(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2016-523573

(P2016-523573A)

(43) 公表日 平成26年8月12日(2016.8.12)

| (51) Int.Cl.            | F 1           | テーマコード (参考) |

|-------------------------|---------------|-------------|

| A 6 1 B 8/14 (2006.01)  | A 6 1 B 8/14  | 4 C 6 O 1   |

| G 0 1 S 7/521 (2006.01) | G 0 1 S 7/521 | 5 D O 1 9   |

| G 0 1 S 15/89 (2006.01) | G 0 1 S 15/89 | 5 J 0 8 3   |

| H 0 4 R 19/00 (2006.01) | H 0 4 R 19/00 | 3 3 0       |

| H 0 4 R 1/02 (2006.01)  | H 0 4 R 1/02  | 3 3 0       |

審査請求 未請求 予備審査請求 未請求 (全 90 頁) 最終頁に続く

|               |                              |          |                                                                                                               |

|---------------|------------------------------|----------|---------------------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2016-501885 (P2016-501885) | (71) 出願人 | 515244151<br>バタフライ ネットワーク, インコーポレイテッド<br>アメリカ合衆国, コネチカット州 O 6 4<br>3 7 ギルフォード, オールド ウィット<br>フィールド ストリート 5 3 0 |

| (86) (22) 出願日 | 平成26年3月13日 (2014. 3. 13)     | (74) 代理人 | 100079108<br>弁理士 稲葉 良幸                                                                                        |

| (85) 翻訳文提出日   | 平成27年10月20日 (2015.10.20)     | (74) 代理人 | 100109346<br>弁理士 大貫 敏史                                                                                        |

| (86) 國際出願番号   | PCT/US2014/025567            | (74) 代理人 | 100117189<br>弁理士 江口 昭彦                                                                                        |

| (87) 國際公開番号   | W02014/151362                | (74) 代理人 | 100134120<br>弁理士 内藤 和彦                                                                                        |

| (87) 國際公開日    | 平成26年9月25日 (2014. 9. 25)     |          |                                                                                                               |

| (31) 優先権主張番号  | 61/798, 851                  |          |                                                                                                               |

| (32) 優先日      | 平成25年3月15日 (2013. 3. 15)     |          |                                                                                                               |

| (33) 優先権主張国   | 米国 (US)                      |          |                                                                                                               |

最終頁に続く

(54) 【発明の名称】モノリシックウルトラソニック撮像デバイス、システム、および方法

## (57) 【要約】

【課題】 従来型アーキテクチャおよび信号処理パラダイムを採用することによる厳しい制限および欠点を改善することである。

【解決手段】 単一チップウルトラソニック撮像解決策を実装するため、オンチップ信号処理を、たとえばデータ帯域幅を減少するために、受信信号経路中に採用することができ、高速シリアルデータモジュールを使用して、デジタルデータストリームとして、オフチップのすべての受信チャネルにデータを移動することができる。オンチップの受信信号のデジタル化によって、進んだデジタル信号処理がオンチップで実施することができる。したがって、单一の半導体基板上に全ウルトラソニック撮像システムの完全な一体化が可能になる。様々な新規の波形生成技法、トランスデューサ構成およびバイアス方法論などが同様に開示される。本明細書に開示される「超音波オンチップ」解決策の構成要素として、HIFU方法を、追加または代替的に採用することができる。

【選択図】 図 2 A

FIG. 2A

**【特許請求の範囲】****【請求項 1】**

ウルトラソニックトランステューサ要素からの信号を処理するための方法であって、前記ウルトラソニックトランステューサ要素と同じ半導体ダイ上に一体化される構成要素を用いて、前記ウルトラソニックトランステューサ要素の出力に対応するアナログ信号をデジタル信号に変換することとを含む、方法。

**【請求項 2】**

前記半導体ダイ上に一体化される少なくとも1つの追加構成要素を用いて、高速シリアルデータストリームとして、前記半導体ダイから前記デジタル信号に対応するデータを送信することとを含む、請求項1に記載の方法。10

**【請求項 3】**

前記半導体ダイ上に一体化される少なくとも1つの追加構成要素を用いて、前記デジタル信号を処理してそのデータ帯域幅を減少させることとを含む、請求項1または2に記載の方法。

**【請求項 4】**

前記少なくとも1つの追加構成要素がデジタル直交復調器を備える、請求項3または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 5】**

前記少なくとも1つの追加構成要素が平均化モジュールを備える、請求項3または他の上記の請求項のいずれか一項に記載の方法。20

**【請求項 6】**

前記少なくとも1つの追加構成要素が整合フィルタを備える、請求項3または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 7】**

前記少なくとも1つの追加構成要素が不整合フィルタを備える、請求項3または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 8】**

前記少なくとも1つの追加構成要素が有限インパルス応答(FIR)フィルタを備える、請求項3または他の上記の請求項のいずれか一項に記載の方法。30

**【請求項 9】**

前記少なくとも1つの追加構成要素が1/2帯域デシメーション低域通過フィルタを備える、請求項3または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 10】**

前記少なくとも1つの追加構成要素がデチャーブモジュールを備える、請求項3または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 11】**

前記半導体ダイ上に一体化される少なくとも1つの追加構成要素を用いて、前記デジタル信号に対応するデータを処理して1つまたは複数の画像形成機能を実施することとを含む、請求項1または他の上記の請求項のいずれか一項に記載の方法。40

**【請求項 12】**

前記1つまたは複数の画像形成機能が、アポディゼーション、逆投影、ファストヒエラルキー逆投影、補間範囲移動または他のフーリエリサンプリング技法、ダイナミックフォーカス、遅延加算処理、およびトモグラフィー再構成からなるグループから選択される少なくとも1つの画像形成機能を含む、請求項11または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 13】**

前記半導体ダイ上に一体化される少なくとも1つの追加構成要素を用いて、前記デジタル信号に対応するデータを処理して1つまたは複数のバックエンド処理機能を実施することとを含む、請求項1または他の上記の請求項のいずれか一項に記載の方法。50

**【請求項 1 4】**

前記 1 つまたは複数のバックエンド処理機能が、ダウンレンジオートフォーカス、クロスレンジオートフォーカス、周波数分散補償、非線形アポディゼーション、リマッピング、圧縮、雑音除去、コンパウンド処理、ドップラ、エラストグラフィ、分光、および基底追跡からなるグループから選択される少なくとも 1 つのバックエンド処理機能を含む、請求項 1 3 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 1 5】**

前記半導体ダイ上に一体化される少なくとも 1 つのマイクロプロセッサを使用して、少なくとも 1 つのデジタル信号処理機能を実施することをさらに含む、請求項 1 または他の上記の請求項のいずれか一項に記載の方法。

10

**【請求項 1 6】**

前記少なくとも 1 つのマイクロプロセッサが使用されて、前記デジタル信号に対応するデータの帯域幅を減少させる、請求項 1 5 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 1 7】**

前記少なくとも 1 つのマイクロプロセッサが使用されて、1 つまたは複数の画像形成機能を実施する、請求項 1 5 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 1 8】**

前記 1 つまたは複数の画像形成機能が、アポディゼーション、逆投影、ファストヒエラルキー逆投影、S to 1 t 補間、ダイナミックフォーカス、遅延加算処理、およびトモグラフィー撮像からなるグループから選択される少なくとも 1 つの画像形成機能を含む、請求項 1 7 または他の上記の請求項のいずれか一項に記載の方法。

20

**【請求項 1 9】**

前記少なくとも 1 つのマイクロプロセッサが使用されて、1 つまたは複数のバックエンド処理機能を実施する、請求項 1 5 または他の上記の請求項のいずれか一項に記載の方法。

。

**【請求項 2 0】**

前記 1 つまたは複数のバックエンド処理機能が、ダウンレンジオートフォーカス、クロスレンジオートフォーカス、周波数分散補償、非線形アポディゼーション、リマッピング、圧縮、雑音除去、コンパウンド処理、ドップラ、エラストグラフィ、分光、および基底追跡からなるグループから選択される少なくとも 1 つのバックエンド処理機能を含む、請求項 1 9 または他の上記の請求項のいずれか一項に記載の方法。

30

**【請求項 2 1】**

前記半導体ダイ上に一体化される少なくとも 1 つの追加構成要素を用いて、前記アナログ信号をデジタル信号に変換する前に、前記アナログ信号を処理して、そこから波形を分離することをさらに含む、請求項 1 または他の上記の請求項のいずれか一項に記載の方法。

。

**【請求項 2 2】**

前記少なくとも 1 つの追加構成要素がアナログ直交復調器を備える、請求項 2 1 または他の上記の請求項のいずれか一項に記載の方法。

40

**【請求項 2 3】**

前記少なくとも 1 つの追加構成要素がアナログデチャーブモジュールを備える、請求項 2 1 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 2 4】**

前記ウルトラソニックトランスデューサ要素が、1 つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルを備える、請求項 1 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 2 5】**

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルが、1 つまたは複数の容量性マイクロマシン加工ウルトラソニックトランスデューサ(

50

CMUT) セルを備える、請求項 2 4 または他の上記の請求項のいずれか一項に記載の方法。

【請求項 2 6】

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランസ്ടେୟୁସାର୍ଲୁଗ୍、1 つまたは複数の C M O S ウルトラソニックトランସ୍ଟେୟୁସା (CUT) セルを備える、請求項 2 4 または他の上記の請求項のいずれか一項に記載の方法。

【請求項 2 7】

半導体ダイ上に一体化される、少なくとも 1 つのウルトラソニックトランସ୍ଟେୟୁସା要素と、

前記半導体ダイ上に一体化され、前記ウルトラソニックトランସ୍ଟେୟୁସା要素の出力に対応するアナログ信号をデジタル信号に変換するように構成されるアナログ - デジタル (ADC) 変換器と

を備える、超音波デバイス。

【請求項 2 8】

前記半導体ダイ上に一体化され、前記半導体ダイからの前記デジタル信号に対応するデータを高速シリアルデータストリームとして送信するように構成される、高速シリアルデータモジュール

をさらに備える、請求項 2 7 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 2 9】

前記半導体ダイ上に一体化され、前記デジタル信号を処理してそのデータ帯域幅を減少させるように構成される、少なくとも 1 つの信号処理モジュール

をさらに備える、請求項 2 7 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 3 0】

前記少なくとも 1 つの信号処理モジュールがデジタル直交復調器を備える、請求項 2 9 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 3 1】

前記少なくとも 1 つの信号処理モジュールが平均化モジュールを備える、請求項 2 9 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 3 2】

前記少なくとも 1 つの信号処理モジュールが整合フィルタを備える、請求項 2 9 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 3 3】

前記少なくとも 1 つの信号処理モジュールが不整合フィルタを備える、請求項 2 9 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 3 4】

前記少なくとも 1 つの信号処理モジュールが有限インパルス応答フィルタを備える、請求項 2 9 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 3 5】

前記少なくとも 1 つの信号処理モジュールが 1 / 2 帯域デシメーション低域通過フィルタを備える、請求項 2 9 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 3 6】

前記少なくとも 1 つの信号処理モジュールがデチャーブモジュールを備える、請求項 2 9 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 3 7】

前記半導体ダイ上に一体化され、前記デジタル信号に対応するデータを処理して、1 つまたは複数の画像形成機能を実施するように構成される、少なくとも 1 つの信号処理モジュール

をさらに備える、請求項 2 7 または他の上記の請求項のいずれか一項に記載の超音波デバ

10

20

30

40

50

イス。

【請求項 3 8】

前記 1 つまたは複数の画像形成機能が、アポディゼーション、逆投影、ファストヒエラルキー逆投影、補間範囲移動または他のフーリエリサンプリング技法、ダイナミックフォーカス、遅延加算処理、およびトモグラフィー再構成からなるグループから選択される少なくとも 1 つの画像形成機能を含む、請求項 3 7 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 3 9】

前記半導体ダイ上に一体化され、前記デジタル信号に対応するデータを処理して、1 つまたは複数のバックエンド処理機能を実施するように構成される、少なくとも 1 つの信号処理モジュール

をさらに備える、請求項 2 7 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 4 0】

前記 1 つまたは複数のバックエンド処理機能が、ダウンレンジオートフォーカス、クロスレンジオートフォーカス、周波数分散補償、非線形アポディゼーション、リマッピング、圧縮、雑音除去、コンパウンド処理、ドップラ、エラストグラフィ、分光、および基底追跡からなるグループから選択される少なくとも 1 つのバックエンド処理機能を含む、請求項 3 9 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 4 1】

前記半導体ダイ上に一体化され、少なくとも 1 つのデジタル信号処理機能を実施するように構成される、マイクロプロセッサ

をさらに備える、請求項 2 7 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 4 2】

前記マイクロプロセッサが、前記デジタル信号に対応するデータの帯域幅を減少させるように構成される、請求項 4 1 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 4 3】

前記マイクロプロセッサが 1 つまたは複数の画像形成機能を実施するように構成される、請求項 4 1 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 4 4】

前記 1 つまたは複数の画像形成機能が、アポディゼーション、逆投影、ファストヒエラルキー逆投影、補間範囲移動または他のフーリエリサンプリング技法、ダイナミックフォーカス、遅延加算処理、およびトモグラフィー撮像からなるグループから選択される少なくとも 1 つの画像形成機能を含む、請求項 4 3 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 4 5】

前記マイクロプロセッサが 1 つまたは複数のバックエンド処理機能を実施するように構成される、請求項 4 1 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 4 6】

前記 1 つまたは複数のバックエンド処理機能が、ダウンレンジオートフォーカス、クロスレンジオートフォーカス、周波数分散補償、非線形アポディゼーション、リマッピング、圧縮、雑音除去、コンパウンド処理、ドップラ、エラストグラフィ、分光、および基底追跡からなるグループから選択される少なくとも 1 つのバックエンド処理機能を含む、請求項 4 5 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 4 7】

前記半導体ダイ上に一体化され、前記 A D C コンバータが前記アナログ信号をデジタル信号に変換する前に、前記アナログ信号を処理して、そこから波形を分離するように構成される、少なくとも 1 つの追加構成要素

10

20

30

40

50

をさらに備える、請求項 27 または他の上記の請求項のいずれか一項に記載のデバイス。

【請求項 48】

前記少なくとも 1 つの追加構成要素がアナログ直交復調器を備える、請求項 47 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 49】

前記少なくとも 1 つの追加構成要素がアナログデチャーブモジュールを備える、請求項 47 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 50】

前記ウルトラソニックトランステューサ要素が、1つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルを備える、請求項 27 または他の上記の請求項のいずれか一項に記載の超音波デバイス。 10

【請求項 51】

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルが、1つまたは複数の容量性マイクロマシン加工ウルトラソニックトランステューサ(CMUT)セルを備える、請求項 50 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 52】

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルが、1つまたは複数の CMOS ウルトラソニックトランステューサ(CUT)セルを備える、請求項 50 または他の上記の請求項のいずれか一項に記載の超音波デバイス。 20

【請求項 53】

ウルトラソニックトランステューサ要素からの信号を処理するための方法であって、前記ウルトラソニックトランステューサ要素と同じ半導体ダイ上に一体化される少なくとも 1 つの構成要素を用いて、前記トランステューサ要素の出力に対応する信号を処理して、そこから波形を分離することを含む、方法。

【請求項 54】

前記少なくとも 1 つの構成要素がアナログ直交復調器を備える、請求項 53 または他の上記の請求項のいずれか一項に記載の方法。

【請求項 55】

前記少なくとも 1 つの構成要素がアナログデチャーブモジュールを備える、請求項 53 または他の上記の請求項のいずれか一項に記載の方法。 30

【請求項 56】

前記ウルトラソニックトランステューサ要素が、1つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルを備える、請求項 53 または他の上記の請求項のいずれか一項に記載の方法。

【請求項 57】

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルが、1つまたは複数の容量性マイクロマシン加工ウルトラソニックトランステューサ(CMUT)セルを備える、請求項 56 または他の上記の請求項のいずれか一項に記載の方法。 40

【請求項 58】

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルが、1つまたは複数の CMOS ウルトラソニックトランステューサ(CUT)セルを備える、請求項 56 または他の上記の請求項のいずれか一項に記載の方法。

【請求項 59】

半導体ダイ上に一体化される、少なくとも 1 つのウルトラソニックトランステューサ要素と、

前記半導体ダイ上に一体化され、前記少なくとも 1 つのウルトラソニックトランステューサ要素の出力に対応する信号を処理して、そこから波形を分離するように構成される、少なくとも 1 つの構成要素と

を備える、超音波デバイス。

【請求項 6 0】

前記少なくとも 1 つの構成要素がアナログ直交復調器を備える、請求項 5 9 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 6 1】

前記少なくとも 1 つの構成要素がアナログデチャーブモジュールを備える、請求項 5 9 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 6 2】

前記少なくとも 1 つのウルトラソニックトランステューサ要素が、1 つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルを備える、請求項 5 9 または他の上記の請求項のいずれか一項に記載の超音波デバイス。 10

【請求項 6 3】

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルが、1 つまたは複数の容量性マイクロマシン加工ウルトラソニックトランステューサ(CMUT)セルを備える、請求項 6 2 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 6 4】

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルが、1 つまたは複数の CMOS ウルトラソニックトランステューサ(CUT)セルを備える、請求項 6 2 または他の上記の請求項のいずれか一項に記載の超音波デバイス。 20

【請求項 6 5】

各々が複数のウルトラソニックトランステューサセルを備える、少なくとも 2 つのウルトラソニックトランステューサ要素を構成するための方法であって、

前記少なくとも 2 つのウルトラソニックトランステューサ要素のうちの一方の中の少なくとも 1 つのウルトラソニックトランステューサセルを、前記少なくとも 2 つのウルトラソニックトランステューサ要素の他方の中の少なくとも 1 つのウルトラソニックトランステューサセルに結合すること

を含む、方法。

【請求項 6 6】

前記結合することが、前記少なくとも 2 つのウルトラソニックトランステューサ要素のうちの前記一方の中の前記少なくとも 1 つのウルトラソニックトランステューサセルを、前記少なくとも 2 つのウルトラソニックトランステューサ要素の前記他方の中の前記少なくとも 1 つのウルトラソニックトランステューサセルに、抵抗性要素を介して結合することを含む、請求項 6 5 または他の上記の請求項のいずれか一項に記載の方法。 30

【請求項 6 7】

前記抵抗性要素がポリシリコン抵抗器を備える、請求項 6 6 または他の上記の請求項のいずれか一項に記載の方法。

【請求項 6 8】

前記結合することが、前記少なくとも 2 つのウルトラソニックトランステューサ要素のうちの異なるものの中の第 1 の対のウルトラソニックトランステューサセルを、第 1 のインピーダンス値を有する第 1 の結合要素と結合することと、前記少なくとも 2 つのウルトラソニックトランステューサ要素のうちの前記異なるものの中の第 2 の対のウルトラソニックトランステューサセルを、前記第 1 のインピーダンス値と異なる第 2 のインピーダンス値を有する第 2 の結合要素と結合することとを含む、請求項 6 5 または他の上記の請求項のいずれか一項に記載の方法。 40

【請求項 6 9】

前記結合することが、前記少なくとも 2 つのウルトラソニックトランステューサ要素のうちの前記一方の中の前記少なくとも 1 つのウルトラソニックトランステューサセルと、前記少なくとも 2 つのウルトラソニックトランステューサ要素の前記他方の中の前記少なくとも 1 つのウルトラソニックトランステューサセルとの間に誘導結合を確立することを

含む、請求項 6 5 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 7 0】**

前記少なくとも 2 つのウルトラソニックトランステューサ要素の前記ウルトラソニックトランステューサセルのうちの少なくともいくつかを混合することをさらに含む、請求項 6 5 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 7 1】**

前記少なくとも 2 つのウルトラソニックトランステューサ要素の各々が、1 つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルを備える、請求項 6 5 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 7 2】**

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルが、1 つまたは複数の容量性マイクロマシン加工ウルトラソニックトランステューサ(CMUT)セルを備える、請求項 7 1 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 7 3】**

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルが、1 つまたは複数の CMOS ウルトラソニックトランステューサ(CUT)セルを備える、請求項 7 1 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 7 4】**

前記少なくとも 2 つのトランステューサ要素の各々の中の少なくともいくつかのトランステューサセルをアポダイズすることをさらに含む、請求項 6 5 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 7 5】**

前記アポダイズすることが、前記少なくとも 2 つのウルトラソニックトランステューサ要素のうちの前記一方の中の前記少なくとも 1 つのトランステューサセル、および前記少なくとも 2 つのトランステューサ要素の前記他方の中の前記少なくとも 1 つのトランステューサセルをアポダイズすることを含む、請求項 7 4 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 7 6】**

各々が複数のウルトラソニックトランステューサセルを備える少なくとも 2 つのウルトラソニックトランステューサ要素を備える、超音波デバイスであって、前記少なくとも 2 つのウルトラソニックトランステューサ要素のうちの一方の中の少なくとも 1 つのウルトラソニックトランステューサセルが、前記少なくとも 2 つのウルトラソニックトランステューサ要素の他方の中の少なくとも 1 つのウルトラソニックトランステューサセルに結合される、超音波デバイス。

**【請求項 7 7】**

前記少なくとも 2 つのウルトラソニックトランステューサ要素のうちの前記一方の中の前記少なくとも 1 つのトランステューサセルが、前記少なくとも 2 つのトランステューサ要素の前記他方の中の前記少なくとも 1 つのトランステューサセルに抵抗性要素を介して結合される、請求項 7 6 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 7 8】**

前記抵抗性要素がポリシリコン抵抗器を備える、請求項 7 7 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 7 9】**

前記少なくとも 2 つのトランステューサ要素のうちの一方が少なくとも第 1 および第 2 のトランステューサセルを備え、前記少なくとも 2 つのトランステューサ要素のうちの他方が少なくとも第 3 および第 4 のトランステューサセルを備え、

前記第 1 のトランステューサセルと第 3 のトランステューサセルが第 1 のインピーダンス値を有する第 1 の結合要素を介して結合され、

前記第 2 のトランステューサセルと第 4 のトランステューサセルが前記第 1 のインピー-

10

20

30

40

50

ダンス値と異なる第2のインピーダンス値を有する第2の結合要素を介して結合される、請求項7\_6または他の上記の請求項のいずれか一項に記載の超音波デバイス。

#### 【請求項8\_0】

前記少なくとも2つのトランスデューサ要素のうちの前記一方の中の前記少なくとも1つのトランスデューサセルと、前記少なくとも2つのトランスデューサ要素の前記他方の中の前記少なくとも1つのトランスデューサセルとの間に誘導結合が確立されるように、前記少なくとも2つのトランスデューサ要素が、構成および配置される、請求項7\_6または他の上記の請求項のいずれか一項に記載の超音波デバイス。

#### 【請求項8\_1】

前記少なくとも2つのトランスデューサ要素の前記トランスデューサセルのうちの少なくともいくつかが混合される、請求項7\_6または他の上記の請求項のいずれか一項に記載の超音波デバイス。 10

#### 【請求項8\_2】

前記少なくとも2つのウルトラソニックトランスデューサ要素の各々が、1つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルを備える、請求項7\_6または他の上記の請求項のいずれか一項に記載の超音波デバイス。

#### 【請求項8\_3】

前記1つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルが、1つまたは複数の容量性マイクロマシン加工ウルトラソニックトランスデューサ(CMUT)セルを備える、請求項8\_2または他の上記の請求項のいずれか一項に記載の超音波デバイス。 20

#### 【請求項8\_4】

前記1つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルが、1つまたは複数のCMOSウルトラソニックトランスデューサ(CUT)セルを備える、請求項8\_2または他の上記の請求項のいずれか一項に記載の超音波デバイス。

#### 【請求項8\_5】

前記少なくとも2つのトランスデューサ要素の各々の中の前記少なくとも1つのトランスデューサセルがアポダイズされる、請求項7\_6または他の上記の請求項のいずれか一項に記載の超音波デバイス。

#### 【請求項8\_6】

前記少なくとも2つのウルトラソニックトランスデューサ要素のうちの前記一方の中の前記少なくとも1つのトランスデューサセル、および前記少なくとも2つのトランスデューサ要素の前記他方の中の前記少なくとも1つのトランスデューサセルがアポダイズされる、請求項8\_5または他の上記の請求項のいずれか一項に記載の超音波デバイス。 30

#### 【請求項8\_7】

ウルトラソニックトランスデューサ要素に電圧でバイアスをかけるための方法であって、

パルサの出力を使用して、前記ウルトラソニックトランスデューサ要素を駆動し、その結果、前記ウルトラソニックトランスデューサ要素がウルトラソニックパルスを放出することと、

少なくともいくつかの場合に、前記パルサが前記ウルトラソニックトランスデューサ要素を駆動するために使用されておらず、その結果、前記ウルトラソニックトランスデューサ要素がウルトラソニックパルスを放出するとき、ウルトラソニックトランスデューサ要素へバイアス信号を印加するために前記パルサの前記出力を使用することとを含む、方法。 40

#### 【請求項8\_8】

前記ウルトラソニックトランスデューサ要素が、1つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルを備える、請求項8\_7または他の上記の請求項のいずれか一項に記載の方法。

#### 【請求項8\_9】

10

20

30

40

50

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルが、1 つまたは複数の容量性マイクロマシン加工ウルトラソニックトランスデューサ(CMUT)セルを備える、請求項 8 8 または他の上記の請求項のいずれか一項に記載の方法。

#### 【請求項 9 0】

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルが、CMOS ウルトラソニックトランスデューサ(CUT)セルを備える、請求項 8 8 または他の上記の請求項のいずれか一項に記載の方法。

#### 【請求項 9 1】

少なくとも 1 つのウルトラソニックトランスデューサ要素と、

前記少なくとも 1 つのウルトラソニックトランスデューサに結合され、少なくともいくつかの場合に、前記少なくとも 1 つのトランスデューサ要素が使用されて受信したウルトラソニックエネルギーを検知するとき、前記パルサの出力が使用されて前記少なくとも 1 つのウルトラソニックトランスデューサ要素にバイアスをかけるように構成および配置されるパルサと

を備える、超音波デバイス。

#### 【請求項 9 2】

前記少なくとも 1 つのウルトラソニックトランスデューサ要素が、1 つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルを備える、請求項 9 1 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

#### 【請求項 9 3】

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルが、1 つまたは複数の容量性マイクロマシン加工ウルトラソニックトランスデューサ(CMUT)セルを備える、請求項 9 2 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

#### 【請求項 9 4】

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルが、1 つまたは複数の CMOS ウルトラソニックトランスデューサ(CUT)セルを備える、請求項 9 2 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

#### 【請求項 9 5】

半導体ダイ上に一体化される少なくとも 1 つのウルトラソニックトランスデューサ要素にバイアスをかけるための方法であって、

前記半導体ダイに印加されるバイアス電圧を使用して前記少なくとも 1 つのウルトラソニックトランスデューサ要素にバイアスをかけること

を含む、方法。

#### 【請求項 9 6】

前記少なくとも 1 つのウルトラソニックトランスデューサ要素が対象物を撮像または治療するために使用されている間、前記対象物に面する前記少なくとも 1 つのウルトラソニックトランスデューサ要素の側に、アースを印加すること

をさらに含む、請求項 9 5 または他の上記の請求項のいずれか一項に記載の方法。

#### 【請求項 9 7】

前記少なくとも 1 つのウルトラソニックトランスデューサ要素が、1 つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルを備える、請求項 9 5 または他の上記の請求項のいずれか一項に記載の方法。

#### 【請求項 9 8】

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルが、1 つまたは複数の容量性マイクロマシン加工ウルトラソニックトランスデューサ(CMUT)セルを備える、請求項 9 7 または他の上記の請求項のいずれか一項に記載の方法。

#### 【請求項 9 9】

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルが、1 つまたは複数の CMOS ウルトラソニックトランスデューサ(CUT)セルを備え

10

20

30

40

50

る、請求項 97 または他の上記の請求項のいずれか一項に記載の方法。

【請求項 100】

半導体ダイ上に一体化される、少なくとも 1 つのウルトラソニックトランスデューサ要素を備え、前記ダイに印加されるバイアス電圧が前記少なくとも 1 つのウルトラソニックトランスデューサ要素にバイアスをかけるためにも使用されるように、前記少なくとも 1 つのウルトラソニックトランスデューサ要素が前記ダイ上で構成および配置される、超音波デバイス。

【請求項 101】

前記超音波デバイスが、前記少なくとも 1 つのウルトラソニックトランスデューサ要素を使用して対象物を撮像または治療するように構成され、撮像または治療の期間前記対象物に面するように構成される前記少なくとも 1 つのウルトラソニックトランスデューサ要素の側がアースに接続される、請求項 100 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

10

【請求項 102】

前記少なくとも 1 つのマイクロマシン加工されたウルトラソニックトランスデューサ要素が、1 つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルを備える、請求項 100 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

20

【請求項 103】

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルが、1 つまたは複数の容量性マイクロマシン加工ウルトラソニックトランスデューサ(CMUT)セルを備える、請求項 102 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 104】

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルが、1 つまたは複数の CMOS ウルトラソニックトランスデューサ(CUT)セルを備える、請求項 102 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 105】

少なくとも 1 つのウルトラソニックトランスデューサ要素にバイアスをかけるための方法であって、

前記少なくとも 1 つのウルトラソニックトランスデューサ要素が対象物を撮像または治療するために使用されている間、前記対象物に面する前記少なくとも 1 つのウルトラソニックトランスデューサ要素の側に、アースを印加することを含む、方法。

30

【請求項 106】

前記少なくとも 1 つのマイクロマシン加工されたウルトラソニックトランスデューサ要素が、1 つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルを備える、請求項 105 または他の上記の請求項のいずれか一項に記載の方法。

40

【請求項 107】

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルが、1 つまたは複数の容量性マイクロマシン加工ウルトラソニックトランスデューサ(CMUT)セルを備える、請求項 106 または他の上記の請求項のいずれか一項に記載の方法。

【請求項 108】

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルが、1 つまたは複数の CMOS ウルトラソニックトランスデューサ(CUT)セルを備える、請求項 106 または他の上記の請求項のいずれか一項に記載の方法。

【請求項 109】

少なくとも 1 つのウルトラソニックトランスデューサ要素を使用して対象物を撮像または治療するように構成され、撮像または治療の期間前記対象物に面するように構成される前記少なくとも 1 つのウルトラソニックトランスデューサ要素の側がアースに接続される

50

、超音波デバイス。

**【請求項 1 1 0】**

前記少なくとも 1 つのウルトラソニックトランステューサ要素が、1 つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルを備える、請求項 1 0 9 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 1 1 1】**

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルが、1 つまたは複数の容量性マイクロマシン加工ウルトラソニックトランステューサ(CMUT)セルを備える、請求項 1 1 0 または他の上記の請求項のいずれか一項に記載の超音波デバイス。 10

**【請求項 1 1 2】**

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルが、1 つまたは複数の CMOS ウルトラソニックトランステューサ(CUT)セルを備える、請求項 1 1 0 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 1 1 3】**

超音波デバイス中で第 1 および第 2 の送信制御回路を構成するための方法であって、前記第 1 および第 2 の送信制御回路の各々が、ウルトラソニックトランステューサ要素のためのパルサを駆動する波形発生器を備える方法において、

前記第 1 の制御回路が送信イネーブル信号を受信するときと、前記第 1 の波形発生器により生成される第 1 の波形が前記第 1 のパルサに印加されるときとの間の第 1 の遅延の長さが、前記第 2 の制御回路が前記送信イネーブル信号を受信するときと、前記第 2 の波形発生器により生成される第 2 の波形が前記第 2 のパルサに印加されるときとの間の第 2 の遅延の長さと異なるように、前記第 1 の送信制御回路と第 2 の送信制御回路を異なって構成すること 20

を含む、方法。

**【請求項 1 1 4】**

前記第 1 および第 2 の送信制御回路を構成する前記ことが、

前記送信イネーブル信号が前記第 1 の波形発生器に到達する前に第 1 の長さの時間だけ前記送信イネーブル信号が遅延されるように前記第 1 の送信制御回路を構成することと、

前記送信イネーブル信号が前記第 2 の波形発生器に到達する前に第 2 の長さの時間だけ前記送信イネーブル信号が遅延されるように前記第 2 の送信制御回路を構成することであって、前記第 2 の長さの時間が前記第 1 の長さの時間と異なることと 30

を含む、請求項 1 1 3 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 1 1 5】**

前記第 1 および第 2 の送信制御回路を構成する前記ことが、

前記第 1 の波形発生器が第 1 の開始周波数を持つように構成することと、

前記第 2 の波形発生器が、前記第 1 の開始周波数と異なる第 2 の開始周波数を持つように構成することと

を含む、請求項 1 1 3 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 1 1 6】**

前記第 1 および第 2 の送信制御回路を構成する前記ことが、

前記第 1 の波形発生器が第 1 の開始位相を持つように構成することと、

前記第 2 の波形発生器が、前記第 1 の開始位相と異なる第 2 の開始位相を持つように構成することと 40

を含む、請求項 1 1 3 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 1 1 7】**

前記第 1 および第 2 の送信制御回路を構成する前記ことが、

前記第 1 の波形発生器により出力される前記第 1 の波形が、前記第 1 の波形が前記第 1 のパルサに到達する前に、第 1 の長さの時間だけ遅延されるように前記第 1 の送信制御回路を構成することと、

10

20

30

40

50

前記第2の波形発生器により出力される前記第2の波形が、前記第2の波形が前記第2のパルサに到達する前に、前記第1の長さの時間と異なる第2の長さの時間だけ遅延されるように前記第2の送信制御回路を構成することと

を含む、請求項113または他の上記の請求項のいずれか一項に記載の方法。

**【請求項118】**

少なくとも第1および第2のウルトラソニックトランスデューサ要素と、

前記第1のウルトラソニックトランスデューサ要素を駆動するように前記第1のウルトラソニックトランスデューサ要素に結合され、その結果、前記第1のウルトラソニックトランスデューサ要素がウルトラソニックパルスを放出する第1のパルサ、

前記第1のパルサに結合され、前記第1の送信制御回路による送信イネーブル信号の受信に応答して、前記第1のパルサに第1の波形を提供する第1の波形発生器、および

前記第1の送信制御回路が前記送信イネーブル信号を受信するときと前記第1の波形が前記第1のパルサに印加されるときとの間の第1の遅延の長さに影響を及ぼす、少なくとも1つの第1の構成要素

を備える第1の送信制御回路と、

前記第2のウルトラソニックトランスデューサ要素を駆動するように前記第2のウルトラソニックトランスデューサ要素に結合され、その結果、前記第2のウルトラソニックトランスデューサ要素がウルトラソニックパルスを放出する第2のパルサ、

前記第2のパルサに結合され、前記第2の送信制御回路による前記送信イネーブル信号の受信に応答して、前記第2のパルサに第2の波形を提供する第2の波形発生器、および

前記第2の送信制御回路が前記イネーブル信号を受信するときと前記第2の波形が前記第2のパルサに印加されるときとの間の第2の遅延の長さに影響を及ぼす、少なくとも1つの第2の構成要素

を備える第2の送信制御回路と

を備え、

前記少なくとも1つの第1の構成要素が前記少なくとも1つの第2の構成要素と異なって構成され、その結果、前記第2の遅延の前記長さが前記第1の遅延の前記長さと異なる、

超音波デバイス。

**【請求項119】**

前記少なくとも1つの第1の構成要素が、前記イネーブル信号を前記第1の波形発生器に提供する前に、第1の数のクロックサイクルだけ前記イネーブル信号を遅延させる第1のシフトレジスタを備え、

前記少なくとも1つの第2の構成要素が、前記イネーブル信号を前記第2の波形発生器に提供する前に、前記第1の数のクロックサイクルと異なる第2の数のクロックサイクルだけ前記イネーブル信号を遅延させる第2のシフトレジスタを備える、

請求項118または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項120】**

前記少なくとも1つの第1の構成要素が、前記第1の波形発生器の開始周波数を決定する第1の値を含む第1のレジスタを含み、

前記少なくとも1つの第2の構成要素が、前記第2の波形発生器の開始周波数を決定する、前記第1の値と異なる第2の値を含む第2のレジスタを含む、

請求項118または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項121】**

前記少なくとも1つの第1の構成要素が、前記第1の波形発生器の開始位相を決定する第1の値を含む第1のレジスタを含み、

前記少なくとも1つの第2の構成要素が、前記第2の波形発生器の開始位相を決定する、前記第1の値と異なる第2の値を含む第2のレジスタを含む、

請求項118または他の上記の請求項のいずれか一項に記載の超音波デバイス。

10

20

30

40

50

**【請求項 1 2 2】**

前記第1の波形発生器により出力される前記第1の波形を、前記第1の波形が前記第1のパルサに到達する前に、第1の長さの時間だけ遅延させる第1の遅延要素を前記少なくとも1つの第1の構成要素が備え、

前記第2の波形発生器により出力される前記第2の波形を、前記第2の波形が前記第2のパルサに到達する前に、前記第1の長さの時間と異なる第2の長さの時間だけ遅延させる第2の遅延要素を前記少なくとも1つの第2の構成要素が備える、

請求項118または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 1 2 3】**

少なくとも第1および第2の波形発生器を構成するための方法であって、

10

前記少なくとも第1および第2の波形発生器の第1および第2の構成可能動作パラメータの値を制御するためにコントローラを使用することを含む、方法。

**【請求項 1 2 4】**

前記コントローラで一連のイベント数を生成することと、

20

前記第1の波形発生器について、前記第1の波形発生器に関連する第1のメモリから前記コントローラにより提供されるイベント数に関連する第1の値を検索し、前記第1の構成可能動作パラメータとして使用するために前記第1の値を前記第1の波形発生器に提供することと、

前記第2の波形発生器について、前記第2の波形発生器に関連する第2のメモリから前記コントローラにより提供される前記イベント数に関連する第2の値を検索し、前記第2の構成可能動作パラメータとして使用するために前記第2の値を前記第2の波形発生器に提供することと

をさらに含む、請求項123または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 1 2 5】**

前記第1および第2の構成可能動作パラメータが前記第1および第2の波形発生器の同じ機能性を制御し、少なくとも1つのイベント数について、前記第1のメモリから検索された前記第1の値と前記第2のメモリから検索された前記第2の値が異なる、請求項124または他の上記の請求項のいずれか一項に記載の方法。

30

**【請求項 1 2 6】**

前記第1および第2の波形発生器の各々にイネーブル信号を送信するために前記コントローラを使用すること

をさらに含む、請求項123または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 1 2 7】**

第1の波形発生器の前記第1の構成可能動作パラメータと第2の波形発生器の前記第2の構成可能動作パラメータのそれぞれが異なる値を有するように設定すること

をさらに含む、請求項123または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 1 2 8】**

少なくとも第1および第2の対応するウルトラソニックトランステューサ要素による送信のための波形を生成するように構成される少なくとも第1および第2の波形発生器であって、前記第1の波形発生器が少なくとも1つの第1の構成可能動作パラメータを含み、前記第2の波形発生器が少なくとも1つの第2の構成可能動作パラメータを含む、少なくとも第1および第2の波形発生器と、

40

前記第1および第2の構成可能動作パラメータの値を制御するように構成されるコントローラと

を備えるデバイス。

**【請求項 1 2 9】**

前記コントローラが一連の送信イベント数を出力するように構成され、

前記第1の波形発生器が、それぞれの送信イベント数に関連する前記第1の構成可能動作パラメータについての値を記憶する第1のイベントメモリに関連し、前記コントローラ

50

から送信されたイベント数を受信して、前記第1の波形発生器にそれによる使用のために、前記第1の構成可能動作パラメータについての対応する記憶された値を出力するように構成され、

前記第2の波形発生器が、それぞれの送信イベント数に関連する前記第2の構成可能動作パラメータについての値を記憶する第2のイベントメモリに関連し、前記コントローラから送信されたイベント数を受信して、前記第2の波形発生器にそれによる使用のために、前記第2の構成可能動作パラメータについての対応する記憶された値を出力するように構成される、

請求項128または他の上記の請求項のいずれか一項に記載のデバイス。

**【請求項130】**

前記コントローラにより出力される少なくとも1つのイベント数について、前記第1のイベントメモリおよび第2のイベントメモリが、前記第1および第2の構成可能動作パラメータについての異なる関連値を記憶する、

請求項129または他の上記の請求項のいずれか一項に記載のデバイス。

**【請求項131】**

前記コントローラが前記第1および第2の波形発生器の各々に送信イネーブル信号を通信するようにさらに構成される、請求項128または他の上記の請求項のいずれか一項に記載のデバイス。

**【請求項132】**

前記第1の構成可能動作パラメータが前記第2の構成可能動作パラメータと異なる値に設定することができる、請求項128または他の上記の請求項のいずれか一項に記載のデバイス。

**【請求項133】**

超音波デバイスを作るための方法であって、少なくとも1つのCMOSウルトラソニックトランステューサ要素と同じ半導体ダイ上にデジタル受信回路を一体化することを含む、方法。

**【請求項134】**

前記ウルトラソニックトランステューサ要素が、1つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルを備える、請求項133または他の上記の請求項のいずれか一項に記載の方法。

**【請求項135】**

前記1つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルが、1つまたは複数の容量性マイクロマシン加工ウルトラソニックトランステューサ(CMUT)セルを備える、請求項134または他の上記の請求項のいずれか一項に記載の方法。

**【請求項136】**

前記1つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルが、1つまたは複数のCMOSウルトラソニックトランステューサ(CUT)セルを備える、請求項134または他の上記の請求項のいずれか一項に記載の方法。

**【請求項137】**

单一の集積回路基板上に形成される、少なくとも1つのCMOSウルトラソニックトランステューサ要素とデジタル受信回路とを備えるデバイス。

**【請求項138】**

前記ウルトラソニックトランステューサ要素が、1つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルを備える、請求項137または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項139】**

前記1つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルが、1つまたは複数の容量性マイクロマシン加工ウルトラソニックトランステューサ(CMUT)セルを備える、請求項138または他の上記の請求項のいずれか一項に記載の超音

10

20

30

40

50

波デバイス。

【請求項 1 4 0】

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランസ്ടේරුසෑセルが、1 つまたは複数の C M O S ウルトラソニックトランස്ടේරුසෑ (CUT) セルを備える、請求項 1 3 8 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

【請求項 1 4 1】

超音波デバイスを作るための方法であって、

少なくとも第 1 および第 2 の送信制御回路ならびに第 1 および第 2 のウルトラソニックトランස്ടේරුසෑ要素に対応する少なくとも第 1 および第 2 の受信制御回路を備える C M O S 回路の上に、少なくとも前記第 1 および第 2 のウルトラソニックトランස്ടේරුසෑ要素を製造すること

を含む、方法。

【請求項 1 4 2】

前記第 1 および第 2 の受信制御回路の各々が、アナログ - デジタル変換器を備える、請求項 1 4 1 または他の上記の請求項のいずれか一項に記載の方法。

【請求項 1 4 3】

前記第 1 および第 2 の受信制御回路の各々が、デジタル信号処理回路をさらに備える、請求項 1 4 2 または他の上記の請求項のいずれか一項に記載の方法。

【請求項 1 4 4】

前記少なくとも第 1 および第 2 のウルトラソニックトランස്ടේරුසෑ要素が、前記 C M O S 回路の上に製造され、そのため、前記第 1 の送信制御回路および前記第 1 の受信制御回路は、両方が前記第 1 のウルトラソニックトランස്ടේරුසෑ要素の下に配設され、前記第 2 の送信制御回路および前記第 2 の受信制御回路は、両方が前記第 2 のウルトラソニックトランස്ടේරුසෑ要素の下に配設される、請求項 1 4 1 または他の上記の請求項のいずれか一項に記載の方法。

【請求項 1 4 5】

前記少なくとも第 1 および第 2 のウルトラソニックトランස്ടේරුසෑ要素を製造する前記ことが、前記 C M O S 回路と同じ半導体基板上に前記少なくとも第 1 および第 2 のウルトラソニックトランස്ടේරුසෑ要素を製造することを含む、請求項 1 4 1 に記載の方法。

【請求項 1 4 6】

前記少なくとも第 1 および第 2 のウルトラソニックトранසෑセルを製造する前記ことが、

前記第 1 のウルトラソニックトランස്ടේරුසෑ要素のために第 1 のパルサを駆動するように結合される第 1 の波形発生器を含むように前記第 1 の送信制御回路を製造することと、

前記第 2 のウルトラソニックトランස്ടේරුසෑ要素のために第 2 のパルサを駆動するように結合される第 2 の波形発生器を含むように前記第 2 の送信制御回路を製造することとを含む、請求項 1 4 1 に記載の方法。

【請求項 1 4 7】

前記第 1 および第 2 のウルトラソニックトランස്ടේරුසෑ要素の各々が、1 つまたは複数のマイクロマシン加工されたウルトラソニックトランස്ടේරුසෑセルを備える、請求項 1 4 1 または他の上記の請求項のいずれか一項に記載の方法。

【請求項 1 4 8】

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランස്ടේරුසෑセルが、1 つまたは複数の容量性マイクロマシン加工ウルトラソニックトランස്ടේරුසෑ (CMUT) セルを備える、請求項 1 4 7 または他の上記の請求項のいずれか一項に記載の方法。

【請求項 1 4 9】

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランස്ടේරුසෑセルが、1 つまたは複数の C M O S ウルトラソニックトランස്ടේරුසෑ (CUT) セルを備え

10

20

30

40

50

る、請求項 147 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 150】**

少なくとも第 1 および第 2 のウルトラソニックトランステューサ要素と、前記少なくとも第 1 および第 2 のウルトラソニックトランステューサ要素の下に配設される CMOS 回路とを備え、

前記 CMOS 回路が、その中に、第 1 および第 2 の送信制御回路ならびに前記第 1 および第 2 のウルトラソニックトランステューサ要素に対応する第 1 および第 2 の受信制御回路を一体化した、超音波デバイス。

**【請求項 151】**

前記第 1 および第 2 の受信制御回路の各々が、アナログ - デジタル変換器を備える、請求項 150 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 152】**

前記第 1 および第 2 の受信制御回路の各々が、デジタル信号処理回路をさらに備える、請求項 151 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 153】**

前記第 1 の送信制御回路および前記第 1 の受信制御回路は、両方が前記第 1 のウルトラソニックトランステューサ要素の下に配設され、前記第 2 の送信制御回路および前記第 2 の受信制御回路は、両方が前記第 2 のウルトラソニックトランステューサ要素の下に配設される、請求項 150 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 154】**

前記第 1 および第 2 のウルトラソニックトランステューサ要素が、前記 CMOS 回路と同じ半導体ダイ上に一体化される、請求項 150 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 155】**

前記第 1 の送信制御回路が、前記第 1 のウルトラソニックトランステューサ要素のために第 1 のパルサを駆動するように結合される第 1 の波形発生器を備え、前記第 2 の送信制御回路が、前記第 2 のウルトラソニックトランステューサ要素のために第 2 のパルサを駆動するように結合される第 2 の波形発生器を備える、請求項 150 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 156】**

前記第 1 および第 2 のウルトラソニックトランステューサ要素の各々が、1つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルを備える、請求項 150 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 157】**

前記 1つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルが、1つまたは複数の容量性マイクロマシン加工ウルトラソニックトランステューサ(CMUT)セルを備える、請求項 156 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 158】**

前記 1つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルが、1つまたは複数の CMOS ウルトラソニックトランステューサ(CUT)セルを備える、請求項 156 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 159】**

ウルトラソニックトランステューサ要素からの信号を処理するための方法であって、

前記ウルトラソニックトランステューサ要素と同じ半導体ダイ上に一体化される構成要素を用いて、前記半導体ダイからの前記ウルトラソニックトランステューサ要素の出力に対応するデータを高速シリアルデータストリームとして送信することを含む、方法。

**【請求項 160】**

10

20

30

40

50

前記ウルトラソニックトランスデューサ要素の出力に対応するアナログ信号をデジタル信号に変換することをさらに含み、

データを送信する前記ことが前記高速シリアルデータストリームとして前記半導体ダイからの前記デジタル信号に対応するデータを送信することを含む、

請求項 159 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 161】**

前記半導体ダイ上に一体化される少なくとも 1 つの追加構成要素を用いて、前記デジタル信号を処理してそのデータ帯域幅を減少させること

をさらに含む、請求項 160 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 162】**

前記少なくとも 1 つの追加構成要素がデジタル直交復調器を備える、請求項 161 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 163】**

前記少なくとも 1 つの追加構成要素が平均化モジュールを備える、請求項 161 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 164】**

前記少なくとも 1 つの追加構成要素が整合フィルタを備える、請求項 161 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 165】**

前記少なくとも 1 つの追加構成要素が不整合フィルタを備える、請求項 161 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 166】**

前記少なくとも 1 つの追加構成要素が有限インパルス応答 (FIR) フィルタを備える、請求項 161 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 167】**

前記少なくとも 1 つの追加構成要素が 1 / 2 帯域デシメーション低域通過フィルタを備える、請求項 161 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 168】**

前記少なくとも 1 つの追加構成要素がデチャーブモジュールを備える、請求項 161 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 169】**

前記半導体ダイ上に一体化される少なくとも 1 つの追加構成要素を用いて、前記アナログ信号をデジタル信号に変換する前に、前記アナログ信号を処理して、そこから波形を分離すること

をさらに含む、請求項 161 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 170】**

前記少なくとも 1 つの追加構成要素がアナログ直交復調器を備える、請求項 169 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 171】**

前記少なくとも 1 つの追加構成要素がアナログデチャーブモジュールを備える、請求項 169 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 172】**

前記ウルトラソニックトランスデューサ要素が、1 つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルを備える、請求項 159 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 173】**

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルが、1 つまたは複数の容量性マイクロマシン加工ウルトラソニックトランスデューサ (CMUT) セルを備える、請求項 172 または他の上記の請求項のいずれか一項に記載の方法。

10

20

30

40

50

**【請求項 174】**

前記1つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルが、1つまたは複数のC M O Sウルトラソニックトランスデューサ(CUT)セルを備える、請求項172または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 175】**

送信する前記ことが、U S Bモジュールを使用して、前記半導体ダイからの前記ウルトラソニックトランスデューサ要素の前記出力に対応する前記データを前記高速シリアルデータストリームとして送信することを含む、

請求項159または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 176】**

前記U S BモジュールがU S B3 . 0モジュールを備える、請求項175または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 177】**

送信する前記ことが、低電圧差動信号(LVDS)リンクを使用して、前記半導体ダイから前記ウルトラソニックトランスデューサ要素の前記出力に対応する前記データを送信することを含む、

請求項159または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 178】**

半導体ダイ上に一体化される、少なくとも1つのウルトラソニックトランスデューサ要素と、

前記半導体ダイ上に一体化され、前記半導体ダイからの前記ウルトラソニックトランスデューサ要素の出力に対応するデータを高速シリアルデータストリームとして送信するように構成される高速シリアルデータモジュールと

を備える、超音波デバイス。

**【請求項 179】**

前記デバイスが、前記半導体ダイ上に一体化され、前記ウルトラソニックトランスデューサ要素の前記出力に対応するアナログ信号をデジタル信号に変換するように構成されるアナログ-デジタル(ADC)変換器をさらに備え、

前記高速シリアルデータモジュールが、前記半導体ダイからの前記デジタル信号に対応するデータを前記高速シリアルデータストリームとして送信するように構成される、

請求項178または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 180】**

前記半導体ダイ上に一体化され、前記デジタル信号を処理してそのデータ帯域幅を減少させるように構成される、少なくとも1つの信号処理モジュール

をさらに備える、請求項179または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 181】**

前記少なくとも1つの信号処理モジュールがデジタル直交復調器を備える、請求項180または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 182】**

前記少なくとも1つの信号処理モジュールが平均化モジュールを備える、請求項180または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 183】**

前記少なくとも1つの信号処理モジュールが整合フィルタを備える、請求項180または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 184】**

前記少なくとも1つの信号処理モジュールが不整合フィルタを備える、請求項180または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 185】**

前記少なくとも1つの信号処理モジュールが有限インパルス応答フィルタを備える、請

10

20

30

40

50

求項 180 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 186】**

前記少なくとも 1 つの信号処理モジュールが 1 / 2 帯域デシメーション低域通過フィルタを備える、請求項 180 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 187】**

前記少なくとも 1 つの信号処理モジュールがデチャーブモジュールを備える、請求項 180 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 188】**

前記半導体ダイ上に一体化され、前記 A D C コンバータが前記アナログ信号をデジタル信号に変換する前に、前記アナログ信号を処理して、そこから波形を分離するように構成される、少なくとも 1 つの追加構成要素

をさらに備える、請求項 179 または他の上記の請求項のいずれか一項に記載のデバイス。

**【請求項 189】**

前記少なくとも 1 つの追加構成要素がアナログ直交復調器を備える、請求項 188 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 190】**

前記少なくとも 1 つの追加構成要素がアナログデチャーブモジュールを備える、請求項 188 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 191】**

前記ウルトラソニックトランステューサ要素が、1 つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルを備える、請求項 178 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 192】**

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルが、1 つまたは複数の容量性マイクロマシン加工ウルトラソニックトランステューサ (CMUT) セルを備える、請求項 191 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 193】**

前記 1 つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルが、1 つまたは複数の C M O S ウルトラソニックトランステューサ (CUT) セルを備える、請求項 191 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 194】**

前記高速シリアルデータモジュールが U S B モジュールを備える、請求項 178 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 195】**

前記 U S B モジュールが U S B 3 . 0 モジュールを備える、請求項 178 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 196】**

前記高速シリアルデータモジュールが低電圧差動信号 (LVDS) リンクモジュールを備える、請求項 178 または他の上記の請求項のいずれか一項に記載の超音波デバイス。

**【請求項 197】**

送信および / または制御回路と同じ半導体ダイ上に一体化される、少なくとも第 1 および第 2 のウルトラソニックトランステューサ要素のために、前記送信および / または制御回路を動作させるための方法であって、

コントローラを使用して、前記少なくとも第 1 および第 2 のウルトラソニックトランステューサ要素のために、前記送信および / または制御回路の動作パラメータの値を制御すること

を含む、方法。

10

20

30

40

50

**【請求項 198】**

前記半導体ダイ上に一体化されないコントローラを用いて、高速シリアルデータリンクを介して、前記送信および／または制御回路に関連する前記レジスタに前記動作パラメータを通信すること

をさらに含む、請求項 197 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 199】**

前記コントローラを使用する前記ことが、前記コントローラを使用して、前記少なくとも第 1 および第 2 のウルトラソニックトランスデューサ要素のために、送信制御回路の波形発生器の動作パラメータの値を制御することを含む、請求項 197 または他の上記の請求項のいずれか一項に記載の方法。

10

**【請求項 200】**

前記コントローラを使用する前記ことが、前記コントローラを使用して、前記少なくとも第 1 および第 2 のウルトラソニックトランスデューサ要素のために、受信制御回路の増幅器の動作パラメータの値を制御することを含む、請求項 197 または他の上記の請求項のいずれか一項に記載の方法。

**【請求項 201】**

半導体ダイ上に一体化される、少なくとも第 1 および第 2 のウルトラソニックトランスデューサ要素と、

前記半導体ダイ上に一体化される、送信および／または制御回路と、

前記少なくとも第 1 および第 2 のウルトラソニックトランスデューサ要素のために、前記送信および／または制御回路の動作パラメータの値を制御するように構成されるコントローラと

20

を備えるデバイス。

**【請求項 202】**

前記コントローラが、前記半導体ダイ上に一体化されず、高速シリアルデータリンクを介して、前記送信および／または制御回路に関連する前記レジスタに前記動作パラメータを通信するように構成される、請求項 201 または他の上記の請求項のいずれか一項に記載のデバイス。

**【請求項 203】**

前記コントローラが、前記少なくとも第 1 および第 2 のウルトラソニックトランスデューサ要素のために、送信制御回路の波形発生器の動作パラメータの値を制御するように構成される、請求項 201 または他の上記の請求項のいずれか一項に記載のデバイス。

30

**【請求項 204】**

前記コントローラが、前記少なくとも第 1 および第 2 のウルトラソニックトランスデューサ要素のために、受信制御回路の増幅器の動作パラメータの値を制御するように構成される、請求項 201 または他の上記の請求項のいずれか一項に記載のデバイス。

**【請求項 205】**

超音波撮像チップと

高密度焦点式超音波 (HIFU) チップと

を備え、

前記超音波撮像チップと前記 HIFU チップが結合され、組み合わされて動作し、画像誘導 HIFU を実施する、デバイス。

40

**【請求項 206】**

单一のチップに一体化された、超音波撮像回路および高密度焦点式超音波 (HIFU) 回路を備え、画像誘導 HIFU を実施するように構成される、デバイス。

**【請求項 207】**

C MOS ウェハ上の超音波トランスデューサ要素の配置と、

前記 C MOS ウェハ上に形成されて超音波トランスデューサ要素の前記配置に電気的に結合される集積回路と

を備え、

50

前記集積回路が約 50Vまでの電圧を駆動するように構成される、デバイス。

【請求項 208】

前記集積回路がサブミクロンノードを備え、前記サブミクロンノードが約 50Vまでの電圧を駆動するように構成される、請求項 207 に記載のデバイス。

【発明の詳細な説明】

【技術分野】

【0001】

関連出願の相互参照

[0001] 本出願は、その全体が参照により本明細書に組み込まれる、2013年3月15日に代理人整理番号第 B1348.70006US00号で出願され、「MONOLITHIC ULTRASONIC IMAGING DEVICES, SYSTEMS AND METHODS」と題する、米国仮特許出願第 61/798,851 号の米国特許法の下の利益を主張する。 10

【0002】

[0002] 本開示の態様は、撮像および / または治療（たとえば、ウルトラソニック撮像および / または治療技術）のためのデバイス、システム、および方法に関する。たとえば、本明細書に開示されるアーキテクチャおよび技法の特定の態様は、全ウルトラソニック撮像システムが単一の半導体基板上に一体化されることを可能にする。したがって、本明細書に記載される特徴および方法論の多くは、シングルチップウルトラソニック撮像ソリューションに関し、または、ウルトラソニック撮像システムの少なくともかなりの部分がシングルチップ上に設けられるデバイスおよびシステムに関する。 20

【背景技術】

【0003】

[0003] 従来型の超音波スキャナは、画像処理に使用することができる、撮像アルゴリズムのタイプを制限する、送受信動作のためのビーム形成を備える線走査などのハードウェア構成を有する。

【0004】

[0004] さらに、ウルトラソニックスキャナの費用および拡張性は、現在業界で主流を占める圧電トランスデューサ技術の限界に近づいてきた。圧電トランスデューサは、依然として、「ダイスアンドフィル（dice and fill）」製造プロセスを使用して作られており、そこでは、個々の圧電素子が切断され、次いで、基板上に個々に配置されてトランスデューサを形成する。そのようなプロセスは、費用がかかり、不均一で、機械加工および配線の拡張性がない傾向がある。 30

【0005】

[0005] 超音波スキャナ中で圧電トランスデューサ配列から電子回路に複数のチャネルのアナログ信号を移送する問題が、超音波撮像の解像度を前進させて高品質 3D 容積撮像を可能にすることに必要な、より大きく、より密度の高いトランスデューサの配列の利用を非常に制限してきた。

【0006】

[0006] 容量性マイクロマシン加工超音波トランスデューサ（CMUT）の製造技法における最近の進歩によって、現在、電子産業を推進しているのと、同じ半導体工場内で高品質超音波トランスデューサを製造することが可能になる。CMUT デバイスは、圧電トランスデューサと比較したときに、優れた帯域幅および音響インピーダンス整合能力も有する。また、CMUT 配列を設計するのに利用可能なフレキシビリティの増加によって、撮像アーティファクトを抑制し、信号品質を改善して、チャネル数を減少することができる、進んだ配列設計技法を可能にする。しかし、これまで提案してきた CMUT 配列を使用するウルトラソニック撮像ソリューションは、従来型アーキテクチャおよび信号処理パラダイムを採用し、したがって厳しい制限および欠点がある。 40

【発明の概要】

【課題を解決するための手段】

50

**【 0 0 0 7 】**

[0007] 本開示は、マイクロマシン加工されたウルトラソニックトランステューサベースのウルトラソニック撮像装置の設計のための、新規なパラダイムの様々な態様を詳述する。いくつかの実施形態では、オンチップ信号処理を、たとえばデータ帯域幅を減少するために受信信号経路中に採用することができ、かつ／または、高速シリアルデータモジュールを使用して、デジタルデータストリームとして、オフチップのすべての受信チャネルにデータを移動することができる。本開示のいくつかの実施形態に従う、オンチップの受信信号のデジタル化によって、進んだデジタル信号処理がオンチップで実施することが可能になり、したがって、単一の半導体基板上に全ウルトラソニック撮像システムの完全、または実質的に完全な一体化が可能になる。いくつかの実施形態では、完全な「超音波システムオンチップ」ソリューションが提供される。

10

**【 0 0 0 8 】**

[0008] いくつかの実施形態では、本明細書に開示されるデバイスおよびアーキテクチャは、たとえば、1つまたは複数の合成開口技法など、1つまたは複数の高度な方法で、完全に一体化することができる。合成開口技法は、たとえば、複数の受信開口の集合から、高解像度画像の形成を可能にすることができる。

**【 0 0 0 9 】**

[0009] 本技術の態様によれば、ウルトラソニックトランステューサ要素からの信号を処理するための方法が提供され、方法は、ウルトラソニックトランステューサ要素と同じ半導体ダイ上に一体化される構成要素を用いて、ウルトラソニックトランステューサ要素の出力に対応するアナログ信号をデジタル信号に変換することを含む。いくつかのそのような実施形態では、次いで、ウルトラソニックトランステューサの出力信号のデジタル表現は、半導体ダイ上で生成され、半導体ダイ上の信号のさらなる処理、および／または半導体ダイからのデジタル信号の送信が容易になる。この様式では、いくつかの実施形態では、超音波デバイスは、単一の半導体ダイ上に、他の構成要素とデジタル的に通信するように構成することができる、一体化されるトランステューサおよび回路を含む。

20

**【 0 0 1 0 】**

[0010] いくつかの実施形態では、方法は、半導体ダイ上に一体化される少なくとも1つの追加構成要素を用いて、高速シリアルデータストリームとして、半導体ダイからデジタル信号に対応するデータを送信することをさらに含む。いくつかの実施形態では、方法は、半導体ダイ上に一体化される少なくとも1つの追加構成要素を用いて、デジタル信号を処理してそのデータ帯域幅を減少させることをさらに含む。少なくともいくつかの実施形態では、そのような帯域幅の減少によって、他の構成要素への、半導体ダイのデジタルデータの送信が容易になる。

30

**【 0 0 1 1 】**

[0011] いくつかの実施形態では、少なくとも1つの追加構成要素は、デジタル直交復調器を備える。いくつかの実施形態では、少なくとも1つの追加構成要素は、平均化モジュールを備える。いくつかの実施形態では、少なくとも1つの追加構成要素は、（たとえば、特定の周波数に整合した）整合フィルタを備え、代替実施形態では、不整合フィルタを備える。いくつかの実施形態では、少なくとも1つの追加構成要素は、有限インパルス応答（FIR: finite impulse response）フィルタを備える。いくつかの実施形態では、少なくとも1つの追加構成要素は、1/2帯域デシメーション低域通過フィルタを備える。いくつかの実施形態では、少なくとも1つの追加構成要素は、ランプ回路（たとえば、デジタルランプ回路）、または伸張回路であってよく、（たとえば、LFM波形といった）信号を時間から周波数に変換するように構成することができる、デチャーブモジュールを備える。

40

**【 0 0 1 2 】**

[0012] いくつかの実施形態では、方法は、半導体ダイ上に一体化される少なくとも1つの追加構成要素を用いて、デジタル信号に対応するデータを処理して、1つまたは複数の画像形成機能を実施することをさらに含む。いくつかのそのような実施形態では、画像形

50

成機能のそのような性能は、超音波画像の形成をもたらす、または超音波画像を形成する結果となり、したがって、いくつかの実施形態では、一体型超音波撮像デバイスが半導体ダイ上に形成される。いくつかの実施形態では、1つまたは複数の画像形成機能は、アポディゼーション、逆投影、ファストヒエラルキー逆投影、補間範囲移動または他のフリエリサンプリング技法、ダイナミックフォーカス、遅延加算処理、およびトモグラフィー再構成からなるグループから選択される少なくとも1つの画像形成機能を含む。少なくともいくつかの実施形態では、そのような機能が使用されて、たとえば、医療関連である画像タイプといった、有利な画像タイプを提供する。

#### 【0013】

[0013] いくつかの実施形態では、方法は、半導体ダイ上に一体化される少なくとも1つの追加構成要素を用いて、デジタル信号に対応するデータを処理し、1つまたは複数のバックエンド処理機能を実施することをさらに含む。いくつかの実施形態では、1つまたは複数のバックエンド処理機能は、ダウンレンジオートフォーカス、クロスレンジオートフォーカス、周波数分散補償、非線形アポディゼーション、リマッピング、圧縮、雑音除去、コンパウンド処理、ドップラ、エラストグラフィ、分光、および基底追跡からなるグループから選択される少なくとも1つのバックエンド処理機能を含む。10

#### 【0014】

[0014] いくつかの実施形態では、方法は、半導体ダイ上に一体化される少なくとも1つのマイクロプロセッサを使用して、少なくとも1つのデジタル信号処理機能を実施することをさらに含む。いくつかの実施形態では、少なくとも1つのマイクロプロセッサが使用されて、デジタル信号に対応するデータの帯域幅を減少させる。いくつかの実施形態では、少なくとも1つのマイクロプロセッサが使用されて、1つまたは複数の画像形成機能を実施する。いくつかの実施形態では、1つまたは複数の画像形成機能は、アポディゼーション、逆投影、ファストヒエラルキー逆投影、S t o l t 補間、ダイナミックフォーカス、遅延加算処理、およびトモグラフィー撮像からなるグループから選択される少なくとも1つの画像形成機能を含む。いくつかの実施形態では、少なくとも1つのマイクロプロセッサが使用されて、1つまたは複数のバックエンド処理機能を実施する。いくつかの実施形態では、1つまたは複数のバックエンド処理機能は、ダウンレンジオートフォーカス、クロスレンジオートフォーカス、周波数分散補償、非線形アポディゼーション、リマッピング、圧縮、雑音除去、コンパウンド処理、ドップラ、エラストグラフィ、分光、および基底追跡からなるグループから選択される少なくとも1つのバックエンド処理機能を含む。20

いくつかの実施形態において、半導体ダイ上に一体化されるマイクロプロセッサを含むことによって、単一の半導体ダイ上の超音波デバイスの実現をさらに容易にする。たとえば、超音波画像の形成で使用するのに好適な超音波データを集めるように構成される超音波撮像デバイスが、いくつかの実施形態で実現される。30

#### 【0015】

[0015] いくつかの実施形態では、方法は、半導体ダイ上に一体化される少なくとも1つの追加構成要素を用いて、アナログ信号をデジタル信号に変換する前に、アナログ信号を処理して、そこから波形を分離することをさらに含む。波形の分離は、いくつかの実施形態で、複数の波形を表す信号に関して使用することができ、選択された信号成分（たとえば、選択された周波数）を分離することを含むことができる。いくつかの実施形態では、少なくとも1つの追加構成要素はアナログ直交復調器を備え、いくつかの実施形態では、アナログデチャーブモジュールを備える。少なくともいくつかの実施形態では、波形の分離によって、ウルトラソニックトランステューサ要素により作り出されるデータの量が減少し、したがって、データ処理および他の構成要素へのデータの転送が容易になる。40

#### 【0016】

[0016] いくつかの実施形態では、ウルトラソニックトランステューサ要素は、1つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルを備える。すなわち、ウルトラソニックトランステューサセルは、個別にまたは組み合わせて、ウルトラソニックトランステューサ要素を形成する。ウルトラソニックトランステューサ要素は50

、そのようなセルが組み合わされるとき、ウルトラソニックトランスデューサセルの任意の好適な組合せから形成することができる。いくつかの実施形態では、1つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルは、1つまたは複数の容量性マイクロマシン加工ウルトラソニックトランスデューサ(CMUT)セルを備える。いくつかの実施形態では、1つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルは、1つまたは複数のCMOSウルトラソニックトランスデューサ(CUT)セルを備える。いくつかの実施形態に従うそのようなセルの使用により、CMOSウェハ上の他の構成要素とウルトラソニックトランスデューサの一体化が容易になる。

#### 【0017】

[0017] 本技術の態様によれば、超音波デバイスが提供され、超音波デバイスは、半導体ダイ上に一体化される、少なくとも1つのウルトラソニックトランスデューサ要素と、半導体ダイ上に一体化され、ウルトラソニックトランスデューサ要素の出力に対応するアナログ信号をデジタル信号に変換するように構成されるアナログ・デジタル(ADC)変換器とを備える。いくつかの実施形態では、そのような構成によって、ウルトラソニックトランスデューサと回路が単一の半導体ダイ上に一体化される、一体型超音波デバイスの実現が容易になる。いくつかの実施形態では、そのようなデバイスは、単一の半導体ダイ上への構成要素の一体化に起因して、サイズが小型である。10

#### 【0018】

[0018] いくつかの実施形態では、超音波デバイスは、半導体ダイ上に一体化され、半導体ダイからのデジタル信号に対応するデータを高速シリアルデータストリームとして送信するように構成される、高速シリアルデータモジュールをさらに備える。いくつかのそのような実施形態では、高速データモジュールの使用によって、オフチップ構成要素との通信が容易になり、したがって、超音波デバイスの機能性を拡張する。たとえば、いくつかの実施形態における超音波デバイスは、いくつかの実施形態でコンピュータ、スマートフォン、またはタブレットである、外部処理構成要素と結合して通信する。20

#### 【0019】

[0019] いくつかの実施形態では、超音波デバイスは、半導体ダイ上に一体化され、デジタル信号を処理してそのデータ帯域幅を減少させるように構成される、少なくとも1つの信号処理モジュールをさらに備える。そのような実施形態では、データ帯域幅の減少によって、超音波デバイスの外部の構成要素との通信が容易になり、その構成要素としては、いくつかの実施形態でコンピュータ、スマートフォン、またはタブレットである、外部処理構成要素が挙げられる。いくつかの実施形態では、通信は、データを外部構成要素に送信することを含む。いくつかの実施形態では、少なくとも1つの信号処理モジュールは、デジタル直交復調器を備える。いくつかの実施形態では、少なくとも1つの信号処理モジュールは、平均化モジュールを備える。いくつかの実施形態では、少なくとも1つの信号処理モジュールは、整合フィルタを備え、代替実施形態では、不整合フィルタを備える。いくつかの実施形態では、少なくとも1つの信号処理モジュールは、有限インパルス応答フィルタを備える。いくつかの実施形態では、少なくとも1つの信号処理モジュールは、1/2帯域デシメーション低域通過フィルタを備える。いくつかの実施形態では、少なくとも1つの信号処理モジュールは、デチャーブモジュールを備える。30

#### 【0020】

[0020] いくつかの実施形態では、超音波デバイスは、半導体ダイ上に一体化され、デジタル信号に対応するデータを処理して、1つまたは複数の画像形成機能を実施するように構成される、少なくとも1つの信号処理モジュールをさらに備える。いくつかの実施形態では、1つまたは複数の画像形成機能は、アポディゼーション、逆投影、ファストヒエラルキー逆投影、補間範囲移動または他のフーリエリサンプリング技法、ダイナミックフォーカス、遅延加算処理、およびトモグラフィー再構成からなるグループから選択される少なくとも1つの画像形成機能を含む。いくつかのそのような実施形態では、画像形成機能のそのような性能は、超音波画像の形成をもたらす、または超音波画像を形成する結果となり、したがって、いくつかの実施形態では、一体型超音波撮像デバイスが半導体ダイ上4050

に形成される。少なくともいくつかの実施形態では、そのような機能が使用されて、たとえば、医療関連である画像タイプといった、有利な画像タイプを提供する。

#### 【0021】

[0021] いくつかの実施形態では、超音波デバイスは、半導体ダイ上に一体化され、デジタル信号に対応するデータを処理して、1つまたは複数のバックエンド処理機能を実施するように構成される、少なくとも1つの信号処理モジュールをさらに備える。これは、以前に記載された理由のために有利な場合がある。いくつかの実施形態では、1つまたは複数のバックエンド処理機能は、ダウンレンジオートフォーカス、クロスレンジオートフォーカス、周波数分散補償、非線形アポディゼーション、リマッピング、圧縮、雑音除去、コンパウンド処理、ドップラ、エラストグラフィ、分光、および基底追跡からなるグループから選択される少なくとも1つのバックエンド処理機能を含む。

10

#### 【0022】

[0022] いくつかの実施形態では、超音波デバイスは、半導体ダイ上に一体化され、少なくとも1つのデジタル信号処理機能を実施するように構成される、マイクロプロセッサをさらに備える。いくつかの実施形態では、マイクロプロセッサは、デジタル信号に対応するデータの帯域幅を減少するように構成され、これは、いくつかの実施形態において、データのさらなる処理、ならびにコンピュータ、スマートフォン、およびタブレットなどの外部構成要素へのデータの通信を容易にするのに有利である。いくつかの実施形態において、半導体ダイ上にマイクロプロセッサを含むことによって、一体型超音波デバイスの実現がさらに容易になる。

20

#### 【0023】

[0023] いくつかの実施形態では、マイクロプロセッサは、1つまたは複数の画像形成機能を実施するように構成される。いくつかの実施形態では、1つまたは複数の画像形成機能は、アポディゼーション、逆投影、ファストヒエラルキー逆投影、補間範囲移動または他のフーリエリサンプリング技法、ダイナミックフォーカス、遅延加算処理、およびトモグラフィー撮像からなるグループから選択される少なくとも1つの画像形成機能を含む。

#### 【0024】

[0024] いくつかの実施形態では、マイクロプロセッサは、1つまたは複数のバックエンド処理機能を実施するように構成される。いくつかの実施形態では、1つまたは複数のバックエンド処理機能は、ダウンレンジオートフォーカス、クロスレンジオートフォーカス、周波数分散補償、非線形アポディゼーション、リマッピング、圧縮、雑音除去、コンパウンド処理、ドップラ、エラストグラフィ、分光、および基底追跡からなるグループから選択される少なくとも1つのバックエンド処理機能を含む。

30

#### 【0025】

[0025] いくつかの実施形態では、デバイスは、半導体ダイ上に一体化され、ADCコンバータがアナログ信号をデジタル信号に変換する前に、アナログ信号を処理して、そこから波形を分離するように構成される、少なくとも1つの追加構成要素をさらに備える。いくつかの実施形態では、少なくとも1つの追加構成要素はアナログ直交復調器を備え、いくつかの実施形態では、アナログデチャーブモジュールを備える。いくつかの実施形態においてそのような処理回路を含むことにより、外部構成要素とデジタル的に通信することができる一体型超音波デバイスの形成がさらに容易になる。

40

#### 【0026】

[0026] いくつかの実施形態では、ウルトラソニックトランステューサ要素は、1つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルを備える。いくつかの実施形態では、1つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルは、1つまたは複数の容量性マイクロマシン加工ウルトラソニックトランステューサ(CMUT)セルを備え、いくつかの実施形態では、1つまたは複数のCMOSウルトラソニックトランステューサ(CUT)セルを備える。いくつかの実施形態に従う、そのようなセルの使用により、CMOSウェハ上の他の構成要素とウルトラソニックトランステューサの一体化が容易になる。

50

## 【0027】

[0027] 本技術の態様によれば、ウルトラソニックトランステューサ要素からの信号を処理するための方法が提供され、方法は、ウルトラソニックトランステューサ要素と同じ半導体ダイ上に一体化される少なくとも1つの構成要素を用いて、トランステューサ要素の出力に対応する信号を処理して、そこから波形を分離することを含む。いくつかの実施形態では、そのような処理がデータの量を減少し、これが今度は、超音波データの収集および送信を容易にする。

## 【0028】

[0028] いくつかの実施形態では、少なくとも1つの構成要素はアナログ直交復調器を備え、いくつかの実施形態では、アナログデチャーブモジュールを備える。いくつかの実施形態では、ウルトラソニックトランステューサ要素は、1つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルを備える。いくつかの実施形態では、1つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルは、1つまたは複数の容量性マイクロマシン加工ウルトラソニックトランステューサ(CMUT)セルを備え、いくつかの実施形態では、1つまたは複数のCMOSウルトラソニックトランステューサ(CUT)セルを備える。いくつかの実施形態に従う、そのようなセルの使用により、CMOSウェハ上の他の構成要素とウルトラソニックトランステューサの一体化が容易になる。

10

## 【0029】

[0029] 本技術の態様によれば、超音波デバイスが提供され、超音波デバイスは、半導体ダイ上に一体化される、少なくとも1つのウルトラソニックトランステューサ要素と、半導体ダイ上に一体化され、少なくとも1つのウルトラソニックトランステューサ要素の出力に対応する信号を処理して、そこから波形を分離するように構成される、少なくとも1つの構成要素とを備える。いくつかの実施形態では、構成要素のそのような構成によって、一体型超音波デバイスの実現が容易になる。波形の分離がデータの量を減少し、これが今度は、超音波データの収集および送信を容易にする。

20

## 【0030】

[0030] いくつかの実施形態では、少なくとも1つの構成要素はアナログ直交復調器を備え、いくつかの実施形態では、少なくとも1つの構成要素はアナログデチャーブモジュールを備える。いくつかの実施形態では、少なくとも1つのウルトラソニックトランステューサ要素は、1つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルを備える。いくつかの実施形態では、1つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルは、1つまたは複数の容量性マイクロマシン加工ウルトラソニックトランステューサ(CMUT)セルを備え、いくつかの実施形態では、1つまたは複数のCMOSウルトラソニックトランステューサ(CUT)セルを備える。いくつかの実施形態に従う、そのようなセルの使用により、CMOSウェハ上の他の構成要素とウルトラソニックトランステューサの一体化が容易になる。

30

## 【0031】

[0031] 本技術の態様によれば、各々が複数のウルトラソニックトランステューサセルを備える、少なくとも2つのウルトラソニックトランステューサ要素を構成するための方法が提供される。方法は、少なくとも2つのウルトラソニックトランステューサ要素のうちの一方の中の少なくとも1つのウルトラソニックトランステューサセルを、少なくとも2つのウルトラソニックトランステューサ要素の他方の中の少なくとも1つのウルトラソニックトランステューサセルに結合することを含む。いくつかの実施形態では、そのような結合によって、ウルトラソニックトランステューサ要素により生成される超音波波形のグレーティングロープが有利に減少する。加えて、いくつかの実施形態では、そのような結合によって、全トランステューサ領域の有益な使用が容易になる。

40

## 【0032】

[0032] いくつかの実施形態では、結合することが、少なくとも2つのウルトラソニックトランステューサ要素のうちの一方の中の少なくとも1つのウルトラソニックトランステ

50

ユーザセルを、少なくとも2つのウルトラソニックトランスデューサ要素の他方の中の少なくとも1つのウルトラソニックトランスデューサセルに、抵抗性要素を介して結合することを含む。いくつかの実施形態では、抵抗性要素は、ポリシリコン抵抗器を備える。そのような抵抗器を使用すること、および抵抗値の好適な選択により、いくつかの実施形態において、ウルトラソニックトランスデューサ要素の性能を最適化する。

#### 【0033】

[0033] いくつかの実施形態では、結合することが、少なくとも2つのウルトラソニックトランスデューサ要素のうちの異なるものの中の第1の対のウルトラソニックトランスデューサセルを、第1のインピーダンス値を有する第1の結合要素と結合することと、少なくとも2つのウルトラソニックトランスデューサ要素のうちの異なるもの中の第2の対のウルトラソニックトランスデューサセルを、第1のインピーダンス値と異なる第2のインピーダンス値を有する第2の結合要素と結合することとを含む。インピーダンス値の好適な選択によって、いくつかの実施形態では、ウルトラソニックトランスデューサ要素の性能を最適化する。いくつかの実施形態では、結合することが、少なくとも2つのウルトラソニックトランスデューサ要素のうちの一方の中の少なくとも1つのウルトラソニックトランスデューサセルと、少なくとも2つのウルトラソニックトランスデューサ要素の他方の中の少なくとも1つのウルトラソニックトランスデューサセルとの間に誘導結合を確立することを含む。

10

#### 【0034】

[0034] いくつかの実施形態では、方法は、少なくとも2つのウルトラソニックトランスデューサ要素のウルトラソニックトランスデューサセルのうちの少なくともいくつかを混合することをさらに含む。

20

#### 【0035】

[0035] いくつかの実施形態では、少なくとも2つのウルトラソニックトランスデューサ要素の各々は、1つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルを備える。いくつかの実施形態に従うそのようなセルの使用により、CMOSウェハ上の他の構成要素とウルトラソニックトランスデューサの一体化が容易になる。

30

#### 【0036】

[0036] いくつかの実施形態では、方法は、少なくとも2つのトランスデューサ要素の各々の中の少なくともいくつかのトランスデューサセルをアポダイズすることをさらに含む。いくつかの実施形態では、アポダイズすることは、少なくとも2つのウルトラソニックトランスデューサ要素のうちの一方の中の少なくとも1つのトランスデューサセル、および少なくとも2つのトランスデューサ要素の他方の中の少なくとも1つのトランスデューサセルをアポダイズすることを含む。

40

#### 【0037】

[0037] 本技術の態様によれば、各々が複数のウルトラソニックトランスデューサセルを備える少なくとも2つのウルトラソニックトランスデューサ要素を備える、超音波デバイスが提供される。少なくとも2つのウルトラソニックトランスデューサ要素のうちの一方の中の少なくとも1つのウルトラソニックトランスデューサセルが、少なくとも2つのウルトラソニックトランスデューサ要素の他方の中の少なくとも1つのウルトラソニックトランスデューサセルに結合される。いくつかの実施形態では、そのような結合によって、ウルトラソニックトランスデューサ要素により生成される超音波波形のグレーティングロープを有利に減少する。加えて、いくつかの実施形態では、そのような結合によって、全トランスデューサ領域の、有益な使用が容易になる。

50

#### 【0038】

[0038] いくつかの実施形態では、少なくとも2つのウルトラソニックトランスデューサ要素のうちの一方の中の少なくとも1つのトランスデューサセルが、少なくとも2つのトランスデューサ要素の他方の中の少なくとも1つのトランスデューサセルに抵抗性要素を介して結合される。いくつかの実施形態では、抵抗性要素は、ポリシリコン抵抗器を備える。

## 【0039】

[0039] いくつかの実施形態では、少なくとも2つのトランスデューサ要素のうちの一方が少なくとも第1および第2のトランスデューサセルを備え、少なくとも2つのトランスデューサ要素のうちの他方が少なくとも第3および第4のトランスデューサセルを備え、第1のトランスデューサセルと第3のトランスデューサセルが第1のインピーダンス値を有する第1の結合要素を介して結合され、第2のトランスデューサセルと第4のトランスデューサセルが第1のインピーダンス値と異なる第2のインピーダンス値を有する第2の結合要素を介して結合される。インピーダンス値の好適な選択によって、いくつかの実施形態では、ウルトラソニックトランスデューサ要素の性能を最適化する。

## 【0040】

[0040] いくつかの実施形態では、少なくとも2つのトランスデューサ要素のうちの一方の中の少なくとも1つのトランスデューサセルと、少なくとも2つのトランスデューサ要素の他方の中の少なくとも1つのトランスデューサセルとの間に誘導結合が確立されるよう、少なくとも2つのトランスデューサ要素が、構成および配置される。

## 【0041】

[0041] いくつかの実施形態では、少なくとも2つのトランスデューサ要素のトランスデューサセルのうちの少なくともいくつかが混合され、いくつかの実施形態において、これが、トランスデューサ要素領域の有益な使用という点で利益をもたらす。

## 【0042】

[0042] いくつかの実施形態では、少なくとも2つのウルトラソニックトランスデューサ要素の各々は、1つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルを備える。いくつかの実施形態に従う、そのようなセルの使用により、CMOSウェハ上の他の構成要素とウルトラソニックトランスデューサの一体化が容易になる。

## 【0043】

[0043] いくつかの実施形態では、少なくとも2つのトランスデューサ要素の各々の中の少なくとも1つのトランスデューサセルがアポダイズされる。いくつかの実施形態では、少なくとも2つのウルトラソニックトランスデューサ要素のうちの一方の中の少なくとも1つのトランスデューサセル、および少なくとも2つのトランスデューサ要素の他方の中の少なくとも1つのトランスデューサセルがアポダイズされる。

## 【0044】

[0044] 本技術の態様によれば、ウルトラソニックトランスデューサ要素に電圧でバイアスをかけるための方法が提供され、方法は、パルサの出力を使用して、ウルトラソニックトランスデューサ要素を駆動し、その結果、ウルトラソニックトランスデューサ要素がウルトラソニックパルスを放出することを含む。パルサは、生成される波形に対応する1つまたは複数のトランスデューサ要素に駆動信号を出力することができる。したがって、少なくともいくつかの実施形態では、パルサは、たとえば波形発生器からの波形を受信し、パルス（たとえば、電圧パルス）を生成して、ウルトラソニックトランスデューサ要素を駆動するのに好適な回路である。加えて、少なくともいくつかの場合に、パルサがウルトラソニックトランスデューサ要素を駆動するために使用されておらず、その結果、ウルトラソニックトランスデューサ要素がウルトラソニックパルスを放出するとき、パルサの出力を、ウルトラソニックトランスデューサ要素へのバイアス信号として印加することができる。少なくともいくつかの実施形態では、そのような動作を使用して、トランスデューサ要素の、安全な高電圧バイアスを実現することができる。

## 【0045】

[0045] 本技術の態様によれば、超音波デバイスが提供され、超音波デバイスは、少なくとも1つのウルトラソニックトランスデューサ要素と、少なくとも1つのウルトラソニックトランスデューサに結合され、少なくともいくつかの場合に、少なくとも1つのトランスデューサ要素が使用されて受信したウルトラソニックエネルギーを検知するとき、パルサの出力が使用されて少なくとも1つのウルトラソニックトランスデューサ要素にバイアスをかけるように構成および配置されるパルサとを備える。

10

20

30

40

50

## 【0046】

[0046] 本技術の態様によれば、半導体ダイ上に一体化される少なくとも1つのウルトラソニックトランスデューサ要素にバイアスをかけるための方法が提供され、方法は、半導体ダイに印加されるバイアス電圧を使用して少なくとも1つのウルトラソニックトランスデューサ要素にバイアスをかけることを含む。いくつかの実施形態では、方法は、少なくとも1つのウルトラソニックトランスデューサ要素が対象物を撮像または治療するために使用されている間、対象物に面する少なくとも1つのウルトラソニックトランスデューサ要素の側に、アースを印加することをさらに含む。そのようなバイアスが、いくつかの実施形態では、ウルトラソニックトランスデューサ要素の安全な動作をもたらし、対象物に対する電気ショックの危険を最小化する。

10

## 【0047】

[0047] 本技術の態様によれば、超音波デバイスが提供され、超音波デバイスは、半導体ダイ上に一体化される、少なくとも1つのウルトラソニックトランスデューサ要素を備える。少なくとも1つのウルトラソニックトランスデューサ要素は、ダイに印加されるバイアス電圧が、少なくとも1つのウルトラソニックトランスデューサ要素にバイアスをかけるためにも使用されるように、ダイ上で構成および配置される。少なくともいくつかの実施形態では、そのような構成を使用して、トランスデューサ要素の、安全な高電圧バイアスを実現する。

## 【0048】

[0048] いくつかの実施形態では、超音波デバイスは、少なくとも1つのウルトラソニックトランスデューサ要素を使用して対象物を撮像または治療するように構成される。撮像または治療の期間対象物に面するように構成される少なくとも1つのウルトラソニックトランスデューサ要素の側がアースに接続され、これが、いくつかの実施形態において、電気ショックの危険を最小化することにより、安全な動作をもたらす。いくつかの実施形態では、少なくとも1つのウルトラソニックトランスデューサ要素は、1つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルを備える。いくつかの実施形態では、1つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルは、1つまたは複数の容量性マイクロマシン加工ウルトラソニックトランスデューサ(CMUT)セルを備え、いくつかの実施形態では、1つまたは複数のCMOSウルトラソニックトランスデューサ(CUT)セルを備える。いくつかの実施形態に従う、そのようなセルの使用により、CMOSウェハ上の他の構成要素とウルトラソニックトランスデューサの一体化が容易になる。

20

30

## 【0049】

[0049] 本技術の態様によれば、少なくとも1つのウルトラソニックトランスデューサ要素にバイアスをかけるための方法が提供され、方法は、少なくとも1つのウルトラソニックトランスデューサ要素が対象物を撮像または治療するために使用されている間、対象物に面する少なくとも1つのウルトラソニックトランスデューサ要素の側に、アースを印加することを含む。そのようなバイアスが、いくつかの実施形態において、電気ショックの危険を最小化することにより、デバイスの安全な動作を容易にする。

40

## 【0050】

[0050] 本技術の態様によれば、超音波デバイスは、少なくとも1つのウルトラソニックトランスデューサ要素を使用して対象物を撮像または治療するように構成される。撮像または治療の期間対象物に面するように構成される少なくとも1つのウルトラソニックトランスデューサ要素の側がアースに接続され、これが、いくつかの実施形態において、電気ショックの危険を最小化することにより、安全な動作をもたらす。

## 【0051】

[0051] 本技術の態様によれば、超音波デバイス中で第1および第2の送信制御回路を構成するために方法が提供され、第1および第2の送信制御回路の各々が、ウルトラソニックトランスデューサ要素のためのパルサを駆動する波形発生器を備え、方法は、第1の制御回路が送信イネーブル信号を受信するとときと、第1の波形発生器により生成される第1

50

の波形が第1のパルサに印加されるときとの間の第1の遅延の長さが、第2の制御回路が送信イネーブル信号を受信するときと、第2の波形発生器により生成される第2の波形が第2のパルサに印加されるときとの間の第2の遅延の長さと異なるように、第1の送信制御回路と第2の送信制御回路を異なって構成することを含む。少なくともいくつかの実施形態では、遅延のそのような制御によって、たとえば有益な超音波撮像機能という点で、有益な動作を実現する。

#### 【0052】

[0052] いくつかの実施形態では、第1および第2の送信制御回路を構成することは、送信イネーブル信号が第1の波形発生器に到達する前に第1の長さの時間だけ送信イネーブル信号が遅延されるように第1の送信制御回路を構成することと、送信イネーブル信号が第2の波形発生器に到達する前に第2の長さの時間だけ送信イネーブル信号が遅延されるように第2の送信制御回路を構成することとを含む。第2の長さの時間は、いくつかの実施形態において、第1の長さの時間と異なる。

10

#### 【0053】

[0053] いくつかの実施形態では、第1および第2の送信制御回路を構成することは、第1の波形発生器が第1の開始周波数を持つように構成することと、第2の波形発生器が、第1の開始周波数と異なる第2の開始周波数を持つように構成することとを含む。いくつかの実施形態では、第1および第2の送信制御回路を構成することは、第1の波形発生器が第1の開始位相を持つように構成することと、第2の波形発生器が、第1の開始位相と異なる第2の開始位相を持つように構成することとを含む。いくつかの実施形態では、第1および第2の送信制御回路を構成することは、第1の波形が第1のパルサに到達する前に、第1の波形発生器により出力される第1の波形が、第1の長さの時間だけ遅延されるように第1の送信制御回路を構成することと、第2の波形が第2のパルサに到達する前に、第2の波形発生器により出力される第2の波形が、第1の長さの時間と異なる第2の長さの時間だけ遅延されるように第2の送信制御回路を構成することとを含む。少なくともいくつかの実施形態では、そのような制御によって、たとえば本明細書に記載されるような超音波撮像で使用する、様々な対象の波形を生成することが容易になる。

20

#### 【0054】

[0054] 本技術の態様によれば、超音波デバイスが提供され、超音波デバイスは、少なくとも第1および第2のウルトラソニックトランステューサ要素と、第1の送信制御回路と、第2の送信制御回路とを備える。第1の送信制御回路は、第1のウルトラソニックトランステューサ要素を駆動するように第1のウルトラソニックトランステューサ要素に結合され、その結果、第1のウルトラソニックトランステューサ要素がウルトラソニックパルスを放出する第1のパルサと、第1のパルサに結合され、第1の送信制御回路による送信イネーブル信号の受信に応答して、第1のパルサに第1の波形を提供する第1の波形発生器とを備え、第1の送信制御回路が送信イネーブル信号を受信するときと第1の波形が第1のパルサに印加されるときとの間の第1の遅延の長さに影響を及ぼす、少なくとも1つの第1の構成要素を含むことができる。第2の送信制御回路は、第2のウルトラソニックトランステューサ要素を駆動するように第2のウルトラソニックトランステューサ要素に結合され、その結果、第2のウルトラソニックトランステューサ要素がウルトラソニックパルスを放出する第2のパルサと、第2のパルサに結合され、第2の送信制御回路による送信イネーブル信号の受信に応答して、第2のパルサに第2の波形を提供する第2の波形発生器と、第2の送信制御回路がイネーブル信号を受信するときと第2の波形が第2のパルサに印加されるときとの間の第2の遅延の長さに影響を及ぼす、少なくとも1つの第2の構成要素とを備える。少なくとも1つの第1の構成要素は、少なくとも1つの第2の構成要素と異なって構成され、その結果、第2の遅延の長さは、第1の遅延の長さと異なる。少なくともいくつかの実施形態では、異なる遅延によって、たとえば、様々な望ましい超音波波形の生成を容易にすることにより、有益な動作を実現する。

30

40

#### 【0055】

[0055] いくつかの実施形態では、少なくとも1つの第1の構成要素は、イネーブル信号

50

を第1の波形発生器に提供する前に、第1の数のクロックサイクルだけイネーブル信号を遅延させる第1のシフトレジスタを備え、少なくとも1つの第2の構成要素は、イネーブル信号を第2の波形発生器に提供する前に、第1の数のクロックサイクルと異なる第2の数のクロックサイクルだけイネーブル信号を遅延させる第2のシフトレジスタを備える。いくつかの実施形態では、少なくとも1つの第1の構成要素が、第1の波形発生器の開始周波数を決定する第1の値を含む第1のレジスタを含み、少なくとも1つの第2の構成要素が、第2の波形発生器の開始周波数を決定する、第1の値と異なる第2の値を含む第2のレジスタを含む。いくつかの実施形態では、少なくとも1つの第1の構成要素が、第1の波形発生器の開始位相を決定する第1の値を含む第1のレジスタを含み、少なくとも1つの第2の構成要素が、第2の波形発生器の開始位相を決定する、第1の値と異なる第2の値を含む第2のレジスタを含む。いくつかの実施形態では、少なくとも1つの第1の構成要素は、第1の波形が第1のパルサに到達する前に、第1の波形発生器により出力される第1の波形を第1の長さの時間だけ遅延させる第1の遅延要素を備え、少なくとも1つの第2の構成要素は、第2の波形が第2のパルサに到達する前に、第2の波形発生器により出力される第2の波形を、第1の長さの時間と異なる第2の長さの時間だけ遅延させる第2の遅延要素を備える。少なくともいくつかの実施形態では、そのような構成によって、たとえば波形パラメータの制御を可能にすることにより、様々な有益な超音波波形の生成が容易になる。

10

#### 【0056】

[0056] 本技術の態様によれば、少なくとも第1および第2の波形発生器を構成するための方法が提供され、方法は、少なくとも第1および第2の波形発生器の第1および第2の構成可能動作パラメータの値を制御するためにコントローラを使用することを含む。少なくともいくつかの実施形態では、そのような制御によって、波形発生器をプログラム可能にし、そのため、波形発生器がプログラムまたは制御されて、たとえば波形パラメータを制御することにより、所望の波形を提供することができる。

20

#### 【0057】

[0057] いくつかの実施形態では、方法は、コントローラで一連のイベント数を生成することと、第1の波形発生器について、第1の波形発生器に関連する第1のメモリからコントローラにより提供されるイベント数に関連する第1の値を検索することと、第1の構成可能動作パラメータとして使用するために第1の値を第1の波形発生器に提供することをさらに含む。方法は、第2の波形発生器について、第2の波形発生器に関連する第2のメモリからコントローラにより提供されるイベント数に関連する第2の値を検索することと、第2の構成可能動作パラメータとして使用するために第2の値を第2の波形発生器に提供することをさらに含む。この様式では、少なくともいくつかの実施形態では、波形発生器により生成される波形の制御を達成することができ、望ましい（たとえば、医療関連の）超音波波形を生成することができる。

30

#### 【0058】

[0058] いくつかの実施形態では、第1および第2の構成可能動作パラメータが、第1および第2の波形発生器の同じ機能性を制御する。少なくとも1つのイベント数について、第1および第2のメモリから検索された第1および第2の値は異なる。

40

#### 【0059】

[0059] いくつかの実施形態では、方法は、第1および第2の波形発生器の各々にイネーブル信号を送信するためにコントローラを使用することをさらに含む。いくつかの実施形態では、方法は、第1の波形発生器の第1の構成可能動作パラメータと第2の波形発生器の第2の構成可能動作パラメータのそれぞれが異なる値を有するように設定することをさらに含む。この様式では、いくつかの実施形態では、たとえば超音波撮像で所望の超音波波形の生成を達成するために使用することができる異なる波形が、異なる波形発生器により生成される。

#### 【0060】

[0060] 本技術の態様によれば、デバイスが提供され、デバイスは、少なくとも第1およ

50

び第2の対応するウルトラソニックトランステューサ要素による送信のための波形を生成するように構成される少なくとも第1および第2の波形発生器であって、第1の波形発生器が少なくとも1つの第1の構成可能動作パラメータを含み、第2の波形発生器が少なくとも1つの第2の構成可能動作パラメータを含む少なくとも第1および第2の波形発生器と、第1および第2の構成可能動作パラメータの値を制御するように構成されるコントローラとを備える。この様式では、波形発生器により作り出される波形の望ましい構成可能性が、いくつかの実施形態で達成される。

#### 【0061】

[0061] いくつかの実施形態では、コントローラは、一連の送信イベント数を出力するように構成される。いくつかの実施形態では、第1の波形発生器は、それぞれの送信イベント数に関連する第1の構成可能動作パラメータについての値を記憶する第1のイベントメモリに関連し、コントローラから送信されたイベント数を受信して、第1の波形発生器にそれによって使用するために、第1の構成可能動作パラメータについての対応する記憶された値を出力するように構成される。いくつかの実施形態では、第2の波形発生器は、それぞれの送信イベント数に関連する第2の構成可能動作パラメータについての値を記憶する第2のイベントメモリに関連し、コントローラから送信されたイベント数を受信して、第2の波形発生器にそれによって使用するために、第2の構成可能動作パラメータについての対応する記憶された値を出力するように構成される。この様式では、いくつかの実施形態で、波形発生器により生成される波形を制御することができ、たとえば超音波撮像を実施するときに所望の波形を達成することができる。

10

20

30

40

50

#### 【0062】

[0062] いくつかの実施形態では、コントローラにより出力される少なくとも1つのイベント数について、第1のイベントメモリおよび第2のイベントメモリは、第1および第2の構成可能動作パラメータについての異なる関連値を記憶する。

#### 【0063】

[0063] いくつかの実施形態では、コントローラは、第1および第2の波形発生器の各々に送信イネーブル信号を通信するようにさらに構成される。

#### 【0064】

[0064] いくつかの実施形態では、第1の構成可能動作パラメータは、第2の構成可能動作パラメータと異なる値に設定することができる。

#### 【0065】

[0065] 本技術の態様によれば、超音波デバイスを作るための方法が提供され、方法は、少なくとも1つのCMOSウルトラソニックトランステューサ要素と同じ半導体ダイ上にデジタル受信回路を一体化することを含む。デジタル受信回路は、ウルトラソニックトランステューサセルまたは要素から信号を受信するように構成されるデジタル回路であつてよい。例が本明細書に記載される。いくつかの実施形態では、そのような構成は、ウルトラソニックトランステューサおよびデジタル回路が同じ半導体ダイ上にあることを可能にすることにより、一体型超音波デバイスを提供する、さもなければ容易にすることができる。小型超音波デバイスがいくつかの実施形態をもたらす。また、デジタル回路によって、外部コンピュータ、スマートフォン、タブレット、または他の処理構成要素など、いくつかの実施形態における外部構成要素とのデジタル通信が容易になる。

#### 【0066】

[0066] 本技術の態様によれば、デバイスが提供され、デバイスは、单一の集積回路基板上に形成される、少なくとも1つのCMOSウルトラソニックトランステューサ要素とデジタル受信回路とを備える。いくつかの実施形態では、そのような構成は、ウルトラソニックトランステューサおよびデジタル回路が同じ半導体ダイ上にあることを可能にすることにより、一体型超音波デバイスを提供する、さもなければ容易にする。小型超音波デバイスがいくつかの実施形態をもたらす。また、デジタル回路によって、外部コンピュータ、スマートフォン、タブレット、または他の処理構成要素など、いくつかの実施形態における外部構成要素とのデジタル通信が容易になる。

## 【0067】

[0067] 本技術の態様によれば、超音波デバイスを作るための方法が提供され、方法は、少なくとも第1および第2の送信制御回路ならびに第1および第2のウルトラソニックトランステューサ要素に対応する少なくとも第1および第2の受信制御回路を備えるCMOS回路の上（たとえば、より高く、またはより後で設けられる処理層の上）に少なくとも第1および第2のウルトラソニックトランステューサ要素を製造することを含む。少くともいくつかの実施形態では、そのような製造によって、ウルトラソニックトランステューサおよび関連する回路を含む一体型超音波デバイスの形成が容易になる。また、デバイスは、記載されたように、回路に対してウルトラソニックトランステューサを配置することに少なくとも部分的に起因して小型となることができる。

10

## 【0068】

[0068] いくつかの実施形態では、第1および第2の受信制御回路の各々は、アナログ-デジタル変換器を備え、いくつかの実施形態では、デジタル信号処理回路をさらに備える。デジタル回路を含むことによって、いくつかの実施形態において、データ処理および外部構成要素とのデジタル通信が容易になる。

## 【0069】

[0069] いくつかの実施形態では、少なくとも第1および第2のウルトラソニックトランステューサ要素は、CMOS回路の上（たとえば、より高く、またはより後で設けられる処理層の上）に製造され、そのため、第1の送信制御回路および第1の受信制御回路は、両方が第1のウルトラソニックトランステューサ要素の下に配設され、第2の送信制御回路および第2の受信制御回路は、両方が第2のウルトラソニックトランステューサ要素の下に配設される。いくつかの実施形態では、回路構成要素は、ウルトラソニックトランステューサの形成の前に完了される処理層上に回路構成要素を製造することができるという意味において、ウルトラソニックトランステューサの下にあってよい。いくつかの実施形態では、ウルトラソニックトランステューサは、回路よりも、基板（たとえば、半導体基板）のデバイス面により近くに置かれる。少くともいくつかの実施形態では、そのような構成によって、小型超音波デバイスを製造することが可能になる。

20

## 【0070】

[0070] いくつかの実施形態では、少なくとも第1および第2のウルトラソニックトランステューサ要素を製造することが、CMOS回路と同じ半導体基板上に少なくとも第1および第2のウルトラソニックトランステューサ要素を製造することを含む。いくつかの実施形態では、少なくとも第1および第2のウルトラソニックトランステューサ要素を製造することが、第1のウルトラソニックトランステューサ要素のために第1のパルサを駆動するように結合される第1の波形発生器を含むように第1の送信制御回路を製造することと、第2のウルトラソニックトランステューサ要素のために第2のパルサを駆動するように結合される第2の波形発生器を含むように第2の送信制御回路を製造することとを含む。一体型超音波デバイスは、いくつかの実施形態において、半導体基板上に信号生成機能性を含んで達成される。

30

## 【0071】

[0071] 本技術の態様によれば、超音波デバイスが提供され、超音波デバイスは、少なくとも第1および第2のウルトラソニックトランステューサ要素と、少なくとも第1および第2のウルトラソニックトランステューサ要素の下に配設されるCMOS回路とを備える。CMOS回路は、その中に、第1および第2のウルトラソニックトランステューサ要素に対応する第1および第2の送信制御回路ならびに第1および第2の受信制御回路を一体化している。少くともいくつかの実施形態では、そのような構成によって、ウルトラソニックトランステューサおよび関連する回路を含む一体型超音波デバイスの形成が容易になる。デバイスは、記載されたように、回路に対してウルトラソニックトランステューサを配置することに少なくとも部分的に起因して小型となることができる。

40

## 【0072】

[0072] いくつかの実施形態では、第1および第2の受信制御回路の各々は、アナログ-

50

デジタル変換器を備える。いくつかの実施形態では、第1および第2の受信制御回路の各々は、デジタル信号処理回路をさらに備える。デジタル回路を含むことによって、いくつかの実施形態において、データ処理および外部構成要素とのデジタル通信が容易になる。

#### 【0073】

[0073] いくつかの実施形態では、第1の送信制御回路および第1の受信制御回路は、両方が第1のウルトラソニックトランステューサ要素の下に配設され、第2の送信制御回路および第2の受信制御回路は、両方が第2のウルトラソニックトランステューサ要素の下に配設される。いくつかの実施形態では、そのような構成によって、小型超音波デバイスを製造することが可能になる。

#### 【0074】

[0074] いくつかの実施形態では、第1および第2のウルトラソニックトランステューサ要素が、CMOS回路と同じ半導体ダイ上に一体化され、このことによって、少なくともいくつかの実施形態において、一体型超音波デバイスの製造が用意になる。

#### 【0075】

[0075] いくつかの実施形態では、第1の送信制御回路が、第1のウルトラソニックトランステューサ要素のために第1のパルサを駆動するように結合される第1の波形発生器を備え、第2の送信制御回路が、第2のウルトラソニックトランステューサ要素のために第2のパルサを駆動するように結合される第2の波形発生器を備える。

#### 【0076】

[0076] いくつかの実施形態では、第1および第2のウルトラソニックトランステューサ要素の各々は、1つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルを備える。いくつかの実施形態では、1つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルは、1つまたは複数の容量性マイクロマシン加工ウルトラソニックトランステューサ(CMUT)セルを備え、いくつかの実施形態では、1つまたは複数のマイクロマシン加工されたウルトラソニックトランステューサセルは、1つまたは複数のCMOSウルトラソニックトランステューサ(CUT)セルを備える。いくつかの実施形態に従う、そのようなセルの使用により、CMOSウェハ上の他の構成要素とウルトラソニックトランステューサの一体化が容易になる。

#### 【0077】

[0077] 本技術の態様によれば、ウルトラソニックトランステューサ要素からの信号を処理するための方法が提供され、方法は、ウルトラソニックトランステューサ要素と同じ半導体ダイ上に一体化される構成要素を用いて、半導体ダイからのウルトラソニックトランステューサ要素の出力に対応するデータを高速シリアルデータストリームとして送信することを含む。いくつかの実施形態におけるそのような動作によって、コンピュータ、スマートフォン、およびタブレットなどの外部処理構成要素へのデータの通信が容易になる。

#### 【0078】

[0078] いくつかの実施形態では、方法は、ウルトラソニックトランステューサ要素の出力に対応するアナログ信号をデジタル信号に変換することと、高速シリアルデータストリームとして半導体ダイからのデジタル信号に対応するデータを送信することを含むデータを送信することとをさらに含む。外部構成要素とのデジタル通信が、いくつかの実施形態で実現される。

#### 【0079】

[0079] いくつかの実施形態では、方法は、半導体ダイ上に一体化される少なくとも1つの追加構成要素を用いて、デジタル信号を処理してそのデータ帯域幅を減少させることをさらに含み、これは、いくつかの実施形態において、データのさらなる処理、ならびにコンピュータ、スマートフォン、およびタブレットなどの外部構成要素へのデータの通信を容易にするのに有利である。いくつかの実施形態では、少なくとも1つの追加構成要素は、デジタル直交復調器を備える。いくつかの実施形態では、少なくとも1つの追加構成要素は、平均化モジュールを備える。いくつかの実施形態では、少なくとも1つの追加構成要素は、整合フィルタを備え、代替実施形態では、不整合フィルタを備える。いくつかの

10

20

30

40

50

実施形態では、少なくとも1つの追加構成要素は、有限インパルス応答(finite impulse response: FIR) フィルタを備える。いくつかの実施形態では、少なくとも1つの追加構成要素は、1/2帯域デシメーション低域通過フィルタを備える。いくつかの実施形態では、少なくとも1つの追加構成要素は、デチャーブモジュールを備える。

#### 【0080】

[0080] いくつかの実施形態では、方法は、半導体ダイ上に一体化される少なくとも1つの追加構成要素を用いて、アナログ信号をデジタル信号に変換する前に、アナログ信号を処理して、そこから波形を分離することをさらに含む。いくつかの実施形態では、そのような処理がデータの量を減少し、これが今度は、超音波データの収集および送信を容易にする。いくつかの実施形態では、少なくとも1つの追加構成要素はアナログ直交復調器を備え、いくつかの実施形態では、アナログデチャーブモジュールを備える。

10

#### 【0081】

[0081] いくつかの実施形態では、送信することは、USBモジュールを使用して、半導体ダイからのウルトラソニックトランスデューサ要素の出力に対応するデータを高速シリアルデータストリームとして送信することを含む。いくつかの実施形態では、USBモジュールは、USB3.0モジュールを備える。いくつかの実施形態では、送信することは、低電圧差動信号(LVDS)リンクを使用して半導体ダイからウルトラソニックトランスデューサ要素の出力に対応するデータを送信することを含む。そのような通信プロトコルによって、外部構成要素と共にウルトラソニックトランスデューサ要素を使用することが容易になる。

20

#### 【0082】

[0082] 本技術の態様によれば、超音波デバイスが提供され、超音波デバイスは、半導体ダイ上に一体化される、少なくとも1つのウルトラソニックトランスデューサ要素と、半導体ダイ上に一体化され、半導体ダイからのウルトラソニックトランスデューサ要素の出力に対応するデータを高速シリアルデータストリームとして送信するように構成される高速シリアルデータモジュールとを備える。高速シリアルデータストリームによって、いくつかの実施形態において、シリアルデータストリームを受信することができるデバイスに関して、超音波デバイスの使用が容易になる。

30

#### 【0083】

[0083] いくつかの実施形態では、デバイスは、半導体ダイ上に一体化され、ウルトラソニックトランスデューサ要素の出力に対応するアナログ信号をデジタル信号に変換するように構成されるアナログ-デジタル(ADC)変換器をさらに備える。いくつかの実施形態では、高速シリアルデータモジュールは、半導体ダイからのデジタル信号に対応するデータを高速シリアルデータストリームとして送信するように構成される。いくつかの実施形態では、そのような動作によって、外部デバイスとの超音波データの通信が容易になる。

#### 【0084】

[0084] いくつかの実施形態では、超音波デバイスは、半導体ダイ上に一体化され、デジタル信号を処理してそのデータ帯域幅を減少させるように構成される、少なくとも1つの信号処理モジュールをさらに備え、これは、いくつかの実施形態において、さらなる処理、ならびにコンピュータ、スマートフォン、およびタブレットなどの外部構成要素への通信を容易にするのに有利である。いくつかの実施形態では、少なくとも1つの信号処理モジュールは、デジタル直交復調器を備える。いくつかの実施形態では、少なくとも1つの信号処理モジュールは、平均化モジュールを備える。いくつかの実施形態では、少なくとも1つの信号処理モジュールは、整合フィルタを備え、代替実施形態では、不整合フィルタを備える。いくつかの実施形態では、少なくとも1つの信号処理モジュールは、有限インパルス応答フィルタを備える。いくつかの実施形態では、少なくとも1つの信号処理モジュールは、1/2帯域デシメーション低域通過フィルタを備える。いくつかの実施形態では、少なくとも1つの信号処理モジュールは、デチャーブモジュールを備える。

40

#### 【0085】

[0085] いくつかの実施形態では、デバイスは、半導体ダイ上に一体化され、ADCコン

50

バータがアナログ信号をデジタル信号に変換する前に、アナログ信号を処理して、そこから波形を分離するように構成される、少なくとも1つの追加構成要素をさらに備える。いくつかの実施形態では、少なくとも1つの追加構成要素はアナログ直交復調器を備え、いくつかの実施形態では、アナログデチャーブモジュールを備える。

#### 【0086】

[0086] いくつかの実施形態では、高速シリアルデータモジュールは、USBモジュールを備える。いくつかの実施形態では、USBモジュールは、USB3.0モジュールを備える。いくつかの実施形態では、高速シリアルデータモジュールは、低電圧差動信号(LVDS)リンクモジュールを備える。そのような通信プロトコルの使用によって、外部構成要素で超音波デバイスの使用が容易になる。

10

#### 【0087】

[0087] 本技術の態様によれば、送信および/または制御回路が設けられるものと同じ半導体ダイ上に一体化される、少なくとも第1および第2のウルトラソニックトランスデューサ要素のために、送信および/または制御回路を動作させるための方法が提供され、方法は、コントローラを使用して、少なくとも第1および第2のウルトラソニックトランスデューサ要素のために、送信および/または制御回路の動作パラメータの値を制御することを含む。少なくともいくつかの実施形態では、そのような制御によって、いくつかの実施形態における望ましい波形の生成が容易になる。

#### 【0088】

[0088] いくつかの実施形態では、方法は、半導体ダイ上に一体化されないコントローラで、高速シリアルデータリンクを介して、送信および/または制御回路に関連するレジスタに動作パラメータを通信することをさらに含む。

20

#### 【0089】

[0089] いくつかの実施形態では、コントローラを使用することは、コントローラを使用して、少なくとも第1および第2のウルトラソニックトランスデューサ要素のために、送信制御回路の波形発生器の動作パラメータの値を制御することを含む。いくつかの実施形態では、コントローラを使用することは、コントローラを使用して、少なくとも第1および第2のウルトラソニックトランスデューサ要素のために、受信制御回路の増幅器の動作パラメータの値を制御することを含む。

30

#### 【0090】

[0090] 本技術の態様によれば、デバイスが提供され、デバイスは、半導体ダイ上に一体化される、少なくとも第1および第2のウルトラソニックトランスデューサ要素と、半導体ダイ上に一体化される、送信および/または制御回路と、少なくとも第1および第2のウルトラソニックトランスデューサ要素のために、送信および/または制御回路の動作パラメータの値を制御するように構成されるコントローラとを備える。いくつかの実施形態では、そのような構成は、超音波画像を形成するのに好適な超音波データを集めるように構成される超音波撮像デバイスなどの、一体型超音波デバイスの少なくとも部分を表す。

#### 【0091】

[0091] いくつかの実施形態では、コントローラは、半導体ダイ上に一体化されず、高速シリアルデータリンクを介して、送信および/または制御回路に関連するレジスタに動作パラメータを通信するように構成される。いくつかの実施形態では、コントローラは、少なくとも第1および第2のウルトラソニックトランスデューサ要素のために、送信制御回路の波形発生器の動作パラメータの値を制御するように構成される。いくつかの実施形態では、コントローラは、少なくとも第1および第2のウルトラソニックトランスデューサ要素のために、受信制御回路の増幅器の動作パラメータの値を制御するように構成される。

40

#### 【0092】

[0092] 本技術の態様によれば、デバイスが提供され、デバイスは、超音波撮像チップ、および高密度焦点式超音波(HIFU)チップを備える。超音波撮像チップとHIFUチップは、結合され、組み合わせて動作して、画像誘導HIFUを実施する。超音波撮像チップ

50

は、好適な構成要素（たとえば、ウルトラソニックトランスデューサおよび回路）を含み、超音波画像を形成するのに好適な超音波データを集めることができる。HIFUチップは、好適な構成要素（たとえば、ウルトラソニックトランスデューサおよび回路）を含み、HIFUエネルギーを印加することができる。いくつかの実施形態では、超音波撮像により集められる超音波データから生じる画像は、HIFUチップによりHIFUの印加を誘導するために使用される。

#### 【0093】

[0093] 本技術の態様によれば、デバイスが提供され、デバイスは、単一のチップに一体化された、超音波撮像回路および高密度焦点式超音波（HIFU）回路を備える。デバイスは、画像誘導HIFUを実施するように構成される。したがって、いくつかの実施形態において、単一のデバイスが、複数の超音波機能を実施するように構成される。

10

#### 【0094】

[0094] 本技術の態様によれば、デバイスが提供され、デバイスは、CMOSウェハ上の超音波トランスデューサ要素の配置、CMOSウェハ上に形成されて超音波トランスデューサ要素の配置に電気的に結合される集積回路を備える。集積回路は約50Vまでの電圧を駆動するように構成される。そのような電圧は、いくつかの実施形態において、高電圧の使用を必要とする可能性がある、HIFUの印加および／または超音波撮像の実施に関して有利である。

#### 【0095】

[0095] いくつかの実施形態では、集積回路は、サブミクロンノードを備える。サブミクロンノードは、約50Vまでの電圧を駆動するように構成される。いくつかの実施形態では、サブミクロンノードとは、約1ミクロン未満であるノードのことを言う場合がある。いくつかの実施形態では、ディープサブミクロンノードとは、約0.3ミクロン未満であるノードのことを言う場合がある。いくつかの実施形態では、ウルトラディープサブミクロンノードとは、約0.1ミクロン未満であるノードのことを言う場合がある。したがって、いくつかの超音波用途で有用な高電圧を維持することが可能である、小型の一体型超音波デバイスが、少なくともいくつかの実施形態で提供される。

20

#### 【0096】

[0096] ウルトラソニックトランスデューサ要素が設けられるまたは使用される、本明細書に記載されたこれらの実施形態の少なくともいくつかでは、ウルトラソニックトランスデューサ要素は、1つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルを備えることができる。いくつかの実施形態では、1つまたは複数のマイクロマシン加工されたウルトラソニックトランスデューサセルは、1つまたは複数の容量性マイクロマシン加工ウルトラソニックトランスデューサ（CMUT）セルを備え、いくつかの実施形態では、1つまたは複数のCMOSウルトラソニックトランスデューサ（CUT）セルを備える。

30

#### 【0097】

[0097] 開示される技術の様々な態様および実施形態は、以下の図を参照して記載されることになる。図は、必ずしも原寸に比例しないことを理解されたい。複数の図に現れるアイテムは、アイテムが現れるすべての図で同じ参照番号により示される。

40

#### 【図面の簡単な説明】

#### 【0098】

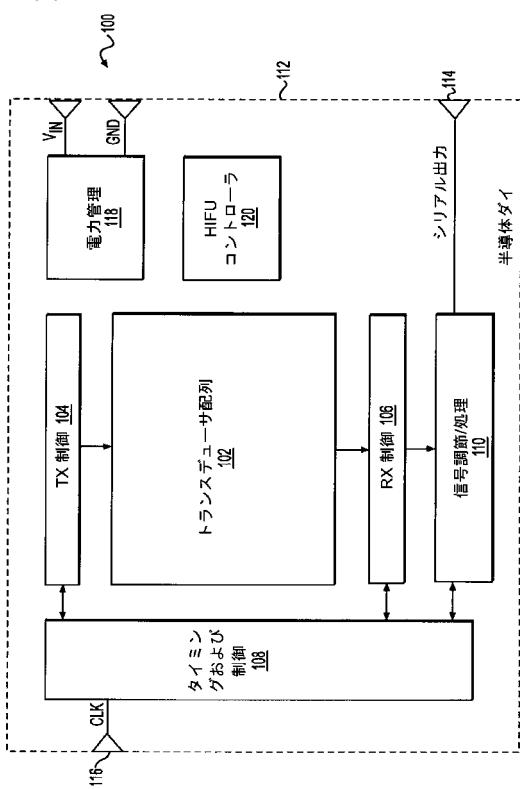

【図1】[0098]本発明の様々な態様を具現化する、モノリシック超音波デバイスの説明に役立つ例を示す図である。

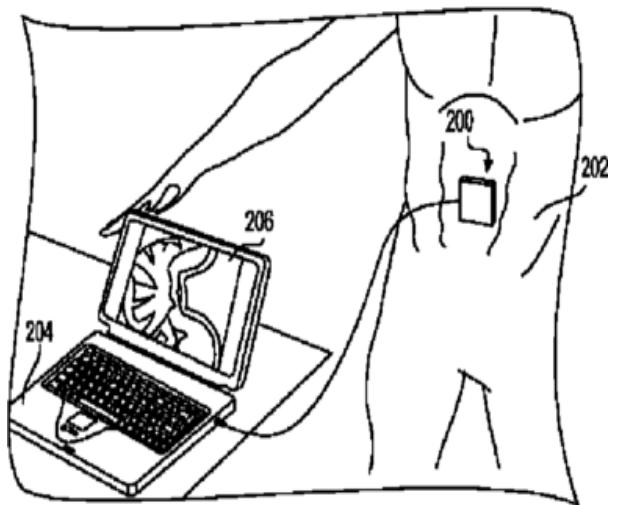

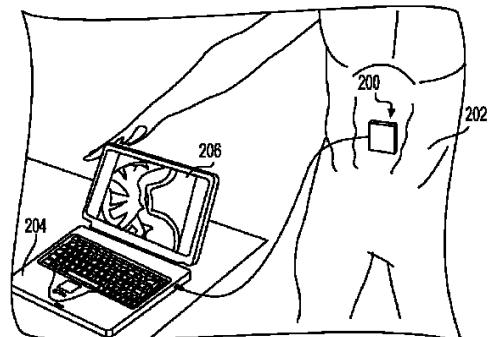

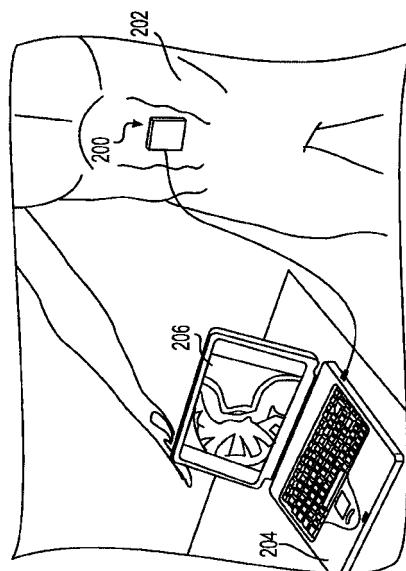

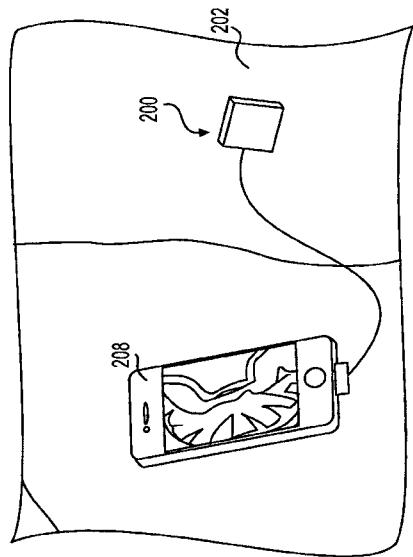

【図2A】[0099]音響信号を送信し、対象物から後方散乱されるパルスのみを受信するように適合される撮像デバイスの例示的な実装を示す図である。

【図2B】音響信号を送信し、対象物から後方散乱されるパルスのみを受信するように適合される撮像デバイスの例示的な実装を示す図である。

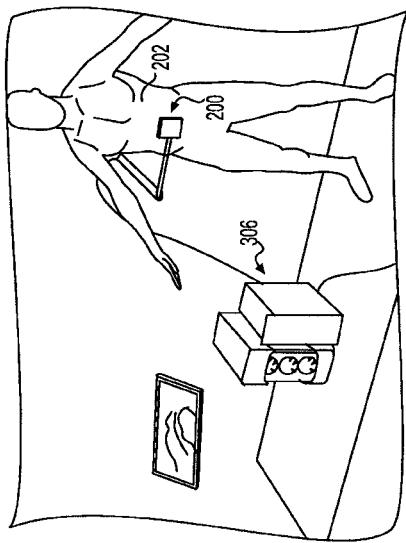

【図3A】[0100]一対の対向する撮像デバイスを採用して対象物を撮像するシステムの例示的な実装を示す図である。

50

【図 3 B】一対の対向する撮像デバイスを採用して対象物を撮像するシステムの例示的な実装を示す図である。

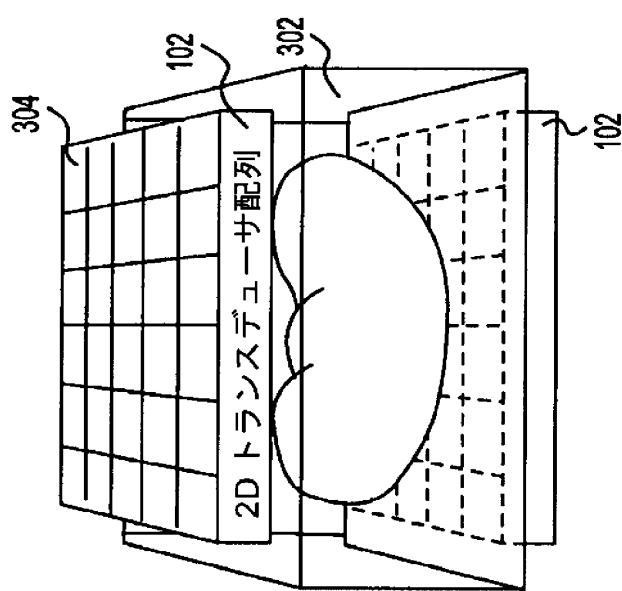

【図 4 A】[0101]トランステューサ配列中の個々のトランステューサ要素が、その要素についての CMOS 回路に関してどのように配置できるのかの説明に役立つ例を示す図である。

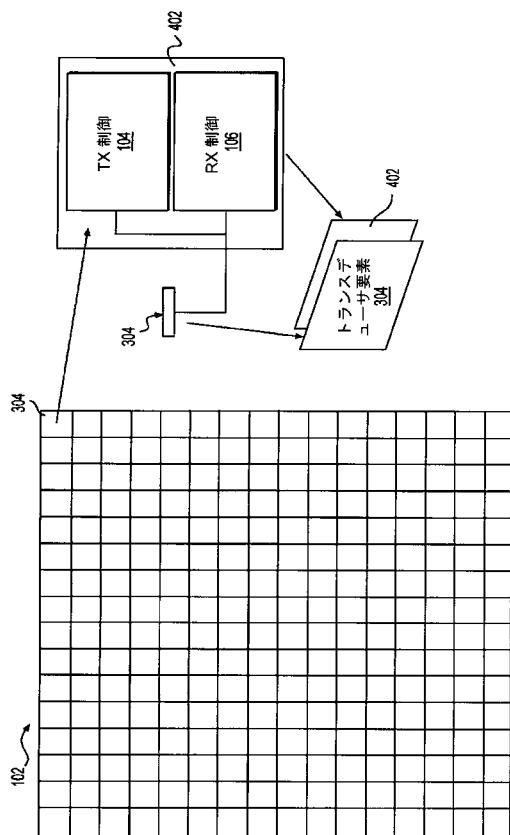

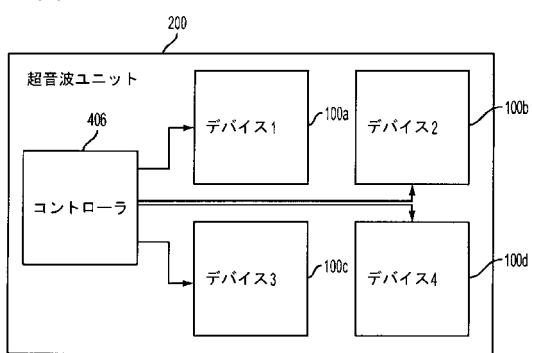

【図 4 B】[0102]コントローラの指示の下で一緒に動作することができる、個々の超音波デバイスのグループを備える、超音波ユニットの説明に役立つ例を示す図である。

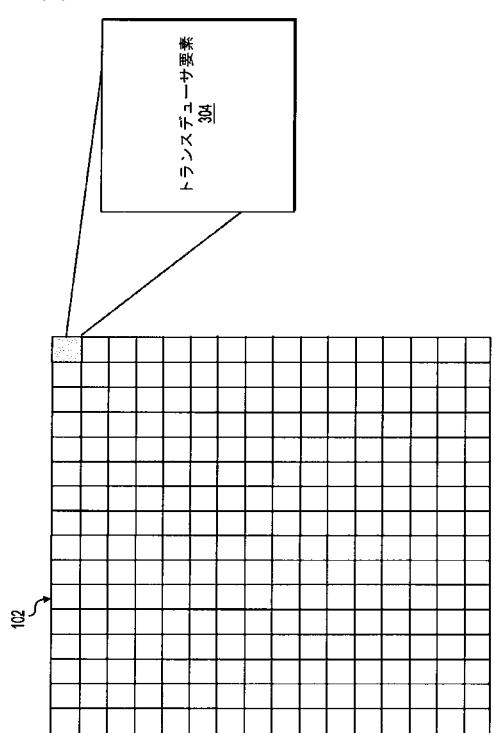

【図 5】[0103]いくつかの実施形態において、単一のトランステューサ要素が、より大きいトランステューサ配列内でどのように収まることができるのかを図示する図である。

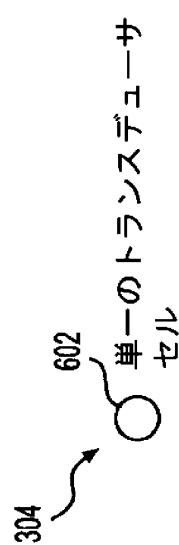

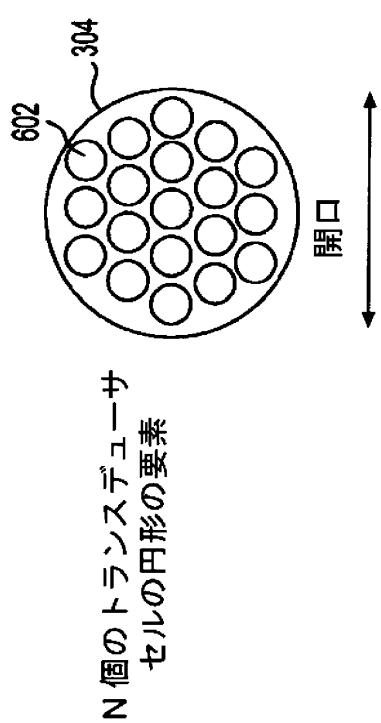

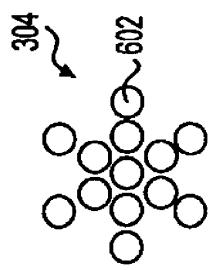

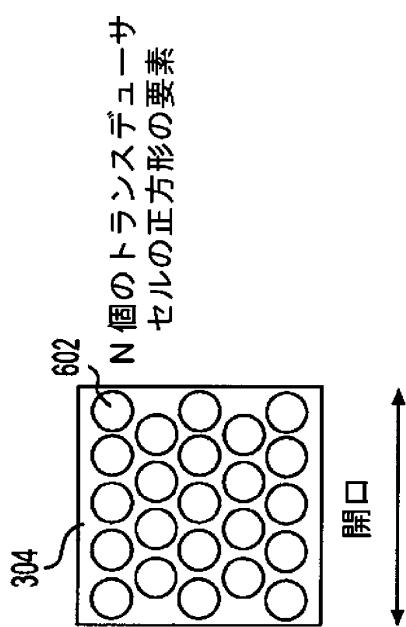

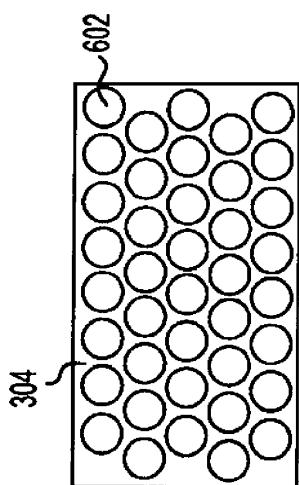

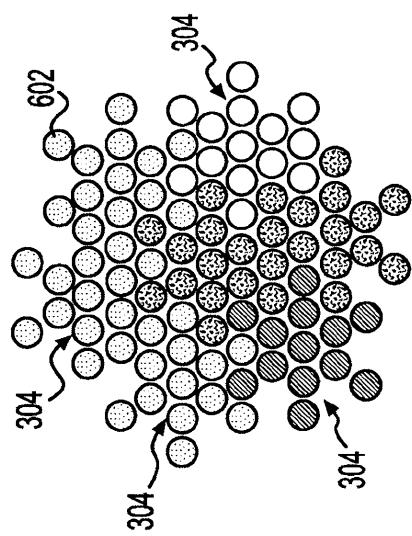

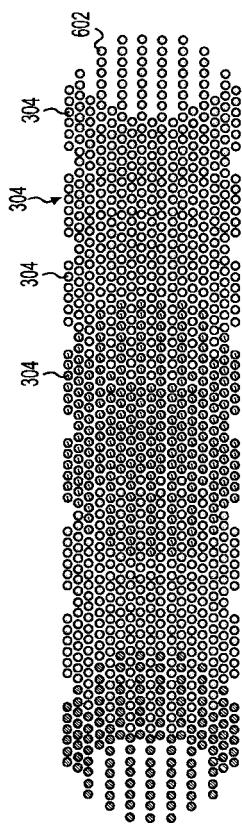

【図 6 A】[0104]配列内の所与のトランステューサ要素が、いくつかの実施形態において、どのように構成することができるのかについての 5 つの異なる例のうちの 1 つを示す図である。

【図 6 B】配列内の所与のトランステューサ要素が、いくつかの実施形態において、どのように構成することができるのかについての 5 つの異なる例のうちの 1 つを示す図である。

【図 6 C】配列内の所与のトランステューサ要素が、いくつかの実施形態において、どのように構成することができるのかについての 5 つの異なる例のうちの 1 つを示す図である。

【図 6 D】配列内の所与のトランステューサ要素が、いくつかの実施形態において、どのように構成することができるのかについての 5 つの異なる例のうちの 1 つを示す図である。

【図 6 E】配列内の所与のトランステューサ要素が、いくつかの実施形態において、どのように構成することができるのかについての 5 つの異なる例のうちの 1 つを示す図である。

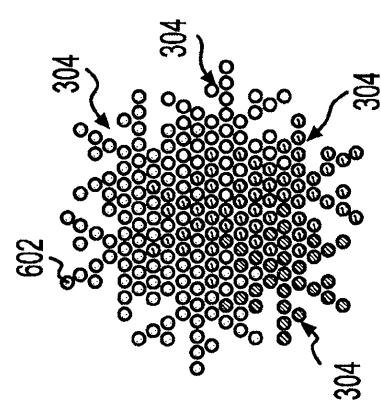

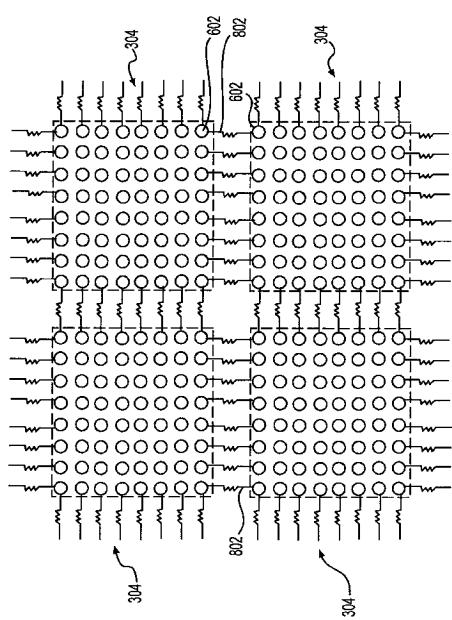

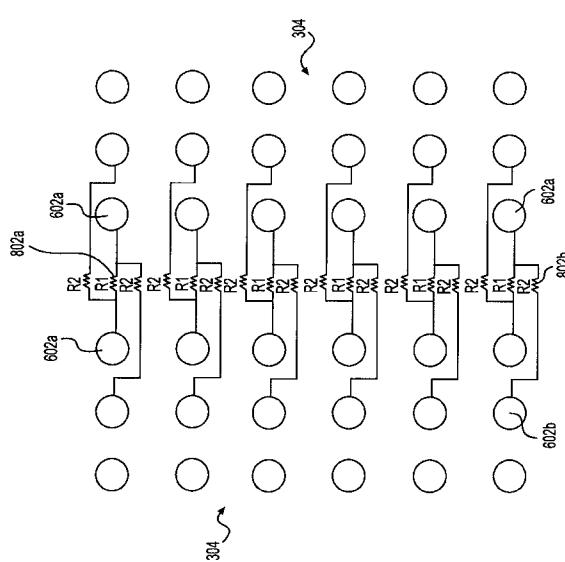

【図 7 A】[0105]グレーティングロープなどを減少させるために、いくつかの実施形態において、トランステューサ要素をどのように混合することができるのかについての例を示す図である。

【図 7 B】グレーティングロープなどを減少させるために、いくつかの実施形態において、トランステューサ要素をどのように混合することができるのかについての例を示す図である。

【図 7 C】グレーティングロープなどを減少させるために、いくつかの実施形態において、トランステューサ要素をどのように混合することができるのかについての例を示す図である。

【図 8】[0106]グレーティングロープなどを減少させるために、いくつかの実施形態において、配列のそれぞれのトランステューサ要素に含まれるトランステューサセルを互いにどのように結合することができるのかについての例を示す図である。

【図 9】グレーティングロープなどを減少させるために、いくつかの実施形態において、配列のそれぞれのトランステューサ要素に含まれるトランステューサセルを互いにどのように結合することができるのかについての例を示す図である。

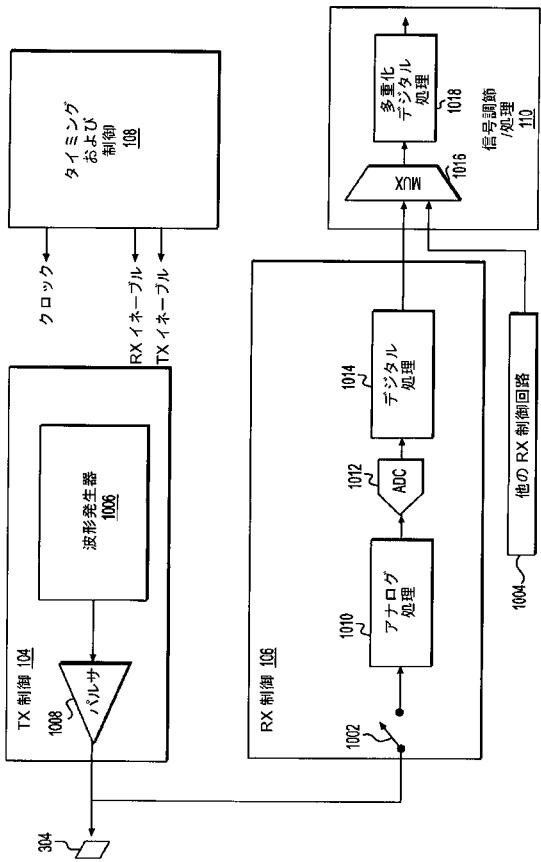

【図 10】[0107]いくつかの実施形態において、どのようにして、所与のトランステューサ要素についての TX 制御回路および RX 制御回路を使用して、要素に通電してウルトラソニックパルスを放出することができるのか、または要素により検知されるウルトラソニックパルスを表す要素からの信号を受信および処理することができるのかについて図示するブロック図である。

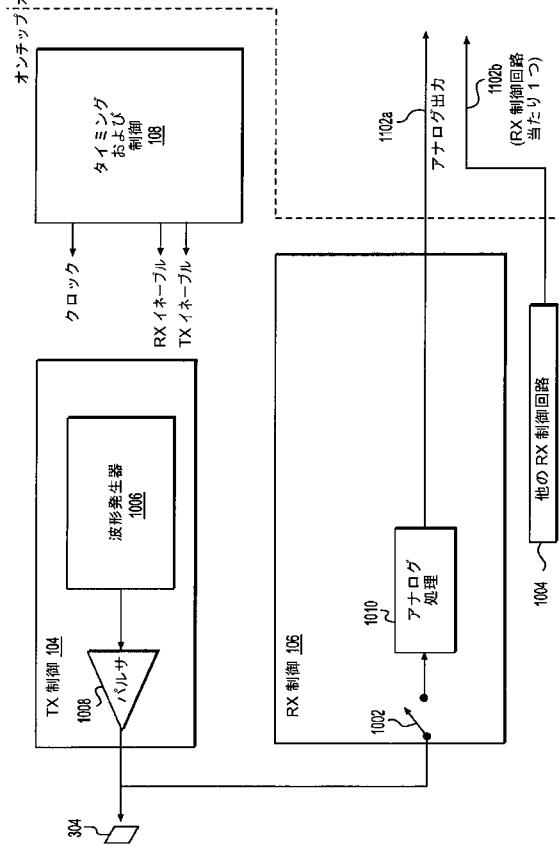

【図 11 A】[0108]受信信号のデジタル処理をオフチップで実施することができる、超音波デバイスの実施形態を図示する図である。

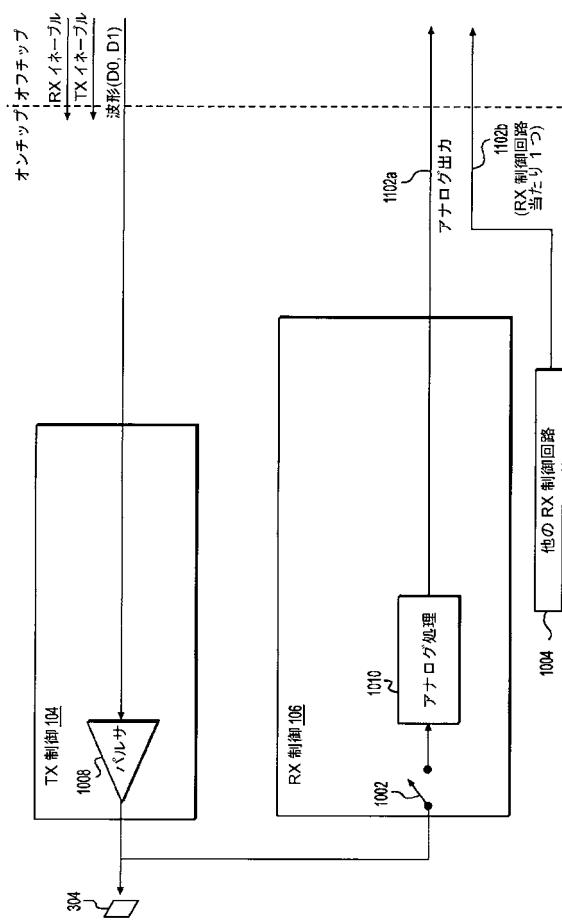

【図 11 B】[0109]波形発生器および他のデジタル回路の一部またはすべてがオフチップで配置することができる、超音波デバイスの実施形態を図示する図である。

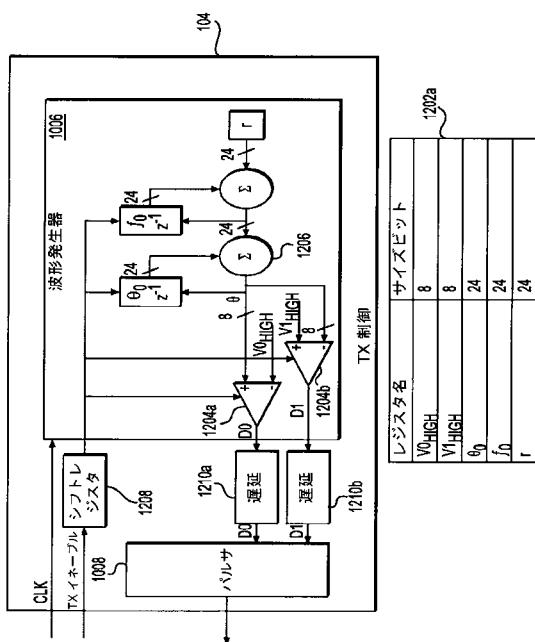

【図 12 A】[0110]トランステューサ配列のあらゆる送信位置において実時間遅延および増幅制御を可能にするように、いくつかの実施形態において、各 TX 制御回路に含むこと

10

20

30

40

50

ができる回路の例を示す図である。

【図12B】トランステューサ配列のあらゆる送信位置において実時間遅延および増幅制御を可能にするように、いくつかの実施形態において、各TX制御回路に含むことができる回路の例を示す図である。

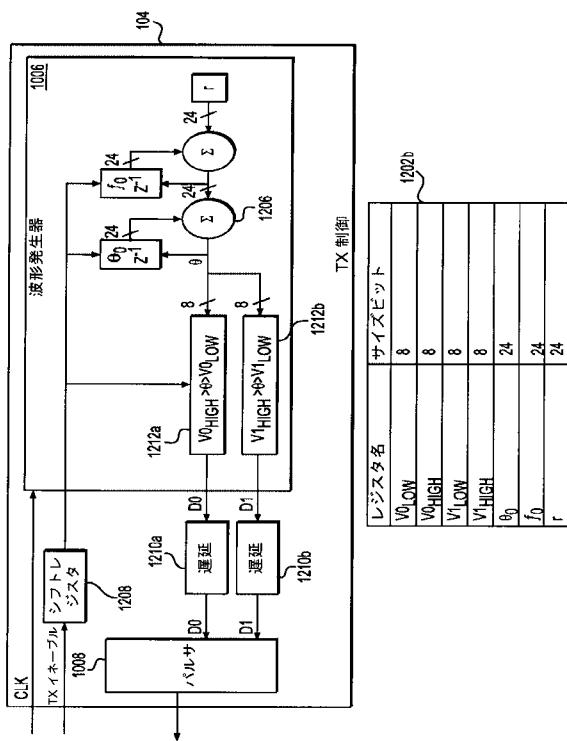

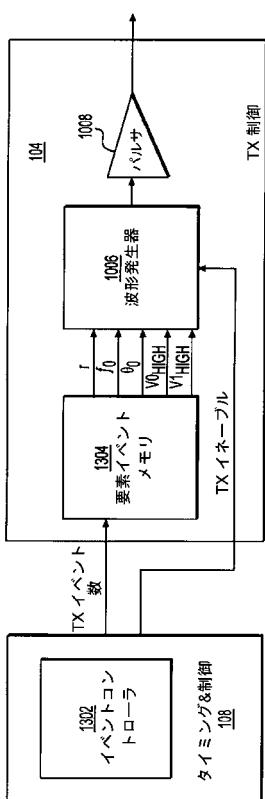

【図13A】[0111]図12A～図12Bの実施形態中の波形発生器により使用されるレジスタに関する値を選択的に決定するため、タイミング&制御回路および各TX制御回路で採用することができる構成要素の説明に役立つ例を示す図である。

【図13B】[0112]TX制御回路および/またはRX制御回路により使用される動作パラメータのうちの1つまたは複数に関する値を選択的に決定するために使用することができる構成要素の例を示す図である。

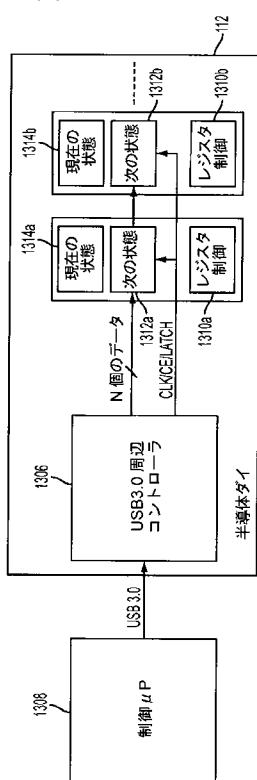

【図14】[0113]いくつかの実施形態において、超音波デバイス中で発生する送信イベントおよび受信イベントの両方を制御するために提供することができる、タイミング&制御回路のイベントコントローラについての入力および出力の例を示す図である。

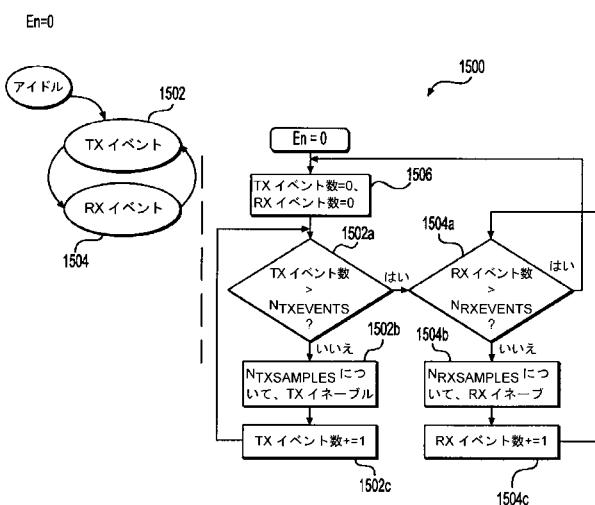

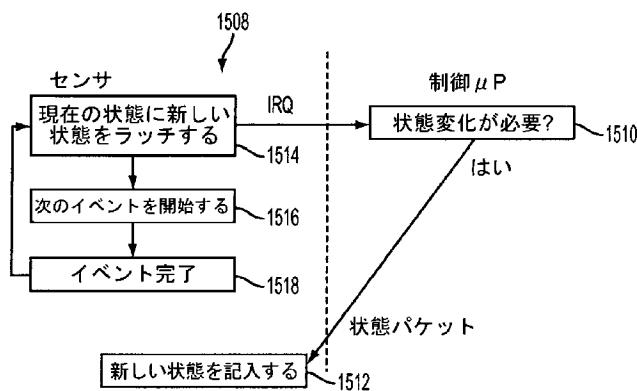

【図15A】[0114]送信および/または受信イベントを制御するための好適な一連の出力を生成するために、図14に示されるイベントコントローラにより実施することができるルーチンの説明に役立つ例を示す図である。

【図15B】[0115]TX制御回路および/またはRX制御回路により使用される1つまたは複数の動作パラメータに関する値を選択的に決定するため、図13Aの実施形態に関連して採用することができるルーチンの説明に役立つ例を示す図である。

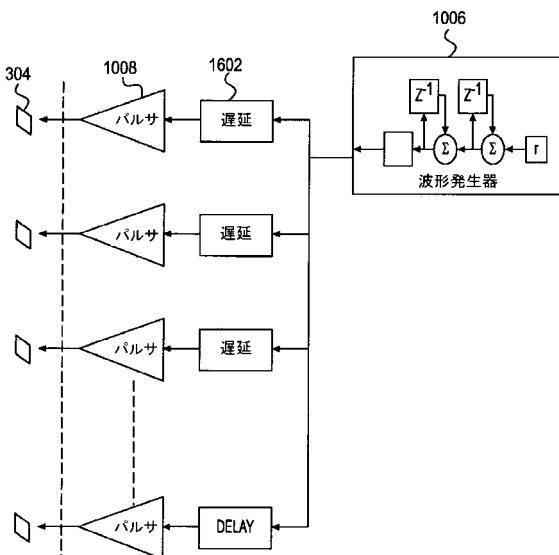

【図16】[0116]単一の波形発生器を2つ以上のTX制御回路により共有することができる、超音波デバイスの代替実装形態を示す図である。

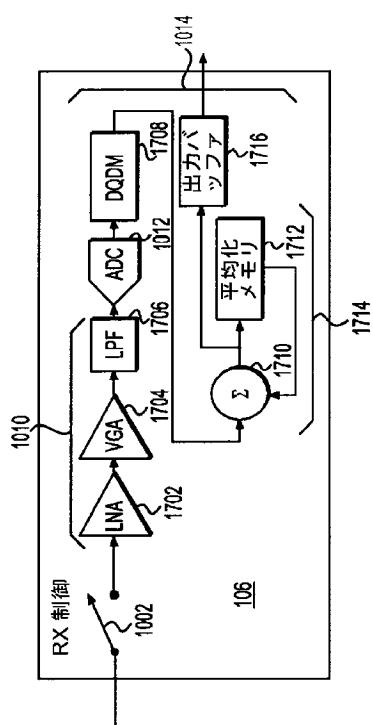

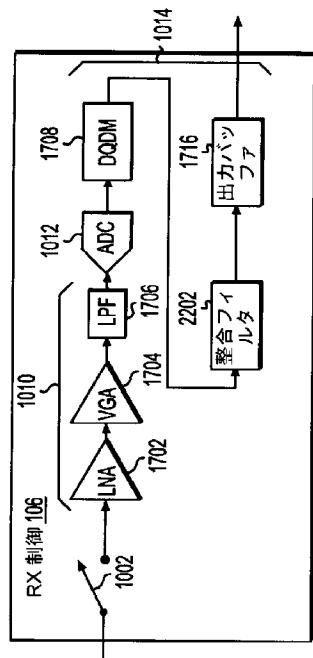

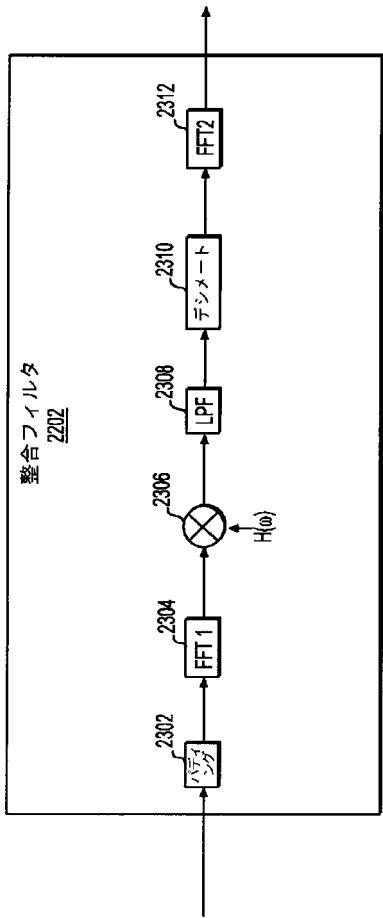

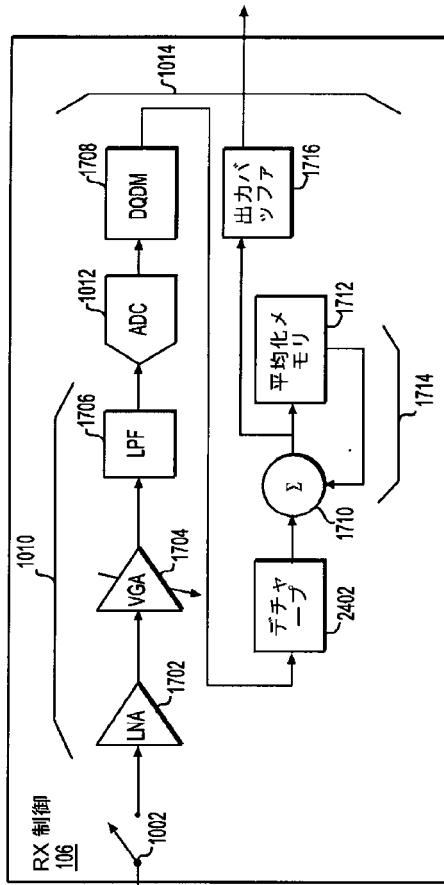

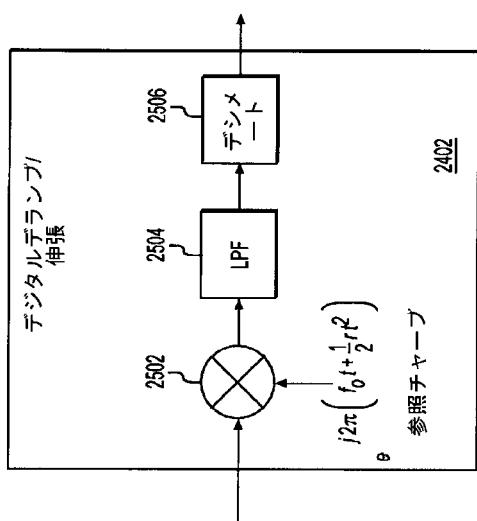

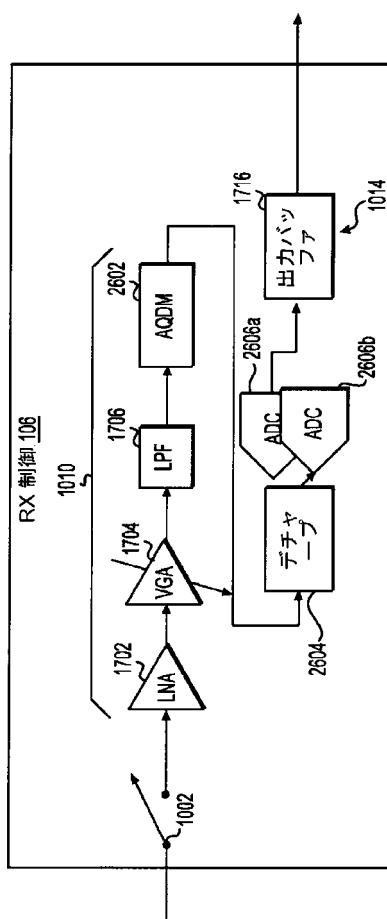

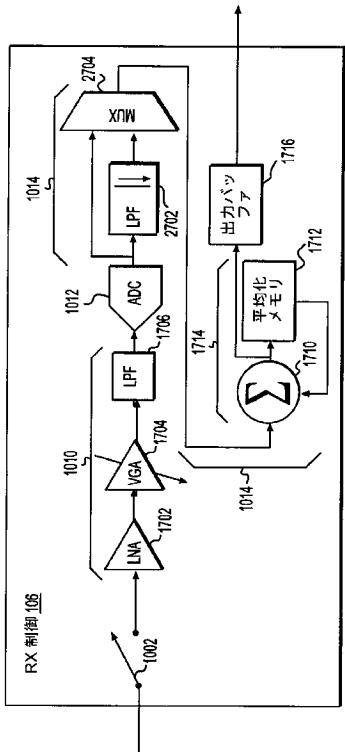

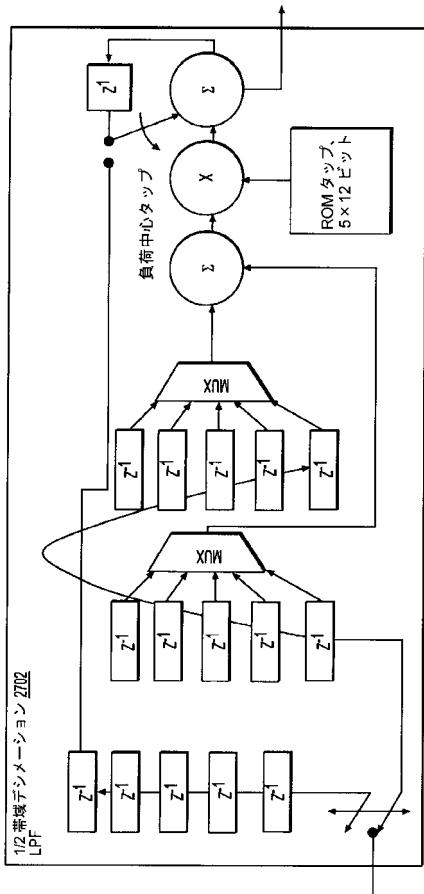

【図17】[0117]図10に示されるRX制御回路のアナログ処理ブロックおよびデジタル処理ブロック内に含むことができる構成要素の説明に役立つ例を示す図である。

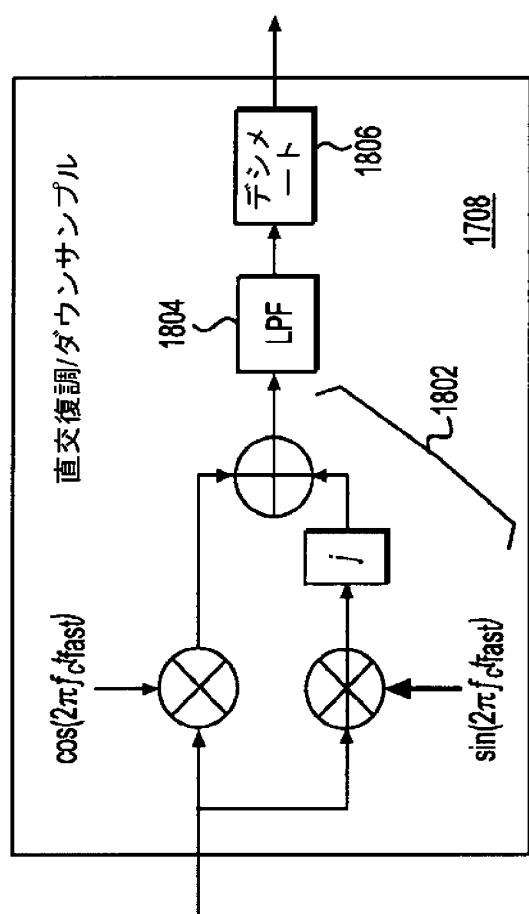

【図18】図10に示されるRX制御回路のアナログ処理ブロックおよびデジタル処理ブロック内に含むことができる構成要素の説明に役立つ例を示す図である。

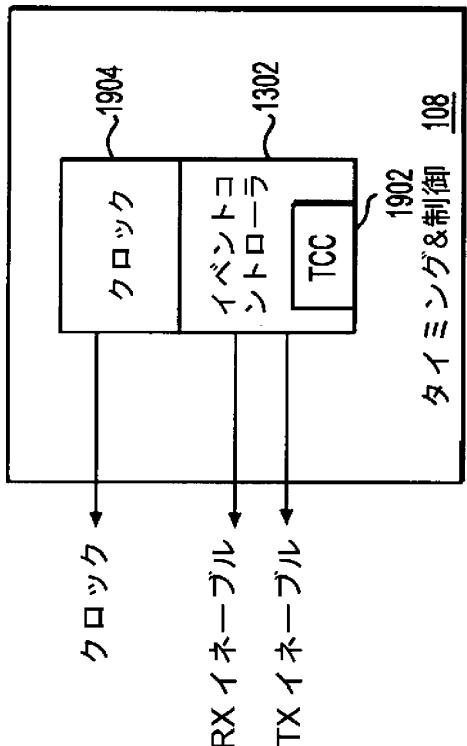

【図19】[0118]図1に示されるタイミング&制御回路の例示的な実装を示す図である。

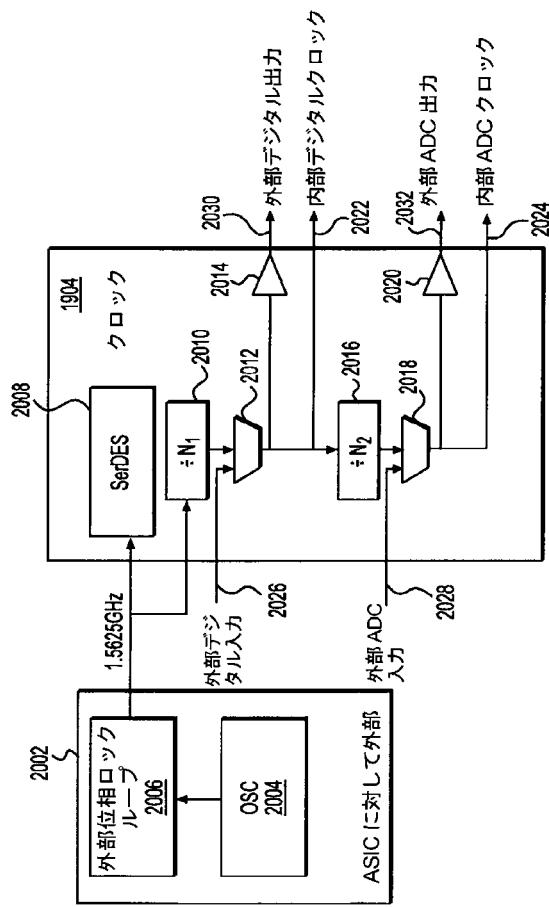

【図20】[0119]図19に示されるクロック生成回路の例示的な実装を示す図である。

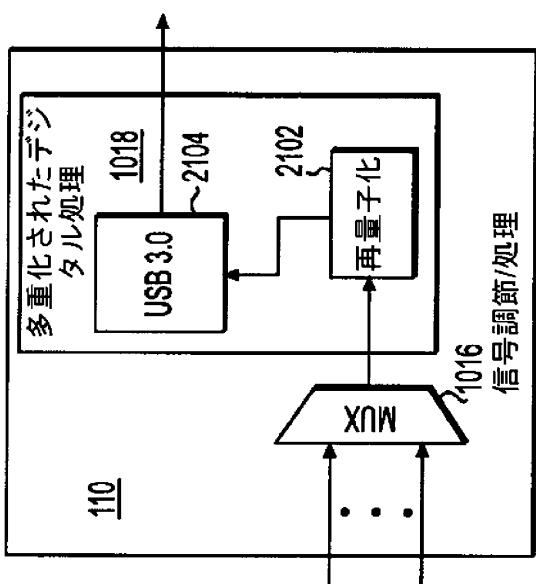

【図21】[0120]図10に示される信号調節/処理回路の多重化されたデジタル処理ブロック中に含むことができる構成要素の説明に役立つ例を示す図である。

【図22】図10に示されるRX制御回路のアナログ処理ブロックおよびデジタル処理ブロック内に含むことができる構成要素の説明に役立つ例を示す図である。

【図23】図10に示されるRX制御回路のアナログ処理ブロックおよびデジタル処理ブロック内に含むことができる構成要素の説明に役立つ例を示す図である。

【図24】図10に示されるRX制御回路のアナログ処理ブロックおよびデジタル処理ブロック内に含むことができる構成要素の説明に役立つ例を示す図である。

【図25】図10に示されるRX制御回路のアナログ処理ブロックおよびデジタル処理ブロック内に含むことができる構成要素の説明に役立つ例を示す図である。

【図26】図10に示されるRX制御回路のアナログ処理ブロックおよびデジタル処理ブロック内に含むことができる構成要素の説明に役立つ例を示す図である。

【図27】図10に示されるRX制御回路のアナログ処理ブロックおよびデジタル処理ブロック内に含むことができる構成要素の説明に役立つ例を示す図である。

【図28】図10に示されるRX制御回路のアナログ処理ブロックおよびデジタル処理ブロック内に含むことができる構成要素の説明に役立つ例を示す図である。

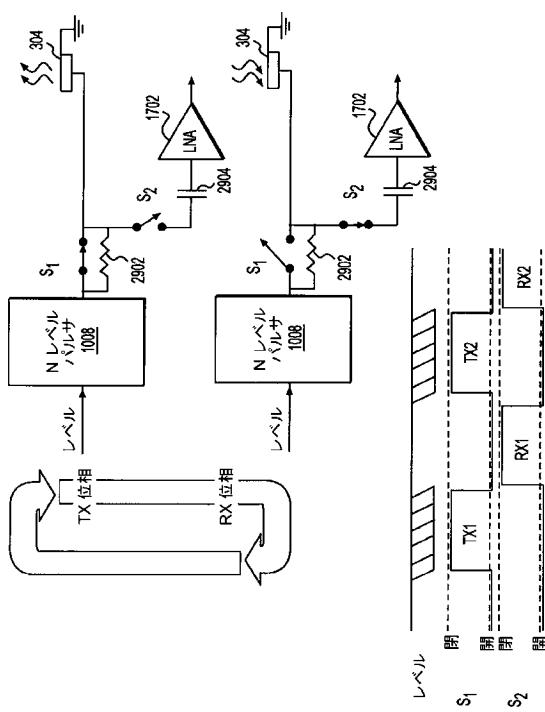

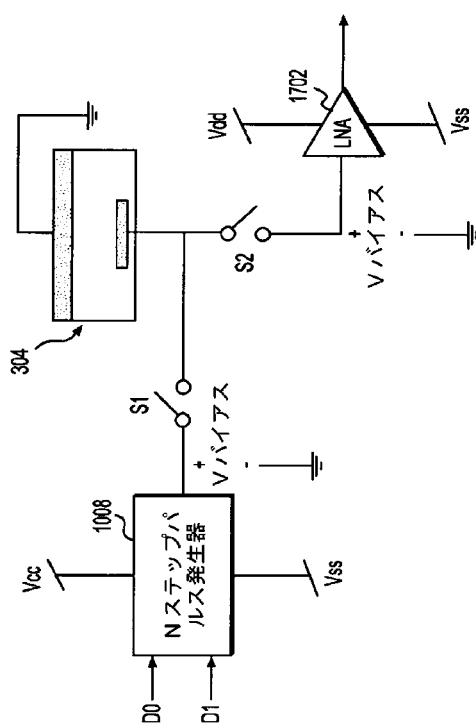

【図29】[0121]配列または他の配置中のトランステューサ要素にバイアスをかけるための技法の例を図示する図である。

【図30】配列または他の配置中のトランステューサ要素にバイアスをかけるための技法の例を図示する図である。

【図31】[0122]図10に示される信号調節/処理回路の多重化されたデジタル処理ブロック中に含むことができる構成要素の例を示す図である。

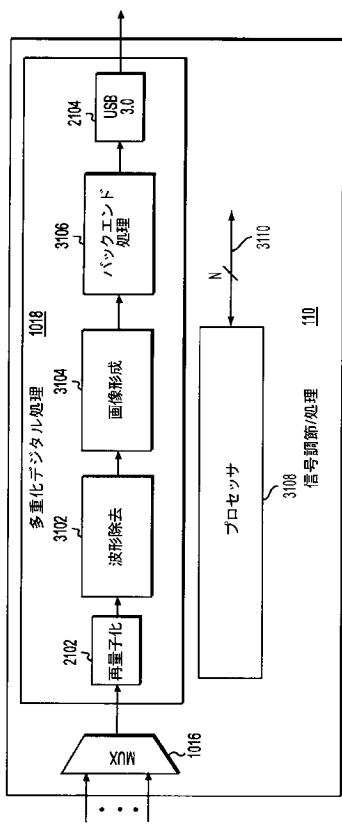

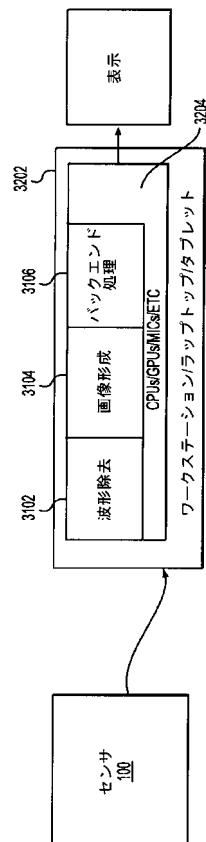

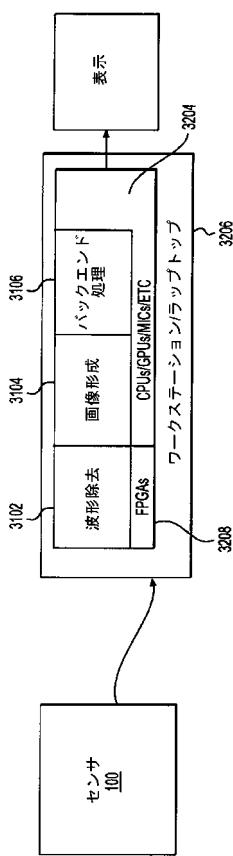

【図32A】[0123]波形除去回路および/もしくはソフトウェア、画像形成回路および/

もしくはソフトウェア、ならびに／またはバックエンド処理回路および／もしくはソフトウェアの一部またはすべてがオフチップで配置することができる実施形態を図示する図である。

【図32B】波形除去回路および／もしくはソフトウェア、画像形成回路および／もしくはソフトウェア、ならびに／またはバックエンド処理回路および／もしくはソフトウェアの一部またはすべてがオフチップで配置することができる実施形態を図示する図である。

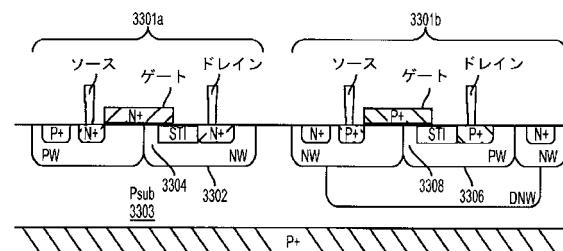

【図33】[0124]いくつかの実施形態において使用することができる、高電圧N MOSおよびPMOSのレイアウトの例を示す図である。

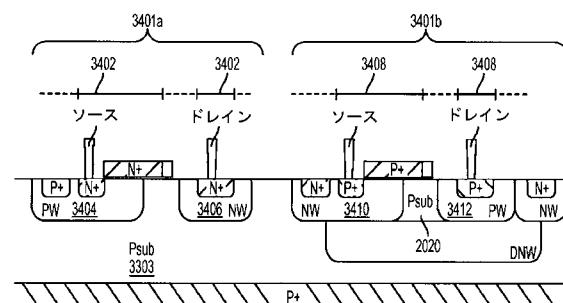

【図34】[0125]いくつかの実施形態において使用することができる、超高電圧N MOSおよびPMOSのレイアウトの例を示す図である。

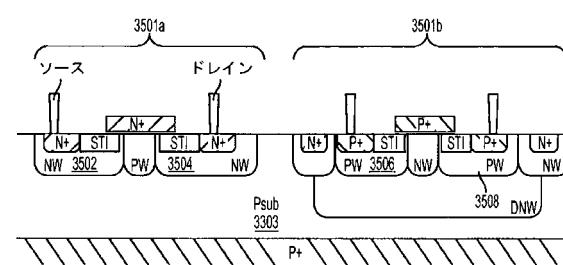

【図35】[0126]いくつかの実施形態において使用することができる、高電圧N MOSおよびPMOSの双方向またはカスコードレイアウトの例を示す図である。

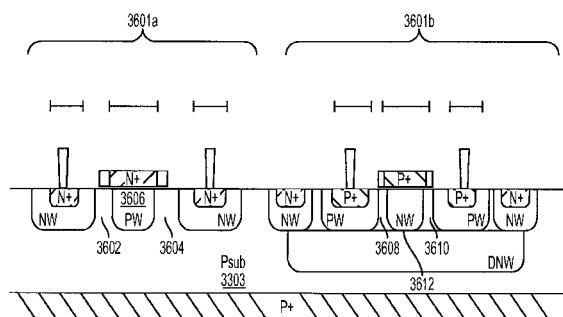

【図36】[0127]いくつかの実施形態において使用することができる、超高電圧N MOSおよびPMOSの双方向またはカスコードレイアウトの例を示す図である。

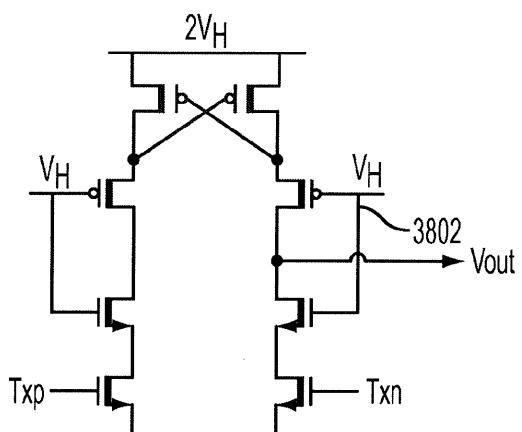

【図37】[0128]いくつかの実施形態において使用することができる高電圧スイッチを備える、高電圧N MOSおよびPMOSのレイアウトを使用するパルサの例を示す図である。

【図38A】[0129]いくつかの実施形態において使用することができる二重電圧パルスドライバの例を示す図である。

【図38B】いくつかの実施形態において使用することができる四重電圧パルスドライバの例を示す図である。

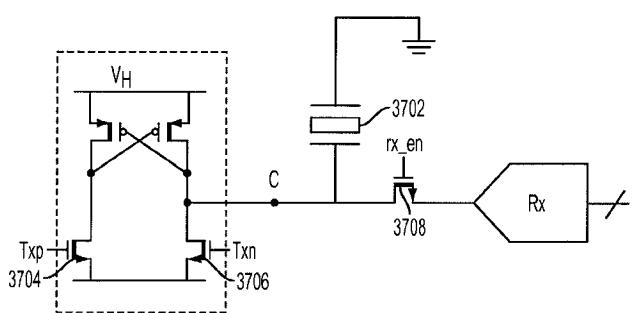

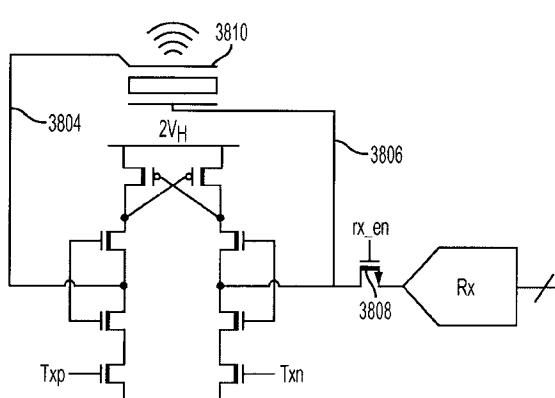

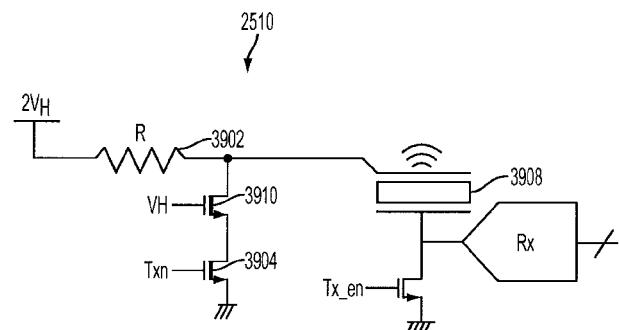

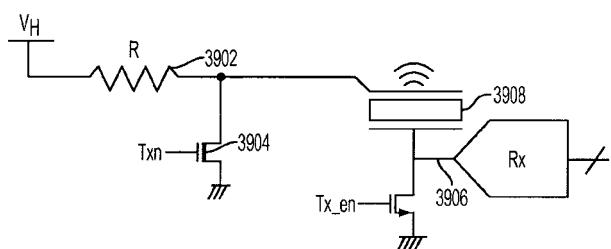

【図39A】[0130]いくつかの実施形態において使用することができる、受信分離スイッチを採用しないパルサの例を示す図である。

【図39B】いくつかの実施形態において使用することができる、受信分離スイッチを採用しないパルサの例を示す図である。

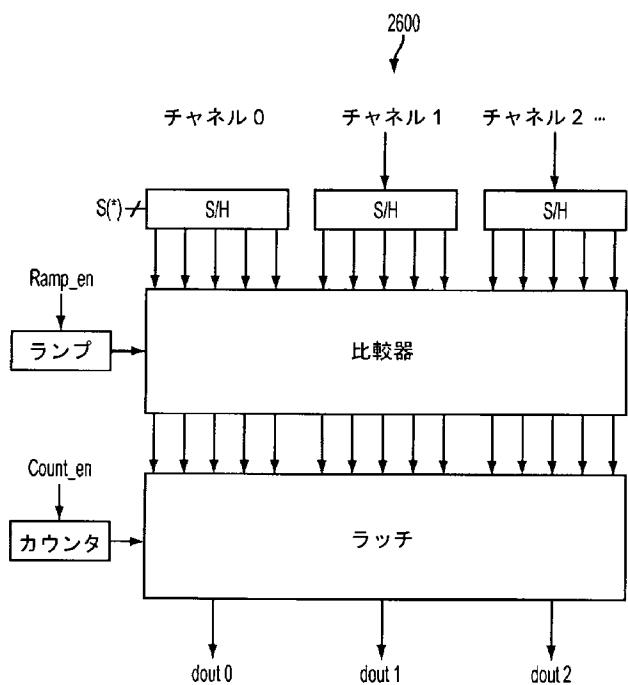

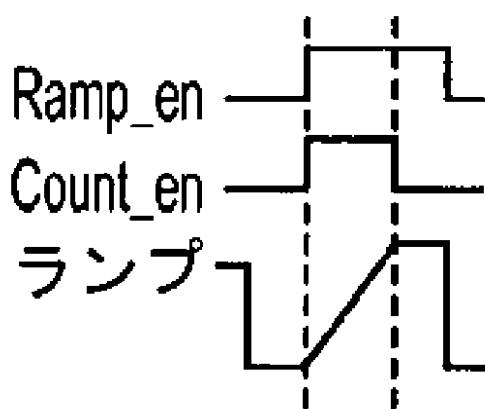

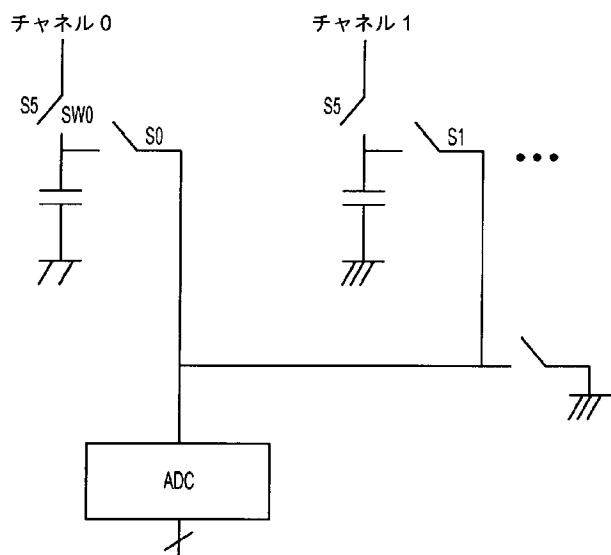

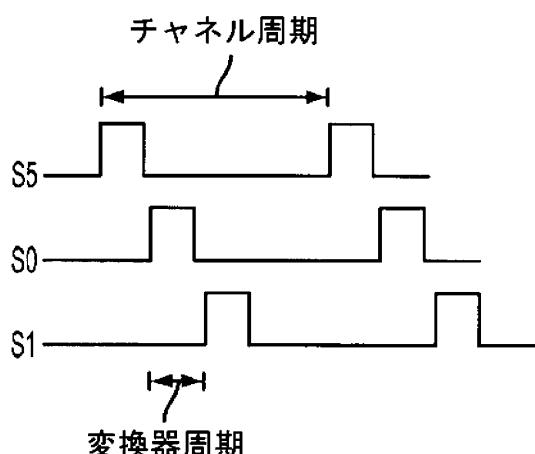

【図40A】[0131]ここで、ADC参照値のうちの1つまたは複数としていくつかの実施形態において採用することができる、時間インターリープされた単一勾配アナログ・デジタル変換器(ADC)の例を示す図である。

【図40B】ここで、ADC参照値のうちの1つまたは複数としていくつかの実施形態において採用することができる、時間インターリープされた単一勾配アナログ・デジタル変換器(ADC)の動作の例を示す図である。

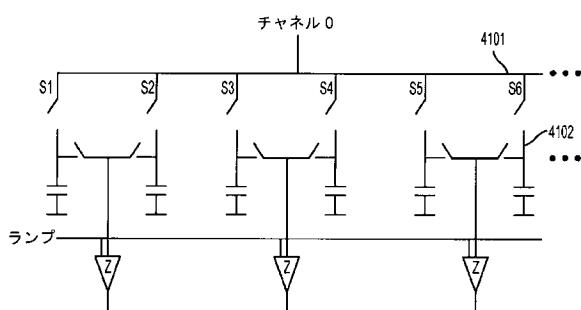

【図41】[0132]いくつかの実施形態において採用することができる、時間インターリープされたサンプルホールド回路の例を示す図である。

【図42A】[0133]ここで参照されるADCのうちの1つまたは複数としていくつかの実施形態において採用することができる、時分割高速ADCの例を示す図である。

【図42B】ここで参照されるADCのうちの1つまたは複数としていくつかの実施形態において採用することができる、時分割高速ADCの動作の例を示す図である。

【発明を実施するための形態】

【0099】

[0134] 本開示のいくつかの実施形態は、CMUT技術の利益を活用し、ウルトラソニックスキャナ中の超音波画像形成処理の最先端を推し進める、新規の装置、システム、および方法を提供する。いくつかの実施形態では、堅牢で高度に一体化された超音波「システムオンチップ」が、完全なデジタル超音波フロントエンドと同じダイ上に製造されるウルトラソニックトランステューサ配列とダイレクトに一体化されて提供される。本開示のいくつかの態様によれば、このアーキテクチャによって、完全デジタル化されたチャネルデータへの十分なアクセスを可能にし、高度な画像形成アルゴリズムを実施するための、最新技術の既製の計算プラットフォームの使用を許可することができる。

【0100】

[0135] この領域での以前の努力は、かなりの程度が、より先進的な技法ではなく標準的なビーム形成を実施することができるASICを設計することによる、標準的な超音波ア

10

20

30

40

50

ーキテクチャの密な一体化に集中され、または、先進的な撮像技法、典型的には拡大縮小可能な集積技術を欠いている高価なデバイスを作り出す技法の実装に集中されてきた。本開示は、先進的な撮像用途で十分に堅牢である、ユニークで、コスト効果的、また拡大縮小可能な一体型超音波プラットフォームオンチップを提供することにより、これらの問題の両方に対処する。

#### 【0101】

[0136] 標準的なビーム形成方法を越えて進むには、単なる時間遅延パルスの送信以上をサポートすることができるアーキテクチャが必要になる。先進的な波形符号化技法を実装するのに十分なフレキシビリティには、トランスデューサ配列中の各要素について、専用のシステムリソースが必要になる。本開示は、たとえば、新規の波形発生器で、この制限を克服する。いくつかの実施形態では、集積回路は、この波形発生器がマルチレベルの（たとえば、3つ以上のレベルの）パルサを制御することをユニークに可能にして、完全な一体型トランスデューサ / CMOS構成で以前には達成されていなかった特徴である、後続の処理における多くの先進的な超音波技法を実装する能力をもたらす。

10

#### 【0102】

[0137] しばしば、超音波受信器アーキテクチャは、複数のチャネルからデータ帯域幅を減らす必要がある。従来型超音波でこれを行う1つの様態は、標準的なビーム形成方法を使用することである。この操作は不可逆であり、多くのより先進的な超音波撮像再構成技法と互換性がない。多くの場合、全チャネルのデータレートは、システムの外部デジタルリンクの帯域幅を超える可能性がある。本明細書に開示されるいくつかの実施形態は、チップを離れるデータについて、かつてないレベルの制御のデータレートを可能にする様態で、全チャネルのデータを使用するフレキシビリティをもたらす新規のアーキテクチャを採用する。

20

#### 【0103】

[0138] 本明細書に詳述される集積回路は、一体型超音波撮像デバイスのために、ユニークに設計される。CMOS接触によって、ダイレクトウェハボンディング、犠牲リリース、フリップチップボンディング、および／または超音波トランスデューサ要素への相互接続を確立するための他の技法が容易になる。

30

#### 【0104】

[0139] 上に記載された態様および実施形態、ならびに追加の態様および実施形態が下でさらに記載される。これらの態様および／または実施形態は、本開示がこの点に関して制限されないので、別個、すべて一緒、または2つ以上の任意の組合せで使用することができる。

40

#### 【0105】

[0140] 図1は、本発明の様々な態様を具現化する、モノリシック超音波デバイス100の説明に役立つ例を示す。示されるように、デバイス100は、1つまたは複数のトランスデューサ配置（たとえば、配列）102、送信（TX）制御回路104、受信（RX）制御回路106、タイミング＆制御回路108、信号調節／処理回路110、電力管理回路118、および／または高密度焦点式超音波（HIFU）コントローラ120を含むことができる。示される実施形態では、図示される要素のすべてが、单一の半導体ダイ112上に形成される。しかし、代替実施形態では、より詳細に下で議論されるように、図示される要素のうちの1つまたは複数を、代わりにオフチップに配置することができることを理解されたい。加えて、図示される例は、TX制御回路104およびRX制御回路106の両方を示すが、（やはり下でより詳細に議論される）代替実施形態では、TX制御回路のみ、またはRX制御回路のみを採用することができる。たとえば、そのような実施形態は、1つまたは複数の送信専用デバイス100が使用されて音響信号を送信し、1つまたは複数の受信専用デバイス100が使用されて、ウルトラソニックで撮像される対象物を通って送信された、または対象物により反射された音響信号を受信する環境で採用することができる。

#### 【0106】

50

[0141] 図示される構成要素のうちの1つまたは複数間の通信は、多くの様態のうちのいずれかで実施できることを理解されたい。いくつかの実施形態では、たとえば、統一されたノースブリッジにより採用されたものなどの、1つまたは複数の高速バス（図示せず）を使用して、高速チップ内通信、または1つまたは複数のオフチップ構成要素との通信を可能にすることができる。

#### 【0107】

[0142] 1つまたは複数のトランステューサ配列102は、多くの形式のうちのいずれかをとることができ、本技術の態様は、必ずしも、トランステューサセルまたはトランステューサ要素の任意の特定のタイプまたは配置を使用する必要がない。実際に、「配列」という用語がこの記載で使用されるが、いくつかの実施形態において、トランステューサ要素は、配列に組織化されなくてよく、代わりに何らかの配列でない様式で配置されてよいことを理解されたい。様々な実施形態では、配列102中のトランステューサ要素の各々は、たとえば、1つもしくは複数のC M U T、1つもしくは複数のC M O Sウルトラソニックトランステューサ（CUT）、および／または1つもしくは複数の他の好適なウルトラソニックトランステューサセルを含むことができる。いくつかの実施形態では、各トランステューサ配列102のトランステューサ要素304は、T X制御回路104および／またはR X制御回路106の電子回路と同じチップ上に形成することができる。ウルトラソニックトランステューサセル、要素、および配置（たとえば、配列）、ならびにC M O S回路が下にあるそのようなデバイスを一体化する方法の多くの例は、その全体の開示が参考により本明細書に組み込まれる、「COMPLEMENTARY METAL OXIDE SEMICONDUCTOR (CMOS) ULTRASONIC TRANSDUCERS AND METHODS FOR FORMING THE SAME」と題し、代理人整理番号第B1348.70007US00号を持ち、2013年3月15日に出願された、米国出願第61/794,744号に詳細に議論されている。10

20

#### 【0108】

[0143] C U Tは、たとえば、C M O Sウェハに形成される空洞を含み、膜が空洞の上にあって、いくつかの実施形態では、空洞を封止する。カバーされる空洞構造からトランステューサセルを形成するために、電極を設けることができる。C M O Sウェハは、トランステューサセルを接続できる集積回路を含むことができる。トランステューサセルとC M O Sウェハを、モノリシックに一体化し、したがって、单一基板（C M O Sウェハ）上に一体型ウルトラソニックトランステューサセルおよび集積回路を形成することができる。30

#### 【0109】

[0144] T X制御回路104は（含まれる場合）、たとえば、撮像のために使用される音響信号を生成するように、トランステューサ配列102の個々の要素、またはトランステューサ配列102内の要素の1つまたは複数のグループを駆動するパルスを生成することができる。R X制御回路106は（含まれる場合）、一方、音響信号がそのような要素に当たったとき、トランステューサ配列102の個々の要素により生成される電気信号を受信して処理することができる。

#### 【0110】

[0145] いくつかの実施形態では、タイミング＆制御回路108は、たとえば、デバイス100の中の他の要素の動作を同期して協調させるために使用されるすべてのタイミングおよび制御信号を生成する役目を果たすことができる。示される例では、タイミング＆制御回路108は、入力ポート116に供給される单一のクロック信号C L Kにより駆動される。クロック信号C L Kは、たとえば、オンチップ回路構成要素のうちの1つまたは複数を駆動するために使用される高周波クロックであってよい。いくつかの実施形態では、クロック信号C L Kは、たとえば、信号調節／処理回路110の中の高速シリアル出力デバイス（図1では図示せず）を駆動するために使用される1.5625G H zもしくは2.5G H zクロック、またはダイ112上の他のデジタル構成要素を駆動するために使用される20M H zまたは40M H zクロックであってよく、タイミング＆制御回路108は、必要に応じて、ダイ112上の他の構成要素を駆動するため、クロックC L Kを分周40

50

または乗算してよい。他の実施形態では、（上で参照されたもののような）異なる周波数の2つ以上のクロックを、オフチップ発生源からタイミング＆制御回路108に別個に供給することができる。タイミング＆制御回路108内に含むことができる好適なクロック発生回路1904の説明に役立つ例は、図19および図20に関して下で議論される。

#### 【0111】

[0146] 電力管理回路118は、たとえば、オフチップ発生源からの1つまたは複数の入力電圧 $V_{IN}$ をチップの動作を実行するために必要な電圧に変換する、さもなければ、デバイス100内の電力消費を管理する役目を果たすことができる。いくつかの実施形態では、たとえば、単一の電圧（たとえば、12V、80V、100V、120Vなど）をチップに供給することができ、電力管理回路118は、必要に応じて、チャージポンプ回路を使用して、または何らかの他のDC-DC電圧変換機構を介して、その電圧をステップアップまたはステップダウンすることができる。他の実施形態では、他のオンチップ構成要素の処理および/または他のオンチップ構成要素への分配のため、複数の異なる電圧を、電力管理回路118に別個に供給することができる。10

#### 【0112】

[0147] 図1に示されるように、いくつかの実施形態では、トランステューサ配列102のうちの1つまたは複数の要素を介してHIFU信号の生成を可能にするように、HIFUコントローラ120を、ダイ112上に一体化することができる。他の実施形態では、トランステューサ配列102を駆動するためのHIFUコントローラを、オフチップ、またはそれどころか、デバイス100とは別個のデバイス内に配置することができる。すなわち、本開示の態様は、超音波撮像能力を持つ、および持たない超音波オンチップHIFUシステムを提供することに関する。しかし、いくつかの実施形態はHIFU能力を持たない場合があり、したがってHIFUコントローラ120を含まない場合があることを理解されたい。20

#### 【0113】

[0148] さらに、HIFU機能性を提供するそれらの実施形態において、HIFUコントローラ120がはっきりした回路を呈さない場合があることを理解されたい。たとえば、いくつかの実施形態では、図1の残りの回路（HIFUコントローラ120以外）は、超音波撮像機能性および/またはHIFUを提供するのに好適であってよく、すなわち、いくつかの実施形態では、同じ共有回路を、撮像システムとして、かつ/またはHIFUのために動作することができる。撮像またはHIFU機能性が発揮されるかどうかは、システムに提供される電力に依存する場合がある。HIFUは、典型的には、超音波撮像よりも高い電力で動作する。したがって、撮像用途に適した第1の電力レベル（または電圧）をシステムに提供することによって、システムを撮像システムとして動作させることができ、一方、より高い電力レベル（または電圧）を提供することによって、システムをHIFU用に動作させることができる。そのような電力管理は、いくつかの実施形態において、オフチップ制御回路により実現することができる。30

#### 【0114】

[0149] 異なる電力レベルを使用することに加えて、撮像およびHIFUへの応用では、異なる波形を利用することができます。したがって、波形発生回路を使用して、撮像システムまたはHIFUシステムのいずれかとしてシステムを動作させるための好適な波形を提供することができる。40

#### 【0115】

[0150] いくつかの実施形態では、システムは、撮像システムおよび（たとえば、画像誘導HIFUを実現することができる）HIFUシステムの両方として動作することができる。いくつかのそのような実施形態では、同じオンチップ回路を利用して両方の機能を実現することができ、2つのモダリティの間で動作を制御するために、好適なタイミングシーケンスが使用される。本開示に記載される様々な実施形態で採用することができる、HIFU実装および動作特徴に関するさらなる詳細が、その全体の内容が参照により本明細書に組み込まれる、「TRANSMISSIVE IMAGING AND RELAT50

ED APPARATUS AND METHODS」と題し、2012年10月17日に出願された、同時係属および共有される米国特許出願第13/654,337号に記載される。

### 【0116】