(12) 发明专利

(10) 授权公告号 CN 103384492 B

(45) 授权公告日 2015. 12. 02

(21) 申请号 201280009568. 9

H04N 5/228(2006. 01)

(22) 申请日 2012. 09. 18

(56) 对比文件

(30) 优先权数据

2011-207465 2011. 09. 22 JP

US 5402769 A, 1995. 04. 04, 全文.

(85) PCT国际申请进入国家阶段日

2013. 08. 19

JP H07194530 A, 1995. 08. 01, 全文.

(86) PCT国际申请的申请数据

PCT/JP2012/073787 2012. 09. 18

JP 2005279125 A, 2005. 10. 13, 全文.

US 2008027284 A1, 2008. 01. 31, 全文.

JP H05168588 A, 1993. 07. 02, 全文.

审查员 任晓帅

(87) PCT国际申请的公布数据

W02013/042647 JA 2013. 03. 28

(73) 专利权人 奥林巴斯株式会社

地址 日本东京都

(72) 发明人 大河文行 小西纯 桥本秀范

田中清洋 松井泰宪

(74) 专利代理机构 北京三友知识产权代理有限

公司 11127

代理人 李辉 于靖帅

(51) Int. Cl.

A61B 1/04(2006. 01)

G02B 23/24(2006. 01)

权利要求书3页 说明书24页 附图22页

(54) 发明名称

内窥镜

(57) 摘要

内窥镜具有：摄像元件，其搭载于插入部的前端部；布线，其传递用于驱动摄像元件的具有多个不同电源电压的电源、驱动摄像元件的驱动信号、从驱动信号所驱动的摄像元件输出的摄像信号、和接地电平；基板，其设有对布线进行转接的连接器；电压比较部，其对多个不同电源电压进行比较；以及电源供给控制部，其根据电压比较部的比较结果，控制针对摄像元件的电源供给。

1. 一种内窥镜, 该内窥镜具有 :

摄像元件, 其搭载于插入部的前端部;

布线, 其传递用于驱动所述摄像元件的具有多个不同电源电压的电源、驱动所述摄像元件的驱动信号、从该驱动信号所驱动的所述摄像元件输出的摄像信号、以及接地电平;

基板, 其设有对所述布线进行转接的连接器;

其特征在于, 所述内窥镜还具有 :

第 1 电压比较部, 其对所述多个不同电源电压进行比较;

电源生成部, 其根据所述多个不同电源电压生成分别与所述多个不同电源电压不同的多个第 2 电源电压;

第 2 电压比较部, 其对所述多个第 2 电源电压进行比较; 以及

电源供给控制部, 其根据所述第 1 电压比较部的比较结果以及所述第 2 电压比较部的比较结果, 控制针对所述摄像元件的电源供给。

2. 根据权利要求 1 所述的内窥镜, 其特征在于,

所述第 1 电压比较部设置在所述基板上, 所述第 1 电压比较部通过对所述多个电源电压和各个规定阈值进行比较, 输出各电源电压是否在正常电压范围内的比较结果, 所述电源供给控制部设置在所述基板上, 在所述第 1 电压比较部的所述比较结果为所述正常电压范围内的条件下, 所述电源供给控制部进行控制以针对所述摄像元件进行电源供给, 在所述第 1 电压比较部的所述比较结果为所述正常电压范围外的情况下, 所述电源供给控制部进行控制以停止针对所述摄像元件进行电源供给。

3. 根据权利要求 2 所述的内窥镜, 其特征在于,

所述电源供给控制部具有告知信号发送部, 在所述第 1 电压比较部的所述比较结果为所述正常电压范围外的异常电压的情况下, 所述告知信号发送部将告知产生所述异常电压的告知信号发送到信号处理装置, 所述信号处理装置以装卸自如的方式连接所述内窥镜, 进行针对所述摄像元件的信号处理。

4. 根据权利要求 3 所述的内窥镜, 其特征在于,

在所述第 1 电压比较部的所述比较结果为所述正常电压范围外的异常电压的情况下, 所述第 1 电压比较部停止被输入所述异常电压的所述电源生成部的动作。

5. 根据权利要求 4 所述的内窥镜, 其特征在于,

所述第 1 电压比较部和所述电源供给控制部使用以可编程的方式构筑的 FPGA 构成。

6. 根据权利要求 5 所述的内窥镜, 其特征在于,

所述电源供给控制部具有告知信号重叠部, 所述告知信号重叠部将所述告知信号重叠在该告知信号以外的其他信号中发送到以装卸自如的方式连接所述内窥镜的所述信号处理装置。

7. 根据权利要求 1 所述的内窥镜, 其特征在于,

所述内窥镜还具有: 减法电路, 其生成分别由所述连接器中的相邻的 2 个连接器触针所转接的具有所述多个不同电源电压的电源中的不同的 2 个电源电压间的差电压; 以及比较电路, 其对所述减法电路所生成的所述差电压和为了检测所述 2 个连接器触针间的短路或绝缘不良而设定的阈值进行比较,

所述电源供给控制部根据所述比较电路的比较结果, 控制针对所述摄像元件的电源供

给。

8. 根据权利要求 3 所述的内窥镜, 其特征在于,

所述内窥镜还具有: 减法电路, 其生成分别由所述连接器中的相邻的 2 个连接器触针所转接的具有所述多个不同电源电压的电源中的不同的 2 个电源电压间的差电压; 以及比较电路, 其对所述减法电路所生成的所述差电压和为了检测所述 2 个连接器触针间的短路或绝缘不良而设定的阈值进行比较,

所述电源供给控制部根据所述比较电路的比较结果, 控制针对所述摄像元件的电源供给。

9. 根据权利要求 6 所述的内窥镜, 其特征在于,

所述内窥镜还具有: 减法电路, 其生成分别由所述连接器中的相邻的 2 个连接器触针所转接的具有所述多个不同电源电压的电源中的不同的 2 个电源电压间的差电压; 以及比较电路, 其对所述减法电路所生成的所述差电压和为了检测所述 2 个连接器触针间的短路或绝缘不良而设定的阈值进行比较,

所述电源供给控制部根据所述比较电路的比较结果, 控制针对所述摄像元件的电源供给。

10. 根据权利要求 4 所述的内窥镜, 其特征在于,

所述基板还具有过大电流检测电路, 所述过大电流检测电路检测从设置在以装卸自如的方式连接所述内窥镜的外部装置内的电源电路供给到所述电源生成部的所述电源的电源电流是否为规定值以上的过大电流, 在所述过大电流检测电路检测到过大电流的情况下, 对被检测为过大电流的电源电流进行切断。

11. 根据权利要求 7 所述的内窥镜, 其特征在于,

所述基板还具有过大电流检测电路, 所述过大电流检测电路检测从设置在以装卸自如的方式连接所述内窥镜的外部装置内的电源电路供给到所述电源生成部的所述电源的电源电流是否为规定值以上的过大电流, 在所述过大电流检测电路检测到过大电流的情况下, 对被检测为过大电流的电源电流进行切断。

12. 根据权利要求 4 所述的内窥镜, 其特征在于,

所述基板还具有电源接通 / 断开控制电路, 在从设置在以装卸自如的方式连接所述内窥镜的外部装置内的电源电路供给到所述电源生成部的所述电源被接通、断开的情况下, 所述电源接通 / 断开控制电路在从所述电源被断开的定时起的较短时间  $t_1$  后切断所述电源生成部生成的所述多个第 2 电源电压, 在从所述电源被接通的定时起的比所述时间  $t_1$  大的时间  $t_2$  后, 进行接通以输出所述电源生成部生成的所述多个第 2 电源电压。

13. 根据权利要求 3 所述的内窥镜, 其特征在于,

所述基板具有: 连接器基板, 其设置在将所述内窥镜以装卸自如的方式连接在所述信号处理装置上的连接器内; 以及前端部基板, 其设置在所述内窥镜的插入部的前端部并连接有所述摄像元件,

所述布线以装卸自如的方式连接所述连接器基板与所述前端部基板之间。

14. 根据权利要求 7 所述的内窥镜, 其特征在于,

所述基板具有: 连接器基板, 其设置在将所述内窥镜以装卸自如的方式连接在所述信号处理装置上的连接器内; 以及前端部基板, 其设置在所述内窥镜的插入部的前端部并连接有所述摄像元件,

接有所述摄像元件，

所述布线以装卸自如的方式连接所述连接器基板与所述前端部基板之间。

15. 根据权利要求 14 所述的内窥镜，其特征在于，

所述基板还具有操作部基板，所述操作部基板配置在所述内窥镜中的设于所述插入部的基端的操作部内，所述布线构成为具有以装卸自如的方式连接所述连接器基板与所述操作部基板之间的第 1 缆线、和以装卸自如的方式连接所述操作部基板与所述前端部基板之间的第 2 缆线。

## 内窥镜

### 技术领域

[0001] 本发明涉及具有摄像元件的内窥镜。

### 背景技术

[0002] 近年来,在医疗用领域和工业用领域中广泛利用设有摄像元件的内窥镜。

[0003] 为了确保向体腔内等的插入性,优选内窥镜具有细径的插入部。

[0004] 并且,搭载于插入部的前端部的摄像元件也使用小型尺寸的元件。为了驱动摄像元件,需要将传送电压不同的多个电源、以电气方式驱动摄像元件的驱动信号、通过施加驱动信号而从摄像元件输出的摄像信号等的由多个信号线构成的缆线贯穿插入到插入部内。

[0005] 并且,固体摄像元件的像素数等根据内窥镜检查的用途而不同的各种内窥镜已经实用化,以装卸自如的方式连接内窥镜的作为信号处理装置的处理器侧的负担也增大。

[0006] 因此,通过在各个内窥镜侧设置生成与搭载于该内窥镜的摄像元件对应的驱动信号、并且对从摄像元件输出的摄像信号进行适于该摄像元件的预处理的电路基板(简称为基板),期望在种类不同的内窥镜的情况下,也使用减轻了负担的共同处理器进行内窥镜检查。

[0007] 在内窥镜内部设有基板的情况下,为了确保良好的组装性等,还需要对缆线(布线)进行转接的小型连接器,在使用小型连接器的情况下,相邻的连接器触针间的间隔也减小。因此,需要应对连接器触针间的短路等的对策。

[0008] 例如在日本国特开 2008-307293 号公报的第 1 现有例中,作为具有搭载于插入部的前端部的摄像元件和电路基板的摄像装置,采用如下构造:将接地信号线结束部配置在错开的位置,容易进行缆线相对于摄像装置的焊接作业。

[0009] 并且,在日本国特开 2008-295589 号公报的第 2 现有例中公开了如下的内窥镜装置:对驱动电源的电压值的变化进行检测,使得在待机状态下也能够使电压检测功能进行动作。

[0010] 但是,上述第 1 和第 2 现有例均未应对连接器触针间的短路。例如存在如下情况:虽然与不同的电源电压连接的连接器触针间处于接近短路的异常状态,但是在内窥镜图像上不会立即成为异常。在这种情况下,可能在内窥镜检查中继续使用该内窥镜。

[0011] 在这种状态下,当用于内窥镜检查时,可能产生如下的不良情况:产生热伤,由于发热等而使针对温度的耐性较弱的电子部件等产生损伤等,在内窥镜检查中无法显示内窥镜图像。

[0012] 因此,期望获得能够迅速检测这种异常状态、能够实施迅速消除该异常状态的对策、能够减少产生内窥镜检查中的不良情况的内窥镜装置。

[0013] 本发明是鉴于上述情况而完成的,其目的在于,提供如下的内窥镜:在使用小型连接器以多个电源电压驱动摄像元件并使基板内的电路进行动作的情况下,也能够迅速检测由于短路等而导致的电源电压的异常状态,容易消除异常状态。

## 发明内容

[0014] 用于解决课题的手段

[0015] 本发明的一个方式的内窥镜具有：摄像元件，其搭载于插入部的前端部；布线，其传递用于驱动所述摄像元件的具有多个不同电源电压的电源、驱动所述摄像元件的驱动信号、从该驱动信号所驱动的所述摄像元件输出的摄像信号、和接地电平；基板，其设有对所述布线进行转接的连接器；电压比较部，其对所述多个不同的电源电压进行比较；以及电源供给控制部，其根据所述电压比较部的比较结果，控制针对所述摄像元件的电源供给。

## 附图说明

[0016] 图 1 是示出本发明的第 1 实施方式中的内窥镜装置的整体结构的图。

[0017] 图 2A 是示出第 1 实施方式的内窥镜中的电气系统的结构的图。

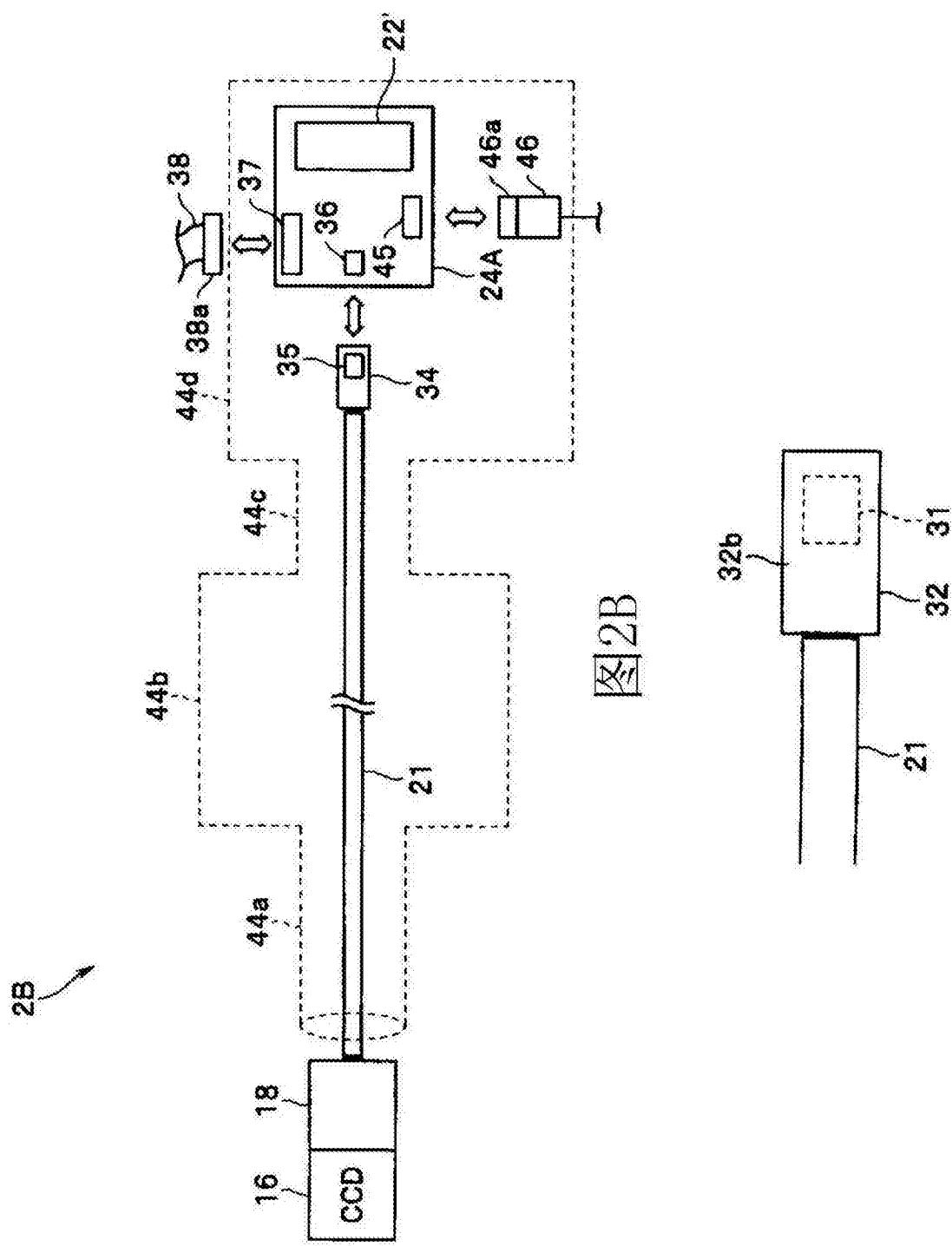

[0018] 图 2B 是示出一部分与图 2A 的内窥镜不同的内窥镜中的电气系统的结构的图。

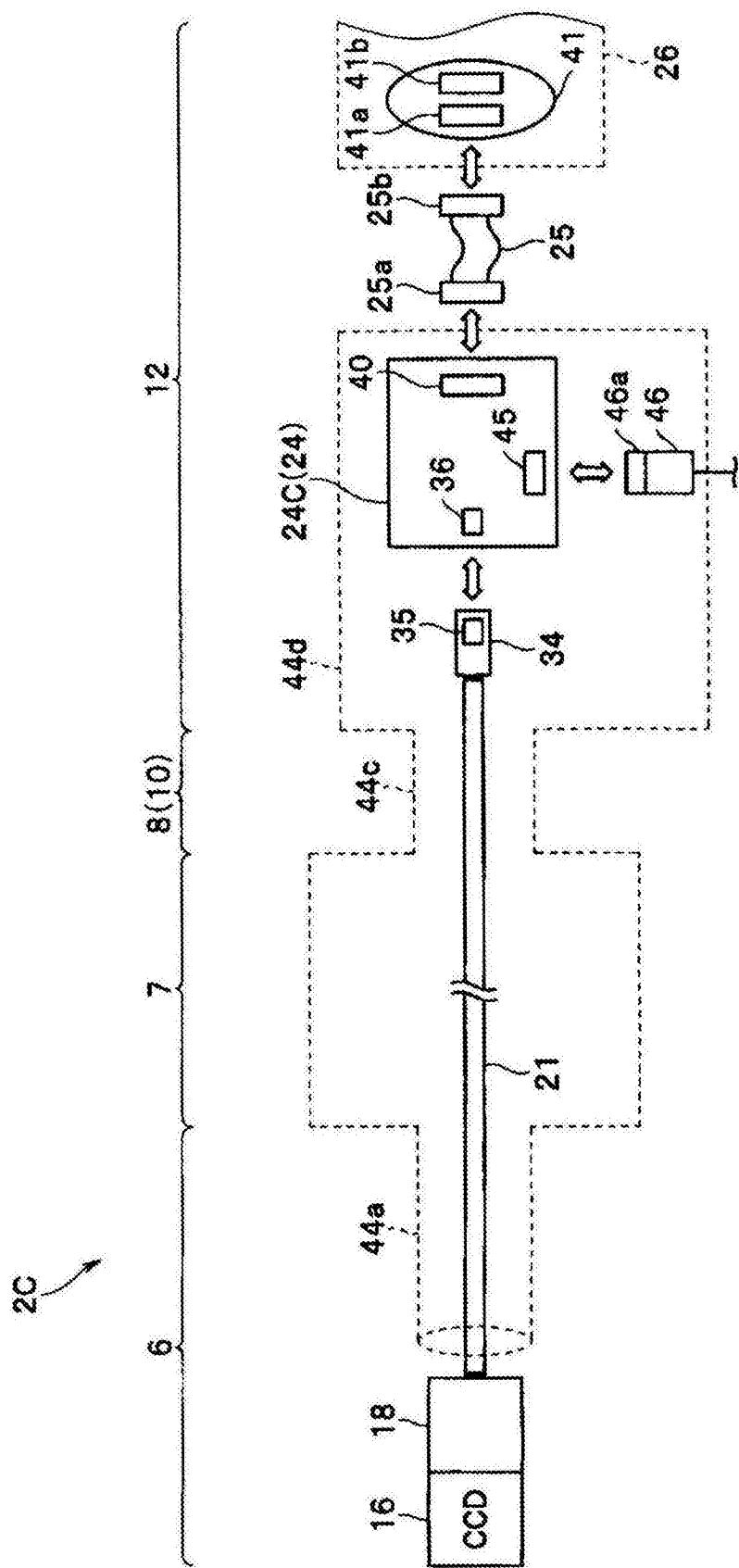

[0019] 图 2C 是示出图 2A 中的微连接器基板的背面的图。

[0020] 图 2D 是示出由一张 A/D 基板形成连接器基板的内窥镜中的电气系统的结构的图。

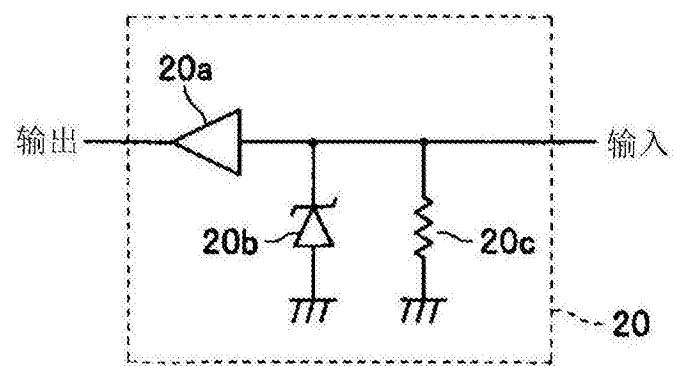

[0021] 图 2E 是示出保护不受静电等影响的输入保护电路的电路结构的电路图。

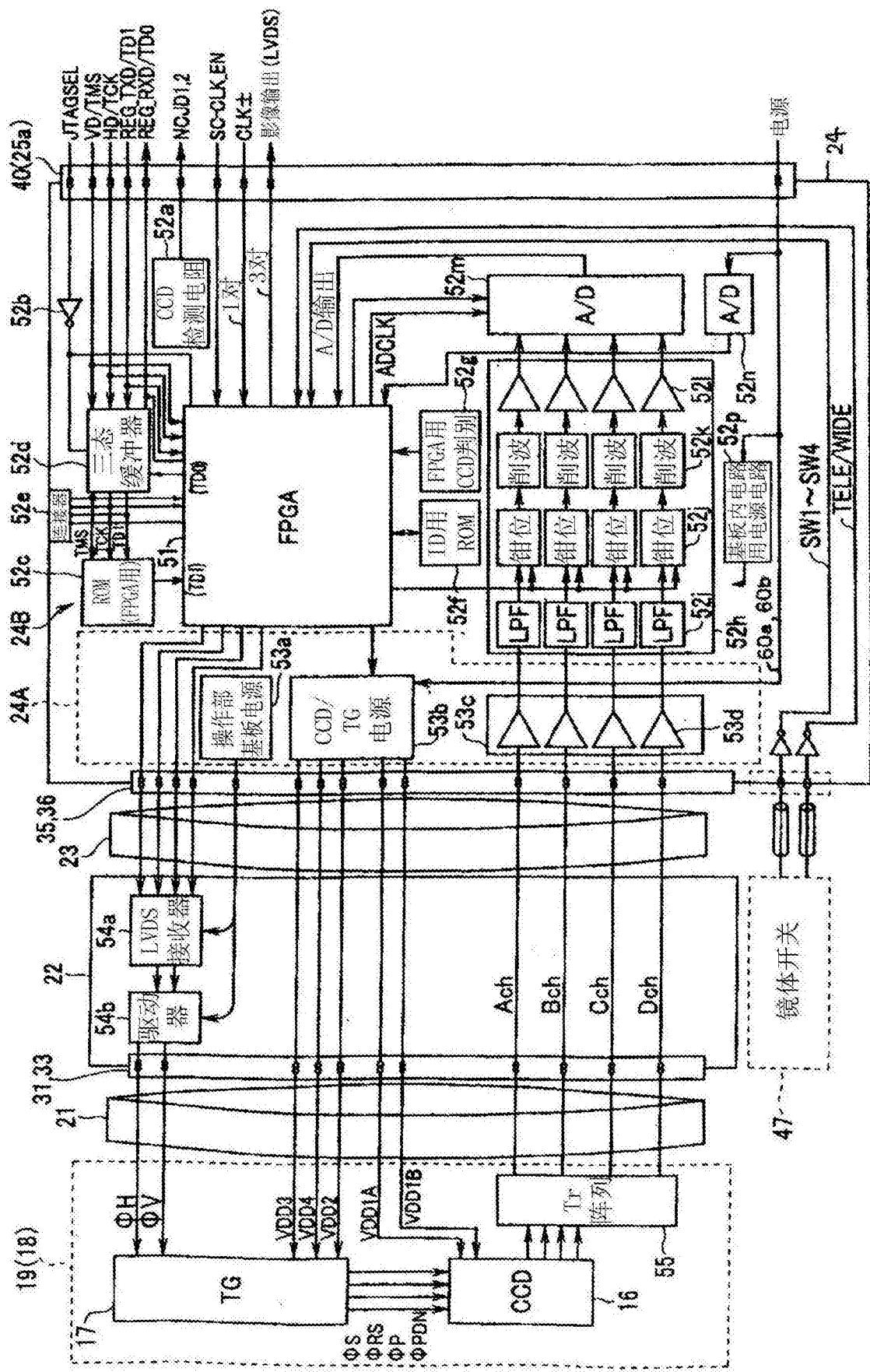

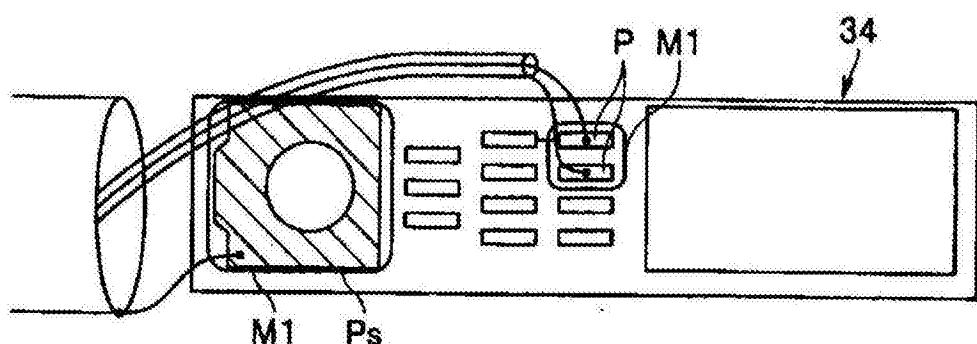

[0022] 图 3 是示出图 2A 的具体结构的图。

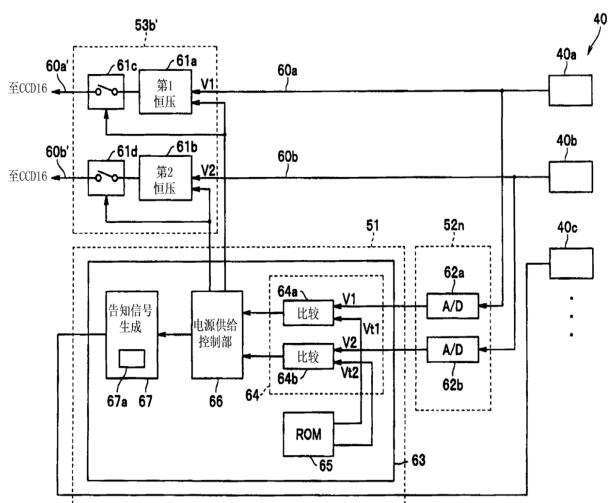

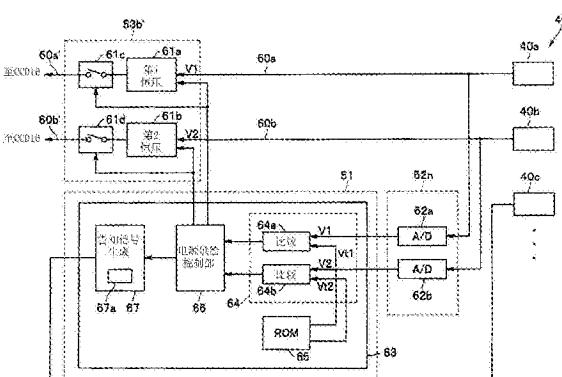

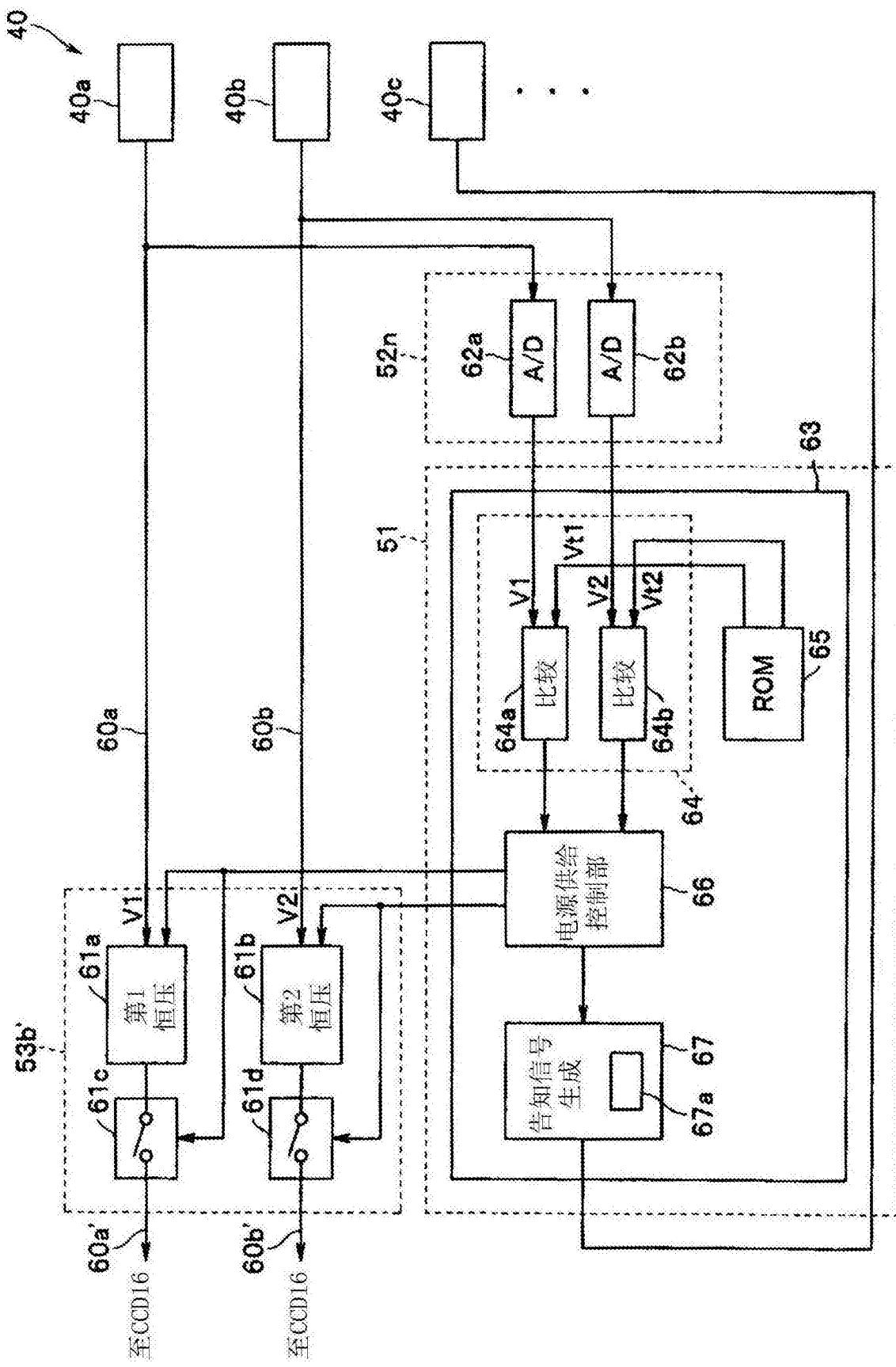

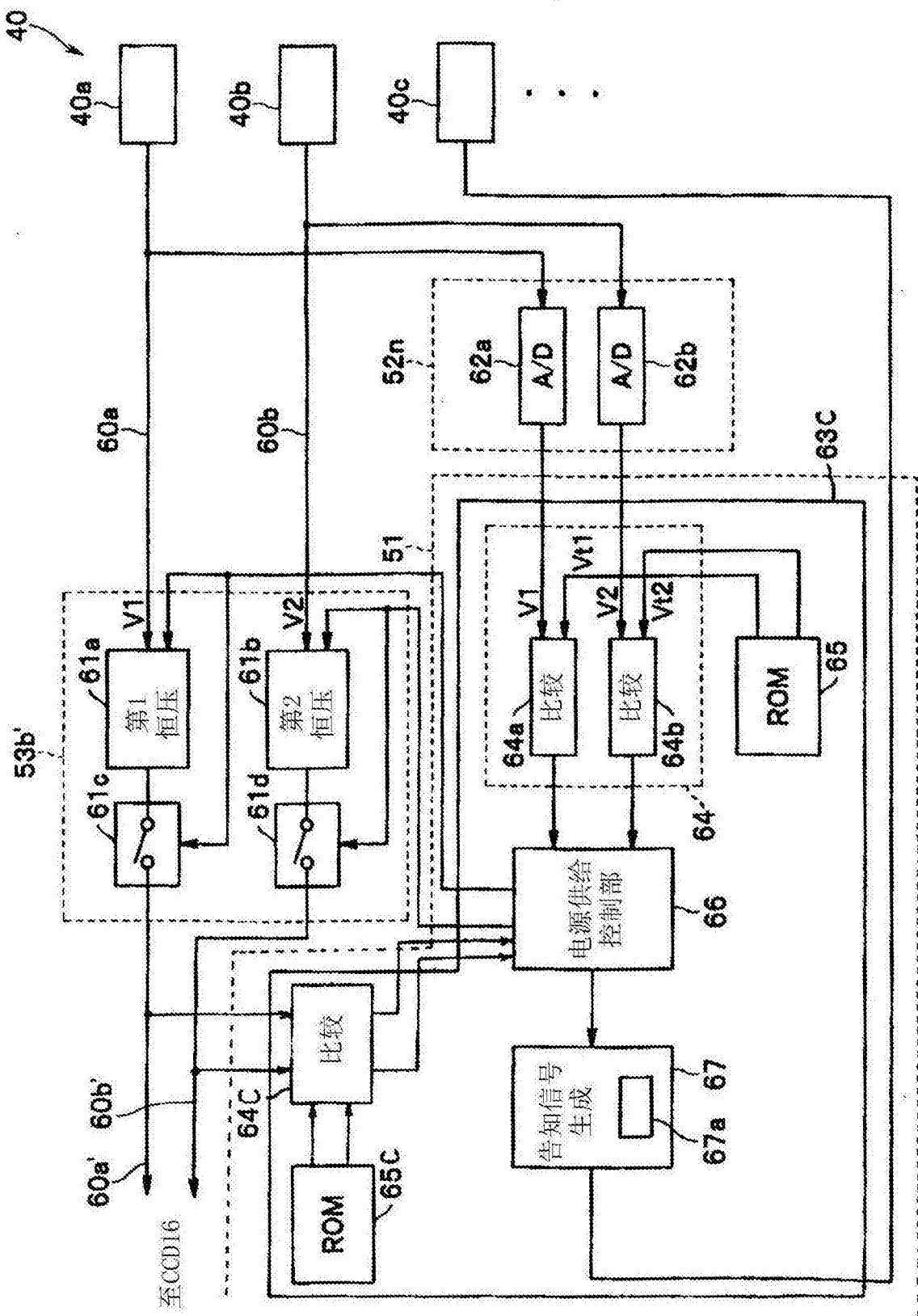

[0023] 图 4A 是示出 CCD 电源电压监视电路的结构的图。

[0024] 图 4B 是示出图 4A 的变形例的 CCD 电源电压监视电路的结构的图。

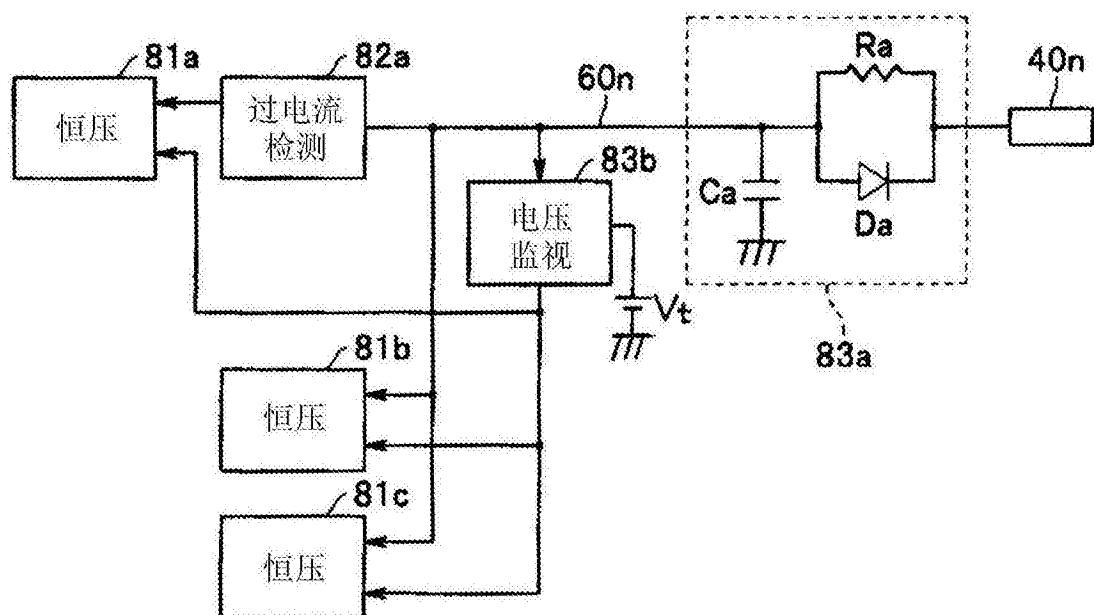

[0025] 图 4C 是示出与 CCD 电源电压监视电路一起设置对 CCD 和定时发生器的电源电压的过电流进行检测的过电流检测电路的结构的图。

[0026] 图 4D 是示出在内窥镜内进行电源接通 / 断开控制的情况下特性的图。

[0027] 图 4E 是示出以图 4D 的特性进行电源接通 / 断开控制的情况下电路结构的图。

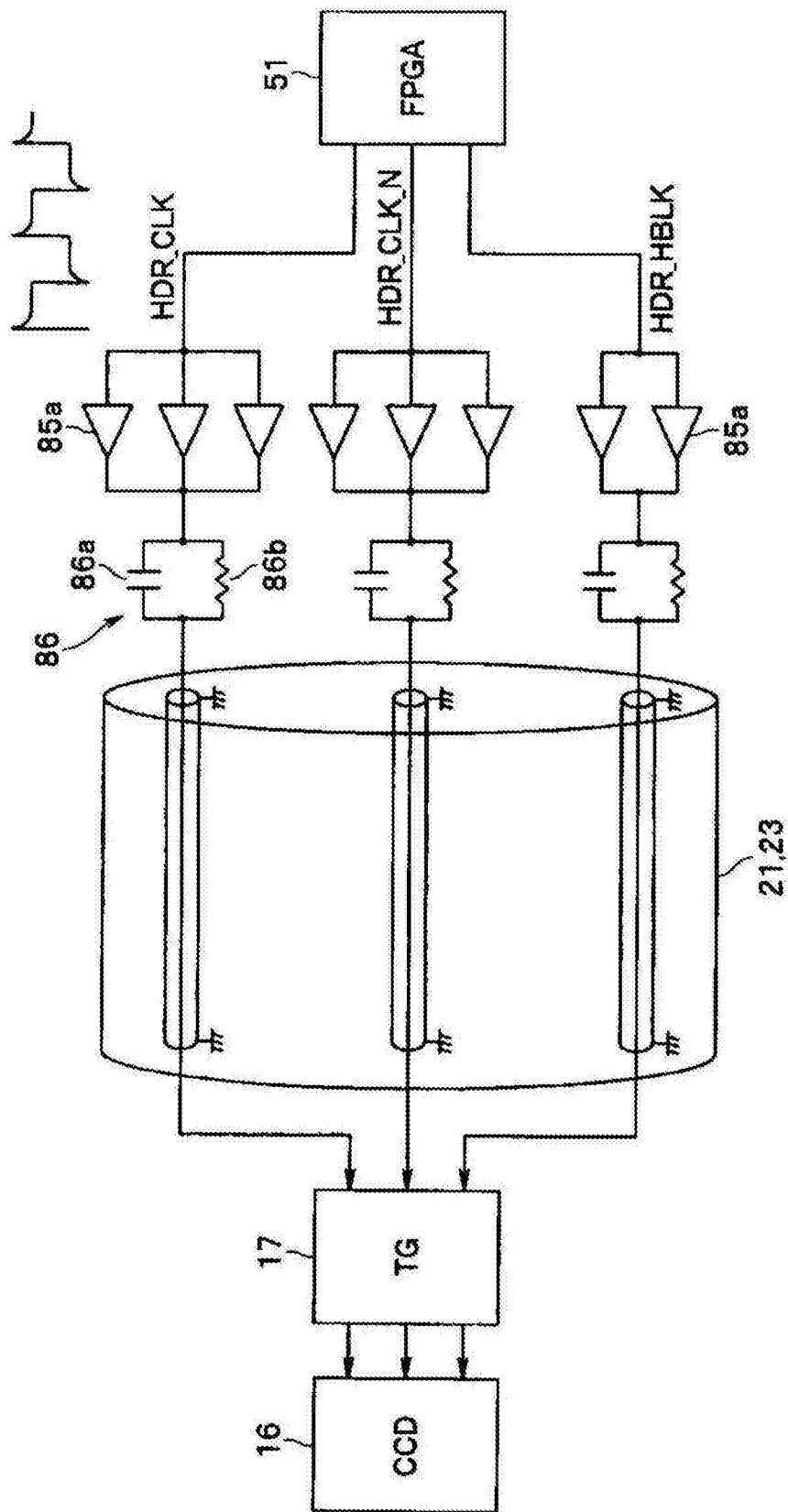

[0028] 图 5A 是示出驱动从 FPGA 连接到定时发生器的缆线的驱动单元的结构的图。

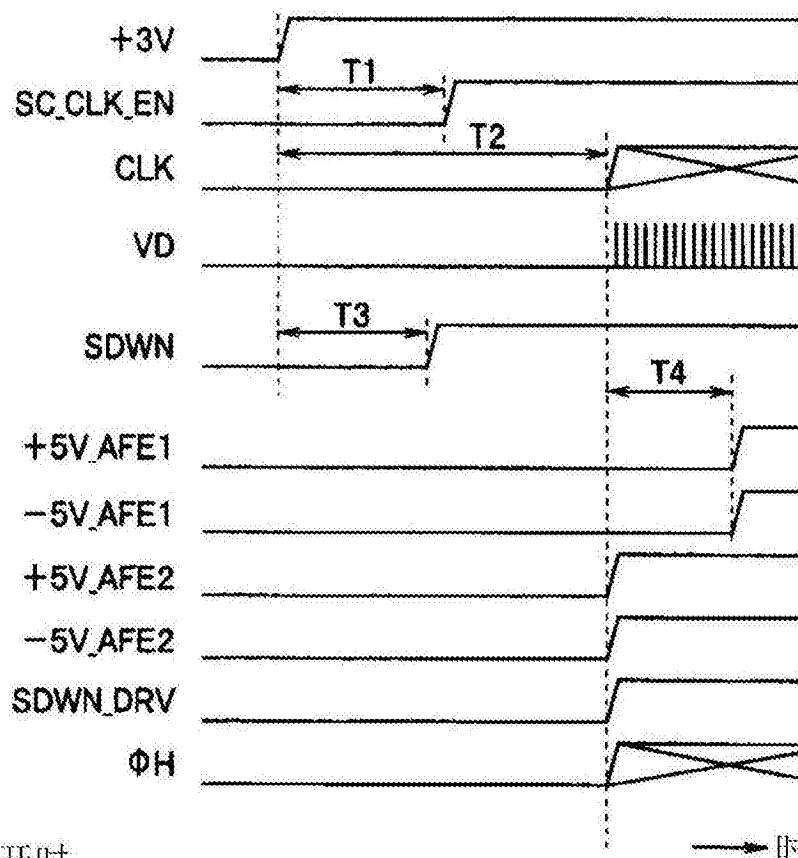

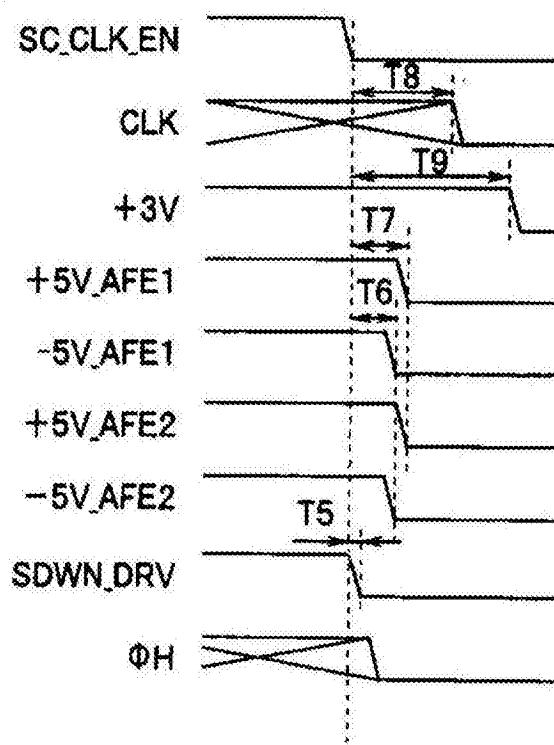

[0029] 图 5B 是示出根据电源接通 / 断开时从处理器侧发送的特定的脉冲信号进行内窥镜侧的电源接通 / 断开等的控制的定时的图。

[0030] 图 5C 是示出生成与从处理器侧输入的时钟对应的输出时钟的情况下进行确定时钟的动作等的 CLK 确定判定电路的结构的图。

[0031] 图 5D 是示出垂直同步信号输出电路的结构的框图。

[0032] 图 5E 是图 5D 的动作说明图。

[0033] 图 6A 是示出经由微连接器对与 CCD 连接的缆线进行转接的构造的图。

[0034] 图 6B 是示出通过微连接器对各种信号线进行转接的情况下连接器触针的配置例的图。

[0035] 图 7 是利用树脂涂敷微连接器基板中的各种信号线的焊接部分的状况的说明图。

[0036] 图 8A 是利用树脂涂敷接口基板中的印刷图案露出的电路部分的状况的说明图。

[0037] 图 8B 是示出图 8A 中的利用树脂涂敷的输入电路部的电路结构的图。

[0038] 图 8C 是示出间歇驱动 CCD 的情况下输入到放大器的 CCD 输出信号的波形的图。

[0039] 图 8D 是示出对休止区域的信号进行削波并对 CCD 的有效像素区域的信号进行放大的放大器的电路结构的图。

[0040] 图 9 是示出在特定的连接器触针间设置未连接的连接器触针的微连接器的图。

- [0041] 图 10A 是示出使用虚设部件来检测腐蚀的产生的腐蚀异常检测装置的结构的图。

- [0042] 图 10B 是示出图 10A 的变形例的虚设部件的结构的图。

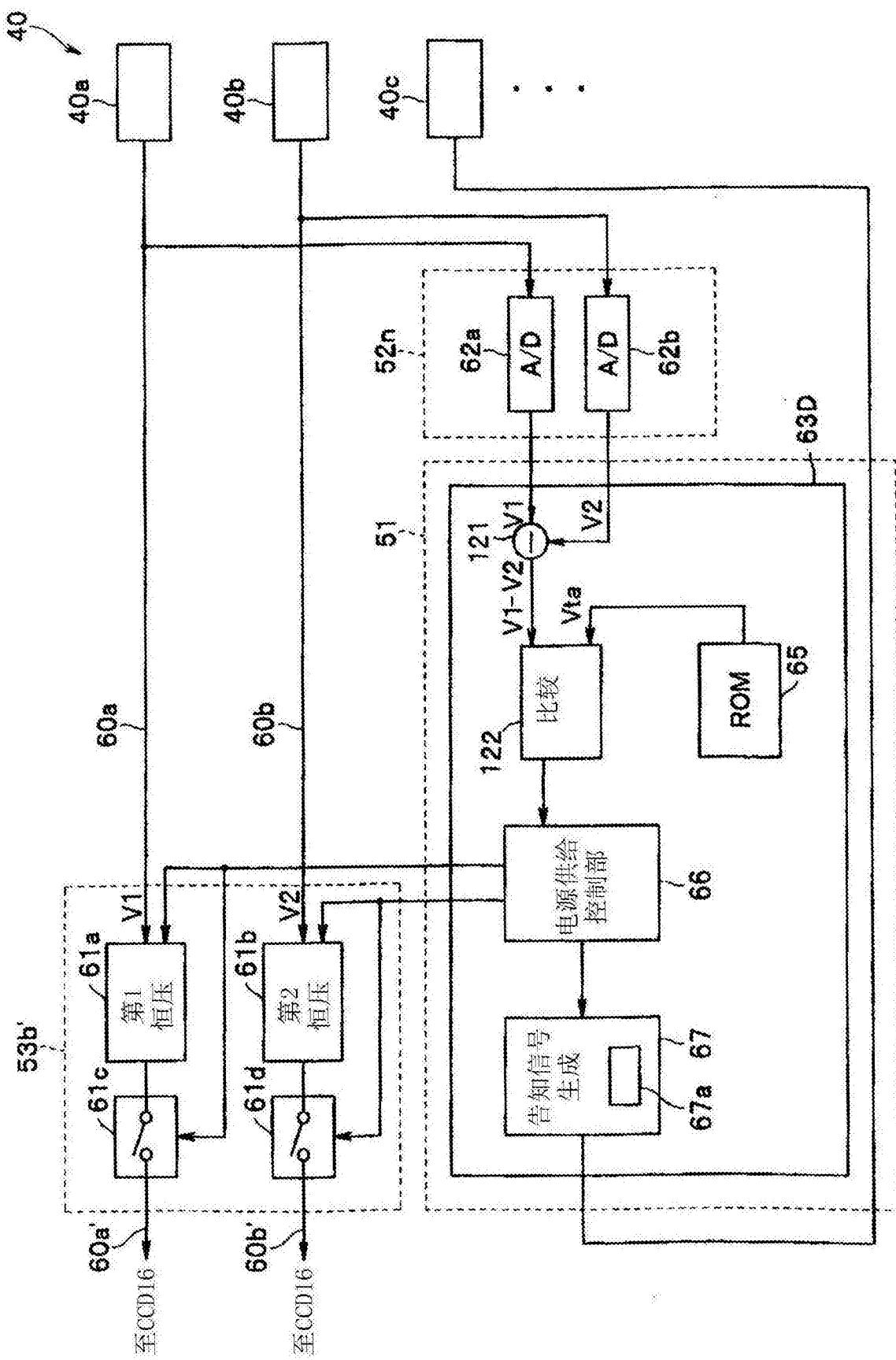

- [0043] 图 11 是示出图 4A 的变形例的 CCD 电源电压监视电路的结构的图。

- [0044] 图 12 是示出图 4A 的其他变形例的 CCD 电源电压监视电路的结构的图。

## 具体实施方式

- [0045] 下面,参照附图对本发明的实施方式进行说明。

- [0046] (第 1 实施方式)

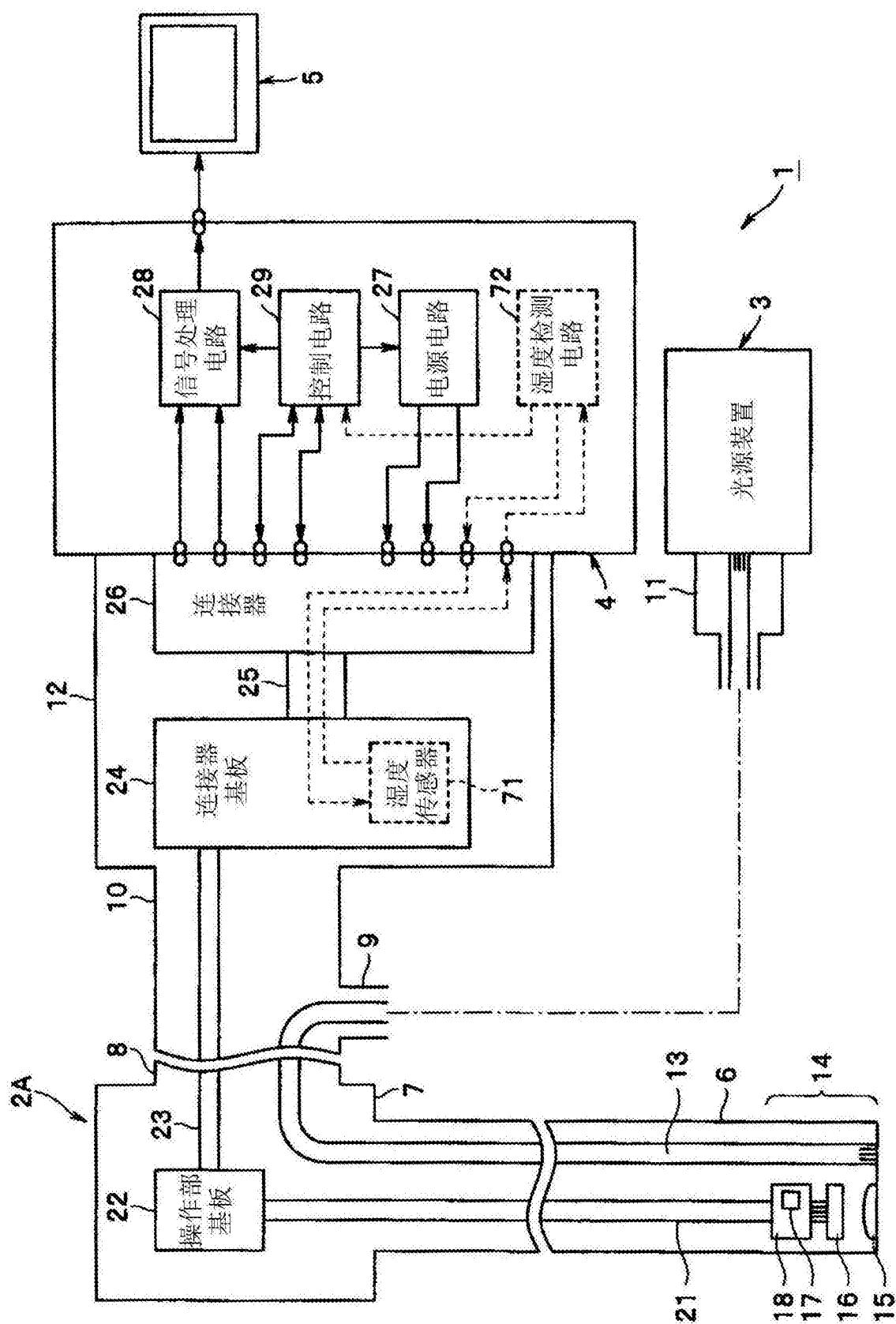

- [0047] 如图 1 所示,本发明的第 1 实施方式的内窥镜装置 1 具有:内窥镜 2A,其具有摄像元件;光源装置 3,其以装卸自如的方式连接内窥镜 2A,对内窥镜 2A 供给照明光;作为信号处理装置的处理器 4,其以装卸自如的方式连接内窥镜 2A,进行信号处理等;以及作为显示装置的监视器 5,其显示由处理器 4 生成的图像信号作为内窥镜图像。

- [0048] 在光源装置 3、处理器 4 上,除了图 1 所示的内窥镜 2A 以外,还能够以装卸自如的方式连接图 2B 所示的内窥镜 2B,能够与内窥镜 2A 的情况同样用于内窥镜检查。另外,图 1 中的虚线所示的结构在后面叙述。

- [0049] 内窥镜 2A 具有被插入体腔内的细长的插入部 6、在该插入部 6 的后端设置的操作部 7、以及从该操作部 7 延伸出的通用缆线 8。通用缆线 8 在其基端附近或中途分支为光导缆线 9 和信号缆线 10。光导缆线 9 的端部的光源用连接器 11 以装卸自如的方式与光源装置 3 连接,信号缆线 10 的端部的信号用连接器 12 以装卸自如的方式与作为内窥镜 2A、2B 的外部装置的处理器 4 连接。

- [0050] 在插入部 6、操作部 7、通用缆线 8 内贯穿插入有传送照明光的光导 13。然后,通过使光源用连接器 11 与光源装置 3 连接,利用光导 13 传送来自光源装置 3 的照明光,从安装在照明窗上的光导前端面射出所传送的照明光,该照明窗设置在插入部 6 的前端部 14 上。并且,也可以构成为,使光源用连接器 11 和信号用连接器 12 为一的连接器与光源装置 3 连接,通过连接光源装置 3 和处理器 4 的缆线与处理器 4 交换信号用连接器 12 的信号。

- [0051] 在前端部 14 上,与照明窗相邻地设有观察窗(摄像窗),在观察窗上安装有形成被照明的患部等被摄体的光学像的物镜 15。在该物镜 15 的成像位置配置有作为摄像元件的电荷耦合元件(简记为 CCD)16。

- [0052] 在本实施方式中,在前端部 14 内的 CCD 16 附近配置有前端部基板 18,该前端部基板 18 包含作为驱动信号生成电路的定时发生器(简记为 TG)17,该定时发生器 17 生成对 CCD 16 进行驱动的驱动信号。

- [0053] 前端部基板 18 经由贯穿插入到插入部 6 内的综合同轴缆线 21 而与设于操作部 7 内的操作部基板 22 连接,该操作部基板 22 经由贯穿插入通用缆线 8 内的综合同轴缆线 23 而与设于信号用连接器 12 的内部的连接器基板 24 连接。

- [0054] 并且,该连接器基板 24 经由细线同轴缆线 25 而与连接器 26 连接,该连接器 6 以装卸自如的方式与处理器 4 连接。

- [0055] 另外,上述综合同轴缆线 21、23、细线同轴缆线 25 构成对 CCD 16 传送(传递)电源、驱动信号等的布线。上述细线同轴缆线 25 成形为,为了组装内窥镜而扭转细线同轴缆线 25 的一部分。

[0056] 在扭转时,可能由于信号传送中使用的 LVDS (Low Voltage Differential Signaling: 低压差分信号) 对分离而使放射噪声增大,为了降低放射噪声,使用双绞线作为细线同轴缆线 25。另外,连接器 26 如图 2A 中说明的那样包含 2 个基板。

[0057] 处理器 4 具有产生摄像元件等的动作所需要的多个不同的电源电压的电源的电源电路 27、对从摄像元件输出的摄像信号进行信号处理的信号处理电路 28、以及包含电源电路 27 和信号处理电路 28 在内的进行控制的控制电路 29。

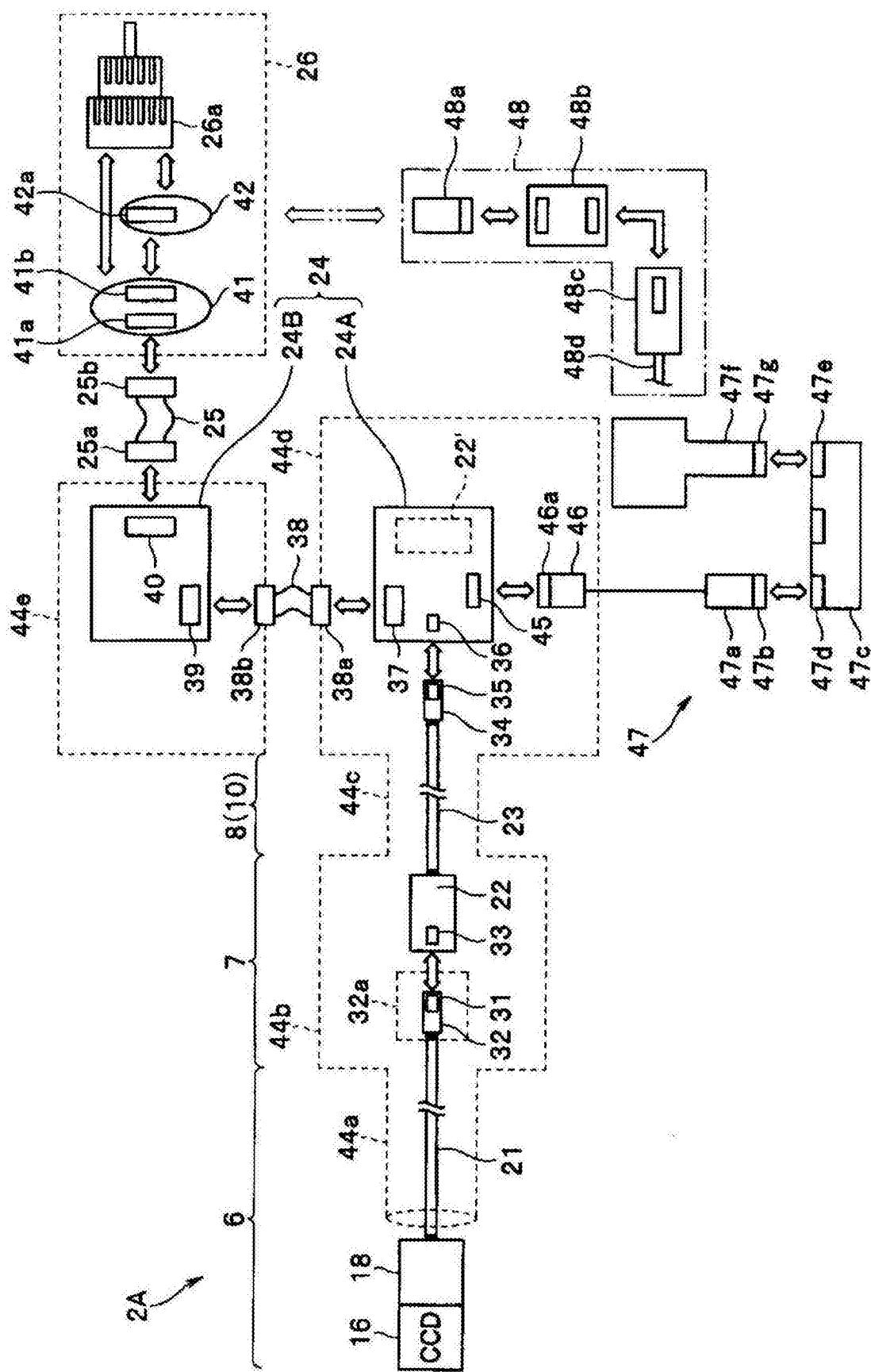

[0058] 图 2A 示出图 1 中的内窥镜 2A 的电气系统的结构。

[0059] 一端 (前端) 通过焊接而与前端部基板 18 连接的综合同轴缆线 21 的另一端 (后端) 通过焊接而与 MC 基板 32 连接,该 MC 基板 32 搭载有作为小型连接器的微连接器 (简记为 MC) 31,该 MC 基板 32 的 MC 31 与操作部基板 22 的微连接器座 (简记为 MC 座) 33 连接。另外,也可以利用 MC、MC 座连接前端部基板 18 和综合同轴缆线 21。MC 基板 32 通过虚线所示的屏蔽壳 32a 而以机械方式固定在操作部基板 22 上。另外,与前端部基板 18 连接的综合同轴缆线 21 在操作部基板 22 中被转接而与综合同轴缆线 23 连接,该综合同轴缆线 23 的基端与连接器基板 24 连接,但是,在内窥镜 2A 中的从插入部 6 到信号缆线 10 的基端的范围内,综合同轴缆线 21、23 的综合缆线 GND 和被该综合缆线 GND 屏蔽的配置在其内侧的各信号用的同轴缆线的 GND 分离。

[0060] 并且,一端 (前端) 通过焊接而与操作部基板 22 连接的综合同轴缆线 23 的另一端 (后端) 通过焊接而与 MC 基板 34 连接,搭载于该 MC 基板 34 上的作为小型连接器的 MC 35 与构成连接器基板 24 的接口基板 (简记为 IF 基板) 24A 的 MC 座 36 连接。

[0061] 在设于该 IF 基板 24A 的连接器座 37 上连接有设于细线同轴缆线 38 的一端的连接器 38a,其另一端的连接器 38b 与搭载有模拟 / 数字转换电路 (简记为 A/D) 的 A/D 基板 24B 的连接器座 39 连接。并且,在设于该 A/D 基板 24B 的作为小型连接器座的连接器座 40 上连接有设于细线同轴缆线 25 的一端的作为小型连接器的连接器 25a,其另一端的连接器 25b 与连接器 26 内的尺寸较大的圆型基板 41 的连接器座 41a 连接。该圆型基板 41 经由连接器 41b、连接器座 42a 而与尺寸较小的圆型基板 42 连接。

[0062] 圆型基板 41、42 通过焊接而与连接器插头 26a 连接。连接器插头 26a 以装卸自如的方式与处理器 4 的连接器插座 (连接器座) 连接。

[0063] 另外,在图 2A 中,连接器基板 24 由 IF 基板 24A 和 A/D 基板 24B 这 2 张基板形成,但是,在后述图 2D 所示的内窥镜 2C 中,连接器基板 24 由 1 张 A/D 基板 24C 构成,该 A/D 基板 24C 包含 IF 基板 24A 的功能。

[0064] 并且,如图 2A 所示,在连接器基板 24 为 IF 基板 24A 和 A/D 基板 24B 的 2 张基板的结构的情况下,也可以在 IF 基板 24A 侧设置存储有缆线长度、缆线长度的校正信息、缆线长度等的检测电路等的 ROM,在 A/D 基板 24B 侧设置存储有与 CCD 16 的像素数、种类等有关的信息的 ROM。另外,在 A/D 基板 24B 的种类增加的情况下,也可以在 IF 基板 24A 侧统一保持与 CCD 16、缆线有关的全部信息,以减少 A/D 基板 24B 的种类。

[0065] 另一方面,在后述的 1 张 A/D 基板 24C 的情况下,也可以统一搭载缆线长度、该缆线长度的校正信息、缆线长度等的检测电路、与 CCD 的种类等有关的信息。

[0066] 如图 2A 中虚线所示,通过基于插入部 6 的外装部件的屏蔽部件 44a 对综合同轴缆线 21 进行屏蔽。并且,该屏蔽部件 44a 与基于操作部 7 的外装部件的屏蔽部件 44b 电连接。

该屏蔽部件 44b 与基于通用缆线 8 的外装部件的屏蔽部件 44c 电连接。而且,屏蔽部件 44c 进一步与信号用连接器 12 的屏蔽部件连接。

[0067] 另外,在图 2A 中,作为信号用连接器 12 的屏蔽部件,分别利用屏蔽部件 44d、44e 对 IF 基板 24A 和 A/D 基板 24B 进行屏蔽。

[0068] 这些屏蔽部件在信号用连接器 12 内的 IF 基板 24A 或 A/D 基板 24B 中的 1 个点或多个点与地线导通(省略图示)。

[0069] 并且,在设于 IF 基板 24A 的连接器座 45 上连接有由柔性基板构成的开关柔性基板 46 的连接器 46a。该开关柔性基板 46 焊接有开关缆线的一端,该开关缆线的另一端通过焊接而与柔性基板 47a 连接,该柔性基板 47a 构成安装于操作部 7 的镜体开关 47。

[0070] 该柔性基板 47a 的连接器 47b 与开关箱柔性基板 47c 的连接器座 47d 连接。在开关箱柔性基板 47c 的连接器座 47e 上还连接有对开关进行转接的开关转接柔性基板 47f 的连接器 47g。并且,在内窥镜 2A 中,还具有检测内窥镜插入形状的插入形状检测单元(简记为 UPD 单元)48。

[0071] 该情况下,如图 2A 中的双点划线所示,在信号用连接器 12 的圆型基板 42 上连接有 UPD 单元 48 的 UPD 柔性基板 48a,该 UPD 柔性基板 48a 经由进行转接的 UPD 转接基板 48b 而与 UPD 基板 48c 连接。该 UPD 基板 48c 与配置在插入部 6 内的 UPD 探针单元 48d 连接。

[0072] 在内窥镜 2A 中,还准备有对物镜 15 的焦点进行切换的未图示的焦点切换单元,该情况下,驱动对物镜 15 的焦点进行切换的致动器的驱动基板与圆型基板 41 连接。

[0073] 另外,MC 基板 32、34、操作部基板 22、IF 基板 24A、A/D 基板 24B、圆型基板 41、42、UPD 转接基板 48b、UPD 基板 48c 是刚性基板,柔性基板 47a、开关箱柔性基板 47c、开关转接柔性基板 47f 由柔性基板构成。

[0074] 图 2B 示出在上述内窥镜 2A 中在操作部 7 中未设置操作部基板 22 的内窥镜。

[0075] 在该内窥镜 2B 中,由于在操作部 7 上未设置操作部基板 22,所以,综合同轴缆线 21 的另一端与信号用连接器 12 内的 MC 34 连接。

[0076] 并且,为了实现与内窥镜 2A 之间的部件的共同化,在 IF 基板 24A 上搭载与操作部基板 22 相同功能的操作部基板 22'。而且,在内窥镜 2B 中,通过使该 IF 基板 24A 的操作部基板 22' 成为动作状态或活性状态(图 2B 中实线所示),在操作部 7 上未设置操作部基板 22 的内窥镜 2B 的情况下,A/D 基板 24B 通过进行与内窥镜 2A 的情况相同的处理,也能够应对任意的内窥镜 2A、2B 的情况。

[0077] 在搭载于内窥镜 2A 的 IF 基板 24A 中,使 IF 基板 24A 内的操作部基板 22' 的功能无效(图 2A 中虚线所示)。由于内窥镜 2B 中的其他结构与内窥镜 2A 相同,所以,省略 A/D 基板 24B 等的图示。另外,IF 基板 24A 和 A/D 基板 24B 在后述 LPF 52i 之前分离。

[0078] 另外,图 2C 示出图 2A 中的 MC 基板 32 的(将设有 MC 31 的面作为表面时的)背面。在 MC 基板 32 的背面形成有整个面为金属面的良接地面 32b。而且,能够通过与良接地面 32b 抵接的屏蔽壳 32a 进行地线的电连接,同时进行 MC 31、MC 座 33 之间的地线(电位)的连接,能够降低不需要的噪声放射等。另外,也可以构成为,在上述屏蔽部件的导电性良好的情况下,如上所述成为形成整个面为金属面的良接地面 32b 的图案,在屏蔽部件的导电性较差的部分中,与良接地面 32b 之间的电连接出现偏差的情况下,不形成良接地面 32b。并且,良接地面 32b 只要具有安装了与屏蔽部件接触的机械触点的金属面即可,也

可以不是整个面的良接地面 32b,而是设置在一部分上的接地面。

[0079] 并且,在本实施方式中,除了图 2A、图 2B 所示的内窥镜 2A、2B 以外,如图 2D 所示,也可以采用连接器基板 24(不是 IF 基板 24A 和 A/D 基板 24B 的 2 张基板的结构)仅为 A/D 基板 24C 的内窥镜 2C 的结构。该内窥镜 2C 与图 2B 的情况同样,采用不在操作部 7 上设置操作部基板 22 的结构。

[0080] 由于其他结构是与图 2B 所示的内窥镜 2B 几乎相同的结构,所以,对同一结构要素标注相同标号并省略其说明。该内窥镜 2C 也能够以装卸自如的方式与处理器 4 连接,处理器 4 在连接该内窥镜 2C 的情况下,与连接内窥镜 2A 或 2B 的情况同样,进行与搭载于内窥镜 2C 的摄像元件等对应的处理。

[0081] 另外,如图 2E 所示,在连接器 26 中的例如圆型基板 41 上设有输入保护电路 20,该输入保护电路 20 保护内窥镜 2A 内的电路不受静电等过大电压影响。从处理器 4 侧经由连接器插头 26a 输入到内窥镜 2A 的信号经由缓冲器 20a 输出到连接器基板 24 侧。

[0082] 通过使过大电压成为规定电压的齐纳二极管(恒压二极管)20b 和下拉的电阻 20c 来保护该缓冲器 20a 的输入端。即,缓冲器 20a 的输入端与齐纳二极管 20b 的阴极连接,该齐纳二极管 20b 的阳极接地,并且,缓冲器 20a 的输入端经由电阻 20c 接地。

[0083] 而且,在对连接器插头 26a 输入静电等过大电压的情况下,通过齐纳二极管 20b 使电压下降到容许的规定电压的齐纳电压,并且,还通过电阻 20c 向接地侧放电,迅速降低过大的电压。另外,齐纳二极管 20b 的齐纳电压被设定为容许的规定电压(例如 10V 左右),并且,电阻 20c 被设定为相对于实际输入的信号而成为较小载荷的电阻值。

[0084] 在图 2E 中示出 1 个输入保护电路 20,但是,也可以针对经由连接器插头 26a 输入到连接器基板 24 侧的多个信号设置同样的输入保护电路 20。

[0085] 另外,相对于从内窥镜 2A 经由连接器插头 26a 向处理器 4 侧输出信号的情况,也可以在输出信号的缓冲器的输出端设置齐纳二极管和电阻 20c,保护缓冲器的输出端不受静电等过大电压影响。

[0086] 图 3 示出内窥镜 2A 中的电气系统的详细结构。在 A/D 基板 24B 内设有作为可编程的 LSI(大规模集成电路)的现场可编程门阵列(Field-Programmable Gate Array(简记为 FPGA))51,该 FPGA 51 负责用于驱动 CCD 16 的同步信号的传送控制、针对各种定时信号的传送处理、从由 CCD 16 输出的摄像信号转换为进行高速信号传送的信号形式的处理、针对电源电压的处理等。

[0087] 而且,FPGA 51 经由连接器 25a 而与处理器 4(的信号处理电路 28 和控制电路 29)侧进行 JTAGSEL、VD/TMS、HD/TCK、REG\_TXD/TDO、REG\_RXD/TDI、NCJD1,2、SC\_CLK\_EN、CLK±、影像输出(LVDS)的收发。

[0088] 并且,从处理器 4 的电源电路 27 向 A/D 基板 24B 供给多个电源电压的电源。

[0089] JTAGSEL 是在利用 JTAG(Joint Test Action Group:联合测试行动小组)从处理器 4 侧改写 ROM 52c 中存储的 FPGA 51 的数据的情况下要利用的信号。

[0090] 并且,VD、HD 表示垂直和水平的同步信号,分别与 TMS(Test Mode Select:测试模式选择)、TCK(Test Clock:测试时钟)进行选择性地使用。

[0091] 并且,REG\_TXD 表示从 FPGA 51 向处理器 4 侧发送发送数据的情况下的信号,与 TDO(Test Data Out:测试数据输出)的信号进行选择性地使用。

[0092] 并且,REG\_RXD 与 FPGA 51 从处理器 4 侧接收接收数据的情况下的信号、TDI (Test Data In : 测试数据输入) 的信号进行选择性地使用。

[0093] NCJD1, 2 表示来自对搭载于各内窥镜 2A 上的 CCD 16 的种类进行检测的 CCD 检测电阻 52a 的信号。

[0094] 并且,SC\_CLK\_EN 是在电源、时钟上升的情况之前 (刚要上升之前) 从处理器 4 向内窥镜 2A 侧的 FPGA 51 通知的脉冲的信号, 并且, 在处理器 4 的电源被断开的情况下, 也提前将该断开的信号通知给 FPGA 51, 能够在内窥镜 2A 侧进行规定的关闭处理 (在后述图 5B 中进行说明)。

[0095] CLK<sub>±</sub> 是从处理器 4 向 FPGA 51 供给的时钟, FPGA 51 进行与 CLK<sub>±</sub> 同步的动作。CLK<sub>±</sub> 采用小振幅、低消耗功率、比较高速的差动接口的 LVDS。

[0096] 影像输出通过 LVDS 而从 FPGA 51 输出到处理器 4 侧。

[0097] JTAGSEL 的信号经由反相器 52b 输入到 FPGA 51, 并且, 对三态缓冲器 52d 的开闭进行控制, 该三态缓冲器 52d 设置在与作为 FPGA 数据的写入用存储器的 ROM52c 连接的信号线上。

[0098] VD/TMS、HD/TCK、REG\_RXD/TDI 的各信号被输入到 FPGA 51 的输入端, 并且, 经由三态缓冲器 52d 输入到 ROM 52c 的输入端。VD/TMS 和 HD/TCK 也被输入到 FPGA 51 的输入端。

[0099] 并且, FPGA 51 的输出端经由三态缓冲器 52d 而与 REG\_RXD/TDO 的信号线连接, FPGA 51 的输出端也与该信号线连接。

[0100] 并且, ROM 52c 的输入输出端可以不经由三态缓冲器 52d 而与连接器 52e 连接, 从该连接器 52e 对 ROM 52c 写入作为决定 LSI 的程序数据的 FPGA 数据, 所述 LSI 由 FPGA 51 以能够编程的方式构筑。并且, ROM 52c 的输入输出端与 FPGA 51 连接。

[0101] 并且, 在 FPGA 51 上连接有存储了与内窥镜 2A 的各固有识别信息 (ID) 有关的信息 (例如机型名等) 的 ID 用 ROM 52f。

[0102] 并且, 在 FPGA 51 上连接有针对 FPGA 判定 CCD 16 的种类等的 FPGA 用 CCD 判别电路 52g。该 FPGA 用 CCD 判别电路 52g 例如由具有判别 CCD 16 的种类的电阻值的电阻构成。

[0103] FPGA 51 对设于操作部基板 22 内的 LVDS 接收器 54a 发送用于生成驱动 CCD 16 的驱动信号所需要的例如 4 个信号。

[0104] LVDS 接收器 54a 对驱动器 54b 进行驱动, 驱动器 54b 将所生成的水平转送信号  $\varphi H$  和垂直转送信号  $\varphi V$  发送到前端部基板 18 的 TG 17。TG 17 将由 4 个信号 (例如  $\varphi S$ 、 $\varphi RS$ 、 $\varphi P$ 、 $\varphi PDN$ ) 构成的 CCD 驱动信号施加给 CCD 16, 进行驱动以输出由 CCD 16 进行光电转换后的信号电荷作为摄像信号。LVDS 接收器 54a 和驱动器 54b 均配置在 IF 基板 24A 上, 在使用操作部基板 22 生成驱动信号的情况下, 穿过配置在 IF 基板 24A 侧的 LVDS 接收器 54a 和驱动器 54b 的电路。另一方面, 在不使用操作部基板 22 的情况下, 通过使用配置在 IF 基板 24A 侧的上述电路, 能够减少 IF 基板 24A 的安装前的基板种类。

[0105] 另外, 在图 3 中, 包含 CCD 16 和前端部基板 18 在内示出为 SIP 19。

[0106] IF 基板 24A 具有对操作部基板 22 供给电源的操作部基板电源电路 53a, 操作部基板电源电路 53a 供给 LVDS 接收器 54a 和驱动器 54b 进行动作所需要的电源。

[0107] 并且, IF 基板 24A 具有设于内窥镜 2A 内的作为电源生成单元的 CCD/TG 电源电路

53b, CCD/TG 电源电路 53b 向 CCD 16 和 TG 17 供给多个电源电压。在图 3 的例子中, CCD/TG 电源电路 53b 经由电源线 60a'、60b' 向 CCD 16 供给不同的电源电压的电源 VDD1A、VDD1B, 向 TG 17 供给 VDD2-VDD4。

[0108] 在本实施方式中, CCD 16 具有输出 4 个通道的信号的输出功能, 关于从 CCD 16 输出的 4 个通道的摄像信号, 从由 4 个晶体管构成的晶体管阵列 (图 3 中简记为 Tr 阵列) 55 输出 4 个通道 (图 3 中简记为 Ach、Bch、Cch、Dch) 的低阻抗的摄像信号。

[0109] 另外, 也可以代替直接对晶体管阵列 55 输出 CCD 16 的输出信号, 而构成为经由相关双重取样电路输出到晶体管阵列 55。

[0110] 4 个通道的摄像信号被输入到 IF 基板 24A 内的第 1 模拟电路 53c。第 1 模拟电路 53c 由分别对所输入的摄像信号进行放大的 4 个放大器 53d 构成。

[0111] 由放大器 53d 分别放大后的摄像信号被输入到 A/D 基板 24B 内的第 2 模拟电路 52h。在第 2 模拟电路 52h 中, 也对应于 4 个通道而设有 4 个通道的电路。例如 Dch 的摄像信号经由 LPF 52i、以黑电平为基准进行钳位的钳位电路 52j、对不需要电平进行削波的削波电路 52k、放大器 52l, 成为第 2 模拟电路 52h 的输出信号。其他通道也采用同样的结构。

[0112] 第 2 模拟电路 52h 的输出信号被输入到 4 个通道的 A/D 转换电路部 (图 3 中简记为 A/D) 52m, 被转换为数字摄像信号。另外, 从 FPGA 51 对 A/D 转换电路部 52m 施加进行 A/D 转换的 A/D 转换用的时钟 ADCLK, A/D 转换电路部 52m 与该时钟 ADCLK 同步地进行 A/D 转换。

[0113] 并且, A/D 转换电路部 52m 将 A/D 转换后的 4 个通道的 A/D 转换输出信号作为 6 对 A/D 转换输出信号 (影像通道、时钟、帧) 输出到 FPGA 51。FPGA 51 从 4 个通道的信号转换为 3 个通道的信号, 向处理器 4 侧输出 3 个通道的 LVDS 方式的影像信号。在 LVDS 方式中, 也期望考虑 EMI。具体内容如下所述。在对搭载于内窥镜 2A 的 CCD 16 进行驱动时, 与影像信号的方式同样, 考虑水平方向的定时和垂直方向的定时。此时, 在水平方向中存在驱动 CCD 16 并从 CCD 16 取出信号的期间、以及不驱动 CCD 16 也不取出信号的期间。如果设后者为 H 消隐, 则为了在 H 消隐中考虑 EMI, 对驱动时钟 (例如 30MHz) 进行分频并生成分频时钟 (30MHz 的 1/2 的 15MHz), 将其重叠在 H 消隐中即可。该情况下, 在通过 LVDS 进行传送的过程中, 进行动作以抑制放射噪声。在垂直方向上的 V 消隐中也同样, 重叠分频时钟即可。并且, 来自电源电路 27 的以多个电源电压 (包含图 4A 所示的 V1、V2) 供给的电源经由电源线 (包含 60a、60b) 供给到 IF 基板 24A 内的 CCD/TG 电源电路 53b (内的 CCD 电源电路 53b'), 并且, 通过 A/D 基板 24B 内的 A/D 转换电路部 52n 转换为数字电压后, 输出到 FPGA 51 (由 FPGA51 构筑的图 4A 所示的 CCD 电源电压监视电路 63)。

[0114] 并且, 如图 3 所示, 在连接器基板 24 中的例如 A/D 基板 24B 内设有基板内电路用电源电路 52p, 该基板内电路用电源电路 52p 产生该连接器基板 24 内的电路 (具体而言为第 1 模拟电路 53c、第 2 模拟电路 53h 等) 进行动作所需要的电源电压。该基板内电路用电源电路 52p 从与处理器 4 的电源电路 27 连接的电源线 60a、60b 生成后述的 +5V\_AFE1、-5V\_AFE1、+5V\_AFE2、-5V\_AFE2 等, 作为电源电压。

[0115] 并且, 操作部 7 的镜体开关 47 经由通用缆线内的同轴缆线、信号用连接器 12 内的波形整形缓冲器而输入到 FPGA 51。例如, 设于镜体开关 47 中的 4 个开关 SW1-SW4 的接通/断开信号、搭载了致动器的情况下望远 (TELE) 和广角 (WIDE) 的操作信号被输入到 FPGA

51。这些开关信息在 FPGA 51 中进行并行 - 串行转换，并经由控制信号线传送到处理器 4。[0116] 图 4A 示出设置在内窥镜 2A 的连接器基板 24 内、监视对 CCD 16 侧供给电源的情况下的电源电压的 CCD 电源电压监视电路 63 的结构。另外，如图 3 所示的 CCD/TG 电源电路 53b 的情况那样，也可以构成为，监视对 CCD 16 侧和 TG 17 侧供给电源的情况下的电源电压。

[0117] 细线同轴连接器座 40 具有通过分别与小型连接器 25a 的连接器触针接触而电连接的连接器座触针 40a、40b、40c、…。另外，连接器座触针 40a、40b 和连接器座触针 40c 经由设有连接器 25a 的细线同轴缆线 25 等，分别与处理器 4 的电源电路 27 的电源输出端和控制电路 29 连接。因此，从处理器 4 侧的电源电路 27 向连接器座触针 40a、40b 供给电源电压（有时简记为电压）V1、V2 的电源。

[0118] 连接器座触针 40a 经由电源线 60a 而与形成（生成与所输入的多个不同的电源电压 V1、V2 不同的多个恒源电压（简记为恒压）的作为电源生成单元的）CCD 电源电路 53b' 的第 1 恒压电路 61a 的输入端连接，连接器座触针 40b 经由电源线 60b 而与形成 CCD 电源电路 53b' 的第 2 恒压电路 61b 的输入端连接。

[0119] 第 1 恒压电路 61a、第 2 恒压电路 61b 从输入到输入端的电源电压 V1、V2 转换为分别不同的规定恒压（图 3 中为 VDD1A、VDD1B），经由电源线 60a'、60b' 分别输出到 CCD 16 的电源端。另外，在到达 CCD 16 的电源端的中途，通过作为小型连接器的 MC 31、35 等对电源线 60a'、60b' 进行转接。

[0120] 并且，电源线 60a、60b 的电源电压通过构成 A/D 转换电路部 52n 的 A/D 转换电路 62a、62b 转换为数字电压后，被输入到 FPGA 51 内（更具体而言由 FPGA 51 的一部分构筑）的 CCD 电源电压监视电路 63。

[0121] CCD 电源电压监视电路 63 具有：比较电路 64a、64b，其对分别由 A/D 转换电路 62a、62b 生成的数字电压 V1、V2 和阈值 Vt1、Vt2 进行比较；作为存储器的 ROM65，其存储分别对比较电路 64a、64b 输出阈值 Vt1、Vt2 的阈值；以及电源供给控制部 66，其被输入比较电路 64a、64b 的比较结果，从而对 CCD 电源电路 53b' 的电源供给的动作进行控制。

[0122] 并且，CCD 电源电压监视电路 63 具有告知信号生成电路 67，在电源供给控制部 66 输出电压异常这样的异常判定信号的情况下，该告知信号生成电路 67 生成用于告知该异常的告知信号。另外，也可以在电源供给控制部 66 的内部设置告知信号生成电路 67。

[0123] 作为阈值的存储单元的 ROM 65 存储比正常状态下的电压 V1、V2 稍小的阈值 Vt1a、Vt2a，并且，存储比电压 V1、V2 稍大的阈值 Vt1b、Vt2b，对比较电路 64a 输出 2 个阈值 Vt1a、Vt1b 作为阈值 Vt1，对比较电路 64b 输出 2 个阈值 Vt2a、Vt2b 作为阈值 Vt2。

[0124] 比较电路 64a、64b 分别是窗口型比较电路，对电压 V1 是否大于阈值 Vt1a、并且电压 V1 是否小于阈值 Vt1b 进行比较，将比较结果输出到电源供给控制部 66。另外，在图 4A 中，利用比较电路 64 示出比较电路 64a 和 64b。

[0125] 电源供给控制部 66 在电压 V1 满足  $V1a \leq V1 \leq Vt1b$  的条件的情况下，判定为电压 V1 是正常范围内的电压，并且，同样在电压 V2 满足  $V2a \leq V2 \leq Vt2b$  的条件的情况下，判定为电压 V2 是正常范围内的电压。

[0126] 另一方面，电源供给控制部 66 在电压 V1 不满足  $V1a \leq V1 \leq Vt1b$  的条件的情况下，判定为电压 V1 处于不正常的异常电压的状态，并且，同样在电压 V2 不满足

$V_{2a} \leq V_2 \leq V_{t2b}$  的条件下,判定为电压  $V_2$  处于不正常的异常电压的状态。

[0127] 并且,电源供给控制部 66 在判定为电压  $V_1$  是异常电压的情况下,进行控制以停止第 1 恒压电路 61a 的(生成恒压电源的)动作,并且,进行控制以断开开关 61c 从而切断从第 1 恒压电路 61a 供给到 CCD 16 的恒压。

[0128] 并且,电源供给控制部 66 在判定为电压  $V_2$  是异常电压的情况下,进行控制以停止第 2 恒压电路 61b 的动作,并且,进行控制以断开开关 61d 从而切断从第 2 恒压电路 61b 供给到 CCD 16 的恒压。

[0129] 也可以将设于第 1 恒压电路 61a 的输出端的开关 61c 设置在第 1 恒压电路 61a 的内部,并断开该开关。在设于第 2 恒压电路 61b 的输出端的开关 61d 的情况下也同样应用。

[0130] 另外,电源供给控制部 66 在判定为电压  $V_1$ 、 $V_2$  均为正常的情况下,继续进行 CCD 电源电路 53b 的动作。

[0131] 并且,告知信号生成电路 67 被输入电源供给控制部 66 判定为电压  $V_1$  或  $V_2$  为异常电压的情况下的异常判定信号时,生成告知电压  $V_1$  或  $V_2$  为异常电压的告知信号。

[0132] 告知信号生成电路 67 具有告知信号发送单元,该告知信号发送单元在向处理器 4 侧传送该告知信号的情况下,不是通过专用传送该告知信号的信号线进行发送,而是在规定定时重叠在其他信号中,通过传送该信号的信号线发送到处理器 4 侧。例如重叠(插入)在图 3 的 REG-TXD/TDO 的信号、垂直同步信号  $VD$  中进行发送。因此,告知信号生成电路 67 具有在本来的控制信号等中重叠告知信号的告知信号重叠电路 67a。该告知信号例如经由连接器触针 40c 发送到处理器 4 的控制电路 29 侧。

[0133] 这样,可以不需要设置很少使用的传送告知信号的专用的信号线。

[0134] 控制电路 29 在接收到重叠在控制信号等中的告知信号的情况下,将该告知信号输出到信号处理电路 28,信号处理电路 28 在影像信号中重叠告知信号。然后,监视器 5 显示内窥镜图像和告知信号。

[0135] 这种结构的内窥镜 2A 的特征在于,具有:作为摄像元件的 CCD 16,其搭载于插入部 6 的前端部 14;作为布线的综合同轴缆线 21、23,其传递用于驱动所述摄像元件的具有多个不同电源电压的电源、驱动所述摄像元件的驱动信号、从由该驱动信号驱动的所述摄像元件输出的摄像信号和接地电平;作为基板的操作部基板 22、连接器基板 24,其设有对所述布线进行转接的微连接器 31、35 等连接器;作为电压比较单元的比较电路 64,其对所述多个不同电源电压进行比较;以及作为电源供给控制单元的电源供给控制部 66,其根据所述电压比较单元的比较结果,控制针对所述摄像元件的电源供给。

[0136] 而且,在本实施方式中,分别监视供给到作为摄像元件的 CCD 16 侧的多个电源电压,判定是否由于电源线 60a、60b 或电源线 60a'、60b' 断线、或者对它们进行转接的小型连接器的连接器触针间的短路(或未导致短路的绝缘不良)等而产生异常电压。在判定为产生了异常电压的异常状态的情况下,电源供给控制部 66 进行切断针对 CCD 16 的电源供给的控制,并且,使告知信号生成电路 67 生成用于告知产生异常电压的告知信号,将其发送到处理器 4 侧。

[0137] 处理器 4 的控制电路 29 将告知信号输出到信号处理电路 28,信号处理电路 28 在影像信号中重叠告知信号。然后,监视器 5 显示内窥镜图像和告知信号,手术医生通过告知信号,能够迅速识别到在电源电压  $V_1$  或  $V_2$  中产生了异常电压。

[0138] 因此,针对产生了异常电压的内窥镜 2A,能够迅速进行与产生该异常电压对应的修理等,能够消除异常状态。并且,能够减小在产生了异常电压的异常状态下继续使用的情况(该情况下,可能产生更严重的异常状态),并且,能够防止在未修理的异常状态下用于下次的内窥镜检查的情况。

[0139] 另外,ROM 65 预先存储用于判定是否是异常电压的阈值的信息,但是,也可以构成为,处理器 4 侧向 FPGA 51 侧发送用于根据实际与该处理器 4 连接的内窥镜 2A 来判定是否是异常电压的阈值的信息,FPGA 51 在 ROM 65 中存储该信息。

[0140] 在该结构的情况下,在初始状态等下,内窥镜 2A 的 FPGA 51 从处理器 4 侧接受上述阈值的信息,使用该信息来判定是否是异常电压。在采用这种结构的情况下,在实际与处理器 4 连接并使用的内窥镜 2A 等的种类不同的情况下(例如针对电源的负载的大小不同的情况下),也能够将阈值设定为更加适当的值。

[0141] 这样,通过将阈值设定为更加适当的值,针对实际与处理器 4 连接的内窥镜 2A 等,能够在更早期的阶段判定电压从正常状态变成异常的异常状态。

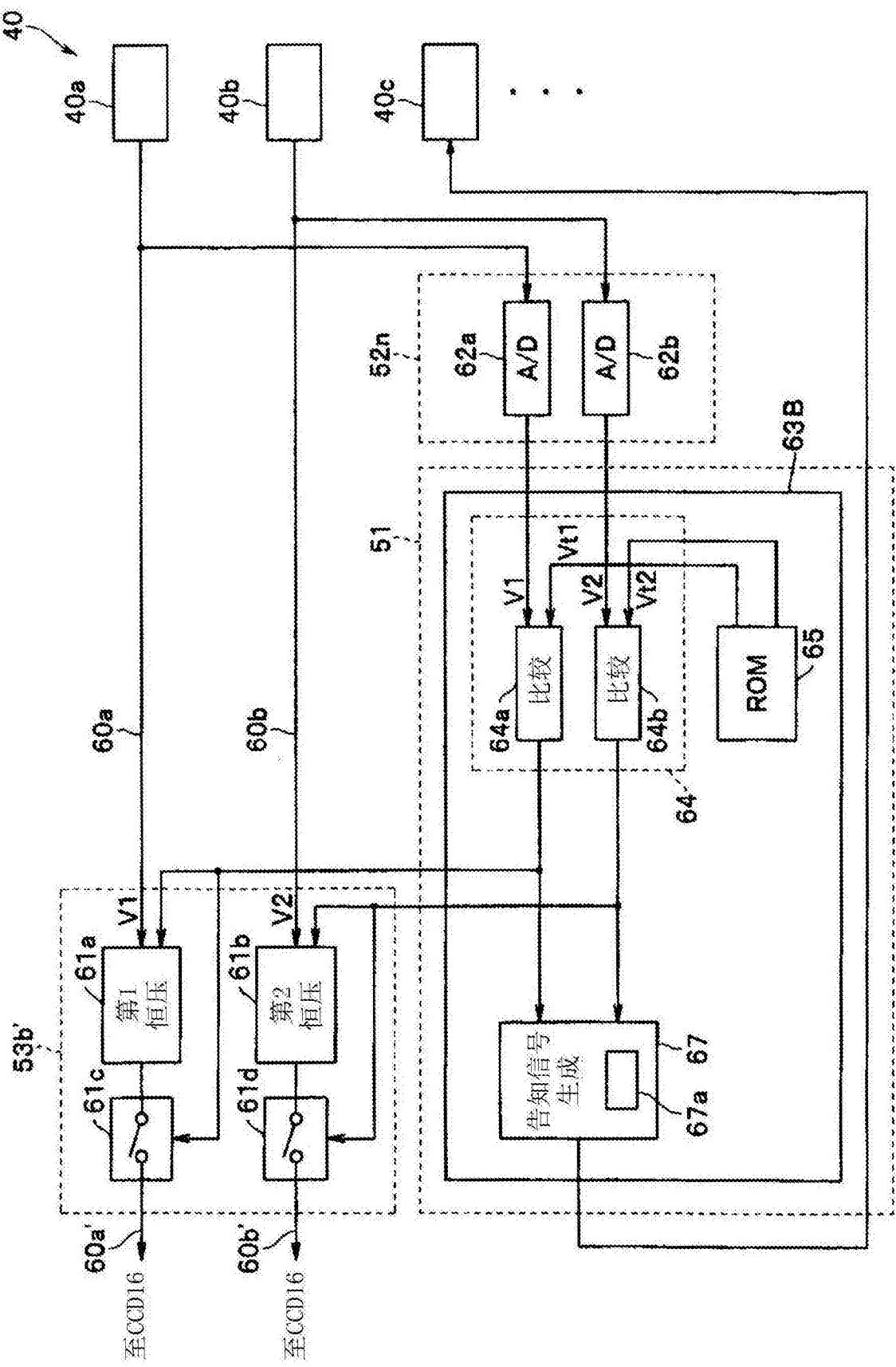

[0142] 在图 4A 的 CCD 电源电压监视电路 63 的结构例中构成为,将作为电压比较单元的比较电路 64 的比较结果输出到作为电源供给控制单元的电源供给控制部 66,电源供给控制部 66 根据比较电路 64 的比较结果来控制针对 CCD 16 的电源供给,但是,也可以采用图 4B 所示的变形例的结构。

[0143] 在图 4B 的 CCD 电源电压监视电路 63B 中构成为,比较电路 64 进行图 4A 中电源供给控制部 66 的控制功能。换言之,作为电压比较单元的比较电路 64 兼有作为电源供给控制单元的电源供给控制部 66 的功能。

[0144] 在图 4B 中构成为,根据构成比较电路 64 的各比较电路 64a、64b 的比较结果,不經由电源供给控制部 66,而分别对第 1 恒压电路 61a 和开关 61c、第 2 恒压电路 61b 和开关 61d 进行控制。

[0145] 即,比较电路 64a 在比较结果为异常电压的情况下,停止第 1 恒压电路 61a 的动作并断开开关 61c,切断针对 CCD 16 侧的电源供给。

[0146] 并且,比较电路 64b 在比较结果为异常电压的情况下,停止第 2 恒压电路 61b 的动作并断开开关 61d,切断针对 CCD 16 侧的电源供给。

[0147] 并且,比较电路 64a、64b 的比较结果被输出到告知信号生成电路 67,在异常电压的情况下,告知信号生成电路 67 将告知信号供给到处理器 4 侧。

[0148] 其他结构与图 4A 的情况相同。除了电压比较单元兼有电源供给控制单元的功能以外,图 4B 的变形例的作用效果与图 4A 的情况几乎相同。

[0149] 另外,如图 4A 或图 4B 所示,不限于监视对 CCD 16 供给多个电源电压的 CCD 电源电路 53b' 的输入侧的多个电源电压的结构,也可以构成为,在还对与 CCD 16 一起搭载于前端部 14 的 TG 17 供给电源电压的电源电路(例如 CCD/TG 电源电路 53b)的输入侧,监视该电源电压,在异常电压的情况下,切断对 TG 17 供给的电源并进行告知。

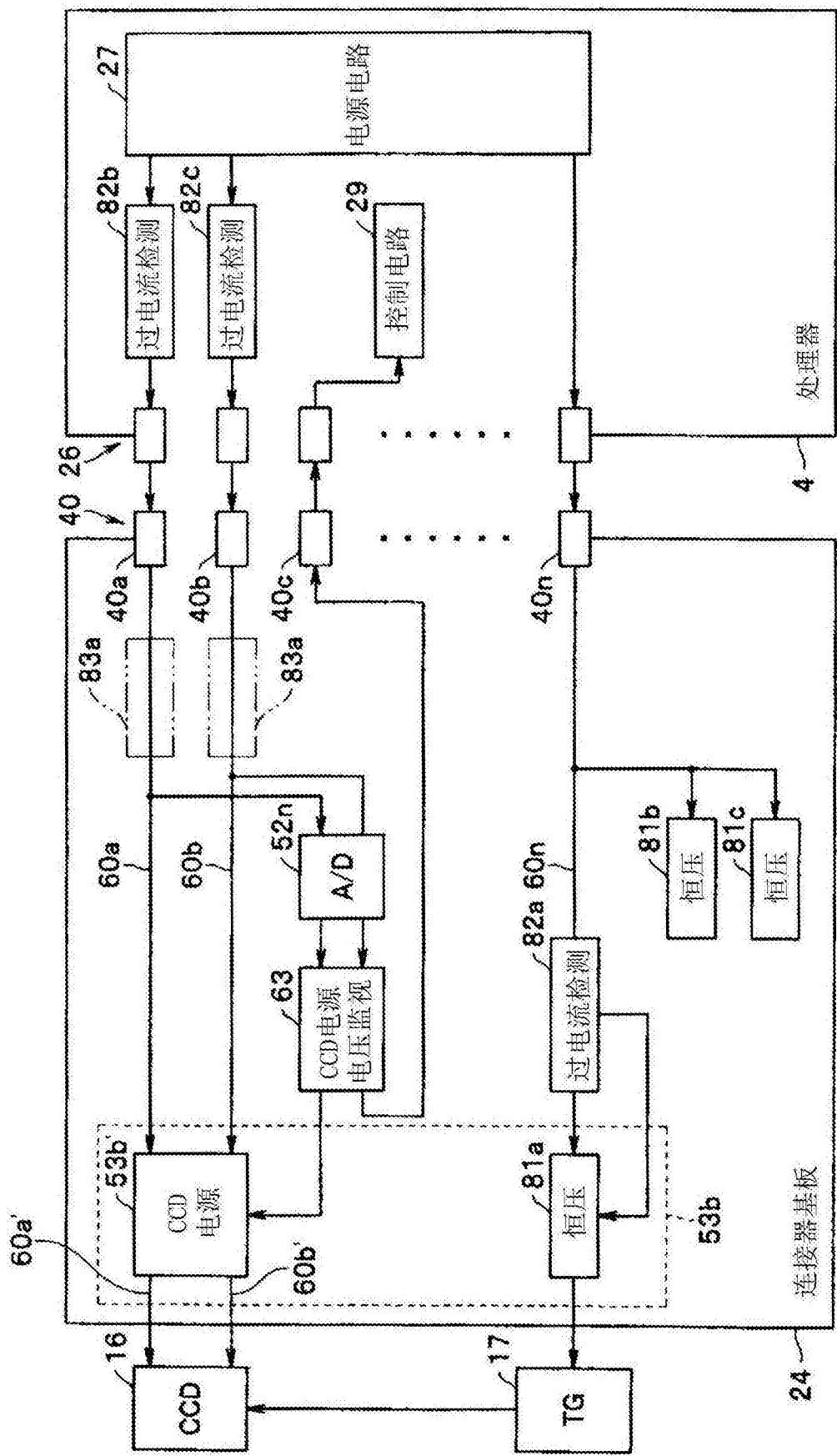

[0150] 并且,在对 CCD 16 侧和 TG 17 侧供给的电源为过大电流(在本说明书中称为过电流)的异常状态的情况下,也可以进行控制以停止(关闭)电源供给。

[0151] 图 4C 示出设置有过电流检测电路 82a-82c 的结构,该过电流检测电路 82a-82c 检测对 CCD 16 供给的电源和对 TG 17 供给的电源是否为过电流的状态,在过电流的情况下停

止电源供给。

[0152] 在图 4C 所示的结构中,在连接器基板 24 内设置有图 4A 中说明的 CCD 电源电路 53b、A/D 转换电路部 52n、CCD 电源电压监视电路 63,并且,设置有对 TG 17 供给电源的恒压电路 81a 和在其前级检测过电流的过电流检测电路 82a。另外,过电流检测电路 82a 具有比较电路,该比较电路对例如与电源线 60n 串联连接的规定值电阻的两端电压和为了判定过电流而预先设定的规定电压值进行比较,在所述电阻的两端电压为规定电压值以上的比较结果的情况下,检测为对恒压电路 81a 供给的电源的电流为阈值以上的过电流的状态。其他过电流检测电路 82b、82c 也采用同样的结构。

[0153] 当预先设定的阈值以上的过电流流过恒压电路 81a 侧时,在与连接器触针 40n 连接的电源线 60n 上设置的过电流检测电路 82a 关闭对恒压电路 81a 侧供给的电源(的电流)。

[0154] 在图 4C 中示出如下结构:仅在内窥镜 2A 内的应当进行监视的电源线 60n 上设置过电流检测电路 82a,关于其他电源线 60a、60b,在处理器 4 侧设置针对 CCD 电源电路 53b 的过电流检测电路 82b、82c。过电流检测电路 82b、82c 在检测到过电流时,关闭从过电流检测电路 82b、82c 供给到 CCD 电源电路 53b' 侧的电源。

[0155] 并且,在图 4C 的结构的情况下,设置有对连接器基板 24 内的电子电路供给电源的恒压电路 81b、81c。CCD 电源电路 53b' 和恒压电路 81a 相当于图 3 的 CCD/TG 电源电路 53b。

[0156] 另外,关于电源线 60a、60b 上设置的双点划线所示的判定用电压生成电路 83a,在图 4E 的说明后进行说明。

[0157] 处理器 4 内的电源电路 27 经由过电流检测电路 82b、82c 对 CCD 电源电路 53b 供给电源,并且,还对恒压电路 81a-81c 供给电源。

[0158] 现有例中的过电流检测电路为如下过程:在检测到过电流时,关闭对恒压电路 81a 供给的电源的电流,但是,当由于关闭而检测到电流低下时解除关闭,成为流过过电流的状态,当检测到该过电流时,再次反复进行关闭。

[0159] 因此,本实施方式中采用的过电流检测电路 82a 构成为,在临时检测到过电流后,在内窥镜 2A 整体的电源断开之前,保持检测到过电流的状态,对上述现有例中的过程进行了改良。另外,其他过电流检测电路 82b、82c 也可以具有与过电流检测电路 82a 的情况相同的功能。

[0160] 在通过过电流检测电路 82a 检测过电流的情况下,也可以根据内窥镜 2A 的种类而具有多个不同的阈值,根据实际使用的内窥镜 2A 来切换阈值(例如,也可以根据内窥镜 2A 的外径不同、前端部的温度不同等而切换阈值)。该情况下,作为用于切换阈值的具体单元,可以在各内窥镜 2A 内装配与内窥镜 2A 的种类对应的电阻值的电阻器。

[0161] 并且,为了切换阈值,也可以利用数字微调器,在 ROM 中存储数字微调器的数值。并且,过电流保护电路 82a-82c 也可以将 CCD 用过电流保护电路和 TG 用过电流保护电路汇总为一个过电流保护电路。并且,可以将全部过电流保护电路 82a-82c 搭载于内窥镜 2A 内,也可以不搭载于内窥镜 2A 内,而搭载于处理器 4 内。

[0162] 并且,也可以构成为,在内窥镜 2A 固有的摄像单元上搭载 ROM 或电阻器,检测电路读取所搭载的 ROM 或电阻器的信息。除此之外,也可以在搭载于内窥镜 2A 内的 MC 基板、A/

D 基板、IF 基板等上搭载上述 ROM 等。

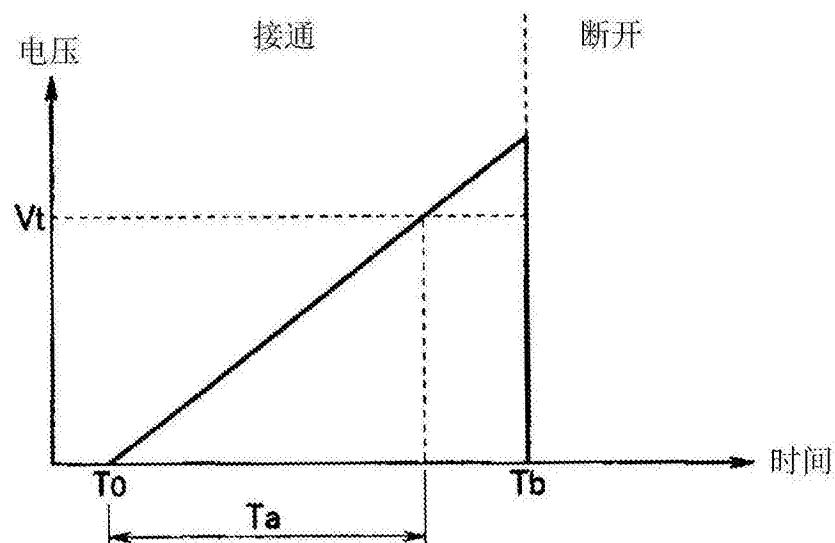

[0163] 并且,在本实施方式中,以图 4D 所示的特性进行内窥镜 2A 侧的电源接通、断开的控制。另外,图 4D 的横轴表示时间,纵轴表示电压。

[0164] 图 4D 示出如下特性:在处理器 4 侧,在从电源接通的时间(定时)T<sub>0</sub> 起的时间 T<sub>a</sub> 后,接通内窥镜 2A 侧的电源,另一方面,在从电源接通的状态起断开电源的情况下,在几乎与电源断开的时间 T<sub>b</sub> 相同的定时或稍微滞后的定时,断开内窥镜 2A 侧的电源。另外,电压 V<sub>t</sub> 表示接通 / 断开电源的阈值。

[0165] 通过以这种特性进行控制,在处理器 4 侧接通 / 断开电源的情况下,能够在内窥镜 2A 侧进行稳定地动作。在电源接通的情况下,由于信号用连接器 12 未适当装配在处理器 4 上的状态、连接器触针的接触不稳定的状态,在内窥镜 2A 侧也可能处于以很快的定时反复进行电源接通 / 断开的状态。

[0166] 因此,当从电源接通的定时起不需要时间而使内窥镜 2A 侧的电源也成为接通状态时,由于以不稳定的电源状态进行动作,由此,无法确保针对供给电源的电路的稳定地动作。

[0167] 因此,在处理器 4 侧的电源接通时,通过进行在内窥镜 2A 侧的电源稳定所需要的时间后接通电源(即,使内窥镜 2A 侧的电源电路成为动作状态)的控制,能够确保内窥镜 2A 侧的稳定地动作。

[0168] 另一方面,在从电源接通的状态起在处理器 4 侧断开电源的情况下,不用像电源接通时那样需要时间,能够在短时间内断开电源(关闭内窥镜 2A 侧的电源电路)。另外,在后述图 5B 中,在短时间内断开电源的情况下的时间为 T<sub>9</sub> 左右。

[0169] 在具有图 4D 所示的特性而进行内窥镜 2A 侧的过程控制的情况下,例如可以通过图 4E 所示的电路结构来实现。

[0170] 在图 4E 中,在图 4C 的例如与过电流检测电路 82a 的输入端连接的电源线 60n 上设置有判定用电压生成电路 83a,该判定用电压生成电路 83a 由电阻 R<sub>a</sub> 和二极管 D<sub>a</sub> 的并联电路以及连接在该并联电路的输出端与地线 GND 之间的电容器 C<sub>a</sub> 构成。

[0171] 并且,在图 4E 中设置有电压监视电路 83b,该电压监视电路 83b 将由该判定用电压生成电路 83a 生成的判定用电压输出到过电流检测电路 82a,并且,监视该判定用电压,对恒压电路 81a、81b、81c 的电源接通 / 断开进行控制。

[0172] 另外,也可以构成为使过电流检测电路 82a 具有电压监视电路 83b 的功能,成为省略电压监视电路 83b 的结构。

[0173] 在图 4E 的结构的情况下,在处理器 4 侧接通电源的情况下,经由电阻 R<sub>a</sub> 而在电容器 C<sub>a</sub> 中流过电流,根据电阻 R<sub>a</sub> 和电容器 C<sub>a</sub> 的时间常数,电容器 C<sub>a</sub> 的电位(电压)随着时间而上升。另外,该情况下,二极管 D<sub>a</sub> 成为反方向,其电阻值远远大于电阻 R<sub>a</sub> 的电阻值。

[0174] 该情况下的上升的时间常数决定图 4D 的特性(电压随着时间而上升的特性)。而且,电压监视电路 83b 具有电源接通控制电路的功能,其进行控制,使得对电容器 C<sub>a</sub> 的电压(即,由判定用电压生成电路 83a 生成的判定用电压)和阈值 V<sub>t</sub> 进行比较,当检测到阈值 V<sub>t</sub> 以上的电压时,接通恒压电路 81a、81b、81c(或从恒压电路 81a、81b、81c 输出电源)。

[0175] 另一方面,在从电源接通的状态起在处理器 4 侧断开电源的情况下,连接器触针 40n 的电压瞬时降低为 0。因此,电容器 C<sub>a</sub> 中蓄积的电荷通过成为顺方向的二极管 D<sub>a</sub> 而在

短时间内被放电,电容器 Ca 的判定用电压在短时间内成为阈值 Vt 以下,电压监视电路 83b 具有电源断开控制电路的功能,其进行控制,使得在短时间内断开恒压电路 81a、81b、81c 的电源。通过进行这种控制,在电源接通的情况下能够确保稳定地动作,在电源断开的情况下能够确保良好的响应性。

[0176] 另外,不限于将判定用电压生成电路 83a 设置在图 4E 所示的电源线 60n 上的情况,例如,如图 4C 的双点划线所示,也可以设置在其他电源线 60a、60b 上。

[0177] 在电源线 60a、60b 设置有判定用电压生成电路 83a 的情况下,CCD 电源电压监视电路 63( 的电源供给控制部 66) 具有图 4E 的电压监视电路 83b 的功能,以图 4D 中说明的特性对 CCD 电源电路 53b' 的电源接通 / 断开进行控制。

[0178] 该情况下,电源供给控制部 66 除了图 4A、图 4C 中说明的控制功能(第 1 控制功能)以外,还具有针对在处理器 4 侧接通 / 断开电源的情况下使 CCD 电源电路 53b' 的电源接通 / 断开的控制功能(第 2 控制功能)。

[0179] 并且,作为从 FPGA 51 经由 TG 17 驱动 CCD 16 的情况下的缆线驱动方法,也可以采用图 5A 的结构,对波形的圆钝进行改善。

[0180] FPGA 51 生成作为 TG 17 请求的例如 3 个时钟的 HDR\_CLK、HDR\_CLK\_N、HDR\_HBLK。从 FPGA 51 输出的 HDR\_CLK、HDR\_CLK\_N、HDR\_HBLK 经由构成缆线驱动电路的缓冲器 85a 以及由电容器 86a 和电阻 86b 的并联电路构成的锐化电路 86,对构成综合同轴缆线 21、23 的各同轴缆线进行驱动。

[0181] 根据时钟而并联连接多个缓冲器 85a,能够满足必要的驱动电流规格。具体而言,在 HDR\_CLK 的情况下并联连接 3 个缓冲器 85a,在 HDR\_CLK\_N 的情况下也并联连接 3 个缓冲器 85a,在 HDR\_HBLK 的情况下并联连接 2 个缓冲器 85a,能够将可以由 1 个缓冲器 85a 驱动的驱动电流增大数倍。

[0182] 并且,通过锐化电路 86 而成为对各时钟的上升波形和下降波形部分进行微分而得到的强调波形(针对 HDR\_CLK 的情况进行图示),在通过同轴缆线而使波形变钝之后,能够对 TG 17 供给近似矩形波的时钟波形。

[0183] 另外,锐化电路 86 的电容器 86a 和电阻 86b 的值根据内窥镜 2A 的种类进行切换,或者设定为适当的值。

[0184] 并且,作为从 FPGA 51 输出的 3 个时钟,有时 TG 17 请求与 FPGA 51 从处理器 4 接收到的时钟的频率相同、且占空比为 50% 的时钟。

[0185] 因此,FPGA 51 将从处理器 4 接收到的时钟倍增为 2 倍后,分频为二分之一,生成占空比为 50% 的时钟。

[0186] 另外,图 5A 示出 3 个时钟 HDR\_CLK、HDR\_CLK\_N、HDR\_HBLK 的情况下的例子,但是,在图 2B 的内窥镜 2B 的情况下,对应于  $\varphi H$  和  $\varphi V$  这 2 个脉冲信号的情况下,但是,可知该情况下也能够同样应用。并且,在内窥镜 2A 的情况下,如图 3 所示,从 FPGA 51 到操作部 7 为 4 个脉冲(LVDS 的  $\varphi H$ 、 $\varphi V$ )的情况下,从操作部 7 到 TG 17 为  $\varphi H$  和  $\varphi V$  这 2 个脉冲信号的情况下,但是,针对该情况也能够应用。

[0187] 并且,FPGA 51 具有被输入对 CCD 判别信号、垂直同步信号 VD、水平同步信号进行复位的 H 复位信号的未图示的计数器电路,在该计数器电路中,生成水平时钟 HCLK、垂直时

钟 VCLK、对 CCD 16 的光学黑（黑电平）的电位进行钳位的钳位脉冲 OBCLP 等的信号。

[0188] 并且，FPGA 51 具有控制信号生成电路（例如 SCP\_SEQ），该控制信号生成电路根据图 3 中说明的 SC-CLK\_EN 的脉冲信号、上述 HCLK 等的驱动的接通 / 断开中使用的信号 SDWN、作为 FPGA 51 内部动作用的垂直同步信号的 VD\_INT、水平同步信号 HD、穿过 LPF 的信号等，生成第 1 模拟电路 53c 用的电源控制信号 (+5V\_AFE1、-5V\_AFE1) 和第 2 模拟电路 53h 用的电源控制信号 (+5V\_AFE2、-5V\_AFE2) 等。

[0189] 在处理器 4 侧，在使用者接通 / 断开电源的情况下，处理器 4 将作为检测到该情况的脉冲信号的 SC-CLK\_EN 发送到内窥镜 2A 内的 FPGA 51，FPGA 51 使用该 SC-CLK\_EN，在内窥镜 2A 内，在规定定时进行各种电源的接通 / 断开控制、CCD 驱动信号的控制。

[0190] 这样，通过利用检测到电源接通 / 断开的脉冲信号来进行各种电源的接通 / 断开控制、CCD 驱动信号的控制，能够迅速执行与电源的接通 / 断开对应的控制。即，当利用处理器 4 和内窥镜 2A 内的 FPGA 51 之间的通信时，在建立通信之前产生时间的延迟，但是，通过利用检测到从处理器 4 侧到 FPGA 51 侧的电源接通 / 断开的脉冲信号，几乎不会产生所述时间的延迟，能够确保良好的响应性。

[0191] 利用上述 SC-CLK\_EN 的脉冲信号，在电源接通时和电源断开时，如图 5B 所示，在规定定时控制时钟 CLK、垂直同步信号 VD、对各种信号进行接通 / 断开控制的 SDWN、第 1 模拟电路 53c 用的电源控制信号 (+5V\_AFE1、-5V\_AFE1)、第 2 模拟电路 53h 用的电源控制信号 (+5V\_AFE2、-5V\_AFE2)、对作为驱动 CCD 6 的驱动信号的  $\varphi H$  进行接通 / 断开的 SDWN\_DRV、水平传送信号  $\varphi H$ （和未图示的  $\varphi V$ ）。

[0192] 在电源接通时，当规定电压（例如 3V）的电源接通时，在从该接通时起的 T1（例如大约 400mS）后，SC-CLK\_EN 从 L 电平上升到 H 电平，并且，在 T2（例如大约 1000mS）后，时钟 CLK 成为动作状态，与此同步地输出垂直同步信号 VD，并且，+5V\_AFE2、-5V\_AFE2、SDWN\_DRV 也上升到 H 电平，成为输出  $\varphi H$  的状态。

[0193] 并且，在从上述接通时起的 T3（例如大约 400mS）后，SDWN 上升。

[0194] 并且，在从时钟 CLK 成为动作状态时起的 T4（例如 500mS）后，+5V\_AFE1、-5V\_AFE1 上升到 H 电平。 $\varphi H$  的输出停止的定时成为与在 FPGA 51 内部生成的 HD 同步停止的定时。由此，能够防止生成不稳定的  $\varphi H$  脉冲，能够稳定地停止  $\varphi H$ 。也可以不是 HD，而与 VD 同步地停止  $\varphi H$ 。

[0195] 另一方面，在电源断开时，首先，SC-CLK\_EN 从 H 电平下降到 L 电平，在从该下降的定时起的 T5（例如大约 300  $\mu$ S）后，SDWN\_DRV 下降，并且，停止输出  $\varphi H$ 。

[0196] 并且，在从 SC-CLK\_EN 的下降的定时起的 T6（例如 15mS）后，-5V\_AFE1、-5V\_AFE2 下降到 L 电平，在从 SC-CLK\_EN 的下降的定时起的 T7（例如 20mS）后，+5V\_AFE1、+5V\_AFE2 下降到 L 电平，稍微在此之后的定时的 T8 后，CLK 停止，进而，在 CLK 停止后的 T9（40mS-50mS 左右）后，规定电压的电源断开。

[0197] 特别在电源断开时，在比电源接通时短的时间后成为断开状态，由此，能够确保良好的响应性。并且，在电源接通时、断开时，均利用 SC-CLK\_EN 进行控制，由此，与利用通信的情况相比，能够确保良好的响应性。

[0198] 另外,在利用通信的情况下也能够实现必要的响应性的情况下,也可以利用通信进行上述控制。并且,也可以在内窥镜 2A 侧设置对电源接通、断开进行检测的检测单元,利用该检测单元的检测信号进行上述控制。

[0199] 另外,搭载于内窥镜 2A 侧的 FPGA 51 等的集成电路 (IC) 具有容错功能,在电源和信号的输入顺序反转的情况下电路也不会被破坏。

[0200] 如图 5B 中说明的那样,例如在电源接通的情况下,在内窥镜 2A 内,进行控制使得在供给电源后使时钟 CLK 等上升 (输入时钟 CLK 等),但是,在该控制的定时由于某种原因而反转的情况下,通过容错功能,也能够保护 FPGA 51 等的 IC 不会被破坏。

[0201] 即,内窥镜 2A 具备具有容错功能的接口,内窥镜 2A 侧的 IC 等不会被破坏。

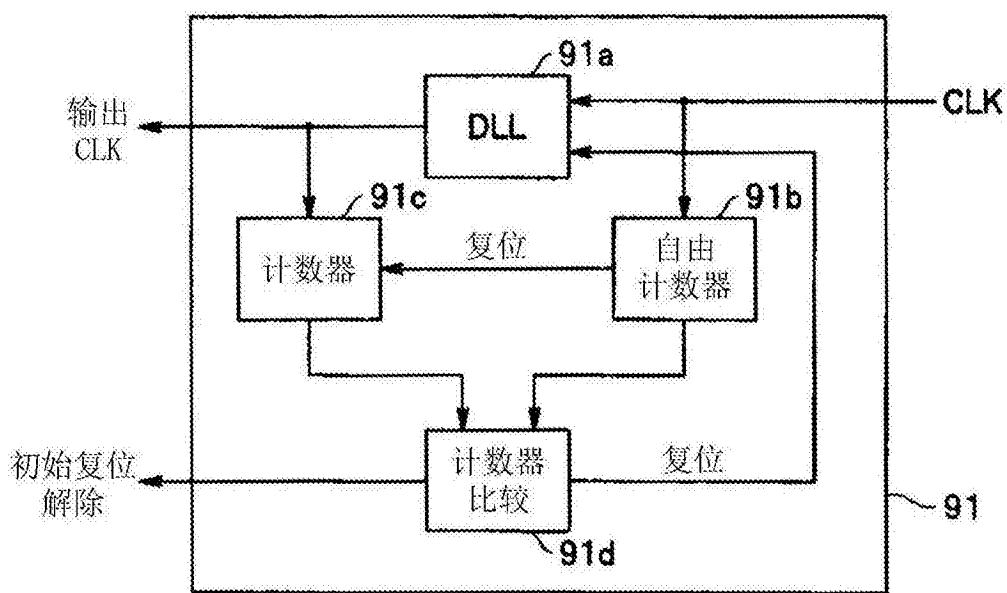

[0202] 并且,FPGA 51 具有 CLK 确定判定电路 91,如图 5C 所示,CLK 确定判定电路 91 进行 CLK 确定以及 CLK 异常的判定,所述 CLK 确定是指确定在电源接通时的起动时从处理器 4 侧输入的时钟 CLK 的起动时的 CLK。

[0203] 从处理器 4 侧输入的 CLK 被输入到对延迟量 (delay 量) 进行调整的 DLL (延迟锁相环) 91a,并且,被输入到自由计数器 91b。DLL 91a 生成作为追随所输入的 CLK 的时钟的输出 CLK 并输出。

[0204] 从 DLL 91a 输出的输出 CLK 作为 CLK 而供给到 FPGA 51 及其他电路,并且被输入到计数器 91c。另外,自由计数器 91b 在开始进行计数动作的情况下,对计数器 91c 进行复位,进行控制以使两个计数器在相同定时对 CLK、输出 CLK 进行计数。

[0205] 自由计数器 91b、计数器 91c 的各计数值被输入到计数器比较电路 91d,在规定定时两个计数器的计数值进入规定范围内的条件下,计数器比较电路 91d 判定为从 DLL 91a 输出的输出 CLK 稳定。

[0206] 在该判定结果的情况下,计数器比较电路 91d 对与输出 CLK 同步进行动作的各电路施加解除 (初始) 复位的信号,使其进行与输出 CLK 同步的动作。不限于起动时,在起动后,如果 DLL 91a 不稳定,则也可以在稳定后解除复位。

[0207] 另一方面,在两个计数器的计数值未进入规定范围内的条件下,计数器比较电路 91d 判定为所输入的 CLK 或 DLL 91a 的动作异常,对 DLL 91a 进行复位。

[0208] 针对这样输入的 CLK,在使用 DLL 91a 生成输出 CLK 的情况下,追加补偿 DLL 91a 的特征的功能,形成 CLK 确定判定电路 91。

[0209] 通过图 5C 所示的 CLK 确定判定电路 91,能够进行控制,使得例如 DLL 91a 由于静电等外界干扰而暂停从而导致从 DLL 91a 输出的输出 CLK 始终异常的情况下,进行复位,进行正常的工作。并且,当所输入的 CLK 的频率或相位存在变动时,有时输出 CLK 的频率在规定期间内成为不稳定,但是,这种情况下,也进行控制使得对 DLL 91a 进行复位而进行稳定的工作。

[0210] 并且,在上述结构的情况下,在起动时 DLL 91a 的输出 CLK 也稳定的情况下,能够使被供给 DLL 91a 输出的输出 CLK 的各电路迅速地开始进行稳定的工作。

[0211] 并且,从处理器 4 侧输入到内窥镜 2A 内的图 5B 所示的 SC-CLK\_EN 的脉冲信号、时钟、同步信号等由于中途的传送缆线而产生延迟,相互产生移相。因此,能够吸收该移相的影响而进行稳定的工作。

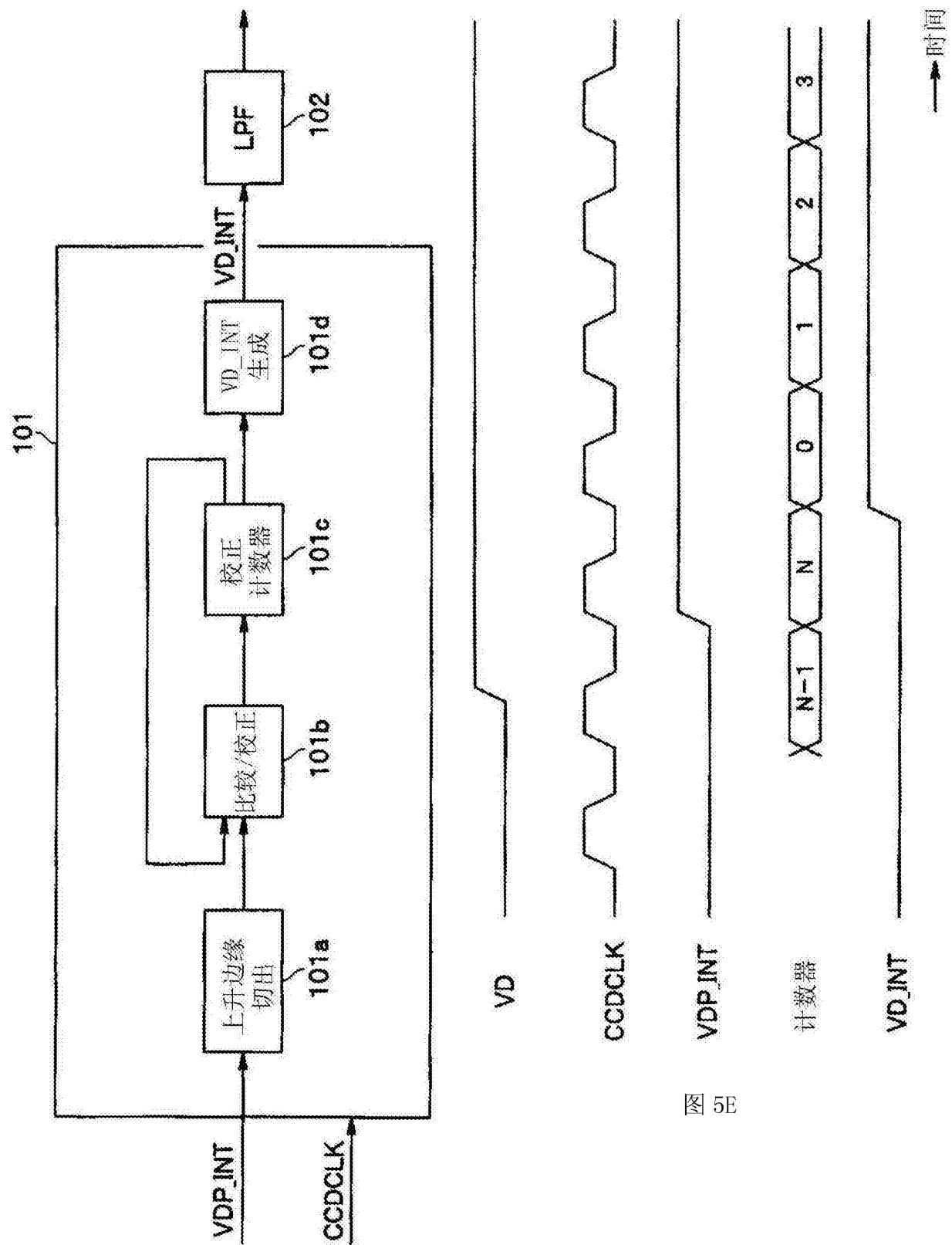

[0212] 图 5D 示出垂直同步信号输出电路 101 的结构,该垂直同步信号输出电路 101 输出

吸收了针对从处理器 4 侧输入到 FPGA 51 的例如垂直同步信号 VDP\_INT 的移相的影响的垂直同步信号 VD\_INT。

[0213] 从处理器 4 输入到垂直同步信号输出电路 101 的 VDP\_INT 通过上升边缘切出电路 101a, 与作为 CCD 时钟的 CCDCLK 同步地切出上升边缘, 在该上升边缘期间内, 使进行比较和校正的比较 / 校正电路 101b 的动作有效。使用切出上升边缘的上升边缘切出电路 101a 进行说明, 但是, 也可以取而代之而使用切出下降边缘的下降边缘切出电路。

[0214] 另外, CCDCLK 被输入到垂直同步信号输出电路 101 内的各电路, 各电路与该 CCDCLK 同步地动作。

[0215] 在每一个垂直同步信号 VD 期间内, 对比较 / 校正电路 101b 输入对 CCDCLK 计数(计测)规定数(图 5E 中为 N)的校正计数器 101c 的计数值。该校正计数器 101c 将计数了规定数的计数值输出到比较 / 校正电路 101b, 并且, 将计数了规定数的定时的脉冲输出到 VD\_INT 生成电路 101d。

[0216] VD\_INT 生成电路 101d 与校正计数器 101c 的输出同步地, 对包含 FPGA 51 的内窥镜 2A 内的各电路输出吸收了移相的垂直同步信号 VD\_INT。

[0217] 比较 / 校正电路 101b 在上升边缘期间内, 对校正计数器 101c 的计数值和规定数进行比较, 根据比较结果对校正计数器 101c 的计数动作进行校正。

[0218] VD\_INT 生成电路 101d 生成与从校正计数器 101c 输出的脉冲同步的垂直同步信号 VD\_INT, 将其输出到使用了降低外界干扰的低通滤波器的 LPF 电路 102。从该 LPF 电路 102 向包含 FPGA 51 的内窥镜 2A 内的各电路供给降低了作为外界干扰的噪声的垂直同步信号 VD\_INT。

[0219] 图 5E 示出图 5D 的定时图。相对于处理器 4 侧生成的垂直同步信号 VD, 实际输入到内窥镜 2A 内的垂直同步信号输出电路 101 的垂直同步信号 VDP\_INT 的相位滞后。

[0220] 该垂直同步信号 VDP\_INT 通过上升边缘切出电路 101a, 切出与 CCDCLK 同步上升的上升边缘, 在该上升边缘期间内, 比较 / 校正电路 101b 有效, 对校正计数器 101c 的计数值和规定数进行比较。

[0221] 在垂直同步信号 VD 和垂直同步信号 VDP\_INT 的相位差为标准的状态下, 计数值为规定数 N, 比较 / 校正电路 101b 进行校正计数器 101c 的计数动作, 直到规定数 N 为止。即, 该情况下, 比较 / 校正电路 101b 不进行校正计数器 101c 的计数动作的校正。此时, 在上升边缘将校正计数器 101c 复位为 0。

[0222] 另一方面, 在垂直同步信号 VDP\_INT 相对于垂直同步信号 VD 的移相(滞后)为 1 个计数的情况下, 比较 / 校正电路 101b 在校正计数器 101c 中设置 1, 进行计数动作(以计数实际被校正的 N+1)。

[0223] 相反地, 在垂直同步信号 VDP\_INT 相对于垂直同步信号 VD 的移相(提前)为 1 个计数的情况下, 比较 / 校正电路 101b 在校正计数器 101c 中设置 N, 进行计数动作(以计数 N-1)。

[0224] 通过这样进行动作, 在移相为 CCDCLK 的 ±1 时钟左右的范围内, 能够生成吸收了该移相的稳定的垂直同步信号 VDP\_INT。在 CCDCLK 的 ±1 以上的相位差的情况下, 在比较 / 校正电路 101b 有效时, 始终将校正计数器 101c 复位为 0。

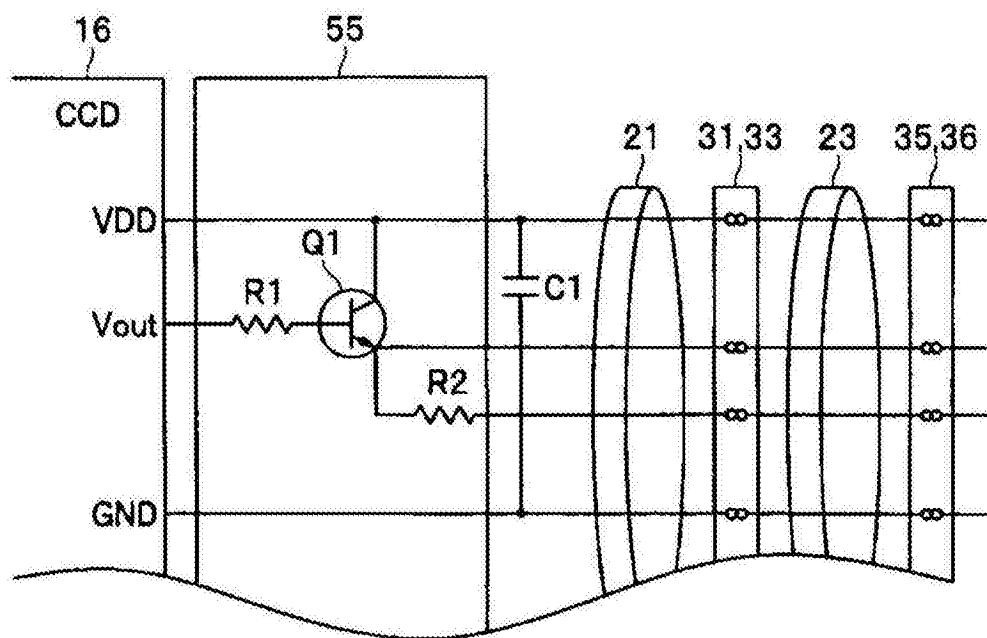

[0225] 图 6A 示出传递 CCD 16 的输出信号等的综合同轴缆线 21、23 和 MC 连接部附近的

结构。另外, MC 连接部表示 MC 和与该 MC 连接的 MC 座, 在图 6A 的情况下, MC 连接部为 MC 31 和 MC 座 33、MC 35 和 MC 座 36。

[0226] 将对 CCD 16 供给电源电压 VDD 的电源端简略记为电源端 VDD。电源端 VDD 经由构成与前端部基板 18 连接的综合同轴缆线 21 的电源线而在 MC 31 和 MC 座 33 处进行 MC 连接(转接)后, 进而, 经由构成综合同轴缆线 23 的电源线而进行基于 MC 35 和 MC 座 36 的 MC 连接, 与 IF 基板 24A 的 CCD/TG 电源电路 53b(参照图 3)连接。

[0227] 并且, 输出 CCD 16 的 CCD 输出信号 Vout 的 CCD 输出端 Vout 经由安装在前端部基板 18 上的电阻 R1 而与构成晶体管阵列 55 的晶体管 Q1 的基极连接, 该晶体管 Q1 集电极与电源端 VDD 连接, 其发射极成为发射极跟随器的信号输出端 Vout, 并且经由电阻 R2 而与输出信号地线 GND(Vout)连接。并且, 电源端 VDD 和地线 GND 经由电容器 C1 连接。

[0228] 和与上述电源端 VDD 连接的电源线的情况同样, 发射极跟随器的信号输出端 Vout 构成综合同轴缆线 21、23, 通过传送摄像信号的信号线, 以中途的 MC 连接的方式进行转接, 与 IF 基板 24A 的放大器 53d 连接。

[0229] 并且, 输出信号地线 GND(Vout)也与上述信号输出端 Vout 的信号线的情况同样, 通过传送(传递)接地电平的接地信号线而与 IF 基板 24A 的未图示的输出信号地线 GND(Vout)连接。

[0230] 并且, 地线 GND 也通过地线而与上述电源线的情况同样, 在中途以 MC 连接的方式进行转接, 与 IF 基板 24A 的未图示的地线 GND 连接。

[0231] 另外, 在图 6A 中, 示出图 3 所示的晶体管阵列 55 中的 1 个通道部分, 针对其他 3 个通道, 也可以应用同样的结构。

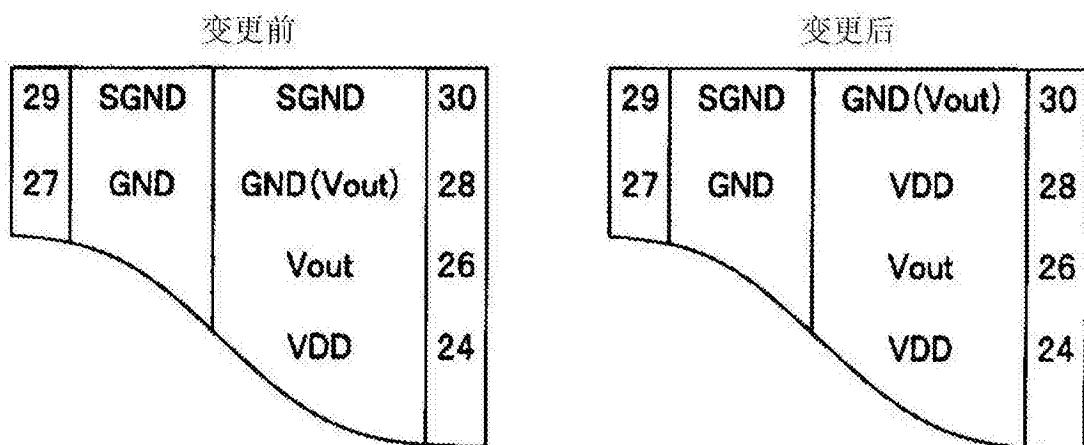

[0232] 在本实施方式中, 如图 6B 所示, 将对各种信号线等进行 MC 连接的连接器触针的配置从变更前的配置变更为变更后所示的配置。在变更前的 MC 连接例中, 编号 30 的连接器触针与屏蔽地线 SGND 连接, 与其相邻的编号 28 的连接器触针与输出信号地线 GND(Vout)连接, 与其相邻的编号 26 的连接器触针与信号输出端 Vout 连接, 与其相邻的编号 24 的连接器触针与电源端 VDD 连接。

[0233] 与此相对, 在变更后的 MC 连接的连接器触针的配置中, 编号 30 的连接器触针与输出信号地线 GND(Vout)连接, 编号 28 的连接器触针与电源端 VDD 连接, 编号 26 的连接器触针与信号输出端 Vout 连接, 编号 24 的连接器触针与电源端 VDD 连接。

[0234] 在利用变更前的连接器触针连接各种信号线的配置状态下, 由于与信号输出端 Vout 相邻地配置输出信号地线 GND(Vout), 所以, 当它们短路(short)时, 在图 6A 所示的晶体管 Q1 中流过过电流, 该情况下, 处理器 4 侧的过电流保护电路检测到该过电流, 关闭电源端 VDD 的电源供给。

[0235] 但是, 在这样相邻的连接器触针间不至于完全短路而输出图像的情况下, 例如当处于以 200 欧姆左右的电阻值短路的状态时, 成为过电流保护电路无法检测为过电流的状态, 继续在晶体管 Q1 中流过过电流, 继续发热。

[0236] 因此, 在本实施方式中, 如变更后的配置所示, 变更为与信号输出端 Vout 相邻地配置电源端 VDD, 利用编号 30 的连接器触针连接输出信号地线 GND(Vout)。

[0237] 在该配置的情况下, 在信号输出端 Vout 成为与电源端 VDD 短路或接近短路的状态的情况下, 无法正常输出图像, 所以, 使用者能够迅速识别为图像异常。并且, 该情况下, 由

于不会在晶体管 Q1 中流过过电流,所以,能够降低由于发热而导致晶体管 Q1 或 CCD 16 故障的可能性。

[0238] 如上所述,通过变更对各种信号线进行 MC 连接的情况下配置,成为容易迅速地识别到产生短路的构造,但是,在本实施方式中采用如下构造:在将各种信号线焊接在 MC、MC 座上的情况下,实施利用树脂覆盖进行了焊接的部位的涂敷,更加有效地防止短路等的产生。

[0239] 图 7 例如示出 MC 基板 34 的背面。图 2A 所示的综合同轴缆线 21 的综合屏蔽件被焊接在屏蔽地线 SGND 用焊盘 Ps 上,由绝缘性的树脂 M1 覆盖(涂敷)。另外,可以利用机械部件铆接综合屏蔽件,也可以通过能够焊接的机械部件进行固定。

[0240] 同样,通过焊接而连接有综合同轴缆线 21 中的各种同轴信号线的信号线(中心导体)的焊盘 P、通过焊接而连接有外侧屏蔽线的焊盘 P 也由绝缘性的树脂 M1 覆盖。在图 7 中仅示出一部分,但是,其余的焊盘 P 的焊接部分也同样由绝缘性的树脂 M1 覆盖。

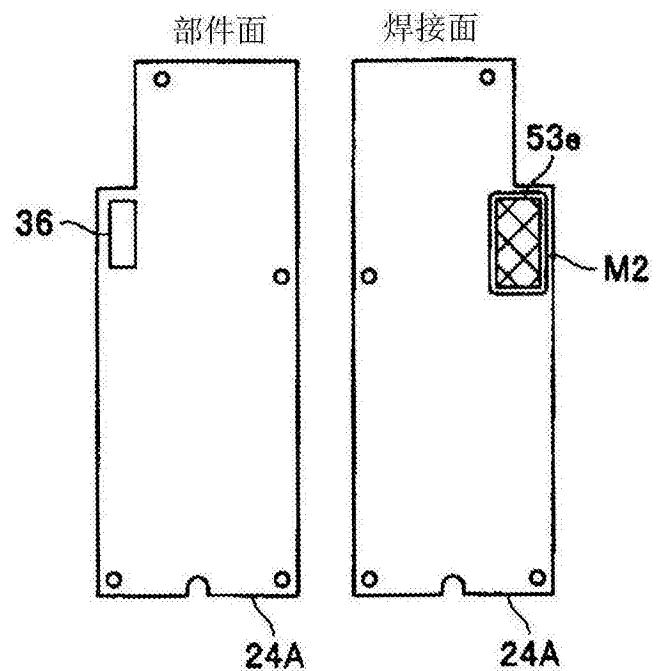

[0241] 并且,图 8A 示出连接器基板 24 中的 IF 基板 24A 的部件面和焊接面(背面),在部件面上设置有连接了 MC 35 的 MC 座 36。

[0242] 并且,在焊接面中,被输入有输出信号 Vout 的放大器 53d(参照图 3)的前级部分的网线(交叉阴影)所示的输入电路部 53e 的印刷图案的布线部分露出,所以,由绝缘性的树脂 M2 覆盖(涂敷)。另外,树脂 M1 和 M2 可以使用相同的树脂。

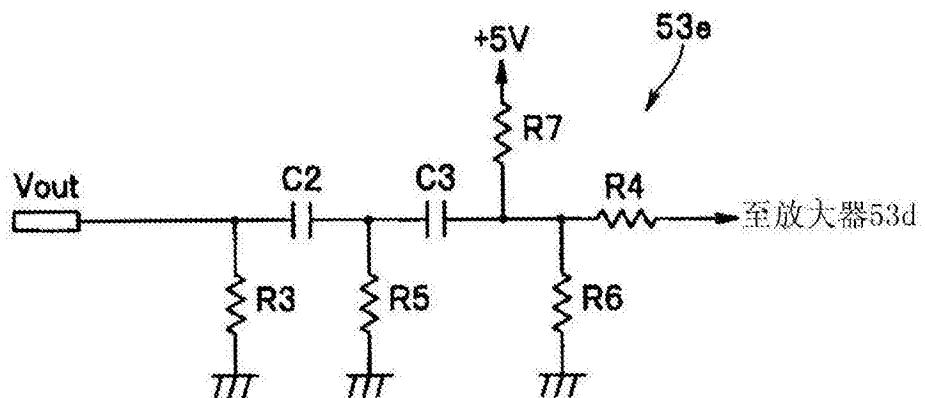

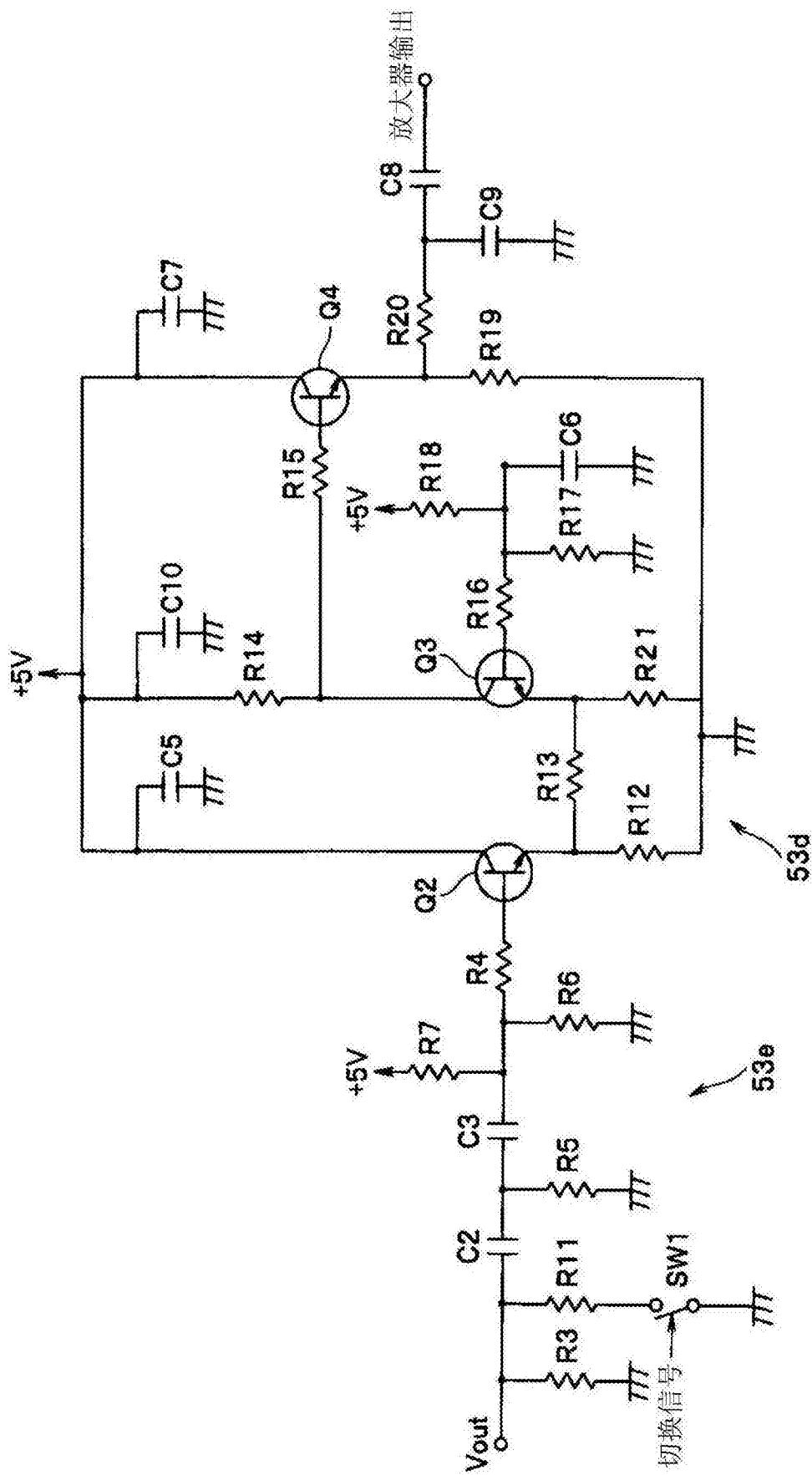

[0243] 图 8B 示出输入电路部 53e 的电路结构。经由 MC 35 输入到输入电路部 53e 的输出信号 Vout 经由电阻 R3 而接地,并且,经由电容器 C2、C3 和电阻 R4 的串联电路输入到放大器 53d。并且,电容器 C2、C3 的连接点经由电阻 R5 而接地。并且,电容器 C3 与电阻 R4 的连接点经由电阻 R6 而接地,并且,经由电阻 R7 而与规定电源端(+5V)连接。

[0244] 如上所述,通过利用绝缘性的树脂 M2 覆盖作为传送输出信号 Vout 的信号线而露出的印刷图案,能够有效防止印刷图案由于湿气等而绝缘不良。不仅是输出信号 Vout,也可以利用绝缘性的树脂涂敷会由于湿气等的影响而引起绝缘不良从而导致发热或热损伤(热伤)的全部电路。

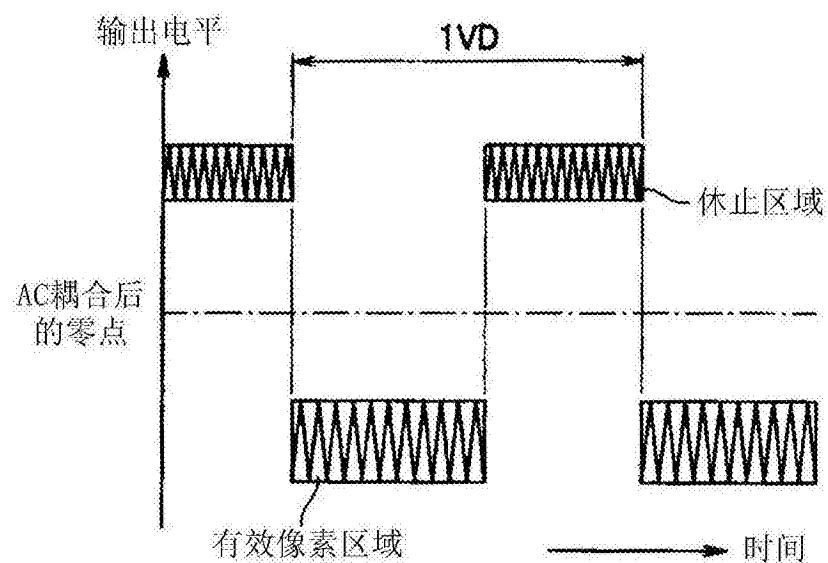

[0245] 并且,在本实施方式中,间歇驱动 CCD 16。具体而言,如图 8C 所示,由于将 1 个垂直同步期间(1 个 VD 所示)作为周期而间歇驱动 CCD 16,所以,CCD 输出信号 Vout 的 DC 电平变动。在 DC 电平变低的驱动期间内,CCD 输出信号 Vout 包含有效像素区域的信号,在 DC 电平变高的休止期间内,不是有效像素区域,而是休止区域的信号。

[0246] 如上所述,在经由输入电路部 53e 将 CCD 输出信号 Vout 直接输入到放大器 53d 的情况下,超过放大器 53d 的后级侧的输入信号的容许范围。因此,作为本实施方式中的放大器 53d,如图 8C 所示,采用如下的电路结构:利用 DC 电平变动的性质,对休止区域的信号进行削波,仅选择性地放大有效像素区域的信号。

[0247] 图 8D 示出对休止区域的信号进行削波的放大器 53d 的电路结构。图 8B 中说明的输入电路部 53e 的输入端还经由电阻 R11 和开关 SW1 的串联电路而接地。即,在图 8D 的电路结构中,在输入端,与电阻 R3 并联地设有电阻 R11 和开关 SW1。

[0248] 该开关 SW1 通过与上述间歇驱动同步的切换信号而接通/断开。具体而言,在驱动期间内,通过(成为 H 电平的)切换信号而接通开关 SW1,在休止期间内断开开关 SW1。而且,输入端在驱动期间内以大约  $910\Omega$  的电阻接地,在休止期间内以  $10k\Omega$  的电阻(具体而

言为 R3) 接地。因此,如图 8C 那样,在驱动期间和休止期间内,CCD 输出信号  $V_{out}$  的 DC 电平变动。

[0249] 经由上述输入电路部 53e 的信号被施加给构成放大器 53d 的晶体管 Q2 的基极,晶体管 Q2 的集电极与规定电源端 (+5V) 连接,并且经由电容器 C5 而接地,晶体管 Q2 的发射极经由电阻 R12 而接地,并且,经由电阻 R13 而与晶体管 Q3 的发射极连接。

[0250] 并且,晶体管 Q3 的发射极经由电阻 21 而接地,晶体管 Q3 的集电极经由电阻 R14 而与规定电源端连接,并且,经由电阻 R15 而与晶体管 Q4 的基极连接。

[0251] 并且,晶体管 Q3 的基极经由电阻 R16 和电阻 R17 而接地。并且,电阻 R16、R17 的连接点经由电容器 C6 而接地,并且经由电阻 R18 而与规定电源端连接。

[0252] 并且,晶体管 Q4 的集电极与规定电源端连接,并且经由电容器 C7 而接地,晶体管 Q4 的发射极经由电阻 R19 而接地,并且经由电阻 R20 和电容器 C8 的串联电路而与放大器 53d 的输出端连接。并且,电阻 R20 和电容器 C8 的连接点经由电容器 C9 而接地。另外,一端连接在晶体管 Q3 上的电阻 R14 的另一端经由电容器 C10 而接地。

[0253] 图 8D 所示的电路结构的作用如下所述。经由输入电路部 53e 输入到放大器 53d 的 CCD 输出信号  $V_{out}$  通过发射极跟随器的晶体管 Q2 而传递到基极接地的晶体管 Q3。由该晶体管 Q3 放大的信号从其集电极通过发射极跟随器的晶体管 Q4 转换为低阻抗而输出。

[0254] 该情况下,如图 8C 所示,在通过晶体管 Q3 放大了休止区域的信号的情况下,晶体管 Q3 的集电极的电压为(全部休止区域的信号)例如 4.8V 的削波电平以上,因此,利用削波电平对全部休止区域的信号进行削波。

[0255] 与此相对,由晶体管 Q3 放大的有效像素区域的信号在晶体管 Q3 的集电极的电压全部为削波电平以下,因此,实质上仅对有效像素区域的信号进行放大并输出。

[0256] 由于这样发挥作用,所以设定为在正电平侧抵消构成放大器 53d 的情况下的 DC 偏压,能够充分放大有效像素区域的信号,另一方面,能够可靠地对休止区域的信号进行削波。

[0257] 通过采用这种结构,通过简单的电路结构,能够仅对 CCD 16 中的有效像素区域的信号进行放大并输出到后级侧。

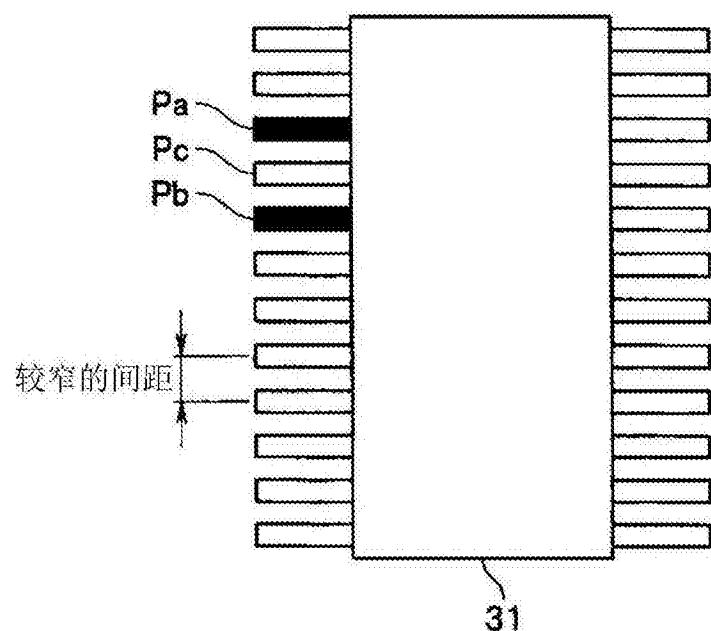

[0258] 进而,在本实施方式中采用如下构造:例如在 MC 31 中的连接器触针间,针对电场强度大的连接器触针间,通过在它们之间配置未连接的连接器触针,能够将配置未连接的连接器触针之前的电场强度降低到其 1/2 左右。

[0259] 在将图 9 的 MC 31 中的相互相邻的连接器触针 Pa、Pb 分配给特定信号或电源的情况下,由于在 MC 31 中各连接器触针间的间距变窄,所以,相邻的连接器触针 Pa、Pb 之间的特定信号或电源的电场强度增大,短路的可能性提高。或者,在电压电平增大的瞬间等,可能导致与相邻的连接器触针间的绝缘不充分。

[0260] 因此,在本实施方式中,采用针对电场强度超过特定值而相邻的连接器触针 Pa、Pb 在两个连接器触针 Pa、Pb 之间配置(均未连接的)未连接的连接器触针 Pc 的构造,防止产生短路及其他异常状态。

[0261] 另外,不限于电场强度大的情况,也可以针对存在较大电压差的连接器触针间、存在较大电流差的连接器触针间配置未连接的连接器触针 Pc。

[0262] 作为图 9 的应用例,不限于 MC 31 的情况,也可以应用于其他的 MC 35、MC 座 33、

36。

[0263] 并且,在本实施方式中,搭载有防止内窥镜 2A 内部的电子部件由于湿度而使特性劣化或腐蚀的传感器。内窥镜 2A 每次用于内窥镜检查时,在药液或高温高湿度环境的状态下进行消毒,并利用清洗装置进行清洗。

[0264] 因此,当长期使用内窥镜 2A 时,湿气可能侵入内窥镜 2A 内部。当在内窥镜 2A 的内部具有规定以上的湿度的状态下进行通电并使用时,与通常的使用状态的情况相比,内窥镜 2A 内的电子部件和基板的劣化和腐蚀加速。

[0265] 因此,如图 1 的虚线所示,在连接器基板 24(内的例如 A/D 基板 24B) 设置用于对内窥镜 2A 内部的湿度进行检测的湿度传感器 71,在处理器 4 内设置有根据湿度传感器 71 的检测信号来检测(计算)内窥镜 2A 内部的湿度的湿度检测电路 72。

[0266] 并且,该湿度检测电路 72 在检测到的湿度为规定阈值以上的高湿度的情况下,对控制电路 29 输出用于警告检测到的湿度处于阈值以上的高湿度状态等的警告信号。控制电路 29 在被输入警告信号时,针对电源电路 27 进行停止对内窥镜 2A 侧供给电源的控制,并且,将警告信号输出到信号处理电路 28。

[0267] 并且,信号处理电路 28 进行信号处理,使得在监视器 5 中显示与警告信号对应的警告消息。该情况下,如以下说明的那样,在内窥镜 2A 侧,在未供给电源的状态下,湿度检测电路 72 驱动湿度传感器 71,根据从湿度传感器 71 输出的检测信号来判定湿度状态,在高湿度的情况下,能够在监视器 5 中显示警告消息。

[0268] 更加优选使用不对内窥镜 2A 侧供给电源就能够通过湿度传感器 71 来检测内窥镜 2A 内的湿度的无源部件构成湿度传感器 71。

[0269] 作为符合这种要求的部件,可以使用检测感湿膜的阻抗变化作为湿度变化的电阻式湿度传感器、检测成对的电极间的静电电容的变化作为湿度变化的电容式湿度传感器。

[0270] 在本实施方式的内窥镜装置 1 中,如上所述,将湿度传感器 71 设置在内窥镜 2A 内部,在检测到内窥镜 2A 内部为高于通常的湿度状态的高湿度状态的情况下,在停止对内窥镜 2A 侧供给电源并有效防止由于高湿度状态下的通电而产生电子部件的劣化和故障的状态下,向使用者警告(告知)处于高湿度状态。并且,通过对使用者进行告知,使用者能够迅速进行解除高湿度状态的修理。

[0271] 并且,也可以不使用上述湿度传感器 71,如以下说明的那样,与内窥镜 2A 内实际使用的电子部件相比,以下使用具有其特性由于湿度而容易劣化的特征的虚设部件。

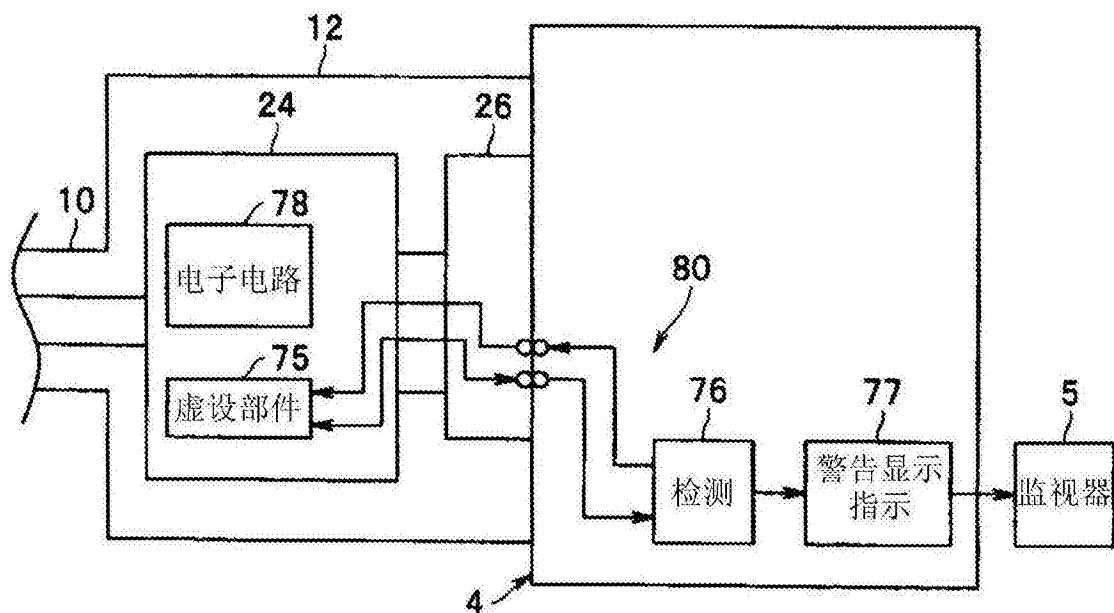

[0272] 图 10A 示出代替设置图 1 的湿度传感器 71 而设置具有上述特征的虚设部件 75 来检测腐蚀的情况的结构。在内窥镜 2A 内的信号用连接器 12 内的连接器基板 24(内的例如 A/D 基板 24B) 上安装虚设部件 75,该虚设部件 75 通过处理器 4 内的检测电路 76 来检测虚设部件 75 的电气特性。检测电路 76 对检测结果和阈值进行比较,判定是否处于由于腐蚀而导致的异常状态。另外,在图 10A 中示出将虚设部件 75 设置在 1 个连接器基板 24 上的情况,但是,也可以将虚设部件 75 设置在内窥镜 2A 内的多个基板上。

[0273] 检测电路 76 在判定为处于异常状态的情况下,将该判定信号输出到警报显示指示电路 77,警报显示指示电路 77 将检测电路 76 检测到异常状态的警报消息输出到监视器 5,对使用者告知产生腐蚀的异常状态。

[0274] 通过虚设部件 75、检测电路 76 和警报显示指示电路 77 构成检测是否产生由于腐

蚀而导致的异常状态的腐蚀异常检测装置 80。

[0275] 另外,在图 10A 中,标号 78 表示由 FPGA 51 等形成的电子电路。

[0276] 作为设置上述虚设部件 75 的情况下的形状和特性,考虑以下要件。作为由于湿气等而导致的特性劣化或由于基板的印刷图案的腐蚀而导致的故障的原因,例如在假设了焊接或元件电镀部的熔析的情况下,考虑如下故障:端子间或露出图案间由于熔析金属而成为短路状态,端子或图案变小而成为开放状态。

[0277] 因此,具有端子间间距比产品中使用的部件窄的图案成为虚设部件 75 的形状要件,能够判别短路和开放的器件成为虚设部件 75 的特性要件。

[0278] 例如在连接器基板 24 的产品中使用的(端子间的)最小间距为 0.5mm 的情况下,将 0402 尺寸 (0.4mm×0.2mm) 的具有数  $k\Omega$  的规定电阻值 R 的电阻器安装在连接器基板 24 上,作为虚设部件 75。

[0279] 然后,通过检测电路 76 来监视上述电阻器的电阻值,在监视到的电阻值为比规定电阻值 R 大  $\Delta$  的阈值  $Rt1 (= R + \Delta)$  以上的情况下、或监视到的电阻值为比规定电阻值小  $\Delta$  的阈值  $Rt2 (= R - \Delta)$  以下的情况下,判定为处于产生腐蚀的异常状态。然后,通过监视器 5 向使用者告知异常状态的判定结果。

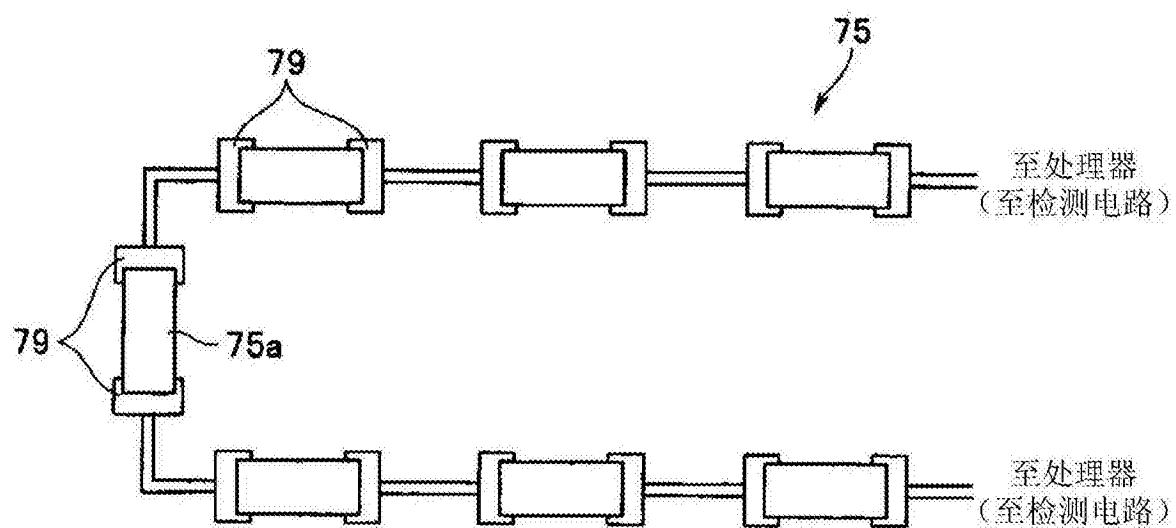

[0280] 在上述说明中,说明了在较窄的端子间安装 1 个电阻器而形成虚设部件 75 的情况,但是,如图 10B 所示,也可以在设置于串联图案上的多个较窄的作为端子的焊盘 79 间分别安装电阻器 75a 来形成虚设部件 75。这样,通过在可能产生腐蚀的宽范围内设置的多个较窄的端子间以串联连接的方式安装多个(图 10B 中为 7 个)电阻器 75a,可以提高检测腐蚀的功能。

[0281] 这样,通过将由于腐蚀而容易产生故障的虚设部件 75 安装在内窥镜 2A 内,能够迅速检测容易产生故障的异常状态并向使用者进行告知,提示进行修理,由此,能够防止或减少在异常状态下使用内窥镜 2A 的情况。

[0282] 如参照图 4A 等说明的那样,根据本实施方式,能够提供如下的内窥镜:在使用小型连接器以多个电源电压驱动摄像元件的情况下,也能够迅速检测由于短路等而导致的电源电压的异常状态,容易迅速地消除异常状态。

[0283] 另外,作为上述内窥镜,主要对内窥镜 2A 的情况进行了说明,但是,可知在具有与所说明的部分有关的结构的内窥镜 2B、2C 的情况下,也同样能够应用。

[0284] 并且,在图 4A-图 4C 中,构成为在作为电压比较单元的比较电路 64 中对 A/D 转换单元进行了 A/D 转换后的数字电压和阈值进行比较,但是,也可以构成为,不设置 A/D 转换单元,而使用对模拟电压和阈值进行比较的模拟电压比较单元。

[0285] 另外,在图 4A-图 4C 中示出具有作为电源生成单元的 CCD 电源电路 53b' 的结构,该 CCD 电源电路 53b' 根据从处理器 4 侧供给的多个电源电压,进一步在内窥镜 2A 内生成不同的多个电源电压,供给到 CCD 16,但是,本发明不限于这种结构的情况。例如,在不具有 CCD 电源电路 53b' 而将处理器 4 所生成的多个电源电压经由电源线 60a、60b 等电源线直接供给到 CCD 16 的结构的情况下也能够应用。

[0286] 并且,如图 4A-图 4C 那样,在采用在内窥镜 2A 内具有 CCD 电源电路 53b' 的结构的情况下,也可以构成为,进一步对从 CCD 电源电路 53b' 输出的多个电源的电源电压进行监视,根据监视结果来控制针对 CCD 16 的电源供给,例如可以采用图 11 所示的结构。另

外,也可以将本结构应用于图 3 所示的基板内电路用电源电路 52p,根据基板内电路用电源电路 52p 的电源电压的监视结果来控制针对基板内电路的电源供给。

[0287] 图 11 所示的 CCD 电源电压监视电路 63C 构成为,在图 4A 的 CCD 电源电压监视电路 63 的结构中进一步具有比较电路 64C 和 ROM 65C。构成为,通过作为第 2 电压比较单元的(如比较电路 64 那样内置 2 个比较电路的)比较电路 64C,分别对经由 CCD 电源电路 53b' 的开关 61c、61d 输出到 CCD 16 的 2 个电源电压和来自 ROM65C 的阈值进行比较,将比较结果输出到电源供给控制部 66。

[0288] 然后,电源供给控制部 66 监视 CCD 电源电路 53b' 的输入端侧和输出端侧的多个电源电压并进行控制,使得在处于正常电压的范围内的判定结果的情况下,直接使 CCD 电源电路 53b' 进行动作,在处于正常电压的范围外的异常电压的判定结果的情况下,切断从 CCD 电源电路 53b' 供给到 CCD 16 侧的电源电压。并且,电源供给控制部 66 进行控制,使得在异常电压的判定结果的情况下,通过告知信号生成电路 67 进行告知。当采用这种结构时,能够更加详细且迅速地检测内窥镜 2A 等内窥镜内的电源的异常状态,能够迅速进行消除该异常状态的对策。

[0289] 另外,在上述图 4A- 图 4C、图 11 等中说明了 CCD 电源电压监视电路,但是,也可以如以下说明的那样,构成为通过对不同的 2 个电源间(产生不同电源电压的 2 个不同电源间)的电压进行比较,检测分别对不同电源电压进行转接的连接器触针间的短路(short)等。

[0290] 图 12 示出 CCD 电源电压监视电路 63D,该 CCD 电源电压监视电路 63D 对由相邻的连接器座触针 40a、40b 进行转接的电源线 60a、60b 的(电源)电压 V1、V2 间的电压进行比较,检测相邻的连接器座触针 40a、40b 间的短路或不至于短路的绝缘不良。

[0291] 关于该 CCD 电源电压监视电路 63D,例如在图 4A 的 CCD 电源电压监视电路 63 中,代替被输入经由 A/D 转换电路 62a、62b 的数字电压 V1、V2 的比较电路 64,设置有生成 2 个电压 V1、V2 间的差电压的作为减法单元的减法器 121 和比较电路 122。另外,不限于应用于图 4A 的情况,也可以应用于图 4B 等。

[0292] 2 个电压 V1、V2 经由通过从较大的电压中减去较小的电压而生成 2 个电压 V1、V2 间的差电压的减法器 121,被输入到作为比较单元的比较电路 122。这里,设较大的电压为 V1(即  $V1 > V2$ ) 进行说明。比较电路 122 对 2 个电压 V1、V2 间的差电压(由减法器 121 生成的电压)  $V1 - V2$  和预先存储在 ROM 65 中的用于判定短路或绝缘不良的电压值即阈值 Vta 进行比较。

[0293] 关于该阈值 Vta 进行说明时,例如在以相当于产生绝缘不良的电阻值来连接连接器座触针 40a、40b 间的情况下,经由减法器 121 输入到比较电路 122 的电压值作为上述阈值 Vta 而预先存储在 ROM 65 中。换言之,在 ROM 65 中存储有用于判定产生成为短路之前的绝缘不良的阈值 Vta 的信息。比较电路 122 对差电压  $V1 - V2$  和阈值 Vta 进行比较,将比较结果输出到电源供给控制部 66。

[0294] 电源供给控制部 66 根据比较结果来控制针对 CCD 16 侧的电源供给。电源供给控制部 66 在比较结果为  $V1 - V2 > Vta$  的情况下,判定为处于未产生短路或绝缘不良的正常状态,在比较结果为  $V1 - V2 \leq Vta$  的情况的情况下,判定为处于产生短路或绝缘不良的异常状态。

[0295] 在正常状态下,满足  $V1-V2>Vta$  的条件,在产生绝缘不良时,比较结果为  $V1-V2 = Vta$  左右,当绝缘不良发展时,成为  $V1-V2<Vta$  的状态。并且,在即将短路的情况下,  $V1-V2<Vta$  成为接近  $0<Vta$  的状态。

[0296] 电源供给控制部 66 在比较结果为  $V1-V2>Vta$  即前者的情况下,继续进行 CCD 电源电路 53b' 的动作。另一方面,在比较结果为  $V1-V2 \leq Vta$  即后者的异常状态的情况下,电源供给控制部 66 停止 CCD 电源电路 53b' 的动作等,并且将异常判定信号输出到告知信号生成电路 67。

[0297] 告知信号生成电路 67 生成用于告知连接器座触针 40a、40b 间产生短路或绝缘不良的异常状态的告知信号,使用告知信号重叠电路 67a 发送到处理器 4 侧。

[0298] 处理器 4 的控制电路 29 将告知信号输出到信号处理电路 28,信号处理电路 28 在影像信号中重叠告知信号。然后,监视器 5 显示内窥镜图像和告知信号,手术医生通过告知信号,能够迅速地识别到连接器座触针 40a、40b 间产生短路或绝缘不良。

[0299] 因此,针对产生了异常状态的内窥镜 2A,能够迅速进行与产生该异常状态对应的修理等,能够消除异常状态。

[0300] 另外,在图 12 中采用如下结构:为了检测是否产生连接器座触针 40a、40b 间的短路或绝缘不良,对由电源线 60a、60b 传送的(电源)电压  $V1$ 、 $V2$  间的差电压和阈值  $Vta$  进行比较,但是,也可以对由其他 2 个电源线(例如  $60a'$ 、 $60b'$ )传送的电源电压间的差电压和对应的阈值进行比较,检测分别转接了其他 2 个电源线的(特别是相邻配置的)连接器触针间是否产生短路或绝缘不良。

[0301] 并且,在图 4A、图 4B 等结构中,也可以进一步追加减法器 121 和比较电路 122,追加检测是否产生连接器座触针 40a、40b 间的短路或绝缘不良的功能。并且,对上述实施方式等进行部分组合等而构成的实施方式也属于本发明。

[0302] 本申请以 2011 年 9 月 22 日在日本申请的日本特愿 2011-207465 号为优先权主张的基础进行申请,上述公开内容被引用到本申请说明书和权利要求书中。

图 1

图 2A

图 2C

图 2D

图 2E

图 3

图 4A

图 4B

图 4C

图 4D

图 4E

图 5A

电源接通时

电源断开时

图 5B

图 5C

图 5D

图 5E

图 6A

图 6B

图 7

图 8A

图 8B

图 8C

图 8D

图 9

图 10A

图 10B

图 11

图 12

|                |                                                                     |         |            |

|----------------|---------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 内窥镜                                                                 |         |            |

| 公开(公告)号        | <a href="#">CN103384492B</a>                                        | 公开(公告)日 | 2015-12-02 |

| 申请号            | CN201280009568.9                                                    | 申请日     | 2012-09-18 |

| [标]申请(专利权)人(译) | 奥林巴斯医疗株式会社                                                          |         |            |

| 申请(专利权)人(译)    | 奥林巴斯医疗株式会社                                                          |         |            |

| 当前申请(专利权)人(译)  | 奥林巴斯株式会社                                                            |         |            |

| [标]发明人         | 大河文行<br>小西纯<br>桥本秀范<br>田中靖洋<br>松井泰宪                                 |         |            |

| 发明人            | 大河文行<br>小西纯<br>桥本秀范<br>田中靖洋<br>松井泰宪                                 |         |            |

| IPC分类号         | A61B1/04 G02B23/24 H04N5/228                                        |         |            |

| CPC分类号         | H04N5/2253 A61B1/00032 A61B1/04 A61B1/045 G02B23/2469 H04N2005/2255 |         |            |

| 代理人(译)         | 李辉                                                                  |         |            |

| 审查员(译)         | 任晓帅                                                                 |         |            |

| 优先权            | 2011207465 2011-09-22 JP                                            |         |            |

| 其他公开文献         | CN103384492A                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                      |         |            |

#### 摘要(译)

内窥镜具有：摄像元件，其搭载于插入部的前端部；布线，其传递用于驱动摄像元件的具有多个不同电源电压的电源、驱动摄像元件的驱动信号、从驱动信号所驱动的摄像元件输出的摄像信号、和接地电平；基板，其设有对布线进行转接的连接器；电压比较部，其对多个不同电源电压进行比较；以及电源供给控制部，其根据电压比较部的比较结果，控制针对摄像元件的电源供给。