(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2017-0030605

(43) 공개일자 2017년03월17일

- (51) 국제특허분류(Int. Cl.)

*B06B 1/02* (2006.01) *A61B 8/00* (2006.01)

*B81B 7/00* (2017.01) *B81C 1/00* (2006.01)

*G01N 29/24* (2006.01)

- (52) CPC특허분류

*B06B 1/0292* (2013.01)

*A61B 8/4483* (2013.01)

- (21) 출원번호 10-2017-7003696

- (22) 출원일자(국제) 2015년07월14일

심사청구일자 없음

- (85) 번역문제출일자 2017년02월09일

- (86) 국제출원번호 PCT/US2015/040342

- (87) 국제공개번호 WO 2016/011000

국제공개일자 2016년01월21일

- (30) 우선권주장

62/024,179 2014년07월14일 미국(US)

(뒷면에 계속)

- (71) 출원인

버터플라이 네트워크, 잉크.

미국 06437 코네티컷주 길포드 올드 웨필드 스트리트 530

- (72) 발명자

로스버그, 조나단, 앤.

미국 06437 코네티컷주 길퍼드 운카스 포인트 로드 215

에일리, 수잔, 애이.

미국 02180 매사추세츠주 스톤팹 던클리 애비뉴 21

(뒷면에 계속)

- (74) 대리인

양영준, 김연송, 백만기

전체 청구항 수 : 총 24 항

(54) 발명의 명칭 마이크로제작된 초음파 트랜스듀서 및 관련된 장치와 방법

**(57) 요약**

상보형 금속 산화물 반도체(CMOS) 기판과 통합된 미세가공된 초음파 트랜스듀서들뿐만 아니라 이러한 디바이스들의 제작 방법들이 설명된다. 제작은 2개의 별개의 웨이퍼 본딩 단계를 수반할 수 있다. 웨이퍼 본딩은 기판(302) 내에 밀봉된 캐비티들(306)을 제작하는 데 이용될 수 있다. 웨이퍼 본딩은 또한, 기판(302)을 CMOS 웨이퍼와 같은 다른 기판(304)에 본딩하는 데 이용될 수 있다. 적어도 제2 웨이퍼 본딩이 저온에서 수행될 수 있다.

**대 표 도**

(52) CPC특허분류

*B81B 7/007* (2013.01)

*B81C 1/00238* (2013.01)

*B81C 1/00301* (2013.01)

*G01N 29/2406* (2013.01)

*B81B 2201/0271* (2013.01)

*B81C 2201/019* (2013.01)

*B81C 2203/036* (2013.01)

*B81C 2203/0792* (2013.01)

*H01L 2224/4813* (2013.01)

(72) 발명자

**파이프, 키스, 지.**

미국 94306 캘리포니아주 팔로 알토 마타데로 애비뉴 635

**산체스, 네바다, 제이.**

미국 06437 코네티컷주 길퍼드 리틀 메도우 로드 1280

**랠스턴, 타일러, 에스.**

미국 06413 코네티컷주 클린턴 비치 파크 로드 56

(30) 우선권주장

14/635,197 2015년03월02일 미국(US)

14/716,152 2015년05월19일 미국(US)

## 명세서

### 청구범위

#### 청구항 1

방법으로서,

내부에 개방된 캐비티들(open cavities)이 형성된 제1 웨이퍼를 제2 웨이퍼와 본딩(bonding)하고 나서 상기 제1 웨이퍼를 약 30 마이크론 미만의 두께로 얇게 함으로써, 복수의 밀봉된 캐비티를 갖는 제작된 기판(engineered substrate)을 형성하는 단계;

450°C를 초과하지 않는 온도에서 상기 제작된 기판을 제3 웨이퍼와 본딩하는 단계; 및

상기 제작된 기판을 상기 제3 웨이퍼와 본딩한 후에, 상기 제2 웨이퍼를 약 30 마이크론 미만의 두께로 얇게 하는 단계

를 포함하는 방법.

#### 청구항 2

제1항에 있어서, 상기 제1 웨이퍼는 실리콘-온-절연체(silicon-on-insulator)(SOI) 웨이퍼이고, 상기 제1 웨이퍼를 얇게 하는 것은 상기 제1 웨이퍼의 핸들 층(handle layer)을 제거하는 것을 포함하는, 방법.

#### 청구항 3

제2항에 있어서, 상기 제2 웨이퍼는 SOI 웨이퍼이고, 상기 제2 웨이퍼를 얇게 하는 것은 상기 제2 웨이퍼의 핸들 층을 제거하는 것을 포함하는, 방법.

#### 청구항 4

제1항에 있어서, 상기 제1 웨이퍼는 도핑된 층(doped layer)을 포함하는 벌크 실리콘 웨이퍼(bulk silicon wafer)이고, 상기 도핑된 층은 약 10 마이크론 미만의 두께를 가지며 상기 제1 웨이퍼의 제1 면에 근접하고, 상기 제1 웨이퍼를 얇게 하는 것은, 상기 제1 웨이퍼를 배면으로부터 상기 도핑된 층까지 얇게 하는 것을 포함하고, 상기 배면은 상기 제1 면의 반대편에 있는, 방법.

#### 청구항 5

제4항에 있어서, 상기 제2 웨이퍼는 약 10 마이크론 미만의 두께를 갖는 도핑된 층을 포함하는 벌크 실리콘 웨이퍼이고, 상기 제2 웨이퍼를 얇게 하는 것은, 상기 제2 웨이퍼를 배면으로부터 상기 제2 웨이퍼의 상기 도핑된 층까지 얇게 하는 것을 포함하는, 방법.

#### 청구항 6

제1항 내지 제5항 중 어느 한 항에 있어서, 상기 제1 웨이퍼를 약 30 마이크론 미만의 두께로 얇게 하는 것은, 상기 제1 웨이퍼를 약 5 마이크론 미만의 두께로 얇게 하는 것을 포함하고, 상기 제2 웨이퍼를 약 30 마이크론 미만의 두께로 얇게 하는 것은, 상기 제2 웨이퍼를 약 5 마이크론 미만의 두께로 얇게 하는 것을 포함하는, 방법.

#### 청구항 7

제1항에 있어서, 상기 제2 웨이퍼는 상기 복수의 밀봉된 캐비티 중 적어도 하나의 캐비티 위에 맴브레인을 형성하고, 상기 제3 웨이퍼는 상보형 금속 산화물 반도체(CMOS) 웨이퍼이며, 상기 방법은 상기 CMOS 웨이퍼 상의 집적 회로를 상기 맴브레인에 접속하는 단계를 더 포함하는, 방법.

#### 청구항 8

제1항 내지 제7항 중 어느 한 항에 있어서, 상기 제1 웨이퍼의 일부는 전기적으로 도전성이고, 상기 제작된 기판을 상기 제3 웨이퍼와 본딩하는 단계는 상기 제1 웨이퍼의 상기 일부와 상기 제3 웨이퍼 상의 전기적 콘택트

(electrical contact) 사이에 전기적 접속을 형성하는 단계를 포함하는, 방법.

### 청구항 9

제8항에 있어서, 상기 제1 웨이퍼의 상기 일부는 전극을 정의하는 패턴으로 도핑되는, 방법.

### 청구항 10

제9항에 있어서, 상기 일부는 단결정 실리콘을 포함하는, 방법.

### 청구항 11

제9항에 있어서, 상기 일부는 폴리실리콘을 포함하는, 방법.

### 청구항 12

제9항에 있어서, 상기 일부는 비정질 실리콘(amorphous silicon)을 포함하는, 방법.

### 청구항 13

제9항에 있어서, 상기 도핑은 제1 영역과 콘택트 영역을 정의하고, 상기 제1 영역과 콘택트 영역은 동일한 도핑 유형을 가지고, 상기 콘택트 영역은 상기 제1 영역보다 높은 도핑 농도를 갖는, 방법.

### 청구항 14

제8항 내지 제13항 중 어느 한 항에 있어서, 상기 제1 웨이퍼의 상기 일부는 상기 제1 웨이퍼의 상기 일부에 인접하게 위치한 적어도 하나의 캐비티의 폭보다 작은 폭을 갖는, 방법.

### 청구항 15

제1항 내지 제14항 중 어느 한 항에 있어서, 상기 제작된 기판을 상기 제3 웨이퍼와 본딩하는 단계는, 공융 본딩(eutectic bond) 또는 열압착 본딩(thermocompression bond) 또는 실리사이드 본딩(silicide bond)을 형성하는 단계를 포함하는, 방법.

### 청구항 16

제1항 내지 제15항 중 어느 한 항에 있어서, 상기 제작된 기판을 상기 제3 웨이퍼와 본딩하는 단계는, 상기 복수의 밀봉된 캐비티를 밀폐식으로 밀봉하는(hermetically sealing) 밀봉 링(seal ring)을 형성하는 단계를 포함하는, 방법.

### 청구항 17

제1항 내지 제16항 중 어느 한 항에 있어서, 복수의 밀봉된 캐비티를 갖는 제작된 기판을 형성하는 단계는, 폭과 깊이를 갖는 적어도 하나의 밀봉된 캐비티를 형성하는 단계를 포함하고, 깊이에 대한 폭의 비율은 50 내지 300인, 방법.

### 청구항 18

제17항에 있어서, 상기 깊이는 약 0.1 마이크론 내지 약 5 마이크론인, 방법.

### 청구항 19

제1항 내지 제18항 중 어느 한 항에 있어서, 상기 제작된 기판을 형성하는 일부로서 그리고 상기 제작된 기판을 상기 제3 웨이퍼와 본딩하기 이전에 어닐링을 수행함으로써 상기 제1 웨이퍼 및/또는 제2 웨이퍼에서 도핑을 활성화하는 단계를 더 포함하는 방법.

### 청구항 20

제1항 내지 제19항 중 어느 한 항에 있어서, 상기 복수의 밀봉된 캐비티 중 적어도 하나의 캐비티를 개봉(unseal)하기 위해 상기 적어도 하나의 캐비티에 대한 개구를 상기 제작된 기판 내에 형성하는 단계를 더 포함하는 방법.

### 청구항 21

제1항 내지 제20항 중 어느 한 항에 있어서, 상기 제1 웨이퍼의 실리콘 산화물 층에 개방된 캐비티들을 형성하는 단계를 더 포함하는 방법.

### 청구항 22

제1항 내지 제21항 중 어느 한 항에 있어서, 상기 제1 웨이퍼를 얇게 한 이후에 상기 제1 웨이퍼에서 복수의 트렌치를 에칭하는 단계를 더 포함하고, 상기 복수의 트렌치는 상기 제1 웨이퍼의 복수의 전극 영역을 정의하는, 방법.

### 청구항 23

제22항 또는 제23항에 있어서, 상기 복수의 트렌치를 절연 재료로 채우는 단계를 더 포함하는 방법.

### 청구항 24

제1항 내지 제23항 중 어느 한 항에 있어서, 상기 제작된 기판을 상기 제3 웨이퍼와 본딩하는 단계는 상기 제작된 기판을 상기 제3 웨이퍼와 모놀리식 통합(monolithically integrating)하는 단계를 포함하는, 방법.

## 발명의 설명

### 기술 분야

[0001]

관련 출원의 상호참조

[0002]

본 출원은, 그 전체가 참조로 본 명세서에 포함되는, 변리사 사건 번호 B1348.70013US00이고, 2014년 7월 14일 출원된, 발명의 명칭이 "Microfabricated Ultrasonic Transducers and Related Apparatus and Methods"인 미국 가출원 제62/024,179호에 대해 35 U.S.C. § 119(e) 하의 혜택을 주장한다.

[0003]

본 출원은 또한, 그 전체가 참조로 본 명세서에 포함되는, 변리사 사건 번호 B1348.70013US02이고, 2015년 5월 19일 출원된, 발명의 명칭이 "Microfabricated Ultrasonic Transducers and Related Apparatus and Methods"인 미국 가출원 제14/716,152호에 대해 35 U.S.C. § 120 하의 혜택을 주장하는, 일부 연속 출원이다.

[0004]

미국 특허 출원 제14/716,152호는, 그 전체가 참조로 본 명세서에 포함되는, 변리사 사건 번호 B1348.70013US01이고, 2015년 3월 2일 출원된, 발명의 명칭이 "Microfabricated Ultrasonic Transducers and Related Apparatus and Methods"인 미국 가출원 제14/635,197호에 대해 35 U.S.C. § 120 하의 혜택을 주장하는, 연속 출원이다.

[0005]

미국 특허 출원 제14/635,197호는, 그 전체가 참조로 본 명세서에 포함되는, 변리사 사건 번호 B1348.70013US00이고, 2014년 7월 14일 출원된, 발명의 명칭이 "Microfabricated Ultrasonic Transducers and Related Apparatus and Methods"인 미국 가출원 제62/024,179호에 대해 35 U.S.C. § 119(e) 하의 혜택을 주장한다.

[0006]

분야

[0007]

본 명세서에 설명되는 기술은 상보형 금속 산화물 반도체(CMOS; complementary metal oxide semiconductor) 트랜스듀서 및 이를 형성하기 위한 방법에 관한 것이다.

## 배경 기술

[0008]

용량성 마이크로제작된 초음파 트랜스듀서(CMUT; Capacitive Micromachined Ultrasonic Transducer)는 마이크로제작된 캐비티 위에 맴브레인을 포함하는 공지된 디바이스이다. 맴브레인은 음향 신호를 전기적 신호로 또는 그 반대로 변환(transduce)하는데 이용될 수 있다. 따라서, CMUT는 초음파 트랜스듀서로서 동작할 수 있다.

[0009]

CMUT를 제작하기 위해 2가지 유형의 프로세스가 이용될 수 있다. 희생층 프로세스는 희생층 위의 제1 기판 상에 CMUT의 맴브레인을 형성한다. 희생층을 제거하면, 맴브레인이 캐비티 위에 매달리게 된다. 웨이퍼 본딩 프로세스는 2개의 웨이퍼를 함께 본딩하여 맴브레인을 갖는 캐비티를 형성한다.

## 발명의 내용

- [0010] 본 출원의 양태는, CMUT의 제작 및 CMOS 웨이퍼와의 통합에 의해 CMOS 초음파 트랜스듀서(CUT; CMOS ultrasonic transducer)를 형성하는 것에 관한 것이다. 본 출원의 양태에 따르면, 2개의 웨이퍼 본딩 단계를 수반하는 웨이퍼-레벨 프로세스가 제공된다. 제1 웨이퍼 본딩 단계는, 2개의 실리콘-온-절연체(SOI) 웨이퍼를 함께 본딩함으로써 밀봉된 캐비티를 형성할 수 있고, 결과적인 본딩된 구조물은 제작된 기판(engineered substrate)으로서 간주된다. 강한 본딩을 달성하는 것을 용이하게 하기 위하여, 예를 들어, 어닐링 동안, 비교적 높은 온도가 이용될 수 있다. 제작된 기판의 2개의 SOI 웨이퍼 중 하나의 핸들 층이 제거된 다음, 제2 웨이퍼 본딩 단계가 수행되어 집적 회로(IC)가 형성된 CMOS 웨이퍼와 제작된 기판을 본딩할 수 있다. 제2 웨이퍼 본딩 단계는 CMOS 웨이퍼 상의 IC에 대한 손상을 피하기 위해 비교적 낮은 온도를 이용할 수 있다. 그 다음, 제작된 기판의 제2 SOI 웨이퍼의 핸들 층이 제거되어, 멤브레인을 제작된 기판의 캐비티 위에 남겨 둘 수 있다. CMOS IC와 제작된 기판 사이의 전기적 접속은 제어 가능한 초음파 트랜스듀서가 실현되는 것을 허용한다.

- [0011] 전술된 웨이퍼-레벨 프로세스는 통합된 CMUT 및 CMOS IC를 갖는 초음파 디바이스를 생성할 수 있다. CMUT의 캐비티는, 제작된 기판을 형성하는데 이용되는 2개의 SOI 웨이퍼의 실리콘 디바이스 층을 나타내는 2개의 실리콘 층 사이에 형성될 수 있다. 그러나 2개의 SOI 웨이퍼의 핸들 층은 완성된 디바이스에 없을 수도 있고, 이것은, 특히, 얇은 디바이스 치수 및 그에 따른 작은 크기를 달성하는 것을 용이하게 한다. 따라서, 이 프로세스는, 일부 양태들에서, 제작된 기판을 CMOS 웨이퍼와 본딩하는 것을 허용하면서 핸들 층을 제거하기에 적절한 단계들을 포함할 수 있다. 스루-실리콘 비아(TSV; thru-silicon via)의 이용은 최종 디바이스에서 없을 수도 있고, 적절한 대안적인 구조물이 결과적인 초음파 트랜스듀서에 전기적 접속을 제공하는 데 이용된다.

- [0012] 본 출원의 또 다른 양태에 따르면, 전술된 SOI 웨이퍼들 중 하나 또는 양쪽 모두 대신에 벌크 실리콘 웨이퍼가 이용될 수 있다. 이러한 경우에, 웨이퍼의 핸들 층을 제거하는 것이 아니라, 예를 들어 벌크 실리콘 웨이퍼의 도핑 층에 의해 표현된 에칭 정지부(etch stop)를 이용하거나 타이밍식 에칭(timed etch)을 이용하여 원하는 지점까지 웨이퍼를 얇게 할 수 있다. 따라서, SOI 또는 벌크 실리콘 웨이퍼 또는 이 둘의 조합을 이용하여 실질적으로 동일한 구조가 달성될 수 있다.

- [0013] 따라서, 본 출원의 양태는, SOI 웨이퍼와 벌크 실리콘 웨이퍼 사이에 캐비티를 개재하여 함께 밀봉함으로써 밀봉된 캐비티를 형성하는 제1 웨이퍼 본딩 단계를 포함하는 웨이퍼-레벨 프로세스를 제공하며, 그 결과의 본딩된 구조물은 제작된 기판으로서 간주된다. 강한 본딩을 달성하는 것을 용이하게 하기 위하여, 예를 들어, 어닐링 동안, 비교적 높은 온도가 이용될 수 있다. 벌크 실리콘 웨이퍼는 얇게 될 수 있으며, 그 후 제2 웨이퍼 본딩 단계가 수행되어 집적 회로(IC) 형성된 CMOS 웨이퍼와 제작된 기판을 본딩할 수 있다. 제2 웨이퍼 본딩 단계는 CMOS 웨이퍼 상의 IC에 대한 손상을 피하기 위해 비교적 낮은 온도를 이용할 수 있다. 그 다음, 제작된 기판의 SOI 웨이퍼의 핸들 층이 제거되어, 멤브레인을 제작된 기판의 캐비티 위에 남겨 둘 수 있다.

- [0014] 본 출원의 한 양태에 따르면, 제1 SOI 웨이퍼의 제1 실리콘 디바이스 층 상의 실리콘 산화물 층에 복수의 캐비티를 형성하는 단계, 제1 SOI 웨이퍼를 제2 SOI 웨이퍼와 본딩한 다음 제1 및 제2 SOI 웨이퍼를 어닐링하는 단계, 및 제1 SOI 웨이퍼의 핸들 층 및 매립된 산화물 층을 제거하는 단계를 포함하는 방법이 제공된다. 이 방법은, 제1 실리콘 디바이스 층을 적어도 하나의 금속 층이 형성된 제3 웨이퍼에 본딩하는 단계, 및 제1 실리콘 디바이스 층을 제3 웨이퍼에 본딩한 후에 제2 SOI 웨이퍼의 핸들 층을 제거하는 단계를 더 포함한다.

- [0015] 본 출원의 한 양태에 따르면, 내부에 개방된 캐비티가 형성된 제1 웨이퍼를 제2 웨이퍼와 본딩하고 나서 제1 웨이퍼를 약 30 마이크론 미만의 두께로 얇게 함으로써 복수의 밀봉된 캐비티를 갖는 제작된 기판을 형성하는 단계를 포함하는 방법이 제공된다. 이 방법은, 450°C를 초과하지 않는 온도에서 제3 웨이퍼와 제작된 기판을 본딩하는 단계와, 제3 웨이퍼와 제작된 기판을 본딩한 후에, 제2 웨이퍼를 약 30 마이크론 미만의 두께로 얇게 하는 단계를 더 포함한다. 일부 실시예에서, 제2 웨이퍼, 또는 그 일부는, 초음파 트랜스듀서의 멤브레인으로서 기능하도록 구성되므로, 얇게 된 이후의 그 두께는 진동을 허용하기에 적절하다. 대조적으로, 이러한 경우에, 제1 웨이퍼가 진동하지 않는 것이 바람직할 수 있고, 따라서 얇게 된 이후 그 두께는 진동을 최소화 또는 방지하기에 충분히 클 수 있다. 추가 실시예에서, 제1 및 제2 웨이퍼 양쪽 모두는, 예를 들어 상이한 주파수들에서 진동하여 다중-주파수 트랜스듀서를 생성하도록 구성될 수 있다. 예를 들어, 제1 멤브레인은 제2 멤브레인의 중심 주파수의 절반에서 공진하도록 구성될 수 있다.

- [0016] 본 출원의 한 양태에 따르면, 제1 SOI 웨이퍼의 제1 실리콘 디바이스 층 상에 실리콘 산화물 층을 형성하는 단계를 포함하는 방법이 제공되고, 제1 SOI 웨이퍼는, 핸들 층, 매립된 산화물(BOX) 층, 및 핸들 층에 가까운 배면과 핸들 층에서 면 전면을 갖는 제1 실리콘 디바이스 층을 가진다. 이 방법은, 실리콘 산화물 층에 복수의 캐비티를 형성하는 단계와, 제2 SOI 웨이퍼의 제2 실리콘 디바이스 층이 실리콘 산화물 층과 접촉하고 복수의

실리콘 산화물 층 내의 복수의 캐비티를 밀봉하도록 제2 SOI 웨이퍼와 제1 SOI 웨이퍼를 본딩하는 단계를 더 포함한다. 이 방법은, 제1 및 제2 SOI 웨이퍼를 함께 본딩한 이후에 어닐링하는 단계를 더 포함하며, 어닐링은 500°C 위의 온도를 이용한다. 이 방법은, 제1 SOI 웨이퍼의 핸들 층을 제거하는 단계, 복수의 캐비티에 대응하는 제1 실리콘 디바이스 층의 복수의 전극 영역을 정의하는 단계, 복수의 캐비티를 에칭하는 단계, 및 복수의 트렌치 절연 재료로 채우는 단계를 더 포함한다. 이 방법은, 제1 실리콘 디바이스 층의 배면 상에 금속 콘택트들을 형성하는 단계를 더 포함하고, 금속 콘택트들 중 적어도 일부는 복수의 전극 영역에 대응한다. 이 방법은, CMOS 웨이퍼 상의 본딩 지점과 접촉하는 제1 실리콘 디바이스 층의 배면 상의 금속 콘택트를 이용하여 제1 실리콘 디바이스 층을 내부에 접적 회로가 형성된 CMOS 웨이퍼와 본딩하는 단계를 더 포함하며, 여기서, 제1 실리콘 디바이스 층과 CMOS 웨이퍼의 본딩은 450°C 아래에서 수행된다. 이 방법은 제2 SOI 웨이퍼의 핸들 층을 제거하는 단계를 더 포함한다.

[0017] 본 출원의 한 양태에 따르면, 내부에 접적 회로가 형성된 CMOS 웨이퍼, 및 CMOS 웨이퍼와 모듈리식으로 통합되고 3개보다 적은 수의 실리콘 층들을 포함하는 기판을 포함하는 장치가 제공된다. 기판의 제1 실리콘 층 및 기판의 제2 실리콘 층은 그 사이에 복수의 캐비티가 개재되어 배치된다.

[0018] 본 출원의 한 양태에 따르면, 내부에 접적 회로가 형성된 CMOS 웨이퍼, 및 CMOS 웨이퍼와 모듈리식으로 통합된 기판을 포함하는 장치가 제공되고, 기판은 CMOS 웨이퍼에 가까운 제1 면과, CMOS 웨이퍼에서 면 제2 면을 가진다. 이 기판은, 제1 면으로부터 제2 면으로의 순서로, 제1 실리콘 층, 제1 실리콘 층과 직접 접촉하고 내부에 복수의 캐비티가 형성된 실리콘 산화물 층, 및 실리콘 산화물과 직접 접촉하고 복수의 캐비티를 위한 맴브레인을 형성하는 제2 실리콘 층을 포함한다.

[0019] 본 출원의 한 양태에 따르면, 서로 본딩된 제1 및 제2 웨이퍼를 갖는 제작된 기판을 본딩하는 방법이 제공된다. 제1 웨이퍼는 제1 웨이퍼의 전극 영역을 격리시키는 격리 트렌치를 갖는다. 이 방법은, IC를 갖는 접적 회로 (IC) 웨이퍼 상에 재분배 층(redistribution layer)을 형성하는 단계, 재분배 층 상에 땀납 범프 어레이 (solder bump array)를 형성하는 단계, 및 제작된 기판의 제1 웨이퍼가 IC 웨이퍼와 제작된 기판의 제2 웨이퍼 사이에 있게 하도록 제작된 기판을 IC 웨이퍼와 땀납 범프 본딩(solder bump bonding)하는 단계를 포함한다. 땀납 범프 어레이의 제1 땀납 범프는 제1 웨이퍼의 전극 영역과 전기적으로 접촉한다.

[0020] 본 출원의 한 양태에 따르면, 서로 본딩된 제1 및 제2 기판을 포함하는 제작된 기판을 포함하는 장치가 제공된다. 제1 기판은 전극 영역을 정의하는 격리 트렌치를 갖는다. 이 장치는 제작된 기판의 제1 기판과 본딩되고 재분배 층을 포함하는 IC를 갖는 접적 회로(IC) 기판을 더 포함한다. 이 장치는 재분배 층 상에 땀납 범프 어레이를 더 포함하여, 제1 기판과 IC 기판 사이에 땀납 범프 본드(solder bump bond)를 형성한다. 땀납 범프 어레이의 제1 땀납 범프는 전극 영역과 전기적으로 접촉한다.

[0021] 여기서 사용되는 용어 "SOI 웨이퍼"는, 핸들 층, 매립 산화물(BOX) 층, 및 BOX 층에 의해 핸들 층으로부터 분리된 실리콘 디바이스 층을 포함하는 통상적인 의미를 갖는다.

[0022] 여기서 사용되는 용어 "제작된 기판"은 기본 실리콘 웨이퍼 또는 표준 SOI 웨이퍼와는 상이하게 제작된 기판을 지칭한다. 제작된 기판은 또한, 복수의 별개의 요소(예를 들어, 복수의 별개의 웨이퍼)를 결합함으로써 형성된 "복합 기판"일 수 있다.

[0023] 본 개시내용 전반에 걸쳐, 용어 "대략"의 사용은, 문맥상 달리 지시하지 않는 한, "정확히"를 포함한다. 예를 들어, 거리가 약 10 마이크론보다 작다는 설명은, 거리가 10 마이크론보다 작은 시나리오를 포함하는 것으로 이해되어야 한다.

### 도면의 간단한 설명

[0024] 본 출원의 다양한 양태 및 실시예들이 이하의 도면들을 참조하여 설명될 것이다. 도면들은 축척비율대로 그려진 것은 아니라는 점을 이해하여야 한다. 복수의 도면들 내에 나타나는 항목들은 이들이 나타나는 모든 도면들에서 동일한 참조 번호로 표시된다.

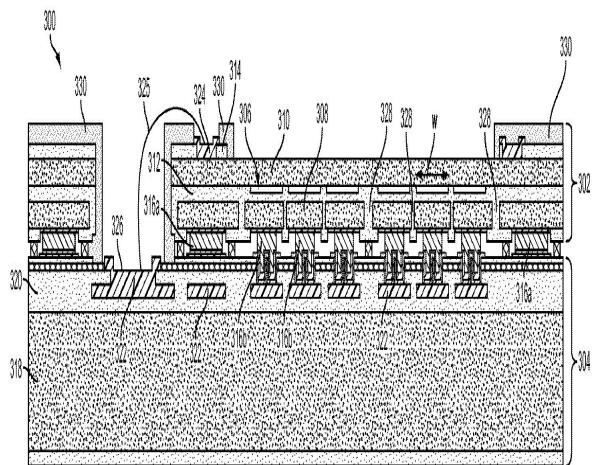

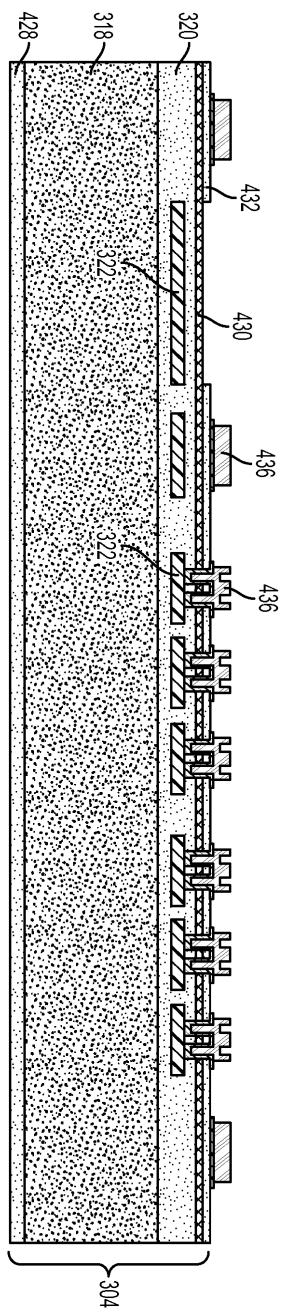

도 1은, 본 출원의 비제한적인 실시예에 따른, CMOS 웨이퍼와 통합된 초음파 트랜스듀서를 제작하기 위한 제작 시퀀스의 플로차트이다.

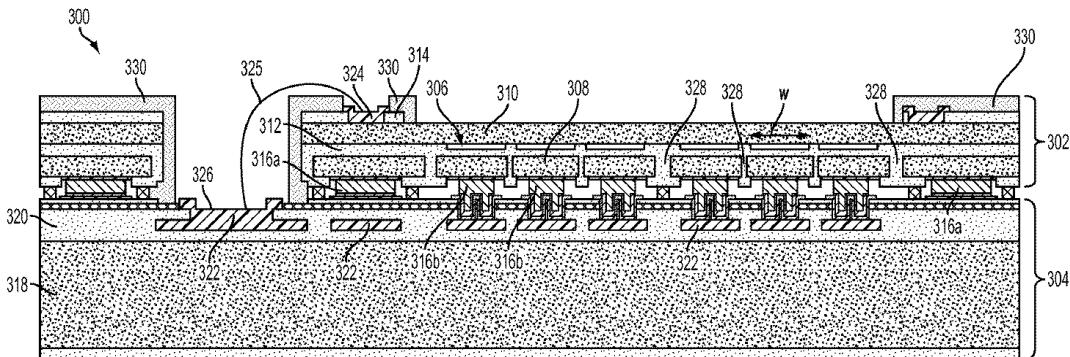

도 2는 도 1의 프로세스(100)의 스테이지의 상세한 예를 나타내는 플로차트이다.

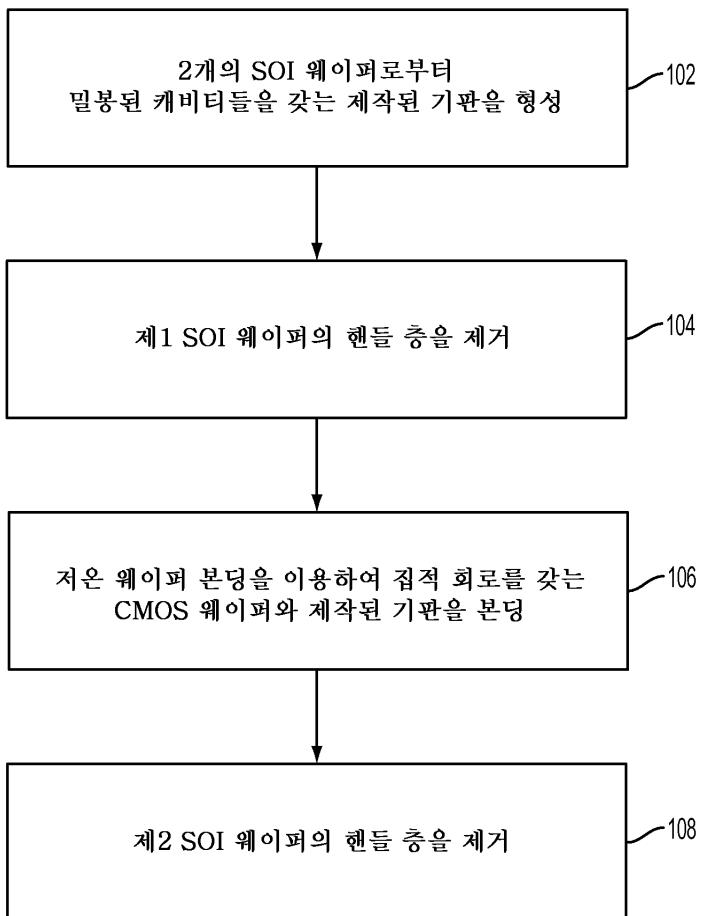

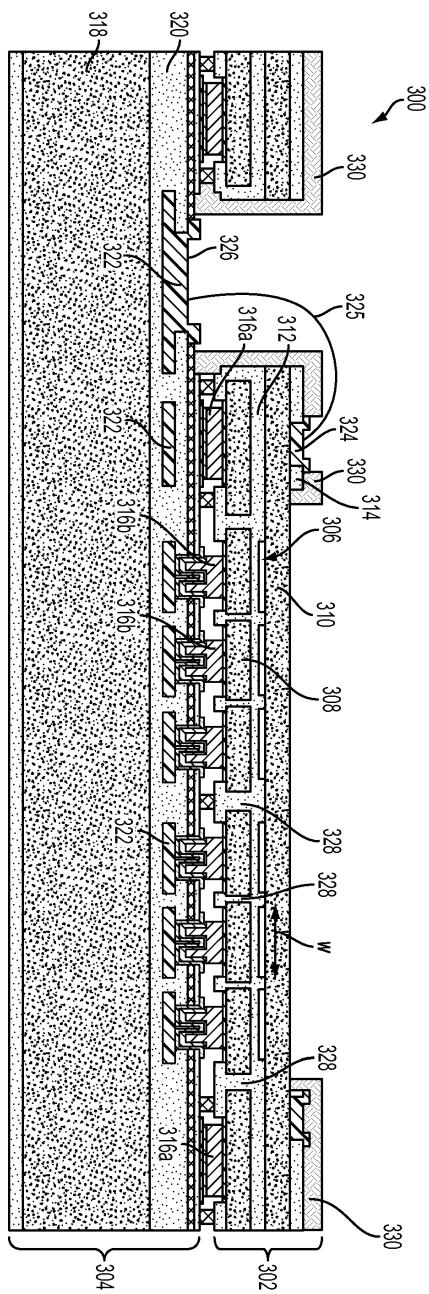

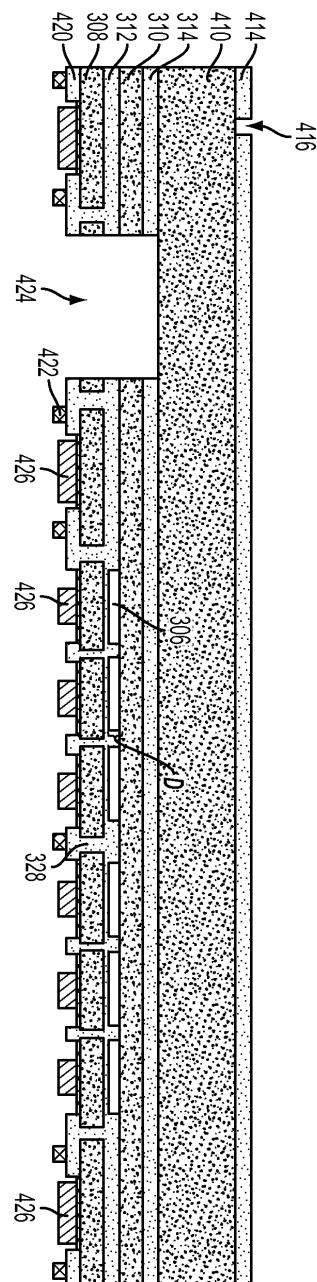

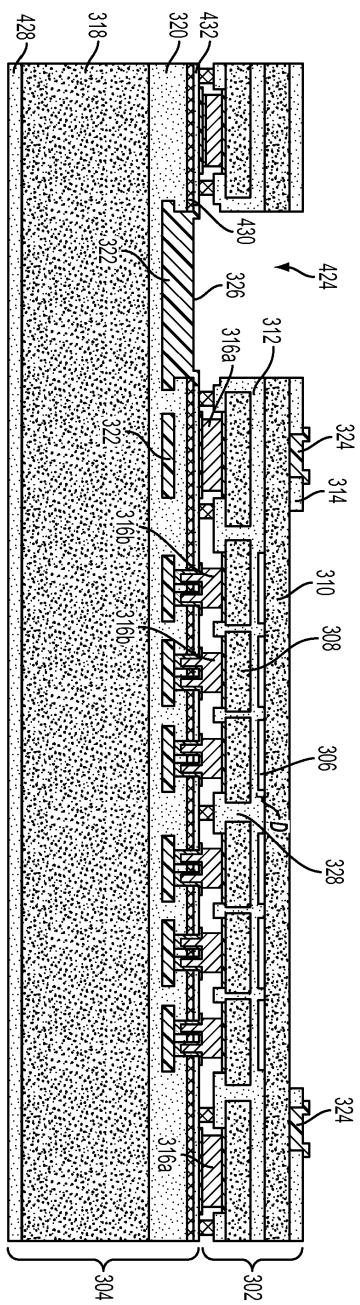

도 3은, 본 출원의 비제한적인 실시예에 따른, 밀봉된 캐비티를 갖는 제작된 기판(engineered substrate)과 통

합된 CMOS 웨이퍼를 포함하는 디바이스의 단면도이다.

도 4a 내지 도 4t는, 본 출원의 비제한적인 실시예에 따른, 도 3의 디바이스를 형성하기 위한, 도 1의 제작 시퀀스와 일치하는 제작 시퀀스를 나타낸다.

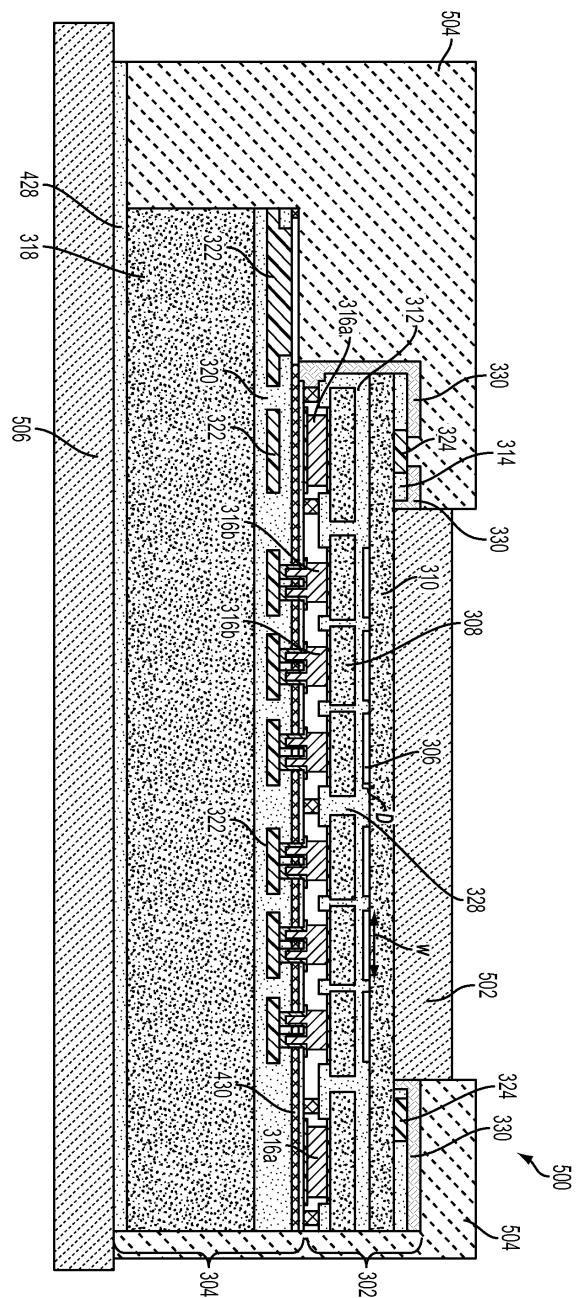

도 5는 추가의 팩키징을 갖는 도 3의 디바이스의 단면도이다.

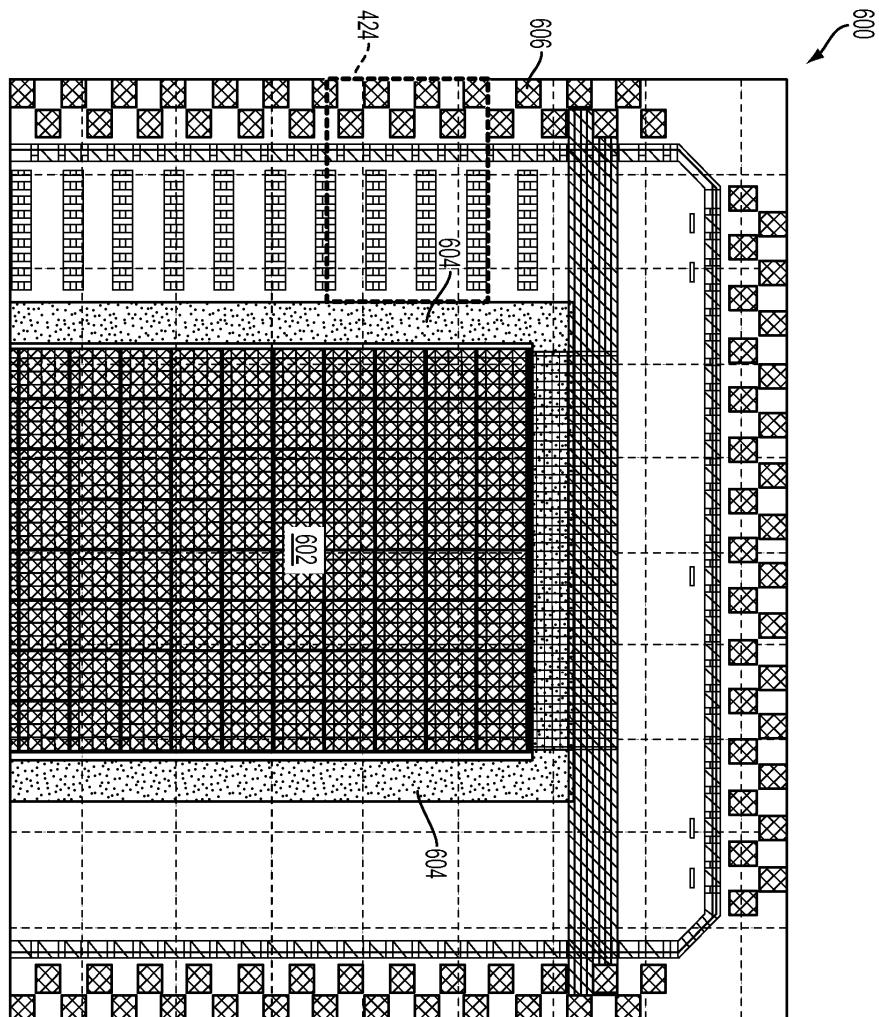

도 6은, 본 출원의 비제한적인 실시예에 따른, 도 3의 디바이스의 피쳐를 포함하는 초음파 디바이스의 평면도이다.

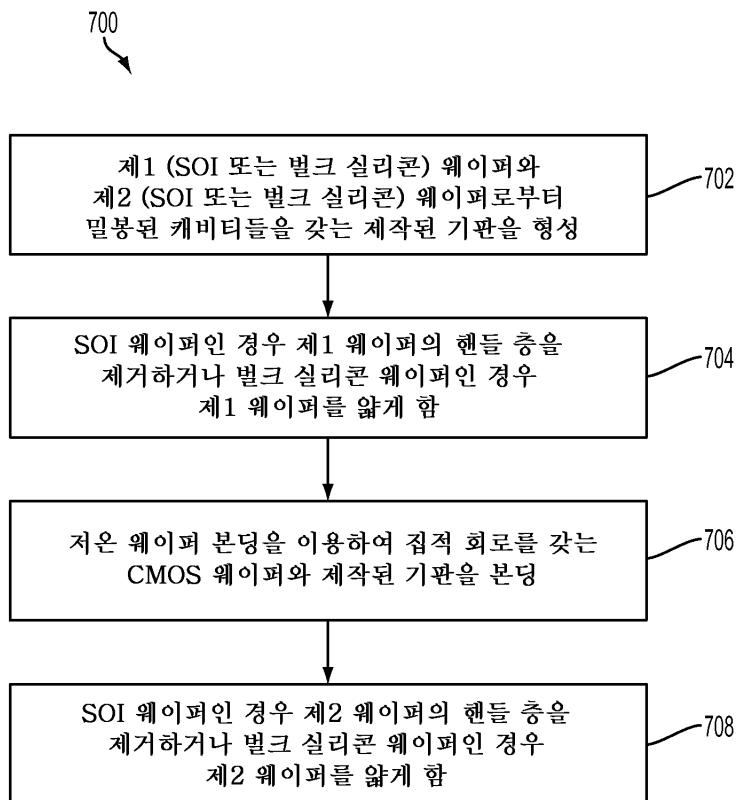

도 7은, 본 출원의 비제한적인 실시예에 따른, 도 1의 방법을 포함하는, CMOS 웨이퍼와 통합된 초음파 트랜스듀서를 제작하기 위한 제작 시퀀스의 플로차트이다.

도 8a 내지 도 8d는, 본 출원의 비제한적인 실시예에 따른, 도 4a 내지 도 4t의 제작 시퀀스의 일부에 대한 변형을 나타낸다.

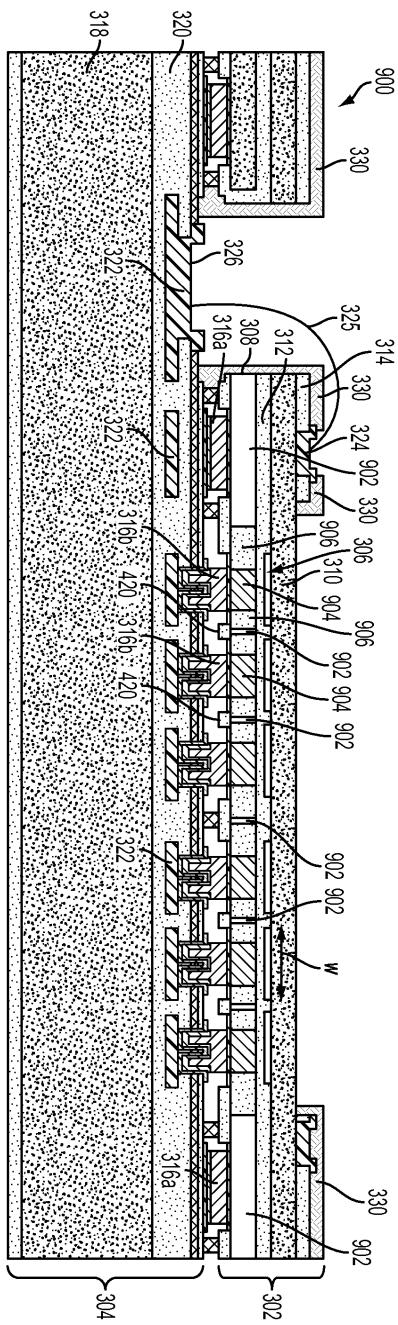

도 9는, 본 출원의 비제한적인 실시예에 따른, 초음파 트랜스듀서의 전극을 정의하기 위해 패터닝된 도핑이 이용되는 도 3의 디바이스(300)의 구현을 나타낸다.

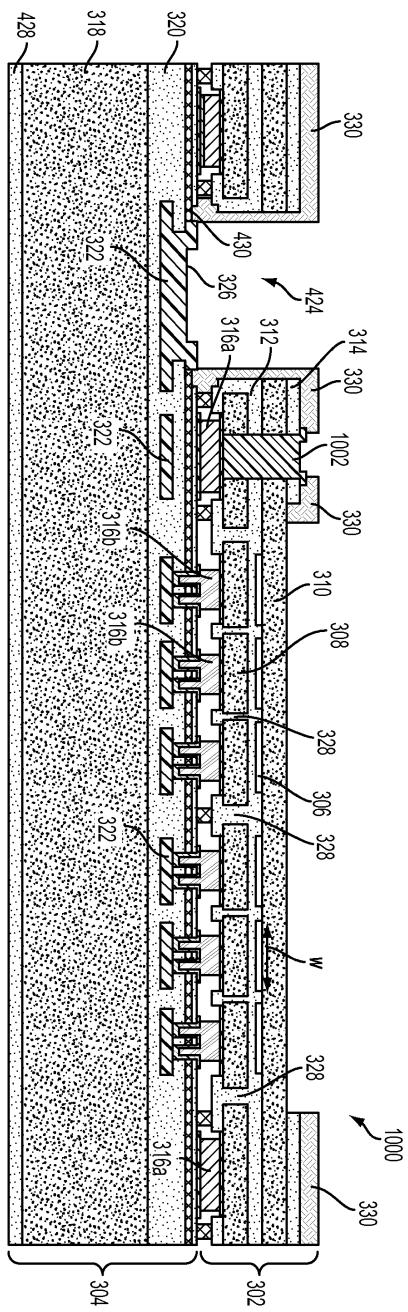

도 10은, 본 출원의 비제한적인 실시예에 따른, 임베딩된 콘택트가 초음파 트랜스듀서 멤브레인에 전기적 접속을 제공하는 도 3의 디바이스(300)의 변형을 나타낸다.

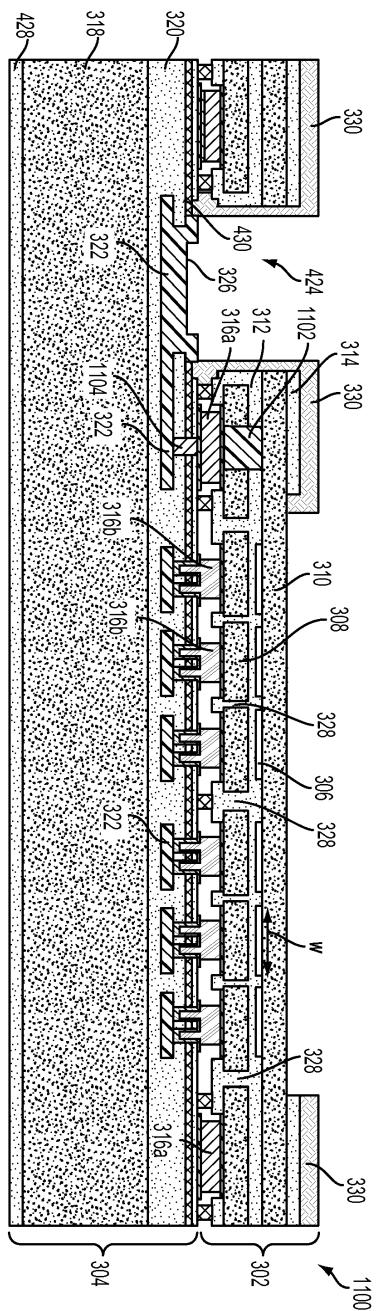

도 11은, 본 출원의 비제한적인 실시예에 따른, 임베딩된 콘택트가 초음파 트랜스듀서 멤브레인으로의 전기적 접속을 제공하는 도 3의 디바이스(300)의 변형 및 도 10의 디바이스의 대안을 나타낸다.

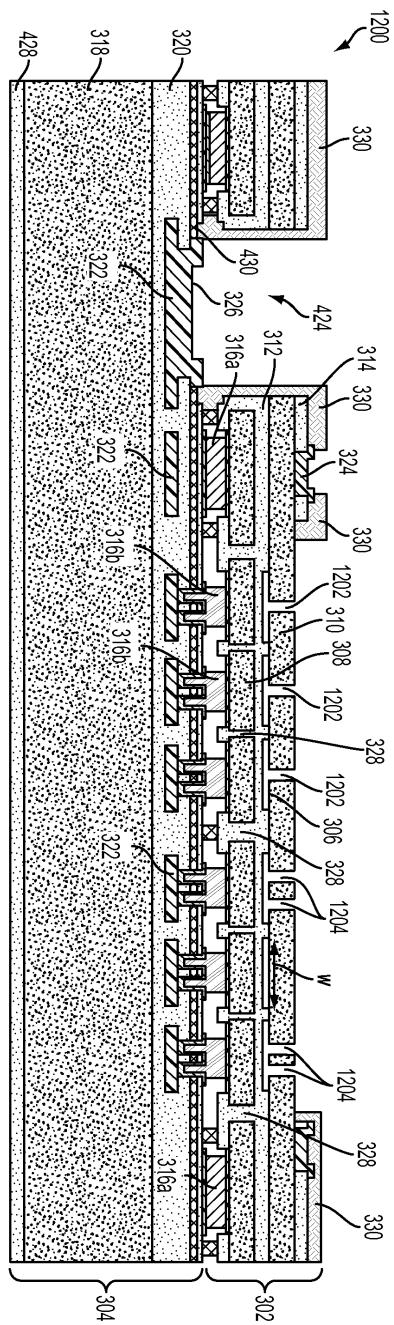

도 12는, 비제한적인 실시예에 따른, 초음파 트랜스듀서의 캐비티가 밀봉되지 않은 도 3의 디바이스(300)의 변형을 나타낸다.

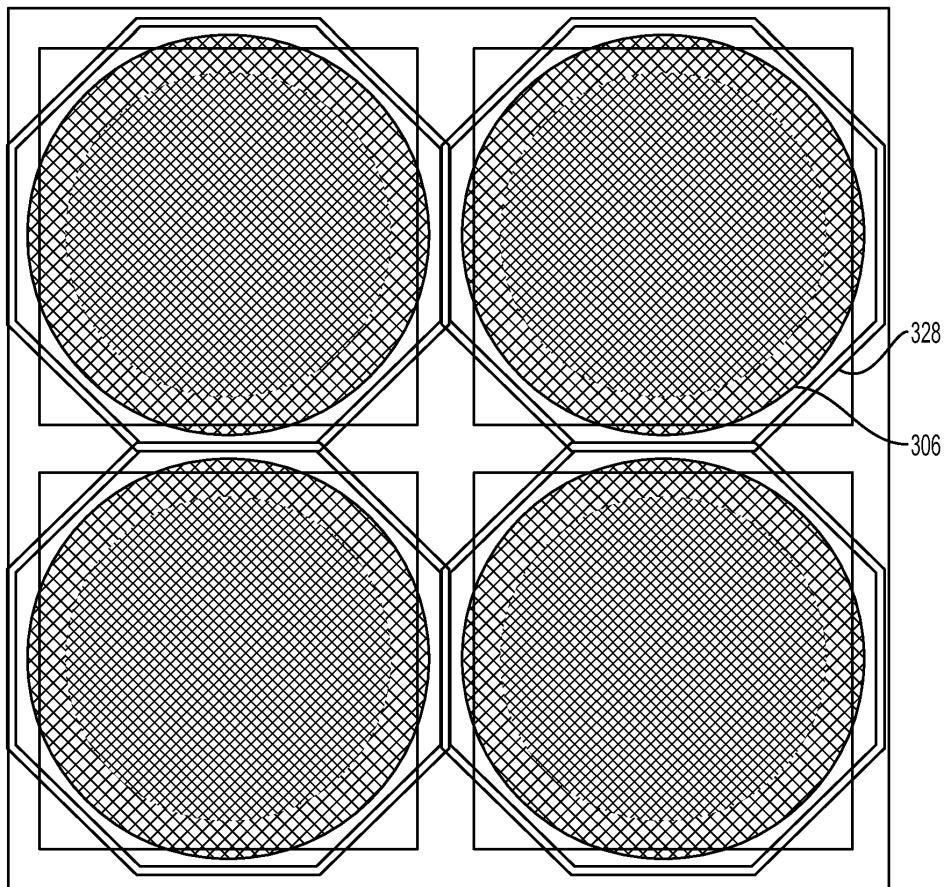

도 13은, 비제한적인 실시예에 따른, 초음파 트랜스듀서들을 격리하는 격리 트렌치 윤곽의 예를 나타내는 평면도이다.

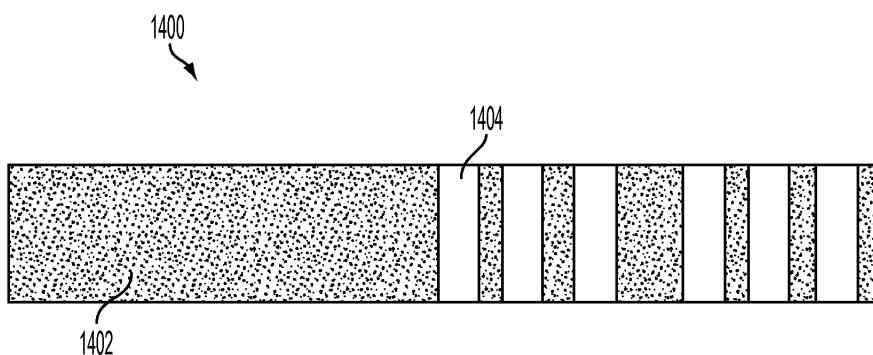

도 14는, 본 출원의 비제한적인 실시예에 따른, 제작된 기판을 제작하는데 이용될 수 있는, TSV를 갖는 실리콘 웨이퍼를 나타낸다.

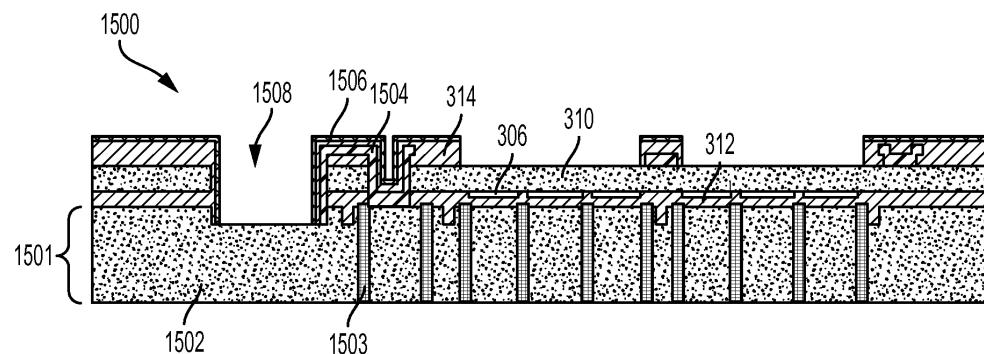

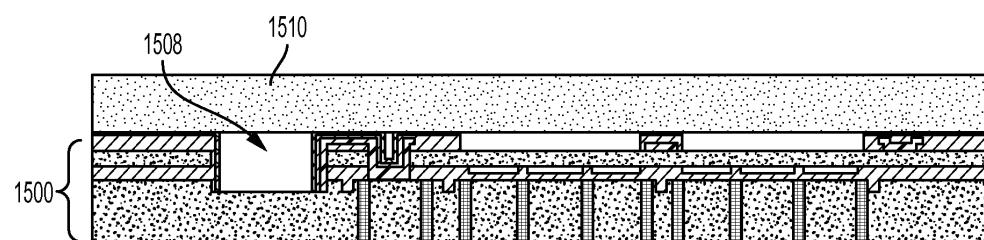

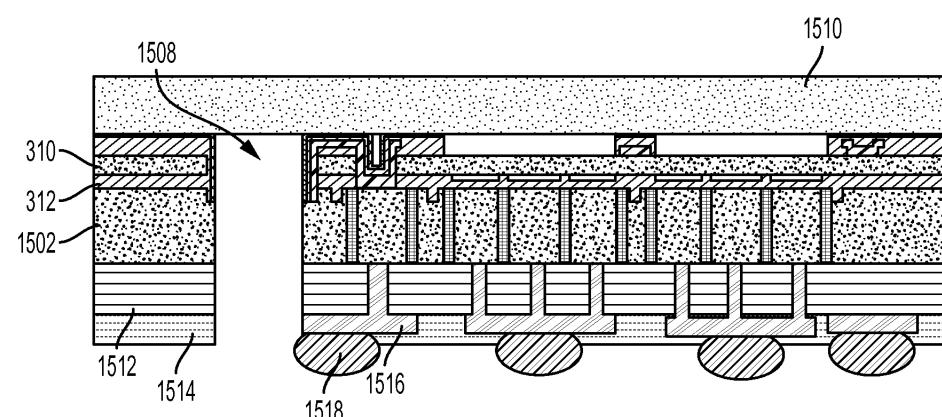

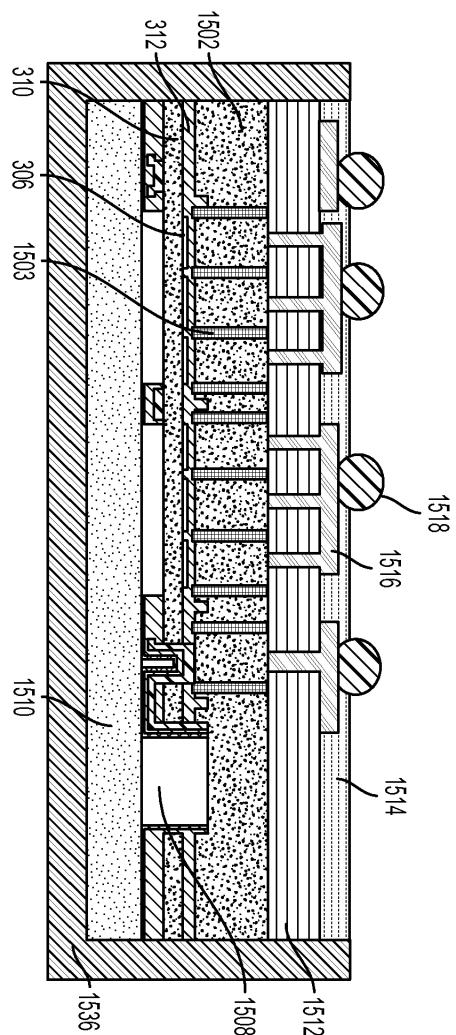

도 15a 내지 도 15f는, 비제한적인 실시예에 따른, 밀봉된 캐비티를 갖는 제작된 기판을 형성하고 제작된 기판을 회로 웨이퍼와 본딩하기 위한 제작 시퀀스를 나타낸다.

도 16은, 비제한적인 실시예에 따른, 제2 웨이퍼로의 웨이퍼-레벨 부착을 위한 땜납 볼들과 함께 준비되고 제작된 기판을 포함하는 재구성된 웨이퍼를 나타낸다.

도 17은, 비제한적인 실시예에 따른, 땜납 볼들이 하나의 웨이퍼 상에만 제공되는 도 15e의 디바이스에 대한 대안을 나타낸다.

### 발명을 실시하기 위한 구체적인 내용

[0025] 본 출원의 양태는, CMUT의 제작 및 CMOS 웨이퍼와의 통합에 의해 CMOS 초음파 트랜스듀서(CUT)를 형성하는 것에 관한 것이다. 설명되는 방법들은, 상업용 반도체 파운드리에서 이용가능한 기술을 이용하여 CMUT를 CMOS 웨이퍼와 통합하여 즉시 이용가능한 공급망을 활용하는데 있어서의 해결과제에 대한, 확장가능하고, 저비용이며, 고수율의 솔루션을 제공한다. 일부 실시예에서, 압전 마이크로제작된 초음파 트랜스듀서(PMUT)가 CMUT 대신에 또는 CMUT에 추가하여 이용된다.

[0026] 본 출원의 한 양태에 따르면, 2개의 웨이퍼 본딩 단계를 포함하는 웨이퍼-레벨 프로세스가 제공되며, 그 중 적어도 하나는 웨이퍼 레벨 팩키징 기술을 이용할 수 있다. 제1 웨이퍼 본딩 단계는, 2개의 실리콘-온-절연체(SOI) 웨이퍼를 함께 본딩함으로써 밀봉된 캐비티를 형성할 수 있고, 결과적인 본딩 구조물은 제작된 기판으로 간주되며, 매립된 캐비티 SOI 웨이퍼를 나타낸다. 강한 본딩을 달성하는 것을 용이하게 하기 위하여, 예를 들어, 어닐링 동안, 비교적 높은 온도가 이용될 수 있다. 제작된 기판의 2개의 SOI 웨이퍼 중 하나의 핸들 층이 제거된 다음, 제2 웨이퍼 본딩 단계가 수행되어 집적 회로(IC)가 형성된 CMOS 웨이퍼와 제작된 기판을 본딩할 수 있다. 제2 웨이퍼 본딩 단계는 CMOS 웨이퍼 상의 IC에 대한 손상을 피하기 위해 비교적 낮은 온도를 이용할 수 있다. 그 다음, 제작된 기판의 제2 SOI 웨이퍼의 핸들 층이 제거될 수 있다.

[0027] 일부 실시예에서, 밀봉된 캐비티를 갖는 제작된 기판을 형성하는데 이용되는 본딩은 융합 본딩을 포함할 수 있

다. 일부 이러한 실시예에서, 본딩은 저온에서 수행될 수 있다. 그러나, 비교적 높은 온도의 어닐링이 강한 본딩을 보장하기 위해 수행될 수 있다. 밀봉된 캐비티의 제작은, CMOS IC 제작의 열 예산(thermal budget)으로부터 분리되는데, 이것은, 이렇게 제작된 기판은 이러한 구조를 CMOS 웨이퍼와 통합하기 이전에 제작되므로, 최종 디바이스에서 IC를 손상시키지 않으면서 비교적 높은 온도의 어닐링을 이용할 수 있기 때문이다.

[0028] 일부 실시예에서, 밀봉된 캐비티를 갖는 제작된 기판을 CMOS 웨이퍼와 통합하기 위해 수행되는 본딩은, 비제한적인 예로서, 열 압축(여기서는 "열 압착"이라고도 함), 공용 본딩, 또는 (한 기판의 실리콘을 충분한 압력 및 온도 하에서 제2 기판 상의 금속과 접촉시켜 금속 실리사이드를 형성하여, 기계적 및 전기적 본딩을 생성하는 본딩인) 실리사이드 본딩을 포함할 수 있다. 이러한 본딩은, CMOS 웨이퍼 상의 IC에 대한 손상을 피할 수 있을 정도로 충분히 낮은 온도에서 수행될 수 있으면서, 여전히 강한 본딩을 제공할 뿐만 아니라 CMOS 웨이퍼 상의 IC와 제작된 기판의 밀봉된 캐비티의 전기적 상호접속을 용이하게 한다. 따라서, 본 출원의 양태는 CMOS 웨이퍼 상에 초음파 트랜스듀서 멤브레인을 형성하기 위해 저온(예를 들어, 450°C 미만) 웨이퍼 본딩을 구현한다. 이 맥락에서의 저온은, 일부 실시예에서는, 450°C 미만, 400°C 미만, 350°C 미만, 200°C 내지 450°C, 그 범위 내의 임의의 온도, 또는 CMOS 웨이퍼 상의 구조물을 보존하기 위한 기타 임의의 적절한 온도일 수 있다. 따라서, 본딩 프로세스뿐만 아니라, CUT를 형성하기 위해 밀봉된 캐비티와 CMOS IC를 통합하기 위한 다른 제작 단계들은, 450°C 위의 임의의 어닐링을 피할 수 있다.

[0029] 본 출원의 한 양태에 따르면, 제작된 기판을 포함하는 장치는 CMOS IC가 형성된 CMOS 웨이퍼와 본딩된다. 제작된 기판은 밀봉된 캐비티를 형성하기 위해 서로 본딩된 복수의 웨이퍼를 포함할 수 있다. 그 다음, 제작된 기판은 CMOS 웨이퍼와 본딩될 수 있다. 제작된 기판은, 진동하는 멤브레인으로서 역할하도록 구성된 하나의 기판과, 진동한다는 것을 의미하지 않는 지지체 역할을 하는 또 다른 기판을 포함할 수 있다. 이 후자의 기판은, 원치않는 진동을 방지하기에 충분히 두껍고(예를 들어, 약 5 마이크론보다 크고), 작은 디바이스 치수에 기여하도록 충분히 얇을 수도 있다(예를 들어, 약 30 마이크론 미만).

[0030] 본 출원의 한 양태에 따르면, 제작된 기판을 포함하는 장치는, CMOS IC가 형성된 CMOS 웨이퍼와 본딩되고, 제작된 기판은, 함께 본딩되어 밀봉된 캐비티를 형성하고 진동하도록 구성된 복수의 웨이퍼를 포함한다. 제작된 기판의 하나의 웨이퍼는 제1 주파수에서 공진하도록 구성될 수 있고, 제작된 기판의 제2 웨이퍼는 상이한 주파수에서 공진하도록 구성될 수 있다. 따라서, 다중-주파수 초음파 트랜스듀서가 생성될 수 있다. 비제한적인 예로서, 하나의 주파수는 전송 동작을 위해, 다른 하나는 수신 동작을 위해 이용될 수 있다. 예를 들어, 비제한적인 예로서, 제1의 더 낮은 주파수가 전송 동작을 위해 이용될 수 있고, 제2의 더 높은 주파수(예를 들어, 더 낮은 주파수의 2배 주파수)가 수신 동작을 위해 이용될 수 있다.

[0031] 전술된 양태들과 실시예들뿐만 아니라 추가적인 양태들과 실시예들이 이하에서 더 설명된다. 이들 양태들 및/또는 실시예들은 개별적으로, 함께, 또는 2개 이상의 임의의 조합으로 이용될 수도 있고, 본 출원은 이 점에서 제한되지 않는다.

[0032] 설명된 바와 같이, 본 출원의 양태는 통합된 CMUT 및 CMOS IC를 가지며 2개의 분리된 본딩 단계를 이용하는 CUT를 제작하는 프로세스를 제공한다. 이 프로세스는, CMOS IC를 갖는 CMOS 웨이퍼와 모놀리식으로 통합된 2개의 실리콘 층 사이에 형성된 캐비티를 갖는 비교적 얇은 제작된 기판을 결과적인 구조가 포함하는 것을 허용할 수 있다. 도 1은 그 프로세스의 한 예를 나타낸다.

[0033] 도시된 바와 같이, 방법(100)은 밀봉된 캐비티를 갖는 제작된 기판의 형성과 함께 스테이지 102에서 시작될 수 있다. 2개의 SOI 웨이퍼는 예를 들어 서로 마주하는 2개의 SOI 웨이퍼의 실리콘 디바이스 층과 함께 본딩될 수 있다. 2개의 SOI 웨이퍼 중 하나 또는 양쪽 모두는, 내부에 형성된 복수의 캐비티를 가질 수 있어서, 2개의 SOI 웨이퍼를 함께 본딩하면 CMUT의 캐비티로서 이용하기에 적절한 밀봉된 캐비티가 형성될 수 있다. 2개의 SOI 웨이퍼 사이의 강한 본딩을 보장하기 위해 고온 처리가 이용될 수 있다. 예를 들어, 저온 융합 본딩 등의, 저온 웨이퍼 본딩에 후속하여, 고온 어닐링이 이용될 수 있다. 따라서, 일부 실시예에서 고온 및 저온의 조합이 제작된 기판을 형성하는데 이용될 수 있다. 이러한 맥락에서의 고온은, 일부 실시예에서는 온도 임계치 450°C 위일 수 있는데, 이 온도 임계치 위에서는 CMOS IC가 통상적으로 손상될 수 있다.

[0034] 2개의 SOI 웨이퍼의 본딩은, 결과적인 밀봉된 캐비티가 낮은 압력(예를 들어, 약  $1 \times 10^{-3}$  Torr와 약  $1 \times 10^{-5}$  Torr 사이의 압력, 약 1 기압 미만의 압력, 또는 기타 임의의 적절한 압력)을 갖도록 진공에서 수행될 수 있다. 일부 실시예에서, 본딩은 비활성 분위기, 예를 들어 N<sub>2</sub>를 이용하여 수행된다.

[0035] 스테이지 104에서, 2개의 SOI 웨이퍼 중 제1 웨이퍼의 핸들 층은 임의의 적절한 방식으로, 예를 들어 그라인딩

과 후속하는 에칭의 조합(a combination of grinding followed by etching)에 의해 제거될 수 있다. 그 결과, 프로세스의 이 시점에서, 제작된 기판은, 3개의 실리콘 층: 제1 SOI 웨이퍼의 실리콘 디바이스 층, 제2 SOI 웨이퍼의 실리콘 디바이스 층, 및 제2 SOI 웨이퍼의 핸들 층을 포함할 수 있다. SOI 웨이퍼의 실리콘 디바이스 층은 얇을 수 있고, 예를 들어, 그 두께가 20 마이크론 이하(예를 들어, 20 마이크론 미만의 범위 내의 임의의 범위 또는 값을 포함한, 10 마이크론, 5 마이크론, 2.5 마이크론, 2 마이크론, 1 마이크론, 또는 그 이하)일 수 있지만, 본 출원인들은 제2 SOI 웨이퍼의 핸들 층이 제작된 기판의 추가 처리를 허용하기에 충분한 구조적 지지를 제공할 수 있다는 것을 인식하였다.

[0036] 스테이지 106에서, 제작된 기판은 접적 회로를 갖는 CMOS 웨이퍼와 본딩되어 접적 디바이스를 형성할 수 있다. 본딩은 CMOS 웨이퍼의 회로에 대한 손상을 방지하기 위해 450°C 아래의 온도에서 수행될 수 있다. 일부 실시예에서, 특히 공용 본딩 및 실리사이드 본딩을 포함한 대안도 역시 가능하지만, 열 압착 본딩이 이용된다. 제1 SOI 웨이퍼의 실리콘 디바이스 층은, 예를 들어 제1 SOI 웨이퍼의 실리콘 디바이스 층의 배면을 CMOS 웨이퍼와 본딩함으로써, CMOS 웨이퍼의 본딩 표면에 근접하게 배치될 수 있다. 따라서, 결과적인 구조는, 순서대로, CMOS 웨이퍼, 제1 실리콘 디바이스 층, 제2 SOI 웨이퍼의 제2 실리콘 디바이스 층, 및 제2 SOI 웨이퍼의 핸들 층을 포함할 수 있다.

[0037] 스테이지 108에서, 제작된 기판의 제2 SOI 웨이퍼의 핸들 층은, 임의의 적절한 방식으로, 예를 들어 그라인딩과 후속하는 에칭의 조합에 의해 제거될 수 있다. 그 결과, 일부 실시예에서, 제작된 기판은, 그 사이에 캐비티들이 있는 2개의 실리콘 층(제작된 기판을 형성하는데 이용되는 SOI 웨이퍼들의 2개의 실리콘 디바이스 층)만을 포함할 수 있다. 2개의 실리콘 층만을 갖는 것은, 다른 이점들 중에서도, 제작된 기판에 대한 얇은 치수의 달성을 용이하게 한다는 것을 포함할 수 있다. 예를 들어, 이 스테이지에서의 제작된 기판은 비교적 얇을 수 있다, 예를 들어, 총 두께가 100 마이크론 미만, 총 두께가 50 마이크론 미만, 총 두께가 30 마이크론 미만, 총 두께가 20 마이크론 미만, 또는 총 두께가 10 마이크론 미만(예를 들어, 약 8 마이크론 또는 약 5 마이크론), 또는 기타 임의의 적절한 두께일 수 있다. 이러한 얇은 두께의 구조물은, 웨이퍼 본딩을 포함한 많은 제작 프로세스에서 생존하기에 충분한 구조적 강성이 부족하다. 따라서, 본 출원의 일부 실시예에 따르면, 제작된 기판은 CMOS 웨이퍼와의 본딩 이후까지 이러한 치수로 감소되지 않아서, 제작된 기판에 기계적 지지를 제공할 수 있다. 또한, 도 7과 관련하여 이하에서 더 설명되는 바와 같이, 일부 실시예에서, 제작된 기판의 2개의 웨이퍼 중 하나가 그 웨이퍼의 진동을 최소화하거나 방지하기에 충분히 두꺼운 것이 바람직하다. 따라서, 제작된 기판은 얇을 수 있지만, 적어도, 예를 들어, 일부 실시예에서는 4 마이크론, 일부 실시예에서는 5 마이크론, 일부 실시예에서는 7 마이크론, 일부 실시예에서는 10 마이크론, 또는 원치 않는 진동을 방지하기 위한 다른 적절한 두께를 가질 수도 있다.

[0038] 기능하는 초음파 트랜스듀서를 제공하기 위해 CMOS 웨이퍼 상의 IC와 제작된 기판의 밀봉된 캐비티 사이에 전기적 접속이 이루어질 수 있다. 예를 들어, CMOS 웨이퍼에 근접한 제작된 기판의 실리콘 디바이스 층은 초음파 트랜스듀서의 하부 전극으로서 역할할 수 있는 반면, CMOS 웨이퍼로부터 면 실리콘 디바이스 층은, 멤브레인으로서 역할할 수 있고, 멤브레인의 동작을 제어하기 위해(예를 들어, 전압을 인가함으로써 멤브레인을 작동시키기(또는 그 진동을 유도하기) 위해) 적절하게 이를 구조물에 전기적 접속이 이루어질 수 있다. 일부 실시예에서, 전기적 접속은 스테이지 106의 본딩에 의해 이루어질 수(또는 적어도 부분적으로 완료될 수) 있다. 예를 들어, 제작된 기판을 CMOS 웨이퍼와 본딩하는 것은, 본딩 재료와 전기적 접속 둘 다로서 역할하는 전도성 본딩 재료(예를 들어, 금속)를 이용하는 것을 수반할 수 있다. 대안으로서, 또는 추가로, 전기적 접속은 CMOS 웨이퍼와 제작된 기판의 본딩에 후속하여 이루어질 수 있다. 예를 들어, 제작된 기판을 CMOS 웨이퍼와 본딩하는 것은, 초음파 트랜스듀서의 하부 전극으로의 전기적 접속을 형성할 수 있으며, 온-칩 금속 인터커넥트 및/또는 와이어 본딩이 후속해서 형성되어 초음파 트랜스듀서의 멤브레인 또는 상부 전극으로의 전기적 접속을 제공할 수 있다.

[0039] 도 2는 방법(100)의 스테이지 102의 구현 예에 관한 추가 상세사항을 제공하지만, 스테이지 102를 구현하기 위한 대안적 방법이 가능하다는 것을 이해해야 한다. 도시된 비제한적인 예에서, 제작된 기판의 캐비티는, 먼저 2개의 SOI 웨이퍼 중 제1 웨이퍼 상의 열 산화물(열 산화에 의해 형성된 산화물)에 캐비티를 형성함으로써 형성될 수 있다. 즉, 제1 SOI 웨이퍼는, 핸들 층(예를 들어, 핸들 실리콘 층), 매립 산화물(BOX) 층, 및 실리콘 디바이스 층을 포함할 수 있으며, 실리콘 디바이스 층을 열 산화함으로써 스테이지 202에서 실리콘 디바이스 층 위에 열 산화물이 형성될 수 있다. 열 산화물은 산화물의 비제한적인 예를 나타내며, 다른 유형의 산화물이 대안적으로서 형성될 수 있다는 것을 이해해야 한다.

[0040] 스테이지 204에서, 캐비티는, 예를 들어 임의의 적절한 에칭에 의해, 제1 SOI 웨이퍼의 열 산화물에 형성될 수

있다. 일부 실시예에서, 캐비티는, 산화물의 (얇은) 층이 캐비티 경계를 정의하도록, 실리콘 디바이스 층에 완전히 도달하지 않는다. 그러나, 다른 실시예들에서, 캐비티는 실리콘 디바이스 층의 표면까지 또는 더욱 연장될 수 있다. 일부 실시예에서, 열 산화물은 실리콘 디바이스 층의 표면까지 예칭될 수 있고, 그 다음, 캐비티가 산화물 층에 의해 정의되도록 열 산화물의 추가 층이 형성될 수 있다.

[0041] 스테이지 206에서, 열 산화물 내에 형성된 캐비티를 갖는 제1 SOI 웨이퍼는, 예를 들어 저온 용합 본딩을 이용하여 제2 SOI 웨이퍼와 본딩될 수 있다. 일부 실시예에서, 제2 SOI 웨이퍼는 핸들 층(예를 들어, 핸들 실리콘 층), BOX 층, 및 실리콘 디바이스 층을 포함하고, 본딩은 제1 SOI 웨이퍼의 열 산화물 층 및 제2 SOI 웨이퍼의 실리콘 디바이스 층과 접촉하여 Si-SiO<sub>2</sub> 본딩을 형성한다. 대안적 실시예에서, 제2 SOI 웨이퍼는 실리콘 디바이스 층 상에 산화물 층을 포함하되, 제1 및 제2 SOI 웨이퍼를 함께 본딩하는 것이 2개의 SOI 웨이퍼의 산화물 층과 직접 접촉하여 SiO<sub>2</sub>-SiO<sub>2</sub> 본딩을 형성하도록 포함된다.

[0042] 2개의 SOI 웨이퍼를 함께 본딩한 결과, 제1 SOI 웨이퍼의 캐비티가 밀봉될 수 있다. 예를 들어, 캐비티는 일부 실시예에서는 진공 밀봉될 수 있지만, 다른 실시예에서는 진공 밀봉이 형성되지 않을 수도 있다.

[0043] 스테이지 208에서, 2개의 SOI 웨이퍼 사이의 강한 본딩의 형성을 용이하게 하기 위해 어닐링이 수행될 수 있다. 전술한 바와 같이, 일부 실시예에서, 어닐링은, 예를 들어, 약 500°C 내지 약 1,500°C(예를 들어, 500°C, 750°C, 1,000°C, 1,250°C)(그 범위 내의 임의의 온도 또는 온도 범위(예를 들어, 약 500°C 내지 약 1,200°C)를 포함함)에서 수행되는 고온 어닐링일 수 있지만, 다른 온도들이 대안적으로 이용될 수 있다. 일부 실시예에서, 어닐링은 약 300°C 내지 약 1,200°C에서 수행될 수 있다.

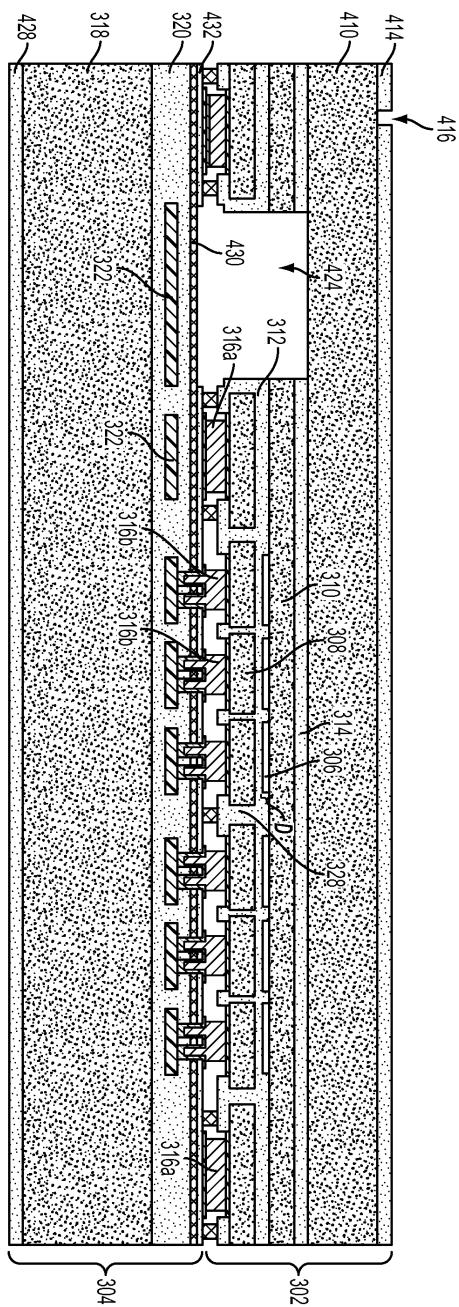

[0044] 도 3은, 본 출원의 비제한적인 실시예에 따른, 밀봉된 캐비티를 갖는 제작된 기판과 통합된 CMOS 웨이퍼를 포함하는 초음파 디바이스의 단면도이다. 디바이스(300)는 도 1 내지 도 2의 방법을 구현함으로써 형성될 수 있다.

[0045] 디바이스(300)는 CMOS 웨이퍼(304)와 통합된 제작된 기판(302)을 포함한다. 제작된 기판(302)은 제1 실리콘 디바이스 층(308)과 제2 실리콘 디바이스 층(310) 사이에 형성된 복수의 캐비티(306)를 포함한다. 제1 및 제2 실리콘 디바이스 층들(308 및 310) 사이에는 실리콘 산화물 층(312)(예를 들어, 실리콘의 열 산화에 의해 형성된 실리콘 산화물)이 형성될 수 있으며, 그 내부에 캐비티(306)가 형성된다. 이 비제한적인 예에서, 제1 실리콘 디바이스 층(308)은 하부 전극으로서 구성될 수 있고 제2 실리콘 디바이스 층(310)은 멤브레인으로서 구성될 수 있다. 따라서, 제1 실리콘 디바이스 층(308), 제2 실리콘 디바이스 층(310), 및 캐비티(306)의 조합은, 초음파 트랜스듀서(예를 들어, CMUT)를 형성할 수 있으며, 그 중 6개가 이 비제한적인 단면도에 도시되어 있다. 하부 전극 또는 멤브레인으로서의 작동을 용이하게 하기 위해, 제1 실리콘 디바이스 층(308) 및 제2 실리콘 디바이스 층(310) 중 하나 또는 양쪽 모두는 도전체로서 작용하도록 도핑될 수 있고, 일부 경우에는 고농도 도핑된다(예를 들어, 10<sup>15</sup> 도펜트/cm<sup>3</sup> 이상).

[0046] 제작된 기판(302)은, 제작된 기판을 형성하는데 이용되는 SOI의 BOX 층을 나타낼 수 있는 제2 실리콘 디바이스 층(310)의 상부에 산화물 층(314)을 더 포함할 수 있다. 일부 실시예들에서 산화물 층(314)은 패시베이션 층으로서 기능할 수 있고, 도시된 바와 같이, 캐비티(306) 위에 존재하지 않도록 패터닝될 수 있다. 이하에서 더 설명되는, 콘택트(324) 및 패시베이션 층(330)은 제작된 기판 상에 포함될 수 있다. 패시베이션 층(330)은 하나 이상의 콘택트(324)로의 액세스를 허용하도록 패터닝될 수 있고, 임의의 적절한 패시베이팅 재료로 형성될 수 있다. 일부 실시예에서, 패시베이션 층(330)은 Si<sub>3</sub>N<sub>4</sub>로 형성되고, 일부 실시예에서는 SiO<sub>2</sub> 및 Si<sub>3</sub>N<sub>4</sub>의 스택에 의해 형성되지만, 대안도 가능하다.

[0047] 제작된 기판(302) 및 CMOS 웨이퍼(304)는 본딩 지점(316a 및 316b)에서 함께 본딩될 수 있다. 본딩 지점은, 예를 들어, CMOS 웨이퍼(304) 상의 층과 제작된 기판(302) 상의 층의 공용 본딩에 의해 형성된 공용 본딩 지점을 나타내거나, 여기서 설명된 기타 임의의 적절한 본딩 유형(예를 들어, 실리사이드 본딩 또는 열 압착 본딩)일 수도 있다. 일부 실시예에서, 본딩 지점들(316a, 316b)은 전도성일 수 있고, 예를 들어 금속으로 형성될 수 있다. 일부 실시예들에서, 본딩 지점(316a)은 본딩 점으로서 유일하게 기능할 수 있고, 일부 실시예들에서는, 예를 들어 도 6과 관련하여 이하에서 더 설명되는 바와 같이 디바이스(300)의 초음파 트랜스듀서들을 밀폐식으로 밀봉하는(hermetically sealing) 밀봉 링(seal ring)을 형성할 수도 있다. 일부 실시예에서, 본딩 지점(316a)은, 제작된 기판과 CMOS 웨이퍼 사이의 전기적 접속을 역시 제공하는 밀봉 링을 정의할 수 있다. 마찬가지로, 본딩 지점(316b)은 일부 실시예에서 이중 목적을 제공할 수 있으며, 예를 들어 본딩 지점 역할을 하고, 또한 제작된 기판(302)의 초음파 트랜스듀서와 CMOS 웨이퍼(304)의 IC 사이에 전기적 접속을 제공할 수 있다. 그 예가 아래에서 더 설명되는, 제작된 기판이 CMOS 웨이퍼와 본딩되지 않는 실시예들에서, 본딩 지점

(316b)은 제작된 기판이 본딩되는 기판 상의 임의의 전기적 구조물에 전기적 접속을 제공할 수 있다.

[0048] CMOS 웨이퍼(304)는, 베이스 층(예를 들어, 벌크 실리콘 웨이퍼)(318), 절연 층(320), 및 금속화부(metallization)(322)를 포함한다. 금속화부(322)는, 알루미늄, 구리 또는 기타 임의의 적절한 금속화 재료로 형성될 수 있고, CMOS 웨이퍼에 형성된 집적 회로의 적어도 일부를 나타낼 수 있다. 예를 들어, 금속화부(322)는 라우팅 층으로서 역할할 수 있고, 하나 이상의 전극을 형성하도록 패터닝될 수 있거나, 다른 기능을 위해 이용될 수 있다. 실제로, CMOS 웨이퍼(304)는 복수의 금속화 층 및/또는 후-처리된 재분배 층을 포함할 수 있지만, 간소화를 위해 단 하나의 금속화부만이 예시되어 있다.

[0049] 본딩 지점(316b)은, CMOS 웨이퍼(304)의 금속화부(322)와 제작된 기판의 제1 실리콘 디바이스 층(308) 사이에 전기적 접속을 제공할 수 있다. 이러한 방식으로, CMOS 웨이퍼(304)의 집적 회로는, 제작된 기판의 초음파 트랜스듀서 전극 및/또는 멤브레인과 통신할 수 있다(예를 들어, 이들에 전기적 신호를 전송하거나 및/또는 이로부터 전기적 신호를 수신할 수 있다). 예시된 실시예에서, 별개의 본딩 지점(316b)이 각각의 밀봉된 캐비티에(및 그에 따라 각각의 초음파 트랜스듀서에 대해) 전기적 접속을 제공하는 것으로 도시되어 있지만, 모든 실시 예가 이러한 방식으로 제한되는 것은 아니다. 예를 들어, 일부 실시예에서, 제공된 전기적 콘택트의 수는 초음파 트랜스듀서의 수보다 적을 수 있다.

[0050] 제2 실리콘 디바이스 층(310)으로 표현되는 초음파 트랜스듀서 멤브레인들에 대한 전기적 콘택트는, 이 비제한적인 예에서, 금속 또는 기타 임의의 적절한 도전성 접촉 재료로 형성될 수 있는 콘택트(324)에 의해 제공된다. 일부 실시예에서, 콘택트(324)와 CMOS 웨이퍼 상의 본딩 패드(326) 사이에 전기적 접속이 제공될 수 있다. 예를 들어, 와이어 본딩(325)이 제공되거나 도전성 재료(예를 들어, 금속)가 디바이스의 상부 표면 상에 퇴적되고 패터닝되어 콘택트(324)로부터 본딩 패드(326)로의 도전성 경로를 형성할 수 있다. 그러나, 콘택트(324)를 CMOS 웨이퍼(304) 상의 IC에 접속하는 대안적 방식들이 이용될 수도 있다. 일부 실시예들에서, 제1 실리콘 디바이스 층(308)으로부터 제2 실리콘 디바이스 층(310)의 하부 측으로 임베딩된 비아(embedded via)가 제공되어, 제2 실리콘 디바이스 층(310)의 상부 측 상의 콘택트(324)에 대한 임의의 필요성을 제거할 수 있다. 예가 도 11과 관련하여 이하에서 설명된다. 이러한 실시예들에서, 제1 및 제2 실리콘 디바이스 층들을 전기적으로 단락시키는 것을 피하기 위해 임의의 이러한 비아에 대해 적절한 전기적 격리가 제공될 수 있다.

[0051] 디바이스(300)는 또한, 도 3에 도시된, 초음파 트랜스듀서(여기서 "초음파 트랜스듀서 요소"로 지칭됨) 그룹 또는 개개의 초음파 트랜스듀서를 전기적으로 격리시키도록 구성된 격리 구조물(예를 들어, 격리 트렌치)(328)을 포함한다. 격리 구조물(328)은 일부 실시예에서 절연 재료로 채워지는 제1 실리콘 디바이스 층(308)을 관통하는 트렌치를 포함할 수 있다. 대안으로서, 격리 구조물(328)은 도 9와 관련하여 이하에서 더 설명되는 바와 같이 적절한 도핑에 의해 형성될 수도 있다. 격리 구조물(328)은 선택사항이다.

[0052] 이제 디바이스(300)의 다양한 피쳐들에 주목한다. 예를 들어, 제작된 기판(302) 및 CMOS 웨이퍼(304) 웨이퍼는 모놀리식으로 통합될 수 있으며, 따라서 초음파 트랜스듀서와 CMOS IC의 모놀리식 통합을 제공할 수 있다는 것을 이해해야 한다. 예시된 실시예에서, 초음파 트랜스듀서는 CMOS IC에 관해 수직으로(또는 적층되어) 배치되어, 초음파 트랜스듀서와 CMOS IC를 통합하는데 요구되는 칩 면적을 감소시킴으로써 컴팩트한 초음파 디바이스의 형성을 용이하게 할 수 있다.

[0053] 또한, 제작된 기판(302)은 단 2개의 실리콘 층(308 및 310)만을 포함하고, 이를 사이에 캐비티(306)가 형성된다. 제1 실리콘 디바이스 층(308) 및 제2 실리콘 디바이스 층(310)은 얇을 수 있고, 예를 들어, 각각은 다른 비제한적인 예들 중에서, 50 마이크론 미만의 두께, 30 마이크론 미만의 두께, 20 마이크론 미만의 두께, 10 마이크론 미만의 두께, 5 마이크론 미만의 두께, 3 마이크론 미만의 두께, 또는 약 2 마이크론의 두께이다. 이러한 치수는, 소형 디바이스를 달성하는데 기여하며, TSV의 필요없이 초음파 트랜스듀서 멤브레인(예를 들어, 제2 실리콘 디바이스 층(310))으로의 전기적 접촉을 용이하게 할 수 있다. TSV는 통상적으로 구현하기에 복잡하고 비용이 많이 소요되므로, 그 이용을 피하면, 제작 수율이 증가하고 디바이스 비용이 감소될 수 있다. 게다가, TSV를 형성하려면 많은 상업용 반도체 파운드리가 소유하지 않는 전문화된 제작 도구가 필요하므로, 이러한 도구의 필요성을 피하면, 디바이스를 형성하기 위한 공급망을 향상시켜, TSV가 이용되는 경우보다 상업적으로 더욱 실용적이게 할 수 있다.

[0054] 도 3에 도시된 바와 같은 제작된 기판(302)은 비교적 얇을 수 있고, 예를 들어, 총 두께가 100 마이크론 미만, 총 두께가 50 마이크론 미만, 총 두께가 30 마이크론 미만, 총 두께가 20 마이크론 미만, 총 두께가 10 마이크론 미만, 또는 기타 임의의 적절한 두께일 수 있다. 이러한 얇은 치수의 중요성은, 구조적 무결성의 결여 및 이러한 얇은 치수의 층으로 다양한 유형의 제작 단계들(예를 들어, 웨이퍼 본딩)을 수행할 수 없다는 측면에서,

여기서 앞서 설명되었다. 따라서, 디바이스(300)에서 이러한 얇은 치수가 달성될 수 있다는 점에 주목할 만하다.

[0055] 또한, 실리콘 디바이스 층들(308, 310)은 단결정 실리콘으로 형성될 수 있다. 단결정 실리콘의 기계적 및 전기적 특성은 이해하고 있으므로, (예를 들어, CMUT의 멤브레인으로서) 초음파 트랜스듀서에서의 이러한 재료의 이용은 초음파 트랜스듀서의 거동의 설계 및 제어를 용이하게 할 수 있다.

[0056] 주목할 가치가 있는 또 다른 피쳐는, CMOS 웨이퍼(304)의 부분들과 제1 실리콘 디바이스 층(308) 사이에는, 이들 2개가 CMOS 웨이퍼(304)의 전체 표면을 덮는 본딩이 아니라 별개의 본딩 지점(316b)에서 본딩되기 때문에 캡이 존재한다는 것이다. 이러한 캡의 중요성은, 제1 실리콘 디바이스 층(308)이 충분히 얇다면 진동할 수도 있다는 것이다. 이러한 진동은 바람직하지 못하며, 예를 들어 제2 실리콘 디바이스 층(310)의 원하는 진동과는 대조적으로 원치않는 진동을 나타낸다. 따라서, 제1 실리콘 디바이스 층(308)이 이러한 진동을 최소화하거나 회피하기에 충분히 두껍다면, 적어도 일부 실시예에서는 유익하다.

[0057] 대안적 실시예에서, 제1 및 제2 실리콘 디바이스 층들(308, 310) 양쪽 모두가 진동하는 것이 바람직할 수 있다. 예를 들어, 이들은 상이한 공진 주파수들을 보이도록 구성되어, 다중-주파수 디바이스를 생성할 수 있다. (일부 실시예들에서 고조파로서 관련될 수 있는) 복수의 공진 주파수들은, 예를 들어, 초음파 트랜스듀서의 상이한 동작 상태들에서 이용될 수 있다. 예를 들어, 제1 실리콘 디바이스 층(308)은 제2 실리콘 디바이스 층(310)의 중심 주파수의 절반에서 공진하도록 구성될 수 있다.

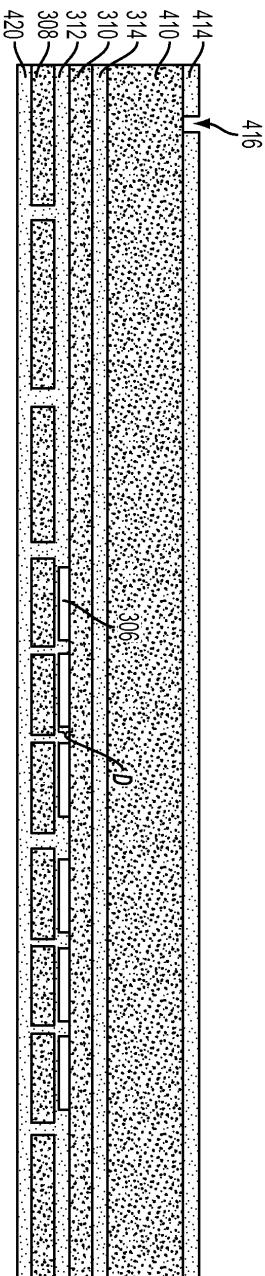

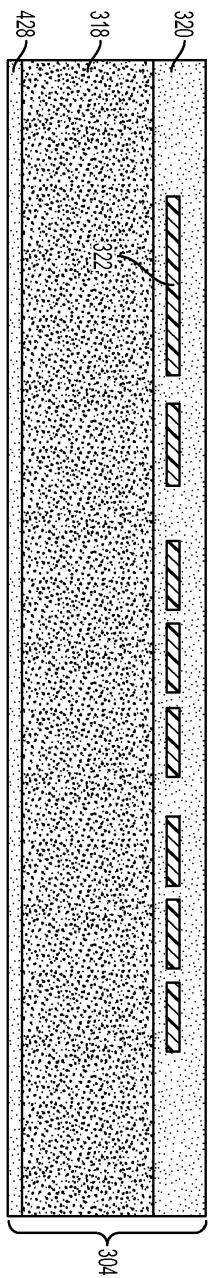

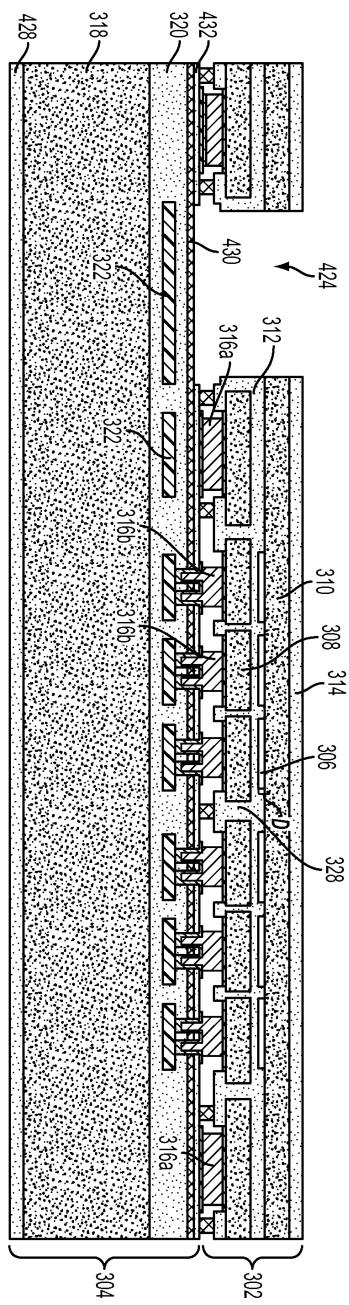

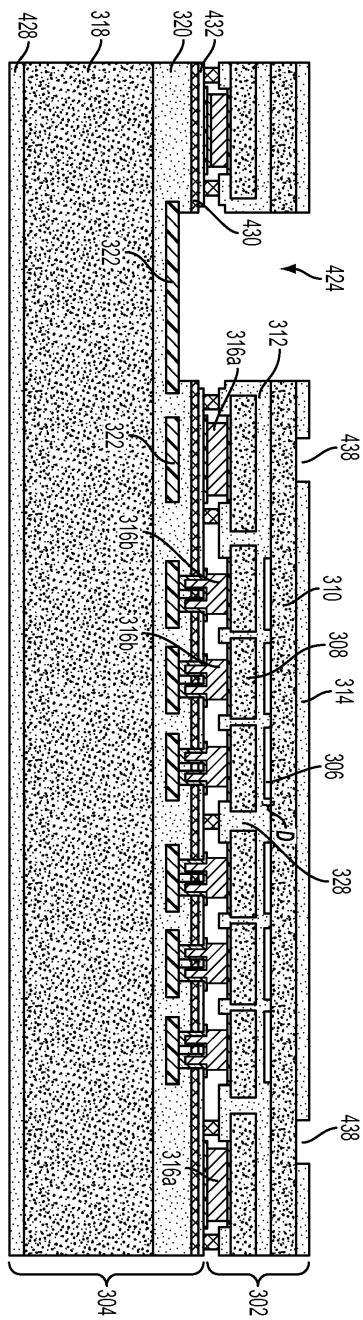

[0058] 도 4a 내지 도 4t는, 본 출원의 비제한적인 실시예에 따른, 도 1의 제작 시퀀스와 일치하는 도 3의 디바이스(300)를 형성하기 위한 제작 시퀀스를 나타낸다. 도 3과 관련하여 앞서 설명된 구조는, 도 4a 내지 도 4t에서 동일한 참조 번호를 유지한다.

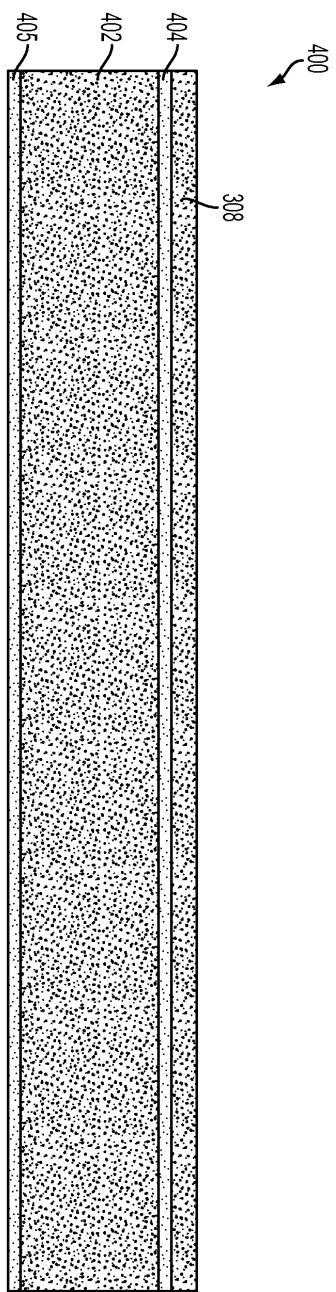

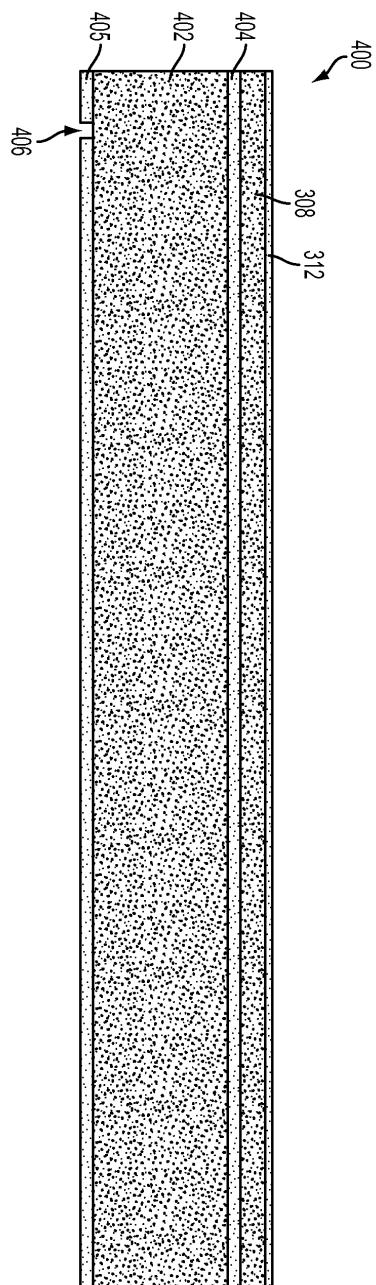

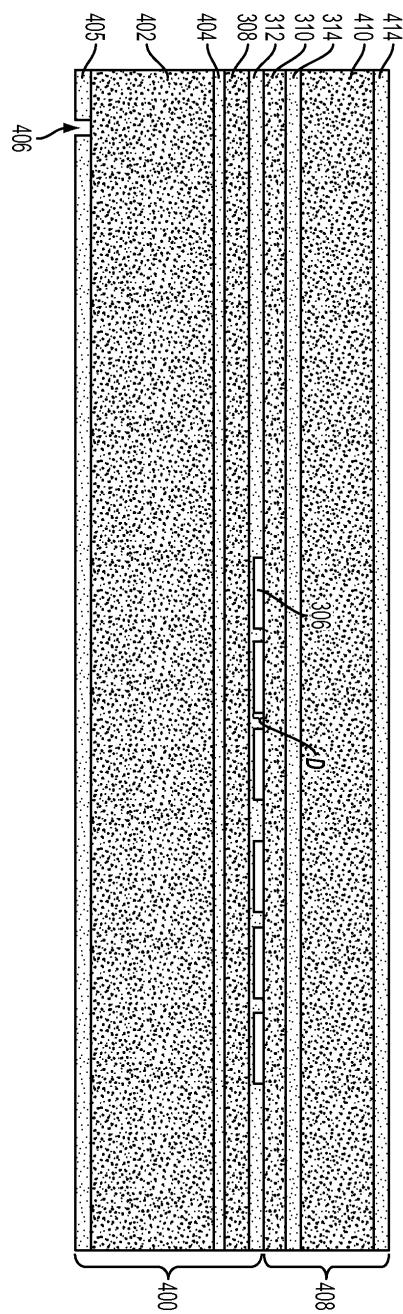

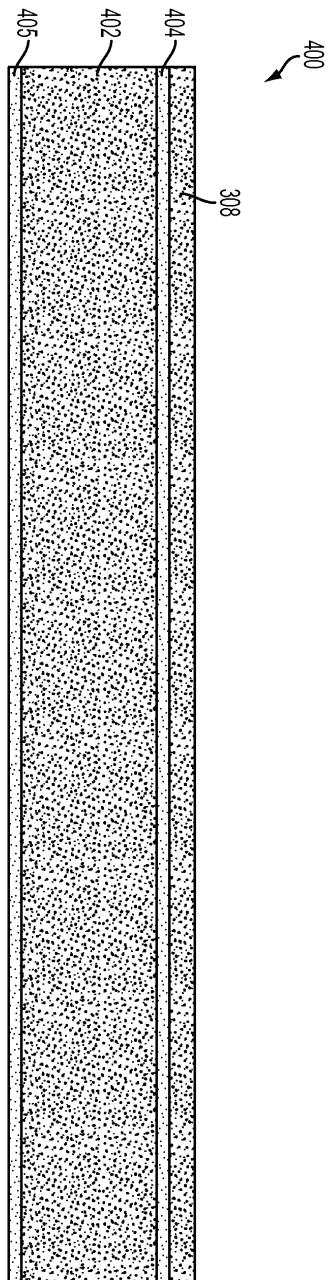

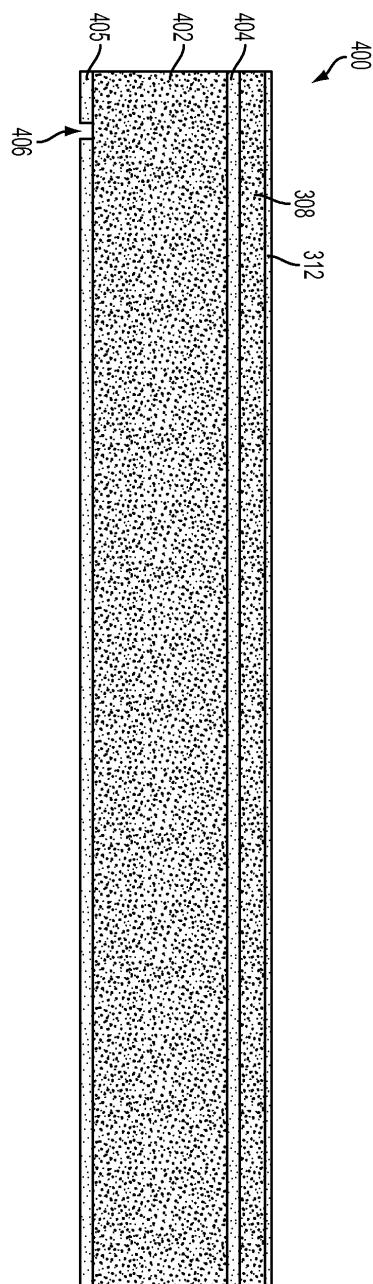

[0059] 처음에, 제1 SOI 웨이퍼(400)와 함께 도 4a에 도시된 바와 같이 시작하는, 제작된 기판의 형성이 설명된다. SOI 웨이퍼(400)는, 핸들 층(402)(예를 들어, 실리콘 핸들 층), BOX 층(404), 및 제1 실리콘 디바이스 층(308)을 포함한다. 산화물 층(405)은 또한, 핸들 층(402)의 배면 상에 제공될 수 있다.

[0060] 제1 실리콘 디바이스 층(308)은 단결정 실리콘으로 형성될 수 있으며, 전술한 바와 같이 일부 실시예에서는 도핑될 수도 있다. 도 3과 관련하여 전술한 바와 같이, 제1 실리콘 디바이스 층(308)은 초음파 트랜스듀서의 하부 전극으로서 역할할 수 있고, 따라서 적절한 도핑은 원하는 전기적 거동을 제공할 수 있다. 또한, 도핑된 실리콘 디바이스 층을 이용하면, 일부 실시예에서 TSV를 이용할 필요가 없다. 일부 실시예에서, 제1 실리콘 디바이스 층(308)은 고농도로 도핑된 P형일 수 있지만, N형 도핑이 대안으로서 이용될 수도 있다. 도핑이 이용될 때, 도핑은 균일하거나, 예를 들어 도 7과 관련하여 이하에서 더 설명되는 격리된 전극을 제공하기 위해 (예를 들어, 패터닝된 영역에 주입함으로써) 패터닝될 수도 있다. 제1 실리콘 디바이스 층(308)은, SOI 웨이퍼가 획득될 때 이미 도핑될 수 있거나, 도핑 방식은 제한적이지 않기 때문에 이온 주입에 의해 도핑될 수도 있다.

[0061] 일부 실시예에서, 제1 실리콘 디바이스 층(308)은 폴리실리콘 또는 비정질 실리콘(amorphous silicon)으로 형성될 수 있다. 어느 경우에나, 제1 실리콘 디바이스 층(308)은 원하는 전기적 거동을 제공하기 위해 적절한 대로 도핑되거나 도핑되지 않을 수도 있다.

[0062] 도 4b에 도시된 바와 같이, 실리콘 산화물 층(312)은 SOI 웨이퍼(400) 상에 형성될 수 있다. 실리콘 산화물 층(312)은 초음파 트랜스듀서의 캐비티(306)를 적어도 부분적으로 정의하기 위해 이용될 수 있고, 따라서 원하는 캐비티 깊이를 제공하기 위해 임의의 적절한 두께를 가질 수 있다. 실리콘 산화물 층(312)은 열적 실리콘 산화물일 수 있지만, 열적 산화물 이외의 산화물들이 대안으로서 이용될 수도 있다는 것을 이해해야 한다.

[0063] 도 4b는 또한, 정렬 마크(406)가 (예를 들어, 산화물 층(405)의 적절한 패터닝에 의해) 형성될 수 있다는 것을 나타낸다. 도 4e와 관련하여 이하에서 더 설명되는 바와 같이, 정렬 마크(406)는 핸들 층(402)이 제거되기 때문에 제2 SOI 웨이퍼에 나중에 전사될 수 있다.

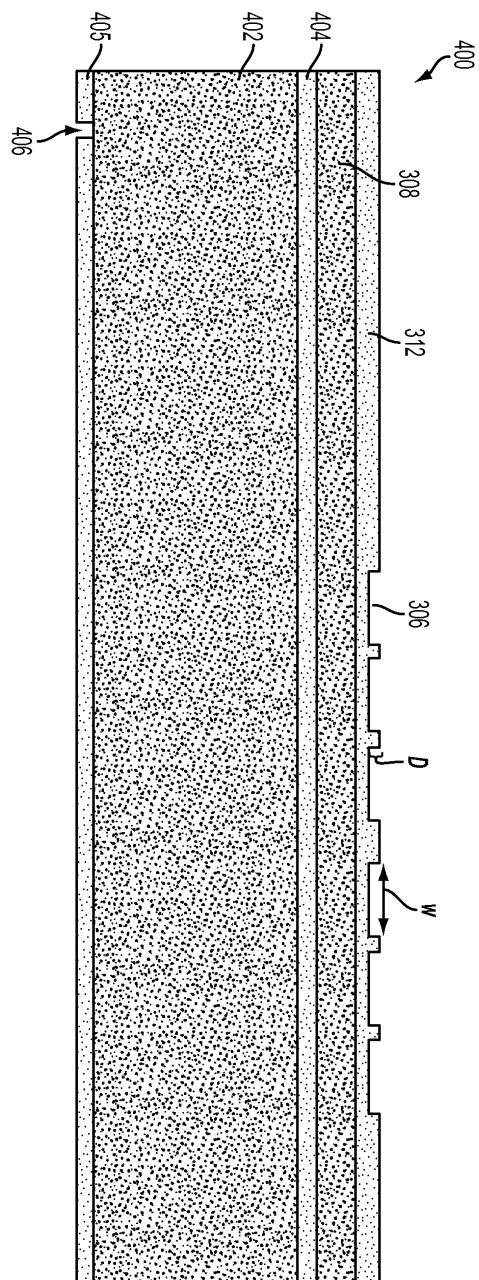

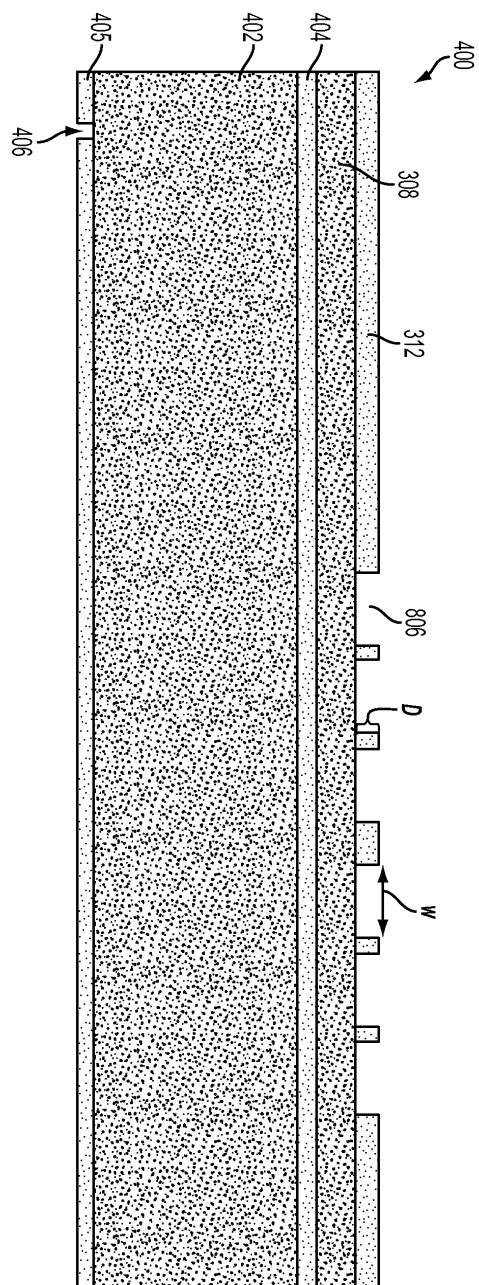

[0064] 도 4c에 도시된 바와 같이, 실리콘 산화물 층(312)은, 임의의 적절한 기술을 이용하여(예를 들어, 적절한 에칭을 이용하여) 캐비티(306)를 형성하도록 패터닝될 수 있다. 이러한 비제한적인 실시예에서, 캐비티(306)는 제1 실리콘 디바이스 층(308)의 표면까지 연장되지 않지만, 대안적인 실시예에서는 연장될 수고 있다. 일부 실시예들에서, 실리콘 산화물 층(312)은 실리콘 디바이스 층의 표면까지 에칭될 수 있고, 그 다음, 산화물 층의 추가 층(예를 들어, 열적 실리콘 산화물)이 형성되되, 산화물 층에 의해 캐비티가 정의되도록 형성될 수 있다. 일부 실시예에서, 캐비티는 제1 실리콘 디바이스 층(308) 내로 연장될 수 있다. 또한, 일부 실시예에서 격리 포스트

(isolation post) 등의 구조물이 캐비티 내에 형성될 수 있다.

[0065] 본 출원의 양태는 이 점에서 제한되지 않기 때문에, 캐비티(306)의 임의의 적절한 개수 및 구성이 형성될 수 있다. 따라서, 6개의 캐비티(306)만이 도 4c의 비제한적인 단면도에 예시되어 있지만, 일부 실시예에서는 더 많은 캐비티가 형성될 수 있다는 것을 이해해야 한다. 예를 들어, 캐비티 어레이(306)는, 원하는 크기의 초음파 트랜스듀서 어레이를 형성하기 위해, 수백 개의 캐비티, 수천 개의 캐비티, 또는 그 이상을 포함할 수 있다.

[0066] 캐비티(306)는, 예를 들어 동작 주파수의 관점에서, 궁극적으로 형성된 초음파 트랜스듀서의 바람직한 동작을 위해 설계된 깊이  $D$ 를 가질 수 있다. 일부 실시예에서, 깊이  $D$ 는, 약 2 마이크론, 약 0.5 마이크론, 약 0.25 마이크론, 약 0.05 마이크론 내지 약 10 마이크론, 약 0.1 마이크론 내지 약 5 마이크론, 약 0.5 마이크론 내지 약 1.5 마이크론, 임의의 깊이 또는 깊이 범위, 또는 기타 임의의 적절한 깊이일 수 있다.

[0067] 캐비티(306)는, 도 3e에 역시 예시된 폭  $W$ 를 가질 수 있다.  $W$ 에 대한 값의 비제한적인 예가 아래에서 더 설명된다. 폭 치수는 또한, 캐비티의 개구 크기를 식별하는데 이용될 수 있고, 따라서 캐비티(306)는 폭  $W$ 에 대해 여기서 설명된 임의의 값의 개구를 가질 수 있다.

[0068] 캐비티(306)는, 초음파 트랜스듀서가 궁극적으로 형성될 때 원하는 맴브레인 형상을 제공하기 위해 (상부 측에서 본) 다양한 형상을 중 하나를 취할 수 있다. 예를 들어, 캐비티(306)는 원형 윤곽 또는 다면 윤곽(예를 들어, 직사각형 윤곽, 6각형 윤곽, 8각형 윤곽)을 가질 수도 있다. 원형 윤곽의 예가 이하에서 설명되는 도 13에 예시되어 있다.

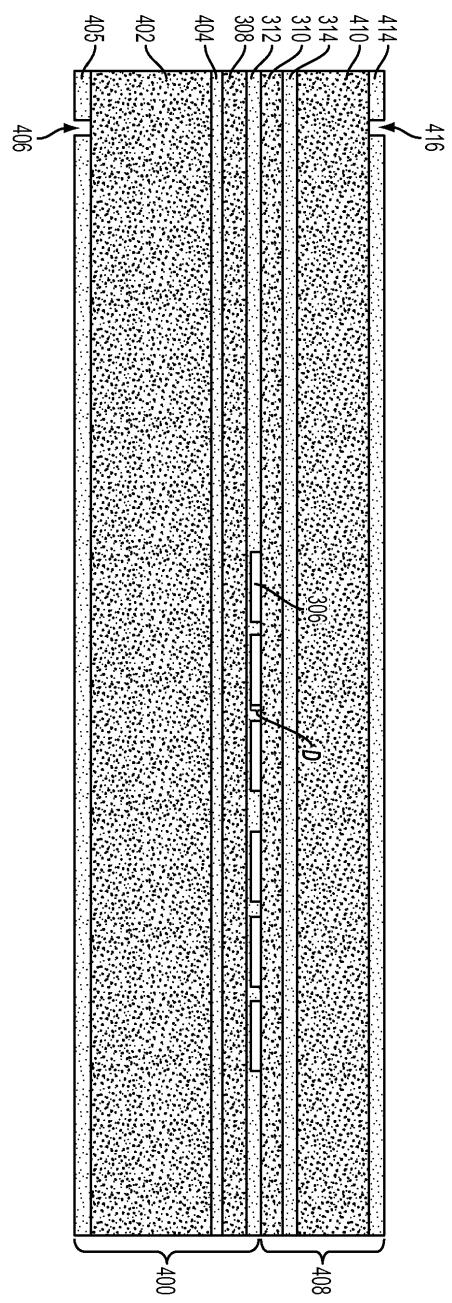

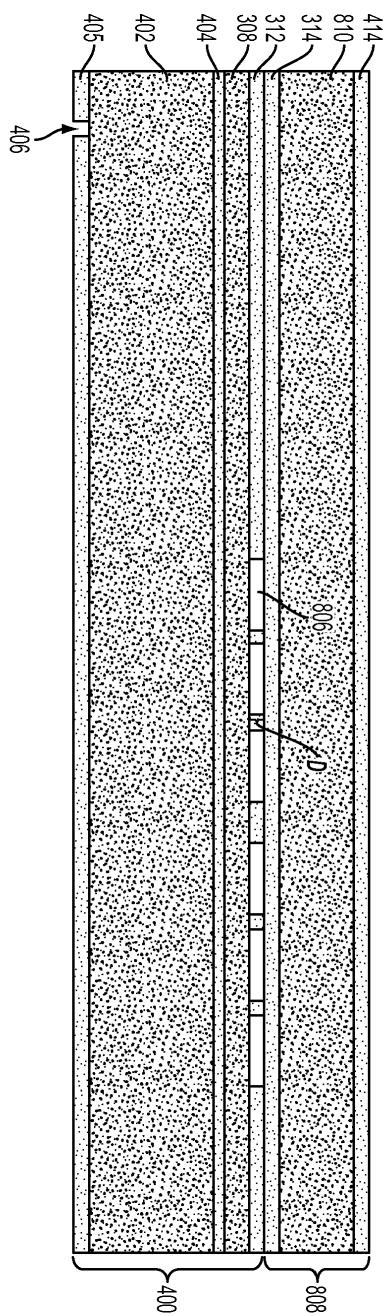

[0069] 도 4d에 도시된 바와 같이, 제1 SOI 웨이퍼(400)는, 제2 핸들 층(예를 들어, 실리콘 핸들 층)(410), 산화물 층(314)(예를 들어, BOX 층), 및 제2 실리콘 디바이스 층(310)을 포함하는 제2 SOI 웨이퍼(408)와 본딩될 수 있다. 제2 SOI 웨이퍼(408)는 산화물 층(414)을 추가로 포함할 수 있다. 본딩은 저온(예를 들어, 450°C 아래의 용융 본딩)에서 수행될 수 있지만, 충분한 본딩 강도를 보장하기 위해 고온(예를 들어, 500°C 초과)에서의 어닐링이 후속될 수도 있다. 제1 및/또는 제2 실리콘 디바이스 층들(308 및 310)이 도핑되는 실시예들에서, 어닐링은 또한, 도핑을 활성화시키는 역할을 할 수 있으며, 이것은 단일 어닐링이 복수의 기능을 수행할 수 있다는 것을 의미한다. 예시된 실시예에서, 본딩은 Si-SiO<sub>2</sub> 본딩일 수 있지만, 대안도 가능하다. 예를 들어, 일부 실시예에서, 제2 SOI 웨이퍼(408)는, 제2 실리콘 디바이스 층(310) 상에 산화물 층(예를 들어, 열적 실리콘 산화물)을 포함하되, 제1 및 제2 SOI 웨이퍼들(400 및 408) 사이의 본딩이 SiO<sub>2</sub>-SiO<sub>2</sub> 본딩이 되도록 포함할 수 있다.

[0070] 제1 실리콘 디바이스 층(308)에서와 같이, 제2 실리콘 디바이스 층(310)은, 단결정 실리콘, 폴리실리콘, 또는 비정질 실리콘일 수 있고, 일부 실시예에서는 도핑될 수도 있다. 이 도핑은 전기적 접속을 제공하기 위해 TSV를 형성할 필요성을 피할 수 있으며, 임의의 적절한 유형 및 레벨일 수도 있다.

[0071] 도 4e에 도시된 바와 같이, 정렬 마크(406)는 정렬 마크(416)로서 제2 SOI 웨이퍼에 전사될 수 있다.

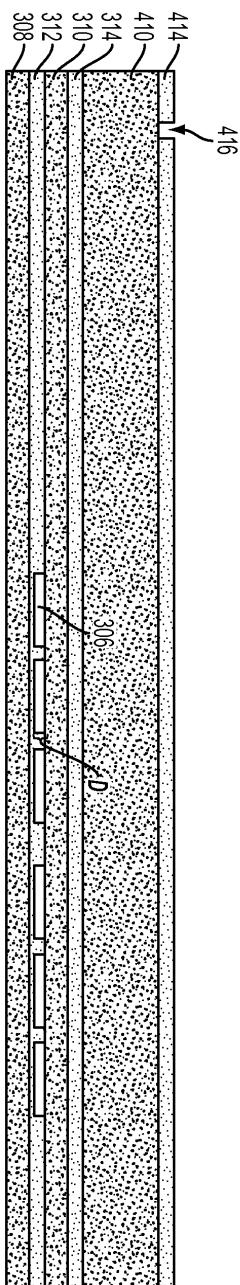

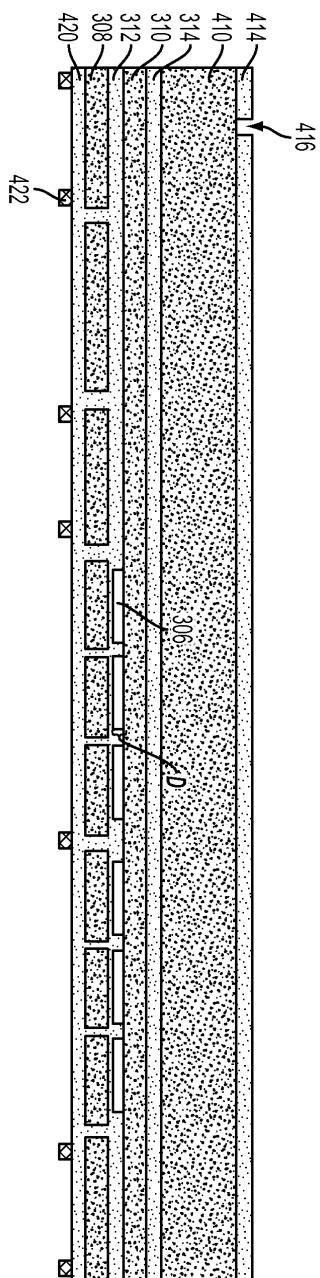

[0072] 그 다음, 도 4f에 도시된 바와 같이, 산화물 층(405), 핸들 층(402), 및 BOX 층(404)은 임의의 적절한 방식으로 제거될 수 있다. 예를 들어, 그라인딩, 에칭, 또는 기타 임의의 적절한 기술 또는 기술들의 조합이 이용될 수 있다. 그 결과, 제1 SOI 웨이퍼(400)로부터 남은 유일한 층은, 제1 실리콘 디바이스 층(308) 및 실리콘 산화물 층(312)을 포함한다. 도 3과 관련하여 앞서 설명된 바와 같이, 이들 층들은 얹을 수도 있다. 그러나, 이들은 그 대응하는 핸들 층과 함께 제2 SOI 웨이퍼(408)에 본딩되기 때문에, 충분한 구조적 무결성이 추가 처리를 위해 유지될 수 있다.

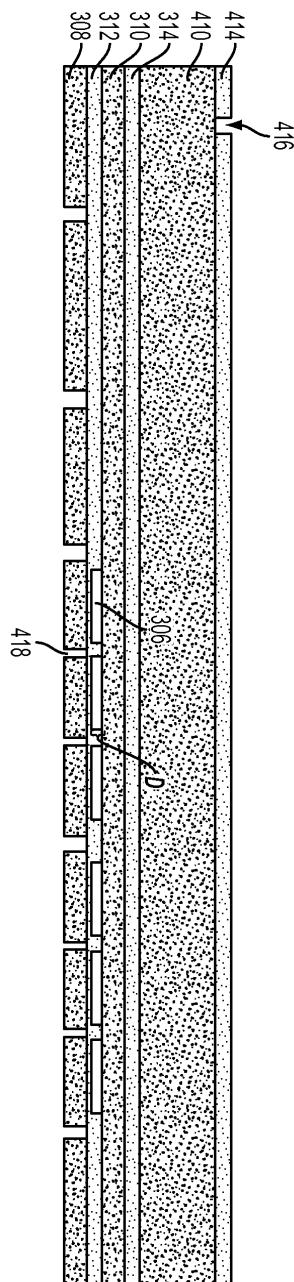

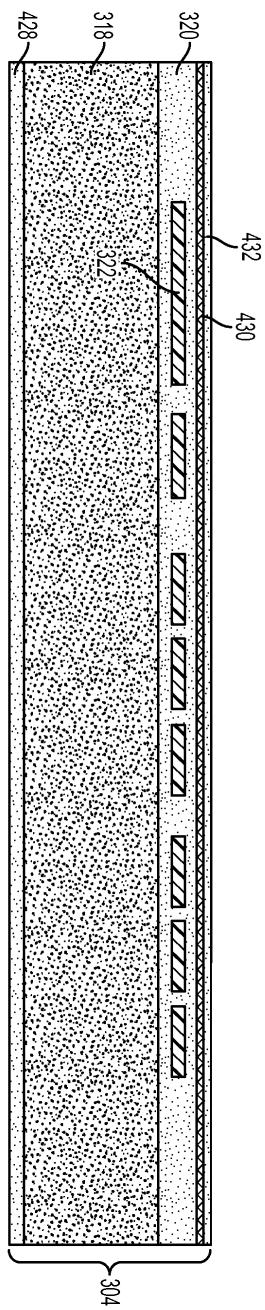

[0073] 도 3의 격리 구조물(328)을 참조하여 앞서 기술된 바와 같이, 일부 실시예들에서, 디바이스(300)의 하나 이상의 초음파 트랜스듀서들을 전기적으로 절연시키는 것이 바람직할 수 있다. 따라서, 도 4g에 도시된 바와 같이, 하나 이상의 격리 트렌치(418)가 제1 실리콘 디바이스 층(308)에 형성될 수 있다. 예시된 실시예에서, 절연 트렌치(418)는, 실리콘 디바이스 층(308)의 배면으로부터 실리콘 산화물 층(312)까지 연장되고, 각각의 격리 트렌치(418)가 접촉하는 위에 놓인 실리콘 산화물 층(312)의 부분(들)보다 (도면에서 좌측으로부터 우측으로의 방향으로) 더 좁아서 실리콘 산화물 층(312)을 통해 캐비티(306) 내로 우연히 편침하는 것을 방지한다. 따라서, 격리 트렌치(418)는 캐비티(306)의 구조적 무결성에 영향을 미치지 않는다. 그러나, 대안적 구성을 가능하다.

[0074] 도 4h는, 임의의 적절한 기술(예를 들어, 적절한 퇴적)을 이용하여 격리 트렌치(418)가 절연 재료(420)(예를 들어, 실리콘 산화물)로 채워질 수 있다는 것을 나타낸다. 예시된 실시예에서, 절연 재료(420)는 격리 트렌치(418)를 완전히 채우며, 트렌치들(418)을 단순하게 정렬(line)하지 않으며, 이것은, 이 스테이지에서 디바이스

의 구조적 무결성에 더욱 기여할 수 있어서, 추가 처리에 더욱 적절하다는 점에 유의해야 한다.

[0075] 도 4i에서, 예를 들어 임의의 적절한 퇴적 및 패터닝 기술을 이용하여, 절연 재료(420)의 하부 표면 상에 흐름 정지 피쳐(422)가 선택사항으로서 형성된다. 흐름 정지 피쳐는 하나 이상의 기능을 수행할 수 있다. 예를 들면, 이들은, 후속해서 퇴적되는 금속 층들의 바람직하지 않은 흐름(flow)을 방지할 수 있다. 대안으로서 또는 추가로, 흐름 정지 피쳐는, 이후에 본딩될 때 제작된 기판과 CMOS 웨이퍼 사이에 원하는 캡을 제공할 수 있다. 따라서, 하나 또는 양쪽 모두의 기능을 달성하기 위해 임의의 적절한 개수의 및 배치의 흐름 정지 피쳐(422)가 제공될 수 있으며, 흐름 정지 피쳐(422)는 임의의 적절한 재료로 형성될 수 있다. 예를 들어, 흐름 정지 피쳐(422)는 일부 비제한적인 실시예에서 실리콘 질화물(SiN)로 형성될 수 있다. 그러나, 전술한 바와 같이, 유동 정지 피쳐(422)의 이용은 선택사항이다. 예를 들어, 이러한 피쳐는, 일부 실시예에서, 예를 들어 제작된 기판을 또 다른 웨이퍼와 본딩시키기 위해 열 압축을 이용할 때 생략될 수도 있다.

[0076] 도 4j에 도시된 바와 같이, 절연 재료(420)는, 제작된 기판을 CMOS 웨이퍼와 나중에 본딩하기 위한 본딩 위치를 형성하기 위한 준비로, (임의의 적절한 에칭 기술을 이용하여) 패터닝될 수 있다. 또한, 패터닝은 도 3과 관련하여 앞서 기술된 격리 구조물(328)을 추가로 정의할 수 있다.

[0077] 도 4k에서, 제1 실리콘 디바이스 층(308), 실리콘 산화물 층(312), 제2 실리콘 디바이스 층(310), 및 산화물 층(314)을 관통하는 말소 영역(clear out region)(424)이 형성될 수 있다. 말소 영역(424)은, 도 6과 관련하여 이하에서 더 설명되는 바와 같이, 초음파 트랜스듀서 그룹들을 서로 격리시킬 수 있다(예를 들어, 별개의 초음파 트랜스듀서 어레이들을 분리). 예를 들어, 일부 실시예에서, 제1 및 제2 실리콘 디바이스 층들(308, 310)은 초음파 트랜스듀서 어레이에 대응하는 영역에만 보유되고, 말소 영역(424)은 초음파 트랜스듀서 어레이들을 분리한다. 말소 영역(424)은, 예를 들어 본딩 패드 또는 다른 전기적 접속 피쳐에 대한 액세스를 허용하는, 초음파 트랜스듀서 어레이의 주변부에서 CMOS 웨이퍼로의 더욱 용이한 액세스를 제공할 수 있다. 말소 영역(424)은, 임의의 적절한 방식으로, 예를 들어, 실리콘 디바이스 층 및 산화물 층을 에칭하기 위한 그라인딩, 깊은 반응성 이온 에칭(DRIE), 및 플라즈마 에칭 중 하나 이상을 이용하여 형성될 수 있다. 일부 실시예에서, 그라인딩과 후속하는 DRIE(grinding followed by DRIE)가 이용된다. 말소 영역(424)을 형성하는 대안적 방식들이 가능하다.

[0078] 그 다음, 도 4l에 도시된 바와 같이, CMOS 웨이퍼와 제작된 기판을 본딩하기 위한 준비로, 제작된 기판 상에 본딩 재료(426)가 형성될 수 있다. 본딩 재료(426)의 유형은 형성될 본딩의 유형에 의존할 수 있다. 예를 들어, 본딩 재료(426)는, 열 압착 본딩, 공용 본딩, 또는 실리사이드 본딩에 적절한 금속일 수 있다. 일부 실시예에서, 본딩 재료는, 도 3 및 본딩 지점(316b)과 관련하여 전술한 바와 같이 전기적 신호가 제작된 기판과 CMOS 웨이퍼 사이에서 전달될 수 있도록 전도성일 수 있다. 예를 들어, 일부 실시예에서, 본딩 재료(426)는 금(gold)일 수 있고 전기 도금에 의해 형성될 수 있다. 일부 실시예들에서, 웨이퍼 레벨 팩키징에 이용되는 재료 및 기술은, 제작된 기판을 CMOS 웨이퍼와 본딩하는 정황에서 적용될 수 있다. 따라서, 예를 들어, 바람직한 접착력, 상호확산 장벽 기능, 및 높은 본딩 품질을 제공하도록 선택된 금속 스택이 이용될 수 있으며, 본딩 재료(426)는 이러한 금속 스택을 포함할 수 있다.

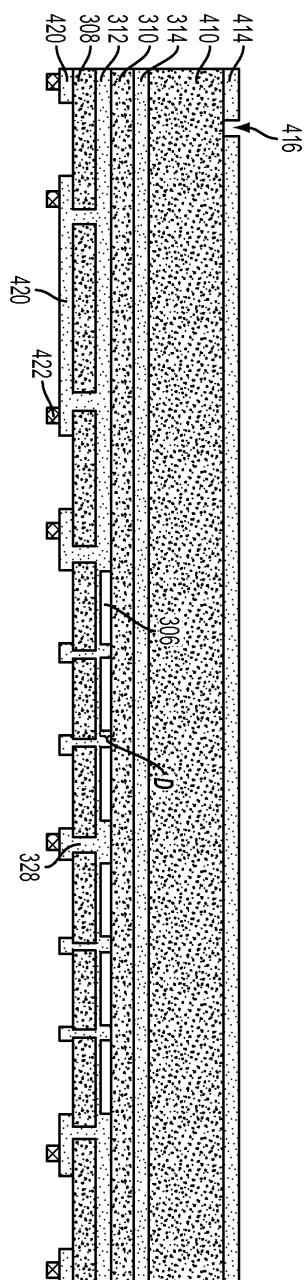

[0079] 도 4m 내지 도 4p는, 제작된 기판과의 본딩을 위한 CMOS 웨이퍼(304)의 준비에 관한 것이다. 도 4m에 도시된 바와 같이, CMOS 웨이퍼(304)는, 베이스 층(예를 들어, 벌크 실리콘 웨이퍼)(318), 절연 층(320), 및 금속화부(322)를 포함한다. 절연 층(428)은 베이스 층(318)의 배면 상에 선택사항으로서 형성될 수 있다.

[0080] 도 4n에 도시된 바와 같이, 층들(430 및 432)이 CMOS 웨이퍼(304) 상에 형성될 수 있다. 층(430)은, 예를 들어 절화물 층일 수 있고, 플라즈마 강화 화학 증착(PECVD)에 의해 형성될 수 있다. 층(432)은, 예를 들어 산화물의 PECVD에 의해 형성된, 산화물 층일 수 있다.

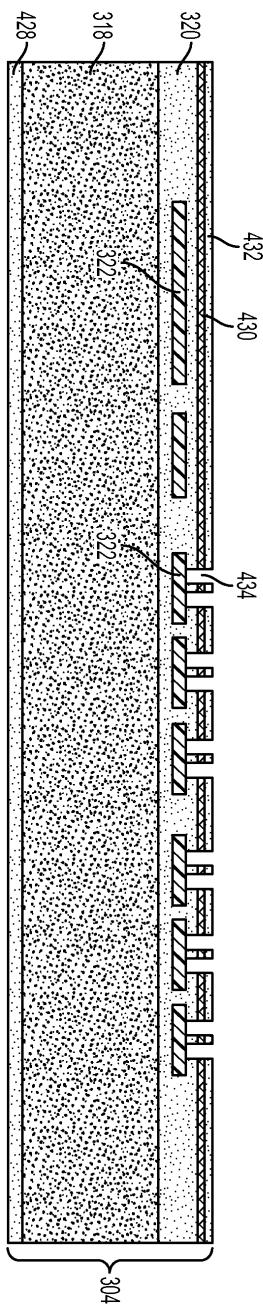

[0081] 도 4o에서, 개구(434)는 층(432)으로부터 금속화부(322)까지 형성될 수 있다. 이러한 개구는 본딩 지점을 형성하기 위한 준비로서 형성될 수 있다. 예를 들어, 도 4p에서, 본딩 재료(436)는, CMOS 웨이퍼(304)와 제작된 기판(302)을 본딩하기 위한 하나 이 상의 적절한 위치에서 (적절한 증착 및 패터닝에 의해) CMOS 웨이퍼(304) 상에 형성될 수 있다. 본딩 재료(436)는, 제작된 기판 상의 본딩 재료(426)와 본딩하기 위한 임의의 적절한 재료일 수 있다. 전술한 바와 같이, 일부 실시예들에서, 저온 공용 본딩이 형성될 수 있고, 이러한 실시예들에서, 본딩 재료(426) 및 본딩 재료(436)는 공용 쌍을 형성할 수 있다. 예를 들어, 본딩 재료(426) 및 본딩 재료(436)는, 인듐-주석(In-Sn) 공용 쌍, 금-주석(Au-Sn) 공용 쌍, 알루미늄-게르마늄(Al-Ge) 공용 쌍, 및 알루미늄-주석-은-구리(Sn-Ag-Cu) 조합을 형성할 수 있다. Sn-Ag-Cu의 경우, 2개의 재료가 본딩 재료(426)로서 제작된 기판 상에 형성되고 나머지 재료는 본딩 재료(436)로서 형성될 수 있다.

- [0082] 도 4q에 도시된 바와 같이, 제작된 기판(302)과 CMOS 웨이퍼(304)는 함께 본딩되어, 일부 실시예에서는 CMOS 웨이퍼(304)의 IC들(예를 들어, 금속화부(322)) 위로 수직으로 배치된 밀봉된 캐비티들(306)을 포함하는 모놀리식 통합형 구조를 생성할 수 있다. 전술한 바와 같이, 이러한 본딩은, 일부 실시예에서, CMOS 웨이퍼(304) 상의 금속화 층 및 다른 커먼트들에 대한 손상을 방지할 수 있는 저온(예를 들어, 450°C 아래)의 이용만을 수반할 수 있다.

- [0083] 예시된 비제한적인 예에서, 본딩은, 본딩 재료(426) 및 본딩 재료(436)가 조합하여 본딩 지점(316a 및 316b)을 형성할 수 있도록 공용 본딩(eutectic bond)일 수 있다. 추가의 비제한적인 예로서, 본딩 재료로서 Au를 이용하여 열 압착 본딩이 형성될 수 있다. 예를 들어, 본딩 재료(426)는, 도금된 Au가 형성된 Ti/TiW/Au의 씨드 층(스페터링 등에 의해 형성됨)을 포함할 수 있고, 본딩 재료(436)는 도금된 Ni/Au가 형성된 (스페터링 또는 기타의 방식으로 형성된) TiW/Au의 씨드 등을 포함할 수 있다. 티타늄 층은 접착 층으로서 역할할 수 있다. TiW 층은 접착 층 및 확산 장벽으로 역할할 수 있다. 니켈은 확산 장벽으로서 역할할 수 있다. Au가 본딩을 형성할 수 있다. 다른 본딩 재료가 대안으로서 이용될 수도 있다.

- [0084] 그 다음, 제2 핸들 층(410) 및 산화물 층(414)은, 도 4r에 도시된 바와 같이 임의의 적절한 방식으로 제거될 수 있다. 예를 들어, 그라인딩 및/또는 에칭이 이용될 수 있다. 산화물 층(314)은 제2 핸들 층(410)을 제거하기 위한 에칭 정지부로서 작용할 수 있다.

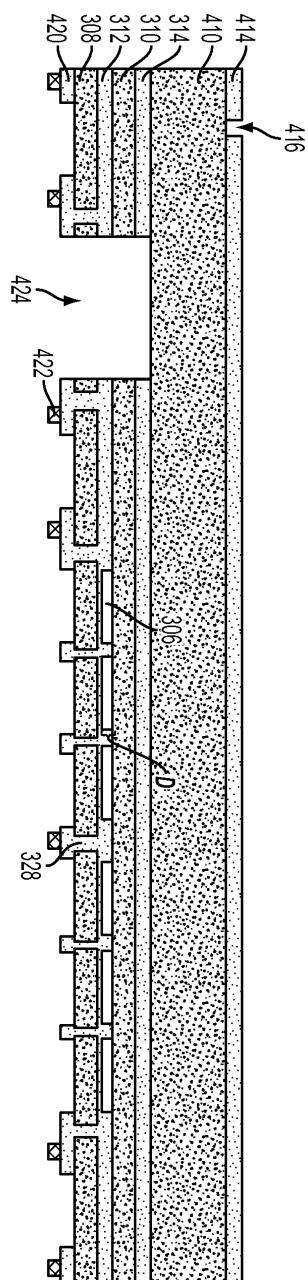

- [0085] 도 4s에 도시된 바와 같이, 산화물 층(314)은 임의의 적절한 에칭 기술을 이용하여 개구(438)를 형성하도록 패터닝될 수 있다. 개구(438)는 CMOS 웨이퍼(304)에 멀리 있는 제2 실리콘 디바이스 층(310)의 배면(또는 상부측)에 대한 액세스를 제공한다. 도 4t에 도시된 바와 같이, 도 3의 콘택트(324) 및 본딩 패드(326)는, 예를 들어 적절한 도전성 재료(예를 들어, 알루미늄, 구리 또는 다른 적절한 재료)를 퇴적하고 패터닝함으로써 형성될 수 있다. 또한, 산화물 층(314)은 선택사항으로서 캐비티(306)를 덮는 영역으로부터 (임의의 적절한 방식으로) 제거될 수 있다. 즉, 산화물 층(314)은 초음파 디바이스의 초음파 트랜스듀서 영역으로부터 제거될 수 있다.

- [0086] 그 다음, 디바이스(300)는 패시베이션 층(330)을 퇴적하고 패터닝함으로써 달성될 수 있다. 도 3과 관련하여 앞서 설명된 바와 같이, 패시베이션 층(330)은 콘택트(324)들 중 하나 이상에 대한 액세스를 제공하도록 패터닝될 수 있다.

- [0087] 이제, 도 4a 내지 도 4t의 제작 시퀀스의 다양한 피쳐들이 주목된다. 예를 들어, 제작 시퀀스가 TSV의 이용을 수반하지 않으므로, TSV가 이용되는 경우보다 프로세스가 덜 비싸고 복잡하다는 것을 이해해야 한다. 결과적으로 프로세스의 수율이 증가할 수 있다.

- [0088] 또한, 이 프로세스는 화학적 기계적 연마(CMP)를 이용하지 않는다. 예를 들어, 설명된 본딩 스테이지들 중 어느 하나에 대한 준비로서 CMP가 이용되지 않으며, 따라서 CMP 단계들이 수행되는 경우에 비해 비용이 감소될 수 있는 한편 본딩 신뢰성(따라서 수율)이 증가될 수 있다. 유사하게, 예시된 제작 시퀀스는 CMOS 웨이퍼와 제작된 기판의 저온 본딩에 대한 어떠한 고밀도 어닐링도 포함하지 않는다는 점에 주목할 만하다. 이러한 어닐링의 이용은 본딩 신뢰성과 그에 따라 수율을 감소시킨다. 또한, 전술한 바와 같이, 초음파 트랜스듀서를 위한 밀봉된 캐비티의 제작은 CMOS 열 예산으로부터 분리되어, 제작된 기판을 웨이퍼와 함께 본딩할 때 고온 처리(예를 들어, 고온 어닐링)의 이용을 허용한다.

- [0089] 밀봉된 캐비티(306)를 형성하는 프로세스는 또한, 원하는 치수 및 간격의 캐비티를 형성하는 것을 용이하게 할 수 있다. 예를 들어, 캐비티(306)는, 약 50 마이크론, 약 5 마이크론 내지 약 500 마이크론, 약 20 마이크론 내지 약 100 마이크론, 그 사이의 임의의 폭 또는 폭 범위, 또는 임의의 다른 적절한 폭들의, 폭  $W$ (도 3 및 도 4c 참조)을 가질 수 있다. 일부 실시예에서, 폭  $W$ 는, 텅빈 부분, 즉, 주변 구조물에 의해 소비되는 영역의 양에 비해 캐비티에 의해 소비되는 영역의 양을 최대화하도록 선택될 수 있다. 캐비티(306)는, 약 2 마이크론, 약 0.5 마이크론, 약 0.25 마이크론, 약 0.05 마이크론 내지 약 10 마이크론, 약 0.1 마이크론 내지 약 5 마이크론, 약 0.5 마이크론 내지 약 1.5 마이크론, 임의의 깊이 또는 깊이 범위, 또는 기타 임의의 적절한 깊이의 깊이  $D$ (도 4c 참조)를 가질 수 있다. 일부 실시예에서, 캐비티는 약 50 마이크론의 폭  $W$ , 및 약 0.2 마이크론의 깊이  $D$ 를 갖는다. 일부 실시예에서, 깊이  $D$ 에 대한 폭  $W$ 의 비율은 50보다 크거나, 100보다 크거나, 150보다 크거나, 30 내지 300의 비율이거나, 또는 기타 임의의 적절한 비율일 수 있다. 이 비율은, 트랜스듀서 멤브레인의 원하는 동작, 예를 들어 목표 주파수에서의 동작을 제공하도록 선택될 수 있다.

- [0090] 캐비티들(306) 사이의 간격은 또한, 캐비티들(306) 사이의 공간의 양이 제작된 기판을 형성할 때 본딩 가능한 영

역에 영향을 준다는 사실에도 불구하고 작게 만들어질 수 있다. 즉, 캐비티들(306) 사이의 거리가 작을수록, 본딩 표면이 적어서 본딩의 어려움을 증가시킨다. 그러나, 산화물 층에서의 캐비티 형성, 저온 융합 본딩, 및 고온 어닐링을 포함한 도 1, 2, 4a 내지 도 4d 및 (이하에서 설명되는) 도 7과 관련하여 여기서 설명된 제작된 기판을 형성하는 프로세스는, 제작된 기판의 높은 본딩 품질 및 수율을 여전히 달성하면서 캐비티(306)를 밀착 배치하는 것을 실용적이게 한다. 일반적으로, 제작된 기판의 형성은 여기서 설명된 기술을 이용하는 열 예산에 의해 제한되지 않으므로, 캐비티들(306) 사이의 본딩 가능한 영역을 최소화하기 위한 설계 규칙을 이용하는데 있어서 유연성이 제공된다. 예를 들어, 다른 가능성들 중에서도, 5 마이크론 미만, 3 마이크론 미만, 또는 2 마이크론 미만의 캐비티들 사이의 간격은, 여기서 설명된 프로세스를 이용하여 달성될 수 있다.

[0091] 디바이스(300)는 일부 실시예에서 추가로 팩키징되거나 및/또는 캡슐화될 수 있다. 예를 들어, 도 5의 팩키징된 디바이스(500)에 의해 도시된 바와 같이, 디바이스(300)는 다이싱되고, 회로 기판, (예를 들어, 일부 실시예에서는 콘택트 핀을 갖는) 플라스틱 팩키지 백킹(plastic package backing), 또는 기타의 기판일 수 있는, 기판(506)과 본딩될 수 있다. 음향 매질(acoustic medium, 502)이 디바이스(300)의 초음파 트랜스듀서 영역 위에 배치될 수 있다. 음향 매질은, 실리콘, 파릴렌(parylene), 또는 원하는 음향 속성을 제공하는 기타 임의의 다른 재료로 형성될 수 있다. 추가 캡슐화는 인캡슐런트(encapsulant)(504)에 의해 제공될 수 있다. 도 3과 관련하여 이전에 기술된 바와 같이, 일부 실시예들에서 와이어 본딩은, 콘택트(324)와, 와이어 본딩(325) 등의 본딩 패드(326) 사이에 형성될 수 있다. 인캡슐런트(504)는, 이러한 와이어 본딩을 덮어 이들을 손상으로부터 보호하도록 배치될 수 있다(따라서 와이어 본딩(325)은 도 5에 도시되지 않음). 임의의 적절한 캡슐화 재료가 이러한 목적에 이용될 수 있다. 따라서, 도 3의 디바이스(300)는 팩키징될 수 있고, 팩키징의 방식은 본 출원의 다양한 양태를 제한하지 않는다는 것을 이해해야 한다.

[0092] 도 6은, 디바이스(300)의 일반적인 구조를 이용할 수 있는 초음파 디바이스의 일부의 평면도를 나타낸다. 도시된 바와 같이, 초음파 디바이스(600)는 도 3과 관련하여 앞서 기술된 CMUT에 대응할 수 있는 초음파 트랜스듀서(602)의 어레이를 포함한다. 밀봉 링(604)은, 간소화를 위해 밀봉 링(604)의 일부분만이 도시되어 있지만, 초음파 트랜스듀서(602)를 실질적으로 또는 완전히 둘러쌀 수 있다. 밀봉 링은 도 3과 관련하여 앞서 기술된 본딩 지점(316a)에 의해 형성될 수 있다. 일부 실시예에서, 밀봉 링(604)은 밀봉을 제공하며, 밀봉은 절단되지 않은 윤곽을 통해 영역을 완전히 둘러싸는 밀봉이다. 일부 실시예에서, 밀봉 링(604)은, 제작된 기판과 CMOS 웨이퍼 상의 피쳐(예를 들어, CMOS 웨이퍼 상의 재배치 라우팅 층, CMOS 웨이퍼 상의 접적 회로 또는 다른 피쳐) 사이의 전기적 상호 접속을 제공한다. 일부 실시예에서, 밀봉 링(604)은 밀봉 및 전기적 상호 접속을 제공한다.

[0093] 도 4k와 관련하여 이전에 기술된 말소 영역(424)이 밀봉 링(604)의 주변 둘레에 제공될 수 있다. 도시된 바와 같이, 말소 영역(424)은 도 3의 본딩 패드(326)에 대응할 수 있는 본딩 패드(606) 등의 다양한 피쳐를 포함할 수 있다.

[0094] 도 4a 내지 도 4t의 제작 시퀀스에 대한 대안이 가능하다. 예를 들어, 제작된 기판(302)을 형성하기 위해 SOI 웨이퍼를 이용하는 것이 아니라, 하나 이상의 벌크 실리콘 웨이퍼가 이용될 수 있다. 예를 들어, 제1 SOI 웨이퍼(400) 및/또는 제2 SOI 웨이퍼(408)는 벌크 실리콘 웨이퍼로 대체될 수 있다. 도 4d를 참조하면, SOI 웨이퍼(400 및 408)를 이용하는 이유는, 핸들 층(402 및 410)이 제거될 때 BOX 층(404 및 314)이 에칭 정지부로서 기능할 수 있기 때문이다. 유사한 기능은 도핑된 층을 생성하는 적절한 도핑을 이용하여 벌크 실리콘 웨이퍼로 달성될 수 있다. 즉, (예를 들어, 실리콘 디바이스 층(308 또는 310)에 대응하고, 이러한 층들에 대해 여기서 설명된 임의의 두께를 갖는) 벌크 실리콘 웨이퍼의 일부는 벌크 실리콘 웨이퍼의 대부분보다 낮은 에칭 속도를 나타내도록 도핑될 수 있다. 그 다음, 벌크 실리콘 웨이퍼는, 도핑된 층에서 느려지거나 사실상 정지할 때까지 (즉, 도핑에 의해 에칭 속도가 변경되는 깊이에서) 배면으로부터 얇게(예를 들어, 에칭)될 수 있다. 이러한 방식으로, 도핑 경사(doping gradient)는 효과적으로 에칭 정지부로서 역할할 수 있고, 따라서 원하는 부분(예를 들어, 실리콘 디바이스 층(308 또는 310)에 대응하는 도핑된 층)만 남기면서 벌크 웨이퍼의 대부분이 제거될 수 있다. 대안으로서, 벌크 실리콘 웨이퍼가 이용되어, 타이밍식 에칭을 이용하여 원하는 두께로 얇게 될 수 있다. 도 4a 내지 도 4t의 제작 시퀀스의 나머지 부분은, SOI 웨이퍼의 이용과 관련하여 설명된 것과 실질적으로 동일한 방식으로 진행될 수 있으며, 따라서 도 3의 디바이스(300)를 생성하기 위해 유사하게 이용될 수 있다. 이러한 방식으로 벌크 실리콘 웨이퍼를 이용하는 한 가지 이점은 SOI 웨이퍼에 비해 비교적 저렴한 비용이다.

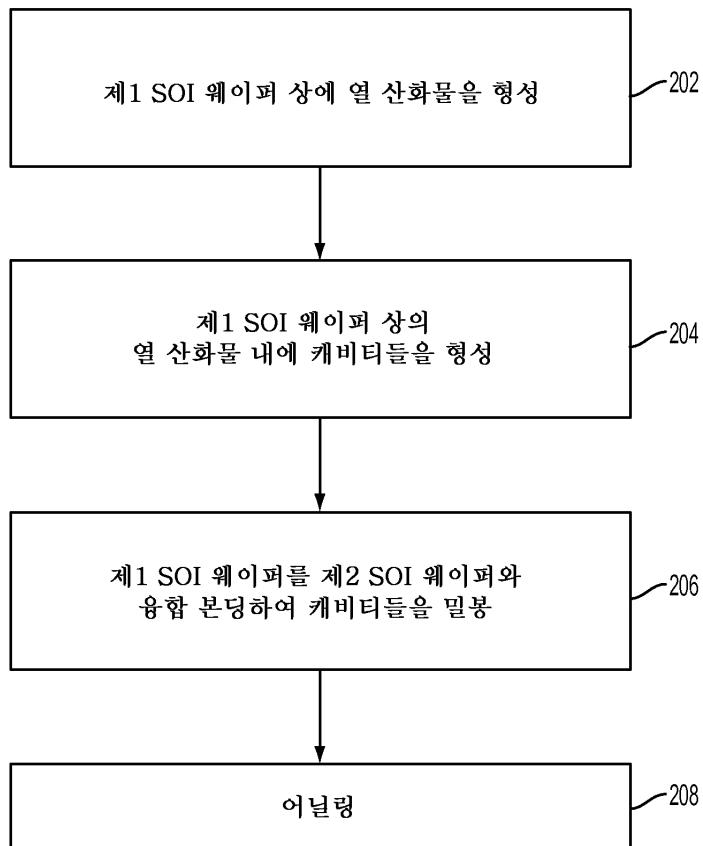

[0095] 상기로부터, 도 1의 방법은, 도 7에서 이루어지는 바와 같이, 특히 SOI 웨이퍼에 대한 제한 없이 일반화될 수 있다는 것을 이해해야 한다. 도시된 바와 같이, 방법(700)은, SOI 웨이퍼 또는 벌크 실리콘 웨이퍼일 수 있는

제1 웨이퍼, 및 SOI 웨이퍼 또는 벌크 실리콘 웨이퍼일 수 있는 제2 웨이퍼로부터, 밀봉된 캐비티를 갖는 제작된 기판의 형성과 함께 스테이지 702에서 시작될 수 있다. 따라서, 방법(700)의 스테이지 702는, 도 1에서와 같이 2개의 SOI 웨이퍼, 2개의 벌크 실리콘 웨이퍼, 또는 1개의 SOI 웨이퍼 및 1개의 벌크 실리콘 웨이퍼의 이용을 수반할 수 있다.

[0096] 스테이지 702에서 이용되는 2개의 웨이퍼 중 하나 또는 양쪽 모두는, 내부에 형성된 복수의 캐비티를 가질 수 있어서, 2개의 웨이퍼를 함께 본딩하면 CMUT의 캐비티로서 이용하기에 적절한 밀봉된 캐비티가 생성될 수 있다. 2개의 웨이퍼 사이의 강한 본딩을 보장하기 위해, 고온 처리가 이용될 수 있다. 예를 들어, 저온 융합 본딩 등의, 저온 웨이퍼 본딩에 후속하여, 고온 어닐링이 이용될 수 있다. 따라서, 일부 실시예에서 고온 및 저온의 조합이 제작된 기판을 형성하는데 이용될 수 있다. 도 1과 관련하여 설명된 바와 같이, 일부 실시예에서는 고온이 임계치 온도 450°C 위일 수 있는데, 이 임계치 온도보다 위에서는 CMOS IC가 일반적으로 손상될 수 있다. 또한, 스테이지 102에서의 본딩과 마찬가지로, 스테이지 702에서 2개의 웨이퍼의 본딩은 전공 상태에서 수행될 수 있다.

[0097] 스테이지 704에서, 제1 웨이퍼의 두께가 변경된다. 제1 웨이퍼가 SOI 웨이퍼라면, 제1 웨이퍼의 핸들 층이 제거된다. 대신에 제1 웨이퍼가 벌크 실리콘 웨이퍼라면, 예를 들어 에칭에 의해 얇게 될 수 있다. 타이밍식 에칭이 이용되거나 벌크 실리콘 웨이퍼는 전술한 바와 같이 에칭 정지부로서 기능하는 도핑 계조(doping gradation)를 포함할 수 있다.

[0098] 스테이지 704의 결과로서, 제1 웨이퍼는 비교적 작은 두께를 가질 수 있다. 예를 들어, 스테이지 704 이후의 제1 웨이퍼의 두께는, 50 마이크론 미만, 30 마이크론 미만, 20 마이크론 미만, 또는 10 마이크론 미만일 수 있다. 이하에서 더 설명하는 바와 같이, 일부 실시예에서, 제1 웨이퍼는 후속해서, CMOS 웨이퍼와 제2 웨이퍼 사이에 배치되도록, CMOS 웨이퍼와 본딩된다. 도 3의 CMOS 웨이퍼(304)와 제1 실리콘 디바이스 층(308) 사이의 캡에 관해 전술된 방식으로 제1 웨이퍼와 CMOS 웨이퍼 사이에 캡이 존재할 수 있다. 본 출원인들은, 이 캡이, 제1 웨이퍼가 너무 얇을 경우 제1 웨이퍼가 진동하는 것을 허용할 수 있다는 것을 이해한다. 이러한 진동은, 예를 들어 초음파 트랜스듀서로부터 원치않는 고조파를 생성할 수 있기 때문에 바람직하지 않을 수 있다. 따라서, 본 출원인들은, 제1 웨이퍼가 이러한 바람직하지 않은 진동을 피하면서 강성을 제공하기에 충분한 두께를 갖는 것이 바람직하다는 것을 인식하였다. 따라서, 한 실시예에 따르면, 제1 웨이퍼의 두께가, 4 마이크론 내지 50 마이크론, 5 마이크론 내지 30 마이크론, 6.5 마이크론 내지 20 마이크론, 8 마이크론 내지 15 마이크론 이거나, 이러한 범위 내의 임의의 두께 또는 두께 범위를 취하도록 스테이지 704가 수행된다. 따라서, 제1 웨이퍼가 얇을 수 있지만, 본 출원인들은 방법(700)의 이 스테이지에서 제2 웨이퍼가 제작된 기판의 추가 처리를 허용하기에 충분한 구조적 지지를 제공할 수 있다는 것을 인식하였다.

[0099] 스테이지 706에서, 제작된 기판은, 도 1의 스테이지 106과 관련하여 설명된 것과 동일한 방식으로 집적 회로를 갖는 CMOS 웨이퍼와 본딩되어 집적 디바이스를 형성할 수 있다. 제1 웨이퍼는, 예를 들어 제1 웨이퍼의 배면을 CMOS 웨이퍼와 본딩함으로써, CMOS 웨이퍼의 본딩 표면에 근접하게 배치될 수 있다. 따라서, 결과적 구조물은, 순서대로, CMOS 웨이퍼, 제1 웨이퍼, 및 제2 웨이퍼를 순서대로 포함할 수 있다. 전술한 바와 같이, 수행된 본딩의 유형에 따라, 예를 들어 도 3의 제1 실리콘 디바이스 층(308) 및 CMOS 웨이퍼(304)와 관련하여 설명된 바와 같이, CMOS 웨이퍼와 제1 웨이퍼 사이에 캡이 존재할 수 있다.

[0100] 스테이지 708에서, 제2 웨이퍼의 두께가 변경된다. 제2 웨이퍼가 SOI 웨이퍼라면, 임의의 적절한 방식으로, 예를 들어 그라인딩과 후속하는 에칭의 조합에 의해, 제작된 기판의 제2 웨이퍼의 핸들 층이 제거된다. 대신에 제2 웨이퍼가 벌크 실리콘 웨이퍼라면, 예를 들어 에칭에 의해 얇게 될 수 있다. 타이밍식 에칭이 이용되거나 또는 벌크 실리콘 웨이퍼는 에칭 정지부로서 기능하는 도핑 계조를 포함할 수 있다.

[0101] 도 1의 방법(100)에서와 같이, 방법(700)은, 일부 실시예에서, CMOS 웨이퍼와 통합된 제작된 기판을 생성하고, 여기서, 제작된 기판은 2개의 실리콘 층만을 포함한다. 이러한 구조는 도 1과 관련하여 이전에 설명된 이점을 갖는다.

[0102] 도 1과 관련하여 설명된 것과 동일한 방식으로 기능하는 초음파 트랜스듀서를 제공하기 위해, CMOS 웨이퍼 상의 IC들과 제작된 기판의 밀봉된 캐비티 사이에 전기적 접속이 이루어질 수 있다.

[0103] 방법(700)에 따라, 도 4a 내지 도 4t의 제작 시퀀스에 대한 대안은, 하나의 SOI 웨이퍼 및 하나의 벌크 실리콘 웨이퍼가 제작된 기판을 형성하는데 이용되는 실시예이다. 도 4a를 참조하면, SOI 웨이퍼(400)는 그 전면 및 배면에 산화물을 갖는 벌크 실리콘 웨이퍼로 대체된다. 즉, 도 4b의 구조에서 BOX 층(404)을 뺀 것이 이용될

수 있다. 그러면, 도 4c에 도시된 것과 동일한 방식으로, 벌크 실리콘 웨이퍼의 전면 상의 실리콘 산화물 층에 캐비티가 형성될 수 있다. 즉, 벌크 실리콘 웨이퍼가 이 실시예에서 이용되기 때문에, 현재의 실시예는 BOX 층(404)이 없을 수 있다는 점에서만 도 4c에 도시된 것과 상이할 수 있다.

[0104] 그 다음, 캐비티를 갖는 벌크 실리콘 웨이퍼는 SOI 웨이퍼(408) 등의 SOI 웨이퍼와 본딩될 수 있다. 따라서, 본 실시예는 BOX 층(404)이 없을 수 있다는 점에서만 도 4d의 구조와 상이할 수 있다.

[0105] 그 후, 본 실시예에서의 처리는 도 4e 내지 도 4t에 도시된 것과 동일한 방식으로 진행될 수 있다.

[0106] 방법(700)과 일치하는 도 4a 내지 도 4t의 제작 시퀀스에 대한 역시 또 다른 대안이, 도 8a 내지 도 8d와 관련하여 예시된다. 여기서, 제작은 도 8a에 도시된 바와 같이 도 4a의 SOI 웨이퍼(400)와 함께 시작된다. 도 8b에 도시된 다음 스테이지는 도 4b의 스테이지와 동일하다.

[0107] 그 다음, 도 8c에 도시된 바와 같이, 캐비티(806)가 실리콘 산화물 층(312)에 형성된다. 캐비티(806)는 실리콘 산화물 층(312)을 통해 연장되어 제1 실리콘 디바이스 층(308) 상에서 멈춘다. 이러한 구성은, 제1 실리콘 디바이스 층(308)이 에칭 정지부로서 역할하는 에칭에 의해 실리콘 산화물 층(312)을 에칭함으로써 달성될 수 있다. 제1 실리콘 디바이스 층(308)을 에칭 정지부로서 이용하는 것은 캐비티(806)의 깊이의 정확한 제어를 용이하게 한다.

[0108] 그 다음, 도 8d에 도시된 바와 같이, (실리콘 산화물 층(312)을 통해 연장되는 캐비티(806)를 갖는) SOI 웨이퍼(400)가 벌크 실리콘 웨이퍼(808)와 본딩된다. 벌크 실리콘 웨이퍼(808)는, 실리콘 층(810), 실리콘 층(810)의 전면 상의 산화물 층(314), 및 실리콘 층(810)의 후면(또는 배면) 상의 산화물 층(414)을 포함한다. 따라서, 이 제작 스테이지에서 캐비티(806)는 밀봉될 수 있다.

[0109] 그 후, 제작은, 도 4e 내지 도 4t에 관하여 도시된 것과 실질적으로 동일한 방식으로 진행될 수 있다. 즉, 도 8d에 도시된 스테이지에 후속하여, 정렬 마크가 벌크 실리콘 웨이퍼에 전사될 수 있다. 그 다음, 도 4f의 구조물과 유사한 구조물을 달성하기 위해, 벌크 실리콘 웨이퍼(808)가 배면(산화물 층(414)이 배치되는 측면)으로부터 얇게 될 수 있다. 이 스테이지로부터, 얇게 된 벌크 실리콘 웨이퍼는, 도 4g 내지 도 4t의 제1 실리콘 디바이스 층(308)과 동일한 방식으로 처리될 수 있다.

[0110] 디바이스와 연관된 다양한 파라미터가 디바이스의 성능을 최적화하도록 선택될 수 있다. 이러한 파라미터의 예로서는, (도 8d의 비제한적인 실시예에서 실리콘 산화물 층(312)의 두께에 의해 결정되는) 캐비티의 깊이  $D$ , 산화물 층(314)의 두께, 캐비티의 폭  $W$ , 캐비티의 피치, 및 결과적 멤브레인의 두께가 포함된다. 예를 들어, 캐비티의 깊이  $D$  및 산화물 층(314)의 두께는, 이미징 모드(imaging mode)에서 초음파 트랜스듀서의 전송 및 수신 기능성을 최적화하고 또한 저전압 동작을 허용하도록 선택될 수 있다. 멤브레인 두께, 캐비티 폭 및 피치는, 고강도 포커싱된 초음파(HIFU) 모드에서 저주파수 동작을 용이하게 하도록 선택될 수 있고, 예로서, 초음파 트랜스듀서의 감도 및 대역폭을 제어하는데 이용될 수 있다.

[0111] 도 4a 내지 도 4t의 제작 시퀀스에 대한 또 다른 대안은, 밀봉된 캐비티(306)에 대응하는 하부 전극의 격리에 관한 것이다. 도 3에 도시된 바와 같이, 격리 구조물(328)이 제공될 수 있으며, 도 4g 내지 도 4j와 관련하여 도시된 바와 같이, 일부 실시예들에서 격리 구조물(328)은 절연 재료로 채워진 트렌치이다. 그러나, 대안적인 격리 구조물이 이용될 수 있으며, 그 중 하나는 제1 실리콘 디바이스 층(308)의 도핑에 의해 형성된 격리 영역을 포함한다. 즉, 격리가 요구되는 각각의 위치에 트렌치(예를 들어, 도 4g의 트렌치(418))를 형성하는 것이 아니라, 예를 들어 하나 이상의 역방향 바이어스된 다이오드를 정의하기 위해 도핑 경계가 대신에 이용될 수 있다. 예가 도 9에 도시되어 있다.

[0112] 도 9의 디바이스(900)는 도핑 경계가 격리 구조물(328)을 생성하는데 이용되는 도 3의 디바이스(300)의 구현을 나타낸다. 도 9에서, 제1 실리콘 디바이스 층(308)은 도핑에서의 차이를 나타내는 3개의 상이한 유형의 영역을 갖는 것으로 도시되어 있다. 영역(902)은 실리콘 재료의 베이스 도핑을 나타낸다. 영역(904)은 전극 영역을 나타내며, 영역(902)과는 반대로 도핑된다. 선택사항적인 영역(906)은, 전극 영역(904)과 동일한 도편트 유형을 갖지만 더 낮은 도핑 농도를 갖는 영역을 나타낸다. 영역들(902 및 904)의 상반되는 도핑의 결과로서, 전극 영역들(904) 사이의 격리는 도시된 바와 같이 적절한 도핑 패턴을 이용함으로써 생성되어 전극 영역들(904) 사이에 p-n 접합을 생성할 수 있다. p-n 접합은 일부 실시예에서 역방향 바이어스될 수 있다.

[0113] 하나의 적절한 도핑 방식은, 영역(902)이 저농도로 도핑된 N형이 되고, 영역(904)이 고농도 도핑된 P형이 되고, 영역(906)이 저농도로 도핑된 P형으로 되는 것이다. 그러나, 대안적인 실시예에서, 영역(902)은 저농도로 도핑된 P형일 수 있고, 영역(904)은 고농도로 도핑된 N형일 수 있고, 영역(906)은 저농도로 도핑된 N형일 수 있다.

어느 시나리오 하에서도, 봉소는 P형 도편트로서 역할할 수 있고, 인 또는 비소는 N형 도편트로서 작용할 수 있지만, 대안들도 가능하다. 영역들(902, 904 및 906)의 도핑 농도는 원하는 전기적 거동을 제공하도록 선택될 수 있다.

[0114] 영역들(902, 904 및 906)의 도핑은 임의의 적절한 방식으로 생성될 수 있다. 일부 실시예에 따르면, (예를 들어, 고온 어닐링을 통한) 이온 주입 및 확산의 조합이 이용될 수 있다. 도 9에 도시된 바와 같이, 영역들(904 및 906)은 제1 실리콘 디바이스 층(308)의 전체 두께를 통해 연장될 수 있으며, 그 두께는 이전에 설명되었다. 이러한 두께를 통해 도핑 영역들(904 및 906)을 연장하기 위해, 예를 들어 750 keV, 1 MeV, 500 keV 내지 2 MeV, 또는 10 MeV까지의 이온 주입이 확산 어닐링과 결합될 수 있고, 그 조합은, 일부 실시예들에서 도핑 영역들(904 및/또는 906)이 제1 실리콘 디바이스 층(308)을 통해 연장될 때까지 반복될 수 있다. 그러나, 이러한 고 에너지 주입은 제1 실리콘 디바이스 층(308) 내로 깊이 관통할 수 있기 때문에, 제1 실리콘 디바이스 층(308)의 더 얕은 깊이도 역시 도핑되도록 보장하기 위해 더 낮은 에너지 주입이 추가로 이용될 수도 있다. 주입(들)의 에너지와 어닐링 지속시간 및 온도는, 일부 도편트가 다른 것보다 더 깊은 깊이에 도달할 수 있기 때문에(예를 들어, 동일한 주어진 주입 에너지에 대해 봉소는 인보다 더 깊이 주입될 수 있다) 이용되는 도편트의 유형에 의존할 수 있다.

[0115] 영역들(902, 904 및 906)의 크기조정은 원하는 전기적 거동을 제공하도록 선택될 수 있다. 예를 들어, 크기조정은, 예를 들어 별개의 전극 영역(904)들 사이에서, 기생 커패시턴스를 감소시키도록 최적화될 수 있다. 영역(904)은 캐비티(306)에 대응하는 전극 영역을 나타내므로, 원하는 전극 크기를 제공하도록 크기조정될 수 있다. 예를 들어, 영역(904)은 캐비티(306)의 폭  $W$ 와 실질적으로 동일한 폭을 가질 수 있지만, 대안적 실시예에서, 영역(904)은 캐비티의 폭  $W$ 보다 작은 폭을 가질 수 있고(도 3 참조), 이것은 죽은(기생) 커패시턴스를 감소시키는데 도움이 될 수 있다.

[0116] 전술한 바와 같이, 영역(906)은 선택사항이며, 따라서 일부 실시예에서는 생략될 수도 있다. 영역(906)은, 전극 영역(904)들 사이의 죽은 커패시턴스를 감소시킬 수 있으며, 따라서 포함될 때 이러한 기능을 수행하기 위한 임의의 적절한 크기조정을 가질 수 있다. 예를 들어, 일부 실시예에서 영역(904)은 전극 영역(904)의 폭에 비해 비교적 클 수 있다. 따라서, 영역들(904 및 906)의 위치는 캐비티(306)에 관한 바람직한 크기조정 및 간격을 제공하도록 제어될 수 있다.

[0117] 영역(902)은 임의의 적절한 전압에 전기적으로 접속될 수 있다. 일부 실시예에서, 영역(902)은 부동성(floating)일 수 있다. 다른 실시예에서, 영역(902)은 바이어스 전압에 결속될 수 있다. 예를 들어, 영역(902)은 P형으로 도핑될 때 전기적으로 접지될 수 있거나, N형으로 도핑될 때 고전압(예를 들어, 고전압 레일)에 결속될 수 있다. 일부 실시예에서, 영역(902)은, 비제한적인 예로서 초음파 촬영 응용의 정황에서 이용될 수 있는 바와 같이 약 20 내지 300 볼트(예를 들어, 약 30 내지 120 볼트, 약 50 내지 250 볼트, 약 60 내지 90 볼트, 또는 이를 범위 내의 임의의 값 또는 임의의 값 범위)의 전압에 결속(tie)될 수 있다. 일부 실시예에서, 영역(902)은 초음파 트랜스듀서용 멤브레인으로서 역할하는 제2 실리콘 디바이스 층(310)을 바이어스하는데 이용되는 것과 동일한(또는 실질적으로 동일한) 전압으로 바이어스될 수 있다.

[0118] 도 9는 제1 실리콘 디바이스 층(308)의 패터닝된 도핑을 나타내지만, 패터닝된 도핑은 또한, 제1 실리콘 디바이스 층(308)에 관해서 설명된 것과 동일한 방식으로 제2 실리콘 디바이스 층(310)에서 이용될 수 있다는 것을 이해해야 한다. 따라서, 상호접속되고 도핑된 초음파 트랜스듀서 멤브레인이 제2 실리콘 디바이스 층(310)에서 형성될 수 있다. 예를 들어, 제2 실리콘 디바이스 층(310)의 더 높은 도핑의 복수의 별개의 영역들은 동일한 도핑 종의 더 낮은 도핑 영역과 교대될 수 있다. 다른 패턴들도 역시 가능하다.

[0119] 제1 및 제2 실리콘 디바이스 층들(308, 310) 양쪽 모두가 도핑되는 실시예들에서, 바람직한 전기적 행동을 제공하도록 2개의 층 사이의 상대적 도핑이 선택될 수도 있다. 예를 들어, 영역(904) 및 제2 실리콘 디바이스 층(310)은 바이어스 전압을 증폭시키기 위해 반대로 도핑되고 상이한 농도로 도핑될 수 있다. 예를 들어, 영역(904)은 P+ 도핑될 수 있고, 제2 실리콘 디바이스 층(310)은 N- 도핑될 수 있다. 이러한 구성은, N 및 P 도핑의 상이한 일함수들로부터 발생하는 캐비티(306)를 가로질러 추가의 전압 강하(예를 들어, 1 볼트 정도)를 생성할 수 있다. 영역(904)이 N형으로 도핑된다면, 제2 실리콘 디바이스 층(310)을 N형으로 도핑하여 일함수로 인한 전압 강하 손실을 피하는 것이 유익할 수 있다.

[0120] 도 4a 내지 도 4t의 제작 시퀀스에 대한 추가적인 대안은 제작된 기판이 본딩되는 품목에 관한 것이다. 설명된 바와 같이, 예를 들어 디바이스(300)와 관련하여, 일부 실시예에서는 제작된 기판이 CMOS 웨이퍼와 본딩된다. 일부 실시예에서, CMOS 웨이퍼는 집적 회로를 포함한다. 일부 실시예에서, CMOS 웨이퍼는 그 위에, 집적 회로

및 처리된 재분배 층을 포함한다. 일부 실시예에서, CMOS 웨이퍼는 그 위에, 처리된 재분배 층만을 포함할 수 있다. 추가적인 대안들도 가능하다. 예를 들어, 제작된 기판은, 대안으로서, 인터포저, 2개의 디바이스(예를 들어, 제작된 기판과, 볼 그리드 어레이 또는 기타의 디바이스 등의 또 다른 디바이스) 중간에 전기적으로(때때로 물리적으로) 구성되고 2개의 디바이스를 전기적으로 결합하도록 구성된 인터커넥트를 갖는 디바이스와 본딩될 수 있다. 일부 실시예에서, 제작된 기판은, 집적 회로를 포함하지 않지만 제1 및/또는 제2 실리콘 디바이스 층과 전기적 신호를 통신하기 위한 배선을 포함할 수 있는 웨이퍼와 본딩될 수 있다. 예를 들어, 일부 실시예에서, 제작된 기판은, 전기적 신호를 더 작거나 더 큰 기판에 재분배하도록 구성되고 그에 따라 여기서는 "재분배 웨이퍼"로 지칭되는 배선 트레이스를 포함하는 웨이퍼와 본딩될 수 있다.

[0121] 추가적인 대안은 제2 실리콘 디바이스 층(310)으로의 전기적 접촉을 이루는 방식에 관한 것이다. 전술한 바와 같이, 도 3의 실시예에서, 예를 들어 와이어 본딩(325)을 이용하여 콘택트(324)와 본딩 패드(326) 사이에 전기적 접촉이 이루어질 수 있다. 도 10에 도시된 바와 같이, 대안적인 구조의 디바이스(1000)는 본딩 지점(316a)으로부터 제2 실리콘 디바이스 층(310)으로의 비아(1002)를 이용한다. 이러한 방식으로, 임베딩된 콘택트가 이용될 수 있고 와이어 본딩이 회피될 수 있다. 일부 실시예들에서, 제1 및 제2 실리콘 디바이스 층들이 전기적으로 격리되는 것이 바람직할 때, 비아(1002)를 제1 실리콘 디바이스 층(308)으로부터 절연시키기 위해 적절한 절연 피쳐들(예를 들어, 절연 라이너(insulating liner))이 이용될 수 있다. 그러나, 전술한 바와 같이, 일부 실시예에서, 제2 실리콘 디바이스 층(310)과 동일한 전위에 제1 실리콘 디바이스 층(308)의 영역(예를 들어, 포함되는 경우, 도 9의 영역(902))을 전기적으로 결속하는 것이 바람직할 수 있으며, 이러한 실시예에서 비아(1002)에는 어떠한 절연 피쳐도 제공되지 않을 수 있다.

[0122] 비아(1002)는, 자신이 통과하는 두께, 즉, 제2 실리콘 디바이스 층(310), 실리콘 산화물 층(312), 및 제1 실리콘 디바이스 층(308)의 두께가 비교적 작기 때문에, 예를 들어, 이러한 구조물에 대해 여기에서 앞서 설명된 임의의 치수를 갖기 때문에, 전통적인 TSV가 아니라는 것을 이해해야 한다.

[0123] 추가적인 대안으로서, 임베딩된 콘택트를 나타내는 비아(1002)는, 제2 실리콘 디바이스 층(310)을 통과하지 않고, 오히려, 적절한 절연 피쳐(예를 들어, 절연 라이너)에 의해 제1 실리콘 디바이스 층(308)으로부터 다시 절연되면서, 본딩 지점(316a)과 캐비티(306)에 근접한 제2 실리콘 디바이스 층(310)의 하부측 사이에서 연장될 수 있다. 디바이스(1100)가 본딩 지점(316a)으로부터 제2 실리콘 디바이스 층(310)의 표면까지 연장되지만 제2 실리콘 디바이스 층(310)을 통과하지 않는 임베딩된 비아(1102)를 포함하는 예가 도 11에 도시되어 있다. 추가적인 인터커넥션(1104)이 금속화부(322)로부터 본딩 지점(316a)까지 제공될 수 있고, 금속화부(322)는 도시된 바와 같이 본딩 패드(326)에 접속되어, 본딩 패드(326)로부터 비아(1102)까지 연속적인 전기적 경로를 형성할 수 있다. 그러나, 비아(1102)로의 전기적 액세스를 제공하기 위한 다른 구성도 역시 가능하다.

[0124] 도 11에서와 같은 구성에서, 비아(예를 들어, 비아(1102))는, 예를 들어, 제작된 기판을 CMOS 웨이퍼와 본딩하기 이전에 (예를 들어, 도 4j에 의해 나타낸 처리 스테이지 이후에) 제1 실리콘 디바이스 층(308) 및 실리콘 산화물 층(312)을 관통하여 제작될 수 있고, 제작된 기판을 CMOS 웨이퍼와 본딩하는 동작은 본딩 지점(316a)으로부터 제2 실리콘 디바이스 층(310)으로의 전기적 접속을 완료할 수 있다. 이러한 구성은, 도 11에 도시된 바와 같이 제2 실리콘 디바이스 층(310)의 상부측 상에서의 임의의 금속에 대한 필요성을 제거할 수 있으며, 제작을 간소화하고 제2 실리콘 디바이스 층(310)에 의해 형성된 초음파 트랜스듀서 멤브레인의 성능을 향상시킬 수 있다.

[0125] 디바이스(300)의 추가적인 대안은 도 10 및 도 11의 디바이스들의 피쳐들을 결합한다. 도 10의 비아(1002)가 포함될 수 있고, 제2 실리콘 디바이스 층(310)의 상부측 상의 금속화부에 접속할 수 있다. 도 11의 인터커넥션(1104)이 또한 포함될 수 있다. 이러한 실시예에서, 와이어 본딩의 필요없이 금속화부(322)로부터 제2 실리콘 디바이스(310)의 상부측 상의 금속화부까지의 전기적 경로가 제공될 수 있다.

[0126] 디바이스(300) 및 도 4a 내지 도 4t의 제작 시퀀스에 대한 추가적인 대안은 캐비티(306)가 밀봉되는지와 관련되어 있다. 전술한 바와 같이, 일부 실시예에서 캐비티(306)는 밀봉된 캐비티일 수 있다. 그러나, 대안적 실시예에서, 캐비티(306)는 밀봉되지 않을 수도 있으며, 예를 들어 캐비티에 대한 하나 이상의 개구가 존재할 수 있다. 예가 도 12에 도시되어 있다.

[0127] 디바이스(1200)는 도 3의 디바이스(300)와 유사하지만, 개구가 제2 실리콘 디바이스 층(310)을 통해 캐비티(306)에 제공된다는 점이 상이하다. 개구의 2개의 상이한 비제한적인 예가 도시되어 있다. 일부 실시예에서, 하나 이상의(그러나 반드시 전부는 아닌) 캐비티들(306) 각각에 대해 단일 개구(1202)가 제공될 수 있다. 일부 실시예에서, 하나 이상의(그러나 반드시 전부는 아닌) 캐비티들 각각에 대해 복수의 개구(1204)가 제공될 수 있

다. 설명을 위해 도 12에는 2개의 상이한 패턴의 개구가 도시되어 있지만, 하나의 패턴(예를 들어, 개구(1202)만 또는 개구(1204)만)이 전체 디바이스(1200)에 이용될 수 있다는 것을 이해해야 한다. 또한, 개구들(1202 및 1204)은 제2 실리콘 디바이스 층(310)을 통해 수직으로 연장되는 것으로 도시되어 있지만, 개구의 다른 경로 및 기하학적 구조가 이용될 수 있다는 것을 이해해야 한다. 예를 들어, 디바이스의 측면을 따라 형성된 트렌치는 캐비티(306)에 액세스하는데 이용될 수 있다.

[0128] 개구들(1202 및/또는 1204)은 임의의 적절한 방식으로 및 디바이스(300)의 임의의 적절한 처리 스테이지에서 형성될 수 있다. 예를 들어, 개구(1202 및/또는 1204)는 적절한 에칭을 이용하여 도 4t에 나타낸 제작 스테이지 이후에 형성될 수 있다.

[0129] 개구(1202 및/또는 1204)의 존재는 초음파 트랜스듀서의 손실 및 경화, 및 궁극적으로 동작 주파수에 영향을 줄 수 있다. 예를 들어, 개구(1202 및/또는 1204)는 개구부가 포함되지 않는 경우보다 디바이스가 더욱 광대역 디바이스로서 동작하게 하여, 개선된 범위의 거동을 야기한다. 개구(1202 및/또는 1204)의 크기는 주파수 특성에 영향을 미치고, 일부 실시예에서는 디바이스(1200)에 대한 헬름홀츠 공진 주파수(Helmholtz resonance frequency)와 일치하도록 선택될 수 있다.

[0130] 따라서, 개구(1202 및/또는 1204)는 원하는 초음파 트랜스듀서 주파수 특성을 제공하는데 유익할 수 있다. 예를 들어, 개구(1202 및/또는 1204)는 (트랜스듀서 매체가 없는) 실외 용도에서 초음파 트랜스듀서에 대해 원하는 주파수 거동을 달성하는 것을 용이하게 할 수 있다.

[0131] 도 13은 밀봉된 캐비티들(306)을 격리시키는 격리 구조물(328)의 형상의 예의 평면도를 나타낸다. 도시된 바와 같이, 한 실시예에서 밀봉된 캐비티(306)는 원형 윤곽을 가질 수 있다. 격리 구조물(328)은, 초음파 트랜스듀서 요소들 사이에, 또는 도 13에 도시된 바와 같이, 개개의 초음파 트랜스듀서들 사이에 충분한 격리를 제공하는 임의의 적절한 형상을 가질 수 있다. 따라서, 일부 실시예들에서, 격리 구조물(328)은 (상부측에서 보았을 때) 밀봉된 캐비티(306)를 실질적으로 또는 완전히 둘러쌀 수 있지만, 대안적 실시예에서는 밀봉된 캐비티를 둘러싸지 않을 수도 있다. 또한, 일부 실시예에서, 격리 구조물은 (상부측에서 보았을 때) 밀봉된 캐비티 내에 윤곽을 가질 수 있다. 예를 들어, 도핑 영역이 도 9와 관련하여 설명된 격리 구조물을 정의하는데 이용될 때, 도핑 영역들은 밀봉된 캐비티의 윤곽보다 작은 격리 구조물의 윤곽을 정의하도록 배치될 수 있다.

[0132] 일부 실시예에서, 격리 구조물(328)은 다면체 윤곽을 가질 수 있다. 예를 들어, 8각형 윤곽이 도 13에 도시되지만, 다른 윤곽(예를 들어, 원형, 직사각형, 6각형, 반원 이상을 정의하는 윤곽 등)이 가능할 수도 있다는 것을 이해해야 한다. 또한, 전술한 바와 같이, 일부 실시예들에서, 격리 구조물은 각각의 캐비티를 개별적으로 둘러싸는 것이 아니라 복수의 캐비티(306)를 둘러쌀 수 있다. 따라서, 격리 구조물에 대한 다양한 구성이 가능하다.

[0133] 디바이스(300) 및 도 4a 내지 도 4t의 제작 시퀀스에 대한 추가적인 대안은 TSV의 이용에 관한 것이다. 전술한 바와 같이, 여기서 설명된 많은 실시예는 TSV의 필요성을 피하는데, 이것은, 예를 들어, 제작의 용이성, 저비용 및 신뢰성 측면에서 상당한 이점을 제공할 수 있다. 그럼에도 불구하고, 일부 실시예에서는 TSV가 이용될 수 있다. 한 예가 도 14과 관련하여 설명된다.

[0134] 일부 실시예에서, TSV를 갖는 웨이퍼는 제작된 기판을 형성하는데 이용될 수 있다. 도 14는 실리콘(1402), 및 6개의 TSV(1404)를 포함하는 웨이퍼(1400)를 나타낸다. 웨이퍼(1400)는, 예를 들어 도 4a 내지 도 4t의 제작 시퀀스에서 SOI 웨이퍼 대신에 이용될 수 있다. 예로서, 웨이퍼(1400)는 제1 SOI 웨이퍼(400) 대신에 이용될 수 있다. 이러한 시나리오에서, 도 4f의 구조는, 제1 실리콘 디바이스 층(308)이 실리콘(1402)으로 대체되고 TSV(1404)가 캐비티(306)와 정렬된다는 점에서 상이할 수 있다. 따라서, TSV(1404)는 전극으로서 기능할 수 있고, 그에 따라, 예를 들어 전극을 형성하기 위해 도 9의 도핑 방식에 대한 대안으로서 이용될 수 있다.

[0135] 도 14와 관련하여 방금 기술된 바와 같이, TSV를 갖는 웨이퍼의 이용을 포함하는 실시예는, TSV가 전극으로서 기능할 수 있기 때문에, 제작된 기판의 밀봉된 캐비티에 대한 하부 전극의 제작을 간소화할 수 있다. 캐비티는 적절한 설계를 통해 TSV와 정렬될 수 있다.

[0136] 지금까지 기술된 제작된 기판을 제작하고 CMOS 웨이퍼와 제작된 기판을 본딩하기 위한 다양한 방법들은 웨이퍼 미세제작 처리 기술과 호환되며, 미세제작 설비에서 수행될 수 있다는 것을 의미한다. 이러한 설비는, 종종 허용되는 재료의 유형 및 수행될 수 있는 처리 단계들과 관련하여 엄격한 기준을 갖고 있다. 다음과 같은 예시적인 기술은, 백엔드 웨이퍼-스케일 팩키징 설비 등의 다른 유형의 설비에서 적어도 부분적으로 수행될 수 있는 프로세스들을 이용한다. 이러한 기술을 이용하는 이점은, 더 낮은 비용일 것이다.

- [0137] 본 출원의 한 양태에 따르면, 웨이퍼 레벨 팩키징 기술은, 여기서 설명된 유형의 제작된 기판을, CMOS 웨이퍼 등의, IC를 갖는 웨이퍼에 본딩하도록 구현될 수 있다. 웨이퍼 레벨 팩키징은 재분배 기술을 이용할 수 있다. 예를 들어, CMOS 웨이퍼 및/또는 제작된 기판은 재분배 층을 추가시킬 수 있다. 땜납 볼 어레이의 형태 또는 다른 것의 형태로, 땜납은, 제작된 기판과 IC 웨이퍼를 함께 본딩하는데 이용될 수 있다. 일부 실시예에서, 처리를 용이하게 하기 위해 캐리어 웨이퍼가 제작된 기판에 부가될 수 있다.

- [0138] 본 출원의 또 다른 양태에 따르면, 소위 팬 아웃(fan out) 또는 팬 인(fan in) 기술이 제작된 기판을 집적 회로 웨이퍼와 본딩하는데 이용될 수 있다. IC 웨이퍼를 포함하는 재구성된 웨이퍼가 형성될 수 있다. 팬 아웃 또는 팬 인 기술은 재구성된 웨이퍼 상에 본딩 위치를 확립하는데 이용될 수 있다. 그 다음, 제작된 기판은 재구성된 웨이퍼와 본딩될 수 있다.

- [0139] 대안으로서, 제작된 기판을 포함하는 재구성된 웨이퍼가 형성될 수 있다. 그 다음, 제작된 기판과 IC 웨이퍼가 함께 본딩될 수 있다. 이러한 처리의 이점은, 제작된 기판 및 IC 웨이퍼가 상이한 크기를 갖는 경우에도 웨이퍼-스케일 본딩이 수행될 수 있다는 것이다.

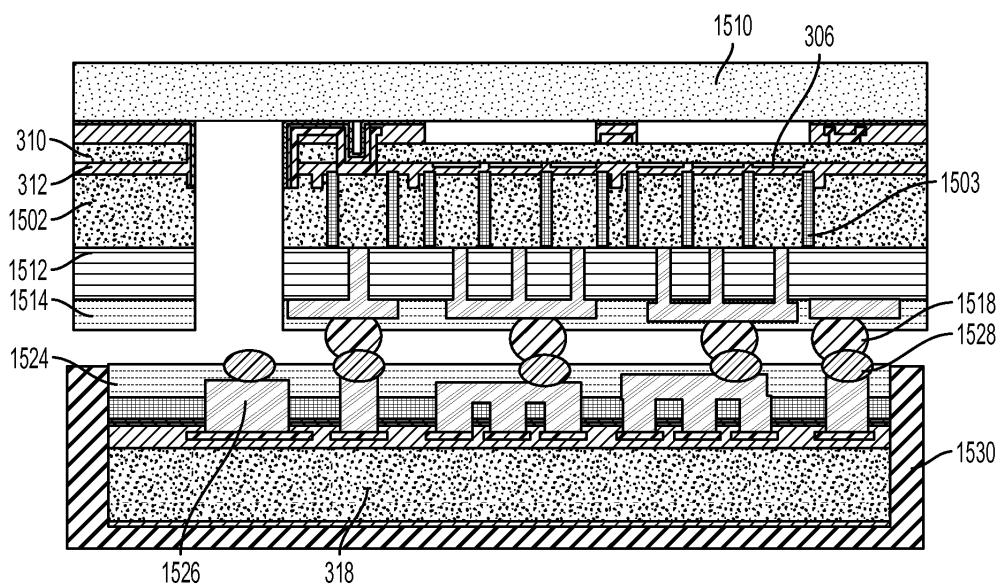

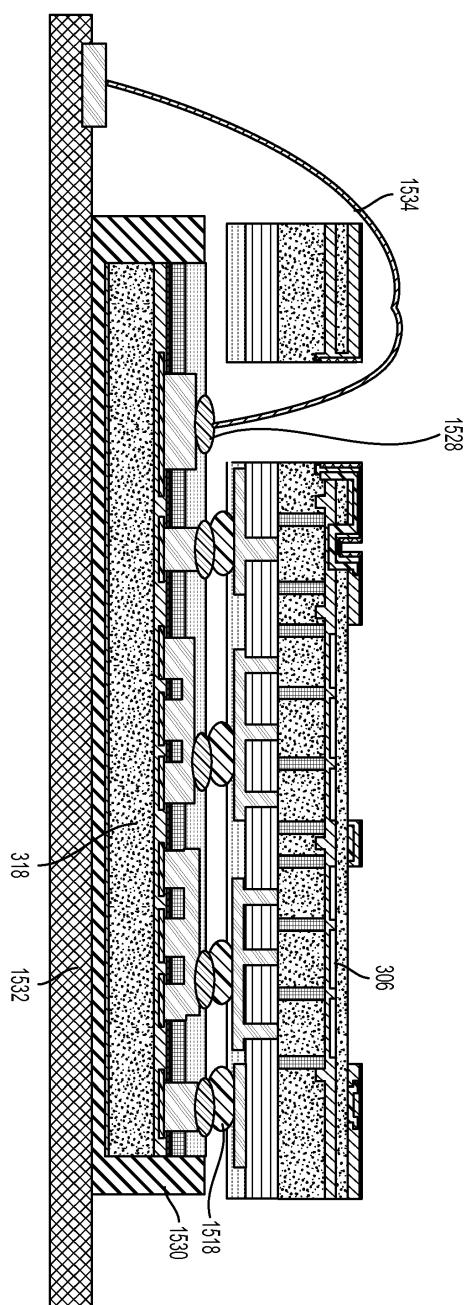

- [0140] 여기서 설명된 유형의 제작된 기판을 IC 웨이퍼와 함께 본딩하는데 있어서 웨이퍼 레벨 팩키징 기술을 이용하는 예가 도 15a 내지 도 15f와 관련하여 설명된다. 도 15a를 참조하면, 제작된 기판(1500)이 제공된다. 제작된 기판(1500)은 앞서 설명된 제작된 기판(302)과 유사하므로, 동일한 참조 번호들 중 일부가 예시되어 있다.

- [0141] 도시된 바와 같이, 제작된 기판(1500)은, 제2 실리콘 디바이스 층(310)과 실리콘 산화물 층(312) 사이에 밀봉된 캐비티(306)가 형성되어 있는 복수의 초음파 트랜스듀서를 포함한다. 제작된 기판(1500)은, 기판(1501)이 SOI 웨이퍼(400) 대신에 포함될 수 있다는 점에서 제작된 기판(302)과는 상이할 수 있다. 기판(1501)은, 절연 재료로 형성된 트렌치(1503)를 갖춘 실리콘 웨이퍼(1502)를 갖는 실리콘 기판일 수 있다. 트렌치(1503)는, 캐비티(306)를 위한 전극으로서 역할할 수 있는 실리콘 웨이퍼(1502)의 영역들을 격리하도록 배치될 수 있다.

- [0142] 일부 실시예에서, 도시된 바와 같이, 트렌치(1503)는 실리콘 웨이퍼(1502)의 두께를 통해 연장될 수 있다. 다른 실시예에서, 트렌치(1503)는, 캐비티(306)에 근접한 실리콘 웨이퍼(1502)의 표면에서 시작하여, 실리콘 웨이퍼(1502)를 통해 부분적으로 연장되질 수 있지만, 실리콘 웨이퍼(1502)의 전체 두께를 통해 연장되지는 않는다. 이러한 상황에서, 기판(1501)은, 나중의 처리 스테이지 동안 트렌치(1503)를 노출시키기 위해 배면(캐비티(306)로부터 면 실리콘 웨이퍼(1502)의 표면)으로부터 얇게 될 수 있다.

- [0143] 일부 실시예에서, 기판(1501)은, 제작된 기판의 초음파 트랜스듀서 구조를 형성하기 위한 처리 단계들의 수행을 허용하기에 충분한 기계적 안정성을 제공하기에 충분히 두꺼울 수 있다. 예를 들어, 기판(1501)은, 그 두께가, 약 400 마이크론, 200 마이크론 내지 500 마이크론, 또는 그 범위 내의 임의의 값 또는 값 범위일 수 있다. 일부 실시예에서, 이하에서 더 설명되는 바와 같이, 기판(1501)은, 트렌치(1503)가 실리콘 웨이퍼(1502)의 전체 두께를 통해 연장되지 않는다면, 트렌치(1503)를 노출시키도록 얇게 될 수 있다. 그러나, 기판(1501)이 얇게 된 일부 이러한 실시예에서도, 추가 처리 단계들을 위한 기계적 안정성을 제공하기에 충분한 두께를 유지할 수 있다. 그러나, 추가적인 대안으로서, 일부 실시예에서, 기판(1501)은, 도 15b와 관련하여 기술되는 바와 같이 임시 캐리어 웨이퍼와 본딩된 이후에 얇게 될 수 있다.

- [0144] 제작된 기판(1500)은, 도전 층 및 패시베이션 층을 각각 나타내는 층들(1504 및 1506)을 포함할 수 있다. 층(1504)은 전기적 콘택트로서 기능할 수 있다. 말소 영역(1508)은, 나중에 제작된 기판(1500)과 본딩되는 CMOS 웨이퍼로의 전기적 접촉을 형성할 것을 예상하여 형성될 수 있다. 따라서, 전기적 콘택트, 금속화부, 패시베이션, 및 패드 개구를 제공하기 위해, 제작된 기판 상에서 상부측 프로세스가 수행될 수 있다는 것을 도 15a로부터 이해해야 한다.

- [0145] 그 다음, 도 15b에 도시된 바와 같이, 제작된 기판(1500)은 캐리어 웨이퍼(1510)와 본딩될 수 있다. 캐리어 웨이퍼(1510)는, 예를 들어 웨이퍼-스케일 팩키징 파운드리에서의 추가 처리를 용이하게 할 수 있다. 캐리어 웨이퍼는, 유리 웨이퍼, 실리콘 웨이퍼, 또는 기타의 적절한 재료일 수 있고, 캐리어 웨이퍼(1510)는, 이하에서 더 설명되는 바와 같이 나중에 제거될 수 있기 때문에, 접착제 또는 다른 적절한 임시 본딩 기술을 이용하여 제작된 기판(1501)과 본딩될 수 있다. 도 15b로부터, 제작된 기판(1500)은 제작된 기판의 디바이스 층에 근접한 캐리어 웨이퍼(1510)와 본딩될 수 있다는 것을 이해해야 한다. 즉, 기판(1501)은 노출된 채로 남을 수 있다.

- [0146] 전술한 바와 같이, 일부 실시예에서, 트렌치(1503)는 실리콘 기판(1502)의 전체 두께를 통해 연장되지 않을 수도 있다. 이러한 실시예에서, 기판(1501)은 캐리어 웨이퍼(1510)와 일단 본딩되면 얇아질 수 있다. 얇게 하는 것은 트렌치(1503)를 노출시키기에 적절한 정도로 수행될 수 있다. 이러한 얇게 하는 것은, 예로서, 그라인딩

또는 스프레이 애칭을 수반할 수 있다. 일부 실시예에서, 트렌치(1503)가 실리콘 기판(1502)을 통해 연장되는 지에 관계없이, 기판(1501)은 제작된 기판에 대해 작은 치수를 제공하도록 얇아질 수 있다. 예를 들어, 기판(1501)은, 50 마이크론 미만, 30 마이크론 미만, 20 마이크론 미만, 10 마이크론 미만, 5 내지 200 마이크론, 또는 이러한 범위 내의 임의의 값 또는 값 범위로 얇게 될 수 있다. 이러한 정도로 기판(1501)을 얇게 하는 것은, 캐리어 웨이퍼(1502)가 구조적 강성을 제공할 수 있다는 점에서 제작된 기판(1500)이 캐리어 웨이퍼(1510)와 본딩됨으로써 촉진될 수 있다.

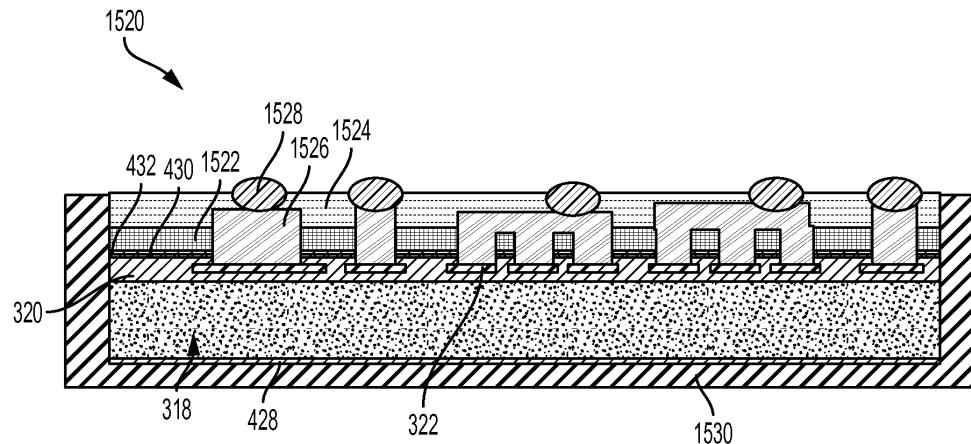

[0147] 그 다음, 도 15b의 구조는, 도 15c에 도시된 바와 같이, 재분배 층을 형성하도록 추가로 처리될 수 있다. 일부 실시예에서, 이러한 추가 처리는 도 15b의 지점까지의 처리와는 상이한 설비에서 이루어질 수 있다. 예를 들어, 도 15b의 지점까지의 처리는 미세제작 설비에서 이루어질 수 있고, 그 다음, 도 15b의 구조가 웨이퍼-스케일 팩키징 파운드리로 운송되고, 나머지 단계들은 웨이퍼-스케일 팩키징 파운드리에서 수행된다. 도 15b에 나타낸 처리 스테이지에서 기판(1501)이 얇아진다면, 이러한 얇게 하는 것이 웨이퍼-스케일 팩키징 파운드리에서 수행될 수도 있다.

[0148] 더 상세하게는, 도 15b의 구조로부터도 15c의 구조에 도달하는 것은, 기판(1501)을 개방시켜서 제작된 기판(1500)의 전체 두께를 관통하여 말소 영역(1508)을 연장시키는 것을 포함할 수 있다. 이것은 임의의 적절한 방식으로 이루어질 수 있다. 일부 실시예에서, 톱(saw)이 사용된다. 그 다음, 유전체 층(1512), 재분배 층(RDL)(1516), 및 유전체 층(1514)이 형성될 수 있다. RDL(1516)은 금속으로 형성될 수 있으며, 도시된 바와 같이 실리콘 기판(1502)과 접촉하도록 제작될 수 있다. 실리콘 기판(1502)은 고농도 도핑될 수 있기 때문에, RDL(1516)은 초음파 트랜스듀서의 동작을 제어하기 위해 전기적 액세스를 제공할 수 있다. 일부 실시예에서, RDL(1516)은, 각각의 초음파 트랜스듀서 디바이스에 대응하는 단일 땜납-가능 전극을 제공하도록 구성될 수 있지만, 다른 구성도 역시 가능하다. 땜납 볼(1518)은, IC 웨이퍼와 제작된 기판의 후속 본딩을 용이하게 하기 위해 선택사항으로서 형성될 수 있다. 대안적인 실시예에서, 땜납은, 이하에서 설명되는, 도 15d와 관련하여 예시된 바와 같이, 회로 웨이퍼 자체 상에 형성될 수 있다.

[0149] 실제로, 유전체 층들(1512 및 1514)은 도 15c의 말소 영역(1508) 내로 연장될 수 있다. 이를 층은 캐리어 웨이퍼(1510)와 접촉할 수 있다. 예시의 간소화를 위해, 그 패턴은 도시되지 않았다. 유전체 층들(1512 및 1514)이 말소 영역(1508) 내로 연장될 때, 이 층들은 캐리어 웨이퍼(1510)가 제거될 때 후속하는 처리 동안 제거될 수 있다.

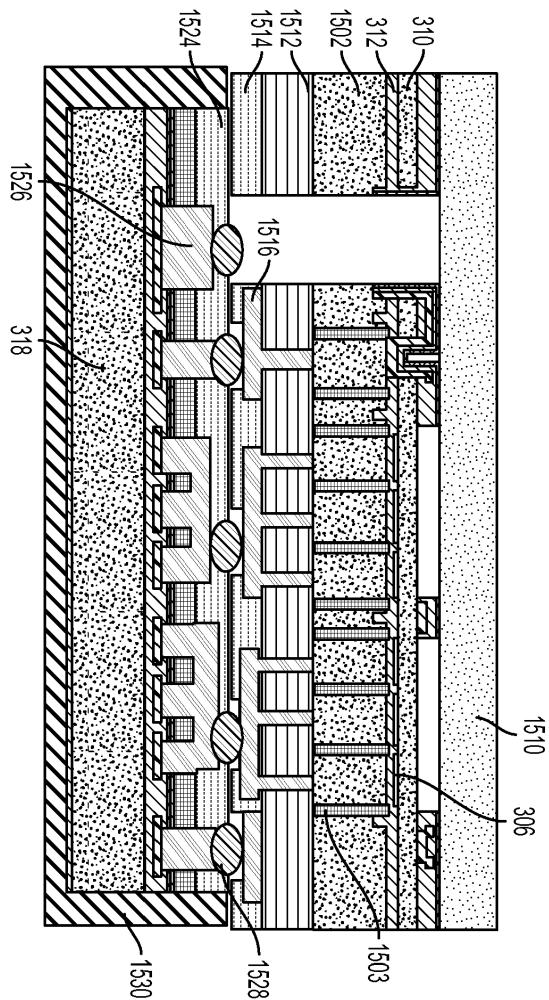

[0150] 도 15d는, 도 15a 내지 도 15c에 도시된 유형의 제작된 기판과 본딩될 수 있는 CMOS 웨이퍼 등의 회로 웨이퍼를 나타낸다. 회로 웨이퍼(1520)는, 앞서 설명된 CMOS 웨이퍼(304)와 공통되는 피쳐들을 가질 수 있으므로, 동일한 참조 번호 중 일부가 나타난다. 그러나, 회로 웨이퍼(1520)는, 제작된 기판과의 본딩을 용이하게 하는 재분배 구조물을 추가적으로 포함한다. 이러한 재분배 구조물은, 유전체 층(1522), RDL(1526), 및 유전체 층(1524)을 포함한다. 땜납 볼(1528)은 본딩을 허용하도록 제공된다.

[0151] 전술한 바와 같이, 일부 실시예에서, 팬 아웃 또는 팬 인 기술은, 제작된 기판 및 디바이스의 제작을 용이하게 하도록 구현될 수 있다. 따라서, 한 예로서, 회로 웨이퍼(1520)는 몰드(1530)를 포함하는 재구성된 웨이퍼의 일부일 수 있다. 몰드(1530)는, 회로 웨이퍼만으로 제공되는 것보다 더 넓은 영역에 걸쳐 접촉 지점들(땀납 볼들(1528))의 일부를 배치하는 것을 허용할 수 있어서, 회로 웨이퍼 및 제작된 기판이 상이한 직경으로 형성되더라도 웨이퍼-레벨 팩키징이 수행되는 것을 허용할 수 있다. 재구성된 웨이퍼가 형성될 때, 임의의 적절한 몰드 재료가 이용될 수 있다.

[0152] 도 15e에 도시된 바와 같이, 그 다음, 제작된 기판과 회로 웨이퍼가 함께 본딩될 수 있다. 이 본딩은 웨이퍼-레벨 본딩일 수 있다. 예시된 실시예에서, 땜납 볼이 제작된 기판과 회로 웨이퍼 양쪽 모두에 도시되어 있지만, 일부 실시예에서는 하나 또는 다른 하나에서만 제공될 수 있다는 것을 이해해야 한다.

[0153] 도 15f에 도시된 바와 같이, 캐리어 웨이퍼(1510)는 그 후 제거될 수 있고, 나머지 디바이스는 다이싱되어 인터포저(1532) 상에 배치될 수 있다. 말소 영역(1508)에 있었던 유전체 층들(1512 및 1514)의 어떠한 잔량도 말소 영역으로부터 제거될 수 있다. 와이어 본딩(1534)은 인터포저로의 전기적 접속을 제공할 수 있다. 그러나 대안들이 가능하다. 예를 들어, 결과적 디바이스는 웨이퍼-적층 구성으로 다른 다이와 적층될 수 있다.

[0154] 도 15a 내지 도 15f의 제작 시퀀스에 대한 대안으로서, 말소 영역(1508)은 상이한 처리 스테이지에서 제작된 기판(1500)의 전체 두께를 관통하여 연장될 수 있다. 도 15b의 구조로부터 도 15c의 구조로 이동할 때 제작된 기판을 통해 말소 영역(1508)을 연장하는 것이 아니라, 도 15b에 도시된 바와 같이 말소 영역이 유지될 수 있다.

유전체 층들(1512, 1514) 및 RDL(1516)이 형성될 수 있다. 제작된 기판은 회로 웨이퍼와 땜납 본딩될 수 있다. 캐리어 웨이퍼(1510)는 제거될 수 있다. 캐리어 웨이퍼(1510)를 제거한 후에, 톱을 이용하여 제작된 기판(1500)의 전체 두께를 통해 말소 영역을 연장시켜, 와이어 본딩 또는 다른 전기 커넥터에 의한 회로 웨이퍼(1520)로의 전기적 액세스를 허용할 수 있다.

[0155] 도 15a 내지 도 15f의 실시예는, 회로 웨이퍼가 재구성된 웨이퍼의 일부로서 형성되는 시나리오를 나타내지만, 다른 실시예는 재구성된 웨이퍼의 일부로서 제작된 기판을 형성한다. 도 16은 한 예를 나타낸다.

[0156] 도 16에 도시된 바와 같이, 제작된 기판(1500)은, 재구성된 웨이퍼를 생성하기 위해 몰드(1536)에 의해 3면에서 실질적으로 캡슐화될 수 있다. 몰드(1536)는 폴리머 또는 다른 적절한 몰딩 재료일 수 있다. 일부 실시예에서, 몰드(1536)는 일시적일 수 있다. 몰드(1536)는, IC 웨이퍼의 치수와 실질적으로 동일한 치수를 갖는 재구성된 웨이퍼를 생성하도록 형성될 수 있다. 그 다음, 제작된 기판 및 IC 웨이퍼를 포함하는 재구성된 웨이퍼는, 일치하는 크기로 인해 더 용이하게 본딩될 수 있다. 몰드(1536)는 그 후 제거될 수 있다. 캐리어 웨이퍼(1510)가 후속해서 제거될 수 있다.

[0157] 따라서, 재구성된 웨이퍼의 이용은 상이한 목적을 가질 수 있다는 것을 이해해야 한다. 일부 실시예에서, 재구성된 웨이퍼는, IC 웨이퍼 상의 전기적 접속의 팬 아웃을 허용하기 위해 이용될 수 있다. 일부 실시예에서, 재구성된 웨이퍼는, 웨이퍼 본딩을 위해 유사한 치수의 웨이퍼를 생성하는데 이용될 수 있다.

[0158] 도 15a 내지 도 15f의 제작에 대한 추가적인 대안으로서, 도 17은 땜납 볼이 IC 웨이퍼에만 제공되는 실시예를 나타낸다. 즉, 도 17은 도 15e와 유사하지만, 땜납 볼(1518)이 생략된 점이 다르다. 대신에, 땜납 볼(1528)은 RDL(1516)에 직접 접촉한다. 도시되지 않은 추가적인 대안에서, 땜납 볼(1518)은 유지되고 땜납 볼(1528)은 생략된다.

[0159] 도 15a 내지 도 15f 및 도 16의 설명으로부터, 본 출원의 실시예들은, 제작된 기판과 회로 웨이퍼 중 하나 또는 양쪽 모두에서 RDL의 웨이퍼-레벨 이용을 제공한다는 것을 이해해야 한다. 웨이퍼들은 함께 본딩될 수 있고, 후속해서 다이싱될 수 있다. 일부 실시예에서, 다이싱된 디바이스는 인터포저 상에 배치되거나, 다이 적층(die stacking) 구성의 일부로서 더 큰 디바이스에 제공될 수 있다.

[0160] 본 출원의 실시예에 따른 RDL의 이용은, 비교적 작은 피처에 전기적 접속을 제공하기 위한 목적일 수 있다는 것을 이해해야 한다. 예를 들어, RDL(1516)은 초음파 트랜스듀서의 전극 영역에 대한 전기적 접촉을 제공할 수 있다. 초음파 트랜스듀서는 작은 치수를 가질 수 있다. 예를 들어, 제작된 기판의 전극 영역은 앞서 열거된 캐비티(306)의 폭  $W$ 과 실질적으로 동일하거나 더 작은 폭을 가질 수 있다. 이러한 RDL 이용은, 본딩 패드에 접속하기 위해 RDL을 이용하는 것과는 대조적이다. 모든 실시예들이 이 점에서 제한되는 것은 아니다.

[0161] 본 출원의 양태들은 하나 이상의 이점을 제공할 수 있으며, 그 중 일부는 앞서 설명되었다. 이제 이러한 이점들의 일부 비제한적 예가 설명된다. 모든 양태들 및 실시예들이 지금 설명되는 모든 이점들을 제공하는 것은 아니라는 것을 이해해야 한다. 또한, 본 출원의 양태는 지금 설명되는 것들에 대한 추가 이점을 제공할 수도 있다는 것을 이해해야 한다.

[0162] 본 출원의 양태는, 모놀리식 접적된 초음파 트랜스듀서 및 CMOS 구조물(예를 들어, CMOS IC)의 형성에 적절한 제작 프로세스를 제공한다. 따라서, (예를 들어, 초음파 콜링 및/또는 고강도 포커싱된 초음파(HIFU)를 위한) 초음파 디바이스로서 동작하는 단일 기판 디바이스가 달성된다.

[0163] 적어도 일부 실시예에서, 프로세스는, 신뢰성이 있을 수 있고(예를 들어, 높은 수율 및/또는 높은 디바이스 신뢰성을 특징으로 하고), 대량으로 확장가능하며, 수행하기에 비교적 저렴할 수 있어서, CUT를 위한 상업적으로 실용적인 제작 프로세스에 기여할 수 있다. TSV의 형성, CMP의 이용, 및 저온 산화물 본딩의 고밀도화 어닐링(densification anneals)의 이용 등의, 복잡하고 값비싼 처리 기술의 이용을 피할 수 있다. 또한, 프로세스는 소형 초음파 디바이스의 제작을 제공하여, 휴대형 초음파 프로브의 생성을 용이하게 할 수 있다.

[0164] 일부 양태들에서, 제작 프로세스는, 미세제작 설비에서 본딩을 수행하는 것에 비해 감소된 비용을 제공하는 웨이퍼-스케일 팩키징 설비에서 회로 웨이퍼와 제작된 기판의 본딩을 허용한다. 또한, 재배포와 팬 아웃 또는 팬인 기술의 이용이 수용될 수 있어서, 상이한 치수를 갖고 있거나 양쪽의 다이가 상이한 치수를 갖고 있을 때에도, 회로 웨이퍼와의 제작된 기판의 본딩을 허용할 수 있다. RDL와 팬 아웃 및/또는 팬 인의 이용은 또한, 회로 웨이퍼의 재설계 또는 회로 웨이퍼와 제작된 기판 사이의 인터페이스 층들의 재설계를 요구하지 않고도, 제작된 기판에서의 설계 변화를 허용할 수 있다.

- [0165] 지금까지 본 출원의 기술의 수 개의 양태와 실시예를 설명하였으므로, 본 기술분야의 통상의 기술자에게는, 다양한 변형, 수정, 및 개선이 용이하다는 것을 이해해야 한다. 이러한 변형, 수정 및 개선은 본 출원에서 설명된 기술의 사상과 범위 내에 포함시키고자 한다. 예를 들어, 본 분야의 통상의 기술자라면, 기능을 수행하고 및/또는 결과 및/또는 여기서 설명된 이점들 중 하나 이상을 얻기 위해 다양한 다른 수단 및/또는 구조를 용이하게 구상할 것이며, 이러한 변형들 및/또는 수정들 각각은 여기서 설명된 실시예의 범위 내에 있는 것으로 간주된다. 통상의 기술자라면, 단지 일상적인 실험만으로, 여기서 설명된 특정한 실시예들에 대한 많은 균등물을 인식하고 확인할 수 있을 것이다. 따라서, 상기 실시예들은 단지 예시로서 제시된 것일 뿐이며, 첨부된 청구항들과 그 균등물의 범위 내에서, 본 발명의 실시예들은 특정적으로 설명된 것과는 다른 방식으로 실시될 수도 있다는 것을 이해해야 한다. 또한, 여기서 설명된 2개 이상의 피쳐, 시스템, 항목, 재료, 키트 및/또는 방법의 임의의 조합은, 이러한 피쳐, 시스템, 항목, 재료, 키트 및/또는 방법이 상호 불일치하지 않는다면, 본 개시내용의 범위 내에 포함된다.

- [0166] 비제한적인 예로서, CMUT를 포함하는 다양한 실시예들이 설명되었다. 대안적 실시예에서, PMUT가, CMUT 대신에 또는 이에 추가하여 이용될 수 있다.

- [0167] 또한, 설명된 바와 같이, 일부 양태는 하나 이상의 방법으로서 구현될 수도 있다. 방법의 일부로서 수행되는 동작들은 임의의 적절한 방식으로 정렬될 수 있다. 따라서, 실시예에서는 순차적 동작들로서 도시되어 있더라도, 일부 동작들을 동시에 수행하는 것을 포함한, 동작들이 예시된 것과는 상이한 순서로 수행되는 실시예들이 구성될 수 있다.

- [0168] 여기서 정의되고 사용된 모든 정의는, 사전적 정의, 참조에 의해 포함된 문서에서의 정의, 및/또는 정의된 용어의 통상의 의미를 통제하는 것으로 이해되어야 한다.

- [0169] 부정관사, "a" 및 "an"은, 본 명세서와 청구항에서 사용될 때, 분명하게 달리 나타내지 않는 한, "적어도 하나"를 의미하는 것으로 이해되어야 한다.

- [0170] 구문 "및/또는"은, 여기 명세서 및 청구항에서 사용될 때, 이와 같이 결합된 요소들, 즉, 일부 경우에는 결합되어 존재하고 다른 경우에는 분리되어 존재하는 요소들의 "어느 하나 또는 양쪽 모두"를 의미하는 것으로 이해되어야 한다. "및/또는"에 의해 열거된 복수의 요소들은 동일한 방식으로, 즉, 이와 같이 결합된 요소들의 "하나 이상"으로서 해석되어야 한다. "및/또는" 구절에 의해 구체적으로 식별되는 요소들 이외의 다른 요소들이, 구체적으로 식별된 이들 요소들과 관련되든 관련되지 않든, 선택사항으로서 존재할 수 있다. 따라서, 비제한적 예로서, "A 및/또는 B"에 대한 언급은, "포함하는" 등의 개방형 용어와 연계하여 사용될 때, 한 실시예에서는, (선택사항으로서 B 이외의 다른 요소를 포함한) A만을 지칭할 수 있고; 또 다른 실시예에서는, (선택사항으로서 A 이외의 요소를 포함한) B만을 지칭할 수 있으며; 역시 또 다른 실시예에서는, (선택사항으로서 다른 요소를 포함한) A와 B 양쪽 모두를 지칭할 수 있다.

- [0171] 여기 명세서와 청구항에서 사용될 때, 하나 이상의 요소의 열거를 참조한 구문 "적어도 하나"는, 요소들의 목록 내의 요소들 중 하나 이상으로부터 선택된 적어도 하나의 요소를 의미하지만, 요소들의 목록 내의 요소들의 각각의 및 모든 요소 중 적어도 하나를 반드시 포함할 필요는 없고 요소들의 목록 내의 요소들의 임의의 조합을 배제하지 않는 것으로 이해되어야 한다. 이 정의는 또한, 구문 "적어도 하나"가 참조하는 요소들의 목록 내에서 구체적으로 식별되는 요소들 이외의 요소들이, 구체적으로 식별되는 요소들과 관련되든 관련되지 않든, 선택사항적으로 존재할 수 있다는 것을 허용한다. 따라서, 비제한적 예로서, "A와 B 중 적어도 하나"(또는, 등가적으로, "A 또는 B 중 적어도 하나", 또는 등가적으로 "A 및/또는 B 중 적어도 하나")는, 한 실시예에서는, B가 존재하지 않는(및 선택사항으로서 B 이외의 요소들을 포함함) 적어도 하나의(선택사항으로서 하나보다 많은) A; 다른 실시예에서는, A가 존재하지 않는(및 선택사항으로서 A 이외의 요소들을 포함함) 적어도 하나의(선택사항으로서 하나보다 많은) B; 또 다른 실시예에서는, 적어도 하나의(선택사항으로서 하나보다 많은) A와 적어도 하나의(선택사항으로서 하나보다 많은) B(및 선택사항으로서 다른 요소들을 포함함) 등을 지칭할 수 있다.

- [0172] 또한, 여기서 사용되는 어법과 용어는 설명을 위한 것으로 간주되어서는 안 된다. 여기서, "내포하는(including)", "포함하는(comprising)", 또는 "갖는(having)", "담고 있는(containing)", "수반하는(involved)" 및 그 파생어들은 이후에 열거되는 항목들과 그 균등물 뿐만 아니라 추가 항목들을 아우르는 것을 의미한다.

- [0173] 상기한 명세서뿐만 아니라 청구항에서, "포함하는(comprising)", "내포하는(including)", "운반하는(carrying)", "갖는(having)", "함유하는(containing)", "수반하는(involved)", "유지하는(holding)", "~로

구성된(composed of~)" 등과 같은 모든 연결 구문은, 제약을 두지 않는(open-ended), 즉, 포함하지만 그것으로 제한되지 않는다는 것을 의미한다. 연결 구문 "~로 이루어진(consisting of~)" 및 "본질적으로 ~로 이루어진 (consisting essentially of~)"만은 각각 폐쇄형 또는 반-폐쇄형 연결 구문일 것이다.

## 도면

### 도면1

100

↓

도면2

102

↓

도면3

도면4a

도면4b

도면4c

도면4d

도면4e

도면4f

도면4g

도면4h

도면4*i*

도면4j

도면4k

도면41

도면4m

도면4n

도면40

도면4p

도면4q

도면4r

도면4s

도면4t

도면5

도면6

## 도면7

도면8a

도면8b

도면8c

도면8d

## 도면9

도면10

도면11

도면12

도면13

도면14

도면15a

도면15b

도면15c

도면15d

도면15e

도면15f

도면16

도면17

|                |                                                                                                                                                                                        |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 微制造的超声换能器和相关的装置和方法                                                                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">KR1020170030605A</a>                                                                                                                                                       | 公开(公告)日 | 2017-03-17 |

| 申请号            | KR1020177003696                                                                                                                                                                        | 申请日     | 2015-07-14 |

| [标]申请(专利权)人(译) | 蝶形网络的大                                                                                                                                                                                 |         |            |

| 申请(专利权)人(译)    | 蝶形网络公司                                                                                                                                                                                 |         |            |

| 当前申请(专利权)人(译)  | 蝶形网络公司                                                                                                                                                                                 |         |            |

| [标]发明人         | ROTHBERG JONATHAN M<br>로스버그조나단엠<br>ALIE SUSAN A<br>에일리수잔에이<br>FIFE KEITH G<br>파이프키스지<br>SANCHEZ NEVADA J<br>산체스네바다제이<br>RALSTON TYLER S<br>랠스턴타일러에스                                    |         |            |

| 发明人            | 로스버그,조나단,엠.<br>에일리,수잔,에이.<br>파이프,키스,지.<br>산체스,네바다,제이.<br>랠스턴,타일러,에스.                                                                                                                   |         |            |

| IPC分类号         | B06B1/02 B81B7/00 B81C1/00 A61B8/00 G01N29/24                                                                                                                                          |         |            |

| CPC分类号         | B06B1/0292 B81B7/007 B81C1/00238 B81C1/00301 A61B8/4483 G01N29/2406 B81B2201/0271<br>B81C2201/019 B81C2203/036 B81C2203/0792 H01L2224/4813 H01L2924/0002 H01L2924/146<br>H01L2924/1461 |         |            |

| 代理人(译)         | Yangyoungjun<br>Gimyeonsong<br>Baekmangi                                                                                                                                               |         |            |

| 优先权            | 62/024179 2014-07-14 US<br>14/635197 2015-03-02 US<br>14/716152 2015-05-19 US                                                                                                          |         |            |

| 其他公开文献         | <a href="#">KR102073317B1</a>                                                                                                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                              |         |            |

**摘要(译)**

下面将解释不仅与互补金属氧化物半导体 ( CMOS ) 基板集成并且是微机械加工的超声换能器的制造方法。制造可以伴随2的单独的晶片键合步骤。当在衬底 ( 302 ) 内制造密封腔 ( 306 ) 时 , 使用晶片键合。此外 , 当基板 ( 302 ) 在类似于CMOS晶片的不同基板 ( 304 ) 处接合时 , 使用晶片接合。至少第二晶片键合可以在低温下进行。