(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2016-0145177

(43) 공개일자 2016년12월19일

- (51) 국제특허분류(Int. Cl.)

*A61B 8/00* (2006.01) *A61B 8/08* (2006.01)

*G01S 15/89* (2006.01) *G01S 7/52* (2006.01)

- (52) CPC특허분류

*A61B 8/4483* (2013.01)

*A61B 8/488* (2013.01)

- (21) 출원번호 10-2016-7032202

- (22) 출원일자(국제) 2015년04월17일

심사청구일자 없음

- (85) 번역문제출일자 2016년11월17일

- (86) 국제출원번호 PCT/US2015/026315

- (87) 국제공개번호 WO 2015/161164

국제공개일자 2015년10월22일

- (30) 우선권주장

61/981,491 2014년04월18일 미국(US)

- (71) 출원인

버터플라이 네트워크, 인크.

미국 06437 코네티컷주 길포드 올드 웨필드 스트리트 530

- (72) 발명자

로스버그, 조나단, 엠.

미국 06437 코네티컷주 길포드 운카스 포인트 로드 215

웰스턴, 타일러, 에스.

- (74) 대리인

양영준, 백만기, 정은진

전체 청구항 수 : 총 30 항

(54) 발명의 명칭 초음파 촬영 압축 방법 및 장치

**(57) 요약**

단일-칩 초음파 촬영 솔루션을 구현하기 위해, 수신 신호 경로에서 온-칩 신호 처리가 채용되어 데이터 대역폭을 감축할 수 있고 출력 데이터 모듈이 모든 수신된 채널에 대한 데이터를 디지털 데이터 스트림으로서 오프-칩으로 이동시키는데 이용될 수 있다. 수신된 신호의 온-칩 디지털화는 진보된 디지털 신호 처리가 온-칩으로 수행되는 것을 허용하므로, 단일의 반도체 기판 상에서의 전체의 초음파 촬영 시스템의 완전한 통합을 허용한다. 수신된 신호의 온-칩 디지털화는 또한, 오프-칩 컴퓨팅에 관한 부담을 감소시키기 위해 초음파 처리 및/또는 전-처리의 온-칩 통합을 가능케 한다. 표준의 상용 출력 인터페이스의 대역폭 요구에 따라 디지털 데이터 스트림으로서의 데이터의 오프-칩 전송을 가능케 하는 데이터 압축 아키텍처들이 개시된다.

**대 표 도**

(52) CPC특허분류

*A61B 8/5207* (2013.01)

*A61B 8/56* (2013.01)

*G01S 15/8915* (2013.01)

*G01S 7/52033* (2013.01)

*G01S 7/52034* (2013.01)

*G01S 7/5208* (2013.01)

(72) 발명자

**산체스, 네바다, 제이.**

미국 06437 코네티컷주 길퍼드 리틀 메도우 로드

1280

**캐스퍼, 앤드류, 제이.**

미국 06413 코네티컷주 클린턴 유닛 205 이스트 메인 스트리트 161

## 명세서

### 청구범위

#### 청구항 1

초음파 디바이스(ultrasound device)로서,

반도체 다이 상에 통합된 적어도 하나의 초음파 트랜스듀서 요소(transducer element);

상기 반도체 다이 상에 통합되고, 상기 적어도 하나의 초음파 트랜스듀서 요소로부터 출력된 신호를 처리하여 디지털 신호를 생성하도록 구성되는 아날로그 대 디지털 변환기(analog to digital converter)(ADC); 및

상기 반도체 다이 상에 통합되고 상기 디지털 신호를 압축함으로써 압축된 신호 –상기 압축된 신호는 데이터 스트림으로서 상기 반도체 다이 외부로 전송되도록 구성됨– 를 생성하도록 구성되는 압축 회로

를 포함하는 초음파 디바이스.

#### 청구항 2

제1항에 있어서, 상기 압축 회로는, 필터, 데시메이션 회로(decimation circuit), 재양자화 회로(re-quantization circuit), 및 산술 로직 유닛(ALU; arithmetic logic unit)을 포함하고, 상기 필터의 출력은 상기 데시메이션 회로의 입력에 결합되며, 상기 데시메이션 회로의 출력은 상기 재양자화 회로의 입력에 결합되고, 상기 재양자화 회로의 출력은 상기 ALU의 입력에 결합되는, 초음파 디바이스.

#### 청구항 3

제1항에 있어서, 상기 압축 회로는 직교 복조 회로(quadrature demodulation circuitry)를 포함하고, 상기 압축 회로는 상기 직교 복조 회로를 이용하여 상기 디지털 신호를 압축하도록 구성되는, 초음파 디바이스.

#### 청구항 4

제1항에 있어서, 상기 압축 회로는 다운샘플링 회로(down-sampling circuitry)를 포함하고, 상기 압축 회로는 상기 다운샘플링 회로를 이용하여 상기 디지털 신호를 압축하도록 구성되는, 초음파 디바이스.

#### 청구항 5

제1항에 있어서, 상기 압축 회로는 필터링 회로를 포함하고, 상기 압축 회로는 상기 필터링 회로를 이용하여 상기 디지털 신호를 압축하도록 구성되는, 초음파 디바이스.

#### 청구항 6

제5항에 있어서, 상기 필터링 회로는 캐스캐이드 적분 콤(CIC; cascade integrating comb) 필터를 포함하고, 상기 압축 회로는 상기 CIC 필터를 이용하여 상기 디지털 신호를 압축하도록 구성되는, 초음파 디바이스.

#### 청구항 7

제1항에 있어서, 상기 압축 회로는 재양자화 회로를 포함하고, 상기 압축 회로는 상기 재양자화 회로를 이용하여 상기 디지털 신호를 압축하도록 구성되는, 초음파 디바이스.

#### 청구항 8

제1항에 있어서, 상기 압축 회로는 산술 로직 유닛을 포함하고, 상기 압축 회로는 상기 산술 로직 유닛을 이용하여 상기 디지털 신호를 처리함으로써 상기 디지털 신호를 압축하도록 구성되는, 초음파 디바이스.

#### 청구항 9

제8항에 있어서, 상기 산술 로직 유닛은, 워드 크기 연장(extending a word size), 비트 쉬프팅(bit shifting), 누산(accumulating), 및 감산(subtracting)으로 이루어진 그룹으로부터 선택된 적어도 하나의 동작

을 상기 디지털 신호에 관해 수행하도록 구성되는, 초음파 디바이스.

#### 청구항 10

제1항에 있어서, 상기 반도체 다이로부터 상기 데이터 스트림을 출력하도록 구성된 출력 인터페이스를 더 포함하는 초음파 디바이스.

#### 청구항 11

제10항에 있어서, 상기 출력 인터페이스는, USB 3.0 인터페이스, USB 3.1 인터페이스, USB 2.0 인터페이스, 썬더볼트(Thunderbolt) 인터페이스, 파이어와이어(Firewire) 인터페이스, 및 기가비트 이더넷(Gigabit Ethernet) 인터페이스로 이루어진 그룹으로부터 선택된 고속 직렬 인터페이스인, 초음파 디바이스.

#### 청구항 12

제1항에 있어서, 상기 압축 회로는 상기 초음파 디바이스의 동작 모드에 적어도 부분적으로 기초하여 상기 디지털 신호를 압축하도록 구성되는, 초음파 디바이스.

#### 청구항 13

제1항에 있어서, 상기 압축 회로는 이미지 재구성 회로를 포함하고, 상기 압축 회로는 상기 디지털 신호에 적어도 부분적으로 기초하여 상기 이미지 재구성 회로를 이용해 이미지 재구성 프로세스의 적어도 일부를 수행함으로써 상기 디지털 신호를 압축하도록 구성되는, 초음파 디바이스.

#### 청구항 14

제13항에 있어서, 상기 이미지 재구성 회로는 베포밍(beamforming) 기술을 이용하여 이미지 재구성 프로세스의 적어도 일부를 수행하도록 구성되는, 초음파 디바이스.

#### 청구항 15

제14항에 있어서, 상기 베포밍 기술은 통합된 배면투사 기술(integrated backprojection technique)을 이용하는 것을 포함하는, 초음파 디바이스.

#### 청구항 16

초음파 트랜스듀서 요소로부터 출력된 신호를 처리하기 위한 방법으로서,

상기 초음파 트랜스듀서 요소와 동일한 반도체 다이 상에 통합된 컴포넌트에 의해, 상기 초음파 트랜스듀서 요소로부터 출력된 신호를 처리하여 디지털 신호를 생성하는 단계; 및

상기 반도체 다이 상에 통합된 적어도 하나의 추가 컴포넌트에 의해, 상기 디지털 신호를 압축함으로써 압축된 신호 –상기 압축된 신호는 데이터 스트림으로서 상기 반도체 다이 외부로 전송되도록 구성됨– 를 생성하는 단계

를 포함하는 방법.

#### 청구항 17

제16항에 있어서, 상기 디지털 신호를 압축하는 것은, 상기 반도체 다이 상에 통합된 필터로 상기 디지털 신호를 필터링하여 필터링된 신호를 생성하는 것, 상기 반도체 다이 상에 통합된 데시메이션 회로로 상기 필터링된 신호를 데시메이팅하여 데시메이트된 신호를 생성하는 것, 상기 반도체 다이 상에 통합된 재양자화 회로로 상기 데시메이트된 신호를 재양자화하여 재양자화된 신호를 생성하는 것, 및 상기 반도체 다이 상에 통합된 산술 로직 유닛(ALU)으로 상기 재양자화된 신호를 처리하는 것을 포함하는, 방법.

#### 청구항 18

제16항에 있어서, 상기 디지털 신호를 압축하는 것은 상기 디지털 신호에 관해 직교 복조를 수행하는 것을 포함하는, 방법.

**청구항 19**

제16항에 있어서, 상기 디지털 신호를 압축하는 것은 상기 디지털 신호를 다운샘플링하는 것을 포함하는, 방법.

**청구항 20**

제16항에 있어서, 상기 디지털 신호를 압축하는 것은 상기 디지털 신호를 필터링하는 것을 포함하는, 방법.

**청구항 21**

제20항에 있어서, 상기 디지털 신호를 필터링하는 것은 상기 반도체 다이 상에 통합된 캐스캐이드 적분 콤(CIC) 필터를 이용하여 상기 디지털 신호를 필터링하는 것을 포함하는, 방법.

**청구항 22**

제16항에 있어서, 상기 디지털 신호를 압축하는 것은 상기 디지털 신호에 관해 재양자화를 수행하는 것을 포함하는, 방법.

**청구항 23**

제16항에 있어서, 상기 디지털 신호를 압축하는 것은 산술 로직 유닛을 이용하여 상기 디지털 신호를 처리함으로써 상기 디지털 신호를 압축하는 것을 포함하는, 방법.

**청구항 24**

제23항에 있어서, 상기 산술 로직 유닛을 이용하여 상기 디지털 신호를 처리함으로써 상기 디지털 신호를 압축하는 것은, 워드 크기 연장, 비트 쉬프팅, 누산, 및 감산으로 이루어진 그룹으로부터 선택된 적어도 하나의 동작을 상기 디지털 신호에 관해 수행하는 것을 포함하는, 방법.

**청구항 25**

제16항에 있어서, 출력 인터페이스를 통해 상기 반도체 다이로부터 상기 데이터 스트림을 출력하는 단계를 더 포함하는 방법.

**청구항 26**

제25항에 있어서, 상기 출력 인터페이스는, USB 3.0 인터페이스, USB 3.1 인터페이스, USB 2.0 인터페이스, 썬더볼트 인터페이스, 파이어와이어 인터페이스, 및 기가비트 이더넷 인터페이스로 이루어진 그룹으로부터 선택된 고속 직렬 인터페이스인, 방법.

**청구항 27**

제16항에 있어서, 상기 디지털 신호를 압축하는 것은, 상기 초음파 트랜스듀서 요소를 포함하는 디바이스의 동작 모드에 적어도 부분적으로 기초하여 상기 디지털 신호를 압축하는 것을 포함하는, 방법.

**청구항 28**

제16항에 있어서, 상기 디지털 신호를 압축하는 것은, 상기 디지털 신호에 적어도 부분적으로 기초하여 이미지 재구성 프로세스의 적어도 일부를 수행하는 것을 포함하는, 방법.

**청구항 29**

제28항에 있어서, 이미지 재구성 프로세스의 적어도 일부를 수행하는 것은, 상기 디지털 신호를 이용하여 뷔퍼 링을 수행하는 것을 포함하는, 방법.

**청구항 30**

제29항에 있어서, 상기 뷔퍼링을 수행하는 것은 통합된 배면투사 기술을 이용하는 것을 포함하는, 방법.

**발명의 설명**

## 기술 분야

- [0001] 관련 출원에 대한 상호참조

- [0002] 본 출원은, 그 전체를 참조로 본 명세서에 포함하는, 대리인 사건 번호 B1348.70009US00 하에서 2014년 4월 18일 출원된 발명의 명칭이 "ULTRASONIC IMAGING COMPRESSION METHODS AND APPARATUS"인 미국 가출원 제 61/981,491호의 35 U.S.C. § 119(e) 하의 혜택을 주장한다.

- [0003] 분야

- [0004] 본 개시내용의 양태는 초음파 촬영 디바이스 및 방법에 관한 것이다.

## 배경 기술

- [0005] 종래의 초음파 스캐너는 일반적으로 이산 트랜스듀서 및 제어 전자회로를 포함한다. 제어 전자회로는 통상적으로 트랜스듀서 내에 통합되지 않고 오히려 별개로 형성되고 하우징된다.

- [0006] 의료 응용에 이용되는 초음파 트랜스듀서 프로브들은 통상적으로, 의료 응용을 위한 초음파 이미지를 생성하기 위해 필요하다면, 많은 양의 데이터를 생성한다. 원하는 이미지의 품질과 복잡성이 높을수록, 통상적으로 더 많은 데이터가 필요하다. 통상적으로, 데이터는 트랜스듀서 프로브로부터 케이블링을 이용하여 별개로 하우징된 제어 전자회로로 전송된다.

## 발명의 내용

- [0007] 본 개시내용은 초음파 트랜스듀서-기반의 촬영기를 이용하여 취득된 데이터의 온-칩 압축을 위한 아키텍처의 다양한 양태를 설명한다. 일부 실시예에서, 온-칩 신호 처리(예를 들어, 데이터 압축)는, 예를 들어, 데이터 대역폭을 감축하기 위해 수신 신호 경로에서 채용될 수 있다. 예를 들어, 여기서 설명되는 일부 온-칩 압축 아키텍처는, 압축된 데이터가 소비자 등급 인터페이스(예를 들어, USB 3.0, USB 3.1, USB 2.0, Thunderbolt, Firewire 등)를 이용하여 디지털 데이터 스트림으로서 오프 칩 전송될 수 있는 범위까지 전체의 실시간 3D 초음파 촬영 데이터를 압축하도록 구성될 수 있다. 수신된 신호의 온-칩 디지털화는 진보된 디지털 신호 처리가 온-칩으로 수행되는 것을 허용하므로, 단일의 반도체 기판 상에서의 전체의 초음파 촬영 시스템의 완전한 또는 실질적으로 완전한 통합을 허용한다. 일부 실시예에서, 완전한 "초음파 시스템 온 칩(ultrasound system on a chip)" 솔루션이 제공된다.

- [0008] 일부 실시예는 초음파 트랜스듀서 요소로부터 출력된 신호를 처리하기 위한 방법에 관한 것이다. 이 방법은, 초음파 트랜스듀서 요소와 동일한 반도체 다이 상에 통합된 컴포넌트로, 초음파 트랜스듀서 요소로부터 출력된 신호를 압축함으로써 압축된 신호를 생성하는 단계를 포함하고, 여기서, 압축된 신호는 데이터 스트림으로서 반도체 다이 외부로 전송되도록 구성된다.

- [0009] 일부 실시예는, 칩에 통합된 초음파 트랜스듀서들의 어레이에 의해 생성된 복수의 초음파 신호의 온-칩 압축을 수행하는 단계를 포함하는 방법에 관한 것이다.

- [0010] 일부 실시예는, 반도체 다이 상에 통합된 적어도 하나의 초음파 트랜스듀서 요소; 반도체 다이 상에 통합되고, 적어도 하나의 초음파 트랜스듀서 요소로부터 출력된 신호를 압축하도록 구성되는 압축 회로를 포함하는 초음파 디바이스에 관한 것으로서, 여기서, 압축된 신호는 반도체 다이 외부로 데이터 스트림으로서 전송되도록 구성된다.

- [0011] 일부 실시예는, 반도체 다이 상에 통합된 적어도 하나의 초음파 트랜스듀서 요소; 및 반도체 다이 상에 통합되고, 적어도 하나의 초음파 트랜스듀서 요소로부터 출력된 신호에 적어도 부분적으로 기초하여 이미지 재구성 프로세스의 적어도 일부를 수행하도록 구성된 이미지 재구성 회로를 포함하는 초음파 디바이스에 관한 것이다.

- [0012] 일부 실시예는, 칩과 통합된 적어도 하나의 초음파 트랜스듀서로부터 출력된 신호에 적어도 부분적으로 기초하여 온-칩 이미지 재구성 프로세스의 적어도 일부를 수행하는 단계를 포함하는 방법에 관한 것이다.

- [0013] 일부 실시예는 초음파 트랜스듀서 요소로부터 출력된 신호를 처리하기 위한 방법에 관한 것이다. 이 방법은, 초음파 트랜스듀서 요소와 동일한 반도체 다이 상에 통합된 컴포넌트로 적어도 하나의 초음파 트랜스듀서 요소로부터 출력된 신호에 적어도 부분적으로 기초하여 이미지 재구성 프로세스의 적어도 일부를 수행하는 단계를 포함한다.

[0014] 일부 실시예는, 반도체 다이 상에 통합되고 촬영 신호를 생성하도록 구성된 적어도 하나의 초음파 트랜스듀서 요소; 초음파 디바이스의 복수의 촬영 동작 모드를 생성하도록 구성된 제어 회로; 및 반도체 다이 상에 통합되고, 선택된 촬영 동작 모드에 적어도 부분적으로 기초하여 복수의 압축 방식들 중 하나를 이용하여 촬영 신호를 압축하도록 구성되는 압축 회로를 포함하는 초음파 디바이스에 관한 것이다.

[0015] 일부 실시예는 적어도 하나의 초음파 트랜스듀서 요소로부터 출력된 신호를 처리하기 위한 방법에 관한 것이다. 이 방법은, 적어도 하나의 초음파 트랜스듀서 요소를 포함하는 초음파 디바이스의 촬영 동작 모드를 결정하는 단계; 및 결정된 (예를 들어, 프로그램된) 촬영 동작 모드에 적어도 부분적으로 기초하여 선택된 복수의 압축 방식들 중 하나를 이용하여 초음파 디바이스에 의해 기록된 데이터를 압축하는 단계를 포함한다.

[0016] 상기 개념들 및 이하에서 더 상세히 논의되는 추가의 개념들의 모든 조합은 (이러한 개념들이 서로 불일치하지 않는다면) 본 명세서에서 개시된 발명 주제의 일부로서 간주된다는 것을 이해해야 한다.

### 도면의 간단한 설명

[0017] 개시된 기술의 다양한 양태 및 실시예들이 이하의 도면들을 참조하여 설명될 것이다. 도면들은 축척비율대로 그려진 것은 아니라는 점을 이해하여야 한다. 복수의 도면들 내에 나타나는 항목들은 이들이 나타나는 모든 도면들에서 동일한 참조 번호로 표시된다.

도 1a는 본 개시내용의 실시예에 따른 초음파 촬영 디바이스의 예시적 아키텍처 블록도를 도시한다;

도 1b는 본 개시내용의 일부 실시예에 따른 추가 컴포넌트들과의 통합시에 도 1a의 예시적 아키텍처를 도시한다;

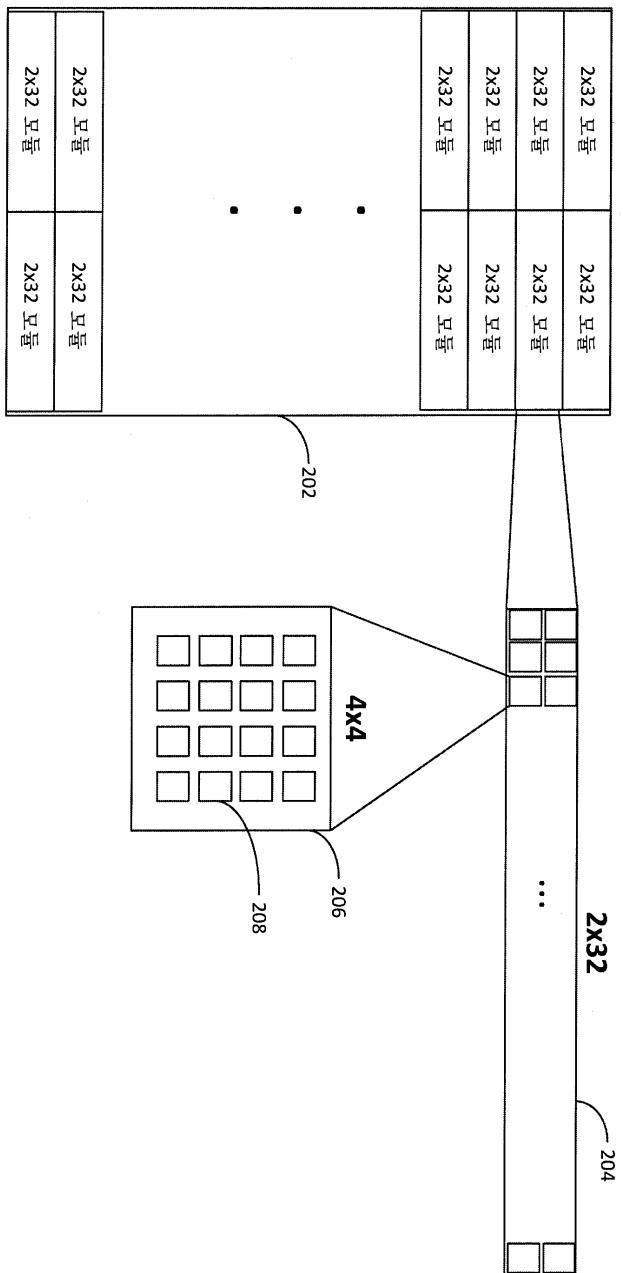

도 2는 본 개시내용의 일부 실시예에 따라 이용되는 어레이 내의 초음파 트랜스듀서 요소들의 개별적으로-제어 가능한 모듈들의 배열의 개략적 예시를 도시한다;

도 3은 본 개시내용의 일부 실시예에 따라, 적어도 일부의 디지털 처리 컴포넌트가 오프 칩 위치해 있는 대안적인 예시적 아키텍처를 도시한다;

도 4는 본 개시내용의 일부 실시예에 따라 이용될 수 있는 시간 이득 보상 회로에 대한 예시적 아키텍처를 도시한다;

도 5는 본 개시내용의 일부 실시예에 따라 포함될 수 있는 데이터 감축 회로에 대한 예시적 아키텍처를 도시한다;

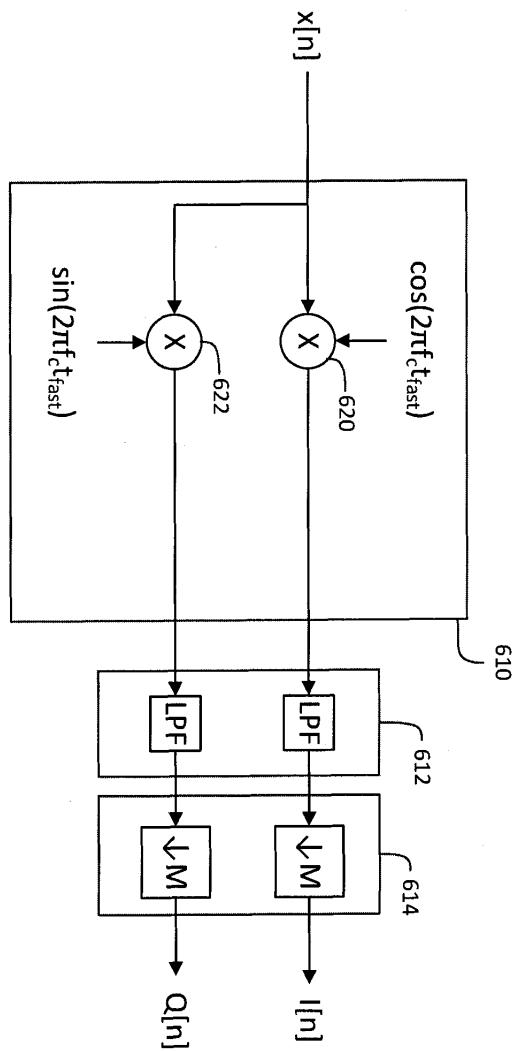

도 6은 도 5에 도시된 데이터 감축 회로의 디지털 처리 블록 내의 데이터 감축을 위한 예시적 아키텍처를 도시한다;

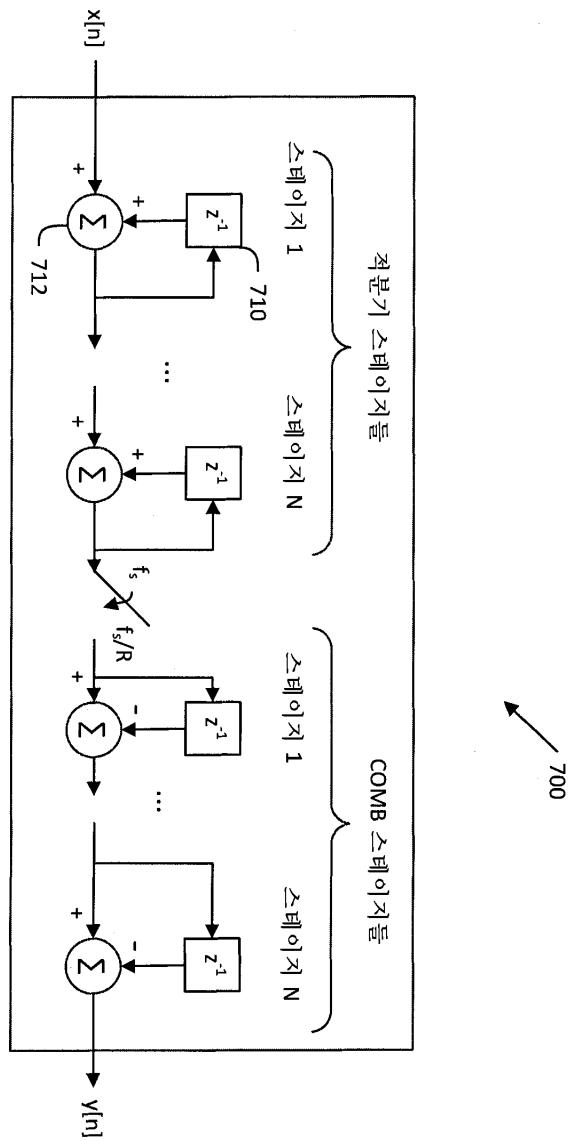

도 7은 본 개시내용의 일부 실시예에 따라 이용될 수 있는 캐스캐이드 적분 콤 회로(cascade integrating comb circuit)에 대한 예시적 아키텍처를 도시한다;

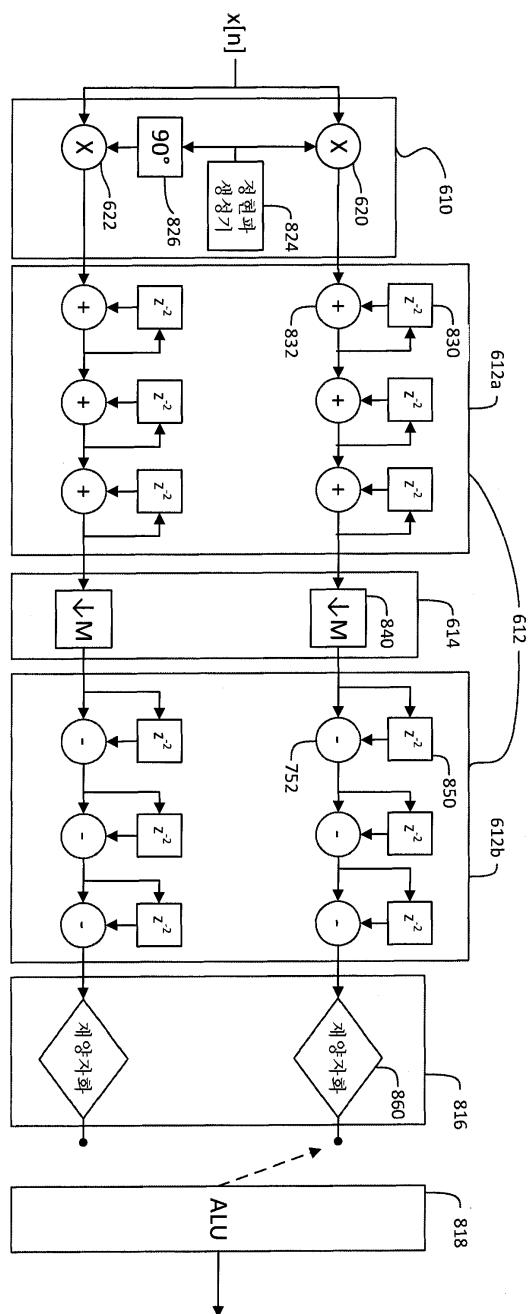

도 8은 본 개시내용의 일부 실시예에 따른 데이터 감축을 수행하기 위한 예시적 회로를 도시한다;

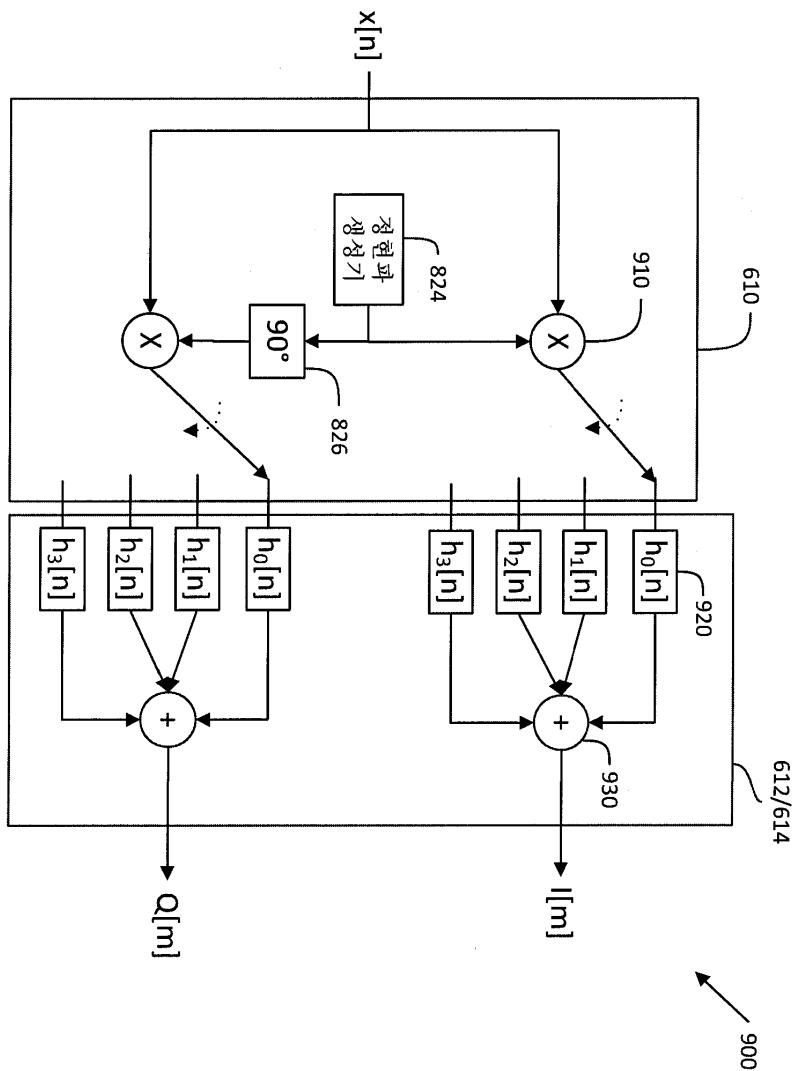

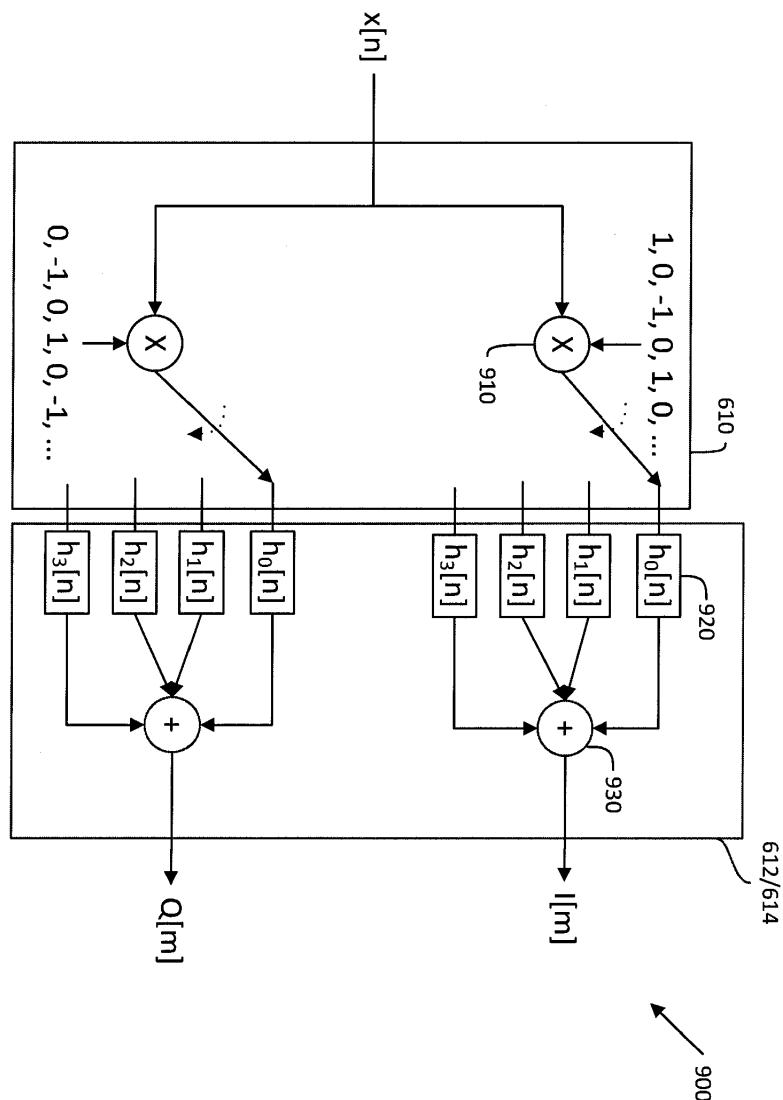

도 9는 본 개시내용의 일부 실시예에 따른 인자 4로 직교 다운샘플링(quadrature downsampling)을 수행하기 위한 예시적 회로를 도시한다;

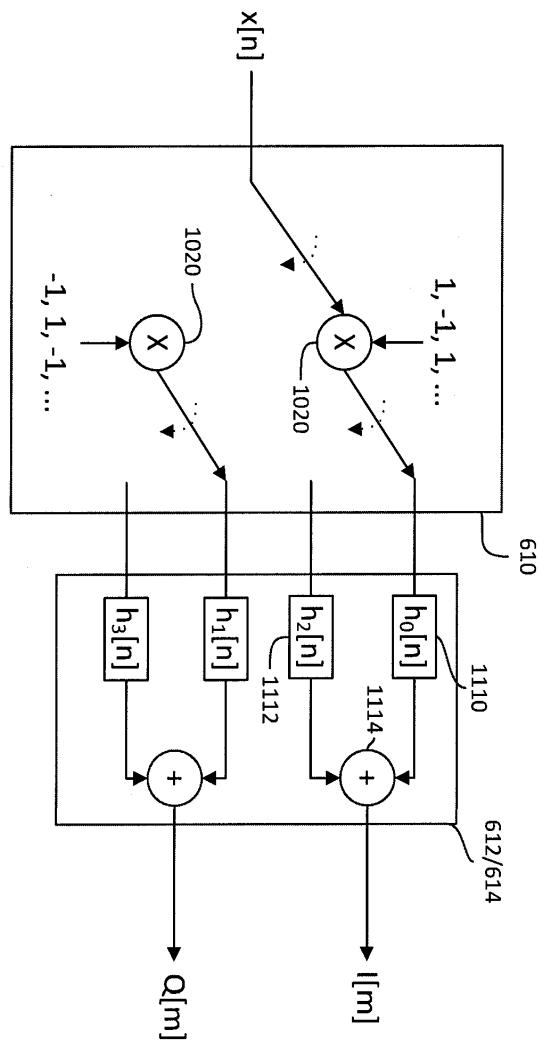

도 10은 본 개시내용의 일부 실시예에 따른 인자 4로 직교 다운샘플링을 수행하기 위한 대안적 회로를 도시한다;

도 11은 본 개시내용의 일부 실시예에 따른 인자 4로 직교 다운샘플링을 수행하기 위한 대안적 회로를 도시한다;

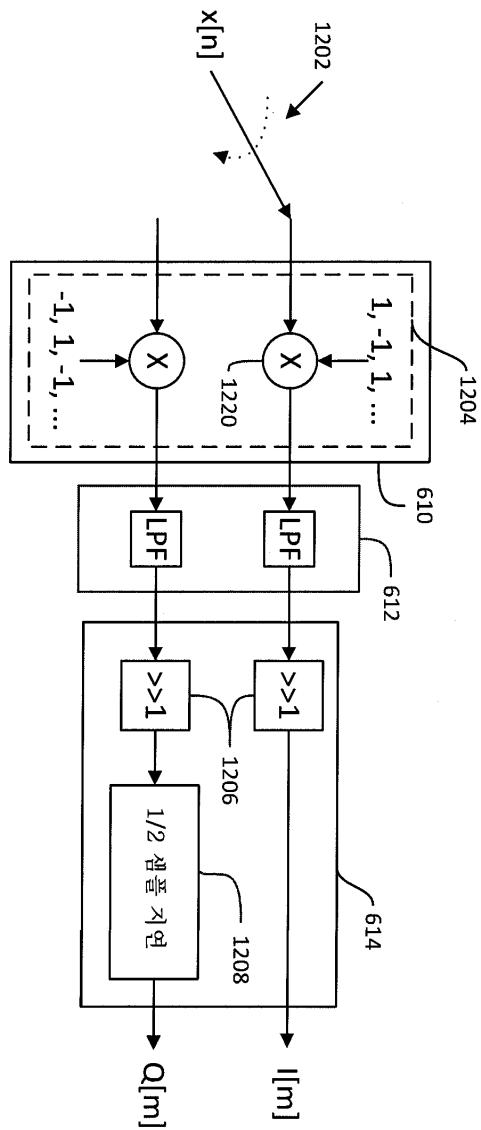

도 12는 본 개시내용의 일부 실시예에 따른 인자 4로 직교 다운샘플링을 수행하기 위한 대안적 회로를 도시한다;

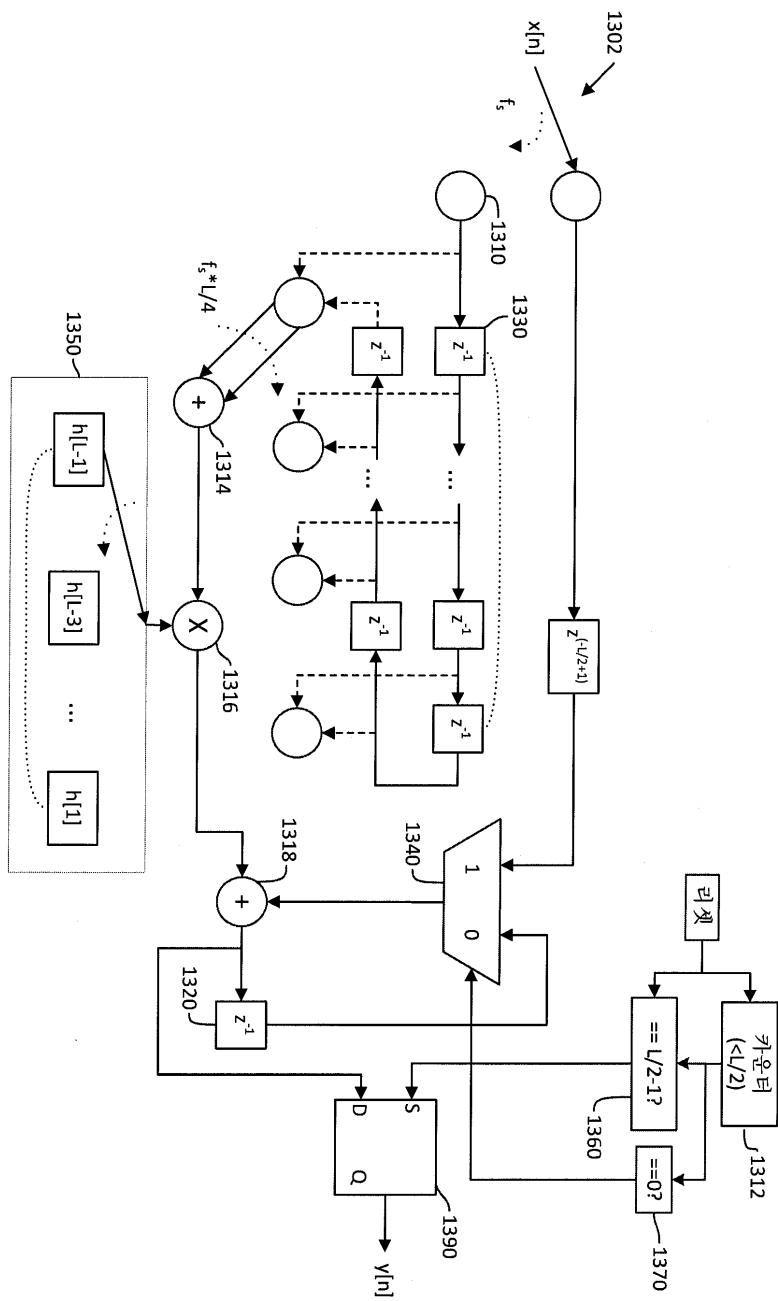

도 13은 본 개시내용의 일부 실시예에 따라 이용될 수 있는 다상 필터(polyphase filter)에 대한 예시적 아키텍처를 도시한다;

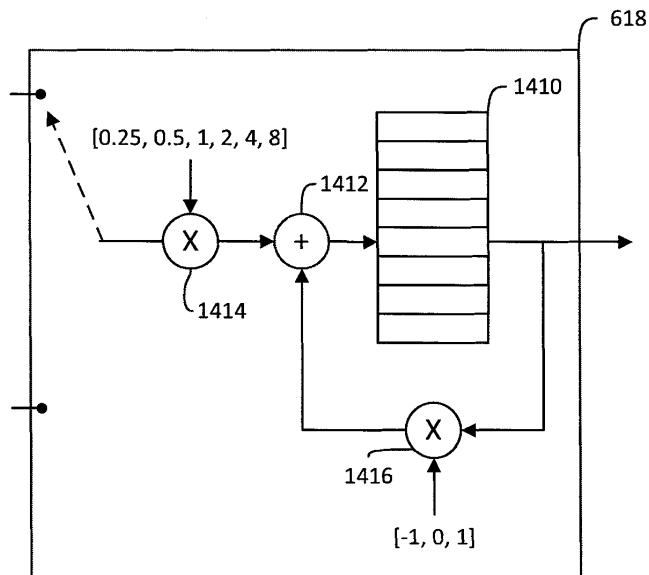

도 14는 본 개시내용의 일부 실시예에 따라 데이터 감축을 제공할 수 있는 산술 로직 유닛(arithmetic logic unit)에 대한 예시적 아키텍처를 도시한다;

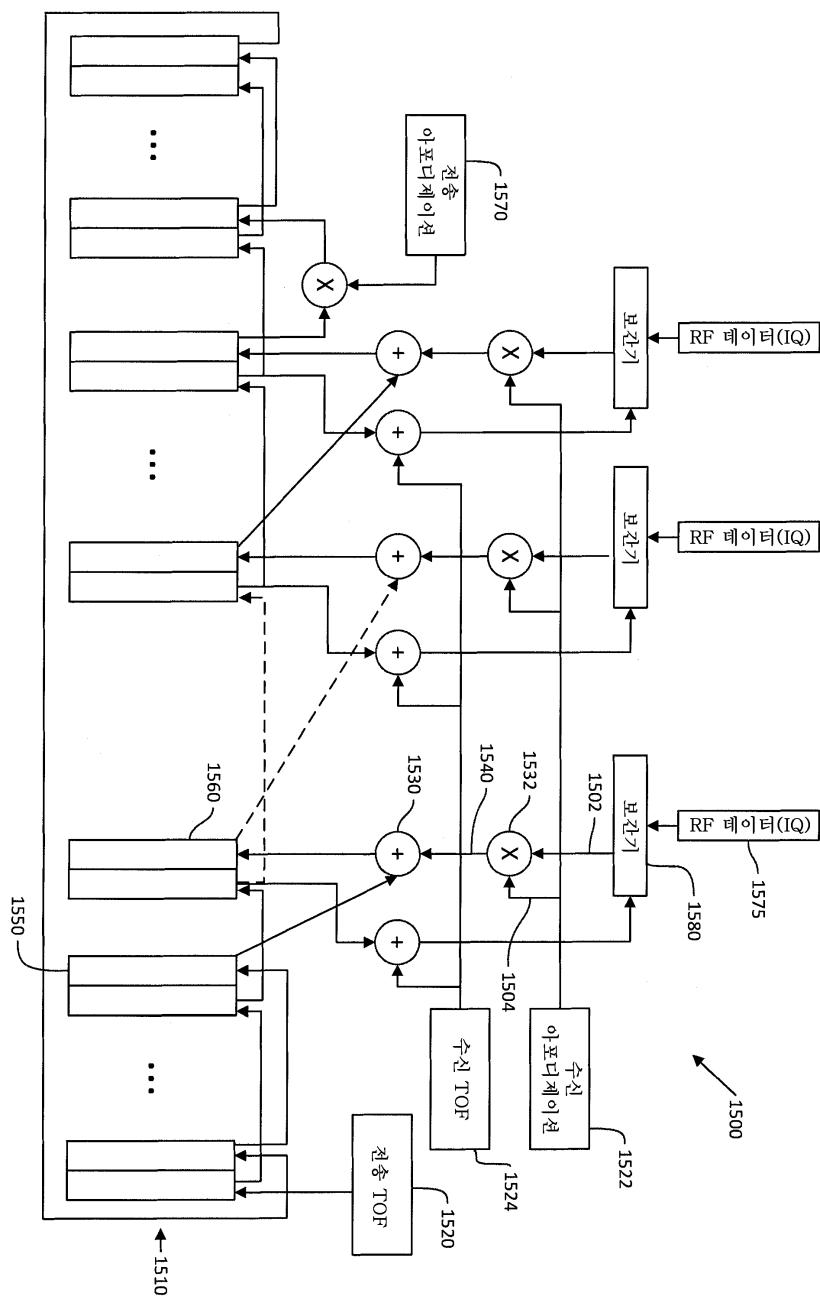

도 15는 본 개시내용의 일부 실시예에 따른 통합된 배면투사 기술(backprojection technique)을 이용한 이미지 형성을 위한 예시적 아키텍처를 도시한다;

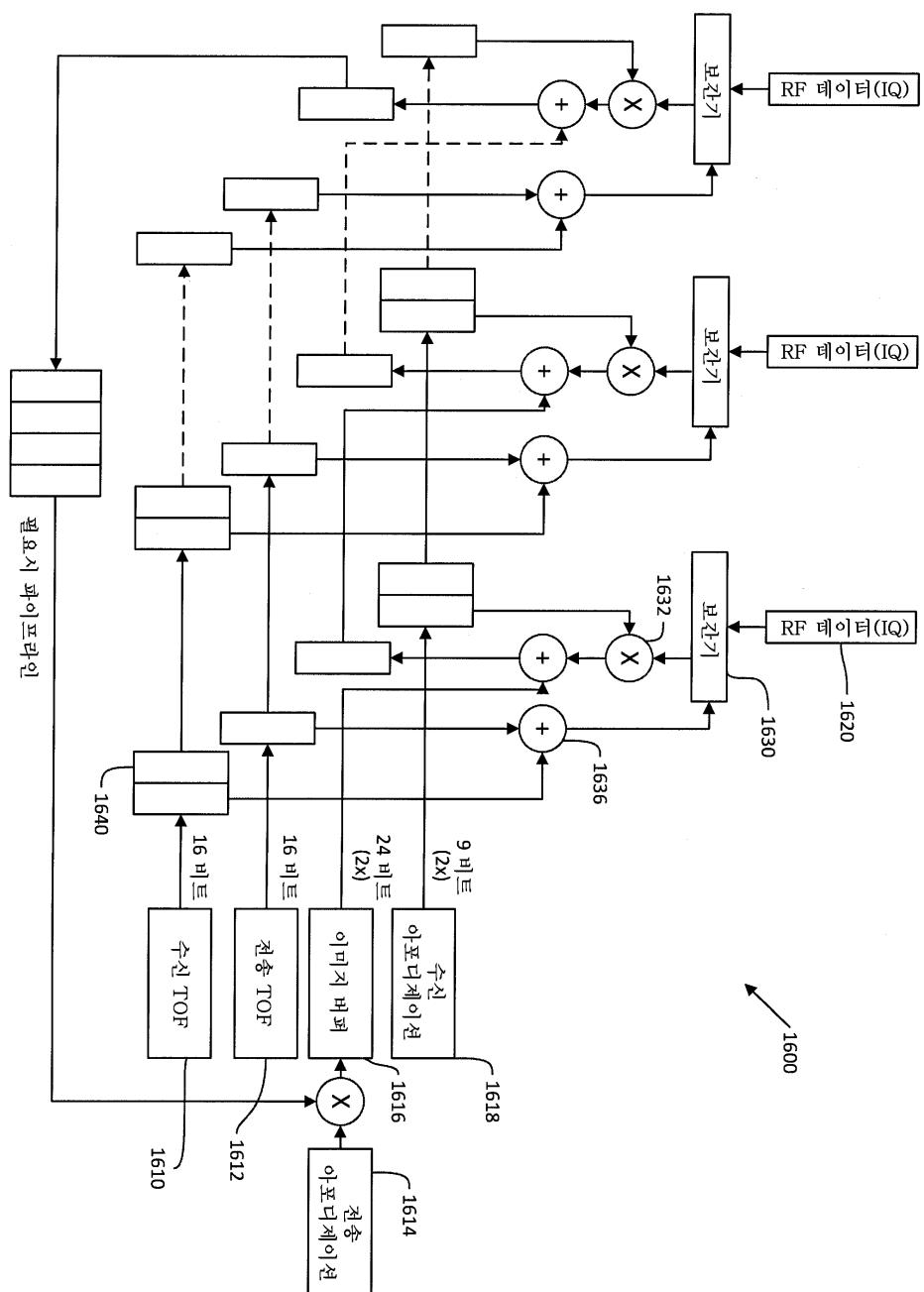

도 16은 본 개시내용의 일부 실시예에 따른 통합된 배면투사 기술을 이용한 이미지 형성을 위한 대안적 아키텍처를 도시한다;

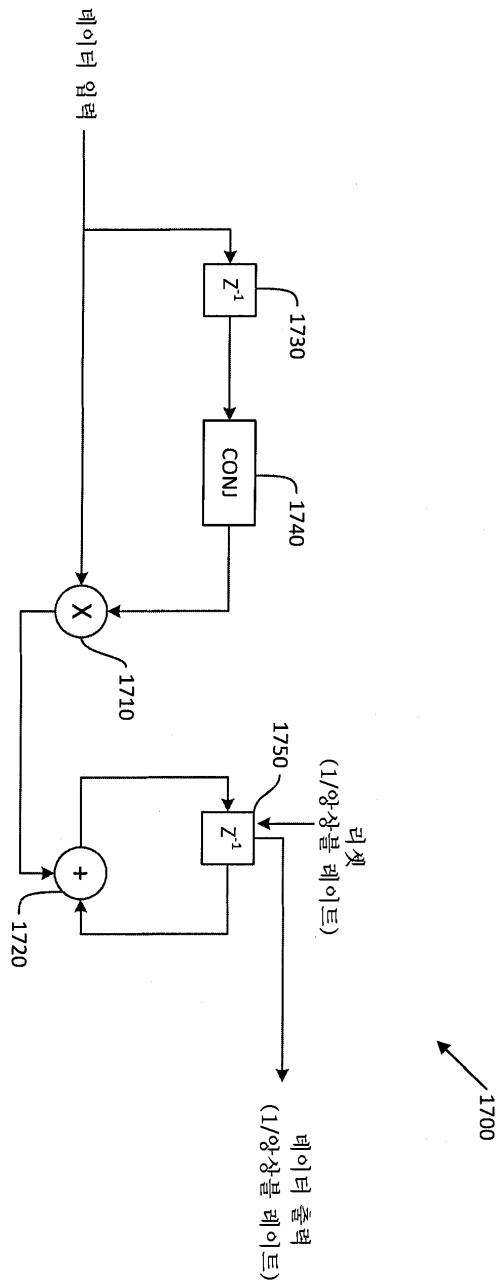

도 17은 본 개시내용의 일부 실시예에 따른 양상을 압축(ensemble compression)을 수행하기 위한 예시적 아키텍처를 도시한다;

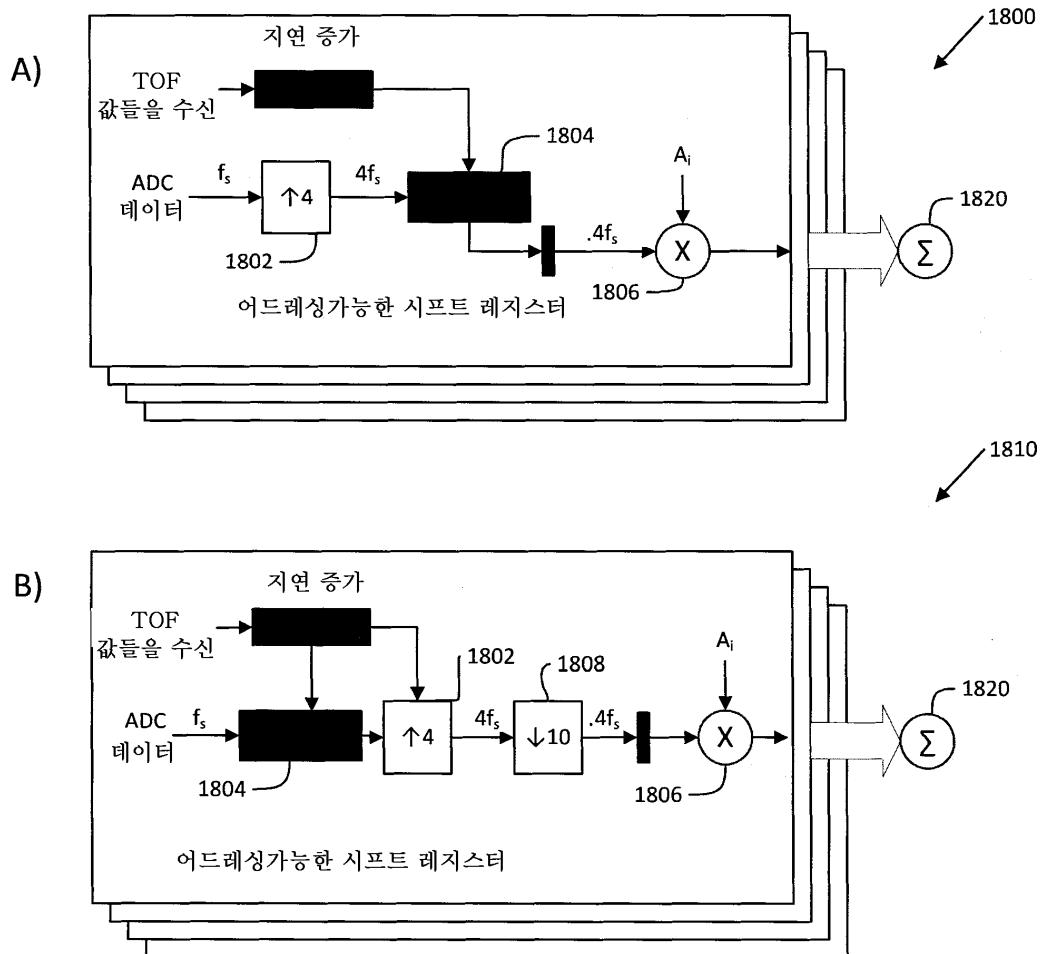

도 18a 및 도 18b는, 본 개시내용의 일부 실시예에 따른, 각각 스트리밍 어드레싱가능 및 파이프라인 지연(streaming addressable and pipeline delay)을 이용한 동적 포커싱을 수행하기 위한 예시적 아키텍처를 도시한다;

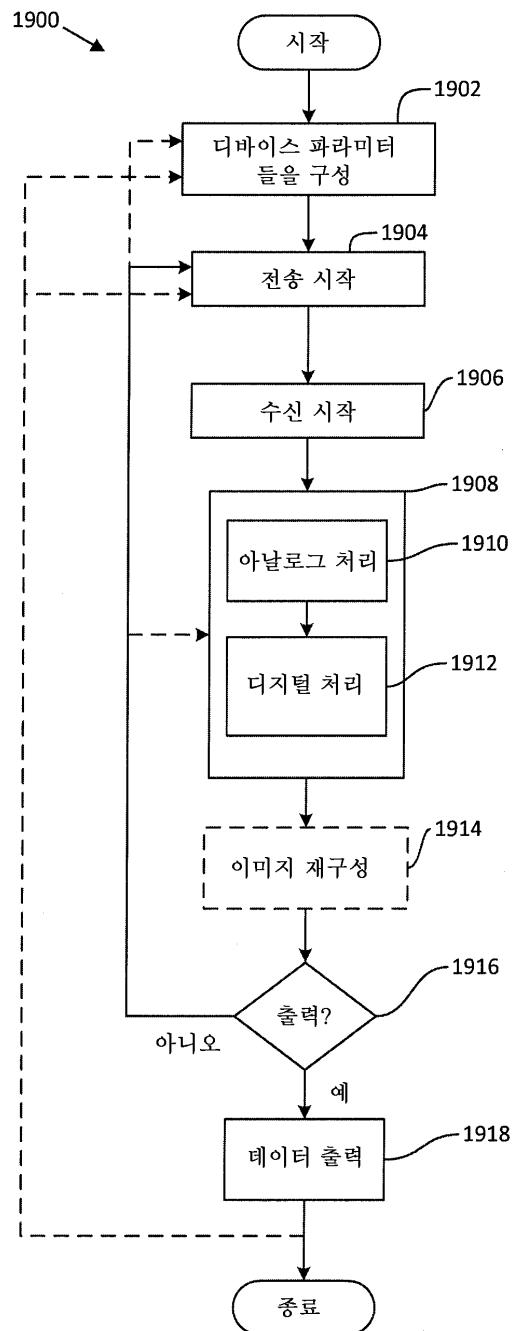

도 19는 본 개시내용은 일부 실시예에 따른 초음파 트랜스듀서 어레이를 동작시키기 위한 예시적 프로세스의 플로차트이다.

### 발명을 실시하기 위한 구체적인 내용

[0018]

출원인들은, 초음파 트랜스듀서 프로브에 의해 수집되고 초음파 이미지를 생성하는데 이용되는 많은 양의 데이터에 의해 부분적으로, 종래의 초음파 스캐너의 제어 회로와 트랜스듀서의 통합이 없는 것이 요구된다는 것을 이해했다. 대응적으로, 출원인들은, 이러한 많은 양의 데이터를 감축시키거나 기타의 방식으로 핸들링하면서 여전히 적절한 품질의 원하는 초음파 이미지 유형들의 생성을 허용하기 위한 적절한 디바이스 구성 및 기술은, 콤팩트한 형태로 초음파 트랜스듀서와 제어 전자회로를 갖는 통합된 초음파 디바이스의 달성을 가능케할 것이라는 것을 이해했다. 본 개시내용은, 데이터 대역폭을 감축시키는 고유하고, 비용-효율적이고, 스케일 가능한 통합된 데이터 압축 기술을 제공하는 한편 진보된 촬영 응용에 대해 충분히 확실한 데이터를 제공함으로써 이 문제를 해결한다. 따라서, 본 출원의 양태는, 통합된 초음파 트랜스듀서(예를 들어, CMOS 초음파 트랜스듀서) 및 회로를 갖는 단일 기판 초음파 디바이스에서 이용될 수 있는 아키텍처를 제공한다.

[0019]

따라서, 본 개시내용의 일부 양태는, 완전 디지털 초음파 전단부(fully digital ultrasound front-end)와 동일한 다이 상에 제작된 초음파 트랜스듀서 어레이들의 직접적인 통합을 갖는 확실하고 고도로 통합된 "초음파 시스템 온 칩"을 제공함으로써 초음파 이미지 처리의 선두부를 푸시하는 처리의 새로운 장치, 시스템, 및 방법을 제공한다. 여기서 사용될 때, "동일한 다이 상에 제작된/통합된"이란, 동일한 기판 상에 통합되거나 3D 칩 팩 키징 기술로 통합된 하나 이상의 적층된 다이를 이용하여 통합된 것을 의미한다. 본 개시내용의 일부 양태에 따르면, 이를 아키텍처들은, 독립된 데이터를 유지하는 디지털화된 채널로의 충분한 액세스를 허용하여, 정교한 이미지 형성 및/또는 처리 알고리즘을 수행하기 위한 최신 기술의 기성품의 컴퓨팅 플랫폼을 허용할 수 있다. 적어도 일부 실시예에서, 고해상도 3D 체적 촬영이, 단지 한 예로서, 여기서 설명되는 데이터 감축 및 핸들링을 위한 디바이스 및 기술들을 이용하여 수행될 수 있다.

[0020]

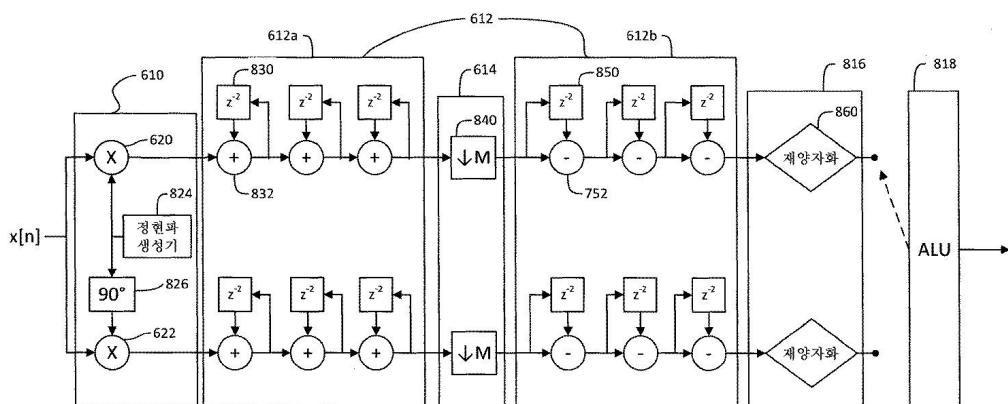

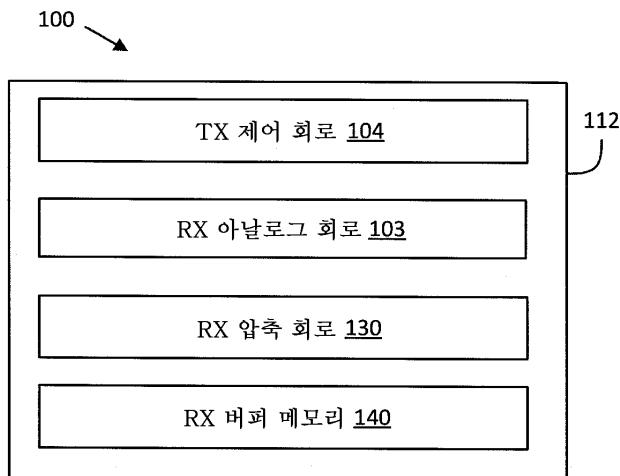

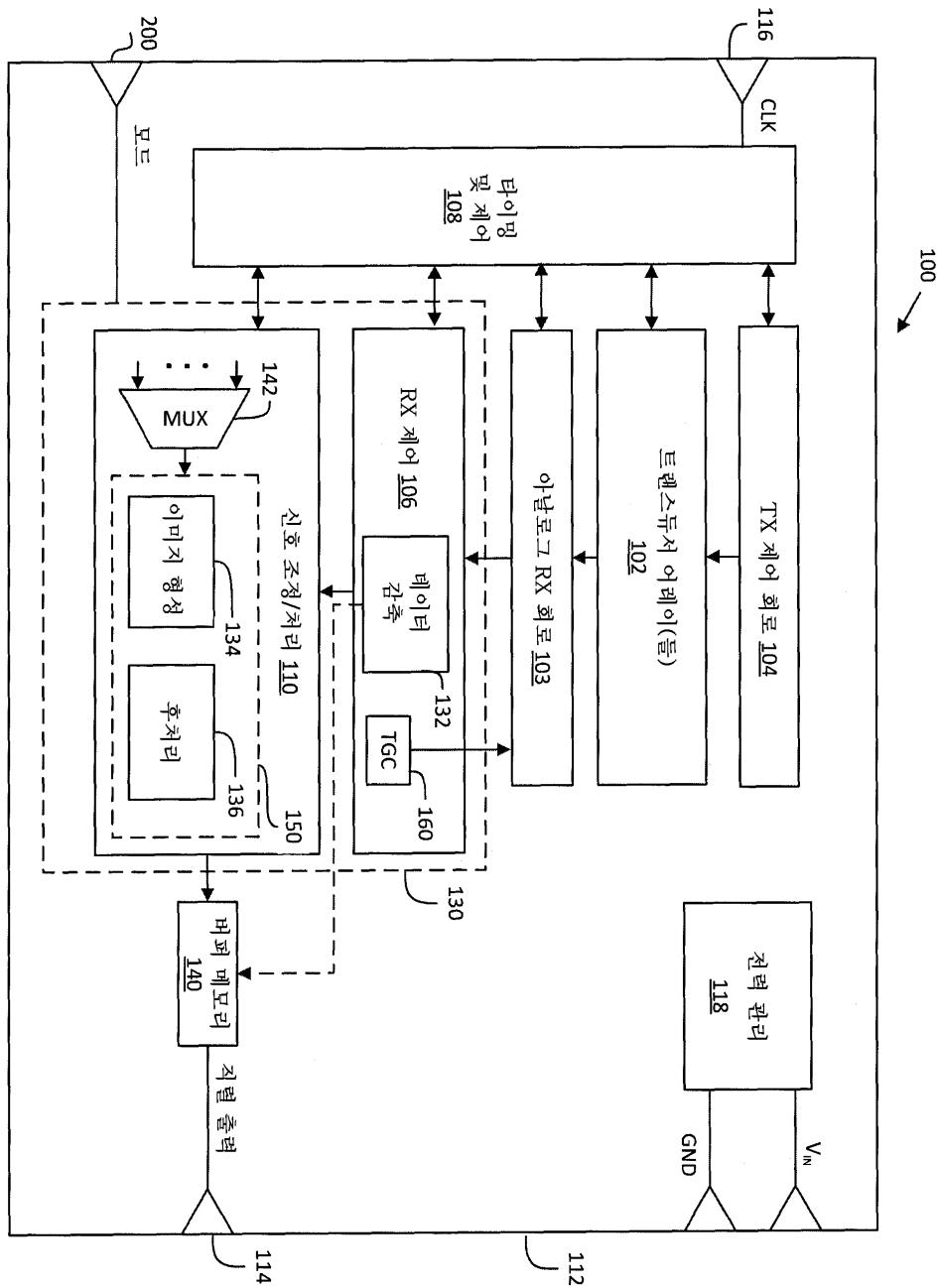

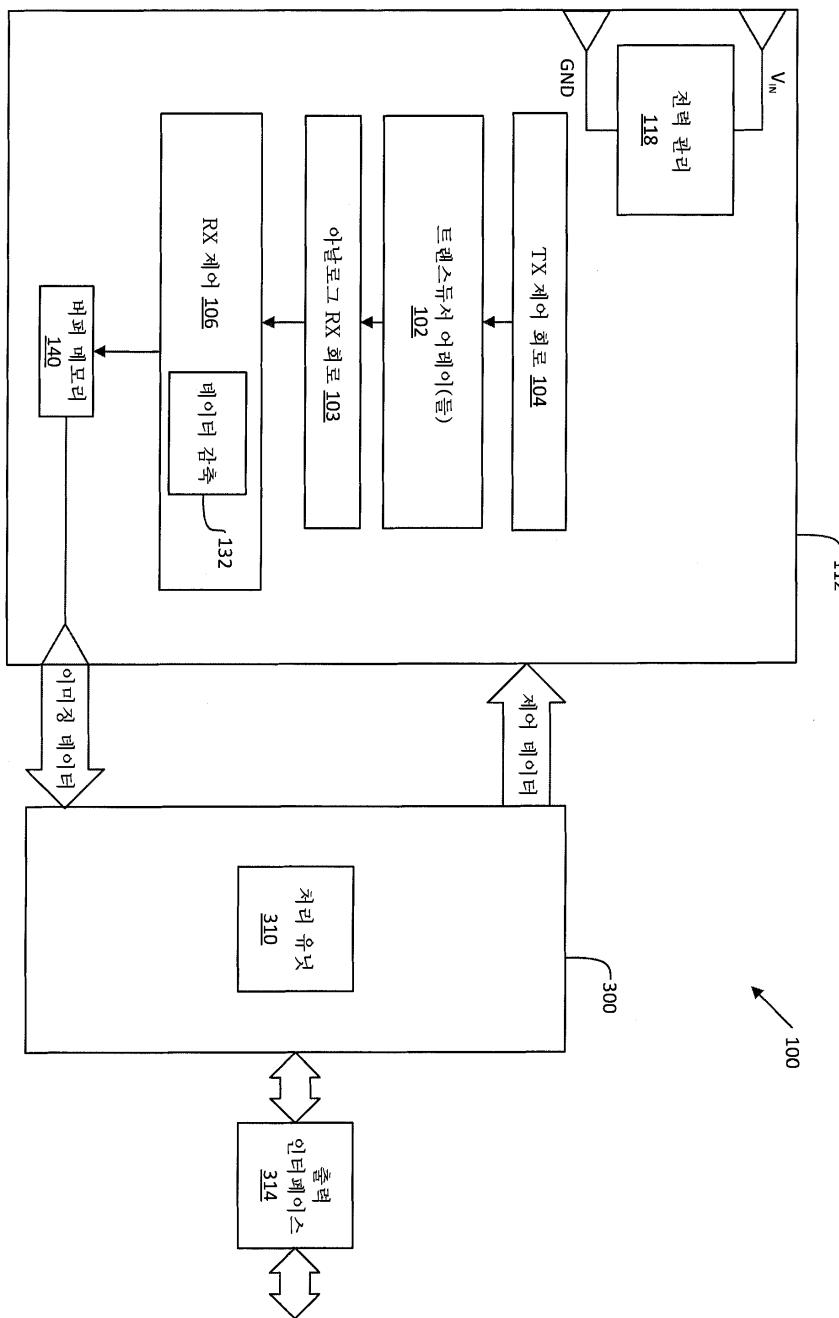

도 1a는 본 개시내용의 다양한 양태를 구현하는 통합된 초음파 디바이스(100)의 예를 도시한다. 도시된 바와 같이, 디바이스(100)는, 전송(TX) 제어 회로(104), 아날로그 수신(RX) 회로(103), 수신(RX) 압축 회로(130), 및 수신(RX) 버퍼 메모리(140)를 포함한 반도체 다이(112) 상에 형성된 복수의 회로를 포함한다. 이들 회로들 각각은 하나 이상의 추가 회로를 포함할 수 있다. 예를 들어, TX 제어 회로(104)는, TX 파형 생성기, TX 파라미터 및 제어 레지스터, 음향 요소들의 어레이를 구동하는 아날로그 필터 회로 및/또는 지연된 파형 분배 기능을 구현하는 회로를 포함할 수 있다.

[0021]

도 1b는, 반도체 다이(112) 상에 포함된 추가 요소들과 함께 도 1a에 도시된 요소들을 포함하는 도 1a의 초음파 디바이스(100)를 도시한다. 예를 들어, 도 1b의 디바이스(100)는, 하나 이상의 트랜스듀서 배열(예를 들어, 어레이)(102), 타이밍 & 제어 회로(108), 및 전력 관리 회로(118)를 추가로 포함한다.

[0022]

아날로그 RX 회로(103)는 복수의 초음파 트랜스듀서 요소로부터 출력된 신호를 처리하는 아날로그 신호 체인 커포넌트들을 포함할 수 있다. 초음파 트랜스듀서 요소들의 초음파 트랜스듀서들은 임의의 적절한 유형일 수 있고, 일부 실시예에서는, 현재 전자기기 산업을 구동하고 있는 바로 그 반도체 파운드리(semiconductor foundry)에서 고품질 초음파 트랜스듀서의 제작을 허용할 수 있는, 용량성 마이크로머신제작된 초음파 트랜스듀서(CMUT; capacitive micromachined ultrasound transducer)이다. 이러한 CMUT는 집적된 회로와 동일한 기판(예를 들어, 실리콘 기판)에 및/또는 동일한 기판 상에 형성될 수 있다.

[0023]

한 양태에서, 아날로그 RX 회로(103)는 복수의 행(예를 들어, 4개의 행)을 포함할 수 있다. 각각의 행은, 초음

파 트랜스듀서 어레이 내의 한 전체 열의 센서들에 대한 아날로그 신호 체인 요소들(예를 들어, 144개 요소)을 포함할 수 있다. 일부 실시예에서, 아날로그 RX 회로(103) 내의 하나 이상의 컴포넌트(예를 들어, 자동 이득 제어 컴포넌트)는, (예를 들어, 신호가 수신된 타이밍에 기초하여 가변 이득을 제공함으로써) 촬영된 물체 내의 상이한 깊이들로부터 수신된 신호들을 보상하는 시간 이득 보상(TGC; time gain compensation) 회로(160)에 의해 제어될 수 있다. TGC 회로(160)는 후술되는 RX 압축 회로(130)의 일부로서 포함될 수 있다. TGC 회로(160)에 대한 예시적 아키텍처는 도 4에 관하여 이하에서 더 상세히 논의된다.

[0024] RX 보상 회로(130)는 아날로그 RX 회로(103)로부터의 출력을 처리하기 위한 회로를 포함할 수 있다. 일부 구현에서, RX 보상 회로(130)는, 이하에서 더 상세히 논의되는 바와 같이, 아날로그 RX 회로(103)로부터 수신된 데이터의 데이터 대역폭을 감축시키도록 구성된 회로를 포함한다. 예를 들어, RX 압축 회로(130)는, 처리된 데이터가 원하는 데이터 레이트로 오프 칩 전송될 수 있도록 온-칩 압축을 제공하기 위해, 필터링, 평균화, 샘플링, 데시메이팅(decimating), 및/또는 기타의 기술을 이용함으로써 수신된 데이터를 처리하도록 구성된 회로를 포함할 수 있다. RX 압축 회로(130)는 데이터 압축을 수행하기 위한 아날로그 및/또는 디지털 컴포넌트를 포함할 수 있고, 실시예들은, 압축 회로의 특정한 양태들이 아날로그 아키텍처, 또는 디지털 아키텍처, 또는 아날로그와 디지털 컴포넌트의 조합을 이용하여 구현되는지에 기초하여 제한되지 않는다. 예를 들어, 동등한 기능을 제공하기 위해, 이하에서 더 상세히 설명되는 디지털 믹싱 회로(digital mixing circuitry)가 아날로그 혼테로다인 회로(analog heterodyning circuit)를 이용하여 대안으로서 구현될 수 있다. 추가적으로, 채널 합산, 동적 지연, 및 주파수 필터링을 포함한 그러나 이것으로 제한되지 않는 다른 피쳐들은, 디지털 및/또는 아날로그 컴포넌트들을 이용하여 구현될 수 있고, 실시예들은 이 점에서 제한되지 않는다.

[0025] RX 압축 회로(130)는 또한, RX 제어 및 파라미터 레지스터를 포함한 다른 컴포넌트들을 포함할 수 있다. 추가적으로, RX 압축 회로(130)는, RX 압축 회로(130)에 의해 처리된 디지털 신호를 압축하는 데 적어도 부분적으로 이용될 수 있는, 다이(112) 상에 통합된 (도시되지 않은) 적어도 하나의 마이크로프로세서와 연관될 수 있다.

[0026] RX 버퍼 메모리(140)는, 이하에서 더 상세히 논의되는 바와 같이, 데이터를 오프 칩 전송하기 이전에 RX 압축 회로(130)의 출력을 임시적으로 저장하도록 구성될 수 있다.

[0027] RX 압축 회로(130)의 일부로서 일부 실시예에서 포함된 컴포넌트들도 역시 도시되어 있다. 앞서 논의된 바와 같이, 본 개시내용의 일부 실시예는, 최대 데이터 대역폭을 갖는 출력 인터페이스(114)와 호환되는 데이터 레이트로 데이터 스트림으로서 반도체 다이(112)로부터의 데이터의 전송을 가능케 하는 데이터 압축 아키텍처를 제공한다. 일부 실시예에서, 데이터 스트림은 직렬 데이터 스트림일 수 있다. (여기서는 "압축 회로"라고도 하는) RX 압축 회로(130)의 컴포넌트들은, 하나 이상의 데이터 압축 기술을 이용하여 데이터 압축을 제공하도록 구성될 수 있고, 그 예가 여기서 설명된다. RX 압축 회로(130)는, 도시된 바와 같이, RX 제어 회로(106)와 신호 조정/처리 회로(110)를 포함한다. RX 제어 회로(106)는, 아날로그 RX 회로(103)의 아날로그 신호 체인 요소들로부터 수신된 데이터를 처리하도록 구성된 데이터 감축 회로(132)를 더 포함한다. 이하에서 더 상세히 논의되는 데이터 감축 회로(132)는, 이미지 재구성 프로세스의 적어도 일부를 수행하기 이전에 신호에 관한 데이터 압축을 수행하도록 구성된 회로를 포함할 수 있다. 일부 실시예에서, 데이터 감축 회로(132)의 적어도 일부의 출력은, 데이터 감축 회로(132)와 버퍼 메모리(140) 사이의 선택사항적인 데이터 경로로 표시된 신호 조정/처리 회로(110)에 의해 추가로 처리되지 않고 버퍼 메모리(140)에 제공될 수 있다.

[0028] 도시된 예에서, 데이터 감축 회로(132)는, 아날로그 압축 회로, 아날로그-대-디지털 변환기(ADC), 및 디지털 압축 회로를 포함할 수 있다. ADC는, 예를 들어, 10-비트, 1, 5, 10, 또는 20 초당 메가-샘플(Msps), 40 Msps, 50 Msps, 또는 80 Msps ADC를 포함할 수 있다. ADC는 대안으로서, 1-비트, 4-비트, 16-비트, 또는 20-비트를 포함한 그러나 이것으로 제한되지 않는 임의의 원하는 해상도를 가질 수 있다. 이용될 수 있는 ADC들의 예시적 유형으로는, 연속 근사화 레지스터(SAR; successive approximation register) ADC, 플래시 ADC, 파이프라인 ADC, 시그마-엘타 ADC, 멀티-슬롭(multi-slop) ADC, 및 시간-인터리빙형 ADC가 포함될 수 있지만 이것으로 제한되지 않는다. 일부 실시예에서, ADC는 수신된 신호의 중심 주파수보다 낮은 레이트로 샘플링됨으로써 관련 데이터를 에일리어싱(aliasing)할 수 있다.

[0029] 데이터 감축 회로(132)에서의 처리를 거친 후, RX 제어 회로들(106) 모두의 출력들(그 개수는, 이 예에서는, 칩 상의 트랜스듀서 요소들의 개수보다 작거나 같음)은 신호 조정/처리 회로(110) 내의 멀티플렉서(MUX)(142)에 전송될 수 있다. 일부 실시예에서, RX 제어 회로의 개수는 칩 상의 트랜스듀서 요소들의 개수와는 상이할 수 있고, 본 개시내용의 실시예들은 이 점에서 제한되지 않는다. MUX(142)는 다양한 RX 제어 회로(106)로부터의 디지털 데이터를 멀티플렉싱하고, MUX(142)의 출력은, 예를 들어, 하나 이상의 출력 포트(114)를 통해 다이(112)

로부터 데이터를 출력하기 이전에, 신호 조정/처리 회로(110) 내의 디지털 신호 처리 블록(150)에 선택사항으로서 제공될 수 있다. 일부 실시예는 MUX(142)를 포함하지 않을 수도 있고, RX 제어 회로(106)로부터의 출력들은 디지털 신호 처리 블록(150)에 직접 제공되거나 및/또는 오프 칩 전송되기 이전에 버퍼(140)에 저장될 수 있다.

[0030] 도시된 바와 같이, 디지털 신호 처리 블록(150)은, 이미지 재구성 프로세스의 적어도 일부를 수행하도록 구성된 이미지 형성 회로(134)를 포함하고, 이미지 형성 회로(134)의 출력은 추가 처리 및/또는 디스플레이를 위해 오프 칩 출력될 수 있다. 디지털 신호 처리 블록(150)은 또한, 추가 데이터 압축을 제공하기 위해 이미지 형성 회로(134)의 출력에서 동작하는 후처리 회로(post-processing circuit)(136)를 포함할 수 있다. 본 개시내용의 실시예에 따른 초음파 촬영기의 일부로서 반도체 다이(112) 상에 형성될 수 있는 데이터 감축 회로(132), 이미지 형성 회로(134), 및 후처리 회로(136) 각각에 대한 예시적 아키텍처가 이하에서 더 상세히 설명된다. 일부 실시예에서, 이하에서 더 상세히 논의된 바와 같이, 디지털 신호 처리 블록(150)의 전부 또는 일부는 오프 칩 형성될 수 있고, 하나 이상의 RX 제어 회로(106)로부터의 데이터는 신호 조정 및 처리 회로(110)에 의한 처리 없이 버퍼 메모리(140)에 저장될 수 있다.

[0031] 이하에서 더 상세히 설명되는 바와 같이, RX 압축 회로(130) 내의 다양한 컴포넌트들은, 수신된 신호로부터의 파형들을 디커플링하고 데이터 링크를 통해 또는 기타의 방식으로 다이(112)로부터 출력되는 데이터의 양을 감축시키도록 역할을 할 수 있다. 따라서 이러한 요소들의 포함은 일부 실시예에 따른 "초음파 온 칩 (ultrasound-on-a-chip)" 솔루션을 가능케 하거나 및/또는 강화시킬 수 있다.

[0032] 도 1b에 도시된 실시예에서, 예시된 컴포넌트들 모두는 단일의 반도체 다이(112) 상에 형성되거나 3D 팩키징 기술을 이용하여 복수의 적층된 통합된 다이스(dice) 상에 형성된다. 그러나, 도 3과 연계하여 이하에서 더 상세히 논의되는 바와 같이, 대안적 실시예에서, 예시된 요소들 중 하나 이상은 그 대신에 오프-칩 위치될 수 있다는 점을 이해해야 한다. 추가로, 예시된 예는 TX 제어 회로(104)와 RX 제어 회로(106) 양쪽 모두를 도시하고 있지만, 대안적 실시예에서, TX 제어 회로만 또는 RX 제어 회로만 채용될 수도 있다. 예를 들어, 이러한 실시예들은, 음향 신호를 전송하기 위해 하나 이상의 전송-전용 디바이스(100)가 이용되고 초음파 촬영중인 대상에 의해 반사되거나 이를 통해 투과된 음향 신호를 수신하기 위해 하나 이상의 수신-전용 디바이스(100)가 이용되는 환경에서 채용될 수 있다.

[0033] 도 2는 복수의 초음파 회로 모듈(204)이 형성되어 있는 기판(202)을 포함하는 초음파 디바이스(100)의 실시예를 도시한다. 도시된 바와 같이, 초음파 회로 모듈(204)은 복수의 초음파 요소(206)를 포함할 수 있다. 초음파 요소(206)는 복수의 초음파 트랜스듀서(208)를 포함할 수 있다. 이러한 모듈형 설계는 임의의 원하는 크기 또는 배열로의 아키텍처의 확장성을 허용한다.

[0034] 예시된 실시예에서, 기판(202)은 72개의 행과 2개의 열을 갖는 어레이로서 배열된 144개의 모듈을 포함한다. 그러나, 초음파 디바이스(100)의 기판은 임의의 적절한 개수의 행과 열을 갖는 모듈들의 2차원 배열로서 배열될 수 있는 임의의 적절한 개수의 초음파 회로 모듈(예를 들어, 적어도 2개의 모듈, 적어도 10개의 모듈, 적어도 100개의 모듈, 적어도 1000개의 모듈, 적어도 5000개의 모듈, 적어도 10,000개의 모듈, 적어도 25,000개의 모듈, 적어도 50,000개의 모듈, 적어도 100,000개의 모듈, 적어도 250,000개의 모듈, 적어도 500,000개의 모듈, 2 내지 백만개의 모듈 등)을 포함하거나, 초음파 회로 모듈들은 기타 임의의 적절한 방식으로 배열될 수도 있다는 것을 이해해야 한다.

[0035] 예시된 실시예에서, 각각의 모듈(204)은 2개의 행과 32개의 열을 갖는 어레이로서 배열된 64개의 초음파 요소들을 포함한다. 그러나, 초음파 회로 모듈(204)은, 임의의 적절한 개수의 행과 열을 갖는 초음파 요소들의 2차원 어레이로서 또는 기타 임의의 적절한 방식으로 배열될 수 있는 임의의 적절한 개수의 초음파 요소(예를 들어, 하나의 초음파 요소, 적어도 2개의 초음파 요소, 적어도 4개의 초음파 요소, 적어도 8개의 초음파 요소, 적어도 16개의 초음파 요소, 적어도 32개의 초음파 요소, 적어도 64개의 초음파 요소, 적어도 128개의 초음파 요소, 적어도 256개의 초음파 요소, 적어도 512개의 초음파 요소, 2개와 1024개 사이의 초음파 요소 등)를 포함할 수 있다는 것을 이해해야 한다.

[0036] 예시된 실시예에서, 각각의 초음파 요소(206)는 4개의 행과 4개의 열을 갖는 2차원 어레이로서 배열된 16개의 초음파 트랜스듀서들을 포함한다. 그러나, 초음파 요소(206)는 임의의 적절한 개수의 행과 열을 갖는 2차원 어레이(정사각형 또는 직사각형)로서 또는 기타 임의의 적절한 방식으로 배열될 수 있는 임의의 적절한 개수의 초음파 트랜스듀서(예를 들어, 하나의, 적어도 2개의, 적어도 4개의, 적어도 16개의, 적어도 25개의, 적어도 36개의, 적어도 49개의, 적어도 64개의, 적어도 81개의, 적어도 100개의, 1개와 200개 사이의 등)를 포함할 수도 있

다는 것을 이해해야 한다. 대안으로서, 초음파 트랜스듀서들은, 6각형 어레이, 3각형 어레이, 및 비스듬한 격자를 포함한 그러나 이것으로 제한되지 않는 기타 임의의 적절한 기하학적 어레이로 배열될 수 있다.

[0037] 각각의 초음파 회로 모듈(204)은 하나 이상의 초음파 요소 외에 회로를 포함하거나 이와 연관될 수 있다. 예를 들어, 초음파 회로 모듈은, 하나 이상의 과형 생성기(예를 들어, 2개의 과형 생성기, 4개의 과형 생성기 등), 인코딩 회로, 및 디코딩 회로를 포함한 그러나 이것으로 제한되지 않는 음파를 전송하는 것과 연관된 회로를 포함할 수 있다. 일부 실시예에서, 초음파 회로 모듈의 전부 또는 일부는 추가로 또는 대안으로서 기타 임의의 적절한 회로를 포함하거나 이와 연관될 수 있다. 예를 들어, 일부 실시예에서, 각각의 모듈(204)은, 앞서 간략히 설명된 바와 같은 및 이하에서 더 상세히 설명되는 바와 같은, 아날로그 신호 체인 요소들 및 디지털 신호 체인 요소들을 포함한 그러나 이것으로 제한되지 않는 수신측 컴포넌트와 연관될 수 있다.

[0038] 일부 실시예에서, 각각의 모듈은 8개의 수신 채널을 포함할 수 있고, 8개의 수신 채널들 각각은, 이하에서 더 상세히 설명되는 바와 같은, 시간 이득 보상 회로를 포함한 그러나 이것으로 제한되지 않는, 단일의 타이밍 및 제어 회로 또는 기타의 제어 요소들과 연관될 수 있다. 추가로, 각각의 모듈은, 모듈의 수신 채널들로부터 신호를 출력하기 위해 아날로그 및/또는 디지털 신호 처리를 수행하는 복수의 컴포넌트와 연관될 수 있다. 예를 들어, 이러한 컴포넌트는, 메모리, 곱셈기 회로, 및 가산기 회로 등의 아날로그 수신 체인의 컴포넌트들 및 디지털 신호 처리 회로의 컴포넌트들을 포함할 수 있지만 이것으로 제한되지 않는다.

[0039] 일부 실시예에서, 초음파 디바이스는, 기판과 통합되고 초음파 회로 모듈들을 서로 접속하여 초음파 회로 모듈들 간에 데이터가 흐르게끔 허용하도록 구성된 모듈 상호접속 회로를 포함할 수 있다. 예를 들어, 디바이스 모듈 상호접속 회로는 인접한 초음파 회로 모듈들 간의 접속을 제공할 수 있다. 이런 방식으로, 초음파 회로 모듈은, 디바이스 상의 하나 이상의 다른 초음파 회로 모듈들에 데이터를 제공하거나 및/또는 이로부터 데이터를 수신하도록 구성될 수 있다.

[0040] 예시된 컴포넌트들 중 하나 이상 간의 통신은 수많은 방식 중 임의의 방식으로 수행될 수 있다는 것을 이해해야 한다. 일부 실시예에서, 예를 들어, 단일화된 노스브리지(Northbridge)에 의해 채용될 수 있는 것 등의, 하나 이상의 고속 버스(미도시)가 고속의 칩내 통신 또는 하나 이상의 오프-칩 컴포넌트들과의 통신을 허용하는데 이용될 수 있다. 일부 실시예에서, 하나 이상의 모듈은 상호접속 네트워크를 이용하여 접속될 수 있다. 예를 들어, 이웃 모듈들이 네트워크를 통해 서로 통신하는 쉬프트 레지스터 링 통신 네트워크(shift register ring communication network)가 이용될 수 있다.

[0041] 일부 실시예에서, 타이밍 & 제어 회로(108)는, 예를 들어, 디바이스(100) 내의 다른 요소들의 동작을 동기화하고 조율하는데 이용되는 모든 타이밍 및 제어 신호들을 생성하는 책임을 질 수 있다. 도시된 예에서, 타이밍 & 제어 회로(108)는 입력 포트(116)에 공급되는 단일 클록 신호 CLK에 의해 구동된다. 클록 신호 CLK는, 예를 들어, 온-칩 회로 컴포넌트들 중 하나 이상을 구동하는데 이용되는 고주파 클록일 수 있다. 일부 실시예에서, 클록 신호 CLK는, 예를 들어, 신호 조정/처리 회로(110)에서의 고속 직렬 출력 디바이스(도 1b에는 미도시)를 구동하는데 이용되는 1.5625GHz 또는 2.5GHz 클록이거나, 다이(112) 상의 다른 디지털 컴포넌트들을 구동하는데 이용되는 20 MHz, 40 MHz, 또는 200MHz (또는 기타 임의의 적절한 속도) 클록이고, 타이밍 & 제어 회로(108)는, 다이(112) 상의 다른 컴포넌트들을 구동하기 위해 필요하다면 클록 CLK를 분할하거나 증배할 수 있다. 다른 실시예에서, (앞서 언급된 것들 등의) 상이한 주파수들 중 2개 이상의 클록이 오프-칩 소스로부터 타이밍 & 제어 회로(108)에 별개로 공급될 수 있다.

[0042] 도시된 예에서, 하나 이상의 출력 포트(114)는 신호 조정/처리 회로(110)의 하나 이상의 컴포넌트들에 의해 생성된 데이터 스트림을 출력할 수 있다. 이러한 데이터 스트림들은, 예를 들어, 다이(112) 상에 통합된, 하나 이상의 USB 2.0 모듈, 하나 이상의 USB 3.0 모듈, 하나 이상의 USB 3.1 모듈, 하나 이상의 썬더볼트(Thunderbolt) 모듈, 하나 이상의 파이어와이어(FireWire) 모듈, 및/또는 하나 이상의 기가비트(Gigabit)(예를 들어, 10 GB, 40 GB, 또는 100 GB) 이더넷 모듈에 의해 생성될 수 있다. 일부 실시예에서, 출력 포트(114) 상에 생성된 신호 스트림은, 클라우드 서비스, 하나 이상의 컴퓨터, 태블릿, 및/또는 스마트폰을 포함한 그러나 이것으로 제한되지 않는 전자 디바이스에 입력으로서 제공될 수 있다. 신호 스트림을 수신하는 하나 이상의 전자 디바이스는, 수치 값들, 1차원, 2차원, 3차원, 및/또는 단층촬영 이미지를 생성 및/또는 디스플레이할 수 있다. 일부 실시예에서, 출력 포트(114) 상에 출력된 신호 스트림은, 도 3과 연계하여 이하에서 논의되는 바와 같이, 추가 처리를 위해 하나 이상의 추가 오프-칩 회로에 제공될 수 있다.

[0043] (이하에서 더 설명되는 바와 같이) 이미지 재구성 능력이 신호 조정/처리 회로(110)에 포함되는 실시예에서, 애플리케이션 실행에 대해 이용 가능한 제한된 양의 처리 능력과 메모리만을 갖는 스마트폰이나 태블릿 등의 비교

적 저전력 디바이스들은 출력 포트(114)로부터의 데이터 스트림만을 이용하여 이미지를 디스플레이할 수 있다. 신호 조정/처리 회로(110)에 포함될 수 있는 고속 직렬 데이터 모듈 및 기타의 컴포넌트들의 예가 이하에서 더 상세히 논의된다. 온-칩 이미지 재구성 프로세스의 적어도 일부를 수행하고 데이터 링크를 이용해 이미지 재구성 프로세스의 적어도 일부의 출력을 오프-칩 전송하는 것은, 본 개시내용의 일부 실시예들에 따라 다양한 정도의 처리 능력을 갖는 광범위한 외부 디스플레이 디바이스들과 함께 이용될 수 있는 통합된 "초음파 온 칩" 솔루션을 가능케 할 수 있는 피쳐들 중 하나이다.

[0044] 다양한 실시예에서, 각각의 RX 제어 회로(106)는, 단일의 트랜스듀서, 단일의 트랜스듀서 요소 내의 2개 이상의 트랜스듀서 그룹, 트랜스듀서 그룹을 포함하는 단일의 트랜스듀서 요소, 모듈 내의 2개 이상의 트랜스듀서 요소 그룹, 2개 이상의 트랜스듀서 요소를 포함하는 단일의 모듈, 어레이(102) 내의 2개 이상의 모듈, 또는 트랜스듀서들의 전체 어레이(102)와 연관될 수 있다.

[0045] 도 1b에 도시된 예에서, 어레이(들)(102) 내의 각각의 트랜스듀서에 대한 별개의 RX 제어 회로(106)가 있지만, 타이밍 & 제어 회로(108)와 신호 조정/처리 회로(110) 각각은 하나의 사례만이 있다. 따라서, 이러한 구현에서, 타이밍 & 제어 회로(108)는 다이(112) 상의 모든 RX 제어 회로(106)의 동작을 동기화하고 조율하는 책임을 질 수 있고, 신호 조정/처리 회로(110)는 다이(112) 상의 RX 제어 회로들(106) 모두로부터의 입력을 핸들링하는 책임을 질 수 있다. 대안으로서, 다이(112)는 복수의 타이밍 & 제어 회로(108)를 포함할 수 있고, 타이밍 & 제어 회로들 각각은 다이 상의 RX 제어 회로 조합들의 서브셋의 동작을 동기화하고 조율하는 책임을 진다.

[0046] 앞서 논의된 바와 같이, 일부 실시예에서, 도 1b와 연계하여 앞서 논의된 수신-경로 디지털 신호 처리 전자회로들 중 적어도 일부는, 초음파 온 칩 아키텍처의 크기를 줄이거나, 초음파 디바이스(100)의 전력 소비를 줄이거나, 하나 이상의 오프-칩 프로세서를 이용하여 진보된 이미지 재구성 능력을 제공하는 것을 포함한 그러나 이것으로 제한되지 않는 기타 임의의 이유로 오프-칩 구현될 수 있다.

[0047] 도 3은 수신-경로 디지털 신호 처리 회로의 일부가 오프-칩 구현되는 초음파 디바이스(100)의 예시적 실시예를 도시한다. 예시된 실시예에서, 필드-프로그래머블 게이트 어레이(FPGA)(300)는 기판(112) 상에 구현된 디바이스(100)의 부분들에 접속된다. FPGA(300)는, 도 1b에 도시된 실시예에서 수행된 것으로 상기에 설명된 적어도 일부의 동작들을 수행하도록 구성된다. 예를 들어, FPGA(300)는, 버퍼 메모리(140)로부터 촬영 데이터를 수신하고 수신된 촬영 데이터에 관한 이미지 재구성 또는 기타 임의의 적절한 동작을 수행하도록 구성된 처리 유닛(310)을 포함할 수 있다. 추가로, FPGA(300)는, 기판(112) 상에 통합된 초음파 디바이스(100)의 부분에 제어 데이터를 전송하도록 구성될 수 있다. 제어 데이터는, 아날로그 TX 회로(104), 아날로그 RX 회로(103), 및 RX 제어 회로(106)를 포함한 그러나 이것으로 제한되지 않는, 전송 제어 회로(104) 및/또는 수신측 회로의 동작을 제어하기 위해 제어 파라미터들을 포함할 수 있다. FPGA(300)는 또한, 앞서 논의된 바와 같이, 디스플레이 및/또는 추가 처리를 위한 임의의 적절한 디바이스로의 전송을 위해 출력 인터페이스(314)에 처리된 촬영 데이터를 전송하도록 구성될 수 있다. 출력 포트(114)를 이용하여 다이(112)와 FPGA(300) 사이에서 데이터를 전송하기 위해 임의의 적절한 데이터 인터페이스가 이용될 수 있고 본 개시내용은 이 점에서 제한되지 않는다. 일부 실시예에서, 디지털 신호 프로세서(DSP), 임베디드 제어기, 또는 기타 임의의 디지털 회로로 칭하는, 수신-경로 디지털 회로의 적어도 일부를 오프-칩 제공하기 위해 FPGA(300)에 추가하여 또는 이에 대한 대안으로서 이용될 수 있다.

[0048] 앞서 논의된 바와 같이, 일부 실시예에서, RX 제어 회로(106)는, 초음파 트랜스듀서 요소들로부터 출력된 신호를 처리하기 위해 아날로그 가변 이득 증폭기(VGA)의 디지털 제어를 제공하도록 구성된 시간 이득 보상(TGC; time gain compensation) 회로(160)를 포함할 수 있다. TGC 회로(160)는, (예를 들어, 상이한 시간들에서 수신된 신호들에 대해 가변 이득을 제공하도록 VGA를 제어함으로써) 촬영된 물체에서의 상이한 깊이들로부터 수신된 신호들을 보상한다.

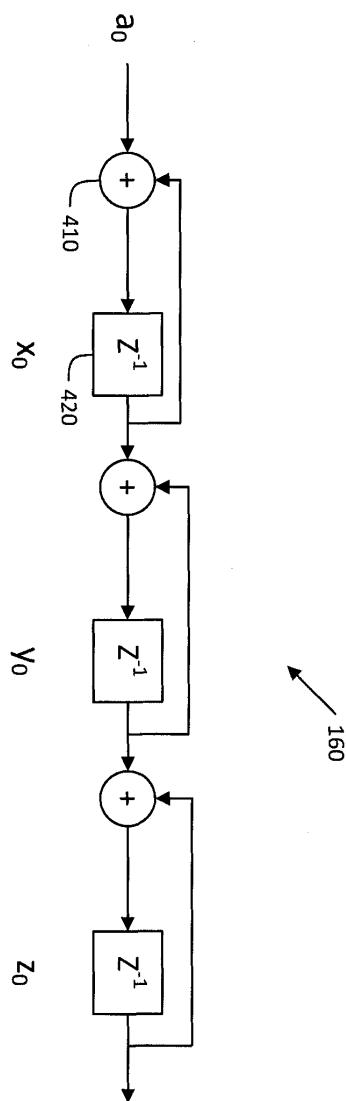

[0049] 한 실시예에서, VGA로부터의 출력은 메모리에 저장되고, VGA 값들은 TGC 회로 업데이트 레이트로 메모리로부터 판독된다. 도 4는, 본 개시내용의 일부 실시예에 따라 이용될 수 있고, TCG 회로의 업데이트 레이트로 메모리로부터 VGA 값들을 판독하는 앞서 언급된 실시예보다 더 적은 메모리와 더 적은 프로그래밍 워드(programming word)를 요구하는 TGC 회로(160)의 예시적 아키텍처를 나타낸다. 예시된 TGC 회로(160)는, 더 얕은 깊이로부터 수신된 신호에 비해 더 깊은 깊이로부터 수신된 신호를 증폭하는, 아날로그 가변 이득 증폭기를 제어하는 다단 합산 제어 회로(multi-stage summing control circuit)로서 구현된다. TGC 회로(160)는 가산기(410)와 지연 요소(420)를 포함하는 제어 회로 요소들을 포함한다.

- [0050] 일부 실시예에서, TGC 회로(160)는, 구간 다항식(piecewise polynomial)을 갖는(즉, 복수의 다항식 세그먼트로 구성된) 가변 이득 증폭기를 위한 보정 이득 프로파일(corrective gain profile)을 모델링하도록 구성될 수 있다. 이득 프로파일은 초음파 트랜스듀서 요소로부터 출력된 신호들을 정합시키도록 (사용자에 의해 수동으로 및/또는 자동으로) 설계될 수 있다. 구간 다항식 모델은, 3차 다항식 모델을 포함한 그러나 이것으로 제한되지 않는 임의의 차수(order)일 수 있다. 구간 다항식을 모델링하기 위한 한 구현은, 도 4에 도시된 바와 같이, 3 개 스테이지(stage)의 적분기 회로를 이용하는 것이다. 더 많거나 더 적은 수의 스테이지를 이용하여 다른 차수의 다항식들이 구현될 수 있다. 일부 실시예에서, 구간 다항식은, 가변 이득 증폭기 회로를 제어하기 위한 제어 신호가 업데이트되는 가변 입력 업데이트 레이트를 이용하여 모델링된다. 제어 신호를 업데이트하기 위한 예시적 입력 업데이트 레이트는 100 kHz 내지 1.25 MHz 범위의 업데이트 레이트를 포함하거나, 100 kHz 아래로부터 칩상의 ADC의 업데이트 레이트(예를 들어, 50 MHz)까지 범위의 업데이트 레이트를 포함하는 다른 적절한 값을 포함할 수 있다. 일부 실시예에서, 제어 신호의 업데이트들 사이의 간격은 불균일하여 가변 입력 업데이트 레이트를 야기한다. 계산 업데이트 레이트 및 출력 업데이트 레이트를 포함한 다른 업데이트 레이트는 내부 레지스터에 기초하거나 일정하거나(예를 들어, 50 MHz, 100 MHz, 또는 200 MHz) 가변적일 수 있다. 특히, 다항식 계수를 업데이트하기 위한 계산 업데이트 레이트는 고정적이거나 가변적일 수 있다. 임의의 적절한 입력, 계산, 및 출력 업데이트 레이트가 대안으로서 이용될 수 있다는 것을 이해해야 한다.

- [0051] 일부 실시예에서, 구간 다항식 함수가 동적으로 계산되고, 선택된 촬영 모델 및/또는 촬영 응용에 기초하여 상이하게 프로그램될 수 있도록, TGC 회로(160)에 의해 제공되는 가변 이득 프로파일의 파라미터화는 프로그램 가능할 수 있다. 예를 들어, 구간 다항식 함수의 복수의 세그먼트들을 프로그램하기 위하여, 파라미터들(예를 들어, x0, y0, 및 z0 및 지속기간)은 TGC 곡선 평가 동안에 동적으로 변하여 후속 다항식 세그먼트들을 구현할 수 있다. 일부 실시예에서, (지속기간 파라미터를 포함한) 모든 파라미터는 다항식 함수의 각각의 구간 세그먼트에 대해 프로그램될 수 있다. 대안으로서, 파라미터들의 서브셋(즉, 모든 파라미터보다 적은 수의 파라미터)은 각각의 세그먼트에 대해 동적으로 변할 수 있다. 예를 들어, 한 구현에서, 다항식 세그먼트들 사이에서 a0 파라미터만이 변한다. 일부 실시예에서, (예를 들어, 8개의 수신 채널을 포함하는) 각각의 모듈은 단일의 TGC 회로(160)와 연관될 수 있다. 대안으로서, 복수의 TGC 회로가 각각의 모듈과 연관될 수도 있고, 실시예는 이 점에서 제한되지 않는다.

- [0052] 압축의 예시적 유형

- [0053] 본 개시내용의 일부 실시예에 따라 제공되는 초음파 촬영 디바이스는, 앞서 논의된, 초음파 트랜스듀서 요소들의 어레이를 이용하여 품질 이미지를 제공하기 위해 많은 양의 초음파 데이터를 기록한다. 이 많은 양의 데이터를 처리하고 최대 데이터 대역폭을 갖는 출력 데이터 인터페이스 모듈을 이용하여 허용 가능한 레이트로 데이터를 오프-칩 전송하기 위해, 일부 실시예는 데이터를 오프-칩 전송하기 이전에 초음파 트랜스듀서 요소들로부터의 데이터를 압축하는 온-칩 회로를 채용한다. 따라서 온-칩 데이터 압축 요소들의 포함은 일부 실시예에 따른 "초음파 온 칩(ultrasound-on-a-chip)" 솔루션을 가능케 하거나 및/또는 강화시킬 수 있다.

- [0054] 일부 실시예에서, 초음파 촬영 응용의 동작 모드 및/또는 촬영 목적에 따라 상이한 유형들의 압축이 선택될 수 있다. 예를 들어, 이용되는 압축의 상이한 유형 또는 양은, 특정한 촬영 응용에 대한 허용 가능한 이미지 품질에 적어도 부분적으로 의존할 수 있다. 본 개시내용의 실시예에 따라 구현될 수 있는 온-칩 압축의 예는, 이하에서 각각 더 상세히 설명되는, 스펙트럼 압축(spectral compression), 조리개 압축(aperture compression), 여기 압축(excitation compression), 앙상블 압축(ensemble compression), 엔트로피 압축(entropy compression), 신호값 압축(signal value compression), 및 선택적 생략 압축(selective omission compression)을 포함하지만, 이것으로 제한되는 않는다.

- [0055] 스펙트럼 압축은 수신된 음향 신호의 주파수 성분(frequency content)에 관해 동작함으로써 데이터를 압축한다. 스펙트럼 압축은, 스펙트럼 대역폭의 양을 원하는 이미지 해상도를 달성하는데 필요한 만큼만으로 크기축소한다. 스펙트럼 압축의 예로서는, 이하에서 각각 더 상세히 설명되는, 직교 복조 및 필터링된 다운샘플링이 포함되지만, 이것으로 제한되지 않는다.

- [0056] 조리개 압축은, 음향 신호의 교차-범위 대역폭(cross-range bandwidth)을 원하는 측방향 이미지 해상도를 달성하는데 필요한 만큼만으로 제한한다. 조리개 압축의 예로서는, 이하에서 각각 더 상세히 설명되는, 필터링된 다운샘플링 및 기타의 필터링 기술이 포함되지만, 이것으로 제한되지 않는다.

- [0057] 여기 압축은, 여기들 사이의 중복 정보가 함께 압축되는 고유한 방식으로 여기를 결합함으로써 데이터를 압축한다. 여기 압축의 비제한적 예는 여기들로부터 이미지를 형성하는 것이고, 여기서 모든 여기는 압축되어 하나의

이미지 재구성을 형성한다.

- [0058] 양상을 압축은 관련 정보를 계산함으로써 양상을 촬영에서 데이터 중복성을 감소시킨다. 양상을 압축의 비제한적 예는, 이하에서 더 상세히 설명되는, 복수의 이미지들이 단일의 복소 속도 및 전력 재구성 프로파일(complex velocity and power reconstruction profile)로 압축되는 도플러 처리이다.

- [0059] 엔트로피 압축은, 오프-칩으로 제공될 때의 데이터 통신에서 중복된 정보를 감소시킨다. 각각의 프레임에 대한 전체 데이터를 인코딩하는 것이 아니라 프레임-내-프레임 차이를 인코딩하는 것이 엔트로피 압축의 비제한적 예이다.

- [0060] 신호값 압축은, 데이터를, 전체 신호의 특성들(예를 들어, 전력, 최대값, 변화량)에서의 원하는 관심대상에 대응하는 값들로 감축시킨다. 신호값 압축의 비제한적 예로서는, 특성묘사 프로세스(characterization process)를 위한 수신된 음향 신호에 대한 운행 시간(time-of-flight)을 결정하는 신호 및 압축 회로에서의 총 전력을 계산하는 압축 회로가 포함된다.

- [0061] 선택적 생략 압축은 전체의 데이터 세트로부터 데이터를 선택적으로 생략함으로써 데이터의 양을 감축시킨다. 선택적 생략 압축의 비제한적 예로서는, 이하에서 더 상세히 설명되는 재양자화, 및 성간 조리개 촬영이 포함된다.

- [0062] 이하에서 더 상세히 논의되는, 초음파 요소들의 어레이로부터 수신된 음향 데이터 신호의 압축을 수행하기 위한 온-칩 회로는 전술된 압축 유형들 중 하나 이상을 수행하도록 구현될 수 있다. 일부 실시예에서, 데이터 신호는 하나 이상의 동작 파라미터 요건에 따라 오프-칩 전송되도록 압축될 수 있다. 예를 들어, 일부 실시예에서, 압축된 데이터 신호는, 초당 4 기가비트보다 작거나 같은 속도로 또는 어떤 다른 적절한 속도로 데이터 스트림으로서 반도체 다이 외부로 전송될 수 있도록 압축된다. 일부 실시예에서, 데이터 신호는 1보다 크지만 2보다 작은 인자로 압축될 수 있다. 일부 실시예에서, 데이터 신호는 적어도 2로서 4보다 작은 인자로 압축될 수 있다. 일부 실시예에서, 데이터 신호는 적어도 4로서 10보다 작은 인자로 압축될 수 있다. 일부 실시예에서, 데이터 신호는 적어도 20으로서 100보다 작은 인자로 압축될 수 있다. 다른 실시예에서, 데이터 신호는 적어도 100으로서 1000보다 작은 인자로 압축될 수 있다. 일부 실시예에서, 데이터 신호는 적어도 1000으로서 10000보다 작은 인자로 압축될 수 있다. 임의의 적절한 양의 압축이 대안으로서 이용될 수 있고, 상기 언급된 압축량에 대한 범위는 단지 예시적 목적으로 제공된 것일 뿐이라는 점을 이해해야 한다.

- [0063] 일부 실시예에서, 초음파 촬영기는 복수의 촬영 모드(예를 들어, 2D, 3D)로 동작하도록 구성될 수 있고, 이용되는 (무압축을 포함한) 압축의 유형 및/또는 양은, 초음파 촬영기의 특정한 동작 모드에 적어도 부분적으로 의존할 수 있다. 예를 들어, 상이한 데이터량을 생성하기 위해 상이한 동작 모드들이 프로그램될 수 있고, 이용되는 압축의 유형 및/또는 양은, 데이터가 출력 인터페이스(314)와 호환되는 원하는 레이트로 오프-칩 제공될 수 있도록, 특정한 동작 모드가 선택될 때 생성된 데이터량에 적어도 부분적으로 기초할 수 있다. 생성된 데이터량이 상이한 동작 모드들에 대해 이용되는 압축의 유형 및/또는 양을 결정하는 한 인자일 수 있지만, 선택된 동작 모드에 대해 이용할 압축의 유형 및/또는 양을 결정할 때 다른 인자들이 추가적으로 또는 대안으로서 고려될 수도 있다는 점을 이해해야 한다. 예를 들어, 특정한 촬영 응용에 대한 이미지 품질 요구가 고려될 수 있다.

- [0064] 초음파 촬영기에 대한 동작 모드의 선택은 임의의 적절한 방식으로 이루어질 수 있다. 예를 들어, 일부 실시예에서, 초음파 촬영기는, 입력 인터페이스(200)를 통해 오프-칩으로부터 수신된 모드 선택 신호(MODE)에 따라 복수의 촬영 모드 중 하나에서 동작할 수 있다. 대안으로서, 초음파 촬영기는, 촬영 동작 모드를 저장하도록 구성된 온-칩 메모리를 포함할 수 있고 (무압축을 포함한) 압축의 양 및/또는 유형은, 온-칩 메모리에 저장된 촬영 동작 모드에 적어도 부분적으로 기초하여 결정될 수 있다.

- [0065] 추가적으로, 압축은 신호 처리 체인 내의 상이한 스테이지들에서 데이터에 적용될 수 있다. 이하에서 더 상세히 논의되는 바와 같이, 수신 신호 처리 체인 내의 데이터 압축은, 이미지 재구성 이전에, 이미지 재구성 동안에, 및/또는 이미지 재구성 이후에 수행될 수도 있다. 이미지 재구성이 부분적으로 또는 전체적으로 오프-칩으로 수행되는 실시예에서, 데이터 압축을 위한 온-칩 아키텍처는 이하에서 더 상세히 논의되는 사전-이미지 형성 압축 기술들 중 하나 이상으로 제한될 수 있다. 이들 스테이지들 각각에서 압축을 제공하기 위한 예시적 기술과 대표적 아키텍처들이 여기서 제공된다.

- [0066] 예시적인 사전-이미지 재구성 압축 아키텍처들

- [0067] 온-칩 데이터 압축은 이미지 재구성 프로세스의 적어도 일부를 수행하기 이전에 달성될 수 있다. 예를 들어,

압축은, 전체 어레이의 요소들을 이용하여 취득된/처리된 전체 세트의 측정치들보다 작은 초음파 트랜스듀서 요소들의 어레이로부터 다수의 측정치들을 선택적으로 취득 및/또는 처리함으로써 달성될 수 있다. 감축된 수의 측정치들을 이용한 압축은 임의의 적절한 방식으로 구현될 수 있다. 일부 실시예에서, 측정치의 수를 감축하는 것은, 측정치의 수를 감축하는 초음파 트랜스듀서 요소에 대한 인코딩 방식을 선택하는 것을 포함한다. 예를 들어, 수정된 하다마르(Hadamard) 행렬 또는 의사랜덤 행렬 등의 인코딩 행렬과 연관된 인코딩 방식이 측정치 수를 감축하기 위해 이용될 수 있다. 이들 유형의 인코딩 방식에서, 각각의 요소에 전송된 신호는 요소의 위치 및 프레임 번호에 기초하여 1, 0 또는 -1로 곱해진다. 주어진 요소에 대한 가중치 시퀀스가 하다마르 또는 의사랜덤 행렬의 열과 동일하도록(각각의 요소는 통상적으로 고유한 열을 가질 것이다) 가중치들이 선택된다.

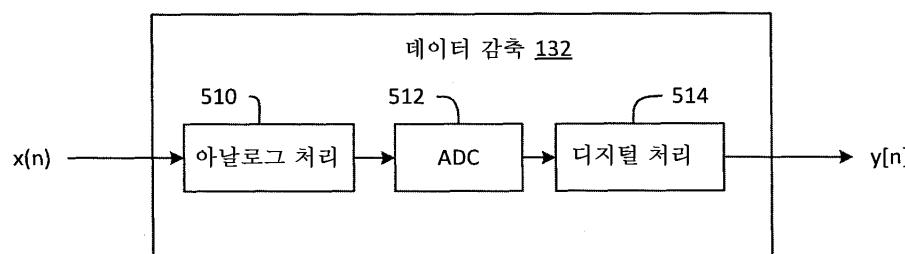

[0068] 일부 실시예에서, 사전-이미지 재구성 데이터 압축은 또한, 앞서 논의된, 데이터 감축 회로(132)의 일부로서 포함된 온-칩 압축 회로 컴포넌트들을 이용함으로써 달성될 수 있다. 도 5는 각각의 RX 제어 회로(106)(예를 들어, 도 1b와 도 3을 참조)의 데이터 감축 회로(132) 내에 포함될 수 있는 컴포넌트들의 블록도를 도시한다. 도 5에 도시된 바와 같이, 데이터 감축 회로(132)는, 아날로그 데이터 압축 기술들을 수행하도록 구성된 아날로그 처리 블록(510)을 포함할 수 있다. 예를 들어, 아날로그 처리 블록(510)은 입력 신호  $x(n)$ 를 필터링하는 저역-통과 필터(LPF)를 포함할 수 있다. 아날로그 처리 블록(510) 내의 LPF는 입력 신호의 안티-에일리어싱(anti-aliasing)을 제공할 수 있다. 일부 실시예에서, LPF는, 예를 들어, 5 MHz 정도의, 10 MHz 정도의, 25 MHz 정도의, 또는 50 MHz 정도의 주파수 컷오프를 갖는 2계 저역-통과 필터를 포함할 수 있다. 그러나, 다른 구현도 가능하고 고려될 수 있다. 예를 들어, 아날로그 처리 블록은 추가로 또는 대안으로서 고역-통과 필터, 대역-통과 필터 또는 입력 신호  $x(n)$ 를 처리하기 위한 기타 임의의 적절한 아날로그 컴포넌트를 포함할 수 있다. 예를 들어, 일부 실시예는 다음과 같은 아날로그 컴포넌트들 중 하나 이상을 포함할 수 있다: 증폭기, 신호 결합기, 감쇠기, 믹서, 및 아날로그 지연 회로. 앞서 논의된 바와 같이, 아날로그 컴포넌트를 이용하여 구현된 여기서 설명된 임의의 데이터 감축 기능은, 적어도 부분적으로, 디지털 컴포넌트를 이용하여 구현될 수 있고, 그 반대도 마찬가지이며, 실시예들은 특정한 데이터 감축 기능이 아날로그 컴포넌트, 디지털 컴포넌트, 또는 아날로그 와 디지털 컴포넌트들의 조합을 이용하여 구현되는지에 기초하여 제한되지 않는다.

[0069] 도시된 데이터 감축 회로(132)는 또한, 아날로그 신호(또는 대안으로서, 아날로그 신호의 필터링된, 또는 기타의 방식으로 처리된 버전)를 디지털 표현으로 변환하도록 구성된 아날로그-대-디지털 변환기(ADC)(512)를 포함한다. 예를 들어, ADC(512)는, 예를 들어, 10-비트, 20Msps, 40Msps, 50Msps, 80Msps ADC, 또는 기타 임의의 적절한 ADC를 포함할 수 있다. 이용될 수 있는 ADC들의 예시적 유형으로는, 연속 근사화 레지스터(SAR) ADC, 플래시 ADC, 파이프라인 ADC, 시그마-델타 ADC, 멀티-슬롭 ADC, 및 시간-인터리빙형 ADC가 포함될 수 있지만 이것으로 제한되지 않는다.

[0070] 신호가 ADC(512)에 의해 디지털 표현으로 변환된 후에, 신호는 데이터 감축 회로(132)의 디지털 처리 블록(514)에 전송된다. 디지털 처리 블록(514)은, 예를 들어, 하나 이상의 디지털 신호 처리 아키텍처를 이용하여 취득된 신호의 디지털 표현의 데이터 대역폭을 감축하도록 구성될 수 있다. 예를 들어, 디지털 신호 처리 아키텍처는, 이하에서 더 상세히 설명되는 바와 같이, 직교 복조, 다운샘플링, 직교 샘플링, 필터링된 다운샘플링, 캐스케이드 적분 콤(CIC; cascade integrating comb) 필터링, 수신 조리개 필터링, 다상 필터링, 재양자화, 및 펠스 압축을 포함한 그러나 이것으로 제한되지 않는 하나 이상의 데이터 감축 기술을 수행하도록 구성될 수 있다.

[0071] 전술된 바와 같이, 일부 실시예는, 초음파 트랜스듀서 요소들에 의해 수신된 많은 양의 데이터가 출력 인터페이스 모듈의 제한된 대역폭과 호환되는 레이트로 오프 칩 전송될 수 있게 하기 위해 데이터 압축의 하나 이상의 스테이지를 제공하는 디지털 신호 처리 컴포넌트를 포함한다. 이러한 압축은 일부 실시예에 따른 초음파 온 칩 솔루션을 가능하게 한다. 일부 실시예에서, 데이터 압축의 스테이지(들) 중 하나 이상은, 앞서 논의된 바와 같이, 초음파 디바이스의 특정한 동작 모드에 따라 인에이블 또는 디스에이블될 수 있다.

[0072] 도 6은 도 5에 도시된 데이터 감축 회로(312)의 디지털 처리 블록(514)의 적어도 일부에 대한 예시적 아키텍처를 도시한다. 예시된 실시예에서, 디지털 처리 블록(514)은 스펙트럼 압축의 형태인 직교 복조(QDM; quadrature demodulation)을 수행한다. QDM은 본 개시내용의 실시예에 따른 초음파 활영 시스템에 의해 처리되고 저장되어야 하는 대역폭의 양을 감축한다. 특히, QDM은 수신된 신호  $x[n]$ 의 디지털화된 버전을 중심 주파수로부터 기저대역으로 다운믹싱한다. 그 다음, 기저대역 신호는, 이하에서 더 상세히 논의되는 바와 같이, 저역-통과 필터링되고 데시메이트될 수 있다. 예시된 QDM 회로는, 수신된 신호로부터 미사용 주파수들을 제거함으로써 무손실(또는 거의 무손실) 감축을 허용할 수 있으므로, 칩으로부터 후속 처리되고 오프로딩될 필요가 있는 디지털 데이터의 양을 상당히 감축시킨다. 이들 컴포넌트들에 의해 달성되는 대역폭 감축은 여기서 설명된 "초

음파 온 침" 실시예들의 수행을 가능케 하고 및/또는 개선하는 것을 도울 수 있다.

[0073] 도 6은, QDM 회로가 복소 입력 신호  $x[n]$ 의 헤수 부분( $I[n]$ )과 직교( $Q[n]$ ) 부분에 대한 2개의 별개의 데이터 스트림으로서 구현될 수 있는 것을 도시한다. 헤테로다인 회로(610)는, 수치-제어형 발진기, 또는  $\cos(2\pi f_c t)$  및  $\sin(2\pi f_c t)$ 를 생성하는데 이용될 수 있는 기타 임의의 적절한 컴포넌트를 포함하고, 여기서, 중심 주파수  $f_c$ 는 특정한 복조량을 제공하도록 선택된다. 복조는, 신호를, 필터링을 위해 0 Hz에 중심을 두도록 또는 어떤 원하는 주파수 범위에 의해 한정되도록 위상 변조할 수 있다. 일부 실시예에서,  $f_c$  를 어레이(들)(102)에서 이용되는 트랜스듀서 셀들의 관심대상 주파수와 정합하는 것이 바람직할 수 있다. 헤테로다인 회로(610)로부터의 헤수 및 직교 데이터 스트림은 출력 이전에 필터링 회로(612)와 데시메이션 회로(614)에 의해 더 처리된다. 필터링 회로(612)는 저역-통과 필터링(LPF)을 수행하는 것으로 예시되어 있다. 그러나, 대역-통과 필터링(BPF) 및 고역-통과 필터링(HPF) 등의 다른 유형의 필터링이 대안으로서 필터링 회로(612)에서 이용될 수 있다는 점을 이해해야 한다. 직교 복조를 제공하기 위한 예시적 회로 아키텍처가 이하에서 더 상세히 설명된다.

[0074] 본 개시내용의 일부 실시예에서, (예를 들어, 필터링 회로(612)에 대한) 필터링 및 (예를 들어, 데시메이션 회로(614)에 대한) 데시메이션을 수행하기 위해 캐스캐이드 적분 콤(CIC) 필터 아키텍처가 이용될 수 있다. 예를 들어, 이러한 CIC 필터 아키텍처는 정확한 지연 시간 인덱스를 이용하여 범위 값을 정확히 계산하는데 이용될 수 있다. 예시적 CIC 필터가 도 7에 도시되어 있다. 도시된 바와 같이, CIC 필터(700)는 지연 요소(710)와 적분기 요소(712)를 포함한다. CIC 필터는 복수(N)의 스테이지를 포함하고 저역-통과 필터로서 작용하는 한편, 입력 데이터 스트림  $x[n]$ 을 데시메이트하여 출력 데이터 스트림  $y[n]$ 을 생성한다. 스테이지 수를 증가시키는 것은 통과대역에서의 더 많은 드롭(droop)을 야기하는 반면, 스테이지 수를 증가시키는 것은 더 양호한 이미지 거부를 야기한다). 일부 구현에서, 통과대역 드롭은 CIC 필터가 데이터에 적용된 후에 적용되는 보상 필터를 이용하여 적어도 부분적으로 해결될 수 있다.

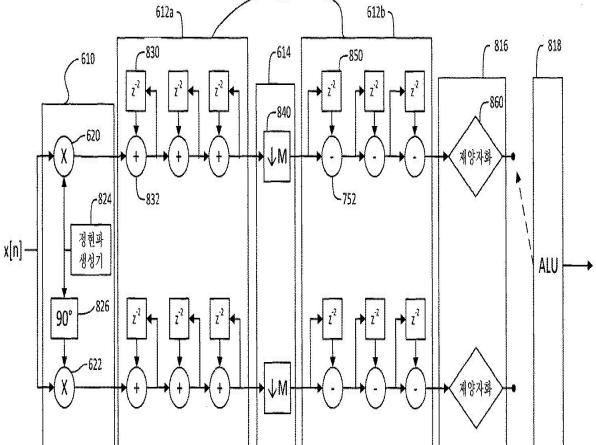

[0075] 도 8은 본 개시내용의 일부 실시예에 따른 직교 복조를 포함한 디지털 데이터 신호 처리를 수행하기 위한 예시적 회로를 도시한다. 예시된 바와 같이, 도 8의 회로는, 디지털 처리 회로에서 구현된 처리의 6개 스테이지를 포함한다. 임의 개수의 디지털 처리 스테이지가 포함될 수 있고, 도 8에 도시된 6-스테이지 구현은 단지 예시를 위해 제공된 것임을 이해해야 한다. 추가로, 초음파 촬영 디바이스의 몇 개 동작 모드는, 특정한 응용에 대한 (무압축을 포함한) 압축의 상이한 양 및/또는 유형을 제공하기 위해 도 8에 설명된 디지털 신호 처리 기능들의 전부가 아닌 일부를 채용할 수 있다. 디지털 신호 처리 컴포넌트들의 모드 선택 및 후속 활성화/비활성화는, 모드 선택을 위한 전술된 기술들을 포함한 그러나 이것으로 제한되지 않는 임의의 적절한 기술을 이용하여 달성될 수 있다.

[0076] 도 8에 도시된 바와 같이, 수신된 디지털 신호  $x[n]$ 은 먼저, 한 쌍의 곱셈기 회로(620, 622), 정현파 생성기(824), 및 위상 쉬프터 요소(826)를 포함하는 헤테로다인 회로(610)에 의해 처리된다. 헤테로다인 회로(610)의 출력은 저역 통과 필터(LPF)(612)에 전달된다. 도 8의 예시적 아키텍처에서, LPF(612)는 적분기 스테이지(612a)와 콤 스테이지(612b)를 포함하는 캐스캐이드 적분 콤(CIC) 필터의 일부로서 도시되어 있다. 임의의 적절한 저역-통과 필터가 LPF(612)에 대해 이용될 수 있지만, 바람직하게는, 이하에서 더 상세히 설명되는 바와 같이, LPF(612)는 헤테로다인 회로(610)의 곱셈 동작으로부터의 고주파 이미지를 거부하고 데시메이션 회로(614)에 의해 제공된 다운샘플링 이전에 신호를 안티-에일리어싱하기에 충분해야 한다는 것을 이해해야 한다.

[0077] 도 8의 예시적 아키텍처에서, 헤테로다인 회로(610)의 출력들은 CIC 필터의 적분기 스테이지(612a)에 제공된다. 도시된 바와 같이, 적분기 스테이지(612a)는 지연 요소(830)와 가산기 요소(832)를 포함한다. 적분기 스테이지(612a)의 출력들은, 수신된 디지털 신호를 다운샘플링 회로(840)를 이용하여 인자  $M$ 에 의해 다운샘플링하는 데시메이션 회로(614)에 전달된다.  $M=2, 4, 6, 8,$  및  $16$ 에 의한 다운샘플링을 포함한 그러나 이것으로 제한되지 않는 임의의 적절한 양의 다운샘플링( $M$ )이 이용될 수 있다.  $M=4$ 의 다운변환은 입력된 데이터량의 절반(샘플 레이트의  $1/4$ ), 그러나 데이터 채널수의 2배)을 생성한다.

[0078] 데시메이션 회로(614)의 출력들은 CIC 필터의 콤 스테이지(612b)에 전달된다. 도시된 바와 같이, 콤 스테이지(612b)는 지연 요소(850)와 감산 요소(852)를 포함한다. 콤 스테이지(612b)의 출력들은 재양자화 회로(816)에 전달되고, 여기서, 디지털 신호의 재양자화는, 이하에서 더 상세히 설명되는 바와 같이, 재양자화 회로(860)를 이용하여 수행된다. 재양자화 회로(816)의 출력들은, 그 예가 도 14에 관하여 이하에서 더 상세히 논의되는, 추가적인 산술 처리를 제공하는 산술 로직 유닛(ALU)(818)에 전달된다. 일부 실시예에서, ALU(818)는 최적화된 통합된 ALU일 수 있다.

- [0079] 디지털 처리 블록(514)의 출력은 디지털 처리 블록(514)과 동일하거나 상이한 기판 상에 형성된 추가적인 처리 스테이지(예를 들어, 이미지 재구성 처리)에 제공될 수 있다. 추가로 또는 대안으로서, 디지털 처리 블록(514)의 출력은 버퍼 메모리에 저장될 수 있고 추가 처리를 위해 출력 인터페이스를 통해 추가 오프-칩 처리 컴포넌트들에 제공될 수 있다.

- [0080] 전술된 바와 같이, 일부 실시예에서, 디지털 처리 블록(514)은, 입력 데이터 신호  $x[n]$ 의 압축을 제공하는 임의의 적절한 개수의 디지털 신호 처리 동작들을 수행하기 위한 회로를 포함할 수 있으며, 본 개시내용의 실시예들은 이 점에서 제한되지 않는다. 예를 들어, 한 실시예에서, 디지털 처리 블록(514)은, 직교 복조 스테이지, 필터링 스테이지, 및 데시메이션 스테이지를 포함할 수 있고, 이들 스테이지들 중 하나 이상은 특정한 촬영 응용의 요건에 기초하여 데이터 압축의 상이한 레벨들을 제공하도록 구성될 수 있다.

- [0081] 도 9는  $M=4$  및 필터  $h[n]$ 을 이용한 QDM 회로의 예시적 다상 아키텍처(900)를 도시한다. 다상 아키텍처(900)는 곱셈기 요소(910)와 가산기 요소(930)를 포함한다. 필터  $h[n]$ 에 기초하여 결정되는 컴포넌트(920)들,  $h_0[n]$ ,  $h_1[n]$ ,  $h_2[n]$ , 및  $h_3[n]$ 은 함께 다상 필터를 구현한다. 필터  $h[n]$ 은, 1/4 대역 필터, 1/2 대역 필터, 대역통과 필터, 또는 고역통과 필터를 포함한 그러나 이것으로 제한되지 않는 임의의 원하는 대역폭을 가질 수 있다. 특정한 필터링 아키텍처의 선택은 데이터의 다운변환 동안 상이한 Nyquist 구역들을 샘플링하는 것을 가능케 한다.

- [0082] 1/4 레이트 복조( $f_c=f_x/4$ )의 특별한 경우에, 도 9의 회로의 복조 부분에 대한 디지털 회로는 도 10에 도시된 바와 같이 단순화될 수 있다. 수치-제어형 발진기(예를 들어, 정현파 생성기(824)와 위상 쉬프터 요소(826))를 대신하여, 데이터 스트림의 하나 걸러 하나의 요소를 샘플링한 다음 샘플들을 교대로 반전시키는 회로가 있다. 일부 실시예에서, ( $f_s*L/4$ 의 레이트로 클록킹되는) 도 10의 아키텍처는 감소된 하드웨어를 허용하는  $h[n]=1$ 의 필터 계수들을 이용하여 더욱 단순화될 수 있다. 이러한 아키텍처는 샘플들을 실행 합(running sum)으로 합산 또는 감산할 수 있는 한 쌍의 누산기를 포함할 수 있다. 실행 합은 원하는 구성에 기초하여 포화(예를 들어, 클립)되거나 랙(wrap)될 수 있다는 것을 이해해야 한다.

- [0083] 도 10의 아키텍처에서 곱셈기(910)로의 입력으로서 제로값 샘플들의 패턴으로 인해, 도 10의 다상 1/2-대역 필터를 구현하는 회로는 도 11에 도시된 바와 같이 더 간소화될 수 있다. 도시된 바와 같이, 곱셈기로의 입력으로서의 제로값 샘플들을 제거함으로써, 필터들  $h_1[n]$  및  $h_3[n]$ 은 신호  $I[m]$ 을 처리하는데 있어서 제거될 수 있고 필터들  $h_0[n]$  및  $h_2[n]$ 은 신호  $Q[m]$ 을 처리하는데 있어서 제거될 수 있다. 도 12에 도시된 바와 같이, 동상(I) 컴포넌트는, 입력 신호  $x[n]$ 을 인자 2로 다운샘플링하고, 하나 걸러 하나의 샘플을 반전(flip)시키고, 데이터를 하나의 샘플만큼 우측 이동시킴으로써 구현될 수 있다. 도 12에 도시된 바와 같은 1/2 샘플 지연을 도입함으로써 동상 컴포넌트의 경우와 동일한 구조가 또한 직교위상(Q) 컴포넌트에 이용될 수 있다. 더 구체적으로는, 도 12에 도시된 1/2-샘플 지연을 구현함으로써 필터들  $h_0[n]$  및  $h_2[n]$ 은 필터들  $h_1[n]$  및  $h_3[n]$ 을 대신하여 재사용될 수 있다. 대안으로서, 1/2 샘플 지연이 직교위상(Q) 컴포넌트가 아니라 동상(I) 컴포넌트의 처리에서 구현된다면, 필터들  $h_1[n]$  및  $h_3[n]$ 은 필터들  $h_0[n]$  및  $h_2[n]$ 을 대신하여 재사용될 수 있다. 따라서, 디지털 처리 블록(514)의 적어도 일부는, 짹수-홀수 샘플러(1202), 복수의 요소(1220)를 포함하는 한 쌍의 인버터(1204), 한 쌍의 우측 쉬프트(1206) 및 1/2 샘플 지연(1208)을 포함하는 디지털 아키텍처로 구현될 수 있다. 데이터 대역폭을 감축하기 위한 데이터 감축 기수들은 이하에서 더 상세히 논의되는 바와 같이  $M > 2$ 에 대한 값을 이용하여 달성될 수 있다. 일부 실시예에서, QDM 회로에 추가하여 또는 이를 대신하여 디지털 처리 블록(514)에 포함될 수 있는 추가 컴포넌트들의 예는, 이하에서 더 상세히 설명된다.

- [0084] 초음파 신호의 디지털 표현을 필터링하고 다운샘플링하기 위한 임의의 적절한 아키텍처가 본 개시내용의 양태에 따라 이용될 수 있다. 전술된 예시적 QDM 회로 아키텍처와 연계하여, 일부 실시예는 다상 필터링 아키텍처를 이용하여 데이터 압축을 제공할 수 있다. 다상 필터링을 위한 예시적 아키텍처와 1/2대역 데시메이팅 필터에 의한 구현예가 도 13과 연계하여 이하에서 설명된다.

- [0085] 이하에서 더 상세히 설명되는 도 13은, 도 9의 일반화된 QDM 회로 아키텍처의 동상 컴포넌트에 관한 1/2-대역 FIR 필터 아키텍처를 도시한다. 직교위상 컴포넌트에 대해 동일한 필터 구조를 이용하기 위하여, Q 컴포넌트로의 입력은 곱셈기에 후속하여 하나의 샘플만큼 전진되고, 필터링되며 데시메이팅된 다음, I와 Q를 가산하기 이전에 1/4-샘플 지연을 적용함으로써 보정될 수 있다. 이 아키텍처는  $2*L-1$  포인트 대칭 1/2-대역 필터를 가정한다(즉, 모든  $n \neq 0$ 에 대해  $h[2*n] = 0$ 이고 모든  $n$ 에 대해  $h[n] - h[-n] = 0$ 도록,  $h[-(L-1)], \dots, h[L-1]$ )

- [0086] 도 13에 도시된 바와 같이, 입력  $x[n]$ 은  $f_s$ 의 레이트로 2개의 다상 브랜치들 사이에서 스위칭한다. 스위치(1302)가 하부 브랜치에 부착될 때, 노드(1310)는 값을 래치하고, 레지스터( $z^{-1}$ )(1330)는 이동(shift)하며, 카운터(1312)가 개시된다. 아키텍처 내의 계산 블록들은  $f_s * L/4$  의 레이트(예를 들어, 각각의 곱셈을 완료하기 위해 하나의 클록 사이클을 가정하여, 2개의 입력 사이클 내에서  $L/2$ 개의 곱셈을 완료하는데 필요한 레이트)로 클록킹된다. 가산기/곱셈기 쌍 내의 가산기(1314)와 곱셈기(1316)는 필터의 대칭 측들을 결합한 다음, 대응하는 필터 계수(예를 들어,  $h[1], \dots, h[L-1]$ )(1350)로 곱함으로써 필터링 단계를 수행한다. 가산기/곱셈기 쌍은 다상 컴포넌트들 모두를 합산하기 위해 필터의 각각의 탭(tap)을 순회한다. 각각의 곱셈의 결과는 가산기(1318)와 레지스터(1320)를 포함하는 누산기에 전송된다. 가산기(1318)는 로직 요소(1340)로부터 값을 추가로 수신한다. 누산기는, 블록(1370)에 의해 결정되는 바와 같이 카운터가 제로와 동일할 때 (예를 들어,  $L/2-1$ 의 지역에 의해 실현될 수 있는) 적절한 중앙 탭과 동일한 값으로 초기화될 수 있다. 블록(1360)에 의해 결정되는 바와 같이 카운터(1312)가  $L/2$ 에 도달할 때, 누산기의 결과는 플립 플롭(1390)에 래칭되고  $y[n]$ 의 값이 출력된다.

- [0087] 복조, 필터링, 및 다운샘플링 회로에 추가하여, 본 개시내용의 일부 실시예에 따른 "초음파 온 칩" 솔루션을 가능케 하거나 및/또는 강화할 데이터 압축의 추가적 또는 대안적 모드를 제공하기 위해 디지털 신호 처리 블록(514)의 일부로서 다른 디지털 회로도 역시 포함될 수 있다. 예를 들어, 일부 실시예는, 디지털 신호에 관해 재양자화를 수행하는 재양자화 회로(616)를 포함한다. 재양자화는 디지털 신호 처리 체인 내의 임의의 적절한 위치에서 구현될 수 있다. 예를 들어, 일부 실시예에서, 재양자화 회로는 아날로그-대-디지털 변환 직후에 구현될 수 있다. 다른 실시예에서, 재양자화 회로는 데이터의 오프-칩 전송 이전에 마지막 단계로서 구현될 수도 있다. 역시 다른 실시예에서, 재양자화 회로는 디지털 신호 처리의 중단 단계로서 구현될 수 있다. 추가로, 일부 실시예는 디지털 신호 처리 체인 내의 상이한 위치들에서 구현된 복수의 재양자화 스테이지를 포함할 수 있다는 것을 이해해야 한다.

- [0088] 비트 절삭, 라운딩(rounding), 및 클립핑을 포함한 그러나 이것으로 제한되지 않는 임의의 적절한 재양자화 기술이 이용될 수 있다. 비트 절삭이 이용되는 실시예에서, 디지털 신호 내의 비트수는, 절삭될 비트수를 나타내는 절삭 레벨에 적어도 부분적으로 기초하여 절삭될 수 있다. 절삭 레벨은, 선택된 촬영 모드 및/또는 원하는 이미지 품질 등의 기타 임의의 적절한 기준에 기초하여 구성가능할 수 있다. 예를 들어, 절삭 레벨은, 출력될 데이터 스트림의 최대 대역폭 및/또는 절삭될 디지털 신호에 대한 예상값들에 적어도 부분적으로 기초하여 결정될 수 있다. 일부 실시예에서, 디지털 신호에 대한 예상값들을 결정하는 것은, 적어도 하나의 이전 취득으로부터의 데이터, 적어도 하나의 이전 프레임으로부터의 데이터, 동일한 프레임 내의 적어도 하나의 이전 샘플로부터의 데이터, 및 적어도 하나의 시간 이득 보상 곡선값 중 하나 이상에 적어도 부분적으로 기초할 수 있다. 예를 들어, 이전 프레임들로부터의 데이터는, 평면과 촬영에 대한 절삭 레벨을 결정하는데 이용될 수 있고, 이전 채널들로부터의 데이터를 이용하는 것은 포커싱된 여기에 대한 절삭 레벨을 결정하는데 이용될 수 있다. 절삭 레벨을 결정하기 위해 이전에 수신된 데이터를 이용하는 이를 응용은 단지 예시를 위한 것이지 제한적인 것은 아니라는 점을 이해해야 한다.

- [0089] 라운딩이 이용되는 실시예에서, 0으로부터 먼 절반 라운딩(rounding half away from zero), 0을 향한 라운딩(rounding towards zero), 항상 라운딩 업(always rounding up), 항상 라운딩 다운(always rounding down), 짹수 라운딩 업(rounding even up), 짹수 라운딩 다운(rounding even down), 홀수 라운딩 업(rounding odd up), 홀수 라운딩 다운(rounding odd down)을 포함한 그러나 이것으로 제한되지 않는 임의의 적절한 라운딩 기술이 채용될 수 있다.

- [0090] 일부 실시예에서, 재양자화 회로는, 예를 들어, 인입 신호의 최대 크기를 결정하고, 모근 신호를 스케일업하여 최대 신호 풀-스케일화한 다음, 신호로부터 하위 N개-비트를 폐기할 수 있다. 다른 실시예에서, 재양자화 회로는 추가로 또는 대안으로서 신호를 로그 공간으로 변환하고 신호의 N개 비트만을 유지할 수도 있다. 역시 다른 실시예에서, 재양자화 회로는, 추가로 또는 대안으로서, Huffman 코딩, 산술 인코딩, 또는 벡터 양자화 기술 중 하나 이상을 채용할 수 있다. 역시 다른 실시예들에서, 노이즈 성형(noise shaping)이 이용될 수도 있다. 노이즈-성형 회로는 실제의 값과 재양자화된 값 사이의 에러(들)를 (직접 또는 간접으로, 예를 들어, 필터를 통해) 다시 입력으로 피드백한다.

- [0091] 초음파 디바이스가 코딩된-여기 펄스 또는 선형 주파수 변조된(LFM) 펄스를 채용하도록 구성되는 일부 실시예에서, 수신-경로 신호 처리 전자회로는 정합된 또는 부정합된 필터를 이용하여 교차-상관에 의해 펄스를 방출된 초음파 파형으로서 압축하는 스테이지를 포함할 수 있다. 펄스 압축은, 유한 임펄스 응답(FIR) 필터를 이용하

는 것 및 고속 푸리에 변환(FFT), 고속 푸리에 역변환(IFFT) 알고리즘을 구현하는 컴포넌트들을 이용하는 것을 포함한 그러나 이것으로 제한되지 않는 임의의 적절한 필터를 이용하여 구현될 수 있다.

[0092] 일부 실시예에서 통합된 최적화된 산술 처리 회로에 의해 추가적인 데이터 압축이 달성될 수 있다. 도 14는 디지털 처리 블록(514)의 일부로서 포함될 수 있는 산술 로직 유닛(ALU)(618)에 대한 예시적 아키텍처를 도시한다. ALU(618)는 디지털 신호의 산술 처리를 수행하여 데이터 압축을 제공하도록 구성될 수 있다. 도 14의 예시적 아키텍처에서, ALU(618)는, 워드 크기 확장, 비트 쉬프팅, 및 누산을 포함한 그러나 이것으로 제한되지 않는 하나 이상의 디지털 신호 처리 동작을 수행하는데 이용될 수 있는, 샘플 메모리(1410)와 가산기(1412) 및 곱셈기(1414, 1416) 등의 디지털 회로 컴포넌트를 포함한다. ALU(618)의 일부 구현은, 베퍼 포화(예를 들어, 클립핑), 랩핑(wrapping), 또는 부호 확장(sign extension)에 대한 융통성을 허용하도록 구성될 수 있다 는 것을 이해해야 한다. 일부 실시예에서, ALU(618)는, 전술된 바와 같이 모듈 내의 각각의 채널의 출력에 관해 동작하도록 구성될 수 있다. 대안으로서, ALU(618)는, 모듈 내의 복수의 채널들의 출력에 관해 동작하도록, 예를 들어 디지털 열 합산을 수행하도록 구성될 수 있다. 본 개시내용의 일부 실시예에 따라 ALU(618)에 의해 수행되는 산술 동작들은, 데이터 감축, 신호 대 잡음비 증가, 상쇄 모드 활영(cancellation mode imaging), 및 하모닉 활영(harmonic imaging) 중 하나 이상을 제공하기 위해 이용될 수 있다. 일부 실시예에서, ALU(618)는 온-칩 통합되는 것이 아니라 대안으로서 오프-칩 제공될 수도 있다.

#### [0093] 예시적 이미지 재구성 압축 아키텍처들

[0094] 본 개시내용에 따른 일부 실시예는, 복수의 통합된 초음파 트랜스듀서들로부터의 출력의 디지털 표현으로부터 이미지 재구성 프로세스의 적어도 일부를 수행하기 위한 온-칩 및/또는 오프-칩 회로를 포함한다. 예를 들어, 도 1b에 도시된 바와 같이, 신호 조정/처리 회로(110)는, 복수의 RX 제어 회로(106)의 출력들에 대응하는 채널-특유의 데이터를 선택하기 위한 기타의 적절한 회로 컴포넌트 또는 MUX(142)로부터 데이터의 스트림을 수신하도록 구성된 이미지 재구성 회로(134)를 포함할 수 있다. 이하에서 더 상세히 논의되는 바와 같이, 이미지 재구성 회로(134)는 이미지 재구성 프로세스의 적어도 일부를 수행하기 위한 온-칩(또는 오프-칩) 아키텍처를 포함할 수 있다. 이미지 재구성 프로세스의 전부 또는 일부를 온-칩으로 수행함으로써, 오프-칩 전송될 필요가 있는 데이터의 양은 상당히 감축되면서, 특정한 활영 응용에 대한 허용가능한 품질의 이미지들의 재구성을 여전히 제공한다. 추가적으로, 일부 실시예에서, 이미지 재구성 프로세스의 적어도 일부로부터의 출력은 오프-칩 전송되기 이전에 추가로 압축될 수 있다. 예를 들어, 도 1b에 도시된 바와 같이, 신호 조정 및 처리 회로(110)는, 이미지 재구성 회로(134)를 이용하여 이미지 재구성 프로세스의 적어도 일부의 출력을 압축하는 후처리 압축 회로(136)를 포함한다. 후처리 압축 회로(136)는, 예를 들어, 원하는(예를 들어, 더 낮은) 해상도에서 재구성된 이미지의 적어도 일부를 출력하기 위한 회로를 포함할 수 있고, 출력 해상도는, 초음파 활영기(100)에 접속된 외부 디바이스의 하나 이상의 디스플레이 및/또는 처리 특성에 기초하여 적어도 부분적으로 선택될 수 있다. 대안으로서, 출력 해상도는 기타 임의의 적절한 기준에 기초하여 선택될 수 있다.

[0095] 온-칩 이미지 재구성 프로세스의 적어도 일부를 수행하기 위한 예시적 기술의 예로서는, 2D 및/또는 3D 이미지를 형성하는데 이용될 수 있는 빔포밍을 이용하는 것이 포함된다. 온-칩 빔포밍 아키텍처의 한 피쳐는, 3D 이미지가, 이미지의 한 방향이 빔포밍되고 또 다른 직교 방향이 후속해서 빔포밍되는 분리가능한 방식으로 형성될 수 있다는 것이다. 예를 들어, 2D 빔포밍 단계들의 0개, 1개, 양쪽 모두가 온-칩으로 수행되는 2개의 2D 빔포밍 스테이지들에 의해 3D 빔포밍이 달성될 수 있다. 이하에서 더 상세히 설명되는 빔포밍 아키텍처는 또한, 전송 및/또는 수신에 관한 상승시에 빔이 포커싱되는 경우에 2D 빔포밍을 수용한다.

[0096] 통합된 배면투사는, 음향 입력 신호들이 이미지의 적어도 일부를 생성하기 위해 운행 시간에 기초하여 등시 곡선(isotemporal curve)으로 다시 투사되는 기술이다. 예시적인 배면투사 알고리즘에서, 명확한 파면(wavefront)을 갖는 초음파가 가정되어, 파면이 타겟 장면 내의 한 지점을 통과하는 임의의 시작 시간에 관한 시간이 결정될 수 있게 한다. 임의의 지점에 대해, 한 지점으로부터 발생하는 구면파가 수신기를 통과하는데 걸리는 시간도 역시 결정될 수 있다. 그러면, 그 지점에 의해 산란된 음파가 수신기에 도달하는데 걸리는 시간이 계산될 수 있다.

[0097] 명확한 파면을 갖는 초음파가 여기되었다고 가정하면, 그 파면이 타겟 장면 내의 한 지점  $\mathbf{r} = (x, z)^T$ 을 통과하는 임의의 시작 시간  $\tau_{tx}(\mathbf{r})$ 이 계산될 수 있다. 임의의 지점에 대해,  $\mathbf{r}$ 에서의 한 지점으로부터 발생하는 구면파가  $\mathbf{r}_k$ 에 위치한 수신기  $k=0, \dots, N-1$ 을 통과하는데 걸리는 시간  $\tau_{tx}(\mathbf{r}, \mathbf{r}_k)$  역시 계산될 수

있다. 그러면, 한 지점  $r$ 에 의해 산란된 음파가 수신기  $k$ 에 도달하는데 걸리는 시간은 다음과 같다.

## 수학식 1

$$[0098] \quad \tau(\mathbf{r}, r_k) = \tau_{tx}(\mathbf{r}) + \tau_{rx}(\mathbf{r}, \mathbf{r}_k)$$

[0099] 각각의 수신기는 전체의 장면에 의해 산란된 음파를 디지털화하고 신호 채널  $x_k(t)$ 를 생성한다. 이 신호는 복소 RF 신호인 것으로 가정된다(예를 들어, 복소 분석). 배면투사 이면의 기본적인 개념은, 각각의 지점  $r$ 로부터, 여기 파라미터가 주어질 경우 시간  $t$ 에서 수신기  $k$ 와 일치하는 산란된 음파를 생성할 수 있는 타겟 장면 내의 모든 장소에 데이터  $x_k(t)$ 를 투사하는 것이다. 이것은 통상적으로, 각각의 수신기  $k$ 에 대해, 각각의 대응하는 지점  $r$ 에 대한 샘플  $x_k(\tau(\mathbf{r}, \mathbf{r}_k))$ 을, 아래 식으로서 각각의 채널에 걸쳐 이들 값들의 가중치 합을 수행하여 계산함으로써 구현된다:

## 수학식 2

$$[0100] \quad y(\mathbf{r}) = \sum_{k=0}^{N-1} a(\mathbf{r}, \mathbf{r}_k) x_k(\tau(\mathbf{r}, \mathbf{r}_k))$$

[0101] 함수  $a(\mathbf{r}, \mathbf{r}_k)$ 은 공간 아포디제이션 함수(spatial apodization function)라 알려져 있고 선택사항으로서 이용된다. 디지털 구현의 한 예에 따르면, 공간과 시간 양쪽 모두가 이산화(discretize)된다:  $\mathbf{r}_{ij} = (i\Delta x, j\Delta z)$  및  $t_n = nT$ , 여기서,  $\Delta x$ ,  $\Delta z$ , 및  $T$ 는, 각각, 측방향 간격, 범위 간격, 및 RF 샘플링 기간이다. 공간적 이산화는, 이미지  $y[i, j]$ 에 대해  $(N_x \times N_z)$ 를 계산할 유한 개수의 지점들이 있다는 것을 암시하고, 시간에서의 이산화는, 이산 신호  $x_k[m]$ 으로부터 값들  $x_k(t_n)$ 을 추출하기 위해 보간이 수행되어야 한다는 것을 암시한다.

[0102] 각각의 수신기는 전체의 장면에 의해 산란된 음파를 디지털화하고 신호 채널을 생성한다. 이 신호는 복소 RF 신호인 것으로 가정될 수 있다(즉, 복소 분석). 배면투사 이면의 기본적인 개념은, 각각의 지점으로부터, 여기 파라미터가 주어질 경우 특정한 시간에서 수신기와 일치하는 산란된 음파를 생성할 수 있는 타겟 장면 내의 모든 장소에 데이터를 투사하는 것이다. 이것은, 각각의 수신기 채널에 대해, 이미지 내의 각각의 지점에 대한 측정된 신호 내의 대응하는 시간 샘플을 계산하고, 각각의 채널에 걸쳐 이들 값들의 가중치 합을 수행함으로써 구현될 수 있다.

[0103] 배면투사는 수신된 과형의 코히어런트 합산(coherent summation)에 의존한다. 수신된 과형의 적절한 시간적 정렬이 이러한 코히어런시에 대해 중요하다. 샘플링된 신호들은 이미지 재구성에 이용되기 때문에, 신호를 적절히 정렬하기 위해 이산적 쉬프트(shift)를 이용하는 능력은 제한된다. 샘플링된 데이터가 최소한으로 오버샘플링되면, 고품질 배면투사 이미지를 달성하기 위해 수신 과형의 보간에 의해 구현된 단편적 샘플 지연(fractional sample delay)을 이용하는 것이 종종 필요하다.

[0104] 디지털 회로에서 고속 배면투사 알고리즘을 실현하는 한 효율적인 방식은, 채널들에 걸쳐 계산을 병렬화하여, 각각의 RF 채널이 그 데이터를 이미지 영역이나 중간 영역으로 독립적으로 및/또는 동시에 배면투사하게 하는 것이다.

[0105] 아키텍처에서 설계된 하나의 예시적 기술은 메모리 재사용을 위해 아포디제이션 및/또는 운행 시간(TOF)에 관한 쉬프트-불변성을 이용하는 것이다. 이것은, TOF에 기초한 보간 인덱스는 각각의 이미지 지점과 트랜스듀서의 상대적 위치에 의존하기 때문이다. 따라서, 한 실시예에서, 수신기 TOF 및/또는 수신 아포디제이션 값들은 스캔 내의 후속 계산들에 대해 재사용될 수 있다. 유사하게, 전송 TOF 및/또는 전송 아포디제이션 값들은, 예를 들어, 값들이 쉬프트-불변성을 보일 때 연속된 스캔들 내에서 재사용될 수 있다. 선택사항으로서, 아포디제이

션은, 예를 들어, 0 및 1로 제약되어, 곱셈기 회로 및 메모리에 대한 필요성을 간소화 또는 제거할 수 있다.

[0106] 이미지 처리를 위한 예시적 아키텍처는 또한, 이미지들을 합성하기 이전의 이미지들을 표현하는 임의 개수의 중간 버퍼들을 이용할 수 있다. 본 개시내용의 실시예에서 이용될 수 있는 또 다른 비제한적 기술은 이미지를 계산시에 이미지 버퍼 메모리의 재사용으로서, 중간 버퍼들의 필요성을 감소 또는 제거한다.

[0107] 이러한 고속 배면투사 알고리즘을 실현하기 위한 2개의 비제한적인 예시적 아키텍처가 여기서 설명된다. 하나는 동일한 수신 운행 시간 정보를 모든 채널에 동시에 배포한다; 다른 하나는 운행 시간 정보를 요소로부터 요소로 순차적으로 쉬프트한다. 이를 아키텍처들의 양쪽 모두의 예가 이하에서 더 상세히 설명된다.

[0108] 도 15는 본 개시내용의 일부 실시예에 따른 배면투사 알고리즘을 구현하기 위한 예시적 아키텍처(1500)를 도시한다. 이 예시된 실시예에서, 버퍼(1510)들은 독립된 메모리들로서 구현된다. 버퍼 내로 들어가는 화살표는 기입 포트에 접속되고, 버퍼를 떠나는 화살표는 판독 포트로부터 나오고 있다.

[0109] 간소화를 위해, 판독 주소는 기입 주소와 동일하다고 가정된다. 그러나, 이것은 반드시 그럴 필요는 없다는 점을 이해해야 한다(예를 들어, 종종 하나 이상의 레지스터 지연이 요구되어, 주소와 판독 사이에 레지스터 지연을 달성한다). 소정 구현에서, 예를 들어, 기입된 데이터는 판독된 데이터로부터 오프셋되어 버퍼 내의 데이터의 순환 쉬프트를 야기할 수 있다. 대안으로서, 메모리는 판독과 기입이 상이한 클록 사이클에서 발생할 수 있도록 처리보다 높은 레이트로 클록킹될 수 있다.

[0110] 배면투사 알고리즘은, 버퍼 내의 각각의 깊이 인덱스에 대한 내측 루프와 각각의 반복 인덱스에 대한 외측 루프를 순차적으로 계산함으로써 구현된다. 반복수는 이용되는 버퍼수에 비례할 수 있지만, 반복수는 수신 아포디제이션의 공간적 지원을 고려함으로써 감소될 수 있다는 것을 이해해야 한다.

[0111] 시퀀싱의 한 비제한적 예는 다음과 같다: (1) 전송 TOF는 전송 TOF 메모리(1520)로부터 메모리 블록으로 다운로드되고, (2) 각각의 내측 루프 사이클에 대해, 단일 주소 카운터는 모든 버퍼들의 판독/기입 위치뿐만 아니라, 아포디제이션(1522), 수신 TOF(1524), 및 전송 TOF(1520) 메모리들을 제어한다. 수신된 TOF 값들과 아포디제이션 값들은 모든 서브시스템들간에 공유될 수 있다. TOF 값들 및/또는 아포디제이션 값들은 미리 계산되어 메모리에 저장되는 것이 아니라 동작 동안에 동등하게 계산될 수 있다는 점에 유의해야 한다.

[0112] 알고리즘의 코어는 각각의 서브시스템 내의 가산기 및 곱셈기(예를 들어, 가산기(1530) 및 곱셈기(1532))에 의해 구현된다. RF 데이터(IQ)(1575)는 입력으로서 수신된다. 곱셈기(예를 들어, 곱셈기(1532))는 보간기(1580)로부터 제공된 보간된 신호 값(1502)과 수신 아포디제이션 값(1504)을 취하여, 아포다이즈된 신호(1540)를 생성하고, 이것을 가산기(예를 들어, 가산기(1530))가 바로 우측의(예를 들어, 버퍼(1550)) 서브시스템으로부터의 이전 버퍼 값과 결합하여 결합된 값을 그 대응하는 버퍼(예를 들어, 버퍼(1560))에 기입한다.

[0113] 반면, 전송 TOF 블록(1520)은 나머지 전송 TOF 값들에서 지속적으로 로딩하고 있다. 특정한 시간에, 현재의 프레임에 대해 관련된 마지막 전송 TOF 값이 버퍼에 기입되었을 것이다. 이 시간 이후에, 다음 여기에 대한 전송 TOF 값이 전송 TOF 버퍼들 내에 로딩되기 시작한다. 이미지 버퍼 값들과 전송 TOF 값들 양쪽 모두가 판독되어 좌측 서브시스템으로 쉬프팅되고, 이미지 값들이 쉬프팅되는 것과 동일한 방식으로 별개 세트의 버퍼들에서 쉬프팅될 수 있다. 대안으로서, 이미지 버퍼 값들과 전송 TOF 값들은 비트별로 결합되어 동일한 메모리에 저장됨으로써, 레이아웃과 설계를 간소화할 수 있다.

[0114] 전송 아포디제이션(1570)은, 각각의 열이 트랜스듀서 내의 최종 요소를 스쳐 지나갈 때 이미지 열들 상에 곱해진다. 이 때, 복소 재구성된 데이터의 크기가 결정됨으로써, 저장되는 데이터를 2의 인자로 감소시킬 수 있다.

[0115] 하나의 프레임(예를 들어, 3D 재구성의 단일의 2D 이미지)을 형성한 후에, 이미지는 디스플레이 또는 추가 처리를 위해 추출되고 프리젠테이션될 수 있다. 그러나, 과정 추출이나 버퍼 리셋없이 프로세스가 계속된다면, 현재의 이미지 상으로의 다음 취득의 코히어런트 합성이 시작할 것이다. 이것이 희망되거나 허용 가능하다면, 추출 및 버퍼들의 리셋 이전에 완전한 프레임에 대해 필요한 모든 여기가 종료할 때까지 대기함으로써 상당한 절감이 이루어질 수 있다.

[0116] 상기의 개요된 접근법은 몇 가지 이점을 가진다. 예를 들어, 이것은 어떠한 큰 멀티플렉서도 이용하지 않으며 이미지를 형성하는데 걸리는 시간은 그 오직 이미지/체적 내의 픽셀/복셀들의 수의 함수이다.

[0117] 도 16은 본 개시내용의 일부 실시예에 따른 배면투사 알고리즘을 구현하기 위한 대안적 아키텍처(1600)를 도시한다. 도시된 바와 같이, 배면투사 아키텍처(1600)는 입력으로서 RF 데이터(IQ)(1620)를 수신하고, 보간기 요소(1630), 곱셈기 요소(1632), 가산기 요소(1636), 및 버퍼 요소들(1616 및 1640)을 포함한다. 일부 실시예에

서, 베퍼 요소(1640)들(예를 들어, 수신 아포디제이션 베퍼들) 중 하나 이상은 더 정교한 촬영 그리드를 협용하기 위해 가변량의 베퍼 요소들을 가질 수 있다. 예시적 아키텍처(1600)는 또한, 전송 아포디제이션 값(1614)과 수신 아포디제이션 값(1618)을 위한 입력 베퍼를 포함한다. 이 예시된 실시예에서, 단일 수신 운행 시간 값을 모든 요소들에 동시에 배포하는 것이 아니라, 수신 운행 정보(1610)는 전송 운행 정보(1612)와 동일한 방식으로 어레이를 가로질러 쉬프트되지만, 절반의 레이트이다. 수신 TOF는 대안으로서, 유사한 결과를 내도록 충분한 베퍼들과 함께 임의의 레이트나 방향으로 값들이 쉬프트될 수 있도록 구현될 수도 있다는 것을 이해해야 한다. 레이트 변경은, 도시된 바와 같이, 각각의 요소 사이에서 추가적인 베퍼에 의해 달성될 수 있다.

[0118] (2N-1)개의 수신 TOF 베퍼들은 하기에 따라 초기화될 수 있다:

$$R_n[j] = \begin{cases} \tau_{\alpha}[n, j], & 0 \leq n < N \\ \tau_{\alpha}[2N-1-n, j], & N \leq n < 2N-1 \end{cases}$$

[0119] N개의 전송 TOF 베퍼들은 하기에 따라 초기화될 수 있다:

$$T_n[j] = \begin{cases} \tau_{\alpha}[0, j], & n = 0 \\ \tau_{\alpha}[N-n, j], & 1 \leq n < N \end{cases}$$

[0120] 수신 파라미터들에 대한 예시적 로딩 방식은 이하의 표에 나타나 있다:

| 반복 | 요소 0               |                    | 요소 1               |                    | 요소 2               |                    | 요소 3               |

|----|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| 1  | R <sub>1</sub> [j] | R <sub>2</sub> [j] | R <sub>3</sub> [j] | R <sub>3</sub> [j] | R <sub>2</sub> [j] | R <sub>1</sub> [j] | R <sub>0</sub> [j] |

| 2  | R <sub>2</sub> [j] | R <sub>3</sub> [j] | R <sub>3</sub> [j] | R <sub>2</sub> [j] | R <sub>1</sub> [j] | R <sub>0</sub> [j] | R <sub>1</sub> [j] |

| 3  | R <sub>3</sub> [j] | R <sub>3</sub> [j] | R <sub>2</sub> [j] | R <sub>1</sub> [j] | R <sub>0</sub> [j] | R <sub>1</sub> [j] | R <sub>2</sub> [j] |

| 4  | R <sub>3</sub> [j] | R <sub>2</sub> [j] | R <sub>1</sub> [j] | R <sub>0</sub> [j] | R <sub>1</sub> [j] | R <sub>2</sub> [j] | R <sub>3</sub> [j] |

| 5  | R <sub>2</sub> [j] | R <sub>1</sub> [j] | R <sub>0</sub> [j] | R <sub>1</sub> [j] | R <sub>2</sub> [j] | R <sub>3</sub> [j] | R <sub>3</sub> [j] |

| 6  | R <sub>1</sub> [j] | R <sub>0</sub> [j] | R <sub>1</sub> [j] | R <sub>2</sub> [j] | R <sub>3</sub> [j] | R <sub>3</sub> [j] | R <sub>2</sub> [j] |

| 7  | R <sub>0</sub> [j] | R <sub>1</sub> [j] | R <sub>2</sub> [j] | R <sub>3</sub> [j] | R <sub>3</sub> [j] | R <sub>2</sub> [j] | R <sub>1</sub> [j] |

[0123]

[0124] 상기 표에서의 음영에 대한 범례는 다음과 같다:

|     |     |     |     |

|-----|-----|-----|-----|

| 열 0 | 열 1 | 열 2 | 열 3 |

|-----|-----|-----|-----|

[0125]

[0126] 전송 파라미터들에 대한 예시적 로딩 방식은 이하의 표에 나타나 있다:

| 반복 | 요소 0               |  | 요소 1               |  | 요소 2               |  | 요소 3               |

|----|--------------------|--|--------------------|--|--------------------|--|--------------------|

| 1  | T <sub>1</sub> [j] |  | T <sub>2</sub> [j] |  | T <sub>3</sub> [j] |  | T <sub>0</sub> [j] |

| 2  | T <sub>2</sub> [j] |  | T <sub>3</sub> [j] |  | T <sub>0</sub> [j] |  | T <sub>1</sub> [j] |

| 3  | T <sub>3</sub> [j] |  | T <sub>0</sub> [j] |  | T <sub>1</sub> [j] |  | T <sub>2</sub> [j] |

| 4  | T <sub>0</sub> [j] |  | T <sub>1</sub> [j] |  | T <sub>2</sub> [j] |  | T <sub>3</sub> [j] |

| 5  | T <sub>1</sub> [j] |  | T <sub>2</sub> [j] |  | T <sub>3</sub> [j] |  | T <sub>0</sub> [j] |

| 6  | T <sub>2</sub> [j] |  | T <sub>3</sub> [j] |  | T <sub>0</sub> [j] |  | T <sub>1</sub> [j] |

| 7  | T <sub>3</sub> [j] |  | T <sub>0</sub> [j] |  | T <sub>1</sub> [j] |  | T <sub>2</sub> [j] |

[0127]

[0128] 전술된 예시적 배면투사 아키텍처들이 2차원 이미지 재구성 프로세스에 관하여 설명된다. 이 아키텍처는 단층 촬영 접근법(즉, 슬라이스들로서 3차원을 구축하는 것)을 이용함으로써, 또는 기타 임의의 적절한 기술을 이용함으로써 3차원으로 확장될 수도 있다.

[0129] 일부 실시예는, 양상을 압축을 이용하여 데이터를 압축하는 도플러 촬영을 채용하도록 구성될 수 있다. 도플러

처리는 시간에 걸쳐 복수의 에코(echo)들에서 위상 이동을 관찰함으로써 조직에서의 속도 측정을 시도한다. 도플러 촬영 시퀀스는 양상블이라 지칭되는 복수의 데이터 취득 프레임들로 구성된다. (패킷 크기라고도 하는) 도플러 양상블의 길이는 통상적으로 8 내지 16 프레임이다.

[0130] 단일의 관심대상 지점으로부터 신호는  $S(t) = A_1 e^{i\phi_0} + A_2 e^{i\phi_1(t)}$  로서 표현될 수 있고, 여기서,  $S(t)$ 는 시간의 함수로서의 구축된 이미지를 내의 관심대상 지점이며,  $A_1$  항은 움직이지 않는 조직 소스(immobile tissue source)로부터 배경 산란을 나타내고,  $A_2$  항은 이동 산란체(scatterer)에 기인한 변하는 신호를 나타낸다. 도플러 처리에서의 해결과제는  $A_1$ 과  $A_2$  사이의 차이의 크기에 기인한다. 이 차이의 크기는 촬영된 조직에 의존한다. 예를 들어, 콩팥에서, 혈류를 포함하는 혈관의 작은 크기로 인해  $A_1$ 은  $A_2$ 보다 40 dB까지 더 클 수 있다; 에코 신호는 조직과 혈액 산란 양쪽 모두를 동시에 포함한다. 경동맥(carotid artery)에서,  $A_1$ 과  $A_2$  사이의 차이는 훨씬 더 작다. 예를 들어, 큰 혈관은 혈액 산란체와 조직 산란체의 완전한 분리를 허용하기 때문에  $A_1$  항은 소정 영역에서 제로일 수도 있다.  $A_1$ 으로부터  $A_2$ 를 격리하는 것은, (클러터 필터(clutter filter)라고도 하는) 장벽 필터(wall filter)를 요구하고, 이하에서 더 상세히 설명된다.

[0131] 데이터의 복수의 취득은 지정된 펄스 반복 주파수(PRF; pulse repetition frequency)에서의 도플러 처리에 대한 양상블을 제공한다. 이 양상블 세트로부터, 속도들이 계산될 수 있다. 종종 장벽 필터는 움직이지 않는 장면 산란체(non-moving scene scatterer)들을 제거하기 위해 구현되며, 여기서, 데이터는 먼저 빔포밍되었다. 이 장벽 필터는, 예를 들어, 유한 임펄스 응답(FIR) 필터 또는 양상블들에 걸친 행렬 곱셈에 의해 구현될 수 있다. 장벽 필터에 대한 다른 옵션들은 무한 임펄스 응답(IIR) 및 고속 푸리에 변환(FFT)을 통한 필터를 포함하지만, 이것으로 제한되지 않는다.  $m = 0 \dots M-1$  이미지들의 양상블에 대한 빔포밍된 이미지는  $\mathbf{Y} = y(\mathbf{r}, m)$ 로 주어진다. 장벽 필터링된 데이터는 하기와 같이 주어진다:

$$\mathbf{Y}_w = \mathbf{Y}\mathbf{W}$$

$$y_w(\mathbf{r}, n) = \sum_{m=0}^{M-1} y(\mathbf{r}, m) w(m, n)$$

[0132] 여기서,  $w(m, n)$ 은 장벽 필터이고, 낮은 주파수들을 제거하기 위해  $M$ 개 필터 값들을 갖는  $M \times N_t$  2D 행렬이 이용되며, 자기상관 값을 계산하기 위해  $N_t$  개 필터들이 이용된다. 가장 간단한 경우  $N_t = M$ 에서,  $N_t$ 의 다른 값들이 대안으로서 이용될 수 있다는 것을 이해해야 한다. 장벽 필터를 설계하고 구현할 때, 필터 응답이 정사각형 또는 비-정사각형 행렬인지를 유의해야 한다.

[0134] 장벽 필터 이후에, 흐름의 파워 및/또는 흐름의 방향을 발견하기 위해 자기상관 함수가 이용될 수 있다. 래그-0 자기상관은 파워 계산을 제공하고 래그-1 자기상관은 흐름 계산을 제공한다. (유의사항: 래그-1 자기상관은 충분한 파워와 컬러 흐름 도플러를 제공할 수 있다.) 래그-1 자기상관은 다음과 같이 주어진다:

$$R_1(\mathbf{r}, \tau) = y_w(\mathbf{r}, \tau+1) y_w^*(\mathbf{r}, \tau), \text{ 여기서 } \tau = 1 \dots N_t - 1$$

[0135]  $y_w(\mathbf{r}, \tau) = s(\mathbf{r}) e^{i\phi\tau}$  가 가정되고, 여기서,  $e^{i\phi\tau}$ 가 프레임들간의 움직임에 기인한 위상 변화를 나타낸다면, 래그-1 상관 값의 위상은  $\phi$ 와 같다.

$$R_1(\mathbf{r}, \tau) = y_w(\mathbf{r}, \tau+1) y_w^*(\mathbf{r}, \tau)$$

$$R_1(\mathbf{r}, \tau) = s(\mathbf{r}) e^{i\phi(\tau+1)} s^*(\mathbf{r}) e^{-i\phi\tau}$$

$$R_1(\mathbf{r}, \tau) = |s(\mathbf{r})|^2 e^{i\phi}$$

[0137]

[0138] 마지막으로, 래그-1 자기상관의 평균 값은 각각의 지점  $\mathbf{r}$ 에 대한 속도의 추정치(또는 래그-0에 대한 파워)를 제곱한다. 평균 값은 먼저 합을 취한 다음  $N_t - 1$ 로 나눔으로써 계산된다. 따라서 도플러 신호는 다음과 같이 주어진다:

$$D(\mathbf{r}) = \frac{1}{N_t - 1} \sum_{k=0}^{N_t-2} R_1(\mathbf{r}, k)$$

[0139] [0140] 디지털 구현에서, 공간은 이산화된다:  $\mathbf{r}_{ij} = (i\Delta x, j\Delta z)$ , 여기서,  $\Delta x, \Delta z$ 는 각각 측방향 간격 및 범위 간격이다. 공간 이산화는, 후방산란체 이미지  $y[i, j]$ 와 도플러 이미지  $D[i, j]$ 에 대한  $(N_x \times N_z)$ 를 계산할 유한한 개수의 지점들이 존재한다는 것을 암시한다.

[0141] 도 17은 본 개시내용의 일부 실시예에 따른 양상을 압축을 이용하여 도플러 촬영을 수행하기 위한 예시적 아키텍처(1700)를 도시한다. 예시된 아키텍처에서, 배면투사 아키텍처(예를 들어, 도 15 및 도 16에 도시된 배면투사 아키텍처)의 하드웨어가 모든 양상을 위한 장벽 필터를 수행하는 이용된다. 그 이후에, 데이터 스트림을 이용하여 데이터가 오프-칩 제공될 때, (함께 누산기를 형성하는) 레지스터(1750) 및 가산기(1720)와 복소 곱셈기(1710)가 래그-1 자기상관 및 마지막으로 도플러 값을 계산하는데 이용된다. 도시된 바와 같이, 도플러 촬영 아키텍처(1700)는 또한, 지역 요소(1730)와 복소 컬렉터 요소(1740)를 포함한다.

[0142] 배면투사 아키텍처는 동작들의 적절한 순서 및 메모리의 재사용을 통반한 행렬 곱셈을 허용한다. 예로서, 도플러 장벽 필터링 행렬 곱셈은, 수신된 아포디제이션 메모리 내에 행렬 계수들을 저장하고 정렬된 인덱스들을 수신 TOF 메모리에 저장함으로써 배면투사 아키텍처 내에서 달성을 수 있다(예시적 순서들에 대해 이하의 표를 참조). 이 사례에서, 수신 TOF 값들은 양상을 대해 동일한 인덱스를 연속적으로 RF 버퍼 내에 반복한다. 특히, 수신 아포디제이션 버퍼 내의 값들은 각각의 양상을 값으로 곱해질 장벽 필터 행렬의 값들을 포함한다. 일단 장벽 필터 값들이 단일의 여기에 대해 곱해지고 나면, 버퍼 값들은 변하지 않고 배면투사 파이프라인을 통과한다. 버퍼 값들은, 양상을 나머지 값들이 장벽 필터의 다음 계수들에 의해 곱해지도록 피드백 된다. 이 프로세스는 행렬 곱셈이 완료될 때까지 반복된다. 도플러 계산에 대해, 계산된 값들이 버퍼를 벗어날 때 데이터를 처리하기 위해 또 다른 처리 유닛이 이용될 수 있다. 이 처리 유닛의 예가 아키텍처(1700)에 나타나 있고  $D[i, j]$  내의 값들을 계산하기 위해 상기 등식들에서 설명된 동작들을 수행한다. 데이터는 레지스터 내에 로딩되고, 래그-1의 자기상관이 계산되고 결과들이 수집된 양상을 위해 결쳐 합산되도록(래그 차이에 대해서는 마이너스 1) 곱해진다. 임의의 바람직한 래그 자기상관을 형성하기 위해 임의의 개수의 레지스터(1730)가 이용되거나 멀티플렉싱될 수 있다는 점에 유의한다.

| 행/열 | 0                        | 1                        | ... | 14                        | 15                        |

|-----|--------------------------|--------------------------|-----|---------------------------|---------------------------|

| 0   | $y(r_{(0,0)}, 0)w(0,0)$  | $y(r_{(0,1)}, 0)w(0,0)$  | ... | $y(r_{(0,14)}, 0)w(0,0)$  | $y(r_{(0,15)}, 0)w(0,0)$  |

| 1   | $y(r_{(0,0)}, 0)w(0,1)$  | $y(r_{(0,1)}, 0)w(0,1)$  | ... | $y(r_{(0,14)}, 0)w(0,1)$  | $y(r_{(0,15)}, 0)w(0,0)$  |

| :   |                          |                          | ... |                           |                           |

| 6   | $y(r_{(0,0)}, 0)w(0,6)$  | $y(r_{(0,1)}, 0)w(0,6)$  | ... | $y(r_{(0,14)}, 0)w(0,6)$  | $y(r_{(0,15)}, 0)w(0,6)$  |

| 7   | $y(r_{(0,0)}, 0)w(0,7)$  | $y(r_{(0,1)}, 0)w(0,7)$  | ... | $y(r_{(0,14)}, 0)w(0,7)$  | $y(r_{(0,15)}, 0)w(0,7)$  |

| 8   | $y(r_{(1,0)}, 0)w(0,0)$  | $y(r_{(1,1)}, 0)w(0,0)$  | ... | $y(r_{(1,14)}, 0)w(0,0)$  | $y(r_{(1,15)}, 0)w(0,0)$  |

| 9   | $y(r_{(1,0)}, 0)w(0,1)$  | $y(r_{(1,1)}, 0)w(0,1)$  | ... | $y(r_{(1,14)}, 0)w(0,1)$  | $y(r_{(1,15)}, 0)w(0,0)$  |

| :   |                          |                          | ... |                           |                           |

| 14  | $y(r_{(1,0)}, 0)w(0,6)$  | $y(r_{(1,1)}, 0)w(0,6)$  | ... | $y(r_{(1,14)}, 0)w(0,6)$  | $y(r_{(1,15)}, 0)w(0,6)$  |

| 15  | $y(r_{(1,0)}, 0)w(0,7)$  | $y(r_{(1,1)}, 0)w(0,7)$  | ... | $y(r_{(1,14)}, 0)w(0,7)$  | $y(r_{(1,15)}, 0)w(0,7)$  |

| :   |                          |                          | ... |                           |                           |

| 504 | $y(r_{(63,0)}, 0)w(0,0)$ | $y(r_{(63,1)}, 0)w(0,0)$ | ... | $y(r_{(63,14)}, 0)w(0,0)$ | $y(r_{(63,15)}, 0)w(0,0)$ |

| 505 | $y(r_{(63,0)}, 0)w(0,1)$ | $y(r_{(63,1)}, 0)w(0,1)$ | ... | $y(r_{(63,14)}, 0)w(0,1)$ | $y(r_{(63,15)}, 0)w(0,0)$ |

| :   |                          |                          | ... |                           |                           |

| 510 | $y(r_{(63,0)}, 0)w(0,6)$ | $y(r_{(63,1)}, 0)w(0,6)$ | ... | $y(r_{(63,14)}, 0)w(0,6)$ | $y(r_{(63,15)}, 0)w(0,6)$ |

| 511 | $y(r_{(63,0)}, 0)w(0,7)$ | $y(r_{(63,1)}, 0)w(0,7)$ | ... | $y(r_{(63,14)}, 0)w(0,7)$ | $y(r_{(63,15)}, 0)w(0,7)$ |

[0143]

[0144] 푸리에 리샘플링 및 전단파 처리(shearwave processing)를 포함한 그러나 이것으로 제한되지 않는 다른 이미지 재구성 기술들도 역시 본 개시내용의 일부 실시예에서의 사용에 대해 고려될 수 있다.

[0145]

도 18a 및 도 18b는 본 개시내용의 일부 실시예에 따라 이용될 수 있는 예시적인 동적 포커스 아키텍처를 도시한다. 동적 포커스 아키텍처는 단일의 여기에 걸쳐 동적인 지연-및-합산 동작을 수행한다. 동적 포커스 범포머는, 라인(또는 평면)을 따라 동일한 시간들로부터의 산란들이 모든 수신 트랜스듀서 요소 사이에서 합산되도록 음향 필드로부터의 반환 신호를 지연시킬 수 있다. 일부 실시예에서, 이것은 단일의 취득에 대한 데이터 모두를 메모리에 저장할 필요는 없는 스트리밍 아키텍처로 이루어진다. 도 18a는, 스트리밍 어드레싱 가능한 지연들이 이용될 때 동적 포커싱을 구현하기 위한 예시적 아키텍처(1800)를 도시한다. 아키텍처(1800)는, 샘플링 레이트  $f_s$ 로 ADC 데이터를 수신하는 업샘플링 요소(1802), 레지스터(1804)(예를 들어, 1024 값 10-비트 어드레싱가능형 쉬프트 레지스터), 곱셈기(1806), 및 가산기(1820)를 포함한다. 임의의 적절한 샘플링 레이트  $f_s$ (예를 들어, 200 MHz, 100 MHz, 50 MHz 등)가 아키텍처(1800)에서 이용될 수 있다는 것을 이해해야 한다. 추가로, 임의의 적절한 크기의 버퍼 또는 레지스터가 이용될 수도 있다. 도 18b는, 파이프라인 지연들이 이용될 때 동적 포커싱을 구현하기 위한 예시적 아키텍처(1810)를 도시한다. 아키텍처(1810)는, 샘플링 레이트  $f_s$ 로 ADC 데이터를 수신하는 레지스터(1804), 업샘플링 요소(1802), 다운샘플링 요소(1808), 곱셈기(1806), 및 적분기(1820)를 포함한다. 임의의 적절한 샘플링 레이트  $f_s$ (예를 들어, 200 MHz, 100 MHz, 50 MHz 등)가 아키텍처(1810)에서 이용될 수 있다는 것을 이해해야 한다. 추가로, 임의의 적절한 크기의 버퍼 또는 레지스터가 이용될 수도 있다.

[0146]

직접 합성(direct compounding)은, 이미지 재구성을 향한 중간 스테이지로서 복수의 여기가 수집되고 함께 가산되는 데이터 감축 기술이다. 초음파 여기 음파장(ultrasonic excitation wavefield)이 쉬프트-불변일 때, 예를 들어, 음파장 압력들이 공간 내의 각각의 지점에 대해 동일하게 쉬프트될 때, 여기는 공간적으로-불변인 것으로 간주된다. 공간적으로-불변의 여기를 합성하는 것은, 재구성시에 감소된 품질 페널티가 수반되는 감축된 데이터 레이트를 허용한다. 한 구현의, 고품질 이미지를 위해 전송한 평면파의 수보다 약간 더 많을 수 있는 다수의 가상 소스를 이용한다. ADC 버퍼에서의 온-칩 가산은 수집시에 데이터를 압축하는 능력을 제공할 수 있다. 가상 소스, 포커싱된 빔, 평면파 및 수개의 다른 공간적으로 불변의 빔들을 포함한 그러나 이것으로 제한되지 않는 다양한 여기로부터 생기는 데이터는 이미지 재구성 이전에 합성될 수 있다.

[0147]

여기서 설명되는 회로의 동작의 양태들은, 데이터 감축 회로를 포함하는 일부 실시예에 따른 초음파 데이터 디바이스를 동작시키기 위한 예시적 프로세스(1900)의 플로차트인 도 19를 참조하여 이하에서 더 설명된다. 프로

세스(1900)는, 전체적으로 또는 부분적으로, 임의의 적절한 초음파 디바이스(예를 들어, 도 1b 및 도 3을 참조하여 설명된 초음파 디바이스(100))에 의해 수행될 수 있다.

[0148] 프로세스(1900)는, 초음파 디바이스의 하나 이상의 파라미터들이 구성되는 스테이지(1902)에서 시작한다. 파라미터들은, 임의의 적절한 방식으로 구성될 수 있고, 실시예들은 이 점에서 제한되지 않는다. 예를 들어, 일부 실시예에서, 초음파 디바이스의 하나 이상의 파라미터를 구성하는 것은, 전송 및/또는 수신 파라미터들을, 디바이스에 정보를 제공하여 그 동작을 제어하는 제어 레지스터들 내에 로딩하는 것을 포함한다. 일부 실시예에서, 하나 이상의 파라미터를 구성하는 것은, 앞서 논의된 바와 같이, 선택되거나 프로그램된 촬영 동작 모드에 기초하여 디바이스 상의 메모리에 저장된 파라미터들에 액세스하는 것을 포함한다. 추가로, 전송 파라미터, 수신 체인 압축 파라미터, 및 시퀀스 타이밍 파라미터를 포함한 그러나 이것으로 제한되지 않는 임의의 적절한 파라미터들이 스테이지(1902)에서 구성될 수 있다.

[0149] 초음파 디바이스에 대한 파라미터(들)가 구성된 후에, 프로세스(1900)는 스테이지(1904)로 진행하고, 그 곳에서 초음파 디바이스가 전송을 시작한다. 예를 들어, 초음파 디바이스의 하나 이상의 컴포넌트는 디바이스 상의 레지스터들 내에 로딩된 전송 파라미터들(스테이지(1902)에서 구성된 전송 파라미터들)에 액세스할 수 있고, 이들 파라미터들에 적어도 부분적으로 기초하여, 초음파 트랜스듀서 어레이의 요소들은 음향 에너지를 전송하도록 지시받을 수 있다.

[0150] 그 다음, 프로세스(1900)는 스테이지(1906)로 진행하고, 그 곳에서, 초음파 트랜스듀서 어레이의 요소들은 전송된 음향 에너지에 응답하여 데이터 수신을 시작한다. 그 다음, 프로세스(1900)는 스테이지(1908)로 진행하고, 그 곳에서, 수신된 데이터는 전술된 수신 신호 처리 체인의 아날로그 및/또는 디지털 컴포넌트들에 의해 처리된다. 일부 실시예에서, 초음파 트랜스듀서 어레이로부터 데이터가 수신됨에 따라 수신된 데이터에 관해 실시간으로 데이터 압축이 수행된다. 다른 실시예에서, 수신된 데이터의 적어도 일부는, 압축되기 이전에 온-칩 메모리에 저장되고, 본 개시내용의 실시예는 이 점에서 제한되지 않는다.

[0151] 스테이지(1910)에 도시된 바와 같이, 및 전술된 바와 같이, 수신된 신호의 적어도 일부의 처리는, 신호들이, 전술된 아날로그 신호 처리 아키텍처를 포함한 그러나 이것으로 제한되지 않는, 아날로그 신호 전자회로에 의한 아날로그 처리(예를 들어, 필터링, 평균화, 시간 이득 보상 회로에 의해 제어되는 가변 이득 증폭 등)를 거치게 하는 것을 포함할 수 있다. 일부 실시예에서, 아날로그 신호 처리 체인의 출력은, 앞서 언급된 바와 같이, 처리된 아날로그 데이터 신호를 디지털 표현으로 변환하는 아날로그-대-디지털 변환기에 제공된다.

[0152] 아날로그 처리 및 아날로그-대-디지털 변환에 이어, 프로세스(1900)는 스테이지(1912)로 진행하고, 그 곳에서, 디지털 신호(들)가, 복조, 필터링, 데시메이션, 재양자화, 및 산술 처리를 위해, 전술된 아키텍처들을 포함한 그러나 이것으로 제한되지 않는 하나 이상의 디지털 압축 아키텍처를 이용하여 압축된다.

[0153] 데이터 압축을 위한 신호 처리에 이어, 프로세스(1900)는 스테이지(1914)로 진행하고, 그 곳에서, 디지털적으로 처리된 신호들은 선택사항으로서 이미지 재구성 프로세스의 적어도 일부를 수행하는데 이용된다. 앞서 논의된 바와 같이, 일부 실시예에서, 수신된 데이터에 기초한 이미지 재구성 프로세스의 적어도 일부는, 초음파 트랜스듀서 어레이와 동일한 기관 상에 형성된 이미지 재구성 컴포넌트들을 이용하여 수행될 수 있다. 다른 실시예에서, 압축된 신호는, 예를 들어, FPGA 또는 기타의 처리 회로(들)를 이용한 이미지 재구성 처리를 위해 오프-칩 전송된다. 일부 실시예에서, 이미지 재구성 프로세스의 일부는 데이터를 오프-칩 전송하기 이전에 데이터 압축을 제공하기 위해 온-칩 수행된다.

[0154] 이미지 재구성 프로세스의 일부가 온-칩 수행되었는지, 부분적으로 온-칩 및 부분적으로 오프-칩 수행되었는지에 관계없이, 프로세스(1900)는 스테이지(1916)로 진행하고, 그 곳에서, 데이터를 오프-칩 출력할지 또는 (예를 들어, 도플러 처리, 하모닉 촬영 강화, 평균화, 또는 기타의 적절한 처리를 위해, 다음 여기로 이전의 여기를 처리할 의도로) 또 다른 여기를 시작할지가 결정된다. 스테이지(1916)에서 데이터를 출력하기로 결정된다면, 프로세스(1900)는 스테이지(1918)로 진행하고, 그 곳에서 데이터는 데이터 스트림으로서 외부 디바이스에 전송된다. 앞서 논의된 바와 같이, 외부 디바이스에 접속된 출력 인터페이스는 대역폭 제한될 수 있고, 출력 인터페이스에 의해 지원되는 레이트로 데이터를 오프-칩 전송할 수 있으면서 초음파 촬영 온 칩(ultrasound imaging-on-a-chip)이 실현되는 것을 가능하게 하기 위해 충분한 데이터 압축을 제공하기 위해 여기서 설명된 아키텍처들이 이용될 수 있다.

[0155] 스테이지(1918)에서 데이터가 출력된 후에, 프로세스(1900)는 선택사항으로서 스테이지(1902) 또는 스테이지(1904)로 복귀할 수 있고, 그 곳에서 더 많은 데이터가 동일하거나 상이한 디바이스 파라미터들을 이용하여 초

음파 디바이스를 이용해 수집될 수 있다. 예를 들어, 프로세스(1900)가 스테이지(1902)로 복귀하면, 디바이스 파라미터들의 전부 또는 서브셋(즉, 전부보다 작은 파라미터)은 초음파 트랜스듀서 어레이로부터의 새로운 여기의 전송 이전에 구성될 수 있다. 대안으로서, 프로세스(1900)가 스테이지(1904)로 복귀한다면, 전송 회로는 디바이스 파라미터들을 수정하지 않고 또 다른 여기를 전송할 것을 지시받을 수 있다.

[0156] 데이터가 출력되지 않아야 한다고 스테이지(1916)에서 결정된다면, 프로세스(1900)는, 예를 들어, 초음파 디바이스의 촬영 모드에 따라 스테이지들(1902, 1904, 또는 1908) 중 하나 이상으로 복귀한다. 이미지 재구성 프로세스의 적어도 일부가 온-칩 수행되는 실시예에서, 프로세스는 스테이지(1902)로 복귀할 수 있고, 그 곳에서 전송 회로는 이미지 데이터의 온-칩 합성을 가능케 하기 위해 상이한 파라미터들에 기초하여 여기를 전송하도록 지시받는다. 예를 들어, 하모닉 촬영에서, ALU 파라미터들은 스테이지(1902)에서 조절될 수 있다. 평균화 또는 도플러 처리에 대해, 프로세스는 스테이지(1904)로 복귀할 수 있고, 그 곳에서, 전송 회로는 파라미터들을 수정하지 않고 또 다른 여기를 전송할 것을 지시받는다. 역시 다른 실시예에서, 프로세스는 스테이지(1908)로 복귀하여 신호를 오프-칩 출력하기 이전에 추가 처리를 수행한다. 프로세스(1900)는, 스테이지(1918)에서 데이터를 오프-칩 출력하기로 결정될 때까지 계속된다. 프로세스(1900)는 예시이고 그 변형들도 생각해 볼 수 있다 는 점을 이해해야 한다.

[0157] 일부 실시예에서, 전술된 기능의 일부 또는 전부를 달성하는데 이용되는 메모리는 온-칩, 즉, 다이(112) 상에 위치할 수 있다. 그러나, 다른 실시예에서, 설명된 기능의 일부 또는 전부를 구현하는데 이용되는 메모리의 일부 또는 전부는 오프-칩 위치할 수 있고, 이 경우 회로의 나머지, 소프트웨어, 및/또는 기타의 컴포넌트들은 다이(112) 상에 위치한다.

[0158] 지금까지 본 개시내용에서 제시된 기술의 수 개의 양태와 실시예들을 설명하였으므로, 본 기술분야의 통상의 기술자에게는, 다양한 변형, 수정, 및 개선이 용이하다는 것을 이해해야 한다. 이러한 변형, 수정 및 개선은 여기서 설명된 기술의 사상과 범위 내에 포함시키고자 한다. 예를 들어, 본 분야의 통상의 기술자라면, 기능을 수행하고 및/또는 결과 및/또는 여기서 설명된 이점들 중 하나 이상을 얻기 위해 다양한 다른 수단 및/또는 구조를 용이하게 구상할 것이며, 이러한 변형들 및/또는 수정들 각각은 여기서 설명된 실시예의 범위 내에 있는 것으로 간주된다. 통상의 기술자라면, 단지 일상적인 실험만으로, 여기서 설명된 특정한 실시예들에 대한 많은 균등물을 인식하고 확인할 수 있을 것이다. 따라서, 상기 실시예들은 단지 예시로서 제시된 것일 뿐이며, 첨부된 청구항들과 그 균등물의 범위 내에서, 본 발명의 실시예들은 특정적으로 설명된 것과는 다른 방식으로 실시될 수도 있다는 것을 이해해야 한다. 또한, 여기서 설명된 2개 이상의 피쳐, 시스템, 항목, 재료, 키트 및/또는 방법의 임의의 조합은, 이러한 피쳐, 시스템, 항목, 재료, 키트 및/또는 방법이 상호 불일치하지 않는다면, 본 개시내용의 범위 내에 포함된다.

[0159] 전술된 실시예들은 다양한 방식들 중 임의의 방식으로 구현될 수 있다. 프로세스 또는 방법의 수행을 수반하는 본 개시내용의 하나 이상의 양태와 실시예들은 프로세스 또는 방법을 수행하거나 수행을 제어하기 위해 디바이스(예를 들어, 컴퓨터, 프로세서, 또는 기타의 디바이스)에 의해 실행가능한 프로그램 명령어를 이용할 수 있다. 이 점에서, 다양한 발명적 개념은, 하나 이상의 컴퓨터 또는 기타의 프로세서 상에서 실행될 때, 전술된 다양한 실시예들 중 하나 이상을 구현하는 방법들을 수행하는 하나 이상의 프로그램으로 인코딩된 컴퓨터 판독 가능한 저장 매체(또는 복수의 컴퓨터 판독가능한 저장 매체)(예를 들어, 컴퓨터 메모리, 하나 이상의 플로피 디스크, 컴팩트 디스크, 광 디스크, 자기 테이프, 플래시 메모리, 필드 프로그래머블 게이트 어레이 또는 기타의 반도체 디바이스 내의 회로 구성, 또는 기타의 유형의 컴퓨터 저장 매체)로 구현될 수 있다. 컴퓨터 판독가능한 매체 또는 매체들은, 저장된 프로그램 또는 프로그램들이 하나 이상의 상이한 컴퓨터 또는 기타의 프로세서에 로딩되어 전술된 양태들 중 다양한 양태를 구현하도록, 이동가능할 수 있다. 일부 실시예에서, 컴퓨터 판독가능한 매체는 비일시적 매체일 수 있다.

[0160] 용어 "프로그램" 또는 "소프트웨어"는 본 명세서에서 전술된 다양한 양태를 구현하기 위해 컴퓨터 또는 기타의 프로세서를 프로그램하도록 채용될 수 있는 임의 유형의 컴퓨터 코드 또는 컴퓨터-실행가능한 명령어 세트를 지칭하기 위해 일반적 의미로 사용된다. 추가적으로, 한 양태에 따르면, 실행될 때 본 개시내용의 방법들을 수행하는 하나 이상의 컴퓨터 프로그램은 단일의 컴퓨터 또는 프로세서 상에 존재할 필요는 없고, 본 개시내용의 다양한 양태를 구현하기 위해 다수의 상이한 컴퓨터 또는 프로세서들간에 모듈식으로 분산될 수도 있다는 점을 이해해야 한다.

[0161] 컴퓨터-실행가능한 명령어는, 하나 이상의 컴퓨터 또는 기타의 디바이스에 의해 실행되는 프로그램 모듈 등의, 많은 형태로 존재할 수 있다. 일반적으로, 프로그램 모듈들은 특정 작업들을 수행하거나 특정 추상 데이터 타

입들을 구현하는 루틴들, 프로그램들, 객체들, 컴포넌트들, 데이터 구조들 등을 포함한다. 전형적으로, 프로그램 모듈의 기능은 다양한 실시예에서 원한다면 결합되거나 분산될 수도 있다.

[0162] 또한, 데이터 구조는 임의의 적절한 형태의 컴퓨터-판독가능한 매체에 저장될 수 있다. 예시의 간소화를 위해, 데이터 구조는 데이터 구조 내의 위치를 통해 관련된 필드들을 갖는 것으로 도시될 수 있다. 이러한 관계는 마찬가지로 필드들간의 관계를 전달하는 컴퓨터-판독가능한 매체 내의 위치들을 갖는 필드들에 대해 스토리지를 할당함으로써 달성될 수 있다. 그러나, 데이터 요소들간의 관계를 설정하는 포인터, 태그 또는 기타의 메커니즘의 이용을 포함한, 데이터 구조 내의 필드들 내의 정보간의 관계를 설정하기 위해 임의의 적절한 메커니즘이 이용될 수 있다.

[0163] 소프트웨어로 구현될 때, 소프트웨어 코드는, 단일의 컴퓨터에 제공되거나 또는 복수의 컴퓨터들 사이에 분산되거나, 임의의 적절한 프로세서 또는 프로세서 집합 상에서 실행될 수 있다.

[0164] 또한, 컴퓨터는, 비제한적 예로서, 랙-탑재형 컴퓨터, 데스크탑 컴퓨터, 랩탑 컴퓨터, 또는 태블릿 컴퓨터 등의, 다수의 형태들 중 임의의 형태로 구현될 수 있다는 점을 이해해야 한다. 추가로, 컴퓨터는, 개인용 디지털 보조도구(PDA), 스마트폰 또는 기타 임의의 적절한 휴대형 또는 고정형 전자 디바이스를 포함한, 일반적으로 컴퓨터로서 간주되지 않지만 적절한 처리 기능을 갖는 디바이스에 임베딩될 수도 있다.

[0165] 또한, 컴퓨터는 하나 이상의 입력 및 출력 디바이스를 가질 수도 있다. 이들 디바이스들은, 특히, 사용자 인터페이스를 프리젠팅하는데 이용될 수 있다. 사용자 인터페이스를 제공하는데 이용될 수 있는 출력 디바이스들의 예로서는, 출력의 시각적 프리젠테이션을 위한 프린터 또는 디스플레이 스크린이나, 출력의 청각적 프리젠테이션을 위한 스피커 또는 기타의 사운드 생성 디바이스가 포함된다. 사용자 인터페이스를 위해 이용될 수 있는 입력 디바이스들의 예로서는, 키보드와, 마우스, 터치패드 및 디지타이징 태블릿 등의 포인팅 디바이스가 포함된다. 또 다른 예로서, 컴퓨터는 음성 인식을 통한 또는 기타의 청각적 형태의 입력 정보를 수신할 수 있다.

[0166] 이러한 컴퓨터들은, 기업 네트워크 등의 근거리 통신망 또는 광역 네트워크, 및 지능형 네트워크(IN) 또는 인터넷을 포함한, 임의의 적절한 형태의 하나 이상의 네트워크에 의해 상호접속될 수 있다. 이러한 네트워크들은 임의의 적절한 기술에 기초할 수 있고 임의의 적절한 프로토콜에 따라 동작할 수 있으며 무선 네트워크, 유선 네트워크 또는 광섬유 네트워크를 포함할 수도 있다.

[0167] 또한, 설명된 바와 같이, 일부 양태는 하나 이상의 방법으로서 구현될 수도 있다. 방법의 일부로서 수행되는 동작들은 임의의 적절한 방식으로 정렬될 수 있다. 따라서, 실시예에서는 순차적 동작들로서 도시되어 있더라도, 소정 동작들을 동시에 수행하는 것을 포함한, 동작들이 예시된 것과는 상이한 순서로 수행되는 실시예들이 구성될 수 있다.

[0168] 여기서 정의되고 사용된 모든 정의는, 사전적 정의, 참조에 의해 포함된 문서에서의 정의, 및/또는 정의된 용어의 통상의 의미를 통제하는 것으로 이해되어야 한다.

[0169] 부정관사("a" 및 "an")는, 본 명세서와 청구항에서 사용될 때, 분명하게 달리 나타내지 않는 한, "적어도 하나"를 의미하는 것으로 이해되어야 한다.

[0170] 구문 "및/또는"은, 여기 본 명세서 및 청구항에서 사용될 때, 이와 같이 결합된 요소들, 즉 어떤 경우에는 결합되어 존재하고 다른 경우에는 분리되어 존재하는 요소들의 "어느 하나 또는 양쪽 모두"를 의미하는 것으로 이해되어야 한다. "및/또는"에 의해 열거된 복수의 요소들은 동일한 방식으로, 즉, 이와 같이 결합된 요소들의 "하나 이상"으로서 해석되어야 한다. "및/또는"에 의해 구체적으로 식별되는 요소들 이외의 다른 요소들이, 구체적으로 식별된 이들 요소들과 관련되지 않든, 선택사항으로서 존재할 수 있다. 따라서, 비제한적 예로서, "A 및/또는 B"에 대한 언급은, "포함하는" 등의 개방형 용어와 연계하여 사용될 때, 한 실시예에서는, (선택사항으로서 B 이외의 다른 요소를 포함한) A만을 지칭할 수 있고; 또 다른 실시예에서는, (선택사항으로서 A 이외의 요소를 포함한) B만을 지칭할 수 있으며; 역시 또 다른 실시예에서는, (선택사항으로서 다른 요소를 포함한) A와 B 양쪽 모두를 지칭할 수 있다.

[0171] 여기 본 명세서와 청구항에서 사용될 때, 하나 이상의 요소의 열거를 참조한 구문 "적어도 하나"는, 요소들의 목록 내의 요소들 중 하나 이상으로부터 선택된 적어도 하나의 요소를 의미하지만, 요소들의 목록 내의 요소들의 각각의 및 모든 요소 중 적어도 하나를 반드시 포함할 필요는 없고 요소들의 목록 내의 요소들의 임의의 조합을 배제하지 않는 것으로 이해되어야 한다. 이 정의는 또한, 구문 "적어도 하나"가 참조하는 요소들의 목록 내에서 구체적으로 식별되는 요소들 이외의 요소들이, 구체적으로 식별되는 요소들과 관련되어지 않든, 선택사항적으로 존재할 수 있다는 것을 허용한다. 따라서, 비제한적 예로서, "A와 B 중 적어도 하나"(또는, 등

가격으로, "A 또는 B 중 적어도 하나", 또는 등가적으로 "A 및/또는 B" 중 적어도 하나")는, 한 실시예에서는, B가 존재하지 않는(및 선택사항으로서 B 이외의 요소를 포함한), 적어도 하나의 A, 선택사항으로서는 하나보다 많은 A를 지칭할 수 있고; 또 다른 실시예에서는, 선택사항으로서 A가 존재하지 않는(및 선택사항으로서 A 이외의 요소를 포함한), 적어도 하나의 B, 선택사항으로서는 하나보다 많은 B를 지칭할 수 있고; 역시 또 다른 실시 예에서는, 적어도 하나의 A, 선택사항으로서 하나보다 많은 A와, 적어도 하나의 B, 선택사항으로서는 하나보다 많은 B(및 선택사항으로서 다른 요소들을 포함)를 지칭할 수 있다.

[0172] 또한, 여기서 사용되는 어법과 용어는 설명을 위한 것이며 제한적인 것으로 간주되어서는 안 된다. 여기서, "내포하는(including)", "포함하는(comprising)", 또는 "갖는(having)", "담고 있는(containing)", "수반하는(involving)" 및 그 파생어들은 이후에 열거되는 항목들과 그 균등물 뿐만 아니라 추가 항목들을 아우르는 것을 의미한다.

[0173] 상기 명세서뿐만 아니라 청구항에서, "포함하는(comprising)", "내포하는(including)", "운반하는(carrying)", "갖는(having)", "함유하는(containing)", "수반하는(involving)", "~로 구성된(composed of~)" 등과 같은 모든 연결 구문은, 제약을 두지 않는(open-ended), 즉, 포함하지만 그것으로 제한되지 않는다는 것을 의미한다. 연결 구문 "~로 이루어진(consisting of~)" 및 "~로 본질적으로 이루어진(consisting essentially of~)"만은 각각 폐쇄형 또는 반-폐쇄형 연결 구문일 것이다.

## 도면

### 도면1a

도면1b

도면2

## 도면3

도면4

도면5

도면6

## 도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

도면16

도면17

## 도면18

## 도면19

|                |                                                                                                                               |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 标题 : 超声波成像压缩方法和设备                                                                                                             |         |            |

| 公开(公告)号        | <a href="#">KR1020160145177A</a>                                                                                              | 公开(公告)日 | 2016-12-19 |

| 申请号            | KR1020167032202                                                                                                               | 申请日     | 2015-04-17 |

| [标]申请(专利权)人(译) | 蝴蝶网络有限公司<br>蝶形网络的大                                                                                                            |         |            |

| 申请(专利权)人(译)    | 蝶形网络公司                                                                                                                        |         |            |

| 当前申请(专利权)人(译)  | 蝶形网络公司                                                                                                                        |         |            |

| [标]发明人         | ROTHBERG JONATHAN M<br>로스버그조나단엠<br>RALSTON TYLER S<br>랠스턴타일러에스<br>SANCHEZ NEVADA J<br>산체스네바다제이<br>CASPER ANDREW J<br>캐스퍼앤드류제이 |         |            |

| 发明人            | 로스버그,조나단,엠.<br>랠스턴,타일러,에스.<br>산체스,네바다,제이.<br>캐스퍼,앤드류,제이.                                                                      |         |            |

| IPC分类号         | A61B8/00 A61B8/08 G01S15/89 G01S7/52                                                                                          |         |            |

| CPC分类号         | A61B8/4483 A61B8/488 A61B8/5207 A61B8/56 G01S15/8915 G01S7/52033 G01S7/52034 G01S7/5208 A61B8/4494 G01S7/52085                |         |            |

| 代理人(译)         | Yangyoungjun<br>Baekmangi<br>Jeongeunjin                                                                                      |         |            |

| 优先权            | 61/981491 2014-04-18 US                                                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                     |         |            |

### 摘要(译)

一种芯片的单芯片超声以实现记录解决方案，从采用所接收的信号的路径，该芯片的信号处理，以减少数据的带宽，并输出该数据模块是关闭的所有接收信道作为数字数据流的数据，可以用来移动。接收信号的片上数字化允许在芯片上执行高级数字信号处理，从而允许整个超声成像系统完全集成在单个半导体衬底上。接收信号的片上数字化还使得能够进行超声处理和/或预处理的片上集成，以减少片外计算的负担。公开了数据压缩体系结构，其根据标准商业输出接口的带宽要求实现数据的片外传输作为数字数据流。卡斯帕，安德鲁，杰伊。