### US009910018B2

# (12) United States Patent Rothberg et al.

### (54) MICROFABRICATED ULTRASONIC TRANSDUCERS AND RELATED APPARATUS AND METHODS

(71) Applicant: **Butterfly Network, Inc.**, Guilford, CT (US)

(72) Inventors: Jonathan M. Rothberg, Guilford, CT (US); Susan A. Alie, Stoneham, MA (US); Keith G. Fife, Palo Alto, CA (US); Nevada J. Sanchez, Guilford, CT (US); Tyler S. Ralston, Clinton, CT

(US)

(73) Assignee: **Butterfly Network, Inc.**, Guilford, CT (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

This patent is subject to a terminal disclaimer.

(21) Appl. No.: 15/177,977

(22) Filed: Jun. 9, 2016

### (65) **Prior Publication Data**

US 2016/0280538 A1 Sep. 29, 2016

### Related U.S. Application Data

- (63) Continuation of application No. 14/716,152, filed on May 19, 2015, now Pat. No. 9,394,162, which is a (Continued)

- (51) **Int. Cl. H01L 29/84** (2006.01) **H01L 21/30** (2006.01)

(Continued)

- (52) **U.S. Cl.**CPC ...... *G01N 29/2406* (2013.01); *A61B 8/4483* (2013.01); *B06B 1/0292* (2013.01); (Continued)

### (10) Patent No.: US 9,910,018 B2

(45) **Date of Patent:** \*Mar. 6, 2018

### (58) Field of Classification Search

### (56) References Cited

### U.S. PATENT DOCUMENTS

5,286,671 A 2/1994 Kurtz et al. 6,430,109 B1 8/2002 Khuri-Yakub et al. (Continued)

### FOREIGN PATENT DOCUMENTS

CN 101640834 A 2/2010 GB 2 467 776 A 8/2010 (Continued)

### OTHER PUBLICATIONS

International Preliminary Report on Patentability dated Oct. 27, 2016 for Application No. PCT/US2015/026290.

(Continued)

Primary Examiner — Su C Kim (74) Attorney, Agent, or Firm — Wolf, Greenfield & Sacks, P.C.

### (57) ABSTRACT

Micromachined ultrasonic transducers integrated with complementary metal oxide semiconductor (CMOS) substrates are described, as well as methods of fabricating such devices. Fabrication may involve two separate wafer bonding steps. Wafer bonding may be used to fabricate sealed cavities in a substrate. Wafer bonding may also be used to bond the substrate to another substrate, such as a CMOS wafer. At least the second wafer bonding may be performed at a low temperature.

### 10 Claims, 26 Drawing Sheets

### US 9,910,018 B2

Page 2

```

7,687,976 B2

7,745,248 B2

Related U.S. Application Data

3/2010 Haider et al.

6/2010 Park et al.

continuation of application No. 14/635,197, filed on

7,759,839 B2

7/2010

Huang

Mar. 2, 2015, now Pat. No. 9,067,779.

7,764,003 B2

7/2010

Huang

7,779,696 B2

8/2010 Huang

7,846,102 B2

12/2010

Kupnik et al.

Provisional application No. 62/024,179, filed on Jul.

7,878,977 B2

2/2011

Mo et al.

14, 2014.

7,880,565 B2

2/2011

Huang

7,888,709 B2

2/2011

Lemmerhirt et al.

7,892,176 B2

2/2011

Wodnicki et al.

(51) Int. Cl.

7,956,510 B2

8,004,373 B2

8,008,105 B2

6/2011

Huang

G01N 29/24

(2006.01)

8/2011

Huang

B81C 1/00

(2006.01)

8/2011

Huang

B06B 1/02

8,008,835 B2

(2006.01)

8/2011

Degertekin

8,018,301 B2

9/2011

A61B 8/00

Huang

(2006.01)

8,076,821 B2

12/2011

Degertekin

B81B 7/00

(2006.01)

8,105,941 B2

1/2012

Huang

(52) U.S. Cl.

8,120,229 B2

2/2012

Huang

CPC ...... B81B 7/007 (2013.01); B81C 1/00238

8,203,912 B2

6/2012

Roest et al.

8,222,065 B1

7/2012

Smeys et al.

(2013.01); B81C 1/00301 (2013.01); B81B

8,241,931 B1

8/2012

Antoine et al.

2201/0271 (2013.01); B81C 2201/019

8,247,945 B2

8/2012

Huang

(2013.01); B81C 2203/036 (2013.01); B81C

8,277,380 B2

10/2012

Daft et al.

2203/0792 (2013.01); H01L 2224/4813

8,309,428 B2

11/2012

Lemmerhirt et al.

(2013.01); H01L 2924/0002 (2013.01); H01L

8,315,125 B2

11/2012

Lemmerhirt et al.

8,327,521 B2

12/2012

Dirksen et al.

2924/146 (2013.01); H01L 2924/1461

12/2012

8,334,133 B2

Federov et al.

(2013.01)

8,345,508 B2

8,345,513 B2

1/2013

Wodnicki et al.

(58) Field of Classification Search

1/2013 Huang

CPC ...... B81C 1/00238; B81C 2203/036; B81C

8,363,514 B2

1/2013 Huang

8,372,011 B2

2201/019; B81C 2203/0792; B06B

2/2013

Degertekin

8,398,554 B2

3/2013 Degertekin

1/0292; H01L 2224/4813; H01L

8,399,278 B2

3/2013

Lemmerhirt et al.

2924/1461; H01L 2924/146; H01L

Kupnik et al.

8,402,831 B2

3/2013

2924/0002

8,429,808 B2

4/2013

Huang

8,451,693 B2

Nikoozadeh et al.

See application file for complete search history.

5/2013

8,483,014 B2

7/2013

Huang

8,526,271 B2

9/2013 Huang

(56)

References Cited

8,559,274 B2

8,563,345 B2

10/2013

Huang

10/2013

Adler et al.

U.S. PATENT DOCUMENTS

8,587,078 B2

11/2013 Huang et al.

8,647,279 B2

2/2014 Daft et al.

9/2002 Fraser

6.443.901 B1

2/2014 Lemmerhirt et al.

8,658,453 B2

6,610,582 B1*

8/2003 Stewart ...... B81C 3/001

8,665,672 B2

3/2014 Soeda et al.

257/E21.088

8,957,564 B1

2/2015 Hiroe et al.

6,645,145 B1

11/2003 Dreschel et al.

9,061,318 B2

6/2015 Rothberg et al.

6,659,954 B2

12/2003

Robinson

9,067,779 B1

Rothberg et al.

6/2015

Degertekin et al.

6.694.817 B2

2/2004

9,242,275 B2

1/2016

Rothberg et al.

8/2004

6,779,387 B2

Degertekin

9,290,375 B2

3/2016

Rothberg et al.

6,795,374 B2

9/2004

Barnes et al

9,386,380 B2

7/2016 Chu et al.

6,831,394 B2

12/2004

Baumgartner et al.

9,394,162 B2

7/2016

Rothberg et al.

6,865,140 B2

3/2005

Thomenius et al.

9,499,392 B2

11/2016 Rothberg et al.

6,958,255 B2

10/2005

Khuri-Yakub et al.

9,499,395 B2

11/2016

Rothberg et al.

7,030,536 B2

4/2006

Smith et al.

9,505,030 B2

11/2016 Rothberg et al.

7,037,746 B1

5/2006

Smith et al.

Rothberg et al.

Degertekin et al

9.533.873 B2

1/2017

7,052,464 B2

5/2006

Wodnicki

2005/0121734 A1

6/2005

7,104,129 B2

9/2006

Nasiri et al.

2005/0177045 A1

8/2005

Degertekin et al.

7,125,383 B2

7,247,246 B2

10/2006

Hoctor et al.

2005/0203397 A1

9/2005

Degertekin

7/2007

Nasiri et al.

2005/0248232 A1

11/2005

Itaya et al.

7,250,353 B2

7/2007

Nasiri et al.

2006/0116585 A1

6/2006

Nguyen et al.

7,257,051 B2

8/2007

Thomenius et al.

2007/0167811 A1

7/2007

Lemmerhirt et al.

7,285,897 B2

10/2007

Fisher et al.

2007/0167812 A1

7/2007

Lemmerhirt et al.

7,312,440 B2

12/2007

Degertekin et al.

2007/0180916 A1

8/2007

Tian et al.

7,313,053 B2

12/2007

Wodnicki

2007/0190680 A1

8/2007

Fukuda et al.

5/2008 Fisher et al.

7,375,420 B2

2007/0215964 A1

Khuri-Yakub et al.

9/2007

7,441,321 B2

10/2008

Baumgartner et al.

2007/0262436 A1

11/2007

Kweon et al.

7,441,447 B2

7,442,570 B2

10/2008

Degertekin et al.

6/2008

Wan

2008/0138922 A1

10/2008

Nasiri et al.

2008/0185669 A1*

8/2008 Kok ...... H04R 19/005

11/2008

7,451,651 B2

Woychik et al.

257/416

7,518,251 B2

4/2009

Fisher et al.

8/2008 Huang

2008/0194053 A1

7,530,952 B2

5/2009

Huang et al.

2008/0290756 A1

11/2008 Huang

Smith et al.

7,545,012 B2

6/2009

2008/0296708 A1

12/2008

Wodnicki et al.

7,557,342 B2

7/2009

Federov et al.

2008/0308920 A1

12/2008 Wan

Huang

Degertekin

7.564.172 B1

7/2009

2009/0122651 A1

5/2009

Kupnik et al.

7,612,483 B2

11/2009

7,612,635 B2

2009/0133820 A1

5/2009

Sato et al.

11/2009

Huang

Khuri-Yakub et al.

2009/0134497 A1

5/2009

Barth et al.

7,615,834 B2

11/2009

7,622,848 B2

2009/0148967 A1

6/2009

Wodnicki et al.

11/2009

Lee et al.

2009/0176375 A1

7,637,149 B2

12/2009

Degertekin et al.

7/2009 Benson et al.

7,646,133 B2

1/2010 Degertekin

2009/0250729 A1

10/2009 Lemmerhirt et al.

```

#### (56)**References Cited**

### U.S. PATENT DOCUMENTS

| 2010/0027830 | A1  | 2/2010  | Hsu et al.         |

|--------------|-----|---------|--------------------|

| 2010/0171153 | A1  | 7/2010  | Yang               |

| 2010/0225200 | A1  | 9/2010  | Kupnik et al.      |

| 2011/0084570 | A1  | 4/2011  | Soeda et al.       |

| 2011/0115333 | A1  | 5/2011  | Ezaki              |

| 2011/0140224 | A1  | 6/2011  | Kropelnicki et al. |

| 2011/0272693 | A1  | 11/2011 | Kobayashi et al.   |

| 2012/0074509 | A1  | 3/2012  | Berg et al.        |

| 2012/0129301 | A1  | 5/2012  | Or-Bach et al.     |

| 2012/0187508 | A1  | 7/2012  | Adler et al.       |

| 2012/0193719 | A1  | 8/2012  | Or-Bach et al.     |

| 2012/0248554 | A1  | 10/2012 | Klein et al.       |

| 2013/0096433 | A1  | 4/2013  | Lemmerhirt et al.  |

| 2013/0116561 | A1  | 5/2013  | Rothberg et al.    |

| 2013/0161702 | A1  | 6/2013  | Chen               |

| 2013/0169110 | A1  | 7/2013  | Jeong et al.       |

| 2013/0175643 | A1  | 7/2013  | Berthelot et al.   |

| 2013/0270967 | A1* | 10/2013 | Dausch B06B 1/0607 |

|              |     |         | 310/365            |

| 2014/0054730 | A1  | 2/2014  | Graham et al.      |

| 2014/0057382 | A1  | 2/2014  | Supino et al.      |

| 2014/0183731 | A1  | 7/2014  | Lin et al.         |

| 2014/0217478 | A1  | 8/2014  | Rothberg et al.    |

| 2014/0219062 | A1  | 8/2014  | Rothberg et al.    |

| 2014/0264660 | A1  | 9/2014  | Rothberg et al.    |

| 2014/0355381 | A1  | 12/2014 | Lal et al.         |

| 2015/0084053 | A1  | 3/2015  | Rothberg et al.    |

| 2015/0156571 | A1  | 6/2015  | Shim et al.        |

| 2015/0175406 | A1  | 6/2015  | Lin et al.         |

| 2015/0251896 | A1  | 9/2015  | Rothberg et al.    |

| 2015/0298170 | A1  | 10/2015 | Rothberg et al.    |

| 2016/0009544 | A1  | 1/2016  | Rothberg et al.    |

| 2016/0009549 | A1  | 1/2016  | Rothberg et al.    |

| 2016/0264400 |     | 9/2016  | Rothberg et al.    |

| 2016/0290969 |     | 10/2016 | Rothberg et al.    |

| 2016/0290970 |     | 10/2016 | Rothberg et al.    |

| 2016/0379973 |     | 12/2016 | Rothberg et al.    |

| 2017/0029271 | A1  | 2/2017  | Rothberg et al.    |

| 2017/0056926 | A1  | 3/2017  | Rothberg et al.    |

|              |     |         |                    |

### FOREIGN PATENT DOCUMENTS

| KR | 10-2013-0134724 A | 12/2013 |

|----|-------------------|---------|

| WO | WO 2009/107940 A2 | 9/2009  |

| WO | WO 2012/017978 A2 | 2/2012  |

| WO | WO 2014/151525 A2 | 9/2014  |

### OTHER PUBLICATIONS

International Preliminary Report on Patentability dated Jan. 26, 2017 for Application No. PCT/US2015/040342.

U.S. Appl. No. 14/172,383, filed Feb. 4, 2014, Rothberg et al. U.S. Appl. No. 15/158,968, filed May 19, 2016, Rothberg et al. U.S. Appl. No. 14/172,840, filed Feb. 4, 2014, Rothberg et al. U.S. Appl. No. 15/042,931, filed Feb. 12, 2016, Rothberg et al. U.S. Appl. No. 14/799,484, filed Jul. 14, 2015, Rothberg et al. U.S. Appl. No. 15/177,899, filed Jun. 9, 2016, Rothberg et al. U.S. Appl. No. 15/178,025, filed Jun. 9, 2016, Rothberg et al.

PCT/US2014/014705, Jul. 1, 2014, International Search Report and Written Opinion.

PCT/US2014/014705, Aug. 20, 2015, International Preliminary Report on Patentability.

PCT/US2014/025924, Nov. 6, 2014, Invitation to Pay Additional

PCT/US2014/025924, Feb. 18, 2015, International Search Report and Written Opinion.

PCT/US2014/025924, Sep. 24, 2015, International Preliminary Report on Patentability.

PCT/US2015/026290, Jun. 29, 2015, International Search Report and Written Opinion.

PCT/US2015/040342, Oct. 29, 2015, International Search Report and Written Opinion.

U.S. Appl. No. 15/581,551, filed Apr. 28, 2017, Rothberg et al. U.S. Appl. No. 15/648,187, filed Jul. 12, 2017, Rothberg et al. International Search Report and Written Opinion dated Jul. 1, 2014 for Application No. PCT/US2014/014705.

International Preliminary Report on Patentability dated Aug. 20, 2015 for Application No. PCT/US2014/014705

Invitation to Pay Additional Fees dated Nov. 6, 2014 for Application No. PCT/US2014/025924.

International Search Report and Written Opinion dated Feb. 18, 2015 for Application No. PCT/US2014/025924.

International Preliminary Report on Patentability dated Sep. 24, 2015 for Application No. PCT/US2014/025924.

International Search Report and Written Opinion dated Jun. 29, 2015 for Application No. PCT/US2015/026290.

International Search Report and Written Opinion dated Oct. 29, 2015 for Application No. PCT/US2015/040342.

Office Communication dated Feb. 13, 2015 for U.S. Appl. No. 14/172,383.

Notice of Allowance dated Dec. 4, 2015 for U.S. Appl. No. 14/172.383.

Office Communication dated Jul. 12, 2016 for U.S. Appl. No. 14/172,840.

Office Communication dated May 21, 2015 for U.S. Appl. No. 14/208.351.

Notice of Allowance dated Sep. 14, 2015 for U.S. Appl. No. 14/208.351.

Notice of Allowance dated Nov. 10, 2015 for U.S. Appl. No.

14/711,145. Office Communication dated May 15, 2015 for U.S. Appl. No.

14/635,197. Office Communication dated Dec. 16, 2015 for U.S. Appl. No.

14/716,152.

[No Author Listed], Sil-Via, TSI & Advanced Features. Silex Microsystems. http://www.silexmicrosystems.com/mems-foundry/ sil-via-tsi-advanced-features/ [last accessed Jan. 6, 2015]. 4 pages. Calmes et al., Highly Integrated 2-D Capacitive Micromachined Ultrasonic Transducers. 1999 IEEE Ultrason Symp. 1999;1163-6. Cha et al., Influences of perforation ratio in characteristics of

capacitive micromachined ultrasonic transducers in air. Sensors Actuators A. 2011;171:191-8. Cheng et al., An Efficient Electrical Addressing Method Using

Through-Wafer Vias for Two-Dimensional Ultrasonic Arrays. 2000 IEEE Ultrasonics Symposium. 2000;2:1179-82.

Cheng et al., Electrical Through-Wafer Interconnects with Sub-PicoFarad Parasitic Capacitance. 2001 Microelectromechan Syst Conf. Aug. 24, 2001;18-21.

Daft et al., Microfabricated ultrasonic transducers monolithically integrated with high voltage electronics. Proc Ultrason Symp. 2004;493-6.

Dixon-Warren, Overview of MEMS microphone technologies for consumer applications. MEMS J. Mar. 8, 2011. http://www. memsjournal.com/2011/03/overview-of-mems-microphone-technologies-for-consumer-applications.html [last accessed Feb. 19,

2014]. 10 pages.

Doody et al., Modeling and Characterization of CMOS-Fabricated Capacitive Micromachined Ultrasound Transducers. Microelectromech Sys. Feb. 1, 2011;20(1):104-18.

Eccardt et al., Micromachined ultrasound transducers with improved coupling factors from a CMOS compatible process. Ultrasonics. Mar. 2000;38:774-80.

Eccardt et al., Surface micromachined ultrasound transducer in CMOS technology. Proc Ultrason Symp. 1996;959-62.

Gurun et al., Front-end CMOS electronics for monolithic integration with CMUT arrays: circuit design and initial experimental results. Proc Ultrason Symp. 2008;390-3.

Helin et al., Poly-SiGe-based CMUT array with high acoustical pressure. MEMS. 2012 IEEE 25th International Conference on Micro Electro Mechanical Systems. Jan. 29, 2012;305-8

Kim et al., Design and Test of a Fully Controllable 64x128 2-D CMUT Array Integrated with Reconfigurable Frontend ASICs for Volumetric Ultrasound Imaging. IEEE. International Ultrasonics Symposium Proceedings. Oct. 7-10, 2012;77-80. doi: 10.1109/ ULTSYM.2012.0019.

### (56) References Cited

### OTHER PUBLICATIONS

Knight et al., Low Temperature Fabrication of Immersion Capacitive Micromachined Ultrasonic Transducers on Silicon and Dielectric Substrates. IEEE Trans Ultrason Ferroelectr Freq Contr. Oct. 2004;51(10):1324-33.

Kupnik et al., CMUT Fabrication Based on a Thick Buried Oxide Layer. Proc IEEE Ultrason Symp. Oct. 2010;2010:547-550. Epub Jun 8, 2012. 10 pages.

Kupnik et al., Wafer-Bonded CMUT Meets CMOS. 2010 CMOS Emerging Technology Workshop. May 21, 2010;1-22.

Lemmerhirt et al., A 32×32 capacitive micromachined ultrasonic transducer array manufactured in standard CMOS. IEEE Trans Ultrason Ferroelectr Freq Control. Jul. 2012;59(7):1521-36. doi: 10.1109/TUFFC.2012.2352.

Lemmerhirt et al., An electronically-scanned CMUT-in-CMOS transducer for hemodialysis vascular access monitoring. Ultrason Symp. 2011 IEEE International Conference. Oct. 18, 2011;2193-6. Lin et al., Packaging of Large and Low-Pitch Size 2D Ultrasonic Transducer Arrays. MEMS Conf. 2010;508-11.

Lu et al., Investigation of thermal stress influence on CMUT in standard CMOS process. Info Auto. 2009 ICIA International Conference. Jun. 22, 2009;1447-51.

Manzanares et al., Air-coupled MUMPs capacitive micromachined ultrasonic transducers with resonant cavities. Ultrason. 2012;52:482-9.

Nikoozadeh et al., Forward-Looking Intracardiac Ultrasound Imaging Using a 1-D CMUT Array Integrated With Custom Front-End Electronics. IEEE Trans Ultrason Ferroelectr Freq Contr. Dec. 2008;55(12):2651-60.

Noble et al., A cost-effective and manufacturable route to the fabrication of high-density 2D micromachined ultrasonic transducer arrays and (CMOS) signal conditioning electronics on the same silicon substrate. Proc Ultrason Symp. 2001;941-5.

Noble et al., Low-temperature micromachined CMUTs with fully-integrated analogue front-end electronics. Proc Ultrason Symp. 2002;1045-50.

Oralkan et al., Volumetric Imaging Using 2D Capacitive Micromachined Ultrasonic Transducer Arrays (CMUTs): Initial Results. 2002 IEEE Ultrason Symp. 2002;1083-6.

Oralkan et al., Volumetric Ultrasound Imaging Using 2-D CMUT Arrays. IEEE Trans Ultrason Ferroelectr Freq Contr. Nov. 2003;50(11):1581-94.

Park et al., Fabrication of Capacitive Micromachined Ultrasonic Transducers via Local Oxidation and Direct Wafer Bonding. J Microelectromechan Syst. Feb. 2011;20(1):95-103.

Torkkeli et al., Capacitative microphone with low-stress polysilicon membrane and high-stress polysilicon backplate. Sensors and Actuators. 2000;85:116-23.

Tsuji et al., Low Temperature Process for CMUT Fabrication with Wafer Bonding Technique. IEEE Intl Ultrason Symp Proc. 2010;551-4.

Um et al., An Analog-Digital-Hybrid Single-Chip RX Beamformer with Non-Uniform Sampling for 2D-CMUT Ultrasound Imaging to Achieve Wide Dynamic Range of Delay and Small Chip Area. IEEE International Solid-State Circuits Conference. Feb. 12, 2014;426-8. Wodnicki et al., Multi-Row Linear CMUT Array Using CMUTs and Multiplexing Electronics. Proc Ultrason Symp. 2009;2696-9.

Wolffenbuttel et al., Low-temperature silicon wafer-to-wafer bonding using gold at eutectic temperature. Sensors and Actuators A. 1994:43:223-9.

Wygant et al., Integration of 2D CMUT Arrays with Front-End Electronics for Volumetric Ultrasound Imaging. IEEE Trans Ultrason Ferroelectr Freq Contr. Feb. 2008;55(2):327-42.

Xu et al., Characterization of improved Capacitive Micromachined Ultrasonic Transducers (CMUTS) using ALD high-[Kappa] dielectric isola. MEMS. 2014 IEEE 27th International Conference on Micro Electro Mechanical Systems. Jan. 26, 2014;584-7.

Yu et al., Dual-bottom-electrode CMUT based on standard CMOS process. NEMS. 2001 IEEE International Conference. Feb. 20, 2011;21-4.

Zahorian et al., Single chip CMUT arrays with integrated CMOS electronics: fabrication process development and experimental results. Proc Ultrason Symp. 2008;386-9.

Zhuang et al., Integration of trench-isolated through-wafer interconnects with 2d capacitive micromachined ultrasonic transducer arrays. Sensors Actuators A. 2007;138:221-9.

Zhuang et al., Wafer-bonded 2-D CMUT arrays incorporating through-wafer trench-isolated interconnects with a supporting frame. IEEE Trans Ultrason Ferroelectr Freq Control. Jan. 2009;56(1):182-92. doi: 10.1109/TUFFC.2009.1018.

<sup>\*</sup> cited by examiner

FIG. 1

FIG. 2

1 5 3

而 ② 4

FIG. 7

FIG. 13

FIG. 14

### MICROFABRICATED ULTRASONIC TRANSDUCERS AND RELATED APPARATUS AND METHODS

## CROSS REFERENCE TO RELATED APPLICATIONS

This application is a continuation, claiming the benefit under 35 U.S.C. § 120, of U.S. patent application Ser. No. 14/716,152 entitled "Microfabricated Ultrasonic Transducers and Related Apparatus and Methods," filed May 19, 2015, which is incorporated herein by reference in its entirety.

U.S. patent application Ser. No. 14/716,152 is a continuation, claiming the benefit under 35 U.S.C. § 120, of U.S. patent application Ser. No. 14/635,197 entitled "Microfabricated Ultrasonic Transducers and Related Apparatus and Methods," filed Mar. 2, 2015, which is incorporated herein by reference in its entirety.

U.S. patent application Ser. No. 14/635,197 claims the benefit under 35 U.S.C. § 119(e) of U.S. Provisional Patent Application Ser. No. 62/024,179 filed Jul. 14, 2014, and entitled "Microfabricated Ultrasonic Transducers and Related Apparatus and Methods," which is incorporated <sup>25</sup> herein by reference in its entirety.

### BACKGROUND

Field

The technology described herein relates to complementary metal oxide semiconductor (CMOS) transducers and methods for forming the same.

Related Art

Capacitive Micromachined Ultrasonic Transducers <sup>35</sup> (CMUTs) are known devices that include a membrane above a micromachined cavity. The membrane may be used to transduce an acoustic signal into an electric signal, or vice versa. Thus, CMUTs can operate as ultrasonic transducers.

Two types of processes can be used to fabricate CMUTs. 40 Sacrificial layer processes form the membrane of the CMUT on a first substrate above a sacrificial layer. Removal of the sacrificial layer results in the membrane being suspended above a cavity. Wafer bonding processes bond two wafers together to form a cavity with a membrane. 45

### BRIEF SUMMARY

Aspects of the present application relate to fabrication and integration of CMUTs with CMOS wafers, thereby forming 50 CMOS ultrasonic transducers (CUTs). According to an aspect of the present application, a wafer-level process is presented involving two wafer bonding steps. A first wafer bonding step may form sealed cavities by bonding together two silicon-on-insulator (SOI) wafers, the resulting bonded 55 structure being considered an engineered substrate. Relatively high temperatures may be used, for example during an anneal, to facilitate achieving a strong bond. A handle layer of one of the two SOI wafers of the engineered substrate may then be removed, after which a second wafer bonding 60 step may be performed to bond the engineered substrate with a CMOS wafer having integrated circuits (ICs) formed thereon. The second wafer bonding step may use a relatively low temperature to avoid damage to the ICs on the CMOS wafer. The handle layer of the second SOI wafer of the 65 engineered substrate may then be removed, leaving a membrane over the cavities of the engineered substrate. Electrical

2

connections between the CMOS IC and the engineered substrate allow for controllable ultrasonic transducers to be realized.

The wafer-level process described above may produce an ultrasound device with integrated CMUTs and CMOS ICs. The cavities of the CMUTs may be formed between two silicon layers representing the silicon device layers of the two SOI wafers used to form the engineered substrate. Yet, the handle layers of the two SOI wafers may be absent in the completed device, which facilitates achieving thin device dimensions and therefore a small size, among other benefits. Thus, the process may, in some aspects, include suitable steps for removing the handle layers while allowing for bonding of the engineered substrate with the CMOS wafer. The use of thru-silicon vias (TSVs) may also be absent in the final device, with suitable alternative structures being used to provide electrical connection to the resulting ultrasonic transducers.

According to another aspect of the present application, a bulk silicon wafer may be used in place of one or both of the SOI wafers described above. In such an instance, rather than removing a handle layer of the wafer, the wafer may be thinned to a desired point, for example using an etch stop represented by a doped layer of the bulk silicon wafer or using a timed etch. Thus, substantially the same structure may be achieved using either SOI or bulk silicon wafers or a combination of the two.

Accordingly, an aspect of the present application provides a wafer-level process including a first wafer bonding step to form sealed cavities by bonding together an SOI wafer and a bulk silicon wafer with cavities between them, the resulting bonded structure being considered an engineered substrate. Relatively high temperatures may be used, for example during an anneal, to facilitate achieving a strong bond. The bulk silicon wafer may be thinned, after which a second wafer bonding step may be performed to bond the engineered substrate with a CMOS wafer having integrated circuits (ICs) formed thereon. The second wafer bonding step may use a relatively low temperature to avoid damage to the ICs on the CMOS wafer. The handle layer of the SOI wafer of the engineered substrate may then be removed, leaving a membrane over the cavities of the engineered substrate.

According to an aspect of the present application, a method is provided comprising forming a plurality of cavities in a layer of silicon oxide on a first silicon device layer of a first SOI wafer, bonding the first SOI wafer with a second SOI wafer and then annealing the first and second SOI wafers, and removing a handle layer and a buried oxide layer of the first SOI wafer. The method further comprises bonding the first silicon device layer to a third wafer having at least one metal layer formed thereon, and removing a handle layer of the second SOI wafer subsequent to bonding the first silicon device layer to the third wafer.

According to an aspect of the present application, a method is provided comprising forming an engineered substrate having a plurality of sealed cavities by bonding a first wafer having open cavities formed therein with a second wafer and then thinning the first wafer to a thickness less than approximately 30 microns. The method further comprises bonding the engineered substrate with a third wafer at a temperature not exceeding 450° C., and subsequent to bonding the engineered substrate with the third wafer, thinning the second wafer to a thickness less than approximately 30 microns. In some embodiments, the second wafer, or a portion thereof, is configured to function as a membrane of an ultrasonic transducer, and therefore its thickness after

being thinned is suitable to allow vibration. By contrast, in such instances it may be desirable for the first wafer not to vibrate, and thus its thickness after being thinned may be sufficiently great to minimize or prevent vibration. In a further embodiment, both the first and second wafers may be 5 configured to vibrate, for example at different frequencies, to create a multi-frequency transducer. For example, the first membrane may be configured to resonate at half the center frequency of the second membrane.

According to an aspect of the present application, a method is provided, comprising forming a layer of silicon oxide on a first silicon device layer of a first SOI wafer, the first SOI wafer including a handle layer, a buried oxide (BOX) layer, and the first silicon device layer having a  $_{15}$ backside proximate the handle layer and a front side distal the handle layer. The method further comprises forming a plurality of cavities in the layer of silicon oxide, and bonding a second SOI wafer with the first SOI wafer such that a second silicon device layer of the second SOI wafer contacts 20 the layer of silicon oxide and seals the plurality of cavities in the layer of silicon oxide. The method further comprises annealing the first and second SOI wafers after bonding them together, the annealing utilizing a temperature above 500° C. The method further comprises removing the handle 25 layer of the first SOI wafer, etching a plurality of trenches in the first silicon device layer defining a plurality of electrode regions of the first silicon device layer corresponding to the plurality of cavities, and filling the plurality of trenches with an insulating material. The method further comprises form- 30 ing metal contacts on the backside of the first silicon device layer, at least some of the metal contacts corresponding to the plurality of electrode regions. The method further comprises bonding the first silicon device layer with a CMOS wafer having integrated circuitry formed therein using the 35 metal contacts on the backside of the first silicon device layer to contact bonding points on the CMOS wafer, wherein bonding the first silicon device layer with the CMOS wafer is performed below 450° C. The method further comprises removing a handle layer of the second SOI wafer.

According to an aspect of the present application, an apparatus is provided, comprising a CMOS wafer having an integrated circuit formed therein, and a substrate monolithically integrated with the CMOS wafer and including fewer than three silicon layers. A first silicon layer of the substrate 45 and a second silicon layer of the substrate are arranged with a plurality of cavities therebetween.

According to an aspect of the present application, an apparatus is provided, comprising a CMOS wafer having an integrated circuit formed therein, and a substrate monolithi- 50 cally integrated with the CMOS wafer, the substrate having a first side proximate the CMOS wafer and a second side distal the CMOS wafer. The substrate comprises, in order from the first side to the second side, a first silicon layer, a layer and having a plurality of cavities formed therein, and a second silicon layer directly contacting the silicon oxide and forming a membrane for the plurality of cavities.

The term "SOT wafer" as used herein has its conventional meaning, including a handle layer, a buried oxide (BOX) 60 layer, and a silicon device layer separated from the handle layer by the BOX layer.

The term "engineered substrate" as used herein refers to a substrate engineered to differ from a basic silicon wafer or standard SOT wafer. An engineered substrate may also be a 65 "composite substrate" formed by combining multiple distinct elements (e.g., multiple distinct wafers).

Throughout this disclosure, the use of the term "approximately" includes "exactly" unless context dictates otherwise. For example, describing a distance as being less than approximately 10 microns is to be understood to include the scenario in which the distance is less than 10 microns.

### BRIEF DESCRIPTION OF DRAWINGS

Various aspects and embodiments of the application will 10 be described with reference to the following figures. It should be appreciated that the figures are not necessarily drawn to scale. Items appearing in multiple figures are indicated by the same reference number in all the figures in which they appear.

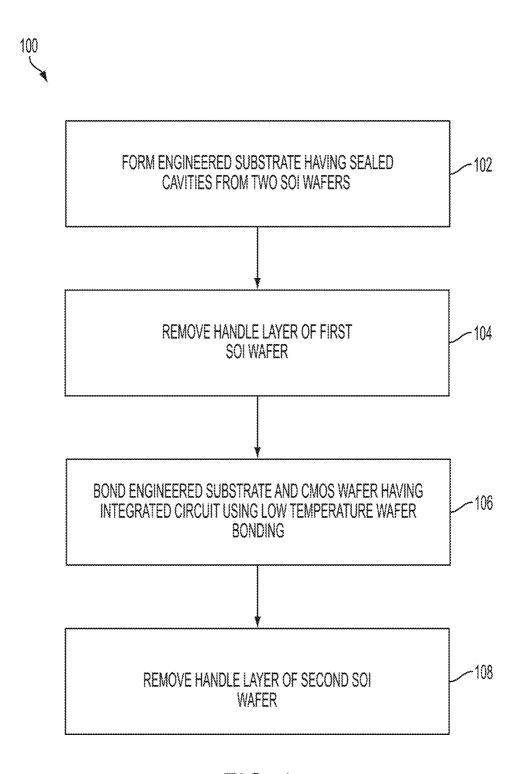

FIG. 1 is a flowchart of a fabrication sequence for fabricating an ultrasonic transducer integrated with a CMOS wafer, according to a non-limiting embodiment of the present application.

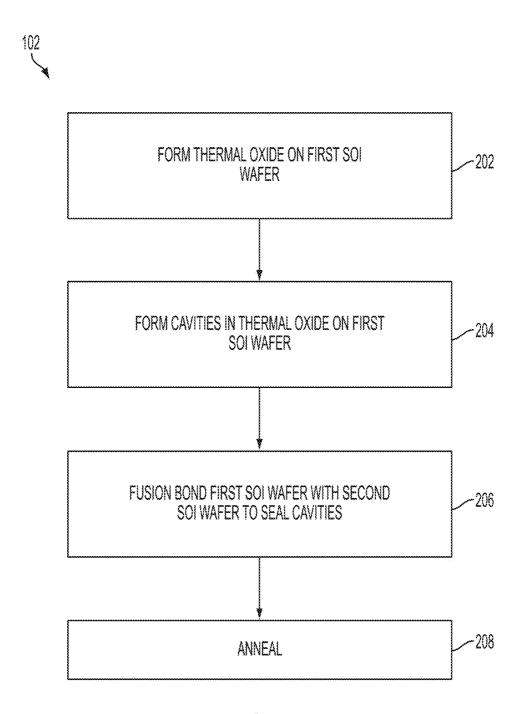

FIG. 2 is a flowchart illustrating a detailed example of a stage of the process 100 of FIG. 1.

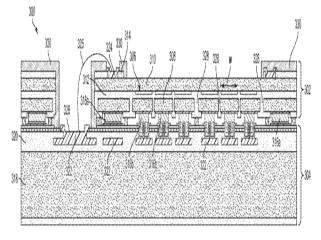

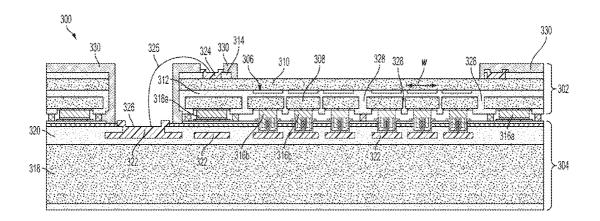

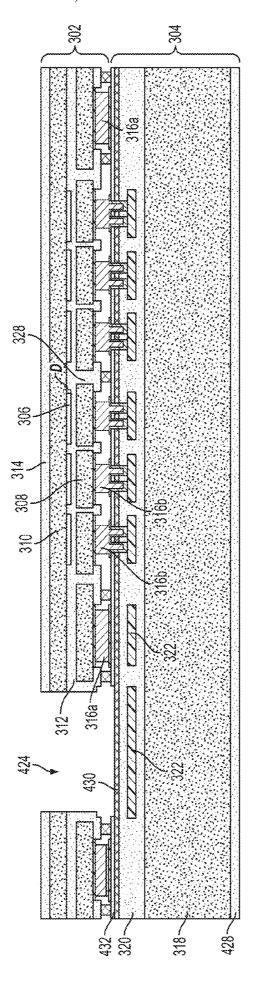

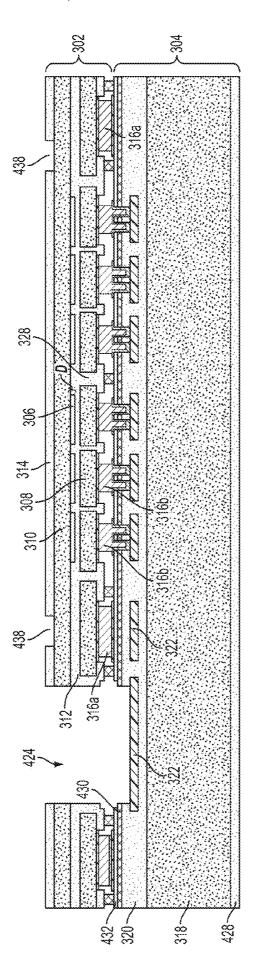

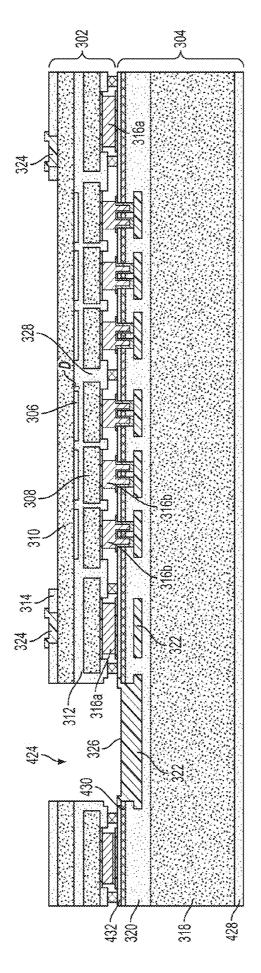

FIG. 3 is a cross-sectional view of a device including a CMOS wafer integrated with an engineered substrate having sealed cavities, according to a non-limiting embodiment of the present application.

FIGS. 4A-4T illustrate a fabrication sequence, consistent with the fabrication sequence of FIG. 1, for forming the device of FIG. 3, according to a non-limiting embodiment of the present application.

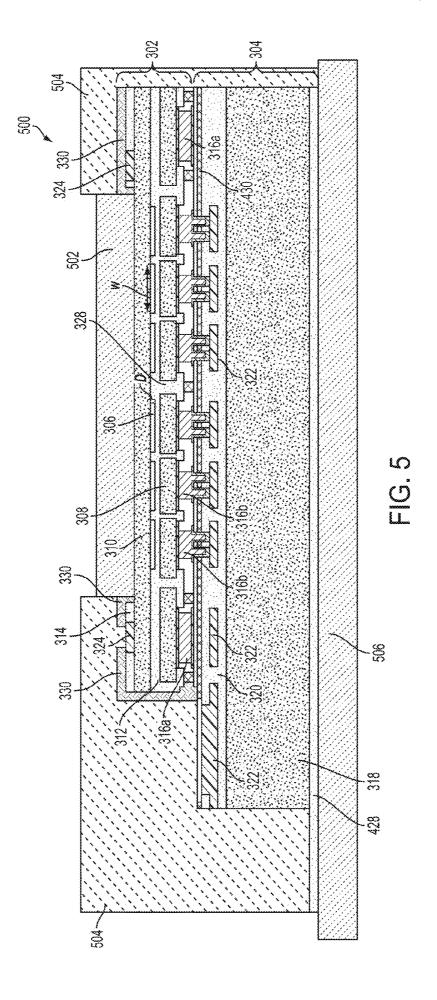

FIG. 5 is a cross-sectional view of the device of FIG. 3 with additional packaging.

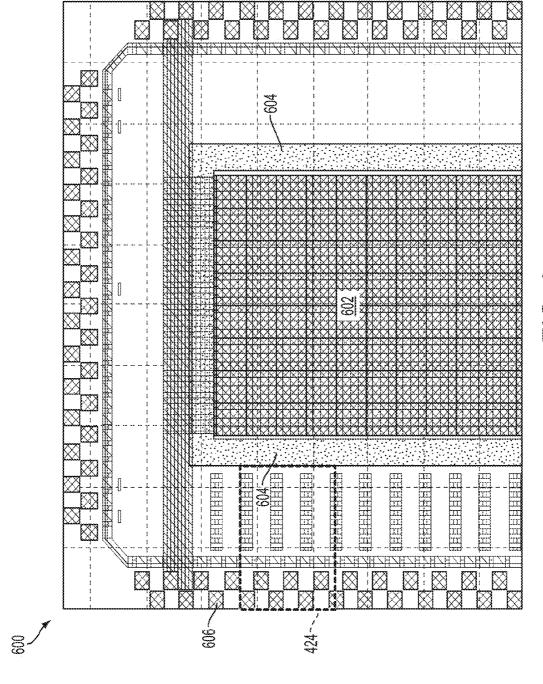

FIG. 6 is a top view of an ultrasound device including features of the device of FIG. 3, according to a non-limiting embodiment of the present application.

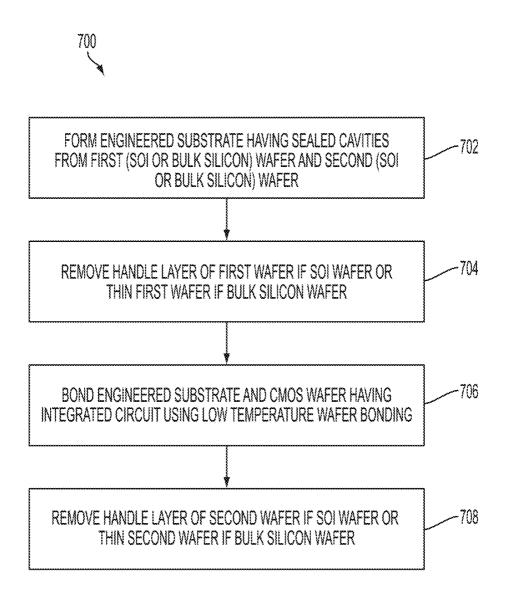

FIG. 7 is a flowchart of a fabrication sequence for fabricating an ultrasonic transducer integrated with a CMOS wafer, and encompasses the method of FIG. 1, according to a non-limiting embodiment of the present application.

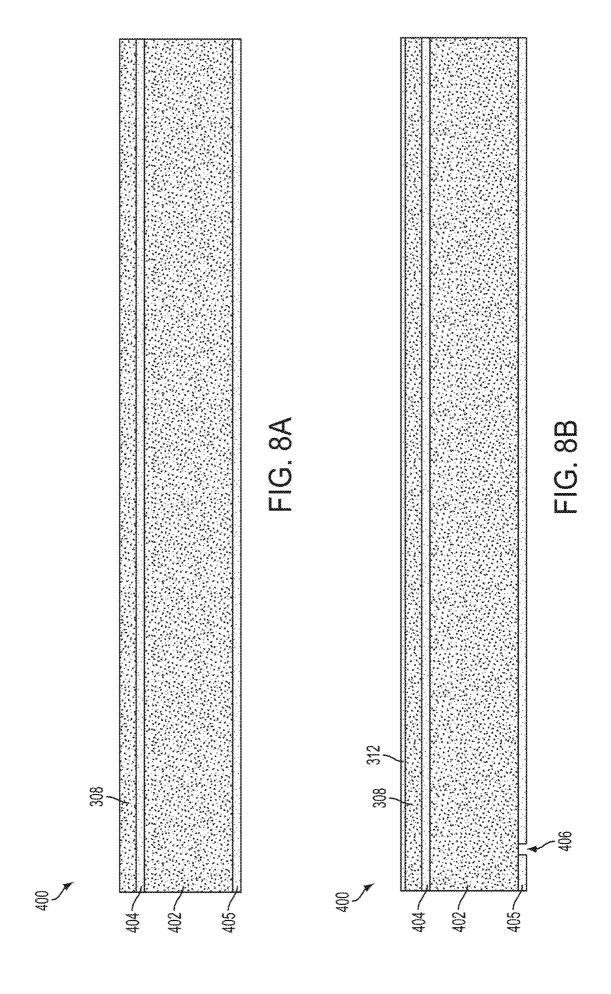

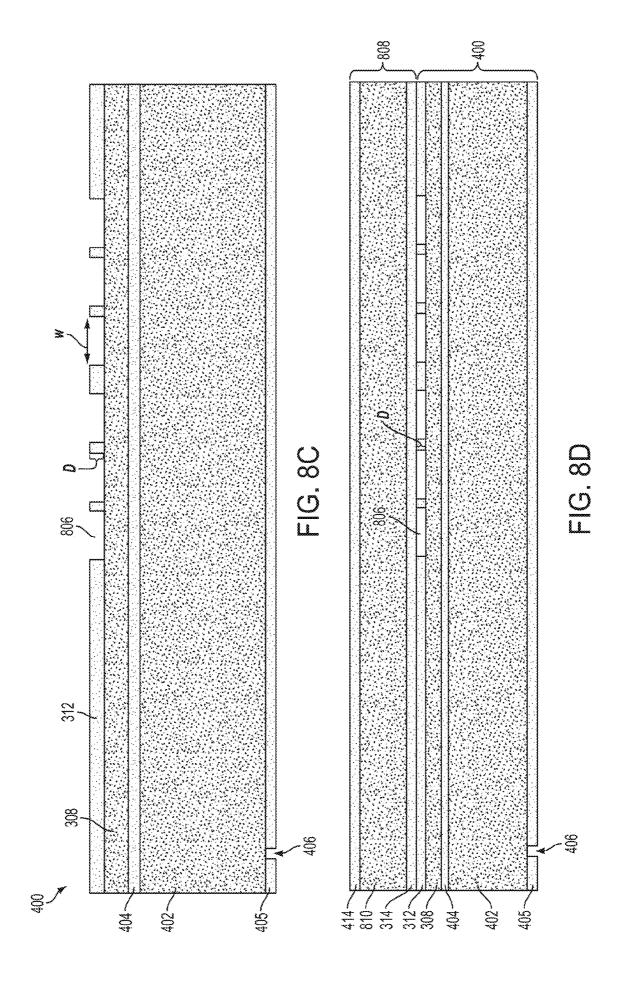

FIGS. 8A-8D illustrate a variation on part of the fabrication sequence of FIGS. 4A-4T, according to a non-limiting embodiment of the present application.

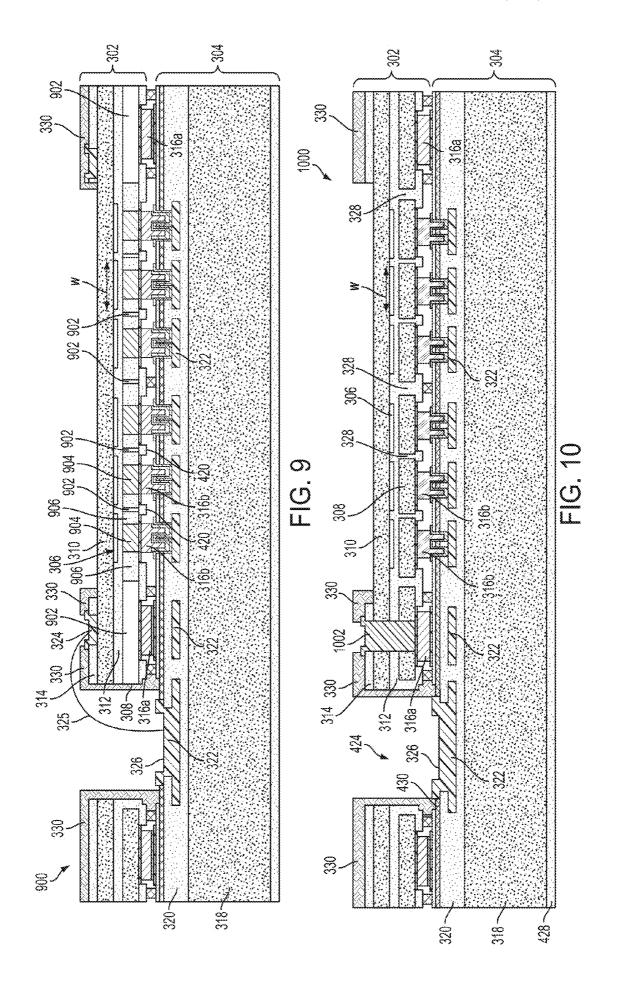

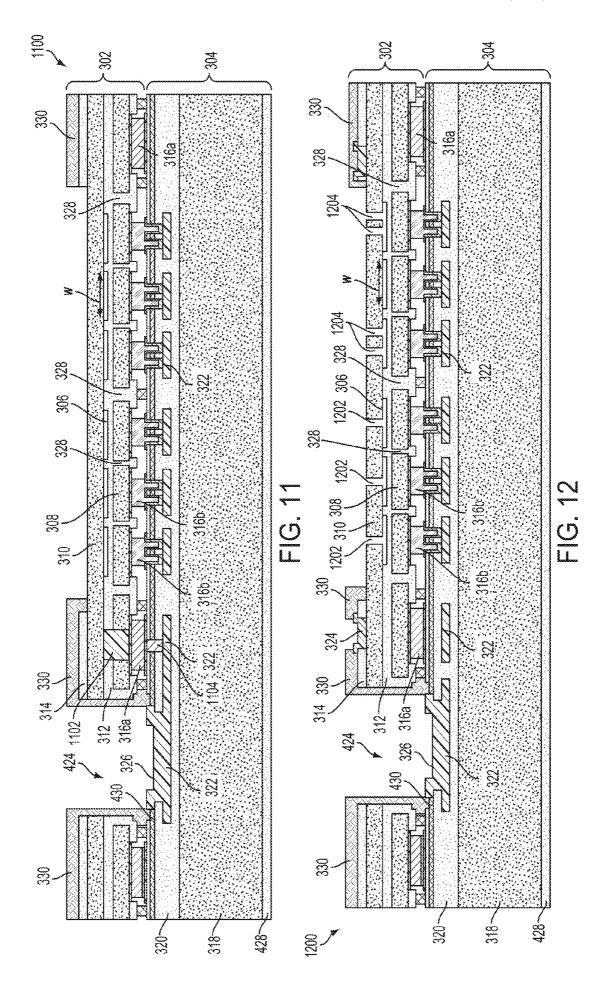

FIG. 9 illustrates an implementation of the device 300 of FIG. 3 in which patterned doping is used to define electrodes of an ultrasonic transducer, according to a non-limiting embodiment of the present application.

FIG. 10 illustrates a variation on the device 300 of FIG. 3 in which an embedded contact provides electrical connection to an ultrasonic transducer membrane, according to a non-limiting embodiment of the present application.

FIG. 11 illustrates a variation on the device 300 of FIG. 3 and an alternative to the device of FIG. 10, in which an embedded contact provides electrical connection to an ultrasonic transducer membrane, according to a non-limiting embodiment of the present application.

FIG. 12 illustrates a variation on the device 300 of FIG. layer of silicon oxide directly contacting the first silicon 55 3 in which the cavities of the ultrasonic transducers are not sealed, according to a non-limiting embodiment.

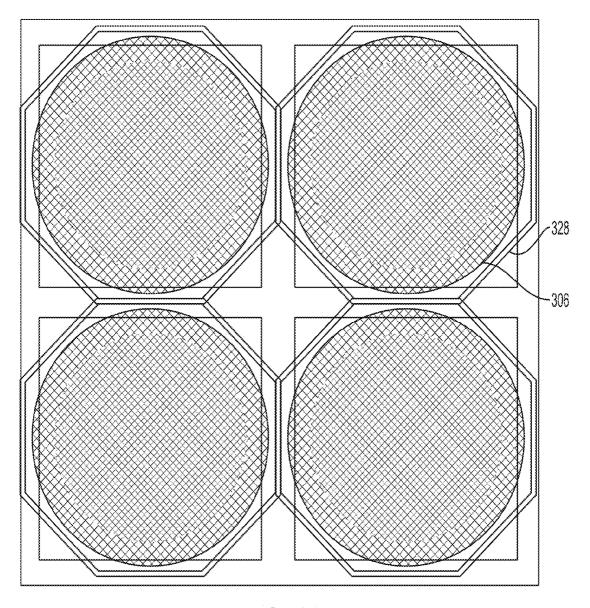

FIG. 13 is a top view illustrating an example of an isolation trench contour isolating ultrasonic transducers, according to a non-limiting embodiment.

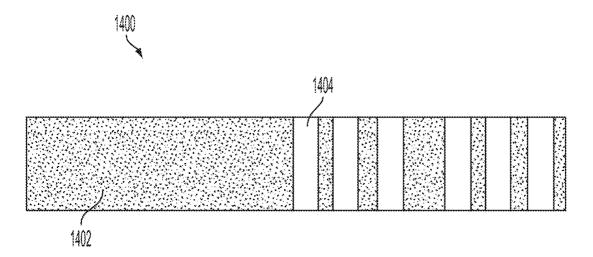

FIG. 14 illustrates a silicon wafer with TSVs, as may be used to fabricate an engineered substrate according to a non-limiting embodiment of the present application.

### DETAILED DESCRIPTION

Aspects of the present application relate to fabrication and integration of CMUTs with CMOS wafers, thereby forming

CMOS ultrasonic transducers (CUTs). The methods described provide scalable, low cost, high yield solutions to the challenge of integrating CMUTs with CMOS wafers using techniques available in commercial semiconductor foundries, thus utilizing a readily available supply chain. In 5 some embodiments, piezoelectric micromachined ultrasonic transducers (PMUTs) are used instead of, or in addition to, CMUTs.

According to an aspect of the present application, a wafer-level process is presented involving two wafer bonding steps, at least one of which may take advantage of wafer level packaging techniques. A first wafer bonding step may form sealed cavities by bonding together two silicon-oninsulator (SOI) wafers, the resulting bonded structure being considered an engineered substrate, and representing a bur- 15 ied cavity SOI wafer. Relatively high temperatures may be used, for example during an anneal, to facilitate achieving a strong bond. A handle layer of one of the two SOI wafers of the engineered substrate may then be removed, after which a second wafer bonding step may be performed to bond the 20 engineered substrate with a CMOS wafer having integrated circuits (ICs) formed thereon. The second wafer bonding step may use a relatively low temperature to avoid damage to the ICs on the CMOS wafer. The handle layer of the removed.

In some embodiments, the bonding used to form the engineered substrate with sealed cavities may include fusion bonding. In some such embodiments, the bonding may be performed at a low temperature. However, a relatively high 30 temperature anneal may be performed to ensure a strong bond. The fabrication of sealed cavities is decoupled from the thermal budget of CMOS IC fabrication since the engineered substrate is fabricated prior to integrating such structures with a CMOS wafer, thus allowing for use of a 35 relatively high temperature anneal without damaging ICs in the final device.

In some embodiments, the bonding performed to integrate the engineered substrate having sealed cavities with the CMOS wafer may include thermal compression (also 40 referred to herein as "thermocompression"), eutectic bonding, or silicide bonding (which is a bond formed by bringing silicon of one substrate into contact with metal on a second substrate under sufficient pressure and temperature to form a metal silicide, creating a mechanical and electrical bond), 45 as non-limiting examples. Such bonding may be performed at temperatures sufficiently low to avoid damage to the ICs on the CMOS wafer, while still providing for a strong bond and also facilitating electrical interconnection of the ICs on the CMOS wafer with the sealed cavities of the engineered 50 substrate. Accordingly, aspects of the present application implement low temperature (e.g., below 450° C.) wafer bonding to form ultrasonic transducer membranes on CMOS wafers. Low temperature in this context may, in some C., between 200° C. and 450° C., any temperature within that range, or any suitable temperature for preserving structures on a CMOS wafer. Thus, the bonding processes as well as other fabrication steps for integrating the sealed cavities with CMOS ICs to form CUTs may avoid any anneals above 60

According to an aspect of the present application, an apparatus including an engineered substrate is bonded with a CMOS wafer having a CMOS IC formed thereon. The engineered substrate may include multiple wafers bonded 65 together to form sealed cavities. The engineered substrate may then be bonded with the CMOS wafer. The engineered

substrate may include one substrate configured to serve as a membrane which vibrates and another substrate serving as a support, and which is not meant to vibrate. This latter substrate may be sufficiently thick (e.g., greater than approximately 5 microns) to prevent unwanted vibration, but also sufficiently thin (e.g., less than approximately 30 microns) to contribute to small device dimensions.

According to an aspect of the present application, an apparatus including an engineered substrate is bonded with a CMOS wafer having a CMOS IC formed thereon and the engineered substrate includes multiple wafers bonded together to form sealed cavities and configured to vibrate. One wafer of the engineered substrate may be configured to resonate at a first frequency and a second wafer of the engineered substrate may be configured to resonate at a different frequency. Thus, a multi-frequency ultrasound transducer may be created. One frequency may be used for transmit operations and the other for receive operations, as a non-limiting example. For example, a first, lower frequency may be used for transmit operations and a second, higher frequency (e.g., twice the frequency of the lower frequency) may be used for receive operations, as a nonlimiting example.

The aspects and embodiments described above, as well as second SOI wafer of the engineered substrate may then be 25 additional aspects and embodiments, are described further below. These aspects and/or embodiments may be used individually, all together, or in any combination of two or more, as the application is not limited in this respect.

> As described, aspects of the present application provide a process for fabricating CUTs having integrated CMUTs and CMOS ICs and utilizing two separate bonding steps. The process may allow for a resulting structure to include a relatively thin engineered substrate having cavities formed between two silicon layers monolithically integrated with a CMOS wafer having CMOS ICs thereon. FIG. 1 illustrates an example of the process.

> As shown, the method 100 may begin at stage 102 with the formation of an engineered substrate having sealed cavities. Two SOI wafers may be bonded together, for example with the silicon device layers of the two SOI wafers facing each other. One or both of the two SOI wafers may have a plurality of cavities formed therein, such that bonding the two SOI wafers together may result in sealed cavities suitable for use as the cavities of CMUTs. To ensure a strong bond between the two SOI wafers, high temperature processing may be used. For example, a high temperature anneal may be used subsequent to a low temperature wafer bond, such as a low temperature fusion bond. Thus, a combination of high and low temperatures may be used in forming the engineered substrate in some embodiments. High temperature in this context may, in some embodiments, be above 450° C., a temperature threshold above which CMOS ICs would typically be damaged.

The bonding of the two SOI wafers may be performed in embodiments, be below 450° C., below 400° C., below 350° 55 vacuum so that the resulting sealed cavities have a low pressure (e.g., a pressure between approximately  $1 \times 10^{-3}$ Torr and approximately  $1 \times 10^{-5}$  Torr, a pressure less than approximately 1 atmosphere, or any other suitable pressure). In some embodiments, the bond is performed in an inert ambient, for example using  $N_2$ .

At stage 104, a handle layer of a first of the two SOI wafers may be removed, in any suitable manner, such as by a combination of grinding followed by etching. As a result, the engineered substrate may, at this point in the process, include three silicon layers: the silicon device layer of the first SOI wafer, the silicon device layer of the second SOI wafer, and the handle layer of the second SOI wafer.

Although the silicon device layers of the SOI wafers may be thin, for example being 20 microns or less in thickness (e.g., 10 microns, 5 microns, 2.5 microns, 2 microns, 1 micron, or less, including any range or value within the range less than 20 microns), Applicants have appreciated that the handle 5 layer of the second SOI wafer may provide sufficient structural support to allow for further processing of the engineered substrate.

At stage 106, the engineered substrate may be bonded with a CMOS wafer having integrated circuitry to form an 10 integrated device. The bonding may be performed at temperatures below 450° C. to prevent damage to the circuitry of the CMOS wafer. In some embodiments, thermocompression bonding is used, although alternatives including eutectic bonding and silicide bonding are also possible, 15 among others. The silicon device layer of the first SOI wafer may be arranged proximate the bonding surface of the CMOS wafer, for example by bonding a backside of the silicon device layer of the first SOI wafer with the CMOS wafer. Thus, the resulting structure may include, in order, a 20 CMOS wafer, a first silicon device layer, a second silicon device layer of the second SOI wafer, and the handle layer of the second SOI wafer.

At stage 108, the handle layer of the second SOI wafer of the engineered substrate may be removed, in any suitable 25 manner, for example by a combination of grinding followed by etching. As a result, in some embodiments, the engineered substrate may include only two silicon layers (the two silicon device layers of the SOI wafers used to form the engineered substrate) between which are the cavities. Hav- 30 ing only two silicon layers may, among other benefits, facilitate achieving thin dimensions for the engineered substrate. For example, the engineered substrate at this stage may be relatively thin, for example being less than 100 microns in total thickness, less than 50 microns in total 35 thickness, less than 30 microns in total thickness, less than 20 microns in total thickness, less than 10 microns in total thickness (e.g., approximately 8 microns or approximately 5 microns), or any other suitable thickness. Structures with such small thicknesses lack sufficient structural rigidity to 40 survive many fabrication processes, including wafer bonding. Thus, according to some embodiments of the present application, the engineered substrate is not reduced to such dimensions until after bonding with the CMOS wafer, which can provide mechanical support to the engineered substrate. 45 Moreover, as described further below in connection with FIG. 7, in some embodiments it is preferable for one of the two wafers of the engineered substrate to be sufficiently thick to minimize or prevent vibration of that wafer. Thus, while the engineered substrate may be thin, it may have a 50 thickness of at least, for example, 4 microns in some embodiments, at least 5 microns in some embodiments, at least 7 microns in some embodiments, at least 10 microns in some embodiments, or other suitable thickness to prevent unwanted vibration.

Electrical connections may be made between the ICs on the CMOS wafer and the sealed cavities of the engineered substrate to provide functioning ultrasonic transducers. For example, the silicon device layer of the engineered substrate proximate the CMOS wafer may serve as a bottom electrode 60 for the ultrasonic transducers while the silicon device layer distal the CMOS wafer may serve as a membrane, and electrical connections may be made to these structures as appropriate to control operation of the membrane (e.g., to actuate (or induce vibration of) the membrane by applying 65 a voltage). In some embodiments, electrical connection may be made (or may be at least partially completed) by the

8

bonding of stage 106. For example, bonding the engineered substrate with the CMOS wafer may involve using conductive bonding materials (e.g., metals) which serve as both bonding materials and electrical connections. Alternatively, or additionally, electrical connections may be made subsequent to bonding of the engineered substrate with the CMOS wafer. For example, bonding the engineered substrate with the CMOS wafer may form electrical connections to a bottom electrode of the ultrasonic transducer, and on-chip metal interconnect and/or wire bonds may be formed subsequently to provide electrical connection to top electrodes or membrane of the ultrasonic transducer.

FIG. 2 provides further detail with respect to an example of the implementation of stage 102 of method 100, although it should be appreciated that alternative manners for implementing stage 102 are possible. In the non-limiting example shown, the cavities of the engineered substrate may be formed by first forming cavities in a thermal oxide (an oxide formed by thermal oxidation) on a first of the two SOI wafers. That is, a first SOI wafer may include a handle layer (e.g., a handle silicon layer), a buried oxide (BOX) layer, and a silicon device layer, on which a thermal oxide may be formed at stage 202 by thermally oxidizing the silicon device layer. It should be appreciated that a thermal oxide represents a non-limiting example of an oxide, and that other types of oxides may alternatively be formed.

At stage 204, cavities may be formed in the thermal oxide of the first SOI wafer, for example by any suitable etching. In some embodiments, the cavities do not completely reach the silicon device layer, such that a (thin) layer of oxide defines the cavity boundaries. However, in other embodiments the cavities may extend to the surface of the silicon device layer or further. In some embodiments, the thermal oxide may be etched to the surface of the silicon device layer and then an additional layer of thermal oxide may be formed such that the cavities are defined by a layer of oxide.

At stage 206, the first SOI wafer, having the cavities formed in the thermal oxide thereon, may be bonded with a second SOI wafer, for example using a low temperature fusion bond. In some embodiments, the second SOI wafer includes a handle layer (e.g., a handle silicon layer), a BOX layer, and a silicon device layer, and the bonding involves making direct contact between the thermal oxide layer of the first SOI wafer and the silicon device layer of the second SOI wafer, thus forming a Si—SiO<sub>2</sub> bond. In an alternative embodiment, the second SOI wafer may include an oxide layer on the silicon device layer, such that bonding the first and second SOI wafers together may involve making direct contact with oxide layers of the two SOI wafers, thus forming a SiO<sub>2</sub>—SiO<sub>2</sub> bond.

As a result of bonding the two SOI wafers together, the cavities in the first SOI wafer may be sealed. For example, the cavities may be vacuum sealed in some embodiments, although in other embodiments a vacuum seal may not be formed.

At stage 208, an anneal may be performed to facilitate formation of a strong bond between the two SOI wafers. As described previously, in some embodiments the anneal may be a high temperature anneal, for example being performed between approximately 500° C. and approximately 1,500° C. (e.g., 500° C., 750° C., 1,000° C., 1,250° C.), including any temperature or range of temperatures within that range (e.g., between approximately 500° C. and approximately 1,200° C.), although other temperatures may alternatively be used. In some embodiments, an anneal may be performed between approximately 300° C. and approximately 1,200° C.

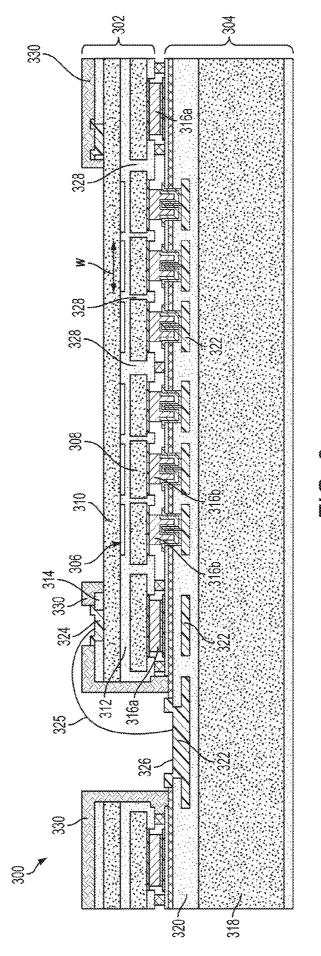

FIG. 3 is a cross-sectional view of an ultrasound device including a CMOS wafer integrated with an engineered substrate having sealed cavities, according to a non-limiting embodiment of the present application. The device 300 may be formed by implementing the methods of FIGS. 1-2.

The device 300 includes an engineered substrate 302 integrated with a CMOS wafer 304. The engineered substrate 302 includes a plurality of cavities 306 formed between a first silicon device layer 308 and a second silicon device layer 310. A silicon oxide layer 312 (e.g., a thermal 10 silicon oxide—a silicon oxide formed by thermal oxidation of silicon) may be formed between the first and second silicon device layers 308 and 310, with the cavities 306 being formed therein. In this non-limiting example, the first silicon device layer 308 may be configured as a bottom 15 electrode and the second silicon device layer 310 may be configured as a membrane. Thus, the combination of the first silicon device layer 308, second silicon device layer 310, and cavities 306 may form an ultrasonic transducer (e.g., a CMUT), of which six are illustrated in this non-limiting 20 cross-sectional view. To facilitate operation as a bottom electrode or membrane, one or both of the first silicon device layer 308 and second silicon device layer 310 may be doped to act as conductors, and in some cases are highly doped (e.g., having a doping concentration greater than 10<sup>15</sup> dop- 25 represented by second silicon device layer 310 is provided ants/cm<sup>3</sup> or greater).

The engineered substrate 302 may further include an oxide layer 314 on top of the second silicon device layer 310, which may represent the BOX layer of an SOI used to form the engineered substrate. The oxide layer 314 may function as a passivation layer in some embodiments and, as shown, may be patterned to be absent over the cavities 306. Contacts 324, described further below, and passivation layer 330 may be included on the engineered substrate. The passivation layer 330 may be patterned to allow access to 35 one or more contacts 324, and may be formed of any suitable passivating material. In some embodiments, the passivation layer 330 is formed of Si<sub>3</sub>N<sub>4</sub> and in some embodiments is formed by a stack of SiO2 and Si3N4, although alternatives

The engineered substrate 302 and CMOS wafer 304 may be bonded together at bond points 316a and 316b. The bond points may represent eutectic bond points, for example formed by a eutectic bond of a layer on engineered substrate 302 with a layer on CMOS wafer 304, or may be any other 45 suitable bond type described herein (e.g., a silicide bond or thermocompression bond). In some embodiments, the bond points 316a and 316b may be conductive, for example being formed of metal. The bond points 316a may function solely as bond points in some embodiments, and in some embodi- 50 ments may form a seal ring, for example hermetically sealing the ultrasonic transducers of the device 300 as described further below in connection with FIG. 6. In some embodiments, the bond points 316a may define a seal ring that also provides electrical connection between the engi- 55 neered substrate and CMOS wafer. Similarly, the bond points 316b may serve a dual purpose in some embodiments, for example serving as bond points and also providing electrical connection between the ultrasonic transducers of the engineered substrate 302 and the IC of the CMOS wafer 60 304. In those embodiments in which the engineered substrate is not bonded with a CMOS wafer, examples of which are described further below, the bond points 316b may provide electrical connection to any electrical structures on the substrate to which the engineered substrate is bonded. 65

The CMOS wafer 304 includes a base layer (e.g., a bulk silicon wafer) 318, an insulating layer 320, and a metalli10

zation 322. The metallization 322 may be formed of aluminum, copper, or any other suitable metallization material, and may represent at least part of an integrated circuit formed in the CMOS wafer. For example, metallization 322 may serve as a routing layer, may be patterned to form one or more electrodes, or may be used for other functions. In practice, the CMOS wafer 304 may include multiple metallization layers and/or post-processed redistribution layers, but for simplicity only a single metallization is illustrated.

The bond points 316b may provide electrical connection between the metallization 322 of CMOS wafer 304 and the first silicon device layer 308 of the engineered substrate. In this manner, the integrated circuitry of the CMOS wafer 304 may communicate with (e.g., send electrical signals to and/or receive electrical signals from) the ultrasonic transducer electrodes and/or membranes of the engineered substrate. In the illustrated embodiments, a separate bond point **316***b* is illustrated as providing electrical connection to each sealed cavity (and therefore for each ultrasonic transducer), although not all embodiments are limited in this manner. For example, in some embodiments, the number of electrical contacts provided may be less than the number of ultrasonic

Electrical contact to the ultrasonic transducer membranes in this non-limiting example by contacts 324, which may be formed of metal or any other suitable conductive contact material. In some embodiments, an electrical connection may be provided between the contacts 324 and the bond pad 326 on the CMOS wafer. For example, a wire bond 325 may be provided or a conductive material (e.g., metal) may be deposited over the upper surface of the device and patterned to form a conductive path from the contacts 324 to the bond pad 326. However, alternative manners of connecting the contacts 324 to the IC on the CMOS wafer 304 may be used. In some embodiments an embedded via may be provided from the first silicon device layer 308 to a bottom side of the second silicon device layer 310, thus obviating any need for the contacts 324 on the topside of the second silicon device layer 310. An example is described below in connection with FIG. 11. In such embodiments, suitable electrical isolation may be provided relative to any such via to avoid electrically shorting the first and second silicon device layers.

The device 300 also includes isolation structures (e.g., isolation trenches) 328 configured to electrically isolate groups of ultrasonic transducers (referred to herein as "ultrasonic transducer elements") or, as shown in FIG. 3, individual ultrasonic transducers. The isolation structures 328 may include trenches through the first silicon device layer 308 that are filled with an insulating material in some embodiments. Alternatively, the isolation structures 328 may be formed by suitable doping as described further below in connection with FIG. 9. Isolation structures 328 are optional.

Various features of the device 300 are now noted. For instance, it should be appreciated that the engineered substrate 302 and CMOS wafer 304 wafer may be monolithically integrated, thus providing for monolithic integration of ultrasonic transducers with CMOS ICs. In the illustrated embodiment, the ultrasonic transducers are positioned vertically (or stacked) relative to the CMOS IC, which may facilitate formation of a compact ultrasound device by reducing the chip area required to integrate the ultrasonic transducers and CMOS IC.

Additionally, the engineered substrate 302 includes only two silicon layers 308 and 310, with the cavities 306 being formed between them. The first silicon device layer 308 and

second silicon device layer 310 may be thin, for example each being less than 50 microns in thickness, less than 30 microns in thickness, less than 20 microns in thickness, less than 10 microns in thickness, less than 5 microns in thickness, less than 3 microns in thickness, or approximately 2 5 microns in thickness, among other non-limiting examples. Such dimensions contribute to achieving a small device and may facilitate making electrical contact to the ultrasonic transducer membrane (e.g., second silicon device layer 310) without the need for TSVs. TSVs are typically complicated and costly to implement, and thus avoiding use of them may increase manufacturing yield and reduce device cost. Moreover, forming TSVs requires special fabrication tools not possessed by many commercial semiconductor foundries, 15 and thus avoiding the need for such tools can improve the supply chain for forming the devices, making them more commercially practical than if TSVs were used.

The engineered substrate 302 as shown in FIG. 3 may be relatively thin, for example being less than 100 microns in total thickness, less than 50 microns in total thickness, less than 30 microns in total thickness, less than 20 microns in total thickness, or any other suitable thickness. The significance of such thin dimensions has been described previously herein in terms of 25 the lack of structural integrity and the inability to perform various types of fabrication steps (e.g., wafer bonding) with layers of such thin dimensions. Thus, it is noteworthy that such thin dimensions may be achieved in the device 300.

Also, the silicon device layers **308** and **310** may be 30 formed of single crystal silicon. The mechanical and electrical properties of single crystal silicon are understood, and thus the use of such materials in an ultrasonic transducer (e.g., as the membrane of a CMUT) may facilitate design and control of the ultrasonic transducer behavior.

Another feature worth noting is that there is a gap between parts of the CMOS wafer 304 and the first silicon device layer 308 since the two are bonded at discrete bond points 316b rather than by a bond covering the entire surface of the CMOS wafer 304. The significance of this gap is that the 40 first silicon device layer 308 may vibrate if it is sufficiently thin. Such vibration may be undesirable, for instance representing unwanted vibration in contrast to the desired vibration of the second silicon device layer 310. Accordingly, it is beneficial in at least some embodiments for the 45 first silicon device layer 308 to be sufficiently thick to minimize or avoid such vibration.

In alternative embodiments, it may be desirable for both the first and second silicon device layers 308 and 310 to vibrate. For instance, they may be constructed to exhibit 50 different resonance frequencies, thus creating a multi-frequency device. The multiple resonance frequencies (which may be related as harmonics in some embodiments) may be used, for example, in different operating states of an ultrasound transducer. For example, the first silicon device layer 55 308 may be configured to resonant at half the center frequency of the second silicon device layer 310.

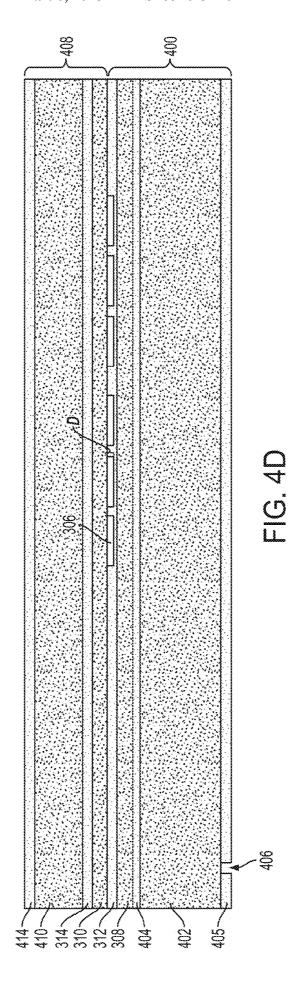

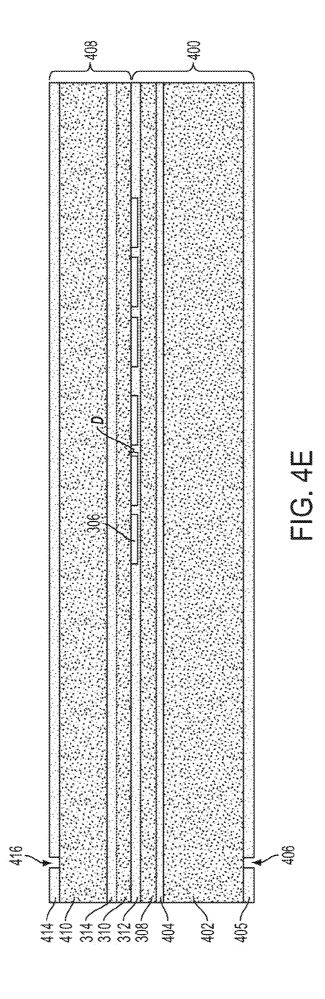

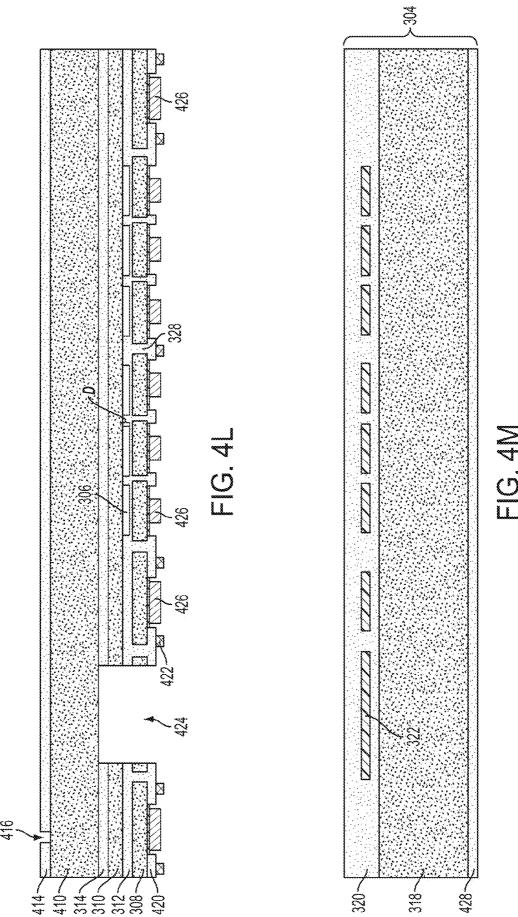

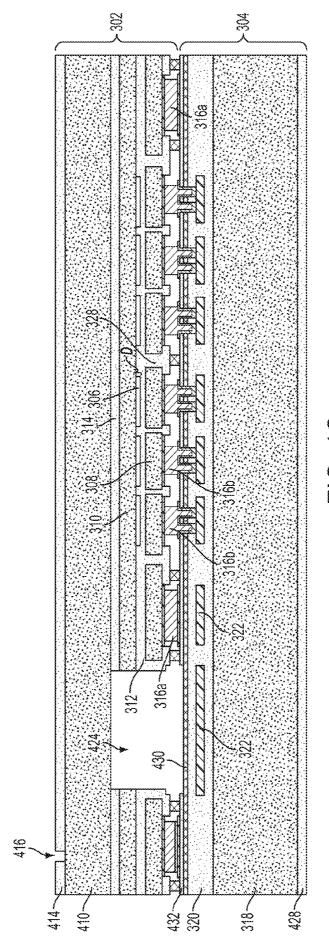

FIGS. 4A-4T illustrate a fabrication sequence for forming the device 300 of FIG. 3 consistent with the fabrication sequence of FIG. 1, according to a non-limiting embodiment 60 of the present application. Structures previously described in connection with FIG. 3 retain the same reference numbers in FIGS. 4A-4T.

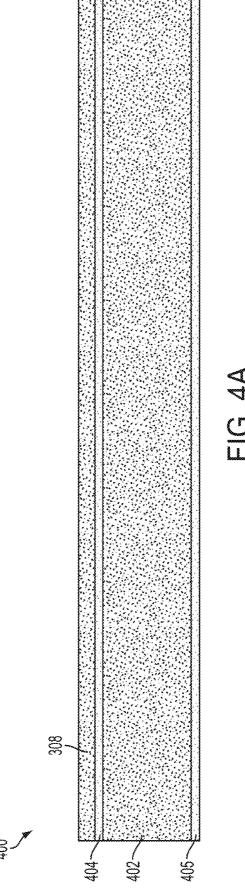

Initially, the formation of the engineered substrate is described, beginning as shown in FIG. 4A with a first SOI 65 wafer 400. The SOI wafer 400 includes a handle layer 402 (e.g., a silicon handle layer), a BOX layer 404, and first

12

silicon device layer 308. An oxide layer 405 may also be provided on the backside of the handle layer 402.

The first silicon device layer 308 may be formed of single crystal silicon and, as previously described, may be doped in some embodiments. As previously described in connection with FIG. 3, the first silicon device layer 308 may serve as a bottom electrode of an ultrasonic transducer, and thus suitable doping may provide desired electrical behavior. Also, using a doped silicon device layer avoids the need for using TSVs in some embodiments. In some embodiments, the first silicon device layer 308 may be highly doped P-type, although N-type doping may alternatively be used. When doping is used, the doping may be uniform or may be patterned (e.g., by implanting in patterned regions), for example to provide isolated electrodes as described further below in connection with FIG. 7. The first silicon device layer 308 may be doped already when the SOI wafer is procured, or may be doped by ion implantation, as the manner of doping is not limiting.

In some embodiments, the first silicon device layer 308 may be formed of polysilicon or amorphous silicon. In either case the first silicon device layer 308 may be doped or not as appropriate to provide desired electrical behavior.

As shown in FIG. 4B, the silicon oxide layer 312 may be formed on the SOI wafer 400. The silicon oxide layer 312 may be used to at least partially define the cavities 306 of the ultrasonic transducers, and thus may have any suitable thickness to provide for a desired cavity depth. Silicon oxide layer 312 may be a thermal silicon oxide, but it should be appreciated that oxides other than thermal oxide may alternatively be used.

FIG. 4B also illustrates that an alignment mark 406 may be formed (e.g., by suitable patterning of the oxide layer 405). As will be explained further below in connection with FIG. 4E, the alignment mark 406 may be later transferred to the second SOI wafer since the handle layer 402 will be removed.

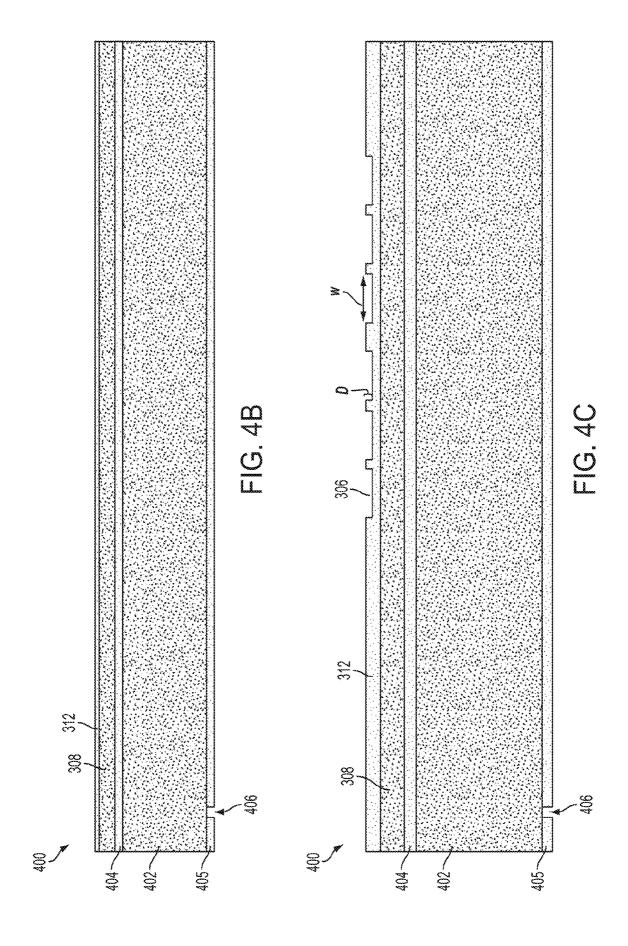

As shown in FIG. 4C, the silicon oxide layer 312 may be patterned to form cavities 306, using any suitable technique (e.g., using a suitable etch). In this non-limiting embodiment, the cavities 306 do not extend to the surface of the first silicon device layer 308, although in alternative embodiments they may. In some embodiments, the silicon oxide layer 312 may be etched to the surface of the silicon device layer and then an additional layer of oxide (e.g., thermal silicon oxide) may be formed such that the cavities are defined by a layer of oxide. In some embodiments, the cavities may extend into the first silicon device layer 308. Also, in some embodiments structures such as isolation posts can be formed within the cavity.

Any suitable number and configuration of cavities 306 may be formed, as the aspects of the application are not limited in this respect. Thus, while only six cavities 306 are illustrated in the non-limiting cross-sectional view of FIG. 4C, it should be appreciated that many more may be formed in some embodiments. For example, an array of cavities 306 may include hundreds of cavities, thousands of cavities, or more to form an ultrasonic transducer array of a desired size.

The cavities 306 may have a depth D designed for desired operation of the ultrasonic transducers ultimately formed, for example in terms of frequency of operation. In some embodiments, the depth D may be approximately 2 microns, approximately 0.5 microns, approximately 0.25 microns, between approximately 0.05 microns and approximately 10 microns, between approximately 0.1 microns and approximately 5 microns, between approximately 0.5 microns and

approximately 1.5 microns, any depth or range of depths in between, or any other suitable depth.

The cavities 306 may have a width W, also illustrated in FIG. 3. Non-limiting examples of values for W are described further below. The width dimension may also be used to 5 identify the aperture size of the cavity, and thus the cavities 306 may have apertures of any of the values described herein for width W.

The cavities 306 may take one of various shapes (viewed from a top side) to provide a desired membrane shape when the ultrasonic transducers are ultimately formed. For example, the cavities 306 may have a circular contour or a multi-sided contour (e.g., a rectangular contour, a hexagonal contour is illustrated in FIG. 13, described below.

As shown in FIG. 4D, the first SOI wafer 400 may be bonded with a second SOI wafer 408 including a second handle layer (e.g., a silicon handle layer) 410, the oxide layer 314 (e.g., a BOX layer), and the second silicon device layer 20 310. The second SOI wafer 408 may additionally include an oxide layer 414. The bonding may be performed at a low temperature (e.g., a fusion bond below 450° C.), but may be followed by an anneal at a high temperature (e.g., at greater than 500° C.) to ensure sufficient bond strength. In those 25 embodiments in which the first and/or second silicon device layers 308 and 310 are doped, the anneal may also serve to activate the doping, meaning that a single anneal may perform multiple functions. In the illustrated embodiment, the bond may be a Si—SiO<sub>2</sub> bond, although alternatives are 30 possible. For example, in some embodiments the second SOI wafer 408 may include an oxide layer (e.g., a thermal silicon oxide) on the second silicon device layer 310, such that the bond between the first and second SOI wafers 400 and 408 may be a SiO<sub>2</sub>—SiO<sub>2</sub> bond.

As with the first silicon device layer 308, the second silicon device layer 310 may be single crystal silicon, polysilicon, or amorphous silicon, and may be doped in some embodiments. The doping may avoid the need to form TSVs to provide electrical connectivity, and may be of any 40 suitable type and level.

As shown in FIG. 4E, the alignment mark 406 may be transferred to the second SOI wafer as alignment mark 416.

Then, as shown in FIG. 4F, the oxide layer 405, handle layer 402, and BOX layer 404 may be removed, in any 45 suitable manner. For example, grinding, etching, or any other suitable technique or combination of techniques may be used. As a result, the only layers remaining from the first SOI wafer 400 include the first silicon device layer 308 and the silicon oxide layer 312. As previously described in 50 connection with FIG. 3, those layers may be thin. However, because they are bonded to the second SOI wafer 408 with its corresponding handle layer, sufficient structural integrity may be retained for further processing.

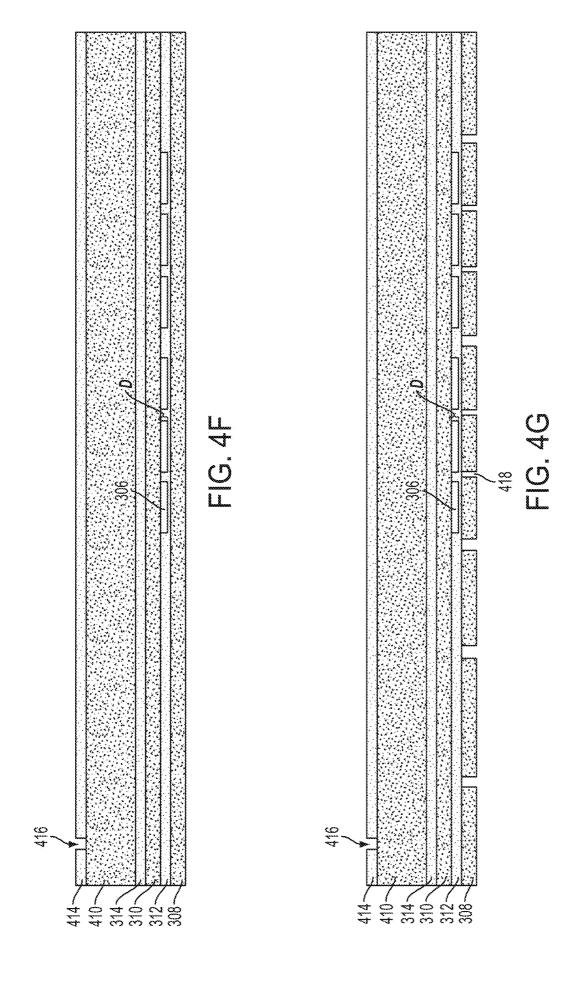

As previously described in reference to isolation struc- 55 tures 328 of FIG. 3, in some embodiments it may be desirable to electrically isolate one or more ultrasonic transducers of the device 300. Thus, as shown in FIG. 4G, one or more isolation trenches 418 may be formed in the first silicon device layer 308. In the illustrated embodiment, the 60 isolation trenches 418 extend from a backside of the silicon device layer 308 to silicon oxide layer 312, and are narrower (in the direction of left to right in the figure) than the portion(s) of the overlying silicon oxide layer 312 to which each isolation trench 418 makes contact to prevent inadver- 65 tently punching through the silicon oxide layer 312 into the cavities 306. Thus, the isolation trenches 418 do not impact

14

the structural integrity of the cavities 306. However, alternative configurations are possible.

FIG. 4H illustrates that the isolation trenches 418 may be filled with an insulating material 420 (e.g., silicon oxide) using any suitable technique (e.g., a suitable deposition). It should be noted that in the embodiment illustrated, the insulating material 420 completely fills the isolation trenches 418 and does not simply line the trenches 418, which may further contribute to the structural integrity of the device at this stage, rendering it more suitable for further processing.

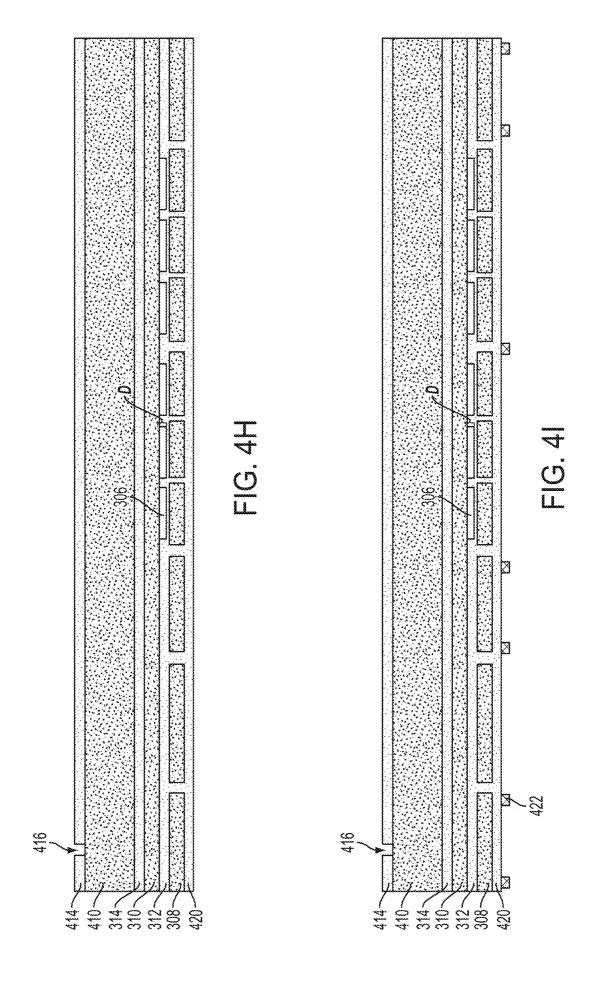

In FIG. 4I, flow stop features 422 are optionally formed on the lower surface of the insulating material 420, for example using any suitable deposition and patterning techcontour, an octagonal contour). An example of a circular 15 nique. The flow stop features may perform one or more functions. For example, they may prevent undesirable flow of metal layers subsequently deposited. Alternatively or additionally, the flow stop features may provide a desired gap between the engineered substrate and CMOS wafer when later bonded. Thus, any suitable number and positioning of the flow stop features 422 may be provided to achieve one or both functions, and the flow stop features 422 may be formed of any suitable material. For example, the flow stop features 422 may be formed of silicon nitride (SiN) in some non-limiting embodiments. However, as described above, the use of flow stop features 422 is optional. For example, such features may be omitted in some embodiments, for example when using thermal compression for bonding the engineered substrate with another wafer.

> As shown in FIG. 4J, the insulating material 420 may be patterned (using any suitable etch technique) in preparation for forming bonding locations for later bonding of the engineered substrate with a CMOS wafer. Also, the patterning may further define the isolation structures 328 described 35 previously in connection with FIG. 3.

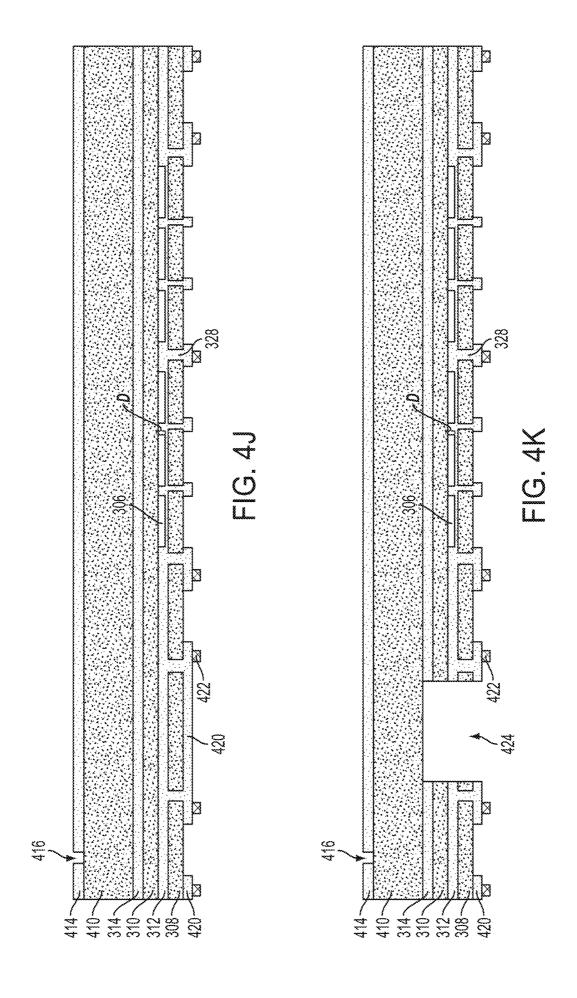

In FIG. 4K, a clear out region 424 may be formed through the first silicon device layer 308, the silicon oxide layer 312, the second silicon device layer 310, and the oxide layer 314. The clear out region 424 may isolate groups of ultrasonic transducers from each other (e.g., separating distinct ultrasonic transducer arrays), as will be described further below in connection with FIG. 6. For example, in some embodiments the first and second silicon device layers 308 and 310 are retained only in a region corresponding to an ultrasonic transducer array, with the clear out region 424 separating ultrasonic transducer arrays. The clear out region 424 may provide easier access to the CMOS wafer at a periphery of the ultrasonic transducer array, for example allowing for access to bond pads or other electrical connection features. The clear out region 424 may be formed in any suitable manner, for example using one or more of grinding, deep reactive ion etching (DRIE) and plasma etches for etching the silicon device layers and oxide layers. In some embodiments, grinding followed by DRIE is used. Alternative manners of forming the clear out region 424 are possible.

Bonding material 426 may then be formed on the engineered substrate in preparation for bonding the engineered substrate with a CMOS wafer, as shown in FIG. 4L. The type of bonding material 426 may depend on the type of bond to be formed. For example, the bonding material 426 may be a metal suitable for thermocompression bonding, eutectic bonding, or silicide bonding. In some embodiments, the bonding material may be conductive so that electrical signals may be communicated between the engineered substrate and the CMOS wafer as previously described in connection with FIG. 3 and bond points 316b. For example, in some embodiments the bonding material 426 may be gold

and may be formed by electroplating. In some embodiments, materials and techniques used for wafer level packaging may be applied in the context of bonding the engineered substrate with the CMOS wafer. Thus, for example, stacks of metals selected to provide desirable adhesion, interdiffusion barrier functionality, and high bonding quality may be used, and the bonding material **426** may include such stacks of metals

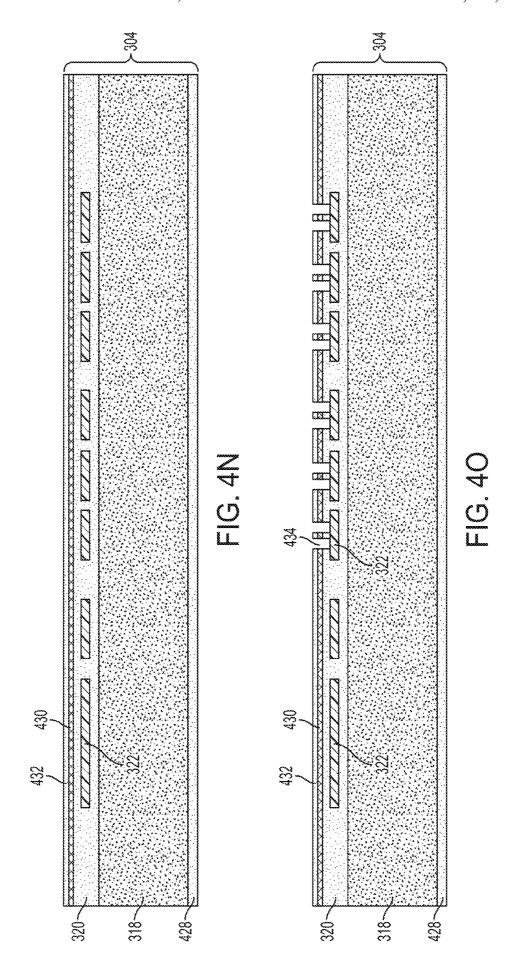

FIGS. 4M-4P relate to preparation of the CMOS wafer 304 for bonding with the engineered substrate. As shown in FIG. 4M, the CMOS wafer 304 includes the base layer (e.g., a bulk silicon wafer) 318, the insulating layer 320, and the metallization 322. An insulating layer 428 may optionally be formed on the backside of the base layer 318.

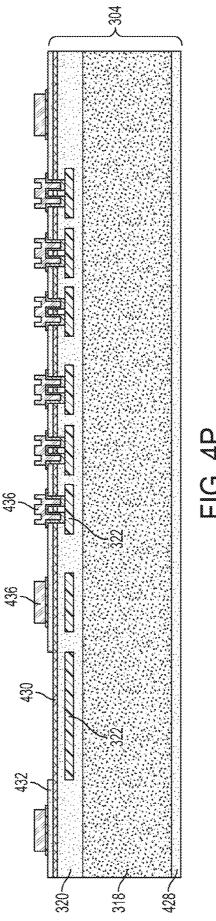

As shown in FIG. 4N, layers 430 and 432 may be formed on the CMOS wafer 304. The layer 430 may be, for example, a nitride layer and may be formed by plasma enhanced chemical vapor deposition (PECVD). The layer 432 may be an oxide layer, for example formed by PECVD 20 of oxide.

In FIG. 4O, openings 434 may be formed from the layer 432 to the metallization 322. Such openings may be made in preparation for forming bonding points. For example, in FIG. 4P, bonding material 436 may be formed on the CMOS 25 wafer 304 (by suitable deposition and patterning) at one or more suitable locations for bonding the engineered substrate 302 with the CMOS wafer 304. The bonding material 436 may be any suitable material for bonding with the bonding material 426 on the engineered substrate. As previously 30 described, in some embodiments a low temperature eutectic bond may be formed, and in such embodiments the bonding material 426 and bonding material 436 may form a eutectic pair. For example, bonding material 426 and bonding material 436 may form an indium-tin (In—Sn) eutectic pair, a 35 gold-tin (Au-Sn) eutectic pair, and aluminum-germanium (Al—Ge) eutectic pair, or a tin-silver-copper (Sn—Ag—Cu) combination. In the case of Sn—Ag—Cu, two of the materials may be formed on the engineered substrate as bonding material 426 with the remaining material formed as bonding 40 material 436.

As shown in FIG. 4Q, the engineered substrate 302 and CMOS wafer 304 may then be bonded together, which in some embodiments results in a monolithically integrated structure including sealed cavities 306 disposed vertically 45 above ICs in the CMOS wafer 304 (e.g., metallization 322). As previously described, such bonding may, in some embodiments, involve only the use of low temperature (e.g., below 450° C.) which may prevent damage to metallization layers and other components on the CMOS wafer 304.

In the non-limiting example illustrated, the bond may be a eutectic bond, such that the bonding material **426** and bonding material **436** may in combination form bond points **316a** and **316b**. As a further non-limiting example, a thermocompression bond may be formed using Au as the 55 bonding material. For instance, the bonding material **426** may include a seed layer (formed by sputtering or otherwise) of Ti/TiW/Au with plated Au formed thereon, and the bonding material **436** may include a seed layer (formed by sputtering or otherwise) of TiW/Au with plated Ni/Au 60 formed thereon. The layers of titanium may serve as adhesion layers. The TiW layers may serve as adhesion layers and diffusion barriers. The nickel may serve as a diffusion barrier. The Au may form the bond. Other bonding materials may alternatively be used.

Next, the second handle layer 410 and oxide layer 414 may be removed in any suitable manner as shown in FIG.

16

4R. For example, grinding and/or etching may be used. The oxide layer 314 may act as an etch stop for removing the second handle layer 410.

As shown in FIG. 4S, the oxide layer 314 may then be patterned to form openings 438 using any suitable etching technique. The openings 438 provide access to a backside (or topside) of the second silicon device layer 310 distal the CMOS wafer 304. As shown in FIG. 4T, the contacts 324 and bond pad 326 of FIG. 3 may then be formed, for example by depositing and patterning a suitable conductive material (e.g., aluminum, copper, or other suitable material). Also, the oxide layer 314 may optionally be removed (in any suitable manner) from regions overlying the cavities 306. That is, the oxide layer 314 may be removed from the ultrasonic transducer region of the ultrasound device.

The device 300 may then be achieved by depositing and patterning the passivation layer 330. As described previously in connection with FIG. 3, the passivation layer 330 may be patterned to provide access to one or more of the contacts 324.

Various features of the fabrication sequence of FIGS. 4A-4T are now noted. For example, it should be appreciated that the fabrication sequence does not involve the use of TSVs, thus making the process less costly and complex than if TSVs were used. The yield of the process may be increased as a result.

Additionally, the process does not utilize chemical mechanical polishing (CMP). For example, CMP is not used in preparation for either of the bonding stages described, and thus the bonding reliability (and therefore yield) may be increased while cost may be decreased compared to if CMP steps were performed. Similarly, it is noteworthy that the illustrated fabrication sequence does not include any densification anneals for the low temperature bond of the engineered substrate with the CMOS wafer. The use of such anneals reduces bonding reliability and therefore yield. Further still, and as previously described, the fabrication of the sealed cavities for the ultrasonic transducers is decoupled from the CMOS thermal budget, thus allowing for use of high temperature processing (e.g., a high temperature anneal) when bonding together the wafers of the engineered substrate.