US 20130261463A1

(19) **United States**

(12) **Patent Application Publication**

**Chiang et al.**

(10) **Pub. No.: US 2013/0261463 A1**

(43) **Pub. Date: Oct. 3, 2013**

(54) **ULTRASOUND 3D IMAGING SYSTEM**

(71) Applicants: **Alice M. Chiang**, Weston, MA (US);

**William M. Wong**, Milton, MA (US);

**Steven R. Broadstone**, Woburn, MA (US)

(72) Inventors: **Alice M. Chiang**, Weston, MA (US);

**William M. Wong**, Milton, MA (US);

**Steven R. Broadstone**, Woburn, MA (US)

(73) Assignee: **TERATECH CORP.**, Burlington, MA (US)

(21) Appl. No.: **13/899,320**

(22) Filed: **May 21, 2013**

**Related U.S. Application Data**

(63) Continuation of application No. 13/498,043, filed on Mar. 23, 2012, filed as application No. PCT/US2007/014526 on Jun. 22, 2007, which is a continuation-in-part of application No. 12/570,856, filed on Sep. 30, 2009, which is a continuation-in-part of application No. PCT/US2009/056995, filed on Sep. 15, 2009, which is a continuation-in-part of application No. 12/286,555, filed on Sep. 30, 2008, now abandoned.

(60) Provisional application No. 61/192,063, filed on Sep. 15, 2008.

**Publication Classification**

(51) **Int. Cl.**

**A61B 8/00** (2006.01)

**A61B 8/14** (2006.01)

**A61B 8/08** (2006.01)

(52) **U.S. Cl.**

CPC ..... **A61B 8/4488** (2013.01); **A61B 8/4444** (2013.01); **A61B 8/54** (2013.01); **A61B 8/488** (2013.01); **A61B 8/52** (2013.01); **A61B 8/565** (2013.01); **A61B 8/145** (2013.01); **A61B 8/466** (2013.01)

USPC ..... **600/447**; 600/459; 600/453

(57) **ABSTRACT**

The present invention relates to an ultrasound imaging system in which the scan head includes a beamformer circuit that performs far field subarray beamforming or includes a sparse array selecting circuit that actuates selected elements. When using a hierarchical two-stage or three-stage beamforming system, three dimensional ultrasound images can be generated in real-time. The invention further relates to flexible printed circuit boards in the probe head. The invention furthermore relates to the use of coded or spread spectrum signaling in ultrasound imaging systems. Matched filters based on pulse compression using Golay code pairs improve the signal-to-noise ratio thus enabling third harmonic imaging with suppressed sidelobes. The system is suitable for 3D full volume cardiac imaging.

FIG.1

Image Plane Scan Pattern

FIG. 2

FIG. 3A

FIG. 3B

FIG. 3C

FIG. 3D

FIG. 3E

FIG. 3F(1)

FIG. 3F(2)

FIG. 3F(4)

|                |                                                                           | Min    | Max     |

|----------------|---------------------------------------------------------------------------|--------|---------|

| <b>tSW_ON</b>  | Time from <b>TR_time</b> or <b>RX_time</b> to switch turn on              | 0 ns   | 1000 ns |

| <b>tSW_OFF</b> | Time from <b>TR_time</b> or <b>RX_time</b> to switch turn off             | 0 ns   | 1000 ns |

| <b>tSETUP</b>  | Config[1:0] set up time before <b>TR_time</b> or <b>RX_time</b> switching | 100 ns |         |

| <b>tHOLD</b>   | Config[1:0] hold time after <b>TR_time</b> or <b>RX_time</b> switching    | 100 ns |         |

| <b>tGAP</b>    | Time gap between <b>TR_Time</b> and <b>RX_time</b> assertion              | 100 ns |         |

FIG. 3G

FIG. 3H

FIG. 31

FIG. 4A

FIG. 4C

FIG. 4D

FIG. 4B

FIG. 4E

FIG. 4F

FIG. 4G

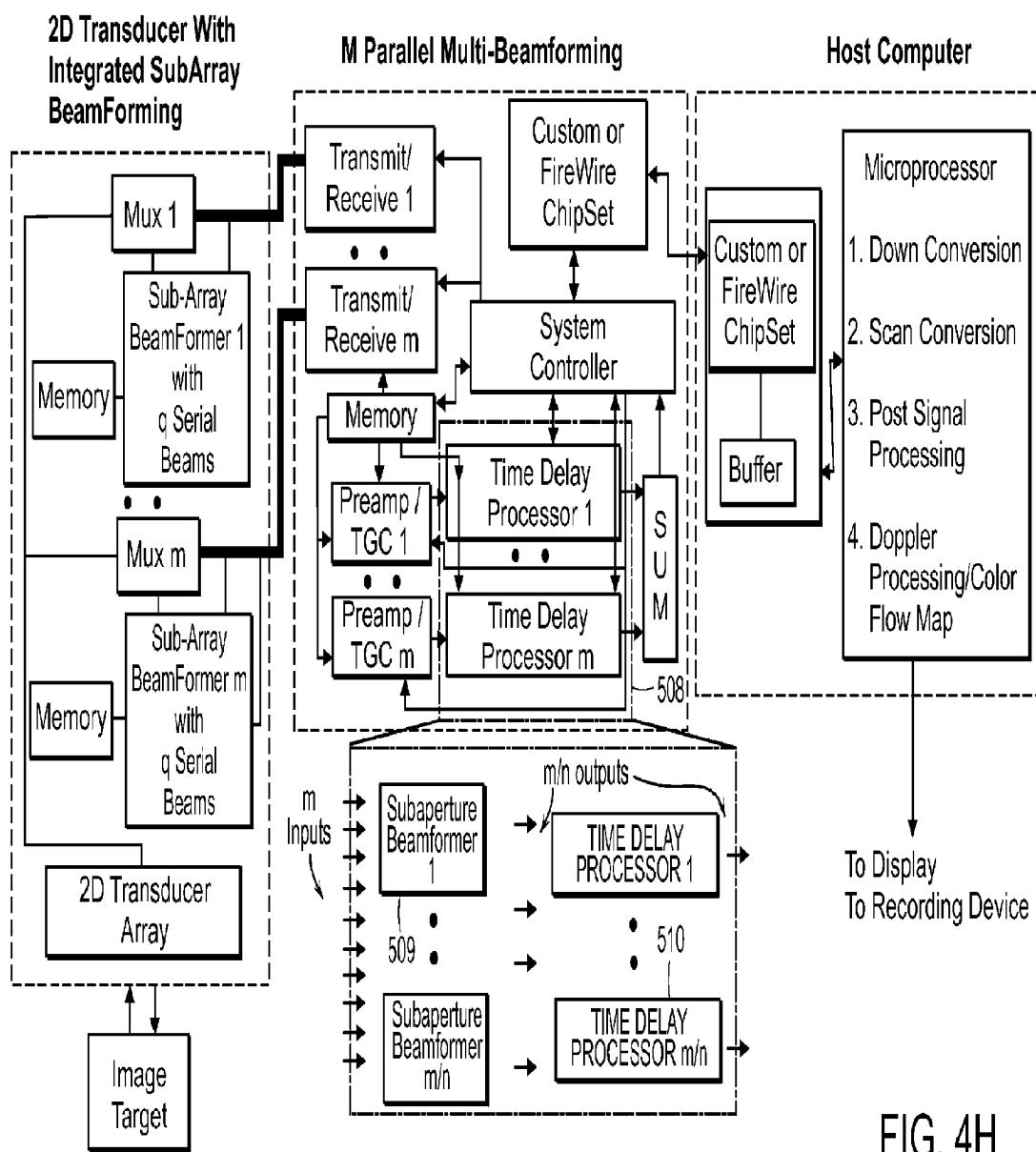

FIG. 4H

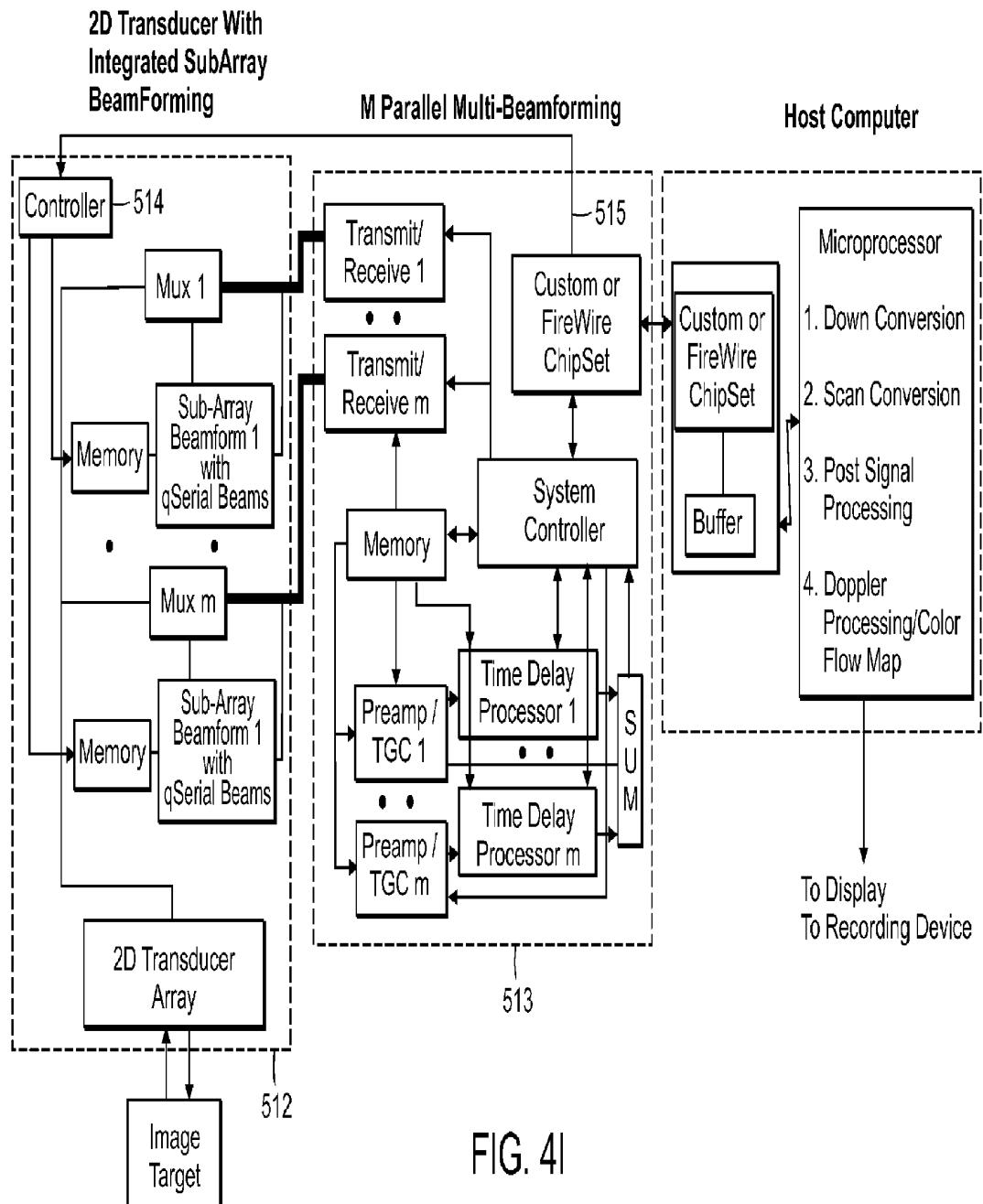

FIG. 4I

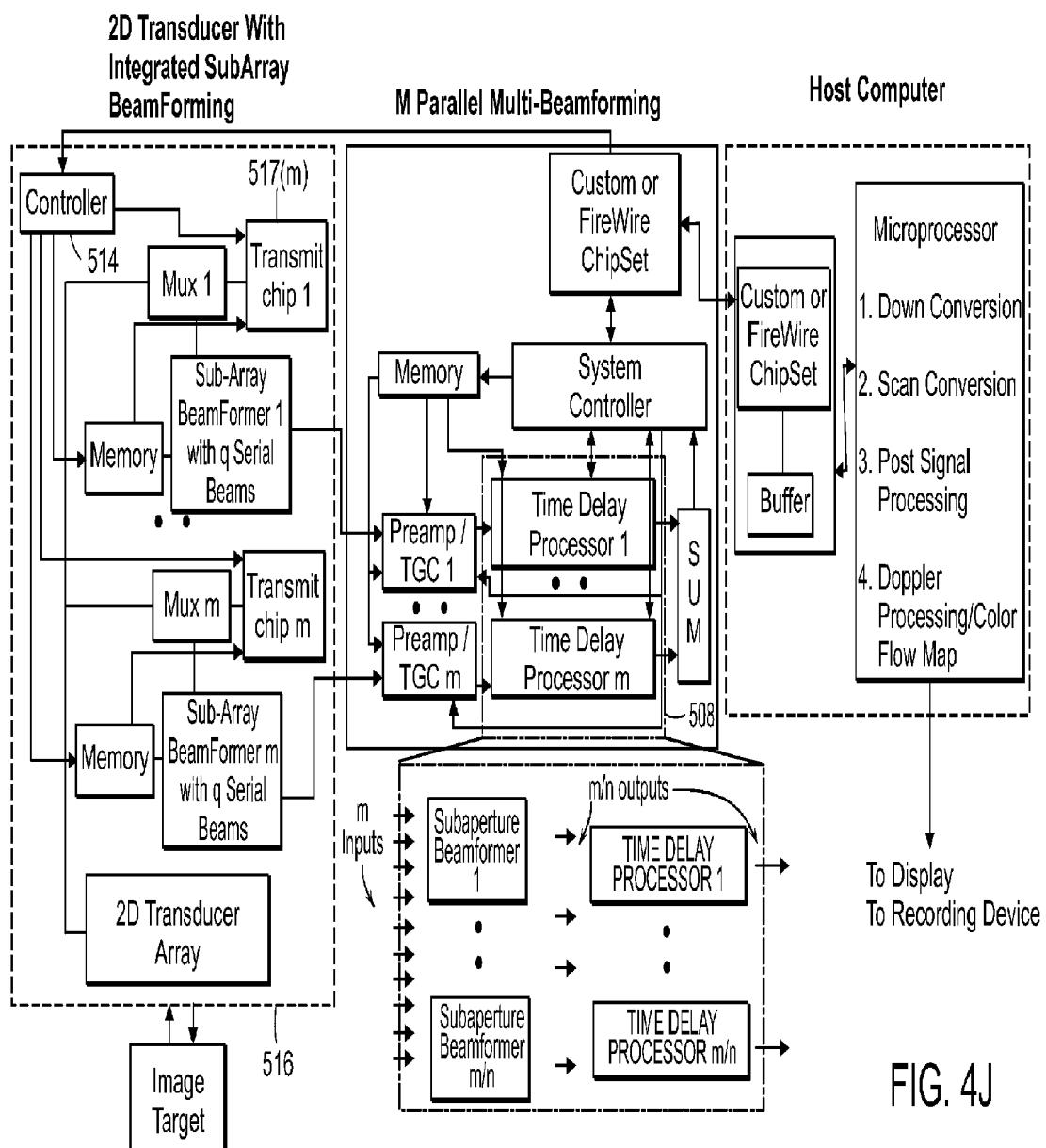

FIG. 5A

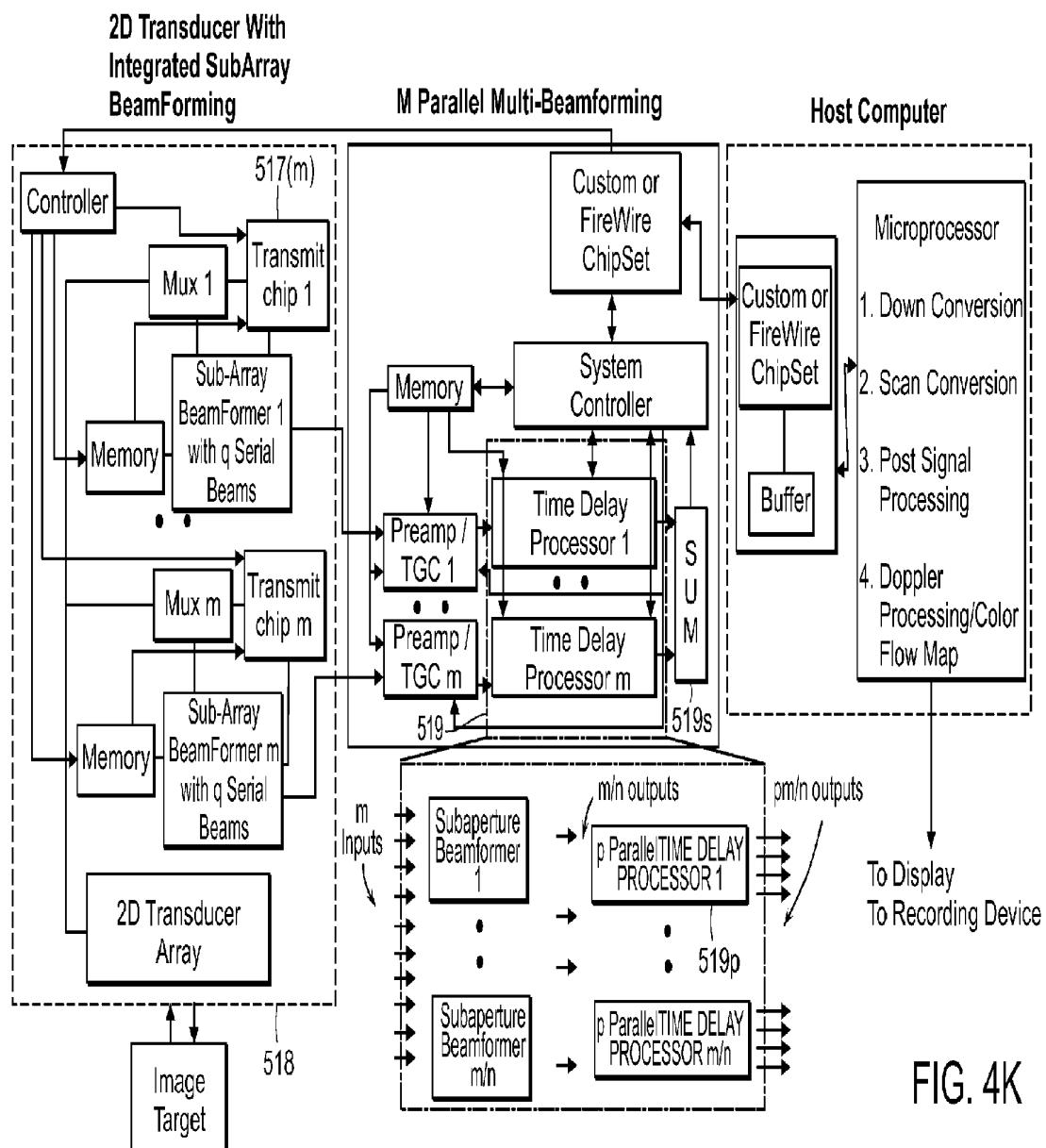

FIG. 6A

## Real-Time 3D/4D Imaging

FIG. 6B

FIG. 8A

**FIG. 8B**

FIG. 9A

FIG. 9B

FIG. 10

**Sparse Array Transmit, Near Fully-Populated Receive Arrays****Receive Sensor Locations 50****FIG. 11**

FIG. 12

FIG. 13

FIG. 14

**FIG. 15**

**FIG. 16**

FIG. 17

FIG. 18

## 2D-ARRAY DIFFERENTIAL DELAY EQUATION

$$f(r, \theta, \varphi) = r \left[ 1 - \sqrt{1 + \frac{x_m^2}{r^2} + \frac{y_m^2}{r^2}} - \frac{2x_m \sin \theta \cos \varphi}{r} - \frac{2y_m \cos \theta \sin \varphi}{r} \right]$$

STEERED TWO-DIMENSIONAL ARRAY

FIG. 19

FIG. 20

**FIG. 21**

**Backend Hierarchical

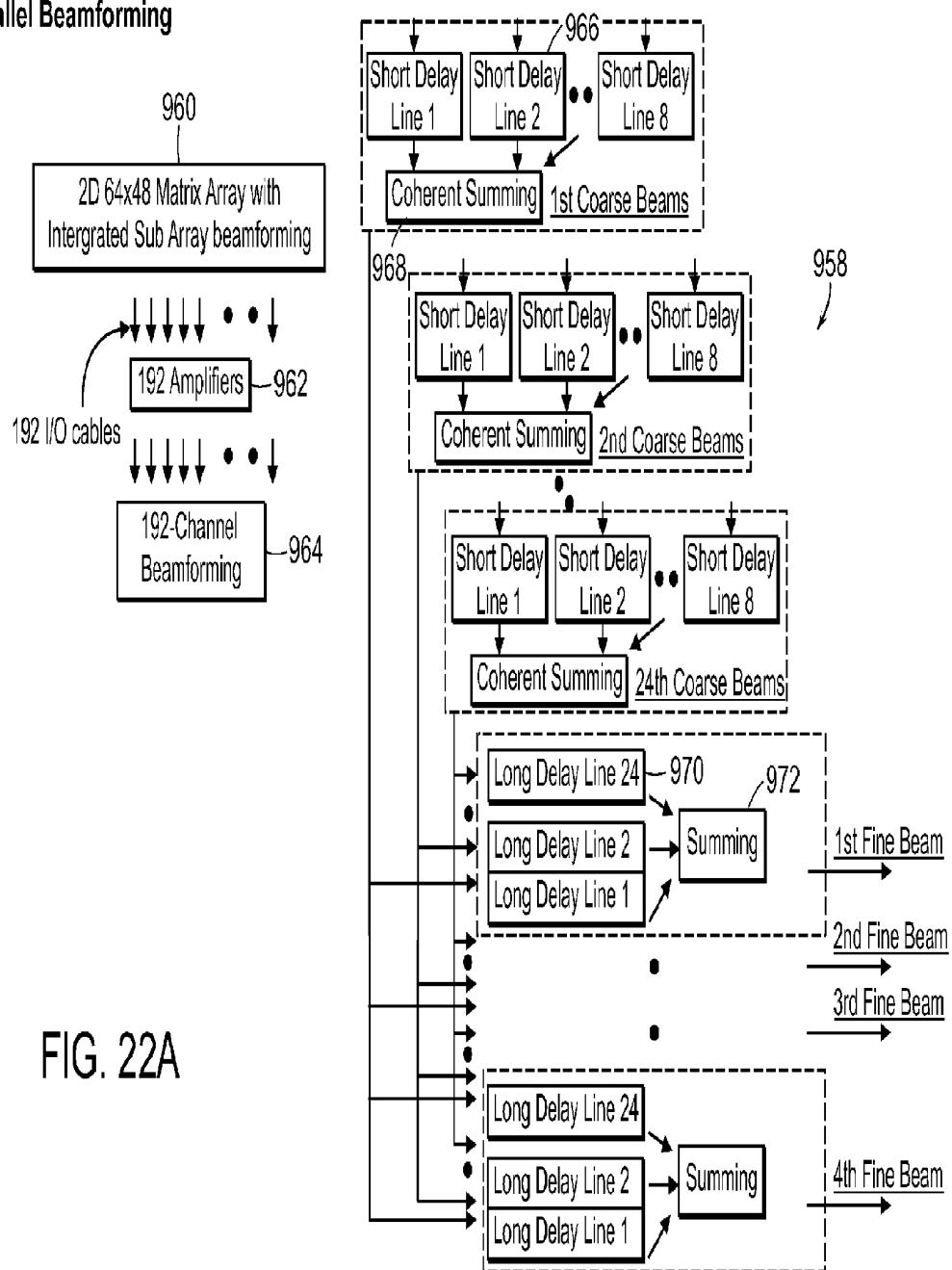

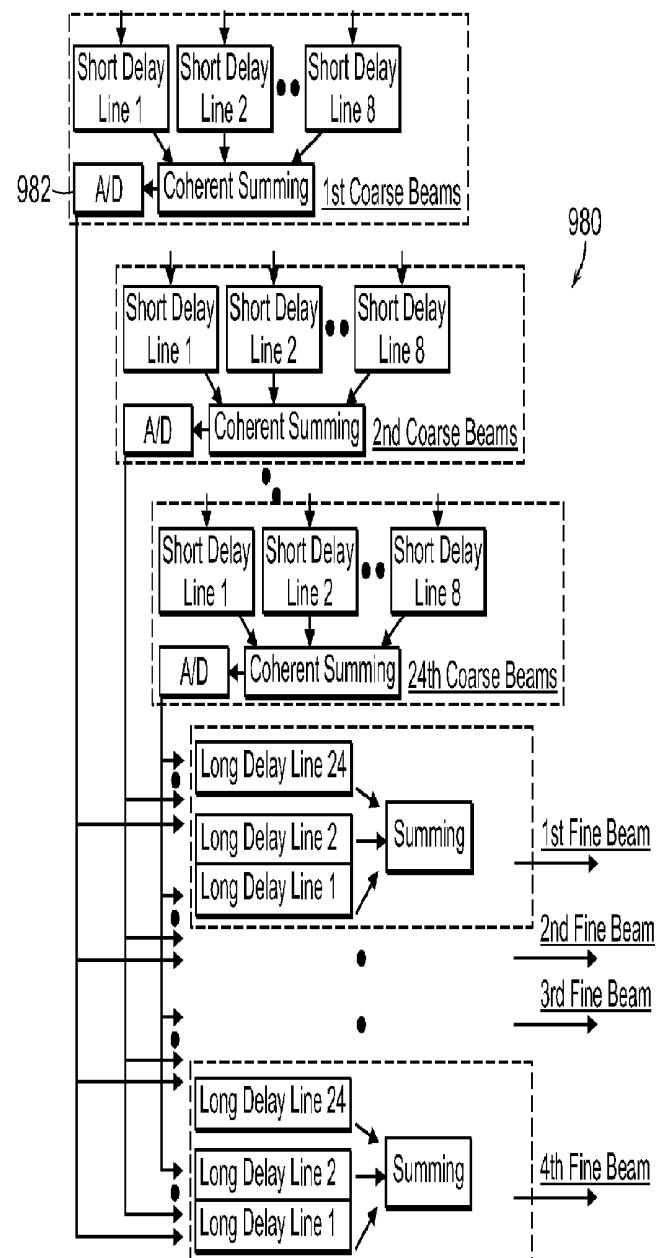

Four Parallel Beamforming****FIG. 22A**

**Backend Hierarchical Four Parallel Beamforming**

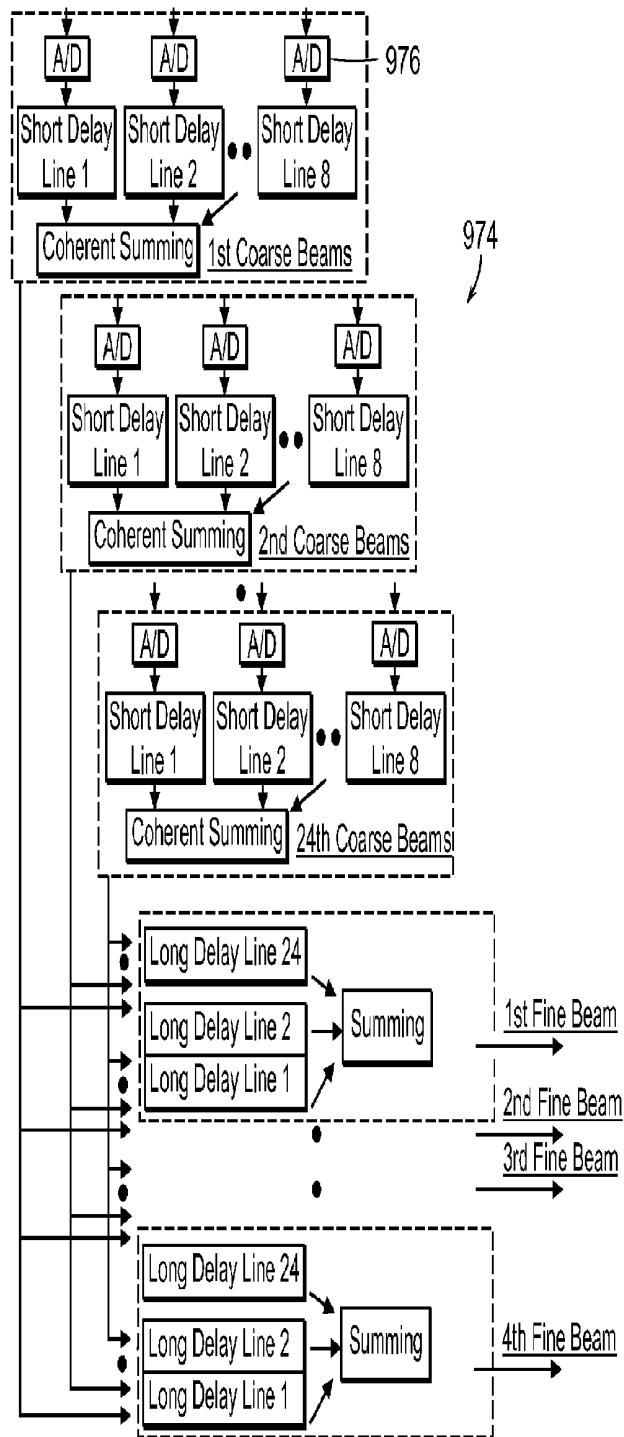

FIG. 22B

**Backend Hierarchical

Four Parallel Beamforming

with Imbedded A to D Converter**

FIG. 22C

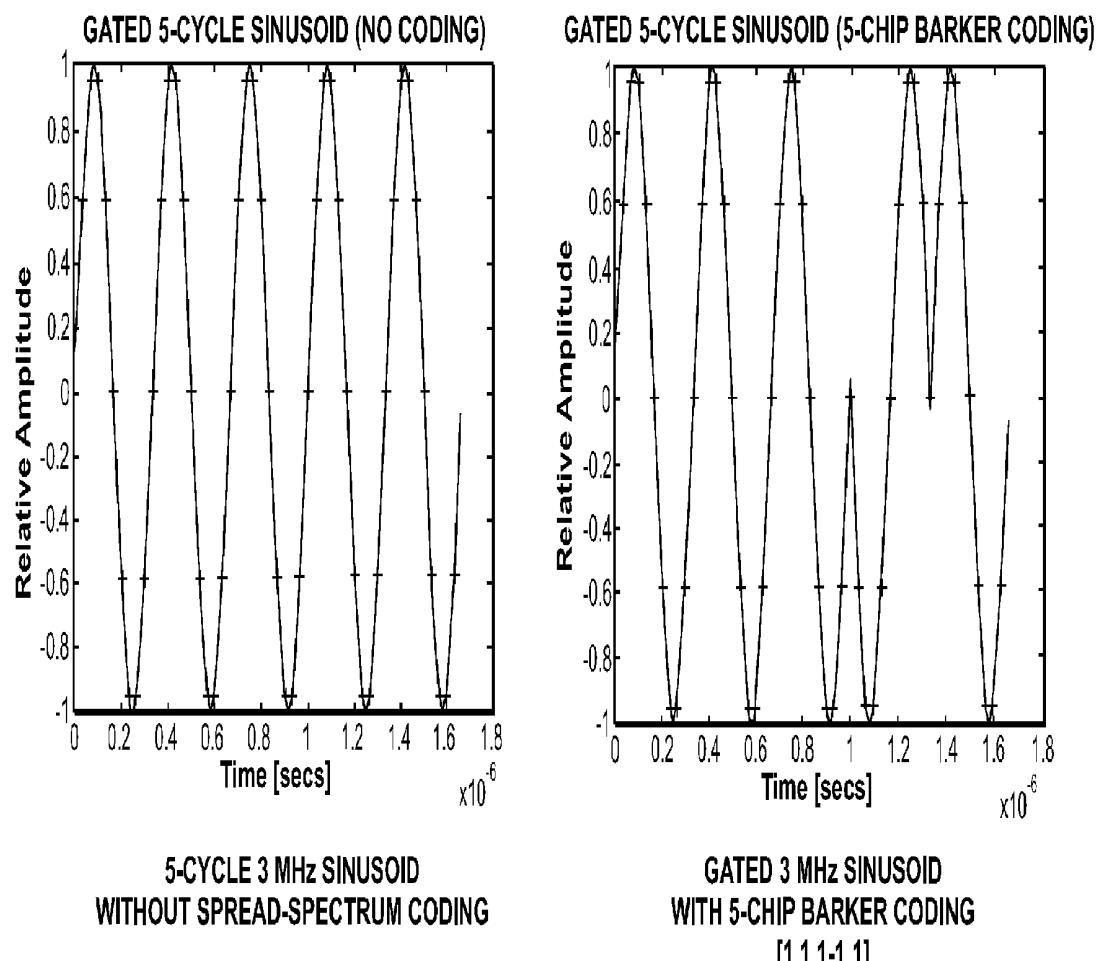

## SPREAD-SPECTRUM EXCITATION TRANSMIT WAVEFORMS

— Continuous

+ Sampled

FIG. 23A

FIG. 23B

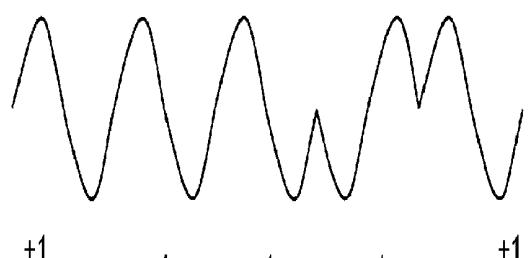

**Oversampled, Spread-Spectrum, Coded Transmit

Waveform**

**FIG. 24A** Base Pulse=1

**FIG. 24B** Base Pulse convolves with

5-chip Barker code

**FIG. 24C** 6 times Oversampled

Transmitted waveform

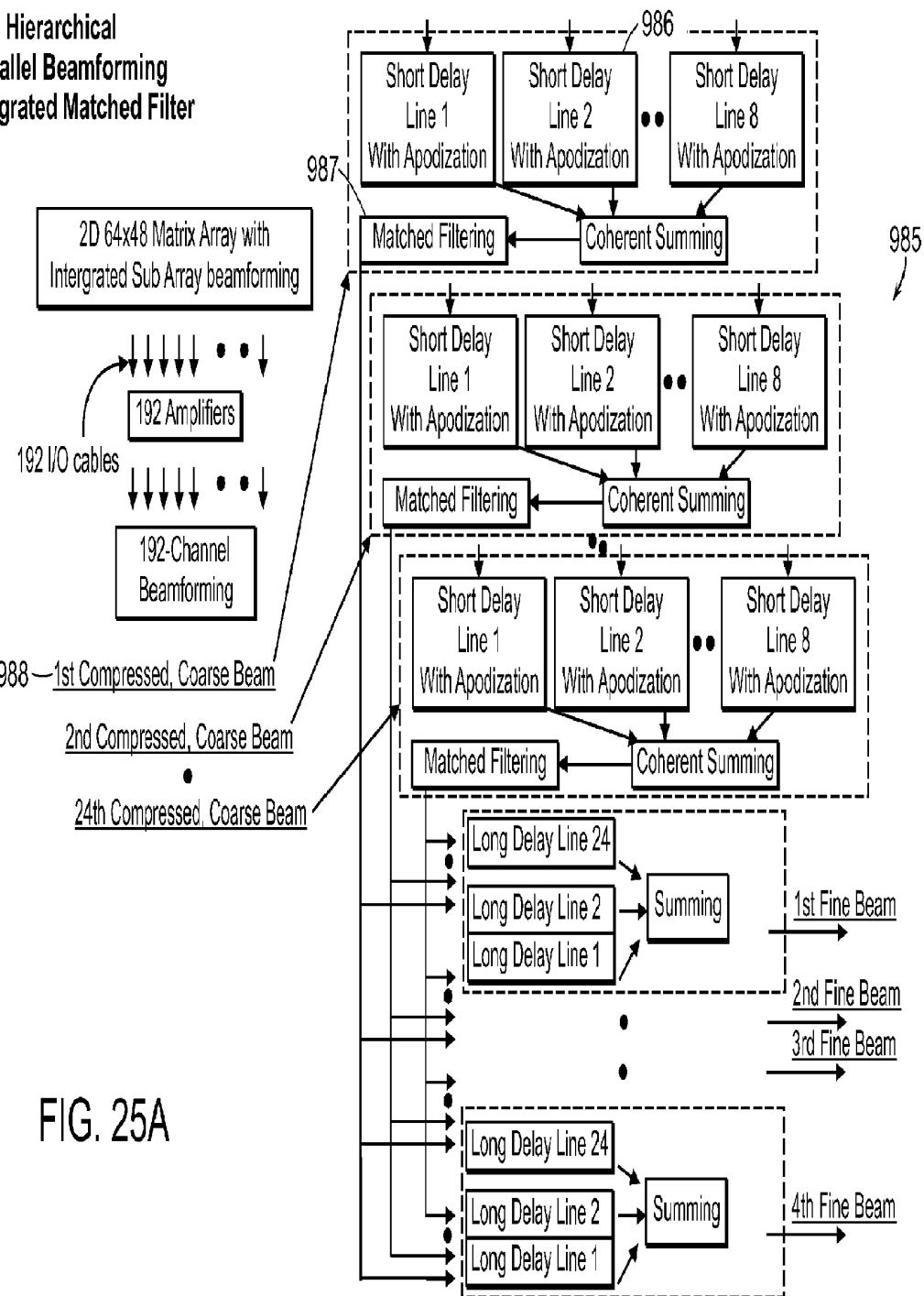

**Backend Hierarchical

Four Parallel Beamforming

with Integrated Matched Filter****FIG. 25A**

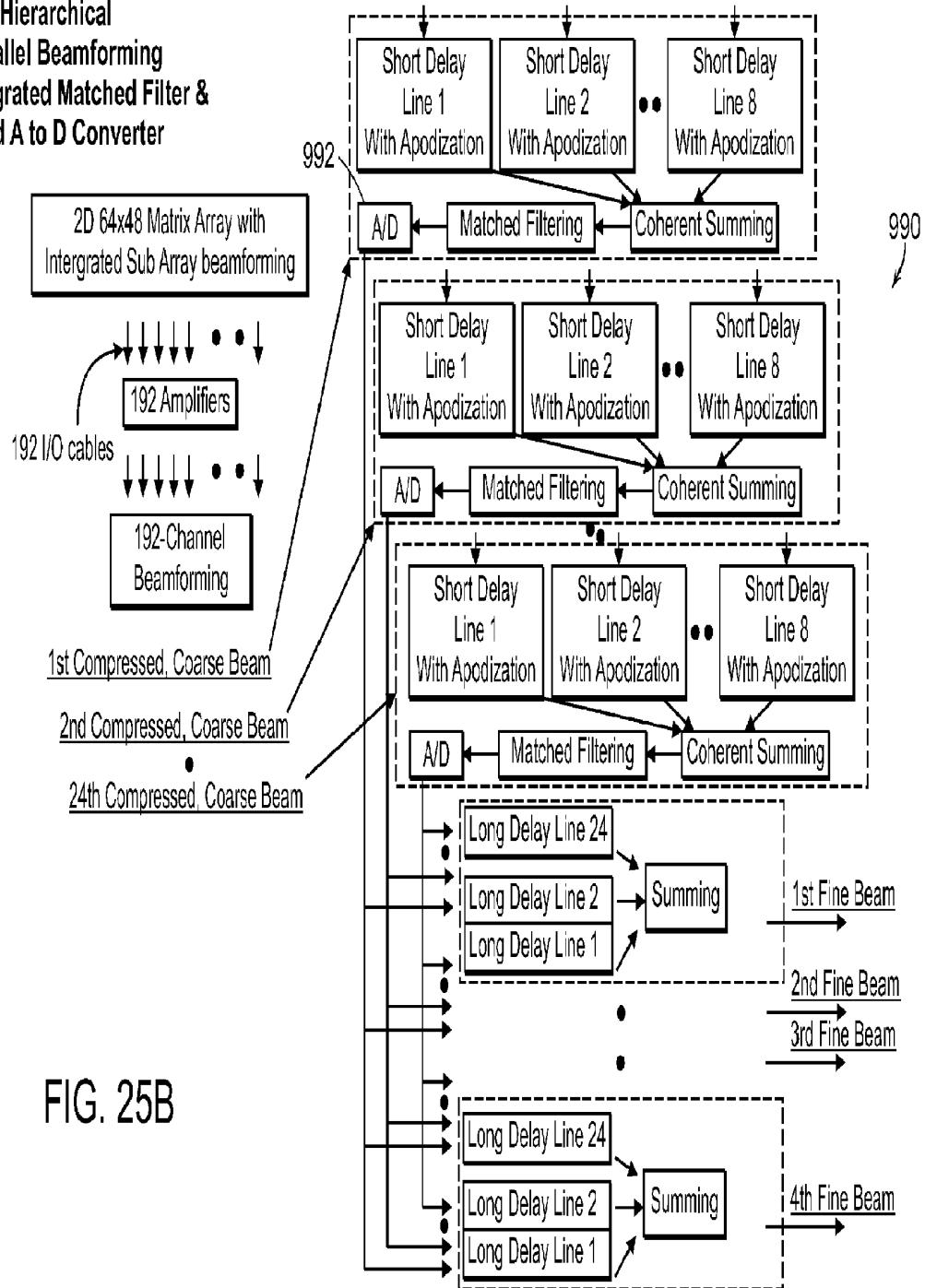

**Backend Hierarchical

Four Parallel Beamforming

with Integrated Matched Filter &

Imbedded A to D Converter**

**FIG. 25B**

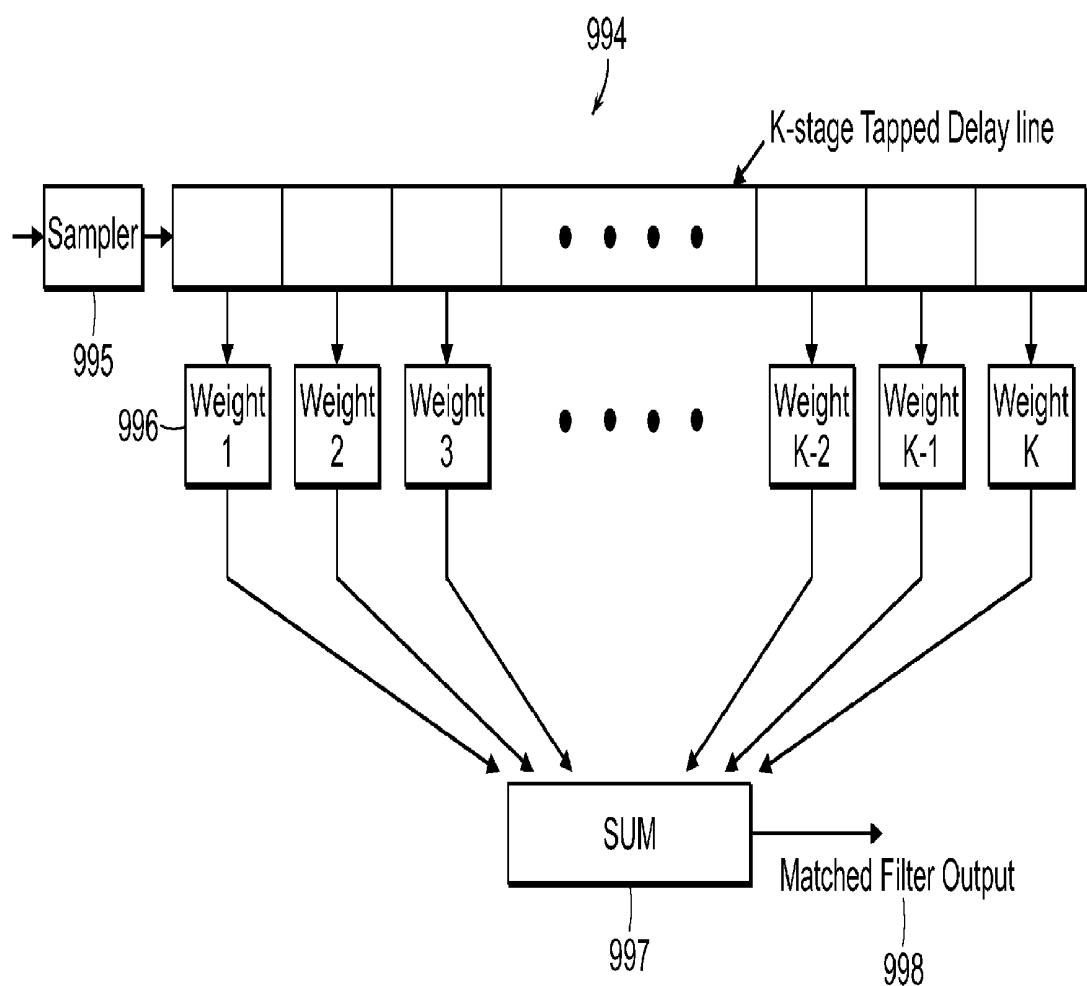

**Matched Filter Implementation**

FIG. 25C

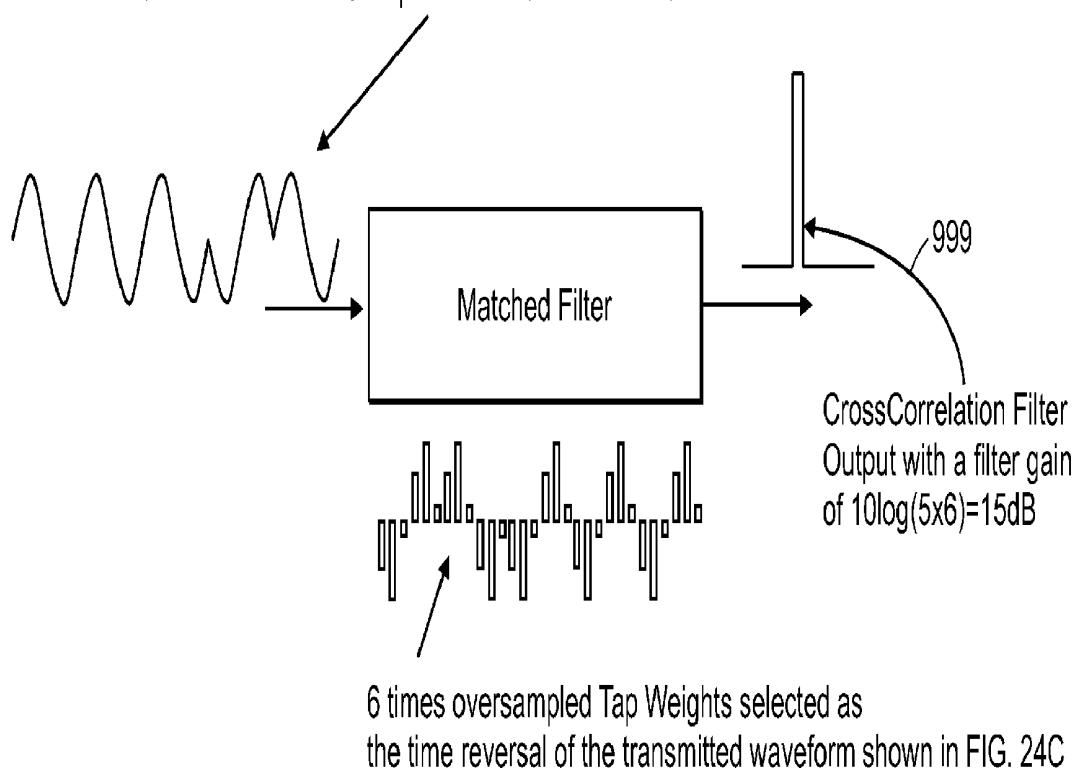

### Cross Correlation Matched Filter Output with Filter Gain

Returned Echoes from the 5-chip Barker code transmitted waveform shown in FIG. 24C

FIG. 25D

FIG. 26A

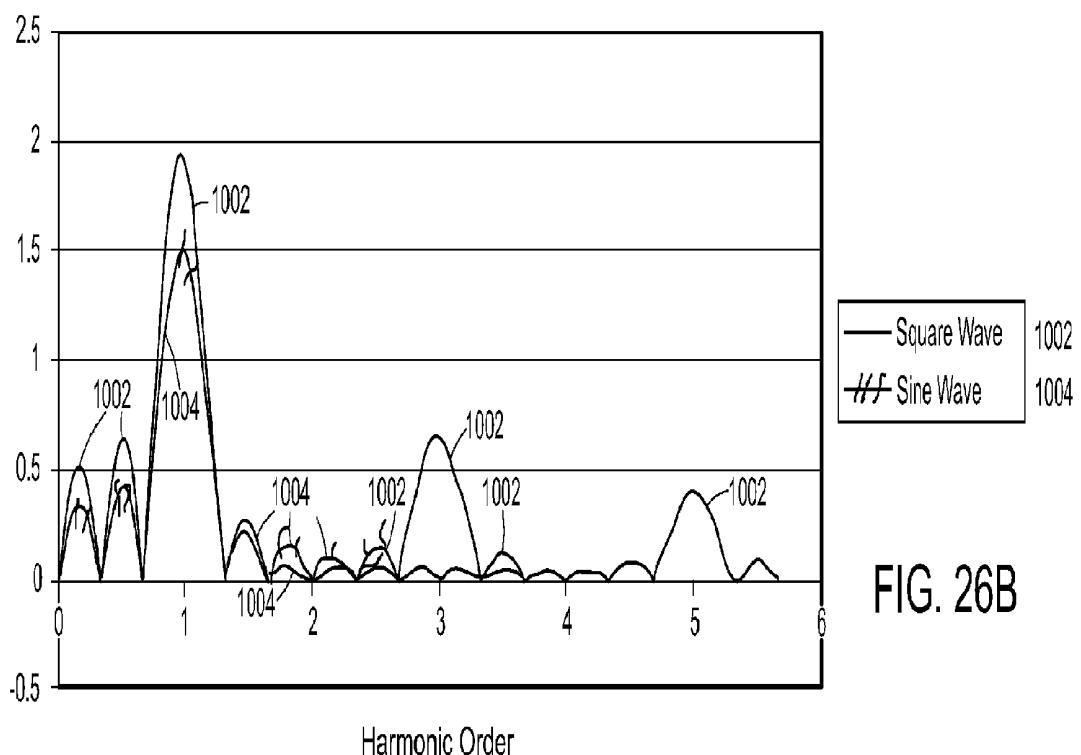

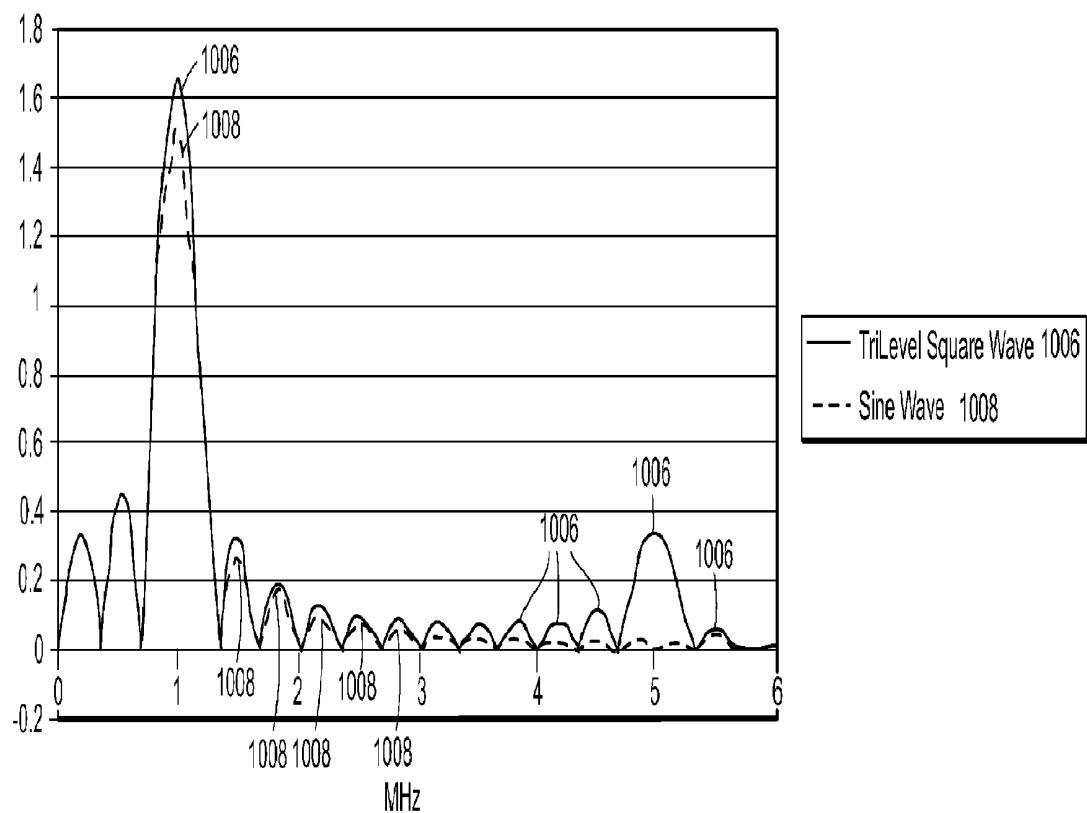

Spectrum of 3 cycles square wave and sinusoidal wave

FIG. 26B

FIG. 26C

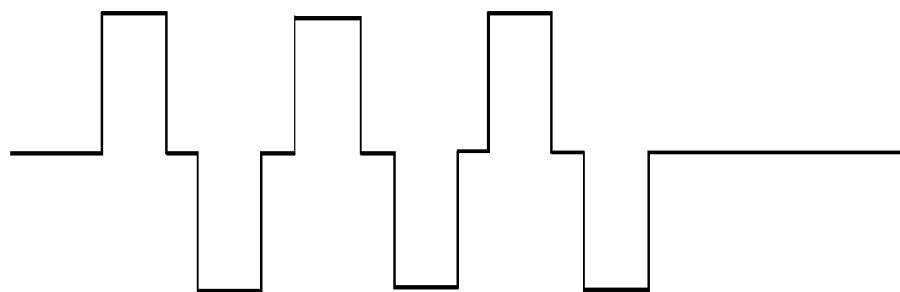

Spectrum of 3 cycles Modified Square Wave and Sinusoidal wave

FIG. 26D

10 bit Golay code

Match filter templates for the 1st code of Golay

1/50

FIG. 27A

Match filter templates for the 2nd code of Golay

1/10

FIG. 27B

Autocorrelation of match filter templates of 1st Golay code

FIG. 27C

Autocorrelation of match filter templates of 2nd Golay code

FIG. 27D

sum of 2 autocorrelations of Golay match filter templates

FIG. 28

3rd harmonic template of the first 10 bit Golay code when 12 over sampling for fundamental and 4 over sampling for 3rd harmonic

-0.015392,-0.055771,0.038076,0.028839,0.046853,0.000259,-0.048214,-0.009984,-0.013817,0.020245,-0.004117,-0.044618,

0.030906,0.022020,0.097704,-0.000757,-0.093799,-0.074193,-0.097050,0.142495,0.042181,0.099716,-0.067330,-0.053362,

0.022042,-0.002163,-0.010761,-0.100456,-0.129251,0.189798,0.088411,0.316329,-0.213122,-0.167861,-0.064531,-0.003720,

0.083276,-0.070915,-0.083733,0.127971,0.020194,-0.014892,0.009126,0.008148,0.040448,0.000549,-0.043114,0.022710,

0.027442,-0.041731,-0.006600,0.008397,-0.007585,0.000156,-0.061273,-0.004199,0.082287,-0.264062,-0.318569,0.481301,

0.108905,0.136914,-0.096247,-0.069733,-0.000691,-0.000256,0.002329,0.040045,0.054824,-0.078496,-0.054176,-0.229860,

0.152626,0.125593,-0.005188,0.001191,-0.000668,-0.054478,-0.065915,0.098890,0.033579,0.090236,-0.060225,-0.049422,

0.032035,0.000060,-0.032161,0.046696,0.054664,-0.083551,-0.014466,0.002113,-0.000411,-0.001898,0.011159,-0.000548,

-0.008619,-0.024835,-0.029946,0.045572,0.001212,-0.037556,0.023807,0.021806,-0.034198,0.000463,0.031978,0.003634,

0.006351,-0.008773,0.001272,0.014401,-0.009098,-0.008516,0.021538,0.000056,-0.021791,0.011059,0.011931,-0.018845,

FIG. 29A

3rd harmonic template of the second 10 bit Golay code when 12 over sampling for fundamental and 4 over sampling for 3rd harmonic

-0.008824,-0.027820,0.018987,0.014484,0.022302,0.000084,-0.022707,-0.009818,-0.013431,0.019342,0.008085,0.026831,-0.017775,-0.014816,0.009059,0.000063,-0.009323,0.016580,0.019067,-0.029635,0.003022,0.047155,-0.030950,-0.025664,0.016604,-0.000309,-0.015470,0.021140,0.030068,-0.042896,-0.024019,-0.083412,0.048176,0.058593,-0.344816,-0.001070,0.349552,-0.102440,-0.094334,0.158912,-0.027233,-0.318685,0.205094,0.182789,-0.153202,0.001818,0.144812,-0.094923,-0.105323,0.162640,0.053721,0.131823,-0.085303,-0.076091,0.284995,-0.002813,-0.270784,-0.104963,-0.139483,0.205625,0.006984,-0.161162,0.106390,0.086570,0.091730,0.000959,-0.096384,-0.032134,-0.041338,0.061265,0.003944,-0.037130,0.023690,0.021028,-0.028005,0.001484,0.020683,0.068112,0.084937,-0.127466,-0.017313,0.030932,-0.021416,-0.013993,-0.116830,-0.000396,0.118731,-0.007615,-0.004045,0.008446,0.010447,0.048092,-0.031976,-0.026087,0.007071,-0.000045,-0.006843,0.023280,0.028564,-0.042842,-0.011970,-0.023449,0.014763,0.014419,-0.073420,0.000537,0.070745,0.018747,0.025976,-0.037990,0.003225,0.055044,-0.036558,-0.029401,-0.016851,-0.000558,0.019591,-0.003528,-0.003314,0.005625,

FIG. 29B

FIG. 30A

FIG. 30B

FIG. 30C

## ULTRASOUND 3D IMAGING SYSTEM

### CROSS REFERENCE TO RELATED APPLICATION

**[0001]** This application is a continuation of Ser. No. 13/498,043 filed on Mar. 23, 2012, application Ser. No. 13/498,043 is a continuation-in-part of U.S. application Ser. No. 12/570,856 filed Sep. 30, 2009, which is a continuation-in-part of International Application No. PCT/US09/56935 filed on Sep. 15, 2009, which is a continuation-in-part of U.S. application Ser. No. 12/286,555 filed on Sep. 30, 2008 and, claims priority to U.S. Application Ser. No. 61/192,063 filed on Sep. 15, 2008 by Chiang et al., entitled: "Ultrasound 3D Imaging System." This application also claims priority to U.S. application Ser. No. 11/474,098 filed Jun. 23, 2006 and of International Application No. PCT/US2007/014526 filed Jun. 22, 2007. The entire contents of the above applications are incorporated herein by reference.

### BACKGROUND OF THE INVENTION

**[0002]** Medical ultrasound imaging has become an industry standard for many medical imaging applications. Techniques have been developed to provide three dimensional (3D) images of internal organs and processes using a two dimensional (2D) transducer array. These systems require thousands of beamforming channels. The power required to operate such systems has resulted in the use of an analog phase shift technique with a digital delay beamformer that results in a compromise of image quality.

**[0003]** There is a continuing need for further improvements in ultrasound imaging technologies enabling improved real-time three dimensional imaging capability. In addition, this improved capability should support continuous real-time display for a fourth dimensional 4D function.

### SUMMARY OF THE INVENTION

**[0004]** The present invention relates to a system for ultrasound medical imaging that provides three dimensional (3D) imaging using a two dimensional (2D) array of transducer elements in a probe housing. Embodiments of the invention provide systems and methods for medical imaging having high resolution and numerous imaging modalities.

**[0005]** In a preferred embodiment, the probe housing contains a first beamforming circuit that transmits beamformed data to a second housing having a second beamforming circuit. The first beamforming circuit provides a far-field sub-array beamforming operation. The resulting beamformed data is transmitted from the scan head to a second housing having the second beam forming circuit that provides near-field beamsteering and beamfocusing.

**[0006]** A preferred embodiment provides a scan head that can be connected to a conventional ultrasound system in which the scan head provides the inputs to the conventional beamforming processing- function. The scan head beamformer can utilise a low power charge domain processor having at least 32 beamforming channels.

**[0007]** A preferred embodiment of the invention employs a sparse array where only a fraction of the transducer elements need to be activated. By selecting the four corner elements of the array to provide proper mean lobe bandwidth, minimizing average sidelobe energy and clutter, eliminating periodicity and maximising peak to side lobe ratio, quality images are produced. To steer the beams across the volume or region of

interest, different transducer elements must be actuated in proper sequence to maintain the peak to sidelobe ratio. The system processor can be programmed to provide the desired sequence for transducer actuation to direct the beam at different angles. Alternatively, a discrete controller can be used to control sparse array actuation. A preferred embodiment provides a scan head with integrated switching circuits for sequentially selecting sparse array actuation elements for sequential multiple beamforming. The scan head can be connected to a conventional ultrasound system in which the scan head provides the inputs to the conventional beamforming processing functions. In another embodiment, the transmit array elements and receive array elements can be operated independently with the transmit elements comprising a sparse array and the receive elements being a near fully populated array. In a preferred embodiment, the multiplexer and beamformer circuits can be integrated into an interface system, or alternatively, into a host processing system, leaving a 2D transducer array mounted in the probe housing.

**[0008]** The present invention utilizes nondestructive sensing at each stage of the delay elements in the beamformer. So with a 65 stage delay line, for example, there are 64 usable outputs with one at each stage. The time resolution can be in the range of:  $\frac{1}{8}\lambda$  to  $\frac{1}{16}\lambda$ .

**[0009]** Using high voltage multiplexers in the probe and the nondestructive sensing allows for time multiplexed sequential beamforming. It is now possible to sequentially change tap selection of each delay line to form multiple beams.

**[0010]** In addition to the three dimensional (3D) display capability, a fourth dimension or time resolved image display can be used to record and display a sequence of images recorded at 10 frames per second or higher, for example. This enables viewing of rapidly changing features such as blood or fluid flow; heart wall movement etc. at video frames rates of 30 frames per second.

**[0011]** Another preferred embodiment of the invention utilizes a three stage beamformer system in which a first stage performs a first beamforming operation on data received from a transducer array, which generates first beamformed data that is followed by a second stage that performs a second beamforming operation to provide second stage beamformed data that is then delivered to a third beamforming stage that performs a third beamforming operation.

**[0012]** The stages can be performed using charge domain processors. Data can also be converted from analog to digital form, before the first stage, or the second stage, at the third stage or thereafter. One stage can utilize parallel beamforming operations and a second stage provides serial beamforming.

**[0013]** A preferred embodiment of the invention performs real time imaging of large volumes such as the human heart without having to take gated images of different portions of the heart in sequence and then stitch the images together. This can be done using beamforming architectures in which multiple beams can be transmitted in a single pulse. This provides for the collection of adult heart images within a single cardiac cycle or heartbeat. This can be done with a narrowband phase shifting beamforming system and/or with a time domain beamforming system. By using parallel and serial beamforming components distributed in the transducer probe housing and the system main processor housing lightweight portable and cart mounted systems can be used for real time full volume cardiac imaging.

[0014] In medical ultrasound imaging, there is a need for harmonic imaging where the transmitted waveform is of one fundamental frequency  $F_o$ , and the received signal of interest is a higher harmonic, generally the 2<sup>nd</sup> harmonic (2  $F_o$ ), or the third harmonic (3  $F_o$ ). The harmonic signal of interest is generated by the image targets in the body, and harmonics in the transmitted waveform are not of interest. Therefore it is important to suppress harmonic components from the transmitted waveform to obtain a clearer response.

[0015] The transmit circuit can generate either square waves or sinusoidal excitations. Square wave pulse generators are generally less costly than sinusoidal pulse generators, and the square wave pulsers are widely used in ultrasound imaging equipment. However a typical square wave itself contains high levels of the third harmonic. The present invention uses a modified square waveform which produces significantly reduced amount of the third harmonic, thus providing substantially improved harmonic imaging using the less expensive wave pulsers.

#### BRIEF DESCRIPTION OF THE DRAWINGS

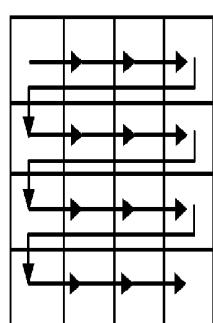

[0016] FIG. 1 illustrates the use of a two dimensional tiled array for ultrasound imaging in accordance with the invention.

[0017] FIG. 2 illustrates a steerable two dimensional array in accordance with the invention.

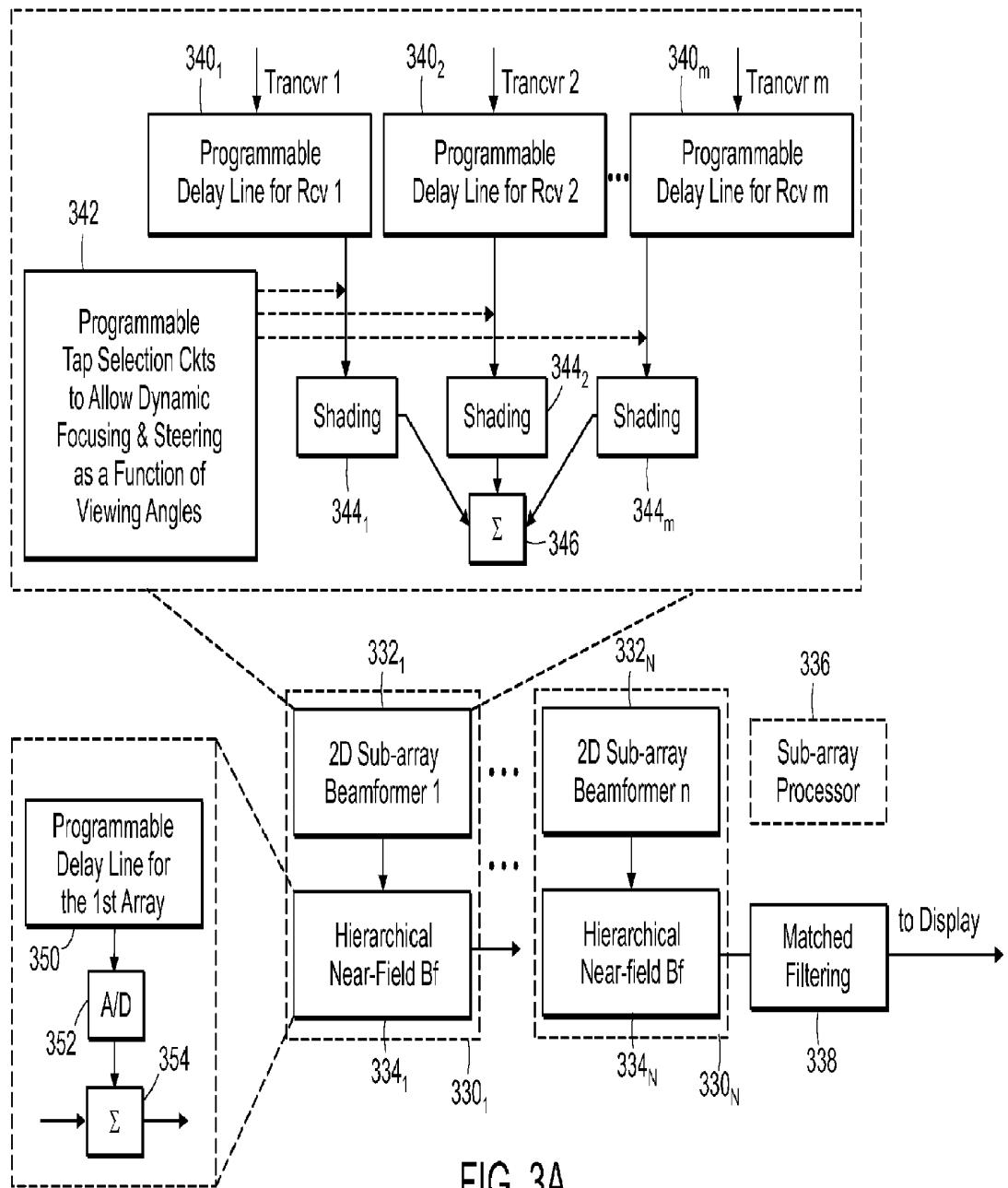

[0018] FIG. 3A illustrates the use of a first beamformer device for far field beamsteering and focusing and a second time delay beamformer for near field beamforming.

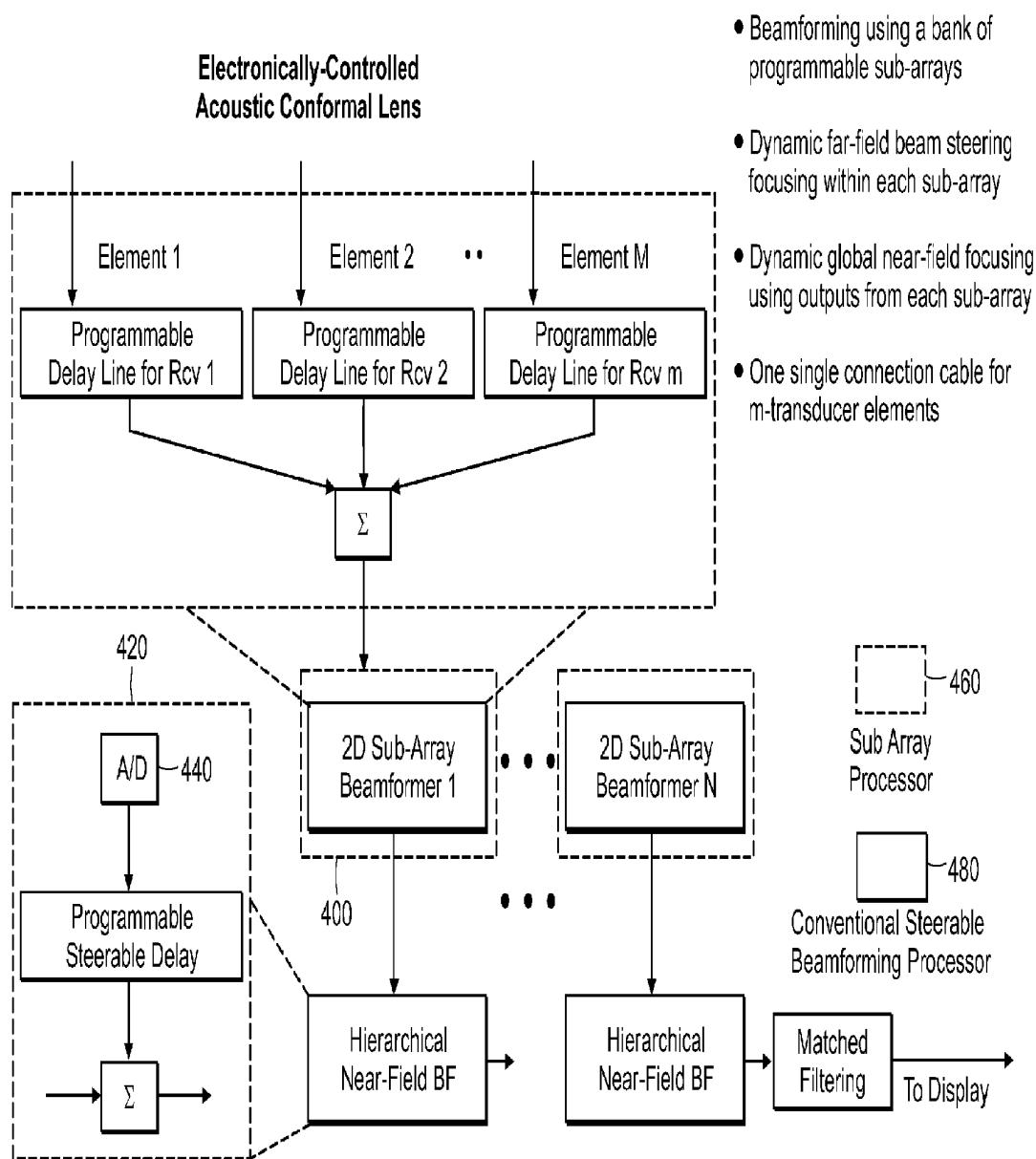

[0019] FIG. 3B illustrates a first analog subarray beamformer forwarding data to a digital beamformer.

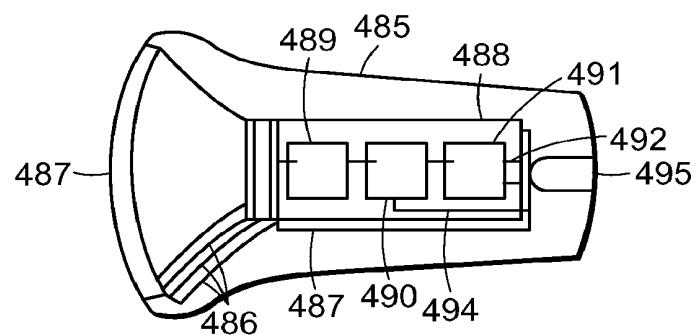

[0020] FIG. 3C illustrates a scanhead for a two dimensional transducer probe.

[0021] FIG. 3D illustrates a preferred embodiment utilizing a flexible circuit board and cable assembly.

[0022] FIG. 3E is a photomicrograph of a preferred embodiment with an integrated circuit beamformer device having 16 channel subarray beamformers that can form 4 sequential beams.

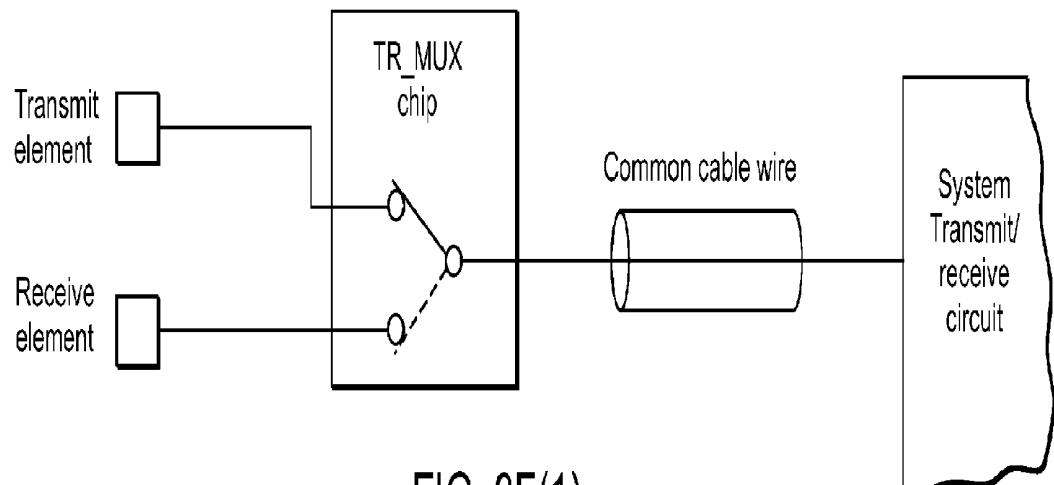

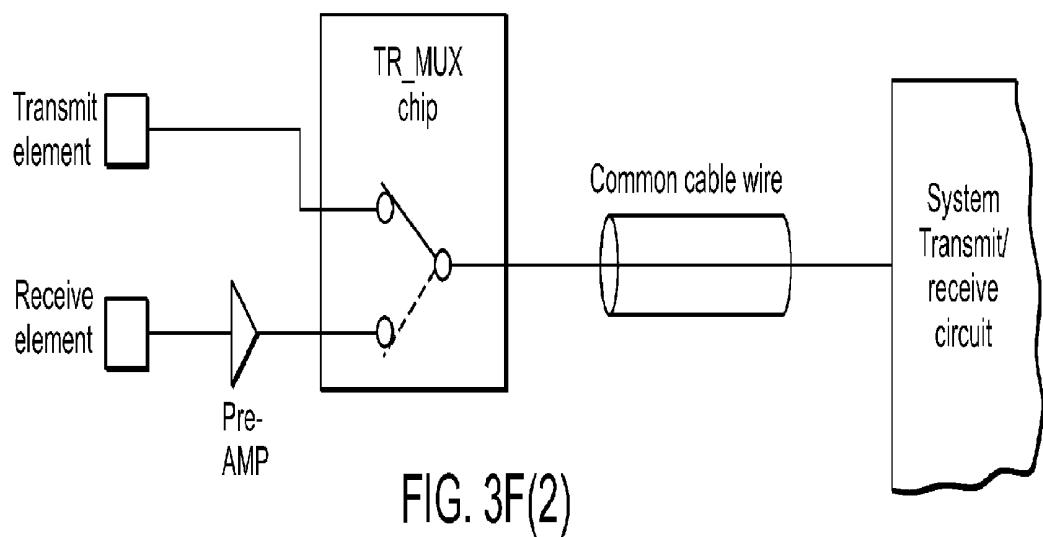

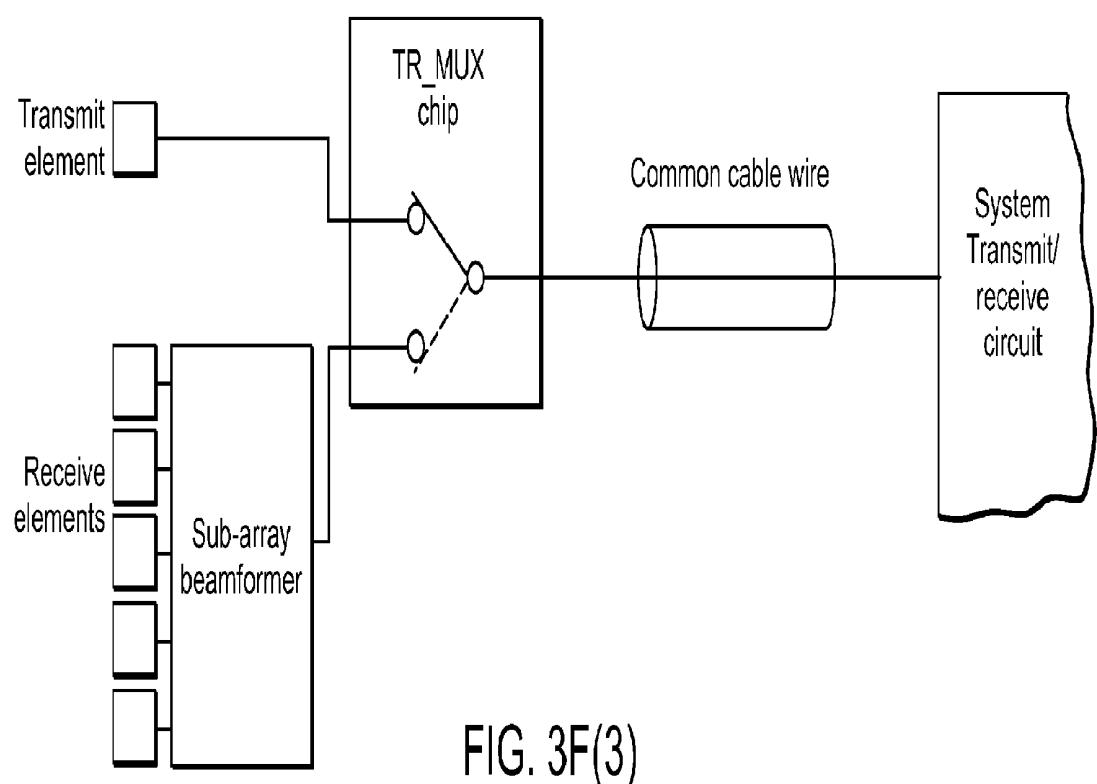

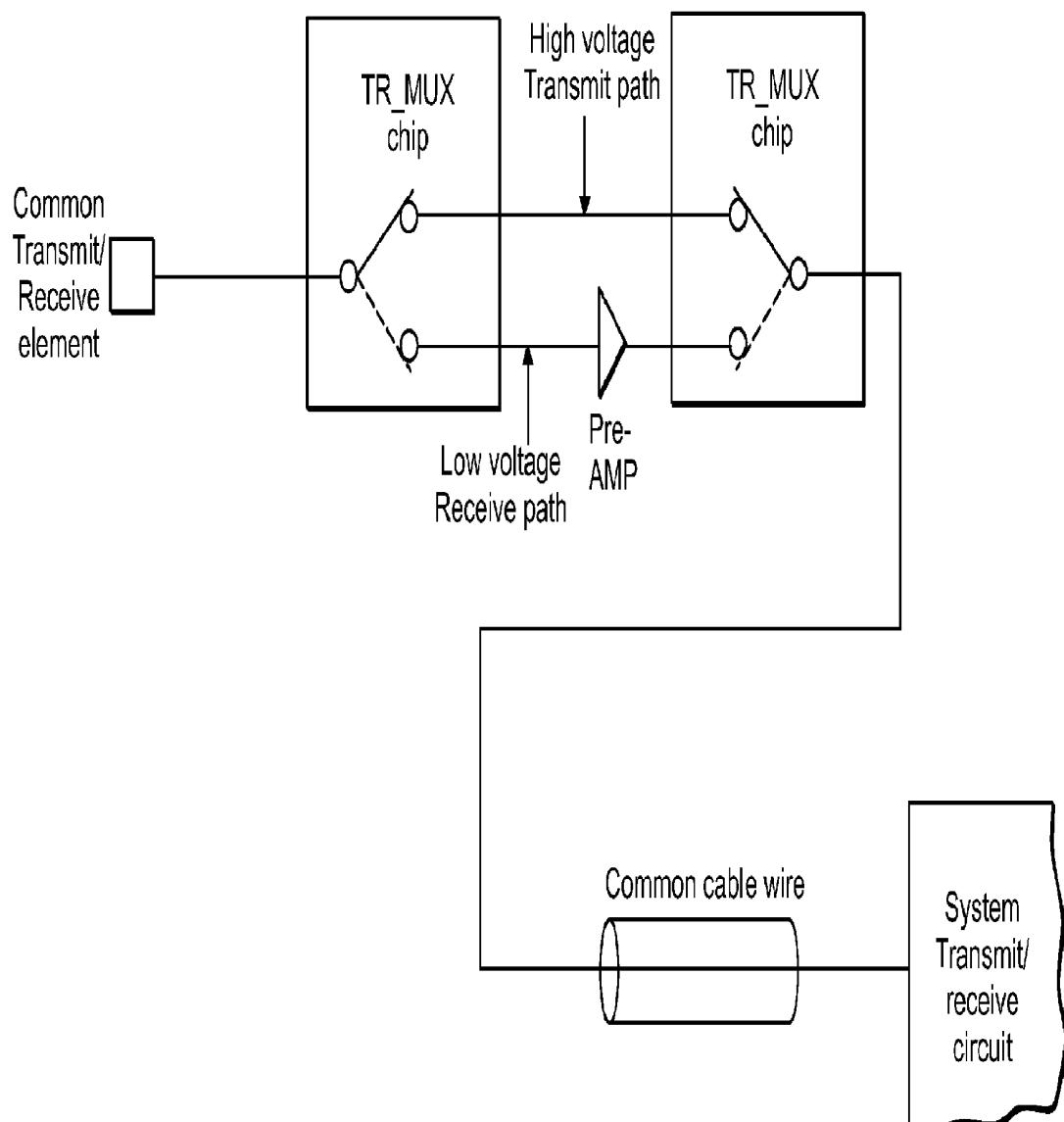

[0023] FIGS. 3F(1)-3F(4) illustrate preferred embodiments of multiplexers used for switching in ultrasound transducer systems.

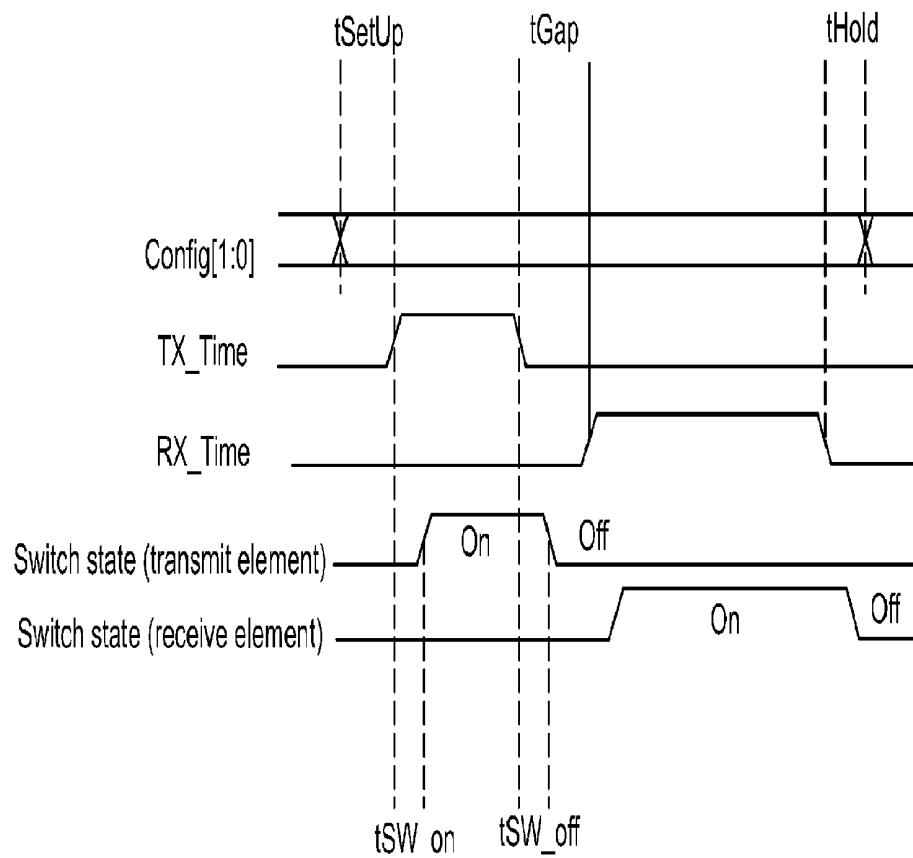

[0024] FIG. 3G illustrates a switch timing diagram in accordance with a preferred embodiment of the invention.

[0025] FIG. 3H is a photomicrograph of a 16 channel high voltage multiplexer integrated circuit chip in accordance with a preferred embodiment of the invention.

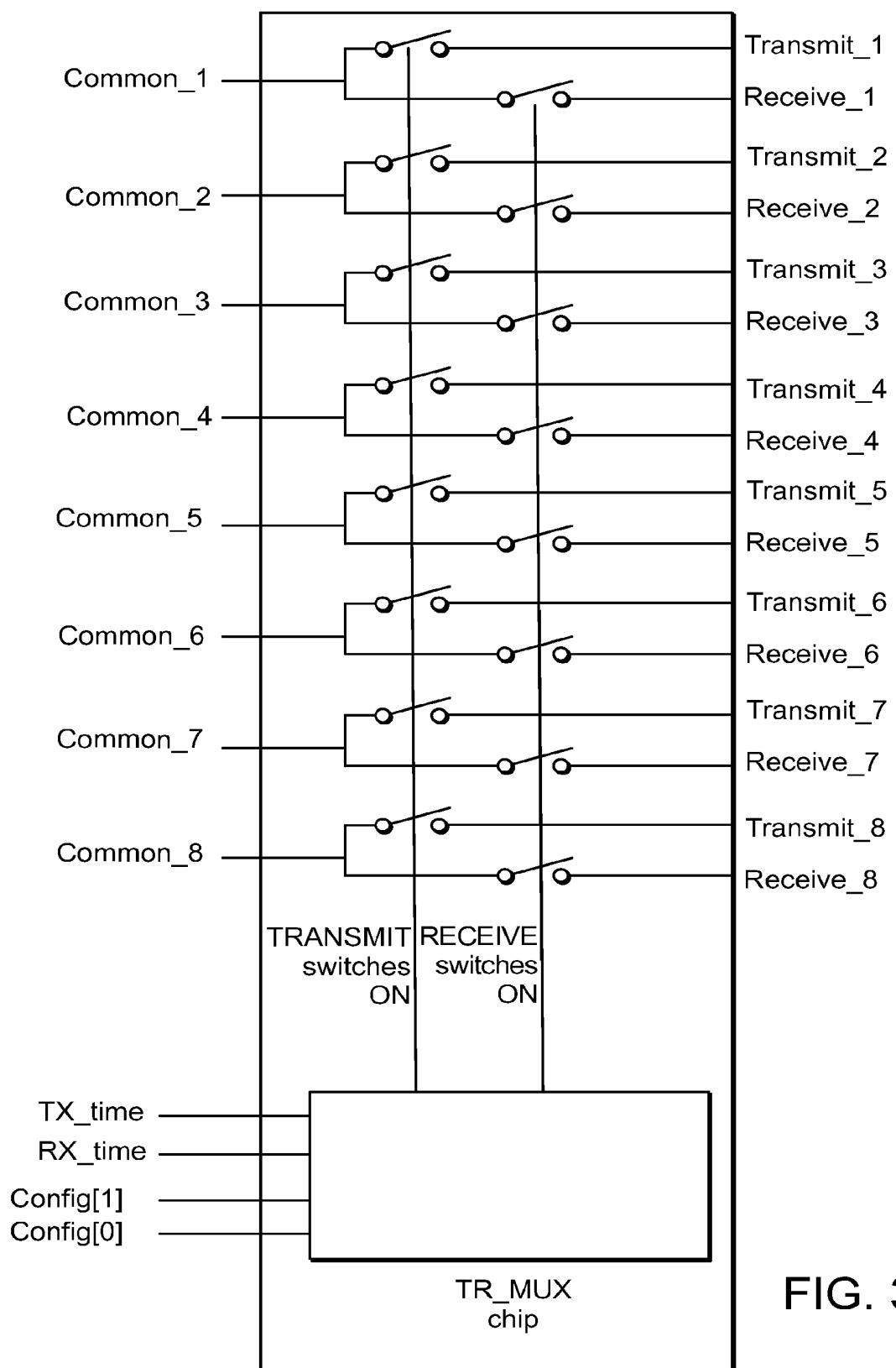

[0026] FIG. 3I is a schematic diagram of an 8 channel multiplexer chip in accordance with a preferred embodiment of the invention.

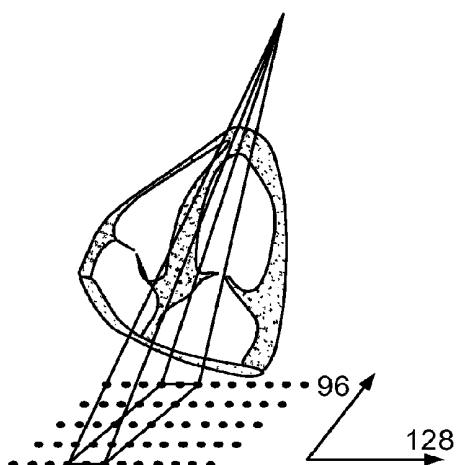

[0027] FIGS. 4A-4D illustrate a gated acquisition sequence for cardiac imaging.

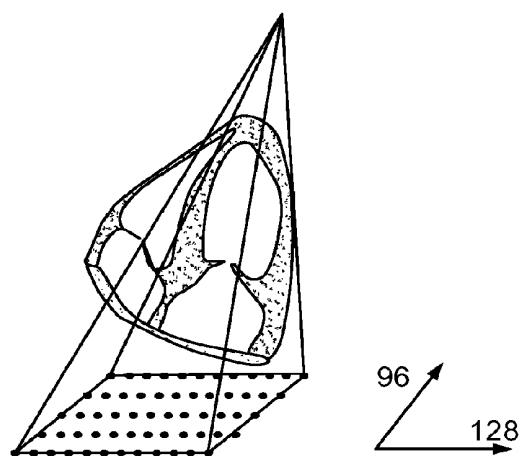

[0028] FIG. 4E illustrates a full cardiac imaging ultrasound scan using a plurality of beams with a single transmit pulse with at least six 3D volumetric images per second.

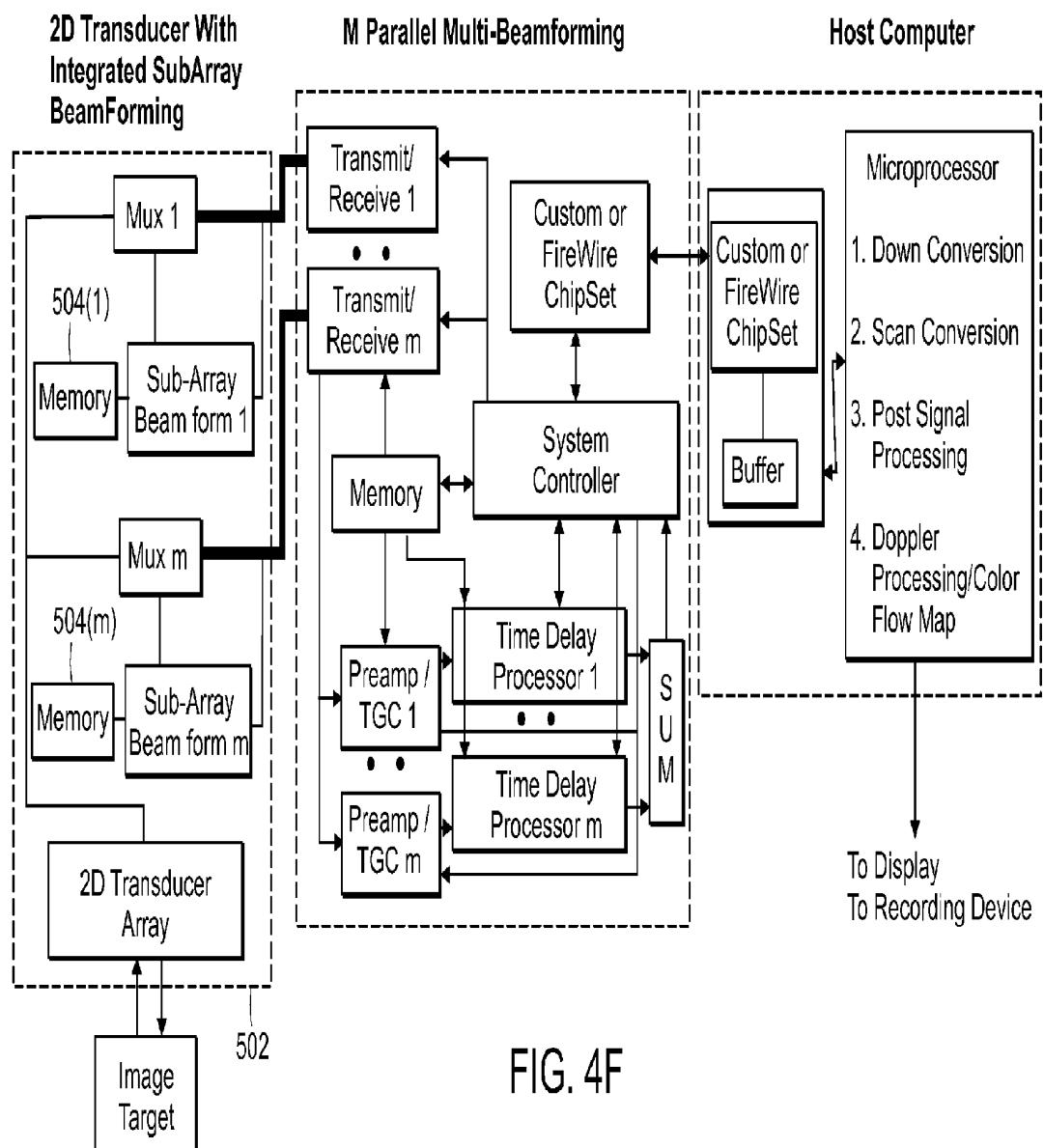

[0029] FIG. 4F illustrates an ultrasound system using a probe such as that shown in FIG. 3C.

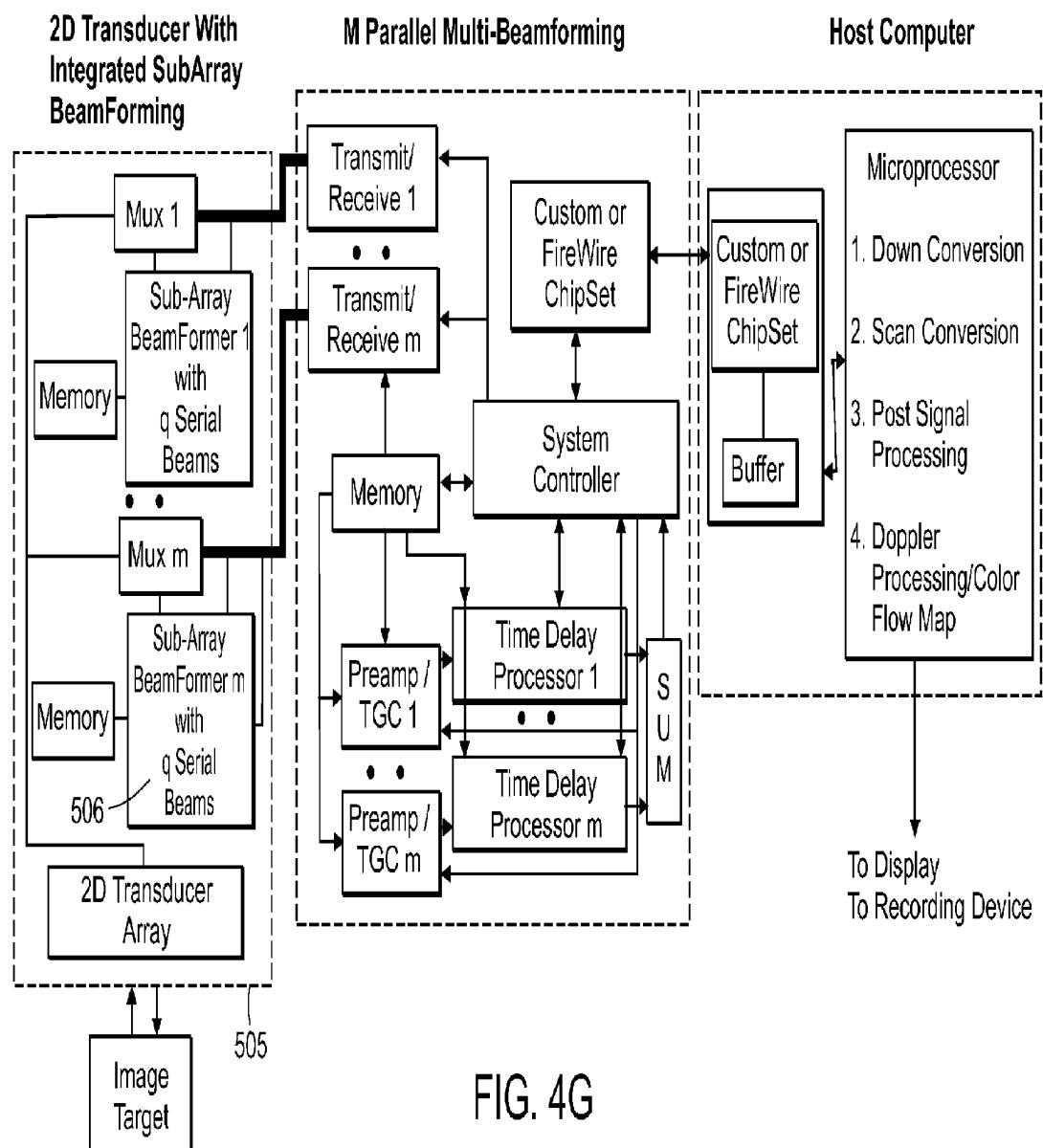

[0030] FIG. 4G illustrates an ultrasound system has a subarray beamformer with serial beam output.

[0031] FIG. 4H illustrates an ultrasound system with a second stage subaperture beamformer (509) that generates an output for a third stage beamformer (510).

[0032] FIG. 4I illustrates an ultrasound system with a controller integrated into the transducer probe housing.

[0033] FIG. 4J illustrates an ultrasound system with a controller and transmission circuit integrated in the transducer probe housing.

[0034] FIG. 4K illustrates an ultrasound system with parallel time delay processors (519P) producing parallel output data.

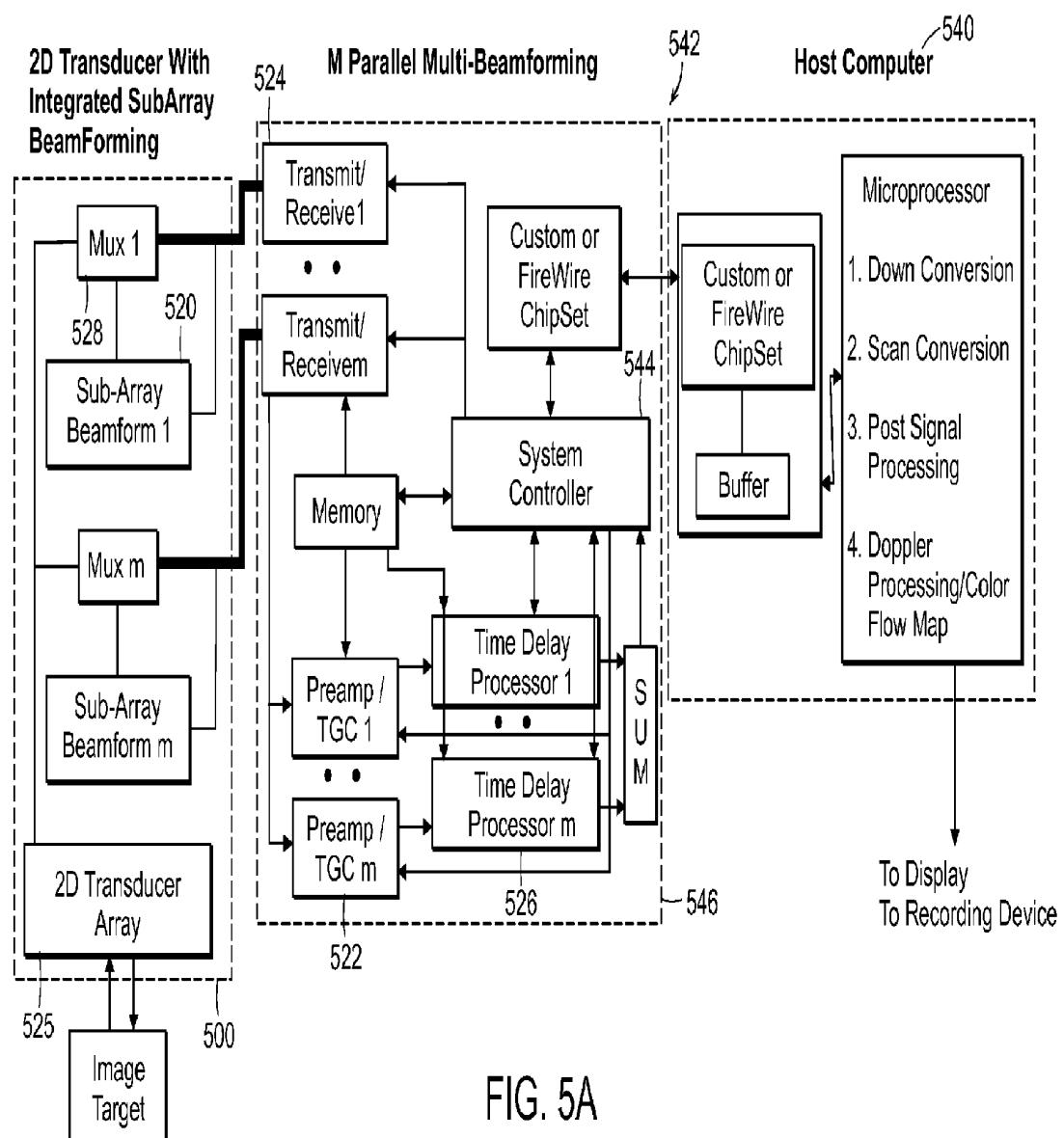

[0035] FIG. 5A illustrates a preferred embodiment of a three dimensional imaging system in accordance with the integrated Subarray scan head invention.

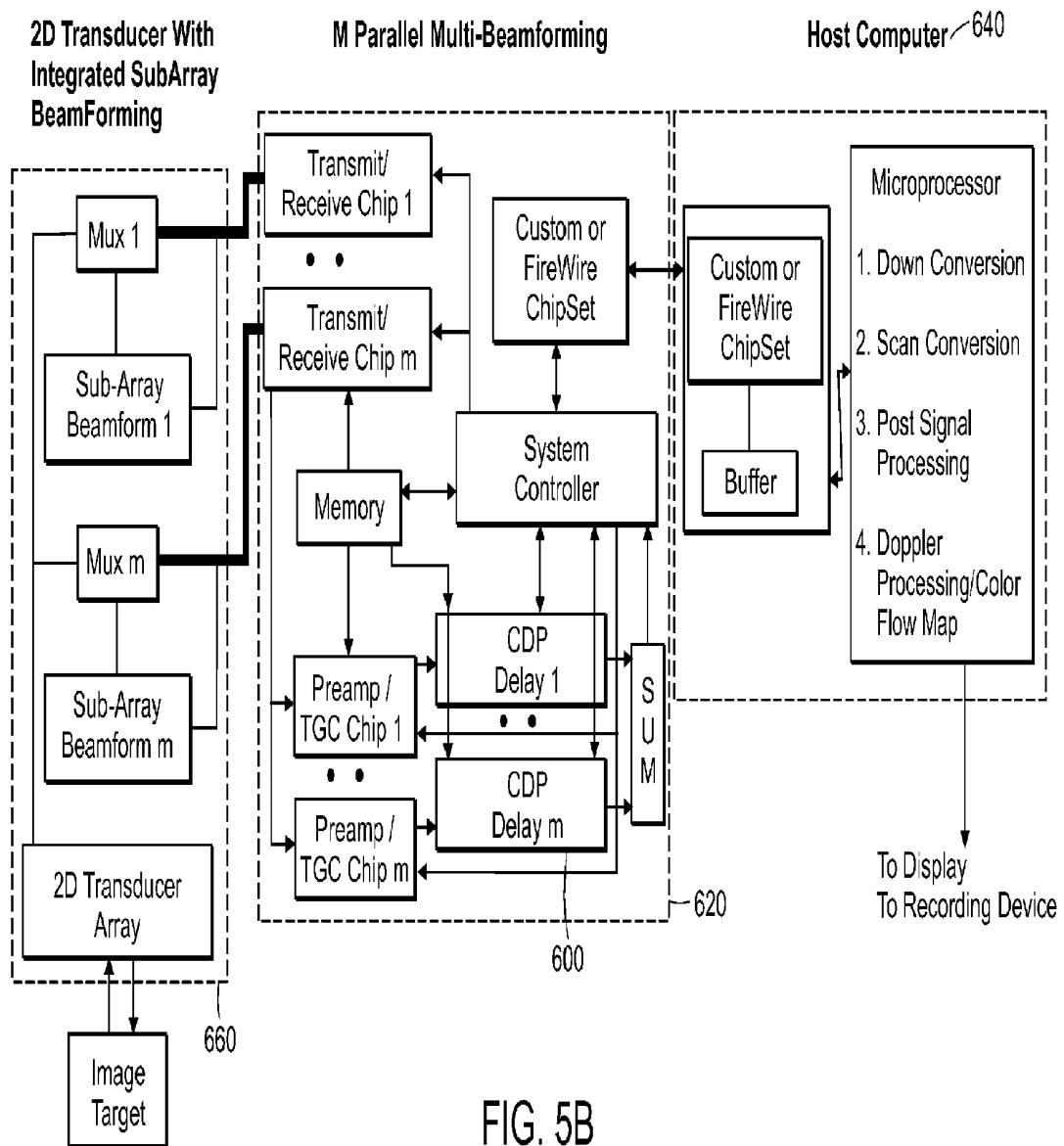

[0036] FIG. 5B illustrates a preferred embodiment of the integrated Subarray scan head invention using a charge domain processor for the 2<sup>nd</sup> time delay beamforming.

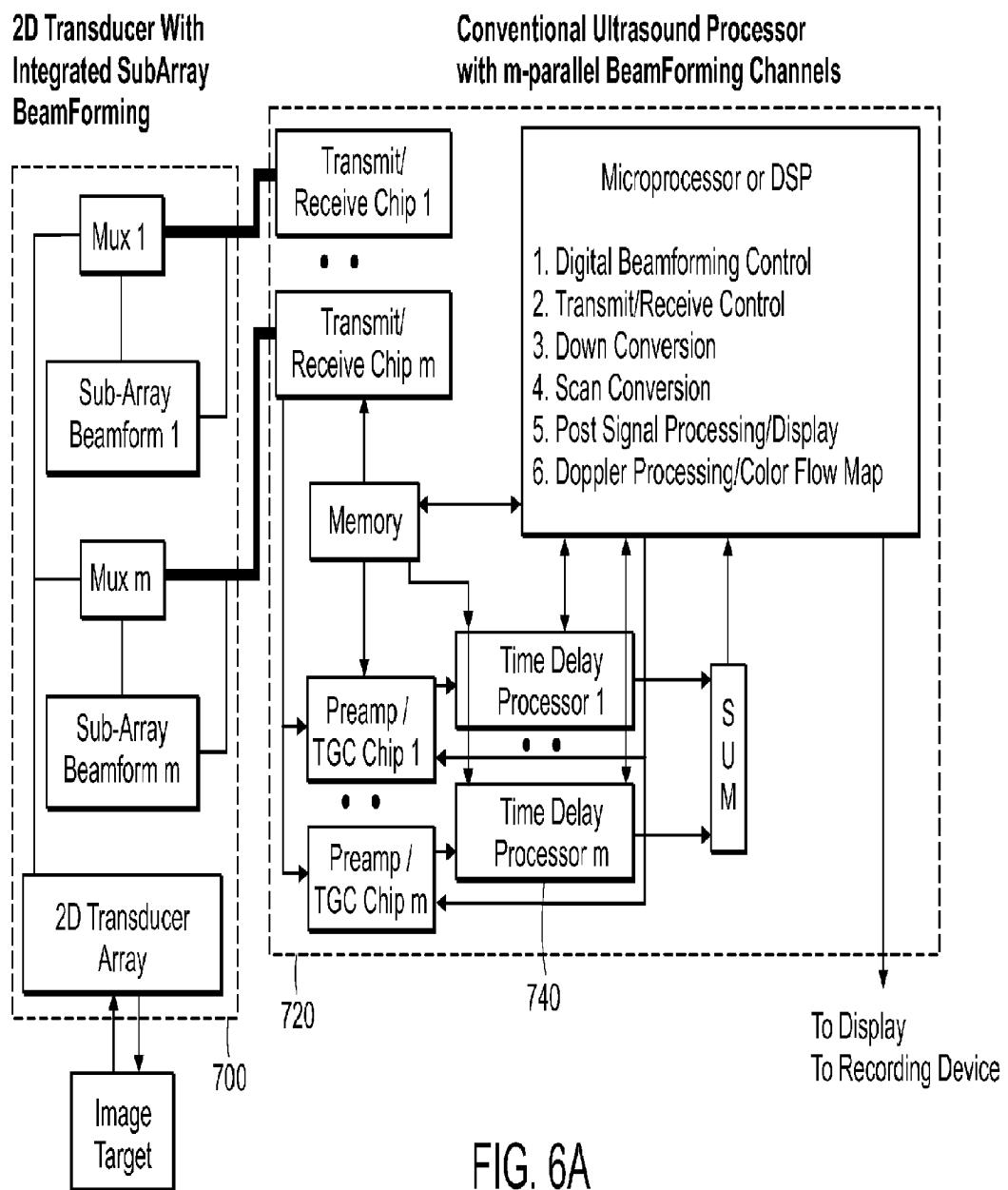

[0037] FIG. 6A illustrates the use of the integrated subarray scan head probe of the present invention with a second stage beamforming ultrasound processor.

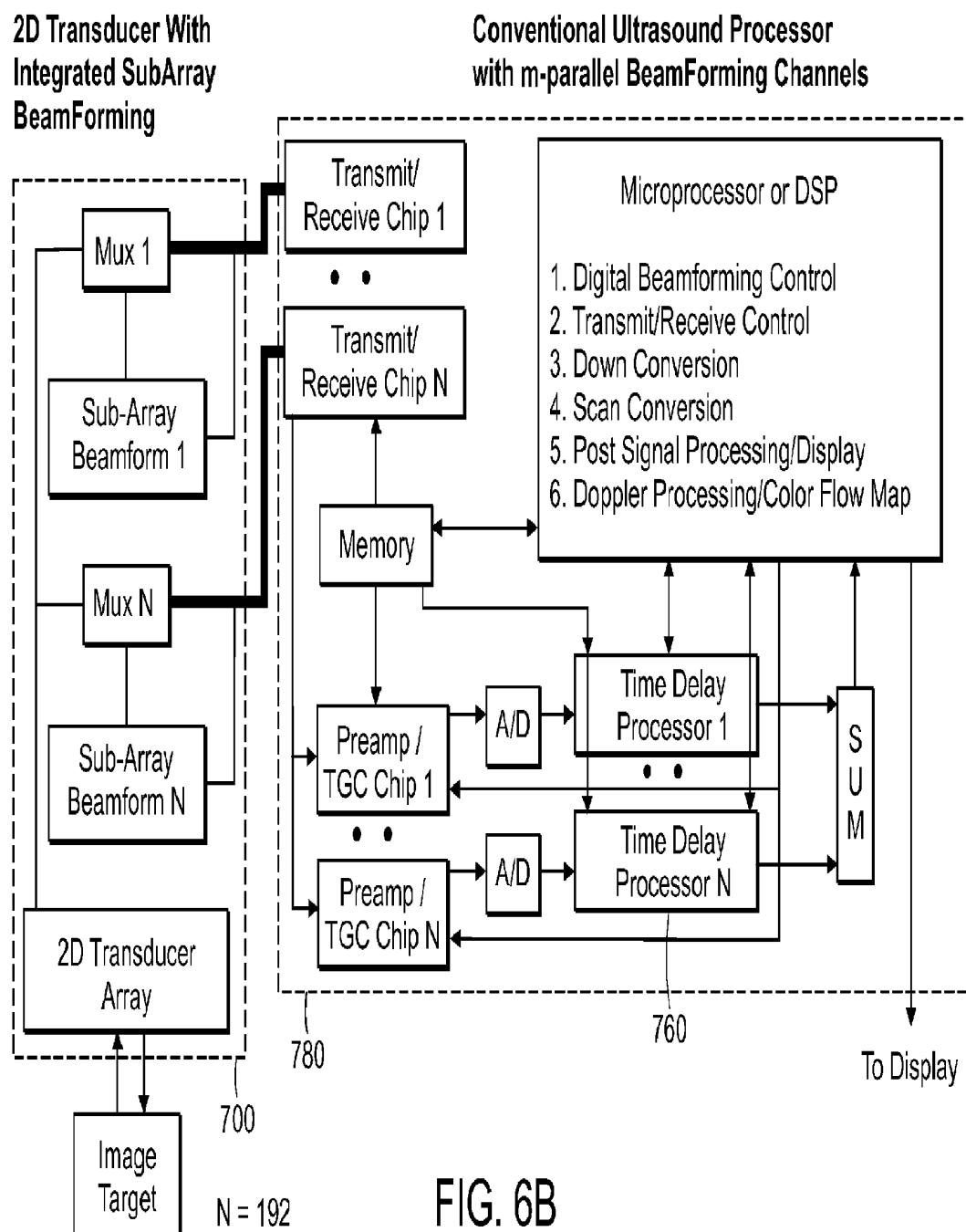

[0038] FIG. 6B illustrates use of the integrated Subarray scan head with a digital beamforming processor.

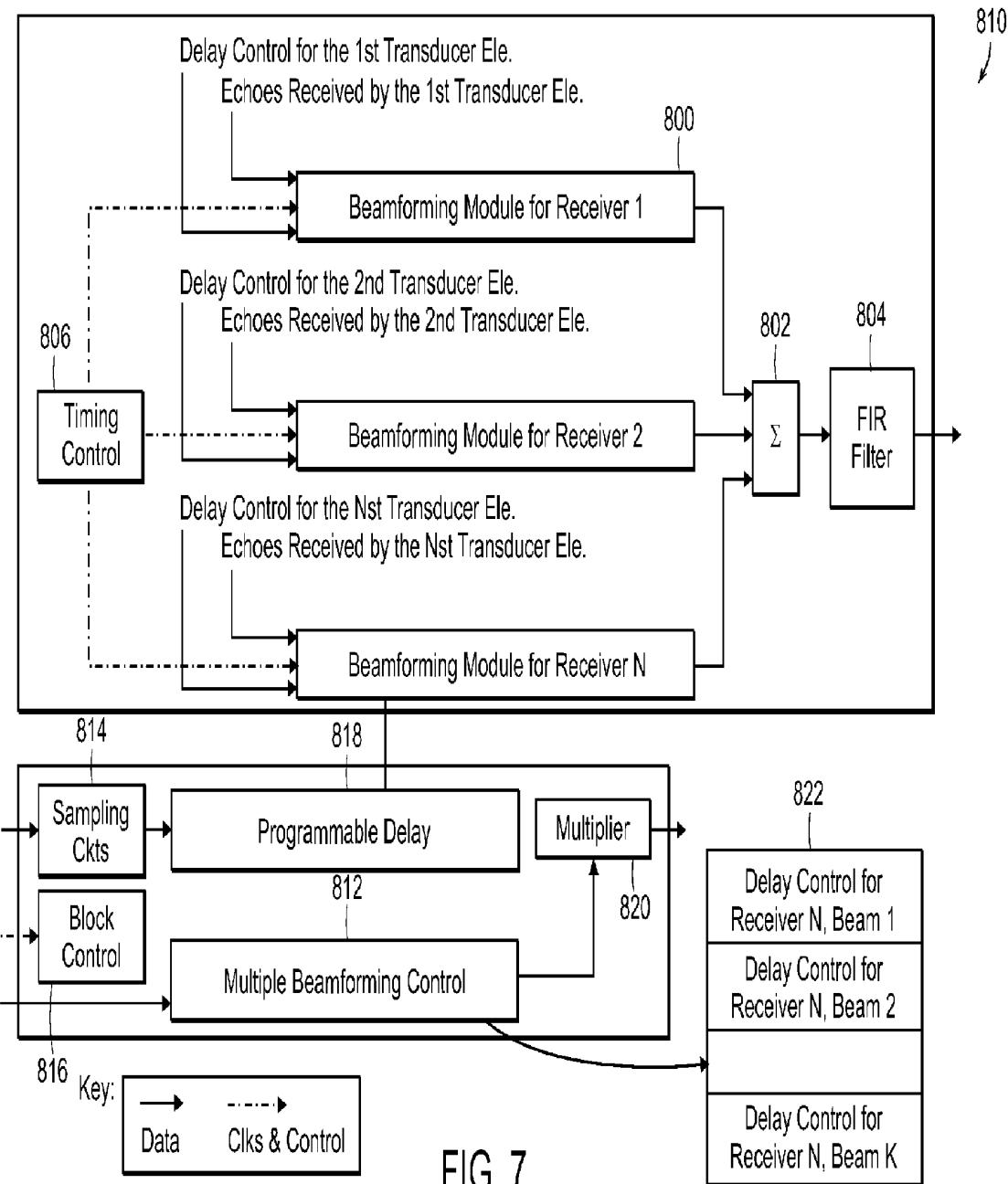

[0039] FIG. 7 illustrates an ultrasound system in accordance with the invention.

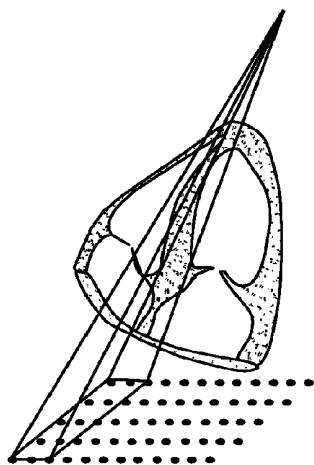

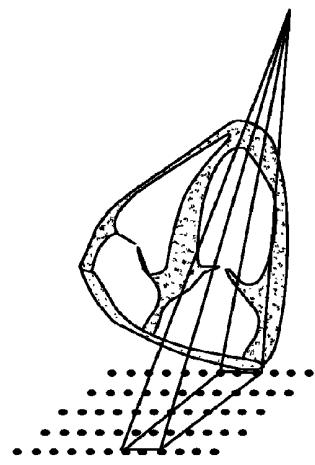

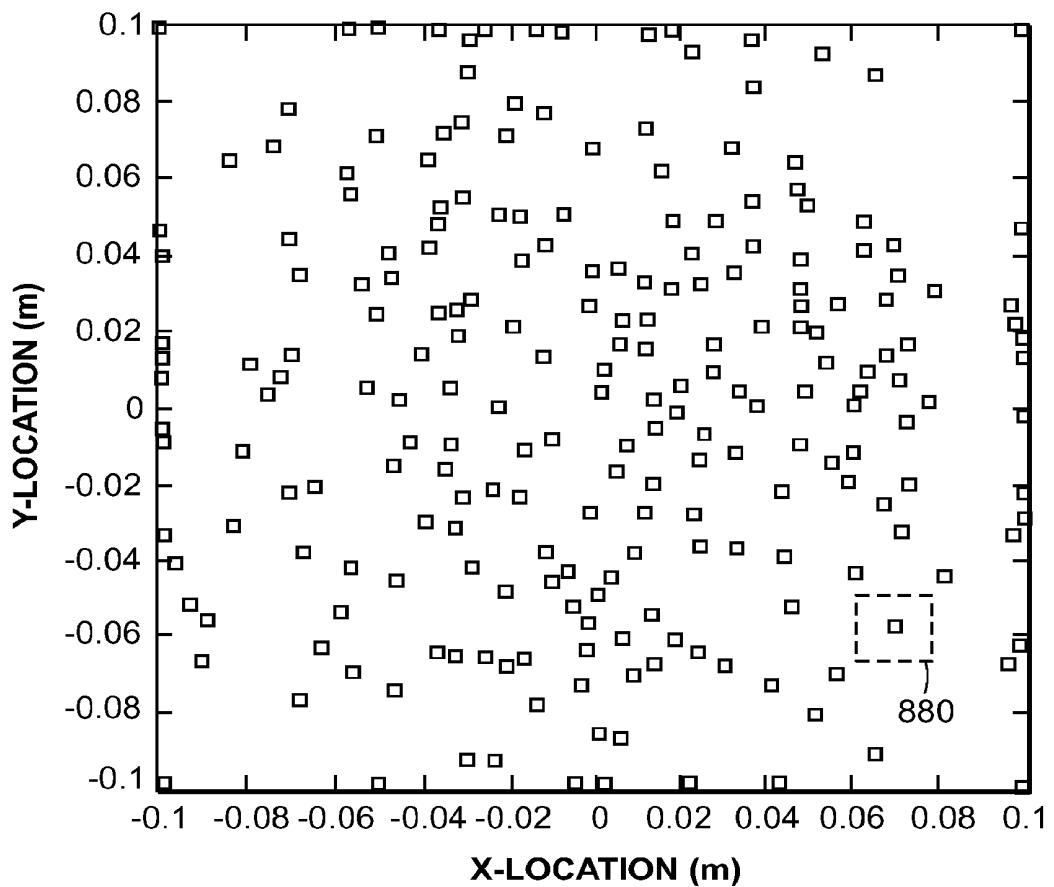

[0040] FIG. 8A illustrates a sparse array used in accordance with the invention.

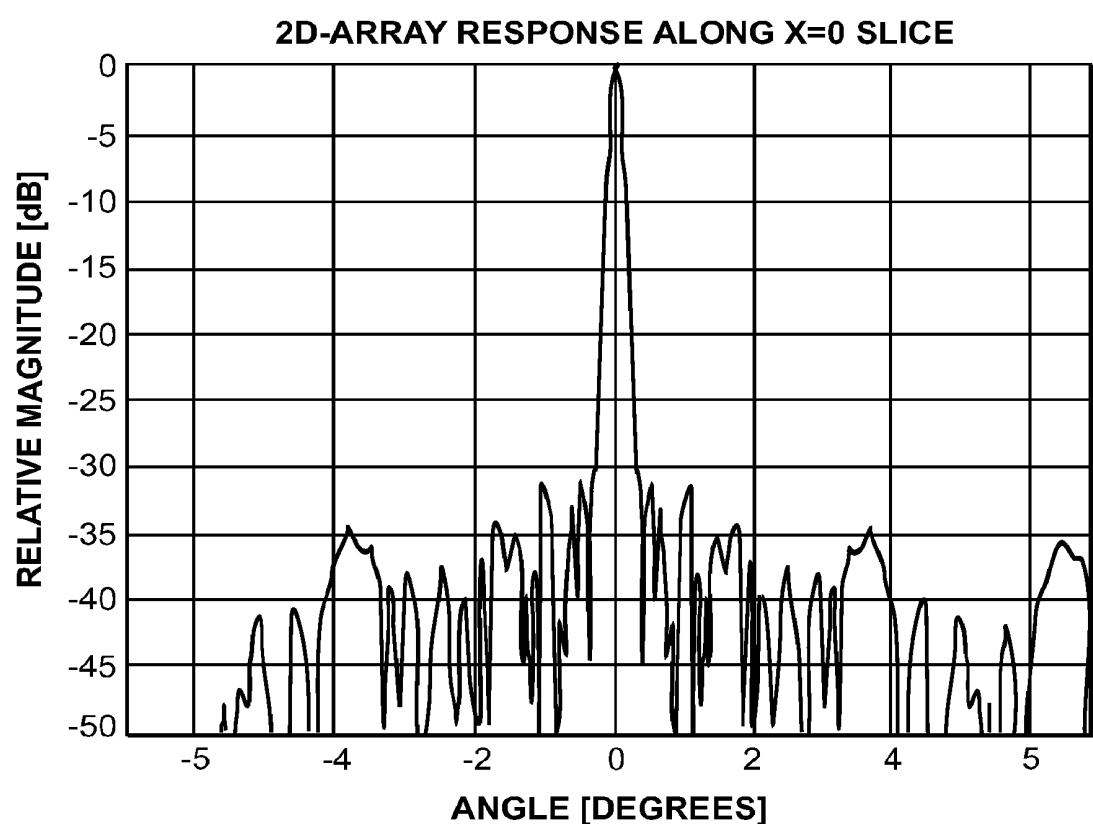

[0041] FIG. 8B graphically illustrates the sparse array performance.

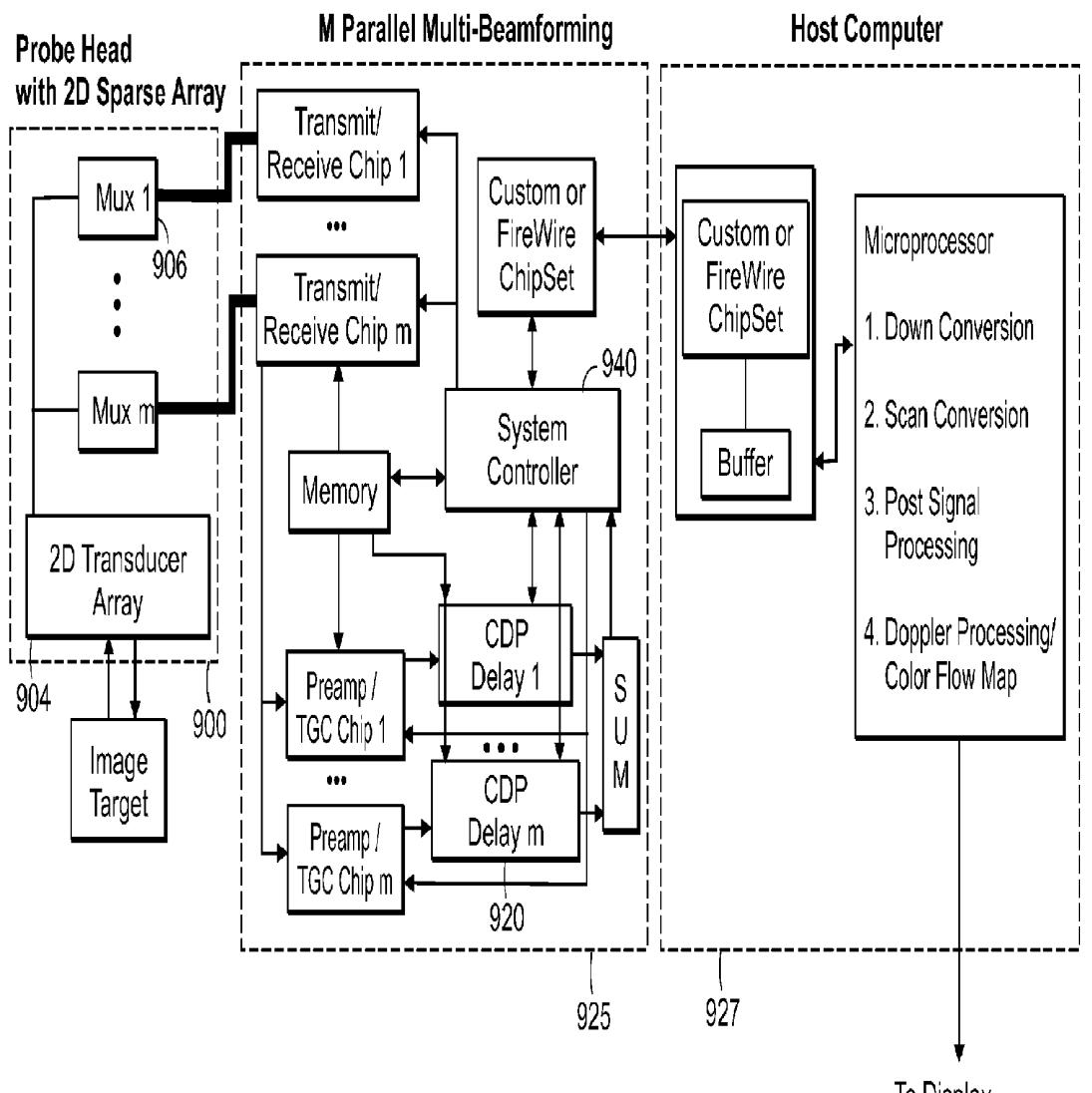

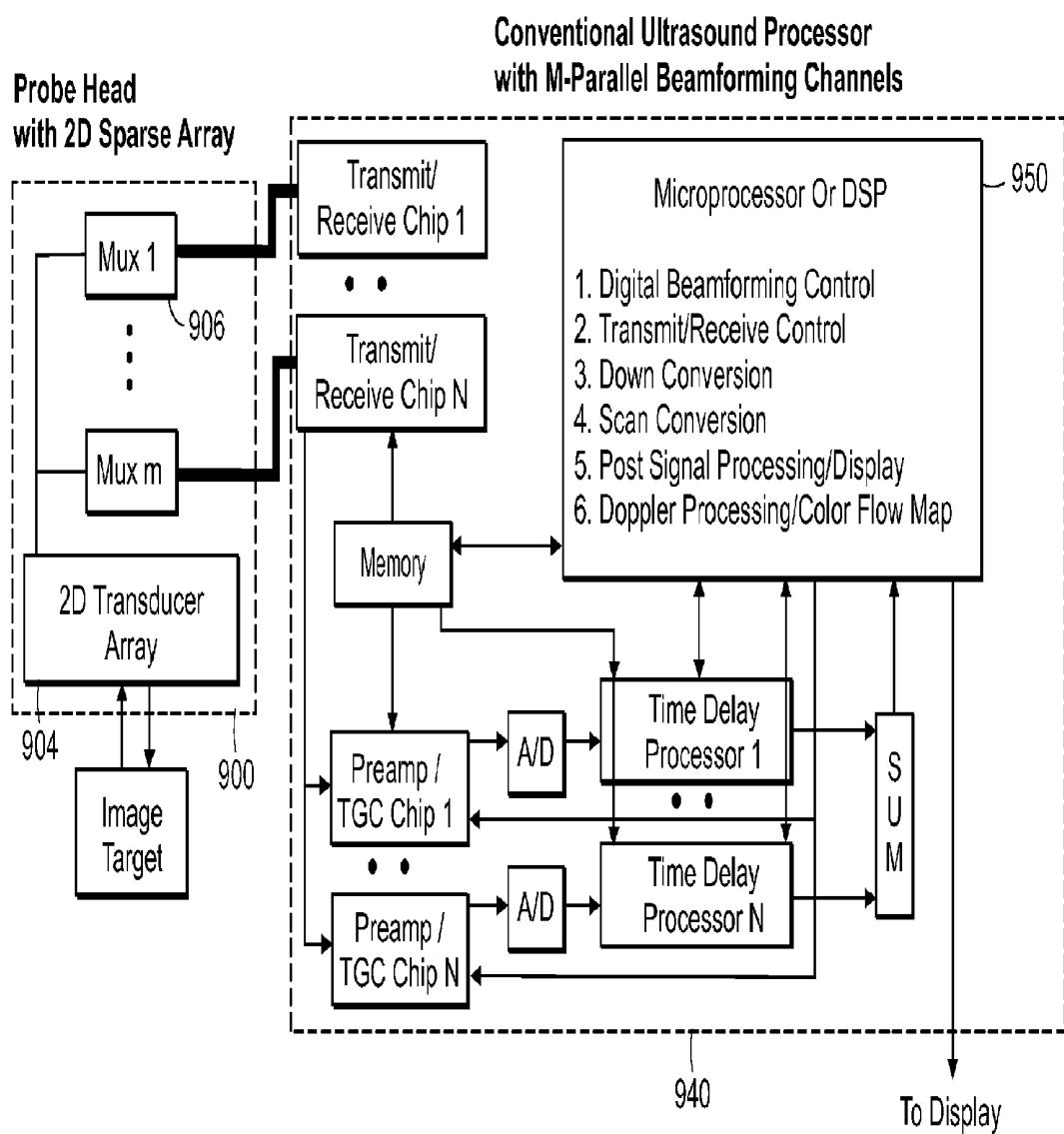

[0042] FIG. 9A illustrates the use of the integrated sparse array scan head probe of the present invention connected to a host system with charge-domain beamforming processing.

[0043] FIG. 9B illustrates the use of the integrated sparse array scan head probe of the present invention connected to a conventional digital ultrasound system with m-parallel beamforming components.

[0044] FIG. 10 illustrates a scan head connected to a portable computer in accordance with a preferred embodiment of the invention.

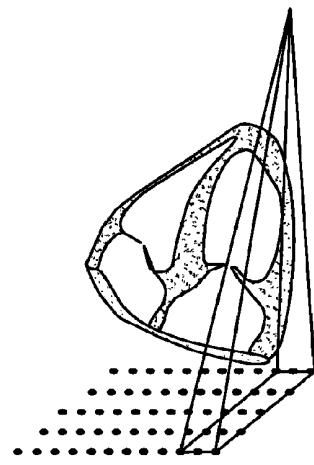

[0045] FIG. 11 illustrates a near fully populated receive array in which the receiving elements are independent of, and do not overlap, the transmit array.

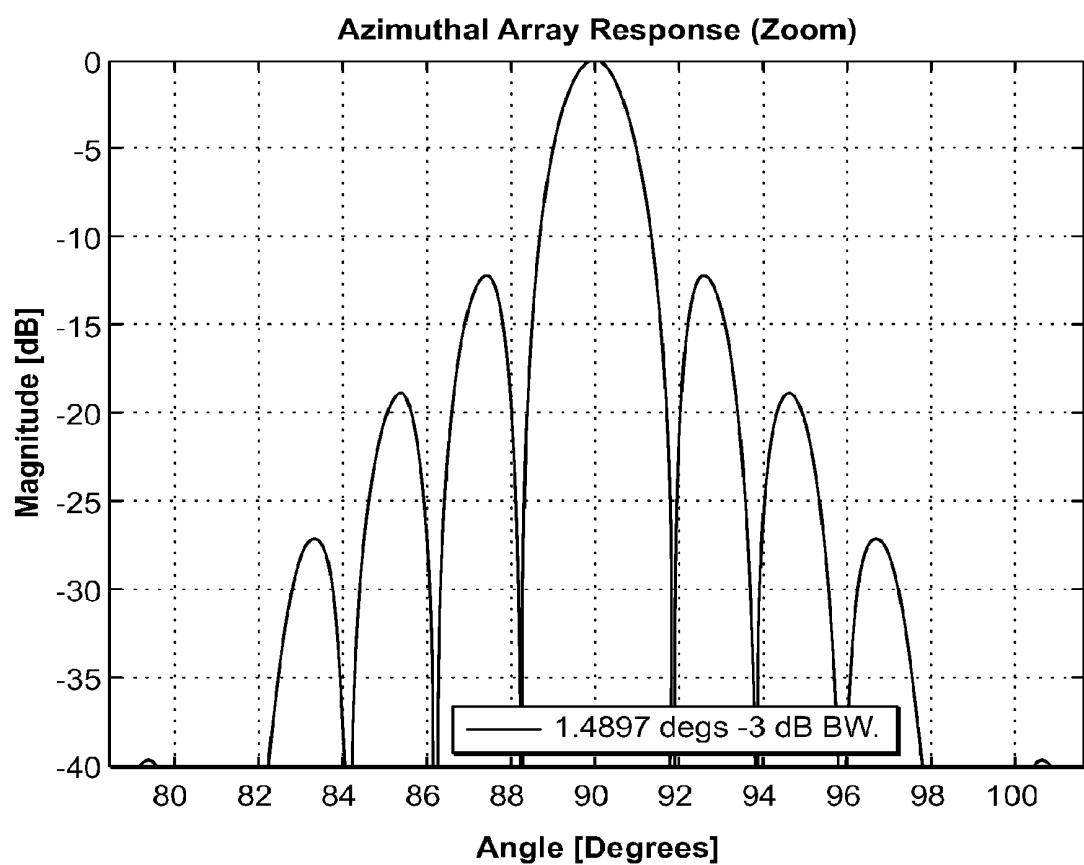

[0046] FIG. 12 graphically illustrates the azimuth and elevation cross-sections of the receive array beampattern.

[0047] FIG. 13 is a magnified portion of the azimuthal beampattern of FIG. 12 showing the mainlobe and sidelobe structure.

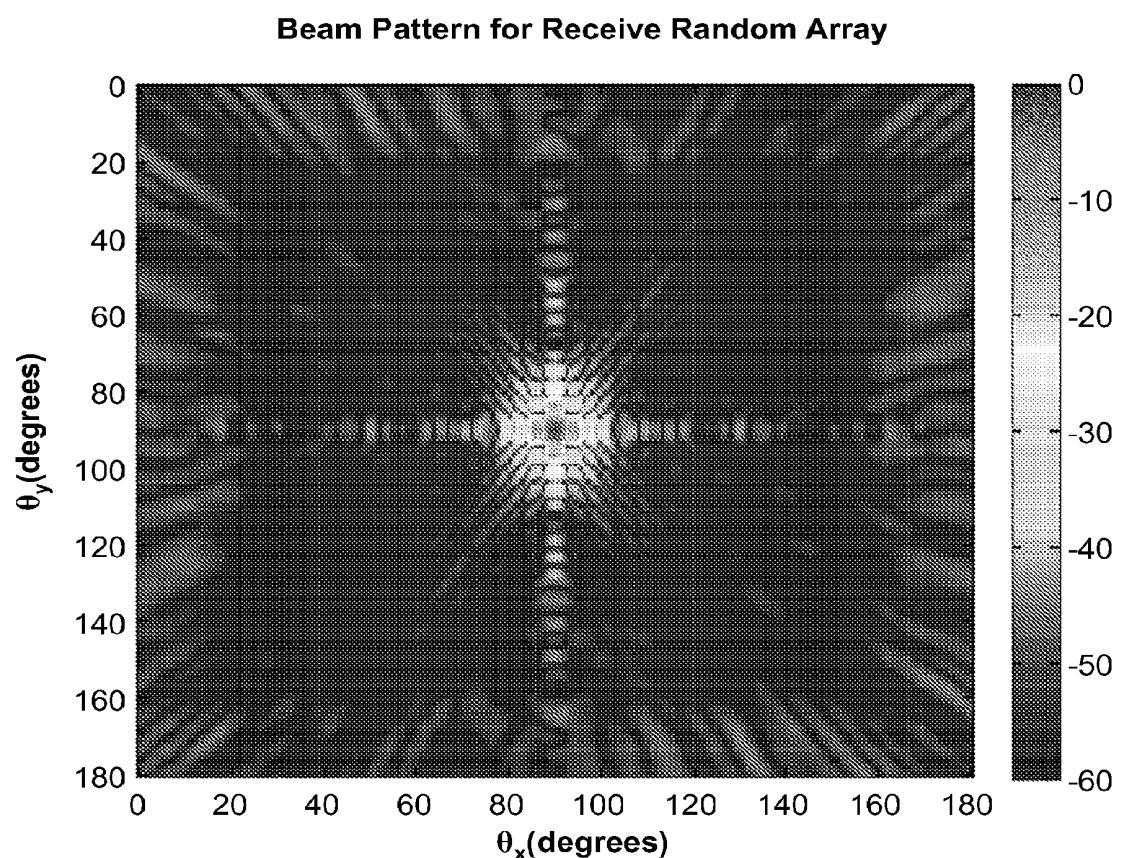

[0048] FIG. 14 illustrates a near fully populated receive array beampattern.

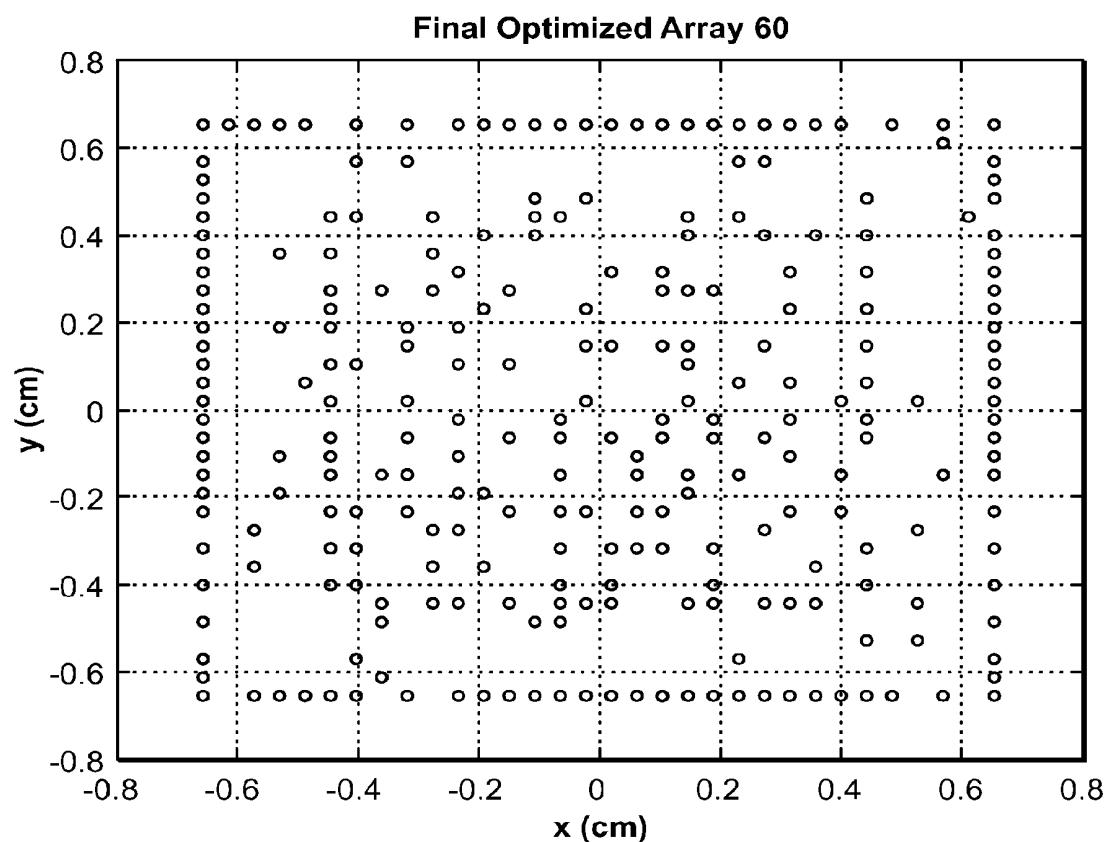

[0049] FIG. 15 shows selected transmit locations for a sparse array in accordance with the invention.

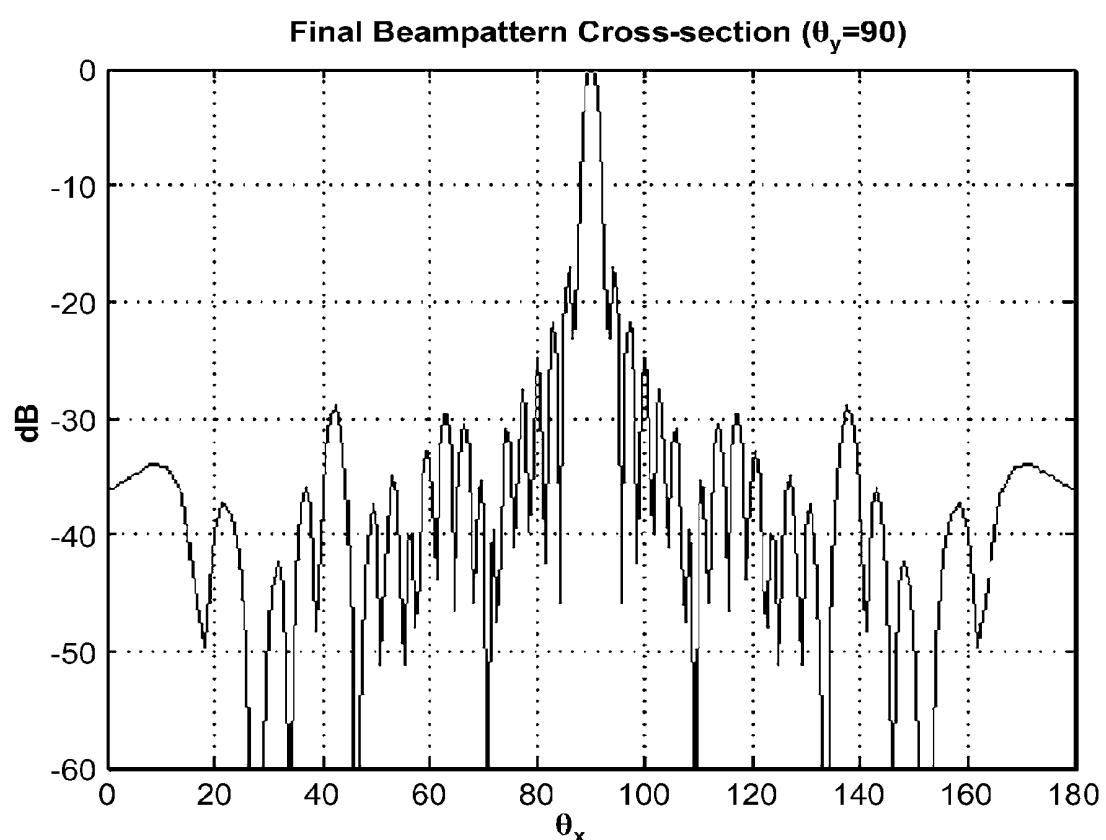

[0050] FIG. 16 illustrates a cross-sectional view of the transmit sparse array beampattern of the embodiment in FIG. 15.

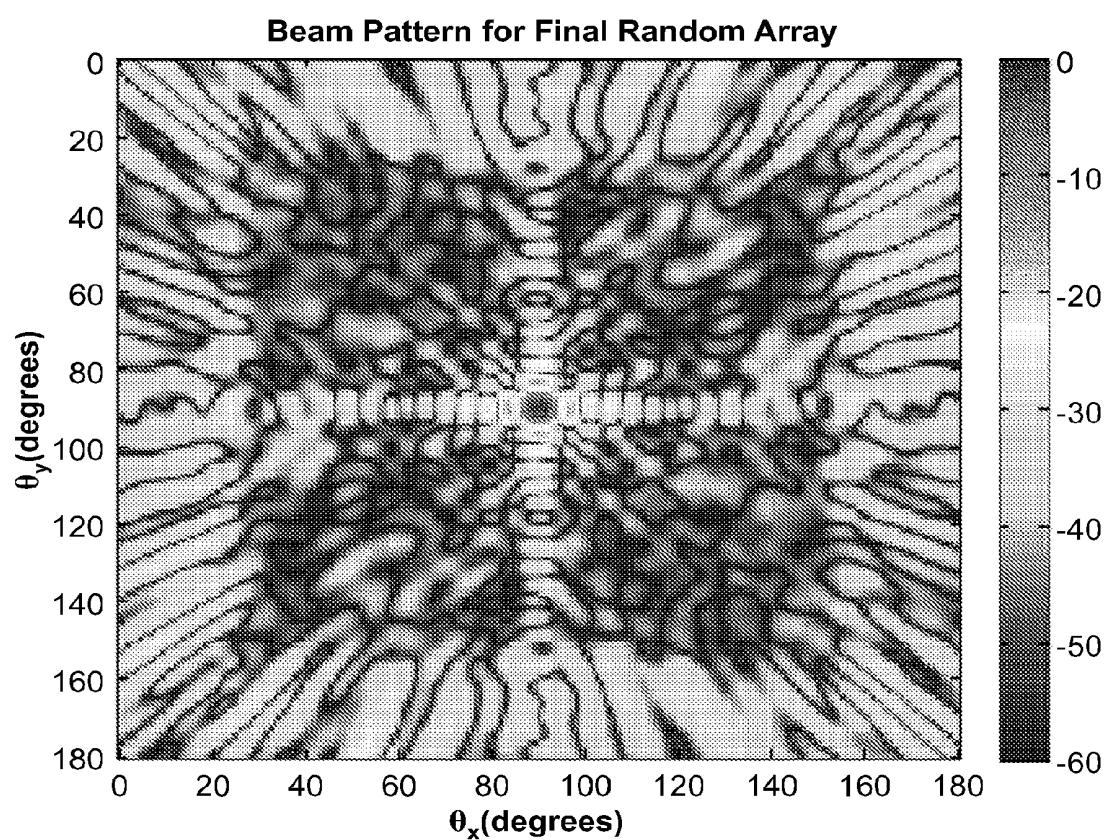

[0051] FIG. 17 illustrates a sparse transmit array beampattern.

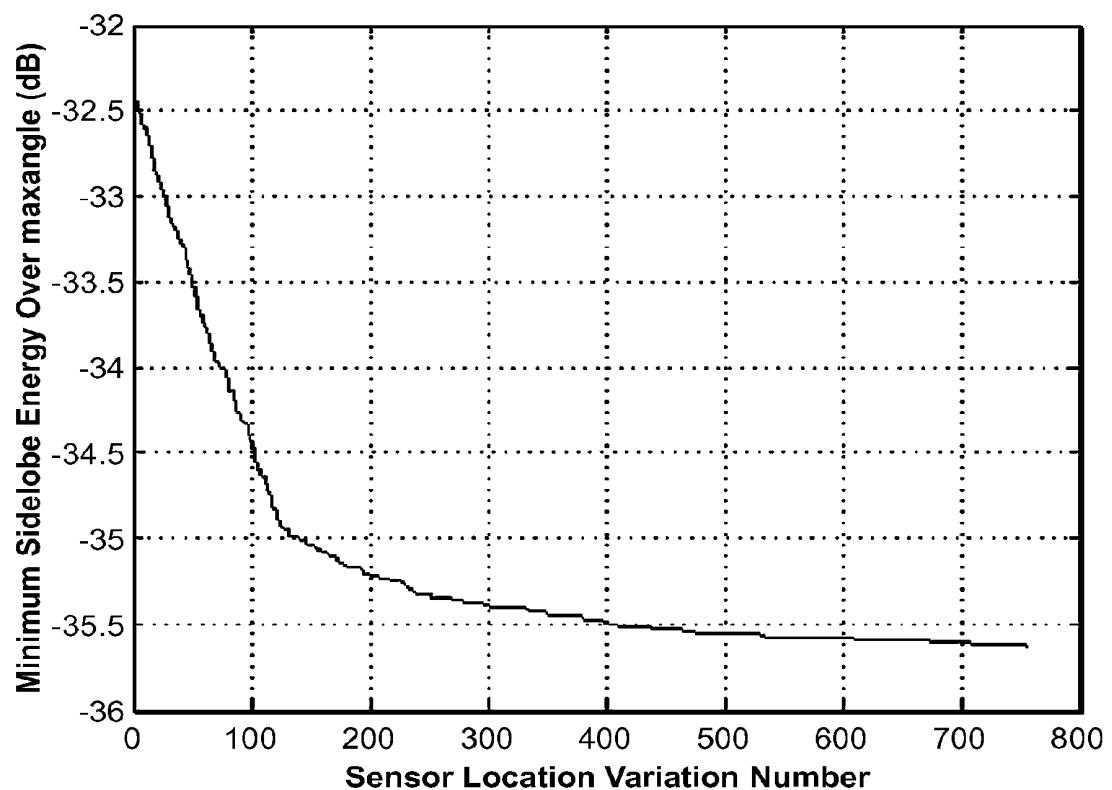

[0052] FIG. 18 illustrates that it is possible to limit, average sidelobe energy to less than -35 dB relative to the central peak of the beampattern.

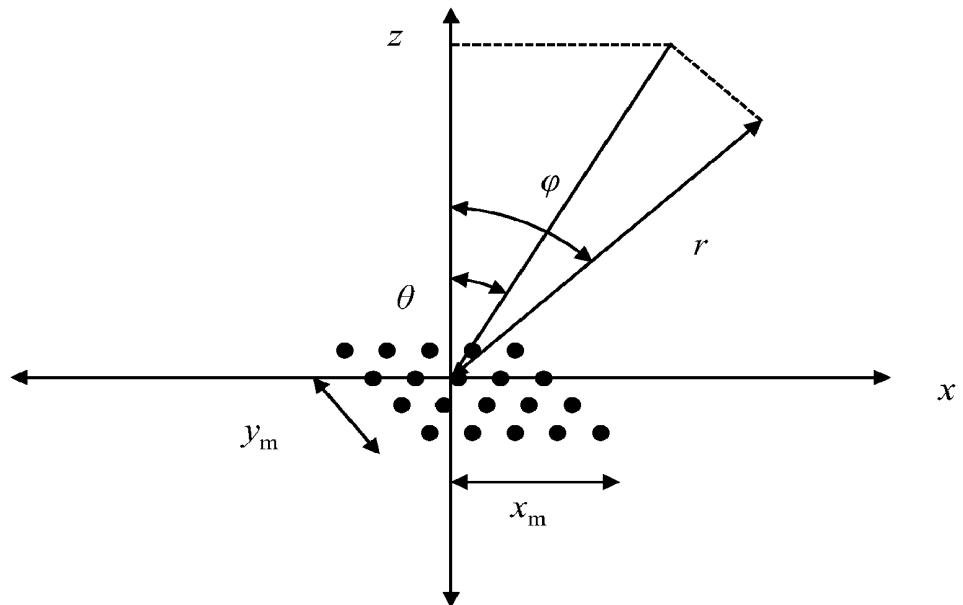

[0053] FIG. 19 illustrates the 2D differential delay equation.

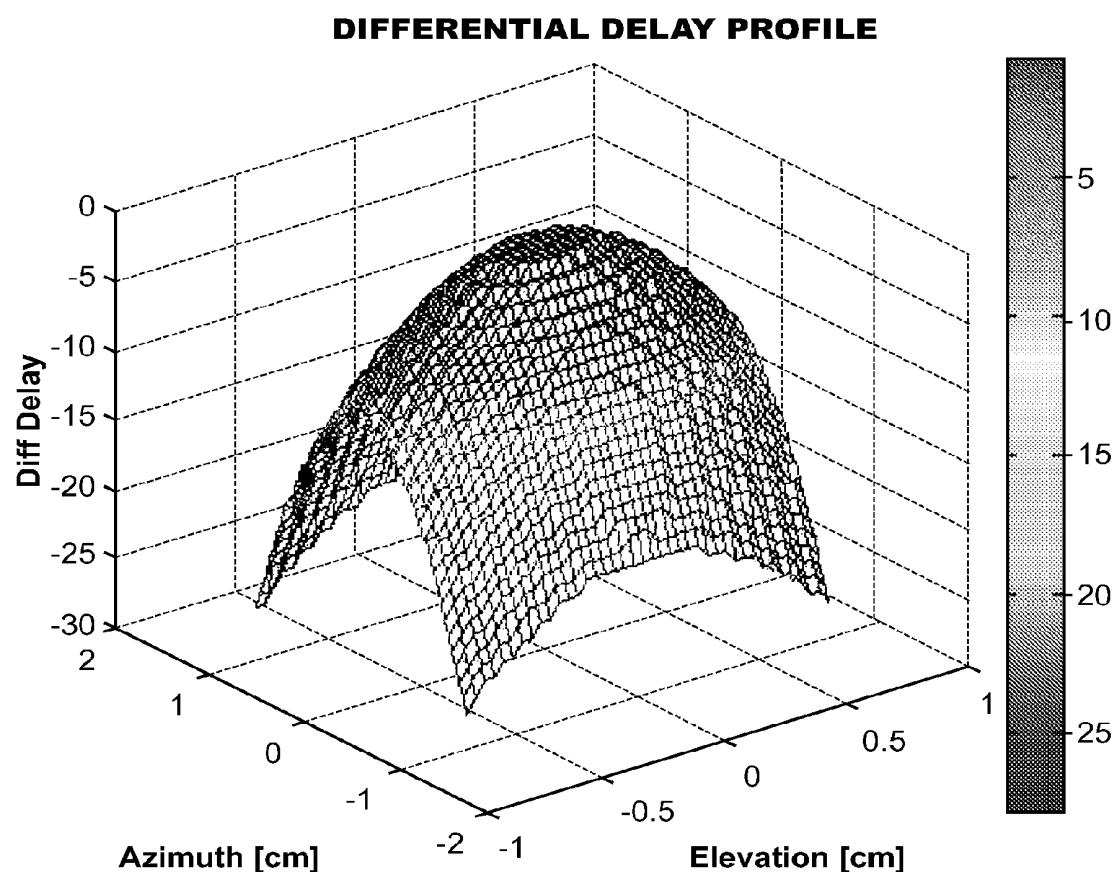

[0054] FIG. 20 illustrates a differential display profile.

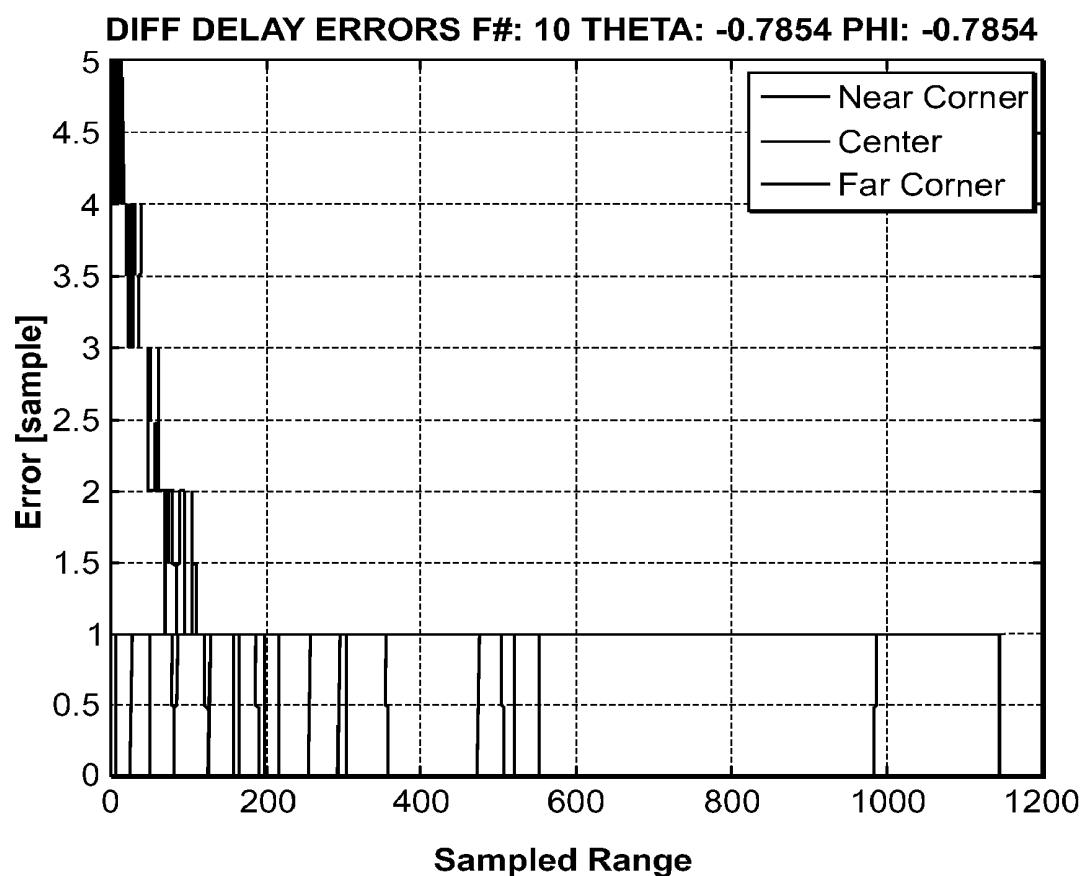

[0055] FIG. 21 illustrates differential delay errors.

[0056] FIGS. 22A-22C illustrate embodiments of system processors in a four parallel beamforming system.

[0057] FIGS. 23A and 23B illustrated non-coded and coded, transmit waveforms for spread spectrum ultrasound transmission.

[0058] FIGS. 24A-24C illustrate a process for forming a transmission signal.

[0059] FIGS. 25A-25D illustrate preferred embodiments including a matched filter.

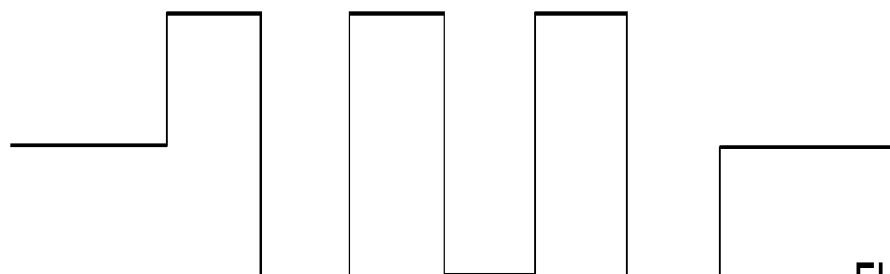

[0060] FIGS. 26A-26D illustrate a square wave signal and modified square wave transmit signals for third harmonic imaging.

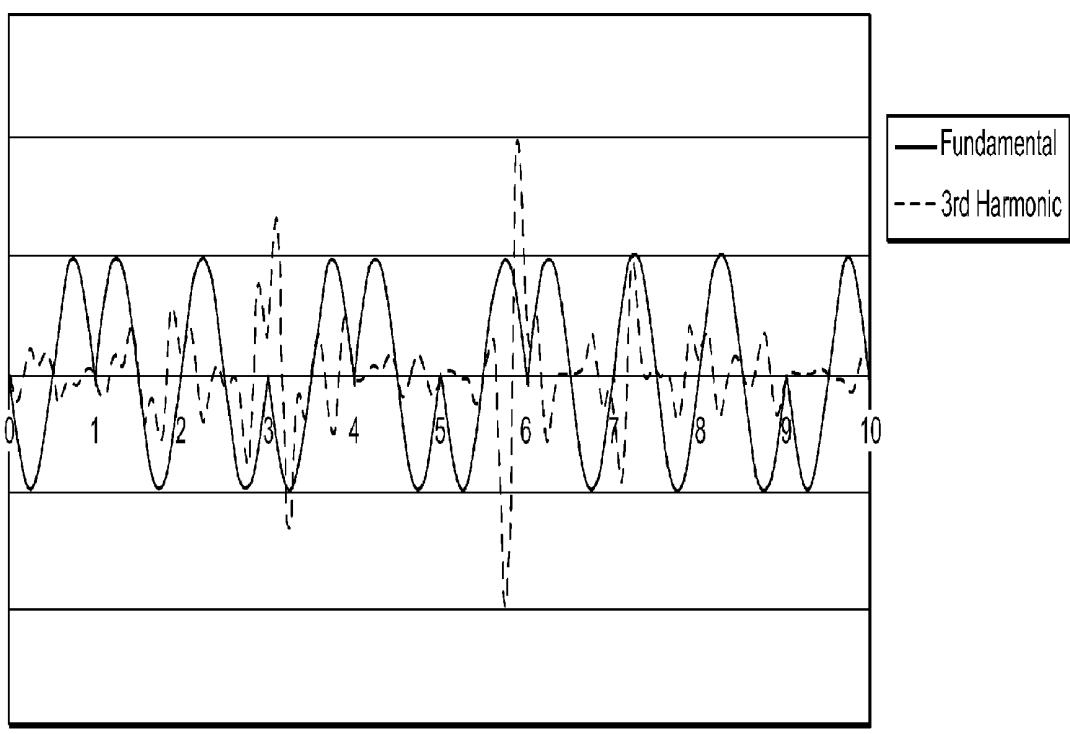

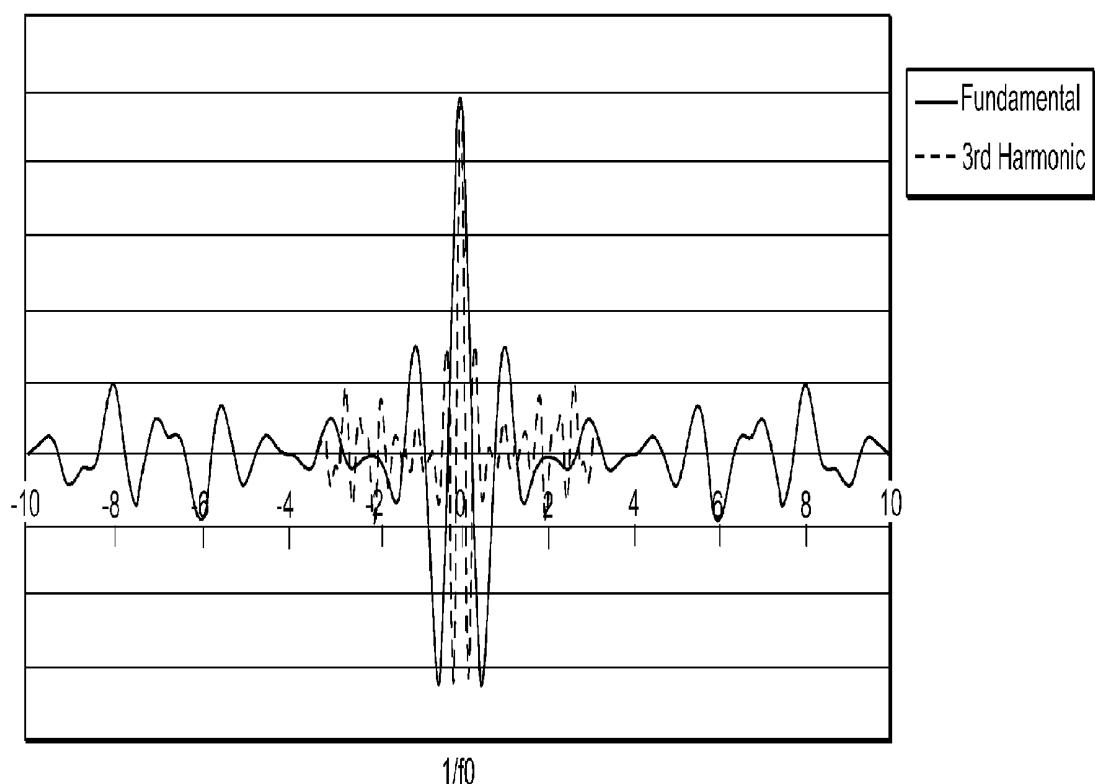

[0061] FIGS. 27A and 27B illustrate match filter template for first and second codes of Golay.

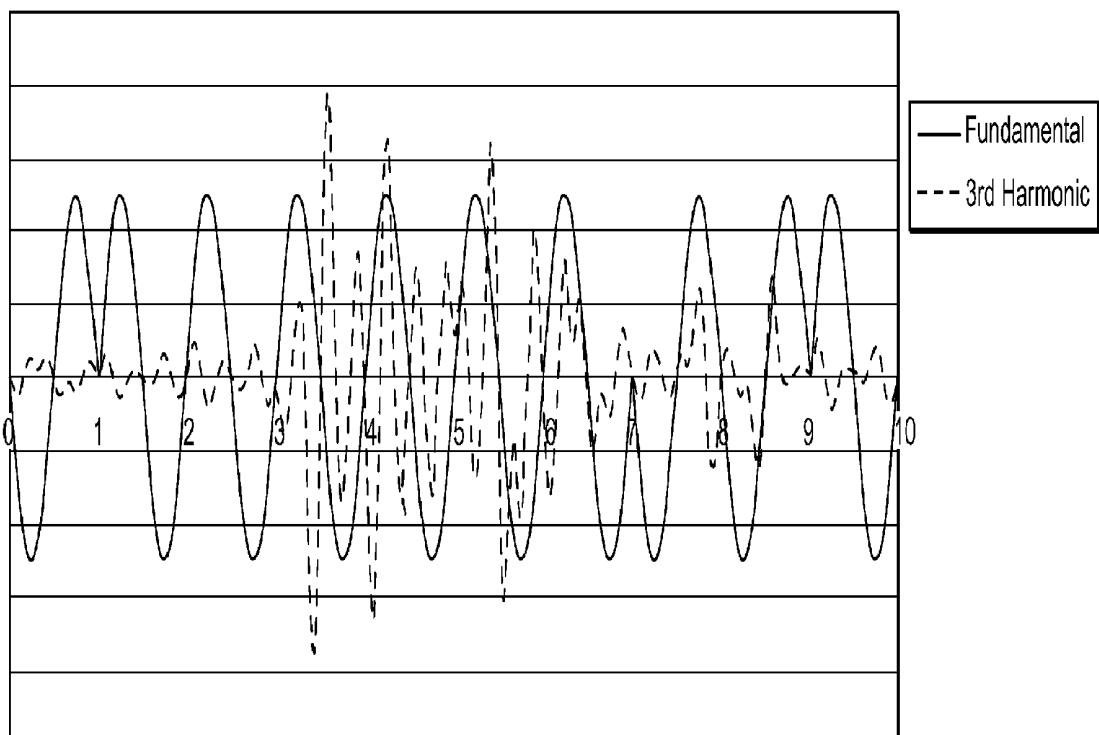

[0062] FIGS. 27C and 27D illustrate the autocorrelation of the fundamental and third harmonics for the filter template of the first and second delay codes.

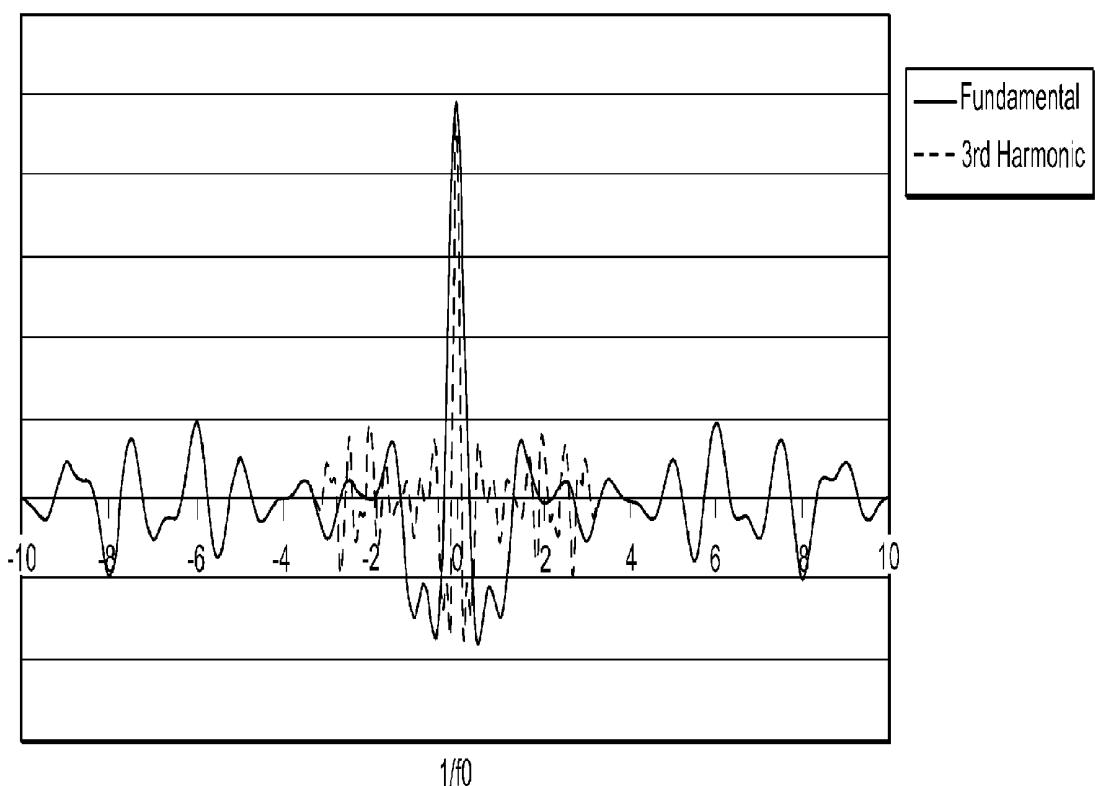

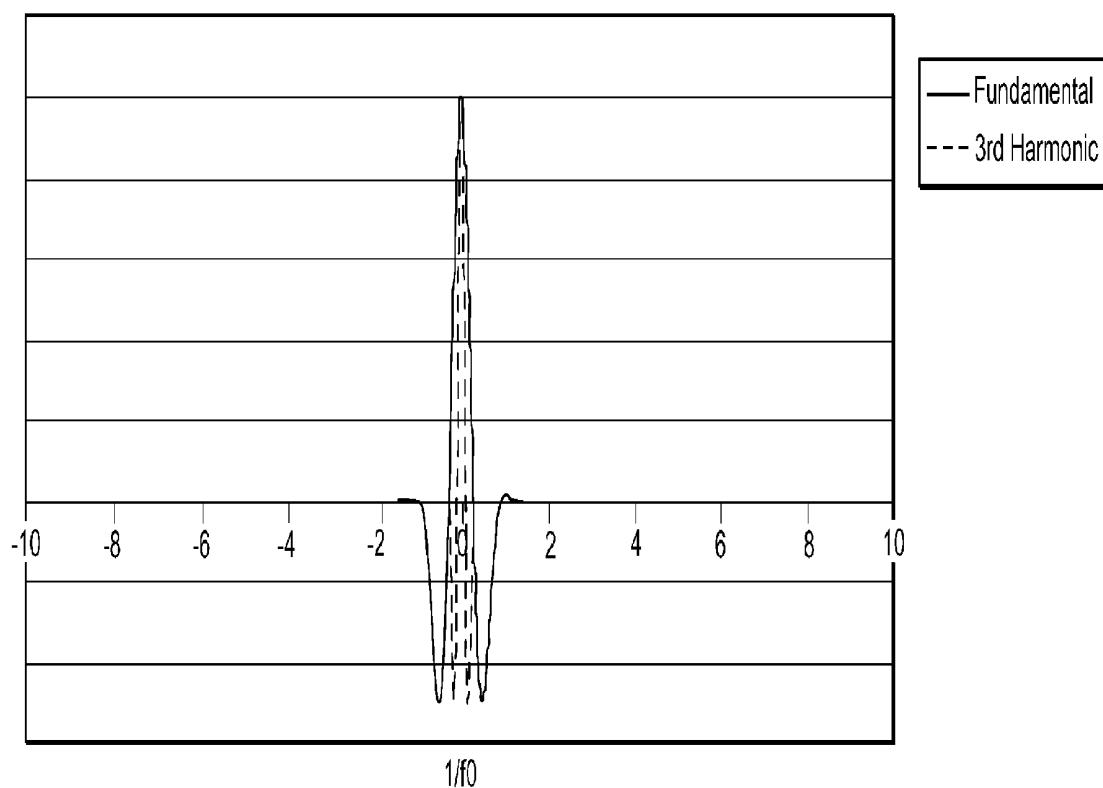

[0063] FIG. 28 shows the sum of the two autocorrelation shown in FIGS. 27C and 27D.

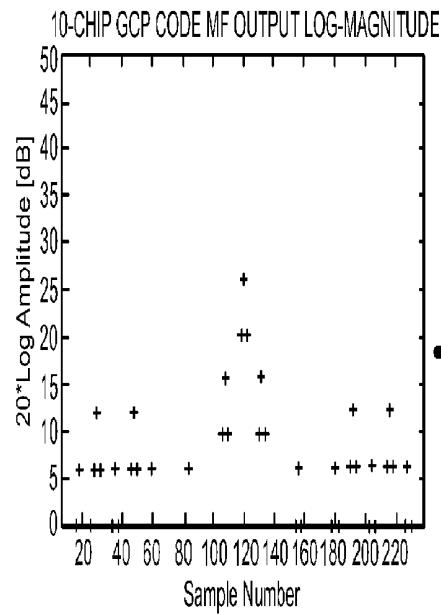

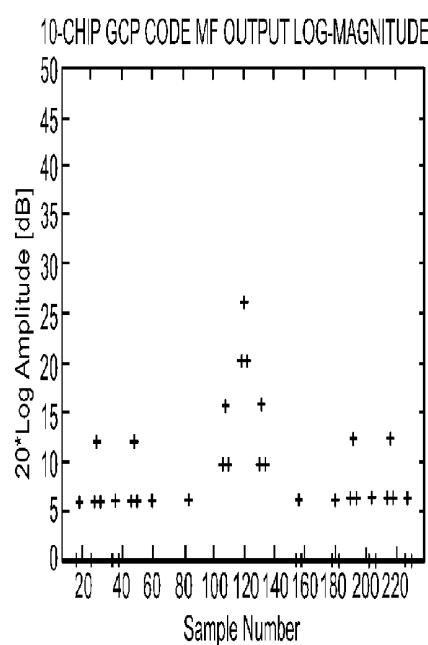

[0064] FIGS. 29A and 29B illustrate examples of the third harmonic template of first and second 10 bit Golay codes.

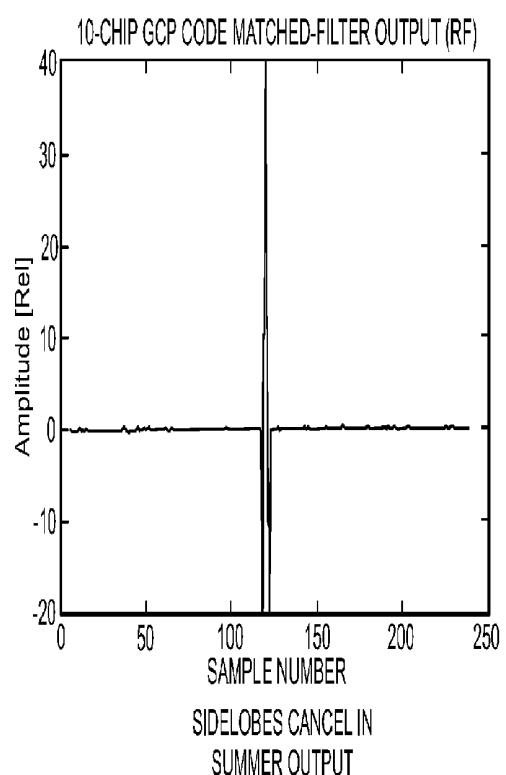

[0065] FIGS. 30A-30C illustrate sidelobe cancellation with the summed output.

#### DETAILED DESCRIPTION OF THE INVENTION

[0066] The objective of the beamforming system is to focus signals received from an image point onto a transducer array. By inserting proper delays in a beamformer to wavefronts that are propagating in a particular direction, signals arriving from the direction of interest are added coherently, while those from other directions do not add coherently or cancel. For real-time three-dimensional applications, separate electronic circuitry is necessary for each transducer element. Using conventional implementations, the resulting electronics rapidly become both bulky and costly as the number of elements increases. Traditionally, the cost, size, complexity and power requirements of a high-resolution beamformer have been avoided by “work-around” system approaches. For real-time three-dimensional high-resolution ultrasound, imaging applications, an electronically steerable two-dimensional beamforming processor based on a delay-and-sum computing algorithm is chosen.

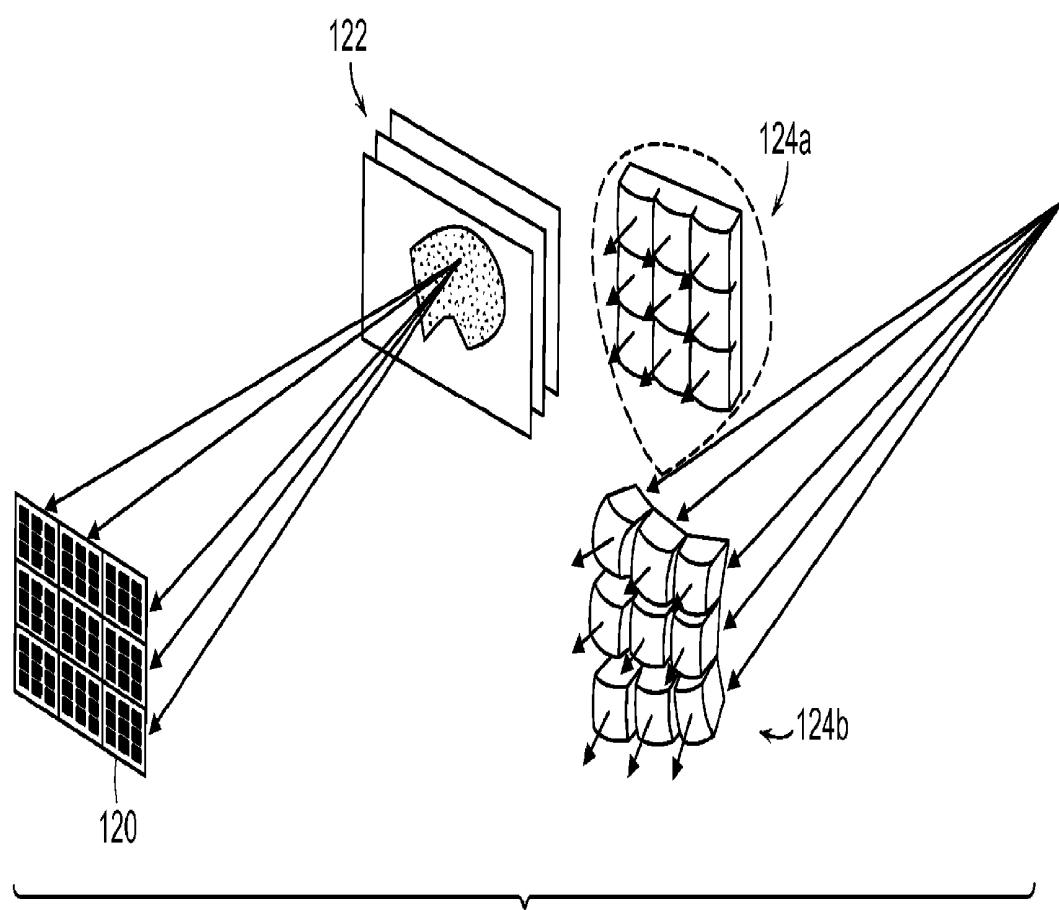

[0067] The concept of an electronically-adjustable acoustic conformal lens is to divide the surface of a 2D transducer array into plane “tiles” of relatively small subarrays. As described in U.S. Pat. No. 6,292,433 the entire contents of which incorporated herein by reference, and illustrated in FIG. 1 the tiles/subarrays 120 are made small enough so that when an object is placed within the field-of-view of the imaging system, the incident radiation 122 from the object toward each “tile” can be treated using a far-field approximation. Additional delay elements are incorporated as second-stage processing to allow all subarrays to be coherently summed (i.e., global near-field beamforming can be achieved by simply delaying and then summing the outputs from all subarrays.) The delay-and-sum beamformer allows each subarray to “look” for signals radiating from a particular direction. By adjusting the delays associated with, each element of the array, the array’s look direction can be electronically steered toward the source of radiation. Thus instead of looking in one direction as seen at 124a, the direction of tiles 120 can be steered in different direction 124b. The delay line requirement for each element in the sub-array can be less than a hundred stages. Only long delays for global summing are needed for the final near field focusing.

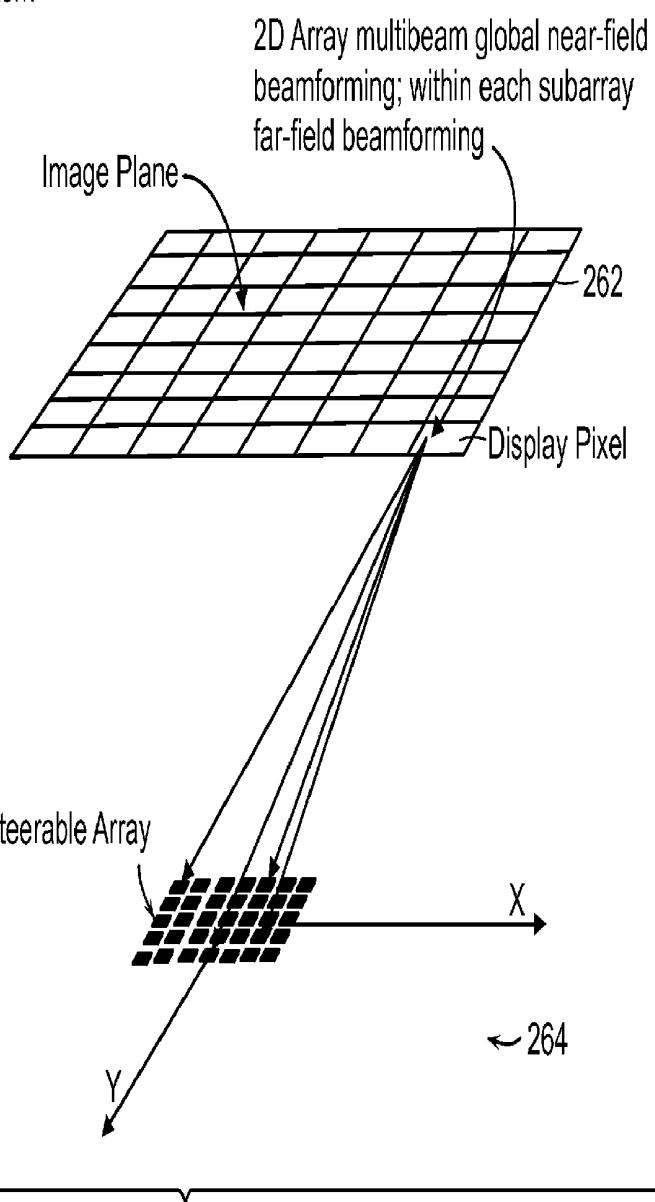

[0068] To scan an image plane using a steerable beamformer system a process such as that shown in FIG. 2 can be used. A raster scan 260 can be used to scan an image plane 262 using a 2D steerable transducer array 264.

[0069] A detailed diagram of an electronically-controlled beamforming system in accordance with the invention is

shown in FIG. 3A. This system consists of a bank of parallel time-delay beamforming processors 330, -330N. Each processor 330 consists of two components: a 2D sub-array beamformer 332 for far-field beamsteering/focusing and an additional time delay processor 334 to allow hierarchical near-field beamforming of outputs from each corresponding subarray. The sub-arrays 332 include m-programmable delay lines 340 with tap selectors 342, multiplexers 344 and summed 346 output. As can be seen in FIG. 3A, for a system with n-sub-arrays, n-parallel programmable 2<sup>nd</sup>-stage near field time delays are needed for individual delay adjustment which are converted with A/D converter 352 to allow all n-parallel outputs be summed 354 coherently, in turn, this summed output is filtered 338 and provides the 3D images of the targeted object. A processor 336 controls sub-array operation.

[0070] Use of the scan head with a second stage digital beamformer is shown in FIG. 3B. In this embodiment, a plurality of N sub-array beamformers 400, which can be near-field beamformers in a preferred embodiment, each receive signals from m transducer elements that have separate delay lines whose outputs are summed and provided to beamformers 420 so that this beamformer can be a conventional system with conventional processor 480. A separate sub-array processor 460 controls beamformers 400.

[0071] Without using this hierarchical subarray far-field and then near-field beamforming approach, for an 80×80 element 2D array, a cable consisting of six thousand and four hundred wires is needed to connect the transducer array to a conventional beamforming system. As shown in FIG. 3A, the number of inputs to each subarray processor equals the total number of delay elements in the subarray, each subarray only has a single output. The number of inputs to the subarray bank equals the number of 2D array elements, and the number of outputs from the subarray bank equals to the total transducer array element number divided by the subarray element number, i.e., the number of outputs from the subarray bank reference to the number of inputs is reduced by a factor equal to the size of the subarray. For example, if one selects to use a 5×5 subarray to implement this hierarchical beamforming concept, after the first stage subarray beamforming, the total number of wires needed to connect to the 2<sup>nd</sup> stage near-field beamforming is reduced by a factor of 25. More specifically, as mentioned above, without using this 2D subarray beamforming, 6400 wires are needed to connect an 80×80 element 2D transducer array to a conventional back-end beamforming system. Using a 5×5 subarray processing bank first, the number of wires required to connect to the backend beamforming system is reduced to 256. Based on the current invention, a bank of 255 5×5 element subarrays Beamformer can be integrated with a 80×80 element 2D array in the scan head, so a cable consisting of 256 wires is adequate to connect the integrated scan head with the back-end near-field beamforming system. It is important to note that 5×5 subarray far-field beamforming processors can be easily integrated in a small size silicon (Si) integrated circuit, eight of such 5×5 subarray beamformers can be integrated on one chip. In this embodiment, only 32 chips or less are integrated into the scan head, thereby reducing the cable size from 6,400 wires down to 256 wires.

[0072] The beamformer processing system is a time domain processor that can simultaneously process the returns of a large 2D array providing a low-power, highly integrated beamformer system capable of real time processing of the

entire array in a portable system. While a system with 132 parallel received channels supports a matrix 2D array probe for a real-time 3D/4D imaging application, the hierarchical multi-stage beamforming can be used with a low-power compact ultrasound system.

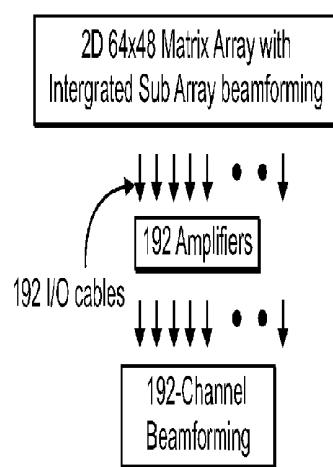

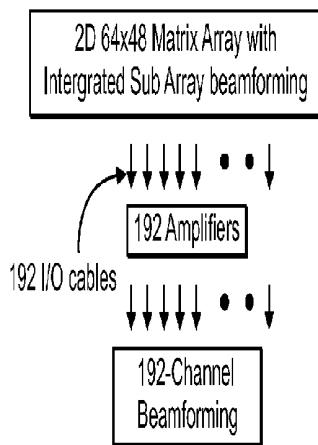

[0073] FIG. 3B demonstrates the hierarchical beamforming architecture in which the beamforming of a group of neighboring receive elements is implemented in two stages, i.e., instead of a single long delay for each of the receive elements, a common long delay is shared by all elements within the group, but each has its own shorter, programmable delay in front of the long delay. Within each group, the outputs from each of the short delays are summed together then applied to the common long-delay. A small group of neighboring- receiving elements having this common long delay characteristic is defined as a “subarray” of the transducer array. For example, for application using a 2D matrix array for real-time 3D imaging, the subarray can be a small array with 4x4, or 5x5 adjacent elements. The first stage programmable delays of each element within this subarray are integrated inside the transducer probe; the summed output from each subarray is then connected to the backend processor. So, for a 64x48 element 2D array (3072 or more transducer elements), if a 4x4 subarray is used for the first stage beamforming, only 192 I/O cable; elements are needed to connect the front-probe to the backend processors.

[0074] In a preferred embodiment, the hierarchical beamforming can also be applied to a one dimensional (1D) array for the real-time 2D imaging application. For example, for a 128-element 1D array, a group of 8 adjacent elements can be grouped together as a subarray. Within each subarray, each of the 8 elements has its own short programmable delay and then the outputs of the eight delays are summed together and then applied to a common long delay. It is important to note that two different methods that can be used for this two-stage implementation. In the first implementation, all the beamforming circuits including both the short and long delays are placed in the back-end processor, so for a 128 element 1D array, 128 connection cables are used as I/O cables between the transducer probe and the backend processor. An alternative implementation is to integrate all the subarray processors within the transducer probe, i.e., for a 128-element array, all 16 subarray processors each with 8 programmable delays are integrated, within the transducer probe, so only 16 cable elements are needed to connect the front-end integrated probe with the back-end processors. Within the back-end, only 16 long delay beamforming circuits are needed to complete the beamforming function. Similarly, for a 64-element array with integrated eight 8-element subarray processors in the probe, the back-end processor can be simplified to only 8 beamforming circuits, only 8 cable elements are needed to connect the front-end integrated probe with the back-end processor. Furthermore, low-power transmit circuitry and A/D converters can be integrated into the front-end probe, so a wireless communication link can be used to connect the front-end probe and the back-end processor. A wireless USB connection or a wireless FireWire connection can be used.

[0075] The construction of a 64x48 element 2D transducer probe 485 with integrated 4x4 sub-array processors is illustrated in FIG. 3C. The 64x48 element 2D array 487 can include stacking 48 rows of 1D arrays each with 64 elements. Connections to the elements of each 64 element 1D transducer array are through a flex cable, so the transducer head assembly can include the 2D transducer array and 48 flex

cables 486. As shown in FIG. 3C, each sub-array can include 4x4 elements (or other rectangular or 2D geometry preferably having at least 16 elements and up to 256 elements per sub-array), the 48 flex cables are grouped into 12 groups, with each adjacent four flex cables connected to a printed circuit board, i.e., flex cables corresponding to the row 1 and row 4 1D transducer array are connected to the first printed circuit board 488, the row 5 to row 8 flex cables are connected to the second printed circuit board 487 and so forth, until the row 45 to row 48 flex cables are connected to the twelfth printed circuit board. One end of each flex cable is connected to the transducer elements and the other end of the flex cable is connected to a 64-element flex connector mounted on the printed circuit board. Within each printed circuit board, there are a 16 4x4 element subarray processors 489 and a high voltage multiplexor crop 491. The subarray processor consists of 16 parallel programmable delay lines each with a low-noise pre-amplifier act its input and a separated programmable multiplier as apodizer and the outputs of the 16 multipliers are summed together to form a single outputs. Within each board, there is also a high-voltage multiplex chip, so to allow the 4x64 element transducer either operated in transmit or receive mode. A memory chip 490 is also mounted on each printed circuit board to store the programming delay for each of the delay lines. There are also power supply cables and digital inputs 492 connected through interface 495 to each printed circuit boards.

[0076] As can be seen in FIG. 3C, the beamforming processor on the printer circuit board has to provide the subarray beamforming function for a total of 64x4 receive elements which are divided into 16 subarrays with each subarray consisting of 4x4 elements, 16 subarray processors each can perform the beamforming function, i.e., time-delay-and-sum function, for 16 receives are incorporated on the printer circuit board. A photomicrograph of a 16 channel subarray beamformer chip is shown in FIG. 3E, for each transmit pulse, the chip is capable of forming 4 sequential beams for 16 receivers. The chip is based on a 0.35  $\mu$ m double-poly, four-metal process. The size of the illustrated chip is 1.2 mmx0.6 mm. Thus, 8 such 4x4 subarray processors can be integrated on one chip with a chip size about 1.2 mm by 5 mm, so the circuit board only requires two such subarray beamforming chips, each including 8 of the 4x4 subarray processors.

[0077] In this chip, there are 16 tapped delay lines, each receiving returns from its corresponding receive element. During the receive mode after a transmission pulse, 4 sequential beams which are summed outputs from the 16 tapped delay lines are formed at every sampling clock. The tap output of each delay line is controlled by a 4-beam time-multiplex buffer memory. With each new digital update, a corresponding non-destructively sensed delayed sample is clocked out of the tapped delay line. With the four digital updates sequentially applied to the buffer memory, four delayed samples for each, of the four beams are then sequentially clocked out.

[0078] The initial tap positions of each delay line are pre-loaded in memory before the scanning starts. During receive mode, at every sampling clock, returned echoes are sampled and clocked into its corresponding delay line. A multiplier is incorporated at the output of each tapped delay line to provide the beamshaping, apodization function. For example, if the center frequency of the transducer is 2 MHz, the tapped delay line samples the returned echo at a 8 MHz rate. The tap outputs are sequentially non-destructively sensed at a 32 MHz rate to generate the 4 beams. That is, after a returned echo loaded

into a delay line, 32 ns latter the tap output of the delay sample of this delay line for the 1<sup>st</sup> beam is clocked out and applied to the multiplier, another 32 ns later, the delayed tap output for the 2<sup>nd</sup> beam is clocked out to the multiplier, the procedure follows, until 128 ns later the tap out for the 4<sup>th</sup> beam is clocked out. The 15 multiplier outputs are summed together to form a single beam; at 32 Mhz rate. It is important to note that for dynamic focusing, each beam needs two digital update bits; one for tap update and one for interpolation. In this chip, each channel has an analog input and a digital input; the two update bits are sequentially loaded into the chip. To support the 4-beam sequential outputs, the two-digital update bits of each beam are dynamically loaded into the chip at a 64 Mhz rate, thereby allowing continuous subarray beamforming function at a 8 Mhz analog input sampling rate. If the range depth is 15 cm, for a 2 Mhz probe oversampled by 4, the total received beamforming includes 2000 points. In this embodiment, the memory she on the circuit board shown in FIG. 3C is  $64 \times 4 \times 4 \times 2 \times 2000 = 4$  Mhits or more. Furthermore, a compression method can be used to reduce the memory size.

[0079] Typically ultrasound transducers use the same element for transmit and receive. The high voltage transmit pulse is sent to a particular element, and the echo from the same element travels back to the system via the same cable wire.

[0080] In some applications, it is desirable, or necessary to use separate elements for transmit and receive. One such application is the use of different, transducer materials for transmit and receive, so that the transmitter and receiver elements can be made with different frequency responses that is a first frequency response and a second frequency responses different from the first frequency response. This is particularly useful for harmonic imaging where the receiver center frequency is double or triple that of the transmitter center frequency. The transmit multiplexer (TR\_MUX) integrated circuit chip allows one single cable wire to connect to the transmit element and the receive element by providing a fast high voltage switch that connects the cable wire to the transmit element during the transmit period, then to one receive element in the receive period as shown in FIG. 3F(1). Off-the-shelf high voltage multiplexer chips are not suitable for this application, as their intended use is to multiplex among elements for aperture selection, a slow process that happens at ultrasound scan line boundaries. In order to support, switching between transmit period and receive period, the switching time needs to be on the order of less than a wave period to a few of wave periods, otherwise there will be a large dead time near the surface of the transducer that cannot be imaged. For example, a switch turn on/off time of 1 micro-second can switch from transmit to receive in one wave period at a 1 MHz transmit frequency, or two wave periods when the transmit frequency goes up to 2 MHz. It can be advantageous to amplify the received, signals as shown in FIG. 3F(2).

[0081] Another application that requires a fast in-the-probe transmit/receive switch is a 2D array probe where the receive elements are first formed into sub-arrays to reduce the number of cable wires for receiving as shown in FIG. 3F(3). The sub-array beamforming circuit is usually a low voltage device, so it is necessary to isolate the sub-array from the cable wire during the high voltage transmit period.

[0082] Yet another application uses two levels of the TR\_MUX chips to allow low voltage amplification circuits be used on a shared transmit/receive element as shown in FIG. 3F(4). The same element is used for transmit and receive. The receive signal is amplified prior to being sent to the system

circuit via the shared cable wire, in this case, the low voltage receive amplification circuitry is detached from she cable and the element during each transmit period, when high voltage pulses are used. During each receive period, the element is attached to the low voltage amplification circuit and then to the cable wire.

[0083] The chip shown in FIG. 3G is a multiplexer fabricated using high voltage CMOS process (>80V). The intended use is for embedding in the acoustic module handle of a medical diagnostic ultrasound probe where either two sets of transducer elements, transmit and receiver, or the subarray beamformed outputs and the transmit element share the same common transducer cable (COM). Multiplexing is achieved with two sets of high voltage switches, capable of handling high voltage bi-polar signals and frequencies up to 20 MHz. The turning on and off of these switches is controlled by two configuration signals (CONFIG[1:0]) and two timing signals, TX\_TIME and RX\_TIME, which indicates when the system is performing transmit or receive. The CONFIG[1:0] can be used to configure the functionality of the port pins, for example, swapping the transmit and receive elements.

[0084] In operation as shown in FIG. 3G, the switches between the transmit elements and the common cable are turned on during the transmit period (TX\_TIME=1), and off during the receive period (RX\_TIME=1). The switches between the receive elements and the common cable are turned off during transmit and turned on during receive. The turn on/off time of the switches is less than 1 microsecond with time skew less than 100 picoseconds, a photomicrograph of a 16 channel high voltage multiplexer integrated circuit chip is shown in FIG. 3H that, was manufactured using a 1 micron, two-poly, two-metal process and has a size of 14 mm×8 mm.

[0085] An implementation of 64 element 1D array with integrated first stage subarray processor can also be implemented using the design of FIG. 3C except that a single 64-element transducer array 491 is connected to a flex cable 497 with one end of the flex cable is connected to each of the transducer element, the other end of the cable is connected to a 64-pin flex connector. The connector is mounted on a printed circuit board. Within the printed circuit, there are eight 8-element subarray processors. Each subarray processor consists of eight programmable delay lines, each delay line has its separated low-noise pre-amplifier and at the output of the delay line, there is an apodiser, i.e., a multiplier for the beamshaping function. The outputs of the eight multipliers are summed together to form a single analog outputs. A high-voltage multiplexer circuit chip is also included on the printed circuit board, to allow the 64 element transducer either operated in transmit or receive mode. A memory chip is also mounted on the printed circuit board to store the programming delay for each of the delay lines. There are also power supply cables and digital inputs connected to each of the printed circuit boards.

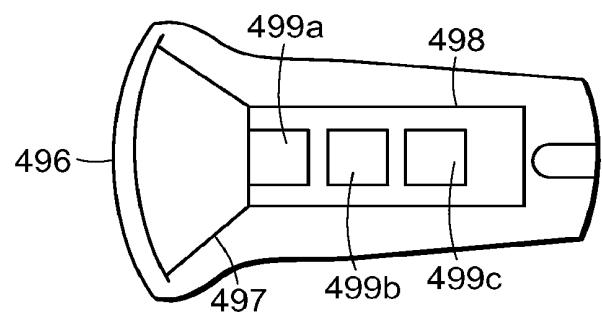

[0086] A preferred embodiment of a 64 element (or more, e.g. 128 or 256 elements) 1D array 496 with integrated subarray processor is shown in FIG. 3D. In this implementation, instead of using a printed circuit board, the subarray processing chip 499a, the high voltage multiplexer circuit chip 449b and the memory chip 449c are mounted on the flexible printed circuit or cable directly (497, 498).

[0087] Alternatively, the beamforming processor can be mounted on a printed circuit board has to provide the subarray

beamforming function for a total of 64 receive elements which are divided into 3 subarrays with each subarray consisting of 8 adjacent elements, 8 subarray processors each can perform the beamforming function, i.e., time-delay-and-sum function, for 8 adjacent receive elements are incorporated on the circuit board. A photomicrograph of a 16 channel subarray beamformer chip shown in FIG. 3E, for each transmit pulse, the chip is capable of forming 4 sequential beams for 16 receivers. The chip also uses the  $0.35\text{ }\mu\text{m}$  double-poly, four-metal process. The size of this chip is  $1.2\text{ mm}\times 0.6\text{ mm}$ . As in the prior embodiment, 4 such 16 subarray processor can easily be integrated on one chip with a chip size about  $1.2\text{ mm}$  by  $2.4\text{ mm}$ , so the board only requires one such subarray beamforming chip.

[0088] As pointed before for dynamic focusing, each beam needs two digital update bits; one for tap update and one for interpolation. To support the 4-beam sequential outputs, the two-digital update bits of each beam are dynamically loaded into the chip at an eight times input-sampling rate, so to allow continuous subarray beamforming function at the analog input sampling rate. If the range depth is 15 cm, for a 2 MHz probe oversampled by 4, the total received beamforming are 2000 points. In the embodiment, the memory size on the board shown in FIG. 3E is  $64\times 4\times 2\times 2000=1\text{ Mbit}$  where compression method can be used to reduce the memory size. The systems described herein can be used with a catheter or probe for insertion within body cavities for cardiac imaging (4D) or other internal organs. The probe or catheter assembly can include a circuit housing with the first plurality of beamformers as described herein.

[0089] Existing are medical ultrasound systems with matrix-array transducers can provide real-time 3D (RT-3D) echocardiography along with state-of-the-art 2D imaging. The major advantages of RT-3D acquisition compared with 2D image include shorter acquisition times, reduced operator dependence, and the ability to manipulate images offline to extract any number of desired views for data analysis. Furthermore, quantitative data regarding Left Ventricle volumes and ejection fraction are more precisely obtained using the 3D technique. Although the term "real-time" is applied to all of the currently available 3D echocardiographic technology, it is important to recognize that in the current scanners, "live 3D" refers to true real-time images that are acquired without electrocardiographic gating. However, this type of real-time 3D imaging has a narrow sector with only a partial volume and is not suitable for imaging the left ventricle.

[0090] To obtain full-volume 3D images in current scanners, electrocardiography is used to gate the image acquisition. Four to 7 subvolumes are acquired over 4 to 7 cardiac cycles and then merged to obtain a complete data set, shown in FIGS. 4A-4D. Note that the healthy adult human heart generally has a volume in a range of  $200\text{--}500\text{ ml/m}^2$ . See, for example, Chikos et al. "Visual assessment of Total Heart volume and Specific Chamber Size from Standard Chest Radiographs," Am. J. Roentgenol 128:375-380, March 1977, the entire contents of which is incorporated herein by reference. Thus it is desirable to image a volume larger than  $200\text{ ml/m}^2$  in order to capture a 3D image of the adult human heart based on a single transmission pulse sequence. Thus, the transducer array has an aperture sufficient to transmit and receive signals within this volume range substantially simultaneously, i.e. in less than one cardiac cycle.

[0091] As indicated, about 128 by 36 beams are required to provide the complete coverage of the left ventricle. In a con-

ventional implementation, during the first cardiac cycle with electrocardiographic gating, 32 by 96 beams are used to acquire part of the 3D image (FIG. 4A). During the second cardiac cycle, the second set of 32 by 96 beams is used to cover the adjacent part of the cardiac image, FIG. 4B. The procedure follows (FIGS. 4C-4D), until the 4<sup>th</sup> cardiac cycle with electrocardiographic gating; the last portion of the cardiac image is then acquired. The four images are then merged together to provide the complete 3D image. This technique offers a wide sector angle and generates a full-volume image after recording a sequence of multiple cardiac cycles. However, stitching artifacts can occur with movement and in patients with arrhythmias and respiratory difficulties, resulting in nondiagnostic images. Therefore, the current RT-3D technique used for echocardiography is near real time, but not truly real time.

[0092] A preferred embodiment of the present invention generates 16 scanning beams for each transmit pulse, as a result, it generates a true "live 3D" image with  $128\times 36$  scanning beams operating at least at a six 3D volumetric images per second, rate. The speed of sound in tissue is about 1500 cm/sec, the round-trip propagation time for a sound wave penetrating a 15-cm depth is about 200 microseconds. For 3D imaging, such as of the heart including both left, and right ventricles, as shown in FIG. 11, 128 $\times$ 96 scanning beams are needed to provide a wide sector view angle. The total round-trip time required for the  $128\times 36$  beams is  $128\times 96\times 200\text{ microseconds}=2.45\text{ seconds}$ . The present invention forms 16 received beams for each transmit pulse, it follows then that only  $2.45/16=0.15\text{ s}$  is needed to generate a single 3D volumetric image with 128 by 36 beams or six 3D volumetric images per second. At a six 3D volumetric images per second rate, the scanner provides real-time 3D diagnostic quality images for coronary artery disease detection. Thus, preferred, embodiments generate at least four full volume cardiac images per second.

[0093] Systems used to generate at least 16 beams for each transmit pulse are shown in the embodiments of FIGS. 4F-4K. systems employing a phase shifting approach can also be used to achieve full volume imaging.

[0094] An ultrasound system using a probe such as that shown in FIG. 3C is illustrated, in the diagram of FIG. 4F in which a 2D transducer with integrated MUX, memory and subarray beamformer. The subarray beamformer has a low-noise input amplifier and memory 504(l), 504(m) in the scan-head 502.

[0095] FIG. 4G illustrates a system with 2D transducer with integrated MUX, memory and subarray beamformer in a probe 505 with serial beam output 506. In this mode, the back-end time delay processor has to run at a rate that is qxtransducer input sampling rate, i.e., if the center frequency of the transducer is 2 MHz, the probe is oversampled at 8 MHz rate. If four serial outputs are generated by the subarray processor, i.e.,  $q=4$ , the back end processor has to run at 32 MHz rate. The subarray beamformer has a low-noise input amplifier

[0096] FIG. 4H illustrates a system with 2D transducer with integrated MUX, memory and subarray beamformer with serial beam output. In this mode, the back-end time delay processor has to run at a rate that is qxtransducer input sampling rate, i.e., if the center frequency of the transducer is 2 MHz, the probe is oversampled at 8 MHz rate. If four serial outputs are generated by the subarray processor, i.e.,  $q=4$ , the back end processor has to run at 32 MHz rate. In this

approach, the back-end processor uses subaperture beamforming system **503**, i.e., the  $n$  adjacent receive channels are grouped together, formed first stage beamforming device **509** and then share a common long delay line **510**. So, the inputs to the back end are  $m$  channels. However, the back-end output to the summing circuits are reduced to  $m/n$  outputs. For example, if the transducer array are  $64 \times 48$  elements, a  $4 \times 4$  subarray is used for subarray beamforming, the total outputs from the integrated probe is then  $64 \times 48 / 16 = 192$  catties, i.e.,  $m=192$ . However, in the current implementation, a subaperture size of 8 is used, i.e.,  $n=8$ , it follows then the total number of long time delay processors are  $132/8=24$ . The subarray beamformer has a low-noise input amplifier.

[0097] FIG. 4I includes the elements of the system shown in FIG. 4G, however, a controller **514** is incorporated in the front-end probe **512**. The controller can be formed on a third circuit board along circuitry for a wireless or cable connection **515** to the external housing **513** which can form an interface to the main system processor or can be integrated into a cart system or a portable system as described herein.

[0098] FIG. 4J is a similar architecture to what described in FIG. 4H, however, a controller **514** is integrated into the front-end, i.e., the interconnection cable are  $m=192$  channels, however sub-aperture beamformers are incorporated into the backend process,  $n$  adjacent receive channels are beamformed first and then applied to the back-end time delay process, if  $n=8$ , the outputs to the summer are only 24 channels. In addition, an optional approach of integrating transmit chips **517(m)** into the front-end integrated probe is used. However, the transmit channel can be located in the back-end processor as indicated in FIG. 4I.

[0099] FIG. 4K is similar to what used in FIG. 4J, however, in the back end processors,  $p$ -parallel beams are formed with each of the subaperture beamformers **519** and parallel delay processor **519P**. So, if  $p=4$ , that is for each output beam from the front-end integrated probe **518**, four parallel beams are formed, each of the 4 outputs are summed together at the summer **519S**. This is how 16 beams are formed for each transmission, i.e., in the probe,  $q=4$ , four serial beams are formed, in the back-end  $p=4$ , four parallel beams are formed. With  $p$  times  $q=16$ . Please note in FIG. 4K, a transmit circuit has also been included in the front-end integrated probe. However, note that the transmit chip can be located at the back-end processor. In addition, in FIGS. 4F-4K a 2D transducer array is used, the architecture can also be used with a 1D transducer array with subaperture beamforming. These systems provide full volume cardiac imaging that can produce video imaging of the heart including left and right ventricles at video rates of at least 4 full volume images per second and preferably 6 full volume images per second or more.

[0100] A preferred embodiment of the invention for 2D array beamforming, each minimizing noise and cable loss with improved S/N performance, are described in FIGS. 5A, 5B, 6A and 6B. In these implementations, the bank, of  $m$  parallel subarray beamforming processors **520** and multiplexers **528** are integrated with the 2D transducer array **525** to create a compact, low-noise, scan head **500**. FIG. 5A depicts a system that the compact scan head is connected to a dedicated, processing module, in which the  $m$ -parallel preamp/TGCs **522** transmit/received chips **524** and the 2<sup>nd</sup> stage time delay processing units **526** are housed. This dedicated processing module communicates with a host computer **540** via FireWire IEEE 1394 or USB or PCI bus **542**. Control and synchronization is performed by the system controller **544**

located in the processing module or housing **546**. FIG. 5B depicts the same architecture as stated in FIG. 5A, except that inside the dedicated processing module, the 2<sup>nd</sup> stage time delay processing units are specifically implemented by using charge-domain programmable (CDP) time-delay lines **600** in housing **620** that is connected to handheld probe **660** and computer housing **648**. FIG. 6B depicts a system that the compact sparse array scan head **700** is connected to a conventional, commercially available time-domain digital ultrasound imaging system **700** with  $n$ -parallel beamforming channels **760**. It is easy to see that in FIG. 6A, the time-delay processor **720** can also be implemented by using CDP time-delay lines **740**. In these embodiments the near-field beamforming is housed **720, 780** in the same housing with other image processing functions. These systems are described in International application No. PCT/US2007/014526 filed Jun. 22, 2007, designating the United States and U.S. application Ser. No. 11/474,098 filed Jun. 23, 2006, both applications being incorporated herein by reference in their entirety.

[0101] By systematically varying beamformer delays and shading along a viewing angle of a 2D transducer array, returned echoes along the line of sight representing the 3D radiation sources can be used, to create the scanned image at the scanned angle. The system can provide continuous real-time large area scanned images throughout a large field of view at 20 frames/s or more. At this frame rate, the system can be used to display continuous 3D images vs. time, thus providing 4D information of the scanned, object. As shown in FIG. 7 a CDP beamforming chip **810**, a time multiplexed, computing structure can be used to generate multiple beams, i.e., for each transmit pulse, the bank of 2D subarray beamformers **818** and its corresponding 2<sup>nd</sup> stage near-field time-delay line are capable of providing multiple beams sequentially. The computing circuits sequentially generate the delays required for forming  $K$  beams. The device operates as follows. Once a set of sampled returned-echoes are loaded in the delay lines with sampling circuits **814**, at time  $t_1$ , the delays required for forming beam 1 are computed **812** within each module **822** and applied in parallel to all delay lines. The sampled return-echoes with proper delays are coherently summed **802** and filtered **804** to form the first beam. At time  $t_2$ , the delays required for forming beam 2 are computed within each module and applied in parallel to all delay lines. The sampled return-echoes with proper delays are coherently summed to form the second beam. The procedure repeats until the  $K$ th beam is coherently formed.

[0102] For example, if a computing circuit with 16-serial addressable outputs is built in with the CDP subarray and the 2<sup>nd</sup> stage time delay lines, for each transmit pulse, 16 beams or scan lines each along a different scan angle can be created. For 256-pulses with a down-range depth of 15 cm. the system can generate 4096-beams with a  $64 \times 64$  pixel resolution at a frame rate of 20 frames/s. The system is fully programmable; the beamforming electronics can be adjusted to zoom-in to a smaller field-of-view for high-resolution or higher frame rate images. For example, using 192-transmit pulses with the same down-range depth of 15 cm, the system can generate 3072-beams with a  $64 \times 43$  pixel resolution at a 30 frame/s frame rate.

[0103] The array described addresses ultrasound imaging applications using a two-dimensional 2 cm $\times$ 2 cm array at a frequency of 3 MHZ. The need for resolution on the order of less than half the wavelength dictates as large an aperture as possible that can be housed within a compact package. To

interrogate a 90 degree scanning volume and also minimize the impact of grating lobes, an element pitch or separation of less than 0.25 mm is desirable, leading to a 80×80 element array. Using the subarray processing technique described above, a scan head with integrated subarray beamforming circuits followed by a 2<sup>nd</sup> stage near-field beamsteering/beamfocusing system provides a practical implementation. However, the implementation still requires at least 32 subarray chips to be integrated on a scan head. An alternative pseudo random array design approach can be used to achieve this resolution with a much less amount of processing components in the scanned head.

[0104] To make a sparse array practical, the combination of low insertion loss and wide bandwidth performance is important for realizing acceptable imaging performance with low illumination levels. Quarter-waves matching layers with low acoustic impedance, but physically solid backing results in a robust array that loses only 3-4 dB in the conversion, of received signal energy to electrical energy. Array bandwidths of 75% or more are typical of this design and construction process. Also, the transducer array employs element positioning and an interconnect system suitable for the beamformer circuitry. The electronics are mounted on printed-circuit boards that are attached to the transducer elements via flexible cables. In practice, a majority of the array elements are connected to outputs using the flexible cables, however, only a small fraction of the total number of elements are wired to the circuit boards. Nevertheless, the large number of array element connections are sufficient to insure a unique pattern of active-element locations in the final array.

[0105] As an example of a sparse array, assuming a 2×2 cm array with 256 active elements, the resulting filling factor is 4%. The output signal to noise ratio of the array is proportional to the number of active elements, so this filling factor corresponds to a loss in sensitivity of -13 dB when compared to a filled, array of the same dimensions. To compensate for this loss, a transmitted signal of wider bandwidth is chosen to increase array sensitivity. In the approach presented here, the sensitivity is increased on the order of 10 dB. Further details regarding sparse array devices can be found in U.S. Pat. No. 6,721,235, the contents of which is incorporated herein by reference.

[0106] Positioning the elements of the array follows the approach in which care must be taken to eliminate any periodicity that would produce grating lobes that compete with the main lobe. Pseudorandom or random arrays can be used (FIG. 8A). The geometry of activated element placement, has been developed to maximize the efficiency of the beamformers while minimizing grating and side lobe clutter. Switching between a plurality of different array patterns is used to provide the most efficient beam pattern at different beam angles relative to the region or volume of interest being scanned. Thus, a first pattern can utilize that illustrated in FIG. 8A, which is then switched to a second pattern for a different scan angle. This can involve selecting a transducer element within a neighborhood 880 surrounding a given element to scan at a second angle.

[0107] The primary goal of the optimization method is to minimize the average side lobe energy. Specifically, this is done by interactively evaluating the optimization criterion:

$$J = \frac{1}{2u_{max}^2} \int \int_s W(u_x, u_y) B(u_x, u_y) du_x du_y, \quad (1)$$

where the weighting function,  $w(u_x, u_y)$ , applies more weight to regions in the array response that require side lobe reduction. The optimization method begins with no weighting (i.e.,  $W(u_x, u_y)=1$ ) and proceeds by choosing successively better weighting functions that satisfy the optimization criterion. Since the side lobes that require the greatest reduction are related to the previously computed beampattern,  $B(u_x, u_y)$ , the weighting is chosen such that  $W(u_x, u_y)=B(u_x, u_y)$ . This is done in an interactive manner until convergence.

[0108] Basically, a random array is capable of producing an imaging point spread function that has a main lobe to average side lobe ratio of  $N$ , where  $N$  is the total number of active elements in the array. For the 256-element sparse array example, the resulting ratio is -13 dB. Using a wide bandwidth approach improves this ratio by 10 dB, Based on the preceding optimization criterion, a pseudorandom placement of the array elements was generated (FIG. 8A).

[0109] FIG. 8B is a plot of the array performance, sensitivity versus cross range, for a 256-element sparsely-sampled array at 3 MHZ. The peak to maximum side lobe level is approximately 30 dB. To improve this performance, the system is configured to achieve the maximum main lobe to clutter level ratio possible, which has been independently verified.

[0110] FIG. 9B depicts a system that the sparse array scan head 900 is connected to a conventional, commercially available time-domain digital ultrasound imaging system 940 with  $m$ -parallel beamforming channels. It is easy to see that in FIG. 9A, the time-delay processor can also be implemented by using CDP time-delay lines 320 in housing 925 that, is connected to a separate computer 927. An array of  $m$  multiplexers 906 is used, to switch between a sequence of scan patterns executed using a software program and system controller 940 or processor 950. The sequence of sparse array patterns is thus selected to scan at different scan angles of an object being imaged to provide 3D ultrasound imaging thereof.

[0111] A commercially available window-based 3D visualization software can be used to visualizing, manipulating, and analyzing the 3D multiple-beams volume image data generated by the electronically-adjustable acoustic conformal lens system. Traditionally, a clinician with 2D ultrasound images for diagnosis would look at the 2D scanned images slice by slice and mentally reconstruct the information into a 3D representation to judge the anatomy of the patient. This procedure requires the clinician to have well-founded experience as well as a highly sophisticated understanding of human anatomy. To create a “complete” image to the 3D structures, the clinician has to take all available slices into account. Looking at hundreds of slices is too time-consuming, even for a single patient. 3D visualisation based on 3D volume data can help overcome this problem by providing the clinician with a 3D representation of the patient’s anatomy reconstructed from the set of multiple-scanned beamforming data.

[0112] A commercially available software tool such as KB-Vol3D of KB-VIS technologies, Chennai, India, provides display or viewing 3D features such as:

[0113] Fast Volume-Rendering

[0114] Shaded Surface Display

[0115] Shaded-Surface module allows easy visualization of surfaces in the volume. Surfaces may be created by intensity-based thresholding. Alternatively, the Seeding option allows selection of specific connected structures of interest.

[0116] MIP (Maximum Intensity Projection) with Radials

[0117] MPR (Multiple-Plane-Reformatting) with Oblique & Double-Oblique and 3D correlation

[0118] MRP Slabs & Multi-Cuts

[0119] Curved MPR

[0120] Color & Opacity Presets with Editor

[0121] Region-Growing and Volume Measurements

[0122] Cutaway Viewing with Slab-Volume and Interactive Real-time VOI

[0123] Volume-interiors are easily visualized using the “Cutaway-Viewing” tool. A Cut-Plane is used to slice through the volume, revealing the interior regions. The cut-plane is easily positioned and oriented using the mouse.

[0124] The VOI (Volume-of-Interest) tool allows interactive, real-time Volume-of-Interest display. The user can isolate and view sub-volumes of interest very easily and in real-time, using easy click-and-drag mouse operation.

[0125] Image Save in Multiple Formats

[0126] Images displayed by KB-Vol3D can be captured to various image formats (including DICOM, JPEG, and BMP etc)

[0127] Movie Capture in AVI Format

[0128] Visualization operations can also be captured to an AVI movie .le and played on Windows Media Player, Quick-Time, and Real Player etc.

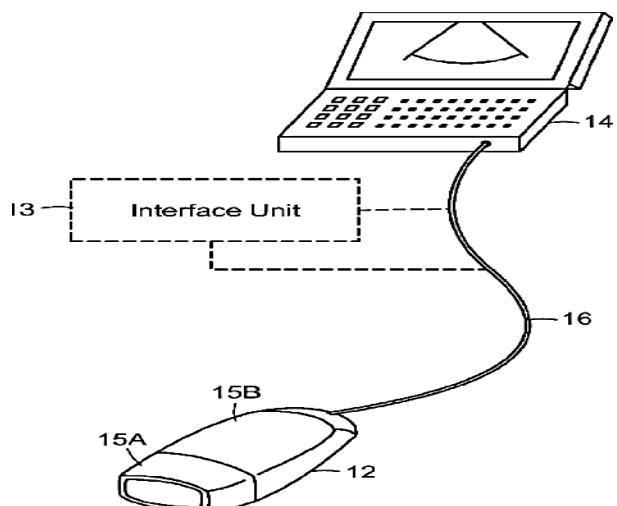

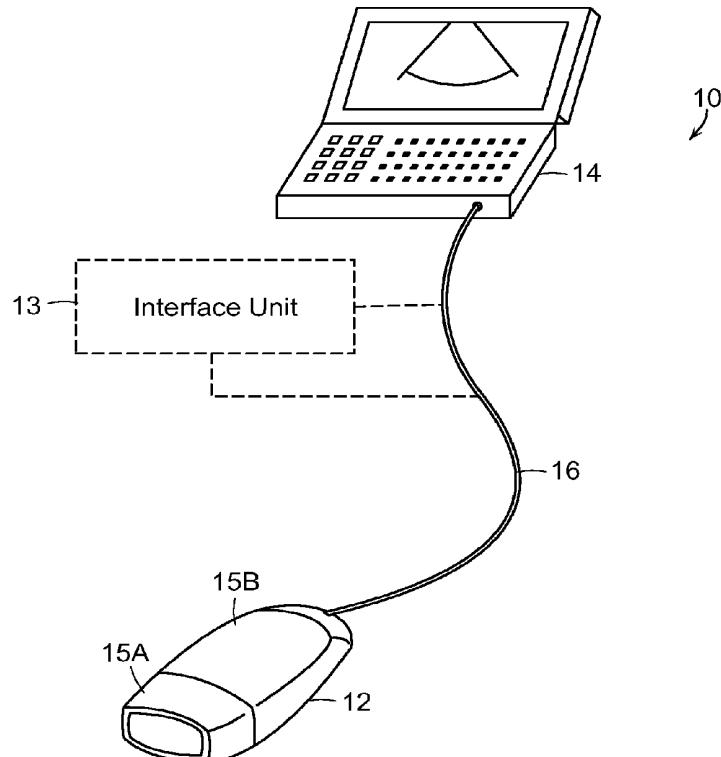

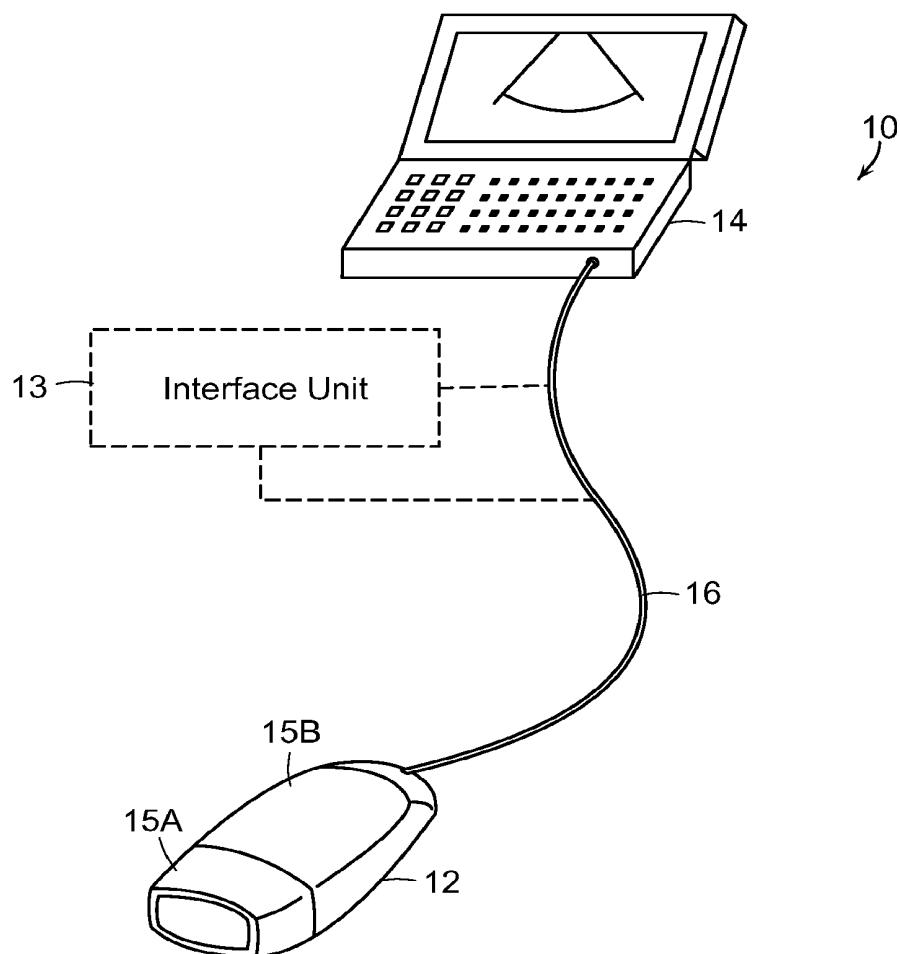

[0129] The invention can be implemented, using a scan head 12 connected to a portable computer 14 as shown in FIG. 10. the ultrasound system 10 can also include a cable 16 to connect the probe 12 to the processor housing 14. Certain embodiments can employ an interface unit 13 which can include a beamformer device. Scan head 12 can include a transducer array 15A (2D) and a circuit housing 15B which can house multiplexer and/or beamforming components as described in detail in U.S. Pat. Nos. 6,106,472 and 6,869,401, the entire contents of these patents being incorporated herein by reference.

[0130] A 2D array configuration using sparse-array for transmission and non-over lapped fully-populated array is used for receiving. For an  $N \times M$  element array, only  $m$ -elements with optimized, sparse array placement are used for transmit tier, and then the remaining  $NM - m$  elements are used as the receiving array. For example, for a  $40 \times 60$ -element 2D array, 256-elements are used as transmit element, the placement of the transmit elements are optimized based, on selection criteria, the remaining 2144 element are used, as received elements. This embodiment simplifies the multiplexer requirement needed for a 2D array, in which cause the multiplexer can be mounted in the interface housing.

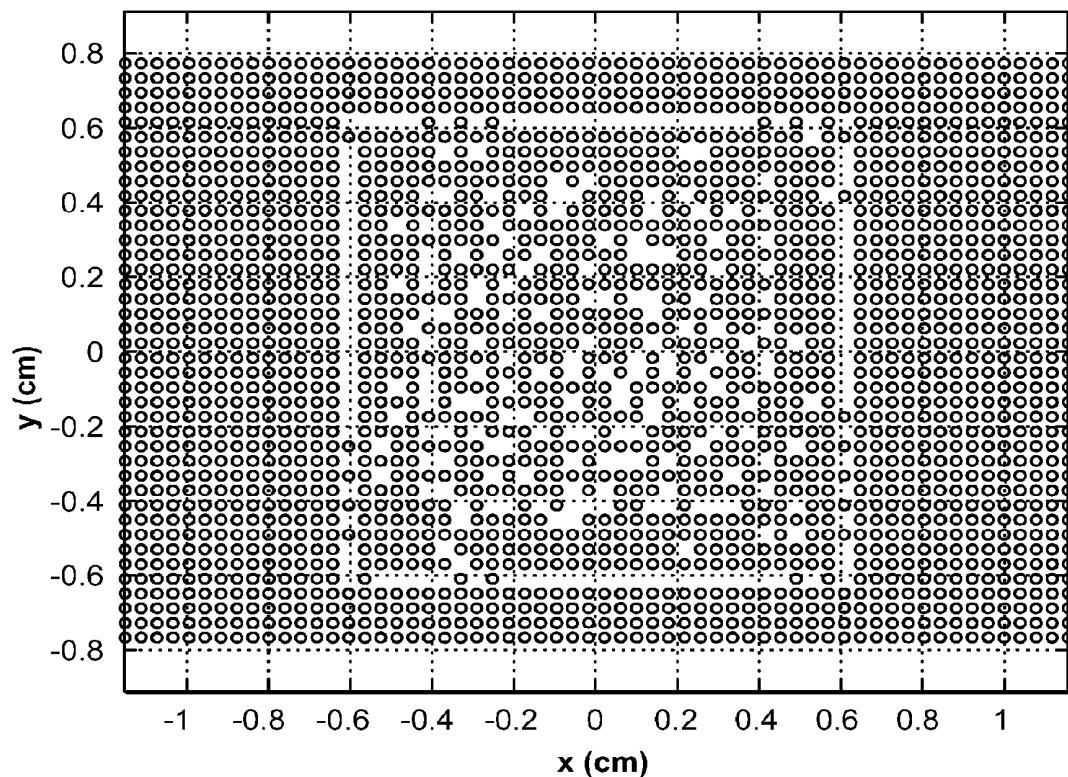

[0131] An example of the element locations for the near fully-populated 40 by 50 receive array 50 is shown in FIG. 11. The 2400-element array is depopulated by the 256 sparse array transmit elements to yield 2144 receive element locations. These elements are independent, and do not overlap the sparse-array transmit elements. In a preferred embodiment the transmit elements constitute less than 25% of the total number of array elements, and preferably less than 15%.

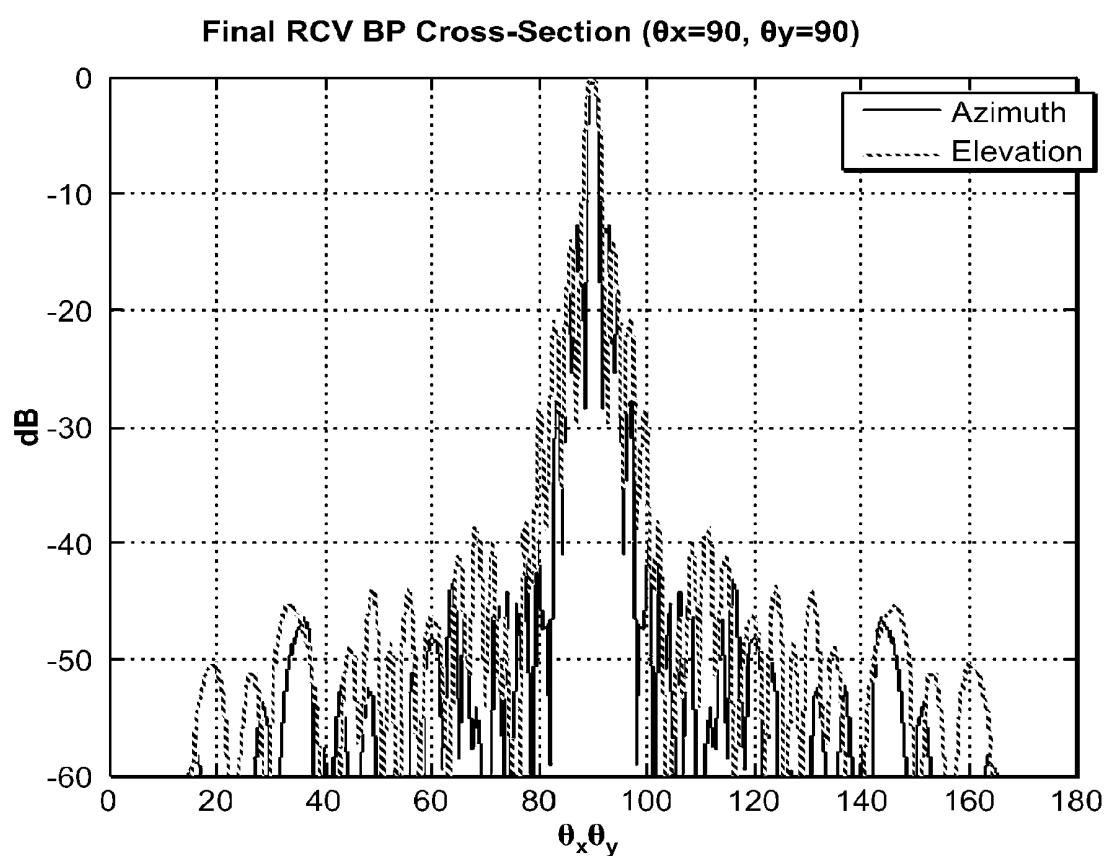

[0132] The azimuth and elevation cross-sections of the beampattern of the above mentioned receive array are shown in FIG. 12. The first sidelobe is approximately -13 dB relative

to the central peak. The grating lobes are less than -30 dB relative to the peak. Given that the 2D array is wider than tall, the azimuthal beamwidth (plotted in blue (solid)) is slightly narrower than the elevation beamwidth (plotted in green (dotted)).

[0133] In FIG. 13, a magnifying view of the above mentioned azimuthal beam pattern demonstrates the detailed mainlobe and sidelobe structure. For this case, the beamwidth is approximately 1.5 degrees. The beam pattern is nearly identical to the fully populated  $60 \times 40$  element, beam pattern. The receive array beam pattern is shown in FIG. 14. As stated above, the received sparse array is comprised of a 2144 elements. There are no sidelobes due to depopulating the center of the array by 256 (transmit) elements.

[0134] An example of the final element locations for the 256 transmit sparse array 60 are shown in FIG. 15. The 256 element locations are confined to the central  $32 \times 32$  elements of the fully populated array. These elements are independent and do not overlap the receive array elements. A cross sectional view of the transmit sparse array beampattern is shown in FIG. 16. The first sidelobe is approximately -17 dB relative to the central peak. The grating lobes are less than -27 dB relative to the peak. The sparse array optimization algorithm minimizes the sidelobe energy  $+/ - 45$  degrees in elevation and  $+/ - 45$  degrees in elevation.

[0135] FIG. 17 demonstrates the beam pattern of the sparse transmit array shown in FIG. 15. The transmit beampattern is designed to uniformly cover a  $4 \times 4$  beam data pyramid. The transmit sparse array is comprised of a 256-element subset of the fully populated 2400-element array (approximately 10% fill). The placement of the transmit/receive array design algorithm required over 750 iterations to minimize the transmit and receive sidelobe energy within the  $+/ - 45$  degree azimuth,  $+/ - 45$  degree elevation region. As shown in FIG. 18, after 750 iterations, the final sparse transmit-array element locations limit the average sidelobe energy to less than -35 dB relative to the central peak of the beampattern.

[0136] A low-power ultrasound system capable of electronically scanning a two-dimensional, 2D, matrix array to generate real-time three-dimensional, 3D, volumetric images with 64 by 64, 4096, scanning beams at a greater than 20 3D images per second is described. For each transmit pulse, the system is capable of generating 16 received beams. In addition, the design is able to drive a one and one-half dimensional array and also support wide-bandwidth encoded transmit waveform for pulse compressing to improve the system sensitivity. Wide bandwidth enables the use of chirped or coded waveforms (PN sequence) that can extend the length of the low power transmit burst without a loss of axial resolution. The combination of these features results in an imaging array with electronic systems that will fit within a portable hand-carried device.

[0137] The beamformer processing system is a time domain processor that will simultaneously process the returns of a large 2D array, the low-power, highly integrated beamformer that provide a real time processing of the entire array and will thus provide a low cost unit that can be hand carried.

[0138] There is a strong need for a real-time 3D ultrasound imaging using a 2D matrix array. In this section, the minimal number of receive beamforming channels required in an ultrasound system to support a real-time 3D imaging is analyzed. It is shown that a minimum of 192 parallel received beamforming channels is required to support a reasonable sized such as  $48 \times 64$ -element array.

[0139] An example of a system having an electronically-adjustable acoustic conformal lens is to divide the surface of a 2D transducer array into plane “tiles” of relatively small subarrays can be formed in U.S. Pat. No. 6,232,433, the contents of which is incorporated herein by reference; beamforming of the entire array can be separated into two stages, first a small-aperture subarray beamforming followed by a second stage large-aperture coherent summing of the outputs from each of the subarrays. As depicted in the tiles/subarrays can be made small enough so that when an object is placed within the field-of-view or the imaging system, the incident radiation from the object toward each “tile” can be treated using a far-field approximation. However, near-field beamforming capability has been incorporated in the actual implementation of the subarray beamforming system to allow a broader application. Additional delay elements are incorporated as second-stage processing to allow all subarrays to be coherently summed. The delay-and-sum beamformer allows each subarray to “look” for signals radiating from a particular direction. By adjusting the delays associated with each element of the array, the array’s look direction can be electronically steered toward the source of radiation. The delay line requirement for each element in the sub-array can be less than a hundred stages. Only long delays for global summing are needed for the final near field focusing. A detailed diagram of an electronically-controlled beamforming system in accordance with the invention is shown in FIG. 14A of U.S. Pat. No. 6,232,433. This system consists of a bank of parallel time-delay beamforming processors. Each processor consists of two components: a 2D sub-array beamformer for small-aperture beamsteering/focusing and an additional time delay processor to allow hierarchical near-field beamforming of outputs from each corresponding subarray. As can be seen in FIG. 14A referenced above for a system with  $m$ -subarrays,  $m$ -parallel programmable 2<sup>nd</sup>-stage near field time delays are needed for individual delay adjustment to allow all in-parallel outputs be summed coherently, in turn, this summed output provides the 3D images of the targeted object.

[0140] It is easy to understand that, without using this hierarchical subarray small aperture and then large aperture beamforming approach, for an 80×80 element 2D array, a cable consisting of six thousand and four hundred wires is needed to connect the transducer array to a conventional beamforming system. As shown in FIG. 14A of U.S. Pat. No. 6,292,433 referenced above, the number of inputs to each subarray processor equals the total number of delay elements in the subarray, each sub-array only has a single output. That is to say, the number of inputs to a subarray equals the number of transducer elements associated with that subarray. The number of subarray outputs equals the total transducer array element number divided by the number of subarrays. For example, if one selects to use a 5×5 subarray to implement this hierarchical beamforming system, after the first stage subarray beamforming, the total number of wires needed to connect to the 2<sup>nd</sup> stage near-field beamforming is reduced by a factor of 25. More specifically, as mentioned above, without using this 2D subarray beamforming, 6400 wires are needed to connect an 80×80 2D transducer array to a conventional back-end beamforming. Using a 5×5 subarray processing bank first, the number of wires required to connect to the backend beamforming system is reduced to 256. Based on this example of the invention, a bank of 256 5×5 element subarrays beamformer can be integrated, with a 80×80 element 2D array in the scan head, so a cable consisting of 256

wires is adequate to connect the integrated scan head with the back-end near-field beamforming system.

[0141] It is important to note that 5×5 subarray small-aperture beamforming processors can be easily integrated in a small size silicon integrated circuit, eight of such 5×5 subarray beamforming can be integrated on one integrated circuit. Note that subarrays have generally between 9 and 64 transducer elements corresponding to a 3×3 subarray up to an 8×8 subarray. The preferred range is at or between 4×4 and a 6×6 array for a square array geometry. Rectangular subarrays can also be used preferably either 3×4, 4×5, or 4×6. Note that a  $\frac{1}{4}\lambda$  error minimum criteria is used. Only 32 integrated circuit devices need be incorporated into the scanhead, it can reduce the cable size from 6,400 wires down, to 256 wires. Similarly, for a 64×48 element 2D array, using a 4×4 subarray processing bank in the transducer housing first, the number of back-end beamforming channels is reduced to 192.