**【特許請求の範囲】****【請求項 1】**

第1の入出力端子がドレイン端子に接続される第1のMOSトランジスタと、第2の入出力端子がドレイン端子に接続される第2のMOSトランジスタとを有し、前記第1のMOSトランジスタのソース端子と前記第2のMOSトランジスタのソース端子が接続されて共有ソース端子を構成し、前記第1のMOSトランジスタのゲート端子と前記第2のMOSトランジスタのゲート端子が接続されて共有ゲート端子を構成する双方向スイッチ回路と、

前記双方向スイッチ回路の前記共有ソース端子及び前記共有ゲート端子に接続され、前記共有ソース端子の電位である共有ソース電位の変動に対して前記共有ゲート端子の電位を同相で追従させ、ゲート制御信号により前記双方向スイッチ回路のオンまたはオフ制御を行う電圧制御回路と、を備えるスイッチ回路。

**【請求項 2】**

請求項1に記載のスイッチ回路において、

前記電圧制御回路は、

第1の電源端子及び前記共有ソース端子に接続され、論理入力端子から入力される入力制御信号を、前記共有ソース電位を基準とする制御信号にレベルシフトを行う第1のラッチ回路と、

前記共有ソース端子に接続され、前記共有ソース電位に基づいて一定の内部電圧を生成する電圧生成回路と、

前記共有ソース端子に接続され、前記内部電圧が電源として入力され、前記制御信号に基づいて前記共有ゲート端子に前記ゲート制御信号を送る第2のラッチ回路と、から構成されるスイッチ回路。

**【請求項 3】**

請求項2に記載のスイッチ回路において、

前記電圧制御回路は、第2の電源端子と前記共有ソース端子に接続されるノイズ除去回路をさらに有し、

前記第1のラッチ回路及び前記電圧生成回路は、前記ノイズ除去回路の入力部に接続され、

前記第2のラッチ回路及び前記共有ソース端子は、前記ノイズ除去回路の出力部に接続され、

前記ノイズ除去回路は、前記第1のラッチ回路の動作により発生する電流と、前記内部電圧を生成するための定電流源からの電流とを、前記共有ソース端子を経由せずに前記第2の電源端子に流すスイッチ回路。

**【請求項 4】**

請求項3に記載のスイッチ回路において、

前記ノイズ除去回路は、ソースフォロア接続される第3のMOSトランジスタと、前記第3のMOSトランジスタのドレイン端子にアノードが接続される第1のダイオードにて構成され、

前記第3のMOSトランジスタのゲート端子に前記共有ソース端子が接続され、前記第3のMOSトランジスタのソース端子に前記第1のラッチ回路と前記電圧生成回路が接続され、前記第1のダイオードのカソードに前記第2の電源端子が接続されるスイッチ回路。

**【請求項 5】**

請求項4に記載のスイッチ回路において、

前記第3のMOSトランジスタのソース端子はノードと接続され、

前記電圧制御回路は、アノードが前記ノードと接続され、カソードが前記共有ソース端子と接続される第2のダイオードを有するスイッチ回路。

**【請求項 6】**

請求項2に記載のスイッチ回路において、

前記電圧制御回路は、前記電圧生成回路の出力部と前記共有ゲート端子の間に接続され、前記共有ゲート端子への前記ゲート制御信号のスルーレート制御を行うスルーレート制

10

20

30

40

50

御回路を備えるスイッチ回路。

【請求項 7】

請求項 6 に記載のスイッチ回路において、

前記スルーレート制御回路は、前記内部電圧が入力されるスルーレート制御抵抗と、前記スルーレート制御抵抗及び前記共有ソース端子に接続されるバッファから構成されるスイッチ回路。

【請求項 8】

請求項 1 に記載のスイッチ回路において、

前記スイッチ回路は、前記双方向スイッチ回路の前記第 2 の入出力端子に接続され、かつ接地される短絡スイッチ回路を備え、

前記双方向スイッチ回路がオフ動作時に前記短絡スイッチ回路はオン動作し、前記双方向スイッチ回路がオン動作時に前記短絡スイッチ回路はオフ動作するスイッチ回路。

【請求項 9】

送信信号を出力する送信回路と、前記送信信号の反射信号を増幅しデジタル信号に変換を行なう受信回路と前記送信回路とを分離するスイッチ回路と、を備え、

前記スイッチ回路は、

前記送信回路の出力部に接続される第 1 の入出力端子がドレイン端子に接続される第 1 の MOS トランジスタと、前記受信回路の入力部に接続される第 2 の入出力端子がドレイン端子に接続される第 2 の MOS トランジスタとを有し、前記第 1 の MOS トランジスタのソース端子と前記第 2 の MOS トランジスタのソース端子が接続されて共有ソース端子を構成し、前記第 1 の MOS トランジスタのゲート端子と前記第 2 の MOS トランジスタのゲート端子が接続されて共有ゲート端子を構成する双方向スイッチ回路と、

前記双方向スイッチ回路の前記共有ソース端子及び前記共有ゲート端子に接続され、前記共有ソース端子の電位である共有ソース電位の変動に対して前記共有ゲート端子の電位を同相で追従させ、ゲート制御信号により前記双方向スイッチ回路のオンまたはオフ制御を行う電圧制御回路と、を備える半導体回路。

【請求項 10】

請求項 9 に記載の半導体回路において、

前記スイッチ回路は前記送信回路と单一半導体基板上に形成される半導体回路。

【請求項 11】

請求項 9 に記載の半導体回路において、

前記電圧制御回路は、

第 1 の電源端子及び前記共有ソース端子に接続され、論理入力端子から入力される入力制御信号を、前記共有ソース電位を基準とする制御信号にレベルシフトを行う第 1 のラッチ回路と、

前記共有ソース端子に接続され、前記共有ソース電位に基づいて一定の内部電圧を生成する電圧生成回路と、

前記共有ソース端子に接続され、前記内部電圧が電源として入力され、前記制御信号に基づいて前記共有ゲート端子に前記ゲート制御信号を送る第 2 のラッチ回路と、から構成される半導体回路。

【請求項 12】

請求項 11 に記載の半導体回路において、

前記電圧制御回路は、第 2 の電源端子と前記共有ソース端子に接続されるノイズ除去回路をさらに有し、

前記第 1 のラッチ回路及び前記電圧生成回路は、前記ノイズ除去回路の入力部に接続され、

前記第 2 のラッチ回路及び前記共有ソース端子は、前記ノイズ除去回路の出力部に接続され、

前記ノイズ除去回路は、前記第 1 のラッチ回路の動作により発生する電流と、前記内部電圧を生成するための定電流源からの電流とを、前記共有ソース端子を経由せずに前記第

10

20

30

40

50

2の電源端子に流す半導体回路。

【請求項 1 3】

請求項 1 2 に記載の半導体回路において、

前記ノイズ除去回路は、ソースフォロア接続される第 3 の MOS トランジスタと、前記第 3 の MOS トランジスタのドレイン端子にアノードが接続される第 1 のダイオードにて構成され、

前記第 3 の MOS トランジスタのゲート端子に前記共有ソース端子が接続され、前記第 3 の MOS トランジスタのソース端子に前記第 1 のラッチ回路と前記電圧生成回路が接続され、前記第 1 のダイオードのカソードに前記第 2 の電源端子が接続される半導体回路。

【請求項 1 4】

請求項 1 3 に記載の半導体回路において、

前記第 3 の MOS トランジスタのソース端子はノードと接続され、

前記電圧制御回路は、アノードが前記ノードと接続され、カソードが前記共有ソース端子と接続される第 2 のダイオードを有する半導体回路。

【請求項 1 5】

請求項 1 1 に記載の半導体回路において、

前記電圧制御回路は、前記電圧生成回路の出力部と前記共有ゲート端子の間に接続され、前記共有ゲート端子への前記ゲート制御信号のスルーレート制御を行うスルーレート制御回路を備える半導体回路。

【請求項 1 6】

請求項 1 5 に記載の半導体回路において、

前記スルーレート制御回路は、前記内部電圧が入力されるスルーレート制御抵抗と、前記スルーレート制御抵抗及び前記共有ソース端子に接続されるバッファから構成される半導体回路。

【請求項 1 7】

請求項 9 に記載の半導体回路において、

前記スイッチ回路は、前記双方向スイッチ回路の前記第 2 の入出力端子に接続され、かつ接地される短絡スイッチ回路を備え、

前記双方向スイッチ回路がオフ動作時に前記短絡スイッチ回路はオン動作し、前記双方向スイッチ回路がオン動作時に前記短絡スイッチ回路はオフ動作する半導体回路。

【請求項 1 8】

第 1 の入出力端子がドレイン端子に接続される第 1 の MOS トランジスタと、第 2 の入出力端子がドレイン端子に接続される第 2 の MOS トランジスタとを有し、前記第 1 の MOS トランジスタのソース端子と前記第 2 の MOS トランジスタのソース端子が接続されて共有ソース端子を構成し、前記第 1 の MOS トランジスタのゲート端子と前記第 2 の MOS トランジスタのゲート端子が接続されて共有ゲート端子を構成する双方向スイッチ回路と、

前記双方向スイッチ回路の前記共有ソース端子に接続され、前記共有ソース端子の電位である共有ソース電位に基づいて一定の内部電位を生成する電圧生成回路と、

入力される制御信号を、前記内部電位または前記共有ソース電位を基準とするゲート制御信号として前記共有ゲート端子に出力し前記双方向スイッチ回路のオンとオフの切替を行うラッチ回路と、を備えるスイッチ回路。

【請求項 1 9】

請求項 1 8 に記載のスイッチ回路において、

前記電圧生成回路は、前記共有ソース端子にアノードが接続されるツェナーダイオードと、前記ツェナーダイオードのカソードに接続される定電流源にて構成されるスイッチ回路。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、半導体集積可能なスイッチ回路技術に関する。

10

20

30

40

50

## 【背景技術】

## 【0002】

従来、超音波診断装置に適用される送受信切り替えスイッチ回路において、2つのMOSトランジスタと、2つのMOSトランジスタのソース共有に接続された双方向主スイッチと、2つのMOSトランジスタの共有ゲートに接続された逆阻止型駆動回路、及び保持回路にてスイッチのオン状態とオフ状態を保持するスイッチ回路があった（例えば、特許文献1参照）。

## 【先行技術文献】

## 【特許文献】

## 【0003】

10

## 【特許文献1】特開2004-363997

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0004】

例えば、医療用超音波診断装置の開発において画像精度向上や多機能化を実現する上で、多チャネル化による分解能の向上が必要となる。これに伴い超音波診断装置に使用される回路規模や消費電力が増大し、装置のアナログフロントエンド部における回路の集積化や消費電力の低減化が継続的に推進されている。

## 【0005】

20

一般に超音波診断装置における送信回路部からの信号は高電圧信号であり、反射信号を受信増幅する受信回路部にとって過負荷となる。そのため、受信回路部前段には送受信切り替えスイッチ(T/Rスイッチ)が挿入される。信号の送信時にはT/Rスイッチをオフ状態にすることで、受信回路の保護回路として働き、受信時はT/Rスイッチをオン状態にすることで、生体から反射される反射信号を受信回路部に通過させる役割を果たす。一方T/Rスイッチを通過する生体からの反射信号は、微小な超音波帯域(数MHz～数十MHz)の信号のため、T/Rスイッチには高帯域、低雑音、低切り替え雑音等の性能が求められる。

## 【0006】

30

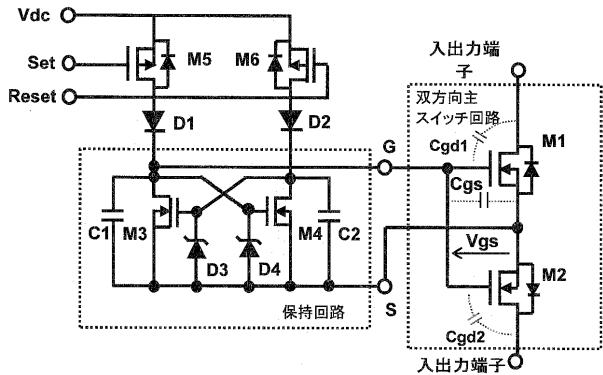

特許文献1に開示されている回路を捉え直した図6のスイッチ回路を比較例として用い、本願課題を説明する。図6の回路は、ソース共有に接続された2つのNMOSトランジスタM1、M2からなる双方向主スイッチ回路、共有ソースに接続されたNMOSトランジスタM3、M4、ツェナーダイオードD3、D4、容量C1、C2、のラッチ回路にて構成された保持回路、主スイッチのスイッチ制御を行なうNMOSトランジスタM5、M6、ダイオードD1、D2とその制御信号入力端子Set、Resetにて構成される。

## 【0007】

30

双方向主スイッチ回路のオン動作はM5をオン、M6をオフにすることで行なわれる。この場合ラッチ回路内C1、及び主スイッチ回路M1、M2におけるゲート-ソース間容量Cgsに電荷がVdc近傍まで充電され、主スイッチ回路がオン動作する。さらに充電後M5をオフにしてもC1、及びCgsの保持電荷により、定常的な電流を必要とせず主スイッチ回路のオン動作を維持することが可能である。また主スイッチ回路のオフ動作はM5をオフ、M6をオンにすることで行なわれる。このときM3のゲート電圧が上昇してオン状態となり、C1、Cgsの保持電荷が共有ソースを通じて放電されることで主スイッチ回路がオフ動作する。

40

## 【0008】

しかし、上記双方向主スイッチ回路のオン状態は充電されたVgs間容量のみで保持されており、また保持回路からの制御信号を主スイッチ回路M1、M2のゲートに直接接続しているため、M1、M2のゲートリーアクによる電荷の放電や、入力信号の電圧変化に対して発生する主スイッチ回路のCgd1、Cgd2、Cgsを介したクロストークにより、保持回路の状態が変化する可能性がある。このため長時間一定のオン/オフ状態を保つことが困難であり誤オン/オフの原因となる。

## 【0009】

また、入出力端子よりGNDから負の高電圧(-HV)が印加された場合、共有ソースSの電圧

50

はM1の寄生ダイオードにより高速に印加電圧に追随するが、共有ゲートGの電圧が即座に追随せずにC1及びM1、M2のゲート-ソース間に瞬間に高電圧が加わり、各々の素子を破壊する可能性がある。

【0010】

以上より本発明の目的は、送信信号または反射信号の電位変動に対しスイッチの誤動作や素子の破壊を起こすことなく、生体からの反射信号を広帯域、低雑音で受信回路に伝送可能なT/Rスイッチ回路を実現することである。

【課題を解決するための手段】

【0011】

本発明の代表的な構成の一例を示すと以下の通りである。

10

【0012】

第1の入出力端子がドレイン端子に接続される第1のMOSトランジスタと、第2の入出力端子がドレイン端子に接続される第2のMOSトランジスタとを有し、第1のMOSトランジスタのソース端子と第2のMOSトランジスタのソース端子が接続されて共有ソース端子を構成し、第1のMOSトランジスタのゲート端子と第2のMOSトランジスタのゲート端子が接続されて共有ゲート端子を構成する双方向スイッチ回路と、双方向スイッチ回路の共有ソース端子及び共有ゲート端子に接続され、共有ソース端子の電位である共有ソース電位の変動に対して共有ゲート端子の電位を同相で追従させ、ゲート制御信号により双方向スイッチ回路のオンまたはオフ制御を行う電圧制御回路と、を備えるスイッチ回路である。

【発明の効果】

20

【0013】

本発明により、送信信号または反射信号の電位変動に対してスイッチの誤動作や素子の破壊を起こすことなく、生体からの反射信号を広帯域、低雑音で伝送するT/Rスイッチを実現することが可能である。

【図面の簡単な説明】

【0014】

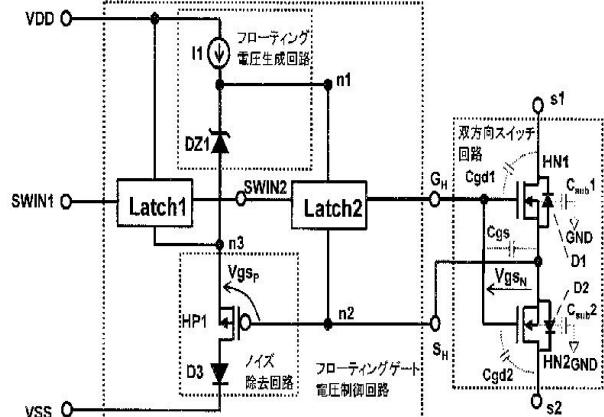

【図1】実施例1のスイッチ回路の構成例を示す図である。

【図2】実施例2のスイッチ回路の構成例を示す図である。

【図3】実施例3のスイッチ回路の構成例を示す図である。

【図4】実施例4のスイッチ回路の構成例を示す図である。

30

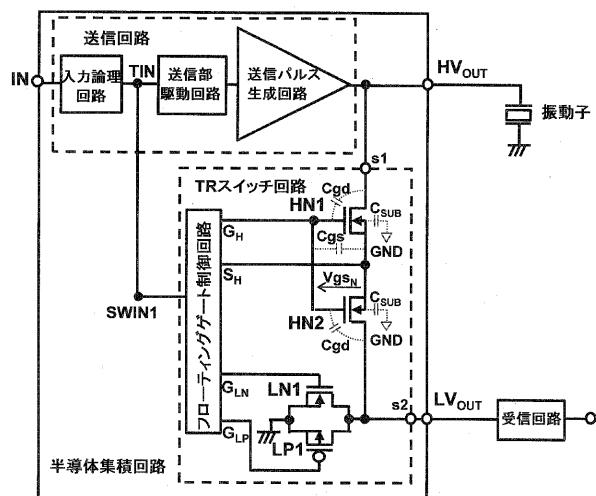

【図5】実施例5の半導体集積回路の構成例を示す図である。

【図6】2つのMOSトランジスタを用いたスイッチ回路の比較例を示す図である。

【発明を実施するための形態】

【0015】

以下に、本発明を実施するための形態を実施例として、図面に基づいて詳細に説明する。実施例の各ブロックを構成する回路素子は公知の低耐圧、高耐圧のCMOSトランジスタ、抵抗、容量、ダイオード、電流源等であり、集積回路技術により単結晶シリコンのような単一の半導体基板上に形成される。

【実施例1】

【0016】

図1は、双方向スイッチ回路とフロー・ティングゲート電圧制御回路とで構成されたスイッチ回路の第1の実施例を示す図である。

40

【0017】

双方向スイッチ回路は、2つのNMOSトランジスタHN1、HN2と2つのNMOSトランジスタの寄生ダイオードD1、D2によって構成されている。NMOSトランジスタHN1、HN2各々のソース端子とゲート端子は共有ソース端子S<sub>H</sub>、及び共有ゲート端子G<sub>H</sub>に接続され、またHN1のドレイン端子は入出力端子s1、HN2のドレイン端子は入出力端子s2に接続されている。2つのNMOSトランジスタHN1、HN2は数程度のオン抵抗を有しており、双方向スイッチ回路のオン抵抗は10数に実現される。

【0018】

50

フローティングゲート電圧制御回路は第1のラッチ回路Latch1と、第2のラッチ回路Latch2と、フローティング電圧生成回路と、ノイズ除去回路からなる。

【0019】

第1のラッチ回路Latch1は、入力端子SWIN1から入力された0Vを基準信号L、基準電源VDDの電位を基準信号Hとしたスイッチ制御入力信号を、共有ソース端子S<sub>H</sub>の電位を基準とした双方方向スイッチ回路制御信号SWIN2にレベルシフト変換を行う。第2のラッチ回路Latch2は、入力されたSWIN2を元に共有ゲート端子G<sub>H</sub>へのゲート制御信号を生成する。フローティング電圧生成回路は、定電流源I1とツエナーダイオードDZ1からなり、双方方向スイッチ回路のオン制御を行うために必要な共有ソースS<sub>H</sub>基準の電圧を生成し、生成された電圧をノードn1からLatch2の電源として供給する。ノイズ除去回路は、PMOSトランジスタHP1を用いHP1のゲート端子と共有ソース端子S<sub>H</sub>を接続したソースフォロア回路と、PMOSトランジスタHP1のドレイン端子にアノードが接続され、基準電源VSSにカソードが接続されたダイオードD3からなる。ノイズ除去回路は、Latch2の基準電位となる共有ソース端子S<sub>H</sub>に接続されたノードn2とLatch1の基準電位となるノードn3を分離し、Latch1とフローティング電圧生成回路から発生する電流を基準電源VSSに流す役割を果たす。

10

【0020】

本スイッチ回路における双方方向スイッチ回路をオンさせるためには、入力端子SWIN1に信号Lを入力する。入力信号を元にLatch1がレベルシフトとして働き、スイッチ回路制御信号SWIN2に共有ソース端子S<sub>H</sub>の電位よりPMOSトランジスタHP1のゲート-ソース間電位V<sub>gs</sub>と分高い電位L'が出力される。

20

【0021】

フローティング電圧生成回路は、基準電源VDDに接続された定電流源I1により、ノードn1の電位が共有ソースS<sub>H</sub>の電位とV<sub>gs</sub>とツエナーダイオードの降伏電圧VZの和となるように電流を流し続ける。

【0022】

Latch2は、ノードn1、及びノードn2の電位を元にオン制御信号SWIN2を受け、共有ゲート端子G<sub>H</sub>に共有ソースS<sub>H</sub>の電位とV<sub>gs</sub>とVZの和となる電位を与える。この動作によりNMOSトランジスタゲート-ソース間にV<sub>gs</sub>とVZの和となる電位が加わり、双方方向スイッチ回路がオン動作する。

30

【0023】

また、双方方向スイッチ回路をオフさせるためには、入力端子SWIN1に信号Hを入力する。入力信号を元にLatch1がレベルシフトとして働き、スイッチ回路制御信号SWIN2に共有ソース端子S<sub>H</sub>の電位とPMOSトランジスタのゲート-ソース間電位V<sub>gs</sub>とツエナーダイオード降伏電圧VZの和となるH'が出力される。

【0024】

Latch2は、オフ制御信号SWIN2を受け、ノードn1及びノードn2の電位を元に共有ゲート端子G<sub>H</sub>は共有ソースS<sub>H</sub>電位と同電位となるようにゲート制御信号を出力する。この動作によりNMOSトランジスタゲート-ソース間の電位差が0となり、双方方向スイッチ回路がオフ動作する。

40

【0025】

上述したスイッチ回路を超音波診断装置におけるT/Rスイッチ回路に適用し、入出力端子s1に送信回路部、入出力端子s2に受信回路部を接続した場合における、スイッチ回路の動作について説明を行う。

【0026】

双方方向スイッチ回路をオンさせ、入出力端子s1から受信信号V1を入出力端子s2へ通過させる場合、共有ソース端子S<sub>H</sub>の電位及びノードn2の電位は、受信信号V1と同電位となる。また、ノードn2の電位変動がPMOSトランジスタHP1のゲート端子に入力されるため、ノードn3の電位はPMOSトランジスタHP1のゲート-ソース間電位V<sub>gs</sub>とV1の和となる。フローティング電圧生成回路は、ノードn3の電位を元にノードn1にVZとV<sub>gs</sub>とV1の和となる電位を生成する。

50

## 【0027】

Latch2は、ノードn1とノードn2の電位を元に共有ゲート端子G<sub>H</sub>にゲート制御信号を与えるため、オン動作時は共有ソース端子S<sub>H</sub>の電位変動に対し、共有ゲート端子G<sub>H</sub>は電位差VZ+Vgspを一定に保ち同相で追従することができる。そのため、双方向スイッチ回路HN1、HN2のゲート-ソース間電位変化 V<sub>gs</sub>=0となり、ゲート-ドレイン間容量C<sub>gd</sub>、及びゲート-ソース間容量C<sub>gs</sub>への充放電が発生しない。このためC<sub>gd</sub>+C<sub>gs</sub>は実質的に0となり、HN1、HN2に発生する対接地容量は基板容量C<sub>sub1</sub>+C<sub>sub2</sub>のみとなる。これにより、素子の破壊を起こすことなく、広帯域の受信信号伝送が可能となる。

## 【0028】

また、熱雑音の原因となるHN1、HN2のオン抵抗は素子サイズを大きくすることで低減可能であるが、トレードオフとして寄生容量が大きくなる。しかし、上記構成によりC<sub>gd</sub>+C<sub>gs</sub>は0となり、寄生容量を大幅に低減しているため、低寄生容量を維持したまま、素子サイズを大きくすることでオン抵抗を低減することができる。その結果、本実施例のスイッチ回路は低雑音の受信信号伝送が可能である。

10

## 【0029】

さらに、Latch1と双方向スイッチ回路の間にLatch2を設けた構成により、入出力端子s1からの電圧変化に対し、C<sub>gd</sub>、C<sub>gs</sub>を介したクロストークが生じても、オン/オフ状態を保持するLatch1には影響が伝わりにくい。このため、本実施例は双方向スイッチ回路の誤動作防止にも有効である。

20

## 【0030】

また、Latch1、Latch2におけるスイッチ切替時に発生する電流や、フローティング電圧生成回路の電流源I1から発生する電流が、双方向スイッチ回路の共有ソース端子S<sub>H</sub>を通して入出力端子s1、s2に流れ込むと、s1、s2に接続される送信回路部、及び受信回路部の抵抗負荷等により電圧ノイズが発生し、通過させる受信信号に重畠される恐れがある。

20

## 【0031】

そこで、本実施例ではノードn2とノードn3の間にノイズ除去回路が接続され、Latch1で行なわれるSWIN1から入力されたスイッチ入力信号のレベルシフトによって発生する電流、及びフローティング電圧生成回路における電流源I1からの電流をPMOSトランジスタHP1のソース-ドレイン間、及びダイオードD3を経由して基準電源VSSへ流している。

30

## 【0032】

このため、ノードn2を通り共有ソース端子S<sub>H</sub>を流れる電流は、Latch2による共有ゲート端子G<sub>H</sub>への制御信号切替時に発生する電流のみとなる。Latch2は、電位差VZ+Vgspである制御信号の切替を行うため、Latch2で発生する電流はLatch1のレベルシフトにて生じる電流に比べ大幅に小さい。ゆえに、非常に低ノイズ特性のT/Rスイッチが実現可能である。

30

## 【0033】

このように、ノードn2とノードn3を接続して同電位とするのではなく、ノードn2とノードn3の間にノイズ除去回路を設けることで、広帯域特性に加えて低ノイズ特性を実現することが可能となる。

40

## 【実施例2】

## 【0034】

図2は、双方向スイッチ回路とフローティングゲート電圧制御回路とで構成されたスイッチ回路の第2の実施例を示す図である。

## 【0035】

本実施例は、図1にて示したスイッチ回路の構成に加え、Latch2の出力端子と共有ゲート端子G<sub>H</sub>の間に、スルーレート制御回路を有することを特徴とする。スルーレート制御回路は、ノードn1、ノードn2に接続されフローティング電圧生成回路にて生成される電位と共有ソース端子S<sub>H</sub>の電位にて動作するバッファBufferを設け、ノードn1とBufferとの間に抵抗R1が接続される構成となる。

## 【0036】

本実施例ではLatch2から出力されたゲート制御信号がBufferを経由することで、ゲート

50

制御信号のスルーレートを変化させる。双方向スイッチ回路をオフからオン動作させる場合、Latch2の出力端子より共有ソース端子の電位とVgspとVZの和となるオン信号が出力され、buffer回路によりオン信号がバッファされる。このとき、ノードn1に接続されたR1により、双方向スイッチ回路のオン動作時のスルーレートを低減させている。

【0037】

その結果、HN1、HN2のゲート寄生容量Cgd、Cgsを充電させる際に入出力端子s1、s2へ流れる電流を低減することが可能である。この電流は外部負荷を通じてノイズの原因となるため、受信時における受信信号へのノイズ重畳を大幅に減らすことが可能である。

【実施例3】

【0038】

図3は、双方向スイッチ回路とフローティングゲート電圧制御回路とで構成されたスイッチ回路の第3の実施例を示す図である。

【0039】

本実施例は、図1にて示したスイッチ回路において、ノイズ除去回路のPMOSトランジスタHP1のゲート端子が接続されているノードn2と、ソース端子が接続されているノードn3にツェナーダイオードDZ2、DZ3を直列に接続したことを特徴とする。DZ2、DZ3の方向はアノード側がノードn3、カソード側がノードn2に接続されている。

【0040】

本実施例の双方向スイッチ回路のゲート制御手段は実施例1と同様である。双方向スイッチ回路をオンさせ、入出力端子s1から受信信号V1を入出力端子s2へ通過させる場合、共有ソース端子S<sub>H</sub>の電位、及びノードn2の電位は受信信号V1と同電位となる。PMOSトランジスタHP1のゲート-ソース間電圧Vgspは受信信号V1に対し、VgspがDZ2とDZ3の閾値電圧の和2VDthより小さいため、Latch1及びI1からの電流は、DZ2、DZ3を経由せずPMOSトランジスタHP1のドレイン-ソース間を経由し、基準電源VSSに流れる。

【0041】

双方向スイッチ回路がオフ動作し、入出力端子s1に超音波診断装置に用いられる一般的な送信回路より+Voutの送信信号が印加された場合、共有ソース端子S<sub>H</sub>の電位は、入出力端子s2の電位にNMOSトランジスタHN2の寄生ダイオードD2の閾値電圧VFが加えられた電位に固定される。このとき送信動作時に入出力端子s2を接地しているとすると、共有ソース端子S<sub>H</sub>の電位はVF(1V以下)となる。このため、双方向スイッチ回路のオン動作時同様にLatch1及びI1からの電流はPMOSトランジスタHP1のドレイン-ソース間経由にて基準電源VSSに流れ、共有ソース端子S<sub>H</sub>と共有ゲート端子G<sub>H</sub>の電位を同電位に保つ。

【0042】

双方向スイッチ回路がオフ動作し、入出力端子s1に超音波診断装置に用いられる一般的な送信回路より-Voutの送信信号が印加された場合、共有ソース端子S<sub>H</sub>の電位はNMOSトランジスタHN1の寄生ダイオードD1を経由して送信信号に追随する。つまり、入出力端子s1の電位にNMOSトランジスタHN1の寄生ダイオードD1の閾値電圧VFが加えられた電位(-Vout+VF)に変化する。このため、PMOSトランジスタHP1のソース端子に接続されるノードn3の電位は-VoutとVFとVgspの和となる。しかし、ノードn3の電位が基準電源VSSとダイオードD3の閾値電圧で決定される電位(VSS+VF)よりも低くなると、PMOSトランジスタHP1はオフ状態となり、Latch1及び定電流源I1からの電流を基準電源VSSに流すことができなくなる。そうすると、ノードn2の電位の急変にノードn3の電位が追随できず、PMOSトランジスタHP1を破壊する恐れがある。

【0043】

これを避けるために、本実施例では、ノードn3にツェナーダイオードDZ2のアノード側、ノードn2にツェナーダイオードDZ3のカソード側を接続し、ノードn3の電位がノードn2の電位に対し2VF以上電位差が生じた場合に、Latch1及びI1からの電流をDZ2、DZ3経由にて共有ソース端子S<sub>H</sub>に流している。

【0044】

このため、入出力端子s1に-Voutの電圧を持つ送信信号が入力されたとしても、ノードn

10

20

30

40

50

2の急激な電位変化にノードn3の電位が追随することで、双方向スイッチ回路のオフ信号を安定に保持し、フローティングゲート電圧制御回路の保護を実現している。

【0045】

また、ダイオードD3をPMOSトランジスタHP1のドレインと基準電源VSS間に挿入することで、ノードn2の電位降下に対してPMOSトランジスタのゲート-ドレイン間に高電圧が印加されることを防いでいるため、PMOSトランジスタHP1は耐圧の低い小型のトランジスタを使用することができる。

【0046】

さらに双方向スイッチ回路がオフ動作し、入出力端子s1に超音波診断装置に用いられる一般的な送信回路より-Voutの送信信号が印加され、一定時間経過後に入出力端子s1より+Voutの送信信号が印加された場合、-Voutから+Voutの送信信号の電位変化に伴い定電流源I1からの電流がノードn2及びノードn3に流れ込み、共有ソース端子S<sub>H</sub>の電位が、-VoutとVFの和から上昇する。入出力端子s2を接地させた場合、送信信号が0Vを超えると、共有ソース端子S<sub>H</sub>はNMOSトランジスタHN2の寄生ダイオードD2の閾値電圧VFに固定され、ノードn3はVFとV<sub>gsp</sub>の和に固定される。

10

【0047】

このとき、PMOSトランジスタHP1はオン状態となり、定電流源I1からの電流は基準電源VSSへ流れる。その後、共有ソース端子及びノードn3の電位が固定されたまま、+Voutの送信信号が入出力端子s1に印加される。このため送信信号±Voutの電位変化に対し、共有ソース端子S<sub>H</sub>および共有ゲート端子G<sub>H</sub>は高速で追従し、双方向スイッチ回路のオフ動作を安定に維持している。

20

【実施例4】

【0048】

図4は、双方向スイッチ回路とフローティングゲート電圧制御回路とで構成されたスイッチ回路の第4の実施例を示す図である。

【0049】

本実施例は、図3にて示したスイッチ回路に加え、入出力端子s2に短絡スイッチ回路を接続したことを特徴とする。

【0050】

短絡スイッチ回路は、PMOSトランジスタLP1とNMOSトランジスタLN1を有する。LP1、LN1のドレインを共通に接続した共有ドレイン端子は、双方向スイッチ回路の入出力端子s2に接続される。LP1、LN1のソースを共通に接続した共有ソース端子は、接地される。LP1のゲート端子にはLP1制御端子G<sub>LP</sub>が接続され、LN1のゲート端子にはLN1制御端子G<sub>LN</sub>が接続され、G<sub>LP</sub>とG<sub>LN</sub>の信号は同時に制御されてLP1とLN1を同時にオンオフ制御可能である。

30

【0051】

短絡スイッチ回路は双方向スイッチ回路と相補的に動作する特徴を有するため、双方向スイッチ回路がオン動作するときに、G<sub>LP</sub>及びG<sub>LN</sub>に信号Lが入力されて短絡スイッチ回路はオフ動作し、双方向スイッチ回路がオフ動作するときに、G<sub>LP</sub>及びG<sub>LN</sub>に信号Hが入力されて短絡スイッチはオン動作する。

【0052】

入出力端子s1に一般的な超音波診断装置に用いられる送信回路が接続され、入出力端子s2と短絡スイッチ回路が接続されるノードn4に受信回路が接続され、双方向スイッチがオフ動作となる場合を検討する。送信回路より入出力端子s1に最大±Voutの送信信号が入力されると、双方向スイッチ回路のNMOSトランジスタ寄生ダイオードD1、またはD2によってクランプされ、入出力端子s2を含むノードn4には送信信号は直接伝送されない。しかし、ノードn4には送信信号からのクロストークにより電位の変動が起こる可能性があり、過大な電位変化によって受信回路側の素子が破壊される恐れがある。

40

【0053】

これを避けるために、本実施例では、双方向スイッチがオフ動作となる送信時に短絡スイッチ回路をオン動作させる。これにより、ノードn4は接地状態となり送信信号からのク

50

ロストークによる電位変動を低減させることができ、ノードn4に接続された受信回路を保護する役割を果たす。

【0054】

以上より、本実施例のスイッチ回路をT/Rスイッチに適用することで、広帯域、低ノイズ特性のスイッチ回路の特徴に加え、受信回路保護回路として高い効果を持ったスイッチ回路の実現が可能である。

【実施例5】

【0055】

図5は、図4に示すスイッチ回路を超音波診断装置におけるT/Rスイッチ回路として適用し、入力された論理信号から送信パルス信号を発生させる送信回路とT/Rスイッチ回路とを单一の半導体基板上にて構成した半導体集積回路の実施例を示す図である。

10

【0056】

送信回路は、入力論理回路、送信部駆動回路、及び送信パルス生成回路からなる。入力論理回路は、入力端子INより入力されたデジタル信号を元に駆動回路制御信号TIN及びT/Rスイッチ回路への制御信号を送る。送信部駆動回路は、駆動回路制御信号TINを送信パルス生成回路の駆動信号に変換する。送信パルス生成回路は、0Vから±100V程度の振幅可変範囲と1MHz～40MHz程度の周波数可変範囲を有する送信パルス信号の生成を行う。

20

【0057】

T/Rスイッチ回路は、実施例4にて述べたように、双方向スイッチ回路と、フローティングゲート電圧制御回路と、短絡スイッチ回路にて構成され、送信回路と受信回路とを分離する。

【0058】

送信回路の出力部は、T/Rスイッチ回路の入出力端子s1と半導体集積回路の出力端子HVoutを経由して、圧電素子にて形成される振動子が接続される。T/Rスイッチ回路の入出力端子s2は、半導体集積回路の出力端子LVoutを経由し、反射信号を受信増幅し、デジタル信号に変換を行なう受信回路が接続される。

30

【0059】

送信信号の送波時はT/Rスイッチ回路をオフ状態にすることで、送信回路より生成された送信信号はHVoutを経由して振動子へ出力され、超音波を発生させる。このとき受信回路に接続されたLVoutは、短絡スイッチ回路がオン状態にあるため0Vに固定され、受信回路保護回路としての役割を果たす。

【0060】

振動子からの反射信号受信時は、T/Rスイッチ回路をオフ状態からオン状態に切り替え、HVoutからの受信信号をLVoutを経由し受信回路へ伝送する。本実施例のT/Rスイッチ回路により低ノイズ特性を実現できるため、超音波診断装置において受信信号を乱すことなく伝送することが可能である。

40

【0061】

このように、本実施例によるT/Rスイッチ回路を用いることで、超音波診断装置において低雑音と広帯域伝送を両立することができる。さらには、T/Rスイッチ回路と送信回路を1チップに組み合わせた半導体集積回路を用いることで、装置の低コスト化、小型化を図ることができる。

【0062】

以上、本発明の実施形態について説明したが、本発明は上述した実施形態に限定されるものではなく、種々実施変形可能であり、上述した各実施形態を適宜組み合わせることが可能であることは当業者に理解されよう。

【符号の説明】

【0063】

D1～D4…ダイオード

HN1～HN2…双方向スイッチNMOSトランジスタ

50

【 図 5 】

【 図 6 】

図 5

図 6

---

フロントページの続き

(72)発明者 花沢 聰

東京都青梅市新町六丁目16番地の3 株式会社日立製作所マイクロデバイス事業部内

(72)発明者 篠宮 敏夫

東京都青梅市新町六丁目16番地の3 株式会社日立製作所マイクロデバイス事業部内

(72)発明者 吉澤 弘泰

東京都青梅市新町六丁目16番地の3 株式会社日立製作所マイクロデバイス事業部内

F ターム(参考) 4C601 EE02 EE10 HH01

5J055 AX22 AX32 BX05 CX00 DX13 DX72 DX83 EX03 EX07 EX16

EY01 EY10 EY12 EY13 EY21 EY29 EZ03 EZ31 EZ62 EZ65

FX12 FX17 GX01

|                |                                                                                                                                                                                                                                                                                                           |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 开关电路和半导体电路                                                                                                                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP2012209763A</a>                                                                                                                                                                                                                                                                             | 公开(公告)日 | 2012-10-25 |

| 申请号            | JP2011073891                                                                                                                                                                                                                                                                                              | 申请日     | 2011-03-30 |

| [标]申请(专利权)人(译) | 株式会社日立制作所                                                                                                                                                                                                                                                                                                 |         |            |

| 申请(专利权)人(译)    | 株式会社日立制作所                                                                                                                                                                                                                                                                                                 |         |            |

| [标]发明人         | 清水哲弘<br>花沢聰<br>篠宮敏夫<br>吉澤弘泰                                                                                                                                                                                                                                                                               |         |            |

| 发明人            | 清水 哲弘<br>花沢 聰<br>篠宮 敏夫<br>吉澤 弘泰                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | H03K17/693 H03K17/16 A61B8/00                                                                                                                                                                                                                                                                             |         |            |

| CPC分类号         | H03K17/6874 G01S7/52017                                                                                                                                                                                                                                                                                   |         |            |

| FI分类号          | H03K17/693.A H03K17/16.D A61B8/00 H03K17/687.G                                                                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 4C601/EE02 4C601/EE10 4C601/HH01 5J055/AX22 5J055/AX32 5J055/BX05 5J055/CX00 5J055<br>/DX13 5J055/DX72 5J055/DX83 5J055/EX03 5J055/EX07 5J055/EX16 5J055/EY01 5J055/EY10 5J055<br>/EY12 5J055/EY13 5J055/EY21 5J055/EY29 5J055/EZ03 5J055/EZ31 5J055/EZ62 5J055/EZ65 5J055<br>/FX12 5J055/FX17 5J055/GX01 |         |            |

| 代理人(译)         | 井上 学<br>戸田裕二                                                                                                                                                                                                                                                                                              |         |            |

| 其他公开文献         | <a href="#">JP5537479B2</a>                                                                                                                                                                                                                                                                               |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                 |         |            |

## 摘要(译)

解决的问题：应用于超声波诊断设备等中，并且在不引起开关故障或元件破坏的情况下，将生物体的反射信号以宽频带且低噪声的形式从生物体传输至接收电路，而不会对发射信号或反射信号的潜在波动造成破坏。实现了T/R开关电路。解决方案：一个共享的源极端子，其中两个MOS晶体管的源极通常串联连接；一个共享的栅极端子，其中一个双向开关电路的栅极端子共同地，以及两个MOS晶体管的漏极连接到输入/输出端子。连接到共享栅极端子和共享源极端子，共享栅极端子的电位在同一相位上跟随共享栅极端子的电位，并且开关ON或OFF信号被共享开关电路由发送到端子的浮栅电压控制电路形成。[选型图]图1

图1