(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-152630

(P2005-152630A)

(43) 公開日 平成17年6月16日(2005.6.16)

(51) Int.Cl.<sup>7</sup>**A61B 8/00**

**GO1N 29/24**

F 1

A 61 B 8/00

G O 1 N 29/24 5 0 2

テーマコード(参考)

2 G O 4 7

4 C 6 O 1

審査請求 未請求 請求項の数 10 O L 外国語出願 (全 32 頁)

(21) 出願番号 特願2004-336211 (P2004-336211)

(22) 出願日 平成16年11月19日 (2004.11.19)

(31) 優先権主張番号 10/719,431

(32) 優先日 平成15年11月21日 (2003.11.21)

(33) 優先権主張国 米国(US)

(71) 出願人 390041542

ゼネラル・エレクトリック・カンパニー

GENERAL ELECTRIC CO

MPANY

アメリカ合衆国、ニューヨーク州、スケネ

クタディ、リバーロード、1番

100093908

弁理士 松本 研一

100105588

弁理士 小倉 博

100106541

弁理士 伊藤 信和

100129779

弁理士 黒川 俊久

最終頁に続く

(54) 【発明の名称】超音波プローブの送受信器回路

## (57) 【要約】

【課題】複数の素子トランステューサ・プローブのサブアーチャの処理。

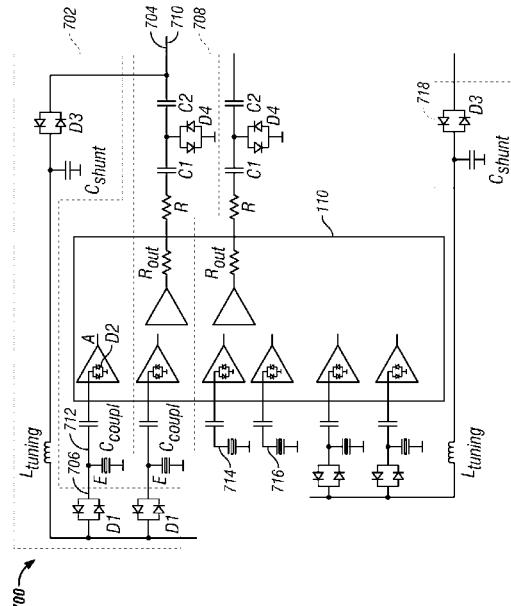

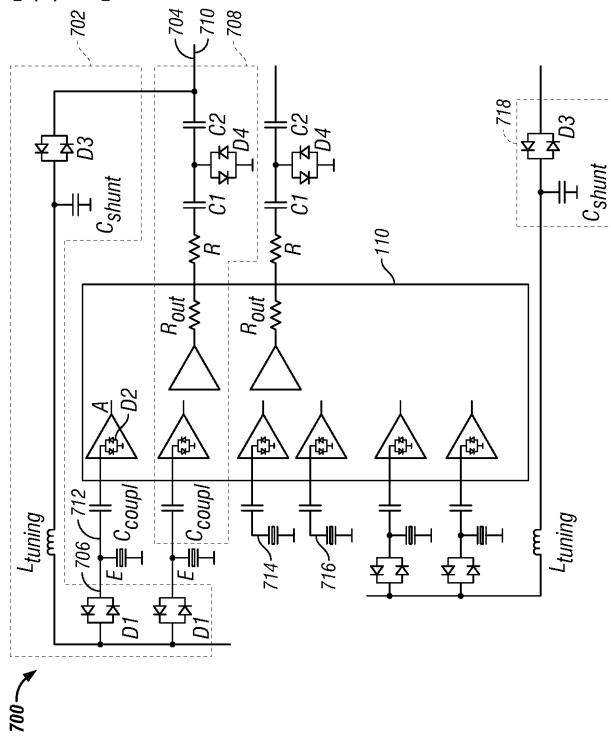

【解決手段】超音波トランステューサ素子の送受信器回路(700)は、送信部分(702)と受信部分(708)とを含む。送信部分(702)は、送信部分入力(704)と、送信部分出力(706)と、該送信部分入力(704)と該送信部分出力(706)との間に結合された受信信号ブロック回路(718)とを含む。受信部分(708)は、受信部分入力(712)と、受信部分出力(710)と、該受信部分入力(712)と該受信部分出力(710)との間に結合された受信信号ブロック回路(718)とを含む。

【選択図】 図7

**【特許請求の範囲】****【請求項 1】**

超音波トランステューサ素子の送受信器回路(700)において、

送信部分入力(704)と、送信部分出力(706)と、該送信部分入力(704)と

前記送信部分出力(706)との間に結合された受信信号ブロック回路(718)とを含

む送信部分(702)と、

受信部分入力(712)と、受信部分出力(710)と、該受信部分入力(712)と

前記受信部分出力(710)との間に結合された受信信号ブロック回路(718)とを含

む受信部分(708)と、

を備える送受信器回路(700)。

10

**【請求項 2】**

前記送信部分出力(706)が前記受信部分入力(712)に結合されていることを特

徴とする請求項1に記載の送受信器回路(700)。

**【請求項 3】**

前記送信部分入力(704)が前記受信部分出力(710)に結合されていることを特

徴とする請求項1に記載の送受信器回路(700)。

**【請求項 4】**

前記送信信号ブロック回路と前記受信信号ブロック回路のうちの少なくとも1つが複数

のクランプダイオードを含むことを特徴とする請求項1に記載の送受信器回路(700)

。

20

**【請求項 5】**

前記受信信号ブロック回路(718)が、前記送信部分出力(706)に結合されたク

ランプダイオードと、前記送信部分入力(704)に結合された逆並列接続ダイオードと

を含むことを特徴とする請求項1に記載の送受信器回路(700)。

**【請求項 6】**

複数のトランステューサ素子間に結合された逆並列接続ダイオードを更に備え、該逆並

列接続ダイオードが送信中に前記複数のトランステューサ素子間で短絡を形成することを

特徴とする請求項1に記載の送受信器回路(700)。

**【請求項 7】**

複数のトランステューサ素子間に結合された逆並列接続ダイオードを更に備え、該逆並

列接続ダイオードが受信中に前記複数のトランステューサ素子間で開回路を形成することを

特徴とする請求項1に記載の送受信器回路(700)。

30

**【請求項 8】**

前記送信信号ブロック回路が、前記受信部分入力(712)に結合されたクランプダイ

オードと、前記受信部分出力(710)に結合されたクランプダイオードとを含むことを

特徴とする請求項1に記載の送受信器回路(700)。

**【請求項 9】**

前記送信部分入力(704)と前記送信部分出力(706)との間に結合された電圧設

定回路を更に備えることを特徴とする請求項1に記載の送受信器回路(700)。

**【請求項 10】**

アレイ状のトランステューサ素子を含むトランステューサアレイ(102)と、

受信信号ブロック回路(718)を介して送信アパーチャを含む送信トランステューサ

素子に結合された送信部分出力(706)と、前記送信トランステューサ素子から選択さ

れた多重化されたトランステューサ素子に結合された受信部分入力(712)とを含む送

受信器回路(700)と、

を備え、

超音波ビーム送信中に、前記送信部分出力(706)が前記多重化されたトランステュ

ーサ素子を駆動し、超音波ビーム受信中に、前記受信部分入力が前記多重化されたトランステ

ューサ素子から受信信号を受け取ることを特徴とする超音波プローブ(100)。

40

**【発明の詳細な説明】**

50

**【技術分野】****【0001】**

本発明は、一般的に、超音波医療用イメージング・システムに関する。より具体的には、本発明は、複数の素子トランスデューサ・プローブのサブアパーチャの処理に関する。

**【背景技術】****【0002】**

医師及び技術者は、通常、診断用途で表示を得て画像を検査するために医療用イメージング・システムを用いる。例えば超音波イメージング・システムにおいて、医師は、心臓が正常に機能しているかどうかを知ろうとして、患者の心臓の画像を取得することができる。時の経過と共に、これらのイメージング・システムは、画像だけでなく、ECGトレース、心拍数などといった付加的な関連診断情報の取得にも次第に精通するようになっていている。10

**【0003】**

超音波システムの2つの主要構成要素は、超音波プローブとビームフォーマである。ビームフォーマは、表示される解剖学的内容物の画像生成の1つの段階として、プローブによって送受信される超音波エネルギーを集束し方向付ける。

**【0004】**

3D超音波の開発は、多数の音響素子を具備する超音波プローブに向かって進んでいる。最新技術の発展は、アパーチャ素子のサブグループ化及び各グループをシステムへ転送される1つの信号に前処理することにより多数のチャネルが低減されることを示唆している。送信は、プローブ内の送信器のみによって、又はアパーチャのサブグループの送信によって同様に処理することができる。20

**【0005】**

勿論、高画質画像は、医師が検査している生理機能を臨床的に評価するのに非常に重要なものである。高画質画像には、例えば、アパーチャの素子のほとんどを送受信双方に用いることが必要な、疎でないアパーチャを使用する必要がある。最新のシステムは、システムの送受信回路間を多重化することによりこれを達成する。従って、プローブの各チャネルは、1本のケーブルでシステムに接続され、送信及び受信の双方に用いることができる。

**【0006】**

送受信のためのアパーチャのサブグループ化の配置及び実施は、画質にとって非常に重要なである。プローブ内に回路を導入することにより、解決しなければならない技術的課題が提起される。また、プローブの受信及び/又は送信回路を用いると、システムの送信/受信スイッチに関する最近の方法では、送受信双方のプローブの全音響チャネルをオフにして用いることはできない。30

**【特許文献1】米国特許第6548837号****【発明の開示】****【発明が解決しようとする課題】****【0007】**

従って、上述の問題及びこれまで経験してきた他の問題を克服する必要性が存在する。40

**【課題を解決するための手段】****【0008】**

1つの実施形態において、プローブが位置付けられる超音波トランスデューサ素子用送受信器回路は、送信部分と受信部分を含む。送信部分は、送信部分入力と、送信部分出力と、送信部分入力及び送信部分出力間に結合される受信信号ブロック回路とを含む。受信部分は、受信部分入力と、受信部分出力と、受信部分入力及び受信部分出力間に結合される送信信号ブロック回路とを含む。送信部分入力は、受信部分出力に結合される。別の実施形態において、送信部分入力は、受信部分出力に結合されない。

**【0009】**

10

20

30

40

50

本発明の他のシステム、方法、特徴、及び利点は、以下の図及び詳細な説明を検討することにより当業者には明らかになるであろう。こうした追加のシステム、方法、特徴、及び利点は、本明細書の説明に含まれており、本発明の範囲内にあり、添付の請求項によって保護されるべきであることが意図される。

#### 【発明を実施するための最良の形態】

##### 【0010】

図面の構成要素は、必ずしも縮尺通りではなく、符号付のシステム及び方法の原理を示すことに重点が置かれる。図中、同じ参照符号は別の図面全体にわたり対応する部分を示している。

##### 【0011】

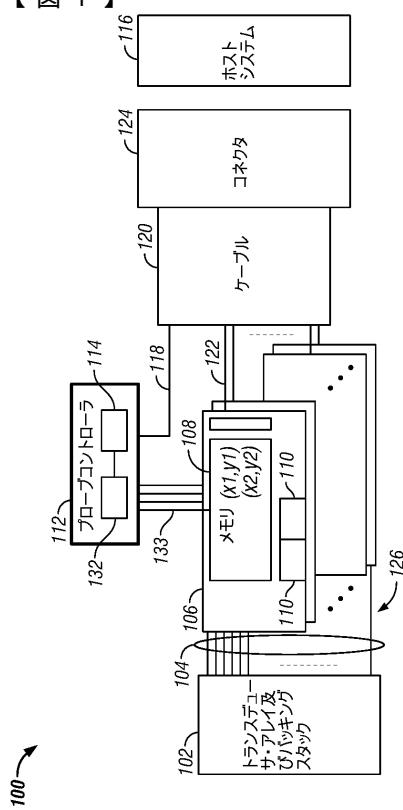

図1は、超音波プロープ100のブロック図を示す。プロープ100は、トランスデューサ・アレイ及びパッキングスタック102（「トランスデューサ・アレイ102」）と、トランスデューサ・ケーブル104と、処理電子機器に対応する複数の処理基板106とを含む。各処理基板106は、メモリ108（以下に述べるように幾何形状RAM、エンコーダRAM、位置レジスタ、及び制御レジスタを含むことができる）及び信号プロセッサ110を含む。また、位置キャッシュメモリ及びコントローラ112（例えば汎用CPU、マイクロコントローラ、PLDなど）も存在し、通信インターフェース114を含む。メモリ108は別個のものとするか、又は信号プロセッサ110の一部として含むことができる。

##### 【0012】

通信インターフェース114は、デジタル信号線118を介して、及び信号ケーブル120を通じてホストシステム116とのデータ交換を確立する。更に、信号ケーブル120は、処理基板106に接続される同軸ケーブル122を含み、送信パルス波形をトランスデューサ・アレイ102に伝送し、ビームフォーミング後に受信信号をホストシステム116に返信する。別の実施形態において、同軸ケーブル122は、受信信号のみを伝送する。プロープ100は、コネクタ124を含むことができ、該コネクタを通じてプロープ100がホストシステム116に取り付けされる。

##### 【0013】

相互接続126は、トランスデューサ可撓性ケーブル104を処理基板106に接続するために備えることができる。相互接続126はこれによって、トランスデューサ可撓性ケーブル104と処理基板106間に電気的接続を確立する。相互接続126はコネクタとすることができますが、他の実施形態もまた好適である。

##### 【0014】

トランスデューサ・アレイ102は、図2に関して以下により詳細に説明されるようにパッキングスタック上に結合される。トランスデューサ可撓性ケーブル104は、パッキングスタックを通じて電気信号が接続される。1つの実施形態においては、48のトランスデューサ可撓性ケーブル104があり、各々が55の信号接続を具備する。従って、トランスデューサ可撓性ケーブル104は、トランスデューサ・アレイ102内の2640ものトランスデューサ素子の送受信号接続に対応するが、以下で説明する実施形態ではより少ない数が使用されている。

##### 【0015】

相互接続126は、トランスデューサ可撓性ケーブル104を処理基板106に接続する。1つの実施形態において、各処理基板106は、トランスデューサ可撓性ケーブル104の6つの面に結合されることにより、330のトランスデューサ素子の信号接続を含む。

##### 【0016】

処理基板106は、可撓性ケーブル104と同様に可撓性材料から形成することができる。処理基板106は、トランスデューサ・アレイ102内の受信アパーチャ上でビームフォーミングを実行する信号プロセッサ110を含む、トランスデューサ・アレイ102の処理電子機器を保持する。処理基板106はまた、送受信間の選択された音響トラン

10

20

30

40

50

デューサ素子を多重化すると共に、音響トランステューサ素子に接続される信号プロセッサ 110 を保護する送受信器回路を保持する。

#### 【0017】

以下でより詳細に説明するように、各信号プロセッサ 110 は、トランステューサ・アレイ 102 上の選択された空間位置に画定された、例えば 4 つの複数の受信サブアーチャを処理することができる。受信サブアーチャは、三角形のサブアーチャとすることができます、これは、例えば、1 素子の列の上に 2 素子の列、その上に 3 素子の列、その上に 4 素子の列、その上に 5 素子の列が配置された 15 の音響トランステューサ素子を含む。更に、各処理基板 106 は、6 つの信号プロセッサを含むことができる。従って、受信方向において、各処理基板 106 は、各々が 15 の音響トランステューサ素子を含む、最大 24 の受信サブアーチャを処理することができる。10

#### 【0018】

全ての超音波ビームにおいて、キャッシュメモリ及びコントローラ 112 は、デジタル信号線 132 ( 例えれば別個の可撓性ケーブルにより伝送される ) を介して、各処理基板 106 上の各信号プロセッサコントローラ 108 に接続される。信号プロセッサコントローラ 108 は、処理基板 106 上に「メモリ」とラベル付けされた別個のブロックとして示されているが、信号プロセッサ 110 の一部として含むこともできる。キャッシュメモリ及びコントローラ 112 は、静的及び動的プローブ設定情報を、信号プロセッサ 110 へ転送する。静的設定情報は典型的には、空間的な素子の位置、電力設定、及び遅延設定マッピングテーブルである。動的情報は典型的には、ビーム毎に変わるサブアーチャの方向情報である。デジタル信号線は、例えれば、各処理基板 106 のクロック・ライン、各処理基板 106 の直列コマンド・データ・ライン、各処理基板 106 に接続される 1 つ又はそれ以上のデータ・ライン、1 つ又はそれ以上の信号プロセッサ 110 の出力イネーブル、及びテスト信号を含むことができる。20

#### 【0019】

キャッシュメモリ及びコントローラ 112 は、例えれば、同期式シリアル・ポートの一部を形成することができるデジタル信号線 118 を介して、ホストシステム 116 と通信する。このために、通信インターフェース 114 及びデジタル信号線 118 は、接地シールド及び中心信号線を具備する同軸ケーブルを含む TIA / EIA - 644 及び IEEE 1592 標準による、低電圧差信号インターフェース LVDS を実装することができる。キャッシュメモリ及びコントローラ 112 は、例えれば、1 - 64M バイトのスタティック・ランダムアクセスメモリ ( SRAM ) といった 1 ブロックのキャッシュメモリ 132 を含む。30

#### 【0020】

キャッシュメモリ及びコントローラ 112 内のキャッシュメモリ 132 の主な目的は、ビームをサブアーチャの設定情報に依存するように保持することである。1 つの実施形態において、これはサブアーチャの方向設定情報とすることができます。これは通常、ページに分割され、各ページは、各ショットに関して必要とされる信号プロセッサ 110 設定情報を含む。キャッシュ・ページに 1 つのスキャンシーケンスの全ショットの情報を載せることにより、この情報はスキャン中にプローブ内で利用可能である。すなわち、スキャン中、各ショットに関するプローブ設定情報は、関連するキャッシュ・メモリ・ポインタをキャッシュメモリ及びコントローラ 112 に転送することにより、信号プロセッサが使用できるようにすることができる。40

#### 【0021】

1 つの実施形態において、キャッシュメモリ及びコントローラ 132 内のキャッシュメモリは、512k ワード × 16 ビット ( 8M ビット ) のものに編成され、128 ワードのページに分割される。キャッシュ・メモリ・ポインタを各ページの最初に設定することができる。キャッシュ・メモリ・ポインタは、例えれば、合計 4096 ページをアドレスすることができる 12 ビットのポインタとすることができる。キャッシュメモリ 132 が 4M ビットのキャッシュのときには、キャッシュ・メモリ・ポインタは、2048 ページにイ50

ンデックスを付ける 11 ビットのポインタとすることができます。信号プロセッサ 110 の連鎖にデータを書き込み、又は該連鎖からデータを読み込むときに、キャッシュ・ページのワードが使用される。各処理基板上の信号プロセッサ 110 のデジタル・データ・ラインは、一連の複数の信号プロセッサ 110 にわたりシフト・レジスタを通じて連鎖化することができる。従って、信号プロセッサ 110 に転送されたデータは、信号プロセッサ 110 を通じて直列に伝播する。ページの最小アドレスを具備するワードからのビットは、データロード時の連鎖における最後の信号プロセッサ 110 へのシフト・レジスタの LSB ビットで終わる。更に、キャッシュメモリ 132 は、キャッシュメモリ及びコントローラ 112 内に示されるが、別の実施形態において、キャッシュメモリ 132 は、キャッシュメモリ及びコントローラ 112 から分離することができる。キャッシュメモリはまた、信号プロセッサ 110 の一部とすることができます。10

【 0 0 2 2 】

プロープ 100 は、例えばホストシステム 116 からの 16 ビットのコマンドに応答する。コマンドの 1 つの例示的な設定が下記の表 1 に示される。コマンドの 4 ビットを用いてコマンドを定義することができると共に、該コマンドのパラメータとして 12 ビットを用いることができる。

【 0 0 2 3 】

【表1】

| 名称               | パラメータ<br>ビット：11-0 | 説明                                | 詳細                                                 |

|------------------|-------------------|-----------------------------------|----------------------------------------------------|

| WR_CTRL_R<br>EG  | 制御レジストリ設定         | 制御／状態レジスタへの書き込み                   | キャッシュメモリ及びコントローラレジスタ                               |

| WR_CACHE_<br>PTR | 11/12ビットポインタ      | キャッシュ・ページ・ポインタ設定                  | キャッシュ・ポインタは、キャッシュメモリから信号プロセッサ110へロードされる次ページの始まりを示す |

| WR_CACHE         |                   | ホストシステム116からキャッシュメモリ132へのページの書き込み | アドレス・ポインタは、書き込まれた各ワードに対して自動的にインクリメントすることができる       |

| LD_SCAN_P<br>AR  |                   | スキャン・パラメータ・ページを信号プロセッサ110連鎖に書き込む  | 各超音波ショットについて更新される                                  |

| LD_CONFIG        |                   | メモリ又はレジスタを信号プロセッサ110にロード          | 静的コンフィギュレーション・データ                                  |

| DELAY_TUN<br>E   | なし                | 遅延較正開始                            | 各信号プロセッサ110は遅延を較正する内部回路を有する                        |

| SAP_RESET        | リセットするもの          |                                   |                                                    |

| RD_CTRL_R<br>EG  | 戻された制御レジスタ値       | 制御／状況レジスタからの読み込み                  | このレジスタはキャッシュメモリ及びコントローラ112の内部にある。                  |

| RD_CACHE_<br>PTR | 戻されたポインタ値         | キャッシュ・ページ・ポインタ・レジスタの読み込み          | 検査及び確認に有効                                          |

| RD_CACHE         | なし                | キャッシュメモリ132からページを読み込む。            | アドレス・ポインタは読み込まれた各ページについて自動的にインクリメントすることができる        |

| RD_CONFIG        |                   | 信号プロセッサ110から設定を読み込む。              | 例えば連鎖の最後の信号プロセッサ110からループ・バックを通す                    |

| CMD_ENABLE       | IDコード             | コマンド実行を有効及び無効にする。                 |                                                    |

コマンドの目的は、プローブを制御するよう設定することである。コマンドは、キャッシュメモリ及びコントローラ112及びノ又は信号プロセッサ110を制御することができる。また、例えば、送信パルスからのノイズに起因する好ましくないコマンドの実行を避けるための保護機構を含むのが望ましい。

#### 【0025】

書き込みキャッシュ・ポインタ(WR\_CACHE\_PTR)コマンドは、メモリ・キャッシュ・ポインタ・レジスタに書き込む。1つの実施形態において、パラメータは12ビットのキャッシュ・ポインタである。キャッシュメモリ132を読み込み/書き込みをする際に、特定のキャッシュ・ポインタが、コマンドのパラメータ領域で使用される。キャッシュ・ワードの読み込み/書き込み中に、キャッシュ・ポインタを自動的にインクリメントすることができる。全ページを転送後、次にポインタは次ページの始まりを示す。8Mビットを超えて使用される場合には、12ビットより長いキャッシュ・ポインタの転送を2つのコマンドとして実行することができる。

#### 【0026】

キャッシュへの書き込み(WR\_CACHE)コマンドは、キャッシュメモリ132へのデータをロードする。データは、キャッシュ・ポインタによって示されたキャッシュ・ページに書き込まれることになる。キャッシュ・ポインタは、各ワードがキャッシュに書き込まれると自動的にインクリメントされる。位置メモリコントローラ112は、このコマンドが受信されるときにコマンド・エコーを送信することができる。

#### 【0027】

スキャン・パラメータのロード(LD\_SCAN\_PAR)コマンドは、スキャン・パラメータを信号プロセッサ110連鎖に書き込む。1つの実施形態において、パラメータは用いられない。このコマンドは、スキャン・パラメータ・ページを信号プロセッサ110へキャッシュ・アドレス・ポインタによって与えられたキャッシュ・ページから書き込む。このコマンドは、EOL信号によってトリガーすることができるが、同様にコマンドとして送信することもできる。

#### 【0028】

データが転送されると、キャッシュメモリ及びコントローラ112は、信号プロセッサ110に計算コマンドを送信し、次の超音波ショットのビームフォーミング遅延の計算を開始する(設定時間を削減するために以前のロードされた設定値を用いる)。キャッシュメモリ132ポインタは、各ワードが信号プロセッサ110に書き込まれると自動的にインクリメントされる。スキャン・パラメータ・ページのサイズは、例えば、128ワードとすることができます。最小アドレスを具備するワードは、最終的には連鎖における最後の信号プロセッサ110のシフト・レジスタの LSB ビットとなる。

#### 【0029】

コンフィギュレーションロード(LD\_CONFIG)コマンドは、静的設定情報を信号プロセッサ110へロードする。静的設定情報は通常、信号プロセッサ110内の空間的素子位置、電力設定、及び遅延設定マッピングテーブルである。コマンドが用いられる度に、1つのキャッシュ・ページが選択されたメモリに書き込まれる。1つよりも多いキャッシュ・ページを必要とするロードもある。

#### 【0030】

信号プロセッサ内で空間的素子位置を保持する幾何形状RAMは、各々が12ビット長である64ワードとして実装することができる。遅延マッピングテーブルを保持するエンコーダRAMは、各々が5ビット長である1024ワードとして実装することができる。スタート・アドレスは、キャッシュメモリ132アドレス・ポインタから取り出される。各ページの後、アドレス・ポインタは次のキャッシュ・ページにインクリメントする。従って、アドレス・ポインタを更新することなく、後続のページをロードすることができる。ページ内で最小アドレスを有するワードは、信号プロセッサ110連鎖内に計時された最初のデータである。従って、最小アドレスのコンテンツは、最終的には特定の処理基板106上の信号プロセッサ110の連鎖における最後の信号プロセッサ110のシフト・

10

20

30

40

50

レジスタの L S B ビットとなる。

【 0 0 3 1 】

遅延チューニング開始 ( D E L A Y \_ T U N E ) コマンドは、信号プロセッサ 110 の内部遅延を較正する処理を開始する。パラメータを用いる必要はない。結果は、信号プロセッサ 110 内に存在するアナログ多目的レジスタに書き込まれる。

【 0 0 3 2 】

S A P リセット ( S A P \_ R \_ S E T ) コマンドは、信号プロセッサ 110 内の内部機能、すなわちアドレス・カウンタを全てリセットする。パラメータは、信号プロセッサ 110 全体か又はサブ機能のみをリセットするかを選択するビット・パターンを指定することができる。

【 0 0 3 3 】

制御レジスタ読み込み ( R D \_ C O N T R O L \_ R E G ) コマンドは、位置メモリコントローラ 112 内の制御レジスタを読み込む。レジスタのコンテンツは、コマンドのパラメータ領域に戻すことができる。

【 0 0 3 4 】

キャッシュ・ポインタ読み込み ( R D \_ C A C H E \_ P T R ) コマンドは、キャッシュメモリ 132 ポインタ・レジスタを読み込む。コマンドがホストシステム 116 にエコーバックされる前に、キャッシュ・ポインタ・レジスタから読み込まれる値は、コマンドのパラメータ領域に戻すことができる。

【 0 0 3 5 】

キャッシュ読み込み ( R D \_ C A C H E ) コマンドは、キャッシュメモリ 132 からホストシステム 116 へのデータを読み込む。コマンドが受信されると、位置メモリコントローラ 112 は、データワードをワードの連続シーケンスとして送ることができる。

【 0 0 3 6 】

S A P からのコンフィギュレーション読み込み ( R D \_ C O N F I G ) コマンドは、パラメータ・ビットで指定される信号プロセッサ 110 からコンフィギュレーション・データを読み込む。コンフィギュレーション・データは、信号プロセッサ 110 から読み込まれ、キャッシュ・ポインタによって示されたキャッシュ・ページのキャッシュメモリ 132 に置かれる。キャッシュ・アドレスは、読み込まれた各ワードについてインクリメントする。第 1 のワードは、最小キャッシュ・アドレス内に置かれる。キャッシュ・アドレスは、終了すると次ページのスタートに調整される。

【 0 0 3 7 】

コマンド・イネーブル ( C M D \_ E N A B L E ) コマンドは、コマンドの実行を有効又は無効にする。キャッシュメモリ 132 からのスキャン・パラメータのロード後、コマンドの実行は、コマンド終了後に無効とされる。それでも尚、無効の間に、位置メモリコントローラ 112 は、コマンド・イネーブルコマンド及び制御レジスタ読み込みコマンドに応答することができる。固有のビット・パターンがパラメータ領域に付加され、このコマンドがコマンド・ライン上に存在するノイズから発生する可能性を低減する。

【 0 0 3 8 】

概要として、以下の段階がスキャン中に起こる。最初に、E O L 信号 ( 前の超音波ショットからの受信データの最後 ) が、キャッシュメモリ及びコントローラ 112 をトリガーし、信号プロセッサ 110 へ計算コマンドを送信し、その後、キャッシュメモリ 132 から信号プロセッサ 110 へ新しいページを送信する。キャッシュメモリ及びコントローラ 112 内のページ・ポインタ・レジスタは、この新しいページのスタート・アドレスを保持する。各アップロードの前に、ホストシステム 116 は、次の超音波ショットのページ・ポインタを、デジタル信号線 118 を下ってキャッシュメモリ及びコントローラ 112 へ送信する。ページのロードが終了すると、肯定応答信号をホストシステム 116 へ返信することができる。ホストシステム 116 はその後、超音波ショットを発射し、超音波データの収集を継続する。最新ショットの収集が終了すると、位置メモリコントローラ 112 は、新しい E O L を受信し、処理が再び新たに開始される。

10

20

30

40

50

## 【0039】

プロープ100がホストシステム116に接続されると、ホストシステム116は、各アパーチャ及び各ビームの設定情報を位置メモリコントローラ112上のS R A Mに送信する。受信ビームフォーミングは、ホストシステム116とプロープ100間で分割される。ホストシステム116は、受信アパーチャ出力の信号プロセッサ110によって駆動されるシステム受信チャネルのビームフォーミング遅延、アパーチャ拡大、及び振幅アポダイゼーションに関与する。

## 【0040】

信号プロセッサ110は、個々の受信サブアパーチャ上でビームフォーミングを行う。

1つの実施形態において、三角形の受信サブアパーチャとして配列される15のトランステューサ素子のグループが、信号プロセッサ110に結合される。信号プロセッサ110は、トランステューサ素子の各々から発生する受信信号の各々に遅延を適用する。信号プロセッサ110はまた、15の受信信号を併せて加算し、受信アパーチャ出力及び同軸ケーブル122を介してホストシステム116にアパーチャ合計を送り返す。

10

## 【0041】

位相遅延を用いる1つの実施形態において、各信号プロセッサ110は、各受信サブアパーチャに対して、15の低ノイズ増幅器、15の位相反転回路、1つのコンデンサ・スイッチング・ネットワーク、及び90度の差動位相シフトに適用される2つの移相器を含む。この実施形態において、差動位相シフトは広帯域である。スイッチング・ネットワークは、移相器への加算のため、潜在的に反転された受信信号に、重み係数を付与する。別の実施形態において、信号プロセッサは遅延線連鎖に基づく。

20

## 【0042】

動作中、各信号プロセッサ110は、各受信サブアパーチャのビームステアリングがホストシステム116によって選択された焦点に向かうように構成される。このため、信号プロセッサ110は、受信アパーチャ内のトランステューサ素子位置、ステアリング方向、及び受信周波数に基づいてビームフォーミング位相シフトを求める。各受信サブアパーチャは、同じ焦点を用いる必要はなく、トランステューサ・アレイ102の中心からより離れた位置にある受信サブアパーチャは、アパーチャ・サイズを動的に増大させることができるように後で作動可能である点に留意されたい。

30

## 【0043】

信号プロセッサ110は、2つの段階で構成される。最初に、プロープ100の初期化中、ホストシステム116は、静的信号プロセッサ設定情報をキャッシュメモリ及びコントローラ112を介して信号プロセッサ110へロードする。この静的情報は、幾何形状情報、すなわち各受信サブアパーチャのトランステューサ素子の空間的(x, y)位置、及び周波数依存変換テーブルを含む。次に、スキャンの前に、動的設定情報が、キャッシュメモリ及びコントローラ112内のキャッシュメモリ132へ送信される。これらのキャッシュ・ページの各々は、1つのショットに関してプロープ内の全てのサブアパーチャのステアリング・パラメータを含む。別の実施形態において、1つよりも多いキャッシュ・ページを用いて、設定情報に関して必要とされるビームを送信することができる。

40

## 【0044】

スキャン中、ホストシステム116は、キャッシュメモリ及びコントローラ112にビーム・インデックスを付加する。これに応答して、キャッシュメモリ及びコントローラ112は、適正なステアリング・パラメータを該キャッシュメモリから信号プロセッサ110へ送信する。次いで、信号プロセッサ110は、トランステューサ素子位置、(方向パラメータによって表される)ステアリング方向に基づいてビームフォーミング遅延を求める。位相遅延を用いる実施形態において、遅延は、周波数依存変換テーブルを用いて位相設定に変換される。

40

## 【0045】

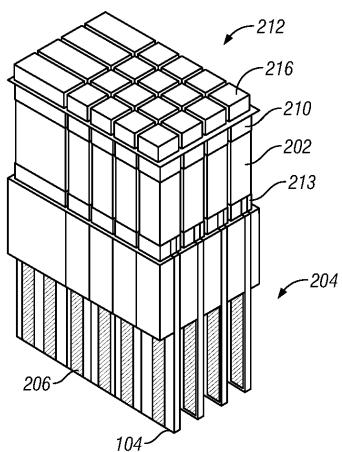

次いで図2を参照すると、該図は、トランステューサ・アレイ102の1つの実施形態を示す。トランステューサ・アレイ102は、電子エネルギーから音響エネルギーへ、及び音

50

響エネルギーから電子エネルギーへ変換する圧電セラミック 202 を含む。圧電セラミック 202 は、トランスデューサ・アレイ 102 の中心に位置付けられる。信号面では、圧電セラミック 202 は、z 軸バッキング層 204 に、トランスデューサ可撓性ケーブル 104 により取り付けられる。

#### 【0046】

トランスデューサ可撓性ケーブル 104 は、高密度信号接続を形成する。セラミック 202、導電性の内部音響整合層 210、及びバッキングブロック 204 の上面は、トランスデューサ可撓性ケーブル 104 内の可撓性回路トレース 206 の各々の上に集められる個別の音響素子 212 を形成する。従って、z 軸バッキングブロック 204 上に信号面 213 が存在する。

10

#### 【0047】

各回路トレース 206 は、トランスデューサ素子 212 の底面、すなわち信号面に接触する。このダイスカット状の整合層 216 は、各素子 212 の上部に取り付けられ、トランスデューサ・アレイ 102 の表面全体に接地接続を形成する。

#### 【0048】

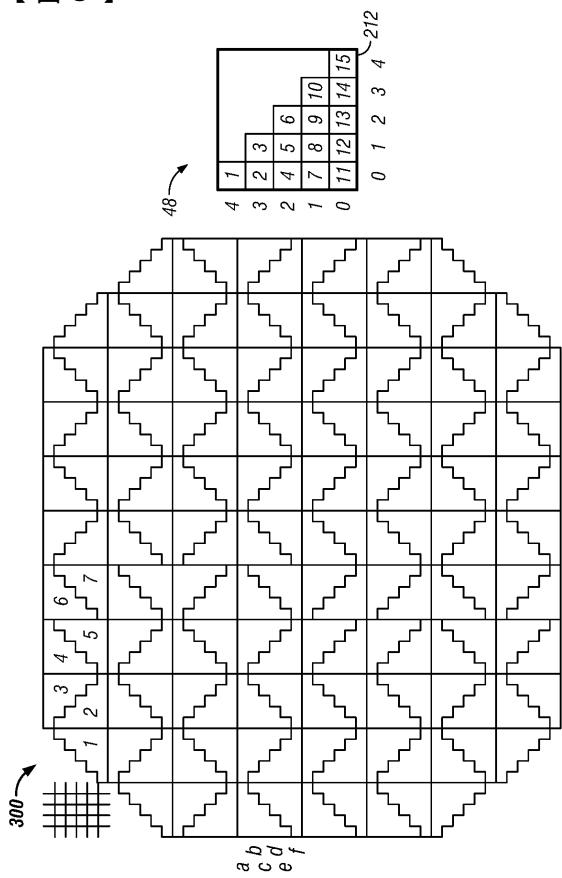

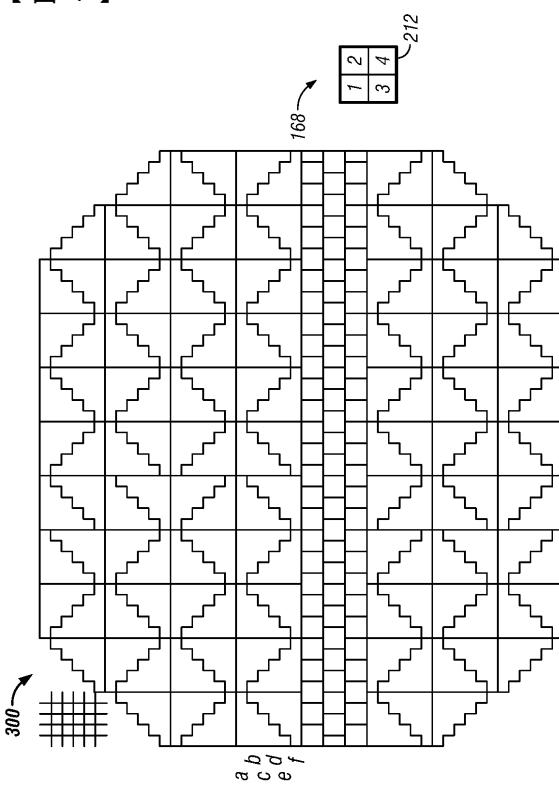

次に、図 3 及び図 4 について、図 3 は、図 1 に示される超音波プローブ内に組み込まれた音響トランスデューサ素子 300 のアレイ全体にわたって配置されている受信サブアーチャを示す。同様に、図 4 は、音響トランスデューサ素子 300 のアレイ全体にわたり配置される特定の受信アーチャと多重化された 1 行の送信サブアーチャを示す。図示される他の行もまた送信素子を含む。1 つの実施形態において、アレイは、横方向に 55 のトランスデューサ素子、縦方向に 48 の素子を含む。

20

#### 【0049】

しかしながら、以下で述べる実施形態において、アレイの角は落とされ、これによってアレイ 300 は八角形となる。全てのトランスデューサ素子は、15 の素子受信サブアーチャにグループ化され、図 3 に示されるように受信方向で用いられる。全ての送信素子もまた、4 つの素子送信サブアーチャにグループ化され、図 4 に示されるように送信方向で用いられる。

#### 【0050】

具体的に図 3 を参照すると、各信号プロセッサ 110 は、各受信サブアーチャの 15 のトランスデューサ素子から生じる 15 の受信信号を、単一システム受信チャネルに結合する。信号プロセッサ 110 は、上述のように、受信信号を加算する前に、各受信信号に遅延を適用する。15 のトランスデューサ素子のグループは、図 3 に示されるように、三角形のアーチャを形成する。従って、トランスデューサ受信アーチャ全体では、 $160 \times 15 = 2400$  のトランスデューサ素子を含む 160 のサブアーチャを含む。別の実施形態において、選択された受信サブアーチャの数及び送信サブアーチャの数は、送受信において利用可能なシステム・チャネルの数、望ましいアーチャのサイズ及び形、並びにトランスデューサ素子のサイズに応じて決まる。

30

#### 【0051】

図 3 に示されるように、拡大した受信アーチャ 48 に関して、各受信アーチャは、 $5 \times 5$  のグリッドのトランスデューサ素子上に形成される。受信アーチャは、5 つのトランスデューサ素子の第 1 の行 (11 - 15 とラベル付けされている)、4 つのトランスデューサ素子の第 2 の行 (7 - 10 とラベル付けされている)、3 つのトランスデューサ素子の第 3 の行 (4 - 6 とラベル付けされている)、2 つのトランスデューサ素子の第 4 の行 (2 - 3 とラベル付けされている)、及び 1 つのトランスデューサ素子の第 5 の行 (1 とラベル付けされている) を含む。各トランスデューサ素子は、そのサブアーチャ内に位置  $x n$ 、 $y n$  を有する。例えば、トランスデューサ素子 14 は、 $x n = 3$ 、 $y n = 0$  に位置付けられる。受信アーチャは、2 つの受信アーチャの組み合わせが、横方向に 5 つのトランスデューサ素子と縦方向に 6 個のトランスデューサ素子の矩形パッチを形成するようにインターロックされる。

40

#### 【0052】

50

図4に関しては、送信アーチャの図示部分は、受信素子アレイ300の第5番目の行に沿って、324のトランステューサ素子を含む。送信素子は、 $2 \times 2$ の素子送信サブアーチャにグループ化され、送信サブアーチャの各々は、同軸ケーブル122でホストシステム116に接続されるシステム送信チャネルの1つに接続される。図4は、拡大された送信サブアーチャ168を示し、2つのトランステューサ素子の第1の行(3-4とラベル付けされている)及び2つのトランステューサ素子の第2の行(1-2とラベル付けされている)を含む。送信サブアーチャは、送信グレーティング・ロープを低減するために横(水平)方向に千鳥配置にされる。

#### 【0053】

縦方向においては、3つの $2 \times 2$ 送信サブアーチャが、6つの受信トランステューサ素子と整列される。縦(垂直方向)において、アレイ300全体は、各々が6行のトランステューサ素子である8つのグループに分割される。送信及び受信サブアーチャの配列は、電子機器分割を構成する。より具体的には、6つの素子行の各グループ(例えば、図3及び図4でa-fとラベル付けされているもの)は、1つの処理基板106に6つのトランステューサ可撓性ケーブル104によって接続される。受信サブアーチャ又は送信サブアーチャは、分割境界線を(2つ又はそれ以上の処理基板の上へ)超えないで、6つの行の全てのトランステューサ素子に関連する処理電子機器は、単一処理基板106内に全体が含まれる。1つの有意な利点は、1つの処理基板106から別の処理基板へアナログ信号を送る必要がないことである。

#### 【0054】

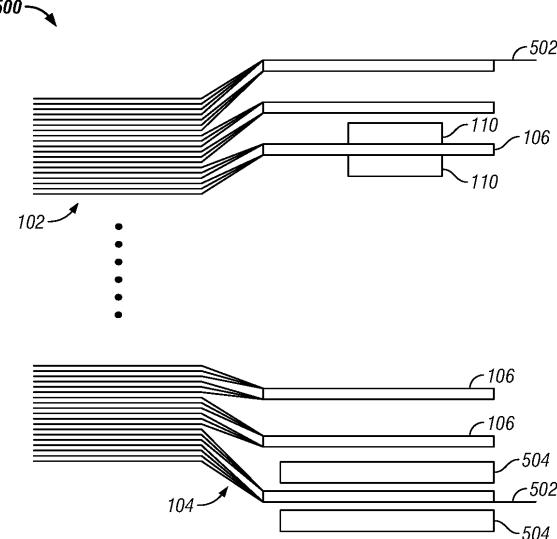

図5は、トランステューサ・アレイ102のバッキングスタック204から生起する48のトランステューサ可撓性ケーブル104の分布500を示す。6つのトランステューサ可撓性ケーブル104が、8つの処理基板106の各々に接続される。トランステューサ可撓性ケーブル104は、これによって、音響トランステューサ素子のアレイ300を処理基板106上の信号プロセッサ(このうち2つは素子110として示される)に接続する。スペーサ504が処理基板106の間に置かれ所望の間隔が得られる。

#### 【0055】

各トランステューサ可撓性ケーブルは、特定の処理基板に接続するように、55のトランステューサ素子の信号経路を備える接続を有する。このために、信号をトランステューサ可撓性ケーブル104から処理基板106に接続するコネクタが設けられる。本明細書で説明される実施形態では、このような処理基板106が8つある。従って、8つの処理基板106は、図5に示されるように、積み重ねられて、48のトランステューサ可撓性ケーブル104を処理基板106へ完全に分配する。

#### 【0056】

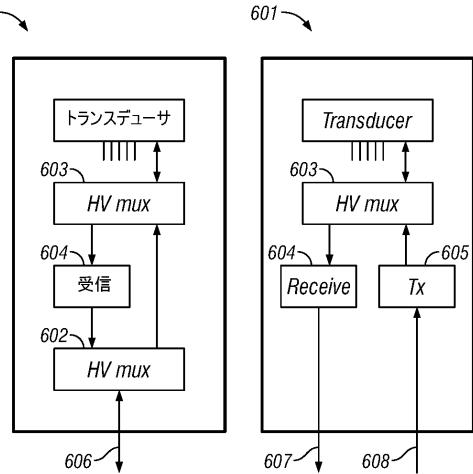

図6は、送受信間の選択された音響トランステューサ素子を多重化すると共に、送受信用のプロープ電子機器を保護するプロープ回路を示す。実施形態600は、送受信双方のシステムに同軸ケーブル606を用いる。この実施形態において、プロープ受信処理回路604は、入力603-604接続及び出力602-604接続の双方に保護回路を有する必要がある。プロープ601の送信回路を具備する別の実施形態においては、受信回路入力603-604接続だけが保護されなければならない。この実施形態において、送信回路の必要性は、ライン608を介したシステムから、又はプロープのキャッシュメモリ及びコントローラ112から制御される。

#### 【0057】

多重回路602及び603は、スイッチ又は受動回路を用いて実装することができる。能動スイッチを具備する実施形態では、制御回路は、信号の流れに対して計時する必要がある。受動回路を用いる実施形態では、図7に示されるように、信号レベルのみに基づいてプロープ回路を保護している。全ての実施形態では、使用されるマルチプレクサ又はスイッチは、通常、圧電トランステューサ素子のピーク間で10から400ボルトの範囲にある高電圧送信電圧に耐えなければならない。他のタイプのトランステューサ素子は、異なる電圧範囲を用いることができる。

10

20

30

40

50

## 【0058】

図7は、送受信器回路700の受動型の実施形態を示すが、これは送受信間の選択された音響トランスデューサ素子を多重化すると共に、音響トランスデューサ素子に接続された信号プロセッサを保護するものである。送受信器回路700は、複数の送信部分を含むが、このうちの1つの702とラベル付けされたものは、送信部分入力704と、送信部分出力706と、送信部分入力704及び送信部分出力706間に配置された2セットの受信信号ブロック回路とを組み込む。図7に示されるように、受信信号ブロック回路は、逆並列接続ダイオードD1、及びコンデンサCshuntに接続された逆並列接続ダイオードD3を含む。

## 【0059】

また、送受信器回路700は、複数の受信部分を含み、そのうちの1つの708とラベル付けされたものは、受信部分出力710と、受信部分入力712と、受信部分入力712及び受信部分出力710間に配置された2セットの送信信号ブロック回路とを組み込む。送信信号ブロック回路は、ダイオードD2に接続されたコンデンサCcouple、及びコンデンサC2に接続される逆並列接続ダイオードD4を含む。受信部分入力712は、トランスデューサ素子から得た受信信号を信号プロセッサ110へ転送する受信信号接続である。

## 【0060】

音響トランスデューサ素子は、送信部分出力706及び受信部分入力712に結合される。送信部分出力706及び受信部分入力712は、トランスデューサ素子で共に接続され、そのうちの1つが図7でEとラベル付けされる。同様に、送信部分入力704及び受信部分出力710は、共に接続される。受信部分出力710は、信号プロセッサ110によって受信方向に駆動される受信サブアパーチャ出力として機能する。従って、受信サブアパーチャ出力は、受信サブアパーチャを介して得られた信号、例えば、三角形の受信サブアパーチャの15のトランスデューサ素子から得られた受信信号から形成されるビームフォーミングされた受信信号を伝送する。

## 【0061】

各送信部分702は、4つのダイオードD1を通じて4つのトランスデューサ素子Eに結合される点に留意されたい。4つのトランスデューサ素子は、上述の $2 \times 2$ の送信サブアパーチャを形成する。同様に、15のトランスデューサ素子Eは、1つの受信サブアパーチャ出力チャネルに組み合わされて加算される。所与の受信サブアパーチャの15の受信部分入力712の各々は、コンデンサCcouple及びダイオードペアD2を含む。出力側において、受信サブアパーチャを介して得られる組み合わせ信号の受信部分出力710の各々は、ダイオードペアD4及びコンデンサC2を含む。

## 【0062】

送受信器回路700によって、トランスデューサ素子Eは、信号受信と信号送信間で多重化が可能であると共に、信号プロセッサ110の入力と出力を保護することができる。すなわち、任意の所与のトランスデューサ素子Eは、送信音響エネルギー及び受信音響エネルギーの双方に用いることができる。

## 【0063】

しかしながら、全てのトランスデューサ素子Eを多重化することは、望ましいものではない。アレイ300のトランスデューサ素子の一部が、受信だけに使用される場合には、トランスデューサ素子Eは、これに結合される送信部分702を有する必要はない。これは図7に示され、受信のみの素子は714及び716でラベル付けされる。更に、送信信号ブロック回路は、受信専用トランスデューサ素子Eは、これに結合される受信部分708を有する必要はなく、受信信号ブロック回路を含む必要もない。従って、例えば、718とラベル付けされる受信信号ブロック回路（並びにCcouple及びD2）は、送信専用チャネルに対して除外することができる。

## 【0064】

10

20

30

40

50

動作中、ホストシステム 116 から来る送信信号（例えば 100 ボルトのパルス）は、ダイオード D3、同調インダクタ  $L_{tuning}$ 、及びダイオード D1 を通過して、トランステューサ素子 E を駆動する。同調インダクタの後、送信信号は 4 つの信号に分かれ、D1 ダイオードの 4 セットを通過し、 $2 \times 2$  の送信サブアパートチャを形成する 4 つのトランステューサ素子に伝わる。

#### 【0065】

図 7 に示されるように、ダイオード D1、D2、D3、D4 は、逆並列ペアのようになる。ダイオードの電圧降下は、送信電圧に比べて小さく、送信中、送信信号に対して有意な影響はない。同調インダクタは、トランステューサ素子 E への電圧設定を与えるように選択される。この回路の共振周波数（つまり、同調インダクタ及び有効静電容量）は、望ましい送信周波数に整合するように調整される。有効静電容量は、トランステューサ素子、寄生シャント静電容量、及び結合コンデンサ  $C_{coupling}$  の並列構成要素で形成される。

10

#### 【0066】

結合コンデンサ  $C_{coupling}$  は、信号プロセッサ 110 入力を送信信号電圧から保護する。信号プロセッサ 110 は、送信電圧まで結合コンデンサを充電するための電流を供給する内部クランプダイオード D2 を含む。従って、結合コンデンサは送信電圧のほぼ全てを占め、ダイオード D2 は、信号プロセッサ 110 入力に存在する電圧をプラス又はマイナス 1 ダイオード電圧降下（例えば 0.7V）に保持する。

#### 【0067】

同軸ケーブル 122 は主に、送信用及び受信用の双方に用いられるので、送信波形も信号プロセッサ 110 出力に（送信ブロック回路なしで）現れる。コンデンサ  $C_2$  及びダイオード D4 は、信号プロセッサ 110 出力を送信電圧から保護する。特に、D4 は信号を 1 ダイオード電圧降下にクランプし、 $C_2$  は信号プロセッサ 110 出力を送信電圧の大部分を占めることにより送信波形から切り離す。送信波形は、同軸ケーブル 122 によって十分にフィルタ処理され、コンデンサ  $C_2$  及び  $C_{coupling}$  の電荷電流を制限する。

20

#### 【0068】

受信中、トランステューサ素子 E からの受信信号は、 $C_{coupling}$  を通過して信号プロセッサ 110 へ伝わる。信号プロセッサ 110 の入力ステージは、 $C_{coupling}$  によって決定されるゲインを有する電荷増幅器 A である。一般に、良好な雑音指数のためには、結合コンデンサのインピーダンスは、トランステューサ素子 E のインピーダンスに比べて小さくなければならない。しかしながら、インピーダンス値が小さいと、送信中の電荷電流が増大する。

30

#### 【0069】

受信中はトランステューサ素子の電圧は小さいので、ダイオード D1 は、開放状態にある。従ってダイオード D1 は、低電圧信号ブロッカーとして動作し、トランステューサ素子 E を互いから切り離す。トランステューサ素子から受信されたエコー信号は、信号プロセッサ 110 内で遅延されて加算され、受信部分出力 710 に供給される。より具体的には、出力信号は、出力抵抗 R 並びにコンデンサ C1 及び C2 を通過して、同軸ケーブル 122 に送られる。ホストシステム 116 の前置増幅器及び同軸ケーブル 122 の静電容量による負荷は、D4 における出力電圧をダイオードのオン電圧よりも小さい程度まで制限するのに十分なほど大きい。従って、ダイオード D4 は、受信中は開回路である。

40

#### 【0070】

抵抗 R は、同軸ケーブル 122 への信号ゲインを効果的に制御する。保護コンデンサ C2 の値は（入力結合コンデンサと類似の）、送信サージ電流と受信インピーダンスとの間のトレードオフである。1 つの実施形態において、コンデンサ C2 は、約 100 pF である。コンデンサ C1 は、出力 DC レベルをクランプダイオード D4 から切り離す。C1 の正確な値は重要でないが、C1 による信号の低下を避けるために、C2 の値の数倍（例えば 1 nF）に設定することができる。

#### 【0071】

10

20

30

40

50

シャント・コンデンサ C shunt は、受信部分出力 710 から受信部分入力 712 へ戻る漏話を低減する。より具体的には、ダイオード D3 は、受信中はオフ状態であるが、この pF 範囲の寄生容量が漏話を生成することになる。シャント・コンデンサは、寄生容量に比べてより大きく、寄生容量よりもはるかに低いインピーダンスを示す。その結果、ダイオード D3 とシャント・コンデンサとが分圧器を形成し、ここでは電圧の大部分が寄生容量で降下し、シャント・コンデンサはわずかな電圧降下しかしない。従って、シャント・コンデンサの低い電圧は、効果的に漏話を制限する。送信中、ダイオードが基本的に短絡されると、シャント・コンデンサは、同軸ケーブル 122 の静電容量に比べて無視できる程の負荷である点に留意されたい。

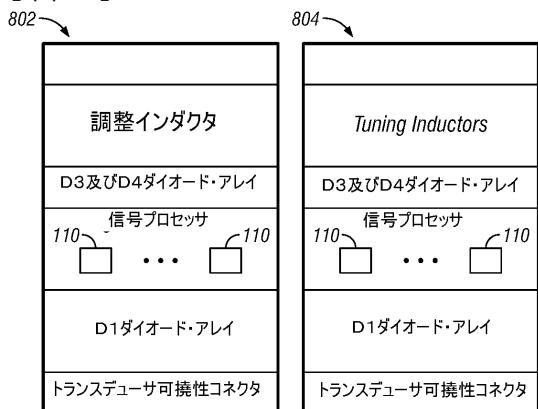

## 【0072】

10

図 8 は、処理基板 106 の底層 802 及び最上層 804 側を示す。図 8 は、図 7 に関して上で詳細に説明しているように、各処理基板 106 に含まれる処理電子機器の例示的な配置図を示す。図 8 に示すように、信号プロセッサ 110 は、処理基板の中央領域を占めると共に、D1 ダイオード・アレイは信号プロセッサ 110 の下に位置付けられ、D3 及び D4 ダイオード・アレイは信号プロセッサ 110 の上に位置付けることができる。

## 【0073】

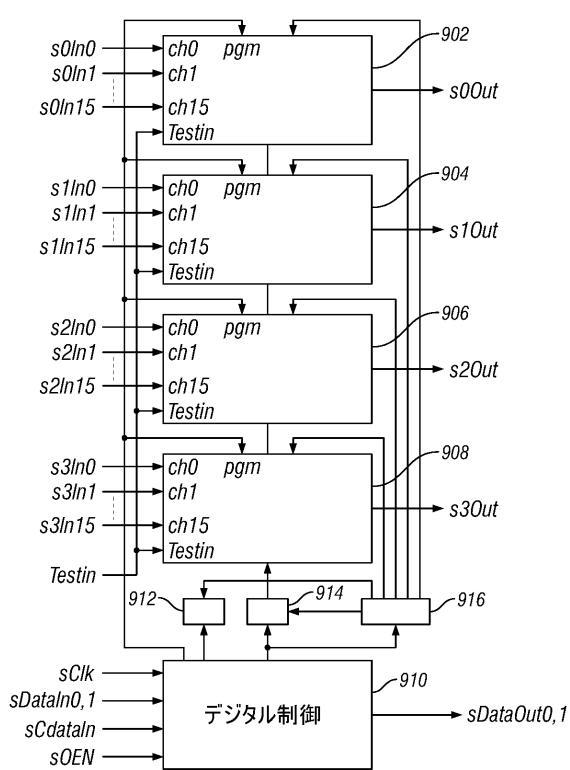

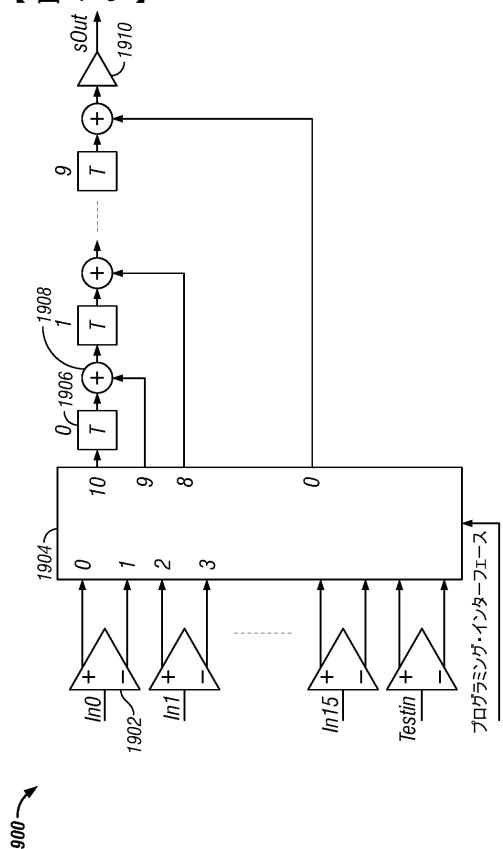

次に図 9 を参照すると、該図は信号プロセッサ 110 のブロック図 900 を示す。信号プロセッサ 110 は、4 つのアパー・チャ・プロセッサ 902、904、906、及び 908 と、デジタル制御ブロック 910 と、遅延調整回路 912 及び回復電圧回路 914 並びにバイアス回路 916 を含むことができるサポート回路とを含む。

20

## 【0074】

各アパー・チャ・プロセッサ 902 - 908 は、16 の受信入力（例えば s0In0 - s0In15）を含むが、これらは、受信サブアパー・チャを形成するトランステューサ素子に接続される。1 つの実施形態において、受信サブアパー・チャは三角形であり、15 のトランステューサ素子から形成される。従って、各サブアパー・チャ・プロセッサ 902 - 908 の 1 つの入力は使用されなくなる。各サブアパー・チャ・プロセッサ 902 - 908 はまた、テスト入力（testin とラベル付けされた）及びデジタル制御入力（pgm とラベル付けされた）を含む。サブアパー・チャ・プロセッサ 902 - 908 は、受信入力信号上でビームフォーミングを行い、受信サブアパー・チャを介して得られたビームフォームされた信号を受信サブアパー・チャ出力（s0Out - s3Out とラベル付けされた）上に出力する。

30

## 【0075】

デジタル制御ブロック 910 は、クロック（sclk、例えば、20MHz のシステムクロック）と、データ（sDataIn0 及び 1、シリアルデータ入力、及び sDataIn、シリアル制御データ入力）と、制御（sOPEN、信号プロセッサ 110 の出力インターフェース）信号とを含む。デジタル制御ブロックはまた、2 つのデータ出力（sDataOut0 及び 1）を含む。データ入力及び出力は、以下に述べるように、信号プロセッサ 110 を直列に連鎖するのに用いることができる。

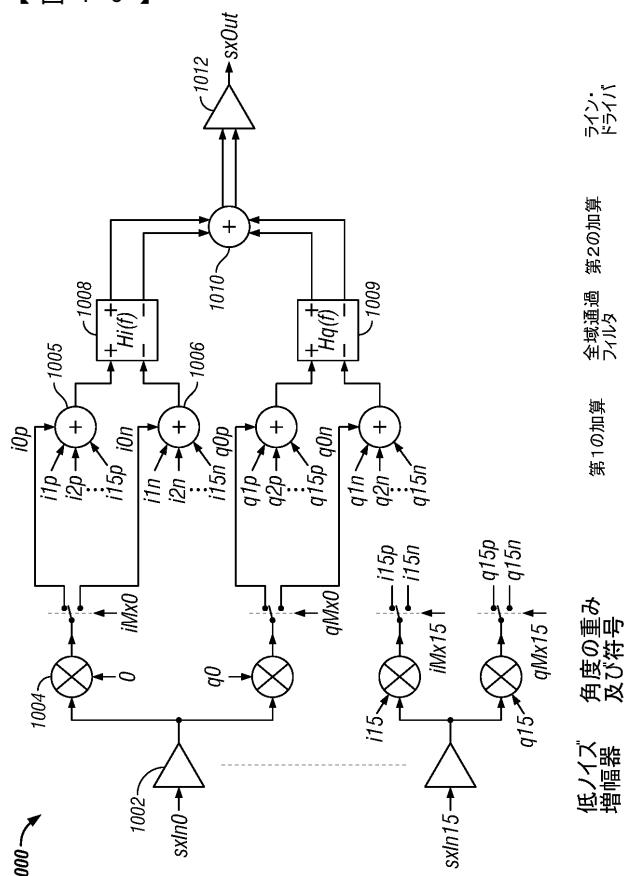

## 【0076】

40

信号プロセッサ 110 内の回路を図 10 に関して以下により詳細に説明する。図 10 は、信号プロセッサ 110 内の狭帯域ビームフォーミング回路 1000 を示す。各受信入力（その 1 つが sXIn0 とラベル付けされている）は、低ノイズ増幅器 1002 と、ミキサーを含む重み付け及び加算ステージ（その 1 つが 1004 とラベル付けされている）と、アナログ加算器（正の加算のアナログ加算器が 1005 とラベル付けされ、負の加算のアナログ加算器が 1006 とラベル付けされている）と、全域通過フィルタ 1008 及び 1009 とを通過する。更に、全域通過フィルタは、第 2 のアナログ加算器（その 1 つが 1010 とラベル付けされている）に接続され、ライン・ドライバ 1012 を通って受信サブアパー・チャ出力（そのうちの 1 つは sXOut とラベル付け）を出る。

## 【0077】

低ノイズ増幅器（LNA）は、電荷感知増幅器であり、外部の結合コンデンサを介して

50

トランステューサ素子からの受信信号を増幅する。LNAのゲインは、外部の結合コンデンサと内部のフィードバック抵抗との比を調整することにより設定することができる。通常、LNAの開ループゲインは高く、典型的な閉ループゲイン(3MHz)は、利用可能な信号範囲を活用するように選択される。

#### 【0078】

LNAは、1つには回復電圧回路914に起因して回復時間が早い。受信信号電圧が回路を飽和状態にまで駆動すると、回復回路が作動して、入力ステージの飽和状態から迅速な回復を確実に行う。

#### 【0079】

図10に示されるように、同相(I)及び直角(Q)信号は、受信信号から生成される。このために、各入力は、全ての入力が加算される前に、望ましいチャネル遅延に応じた重みと符号が与えられる。多入力増幅器は、各入力に対して個別に選択可能な入力コンデンササイズを使用することによって重み付け及び加算を行う。完全差動増幅器を加算に用いることができる。各入力の符号は、正の加算ノード1005か又は負の加算ノード1006のいずれかに入力を供給することによって設定される。

#### 【0080】

1つの実施形態において、信号プロセッサ110は、以下の表2及び表3に示される22.5度の定量化の重みを用いる。

#### 【0081】

【表2】

| 位相                               | $I_{Mx}$ | $q_{Mx}$ |

|----------------------------------|----------|----------|

| $0 \leq \text{位相} < P_i / 2$     | 1        | 1        |

| $P_i / 2 \leq \text{位相} < P_i$   | -1       | 1        |

| $P_i \leq \text{位相} < 3P_i / 2$  | -1       | -1       |

| $3P_i / 2 \leq \text{位相} < 2P_i$ | 1        | -1       |

#### 【0082】

【表3】

| 位相         | $I_n$ | $q_n$ |

|------------|-------|-------|

| 0          | 1     | 0     |

| $p_i / 8$  | 0.924 | 0.383 |

| $p_i / 4$  | 0.707 | 0.707 |

| $3p_i / 8$ | 0.383 | 0.924 |

| $P_i / 2$  | 0     | 1     |

| X          | 0     | 0     |

#### 【0083】

第2のアナログ加算器を有する加算ステージ1010は更に、使用可能範囲の信号の振れを平均化する減衰を含むことができる。

#### 【0084】

全域通過フィルタは、I及びQ信号に対して、対象の周波数帯域にわたる位相誤差の差異を最小化するように選択された位相遅延を加える。各フィルタは、s平面に与えられる一次伝達関数 $H(s) = (1 - st) / (1 + st)$ を有し、ここでtはフィルタのRC時定数である。伝達関数は、アクティブ・フィードバックと抵抗及びクロスカップルのコンデンサを用いて実現することができる。より具体的には、全域通過フィルタは、その後に抵抗が続く非反転バッファとして、コンデンサと直列の反転バッファと並列にして実装することができる(図20参照)。

#### 【0085】

1つの実施形態において、全域通過フィルタ1008は、 $RC = 25\text{ns}$ を有し、全域通過フィルタ1009は、3MHzで $RC = 145\text{ns}$ を有する。 $i_{Mx}$ 、 $q_{Mx}$ 、 $i_n$

10

20

30

40

50

、及び $q_n$ の決定について、図15及び表4を参照して以下に説明する。

#### 【0086】

ライン・ドライバ1012は、ビームフォーミングされた受信信号を駆動してホストシステム116へ戻す。ライン・ドライバ1012は、アナログ加算器と差動増幅器の組み合わせとして接続された極めて大きな入力ステージを具備するオペアンプを用いることができる。この方法において、I及びQチャネルからの信号は、加算されて単一の最終出力に変換される。組み合わされた第2の加算ステージのゲイン及びライン・ドライバは、望ましい出力範囲を与えるように選択される。

#### 【0087】

遅延調整回路912は、全域通過フィルタの時定数を変えることができるプロセス変動及び動作条件を考慮するように含まれる。時定数を制御するために、調整回路912が含まれる。

#### 【0088】

バイアス回路916は、信号プロセッサ110内のアナログ・モジュールへのバイアス電流を制御する。電源電圧は、基準電圧として用いることができる。1つの実施形態において、バイアス電流は、信号プロセッサ110により分配されて、異なるアナログ・モジュールに必要なバイアス電流を供給する。

#### 【0089】

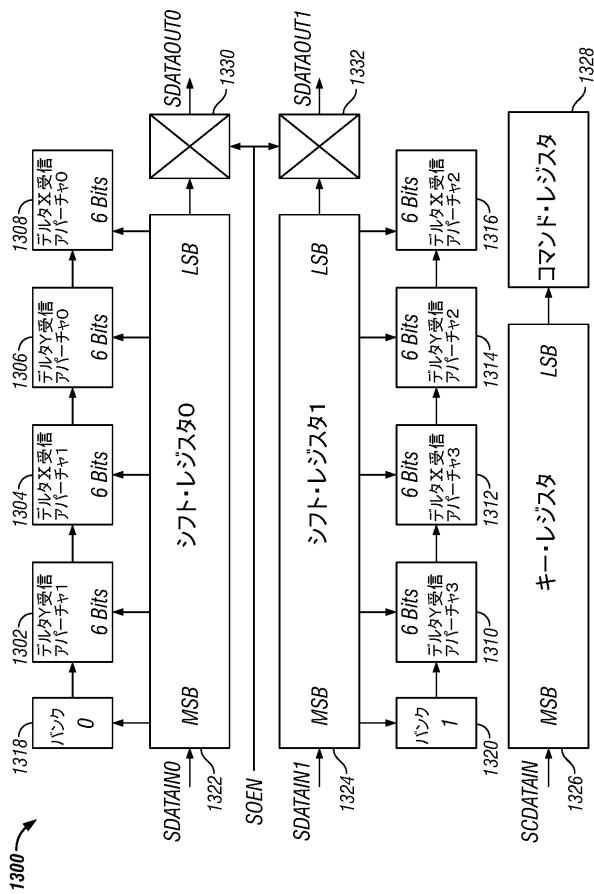

次に図13を参照すると、デジタル制御ブロック910内に含まれる信号プロセッサ110のデジタル・インターフェース1300のブロック図が示されている。デジタル・インターフェース1300は、4セットの6ビットレジスタ/メモリ1302及び1304、1306及び1308、1310及び1312、1314及び1316を含み、信号プロセッサ110によって処理される4つの受信アパートチャのデルタY及びデルタX傾斜パラメータを記憶する。デジタル・インターフェース1300はまた、2つの1ビットのバンク・メモリ1318、1320と、2つのデータシフトレジスタ1322、1324と、多ビットのキー・レジスタ1326と、多ビットのコマンド・レジスタ1328とを含む。トライステイト・バッファ1330及び1332により、インターフェース1300は、その出力をSOEN信号の制御下で高インピーダンス状態に置くことができる。

#### 【0090】

インターフェース1300を用いて、信号プロセッサ110をプログラムし、設定し、読み込むことができる。インターフェース1300は、1つのコマンド・ライン(SCD ATAIN)と、2つのデータ・ライン(SDATAIN0、1)と、1つのイネーブル・ライン(SOEN)と、1つのクロック・ラインSCLK(図示せず)とを含む。SDATAIN0及びSDATAIN1ラインは、シリアルデータ入力を2つのデータシフトレジスタ1322、1324(SHIFTREGISTER0、1とラベル付け)に供給し、SCDATINは、シリアルデータ入力を制御データシフトレジスタに供給する。1つの実施形態において、データシフトレジスタは25ビット長とすることができ、制御シフト・レジスタは36ビット長とすることができる。

#### 【0091】

信号プロセッサ110は通常、超音波送信中にデジタル入力線がランダムな値を仮定することが予想される厳しい環境で用いられる。デジタル・インターフェースを通じて誤ったデータ及びコマンドを得ることのないように、イネーブル信号として32ビットのキー・レジスタが用いられる。キー・レジスタに(信号プロセッサ110に事前に選択されて事前設定されたキーに比べて)正確なキーがあるときに、デジタルコントローラは4ビットのコマンド・レジスタ内にあるコマンドを実行する。

#### 【0092】

データ・ラインは、SCLKデータ・クロックにより制御されるレジスタに同時にシフトすることができる。SLCKは、例えば20MHzで作動する。インターフェース1300はまた、SDATAOUT0及びSDATAOUT1とラベル付けされた2つのデジタル出力を含む点に留意されたい。これらの出力は、データシフトレジスタの出力であり

10

20

30

40

50

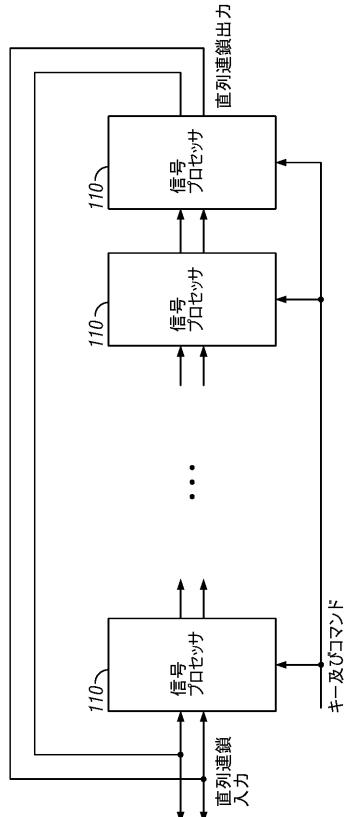

、複数の信号プロセッサ 110 を連鎖的に接続するように用いることができる（図 14 参照）。信号プロセッサ 110 からの出力データは、直列の連鎖を通じてシフトされ、連鎖の最後の信号プロセッサ 110 から読み出される。

#### 【0093】

出力バスは、連鎖的に入力バスに接続されるので、該連鎖に書き込むときに、S O E N 信号を用いて、最後の信号プロセッサ 110 の出力をトライステート・モード（H i Z モード）に置くことができる。シリアル・バスを介してデータを読み込むときに、S O E N を用いて、最後の信号プロセッサ 110 からの出力を有効にすることができる。

#### 【0094】

1つの実施形態において、36ビットの制御データ・レジスタは、32ビットのキー・レジスタ及び4ビットのコマンド・レジスタを含む。S C D A T A I N ラインは、処理基板 106 上の全ての信号プロセッサ 110 への別個の信号線とすることができます。更に、図 13 に示されるように、直列シフト・レジスタは最上位ビット（M S B）からシフトされる。すなわち、コマンド及びデータは、L S B のシフトが最初である。

#### 【0095】

また図 13 に示されるものは、6ビットの傾斜パラメータ・メモリであり、これは、信号プロセッサ 110 によって処理される4つの受信サブアーチャの位置情報を記憶する。6ビットのメモリのペア 1302、1304 は、受信サブアーチャのデルタ Y 及びデルタ X 傾斜情報を記憶し、6ビットのメモリのペア 1306、1308 は、第 2 の受信サブアーチャのデルタ Y 及びデルタ X 傾斜パラメータを記憶する。同様に、6ビットのメモリのペア 1310、1312 は、第 3 の受信サブアーチャのデルタ Y 及びデルタ X 傾斜パラメータを記憶し、6ビットのメモリのペア 1314、1316 は、第 4 の受信アーチャのデルタ Y 及びデルタ X 傾斜パラメータを記憶する。次に、信号プロセッサの静的情報（幾何形状 R A M、設定レジスタ、エンコーダ R A M など）をロードすると、シフト・レジスタ区域は、ロードされたデータに適合されている。

#### 【0096】

簡単に図 14 を参照すると、該図は信号プロセッサ 110 の直列連鎖 1400 を示している。直列連鎖 1400 は、S D A T A O U T 0、S D A T A O U T 1、S D A T A I N 0、及び S D A T A I N 1 信号線を通じて接続される。また、クロック・ライン、ラッチ・ライン、及び（書き込みに対するパラメータ・レジスタのいずれかを選択するための）パラメータ選択ラインも備えることができる。

#### 【0097】

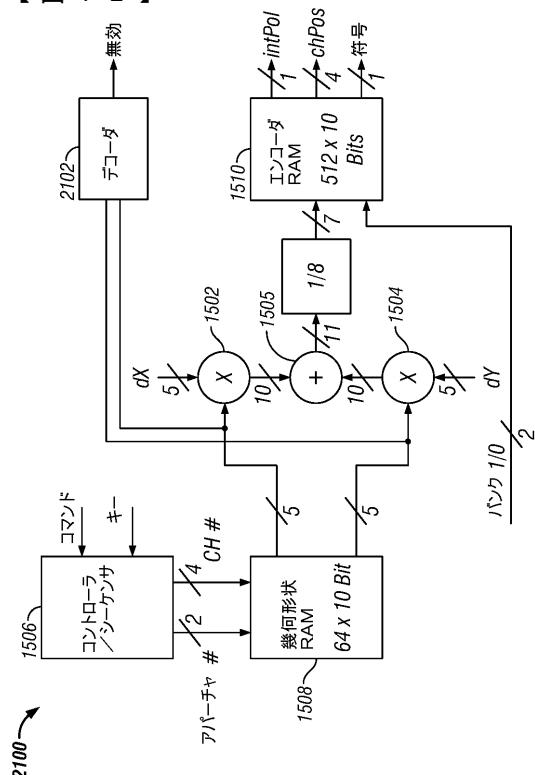

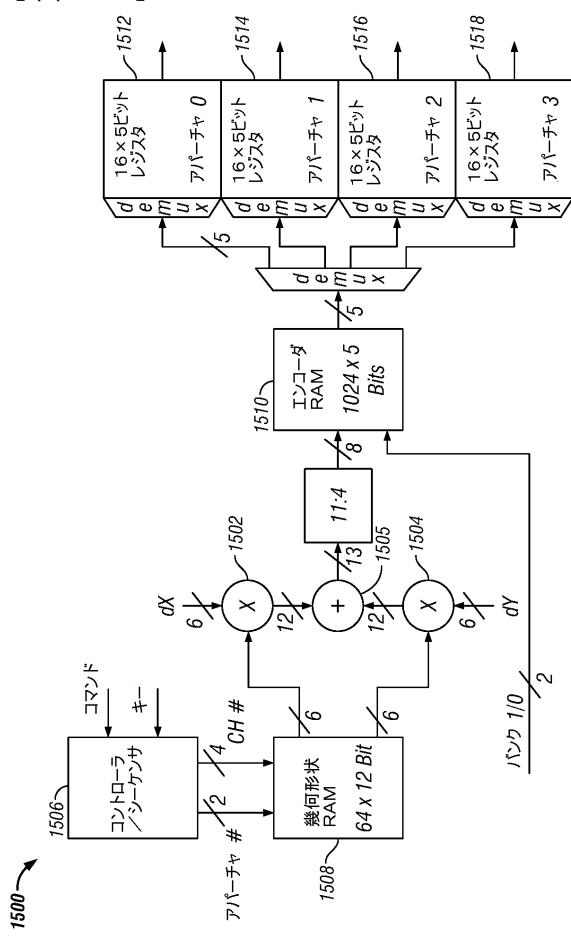

次に図 15 を参照すると、該図は信号プロセッサ 110 内のクロスポイント・コントローラ 1500 を示し、これは、シリアルインターフェース（図 13 参照）を通じてロードされたデルタ X、デルタ Y 傾斜に基づいて信号プロセッサ 110 に割り当てられた4つの受信サブアーチャを処理するための新たな制御値を計算する。クロスポイント・コントローラ 1500 は、各アーチチャの 16 の新たな遅延設定値を新たな傾斜パラメータのデルタ X、デルタ Y に基づいて計算する。遅延設定値は、幾何形状 R A M の内容及び新たな傾斜パラメータのデルタ X、デルタ Y に基づいて計算される。対応する位相遅延は、選択されたエンコーダ R A M バンク内のロックアップから検出される。

#### 【0098】

このために、クロスポイント・コントローラ 1500 は、乗算器 1502、1504 及びアナログ加算器 1505 を含む。クロスポイント・コントローラ 1500 はまた、コントローラ 1506 と、幾何形状 R A M 1508 と、エンコーダ R A M 1510 とを含む。4 セット（各受信サブアーチャに 1 つ）の 16 の 5 ビット位相設定レジスタ 1512、1514、1516、及び 1518 が備えられる（合計 64 の 5 ビットレジスタ）。これらの遅延設定レジスタは、後述するように、信号プロセッサ 110 により処理される各受信サブアーチャの遅延設定制御ビットを記憶する。

#### 【0099】

幾何形状 R A M 1508 は、受信サブアーチャ内の受信信号チャネル n と対応するト

10

20

30

40

50

ランスデューサ位置 ( $x_n$ 、 $y_n$ ) との間の関係を保持する。エンコーダ RAM1510 は、コード化した遅延と狭帯域ビームフォーミングの図 10 に示されるハードウェア設定 ( $iMx_n$ 、 $in$ 、 $qMx_n$ 、 $qn$ ) との間の関係を保持する。或いはまた、エンコーダ RAM1510 は、望ましい遅延とクロスポイント・スイッチ制御信号  $intP_01$  及び  $chPos(4)$  と、図 19 に示される広帯域ビームフォーミング回路の符号との間の関係を保持する。プロセッサ 110 により処理される 4 つのサブアパートチャ各々について、パラメータの  $\Delta X_n$  はサブアパートチャ  $n$ 、 $n = 0, 1, 2, 3$  の  $x$  傾斜を表し、 $\Delta Y_n$  はサブアパートチャ  $n$ 、 $n = 0, 1, 2, 3$  の  $y$  傾斜を表す。

#### 【0100】

有効キーがキー・レジスタ内で検出されて、開始クロスポイント計算コマンドが選択されると、クロスポイント・コントローラ 1500 は、サブアパートチャ 0、1、2、及び 3 の新たなレジスタ値を計算する。最大 16 の受信信号が各受信サブアパートチャに寄与することができるので、合計 64 の計算が実行される。図 15 に示される  $\Delta X$  値及び  $\Delta Y$  値は、各々の新たな設定の前にシリアルインターフェースからロードされた値である。以前の設定計算中にロードされた  $\Delta X$  及び  $\Delta Y$  の 8 つの値の全ては、図 13 に示すように 2 つの 24 ビット・バスを介してクロスポイント・コントローラ 1500 が利用可能である。

#### 【0101】

設定時間を短縮するため、信号プロセッサが現在の設定を計算している間に、次の計算に用いられることになるデータがシフトされてロードされる。現在の計算が終了したときには、新たな  $\Delta X$  及び  $\Delta Y$  データは既にロードされており、次の設定計算の準備がなされる。

#### 【0102】

計算を開始するために、所望のコマンドに割り当てられたキー値及びビット・コードと共にキー及びコマンド・レジスタがロードされる。計算が開始されると、乗算器 1502、1504 の入力にアパートチャ 0 の  $\Delta X$  及び  $\Delta Y$  値が加えられる。該計算によりシーケンサ 1506 が制御される。シーケンサ 1506 は、64 の受信信号入力 (4 サブアパートチャ  $\times$  サバパートチャ当たりに 16 の受信入力) の全てを通じて循環するアップ・カウンタとして実行される。シーケンサ 1506 は、幾何形状 RAM1508 のアドレス・バスに接続される。一般に、1 つのサブアパートチャのデータは、次のサブアパートチャに進む前に計算される。

#### 【0103】

シーケンサ 1506 はまた、エンコーダ RAM1510 からの信号を正確なアナログ・サブアパートチャ・レジスタ 1302 - 1314 へ送ること、並びに正確な  $\Delta X$  及び  $\Delta Y$  データをクロスポイント・コントローラ 1500 へ多重化することを制御する。狭帯域ビームフォーミングの 1 つの実施形態において、エンコーダ RAM1510 からの出力は、5 ビットのワードであり、 $sap\_data[4:0]$  と呼ばれ、 $sX\_m\_controlX()$  にマッピングされる。

#### 【0104】

$sX\_m\_controlX()$  は、図 10 に示されるビームフォーミング回路の制御信号にマッピングされる。5 ビットの  $sX\_m\_control4...0(Y)$  は、Y チャネル (受信信号) に対するアパートチャ X の角度の重み及び符号を直接制御する。ビット値から角度の重み及び符号への変換は表 4 で与えられる。すなわち、エンコーダ RAM1510 は、狭帯域ビームフォーミングにおいて、遅延値からマルチプレクサ符号 ( $iMx_n$  及び  $qMx_n$ ) と I 及び Q スケーリング ( $in$  及び  $qn$ ) とにマッピングする。これらのパラメータは、16 の位相角を実行し、所与の遅延を具備する信号を除外できるように、 $in = qn = 0$  もまた選択することができる。その結果、エンコーダ RAM1510 のワード長は 5 ビットである。或いは、エンコーダ RAM1510 のビットは、係数及びマルチプレクサの値を直接選択することができる (例えば、各マルチプレクサに 1 ビットを用いると、表 3 の 6 つのゲインペアの各々を選択するようにデコーダに 3 ビットが具備され

10

20

30

40

50

る)。

【0 1 0 5】

【表4】

| #      | bit4 | bit3 | bit2 | bit1 | bit0 | iMxn | in    | qMxn | qn    | 位相                |

|--------|------|------|------|------|------|------|-------|------|-------|-------------------|

| 0      | 0    | 0    | 0    | 0    | 0    | 1    | 1.0   | X    | 0.0   | 0                 |

| 1      | 0    | 0    | 0    | 0    | 1    | 1    | 0.924 | 1    | 0.383 | $\frac{\pi}{8}$   |

| 2      | 0    | 0    | 0    | 1    | 0    | 1    | 0.707 | 1    | 0.707 | $\frac{\pi}{4}$   |

| 3      | 0    | 0    | 0    | 1    | 1    | 1    | 0.383 | 1    | 0.924 | $\frac{3\pi}{8}$  |

| 4      | 0    | 0    | 1    | 0    | 0    | X    | 0.0   | 1    | 1.0   | $\frac{\pi}{2}$   |

| 5      | 0    | 0    | 1    | 0    | 1    | -1   | 0.383 | 1    | 0.924 | $\frac{5\pi}{8}$  |

| 6      | 0    | 0    | 1    | 1    | 0    | -1   | 0.707 | 1    | 0.707 | $\frac{3\pi}{4}$  |

| 7      | 0    | 0    | 1    | 1    | 1    | -1   | 0.924 | 1    | 0.383 | $\frac{7\pi}{8}$  |

| 8      | 0    | 1    | 0    | 0    | 0    | -1   | 1.0   | X    | 0.0   | $\pi$             |

| 9      | 0    | 1    | 0    | 0    | 1    | -1   | 0.924 | -1   | 0.383 | $\frac{9\pi}{8}$  |

| 10     | 0    | 1    | 0    | 1    | 0    | -1   | 0.707 | -1   | 0.707 | $\frac{5\pi}{4}$  |

| 11     | 0    | 1    | 0    | 1    | 1    | -1   | 0.383 | -1   | 0.924 | $\frac{11\pi}{8}$ |

| 12     | 0    | 1    | 1    | 0    | 0    | X    | 0.0   | -1   | 1.0   | $\frac{3\pi}{2}$  |

| 13     | 0    | 1    | 1    | 0    | 1    | 1    | 0.383 | -1   | 0.924 | $\frac{13\pi}{8}$ |

| 14     | 0    | 1    | 1    | 1    | 0    | 1    | 0.707 | -1   | 0.707 | $\frac{7\pi}{4}$  |

| 15     | 0    | 1    | 1    | 1    | 1    | 1    | 0.924 | -1   | 0.383 | $\frac{15\pi}{8}$ |

| 16..31 | 1    | X    | X    | X    | X    | X    | 0.0   | X    | 0.0   | X                 |

10

20

30

40

50

## 【0106】

計算は、2の補数表示により行うことができる。再び図15を参照すると、デルタX及びデルタY並びに幾何形状RAMデータは、アナログ加算器1505において乗算及び加算される。この計算は、13ビット出力を生成する。デルタX及びデルタYは、同時には最大にならないので、計算において2つのMSBは常に同じであり、信号のMSBは切り捨てることができる。図15に示される実施形態において、4つのLSBを切り捨てることで精度は8ビットまで低減される。

## 【0107】

クロスポイント・コントローラ1500は、信号プロセッサ110により処理される全ての受信アーチャ「m」に対して全トランスデューサ素子受信入力「n」を順に配列する。クロスポイント・コントローラ1500は、以下のように、各受信信号に導入されることになる遅延のスケーリングされたバージョンを決定するものとみなすことができる。

フロア( (x(m, n) \* デルタX(m) + y(m, n) \* デルタY(m)) / 16 )

ここで、n = 0, 1, ..., 15、及び、m = 0, 1, 2, 3である。

## 【0108】

x(m, n)及びy(m, n)は、受信アーチャmのn番目の入力に結合されたトランシスデューサ素子の幾何形状的位置である点に留意されたい。各位置は、幾何形状RAM1508によりインデックスが付けられ、処理回路基板106の配置中にルーティングのフレキシビリティが付加される。傾斜パラメータデルタX(m)及びデルタY(m)は、所与の受信サブアーチャmの全ての受信信号について一定に維持することもできるが、通常はサブアーチャによって変化する。

## 【0109】

計算された遅延は、エンコーダRAM1510内のテーブルインデックスにより物理的遅延に変換される。

## 【0110】

幾何形状RAM1508に関しては、6ビットのアドレスを取り、12ビットのデータを記憶する。幾何形状RAM1508へのデータのロードを開始するために、アドレス・カウンタをリセットするようコマンドRESET\_ADDRESS\_COUNTERSが出される。その後、次のコマンドは、LOAD\_GEOGRAMであり、これはアドレス・カウンタによって示された現在のアドレスにデータを書き込み、アドレス・カウンタを自動的にインクリメントする。データ幅が12ビットであるため、1つのシフト/ロード処理は、幾何形状RAM1508内に4データワードをロードすることになる。従って、アドレス・カウンタは、各ロードにつき4つずつインクリメントされることになる。

## 【0111】

エンコーダRAM1510は、超音波プローブ100の4つの異なる周波数設定を反映する、4つのバンクに分割される。シリアルインターフェースからロードされたバンク0及びバンク1のレジスタは、いずれのバンクを用いるかを指定する。計算からの8ビットと併せて、これらは、 $1024 \times 5$ ビットRAMのエンコーダRAMアドレスを構成する。

## 【0112】

エンコーダRAM1510は、10ビットのアドレス・バスと5ビットのデータ・バスとを有する。エンコーダRAM1510にデータのロードを開始するために、アドレス・カウンタをリセットするようコマンドRESET\_ADDRESS\_COUNTERSが出される。次のコマンドはLOAD\_ENC\_RAMであり、これはアドレス・カウンタ及びバンク0/1レジスタによって示された現在のアドレスにデータを書き込み、アドレス・カウンタを自動的にインクリメントする。データ幅が5ビットであるため、1つのシフト/ロード処理は、RAM1510に8つのアーチャ制御データワードをロードすることになる。従って、アドレス・カウンタは各ロードにつき8つずつインクリメントされることになる。

## 【0113】

10

20

30

40

50

直列のシフト・レジスタの双方のビット [ 19 : 0 ] は、RAMへのデータ用に用いられる。直列シフト・レジスタ0のビット24は、エンコーダRAM1510のバンク0制御信号にマッピングされ、直列シフト・レジスタ1のビット24は、バンク1制御信号にマッピングされる。バンク0 / 1レジスタ(図13参照)は、どちらのバンクにロードするかを制御する。1つの実施形態において、位置メモリコントローラ112は、4ビットのコマンドを信号プロセッサ110に送信する。コマンドは、コマンド・レジスタ1328内の信号プロセッサ110の中にシフトされる。例示的なコマンドを下記の表5に表す。

## 【0114】

【表5】

| 名称                  | コマンド                                            |

|---------------------|-------------------------------------------------|

| RESET               | 信号プロセッサを既知の状態に置く                                |

| LOAD_X_Y_Data       | デルタX及びデルタY及びエンコーダ・バンクをシフト・レジスタからロードする           |

| RESET_ADDR_COUNTERS | 信号プロセッサへの読み書きのため、全てのアドレス・カウンタをリセットする            |

| LOAD_Geom_RAM       | 幾何形状RAMに4データワードをロードする                           |

| LOAD_ENC_RAM        | エンコーダRAMに8データワードをロードする                          |

| CALCULATE           | 新たなアパーチャビームフォーミング値を計算                           |

| DELAY_TUNING_START  | アナログ調整及び較正処理を開始                                 |

| WRITE_ANALOG_MP_REG | 信号プロセッサ内のアナログ多目的レジスタに書き込む                       |

| READ_ANALOG_MP_REG  | 1322、1324に対して、例えば遅延調整からの遅延測定を含む、アナログ多目的レジスタを加える |

| READBACK_REGS       | 信号プロセッサの内部レジスタを読み出す                             |

| WRITE_REGS          | 信号プロセッサの内部レジスタに直接書き込む                           |

| LOAD_PD_REG         | アナログ出力低減レジスタを書き込む                               |

## 【0115】

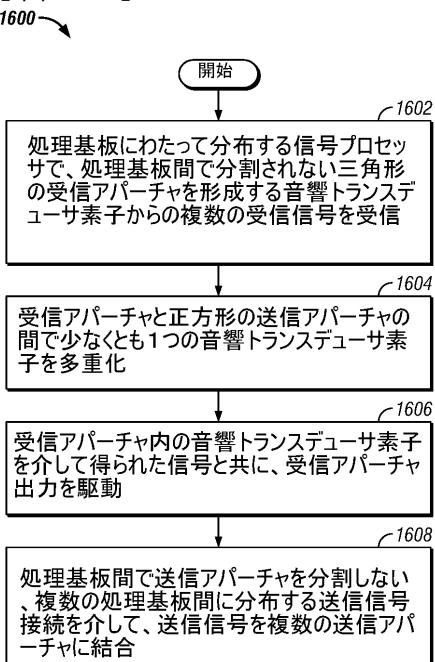

図16は、図1に示す超音波プローブ100がサブアパーチャ処理を実行する段階1600をまとめている。プローブ100は、処理基板106にわたって分配された信号プロセッサ110において、音響トランスデューサ素子からの複数の受信信号を受信する(段階1602)。トランスデューサ素子は、三角形の受信サブアパーチャを形成することができるが、これは処理基板毎に分割されるのではなく所与の信号プロセッサ110によって全体的に処理される。受信(及び送信)動作中、プローブ100は、受信サブアパーチャと正方形の送信サブアパーチャ間で少なくとも1つの音響トランスデューサ素子を多重化する(段階1604)。

## 【0116】

ビームフォーミング後、信号プロセッサ110は、受信サブアパーチャの音響トランスデューサ素子を介して得られたビームフォーミング信号を有する受信サブアパーチャ出力を駆動する(段階1606)。送信方向において、プローブは、複数の処理基板間に分布する送信信号接続を介して送信信号を複数の送信サブアパーチャに結合することができる(段階1608)。受信アパーチャと同様に、所与のサブアパーチャの送信信号接続は、複数の処理基板106にわたって分割されるのではなく所与の処理基板106上に全て備

10

20

30

40

50

えることができる。

【0117】

複数の処理基板間で、送信又は受信サブアーチャを分割しないことにより、ホストシステム116と処理基板106間にトランスデューサ・アレイ102への効率的な信号のルーティングが形成される。各処理基板106は、固有の送信及び受信サブアーチャを処理するので、交差接続信号又はルーティングを処理基板106間に備える必要がない。

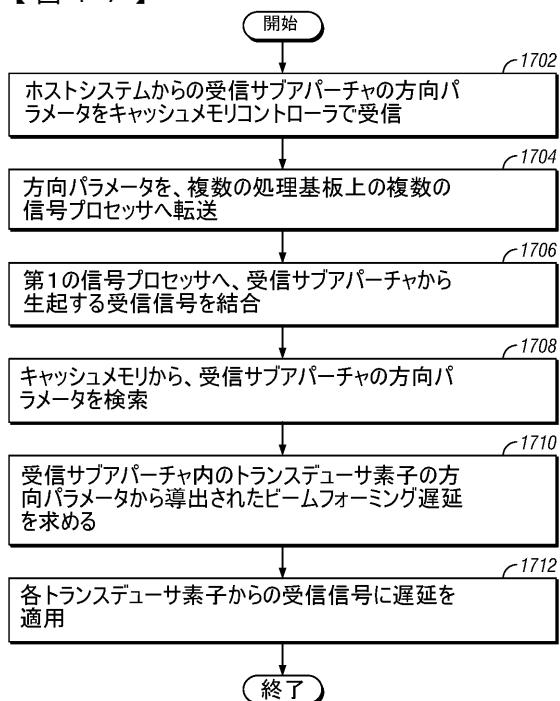

【0118】

図17は、図1に示す超音波プローブ100が該プローブ100のビームフォーミングを実行することができる段階1700をまとめている。プローブ100は、キャッシュメモリ及びコントローラ112でホストシステム116からの受信サブアーチャの傾斜値(例えばデルタX及びデルタYデータ)などの複数の方向パラメータを受信する(段階1702)。次いで、キャッシュメモリ及びコントローラ112は、方向パラメータを複数の処理基板106上の複数の信号プロセッサ110に転送する(段階1704)。

【0119】

プローブ100は、受信サブアーチャから生起する受信信号を信号プロセッサ110に結合する(段階1706)。信号プロセッサ110は、直列入力レジスタ(例えば1302-1304、1306-1308、1310-1312、又は1314-1316)から、受信サブアーチャの方向パラメータを検索する(段階1708)。方向パラメータに基づいて、信号プロセッサは、受信サブアーチャ内のトランスデューサ素子のビームフォーミング遅延を求め(段階1710)、各それぞれのトランスデューサ素子からの受信信号に遅延を適用する(段階1712)。

【0120】

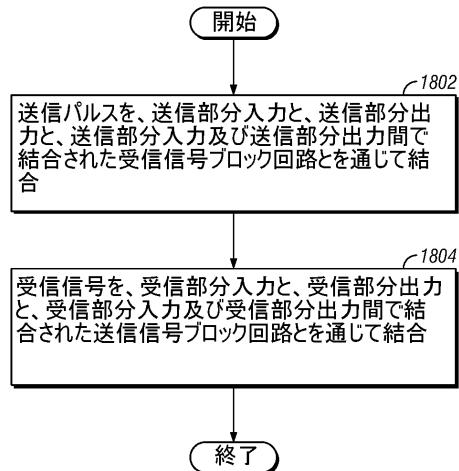

図18は、図1に示される超音波プローブ100の段階1800を示す(例えば、送受信器回路700を用いて、受信アーチャと送信アーチャ間で多重化された音響トランスデューサ素子にエネルギーを送受信するように行うことができる)。回路700は、送信パルスを、送信部分入力704と、送信部分出力706と、送信部分入力704及び送信部分出力706間に結合された受信信号ブロック回路D1、D3、及びCshuntを通じて結合する(段階1802)。送受信器回路700はまた、受信信号を、受信部分入力712と、受信部分出力710と、受信部分入力712及び受信部分出力710間に結合された送信信号ブロック回路C2とD4、CcoupleとD2を通じて結合する(段階1804)。

【0121】

次に図19を参照すると、該図は、アーチャ・プロセッサ902-908内のビームフォーミング回路の別の実施形態のブロック図1900を示す。ビームフォーミング回路1900は、プリアンプ1902を含み、受信アーチャ内の16の受信チャネルの各々に1つと検査用に1つとを含む。プリアンプ1902は、 $34 \times 11$ のクロスポイント・マトリクス1904に接続され、これは、直列に遅延ラインを形成する0から10の遅延素子1906及び加算ノード1908を通じて受信信号をフレキシブルに接続するものである。ライン・ドライバ1910は、組み合わされた信号をホストシステム116に送り戻す。

【0122】

クロスポイント・マトリクス1904は、遅延ラインの任意のノードへの任意の受信チャネルの接続をサポートする。幾つかのチャネルが遅延ラインの同じノードに接続されると、該ノードの出力は、それぞれの入力信号の合計となる。任意のチャネルは加算ノードに入る前に変換することができ、任意のチャネルは、任意選択的に2つの隣接加算ノードに同時に接続することができる。この場合、有効ゲインが各々について約6dBだけ低減されるように信号が分割されることになる。

【0123】

ビームフォーミング回路1900が使用されると、クロスポイント・コントローラ1500は、ビームフォーミング回路1900に信号intP01、chPos(4)を出力

10

20

30

40

50

する。

【0124】

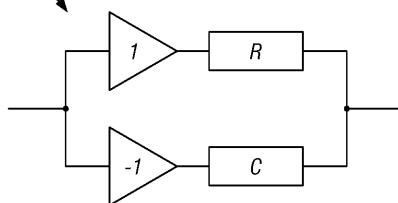

図11は、全域通過フィルタのセルの1つの実施形態を示す(例えばフィルタ・セル1906)。図のように、全域通過フィルタは、その後に抵抗Rが続く非反転バッファとして、コンデンサCと直列の反転バッファと並列にして実装することができる。各フィルタ・セルは、位相遅延T = 2RC、及び伝達関数Hc(w) = (1 - j(wT/2)) / (1 + j(wT/2))を有する。

【0125】

図12は、ビームフォーミング回路1900に用いられるクロスポイント・コントローラ2100を示し、クロスポイント・マトリクス1904内にスイッチをプログラムし、トリガー事象に対して開始し、スキャン・パラメータのラッチバージョンに対して動作する。クロスポイント・コントローラ2100は、信号プロセッサ110によって処理される全ての受信アパートチャ「m」に対して全てのトランスデューサ素子の受信入力「n」を順に配列する。クロスポイント・コントローラ2100は、以下のように各受信信号に導入されることになる遅延の事前スケーリングされたバージョンを決定するものとみなすことができる。フロア(((x(m,n)\*デルタX(m)+y(m,n)\*デルタY(m))/8)ここでn=0、1、…15、及び、m=0、1、2、3である。

【0126】

x(m,n)及びy(m,n)は、受信アパートチャmのn番目の入力に結合されたトランスデューサ素子の、幾何形状的位置である点に留意されたい。コード(又は任意選択的に、又は追加して、chPosのオーバーフロー)を検出し、チャネル無効出力信号をアサートするためのデコーダ2102を用いることによってアパートチャmのチャネルnを(例えば電源管理のため)無効にする予約コードを定める(例えばx(m,n)、y(m,n) = -16、-16)ことができる。位置は、幾何形状RAM1508を通じてインデックスが付けられ、処理回路基板106の配置中にルーティングのフレキシビリティが付加される。スケール係数デルタX(m)及びデルタY(m)は、所与の受信アパートチャmの全ての受信信号について一定に維持することができる。

【0127】

事前遅延は、エンコーダRAM1510のテーブルインデックスにより物理的遅延に変換される。1つの実施形態において、エンコーダRAM1510の出力は、6ビットを含み、すなわち、1ビットはintPos、4ビットはchPos、及び1ビットはsignである。chPosビットは、クロスポイント・マトリクス1904の対応するスイッチを開成する。制御ビットintPosが設定されると、スイッチ1+chPosもまた設定されることになる。サイン・ビットは、入力信号の非反転又は反転バージョンを選択する。

【0128】

本発明の様々な実施形態を説明してきたが、本発明の範囲にある多くの実施形態が及び具現化が可能であることは当業者には明らかであろう。

【図面の簡単な説明】

【0129】

【図1】ホストシステムと通信する超音波プローブのブロック図。

【図2】図1に示される超音波プローブで用いることができる音響トランスデューサ素子のアレイを含むトランスデューサ・スタック。

【図3】図1に示される超音波プローブに組み込まれた音響トランスデューサ素子のアレイ全体に配置された受信アパートチャ。

【図4】図1に示される超音波プローブに組み込まれた音響トランスデューサ素子のアレイ全体に配置された受信アパートチャと多重化された送信アパートチャ。

【図5】プローブの音響トランスデューサ素子のアレイを処理基板の信号プロセッサに接続するための8つの処理基板に接続された48のトランスデューサ可撓性ケーブルの分布。

【図6】送受信間で選択された音響トランステューサ素子を多重化すると共に、音響トランステューサ素子に接続された信号プロセッサを保護する送受信器回路。

【図7】送受信間で選択された音響トランステューサ素子を多重化すると共に、音響トランステューサ素子に接続された信号プロセッサを保護する受動回路を用いる送受信器回路の1つの実施形態。

【図8】処理基板によって伝送される電子機器の推奨配置領域を含む、処理基板の正面及び裏面図。

【図9】図1に示される超音波プローブに用いるのに好適な信号プロセッサのブロック図。

。

【図10】信号プロセッサの狭帯域ビームフォーミング回路。 10

【図11】全域通過フィルタのセル。

【図12】クロスポイント・コントローラの第2の実施形態。

【図13】信号プロセッサのデジタル・インターフェースのブロック図。

【図14】直列連鎖的に接続される信号プロセッサ。

【図15】信号プロセッサに割り当てられる4つの受信サブアパートを処理するための新たな制御値を計算する信号プロセッサのクロスポイント・コントローラ。

【図16】図1に示される超音波プローブがサブアパート処理を実行するために行うことができる段階。

【図17】図1に示される超音波プローブがプローブ内でビームフォーミングを実行するために行うことができる段階。 20

【図18】図1に示される超音波プローブが受信アパートと送信アパートの間で多重化された音響トランステューサ素子にエネルギーを送受信するために行うことができる段階。

。

【図19】信号プロセッサのビームフォーミング回路の別の実施形態。

【符号の説明】

【0130】

110 信号プロセッサ

700 送受信器回路

702 送信部分

704 送信部分入力

706 送信部分出力

708 受信部分

710 受信部分出力

712 受信部分入力

718 受信信号ブロック回路

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

ライン

ドライバ全域通過 第2の加算

プリズマ第1の加算

低ノイズ

増幅器

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

---

フロントページの続き

(72)発明者 ケル・クリストファーセン

ノルウェー、0379・オスロ、モンテベロヴェイエン・7番

(72)発明者 ゲイル・アルトヴェイト・ハウゲン

ノルウェー、エヌ-0586・オスロ、シンセンヴェイエン・79番

(72)発明者 ペル・アルネ・リンネルッド

ノルウェー、3189・ホルテン、オアフーグルスティエン・60番

F ターム(参考) 2G047 AA12 AC13 EA07 GB02 GB21

4C601 BB03 EE01 GB01 GB06

【外國語明細書】

2005152630000001.pdf

|                |                                                                                                    |         |            |

|----------------|----------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 超声探头收发电路                                                                                           |         |            |

| 公开(公告)号        | <a href="#">JP2005152630A</a>                                                                      | 公开(公告)日 | 2005-06-16 |

| 申请号            | JP2004336211                                                                                       | 申请日     | 2004-11-19 |

| [标]申请(专利权)人(译) | 通用电气公司                                                                                             |         |            |

| 申请(专利权)人(译)    | 通用电气公司                                                                                             |         |            |

| [标]发明人         | ケルクリストファーセン<br>ゲイルアルトヴェイトハウゼン<br>ペルアルネリンネルッド                                                       |         |            |

| 发明人            | ケル・クリストファーセン<br>ゲイル・アルトヴェイト・ハウゼン<br>ペル・アルネ・リンネルッド                                                  |         |            |

| IPC分类号         | G01N29/24 A61B8/00 B06B1/02 G01S7/52 G01S7/521 G01S15/89 G10K11/34                                 |         |            |

| CPC分类号         | G01S7/52079 A61B8/4494 G01S7/5202 G01S15/8925                                                      |         |            |

| FI分类号          | A61B8/00 G01N29/24.502                                                                             |         |            |

| F-TERM分类号      | 2G047/AA12 2G047/AC13 2G047/EA07 2G047/GB02 2G047/GB21 4C601/BB03 4C601/EE01 4C601/GB01 4C601/GB06 |         |            |

| 代理人(译)         | 松本健一<br>小仓 博<br>伊藤亲                                                                                |         |            |

| 优先权            | 10/719431 2003-11-21 US                                                                            |         |            |

| 其他公开文献         | <a href="#">JP4774205B2</a>                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                          |         |            |

### 摘要(译)

要解决的问题：处理多个元件换能器探头的子孔径。超声换能器元件收发器电路(700)包括发射器部分(702)和接收器部分(708)。发送部分(702)包括发送部分输入(704)，发送部分输出(706)和接收信号块电路(耦合在发送部分输入(704)和发送部分输出(706)之间)。718)。接收部分(708)包括接收部分输入(712)，接收部分输出(710)和接收信号块电路(耦合在接收部分输入(712)和接收部分输出(710)之间)。718)。[选择图]图7