(19)日本国特許庁 (JP)

(12) **公開特許公報** (A) (11)特許出願公開番号

**特開2001-292496**

(P2001-292496A)

(43)公開日 平成13年10月19日(2001.10.19)

| (51) Int.CI <sup>7</sup> | 識別記号 | 庁内整理番号 | F I           | 技術表示箇所 |

|--------------------------|------|--------|---------------|--------|

| H 0 4 R 17/00            | 332  |        | H 0 4 R 17/00 | 332 Y  |

|                          | 330  |        |               | 330 G  |

|                          |      |        |               | 330 H  |

| A 6 1 B 8/00             |      |        | A 6 1 B 8/00  |        |

| G 0 1 N 29/24            | 502  |        | G 0 1 N 29/24 | 502    |

審査請求 未請求 請求項の数 90 L (全 14数)

(21)出願番号 特願2001-27451(P2001-27451)

(22)出願日 平成13年2月2日(2001.2.2)

(31)優先権主張番号 特願2000-25470(P2000-25470)

(32)優先日 平成12年2月2日(2000.2.2)

(33)優先権主張国 日本(JP)

(71)出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(72)発明者 橋本 新一

栃木県大田原市下石上字東山1385番の1 株式会社東芝那須工場内

(72)発明者 手塚 智

栃木県大田原市下石上字東山1385番の1 株式会社東芝那須工場内

(74)代理人 100058479

弁理士 鈴江 武彦 (外6名)

(54)【発明の名称】 二次元アレイ型超音波プローブ

(57)【要約】

【課題】 小さい振動素子ピッチであっても、各振動素子の音響特性を劣化させることなく各振動素子から信号が引き出し可能で、IC基板を容易に接続可能な2次元アレイ型超音波プローブを提供する。

【解決手段】 本発明は2次元アレイプローブの電極取り出し構造に関し、パッキング材20中を通した信号線22の一端である信号電極221を振動素子16の配列面と平行に電極パターンとして2次元配列した二次元トランスデューサと、当該信号電極221の電極パターンと同様の電極パターンを形成した中継基板30と、当該中継基板30と垂直に連結するIC基板40と、を接続して構成した2次元アレイプローブ。

## 【特許請求の範囲】

【請求項1】二次元状に配列された超音波振動子と、前記超音波振動子に設けられ、当該超音波振動子からの電気信号を受信する信号電極と、前記超音波振動子を制動する負荷材と、前記信号電極から前記負荷材を通して所定のピッチで引き出される複数の信号線と、複数の第1の電極が前記信号線の所定のピッチと同ピッチで設けられた第1の面と、前記第1の電極と電気的に接続された複数の第2の電極が前記所定のピッチより広いピッチで設けられた第2の面と、を有し、前記信号線と前記第1の電極とを対応して接続することで、前記第1の面から前記第2の面にかけて前記信号線間のピッチを広げる第1の基板と、前記第2の電極に接続され前記電気信号に関する処理を行う信号処理手段を実装し、前記第1の基板と略垂直に設けられた第2の基板と、を具備することを特徴とする二次元アレイ型超音波プローブ。

【請求項2】前記複数の信号線は、前記振動子の二次元状の配列面に対して略垂直に引き出されていることを特徴とする請求項1記載の二次元アレイ型超音波プローブ。

【請求項3】前記第1の基板は、前記第2の面に於いて前記第2の電極を有する複数の孔を有し、前記第2の基板は、前記孔と同一ピッチで形成され、所定の接続パターンによって前記制御手段と電気的に接続されている複数の接続ピンを有し、前記制御手段は、前記孔に差し込まれた前記接続ピンを介して前記第2の電極と電気的に接続されること、を特徴とする請求項1又は2記載の二次元アレイ型超音波プローブ。

【請求項4】前記第2の基板は、前記所定の接続パターンを変更する変更手段を有することを特徴とする請求項3記載の二次元アレイ型超音波プローブ。

【請求項5】前記変更手段は、所定の接続パターンを有した前記第2の基板に脱着可能なプレートであること、を特徴とする請求項4記載の二次元アレイ型超音波プローブ。

【請求項6】前記複数の第1の電極のうちの一部は、アース接続されていることを特徴とする請求項1乃至5のうちいずれか一項記載の二次元アレイ型超音波プローブ。

【請求項7】前記第2の電極の数は、前記第1の電極の数よりも少ない構成であることを特徴とする請求項1乃至6のうちいずれか一項記載の二次元アレイ型超音波プローブ。

【請求項8】前記第1の基板は多層基板であり、前記第1の電極の前記所定ピッチを広げるための複数の配線パターンが形成された少なくとも一つの配線パターン層

10

と、

前記複数の第1の電極の一つと、前記複数の配線パターンのうちの一つと、前記複数の第2の電極の一つとを電気的に接続する複数の接続手段と、を有し、

前記信号線間のピッチは、前記配線パターン層の配線パターンによって拡大されていること、を特徴とする請求項1記載の二次元アレイ型超音波プローブ。

【請求項9】前記複数の第1の電極は、超音波送信用電極と、超音波受信用電極と、アース電極とから成り、前記第2の電極は、複数の配線パターンによって前記超音波送信用電極に対応する電極毎、及び前記超音波受信用電極に対応する電極毎に整列されていること、を特徴とする請求項8記載の二次元アレイ型超音波プローブ。

## 【発明の詳細な説明】

## 【0001】

【発明の属する技術分野】本発明は、超音波診断装置や超音波探傷装置等に用いられる超音波探触子に関し、特に、圧電振動子をマトリックス状に配列した2次元アレイ型超音波プローブに関する。

## 【0002】

【従来の技術】従来、超音波診断装置に使用する超音波プローブの一つに、図18(a)に示すように、短冊状(細長い直方体状)の圧電素子をアレイ状に配列した1次元のアレイプローブがある。一般に、この1次元のアレイプローブは、電子走査法と呼ばれる超音波走査方式によって被検体に超音波を走査し、診断する場合に使用されている。ここで、電子走査法とは、アレイ状の超音波振動子それぞれに遅延時間を与え、送信パルスや受信信号のフォーカスをかける方法である。この電子走査法によれば、送受信超音波ビームのフォーカス点を高速に変更することが可能であり、現在の超音波走査方式の主流となっている。

【0003】しかし、一次元アレイプローブによる電子走査では、圧電素子の配列方向の面内における電子フォーカスや超音波ビームの走査は可能であるが、配列方向と直交する方向(すなわち前記超音波走査面の法線方向)には、音響レンズのみによるフォーカスしか行うことことができず、フォーカス点の変更は狭い範囲に限られてしまい、ダイナミックなフォーカスは不可能である。また、アレイ素子の配列が1次元配列となっているため、超音波ビームを2次元的にしか走査することが出来ない。

【0004】一方、近年に於いて、超音波ビームのフォーカスを全方位的にダイナミックフォーカスしたり、超音波ビームの三次元的走査が可能なアレイ超音波プローブ、及びこのアレイ超音波プローブにより収集された被検体からの超音波に基いて三次元超音波画像を生成し表

50

示するシステムの検討が進んできている。超音波ビームの三次元走査は、上述の一次元アレイプローブとメカニカルな走査機構を組み合わせることで実現することができる。しかし、超音波の全方位的なフォーカシング、高速な三次元走査の実現は、一次元アレイプローブでは困難である。

【0005】この超音波の全方位的なフォーカシングや高速な三次元走査を実現する超音波プローブとして、図18(b)に示すように、一次元アレイプローブと比較して更に多数の超音波素子をマトリックス状等に配列し10 2次元アレイ超音波プローブがある。

【0006】この2次元アレイ超音波プローブを実現する手段は、以前から多数の提案が検討されている。例えば、U.S.P.5,267,221に於いては、パッキング材に穴構造を設け、信号リードを引き出す構造が提案されており、特開昭62-2799に於いては、振動子配列に対応する基板を積層して信号引き出し部を構成する構造が提案されている。これらに開示されている2次元アレイ超音波プローブの構造は、1素子の音響特性を良好に保つことを可能としている。また、U.S.P.5,311,095に於いては、信号取りだしのための積層基板80を振動子直下に配した構造等を提案しており、素子ピッチを小さくしても比較的容易に信号引き出し可能な構造が開示されている。

#### 【0007】

【発明が解決しようとする課題】しかしながら、2次元アレイ超音波プローブに於いては、一振動素子が小さく配列ピッチが小さいため、各素子から信号線の引き出し、超音波素子の音響特性の維持、I.C.等の実装等が困難になる。既に提案されている2次元アレイ超音波プローブでは、さらに素子ピッチを小さくした場合、電気回路やケーブルに、取り出したリード線を接続したり、あるいは基板にI.C.等を実装することが困難になる。また、素子ピッチを小さくしても比較的容易に信号引き出し可能なU.S.P.5,311,095に示されたような引き出し基板を用いた場合でも、基板による素子への音響的な影響(素子特性の劣化)が生じてしまう。

【0008】これらの点についてさらに詳しく検討すると、以下のようなである。

【0009】例えば、2次元アレイ状の各超音波振動子から信号電極を取り出すために信号取り出しのための回路基板を振動子直下に設ける方法では、回路基板が音響的に悪影響を与えないようにしなくてはならない。しかし、振動子の背面に設ける音響負荷材(パッキング材)と振動子の間に回路基板を設けることになり、音響的特性劣化は避けられないため、現実的には困難である。

【0010】また、2次元状のアレイ素子から信号線を素子配列面と概垂直に引き出す場合、このように引き出すことでパッキング材を従来と同様に設けることは可能となり、信号線の影響も小さくすることが可能である

が、2次元アレイプローブの素子配列が多数になり素子ピッチが小さくなるにつれ、信号線に付加する回路基板の接続が困難になるという問題が生じる。すなわち、例えば振動子の配列ピッチが0.5mmとなれば、それから引き出される信号線の配列ピッチも当然0.5mm程度となり信号線に付加する回路基板も0.5mmピッチで配列する必要が生じる。当然それ以下のピッチでも同様である。

#### 【0011】

【課題を解決するための手段】本発明は、上述した問題に鑑みてなされたもので、電気回路を付加した2次元アレイプローブに於いて、2次元状に配列された各超音波振動素子の音響特性を維持しつつ、2次元アレイプローブの素子ピッチがマトリックスの各配列方向に従来1次元プローブの素子配列ピッチ程度に小さくなっても信号線の引き出しが可能で、かつ信号線に電気回路を設けた回路基板を容易に接続することができる超音波プローブを提供することを目的とする。

【0012】上記目的を達成するために、本発明は、以下の特徴を具備するものである。

【0013】請求項1記載の発明は、二次元状に配列された超音波振動子と、前記超音波振動子に設けられ、当該超音波振動子からの電気信号を受信する信号電極と、前記超音波振動子を制動する負荷材と、前記信号電極から前記負荷材を通して所定のピッチで引き出される複数の信号線と、複数の第1の電極が前記信号線の所定のピッチと同ピッチで設けられた第1の面と、前記第1の電極と電気的に接続された複数の第2の電極が前記所定のピッチより広いピッチで設けられた第2の面と、を有し、前記信号線と前記第1の電極とを対応して接続することで、前記第1の面から前記第2の面にかけて前記信号線間のピッチを広げる第1の基板と、前記第2の電極に接続され前記電気信号に関する処理を行う信号処理手段を実装し、前記第1の基板と略垂直に設けられた第2の基板とを具備することを特徴とする二次元アレイ型超音波プローブである。

【0014】請求項1記載の発明によれば、制御手段を付加した2次元アレイプローブに於いて、超音波振動子のピッチが小さくなつた場合であつても、2次元状に配列された各超音波振動素子の音響特性を維持しつつ、信号線の引き出しが可能で、かつ信号線に制御手段を設けた基板を容易に接続することができる超音波プローブを実現することができる。

【0015】請求項2記載の発明は、請求項1記載の二次元アレイ型超音波プローブにおいて、前記複数の信号線は、前記振動子の二次元状の配列面に対して略垂直に引き出されていることを特徴とするものである。

【0016】請求項3記載の発明は、請求項1又は2記載の二次元アレイ型超音波プローブにおいて、前記第1の基板は、前記第2の面に於いて前記第2の電極を有す

る複数の孔を有し、前記第2の基板は、前記孔と同一ピッチで形成され、所定の接続パターンによって前記制御手段と電気的に接続されている複数の接続ピンを有し、前記制御手段は、前記孔に差し込まれた前記接続ピンを介して前記第2の電極と電気的に接続されることを特徴とするものである。

【0017】請求項4記載の発明は、請求項3記載の二次元アレイ型超音波プローブにおいて、前記第2の基板は、前記所定の接続パターンを変更する変更手段を有することを特徴とするものである。

【0018】請求項5記載の発明は、請求項4記載の二次元アレイ型超音波プローブにおいて、前記変更手段は、所定の接続パターンを有した前記第2の基板に脱着可能なプレートであることを特徴とするものである。

【0019】請求項6記載の発明は、請求項1乃至5のうちいずれか一項記載の二次元アレイ型超音波プローブにおいて、前記複数の第1の電極のうちの一部は、アース接続されていることを特徴とするものである。

【0020】請求項7記載の発明は、請求項1乃至6のうちいずれか一項記載の二次元アレイ型超音波プローブにおいて、前記第2の電極の数は、前記第1の電極の数よりも少ない構成であることを特徴とするものである。

【0021】請求項2～請求項7記載のうちいずれか一項記載の発明によても、制御手段を附加した2次元アレイプローブに於いて、超音波振動子のピッチが小さくなつた場合であつても、2次元状に配列された各超音波振動素子の音響特性を維持しつつ、信号線の引き出しが可能で、かつ信号線に制御手段を設けた基板を容易に接続することができる超音波プローブを実現することができる。

【0022】請求項8記載の発明は、請求項1記載の二次元アレイ型超音波プローブであつて、前記第1の基板は多層基板であり、前記第1の電極の前記所定ピッチを広げるための複数の配線パターンが形成された少なくとも一つの配線パターン層と、前記複数の第1の電極の一つと、前記複数の配線パターンのうちの一つと、前記複数の第2の電極の一つとを電気的に接続する複数の接続手段と、を有し、前記信号線間のピッチは、前記配線パターン層の配線パターンによって拡大されていることを特徴とするものである。

【0023】請求項8記載の発明によれば、第1の基板は少なくとも一つの配線パターン層を有しており、各第1の電極から引き出された信号線のピッチ幅は、配線パターン層に形成されたパターン配線によって拡大され、第2の電極に接続される。従つて、超音波振動子が小さく配列ピッチが小さい二次元アレイ型超音波プローブであつても、各素子から信号線の引き出し、超音波素子の音響特性の維持、I C等の制御手段の実装等を容易に実現することができる。

【0024】請求項9記載の発明は、請求項1記載の二

次元アレイ型超音波プローブであつて、前記複数の第1の電極は、超音波送信用電極と、超音波受信用電極と、アース電極とから成り、前記第2の電極は、複数の配線パターンによって前記超音波送信用電極に対応する電極毎、及び前記超音波受信用電極に対応する電極毎に整列されていることを特徴とするものである。

【0025】請求項9記載の発明によれば、各第1の電極配列が送信用電極と受信用電極とを無作為に混在させた状態であつても、各第2の電極が送信用電極或いは受信用電極であるのか容易に把握することができる。また、前記第2の基板の電回路を単純化することができ、第2の基板の種類を少なくすることができる。

【0026】

【発明の実施の形態】以下、本発明の第1の実施形態～第4の実施形態を図面に従つて説明する。

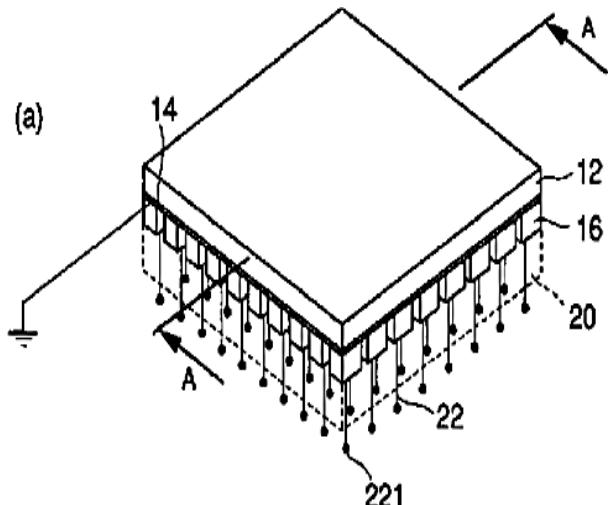

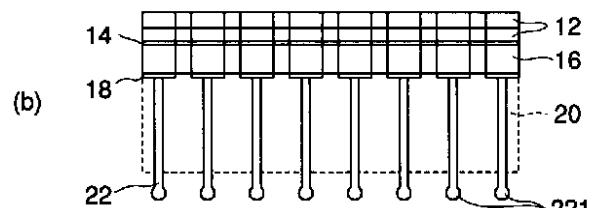

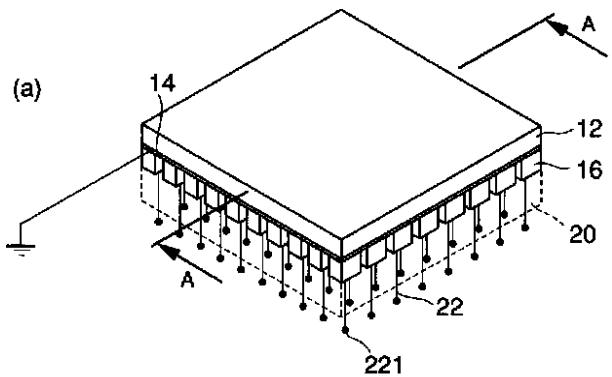

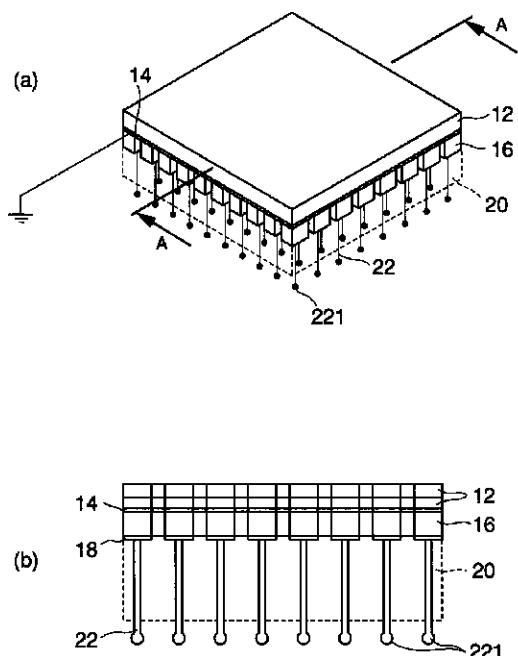

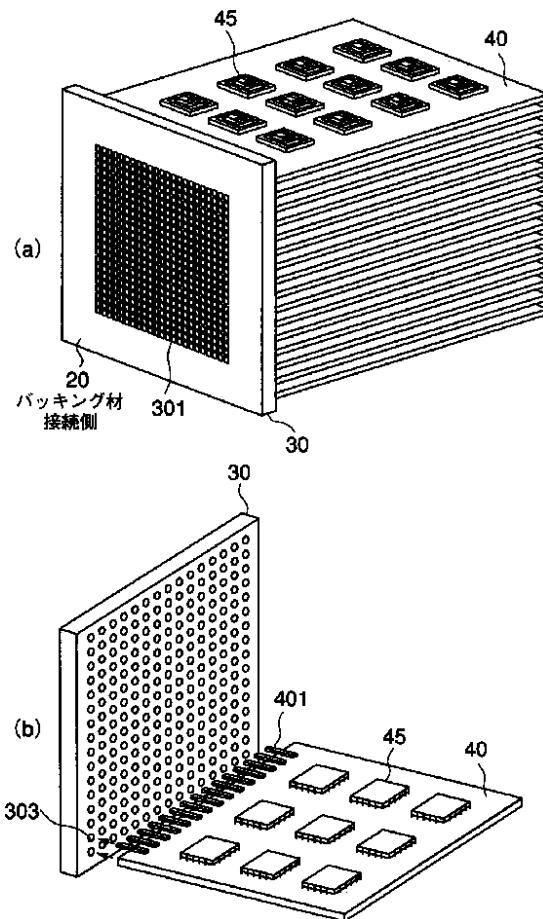

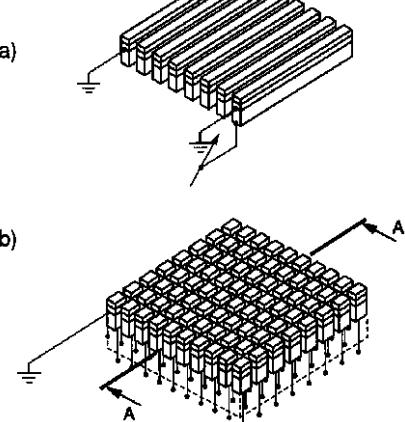

【0027】(第1の実施形態)図1は、本発明の第1の実施形態に係る二次元アレイ超音波プローブが有する二次元アレイ超音波トランスデューサ10の概略図である。図1(a)は、2次元アレイ超音波トランスデューサ1の斜視図であり、図1(b)は、図1(a)に於いて矢印方向から見たA-A断面図である。

【0028】図1(a)に於いて、2次元アレイ超音波トランスデューサ10は、音響整合層12、アース電極14、振動素子(圧電体)16、信号電極18、パッキング材20(負荷材相)、信号線22、を具備する構成となっている。

【0029】音響整合層12は、図示していない被検体と振動素子12との間に位置するように設けられており、被検体と振動素子12との音響インピーダンスの整合をとるものである。

【0030】アース電極14は、各振動素子16の一端に設けられている。アース電極14は、圧電効果を得るために各振動素子16に電力を印加するための電極であり、アース接続されている。

【0031】振動素子(圧電体)16は、2成分系或いは3成分系の圧電セラミックス等から成る圧電素子であり、2次元マトリックス状に配列されている。この振動素子16の2次元的配列により、超音波の全方位的なフォーカシングと高速な三次元走査が可能である。

【0032】信号電極18は、各振動素子16の他端(すなわち、アース電極14とは異なる一端)に設けられており、圧電効果のための電力印加や被検体から受波した超音波に基く電気信号を入力する電極である。

【0033】パッキング材20は、振動素子16の背面に設けられており、当該振動素子16を機械的に支持する。また、パッキング材20は、超音波パルスを短くするため、振動素子16を制動している。このパッキング材20は、後述する信号線端部221が振動素子16と同じ配列ピッチとなるように、信号電極18から振動素子16の配列面と垂直な方向に信号線22を引き出し

可能な経路が形成されている。このようなパッキング材20は、板状のパッキング材と信号線パターンを張り合わせ、その板厚みが配列ピッチと同じになるような薄いパッキングを積み重ねなる等により作成することが可能である。また、このパッキング材20の厚さは、トランスデューサの音響的特性を良好に保つため、使用する超音波周波数の波長に対して十分な厚さ（十分減衰される厚さ）にとるものとする。

【0034】信号線22は、その一端に於いて信号線端部221を有している。また、他端に於いては各振動素子12の信号電極18と接続されており、振動素子16の配列面と垂直な方向に、信号電極18から伸延して、パッキング材20中の経路を通し信号線端部221が引き出されている。従って、信号線端部221は、振動子と反対側のパッキング材20の面に於いて、2次元アレイ状に並んだ構成となっている。

【0035】なお、本実施形態に係る信号線端部221の配列は、振動素子16と同じ配列ピッチのまま、すなわち電極配列と同様に並んだ例を示しているが、信号線端部221の配線ピッチを素子ピッチより大きくとることも可能である。例えば、上述した板状パッキングと信号線パターンとを張り合わせて信号線の2次元配列を作る場合等では、張り合わせる信号線パターンを信号線端部221方向に進むに従って広がるようなパターンにすることで実現できる。

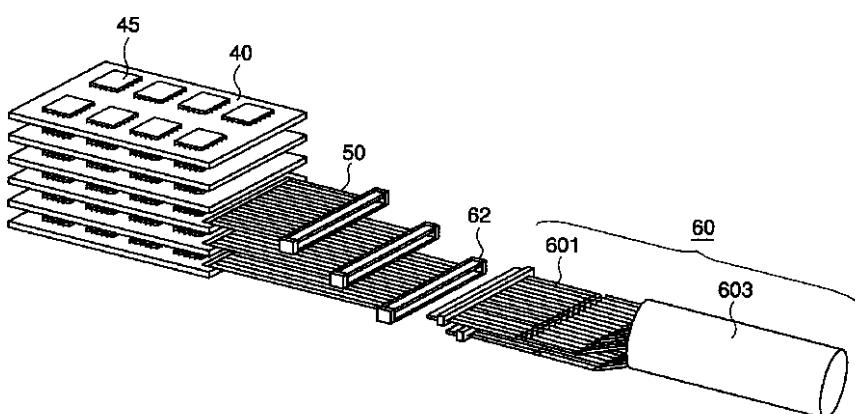

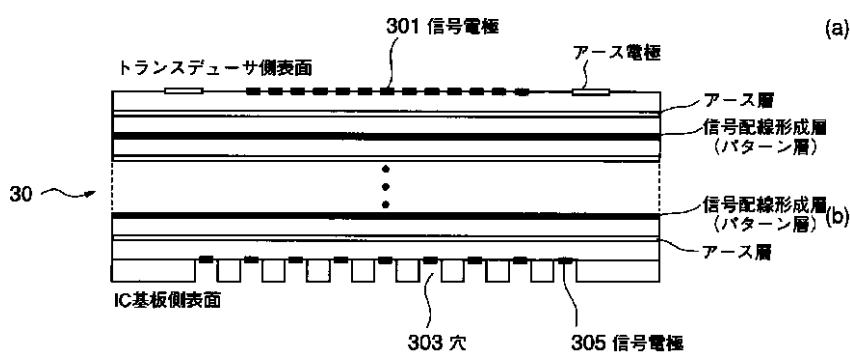

【0036】図2は、本発明の第1の実施形態に係る二次元アレイ超音波プローブが有する、上述したトランスデューサ10と接続される中継基板30と、中継基板30に略垂直に設けられる第1のIC基板40と、を示した概略図である。図2(a)は、中継基板30と第1のIC基板40とをパッキング材20接続側から見た斜視図である。また、図2(b)は、パッキング材20接続側に対し反対側から見た中継基板30の斜視図であり、中継基板30と第1のIC基板40との接続を説明するための図である。

【0037】中継基板30は、図2(a)に示すように、一方の面に於いて信号線端部221と接続される信号取り出し電極301を有し、図2(b)に示すように、他方の面に於いて後述する第1のIC基板40の接続ピン401を支持する穴(孔)303を有しており(以下、信号取り出し電極301を有する面を第1の面310、穴303を有する面を第2の面312と呼ぶことにする)、トランスデューサ10とIC基板40との電気的接続の中継を担っている。第1の面310の信号取り出し電極301は、信号線端部221の配列ピッチに合わせて二次元アレイ状に形成されており、対応する信号線端部221に接続される。第2の面312の穴303は、その底部に於いて、後述する接続ピン401に接続される電極305を有している。また、穴303の配列ピッチは、信号取り出し電極301の配列ピッチと

比較して大きなものとなっている。これは、中継基板30を多層基板で構成し、中間層にピッチを拡大していくようなパターンを設けることで実現できる。

【0038】第1のIC基板40は、送受信信号を処理する(増幅、切り替え等)IC45を実装しているリジッド基板である。この第1のIC基板40は、第1のIC基板40の一端の両面に、前記穴303の形状、配列ピッチに合わせた接続ピン401を有している。第1のIC基板40は、当該両面の接続ピン401を穴303内に差し込む形で中継基板30に接続される。このとき、接続穴303の底面に半田層を設け接続時に半田を溶融することで、電気的接続(接続ピン401と電極305との接続)、及び機械的接続(穴303による接続ピン401の支持)をとることが可能である。

【0039】一般に、トランスデューサ10の振動素子数が増加すると、実装するIC45の数も多数となる。本発明に係る二次元アレイ超音波プローブは二次元トランスデューサ10を有するため、多くのICを実装する必要がある。従って、IC実装面積を広く確保しなければならない。本発明に係る二次元アレイ超音波プローブでは、以下に述べるように、中継基板と垂直に複数枚のIC基板を所定のピッチで接続し、広いIC実装面積を確保する構成となっている。

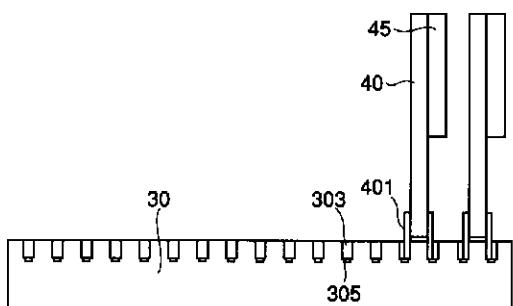

【0040】図3、4は、第1のIC基板40と中継基板30との接続を説明するための図である。図3は、各IC基板45が同一の向きとなる接続方法であり、図4は、各IC45が向き合うような接続方法を示している。

【0041】上述したように、接続ピン401を第1のIC基板40の両面に設け、例えば図3、図4に示すように、第1のIC基板40の厚さを穴303の列ピッチと同程度とすることで、第1のIC基板40の配列ピッチが穴303の2列分(すなわち、IC基板の配列ピッチは電極配列ピッチの2倍)となるように、複数枚の第1のIC基板40を中継基板30に接続することができる。また、接続ピン401を3列分あるいは4列分設けることにより、第1のIC基板40の配列ピッチをさらに大きくとることも可能である。

【0042】また、第1のIC基板40のIC45実装形態は、図3に示した一般的な形態以外に、図4に示すように隣接するIC基板40間でIC45の実装位置を変えた両面実装や、更なる高密度実装にすることも可能である。

【0043】この様な構成によれば、中継基板30による信号電極305のピッチ拡大、第1のIC基板40で接続に使用する接続ピン401の複数列形成により、トランスデューサ10の素子配列ピッチに対して十分大きなピッチで複数の第1のIC基板40を配列することができる。その結果、IC基板厚みがある程度厚くでき(例えば、素子ピッチは0.2~0.5mm程度である

のに対し、IC基板配列ピッチはその2倍から4倍以上とすることも可能である)作成を容易にするばかりでなく、ICの実装や第1のIC基板40へのケーブル接続等を容易にすることが可能となる。

【0044】次に、二次元トランステューサ10と、複数枚の第1のIC基板40が設けられた中継基板30との接続について説明する。

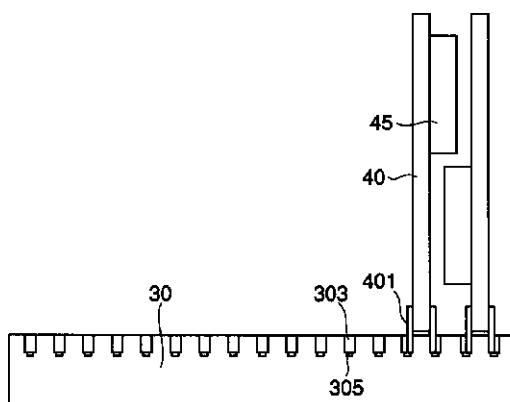

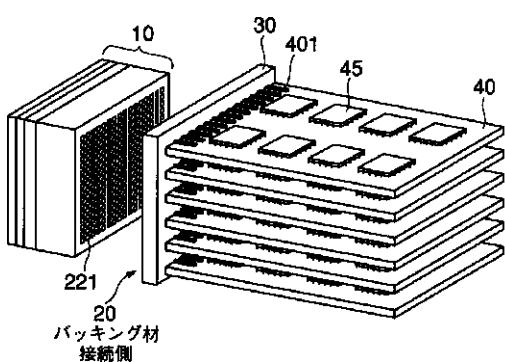

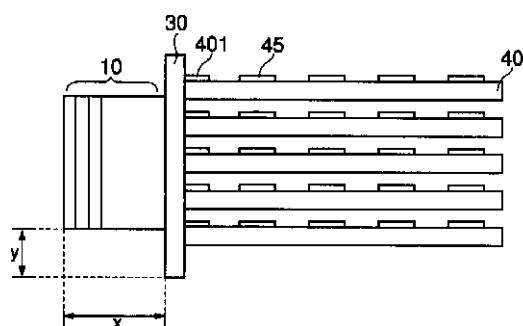

【0045】図5は、図1に示した二次元トランステューサ10と、図2に示した第1のIC基板40が設けられた中継基板30との接続を説明するための図である。

【0046】上述したように、バッキング材20の一面に形成された信号線端部221と中継基板30の信号取り出し電極301とは、同じ配列ピッチで二次元アレイ状に配列されているから、二次元トランステューサ10と中継基板30とは、各信号電極7と各信号取り出し電極301とを対応させ、一括して異方性導電フィルムやバンプ接続等の方法で接続することができる。

【0047】従って、本発明に係る二次元アレイ超音波プローブは、バッキング材20を貫いて信号電極18からの信号線19を引き出している。バッキング材20背面(下層)には、バッキング材相を通過した信号線と接続する中継基板30と送受信信号に対して増幅や切り替え等を行うICを実装するための第1のIC基板40とが設けられている。中継基板30とIC基板40とは、垂直に連結した構造となっている。

【0048】図6は、本発明の第1の実施形態に係る二次元アレイ超音波プローブと超音波診断装置本体とを接続するケーブル60と、上述した第1のIC基板40とを接続する機構を説明するための図である。

【0049】図6に於いて、ケーブル60は、超音波診断装置本体と第1のIC基板40等との電気的接続を取るケーブルである。このケーブル60は、ケーブルアセンブリ用FPC601(フレキシブルプリント基板)と、当該ケーブルアセンブリ用FPC601を覆うカバー603とによって構成されており、柔軟性を備えている。

【0050】ケーブル接続基板50は、上述した第1のIC基板40とケーブル60とを接続するための基板である。当該ケーブル接続基板50は、柔軟性を備えたFPCで出来ており、その一端は、第1のIC基板40における接続ピン401が設けられた一端とは反対側の一端に電気的に接続されている。

【0051】コネクタ62は、ケーブル接続基板50の他端及びケーブルアセンブリ用FPC601の一端にそれぞれ設けられている。このコネクタ62によって、ケーブル接続基板50とケーブルアセンブリ用FPC601とは電気的に接続される。

【0052】次に、上記のように構成した二次元アレイ超音波プローブの作用を説明する。

【0053】本実施形態に示した構造では、バッキング

材20の厚みは、使用する超音波周波数の波長に対して十分な厚さ(十分減衰される厚さ)にとる構成となっているから、超音波トランステューサの振動素子の音響特性を劣化させることなく信号線を引き出すことができる。従って、2次元アレイ素子の素子数が増大した場合、また、素子ピッチが従来プローブ並に小さくなった場合であっても、2次元アレイ状に配列した電極同士を、ACF等の微細パターン接続法を用いて面接続可能である。

【0054】信号線の引き出しを行う中継基板30は、2次元アレイ素子の配列面と概平行な面内に信号取り出し電極を配列する構成になっている。その結果、従来のアレイ素子ピッチと同程度の素子ピッチを有する2次元アレイ素子であっても信号の取り出しが容易となる。

【0055】また、中継基板30によって、第2の面312に形成された穴303の配列ピッチ(すなわち、電極305の配列ピッチ)は、第1の面310に形成された信号取り出し電極301の配列ピッチよりも大きくする構成であるから、送受信信号のためのICを実装する第1のIC基板40と中継基板30との接続を容易に行うことができる。この構成は、振動素子が小さい場合に特に実益がある。

【0056】第1のIC基板40には、中継基板30との接続のための接続ピン401を複数列設け、第1のIC基板40の数を電極305の列数または行数よりも少なくした構成となっている。従って、第1のIC基板40の配列ピッチを大きくすることができ、ICの実装やケーブル接続等を容易に行うことができる。さらに、製造コストも低くすることが可能となる。

【0057】バッキング材相を通過した信号線22と接続する中継基板30と、送受信信号に対して増幅や切り替え等を行うICを実装するための第1のIC基板40とを個別に設け、略垂直に連結した構成となっている。従って、従来の二次元アレイ超音波プローブと比してIC実装面積を十分広く確保することができ、複数のIC基板の効率的な接続が可能である。また、送受信信号に対して増幅や切り替えを行うICの設置は、超音波振動素子配列面とは概垂直な面内で行うことが出来るから、当該配置を障害なく容易に行うことが出来る。

【0058】また、第1のIC基板40に接続するケーブル接続基板50とケーブルアセンブリ用FPC601とをコネクタ62で接続する構成となっている。また、IC基板はICの実装を高密度に行えるようにリジット基板を利用することで強固な構造体を形成している。従って、ケーブル60と第1のIC基板40との接続、組立の作業性を良くし、ケーブル接続部の柔軟性により破損しにくい構造となっている。

【0059】以上述べた構成によれば、以下の効果を得ることができる。

【0060】電気回路を付加した2次元アレイ型超音波

プローブに於いて、二次元上配列の各配列方向に素子ピッチが小さくなつた場合であつても、各超音波振動素子16の音響特性を劣化させず、信号線22を引き出すことが可能であり、当該引き出した信号線22にIC45を設けたIC基板40を容易に接続することができる。【0061】以上、本発明を第1実施形態に基いて説明したが、上記実施形態に限定されるものではなく、例えば以下に示すように、その要旨を変更しない範囲で種々変形可能である。

【0062】上述した中継基板30は、第1の面に於いて、信号線端部221と接続される所定ピッチの信号取り出し電極301を有し、第2の面に於いて、信号取り出し電極301のピッチより大きなピッチで形成された、接続ピン401を支持する穴303及び当該穴303にある電極305を有している。この信号取り出し電極301と電極305との対応は、必要に応じて変形可能な構成であつてもよい。

【0063】すなわち、すべての第1面の信号取り出し電極301からの電気信号を、第2面の電極305から取り出す必要はなく、例えば、信号線端部221のいくつかからアース接続をとる形態、或いは信号取り出し電極301からの電気信号を間引いて電極305から取り出す形態とし、信号取り出し電極301と電極305との数を対応させない構成であつてもよい。また、第1の面310の信号取り出し電極301と第2の面312の電極305との電気的接続の対応のさせ方は、任意であつてかまわぬ。

【0064】(第2の実施形態)第1の実施形態で述べたように、2次元アレイ超音波プローブは、超音波素子を2次元アレイ状に配列することで、超音波ビームの走査を三次元的に行なうことを1つの目的としている。従つて、従来の1次元アレイプローブと同程度の分解能を得るためにには、一方の素子配列数や素子配列ピッチを1次元アレイプローブと同程度であることが好ましい。例えば、現状のセクタプローブ(1次元アレイプローブ)は、100素子前後の素子数を利用している。従つて、二次元の各方向についてこのセクタプローブと同程度の分解能を得るためにには、 $100 \times 100 = 10000$ 素子もの素子数を確保することが必要である。しかし、現在では、10000素子もの素子を使用するシステムを実現することは、プローブの製造性等の観点から困難くなっている。

【0065】この問題の解決策の一つとして、2次元アレイ超音波プローブの利用に於いて、スパースアレイという利用方法がある。これは、多数ある2次元アレイプローブ素子配列の中から、振動素子をランダムに抽出選択し、使用する振動素子数を減少させることにより、構造上の課題を解決する方法である。この方法の長所の一つは、ランダムな素子を選択することで、素子配列により生じるグレーティングローブやサイドローブといった

虚像の発生原因を抑制することができるることである。

【0066】しかし、このスパースアレイを可能とする二次元超音波プローブに於いては、上述した第1のIC基板40上に形成される信号線の数やパターンは、各第1のIC基板40ごとに変わる可能性が高い。すなわち回路パターンの異なる多数のIC基板を必要とすることに他なり、プローブのコストを高くする要因となってしまう。

【0067】第2の実施形態は、本発明に係る二次元アレイ型超音波プローブをスパースアレイに適用し、プローブのコストを低くできる例について説明する。この例は、第1のIC基板40上に実装された各ICと接続ピン401との電気的接続パターンは、第1のIC基板40毎に特定のパターンとなる第1の実施形態に対し、各IC基板上の各ICと接続ピン401との電気接続パターンを必要に応じて変更可能としたものである。

【0068】すなわち、第2の実施形態に係る二次元アレイ型超音波プローブが具備するIC基板は、基板内にパターン変更部71を有しており、利用する素子のパターンが異なる場合であつても同一のIC基板が使用できるようになっている。以下、パターン変更部の具体的な実現方法を示す。

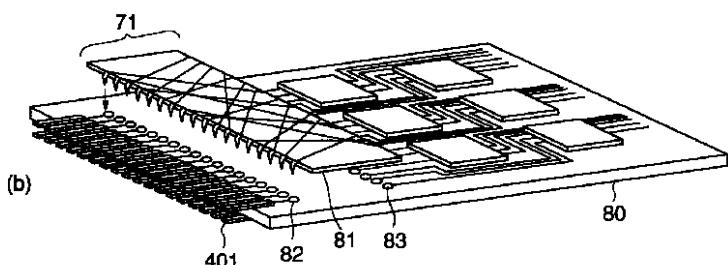

【0069】図7(a)は、ICと接続ピン401との接続パターンを変更可能な第2のIC基板70を示している。

【0070】図7(a)に於いて、第2のIC基板70は、信号線の途中にジャンパー線74を接続するためのジャンパー端子72、73を設け、ジャンパー端子12、13間を所望の接続パターンに変更可能としたパターン変更部71を具備している。ある接続パターンを別の接続パターンに変更したければ、新たなジャンパー線の接続設定を行なえばよい。また、不必要的端子をアースに落とすことも可能である。

【0071】図7(b)は、ICと接続ピン401との接続パターンを変更可能な第3のIC基板80を示している。

【0072】図7(b)に於いて、第3のIC基板80は、ソケット形状の端子82、83、予め接続パターンが作成されたソケット81を具備している。そして、ソケット81を端子82、83に差し込むことで、パターン変更を可能な構成となっている。また、必要に応じて、他の接続パターンを有するソケット81にすることで、所望の接続パターンに変更することが可能である。さらに、ソケット81の接続パターン変更により、不必要的端子をアースに落とすことも可能である。

【0073】従つて、この様な構成によれば、IC基板内に信号ラインの引き回しパターンを変更可能なパターン変更部71或いはソケット81を設け、IC基板内で処理する信号線の数や接続パターンが各IC基板で異なる場合であつても、同一のIC基板を使用することがで

きる。その結果、例えば、マトリックス状に多数の素子が配列された2次元アレイ型超音波プローブに於いて、選択的に素子を使用するスパースアレイ型の利用形態をとった場合でも、IC基板の種類を少なく抑制することが可能となり、コスト上昇を抑制することが出来る。また、信号線の数や接続パターンの変更も容易となり、作業性の向上も期待することができる。

【0074】(第3の実施形態)第3の実施形態では、第2の実施形態で述べたスパースアレイ型の2次元アレイ超音波プローブに於いて、ランダムな素子配列ごとにIC実装基板を多数作らず、プローブ構造を簡素化した2次元アレイプローブを実現する例を示す。

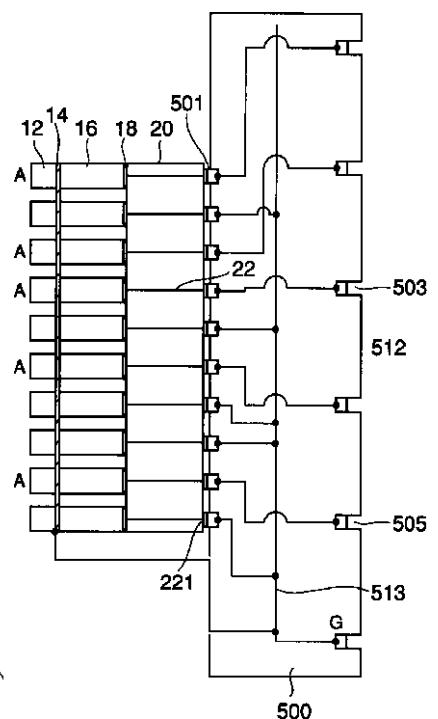

【0075】第2の実施形態で説明したように、スパースアレイ型2次元アレイ超音波プローブは、マトリックス状に2次元配列された超音波素子の全てを使用するものではない。従って、使用する素子のみを接続する場合、非スパースアレイ型2次元アレイ超音波プローブと比較して、必要な信号線数を当然少なくすることが出来る。すなわち、第2の実施形態では、2次元アレイの各素子を有効な素子とするか無効な素子とするかの選択をIC基板上のパターン変更部71で行っている。これに対し、第3の実施形態は、この選択を中継基板(図8参照)内で行ってしまうものである。

【0076】図8に、第3の実施形態に係るスパースアレイ型の2次元アレイ超音波プローブの概念構成図を示す。図8は側方断面図であるためアレイ配列を1次元に示しているが、実際には2次元配列に適用するものである。

【0077】図8に於いて、2次元アレイ超音波プローブは、二次元アレイ型超音波トランスデューサ10と中継基板500と、図示していない第1のIC基板40等を具備している。

【0078】二次元アレイ型超音波トランスデューサ10は、図1同様な振動素子16と音響整合層12、バッキング材20等から成る。また、振動子電極として共通電極14と信号電極18とが設けられており、信号電極18にはバッキング材内を通る信号線22が接続され信号線端部221に引き出され、2次元アレイ状に配列された構成となっている。

【0079】中継基板500は、信号線端部221に対応した信号線取り出し電極501を有しており、2次元配列された信号線端部221と接続される。中継基板500は、多層プリント配線基板となっており、信号取り出し電極501は有効な素子部では図示していないIC基板と接続する側の面512面に引き回されIC基板と接続する電極505に至っている。なお、IC基板は、スパースアレイとして使用される素子を制御するもののみ実装される。

【0080】また、無効な素子部の信号引き出し電極501は、アースライン513に落とされ共通接続されて50

いる。電極505に接続するIC基板等は前述と同様であるが、本実施形態では信号線取り出し電極501よりもIC基板接続電極505の数が少ない構成となっている。

【0081】この様な構成によれば、スパースアレイとして使用する素子のみから信号線を取り出し、当該取り出された信号線と使用する素子分のIC基板とを接続する構成となる。従って、IC基板を接続する接続電極505及び接続穴503の数を信号取り出し電極501よりも少なくでき、穴503の配列ピッチを広くすることが可能となる。その結果、ICの実装がより容易となり、またケーブル接続など容易にすることが可能となる。

【0082】さらに、IC基板に接続する電極505の配置は、中継基板内で信号引き出し電極501から複数層のプリントパターンで引き回すことで自在に配置することが可能であり、スパースアレイの素子配置によらず任意の配置が可能となる。すなわち、スパースアレイで有効素子配置が各列毎に異なっていても、IC基板の配線パターンを全て異なるものにする必要はなく、少ない種類のIC基板で対応可能となる。極論すればIC基板を1種類にすることも可能である。

【0083】従って、本実施形態によれば、何種類ものIC基板を作ることなく1種類のIC基板を効率的に使用でき、またIC基板接続部のピッチも大きくすることが可能となる。その結果、製造し易く、安価な2次元アレイ超音波プローブを実現することができる。

【0084】なお、本実施形態で説明した2次元アレイ超音波プローブは、中継基板500と第2の実施形態で示した第2のIC基板70とを組み合わせた配線パターン形成も可能である。

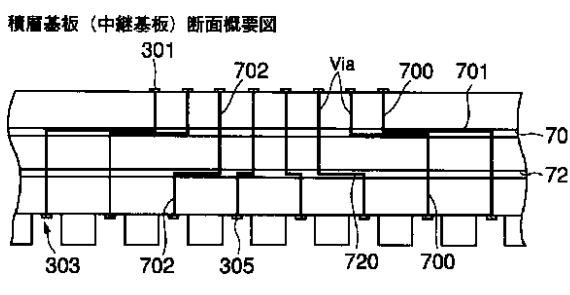

【0085】(第4の実施形態)第4の実施形態では、中継基板を多層の基板によって構成することで、特に良好な信号取り出しを実現する二次元超音波アレイプローブを、図面に基づいて説明する。

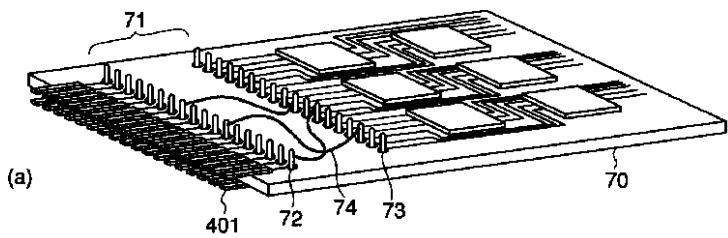

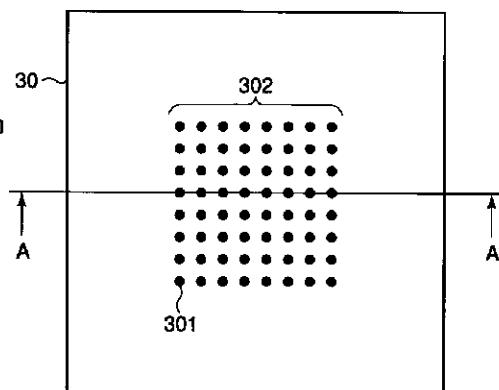

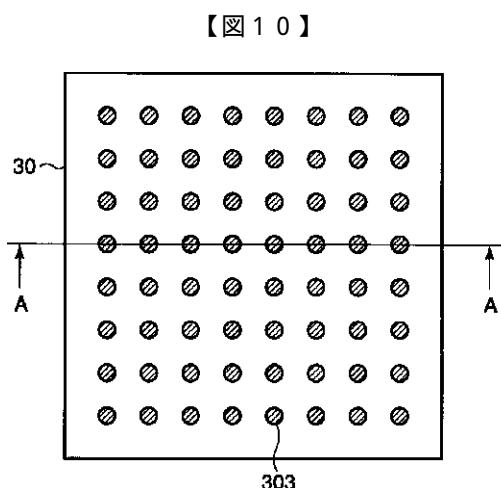

【0086】図9は、本実施形態に係る二次元超音波アレイプローブが有する中継基板30のトランスデューサ接続面(すなわち、バッキング材接続側20)を示している。

【0087】図10は、本実施形態に係る二次元超音波アレイプローブが有する中継基板30のIC基板接続面(すなわち、バッキング材接続側20に対して反対側の面)を示している。同図においては、穴303及び当該穴303中に存する電極305(図示せず)が、図9に示した電極301よりも大きなピッチによって配列されている。

【0088】図11は、図9或いは図10の直線A-Aに沿った中継基板30の概略断面図であり、複数のパターン層基板(本図では、n枚)から構成されていることを示している。

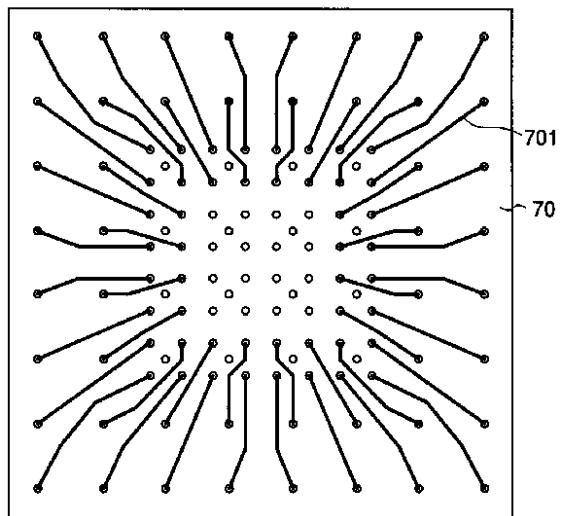

【0089】本実施形態に係る二次元超音波アレイプローブの重要な点の一つは、中継基板が複数のパターン層基板によって構成された多層基板となっていることである。この複数のパターン層基板のそれぞれに形成された複数のパターン配線によって、図9に示したトランスデューサ接続面の電極301から取り出される信号配線は、図10に示すような大きなピッチで整列して取り出される。なお、パターン層基板の数nは、使用する或いは備え付けられる振動素子16の数に依存する。以下、n=2の場合を例として、多層基板から成る中継基板30の具体例を説明する。

【0090】(実施例)図12は、2枚のパターン層基板(すなわち、n=2)を有する、図9或いは図10の直線A-Aに沿った中継基板30の断面図である。

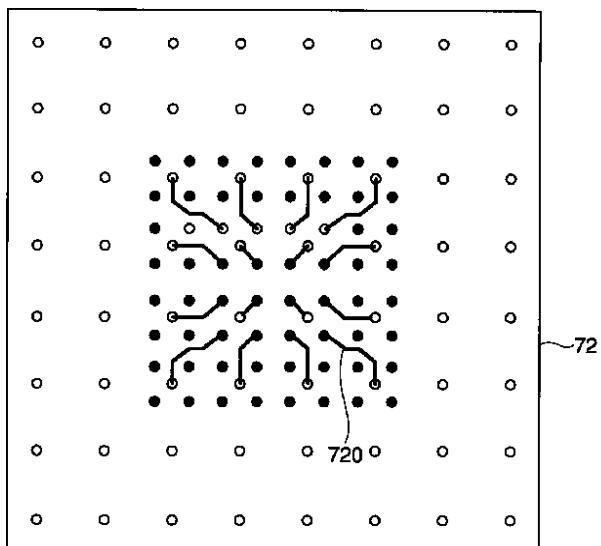

【0091】また図13は、第1のパターン層基板70のトランスデューサ側上面図を示しており、図14は、第2のパターン層基板72のトランスデューサ側上面図を示している。

【0092】図12に示すように、中継基板30のトランスデューサ側接続面に設けられた各電極301から取り出された電気配線の一部は、ビアホール700によって第1のパターン層70に引き出される。引き出された各電気配線は、第1のパターン層基板70において図13に示すパターン配線701によってより大きなピッチ幅に拡大され、ビアホール700によって中継基板30のIC基板接続面へと引き出される。

【0093】また、トランスデューサ側接続面に設けられた各電極301から取り出された残余の電気配線は、図12に示すようにビアホール702によって第2のパターン層72に引き出される。引き出された各電気配線は、第2のパターン層基板72において図14に示すパターン配線720によってより大きなピッチ幅に拡大され、ビアホール702によって中継基板30のIC基板接続面へと引き出される。

【0094】本実施例は、n=2の場合を示しているが、例えば多くの振動素子を有する二次元超音波アレイプローブであっても、さらに多くのパターン層基板を設けることで対応することが可能である。

【0095】なお、当然ではあるが、各パターン層基板の電気配線パターンは任意である。すなわち、トランスデューサ側接続面に設けられた電極301とIC基板接続面に設けられた電極305とを一対一に対応させるためのものであり(但し、アース配線はこの限りではない。)、且つ中継基板30のトランスデューサ側接続面からIC基板接続面にかけて電気配線のピッチを広げるものであれば、どのようなものであっても構わない。また、一の信号配線を、複数のパターン層基板に渡って段階的に電気配線のピッチを広げる構成であっても、同様の目的を達成することができる。

【0096】次に、中継基板30の受信電極と送信電極

との割り当て例について、図面を参照しながら説明する。

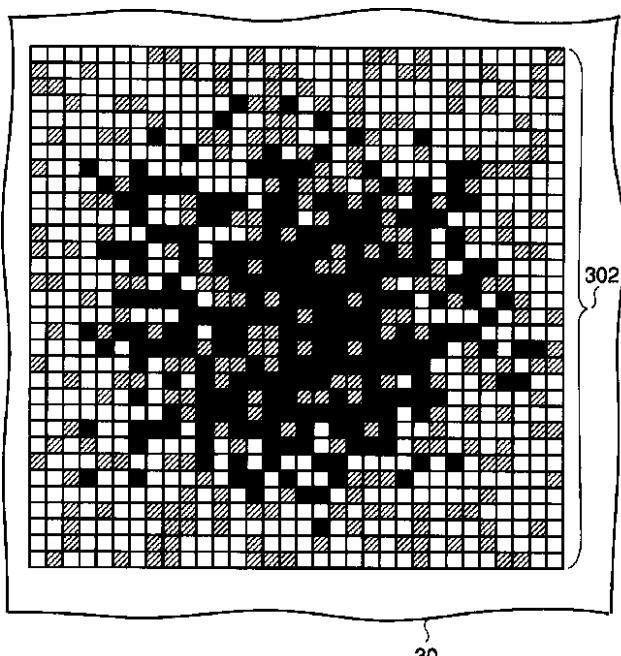

【0097】図15は、中継基板30のトランスデューサ側接続面に存在する電極アレイ302を構成する電極301の割り当て例を模式的に示した図である。同図において、斜線に塗られた矩形は送信電極、黒く塗りつぶされた矩形は受信電極、白色の矩形はアース電極にそれぞれ割り当てられた電極301を示している。

【0098】図15からわかるように、送信電極は電極アレイ302の中心部(すなわち、二次元超音波アレイプローブの超音波照射面中心部)付近に集められている。これは、反射波情報を増やす観点から照射ビーム口径を小さくするためである。一方、受信電極は電極アレイ302全体に散りばめられている。これは、受信口径を大きくすることでよりシャープな反射波を受信するためである。従って、この様な電極割り当てを行えば、より精度の高い超音波送受信が可能である。

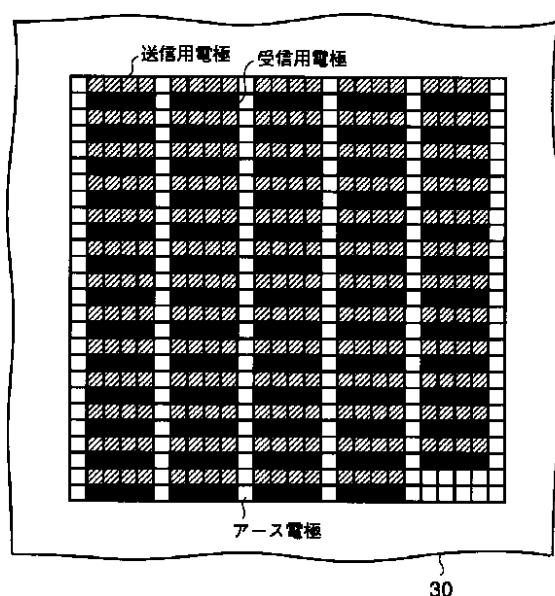

【0099】図16は、図20の中継基板30のIC接続面に存在する電極アレイ306を構成する電極305の割り当て例を模式的に示した図である。斜線矩形が送信電極、黒色矩形が受信電極、白色矩形がアース電極にそれぞれ対応するのは、図15と同様である。

【0100】図16からわかるように、複数のパターン層基板によって引き出された電気配線は、送信電極及び受信電極ごとに整列されている。また、アース電極は4個の送受信電極毎に配列されている。従って、本中継基板30に接続されるIC基板40の接続ピン401(例えば、図3又は図4参照)は、一方の面に配列されたものは送信信号の為のピンとなり、他方の面に接続されたものは受信のためのピンとなる。例えばこの様な電極割り当てを行うことによって、IC基板70等の接続ピン401と送信用電極或いは受信用電極との対応、すなわちIC45の接続ピン401と送信用電極或いは受信用電極との対応形態を容易に把握することができる。この形態は、例えばIC基板70等やIC45の交換等において実益がある。また、IC基板70等の電気回路を単純化することができる。さらに、IC基板70等の形態を統一的に扱うことが可能であり、従ってIC基板70等の種類は少なくて済む。

【0101】なお、上記例では、送信電極と受信電極とを異なる電極301、305に割り当てたが、同一の電極301、305が超音波の送受信を担う構成であってもよい。また、一部の電極301、305が超音波の送受信を担い、残余の電極301、305には送信電極と受信電極とを別々に割り当てる構成であってもよい。

【0102】以上述べた様に、中継基板30が多層化されており、トランスデューサから引き出された信号配線は、そのピッチ幅が中継基板30の各層に形成されたパターン配線によって拡大され、IC基板接続側に整列して引き出される。従って、一振動素子が小さく配列ピッ

チが小さい二次元超音波アレイプローブであっても、各素子から信号線の引き出し、超音波素子の音響特性の維持、IC等の実装等を容易に実現することができる。

【0103】以上、本発明を実施形態に基づき説明したが、本発明の思想の範疇において、当業者であれば、各種の変更例及び修正例に想到し得るものであり、それら変形例及び修正例についても本発明の範囲に属するものと了解される。例えば以下(1)、(2)に示すように、その要旨を変更しない範囲で種々変形可能である。

【0104】(1)上記各実施形態で示した二次元超音波アレイプローブは、それぞれ別体であるトランスデューサ10、中継基板30、IC45を備えたIC基板70等を組合わせて構成される。設計によっては、トランスデューサ10の中継基板30接続面サイズよりも中継基板30のトランスデューサ10接続面サイズが大きくなる場合がある。この場合において、トランスデューサ10と中継基板30とを接続すれば、例えば図17に示すように、中継基板30の周縁部がトランスデューサ10の輪郭より大きな形態となる。

【0105】一般に、二次元超音波アレイプローブは、検査対象物、例えば人体の一部に当接して使用される。従って、トランスデューサ10の輪郭からはみ出る中継基板30の周縁部があまりに大きいと、作業性に影響を及ぼすことがある。

【0106】本発明者らの研究によれば、トランスデューサ10の超音波照射方向の長さxは、トランスデューサ10の輪郭からはみ出る中継基板30の周縁部の長さyよりも長ければ(すなわち、 $x > y$ であれば)、二次元超音波アレイプローブの使用は良好である。なお、長さxの調整は、例えばバッキング材の長さの調整によって容易に実現することができる。

【0107】(2)第4の実施形態においては、別途形成されたパターン配線基板を積層して形成された中継基板を示した。これに対し、各層を順次積み重ねて多層化した中継基板であっても、同様の効果を得ることができる。

【0108】以上述べた本願発明は各実施形態は可能な限り適宜組み合わせて実施してもよく、その場合組合せた効果が得られる。さらに、上記実施形態には種々の段階の発明が含まれており、開示される複数の構成要件における適宜な組合せにより種々の発明が抽出され得る。例えば、実施形態に示される全構成要件から幾つかの構成要件が削除されても、発明が解決しようとする課題の欄で述べた課題が解決でき、発明の効果の欄で述べられている効果の少なくとも1つが得られる場合には、この構成要件が削除された構成が発明として抽出され得る。

【0109】

【発明の効果】以上本発明によれば、電気回路を付加した2次元アレイプローブに於いて、素子ピッチが小さく

10 10 20 30 40 50

なった場合であっても、2次元状に配列された各超音波振動素子の音響特性を維持しつつ、信号線の引き出しが可能で、かつ信号線に電気回路を設けた回路基板を容易に接続することができる超音波プローブを実現することができる。

【図面の簡単な説明】

【図1】図1は、本発明に係る二次元アレイ超音波プローブが有する二次元アレイ超音波トランスデューサ10の概略図。

【図2】図2は、トランスデューサ10と接続される中継基板30と中継基板30に略垂直に設けられる第1のIC基板40とを示した概略図。

【図3】図3は、中継基板とIC基板との接続方法を示す図。

【図4】図4は、中継基板とIC基板との接続方法の他の例を示す図。

【図5】図5は、二次元トランスデューサ10と、第1のIC基板40が設けられた中継基板30との接続を説明するための図。

【図6】図6は、本発明に係る二次元アレイ超音波プローブが有するケーブル60と、第1のIC基板40とを接続する機構を説明するための図。

【図7】図7は、ICと接続ピンとの接続パターンを変更可能なIC基板を示す図。

【図8】図8は、第3の実施形態に係るスパースアレイ型の2次元アレイ超音波プローブの概念構成を示す図。

【図9】図9は、第4の実施形態に係る二次元超音波アレイプローブが有する中継基板30のトランスデューサ接続面を示している。

【図10】図10は、第4の実施形態に係る二次元超音波アレイプローブが有する中継基板30のIC基板接続面を示している。

【図11】図11は、図9或いは図10の直線A-Aに沿った中継基板30の断面図である。

【図12】図12は、2枚のパターン層基板を有する、図9或いは図10の直線A-Aに沿った中継基板30の断面図である。

【図13】図13は、第1のパターン層基板70のトランスデューサ側上面図を示している。

【図14】図14は、第2のパターン層基板72のトランスデューサ側上面図を示している。

【図15】図15は、中継基板30のトランスデューサ側接続面に存在する電極アレイ302を構成する電極301の割り当て例を模式的に示した図である。

【図16】図16は、中継基板30のIC接続面に存在する電極アレイ306を構成する電極305の割り当て例を模式的に示した図である。

【図17】図17は、トランスデューサと中継基板との好ましいサイズ比を説明するための図である。

【図18】従来の二次元アレイ超音波プローブが有する

二次元トランスデューサの概略構成図。

【符号の説明】

- 10 ...トランスデューサ

- 12 ...音響整合層

- 14 ...アース電極

- 16 ...振動素子

- 18 ...信号電極

- 19 ...信号線

- 22 ...信号線

- 30 ...中継基板

- 40 ...I C基板

- 50 ...ケーブル接続基板

- 60 ...ケーブル

- 62 ...コネクタ

- 70 ...I C基板

- 71 ...パターン変更部

- 72, 73 ...ジャンパー端子

- 74 ...ジャンパー線

- \* 80 ...I C基板

- 81 ...ソケット

- 82, 83 ...端子

- 221 ...信号線端部

- 301 ...電極

- 303 ...穴

- 305 ...電極

- 310 ...第1の面

- 312 ...第2の面

- 10401 ...接続ピン

- 500 ...中継基板

- 501 ...電極

- 503 ...接続穴

- 505 ...接続電極

- 512 ...面

- 513 ...アースライン

- 603 ...カバー

\*

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図8】

【図12】

【図17】

【図7】

【図9】

【図13】

パターン層のパターン例

【図11】

【図18】

【図14】

【図15】

【図16】

|                |                                                                                                                                                                                                                                                                |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 二维阵列式超声探头                                                                                                                                                                                                                                                      |         |            |

| 公开(公告)号        | <a href="#">JP2001292496A</a>                                                                                                                                                                                                                                  | 公开(公告)日 | 2001-10-19 |

| 申请号            | JP2001027451                                                                                                                                                                                                                                                   | 申请日     | 2001-02-02 |

| [标]申请(专利权)人(译) | 株式会社东芝                                                                                                                                                                                                                                                         |         |            |

| 申请(专利权)人(译)    | 东芝公司                                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | 橋本新一<br>手塚智                                                                                                                                                                                                                                                    |         |            |

| 发明人            | 橋本 新一<br>手塚 智                                                                                                                                                                                                                                                  |         |            |

| IPC分类号         | G01N29/24 A61B8/00 H04R17/00                                                                                                                                                                                                                                   |         |            |

| FI分类号          | H04R17/00.332.Y H04R17/00.330.G H04R17/00.330.H A61B8/00 G01N29/24.502 G01N29/24                                                                                                                                                                               |         |            |

| F-TERM分类号      | 2G047/EA11 2G047/GB02 2G047/GB21 4C301/EE12 4C301/EE20 4C301/GB09 4C301/GB19 4C601 /BB03 4C601/GB11 4C601/GB19 4C601/GB20 4C601/GB30 4C601/GB41 5D019/AA21 5D019/AA25 5D019/AA26 5D019/BB26 5D019/BB28 5D019/BB29 5D019/EE06 5D019/FF04 5D019/GG05 5D019 /GG11 |         |            |

| 优先权            | 2000025470 2000-02-02 JP                                                                                                                                                                                                                                       |         |            |

| 其他公开文献         | <a href="#">JP4521126B2</a>                                                                                                                                                                                                                                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                      |         |            |

## 摘要(译)

解决的问题：提供一种二维阵列型超声波探头，其中即使在较小的振动元件节距的情况下，也可以从每个振动元件引出信号线而不会劣化每个振动元件的声学特性，并且可以容易地连接IC基板。提供。二维阵列探针的电极引出结构技术领域本发明涉及一种二维阵列探针的电极引出结构，其中，作为信号线22的一端的信号电极221，其穿过背衬材料20而二维地布置为与振动元件16的布置面平行的电极图案。通过连接二维换能器，在其上形成有与信号电极221的电极图案相似的电极图案的中继基板30，以及垂直连接至中继基板30的IC基板40而构成的二维阵列探针。