(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2013-175879

(P2013-175879A)

(43) 公開日 平成25年9月5日(2013.9.5)

(51) Int.Cl.

H04R 17/00 (2006.01)

A61B 8/00 (2006.01)

F 1

H04R 17/00

A61B 8/00

H04R 17/00

テーマコード(参考)

4C601

5D019

審査請求 未請求 請求項の数 13 O L (全 14 頁)

(21) 出願番号

(22) 出願日特願2012-38402 (P2012-38402)

平成24年2月24日 (2012.2.24)

(71) 出願人 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100090479

弁理士 井上 一

(74) 代理人 100104710

弁理士 竹腰 昇

(74) 代理人 100124682

弁理士 黒田 泰

(72) 発明者 中村 友亮

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

(72) 発明者 鶴野 次郎

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

最終頁に続く

(54) 【発明の名称】超音波トランステューサー素子チップおよびプローブ並びに電子機器および超音波診断装置

## (57) 【要約】

【課題】薄型で、かつ、基板の厚み方向に十分な強度を有する超音波トランステューサー素子チップは提供される。

【解決手段】基板21にはアレイ状に複数の開口45が配置される。開口45同士は仕切り壁51で相互に隔てられる。個々の開口45ごとに超音波トランステューサー素子23が設けられる。基板21の裏面には板状部材52が固定される。仕切り壁51の壁厚みtは仕切り壁51の壁高さHに比べて小さい。

【選択図】図4

**【特許請求の範囲】****【請求項 1】**

複数の開口がアレイ状に配置された基板と、

個々の前記複数の開口に設けられる超音波トランスデューサー素子と、

前記基板の前記超音波トランスデューサー素子が設けられる面とは反対側の面に固定され、前記基板の厚み方向からの平面視で前記複数の開口の少なくとも1つ以上を覆う板状部材とを備え、

前記複数の開口の間の仕切り壁部では、壁厚みが壁高さより小さい

ことを特徴とする超音波トランスデューサー素子チップ。

**【請求項 2】**

請求項1に記載の超音波トランスデューサー素子チップにおいて、前記板状部材は個々の前記仕切り壁部に少なくとも1カ所の接合域で接合されることを特徴とする超音波トランスデューサー素子チップ。

**【請求項 3】**

請求項1または2に記載の超音波トランスデューサー素子チップにおいて、前記開口の輪郭は四角形で規定されることを特徴とする超音波トランスデューサー素子チップ。

**【請求項 4】**

請求項3に記載の超音波トランスデューサー素子チップにおいて、前記四角形は対向する2辺の長辺を有し、前記仕切り壁部の前記接合域は前記長辺の中央位置を含む領域であることを特徴とする超音波トランスデューサー素子チップ。

**【請求項 5】**

請求項4に記載の超音波トランスデューサー素子チップにおいて、前記仕切り壁部の前記接合域は前記長辺の全長を含む領域であることを特徴とする超音波トランスデューサー素子チップ。

**【請求項 6】**

請求項5に記載の超音波トランスデューサー素子チップにおいて、前記仕切り壁部は前記長辺の全長にわたって前記開口同士の間の全面で面接合されることを特徴とする超音波トランスデューサー素子チップ。

**【請求項 7】**

請求項3に記載の超音波トランスデューサー素子チップにおいて、前記仕切り壁部の前記接合域は前記四角形の各辺に少なくとも1カ所ずつ配置されることを特徴とする超音波トランスデューサー素子チップ。

**【請求項 8】**

請求項7に記載の超音波トランスデューサー素子チップにおいて、前記仕切り壁部の前記接合域は前記四角形を途切れなく囲むことを特徴とする超音波トランスデューサー素子チップ。

**【請求項 9】**

請求項8に記載の超音波トランスデューサー素子チップにおいて、前記仕切り壁部は前記四角形の全周にわたって前記開口同士の間の全面で面接合されることを特徴とする超音波トランスデューサー素子チップ。

**【請求項 10】**

請求項1～9のいずれか1項に記載の超音波トランスデューサー素子チップと、前記超音波トランスデューサー素子チップを支持する筐体とを備えることを特徴とするプローブ。

**【請求項 11】**

請求項10に記載のプローブと、前記プローブに接続されて、前記超音波トランスデューサー素子の出力を処理する処理回路とを備えることを特徴とする電子機器。

**【請求項 12】**

請求項10に記載のプローブと、前記プローブに接続されて、前記超音波トランスデューサー素子の出力を処理し、画像を生成する処理回路と、前記画像を表示する表示装置と

10

20

30

40

50

を備えることを特徴とする超音波診断装置。

【請求項 1 3】

請求項 1 ~ 9 のいずれか 1 項に記載の超音波トランステューサー素子チップと、前記超音波トランステューサー素子チップを支持する筐体とを備えることを特徴とするプローブヘッド。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、超音波トランステューサー素子チップ、および、それを利用したプローブ、並びに、そういうプローブを利用した電子機器および超音波診断装置等に関する。 10

【背景技術】

【0 0 0 2】

例えば特許文献 1 に開示されるように、超音波トランステューサー素子チップは基板を備える。基板には複数の開口が形成される。個々の開口に超音波トランステューサー素子が設けられる。超音波トランステューサー素子は振動膜を備える。振動膜は基板の表面から開口を塞ぐ。

【先行技術文献】

【特許文献】

【0 0 0 3】

【特許文献 1】特開 2011 - 82624 号公報 20

【特許文献 2】特開 2011 - 77918 号公報

【発明の概要】

【発明が解決しようとする課題】

【0 0 0 4】

基板に開口が形成されると、基板の強度は低下する。基板の厚み方向の力に対して強度が不足する。超音波トランステューサー素子チップが被検体に押し付けられると、超音波トランステューサー素子が破損することがあった。

【0 0 0 5】

本発明の少なくとも 1 つの態様によれば、薄型で、かつ、基板の厚み方向に十分な強度を有する超音波トランステューサー素子チップは提供することができる。 30

【課題を解決するための手段】

【0 0 0 6】

(1) 本発明の一態様は、複数の開口がアレイ状に配置された基板と、個々の前記複数の開口に設けられる超音波トランステューサー素子と、前記基板の前記超音波トランステューサー素子が設けられる面とは反対側の面に固定され、前記基板の厚み方向からの平面視で前記複数の開口の少なくとも 1 つ以上を覆う板状部材とを備え、前記複数の開口の間の仕切り壁部では、壁厚みが壁高さより小さい超音波トランステューサー素子チップに関する。

【0 0 0 7】

こうした超音波トランステューサー素子チップでは超音波トランステューサー素子は薄型に形成されることができる。超音波トランステューサー素子は薄型の基板に形成されることができる。板状部材が基板に固定されても、超音波トランステューサー素子チップは薄型に形成されることができる。同時に、板状部材は基板の強度を補強する。特に、仕切り壁部で壁厚みが壁高さよりも小さいことから、断面係数の関係で仕切り壁部では基板の厚み方向に十分な剛性が確保されることができる。基板の厚み方向の力は仕切り壁部を伝って板状部材で支持されることができる。こうして超音波トランステューサー素子チップは基板の厚み方向に十分な強度を有することができる。ここで、仕切り壁部は、隣接する開口の空間同士の間に挟まれる基板の部位に相当する。壁厚みは仕切り壁部の厚みすなわち開口同士の距離に相当する。仕切り壁部の壁面が平面で構成される場合には、壁厚みはその壁面に直交する垂線の長さで規定されることができる。壁高さは基板の厚み方向に規

10

20

30

40

50

定される壁面の長さで規定されることがある。

【0008】

(2) 前記板状部材は個々の前記仕切り壁部に少なくとも1カ所の接合域で接合されることがある。仕切り壁部が板状部材に接合されると、仕切り壁部の動きは板状部材で拘束される。したがって、仕切り壁部の振動は防止されることがある。その結果、超音波トランスデューサー素子同士のクロストークは防止されることがある。しかも、こうして仕切り壁部の動きが拘束されると、超音波トランスデューサー素子の超音波振動に対して仕切り壁部の振動の作用は回避されることがある。超音波トランスデューサー素子ではクリアな振動モードの超音波振動が得られる。こうして仕切り壁部の振動が回避されると、超音波振動の振幅の低下も抑制されることがある。

10

【0009】

(3) 前記開口の輪郭は四角形で規定されることがある。四角い輪郭同士の開口が隣り合うと、仕切り壁部は均一な壁厚みで形成される。特に、超音波トランスデューサー素子の密集度が高まれば高まるほど、仕切り壁部の壁厚みは均一に減少する。したがって、仕切り壁部の剛性は著しく弱まる。こうしたときに仕切り壁部が板状部材に連結されれば、仕切り壁部の振動は効果的に防止されることがある。

【0010】

(4) 前記四角形は対向する2辺の長辺を有することができ、前記仕切り壁部の前記接合域は前記長辺の中央位置を含む領域であることがある。こうして仕切り壁部のうち振動振幅の大きい部位が板状部材に接合される。その結果、仕切り壁部の振動は効果的に防止されることがある。

20

【0011】

(5) 前記仕切り壁部の前記接合域は前記長辺の全長を含む領域であることがある。こうして長辺の全長にわたって仕切り壁部が板状部材に接合されれば、仕切り壁部の振動は確実に防止されることがある。

【0012】

(6) 前記仕切り壁部は前記長辺の全長にわたって前記開口同士の間の全面で面接合されることがある。こうして長辺の全長にわたって開口同士の間で全面で仕切り壁部が板状部材に面接合されれば、仕切り壁部の振動は確実に防止されることがある。

30

【0013】

(7) 前記仕切り壁部の前記接合域は前記四角形の各辺に少なくとも1カ所ずつ配置されることがある。こうして四角形の各辺で仕切り壁部が板状部材に接合されれば、仕切り壁部の振動は確実に防止されることがある。

【0014】

(8) 前記仕切り壁部の前記接合域は前記四角形を途切れなく囲むことができる。こうして四角形の全域で仕切り壁部が板状部材に接合されれば、仕切り壁部の振動は確実に防止されることがある。

【0015】

(9) 前記仕切り壁部は前記四角形の全周にわたって前記開口同士の間の全面で面接合されることがある。こうして四角形の全周にわたって開口同士の間で全面で仕切り壁部が板状部材に面接合されれば、仕切り壁部の振動は確実に防止されることがある。

40

【0016】

(10) 超音波トランスデューサー素子チップはプローブに組み込まれて利用されることができる。プローブは、超音波トランスデューサー素子チップと、前記超音波トランスデューサー素子チップを支持する筐体とを備えることができる。

【0017】

(11) プローブは電子機器に組み込まれて利用されることがある。電子機器は、プローブと、前記プローブに接続されて、前記超音波トランスデューサー素子の出力を処理する処理回路とを備えることができる。

【0018】

50

(12) 同様にプローブは超音波診断装置に組み込まれて利用されることができる。超音波診断装置は、プローブと、前記プローブに接続されて、前記超音波トランスデューサー素子の出力を処理し、画像を生成する処理回路と、前記画像を表示する表示装置とを備えることができる。

【0019】

(13) 超音波トランスデューサー素子チップはプローブヘッドに組み込まれて利用されることができる。プローブヘッドは、超音波トランスデューサー素子チップと、前記超音波トランスデューサー素子チップを支持する筐体とを備えることができる。

【図面の簡単な説明】

【0020】

【図1】一実施形態に係る電子機器の一具体例すなわち超音波診断装置を概略的に示す外観図である。

【図2】超音波プローブの拡大正面図である。

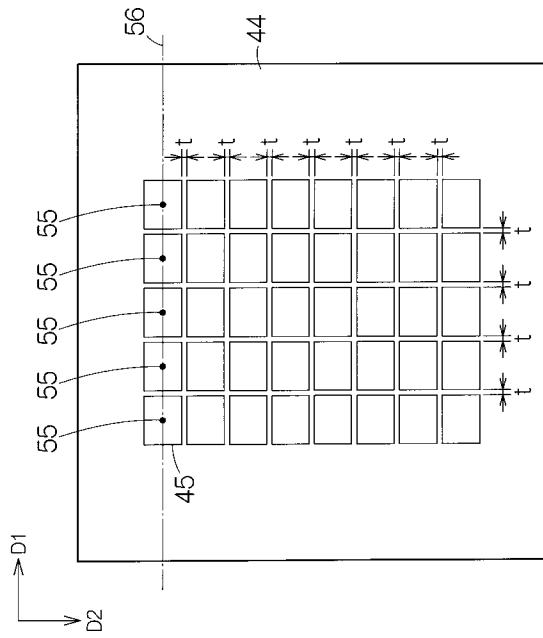

【図3】超音波トランスデューサー素子チップの拡大平面図である。

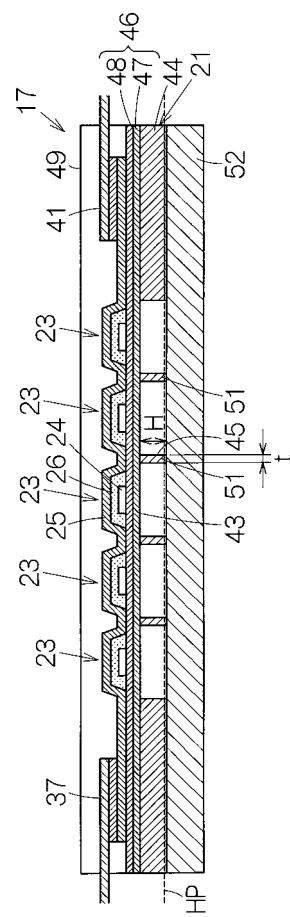

【図4】図3の4-4線に沿った断面図である。

【図5】基体の裏面の平面図である。

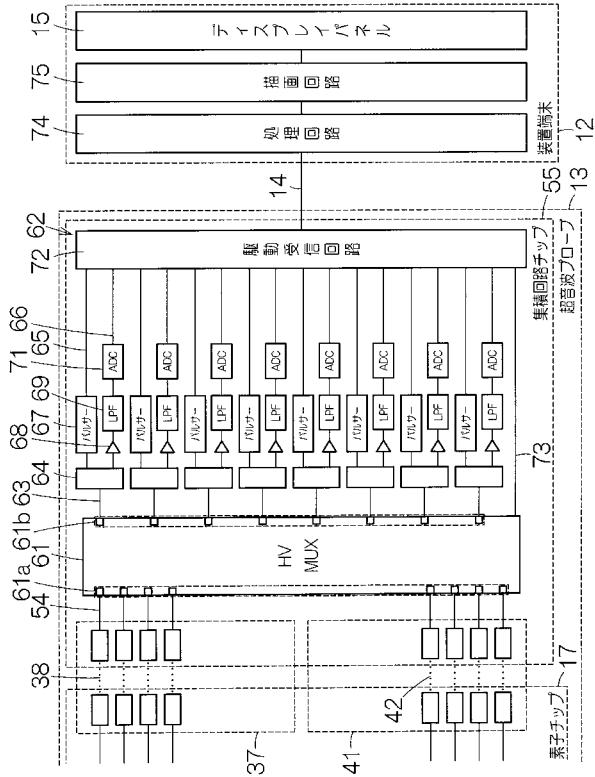

【図6】超音波診断装置の回路構成を概略的に示すブロック図である。

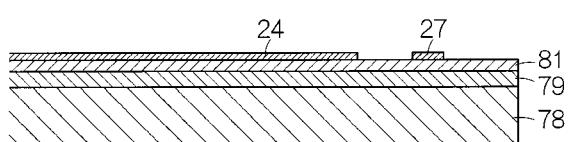

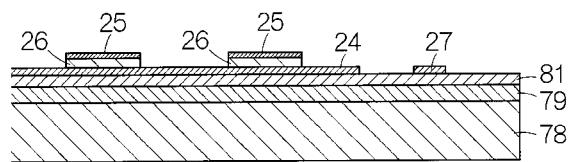

【図7】シリコンウェハー上に形成された可撓膜および下部電極を概略的に示す部分拡大垂直断面図である。

【図8】下部電極上に形成された圧電体膜および上部電極を概略的に示す部分拡大垂直断面図である。

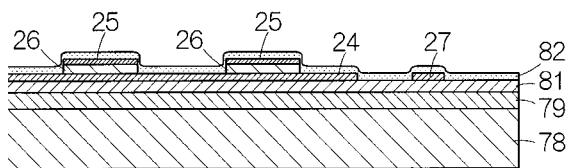

【図9】シリコンウェハーを覆う導電膜を概略的に示す部分拡大垂直断面図である。

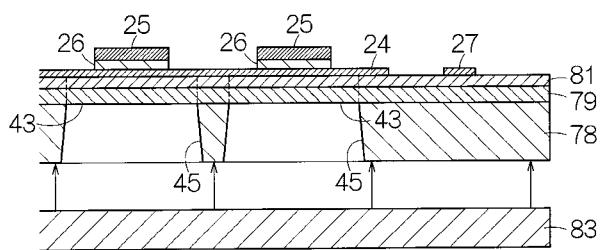

【図10】シリコンウェハーに形成された開口および補強板用のウエハーを概略的に示す部分拡大垂直断面図である。

【発明を実施するための形態】

【0021】

以下、添付図面を参照しつつ本発明の一実施形態を説明する。なお、以下に説明する本実施形態は、特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。

【0022】

(1) 超音波診断装置の全体構成

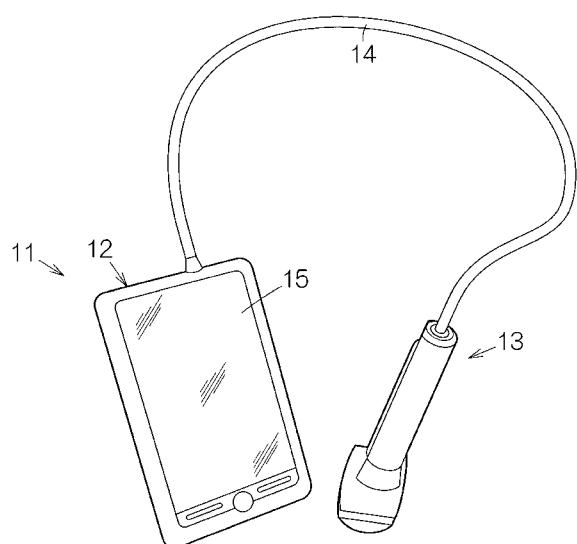

図1は本発明の一実施形態に係る電子機器の一具体例すなわち超音波診断装置11の構成を概略的に示す。超音波診断装置11は装置端末12と超音波プローブ(プローブ)13とを備える。装置端末12と超音波プローブ13とはケーブル14で相互に接続される。装置端末12と超音波プローブ13とはケーブル14を通じて電気信号をやりとりする。装置端末12にはディスプレイパネル(表示装置)15が組み込まれる。ディスプレイパネル15の画面は装置端末12の表面で露出する。装置端末12では、後述されるように、超音波プローブ13で検出された超音波に基づき画像が生成される。画像化された検出結果がディスプレイパネル15の画面に表示される。

【0023】

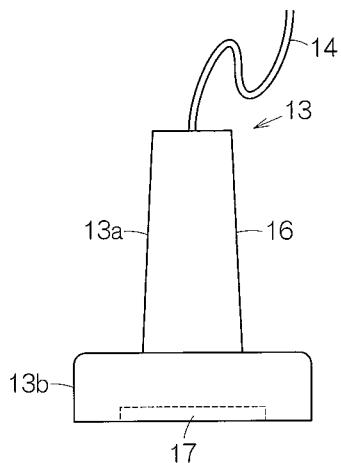

図2に示されるように、超音波プローブ13は筐体16を有する。筐体16内には超音波トランスデューサー素子チップ(以下「素子チップ」という)17が収容される。素子チップ17の表面は筐体16の表面で露出することができる。素子チップ17は表面から超音波を出力するとともに超音波の反射波を受信する。その他、超音波プローブ13は、プローブ本体13aに着脱自在に連結されるプローブヘッド13bを備えることができる。このとき、素子チップ17はプローブヘッド13bの筐体16内に組み込まれることができる。

【0024】

(2) 超音波トランスデューサー素子チップの構成

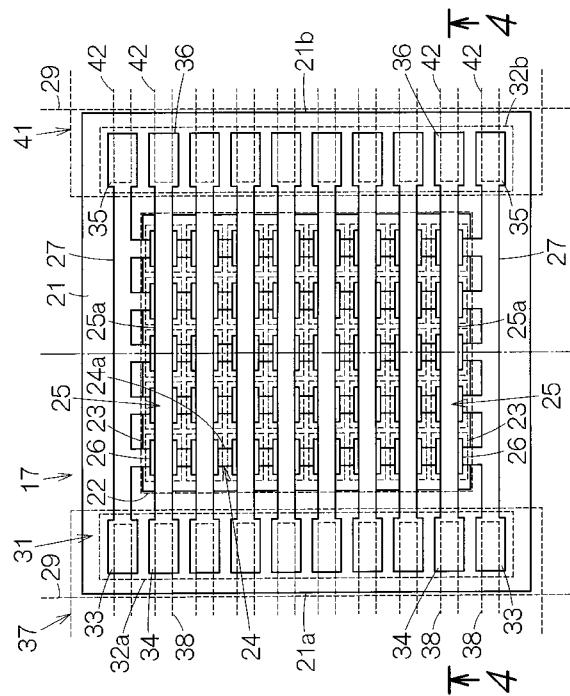

図3は一実施形態に係る素子チップ17の平面図を概略的に示す。素子チップ17は基

10

20

30

40

50

板21を備える。基板21の表面には素子アレイ22が形成される。素子アレイ22は超音波トランスデューサー素子(以下「素子」という)23の配列で構成される。配列は複数行複数列のマトリクスで形成される。個々の素子23は圧電素子部を備える。圧電素子部は下部電極24、上部電極25および圧電体膜26で構成される。個々の素子23ごとに下部電極24および上部電極25の間に圧電体膜26が挟み込まれる。

#### 【0025】

下部電極24は複数本の第1導電体24aを有する。第1導電体24aは配列の行方向に相互に平行に延びる。1行の素子23ごとに1本の第1導電体24aが割り当てられる。1本の第1導電体24aは配列の行方向に並ぶ素子23の圧電体膜26に共通に配置される。第1導電体24aの両端は1対の引き出し配線27にそれぞれ接続される。引き出し配線27は配列の列方向に相互に平行に延びる。したがって、全ての第1導電体24aは同一長さを有する。こうしてマトリクス全体の素子23に共通に下部電極24は接続される。

10

#### 【0026】

上部電極25は複数本の第2導電体25aを有する。第2導電体25aは配列の列方向に相互に平行に延びる。1列の素子23ごとに1本の第2導電体25aが割り当てられる。1本の第2導電体25aは配列の列方向に並ぶ素子23の圧電体膜26に共通に配置される。列ごとに素子23の通電は切り替えられる。こうした通電の切り替えに応じてラインスキャンやセクタースキャンは実現される。1列の素子23は同時に超音波を出力することから、1列の個数すなわち配列の行数は超音波の出力レベルに応じて決定することができる。行数は例えば10~15行程度に設定されればよい。図中では省略されて5行が描かれる。配列の列数はスキャンの範囲の広がりに応じて決定することができる。列数は例えば128列や256列に設定されればよい。図中では省略されて8列が描かれる。その他、配列では千鳥配置が確立されてもよい。千鳥配置では偶数列の素子23群は奇数列の素子23群に対して行ピッチの2分の1ですらされればよい。奇数列および偶数列の一方の素子数は他方の素子数に比べて1つ少なくてよい。さらにまた、下部電極24および上部電極25の役割は入れ替えられてもよい。すなわち、マトリクス全体の素子23に共通に上部電極が接続される一方で、配列の列ごとに共通に素子23に下部電極が接続されてもよい。

20

#### 【0027】

30

基板21の外縁は、相互に平行な1対の直線29で仕切られて対向する第1辺21aおよび第2辺21bを有する。素子アレイ22の輪郭と基板21の外縁との間に広がる周縁領域31には、第1辺21aと素子アレイ22の輪郭との間に1ラインの第1端子アレイ32aが配置され、第2辺21bと素子アレイ22の輪郭との間に1ラインの第2端子アレイ32bが配置される。第1端子アレイ32aは第1辺21aに平行に1ラインを形成することができる。第2端子アレイ32bは第2辺21bに平行に1ラインを形成することができる。第1端子アレイ32aは1対の下部電極端子33および複数の上部電極端子34で構成される。同様に、第2端子アレイ32bは1対の下部電極端子35および複数の上部電極端子36で構成される。1本の引き出し配線27の両端にそれぞれ下部電極端子33、35は接続される。引き出し配線27および下部電極端子33、35は素子アレイ22を二等分する垂直面で対称に形成されればよい。1本の第2導電体25aの両端にそれぞれ上部電極端子34、36は接続される。第2導電体25aおよび上部電極端子34、36は素子アレイ22を二等分する垂直面で対称に形成されればよい。

40

#### 【0028】

50

基板21には第1フレキシブルプリント基板(以下「第1フレキ」という)37が連結される。第1フレキ37は第1端子アレイ32aに覆い被さる。第1フレキ37の一端には下部電極端子33および上部電極端子34に個別に対応して導電線すなわち第1信号線38が形成される。第1信号線38は下部電極端子33および上部電極端子34に個別に向き合わせられ個別に接合される。同様に、基板21には第2フレキシブルプリント基板(以下「第2フレキ」という)41が覆い被さる。第2フレキ41は第2端子アレイ32

b に覆い被さる。第 2 フレキ 4 1 の第 1 端 4 1 a には下部電極端子 3 5 および上部電極端子 3 6 に個別に対応して導電線すなわち第 2 信号線 4 2 が形成される。第 2 信号線 4 2 は下部電極端子 3 5 および上部電極端子 3 6 に個別に向き合わせられ個別に接合される。

#### 【0029】

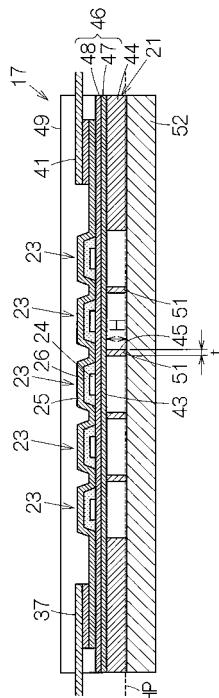

図 4 に示されるように、個々の素子 2 3 は振動膜 4 3 を有する。振動膜 4 3 の構築にあたって基板 2 1 の基体 4 4 には個々の素子 2 3 ごとに開口 4 5 が形成される。開口 4 5 は基体 4 4 に対してアレイ状に配置される。基体 4 4 の表面には可撓膜 4 6 が一面に形成される。可撓膜 4 6 は、基体 4 4 の表面に積層される酸化シリコン (SiO<sub>2</sub>) 層 4 7 と、酸化シリコン層 4 7 の表面に積層される酸化ジルコニウム (ZrO<sub>2</sub>) 層 4 8 とで構成される。可撓膜 4 6 は開口 4 5 に接する。こうして開口 4 5 の輪郭に対応して可撓膜 4 6 の一部が振動膜 4 3 として機能する。酸化シリコン層 4 7 の膜厚は共振周波数に基づき決定されることができる。

10

#### 【0030】

振動膜 4 3 の表面に下部電極 2 4 、圧電体膜 2 6 および上部電極 2 5 が順番に積層される。下部電極 2 4 には例えればチタン (Ti) 、イリジウム (Ir) 、白金 (Pt) およびチタン (Ti) の積層膜が用いられることができる。圧電体膜 2 6 は例えればジルコン酸チタン酸鉛 (PZT) で形成されることがある。上部電極 2 5 は例えればイリジウム (Ir) で形成されることがある。下部電極 2 4 および上部電極 2 5 にはその他の導電材が利用されてもよく、圧電体膜 2 6 にはその他の圧電材料が用いられてもよい。ここでは、上部電極 2 5 の下で圧電体膜 2 6 は完全に下部電極 2 4 を覆う。圧電体膜 2 6 の働きで上部電極 2 5 と下部電極 2 4 との間で短絡は回避されることがある。

20

#### 【0031】

基板 2 1 の表面には保護膜 4 9 が積層される。保護膜 4 9 は例えれば全面にわたって基板 2 1 の表面に覆い被さる。その結果、素子アレイ 2 2 や第 1 および第 2 端子アレイ 3 2 a 、3 2 b 、第 1 および第 2 フレキ 3 7 、4 1 の第 1 端 3 7 a 、4 1 a は保護膜 4 9 で覆われる。保護膜 4 9 には例えればシリコーン樹脂膜が用いられることがある。保護膜 4 9 は、素子アレイ 2 2 の構造や、第 1 端子アレイ 3 2 a および第 1 フレキ 3 7 の接合、第 2 端子アレイ 3 2 b および第 2 フレキ 4 1 の接合を保護する。

#### 【0032】

マトリクスの行方向および列方向に隣接する開口 4 5 同士の間には仕切り壁 5 1 が区画される。開口 4 5 同士は仕切り壁 5 1 で仕切られる。仕切り壁 5 1 の壁厚み t は開口 4 5 の空間同士の間隔に相当する。仕切り壁 5 1 は相互に平行に広がる平面内に 2 つの壁面を規定する。壁厚み t は壁面同士の距離に相当する。すなわち、壁厚み t は壁面に直交して壁面同士の間に挟まれる垂線の長さで規定されることがある。仕切り壁 5 1 の壁高さ H は開口 4 5 の深さに相当する。開口 4 5 の深さは基体 4 4 の厚みに相当する。したがって、仕切り壁 5 1 の壁高さ H は基体 4 4 の厚み方向に規定される壁面の長さで規定されることがある。基体 4 4 は均一な厚みを有することから、仕切り壁 5 1 は全長にわたって一定の壁高さ H を有することができる。仕切り壁 5 1 の壁厚み t が縮小されれば、振動膜 4 3 の配置密度は高められる。素子チップ 1 7 の小型化に寄与することができる。壁厚み t に比べて仕切り壁 5 1 の壁高さ H が大きければ、素子チップ 1 7 の曲げ剛性は高められることがある。こうして開口 4 5 同士の間隔は開口 4 5 の深さよりも小さく設定される。

30

#### 【0033】

基体 4 4 の裏面には補強板 (板状部材) 5 2 が固定される。補強板 5 2 の表面に基体 4 4 の裏面が重ねられる。補強板 5 2 の表面は仮想平面 HP 内で広がる。基体 4 4 の裏面も仮想平面 HP 内で広がることから、基体 4 4 の裏面は最大限に広い面積で補強板 5 2 の表面に接することができる。補強板 5 2 は素子チップ 1 7 の裏面で開口 4 5 を閉じる。補強板 5 2 は基体 4 4 の厚み方向からの平面視で開口 4 5 を覆う。補強板 5 2 はリジッドな基材を備えることができる。補強板 5 2 は例えればシリコン基板から形成されることがある。基体 4 4 の板厚は例えれば 100  $\mu\text{m}$  程度に設定され、補強板 5 2 の板厚は例えれば 100 ~ 150  $\mu\text{m}$  程度に設定される。ここでは、仕切り壁 5 1 は補強板 5 2 に結合される。補

40

50

強板 5 2 は個々の仕切り壁 5 1 に少なくとも 1 力所の接合域で接合される。接合にあたって接着剤は用いられることがある。

【 0 0 3 4 】

図 5 に示されるように、開口 4 5 は第 1 方向 D 1 に列を形成する。開口 4 5 の輪郭形状の図心 5 5 は第 1 方向 D 1 の 1 直線 5 6 上で等ピッチに配置される。開口 4 5 は 1 つの輪郭形状の複写で象られることから、同一形状の開口 4 5 が一定のピッチで繰り返し配置される。開口 4 5 の輪郭 4 5 a は例えば四角形に規定される。具体的には矩形に形成される。矩形の長辺は第 1 方向 D 1 に合わせ込まれる。こうして開口 4 5 は矩形の輪郭 4 5 a を有することから、仕切り壁 5 1 は全長にわたって一定の壁厚み  $t$  を有することができる。このとき、仕切り壁 5 1 の接合域は長辺の中央位置を含む領域であればよい。特に、仕切り壁 5 1 の接合域は長辺の全長を含む領域であればよい。仕切り壁 5 1 は長辺の全長にわたって開口 4 5 同士の間の全面で補強板 5 2 に面接合されることができる。さらに、仕切り壁 5 1 の接合域は四角形の各辺に少なくとも 1 力所ずつ配置されることができる。仕切り壁 5 1 の接合域は四角形を途切れなく囲むことができる。仕切り壁 5 1 は四角形の全周にわたって開口 4 5 同士の間の全面で補強板 5 2 に面接合されることができる。

10

【 0 0 3 5 】

( 3 ) 超音波診断装置の回路構成

図 6 に示されるように、集積回路はマルチプレクサー 6 1 および送受信回路 6 2 を備える。マルチプレクサー 6 1 は素子チップ 1 7 側のポート群 6 1 a と送受信回路 6 2 側のポート群 6 1 b とを備える。素子チップ 1 7 側のポート群 6 1 a には第 1 配線 5 4 経由で第 1 信号線 3 8 および第 2 信号線 4 2 が接続される。こうしてポート群 6 1 a は素子アレイ 2 2 に繋がる。ここでは、送受信回路 6 2 側のポート群 6 1 b には集積回路チップ 5 5 内の規定数の信号線 6 3 が接続される。規定数はスキャンにあたって同時に出力される素子 2 3 の列数に相当する。マルチプレクサー 6 1 はケーブル 1 4 側のポートと素子チップ 1 7 側のポートとの間で相互接続を管理する。

20

【 0 0 3 6 】

送受信回路 6 2 は規定数の切り替えスイッチ 6 4 を備える。個々の切り替えスイッチ 6 4 はそれぞれ個別に対応の信号線 6 3 に接続される。送受信回路 6 2 は個々の切り替えスイッチ 6 4 ごとに送信経路 6 5 および受信経路 6 6 を備える。切り替えスイッチ 6 4 には送信経路 6 5 と受信経路 6 6 とが並列に接続される。切り替えスイッチ 6 4 はマルチプレクサー 6 1 に選択的に送信経路 6 5 または受信経路 6 6 を接続する。送信経路 6 5 にはパルサー 6 7 が組み込まれる。パルサー 6 7 は振動膜 5 2 の共振周波数に応じた周波数でパルス信号を出力する。受信経路 6 6 にはアンプ 6 8 、ローパスフィルター ( L P F ) 6 9 およびアナログデジタル変換器 ( A D C ) 7 1 が組み込まれる。個々の素子 2 3 の検出信号は増幅されてデジタル信号に変換される。

30

【 0 0 3 7 】

送受信回路 6 2 は駆動 / 受信回路 7 2 を備える。送信経路 6 5 および受信経路 6 6 は駆動 / 受信回路 7 2 に接続される。駆動 / 受信回路 7 2 はスキャンの形態に応じて同時にパルサー 6 7 を制御する。駆動 / 受信回路 7 2 はスキャンの形態に応じて検出信号のデジタル信号を受信する。駆動 / 受信回路 7 2 は制御線 7 3 でマルチプレクサー 6 1 に接続される。マルチプレクサー 6 1 は駆動 / 受信回路 7 2 から供給される制御信号に基づき相互接続の管理を実施する。

40

【 0 0 3 8 】

装置端末 1 2 には処理回路 7 4 が組み込まれる。処理回路 7 4 は例えば中央演算処理装置 ( C P U ) やメモリーを備えることができる。超音波診断装置 1 1 の全体動作は処理回路 7 4 の処理に従って制御される。ユーザーから入力される指示に応じて処理回路 7 4 は駆動 / 受信回路 7 2 を制御する。処理回路 7 4 は素子 2 3 の検出信号に応じて画像を生成する。画像は描画データで特定される。

【 0 0 3 9 】

装置端末 1 2 には描画回路 7 5 が組み込まれる。描画回路 7 5 は処理回路 7 4 に接続さ

50

れる。描画回路 7 5 にはディスプレイパネル 1 5 が接続される。描画回路 7 5 は処理回路 7 4 で生成された描画データに応じて駆動信号を生成する。駆動信号はディスプレイパネル 1 5 に送り込まれる。その結果、ディスプレイパネル 1 5 に画像が映し出される。

#### 【0040】

##### (4) 超音波診断装置の動作

次に超音波診断装置 1 1 の動作を簡単に説明する。処理回路 7 4 は駆動 / 受信回路 7 2 に超音波の送信および受信を指示する。駆動 / 受信回路 7 2 はマルチプレクサー 6 1 に制御信号を供給するとともに個々のパルサー 6 7 に駆動信号を供給する。パルサー 6 7 は駆動信号の供給に応じてパルス信号を出力する。マルチプレクサー 6 1 は制御信号の指示に従ってポート群 6 1 b のポートにポート群 6 1 a のポートを接続する。パルス信号はポートの選択に応じて下部電極端子 3 3、3 5 および上部電極端子 3 4、3 6 を通じて列ごとに素子 2 3 に供給される。パルス信号の供給に応じて振動膜 4 3 は振動する。その結果、対象物（例えば人体の内部）に向けて所望の超音波は発せられる。

#### 【0041】

超音波の送信後、切り替えスイッチ 6 4 は切り替えられる。マルチプレクサー 6 1 はポートの接続関係を維持する。切り替えスイッチ 6 4 は送信経路 6 5 および信号線 6 3 の接続に代えて受信経路 6 6 および信号線 6 3 の接続を確立する。超音波の反射波は振動膜 4 3 を振動させる。その結果、素子 2 3 から検出信号が出力される。検出信号はデジタル信号に変換されて駆動 / 受信回路 7 2 に送り込まれる。

#### 【0042】

超音波の送信および受信は繰り返される。繰り返しにあたってマルチプレクサー 6 1 はポートの接続関係を変更する。その結果、ラインスキャンやセクタスキャンは実現される。スキャンが完了すると、処理回路 7 4 は検出信号のデジタル信号に基づき画像を形成する。形成された画像はディスプレイパネル 1 5 の画面に表示される。

#### 【0043】

素子チップ 1 7 では素子 2 3 は薄型に形成されることができる。素子 2 3 は薄型の基板 2 1 に形成されることができる。補強板 5 2 が基板 2 1 に固定されても、素子チップ 1 7 は薄型に形成されることができる。同時に、補強板 5 2 は基板 2 1 の強度を補強する。特に、仕切り壁 5 1 で壁厚  $m$  が壁高さ  $H$  よりも小さいことから、断面係数の関係で仕切り壁 5 1 では基板 2 1 の厚み方向に十分な剛性が確保されることができる。基板 2 1 の厚み方向の力は仕切り壁 5 1 を伝って補強板 5 2 で支持されることができる。こうして素子チップ 1 7 は基板 2 1 の厚み方向に十分な強度を有することができる。そして、基板 2 1 の板厚が例えば  $100 \mu m$  程度に設定されても、補強板 5 2 は基板 2 1 の破損を防止することができる。その一方で、バルク型の超音波トランスデューサー素子で素子アレイが構成される場合には、基板の板厚は数  $mm$  程度に設定される。たとえ補強板 5 2 が接合されても、本実施形態に係る素子チップ 1 7 の厚みは、バルク型の超音波トランスデューサー素子で素子アレイが構成される場合に比べて確実に縮小されることができる。加えて、振動膜 4 3 の音響インピーダンスはバルク型の超音波トランスデューサー素子に比べて人体のそれに近いことから、素子チップ 1 7 ではバルク型の超音波トランスデューサー素子に比べて音響インピーダンスの整合層が省略されることができる。こういった整合層の省略は素子チップ 1 7 の薄型化にさらに寄与することができる。

#### 【0044】

補強板 5 2 は個々の仕切り壁 5 1 に少なくとも 1 力所の接合域で接合される。仕切り壁 5 1 が補強板 5 2 に接合されると、仕切り壁 5 1 の動きは補強板 5 2 で拘束される。したがって、仕切り壁 5 1 の振動は防止されることがある。その結果、素子 2 3 同士のクロストークは防止されることがある。しかも、こうして仕切り壁 5 1 の動きが拘束されると、素子 2 3 の超音波振動に対して仕切り壁 5 1 の振動の作用は回避されることがある。素子 2 3 ではクリアな振動モードの超音波振動が得られる。こうして仕切り壁 5 1 の振動が回避されると、超音波振動の振幅の低下も抑制されることがある。その一方で、仕切り壁 5 1 が動くと、振動膜 4 3 の上下振動モードよりも低い周波数の歪んだ振動モード

10

20

30

40

50

が現れる。しかも、仕切り壁 5 1 が動く分だけ振動膜 4 3 の運動エネルギーが減少し振動の振幅が低下してしまう。

【0045】

四角い輪郭同士の開口 4 5 が隣り合うと、仕切り壁 5 1 は均一な壁厚み  $t$  で形成することができる。したがって、素子 2 3 の密集度は高められることができる。こうして素子 2 3 の密集度が高まれば高まるほど、仕切り壁 5 1 の壁厚み  $t$  は均一に減少する。したがって、仕切り壁 5 1 の剛性は著しく弱まる。こうしたときに仕切り壁 5 1 が補強板 5 2 に連結されれば、仕切り壁 5 1 の振動は効果的に防止されることがある。

【0046】

仕切り壁 5 1 の接合域は長辺の中央位置を含む領域であることができる。仕切り壁 5 1 のうち振動振幅の大きい部位が補強板 5 2 に接合される。その結果、仕切り壁 5 1 の振動は効果的に防止されることがある。しかも、仕切り壁 5 1 の接合域は長辺の全長を含む領域であることができる。こうして長辺の全長にわたって仕切り壁 5 1 が補強板 5 2 に接合されれば、仕切り壁 5 1 の振動は確実に防止されることがある。さらに、仕切り壁 5 1 は長辺の全長にわたって開口 4 5 同士の間の全面で面接合されることがある。こうして長辺の全長にわたって開口 4 5 同士の間で全面で仕切り壁 5 1 が補強板 5 2 に面接合されれば、仕切り壁 5 1 の振動は確実に防止されることがある。

【0047】

仕切り壁 5 1 の接合域は四角形の各辺に少なくとも 1 力所ずつ配置されればよい。こうして四角形の各辺で仕切り壁 5 1 が補強板 5 2 に接合されれば、仕切り壁 5 1 の振動は確実に防止されることがある。しかも、仕切り壁 5 1 の接合域は四角形を途切れなく囲むことができる。こうして四角形の全域で仕切り壁 5 1 が補強板 5 2 に接合されれば、仕切り壁 5 1 の振動は確実に防止されることがある。その上、仕切り壁 5 1 は四角形の全周にわたって開口 4 5 同士の間の全面で面接合されることがある。こうして四角形の全周にわたって開口 4 5 同士の間で全面で仕切り壁 5 1 が補強板 5 2 に面接合されれば、仕切り壁 5 1 の振動は確実に防止されることがある。

【0048】

(5) 超音波トランステューサー素子チップの製造方法

図 7 に示されるように、シリコンウエハー 7 8 の表面で個々の素子チップ 1 7 ごとに下部電極 2 4 、引き出し配線 2 7 および下部電極端子 3 3 、 3 5 (図 7 以降では図示されず) が形成される。下部電極 2 4 、引き出し配線 2 7 および下部電極端子 3 3 、 3 5 の形成に先立ってシリコンウエハー 7 8 の表面には酸化シリコン膜 7 9 および酸化ジルコニウム膜 8 1 が相次いで形成される。酸化ジルコニウム膜 8 1 の表面には導電膜が形成される。導電膜はチタン、イリジウム、白金およびチタンの積層膜で構成される。フォトリソグラフィ技術に基づき導電膜から下部電極 2 4 、引き出し配線 2 7 および下部電極端子 3 3 、 3 5 は成形される。

【0049】

図 8 に示されるように、下部電極 2 4 の表面で個々の素子 2 3 ごとに圧電体膜 2 6 および上部電極 2 5 が形成される。圧電体膜 2 6 および上部電極 2 5 の形成にあたってシリコンウエハー 7 8 の表面には圧電材料膜および導電膜が成膜される。圧電材料膜は P Z T 膜から構成される。導電膜はイリジウム膜から構成される。フォトリソグラフィ技術に基づき個々の素子 2 3 ごとに圧電材料膜および導電膜から圧電体膜 2 6 および上部電極 2 5 が成形される。

【0050】

続いて、図 9 に示されるように、シリコンウエハー 7 8 の表面に導電膜 8 2 が成膜される。導電膜 8 2 は個々の素子チップ 1 7 内で列ごとに上部電極 2 5 を相互に接続する。そして、フォトリソグラフィ技術に基づき導電膜 8 2 から上部電極 2 5 および上部電極端子 3 4 、 3 6 が成形される。

【0051】

その後、図 10 に示されるように、シリコンウエハー 7 8 の裏面からアレイ状の開口 4

10

20

30

40

50

5 が形成される。開口 4 5 の形成にあたってエッティング処理が施される。酸化シリコン膜 7 9 はエッティングストップ層として機能する。酸化シリコン膜 7 9 および酸化ジルコニウム膜 8 1 に振動膜 4 3 は区画される。開口 4 5 の形成後、シリコンウエハー 7 8 の裏面に補強板用のウエハー 8 3 の表面が重ね合わせられる。ウエハー 8 3 には例えばリジッドな絶縁性基板が用いられることができる。絶縁性基板にはシリコンウエハーが用いられることが可能である。接合にあたって例えば接着剤が用いられることがある。接合後、シリコンウエハー 7 8 から個々の素子チップ 1 7 は切り出される。

【0052】

なお、上記のように本実施形態について詳細に説明したが、本発明の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。したがって、このような変形例はすべて本発明の範囲に含まれる。例えば、明細書または図面において、少なくとも一度、より広義または同義な異なる用語とともに記載された用語は、明細書または図面のいかなる箇所においても、その異なる用語に置き換えることができる。また、超音波診断装置 1 1、超音波プローブ 1 3、素子チップ 1 7、素子 2 3 等の構成および動作も本実施形態で説明したものに限定されず、種々の変形が可能である。

10

【符号の説明】

【0053】

1 1 電子機器（超音波診断装置）、1 3 プローブ（超音波プローブ）、1 3 b プローブヘッド、1 5 表示装置（ディスプレイパネル）、1 6 筐体、1 7 超音波トランステューサー素子チップ、2 1 基板、2 3 超音波トランステューサー素子、4 5 開口、5 1 仕切り壁部（仕切り壁）、5 2 板状部材（補強板）。

20

【図 1】

【図 2】

【図3】

【 図 5 】

【 四 4 】

【 四 6 】

【図7】

【図8】

【図10】

【図9】

---

フロントページの続き

(72)発明者 清瀬 摂内

長野県諏訪市大和3丁目3番5号 セイコーホームズ株式会社内

Fターム(参考) 4C601 EE10 GB06 GB41

5D019 AA20 BB02 BB19 EE03 FF04

|                |                                                                                                                                                                                 |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | <无法获取翻译>                                                                                                                                                                        |         |            |

| 公开(公告)号        | <a href="#">JP2013175879A5</a>                                                                                                                                                  | 公开(公告)日 | 2015-04-09 |

| 申请号            | JP2012038402                                                                                                                                                                    | 申请日     | 2012-02-24 |

| [标]申请(专利权)人(译) | 精工爱普生株式会社                                                                                                                                                                       |         |            |

| 申请(专利权)人(译)    | 精工爱普生公司                                                                                                                                                                         |         |            |

| [标]发明人         | 中村友亮<br>鶴野次郎<br>清瀬撰内                                                                                                                                                            |         |            |

| 发明人            | 中村 友亮<br>鶴野 次郎<br>清瀬 撰内                                                                                                                                                         |         |            |

| IPC分类号         | H04R17/00 A61B8/00                                                                                                                                                              |         |            |

| CPC分类号         | B06B1/0629 A61B8/4427 A61B8/4488 A61B8/4494 B06B1/0622 H01L41/053                                                                                                               |         |            |

| FI分类号          | H04R17/00.330.G A61B8/00 H04R17/00.332.A                                                                                                                                        |         |            |

| F-TERM分类号      | 4C601/EE10 4C601/GB06 4C601/GB41 5D019/AA20 5D019/BB02 5D019/BB19 5D019/EE03 5D019/FF04 2G047/AC13 2G047/CA01 2G047/DB02 2G047/GB02 2G047/GB17 2G047/GB21 2G047/GG35 2G047/GH06 |         |            |

| 代理人(译)         | 井上 一<br>黒田靖                                                                                                                                                                     |         |            |

| 其他公开文献         | JP5990930B2<br>JP2013175879A                                                                                                                                                    |         |            |

### 摘要(译)

超声换能器元件芯片包括基板，多个超声换能器元件和板状构件。基板包括分隔壁部分，该分隔壁部分限定以阵列图案布置的多个开口。隔壁部分的壁厚小于隔壁部分的壁高。每个超声换能器元件设置在每个开口中。板状构件固定在基板的与基板的表面相对的表面上，在基板的表面上设置有超声波换能器元件。在沿着基板的厚度方向看的平面图中，板状构件覆盖至少一个开口。