(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2018-75182

(P2018-75182A)

(43) 公開日 平成30年5月17日(2018.5.17)

(51) Int.Cl.

A 6 1 B 8/14 (2006.01)

F 1

A 6 1 B 8/14

テーマコード(参考)

4 C 6 0 1

審査請求 未請求 請求項の数 15 O L (全 18 頁)

(21) 出願番号

特願2016-218984 (P2016-218984)

(22) 出願日

平成28年11月9日 (2016.11.9)

(71) 出願人 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(74) 代理人 110001689

青稜特許業務法人

(72) 発明者 梶山 新也

東京都千代田区丸の内一丁目6番6号 株式会社日立製作所内

(72) 発明者 中川 樹生

東京都千代田区丸の内一丁目6番6号 株式会社日立製作所内

F ターム(参考) 4C601 EE09 EE15 GB18 HH21 JB06

JB09 JB60

(54) 【発明の名称】アナログ加算回路、それを用いた超音波探触子、および超音波診断装置

## (57) 【要約】

## 【課題】

低消費電力で広帯域なアナログ加算回路を実現する。

## 【解決手段】

其々が超音波振動子に接続された、複数の入力端子と、複数の入力端子と一対一に対応する、複数の受信回路と、複数の受信回路の其々が備える、入力端子から得られる信号に基づく電荷を貯える信号キャパシタと、複数の受信回路の信号キャパシタの出力を統合する出力配線と、を有する超音波探触子である。この超音波探触子では、複数の受信回路の信号キャパシタに貯えた電荷を、複数の受信回路の信号キャパシタで再配分することで、複数の入力端子から得られる信号を統合し、信号キャパシタおよび出力配線の寄生キャパシタの電荷を定期的に所定値に設定することで、信号キャパシタおよび寄生キャパシタの電荷の充放電履歴をリセットすることを特徴とする。

## 【選択図】図 1

**【特許請求の範囲】****【請求項 1】**

複数の入力端子と、

前記複数の入力端子の其々に対応する、複数のサンプルホールド回路ブロックと、

前記複数のサンプルホールド回路ブロックの出力を入力として、一つの出力を生成する

マルチプレクサを備え、

前記複数のサンプルホールド回路ブロックの其々は、第1の容量と、第2の容量と、第

3の容量と、を備え、

前記第1の容量と前記マルチプレクサを接続する第1の配線と、前記第2の容量と前記

マルチプレクサを接続する第2の配線と、前記第3の容量と前記マルチプレクサを接続す

る第3の配線と、を備え、

前記第1の容量、第2の容量、および第3の容量の其々に対して、

前記入力端子と接続し、前記マルチプレクサと切断する第1の状態、

前記マルチプレクサと接続し、前記入力端子と切断する第2の状態、

所定電位に接続し、前記入力端子およびマルチプレクサと切断する第3の状態、

の3つの状態を排他的に設定するスイッチを備え、

前記第1の容量と前記マルチプレクサの間に配置され、前記第3の状態において、前記

第1の配線を前記所定電位に接続するための第1のリセットスイッチと、

前記第2の容量と前記マルチプレクサの間に配置され、前記第3の状態において、前記

第2の配線を前記所定電位に接続するための第2のリセットスイッチと、

前記第3の容量と前記マルチプレクサの間に配置され、前記第3の状態において、前記

第3の配線を前記所定電位に接続するための第3のリセットスイッチと、

を備えるアナログ加算回路。

**【請求項 2】**

前記第1のリセットスイッチは、前記第1の配線の寄生容量の電荷をリセットし、

前記第2のリセットスイッチは、前記第2の配線の寄生容量の電荷をリセットし、

前記第3のリセットスイッチは、前記第3の配線の寄生容量の電荷をリセットする、

請求項1記載のアナログ加算回路。

**【請求項 3】**

前記複数のサンプルホールド回路ブロックは、半導体集積回路装置内にアレイ状に配列

されてアレイ領域を形成しており、

前記第1のリセットスイッチ、第2のリセットスイッチ、および、第3のリセットスイ

ッチは、前記アレイ領域外に配置されている、

請求項1記載のアナログ加算回路。

**【請求項 4】**

前記3つの状態を排他的に設定するスイッチは、

前記第1の配線の、前記第1の容量と前記第1のリセットスイッチの間に配置された第

1の接続スイッチと、

前記第2の配線の、前記第2の容量と前記第2のリセットスイッチの間に配置された第

2の接続スイッチと、

前記第3の配線の、前記第3の容量と前記第3のリセットスイッチの間に配置された第

3の接続スイッチと、を含む、

請求項3記載のアナログ加算回路。

**【請求項 5】**

其々が超音波振動子に接続された、複数の入力端子と、

前記複数の入力端子と一対一に対応する、複数の受信回路と、

前記複数の受信回路の其々が備える、前記入力端子から得られる信号に基づく電荷を貯

える信号キャパシタと、

前記複数の受信回路の信号キャパシタの出力を統合する出力配線と、を有し、

前記複数の受信回路の信号キャパシタに貯えた電荷を、該複数の受信回路の信号キャパ

10

20

30

40

50

シタで再配分することで、前記複数の入力端子から得られる信号を統合し、

前記信号キャパシタおよび前記出力配線の寄生キャパシタの電荷を定期的に所定値に設定することで、前記信号キャパシタおよび前記寄生キャパシタの電荷の充放電履歴をリセットすることを特徴とする超音波探触子。

【請求項 6】

請求項 5において、

前記信号キャパシタおよび前記寄生キャパシタの電荷を定期的に所定値に設定する際に

、前記信号キャパシタおよび前記寄生キャパシタに印加される電圧をアナログ信号のコモン電圧近傍とすることを特徴とする超音波探触子。

10

【請求項 7】

請求項 5において、

前記信号キャパシタに対して、クロックに同期して動作する離散時間サンプリング系を備え、

前記クロックに同期して、信号のサンプル、信号のホールド、前記信号キャパシタおよび前記寄生キャパシタの電荷の充放電履歴のリセット、の 3 インタリーブ動作を交互に行うことを特徴とする超音波探触子。

【請求項 8】

請求項 7において、

前記 3 インタリーブ動作を交互に行う 3 つのサンプルホールド回路を有し、

20

前記 3 つのサンプルホールド回路の其々は、前記信号キャパシタを備え、

前記 3 つのサンプルホールド回路の出力をアナログマルチプレクサにより交互に出力することを特徴とする超音波探触子。

【請求項 9】

請求項 8において、

前記 3 つのサンプルホールド回路と、前記アナログマルチプレクサと、前記アナログマルチプレクサの後段回路の接続において、

前記 3 つのサンプルホールド回路と前記アナログマルチプレクサの間の 3 本の配線の長さが、前記アナログマルチプレクサと前記後段回路の間の配線の長さより長いことを特徴とする超音波探触子。

30

【請求項 10】

請求項 8において、

前記 3 つのサンプルホールド回路を一組としたサンプルホールド回路ブロックがアレイ状に並んでおり、

前記サンプルホールド回路ブロックから、アレイの外側に配置された前記アナログマルチプレクサまでの配線長が、前記サンプルホールド回路ブロックの位置に依らず等長であることを特徴とする超音波探触子。

【請求項 11】

請求項 5において、

前記入力端子の其々は、1 対の差動入力端子であり、

40

前記差動入力端子は前記信号キャパシタの 2 つの電極にスイッチを介して接続されることで、差動信号を前記信号キャパシタに保持することを特徴とする超音波探触子。

【請求項 12】

超音波探触子と本体装置から構成される超音波診断装置であって、

前記超音波探触子は、

複数の超音波振動子と、

前記超音波振動子の其々に対応する、複数のサンプルホールド回路ブロックと、

前記複数のサンプルホールド回路ブロックの出力を入力とするマルチプレクサと、

前記サンプルホールド回路ブロックと前記マルチプレクサを接続する出力配線と、

を備え、

50

前記マルチプレクサの出力は、後段回路を介して前記本体装置に入力され、

前記サンプルホールド回路ブロックの其々は、前記超音波振動子の検出信号に基づく電荷を貯える信号キャパシタを備え、

前記出力配線を定期的に所定電位に接続するリセットスイッチを備える、

ことを特徴とする超音波診断装置。

【請求項 1 3】

前記サンプルホールド回路ブロックは、アレイ状に配列され、

前記マルチプレクサは前記アレイ状の配列の外部に配置され、

前記リセットスイッチは、前記アレイ状の配列の外部に配置され、前記出力配線を前記所定電位に接続する寄生キャパシタリセットスイッチであり、

10

さらに、前記アレイ状の配列の内部に配置され、前記信号キャパシタを前記所定電位に接続する信号キャパシタリセットスイッチを備え、

前記信号キャパシタリセットスイッチと寄生キャパシタリセットスイッチは、同期して動作する、

請求項 1 2 記載の超音波診断装置。

【請求項 1 4】

前記サンプルホールド回路ブロックは、3個一組の前記信号キャパシタを備え、

該3個の信号キャパシタは、

20

前記超音波振動子からの信号をサンプルする第1の状態、

前記マルチプレクサに信号を出力する第2の状態、

前記所定電位に接続される第3の状態、

の3つの状態を順次排他的に設定される、

請求項 1 3 記載の超音波診断装置。

【請求項 1 5】

前記サンプルホールド回路ブロックと前記出力配線は、半導体集積回路内に形成されている、

請求項 1 4 記載の超音波診断装置。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、超音波診断装置の構成要素である超音波探触子に搭載されて、1次元あるいは2次元に繰り返し配置されたアレイ状の各振動子からの受信信号を超音波振動子毎に独立に遅延させフォーカスを行う遅延加算整相に必要なアナログ加算回路を、広帯域かつ低消費電力で実現する技術に関するものである。

30

【背景技術】

【0 0 0 2】

超音波診断装置は人体に非侵襲で安全性の高い医療診断機器であり、X線診断装置、MRI (Magnetic Resonance Imaging) 装置などの他の医用画像診断装置に比べ、装置規模が小さく、また、超音波探触子を体表から当てるだけの簡単な操作により、例えば、心臓の脈動や胎児の動きといった検査対象の動きの様子をリアルタイムで表示可能な装置であることから、今日の医療において重要な役割を果たしている。

40

【0 0 0 3】

超音波診断装置においては、超音波探触子に内蔵されている複数の振動子それぞれに高電圧の駆動信号を供給することで、超音波を被検体内に送信する。被検体内において生体組織の音響インピーダンスの差異によって生ずる超音波の反射波を複数の振動素子それぞれにて受信し、超音波探触子が受信した反射波に基づいて画像を生成する。

【0 0 0 4】

具体的には、送信においては、複数の振動子に独立な遅延を与えて振動子を駆動することで音響パルスをフォーカスし、超音波のビームフォーミングおよびビーム走査を行う。

50

受信においては、生体内の反射点から各振動子への距離の違いを補償するため、複数の振動子に独立な遅延を与えて信号の位相をコヒーレントにそろえ、これを加算するという整相加算処理を行う。このように、アナログ信号の遅延および加算は超音波診断装置において必須の信号処理となっている。

【0005】

近年、3次元立体画像を得られる超音波診断装置が開発されてきており、3次元立体画像から任意の断面を特定して断層像を得ることで、検査効率を向上させることが出来る。3次元の撮像のためには、超音波探触子内の振動子を、従来の1次元配列から2次元配列、すなわち2Dアレイとする必要があり、振動子数が従来の超音波探触子に対して2乗で増加する。この場合に、超音波探触子と本体装置を接続するケーブルの本数を2乗で増やすことは困難であるため、超音波探触子内で整相加算して本数を減らした受信信号を本体装置にケーブルを介して転送する必要がある。このような超音波探触子内の整相加算を実現するには、送受信と整相加算の機能をビームフォーマーICとして実現し、IC内には振動子毎に送受信回路を配置して振動子と電気的に1対1で接続する必要がある。

10

【0006】

2Dアレイ超音波探触子においては、整相加算を行うICを探触子内に搭載する必要があり、数千から1万以上の送受信回路がICに搭載される。探触子は体表に直接接触するので発熱を抑える必要があり、ICの低消費電力化は重要な課題である。

【0007】

また、超音波の周波数が高いほど生体内での減衰が大きくなるものの、超音波エコーから得られる画像の空間分解能は向上するため、超音波の周波数は可能な限り高くして受信回路の帯域を広く取りたい。広帯域な受信回路を前述のように低消費電力で実現することが必要となる。

20

【0008】

整相処理に必要なアナログ信号の加算を実現する回路として、オペアンプを用いて電流で信号を加算するような回路が考えられるが、オペアンプは定常電流バイアスをかけて動作させるために回路の消費電力が大きくなる。低消費電力でアナログ加算を行う回路として、キャパシタに信号電荷を貯めて電荷で信号加算を行うようなパッシブなアナログ加算回路が考えられる。

30

【0009】

このようなキャパシタの電荷履歴をキャンセルする回路の例として、複数キャパシタを用いた遅延回路が特許文献1に提案されている。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】国際公開 WO 2015/128974 A1

【発明の概要】

【発明が解決しようとする課題】

【0011】

スイッチとキャパシタのみを用いてパッシブ動作で電荷加算する回路の場合、低インピーダンスでバッファリングする回路がないために寄生容量の影響を強く受け、アナログ加算回路としての帯域が寄生容量により劣化することが懸念される。とくに、信号電荷を貯めるキャパシタと寄生容量の間で電荷のシェアが行われるために、クロック同期で動作する離散時間サンプリング系の回路を構成した場合、前クロックサイクルで信号電荷用キャパシタおよび寄生容量に蓄えられた電荷の履歴の影響を受ける。

40

【0012】

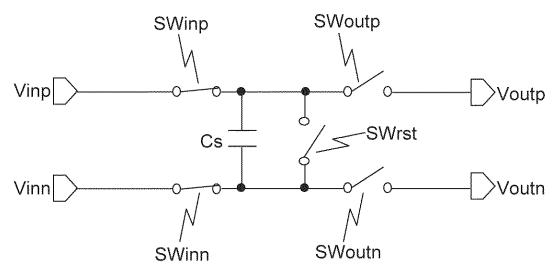

図13は、本発明の課題を説明するために、特許文献1の図16を発明者の視点で描き直したものである。図13の回路は、複数キャパシタにアナログ電圧を順番に保持し、所定時間後に読み出すことでアナログ信号を遅延させるものである。図13の例においては、差動アナログ信号電圧入力 $V_{inp}$ ,  $V_{inn}$ の差をキャパシタ $C_s$ に電荷として蓄え

50

るが、入力信号を蓄える前の初期状態に依存して蓄積する電荷に変化が生じるため、キャパシタに電圧レベルが電荷として蓄積される前にキャパシタ電荷をリセットすることが有効である点が示されている。すなわち前段回路の出力インピーダンスは理想的な0でなく、0より高いインピーダンスをもつためにこのような初期電荷状態に依存する。

【0013】

$SW_{inp}$ と $SW_{inn}$ をオンさせることで前段から電圧駆動されて $C_s$ に蓄積された電荷は、 $SW_{outp}$ と $SW_{outn}$ をオンさせることで電圧として後段に出力され、さらに $SW_{rst}$ をオンすることで $C_s$ の電荷はリセットされて次に $SW_{inp}$ と $SW_{inn}$ をオンさせて $C_s$ に電荷が蓄積される前に初期状態に戻る。

【0014】

しかしながら、図13の回路の後段の負荷を考慮した場合、たとえば $V_{outp}$ 、 $V_{outn}$ に大きな入力容量を持つ回路が接続された場合、あるいは次段回路までの距離が遠く、大きな配線の寄生容量が付いてしまう場合、 $SW_{outp}$ と $SW_{outn}$ がオンした場合に $C_s$ とこの負荷容量で電荷のシェアが行われるが、 $C_s$ の信号電荷は $SW_{rst}$ によりリセットできても、負荷容量に蓄積された電荷のリセットは行えない。

【0015】

特許文献1には、 $SW_{outp}$ と $SW_{outn}$ をオンさせて信号を出力した後、または信号を電荷として蓄積する前にリセットを行うことが望ましいとの記載があるが、出力に接続される負荷容量についての記載はない。また、特許文献1の図13には、オペアンプを用いて出力をバッファリングする構成が開示されているが、オペアンプのような定常バイアス電流を消費する回路を用いた場合には消費電力が増加するという問題がある。

【0016】

このような点から、信号を電荷で蓄積するサンプルホールド回路を用いながら、オペアンプのような定常バイアス電流を消費するバッファ回路を用いることなく、出力の負荷容量が大きな場合においても信号電荷蓄積用のキャパシタおよび出力負荷容量の両方に蓄積された電荷をリセットすることで電荷履歴をキャンセルし、広帯域な回路を実現することが求められる。

【0017】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0018】

上記課題を達成するための本願発明の一側面は、複数の入力端子と、複数の入力端子の其々に対応する、複数のサンプルホールド回路ブロックと、複数のサンプルホールド回路ブロックの出力を入力として、一つの出力を生成するマルチブレクサを備えるアナログ加算回路である。この回路では、複数のサンプルホールド回路ブロックの其々は、第1の容量と、第2の容量と、第3の容量と、を備える。また、第1の容量とマルチブレクサを接続する第1の配線と、第2の容量とマルチブレクサを接続する第2の配線と、第3の容量とマルチブレクサを接続する第3の配線と、を備える。そして、第1の容量、第2の容量、および第3の容量の其々に対して、入力端子と接続し、マルチブレクサと切断する第1の状態、マルチブレクサと接続し、入力端子と切断する第2の状態、所定電位に接続し、入力端子およびマルチブレクサと切断する第3の状態、の3つの状態を排他的に設定するスイッチを備える。また、第1の容量とマルチブレクサの間に配置され、第3の状態において、第1の配線を所定電位に接続するための第1のリセットスイッチと、第2の容量とマルチブレクサの間に配置され、第3の状態において、第2の配線を所定電位に接続するための第2のリセットスイッチと、第3の容量とマルチブレクサの間に配置され、第3の状態において、第3の配線を所定電位に接続するための第3のリセットスイッチと、を備える。

【0019】

本願発明の他の一側面は、其々が超音波振動子に接続された、複数の入力端子と、複数

10

20

30

40

50

の入力端子と一対一に対応する、複数の受信回路と、複数の受信回路の其々が備える、入力端子から得られる信号に基づく電荷を貯える信号キャパシタと、複数の受信回路の信号キャパシタの出力を統合する出力配線と、を有する超音波探触子である。この超音波探触子では、複数の受信回路の信号キャパシタに貯えた電荷を、複数の受信回路の信号キャパシタで再配分することで、複数の入力端子から得られる信号を統合し、信号キャパシタおよび出力配線の寄生キャパシタの電荷を定期的に所定値に設定することで、信号キャパシタおよび寄生キャパシタの電荷の充放電履歴をリセットすることを特徴とする。

【0020】

本発明のさらに他の一側面は、超音波探触子と本体装置から構成される超音波診断装置である。この装置では、超音波探触子は、複数の超音波振動子と、超音波振動子の其々に対応する、複数のサンプルホールド回路ブロックと、複数のサンプルホールド回路ブロックの出力を入力とするマルチブレクサと、サンプルホールド回路ブロックとマルチブレクサを接続する出力配線と、を備える。そして、マルチブレクサの出力は、後段回路を介して本体装置に入力される。また、サンプルホールド回路ブロックの其々は、超音波振動子の検出信号に基づく電荷を貯える信号キャパシタを備える。また、出力配線を定期的に所定電位に接続するリセットスイッチを備える。

10

【発明の効果】

【0021】

低消費電力で広帯域なアナログ加算回路を実現する。

20

【図面の簡単な説明】

【0022】

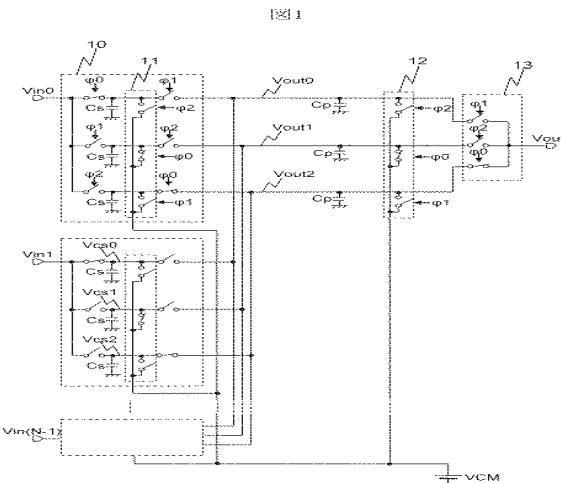

【図1】本発明の実施例のアナログ加算回路の構成を示した回路図である。

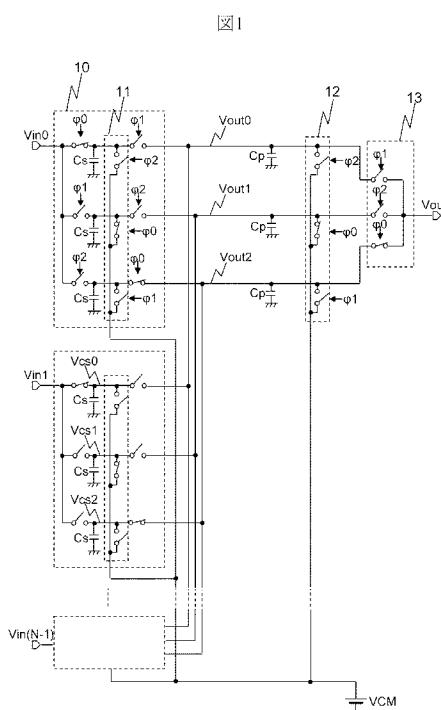

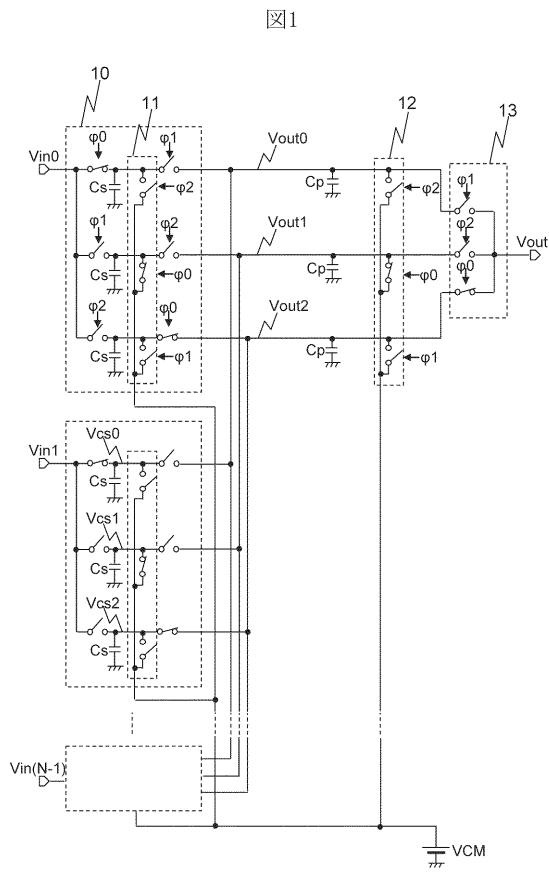

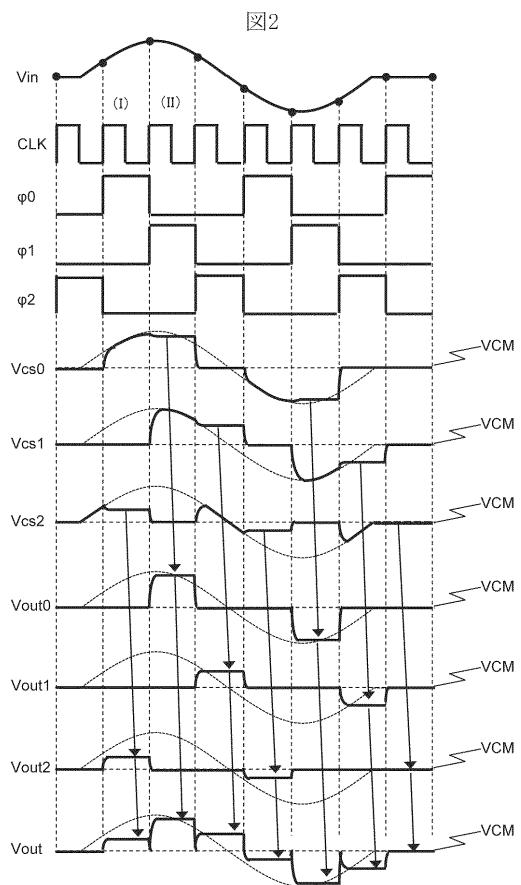

【図2】図1のアナログ加算回路の動作を説明するタイミングチャートである。

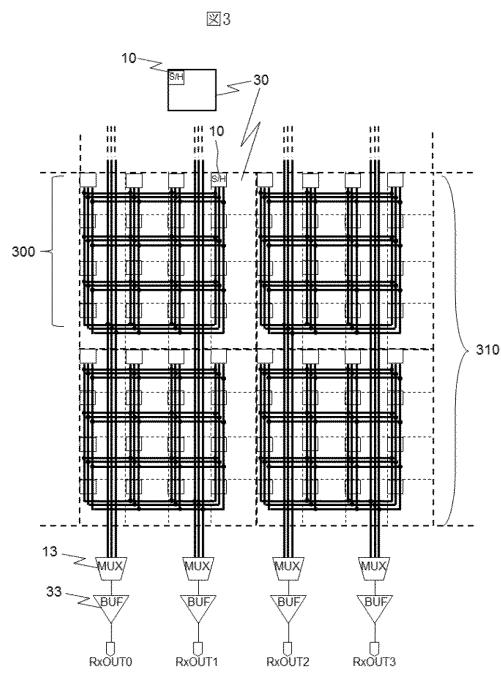

【図3】実施例のアナログ加算回路の物理的レイアウト例を示す平面図である。

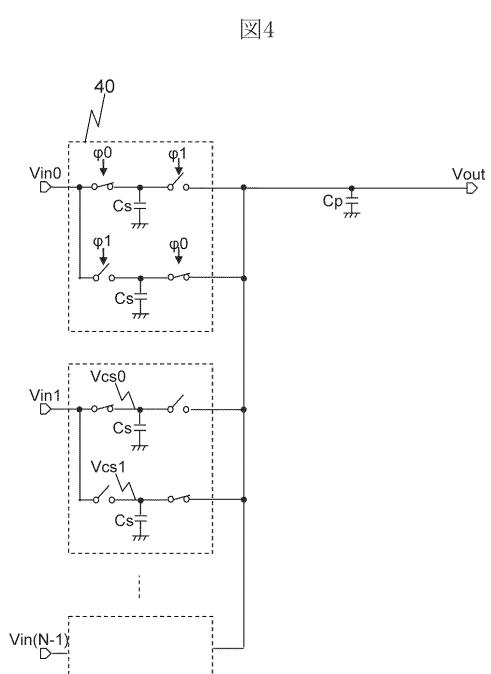

【図4】電荷履歴リセットの加算回路帯域に与える効果を説明するために、電荷履歴をリセットしない場合の離散時間サンプリングアナログ加算回路の構成を示した回路図である。

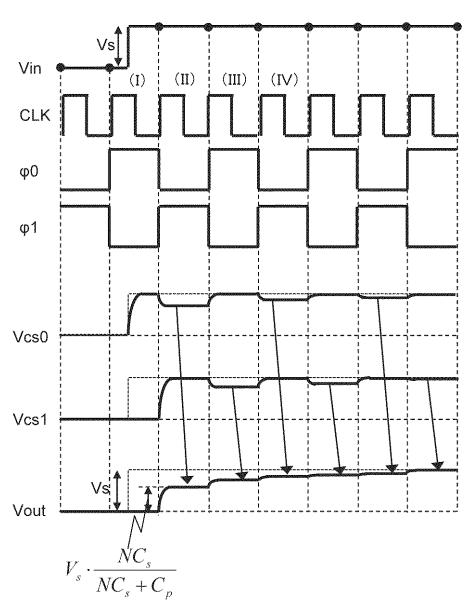

【図5】図4のアナログ加算回路のステップ入力時の動作を説明するタイミングチャートである。

30

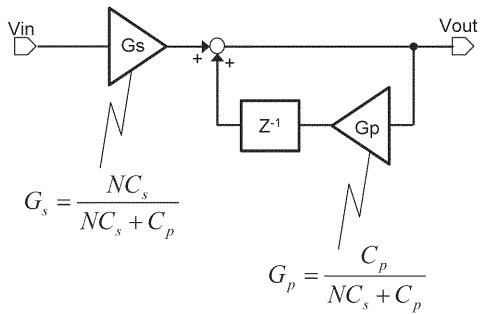

【図6】図4のアナログ加算回路の信号フローと伝達関数を示した回路ブロック図である。

【図7】図1のアナログ加算回路のステップ入力時の動作を説明するタイミングチャートである。

【図8】図1のアナログ加算回路の信号フローと伝達関数を示した回路ブロック図である。

40

【図9】図1と図4のアナログ加算回路の周波数特性を示したグラフ図である。

【図10】本発明の別の実施例として、差動入力、シングルエンド出力のアナログ加算回路の構成を示した回路図である。

40

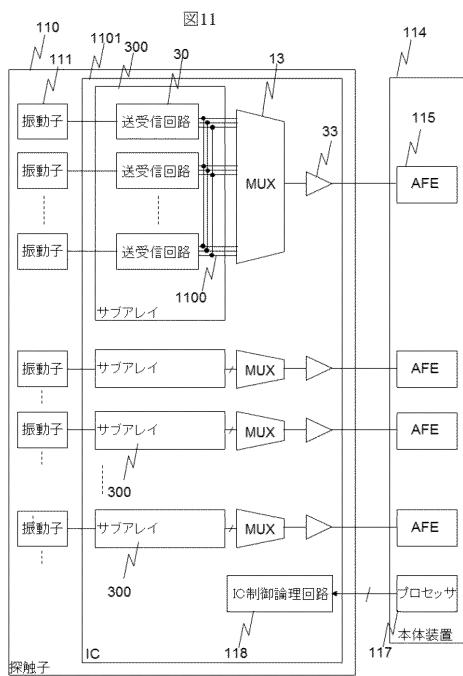

【図11】実施例が適用される超音波診断装置のシステム構成例を示したブロック図である。

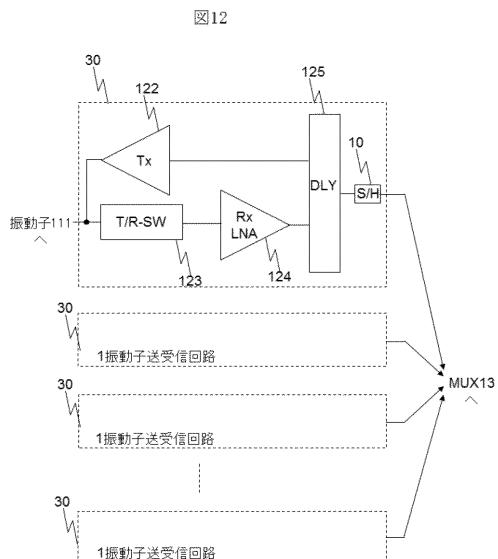

【図12】実施例が適用される超音波探触子内ICの送受信回路の構成例を示したブロック図である。

50

【図13】比較例の回路図である。

【発明を実施するための形態】

【0023】

本実施例において開示される発明のうち代表的なものの概要を簡単に説明すれば、下記の通りである。すなわち、サンプルホールド回路を用いて電荷でアナログ信号を加算するアナログ加算回路において、信号電荷を蓄積するキャパシタ、およびサンプルホールド回路の出力に接続される負荷容量の両方の電荷を定期的にリセットすることで電荷履歴の影響を排除し、アナログ加算回路の負荷容量が大きな場合においても広帯域なアナログ加算

50

処理を低消費電力で実現している。

【0024】

これにより、定常バイアス電流を消費するバッファ回路を用いることなく、スイッチとキャパシタのみで構成されるパッシブな回路のみで広帯域なアナログ加算回路を実現出来る。また、これにより、高い周波数の超音波を扱う受信回路が実現出来、超音波の周波数が高いほど生体内での減衰は増大するものの、エコー画像の空間分解能は向上するため、空間分解能が高い超音波画像診断装置を実現することが出来る。また、アナログ加算回路が搭載されるICの電力を低減することが出来、ICが搭載される超音波探触子の発熱を抑制することが可能となる。

【0025】

図1に本実施例における離散時間アナログ加算回路の構成を示す。Vin0、Vin1、…、Vin(N-1)のN端子のアナログ電圧入力を受けてVoutに加算された信号を出力する。超音波診断装置の場合には、アナログ電圧入力は複数の超音波振動子のそれぞれから得られる信号であり、図1に示す加算回路により、被検査物の所定箇所から得られる情報を取得することができる。また、図1の加算回路は超音波探触子に内蔵され、例えば、半導体集積回路で構成される。Voutから出力される加算された出力信号は、必要な後段回路を経由して、ケーブルなどを介して装置本体へ送られる。

10

【0026】

N個のサンプルホールド回路ブロック10は同一構成であり、N端子のアナログ電圧入力を其々入力としている。Csは入力信号電圧を電荷として保持するためのキャパシタ(信号キャパシタ)であり、Cpは配線寄生容量(寄生キャパシタ)を想定している。すなわち、後述するように2Dアレイ超音波探触子用のICにおいては、加算出力をアレイ内からアレイ外へと長い配線で布線する必要があり、Cpが付いたVout0、Vout1、Vout2の3本の配線はアレイ内からアレイ外へと布線される配線のために大きな寄生容量Cpが付くと仮定している。アナログマルチプレクサ13はアレイの外に配置され、Voutに接続される後段回路は近接して配置することが可能なため、Voutの負荷は小さく、サンプルホールド回路ブロック10からリセットスイッチ12およびアナログマルチプレクサ13までの距離が長く、この部分の配線寄生容量Cpのみが問題となるものとする。

20

【0027】

この例では、サンプルホールド回路ブロック10には3つのサンプルホールド回路が含まれている。アナログマルチプレクサ13とアナログマルチプレクサ13の後段回路の接続においては、3つのサンプルホールド回路とアナログマルチプレクサ13の間の3本の配線の長さが、アナログマルチプレクサ13と後段回路の間の配線の長さより長く構成している。

30

【0028】

制御信号0、1、2により、リセットスイッチ11および12がオンまたはオフに制御される。各超音波振動子毎に配置される3インタリーブのサンプルホールド回路ブロック10は、アレイ内に配置される。電荷履歴をリセットするためのリセットスイッチ11および12については、リセットスイッチ11はCsの電荷をリセットするためにアレイ内に配置される必要があり、リセットスイッチ12は特に制限されないが、配線寄生容量Cp電荷をリセットするスイッチであり、アレイ外に配置されることが望ましい。また、VCMは信号のコモン電位である。

40

【0029】

本アナログ加算回路はCsに蓄積された電荷CsVin0、CsVin1、…、CsVin(N-1)をN個のCsで再配分する動作を行うため、仮に配線寄生容量Cpの影響がなくCp=0Fとした場合には、(数1)の出力Voutが得られるため、正確にはN入力を加算するのではなく平均化する回路であるが、加算してさらに1/Nに減衰していると考えればよいので、便宜上加算回路と呼ぶことにする。

【0030】

50

## 【数1】

$$\begin{aligned}

V_{out} &= \frac{C_s V_{in0} + C_s V_{in0} + \cdots + C_s V_{in(N-1)}}{NC_s} \\

&= \frac{C_s (V_{in0} + V_{in0} + \cdots + V_{in(N-1)})}{NC_s} \\

&= \frac{V_{in0} + V_{in0} + \cdots + V_{in(N-1)}}{N}

\end{aligned}$$

10

## 【0031】

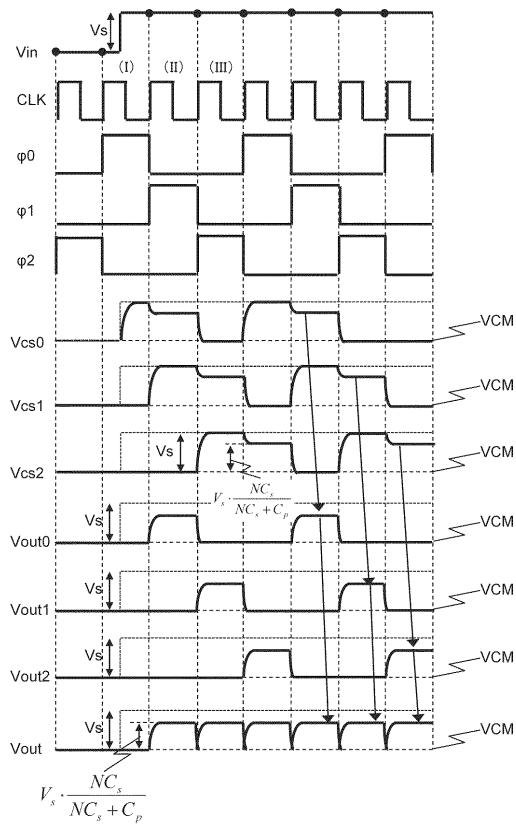

図2に本実施例における加算動作の原理を理解するためのタイミングチャートを示す。V<sub>in</sub>は図1のV<sub>in0</sub>、V<sub>in1</sub>、…、V<sub>in(N-1)</sub>がすべて同一の波形と仮定したときの電圧入力信号である。同一のN系統のV<sub>in</sub>信号が平均化されて、理想的にはV<sub>in</sub>が離散時間サンプリングされた信号がV<sub>out</sub>として出力される。

## 【0032】

0、1、2はスイッチの制御信号であり、図示されるようにクロックCLKに同期して3相のパルス信号として生成される。3相信号は、図1中の3インタリーブのサンプルホールド回路ブロック10のサンプル、ホールド、リセット動作に対応している。

20

## 【0033】

たとえば図2において、左から2番目のクロックサイクル(I)にみられるように、0がHiレベルで図1中の容量ノードV<sub>cs0</sub>が入力V<sub>in</sub>にトラックしているフェーズでは、V<sub>cs1</sub>はCsの電荷をリセットするフェーズにあり、V<sub>cs2</sub>はCsに保持されたV<sub>in</sub>をV<sub>out2</sub>に出力するフェーズにある。

## 【0034】

次のクロックサイクル(II)では図2のように、1のみがHiレベルとなるので、V<sub>cs0</sub>がホールド、V<sub>cs1</sub>がサンプル、V<sub>cs2</sub>がリセットのフェーズとなる。このように3インタリーブの動作を繰り返し、図1の長い配線V<sub>out0</sub>、V<sub>out1</sub>、V<sub>out2</sub>にはホールドされた状態のみが3インタリーブで交互に出力される。図1のアナログマルチプレクサ13でV<sub>out0</sub>、V<sub>out1</sub>、V<sub>out2</sub>の3つをマルチプレクスしてV<sub>out</sub>に加算結果を出力する。

30

## 【0035】

図1のVCMは信号のコモンレベルであり、Cs信号電荷のリセット先である。リセットフェーズにおいては、CsにはVCM電圧(コモン電圧)が強制的に印加される。このように信号のコモンレベルにリセットすることにより、入力信号サンプルのフェーズ、すなわち入力信号をサンプルする場合のCsの初期電位は常に信号振幅中心のVCMとなる。サンプル時の静定を0Vから開始、あるいは電源電圧Vddから開始でなく信号振幅中心から開始することで、静定を早くすることができるため、このようにリセット先をコモン電位VCMとするのが望ましい。

40

## 【0036】

以上のサンプル、ホールド、リセットの3インタリーブ動作、さらに信号電荷を蓄えるキャパシタCsをリセットする図1中のリセットスイッチ11、配線寄生容量Cpをリセットするリセットスイッチ12により、CsとCpの両方の電荷履歴をリセットした電荷加算動作がパッシブで実現可能となり、広帯域な離散時間アナログ加算回路を実現できる。

## 【0037】

50

なお、図2のV<sub>c s 0</sub>、V<sub>c s 1</sub>、V<sub>c s 2</sub>波形において、サンプルフェーズで入力信号をトラックした後、ホールドのフェーズで保持電圧が若干シフトした図としている。これは、N×C<sub>s</sub>とC<sub>p</sub>で電荷のシェアが起こるために電圧変動が生じることを示している。後述するように、C<sub>s</sub>とC<sub>p</sub>は常にサンプルフェーズ前に履歴がリセットされているため、電荷のシェアは常に固定された既知のC<sub>p</sub>電荷とN×C<sub>s</sub>で行われるので問題とならない。前サイクルで信号に依存したC<sub>p</sub>電荷が残留してしまうことが問題になる。

#### 【0038】

図3に本実施例のアナログ加算回路の物理的レイアウト例を示す。このような回路は、例えば超音波探触子内に配置される1チップの集積回路として構成することができる。この場合には、R<sub>x</sub>OUT<sub>0</sub>～R<sub>x</sub>OUT<sub>3</sub>は、I<sub>C</sub>の出力端子を構成する。図3のレイアウトでは、超音波振動子毎に配置される1チャネルの送受信回路30がアレイ状に配置されている。また、4×4=16チャネルの受信信号を加算して1本に束ねることを仮定している。ここでは、16チャネル分の送受信回路が一つのサブアレイ300に属するものとし、4個のサブアレイを配置してアレイ310を構成しているが、個数の増減は可能である。送受信回路30は其々、例えばI<sub>C</sub>のバンプを介して超音波振動子と接続される。なお、便宜上本明細書では、出力信号が加算により束ねられるグループであり、物理的にアレイ内に配置される回路（超音波振動子およびマルチプレクサ13は含まない）をサブアレイ300ということにする。

#### 【0039】

送受信回路30の一つを抜き出して図3上方に示す。1チャネルの送受信回路30内には、サンプルホールド回路ブロック10が配置されており、これは図1のサンプルホールド回路ブロック10に相当する。サンプルホールド回路ブロック10からの3本の出力配線が、加算単位である16チャネルでショートされ、アレイ310の外まで布線される。アレイ310上の布線が長いために、大きな寄生容量が付くことは図1のC<sub>p</sub>の説明で述べた通りである。

#### 【0040】

各アナログマルチプレクサ13は、1つのサブアレイ300からの3本の出力線を入力とする。これは、図1のアナログマルチプレクサ13に相当する。図示されないが、図1の配線寄生容量リセット用のリセットスイッチ12はアナログマルチプレクサ13の近傍に配置されることが望ましい。アナログマルチプレクサ13の後段には、I<sub>C</sub>出力をバッファして、超音波探触子と本体装置を接続するケーブルを駆動するためのケーブルバッファ回路33を備える。

#### 【0041】

アナログマルチプレクサ13とケーブルバッファ回路33は、アレイ310の外部において近接して置けるため、アナログマルチプレクサ13の出力に付く寄生容量は大きな問題とはならない。仮にアナログマルチプレクサ13をアレイ内に配置した場合、アナログマルチプレクサ13の出力に付く寄生容量は大きくなってしまうので、加算回路の帯域が劣化する。本実施例においては、信号電荷を蓄積するキャパシタと配線寄生容量の電荷履歴のリセットを3インタリーブ動作で実現し、電荷履歴がリセットされた3本の出力配線をアナログマルチプレクスして1本の出力とするため、本実施例の効果が発揮されるためには図3のように3本の配線をアレイ310の外まで布線しておいて、アレイ外でマルチプレクスすることが望ましい。

#### 【0042】

また、振動子毎のチャネルを束ねる加算単位であるサブアレイ300の位置によらず、サブアレイ300からアナログマルチプレクサ13までの配線寄生容量が等負荷であることが、各加算回路の特性をそろえてサブアレイ間の特性ばらつきを低減するという目的を鑑みれば望ましい。図3に示すように、サブアレイ300からアナログマルチプレクサ13までの配線長が、アレイ310の外側のサブアレイでも内側のサブアレイでも等長となるように、サンプルホールド回路ブロック10の出力である3本の配線をアレイ310の下端から、図示されないが反対側の上端まで布線すること等で等長とすることができます。

10

20

30

40

50

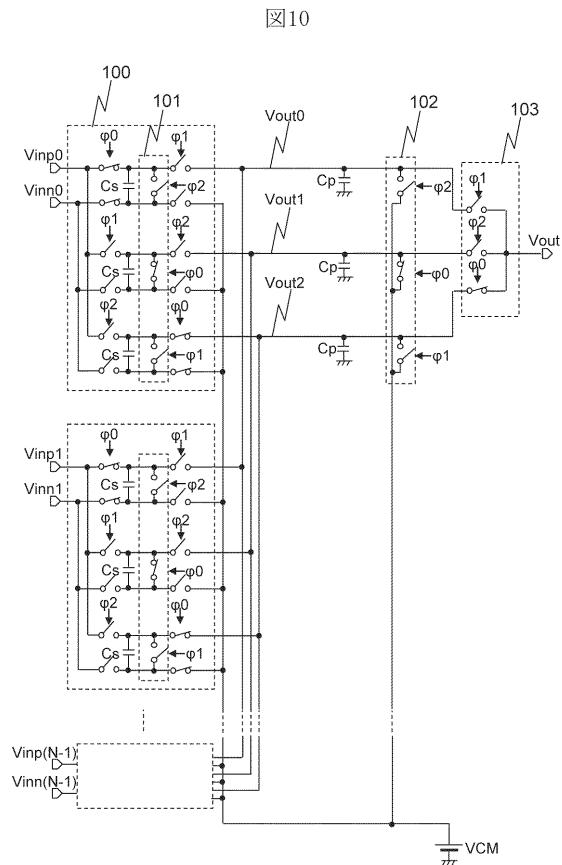

## 【0043】

本実施例における、電荷履歴リセットの加算回路帯域に与える効果を説明するために、図4に電荷履歴をリセットしない場合の離散時間サンプリングアナログ加算回路を、図5にこの動作を示すステップ入力時のタイミングチャートを、図6に図4の回路に相当する伝達関数を、さらに図7に本実施例の図1のステップ入力時のタイミングチャートを、図8に本実施例の図1に相当する伝達関数を示す。

## 【0044】

図4の比較例において、回路40は振動子毎に配置される送受信回路内の加算回路である。サンプル、ホールドの2インタリーブ動作であり、一方のキャパシタCsに入力信号をサンプルしているフェーズで、もう一方のCsに電荷で蓄積された信号を出力し、この出力は各チャネルで互いにショートされているため、電荷の再配分により加算、正確には平均化動作が実現できる。回路40の出力配線はアレイの外まで布線されるために長く、配線寄生容量Cpが大きいと仮定する。

10

## 【0045】

図5は図4の回路において、各入力に同一のステップ入力を与えたときの動作を示すタイミングチャートである。0と1により入力信号のサンプルと、キャパシタCsに保持された電圧の出力の2インタリーブ動作が行われる。キャパシタCsのノードVcs0、Vcs1において、例えばVcs0に注目すると、サンプルフェーズであるクロックサイクル(I)ではVc電位はステップ入力の変動Vsを追隨して静定する。しかしながらCsに保持された電圧を出力するホールドフェーズのクロックサイクル(II)において、NxCsとCpで電荷のシェアが行われ、Vcs電圧が変動する。次のサンプルフェーズのクロックサイクル(III)ではVcsはVsに追隨するが、その次のホールドフェーズ(IV)では、以前のホールドフェーズでCpに蓄積された電荷とVsに対応してCsに蓄積された電荷Cs・Vsの電荷のシェアで決まる電位までVsが変動する。このように、配線寄生容量Cpには、以前のホールドフェーズでの電荷が蓄積されており、NxCsとCpの電荷シェアで決まる電位は常にCp電荷履歴の影響を受けることになる。

20

## 【0046】

ステップ入力後の最初のステップ出力のサイクルでは、Cpに電荷が残っていないために、次の(数2)のようになる。

30

## 【0047】

## 【数2】

$$V_{out} = V_s \cdot \frac{NC_s}{NC_s + C_p}$$

## 【0048】

しかし、この後はNxCsとCpで電荷のシェアを繰り返しながら図5のVout波形に示すように徐々にVsに漸近していくという動作になる。すなわちCpの電荷履歴の影響を受けて、ステップ入力を与えた場合に出力は理想的なステップ出力とはならず、徐々にVsに漸近していくくなった波形となる。周波数応答としては、アナログ加算回路としての帯域がCp電荷履歴により劣化しているようにみえ、NxCsとCpの関係で帯域が決まる。

40

## 【0049】

図6に、図4の回路の伝達関数を示す。電荷履歴によるフィードバックパスがあるために、Cpの影響を受けた伝達関数となる。

## 【0050】

図7には、リセット動作を追加した本実施例の図1の回路にステップ入力を与えた場合の動作タイミングチャートを示す。Vcs0、Vcs1、Vcs2は図1の信号電荷蓄積

50

キャパシタ  $C_s$  のノードである。サンプルフェーズでステップ入力の最大電位  $V_s$  までト ラックした後（例えばクロックサイクル（I）の  $V_{c_s 0}$ ）、 $N \times C_s$  と  $C_p$  で電荷のシェアが行われて電位は低下する（例えばクロックサイクル（II）の  $V_{c_s 0}$ ）。しかしながら、 $C_s$  および  $C_p$  はサンプルホールドを行う前に必ずリセットされており（例えばクロックサイクル（III）の  $V_{c_s 0}$ ）、 $C_p$  電荷初期状態が決まっているため、 $N \times C_s$  と  $C_p$  で電荷シェアされた後の電位は必ず（数2）で表される電位となる。

#### 【0051】

この結果、 $C_p$  の電荷履歴の影響なく、図7最下段の波形  $V_{out}$  のように、ステップ入力に対して常にコモン電位  $V_{CM}$  から（数2）で表される電位まで毎サイクル静定する出力となり、図5のような  $V_s$  に徐々に漸近するなまつた波形ではなく、（数2）で表現されるように固定の減衰率で減衰はするもののステップ出力を出力できることになる。

10

#### 【0052】

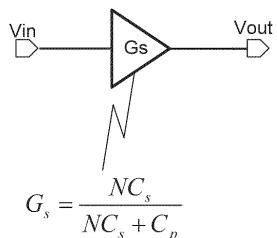

図8に本実施例の構成である図1の回路の伝達関数を示す。 $C_s$  と  $C_p$  の電荷履歴をリセットすることにより図6のフィードバックパスが無くなり、以下の（数3）で表される伝達関数となる。 $N \times C_s$  と  $C_p$  の電荷シェアの影響で（数3）の固定の減衰率をもつ。

#### 【0053】

#### 【数3】

$$\frac{V_{out}}{V_{in}} = G_s = \frac{NC_s}{NC_s + C_p}$$

20

#### 【0054】

図9に、本実施例の図1の回路と、リセット動作を行わない図4の回路の周波数特性を示す。リセットしない場合は図5のタイミングチャートのように  $V_{out}$  は  $V_s$  に追随し、0 dB の直流利得を実現できる。ただしステップ入力に対する応答のなまりにみられるように、帯域は  $C_p$  の電荷履歴の影響を受けて劣化する。一方リセット動作を行った場合、図7のタイミングチャートに示されるように  $V_{out}$  は（数2）で表される電位以上には上昇しないので、直流利得すなわち減衰率は（数3）となる。ただしステップ入力に対してステップ出力の応答が得られるため、帯域はリセットしない場合に対して改善し、実際の帯域は  $C_p$  の電荷履歴でなく、回路の構成要素であるスイッチのオン抵抗とキャパシタで決まる時定数で律速される。

30

#### 【0055】

なお、（数1）～（数3）中のキャパシタなどの実際の数値については、装置の設計や用途により、種々適用が可能であり制限されるものではない。

#### 【0056】

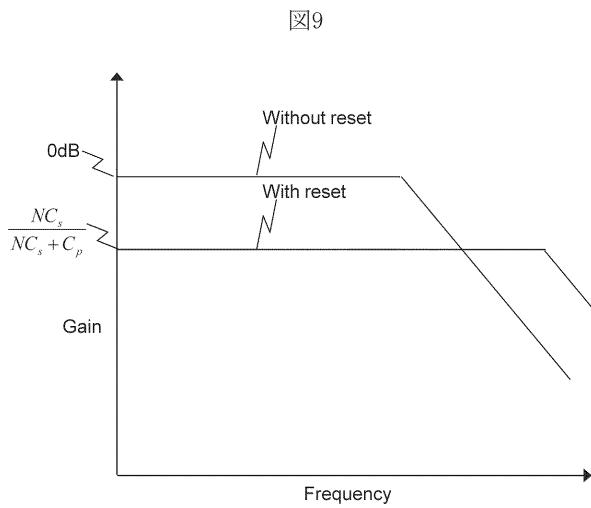

図10には本実施例が適用される、図1と別の実施例を示している。図1はシングルエンド入力、シングルエンド出力のアナログ加算回路であるが、図10の実施例では差動入力、シングルエンド出力の構成としている。

40

#### 【0057】

超音波診断装置では、超音波の生体内伝播における非線形性を利用して、信号の2次高調波を用いてイメージングを行うティッシュハーモニックイメージング（Tissue Harmonic Imaging : THI）が用いられている。信号の2次高調波を検出するためには受信回路の非線形性による2次高調波を低減する必要があり、回路の差動化は2次高調波抑制に効果が高いことは広く知られている。

#### 【0058】

図10の構成では、差動アナログ信号電圧入力  $V_{in p}$ 、 $V_{inn}$  間電圧をキャパシタ

50

$C_s$  に保持させる。これを、VCM電位をコモン電位として  $V_{out0}$ 、 $V_{out1}$ 、 $V_{out2}$  に出力してマルチブレクサ 103 によりマルチブレクスを行う。この構成により、アナログ加算回路の前段に、差動出力の回路を接続できる。差動回路は前述のように2次高調波抑制に効果が高いため、THIに適した受信回路を実現でき、超音波診断装置としての画質向上を図ることができる。

#### 【0059】

図11には上記実施例の加算回路が適用される、3次元撮像のための2次元アレイ振動子を持つ超音波探触子とシステム構成を示している。超音波探触子 110（いわゆるプローブで、例えば手に持って測定部位に当てるような操作ができるようになっている）内には各振動子 111 に対して送受信回路 30 が配置され、受信信号はアナログマルチブレクサ 13 を経て本体装置 114 内の AFE（アナログフロントエンド）115 に送られる。加算される振動子チャネルのグルーピング単位がサブアレイ 300 を構成する。

10

#### 【0060】

既に説明した図1、図3のアナログ加算回路との関係を補足しつつ、装置構成の一例を説明する。送受信回路 30 はそれぞれ図1と図3に示したサンプルホールド回路ブロック 10 を備えている。送受信回路 30 は図3に示したように、アレイ状の配置を持って IC 内に配置されている。3本の配線 1100 は、IC 1101 内でサンプルホールド回路ブロック 10 とアナログマルチブレクサ 13 を接続する。3本の配線には、図1で示したリセットスイッチ 11 や 12 も配置される。この構成により、送受信回路 30 の出力信号の電荷を3本の配線をショートすることで再分配し、平均を取る動作になる。加算された3本の出力のうち、電圧ホールド以外の期間を隠蔽するためにマルチブレクサ 13 が挿入され、電圧をホールドしている1本をマルチブレクサで取り出している。

20

#### 【0061】

本体装置内のプロセッサ 117 は超音波探触子内 IC 1101 を制御する IC 制御論理回路 118 に制御信号を送り、IC 制御論理回路 118 はこれに応じて送受信の切換や超音波フォーカスのための遅延の制御を行う。特に制限されないが、送信回路がリニアアンプ方式でなくパルサ方式の場合、波形はデジタル値としてパルサに送られるため、IC 制御論理回路 118 は、パルサが送波する波形データを記憶する波形メモリを含む。

30

#### 【0062】

図12にはサブアレイ 300 内の送受信回路 30 の構成が示されている。1振動子あたりの送受信回路 30 には、高耐圧 MOS で構成され、高圧信号を生成し振動子 111 を駆動する送信回路 122、送信時にオフ状態となり高圧信号から低圧系受信回路を保護し、受信時には微小信号を通過させる送受分離スイッチ 123、低圧系の受信低雑音増幅器（Low Noise Amplifier: LNA）124、送信信号を遅延させビームフォーミングを行い、さらには受信信号を遅延させて整相を行う微小遅延回路 125 が含まれる。微小遅延回路 125 には、サンプルホールド回路ブロック 10 が接続される。各微小遅延回路で整相された受信信号は、アナログマルチブレクサ 13 でマルチブレクスされて本体装置に伝送される。

#### 【0063】

以上説明した実施例では、低消費電力かつ広帯域なアナログ加算回路を提供することができる。とくに、2Dアレイ超音波探触子用の IC において、アレイ上の受信回路からアレイ外に長い配線を布線し寄生容量が大きくなつた場合においても広帯域な加算処理を実現することができる。

40

#### 【0064】

また、サンプルホールド回路を用いて電荷でアナログ信号を加算するアナログ加算回路において、信号電荷を蓄積するキャパシタ、およびサンプルホールド回路の出力に接続される負荷容量の両方の電荷を定期的にリセットすることで電荷履歴の影響を排除することができる。

#### 【0065】

以上説明した実施例は、超音波診断装置に接続される超音波探触子内の IC に搭載する

50

ことで効果を発揮する。本実施例を用いれば、超音波受信の整相に必要となるアナログ加算回路の広帯域化を低消費電力のまま実現出来る。これにより高い周波数の超音波を扱う受信回路が実現出来、空間分解能が高い超音波画像診断装置を実現することが出来る。また、アナログ加算回路が搭載されるICの電力を低減することが出来、ICが搭載される超音波探触子の発熱を抑制することが可能となる。すなわち本実施例は、広帯域のアナログ加算回路を低消費電力で実現する、ひいては高性能な超音波探触子を低発熱で実現するための技術として効果を発揮する。

## 【符号の説明】

## 【0066】

|                    |                                   |        |

|--------------------|-----------------------------------|--------|

| N                  | 加算される信号本数                         | 10     |

| C <sub>s</sub>     | 信号電圧保持用キャパシタ                      |        |

| C <sub>p</sub>     | 配線寄生容量                            |        |

| V <sub>in</sub> *  | 電圧入力                              |        |

| V <sub>out</sub> * | 電圧出力                              |        |

| V <sub>cs</sub> *  | キャパシタ電圧                           |        |

| V <sub>CM</sub>    | 信号コモン電位                           |        |

| *                  | スイッチオンオフ制御信号                      |        |

| C <sub>L</sub> K   | 基準クロック                            |        |

| A <sub>D</sub> D   | アナログ加算回路                          |        |

| MUX                | アナログマルチプレクサ                       | 20     |

| BUF                | バッファ                              |        |

| V <sub>s</sub>     | ステップ入力電圧振幅                        |        |

| Z <sup>-1</sup>    | 1クロックサイクル遅延                       |        |

| A <sub>F</sub> E   | アナログフロントエンド                       |        |

| IC                 | I n t e g r a t e d C i r c u i t | 集積回路   |

| T <sub>x</sub>     | 送信回路                              |        |

| T/R-SW             | 送受分離スイッチ                          |        |

| R <sub>x</sub>     | 受信回路                              |        |

| LNA                | L o w N o i s e A m p l i f i e r | 低雑音増幅器 |

| DLY*               | アナログ遅延回路                          |        |

| SW*                | スイッチ                              | 30     |

【図1】

【図2】

【図3】

【図4】

【図5】

図5

【図6】

図6

$$\frac{V_{out}}{V_{in}} = \frac{G_s}{1 - G_p z^{-1}}$$

【図7】

図7

【図8】

図8

$$\frac{V_{out}}{V_{in}} = G_s = \frac{N C_s}{N C_s + C_p}$$

【圖 9】

【図10】

【 図 1 1 】

【 図 1 2 】

【図 13】

図13

|                |                                                                              |         |            |

|----------------|------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 模拟加法电路，使用其的超声波探头，以及超声波诊断装置                                                   |         |            |

| 公开(公告)号        | <a href="#">JP2018075182A</a>                                                | 公开(公告)日 | 2018-05-17 |

| 申请号            | JP2016218984                                                                 | 申请日     | 2016-11-09 |

| [标]申请(专利权)人(译) | 株式会社日立制作所                                                                    |         |            |

| 申请(专利权)人(译)    | 株式会社日立制作所                                                                    |         |            |

| [标]发明人         | 梶山新也<br>中川樹生                                                                 |         |            |

| 发明人            | 梶山 新也<br>中川 樹生                                                               |         |            |

| IPC分类号         | A61B8/14                                                                     |         |            |

| FI分类号          | A61B8/14                                                                     |         |            |

| F-TERM分类号      | 4C601/EE09 4C601/EE15 4C601/GB18 4C601/HH21 4C601/JB06 4C601/JB09 4C601/JB60 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                    |         |            |

### 摘要(译)

[问题] 实现低功耗，高带宽的模拟加法器电路。[解决方案] 从每个都连接到超声换能器的输入端子获得，具有多个输入端子，以一对一的方式对应于多个输入端子的多个接收电路以及多个接收电路。它是一种超声波探头，具有一个信号电容器，该信号电容器根据信号存储电荷；输出布线，对多个接收电路的信号电容器的输出进行积分。在该超声波探头中，在多个接收电路的信号电容器中蓄积的电荷通过多个接收电路的信号电容器而被再分配，从而对从多个输入端子获得的信号进行积分。通过周期性地将输出布线的寄生电容器的电荷设置为预定值，来重置信号电容器和寄生电容器的电荷的充电和放电历史。[选型图]图1