**【特許請求の範囲】****【請求項 1】**

超音波の送受信に関する第1の制御パラメータを記憶する第1のメモリと、

一回の前記超音波の送受信に必要な前記第1の制御パラメータの量に基づいて、当該第

1の制御パラメータの転送量を設定し、設定した転送量の前記第1の制御パラメータをま

とめて転送する転送制御部と、

前記転送された前記第1の制御パラメータを一時的に記憶する第2のメモリと

を備える超音波診断装置。

**【請求項 2】**

前記転送制御部は、一回の前記超音波の送受信に必要な前記第1の制御パラメータの量

に応じて、前記転送量を設定する請求項1に記載の超音波診断装置。 10

**【請求項 3】**

前記転送制御部は、一回の前記超音波の送受信に必要な前記第1の制御パラメータの量

、及び前記第2のメモリに記憶されている前記第1の制御パラメータの量を比較し、当該

比較結果に基づいて前記転送量を設定する請求項1に記載の超音波診断装置。

**【請求項 4】**

前記転送制御部は、前記第2のメモリに記憶されている前記第1の制御パラメータの量

に応じて、前記超音波の送受信に関する第2の制御パラメータの転送量を設定する請求項

1乃至3のうちいずれかに記載の超音波診断装置。

**【請求項 5】**

前記第1の制御パラメータは、超音波の送信に必要な送信パラメータ、超音波の受信に

必要な受信パラメータ、超音波のエコー信号の信号処理に必要な信号処理パラメータを含

み、

前記転送制御部は、一回の前記超音波の送受信に必要な前記送信パラメータの量、前記

受信パラメータの量、及び前記信号処理パラメータ量に基づいて、前記送信パラメータ、

前記受信パラメータ、又は前記信号処理パラメータの転送順を設定する請求項1乃至4の

うちいずれかに記載の超音波診断装置。

**【請求項 6】**

超音波の送受信に関する第1の制御パラメータを記憶する第1のメモリ、及び前記第1

のメモリから転送される前記第1の制御パラメータを一時的に記憶する第2のメモリを具

備するコンピュータに、 30

一回の前記超音波の送受信に必要な前記第1の制御パラメータの量に基づいて、当該第

1の制御パラメータの転送量を設定し、設定した転送量の前記第1の制御パラメータをま

とめて転送する転送制御機能を実現させる、

制御プログラム。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明の実施形態は、超音波診断装置、及び制御プログラムに関する。

**【背景技術】****【0002】**

一般に、超音波診断装置における超音波の送受信に関する処理は、診断モード毎に送受

信条件に応じて決定されるパルス繰り返し期間 (P R I : Pulse Repetition Interval)

毎に行われる。例えば、超音波診断装置は、1つのP R Iに必要な数、すなわち一回の送

受信に必要な数の超音波送受信に関する制御パラメータをR A M (Random Access Memory

)等の記憶回路から読み出し、読み出した制御パラメータを例えば超音波送受信に関する

処理を行う送信回路、受信回路、及び信号処理回路へ転送する。送信回路、受信回路、及

び信号処理回路は、受信した制御パラメータに基づいて、対応するP R Iにおいて超音波

送受信に関する処理を実行する。

**【0003】**

10

20

30

40

50

ここで、超音波診断装置は、例えば送信回路に送信パラメータを転送する送信回路 I F (Interface)、受信回路に受信パラメータを転送する受信回路 I F、及び信号処理回路に信号処理パラメータを転送する信号処理回路 I F を有している。さらに、送信回路 I F、受信回路 I F、及び信号処理回路 I F は、記憶回路から送信回路、受信回路、及び信号処理回路へ転送される制御パラメータを一時的に記憶する内部メモリをそれぞれ有している。このとき、PRI 毎に超音波の送受信に関する処理を遅滞なく実行するには、例えば、PRI のうち送信準備期間の前に、当該 PRI において用いる制御パラメータを、送信回路 I F、受信回路 I F、及び信号処理回路 I F がそれぞれ有する内部メモリへ転送しておく必要がある。

## 【0004】

10

一方、超音波診断装置では、制御パラメータが転送される内部バスが、転送を要求する複数の転送要求者により共有されている。例えば、内部バスは、記憶回路に記憶された制御パラメータを送信回路 I F、受信回路 I F、及び信号処理回路 I F がそれぞれ有する内部メモリへ転送するメモリ I F、入力インターフェースを介して入力された制御パラメータを送信回路 I F、受信回路 I F、及び信号処理回路 I F がそれぞれ有する内部メモリへ転送するホスト制御回路 I F 等により共有されている。この内部バスの使用権は、例えば一つの調停回路によりラウンドロビン方式で管理されている。このラウンドロビン方式の下では、例えばメモリ I F、及びホスト制御回路 I F は、調停回路に対して制御パラメータの転送のために内部バスの使用権をそれぞれ要求する。そして、調停回路は、メモリ I F、又はホスト制御回路 I F に対して、均等に内部バスの使用権を与える。メモリ I F は、調停回路から内部バスの使用権を与えられると、例えば記憶回路に記憶された送信パラメータを送信回路 I F が有する内部メモリに一度転送する。また、ホスト制御回路 I F は、調停回路から内部バスの使用権を与えられると、例えば入力インターフェースを介して入力された受信パラメータを受信回路 I F に一度転送する。

20

## 【0005】

しかしながら、このようなラウンドロビン方式に基づく転送では、調停回路から内部バスの使用権を与えられたメモリ I F、及びホスト制御回路 I F が一度に転送できる制御パラメータの転送量は、所定の量、例えば 1 Q W (Quad Word) に固定されていた。このため、一回の送受信に必要な制御パラメータの数に増加に対し、転送完了に必要な転送回数が比例的に増加する。このように転送回数が増加すると、例えば制御パラメータを転送する際に必ず付加されるアドレスデータ等を転送する時間の分だけ転送時間が比例的に増加する。

30

## 【0006】

また、例えばメモリ I F を介して記憶回路から送信回路 I F が有する内部メモリへ送信パラメータを複数回転送する場合に、ホスト制御回路 I F が内部バスの使用権を要求していない場合でも、メモリ I F は、転送動作間ににおいて所定の期間待機する必要があった。このとき、一回の送受信に必要な制御パラメータの数に対して転送回数が比例的に増加すると、転送回数に対応する転送動作間の待機時間の分だけ転送時間が比例的に増加する。したがって、制御パラメータの転送効率が悪くなってしまう。

40

## 【先行技術文献】

## 【特許文献】

## 【0007】

## 【特許文献 1】特開 2017-153683 号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0008】

発明が解決しようとする課題は、超音波送受信に関する制御パラメータの転送効率を向上させることにある。

## 【課題を解決するための手段】

## 【0009】

50

実施形態によれば、超音波診断装置は、第1のメモリ、制御部、及び第2のメモリを備える。第1のメモリは、超音波の送受信に関する第1の制御パラメータを記憶する。制御部は、一回の前記超音波の送受信に必要な前記第1の制御パラメータの量に基づいて、当該第1の制御パラメータの転送量を設定し、設定した転送量で前記第1の制御パラメータを転送する。第2のメモリは、前記転送された前記第1の制御パラメータを一時的に記憶する。

【図面の簡単な説明】

【0010】

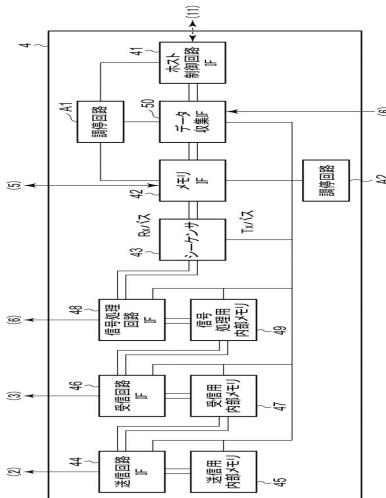

【図1】図1は、実施形態に係る超音波診断装置の構成を示す図である。

10

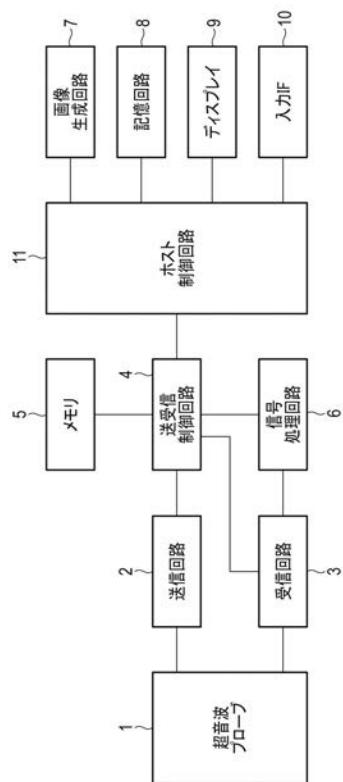

【図2】図2は、図1に示される送受信制御回路の内部構成を示すブロック図である。

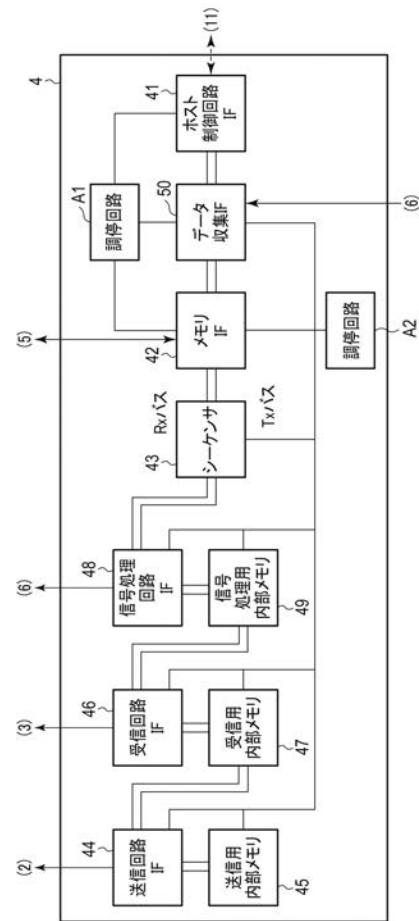

【図3】図3は、実施形態に係る調停回路によるR×バスの使用権の管理方法について説明するための図である。

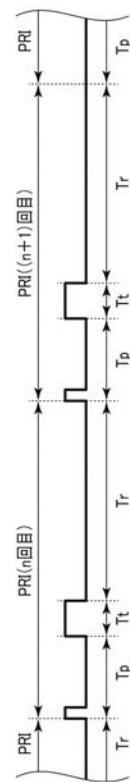

【図4】図4は、実施形態に係るシーケンサがメモリから制御パラメータを転送する期間を説明するための図である。

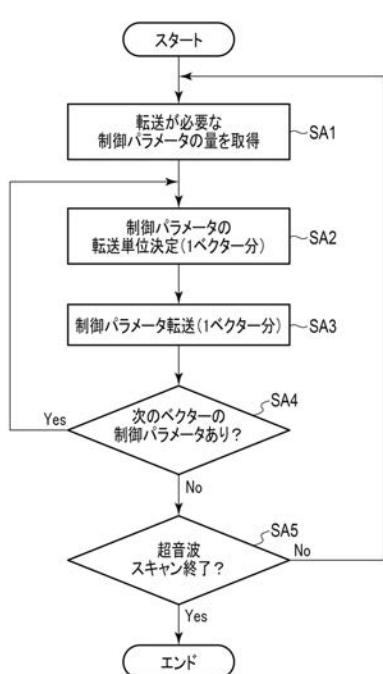

【図5】図5は、実施形態に係る超音波診断装置が制御パラメータの転送量を制御する際のシーケンサの動作を示すフローチャートである。

20

【図6】図6は、実施形態に係る制御パラメータ関連情報の内容を示す図である。

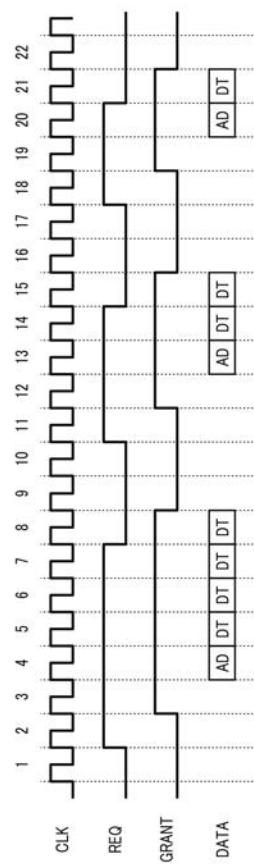

【図7】図7は、実施形態に係るシーケンサによる制御パラメータの転送量制御について説明するための図である。

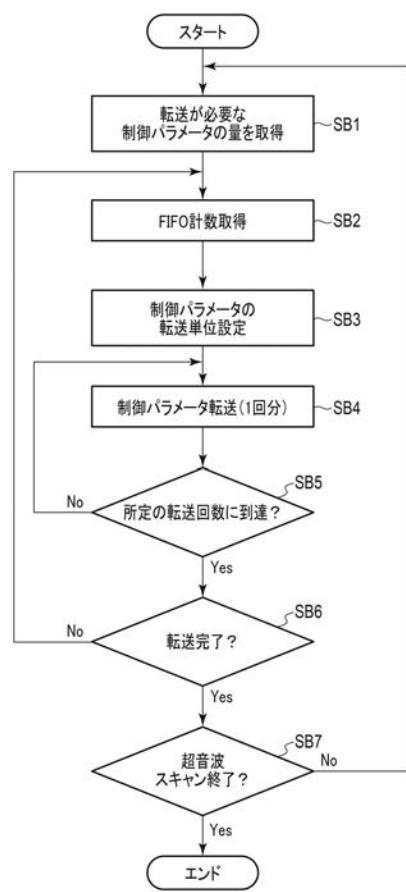

【図8】図8は、変形例に係る超音波診断装置が制御パラメータの転送量を制御する際のシーケンサの動作を示すフローチャートである。

30

【図9】図9は、変形例に係る制御パラメータ関連情報の内容を示す図である。

【図10】図10は、変形例に係るシーケンサによる制御パラメータの転送量制御について説明するための図である。

【発明を実施するための形態】

【0011】

以下、実施の形態について、図面を参照して説明する。

【0012】

本実施形態に係る超音波診断装置を図1のブロック図を参照して説明する。

【0013】

図1に示されるように、本実施形態に係る超音波診断装置は、超音波プローブ1、送信回路2、受信回路3、送受信制御回路4、メモリ5、信号処理回路6、画像生成回路7、記憶回路8、ディスプレイ9、入力インターフェース(IF:Interface)10、及びホスト制御回路11を備えている。

【0014】

超音波プローブ1は、送信回路2から供給される送信信号を超音波信号に変換し、被検体へ送信する。また、超音波プローブ1は、被検体より反射してきた超音波エコー信号を受信し、電気信号に変換して受信回路3に出力する。

【0015】

送信回路2は、送受信制御回路4から与えられるパルス繰り返し周波数(PRF: Pulse Repetition Frequency)、送信位置、送信開口、送信遅延等の送信パラメータに従って、超音波プローブ1から所望の超音波信号が送信されるように駆動する。

40

【0016】

受信回路3は、送受信制御回路4から与えられる受信素子位置、受信開口、受信遅延、受信座標等の受信パラメータに従って超音波プローブ1で取得される超音波エコー信号からビームデータを生成する。

【0017】

送受信制御回路4は、超音波の送受信に関する処理を実行する送受信処理回路を制御するプロセッサである。具体的には、送受信制御回路4は、ホスト制御回路11からの指示に従い、送信回路2、受信回路3、信号処理回路6等の送受信処理回路を制御する。送受

50

信制御回路4は、診断モード毎に送受信条件に応じたPRIを決定し、PRI毎に送信パラメータ転送、受信パラメータ転送、信号処理パラメータ転送、超音波信号の送信、超音波エコー信号の受信を制御する。ここで、診断モードとは、例えば、Bモード、Bモード+Cモード、Bモード+PWモード、Bモード+Mモード、及びCWモード等である。また、送受信条件とは、例えば、走査対象範囲における視野深度の変更、関心領域(ROI:Region of Interest)サイズ変更、カーソル移動、信号強度変更、及びスケール変更等である。

【0018】

送受信制御回路4は、ホスト制御回路11から指示された送受信条件等に応じて制御パラメータを送受信処理回路へ転送する。制御パラメータは、例えば、送信パラメータ、受信パラメータ、信号処理パラメータの総称である。送受信制御回路4は、ホスト制御回路11から指示されたビーム数、フレーム数、フレームレート、走査方向、走査対象範囲における視野深度等に応じて、メモリ5に記憶されたPRF、送信位置、送信開口、送信遅延等の送信パラメータを送信回路2へ転送する。また、送受信制御回路4は、受信素子位置、受信開口、受信遅延、受信座標等の受信パラメータを受信回路3へ転送する。また、送受信制御回路4は、デジタルフィルタ処理条件等の信号処理パラメータを信号処理回路6へ転送する。また、送受信制御回路4は、信号処理回路6において当該ビームデータから生成された処理データをホスト制御回路11を介して画像生成回路7へ出力する。

10

【0019】

なお、送受信制御回路4は、特定用途向け集積回路(ASIC:Application Specific Integrated Circuit)、プログラマブル論理デバイス(例えば、単純プログラマブル論理デバイス(SPLD:Simple Programmable Logic Device)、および複合プログラマブル論理デバイス(CPLD:Complex Programmable Logic Device))の少なくとも一つにより構成されてもよい。

20

【0020】

メモリ5は、本実施形態に係る超音波診断装置が備える各種回路を制御するための制御パラメータを記憶するRAM(Random Access Memory)である。メモリ5に記憶される制御パラメータ(第1の制御パラメータ)は、ホスト制御回路11からの出力により更新可能である。メモリ5は、各種超音波スキャンモード、接続する超音波プローブ1、並列同時受信数等の情報に応じて設定される、送信回路2の送信パラメータと、受信回路3の受信パラメータと、信号処理回路6の信号処理パラメータとを記憶する。

30

【0021】

例えば、メモリ5は、送信パラメータとして、送信位置、送信遅延、送信開口を記憶する。また、メモリ5は、受信パラメータとして、受信素子位置、受信開口、受信遅延、受信座標を記憶する。また、メモリ5は、信号処理パラメータとして、デジタルフィルタ係数を記憶する。また、制御パラメータは、実質的なデータとヘッダ情報とを含む。ヘッダ情報は、転送先アドレスを含み、制御パラメータは当該転送先アドレスに対応する送受信処理回路へ転送される。

30

【0022】

信号処理回路6は、受信回路3から出力されたビームデータにフィルタリング処理等の信号処理を施した処理データを生成する。信号処理回路6は、生成した処理データを、送受信制御回路4を介してホスト制御回路11へ出力する。なお、信号処理回路6は、転送可能な配線方式の関係上、送受信制御回路4を経由して、処理データをホスト制御回路11へ出力しているが、信号処理回路6からホスト制御回路11への専用の転送経路を設けてもよい。

40

【0023】

画像生成回路7は、ホスト制御回路11から出力された処理データをスキャンコンバートして、被検体に関する二次元または三次元の超音波画像を生成する。

【0024】

また、記憶回路8は、比較的大容量のデータを記憶可能なHDD(Hard Disk Drive)

50

および S S D (Solid State Drive) 等である。例えば、記憶回路 8 は、入力インターフェース 10 を介して入力される記憶操作に従い、画像生成回路 7 で生成された各種超音波画像データ、及び当該各種超音波画像データに付加された付加情報等を記憶する。なお、記憶回路 8 は、H D D 等の磁気ディスク以外にも、光磁気ディスクや C D (Compact Disc) 、 D V D (Digital Versatile Disc) 等の光ディスクを利用してよい。また、記憶回路 8 の記憶領域は、超音波診断装置内にあってもよいし、ネットワークで接続された外部記憶装置内にあってもよい。

【 0 0 2 5 】

ディスプレイ 9 は、ホスト制御回路 11 による制御に従い、画像生成回路 7 において生成された超音波画像、および各種の診断用パラメータ等を表示する。ディスプレイ 9 としては、例えば、C R T ディスプレイ (Cathode Ray Tube Display) 、液晶ディスプレイ (L C D : Liquid Crystal Display) 、有機 E L ディスプレイ (O E L D : Organic Electro Luminescence Display) 、プラズマディスプレイまたは当技術分野で知られている他の任意のディスプレイが適宜利用可能である。

10

【 0 0 2 6 】

入力インターフェース 10 は、トラックボール、スイッチボタン、マウス、キーボード、操作面へ触れることで入力操作を行うタッチパッド、および表示画面とタッチパッドとが一体化されたタッチパネルディスプレイ等によって実現される。入力インターフェース 10 は、超音波診断装置に対して各種の診断モードや診断モードに付随する制御パラメータを設定するための入力デバイスである。入力インターフェース 10 は、操作者から受け取った入力操作を電気信号へ変換しホスト制御回路 11 へ出力する。なお、本実施形態において、入力インターフェース 10 は、トラックボール、スイッチボタン、マウス、キーボード等の物理的な操作部品を備えるものだけに限られない。例えば、装置とは別体に設けられた外部の入力機器から入力操作に対応する電気信号を受け取り、この電気信号をホスト制御回路 11 へ出力する電気信号の処理回路も入力インターフェース 10 の例に含まれる。

20

【 0 0 2 7 】

ホスト制御回路 11 は、入力インターフェース 10 で設定された診断モードや各種パラメータに基づいて、超音波診断装置における各構成の制御を実行する。ホスト制御回路 11 は、ハードウェア資源として、C P U や M P U (Micro Processing Unit) 等のプロセッサと、R O M (Read Only Memory) や R A M 等のメモリとを含む。ホスト制御回路 11 のメモリは、画像収集プログラムを記憶する。ホスト制御回路 11 のプロセッサは、入力インターフェース 10 からの入力信号に基づいて、メモリに記憶された画像収集プログラムを実行することにより、超音波診断装置における各構成の制御を実行する。例えば、ホスト制御回路 11 は、入力インターフェース 10 からの入力信号に基づく制御パラメータ (第 2 の制御パラメータ) を、送受信制御回路 4 を介して各送受信処理回路へ転送する。例えば、ホスト制御回路 11 は、当該制御パラメータ (受信パラメータ) として、入力インターフェース 10 からの入力信号に基づく T G C (Time Gain Control) を変更するための T G C パラメータ (ゲイン値) を、送受信制御回路 4 を介して受信回路 3 へ転送する。

30

【 0 0 2 8 】

(送受信制御回路 4 の内部構成)

40

次に、実施形態における送受信制御回路 4 の内部構成について詳しく説明する。

【 0 0 2 9 】

図 2 は、図 1 に示される送受信制御回路 4 の内部構成を示すブロック図である。送受信制御回路 4 は、ホスト制御回路インターフェース 4 1 (以下、ホスト制御回路 I F 4 1 と称する) 、メモリインターフェース 4 2 (以下、メモリ I F 4 2 と称する) 、シーケンサ 4 3 、送信回路インターフェース 4 4 (以下、送信回路 I F 4 4 と称する) 、送信回路 I F 4 4 専用の内部メモリ 4 5 、受信回路インターフェース 4 6 (以下、受信回路 I F 4 6 と称する) 、受信回路 I F 4 6 専用の内部メモリ 4 7 、信号処理回路インターフェース 4

50

8（以下、信号処理回路IF48と称する）、信号処理回路IF48専用の内部メモリ49、データ収集インターフェース50（以下、データ収集IF50と称する）、調停回路（Arbiter、アービタ回路とも呼ばれる）A1、及び調停回路A2を備える。実施形態における送受信制御回路4は、超音波送受信における機能毎に、送受信処理回路インターフェース（以下、送受信処理回路IFと称する）、内部メモリ、及び調停回路を設けた機能別回路構成を有する。

#### 【0030】

ホスト制御回路IF41、メモリIF42、シーケンサ43、送信回路IF44、内部メモリ45、受信回路IF46、内部メモリ47、信号処理回路IF48、内部メモリ49、データ収集IF50は、共用の内部バスにより接続されている。

10

#### 【0031】

ホスト制御回路IF41は、外部バスを介してホスト制御回路11に接続される。ホストIF41は、超音波診断装置の送受信開始前において、ホスト制御回路11から転送された制御パラメータをメモリIF42を介してメモリ5へ予め転送しておく。また、ホスト制御回路IF41は、超音波診断装置の送受信開始後において、ホスト制御回路11から転送された制御パラメータを送信回路IF44、受信回路IF46、又は信号処理回路IF48に転送する。

#### 【0032】

メモリIF42は、外部バスを介してメモリ5に接続される。メモリIF42は、メモリ5に記憶された制御パラメータを、対応する内部メモリ45、内部メモリ47、及び内部メモリ49へ転送する。

20

#### 【0033】

データ収集IF50は、外部バスを介して信号処理回路6に接続される。データ収集IF50は、信号処理回路6で生成された処理データをホスト制御回路11へ転送する。

#### 【0034】

シーケンサ43は、制御パラメータの転送を制御するプロセッサである。シーケンサ43は、例えば、診断モード毎に送受信条件に応じてPRIを決定する。PRIを決定するためのPRI情報は、ホスト制御回路11からシーケンサ43に通知される。また、シーケンサ43は、メモリIF42を介し、PRIとは非同期に、メモリ5から制御パラメータを読み出して、読み出した制御パラメータを内部メモリ45、内部メモリ47、又は内部メモリ49に転送する。このとき、シーケンサ43は、メモリIF42から内部メモリ45、内部メモリ47、又は内部メモリ49へ転送する制御パラメータの転送量を制御する。シーケンサ43による制御パラメータの転送量制御の詳細については後述する。

30

#### 【0035】

送信回路IF44は、外部バスを介して送信回路2に接続される。送信回路IF44は、内部メモリ45に記憶された送信パラメータを送信回路2へ転送する。このとき、内部メモリ45に記憶されている送信パラメータは、FIFO(First In First Out)方式で処理される。また、送信回路IF44は、ホスト制御回路IF41から転送された送信パラメータを送信回路2へ転送する。内部メモリ45は、例えば格納する送信パラメータの数について所定の上限が設けられたFIFOキューを有している。

40

#### 【0036】

受信回路IF46は、外部バスを介して受信回路3に接続される。受信回路IF46は、内部メモリ47に記憶された受信パラメータを受信回路3へ転送する。このとき、内部メモリ47に記憶されている受信パラメータは、FIFO方式で処理される。また、受信回路IF46は、ホスト制御回路IF11から転送された受信パラメータを受信回路3へ転送する。内部メモリ47は、例えば格納する受信パラメータの数について所定の上限が設けられたFIFOキューを有している。

#### 【0037】

信号処理回路IF48は、外部バスを介して信号処理回路6に接続される。信号処理IF48は、内部メモリ49に記憶された信号処理パラメータを信号処理回路6へ転送する

50

。このとき、内部メモリ 4 9 に記憶されている信号処理パラメータは、FIFO 方式で処理される。また、信号処理回路 IF 4 8 は、ホスト制御回路 IF 4 1 から転送された信号処理パラメータを信号処理回路 6 へ転送する。内部メモリ 4 9 は、例えば格納する信号処理パラメータの数について所定の上限が設けられた FIFO キューを有している。

【0038】

ホスト制御回路 IF 4 1 から内部メモリ 4 5 の方向への内部バスを R × バスと呼称する。例えば、R × バスは、メモリ IF 4 2 から内部メモリ 4 5 、内部メモリ 4 7 、及び内部メモリ 4 9 への制御パラメータの転送、又はホスト制御回路 IF 4 1 から送信回路 2 、受信回路 3 、及び信号処理回路 6 への制御パラメータの転送に使用する。また、内部メモリ 4 5 からホスト制御回路 IF 4 1 の方向への内部バスを T × バスと呼称する。例えば、T × バスは、内部メモリ 4 5 から送信回路 IF 4 4 、内部メモリ 4 7 から受信回路 IF 4 6 、及び内部メモリ 4 9 から信号処理回路 IF 4 8 への制御パラメータの転送に使用する。

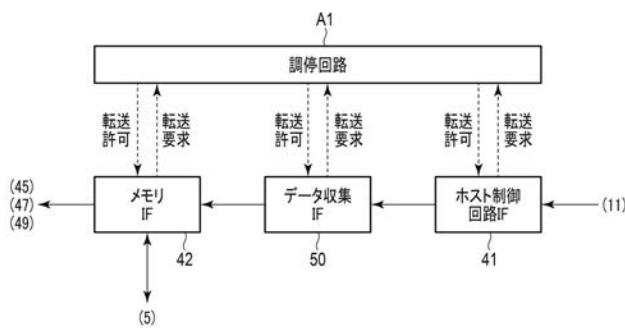

【0039】

調停回路 A 1 は、ホスト制御回路 IF 4 1 、メモリ IF 4 2 、及びデータ収集 IF 5 0 からの要求（リクエスト）に応じて、R × バスの使用権を管理する。調停回路 A 1 は、ホスト制御回路 IF 4 1 と、メモリ IF 4 2 と、データ収集 IF 5 0 とに接続される。

【0040】

調停回路 A 1 は、例えば、ホスト制御回路 IF 4 1 による R × バスを介した各送受信処理回路インターフェースへの制御パラメータの転送要求と、メモリ IF 4 2 による R × バスを介した各内部メモリへの制御パラメータの転送要求と、データ収集 IF 5 0 による R × バスを介した各送受信処理回路インターフェースへの制御パラメータの転送要求とに応じて、例えばラウンドロビン方式により、ホスト制御回路 IF 4 1 、メモリ IF 4 2 、及びデータ収集 IF 5 0 に対してそれぞれ R × バスの使用権を与える。

【0041】

図 3 は、本実施形態に係る調停回路 A 1 による R × バスの使用権の管理（調停）方法について説明するための図である。図 3 によれば、ホスト制御回路 IF 4 1 、メモリ IF 4 2 、及びデータ収集 IF 5 0 は、R × バスの使用権を調停回路 A 1 に対して要求する。調停回路 A 1 は、R × バスの使用権を要求するホスト制御回路 IF 4 1 、メモリ IF 4 2 、及びデータ収集 IF 5 0 に対し、ラウンドロビン方式により当該要求を許可する。これにより、ホスト制御回路 IF 4 1 、メモリ IF 4 2 、及びデータ収集 IF 5 0 の要求に対して、R × バスの使用権が均等に許可される。R × バスの使用権の要求が調停回路 A 1 により許可された場合、ホスト制御回路 IF 4 1 、メモリ IF 4 2 、及びデータ収集 IF 5 0 は、R × バスを使用して各種制御パラメータの転送を行うことができる。

【0042】

ここで、ラウンドロビン方式において、メモリ IF 4 2 は、例えば、ホスト制御回路 IF 4 1 、及び / 又はデータ収集 IF 5 0 から調停回路 A 1 に対して転送要求されている場合、制御パラメータを一回転送する毎に、調停回路 A 1 に対する要求を一旦終了してホスト制御回路 IF 4 1 、及び / 又はデータ収集 IF 5 0 に対して R × バスの使用権を譲渡しなければならない。また、メモリ IF 4 2 は、ホスト制御回路 IF 4 1 、及びデータ収集 IF 5 0 から調停回路 A 1 に対して転送要求されていない場合であっても、調停回路 A 1 に対する要求を一旦終了しなければならない。このため、メモリ IF 4 2 は、連続して制御パラメータを転送する場合、転送動作間に所定のクロック数分、例えば 4 クロック分休止期間を設けて転送する必要がある。

【0043】

調停回路 A 2 は、メモリ IF 4 2 、シーケンサ 4 3 、送信回路 IF 4 4 、受信回路 IF 4 6 、信号処理回路 IF 4 8 、及びデータ収集 IF 5 0 からの要求に応じて、T × バスの使用権を管理する。調停回路 A 2 は、メモリ IF 4 2 と、シーケンサ 4 3 と、送信回路 IF 4 4 と、内部メモリ 4 5 と、受信回路 IF 4 6 と、内部メモリ 4 7 と、信号処理回路 IF 4 8 と、内部メモリ 4 9 と、データ収集 IF 5 0 とに接続される。

【0044】

10

20

30

40

50

調停回路 A 2 は、T × バスの使用権について、例えば、送信回路 I F 4 4 によるホスト制御回路 I F 4 1 への送信パラメータの転送要求と、受信回路 I F 4 6 によるホスト制御回路 I F 4 1 への受信パラメータの転送要求と、信号処理回路 I F 4 8 によるホスト制御回路 I F 4 1 への信号処理パラメータの転送要求と、シーケンサ 4 3 によるメモリ I F 4 2 への制御パラメータの転送要求と、メモリ I F 4 2 によるホスト制御回路 I F 4 1 への制御パラメータの転送要求と、データ収集 I F 5 0 によるホスト制御回路 I F 4 1 への処理データの転送要求とに応じて、例えばラウンドロビン方式により、送信回路 I F 4 4 、受信回路 I F 4 6 、信号処理回路 I F 4 8 、シーケンサ 4 3 、メモリ I F 4 2 、及びデータ収集 I F 5 0 に対してそれぞれ T × バスの使用権を与える。

【0045】

10

次に、本実施形態に係るシーケンサ 4 3 による制御パラメータの転送量制御の詳細について、図を参照して説明する。

【0046】

まず、本実施形態に係るシーケンサ 4 3 がメモリ 5 から制御パラメータを転送する期間について説明する。図 4 は、本実施形態に係るシーケンサ 4 3 がメモリ 5 から制御パラメータを転送する期間を説明するための図である。図 4 に示すように、シーケンサ 4 3 は、PRI 毎に用いられる超音波送受信に関する制御パラメータの転送を制御する。PRI には、送信準備期間 T p 、送信期間 T t 、及び受信期間 T r が含まれる。送信準備期間 T p には、メモリ 5 に記憶されていた制御パラメータを送信回路 2 、受信回路 3 、及び信号処理回路 6 へ転送する転送期間が含まれる。例えば、図 4 に示される n ( n は自然数 ) 回目の送受信における送信準備期間 T p において、 n 回目の送受信に必要な送信パラメータが内部メモリ 4 5 から送信回路 2 へ転送される。また、図 4 に示される n 回目の送受信における送信準備期間 T p において、 n 回目の送受信に必要な受信パラメータが内部メモリ 4 7 から受信回路 3 へ転送される。また、図 4 に示される n 回目の送受信における送信準備期間 T p において、 n 回目の送受信に必要な信号処理パラメータが内部メモリ 4 9 から信号処理回路 6 へ転送される。送信期間 T t は、例えば、超音波信号の送信期間である。受信期間 T r は、例えば、超音波エコー信号の受信期間である。

20

【0047】

30

シーケンサ 4 3 は、例えば、図 4 に示される n 回目の送受信における送信準備期間 T p が開始されるまでに、少なくとも n 回目の送受信に必要な制御パラメータをメモリ I F 4 2 から各内部メモリに転送する。内部メモリ 4 5 に転送された n 回目の送受信に必要な送信パラメータは、 n 回目の送受信における送信準備期間 T p において、送信回路 I F 4 4 により内部メモリ 4 5 から送信回路 2 へ転送される。

【0048】

40

また、シーケンサ 4 3 は、例えば、図 4 に示される ( n + 1 ) 回目の送受信における送信準備期間 T p が開始されるまでに、少なくとも ( n + 1 ) 回目の送受信に必要な送信パラメータをメモリ I F 4 2 から内部メモリ 4 5 に転送する。内部メモリ 4 5 に転送された送信パラメータは、 ( n + 1 ) 回目の送受信における送信準備期間 T p において、送信回路 I F 4 4 により内部メモリ 4 5 から送信回路 2 へ転送される。なお、シーケンサ 4 3 は、受信パラメータ、及び信号処理パラメータについても、送信パラメータと同様に転送する。

【0049】

次に、本実施形態に係るシーケンサ 4 3 が制御パラメータの転送量を制御する流れについて説明する。図 5 は、本実施形態に係る超音波診断装置が制御パラメータの転送量を制御する際のシーケンサ 4 3 の動作の例を示すフローチャートである。以下の説明では、シーケンサ 4 3 は、超音波スキャンが開始されてから終了されるまでの間、超音波送受信に関する制御パラメータの転送を制御するものとする。また、シーケンサ 4 3 、データ収集 I F 5 0 、及びホスト制御回路 I F 4 1 のうち、シーケンサ 4 3 のみが調停回路 A 1 に対して転送要求しているものとする。

【0050】

50

また、シーケンサ43は、当該シーケンサ43が備える不図示の内部メモリに、必要な各種制御パラメータの量を表す制御パラメータ関連情報を記憶しているものとする。この制御パラメータ関連情報は、ホスト制御回路11からシーケンサ43に予め供給されているものとする。制御パラメータ関連情報は、メモリ5から各送受信回路に対応する内部メモリに転送することが必要な制御パラメータの数を、例えば、ベクター毎、及び送受信回路毎に表している。1ベクターは、例えば一回の超音波送受信を表す。一回の超音波送受信に必要な制御パラメータの数は、例えば、チャンネル数、ビームの並列同時受信数、及び新たな超音波診断サービスの開始に伴い必要となるパラメータ等により変動する。

#### 【0051】

図6は、本実施形態に係る制御パラメータ関連情報の内容の例を示す図である。図6に示される制御パラメータ関連情報は、例えば、先頭(ベクター番号0)のベクターについて、送信パラメータの数が7、受信パラメータの数が5、及び信号処理パラメータの数が3であることを表す。また、図6に示される制御パラメータ関連情報は、例えば、2番目(ベクター番号1)のベクターについて、送信パラメータの数が10、受信パラメータの数が8、及び信号処理パラメータの数が6であることを表す。なお本実施形態では、例えば、制御パラメータの数1は1QWを表すものとする。なお、図6に示される制御パラメータ関連情報には、少なくとも2つのベクターに対応する制御パラメータの数に関する情報が含まれているものとする。

10

#### 【0052】

また、シーケンサ43は、制御パラメータをメモリ5から内部メモリ45、内部メモリ47、及び内部メモリ49のいずれかに1度転送すると、その後4クロックの間メモリ5から制御パラメータの転送を行わないものとする。

20

#### 【0053】

図5において、シーケンサ43は、超音波スキャンが開始されると、転送が必要な制御パラメータの量を取得する(ステップSA1)。具体的には、シーケンサ43は、不図示の内部メモリ(若しくはメモリ5)に記憶されている制御パラメータ関連情報を参照し、ベクター番号毎の送信パラメータの数、受信パラメータの数、及び信号処理パラメータの数を取得する。

#### 【0054】

シーケンサ43は、取得した制御パラメータの量に応じて、当該制御パラメータの転送量を設定する(ステップSA2)。具体的には、例えば、シーケンサ43は、ベクター番号0に対応する制御パラメータについて、制御パラメータの数が多い順に、送信パラメータ、受信パラメータ、及び信号処理パラメータに対して、転送に関する優先度を設定する。具体的には、シーケンサ43は、ベクター番号0に対応する送信パラメータの数、受信パラメータの数、及び信号処理パラメータの数が7、5、及び3であるため、送信パラメータ、受信パラメータ、及び信号処理パラメータの順に転送されるように、各パラメータに対して転送に関する優先度を設定する。これにより、シーケンサ43は、最も優先度の高い制御パラメータを送信パラメータと認識する。また、シーケンサ43は、次に優先度の高い制御パラメータを受信パラメータと認識する。また、シーケンサ43は、最も優先度の低い制御パラメータを信号処理パラメータと認識する。

30

#### 【0055】

次に、シーケンサ43は、送信パラメータの数が7であるため、転送する送信パラメータの転送量を、例えば7以下の値のうち2の2乗である4つの送信パラメータに対応する4QWに設定する。また、ベクター番号0に対応する送信パラメータについて、シーケンサ43は、次に送信する送信パラメータの転送量を、例えば残りの3以下の値のうち2の1乗に対応する2QWに設定する。また、ベクター番号0に対応する送信パラメータについて、シーケンサ43は、次に送信する送信パラメータの転送量を、次に送信する送信パラメータの転送量を、例えば残りの1以下の値のうち2の0乗に対応する1QWに設定する。なお、転送量は、1QW以上であればどのように設定されてもかまわない。

40

#### 【0056】

50

また、シーケンサ43は、ベクター番号0に対応する受信パラメータについて、例えば、一回目の送信の転送量を5以下の値のうち2の2乗に対応する4QW、2回目の送信の転送量を残りの1以下の値のうち2の0乗に対応する1QWに設定する。

#### 【0057】

また、シーケンサ43は、ベクター番号0に対応する信号処理パラメータについて、例えば、一回目の送信の転送量を3以下の値のうち2の1乗に対応する2QW、2回目の送信の転送量を残りの1以下の値のうち2の0乗に対応する1QWに設定する。

#### 【0058】

次に、シーケンサ43は、ベクター番号0に対応する制御パラメータについて、メモリIF42を介し、ステップSA2において設定した優先度、及び転送量に基づいて、送信パラメータ、受信パラメータ、及び信号処理パラメータを、メモリ5から内部メモリ45、内部メモリ47、及び内部メモリ49にそれぞれ送信する(ステップSA3)。具体的には、まず、シーケンサ43は、例えば、メモリIF42を介し、調停回路A1から4QW分の送信パラメータを転送可能なR×バスの使用権を要求する。シーケンサ43は、当該要求した使用権が調停回路A1により与えられると、与えられた使用権に相当する期間において、4QW分の送信パラメータをメモリ5から内部メモリ45に送信する。

10

#### 【0059】

そして、シーケンサ43は、例えばベクター番号0に対応する制御パラメータについて、送信パラメータを4QW、2QW、及び1QWの転送量で順番に3回転送する。次に、シーケンサ43は、受信パラメータを3QW、及び2QWの転送量で順番に2回転送する。最後に、シーケンサ43は、信号処理パラメータを2QW、及び1QWの転送量で順番に2回転送する。

20

#### 【0060】

なお、シーケンサ43は、制御パラメータの転送前に、内部メモリ45、内部メモリ47、及び内部メモリ49がそれぞれ有する FIFOキューに格納されている制御パラメータの数が予め設定された上限値に達しているか否かを判定するものとする。本実施形態では、内部メモリ45、内部メモリ47、及び内部メモリ49がそれぞれ有する FIFOキューに格納されている制御パラメータの数は、予め設定された上限値に達しておらず、FIFOキューの空き容量は十分確保されているものとする。

30

#### 【0061】

また、シーケンサ43は、設定した転送に関する優先度に基づいて、同一のベクター番号の制御パラメータについて、例えば、送信パラメータを一回送った後、1ベクター分の送信パラメータを全て転送していない場合であっても、続けて送信パラメータを転送するのではなく、送信パラメータの転送に続けて受信パラメータ、及び信号処理パラメータの順に転送するようにしてもよい。具体的には、シーケンサ43は、例えばベクター番号0に対応する制御パラメータについて、送信パラメータ4QW、受信パラメータ3QW、及び信号処理パラメータ2QWの順番で転送するようにしてもよい。

30

#### 【0062】

図7は、本実施形態に係るシーケンサ43による制御パラメータの転送量制御の例について説明するための図である。図7は、ベクター番号0に対応する送信パラメータを転送する際のタイミングチャートを表している。図7に示される「CLK」が付された波形は、送受信制御回路4等のシステムクロックに関する連続パルス波形を表している。図6では、1番目のクロックから22番目のクロックまでの連続パルス波形が描かれている。

40

#### 【0063】

また、図7に示される「REQ」が付された波形は、シーケンサ43により調停回路A1に対するR×バスの使用権が転送要求された期間を表している。図7によれば、図7に示されるシステムクロックに関する連続パルス波形のうち、2クロックから7クロックまでの期間、11クロックから14クロックまでの期間、及び18クロックから20クロックまでの期間において、シーケンサ43は、調停回路A1に対し、メモリIF42についてR×バスの使用権を要求している。

50

## 【0064】

また、図7に示される「GRANT」が付された波形は、上記要求に応じて、メモリIF42についてRxバスの使用権が許可された期間を表している。図7によれば、図7に示されるシステムクロックに関する連続パルス波形のうち、3番目のクロックから8番目のクロックに対応する期間、12クロックから15クロックまでの期間、及び19クロックから21クロックまでの期間において、シーケンサ43は、調停回路A1から、メモリIF42についてRxバスの使用権を許可されている。

## 【0065】

図7によれば、シーケンサ43は、図5に示されるステップSA2で決定した制御パラメータの転送量に基づいて、制御パラメータを、例えば、送信回路IF44に対応する内部メモリ45に3回連続で転送している。図7に示される「AD」が付された領域は、例えば転送先アドレスを含むヘッダ情報を送信する期間を表す。図7に示される「DT」が付された領域は、例えば制御パラメータの値を含む実質的なデータを送信する期間を表す。

10

## 【0066】

図7において、シーケンサ43は、4クロックから8クロックまでに対応する期間において4QW分の制御パラメータを転送している。また、シーケンサ43は、13クロックから15クロックまでに対応する期間において、2QW分の制御パラメータを転送している。また、シーケンサ43は、20クロックから21クロックまでに対応する期間において、1QW分制御パラメータを転送している。これにより、シーケンサ43は、ベクター番号0に対応する送信パラメータを全て内部メモリ45に転送できる。従来、一回に転送できる制御パラメータの量は、1QW分と固定されていたため、7QW分の制御パラメータを転送するには、7回転送する必要がった。このため、本実施形態に係るシーケンサ43によれば、転送回数を7回から3回に削減することが可能となる。

20

## 【0067】

図5に戻って、シーケンサ43は、次のベクターの制御パラメータが存在するか否か判定する(ステップSA4)。

## 【0068】

シーケンサ43は、次のベクターであるベクター番号1に対応する制御パラメータが存在するため(ステップSA4のYes)、ベクター番号1に対応する制御パラメータについて、ベクター番号0に対応する制御パラメータと同様に、転送に関する優先度、及び転送量を設定する(ステップSA2)。

30

## 【0069】

次に、シーケンサ43は、ベクター番号1に対応する制御パラメータについて、ベクター番号0に対応する制御パラメータと同様に、メモリIF42を介し、ステップSA2において設定した優先度、及び転送量に基づいて、送信パラメータ、受信パラメータ、及び信号処理パラメータを、メモリ5から内部メモリ45、内部メモリ47、及び内部メモリ49にそれぞれ送信する(ステップSA3)。

## 【0070】

さらに、シーケンサ43は、ベクター番号2以降に対応する制御パラメータについても、ベクター番号0、及び1に対応する制御パラメータと同様に、転送に関する優先度、及び転送量を設定する(ステップSA2)。そして、シーケンサ43は、ベクター番号2以降に対応する制御パラメータについても、ベクター番号0、及び1に対応する制御パラメータと同様に、メモリIF42を介し、ステップSA2において設定した優先度、及び転送量に基づいて、送信パラメータ、受信パラメータ、及び信号処理パラメータを、メモリ5から内部メモリ45、内部メモリ47、及び内部メモリ49にそれぞれ送信する(ステップSA3)。

40

## 【0071】

シーケンサ43は、ステップSA4において、次のベクターの制御パラメータが存在しない場合(ステップSA4のNo)、超音波スキャンが終了したか否か判定する(ステッ

50

プ S A 5 )。

【 0 0 7 2 】

シーケンサ 4 3 は、超音波スキャンが終了していない場合 (ステップ S A 5 の N o ) 、転送が必要な制御パラメータの量を再び取得する (ステップ S A 1 )。具体的には、シーケンサ 4 3 は、不図示の内部メモリに記憶されている制御パラメータ関連情報を参照し、例えば、ステップ S A 2 からステップ S A 5 までの処理を実行している間に新たにホスト制御回路 1 1 からシーケンサ 4 3 に供給された制御パラメータ関連情報について、ベクターパス号毎の送信パラメータの数、受信パラメータの数、及び信号処理パラメータの数を取得する。

【 0 0 7 3 】

シーケンサ 4 3 は、新たに取得した制御パラメータについて、ステップ S A 2 からステップ S A 5 までの処理を再び実行する。

【 0 0 7 4 】

シーケンサ 4 3 は、ステップ S A 5 において超音波スキャンが終了している場合 (ステップ S A 5 の Y e s ) 、転送制御処理を終了する。

【 0 0 7 5 】

以上のように、本実施形態に係る超音波診断装置が備えるメモリ 5 は、超音波の送受信に関する制御パラメータを記憶している。また、シーケンサ 4 3 は、一回の前記超音波の送受信に必要な制御パラメータの量に基づいて、当該制御パラメータの転送量を設定し、設定した転送量の制御パラメータをまとめて転送する。また、超音波診断装置が備える内部メモリ 4 5 、 4 7 、及び 4 9 は、転送された制御パラメータを一時的に記憶する。

【 0 0 7 6 】

これにより、例えば、一回の超音波の送受信に必要な制御パラメータの量が多い場合であっても、制御パラメータの転送量を大きくする、すなわち一度に転送する制御パラメータを複数まとめてバースト転送することが可能となる。よって、転送回数を削減することが可能となり、削減された転送回数に対応する転送動作間の待機時間、及び、転送先アドレスを示すアドレスデータの転送時間分だけ所要時間を削減することができる。

【 0 0 7 7 】

したがって、超音波送受信に関する制御パラメータの転送効率を向上させることが可能となる。

【 0 0 7 8 】

( 变形例 )

上記実施形態では、超音波診断装置が備えるシーケンサ 4 3 が、制御パラメータ関連情報を参照し、一回の超音波の送受信に必要な制御パラメータの量を認識して、認識した制御パラメータの量に応じて、各内部メモリに転送する当該制御パラメータの転送量を設定する場合について説明した。变形例では、超音波診断装置が備えるシーケンサ 4 3 が、各内部メモリに転送された制御パラメータの量に応じて、各内部メモリに転送する当該制御パラメータの転送量を設定する場合について説明する。

【 0 0 7 9 】

変形例に係る超音波診断装置の構成及び機能は、図 1 及び図 2 に示される超音波診断装置の構成及び機能と同様である。

【 0 0 8 0 】

次に、以上のように構成された変形例に係る超音波診断装置による動作を、シーケンサ 4 3 の処理手順に従って説明する。図 8 は、変形例に係る超音波診断装置が制御パラメータの転送量を制御する際のシーケンサ 4 3 の動作を示すフローチャートである。

【 0 0 8 1 】

以下の説明では、上記実施形態と同様に、シーケンサ 4 3 は、超音波スキャンが開始されてから終了されるまでの間、超音波送受信に関する制御パラメータの転送を制御するものとする。また、シーケンサ 4 3 は、当該シーケンサ 4 3 が備える不図示の内部メモリ (若しくはメモリ 5 ) に、必要な各種制御パラメータの量を表す制御パラメータ関連情報を

10

20

30

40

50

記憶しているものとする。この制御パラメータ関連情報は、ホスト制御回路 11 からシーケンサ 43 に予め供給されているものとする。

【0082】

図 9 は、変形例に係る制御パラメータ関連情報の内容の例を示す図である。図 9 に示される制御パラメータ関連情報は、例えば、先頭（ベクター番号 0）のベクターについて、送信パラメータの数が 100、受信パラメータの数が 50、及び信号処理パラメータの数が 20 であることを表す。また、図 9 に示される制御パラメータ関連情報は、例えば、2 番目（ベクター番号 1）のベクターについて、送信パラメータの数が 50、受信パラメータの数が 25、及び信号処理パラメータの数が 15 であることを表す。なお、図 9 に示される制御パラメータ関連情報には、少なくとも 2 つのベクターに対応する制御パラメータの数に関する情報が含まれているものとする。

10

【0083】

また、シーケンサ 43 は、制御パラメータをメモリ 5 から各送受信回路に対応する内部メモリのいずれかに 1 度転送すると、その後 4 クロックの間メモリ 5 から制御パラメータの転送を行えないものとする。また、内部メモリ 45、内部メモリ 47、及び内部メモリ 49 には、メモリ 5 から内部メモリ 45、内部メモリ 47、及び内部メモリ 49 へそれぞれ転送された制御パラメータの数を示す FIFO 計数が記憶されているものとする。FIFO 計数は、例えば、内部メモリ 45、内部メモリ 47、及び内部メモリ 49 に制御パラメータが転送される度に、送信回路 IF44、受信回路 IF46、及び信号処理回路 IF48 により、それぞれ転送された数だけ加算されるものとする。

20

【0084】

図 8 において、シーケンサ 43 は、超音波スキャンが開始されると、転送が必要な制御パラメータの量を取得する（ステップ SB1）。具体的には、シーケンサ 43 は、不図示の内部メモリに記憶されている制御パラメータ関連情報を参照し、ベクター番号毎の送信パラメータの数、受信パラメータの数、及び信号処理パラメータの数を取得する。

20

【0085】

シーケンサ 43 は、FIFO 計数を取得する（ステップ SB2）。具体的には、シーケンサ 43 は、内部メモリ 45、内部メモリ 47、及び内部メモリ 49 に記憶されている FIFO 計数をそれぞれ参照する。このとき、内部メモリ 45、内部メモリ 47、及び内部メモリ 49 に記憶されている FIFO 計数は、それぞれ 0 であるものとする。

30

【0086】

次に、シーケンサ 43 は、ステップ SA1 において取得した制御パラメータの量、及び、ステップ SA2 において取得した FIFO 計数に基づいて、制御パラメータの転送量を設定する（ステップ SB3）。具体的には、シーケンサ 43 は、取得した制御パラメータの数と、及び取得した FIFO 計数とを比較する。シーケンサ 43 は、FIFO 計数が制御パラメータの数より大きい場合、転送量を最小の転送量（MIN）、例えば 1QW に設定する。また、シーケンサ 43 は、FIFO 計数が制御パラメータの数以下である場合、転送量を最大の転送量（MAX）、例えば 4QW に設定する。

30

【0087】

より具体的には、シーケンサ 43 は、ベクター番号 0 に対応する送信パラメータの数と、内部メモリ 45 から取得した FIFO 計数とを比較する。シーケンサ 43 は、FIFO 計数が送信パラメータの数より小さいため、転送量を最大の転送量である 4QW に設定する。また、シーケンサ 43 は、ベクター番号 0 に対応する受信パラメータの数と、内部メモリ 47 から取得した FIFO 計数とを比較する。シーケンサ 43 は、FIFO 計数が受信パラメータの数より小さいため、転送量を最大の転送量である 4QW に設定する。また、シーケンサ 43 は、ベクター番号 0 に対応する信号処理パラメータの数と、内部メモリ 49 から取得した FIFO 計数とを比較する。シーケンサ 43 は、FIFO 計数が信号処理パラメータの数より小さいため、転送量を最大の転送量である 4QW に設定する。

40

【0088】

次に、シーケンサ 43 は、メモリ IF42 を介し、ステップ SB3 において設定した転

50

送量に基づいて、まず、メモリ 5 から内部メモリ 4 5 に送信パラメータを 4 Q W 転送する（ステップ S B 4）。

【0089】

シーケンサ 4 3 は、ステップ S B 4 において転送した回数が所定の転送回数に到達したか否か判定する（ステップ S B 5）。このとき、所定の転送回数は、内部メモリ 4 9 に記憶される信号処理パラメータの数がベクター番号 0 に対応する信号処理パラメータの数 2 0 に到達するまでに必要な転送回数であるものとする。具体的には、内部メモリ 4 9 に記憶されている信号処理パラメータの数は 0 であり、送信パラメータ、受信パラメータ、及び信号処理パラメータの順で 4 Q W ずつ送信されるため、所定の転送回数は 1 5 である。シーケンサ 4 3 は、転送した回数は一回であるため（ステップ S B 5 の N o）、次に、メモリ 5 から内部メモリ 4 7 に受信パラメータを 4 Q W 転送する（ステップ S B 4）。

10

【0090】

そして、シーケンサ 4 3 は、転送回数が 1 5 に到達するまで、例えば、送信パラメータ、受信パラメータ、及び信号処理パラメータの順で、ステップ S B 4 の転送処理を実行する。

【0091】

シーケンサ 4 3 は、1 5 回目の転送処理において、信号処理パラメータを 4 Q W 転送すると（ステップ S B 4）、転送した回数が所定の転送回数に到達したと判定し（ステップ S B 5 の Y e s）し、転送が完了したか否か判定する（ステップ S B 6）。

20

【0092】

シーケンサ 4 3 は、例えば、制御パラメータ関連情報が示す制御パラメータを全て送信していないため、転送が完了していないと判定し（ステップ S B 6 の N o）、内部メモリ 4 5、内部メモリ 4 7、及び内部メモリ 4 9 に記憶されている F I F O 計数をそれぞれ取得する（ステップ S B 2）。

【0093】

次に、シーケンサ 4 3 は、ステップ S A 1 において取得した制御パラメータの量、及び、ステップ S A 2 において取得した最新の F I F O 計数に基づいて、制御パラメータの転送量を設定する（ステップ S B 3）。

【0094】

具体的には、シーケンサ 4 3 は、ベクター番号 0 に対応する送信パラメータの数と、内部メモリ 4 5 から取得した F I F O 計数とを比較する。シーケンサ 4 3 は、F I F O 計数が送信パラメータの数 1 0 0 より小さいため、転送量を最大の転送量である 4 Q W に設定する。また、シーケンサ 4 3 は、ベクター番号 0 に対応する受信パラメータの数と、内部メモリ 4 7 から取得した F I F O 計数とを比較する。シーケンサ 4 3 は、F I F O 計数が受信パラメータの数 5 0 より小さいため、転送量を最大の転送量である 4 Q W に設定する。また、シーケンサ 4 3 は、ベクター番号 0 に対応する信号処理パラメータの数と、内部メモリ 4 9 から取得した F I F O 計数とを比較する。シーケンサ 4 3 は、F I F O 計数が信号処理パラメータの数 2 0 と等しいため、転送量を最小の転送量である 1 Q W に設定する。これにより、信号処理パラメータの転送量は、4 Q W から 1 Q W に変更される。

30

【0095】

次に、シーケンサ 4 3 は、転送回数が所定の回数に達するまで、ステップ S B 4 及びステップ S B 5 を繰り返し実行する。このとき、所定の回数は、内部メモリ 4 7 に記憶される受信パラメータの数がベクター番号 0 に対応する受信パラメータの数 5 0 に到達するまでに必要な転送回数であるものとする。具体的には、内部メモリ 4 7 に記憶されている受信パラメータの数は 2 0 であり、送信パラメータ、受信パラメータ、及び信号処理パラメータの順で 4 Q W、4 Q W、1 Q W ずつ送信されるため、所定の転送回数は 3 9 である。

40

【0096】

そして、シーケンサ 4 3 は、転送回数が 3 9 に到達するまで、送信パラメータ、受信パラメータ、及び信号処理パラメータの順で、ステップ S B 4 の転送処理を実行する。

【0097】

50

シーケンサ43は、39回目の転送処理において、信号処理パラメータを1QW転送すると(ステップSB4)、転送した回数が所定の転送回数に到達したと判定し(ステップSB5のYes)、転送が完了したか否か判定する(ステップSB6)。

【0098】

シーケンサ43は、例えば、制御パラメータ関連情報が示す制御パラメータを全て送信していないため、転送が完了していないと判定し(ステップSB6のNo)、内部メモリ45、内部メモリ47、及び内部メモリ49に記憶されているFIFO計数をそれぞれ取得する(ステップSB2)。

【0099】

以下、シーケンサ43は、制御パラメータ関連情報が示す制御パラメータの転送が全て完了するまで、ステップSB2からステップSB6までの処理を繰り返し実行する。

10

【0100】

シーケンサ43は、制御パラメータ関連情報が示す制御パラメータの転送が全て完了すると(ステップSB6のYes)、超音波スキャンが終了したか否か判定する(ステップSB7)。

【0101】

シーケンサ43は、超音波スキャンが終了していない場合(ステップSB7のNo)、転送が必要な制御パラメータの量を再び取得する(ステップSB1)。具体的には、シーケンサ43は、不図示の内部メモリに記憶されている制御パラメータ関連情報を参照し、例えば、ステップSB2からステップSB7までの処理を実行している間に新たにホスト制御回路11からシーケンサ43に供給された制御パラメータ関連情報について、ベクターパターン毎の送信パラメータの数、受信パラメータの数、及び信号処理パラメータの数を取得する。

20

【0102】

シーケンサ43は、新たに取得した制御パラメータについて、ステップSB2からステップSB7までの処理を再び実行する。

【0103】

シーケンサ43は、超音波スキャンが終了している場合(ステップSB7のYes)、転送制御処理を終了する。

30

【0104】

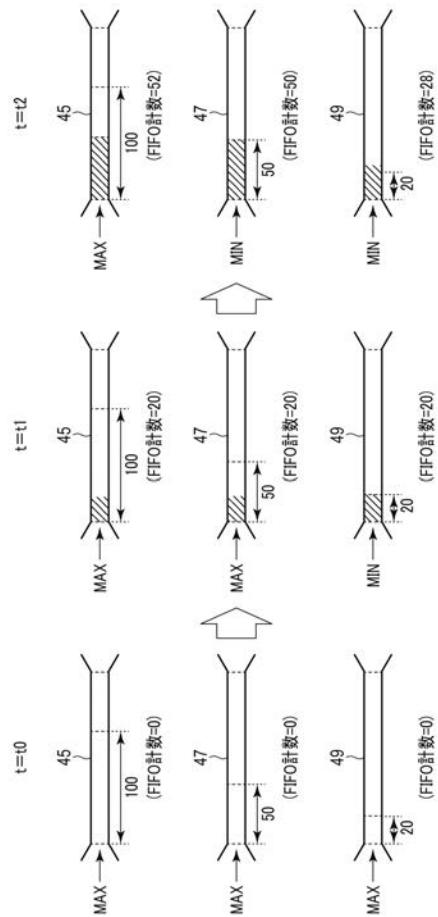

図10は、変形例に係るシーケンサ43による制御パラメータの転送量制御について説明するための図である。

【0105】

シーケンサ43は、図10に示される時点 $t = t_0$ において、図8に示されるステップSB2を実行し、内部メモリ45、内部メモリ47、及び内部メモリ49に記憶されているFIFO計数をそれぞれ取得する。図10に示されるように、時点 $t = t_0$ では、内部メモリ45、内部メモリ47、及び内部メモリ49のFIFOキューに制御パラメータは滞留していない。このため、シーケンサ43は、図8に示されるステップSB3において、内部メモリ45、内部メモリ47、及び内部メモリ49に対して転送するデータの転送量をそれぞれMAX、例えば4QWにそれぞれ設定する。そして、シーケンサ43は、調停回路A1にR×バスの使用権を要求し、例えば、送信パラメータ、受信パラメータ、及び信号処理パラメータを、送信パラメータ、受信パラメータ、及び信号処理パラメータの順で内部メモリ45、内部メモリ47、及び内部メモリ49にそれぞれ繰り返し転送する。

40

【0106】

シーケンサ43は、図10に示される時点 $t = t_1 (> t_0)$ において、図8に示されるステップSB5を実行し、ベクターパターン0について転送すべき20の信号処理パラメータを全て内部メモリ49に転送し終えたと認識する(ステップSB5のYes)。その後、シーケンサ43は、図8に示されるステップSB2において、内部メモリ45、内部メモリ47、及び内部メモリ49に記憶されているFIFO計数をそれぞれ取得する。そし

50

て、シーケンサ43は、図8に示されるステップSB3を実行し、内部メモリ49に対して転送するデータの転送量をMIN、例えば1QWに変更する。そして、シーケンサ43は、例えば、送信パラメータ、受信パラメータ、及び信号処理パラメータを、送信パラメータ、受信パラメータ、及び信号処理パラメータの順で内部メモリ45、内部メモリ47、及び内部メモリ49にそれぞれ繰り返し転送する。

#### 【0107】

シーケンサ43は、図10に示される時点  $t = t_2 (> t_1)$ において、図8に示されるステップSB5を実行し、ベクター番号0について転送すべき52の信号処理パラメータを全て内部メモリ49に転送し終えたと認識する(ステップSB5のYess)。その後、シーケンサ43は、図8に示されるステップSB2において、内部メモリ45、内部メモリ47、及び内部メモリ49に記憶されている FIFO計数をそれぞれ取得する。そして、シーケンサ43は、図8に示されるステップSB3を実行し、内部メモリ47に対して転送するデータの転送量をMIN、例えば1QWに変更する。そして、シーケンサ43は、例えば、送信パラメータ、受信パラメータ、及び信号処理パラメータを、送信パラメータ、受信パラメータ、及び信号処理パラメータの順で内部メモリ45、内部メモリ47、及び内部メモリ49にそれぞれ繰り返し転送する。

10

#### 【0108】

このように、シーケンサ43は、1ベクター内の送信パラメータの量、受信パラメータの量、及び信号処理パラメータの量に差がある場合、一回の超音波送受信に必要な量が相対的に多い制御パラメータを優先的にバースト転送することができる。これにより、一回の超音波送受信に必要な量が相対的に多い制御パラメータの転送回数を削減することができとなり、削減された転送回数に対応する転送動作間の待機時間、及び、転送先アドレスを示すアドレスデータの転送時間分だけ所要時間を削減することができる。

20

#### 【0109】

##### [他の実施形態]

なお、この発明は上記実施形態に限定されるものではない。上記実施形態、及び変形例では、メモリIF42から調停回路A1に対して送信パラメータ、受信パラメータ、信号処理パラメータ等の制御パラメータの転送が要求される場合について説明したがこれに限定されない。シーケンサ43は、例えば、メモリIF42から調停回路A1に対する制御パラメータの転送要求と、ホスト制御回路IF41から調停回路A1に対する制御パラメータの転送要求とが競合する場合について、内部メモリ45、内部メモリ47、及び内部メモリ49に記憶されている FIFO計数の値に応じて、制御パラメータの転送量を設定するようにしてもよい。

30

#### 【0110】

具体的には、シーケンサ43は、内部メモリ45、内部メモリ47、及び内部メモリ49に記憶されている FIFO計数の値が、例えば、7、5、3であった場合、ホスト制御回路IF41から送信回路IF44、受信回路IF46、及び信号処理回路IF48に転送する制御パラメータの転送量を、4QW、4QW、及び1QWにそれぞれ設定する。シーケンサ43は、設定した転送量に基づいて、ホスト制御回路IF41を介し、ホスト制御回路11から送信回路IF44、受信回路IF46、及び信号処理回路IF48へ制御パラメータをそれぞれ転送する。なお、シーケンサ43は、内部メモリ45、内部メモリ47、及び内部メモリ49に記憶されている FIFO計数の合計値に基づいて、ホスト制御回路11から送信回路IF44、受信回路IF46、及び信号処理回路IF48へ転送される制御パラメータの転送量を設定するようにしてもよい。

40

#### 【0111】

ホスト制御回路11から送信回路IF44、受信回路IF46、及び信号処理回路IF48へ転送される制御パラメータの転送量は1QWである場合が多い。メモリIF42から調停回路A1に対する制御パラメータの転送要求と、ホスト制御回路IF41から調停回路A1に対する制御パラメータの転送要求とが競合する場合、ラウンドロビン方式の下では、調停回路A1は、例えば、メモリIF42及びホスト制御回路IF41に対して要

50

求に応じて均等に R × バスの使用権を許可しなければならない。このため、ホスト制御回路 I F 4 1 から調停回路 A 1 に対する制御パラメータの転送要求の回数が多い場合には、メモリ I F 4 2 が調停回路 A 1 により R × バスの使用権を許可される回数が相対的に少なくなってしまう場合ある。

【 0 1 1 2 】

他の実施形態に係るシーケンサ 4 3 によれば、F I F O 計数、すなわち内部メモリ 4 5 、内部メモリ 4 7 、及び内部メモリ 4 9 転送された制御パラメータの量に応じて、ホスト制御回路 I F 4 1 から送信回路 I F 4 4 、受信回路 I F 4 6 、及び信号処理回路 I F 4 8 へ制御パラメータをバースト転送する。このため、最小の転送量である 1 Q W ずつ転送する場合と比して、制御パラメータの転送回数を削減することができ、ホスト制御回路 I F 4 1 から調停回路 A 1 に対する転送要求の回数を削減することができる。したがって、相対的に、メモリ I F 4 2 から調停回路 A 1 に対する制御パラメータの転送要求が許可される回数を増加させることができ、メモリ I F 4 2 から内部メモリ 4 5 、内部メモリ 4 7 、及び内部メモリ 4 9 へ転送される制御パラメータの転送速度を向上することができる。

10

【 0 1 1 3 】

また、実施形態に係る各機能は、当該処理を実行するプログラムをワークステーション等のコンピュータにインストールし、これらをメモリ上で展開することによっても実現することができる。このとき、コンピュータに当該手法を実行させることのできるプログラムは、磁気ディスク（ハードディスクなど）、光ディスク（C D - R O M 、D V D など）、半導体メモリなどの記憶媒体に格納して頒布することも可能である。

20

【 0 1 1 4 】

上記説明において用いた「プロセッサ」という文言は、例えば、C P U (Central Processing Unit) 、G P U (Graphics Processing Unit) 、或いは、特定用途向け集積回路 (Application Specific Integrated Circuit : A S I C ) 、プログラマブル論理デバイス（例えば、単純プログラマブル論理デバイス (Simple Programmable Logic Device : S P L D ) 、複合プログラマブル論理デバイス (Complex Programmable Logic Device : C P L D ) 、及びフィールドプログラマブルゲートアレイ (Field Programmable Gate Array : F P G A ) ）等の回路を意味する。プロセッサは記憶回路に保存されたプログラムを読み出し実行することで機能を実現する。なお、本実施形態の各プロセッサは、プロセッサごとに単一の回路として構成される場合に限らず、複数の独立した回路を組み合わせて 1 つのプロセッサとして構成し、その機能を実現するようにしてもよい。さらに、図 1 における複数の構成要素を 1 つのプロセッサへ統合してその機能を実現するようにしてもよい。

30

【 0 1 1 5 】

以上説明した少なくとも 1 つの実施形態によれば、超音波送受信に関する制御パラメータの転送効率を向上させることができる。

【 0 1 1 6 】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれると同様に、特許請求の範囲に記載された発明とその均等の範囲に含まれるものである。

40

【 符号の説明 】

【 0 1 1 7 】

- 1 ... 超音波プローブ

- 2 ... 送信回路

- 3 ... 受信回路

- 4 ... 送受信制御回路

50

- 5 … メモリ

6 … 信号処理回路

7 … 画像生成回路

8 … 記憶回路

9 … ディスプレイ

10 … 入力インターフェース

11 … ホスト制御回路

41 … ホスト制御回路インターフェース

42 … メモリインターフェース

43 … シーケンサ

44 … 送信回路インターフェース

45、47、49 … 内部メモリ

46 … 受信回路インターフェース

48 … 信号処理回路インターフェース

50 … データ収集インターフェース

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

| ベクター番号 | 送信パラメータの数 | 受信パラメータの数 | 信号処理パラメータの数 |

|--------|-----------|-----------|-------------|

| 0      | 7         | 5         | 3           |

| 1      | 10        | 8         | 6           |

| ...    | ...       | ...       | ...         |

【図7】

【図8】

【図9】

| ペクター番号 | 送信パラメータの数 | 受信パラメータの数 | 信号処理パラメータの数 |

|--------|-----------|-----------|-------------|

| 0      | 100       | 50        | 20          |

| 1      | 50        | 25        | 15          |

| ...    | ...       | ...       | ...         |

【図10】

---

フロントページの続き

(72)発明者 崔 載鎬

栃木県大田原市下石上1385番地 キヤノンメディカルシステムズ株式会社内

Fターム(参考) 4C601 EE07 HH14 LL01

|           |                                  |         |            |

|-----------|----------------------------------|---------|------------|

| 专利名称(译)   | 超声诊断设备和控制程序                      |         |            |

| 公开(公告)号   | <a href="#">JP2019141170A</a>    | 公开(公告)日 | 2019-08-29 |

| 申请号       | JP2018026354                     | 申请日     | 2018-02-16 |

| [标]发明人    | 崔載鎬                              |         |            |

| 发明人       | 崔載鎬                              |         |            |

| IPC分类号    | A61B8/14                         |         |            |

| FI分类号     | A61B8/14                         |         |            |

| F-TERM分类号 | 4C601/EE07 4C601/HH14 4C601/LL01 |         |            |

| 代理人(译)    | 河野直树<br>井上 正<br>肯·鶴饲             |         |            |

| 外部链接      | <a href="#">Espacenet</a>        |         |            |

### 摘要(译)

要解决的问题：提高与超声波发送/接收相关的控制参数的传输效率。根据实施例，超声诊断设备包括第一存储器，控制单元和第二存储器。第一存储器存储与超声波的发送/接收有关的第一控制参数。控制单元基于一次发送和接收超声波所需的第一控制参数的量来设置第一控制参数的传送量，并且设置传送量的第一控制传输参数。第二存储器临时存储传送的第一控制参数。[选择]图2