(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5690900号 (P5690900)

(45) 発行日 平成27年3月25日(2015.3.25)

(24) 登録日 平成27年2月6日(2015.2.6)

(51) Int.Cl.

A 6 1 B 8/00 (2006.01)

A 6 1 B 8/00

FL

請求項の数 13 外国語出願 (全 93 頁)

(21) 出願番号 特願2013-204411 (P2013-204411) (22) 出願日 平成25年9月30日 (2013.9.30)

(62) 分割の表示 特願2008-539044 (P2008-539044)

の分割

原出願日 平成18年11月2日 (2006.11.2) (65) 公開番号 特開2014-465 (P2014-465A) (43) 公開日 平成26年1月9日 (2014.1.9) 審査請求日 平成25年9月30日 (2013.9.30)

(31) 優先権主張番号 60/733,089

(32) 優先日 平成17年11月2日 (2005.11.2)

(33) 優先権主張国 米国 (US) (31) 優先権主張番号 60/733,091

(32) 優先日 平成17年11月2日 (2005.11.2)

(33) 優先権主張国 米国(US)

(73) 特許権者 504461529

ビジュアルソニックス インコーポレイテ

ッド

カナダ国 エム4エヌ 3エヌ1 オンタ リオ, トロント, ヤング ストリート 3080, スイート 6100, ボ

ックス 66

(74)代理人 100078282

弁理士 山本 秀策

(74)代理人 100113413

弁理士 森下 夏樹

(72)発明者 ジェームス メヒ

カナダ国 エル4ジェイ 7エックス1 オンタリオ, ソーンヒル, ヤング ス トリート 7250, ユニット 206

最終頁に続く

(54) 【発明の名称】高周波数アレイ超音波システム

### (57)【特許請求の範囲】

### 【請求項1】

アレイド超音波イメージングシステム(1600)用のデジタル送信ビーム成形器(1 605)であって、

前記デジタル送信ビーム成形器は、

1 つまたは複数のフィールドプログラマブルゲートアレイ(FPGA)であって、各F PGAがFPGAクロック周波数(FPGA fc)を有する、FPGAと、

二重データレート出力を有する並列/直列変換器(2212、2213)と

#### を備え、

前記デジタル送信ビーム成形器は、正の送信パルスの微細遅延および正のパルス幅と負の送信パルスの微細遅延および負のパルス幅とをそれぞれの波形ワード(2202、2203)にデジタルで符号化することにより、 $[1/(2\times FPGA\ fc)]$ 以下の遅延分解能時間で  $1.5\ MHz \sim 8.0\ MHz$  の範囲内の送信中心周波数を有する超音波信号であって、前記正の送信パルスおよび前記負の送信パルスを備える超音波信号を送信するように構成され、それにより、前記正のパルス幅および前記負のパルス幅は、前記遅延分解能時間の増分において個々に調節可能であり、前記波形ワードは、前記超音波信号を生成するために前記並列/直列変換器により直列ビット流に変換される、デジタル送信ビーム成形器(1.6.0.5)。

# 【請求項2】

前記送信中心周波数は、調節可能である、請求項1に記載のデジタル送信ビーム成形器

# (1605)。

### 【請求項3】

<u>前記送信された超音波信号は、複数の送信サイクルを含み、前記送信サイクルの数が調</u>節可能である、請求項1に記載のデジタル送信ビーム成形器(1605)。

### 【請求項4】

前記デジタル送信ビーム成形器は、アレイド超音波振動子(1601)と動作可能に接続されるように構成され、前記アレイド超音波振動子は、線形アレイ振動子(2302)、位相アレイ振動子、二次元アレイ振動子および曲線アレイ振動子から成る群から選択される、請求項1に記載のデジタル送信ビーム成形器(1605)。

# 【請求項5】

<u>前記送信中心周波数は、15MHz~約55MHzである、請求項1に記載のデジタル</u>送信ビーム成形器(1605)。

### 【請求項6】

<u>前記ビットワード(2202、2203)は、最大で16ビットワードである、請求項</u>1に記載のデジタル送信ビーム成形器(1605)。

#### 【請求項7】

F P G A f c は、前記 1 つまたは複数の F P G A の動作可能な最高周波数である、請求項 1 に記載のデジタル送信ビーム成形器 ( 1 6 0 5 )。

#### 【請求項8】

\_\_\_アレイド超音波イメージングシステム(1600)用の信号処理ユニット(1620) であって、\_\_

前記信号処理ユニットは、

請求項1~7のいずれかに記載のデジタル送信ビーム成形器(1605)を備えるデジタル送信ビーム成形器サブシステムと、

デジタル受信ビーム成形器サブシステム(1603)と、

フロントエンド電子回路モジュール(1602)と、

ビーム成形器制御装置モジュール(1604)と、

信号処理モジュール(1715)と、

コンピュータユニット(1717)と

# を備え、

<u>前記信号処理ユニットは、複数の要素を有するアレイド超音波振動子(1601)から</u>受信超音波信号を取得するように構成される、信号処理ユニット(1620)。

# 【請求項9】

前記送信された超音波信号が、複数の正の半波サイクル部分から成り、各々の正の半波サイクル部分が、少なくとも1つの前記正の送信パルスから成り、前記送信された超音波信号が、さらに、複数の負の半波サイクル部分から成り、各々の負の半波サイクル部分が、少なくとも1つの前記負の送信パルスから成り、各々の正の送信パルスの持続時間が、各々の正の半波サイクル部分について調節可能であり、各々の負の送信パルスの持続時間が、各々の負の半波サイクル部分について調節可能である、請求項8に記載の信号処理ユニット(1620)。

# 【請求項10】

各々の前記正の半波サイクル内の前記少なくとも1つの前記正の送信パルスの各々の微細遅延が調節可能であり、各々の負の半波サイクル内の前記少なくとも1つの前記負の送信パルスの各々の微細遅延が調節可能である、請求項9に記載の信号処理ユニット(1620)。

# 【請求項11】

前記フロントエンド電子回路モジュール(1602)は、交換可能な差込みモジュールとして構成される、請求項8、9または10に記載の信号処理ユニット(1620)。

### 【請求項12】

送信中心周波数で超音波信号を被検体内に送信する複数の要素を有するアレイド超音波

10

30

20

40

#### 振動子(1601)と、

請求項8~11のいずれかに記載の信号処理ユニット(1620)であって、前記アレイド超音波振動子と動作可能に接続される信号処理ユニットと、

を備え、前記信号処理ユニットは、複数の要素を有する前記アレイド超音波振動子から、少なくとも15MHzの周波数を有する受信超音波信号を取得するように適合される、超音波イメージングシステム(1600)。

#### 【請求項13】

前記アレイド超音波振動子(1601)は、線形アレイ振動子(2302)、位相アレ イ振動子、二次元アレイ振動子および曲線アレイ振動子から成る群から選択される、請求 項12に記載の超音波イメージングシステム(1600)。

【発明の詳細な説明】

【技術分野】

[0001]

(関連出願の参照)

本願は、2005年11月2日出願の米国仮特許出願第60/733,091号の利益を主張し、2005年11月2日出願の米国仮特許出願第60/733,089号の利益を主張する。上記出願の両方が、本明細書において完全に援用され、本明細書の一部を構成する。

### 【背景技術】

[0002]

アレイド振動子を使用する超音波エコグラフィシステムは、所望の画像分解能がミリメートル台であるヒトの臨床用途に使用されてきた。こうした臨床システム内の動作周波数は、一般に10MHz未満である。しかし、このような低動作周波数の場合、こうしたシステムは、比較的高分解能を必要とするイメージング、たとえば、マウスなどの小動物、またはヒトの小さい組織構造をイメージングするのには適さない。

[0003]

さらに、小動物イメージング用途は、現在利用可能なイメージングシステムによって満たすことができないいくつかの難しい要件を提示する。生体マウスの心拍数は毎分500ビートという高さなので、高いフレームレート能力が必要である。イメージングされる領域の幅、つまり視野も、検査される組織全体を含むのに十分でなければならない。

[0004]

15MHzを超える周波数でイメージングするための超音波システムは、単一素子振動子を使用して開発されてきた。しかし、アレイド振動子は、単一素子振動子システムと比べてより良好な画像品質を提供し、より高度の取得フレームレートを達成することができ、その他の利点を提供することができる。本発明による実施態様は、上記を含む現在の技術の多くの問題を克服する。

## 【発明の概要】

【課題を解決するための手段】

[00005]

本明細書では、複数の素子を有する超音波振動子から受信超音波信号を取得するように構成された信号処理ユニットから成る超音波信号取得システムおよび方法を提供する。このシステムは、少なくとも5.0ミリメートル(mm)の視野を有する固定振動子を使って、少なくとも毎秒20フレーム(fps)のフレームレートで、少なくとも15メガヘルツ(MHz)の周波数を有する超音波信号を受信するように構成することができる。この信号処理ユニットは、取得超音波信号から超音波画像をさらに生成することができる。振動子は、線形アレイ振動子、位相アレイ振動子、二次元(2-D)アレイ振動子、または曲線アレイ振動子で良いが、これらだけに限らない。このシステムは、こうした振動子を備えるか、またはこうした振動子で動作するように構成することができる。

# [0006]

また、本明細書では、少なくとも15MHzの送受信で動作する超音波振動子から受信

10

20

30

50

超音波信号を取得するための処理ユニットであって、直交サンプリングを使用して超音波信号を取得する信号サンプラを備える処理ユニットを備える超音波信号取得システムおよび方法も提供する。

### [0007]

本発明のその他の利点は、以下の明細書に部分的に記載され、この明細書から部分的に明らかになるか、または本発明の実践により知ることができる。本発明の利点は、添付の請求の範囲で特に指摘される素子および組合せによって実現および達成されるであろう。上記の一般的な説明および以下の詳細な説明は共に、単に例示および説明するためのものであり、請求項に係る本発明を制限するものではない。

例えば、本発明は以下の項目を提供する。

10

20

# (項目1)

超音波イメージングシステムであって、

送信超音波信号を被検体内に、最大で少なくとも 5 5 メガヘルツ(MHz)の送信中心 周波数で送信するための複数の素子を有するアレイド超音波振動子と、

前記アレイド超音波振動子と動作可能に接続する信号処理ユニットであって、前記信号 処理ユニットがさらに、

1 つまたは複数のフィールドプログラマブルゲートアレイ(FPGA)から成るデジタル送信ビーム成形器サブシステムであって、各々がFPGAクロック周波数(FPGA f c )を有し、前記デジタル送信ビーム成形器サブシステムが、少なくとも[1/(2 x F P G A f c )]以上の遅延分解能時間を有するサブシステムと、

受信ビーム成形器サブシステムと、

フロントエンド電子回路モジュールと、

ビーム成形器制御装置モジュールと、

信号処理モジュールと、

コンピュータユニットと

を備える前記信号処理ユニットとから成り、

前記信号処理ユニットが、少なくとも15MHzの周波数を有する受信超音波信号を、 複数の素子を有する前記アレイド超音波振動子から取得するように構成される超音波イメ ージングシステム。

(項目2)

30

40

<u>前記デジタル送信ビーム成形器サブシステムが、二重データレート(DDR)出力を有</u>する並列 / 直列変換器を備え、

前記デジタル送信ビーム成形器サブシステムが、前記送信超音波信号の微細遅延および半周期部分を、前記並列/直列変換器によって直列ビット流に変換されるビットワードに符号化することによって、少なくとも[1/(2×FPGA fc)]以上の遅延分解能時間で最大少なくとも55MHzの送信中心周波数を有する超音波信号を送信するように構成される、項目1に記載の超音波イメージングシステム。

# (項目3)

前記デジタル送信ビーム成形器サブシステムが、前記送信超音波信号の微細遅延および半周期部分を、前記並列 / 直列変換器によって直列ビット流に変換される16ビットワードに符号化することによって、少なくとも[1 / (2×FPGA fc)]以上の遅延分解能時間で大少なくとも55MHzの送信中心周波数を有する超音波信号を送信するように構成される、項目2に記載の超音波イメージングシステム。

(項目4)

前記送信超音波信号が、正のパルス波を有する正の送信パルスと、負のパルス波を有する負の送信パルスとから成り、前記正のパルス波および前記負のパルス波が個々に調節可能である、項目 2 に記載の超音波イメージングシステム。

### (項目5)

前記送信超音波信号が、複数の正の半波サイクル部分から成り、各々の正の半波サイクル部分が、少なくとも 1 つの前記正の送信パルスから成り、前記送信超音波信号が、さら

に複数の負の半波サイクル部分から成り、各々の負の半波サイクル部分が、少なくとも 1 つの負の送信パルスから成り、各々の正の送信パルスが、各々の正の半波サイクル部分の 持続時間で調節可能であり、各々の負の送信パルスが、各々の負の半波サイクル部分の 続時間で調節可能である、項目 4 に記載の超音波イメージングシステム。

### (項目6)

各々の正の半波サイクル内の前記少なくとも1つの前記正の送信パルスの各々の微細遅延が調節可能であり、各々の負の半波サイクル内の前記少なくとも1つの前記複数の送信パルスの各々の微細遅延が調節可能である、項目5に記載の超音波イメージングシステム

0

# (項目7)

10

<u>前記送信超音波信号が、送信サイクル数から成り、前記送信サイクル数が調節可能であ</u>る、項目 4 に記載の超音波イメージングシステム。

# (項目8)

<u>前記フロントエンド電子回路モジュールが、交換可能な差込みモジュールとして構成さ</u>れる、項目1に記載の超音波イメージングシステム。

# (項目9)

前記信号処理ユニットが、前記受信超音波信号を前記アレイド超音波振動子から取得するように構成され、前記アレイド超音波振動子が、線形アレイ振動子、位相アレイ振動子、二次元(2 - D)アレイ振動子、曲線アレイ振動子から成る群から選択される、項目 1 に記載の超音波イメージングシステム。

20

30

40

# (項目10)

前記送信超音波信号が、約15MHz~少なくとも55MHzの送信中心周波数を有する、項目1に記載の超音波イメージングシステム。

### (項目11)

器 c h 取得超音波信号が、約15MHz~約55MHzの送信中心周波数を有する、項目1に記載の超音波イメージングシステム。

### (項目12)

アレイド超音波イメージングシステム用の信号処理ユニットであって、

最大少なくとも55 MHzの送信中心周波数で動作するように構成されたデジタル送信ビーム成形器サブシステムであって、前記デジタル送信ビーム成形器サブシステムが、さらに1つまたは複数のフィールドプログラマブルゲートアレイ(FPGA)から成り、各々が、FPGAクロック周波数(FPGA fc)を有し、前記デジタル送信ビーム成形器サブシステムが、少なくとも[1/(2×FPGA fc)]以上の遅延分解能時間を有するデジタル送信ビーム成形器サブシステムと、

デジタル受信ビーム成形器サブシステムと、

フロントエンド電子回路モジュールと、

ビーム成形器制御装置モジュールと、

信号処理モジュールと、

コンピュータユニットとを備え、

<u>前記信号処理ユニットが、複数の素子を有するアレイド超音波振動子から受信超音波信</u>号を取得するように構成される信号処理ユニット。

(項目13)

前記デジタル送信ビーム成形器サブシステムが、二重データレート(DDR)出力を有する並列 / 直列変換器をさらに備え、

前記デジタル送信ビーム成形器サブシステムが、前記送信超音波信号の微細遅延および 半周期部分を、前記並列 / 直列変換器によって直列ビット流に変換されるビットワードに 符号化することによって、少なくとも [ 1 / (2 × F P G A f c ) ] 以上の遅延分解能 時間で最大少なくとも 5 5 M H z の送信中心周波数を有する超音波信号を送信するように 構成される、項目 1 2 に記載の信号処理ユニット。

# (項目14)

前記デジタル送信ビーム成形器サブシステムが、前記送信超音波信号の微細遅延および 半周期部分を、前記並列 / 直列変換器によって直列ビット流に変換された 1 6 ビットワー ドに符号化することによって、少なくとも [ 1 / (2 x F P G A f c)]以上の遅延分 解能時間で最大少なくとも 5 5 M H z の送信中心周波数を有する超音波信号を送信するよ うに構成される、項目 1 3 に記載の信号処理ユニット。

# (項目15)

前記送信超音波信号が、正の送信パルス波、および負の送信パルス波から成り、前記送信パルス波および負のパルス波が別個に調節可能である、項目 1 3 に記載の信号処理ユニット。

# (項目16)

<u>前記送信超音波信号が、送信サイクル数から成り、前記送信サイクル数が調節可能である、項目15に記載の信号処理ユニット。</u>

# (項目17)

<u>前記フロントエンド電子回路モジュールが、交換可能な差込みモジュールとして構成さ</u>れる、項目12に記載の信号処理ユニット。

# (項目18)

前記信号処理ユニットが、前記受信超音波信号を前記アレイド超音波振動子から取得するように構成され、前記アレイド超音波振動子が、線形アレイ振動子、位相アレイ振動子、二次元(2-D)アレイ振動子、曲線アレイ振動子から成る群から選択される、項目12に記載の信号処理ユニット。

# (項目19)

<u>前記送信中心周波数が、約15MHz~少なくとも55MHzである、項目12に記載</u>の信号処理ユニット。

# (項目20)

<u>前記送信中心周波数が約15MHz~約55MHzである、項目12に記載の信号処理</u> ユニット。

# (項目21)

アレイド超音波イメージングシステム用のデジタル送信ビーム成形器であって、

<u>各々がFPGAクロック周波数(FPGA fc)を有する1つまたは複数のFPGAと、</u>

二重データレート(DDR)出力を有する並列/直列変換器とを備え、

前記デジタル送信ビーム成形器が、前記送信超音波信号の微細遅延および半周期部分を 、前記並列 / 直列変換器によって直列ビット流に変換されるビットワードに符号化するこ とによって、少なくとも [ 1 / ( 2 × F P G A f c ) ] 以上の遅延分解能時間で最大少 なくとも 5 5 M H z の送信中心周波数を有する超音波信号を送信するように構成される送 信ビーム成形器。

### (項目22)

前記送信超音波信号が、正の送信パルス波および負の送信パルス波から成り、前記送信 パルス波および負の送信パルス波が個々に調節可能である、項目 2 1 に記載のデジタル送 信ビーム成形器。

# (項目23)

前記送信超音波信号が送信サイクル数から成り、前記送信サイクル数が調節可能である、項目 2 2 に記載のデジタル送信ビーム成形器。

# (項目24)

前記デジタル送信ビーム成形器が、アレイド超音波振動子と動作可能に接続され、前記アレイド超音波振動子が、線形アレイ振動子、位相アレイ振動子、二次元(2-D)アレイ振動子、および曲線アレイ振動子から成る群から選択される、項目21に記載のデジタル送信ビーム成形器。

#### (項目25)

前記送信中心周波数が約15MHz~少なくとも55MHzである、項目21に記載の

10

20

30

30

40

デジタル送信ビーム成形器。

(項目26)

前記送信中心周波数が、約15MHz~約55MHzである、項目21に記載のデジタル送信ビーム成形器。

(項目27)

前記デジタル送信ビーム成形器が、前記送信超音波信号の微細遅延および半周期部分を 、前記並列 / 直列変換器によって直列ビット流に変換される 1 6 ビットワードに符号化す ることによって、少なくとも [ 1 / (2 x F P G A f c ) ] 以上の遅延分解能時間で最 大少なくとも 5 5 M H z の送信中心周波数を有する超音波信号を送信するように構成され る、項目 2 1 に記載のデジタル送信ビーム成形器。

10

(項目28)

超音波イメージングシステムであって、

最大少なくとも55メガヘルツ(MHz)の送信中心周波数で、送信超音波信号を被検体内に送信するための複数の素子を有するアレイド超音波振動子と、

前記アレイド超音波振動子に動作可能に接続された信号処理ユニットと

を備え、前記信号処理ユニットがさらに、

デジタル送信ビーム成形器サブシステムと、

受信ビーム成形器サブシステムと、

フロントエンド電子回路モジュールと、

ビーム成形制御モジュールと、

20

直交サンプリングを使用し、受信サンプリング周波数を有する信号処理モジュールと

<u>コンピュータ</u>ユニットとから構成され、

<u>前記受信サンプリング周波数が選択的に選択されるように構成される超音波イメージン</u>グシステム。

(項目29)

前記受信サンプリング周波数が、前記送信中心周波数とは異なる周波数で選択される、 項目 2 8 に記載の超音波イメージングシステム。

(項目30)

<u>前記受信サンプリング周波数が、前記送信中心周波数と同じ周波数で選択される、項目</u> 2 8 に記載の超音波イメージングシステム。 30

(項目31)

前記デジタル送信ビーム成形器サブシステムが、前記受信サンプリング周波数が前記送信焦点深度に依存するように、送信焦点深度をさらに含む、項目28に記載の超音波イメージングシステム。

(項目32)

<u>前記受信サンプリング周波数が、前記送信焦点深度が増加するにつれて減少する、項目</u>30に記載の超音波イメージングシステム。

(項目33)

前記デジタル送信ビーム成形器サブシステムが、二重データレート(DDR)出力を有する並列 / 直列変換器をさらに備え、

前記デジタル送信ビーム成形器が、前記送信超音波信号の微細遅延および半周期部分を、前記並列 / 直列変換器によって直列ビット流に変換されるビットワードに符号化することによって、少なくとも [ 1 / (2 x F P G A f c )]以上の遅延分解能時間で最大少なくとも 5 5 M H z の送信中心周波数を有する超音波信号を送信するように構成される、項目 2 8 に記載の超音波イメージングシステム。

(項目34)

前記デジタル送信ビーム成形器サブシステムが、前記送信超音波信号の微細遅延および 半周期部分を、前記並列/直列変換器によって直列ビット流に変換される16ビットワー ドに符号化することによって、少なくとも[1/(2×FPGA fc)]以上の遅延分

50

解能時間で最大少なくとも55MHzの送信中心周波数を有する超音波信号を送信するように構成される、項目33に記載の超音波イメージングシステム。

# (項目35)

前記送信超音波信号が、正の送信パルス波および負の送信パルス波から成り、前記送信 パルス波および負の送信パルス波が個々に調節可能である、項目33に記載の超音波イメ ージングシステム。

# (項目36)

<u>前記送信超音波信号が、送信サイクル数から成り、前記送信サイクル数が調節可能であ</u>る、項目35に記載の超音波イメージングシステム。

### (項目37)

<u>前記フロントエンド電子回路モジュールが、交換可能な差込みモジュールとして構成される、項目28に記載の超音波イメージングシステム。</u>

# (項目38)

前記信号処理ユニットが、前記受信超音波信号を前記アレイド超音波振動子から取得するように構成され、前記アレイド超音波振動子が、線形アレイ振動子、位相アレイ振動子、二次元(2-D)アレイ振動子、および曲線アレイ振動子から成る群から選択される、項目28に記載の超音波イメージングシステム。

# (項目39)

前記送信超音波信号が、約15MHz~少なくとも55MHzの送信中心周波数を有する、項目28に記載の超音波イメージングシステム。

# (項目40)

前記送信超音波信号が、約15MHz~約55MHzの送信中心周波数を有する、項目 2 8 に記載の超音波イメージングシステム。

### (項目41)

超音波イメージングシステムであって、

最大少なくとも55メガヘルツ(MHz)の送信中心周波数で、送信超音波信号を被検体内に送信するための複数の素子を有するアレイド超音波振動子であって、前記前記アレイド超音波振動子が、少なくとも5.0ミリメートル(mm)の視野を有する前記アレイド超音波振動子と、

前記アレイド超音波振動子と動作可能に接続される信号処理ユニットであって、

前記処理ユニットが、デジタル送信および受信ビーム成形器サブシステムと、フロント エンド電子回路モジュールと、ビーム成形器制御装置および信号処理モジュールと、コン ピュータユニットとをさらに備える信号処理ユニットとを備え、

前記信号処理ユニットが、複数の素子を有する前記アレイド超音波振動子から、少なくとも毎秒20フレーム(fps)のフレームレートで受信超音波信号を取得するように構成され、前記受信超音波信号が少なくとも15MHzの周波数を有する超音波イメージングシステム。

# (項目42)

<u>前記信号処理ユニットが、前記受信超音波信号から超音波画像をさらに生成する、項目</u> 4 1 に記載のシステム。

# (項目43)

前記受信超音波信号が、前記取得レートより低速の表示レートで超音波画像を生成するように、前記信号処理ユニットによって処理される、項目42に記載のシステム。

#### (項目44)

前記生成された超音波画像の表示レートが約100fps以下である、項目43に記載のシステム。

#### (項目45)

前記生成された超音波画像の表示レートが約30fps以下である、項目44に記載の システム。

# (項目46)

20

10

30

40

前記超音波画像が、Bモード、Mモード、ドップラーモード、RFモード、3-Dモードから成る群から選択される超音波モードの前記信号処理ユニットによって生成される、項目42に記載のシステム。

### (項目47)

前記信号処理ユニットが、前記受信超音波信号を前記アレイド超音波振動子から取得するように構成され、前記アレイド超音波振動子が、線形アレイ振動子、位相アレイ振動子、二次元(2-D)アレイ振動子、および曲線アレイ振動子から成る群から選択される、項目41に記載のシステム。

### (項目48)

前記アレイド超音波振動子が、少なくとも15MHzの中心動作周波数を有し、前記アレイド超音波振動子が、前記アレイド超音波振動子の送信中心周波数における音の波長の 2.0倍以下の素子ピッチを有する、項目41に記載のシステム。

# (項目49)

<u>前記アレイド超音波振動子が、前記アレイド超音波振動子の送信中心周波数における音</u>の波長の1.5倍以下の素子ピッチを有する、項目41に記載のシステム。

#### (項目50)

前記デジタル受信ビーム成形器サブシステムが、少なくとも 1 つのフィールドプログラマブルゲートアレイ(FPGA)デバイスを使用することを含む、項目 4 1 に記載のシステム。

### (項目51)

前記デジタル送信ビーム成形器サブシステムが、少なくとも1つのフィールドプログラマブルゲートアレイ(FPGA)デバイスを使用することを含む、項目41に記載のシステム。

# (項目52)

フロントエンド電子回路モジュールが、送信回路および受信チャネルをさらに備え、前記送信回路が、2つの電界効果トランジスタ(FET)を介して、中心タップ巻線を含む変換器に接続された送信電源電圧を備え、前記受信チャネルに対する入力が、前記変換器の前記二次巻線の第2端部に接続され、その結果、前記送信電源電圧が実質的にゼロに設定され、前記2つのFETに電源が投入され、前記受信チャネルが信号を受信し、前記変換器が送信信号を生成し、前記送信回路が信号を送信する時に、前記送信信号を前記アレイド超音波振動子に結合する、項目41に記載のシステム。

# (項目53)

前記フロントエンド電子回路モジュールが、各々の受信チャネルに 2 つ以上の信号サンプラをさらに備える、項目 5 2 に記載のシステム。

### (項目54)

前記信号サンプラがアナログデジタル変換器である、項目53に記載のシステム。

# (項目55)

<u>前記信号サンプラが直交サンプリングを使用して、受信信号をサンプリングする、項目</u> 5 3 に記載のシステム。

# (項目56)

<u>前記信号サンプラが、90°位相が外れたサンプリングクロックを備える、項目55に</u> 記載のシステム。

# (項目57)

<u>前記サンプリングクロックが、受信超音波信号の前記中心周波数にほぼ等しい受信クロック期間を有する、項目56に記載のシステム。</u>

# (項目58)

受信クロック期間未満の遅延分解能が、取得信号を処理するために使用される、項目 57 に記載のシステム。

### (項目59)

前記遅延分解能が、前記受信クロック期間の1/16である、項目58に記載のシステ

20

10

30

30

40

### ム。

# (項目60)

複数の素子を有する前記アレイド超音波振動子の各々の素子が、受信チャネルに動作可能に接続される、項目 4 1 に記載のシステム。

### (項目61)

\_\_複数の素子を有する前記アレイド超音波振動子の素子の数が、受信チャネルの数より多い、項目60に記載のシステム。

# (項目62)

複数の素子を有する前記アレイド超音波振動子が、少なくとも32個の受信チャネルに動作可能に接続される少なくとも64個の素子を備える、項目60に記載のシステム。

10

# (項目63)

<u>複数の素子を有する前記アレイド超音波振動子が、64個の受信チャネルに動作可能に</u>接続される256個の素子を備える、項目60に記載のシステム。

# (項目64)

複数の素子を有する前記アレイド超音波振動子が、128個の受信チャネルに動作可能 に接続される256個の素子を備える、項目60に記載のシステム。

# (項目65)

複数の素子を有する前記アレイド超音波振動子が、256個の受信チャネルに動作可能に接続される256個の素子を備える、項目60に記載のシステム。

### (項目66)

20

\_\_\_\_\_複数の素子を有する前記アレイド超音波振動子が、256個の素子を備える、項目60 に記載のシステム。

# (項目67)

5 1 2 本の超音波ラインが生成され、前記被検体内に送信され、前記生成された超音波画像の各々のフレームごとに、前記被検体から受信される、項目 6 6 に記載のシステム。 (項目 6 8)

256本の超音波ラインが生成され、前記被検体内に送信され、前記生成された超音波画像の各々のフレームごとに、前記被検体から受信される、項目66に記載のシステム。 (項目69)

30

少なくとも2本の超音波ラインが生成され、前記被検体内に送信され、前記生成された 超音波画像の各々のフレームごとに、前記アレイの各々の素子において前記被検体から受 信される、項目41に記載のシステム。

# (項目70)

1本の超音波ラインが生成され、前記被検体内に送信され、前記生成された超音波画像 の各々のフレームごとに、前記アレイの各々の素子において前記被検体から受信される、 項目 4 1 に記載のシステム。

### (項目71)

前記受信超音波信号が、毎秒少なくとも 2 0 0 フレーム数 ( f p s ) の取得レートで取得される、項目 7 0 に記載のシステム。

### (項目72)

40

50

<u>複数の素子を有する前記アレイド超音波振動子が、前記振動子の前記中心送信周波数の</u>波長に等しい距離だけ分離される、項目 4 1 に記載のシステム。

# (項目73)

<u>前記中心送信周波数が、15MHz、20MHz、30MHz、40MHz、50MH</u>z、および55MHzから成る群から選択される、項目72に記載のシステム。

# (項目74)

\_\_複数の素子を有する前記アレイド超音波振動子の長さが前記振動子の視野に等しい、項目41に記載のシステム。

### (項目75)

複数の素子を有する前記アレイド超音波振動子が、約15MHz~約80MHzの範囲

<u>内の中心周波数で、前記被検体内に送信超音波を送信することができる、項目41に記載</u>のシステム。

# (項目76)

<u>前記受信超音波信号が、少なくとも200fpsのフレームレートで取得される、項目</u>41に記載のシステム。

# (項目77)

<u>前記受信超音波信号が、約100fps~約200fpsのフレームレートで取得される、項目41に記載のシステム。</u>

## (項目78)

<u>前記超音波画像が、約150ミクロン(μm)以下の方位分解能を有する、項目41に</u>記載のシステム。

#### (項目79)

前記超音波画像が、約75ミクロン(μm)以下の距離分解能を有する、項目78に記載のシステム。

### (項目80)

前記超音波画像が、約30ミクロン(μm)以下の空間分解能を有する、項目79に記載のシステム。

# (項目81)

前記送信超音波信号が、約1.0mm~約30.0mmの深さで集束することが可能な、項目41に記載のシステム。

# (項目82)

<u>前記送信超音波信号が、約3.0mm~約10.0mmの深さで集束することが可能な</u> <u>、項目81に記載のシステム。</u>

# (項目83)

前記送信超音波信号が、約2.0mm~約12.0mmの深さで集束することが可能な 、項目81に記載のシステム。

#### (項目84)

前記送信超音波信号が、約1.0mm~約6.0mmの深さで集束することが可能な、 項目81に記載のシステム。

### (項目85)

<u>前記送信超音波信号が、約3.0mm~約8.0mmの深さで集束することが可能な、</u>項目81に記載のシステム。

### (項目86)

前記送信超音波信号が、約5.0mm~約18.0mmの深さで集束することが可能な 、項目81に記載のシステム。

# (項目87)

超音波画像を生成するシステムであって、

最大少なくとも55メガヘルツ(MHz)の中心動作周波数で超音波を生成して被検体内に送信し、超音波信号を前記被検体から受信するための複数の素子を有するアレイド超音波振動子と、

超音波画像フレームを生成するための処理ユニットであって、前記アレイド超音波振動子の各々の素子が、2本以上の超音波ラインを前記被検体内に送信し、前記生成された超音波画像の各々のフレームについて2本以上のエコー超音波ラインを前記被検体から受信する処理ユニットと

# を備えるシステム。

# (項目88)

前記アレイド超音波振動子が、線形アレイ振動子、位相アレイ振動子、二次元(2-D)アレイ振動子、および曲線アレイ振動子から成る群から選択される、項目87に記載のシステム。

# (項目89)

20

10

30

40

前記アレイド超音波振動子の中心動作周波数が少なくとも 1 5 M H z であり、前記アレイド超音波振動子が、前記アレイド超音波振動子の送信中心周波数における音の波長の 2 倍以下に等しい素子ピッチを有する、項目 8 7 に記載のシステム。

(項目90)

超音波画像を生成するシステムであって、

最大少なくとも55メガヘルツ(MHz)の周波数で超音波を生成して被検体内に送信 し、超音波信号を前記被検体から受信するための複数の素子を有するであって、各々の素 子が、受信チャネルに動作可能に接続されるアレイド超音波振動子と、

前記受信超音波信号を取得し、超音波画像を前記取得信号から生成するための処理ユニットであって、前記処理ユニットが、前記信号を取得するための直交サンプリングを使用する複数の信号サンプラを含む処理ユニットと

10

を備えるシステム。

(項目91)

前記超音波画像が、Bモード、Mモード、ドップラーモード、RFモード、および3-Dモードから成る群から選択される超音波モードで生成される、項目90に記載のシステム。

(項目92)

前記アレイド超音波振動子が、線形アレイ振動子、位相アレイ振動子、二次元(2 - D ) アレイ振動子、および曲線アレイ振動子から成るく群から選択される、項目 9 0 に記載のシステム。

20

30

40

(項目93)

前記アレイド超音波振動子が、少なくとも20MHzの中心動作周波数を有し、前記アレイド超音波振動子が前記アレイド超音波振動子の送信中心周波数における音の波長の2倍以下に等しい素子ピッチを有する、項目90に記載のシステム。

(項目94)

<u>前記アレイド超音波振動子の各々の素子が、受信チャネルに動作可能に接続される、項</u>目 9 0 に記載のシステム。

(項目95)

<u>前記アレイド超音波振動子の素子の数が受信チャネルの数より多い、項目94に記載の</u>システム。

(項目96)

前記処理ユニットが、各々の受信チャネルの 2 つ以上の信号サンプラを含む、項目 9 4 に記載のシステム。

(項目97)

前記信号サンプラがアナログデジタル変換器である、項目96に記載のシステム。

(項目98)

<u>前記信号サンプラが、90°位相が外れたサンプリングクロックを備える、項目97に</u>記載のシステム。

(項目99)

<u>前記サンプリングクロックが、受信超音波信号の中心周波数にほぼ等しい受信クロック</u> 期間を有する、項目 9 8 に記載のシステム。

(項目100)

受信クロック期間未満の遅延分解能が、前記取得信号を処理するために使用される、項目 9 9 に記載のシステム。

(項目101)

\_\_前記遅延分解能が、前記受信クロック期間の1/16である、項目100に記載のシステム。

(項目102)

取得信号が、補間フィルタリング法を使用して処理される、項目90に記載のシステム

50

## (項目103)

前記処理ユニットが受信ビーム成形器を備え、前記受信ビーム成形器が、少なくとも 1 つのフィールドプログラマブルゲートアレイ(FPGA)デバイスを使用してインプリメントされる、項目 9 0 に記載のシステム。

### (項目104)

前記処理ユニットが送信ビーム成形器を備え、前記送信ビーム成形器が、フィールドプログラマブルゲートアレイ(FPGA)デバイスを使用してインプリメントされる、項目90に記載のシステム。

### (項目105)

超音波画像を生成するためのシステムであって、

最大少なくとも55メガヘルツ(MHz)の周波数、および少なくとも500ヘルツ(Hz)のパルス繰返し周波数(PRF)における超音波を生成して被検体内に送信するための複数の素子を有するアレイド超音波振動子と、

カラーフロードップラー超音波画像を前記受信超音波から生成するための処理ユニット と

を備えるシステム。

## (項目106)

前記アレイド超音波振動子が、線形アレイ振動子、位相アレイ振動子、二次元(2 - D ) アレイ振動子、および曲線アレイ振動子から成る群から選択される、項目 1 0 5 に記載のシステム。

(項目107)

前記アレイド超音波振動子が、少なくとも20MHzの中心動作周波数を有し、前記アレイド超音波振動子が、前記アレイド超音波振動子の送信中心周波数における音の波長の2倍以下に等しい素子ピッチを有する、項目105に記載のシステム。

(項目108)

前記 P R F が約 5 0 0 H z ~ 約 7 5 K H z である、項目 1 0 5 に記載のシステム。

### (項目109)

超音波画像を生成するためのシステムであって、

最大少なくとも55メガヘルツ(MHz)の周波数、および少なくとも500ヘルツ(Hz)のパルス繰返し周波数(PRF)における超音波を生成して被検体内に送信し、超音波を前記被検体から受信するための複数の素子を有するアレイド超音波振動子であって、前記アレイド超音波振動子が、少なくとも5.0ミリメートル(mm)の視野を有するアレイド超音波振動子と、

# (項目104)

前記アレイド超音波振動子が、線形アレイ振動子、位相アレイ振動子、二次元(2 - D ) アレイ振動子、曲線アレイ振動子から成る群から選択される、項目 1 0 9 に記載のシステム。

### (項目105)

前記アレイド超音波振動子が、少なくとも15MHzの中心動作周波数を有し、前記アレイド超音波振動子が、前記アレイド超音波振動子の送信中心周波数における音の波長の少なくとも2倍以下に等しい素子ピッチを有する、項目109に記載のシステム。

(項目106)

<u>前記PRFが約500Hz~約150KHzである、項目109に記載のシステム。</u> (項目113)

### 超音波画像を生成するシステムであって、

最大少なくとも15メガヘルツ(MHz)の周波数における超音波を生成して被検体内に送信し、超音波信号を前記被検体から受信するための複数の素子を有するアレイド超音波振動子であって、前記アレイド超音波振動子が少なくとも2.0ミリメートル(mm)

10

20

30

- -

40

## の視野を有するアレイド超音波振動子と、

毎秒少なくとも300フレーム数(fps)の取得レートで前記受信超音波信号を取得し、超音波画像を前記取得信号から生成するための処理ユニットと

を備えるシステム。

(項目114)

前記アレイド超音波振動子が、線形アレイ振動子、位相アレイ振動子、二次元(2-D)アレイ振動子、および曲線アレイ振動子から成る群から選択される、項目113に記載のシステム。

(項目115)

前記アレイド超音波振動子が、少なくとも20MHzの中心動作周波数を有し、前記アレイド超音波振動子が、前記アレイド超音波振動子の送信中心周波数における音の波長の2倍以下に等しい素子ピッチを有する、項目113に記載のシステム。

(項目116)

F P G A f c が、前記 1 つまたは複数の F P G A の動作可能な最高周波数である、項目 1 に記載の超音波イメージングシステム。

(項目117)

F P G A f c が、前記 1 つまたは複数の F P G A の動作可能な最高周波数である、項目 1 2 に記載の信号処理ユニット。

(項目118)

FPGA fcが、前記1つまたは複数のFPGAの動作可能な最高周波数である、項目21に記載のデジタル送信ビーム成形器。

【図面の簡単な説明】

[0008]

【図1】図1は、計算動作環境のブロック図形式の表現である。

【図2】図2A~2Cは、本発明の例示的な略図によるPZTスタックの例示的な上面図、下面図および断面図であり、上面図は、PZTスタックの上部および下部において、上にあるレンズから外側に延在する接地電気層の部分を示し、下面図は、長手方向に延在する縁部において、個々の信号電極素子間の誘電体層の露出部分を示す(理解されるとおり、個別化信号電極素子-PZTスタックの素子1つ当たり1つの信号電極を示す線は、PZTスタックの中心部分に示されていない)。

【図3】図3Aは、図2A~2CのPZTスタックと共に使用されるインターポーザの上面平面図であり、振動子の中心開口部の隣接部分から外側に延在する電気トレースと、インターポーザの上部および下部部分に位置する電気トレースとを示し、インターポーザの表面の一部分に配置される誘電体層であって、インターポーザの長手方向軸に平行な軸に沿って位置する千鳥状のウェルのアレイを画定し、各々のウェルが、インターポーザの電気トレースと連通する誘電体層を示し、PZTスタックが誘電体層上に実装され、熱が加えられるとはんだが融解し、個々の素子信号電極と、インターポーザ上の個々のトランスとの間に所望の電気的に導通を形成するように、誘電体層内の各々のウェル内に実装されるはんだペーストボールバンプをさらに示す。図3Bは、図3Aの下にあるインターポーザの誘電体層の千鳥状ウェル、および電気トレースの部分拡大図であり、ウェルは、はんだペーストボールバンプを収納するサイズになっている。

【図4】図4Aは、誘電体層上に実装された図2AのPZTスタック、および図3Aのインターポーザの上面平面図である。図4Bは、誘電体層上に実装された図2AのPZTスタック、および図3Aのインターポーザの上面平面図であり、PZTスタックと、下にあるインターポーザと、これらの間に実装され、インターポーザ上の個々の素子信号電極と電気トレースとの間に電気接続を形成するはんだペーストボールバンプとの間の実装関係を示すために透明な層としてPZTスタックが示されている。

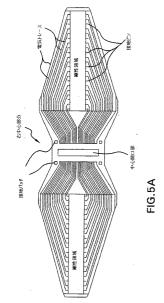

【図5A】図5Aは、本発明の振動子が実装される例示的な回路基板であって、複数の基板電気トレースが回路基板上に形成され、各々の基板電気トレースが、振動子の電気トレースに結合するように構成された近位端と、コネクタ、たとえばそれを通して信号を伝達

10

20

30

40

するためのケーブルに結合するように構成された遠位端とを有する回路基板の略上面平面 図である。

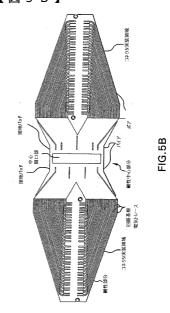

【図5B】図5Bは、75ミクロンピッチを有する例示的な256素子アレイを実装するための例示的な回路基板の上面平面図である。

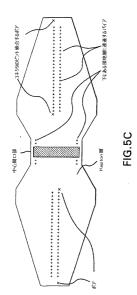

【図5C】図5Cは、回路基板の下にある接地層と連通する図5Bの回路基板のバイアの上面平面図である。

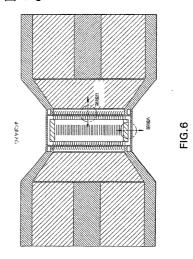

【図6】図6は、例示的な回路基板の一部分の上面平面図であり、領域Aには、インターポーザ上の電気トレースにワイヤボンドされ、その結果、回路基板の接地パッドにワイヤボンドされる振動子の接地電極層を示し、さらに、領域Bには、回路基板の個々の基板電気トレースにワイヤボンドされる振動子の個々の電気トレースを示す。

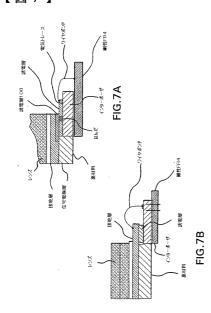

【図7】図7Aは、図6の領域Aの部分拡大断面図であり、はんだペーストボールバンプの周囲、およびPZTスタックとインターポーザとの間に配置された誘電体層を示す。図7Bは、図6の領域Bの部分拡大断面図であり、PZTスタックとインターポーザとの間の誘電体層を示す。

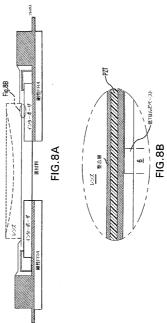

【図8】図8Aおよび8Bは、回路基板の一部分に実装された例示的な振動子の部分断面図を示す。

【図9】図9は、回路基板の一部分に実装された例示的な振動子の領域Bの拡大部分図を示す。

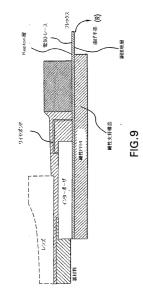

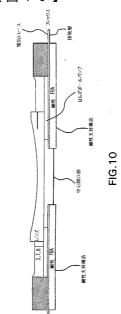

【図10】図10は、インターポーザを備えない振動子の部分拡大断面図であり、下にある回路基板上に実装されたはんだペーストボールバンプであって、各々のボールバンプが、回路基板の1つの基板電気トレース上に実装されているはんだペーストボールバンプを示し、PZTスタックの個々の素子信号電極が、個々のボールバンプを介して、回路基板の個々の基板電気トレースに電気的に導通するように、個々の基板電気トレース上に実装されたPZTスタックを示す。

【図11】図11Aは、回路基板の接地パッドにワイヤボンドされたインターポーザを備えない振動子の接地電極層を示す図10の部分拡大断面図である。図11Bは、回路基板の電気トレースと、PZTスタックの素子信号電極との間に配置され、これらの電気トレースおよび素子信号電極と電気的に連通するボールバンプを示す図10の部分拡大断面図である。

【図12A】図12Aは、フレックス回路基板、およびこの回路基板に実装された1対の Samtec BTH-090 コネクタを示す略図である。

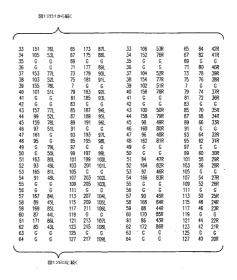

【 図 1 2 B - 1 】図 1 2 B は、図 5 B および 1 2 A に示すコネクタの例示的なピン配列テーブルである。

【 図 1 2 B - 2 】 図 1 2 B は、図 5 B および 1 2 A に示すコネクタの例示的なピン配列テーブルである。

【 図 1 2 B - 3 】 図 1 2 B は、図 5 B および 1 2 A に示すコネクタの例示的なピン配列テーブルである。

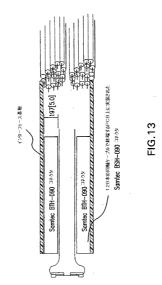

【図13】図13は、1対のBSH-090コネクタを介して、フレックス回路基板上のSamtec BTH-090 コネクタの対に動作可能に結合された個々の同軸ケーブルの側面図を示す略図である。

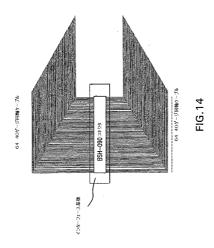

【図14】図14は、BSH-090コネクタの1つに接続されたケーブル内の同軸リードの半分の例示的な平面図を示す略図である。

【図15A】図15Aは、折り畳まれたフレックス回路基板に接続された医療用ケーブル組立体の遠位端の例示的な平面図を示し、ケーブルの近位端(図示しない)はマルチピン ZIFコネクタを備え、このコネクタは、超音波システムとインターフェースし、本発明の1つまたは複数の態様を実施するために使用される。

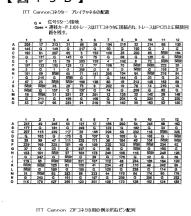

【図15B】図15Bは、例示的なZIFコネクタ、たとえばITT Cannon DLM6コネクタを有するマルチピンZIFコネクタに対する医療用ケーブル組立体の個々の同軸ケーブルの例示的な終端ピン配列を示す。

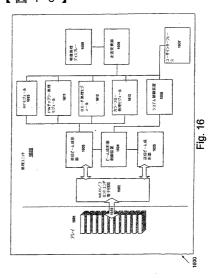

【図16】図16は、例示的な超音波イメージングシステムを示すブロック図である。

10

20

30

40

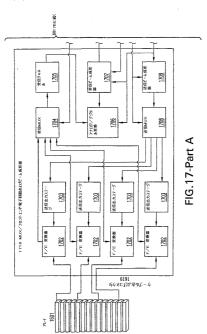

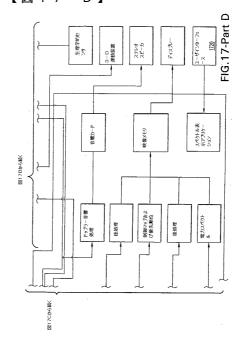

【図17-A】図17は、図16に示されている例示的な超音波イメージングシステムを さらに示すブロック図である。

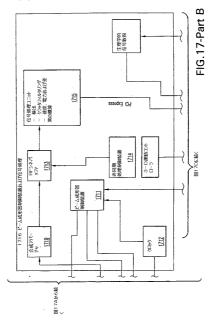

【 図 1 7- B 】図 1 7 は、図 1 6 に示されている例示的な超音波イメージングシステムを さらに示すブロック図である。

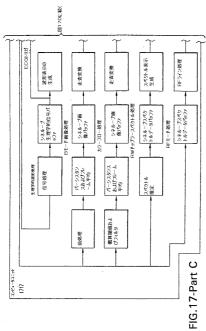

【図17-C】図17は、図16に示されている例示的な超音波イメージングシステムを さらに示すブロック図である。

【図17-D】図17は、図16に示されている例示的な超音波イメージングシステムを さらに示すブロック図である。

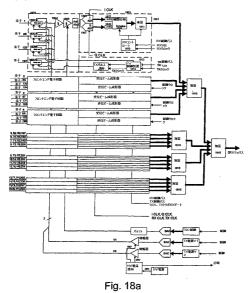

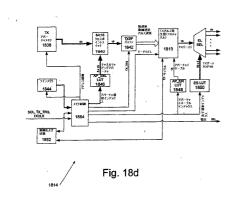

【図18a】図18aは、例示的な受信ビーム成形器、送信ビーム成形器、フロントエン ド電子回路、および関連する構成要素を示す略図である。

【図18b】図18bは、図18aに示されているフロントエンド電子回路のさらに詳細 を示す例示的な実施態様である。

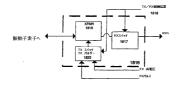

【図18c】図18cは、本発明による一実施態様の受信コントローラの例示的な実施態 様である。

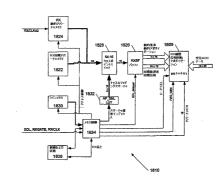

【図18d】図18dは、本発明による一実施態様の例示的な送信コントローラ(TXコ ントローラ)の図である。

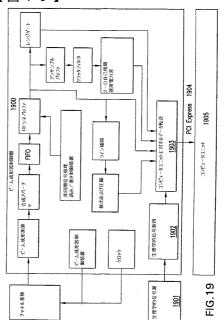

【図19】図19は、例示的なビーム成形器制御盤を示すシステム信号処理ブロック図で

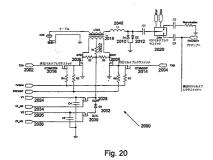

【図20】図20は、TX/RXスイッチおよびパルサー、並びに関連回路構成の略図で ある。

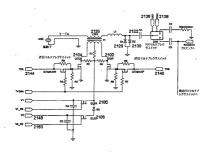

【図21】図21は、TX/RXスイッチおよびパルサー、並びに関連回路構成を示す別 の実施態様の略図である。

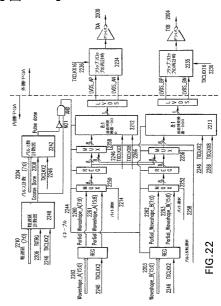

【図22】図22は、例示的な送信ビーム成形器制御のブロック図である。

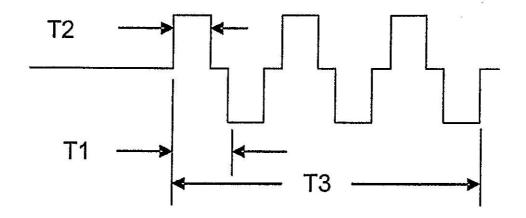

【図22A】図22A~22Cは、例示的な波形を使用して、「A」および「B」信号の 微細遅延、パルス幅、および不感時間を変更する方法を示す。

【図22B】図22A~22Cは、例示的な波形を使用して、「A」および「B」信号の 微細遅延、パルス幅、および不感時間を変更する方法を示す。

【図22C】図22A~22Cは、例示的な波形を使用して、「A」および「B」信号の 微細遅延、パルス幅、および不感時間を変更する方法を示す。

【図23】記載無し

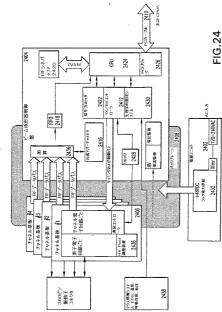

【図24】図24は、例示的な超音波イメージングシステムのシステム電子回路の概要を 示す。

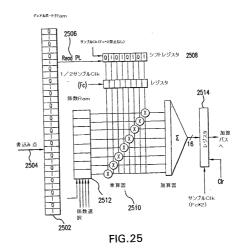

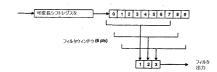

【図25】図25は、直交サンプリングの例示的な単一チャネル遅延スキームを示す。

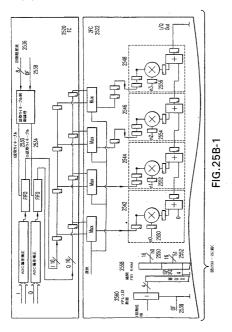

【図25B-1】図25Bは、本発明の一実施態様による補間フィルタ、位相回転、およ び動的アポダイゼーションを実施する別の方法である。

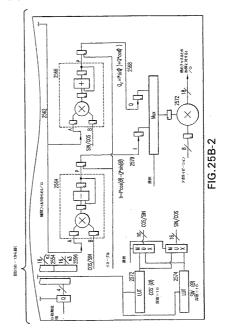

【図25B-2】図25Bは、本発明の一実施態様による補間フィルタ、位相回転、およ び動的アポダイゼーションを実施する別の方法である。

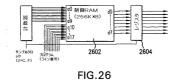

【図26】図26は、受信制御信号を記憶するための例示的な制御RAMを示す。

【図26A】図26Aは、アレイド振動子の中心および外側素子の例示的なビーム成形器 遅延制御信号を示す。

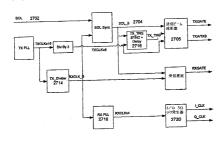

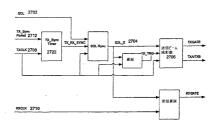

【図27】図27は、例示的な送信/受信同期スキームのブロック図である。

【図27A】図27Aは、別の例示的な送信/受信同期スキームのブロック図である。

【図28】図28は、ビーム成形器出力記憶装置の例示的なRFメモリバッファを示す。

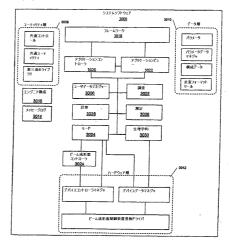

【図29】図29は、例示的な超音波イメージングシステムの例示的なシステムソフトウ ェアの概要を示す。

【図30】図30は、例示的な超音波イメージングシステムのメインシステムソフトウェ アのアプリケーションの概要である。

【図31】図31は、例示的な超音波イメージングシステムの例示的なモジュラーシステ ムを示す。

【図32】図32は、例示的な送信周波数、半周期時間、およびパルス持続時間を示す。

10

20

30

40

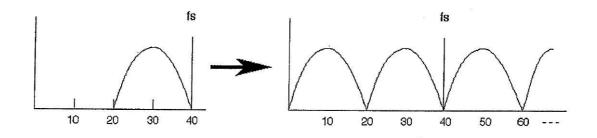

- 【図33】図33は、30MHz信号スペクトルの例示的な帯域幅サンプリングを示す。

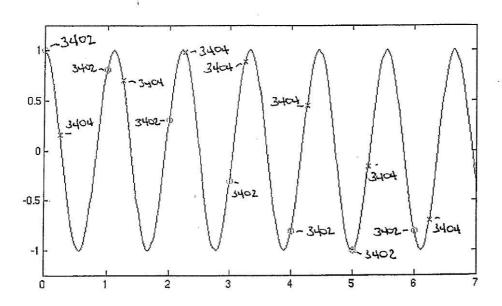

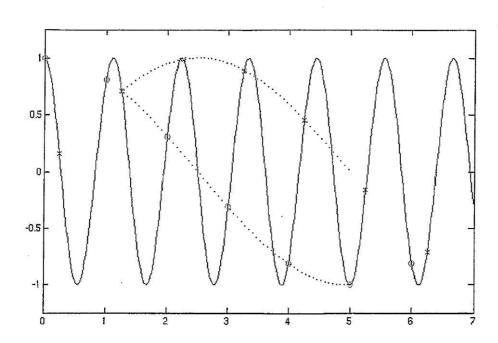

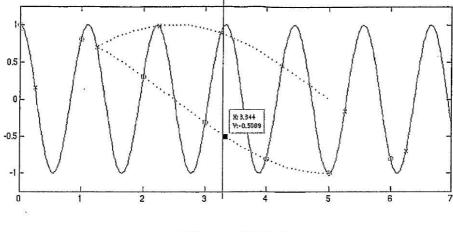

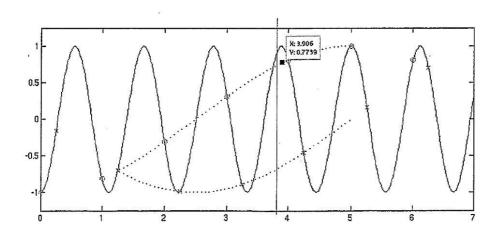

- 【図34】図34は、サンプル周波数の0.9倍で直交サンプリングされた例示的な正弦波を示す。

- 【 図 3 4 A 】 図 3 4 A は、 Q および I サンプリング点に対する図 3 4 の 1 6 のサンプル点の例示的な図である。

- 【図34B】図34Bは、Qおよび I サンプルの間に点  $0 \sim 3$  を補間する 8 つのサンプルのウィンドウの例示的な図である。

- 【図34C】図34Cは、点4~15を補間するために、1つのサンプルだけ前方の移動する図34の例示的なウィドウである。

- 【図35】図35は、ⅠおよびQ波形の例示的な補間点を示す。

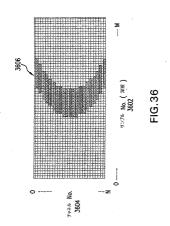

- 【図36】図36は、線形アレイから単一光線ラインを取得するための例示的な直交サンプルを示す。

- 【図37】図37Aおよび37Bは、同じ範囲点だが、半波長に応じて異なる光路長を有する範囲点から返される2つの例示的なチャネル信号を示す。

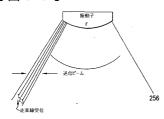

- 【図38】図38は、例示的な曲線アレイ振動子による3~1マルチライン走査を示す。

- 【図39】図39は、補間遅延法の概念的な実施を示す。

- 【図40】図40は、補間遅延法の例示的な3-1マルチライン動作を示す。

- 【図41】図41は、相補型(Complimentary)ヒルベルト変換フィルタの 概略設計図を示す。 本明細書に含まれ、本明細書を構成する添付の図面は、本発明によ るいくつかの実施態様およびその説明を示し、本発明の原理を説明する上で役に立つ。

【発明を実施するための形態】

#### [0009]

本発明は、本発明の以下の詳細な説明、この説明に含まれる実施例、図面、並びに上記および以下の説明を参照することにより、より容易に理解されるであろう。

#### [0010]

本発明の化合物、組織生物、物品、デバイス、および / または方法を開示および説明する前に、本発明は、特定の方法、特定の構成要素、または特定のコンピュータアーキテクチャに限られるのではなく、これらは、当然変化することを理解するべきである。また、本明細書で使用される専門用語は、特定の実施態様のみを説明するためのものであり、制限することを意図するのではないと考えるべきである。本明細書および添付の請求の範囲に使用されるとおり、単数形の不定冠詞および定冠詞は、文脈上明らかにそうではない場合を除いて、複数の指示対象を含む。したがって、たとえば、「1つの処理ユニット」または「1つの受信チャネル」と言及する場合、2つ以上のこうした処理ユニットまたは受信チャネルなどを含む。

# [0011]

範囲は、本明細書では、「ほぼ」特定のある値から、および/または「ほぼ」特定の別の値まで表現される。このような範囲を表現する場合、別の実施態様は、ある特定の値から、および/または他の特定の値までを含む。同様に、値が、先行詞の「約」を使用して近似値として表現される場合、特定の値が別の実施態様を構成すると考えられる。さらに、各々の範囲の端点は、他の端点に関連する場合、および他の端点に関係ない場合の両方で重要である。「任意の」または「任意に」とは、以下で説明する事象または状況が生じるか、または生じないこと、およびこの記述は、前記の事象または状況が生じる事例、およびこうした事象または状況が生じない事例を含むことを意味する。

# [0012]

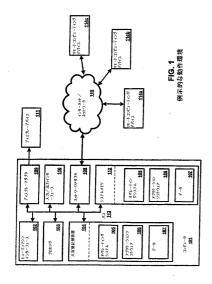

本明細書に開示される例示的なシステムの態様は、汎用計算デバイス、たとえば図1に示すコンピュータ101の形式のデバイスを介して実施することができる。コンピュータ101の構成要素としては、1つまたは複数のプロセッサまたは処理ユニット103と、システムメモリ112に結合するシステムバス113とが挙げられるが、これらだけに限らない。

# [0013]

50

10

20

30

20

30

40

50

システムバス113は、1つまたは複数のいくつかの可能なタイプのバス構造、たとえ ばメモリバスまたはメモリコントローラ、周辺機器用バス、アクセラレイティッドグラフ ィックスポート、およびプロセッサ、または多様なバスアーキテクチャの何れかを使用す るローカルバスを表す。一例として、このようなアーキテクチャとしては、業界標準アー キテクチャ(ISA)バス、マイクロチャネルアーキテクチャ(MCA)バス、強化IS A(EISA)バス、ビデオ周辺機器関連標準化団体(VESA)ローカルバス、および メザニンバスとしても知られるペリフェラルコンポーネントインターコネクト(PCI) バスを挙げることができる。このバス、および本明細書に記載されているすべてのバスは 、有線または無線ネットワーク接続で実施することもできる。バス113、および本明細 書に記載されているすべてのバスは、有線または無線ネットワーク接続で実施することも でき、プロセッサ103、大容量記憶装置104、オペレーティングシステム105、ア プリケーションソフトウェア106、データ107、ネットワークアダプタ108、シス テムメモリ112、入力/出力インターフェース110、ディスプレーアダプタ109、 ディスプレーデバイス111、およびヒューマンマシンインターフェース102を含むサ ブシステムの各々は、1つまたは複数のリモートコンピューティングデバイス114a、 b、c内の、この形式のバスを介して接続された物理的に別個の位置に含み、実際上、完 全分散システムを実施することができる。

#### [0014]

コンピュータ 1 0 1 は、一般に、様々なコンピュータ可読媒体を含む。このような媒体は、コンピュータ 1 0 1 がアクセス可能な何らかの利用可能な媒体で良く、揮発性および不揮発性媒体、取り外し可能および取り外し不能媒体の両方を含む。システムメモリ 1 1 2 は、ランダムアクセスメモリ(RAM)などの揮発性メモリ、および / または読み出し専用メモリ(ROM)などの不揮発性メモリの形式のコンピュータ可読媒体を含む。システムメモリ 1 1 2 は、一般に、データ 1 0 7 などのデータ、および / または処理ユニット 1 0 3 に直接アクセス可能であるか、および / または処理ユニット 1 0 3 上で現在動作しているアプリケーションソフトウェア 1 0 6 を含む。

### [0015]

コンピュータ101は、その他の取り外し可能/取り外し不能、揮発性/不揮発性コンピュータ記憶媒体も含む。一例として、図1は、コンピュータコード、コンピュータ可読命令、データ構造、プログラムモジュール、およびコンピュータ101のその他のデータの不揮発性記憶装置を提供可能な大容量記憶装置104を示す。たとえば、大容量記憶装置104は、ハードディスク、取り外し可能なハードディスク、磁気カセットもしくはその他の磁気記憶デバイス、フラッシュメモリカード、CD-ROM、デジタルバーサタイルディスク(DVD)もしくはその他の光学式記憶装置、ランダムアクセスメモリ(RAM)、読み出し専用メモリ(ROM)、電気的消去可能プログラム可能読出し専用メモリ(EEPEROM)などで良い。

# [0016]

任意の数のプログラムモジュールは、一例としてオペレーティングシステム105およびアプリケーションソフトウェア106を含む大容量記憶装置104上に記憶することができる。オペレーティングシステム105およびアプリケーションソフトウェア106の各々(または、これらの組合せ)は、プログラミングの要素、およびアプリケーションソフトウェア106を含む。データ107も、大容量記憶装置104上に記憶することができる。データ104は、当該技術分野で周知されている1つまたは複数のデータベースの何れかに記憶することができる。こうしたデータベースの例としては、DB2(登録商標)、Microsoft(登録商標)、Access、Microsoft(登録商標)、SQL Server、Oracle(登録商標)、mySQL、PostgreSQLなどが挙げられる。データベースは集中させるか、または複数のシステム全体に分散させることができる。

#### [0017]

ユーザは、入力デバイス(図示しない)を介してコンピュータ101内にコマンドおよ

20

30

40

50

び情報を入力することができる。こうした入力デバイスの例としては、キーボード、ポインティングデバイス(たとえば、「マウス」)、マイクロフォン、ジョイスティック、シリアルポート、スキャナなど挙げられるが、これらだけに限らない。上記およびその他の入力デバイスは、システムバス113に結合されるヒューマンマシンインターフェース102を介して処理ユニット103に接続することができるが、その他のインターフェースおよびバス構造、たとえばパラレルポート、ゲームポート、またはユニバーサルシリストスに、ユーザは、1つまたは複数の上記の入力デバイスから選択することができる。任日をに、ユーザは、1つまたは複数の上記の入力デバイスから選択することができる。任日をに、ユーザは、トグルスイッチ、スライダー、可変抵抗器、およびその他のユーザインターフェースデバイスなど、様々な制御デバイスも含むことができる。ユーザインターフェースは、処理ユニット103に接続することができる。ユーザインターフェースは、処理ユニット103の接続するか、または接続しない状態で、本明細書に記載されている例示的なシステムのその他の機能ブロックに接続することも可能である。

### [0018]

ディスプレーデバイス111は、ディスプレーアダプタ109などのインターフェースを介して、システムバス113に接続することもできる。たとえば、ディスプレーデバイスは、モニターまたはLCD(液晶ディスプレー)で良い。ディスプレーデバイス111のほかに、出力周辺デバイスは、入力/出力インターフェース110を介してコンピュータ101に接続可能なスピーカ(図示しない)およびプリンタ(図示しない)などの構成要素を含むことができる。

### [0019]

コンピュータ101は、1つまたは複数のリモートコンピューティングデバイス114 a、b、cに対する論理接続を使用して、ネットワーク環境で動作することができる。一 例として、リモートコンピューティングデバイスは、パーソナルコンピュータ、ポータブ ルコンピュータ、サーバー、ルーター、ネットワークコンピュータ、ピアデバイス、また はその他の共通ネットワークノードなどで良い。コンピュータ101とリモートコンピュ ーティングデバイス114a、b、c間の論理接続は、ローカルエリアネットワーク(L AN)および汎用広域ネットワーク(WAN)を介して行うことができる。こうしたネッ トワーク接続は、ネットワークアダプタ108を介して行うことができる。ネットワーク アダプタ108は、有線または無線環境の両方にインプリメントすることができる。こう したネットワーク環境は、オフィス、企業内コンピュータネットワーク、イントラネット . インターネット115では一般的である。リモートコンピュータ114a、b、cは、 サーバー、ルーター、ピアデバイス、またはその他の共通ネットワークノードで良く、一 般に、コンピュータ101に関して上記で述べたすべての、または何れかの要素を含む。 ネットワーク環境では、プログラムモジュールおよびデータは、リモートコンピュータ1 14a、b、c上に記憶される。論理接続は、LANおよびWANを含む。その他の接続 方法を使用することもでき、ネットワークは、「ワールドワイドウェブ」またはインター ネットなどを含む。

### [0020]

実例を挙げるため、アプリケーションプログラム、およびオペレーティングシステム105などのその他の実行可能プログラムは、本明細書では別個のブロックとして示されているが、こうしたプログラムおよび構成要素は、コンピュータ101の様々な記憶構成要素内に様々な時点で存在し、コンピュータのデータプロセッサによって実行される。アプリケーションソフトウェア106のインプリメンテーションは、ある形式のコンピュータ可読媒体上に記憶されるか、またはこうしたコンピュータ可読媒体を通して送信される。コンピュータ可読媒体は、コンピュータがアクセス可能な何らかの利用可能な媒体で良い。制限するのではなく一例として、コンピュータ可読媒体は、「コンピュータ記憶媒体」は、コンピュータ記憶媒体」および「通信媒体」を含み、「コンピュータ記憶媒体」は、コンピュータ可読命令、データ構造、プログラムモジュール、またはその他のデータなどの情報を記憶するための何ら

かの方法または技術でインプリメントされる揮発性および不揮発性、取外し可能および取外し不能媒体を含む。コンピュータ記憶媒体としては、RAM、ROM、EEPROM、フラッシュメモリもしくはその他のメモリ技術、CD-ROM、デジタルバーサタイルディスク(DVD)、またはその他の光学式記憶装置、磁気カセット、磁気テープ、磁気ディスク記憶装置もしくはその他の磁気記憶デバイス、または所望の情報を記憶するために使用することができ、コンピュータがアクセス可能なその他の何らかの媒体が挙げられるが、これらだけに限らない。開示された方法のインプリメンテーションは、ある形式のコンピュータ可読媒体上に記憶されるか、またはこうしたコンピュータ可読媒体を通して送信される。

# [0021]

開示された方法の処理は、ソフトウェア構成要素によって実施することができる。開示された方法は、1つまたは複数のコンピュータまたはその他のデバイスによって実行されるコンピュータ実行可能命令、たとえばプログラムモジュールに一般的に関連して説明する。一般に、プログラムモジュールは、特定のタスクを実行するか、または特定の抽象データタイプをインプリメントするコンピュータコード、ルーチン、プログラム、オブジェクト、コンピュータデータ構造などを含む。開示された方法は、グリッドベースおよび分散計算環境で実施しても良い。分散計算環境では、プログラムモジュールは、メモリ記憶デバイスを含むローカルおよびリモートコンピュータ記憶媒体の両方に配置される。

# [0022]

図示され、本明細書に記載されている例示的なシステムの態様は、ハードウェア、ソフトウェア、およびこれらの組合せの様々な形式でインプリメントすることが可能である。ハードウェアのインプリメンテーションは、当該技術分野で周知されている以下の技術の何れか、またはこれらの組合せを含むことができる:分散電子回路構成要素、データ信号上で論理関数をインプリメントする t まえの論理ゲートを有する分散論理回路、適切なイートを有する、アプリケーション特有の集積回路、プログラム可能なゲートアレイ(EPGA)など。ソフトウェアは(PGA)、フィールドプログラマブルゲートアレイ(EPGA)など。ソフトウェアはは治理関数をインプリメントするために実行可能な命令の順序付きリストを含み、命令実力システム、装置またはデバイス、たとえばコンピュータベースのシステム、プロセッサを含むシステム、または命令実行システム、装置、またはデバイスから命令をフェッチするか、または命令を実行することが可能なその他のシステムによって使用されるか、または元れらに関連して使用される何らかのコンピュータ可読媒体内に埋め込むことができる。

# [0023]

例示的なシステムの態様は、コンピュータ化システムにインプリメントすることができる。たとえば計算ユニット101を含む例示的なシステムの態様は、多数のその他の一般的な用途または特殊な用途の計算システム環境または構成で動作可能である。このシステムおよび方法と共に使用するのに適する周知の計算システム、環境、および/または構成の例としては、パーソナルコンピュータ、サーバーコンピュータ、ラップトップデバイス、およびマルチプロセッサシステムが挙げられるが、これらだけに限らない。追加の実施例としては、セットトップボックス、プログラム可能な家庭用電化製品、ネットワークPC、ミニコンピュータ、メインフレームコンピュータ、上記システムまたはデバイスなどの何れかを含む分散計算環境が挙げられる。

# [0024]

例示的なシステムの態様は、コンピュータによって実行されるプログラムモジュールなど、コンピュータ命令に一般的に関連して説明することができる。一般に、プログラムモジュールは、特定のタスクを実行するか、または特定の抽象データタイプをインプリメントするルーチン、プログラム、オブジェクト構成要素、データ構造などを含む。システムおよび方法は、タスクが、通信ネットワークを通してリンクされるリモート処理デバイスによって実行される分散計算環境でも実施される。分散計算環境では、プログラムモジュールは、メモリ記憶デバイスを含むローカルおよびリモートコンピュータ記憶媒体の両方に配置される。

10

20

30

#### [0025]

多くの可能なアプリケーションの中では、上記の実施態様は、小動物の長手方向イメージング調査における解剖学的構造、および血流力学的機能のインビボでの可視化、評価、および測定を可能にする。このシステムは、非常に高度の分解能、画像の均一性、被写界深度、調節可能な送信焦点深度、複数の用途のための複数の送信焦点領域を有する画像を提供することができる。たとえば、超音波画像は、被検体またはその解剖学的部分、たとえば心臓または心臓弁の画像で良い。画像は血液でも良く、腫瘍の血管新生の評価を含む用途に使用することができる。このシステムは、針注射を案内するために使用可能である

[0026]

上記の実施態様は、ヒトの臨床、医療、製造(たとえば、超音波検査など)、または 1 5 M H z 以上の送信周波数で画像を生成することが望ましいその他の用途にも使用可能である。

# [0027]

上記のシステムによる実施態様は、本明細書で詳細に説明されている以下の1つまたは複数を備えることができる:1つまたは複数の信号および画像処理機能から成る処理システムに動作可能に接続することができるアレイ振動子;デジタル送信および受信ビーム成形器サブシステム;アナログフロントエンド電子回路;デジタルビーム成形器コントローラサブシステム;高電圧サブシステム;コンピュータモジュール;電源モジュール;ユーザインターフェース;ビーム成形器を作動させるためのソフトウェア;走査変換器、および本明細書に記載するその他のシステム特徴。

#### [0028]

システムに使用されるアレイド振動子は、走査ヘッド内に組み込むことができ、走査ヘッドは、一実施態様ではイメージング時に固定具に取付けられ、その結果、操作者が、通常「フリーハンド」イメージングから生じる振動および動揺がない状態で画像を取得することを可能にする。小動物の被検体は、麻酔設備、および走査ヘッドを被検体に対して自在に配置する手段にアクセスする加熱プラットフォーム上に配置しても良い。走査ヘッドは、イメージング時に固定具に取り付けることができる。固定具は、様々な特徴、たとえば3次元における運動の自由、回転の自由、迅速な解放機構などを有することができる。固定具は、「レールシステム」装置の一部で良く、加熱マウスプラットフォームと一体化することができる。

# [0029]

システムは、小動物のイメージングに使用されるプラットフォームおよび装置であって、操作が容易なプローブ保持装置を有する「レールガイド」タイプのプラットフォームを含むプラットフォームおよび装置に使用することができる。たとえば、上記のシステムは、マルチレールイメージングシステム、米国特許出願第10/683,168号「Integrated Multi‐Rail Imaging System」、米国特許出願第10/053,748号「Integrated Multi‐Rail Imaging System」、米国特許出願第10/683,870号で、2005年2月8日に発行された現在の米国特許第6,851,392号「Small Animal Mount Assembly」、および米国特許出願第11/053,653号「Small Animal Mount Assembly」に記載されている小動物実装組立体と共に使用することができ、これらは各々、引用することにより全体として本明細書に援用する。

### [0030]

小動物はイメージング時に麻酔されて、心拍数および体温などの重要な生理学的パラメータを監視することができる。したがって、システムの実施態様は、処理および表示用のECGおよび温度信号を取得するための手段を備える。システムの一実施態様は、ECG、呼吸作用、または血圧波形などの生理学的波形を表示することもできる。

# [0031]

10

20

30

20

30

40

50

### 概要

本明細書では、複数の素子を有する超音波振動子から受信超音波信号を取得するように構成された信号処理ユニットを含む超音波信号取得システムの実施態様を提供する。シュテムは、少なくとも毎秒20フレーム(fps)のフレームレートで、少なくとも55 M H z )の周波数を有する超音波信号を受信するように構成される。その他の実施態様とといって、の間波数を有する超音波信号を受信するように構成される。その他の実施態様とといっては、の間に表している。とのでは、50、100、または200(fps)の取得レートで取得することができる。その他の実施例では、受信超音波信号は、約100fps~200fpsの範囲内のフレームレートで取得することができる。いくつかの例示的な態様では、振動子の長さは視野に等しい。視野は、心臓学用の小動物の心臓がのに十分な広さにするに、振動子の長さは視野に等したの臓学用の小動物の心臓がにまるにするにできる。一実施態様では、振動子の双方向帯域幅は、約50%~100%で良い。促動子が超音波の送信機、および受信器の両方として使用される時に生じる振動子の帯域幅を意味し、の送信機、および受信器の両方として使用される時に生じる振動子の帯域幅は、二乗単方向スペクトルの帯域幅である。

### [0032]

処理ユニットは、取得超音波信号から超音波画像を生成する。取得した信号は、取得レートより遅い表示レートで超音波画像を生成するように処理される。任意に、生成超音波画像は、100fps以下の表示レートを有することが可能である。たとえば、生成超音波画像は、30fps以下の表示レートを有する。視野は、約2.0mm の範囲を有することができる。比較的小さい視野を使用する場合、処理ユニットは、少なくとも毎秒300pp つフレーム数(ps の取得レートで受信超音波信号を得することができる。その他の実施例では、取得レートは、毎秒ps の、ps 00 またはそれ以上のフレーム数(ps 70 で良い。

### [0033]

$30\,\text{MHz}$  の中心周波数の振動子が使用される一実施態様では、開示されたシステムを使用して生成された画像は、約150S クロン( $\mu$ m)以下の方位分解能、および約75S クロン( $\mu$ m)以下の距離分解能を有する。たとえば、画像は、約30S クロン( $\mu$ m)の距離分解能を有することができる。さらに、本発明による実施態様は、約 $1.0\,\text{mm}$  ~約 $30.0\,\text{mm}$  の深さで集束する超音波を送信する。たとえば、送信された超音波は、約 $3.0\,\text{mm}$  ~約 $10.0\,\text{mm}$  の深さで集束することが可能である。他の実施例では、送信された超音波は、約 $2.0\,\text{mm}$  ~約 $12.0\,\text{mm}$  ~約 $1.0\,\text{mm}$  ~約 $1.0\,\text{mm}$  ~的 $1.0\,\text{mm}$

### [0034]

# 振動子

様々な実施態様では、振動子としては、線形アレイ振動子、位相アレイ振動子、二次元(2-D)アレイ振動子、または曲線アレイ振動子が挙げられるが、これらだけに限らない。線形アレイは、一般に平坦であり、つまりすべての素子は、同じ(平坦な)平面に存在する。曲線線形アレイは、一般に、素子が曲線状平面内に存在するように構成される。本明細書に記載されている振動子は、「固定」振動子である。「固定」という用語は、振動子アレイが、所望の動作パラメータを達成するか、または超音波データのフレームを取得するために、超音波の送信または受信時に、方位角方向の運動を利用しないことを意味のように、「固定」という用語は、振動子が、動作時に走査ヘッド、プローブ、またはこれらの部分に対して、方位角方向または左右方向に移動しないことも意味する。上記のように固定されている上記の振動子は、全体的に、「アレイ」、「振動子」、「超音波振動子」、「超音波下レイ」、「アレイ振動子」、「超音波振動子」、もしくはこれらの組合せとして記載されるか、または当業者が超音波振動子を意味すると認識す

20

30

40

50

ると思われるその他の用語で記載される。本明細書に記載される振動子は、超音波フレーム間で移動することが可能性であり、たとえば、超音波データのフレームを取得した後の走査平面間で移動することが可能だが、このような移動は、振動子の動作に必須ではない。しかし、当業者が理解するとおり、本発明のシステムの振動子は、イメージングされたオブジェクトに対して移動することが可能だが、動作パラメータに関しては固定された状態を維持する。たとえば、振動子は、動作時に被検体に対して移動し、走査平面の位置を変更するか、または被検体もしくはその下にある生体構造の異なる視界を取得することが可能である。

# [0035]

アレイド振動子は、多数の素子から構成される。一実施態様では、本発明の1つまたは複数の態様を実施するために使用される振動子は、少なくとも64個の素子を含む。一態様では、振動子は256個の素子を含む。振動子の素子は、振動子の中心送信周波数の波長の約2分の1の波長から約2倍の波長に相当する距離だけ離すことができる(本明細書では、「素子と呼ぶ)。一態様では、振動子の素子は、振動子の中心送信周波数のは、15MHzに等しいか、または15MHzより大きい。たとえば、中心送信周波数は、約15MHzに等しいか、または15MHzより大きい。たとえば、中心送信周波数は、約15MHzに等しいか、または15MHzより大きい。たとえば、中心送信周波数は、約15MHzに多のMHz、30MHz、30MHz、50MHz、55MHz、550MHz、15MHzの範囲内の心周波数で、超音波を被検体内に送信する。本発明による一実施態様では、振動子の心周波数では、超音波振動子は、振動子は、振動子の送信中心周波数にも15MHzの中心動作周波数を有し、振動子は、振動子の送信中心周波数における音の波長の1.5倍以下に等しい素子ピッチを有することも可能である。

#### [0036]

非制限的な実施例では、上記のシステムと共に使用される1つの振動子としては、特に、2005年4月20日に提出された米国特許出願第11/109,986号「Arrayed Ultrasonic Transducer」で、2005年12月8日に米国特許出願公報2005/0272183 A1として公告された振動子が挙げられ、この特許出願は、引用することにより全体として本明細書に援用され、本明細書の一部を構成する。この振動子は、可変パルシングおよび遅延機構を使用して電子的にステアリング可能な圧電素子のアレイも含む。本発明の様々な実施態様による処理システムは、1つまたは複数の振動子または走査ヘッドのインターフェースとして、複数の振動子ポートを含む。上記のとおり、走査ヘッドは、手で持つか、またはレールシステムに取り付けることができ、走査ヘッドのケーブルは可撓性で良い。

# [0037]

システムが振動子を含むか、または別に取得した振動子と共に使用するように構成されるかどうかに関わらず、振動子の各々の素子は、処理ユニットの受信チャネルに動作可能に接続することができる。任意に、振動子の素子の数は、受信チャネルの数より多い。たとえば、振動子は、少なくとも32の受信チャネルに動作可能に接続される少なくとも64の素子を含む。一態様では、256の素子は、64の受信チャネルに動作可能に接続される。別の態様では、256の素子は、128の受信チャネルに動作可能に接続される。さらに別の態様では、256の素子は、256の受信チャネルに動作可能に接続される。各々の素子も、送信チャネルに動作可能に接続することができる。

# [0038]

#### サンプリング

このシステムは、各々の受信チャネルに1つまたは複数の信号サンプラをさらに含むことができる。信号サンプラは、アナログデジタル変換器(ADC)で良い。信号サンプラは、受信信号を直接サンプリングするための直接サンプリング技術を使用することができる。任意に、信号サンプラは、帯域幅サンプリングを使用して、受信信号をサンプリングをすることができる。別の態様では、信号サンプラは、直交サンプリングを使用して、受信

20

30

40

50

信号をサンプリングすることができる。任意に、直交サンプリングでは、信号サンプラは、位相が90°変位したサンプリングクロックを含む。また、直交サンプリングでは、サンプリングクロックは受信期間も有し、受信クロック周波数は、受信超音波信号の中心周波数にほぼ等しくて良いが、送信周波数とは異なる。たとえば、多くの状況では、受信信号の中心周波数は、イメージングされる組織内の周波数依存減衰により、送信信号の中心周波数より低く変位した。こうした状況では、受信サンプルクロック周波数は、送信周波数より低くて良い。

### [0039]

取得信号は、補間フィルタリング法を使用して処理することができる。補間フィルタリング法を使用すると、遅延分解能を使用することができ、遅延分解能は受信クロック期間より低い可能性である。例示的な態様では、遅延分解能は、たとえば、受信クロック期間の1/16が可能である。

## [0040]

処理ユニットは、受信ビーム成形器を備えることができる。受信ビーム成形器は、少なくとも1つのフィールドプログラマブルゲートアレイ(FPGA)デバイスを使用してインプリメントすることができる。処理ユニットは、送信ビーム成形器を備えることもできる。送信ビーム成形器は、少なくとも1つのFPGAデバイスを使用してインプリメントすることも可能である。

# [0041]

一態様では、512本の超音波ラインが生成され、被検体内に送信され、生成された超音波画像の各々のフレームごとに、被検体から受信される。さらに他の態様では、256本の超音波ラインを生成することも可能であり、被検体内に送信され、生成された超音波画像の各々のフレームごとに、被検体から受信される。別の態様では、少なくとも2本の超音波ラインを生成することが可能であり、被検体内に送信され、生成された超音波画像の各々のフレームごとに、アレイの各々の素子において被検体から受信される。任意に1本の超音波ラインが生成され、被検体内に送信され、生成された超音波画像の各々のフレームごとに、アレイの各々の素子において被検体から受信される。

#### [0042]

本明細書に記載の超音波システムは、複数のイメージングモードで使用することができ る。たとえば、システムは、Bモード、Mモード、パルス波(PW)ドップラーモード、 パワードップラーモード、カラーフロードップラーモード、 R F - モード、および 3 - D モードで画像を生成するために使用することができる。システムは、方向速度カラーフロ ー、パワードップラーイメージング、組織ドップラーイメージングを含むカラーフローイ メージングモードで使用することができる。システムは、高パルス繰返し周波数(PRF )を有するステアリングされた PWドップラーを使用することも可能である。システムは 、心臓学、またはこうした技術が望ましいその他の用途のために、同時Bモードと共にM モードで使用することも可能である。システムは、任意に二重および三重モードに使用す ることができ、この場合、Mモード、およびPWドップラー、および/またはカラーフロ ーモードが、リアルタイムでBモードと同時に実行される。Bモードまたはカラーフロー モード情報が三次元領域上で取得され、 3 - D表面レンダリングディスプレーに表示され る3-Dモードも、使用することが可能である。ラインベースの画像構成または「KEV 」モードは、心臓学か、または画像情報がいくつかの心周期で取得されて結合され、非常 に高度のフレームレートディスプレーを提供するその他の用途に使用することができる。 ラインベースの画像再現法は、米国特許出願第10/736,232号で、2006年5 月30日に発行された現在の米国特許第7,052,460号「System for Producing an Ultrasound Image Using Line Based Image Reconstruction」に記載されており、この特 許は、引用することにより全体として本明細書に包含し、本明細書の一部を構成する。こ うしたラインベースのイメージング法は、高フレーム取得レートが望ましい場合、たとえ

ば急速に鼓動するマウスの心臓をイメージングする場合に画像を形成するために組み込む

ことができる。 R F 取得モードでは、生 R F データを取得して表示し、オフライン分析に使用することができる。

### [0043]

一実施態様では、振動子は、少なくとも500ヘルツ(Hz)のパルス繰返し周波数(PRF)で送信することができる。システムは、カラーフロードップラー超音波画像を受信超音波から生成する処理ユニットをさらに備えることができる。任意に、PRFは約100Hz~約150KHzである。MモードまたはRFモードでは、PRFは、約100Hz~約10KHzである。ドップラーモードの場合、PRFは、約500Hz~約150KHzで良い。MモードおよびRFモードの場合、PRFは、約50Hz~約10KHzで良い。

[0044]

例示的なアレイド振動子

次に、図2A~15Bを参照すると、本発明の一実施態様による回路基板は、例示的な振動子を収納するように構成され、少なくとも1つの従来のコネクタに接続するようにさらに構成される。本明細書に記載するとおり、要求された信号の送信および/または供給用のケーブルと相補的に接続するように構成することができる。図を参照すると、回路基板の微細な詳細により、別様に指示されていない限り、図面は、相補的な回路基板および関連するマルチ素子アレイを単に表している。図5A~5Cは、75ミクロンピッチを有する256個の素子アレイ用の例示的な回路基板の様々な図を示す。

[0045]

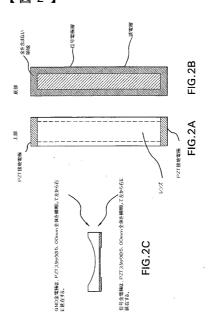

次に、特に図2A~4Bを参照すると、例示的な回路基板と共に使用される例示的な振動子が示されている。図2A~4Bでは、例示的なPZTスタックの略図の例示的な上部、下部、および断面図が示されている。図2Aは、PZTスタックの上面図を示し、PZTスタックの上部および下部部分から延在する接地電気層の部分を表す。一態様では、接地電気層は、PZTスタックの全幅に延在する。図2Bは、PZTスタックの下面図を示す。この態様では、PZTスタックの長手方向に延在する縁部に沿って、PZTスタックは、個々の信号電極素子間の誘電体層の露出部分を形成する。別の態様では、信号素子は、PZTスタックの全幅に延在する。図面で分かるとおり、PZTスタックの下にある「中心部分」には、個別化信号電極素子を示すラインが示されていない。図面でさらに分かるとおり、PZTスタックの素子ごとに1つの信号電極があり、たとえば256個の素子アレイには、256個の信号電極がある。

[0046]

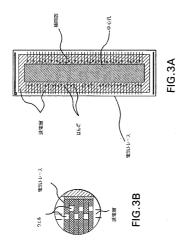

図3 A は、図2 A ~ CのPZTスタックと共に使用されるインターポーザの上面平面図であり、インターポーザの中心開口部に隣接して外側に延在する電気トレースを含む。インターポーザは、このインターポーザの上部および下部部分に位置する接地電気トレースをさらに含む。

[0047]

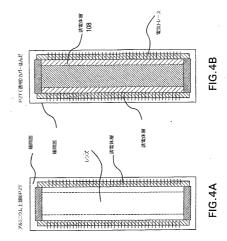

インターポーザは、このインターポーザの中心開口部の周囲のインターポーザ上面の一部に配置された誘電体層をさらに含む。この態様では、さらに図3Bを参照すると、誘電体層は、千鳥状のウェルの2つのアレイを画定し、1つのアレイは、中心開口部の各々の側にあり、インターポーザの長手方向軸に平行な軸に沿って延在する。各々のウェルは、インターポーザの電気トレースと連通する。はんだペーストは、誘電体層内の各々のウェルを充填するために使用することができ、PZTスタックが誘電体層上に実装されて、熱が加えられた時に、はんだが融解して、インターポーザ上の個々の素子信号電極と個々のトランス間に所望の電気的に導通を形成する。

[0048]

図4Aは、図3Aのインターポーザの誘電体層上に実装された図2AのPZTスタックの上面平面図である。本発明を分かりやすくするために、図4Bは、誘電体層上に実装された図2AのPZTスタック、および図3Aのインターポーザの上面平面図を示し、PZTスタックは、透明画として示されている。これは、PZTスタックと、下にある誘電体

10

20

30

40

層 / インターポーザとの実装関係を示し、これらの間に実装されたはんだペーストは、インターポーザ上の個々の素子信号電極と電気トレースとの間に電気接続を形成する。

### [0049]

次に、図5Aを参照すると、本発明の振動子が実装される例示的な回路基板の略上面平面図が示されている。一態様では、回路基板の少なくとも一部分は可撓性で良い。一実施態様では、回路基板は、下部銅接地層の上面に実装された下部銅接地層およびKapton(商標)層を含む。一態様では、回路基板は、下にある複数の実質的に剛性の支持構造を含むこともできる。この態様では、回路基板の中心開口部を囲む中心部分は、下部銅接地層の下面に実装された剛性の支持構造を有することができる。さらに他の態様では、コネクタを取り付けることが可能な回路基板の部分も、下部銅接地層の下面に実装された剛性支持構造を有することができる。

#### [0050]

回路基板は、Kapton(商標)層の上面に形成された複数の基板電気トレースをさらに含み、各々の基板電気トレースは、振動子の電気トレース、およびコネクタ、たとえば信号通信が行われるケーブルに結合するように構成された遠位端に結合するように構成される。一態様では、各々の電気トレースを形成する回路の長さは、実質的に一定のインピーダンスを有する。

## [0051]

回路基板は、複数のバイアも含み、これらのバイアは、Kapton(商標)層を貫通し、下にある接地層と連通して、信号リターンパス、または信号接地パスを形成することができる。さらに、回路基板は、複数の接地ピンも含む。各々の接地ピンは、回路基板の接地層に結合される近位端と(Kapton層内のバイアの1つを貫通する)、コネクタに結合するように構成された遠位端とを有する。

#### [0052]

図5 B は、7 5 ミクロンピッチを有する例示的な 2 5 6 素子アレイを実装するための例示的な回路基板の上面平面図であり、図5 C は、回路基板の下にある接地層と連通する図5 B の回路基板のバイアの上面平面図である。図 5 B は、コネクタのピンを収納するサイズおよび形状のボアを回路基板に画定し、コネクタが回路基板の部分に実装されると、個々の電気トレースおよび接地ピンとコネクタとの正確な位置合わせが行われる。

### [0053]

図6は、例示的な回路基板の一部分の部分拡大上面平面図を示し、領域Aには、インターポーザ上の電気トレースにワイヤボンドされ、その結果、回路基板の接地パッドにワイヤボンドされる振動子の接地電極層が示されている。回路基板の接地パッドは、Kapton(商標)層内のバイアを通して、下にある下部銅接地層と連通する。図示のとおり、領域Bでは、振動子の個々の電気トレースが、回路基板の個々の基板電気トレースにワイヤボンドされている。次に、図8Aを参照すると、一態様では、回路基板の中心開口部は、振動子の裏材料の下にある。図7Aは、回路基板の一部分に実装された例示的な振動子の領域Bの拡大部分図である。

### [0054]

次に、図11A~11Bを参照すると、回路基板の実質的に剛性の中心部分に対する、インターポーザを含まない振動子の実装が示されている。この実施態様では、殆どのワイヤボンドをなくすことが可能である。この態様では、PZTスタックは、たとえば、一連の金ボールバンプにより回路基板に直接表面実装される。金ボールバンプ手段は、従来の表面実装技術であり、上記の表面実装技術と一致する別のタイプの表面実装技術を示す。この実施例では、回路基板の剛化された中心部分は、インターポーザと同じ機能性を提供することができる。PZTスタックの接地電極から回路基板の接地までのワイヤボンド、またはその他の電気接続部は、組み立てられたデバイスの信号リターンに匹敵させる必要がある。図11Aは、回路基板の接地パッドにワイヤボンドされた振動子(インターポーザを含まない)の接地電極層を示す。

### [0055]

50

20

10

30

20

30

40

50

一態様では、器ボールバンプは、回路基板上に直接適用される。各々のボールバンプは、回路基板の1つの電気トレースと連通させて配置される。PZTスタックが適用されると、PZTスタックは回路基板の電気トレースと整列し、ボールバンプを介して電気的な導通が行われる。PZTスタックは、たとえば、a)UV硬化性の欠肉を使用する;b)ACFテープを使用する;c)純粋なインジウムはんだをPZTまたは回路基板の電極上に電気めっきし、インジウムをリフローさせて、PZT上の信号電極と、回路基板上の気ボールバンプとの間などにはんだ接合部を形成することにより回路基板に固定されるが、これらに制限する意図はない。

# [0056]

アレイド振動子は、図2A~11に示す可撓性回路を使用して、システムの処理ユニッ トに動作可能に接続することができる。次に、図12~15を参照すると、フレックス回 路は、BTHコネクタと動作可能に接続することができる。BTHコネクタは共通であり 、様々なサイズのコネクタがある。BTHコネクタは、BSHコネクタと嵌合する多数の ピンを備える。ピンの数は、フレックスの対応するトレースのアレイ素子の数より少なく とも1つ多くすることができる。たとえば、ピンの数は、フレックスの対応するトレース のアレイ素子の数の2倍に等しくて良い。したがって、一実施例では、2×180=36 0のピンを、256個素子アレイの可撓性回路上の256個のトレースに使用することが できる。別の実施例では、256個のピンは、例示的な256素子アレイに使用すること ができる。BSHコネクタは、BTH内に接続可能に着座させることができる。BSHコ ネクタは、複数の同軸ケーブルで終端するプリント回路基板などのインターフェースと動 作可能に接続される。複数の同軸ケーブルから形成される比較的大きい共通ケーブルは、 ZIF端部で終端させて、ZIFレセプタクルまたはインターフェース部位において、超 音波システムの処理ユニットとインターフェースさせることができる。使用可能な例示的 な ZIFコネクタは、ニューヨーク州、ホワイトプレインズのITT Corporat ionから市販されている360ピンDLM6 ITT Cannon ZIF(商標) コネクタである。しかし、当業者には明らかなとおり、別のZIF(商標)コネクタを処 理ユニットとインターフェースするために使用することができ、こうしたコネクタは、お およそ360個のピンを有することが可能である。

### [0057]

接続は、ケーブル、またはケーブルの束から構成することができる。ケーブルは、アレイの各々の素子を1対1の関係で処理ユニットに接続することができ、つまり、各々の素子は、それ自体の信号および接地リードを使って、処理ユニット内の指定の接続点に電気的に接続することができ、その結果、複数の個々の素子接続部が一緒に束ねられて、全体のケーブルを形成する。任意に、各々の個々の電気接続部は束から取り外すことができ、物理的に1つのケーブルまたはケーブル組立体を形成するわけではない。

# [0058]

適切なケーブルは、同軸ケーブル、捩られた対、および銅合金配線で良い。その他の接続手段は、非物理的な接続方法、たとえばRFリンク、赤外線リンク、および適切な送信および受信構成要素が含まれる類似の技術を介して行われる。

#### [0059]

個々の素子の接続は、処理ユニットに対する接続アレイ素子に一般に使用される他言うの同軸ケーブルを含むことができる。これらの同軸ケーブルは、低損失タイプで良い。同軸ケーブルは、中心導体、および中心導体から絶縁され、外側絶縁層内に入れられたあるタイプの外側シールディングを一般に含む。これらの同軸ケーブルは、アレイに使用するのに適する公称インピーダンスを有することができる。一例の公称インピーダンスは、50以上、たとえば50、52、73、75、または80で良い。

#### [0060]

本明細書に記載されている1つまたは複数の超音波イメージングシステムと共に使用される例示的な医療用ケーブルは、40AWGの少なくとも256本の同軸ケーブルで、公称インピーダンスが約75 、同軸ケーブルの長さが約2.0mの同軸ケーブルを含む。

長さは、2.0m未満か、または2.0mを超えて良い。医療用ケーブルのジャケットの長さは、ケーブルの長さに適合し、電気シールディング用の追加の金属シースを含むことができ、PVCまたはその他の可撓性材料から製造することができる。

### [0061]

本明細書に記載されているものを含むアレイ振動子を処理ユニットに接続するケーブルおよび接続部は、Precision Interconnect-TYCO Electronics(デラウェア州、ウィルミントンのTyco Electronics Corporation)などの会社が製造することができる。

# [0062]

例示的なケーブルは、近位端に、フレックス / 歪緩和、同軸ケーブルと Z I F (商標) ピンとをインターフェースする12 P C B、360ピン I T T C a n n o n Z I F (商標) コネクタ、および作動ハンドル(D L M 6 - 360タイプ)、並びにコネクタ周囲の遮蔽ケーシングをさらに含む。例示的なケーブルは、遠位端に、2つの P C B で終端し、同軸ケーブルとフレックス回路基板とをインターフェースするフレックス / 歪緩和ケーブルであって、各々の P C B が、1 B S H - 090-01-L-D-A S a m t e c コネクタ(インディアナ州、ニューオールバニーの S a m t e c 、 I n c . )を有し、各々の P C B が、75 の独特なインピーダンストレースを有し、ケーブルが千鳥状配置の P C B の両側から終端するケーブルを含むことができる。

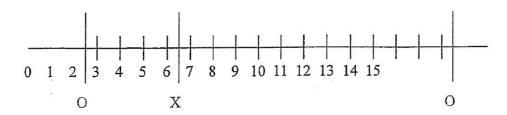

#### [0063]

ケーブルは、大きいケーブルを含む複数の同軸ケーブルを固定および接続する「フレックス回路」法を使用することができる。例示的な実施態様では、アレイは、256個の素子を有する。アレイは、フレックス回路の中心領域に実装される。フレックス回路は、奇数の番号が付いた素子1、3、5、7...255が、J1というラベルが付いたBTH - 090コネクタを有するフレックスの左端部上で終端し、偶数番号が付いた素子2、4、6、8...256が、J3というラベルが付いたBTH - 090コネクタを有するフレックスの右端部で終端する両端を有する。両端では、これらの素子は、GND(信号リターン)ピンが、コネクタ全体に繰り返しパターンで均一に分散している個々のコネクタの上および下の列に沿って順に終端する。

### [0064]

この繰返しパターンは、以下のとおり、フレックスの外側縁部からフレックスの中心領域に向かって画定される:

- 2つの信号ピン、GND

- 3つの信号ピン、GND

- 2つの信号ピン、GND

- 3 つの信号ピン . . .

. . . . G N D

- 3つの信号ピン、GND

- 2つの信号ピン、GND

- 2つの信号ピン、GND。

#### [0065]

折り畳まれたフレックス回路であって、アレイが、フレックスの中心アレイに実装されているフレックス回路の側面図を示す略図は、図12Aに示され、フレックス回路上のコネクタの関連するピン配列テーブルは、図12Bに示されている。

# [0066]

フレックス回路は、上記の例示的なケーブルに接続することができる。フレックス回路は、Precision Interconnect・Tyco Electronicsの医療用ケーブル組立体に接続することができる。フレックスからZIF(商標)コネクタまでの、たとえば電気接続は、2つの走査ヘッドPCBと、これに続く同軸ケーブルの束、および各々が、ZIF(商標)ピン内に挿入された2×15コネクタを有する12本の短いPCBによって行うことができる。

10

20

30

40

### [0067]

### [0068]

図13は、2つの走査ヘッドPCBの構造を示す。図14は、PCBをどのようにフレックス回路に接続することができるかを示し、同軸ケーブルのリボンをPCBにはんだ付けすることを可能にする千鳥状態を示す。2つの走査ヘッドPCBがある。左の基板は、フレックス上のJ1コネクタに接続することができ、右の基板は、J3コネクタに接続することができる。各々の走査ヘッドPCBは、1つのBSH-090コネクタを有することができる。各々の走査ヘッドのトレースのピン配列は、J1およびJ3コネクタのピン配列に一致適合させることができる。

# [0069]

### ZIFコネクタ

例示的な医療用ケーブルは、図15Aに部分的に示すように、処理ユニットに接続するケーブルの端部である近位端にZIFコネクタを備える。当業者は、ケーブル組立体のいくつかの構造が可能であることを理解するであろう。図15Bは、例示的なZIFコネクタに使用可能なピン配列を示す。Gというラベルを付けられたピンは、信号リターンピンである。N/Cというラベルを付けられたピンは同軸ケーブルで終端せず、これらのピンは、シャーシ接地を保護するか、または特定されていないその他の機能として使用するために留保される。N/Cピンは、単にZIF筐体を取り外し、ZIFに接続される12個のPCBの何れかの未使用のトレースのはんだを除去することによって接近することができる。

### [0070]

ZIFコネクタに接続するために使用される12個の個々のPCBは、基板の一方または両方の側に接続される同軸ケーブルを有する。PCBの一方の縁部は、ZIFコネクタ(Saintec SSWまたは等価なもの)内に挿入するのに適するコネクタを有することができ、各々のPCBは、正しい同軸ケーブルを正しいZIFピンに接続するために必要な適切なトレースおよびバイアを有するべきである。

### [0071]

各々の P C B は、 S a m t e c S S W または等価なもの、 2 列の 1 5 個のピンを有するコネクタを有することができるが、同軸ケーブルの数は、図 1 5 B に示すように 1 2 個の P C B によって異なる。  $2 \times 1$  5 コネクタ上のピンの一般的な配置は普遍的であり、表 1 に示されている。

### [0072]

12個のPCBの1つは、図15Bに示すとおり、EEPROMを含むトレースのレイアウトに備えを必要とする。12個のPCBの2つは、アレイ組立体内部に含まれる特定のアレイ構造を特定するPROBE ID番号を提供するために、必要に応じてピンのいくつかを終端させることが必要である。

# [0073]

様々な接続方法を使用することができ、様々なスタイルのコネクタが挙げられる。これらの様々な接続方法では、インピーダンスは、30MHzの中心周波数において75 で良い。

### [0074]

10

20

30

#### 【表1】

表1 ITTコネクタに差し 込まれるZIF PCBのコネクタ 端部における 接続部のレイア ウト

#### 一般的なパターン

超音波システム

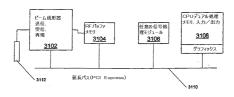

本発明による超音波システム1600の例示的な実施態様を図16に示す。図16は、例示的な超音波イメージングシステム1600を示すブロック図である。様々な図面に示されているブロックは、システム1600の一実施態様内で行われるプロセスの機能表現で良い。しかし、実際上、機能は、システム1600内のいくつかの位置またはモジュール全体で行われる。

[0075]

例示的なシステム1600は、アレイ振動子1601、ケーブル1619、および処理ユニット1620を備える。ケーブル1619は、処理ユニット1620およびアレイ振動子1601を接続する。処理ユニットは、ソフトウェアおよびハードウェア構成要素を含む。処理ユニットは、マルチプレクサ(MUX)/フロントエンド電子回路1602、受信ビーム成形器1603、ビーム成形器制御装置1604、送信ビーム成形器1605、システム制御装置1606、ユーザインターフェース1607、走査変換器1608、映像処理ディスプレーユニット1609、および1つまたは複数のMモード処理モジュール(図示しない)を含む処理モジュール、PWドップラー処理モジュール1611、Bモード処理モジュール1612、カラーフロー処理モジュール1613、3・Dモード処理モジュール1615を含むことができる。例示的なシステムの中心周波数範囲は、約15~55MHz以上で良い。帯域幅の外側縁部から測定した場合、例示的なシステムの周波数範囲は、約10~80MHz以上で良い。

[0076]

アレイ振動子1601は、MUX/フロントエンド電子回路(MUX/FEE)160 2 において、処理ユニット1620とインターフェースする。MUX/FEE1602の MUX部分は、複数の電気パスをより少数の電気パスに電子的に切り換えるか、または接 続することが可能なマルチプレクサである。アレイ振動子1601は、電気エネルギーを 超音波エネルギーに、およびこの逆に変換し、MUX/FEE1602に電気的に接続される。

[0077]

MUX/FEE1602は、アレイの素子の一定のサブセット、つまりアクティブアパーチャの素子に接続される送信波形を生成する電子回路を含む。素子のサブセットは、アレイ振動子1601のアクティブアパーチャと呼ばれる。MUX/FEE1602の電子回路は、アレイのアクティブアパーチャを受信チャネルの電子回路にも接続する。作動時、アクティブアパーチャは、アレイ振動子1601の周囲で、本明細書に記載された構成要素によって決定される方法で移動する。

[0078]

MUX/FEE1602は、アクティブアパーチャの素子を例示的なシステムの送信お

10

20

30

40

20

30

40

50

よび受信チャネルに切換え可能に接続する。本発明の256素子アレイ振動子の例示的な実施態様では、最大64個のアクティブアパーチャに切換え可能に接続可能な64個の送信チャネルおよび64個の受信チャネルがある。最大64個のアクティブアパーチャは連続している。本発明の特定の実施態様では、別個の送信MUXおよび別個の受信MUXがある。本発明のその他の実施態様は、送信チャネルおよび受信チャネルの両方でMUXを共有する。

#### [0079]

例示的な超音波システム1600の送信サイクル時、MUX/FEE1602のフロントエンド電子回路部分は、アレイ振動子1601のアクティブアパーチャの素子に高電圧信号を供給する。一態様では、受信チャネルおよび送信チャネルは、アレイ振動子1601の素子に共通の接続点を有するため、フロントエンド電子回路は、受信チャネルの保護回路も提供し、受信チャネルを高電圧送信信号から保護することができる。保護は、受信チャネル内に漏れるか、または通過する可能性がある送信信号の量を、受信電子回路に損傷を生じない安全レベルに制限する絶縁回路構成の形式で良い。MUX/FEE1602の特徴としては、送信側における迅速な立上がり時間、および送信および受信チャネル上における高帯域幅が挙げられる。

### [0800]

MUX/FEE1602は、信号を送信ビーム成形器1605からアレイ振動子1601に通過させる。例示的な実施態様では、送信ビーム成形器1605は、別個の波形を生成し、アクティブアパーチャの各々の素子に供給する。例示的な実施態様では、アクティブアパーチャの各々の素子の波形は同じである。別の態様では、アクティブアパーチャの各々の素子の波形は、すべて同じというわけではなく、実施態様によっては、異なる中心周波数を有する。

#### [0081]

例示的な一実施態様では、各々の別個の送信波形は、それぞれに関連する遅延を有する。各々の素子の波形の遅延の分布は、遅延プロファイルと呼ばれる。遅延プロファイルは、送信音響ビームを所望の焦点に所望どおりに集束させるように計算される。特定のアクイルをでは、送信音響ビーム軸は、アレイ1601の平面に垂直であり、ビーム軸は、アレイ1601と交差する。遅延プロファイルも、ビームがアレイ1601の平面に垂直ではないように、ビームをステアリングすることができる。本発明の例示的な態様では、1/16の遅延分解能を使用することができる。あるいは、言い換えれば、送信中心周波数の中心周波数の期間の1/16は、別の遅延分解能だが、本発明の範囲内で考えられる。たとえば、50MHzの中心周波数では、期間は20ナノ秒であるから、期間の1/16は1.25ナノ秒であり、これは、音響ビームを集束させるために使用される例示的な遅延分解能である。遅延分解能は、期間の1/16番目とは異なる場合があり、たとえば、1/16番目より小さい遅延分解能(たとえば、1/16番目とは異なる場合があり、および1/16番目より小さい遅延分解能(たとえば、1/12、1/8など)は、本発明の範囲内であると考えられることが分かるであろう。

### [0082]

受信ビーム成形器 1 6 0 3 は、MUX / FEE1602を介して、アレイ振動子 1 0 1 のアクティブアパーチャの素子に接続することもできる。送信時、音響信号は、被検体内に浸透し、被検体の組織から反射信号を生成する。反射信号は、アレイ振動子 1 6 0 1 のアクティブアパーチャの素子によって受信され、アクティブアパーチャの各々の素子から放射されるアナログ電気信号に変換される。電気信号がサンプリングされ、信号は、受信ビーム成形器 1 6 0 3 内でアナログからデジタル信号に変換される。本発明の実施態様は、直交サンプリングを使用して、受信信号のデジタル化を行う。システム 1 6 0 0 の受信サイクルでは、アレイ振動子 1 6 0 1 は、ビーム成形器制御装置 1 6 0 4 によって決定される受信アパーチャも有し、ビーム成形器制御装置 1 6 0 4 は、受信ビーム成形器 1 6 0 3 に対して、アレイの

20

30

40

50

どの素子をアクティブアパーチャ内に含み、どの遅延プロファイルを使用するかを知らせる。例示的な実施態様の受信ビーム成形器 1 6 0 3 は、デジタルビーム成形器である。

#### [0083]

受信ビーム成形器 1 6 0 3 は、遅延をアクティブアパーチャの各々の素子の受信信号内に遅延を導入する。この遅延は、遅延プロファイルと総称される。受信遅延プロファイルは、経過時間、つまりイメージングされる組織内に超音波が送信される時に、経過した時間に基づいて動的に調節することができる。経過時間は、受信ビーム成形器を組織内の焦点の 1 点に集束させるために使用される。つまり、受信ビームは、送信ビームの経過時間に関する情報を含む遅延プロファイルを使用して調節される。

#### [0.084]

アクティブアパーチャの各々の素子からの受信信号は合計され、合計は、遅延プロファイルを含む。合計受信信号は、ユーザインターフェース1607、およびユーザの入力に基づいて動作するシステム制御装置1606によって選択されるように、受信チャネルに沿って、受信ビーム成形器1603から、図16に示さないものも含み)1つまたは複数の処理モジュール1611、1612、1613、および/または1615流れる。

#### [0085]

ビーム成形器制御装置1604は、送信ビーム成形器1605および受信ビーム成形器1603を介してMUX/FEE1602に接続される。ビーム成形器制御装置1604は、システム制御装置1606にも接続される。ビーム成形器制御装置1604は、MUX/FEE1602に情報を提供し、その結果、アレイ振動子1601の所望の素子は、アクティブアパーチャを形成するように接続される。また、ビーム成形器制御装置1604は、特定のビームの受信に使用される遅延プロファイルを生成し、受信ビーム成形器1603に送信する。本発明の実施態様では、受信遅延プロファイルは、経過時間に基づいて、繰返し更新することができる。ビーム成形器制御装置1604は、送信遅延プロファイルも生成し、送信ビーム成形器1605に送信する。

#### [0086]

システム制御装置1606は、当業者が周知している方法で動作する。システム160 0は、ユーザインターフェース1607から入力を取得し、制御情報をシステム1600 の様々な構成要素に提供し、選択された動作モードになるようにシステム1600を構成 する。走査変換器1608は、当該技術分野で周知の方法で動作し、1つまたは複数の処理モジュールから生成された生画像データを取得して、この生画像データを、映像処理 / ディスプレー1609によって表示可能な画像に変換する。動作の処理モードでは、画像 は、画像の映像特性が、ディスプレーの映像特性と同じであれば、走査変換器1608を 使用しないで表示することができる。

### [0087]

処理モジュールは、本明細書に特記しない限り、当業者が周知している方法で機能する。 PWドップラーモジュール1611、およびカラーフロー処理モジュール1613では、パルス繰返し周波数(PRF)は、本発明の実施態様の高い中心周波数により高い可能性がある。測定される最大非エイリアス速度は、PRFに比例し、送信中心周波数に反比例する。特定の送信中心周波数が、当業者が周知している方法で計算されると仮定すると、PRFは、非エイリアス測定を可能にするために必要である。使用される送信中心周波数が、15~55MHz以上であり、血流速度が、1m/秒という速さ、および場合によっては1m/秒を超えると仮定すると、こうした速度から生じるドップラー信号の非エイリアス測定は、PWドップラーを150KHz以下にするために、PRFを必要とする。本発明の実施態様は、150KHz以下のPRFを支持するPWドップラーモードを有し、このモードは、中心周波数が30MHzの場合、移動する目標の速度ベクトルと超音波ビーム軸との間の角度が0度の状態で、1.9m/秒以下の血流速度の非エイリアス測定を可能にする。

#### [0088]

特定に実施態様では、RFモジュール1615は補間を使用する。使用されるサンプリ

20

30

40

50

ング方法が直交サンプリングである場合、RF信号は、当業者が周知のゼロパディングお よびフィルタリングによって、直交ベースバンドサンプルから再現することができる。N y q u i s t サンプリングを使用する場合、 R F 信号が直接サンプリングされるため、再 現は不要である。特定の実施態様では、RFモジュール1615は、受信ビーム成形器出 力の直交サンプルからRF信号を生構成する。サンプリングは、受信信号の中心周波数で 行われるが、直交の場合、信号のベースバンド直交表現が与えられる。RF信号は、直交 サンプリングされたデータ流を最初にゼロパディングすることによって生成され、ゼロの 数は、所望の補間信号サンプルレートによって決定される。次に、複合帯域フィルタは、 ゼロパディングされたデータ流に適用され、fsがサンプル周波数であるfs/2~3f s / 2 の周波数帯域外にあるゼロパディングされた信号の周波数成分を拒絶する。フィル タリング後の結果は、元のRF信号の複素表現である。次に、RF信号は、メインコンピ ュータユニットに送られ、デジタルフィルタリング、並びに包絡線検波および表示など、 その他の処理が行われる。RF信号の実数部または複素表現が表示される。たとえば、特 定の走査ラインに関して取得されたRFデータが処理され、表示される。あるいは、多数 のパルスエコーリターンを平均した特定の走査ラインからのRFデータを表示することが できるか、または多数の異なる走査ラインから取得したRFデータを平均し、表示するこ とができる。RFデータの取得に使用される走査ラインは、Bモード画像上に重なったカ ーソルラインを配置することによって、ユーザが、Bモードの評価に基づいて指定するこ とができる。RFデータの高速フーリエ変換(FFT)を計算して、表示することもでき る。RFデータの取得およびBモードデータの取得は、リアルタイムで同時に、両方のモ ードからの情報を表示することができるように、インターリーブすることができる。EC G信号などの生理学的信号の取得も、RFデータの取得と同時に行うことができる。EC G波形は、RFデータが取得されている間に表示することができる。RFデータの取得の タイミングは、ECG波形内のユーザが画定した点と同期させて、それによって、心周期 時に特定回数だけRFデータを参照することが可能になる。RFデータを記録して、その 後のある時点で処理および評価することができる。

### [0089]

図17は、本発明の一実施態様の構成要素をさらに示すシステム1600のブロック図を示す。アレイ振動子1601は、ケーブル1619を介してフロントエンド変換器1702に接続される。ケーブル1619は、アレイ振動子1601の素子からフロントエンド変換器1702までの信号経路を含む。ケーブルの例示的な実施態様は、本明細書で説明されており、個々のマイクロ同軸ケーブルを含む。さらに、コネクタは、ケーブル1619の一方の端部または両方の端部に使用することができる。本発明の一態様では、素子の数の2倍に相当するピンを有するコネクタを使用することができ、例示的なコネクタは、本明細書で説明されている。アレイ振動子1601の各々の素子では、信号および接地パスを使用することができる。本発明のその他の実施態様では、接地接続は、素子群ごとに共用される。あるいは、MUX/フロントエンド電子回路1702、1703、1704、1708は、線形振動子アレイ1601用の筐体内に配置することができる。

# [0090]

図17は、フロントエンド変換器1702および送信出力ステージ1703が各々の素子に存在する比較的大きいシステム1600の例として、アレイ振動子1601の4つの素子のための回路構成の代表的な詳細を示す。256素子のアレイ振動子1601を有する一実施態様の場合、256個のフロントエンド変換器1702および送信出力ステージ1703について、以下でさらに完全に説明する。受信時、アレイ振動子1601の素子からの電気信号は、フロントエンド変換器1702を通過して、受信マルチプレクサ1704内に入る。受信マルチプレクサ1704は、どの素子およびフロントエンド変換器を受信チャネル1705に接続するかを選択する。受信チャネル1705は、低雑音増幅器およびタイムゲインコントロールを備え、両者について、以下でさらに完全に説明する。信号は、次に、受信チャネル1705からアナログデジタル変換1706内に至り、そこでデジタル化される。デジタル受信信号は、次に、デジタルビーム成形器である受信ビー

20

30

40

50

ム成形器1707内に入る。ブロック1707では、ビーム成形器制御装置内で生成され た遅延プロファイルは、受信信号に適用される。受信ビーム成形器1707からの信号は 、合成アパーチャメモリ1710内に移動する。合成アパーチャメモリは、2つの連続す る超音波ラインからの受信データを追加する。超音波ラインは、超音波パルスが組織内に 送信された後に受信される超音波エコーを返すことによって生じるデータであると考えら れる。合成アパーチャイメージングは、当業者が理解するように実施される。部分的には . 合成アパーチャイメージングは、送信または受信アパーチャの有効サイズを増加する方 法を意味する。たとえば、ビーム成形器内に64個のチャネルがある場合、1本の超音波 ラインデータの受信時に、64個の送信チャネル、および64個の受信チャネルを使用す ることができる。合成アパーチャイメージングは、合計2本の超音波データラインを使用 する。第1超音波ラインは、素子33から96にわたる受信アパーチャを使って取得する ことができる。第2超音波ラインは、素子1~32および97~128に位置する2つの ブロックに区分されたアパーチャを使って受信される。両方の超音波ラインは、同じ送信 アパーチャを使用する。2本の超音波ラインを加算する場合、受信アパーチャが、素子1 から128に位置する128個のチャネルから成るとして、結果として得られる超音波ラ インは、受信された超音波ラインと本質的に同じだが、2本の超音波データラインを取得 するために必要な期間に、イメージングされる組織に感知可能な動きはないことが条件で ある。この場合、フレームレートは2分の1に低下するため、1本ではなく2本の超音波 ラインが必要である。2つの受信アパーチャは、一緒に128個の素子のアパーチャを形 成する限り、異なる方法で配置することができる。あるいは、送信アパーチャのサイズは 、受信アパーチャを同じに維持しながら、増加させることができる。2本を超える超音波 ラインは、アパーチャを2倍に増加するために使用することができる。合成アパーチャメ モリ1710からの信号は、次に、RFシネバッファ1713内に記憶され、このRFシ ネバッファ1713は、同期処理制御モジュール1714によって制御されるように、多 くの受信RFラインを記憶する大型メモリである。バッファされた受信信号は、次に、適 切な速度で信号処理ユニット1715内に読み込まれる。信号処理ユニット1715は、 ビーム成形器制御盤上において、専用CPUで実施される。受信信号は、信号処理ユニッ ト1715からコンピュータユニット1717に送られ、ユーザが選択したモードに従っ てさらに処理される。コンピュータユニット1717による受信信号の処理は、一般に、 本明細書に特記する場合を除いて、当業者が周知するタイプである。

### [0091]

一実施態様では、コンピュータユニット1717は、図17に示すとおり、コンピュータユニット1717は、システムの動作モードに従って信号を処理するように構成されたシステムソフトウェアを含む。たとえば、メインコンピュータユニット1717のシステムソフトウェアは、Bモードプロセッサを実行するように構成され、たとえば、前処理、パーシスタンス処理、シネループ画像バッファ、走査変換、イメージパン、ズーム、おフーフローイメージング(CFI)のための処理を実行するように構成することもでき、カラーマップ、および優先度を含む。メインコンピュータユニット1717のシステムソフトウェアは、PWドップラーのたとえば、シネループCFI画像バッファ、走査変換、カラーマップ、および優先度を含む。メインコンピュータユニット1717のシステムソフトウェアは、PWドップラーのための処理を実行するように構成することもでき、たとえば、スペクトル推定(FFT)、推定値フィルタリング、シネループスペクトルデータバッファ、スペクトル表示の生成、後処理、ダイナミックレンジ、および音響処理を含む。

#### [0092]

図17のシステムの実施態様は、ユーザインターフェースパネル1720も備える。この実施態様では、ユーザインターフェースパネル1720は、殆どの臨床超音波システムに見られる標準ユーザインターフェースに類似している。たとえば、Bモードユーザインターフェースは、画像の奥行き、画像のサイズ、二重画像作動、二重画像左/右選択、フリップ画像上/下、およびズームを含む画像フォーマット制御装置を有する。送信制御装

20

30

40

50

置は、送信電力(送信振幅)、送信焦点領域の位置、送信域の数の選択、送信周波数、およびサイクル数を含む。画像最適化制御装置は、Bモードゲイン、TGCスライダー、前処理、パーシスタンス、ダイナミックレンジ、フレームレート/分解能制御、および後処理曲線を含む。

### [0093]

モード依存インターフェース制御装置のもう1つの例として、カラーフローイメージングユーザインターフェースは、カラーフローモード選択(たとえば、カラーフロー速度、パワードップラー、組織ドップラー)、トラックボール、ステアリング角度、カラーボックスの位置 / サイズの選択(選択後、トラックボールを使用して、位置またはサイズを調節する)、プリセットリコール、プリセットメニュー、およびカラーマップ反転を含む画像フォーマット制御装置を有する。送信制御は、送信電力(送信振幅)、送信焦点領域の位置、および送信周波数を含む。画像最適化制御は、カラーフローゲイン、ゲートサイズ、PRF(速度スケールの変更)、クラッタフィルタの選択、クラッタフィルタの選択、フレームレート / 分解能の制御、前処理の選択、パーシスタンス、ダイナミックレンジ(パワードップラーの場合のみ)、およびカラーマップの選択を含む。

#### [0094]

ユーザインターフェースのさらに別の実施例は、PWドップラーモードの選択、トラックボール、PWカーソルの作動(トラックボールは、サンプルボリューム位置を調節するために使用される)、サンプルボリュームサイズ、ドップラーステアリング角度、掃引速度、更新(同時または間隔更新イメージングを選択)、音響ボリューム制御、および流れベクトルの角度を含むPWドップラーフォーマット制御装置を有するPWドップラーユーザインターフェースである。送信制御は、送信電力(送信振幅)および送信周波数を含む。スペクトル表示最適化制御は、ドップラーゲイン、スペクトル表示のサイズ、PRF(速度スケールの変更)、クラッタフィルタの選択、前処理およびダイナミックレンジを含む。

### [0095]

例示的なMモードのユーザインターフェースは、Mモードカーソル作動、トラックボール(カーソルの位置決めに使用)、ストリップサイズ、および掃引速度を含む画像フォーマット制御を有する。送信制御は、送信電力(送信振幅)、送信焦点領域の位置、送信周波数、およびサイクル数を含む。画像最適化制御は、Mモードゲイン、前処理、ダイナミックレンジ、および後処理を含む。

# [0096]

例示的なRFモードユーザインターフェースは、たとえば、RFライン位置、RFゲート、取得したRFラインの数、RF領域の動作、RF領域の位置、RF領域のサイズ、領域内のRFラインの数、平均化、およびBモードインターリーブディスエーブルを含むRFライン取得制御を有する。送信制御は、送信電力(送信振幅)、送信焦点領域の位置、送信「番号、送信周波数、サイクル数、取得PRFおよびステアリング角度を含む。受信処理制御は、RFモードゲイン、フィルタタイプと順序、ウィンドウのタイプ、および平均化されたライン数を含む。

### [0097]

受信信号のデジタルサンプルは、データが取得されるレートと一般に異なるレートで処理される。こうした処理は、本明細書では、「非同期信号処理」と記載する。処理レートは、データが表示されるレートであり、一般に毎秒約30フレーム数(fps)である。しかし、理解されるように、データは、最高で取得レートのレートで表示されるか、または約30fps未満で表示することができる。データは、本発明の特定の実施態様では、はるかに迅速なフレームレート、毎秒約300フレーム、または望ましい診断情報を取得するのに必要な速度で取得することができる。たとえば、迅速に移動する解剖学的構造、たとえば心臓弁の画像データは、比較的速いフレームレートを使用して取得され、次に比較的遅いフレームレートで表示することができる。データ取得レートは、30fps未満、30fps、または30fpsを超えて良い。たとえば、取得レートは、50、100

20

30

40

50

、200、300、またはそれ以上のfpsで良い。

#### [0098]

表示レートは、ヒトの眼が処理可能なレートを超えないように設定することができる。 取得可能なフレームによっては、表示の際にスキップすることができるが、受信ビーム成 形器の出力からのすべてのデータは、RFシネバッファ1713などのRFデータバッフ ァに記憶される。データは、RFデータと呼ばれることもあり、あるいはデータを取得す るために使用されるサンプリング方法で呼ばれることもある(たとえば、直交サンプリン グの場合、データは、ベースバンド直交データと呼ぶこともできる)。直交またはRFデ ータは、表示前に処理される。処理は計算集約的であり、使用する処理量を減少すると有 利であり、これは、取得レートではなく、表示レートで表示されるフレームのみを処理す ることによって達成される。表示の際にスキップされたフレームは、ライブイメージング が停止するか、またはシステムが「凍結」されると閲覧することができる。RFバッファ 1713内のフレームは、比較的低いレートで検索、処理、および再生することができ、 たとえば、取得レートが毎秒300フレームである場合、毎秒30フレームにおけるフレ 一ムごとの再生は、通常の10分の1の遅さになるが、操作者は、画像の迅速な変化を見 ることが可能になる。再生機能は、一般に、当業者によって「シネループ」機能と呼ばれ ている。画像は、様々なレートで再生するか、フレームごとに、後方、および前方に再生 することができる。

# [0099]

図17に示すシステム1600は、当業者が、システムの機能として望ましいと認識すると思われる様々な項目を含むことができ、たとえば、クロック1712、メモリ、音声カードおよびスピーカ、映像カードおよびディスプレーなど、並びに図17に示すその他の機能ブロックがある。

#### [0100]

図18aおよび18bは、MUX/フロントエンド電子回路1702、1703、1704、1708の一実施態様、並びに本発明の一実施態様による受信ビーム成形器1707および送信ビーム成形器1709の機能の追加の詳細を示す。図18aに示す実施態様では、チャネル、たとえば受信チャネルはノードに接続することができ、このノードは、図18aに示すように、切換え回路または多重化回路を通して、たとえば、アレイ振動子照符号1、65、129、および193の素子に切換え可能に接続され、これらの4つの素子の1つのみが、任意の特定の時にチャネル1 1801に接続される。これは、本質的に、システム1600の受信サイクルにおけるMUX/フロントエンド電子回路1702、1703、1704、1708の多重化機能の実行である。あるチャネルに切換え可能に接続される4つの素子の割当ては、素子の特定のサブセットの連続素子が、アクティブアパーチャを含むように行われる。たとえば、アレイ振動子が、256個の素子から成る場合、64個以下の素子が、アクティブアパーチャを含むサブセットを形成することができる。

# [0101]

受信サイクルのアレイ振動子1601の素子の多重化は、フロントエンド1802の例示的な図(図18b)に示されているRXスイッチ1817によって行うことができる。ビーム成形器制御装置1711からの制御信号1818は、どのRXスイッチ1817を作動させ、それによって、モジュール1802の4つの利用可能な素子の選択された素子を受信チャネルに接続するかを決定する。当業者が理解するとおり、図18aおよび18bにに示す多重化スキームは、異なる数の素子(256個の素子以外)、および異なる最大アクティブアパーチャサイズ(最大64個の素子以外)の振動子に適用することができる。

## [0102]

図 1 8 b に示す例示的なフロントエンド 1 8 1 6 は、以下で招請に説明するとおり、変換器 1 8 1 9 およびパルサー 1 8 2 0 も備える。一態様では、フロントエンド 1 8 1 6 は

20

30

40

50

、上記のとおり、受信チャネルを送信波形から絶縁する。

# [0103]

選択されたアレイ振動子素子からの受信信号は、低雑音増幅器(LNA)1804に送 られる。増幅された信号は、LNA1804から、タイムゲインコントロール(TGC) 1805に送られる。経過時間は、受信反射信号の深さに比例するため、深さ依存ゲイン 制御とも呼ばれる。超音波システムでは、超音波の送信から時間が経過すると、選択され た信号もこうした減衰を生じる。TGC1805は、時間依存性関数に応じて受信信号を 増幅し、この減衰を補償する。時間依存TGCゲインを決定するために使用可能な要素は 、経過時間、調査される被検体または被検組織の組織の特性、および用途(たとえば、画 像診断法)である。ユーザは、ユーザインターフェースパネル1607におけるTGC制 御を調節することによって、ゲインを深さの関数として指定することもできる。各実施態 様は、たとえば、Analog Devices(マサチューセッツ州、ノーウッド)の AD8332または類似のデバイスを使用して、LNA1804およびTGC1805の 機能を実行することができる。受信信号は、TGC1805から、受信ビーム成形器18 03に入り、サンプラーによって、この実施態様ではアナログデジタル変換器1807お よび1808によってサンプリングされる。本発明によるその他の実施態様では、サンプ リングが、Nyauistレートを超えるレート、たとえばNyauistレートの 2 倍 または3倍で行われる場合、1つのアナログデジタル変換器のみが使用され、Nyqui stレートでは、信号の最高周波数の少なくとも2倍のレートで、個々の素子から超音波 信号がサンプリングされる。

## [0104]

本発明のその他の実施態様では、直交サンプリングが使用され、2つのアナログデジタル変換器、つまり「I」および「Q」サンプラーが使用される。受信ビーム成形器1803の例示的な実施態様では、受信信号は、ブロック1807および1808で、直交サンプリングアナログデジタル変換器(ADC)を使用してデジタル化され、サンプリングクロックが、90°位相が外れいてる2つのADCがチャネルごとに必要である。使用されるサンプルレートは、受信信号の中心周波数で良い。比較すると、直接サンプリングは、理論上、受信信号の最高周波数成分の少なくとも2倍のサンプリングレートを使用するが、事実上、少なくとも3倍のサンプリングレートが好ましい。直接サンプリングは、チャネルごとに1つのADCを使用する。

## [0105]

サンプリング後、現在のデジタル化受信信号は、フィールドプログラマブルゲートアレイ(FPGA)内に送られ、受信ビームの形成に関連する様々な機能がインプリメントされる。FPGA内では、デジタル化受信信号には、ADCのDCオフセットの補正が行われる。各々のADCは、異なるDCオフセット補正値を有する。DCオフセットは、ADCの出力部で得られる多数のデジタルサンプルを平均化することによって決定され、たとえば、システム始動時の校正期間中、受信チャネル入力部に信号は存在しない。デジタル化信号は、次に、FIFOバッファ1822内に送られ、各々のサンプルは、適切な遅延プロファイルをインプリメントすることができる。粗遅延は、信号を1つまたは複数のサンプル点だけシフトさせて、所望の遅延を取得することによってインプリメントすることができる。たとえば、所望の遅延が1サンプル期間である場合、1サンプルだけ適切な方向にシフトすることによって、適切な遅延を有する信号が得られる。しかし、サンプル期間に等しくない値の遅延が望ましい場合、補間フィルタ1809を使用して、微細遅延をインプリメントすることができる。

#### [0106]

デジタル化受信信号は、FIFOバッファ1822から補間フィルタ内に送られ、微細遅延の計算が行われる。補間フィルタ1809は、サンプル期間が、適切な微細遅延分解能を超えるシステムに使用される。たとえば、サンプルレートは、超音波信号の中心周波数であり、50MHzである場合、サンプルレートは20ナノ秒ごとに1サンプルである。しかし、1.25ナノ秒の遅延分解能(20ナノ秒の1/16)は、所望の画像品質を

提供するために特定の実施態様に使用されるが、その他の遅延分解能は、本発明の範囲内 ので考えられる。補間フィルタ1809は、適時に、サンプリングされた点以外の点にお ける信号の値を計算するために使用される。補間フィルタ1809は、サンプリングされ た信号の同相および直交部分に適用される。補間フィルタ1809の実施態様は、有限イ ンパルス応答(FIR)フィルタを備える。各々のフィルタの係数は、経過時間に基づい てサンプルごとに、ビーム成形器制御装置によって動的に更新することができる。補間フ ィルタによる処理の後、位相回転は、同相および直交成分に適切な係数を乗算する乗算器 1811によって適用することができる。位相回転は、ADCサンプル周波数に対する正 しい位相を補間サンプルに組み入れるために使用される。RXコントローラ1810は、 FIFOモジュールおよび補間フィルタを制御する。受信遅延は動的に更新されるため、 各々のチャネルにおける補間フィルタ係数は、一定の間隔で変更する必要がある。FIF Oによってインプリメントされる遅延も、一定の間隔で変更する必要がある。また、受信 アパーチャのサイズは動的に調節されるため、各々のチャネルは、超音波信号の受信時の 特定の時間にアクティブになり、チャネルは、「乗算」モジュール1811において0で はなく1を乗算することによって作動される。また、乗算モジュール1811は、0と1 との間の値である「重量」を受信アパーチャ内の各々のチャネルに個々に適用することが できる。アポダイゼーションとして周知されているこのプロセスは、当業者が周知してい る。補間サンプルに乗算される値は、超音波信号の受信時に動的に拡大するアポダイズド 受信アパーチャをインプリメントするように、時間に応じて異なる。

# [0107]

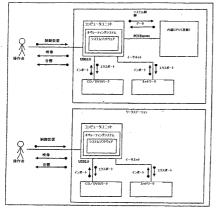

図18cは、本発明による実施態様の受信コントローラ(R X コントローラ)の例示的な実施態様である。受信コントローラ1810は、正しい遅延プロファイル、アパーチャサイズ、および受信アポダイゼーションデータを、補間および位相回転アポダイゼーションデータを、補間および位相回転アポダイゼーションをインプリメントする処理ブロック1809内にプログラムするために使用される。図18cの受信コントローラ1810は、初期パラメータ(初期粗遅延、初期位相)を開始(S O L )トリガごとに1回設定し、動的パラメータ(動的集束、動的アポダイゼーション)を受信クロック(R X C L K )期間ごとに1回設定する。初期受信遅延プロファイルは、R X 初期アパーチャメモリ1822内に記憶される。動的受信遅延プロファイルは、R X 動的アパーチャメモリ1824内に記憶される。遅延プロファイルは、S O L トリガの前に、64:16交差スイッチ1828を介して、R X B F バッファ1826内にロードされる。交差スイッチ1828は、64のアパーチャチャネル構成のうちの16を選択する。これらは、単一チャネル基板上に存在する16の受信チャネルをプログラムするために使用される。

# [0108]

各々の受信ラインの構成は、ラインメモリ1830内に記憶される。ラインメモリ1830内の各々のライン構成は、アパーチャ選択インデックス、モード選択、およびアパーチャイネーブルを含む。アパーチャ選択インデックスは、チャネルマッピングアパーチャを決定するために使用される。モード選択は、複数の遅延プロファイルにアクセスするために使用される。アパーチャイネーブルインデックスは、最初のアパーチャサイズを制御する。アパーチャ選択ルックアップテーブル(AP\_SEL LUT)1832は、可能な構成の数を減少させ、その結果、ラインメモリ内に記憶する必要があるビット数を減少させる方法である。AP\_SEL LUT1832は、再プログラム可能である。

# [0109]

メモリ制御装置1834は、ライン構成を復号する状態マシンである。状態マシンは、制御および状態メモリ1836によって構成される。状態マシンは、異なるモード(たとえば、Bモード、カラーフローモード、PWドップラーモードなど)の場合は別様に構成される。メモリ制御装置1834は、RXBFバッファ1826内へのアパーチャメモリのロードを制御し、SOL\_delayedおよびFIFO\_WEN信号を生成する。パルスSOL\_delayedは、RXCLK期間で、初期遅延パラメータをRX位相回転およびRXアポダイゼーションブロック1809内に転送するために使用される。動的受

10

20

30

40

20

30

40

50

信パラメータは、次に、各々の後続のRXCLK期間で転送される。FIFO\_WEN信号は、RX補間フィルタ用のFIFOへの受信ADCデータ取得を開始する。

# [0110]

制御および状態メモリ1836は、受信長さなどの共通パラメータも含む。受信長さパラメータは、各々のラインのために、どの位の受信サンプルを収集するかを決定する。

# [0111]

受信チャネルの数を増加すると、比較的大きい受信アパーチャが可能になり、その結果、方位分解能および浸透を改善することによって、深いイメージングに有利になる可能性があることが分かるであろう。合成アパーチャモードは、64を超えるアパーチャを使用することを可能にするが、フレームレートの減少という犠牲を伴う。受信チャネルの数が増加すると、これは、フレームレートに不利益がない状態で行うことができる。

#### [0112]

本発明による位置実施態様では、受信ビーム成形器 1 8 0 3 は、マルチラインビーム成形を可能にする。マルチラインビ・ム成形は、複数の受信ラインを同時に処理することによって、比較的高いフレームレートが可能になる。フレームレートが、平行受信ラインの数に等しい係数だけ増加する。ビーム成形は、複数の受信アパーチャについて同時に行われるため、補間フィルタ 1 8 0 9 による比較的高度のデータ処理レートが使用される。受信ビーム成形器からホスト C P U に転送されるデータ量は、平行受信ラインの数に等しい係数だけ増加するであろう。送信ビームは広がり、複数の受信ラインと重なる。

# [0113]

各々の受信ビーム成形器 1 8 0 3 からの信号は、次に、加算器 1 8 1 5 によって加算される。加算された信号は、一定の深さから反射される、一定時期における受信信号を表す。加算された受信信号は、次に、以前に説明し、図 1 7 に示すモジュールを通って、ユーザが選択した動作モードに適する処理モジュールに至る。

#### [0114]

システム1600の送信動作サイクル時に、選択された送信出力ステージは、送信チャネルに接続され、アクティブアパーチャを形成する。この態様では、多重化は、送信出力ステージ以前に行われる。たとえば、以前に説明したとおり、送信チャネル1 1801は、図18aおよび図18bの参照符号1、65、129、および193の素子に応じて、送信出力ステージに切換え可能に接続され、その結果、これらの4つの送信出力ステージの1つだけが、ある一定の時に送信チャネル1 1801に接続される。図18aおよび18bでは、送信チャネル2は、素子2、66、130および194などに応じて、送信出力ステージに切換え可能に接続することができることも分かる。これは、システムの送信サイクル時におけるMUX/フロントエンド電子回路1702、1703、1704、1708の多重化機能の動作である。

# [0115]

図20を参照すると、多重化された送信信号は、TXA 2002およびTXB 2004によって支持される信号の対であり、図20に示すように、送信パルサーMOSFETQTDN 2006およびQTDP 2008のゲートを駆動する。これらの信号2002、2004は、十分に低レベルの単極信号であるから、MOSFETタイプのスイッチによる多重化を使用することができる。送信チャネルに切換え可能に接続された4つの送信出力ステージの割当ては、素子の任意の特定のサブセットの連続素子が、アクティブな送信アパーチャを含むことができるように行われる。たとえば、256個の素子から成るアレイ振動子の場合、64個以下の素子が、アクティブな送信アパーチャを含むサブセットを形成することができる。

# [0116]

任意に、送信多重化は、比較的高電圧の双極信号を収容可能な多重化回路構成を使用して、送信出力ステージ後に行うことができる。

#### [0117]

再び18a~13dを参照すると、送信ビーム成形器1812は、特定の遅延が波形に

存在する送信波形を生成し、この場合、波形は、遅延プロファイルごとに適切な時間まで送信されない。送信波形は、デジタル信号を含む低電圧信号で良い。任意に、送信波形は、電気エネルギーを超音波エネルギーに変換するために、アレイ振動子によって使用される高電圧信号で良い。変換器 1 8 1 9 およびパルサー 1 8 2 0 の動作については、以下でさらに詳細に説明する。

# [0118]

送信ビーム成形の処理時に、アクティブ送信アパーチャ内の1つまたは複数の各送信チャネルは、基準制御信号と比べて遅延させることが可能な送信波形を生成することができる。送信チャネルの数は、最大送信アパーチャサイズを決定する。送信チャネルの数を増加する利点は、深いイメージングの方位分解能および浸透の改善である。様々な実施態態では、アレイ振動子は64個の送信チャネルを有するか、または96もしくは128個の送信チャネルを有して良い。この遅延は、チャネルごとに異なる可能性があり、総称的に、遅延は、送信遅延プロファイルと呼ばれる。送信ビーム成形は、送信波形に重み関数のに、選延は、送信遅延プロファイルと呼ばれる。送信ビーム成形は、送信波形に重み関数のによることも含み、これは、当業者には「アポダイゼーション」として周知された波形の版幅の間々の制御を使用する。画像品質に対する利点は、受信ビームプロファイルにおけるプロセスである。送信アポダイゼーションは、各々のチャネルで送信された波形の個々の制御を使用する。画像品質に対する利点は、受信ビームプリアスローブは、側面ローブまたは格子ローブの可能性がある。各々の送信器の出力ステージは、個々に制御された電源、および制御ハードウェアを有する。

# [0119]

送信波形整形は、送信信号としての任意波形の生成、つまり送信波形の振幅および位相の生成を含む。この利点は、送信信号のスペクトルの整形による距離分解能の改善である。コード化励起などの技術は、距離分解能を損失せずに浸透を改善するために使用される

## [0120]

本明細書に記載されている送信ビーム成形器1812は、FPGAデバイスを有する一実施態様にインプリメントされる。たとえば、送信クロック周期の1/16の遅延分解能を提供する送信ビーム成形器1812の代表的なインプリメンテーションは、送信クロック周波数の16倍のクロックを必要とする。本明細書に記載されているシステムの周波数範囲では、これは、50MHzの16倍の最大クロック周波数、つまり800MHzを意味し、代表的なFPGAデバイスは、このレートのクロック周波数をサポートする。しかし、以下に記載する送信ビーム成形器1812のイメージングは、送信クロック周波数の8倍のみのFPGAの範囲内のクロック周波数を使用する。

# [0121]

送信ビーム成形器の各々のチャネルは、TXコントローラ1814およびTxパルス発生器1813から成る。TXコントローラ1814は、たとえば、超音波ライン番号と呼ばれるパラメータ(光線番号としても周知されている)を使用して、送信マルチプレクサの適切な構成を介してアクティブ送信アパーチャを選択する。光線番号値は、物理アレイに対する超音波走査ラインの始点を特定する。光線番号に基づいて、遅延値は、アクティブ送信アパーチャ内の各々の送信チャネルに割り当てられる。TXパルス発生器1813は、本明細書に記載する波形パラメータおよび制御信号を使用して、各々の送信チャネルの送信波形を生成する。

# [0122]

図18dは、本発明による実施態様における例示的な送信コントローラ(TXコントローラ)の図である。送信コントローラ1814は、正しい遅延プロファイル(各々のチャネルの粗遅延および微細遅延)、並びに各々のラインの送信波形を使って、TXパルス発生器1813をプログラムするために使用される。送信コントローラ1814は、各々のラインの前に、TXパルス発生器1813を再プログラムする。各々のラインは、送信アパーチャを形成するために使用されるアレイ素子の特定のサブセットを必要とする。アパーチャ内の各々のアレイ素子は、TXパルス発生器1813内のチャネルに接続する必要

10

20

30

40

があり、送信チャネルは、所望の送信遅延プロファイルによる遅延を有する所望の送信波 形を生成するように構成しなければならない。

### [0123]

アパーチャ全体の遅延プロファイルおよび送信波形は、TXアパーチャメモリ1838内に記憶される。複数の遅延プロファイルは、TXアパーチャメモリ1838内に記憶することができる。複数の焦点域が使用されるBモードイメージング、ドップラーモードの焦点深さおよび送信波形が、Bモードに使用されるものとは異なるPWドップラーおびカラーフローイメージングモードの場合、複数の遅延プロファイルが必要である。この例示的な実施態様では、TXアパーチャメモリ1838は遅延プロファイルを含み、64チャネルアパーチャパルス波形データを送信する。各々のチャネル基板上には、16個の送信チャネルがあり、各々の送信チャネルは、送信出力ステージを介して、4つの異なるアレイ素子の1つに接続することができる。64:16交差スイッチ1840は、正しい送信波形データセットを16チャネルの各々に経路指定するために使用される。他の48チャネルの制御は、他のチャネル基板上にインプリメントされる。TXBFバッファ1842は、開始(SOL)トリガ以前に、TXパルス発生器のデータを一時的に記憶する。TX\_TRGトリガは、データをTXBFバッファ1842からTXパルス発生器1813に、1つのTXCLK期間で移動させる。

#### [0124]

各々の送信ラインの構成は、ラインメモリ1844内に記憶される。ラインメモリ1844内の各々のライン構成は、以下の情報を含む:アパーチャ選択インデックス、モード選択、アパーチャイネーブルインデックス、および素子選択インデックス。アパーチャ選択インデックスは、チャネルマッピングアパーチャを決定するために使用される。モード選択は、複数の遅延プロファイルにアクセスするために使用される。アパーチャイネーブルインデックスは、アパーチャのサイズを制御する。素子選択インデックスは、送信チャネルまたは受信チャネルより多いアレイ素子が存在する場合、どの素子がアクティブかを制御する。アパーチャ選択、アパーチャイネーブル、および素子選択ルックアップテーブル(AP\_SEL LUT1846、AP\_EN LUT1848、ES LUT1850)のインデックス付けは、可能な構成の数、ひいてはラインメモリ1844内に記憶する必要があるビット数を減少させる方法である。ルックアップテーブルはすべて、再プログラム可能である。

## [0125]

制御および状態メモリ1852は、SOLの数(TXサイクル)、フレーム内のライン数などの共通のパラメータを含み、さらに、モリ制御ブロック1854内のメモリ制御ブロック1854内の状態マシンを構成する。メモリ制御装置1854は、アパーチャ選択、アパーチャイネーブル、および素子選択ライン情報を復号する状態マシンである。

# [0126]

図20を参照すると、送信波形は、実際上「A」および「B」信号と呼ばれる2つの信号であり、一方の信号は、パルサードライブMOSFET QTDN62006のゲートに適用され、他方の信号は、パルサードライブMOSFET QTDP2008に適用されることが分かる。「B」信号は、送信クロックの期間の1/2だけ遅延する以外、「A」信号と同じで良い。各々の送信波形に適用される遅延は、「粗遅延」および「微細遅延」の2つの成分に分割される。粗遅延は、送信周波数期間の1/2の単位で良く、微細遅延は、送信周波数期間の1/2の単位で良く、微細遅延は、送信周波数期間の1/2の単位で良く、微細遅延は、送信周波数期間の1/16の単位で良いが、微細遅延の他の単位は本発明の範囲内であると考えられる。調節可能な送信波形のその他の態様は、送信される中心周波数、パルス波、サイクル数、および「不感時間」である。「不感時間」は、2つの出力ステージMOSFET、QTDN2006およびQTDP2008のどちらも電源が入っていない出力パルスの最初の半周期後の時間間隔である。送信中心周波数、パルス波、および不感時間の変更は、振動子素子に対する最終的な送信信号の周波数成分を変更するために使用される。

[0127]

10

20

30

20

30

40

50

次に、図22~22Cを参照すると、本発明による一実施態様では、1つの送信パルス生成回路2200が、各々の送信ビーム成形器チャネルのために使用される。16ビットA波形ワード2202は、A信号の微細遅延、パルス波、および不感時間を符号化するために使用される。26ビットB波形ワード2203は、B信号の微細遅延、パルス波、および不感時間を符号化するために使用される。波形ワード2202、2203は、たとえばFPGA内のメモリ内に記憶することができる。送信出力信号の周波数は、送信クロックの周波数によって決定される。制御入力は、FPGA内にインプリメントされる送信コントローラ1814から由来する。これらは、以下で説明し、図22~22Cに示すパルス計数2204、TXTRG2206、および様々なクロックで良い。

# [0128]

送信パルスの生成は、TXTRGパルス2206が、チャネル制御盤1814から受信されると開始する。TXTRG信号2206は、送信ビーム成形器チャネルに送信され、送信ビーム成形器の遅延が参照される信号である。TXTRGパルス2206は、TXCLK2 2246で示される送信周波数クロックサイクルの1/2間隔の計算を開始する。現在のハードウェアインプリメンテーションは、送信クロックの2倍のクロックを使用する。粗遅延2210は、クロックTXCLK2 2246によって計時される粗遅延計数器2248によってインプリメントされる。信号TXTRG2206は、計算を開始させる。

## [0129]

COARSE DONE信号2208は、TXCLK2 2246のクロックサイクル 数が、粗遅延入力変数値2210に達した時に生成される。COARSE DONE信号 2208は、マルチプレクサ2250および2252から成るバイト選択回路、マルチプ レクサ 2 2 5 4 および 2 2 5 6 から成るパルス反転選択回路、並びに 8 : 1 並列 / 直列回 路2212および2213を可能にする。16ビット波形ワード2202および2203 は、16ビットレジスタ2216および2217内に転送される。A波形レジスタ221 6の出力は、部分波形: Partial \_ Waveshape \_ A (7:0) 2 2 6 0 お よびPartial\_Waveshape\_A(15:8)2261から成る。Part i a l \_\_W a v e s h a p e \_\_ A ( 7 : 0 ) 2 2 6 0 は、マルチプレクサ 2 2 5 4 および 2 2 5 6 から成るパルス反転回路を介して、8:1並列/直列回路2212または8:1 並列/直列回路2213に転送される。Partial\_Waveshape\_A(7: 0)2260の転送後、Partial\_Waveshape\_A(15:8)2261 は、マルチプレクサ2254および2256から成るパルス反転回路を介して、8:1並 列/直列回路2212または8:1並列/直列回路2213に転送される。バイト選択信 号 2 2 1 4 は、P a r t i a l \_ W a v e s h a p e \_ A ( 7 : 0 ) 2 2 6 0 またはP a r t i a l \_\_W a v e s h a p e \_\_A ( 1 5 : 8 ) 2 2 6 1 のどちらを多重化して、パル ス反転回路に送るかを制御する。こうして、Waveshape A2202は、8:1 並列/直列回路に転送され、1ビットデータ流に直列化される。

### [0130]

図 2 2 から分かるとおり、W a v e s h a p e \_\_ B 2 2 0 3 の転送は、同様に行われる

# [0131]

8:1並列/直列回路2212および2213は、二重データレート(DDR)出力を有する。COARSE DONE2208は、出力パルスの数の計算を開始する。パルス数計数器が、パルス数の計算を終了する場合、イネーブル信号224は低くなり、レジスタ2216および2217は部分波形の出力を停止する。「A」位相2202の16ビット波形は、2つのTXCLK2 2246サイクルで1つの直列ビットに転換される。「B」位相2203の16ビット波形も、2つのTXCLK2 2246サイクルで1つの直列ビットに転換される。パルス反転は、信号が並列/直列回路に送信される前に、「A」および「B」位相をスワッピングすることによって達成される。信号スワップは、パルス反転信号2258が、パルス反転MUX回路2254および2256で可能になる場合

に行われる。

## [0132]

二重データレート(DDR)出力を有する8:1並列/直列回路は、送信クロックの8倍の周波数のTXCLK8 2266を使って計時される。DDR出力では、波形は、送信クロック周波数の16倍のレートでシフトアウトされる。8:1並列/直列回路2212または8:1並列/直列回路2213からの信号は、LVDS規格を使用してFPGAから転送された後、クロックTXCLK16 2236によって再同期化される。

# [0133]

「A」位相信号は、低ジッター正エミッター結合論理(PECL)フリップフロップ 2 2 3 4、および低ジッタークロック、TXCLK 1 6 2 2 3 6によって、送信周波数の 1 6倍で再同期化される。これは、FPGA内部の回路によって加わるジッターを排除することができる。「B」位相信号も、フリップフロップ 2 2 3 5によって再同期化される

[0134]

「A」および「B」信号は共に、個々のドライバ回路 2 2 3 8 、 2 2 4 0 に行き、それぞれのカレントドライブの機能を増加させる。ドライバの出力は、信号 T X B 2 0 0 4 および T X A 2 0 0 2 になり、フロントエンド回路 2 0 0 0 内の送信マルチプレクサに接続する。

[0135]

波形データ2202および2203の再送信は、パルス計数器2242が、パルス計数 入力変数2204によって指定される数に達し、イネーブル信号2244が状態を変える までで続く。

[0136]

波形 A 2 2 0 2 を構成する 1 6 ビットワードは、ある送信サイクルから次の送信サイクルに変化する。同じことは、Waveshape\_B2203にも適用される。これは、あるサイクルから次のサイクルまで、任意に指定されるパルス波を有する送信波形の生成を可能にする。Waveshape\_A2201およびWaveshape\_B2203は、個々に指定される。たとえば、奇数または偶数の送信波形が生成される。

[0137]

図22A~22Cは、「A」および「B」信号の微細遅延、パルス波、および不感時間を変更するために、波形データをどのように使用するかを示す。この実施例では、「B」出力は、送信周波数期間の1/2だけ遅延することを除いて、「A」出力と同じである。図22Cは、「A」および「B」位相で任意の波形を生成できることを示す。Ny Waveshape\_Aは、その前の波形とは異なり、任意のWaveshape\_Bはその前の波形とは異なる。図22Cの実施例では、Waveshape\_A1(15:0)およびWaveshape\_A3(15:0)に使用される16ビット波形は、別の波形と異なる。この実施例では、Waveshape\_B(15:0)は2回繰り返されるが、Waveshape\_Bが前のWaveshape\_Bと異なるように指定することが可能である。AおよびB波形は独立しており、コード化励起法、たとえば造影剤イメージングおよび非線形イメージングを伴う用途に私用される送信波形をインプリメントするために使用することができる。

[0138]

TXPower信号(図18bに「TX高電圧」として示す)は、送信パルサーの出力の振幅を制御することができる。このインプリメンテーションに示されるとおり、TXPowerはすべての送信チャネルに共通である。任意に、各々の送信チャネルの出力パルスの振幅は、個々に制御することができる。

[0139]

図19は、例示的なビーム成形器制御盤1900を示すシステム信号処理ブロック図である。ビーム成形器制御盤1900は、ビーム成形器制御装置、および信号処理ブロック1716の例示的な実施態様である。ビーム成形器制御盤1900の構造および動作は、

10

20

30

40

20

30

40

50

当業者に一般的に周知されている。例示的なシステムの実施態様は、たとえば、ECG、呼吸作用、被検体の体温、または血圧の1つまたは複数の生理学的信号源1901を取得、処理、および表示する機能を有することが可能である。生理学的信号取得プロック1902は、こうしたタイプの生理学的信号を取得できる信号取得モジュールを含むことができる。

## [0140]

コンピュータユニット 1 9 0 3 へのデータ転送は、データをビーム成形器制御盤 1 9 0 0 からコンピュータユニット 1 9 0 5 に転送する。各実施態様は、この転送のために、当該技術分野で周知されている P C I E x p r e s s バス 1 9 0 4、または類似のバスを使用することができる。

# [0141]

図20は、フロントエンド回路変換器1702、送信出力ステージ1703、並びに受信MUX1704および送信MUX1708の例示的な略図2000である。その他の例示的なフロントエンド回路も、上記のシステムと共に使用することができる。たとえば、米国特許第6,083,164号「Ultrasound Front-End Circuit Combining the Transmitter and Automatic Transmit/Receive Switch」に記載されているフロントエンド回路を使用することができ、この特許は、引用することにより全体的に本明に援用し、本明細書の一部を構成する。図20に示す例示的な回路2000は、素子がクティブアパーチャの一部である場合に、素子を受信チャネルに接続する多重化機能を提供する。また、フロントエンド回路は、本明細書に記載するとおり、受信チャネルを送信チャネルから絶縁する。送信出力ステージは、送信パルス発生器1813からの送信波形を受信し、その結果、送信パルス情報を送信高電圧と結合し、アクティブ送信アパーチャの一部である素子において高電圧波形を生成する。

# [0142]

図20に示す例示的な略図では、送信パルシングは、D1 2010、D2 2012 QTDP 2008, QTDN 2006, QTXMUXP 2014, QTXMUX - 2016およびT1 - 2018によって行われる。送信時、アクティブ送信アパーチ ャ内に含まれる送信出力ステージは、QTXMUXP 2014およびQTXMUXN 2016の電源を投入することによって接続され、ゲート駆動信号TXA 2002およ びTXB 2004がQTDN 2006およびQTDP 2008に到達することを可 能にする。送信パルシングの際、QTDN 2006またはQTDP 2008は、意図 する送信波形を生成するのに必要なタイミングで個々に電源が投入される。パルサー出力 は、二次変換器LTXS 2038の左端に出現し、右端は、D1 2010およびD2 2012によって0V付近にクランプされ、D1 2010およびD2 2012は、 たとえば通常の高速シリコンスイッチングダイオードで良い。アクティブパルシングの際 、受信多重化スイッチSW1 2020も電源が切られ、付加的な隔離が提供される。送 信パルサーの出力の振幅は、T1 2018~R1 2022の一次の中心タップに印加 される送信電源電圧によって決定される。2つの電圧源V1 2024およびV2 26が利用可能であり、V1 2024はV2 2026より大きい。これらの電圧源は . FETスイッチQLSH 2028、QLSL 2030およびダイオードD3 3 2 に示すように、R 1 2 0 2 2 で共通ノードに接続される。電源電圧の一方または他 方は、制御信号 V 1 N E 2 0 3 4 および V 2 N E 2 0 3 6 を使用して、Q L S H 2028またはQLSL 2030の電源を入れることによって選択される。ダイオー 2032は、V1 2024がR1 2022に接続されると、電流がV1 024からV2 2026に流れるのを防止するのに役立つ。この構成は、電圧記憶キャ パシタC4およびC5に保持される電源電圧を充電または放電する必要をなくすため、送 信電源電圧を2つのレベル間で迅速に切り換えることを可能にする。

#### [0143]

受信切換えは、QTDP 2008、QTDN 2006、QLSH 2028、QL

SL 2030およびSW1 2020によって行われる。SW1 2020は、GaASPHEMT(ガリウムヒ素擬似格子整合高電子移動トランジスタ)などのタイプの単極単投(SPST)または単極双投(SPDT)スイッチで良い。あるいは、受信多重化スイッチは、その他のタイプの電界効果トランジスタまたは双極トランジスタと共にインプリメントされる。SW1 2020は、SPDTスイッチである場合、図20に示すように構成され、一方の端子は終端抵抗器に接続され、他方の端子は受信チャネル入力に接続される。SW1 2020がSPSTスイッチである場合、終端抵抗器に接続される端子、および終端抵抗器は取り除かれる。

## [0144]

受信間隔では、受信多重化スイッチは、アレイ素子および受信チャネル間が接続するよ うに構成される。パルサードライブMOSFETQTDN 2006およびQTDP 008は共に、受信時に電源が投入され、QLSH 2028、QLSL 2030、Q TXMUXN 2016およびQTXMUXP 2014は電源が切られる。その結果、 LTXS 2038は、その漏れインダクタンスを受信信号と直列のインピーダンスとし て主に提示する。受信信号が、順方向バイアスD1 2010またはD2 2012には 小さすぎる場合、これらのダイオードは、接合キャパシンタスに支配される高いシャント インピーダンスを提示する。L1 2040および漏れインダクタンスLTXS 203 8は、受信モードの入力インピーダンスを平均にして、D1 2010、D2 2012 の接合キャパシンタス、および受信マルチプレクサを形成する連結スイッチのキャパシタ ンスを補償する。フロントエンド回路の別のインプリメンテーションでは、図21に示す ように、信号RXCLMPは排除され、その機能はTXAおよびTXBによって実行され る。この回路の送信機能は、図20の回路と同じであり、QTXMUXNおよびQTXM UXPは、信号TxDriveNおよびTXDrivePをゲート制御する。受信モード では、QTXMUXNおよびQTXMUXPは電源が切られ、その結果、信号TXAおよ びTXBを遮断する。レジスタR8およびR9はQTXMUXNおよびQTXMUXPを シャントし、その結果、TXAおよびTXBは、受信モードの持続時間だけ高く駆動され 、QTDNおよびQTDPのゲート上の電圧は徐々に増加し、これらのMOSFETスイ ッチが滑らかに作動する。受信モードの場合のQTDNおよびQTDPの滑らかな作動は 、図20の回路の信号RXCLMPによって制御される。図21では、レジスタR5およ びR6は、QTDNおよびQTDPのゲート上で電圧を取り、送信動作後に、送信多重化 スイッチの電源が切れると接地する。

# [0145]

パルサーは、スイッチ選択可能なレベルの電源と共に中心タップ変換器およびNMOSFETを使用し、名目上方形波を生成する。供給スペクトルを制御するには、制御インピーダンス同軸ケーブルを介して振動子素子に接続する時に、直列およびシャント抵抗を使用する。これらは、パルサーの動作時にソースインピーダンスの時間変化を減少させ、送信パルスの直後の間隔で、振動子の終了を送り返す役割を果たす。最終ステージのMOSFETの駆動回路は、この略図には示されていない。この回路(以下のとおり、マルチプレクサの遠端にある)は、個々に切り換えられるMOSFETパルス増幅器、または必要な駆動を提供するのに十分なCMOSバッファの集合である。

# [0146]

パルサーに必要な変換器は、PCB上プリントされた巻線として構築され、PCBの両側に固締された小型フェライトスラブによって、巻線の周囲が補強される。この技術は、フェライトスラブを適切にパッケージすることができれば、自動化組立てに適する。

### 【実施例】

# [0147]

以下の実施例は、本明細書の請求項に係る物品、デバイス、および / または方法の製造および評価方法の完全な開示および説明を当業者に提供するものであり、本発明を単に例示的に示すことを意図しており、発明者が考える発明の範囲を制限することを意図するものではない。数(たとえば、数量、温度など)には正確を期すように注意を払ったが、多

10

20

30

40

少の誤差および偏差はあると思われる。

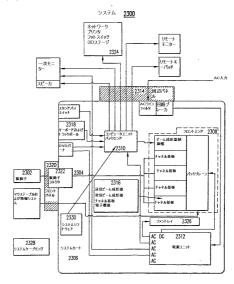

## [0148]

# 実施例1

図23は、本発明の一実施態様による例示的なシステムを示すブロック図である。例示的なシステム2300は、たとえば最大256の素子を有する線形アレイと結合される。マイクロ同軸ケーブル2304の束は、アレイ2302と処理ユニット2306との間の信号の送信を提供する。例示的なシステムは、処理ユニットをさらに備える。

# [0149]

処理ユニット2306は、2つの主なサブシステムに仕切られる。第1のサブシステムは、フロントエンド2308であり、ビーム成形器、フロントエンド電子回路、ビーム成形器コントローラ、および信号処理モジュールを備える。第2のサブシステムは、コンピュータユニット2310、またはバックエンドである。フロントエンドサブシステム2308は、送信信号の生成、受信信号の取得、および信号処理に関連する。バックエンド2310は、既製のPCマザーボードで良く、これは、システム制御、信号および画像処理、画像表示、データ管理、並びにユーザインターフェースに関連する。データは、たとえば、当業者が当該技術分野で周知するとおり、PCIExpressバスによって、フロントおよびバックエンドサブシステム間で転送される。

#### [0150]

受信信号を処理するモジュールは、本明細書で以前に記載したとおり、受信ビーム成形器である。送信信号を生成するサブシステムは、やはり本明細書で以前に記載したとおり、送信ビーム成形器である。送信および受信ビーム成形器の各々のチャネルは、アレイ2302内の別個の素子に接続される。各々の素子における個々の送信または受信信号の遅延および振幅を変えることによって、ビーム成形器は、深さの関数としての焦点深度、アパーチャサイズ、およびアパーチャウィンドウを調節することができる。図23の例示的なシステムは、当業者が当該技術分野で周知している1つまたは複数の様々な超音波動作モードをサポートする。これらのモードを以下の表2に記載する。

# 【 0 1 5 1 】 【表 2 】

表2 サポートされるモード