(19)日本国特許庁( J P )

(12) 公開特許公報 ( A ) (11)特許出願公開番号

特開2002 - 177266

(P2002 - 177266A)

(43)公開日 平成14年6月25日(2002.6.25)

(51) Int.CI<sup>7</sup>

識別記号

A 6 1 B 8/00

F I

A 6 1 B 8/00

テ-マコード(参考)

4 C 3 0 1

審査請求 未請求 請求項の数 100 L (全 11数)

(21)出願番号 特願2001 - 342403(P2001 - 342403)

(22)出願日 平成13年11月7日(2001.11.7)

(31)優先権主張番号 710985

(32)優先日 平成12年11月9日(2000.11.9)

(33)優先権主張国 米国(US)

(71)出願人 590000248

コニンクレッカ フィリップス エレクトロニクス エヌ ヴィ

KONINKLIJKE PHILIPS

S ELECTRONICS N.V.

オランダ国 5621 ベーアー アイント-

フェン フルーネヴァウツウェッハ 1

(74)代理人 100070150

弁理士 伊東 忠彦

最終頁に続く

(54)【発明の名称】携帯用及び機器構成可能な超音波画像形成システム

(57)【要約】

【課題】 様々なトランスデューサアレイタイプ及び処理技術に容易に機器構成することができ、プロセッサ及びソフトウェアの拡張を容易に収容することができる携帯用の画像形成システムを提供する。

【解決手段】 携帯用、機器構成可能な超音波システム100は、携帯用、機器構成可能な超音波プロセッサ102に接続され、超音波画像を展開するフェーズド超音波トランスデューサアレイ200を使用する。セクタフェーズドアレイと共に使用される時、本超音波システム100は、トランスデューサアレイ200におけるそれぞれの要素204に関連付けられた処理チャネルを使用して、超音波画像を形成する。リニア又はカーブドリニアトランスデューサアレイと使用する時、超音波プロセッサ102は、トランスデューサアレイよりも少ない処理チャネルを使用して、超音波画像を形成する。超音波プロセッサ102は、スケーラブルであり、プロセッサ、ソフトウェア及びトランスデューサアレイのパラエティを使用して、多数の異なる超音波画像を形成することができる。

**【特許請求の範囲】**

【請求項1】 それぞれが超音波信号を処理するために配置される複数のトランスデューサ素子を含むフェーズド超音波トランスデューサアレイと、前記トランスデューサ素子のそれぞれに対応する前記超音波信号のそれぞれを受けて、超音波画像に処理するために配置される携帯用、機器構成可能なプロセッサと、を備える機器構成可能な超音波画像形成システム。

【請求項2】 前記フェーズド超音波トランスデューサアレイは、セクタフェーズドアレイである、請求項1記載の超音波画像形成システム。

【請求項3】 前記携帯用、機器構成可能なプロセッサはモジュラープロセッサを含む、請求項1記載の超音波画像形成システム。

【請求項4】 前記モジュラープロセッサは標準的なパーソナルコンピュータツール及びコンパイラを使用する、請求項3記載の超音波画像形成システム。

【請求項5】 前記携帯用、機器構成可能なプロセッサはモジュラーメモリを含む、請求項1記載の超音波画像形成システム。

【請求項6】 前記携帯用、機器構成可能なプロセッサは、前記トランスデューサ素子のそれぞれから前記超音波信号のそれぞれを受けるために配置されるスケーラブルなフロントエンドプロセッサと、

前記トランスデューサ素子のそれぞれからの前記超音波信号を成形してビーム成形された信号にするためのスケーラブルビームフォーマ回路と、をさらに備える請求項1記載の超音波画像形成システム。

【請求項7】 前記携帯用、機器構成可能なプロセッサは、

セクタ、リニア、カーブドリニア及びコンビネーションフォーマットアレイからなるグループから選択された超音波モジュラーアレイからの超音波信号を処理することができるスキャンコンバータをさらに備える、請求項1記載の超音波画像形成システム。

【請求項8】 代替的な画像形成アプリケーションを有する、請求項1記載の超音波画像形成システム。

【請求項9】 代替的な動作モードをさらに備える、請求項1記載の超音波画像形成システム。

【請求項10】 変更可能な処理アルゴリズム及び動作特性を有する、請求項1記載の超音波画像形成システム。

**【発明の詳細な説明】**

**【0001】**

【発明の属する技術分野】本発明は、一般に超音波画像形成システムに関し、特に、携帯用及び機器構成可能な超音波画像形成システムに関する。

**【0002】**

【従来の技術】超音波画像形成システムが普及してきて

おり、非破壊検査及び医療の応用に一般に使用されている。医療分野での超音波画像形成システムにより、人体の内部構造を実時間で非侵入的に見ることができる。

【0003】画像形成システムは、携帯式でありことが好ましく、病院の緊急室、病院の周囲及び個人的な業務用途のような、移動性が要求される用途において使用することができる。

【0004】さらに、画像形成システムは、医療産業の予算の拘束に見合うように安価であるべきであり、バッテリにとって上記用途の幾つかにおいて必要とされる動作を可能にするために最小の電力が要求されるべきである。

【0005】これまで、超音波画像形成システムは、ケーブルを使用した超音波プローブアセンブリに接続される大きな処理及び表示ユニットから構成されていた。プローブアセンブリは、問い合わせパルスを送信し、ターゲットからの反射された超音波エネルギーを受信する超音波トランスデューサを含んでいた。処理及び表示ユニットは、全ての処理システム、及びユーザに画像が提供されるディスプレイを含んでいた。

**【0006】**

【発明が解決しようとする課題】残念ながら、これらの処理及び表示システムは、異なるエンドユーザのニーズに容易に適合することができなかった。これら従来のシステムは、異なるエンドユーザのニーズを収容するための高価な再設計を典型的に必要としていた。システムは、多用する市場のニーズを処理するために著しい再設計が必要とされる複雑な対話を有するプリント回路基板を使用して設計されていた。

【0007】超音波画像形成システムは更に開発され、電子工学的な集積化及び小型化により、システムはサイズがより小さくなっている。これらより小さなユニットは、プローブアセンブリ、メイン処理ユニット及び表示ユニットの間で処理機能の幾つかを分割する場合がある。

【0008】残念ながら、これらのより小さなシステムであっても、異なるトランスデューサアレイ、処理技術又はソフトウェアの拡張に適合することが依然として難しい。

【0009】したがって、様々なトランスデューサアレイタイプ及び処理技術に容易に機器構成することができ、プロセッサ及びソフトウェアの拡張を容易に収容することができる携帯用の画像形成システムを有することが望まれる。

**【0010】**

【課題を解決するための手段】本発明は、携帯用及び機器構成可能な(configurable)超音波画像形成システムを提供する。該システムは、様々なトランスデューサアレイ及び処理技術をサポートするために容易に機器構成することができ、プロセッサ及びソフトウェアの拡張を

容易に可能にする。携帯用、機器構成可能な超音波システムは、受信した超音波エネルギーを処理して可視画像にするために、様々なトランステューサアレイ及びビーム成形回路の使用を組んでいる。

【0011】本超音波システムは、モジュラープロセッサ及びモジュラーメモリ要素を含む携帯用、機器構成可能なプロセッサを含んでいる。ソフトウェア及びハードウェアの両者におけるシステム設計のモジュール性は、システム設計の他の態様に対する最小の影響により、システムのアップグレード及びエンハンスメントを容易にする。

10

【0012】モジュール性の例は、单一化されたメモリの使用であり、システムのバランスに対する最小の影響により、ソフトウェアのアップグレード及びエンハンスメントが可能となる。携帯用及び機器構成可能な超音波画像形成システムにより、代替的な画像形成アプリケーション及び動作モードが可能となり、該システムは、携帯用及び機器構成可能な超音波画像形成システムに対して高度な機器構成を提供する変更可能な処理アルゴリズム及び動作特性を含んでいる。

【0013】図面における構成要素は、互いに関連して縮尺する必要はなく、本発明の原理を明らかに例示するために重きが置かれている。さらに、図面において、同じ参照符号は、異なる図面を通して対応する部材を示している。

#### 【0014】

【発明の実施の形態】本発明は、セクタフェーズドトランステューサアレイ技術を特に参照して以下に記載するが、本発明は、いずれかのタイプのトランステューサアレイ技術を使用した超音波画像形成システムに適用することができる。

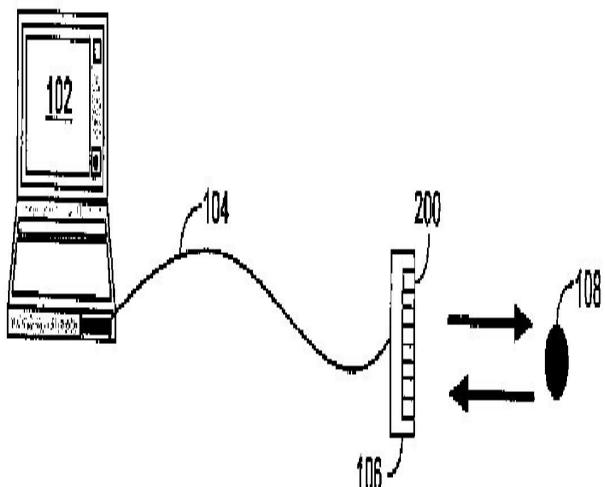

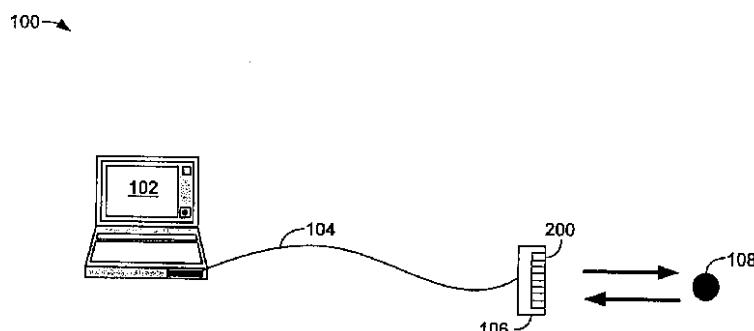

【0015】図面を参照して、図1は、本発明の1態様による携帯用、機器構成可能な超音波システム100を例示する図である。携帯用、機器構成可能な超音波システム100は、インタフェースケーブル104を介してプローブアセンブリ106に接続されている携帯用のプロセッサ102を含んでいる。

【0016】プローブアセンブリ106は、セクタフェーズドトランステューサアレイ200を含んでおり、該アレイは、ターゲット108に超音波エネルギーを送信し、ターゲット108からの反射された超音波エネルギーを受信する。携帯用、機器構成可能なプロセッサ102は、受信された超音波エネルギーを処理する。

【0017】処理の後、受信された超音波エネルギーから生成された2次元(2-D)画像は、次いで、携帯用、機器構成可能なプロセッサ102に組込まれている液晶表示装置(LCD)上に表示される。

【0018】プローブアセンブリ106は、ターゲット108から受信された超音波エネルギーの幾つかを複数のサブビームに処理することができる追加の処理回路を50

含んでいてよい。これらサブビームは、トランステューサ要素の数よりも少ない信号数を使用して、プローブアセンブリ106における全てのトランステューサから受信されたエネルギーを表している。

【0019】サブビーム成形は、インタフェースケーブル104を介して、プローブアセンブリ106と携帯用プロセッサ102の間で通信されなければならない信号数を減少する。かかるシステムは、一般に譲渡され、係属中である米国特許出願シリアル番号第XXX号、“SUB-BEAMFORMING APPARATUS AND METHOD FOR A PORTABLE ULTRASOUND IMAGING SYSTEM”(代理人書類番号10004033)、譲渡シリアル番号第XXX号、及びXXX出願に開示されており、その本文は参照により本明細書に組込まれる。

【0020】さらに、プローブアセンブリは、アナログ信号処理を使用したサブビーム成形のための方法論を含んでおり、Savordに一般に譲渡された米国特許第6,013,032号、2000年1月11日発行、及びSavordに一般に譲渡された米国特許第5,997,479号、1999年12月7日発行に開示されており、両特許の本文は参照により本明細書に組込まれる。

20

【0021】プローブアセンブリ106は、1つ又は複数の送信の特定用途向け集積回路ASICを含んでいてよい。該ASICは、プローブアセンブリ106内に含まれるトランステューサアレイ200に高電圧パルスを送信する。

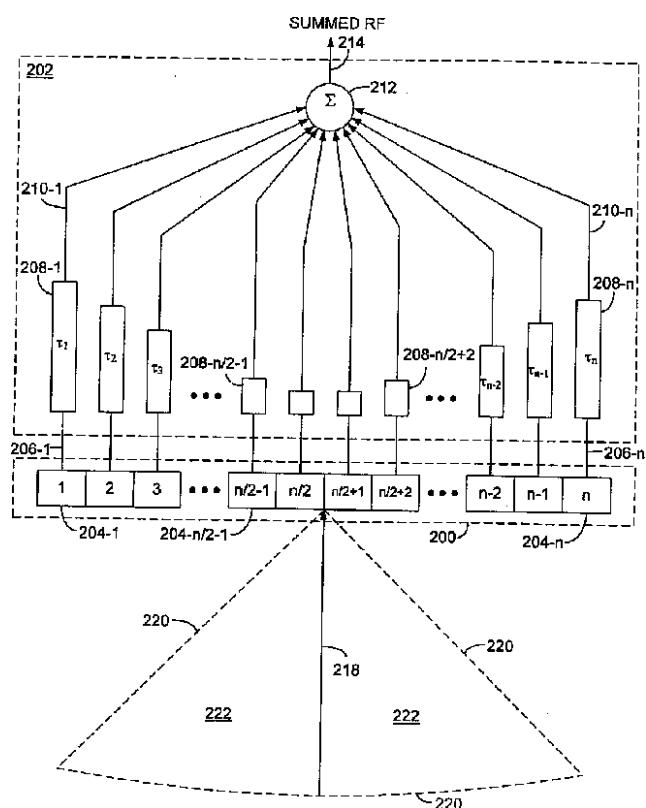

【0022】図2は、プローブアセンブリ106(図1)において配置されるセクタフェーズドトランステューサアレイ200、及び携帯用、機器構成可能なプロセッサ102(図1)において配置されるフェーズドアレイビームフォーマ202を例示する図である。

【0023】フェーズドアレイビームフォーマ202は、上述したサブビームフォーマアプローチとは対照的に、セクタフェーズドアレイビームフォーマの機能的な態様を例示するために適した遅延構成を含んでいる。該アプローチは、“SUB-BEAMFORMING APPARATUS AND METHOD FOR A PORTABLE ULTRASOUND IMAGING SYSTEM”(代理人書類番号10004033)と題された特許出願、米国特許第6,013,032号、及び米国特許第5,997,479号に上述されたものである。

【0024】トランステューサアレイ200は、セクタフェーズドアレイ超音波トランステューサである。図2において示されるようなトランステューサアレイ200は、複数の各トランステューサ要素204-1~204-nを含む、n要素のセクタフェーズドアレイを含んでいる。トランステューサ要素204-1~204-nのそれぞれは、複数の対応するコネクション206-1~206-nを介して、対応する遅延要素208-1~208-nに接続している。

【0025】遅延要素208-1~208-nは、図2

において示される代表的な中央の受信ライン218(セクタスキャンラインとも呼ぶ)について、受信ビームを成形する。この1つの特定のセクタスキャンライン218についての遅延要素は、トランステューサアレイ200の中央について対称である。遅延要素208-1は、遅延要素208-nと同じ遅延を有し、遅延要素208-n/2-1は、遅延要素208-n/2+2と同じ遅延を有する。

【0026】最も外側の遅延要素208-1から、遅延要素208-n/2-1のような中央の要素までの遅延は、遅延要素がセクタスキャンライン218に、すなわち受信ターゲット108(図1)により近くなるにつれて必要とされる低減された遅延のために、単調に減少する。中央ラインでないラインについては対称性がないため、ユニークな遅延経路が遅延要素208-1~208-nのそれぞれに関連付けられている。

【0027】遅延要素208-1~208-nのそれぞれは、対応するコネクション210-1~210-nを介して、加算要素212に接続される。コネクション214上の加算要素212の出力は、それぞれの超音波トランステューサ要素204-1~204nから受信された加算されたRFエネルギーである。

【0028】コネクション206-1~206-nは、インターフェースケーブル104に典型的に含まれており、フェーズドアレイビームフォーマ202は、図1において示される携帯用の、機器構成可能なプロセッサ104において配置されている。しかし、フェーズドアレイビームフォーマ202は、プロープアレイアセンブリ106(図1)内に含まれるサブビームフォーマとして分割することもできる。

【0029】かかる配置において、サブビームフォーマの出力により形成されるコネクションの低減されたセットは、図1において示されるケーブル104において含まれる。なお、上述したセクタフェーズドアレイを使用する一方で、本発明は、リニアアレイ、カーブドリニアアレイのような他のタイプのフェーズドアレイを使用して実現することができる。

【0030】動作の間、n要素のセクタフェーズドアレイ200は、電気的に操縦して、超音波エネルギーのビームを集束し、参照番号222を使用して定義され、ライン220により定義されるセクタの境界線により境界付けられるセクタに問い合わせる。セクタ222は、セクタフェーズドトランステューサアレイ200を使用して、多数の連続した超音波トランステューサパルスにより問い合わせられた典型的な領域の代表である。

【0031】セクタフェーズドトランステューサアレイ200の重要な使用領域は、異なる形状のバラエティで定義することができる。たとえば、形状は、中央の一方に関して他方よりも多いスキャンラインを有する非対称なセクタとすることもできる。形状は、最も深い深

さでの曲率の半径が無いことを示す三角形の形状とすることもできる。また、上述したように、アレイは、セクタフェーズドアレイでなくてもよいが、カーブドリニアアレイ(CLA)又はリニアアレイであってもよい。かかるアレイは、環状、矩形、延長されたセクタサイドを有する矩形、当該技術分野において公知である多数の他の領域、のような重要な領域である。

【0032】典型的に、セクタフェーズドアレイについて、100又は100を超える分離されたスキャンライン、そのうちの例示的な1つはセクタスキャンライン218として例示されており、セクタ222により示される重要な領域を問い合わせるために使用される。集束された送信パルスが特定のスキャン方向を問い合わせるために使用された後、ターゲット108(図1)から受信された超音波エネルギーを表す問い合わせの送信に続く受信ラインは、n要素のセクタフェーズドアレイ200により受信される。

【0033】典型的な送信/受信スキャンラインは、図2においてセクタスキャンライン218として示されている。とりわけ、n要素のセクタフェーズドアレイ200の配置は、超音波トランステューサ要素204-1~204-nのそれぞれが対応する遅延チャネルに関連することを保証する。これら遅延された信号は、加算要素212において加算され、コネクション214上の加算されたRF信号を発生する。

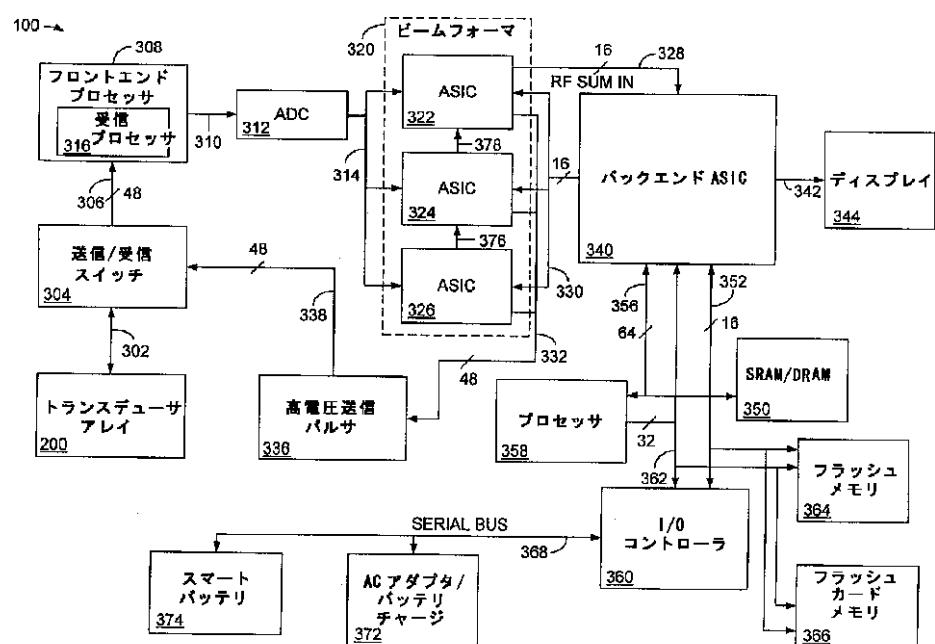

【0034】図3は、図1の携帯用、機器構成可能な超音波システム100を例示するブロック図である。携帯用、機器構成可能な超音波システム100は、コネクション302を介して、送信/受信(T/R)スイッチ304と通信するセクタフェーズドアレイ200を含んでいる。

【0035】1実施の形態では、セクタフェーズドアレイ200は、プロープアセンブリ106(図1)において配置されており、図3のコネクション302は、図1のインターフェースケーブル104内に接続されている。T/Rスイッチ304は、受信された超音波エネルギーから送信パルスを分離し、コネクション306を介して受信された信号をプロセッサ308に転送する。プロセッサ308は、典型的に「フロントエンドプロセッサ」と呼ばれる。

【0036】例示的に、セクタフェーズドアレイ200は、48個のトランステューサ要素、したがって48本の信号チャネルを含んでいる。しかし、セクタフェーズドトランステューサアレイ200は、1つ又は複数のトランステューサアレイを含んでいてもよい。さらに、図3において1つのブロックを使用して例示されているが、フロントエンドプロセッサ308は、1つ又は複数のASICとして実現されていてもよい。

【0037】T/Rスイッチ304もまた、隔離された回路として機能する。これにより、高電圧送信パルサ3

36により(以下に記載される)コネクション338を介して、供給された送信エネルギーが、コネクション306を介して感度の高いフロントエンドプロセッサ308に移動することが防止される。

【0038】フロントエンドプロセッサ308は、受信プロセッサ316を含んでいる。該プロセッサは、セクタフェーズドトランステューサアレイ200内のトランステューサ要素204-1~204-nのそれぞれからの超音波エネルギー信号を受け、受信信号の増幅とフィルタリングを実行する。

【0039】フロントエンドプロセッサ308の出力は、コネクション310を介してアナログ/デジタル変換器(ADC)312に供給される。ADC312は、コネクション310に関するそれぞれのチャネルについて、サンプルをデジタル化し、それぞれのチャネルについて8ビットデジタルビットストリームをコネクション314を介してビームフォーマ320に供給する。

【0040】コネクション314に関する適切なチャネルは、ビームフォーマ320内のASIC322,324及び326のそれぞれに供給される。カスケード接続における3つのASIC322,324及び326を使用して例示されているが、トランステューサアレイ200内のトランステューサ要素の数(及び対応するチャネルの数)に依存して、1つ又は複数のASICがビームフォーマ320内に使用されてもよく、それぞれのASICと関連付けされてもよい。

【0041】ASIC322,324及び326のそれぞれもまた、コネクション332を介して低電圧の送信タイミング信号を提供し、高電圧送信パルサ336を駆動する。1つのブロックを使用して例示されているが、トランステューサ要素204-1~204-n(図2)のそれぞれを駆動するために使用される1つの高電圧送信パルサ336が存在する。

【0042】さらに、低電圧の送信パルサ信号機能及び/又は高電圧の送信パルサは、1つ又は複数のASICに組込まれていてもよい。また、さらに、T/Rスイッチ304、フロントエンドプロセッサ308、及び高電圧送信パルサ336は、いずれかのコンピネーションにおいて1つ又は複数のASICに組まれていてよい。

【0043】ビームフォーマ320内のASIC322,324及び326のそれぞれは、セクタフェーズドアレイ200から受信された48個のチャネルに対応する48個の信号のうちの16個を処理する。それぞれのASICは、16個のチャネルのみを所有するので、ビームフォーマ320における最後のASICが到達するまで、それぞれのASICは、処理されるチャネルを含んでいるデジタル中間RF加算信号を別のASICに供給する。

【0044】たとえば、ASIC326は、16ビット50

の中間RF加算デジタル出力をコネクション376を介してASIC324に供給し、ASIC324は、その16ビット中間RF加算(32チャネルを含む)デジタル出力をコネクション378を介してASIC322に提供する。ビームフォーマ320の結合された出力は、コネクション328を介してASIC322から取られ、16ビットのビーム成形された信号としてプロセッサ340に“RF SUM IN”として供給される。

【0045】プロセッサ340は、典型的に「バックエンド」プロセッサと呼ばれ、典型的に1つ又は複数のASICで実現される。したがって、典型的にバックエンドASICと呼ばれる。例示の目的のために、1つのビームフォーマが使用される。しかし、並列のビームフォーマは、ADC312の出力を共有するビームフォーマASIC(又は現在のASIC内に並列処理を加える)の並列のセットを有することにより、容易に実現することができる。

【0046】結果は、2つの分離した受信ビームを独立にビーム成形することができる2つの分離したビームフォーマ出力である。並列のビームを使用することにより、フレームレートの増加のような利点が提供される。

【0047】バックエンドASIC340は、多くの処理機能を実行し、図4に関してより詳細に記載される。バックエンドASIC340もまた、ビームフォーマ320内のASIC322,324及び326がビーム成形機能を実行することができ、コネクション332に関して低電圧の送信信号タイミングパルスを発生するために必要な送信タイミングを実行することができる係数データをコネクション330を介してビームフォーマ320に提供する。

【0048】高電圧送信パルサ336は、ディスクリート素子を使用して、又はASICにおいて実現することができる。いずれの構成においても、低電圧の送信タイミング信号は、コネクション332を介してビームフォーマ320から取られ、高電圧送信パルサ336に供給される。

【0049】送信パルサ336は、コネクション338を介して48個の送信パルスをT/Rスイッチ304に供給する。T/Rスイッチ304は、セクタフェーズドアレイ200内の対応するトランステューサ要素204-1~204-nのそれぞれにコネクション302を介してこれら送信パルスを進路決定する。

【0050】並列受信ビームフォーマについて、送信ビームは、並列に隣接して受信されるビームが1つの送信ビームから成形することができるよう、適切な低電圧送信タイミング信号により広くされる。

【0051】バックエンドASIC340は、コネクション328を介して供給されるRF SUM IN信号を処理し、ディスプレイ344上に表示されるコネクション342を介して超音波画像を提供する。ディスプレイ34

4は、液晶ディスプレイ(ＬＣＤ)、又は超音波画像データを表示することができるいすれか他のディスプレイとすることもできる。バックエンドASIC340もまた、双方向データバス356を介してメモリ素子350と通信することができる。

【0052】メモリ素子350は、ステティック/ダイナミックランダムアクセスメモリ要素であり、32メガバイト又はそれ以上のサイズであることが好ましく、ユニファイドメモリ(unified memory)として実現されることが好ましい。ユニファイドメモリは、Dowdellに対して一般に譲渡された米国特許第6,106,468号、2000年8月22日付け発行、に記載されており、その本文は参照により本明細書に組み込まれる。

【0053】メモリ要素350は、即時性のデータ記憶、処理コードの記憶、テーブル及びバックエンドASIC340により使用される他の実行可能なソフトウェアのために使用される。

【0054】また、バックエンドASIC340は、双方向データバス356を介してプロセッサ358と通信する。プロセッサ358は、商標POWERPCの下で市販されている7xxシリーズプロセッサであることが好ましい。該商標は、モトローラ社の登録商標である。しかし、受信された超音波信号を処理するために適したいすれか他のプロセッサを使用することができる。

【0055】プロセッサ358は、たとえば、32ビット幅のアドレスバス362を介してバックエンドASIC340、メモリ要素350及びフラッシュカードメモリ366と通信する。本発明の態様によれば、メモリ要素350及びプロセッサ358は、ASICから外部であり、モジュール性を有して実現される。したがって、重要なシステムの影響なしに、これらはスケーラブルであり、アップグレード可能であり、交換可能である。

【0056】たとえば、メモリ要素350は、携帯用の、機器構成可能な超音波システム100内のいすれか他の要素に影響を与えることなしに、アップグレードすることができる。同様に、プロセッサ358は、携帯用の、機器構成可能な超音波システム100内のいすれか他の要素に影響を与えることなしに、アップグレードすることができる。

【0057】さらに、プロセッサ358は、標準的なパーソナルコンピュータ(PC)ツール及びコンパイラを使用する。ここで使用されるように、用語「モジュール」は、プロセッサ358又はメモリ要素350のいすれもASICデバイスに埋め込まれていないことを示している。

【0058】このようなやり方で、携帯用の、機器構成可能な超音波システム100は、最小のシステムの影響によりアップグレードすることができる。これらの要素がASIC内に組込まれていないことにより、高価で時間消費するASIC再設計の必要がなく、急速で簡単な

メモリ及び計算上のアップグレードが可能となる。

【0059】アップグレードにより、腹部、産科、婦人科医学、脈管及び小さな部分のような、現在の心臓の焦点合わせを超えた代替的な画像形成の応用が可能となる。

【0060】経食道断層心エコー(TEE)の使用であっても、アップグレード可能なソフトウェア及びTEEプロープを用いて可能となる。システムは、代替的な動作モードを可能にする。たとえば、当業者には知られているように、ライン添え継ぎのような代替的なスキャニングフォーマットを携帯用の、機器構成可能な超音波システムに組むことができ、それぞれの送信ラインが開口及びパルス形状を通して達成される異なる焦点距離を有する複数の送信ラインからの復号受信ラインを達成することができる。

【0061】さらに、他のスキャニングフォーマットは、セクタスキャニング、カーブドリニアスキャニング及びリニアスキャニングフォーマットを含み、代替的な開口モードは、フル、スプリット、パラレル及びノンパラレル或いはそれらのいすれかの結合を含んでいる。

【0062】ソフトウェアのアップグレード可能であること、及びハードウェアの柔軟な設計により、変更可能な周波数出力及び接続可能にされたトランステューサの使用のように、変更可能な動作周波数を有する複数のトランステューサを使用することができる。さらに、ユニファイドメモリ要素350により、ガンマ補正に基づく制御、変更可能なソフトウェアの使用が可能となる。

【0063】本発明の実施の形態は、カラーフローマッピングを実現するためのソフトウェアアルゴリズムを含んでいる。カラーフローアルゴリズムは、機器構成可能な設計の柔軟性を示す。パワードップラアプローチを使用した脳血管撮影による画像形成は、現在の設計により容易に実現することができる。

【0064】脳血管撮影による画像形成は、カラーフローマッピングアルゴリズムから派生している。当該技術分野においてソフトウェアを容易に変更することができることと、ユニファイドメインメモリとの結合により、容易なソフトウェアのアップグレードが可能となる。全てのかかるソフトウェアは、メモリ要素350において含まれており、プロセッサ358において実行される。

【0065】また、本発明の実施の形態は、パルス波ドップラ画像形成を実行するためにアップグレードされるソフトウェアとすることもできる。同相及び直交位相チャネルのためのクアドラチャーキュムレータのような必要な構成要素をバックエンドASIC340に組込むことができる。

【0066】バックエンドASICは、たとえば16ビット幅を有する双方向データバス352を介して、I/Oコントローラ、フラッシュメモリ要素364及びフラッシュカードメモリ366と通信する。I/Oコントロ

ーラ360は、携帯用、機器構成可能な超音波システム100の入力及び出力タスクを制御する。たとえば、I/Oコントローラ360は、携帯用、機器構成可能な超音波システム100に情報を伝達するためのキーボード入力を含んでおり、周辺装置(図示せず)の接続のためのシリアル及びパラレルポートを含んでいる。

【0067】フレッシュメモリ要素364は、非揮発性メモリであり、超音波システム100が機能することを可能にする現在の実行可能なソフトウェアファイル(「ランタイムコード」と呼ばれることがある)を記憶するために使用される。フラッシュカードメモリ366は、取り外し可能な記憶メディアであり、携帯用、機器構成可能な超音波システム100により実行されるオペレーティングシステムを便利に更新するために使用される。

【0068】さらに、携帯用、機器構成可能な超音波システム100は、変更可能な処理アルゴリズムを使用して、異なる画像形成アプリケーション、スキャニングフォーマット、動作モード及び開口モードを実行する。これら変更可能な処理アルゴリズムは、メモリ要素350に記憶され、プロセッサ358により実行されるソフトウェアで実現される。変更可能な処理アルゴリズムは、モジュール性を有するフォーマットであり、I/Oコントローラ360を介してフラッシュカードメモリ366の使用を通して更新することができる。

【0069】このようにして、ソフトウェアのアップグレードは、超音波システム100に供給することができ、簡単な、移動可能なフラッシュカードメモリ要素366を使用することにより、フラッシュメモリ要素364において記憶することができる。

【0070】また、I/Oコントローラ360は、シリアルバス368を介して、スマートバッテリ374及び交流(AC)アダプタ/バッテリチャージャ372と通信する。ACアダプタ/バッテリチャージャ372は、携帯用、機器構成可能な超音波システム100に電力を供給し、スマートバッテリ374を充電する。

【0071】さらに、携帯用、機器構成可能な超音波システム100は、バッテリがシステムに取り付けられていない時にスマートバッテリを充電するために、分離したスタンドアローンバッテリチャージャ(図示せず)を含んでいてもよい。

【0072】また、シリアルバス368は、I/Oコントローラ360を介して、試験及び診断装置の接続を可能にする。シリアルバス368を使用することにより、メモリ要素350、全てのASIC322, 324, 326, 340等における内部レジスタをはじめとして、内部プロセッサ358の内部プロセッサレジスタは、Joint Test Access Group(JTAG)インターフェースを使用した外部の試験装置を使用して問い合わせができる。

【0073】JTAGは、Standard Test Access Port and Boundary Scan Architectureとして知られているIEE標準(1149.1)であり、ASIC及びプロセッサのようなファインピッチ、ハイピンカウントパッケージのための試験実施性を提供するために使用される。当業者であれば、JTAG標準に精通しているであろう。

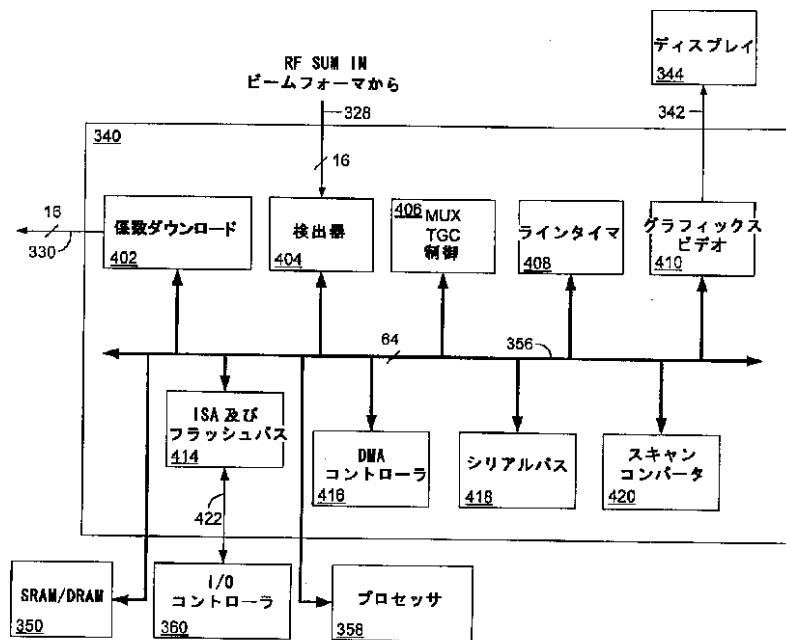

【0074】図4は、図3のバックエンドASIC340を例示するブロック図である。バックエンドASIC340は、ビームフォーマ320(図3)内のASIC322, 324及び326のそれぞれをロードするために使用される係数データを供給する係数ダウンロード要素402を含んでいる。このデータにより、ビームフォーマ320におけるASICは、受信された信号に関するビーム成形を実行して、上述したような低電圧の送信信号タイミング情報を提供する。

【0075】RF SUM INとラベル付けされたビーム成形されたデジタル信号は、コネクション328を介して検出器328に供給される。検出器404は、コネクション328を介してデジタル信号を受け、他の機能の間で時間利得補償(TGC)を提供してもよい。ターゲット内の複数の深さから超音波信号を受けた時にTGCは使用される。

【0076】かかる瞬間ににおいて、超音波エネルギーの深さに関する増加する経過時間を補償するために、利得が対応して典型的に増加される。また、検出器404は、フィルタリングを提供し、検出機能を実行する。該検出機能は、信号に含まれる位相及び振幅情報を保持し、入力RF信号をベースバンド信号に変換する。

【0077】検出は、コネクション28上で生成されたRFデータストリームを対数振幅データに変換することを含む。該対数振幅データは、2次元カラーフローイメージングにおける使用のためのベースバンド直交データと共に、2次元の解剖学的画像形成について標本化されたものである。並列のビーム成形について、検出器は、2つの受信ビームを処理するために複製される。

【0078】検出の後、データは、解剖学的な画像形成のための対数で検出された振幅データの形式であり、コネクション328を介してビームフォーマ320から受信されたRF信号の直交する検出された成分(同相及び直交相)である。このデータは、メモリ要素350に記憶される。情報は、検出器404から双方向データバス356を介してメモリ要素350に転送される。双方向バス356は、たとえば、64ビット幅である。

【0079】トランスデューサアレイ200(図2)により転送されるセクタスキャンライン(図2のセクタスキャンライン218として典型的に示される)のそれについて、RFデータのラインは、上述したようにメモリ要素350に記憶される。この処理は、所望の横方向の解像度及び空間適用範囲に準じた量により進められるセクタスキャンラインのそれぞれで続く。

【0080】たとえば、トランステューサアレイ200により転送されるそれぞれのラインは、前に転送されたラインとは異なる角度である。セクタスキャンライン218のそれぞれについて、検出器は、完全なデータフレームがメモリ要素350内に記憶されるまで、RFエネルギーを検出してメモリ要素350に値を記憶する。このデータフレームは、音響データフレームと呼ぶことにする。

【0081】完全な音響フレームがメモリ350において捕捉された時、プロセッサ358は、次の音響フレームが書込まれるメモリ要素350における位置を示すメモリ要素350におけるポインタを供給する。最後の音響データフレームを含む（メモリポインタによりタグ付けされた）メモリ350における前の位置は、そのまま残される。

【0082】最後に取得された音響フレームは、メモリ要素350に記憶され、スキャンコンバータ420は、最後の音響フレームが記憶されるメモリ350における位置を示すポインタをプロセッサ358から受ける。スキャンコンバータ420は、該既往された音響データ内の連続的な音響スキャンラインを使用して、双方データバス356を介してメモリ350の別の位置に転送するために、スキャン変換されたセクタスライスを作成する。

【0083】セクタスライスは、2つの隣接する音響スキャンラインの間の画像領域として定義される。スキャンコンバータ420は、現在の音響フレームについての全ての音響データがスキャン変換されるまで、追加のスライスの処理を続ける。スキャンコンバータ420は、音響フレームを完了し、スキャンコンバータ420が現在の及び音響フレームを完了したことを示す割り込みがプロセッサ358に送出される。

【0084】プロセッサ358により割り込みが受信された時、画像フレームデータは、コネクション342を介してディスプレイ344に出力するために、グラフィックビデオ要素410の制御下で、双方向データバス356を介して、ラスタ方式でメモリ350から読み出される。グラフィックビデオ要素410は、ディスプレイ344を見るためにコネクション342を介してディスプレイへのラスタ読出しに並行して、音響フレームを有するテキスト及びカーソルのような全てのグラフィックオーバレイを結合する。

【0085】ダイレクトメモリアクセス（DMA）コントローラ416は、双方向のデータバス356上を流れる全てのデータについてのゲーティング機能としての役割を果たす。たとえば、DMAコントローラ416は、スキャンコンバータ420又は検出器404がメモリ要素350にアクセスすることができるか判定する。DMAコントローラ416は、当業者には公知である動作を行う。

【0086】International standards architecture（ISA）及びフラッシュバス要素414は、専用ライン422を介して、I/Oコントローラ360により使用される外部のフラッシュメモリに伝達する。I/Oコントローラにより使用されるフラッシュメモリは、明瞭さのために省略されており、I/Oコントローラ360をサポートするのみに使用され、図3のフラッシュメモリ要素364又はフラッシュカードメモリ366と混同すべきではない。

【0087】フラッシュメモリ要素364は、不揮発性メモリ記憶を提供し、ランタイムソフトウェアを含んでいる。フラッシュカード366は、取り外し可能な記録メディアであり、改訂又はアップグレード入手することができる時に、オペレーティングソフトウェアの変更及びアップグレードのために使用される。さらに、画像はバックエンドASIC340から読むことができ、及び他のシステムに移すためにフラッシュカード366に書込むことができる。

【0088】ラインタイマ408は、一連のタイマを表示しており、プロセッサ358により使用されてタイミング及び制御機能を提供する。図4に関して記載される全ての機能についてタイミングが取られているため、ラインタイマ408は、この予備のタイミング機能を提供し、プロセッサ358からタイミングの責任をなくす。

【0089】マルチブレクサ（MUX）TGC制御要素406は、リニア又はカーブドリニアアレイトランステューサが使用される場合に使用される。かかる場合において、MUX TGC制御要素406のマルチブレクサ機能は、リニア又はカーブドリニアアレイの要素のそれを多重化する。リニア又はカーブドリニアアレイが使用される時、低減された数の要素が所与の時間で処理され、全体の数の要素よりも少ない数の要素が所与の時間で運用される。

【0090】当業者であれば認識されるように、チャネル処理に関する要素の再整理が必要となる。MUX TGC制御要素406のTGC部分は、上述したように、フロントエンド及びバックエンド時間利得補償の両者を提供する。バックエンドTGCは、図4における検出器404において実行され、フロントエンドTGCは、図3のフロントエンドプロセッサ308において実行される。

【0091】さらに、軽いコンポーネントの統合及び賢明な選択を通して、フェーズドチュ音波トランステューサアレイ及び機器構成可能な超音波プロセッサは、8ボンドより軽く構成することができる。

【0092】本発明の原理から実質的に逸脱せずに、上述した本発明の好適な実施の形態に対して、多くの変更及びバリエーションを行ってもよいことは、当業者であれば明らかであろう。たとえば、本発明は、様々な超音波トランステューサアレイ技術、及び異なるビーム成形

方法と共に使用されてもよい。全てのかかる変更及びバリエーションは、特許請求の範囲において定義される本発明の範囲内で本明細書に含まれることが意図されている。

**【図面の簡単な説明】**

**【図1】**本発明の1態様により構成される、携帯用、機器構成可能な超音波システムを示す図である。

**【図2】**図1の携帯用、プローブアセンブリに配置されるセクタフェーズドトランステューサアレイ、及び機器構成可能なプロセッサ102において配置されるフェー<sup>10</sup>ズドアレイビームフォーマを例示する図である。

**【図3】**図1の携帯用、機器構成可能な超音波システムを例示するブロック図である。

**【図4】**図3のバックエンドプロセッサを例示するブロ<sup>10</sup>ック図である。

**【符号の説明】**

100：(携帯用、機器構成可能な)超音波システム

102：プロセッサ

104：インタフェースケーブル

106：プローブアセンブリ

108：ターゲット

200：トランステューサアレイ

202：フェーズドアレイビームフォーマ

204 - 1 ~ 204 - n：トランステューサ素子

206 - 1 ~ 206 - n：コネクション

208 - 1 ~ 208 - n：遅延素子

210 - 1 ~ 210 - n：コネクション

212：加算素子

214：コネクション

218：中央の受信ライン

\*220：ライン

222：セクタ

302, 306, 310：コネクション

304：送信／受信スイッチ

308：フロントエンドプロセッサ

312：アナログ／デジタル変換器(ADC)

314：コネクション

316：受信プロセッサ

320：ビームフォーマ

322, 324, 326：ASIC

336：高電圧送信パルサ

340：バックエンドASIC

344：ディスプレイ

350：SRAM/DRAM

358：プロセッサ

360：I/Oコントローラ

364：フラッシュメモリ

366：フラッシュカードメモリ

372：交流(AC)アダプタ/バッテリチャージャ

20

374：スマートバッテリ

402：係数ダウンロード

404：検出器

406：MUX TGC制御

408：ラインタイマ

410：グラフィックビデオ

414：ISA及びフラッシュバス

416：DMAコントローラ

418：シリアルバス

\*30 420：スキャンコンバータ

**【図1】**

【図2】

【図3】

【図4】

## フロントページの続き

(71)出願人 590000248

G roenewoudseweg 1,

5621 BA Eindhoven, Th

e Netherlands

(72)発明者 スティーヴン シー リーヴィット

アメリカ合衆国, メイン 04544, イース

ト ブースペイ, リーヴィット ロード

1, ヘンリー ロード(オフ バック ナ

ロウ ロード)

(72)発明者 ジョセフ アール ファロン

アメリカ合衆国, マサチューセッツ

01921, ボックスフォード, ワиндミア

ドライヴ 4

(72)発明者マイケル ピー アンソニー

アメリカ合衆国, マサチューセッツ

01810, アンドーヴァー, チェスナット

ストリート 38

(72)発明者 テオドア ピー ファツィオリ

アメリカ合衆国, ニューハンプシャー

03079, セイラ, アルタ アヴェニュ 21

(72)発明者 チャールズ アール ダウデル

アメリカ合衆国, ニューハンプシャー

03062, ナッシュア, ローズクリフ ドラ

イヴ 27

F ターム(参考) 4C301 AA02 BB01 BB02 BB22 EE16

EE17 GB03 GB04 GB06 HH07

HH11 HH21 HH33 HH40 JB29

LL04

|                |                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 便携式可配置超声成像系统                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP2002177266A</a>                                                                                                                                                                                                                                                                                                                                                                               | 公开(公告)日 | 2002-06-25 |

| 申请号            | JP2001342403                                                                                                                                                                                                                                                                                                                                                                                                | 申请日     | 2001-11-07 |

| [标]申请(专利权)人(译) | 皇家飞利浦电子股份有限公司                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 申请(专利权)人(译)    | 皇家飞利浦电子股份有限公司的Vie                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | スティーヴン・シーリー・ヴィット<br>ジョセフ・アール・ファロン<br>マイケル・ピー・アンソニー<br>テオドア・ピーファツィオリ<br>チャールズ・アール・ダウデル                                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人            | スティーヴン・シーリー・ヴィット<br>ジョセフ・アール・ファロン<br>マイケル・ピー・アンソニー<br>テオドア・ピーファツィオリ<br>チャールズ・アール・ダウデル                                                                                                                                                                                                                                                                                                                       |         |            |

| IPC分类号         | A61B8/00 G01S7/52 G01S7/531 G01S15/89                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| CPC分类号         | G01S15/899 A61B8/4427 G01S7/52033 G01S7/52044 G01S7/52073 G01S15/8909 G01S15/8979                                                                                                                                                                                                                                                                                                                           |         |            |

| FI分类号          | A61B8/00                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| F-TERM分类号      | 4C301/AA02 4C301/BB01 4C301/BB02 4C301/BB22 4C301/EE16 4C301/EE17 4C301/GB03 4C301/GB04 4C301/GB06 4C301/HH07 4C301/HH11 4C301/HH21 4C301/HH33 4C301/HH40 4C301/JB29 4C301/LL04 4C601/BB05 4C601/BB06 4C601/BB21 4C601/BB23 4C601/EE13 4C601/EE14 4C601/GB01 4C601/GB03 4C601/GB04 4C601/HH14 4C601/HH29 4C601/JB01 4C601/JB03 4C601/JB08 4C601/JB34 4C601/JB45 4C601/JB55 4C601/LL01 4C601/LL02 4C601/LL26 |         |            |

| 代理人(译)         | 伊藤忠彦                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 优先权            | 09/710985 2000-11-09 US                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

## 摘要(译)

要解决的问题：提供一种便携式图像形成系统，该系统可以轻松配置为各种换能器阵列类型和处理技术，并可以轻松容纳处理器和软件的扩展。便携式设备可配置超声系统100使用连接到便携式设备可配置超声处理器102的相控超声换能器阵列200来产生超声图像。当与扇形相控阵列一起使用时，超声系统100使用与换能器阵列200中的每个元件204相关的处理通道来形成超声图像。当与线性或弯曲的线性换能器阵列一起使用时，超声处理器102使用比换能器阵列更少的处理通道来形成超声图像。超声处理器102是可缩放的，并且可以使用多种处理器，软件和换能器阵列来形成许多不同的超声图像。