## [12] 发明专利申请公布说明书

[21] 申请号 200810241926.4

[43] 公开日 2009 年 7 月 8 日

[11] 公开号 CN 101474081A

[22] 申请日 2008.12.30

[21] 申请号 200810241926.4

[71] 申请人 深圳市蓝韵实业有限公司

地址 518034 广东省深圳市福田区景田路碧

景园 E 栋 408-413 室

[72] 发明人 兰 海 黄嘉熙 蒋颂平

权利要求书 2 页 说明书 6 页 附图 2 页

### [54] 发明名称

一种连续多普勒超声成像系统正交本振信号

产生装置

### [57] 摘要

本发明公开了一种连续多普勒超声成像系统正交本振信号产生装置，包括现场可编程门阵列 FPGA、晶振、第一数模转换器和第二数模转换器，所述现场可编程门阵列 FPGA 的输出端与第一数模转换器和第二数模转换器的输入端相连，所述晶振分别与所述现场可编程门阵列 FPGA、第一数模转换器和第二数模转换器相连，所述晶振用于向所述现场可编程门阵列 FPGA、第一数模转换器和第二数模转换器提供同步时钟信号，所述现场可编程门阵列 FPGA 用于根据输入的相位值向第一数模转换器输出与该相位值相应的正弦值，向第二数模转换器输出与该相位值相应的余弦值，第一数模转换器用于将所述正弦值转换为相应的模拟信号，第二数模转换器用于将所述余弦值转换为相应的模拟信号。

1、一种连续多普勒超声成像系统正交本振信号产生装置，其特征在于：包括现场可编程门阵列FPGA、晶振、第一数模转换器和第二数模转换器，所述现场可编程门阵列FPGA的输出端与第一数模转换器和第二数模转换器的输入端相连，所述晶振分别与所述现场可编程门阵列FPGA、第一数模转换器和第二数模转换器相连，所述晶振用于向所述现场可编程门阵列FPGA、第一数模转换器和第二数模转换器提供同步时钟信号，所述现场可编程门阵列FPGA用于根据输入的相位值向第一数模转换器输出与该相位值相应的正弦值，向第二数模转换器输出与该相位值相应的余弦值，第一数模转换器用于将所述正弦值转换为相应的模拟信号，第二数模转换器用于将所述余弦值转换为相应的模拟信号。

2、根据权利要求 1 所述的连续多普勒超声成像系统正交本振信号产生装置，其特征在于：还包括第一低通滤波器，第一数模转换器的输出端与第一低通滤波器相连。

3、根据权利要求 2 所述的连续多普勒超声成像系统正交本振信号产生装置，其特征在于：还包括第二低通滤波器，第二数模转换器的输出端与第二低通滤波器相连。

4、根据权利要求 3 所述的连续多普勒超声成像系统正交本振信号产生装置，其特征在于：第一低通滤波器设为二阶巴特沃兹滤波器。

5、根据权利要求 4 所述的连续多普勒超声成像系统正交本振信号产生装置，其特征在于：第二低通滤波器设为二阶巴特沃兹滤波器。

6、根据权利要求 5 所述的连续多普勒超声成像系统正交本振信号产生装置，其特征在于：所述晶振设为有源晶振。

---

7、根据权利要求 6 所述的连续多普勒超声成像系统正交本振信号产生装置，其特征在于：在所述现场可编程门阵列 FPGA 内设置相位累加器，所述相位累加器用于将上一时钟的相位值和相位增量相加后生成当前的相位值。

8、根据权利要求 7 所述的连续多普勒超声成像系统正交本振信号产生装置，其特征在于：在所述现场可编程门阵列 FPGA 内设置正弦值查找表，所述正弦值查找表根据当前的相位值输出对应的正弦值。

9、根据权利要求 7 所述的连续多普勒超声成像系统正交本振信号产生装置，其特征在于：在所述现场可编程门阵列 FPGA 内设置余弦值查找表，所述余弦值查找表根据当前的相位值输出对应的余弦值。

10、根据权利要求 8 或 9 所述的连续多普勒超声成像系统正交本振信号产生装置，其特征在于：所述二阶巴特沃兹滤波器的 3dB 截至频率设置为 3MHz。

## 一种连续多普勒超声成像系统正交本振信号产生装置

### 技术领域

本发明涉及超声成像设备技术领域，具体涉及一种连续多普勒(CW Doppler)超声成像系统正交本振信号产生装置。

### 背景技术

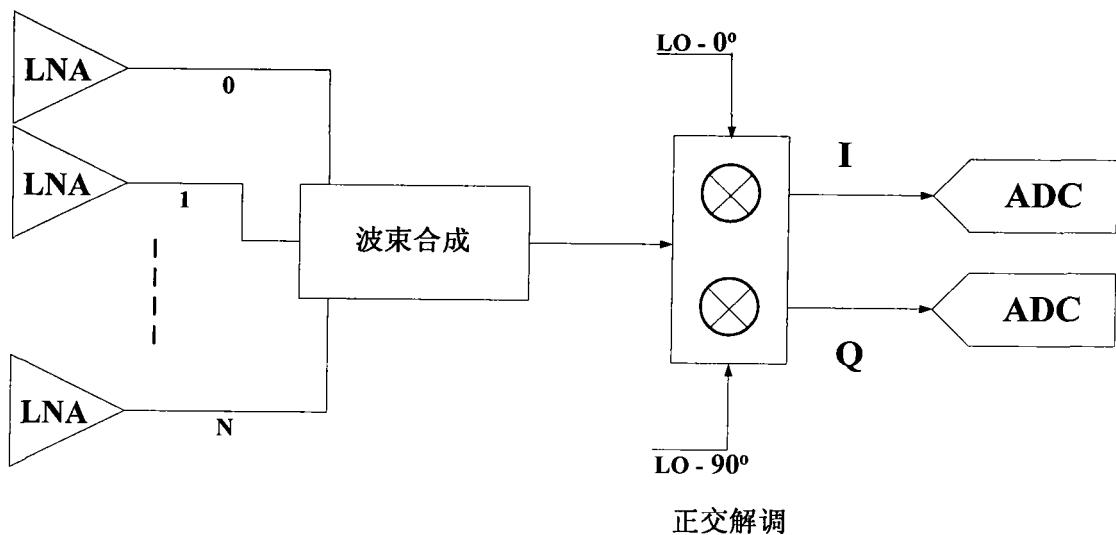

连续多普勒成像系统中 CW 模式通常是这样工作的：探头的一部分阵元用于发射，另外一部分阵元用于接收。这样就可以将 CW 用于流速较快的血流信号的测量而不会发生混叠的现象。CW 模式常用的处理方式如图 1 所示，各通道的回波信号先通过前置低噪声放大器(LNA)进行预放大，再将各个接收通道进行波束合成，然后将合成后的信号进行正交解调(I/Q Demodulate)，最后进行模数转换(ADC)。其中正交解调的目的是区分多普勒信号是正向频移还是负向频移。如果 I 通道的解调的输出相位滞后 Q 通道的输出相位，则说明该多普勒频移信号是正向频移信号(血流方向流向探头)；如果 I 通道的解调的输出相位超前 Q 通道的输出相位，则说明该多普勒频移信号是反向频移信号(血流方向远离探头)。

在现有的连续多普勒超声成像系统中，使用专用的集成电路(ASIC)来产生相位相差 90 度的正交本振信号，专用集成电路设计复杂，价格昂贵。

### 发明内容

本发明要解决的技术问题是提供一种连续多普勒超声成像系统正交本振信号产生装置，克服现有技术的连续多普勒成像系统使用专用的集成电路产生正交本振信号，设计复杂、生产成本高的缺陷。

本发明为解决上述技术问题所采用的技术方案为：

一种连续多普勒超声成像系统正交本振信号产生装置，包括现场可编程门阵列FPGA、晶振、第一数模转换器和第二数模转换器，所述现场可编程门阵列FPGA的输出端与第一数模转换器和第二数模转换器的输入端相连，所述晶振分别与所述现场可编程门阵列FPGA、第一数模转换器和第二数模转换器相连，所述晶振用于向所述现场可编程门阵列FPGA、第一数模转换器和第二数模转换器提供同步时钟信号，所述现场可编程门阵列FPGA用于根据输入的相位值向第一数模转换器输出与该相位值相应的正弦值，向第二数模转换器输出与该相位值相应的余弦值，第一数模转换器用于将所述正弦值转换为相应的模拟信号，第二数模转换器用于将所述余弦值转换为相应的模拟信号。

所述的连续多普勒超声成像系统正交本振信号产生装置，其中还包括第一低通滤波器，第一数模转换器的输出端与第一低通滤波器相连。

所述的连续多普勒超声成像系统正交本振信号产生装置，其中还包括第二低通滤波器，第二数模转换器的输出端与第二低通滤波器相连。

所述的连续多普勒超声成像系统正交本振信号产生装置，其中第一低通滤波器设为二阶巴特沃兹滤波器。

所述的连续多普勒超声成像系统正交本振信号产生装置，其中第二低通滤波器设为二阶巴特沃兹滤波器。

所述的连续多普勒超声成像系统正交本振信号产生装置，其中所述晶振设为有源晶振。

所述的连续多普勒超声成像系统正交本振信号产生装置，其中在所述现场可编程门阵列 FPGA 内设置相位累加器，所述相位累加器用于将上一时钟的相位值和相位增量相加后生成当前的相位值。

所述的连续多普勒超声成像系统正交本振信号产生装置，其中在所述现场可编程门阵列 FPGA 内设置正弦值查找表，所述正弦值查找表根据当前的相位值输出对应的正弦值。

所述的连续多普勒超声成像系统正交本振信号产生装置，其中在所述现场可编程门阵列 FPGA 内设置余弦值查找表，所述余弦值查找表根据当前的相位值输出对应的余弦值。

所述的连续多普勒超声成像系统正交本振信号产生装置，其中所述二阶巴特沃兹滤波器的 3dB 截至频率设置为 3MHz。

本发明的有益效果：本发明连续多普勒超声成像系统正交本振信号产生装置使用现场可编程门阵列FPGA实现直接数字合成(DDS, Direct Digital Synthesizer)技术来产生正交本振信号，大大降低了设计复杂度，并降低了生产成本。

### 附图说明

本发明包括如下附图：

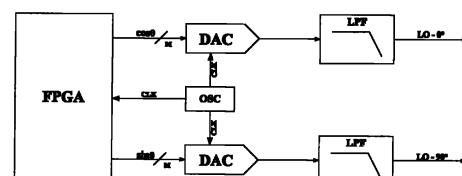

图 1 为现有技术使用正交本振信号的装置示意图；

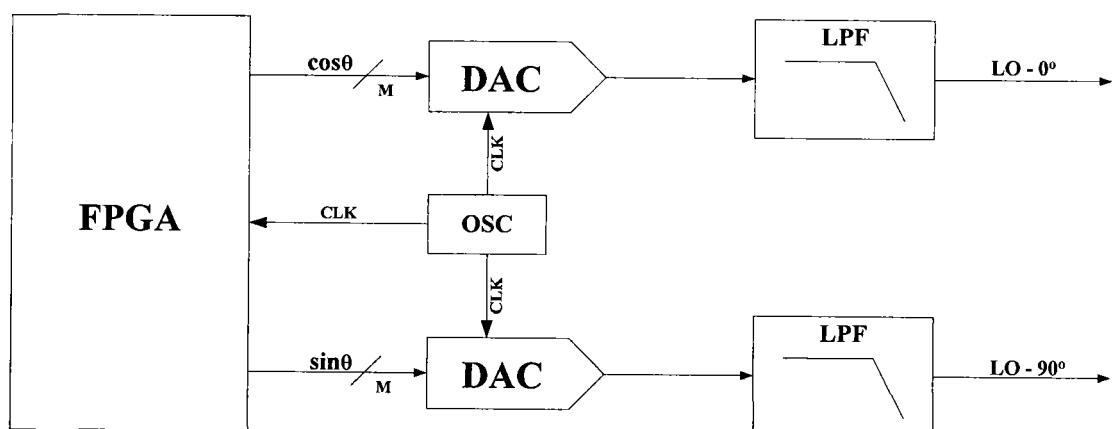

图 2 为本发明连续多普勒超声成像系统正交本振信号产生装置示意图；

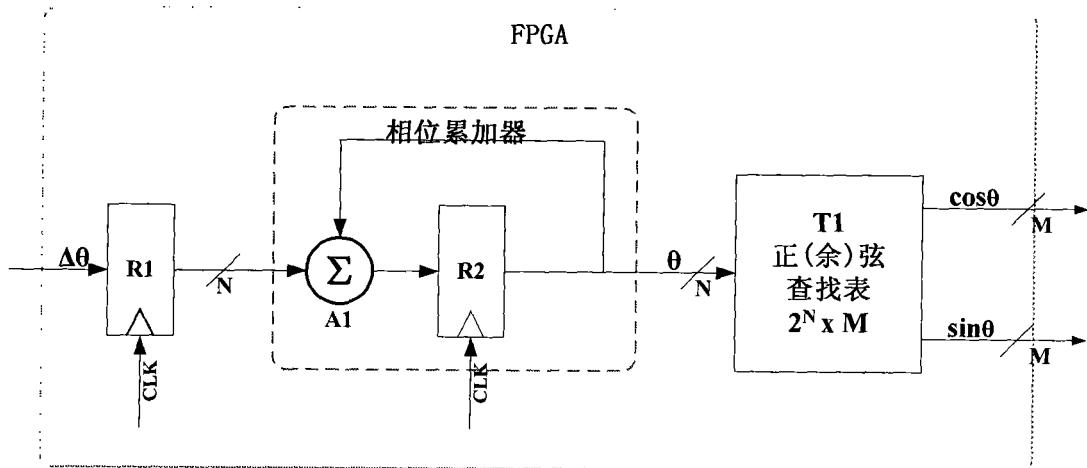

图 3 为本发明 FPGA 中生成正交数字信号的逻辑组件示意图。

### 具体实施方式

下面根据附图和实施例对本发明作进一步详细说明：

如图 2 所示，本发明连续多普勒超声成像系统正交本振信号产生装置由现场可编程门阵列 FPGA，有源晶振 OSC，两个数模转换器 DAC 和两个低通滤波器 LPF 构成。

有源晶振 OSC 产生同步时钟信号供现场可编程门阵列 FPGA 和数模转换器 DAC 使用，由于正交本振信号 LO 信号对相位要求很严格，所以使用高稳定度的有源晶振来减少时钟的抖动。

现场可编程门阵列 FPGA 根据输入的相位值，输出该相位对应的正弦值和余弦值。这些正弦值和余弦值是位宽为 M 的数字信号。

数模转换器 DAC 将现场可编程门阵列 FPGA 输出的数字信号转换为模拟信号，其输出即为正弦值和余弦值对应的一定幅度的模拟信号。

低通滤波器 LPF 将锯齿形的数模转换器 DAC 输出信号平滑为需要的正余弦信号，其截至频率设置为比需要的正交本振信号 LO 频率略高的一个值。

正交输出的条件是现场可编程门阵列 FPGA 的输出为正交的数字信号，现场可编程门阵列 FPGA 中产生正交数字信号的逻辑组件如图 3 所示，其中  $\Delta\theta$  为输入的相位增量，用位宽为 N 的数字信号表示，输出本振频率由下列公式决定：

$$F_{LO} = (F_{clk} * \Delta\theta) / 2^N$$

公式中， $F_{LO}$  为需要的本振频率， $F_{clk}$  为现场可编程门阵列 FPGA 的时钟频率。

$R1$  为寄存器，在时钟的上升(或下降)沿锁存输入的  $\Delta\theta$ 。 $\Delta\theta$  进入相位累加器，相位累加器由加法器 A1 和寄存器  $R2$  构成。加法器将上一时钟的相位和相位增量  $\Delta\theta$  相加生成当前的相位值，并在时钟的上升(或下降)沿锁存进  $R2$ 。 $R2$  输出即为当前相位  $\theta$ ，其位宽也为 N。

$T1$  为正弦(或余弦)查找表，根据输入的相位值  $\theta$ ，从表中可以查找出该相位值  $\theta$  对应的正弦值或余弦值。这些正弦值或余弦值预先存储于

在现场可编程门阵列 FPGA 的随机读写存储器(RAM)中。由于正弦或余弦都是周期信号，并且将余弦信号滞后  $\pi/2$  相位后其形状和正弦信号一样，所以在该查找表只需要保存一个周期的正弦值或者余弦值。查找表 T1 的深度为  $2^N$ ，宽度为 M。当输出相位值  $\theta$  为  $0 \sim 2^N$  范围内的任意一个值时，可以从查找表中找到一个对应的位宽为 M 的正弦值  $\sin\theta$  或余弦值  $\cos\theta$ 。

一个具体实施例：

利用本发明连续多普勒超声成像系统正交本振信号产生装置产生 2.5MHz 的正交本振信号用于超声回波信号的解调。

时钟(clk)频率为 40MHz，选用相位增量  $\Delta\theta$  的位宽 N = 16，正弦(或余弦)值位宽 M = 10。根据前面的公式可以计算得到：

$$\begin{aligned}\Delta\theta &= (F_{LO} * 2^N) / F_{clk} = (2.5M * 2^{16}) / 40M \\ &= (4096)_{10} = (0001\ 0000\ 0000\ 0000)_2\end{aligned}$$

所以需要向现场可编程门阵列 FPGA 发送  $\Delta\theta = (0001\ 0000\ 0000\ 0000)_2$  即可产生 2.5MHz 的输出频率。

相位累加器在每个时钟周期，根据上一时钟的相位和相位增量  $\Delta\theta$  相加生成当前的相位值  $\theta$ 。

查找表 T1 中保存深度为  $2^{16}$ ，宽度为 10 的余弦幅度值。在每个时钟周期，T1 根据输入的相位  $\theta$ ，查找出余弦输出  $\cos\theta$ ；同时查找出滞后  $\pi/2$  相位的正弦输出  $\sin\theta = \cos(\theta - \pi/2)$ 。

数模转换器 DAC 选用 10bit、40MHz 的数模转换器，将现场可编程门阵列 FPGA 输出的  $\sin\theta$ 、 $\cos\theta$  数字信号转换为模拟信号。

低通滤波器(LPF)使用 2 阶巴特沃兹滤波器，其 3dB 截至频率设置为 3MHz，这样可以平滑输出 2.5MHz 的本振信号。

本领域技术人员不脱离本发明的实质和精神，可以有多种变形方案实现本发明，以上所述仅为本发明较佳可行的实施例而已，并非因此局

---

限本发明的权利范围，凡运用本发明说明书及附图内容所作的等效结构变化，均包含于本发明的权利范围之内。

图1

图2

图3

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种连续多普勒超声成像系统正交本振信号产生装置                        |         |            |

| 公开(公告)号        | <a href="#">CN101474081A</a>                   | 公开(公告)日 | 2009-07-08 |

| 申请号            | CN200810241926.4                               | 申请日     | 2008-12-30 |

| [标]申请(专利权)人(译) | 深圳市蓝韵实业有限公司                                    |         |            |

| 申请(专利权)人(译)    | 深圳市蓝韵实业有限公司                                    |         |            |

| 当前申请(专利权)人(译)  | 深圳市蓝韵实业有限公司                                    |         |            |

| [标]发明人         | 兰海<br>黄嘉熙<br>蒋颂平                               |         |            |

| 发明人            | 兰海<br>黄嘉熙<br>蒋颂平                               |         |            |

| IPC分类号         | A61B8/06                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

## 摘要(译)

本发明公开了一种连续多普勒超声成像系统正交本振信号产生装置，包括现场可编程门阵列FPGA、晶振、第一数模转换器和第二数模转换器，所述现场可编程门阵列FPGA的输出端与第一数模转换器和第二数模转换器的输入端相连，所述晶振分别与所述现场可编程门阵列FPGA、第一数模转换器和第二数模转换器相连，所述晶振用于向所述现场可编程门阵列FPGA、第一数模转换器和第二数模转换器提供同步时钟信号，所述现场可编程门阵列FPGA用于根据输入的相位值向第一数模转换器输出与该相位值相应的正弦值，向第二数模转换器输出与该相位值相应的余弦值，第一数模转换器用于将所述正弦值转换为相应的模拟信号，第二数模转换器用于将所述余弦值转换为相应的模拟信号。