## [12] 发明专利申请公开说明书

[21] 申请号 02142563.9

[43] 公开日 2003 年 10 月 29 日

[11] 公开号 CN 1451356A

[22] 申请日 2002.7.30 [21] 申请号 02142563.9

[74] 专利代理机构 中国专利代理(香港)有限公司

[30] 优先权

代理人 张志醒

[32] 2001.7.31 [33] US [31] 09/919524

[71] 申请人 皇家菲利浦电子有限公司

地址 荷兰艾恩德霍芬

[72] 发明人 M·P·安东尼

权利要求书 4 页 说明书 7 页 附图 4 页

[54] 发明名称 用模拟随机存取存储器的束形成系统

## [57] 摘要

本发明涉及用模拟随机存取存储器的束形成系统。每个束形成信道用一个模拟随机存取存储器元件(RAM)的结构简单成本低的超声束形成系统。系统包括处理器和超声转换器阵列。超声转换器阵列有多个转换器元件，每个转换器元件与一个信道相关。系统还包括用于接收来自每个转换器元件的输出信号的束形成器，和位于束形成器中与每个信道相关的延迟元件。延迟元件包括模拟随机存取存储元件。

1. 一种超声成像系统，包括：

5       超声转换器阵列，它有多个转换器元件，每个转换器元件与多个信道中的一个信道相关；

束形成器，用于接收来自所述多个转换器元件的其中每一个的输出信号；和

延迟元件，位于所述束形成器中并与所述信道的其中每一个相关，其中，所述延迟元件包括模拟随机存取存储器（RAM）元件。

10      2. 按照权利要求1的超声成像系统，其特征在于，所述延迟元件还包括：

第一移位寄存器，它有多个第一存储器单元，所述第一移位寄存器配置成循环移位寄存器，“逻辑1”通过所述多个第一存储器单元的其中每一个循环；

15      多个第一开关，所述多个第一开关的其中每一个与所述第一移位寄存器中的所述多个第一存储单元的其中一个相关；

第二移位寄存器，它包括多个第二存储器单元，所述第二移位寄存器配置成循环移位寄存器，其中“逻辑1”通过所述多个第二存储器单元的其中每一个循环；

20      多个第二开关，所述多个第二开关的其中每一个与所述第二移位寄存器中的所述多个第二存储单元的其中一个相关；

容性元件，它与所述第一移位寄存器和第二移位寄存器中的所述多个存储器单元的其中每一个相关；和

25      加到所述第二移位寄存器中的所述多个存储器单元的其中每一个的控制信号，所述控制信号使所述第二移位寄存器暂停运行，以便在所述第一移位寄存器中的存储器单元与所述第二移位寄存器中相应的存储器单元之间建立延迟。

3. 按照权利要求2的超声成像系统，其特征在于，所述多个第一开关的其中每一个响应所述第一存储器单元中的其中之一出现的“逻辑1”而闭合，所述多个第二开关的其中每一个响应所述第二存储器单元中的其中之一出现

的“逻辑 1”而闭合，所述控制信号引起所述第一与第二开关闭合的时间之间的延迟。

4. 按照权利要求 3 的超声成像系统，其特征在于，来自所述多个转换器元件的其中每一个的输出信号加到位于所述束形成器中的多个延迟元件中的其中每一个上。

5

5. 按照权利要求 3 的超声成像系统，其特征在于，所述延迟修改从所述多个转换器元件的其中每一个中来的输出信号。

6. 按照权利要求 5 的超声成像系统，其特征在于，组合多个输出信号以形成束形成信号。

10 7. 一种用于形成超声信号的方法，所述方法包括以下步骤：

从有多个转换器元件的超声转换器阵列产生超声信号，每个转换器元件与多个信道中的其中之一相关。

给束形成器供给所述超声信号；和

用位于所述束形成器中并与所述信道的其中每一个相关的延迟元件来修改所述超声信号，其中，所述延迟元件包括模拟随机存取存储器元件。

15

8. 按照权利要求 7 的方法，其特征在于，还包括以下步骤：

提供具有多个第一存储器单元的第一移位寄存器，所述第一移位寄存器配置成循环移位寄存器，其中“逻辑 1”通过所述多个第一存储器单元的其中每一个循环；

20 提供多个第一开关，所述多个第一开关的其中每一个与所述第一移位寄存器中的所述多个第一存储单元的其中每一个相关；

提供具有多个第二存储器单元的第二移位寄存器，所述第二移位寄存器配置成循环移位寄存器，其中“逻辑 1”通过所述多个第二存储器单元的其中每一个循环；

25 提供多个第二开关，所述第二开关的其中每一个与所述第二移位寄存器中的所述多个第二存储单元的其中之一相关；

提供容性元件，它与所述第一移位寄存器和所述第二移位寄存器中的所述多个存储器单元的其中每一个相关；和

向所述第二移位寄存器中的所述多个存储器单元的其中每一个提供控

制信号，所述控制信号使所述第二移位寄存器暂停运行，以便在所述第一移位寄存器中的存储器单元与所述第二移位寄存器中相应的存储器单元之间建立延迟。

9. 按照权利要求 8 的方法，其特征在于，还包括以下步骤：

5 响应所述第一存储器单元的其中之一中出现的“逻辑 1”而闭合所述多个第一开关的其中每一个；和

响应所述第二存储器单元的其中之一中出现的“逻辑 1”而闭合所述多个第二开关的其中每一个，其中所述控制信号引起所述第一与所述第二开关闭合的时间之间的延迟。

10 10. 按照权利要求 9 的方法，其特征在于，还包括以下步骤：把来自所述多个转换器元件的其中每一个的输出信号加到位于所述束形成器中的多个延迟元件的其中每一个上。

11. 按照权利要求 9 的方法，其特征在于，还包括以下步骤：修改从所述多个转换器元件的其中每一个来的输出信号。

15 12. 按照权利要求 11 的方法，其特征在于，还包括以下步骤：组合多个输出信号以形成束形成信号。

13. 一种计算机可读媒体具有形成超声信号用的程序，所述程序包括用于以下步骤的逻辑：

20 从具有多个转换器元件的超声转换器阵列产生超声信号，每个转换器元件与多个信道的其中之一相关；

给束形成器供给所述超声信号，和

用位于所述束形成器中并与所述信道的其中每一个相关的延迟元件来修改所述超声信号，其中所述延迟元件包括模拟随机存取存储器元件。

14. 按照权利要求 13 的程序，其特征在于，还包括用于以下步骤的逻辑：

25 提供具有多个第一存储器单元的第一移位寄存器，所述第一移位寄存器配置成循环移位寄存器，其中“逻辑 1”通过所述多个第一存储器单元的其中每一个循环；

提供多个第一开关，所述多个第一开关的其中每一个与所述第一移位寄存器中的所述多个第一存储单元的其中之一相关；

提供具有多个第二存储器单元的第二移位寄存器，所述第二移位寄存器配置成循环移位寄存器，其中“逻辑 1”通过所述多个第二存储器单元的其中每一个循环；

5 提供多个第二开关，所述第二开关的其中每一个与所述第二移位寄存器中的所述多个第二存储位置中的一个第二存储单元的其中每一个相关；

提供容性元件，它与所述第一移位寄存器和所述第二移位寄存器中的所述多个存储器单元的其中每一个相关；和

10 向所述第二移位寄存器中的所述多个存储器单元的其中每一个提供控制信号，所述控制信号使所述第二移位寄存器暂停运行，以便在所述第一移位寄存器中的存储器单元与所述第二移位寄存器中相应的存储器单元之间建立延迟。

15. 按照权利要求 14 的程序，其特征在于，还包括用于以下步骤的逻辑：

响应所述第一存储器单元的其中之一中出现“逻辑 1”而闭合所述多个第一开关的其中每一个，和

15 响应一个所述第二存储器单元的其中之一中出现“逻辑 1”而闭合所述多个第二开关的其中每一个，其中所述控制信号引起所述第一与所述第二开关闭合的时间之间的延迟。

16. 按照权利要求 15 的程序，其特征在于，还包括用于以下步骤的逻辑：

把从所述多个转换器元件的其中每一个来的输出信号加到位于所述束形成器中的多个延迟元件的其中每一个上。

17. 按照权利要求 15 的程序，其特征在于，还包括用于以下步骤的逻辑：修改来自所述多个转换器元件的其中每一个的输出信号。

18. 按照权利要求 17 的程序，其特征在于，还包括用于以下步骤的逻辑：组合多个输出信号以形成束形成信号。

---

## 用模拟随机存取存储器的束形成系统

5

### 技术领域

本发明总的涉及超声成像系统，更具体涉及用于超声成像系统中使用模拟随机存取存储器（RAM）元件的束形成系统。

### 背景技术

有时，可用超声成像系统进行无损伤测试和用于医疗中。医用超声成像能实时无损伤地观看人体内部结构。超声成像系统能二维成像或三维成像。

超声成像系统，包括其它许多元件，其中有超声探针（包括超声转换器阵列），处理和控制电子元件（包括发送和接收束形成器），显示器，电缆线，它使超声探针连接到处理和控制电子元件。超声转换器通常构成为一维或二维阵列。一维转换器阵列包括纵向配置的一行超声转换器元件。二维超声转换器阵列通常包括按行和列配置的多个超声转换器元件。

无论超声转换器阵列如何配置，发送脉冲时，转换器元件把电能转换成声能，并按目标方向发送。声能从目标反射再回到转换器元件。转换器元件收到的声能转换成电信号，并作为接收信号传到与超声成像系统关连的接收处理电路。典型的二维超声转换器阵列包括成百上千的单个转换器元件。每个转换器元件供给的电信号多路复用至少量信道中，之后，耦合到处理电路。

每个转换器元件接收声能时，通常要求改变信号特性，以改善超声成像。这种改变信号的方式使一个信道中的信号相对于其它信道中的信号延迟。这通常叫做束形成。通过使用束形成可以改变接收信号的分量来改善显示的超声图像。常规的束形成技术通常用多个束形成元件，它对每个接收信道用复杂的数字式处理电路。因此，这需用复杂的处理元件并增大了超声系统的成本。

因此，要求超声成像系统中的每个信道有价格低而结构简单的束形成系统。

### 发明内容

简单价格低廉的超声束形成系统中每个束形成信道用模拟随机存取存储器（RAM）元件。系统包括处理器和超声转换器阵列。超声转换器阵列包括多个转换器元件，每个转换器元件与多个信道中的一个信道关连，系统还包括束形成器，它适合接收从每个转换器元件输出的信号，以及设在束形成器中的延迟元件并与每个信道关连，延迟元件包括模拟随机存取存储器（RAM）元件。

本领域的技术人员通过参见附图和以下的详细描述将会理解本发明的其它系统，方法，特征和优点。本说明书中描述的这些附加的系统，方法，特征和优点也包括在所附权利要求书中界定的要求保护的发明范围内。

### 附图说明

参见以下附图能更好理解本发明。附图中的元件没有标注相互间的尺寸关系，只是为了清楚展示发明的原理突出展示了这些元件的位置。

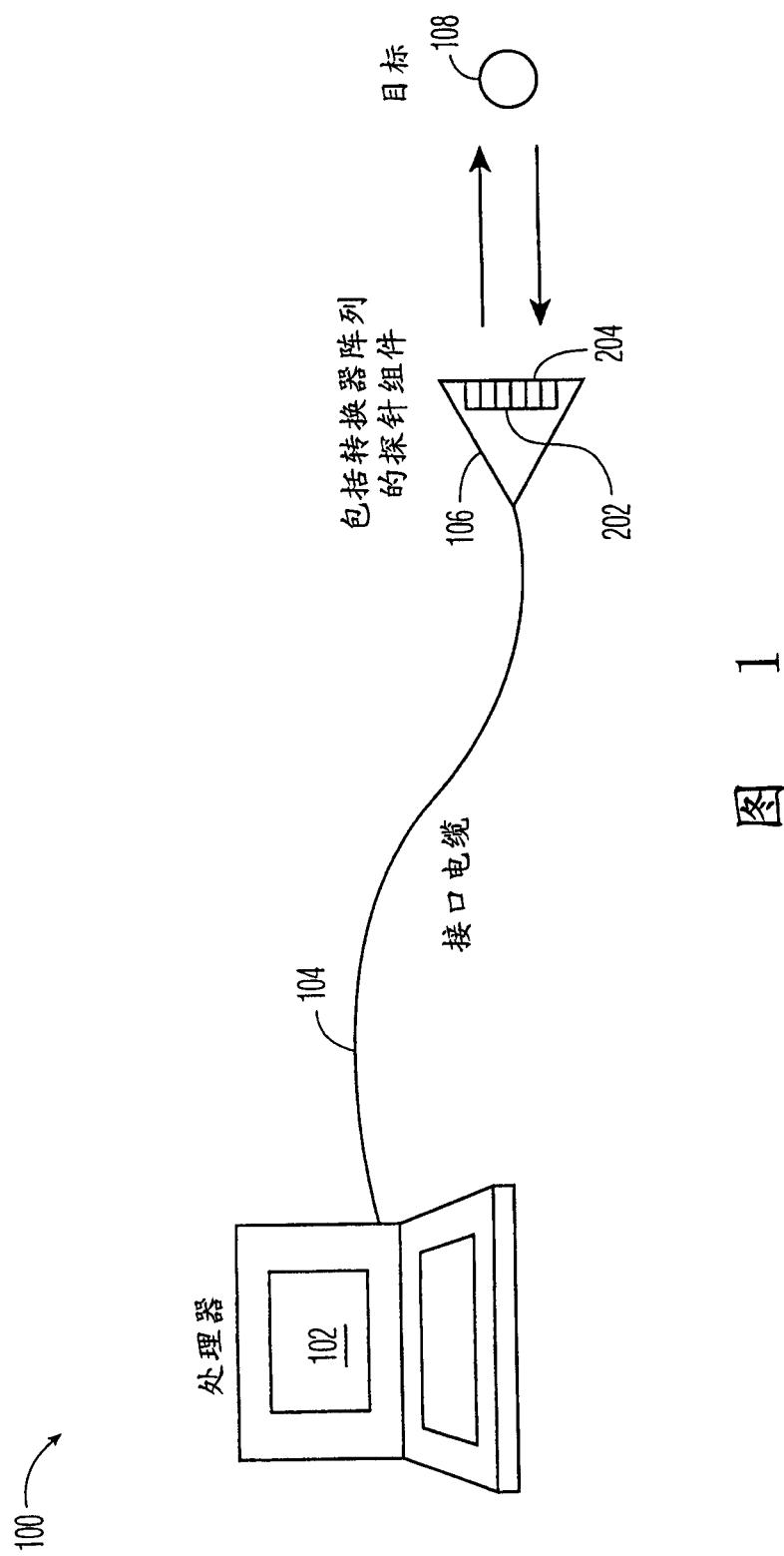

- 15      图1是简化的超声系统示意图；

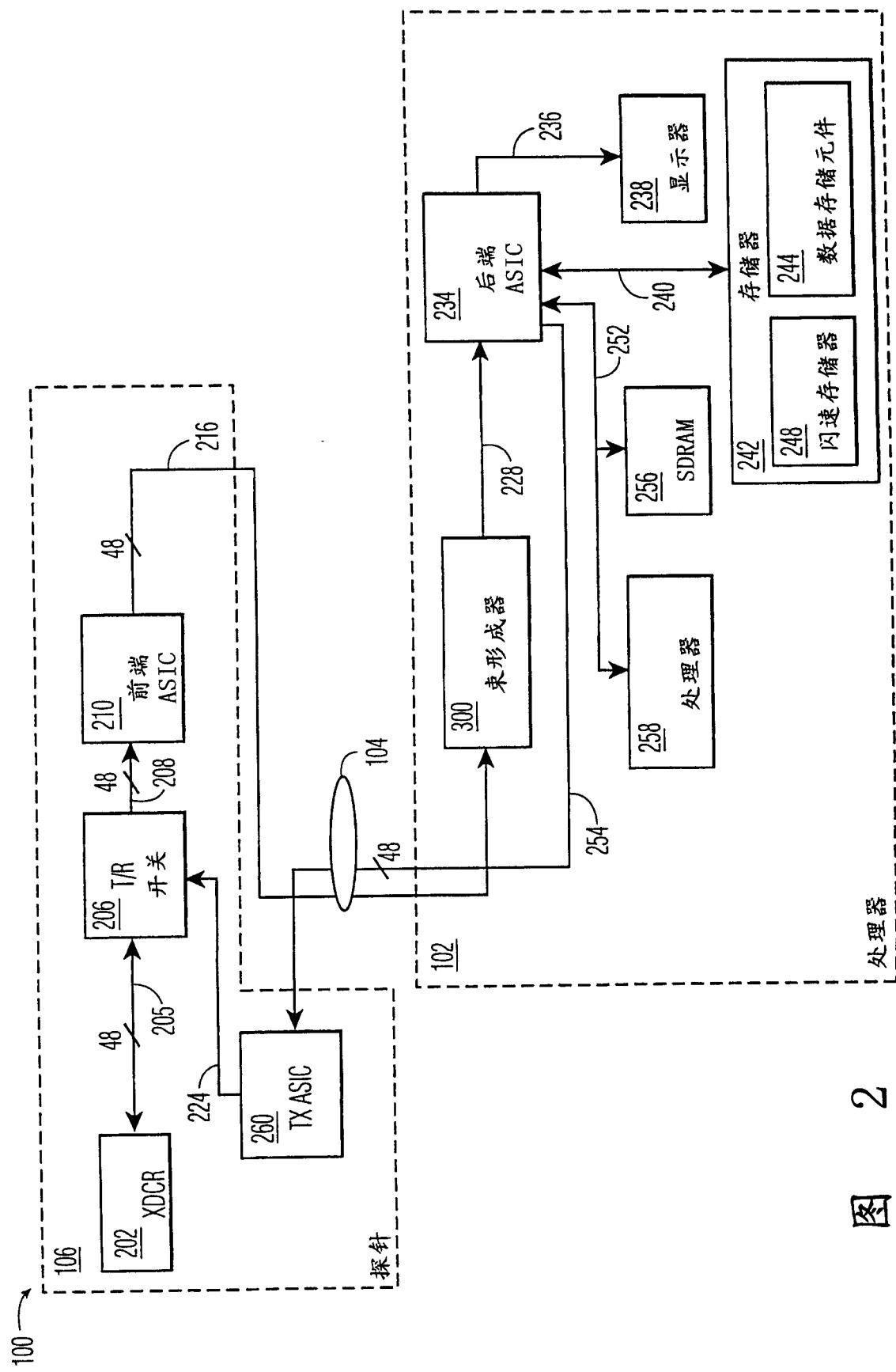

图2是图1所示超声系统的示意图；

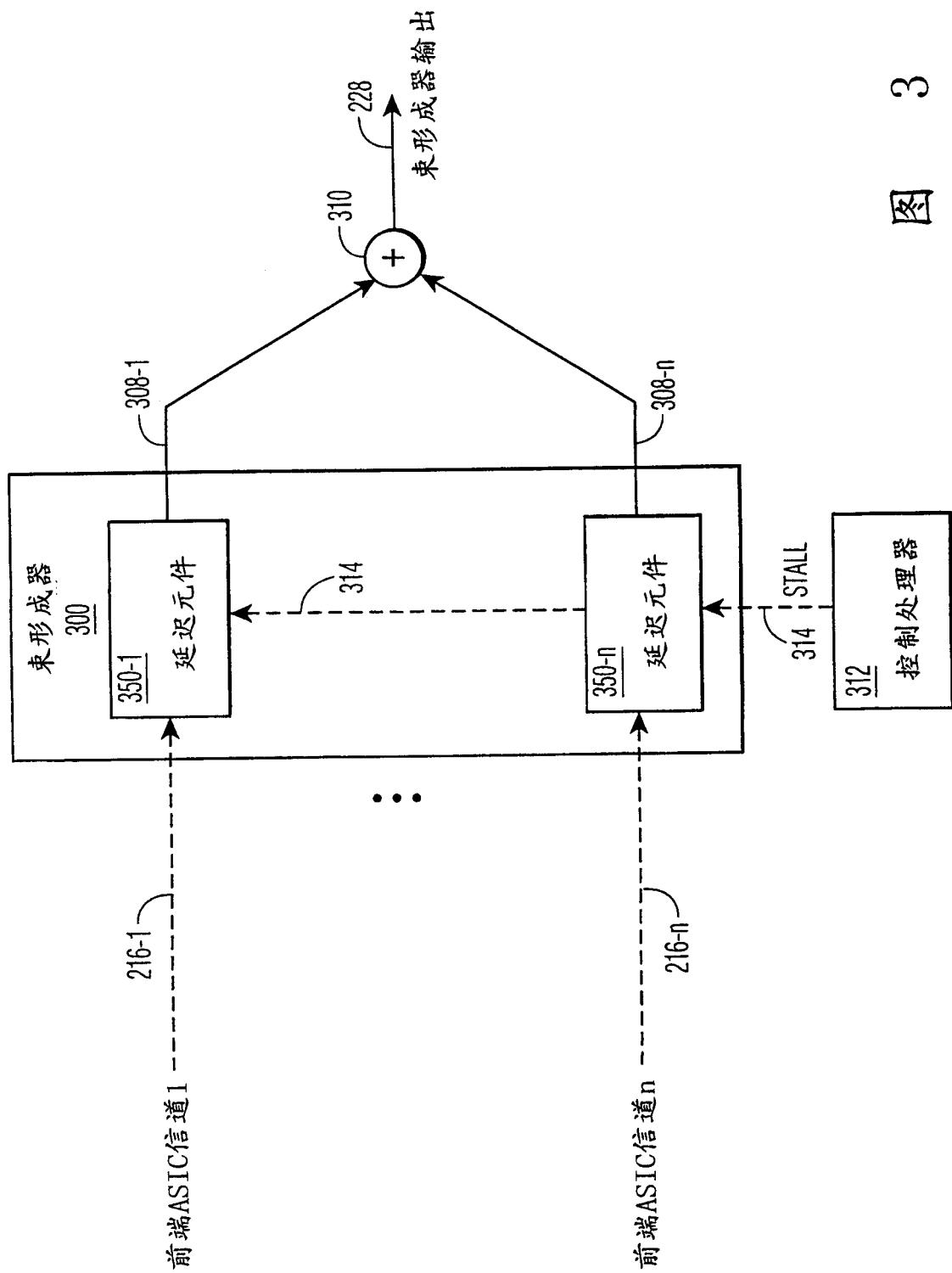

图3是图2中的束形成器的示意图；

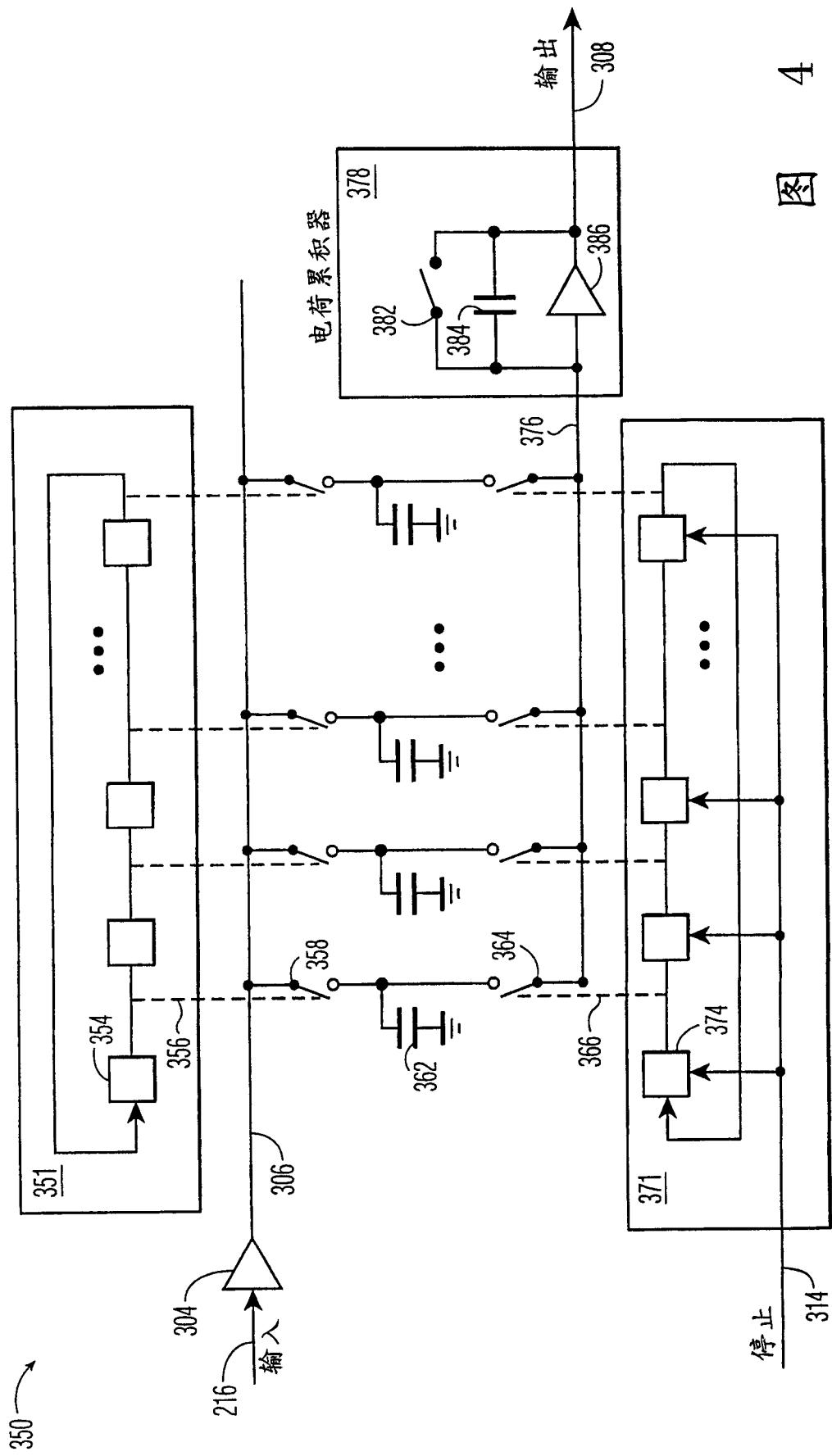

图4是图3中延迟元件的示意图。

### 具体实施方式

本发明的束形成系统可按硬件，软件，固件及其组合方式实施。优选实施例中，束形成系统用硬件和软件或固件的组合实现，它存储在存储器中和用合适的指令执行系统执行。如果在硬件中实现，作为另一实施例，束形成系统用以下任何一种技术或它们的组合实现，这些技术是本行业的公知技术，包括：有多个逻辑门的分立逻辑电路，根据数据信号实现逻辑功能；用组合逻辑门的专用集成电路（ASIC）；可编程门阵列(PGA)；现场可编程门阵列（FPGA）等。

束形成系统的软件部分包括用于实现逻辑功能的可执行指令的有序列表，能在任何计算机可读媒体中实施，能用于或与指令执行系统、设备或装置

相关，诸如以计算机为基础的系统，装有处理器的系统，或可以从指令执行系统、设备或装置读出执行指令的其它系统。该文文本中的“计算机可读媒体”可以是指用于或与指令执行系统、设备或装置相关的任何装置，其可以包含、存储、通信、传播或传输程序。计算机可读媒可以是电子、磁、光、电磁、红外、或半导体系统，设备，装置或传播媒体，但不限于这些媒体。计算机可读媒体的更具体例子(非穷举罗列)包括：有一根或多根布线的电连接(电子的)，便携式计算机磁盘，随机存取存储器(RAM)(电子的)，只读存储器(ROM)(电子的)，可擦除可编程只读存储器(EPROM或闪速存储器)(电子的)，光纤(光的)和可移动只读光盘(CDROM)(光的)。注意，计算机可读媒体甚至是纸或程序打印在上面的其它合适的媒体，例如用光扫描纸或其它媒体能电子捕获程序，之后，按需要用合适的方式编译，解释或进行其它处理，之后，存储在计算机存储器中。

现在再看图1，图1是按本发明的简化超声系统100的构成示意图。超声系统100包括经接口电缆104连接到探针组件106的处理器102。处理器102可以是便携式处理器，也可以是大的办公型全特征超声处理系统。探针组件106包括：有多个超声转换器元件的超声转换器阵列202；用数字204指示的样品。超声转换器阵列可以是一维阵列或二维阵列。而且，超声转换器阵列可以是对阵列中每个元件204在接收和发送周期能单独控制的二维阵列。有时这种阵列叫做“矩阵阵列”。矩阵阵列包括按二维邻接配置的转换器元件。

探针组件106朝目标108传送声能和接收从目标108反射的声能。转换器阵列202接收从目标108反射的声能，每个转换器元件204把收到的声能转换成电信号。如果探针组件包括处理电路，则探针组件中能部分处理收到的声能和转送到处理器102进行另外的处理。处理后，由收到的声能产生的图像显示在与处理器102结合在一起的显示器上。

图2是图1所示超声系统100的结构方框图。图2中只画出能实现本发明的一个超声系统的结构，注意，其它超声系统结构也能用本发明，探针组件106包括转换器阵列202。转换器阵列202包括配置成相阵列、直线性阵列、曲线性阵列或矩阵阵列的大量单个超声转换器元件204(见图1)，但不限于这些阵列形式，认为所公开的系统中能用任何转换器阵列，但是，为便于描述，

用 48 个元件的相阵列转换器。转换器阵列 202 经连接线 205 把 48 个信号（每个转换器元件用一个信道）传送到发送/接收（T/R）开关 206。T/R 开关 206 有隔离发送能与接收能的转换功能。T/R 开关 206 经连接线 208 与多个处理器连通，通常叫做“前端”ASIC，图中画出一个前端 ASIC210 样品。前端 ASIC210 通常是模拟 ASIC 器件，它经连接线 208 接收 48 个超声转换器信号的一部分，同时，图中画出的是用单个前端 ASIC210，而通常是多个前端 ASIC 处理经连接线 208 收到的全部 48 个超声转换器信号。

前端 ASIC210 执行功率放大，滤波和前端时间增益补偿（TGC）功能。接收来自多重深度中的目标的超声信号时要求 TGC。该例中，为了补偿与超声能深度相关的加长了的行程时间，通常要相应地提高增益。行程时间是指超声能从转换器元件传送到目标再返回到转换器元件所需的传送时间。前端 ASIC210 经连接线 212 给多个模拟/数字转换器（ADC）供给经放大的、已滤波的和经增益补偿的超声能信号，图中数字 214 指出这样的一个样品。多个 ADC214 用例如 8 位转换器技术把连接线 212 上的 48 个模拟信号转换成数字位流。ADC214 经连接线 216 给束形成器 300 供给数位流。尽管只画出一个方框，前端 ASIC210 和 ADC214 能重复实施，足够处理从转换器阵列 202 中包括的多个转换器元件收到的多个信号。

束形成器 300 包括多个延迟元件，每个延迟元件对应 48 个信道中的一个信道，成形表示从转换器阵列 202 收到的能量的信号。加法器 230 中组合在连接线 228 上的束形成器 300 的输出，使得在连接线 232 上供给单个束形成输出信号。连接线 232 上的单个束形成输出信号供给通常叫做“后端 ASIC”234 的处理器。后端 ASIC234 具有检测和附加的后端 TGC 功能，检测包括将连接线 232 上产生的无线电频率（RF）数据流转换成用于二维组织成像的对数量取样数据以及二维彩色流成像用的基带积分数据。

可用多个 ASIC 实现的后端 ASIC234 经连接线 252 与处理器 258 和与静态/动态随机存取存储器（SDRAM）256 连通。处理器 258 通过执行 SDRAM256 和闪速存储器 248 中存储的码来控制超声系统 100 的操作和功能，而且处理器 258 可以是 Motorola 公司生产的 7XXPower PC<sup>TM</sup> 系列处理器，但这只是便于说明而不是作为限制例。而且，束形成器 300 中包括的模拟 RAM（这在以下

还会详细描述)是处理器 258 访问的存储元件 242 的一部分。后端 ASIC234 还经连接线 240 与存储元件 242 连通。存储元件 242 包括闪速存储器 248 和数据存储元件 244。数据存储元件 244 可用于初始加载闪速存储器 248，也能用于输出显示器 238 上显示的信息。尽管图中画的是用分立的连接线，处理器 5 258、SDRAM256 和存储器 242 也可在公共总线上连通。

后端 ASIC234 还有扫描转换器功能，用于提供通过连接线 236 在显示器 238 上显示的超声图像。例如，显示器 238 是用来观看探针组件 106 和处理器 102 产生的超声图像的液晶显示(LCD)监视器。尽管为了表示清楚图中没画，但便携式处理器 102 还包括电源，如电池或 AC 适配器，用于给图 2 中所示的 10 全部元件供电。后端 ASIC234 还通过连接线 254 与传送 ASIC260 连通。与上述的其它 ASIC 相同，传送 ASIC260 通常作为多个 ASIC 实现，为了简化只用单个传送 ASIC260 来描述。传送 ASIC260 产生用于激励转换器阵列 202 中的 15 转换器元件 204 的传送脉冲。传送脉冲经连接线 224 连通到 T/R 开关 206。连接线 216 和 254 组合形成图 1 的接口电缆 104。某些应用中，TX ASIC260 的功能性可结合到前端 ASIC210，其它应用中，TX ASIC 的功能可结合到处理器 102 中。

图 3 是图 2 中束形成器 300 的框图。1 至 n 个信道中的每个处理信道接收来自转换器元件 204-1 至 204-n 的其中之一的信号。而且，由于处理信道相同，所以只描述一个信道。接收信号处理中，每个转换器元件 204 接收来自目标的 20 声能和把声能转换成电信号。电信号经连接线 216-1 供给放大器 304-1。放大器 304-1 把接收信号放大到允许用束形成器 300 进一步处理的电平。放大的接收信号经连接线 306-1 供给设在束形成器 300 的相应的延迟元件 350-1。如本例所示，设有 48 个转换器元件，每个转换器元件包括一个信道。因此，48 个信道中的每个信道有要供给束形成器 300 中的一个延迟元件 350 的信号。因此，束形成器 300 中有 48 个延迟元件 350。 25

每个延迟元件 350 包括一个模拟随机存取存储器(RAM)元件，并用由控制处理器 312 经连接线 314 供给的控制信号控制。连接线 314 上的信号根据来自控制处理器 312 的信号暂停每个延迟元件。在由控制处理器 312 确定的适当时间，延迟元件 350-1 的输出经连接线 308-1 供给加法元件 310。加法元件 310

组合每个延迟元件 350 的输出和在连接线 228 上提供束形成信号输出。

图 4 是图 3 所示延迟元件 350 的电路图。接收信号经连接线 216 供给放大器 304。放大器 304 的输出经连接线 306 供给多个写入开关；数字 358 指示一个实施。连接线 306 上的输入信号经写入开关 358 被取样，每一个连续的抽样保持在相应的容性元件 362 中。在延迟的时间，经读出开关 364 从容性元件 362 读出容性元件 362 中保持的电荷。从容性元件 362 读出信号并送到连接线 376 上，用电荷累集器 378 收集和处理。连接线 308 上的电荷累集器 378 的输出是每个延迟元件 350 的延迟的信道输出。

写入开关 358 用数字逻辑“1”或“逻辑 1”控制，在写入移位寄存器 351 中循环。写入移位寄存器 351 包括多个寄存器单元，354 指示了其中的一个例子。每个寄存器单元 354 对应于一个写入开关 358。寄存器单元 354 中出现“逻辑 1”时，相应的写入开关 358 经连接线 356 上的信号起动。闭合时，写入开关 358 引起连接线 306 上出现的信号存入相应的容性元件 362 中。由于逻辑 1 经写入移位寄存器 351 中的每个寄存器单元 354 循环，所以每个写入开关 358 按连续取样时钟信号依次起动。每个写入开关 358 闭合时，连接线 306 上的输入信号的瞬时值储存在相应的容性元件 362 上。每写入容性元件 362 的整个阵列时，“逻辑 1”循环回第 1 移位寄存器单元 354，由此起动第 1 写入开关 358。实质上，写入移位寄存器 351 是“模拟环形缓冲区”，写入移位寄存器 351 的长度通常大于信道之间所需的最大延迟，以满足收到的束的聚焦和控制要求。

读出移位寄存器 371 还进位循环“逻辑 1”，它相对于写入寄存器 351 中循环的“逻辑 1”延迟。因此，在给出的取样写入一个容性元件 362 后的时间，有关容性元件 362 的相应的读出开关 364 关闭。“逻辑 1”出现在寄存器单元 374 时，移位寄存器 374 经连接线 366 控制读出开关 364，读出开关 364 闭合且容性元件 362 中存储的值读出到连接线 376 上。那时容性元件 362 上的电荷经连接线 376 传送到电荷累积器 378。电荷累积器 378 包括放大器 386、容性元件 384 和开关 382。电荷累积器 378 接收连接线 376 上的连续信号和在连接线 308 上供给连续时间变化电压输出。

给出的取样写入容性元件 362 与读出容性元件 362 的取样之间的延迟是加

到该信号信道的聚焦/控制延迟。该延迟具有一个取样时钟周期的分辨率。在本实施例中约为  $1/4 \lambda$ ， $\lambda$  是接收信号波长。用与数字式扫描器件中用的方法相类似的可选择的滤波级（没画）能供给附加的延迟分辨率。但是，这里所描述的系统中，这些滤波器是模拟滤波器而不是数字式滤波器。

5 用从控制处理器（图3中312所指）经连接线314供给的停止信号314可以动态改变读出延迟时间，要求停止信号314时，读出移位寄存器371中循环的“逻辑1”不会超前，而写入移位寄存器351中循环的“逻辑1”继续超前。结果，只要连接线314上要求停止信号，读出时间就落在写入时间后面很远。按此方式，能控制连接线216上的输入与连接线308上的输出之间的延迟。延迟元件350的输出加到连接线308上（图3中的加法装置310中），在连接线228上形成组和信号并形成束形成信号输出（图3）。

10 本行业技术人员应了解，在不脱离本发明原理的前提下，上述的本发明的优选实施例还会做出各种改进和变化。例如，本发明能用于任何超声成像系统，所有这些改进和变化均属于后附的权利要求书界定的要求保护的本发明范围。

15

图 1

|                |                                                  |         |            |

|----------------|--------------------------------------------------|---------|------------|

| 专利名称(译)        | 用模拟随机存取存储器的束形成系统                                 |         |            |

| 公开(公告)号        | <a href="#">CN1451356A</a>                       | 公开(公告)日 | 2003-10-29 |

| 申请号            | CN02142563.9                                     | 申请日     | 2002-07-30 |

| [标]申请(专利权)人(译) | 皇家飞利浦电子股份有限公司                                    |         |            |

| 申请(专利权)人(译)    | 皇家飞利浦电子有限公司                                      |         |            |

| 当前申请(专利权)人(译)  | 皇家飞利浦电子有限公司                                      |         |            |

| [标]发明人         | MP安东尼                                            |         |            |

| 发明人            | M·P·安东尼                                          |         |            |

| IPC分类号         | G01N29/26 A61B8/00 G01S15/89 G10K11/34 G01N29/00 |         |            |

| CPC分类号         | G01S15/8915 G01S7/5208 G10K11/346                |         |            |

| 优先权            | 09/919524 2001-07-31 US                          |         |            |

| 其他公开文献         | CN1287739C                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">SIPO</a>   |         |            |

### 摘要(译)

本发明涉及用模拟随机存取存储器的束形成系统。每个束形成信道用一个模拟随机存取存储器元件(RAM)的结构简单成本低的超声束形成系统。系统包括处理器和超声转换器阵列。超声转换器阵列有多个转换器元件，每个转换器元件与一个信道相关。系统还包括用于接收来自每个转换器元件的输出信号的束形成器，和位于束形成器中与每个信道相关的延迟元件。延迟元件包括模拟随机存取存储元件。