# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

*H01L* 51/00 (2006.01) *H01L* 27/32 (2006.01) *H01L* 51/52 (2006.01) *H01L* 51/56 (2006.01)

(52) CPC특허분류

HO1L 51/0097 (2013.01) HO1L 27/3276 (2013.01)

(21) 출원번호

10-2016-0097571

(22) 출원일자

2016년07월29일

심사청구일자 입

없음

(11) 공개번호 10-2018-0014404

(43) 공개일자 2018년02월08일

(71) 출원인

#### 엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

# 장이식

경기도 파주시 문산읍 당동1로 67 208동 303호 ( 당동리,파주현대힐스테이트2차아파트)

#### 정유호

경기도 파주시 한빛로 70, 520동 1801호(야당동, 한빛마을5단지 캐슬&칸타빌)

#### 최영석

경기도 파주시 책향기로 441, 1005동 902호(동패동, 책향기마을동문굿모닝힐아파트)

(74) 대리인

특허법인인벤투스

전체 청구항 수 : 총 17 항

### (54) 발명의 명칭 유기발광 표시장치 및 그 제조방법

### (57) 요 약

본 발명의 일 실시예에 따른 플렉서블 표시장치가 개시된다. 플렉서블 표시장치는, 표시 영역, 표시 영역에서 연장된 패드 영역 및 패드 영역에서 연장된 벤딩 영역을 구비하는 플렉서블 기판, 플렉서블 기판 상에 배치되고, 복수 개의 층을 구비하며, 벤딩 영역에서의 두께가 벤딩 영역을 제외한 다른 영역에서의 두께보다 얇은 제1 버퍼층, 패드 영역에서 제1 버퍼층 상에 배치되는 제1 보호부재, 패드 영역에서, 제1 보호부재 상에 배치되는 제1 절연층, 제1 절연층 상에 배치되며, 표시 영역으로부터 연장되는 게이트 배선, 패드 영역에서 게이트 배선 상에 배치되는 제2 절연층, 게이트 배선과 전기적으로 연결되는 연결 배선 및 연결 배선을 덮는 제2 버퍼층을 포함하고, 연결 배선의 일 부분은 패드 영역에서 제2 절연층 상에 배치되며, 일 부분 이외의 부분은 벤딩 영역에서 상기 제1 버퍼층 상에 배치된다.

### 대표도

# (52) CPC특허분류

**H01L 51/5253** (2013.01)

**H01L 51/56** (2013.01)

H01L 2251/5338 (2013.01)

HO1L 2251/558 (2013.01)

# 명세서

# 청구범위

# 청구항 1

표시 영역, 상기 표시 영역에서 연장된 패드 영역 및 상기 패드 영역에서 연장된 벤딩 영역을 구비하는 플렉서 블 기판;

상기 플렉서블 기판 상에 배치되고, 복수 개의 충을 구비하며, 상기 벤딩 영역에서의 두께가 상기 벤딩 영역을 제외한 다른 영역에서의 두께보다 얇은 제1 버퍼층;

상기 패드 영역에서 제1 버퍼층 상에 배치되는 제1 보호부재;

상기 패드 영역에서, 상기 제1 보호부재 상에 배치되는 제1 절연층;

상기 제1 절연층 상에 배치되며, 상기 표시 영역으로부터 연장되는 게이트 배선;

상기 패드 영역에서 상기 게이트 배선 상에 배치되는 제2 절연층;

상기 게이트 배선과 전기적으로 연결되는 연결 배선; 및

상기 연결 배선을 덮는 제2 버퍼층을 포함하고,

상기 연결 배선의 일 부분은 상기 패드 영역에서 상기 제2 절연층 상에 배치되며, 상기 일 부분 이외의 부분은 상기 벤딩 영역에서 상기 제1 버퍼층 상에 배치되는 것을 특징으로 하는 플렉서블 표시장치.

### 청구항 2

제1 항에 있어서,

상기 제1 보호부재는, 인접한 또 다른 제1 보호부재와 이격되도록 구비된 것을 특징으로 하는 플렉서블 표시장치.

# 청구항 3

제2 항에 있어서,

상기 제1 보호부재는, 상기 벤딩 영역에서 제1 절연층과 제1 버퍼층의 일 부분이 동일한 패터닝장비로 제거될 수 있도록 구비되는 것을 특징으로 하는 플렉서블 표시장치.

# 청구항 4

제 3항에 있어서,

상기 플렉서블 표시장치는, 상기 표시 영역에서 상기 제1 버퍼층 상에 배치되는 박막트랜지스터 보호부재를 더 포함하고

상기 제1 보호부재는 상기 박막트랜지스터 보호부재와 동일한 물질인 것을 특징으로 하는 플렉서블 표시장치.

# 청구항 5

제1 항에 있어서,

상기 플렉서블 표시장치는, 상기 제1 절연층과 상기 제2 절연층 사이에 배치되는 제2 보호부재를 더 포함하는 것을 특징으로 하는 플렉서블 표시장치.

#### 청구항 6

제5 항에 있어서,

상기 제2 보호부재는, 상기 게이트 배선과 동일한 물질인 것을 특징으로 하는 플렉서블 표시장치.

### 청구항 7

제5 항에 있어서,

상기 제2 보호부재는, 상기 제1 보호부재와 상기 인접한 제1 보호부재 사이에서 플렉서블 기판이 노출되어, 이물이 존재하는 것을 억제하도록 구비된 것을 특징으로 하는 플렉서블 표시장치.

### 청구항 8

제7 항에 있어서,

상기 제2 보호부재는, 상기 연결 배선과 인접한 또 다른 연결 배선이 쇼트(short)되는 것을 방지하는 것을 특징 으로 하는 플렉서블 표시장치.

#### 청구항 9

제5 항에 있어서.

상기 제2 보호부재의 끝단은, 상기 제2 절연층의 끝단보다 내측에 위치하도록 구비된 것을 특징으로 하는 플렉 서블 표시장치.

# 청구항 10

표시 영역, 상기 표시 영역에서 연장된 패드 영역 및 상기 패드 영역에서 연장된 벤딩 영역을 구비하는 플렉서 블 기판 상에 복수 개의 층을 구비한 제1 버퍼층을 형성하는 단계;

상기 패드 영역 및 상기 벤딩 영역에 있는 상기 제1 버퍼층의 일 부분 상에 제1 보호부재를 패터닝(patterning)하는 단계;

상기 제1 보호부재를 덮도록, 상기 제1 버퍼층 상에 제1 절연층을 형성하는 단계;

상기 제1 절연층 상에 상기 표시 영역으로부터 연장된 게이트 배선 및 상기 게이트 배선을 덮는 제2 절연층을 순차적으로 형성하는 단계;

상기 벤딩 영역에 있는 상기 제1 보호부재를 노출시키 단계;

상기 노출된 제1 보호부재를 식각(etching)하는 단계;

상기 게이트 배선과 전지적으로 연결되도록 상기 패드 영역의 제2 절연층 및 상기 벤딩 영역의 제1 버퍼층 상에 연결 배선을 형성하는 단계; 및

상기 연결 배선을 덮는 제2 버퍼층을 형성하는 단계를 포함하는 플렉서블 표시장치 제조 방법.

# 청구항 11

제10 항에 있어서,

상기 플렉서블 표시장치의 제조 방법은, 상기 노출된 제1 보호부재를 식각하는 단계 후 상기 벤딩 영역에 있는 제1 버퍼층을 식각(etching)하는 단계를 더 포함하는 것을 특징으로 하는 플렉서블 표시장치 제조 방법.

#### 청구항 12

제11 항에 있어서,

상기 제1 버퍼층을 식각하는 단계는, 상기 제1 보호부재를 노출시키는 단계와 동일만 패터닝장비를 사용하여 식각(etching)하는 것을 특징으로 하는 플렉서블 표시장치 제조 방법.

### 청구항 13

제10 항에 있어서,

상기 제1 보호부재를 패터닝하는 단계는, 상기 제1 보호부재가 인접한 또 다른 제1 보호부재와 패드 영역 및 벤딩 영역에서 이격되도록 패터닝되는 것을 특징으로 하는 플렉서블 표시장치 제조 방법.

# 청구항 14

제10 항에 있어서,

상기 게이트 배선을 형성하는 단계는, 상기 패드 영역 및 벤딩 영역에서 상기 제1 절연층의 일 부분을 덮는 제2 보호부재를 형성하는 단계를 포함하는 것을 특징으로 하는 플렉서블 표시장치 제조 방법.

# 청구항 15

제14 항에 있어서,

상기 제1 보호부재를 노출시키는 단계는, 상기 벤딩 영역에서 상기 제2 보호부재로 덮이지 않은 상기 제1 절연 층 부분을 습식 식각(wet-etching)하는 것을 특징으로 하는 플렉서블 표시장치 제조 방법.

#### 청구항 16

제15 항에 있어서.

상기 노출된 제1 보호부재를 식각하는 단계는, 상기 제2 보호부재와 상기 노출된 제1 보호부재를 함께 식각하는 것을 특징으로 하는 플렉서블 표시장치 제조 방법.

# 청구항 17

제15 항에 있어서,

상기 노출된 제1 보호부재를 식각하는 단계는, 상기 패드 영역에 있는 상기 제2 보호부재와 상기 노출된 제1 보호부재를 함께 식각하여, 상기 제2 보호부재의 끝단이 상기 제2 절연층의 끝단보다 내측에 위치하도록 형성되는 것을 특징으로 하는 플렉서블 표시장치의 제조 방법.

# 발명의 설명

# 기 술 분 야

[0001] 본 명세서는 플렉서블 표시장치 및 이의 제조 방법에 관한 것이다.

### 배경기술

- [0002] 다양한 정보를 화면으로 구현해 주는 영상표시장치는 정보 통신 시대의 핵심 기술로 더 얇고 더 가볍고 휴대가 가능하면서도 고성능의 방향으로 발전하고 있다. 이에 유기발광 소자의 발광량을 제어하여 영상을 표시하는 유기발광 표시장치 등이 각광받고 있다.

- [0003] 유기발광 소자는 전극 사이의 얇은 발광층을 이용한 자발광 소자로 박막화가 가능하다는 장점이 있다. 일반적인 유기발광 표시장치는 기판에 화소구동 회로와 유기발광 소자가 형성된 구조를 갖고, 유기발광 소자에서 방출된 빛이 기판 또는 배리어층을 통과하면서 화상을 표시하게 된다.

- [0004] 유기발광 표시장치는 별도의 광원장치 없이 구현되기 때문에, 플렉서블(flexible) 표시장치로 구현되기에 용이하다. 이때, 플라스틱, 박막 금속(metal foil) 등의 플렉서블 재료가 유기발광 표시장치의 기판으로 사용된다.

- [0005] 한편, 유기발광 표시장치가 플렉서블(flexible) 표시장치로 구현되는 경우에, 그 유연한 성질을 이용하여 표시 장치의 여러 부분을 휘거나 구부리려는 연구가 수행되고 있다. 이러한 연구는 주로 새로운 디자인과 UI/UX를 위해 수행되고 있으며, 일각에서는 표시장치 모서리의 면적을 줄이기 위해 이러한 연구가 수행되기도 한다.

# 발명의 내용

# 해결하려는 과제

- [0006] 본 명세서는 제조 공정을 단순화한 플렉서블 표시장치 및 이의 제조방법을 제공하는 것을 목적으로 한다.

- [0007] 본 명세서의 과제들은 이상에서 언급한 과제들로 제한되지 않으며, 언급되지 않은 또 다른 과제들은 아래의 기

재로부터 당업자에게 명확하게 이해될 수 있을 것이다.

### 과제의 해결 수단

- [0008] 본 명세서의 일 실시예에 따라 플렉서블 표시장치가 제공된다. 플렉서블 표시장치는, 표시 영역, 표시 영역에서 연장된 패드 영역 및 패드 영역에서 연장된 벤딩 영역을 구비하는 플렉서블 기판, 플렉서블 기판 상에 배치되고, 복수 개의 층을 구비하며, 벤딩 영역에서의 두께가 벤딩 영역을 제외한 다른 영역에서의 두께보다 얇은 제1 버퍼층, 패드 영역에서 제1 버퍼층 상에 배치되는 제1 보호부재, 패드 영역에서, 제1 보호부재 상에 배치되는 제1 절연층, 제1 절연층 상에 배치되며, 표시 영역으로부터 연장되는 게이트 배선, 패드 영역에서 게이트 배선 상에 배치되는 제2 절연층, 게이트 배선과 전기적으로 연결되는 연결 배선 및 연결 배선을 덮는 제2 버퍼층을 포함하고, 연결 배선의 일 부분은 패드 영역에서 제2 절연층 상에 배치되며, 일 부분 이외의 부분은 벤딩 영역에서 제1 버퍼층 상에 배치된다.

- [0009] 제1 보호부재는, 인접한 또 다른 제1 보호부재와 이격되도록 구비될 수 있다.

- [0010] 제1 보호부재는, 벤딩 영역에서 제1 절연층과 제1 버퍼층의 일 부분이 동일한 패터닝장비로 제거될 수 있도록 구비될 수 있다.

- [0011] 플렉서블 표시장치는, 표시 영역에서 제1 버퍼층 상에 배치되는 박막트랜지스터 보호부재를 더 포함하고, 제1 보호부재는 박막 트랜지스터 보호부재와 동일한 물질일 수 있다.

- [0012] 플렉서블 표시장치는, 제1 절연층과 제2 절연층 사이에 배치되는 제2 보호부재를 더 포함할 수 있다.

- [0013] 제2 보호부재는, 게이트 배선과 동일한 물질일 수 있다.

- [0014] 제2 보호부재는, 제1 보호부재와 인접한 제1 보호부재 사이에서 플렉서블 기판이 노출되어, 이물이 존재하는 것을 방지하도록 구비될 수 있다.

- [0015] 제2 보호부재는, 연결 배선과 인접한 또 다른 연결 배선이 쇼트(short)되는 것을 방지할 수 있다.

- [0016] 제2 보호부재의 끝단은, 제2 절연층의 끝단보다 내측에 위치하도록 구비될 수 있다.

- [0017] 본 명세서의 일 실시예에 따른 플렉서블 표시장치의 제조 방법은 표시 영역, 표시 영역에서 연장된 패드 영역 및 패드 영역에서 연장된 벤딩 영역을 구비하는 플렉서블 기판 상에 복수 개의 충을 구비한 제1 버퍼충을 형성하는 단계, 패드 영역 및 벤딩 영역에 있는 제1 버퍼충의 일 부분 상에 제1 보호부재를 패터닝(patterning)하는 단계, 제1 보호부재를 덮도록, 제1 버퍼충 상에 제1 절연충을 형성하는 단계, 제1 절연충 상에 표시 영역으로부터 연장된 게이트 배선 및 게이트 배선을 덮는 제2 절연충을 순차적으로 형성하는 단계, 벤딩 영역에 있는 제1 보호부재를 노출시키 단계, 노출된 제1 보호부재를 식각(etching)하는 단계, 게이트 배선과 전지적으로 연결되도록 패드 영역의 제2 절연충 및 기 벤딩 영역의 제1 버퍼충 상에 연결 배선을 형성하는 단계 및 연결 배선을 덮는 제2 버퍼충을 형성하는 단계를 포함한다.

- [0018] 플렉서블 표시장치의 제조 방법은, 노출된 제1 보호부재를 식각하는 단계 후 벤딩 영역에 있는 제1 버퍼층을 식각(etching)하는 단계를 더 포함할 수 있다.

- [0019] 제1 버퍼층을 식각하는 단계는, 제1 보호부재를 노출시키는 단계와 동일만 패터닝장비를 사용하여 식각 (etching)할 수 있다.

- [0020] 제1 보호부재를 패터닝하는 단계는, 제1 보호부재가 인접한 또 다른 제1 보호부재와 패드 영역 및 벤딩 영역에 서 이격되도록 패터닝될 수 있다.

- [0021] 게이트 배선을 형성하는 단계는, 패드 영역 및 벤딩 영역에서 제1 절연층의 일 부분을 덮는 제2 보호부재를 형성하는 단계를 포함할 수 있다.

- [0022] 제1 보호부재를 노출시키는 단계는, 벤딩 영역에서 제2 보호부재로 덮이지 않은 제1 절연층 부분을 습식 식각 (wet-etching)할 수 있다.

- [0023] 노출된 제1 보호부재를 식각하는 단계는, 제2 보호부재와 노출된 제1 보호부재를 함께 식각할 수 있다.

- [0024] 노출된 제1 보호부재를 식각하는 단계는, 패드 영역에 있는 제2 보호부재와 노출된 제1 보호부재를 함께 식각하여, 제2 보호부재의 끝단이 제2 절연층의 끝단보다 내측에 위치하도록 형성될 수 있다.

[0025] 기타 실시예의 구체적인 사항들은 상세한 설명 및 도면들에 포함되어 있다.

# 발명의 효과

- [0026] 본 명세서의 실시예들은, 굴곡 영역을 1차 식각할 때와 2차 식각할 때 동일한 마스크를 사용하여 굴곡 영역 간의 균일도를 향상시킨 플렉서블 표시장치를 제공할 수 있다.

- [0027] 더 구체적으로, 본 명세서의 실시예들은, 굴곡 영역을 1차 식각할 때와 2차 식각할 때 동일한 마스크 장비를 사용하여 제조 공정이 단순화된 플렉서블 표시장치를 제공할 수 있다.

- [0028] 이에 따라 본 명세서의 실시예에 따른 유기발광 표시장치는 향상될 수 있다. 본 명세서의 실시예들에 따른 효과는 이상에서 예시된 내용에 의해 제한되지 않으며 더욱 다양한 효과들이 본 명세서 내에 포함되어 있다.

# 도면의 간단한 설명

- [0029] 도 1은 전자장치에 포함될 수 있는 예시적인 플렉서블 표시장치를 도시한다.

- 도 2는 평평한 부분과 굴곡 부분의 예시적인 배치를 나타낸다.

- 도 3a 및 3b는 본 명세서의 실시예에 따른 플렉서블 표시장치의 표시 영역의 배치를 나타낸다.

- 도 4는 본 명세서의 일 실시예에 따른 플렉서블 표시장치의 적충 구조를 개략적으로 나타낸 단면도이다.

- 도 5는 본 명세서의 실시예에 따른 굴곡 패턴의 평면도 및 단면도이다.

- 도 6a 내지 6c는 플렉서블 표시장치에서 구성 요소들의 예시적인 배치를 보여주는 개략적인 단면도이다.

- 도 7a 및 7b는 다층 구조 도선의 예시적인 구조를 도시한다.

- 도 8은 변형 저감 설계의 몇몇 예를 도시한다.

- 도 9a 및 9b는 다수의 부배선을 갖는 배선 구조의 개략적인 도면을 나타낸다.

- 도 10은 다이아몬드 배선 디자인을 갖는 여러 예시적인 배선 구조를 도시한다.

- 도 11a 및 11b는 예시적인 배선 구조의 개략적인 단면도를 나타낸다.

- 도 12a 및 12b는 수정된 부분을 갖는 예시적인 변형 저감 배선 구조의 개략적인 도면을 나타낸다.

- 도 13은 본 명세서의 일 실시예에 따른 플렉서블 표시장치의 단면도이다.

- 도 14a 내지 도 14q는 본 명세서의 일 실시예에 따른 플렉서블 표시장치의 제조 단계를 나타낸 도면이다.

- 도 15는 본 명세서의 또 다른 일 실시예에 따른 플렉서블 표시장치의 단면도이다.

- 도 16은 본 명세서의 또 다른 일 실시예에 따른 플렉서블 표시장치의 단면도이다.

- 도 17a 내지 도 17r은 본 명세서의 또 다른 일 실시예에 따른 플렉서블 표시장치의 제조 순서를 나타내는 도면이다.

- 도 18a 내지 도 18r은 본 명세서의 또 다른 일 실시예에 따른 플렉서블 표시장치의 제조 순서를 나타내는 도면 이다.

# 발명을 실시하기 위한 구체적인 내용

- [0030] 본 발명의 이점 및 특징, 그리고 그것들을 달성하는 방법은 첨부되는 도면과 함께 상세하게 후술되어 있는 실시 예들을 참조하면 명확해질 것이다. 그러나 본 발명은 이하에서 개시되는 실시 예들에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 것이며, 단지 본 실시 예들은 본 발명의 개시가 완전하도록 하며, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 발명의 범주를 완전하게 알려주기 위해 제공되는 것이며, 본 발명은 청구항의 범주에 의해 정의될 뿐이다.

- [0031] 본 발명의 실시 예를 설명하기 위한 도면에 개시된 형상, 크기, 비율, 각도, 개수 등은 예시적인 것이므로 본 발명이 도시된 사항에 한정되는 것은 아니다. 명세서 전체에 걸쳐 동일 참조 부호는 동일 구성 요소를 지칭한다. 또한, 본 발명을 설명함에 있어서, 관련된 공지 기술에 대한 구체적인 설명이 본 발명의 요지를 불필

요하게 흐릴 수 있다고 판단되는 경우 그 상세한 설명은 생략한다.

- [0032] 본 명세서에서 언급된 '포함한다', '갖는다', '이루어진다' 등이 사용되는 경우 '~만'이 사용되지 않는 이상 다른 부분이 추가될 수 있다. 구성 요소를 단수로 표현한 경우에 특별히 명시적인 기재 사항이 없는 한 복수를 포함하는 경우를 포함한다.

- [0033] 구성 요소를 해석함에 있어서, 별도의 명시적 기재가 없더라도 오차 범위를 포함하는 것으로 해석한다.

- [0034] 위치 관계에 대한 설명일 경우, 예를 들어, '~상에', '~상부에', '~하부에', '~옆에' 등으로 두 부분의 위치 관계가 설명되는 경우, '바로' 또는 '직접'이 사용되지 않는 이상 두 부분 사이에 하나 이상의 다른 부분이 위치할 수도 있다.

- [0035] 시간 관계에 대한 설명일 경우, 예를 들어, '~후에', '~에 이어서', '~다음에', '~전에' 등으로 시간적 선후 관계가 설명되는 경우, '바로' 또는 '직접'이 사용되지 않는 이상 연속적이지 않은 경우도 포함할 수 있다.

- [0036] 제1, 제2 등이 다양한 구성요소들을 서술하기 위해서 사용되나, 이들 구성요소들은 이들 용어에 의해 제한되지 않는다. 이들 용어들은 단지 하나의 구성요소를 다른 구성요소와 구별하기 위하여 사용하는 것이다. 따라서, 이하에서 언급되는 제1 구성요소는 본 발명의 기술적 사상 내에서 제2 구성요소일 수도 있다.

- [0037] "X축 방향", "Y축 방향" 및 "Z축 방향"은 서로 간의 관계가 수직으로 이루어진 기하학적인 관계만으로 해석되어 서는 아니 되며, 본 발명의 구성이 기능적으로 작용할 수 있는 범위 내에서보다 넓은 방향성을 가지는 것을 의미할 수 있다.

- [0038] "적어도 하나"의 용어는 하나 이상의 관련 항목으로부터 제시 가능한 모든 조합을 포함하는 것으로 이해되어야한다. 예를 들어, "제 1 항목, 제 2 항목 및 제 3 항목 중에서 적어도 하나"의 의미는 제 1 항목, 제 2 항목 또는 제 3 항목 각각 뿐만 아니라 제 1 항목, 제 2 항목 및 제 3 항목 중에서 2개 이상으로부터 제시될 수 있는모든 항목의 조합을 의미할 수 있다.

- [0039] 본 명세서에서 플렉서블(flexible) 디스플레이 장치는 연성이 부여된 디스플레이 장치를 의미하는 것으로, 굽힘이 가능한(bendable) 디스플레이 장치, 롤링이 가능한(rollable) 디스플레이 장치, 깨지지 않는(unbreakable) 디스플레이 장치, 접힘이 가능한(foldable) 디스플레이 장치 등과 동일한 의미로 사용될 수 있다. 본 명세서에서 플렉서블 유기 발광 표시장치는 다양한 플렉서블 디스플레이 장치 중 일 예이다.

- [0040] 본 발명의 여러 실시 예들의 각각 특징들이 부분적으로 또는 전체적으로 서로 결합 또는 조합 가능하고, 기술적으로 다양한 연동 및 구동이 가능하며, 각 실시 예들이 서로에 대하여 독립적으로 실시 가능할 수도 있고 연관관계로 함께 실시할 수도 있다.

- [0041] 도면에서 나타난 각 구성의 크기 및 두께는 설명의 편의를 위해 도시된 것이며, 본 발명이 도시된 구성의 크기 및 두께에 반드시 한정되는 것은 아니다. 이하, 첨부된 도면을 참조하여 본 발명의 다양한 실시예들을 상세히 설명한다.

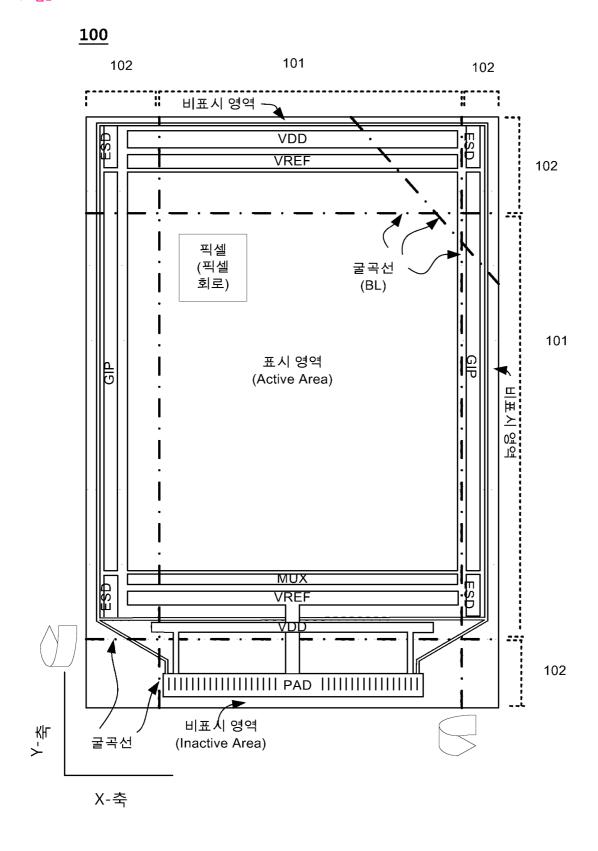

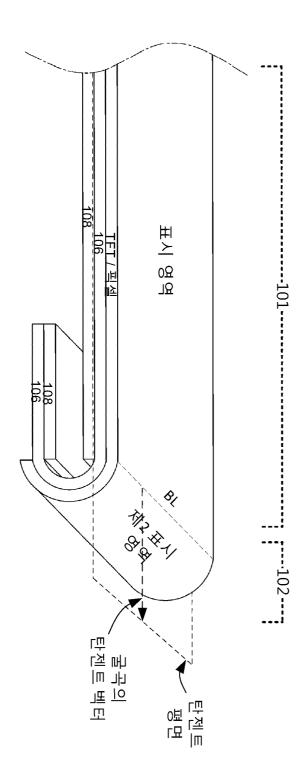

- [0042] 도 1은 전자장치에 포함될 수 있는 예시적인 플렉서블 표시장치를 도시한다.

- [0043] 도 1을 참조하면, 상기 플랙서블 표시장치(100)는 적어도 하나의 표시 영역(active area)을 포함하고, 상기 표시 영역에는 픽셀들의 어레이(array)가 형성된다. 하나 이상의 비표시 영역(in표시 영역)이 상기 표시 영역의 주위에 배치될 수 있다. 즉, 상기 비표시 영역은, 표시 영역의 하나 이상의 측면에 인접할 수 있다. 도 1에서, 상기 비표시 영역은 사각형 형태의 표시 영역을 둘러싸고 있다. 그러나, 표시 영역의 형태 및 표시 영역에 인접한 비표시 영역의 형태/배치는 도 1에 도시된 예에 한정되지 않는다. 상기 표시 영역 및 상기 비표시 영역은, 상기 플렉서블 표시장치(100)를 탑재한 전자장치의 디자인에 적합한 형태일 수 있다. 상기 표시 영역의 예시적형태는 오각형, 육각형, 원형, 타원형 등이다.

- [0044] 상기 표시 영역 내의 각 픽셀은 픽셀 회로와 연관될 수 있다. 상기 픽셀 회로는, 백플레인(backplane) 상의 하나 이상의 스위칭 트랜지스터 및 하나 이상의 구동 트랜지스터를 포함할 수 있다. 각 픽셀 회로는, 상기 비표시 영역에 위치한 게이트 드라이버 및 데이터 드라이버와 같은 하나 이상의 구동 회로와 통신하기 위해, 게이트 라인 및 데이터 라인과 전기적으로 연결될 수 있다.

- [0045] 상기 구동 회로는, 도 1에 도시된 것처럼, 상기 비표시 영역에 TFT(thin film transistor)로 구현될 수 있다. 이러한 구동 회로는 GIP(gate-in-panel)로 지칭될 수 있다. 또한, 데이터 드라이버 IC와 같은 몇몇 부품들은, 분리된 인쇄 회로 기판에 탑재되고, FPCB(flexible printed circuit board), COF(chip-on-film), TCP(tape-

carrier-package) 등과 같은 회로 필름을 이용하여 상기 비표시 영역에 배치된 연결 인터페이스(패드/범프, 핀등)와 결합될 수 있다. 상기 비표시 영역은 상기 연결 인터페이스와 함께 구부러져서, 상기 인쇄 회로(COF, PCB 등)는 상기 플렉서블 표시장치(100)의 뒤편에 위치될 수 있다.

- [0046] 상기 플렉서블 표시장치(100)는, 다양한 신호를 생성하거나 표시 영역내의 픽셀을 구동하기 위한, 다양한 부가 요소들 포함할 수 있다. 상기 픽셀을 구동하기 위한 부가 요소는 인버터 회로, 멀티플렉서, 정전기 방전 회로 (electro static discharge) 등을 포함할 수 있다. 상기 플렉서블 표시장치(100)는 픽셀 구동 이외의 기능과 연관된 부가 요소도 포함할 수 있다. 예를 들어, 상기 플렉서블 표시장치(100)는 터치 감지 기능, 사용자 인증 기능(예: 지문 인식), 멀티 레벨 압력 감지 기능, 촉각 피드백(tactile feedback) 기능 등을 제공하는 부가 요소들을 포함할 수 있다. 상기 언급된 부가 요소들은 상기 비표시 영역 및/또는 상기 연결 인터페이스와 연결된 외부 회로에 위치할 수 있다.

- [0047] 상기 플렉서블 표시장치(100)의 여러 부분들은 굴곡선(BL)을 따라 구부러질 수 있다. 상기 굴곡선(BL)은 수평으로(예: 도 1의 X 방향), 수직으로(예: 도 1의 Y 방향), 또는 대각선으로 연장될 수 있다 따라서, 상기 플렉서블 표시장치(100)는, 요구되는 디자인에 기초하여, 수평, 수직, 대각선 방향의 조합으로 구부러질 수 있다.

- [0048] 언급한 대로, 상기 플렉서블 표시장치(100)의 하나 이상의 모서리(edge)는, 상기 굴곡선(BL)을 따라 중앙 부분 (central portion, 101)에서 멀어지도록 구부러질 수 있다. 비록 상기 굴곡선(BL)이 상기 플렉서블 표시장치(100)의 모서리와 가깝게 위치하도록 도시되었지만, 상기 굴곡선(BL)은 상기 중앙 부분(101)을 가로질러 연장되거나, 상기 플렉서블 표시장치(100)의 하나 이상의 꼭지점(corner)에서 대각선으로 연장될 수 있다. 이러한 구조는 상기 플렉서블 표시장치(100)가 폴더블(foldable) 표시장치가 되거나, 또는 접히는 양면에 표시가 이뤄지는 표시장치가 되도록 할 수 있다.

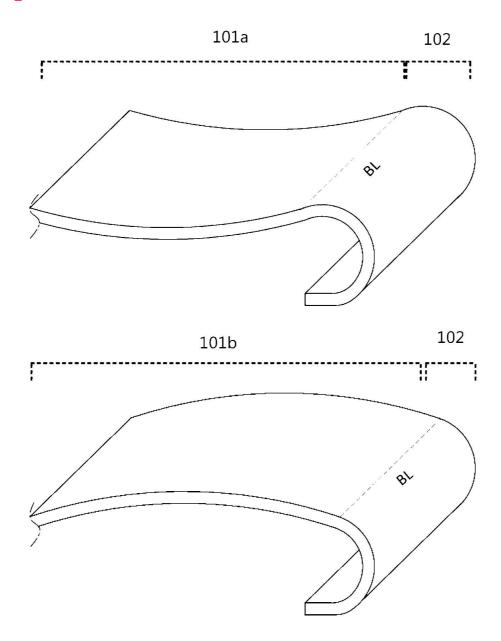

- [0049] 상기 플렉서블 표시장치(100)의 하나 이상의 부분이 구부러질 수 있으므로, 상기 플렉서블 표시장치(100)는 실 질적으로 평평한(flat) 부분 및 굴곡진 부분으로 정의될 수 있다. 플렉서블 표시장치(100)의 일 부분은 실질적으로 평평(flat)한, 중앙 부분(101)으로 지칭될 수 있다. 플렉서블 표시장치(100)의 일 부분은 소정의 각도로 구부러지며, 이러한 부분은 굴곡 부분(102)으로 지칭될 수 있다. 상기 굴곡 부분(102)은, 소정의 굴곡 반지름으로 실제로 휘어지는 굴곡 구간(bended section)을 포함한다.

- [0050] "실질적으로 평평한" 이라는 용어에는 완벽히 평평하지는 않은 부분도 포함된다. 예를 들어, 도 2에 묘사된 오목한 중앙 부분(101a) 및 볼록한 중앙 부분(101b)도 어떤 실시예에서는 실질적으로 평평한 부분으로 기술될 수 있다. 도 2에서, 하나 이상의 굴곡 부분(102)이 오목한 중앙 부분(101a) 또는 볼록한 중앙 부분(101b)의 옆에 존재하고, 굴곡선(BL)을 따라 굴곡 축에 대한 각도를 갖고 안쪽 또는 바깥쪽으로 구부러진다. 굴곡 부분(102)의 굴곡 반지름은 중앙 부분(101a, 101b)의 굴곡 반지름보다 작다. 다시 말해서, "실질적으로 평평한 부분"이라는 용어는 인접한 구간보다 더 작은 곡률을 갖는 부분을 의미한다.

- [0051] 굴곡선(BL)의 위치에 따라서 굴곡선의 일 측에 있는 부분은 플렉서블 표시장치(100)의 중앙을 향해 위치하는 반면, 굴곡선의 타 측에 있는 부분은 플렉서블 표시장치(100)의 모서리을 향해 위치한다. 플렉서블 표시장치(100)의 중앙을 향해 놓이는 부분은 중앙 부분이라 언급될 수 있고 플렉서블 표시장치(100)의 모서리를 향해 놓이는 부분은 모서리 부분이라 언급될 수 있다. 항상 그런 것은 아니지만, 플렉서블 표시장치(100)의 중앙부분은 실질적으로 평평하고, 모서리 부분은 굴곡 부분일수 있다. 실질적으로 평평한 부분은 모서리 부분에도 위치할수 있다는 점은 언급되어야 한다. 그리고, 플렉서블 표시장치(100)의 몇몇 형상에서, 굴곡 구간은 두 개의 실질적으로 평평한 부분 사이에 놓일 수 있다.

- [0052] 언급한 대로, 비표시 영역을 구부리면, 비표시 영역이 표시장치의 앞면에서는 안보이거나 최소로만 보이게 된다. 비표시 영역 중 표시장치의 앞면에서 보이는 일부는 베젤(bezel)로 가려질 수 있다. 상기 베젤은 독자적인 구조물, 또는 하우징이나 다른 적합한 요소로 형성될 수 있다. 비표시 영역 중 표시장치의 앞면에서 보이는일부는 블랙 잉크(예: 카본 블랙으로 채워진 폴리머)와 같은 불투명한 마스크 층 아래에 숨겨질 수도 있다. 이러한 불투명한 마스크 층은 플랙서블 표시장치(100)에 포함된 다양한 층(터치센서층, 편광층, 덮개층 등) 상에 마련될 수 있다.

- [0053] 몇몇 실시예에서 플렉서블 표시장치(100)의 굴곡 부분은, 이미지를 표시할 수 있는 표시 영역을 포함할 수 있다. 이러한 표시 영역을 이하에서는 제2 표시 영역이라 호칭한다. 즉, 표시 영역의 적어도 일부 픽셀이 굴곡 부분에 포함되도록 굴곡선(BL)이 표시 영역 내에 놓일 수 있다.

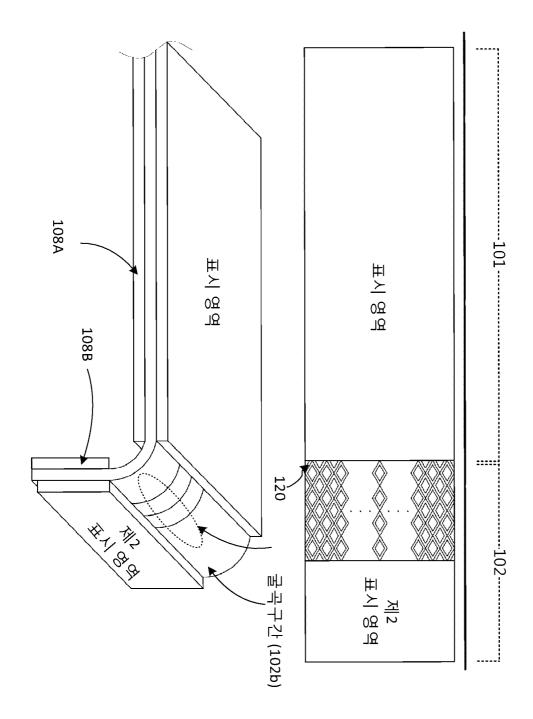

- [0054] 도 3a 및 3b는 각각 본 명세서의 실시예에 따른 플렉서블 표시장치(100)의 표시 영역의 배치를 나타낸다.

- [0055] 도 3a의 형상에서, 제2 표시 영역 내의 픽셀 매트릭스는, 중앙 부분(101)의 표시 영역으로부터 연속적으로 연장될 수 있다. 또 다르게는, 도 3b의 형상에서, 굴곡 부분(102) 내의 제2 표시 영역과 중앙 부분(101) 내의 표시 영역은, 굴곡 구간을 사이에 두고 서로 분리될 수 있다. 중앙 부분(101)과 굴곡 부분(102)은 몇몇 부품들은, 굴곡 구간을 가로질러 놓인 하나 이상의 도선(120)을 통해 전기적으로 연결될 수 있다.

- [0056] 제2 표시 영역의 픽셀과 중앙 표시 영역의 픽셀은 구동 회로(예: 게이트 드라이버, 데이터 드라이버 등)에 의해 마치 동일 매트릭스에 있는 것처럼 구동될 수 있다. 이때, 제2 표시 영역의 픽셀과 중앙 표시 영역의 동일한 구동 회로들에 의해 동작될 수 있다. 예를 들어, 중앙 표시 영역의 N번째 행 픽셀과 제2 표시 영역의 N번째 행 픽셀은, 같은 게이트 드라이버로부터 게이트 신호를 수신하도록 구비될 수 있다. 도 3b와 같이, 굴곡 구간을 가로 지르는 게이트 배선의 일부 또는 상기 두 표시 영역들의 게이트 배선을 연결하는 브릿지(bridge)는 변형 저감형상을 가질 수 있다.

- [0057] 제2 표시 영역의 기능에 따라서는, 제2 표시 영역의 픽셀이 중앙 표시 영역의 픽셀과 분리되어 구동될 수도 있다. 즉, 제2 표시 영역의 픽셀은, 표시 영역의 픽셀 매트릭스와는 분리된 독립된 매트릭스로 구동회로에 인식될수 있다. 이 경우, 제2 표시 영역의 픽셀은, 중앙 표시 영역의 픽셀에 신호를 공급하는 구동회로와는 다른 하나이상의 분리된 구동회로로부터 신호를 수신할 수 있다.

- [0058] 그 형상에 상관없이, 굴곡 부분의 제2 표시 영역은 플렉서블 표시장치(100)의 2차 표시 영역으로 기능할 수 있다. 또한, 제2 표시 영역의 크기는 특별히 제한되지 않는다. 제2 표시 영역의 크기는 전자장치에 내장된 기능에 의존할 수 있다. 예를 들어, 제2 표시 영역은 GUI(graphical user interface), 버튼, 문자 메시지 등과 같은 이미지 및/또는 문자를 제공하는 데에 사용될 수 있다. 몇몇 경우에, 제2 표시 영역은 여러 목적(예: 상태 표시)의 다양한 색의 빛을 제공하는 데에 사용될 수 있고, 이때 제2 표시 영역의 크기는 중앙 부분 내의 표시 영역만큼 클 필요는 없다.

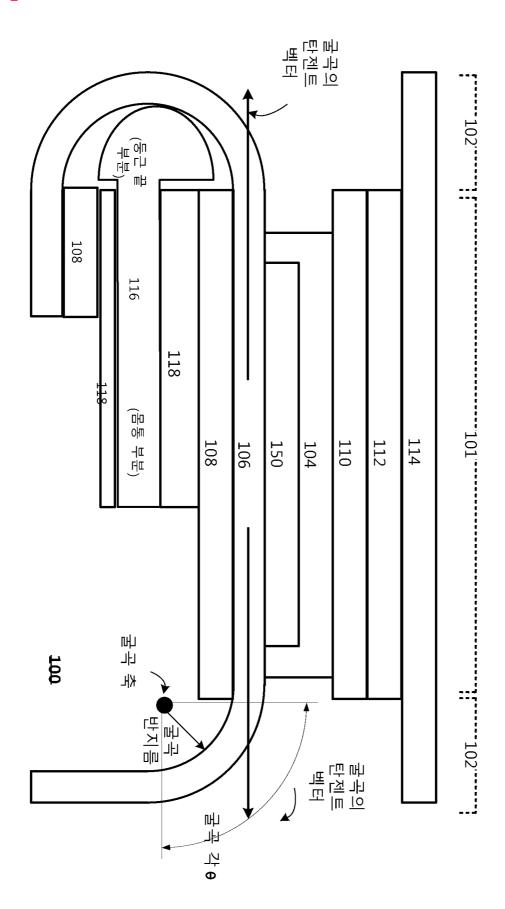

- [0059] 도 4는 본 명세서의 일 실시예에 따른 플렉서블 표시장치의 적층 구조를 개략적으로 나타낸 단면도이다.

- [0060] 도 4에서는 설명의 편의를 위하여, 상기 중앙 부분(central portion, 101)은 실질적으로 평평하고, 상기 굴곡 부분(102)은 상기 플렉서블 표시장치(100)의 모서리에 있는 것으로 도시되었다. 도시된 것처럼, 하나 이상의 굴 곡 부분(102)은, 굴곡축에 대한 굴곡각 Θ 및 굴곡 반지름 R을 갖고 상기 중앙 부분(101)으로부터 바깥쪽으로 구부러질 수 있다. 상기 각 굴곡 부분(102)의 크기는 동일할 필요는 없다. 즉, 각 굴곡 부분(102)에서 굴곡선 (BL)으로부터 베이스 층(106)의 외곽 모서리까지의 길이는 서로 다를 수 있다. 또한, 굴곡 축 둘레의 굴곡 각 Θ 및 상기 굴곡축으로부터의 곡률 반지름 R은 굴곡 부분(102)마다 다를 수 있다.

- [0061] 도 4에 도시된 예에서, 상기 굴곡 부분(102)의 오른쪽은 90°의 굴곡각 θ를 갖고, 상기 굴곡 부분(102)은 실질 적으로 평면인 구간을 포함한다. 굴곡 부분(102)은 더 큰 굴곡각 θ로 구부러져, 상기 플렉서블 표시장치(100)의 왼쪽 굴곡 부분(102)과 같이, 굴곡 부분(102)의 일 부분이 중앙 부분(101)의 아래로 갈 수 있다. 또한, 굴곡 부분(102)은 90°이하의 굴곡각 θ로 구부러질 수도 있다.

- [0062] 몇몇 실시예에서, 상기 굴곡 부분(102)의 곡률 반지름(radius of curvatures)은 약 0.1 mm에서 약 10 mm 사이일 수 있고, 바람직하게는 약 0.1 mm에서 약 5 mm 사이 또는, 약 0.1 mm에서 약 1 mm 사이, 또는 약 0.1 mm에서 약 0.5 mm 사이일 수 있다. 몇몇 실시예에서, 굴곡 부분(102)에서의 곡률 반지름은 0.5 mm보다 작을 수 있다.

- [0063] 상기 플렉서블 표시장치(100)의 특정 부분에서의 강도 및/또는 견고성을 증가시키기 위해, 하나 이상의 지지층 (108)이 상기 베이스 층(106)의 하부에 제공될 수 있다. 예를 들어, 상기 지지층(108)은 상기 중앙 부분(101)의 아래쪽 면에 제공될 수 있다. 상기 지지층(108)은 더 큰 유연성이 필요한 굴곡 구간에는 제공되지 않을 수 있다. 상기 지지층(108)은 상기 중앙 부분(101) 아래에 위치한 굴곡 부분(102) 상에 제공될 수 있다. 특정 부분의 강도를 높이면, 상기 플렉서블 표시장치(100)에 다양한 부품들을 정확히 구성하고 배치하는 데에 도움이 된다. 상기 베이스 층(106)에 상기 지지층(108)보다 더 큰 탄성을 갖는 경우에, 상기 지지층(108)은 상기 베이스 층(106)에서의 갈라짐(crack) 발생을 억제하는 데에 기여할 수 있다.

- [0064] 상기 베이스 충(106) 및 상기 지지충(108)은 폴리이미드, 폴리에틸렌 나프탈레이트(PEN), 폴리에틸렌 테레플레이트, 기타 적합한 폴리머의 조합으로 구성된 박형 플라스틱 필름으로 만들어질 수 있다. 상기 베이스 충(106) 및 상기 지지충(108)의 형성에 사용될 수 있는 다른 적합한 물질은 박형 유리, 유전체로 차폐된 금속 호일 (metal foil), 다충 폴리머, 나노 파티클 또는 마이크로 파티클과 조합된 고분자 물질이 포함된 고분자 필름 등일 수 있다. 상기 플렉서블 표시장치(100)의 여러 부분에 제공되는 지지충(108)이 모두 동일한 물질일 필요는

없다. 예를 들어, 박형 유리층이 중앙 부분(101)에 대한 지지층(108)으로 사용되면서, 플라스틱 필름이 모서리 부분에 대한 지지층(108)으로 사용될 수 있다.

- [0065] 상기 베이스 층(106) 및 상기 지지층(108)의 두께 또한 상기 플렉서블 표시장치(100)의 디자인에 있어서 고려할 사항이다. 한 관점에서, 만약 상기 베이스 층(106)이 과도한 두께를 갖는다면, 상기 베이스 층(106)이 작은 곡률 반경으로 구부러지는 것이 어렵다. 또, 상기 베이스 층(106)의 과도한 두께는, 굴곡 시에 그 위에 배치된 부품에 기계적 스트레스를 가중시킨다. 그러나, 다른 관점에서, 상기 베이스 층(106)이 너무 얇다면, 그 위에 배치된 부품들을 지탱할 기판으로서 너무 약하다.

- [0066] 이와 같은 요구 조건을 만족시키기 위해, 상기 베이스 층(106)은 약 5μm에서 약 50μm의 두께를 가질 수 있다, 바람직하게는, 상기 베이스 층(106)은 약 5μm에서 약 30μm의 범위나, 약 5μm에서 약 16μm의 범위의 두께를 가질 수 있다. 상기 지지층(108)은 약 100μm에서 약 125μm, 약 50μm에서 약 150μm, 약 75μm에서 200μm, 150μm 이하, 또는 100μm 이상의 두께를 가질 수 있다.

- [0067] 일 실시예에서, 약  $10 \, \mu$  m에서 약  $16 \, \mu$  m 사이의 두께를 갖는 폴리이미드 층이 상기 베이스 층(106)으로 사용되고, 약  $50 \, \mu$  m에서 약  $125 \, \mu$  m 사이의 두께를 갖는 폴리에틸렌 테레프탈레이트(PET) 층이 상기 지지층(10 8)으로 사용된다. 다른 실시예에서, 약  $10 \, \mu$  m에서 약  $16 \, \mu$  m 사이의 두께를 갖는 폴리이미드 층이 상기 베이스 층(106)으로 사용되고, 약  $50 \, \mu$  m에서 약  $200 \, \mu$  m 사이의 두께를 갖는 박형 유리가 상기 지지층(108)으로 사용된다. 또 다른 실시예에서는, 박형 유리가 상기 베이스 층(106)으로 사용되고, 상기 베이스 층(106)은 파손을 피하기 위해 상기 지지층(108)으로 기능하는 폴리이미드 층을 가진다.

- [0068] 제조 과정에서 상기 플렉서블 표시장치(100)의 몇몇 부분들은 외부 광에 노출될 수 있다. 상기 부품들을 제조하는데 쓰이는 물질 또는 상기 부품들 그 자체는, 플렉서블 표시장치(100) 제조 중의 광 노출에 의해 원치 않는 상태 변화(예: TFT에서의 임계 전압 천이 등)를 겪는다. 상기 플렉서블 표시장치(100)의 몇몇 부분은, 다른 부분에 비하여 상기 외부 광에 과도하게 노출된다. 그리고 이는 표시 불균일(예: mura, shadow defects 등)을 야기할 수 있다. 이러한 문제를 최소화하기 위해, 상기 베이스 층(106) 및/또는 상기 지지층(108)은, 외부 광의양을 줄일 수 있는 물질을 하나 이상 포함할 수 있다.

- [0069] 예를 들어, 상기 광 차단 물질은, 상기 베이스 충(106)의 구성 물질(폴리이미드, 기타 폴리머)에 혼합된 염화 카본 블랙이다. 이와 같이 상기 베이스 충(106), 광 차단 기능을 제공하는 셰이드(shade)를 가진 폴로이미드로 부터 형성될 수 있다. 이러한 베이스 충(106)은, 상기 플렉서블 표시장치(100)의 전면에서 입사하는 외부 광의 반사를 줄임으로써, 가시성(visibility)을 향상시킬 수 있다.

- [0070] 상기 베이스 층(106) 대신에, 상기 플렉서블 표시장치(100)의 후면(즉, 상기 지지층(108)이 부착된 면)으로부터 입사하는 광의 양을 줄이기 위해, 상기 지지층(108)이 광 차단 물질을 포함할 수도 있다. 상기 지지층(108)의 구성 물질은, 위에서 설명한 것과 유사하게, 하나 이상의 광 차단 물질과 혼합될 수 있다. 더 나아가, 상기 베이스 층(106) 및 상기 지지층(108)이 모두 하나 이상의 광 차단 물질을 포함할 수 있다. 여기서, 상기 베이스 층(106) 및 상기 지지층(108)에 사용되는 광 차단 물질이 동일할 필요는 없다.

- [0071] 상기 베이스 충(106) 및 상기 지지충(108)이 불요한 외부 광을 차단하게 만드는 것은 표시 균일성을 향상시키고 반사를 감소시키지만, 부품들을 정확하게 배치하기 위한 정렬 표식(alignment marks), 또는 제조 공정의 수행을 위한 정렬 표식을 인식하는 것이 어려워질 수 있다. 예를 들어, 상기 충(layer)들의 배치는 중첩 부분의 외곽을 비교하여 결정되기 때문에, 부품들을 상기 베이스 충(106) 상에 정확히 배치하거나, 또는 상기 플렉서블 표시장치(100)의 구부러짐 중에 정렬하는 것이 더 어려울 수 있다. 이에 더하여, 만약 상기 베이스 충(106) 및/또는 상기 지지충(108)이 과도한 범위의 광 스펙트럼(즉, 가시광, 자외선, 적외선 스펙트럼의 과장)을 차단한다면 상기 플렉서블 표시장치(100)내의 잔해 또는 이물질을 확인하는 것이 문제될 수 있다.

- [0072] 따라서, 몇몇 실시예에서, 상기 베이스 층(106) 및/또는 상기 지지층(108)에 포함되는 광 차단 물질은, 특정 편광 및/또는 하나 이상의 제조/검사 과정에서 사용되는 특정 파장 범위 이내의 광은 통과하도록 구성된다. 일 예로서, 상기 지지층(108)은 품질 검사 및/또는 정렬 과정에서 사용되는 광(예: UV, IR)은 통과시키되, 가시광 파장 범위의 광은 차단할 수 있다. 상기 제한된 범위의 파장은, 상기 베이스 층(106)이 광 차단 물질을 포함하였을 경우에. 베이스 층(106)에 부착된 인쇄 회로 필름에 의해 생기는 음영이 야기하는, 표시장치의 불균일성 문제를 줄이는데 도움이 된다.

- [0073] 상기 베이스 층(106) 및 상기 지지층(108)은 특정 형태의 광을 차단시키거나 통과시키는 일을 함께 수행할 수 있다. 예를 들어, 상기 지지층(108)는 해당 광이 상기 베이스 층(106)을 통과하지 못하도록, 광의 편광을 변화

시킬 수 있다. 이와 같이, 특정 형태의 광은, 상기 플렉서블 표시장치(100)의 제조 중에 여러 가지 목적을 위해 상기 지지층(108)을 통과할 수 있지만, 상기 베이스 층(106)의 반대 면에 배치된 부품들에 불필요한 영향을 주지 않도록, 상기 베이스 층(106)을 통과할 수는 없다.

- [0074] 상기 플렉서블 표시장치(100)의 백플레인(backplane)이 상기 베이스 층(106) 상에 구현된다. 몇몇 실시예에서, 상기 플렉서블 표시장치(100)의 백플레인은, LTPS(low temperature poly silicon) 반도체 층을 활성층(active layer)으로서 사용한 TFT와 함께 구현된다. 일 예에서, 상기 베이스 층(106) 상의 픽셀 회로 및 구동 회로(예: GIP)들은 NMOS LTPS TFT로 구현될 수 있다. 다른 예에서, 상기 상기 플렉서블 표시장치(100)의 백플레인은 NMOS LTPS TFT 및 PMOS LTPS TFT의 조합으로 구현될 수 있다. 예를 들어, 상기 베이스 층(106) 상의 구동 회로(예: GIP)는, 게이트 라인 상의 스캔 신호를 제어하기 위한 배선 수를 줄이기 위해, 하나 이상의 CMOS 회로를 포함할 수 있다.

- [0075] 그리고, 몇몇 실시예에서, 상기 플렉서블 표시장치(100)는, 비표시 영역 및/또는 표시 영역 내의 픽셀 회로에 구동 회로들을 구현하기 위해, 여러 종류의 TFT를 채용할 수 있다. 즉, 상기 플렉서블 표시장치(100)의 백플레인을 구현하기 위해, 산화물(oxide) 반도체 TFT 및 LTPS TFT의 조합이 사용될 수 있다. 상기 백플레인에서, 상기 TFT의 유형은 동작 조건 및/또는 관련된 회로 내의 TFT 요구 조건에 따라서 선택될 수 있다

- [0076] LTPS TFT는 일반적으로 작은 프로파일(profile)에서도 우수한 캐리어(carrier) 이동도(mobility)를 나타내어, 집적된 구동 회로를 구현하는데 적합하다. 상기 우수한 캐리어 이동도는 LTPS TFT를 빠른 동작 속도를 요하는 부품에 이상적으로 만든다. 상기 언급된 장점에도 불구하고, 다결정 실리콘 반도체 층의 그레인 경계(grain boundary) 때문에 초기 임계 전압(initial threshold voltage)이 LTPS TFT들 간에 다를 수 있다.

- [0077] IGZO(indium-gallium-zinc-oxide) 반도체 층(이하에서는 산화물 TFT로 지칭)과 같은 산화물(oxide) 기반의 반도체 층을 채용한 TFT는, 상기 LTPS TFT와 많은 측면에서 다르다. 상기 LTPS TFT에 비하여 낮은 이동도에도 불구하고, 상기 산화물 TFT는 일반적으로 전력 효율에서 상기 LTPS TFT보다 더 유리하다. 오프 상태에서 상기 산화물 TFT의 낮은 누설 전류(leakage current)는 액티브 상태를 더 오래 지속시킨다. 이는 픽셀을 구동하기 위해 높은 프레임 레이트(frame rate)가 필요하지 않을 때, 감소된 프레임 레이트에서 픽셀을 구동하는 데에 중요한 장점이 될 수 있다.

- [0078] 일 예로서, 상기 플렉서블 표시장치(100)는 표시 영역의 전부 또는 일부의 픽셀이 특정 조건 하에서는 감소된 프레임 레이트에서 구동되는 특성을 지닐 수 있다. 이러한 설정에서, 상기 픽셀은, 상기 플렉서블 표시장치 (100)에 표시되는 컨텐츠에 의존하여 감소된 비율로 새로 고침(refresh)될 수 있다. 또한, 정지된 이미지 데이터(예: 사용자 인터페이스, 텍스트)를 표시하는 일부의 표시 영역은, 빨리 변하는 이미지 데이터(예: 영화)를 표시하는 다른 부분의 표시 영역에 비해 더 낮은 비율로 새로 고침될 수 있다. 감소된 새로 고침 비율로 구동되는 픽셀은, 데이터 신호가 픽셀에 제공되지 않는 공백 기간(blank period)이 증가할 수 있다. 이는 픽셀에 같은 이미지 데이터를 제공함으로써 소비되는 전력을 최소화할 것이다. 이러한 실시예에서, 픽셀 회로 및/또는 상기 구동 회로를 구현하는 몇몇 TFT는, 상기 공백 기간 동안의 누설 전류를 최소화하기 위해, 산화물 TFT로 형성될 수 있다 상기 픽셀 회로 및/또는 상기 구동 회로에서 누설 전류를 줄임으로써, 상기 픽셀은 디스플레이가 감소된 비율로 새로 고침될 때에도 더 안정적인 휘도 레벨을 달성할 수 있다.

- [0079] 상기 산화물 TFT의 다른 특성은, 트랜지스터 간의 초기 임계 전압 변화 문제를 LTPS TFT만큼 많이 겪지 않는다는 점이다. 이러한 측면은 상기 플렉서블 표시장치(100)의 크기가 증가할 때 중대한 장점이 될 수 있다 또한, 바이어스 스트레스(bias stress) 하에서의 LTPS TFT와 산화물 TFT 사이의 임계값 이동이 다르다.

- [0080] 상기 언급된 LTPS TFT 및 산화물 TFT의 특징을 고려하여, 상기 플렉서블 표시장치(100)의 몇몇 실시예들은 하나의 백플레인에 LTPS TFT 및 산화물 TFT을 조합하여 적용할 수 있다. 특히, 상기 플렉서블 표시장치(100)의 몇몇 실시예는, 비표시 영역에 구동 회로(예: GIP)를 구현하기 위해 LTPS TFT를 채용하고, 표시 영역에 픽셀 회로를 구현하기 위해 산화물 TFT를 적용할 수 있다. LTPS TFT의 우수한 캐리어 이동도 때문에, 산화물 TFTs로 구현된 구동 회로에 비해, LTPS TFT로 구현된 구동 회로는 더 빠른 속도로 동작할 수 있다. 이에 더하여, LTPS TFT에 의해 더 집적된 구동 회로가 제공될 수 있고, 이로써 비표시 영역의 크기가 감소될 수 있다. 픽셀 회로에 사용되는 산화물 TFT의 우수한 전압 유지 비율에 의해, 픽셀에서의 누설 전류는 감소될 수 있다. 또한 이는 누설 전류에 의해 야기되는 디스플레이 결함을 최소화하면서, 표시 영역의 특정 부분에서, 또는 기 설정된 조건(예: 정지 영상을 표시할 때) 하에서 감소된 프레임 레이트로 픽셀을 구동하도록 한다

- [0081] 몇몇 실시예에서, 픽셀 회로는 산화물 TFT로 구현되면서, 구동 회로는, N-형 LTPS TFT 및 P-형 LTPS TFT의 조합

으로 구현될 수 있다. 예를 들어, N-형 LTPS TFT 및 P-형 LTPS TFT는 CMOS 게이트 드라이버(예: CMOS GIP, 데이터 드라이버)를 구현하기 위해 사용될 수 있다. 반면, 산화물 TFT는 상기 픽셀 회로의 적어도 몇몇 부분에 적용될 수 있다. 전체가 P-형 또는 N-형 LTPS TFT로 형성된 GIP와는 다르게, 상기 CMOS 게이트 드라이버로부터의 게이트 출력 신호는, DC 신호 또는 논리 하이(high)/로우(low) 신호에 의해 제어될 수 있다. 이로써 게이트 라인이 공백 기간 중에 더 안정적으로 제어되어, 픽셀 회로로부터의 전류 누설과 의도하지 않은 픽셀의 활성화가억제된다.

- [0082] 상기 백플레인 상의 CMOS 게이트 드라이버 또는 인버터 회로는 LTPS TFT 및 산화물 TFT의 조합으로 구현될 수 있다. 예를 들어, P-형 LTPS TFT 및 N-형 산화물 TFT가 CMOS 회로를 구현하기 위해 사용될 수 있다. 또한, 상기 표시 영역의 픽셀 회로는, LTPS TFT 및 산화물 TFT를 모두 사용하여 구현될 수 있다. 픽셀 회로 및/또는 구동 회로에 두 종류의 TFT를 적용할 때, 오프 상태 중에 산화물 TFT들 사이의 노드에 남아있는 바이어스를 없애고, 바이어스 스트레스(예: PBTS, NBTS)를 최소화하기 위해, LTPS TFT는 전략적으로 회로 내부에 놓일 수 있다. 추가적으로, 회로 내의 저장 커패시터(storage capacitor)와 연결되는 TFT는, 누설 전류를 최소화하기 위해 산화물 TFT로 형성될 수 있다.

- [0083] 유기발광소자(OLED)층은 상기 베이스 층(106)상에 배치된다. 상기 유기발광소자층(150)은 다수 개의 OLED 소자를 포함한다. OLED 소자는, 베이스 층(106) 상에 구현된 픽셀 회로 및 구동 회로, 상기 베이스 층(106) 상의 연결 인터페이스와 연결된 외부의 다른 구동회로에 의해 제어된다. 상기 OLED층은 특정 색상(예: red, green, blue)의 광을 방출하는 유기발광물질 층을 포함한다. 몇몇 실시예에서, 상기 유기발광물질 층은 백색 광(본질적으로는 여러 색상의 광의 조합)을 방출할 수 있는 적층 구조를 가질 수 있다.

- [0084] 상기 봉지층(104)은 상기 유기발광소자층(150)을 공기와 습기로부터 보호하기 위해 제공된다. 상기 봉지층(104)은 공기와 습기의 침투를 감소시키기 위한 여러 물질 층을 포함할 수 있다. 몇몇 실시예에서, 상기 봉지층 (104)은 박형 필름 형상으로 제공될 수 있다.

- [0085] 상기 플렉서블 표시장치(100)는 표시 특성(예: 외부 광 반사, 색 정확도, 휘도 등)을 제어하기 위해 편광충 (110)을 포함할 수 있다. 또한, 상기 커버충(114)은 상기 플렉서블 표시장치(100)를 보호하기 위해 사용될 수 있다.

- [0086] 커버층(114)의 일 면 및/또는 상기 편광층(110)의 적어도 한 면의 내부에, 사용자의 터치 입력을 감지하기 위한 전극이 형성될 수 있다. 필요하다면, 터치 감지 전극 및/또는 터치 입력 감지와 연관된 다른 부품이 구비된 독립된 층(이하에서는 터치센서층(112)으로 지칭)이 상기 플렉서블 표시장치(100) 내에 제공될 수 있다. 상기 터치 감지 전극(예: 터치 구동/감지 전극)은 인듐 주석 산화물, 그래핀(graphene)과 같은 탄소 기반 물질, 탄소나노튜브, 전도성 고분자, 다양한 전도성/비전도성 물질의 혼합물로 만들어진 하이브리드 물질 등의 투명 전도성 물질로 형성될 수 있다. 또한, 금속 메쉬(metal mesh), 예컨대, 알루미늄 메쉬, 은 메쉬 등이 상기 터치 감지 전극으로 사용될 수 있다.

- [0087] 상기 터치센서층(112)은 하나 이상의 변형 유전체 물질을 포함할 수 있다. 하나 이상의 전극은 상기 터치센서층 (112)과 인터페이스 되거나 상기 터치센서층(112) 부근에 위치할 수 있고, 전극 상의 전기적 변화를 측정하는 신호를 읽을 수 있다. 상기 측정은 분석되어 상기 플렉서블 표시장치(100)에 입력된 압력의 양이 여러 례벨로 평가된다.

- [0088] 몇몇 실시예에서, 상기 터치 감지 전극은 사용자 입력의 위치를 확인하고, 사용자 입력의 압력을 평가하는 데에 활용될 수 있다. 상기 터치 입력 위치 확인과 터치 압력 측정은, 상기 터치센서층(112)의 일 면에 있는 터치 감지 전극의 커패시턴스 변화를 측정함으로써 수행될 수 있다. 상기 터치 감지 전극 및/또는 다른 전극은 터치 입력에 의한 플렉서블 표시장치(100) 상의 압력을 나타내는 신호를 측정하는 데에 사용될 수 있다. 이러한 신호는 터치 신호와 동시에 또는 다른 타이밍에 터치 감지 전극으로부터 획득된다.

- [0089] 상기 터치센서층(112)에 포함된 변형 물질은 전기 활성화 물질일 수 있고, 상기 물질의 진폭 및/또는 진동수는 전기 신호 및/또는 전기장에 의해 제어된다 이러한 변형 물질은 피에조 세라믹(piezo ceramic), 전기 활성화 고 분자(electro-active-polymer) 등을 포함한다. 따라서, 상기 터치 감지 전극 및/또는 별도의 전극은 상기 변형 물질을 활성화하여 상기 플렉서블 표시장치(100)를 원하는 방향으로 구부리도록 할 수 있다. 추가적으로, 상기 전기 활성화 물질은 활성화되어 원하는 진동수로 진동하여, 플렉서블 표시장치(100) 상에서 촉각(tactile) 및/또는 감촉(texture) 피드백을 제공한다. 상기 플렉서블 표시장치(100)는 다수의 전기 활성화 물질을 채용하여 상기 플렉서블 표시장치(100)의 구부러짐이나 진동이 동시에 또는 다른 타이밍에 제공되도록 할 수 있다. 이러

한 조합은 상기 플렉서블 표시장치(100)로부터 사운드 웨이브(sound wave)를 만드는 데에 사용될 수 있다.

- [0090] 일부 구성 요소들은 굴곡선(BL)을 따른 플렉서블 표시장치(100)의 굴곡을 어렵게 할 수 있다. 지지층(108), 터치센서층(112), 편광층(110) 등과 같은 몇몇 구성 요소들은, 플렉서블 표시장치(100)에 강도를 추가할 수 있다. 또한, 상기 구성 요소들의 두께는 상기 플렉서블 표시장치(100)의 중립 면(neutral plane)을 이동시키고, 그에따라 상기 구성요소 중 일부는 다른 요소보다 더 큰 굴곡 스트레스를 만든다.

- [0091] 상기 플렉서블 표시장치(100)의 더 용이한 굴곡 및 신뢰성 향상을 위해, 굴곡 부분(102)에서 구성 요소들의 구성은 상기 중앙 부분(101)에서와 다르다. 상기 중앙 부분(101)에 존재하는 몇몇 구성 요소들은 상기 굴곡 부분(102)에는 배치되지 않거나, 다른 두께로 제공된다. 상기 지지층(108), 상기 편광층(110), 상기 터치센서층(112), 컬러필터층 및/또는 플렉서블 표시장치(100)의 굴곡을 방해하는 다른 구성 요소들은 상기 굴곡 부분(102)에 없을 수 있다. 상기 굴곡 부분(102)을 사용자가 볼 수 없거나 액세스할 수 없다면, 위와 같은 구성 요소들은 필요하지 않다.

- [0092] 사용자에게 정보를 제공하기 위해, 제2 표시 영역이 상기 굴곡 부분(102)에 있지만, 상기 제2 표시 영역에 의해 제공되는 정보의 용도 및/또는 형태에 따라 상기의 구성 요소들 중 일부는 필요치 않다. 예를 들어, 상기 제2 표시 영역이 단지 색상을 발광하거나, 명암 조합(예: 흰색 바탕에 검정색 텍스트 또는 아이콘)으로만 텍스트 또는 단순한 GUI를 표시한다면, 편광층(110) 및/또는 컬러필터층은 상기 굴곡 부분(102)에 불필요하다. 또한, 상기 굴곡 부분(102)에는, 터치 기능이 불필요하다면, 터치센서층(112)이 없을 수 있다. 정보를 표시하기 위한 보조 표시 영역이 굴곡 부분(102)에 제공되지 않더라도, 필요하다면, 상기 굴곡 부분(102)은 터치센서층(112) 및/또는 전기 활성화 물질 층을 포함할 수 있다.

- [0093] 굴곡 구간은 굴곡 스트레스에 의해 가장 큰 영향을 받기 때문에, 굴곡 구간 상의 부품에 여러 가지 스트레스 저 감 구조가 적용된다. 이를 위해서, 상기 중앙 부분(101)에 있는 구성 요소 중 일부는, 상기 굴곡 부분(102) 상의 적어도 일 부분에 존재하지 않는다. 상기 굴곡 구간에서 구성 요소를 선택적으로 제거하여, 상기 중앙 부분(101)과 상기 굴곡 부분(102) 있는 부품들 사이의 분리가 이루어짐으로써, 상기 굴곡 구간이 각 구성 요소들로 부터 자유롭게 된다.

- [0094] 도 4에 도시된 바와 같이, 상기 중앙 부분(101)에 있는 지지층(108) 및 상기 굴곡 부분(102)에 있는 지지층 (108)은, 상기 굴곡 구간(102b)에 지지층(108)이 없음으로 인하여 서로 이격될 수 있다. 상기 베이스 층(106)에 부착된 지지층(108) 대신에, 상기 베이스 층(106)의 아래 굴곡 구간에 끝 부분이 둥근(rounded) 지지 부재(11 6)가 배치될 수 있다. 다양한 다른 구성 요소들, 예를 들어 상기 편광층(110), 상기 터치센서층(112) 등이 상기 굴곡 구간에 존재하지 않을 수 있다. 상기 구성 요소의 제거는 절단, 에칭(wet etching, dry etching), 스크라이빙(scribing), 기타 적절한 방식을 통해 이루어질 수 있다. 절단이나 기타 제거 대신에, 상기 구성 요소의 분할 조각이 선택된 부분에(예: 중앙 부분 및 굴곡 부분) 형성되어, 굴곡 구간에 해당 구성 요소가 없도록 할 수 있다. 상기 굴곡 부분(102)으로부터 완전히 제거되는 대신에, 몇몇 구성 요소들은 굴곡 스트레스를 줄이기 위해 굴곡선 및/또는 굴곡 구간 내의 일 부분을 따라 굴곡 패턴을 가질 수 있다.

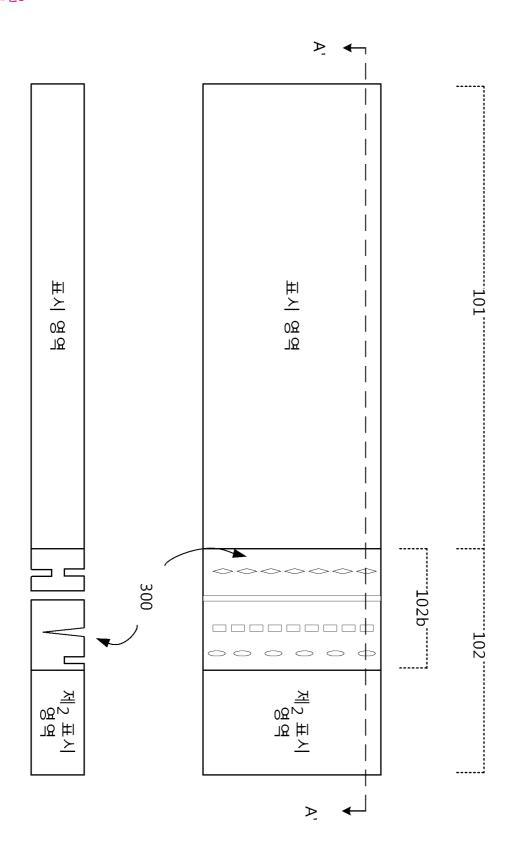

- [0095] 도 5는 본 명세서의 실시예에 따른 굴곡 패턴의 평면도 및 단면도이다.

- [0096] 상기 굴곡 패턴(300)은 몇몇 구성 요소에 적용될 수 있다. 상기 굴곡 패턴(300)은 지지층(108), 편광층(110), 터치센서층(112) 등에 사용될 수 있다.

- [0097] 상기 플렉서블 표시장치(100)은 하나 이상의 굴곡 패턴(300)을 활용할 수 있다. 부품들에 사용되는 굴곡 패턴의 수 및 굴곡 패턴의 형태는 제한되지 않는다. 필요하다면, 상기 패턴(300)의 깊이는, 부품을 완전히 통과하지만 각 층을 부분적으로만 침투하는 정도일 수 있다. 도전선을 덮는 보호층(passivation layer) 뿐만 아니라, 상기 베이스 층(106)과 TFT 사이의 버퍼층에도 굴곡 스트레스를 줄이기 위해 굴곡 패턴이 마련될 수 있다.

- [0098] 언급한 바와 같이, 상기 지지층(108)은 상기 베이스 층(106)의 용이한 굴곡을 위해 상기 굴곡 구간에 존재하지 않는다. 그러나, 상기 지지층(108)의 부재함으로 인해, 상기 굴곡 구간의 곡률(curvature)은 외력에 의해 쉽게 변형된다. 상기 베이스 층(106)을 지지하고 상기 굴곡 구간의 곡률을 유지하기 위해, 상기 플렉서블 표시장치 (100)는 지지 부재(116)를 포함할 수 있고, 상기 지지 부재는 맨드릴(mandrel)로 호칭될 수 있다. 도 2에 도시된 상기 지지 부재(116)는, 몸통 부분(body portion) 및 끝 부분(end portion)을 포함한다. 상기 베이스 층 (106) 및 상기 지지 부재(116)는, 둥근(rounded) 끝 부분이 상기 굴곡 구간에 대응하여 상기 베이스 층(106)의 아래 면에 위치하도록 배치된다.

- [0099] 굴곡 부분(102)이 플렉서블 표시장치(100)의 모서리에 있는 실시예에서, 상기 지지 부재(116)는 상기 플렉서블

표시장치(100)의 모서리에 위치할 수 있다. 이러한 설정에서, 상기 베이스 층(106)의 일 부분은, 도 2에 도시된 것처럼, 상기 지지 부재(116)의 끝 부분을 감싸고 상기 지지 부재(116)의 아래 면에 위치하게 된다. 상기 비표시 영역에 있는 다양한 회로 및 부품들(구동 IC, COF(connecting chip-on-flex)과의 연결 인터페이스, 인쇄 회로 기판 등)은 플렉서블 표시장치(100)의 뒤 편에 위치한 베이스 층(106) 상에 제공될 수 있다. 이와 같은 방식으로, 연성 부품이 아니더라도 상기 표시 영역의 아래에 위치할 수 있다.

- [0100] 상기 지지 부재(116)는 폴리카보네이트(PC), 폴리이미드(PI), 폴리에틸렌 나프탈레이트(PEN), 폴리에틸렌 테레 프탈레이트(PET) 등과 같은 플라스틱 물질로 형성될 수 있다. 상기 플라스틱 물질로 만들어진 지지 부재(116)의 강도는, 상기 지지 부재(116) 두께 및/또는 강도를 증가시키는 첨가물에 의해 제어될 수 있다. 상기 지지 부재 (116)는 원하는 색상(예: 검정, 흰색 등)으로 형성될 수 있다. 그리고, 상기 지지 부재(116)는 유리, 세라믹, 금속 등 단단한 물질 또는 그 조합으로 만들어질 수 있다.

- [0101] 상기 지지 부재(116)의 끝 부분의 크기 및 형태는, 상기 굴곡 구간에서 원하는 최저 곡률에 의존하여 변할 수 있다. 몇몇 실시예에서, 상기 끝 부분 및 상기 몸통 부분의 두께는 실질적으로 동일할 수 있다. 다른 실시예에서, 상기 평면 형상의 몸통 부분은 끝 부분보다 얇을 수 있다. 더 얇은 몸통 부분을 가지고, 상기 지지 부재 (116)는, 플렉서블 표시장치(100)의 불필요한 두께 증가를 피하면서 상기 굴곡 구간(102b)을 지지할 수 있다.

- [0102] 상기 지지 부재(116)의 끝 부분에 의해 상기 굴곡 구간이 지지되기 때문에, 상기 플렉서블 표시장치(100)의 중 앙 부분(101)을 향해 연장된 상기 몸통 부분은, 표시 영역까지 연장될 필요는 없다. 상기 몸통 부분이 여러 가지 이유로 상기 표시 영역 아래까지 연장될 수 있다면, 상기 끝 부분으로부터 반대쪽 끝을 향한 상기 몸통 부분의 길이는, 상기 지지 부재(116)를 지지할 표면 영역까지의 길이면 충분하다.

- [0103] 상기 플렉서블 표시장치(100) 내에서 상기 지지 부재(116)를 안전하게 하기 위해, 상기 지지 부재(116)의 표면에 접착층(118)이 제공될 수 있다. 상기 접착층(118)은 감압 접착제(pressure-sensitive adhesive), 거품형 접착제(foam-type adhesive), 액상 접착제(liquid adhesive), 광 경화 접착제(light-cured adhesive) 또는 다른적합한 접착 물질을 포함할 수 있다. 몇몇 실시예에서, 상기 접착층(118)은 압축될 수 있는 물질로 형성되거나그를 포함하여, 상기 접착층(118)에 의해 접착된 부분에 대해 완충재로 기능할 수 있다 일 예로서, 상기 접착층(118)의 구성 물질은 압축 가능할 수 있다. 상기 접착층(118)은 다층 구조로 형성될 수 있고, 상기 다층구조는, 접착 물질 층의 상부 및 하부 층 사이에 놓인 완충층(예: polyolefin foam)을 포함한다.

- [0104] 상기 접착층(118)은 상기 지지 부재(116)의 몸통 부분의 상부 및 하부 표면 중 어느 하나 이상에 위치할 수 있다. 상기 플렉서블 표시장치(100)의 굴곡 부분(102)이 상기 지지 부재의 끝 부분을 감쌀 때, 접착층(118)은 몸통 부분의 하부 표면(즉, 후면과 마주하는 면) 및 상부 표면(즉, 전면과 마주하는 면) 모두에 제공될 수 있다. 필요하다면, 상기 지지 부재(116)의 끝 부분과 상기 베이스 층(106)의 안쪽 표면 사이에 접착층(118)이 제공될수 있다.

- [0105] 굴곡되는 중에, 상기 지지 부재(116)의 일 면 상에 있는 플렉서블 표시장치(100)의 일 부분은 상기 지지 부재 (116)를 향해 당겨질 수 있고, 상기 베이스 층(106)은 상기 끝 부분의 최상단 및 최하단 모서리에 의해 충격을 받을 수 있다. 이에 상기 접착층(118)의 높이와, 상기 지지 부재(116) 및 상기 베이스 층(106) 사이의 지지층 (108)의 높이는, 끝 부분의 최상단 모서리와 상기 접착층(118)이 위치한 몸통 부분의 표면 사이의 수직 거리 이상이다. 다시 말해, 상기 끝 부분과 상기 몸통 부분 사이의 두께 차이로 생기는 공간의 높이는, 상기 지지층 (108)과 상기 접착층(118)의 두께를 합한 것 보다 작거나 같다.

- [0106] 상기 지지 부재(116)의 형태에 따라, 상기 몸통 부분의 상부 및 하부 표면 상에 있는 상기 접착층(118)의 두께는 다를 수 있다. 예를 들어, 상기 끝 부분보다 얇은 몸통 부분은, 상기 상기 끝 부분의 중심에서는 존재하지 않을 수 있다. 이 경우에, 상기 지지 부재(116)의 일 측 상의 공간은 반대 측 상의 공간보다 클 수 있다.

- [0107] 다른 예에서, 상기 끝 부분의 가장 낮은 모서리는 상기 몸통 부분의 바닥 선 안쪽에 있어서, 오직 몸통 부분의 일 측 상에만 공간이 만들어진다. 이 경우에, 상기 몸통 부분의 일 측 상에 있는 접착충(118)은 반대 측 보다 두꺼울 수 있다.

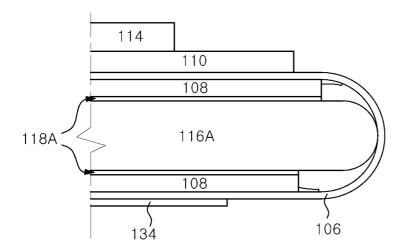

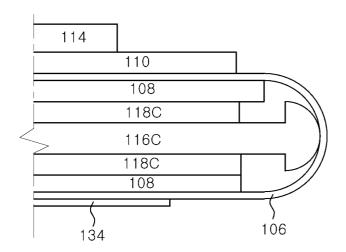

- [0108] 도 6a, 6b 및 6c는 플렉서블 표시장치(100)의 여러 실시예에서 구성 요소들의 예시적인 배치를 보여주는 개략적 인 단면도이다.

- [0109] 일 구성예로, 도 6a에서, 지지 부재(116A)의 등근 끝 부분(rounded end portion) 및 길게 늘어진 몸통 부분 (elongated body portion)의 두께는 실질적으로 동일할 수 있다. 이러한 지지 부재(116A)는 플라스틱 물질로 형성될 수 있다. 상기 지지 부재(116A)는 접힌 박형 금속 시트(예: SUS)로 형성될 수 있다. 이때 금속 시트의 접

힌 모서리는 지지 부재(116A)의 둥근 끝 부분으로 기능할 수 있다. 금속 시트가 지지 부재를 형성하는 데에 사용될 때에도, 끝 부분은 몸통 부분보다 더 두꺼울 수 있다. 예를 들어, 몸통 부분이 접힌 모서리보다 더 얇아지도록 접힌 금속 시트의 일 부분에 압력이 가해질 수 있다.

- [0110] 도 6a에서, 접착충(118A)이 지지 부재(116A)의 상면, 하면 및 둥근 끝 부분의 표면에 적용된 것으로 도시되었다. 두께 둥근 부분 및 몸통 부분에서 지지 부재(116A)의 두께가 거의 같기 때문에, 접착충(118A)은 지지 부재(116A)의 표면 상에서 실질적으로 균일한 두께를 갖는다. 그러나, 접착충(118A)은 지지 부재(116A)의 선택된 부분에서 더 얇거나 두꺼울 수 있다.

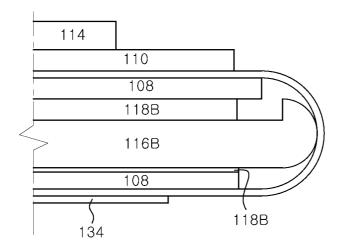

- [0111] 다른 구성예로서, 지지 부재(116)의 길게 늘어진 몸통 부분(elongated body portion)의 두께는 둥근 끝 부분 (rounded end portion)보다 얇을 수 있다. 이 경우, 도 6b에서와 같이 지지 부재(116B)가 평평한 바닥을 가지면, 몸통 부분의 아래 표면은 끝 부분의 가장 낮은 모서리와 일직선을 이룬다. 이러한 예시적 구성에서, 지지 부재(116B)는 앞서 언급된 플라스틱 물질(예: polycarbonate 등) 또는 그 조합으로 형성될 수 있다. 또한, 몸통 부분의 상부 표면에 마련된 접착충(118B)은, 몸통 부분의 하부 표면에 마련된 접착충(118B)보다 더 두껍다. 하부 표면에 있는 접착충(118B)은 그렇지 않은 반면, 몸통 부분의 상부 표면에 있는 접착충(118B)은 완충층을 포함할 수 있다.

- [0112] 도 6에 도시된 다른 구성예에서는, 지지 부재(116C)의 몸통 부분의 상부 또는 하부 표면 어느 것도 둥근 부분의 최고/최저 모서리와 일직선상에 있지 않다. 지지 부재(116C)는 앞서 언급된 플라스틱 물질(예: polycarbonate 등) 또는 그 조합으로 형성될 수 있다. 이 예에서, 몸통 부분은 대칭적이지 않고 (즉, 둥근 부분의 최하단 모서리에 더 가까운), 몸통 부분의 위 표면의 접착층(118C)은 아래 표면의 접착층(118C)보다 더 두껍다

- [0113] 하부 표면에 있는 접착충(118B)은 그렇지 않은 반면, 몸통 부분 위 표면의 접착충(118C)은 상술한 완충충을 포함할 수 있다.

- [0114] 도 6a 내지 6c의 에시적 구성에서, 지지 부재(116) 위쪽의 지지층(108)은 굴곡 구간을 향해 봉지층(114)보다 더 연장될 수 있다. 다시 말해서, 굴곡 구간을 향한 베이스 층(106)의 일부는 봉지층(114)에 의해 덮이지 않지만, 그 아래에 지지층(108)은 마련된다. 지지층(108)의 남은 길이는 굴곡 구간에서 곡률의 유지를 도울 수 있다. 지지 부재(116)의 아래 지지층(108)의 모서리는 굴곡 구간으로부터 멀리 이동할 수 있다. 몇몇 실시예에서, 굴곡 구간을 향한 지지층(108)의 모서리에는 테두리(flange)가 마련될 수 있다. 상기 테두리는 도 6a에서처럼 굴곡 구간을 향해 더 연장될 수 있다. 일 예로, 지지층(108)이 뾰족한 모서리를 갖도록, 상기 테두리는 절삭 또는 패터성으로 만들어질 수 있다. 다른 예로, 상기 테두리는 적어도 둘 이상의 지지층을 모서리가 서로 빗겨나도록 쌓아서 마련될 수 있다. 도 6b 및 6c에서는 생략되었지만, 상기 테두리는 해당 실시예에도 제공될 수 있다.

- [0115] 도 6a 내지 6c에 기술된 구성은 예시적일 뿐이다. 몸통 부분의 위치에 상관없이 동일한 두께를 갖는 접착층이 지지 부재의 상부 및 하부 표면 상에 제공될 수 있다. 그리고, 지지 부재의 위 또는 아래 표면 상의 접착층은 완충층을 포함할 수 있다.

- [0116] 복수의 도선들이 다양한 부품들 사이의 전기적 연결을 위해 플렉서블 표시장치(100)에 포함된다. 표시 영역 및 비표시 영역에 제조되는 회로들은 하나 이상의 도선을 통해 다양한 신호들을 전송하여 여러 기능을 제공할 수 있다. 몇몇 도선들은 중앙 부분 및 굴곡 부분에 있는 회로 및/또는 다른 부품들 사이의 상호연결을 위해 사용될수 있다.

- [0117] 도선(conductive line)은 플렉서블 표시장치(100) 내의 한 지점에서 다른 지점으로 전기적 신호, 전력 및/또는 전압을 전달하는 도전성 경로를 지칭한다. 상기 도선은, 비표시 영역의 표시구동 회로(예: 게이트 드라이버, 데이터 드라이버)에서 표시 영역의 픽셀 회로로 신호를 전달하는 게이트 라인/데이터 라인, TFT의 소스/드레인 전 극을 포함할 수 있다. 마찬가지로 터치감지 전극, 압력감지 전극, 지문감지 전극과 같은 도선들이 플렉서블 표시장치(100) 상의 터치입력 감지 또는 지문 인식을 위한 신호를 제공할 수 있다 또한, 도선들은 중앙 부분 표시 영역의 부품과 굴곡 부분 제2 표시 영역의 부품 사이의 상호연결을 제공할 수 있다.

- [0118] 플렉서블 표시장치(100)의 도선들은 전기적/비전기적 요구를 만족하도록 주의깊게 설계되어야 한다. 예를 들어, 도선은 특정한 최소 저항 수준을 가질 수 있는데 상기 저항 수준은 도선을 통해 전달될 신호의 종류에 따라 변할 수 있다. 몇몇 도선은 실질적으로 평평한 부분에서 굴곡 부분으로 보내질 수 있다. 이러한 도선들은 기계적/전기적 견고함을 유지하기에 충분한 유연성을 보여야한다. 이를 위하여, 플렉서블 표시장치(100)의 몇몇 도선은 다층(multi-layered) 구조를 갖는다.

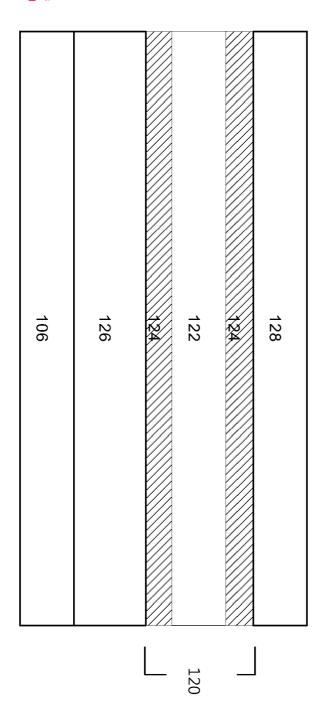

- [0119] 도 7a 및 7b는 각각 다층 구조 도선의 예시적인 적층 구조를 도시한다.

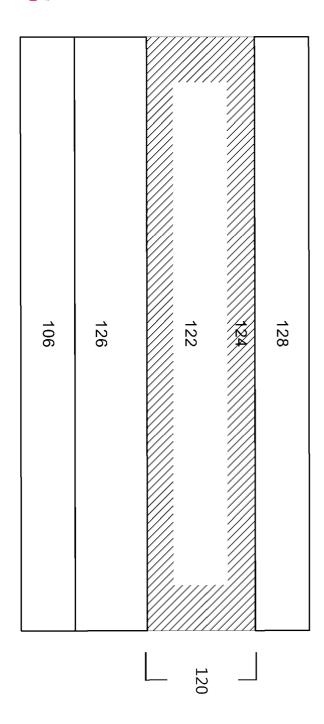

- [0120] 도 7a를 참조하면, 도선(120)은 제1 도전층(122)이 제2 도전층(124)들 사이에 끼워진 다층 구조를 갖는다. 제1 도전층(122)은 제2 도전층(124)보다 낮은 전기 저항을 갖는 물질로 형성될 수 있다. 제1 도전층(122)은 구리, 알루미늄, 투명 도전성 산화물, 기타 플렉서블 도전체 등의 물질을 포함하나, 이에 제한되는 것은 아니다.

- [0121] 제2 도전층(124)은 제1 도전층(122) 위에 적충될 때 충분히 작은 옴 접촉 저항(ohmic contact resistance)을 나타내는 도전성 물질로 형성된다. 다층 도선(120)에서 도전층 사이의 낮은 접촉 저항은 도전층 물질을 선택할 때 고려하는 유일한 인자는 아니다. 엄격한 전기적 및 열적 요구(예: 저항, 발열 등)를 충족하면서, 도선(120)물질은 최소한의 기계적 강도 요건(예: Young's modulus)도 충족시켜야 한다 즉, 제1 도전층(122)과 제2 도전층 (124)은 모두 충분한 유연성을 나타내는 물질로 형성되어야 한다.

- [0122] 따라서, 몇몇 실시예에서 플렉서블 표시장치(100)의 적어도 일부 도선(120)들은 알루미늄(Al), 티타늄(Ti), 몰리브덴(Mo), 구리(Cu) 층에서 선택된 둘 이상의 층으로 형성될 수 있다. 이러한 조합의 예로, 티타늄 층 사이에 끼워진 알루미늄 층(Ti/Al/Ti), 상하의 몰리브덴 층 사이에 있는 알루미늄 층(Mo/Al/Mo), 티타늄 층 사이에 끼워진 구리 층(Ti/Cu/Ti), 상하의 몰리브덴 층 사이에 있는 구리 층(Mo/Cu/Mo) 등이 있다. 물론 다른 도전성 물질도 제1/제2 층으로 사용될 수 있다.

- [0123] 플렉서블 표시장치(100)를 채용한 전자기기, 예컨대 웨어러블 전자기기 또는 수중 전자기기는, 플렉서블 표시장치(100)를 습기 많은 환경에 노출할 수 있다. 어떤 경우에는, 수분이 도선(120)에 도달할 수 있다. 비유사 금속 및 합금은 다른 전극 전위를 갖고, 둘 이상이 전해질에서 접촉하면 한 금속은 애노드로, 다른 금속은 캐소드로 행동한다. 비유사 금속 사이의 전위차는 애노드 부재의 부식을 촉진하는데, 그것은 다층 도선(120)의 제1 도전 층(122) (예: Ti/Al/Ti 적층의 Al 층)일 것이다. 애노드 금속이 녹아 전해질이 되고 캐소드 금속 위에 쌓인다.

- [0124] 상술된 다층 도선(120)을 사용할 때 제1 도전층(122) 및 제2 도전층(124) 모두를 노출시키는 표면은 갈바닉 부식(galvanic corrosion)의 시작점이 될 수 있다. 따라서, 상기 플렉서블 표시장치(100)의 몇몇 실시예에서, 적어도 일부의 도선(120)에는, 도 7b와 같이 제1 도전층(122)의 외부 표면이 제2 도전층(124)에 의해 둘러싸인 구조가 마련된다 이러한 형상은 전해질이 제1 도전층(122) 및 제2 도전층(124) 모두와 접촉하지 않도록 막음으로써, 제1 도전층(122)이 갈바닉 부식에 의해 손실되는 것을 최소화한다

- [0125] 이러한 다층 도선(120)은, 제1 도전층(122)을 위한 물질(예: Al)을 제2 도전층(124) (예: Ti) 위에 적층하여 제작될 수 있다 여기서, 제1 도전층(122) 아래의 제2 도전층(124)은 더 큰 폭을 가질 수 있다. 식각(etch) 저지물질이 상기 두 개층 위에 형성되고, 원하는 배선형태로 도선이 형성되도록 식각(예: dry etch, wet etch 등)된다. 식각 저지물질을 벗겨낸 후에, 제2 도전층(124)이 (예: Ti) 상기 구조(즉, Ti/Al) 위에 적층된다. 제1도전층(122) 상에 적층되는 제2 도전층(124)의 폭은, 제1 도전층(122)의 바깥쪽 표면을 덮도록, 제1도전층(122)의 폭에 비해 더 클 수 있다. 원하는 도선 배치 설계에 따라 다층 도선을 형성하기 위해 다음의 식각 및식각 저지물질 제거 단계가 수행된다. 상술한 다층 도선 형성 과정은 예시적일 뿐이다. 따라서, 다층 도선의제조에서 몇몇 과정이 추가 및/또는 생략될 수 있다.

- [0126] 도선의 배선 설계(trace design)는, 도선의 전기적/기계적 성질에 영향을 미칠 수 있는 중요한 요인이다. 전기적/기계적 요구를 만족하기 위해, 도선의 일 부분은 다른 부분과 다르게 구성될 수 있다. 플렉서블 표시장치(100)의 굴곡 구간에 또는 부근에 있는 도선의 일 부분에는 굴곡 스트레스 조절을 위한 구조가 마련된다.

- [0127] 도선 부근 절연층의 굴곡 스트레스 조절은 도선 자체의 변형 조절만큼 중요하다. 도선(120)의 위 및/또는 아래에 놓인 버퍼층(126), 보호층(128), 게이트 절연층(GI), 층간 절연층(ILD)과 같은 다양한 절연층은 무기 물질을 포함할 수 있다 무기 물질로 형성된 층, 예컨대 산화실리콘(silicon oxide) 층, 질화실리콘(silicon nitride)층은 일반적으로 도선의 금속 층보다 더 갈라지기 쉽다. 도선이 갈라짐(crack) 없이 굴곡 스트레스를 견딜만한충분한 유연성을 가질 때조차, 절연층에서 발생한 갈라짐이 도선으로 전파되어 전기적 연결이 나쁜 곳을 만들수 있다.

- [0128] 도선의 굴곡 스트레스를 감소시키는 배선 설계로서, 도선(120)의 위 및/또는 아래의 절연층 중 일부는, 갈라짐을 최소화하기 위해 패터닝될 수 있다. 습식 식각(wet etching) 및/또는 건식 식각(dry etching) 같은 다양한 절연층 패터닝 기법이 배선 구조에 대응하는 절연층의 형상을 만들기 위해 사용될 수 있다. 절연층, 특히 도선주위의 무기 물질 기반의 절연층의 생략은, 갈라짐 발생 기회를 줄일 뿐만 아니라 그 전파 경로도 없앤다. 설명의 편의를 위해, 도선(120) 및 도선(120)의 적어도 일부를 덮는 절연층의 배치 구성을 이하에서는 "배선 구조 (wire trace)"라 칭한다.

- [0129] 언급한 바와 같이 도선 및 도선을 덮는 절연층에 대한 설계는 배선 구조의 견고함을 증가시키는 데에 중요한 역할을 한다. 두께와 폭부터 각각의 굴곡 방향에 대한 배선 조각의 펼쳐짐 각도에 이르기까지 다양한 요인들이 배선 구조의 설계와 연관되어 있다. 이에 더하여, 도선(120) 및 절연층 배치와 관련된 많은 다른 요인들이 배선의설치 및 방향에 기반하여 특별히 조율된다.

- [0130] 배선 구조가 연장되는 방향이 곡률의 탄젠트 벡터(tangent vector)에 더 맞춰질수록, 굴곡 스트레스에 기인한 배선의 변형은 더 커질 것이다. 다시 말해서, 곡률의 탄젠트 벡터에 평행한 배선 조각의 길이가 줄어들면, 배선 구조는 굴곡 스트레스에 더 잘 견딜 것이다. 배선 구조가 연장되는 방향과 무관하게, 언제나 배선 구조 내에 굴곡 방향에서 측정되는 부분이 있다. 그러나, 배선 구조에 변형 저감 설계를 적용함으로써, 굴곡 방향에 평행하게 정렬된 각 연속적인 측정가능 부분(즉, 조각)의 길이는 줄어들 수 있다.

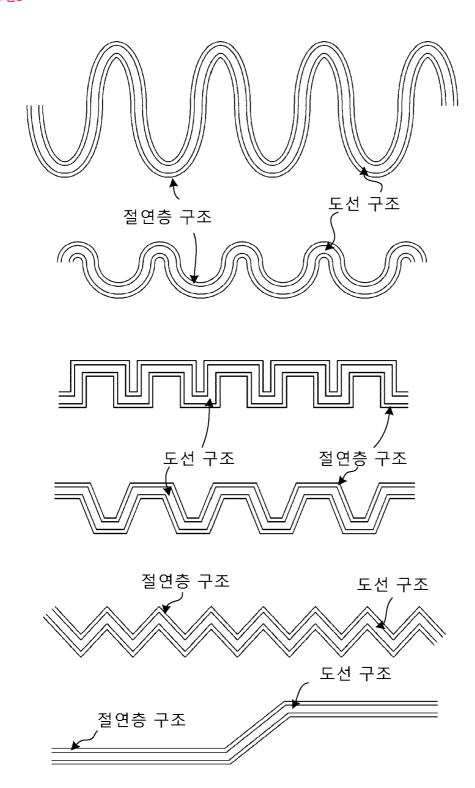

- [0131] 도 8은 변형 저감 배선 설계의 몇몇 예를 도시한다.

- [0132] 도 8에 도시된 사인파(sine-wave), 구형파(square-wave), 톱니, 물결, 빗금 형상 중 하나 이상의 설계가 배선 구조에 사용될 수 있다. 이러한 변형 저감 설계를 적용하면, 곡률의 탄젠트 벡터에 비스듬한 방향으로 정렬된 배선 부분이 증가된다. 이는 굴곡 방향에 평행하게 직선으로 연장하는 배선 조각의 길이를 제한한다.

- [0133] 플렉서블 표시장치를 구부림으로 인한 배선 구조 내의 갈라짐은 통상적으로 무기 절연층(inorganic insulation layer)에서 시작하기 때문에, 곡률의 탄젠트 벡터와 정렬된 절연층의 길이도 최소화되는 것이 중요하다. 한 선의 변형 저감 설계 내에서, 도선의 표면과 만나는 패턴화된 무기 절연층의 너비뿐만 아니라 도선의 너비 및 형상도 최소로 유지되어야 한다.

- [0134] 도 8에 도시된 변형 저감 배치 설계는 단지 예시적이며, 플렉서블 표시장치(100)의 여러 실시예에서 굴곡 방향에 평행한 배선 조각을 줄이기 위한 다른 배치 설계들이 사용될 수 있다. 그리고, 몇몇 배선 구조는, 전기적 및 /또는 기계적 요구에 따라, 플렉서블 표시장치(100) 내의 다른 배선 구조와는 상이한 변형 저감 배치 설계를 채용할 수 있다. 예를 들어, 데이터 신호 라인에 사용되는 변형 저감 배치 설계는 전원 라인의 변형 저감 배치 설계와 다를 수 있다.

- [0135] 전고성을 더 향상하기 위해, 배선 구조는, 특정한 간격으로 반복하여 나눠지고 모여드는 배치 설계를 이용할 수 있다. 다시 말해서, 배선 구조는, 연결 링크가 이어진 사슬을 닮은 배선을 형성하도록, 적어도 두 개의 부배선 (sub-trace)을 포함한다. 나눠지고 모이는 각도가 각 링크의 모양을 정의하고, 각 링크의 모양은 굴곡 방향에 평행한 직선에서 측정 가능한 배선 조각의 길이를 제한한다.

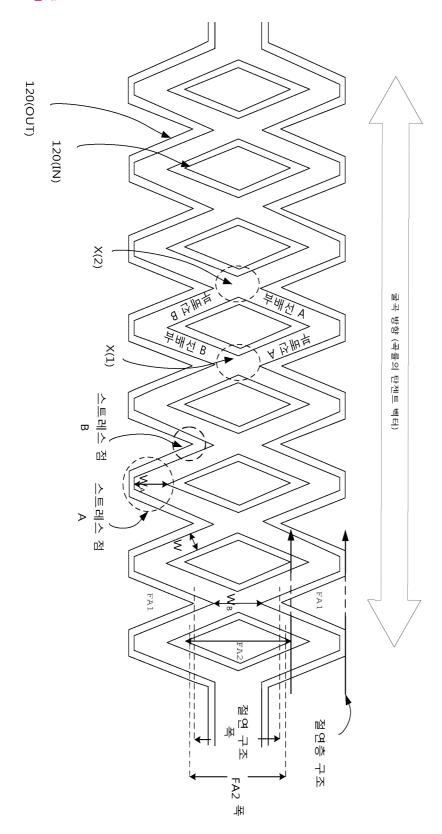

- [0136] 도 9a를 참조하면, 도선(120)은 각 마디(joint) X에서 나눠지고 모이는 부배선 A 및 부배선 B를 포함한다. 제1 마디 X(1) 및 제2 마디 X(2) 사이에, 부배선 A의 일 부분이 곡률의 탄젠트 벡터로부터 멀어지는 각도로 제1 방향에서 기설정된 거리만큼 확장되고 부배선 A의 또 다른 부분은 제2 방향으로 확장된다. 부배선 B는 부배선 A와 유사한 방식으로, 하지만 곡률의 탄젠트 벡터에 대해서는 반대 방향으로 꺾인다. 두 인접한 마디 사이에 부배선 이 배열되는 거리 및 방향은, 부배선에 의해 둘러싸인 개방 영역뿐만 아니라 사슬에서 링크의 모양과 크기를 정의한다. 이 예에서, 제1 마디 X(1) 및 제2 마디 X(2), 즉, 링크 사이에서 도선(120)의 모양은 부배선 A와 부배선 B로 둘러싸인 개방 영역을 가진 다이아몬드 모양이다. 추가적인 마디 X와 함께, 도선(120)은 다이아몬드 모양 링크의 사슬을 형성하고, 이러한 배선은 다이아몬드 배선으로 지칭될 수 있다.

- [0137] 도 8에 도시된 나눠짐이 없는 변형 저감 배선 설계와 비교하여, 도 9a에 도시된 변형 저감 배선 설계는 전기적 특성에 중대한 이점을 제공할 수 있다. 예를 들어, 나뉨/모임 배선 설계가 있는 배선 구조는, 도 8의 산 배선, 사인파 배선, 또는 다른 단일 도선 형태의 변형 저감 설계가 적용된 배선 구조에 비해 훨씬 더 낮은 전기 저항을 갖는다. 이에 더하여, 부배선은 한쪽 배선이 손상되었을 경우에 예비 통로로 기능할 수 있다.

- [0138] 도선(120)의 표면을 덮는 절연층 또한 도선(120)의 배선 구조에 대응하는 배치 설계로 패턴화된다 이때, 부배선 A와 부배선 B로 둘러싸인 개방 영역은 무기 절연층이 없거나, 도선(120) 구조의 아래 및/또는 위의 영역에 비해 더 얇은 무기 절연층을 갖는다. 이때, 굴곡 방향에 평행한 직선에서 측정 가능한 절연층의 길이는, 갈라짐 발생 및 전파를 줄이도록, 제한될 수 있다.

- [0139] 다수의 부배선에 기초한 변형 저감 설계에 대하여 다양한 추가적 요인들이 고려되어야 한다. 나뉨/모임 각도 및 두 인접 마디 X 사이에 있는 부배선의 길이는, 마디 X 및 부배선이 두 인접 마디 X. 사이에서 방향을 바꾸는 바깥쪽 꼭지점에서, 무기 절연층을 위한 오프셋(offset)을 제공해야 한다. 달리 말하면, 두 마디 X 사이에서 부배선으로 둘러싸인 개방 영역은, 배선의 무기 절연층 구조가 굴곡 방향에 평행하게 연장하는 길이를 최소화하는

크기 및 모양을 가져야 한다.

- [0140] 도 9a에 설명된 다이아몬드 배선 설계에서, 도선(120)을 덮는 버퍼층(126) 및 보호층(128)은 도선(120)의 바깥쪽 구조(즉, 바깥쪽 모서리)로부터 소정의 여유(margin)를 두고 패터닝된다. 소정의 여유을 갖고 도선(120)을 덮으며 남아있는 절연층 외에는, 부배선 A와 B로 둘러싸인 개방 영역(FA2)에는 절연층이 없다. 이와 같이, 절연층의 배치 구조는 도선(120)의 배치 설계와 상응하여 형성된다. 굴곡 방향과 직교하는 방향으로 측정된, 절연층이 없는 개방 영역의 길이는. 같은 방향으로 측정된 마디 X에서의 무기 절연층 구조의 폭보다 더 크다. 이 설정에서, 마디 X 옆의 영역뿐만 아니라 부배선 A와 B로 둘러싸인 개방 영역(FA2)은 무가 절연층이 없거나, 감소된수의 무기 절연층을 갖게 될 수 있다.

- [0141] 도 9a를 참조하면, 절연층 없는 영역 FA1은, 두 마디 X(1)와 X(2) 사이의 부배선 A 및 부배선 B의 절연층이 연속적인 직선으로 확장되는 것을 막는다. 마찬가지로, 절연층 없는 영역 FA2는 두 마디 X(1)와 X(2) 사이의 절연층이 연속적인 직선으로 확장되는 것을 막는다. 따라서, 곡률의 탄젠트 벡터에 대해 정렬된 각 절연층 배열 조각들의 길이는 최소화된다. 곡률의 탄젠트 벡터에 대해 정렬된 각 절연층 배열 조각들의 길이를 더 줄이는 것은, 도선(120)의 폭 및 도선(120)의 모서리 너머 절연층의 마진을 줄임으로써 얻어진다.

- [0142] 도선 폭의 감소는 전기 저항을 플렉서블 표시장치(100) 내의 특정 용도에 비해 몹시 크게 만들기 때문에, 도 8에서 설명된 단일 도선 변형 저감 배선 설계에서 도선(120) 폭의 감소량은 제한적이다. 그러나, 도 9a의 나뉨/모임 배선 설계에서, 도선(120)의 폭 및 절연층 구조는, 필요한 전기적 특성을 만족하면서도, 줄어들 수 있다.

- [0143] 부배선의 굴곡 방향에 대한 더 큰 나뉨/모임 각도는, 곡률의 탄젠트 벡터를 따라 연장하는 도선(120) 및 절연층 구조의 길이를 크게 줄인다. 따라서, 높은 굴곡 스트레스 지역에서 부배선의 나뉨/모임 각도를 선택적으로 증가 시킴으로써, 배선 구조에서 갈라짐(crack) 발생할 가능성이 더 낮아진다.

- [0144] 부배선의 나뉨 각도는 다이아몬드 배선 설계에서 두 인접 마디 X 사이의 거리에 영향을 줄 수 있다. 마디 X 사이의 거리가 전체 배선에 걸쳐 균일할 필요는 없다. 배선이 나눠지고 모이는 간격은, 배선 구조의 특정 부분에 가해지는 굴곡 스트레스의 정도에 기초하여 한 배선 내에서 변할 수 있다. 더 큰 굴곡 스트레스가 가해지는 영역(예: 더 작은 굴곡 반지름을 갖는 영역, 더 큰 굴곡 각을 갖는 영역)을 향하는 배선의 특정 부분에서 마디 X 사이의 거리는 점진적으로 짧아질 수 있다. 반대로, 더 작은 굴곡 스트레스가 가해지는 영역을 향할 때, 마디 X 사이의 거리는 점진적으로 멀어질 수 있다.

- [0145] 변형 저감 배선 설계를 가져도, 배선의 일부 지점(즉, 스트레스 점)에 불가피한 굴곡 스트레스는 남아있다. 스트레스 점의 위치는 굴곡 방향과 배선의 모양에 크게 의존한다. 이에 따라, 주어진 굴곡 방향에 대해, 배선 구조는 남아있는 굴곡 스트레스가 원하는 부분에 집중되도록 설계될 수 있다. 배선 내의 스트레스 점을 알면, 배선 구조가 굴곡 스트레스를 더 오래 견디도록, 갈라짐 저지 영역이 그 스트레스 점에 마련될 수 있다.

- [0146] 도 9a를 다시 참조하면, 다이아몬드 배선 설계를 갖는 배선 구조가 굴곡 방향으로 구부러질 때, 굴곡 스트레스는 각진 꼭지점(즉, 각 다이아몬드 모양 링크의 정점)에 집중되는 경향이 있는데, 이를 스트레스 점 A 및 스트레스 점 B로 표시하였다. 이와 같이, 갈라짐은 배선 구조의 안쪽과 바깥쪽 사이에서 시작되고 확대되기 쉽다. 예를 들어, 스트레스 점 A에서, 갈라짐은 안쪽 배선 120(IN)에서 시작되어 바깥쪽 배선 120(OUT)으로 진행될 수 있다. 유사하게, 스트레스 점 B에서, 갈라짐은 바깥쪽 배선 120(OUT)에서 시작되어 안쪽 배선 120(IN)으로 진행될 수 있다.

- [0147] 따라서, 스트레스 점 A에서 도선(120)의 폭은, 갈라짐 저지 영역 역할을 위해, 선택적으로 증가할 수 있다. 도 9a에서 설명하였듯이, 굴곡 방향에 수직으로 측정된, 스트레스 점 A 및 B에서 도선(120)의 폭(WA, WB)은, 스트레스 점 A와 B 사이 부분에서의 도선(120) 폭(W) 보다 더 클 수 있다. 스트레스 점에서의 추가 폭은, 스트레스 점에서의 갈라짐이 커져서 완전히 절단되기 전까지 도선(120)이 더 오래 지탱하도록 만들 수 있다.

- [0148] 굴곡 방향에 정렬된 절연층 구조의 연속적인 부분의 길이는 최소로 유지되어야 한다. 스트레스 점 A 및 B에서 도선(120)의 폭을 증가시키면, 각각의 절연층 구조의 폭이 필연적으로 증가하고, 이는 굴곡 방향에 평행하게 정렬된 절연층 구조를 길어지도록 만든다.

- [0149] 따라서, 몇몇 실시예에서, 스트레스 점 A에서 곡률의 탄젠트 벡터에 수직 방향으로 측정된 도선(120)의 폭은, 약 2.5 마이크로미터(μm)에서 약 8 μm 사이, 바람직하게는 약 3.5 μm 에서 약 6 μm 사이, 더 바람직하게는 약 4.5 μm 에서 약 8.5 μm 사이일 수 있고, 보다 더 바람직하게는 약 4.0 μm 일 수 있다. 스트레스 점 B에서 도선(120)의 폭은 스트레스 점 A에서의 도선(120) 폭과 비슷하게 유지되어야 한다. 이와 같이, 스트레스 점 B에서 도선(120)의 폭은 약 2.5 μm 에서 약 8 μm 사이, 바람직하게는 약 3.5 μm 에서 약 6 μm 사이, 더 바람직

하게는 약  $4.5~\mu m$  에서 약  $8.5~\mu m$  사이일 수 있고, 보다 더 바람직하게는 약  $4.0~\mu m$  일 수 있다. 부배선 A와 부배선 B가 스트레스 점 B에서 모이기 때문에, 스트레스 점 B에서 도선(120)의 폭은 스트레스 점 A에서의 폭보다 더 길 수 있다.

- [0150] 몇몇 실시예에서, 안쪽 배선 120(IN) 및 바깥쪽 배선 120(OUT) 중 하나는, 갈라짐이 양쪽 측면에서 발생할 경우를 최소화하기 위해, 스트레스 점 A에서의 다른 배선만큼 날카롭게 꺾이지 않을 수 있다. 도 9a에서 설명된 실시예에서, 안쪽 배선 120(IN)은, 스트레스 점 A에서의 바깥쪽 배선 120(OUT)보다 보다 더 날카롭게 꺾인다. 그러나, 다른 실시예에서, 바깥쪽 배선 120(OUT)이 스트레스 점 A에서의 안쪽 배선 120(IN)보다 더 날카롭게 꺾일수 있다. 도 9a의 묘사에서 두 경우에, 덜 날카롭게 꺾인 배선은, 바깥쪽 배선 120(OUT)처럼 직선보다는 더 등 글게 될 수 있다. 그리고, 스트레스 점 A에서 안쪽 배선 120(IN)과 바깥쪽 배선 120(OUT) 모두 둥글게 될 수 있다

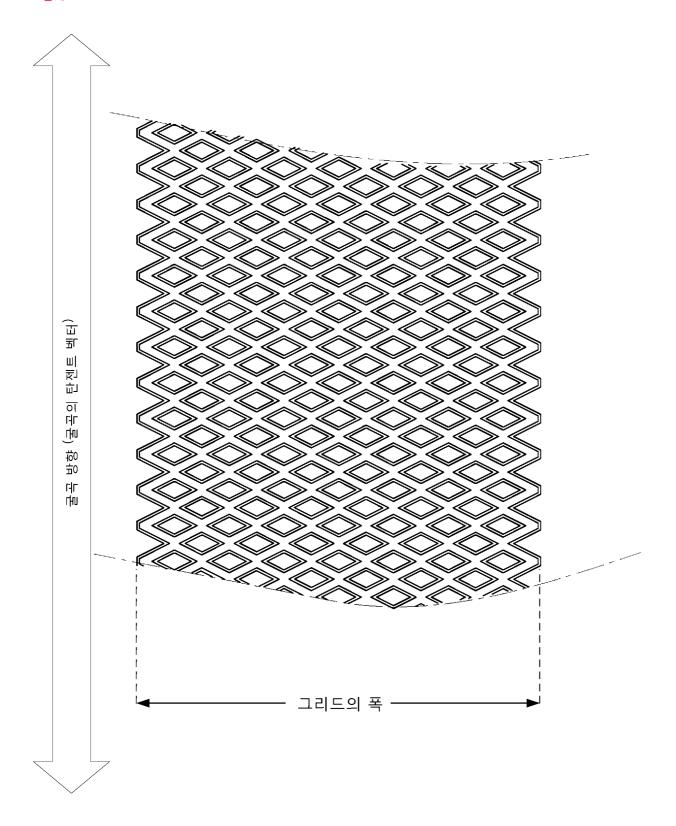

- [0151] 배선 구조는 더 많은 수의 부배선으로 나눠져서 그리드(grid) 형상처럼 배열된 연속 링크가 될 수 있다. 일 예로서, 배선 구조는 도 9b와 같이 다이아몬드 배선의 거미줄처럼 구성될 수 있다. 이러한 배선 설계는, 배선이다수 지점으로 공통 신호를 전달할 때, 또는 배선이 매우 낮은 전기 저항을 요구할 때 특히 유용하다 예를들어, 플렉서블 표시장치(100)에서 VSS 라인 및 VDD 라인은, 특히 상기 라인들이 굴곡 구간을 건너도록 배열되는 경우에, 상기 그리드 배선 구조를 가질 수 있다. 그리드 배선 구조에서 부배선의 수와 모양 중 어느 것도 도 9b의 예시에 의해 제한되지 않는다.

- [0152] 몇몇 실시예에서, 그리드의 폭은 플렉서블 표시장치(100) 내의 양 끝 사이에서 줄어들거나 늘어날 수 있다. 또한, 도 9b에 도시된 그리드 배선 구조는 도 9a의 다이아몬드 배선을 형성하기 위해 또는 나눠짐 없는 변형 저감배선을 형성하기 위해, 다시 수렴할 수도 있다. 몇몇 경우에, 그리드 형상 배선 구조의 각 다이아몬드-배선의 크기는, 저항을 줄이기 위해, 다이아몬드 배선 사슬의 각 다이아몬드 배선의 크기보다 더 클 수 있다

- [0153] 굴곡 방향으로부터 멀어지게 꺾이는 부분 때문에, 변형 저감 배선 설계를 갖는 배선 구조는 플렉서블 표시장치 (100) 내에 더 큰 라우팅(routing) 영역을 필요로 할 수 있다. 플렉서블 표시장치(100)의 모서리에 있는 비표시 영역이 구부러지는 실시예에서, 배선 구조를 수용하기 위해 라우팅 영역을 증가시키는 것은, 숨겨져야 할 비표시 영역의 크기를 증가시키는 것이다.

- [0154] 따라서, 변형 저감 설계를 적용한 배선 구조는 인접 배선 간에 촘촘한 간격으로 배치되어야 한다. 예를 들어, 변형 저감 설계를 갖는 두 인접한 배선은 각각 볼록한 측면과 오목한 측면을 가진 비선형 구간을 포함할 수 있다. 상기 두 인접 배선은, 제1 배선 구조의 비선형 구간의 볼록한 측면이 제2 배선 구조의 비선형 구간의 오목한 측면 옆에 위치하도록, 배열될 수 있다. 상기 두 배선 사이의 간격이 배선 구조의 모양과 크기에 의해 제한되기 때문에, 제1 배선 구조의 변형 저감 설계에서 비선형 구간은, 제2 배선 구조의 변형 저감 설계에서의 비선형 구간보다 더 클 수 있다. 물론, 제1 배선 구조 및 제2 배선 구조 중 하나는 다른 배선 구조의 비선형 구간을 더 잘 수용하기 위해 다른 변형 저감 설계를 가질 수 있다.

- [0155] 예를 들어, 나란히 배열된 둘 이상의 배선 구조는 각각 변형 저감 설계가 적용될 수 있고, 각 배선 구조는 다수의 수축 구역(indented section)과 팽창 구역(distended section)을 가질 수 있다. 이러한 경우에, 한 배선 구조의 팽창 구역이 인접 배선 구조의 수축 구역 옆에 놓이도록 배열될 수 있다.

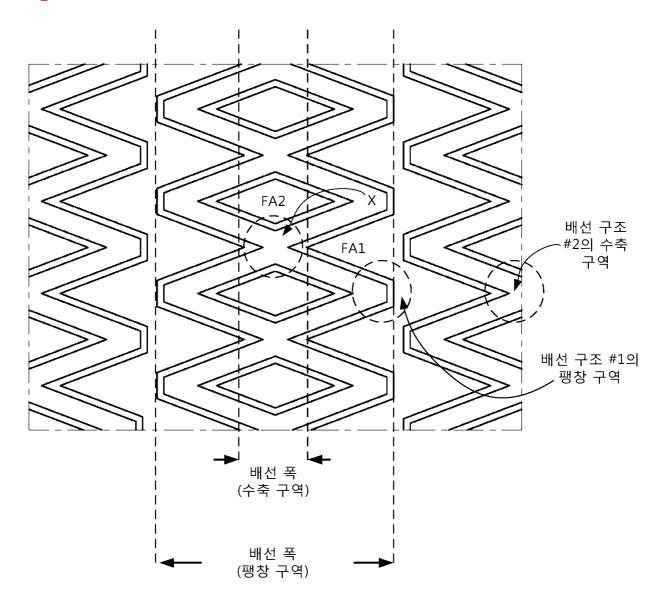

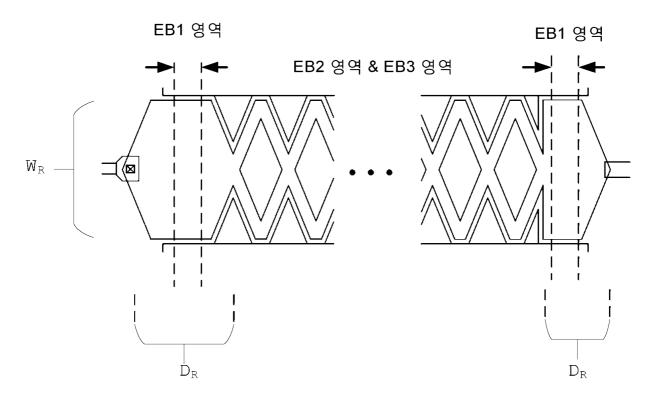

- [0156] 도 10은 다이아몬드 배선 디자인을 갖는 여러 배선 구조의 예시적인 배열을 도시한다.

- [0157] 부배선의 나뉨은 팽창 구역을 만들어 배선 구조의 레이아웃을 넓히는 반면, 부배선의 모임은 수축 구역을 만들어 배선 구조의 레이아웃을 좁힌다. 따라서, 레이아웃 관점에서, 배선 구조의 수축 구역은 마디 X에 있고, 반면 배선 구조의 팽창 구역은 부배선들의 나뉨/모임 각도가 두 인접 마디 X 사이에서 변하는 지점에 있다.

- [0158] 도 10에 보이듯이, 제1 배선 구조의 마디 X와 제2 배선 구조의 마디 X는 엇갈린 위치에 배치된다. 이러한 배치에서, 제1 배선 구조의 팽창 구역에서 다이아몬드 형상의 꼭지점은, 인접한 배선 구조의 수축 구역에 있는 마디 X 옆에 놓인다. 이러한 배선 구조들의 엇갈린 배치는, 배선의 근접에 기인한 전기적 잡음을 낮추는데 도움이 될수 있고, 따라서 배선들 사이의 거리를 줄일 수 있다. 배선들 사이의 촘촘한 간격은, 한 배선 구조의 팽창 구역을 인접 배선 구조의 수축 구역을 향해 가깝게 위치하도록 배치함으로써 가능해질 수 있다. 예를 들어, 한 배선 구조의 넓은 부분에 있는 꼭지점은 개방 영역 FA1에 놓일 수 있다, 개방 영역 FA1는 인접한 배선 구조 내의 부배선의 길이 및 나뉨/모임 각도에 의해 만들어진다. 이와 같이 엇갈린 배치는, 배선 구조들이 차지하는 총 공간을 감소시키면서 배선들 사이의 소정 최소 거리를 유지하도록 한다.

- [0159] 도 11a 및 11b는 본 명세서의 실시예에 따른 플렉서블 표시장치에서 사용되는 예시적인 배선 구조의 개략적인

단면도를 나타낸다.

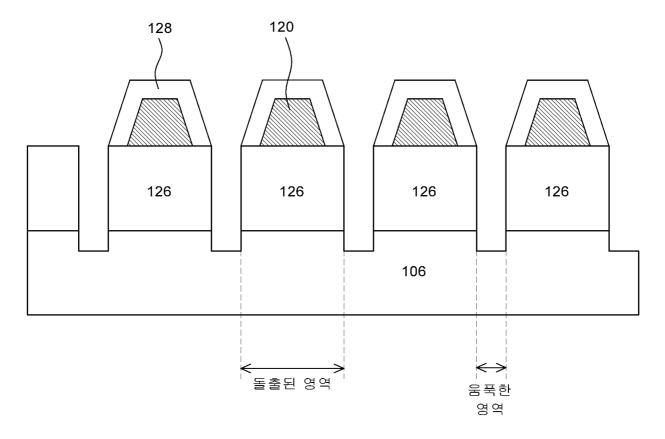

- [0160] 언급한 것처럼, 갈라짐(crack)은 주로 무기 절연층으로부터 개시된다. 따라서, 갈라짐이 생기기 쉬운 영역에서 무기 절연층을 선택적으로 제거함으로써, 갈라짐의 전파가 억제될 수 있다. 이를 위해, 하나 이상의 무기 절연층 및/또는 무기물 층을 포함한 절연층 더미가 플렉서블 표시장치(100)의 여러 부분에서 선택적으로 식각될 수 있다.

- [0161] 예를 들어, 도선(120) 아래의 절연층이 식각될 수 있다. 도선(120) 아래의 절연층은 버퍼층(126)일 수 있는데, 버퍼층은 하나 이상의 무기물 층(inorganic layer)을 포함할 수 있다. 버퍼층(126)은 하나 이상의 질화실리콘 (SiNx) 층 및/또는 산화실리콘(SiO<sub>2</sub>) 층으로 형성될 수 있다. 하나의 구성으로서, 버퍼층(126)은 SiNx 층과 SiO<sub>2</sub> 층이 교대로 적층되어 형성될 수 있다. 버퍼층(126)은 베이스 층(106) 위 및 TFT 아래에 배치된다.

- [0162] 플렉서블 표시장치(100)의 더 쉬운 구부림을 도모하기 위해, 버퍼층(126)의 일부는 굴곡 부분에서 식각될 수 있다. 따라서, 실질적으로 평평한 부분의 버퍼층(126)은 굴곡 부분의 버퍼층(126)보다 더 두꺼울 수 있다. 버퍼층 (126)이 다수의 부계층(sub-layer)으로 형성될 때, 실질적으로 평평한 부분의 버퍼층(126)은 굴곡 부분의 버퍼층에 비해 하나 이상 더 추가된 부계층을 포함할 수 있다.

- [0163] 예를 들어, 실질적으로 평평한 부분에 있는 버퍼층(126)은 SiNx 및 SiO<sub>2</sub>의 여러 층을 포함할 수 있고, 굴곡 부분에 있는 버퍼층(126)은 SiNx 및 SiO<sub>2</sub>의 한 층을 포함할 수 있다. 또한 굴곡 부분의 일 부분에 SiNx 또는 SiO<sub>2</sub> 중 하나의 층만을 갖는 것도 가능하다. 일 구성예로, 버퍼층(126) 내의 각 층은 약 1000Å의 두께를 가질 수 있다. 이와 같이, 굴곡 부분에서 버퍼층(126)의 두께는 약 100Å에서 약 2000Å의 범위일 수 있다.

- [0164] 플렉서블 표시장치(100)의 실질적으로 평평한 부분에서, 추가적 무기물 층이 TFT의 반도체 층 바로 아래에 마련될 수 있는데, 이는 액티브 버퍼(active buffer)로 칭해질 수 있다. 몇몇 실시예에서, TFT의 반도체 층과 가장가까이 위치한 무기물 층은, 버퍼층(126) 내의 개별 무기물 층 보다 더 두꺼울 수 있다.

- [0165] 굴곡 구간 내의 버퍼층(126)은, 도선(120) 아래의 버퍼층(126)은 온전히 두면서, 베이스 층(106)을 노출하도록 더 식각될 수 있다. 다시 말해서, 굴곡 부분에 움푹한 영역과 돌출된 영역이 마련된다. 돌출된 영역은 베이스 층(106) 상에 마련된 버퍼층(126)을 포함하고, 반면에 움푹한 영역은 버퍼층(126)이 그 위에 배치되지 않은 노출된 베이스 층(106)을 갖는다.

- [0166] 도 11a에 도시된 예시적인 구성에서, 도선(120)은 돌출된 영역 상에 위치하고, 보호층(128)은 돌출된 영역 상의 도선(120) 위에 위치한다. 보호층(128)이 움푹한 영역 위에 퇴적되지 않아도, 보호층(128)은 건식 또는 습식 식각에 의해 움푹한 영역으로부터 제거될 수 있다. 이와 같이, 움푹한 영역에는 보호층(128)이 실질적으로 없어질수 있다. 보호층(128)을 움푹한 영역으로부터 식각할 때, 베이스 층(106)의 일부도 식각될 수 있다. 따라서, 움푹한 영역에서 베이스 층(106)의 두께는 다른 곳에서의 베이스 층(106) 두께보다 작을 수 있다. 도 11a과 같이 버퍼층(126)이 식각될 때, 버퍼층(126)의 일부에서 다른 부분으로 갈라짐이 전파되는 것은 움푹한 영역의 공간에 의해 저지된다. 유사하게, 보호층(128)에 의한 갈라짐 전파도 움푹한 영역의 공간에 의해 저지된다. 따라서, 갈라짐 전파에 의한 도선(120)의 손상이 감소된다.

- [0167] 도 11b에 도시된 다른 구성에서, 움푹한 영역은 특정 깊이로 식각된 베이스 충(106)을 포함하고, 도선(120)은 움푹한 영역의 베이스 충(106) 상에 중착된다. 이 설정에서, 도선(120) 부분은 베이스 충(106) 내에 배치된다. 또한 도선(120)의 일 부분은 돌출된 영역에 마련된 버퍼층(126)의 일부 상에 중착된다. 보호층(128)은 도선(120) 위에 중착되고, 움푹한 영역 내에 도선(120)을 노출시키기 위해 식각될 수 있다.

- [0168] 따라서, 보호층(128)은 돌출된 영역 위에 위치한 도선(120) 상에 남는다. 이 구성에서, 버퍼층(126) 위에 남은 보호층(128)은 다층 도선(120)의 측부의 단면을 덮음으로써 갈바닉 부식을 억제할 수 있다. 버퍼층(126)에서 발생된 갈라짐이 버퍼층(126) 내의 빈 공간 벽 위에 있는 도선(120)으로 침투할 수 있지만, 베이스 층(106) 내에 위치한 도선(120)에 도달하기는 어렵다.

- [0169] 도선(120)이 상술한 다층 구조를 가질 때, 움푹한 영역에 있는 도선(120)의 일 부분은 보호층(128)으로 덮일 필요가 없다. 보호층(128)이 움푹한 영역에서 도선(120)의 표면으로부터 제거되면, 보호층(128)으로부터의 갈라짐전파는 방지될 수 있다. 그리고, 일반적으로 갈바닉 부식은 버퍼층(126) 위에 있는 도선(120)의 모서리에서 시작하고, 따라서 버퍼층(126) 상의 도선(120)과 베이스 층(106)의 도선(120)이 서로 충분히 떨어져 있다면, 버퍼층(126) 위 도선(120)의 모서리를 덮는 보호층(128)은 필요하지 않을 수 있다. 도 11a 및 11b에 도시된 구성은, 굴곡 구간의 배선 구조를 위해 도 8, 9a 및 9b의 변형 저감 배선 패턴과 함께 사용될 수 있다. 굴곡 구간 외에

도, 몇몇 실시예에서 상기 패턴화된 절연층은, COF 부착 영역과 굴곡 구간 사이의 라우팅 영역 사이와, 표시 영역과 굴곡 구간 사이의 라우팅 영역에도 마련될 수 있다.

- [0170] 그리고, 상술된 패턴화된 절연층은 표시 영역에 제공될 수도 있다. 그러나, TFT 부근의 무기 절연층을 제거하면 부품의 전기적 특성에 영향을 미칠 수 있다. 예를 들어, 버퍼층(126)의 일부가 제거되면 원치 않는 TFT의 임계 전압 이동이 초래될 수 있다. TFT의 안정성을 유지하기 위해서, 추가적인 차폐 금속(shield metal)이 TFT의 반도체 층 아래에 형성될 수 있다. 차폐 금속 층은 버퍼층(126) 아래 또는 버퍼층(126)의 무기물 층들 사이에 있을 수 있다. 몇몇 실시예에서, 차폐 금속 층은 TFT의 소스 전극 또는 게이트 전극과 전기적으로 연결될 수 있다.

- [0171] 플렉서블 표시장치(100)의 여러 곳에 있는 절연층의 패터닝에 더하여, 굴곡을 위해 플렉서블 표시장치(100)의 몇몇 영역에서 다른 구조적 요소가 제거되거나 단순화될 수 있다. 예를 들어, 터치센서층(112), 편광층(110) 등이 굴곡 구간에 없을 수 있다. 이러한 요소들의 제거 또는 단순화는 배선 구조가 지나갈 수도 있는 다수의 비평 탄 표면을 만들 것이다.

- [0172] 배선 구조가 이러한 비평탄 표면에 있을 때, 배선 구조의 일 부분은 타 부분과는 다른 평면에 놓일 수 있다. 다른 평면에 있는 부분들이 있기에, 굴곡 스트레스 및 그에 기인한 변형의 양과 방향은 배선 구조 내에서도 다를 수 있다. 이 차이를 수용하기 위해, 배선 구조의 변형 저감 설계는 비평탄 표면에 있는 배선 구조를 위한 수정된 배치 설계를 포함할 수 있다.

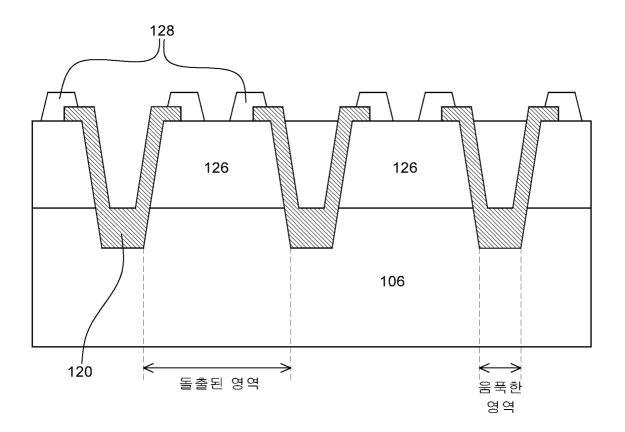

- [0173] 도 12a는 플렉서블 표시장치(100)의 예시적인 백플레인을 도시한 확대 단면도이다.

- [0174] 상기 표시장치는, 신뢰성있인 굴곡을 위해 굴곡 부분에서 다수의 절연층이 제거되었다.

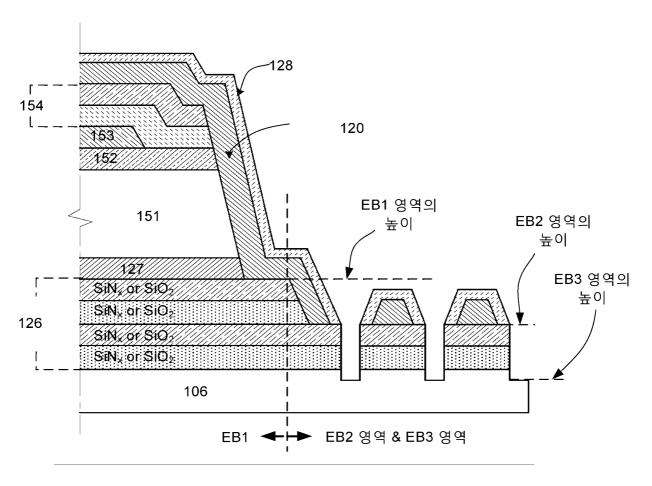

- [0175] 다수의 유기물 및 무기물 층이 베이스 층(106)과 유기발광소자층(150) 사이에 형성될 수 있다. 이 예시에서, 버 퍼충(126) 역할을 하도록 베이스 층(106) 상에 SiNx 및 SiO<sub>2</sub> 층이 번갈아 적충될 수 있다. TFT의 반도체 층 (151)은 액티브 버퍼층(127)과 SiO<sub>2</sub> 층으로 만들어진 게이트 절연층(152) 사이에 끼워질 수 있다. TFT의 게이트 (152)는 게이트 절연층 (152) 상에 배치되고, 다층 구조를 갖는 금속층(TFT의 소스/드레인과 동일 금속)은 층간 절연층(154)와 보호층(128) 사이에 놓인다. 여기서, 층간 절연층(154)은 SiNx 및 SiO<sub>2</sub>의 적층으로 형성될 수 있고, 보호층(128, passivation layer)은 SiNx로 형성될 수 있다. 그 후에, 보호층(128) 위에 평탄화층이 배치되고, OLED의 애노드가 그 위에 놓인다.

- [0176] 상술한 바와 같이, 변형 저감 설계의 사용은 굴곡 부분에 있는 배선 구조의 일부분에 제한되지 않는다. 또한, 변형 저감 설계는 굴곡 구간 바깥에 있는 라우팅 영역의 배선 구조에 적용될 수 있다. 이러한 라우팅 영역의 배선 구조를 위한 변형 저감 설계의 사용은, 배선 구조의 굴곡 스트레스에 대한 향상된 보호를 가져올 수 있다.

- [0177] 그러나, 라우팅 영역에서 베이스 층(106)과 유기발광소자층(150) 사이에 있는 다수의 유기 및/또는 무기물 층은 플렉서블 표시장치(100)의 굴곡을 용이하게 하기 위해 제거될 수 있다. 이러한 유기물 및/또는 무기물 층은, 층 간 절연층(154), 게이트 절연층(152), 버퍼층(126, 127), 보호층(128), 편광층 등에 포함될 수도 있는데, 플렉서블 표시장치(100)의 굴곡 부분에는 없을 수도 있다. 이러한 층들 중 일부는 식각 공정에 의해 특정 영역에서 제거될 수 있다.

- [0178] 일 예로서, 버퍼층(126) 상에 있는 복수의 절연층은 제1 식각 과정(EB1)에 의해 제거될 수 있다. 제1 식각 과정(EB1) 다음에는 액티브 버퍼(127) 및 버퍼층(126)의 일부(예: SiNx 층 및 SiO<sub>2</sub> 층의 적층)가 제거되는 제2 식각 과정(EB2)이 뒤따른다. 이러한 식각 과정은 도 12a에 도시된 것과 같은 다수의 단차(계단) 영역을 만든다. 상기 단차 영역은 하나 이상의 수직으로 경사진 표면 및 수평으로 평탄한 표면을 가지고, 그 위에는 도선이 배치된다. 수직으로 경사진 표면 및 수평으로 평탄한 표면에 놓인 도선은 절연층에 의해 마련된 높은 계단 및 낮은 계단 사이의 영역과 같은 다수의 굴곡 지점을 가질 수 있다.

- [0179] 플렉서블 표시장치(100)가 굴곡 방향으로 구부러질 때, 도선은 단차 영역 및 그 부근에서 더 큰 변형을 겪는다. 다양한 연구와 실험에서 갈라짐 가능성은 EB1 영역 및 EB2 영역 사이의 단차 영역을 가로지르는 배선에서 특히 높다는 점이 지적되었다. 따라서, 몇몇 실시예에서 변형 저감 설계는, 절연층에 의해 만들어진 높은 단과 낮은 단 사이의 단차 영역 및 그 부근에 강화 부분을 갖는다.

- [0180] 도 12b에 도시된 예에서, 배선 구조는 양 끝에서 단순한 직선 배선을 갖는다. 그러나, 굴곡 구간 EB1과 EB2를 가로지르는 도선(120)의 일부분이 수정된 배선 설계로 강화된다. 수정된 부분에서, 도선(120)은, EB1 및 EB2 영

역 부근의 절연층으로부터 시작된 갈라짐에도 도선(120)의 보호를 보장하도록, 추가 폭 WR을 갖는 더 넓은 폭을 갖게 된다. 수정된 배선 설계에서 제공되는 거리 DR은, 제1 높이면 (예: EB1 영역의 높이)과 제2 높이면(예: EB2 영역의 높이) 사이의 거리뿐만 아니라 식각 과정에서 식각되는 절연층의 두께에 의존한다.

- [0181] 수정된 부분이 적용된 배선 구조의 변형 저감 설계는 도 12b에 설명된 디자인에 제한되지 않는다. 변형 저감 설계의 다양한 실시예는 다른 높이의 단차 영역에 대응하는 배선의 특정 부분을 위한 수정된 배선 설계를 포함할 수 있다.

- [0182] 항상 그런 것은 아니지만, 굴곡 구간에 인접한 라우팅 영역은 플렉서블 표시장치(100)의 실질적으로 평평한 부분일 수 있다. 이 경우에, EB1 및 EB2 영역은, 굴곡 부분에서 굴곡 구간의 시작 또는 바로 바깥에 위치할 수 있고, 배선 구조는 강화 부분을 가지게 될 수 있다.

- [0183] 강화된 도선(120) 부분의 증가 폭 WR은, 곡률이 상대적으로 작은 굴곡 구간의 시작과 끝 및 그 부근에서 본 목적에 부합한다. 배선 구조의 더 넓은 폭 WR 및 수정된 배선 부분이 적용된 길이는, 굴곡 방향에 평행하게 정렬된 배선의 길이를 증가시킬 수 있다. 이 것은 더 큰 굴곡 반지름 지역에서 굴곡 스트레스에 버티도록, 배선 구조를 더 단단하게 만들 것이다.

- [0184] 이와 같은 이유로, 강화 부분이 있는 거리 DR은, 강화 도선 부분이 굴곡 구간으로 너무 많이 연장되지 않도록 제한되어야 한다. 따라서, 강화 도선 부분의 거리 DR은, 강화 도선 부분의 배선이 소정의 임계 굴곡각보다 더 구부러지는 굴곡 구간을 넘어 연장하지 않도록 제한될 수 있다. 일 예로서, 강화 도선 부분은 탄젠트 평면으로 부터 30° 구부러지는 지점을 넘어 연장하지 않을 수 있다. 임계 굴곡 각은 20° 보다 작을 수 있고, 10° 또는 7° 이하일 수도 있다.

- [0185] 단차 영역에 강화 부분이 마련된 배선 구조는, 굴곡 구간을 가로질러 확장하여 COF의 패드 또는 다른 부품들로 연결될 수 있다. 이러한 예에서, (EB1 및 EB2와 유사한) 추가적인 단차 영역이 굴곡 구간의 반대쪽 끝 또는 그 부근에 존재할 수 있다. 이러한 굴곡 지점 또는 그 부근에 있는 도선은, 도 12b처럼, 배선 구조의 수정된 부분과 비슷한 방식으로 반대쪽 끝이 강화될 수 있다. 원한다면, 굴곡 구간의 반대쪽 끝의 단차 영역 또는 그 부근에 있는 도선 강화 부분은, 도 12b에 설명된 것과는 다른 모양을 가질 수 있다.

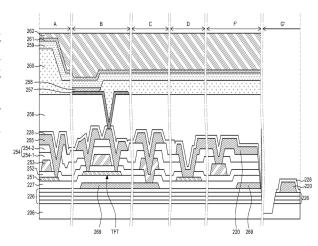

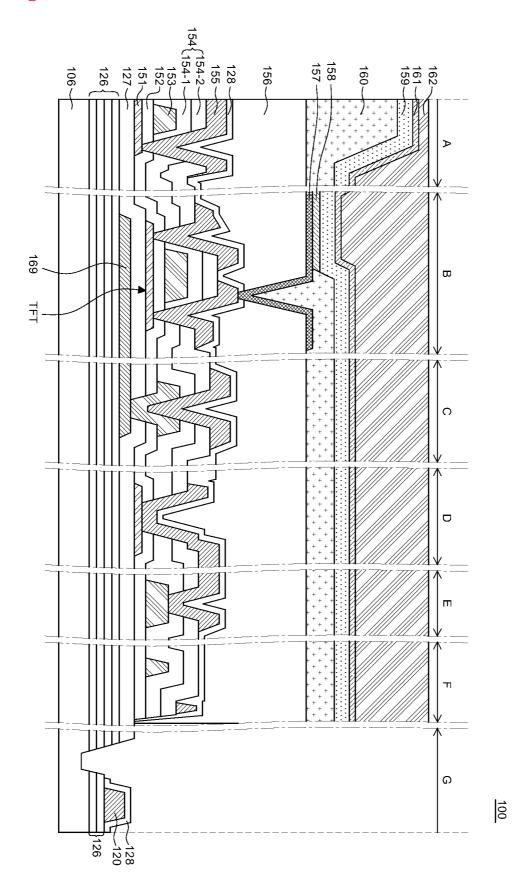

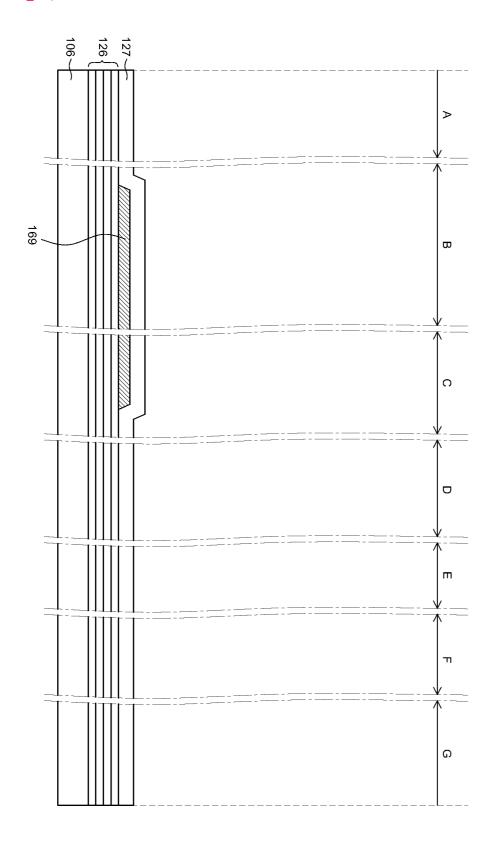

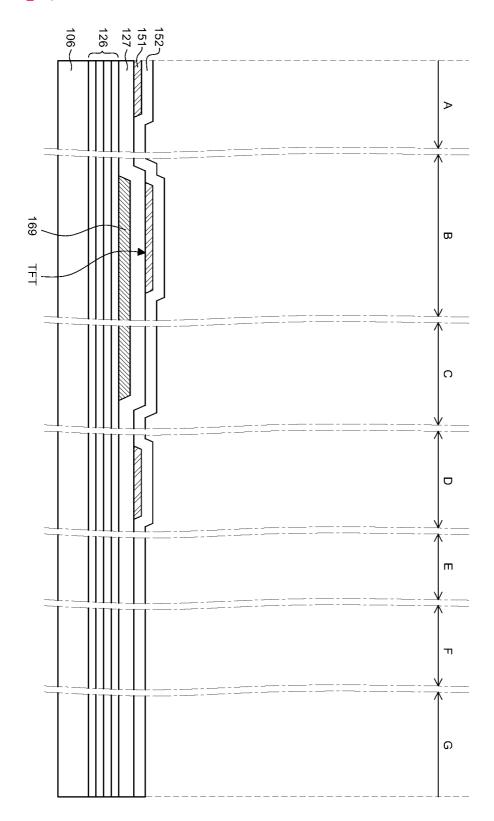

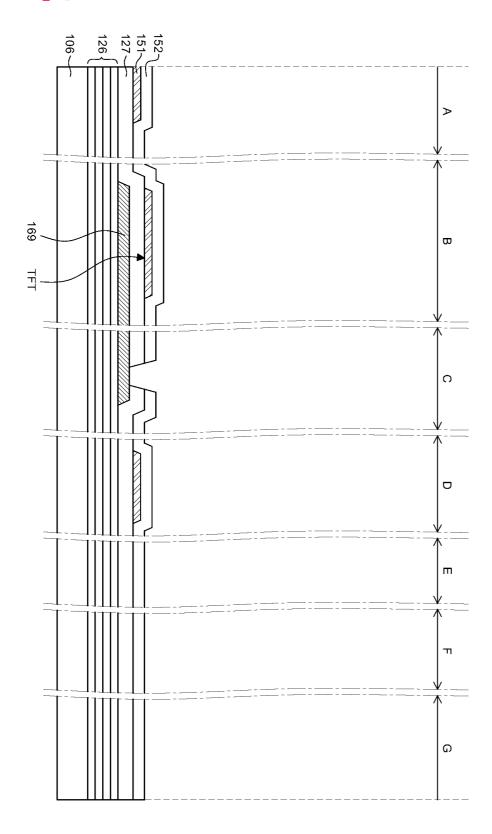

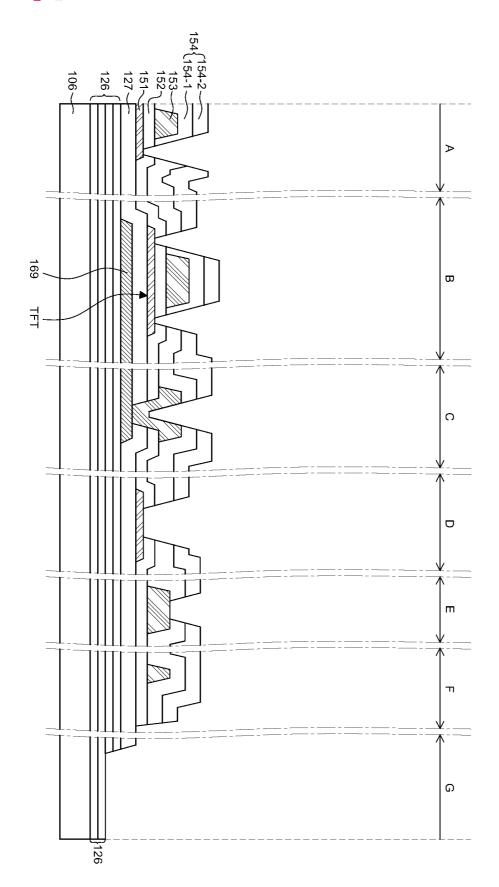

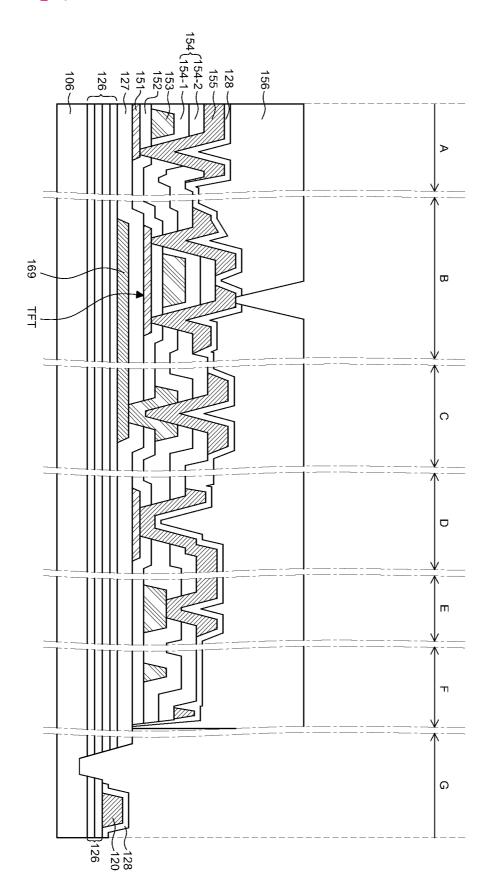

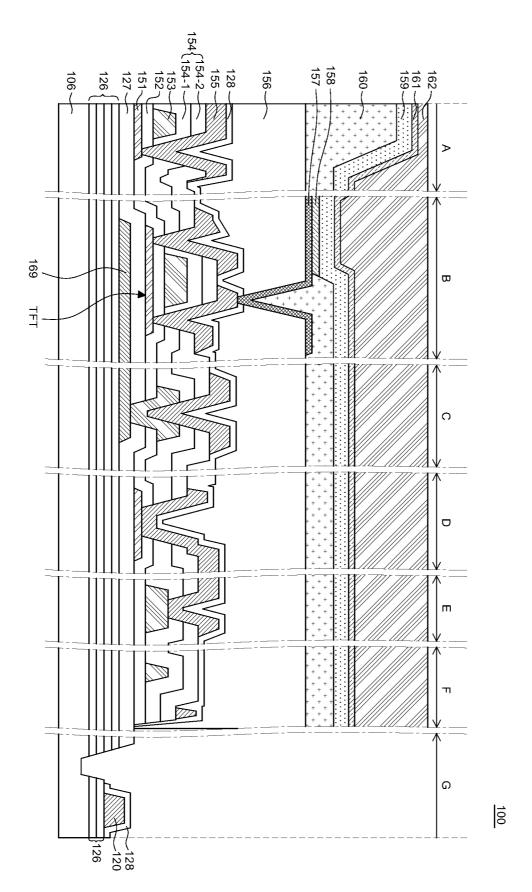

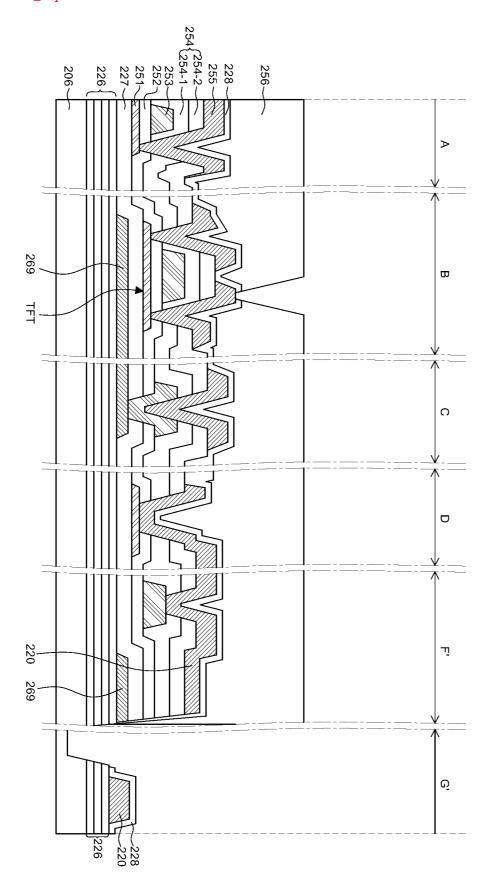

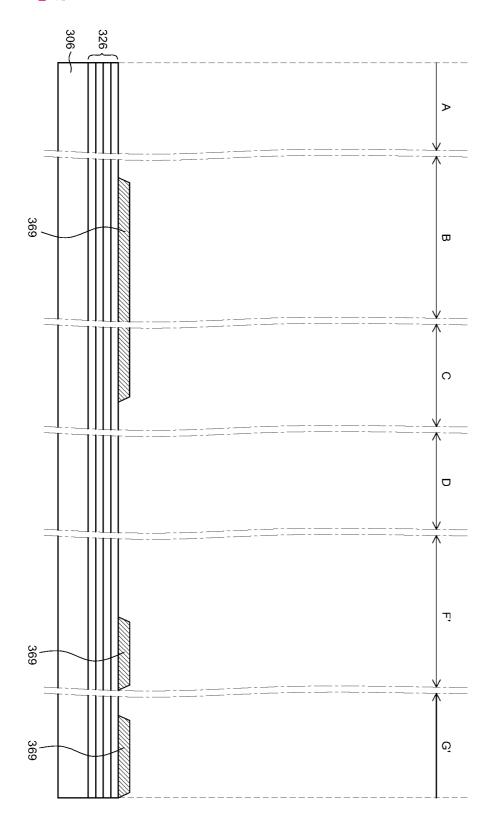

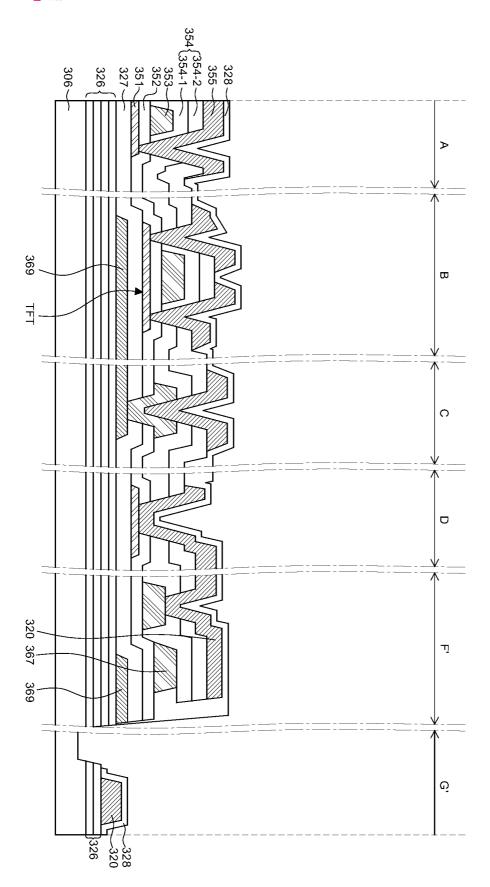

- [0186] 도 13은 본 명세서의 일 실시예에 따른 플렉서블 표시장치의 단면도이다.

- [0187] 상기 플렉서블(flexible) 표시장치는 가요성(flexibility)이 부여된 표시장치를 의미하는 것으로, 구부릴 수 있는(bendable) 표시장치, 말수있는(rollable) 표시장치, 깨지지 않는(unbreakable) 표시장치, 접을 수 있는 (foldable) 표시장치 등과 동일한 의미로 사용될 수 있다. 이하에서 서술되는 플렉서블 유기발광 표시장치는, 도 1 내지 도 12에서 설명된 다양한 구조 및 설계가 반영된 플렉서블 표시장치 중 일 예이다.

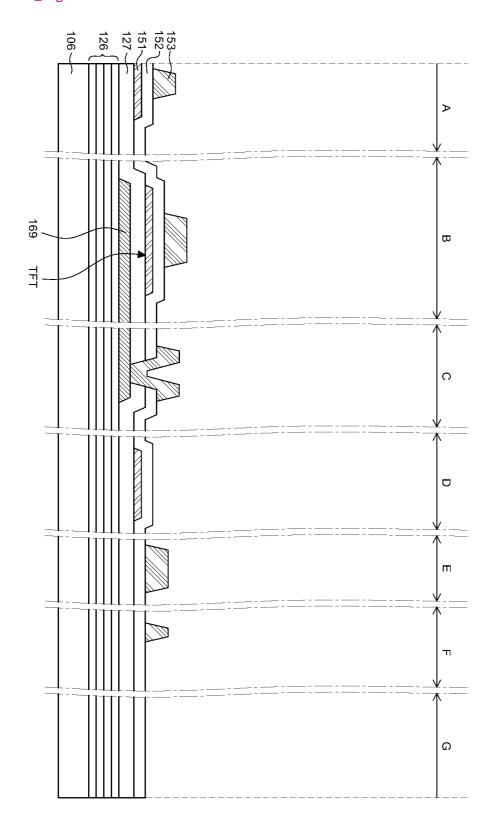

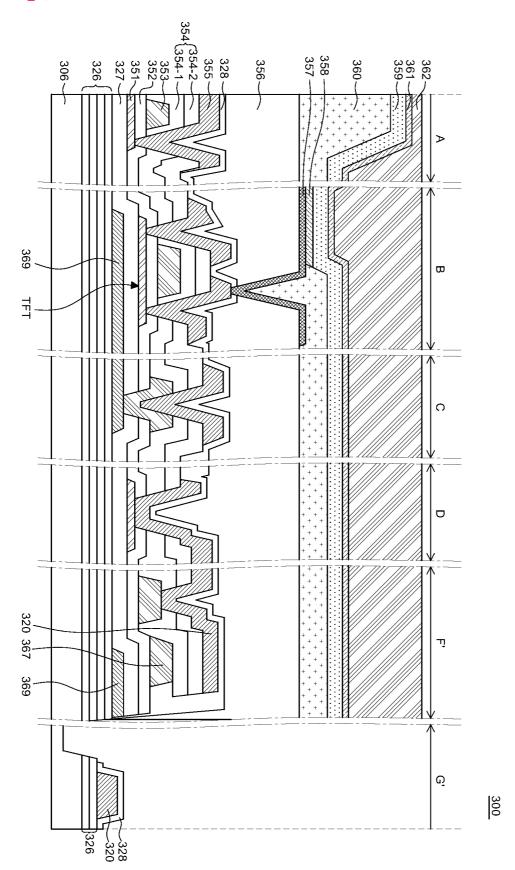

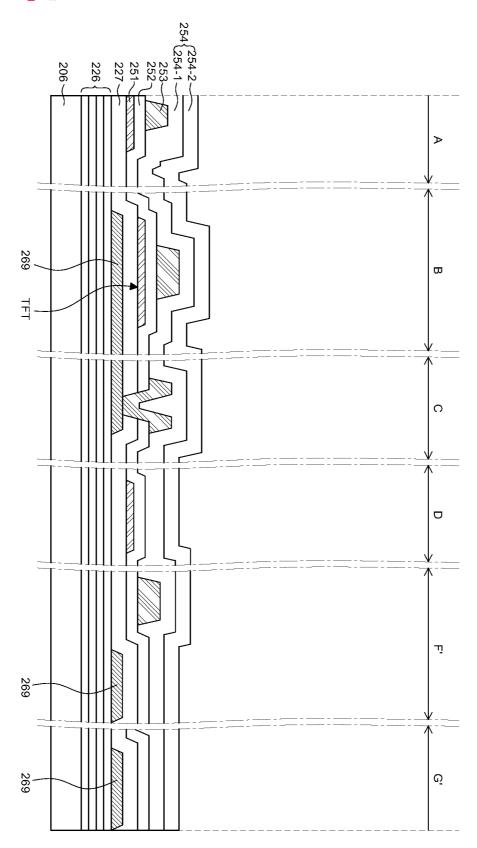

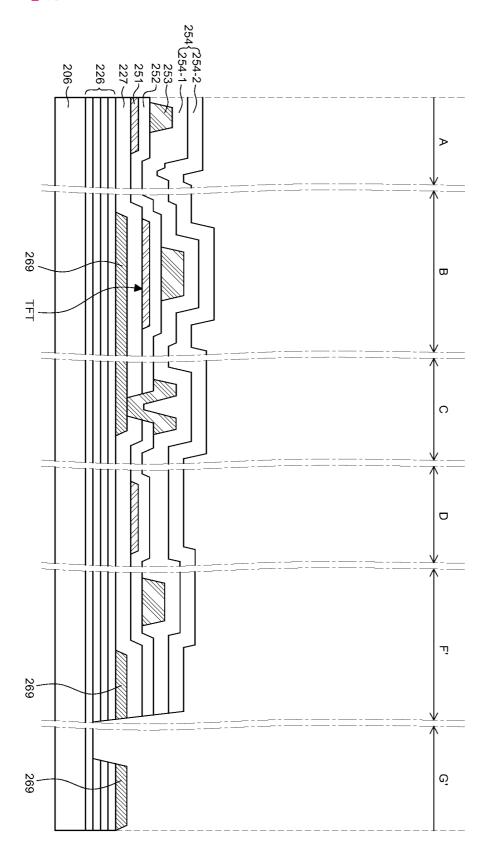

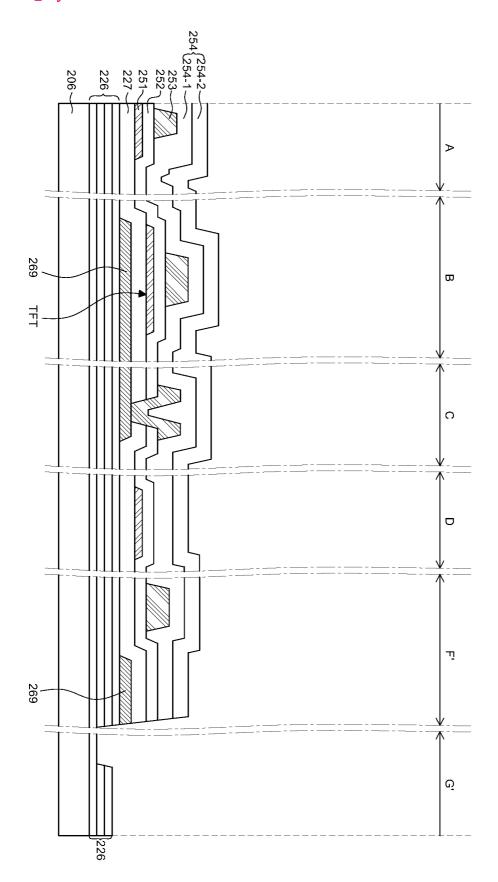

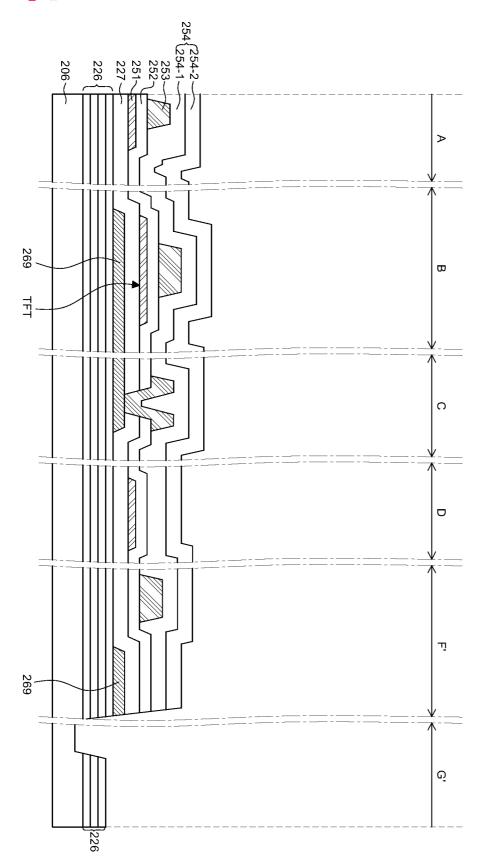

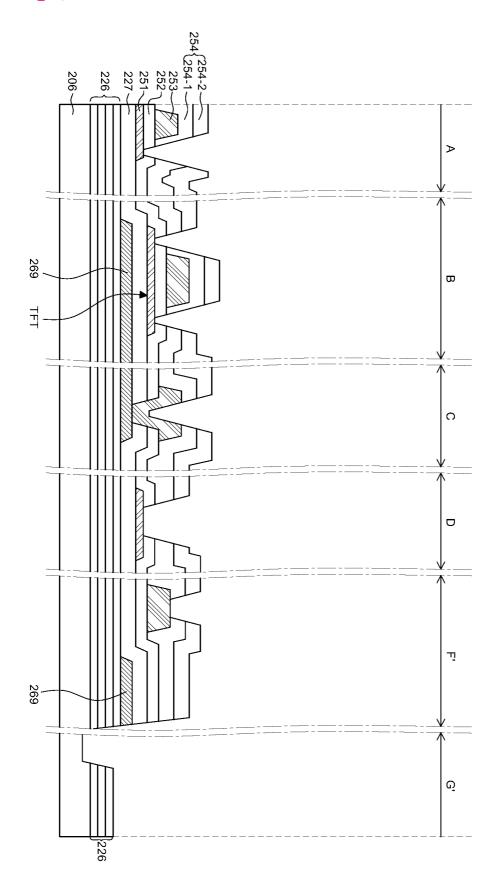

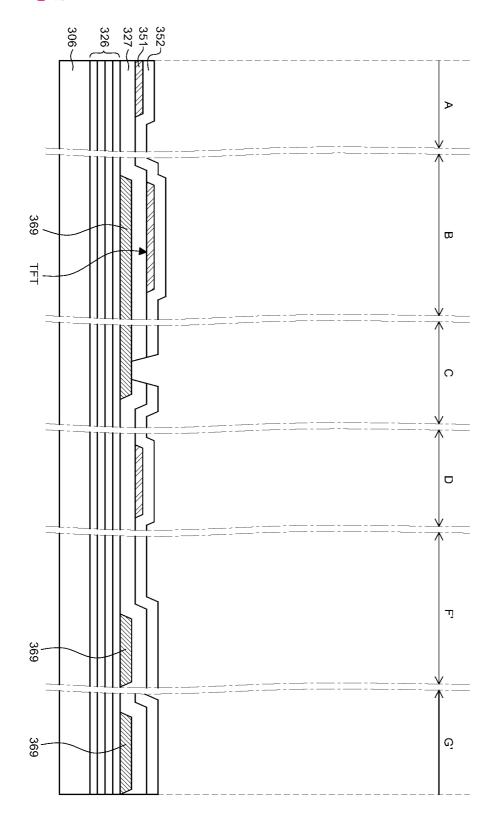

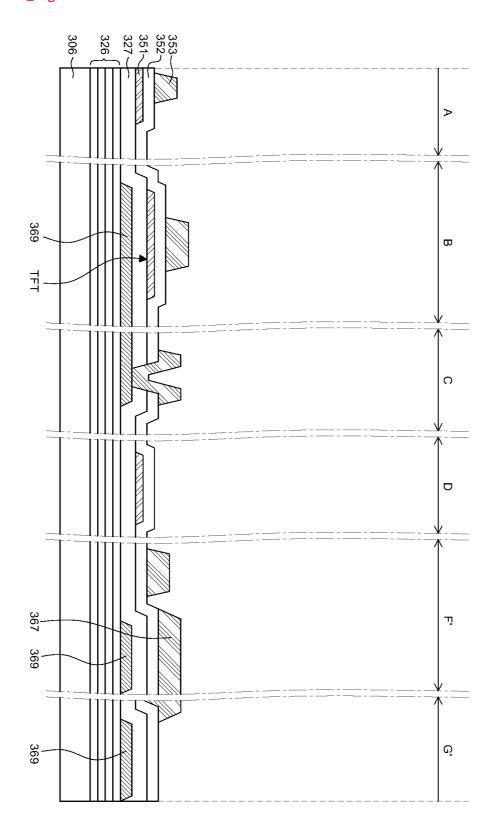

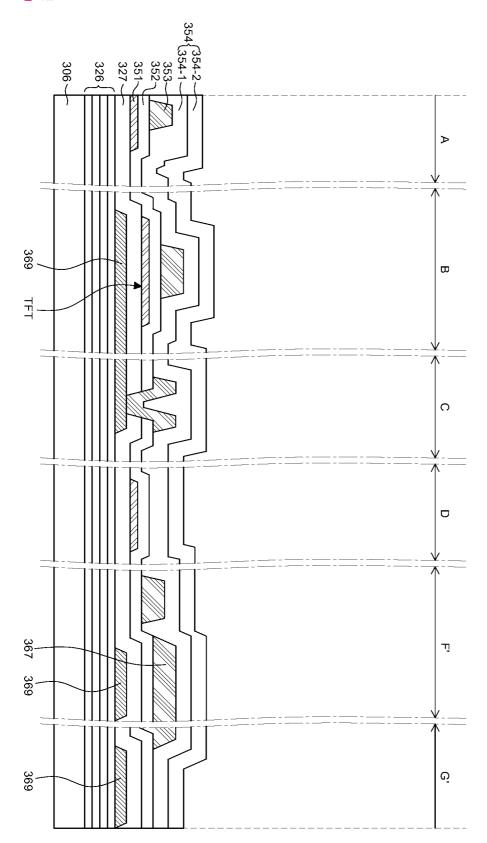

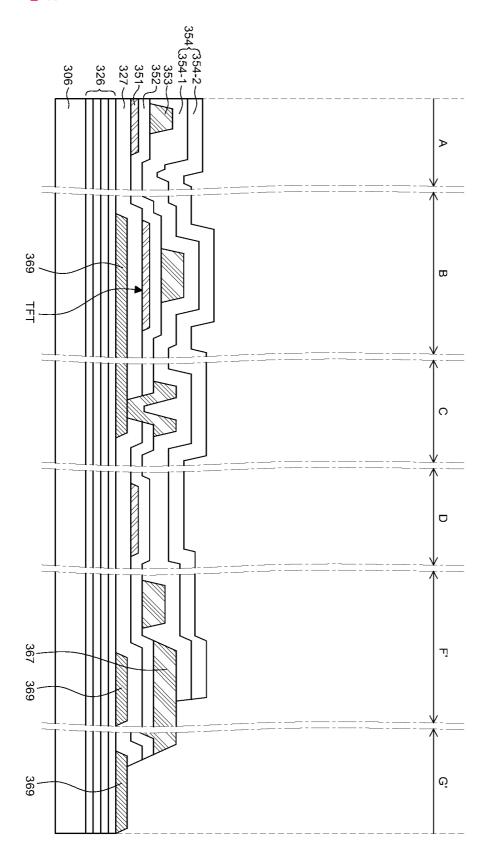

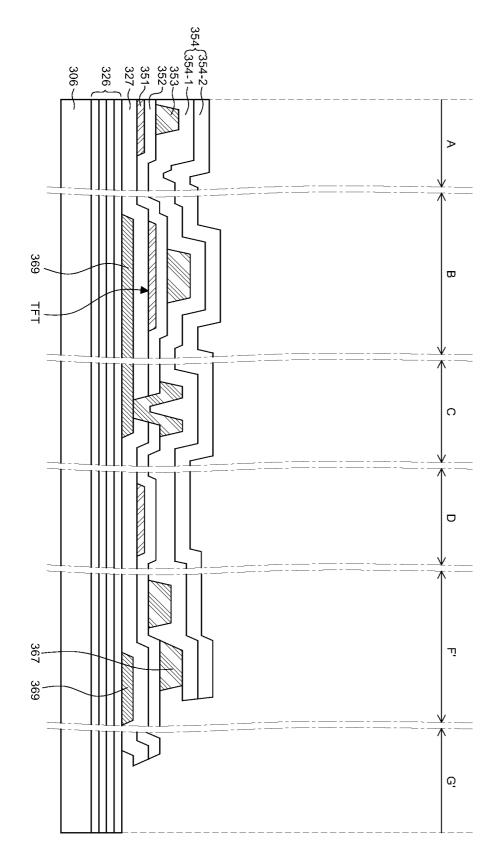

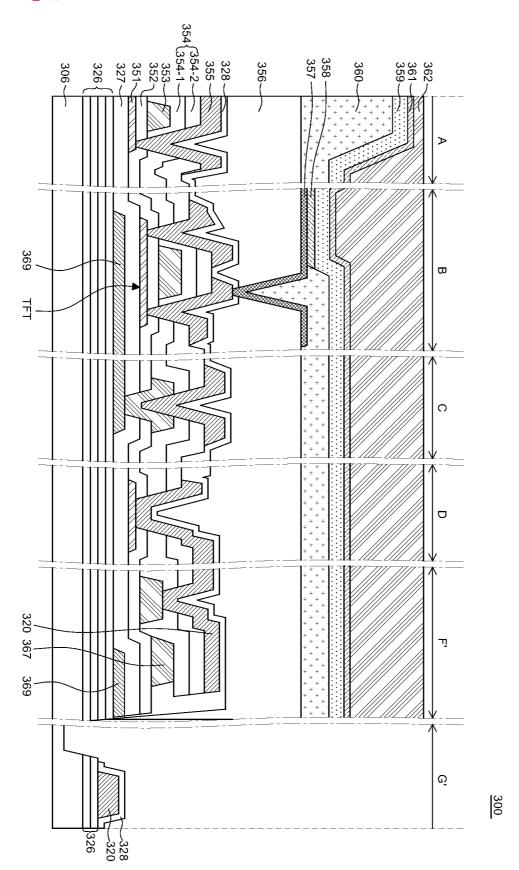

- [0188] 상기 플렉서블 표시장치는 도 1과 같이 표시 영역 및 비표시 영역을 포함할 수 있다. 도 13에서는 비표시 영역이 표시 영역의 바깥쪽을 두르면서, 굴곡 구간(G)을 포함하고 있는 것으로 도시하였지만 본 발명의 사상이 이에 제한되는 것은 아니다. 또한 도 13은 표시 영역의 유기발광소자층, 비표시 영역, 굴곡 구간 등의 특정 지점 (A~G)에서 추출한 단면도를 연결하여 도시한 것이다. 예시적으로서, A는 데이터 신호(전압)를 저장하는 저장 커패시터(storage capacitor)가 있는 영역을 개념적으로 도시한 부분이다. B는 유기발광소자 와 접속된 박막트랜지스터(TFT: thin film transistor)가 있는 영역을 개념적으로 도시한 부분이다. C는 하부보호금속(169)이 게이트 물질(153) 및 소스/드레인 물질(155)과 연결된 컨택 홀 영역을 개념적으로 도시한 부분이다. B는 게이트 물질(153)과 소스/드레인 물질(155)이 연결된 컨택 홀 영역을 개념적으로 도시한 부분이다. E는 게이트 물질(153)과 소스/드레인 물질(155)이 전기적으로 연결된 영역을 개념적으로 도시한 부분이다. F는 스캔 신호(또는 주사 신호)를 공급하는 게이트 라인들이 배치된 영역을 개념적으로 도시한 부분이다. G는 굴곡 구간을 개념적으로 도시한 부분이다.

- [0189] 이하에서는 도 13에 도시된 각 충(layer)들을 설명한다. A~G 지점에 도시된 충들은, 각각 같은 공정을 통해 구조화된 충들이다. 즉, A~G 지점의 '반도체 충'(151)은 모두 X 공정에서 형성되고, '게이트 물질(153)'은 Y 공정에서 형성되며 나머지 충들도 마찬가지이다.

- [0190] 베이스 충(106)은 플렉서블 표시장치의 여러 구성 요소들을 지지한다. 상기 베이스 충(106)이 플라스틱으로 이루어진 경우, 플라스틱 필름 또는 플라스틱 기판으로 지칭될 수 있다. 예를 들어, 상기 베이스 충(106)은 폴리에스터계 고분자, 실리콘계 고분자, 아크릴계 고분자, 폴리올레핀계 고분자 및 이들의 공중합체로 이루어진 군에서 선택된 하나를 포함하는 필름 형태일 수 있다. 구체적으로, 상기 베이스 충(106)은 폴리에텔렌테레프탈레이트(PBT), 폴리부틸렌테레프탈레이트(PBT), 폴리실란(polysilane), 폴리실록산(polysiloxane), 폴리실라잔

(polysilazene), 폴리카르보실란(polycarbosilane), 폴리아크릴레이트(polyacrylate), 폴리메타크릴레이트 (polymethacrylate), 폴리메티크릴레이트(polymethylacrylate), 폴리메틸메타크릴레이트 (polymethylmetacrylate), 폴리메틸메타크릴레이트 (polyethylmetacrylate), 폴리에틸메타크릴레이트 (polyethylmetacrylate), 사이클릭 올레핀 코폴리머(COC), 사이클릭 올레핀 폴리머(COP), 폴리에틸렌(PE), 폴리프로필렌(PP), 폴리이미드(PI), 폴리스타이렌(PS), 폴리아세탈(POM), 폴리에테르에테르케톤(PEEK), 폴리에스 테르설폰(PES), 폴리테트라플루오로에틸렌(PTFE), 폴리비닐클로라이드(PVC), 폴리카보네이트(PC), 폴리비닐리덴 플로라이드(PVDF), 퍼플루오로알킬 고분자(PFA), 스타이렌아크릴나이트릴코폴리머(SAN) 및 이들의 조합으로 이루어진 군에서 선택된 하나를 포함할 수 있다. 이 물질 중에서, 폴리이미드는 고온의 공정에 적용될 수 있고, 코팅이 가능한 재료이기에 플라스틱 기판으로 많이 사용된다.투명 플렉서블 표시장치에서는, 상기 베이스 층 (106)이 투명한 가요성의 물질로 이루어질 수 있다.

- [0191] 버퍼층(126, 127)은 베이스 층(106) 또는 하부의 충들에서 유출되는 알칼리 이온 등과 같은 불순물로부터 박막 트랜지스터를 보호하기 위한 기능 층이다. 상기 버퍼층은 멀티 버퍼(multi buffer, 126) 및/또는 액티브 버퍼 (active buffer, 127)를 포함할 수 있다.

- [0192] 멀티 버퍼층(126)은 상기 베이스 층(106) 상에 위치한다. 상기 멀티 버퍼층(126)은 질화실리콘(SiNx) 및 산화실리콘(SiOx)이 교대로 적층되어 이루어질 수 있으며, 베이스 층(106)에 침투한 수분 및/또는 산소가 확산되는 것을 지연시킬 수 있다. 멀티 버퍼층(126)은 베이스 층(106)의 물질이나 그 위에 형성되는 층의 종류에 따라 더 배치되거나 제거될 수 있다. 예를 들어, 상술한 것과 같이 굴곡 구간에서 갈라짐(crack) 발생을 억제하기 위하여, 비표시 영역에는 멀티 버퍼층이 표시 영역보다 더 적게 배치되거나 혹은 멀티 버퍼층이 제거될 수 있다.

- [0193] 액티브 버퍼층(127)은 멀티 버퍼층(126) 상에 위치할 수 있다. 상기 액티브 버퍼(127)는 트랜지스터의 반도체 층(151)을 보호하며, 베이스 층(106)으로부터 유입되는 다양한 종류의 결함을 차단하는 기능을 수행한다. 상기 액티브 버퍼(126)는 비정질 실리콘(a-Si) 등으로 형성될 수 있다. 박막트랜지스터는 반도체 층(151), 게이트 절 연충(152), 게이트(153), 충간 절연막(154), 소스 및 드레인(155)이 순차적으로 배치된 형태일 수 있다. 상기 박막트랜지스터는 P형 TFT 또는 N형 TFT일 수 있다. 상기 P형(P-type) TFT는, PMOS로, 상기 N형(N-type) TFT는 NMOS로 호칭되기도 한다.

- [0194] 반도체 층(151)은 상기 액티브 버퍼층(127) 상에 위치한다. 이때 반도체 층(151) 폭은 하부보호금속(159)의 폭보다 작게 형성될 수 있으나, 이에 한정되지 않는다. 반도체 층(151)은 다결정 실리콘(polycrystalline silicon)으로 만들어질 수 있으며, 이 경우 소정의 영역이 불순물로 도핑될 수도 있다. 또한, 반도체 층(102)은 비정질 실리콘(amorphous silicon), 유기 반도체 물질 또는 산화물(oxide)로 형성될 수 있다.

- [0195] 게이트 절연층(152)은 반도체 층(151) 상에 위치할 수 있다. 게이트 절연층(Gate Insulator)은 게이트(153)과 반도체 층(151) 사이를 절연한다. 게이트 절연층(152)은 실리콘 산화물(SiOx) 또는 실리콘 질화물(SiNx) 등과 같은 절연성 무기물로 형성될 수 있으며, 이외에도 절연성 유기물 등으로 형성될 수도 있다.

- [0196] 게이트 절연충(152)을 구성하는 실리콘 산화막(SiOx) 및 실리콘 질화막(SiNx) 등은 금속에 비해 가요성이 떨어 진다. 따라서 굴곡 구간의 가요성을 향상시키기 위해, 굴곡 구간의 게이트 절연충은 제거될 수 있다.

- [0197] 게이트 물질(153)은 게이트 절연층(152) 상에 위치한다. 게이트 물질(153)은 몰리브덴(Mo), 알루미늄(Al), 크롬 (Cr), 금(Au), 티타늄(Ti), 니켈(Ni), 네오디뮴(Nd) 및 구리(Cu) 중 어느 하나 또는 이들의 합금으로 이루어질 수 있으나, 이에 한정되지 않으며, 다양한 물질로 형성될 수 있다. 또한, 게이트 물질(153)은 단일층 또는 다중 층일 수도 있다. 게이트 물질(153)은, B지점에서와 같이 박막트랜지스터의 게이트 전극으로 사용되는 것 외에도, A 지점에서와 같이 특정 커패시턴스를 형성하거나, C 지점과 같이 연결 전극으로 사용되기도 한다.

- [0198] 충간 절연충154)은 게이트 물질(153) 상에 위치한다. 충간 절연충(154)은 게이트 절연충(152)과 동일한 물질인, 실리콘 산화막(SiOx), 실리콘 질화막(SiNx) 또는 이들의 다중층 등으로 형성될 수 있으나, 이에 한정되지 않는다. 한편, 충간 절연막(154)과 게이트 절연충(152)의 선택적 제거를 통해 반도체 충(151) 및/또는 게이트 물질(153)이 노출되는 컨택 홀(contact hole)이 형성될 수 있다.

- [0199] 소스/드레인 물질(155)은 충간 절연충(154) 상에 위치한다. 소스/드레인 물질(155)은 몰리브덴(Mo), 알루미늄 (Al), 크롬(Cr), 금(Au), 티타늄(Ti), 니켈(Ni), 네오디뮴(Nd) 및 구리(Cu) 중 어느 하나 또는 이들의 합금으로 이루어질 수 있으나, 이에 한정되지 않으며, 다양한 물질로 형성될 수 있다. 또한, 소스/드레인 물질(155)은 단일층 또는 다중층일 수도 있다. 소스/드레인 물질(155)은, B지점에서와 같이 박막트랜지스터의 소스/드레인 전극으로 사용되는 것 외에도, A 지점에서와 같이 특정 커패시턴스를 형성하거나, C 지점과 같이 연결 전극으로

사용되기도 한다. 또한 소스/드레인 물질(155)은 F, G 지점과 같이 도선(120)을 형성하기도 한다. 도 13에 도시된 도선(120)은 상술한 변형 저감 배선 구조의 일 부분일 수 있다.

- [0200] 하부보호금속(169)은 멀티 버퍼층(126) 상에 위치할 수 있다. 또한 하부보호금속(BSM: Bottom Shield Metal)은 박막트랜지스터( 하부에 위치할 수 있다. 예를 들어 하부보호금속은 박막 트랜지스터의 반도체 층 대응하여 액티브 버퍼층 하부에 위치할 수 있다. 하부보호금속(169)은 모든 트랜지스터의 반도체 층 하부에 위치할 수도 있고, 필요에 따라 특정 트랜지스터(예: 구동 트랜지스터)의 반도체 층 하부에만 위치할 수도 있다. 이때 하부보호금속(169)은 레이저 및 외부로부터 유입되는 광으로부터, 박막 트랜지스터의 소자 특성, 예를 들어 문턱 접압 또는 on/off 접압이 변동되는 것을 방지하여 픽셀 간 휘도 불균형을 방지할 수 있다. 또한 하부보호금속(109)은 외부로부터 유입되는 수분으로부터 상기 트랜지스터의 소자 특성(예: 문턱 전압 등)이 변동되는 것을 억제한다. 이로써 상기 하부보호금속(BSM: Bottom Shield Metal)은 픽셀 간 휘도 불균형(얼룩, 잔상으로 나타남)을 방지할수 있다. 더 나아가, 상기 하부보호금속(169)은, 플렉서블 유기발광 표시장치의 제조 공정(예: 유리기판을 떼어내는 과정)에서, 트랜지스터가 물리적으로 손상되는 것을 최소화할 수도 있다.

- [0201] 하부보호금속(169)은 박막 트랜지스터를 구성하는 게이트 전극(153) 과 동일한 물질로 형성될 수 있다. 한편, 하부보호금속(109)은 금속 재질이기 때문에, 소정의 커패시턴스(capacitance)를 형성하는 소자가 되기도 한다. 이때, 하부보호금속(169)이 전기적으로 플로팅(floating) 되어있으면 커패시턴스의 변동이 나타나고, 박막 트랜지스터들 각각의 문턱전압의 쉬프트 양이 다양해 질 수 있으며, 이것은 의도하지 않은 시각적 결함(예를 들어, 휘도 변화)을 발생시킬 수 있다. 따라서, 연결부재를 통해 하부보호금속(169)을 소스/드레인 전극 또는 게이트 전극에 접지하여 커패시턴스가 일정하게 유지되도록 할 수 있다.

- [0202] 하부보호금속(169)이 박막 트랜지스터의 소스 전극 또는 드레인 전극에 연결되는 경우, 하부보호금속 및 하부보 호금속에 연결된 전극 사이에 등전위가 형성될 수 있다. 하부보호금속 및 하부보호금속에 연결되는 전극들 사이의 전압 차이가, 박막 트랜지스터의 게이트 전극과 소스 전극 사이의 전압차(즉, VGS) 보다 작다면, 하부보호금속(169)가 박막 트랜지스터의 문턱전압에 미치는 영향은 최소화될 수 있다.

- [0203] 하부보호금속(169)은 게이트 전극과 연결되는 경우, 게이트 전극(153)과 하부보호금속(169)에 동일한 전압이 공급될 수 있다. 이때 상기 하부보호금속(169)이 박막 트렌지스터의 보조 게이트 전극으로서 동작할 수 있다. 하부보호금속 상에 위치하는 액티브의 표면에 추가적인 채널 영역이 제공될 수 있다. 따라서 박막 트랜지스터의 크기를 실질적으로 증가시키는 것 없이, 박막 트랜지스터의 이동도를 증가시킬 수 있다. 즉, 박막 트랜지스터의 전류 구동 능력을 향상시킬 수도 있다.

- [0204] 보호층(128)은 소스/드레인 물질(155) 상에 위치한다. 보호층(128)은 상기 소스/드레인 물질(155)을 보호한다. 보호층(128)의 선택적 제거를 통해 소스/드레인 물질(155이 노출되는 컨택 홀(contact hole)이 형성될 수 있다. 보호층(128)은 제2 버퍼층으로 지칭될 수 있으며, 이하에서는 보호층(128)과 제2 버퍼층을 동일한 구성요소로 지칭한다.

- [0205] 평탄화층(156)은 보호층 상에 위치한다. 평탄화층(156)은 박막트랜지스터를 보호하고 그 상부를 평평하게 한다. 평탄화층(156)은, 아크릴계 수지(polyacrylates resin), 에폭시 수지(epoxy resin), 페놀 수지(phenolic resin), 폴리아미드계 수지(polyamides resin), 폴리이미드계 수지(polyimides resin), 불포화 폴리에스테르계 수지(unsaturated polyesters resin), 폴리페닐렌계 수지(poly-phenylenethers resin), 폴리페닐렌설파이드계 수지(polyphenylenesulfides resin) 및 벤조사이클로부텐(benzocyclobutene) 중 하나 이상의 물질로 형성될 수 있으나, 이에 한정되지 않는다. 평탄화층(156)은 단층으로 형성되거나 이중 혹은 다중 층으로 구성될 수도 있는 등 다양한 변형이 가능하다.

- [0206] 유기발광소자는 제1 전극(112), 유기발광 층(158), 제2 전극(159)이 순차적으로 배치된 형태일 수 있다. 즉, 유기발광소자는 평탄화층(156) 상에 형성된 제1 전극(112), 제1 전극(112) 상에 위치한 유기발광 층(158) 및 유기발광 층(158) 상에 위치한 제2 전극(159)으로 구성될 수 있다.

- [0207] 제1 전극(157)은 컨택 홀을 통해 구동 박막트랜지스터의 전극(108)과 전기적으로 연결된다. 제1 전극(157)은 박막 트랜지스터의 타입에 따라 애노드 또는 캐소드의 역할을 할 수 있다. 유기발광 표시장치(100)가 하부 발광 (bottom emission) 방식인 경우, 상기 제1 전극(157)은 일함수 값이 비교적 큰 투명 도전성 물질(인듐-틴-옥사이드(ITO) 또는 인듐-징크-옥사이드(IZO) 등)일 수 있다. 유기발광 표시장치(100)가 상부 발광(top emission) 방식인 경우, 제1 전극(157)은 반사율이 높은 불투명한 도전 물질로 만들어질 수 있다. 예를 들면, 제1 전극(157)은 은(Ag), 알루미늄(Al), 금(Au), 몰리브덴(Mo), 텅스텐(W), 크롬(Cr) 또는 이들의 합금(예:

APC(Ag; Pb; Cu)) 등으로 형성될 수 있다.

- [0208] 뱅크(160)는 평탄화충 상에 발광 영역을 제외한 나머지 영역에 위치한다. 이때 뱅크는 제1 전극(157)의 일 부분을 노출시키는 개구 영역을 형성할 수 있다. 뱅크(160)는 실리콘 질화막(SiNx), 실리콘 산화막(SiOx)와 같은 무기 절연 물질 또는 BCB, 아크릴계 수지 또는 이미드계 수지와 같은 유기 절연물질로 만들어질 수 있다.

- [0209] 유기발광 층(158)이 뱅크(160)에 의해 노출된 제1 전극(112) 상에 위치한다. 유기발광 층(158)은 발광층, 전자 주입층, 전자수송층, 정공수송층, 정공주입층 등을 포함할 수 있다.

- [0210] 제2 전극(159)이 유기발광층(158) 상에 위치한다. 유기발광 표시장치(100)가 상부 발광(top emission) 방식인 경우, 제2 전극(159)은 인듐 틴 옥사이드(Indium Tin Oxide; ITO) 또는 인듐 징크 옥사이드(Induim Zinc Oxide; IZO) 등과 같은 투명한 도전 물질로 형성됨으로써 유기발광 층(158)에서 생성된 광을 제2 전극(159) 상부로 방출시킨다.

- [0211] 보호층(161)과 봉지층(162)이 제2 전극(159) 상에 위치한다. 상기 보호층(passivation layer)과 봉지층 (encapsulation layer)은, 발광 재료와 전극 재료의 산화를 방지하기 위하여, 외부로부터의 산소 및 수분 침투를 막는다. 유기발광소자가 수분이나 산소에 노출되면, 발광 영역이 축소되는 화소 수축(pixel shrinkage) 현상이 나타나거나, 발광 영역 내 흑점(dark spot)이 생길 수 있다. 상기 보호 층(161) 및/또는 상기 봉지층(162)은 유리, 금속, 산화 알루미늄(AlOx) 또는 실리콘(Si) 계열 물질로 이루어진 무기막으로 구성되거나, 또는 유기막과 무기막이 교대로 적층된 구조일 수도 있다. 무기막은 수분이나 산소의 침투를 차단하는 역할을 하고, 유기막은 무기막의 표면을 평탄화하는 역할을 한다. 봉지 층을 여러 겹의 박막 층으로 형성하는 이유는, 단일 층에 비해 수분이나 산소의 이동 경로를 길고 복잡하게 하여, 유기발광소자까지 수분/산소의 침투를 어렵게 만들려는 것이다. 또는 상기 봉지층(162)은 배리어 필름(barrier film)일 수 도 있다.

- [0212] 봉지층(162) 상에 편광 필름, 터치 패널(필름), 상면 커버 등이 더 위치할 수도 있다.

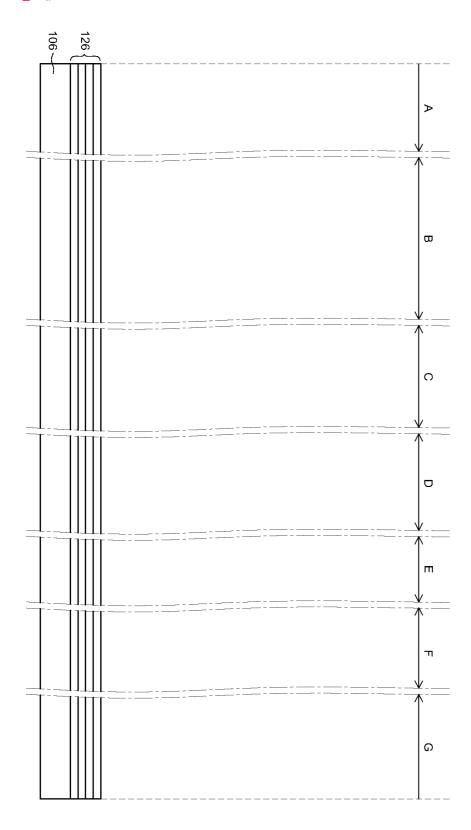

- [0213] 도 14a 내지 도 14q는 본 명세서의 일 실시예에 따른 플렉서블 표시장치의 제조 단계를 나타낸 도면이다.

- [0214] 도 14a는 베이스 층(106) 및 멀티 버퍼층(126)을 형성하는 단계를 도시한다.

- [0215] 베이스 층(106)은, 우선 보조 기판(캐리어 기판) 상에 희생층이 형성된 후, 상기 희생층 상에 형성될 수 있다. 베이스 층(106)은, 예를 들어, 스핀 코팅(spin coating) 방식으로 형성될 수 있다. 즉, 베이스 층(106)을 형성하는 물질을 포함한 액상 물질을 희생층 상에 위치시킨 후, 보조 기판을 고속으로 회전시켜, 두께가 균일한 베이스 층(106)이 형성될 수 있다. 또한 베이스 층(106)은 롤 코팅(roll coating) 방식 또는 슬릿 코팅(slit coating) 방식으로 형성될 수도 있다. 상기 두 방식은 스핀 코팅 방식에 비해 두께 균일도는 낮아도, 생산 효율성은 높을 수 있다.

- [0216] 멀티 버퍼층(126)은 베이스 층(106) 상에 적층된다. 멀티 버퍼층(126)은 실리콘 산화막(SiOx), 실리콘 질화막(SiNx) 또는 이들의 다중 층 등으로 구성될 수 있다. 이때 멀티 버퍼층(126)을 구성하는 실리콘 산화막(SiOx), 실리콘 질화막(SiNx) 등은 베이스 층(106)의 전면에 증착(deposition)될 수 있다. 이때 멀티 버퍼층(126)은 화학기상증착(Chemical Vapor Deposition; CVD) 공정, 플라즈마 화학기상증착(Plasma Enhanced Chemical Vapor Deposition; PECVD) 공정 등을 통해 증착될 수 있으나, 이에 한정되지는 않는다.

- [0217] 도 14b는 하부보호금속을 형성하는 단계를 도시한다.

- [0218] 하부보호금속(169)은 멀티 버퍼층(126) 상에 형성된다. 이때 하부보호금속(169)은 박막 트랜지스터의 하부 및/ 또는 기타 필요한 부분에 위치한다. 하부보호금속(169)은 박막 트랜지스터를 구성하는 게이트 전극과 동일한 물질로 형성될 수 있다. 예를 들어 하부보호금속은 몰리브덴(Mo)과 같은 물질로 형성될 수 있으나, 이에 한정되지 않는다. 이때 하부보호금속(169)은 마스크(mask) 공정(또는 포토리소그래피 공정)을 통해서 형성될 수 있다. 즉, 하부보호금속(169)은, 하부보호금속(169)이 위치하는 영역에 마스크를 사용하는 스퍼터링(sputtering) 공정을 통해 형성될 수 있다. 또는 하부보호금속(169)은, 멀티버퍼층(126) 전면에 금속을 증착한 후에 감광수지 (photoresist) 도포, 패터닝된 마스크를 통한 노광, 현상, 식각 및 감광수지 제거 과정을 통해 형성될 수도 있다.

- [0219] 도 14c는 액티브 버퍼층을 형성하는 단계를 도시한다.

- [0220] 액티브 버퍼(127)는 멀티 버퍼층(126) 및/또는 하부보호금속(169) 상에 형성될 수 있다. 이때 액티브 버퍼층 (127)은 하부보호금속(169)을 덮을 수 있다. 액티브 버퍼(127)는 비정질 실리콘(a-Si) 등으로 형성될 수

있으며, 베이스 층(106) 및/또는 하부보호금속(169)의 상부 전면에 적층될 수 있다.

- [0221] 도 14d는 반도체 층을 형성하는 단계를 도시한다.

- [0222] 반도체 층(151)은 액티브 버퍼(127) 상에 형성될 수 있다. 박막트랜지스터 영역(B 지점)에 형성되는 반도체 층 (151)은 하부보호금속(169)의 좌우 폭보다 작게 형성될 수 있다. 또한 반도체 층(151)는 A 지점 및 D 지점에 형성될 수도 있다. 이때 반도체 층(151)는 마스크 공정을 통해서 형성될 수 있다. 예를 들어, 반도체 층(151)은 패터닝 하려는 영역에 마스크를 사용하는 증착(deposition) 공정을 통해 지정된 영역에만 위치될 수 있다. 또는 반도체 층(151)은, 액티브버퍼(127) 전면에 반도체(Si, Ge 등)를 증착한 후에, 감광수지(photoresist) 도포, 패터닝 마스크를 통한 노광, 현상, 식각 및 감광수지 제거 과정을 통해 형성될 수도 있다.

- [0223] 도 14e는 게이트 절연층을 형성하는 단계를 도시한다.

- [0224] 게이트 절연층(152)은 반도체 층(151) 및/또는 액티브 버퍼층(127) 상에 형성될 수 있다. 이때 게이트 절연층 (152)은 반도체 층(151)를 덮을 수 있다. 게이트 절연층(152)은 절연성 무기물(실리콘 산화막(Si0x), 실리콘 질화막(SiNx) 등), 절연성 유기물 등으로 형성될 수 있다. 게이트 절연층(152)은 반도체 층(151) 및/또는 액티브 버퍼층(127) 상의 전면에 적층될 수 있다.

- [0225] 게이트 절연층(152)이 형성된 후, 박막트랜지스터의 반도체 층(151)에 채널 영역(channel region)을 형성하기 위해, 채널 도핑(channel doping) 과정이 수행될 수 있다. 상기 채널 도핑은 마스크 공정을 통해서 형성될 수 있다. 예컨대, 채널 영역을 형성하고자 하는 반도체 층(151)의 부분과 대응되도록 마스크를 배치한 후, 개구 영역을 통해 불순물(이온)을 소정 영역에 주입하는 도핑 공정이 수행될 수 있다. 이때 반도체 층(151)의 채널 영역에는 붕소(boron) 등의 13족 원소가 도핑되거나(NMOS), 또는 인(phosphorus) 등의 15족 원소가 도핑될 수 있으나(PMOS), 이에 한정되지는 않는다.

- [0226] 박막트랜지스터의 반도체 층(151)에 채널 영역을 형성한 후, 반도체 층(151)의 (채널 영역을 제외한) 나머지 영역에 도체화 영역(저항 영역)을 형성하는 공정(예: 스토리지 도핑(storage doping) 과정)이 수행될 수 있다. 상기 도체화 영역은 다른 지점에 있는 반도체에도 형성될 수 있다. 예를 들어, B 지점의 반도체 층이 도핑될 때, A 지점에 있는 반도체 층(151), D 지점에 있는 반도체 층(151) 등이 함께 도핑될 수 있다.

- [0227] 이때 도체화 영역은 마스크 공정을 통해 형성될 수 있다. 예를 들어, 반도체 층(151)의 전부 또는 일 부분과 대응되도록 마스크를 배치한 후 도핑 공정이 수행될 수 있다. 반도체 층(151)의 도체화 영역은 인(phosphorus) 등의 15족 원소로 도핑되거나(NMOS), 붕소(boron) 등의 13족 원소가 도핑될 수 있으나(PMOS), 이에 한정되지 않는다. 또한 도체화 영역은 이온이 고농도로 도핑되는데,. 이에 상기 도핑을 № 도핑이라 지칭하기도 한다. 이러한 공정을 통하여, B 지점의 반도체 층(151) 중에서 소스/드레인 전극과 접촉할 부분, 커패시터의 일 전극으로 기능할 A 지점의 반도체 층(151), D 지점의 반도체 층(151) 등이 도체화된다.

- [0228] 도 14f는 액티브 버퍼 및 게이트 절연층에 컨택 홀을 형성하는 단계를 도시한다.

- [0229] 컨택 홀은 단일 마스크 공정을 통해 액티브 버퍼(127) 및 게이트 절연층(152)을 뚫고 형성될 수 있다. 이때 컨택 홀을 통해서 하부보호금속(169) 일 부분이 노출된다. 이 공정에서, 일 에로, 게이트 절연층(152) 상에 포토레지스트(Photoresist; PR)와 같은 감광수지를 도포한 후, 마스크를 사용하여 특정 영역의 감광수지에만 선택적으로 광을 조사할 수 있다. 이어서, 노광된 감광수지를 현상하고 나면, 광이 조사된 부부의 감광수지는 제거될수 있다. (감광성 물질이 포지티브 타입인 경우) 이에 게이트 절연층(152)은 감광수지가 제거된 부분에서 노출된다. 이때 제거되지 않고 남은 감광수지를 마스크로 하여, 게이트 절연층(152)의 노출된 부분을 식각할 수 있다. 이후, 게이트 절연층(152) 상에 있는 감광수지가 애싱(ashing) 공정으로 제거되면, 게이트 절연층(152) 및 액티브 버퍼층(127)의 컨택 홀이 완성된다.

- [0230] 도 14g는 게이트 물질을 패터닝하는 단계를 도시한다.

- [0231] 게이트 물질(153)은 게이트 절연층(152) 상에 형성된다. 이때 B 지점에 형성된 게이트 물질(153)은 반도체 층 (151)과 수직 방향으로 중첩될 수 있다. C 지점에 형성된 게이트 물질(153)은 컨택 홀을 통해 하부보호금속 (169)과 전기적으로 연결될 수 있다. 하부보호금속(169)과 전기적으로 연결된 게이트 물질(153)은 도선으로 사용될 수 있다. 이때 게이트 물질(153)을 특정 위치에 형성하는 공정은, 하부보호금속(169)을 형성하는 공정과 유사한 방식으로 수행될 수 있다.

- [0232] 게이트 물질(153)이 형성된 후, 반도체 층(151)의 채널 영역과 도체화 영역 사이에 LDD(lightly doped drain)

영역을 형성하기 위해, 반도체 층(151)에 특정 불순물을 도핑할 수 있다. 이때 LDD 영역은 반도체 층에서 채널 영역과 도체화 영역 사이에 형성되어, 상기 두 영역 간의 전자의 이동을 용이하게 할 수 있다. 이때 LDD 영역은 마스크 공정을 통해서 형성될 수 있다. 구체적으로 반도체 층(151)의 LDD 영역과 대응되도록, 마스크를 배치한 후 (또는 게이트 물질이 마스크가 되어) 소정 영역에 이온을 주입할 수 있다. 이때 LDD 영역은 인(phosphorus) 등의 15족 원소로 도핑될 수 있으나(NMOS), 이에 한정되지 않는다. 또한 LDD 영역을 형성할 때 불순물(이온)은 도체화 영역과 비교하여 저농도로 도핑된다. 예를 들어 LDD 영역은 도체화 영역보다 1000배 정도 농도가 낮게 도핑될 수 있다. 이에 LDD 도핑을 N 도핑이라 지칭하기도 한다. 전자가 도체화 영역에서 채널 영역으로 이동할 때, 버퍼 영역인 LDD 영역에 의해 OFF 전류가 안정화되어 소자 신뢰성이 향상될 수 있다.

- [0233] 도 14h는 층간 절연층을 형성하는 단계를 도시한다.

- [0234] 충간 절연충(154)은 게이트 절연충(152)상 및/또는 게이트 물질(153) 상에 형성될 수 있다. 이때 충간 절연충은 (154) 게이트 물질(153)을 덮을 수 있다. 충간 절연충(154)은 실리콘 산화막(SiOx), 실리콘 질화막(SiNx) 또는 이들의 다중층 등으로 형성될 수 있으나 이에 한정되지 않는다. 충간 절연충(154)은 베이스 충(106) 및/또는 게이트 물질(153)의 상부 전면에 중착될 수 있다. 도시된 대로 충간 절연충(154)은 2개 충으로 구성될 수도 있지만, 그 이상 또는 그 이하의 개수로 구성될 수도 있다.

- [0235] 도 14i는 굴곡 구간(G)을 1차 식각하는 단계를 도시한다.

- [0236] 굴곡 구간에 형성된 층간 절연층(154) 및 게이트 절연층(152)은 마스크 공정을 통해 식각되어 제거될 수 있다. 이때의 마스크 공정은 감광수지 도포, 패터닝 마스크를 통한 노광, 현상, 식각 및 감광수지 제거 과정을 포함할 수 있다.

- [0237] 도 14j는 굴곡 구간(G)을 2차 식각하는 단계를 도시한다.

- [0238] 베이스 층(106)의 굴곡 구간에 형성된 액티브 버퍼(127) 및 적어도 일부의 멀티 버퍼층(126)은 마스크 공정을 통해 식각되어 제거될 수 있다. 이때의 마스크 공정은 상기 1차 식각 공정과 유사하게 감광수지 도포, 패터닝 마스크를 통한 노광, 현상, 식각 및 감광수지 제거 과정 순으로 진행될 수 있다. 굴곡 구간(G)이 2차 식각되면, 굴곡 구간의 멀티 버퍼층(126)은 표시 영역의 멀티 버퍼층(126) 보다 얇아질 수 있다. 즉, 굴곡 구간의 멀티 버퍼층(126)은 표시 영역의 멀티 버퍼층(126) 보다 더 적은 개수의 무기물 층을 가질 수 있다.

- [0239] 도 14k는 층간 절연층 및 게이트 절연층에 컨택 홀을 형성하는 단계를 도시한다.

- [0240] 상기 컨택 홀은 단일 마스크 공정을 통해 층간절연층(154) 및 게이트 절연층(152)을 뚫고 형성될 수 있다. 이때 컨택 홀을 통해서 반도체 층(151)의 일 부분이 노출된다. 이때의 공정은 도 14f의 컨택 홀 생성 공정과 유사하 게 감광수지 도포, 패터닝 마스크를 통한 노광, 현상, 식각 및 감광수지 제거 과정 순으로 진행될 수 있다.

- [0241] 도 141는 소스/드레인 물질을 형성하는 단계를 도시한다.

- [0242] 소스/드레인 물질(155)은 층간 절연층(154) 상에 형성된다. 이때 소스/드레인 물질(155)은 층간 절연막(154)에 마련된 컨택 홀을 통해 반도체 층(151)와 전기적으로 연결될 수 있다. 또한 소스/드레인 물질(155)은 C 지점에 서는 층간 절연층(154)에 마련된 컨택 홀을 통해 게이트 물질(153)과 전기적으로 연결될 수 있다.

- [0243] 같은 공정에서 도선(120)은 굴곡 구간(G)의 멀티 버퍼층(126) 상에 형성될 수 있다. 예를 들어, 도선(120) 및 소스/드레인 물질(155)은 패터닝 하려는 영역에 마스크를 사용하는 스퍼터링(sputtering) 공정을 통해 형성될 수 있다. 이때 도선(120)은 소스/드레인 물질(155)과 같은 물질(예: Cu, Mo/Ti 등)로 형성된다.

- [0244] 도 14m는 굴곡 구간(G)을 3차 식각하는 단계를 도시한다.

- [0245] 3차 식각 전에 소스/드레인 물질(155) 상에 보호층(128)을 형성할 수 있다. 보호층(128)은 소스/드레인 물질 (155)의 상부 전면에 형성될 수 있다. 이때 보호층(128)은 표시 영역의 소스/드레인 물질(155) 및 굴곡 구간 (G)의 도선(120)을 덮도록 형성될 수 있다.

- [0246] 보호층(128)이 형성된 후, 굴곡 구간(G)에 형성된 보호층의 일부는 마스크 공정을 통해 식각되어 제거될 수 있다. 이때 베이스 층(106)의 일 부분도 제거될 수 있다. 이때의 마스크 공정은 1차 식각 및 2차 식각 공정과 유사하게 감광수지 도포, 패터닝 마스크를 통한 노광, 현상, 식각 및 감광수지 제거 과정 순으로 진행될 수 있다.

- [0247] 도 14n는 보호층에 컨택 홀을 형성하는 단계를 도시한다.

- [0248] 상기 컨택 홀은 단일 마스크 공정을 통해 보호층(128)을 뚫고 형성될 수 있다. 이때 컨택 홀을 통해서 소스/드

레인 물질(155)의 일 부분이 노출된다. 이때의 공정은 도 14f 또는 도 14k의 공정과 유사하게 감광수지 도포, 패터닝 마스크를 통한 노광, 현상, 식각 및 감광수지 제거 과정 순으로 진행될 수 있다.

- [0249] 도 140는 평탄화층을 형성하는 단계를 도시한다.

- [0250] 평탄화층(156)은 보호층(128)의 상부 전면에 적충될 수 있다. 이때 굴곡 구간(G)에는 적충되지 않을 수 있다. 이후 평탄화층(156)은 마스크 공정을 통해 컨택 홀을 구비할 수 있다. 평탄화층(156)이 구비한 컨택 홀은 보호 층(128)이 구비한 컨택 홀과 대응되도록 형성될 수 있다. 따라서 상기 컨택 홀들을 통해서 소스 또는 드레인 전 극의 일 부분이 노출될 수 있다. 또한 평탄화층(156)은 단층 또는 다층으로 형성될 수 있다..

- [0251] 도 14p는 제1 전극을 형성하는 단계를 도시한다.

- [0252] 제1 전극(157)은 평탄화층(156) 상에 형성된다. 이때 제1 전극(157)은 평탄화층(156) 및 보호층(128)이 구비한 콘택 홀을 통해 소스 전극 또는 드레인 전극과 전기적으로 연결될 수 있다. 제1 전극(157)은 마스크 공정을 통해서 패터닝 될 수 있다.

- [0253] 도 14q는 뱅크를 형성하는 단계를 도시한다.

- [0254] 뱅크(160)는 평탄화층(156) 상에 형성될 수 있다. 이때 뱅크(160)는 제1 전극(157)의 일 부분을 노출시키는 개구 영역을 구비하도록 형성될 수 있다. 이때 뱅크(160)는 마스크 공정을 통해서 패터닝될 수 있다. 뱅크(160)를 형성한 후, 유기발광 층(158), 제2 전극(159), 보호막(161) 및 봉지층(162)을 순차적으로 형성한다.

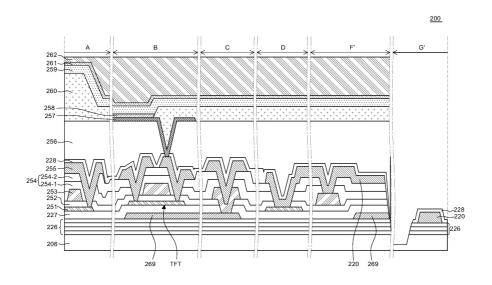

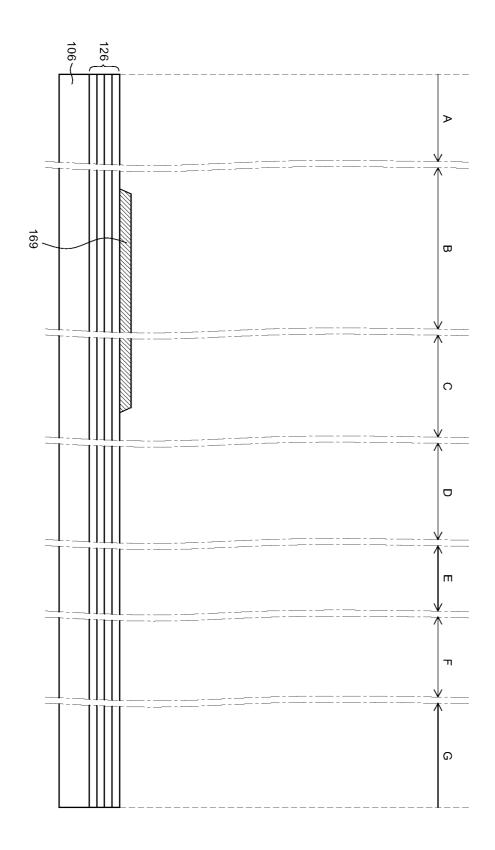

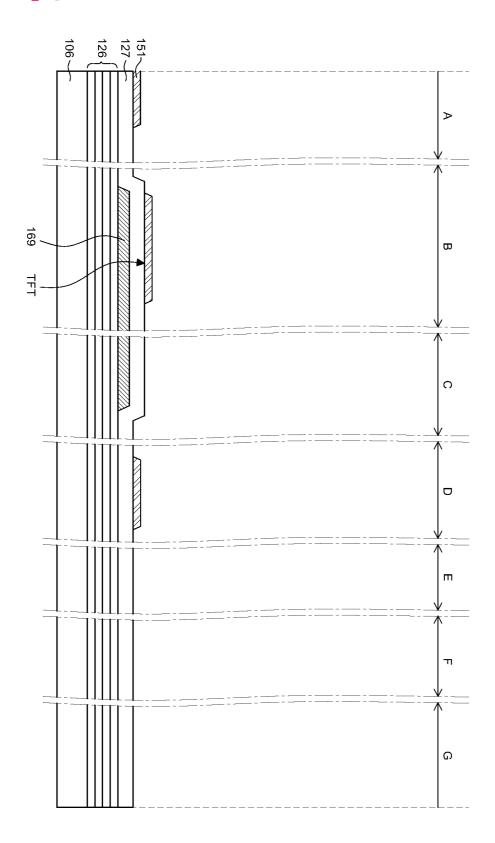

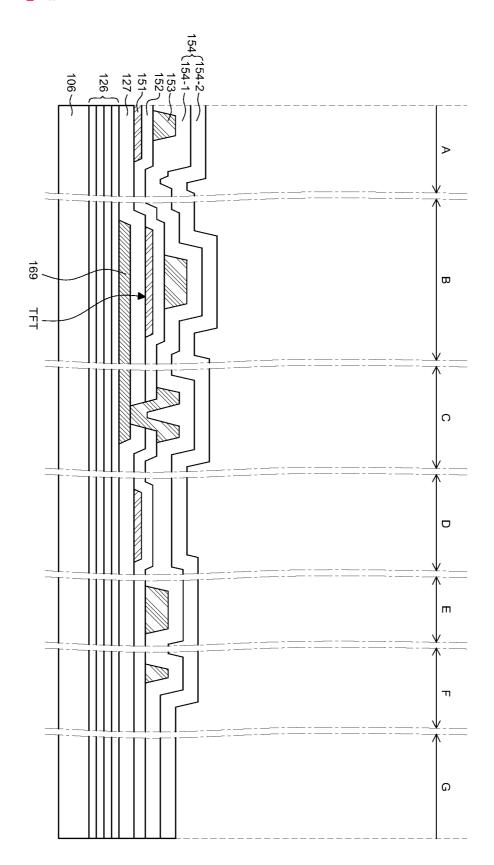

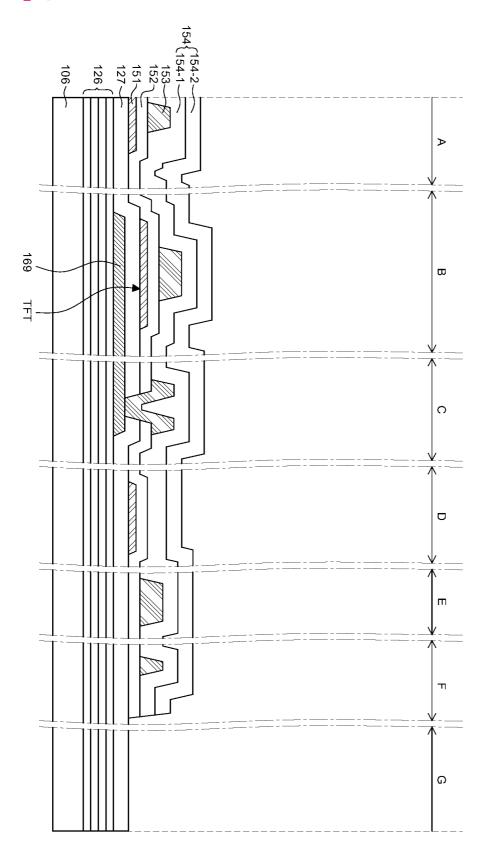

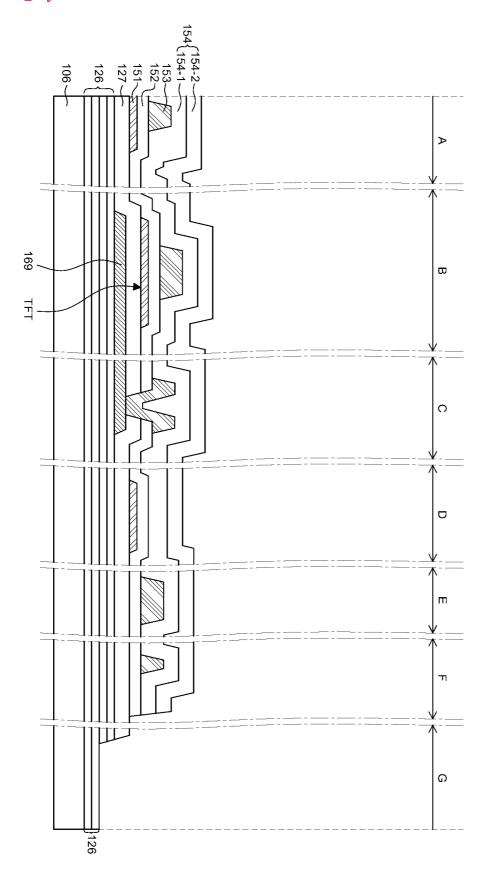

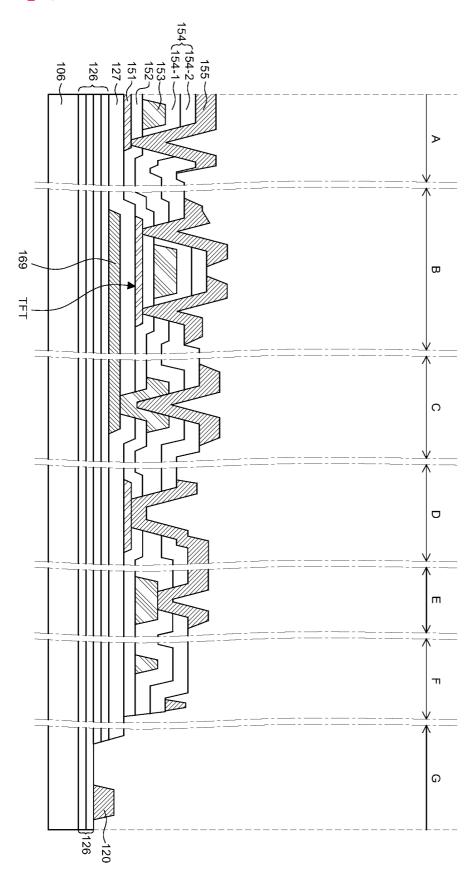

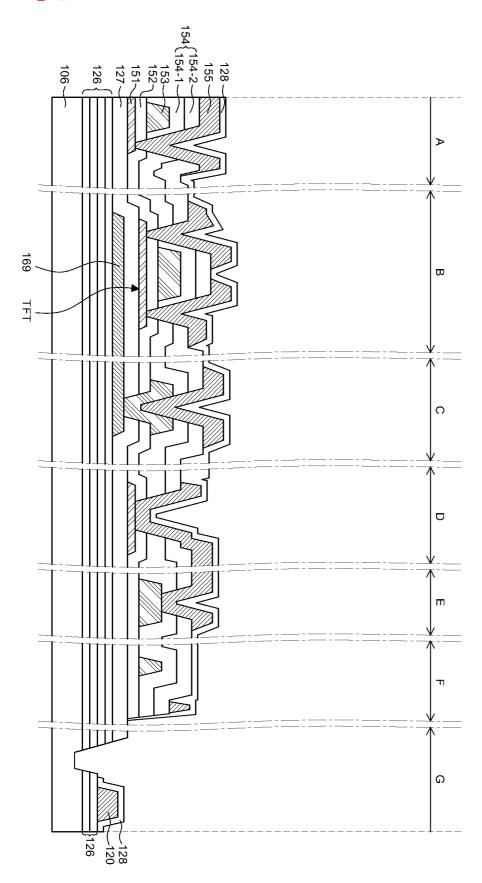

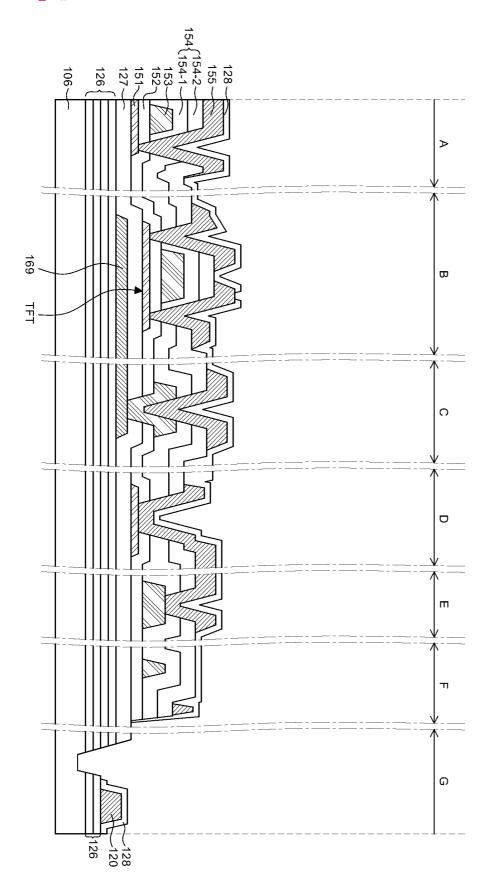

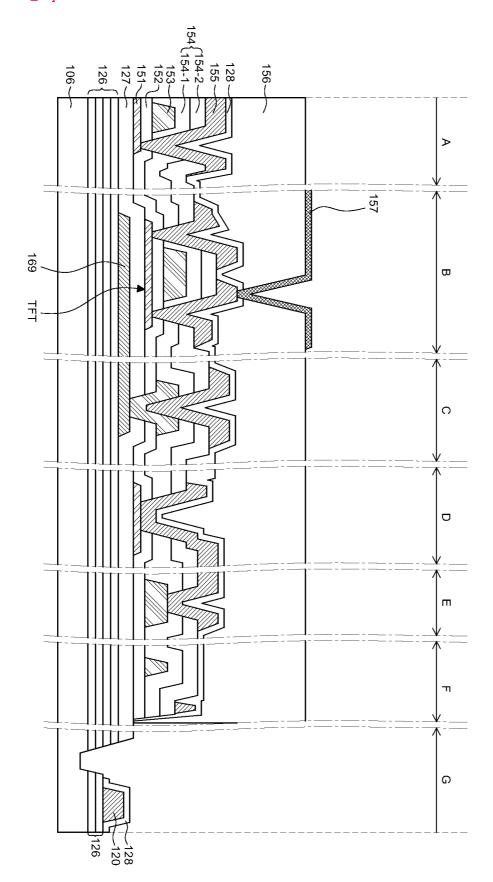

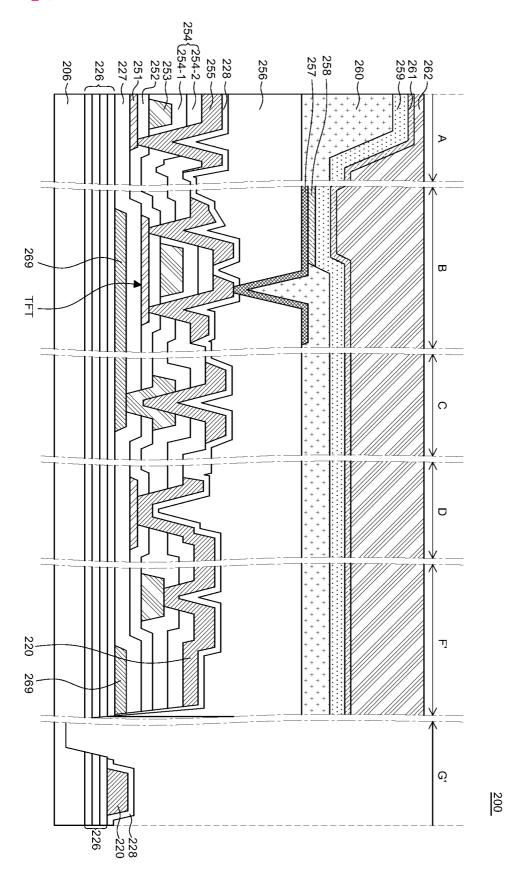

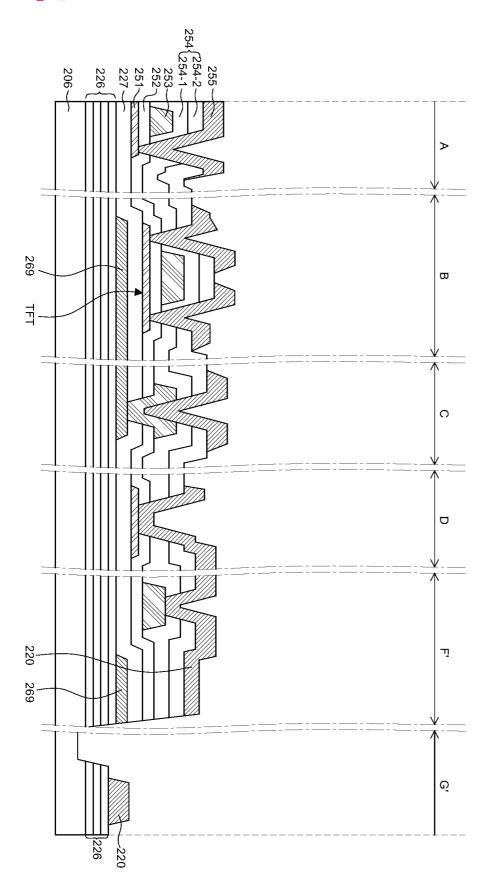

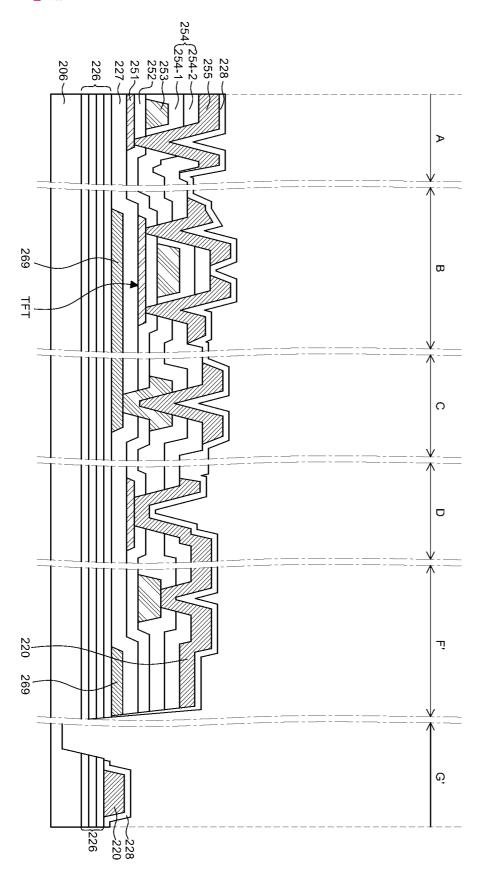

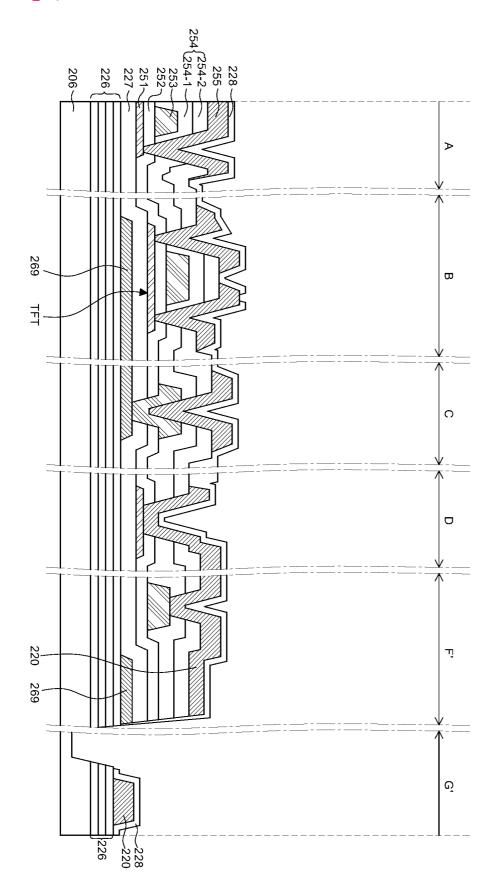

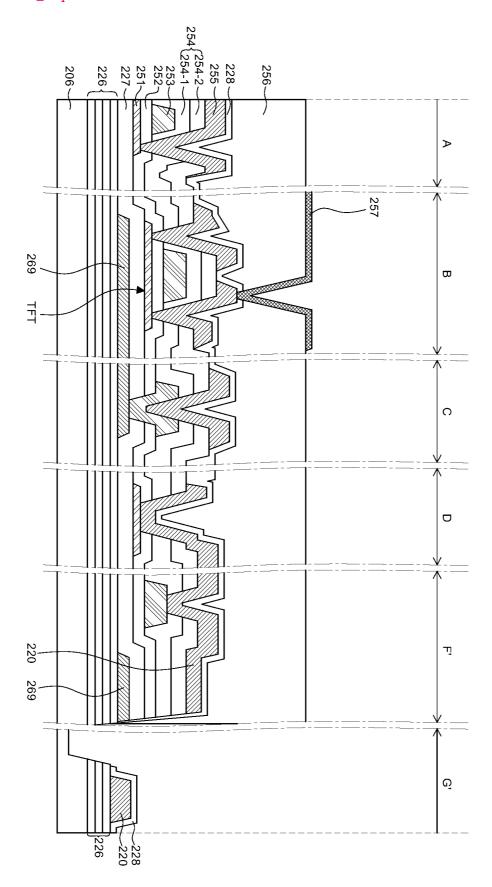

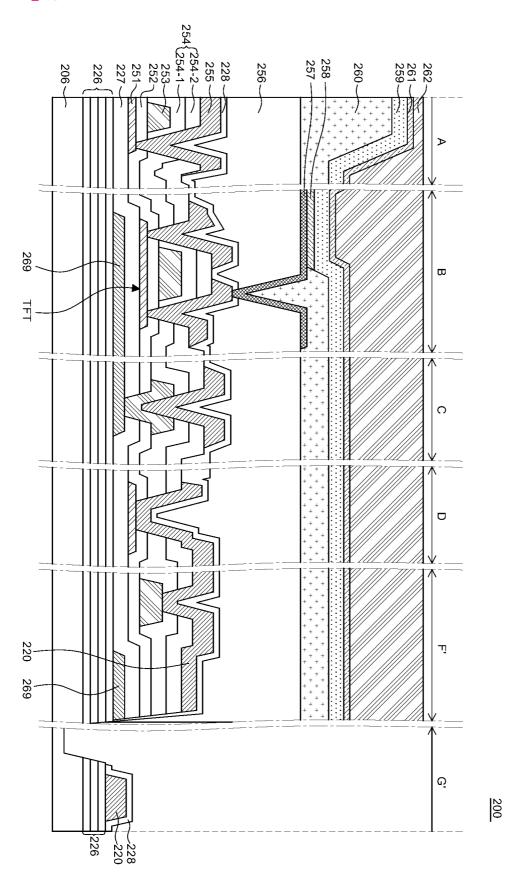

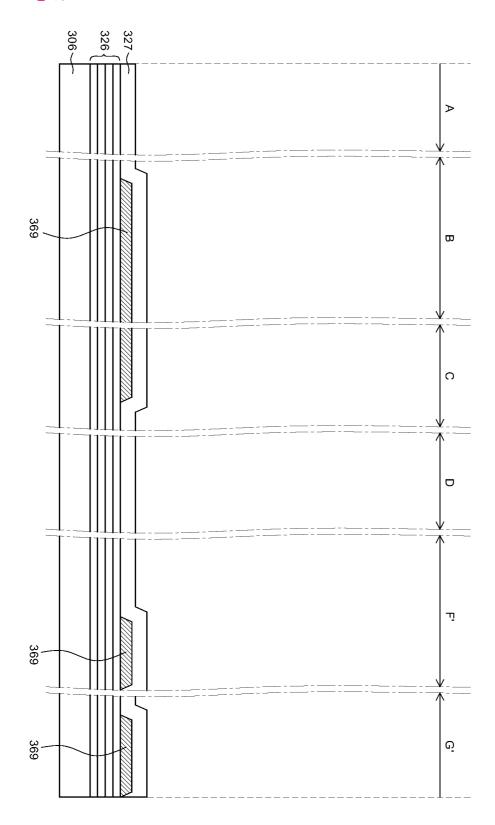

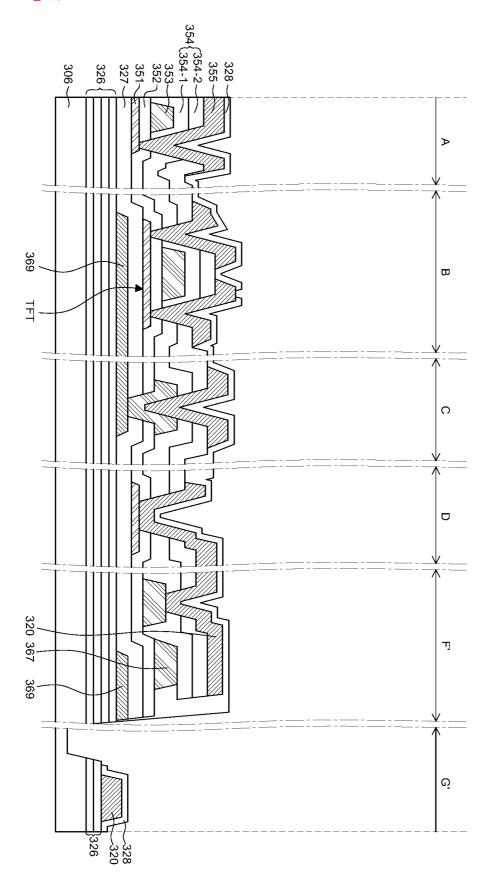

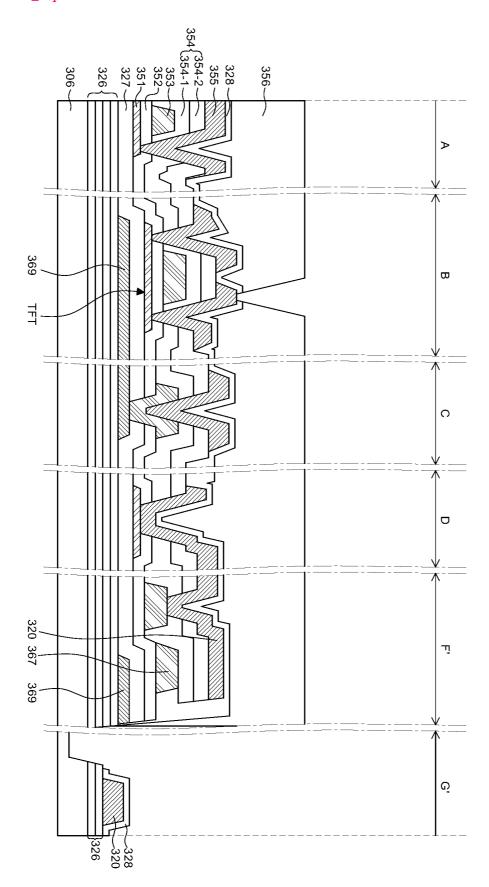

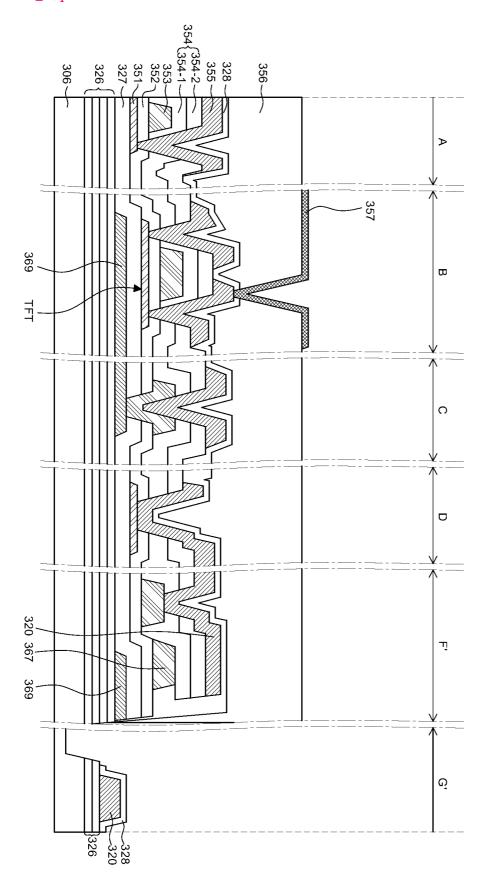

- [0255] 도 15는 본 명세서의 또 다른 일 실시예에 따른 플렉서블 표시장치의 단면도이다.

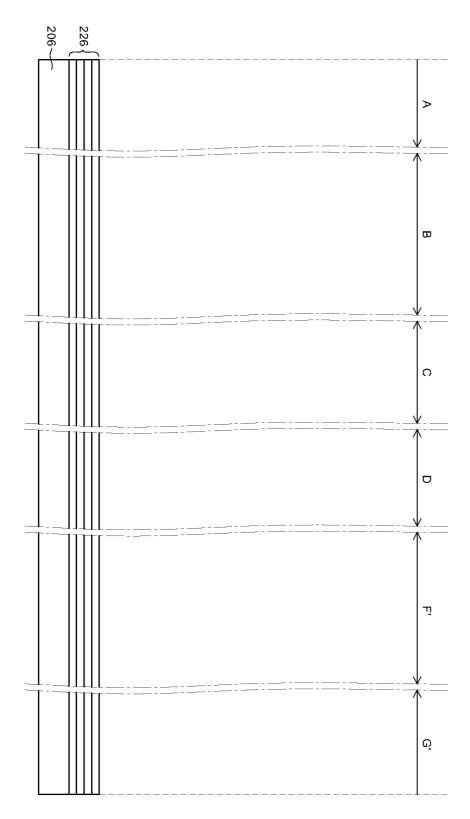

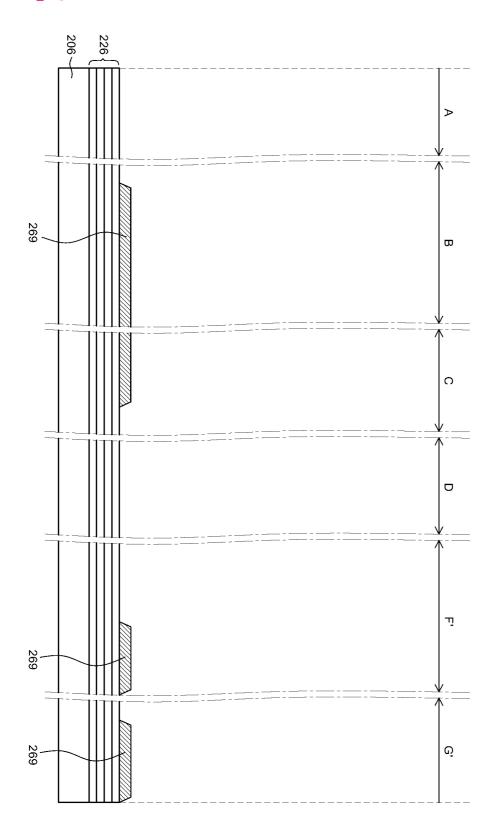

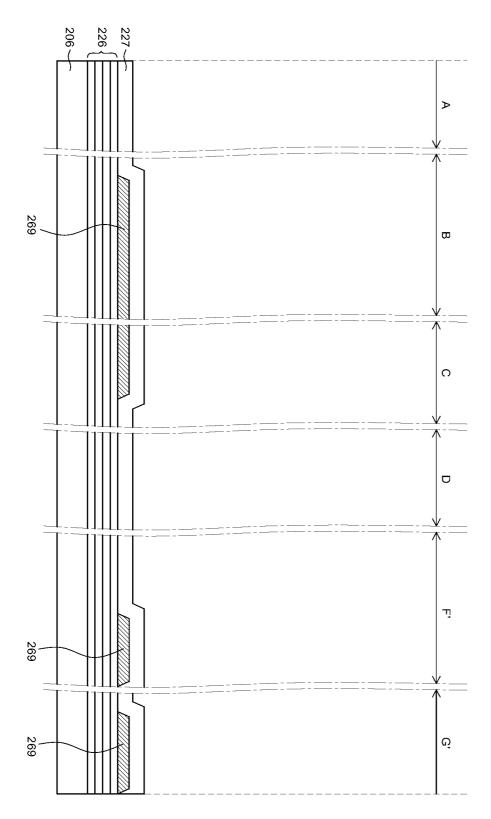

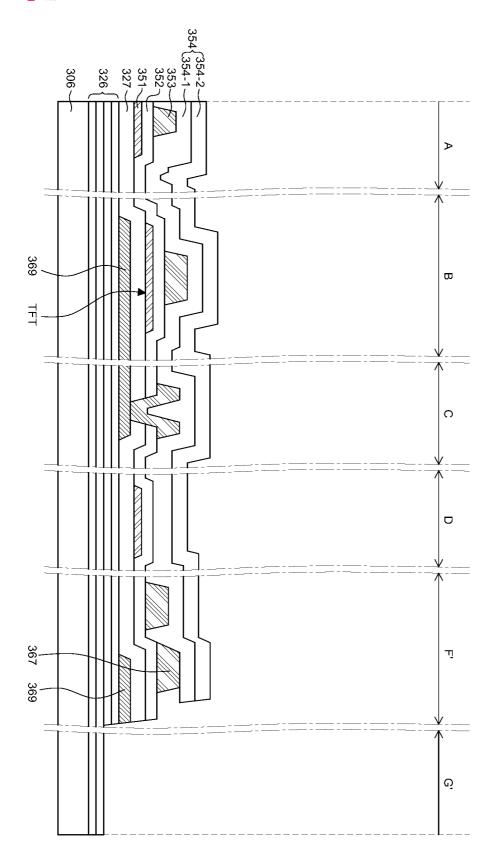

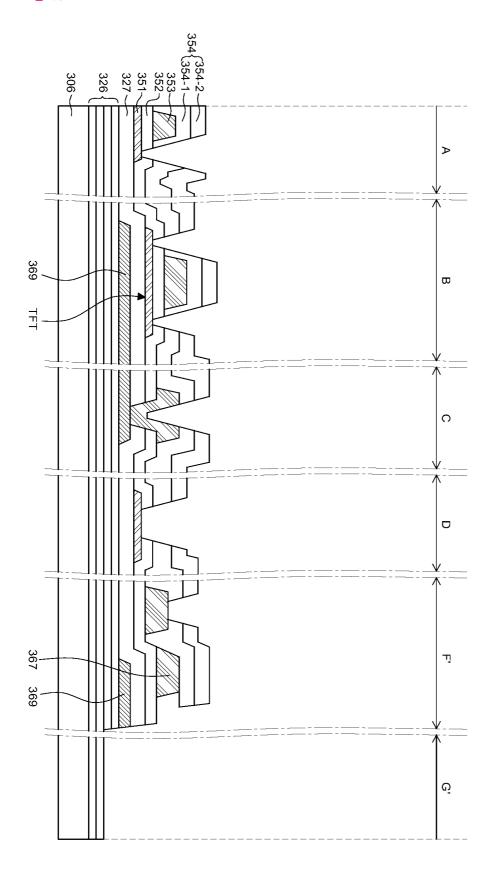

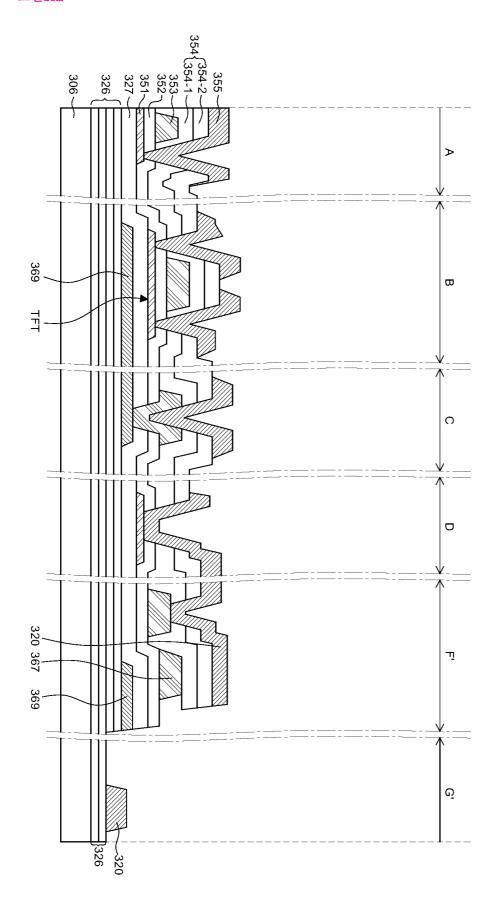

- [0256] 상기 플렉서블 표시장치(200)는 도 1과 같이 표시 영역 및 비표시 영역을 포함할 수 있다. 도 15에서는 비표시 영역이 표시 영역의 바깥쪽을 두르고 있으며, 굴곡 구간(G')을 포함하고 있는 것으로 도시하였지만 본 발명의 사상이 이에 제한되는 것은 아니다. 또한 도 15는 표시 영역 및 비표시 영역 위의 복수의 지점(A~G')에서 추출한 단면도를 연결하여 도시한 것이다.

- [0257] A는 스토리지 캐패시터(Storage Capacitor) 영역을 개념적으로 도시한 부분이다. 스토리지 캐패시터 영역은 박 막트랜지스터를 구동하기 위한 데이터 전압을 저장하는 스토리지 캐피시터가 있는 영역을 의미한다.

- [0258] B는 박막트랜지스터 영역을 개념적으로 도시한 부분이다. 박막트랜지스터 영역은 전원과 유기발광소자 사이에 접속되어, 유기발광소자에 전류를 공급하는 박막트랜지스터가 있는 영역을 의미한다.

- [0259] C는 하부보호금속 컨택 홀(BSM-contact hole) 영역을 개념적으로 도시한 부분이다. 하부보호금속 컨택 홀 영역은 하부보호금속이 배선으로 사용되는 게이트 물질과 전기적으로 연결되어 전류를 공급받는 영역을 의미한다.

- [0260] D는 반도체 층 컨택 홀(ACT-contact hole) 영역을 개념적으로 도시한 부분이다. 반도체 층 컨택 홀 영역은 배선으로 사용되는 반도체 층과 구동 배선이 전기적으로 연결되는 영역을 의미한다.

- [0261] F'는 패드(Pad) 영역을 개념적으로 도시한 부분이다. 패드 영역은 표시 영역에서 연장된 영역으로 벤딩 영역의 연결 배선과 연결되는 구동 배선이 배치된 영역을 의미한다.

- [0262] G'는 굴곡(Bending) 영역(또는 벤딩 영역)을 개념적으로 도시한 부분이다. 굴곡 영역은 패드 영역에서 연장된 영역으로, 표시 영역의 화소 전극과 외부모듈을 연결하는 연결 배선이 배치되는 영역을 의미한다.

- [0263] 이하에서는 도 15에 도시된 각 충(layer)들을 설명한다. 도시된 각각의 충들은 동일한 공정을 통해 구조화된 충들이다.

- [0264] 베이스 층(또는 플렉서블 기판)(206)은 플렉서블 표시장치의 여러 구성 요소들을 지지한다. 상기 베이스 층 (206)이 플라스틱으로 이루어진 경우, 플라스틱 필름 또는 플라스틱 기판으로 지칭될 수 있다. 예를 들어, 상기 베이스 층(206)은 폴리에스터계 고분자, 실리콘계 고분자, 아크릴계 고분자, 폴리올레핀계 고분자 및 이들의 공 중합체로 이루어진 군에서 선택된 하나를 포함하는 필름 형태일 수 있다. 구체적으로, 상기 베이스 층(206)은 폴리에텔렌테레프탈레이트(PET), 폴리부틸렌테레프탈레이트(PBT), 폴리실란(polysilane), 폴리실록산 (polysiloxane), 폴리실라잔(polysilazene), 폴리카르보실란(polycarbosilane), 폴리아크릴레이트 (polyacrylate), 폴리메타크릴레이트(polymethacrylate), 폴리메틸아크릴레이트(polymethylacrylate), 폴리메틸메타크릴레이트 (polyethylmetacrylate), 폴리메틸아크릴레이트(polyethylacylate), 폴리에틸메타크릴레이트 (polyethylmetacrylate), 사이클릭 올레핀 코폴리머(COC), 사이클릭 올레핀 폴리머(COP), 폴리에틸렌(PE), 폴리프로필렌(PP), 폴리이미드(PI), 폴리스타이렌(PS), 폴리아세탈(POM), 폴리에테르에테르케톤(PEEK), 폴리에스

테르설폰(PES), 폴리테트라플루오로에틸렌(PTFE), 폴리비닐클로라이드(PVC), 폴리카보네이트(PC), 폴리비닐리덴 플로라이드(PVDF), 퍼플루오로알킬 고분자(PFA), 스타이렌아크릴나이트릴코폴리머(SAN) 및 이들의 조합으로 이루어진 군에서 선택된 하나를 포함할 수 있다. 이 물질 중에서, 폴리이미드는 고온의 공정에 적용될 수 있고, 코팅이 가능한 재료이기에 플라스틱 기판으로 많이 사용된다. 투명 플렉서블 표시장치에서는, 상기 베이스 층 (106)이 투명한 가요성의 물질로 이루어질 수 있다.

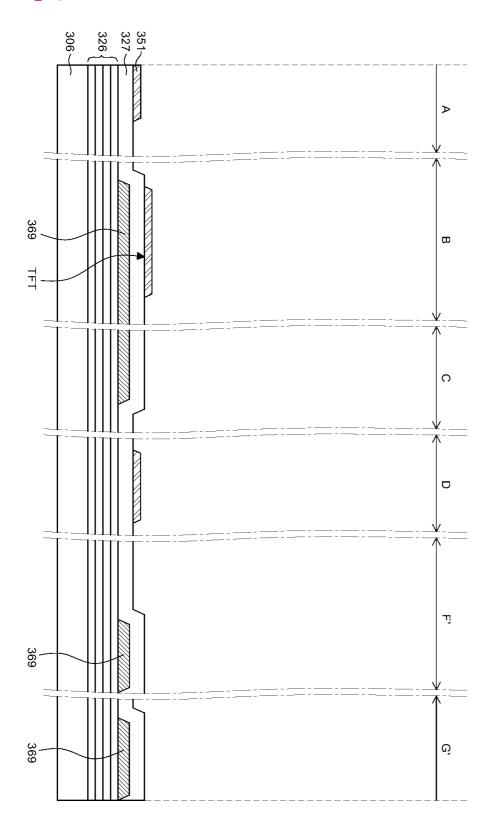

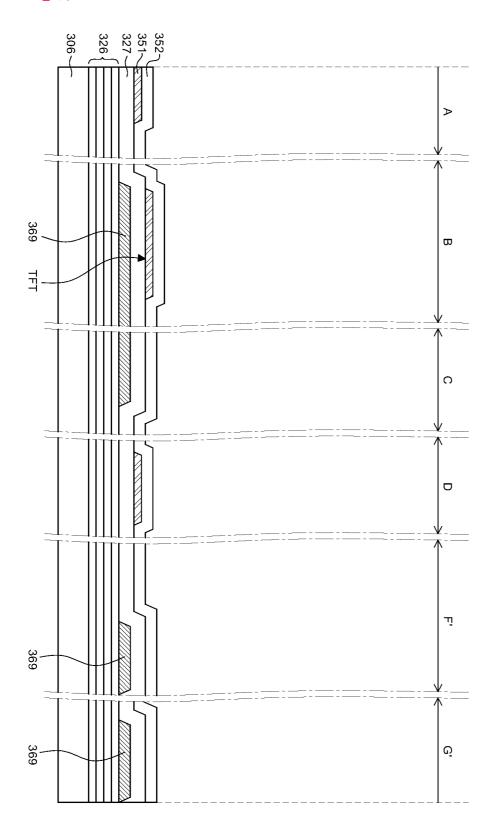

- [0265] 버퍼층(226, 227)은 베이스 층(206) 또는 하부의 층들에서 유출되는 알칼리 이온 등과 같은 불순물로부터 박막 트랜지스터를 보호하기 위한 기능 층이다. 상기 버퍼층은 멀티 버퍼(multi buffer, 226) 및/또는 액티브 버퍼 (active buffer, 227)를 포함할 수 있다.

- [0266] 멀티 버퍼층(또는 제1 버퍼층)(226)은 상기 베이스 층(206) 상에 위치한다. 이때 상기 멀티 버퍼층(226)은 복수 개의 층을 구비할 수 있다. 상기 멀티 버퍼층(226)은 질화실리콘(SiNx) 및 산화실리콘(SiOx)이 교대로 적층되어 이루어질 수 있으며, 베이스 층(206)에 침투한 수분 및/또는 산소가 확산되는 것을 지연시킬 수 있다. 멀티 버퍼층(226)은 베이스 층(206)의 물질이나 그 위에 형성되는 층의 종류에 따라 더 배치되거나 제거될 수 있다. 예를 들어, 상술한 것과 같이 굴곡 영역에서 갈라짐(crack) 발생을 억제하기 위하여, 비표시 영역에는 멀티 버퍼층(226)이 표시 영역보다 더 적게 배치되거나 혹은 멀티 버퍼층(226)이 제거될 수 있다. 즉, 멀티 버퍼층(226)은 굴곡 구간(G')에서의 두께가 다른 구간에서의 두께보다 얇을 수 있다.

- [0267] 액티브 버퍼(또는 제1 절연층)(227)는 멀티 버퍼층(226) 상에 위치할 수 있다. 특히, 액티브 버퍼(227)는 패드 구간(F')에서 하부보호금속(269)(또는 제1 보호부재) 상에 배치될 수 있다. 상기 액티브 버퍼(227)는 박막트랜 지스터의 반도체 층(251)을 보호하며, 베이스 층(206)으로부터 유입되는 다양한 종류의 결함을 차단하는 기능을 수행한다. 상기 액티브 버퍼(226)는 비정질 실리콘(a-Si) 등으로 형성될 수 있다. 박막트랜지스터는 반도체 층(251), 게이트 절연층(252), 게이트 물질(253), 층간 절연층(254), 소스 및 드레인 전극(255)이 순차적으로 배치된 형태일 수 있다.

- [0268] 반도체 층(251)은 상기 액티브 버퍼(227) 상에 위치한다. 이때 반도체 층(251) 폭은 하부보호금속(259)의 폭보다 작게 형성될 수 있으나, 이에 한정되지 않는다. 반도체 층(251)은 다결정 실리콘(polycrystalline silicon)으로 만들어질 수 있으며, 이 경우 소정의 영역이 불순물로 도핑될 수도 있다. 또한, 반도체 층(202)은 비정질실리콘(amorphous silicon), 유기 반도체 물질 또는 산화물(oxide)로 형성될 수 있다.

- [0269] 게이트 절연층(252)은 반도체 층(251) 상에 위치할 수 있다. 게이트 절연층(Gate Insulator)(252)은 게이트 물 절(253)과 반도체 층(251) 사이를 절연한다. 게이트 절연층(252)은 산화실리콘(SiOx) 또는 질화실리콘(SiNx) 등 과 같은 절연성 무기물로 형성될 수 있으며, 이외에도 절연성 유기물 등으로 형성될 수도 있다.

- [0270] 게이트 절연층(252)을 구성하는 산화실리콘(SiOx) 및 질화실리콘(SiNx) 등은 금속에 비해 가요성이 떨어진다. 따라서 굴곡 구간(G')의 가요성을 향상시키기 위해, 굴곡 구간(G')의 게이트 절연층(252)은 제거될 수 있다.

- [0271] 게이트 물질(253)은 게이트 절연층(252) 상에 위치한다. 게이트 물질(253)은 몰리브덴(Mo), 알루미늄(Al), 크롬 (Cr), 금(Au), 티타늄(Ti), 니켈(Ni), 네오디뮴(Nd) 및 구리(Cu) 중 어느 하나 또는 이들의 합금으로 이루어질 수 있으나, 이에 한정되지 않으며, 다양한 물질로 형성될 수 있다. 또한, 게이트 물질(253)은 단일층 또는 다중 층일 수도 있다.

- [0272] B 지점에 있는 게이트 물질(253)은 박막트랜지스터를 구동하기 위한 반도체 층(251)와 중첩될 수 있다.

- [0273] C 지점에 있는 게이트 물질(253)은 게이트 절연층(252) 및 액티브 버퍼(227)가 구비한 컨택 홀을 통해 반도체 층(251) 하부에 위치한 하부보호금속(269)과 전기적으로 연결될 수 있다. 이때 게이트 물질(253)은 배선으로 사용되어 하부보호금속(269)과 구동 배선(255)을 전기적으로 연결할 수 있다. 따라서 상기 구동 배선(255)으로부터 공급된 전류는 배선으로 사용되는 게이트 물질(253)을 통해 하부보호금속(269)에 공급될 수 있다. 또한 배선으로 사용되는 게이트 물질(253)은 액티브 버퍼(227) 상에 배치되며, 표시 영역으로부터 연장되어 패드 구간 (F')에 위치할 수 있다. 이때 게이트 물질(253)은 게이트 배선(253)이라 할 수 있다.

- [0274] 이때 표시 영역으로부터 연장된 게이트 배선(253)은 패드 구간(F')에 배치된 연결 배선(220)과 전기적으로 연결 될 수 있다.

- [0275] 충간 절연층(또는 제2 절연층)(254)은 게이트 물질(253) 상에 위치한다. 또한 충간 절연층(254)은 패드 구간 (F')에서 게이트 배선(253) 상에 위치한다.

- [0276] 층간 절연층(254)은 게이트 절연층(252)과 동일한 물질인, 산화실리콘(SiOx), 질화실리콘(SiNx) 또는 이들의 다

중층 등으로 형성될 수 있으나, 이에 한정되지 않는다. 층간 절연층(254)과 게이트 절연층(252)의 선택적 제거를 통해 소스 및 드레인 영역이 노출되는 컨택 홀(contact hole)이 형성될 수 있다.

- [0277] 구동 배선(255)은 층간 절연층(254) 상에 위치한다. 이때 B 지점에 있는 구동 배선(255)은 반도체 층(251)와 일부 영역에서 중첩될 수 있다. 구동 배선(255)은 층간 절연층(254)과 게이트 절연층(252)이 구비한 컨택 홀을 통해 노출된 반도체 층(251)의 소스 및 드레인 영역과 전기적을 연결될 수 있다. 이때 구동 배선(255)은 소스/드레인 전극으로 사용되어 반도체 층(251)에 전류를 공급할 수 있다.

- [0278] 하부보호금속(또는 제1 보호부재)(269)은 멀티 버퍼층(226) 상에 위치할 수 있다. 또한 하부보호금속(BSM: Bottom Shield Metal)(269)은 박막트랜지스터(TFT: Thin Film Transistor) 하부에 위치할 수 있다. 예를 들어 하부보호금속(269)은 박막트랜지스터DD(TFT)의 반도체 층 대응하여 액티브 버퍼층(227) 하부에 위치할 수 있다.

- [0279] 하부보호금속(269)은 모든 트랜지스터의 반도체 층 하부에 위치할 수도 있고, 필요에 따라 특정 트랜지스터(예: 구동 트랜지스터)의 반도체 층 하부에만 위치할 수도 있다. 이때 하부보호금속(269)은 레이저 및 외부로부터 유입되는 광으로부터, 박막트랜지스터의 소자 특성, 예를 들어 문턱 접압 또는 on/off 전압이 변동되는 것을 방지하여 픽셀 간 휘도 불균형을 방지할 수 있다. 또한 하부보호금속(269)은 외부로부터 유입되는 수분으로부터 상기 트랜지스터의 소자 특성(예: 문턱 전압 등)이 변동되는 것을 억제한다. 이로써 상기 하부보호금속(BSM: Bottom Shield Metal)(269)은 픽셀 간 휘도 불균형(얼룩, 잔상으로 나타남)을 방지할 수 있다. 더 나아가, 상기하부보호금속(269)은, 플렉서블 표시장치(200)의 제조 공정(예: 유리기판을 떼어내는 과정)에서, 트랜지스터가물리적으로 손상되는 것을 최소화할 수도 있다. 즉, 하부보호금속(269)은 박막트랜지스터(TFT) 하부에 배치되어, 박막트랜지스터(TFT)를 보호할 수 있다. 이때 하부보호금속(269)은 박막트랜지스터(TFT) 보호부재라고 할 수 있다.

- [0280] 하부보호금속(269)은 박막트랜지스터를 구성하는 게이트 물질(253)과 동일한 물질로 형성될 수 있다. 한편, 하부보호금속(209)은 금속 재질이기 때문에, 소정의 커패시턴스(capacitance)를 형성하는 소자가 되기도 한다. 이때, 하부보호금속(269)이 전기적으로 플로팅(floating) 되어있으면 커패시턴스의 변동이 나타나고, 박막트랜지스터들 각각의 문턱전압의 쉬프트 양이 다양해 질 수 있으며, 이것은 의도하지 않은 시각적 결함(예를 들어, 휘도 변화)을 발생시킬 수 있다. 따라서, 연결부재를 통해 하부보호금속(269)을 소스/드레인 전극 또는 게이트 물질에 접지하여 커패시턴스가 일정하게 유지되도록 할 수 있다.

- [0281] 하부보호금속(269)이 박막트랜지스터의 소스 전극 또는 드레인 전극에 연결되는 경우, 하부보호금속(269) 및 하부보호금속(269)에 연결된 전극 사이에 등전위가 형성될 수 있다. 하부보호금속(269) 및 하부보호금속(269)에 연결되는 전극들 사이의 전압 차이가, 박막트랜지스터의 게이트 물질과 소스 전극 사이의 전압차(즉, VGS) 보다 작다면, 하부보호금속(269)가 박막트랜지스터의 문턱전압에 미치는 영향은 최소화될 수 있다.

- [0282] 하부보호금속(269)은 게이트 물질(253)과 연결되는 경우, 게이트 물질(253)과 하부보호금속(269)에 동일한 전압이 공급될 수 있다. 이때 상기 하부보호금속(269)이 박막트랜지스터의 보조 게이트 물질로서 동작할 수 있다. 하부보호금속(269) 상에 위치하는 반도체 층의 표면에 추가적인 채널 영역이 제공될 수 있다. 따라서 박막트랜지스터의 크기를 실질적으로 증가시키는 것 없이, 박막트랜지스터의 이동도를 증가시킬 수 있다. 즉, 박막트랜지스터의 전류 구동 능력을 향상시킬 수도 있다.

- [0283] 또한 하부보호금속(269)은 패드 구간(F')에서 멀티 버퍼층(226) 상에 배치될 수 있다. 이때 하부보호금속(269)은, 하부보호금속(269) 상에 배치되는 연결 배선(220) 간의 쇼트(short)(또는 전기적 연결)를 방지하기 위해 인접한 또 다른 하부보호금속(269)과 이격되도록 구비될 수 있다.

- [0284] 또한 패드 구간(F')에 배치된 하부보호금속(269)은 플렉서블 표시장치(200)의 표시 영역에 배치된 하부보호금속 (269)(또는 박막트랜지스터 보호부재)과 동일한 물질일 수 있다. 이때 패드 구간(F') 및 표시 영역에 형성되는 하부보호금속(269)을 함께 형성하여, 플렉서블 표시장치(200)의 제조 공정은 단순화될 수 있다.

- [0285] 패드 구간(F')에 배치된 하부보호금속(269)은 플렉서블 표시장치(200)를 제조 하기 위해 플렉서블 표시장치(200)의 굴곡 구간(G')을 식각하는 공정 중, 상기 하부보호금속(269) 밑에 배치된 멀티 버퍼층(226)을 보호할 수 있다. 이때 멀티 버퍼층(226)의 일 부분과 상기 멀티 버퍼층(226) 상에 있는 액티브 버퍼층(227)을 동일한 패터닝 장비로 제거할 수 있다. 따라서 플렉서블 표시장치(200)의 제조 공정은 단순화될 수 있다.

- [0286] 연결 배선(220)은 베이스 층(206)의 비표시 영역에 배치된다. 연결 배선(220)은 베이스 층(206)의 비표시 영역의 패드 구간(F') 및 굴곡 구간(G')에 배치된 멀티 버퍼층(226) 상에 배치될 수 있다. 구체적으로, 연결 배선 (220)의 일 부분은 베이스 층(206)의 패드 구간(F')에 배치된 층간 절연층(254) 상에 배치된다. 이때 연결 배선

(220)은 패드 구간(F')에 배치된 게이트 배선(253)과 전기적으로 연결될 수 있다. 또한 연결 배선(220)의 일 부분 이외의 부분은 베이스 층(206)의 굴곡 구간(G')에 배치된 멀티 버퍼층(226) 상에 배치될 수 있다. 베이스 층 (206)의 굴곡 구간(G')이 벤딩될 때 연결 배선(220)은 벤딩될 수 있다. 연결 전극(220)은 표시장치의 표시 영역의 화소 전극과 비표시 영역에 배치되는 외부 모듈, 예를 들어 FPCB(flexible printed circuit board), COF(chip on film) 등을 전기적으로 연결할 수 있다.

- [0287] 보호층(228)(또는 제2 버퍼층)은 구동 배선(255) 상에 위치한다. 보호층(228)은 상기 박막트랜지스터를 보호하는 기능을 한다. 또한 보호층(228)은 굴곡 구간(G')에 배치된 연결 배선(220)을 덮어서 보호할 수 있다.

- [0288] 평탄화층(256)은 보호층(228) 상에 위치한다. 평탄화층(256)은 박막트랜지스터를 보호하고 그 상부를 평평하게한다. 평탄화층(256) 및 보호층(228)은 선택적 제거를 통해 소스 또는 드레인 전국이 노출되는 컨택 홀(contact hole)을 구비할 수 있다. 소스 또는 드레인 전국은 상기 노출된 컨택 홀을 통해 제1 전국(257)과 전기적으로 연결될 수 있다.

- [0289] 평탄화층(256)은, 아크릴계 수지(polyacrylates resin), 에폭시 수지(epoxy resin), 페놀 수지(phenolic resin), 폴리아미드계 수지(polyamides resin), 폴리이미드계 수지(polyimides resin), 불포화 폴리에스테르계 수지(unsaturated polyesters resin), 폴리페닐렌계 수지(poly-phenylenethers resin), 폴리페닐렌설파이드계 수지(polyphenylenesulfides resin) 및 벤조사이클로부텐(benzocyclobutene) 중 하나 이상의 물질로 형성될 수 있으나, 이에 한정되지 않는다. 평탄화층(256)은 단층으로 형성되거나 이중 혹은 다중 층으로 구성될 수도 있는 등 다양한 변형이 가능하다.