(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2019년02월15일

(11) 등록번호 10-1948171

(24) 등록일자 2019년02월08일

(51) 국제특허분류(Int. Cl.)

*H01L 51/50* (2006.01) *H01L 29/786* (2006.01)

*H05B 33/10* (2006.01)

(21) 출원번호 10-2012-0078863

(22) 출원일자 2012년07월19일

심사청구일자 2017년06월27일

(65) 공개번호 10-2014-0013166

(43) 공개일자 2014년02월05일

(56) 선행기술조사문헌

KR1020120046356 A\*

KR1020120066491 A\*

KR1020030058148 A\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

**엘지디스플레이 주식회사**

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

**정영기**

경기 고양시 일산서구 칸텍스로 300, 1401동 308호 (주엽동, 문촌마을14단지아파트)

**조성필**

경기 파주시 쇠재로 30, 711동 306호 (금촌동, 서원마을아파트)

(뒷면에 계속)

(74) 대리인

**네이트특허법인**

전체 청구항 수 : 총 12 항

심사관 : 박정근

#### (54) 발명의 명칭 유기발광소자표시장치 및 그 제조방법

(57) 요약

본 발명은 기판 상에 반도체패턴과, 상기 반도체패턴과 동일한 물질로 이루어지며 불순물 이온이 도핑된 제1스토리지전극과; 상기 반도체패턴 및 제1스토리지전극 상에 형성된 게이트절연막과; 상기 게이트절연막 상에, 상기 제1스토리지전극에 대응되며 제1도전층으로 이루어진 제2스토리지전극과, 상기 반도체패턴의 채널영역에 대응되

(뒷면에 계속)

대표도 - 도2

며 상기 제1도전층을 포함한 다중층으로 이루어진 게이트전극과; 상기 제2스토리지전극 및 게이트전극 상에 형성된 층간절연막과; 상기 층간절연막 상에, 상기 반도체패턴의 소스영역 및 드레인영역과 연결되는 소스전극 및 드레인전극과, 상기 제3스토리지전극에 대응되며 상기 제1스토리지전극과 전기적으로 연결되는 제3스토리지전극과; 상기 소스전극 및 드레인전극과 상기 제3스토리지전극 상에 형성된 제1보호막과; 상기 제1보호막 상에, 상기 드레인전극과 연결되는 연결전극과, 상기 제3스토리지전극에 대응되며 상기 제2스토리지전극과 전기적으로 연결되는 제4스토리지전극과; 상기 연결전극과 연결되는 유기발광다이오드를 포함하는 유기발광소자표시장치를 제공한다.

(72) 발명자

**신동채**

경기 파주시 문산읍 당동1로 11, 605동 602호 (자연엔꿈에그린6단지아파트)

**정인상**

경기도 파주시 월롱면 엘씨디로 201 E동 214호 (덕은리, 정다운마을)

## 명세서

### 청구범위

#### 청구항 1

기판 상에 배치된 반도체패턴 및 상기 반도체패턴과 동일한 물질로 이루어져 불순물 이온이 도핑된 제1스토리지전극;

상기 반도체패턴 및 제1스토리지전극 상에 형성된 게이트절연막;

제1도전층으로 이루어져 상기 제1스토리지전극에 대응되는 영역의 게이트절연막 상에 배치된 제2스토리지전극 및 상기 제1도전층을 포함한 다중층으로 구성되어 상기 반도체패턴의 채널영역에 대응하는 영역의 게이트절연막 상에 배치된 게이트전극;

상기 제2스토리지전극 및 게이트전극 상에 형성된 충간절연막;

상기 충간절연막 상에 배치되고 상기 반도체패턴의 소스영역 및 드레인영역과 연결되는 소스전극과 드레인전극 및 상기 제2스토리지전극에 대응되는 영역의 충간절연막 상에 배치되고 상기 제1스토리지전극과 전기적으로 연결되는 제3스토리지전극;

상기 소스전극 및 드레인전극과 상기 제3스토리지전극 상에 형성된 제1보호막;

상기 제1보호막 상에 배치되어 상기 드레인전극과 연결되는 연결전극 및 상기 제3스토리지전극에 대응되는 영역의 제1보호막 상에 배치되고 상기 제2스토리지전극과 전기적으로 연결되는 제4스토리지전극;

상기 연결전극과 제4스토리지전극 상에 형성된 제2보호막;

상기 제2보호막 위에 형성된 유기발광다이오드로 구성되며,

상기 유기발광 다이오드는 상기 연결전극과 연결되는 제1전극과 제2전극 및 그 사이의 유기발광층으로 구성되며, 상기 제1전극은 제4스토리지전극 상부로 연장되어 상기 제1전극과 제4스토리지전극이 제2보호막을 사이에 두고 배치되는 유기발광소자표시장치.

#### 청구항 2

제 1 항에 있어서,

상기 소스전극 및 드레인전극과 동일층에 형성되며, 상기 제2 및 4스토리지전극을 전기적으로 연결하는 브릿지전극

을 포함하는 유기발광소자표시장치.

#### 청구항 3

제 1 항에 있어서,

상기 제1도전층은 200Å 내지 500Å의 두께를 갖는 유기발광소자표시장치.

#### 청구항 4

제 2 항에 있어서,

상기 충간절연막에는 상기 제2스토리지전극과 브릿지패턴 사이의 연결을 위한 제1브릿지콘택홀이 형성되고,

상기 제1보호막에는 상기 브릿지전극과 제4스토리지전극 사이의 연결을 위한 제2브릿지콘택홀이 형성되는

유기발광소자표시장치.

#### 청구항 5

제 1 항에 있어서,

상기 연결전극과 유기발광다이오드 사이의 연결을 위한 연결콘택홀이 형성된 제2보호막을 포함하는 유기발광소자표시장치.

#### 청구항 6

기판 상에 반도체패턴과 상기 반도체패턴과 동일한 물질로 이루어진 제1스토리지전극을 형성하는 단계;

상기 반도체패턴 및 제1스토리지전극 상에 게이트절연막을 형성하는 단계;

상기 제1스토리지전극에 대응되는 영역의 게이트절연막 상에 제1도전층으로 이루어진 제2스토리지전극을 형성하고 상기 반도체패턴의 채널영역에 대응되는 영역의 게이트절연막 상에 상기 제1도전층을 포함한 다중층으로 이루어진 게이트전극을 형성하는 단계;

상기 게이트전극을 도핑마스크로 도핑공정을 진행하여 상기 제1스토리지전극을 불순물 이온으로 도핑하는 단계;

상기 제2스토리지전극 및 게이트전극 상에 충간절연막을 형성하는 단계;

상기 충간절연막 상에 상기 반도체패턴의 소스영역 및 드레인영역과 연결되는 소스전극 및 드레인전극을 형성하고, 상기 제2스토리지전극에 대응되는 영역의 충간절연막 상에 상기 제1스토리지전극과 전기적으로 연결되는 제3스토리지전극을 형성하는 단계;

상기 소스전극 및 드레인전극과 상기 제3스토리지전극 상에 제1보호막을 형성하는 단계;

상기 제1보호막 상에 상기 드레인전극과 연결되는 연결전극을 형성하고, 상기 제3스토리지전극에 대응되는 영역의 제1보호막 상에 상기 제2스토리지전극과 전기적으로 연결되는 제4스토리지전극을 형성하는 단계;

상기 연결전극과 연결되는 제1전극과 제2전극 및 그 사이의 유기발광층을 포함하는 유기발광다이오드를 형성하는 단계를 포함하며,

상기 제1전극은 제4스토리지전극 상부로 연장되어 상기 제1전극과 제4스토리지전극이 제2보호막을 사이에 두고 배치되는 유기발광소자표시장치 제조방법.

#### 청구항 7

제 6 항에 있어서,

상기 소스전극 및 드레인전극 형성시, 상기 제2 및 4스토리지전극을 전기적으로 연결하는 브릿지전극을 형성하는 단계

를 포함하는 유기발광소자표시장치 제조방법.

#### 청구항 8

제 6 항에 있어서,

상기 제1도전층은 200Å 내지 500Å의 두께를 갖는 유기발광소자표시장치 제조방법.

#### 청구항 9

제 6 항에 있어서,

상기 게이트전극은 제1도전층 상에 위치하는 제2도전층을 포함하고, 상기 제1도전층과 제2도전층은 서로 상이한 에친트로 식각되는 유기발광소자표시장치 제조방법.

### 청구항 10

제 9 항에 있어서,

상기 제1도전층은 투명 도전성 물질이나 MoTi로 이루어지고, 상기 제2도전층은 Mo로 이루어지는 유기발광소자표시장치 제조방법.

### 청구항 11

제 7 항에 있어서,

상기 제2스토리지전극과 브릿지패턴 사이의 연결을 위한 제1브릿지콘택홀을 상기 층간절연막에 형성하는 단계;

상기 브릿지전극과 제4스토리전극 사이의 연결을 위한 제2브릿지콘택홀을 상기 제1보호막에 형성하는 단계를 포함하는 유기발광소자표시장치 제조방법.

### 청구항 12

제 6 항에 있어서,

상기 연결전극과 유기발광다이오드 사이의 연결을 위한 연결콘택홀이 형성된 제2보호막을 형성하는 단계를 포함하는 유기발광소자표시장치 제조방법.

## 발명의 설명

### 기술 분야

[0001]

본 발명은 유기발광소자표시장치에 관한 것으로서, 보다 상세하게는, 유기발광소자표시장치 및 그 제조방법에 관한 것이다.

### 배경 기술

[0002]

정보화 사회가 발전함에 따라 화상을 표시하기 위한 표시장치에 대한 요구가 다양한 형태로 증가하고 있으며, 근래에는 액정표시장치(LCD : liquid crystal display), 플라즈마표시장치(PDP : plasma display panel), 유기 발광소자표시장치 (OLED : organic light emitting diode display)와 같은 여러가지 평판표시장치(flat display device)가 활용되고 있다.

[0003]

이들 평판표시장치 중에서, 유기발광소자표시장치는 소형화, 경량화, 박형화, 저전력 구동의 장점을 가지고 있어, 최근에 널리 사용되고 있다.

[0004]

유기발광소자표시장치로서는, 매트릭스형태로 배치된 화소 각각에 스위칭트랜지스터가 형성된 액티브매트릭스 타입(active matrix type)의 유기발광소자표시장치가 현재 보편적으로 사용되고 있다.

[0005]

화소영역에는 구동트랜지스터와 유기발광다이오드가 구성되며, 또한 구동트랜지스터의 게이트전극에 인가되는 전압을 유지하기 위한 스토리지 커패시터(storage capacitor)가 구성된다.

[0006]

종래에는 스토리지 커패시터를 구성함에 있어, 단일 또는 2중 커패시터 구조 즉 최대 2중 커패시터 구조를 채택하였다. 단일 커패시터 구조는 두개의 스토리지 전극을 사용하는 구조이며, 2중 커패시터 구조는 3개의 스토리

지 전극을 사용하는 구조이다.

[0007] 이와 같은 스토리지 전극은, 유기발광소자표시장치에서 적층된 금속 박막 등을 사용하여 구성된다.

[0008] 스토리지 커패시터 용량은 면적이 커질수록 용량이 커지게 된다. 따라서, 종래와 같이 최대 2중 커패시터 구조가 사용되는 경우에는, 충분한 커패시터 용량을 확보하기 위해 면적을 넓힐 수 밖에 없다. 이는, 화소영역에서 스토리지영역이 차지하는 면적이 커져야 하는 것을 의미한다.

[0009] 이로 인해, 개구율이 감소하게 되며, 이는 고해상도 표시장치 개발에 장애로 작용하게 된다.

## 발명의 내용

### 해결하려는 과제

[0010] 본 발명은, 스토리지영역을 감소시켜 개구율을 향상시킬 수 있는 유기발광소자표시장치 및 그 제조방법을 제공하는 데 과제가 있다.

### 과제의 해결 수단

[0011] 전술한 바와 같은 과제를 달성하기 위해, 본 발명은 기판 상에 반도체패턴과, 상기 반도체패턴과 동일한 물질로 이루어지며 불순물 이온이 도핑된 제1스토리지전극과; 상기 반도체패턴 및 제1스토리지전극 상에 형성된 게이트 절연막과; 상기 게이트절연막 상에, 상기 제1스토리지전극에 대응되며 제1도전층으로 이루어진 제2스토리지전극과, 상기 반도체패턴의 채널영역에 대응되며 상기 제1도전층을 포함한 다중층으로 이루어진 게이트전극과; 상기 제2스토리지전극 및 게이트전극 상에 형성된 층간절연막과; 상기 층간절연막 상에, 상기 반도체패턴의 소스영역 및 드레인영역과 연결되는 소스전극 및 드레인전극과, 상기 제3스토리지전극에 대응되며 상기 제1스토리지전극과 전기적으로 연결되는 제3스토리지전극과; 상기 소스전극 및 드레인전극과 상기 제3스토리지전극 상에 형성된 제1보호막과; 상기 제1보호막 상에, 상기 드레인전극과 연결되는 연결전극과, 상기 제3스토리지전극에 대응되며 상기 제2스토리지전극과 전기적으로 연결되는 제4스토리지전극과; 상기 연결전극과 연결되는 유기발광다이오드를 포함하는 유기발광소자표시장치를 제공한다.

[0012] 여기서, 상기 소스전극 및 드레인전극과 동일층에 형성되며, 상기 제2 및 4스토리지전극을 전기적으로 연결하는 브릿지전극을 포함할 수 있다.

[0013] 상기 제1도전층은  $200\text{ \AA}$  내지  $500\text{ \AA}$ 의 두께를 가질 수 있다.

[0014] 상기 층간절연막에는 상기 제2스토리지전극과 브릿지패턴 사이의 연결을 위한 제1브릿지콘택홀이 형성되고, 상기 제1보호막에는 상기 브릿지전극과 제4스토리전극 사이의 연결을 위한 제2브릿지콘택홀이 형성될 수 있다.

[0015] 상기 연결전극과 유기발광다이오드 사이의 연결을 위한 연결콘택홀이 형성된 제2보호막을 포함할 수 있다.

[0016] 다른 측면에서, 본 발명은 기판 상에 반도체패턴과, 상기 반도체패턴과 동일한 물질로 이루어진 제1스토리지전극을 형성하는 단계와; 상기 반도체패턴 및 제1스토리지전극 상에 게이트절연막을 형성하는 단계와; 상기 게이트절연막 상에, 상기 제1스토리지전극에 대응되며 제1도전층으로 이루어진 제2스토리지전극과, 상기 반도체패턴의 채널영역에 대응되며 상기 제1도전층을 포함한 다중층으로 이루어진 게이트전극을 형성하는 단계와; 상기 게이트전극을 도핑마스크로 도핑공정을 진행하여, 상기 제1스토리지전극을 불순물 이온으로 도핑하는 단계와; 상기 제2스토리지전극 및 게이트전극 상에 층간절연막을 형성하는 단계와; 상기 층간절연막 상에, 상기 반도체패턴의 소스영역 및 드레인영역과 연결되는 소스전극 및 드레인전극과, 상기 제3스토리지전극에 대응되며 상기 제1스토리지전극과 전기적으로 연결되는 제3스토리지전극을 형성하는 단계와; 상기 소스전극 및 드레인전극과 상기 제3스토리지전극 상에 제1보호막을 형성하는 단계와; 상기 제1보호막 상에, 상기 드레인전극과 연결되는 연결전극과, 상기 제3스토리지전극에 대응되며 상기 제2스토리지전극과 전기적으로 연결되는 제4스토리지전극을 형성하는 단계와; 상기 연결전극과 연결되는 유기발광다이오드를 형성하는 단계를 포함하는 유기발광소자표시장치 제조방법을 제공한다.

[0017] 여기서, 상기 소스전극 및 드레인전극 형성시, 상기 제2 및 4스토리지전극을 전기적으로 연결하는 브릿지전극을 형성하는 단계를 포함할 수 있다.

- [0018] 상기 제1도전층은 200Å 내지 500Å의 두께를 가질 수 있다.

- [0019] 상기 게이트전극은 제1도전층 상에 위치하는 제2도전층을 포함하고, 상기 제1도전층과 제2도전층은 서로 상이한 에친트로 식각될 수 있다.

- [0020] 상기 제1도전층은 투명 도전성 물질이나 MoTi로 이루어지고, 상기 제2도전층은 Mo로 이루어질 수 있다.

- [0021] 상기 제2스토리지전극과 브릿지패턴 사이의 연결을 위한 제1브릿지콘택홀을 상기 층간절연막에 형성하는 단계와; 상기 브릿지전극과 제4스토리전극 사이의 연결을 위한 제2브릿지콘택홀을 상기 제1보호막에 형성하는 단계를 포함할 수 있다.

- [0022] 상기 연결전극과 유기발광다이오드 사이의 연결을 위한 연결콘택홀이 형성된 제2보호막을 형성하는 단계를 포함할 수 있다.

### 발명의 효과

- [0023] 본 발명에서는, 제1 내지 4스토리지전극을 구성하여 3중 구조의 스토리지 커패시터를 구현할 수 있게 된다. 이에 따라, 면적 대비 스토리지 용량이 향상될 수 있게 된다. 따라서, 종래에 비해, 스토리지영역이 차지하는 면적이 감소될 수 있게 되어, 결과적으로 개구율이 향상될 수 있게 된다.

### 도면의 간단한 설명

- [0024] 도 1은 본 발명의 실시예에 따른 유기발광소자표시장치를 개략적으로 도시한 회로도.

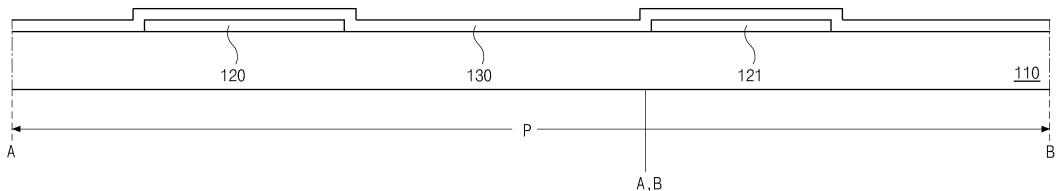

도 2는 본 발명의 실시예에 따른 유기발광소자표시장치를 개략적으로 도시한 평면도.

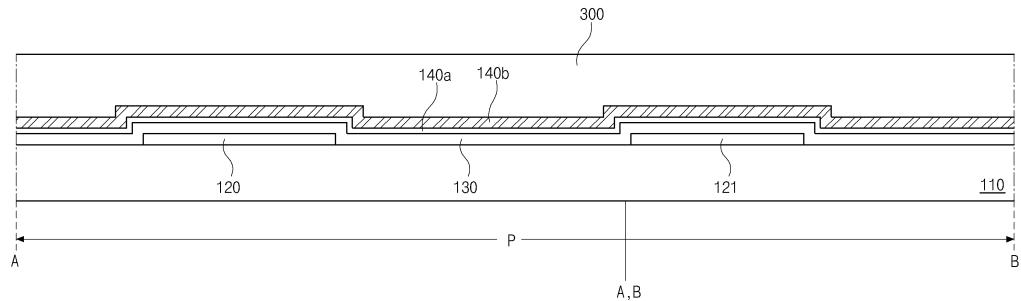

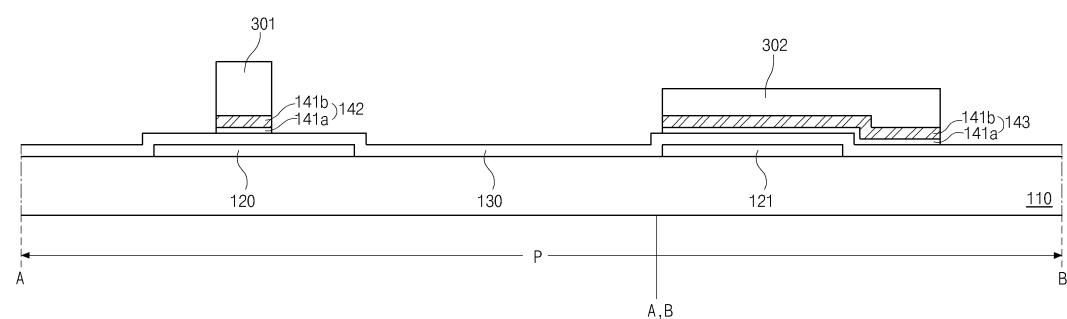

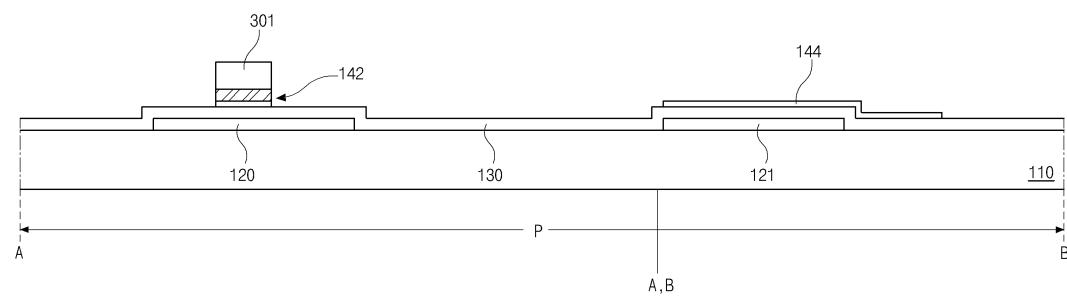

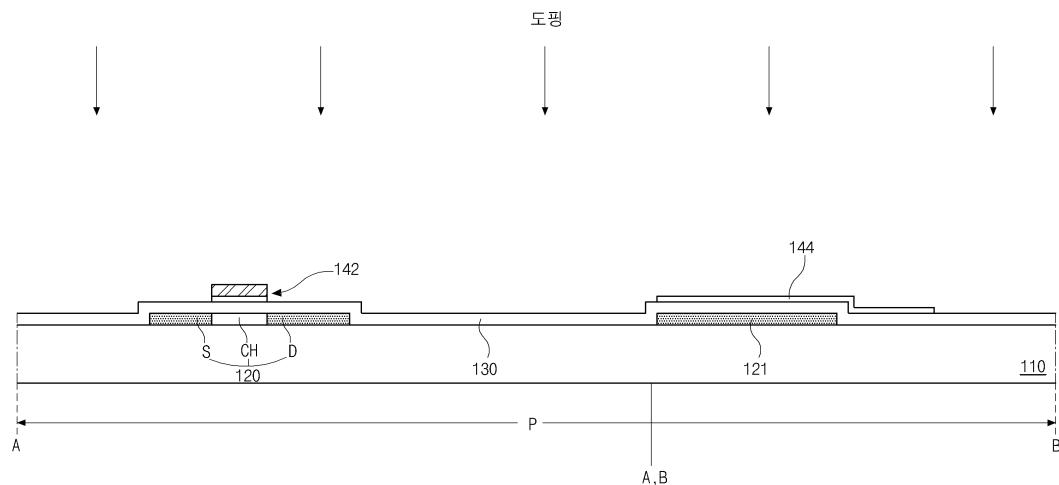

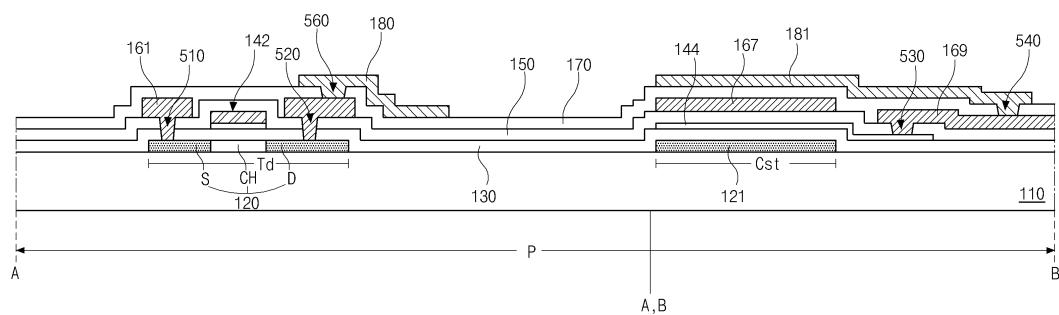

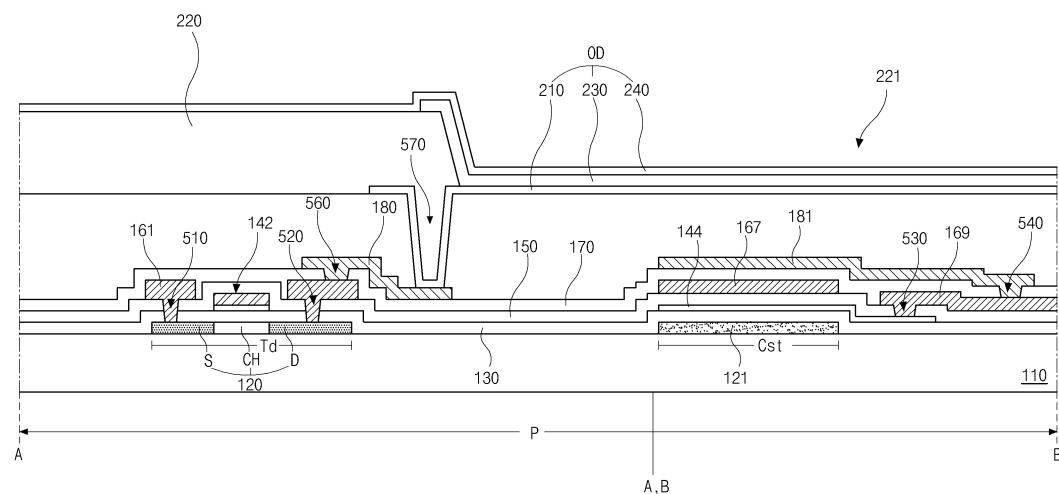

도 3은 도 2의 절단선 A-A 및 B-B를 따라 단면도.

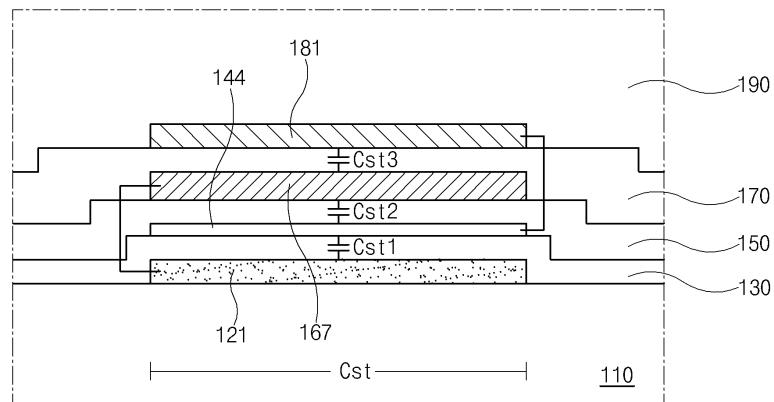

도 4는 본 발명의 실시예에 따른 유기발광소자표시장치의 스토리지 커패시터를 도시한 단면도.

도 5a 내지 5g는 본 발명의 실시예에 따른 유기발광소자표시장치를 제조하는 방법을 도시한 단면도.

### 발명을 실시하기 위한 구체적인 내용

- [0025] 이하, 도면을 참조하여 본 발명의 실시예를 설명한다.

- [0026] 도 1은 본 발명의 실시예에 따른 유기발광소자표시장치를 개략적으로 도시한 회로도이고, 도 2는 본 발명의 실시예에 따른 유기발광소자표시장치를 개략적으로 도시한 평면도이고, 도 3은 도 2의 절단선 A-A 및 B-B를 따라 단면도이고, 도 4는 본 발명의 실시예에 따른 유기발광소자표시장치의 스토리지 커패시터를 도시한 단면도이다.

- [0027] 본 발명의 실시예에서는, 설명의 편의를 위해, 각 화소영역에 3개의 트랜지스터 및 1개의 커패시터가 구성된 3T1C 구조를 예로 들어 설명한다. 물론, 이는 일례로서, 그 외의 다양한 구조로서 예를 들면 2T1C, 4T1C, 5T1C, 6T1C 등과 같은 구조에도 본 발명의 실시예가 적용될 수 있을 것이다.

- [0028] 그리고, 화소영역에 구성된 3개의 트랜지스터는 실질적으로 동일한 구조를 갖게되는바, 구동트랜지스터를 위주로 하여 설명하며 3개의 트랜지스터를 구성하는 구성요소에는 동일한 도면부호를 사용할 수 있다. 또한, 도 2는 스토리지 커패시터를 위주로 도시하였다.

- [0029] 도 1 내지 3을 참조하면, 본 발명의 실시예에 따른 유기발광소자표시장치(100)에는 매트릭스 형태로 배치된 다수의 화소영역(P)이 정의되어 있다. 각 화소영역(P)에는, 스위칭트랜지스터(Ts)와 구동트랜지스터(Td)와 발광제어트랜지스터(Te)와 유기발광다이오드(OD)와 3중 구조의 스토리지 커패시터(Cst)가 구성될 수 있다.

- [0030] 스위칭트랜지스터(Ts)는 대응되는 게이트배선 및 데이터배선(140, 160)과 연결되며, 게이트배선(140)에 인가된 게이트신호에 따라 턴온(turn-on)된다. 스위칭트랜지스터(Ts)가 턴온되면, 이에 동기하여 데이터배선(160)을 통해 전달된 데이터전압이 구동트랜지스터(Td)의 게이트전극(142)에 인가된다.

- [0031] 이에 따라, 구동트랜지스터(Td)는 턴온되어 발광전류가 채널영역(CH)을 통해 흐르게 된다. 여기서, 발광전류의

크기는 인가된 데이터전압의 크기에 따라 결정되는데, 예를 들면 데이터전압에 비례 관계로 발광전류의 크기가 결정된다.

[0032] 이와 같은 발광전류가 유기발광다이오드(OD)에 공급되면, 발광전류의 크기에 따라 대응되는 휘도를 갖는 빛이 방출되게 된다.

[0033] 한편, 발광제어트랜지스터(Te)는 유기발광다이오드(OD)의 턴온/턴오프를 제어하게 된다. 즉, 발광제어트랜지스터(Te)가 턴온되면 구동트랜지스터(Td)에 구동전압(Vdd)이 인가될 수 있게 되므로, 데이터전압에 대응되는 발광전류가 발생되어 유기발광다이오드(OD)에 공급될 수 있게 된다. 반면에, 발광제어트랜지스터(Te)가 턴오프되면 구동트랜지스터(Td)에 구동전압(Vdd)이 인가될 수 없게 되므로, 발광전류는 발생되지 않고 유기발광다이오드(OD)는 턴오프 상태가 된다.

[0034] 게이트배선 및 데이터배선(140, 160)은 서로 교차하도록 구성되는데, 예를 들면 게이트배선(140)은 제1방향으로 연장되며 데이터배선(160)은 제2방향으로 연장된다.

[0035] 한편, 발광제어트랜지스터(Te)와 연결되는 발광제어배선(145)이 더욱 구비될 수 있다. 발광제어배선(145)은 게이트배선(140)과 동일층에 동일한 물질로 형성되며, 제1방향을 따라 연장되고 게이트배선(140)과 이격되어 구성될 수 있는데, 이에 한정되지는 않는다.

[0036] 그리고, 구동전압(Vdd)을 전달하는 전원배선(165)이 더욱 구비될 수 있다. 전원배선(165)은 데이터배선(160)과 동일층에 동일한 물질로 형성되며, 제2방향을 따라 연장되고 데이터배선(160)과 이격되어 구성될 수 있는데, 이에 한정되지는 않는다.

[0037] 전술한 스위칭트랜지스터(Ts)와 구동트랜지스터(Td)와 발광제어트랜지스터(Te)는 실질적으로 동일한 구조로 형성된다. 이와 관련하여, 구동트랜지스터(Td)를 예로 들어 설명한다.

[0038] 구동트랜지스터(Td)는 반도체패턴(120)과, 게이트전극(142)과, 소스전극 및 드레인전극(161, 163)을 포함한다. 반도체패턴(120)은 기판(110) 상에 형성되며 결정질 실리콘으로 이루어질 수 있다. 반도체패턴(120)은 채널영역(CH)과 소스영역 및 드레인영역(S, D)을 포함할 수 있다. 채널영역(CH)은 반도체패턴(120)의 중심부분에 위치하며, 정공 또는 전자의 이동영역으로서 순수한 결정질 실리콘으로 구성될 수 있다. 한편, 소스영역 및 드레인영역은 채널영역(CH)의 양측부분에 각각 위치하며, n+ 또는 p+ 이온과 같은 불순물 이온이 도핑된 결정질 실리콘으로 구성될 수 있다.

[0039] 이와 같은 반도체패턴(120) 상에는 게이트절연막(130)이 형성되며, 게이트절연막(130) 상에는 채널영역(CH)에 대응하여 게이트전극(142)이 구성될 수 있다.

[0040] 게이트전극(142) 상에는 층간절연막(150)이 형성되며, 층간절연막(150) 상에는 소스전극 및 드레인전극(161, 163)이 구성될 수 있다. 층간절연막(150)에는 소스영역 및 드레인영역(S, D)을 각각 노출하는 소스콘택홀 및 드레인콘택홀(510, 520)이 구성될 수 있다. 이와 같은 소스콘택홀 및 드레인콘택홀(510, 520) 각각을 통해, 소스전극 및 드레인전극(161, 163)은 대응되는 소스영역 및 드레인영역(S, D)에 접촉할 수 있게 된다.

[0041] 한편, 구동트랜지스터(Td)와 전기적으로 연결되는 유기발광다이오드(OD)는 제1 및 2전극(210, 240)과 이를 전극 사이에 구성된 유기발광층(230)을 포함할 수 있다.

[0042] 제1전극(210)은 구동트랜지스터(Td)의 드레인전극(163)과 연결되는데, 본 발명의 실시예에 따르면 이를 사이의 연결을 위해 연결전극(180)이 구성될 수 있다.

[0043] 이와 관련하여, 연결전극(180)은 제1보호막(170) 상에 형성되며, 제1보호막(170)에는 구동트랜지스터(Td)의 드레인전극(163)을 노출하는 제1연결콘택홀(560)이 형성될 수 있다. 이와 같은 제1연결콘택홀(560)을 통해, 연결전극(180)은 드레인전극(163)과 접촉할 수 있게 된다.

[0044] 한편, 연결전극(180) 상에는 제2보호막(190)이 형성될 수 있다. 제2보호막(190)은 평탄화막으로서 기능할 수 있는데, 이에 따라 제2보호막(190) 상에 형성되는 제1전극(210)은 실질적으로 평탄하게 형성될 수 있다. 제2보호막(190)에는 제2연결콘택홀(570)이 형성될 수 있다. 이와 같은 제2연결콘택홀(570)을 통해, 제1전극(210)은 연결전극(180)과 접촉할 수 있게 된다.

- [0045] 위와 같은 구성을 통해, 유기발광다이오드(OD)는 구동트랜지스터(Td)와 전기적으로 연결될 수 있게 된다.

- [0046] 한편, 제1전극(210) 상에는 화소영역(P)의 경계를 따라 뱅크층(220)이 형성될 수 있다. 이와 같은 뱅크층(220)은 개구부(221)를 구비하게 되며, 개구부(221)에는 유기발광층(230)이 형성될 수 있다. 한편, 유기발광층(230)은 뱅크층(220)과 끝단이 중첩되도록 개구부(221)에서 연장되어 형성될 수 있다.

- [0047] 유기발광층(230) 상에는 실질적으로 기판(110) 전면에 걸쳐 제2전극(240)이 구성될 수 있다. 즉, 제1전극 및 유기발광층(210, 230)은 화소영역별로 패터닝되어 구성되며, 제2전극(240)은 모든 화소영역(P)에 걸쳐 일체로 구성될 수 있다.

- [0048] 한편, 본 발명의 실시예에서는 스토리지 커패시터(Cst)를 3중 구조로 구성하게 되는데, 이에 대해 보다 상세하게 설명한다.

- [0049] 본 발명의 실시예에 따른 스토리지 커패시터(Cst)는 제1 내지 4스토리지전극(121, 144, 167, 181)을 포함할 수 있다.

- [0050] 제1스토리지전극(121)은 반도체패턴(120)과 동일한 물질로 동일층에 형성될 수 있다. 이처럼, 반도체 물질로 제1스토리지전극(121)이 구성되는데, 제1스토리지전극(121)이 전극으로서 기능을 발휘할 수 있을 정도의 도전성을 갖기 위해, 제1스토리지전극(121)은 소스영역 및 드레인영역(S, D)과 같이 불순물이 도핑된 결정질 실리콘으로 이루어질 수 있다.

- [0051] 제2스토리지전극(144)은, 게이트절연막(130)이 개재된 상태로 제1스토리지전극(121)과 대응되도록 구성된다. 이와 같은 제2스토리지전극(144)은 게이트전극(142)과 동일층에 형성될 수 있다. 여기서, 게이트전극(142)은 다중층 구조 예를 들면 2중층 구조로 구성될 수 있으며, 제2스토리지전극(144)은 게이트전극(142)의 최하부층을 사용한 단일층 구조로 구성될 수 있다.

- [0052] 이와 관련하여, 게이트전극(142)이 2중층 구조로 구성되는 경우에, 하부층인 제1도전층(141a)은 도핑공정시 불순물 이온이 투과될 수 있도록 형성되는 것이 바람직하다. 그리고, 상부층인 제2도전층(141b)은 저저항 도전성 물질로 이루어질 수 있다. 이와 같은 경우에, 제2스토리지전극(144)은 게이트전극(142)의 제1도전층(141a)으로 구성될 수 있게 된다.

- [0053] 이와 관련하여, 제1도전층(141a)은 불순물 이온이 투과될 수 있도록 얇은 두께로 구성되는데, 예를 들면 200Å 내지 대략 500Å의 두께를 갖도록 구성되는 것이 바람직하다.

- [0054] 그리고, 제2도전층(141b)은 제1도전층(141a)에 비해 저항이 낮은 금속물질로 이루어지는 것이 바람직하다. 또한, 제1도전층(141a)과 제2도전층(141b)은 식각 특성이 서로 상이한 물질로 이루어지는 것이 바람직하다. 즉, 제1 및 2도전층(141a, 141b)은 서로 다른 에친트로 식각되는 것이 바람직하다.

- [0055] 이와 관련하여 예를 들면, 제1도전층(141a)은 투명 도전성 물질인 ITO(indium-tin-oxide), IZO(indium-zinc-oxide) 또는 ITZO(indium-tin-zinc-oxide)나, MoTi(molybdenum titanium)로 구성될 수 있는데, 이에 한정되지는 않는다. 그리고, 제2도전층(141b)은 Mo(molybdenum)를 사용할 수 있는데, 이에 한정되지는 않는다.

- [0056] 한편, 게이트배선 및 발광제어배선(140, 145)은 게이트전극(142)과 동일한 다중층 구조로 구성된다.

- [0057] 제3스토리지전극(167)은 충간절연막(150)이 개재된 상태로 제2스토리지전극(144)과 대응되도록 구성된다. 이와 같은 제3스토리지전극(144)은 소스전극 및 드레인전극(161, 163)과 동일층에 동일한 물질로 형성될 수 있다.

- [0058] 제4스토리지전극(181)은 제1보호막(170)이 개재된 상태로 제3스토리지전극(167)과 대응되도록 구성된다. 이와 같은 제4스토리지전극(181)은 연결전극(180)과 동일층에 동일한 물질로 형성될 수 있다.

- [0059] 전술한 제1 내지 4스토리지전극(121, 144, 167, 181)에 있어, 제1 및 2스토리지전극(121, 144) 사이와 제2 및 3스토리지전극(144, 167) 사이와 제3 및 4스토리지전극(167, 181) 사이 각각에는 스토리지 커패시터(Cst1 내지 Cst3)가 형성될 수 있는데, 설명의 편의를 위해, 이와 같이 형성되는 스토리지 커패시터를 제1 내지 3부(sub)스토리지 커패시터(Cst1 내지 Cst3)로 칭한다.

- [0060] 그리고, 제1 및 3스토리지전극(121, 167)은 전기적으로 연결되며, 제2 및 4스토리지전극(144, 181)은 전기적으로 연결될 수 있다. 이와 같은 연결 관계에 따라, 제1 및 3스토리지전극(121, 167)은 하나의 스토리지전극으로 기능하고 제2 및 4스토리지전극(144, 181)은 하나의 대향 스토리지전극으로서 기능하여, 본 발명의 실시예에 따른

스토리지 커패시터(Cst)를 구성할 수 있게 된다. 즉, 3개의 부스토리지 커패시터(Cst1 내지 Cst3)를 구성함으로써 3중 구조의 스토리지 커패시터(Cst)를 구현할 수 있게 된다.

[0061] 이처럼, 본 발명의 실시예에서는 4개의 스토리지전극(121, 144, 167, 181)을 사용하여 스토리지 커패시터(Cst)를 구성할 수 있게 되므로, 스토리지영역의 면적을 감소시킬 수 있게 된다. 즉, 단일 또는 2중 구조를 사용하는 종래에 비해, 본 발명의 실시예에서는 3중 구조를 채택함에 따라, 스토리지전극 사이의 거리가 줄어들게 되므로 스토리지영역의 면적 대비 용량이 향상될 수 있게 된다. 따라서, 종래와 동일한 용량을 구현함에 있어, 종래에 비해 보다 적은 면적이 사용될 수 있게 된다. 이에 따라 스토리지영역의 면적이 감소되어, 결과적으로 화소영역의 개구율이 증가되는 효과가 발휘될 수 있게 된다.

[0062] 한편, 본 발명의 실시예에 있어서, 제1 및 3스토리지전극(121, 167)은 구동트랜지스터(Td)의 소스전극(161) 측에 연결되며, 제2 및 4스토리지전극(144, 181)은 구동트랜지스터(Td)의 게이트전극(142) 측에 연결된다.

[0063] 여기서, 제1 및 3스토리지전극(121, 167) 사이의 연결은, 게이트절연막 및 충간절연막(130, 150)에 형성된 콘택홀을 통해 이루어질 수 있다. 한편, 본 발명의 실시예에서는 구동트랜지스터(Td)의 소스콘택홀(510)이 제1 및 3스토리지전극(121, 167)을 연결하는 콘택홀로서 기능할 수 있다.

[0064] 이와 관련하여, 제1스토리지전극(121)은 구동트랜지스터(Td)의 반도체패턴(120)으로부터 연장되어 형성될 수 있으며, 제3스토리지전극(167)은 구동트랜지스터(Td)의 소스전극(161)으로부터 연장되어 형성될 수 있다. 이에 따라, 소스콘택홀(510)을 통한 소스영역(S)과 소스전극(161)의 연결을 통해, 제1 및 3스토리지전극(121, 167)이 연결될 수 있게 된다.

[0065] 한편, 발광제어트랜지스터(Te)의 드레인전극(163)은 구동트랜지스터(Td)의 소스전극(161)과 연결되는데, 본 발명의 실시예에서는 구동트랜지스터(Td)의 소스전극(161)이 발광제어트랜지스터(Te)의 드레인전극(163)으로 겸용되는 경우를 예로 들어 도시하였다. 그리고, 발광제어트랜지스터(Te)의 반도체패턴(120)은 제1스토리지전극(121)으로부터 연장되어 형성될 수 있다.

[0066] 제2 및 4스토리지전극(144, 181) 사이의 연결은 예를 들면 이를 사이에 위치하는 브릿지패턴(169)을 통해 이루어질 수 있다. 브릿지패턴(169)은 소스전극 및 드레인전극(161, 163)과 동일층 동일물질로 구성될 수 있으며, 제1 및 2브릿지콘택홀(530, 540) 각각을 통해 제2 및 4스토리지전극(144, 181)과 연결될 수 있다. 여기서, 제1 브릿지콘택홀(530)은 충간절연막(150)에 형성되며, 이를 통해 브릿지패턴(169)이 제2스토리지전극(144)과 접촉할 수 있다. 그리고, 제2브릿지콘택홀(540)은 제1보호막(170)에 형성되며, 이를 통해 브릿지패턴(169)이 제4스토리지전극(181)과 접촉할 수 있다. 여기서, 브릿지패턴(169)은 스위칭트랜지스터(Ts)의 드레인전극(163)으로부터 연장되어 형성될 수 있다.

[0067] 한편, 브릿지패턴(169)과 제4스토리지전극(181)은 게이트배선(140) 상에서 접촉될 수 있으며, 이를 위해 제2브릿지콘택홀(530)은 게이트배선(140) 상에 형성될 수 있다. 이와 같이 구성하는 경우에, 브릿지패턴(169)과 제4스토리지전극(181)의 연결을 위한 영역 확보를 의해 스토리지영역이 감소되는 것을 방지할 수 있다. 즉, 스토리지영역 확보가 보다 효율적으로 이루어질 수 있게 된다.

[0068] 한편, 이와는 달리, 제2브릿지콘택홀(530)은 게이트배선(140) 이외의 영역에서 형성될 수 있다. 이와 같은 경우에, 스토리지영역 확보 측면에서 게이트배선(140)에 근접하여 형성되는 것이 바람직하다.

[0069] 그리고, 구동트랜지스터(Td)의 게이트전극(142)은 스위칭트랜지스터(Ts)의 드레인전극(163)과 연결되는데, 이와 관련하여 예를 들면 구동트랜지스터(Td)의 게이트전극(142)은 브릿지패턴(169)과 접촉함으로써 스위칭트랜지스터(Ts)의 드레인전극(163)과 연결되도록 구성될 수 있다. 이를 위해, 충간절연막(150)에는 구동트랜지스터(Td)의 게이트전극(142)을 노출하는 게이트콘택홀(550)이 형성될 수 있으며, 이를 통해 브릿지패턴(169)과 구동트랜지스터(Td)의 게이트전극(142)이 접촉하도록 구성될 수 있다.

[0070] 한편, 위와 같은 경우는 제2스토리지전극(144)과 구동트랜지스터(Td)의 게이트전극(142)이 별개로 패터닝된 경우로서, 이와는 달리 구동트랜지스터(Td)의 게이트전극(142)이 제2스토리지전극(144)으로부터 연장되어 형성될 수 있다. 이와 같은 경우에는, 제1브릿지콘택홀(530)을 통해, 스위칭트랜지스터(Ts)의 드레인전극(163)과 구동트랜지스터(Td)의 게이트전극(142)이 전기적으로 연결될 수 있게 된다. 즉, 제1브릿지콘택홀(530)이 게이트콘택홀(550)의 기능을 겸할 수 있게 된다.

[0071] 전술한 바와 같이, 본 발명의 실시예에 따르면 제1 내지 4스토리지전극(121, 144, 167, 181)을 구성하여 3중 구

조의 스토리지 커페시터(Cst)를 구현할 수 있게 된다. 이에 따라, 면적 대비 스토리지 용량이 향상될 수 있게 된다. 따라서, 종래에 비해, 스토리지영역이 차지하는 면적이 감소될 수 있게 되어, 결과적으로 개구율이 향상될 수 있게 된다.

[0072] 이와 관련하여, 아래의 표1을 참조할 수 있다.

표 1

|                                | 종래(2중 구조)          | 실시예(3중 구조)         |

|--------------------------------|--------------------|--------------------|

| 스토리지 용량                        | 240 pF             | 240 pF             |

| 제1부스토리지 용량                     | -                  | 97 pF              |

| 제2부스토리지 용량<br>(종래의 제1부스토리지 용량) | 108 pF             | 65 pF              |

| 제3부스토리지 용량<br>(종래의 제2부스토리지 용량) | 132 pF             | 79 pF              |

| 스토리지 면적                        | 670um <sup>2</sup> | 400um <sup>2</sup> |

| 스토리지 면적비                       | 100%               | 60%                |

| 화소영역 대비 스토리지 면적비               | 13%                | 8%                 |

[0074] 표 1은 7인치 HD(high definition) 모델에서의 시뮬레이션(simulation) 결과를 도시하고 있다.

[0075] 이를 살펴보면, 대략 240 pF의 스토리지 용량을 확보함에 있어, 종래의 스토리지 면적 대비 실시예의 스토리지 면적은 대략 60% 정도가 요구됨을 알 수 있다. 이에 따라, 화소영역 대비 스토리지 면적은 대략 8%를 차지하여, 종래 대비 5% 정도의 개구율이 증가하게 됨을 알 수 있다.

[0076] 이처럼, 본 발명의 실시예에 따르면, 스토리지 면적을 감소시킬 수 있어 개구율이 향상되는 효과를 발휘할 수 있게 된다.

[0077] 이하, 도 5a 내지 5g를 참조하여 본 발명의 실시예에 따른 유기발광소자표시장치를 제조하는 방법을 설명한다.

[0078] 도 5a 내지 5g는 본 발명의 실시예에 따른 유기발광소자표시장치를 제조하는 방법을 도시한 단면도이다.

[0079] 먼저, 도 5a에 도시한 바와 같이, 기판(110) 상에 비정질 실리콘을 증착하여 반도체층을 형성한다. 한편, 반도체층 형성 이전에 벼파층을 형성하고, 그 상부에 반도체층을 형성할 수 있다.

[0080] 다음으로, 반도체층에 대해 결정화 공정을 진행하여 결정질 실리콘으로 이루어진 반도체층을 형성한다. 다음으로, 반도체층에 대해 마스크 공정을 진행하여 이를 패터닝함으로써, 반도체패턴(120)과 제1스토리지전극(121)을 형성한다.

[0081] 다음으로, 반도체패턴(120)과 제1스토리지전극(121) 상에 게이트절연막(130)을 형성한다. 게이트절연막(130)은 무기절연물질로서 예를 들면 산화실리콘(SiO<sub>2</sub>)이나 질화실리콘(SiNx)이 사용될 수 있다.

[0082] 다음으로, 도 5b에 도시한 바와 같이, 게이트절연막(130) 상에 제1도전층 및 제2도전층(140a, 140b)을 순차적으로 형성하고, 그 상부에 포토레지스터층(300)을 증착한다.

[0083] 여기서, 제1도전층(140a)은 이후의 도핑공정시에 불순물 이온이 투과될 수 있을 정도로 얇은 두께를 갖는 것이 바람직하다. 이를 위해, 제1도전층(140a)은 200Å 내지 500Å의 두께로 형성될 수 있다.

[0084] 그리고, 제2도전층(140b)은 제1도전층(140a)에 비해 저항이 낮은 금속물질로 구성할 수 있다.

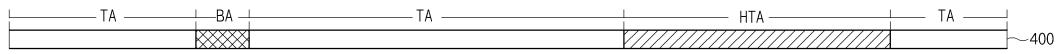

[0085] 다음으로, 포토레지스트층(300) 상부에 포토마스크(400)를 위치시킨다. 포토마스크(400)는 투과부(TA)와 반투과부(HTA)와 차단부(BA)를 포함할 수 있다. 투과부(TA)는 입사된 빛을 투과시키고, 차단부(BA)는 입사된 빛을 차단시키며, 반투과부(HTA)는 입사된 빛을 일부분 투과시키게 된다. 반투과부(HTA)는 슬릿(slit) 또는 반투과막으로 구성될 수 있다. 이처럼, 반투과부(HTA)를 갖는 포토마스크(400)는 슬릿 마스크 또는 하프톤(halftone) 마스크로 불리워진다.

[0086] 한편, 본 발명의 실시예에서는, 설명의 편의를 위해, 파지티브 타입(positive type)의 포토레지스트층(300)이 사용되는 경우를 예로 든다.

- [0087] 이와 같은 경우에, 차단부(BA)는 반도체패턴(120)의 중앙부로서 게이트전극(도 5c의 142 참조)이 형성될 영역에 대응하여 위치할 수 있으며, 또한 게이트배선 및 발광제어배선(도 2의 140 및 145 참조)이 형성될 영역에 대응하여 위치할 수 있다. 반투과부(HTA)는 제2스토리지전극(도 5d의 144 참조)이 형성될 영역으로서 스토리지영역에 대응하여 위치할 수 있다. 투과부(TA)는 차단부(BA)와 반투과부(HTA)가 배치된 부분 이외의 부분에 배치된다.

- [0088] 이와 같이 포토마스크(400)를 배치한 상태에서 노광 공정이 진행되고, 그 후에 포토레지스트층(300)을 현상한다.

- [0089] 이에 따라, 도 5c에 도시한 바와 같이, 차단부(BA)에 대응되는 영역에는 제1두께를 갖는 제1포토레지스트패턴(301)이 형성되고, 반투과부(HTA)에 대응되는 영역에는 제1두께보다 작은 제2두께를 갖는 제2포토레지스트패턴(302)이 형성된다.

- [0090] 다음으로, 제1 및 2포토레지스트패턴(301, 302)을 식각마스크로 하여 제1식각공정이 진행된다. 이에 따라, 노출된 제1 및 2도전층(140a, 140b)은 제거되어, 제1 및 2포토레지스터패턴(301, 302) 하부에는 패턴된 제1 및 2도전층(141a, 141b)이 남겨지게 된다. 여기서, 제1포토레지스터패턴(301) 하부의 패턴된 제1 및 2도전층(141a, 141b)은 게이트전극(142)을 구성하며, 또한 게이트배선(140)과 발광제어배선(145)을 구성하게 된다. 한편, 제2포토레지스트패턴(302) 하부의 패턴된 제1 및 2도전층(141a, 141b)은 스토리지패턴(143)을 구성한다.

- [0091] 다음으로, 도 5d에 도시한 바와 같이, 제1 및 2포토레지스트패턴(301, 302)에 대해 애싱(ashing) 공정이 수행된다. 이에 따라, 제2포토레지스트패턴(302)은 제거되어 그 하부의 스토리지패턴(143)은 노출된다. 한편, 제1포토레지스트패턴(301)은 그 두께가 감소된 상태로 남겨지게 된다.

- [0092] 다음으로, 애싱된 제1포토레지스트패턴(301)을 식각마스크로 하여 제2식각공정이 진행된다. 이에 따라, 스토리지패턴(143)의 제2도전층(141b)이 제거되며 하부의 제1도전층(141a)이 남겨지게 된다. 이처럼 남겨진 제1도전층(141a)은 제2스토리지전극(144)에 해당된다.

- [0093] 위와 같이 하나의 마스크공정을 통해, 2중층 구조의 게이트전극(142)을 형성하며, 단일층 구조의 제2스토리지전극(144)을 형성할 수 있다.

- [0094] 한편, 이와는 다른 예로서, 2개의 마스크공정을 통해, 게이트전극 및 제2스토리지전극(142, 144)을 형성할 수 있다. 이와 같은 경우에는, 제1도전층(140a)을 증착한 후 제1마스크공정을 진행하여 게이트전극(142)의 하부층인 패턴된 제1도전층(141a)과 제2스토리지전극(144)을 형성하고, 다음으로 제2도전층(140b)을 증착한 후 제2마스크공정을 진행하여 게이트전극(142)의 상부층인 패턴된 제2도전층(141b)을 형성할 수 있다.

- [0095] 한편, 전술한 제1 및 2도전층(140a, 141a 및 140b, 141b)은 서로 다른 에친트로 식각되는 것이 바람직하다. 이와 관련하여, 만약 제2식각공정에서 제2도전층(141b)을 제거함에 있어, 제1도전층(141b)이 식각된다면 제1도전층(141b)의 과식각에 따라 제2스토리지전극(144)이 원하는 형태로 형성될 수 없게 될 것이다. 따라서, 제1도전층용 에친트는 제2도전층(140b, 141b)과 반응하지 않고 마찬가지로 제2도전층용 에친트는 제1도전층(140a, 141b)과 반응하지 않도록 구성하는 것이 바람직할 것이다.

- [0096] 다음으로, 제2식각공정이 완료되면, 스트립공정이 수행되어 제1포토레지스트패턴(301)을 제거하게 된다.

- [0097] 다음으로, 도 5e에 도시한 바와 같이, n<sup>+</sup> 또는 p<sup>+</sup> 이온과 같은 불순물 이온을 사용한 도핑공정이 수행된다. 도핑공정에서는, 게이트전극(142)의 상부층인 제2도전층(141b)은 도핑마스크로 기능하게 된다. 따라서, 불순물 이온은, 게이트전극(142)에 의해 가려지지 않는 반도체패턴(120)의 양측부분에 도핑되며, 이에 따라 반도체패턴(120)의 양측부분은 소스영역 및 드레인영역(S, D)으로서 기능하게 된다. 한편, 도핑되지 않은 반도체패턴(120)의 중앙부분은 채널영역(CH)으로서 기능하게 된다.

- [0098] 한편, 도핑공정시에는 제1스토리지전극(121) 또한 불순물 이온으로 도핑되어 도전특성을 갖게 된다. 이와 관련하여, 제1스토리지전극(121) 상부에는 제2스토리지전극(144)이 구성되는데, 제2스토리지전극(144)은 불순물 이온을 통과시킬 수 있을 정도의 얇은 두께를 갖는 제1도전층(141a)로 구성되어 있는바, 제1스토리지전극(121)은 불순물 이온으로 충분히 도핑될 수 있게 된다.

- [0099] 한편, 전술한 바에는, 제1포토레지스터패턴(301)을 제거한 후에 도핑공정이 진행되는 것을 예로 들어 설명하였다. 다른 예로서, 제1포토레지스터패턴(301)이 게이트전극(142) 상에 남겨진 상태에서 전술한 도핑공정이 수행될 수도 있다.

- [0100] 다음으로, 도 5f에 도시한 바와 같이, 게이트전극(142) 상에 층간절연막(150)을 형성한다. 이와 같은 층간절연막(150)은, 무기절연물질로서 산화실리콘( $\text{SiO}_2$ ) 또는 질화실리콘( $\text{SiNx}$ )을 사용한 단일층 또는 이들을 사용한 이중층 구조로 형성될 수 있다.

- [0101] 다음으로, 마스크공정을 진행하여, 소스영역 및 드레인영역(S, D)을 노출하는 소스콘택홀 및 드레인콘택홀(510, 520)을 게이트절연막 및 층간절연막(130, 150)에 형성한다. 한편, 이와 같은 마스크공정에서, 제2스토리지전극(144)의 일부를 노출하는 제1브릿지콘택홀(530)을 층간절연막(150)에 형성한다. 그리고, 해당 마스크공정에서는, 구동트랜지스터(Td)의 게이트전극(142)을 노출하는 게이트콘택홀(도 2의 550)이 층간절연막(150)에 형성될 수 있다.

- [0102] 다음으로, 층간절연막(150) 상에 금속물질을 증착하고, 그 후에 마스크공정을 진행하여 소스전극 및 드레인전극(161, 163)과 제3스토리지전극(167)과 브릿지패턴(169)을 형성한다. 한편, 이와 같은 공정에서, 데이터배선(160)과 전원배선(165)을 형성한다.

- [0103] 전술한 바와 같은 공정을 통해, 반도체패턴(120), 게이트전극(142), 소스전극 및 드레인전극(161, 163)을 포함하는 구동트랜지스터(Td)를 형성할 수 있게 되며, 또한 이와 같은 구조를 갖는 스위칭트랜지스터 및 발광제어트랜지스터(도 2의 Ts, Te 참조)가 형성될 수 있게 된다.

- [0104] 소스전극 및 드레인전극(161, 163) 각각은 소스콘택홀 및 드레인콘택홀(510, 520)을 통해 소스영역 및 드레인영역(S, D)과 접촉할 수 있게 된다.

- [0105] 그리고, 제3스토리지전극(167)은 제1스토리지전극(121)과 전기적으로 연결된다. 이와 관련하여, 제3스토리지전극(167)은 구동트랜지스터(Td)의 소스전극(161)과 연결되어 있고, 제1스토리지전극(121)은 구동트랜지스터(Td)의 소스영역(S)과 연결되어 있으므로, 소스콘택홀(510)을 통한 소스전극(161) 및 소스영역(S)의 연결을 통해 제1 및 3스토리지전극(121, 167)은 전기적으로 연결될 수 있다. 한편, 이와 달리, 제1 및 3스토리지전극(121, 167)을 직접적으로 연결하기 위한 별도의 콘택홀이 구비될 수 있는데, 이는 소스콘택홀(510) 형성시에 형성될 수 있을 것이다.

- [0106] 브릿지패턴(169)은 제1브릿지콘택홀(530)을 통해 제2스토리지전극(144)과 접촉하게 된다.

- [0107] 다음으로, 소스전극 및 드레인전극(161, 163) 상에 제1보호막(170)을 형성한다. 이와 같은 제1보호막(150)은, 무기절연물질로서 산화실리콘( $\text{SiO}_2$ ) 또는 질화실리콘( $\text{SiNx}$ )을 사용한 단일층 또는 이들을 사용한 이중층 구조로 형성될 수 있다.

- [0108] 다음으로, 마스크공정을 진행하여, 구동트랜지스터(Td)의 드레인전극(163)을 노출하는 제1연결콘택홀(560)과 브릿지패턴(169)를 노출하는 제2브릿지콘택홀(540)을 제1보호막(150)에 형성한다.

- [0109] 다음으로, 제1보호막(150) 상에 금속물질을 증착하고, 그 후에 마스크공정을 진행하여 연결전극(180)과 제4스토리지전극(181)을 형성한다.

- [0110] 연결전극(180)은 제1연결콘택홀(560)을 통해 드레인전극(163)과 접촉하게 된다.

- [0111] 제4스토리지전극(181)은 제2브릿지콘택홀(540)을 통해 브릿지전극(169)과 접촉하게 된다. 이에 따라, 제4스토리지전극(181)은 브릿지전극(169)을 통해 제2스토리지전극(144)과 전기적으로 연결될 수 있게 된다.

- [0112] 전술한 바와 같은 공정을 통해, 제1 내지 4스토리지전극(121, 144, 167, 181)을 형성하여 3중 구조의 스토리지커패시터(Cst)를 구성할 수 있게 된다.

- [0113] 다음으로, 도 5g에 도시한 바와 같이, 연결전극(180) 상에 제2보호막(190)을 형성한다. 이와 같은 제2보호막(190)은 연결전극(180)이 형성된 기판(110)의 단차를 완화하기 위한 평탄화막으로서 기능할 수 있다. 제2보호막(190)은 예를 들면 유기절연물질로 이루어질 수 있다.

- [0114] 다음으로, 제2보호막(190)에 대해 마스크공정을 진행하여, 연결전극(180)을 노출하는 제2연결콘택홀(570)을 형성한다.

- [0115] 다음으로, 제2보호막(190) 상에 화소영역(P) 별로 제1전극(210)을 형성한다.

- [0116] 다음으로, 제1전극(210) 상에 화소영역(P)의 경계를 따라 뱅크층(220)을 형성한다. 뱅크층(220)에는 제1전극(210)을 노출하는 개구부(221)가 형성될 수 있다.

- [0117] 다음으로, 제1전극(210) 상에 개구부(221)를 따라 유기발광층(230)을 형성한다. 다음으로, 유기발광층(230) 상에 제2전극(240)을 형성한다.

- [0118] 제1 및 2전극(210, 240)과 이들 사이의 유기발광층(230)은 유기발광다이오드(OD)를 구성하게 된다.

- [0119] 전술한 바와 같은 공정을 통해, 유기발광소자표시장치용 어레이기판이 형성될 수 있다.

- [0120] 한편, 전술한 바와 같이 제조된 어레이기판과 대향기판으로서 예를 들면 인캡슐레이션기판을 합착하여, 유기발광소자표시장치를 완성할 수 있다.

- [0121] 전술한 바와 같이, 본 발명의 실시예에 따르면 제1 내지 4스토리지전극을 구성하여 3중 구조의 스토리지 커패시터를 구현할 수 있게 된다. 이에 따라, 면적 대비 스토리지 용량이 향상될 수 있게 된다. 따라서, 종래에 비해, 스토리지영역이 차지하는 면적이 감소될 수 있게 되어, 결과적으로 개구율이 향상될 수 있게 된다.

- [0122] 전술한 본 발명의 실시예는 본 발명의 일예로서, 본 발명의 정신에 포함되는 범위 내에서 자유로운 변형이 가능하다. 따라서, 본 발명은, 첨부된 특허청구범위 및 이와 등가되는 범위 내에서의 본 발명의 변형을 포함한다.

### 부호의 설명

- |                        |               |

|------------------------|---------------|

| [0123] 100: 유기발광소자표시장치 | 120: 반도체패턴    |

| 121: 제1스토리지전극          | 140: 게이트배선    |

| 142: 게이트전극             | 144: 제2스토리지전극 |

| 145: 발광제어배선            | 160: 데이터배선    |

| 161: 소스전극              | 163: 드레인전극    |

| 165: 전원배선              | 167: 제3스토리지전극 |

| 169: 브릿지전극             | 180: 연결전극     |

| 181: 제4스토리지전극          | 510: 소스콘택홀    |

| 520: 드레인콘택홀            | 530: 제1브릿지콘택홀 |

| 540: 제2브릿지콘택홀          | 550: 게이트콘택홀   |

| 560: 제1연결콘택홀           | 570: 제2연결콘택홀  |

| Ts: 스위칭트랜지스터           | Td: 구동트랜지스터]  |

| Te: 발광제어트랜지스터          |               |

## 도면

## 도면1

100

## 도면2

## 도면3

## 도면4

## 도면5a

## 도면5b

## 도면5c

제 1 식각

## 도면5d

제 2 식각

## 도면5e

## 도면5f

## 도면5g

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | OLED显示装置及其制造方法                                 |         |            |

| 公开(公告)号        | <a href="#">KR101948171B1</a>                  | 公开(公告)日 | 2019-02-15 |

| 申请号            | KR1020120078863                                | 申请日     | 2012-07-19 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                       |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                      |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                      |         |            |

| [标]发明人         | 정영기<br>조성필<br>신동채<br>정인상                       |         |            |

| 发明人            | 정영기<br>조성필<br>신동채<br>정인상                       |         |            |

| IPC分类号         | H01L51/50 H01L29/786 H05B33/10                 |         |            |

| CPC分类号         | H01L27/124 H01L27/1255 H01L27/3265 H01L27/3274 |         |            |

| 审查员(译)         | 朴贞根                                            |         |            |

| 其他公开文献         | KR1020140013166A                               |         |            |

| 外部链接           | <a href="#">Espacenet</a>                      |         |            |

**摘要(译)**

根据本发明的一个方面，提供了一种半导体器件，包括：第一存储电极，该第一存储电极由在基板上的半导体图案形成，与该半导体图案相同的材料并且掺杂有杂质离子；栅绝缘膜形成在半导体图案和第一存储电极上；栅绝缘层上的第二存储电极，对应于第一存储电极并由第一导电层形成的第二存储电极，对应于半导体图案的沟道区并包括第一导电层的多层栅电极；层间绝缘膜形成在第二存储电极和栅电极上；源电极和漏电极连接到半导体图案的源区和漏区，第三存储电极对应于第三存储电极并电连接到第一存储电极；第一钝化层形成在源电极，漏电极和第三存储电极上；连接电极，其连接到第一钝化层上的漏极，第四存储电极，其对应于第三存储电极并电连接到第二存储电极；提供一种有机发光二极管显示装置，该有机发光二极管显示装置包括连接至连接电极的有机发光二极管。