(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2019-0069730

(43) 공개일자 2019년06월20일

(51) 국제특허분류(Int. Cl.)

*H01L 27/32* (2006.01)

(52) CPC특허분류

*H01L 27/3211* (2013.01)

*H01L 27/3246* (2013.01)

(21) 출원번호 10-2017-0169932

(22) 출원일자 2017년12월12일

심사청구일자 없음

(71) 출원인

엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

송은지

경기도 파주시 월롱면 엘지로 245

김준동

경기도 파주시 월롱면 엘지로 245

(74) 대리인

박영복

전체 청구항 수 : 총 4 항

(54) 발명의 명칭 OLED 표시 패널

### (57) 요 약

본 발명은 화소 어레이 내에서 동일 칼라 서브 화소 간 휘도 편차를 최소화 하기 위한 OLED 표시 패널에 관한 것으로, TRD 구조를 갖는 OLED 표시 장치에 있어서, 인접한 3개의 R, G, B 서브 화소들이 하나의 단위 화소를 구성하도록 제 1 방향으로 배치되는 복수개의 R, G, B 서브 화소들과, 각 단위 화소의 R- 서브 화소와 G-서브 화소 사이에 하나의 데이터 라인이 제 2 방향으로 배열되어 단위 화소를 각 단위 화소를 구동하도록 구성되는 복수개의 데이터 라인과, 각 데이터 라인에 연결되고 상기 제 1 방향으로 배열되어 각 단위 화소 별로 각 서브 화소에 데이터 전압을 공급하는 복수개의 보조 데이터 라인을 구비한 것이다.

### 대 표 도 - 도4

(52) CPC특허분류

**H01L 27/3276** (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

TRD 구조를 갖는 OLED 표시 장치에 있어서,

인접한 3개의 R, G, B 서브 화소들이 하나의 단위 화소를 구성하도록 제 1 방향으로 배치되는 복수개의 R, G, B 서브 화소들;

각 단위 화소의 R- 서브 화소와 G-서브 화소 사이에 하나의 데이터 라인이 제 2 방향으로 배열되어 단위 화소를 구동하도록 구성되는 복수개의 데이터 라인; 그리고,

각 데이터 라인에 연결되고 상기 제 1 방향으로 배열되어 각 단위 화소 별로 각 서브 화소에 데이터 전압을 공급하는 복수개의 보조 데이터 라인을 구비한 OLED 표시 패널.

#### 청구항 2

제 1 항에 있어서,

상기 복수개의 데이터 라인은, 제 1 내지 제 4 단위 화소들을 각각 구동하기 위한 제 1 내지 제 4 데이터 라인들을 구비하고,

상기 복수개의 보조 데이터 라인은,

상기 제 1 데이터 라인에 연결되고 상기 제 1 방향으로 배열되어 제 1 단위 화소의 서브 화소들에 데이터 전압을 공급하는 제 1 보조 데이터 라인과,

상기 제 2 데이터 라인에 연결되고 상기 제 1 방향으로 배열되어 제 2 단위 화소의 서브 화소들에 데이터 전압을 공급하는 제 2 보조 데이터 라인과,

상기 제 3 데이터 라인에 연결되고 상기 제 1 방향으로 배열되어 제 3 단위 화소의 서브 화소들에 데이터 전압을 공급하는 제 3 보조 데이터 라인과,

상기 제 4 데이터 라인에 연결되고 상기 제 1 방향으로 배열되어 제 4 단위 화소의 서브 화소들에 데이터 전압을 공급하는 제 4 보조 데이터 라인을 구비하는 OLED 표시 패널.

#### 청구항 3

제 1 항에 있어서,

제 1 단위 화소와 제 2 단위 화소 사이에 상기 제 2 방향으로 배열되는 제 1 정전압 라인과,

제 3 단위 화소와 제 4 단위 화소 사이에 상기 제 2 방향으로 배열되는 제 2 정전압 라인과,

상기 복수개의 R, G, B 서브 화소들의 일측에 상기 제 2 방향으로 배열되는 초기화 라인과,

상기 제 2 단위 화소와 상기 제 3 단위 화소 사이에 상기 제 2 방향으로 배열되는 기준 전압 라인을 더 포함하는 OLED 표시 패널.

#### 청구항 4

제 3 항에 있어서,

상기 제 1 및 제 2 정전압 라인에 연결되고 상기 제 1 방향으로 배열되어 상기 복수개의 R, G, B 서브 화소들에 정전압을 공급하는 보조 정전압 라인과,

상기 기준 전압 라인에 연결되고 상기 제 1 방향으로 배열되어 상기 복수개의 R, G, B 서브 화소들에 기준 전압을 공급하는 보조 기준 전압 라인과,

상기 초기화 라인에 연결되고 상기 제 1 방향으로 배열되어 상기 복수개의 R, G, B 서브 화소들에 초기화 전압

을 공급하는 보조 초기화 라인을 더 구비하는 OLED 표시 패널.

## 발명의 설명

### 기술 분야

[0001]

본 발명은 OLED 표시 패널에 관한 것으로, 특히 화소 어레이 내에서 동일 칼라 서브 화소 간 휘도 편차를 저감하기 위한 OLED 표시 패널에 관한 것이다.

### 배경 기술

[0002]

최근 디지털 데이터를 이용하여 영상을 표시하는 평판 표시 장치로는 액정을 이용한 액정 표시 장치(Liquid Crystal Display; LCD), 유기 발광 다이오드(Organic Light Emitting Diode; 이하 OLED)를 이용한 OLED 표시 장치 등이 대표적이다.

[0003]

이들 중 OLED 표시 장치는 전자와 정공의 재결합으로 유기 발광층을 발광시키는 자발광 소자로 휘도가 높고 구동 전압이 낮으며, 응답 시간이 수 마이크로 초( $\mu$ s) 정도로 동화상 구현이 쉽고, 시야각 제한이 없으며 저온에서도 안정적이라는 장점이 있으며, 박막화가 가능하여 차세대 표시 장치로 기대되고 있다.

[0004]

OLED 표시 패널을 구성하는 다수의 화소 각각은 애노드 및 캐소드 사이의 유기 발광층으로 구성된 OLED 소자와, OLED 소자를 독립적으로 구동하는 화소 회로를 구비한다. 상기 화소 회로는 데이터 전압을 스토리지 커패시터에 공급하는 스위칭 트랜지스터(Thin Film Transistor; TFT)와, 스토리지 커패시터에 충전된 구동 전압에 따라 구동 전류를 제어하여 OLED 소자로 공급하는 구동 트랜지스터 등을 포함하고, OLED 소자는 구동 전류에 비례하는 광을 발생한다.

[0005]

이러한 구조의 OLED 표시 패널에서 특히 구동 트랜지스터는 OLED 소자에 흐르는 전류의 양을 조절하여 영상의 계조를 표시하도록 하는 것으로서 화상 품질에 중요한 역할을 한다.

[0006]

그러나, 하나의 표시 패널 내에서도, 공정 편차와 경시 변화의 이유로, 각 화소 간 구동 트랜지스터의 전기적 특성 편차, 즉 문턱전압( $V_{th}$ ) 및 전자 이동도(mobility)의 편차가 발생하며, 각 OLED 소자들에 흐르는 전류가 일정하지 않아 원하는 계조를 구현하지 못하는 문제가 발생하게 된다.

[0007]

이를 해결하기 위하여, OLED 표시 장치는 각 화소의 구동 트랜지스터의 특성을 센싱하고 센싱값을 이용하여 각 화소에 공급될 데이터를 보상하는 방법을 이용하고 있다.

[0008]

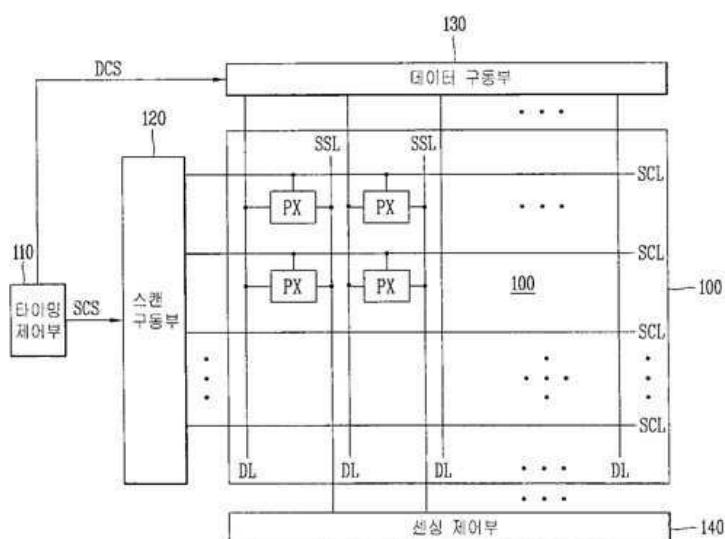

도 1은 일반적인 OLED 표시 장치를 간략히 나타내는 구성도이다.

[0009]

일반적인 OLED 표시 장치는, 도 1에 도시한 바와 같이, 복수의 화소(PX)가 정의되는 OLED 표시 패널(100)과, 상기 OLED 표시 패널(100)과 연결되는 각종 제어부 및 구동부(110 ~ 140)를 포함한다.

[0010]

상기 OLED 표시 패널(100)은 유기기판 또는 플라스틱 기판상에 서로 교차되도록 복수의 스캔 라인(SCL) 및 데이터 라인(DL)이 배치되고, 상기 스캔 라인(SCL) 및 데이터 라인(DL)이 교차하는 지점에 각각 적, 녹 및 청에 해당하는 계조를 표시하는 서브-화소(PX)들이 정의된다. 또한, 각 서브-화소(PX)들은 문턱 전압( $V_{th}$ ) 및 전자 이동도( $\mu$ )를 센싱하기 위한 센싱 라인(SSL)과 연결되어 있으며, 도시되어 있지 않지만 상기 OLED 표시 패널(100)에는 전원 전압(EVDD) 및 접지 전압(ELVSS)을 공급하기 위한 각종 라인들이 더 형성된다.

[0011]

상기 스캔 라인(SCL)들은 스캔 신호(SCAN)를 출력하는 스캔 구동부(120)와 연결되고, 상기 데이터 라인(DL)들은 데이터 전압(Vdata)을 출력하는 데이터 구동부(130)와 연결되어 있다.

[0012]

또한, 상기 OLED 표시 패널(100)에 형성되는 센싱 라인(SSL)은 화소(PX)에 흐르는 싱크 전류를 통해 구동 박막 트랜지스터의 전기적 특성을 센싱하는 센싱 제어부(140)와 연결되어 있다.

[0013]

타이밍 제어부(110)는 외부로부터 인가되는 영상 데이터와, 클럭 신호, 수직 및 수평 동기신호 등의 타이밍 신호를 인가 받아 스캔 제어신호(GCS), 데이터 제어신호(DCS) 및 센싱 구동 제어신호(SCS) 등의 제어신호를 생성한다.

[0014]

상기 스캔 구동부(120)는 상기 타이밍 제어부(110)로부터 스캔 제어신호(SCS)에 대응하여 각 스캔 라인(SCL)에 스캔 신호(SCAN)을 순차적으로 인가한다. 이러한 스캔 구동부(120)는 통상의 소프트 레지스터로 구현될 수 있다.

- [0015] 상기 데이터 구동부(130)는 상기 타이밍 제어부(110)로부터 인가되는 디지털 파형의 영상 신호(RGB)를 입력 받아, 화소(PX)가 처리할 수 있는 계조값을 갖는 아날로그 전압형태의 데이터 전압(Vdata)으로 변환하고, 또한 입력되는 데이터 제어신호(DCS)에 대응하여 데이터 전압(Vdata)을 데이터 라인(DL)을 통해 각 서브-화소(PX)에 공급한다.

- [0016] 상기 센싱 제어부(140)는 상기 타이밍 제어부(110)의 제어에 따라 OLED 표시 장치의 전원 온/오프 직후 또는 기타 사용자에 의해 지정된 시점에 구동 박막트랜지스터(DR-TFT)의 문턱전압(Vth) 및 이동도 특성을 외부보상 방식 및 내부보상 방식을 병행하여 센싱하고, 센싱된 결과를 데이터 전압(Vdata)에 반영하여 구동 박막 트랜지스터(DR-TFT)특성 편차를 보상하는 역할을 한다.

- [0017] 일례로서, 정상 서브-화소(PX)에서 구동 트랜지스터의 출력 전류값은 구동 트랜지스터의 문턱 전압 및 전자 이동도 특성이 반영된다. 이에 따라 열화가 발생되면 구동 트랜지스터에 의한 전류값이 달라지게 되고 그 전류를 싱크하여 문턱전압 및 이동도의 변동값을 측정할 수 있다. 따라서, 상기 센싱 제어부(140)는 측정된 결과를 데이터 전압(Vdata)에 반영되도록 함으로서 구동 트랜지스터의 특성변화를 보상하게 된다.

- [0018] 이와 같은 OLED 표시 패널(100)에서, 화소 영역을 늘리기 위해 데이터 라인 수를 줄이고, 하나의 데이터 라인으로 3개의 서브 화소를 구동하는 TRD(Triple rate driving) 구조의 OLED 표시 패널이 제안되었다.

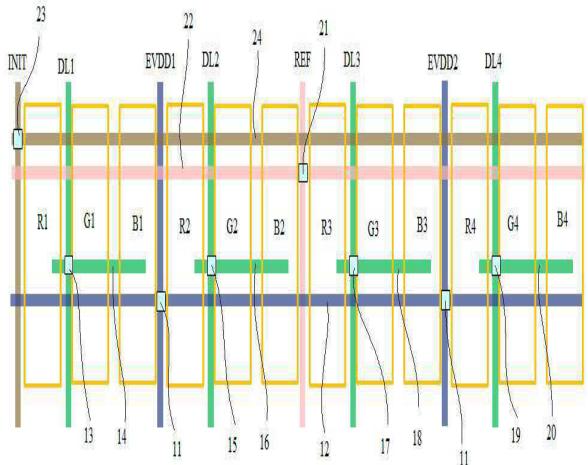

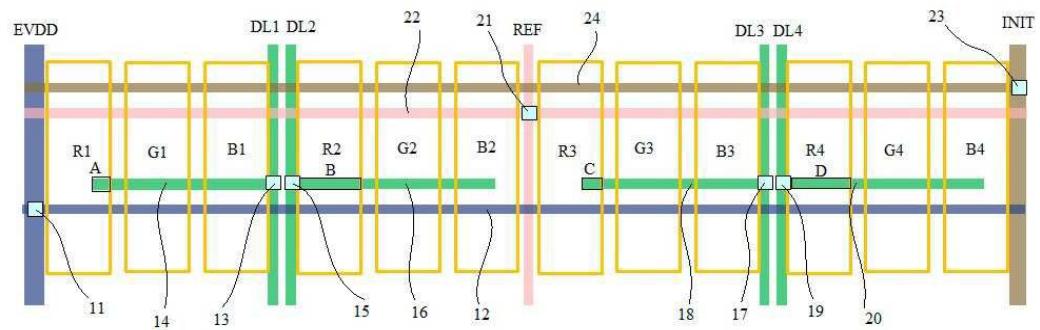

- [0019] 도 2는 종래의 TRD 구조의 OLED 표시 패널의 모식도이다.

- [0020] 종래의 TRD 구조의 OLED 표시 패널은, 도 2에 도시한 바와 같이, 복수개의 R, G, B 서브 화소(R1, G1, B1, R2, G2, B2, R3, G3, B3, R4, G4, B4)가 수평 방향으로 배치된다. 인접한 3개의 R, G, B 서브 화소((R1, G1, B1), (R2, G2, B2), (R3, G3, B3), 또는 (R4, G4, B4))가 하나의 단위 화소를 구성한다.

- [0021] 4개의 단위 화소를 기준으로 하나의 정전압 라인(EVDD)과, 하나의 기준 전압 라인(REF) 및 하나의 초기화 라인(INIT)가 각각 수직 방향으로 배열되고, 각 단위 화소당 하나의 데이터 라인(DL1, DL2, DL3, DL4)이 수직 방향으로 배열된다.

- [0022] 즉, 4개의 단위 화소를 기준으로, 정전압 라인(EVDD)이 맨 좌측에 수직 방향으로 배치되고, 초기화 라인(INIT)이 맨 우측에 수직 방향으로 배치되며, 기준 전압 라인(REF)은 제 2 단위 화소((R2, G2, B2)와 제 3 단위 화소(R3, G3, B3) 사이에 수직 방향으로 배열된다.

- [0023] 그리고, 제 1 단위 화소(R1, G1, B1)와 제 2 단위 화소(R2, G2, B2) 사이에 2개의 데이터 라인(DL1, DL2)이 수직 방향으로 배치되고, 제 3 단위 화소(R3, G3, B3)와 제 4 단위 화소(R4, G4, B4) 사이에 2개의 데이터 라인(DL3, DL4)이 수직 방향으로 배치된다.

- [0024] 또한, 제 1 콘택 홀(11)을 통해 상기 정전압 라인(EVDD)에 연결되고 수평 방향으로 배열되어 4개의 단위 화소의 각 서브 화소에 정전압을 공급하는 보조 정전압 라인(12)을 더 구비한다.

- [0025] 제 2 내지 제 5 콘택 홀(13, 15, 17, 19)을 통해 각 데이터 라인(DL1, DL2, DL3, DL4)에 연결되고 수평 방향으로 배열되어 각 단위 화소 별로 각 서브 화소에 데이터 전압을 공급하는 보조 데이터 라인(14, 16, 18, 20)을 더 구비한다.

- [0026] 제 6 콘택 홀(21)을 통해 상기 기준 전압 라인(REF)에 연결되고 수평 방향으로 배열되어 4개의 단위 화소의 각 서브 화소에 기준 전압을 공급하는 보조 기준 전압 라인(22)을 더 구비한다.

- [0027] 제 7 콘택 홀(23)을 통해 상기 초기화 라인(INIT)에 연결되고 수평 방향으로 배열되어 4개의 단위 화소의 각 서브 화소에 초기화 전압을 공급하는 보조 초기화 라인(24)을 더 구비한다.

- [0028] 여기서, 상기 기준 전압 라인(REF) 및 상기 보조 기준 전압 라인(22)과 상기 초기화 라인(INIT) 및 상기 보조 초기화 라인(24)은, 상기에서 언급한 바와 같이, 각 서브 화소들의 문턱 전압(Vth) 및 전자 이동도( $\mu$ )를 센싱하기 위해 사용된다.

- [0029] 이와 같이 구성되는 종래의 TRD 구조의 OLED 표시 패널에 있어서는 다음과 같은 문제점이 있다.

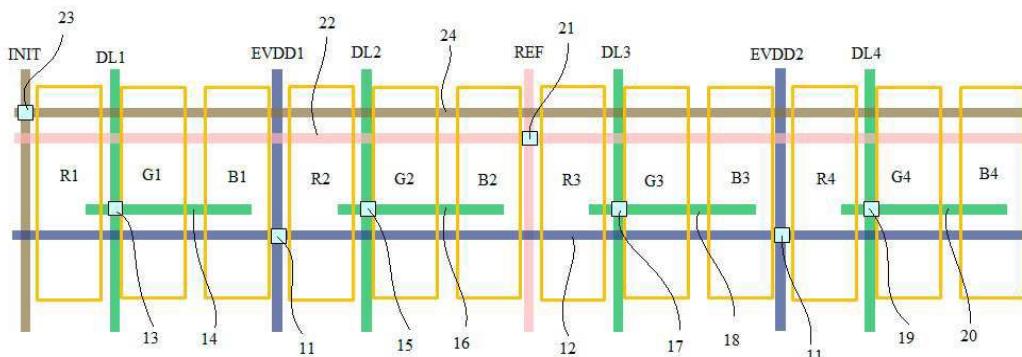

- [0030] 도 3은 종래의 TRD 구조 OLED 표시 패널의 휘도 편차를 설명하기 위한 모식도이다.

- [0031] 도 2에서 설명한 바와 같이, TRD 구조 OLED 표시 패널은 제 1 단위 화소(R1, G1, B1)와 제 2 단위 화소(R2, G2, B2) 사이에 2개의 데이터 라인(DL1, DL2)이 수직 방향으로 배치되고, 제 3 단위 화소(R3, G3, B3)와 제 4 단위 화소(R4, G4, B4) 사이에 2개의 데이터 라인(DL3, DL4)이 수직 방향으로 배치되며, 제 2 내지 제 5 콘택

홀(13, 15, 17, 19)을 통해 각 데이터 라인(DL1, DL2, DL3, DL4)에 연결되도록 수평 방향으로 복수개의 보조 데이터 라인(14, 16, 18, 20)이 배치되어 각 단위 화소의 각 서브 화소에 데이터 전압을 공급한다.

[0032] 도 3에서는 각 단위 화소의 R 서브 화소들(R1, R2, R3, R4)과 상기 보조 데이터 라인(14, 16, 18, 20)이 중첩되는 면적을 도시하였다.

[0033] 상기 보조 정전압 라인(12), 상기 보조 기준 전압 라인(22) 및 상기 보조 초기화 라인(24)은 모든 서브 화소와 중첩되는 면적이 거의 동일하다.

[0034] 그러나, 각 단위 화소별로 동일 칼라 서브 화소들 간에 상기 보조 데이터 라인(14, 16, 18, 20)과 서브 화소가 중첩되는 면적이 다르다. 이로 인하여, 각 단위 화소별로 동일 칼라 서브 화소들 간에 기생 커패시턴스가 다르므로 휘도 편차가 발생한다.

[0035] 즉, 제 1 단위 화소(R1, G1, B1)의 R 서브 화소(R1)와 상기 보조 데이터 라인(14)이 중첩되는 면적(A)과 제 3 단위 화소(R3, G3, B3)의 R 서브 화소(R3)와 상기 보조 데이터 라인(18)이 중첩되는 면적(C)은 상대적으로 작고, 제 2 단위 화소(R2, G2, B2)의 R 서브 화소(R2)와 상기 보조 데이터 라인(16)이 중첩되는 면적(B)과 제 4 단위 화소(R4, G4, B4)의 R 서브 화소(R4)와 상기 보조 데이터 라인(20)이 중첩되는 면적(D)은 상대적으로 크다.

[0036] 마찬가지로, 제 2 단위 화소(R2, G2, B2)의 B 서브 화소(B2)와 상기 보조 데이터 라인(16)이 중첩되는 면적과 제 4 단위 화소(R4, G4, B4)의 B 서브 화소(B4)와 상기 보조 데이터 라인(20)이 중첩되는 면적은 상대적으로 작고, 제 1 단위 화소(R1, G1, B1)의 B 서브 화소(B1)와 상기 보조 데이터 라인(14)이 중첩되는 면적과 제 3 단위 화소(R3, G3, B3)의 B 서브 화소(B3)와 상기 보조 데이터 라인(18)이 중첩되는 면적은 상대적으로 크다.

[0037] 이와 같이, 동일 칼라 서브 화소들 간에 상기 보조 데이터 라인과 서브 화소가 중첩되는 면적 편차로 인하여 동일 칼라 서브 화소들 간에 휘도 편차가 발생하게 된다.

[0038] 즉, 9.7인치 QXGA급 해상도를 갖는 OLED 패널에서, 각 단위 화소의 R 서브 화소들(R1, R2, R3, R4)의 기생 커패시턴스 편차가 약 3.3fF 정도이고, 각 단위 화소의 R 서브 화소들(R1, R2, R3, R4)의 OLED 소자에 흐르는 전류 편차는 63 그레이 기준 26.8% 정도였다. 따라서, 동일 칼라 서브 화소들 간에 휘도 편차가 심하게 발생하였다.

## 발명의 내용

### 해결하려는 과제

[0039] 본 발명은 상기와 같은 종래의 문제점을 해결하기 위한 것으로, 화소 어레이 내에서 동일 칼라 서브 화소 간 휘도 편차를 최소화 할 수 있는 OLED 표시 패널을 제공하는데 그 목적이 있다.

### 과제의 해결 수단

[0040] 상기와 같은 목적을 달성하기 위한 본 발명에 따른 OLED 표시 패널은, TRD 구조를 갖는 OLED 표시 장치에 있어서, 인접한 3개의 R, G, B 서브 화소들이 하나의 단위 화소를 구성하도록 제 1 방향으로 배치되는 복수개의 R, G, B 서브 화소들과, 각 단위 화소의 R- 서브 화소와 G-서브 화소 사이에 하나의 데이터 라인이 제 2 방향으로 배열되어 각 단위 화소를 구동하도록 구성되는 복수개의 데이터 라인들과, 각 데이터 라인에 연결되고 상기 제 1 방향으로 배열되어 각 단위 화소 별로 각 서브 화소에 데이터 전압을 공급하는 복수개의 보조 데이터 라인들을 구비함에 그 특징이 있다.

[0041] 여기서, 제 1 단위 화소와 제 2 단위 화소 사이에 상기 제 2 방향으로 배열되는 제 1 정전압 라인과, 제 3 단위 화소와 제 4 단위 화소 사이에 상기 제 2 방향으로 배열되는 제 2 정전압 라인과, 상기 복수개의 R, G, B 서브 화소들의 일측에 상기 제 2 방향으로 배열되는 초기화 라인과, 상기 제 2 단위 화소와 상기 제 3 단위 화소 사이에 상기 제 2 방향으로 배열되는 기준 전압 라인과, 상기 제 1 및 제 2 정전압 라인에 연결되고 상기 제 1 방향으로 배열되어 상기 복수개의 R, G, B 서브 화소들에 정전압을 공급하는 보조 정전압 라인과, 상기 기준 전압 라인에 연결되고 상기 제 1 방향으로 배열되어 상기 복수개의 R, G, B 서브 화소들에 기준 전압을 공급하는 보조 기준 전압 라인과, 상기 초기화 라인에 연결되고 상기 제 1 방향으로 배열되어 상기 복수개의 R, G, B 서브 화소들에 초기화 전압을 공급하는 보조 초기화 라인을 더 구비함을 특징으로 한다.

## 발명의 효과

- [0042] 상기와 같은 특징을 갖는 본 발명에 따른 OLED 표시 패널에 있어서는 다음과 같은 효과가 있다.

- [0043] 즉, 인접한 3개의 R, G, B 서브 화소들이 하나의 단위 화소를 구성하도록 수평 방향으로 복수개의 R, G, B 서브 화소들을 배치하고, 각 단위 화소를 구동하기 위해, 각 단위 화소의 R-서브 화소와 G-서브 화소 사이에 수직 방향으로 복수개의 데이터 라인들을 배치하며, 각 데이터 라인에 연결되도록 각 단위 화소 별로 복수개의 보조 데이터 라인들을 수평 방향으로 배치하므로, 동일 칼라 서브 화소들 간에 휘도 편차가 최소화 되었다.

- [0044] 즉, 제 1 단위 화소(R1, G1, B1)의 R 서브 화소(R1)와 상기 보조 데이터 라인(14)이 중첩되는 면적(A)과, 제 2 단위 화소(R2, G2, B2)의 R 서브 화소(R2)와 상기 보조 데이터 라인(16)이 중첩되는 면적(A)과, 제 3 단위 화소(R3, G3, B3)의 R 서브 화소(R3)와 상기 보조 데이터 라인(18)이 중첩되는 면적(A)과, 제 4 단위 화소(R4, G4, B4)의 R 서브 화소(R4)와 상기 보조 데이터 라인(20)이 중첩되는 면적(A)들은 서로 동일하고, 제 1 단위 화소(R1, G1, B1)의 B 서브 화소(B1)와 상기 보조 데이터 라인(14)이 중첩되는 면적(B)과, 제 2 단위 화소(R2, G2, B2)의 B 서브 화소(B2)와 상기 보조 데이터 라인(16)이 중첩되는 면적(B)과, 제 3 단위 화소(R3, G3, B3)의 B 서브 화소(B3)와 상기 보조 데이터 라인(18)이 중첩되는 면적(B)과, 제 4 단위 화소(R4, G4, B4)의 B 서브 화소(B4)와 상기 보조 데이터 라인(20)이 중첩되는 면적(A)들은 서로 동일하며, 제 1 단위 화소(R1, G1, B1)의 G 서브 화소(G1)와 상기 보조 데이터 라인(14)이 중첩되는 면적과, 제 2 단위 화소(R2, G2, B2)의 G 서브 화소(G2)와 상기 보조 데이터 라인(16)이 중첩되는 면적과, 제 3 단위 화소(R3, G3, B3)의 G 서브 화소(G3)와 상기 보조 데이터 라인(18)이 중첩되는 면적과, 제 4 단위 화소(R4, G4, B4)의 G 서브 화소(G4)와 상기 보조 데이터 라인(20)이 중첩되는 면적들은 서로 동일하여, 동일 칼라 서브 화소들 간에 휘도 편차가 최소화 되었다.

- ### 도면의 간단한 설명

- [0045] 도 1은 일반적인 OLED 표시 장치를 간략히 나타내는 구성도

도 2는 종래의 TRD 구조의 OLED 표시 패널의 모식도

도 3은 종래의 TRD 구조 OLED 표시 패널의 휘도 편차를 설명하기 위한 모식도

도 4는 본 발명에 따른 TRD 구조의 OLED 표시 패널의 모식도

도 5는 본 발명에 따른 TRD 구조 OLED 표시 패널의 휘도 편차를 설명하기 위한 모식도

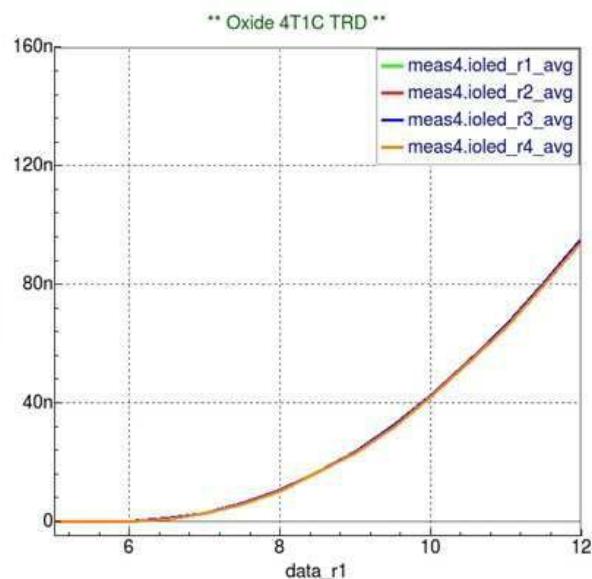

도 6은 종래의 TRD 구조의 OLED 표시 패널의 R 서브 화소들의 I-V 특성 그래프

도 7은 본 발명에 따른 TRD 구조의 OLED 표시 패널의 R 서브 화소들의 I-V 특성 그래프

- ### 발명을 실시하기 위한 구체적인 내용

- [0046] 상기와 같은 특징을 갖는 본 발명에 따른 TRD 구조의 OLED 표시 패널을 첨부된 도면을 참조하여 보다 상세히 설명하면 다음과 같다.

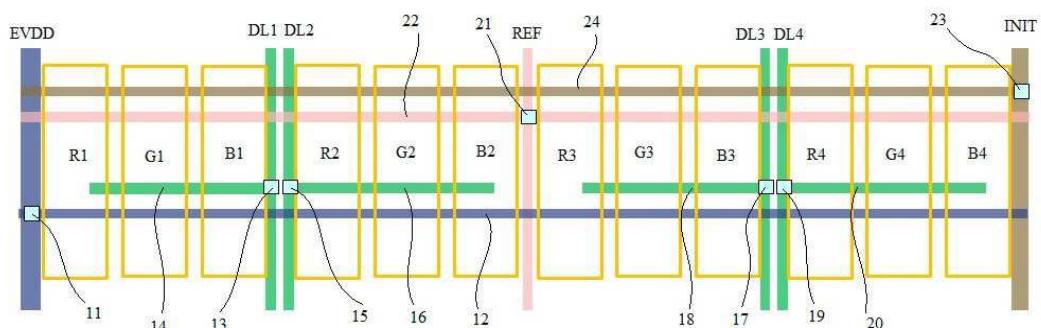

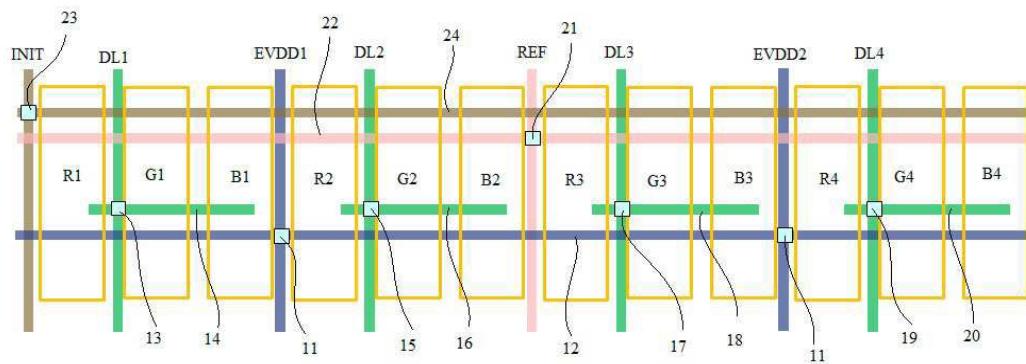

- [0047] 도 4는 본 발명에 따른 TRD 구조의 OLED 표시 패널의 모식도이다.

- [0048] 본 발명에 따른 TRD 구조의 OLED 표시 패널은, 도 4에 도시한 바와 같이, 복수개의 R, G, B 서브 화소(R1, G1, B1, R2, G2, B2, R3, G3, B3, R4, G4, B4)가 수평 방향으로 배치된다. 인접한 3개의 R, G, B 서브 화소((R1, G1, B1), (R2, G2, B2), (R3, G3, B3), 또는 (R4, G4, B4))가 하나의 단위 화소를 구성한다.

- [0049] 4개의 단위 화소를 기준으로 2개의 정전압 라인(EVDD1, EVDD2)과, 하나의 기준 전압 라인(REF) 및 하나의 초기화 라인(INIT)가 각각 수직 방향으로 배열되고, 각 단위 화소당 하나의 데이터 라인(DL1, DL2, DL3, DL4)이 수직 방향으로 배열된다.

- [0050] 즉, 4개의 단위 화소를 기준으로, 제 1 단위 화소(R1, G1, B1)와 제 2 단위 화소(R2, G2, B2) 사이에 제 1 정전압 라인(EVDD1)이 수직 방향으로 배열되고, 제 3 단위 화소(R3, G3, B3)와 제 4 단위 화소(R4, G4, B4) 사이에 제 2 정전압 라인(EVDD2)이 수직 방향으로 배열된다.

- [0051] 상기 초기화 라인(INIT)은 4개의 단위 화소를 기준으로 맨 좌측에 수직 방향으로 배열되며, 상기 기준 전압 라인(REF)은 제 2 단위 화소((R2, G2, B2)와 제 3 단위 화소(R3, G3, B3) 사이에 수직 방향으로 배열된다.

- [0052] 그리고, 각 단위 화소 내에 복수개의 데이터 라인(DL1, DL2, DL3, DL4)이 수직 방향으로 배열된다.

- [0053] 구체적으로, 제 1 단위 화소(R1, G1, B1)를 구동하기 위한 제 1 데이터 라인(DL1)은 제 1 단위 화소(R1, G1,

B1)의 R- 서브 화소(R1)와 G-서브 화소(G1) 사이에 수직 방향으로 배열되고, 제 2 단위 화소(R2, G2, B2)를 구동하기 위한 제 1 데이터 라인(DL2)은 제 2 단위 화소(R2, G2, B2)의 R- 서브 화소(R2)와 G-서브 화소(G2) 사이에 수직 방향으로 배열되며, 제 3 단위 화소(R3, G3, B3)를 구동하기 위한 제 3 데이터 라인(DL3)은 제 3 단위 화소(R3, G3, B3)의 R- 서브 화소(R3)와 G-서브 화소(G3) 사이에 수직 방향으로 배열되고, 제 4 단위 화소(R4, G4, B4)를 구동하기 위한 제 4 데이터 라인(DL4)은 제 4 단위 화소(R4, G4, B4)의 R- 서브 화소(R4)와 G-서브 화소(G4) 사이에 수직 방향으로 배열된다.

[0054] 또한, 2개의 제 1 콘택 훌(11)을 통해 상기 제 1 및 제 2 정전압 라인(EVDD1, EVDD2)에 연결되고 수평 방향으로 배열되어 4개의 단위 화소의 각 서브 화소에 정전압을 공급하는 보조 정전압 라인(12)을 더 구비한다.

[0055] 제 2 내지 제 5 콘택 훌(13, 15, 17, 19)을 통해 각 데이터 라인(DL1, DL2, DL3, DL4)에 연결되고 수평 방향으로 배열되어 각 단위 화소 별로 각 서브 화소에 데이터 전압을 공급하는 복수개의 보조 데이터 라인(14, 16, 18, 20)을 더 구비한다.

[0056] 즉, 상기 제 2 콘택 훌(13)을 통해 상기 제 1 단위 화소(R1, G1, B1)를 구동하기 위한 제 1 데이터 라인(DL1)에 연결되고 수평 방향으로 배열되어 제 1 단위 화소의 서브 화소들(R1, G1, B1)에 제 1 데이터 전압을 공급하는 제 1 보조 데이터 라인(14)과, 상기 제 3 콘택 훌(15)을 통해 상기 제 2 단위 화소(R2, G2, B2)를 구동하기 위한 제 2 데이터 라인(DL2)에 연결되고 수평 방향으로 배열되어 제 2 단위 화소의 서브 화소들(R2, G2, B2)에 제 2 데이터 전압을 공급하는 제 2 보조 데이터 라인(16)과, 상기 제 4 콘택 훌(17)을 통해 상기 제 3 단위 화소(R3, G3, B3)를 구동하기 위한 제 3 데이터 라인(DL3)에 연결되고 수평 방향으로 배열되어 제 3 단위 화소의 서브 화소들(R3, G3, B3)에 제 3 데이터 전압을 공급하는 제 3 보조 데이터 라인(18)과, 상기 제 5 콘택 훌(19)을 통해 상기 제 4 단위 화소(R4, G4, B4)를 구동하기 위한 제 4 데이터 라인(DL4)에 연결되고 수평 방향으로 배열되어 제 4 단위 화소의 서브 화소들(R4, G4, B4)에 제 4 데이터 전압을 공급하는 제 4 보조 데이터 라인(20)을 더 구비한다.

[0057] 제 6 콘택 훌(21)을 통해 상기 기준 전압 라인(REF)에 연결되고 수평 방향으로 배열되어 4개의 단위 화소의 각 서브 화소에 기준 전압을 공급하는 보조 기준 전압 라인(22)을 더 구비한다.

[0058] 제 7 콘택 훌(23)을 통해 상기 초기화 라인(INIT)에 연결되고 수평 방향으로 배열되어 4개의 단위 화소의 각 서브 화소에 초기화 전압을 공급하는 보조 초기화 라인(24)을 더 구비한다.

[0059] 여기서, 상기 기준 전압 라인(REF) 및 상기 보조 기준 전압 라인(22)과 상기 초기화 라인(INIT) 및 상기 보조 초기화 라인(24)은 상기에서 언급한 바와 같이, 각 서브 화소들의 문턱 전압(Vth) 및 전자 이동도(?)를 센싱하기 위해 사용된다.

[0060] 이와 같이 구성되는 본 발명에 따른 TRD 구조의 OLED 표시 패널에 있어서는 동일 칼라 서브 화소 간의 휘도 편차가 최소화 된다.

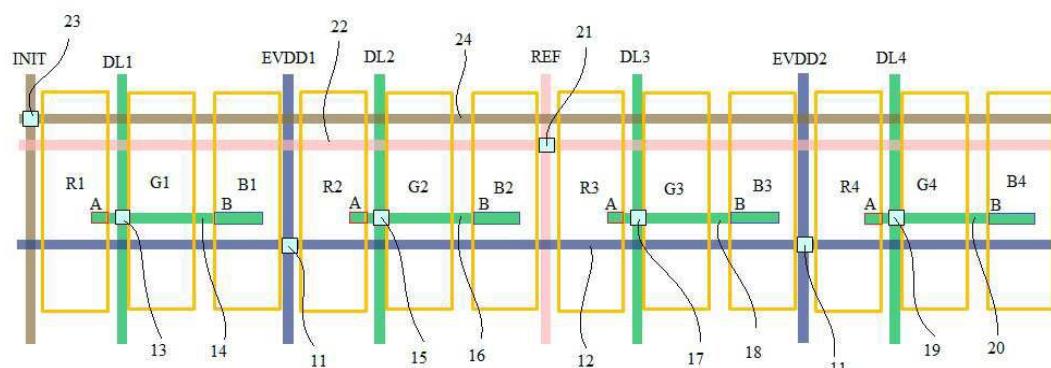

[0061] 도 5는 본 발명에 따른 TRD 구조 OLED 표시 패널의 휘도 편차를 설명하기 위한 모식도이다.

[0062] 도 4에서 설명한 바와 같이, 본 발명에 따른 TRD 구조 OLED 표시 패널은 제 1 단위 화소(R1, G1, B1)를 구동하기 위한 제 1 데이터 라인(DL1)은 제 1 단위 화소(R1, G1, B1)의 R- 서브 화소(R1)와 G-서브 화소(G1) 사이에 수직 방향으로 배열되고, 제 2 단위 화소(R2, G2, B2)를 구동하기 위한 제 1 데이터 라인(DL2)은 제 2 단위 화소(R2, G2, B2)의 R- 서브 화소(R2)와 G-서브 화소(G2) 사이에 수직 방향으로 배열되며, 제 3 단위 화소(R3, G3, B3)를 구동하기 위한 제 3 데이터 라인(DL3)은 제 3 단위 화소(R3, G3, B3)의 R- 서브 화소(R3)와 G-서브 화소(G3) 사이에 수직 방향으로 배열되고, 제 4 단위 화소(R4, G4, B4)를 구동하기 위한 제 4 데이터 라인(DL4)은 제 4 단위 화소(R4, G4, B4)의 R- 서브 화소(R4)와 G-서브 화소(G4) 사이에 수직 방향으로 배열된다.

[0063] 또한, 제 2 콘택 훌(13)을 통해 제 1 데이터 라인(DL1)에 연결되고 수평 방향으로 제 1 보조 데이터 라인(14)이 배치되어 제 1 단위 화소(R1, G1, B1)의 각 서브 화소(R1, G1, B1)에 데이터 전압을 공급하고, 제 3 콘택 훌(15)을 통해 제 2 데이터 라인(DL2)에 연결되고 수평 방향으로 제 2 보조 데이터 라인(16)이 배치되어 제 2 단위 화소(R2, G2, B2)의 각 서브 화소(R2, G2, B2)에 데이터 전압을 공급한다.

[0064] 제 4 콘택 훌(17)을 통해 제 3 데이터 라인(DL3)에 연결되고 수평 방향으로 제 3 보조 데이터 라인(18)이 배치되어 제 3 단위 화소(R3, G3, B3)의 각 서브 화소(R3, G3, B3)에 데이터 전압을 공급하고, 제 5 콘택 훌(19)을 통해 제 4 데이터 라인(DL4)에 연결되고 수평 방향으로 제 4 보조 데이터 라인(20)이 배치되어 제 4 단위 화소(R4, G4, B4)의 각 서브 화소(R4, G4, B4)에 데이터 전압을 공급한다.

- [0065] 여기서, 상기 기준 전압 라인(REF), 상기 초기화 라인(INIT), 각 데이터 라인(DL1, DL2, DL3, DL4), 및 각 보조 라인(14, 16, 18, 20, 22, 24)의 선폭은 종래와 같다. 그러나, 종래에는 4개의 단위 화소를 기준으로 하나의 정전압 라인(EVDD)을 배치하였으나, 전류/저항 드롭(IR drop)이 증가됨을 방지하기 위하여 본 발명에서는 4개의 단위 화소를 기준으로 2개의 정전압 라인(EVDD1, EVDD2)을 배치하였다.

- [0066] 종래에는 정전압 라인의 선폭을 약 9 $\mu$ m로 하였으나, 본 발명에는 2개의 정전압 라인(EVDD1, EVDD2)을 배치하는 대신에, 각 정전압 라인((EVDD1, EVDD2)의 선폭을 약 5 $\mu$ m로 하였다.

- [0067] 도 5에서는 각 단위 화소의 R 서브 화소들(R1, R2, R3, R4)과 상기 보조 데이터 라인(14, 16, 18, 20)이 중첩되는 면적이, 각 단위 화소의 B 서브 화소들(B1, B2, B3, B4)과 상기 보조 데이터 라인(14, 16, 18, 20)이 중첩되는 면적을 도시하였다.

- [0068] 상기 보조 정전압 라인(12), 상기 보조 기준 전압 라인(22) 및 상기 보조 초기화 라인(24)은 모든 서브 화소와 중첩되는 면적이 거의 동일하다.

- [0069] 또한, 각 단위 화소 별로 동일 칼라 서브 화소들 간에 상기 보조 데이터 라인(14, 16, 18, 20)과 서브 화소가 중첩되는 면적이 동일하게 된다. 이로 인하여, 각 단위 화소별로 동일 칼라 서브 화소들 간에 기생 커패시턴스가 동일하므로 휘도 편차가 최소화 된다.

- [0070] 즉, 제 1 단위 화소(R1, G1, B1)의 R 서브 화소(R1)와 상기 보조 데이터 라인(14)이 중첩되는 면적(A)과, 제 2 단위 화소(R2, G2, B2)의 R 서브 화소(R2)와 상기 보조 데이터 라인(16)이 중첩되는 면적(A)과, 제 3 단위 화소(R3, G3, B3)의 R 서브 화소(R3)와 상기 보조 데이터 라인(18)이 중첩되는 면적(A)과, 제 4 단위 화소(R4, G4, B4)의 R 서브 화소(R4)와 상기 보조 데이터 라인(20)이 중첩되는 면적(A)들은 서로 동일하다.

- [0071] 또한, 제 1 단위 화소(R1, G1, B1)의 B 서브 화소(B1)와 상기 보조 데이터 라인(14)이 중첩되는 면적(B)과, 제 2 단위 화소(R2, G2, B2)의 B 서브 화소(B2)와 상기 보조 데이터 라인(16)이 중첩되는 면적(B)과, 제 3 단위 화소(R3, G3, B3)의 B 서브 화소(B3)와 상기 보조 데이터 라인(18)이 중첩되는 면적(B)과, 제 4 단위 화소(R4, G4, B4)의 B 서브 화소(B4)와 상기 보조 데이터 라인(20)이 중첩되는 면적(A)들은 서로 동일하다.

- [0072] 물론, 제 1 단위 화소(R1, G1, B1)의 G 서브 화소(G1)와 상기 보조 데이터 라인(14)이 중첩되는 면적과, 제 2 단위 화소(R2, G2, B2)의 G 서브 화소(G2)와 상기 보조 데이터 라인(16)이 중첩되는 면적과, 제 3 단위 화소(R3, G3, B3)의 G 서브 화소(G3)와 상기 보조 데이터 라인(18)이 중첩되는 면적과, 제 4 단위 화소(R4, G4, B4)의 G 서브 화소(G4)와 상기 보조 데이터 라인(20)이 중첩되는 면적들은 서로 동일하다.

- [0073] 이와 같이, 동일 칼라 서브 화소들 간에 상기 보조 데이터 라인과 서브 화소가 중첩되는 면적이 서로 동일하므로 동일 칼라 서브 화소들 간에 휘도 편차가 최소화 된다.

- [0074] 즉, 9.7인치 QXGA급 해상도를 갖는 OLED 패널에서, 각 단위 화소의 R 서브 화소들(R1, R2, R3, R4)의 기생 커패시턴스 편차가 약 0.2fF 정도이고, 각 단위 화소의 R 서브 화소들(R1, R2, R3, R4)의 OLED 소자에 흐르는 전류 편차는 63 그레이 기준 1.1% 정도였다. 따라서, 동일 칼라 서브 화소들 간에 휘도 편차가 최소화 된다.

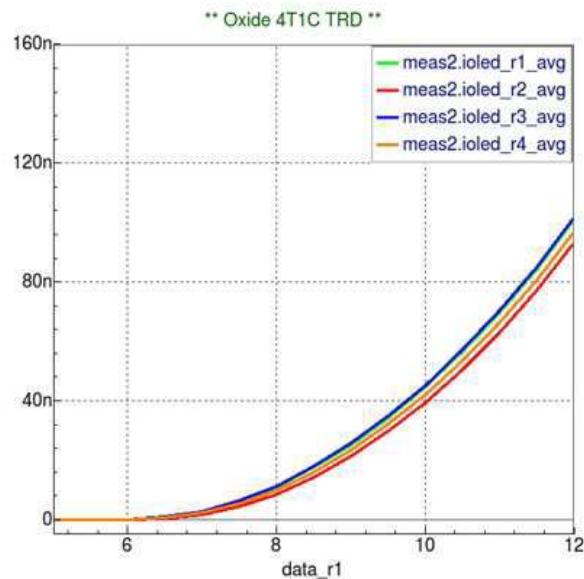

- [0075] 도 6는 종래의 TRD 구조의 OLED 표시 패널의 R 서브 화소들의 I-V 특성 그래프이고, 도 7는 본 발명에 따른 TRD 구조의 OLED 표시 패널의 R 서브 화소들의 I-V 특성 그래프이다.

- [0076] 도 6에 도시한 바와 같이, 종래의 TRD 구조의 OLED 표시 패널은 각 단위 화소의 R 서브 화소들(R1, R2, R3, R4)의 기생 커패시턴스 편차가 약 3.3fF 정도이고, 각 단위 화소의 R 서브 화소들(R1, R2, R3, R4)의 OLED 소자에 흐르는 전류 편차는 63 그레이 기준 26.8% 정도이므로, 각 단위 화소의 R 서브 화소들(R1, R2, R3, R4)에 동일 데이터 전압을 인가하더라도 각 단위 화소의 R 서브 화소들(R1, R2, R3, R4)의 OLED 소자에 흐르는 전류가 다르게 나타났다. 따라서, 동일 칼라 서브 화소들 간에 휘도 편차가 심하게 발생하였다.

- [0077] 반면, 도 7에 도시한 바와 같이, 본 발명에 따른 TRD 구조의 OLED 표시 패널은 각 단위 화소의 R 서브 화소들(R1, R2, R3, R4)의 기생 커패시턴스 편차가 약 0.2fF 정도이고, 각 단위 화소의 R 서브 화소들(R1, R2, R3, R4)의 OLED 소자에 흐르는 전류 편차가 1.1% 정도이므로, 각 단위 화소의 R 서브 화소들(R1, R2, R3, R4)에 동일 데이터 전압을 인가하면 각 단위 화소의 R 서브 화소들(R1, R2, R3, R4)의 OLED 소자에 흐르는 전류가 거의 비슷하였다. 따라서, 동일 칼라 서브 화소들 간에 휘도 편차가 최소화 된다.

- [0078] 이상 설명한 내용을 통해 당업자라면 본 발명의 기술사항을 일탈하지 아니하는 범위에서 다양한 변경 및 수정이 가능함을 알 수 있을 것이다. 따라서, 본 발명의 기술적 범위는 명세서의 상세한 설명에 기재된 내용으로 한정

되는 것이 아니라 특히 청구의 범위에 의해 정하여져야만 할 것이다.

### 부호의 설명

[0079] DL1, DL2, DL3, DL4: 데이터 라인

EVDD1, EVDD2: 정전압 라인

REF: 기준 전압 라인

INIT: 초기화 라인

11, 13, 15, 17, 19, 21, 23: 콘택 홀

12: 보조 정전압 라인

14, 16, 18, 20: 보조 데이터 라인

22: 보조 기준 전압 라인

24: 보조 초기화 라인

### 도면

#### 도면1

#### 도면2

**도면3****도면4****도면5**

## 도면6

## 도면7

|                |                                     |         |            |

|----------------|-------------------------------------|---------|------------|

| 专利名称(译)        | OLED显示屏                             |         |            |

| 公开(公告)号        | <a href="#">KR1020190069730A</a>    | 公开(公告)日 | 2019-06-20 |

| 申请号            | KR1020170169932                     | 申请日     | 2017-12-12 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                            |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                           |         |            |

| [标]发明人         | 송은지<br>김준동                          |         |            |

| 发明人            | 송은지<br>김준동                          |         |            |

| IPC分类号         | H01L27/32                           |         |            |

| CPC分类号         | H01L27/3211 H01L27/3246 H01L27/3276 |         |            |

| 代理人(译)         | Bakyoungbok                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>           |         |            |

### 摘要(译)

本发明涉及一种用于使像素阵列中的相同颜色的子像素之间的亮度变化最小的OLED显示面板，在具有TRD结构的OLED显示装置中，三个相邻的R，G和B子像素具有一个单位像素。一个数据线在第二方向上布置在沿第一方向布置的多个R，G和B子像素之间，并且每个单位像素的R子像素和G子像素形成单位像素。提供多条数据线和多条辅助数据线，多条数据线被配置为驱动每个单位像素，多条辅助数据线被连接到每条数据线并沿第一方向布置，并为每个单位像素向每个子像素提供数据电压。