# (19) 대한민국특허청(KR)(12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

**H01L 27/32** (2006.01) **H01L 51/52** (2006.01)

(52) CPC특허분류

**H01L 27/3258** (2013.01) **H01L 27/3211** (2013.01)

(21) 출원번호 10-2016-0059060

(22) 출원일자 2016년05월13일

심사청구일자 없음

(11) 공개번호 10-2017-0128000

(43) 공개일자 2017년11월22일

(71) 출원인

#### 엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

### 송창욱

서울특별시 송파구 충민로6길 14, 603-404 (장지 동, 송파파인타운6단지)

#### 강임국

경기도 파주시 교하로 70, 307동 1302호 (목동동, 산내마을3단지아파트)

#### 박상무

경기도 고양시 일산동구 위시티4로 46, 211동 80 2호 (식사동, 위시티일산자이2단지아파트)

(74) 대리인

특허법인네이트

전체 청구항 수 : 총 11 항

#### (54) 발명의 명칭 유기발광표시장치

#### (57) 요 약

본 발명은, 백색 화소영역과 인접한 컬러 화소영역의 제 1 전극(애노드)이 화소영역의 모서리에서 돌출부를 갖는 유기발광표시장치를 제공한다.

따라서, 제 1 전국이 뱅크층에 의해 완전히 덮이고 제 1 전국과 제 2 전국(캐소드) 간 전기적 쇼트 문제가 방지된다.

#### 대 표 도 - 도5

### (52) CPC특허분류

**H01L 27/322** (2013.01)

**H01L 27/3246** (2013.01)

**H01L 27/3248** (2013.01)

**H01L 27/3262** (2013.01)

**H01L 27/3276** (2013.01)

**H01L 51/5209** (2013.01)

H01L 2251/558 (2013.01)

### 명 세 서

#### 청구범위

#### 청구항 1

인접한 제 1 및 제 2 화소 영역 각각에 위치하는 박막트랜지스터와;

상기 박막트랜지스터를 덮는 보호층과;

상기 제 1 화소 영역에 대응하여 상기 보호층 상에 위치하는 컬러필터층과;

상기 제 1 컬러필터층을 덮는 평탄화층과;

상기 제 2 화소 영역에 대응하는 투명 절연층과;

상기 제 1 및 제 2 화소 영역 각각에 위치하며 상기 박막트랜지스터에 연결되고, 상기 평탄화층 상에 위치하는 제 1 전극과;

상기 제 1 전극의 가장자리를 덮는 뱅크층과;

상기 제 1 전극 상에 위치하는 유기발광층과;

상기 유기발광층 상에 위치하는 제 2 전극을 포함하고,

상기 제 1 화소 영역의 상기 제 1 전극은 상기 제 2 화소 영역에 인접한 모서리에서 제 1 돌출부를 갖는 유기발 광표시장치.

#### 청구항 2

제 1 항에 있어서,

상기 제 1 컬러필터층은 적색, 녹색 및 청색 컬러필터층 중 어느 하나인 유기발광표시장치.

### 청구항 3

제 1 항에 있어서.

상기 제 2 화소 영역이 사이에 위치하도록 상기 제 2 화소 영역에 인접한 제 3 화소영역에 대응하여 상기 보호 층 상에 위치하는 제 2 컬러필터층을 포함하고,

상기 제 3 화소 영역의 상기 제 1 전극은 상기 제 2 화소 영역과 인접한 모서리에서 제 2 돌출부를 갖는 유기발 광표시장치.

#### 청구항 4

제 3 항에 있어서,

상기 제 1 컬러필터층은 적색, 녹색 및 청색 컬러필터층 중 어느 하나이고, 상기 제 2 컬러필터층은 적색, 녹색 및 청색 컬러필터층 중 다른 하나인 유기발광표시장치.

#### 청구항 5

제 3 항에 있어서,

상기 제 3 화소영역의 변에서 상기 뱅크층과 상기 제 1 전극은 제 1 폭만큼 중첩하고, 상기 제 3 화소영역의 모

서리에서 상기 뱅크층과 상기 제 1 전극은 상기 제 1 폭보다 큰 제 2 폭만큼 중첩하는 유기발광표시장치.

### 청구항 6

제 3 항에 있어서.

상기 제 3 화소 영역의 상기 제 1 전극은 끝에서 제 1 폭을 갖고 중앙에서 상기 제 1 폭보다 작은 제 2 폭을 갖는 유기발광표시장치.

#### 청구항 7

제 1 항에 있어서,

상기 제 1 화소 영역의 상기 제 1 전극은 끝에서 제 1 폭을 갖고 중앙에서 상기 제 1 폭보다 작은 제 2 폭을 갖는 유기발광표시장치.

#### 청구항 8

제 6 항 또는 제 7 항에 있어서,

상기 제 2 화소 영역의 제 1 전극은 끝과 중앙에서 동일한 폭을 갖는 유기발광표시장치.

#### 청구항 9

제 3 항에 있어서,

상기 제 2 화소 영역과 상기 제 3 화소 영역의 상기 제 1 전극은 끝에서 제 1 거리만큼 이격되고 중앙에서 상기 제 1 거리보다 큰 제 2 거리만큼 이격되는 유기발광표시장치.

#### 청구항 10

제 1 항에 있어서.

상기 제 1 화소 영역과 상기 제 2 화소 영역의 상기 제 1 전극은 끝에서 제 1 거리만큼 이격되고 중앙에서 상기 제 1 거리보다 큰 제 2 거리만큼 이격되는 유기발광표시장치.

### 청구항 11

제 1 항에 있어서.

상기 제 1 화소영역의 변에서 상기 뱅크층과 상기 제 1 전극은 제 1 폭만큼 중첩하고, 상기 제 1 화소영역의 모 서리에서 상기 뱅크층과 상기 제 1 전극은 상기 제 1 폭보다 큰 제 2 폭만큼 중첩하는 유기발광표시장치.

### 발명의 설명

#### 기술분야

[0001] 본 발명은 유기발광표시장치에 관한 것으로, 특히 유기발광다이오드의 제 1 및 제 2 전극 간 전기적 쇼트를 방지할 수 있는 유기발광표시장치에 관한 것이다.

#### 배경기술

[0002] 정보화 사회가 발전함에 따라 화상을 표시하기 위한 표시장치에 대한 요구가 다양한 형태로 증가하고 있다. 종

래의 음극선관 표시장치(CRT)를 대신하여 액정표시장치(liquid crystal display (LCD) device), 플라즈마 표시 장치(plasma display panel (PDP)) 또는 유기발광표시장치(organic light emitting display(OLED) device) 표 시장치를 포함하는 평판표시장치가 활발하게 연구되고 있다.

- [0003] 유기발광표시장치는 높은 휘도와 낮은 동작 전압 특성을 갖는다. 또한, 스스로 빛을 내는 자체 발광형이기 때문에 대조비(contrast ratio)가 크고, 초박형 디스플레이의 구현이 가능하며, 응답시간이 짧고 시야각이 넓은 장점을 갖는다.

- [0004] 도 1은 종래 유기발광표시장치의 개략적인 회로도이다.

- [0005] 도 1에 도시한 바와 같이, 유기발광표시장치에는, 서로 교차하여 제 1 및 제 2 화소영역(P1, P2)을 정의하는 게이트배선(GL), 데이터배선(DL) 및 파워배선(PL)이 형성되고, 화소영역(P)에는, 스위칭 박막트랜지스터(Ts), 구동 박막트랜지스터(Td), 스토리지 커패시터(Cst), 유기발광다이오드(D)가 형성된다.

- [0006] 스위칭 박막트랜지스터(Ts)는 게이트배선(GL) 및 데이터배선(DL)에 연결되고, 구동 박막트랜지스터(Td) 및 스토리지 커패시터(Cst)는 스위칭 박막트랜지스터(Ts)와 파워배선(PL) 사이에 연결되고, 유기발광다이오드(D)는 구동 박막트랜지스터(Td)에 연결된다.

- [0007] 이러한 유기발광표시장치의 영상표시 동작을 살펴보면, 게이트배선(GL)에 인가된 게이트신호에 따라 스위칭 박막트랜지스터(Ts)가 턴-온(turn-on) 되면, 데이터배선(DL)에 인가된 데이터신호가 스위칭 박막트랜지스터(Ts)를 통해 구동 박막트랜지스터(Td)의 게이트전극과 스토리지 커패시터(Cst)의 일 전극에 인가된다.

- [0008] 구동 박막트랜지스터(Td)는 게이트전극에 인가된 데이터신호에 따라 턴-온 되며, 그 결과 데이터신호에 비례하는 전류가 파워배선(PL)으로부터 구동 박막트랜지스터(Td)를 통하여 유기발광다이오드(D)로 흐르게 되고, 유기발광다이오드(D)는 구동 박막트랜지스터(Td)를 통하여 흐르는 전류에 비례하는 휘도로 발광한다.

- [0009] 이때, 스토리지 커패시터(Cst)에는 데이터신호에 비례하는 전압으로 충전되어, 일 프레임(frame) 동안 구동 박막트랜지스터(Td)의 게이트전극의 전압이 일정하게 유지되도록 한다.

- [0010] 따라서, 유기발광표시장치는 게이트신호 및 데이터신호에 의하여 원하는 영상을 표시할 수 있다.

- [0011] 최근에는, 유기발광다이오드(D)가 백색을 발광하고 컬러필터충을 구비하여 컬러 영상을 표시하는 구조의 유기발 광표시장치가 제안되었다.

- [0012] 이와 같은 유기발광표시장치에는, 구동 박막트랜지스터(Td)를 덮는 보호층 상에 컬러필터층이 형성되고, 컬러필터층을 덮는 평탄화층이 더 형성된다. 이 경우, 평탄화층을 패터닝하기 위한 마스크 공정이 추가되어 제조 공정이 복잡해지고 제조 원가가 증가하는 문제가 발생한다.

#### 발명의 내용

### 해결하려는 과제

[0013] 본 발명에서는, 컬러필터층과 평탄화층 형성에 따른 제조 공정 및 제조 원가 증가의 문제를 해결하고자 한다.

#### 과제의 해결 수단

[0014] 위와 같은 과제의 해결을 위해, 본 발명은, 백색 화소영역과 인접한 컬러 화소영역의 제 1 전극(애노드)이 화소 영역의 모서리에서 돌출부를 갖는 유기발광표시장치를 제공한다.

#### 발명의 효과

- [0015] 본 발명에 따른 유기발광표시장치에서는, 보호층과, 컬러필터층에 의한 단차를 평탄화하기 위한 평탄화층을 하나의 마스크 공정에 의해 패터닝함으로써, 제조 공정이 단순해지고 제조 원가가 절감된다.

- [0016] 또한, 백색 화소영역과 인접한 컬러 화소영역의 제 1 전극(애노드)이 화소영역의 모서리에서 돌출부를 가져 제 1 전극의 가장자리가 뱅크층에 의해 완전히 덮인다. 따라서, 유기발광다이오드의 제 1 전극(애노드)과 제 2 전 극(캐소드) 간 전기적 쇼트를 방지할 수 있다.

### 도면의 간단한 설명

[0017] 도 1은 종래 유기발광표시장치의 개략적인 회로도이다.

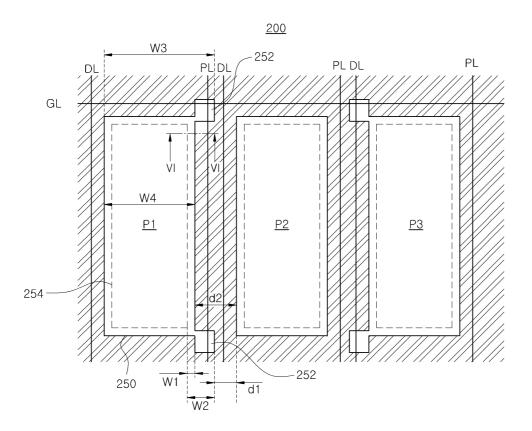

도 2는 본 발명의 제 1 실시예에 따른 유기발광표시장치의 개략적인 평면도이다.

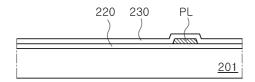

도 3은 본 발명의 제 1 실시예에 따른 유기발광표시장치의 개략적인 단면도이다.

도 4a 내지 도 4g는 본 발명의 제 1 실시예에 따른 유기발광표시장치의 제조 공정을 보여주는 개략적인 단면도이다.

도 5는 본 발명의 제 2 실시예에 따른 유기발광표시장치의 개략적인 평면도이다.

도 6a 내지 도 6g는 본 발명의 제 2 실시예에 따른 유기발광표시장치의 제조 공정을 보여주는 개략적인 단면도이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0018] 본 발명은, 인접한 제 1 및 제 2 화소 영역 각각에 위치하는 박막트랜지스터와, 상기 박막트랜지스터를 덮는 보호층과, 상기 제 1 화소 영역에 대응하여 상기 보호층 상에 위치하는 컬러필터층과, 상기 제 1 컬러필터층을 덮는 평탄화층과, 상기 제 2 화소 영역에 대응하는 투명 절연층과, 상기 제 1 및 제 2 화소 영역 각각에 위치하며 상기 박막트랜지스터에 연결되고, 상기 평탄화층 상에 위치하는 제 1 전극과, 상기 제 1 전극의 가장자리를 덮는 뱅크층과, 상기 제 1 전극 상에 위치하는 유기발광층과, 상기 유기발광층 상에 위치하는 제 2 전극을 포함하고, 상기 제 1 화소 영역의 상기 제 1 전극은 상기 제 2 화소 영역에 인접한 모서리에서 제 1 돌출부를 갖는 유기발광표시장치를 제공한다.

- [0019] 본 발명의 유기발광표시장치에 있어서, 상기 제 1 컬러필터층은 적색, 녹색 및 청색 컬러필터층 중 어느 하나일 수 있다.

- [0020] 본 발명의 유기발광표시장치는, 상기 제 2 화소 영역이 사이에 위치하도록 상기 제 2 화소 영역에 인접한 제 3 화소영역에 대응하여 상기 보호층 상에 위치하는 제 2 컬러필터층을 포함하고, 상기 제 3 화소 영역의 상기 제 1 전극은 상기 제 2 화소 영역과 인접한 모서리에서 제 2 돌출부를 가질 수 있다.

- [0021] 본 발명의 유기발광표시장치에 있어서, 상기 제 1 컬러필터층은 적색, 녹색 및 청색 컬러필터층 중 어느 하나이고, 상기 제 2 컬러필터층은 적색, 녹색 및 청색 컬러필터층 중 다른 하나일 수 있다.

- [0022] 본 발명의 유기발광표시장치에 있어서, 상기 제 3 화소영역의 변에서 상기 뱅크층과 상기 제 1 전극은 제 1 폭만큼 중첩하고, 상기 제 3 화소영역의 모서리에서 상기 뱅크층과 상기 제 1 전극은 상기 제 1 폭보다 큰 제 2 폭만큼 중첩할 수 있다.

- [0023] 본 발명의 유기발광표시장치에 있어서, 상기 제 3 화소 영역의 상기 제 1 전극은 끝에서 제 1 폭을 갖고 중앙에서 상기 제 1 폭보다 작은 제 2 폭을 가질 수 있다.

- [0024] 본 발명의 유기발광표시장치에 있어서, 상기 제 1 화소 영역의 상기 제 1 전극은 끝에서 제 1 폭을 갖고 중앙에서 상기 제 1 폭보다 작은 제 2 폭을 가질 수 있다.

- [0025] 본 발명의 유기발광표시장치에 있어서, 상기 제 2 화소 영역의 상기 제 1 전극은 끝과 중앙에서 동일한 폭을 가질 수 있다.

- [0026] 본 발명의 유기발광표시장치에 있어서, 상기 제 2 화소 영역과 상기 제 3 화소 영역의 상기 제 1 전극은 끝에서 제 1 거리만큼 이격되고 중앙에서 상기 제 1 거리보다 큰 제 2 거리만큼 이격될 수 있다.

- [0027] 본 발명의 유기발광표시장치에 있어서, 상기 제 1 화소 영역과 상기 제 2 화소 영역의 상기 제 1 전극은 끝에서 제 1 거리만큼 이격되고 중앙에서 상기 제 1 거리보다 큰 제 2 거리만큼 이격될 수 있다.

- [0028] 본 발명의 유기발광표시장치에 있어서, 상기 제 1 화소영역의 변에서 상기 뱅크층과 상기 제 1 전극은 제 1 폭만큼 중첩하고, 상기 제 1 화소영역의 모서리에서 상기 뱅크층과 상기 제 1 전극은 상기 제 1 폭보다 큰 제 2 폭만큼 중첩할 수 있다.

- [0029] 이하, 본 발명에 따른 바람직한 실시예를 도면을 참조하여 설명한다.

- [0030] -제 1 실시예-

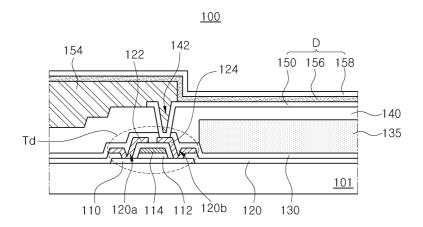

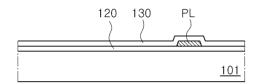

- [0031] 도 2는 본 발명의 제 1 실시예에 따른 유기발광표시장치의 개략적인 평면도이고, 도 3은 본 발명의 제 1 실시예

- 에 따른 유기발광표시장치의 개략적인 단면도이다.

- [0032] 도 2에 도시된 바와 같이, 본 발명의 제 1 실시예에 따른 유기발광표시장치(100)에서, 제 1 방향으로 게이트 배선(GL)이 연장되고, 제 2 방향으로 데이터 배선(DL) 및 파워 배선(PL)이 연장된다.

- [0033] 상기 게이트 배선(GL)과 상기 데이터 배선(DL)은 서로 교차하여 제 1 및 제 2 화소 영역(P1, P2)을 정의한다. 도시하지 않았으나, 상기 제 1 및 제 2 화소 영역(P1, P2) 각각에는 스위칭 박막트랜지스터와, 구동 박막트랜지스터와, 유기발광다이오드와 스토리지 커패시터가 위치한다.

- [0034] 상기 제 1 화소 영역(P1)은 컬러 화소 영역이고, 상기 제 2 화소 영역(P2)은 백색 화소 영역이다. 즉, 상기 제 1 화소 영역(P1)에는 컬러필터층(미도시)이 형성되고, 상기 제 2 화소 영역(P2)에는 컬러필터층이 형성되지 않는다.

- [0035] 도 3에 도시된 바와 같이, 기판(101) 상에 구동 박막트랜지스터(Td)가 형성된다. 한편, 상기 기판(101) 상에 산화실리콘 또는 질화실리콘과 같은 버퍼층(미도시)이 형성되고, 상기 구동 박막트랜지스터(Td)가 상기 버퍼층 상에 형성될 수도 있다.

- [0036] 상기 구동 박막트랜지스터(Td)는 반도체층(110), 게이트 전극(112), 소스 전극(122) 및 드레인 전극(124)을 포함한다.

- [0037] 상기 반도체충(110)은 상기 버퍼충(102) 상에 형성된다. 예를 들어, 상기 반도체충(110)은 산화물 반도체 물질로 이루어지거나 다결정 실리콘으로 이루어질 수 있다.

- [0038] 상기 반도체층(110)이 산화물 반도체 물질로 이루어질 경우 상기 반도체층(110) 하부에는 차광패턴(도시하지 않음) 이 형성될 수 있으며, 차광패턴은 상기 반도체층(110)으로 빛이 입사되는 것을 방지하여 상기 반도체층(110)이 빛에 의해 열화되는 것을 방지한다. 이와 달리, 상기 반도체층(110)은 다결정 실리콘으로 이루어질 수도 있으며, 이 경우 상기 반도체층(110)의 양 가장자리에 불순물이 도핑되어 있을 수 있다.

- [0039] 상기 반도체충(110) 상부에는 절연물질로 이루어진 게이트 절연막(112)이 형성된다. 상기 게이트 절연막(112)은 산화 실리콘 또는 질화 실리콘과 같은 무기절연물질로 이루어질 수 있다.

- [0040] 상기 게이트 절연막(112) 상에는 금속과 같은 도전성 물질로 이루어진 게이트 전극(114)이 상기 반도체충(110)의 중앙에 대응하여 형성된다. 상기 게이트 전극(114)은 스위칭 박막트랜지스터(미도시)에 연결된다.

- [0041] 상기 게이트 절연막(112)이 상기 게이트 전극(114)과 동일한 형상인 것이 보여지고 있다. 이와 달리, 상기 게이트 절연막(112)은 상기 기판(101)의 전면에 형성될 수도 있다.

- [0042] 상기 게이트 전극(114) 상부에는 절연물질로 이루어진 층간 절연막(120)이 상기 기판(101) 전면에 형성된다. 상기 층간 절연막(120)은 산화 실리콘이나 질화 실리콘과 같은 무기 절연물질로 형성되거나, 벤조사이클로부텐(benzocyclobutene)이나 포토 아크릴(photo-acryl)과 같은 유기 절연물질로 형성될 수 있다.

- [0043] 상기 층간 절연막(120)은 상기 반도체층(110)의 양측을 노출하는 제 1 및 제 2 콘택홀(120a, 120b)을 갖는다. 상기 제 1 및 제 2 콘택홀(120a, 120b)은 상기 게이트 전극(114)의 양측에 상기 게이트 전극(114)과 이격되어 위치하다.

- [0044] 상기 층간 절연막(120) 상에는 금속과 같은 도전성 물질로 이루어지는 소스 전극(122)과 드레인 전극(124)이 형성된다.

- [0045] 상기 소스 전극(122)과 상기 드레인 전극(124)은 상기 게이트 전극(114)을 중심으로 이격되어 위치하며, 각각 상기 제 1 및 제 2 콘택홀(120a, 120b)을 통해 상기 반도체층(110)의 양측과 접촉한다. 상기 소스 전극(122)은 상기 파워 배선(미도시)에 연결된다.

- [0046] 상기 반도체층(110)과, 상기 게이트 전극(114), 상기 소스 전극(122), 상기 드레인 전극(124)은 상기 구동 박막 트랜지스터(Td)를 이루며, 상기 구동 박막트랜지스터(Td)는 상기 반도체층(110)의 상부에 상기 게이트 전극(114), 상기 소스 전극(122) 및 상기 드레인 전극(124)이 위치하는 코플라나(coplanar) 구조를 가진다.

- [0047] 이와 달리, 구동 박막트랜지스터(Td)는 반도체충의 하부에 게이트 전국이 위치하고 반도체충의 상부에 소스 전 국과 드레인 전국이 위치하는 역 스태거드(inverted staggered) 구조를 가질 수 있다. 이 경우, 반도체충은 비 정질 실리콘으로 이루어질 수 있다.

- [0048] 또한, 상기 구동 박막트랜지스터(Td)를 덮으며 보호층(130)이 형성된다. 상기 보호층(130)은 산화실리콘 또는

- 질화실리콘과 같은 무기절연물질로 이루어질 수 있다.

- [0049] 상기 보호층(130) 상에는 제 1 화소영역(도 2의 P1)의 표시영역에 대응하여 컬러필터층(135)이 형성된다. 상기 컬러필터층(135)은 적색, 녹색 및 청색 컬러필터 패턴을 포함할 수 있다.

- [0050] 상기 보호층(130) 및 상기 컬러필터층(135)을 덮는 평탄화층(140)이 기판(101)의 전면에 형성된다.

- [0051] 상기 평탄화층(140)은 감광 특성(photo-sensitive property)을 갖고 투명한 유기절연물질을 포함한다. 예를 들어, 평탄화층(140)은 포토-아크릴(photo-acryl) 또는 폴리이미드(polyimide)로 이루어질 수 있다.

- [0052] 한편, 백색 화소 영역인 제 2 화소 영역(도 2의 P2)에는 컬러필터층(135) 없이 상기 평탄화층(140)과 동일 물질로 이루어지는 투명 절연층(미도시)이 형성된다.

- [0053] 상기 제 1 화소 영역(P1)에서, 상기 평탄화층(140)과 상기 보호층(130)에는 상기 구동 박막트랜지스터(Td)의 드 레인 전극(124)을 노출하는 드레인 콘택홀(142)이 형성된다. 한편, 제 2 화소 영역(P2)에서는 상기 투명 절연층 과 상기 보호층(130)을 통해 드레인 콘택홀(142)이 형성될 수 있다.

- [0054] 상기 평탄화충(140) 상에는 상기 드레인 콘택홀(142)을 통해 상기 구동 박막트랜지스터(Td)의 드레인 전극(124)에 연결되는 제 1 전극(150)이 형성된다.

- [0055] 상기 제 1 전극(150)은 일함수 값이 비교적 높은 물질로 이루어져 양극(anode) 역할을 한다. 예를 들어, 상기 제 1 전극(150)은 인듐-틴-옥사이드(indium-tin-oxide, ITO) 또는 인듐-징크-옥사이드(indium-zinc-oxide, IZO)와 같은 투명 도전성 물질로 이루어질 수 있다.

- [0056] 또한, 상기 제 1 전극(150)의 가장자리를 덮는 뱅크충(154)이 형성된다. 즉, 상기 뱅크충(154)은 상기 제 1 및 제 2 화소 영역(P1, P2)을 둘러싸는 격자 형상을 갖는다.

- [0057] 상기 제 1 전극(150)의 중앙부에는 유기발광층(156)이 형성된다. 상기 유기발광층(156)은 백색을 발광하는 유기 발광물질을 포함한다.

- [0058] 상기 유기발광충(158) 상에는 제 2 전극(158)이 형성된다. 상기 제 2 전극(158)은 비교적 일함수 값이 작은 물질로 이루어져 음극(cathode) 역할을 한다. 예를 들어, 상기 제 2 전극(258)은 알루미늄 또는 알루미늄 합금 (Al:Mg)으로 이루어질 수 있다.

- [0059] 서로 마주하는 제 1 전극(150) 및 제 2 전극(158)과 이들 사이에 개재된 유기발광층(156)은 유기발광다이오드 (D)를 구성하며, 상기 유기발광다이오드(D)는 백색 발광 타입니다.

- [0060] 전술한 유기발광표시장치(100)에서, 상기 유기발광다이오드(D)는 백색을 발광하고 상기 컬러필터층(135)에 의해 풀컬러 영상이 구현되며, 상기 유기발광다이오드(D)로부터의 빛은 상기 기판(101)을 통하여 영상이 표시된다.

- [0061] 또한, 컬러필터층(135)을 덮는 평탄화층(140)이 형성되더라도, 상기 평탄화층(140)과 보호층(130)을 하나의 마스크 공정에 의해 패터닝하기 때문에 제조 공정이 증가하지 않는다.

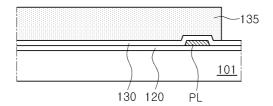

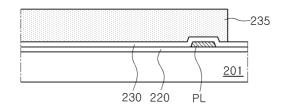

- [0062] 도 4a 내지 도 4g는 본 발명의 제 1 실시예에 따른 유기발광표시장치의 제조 공정을 보여주는 개략적인 단면도 이며 도 2의 IV-IV을 따라 절단한 단면을 보여준다.

- [0063] 도 3과 도 4a에서 보여지는 바와 같이, 기판(101) 상에 반도체 물질을 증착하고 마스크 공정을 진행하여 반도체 층(110)을 형성한다.

- [0064] 다음, 상기 반도체충(110) 상에 무기절연물질과 금속물질을 순차 적충하고 하나의 마스크 공정을 진행하여 동일 한 형상을 갖는 게이트 절연막(112)과 게이트 전극(114)을 형성한다. 또한, 제 1 방향을 따라 연장되는 게이트 배선(도 2의 GL)을 형성한다.

- [0065] 다음, 상기 게이트 전극(114)을 덮고 제 1 및 제 2 콘택홀(120a, 120b)을 갖는 층간 절연막(120)을 형성한다.

- [0066] 다음, 상기 층간 절연막(120) 상에 금속물질을 증착하고 마스크 공정을 진행하여 데이터 배선(도 2의 DL), 파워 배선(PL), 소스 전극(122) 및 드레인 전극(124)을 형성한다.

- [0067] 다음, 상기 데이터 배선(DL), 파워 배선(PL), 소스 전극(122) 및 드레인 전극(124)을 덮는 보호층(130)을 형성한다.

- [0068] 다음, 도 4b에서 보여지는 바와 같이, 상기 보호층(130) 상에 컬러 안료를 포함하는 컬러필터층(135)을 형성한

- 다. 이때, 상기 제 2 화소 영역(P2)에는 컬러필터층(135)이 형성되지 않는다.

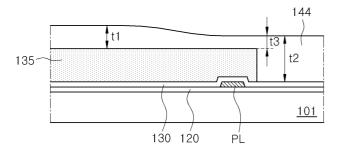

- [0069] 다음, 도 4c에서 보여지는 바와 같이, 상기 컬러필터층(135)과 상기 보호층(130) 상에 투명 절연물질을 코팅하여 투명 절연물질층(144)을 형성한다. 예를 들어, 상기 투명 절연물질은 포토-아크릴(photo-acryl) 또는 폴리이미드(polyimide)일 수 있다.

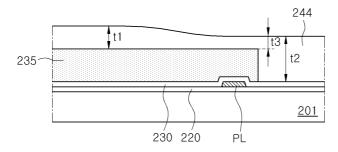

- [0070] 상기 투명 절연물질층(144)은, 제 1 화소 영역(도 2의 P1)에서 컬러필터층(135) 상에 위치하며 제 1 두께(t1)를 갖고, 상기 제 2 화소 영역(도 2의 P2)에서 보호층(130) 상에 위치하며 상기 제 1 두께(t1)보다 큰 제 2 두께(t2)를 갖는다. 한편, 상기 제 1 및 제 2 화소 영역(P1, P2)의 경계에서 상기 컬러필터층(135)과 상기 보호층(130)의 단차에 의해 상기 투명 절연물질층(144)은 상기 제 1 두께(t1)보다 작은 제 3 두께(t3)를 갖는다.

- [0071] 다음, 상기 투명 절연물질층(144)에 대하여 마스크 공정을 진행하여 드레인 콘택홀(도 3의 142)에 대응하는 투명 절연물질층(144)을 제거한다.

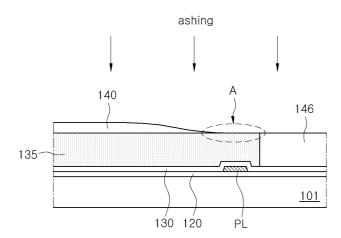

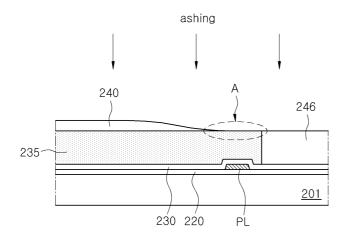

- [0072] 도 4d에 도시된 바와 같이, 상기 투명 절연물질층(144)에 대하여 애싱(ashing) 공정을 진행함으로써, 제 1 화소 영역(P1)의 컬러필터층(135) 상에 평탄화층(140)을 형성하고 제 2 화소 영역(P2)의 보호층(130) 상에 투명 절연 층(146)을 형성한다.

- [0073] 드레인 콘택홀(도 3의 142)이 형성될 영역에 투명 절연물질이 남게 되면 보호층(130)의 식각 공정이 불충분하게 진행되기 때문에, 제 1 애싱 공정을 진행하여 드레인 콘택홀(142) 형성 영역의 잔류 투명 절연물질을 완전히 제거하여 보호층(130)을 노출시킨다.

- [0074] 다음, 노출된 보호층(130)을 식각함으로써, 드레인 콘택홀(142)을 형성한다. 즉, 본 발명에서는, 상기 평탄화층 (140)과 상기 보호층(130)이 하나의 마스크 공정에 의해 패터닝되기 때문에, 제조 공정이 증가하지 않는다.

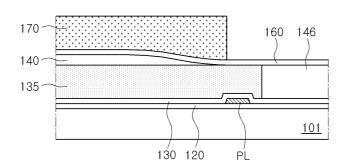

- [0075] 다음, 도 4e에 도시된 바와 같이, 상기 평탄화층(140)과 상기 투명 절연층(146) 상에 투명 도전 물질층(160)을 형성하고, 상기 투명 도전 물질층(160) 상에 포토레지스트 패턴(170)을 형성한다.

- [0076] 상기 투명 도전 물질층(160)은 ITO 또는 IZO와 같은 투명 도전 물질로 이루어질 수 있다.

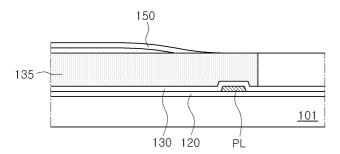

- [0077] 다음, 도 4f에 도시된 바와 같이, 상기 포토레지스트 패턴(170)을 이용한 마스크 공정을 진행함으로써, 상기 평 탄화층(150) 상에 제 1 전극(150)을 형성한다.

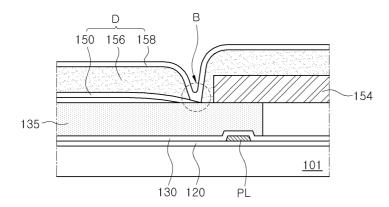

- [0078] 다음, 도 4g에 도시된 바와 같이, 상기 제 1 전극(150)의 가장자리를 덮도록 뱅크층(154)을 형성한다. 다음, 상기 제 1 전극(150) 상에 유기발광층(156)과 제 2 전극(158)을 순차 적층시켜 유기발광다이오드(D)를 형성한다.

- [0079] 상기 제 1 전극(150)과 상기 제 2 전극(158) 간 쇼트를 방지하기 위해, 상기 제 1 전극(150)의 가장자리는 상기 뱅크층(154)에 의해 완전히 덮여야 한다.

- [0080] 그러나, 투명 절연물질층(144)은 컬러필터층(135)의 가장자리에서 다른 부분보다 작은 제 3 두께(t3)를 갖기 때문에(도 4c), 애성 공정에 의해 컬러필터층(135)의 가장자리에서 투명 절연물질층이 모두 제거되어 컬러필터층 (135)의 가장자리가 노출된다. (도 4d의 "A" 부분)

- [0081] 애싱 공정 후, 증착되는 투명 도전 물질층(160)은 컬러필터층(135)의 가장자리와 접촉하게 되고 (도 4e), 마스크 공정을 진행하면 제 1 전극(150)은 원하는 폭보다 작은 폭을 가지며 형성된다.

- [0082] 즉, 안료를 포함하는 컬러필터층(135)과 접촉된 투명 도전 물질층(160)은 식각 바이어스(etch bias)가 증가하여, 포토레지스트 패턴(170) 내측 부분까지 식각된다. 다시 말해, 컬러필터층(135)과의 접촉에 의해 투명 도전 물질층(160)이 과식각(over-etch)되어 제 1 전극(150)의 폭이 원하는 폭보다 작아진다.

- [0083] 따라서, 뱅크층(154)이 제 1 전극(150)의 가장자리를 덮지 못하게 되고, 상기 제 1 전극(150) 상부에 적층되는 제 2 전극(158)이 제 1 전극(150)과 접촉하여 전기적 쇼트가 발생한다. (도 4g의 "B" 부분) 이와 같은 문제는 제 2 화소 영역(도 2의 P2)에 인접한 제 1 화소 영역(도 2의 P1)의 두 모서리에서 심각하게 발생한다.

- [0084] -제 2 실시예-

- [0085] 도 5는 본 발명의 제 2 실시예에 따른 유기발광표시장치의 개략적인 평면도이다.

- [0086] 도 5에 도시된 바와 같이, 본 발명의 제 2 실시예에 따른 유기발광표시장치(200)에서, 제 1 방향으로 게이트 배선(GL)이 연장되고, 제 2 방향으로 데이터 배선(DL) 및 파워 배선(PL)이 연장된다.

- [0087] 상기 게이트 배선(GL)과 상기 데이터 배선(DL)은 서로 교차하여 제 1 내지 제 3 화소 영역(P1, P2, P3)을 정의

한다. 도시하지 않았으나, 상기 제 1 내지 제 3 화소 영역(P1, P2, P3) 각각에는 스위칭 박막트랜지스터와, 구 동 박막트랜지스터와, 유기발광다이오드와 스토리지 커패시터가 위치한다.

- [0088] 상기 제 1 및 제 3 화소 영역(P1, P3)은 컬러 화소 영역이고, 상기 제 1 및 제 3 화소 영역(P1, P3) 사이에 위치하는 상기 제 2 화소 영역(P2)은 백색 화소 영역이다. 즉, 상기 제 1 및 제 3 화소 영역(P1, P3)에는 컬러필터층(미도시)이 형성되고, 상기 제 2 화소 영역(P2)에는 컬러필터층이 형성되지 않는다.

- [0089] 상기 제 1 내지 제 3 화소 영역(P1, P2, P3) 각각에는 판 형상의 제 1 전극(250)이 형성된다. 상기 제 1 전극 (250)은 구동 박막트랜지스터의 드레인 전극에 연결된다.

- [0090] 예를 들어, 상기 제 1 내지 제 3 화소 영역(P1, P2, P3) 각각은 직사각형 형상을 갖고, 상기 제 1 전극(250) 역 시 직사각형 형상을 갖는다.

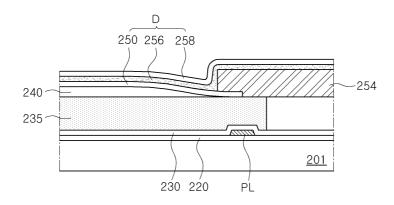

- [0091] 한편, 상기 제 2 화소 영역(P2)과 마주하는 제 1 화소 영역(P1)의 제 1 변의 양 단에서 상기 제 1 전극(250)은 돌출부(252)를 갖는다. 즉, 상기 제 1 화소 영역(P1)의 제 1 전극(250)은 상기 제 2 화소 영역(P2)에 근접한 모 서리에서 돌출부(252)를 갖는다.

- [0092] 상기 돌출부(252)는 사각형 형상을 갖는다. 이와 달리, 상기 돌출부(252)는 마름모, 원형, 타원형 형상을 가질 수도 있으며, 그 형상은 이에 한정되지 않는다.

- [0093] 다시 말해, 상기 제 1 화소 영역(P1)의 변에서 상기 뱅크층(254)과 상기 제 1 전극(250)은 제 1 폭(W1)만큼 중첩하고, 상기 제 1 전극(250)은 상기 제 1 화소 영역(P2)의 모서리에 대응하여 돌출부(252)를 포함하기 때문에 상기 제 1 화소 영역(P1)의 모서리에 상기 뱅크층(254)과 상기 제 1 전극(250)은 상기 제 1 폭(W1)보다 큰 제 2 폭(W2)만큼 중첩한다.

- [0094] 이와 달리, 상기 제 1 화소 영역(P1)의 제 1 변과 반대측인 제 2 변의 양단에 위치하는 모서리에서 상기 제 1 전극(250)은 돌출부를 갖지 않는다.

- [0095] 또한, 상기 제 2 화소 영역(P2)과 마주하는 제 3 화소 영역(P3)의 제 1 변의 양 단에서 상기 제 1 전극(250)은 돌출부(252)를 갖는다. 즉, 상기 제 3 화소 영역(P3)의 제 1 전극(250)은 상기 제 2 화소 영역(P2)에 근접한 모 서리에서 돌출부(252)를 갖는다.

- [0096] 다시 말해, 상기 제 3 화소 영역(P3)의 변에서 상기 뱅크층(254)과 상기 제 1 전극(250)은 제 1 폭(W1)만큼 중첩하고, 상기 제 1 전극(250)은 상기 제 1 화소 영역(P2)의 모서리에 대응하여 돌출부(252)를 포함하기 때문에 상기 제 3 화소 영역(P3)의 모서리에 상기 뱅크층(254)과 상기 제 1 전극(250)은 상기 제 1 폭(W1)보다 큰 제 2 폭(W2)만큼 중첩한다.

- [0097] 이에 따라, 돌출부(252)를 포함하는 제 1 및 제 3 화소 영역(P1, P3)의 제 1 전극(250)은 끝에서 제 3 폭(W3)을 갖고 중앙에서 상기 제 3 폭(W3)보다 작은 제 4 폭(W4)을 갖는다.

- [0098] 따라서, 상기 제 1 화소 영역(P1)과 상기 제 2 화소 영역(P2)의 상기 제 1 전극(250)은 끝에서 제 1 거리(d1)만 큼 이격되고 중앙에서 상기 제 1 거리(d1)보다 큰 제 2 거리(d2)만큼 이격된다. 또한, 상기 제 2 화소 영역(P 2)과 상기 제 3 화소 영역(P3)의 상기 제 1 전극(250) 역시 중앙에서 끝부분보다 큰 거리만큼 이격된다.

- [0099] 이와 달리, 상기 제 3 화소 영역(P3)의 제 1 변과 반대측인 제 2 변의 양단에 위치하는 모서리에서 상기 제 1 전극(250)은 돌출부를 갖지 않는다.

- [0100] 즉, 백색 화소인 제 2 화소 영역(P1, P2)과 인접한 제 1 및 제 3 화소 영역(P1, P3)에서, 제 1 전극(250)은 제 2 화소 영역(P1, P2) 방향의 모서리에 대응하여 돌출부(252)를 포함한다.

- [0101] 한편, 제 2 화소 영역(P2)에서 상기 제 1 전극(250)은 돌출부를 갖지 않는다. 즉, 제 2 화소 영역(P2)에서 제 1 전극(250)은 끝과 중앙에서 동일한 폭을 갖는다.

- [0102] 전술한 바와 같이, 본 발명의 제 2 실시예에 따른 유기발광표시장치(200)에서는, 백색 화소와 인접한 컬러 화소에서 제 1 전극(250)의 모서리에 돌출부(252)를 형성함으로써, 제 1 실시예의 유기발광표시장치에서와 같이 제 1 전극이 과식각되더라도 제 1 전극의 가장자리가 뱅크층에 의해 완전히 덮인다. 따라서, 제 1 전극과 제 2 전 극 간 전기적 쇼트 문제를 방지할 수 있다.

- [0103] 도 6a 내지 도 6g는 본 발명의 제 2 실시예에 따른 유기발광표시장치의 제조 공정을 보여주는 개략적인 단면도 이다.

- [0104] 기판(201) 상에 반도체 물질을 증착하고 마스크 공정을 진행하여 반도체충(도 3의 110)을 형성한다.

- [0105] 다음, 상기 반도체층(110) 상에 무기절연물질과 금속물질을 순차 적층하고 하나의 마스크 공정을 진행하여 동일 한 형상을 갖는 게이트 절연막(도 3의 112)과 게이트 전극(도 3의 114)을 형성한다. 또한, 제 1 방향을 따라 연장되는 게이트 배선(도 2의 GL)을 형성한다.

- [0106] 다음, 도 6a에서 보여지는 바와 같이, 상기 게이트 전극(114)을 덮고 제 1 및 제 2 콘택홀(도 3의 120a, 120b)을 갖는 층간 절연막(120)을 형성한다.

- [0107] 다음, 상기 충간 절연막(120) 상에 금속물질을 중착하고 마스크 공정을 진행하여 데이터 배선(도 2의 DL), 파워배선(PL), 소스 전극(도 3의 122) 및 드레인 전극(도 3의 124)을 형성한다.

- [0108] 다음, 상기 데이터 배선(DL), 파워 배선(PL), 소스 전극(122) 및 드레인 전극(124)을 덮는 보호층(230)을 형성하다.

- [0109] 다음, 도 6b에서 보여지는 바와 같이, 제 1 및 제 3 화소 영역(P1, P3)에 대응하여 상기 보호층(230) 상에 컬러 안료를 포함하는 컬러필터층(235)을 형성한다. 이때, 상기 제 2 화소 영역(P2)에는 컬러필터층(235)이 형성되지 않는다. 예를 들어, 상기 제 1 화소 영역(P1)에는 적색, 녹색 및 청색 컬러필터층 중 어느 하나가 형성되고, 상기 제 3 화소 영역(P3)에는 이들 중 다른 하나가 형성될 수 있다.

- [0110] 다음, 도 6c에서 보여지는 바와 같이, 상기 컬러필터층(235)과 상기 보호층(230) 상에 투명 절연물질을 코팅하여 투명 절연물질층(244)을 형성한다. 예를 들어, 상기 투명 절연물질은 포토-아크릴(photo-acryl) 또는 폴리이미드(polyimide)일 수 있다.

- [0111] 상기 투명 절연물질층(244)은, 제 1 화소 영역(도 5의 P1)에서 컬러필터층(235) 상에 위치하며 제 1 두께(t1)를 갖고, 상기 제 2 화소 영역(도 2의 P2)에서 보호층(230) 상에 위치하며 상기 제 1 두께(t1)보다 큰 제 2 두께 (t2)를 갖는다. 한편, 상기 제 1 및 제 2 화소 영역(P1, P2)의 경계에서 상기 컬러필터층(235)과 상기 보호층 (230)의 단차에 의해 상기 투명 절연물질층(244)은 상기 제 1 두께(t1)보다 작은 제 3 두께(t3)를 갖는다.

- [0112] 한편, 제 3 화소 영역(도 5의 P3)와 제 2 화소 영역(P2)의 경계에서도 도 6c에서와 유사한 구조가 된다.

- [0113] 다음, 상기 투명 절연물질층(244)에 대하여 마스크 공정을 진행하여 드레인 콘택홀(도 3의 142)에 대응하는 투명 절연물질층(244)을 제거한다.

- [0114] 도 6d에 도시된 바와 같이, 상기 투명 절연물질층(244)에 대하여 애싱(ashing) 공정을 진행함으로써, 제 1 화소 영역(P1)의 컬러필터층(235) 상에 평탄화층(240)을 형성하고 제 2 화소 영역(P2)의 보호층(230) 상에 투명 절연 층(246)을 형성한다.

- [0115] 드레인 콘택홀(도 3의 142)이 형성될 영역에 투명 절연물질이 남게 되면 보호층(230)의 식각 공정이 불충분하게 진행되기 때문에, 제 1 애싱 공정을 진행하여 드레인 콘택홀(142) 형성 영역의 잔류 투명 절연물질을 완전히 제 거하여 보호층(230)을 노출시킨다.

- [0116] 다음, 노출된 보호층(230)을 식각함으로써, 드레인 콘택홀(142)을 형성한다. 즉, 본 발명에서는, 상기 평탄화층 (240)과 상기 보호층(230)이 하나의 마스크 공정에 의해 패터닝되기 때문에, 제조 공정이 증가하지 않는다.

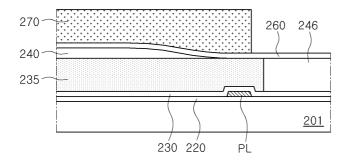

- [0117] 다음, 도 6e에 도시된 바와 같이, 상기 평탄화층(240)과 상기 투명 절연층(246) 상에 투명 도전 물질층(260)을 형성하고, 상기 투명 도전 물질층(260) 상에 포토레지스트 패턴(270)을 형성한다.

- [0118] 상기 포토레지스트 패턴(270)은 제 1 전극(도 5의 250)에 대응하여 형성된다. 즉, 상기 포토레지스트 패턴(270)은 제 2 화소 영역(도 5의 P2)에서 직사각형 형상을 갖고, 상기 제 1 및 제 3 화소 영역(도 5의 P1, P3)에서 는 모서리에 돌출부가 형성된 직사각형 형상을 갖는다.

- [0119] 상기 투명 도전 물질층(260)은 ITO 또는 IZO와 같은 투명 도전 물질로 이루어질 수 있다.

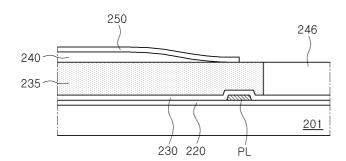

- [0120] 다음, 도 6f에 도시된 바와 같이, 상기 포토레지스트 패턴(270)을 이용한 마스크 공정을 진행함으로써, 상기 평 탄화층(250) 상에 제 1 전극(250)을 형성한다. 상기 제 2 화소 영역(P2)에서 제 1 전극(250)은 투명 절연층 (246) 상에 형성된다.

- [0121] 다음, 도 6g에 도시된 바와 같이, 상기 제 1 전극(250)의 가장자리를 덮도록 뱅크층(254)을 형성한다. 다음, 상기 제 1 전극(250) 상에 유기발광층(256)과 제 2 전극(258)을 순차 적층시켜 유기발광다이오드(D)를 형성한다.

- [0122] 본 발명의 제 2 실시예에 따른 유기발광표시장치(100)에서는, 컬러필터층(235)의 가장자리에서 투명 절연물질층 (244)이 모두 제거되어 컬러필터층(235)이 노출되고 (도 6c), 투명 도전 물질층(260)이 컬러필터층(235)과 접촉하여 과식각되더라도 제 1 및 제 3 화소 영역(P1, P3)의 모서리에서 제 1 전극(250)이 돌출부(252)를 포함하기 때문에 제 1 전극(250)의 가장자리는 뱅크층(254)에 의해 완전히 덮인다.

- [0123] 따라서, 제 1 전극(250)과 제 2 전극(258) 간 전기적 쇼트가 발생되지 않는다.

- [0124] 상기에서는 본 발명의 바람직한 실시예를 참조하여 설명하였지만, 해당 기술분야의 통상의 기술자는 하기의 특허청구범위에 기재된 본 발명의 기술적 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다.

#### 부호의 설명

[0125] 101, 201: 기판 110, 210: 반도체층

112, 212: 게이트 절연막 114, 214: 게이트 전극

120, 220: 층간 절연막 122, 222: 소스 전극

124, 224: 드레인 전극 130, 230: 보호층

135, 235: 컬러필터층 140, 240: 평탄화층

146, 246: 투명 절연층 150, 250: 제 1 전극

252: 돌출부 154, 254: 뱅크층

156, 256: 유기발광층 158, 258: 제 2 전극

Td: 구동 박막트랜지스터 D: 유기발광다이오드

### 도면

### 도면1

# 도면2

# 도면3

# 도면4a

# *도면4b*

## *도면4c*

# *도면4d*

# *도면4e*

# *도면4f*

# 도면4g

# 도면5

## 도면6a

# *도면6b*

## 도면6c

# *도면6d*

# *도면6e*

# *도면6f*

# 도면6g

| 专利名称(译)        | 相关技术的描述                                                                                                     |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | KR1020170128000A                                                                                            | 公开(公告)日 | 2017-11-22 |

| 申请号            | KR1020160059060                                                                                             | 申请日     | 2016-05-13 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                    |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                                                                   |         |            |

| [标]发明人         | SONG CHANG WOOK<br>송창욱<br>KANG IM KUK<br>강임국<br>PARK SANG MOO<br>박상무                                        |         |            |

| 发明人            | 송창욱<br>강임국<br>박상무                                                                                           |         |            |

| IPC分类号         | H01L27/32 H01L51/52                                                                                         |         |            |

| CPC分类号         | H01L27/3258 H01L27/322 H01L27/3248 H01L27/3246 H01L27/3262 H01L27/3211 H01L27/3276 H01L51/5209 H01L2251/558 |         |            |

| 外部链接           | Espacenet                                                                                                   |         |            |

|                |                                                                                                             |         |            |

### 摘要(译)

本发明提供一种有机发光显示装置,其中与白色像素域相邻的彩色像素域的第一电极(阳极)在像素区域的边缘处具有突出部分。因此,防止了第一电极被堤层完全覆盖并与第一电极和第二电极(阴极)一起移动的电短路问题。