(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2017-0019022

(43) 공개일자 2017년02월21일

(51) 국제특허분류(Int. Cl.)

*G09G 3/32* (2016.01)

(52) CPC특허분류

*G09G 3/3208* (2013.01)

*G09G 2330/06* (2013.01)

(21) 출원번호 10-2015-0112600

(22) 출원일자 2015년08월10일

심사청구일자 없음

(71) 출원인

삼성디스플레이 주식회사

경기도 용인시 기흥구 삼성로 1 (농서동)

(72) 발명자

이승규

경기도 용인시 기흥구 삼성로 1 (농서동)

박경진

경기도 용인시 기흥구 삼성로 1 (농서동)

(뒷면에 계속)

(74) 대리인

장신섭, 문용호, 이용우

전체 청구항 수 : 총 11 항

(54) 발명의 명칭 발광제어 구동부 및 이를 포함하는 유기전계발광 표시장치

### (57) 요 약

본 발명에 의한 발광제어 구동부는, 복수의 스테이지들을 구비하는 발광제어 구동부에 있어서, 상기 스테이지들 각각은, 발광제어신호를 출력하는 출력단자와 제1 전원 사이에 접속되며, 게이트 전극이 제1 노드에 접속되는 제1 트랜지스터; 상기 출력단자와 제2 전원 사이에 접속되며, 게이트 전극이 제2 노드에 접속되는 제2 트랜지스터;

(뒷면에 계속)

### 대 표 도 - 도3

상기 제2 전원과 상기 제2 노드 사이에 접속되며, 게이트 전극이 상기 제1 노드에 접속되는 제3 트랜지스터; 시작신호 또는 이전 스테이지의 발광제어신호를 입력받는 시작단자와 상기 제1 노드 사이에 접속되며, 게이트 전극이 제1 입력단자에 접속되는 제4 트랜지스터; 및 제2 입력단자와 상기 제1 노드 사이에 접속되는 제1 캐패시터를 포함하되, 첫번째 스테이지를 제외한 홀수번째 스테이지들의 제1 입력단자는 이전 스테이지의 제2 입력단자에 연결된 제1 서브 클럭신호선에 접속되고, 제2 입력단자는 제2 메인 클럭신호선 및 다음 스테이지의 제1 입력단자에 연결된 제2 서브 클럭신호선에 접속되며, 짹수번째 스테이지들의 제1 입력단자는 이전 스테이지의 제2 입력단자에 연결된 제2 서브 클럭신호선에 접속되고, 제2 입력단자는 제1 메인 클럭신호선 및 다음 스테이지의 제1 입력단자에 접속된 제1 서브 클럭신호선에 접속된다.

(72) **발명자**

**박현애**

경기도 용인시 기흥구 삼성로 1 (농서동)

**변민우**

경기도 용인시 기흥구 삼성로 1 (농서동)

## 명세서

### 청구범위

#### 청구항 1

복수의 스테이지들을 구비하는 발광제어 구동부에 있어서, 상기 스테이지들 각각은, 발광제어신호를 출력하는 출력단자와 제1 전원 사이에 접속되며, 게이트 전극이 제1 노드에 접속되는 제1 트랜지스터; 상기 출력단자와 제2 전원 사이에 접속되며, 게이트 전극이 제2 노드에 접속되는 제2 트랜지스터; 상기 제2 전원과 상기 제2 노드 사이에 접속되며, 게이트 전극이 상기 제1 노드에 접속되는 제3 트랜지스터; 시작신호 또는 이전 스테이지의 발광제어신호를 입력받는 시작단자와 상기 제1 노드 사이에 접속되며, 게이트 전극이 제1 입력단자에 접속되는 제4 트랜지스터; 및 제2 입력단자와 상기 제1 노드 사이에 접속되는 제1 캐패시터를 포함하되, 첫번째 스테이지를 제외한 홀수번째 스테이지들의 제1 입력단자는 이전 스테이지의 제2 입력단자에 연결된 제1 서브 클럭신호선에 접속되고, 제2 입력단자는 제2 메인 클럭신호선 및 다음 스테이지의 제1 입력단자에 연결된 제2 서브 클럭신호선에 접속되며, 짹수번째 스테이지들의 제1 입력단자는 이전 스테이지의 제2 입력단자에 연결된 제2 서브 클럭신호선에 접속되고, 제2 입력단자는 제1 메인 클럭신호선 및 다음 스테이지의 제1 입력단자에 접속된 제1 서브 클럭신호선에 접속되는 발광제어 구동부.

#### 청구항 2

제 1 항에 있어서,

상기 제1 메인 클럭신호선 및 상기 제1 서브 클럭신호선은 제1 클럭신호를 전송하고,

상기 제2 메인 클럭신호선 및 상기 제2 서브 클럭신호선은 제2 클럭신호를 전송함을 특징으로 하는 발광제어 구동부.

#### 청구항 3

제 2 항에 있어서,

상기 제1 클럭신호와 상기 제2 클럭신호는 하이전압과 로우전압이 서로 교대로 반복되어 인가됨을 특징으로 하는 발광제어 구동부.

#### 청구항 4

제 3 항에 있어서,

상기 제1 서브 클럭신호선은 상기 짹수번째 스테이지들의 제2 입력단자 및 상기 홀수번째 스테이지들의 제1 입력단자에 접속되며,

상기 제2 서브 클럭신호선은 상기 홀수번째 스테이지들의 제2 입력단자 및 상기 짹수번째 스테이지들의 제1 입력단자에 접속됨을 특징으로 하는 발광제어 구동부.

#### 청구항 5

제 4 항에 있어서,

상기 첫번째 스테이지의 시작단자는 상기 시작신호를 공급받으며,

상기 첫번째 스테이지를 제외한 스테이지들의 시작단자는 이전 스테이지의 발광제어신호를 공급받음을 특징으로

하는 발광제어 구동부.

### 청구항 6

제 5 항에 있어서,

상기 첫번째 스테이지의 제1 입력단자는 상기 제1 메인 클럭신호선을 통해 상기 제1 클럭신호를 입력받고,

상기 첫번째 스테이지를 제외한 홀수번째 스테이지들의 제1 입력단자는 상기 제1 서브 클럭신호선을 통해 상기 제1 클럭신호를 입력받고,

상기 홀수번째 스테이지들의 제2 입력단자는 상기 제2 메인 클럭신호선을 통해 상기 제2 클럭신호를 입력받음을 특징으로 하는 발광제어 구동부.

### 청구항 7

제 5 항에 있어서,

상기 짹수번째 스테이지들의 제1 입력단자는 상기 제2 서브 클럭신호선을 통해 상기 제2 클럭신호를 입력받고, 제2 입력단자는 상기 제1 메인 클럭신호선을 통해 상기 제1 클럭신호를 입력받음을 특징으로 하는 발광제어 구동부.

### 청구항 8

제 1 항에 있어서,

상기 제1 노드와 제8 트랜지스터 사이에 접속되며, 게이트 전극이 제2 입력단자에 접속되는 제5 트랜지스터;

상기 제1 입력단자와 제3 노드 사이에 접속되며, 게이트 전극이 상기 제1 노드에 접속되는 제6 트랜지스터;

상기 제1 전원과 상기 제3 노드 사이에 접속되며, 게이트 전극이 상기 제1 입력단자에 접속되는 제7 트랜지스터;

상기 제2 전원과 상기 제5 트랜지스터 사이에 접속되며, 게이트 전극이 상기 제3 노드에 접속되는 제8 트랜지스터;

상기 제2 입력단자와 제10 트랜지스터 사이에 접속되며, 게이트 전극이 상기 제3 노드에 접속되는 제9 트랜지스터;

상기 제9 트랜지스터와 상기 제2 노드 사이에 접속되며, 게이트 전극이 상기 제2 입력단자에 접속되는 제10 트랜지스터; 및

상기 제10 트랜지스터와 상기 제3 노드 사이에 접속되는 제2 캐패시터를 더 포함함을 특징으로 하는 발광제어 구동부.

### 청구항 9

제 8 항에 있어서,

상기 제2 캐패시터는 상기 제9 트랜지스터의 게이트 전극과 제1 전극 사이에 접속됨을 특징으로 하는 발광제어 구동부.

### 청구항 10

제 8 항에 있어서,

상기 제2 전원과 상기 제2 노드 사이에 접속되는 제3 캐패시터를 더 포함함을 특징으로 하는 발광제어 구동부.

### 청구항 11

주사선들, 데이터선들 및 발광제어선들과 접속되는 화소들을 포함하는 화소부;

상기 주사선들을 통해 각 화소에 주사신호를 공급하는 주사 구동부;

상기 데이터선들을 통해 각 화소에 데이터신호를 공급하는 데이터 구동부; 및

상기 발광제어선들과 각각 접속되는 복수의 스테이지들을 포함하며, 상기 발광제어선들을 통해 각 화소에 발광제어신호를 공급하는 발광제어 구동부를 포함하고,

상기 스테이지들 각각은,

발광제어신호를 출력하는 출력단자와 제1 전원 사이에 접속되며, 게이트 전극이 제1 노드에 접속되는 제1 트랜지스터;

상기 출력단자와 제2 전원 사이에 접속되며, 게이트 전극이 제2 노드에 접속되는 제2 트랜지스터;

상기 제2 전원과 상기 제2 노드 사이에 접속되며, 게이트 전극이 상기 제1 노드에 접속되는 제3 트랜지스터;

시작신호 또는 이전 스테이지의 발광제어신호를 입력받는 시작단자와 상기 제1 노드 사이에 접속되며, 게이트 전극이 제1 입력단자에 접속되는 제4 트랜지스터; 및

제2 입력단자와 상기 제1 노드 사이에 접속되는 제1 캐패시터를 포함하되,

첫번째 스테이지를 제외한 홀수번째 스테이지들의 제1 입력단자는 이전 스테이지의 제2 입력단자에 연결된 제1 서브 클럭신호선에 접속되고, 제2 입력단자는 제2 메인 클럭신호선 및 다음 스테이지의 제1 입력단자에 연결된 제2 서브 클럭신호선에 접속되며,

짝수번째 스테이지들의 제1 입력단자는 이전 스테이지의 제2 입력단자에 연결된 제2 서브 클럭신호선에 접속되고, 제2 입력단자는 제1 메인 클럭신호선 및 다음 스테이지의 제2 입력단자에 접속된 제1 서브 클럭신호선에 접속되는 유기전계발광 표시장치.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 발광제어 구동부 및 이를 포함하는 유기전계발광 표시장치에 관한 것으로, 특히 정전기에 의한 손상을 방지할 수 있는 발광제어 구동부 및 이를 포함하는 유기전계발광 표시장치에 관한 것이다.

### 배경 기술

[0002] 최근 음극선관(Cathode Ray Tube)의 단점인 무게와 부피를 줄일 수 있는 각종 표시장치들이 개발되고 있다. 표시장치로는 액정 표시장치(Liquid Crystal Display Device), 전계방출 표시장치(Field Emission Display Device), 플라즈마 표시패널(Plasma Display Panel) 및 유기전계발광 표시장치(Organic Light Emitting Display Device) 등이 있다.

[0003] 표시장치 중 유기전계발광 표시장치는 전자와 정공의 재결합에 의하여 빛을 발생하는 유기발광 다이오드를 이용하여 영상을 표시한다. 이러한 유기전계발광 표시장치는 빠른 응답속도를 가짐과 동시에 낮은 소비전력으로 구동되는 장점이 있다. 일반적인 유기전계발광 표시장치는 화소마다 형성되는 트랜지스터를 이용하여 데이터 신호에 대응하는 전류를 유기발광 다이오드로 공급함으로써 유기발광 다이오드에서 빛이 발생되도록 한다.

[0004] 이와 같은 유기전계발광 표시장치는 데이터선들로 데이터신호를 공급하기 위한 데이터 구동부, 주사선들로 주사신호를 순차적으로 공급하기 위한 주사 구동부, 발광제어선들로 발광제어신호를 공급하기 위한 발광제어 구동부 및 데이터선들, 주사선들 및 발광제어선들과 접속되는 복수의 화소를 구비하는 화소부를 포함한다.

[0005] 화소부에 포함된 화소들은 해당 주사선으로 주사신호가 공급될 때 선택되어 데이터선으로부터 데이터신호를 공급받는다. 데이터신호를 공급받은 화소들은 데이터신호에 대응하는 휘도의 빛을 생성하면서 소정의 영상을 표시한다. 여기서, 화소들의 발광시간은 발광제어선들로부터 공급되는 발광제어신호에 의하여 제어된다. 일반적으로 발광제어신호는 하나의 주사선 또는 두 개의 주사선들로 공급되는 주사신호와 중첩되도록 공급되면서 데이터신호가 공급되는 화소들을 비발광 상태로 설정한다.

[0006] 이를 위하여, 발광제어 구동부는 발광제어선들 각각과 접속되는 복수의 스테이지들을 구비한다. 각각의 스테이지는 복수의 클럭신호들을 입력받고, 입력된 클럭신호들에 응답하여 발광제어신호를 출력한다.

[0007] 이러한 스테이지들 각각은 다수의 트랜지스터들과 캐패시터로 구성될 수 있다. 그런데, 외부로부터 유입된 정전기가 스테이지를 구성하는 트랜지스터의 게이트에 직접적으로 가해지는 경우, 발광제어 구동부가 손상되고, 화재 등의 위험이 발생할 수 있다.

## 발명의 내용

### 해결하려는 과제

[0008] 따라서, 본 발명의 목적은 정전기에 의한 손상을 방지할 수 있는 발광제어 구동부 및 이를 포함하는 유기전계발광 표시장치를 제공하는 것이다.

### 과제의 해결 수단

[0009] 본 발명의 실시예에 의한 발광제어 구동부는, 복수의 스테이지들을 구비하는 발광제어 구동부에 있어서, 상기 스테이지들 각각은, 발광제어신호를 출력하는 출력단자와 제1 전원 사이에 접속되며, 게이트 전극이 제1 노드에 접속되는 제1 트랜지스터; 상기 출력단자와 제2 전원 사이에 접속되며, 게이트 전극이 제2 노드에 접속되는 제2 트랜지스터; 상기 제2 전원과 상기 제2 노드 사이에 접속되며, 게이트 전극이 상기 제1 노드에 접속되는 제3 트랜지스터; 시작신호 또는 이전 스테이지의 발광제어신호를 입력받는 시작단자와 상기 제1 노드 사이에 접속되며, 게이트 전극이 제1 입력단자에 접속되는 제4 트랜지스터; 및 제2 입력단자와 상기 제1 노드 사이에 접속되는 제1 캐패시터를 포함하되, 첫번째 스테이지를 제외한 홀수번째 스테이지들의 제1 입력단자는 이전 스테이지의 제2 입력단자에 연결된 제1 서브 클럭신호선에 접속되고, 제2 입력단자는 제2 메인 클럭신호선 및 다음 스테이지의 제1 입력단자에 연결된 제2 서브 클럭신호선에 접속되며, 짹수번째 스테이지들의 제1 입력단자는 이전 스테이지의 제2 입력단자에 연결된 제2 서브 클럭신호선에 접속되고, 제2 입력단자는 제1 메인 클럭신호선 및 다음 스테이지의 제1 입력단자에 접속된 제1 서브 클럭신호선에 접속된다.

[0010] 일 실시예에서, 상기 제1 메인 클럭신호선 및 상기 제1 서브 클럭신호선은 제1 클럭신호를 전송하고, 상기 제2 메인 클럭신호선 및 상기 제2 서브 클럭신호선은 제2 클럭신호를 전송할 수 있다. 일 실시예에서, 상기 제1 클럭신호와 상기 제2 클럭신호는 하이전압과 로우전압이 서로 교대로 반복되어 인가될 수 있다.

[0011] 일 실시예에서, 상기 제1 서브 클럭신호선은 상기 짹수번째 스테이지들의 제2 입력단자 및 상기 홀수번째 스테이지들의 제1 입력단자에 접속되며, 상기 제2 서브 클럭신호선은 상기 홀수번째 스테이지들의 제2 입력단자 및 상기 짹수번째 스테이지들의 제1 입력단자에 접속될 수 있다. 일 실시예에서, 상기 첫번째 스테이지의 시작단자는 상기 시작신호를 공급받으며, 상기 첫번째 스테이지를 제외한 스테이지들의 시작단자는 이전 스테이지의 발광제어신호를 공급받을 수 있다.

[0012] 일 실시예에서, 상기 첫번째 스테이지의 제1 입력단자는 상기 제1 메인 클럭신호선을 통해 상기 제1 클럭신호를 입력받고, 상기 첫번째 스테이지를 제외한 홀수번째 스테이지들의 제1 입력단자는 상기 제1 서브 클럭신호선을 통해 상기 제1 클럭신호를 입력받고, 상기 홀수번째 스테이지들의 제2 입력단자는 상기 제2 메인 클럭신호선을 통해 상기 제2 클럭신호를 입력받을 수 있다.

[0013] 일 실시예에서, 상기 짹수번째 스테이지들의 제1 입력단자는 상기 제2 서브 클럭신호선을 통해 상기 제2 클럭신호를 입력받고, 제2 입력단자는 상기 제1 메인 클럭신호선을 통해 상기 제1 클럭신호를 입력받을 수 있다.

[0014] 일 실시예에서, 상기 제1 노드와 제8 트랜지스터 사이에 접속되며, 게이트 전극이 제2 입력단자에 접속되는 제5 트랜지스터; 상기 제1 입력단자와 상기 제3 노드 사이에 접속되며, 게이트 전극이 상기 제1 노드에 접속되는 제6 트랜지스터; 상기 제1 전원과 상기 제3 노드 사이에 접속되며, 게이트 전극이 상기 제1 입력단자에 접속되는 제7 트랜지스터; 상기 제2 전원과 상기 제5 트랜지스터 사이에 접속되며, 게이트 전극이 상기 제3 노드에 접속되는 제8 트랜지스터; 상기 제2 입력단자와 제10 트랜지스터 사이에 접속되며, 게이트 전극이 상기 제3 노드에 접속되는 제9 트랜지스터; 상기 제9 트랜지스터와 상기 제2 노드 사이에 접속되며, 게이트 전극이 제2 입력단자에 접속되는 제10 트랜지스터; 및 상기 제10 트랜지스터와 상기 제3 노드 사이에 접속되는 제2 캐패시터를 더 포함할 수 있다.

[0015] 일 실시예에서, 상기 제2 캐패시터는 상기 제9 트랜지스터의 게이트 전극과 제1 전극 사이에 접속될 수 있다. 일 실시예에서, 상기 제2 전원과 상기 제2 노드 사이에 접속되는 제3 캐패시터를 더 포함할 수 있다.

[0016] 본 발명의 실시예에 의한 유기전계발광 표시장치는, 주사선들, 데이터선들 및 발광제어선들과 접속되는 화소들을 포함하는 화소부; 상기 주사선들을 통해 각 화소에 주사신호를 공급하는 주사 구동부; 상기 데이터선들을 통

해 각 화소에 데이터신호를 공급하는 데이터 구동부; 및 상기 발광제어선들과 각각 접속되는 복수의 스테이지들을 포함하며, 상기 발광제어선들을 통해 각 화소에 발광제어신호를 공급하는 발광제어 구동부를 포함하고, 상기 스테이지들 각각은, 발광제어신호를 출력하는 출력단자와 제1 전원 사이에 접속되며, 게이트 전극이 제1 노드에 접속되는 제1 트랜지스터; 상기 출력단자와 제2 전원 사이에 접속되며, 게이트 전극이 제2 노드에 접속되는 제2 트랜지스터; 상기 제2 전원과 상기 제2 노드 사이에 접속되며, 게이트 전극이 상기 제1 노드에 접속되는 제3 트랜지스터; 시작신호 또는 이전 스테이지의 발광제어신호를 입력받는 시작단자와 상기 제1 노드 사이에 접속되며, 게이트 전극이 제1 입력단자에 접속되는 제4 트랜지스터; 및 제2 입력단자와 상기 제1 노드 사이에 접속되는 제1 캐패시터를 포함하되, 첫번째 스테이지를 제외한 홀수번째 스테이지들의 제1 입력단자는 이전 스테이지의 제2 입력단자에 연결된 제1 서브 클럭신호선에 접속되고, 제2 입력단자는 제2 메인 클럭신호선 및 다음 스테이지의 제1 입력단자에 연결된 제2 서브 클럭신호선에 접속되며, 짹수번째 스테이지들의 제1 입력단자는 이전 스테이지의 제2 입력단자에 연결된 제2 서브 클럭신호선에 접속되고, 제2 입력단자는 제1 메인 클럭신호선 및 다음 스테이지의 제2 입력단자에 접속된 제1 서브 클럭신호선에 접속된다.

### 발명의 효과

[0017]

이와 같은 본 발명에 의하면, 현재 스테이지의 입력단자는 이전 스테이지의 캐패시터에 연결된 입력단자에 연결된 서브 클럭신호선에 접속됨으로써, 서브 클럭신호선과 연결되는 트랜지스터의 게이트에 정전기가 직접적으로 가해지는 현상을 방지하고, 발광제어 구동부의 손상과 화재 등의 위험을 방지할 수 있다.

### 도면의 간단한 설명

[0018]

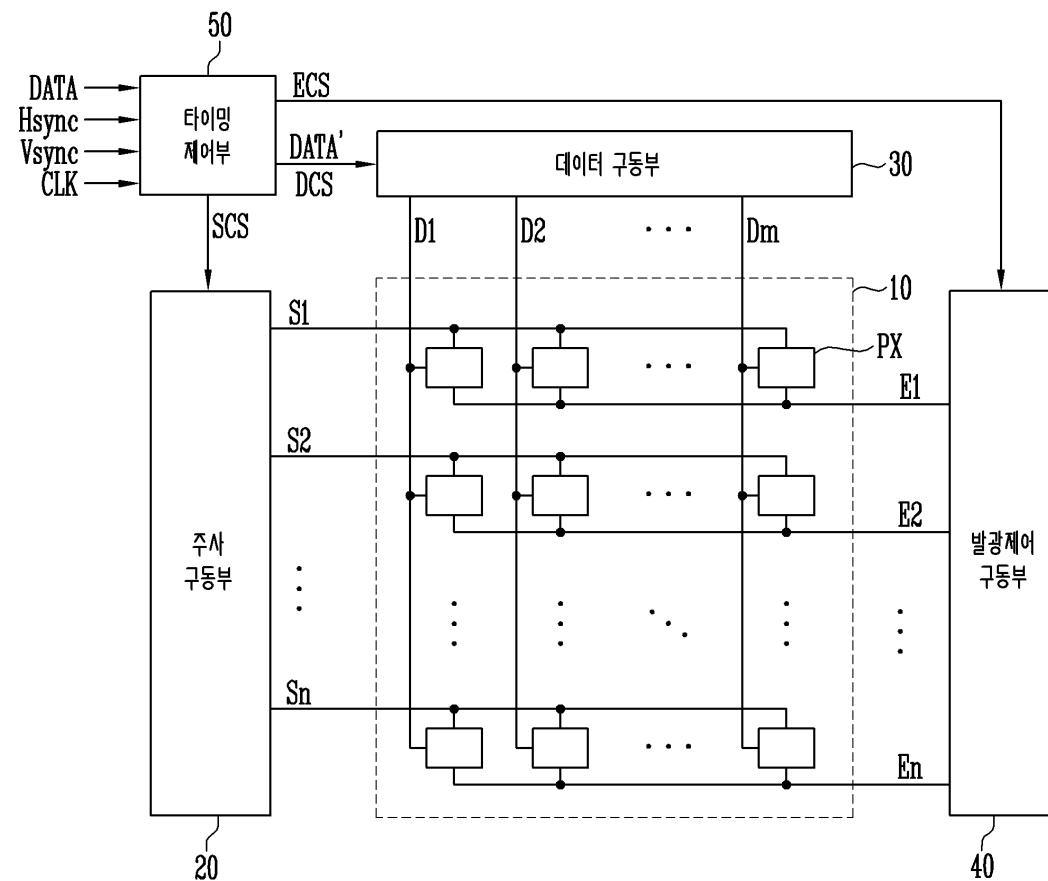

도 1은 본 발명의 일 실시예에 따른 유기전계발광 표시장치의 개략적인 구성도이다.

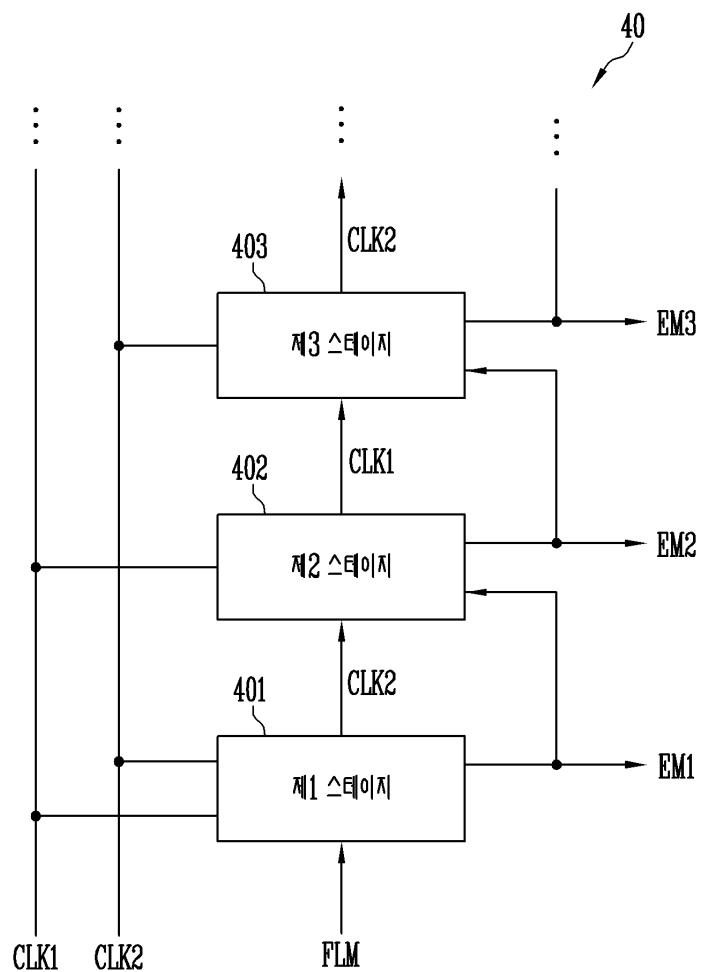

도 2는 도 1에 도시된 발광제어 구동부의 세부 구성도이다.

도 3은 도 2에 도시된 스테이지들의 회로도이다.

도 4는 도 3에 도시된 제1 스테이지의 동작을 나타내는 파형도이다.

### 발명을 실시하기 위한 구체적인 내용

[0019]

이하, 첨부된 도면을 참조하여 본 발명의 실시예를 보다 상세히 설명하도록 한다.

[0020]

도 1은 본 발명의 일 실시예에 따른 유기전계발광 표시장치의 개략적인 구성도이다.

[0021]

도 1을 참조하면, 본 발명의 일 실시예에 따른 유기전계발광 표시장치는 화소부(10), 주사 구동부(20), 데이터 구동부(30), 발광제어 구동부(40) 및 타이밍 제어부(50)를 포함할 수 있다.

[0022]

화소부(10)는 주사선들(S1~Sn), 데이터선들(D1~Dm) 및 발광제어선들(E1~En)과 접속되어 매트릭스 형태로 배열된 복수의 화소들(PX)을 포함한다. 화소들(PX)은 주사선들(S1~Sn)을 통해 주사신호를 입력받고, 데이터선들(D1~Dm)을 통해 데이터신호를 입력받고, 발광제어선들(E1~En)을 통해 발광제어신호를 입력받는다. 화소들(PX)은 주사선들(S1~Sn)로부터 주사신호가 공급될 때 데이터선들(D1~Dm)로부터 공급되는 데이터 신호에 대응하는 휘도로 발광한다.

[0023]

주사 구동부(20)는 복수의 주사선들(S1~Sn)과 연결되며, 타이밍 제어부(50)의 주사구동 제어신호(SCS)에 응답하여 주사신호를 생성하고, 생성된 주사신호를 주사선들(S1~Sn)로 출력한다. 주사 구동부(20)는 복수개의 스테이지 회로로 구성될 수 있으며, 주사선들(S1~Sn)로 주사신호가 순차적으로 공급되면 화소들(PX)이 수평라인 단위로 선택된다.

[0024]

데이터 구동부(30)는 복수의 데이터선들(D1~Dm)과 연결되며, 타이밍 제어부(50)의 데이터구동 제어신호(DCS)와 영상 데이터(DATA')에 기초하여 데이터신호를 생성하고, 생성된 데이터신호를 데이터선들(D1~Dm)로 출력한다. 데이터선들(D1~Dm)로 공급된 데이터신호는 주사신호가 공급될 때마다 주사신호에 의해 선택된 화소들(PX)로 공급된다. 그러면, 화소들(PX)은 데이터신호에 대응하는 전압을 충전할 수 있다.

[0025]

발광제어 구동부(40)는 복수의 발광제어선들(E1~En)과 연결되며, 타이밍 제어부(50)의 발광구동 제어신호(ECS)에 응답하여 발광제어신호를 생성하고, 생성된 발광제어신호를 발광제어선들(E1~En)로 출력한다. 발광제어 구동부(40)는 복수개의 스테이지 회로로 구성될 수 있으며, 발광제어선들(E1~En)로 발광제어신호를 공급하여 화소들(PX)의 발광기간을 제어한다.

- [0026] 타이밍 제어부(50)는 영상 데이터(DATA) 및 이의 표시를 제어하기 위한 동기신호들(Hsync, Vsync) 및 클럭신호(CLK) 등을 입력 받는다. 타이밍 제어부(50)는 입력되는 영상 데이터(DATA)를 영상 처리하여 화소부(10)의 영상 표시에 적합하도록 보정된 영상 데이터(DATA')를 생성하여 데이터 구동부(30)에 출력한다. 또한, 타이밍 제어부(50)는 상기 동기신호들(Hsync, Vsync)과 클럭신호(CLK)에 기초하여 주사 구동부(20), 데이터 구동부(30) 및 발광제어 구동부(40)의 구동을 제어하기 위한 구동 제어신호들(SCS, DCS, ECS)을 생성할 수 있다. 구체적으로, 타이밍 제어부(50)는 주사구동 제어신호(SCS)를 생성하여 주사 구동부(20)로 공급하고, 데이터구동 제어신호(DCS)를 생성하여 데이터 구동부(30)로 공급하며, 발광구동 제어신호(ECS)를 생성하여 발광제어 구동부(40)로 공급할 수 있다.

- [0027] 도 2는 도 1에 도시된 발광제어 구동부의 세부 구성도이다.

- [0028] 도 2를 참조하면, 본 발명의 발광제어 구동부(40)는 발광제어선들(E1~En)로 발광제어신호를 공급하기 위하여 복수의 스테이지들(401, 402, 403, ...)을 구비한다. 단, 본 실시예에서는 설명의 편의를 위하여 3개의 스테이지(401, 402, 403)만을 도시하기로 한다. 스테이지들(401, 402, 403)은 시작신호(FLM)와 제1 및 제2 클럭신호들(CLK1, CLK2)에 의하여 구동되며, 각각의 발광제어신호(EM1, EM2, EM3)를 출력한다. 타이밍 제어부(50)로부터의 발광구동 제어신호(ECS)는 시작신호(FLM)와 제1 및 제2 클럭신호들(CLK1, CLK2)를 포함할 수 있다.

- [0029] 스테이지들(401, 402, 403) 중 제1 스테이지(401)는 시작신호(FLM)를 입력받으며, 제1 스테이지(401)를 제외한 스테이지들(402, 403)은 이전 스테이지의 발광제어신호(EM2, EM3, EM4)를 입력받는 구조를 갖는다. 또한, 제1 스테이지(401)는 제1 및 제2 클럭신호들(CLK1, CLK2)을 직접적으로 입력받으며, 제1 스테이지(401)를 제외한 스테이지들(402, 403)은 제1 및 제2 클럭신호들(CLK1, CLK2) 중 어느 하나를 이전 스테이지로부터 전달받는다. 구체적으로, 제1 스테이지(401)를 제외한 홀수번째 스테이지인 제3 스테이지(403)는 제1 클럭신호(CLK1)를 이전 스테이지로부터 전달받고, 제2 클럭신호(CLK2)를 직접적으로 입력받는다. 짝수번째 스테이지인 제2 및 제4 스테이지(402, 404)는 각각 제1 클럭신호(CLK1)를 직접적으로 입력받고, 제2 클럭신호(CLK2)는 이전 스테이지로부터 전달받는다.

- [0030] 제1 스테이지(401)는 시작신호(FLM)와 제1 및 제2 클럭신호들(CLK1, CLK2)에 응답하여 제1 발광제어신호(EM1)를 출력하고, 제2 스테이지(402)로 제2 클럭신호(CLK2)와 제1 발광제어신호(EM1)를 전달한다. 제2 스테이지(402)는 직접적으로 입력되는 제1 클럭신호(CLK1)와 제1 스테이지(401)로부터 전달된 제2 클럭신호(CLK2) 및 제1 발광제어신호(EM1)에 응답하여 제2 발광제어신호(EM2)를 출력하고, 제3 스테이지(403)로 제1 클럭신호(CLK1)와 제2 발광제어신호(EM2)를 전달한다. 제3 스테이지(403)는 직접적으로 입력되는 제2 클럭신호(CLK2)와 제2 스테이지(402)로부터 전달된 제1 클럭신호(CLK1) 및 제2 발광제어신호(EM2)에 응답하여 제3 발광제어신호(EM3)를 출력하고, 제4 스테이지(미도시)로 제2 클럭신호(CLK2)와 제3 발광제어신호(EM3)를 전달한다.

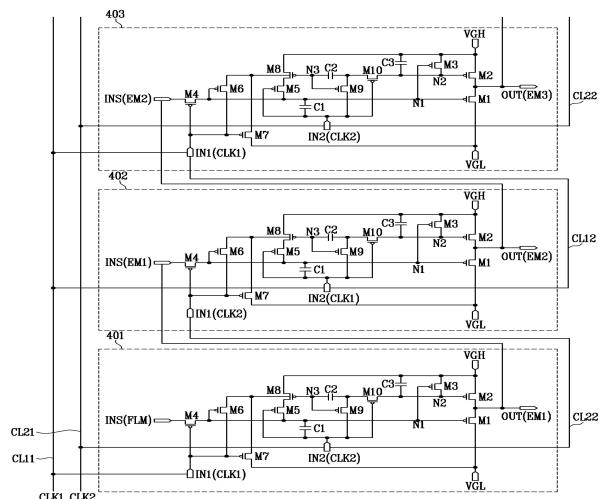

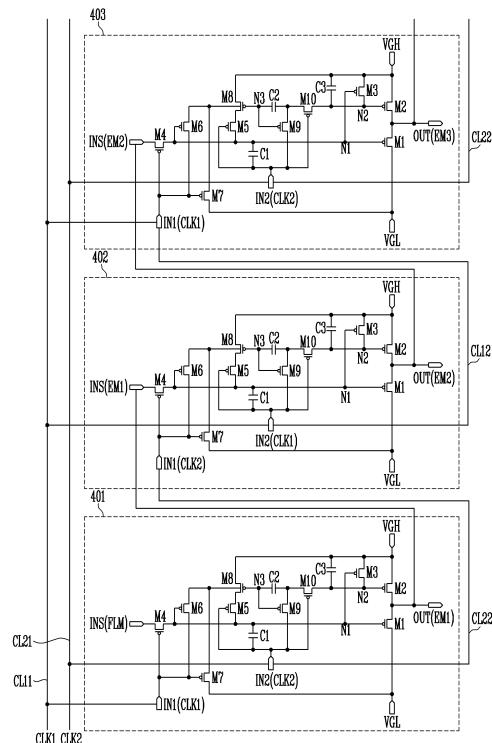

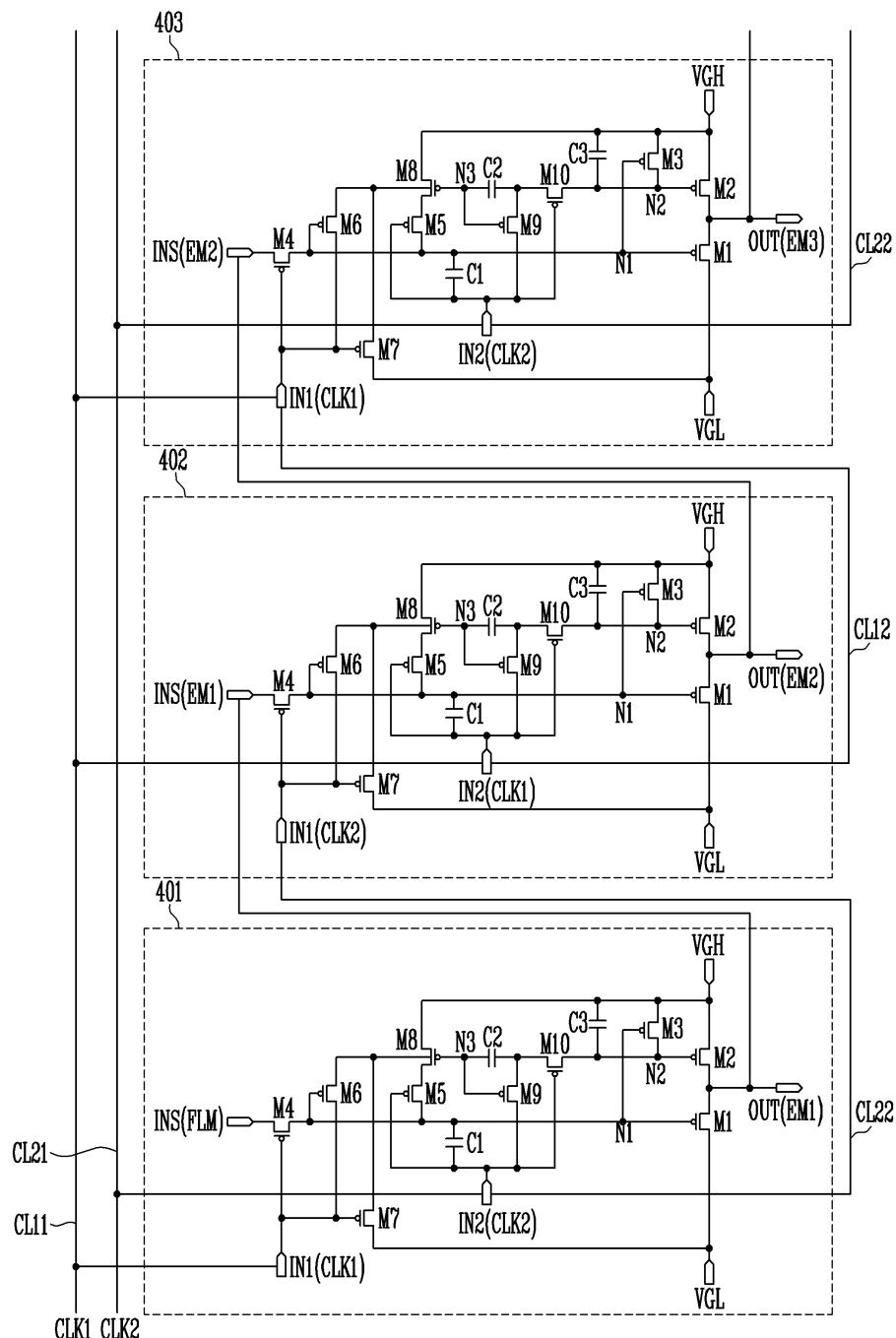

- [0031] 도 3은 본 발명의 도 2에 도시된 스테이지들의 회로도이다.

- [0032] 도 3을 참조하면, 본 발명의 일 실시예에 따른 스테이지들(401, 402, 403) 각각은 제1 내지 제10 트랜지스터(M1 내지 M10)와 제1 내지 제3 캐패시터(C1 내지 C3)를 포함한다. 제1 메인 클럭신호선(CL11)과 제1 서브 클럭신호선(CL12)은 제1 클럭신호(CLK1)를 전송하고, 제2 메인 클럭신호선(CL21)과 제2 서브 클럭신호선(CL22)은 제2 클럭신호(CLK2)를 전송한다.

- [0033] 제1 트랜지스터(M1)는 발광제어신호를 출력하는 출력단자(OUT)와 제1 전원(VGL) 사이에 접속되며, 게이트 전극이 제1 노드(N1)에 접속된다. 이와 같은 제1 트랜지스터(M1)는 제1 노드(N1)에 인가되는 전압에 대응하여 출력단자(OUT)의 전압을 제어한다. 예컨대, 제1 트랜지스터(M1)가 턴-온되면 로우(low)전압의 제1 전원(VGL)이 출력단자(OUT)로 공급되고, 출력단자(OUT)는 로우전압의 발광제어신호를 출력한다.

- [0034] 제2 트랜지스터(M2)는 출력단자(OUT)와 제2 전원(VGH) 사이에 접속되며, 게이트 전극이 제2 노드(N2)에 접속된다. 이와 같은 제2 트랜지스터(M2)는 제2 노드(N2)에 인가되는 전압에 대응하여 출력단자(OUT)의 전압을 제어한다. 예컨대, 제2 트랜지스터(M2)가 턴-온되면 하이(high)전압의 제2 전원(VGH)이 출력단자(OUT)로 공급되고, 출력단자(OUT)는 하이전압의 발광제어신호를 출력한다.

- [0035] 제3 트랜지스터(M3)는 제2 전원(VGH)과 제2 노드(N2) 사이에 접속되며, 게이트 전극이 제1 노드(N1)에 접속된다. 이와 같은 제3 트랜지스터(M3)는 제1 노드(N1)에 인가되는 전압에 대응하여 턴-온 또는 턴-오프되면서 제2 노드(N2)의 전압을 제어한다. 예컨대, 제3 트랜지스터(M3)는 제1 노드(N1)로 로우전압이 인가되는 경우 턴-온되어 제2 노드(N2)로 하이전압의 제2 전원(VGH)을 공급한다. 따라서, 제1 노드(N1)로 로우전압이 인가되는 경우 제2 노드(N2)로는 하이전압이 공급되므로, 제1 및 제2 트랜지스터(M1, M2)는 서로 다른 시간에 턴-온 또는

턴-오프된다.

[0036] 제4 트랜지스터(M4)는 시작단자(INS)와 제1 노드(N1) 사이에 접속되며, 게이트 전극이 제1 입력단자(IN1)에 접속된다. 제4 트랜지스터(M4)는 제1 입력단자(IN1)로 공급되는 제1 클럭신호(CLK1) 또는 제2 클럭신호(CLK2)에 응답하여 턴-온 또는 턴-오프된다. 제4 트랜지스터(M4)가 턴-온되면 시작단자(INS)와 제1 노드(N1)가 전기적으로 접속된다. 제4 트랜지스터(M4)가 턴-온되면, 시작신호(FLM) 또는 이전 스테이지의 발광제어신호가 제1 노드(N1)로 공급되고, 제1 트랜지스터(M1)는 제1 노드(N1)의 전압에 대응하여 턴-온된다.

[0037] 여기서, 시작단자(INS)는 시작신호(FLM) 또는 이전 스테이지의 발광제어신호를 입력받는다. 첫번째 스테이지의 시작단자(INS)는 시작신호(FLM)를 입력받고, 첫번째 스테이지를 제외한 스테이지의 시작단자(INS)는 이전 스테이지의 발광제어신호를 입력받는다. 예컨대, 제1 스테이지(401)의 시작단자(INS)는 시작신호(FLM)를 입력받는다. 제2 스테이지(402)의 시작단자(INS)는 제1 스테이지(401)의 출력단자(OUT)에 접속되어 제1 발광제어신호(EM1)를 입력받는다. 제3 스테이지(403)의 시작단자(INS)는 제2 스테이지(402)의 출력단자(OUT)에 접속되어 제2 발광제어신호(EM2)를 입력받는다.

[0038] 제1 입력단자(IN1)는 제1 클럭신호(CLK1) 또는 제2 클럭신호(CLK2)를 입력받는다. 구체적으로, 첫번째 스테이지를 제외한 홀수번째 스테이지들의 제1 입력단자(IN1)는 이전 스테이지의 제2 입력단자(IN2)에 연결된 제1 서브클럭신호선(CL12)에 접속되고, 제1 서브클럭신호선(CL12)을 통해 제1 클럭신호(CLK1)를 입력받는다. 단, 첫번째 스테이지는 이전 스테이지가 없으므로, 첫번째 스테이지의 제1 입력단자(IN1)는 제1 메인 클럭신호선(CL11)에 접속되고, 제1 메인 클럭신호선(CL11)을 통해 제1 클럭신호(CLK1)를 입력받는다. 짹수번째 스테이지들의 제1 입력단자(IN1)는 이전 스테이지의 제2 입력단자(IN2)에 연결된 제2 서브클럭신호선(CL22)에 접속되고, 제2 서브클럭신호선(CL22)을 통해 제2 클럭신호(CLK2)를 입력받는다.

[0039] 예를 들면, 제1 스테이지(401)의 제1 입력단자(IN1)는 제1 메인 클럭신호선(CL11)을 통해 제1 클럭신호(CLK1)를 입력받는다. 제2 스테이지(402)의 제1 입력단자(IN1)는 제1 스테이지(401)의 제2 입력단자(IN2)에 연결된 제2 서브클럭신호선(CL22)에 접속되고, 제2 서브클럭신호선(CL22)을 통해 제2 클럭신호(CLK2)를 입력받는다. 제3 스테이지(403)의 제1 입력단자(IN1)는 제2 스테이지(402)의 제2 입력단자(IN2)에 연결된 제1 서브클럭신호선(CL12)에 접속되고, 제1 서브클럭신호선(CL12)을 통해 제1 클럭신호(CLK1)를 입력받는다.

[0040] 제5 트랜지스터(M5)는 제1 노드(N1)와 제8 트랜지스터(M8) 사이에 접속되며, 게이트 전극이 제2 입력단자(IN2)에 접속된다. 제5 트랜지스터(M5)는 제2 입력단자(IN2)로 공급되는 제1 클럭신호(CLK1) 또는 제2 클럭신호(CLK2)에 응답하여 턴-온 또는 턴-오프된다. 예컨대, 제2 입력단자(IN2)로 로우전압의 제1 클럭신호(CLK1) 또는 제2 클럭신호(CLK2)가 인가되는 경우 제5 트랜지스터(M5)가 턴-온된다.

[0041] 여기서, 제2 입력단자(IN2)는 제1 클럭신호(CLK1) 또는 제2 클럭신호(CLK2)를 입력받는다. 구체적으로, 홀수번째 스테이지들의 제2 입력단자(IN2)는 제2 메인 클럭신호선(CL21)에 접속되며, 제2 메인 클럭신호선(CL21)을 통해 제2 클럭신호(CLK2)를 입력받는다. 또한, 홀수번째 스테이지들의 제2 입력단자(IN2)는 다음 스테이지의 제1 입력단자(IN1)에 연결된 제2 서브클럭신호선(CL22)에 접속된다. 짹수번째 스테이지들의 제2 입력단자(IN2)는 제1 메인 클럭신호선(CL11)에 접속되고, 제1 메인 클럭신호선(CL11)을 통해 제1 클럭신호(CLK1)를 입력받는다. 또한, 짹수번째 스테이지들의 제2 입력단자(IN2)는 다음 스테이지의 제1 입력단자(IN1)에 접속된 제1 서브클럭신호선(CL12)에 접속된다.

[0042] 예를 들면, 제1 스테이지(401)의 제2 입력단자(IN2)는 제2 메인 클럭신호선(CL21)을 통해 제2 클럭신호(CLK2)를 입력받고, 제2 스테이지(402)의 제1 입력단자(IN1)에 연결된 제2 서브클럭신호선(CL22)에 접속된다. 즉, 제1 스테이지(401)로 공급된 제2 클럭신호(CLK2)는 제1 스테이지(401)를 경과하여 제2 스테이지(402)로 전달된다. 제2 스테이지(402)의 제2 입력단자(IN2)는 제1 메인 클럭신호선(CL11)을 통해 제1 클럭신호(CLK1)를 입력받고, 제3 스테이지(403)의 제1 입력단자(IN1)에 접속된 제1 서브클럭신호선(CL12)에 접속된다. 즉, 제2 스테이지(402)로 공급된 제1 클럭신호(CLK1)는 제2 스테이지(402)를 경과하여 제3 스테이지(403)로 전달된다.

[0043] 제1 캐패시터(C1)는 제2 입력단자(IN2)와 제1 노드(N1) 사이에 접속된다. 제1 캐패시터(C1)는 제2 입력단자(IN2)로 공급되는 제1 클럭신호(CLK1) 또는 제2 클럭신호(CLK2)에 대응하여 제1 노드(N1)의 전압을 제어한다.

[0044] 제6 트랜지스터(M6)는 제1 입력단자(IN1)와 제3 노드(N3) 사이에 접속되며, 게이트 전극이 제1 노드(N1)에 접속된다. 이와 같은 제6 트랜지스터(M6)는 제1 노드(N1)에 인가되는 전압에 대응하여 턴-온 또는 턴-오프되면서 제3 노드(N3)의 전압을 제어한다. 예컨대, 제6 트랜지스터(M6)는 제1 노드(N1)로 로우전압이 인가되는 경우 턴-온되어 제1 입력단자(IN1)에 인가되는 제1 클럭신호(CLK1) 또는 제2 클럭신호(CLK2)에 대응되는 전압을 제3 노드

(N3)로 공급한다.

[0045] 제7 트랜지스터(M7)는 제1 전원(VGL)과 제3 노드(N3) 사이에 접속되며, 게이트 전극이 제1 입력단자(IN1)에 접속된다. 이와 같은 제7 트랜지스터(M7)는 제1 입력단자(IN1)로 공급되는 제1 클럭신호(CLK1) 또는 제2 클럭신호(CLK2)에 응답하여 턴-온 또는 턴-오프되면서 제3 노드(N3)의 전압을 제어한다. 예컨대, 제7 트랜지스터(M7)는 제1 입력단자(IN1)로 로우전압의 제1 클럭신호(CLK1) 또는 제2 클럭신호(CLK2)가 인가되는 경우 턴-온되어 로우전압의 제1 전원(VGL)을 제3 노드(N3)로 공급한다.

[0046] 제8 트랜지스터(M8)는 제2 전원(VGH)과 제5 트랜지스터(M5) 사이에 접속되며, 게이트 전극이 제3 노드(N3)에 접속된다. 이와 같은 제8 트랜지스터(M8)는 제3 노드(N3)에 인가되는 전압에 대응하여 턴-온 또는 턴-오프되면서 제2 전원(VGH)과 제5 트랜지스터(M5)를 전기적으로 접속시키거나 차단시킨다.

[0047] 제9 트랜지스터(M9)는 제2 입력단자(IN2)와 제10 트랜지스터(M10) 사이에 접속되며, 게이트 전극이 제3 노드(N3)에 접속된다. 이와 같은 제9 트랜지스터(M9)는 제3 노드(N3)에 인가되는 전압에 대응하여 턴-온 또는 턴-오프되면서, 제2 입력단자(IN2)와 제10 트랜지스터(M10)를 전기적으로 접속시키거나 차단시킨다.

[0048] 제10 트랜지스터(M10)는 제9 트랜지스터(M9)와 제2 노드(N2) 사이에 접속되며, 게이트 전극이 제2 입력단자(IN2)에 접속된다. 제10 트랜지스터(M10)는 제2 입력단자(IN2)로 공급되는 제1 클럭신호(CLK1) 또는 제2 클럭신호(CLK2)에 응답하여 턴-온 또는 턴-오프된다. 예컨대, 제2 입력단자(IN2)로 로우전압의 제1 클럭신호(CLK1) 또는 제2 클럭신호(CLK2)가 인가되는 경우 제10 트랜지스터(M10)가 턴-온되어 제9 트랜지스터(M9)와 제2 노드(N2)가 전기적으로 접속된다.

[0049] 제2 캐패시터(C2)는 제3 노드(N3)와 제10 트랜지스터(M10) 사이에 접속된다. 제2 캐패시터(C2)는 제9 트랜지스터(M9)의 게이트 전극과 제1 전극 사이에 접속된다. 이와 같은 제2 캐패시터(C2)는 양 단의 전압차에 대응하는 전압을 충전하고 플로팅시 전압차를 유지한다.

[0050] 제3 캐패시터(C3)는 제2 전원(VGH)과 제2 노드(N2) 사이에 접속된다. 이와 같은 제3 캐패시터(C3)는 제2 전원(VGH)과 제2 노드(N2) 사이의 전압차에 대응하는 전압을 충전하고 플로팅시 전압차를 유지한다.

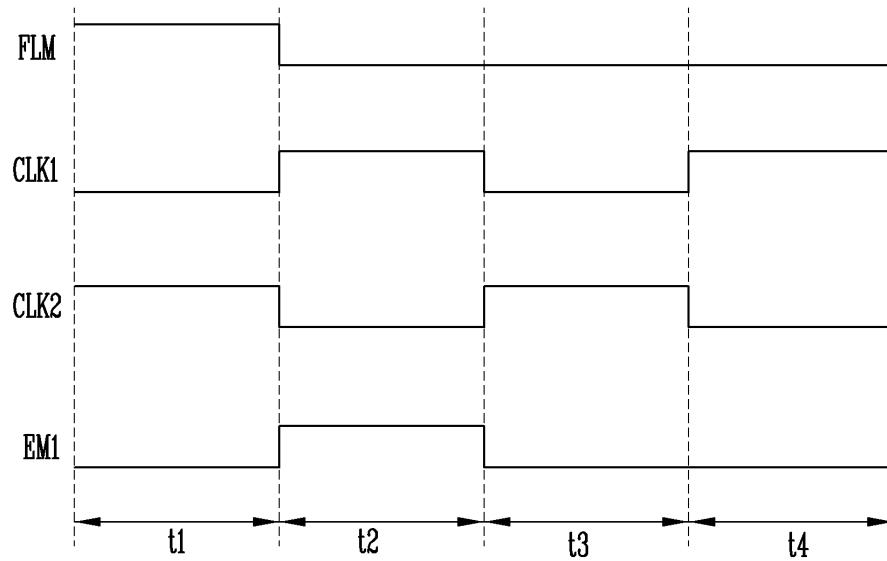

[0051] 도 4는 도 3에 도시된 제1 스테이지의 동작을 나타내는 과정도이다.

[0052] 전술된 도 3과 함께 도 4를 참조하면, 제1 스테이지(401)는 시작단자(INS)로 시작신호(FLM)를 입력받고, 제1 입력단자(IN1)로 제1 클럭신호(CLK1)를 입력받으며, 제2 입력단자(IN2)로 제2 클럭신호(CLK2)를 입력받는다. 그리고, 제1 스테이지(401)의 출력단자(OUT)는 제1 발광제어신호(EM1)를 출력한다. 여기서, 제1 클럭신호(CLK1)와 제2 클럭신호(CLK2)는 하이전압과 로우전압이 서로 교대로 반복되어 인가된다.

[0053] 먼저, 제1 기간(t1) 동안, 시작신호(FLM)는 하이전압이고, 제1 클럭신호(CLK1)는 로우전압이고, 제2 클럭신호(CLK2)는 하이전압이다. 제1 클럭신호(CLK1)가 로우전압이면 제4 및 제7 트랜지스터(M4, M7)는 턴-온된다. 턴-온된 제4 트랜지스터(M4)를 통해 하이전압의 시작신호(FLM)가 제1 노드(N1)로 공급된다. 제1 노드(N1)가 하이전압이면 제1, 제3 및 제6 트랜지스터(M1, M3, M6)는 턴-오프된다. 또한, 턴-온된 제7 트랜지스터(M7)를 통해 로우전압의 제1 전원(VGL)이 제3 노드(N3)로 공급된다. 제3 노드(N3)가 로우전압이면 제8 및 제9 트랜지스터(M8, M9)는 턴-온된다.

[0054] 한편, 제2 클럭신호(CLK2)가 하이전압이면 제5 및 제10 트랜지스터(M5, M10)는 턴-오프된다. 제2 노드(N2)에 전압을 공급하는 제3 및 제10 트랜지스터(M3, M10)가 턴-오프 상태이므로, 제2 트랜지스터(M2)의 게이트 전극은 플로팅되어 이전 상태를 유지한다. 출력단자(OUT)의 전압을 제어하는 제1 트랜지스터(M1)는 턴-오프되고 제2 트랜지스터(M2)의 이전 상태가 턴-오프 상태라면, 출력단자(OUT)는 플로팅되고 이전 상태의 전압을 유지한다. 본 실시예에서 출력단자(OUT)의 이전 상태는 로우전압임을 가정한다. 따라서, 제1 기간(t1) 동안 제1 스테이지(401)는 로우전압의 제1 발광제어신호(EM1)를 출력한다.

[0055] 다음으로, 제2 기간(t2) 동안, 시작신호(FLM)는 로우전압이고, 제1 클럭신호(CLK1)는 하이전압이고, 제2 클럭신호(CLK2)는 로우전압이다. 제1 클럭신호(CLK1)가 하이전압이면 제4 및 제7 트랜지스터(M4, M7)는 턴-오프된다. 제3 노드(M3)에 전압을 공급하는 제6 및 제7 트랜지스터(M4, M7)가 턴-오프되므로, 제3 노드(M3)는 플로팅되어 이전 상태인 로우전압을 유지한다. 제3 노드(N3)가 로우전압이면 제8 및 제9 트랜지스터(M8, M9)는 턴-온된다.

[0056] 한편, 제2 클럭신호(CLK2)가 로우전압이면 제5 및 제10 트랜지스터(M5, M10)는 턴-온된다. 턴-온된 제5 및 제8 트랜지스터(M5, M8)를 통해 하이전압의 제2 전원(VGH)이 제1 노드(N1)에 공급된다. 제1 노드(N1)가 하이전압이면 제1, 제3 및 제6 트랜지스터(M1, M3, M6)는 턴-오프된다. 또한, 턴-온된 제9 및 제10 트랜지스터(M9, M10)를

통해 로우전압의 제2 클럭신호(CLK2)가 제2 노드(N2)에 공급된다. 제2 노드(N2)가 로우전압이면 제2 트랜지스터(M2)는 턴-온되어 하이전압의 제2 전원(VGH)이 출력단자(OUT)에 공급된다. 따라서, 제2 기간(t2) 동안 제1 스테이지(401)는 하이전압의 제1 발광제어신호(EM1)를 출력한다.

[0057] 다음으로, 제3 기간(t3) 동안, 시작신호(FLM)는 로우전압이고, 제1 클럭신호(CLK1)는 로우전압이고, 제2 클럭신호(CLK2)는 하이전압이다. 제1 클럭신호(CLK1)가 로우전압이면 제4 및 제7 트랜지스터(M4, M7)는 턴-온된다. 턴-온된 제4 트랜지스터(M4)를 통해 로우전압의 시작신호(FLM)가 제1 노드(N1)로 공급된다. 제1 노드(N1)가 로우전압이면 제1, 제3 및 제6 트랜지스터(M1, M3, M6)는 턴-온된다. 턴-온된 제1 트랜지스터(M1)를 통해 로우전압의 제1 전원(VGL)이 출력단자(OUT)에 공급된다. 또한, 턴-온된 제3 트랜지스터(M3)를 통해 하이전압의 제2 전원(VGH)이 제2 노드(N2)에 공급된다. 제2 노드(N2)가 하이전압이면 제2 트랜지스터(M2)는 턴-오프된다. 따라서, 제3 기간(t3) 동안 제1 스테이지(401)는 로우전압의 제1 발광제어신호(EM1)를 출력한다.

[0058] 다음으로, 제4 기간(t4) 동안, 시작신호(FLM)는 로우전압이고, 제1 클럭신호(CLK1)는 하이전압이고, 제2 클럭신호(CLK2)는 로우전압이다. 제1 클럭신호(CLK1)가 하이전압이면 제4 및 제7 트랜지스터(M4, M7)는 턴-오프된다. 제1 노드(N1)는 플로팅되어 이전 상태인 제3 기간(t3)의 로우전압을 유지한다. 제1 노드(N1)가 로우전압이면 제1, 제3 및 제6 트랜지스터(M1, M3, M6)는 턴-온된다. 턴-온된 제1 트랜지스터(M1)를 통해 로우전압의 제1 전원(VGL)이 출력단자(OUT)에 공급된다. 또한, 턴-온된 제3 트랜지스터(M3)를 통해 하이전압의 제2 전원(VGH)이 제2 노드(N2)에 공급된다. 제2 노드(N2)가 하이전압이면 제2 트랜지스터(M2)는 턴-오프된다. 따라서, 제4 기간(t4) 동안 제1 스테이지(401)는 로우전압의 제1 발광제어신호(EM1)를 출력한다.

[0059] 다른 실시예에서, 제1 스테이지(401)를 제외한 n번째 스테이지들의 경우, 시작신호(FLM)는 (n-1)번째 스테이지의 발광제어신호로 대치되고, 제1 발광제어신호(EM1)는 제n 발광제어신호로 대치되어 설명될 수 있을 것이다.

[0060] 이와 같은 본 발명에 의하면, 현재 스테이지의 입력단자는 이전 스테이지의 캐패시터에 연결된 입력단자에 연결된 서브 클럭신호선에 접속됨으로써, 서브 클럭신호선과 연결되는 트랜지스터의 게이트에 정전기가 직접적으로 가해지는 현상을 방지하고, 발광제어 구동부의 손상과 화재 등의 위험을 방지할 수 있다.

[0061] 본 발명의 기술 사상은 상기 바람직한 실시예에 따라 구체적으로 기술되었으나, 상기한 실시예는 그 설명을 위한 것이며 그 제한을 위한 것이 아님을 주의하여야 한다. 또한, 본 발명의 기술 분야의 통상의 지식을 가진 자라면 본 발명의 기술 사상의 범위 내에서 다양한 변형예가 가능함을 이해할 수 있을 것이다.

### 부호의 설명

[0062] 10: 화소부 20: 주사 구동부

30: 데이터 구동부 40: 발광제어 구동부

50: 타이밍 제어부

도면

도면1

도면2

## 도면3

도면4

|                |                                                                                                                           |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 标题 : 发光控制驱动器和包括其的有机发光显示装置                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">KR1020170019022A</a>                                                                                          | 公开(公告)日 | 2017-02-21 |

| 申请号            | KR1020150112600                                                                                                           | 申请日     | 2015-08-10 |

| [标]申请(专利权)人(译) | 三星显示有限公司                                                                                                                  |         |            |

| 申请(专利权)人(译)    | SAMSUNG DISPLAY CO.LTD.                                                                                                   |         |            |

| 当前申请(专利权)人(译)  | SAMSUNG DISPLAY CO.LTD.                                                                                                   |         |            |

| [标]发明人         | LEE SEUNG KYU<br>이승규<br>PARK KYOUNG JIN<br>박경진<br>PARK HYUN AE<br>박현애<br>BYUN MIN WOO<br>변민우                              |         |            |

| 发明人            | 이승규<br>박경진<br>박현애<br>변민우                                                                                                  |         |            |

| IPC分类号         | G09G3/32                                                                                                                  |         |            |

| CPC分类号         | G09G3/3208 G09G2330/06 G09G3/3266 G09G2300/0861 G09G2310/0286 G09G2330/04 G09G3/3258 G09G3/3275 G09G2300/0426 G09G2310/08 |         |            |

| 代理人(译)         | 강신섭<br>Munyongho<br>Yiyongwoo                                                                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                 |         |            |

## 摘要(译)

该摘要目前正在准备中。更新的KPA将于2017年5月10日之后提供。\*本标题 ( 54 ) 和代表图显示为申请人提交的.COPYRIGHT KIPO 2017