# (19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

**H01L 27/32** (2006.01)

(21) 출원번호 **10-2014-0193578**

(22) 출원일자2014년12월30일

심사청구일자 없음

(11) 공개번호 10-2016-0083243

(43) 공개일자

(71) 출원인

엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

2016년07월12일

(72) 발명자

유석종

경기도 파주시 쇠재로 30 706동 1203호 (금촌 동,서원마을아파트)

성낙진

경기도 파주시 가온로 245 (와동동, 가람마을10단지 동양엔파트월드메르디앙) 1007동 802호

(74) 대리인

김은구, 송해모

전체 청구항 수 : 총 9 항

(54) 발명의 명칭 유기발광표시장치

### (57) 요 약

본 발명은, 서브픽셀들이 배치된 유기발광표시패널, 감마기준전압들을 공급하는 감마기준전압 공급부, 감마기준전압들 중 일부를 이용하여 저전압 감마기준전압들을 공급하는 저계조 감마기준전압 공급부, 문턱전압 센싱 시각 서브픽셀 내 센싱 노드의 전압을 센싱하고 구동시 데이터가 저계조인 경우 저계조 감마기준전압 공급부로부터 공급된 감마기준전압들을 토대로 각 서브픽셀에 데이터 전압을 공급하는 데이터 구동부 및 데이터 구동부를 제어하며 데이터 구동부의 센싱된 전압을 토대로 보상 프로세스를 수행하는 타이밍 컨트롤러를 포함하는 유기발광표시장치에 관한 것이다.

## 대표도

1100

## 명세서

### 청구범위

### 청구항 1

서브픽셀들이 배치된 유기발광표시패널;

감마기준전압들을 공급하는 감마기준전압 공급부;

상기 감마기준전압들 중 일부를 이용하여 저전압 감마기준전압들을 공급하는 저계조 감마기준전압 공급부;

문턱전압 센싱 시 상기 각 서브픽셀 내 센싱 노드의 전압을 센싱하고, 구동시 데이터가 저계조인 경우 상기 저계조 감마기준전압 공급부로부터 공급된 감마기준전압들을 토대로 상기 각 서브픽셀에 데이터 전압을 공급하는 데이터 구동부; 및

상기 데이터 구동부를 제어하며, 상기 데이터 구동부의 센싱된 전압을 토대로 보상 프로세스를 수행하는 타이밍 컨트롤러를 포함하는 유기발광표시장치.

#### 청구항 2

제1항에 있어서.

상기 데이터 구동부는 상기 데이터가 저계조가 아닌 경우 상기 감마기준전압 공급부로부터 공급된 상기 감마기 준전압을 토대로 상기 각 서브픽셀에 대한 데이터 전압을 공급하는 유기발광표시장치.

#### 청구항 3

제1항에 있어서.

상기 저계조 감마기준전압 공급부는 상기 데이터 구동부 내에 위치하는 패킷 감마기준전압 공급부인 유기발광표 시장치.

#### 청구항 4

제1항에 있어서,

상기 저계조 감마기준전압 공급부는 상기 감마기준전압 공급부와 별도로 상기 데이터 구동부 외부에 위치하는 감마기준전압 공급부인 유기발광표시장치.

#### 청구항 5

제3항에 있어서,

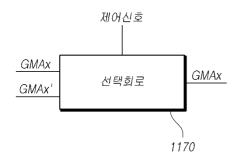

상기 데이터 구동부는, 상기 타이밍 컨트롤러로부터 공급되는 제어신호에 따라, 상기 감마기준전압 공급부와 상기 저계조 감마기준전압 공급부로부터 공급된 감마기준전압들 중 하나를 선택하는 선택회로를 추가로 포함하는 유기발광표시장치.

#### 청구항 6

제5항에 있어서,

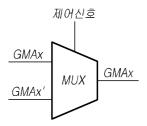

상기 선택회로는, 멀티플렉서인 유기발광표시장치.

## 청구항 7

제2항에 있어서.

상기 데이터 구동부는 상기 문턱전압 센싱 시 상기 각 서브픽셀 내 센싱 노드의 전압을 센싱하는 아날로그 디지털 컨버터 및 상기 타이밍 컨트롤러로부터 수신한 상기 데이터를 상기 데이터 전압으로 변환하여 각 서브픽셀에데이터 전압을 공급하는 디지털 아날로그 컨버터를 포함하며,

상기 아날로그 디지털 컨버터가 각 서브픽셀 내 센싱 노드의 전압을 센싱하는 해상도와 상기 디지털 아날로그 컨버터가, 데이터가 저계조인 경우, 상기 상기 데이터를 상기 데이터 전압으로 변환하는 해상도가 동일한 유기 발광표시장치.

#### 청구항 8

제2항에 있어서,

상기 데이터 구동부는 상기 문턱전압 센싱 시 상기 각 서브픽셀 내 센싱 노드의 전압을 센싱하는 아날로그 디지털 컨버터 및 상기 타이밍 컨트롤러로부터 수신한 상기 데이터를 상기 데이터 전압으로 변환하여 각 서브픽셀에 데이터 전압을 공급하는 디지털 아날로그 컨버터를 포함하며,

상기 디지털 아날로그 컨버터가, 상기 데이터가 저계조가 아닌 경우 상기 데이터를 상기 데이터 전압으로 변환하는 해상도보다 상기 데이터가 저계조인 경우 상기 데이터를 상기 데이터 전압으로 변환하는 해상도가 높은 유기발광표시장치.

#### 청구항 9

제1항에 있어서,

상기 각 서브픽셀은,

유기발광다이오드와,

상기 데이터 전압이 인가되는 제1노드와, 상기 유기발광다이오드의 제1전극과 연결된 제2노드와, 구동전압 라인과 전기적으로 연결된 제3노드를 갖는 구동 트랜지스터와,

상기 데이터 전압을 공급하는 상기 데이터 라인과 상기 구동 트랜지스터의 제1노드 사이에 전기적으로 연결된 제1트랜지스터와,

기준전압을 공급하는 기준전압 라인과 상기 구동 트랜지스터의 제2노드 사이에 전기적으로 연결된 제2트랜지스 터와,

상기 구동 트랜지스터의 제1노드와 제2노드 사이에 전기적으로 연결된 캐패시터를 포함하는 유기발광표시장치.

#### 발명의 설명

#### 기술분야

[0001] 본 발명은 영상을 표시하는 유기발광표시장치에 관한 것이다.

#### 배경기술

- [0002] 최근, 표시장치로서 각광받고 있는 유기발광표시장치는 스스로 발광하는 유기발광다이오드(OLED: Organic Light Emitting Diode)를 이용함으로써 응답속도가 빠르고, 발광효율, 휘도 및 시야각 등이 큰 장점이 있다.

- [0003] 이러한 유기발광표시장치는 유기발광다이오드가 포함된 서브픽셀을 매트릭스 형태로 배열하고 스캔 신호에 의해 선택된 화소들의 밝기를 제어한다. 이러한 유기발광표시장치의 각 서브픽셀은, 유기발광다이오드 이외에도, 유기발광다이오드를 구동하기 위한 구동 회로를 포함한다. 이러한 각 서브픽셀 내 유기발광다이오드의 구동 회로는, 트랜지스터 및 스토리지 캐패시터 등을 포함한다. 이러한 구동 회로 내 트랜지스터는 문턱전압, 이동도 등의 고유 특성치를 갖는다.

- [0004] 한편, 구동 회로 내 트랜지스터(특히, 유기발광다이오드로 전류를 공급하는 구동 트랜지스터)는 구동시간이 길 어지게 되면, 열화(Degradation)가 진행되어, 트랜지스터의 고유 특성치가 변할 수 있다. 이에 따라, 각 트랜지스터 간의 고유 특성치의 편차가 발생한다. 이러한 트랜지스터 간의 고유 특성치의 편차는, 각 서브픽셀 간 휘도 편차를 발생시켜 화상 품질을 저하하는 주요 요인이 될 수 있다. 따라서, 각 서브픽셀 내 트랜지스터의 특성치를 센싱하여 이를 보상해줄 수 있는 기능이 개발되었다.

- [0005] 한편, 각 서브픽셀 내 트랜지스터의 문턱전압 등의 고유 특성치를 센싱하여 보상해주기 위해서, 각 서브픽셀에 서의 특정 센싱 노드를 어떠한 전압 값으로 초기화시킨 이후, 변화시켜, 특정 센싱 노드의 포화한 전압을 센싱

(측정) 하여 센싱된 전압을 토대로 트랜지스터의 문턱전압 등의 고유 특성치를 보상해준다.

[0006] 이러한 트랜지스터의 문턱전압 등의 고유 특성치를 보상하는 방식은 시간 경과후 구동 트랜지스터의 문턱전압 등의 고유 특성치가 변화하는 것을 반영하지 못하는 문제점이 있다. 또한 이 방식은 유기발광표시장치에 포함되는 센서와 보상부의 해상도가 달라 문턱전압 등의 고유 특성치를 완벽하게 보상하지 못해 저계조의 휘도의 화면에서 얼룩이 나타나는 문제점이 있었다.

## 발명의 내용

#### 해결하려는 과제

[0007] 본 발명의 목적은, 문턱전압 보상이 보다 완벽하여 저계조의 휘도의 화면에서 얼룩이 나타나지 않는 유기발광표 시장치를 제공하는 데 있다.

#### 과제의 해결 수단

[0008] 일측면에서 본 발명은, 서브픽셀들이 배치된 유기발광표시패널, 감마기준전압들을 공급하는 감마기준전압 공급부, 감마기준전압들 중 일부를 이용하여 저전압 감마기준전압들을 공급하는 저계조 감마기준전압 공급부, 문탁전압 센싱 시 각 서브픽셀 내 센싱 노드의 전압을 센싱하고 구동시 데이터가 저계조인 경우 저계조 감마기준전압 압 공급부로부터 공급된 감마기준전압들을 토대로 각 서브픽셀에 데이터 전압을 공급하는 데이터 구동부 및 데이터 구동부를 제어하며 데이터 구동부의 센싱된 전압을 토대로 보상 프로세스를 수행하는 타이밍 컨트롤러를 포함하는 유기발광표시장치에 관한 것이다.

#### 발명의 효과

[0009] 이상에서 설명한 바와 같은 본 발명에 의하면, 표시장치의 문턱전압을 보다 정밀한 단위로 보상하여 저계조의 휘도의 화면에서 얼룩이 나타나지 않을 수 있다.

#### 도면의 간단한 설명

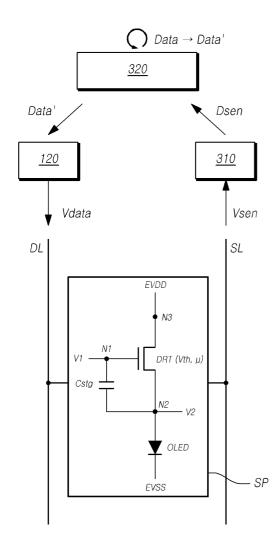

[0010] 도 1은 본 실시예들에 따른 유기발광표시장치(100)의 구성도이다.

도 2는 본 실시예들에 따른 유기발광표시장치(100)의 서브픽셀의 간략화된 등가회로도를 예시적으로 나타낸다.

도 3은 본 실시예들에 따른 유기발광표시장치(100)의 보상 구성을 나타낸다.

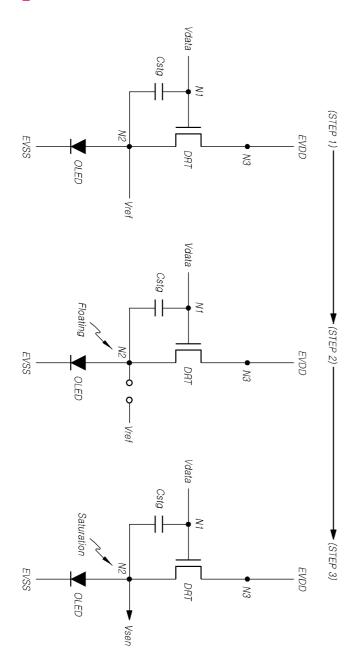

도 4는 본 실시예들에 따른 유기발광표시장치(100)의 센싱 모드 구간에서 센싱 동작 단계를 나타낸다.

도 5는 본 실시예들에 따른 유기발광표시장치(100)의 센싱 모드 구간에서, 구동전압 및 데이터 전압의 기본적인 신호 파형과, 센싱 노드의 전압 변화를 나타낸 도면이다.

도 6은 본 실시예들에 따른 유기발광표시장치(100)의 서브픽셀의 센싱 및 보상 구성을 나타낸 도면이다.

도 7은 본 실시예들에 따른 유기발광표시장치(100)의 서브픽셀의 초기 문턱전압 센싱 및 보상 구성을 나타낸 도면이다.

도 8은 문턱전압 센싱 및 보상시 문턱전압의 전압 변화를 나타낸 도면이다.

도 9는 문턱전압 센싱 및 보상시 데이터 전압의 기본적인 신호 파형과, 위치에 따른 문턱전압의 전압 변화를 나타낸 도면이다.

도 10은 본 실시예들에 따른 유기발광표시장치(100)의 서브픽셀의 문턱전압 업데이트 센싱 및 보상 구성을 나타낸 도면이다.

도 11은 문턱전압 업데이트 센싱 및 보상시 문턱전압의 변화량을 나타낸 도면이다.

도 12는 문턱전압 업데이트 센싱 및 보상시 위치에 따른 데이터 전압 및 데이터 보상량, 문턱전압의 변화량의 변화를 나타낸 도면이다.

도 13은 본 실시예들에 따른 유기발광표시장치(100)의 서브픽셀의 센싱 및 보상 구성을 나타낸 도면이다.

도 14는 문턱전압 센싱 및 보상시 문턱전압의 전압 변화를 나타낸 도면이다.

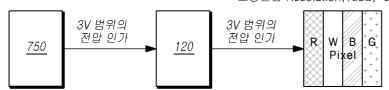

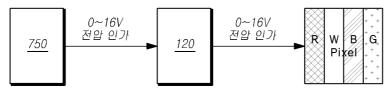

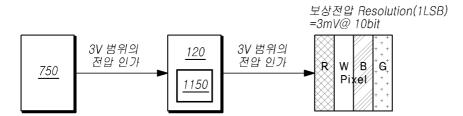

- 도 15는 데이터 전압(Vdata) 출력 전압 해상도에 따른 센싱 전압 오차 발생을 도시하고 있다.

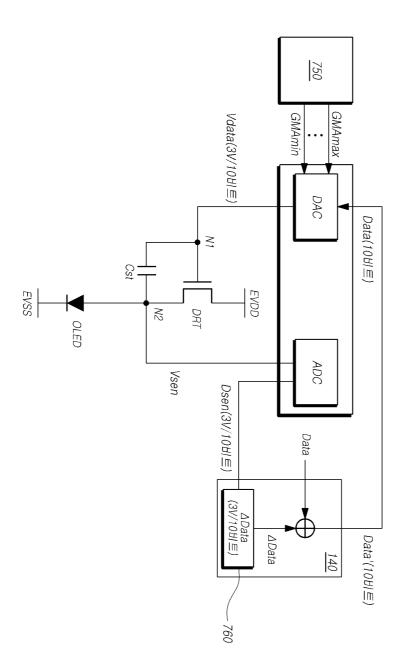

- 도 16은 본 실시예들에 따른 유기발광표시장치(100)의 서브픽셀의 센싱 및 보상 구성을 나타낸 도면이다.

- 도 17은 문턱전압 센싱시 데이터 구동부에 인가되는 감마기준전압을 도시하고 있다.

- 도 18은 문턱전압 센싱시 데이터 구동부에 인가되는 감마기준전압 가변에 따른 문턱전압의 센싱된 전압 오차 개선을 도시하고 있다.

#### 발명을 실시하기 위한 구체적인 내용

- [0011] 이하, 본 발명의 일부 실시예들을 예시적인 도면을 참조하여 상세하게 설명한다. 각 도면의 구성요소들에 참조 부호를 부가함에 있어서, 동일한 구성요소들에 대해서는 비록 다른 도면상에 표시되더라도 가능한 한 동일한 부호를 가질 수 있다. 또한, 본 발명을 설명함에 있어, 관련된 공지 구성 또는 기능에 대한 구체적인 설명이 본 발명의 요지를 호릴 수 있다고 판단되는 경우에는 그 상세한 설명은 생략할 수 있다.

- [0012] 또한, 본 발명의 구성 요소를 설명하는 데 있어서, 제 1, 제 2, A, B, (a), (b) 등의 용어를 사용할 수 있다. 이러한 용어는 그 구성 요소를 다른 구성 요소와 구별하기 위한 것일 뿐, 그 용어에 의해 해당 구성 요소의 본질, 차례, 순서 또는 개수 등이 한정되지 않는다. 어떤 구성 요소가 다른 구성요소에 "연결", "결합" 또는 "접속"된다고 기재된 경우, 그 구성 요소는 그 다른 구성요소에 직접적으로 연결되거나 또는 접속될 수 있지만, 각구성 요소 사이에 다른 구성 요소가 "개재"되거나, 각 구성 요소가 다른 구성 요소를 통해 "연결", "결합" 또는 "접속"될 수도 있다고 이해되어야 할 것이다.

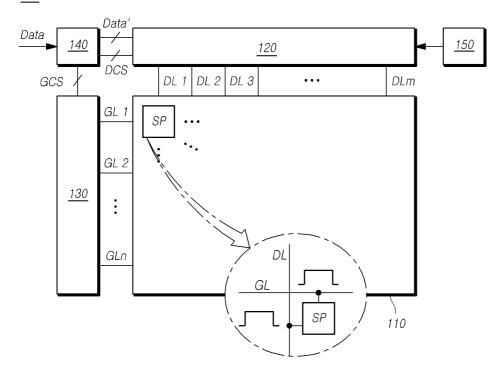

- [0013] 도 1은 본 실시예들에 따른 유기발광표시장치(100)의 구성도이다.

- [0014] 도 1을 참조하면, 본 실시예들에 따른 유기발광표시장치(100)는, 유기발광표시패널(110), 데이터 구동부(120), 게이트 구동부(130), 타이밍 컨트롤러(140) 등을 포함한다.

- [0015] 유기발광표시패널(110)에는, 제1방향으로 다수의 데이터 라인(DL: Data Line)이 배치되고, 제1방향과 교차하는 제2방향으로 다수의 게이트 라인(GL: Gate Line)이 배치되며, 다수의 서브픽셀(SP: Sub Pixel)이 매트릭스 타입으로 배치된다. 데이터 구동부(120)는, 데이터 라인들로 데이터 전압을 공급하여 데이터 라인들을 구동한다. 게이트 구동부(130)는, 게이트 라인들로 스캔 신호를 순차적으로 공급하여 게이트 라인들을 순차적으로 구동한다. 타이밍 컨트롤러(140)는, 데이터 구동부(120) 및 게이트 구동부(130)로 제어신호를 공급하여, 데이터 구동부(120) 및 게이트 구동부(130)를 제어한다.

- [0016] 타이밍 컨트롤러(140)는, 각 프레임에서 구현하는 타이밍에 따라 스캔을 시작하고, 호스트 시스템에서 입력되는 영상 데이터(Data)를 데이터 구동부(120)에서 사용하는 데이터 신호 형식에 맞게 전환하여 전환된 영상 데이터 (Data')를 출력하고, 스캔에 맞춰 적당한 시간에 데이터 구동을 통제한다.

- [0017] 게이트 구동부(130)는, 타이밍 컨트롤러(140)의 제어에 따라, 온(0n) 전압 또는 오프(0ff) 전압의 스캔 신호를 게이트 라인들로 순차적으로 공급하여 게이트 라인들을 순차적으로 구동한다.

- [0018] 게이트 구동부(130)는, 구동 방식에 따라서, 유기발광표시패널(110)의 양측에 위치할 수도 있고, 경우에 따라서는, 한 측에만 위치할 수도 있다.

- [0019] 또한, 게이트 구동부(130)는, 다수의 게이트 드라이버 집적회로들을 포함할 수 있는데, 이러한 다수의 게이트 드라이버 집적회로들은, 테이프 오토메티드 본딩(TAB: Tape AuTrmated Bonding) 방식 또는 칩 온 글래스(COG) 방식으로 표시패널(110)의 본딩 패드(Bonding Pad)에 연결되거나, GIP(Gate In Panel) 타입으로 구현되어 유기 발광표시패널(110)에 직접 배치될 수도 있으며, 경우에 따라서, 유기발광표시패널(110)에 집적화되어 배치될 수도 있다.

- [0020] 위에서 언급한 다수의 게이트 드라이버 집적회로들 각각은 쉬프트 레지스터, 레벨 쉬프터 등을 포함할 수 있다.

- [0021] 데이터 구동부(120)는, 특정 게이트 라인이 열리면, 타이밍 컨트롤러(140)로부터 수신한 영상 데이터(Data')를 아날로그 형태의 데이터 전압(Vdata)으로 변환하여 데이터 라인들로 공급함으로써, 데이터 라인들을 구동한다.

- [0022] 데이터 구동부(120)는, 다수의 소스 드라이버 집적회로들을 포함할 수 있는데, 이러한 다수의 소스 드라이버 집 적회로들은, 테이프 오토메티드 본딩(TAB: Tape AuTrmated Bonding) 방식 또는 칩 온 글래스(COG) 방식으로 유기발광표시패널(110)의 본딩 패드(Bonding Pad)에 연결되거나, 유기발광표시패널(110)에 직접 배치될 수도 있으

며, 경우에 따라서, 유기발광표시패널(110)에 집적화되어 배치될 수도 있다.

- [0023] 위에서 언급한 다수의 소스 드라이버 집적회로들 각각은, 쉬프트 레지스터, 래치, 디지털 아날로그 컨버터(DAC: Digital Analog Converter), 출력 버터 등을 포함하고, 경우에 따라서, 서브픽셀 보상을 위해 아날로그 전압 값을 센싱하여 디지털 값으로 변환하고 센싱 데이터를 생성하여 출력하는 아날로그 디지털 컨버터(ADC: Analog Digital Converter)를 더 포함할 수 있다.

- [0024] 다수의 소스 드라이버 집적회로들은, 칩 온 필름(COF: Chip On Film) 방식으로 구현될 수 있다. 다수의 소스 드라이버 집적회로들 각각에서, 일 단은 적어도 하나의 소스 인쇄회로기판(Source Printed Circuit Board)에 본딩되고, 타 단은 유기발광표시패널(110)에 본딩된다.

- [0025] 한편, 위에서 언급한 호스트 시스템은 입력 영상의 디지털 비디오 데이터(Data)와 함께, 수직 동기 신호 (Vsync), 수평 동기 신호(Hsync), 입력 데이터 인에이블(DE: Data Enable) 신호, 클럭 신호(CLK) 등을 포함하는 각종 타이밍 신호들을 타이밍 컨트롤러(140)로 전송한다.

- [0026] 타이밍 컨트롤러(140)는, 호스트 시스템으로부터 입력된 데이터(Data)를 데이터 구동부(120)에서 사용하는 데이터 신호 형식에 맞게 전환하여 전환된 영상 데이터(Data')를 출력하는 것 이외에, 데이터 구동부(120) 및 게이트 구동부(130)를 제어하기 위하여, 수직 동기 신호(Vsync), 수평 동기 신호(Hsync), 입력 DE 신호, 클럭 신호 등의 타이밍 신호를 입력받아, 각종 제어 신호들을 생성하여 데이터 구동부(120) 및 게이트 구동부(130)로 출력한다.

- [0027] 예를 들어, 타이밍 컨트롤러(140)는, 게이트 구동부(130)를 제어하기 위하여, 게이트 스타트 펄스(GSP: Gate Start Pulse), 게이트 쉬프트 클럭(GSC: Gate Shift Clock), 게이트 출력 인에이블 신호(GOE: Gate Output Enable) 등을 포함하는 게이트 제어 신호들(GCSs: Gate Control Signals)을 출력한다. 게이트 스타트 펄스(GSP)는 게이트 구동부(130)를 구성하는 게이트 드라이버 집적회로들의 동작 스타트 타이밍을 제어한다. 게이트 쉬프트 클럭(GSC)은 게이트 드라이버 집적회로들에 공통으로 입력되는 클럭 신호로서, 스캔 신호(게이트 펄스)의 쉬프트 타이밍을 제어한다. 게이트 출력 인에이블 신호(GOE)는 게이트 드라이버 집적회로들의 타이밍 정보를 지정하고 있다.

- [0028] 타이밍 컨트롤러(140)는, 데이터 구동부(120)를 제어하기 위하여, 소스 스타트 펄스(SSP: Source Start Pulse), 소스 샘플링 클럭(SSC: Source Sampling Clock), 소스 출력 인에이블 신호(SOE: Souce Output Enable) 등을 포함하는 데이터 제어 신호들(DCSs: Data Control Signals)을 출력한다. 소스 스타트 펄스(SSP)는 데이터 구동부(120)를 구성하는 소스 드라이버 집적회로들의 데이터 샘플링 시작 타이밍을 제어한다. 소스 샘플링 클럭 (SSC)은 소스 드라이버 집적회로들 각각에서 데이터의 샘플링 타이밍을 제어하는 클럭 신호이다. 소스 출력 인에이블 신호(SOE)는 데이터 구동부(120)의 출력 타이밍을 제어한다. 경우에 따라서, 데이터 구동부(120)의 데이터 전압의 극성을 제어하기 위하여, 데이터 제어 신호들(DCSs)에 극성 제어 신호(POL)가 더 포함될 수 있다. 데이터 구동부(120)에 입력된 데이터(Data')가 mini LVDS(Low Voltage Differential Signaling) 인터페이스 규격에 따라 전송된다면, 소스 스타트 펄스(SSP)와 소스 샘플링 클럭(SSC)은 생략될 수 있다.

- [0029] 도 1을 참조하면, 유기발광표시장치(100)는, 유기발광표시패널(110), 데이터 구동부(120) 및 게이트 구동부 (130) 등으로 각종 전압 또는 전류를 공급해주거나 공급할 각종 전압 또는 전류를 제어하는 전원 컨트롤러(150)를 더 포함할 수 있다.

- [0030] 이러한 전원 컨트롤러(150)는 전원 관리 집적회로(PMIC: Power Management IC)라고도 한다.

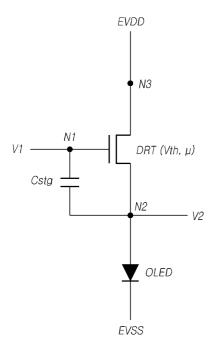

- [0031] 도 2는 본 실시예들에 따른 유기발광표시장치(100)의 서브픽셀의 간략화된 등가회로도를 예시적으로 나타낸다.

- [0032] 도 2를 참조하면, 유기발광표시장치(100)의 각 서브픽셀은, 기본적으로, 유기발광다이오드(OLED: Organic Light Emitting Diode)와, 유기발광다이오드(OLED)를 구동하는 구동 회로로 구성된다. 구동 회로는, 기본적으로, 유기발광다이오드(OLED)로 전류를 공급하여 유기발광다이오드(OLED)를 구동하는 구동 트랜지스터(DRT: Driving Transister)를 포함한다.

- [0033] 이러한 구동 트랜지스터(DRT)의 제1노드(N1)는, 게이트 노드로서, V1 전압이 인가된다. 구동 트랜지스터(DRT)의 제2노드(N2)는, 소스 노드 또는 드레인 노드로서, V2 전압이 인가된다. 구동 트랜지스터(DRT)의 제3노드(N3)는, 드레인 노드 또는 소스 노드로서, 구동전압(EVDD: Driving Voltage)이 인가된다. 여기서, V1 전압은 해당 서브 픽셀에 대응되는 데이터 전압(Vdata)일 수 있다. V2 전압은 V1 전압과 일정 전위차가 나는 전압으로서, 일예로, 기준전압(Vref: Reference Voltage)일 수 있다.

- [0034] 구동 회로는, 구동 트랜지스터(DRT)의 N1 노드와 N2 노드 사이에 연결되는 스토리지 캐패시터(Cstg: Storage Capacitor)를 포함할 수 있다. 이러한 스토리지 캐패시터(Cstg)는 한 프레임 동안 일정 전압을 유지시켜 준다.

- [0035] 도 2는 각 서브픽셀의 회로적인 구성을 간략화하여 등가적으로 나타낸 것으로서, 실제적으로, 각 서브픽셀에서 유기발광다이오드(OELD)를 구동하는 구동 회로는, 구동 트랜지스터(DRT) 및 스토리지 캐패시터(Cstg) 이외에, 하나 이상의 트랜지스터를 더 포함할 수 있고, 경우에 따라서는, 하나 이상의 캐패시터를 더 포함할 수 있다.

- [0036] 한편, 각 서브픽셀 내 트랜지스터, 특히, 구동 트랜지스터(DRT)는 문턱전압(Vth: Threshold Voltage), 이동도 (µ: Mobility) 등의 고유한 특성치를 갖는다.

- [0037] 트랜지스터(특히, 구동 트랜지스터(DRT))는 구동시간이 길어지게 되면, 열화(Degradation)가 진행되어, 트랜지스터의 고유 특성치가 변할 수 있다. 이에 따라, 각 트랜지스터 간의 고유 특성치의 편차가 발생한다. 이러한 트랜지스터 간의 고유 특성치의 편차는, 각 서브픽셀 간 휘도 편차를 발생시켜 화상 품질을 저하하는 주요 요인이 될 수 있다.

- [0038] 이에, 본 실시예들에 따른 유기발광표시장치(100)는 서브픽셀 간 휘도 편차를 보상해주기 위한 보상 기능을 제공하는 보상 구성을 포함한다.

- [0039] 도 3은 본 실시예들에 따른 유기발광표시장치(100)의 보상 구성을 나타낸다.

- [0040] 도 3을 참조하면, 본 실시예들에 따른 유기발광표시장치(100)는 센서(310), 보상부(320), 데이터 구동부(120) 등을 포함한다.

- [0041] 센서(310)는, 각 서브픽셀(SP) 내 센싱 노드(SN: Sensing Node)의 전압을 센싱하고, 센싱된 전압(Vsen)을 토대로, 센싱데이터(Dsen)를 보상부(320)로 전송한다. 이러한 센서(310)는, 일 예로, 아날로그 디지털 컨버터(ADC: Analog Digital Converter)일 수 있다.

- [0042] 아날로그 디지털 컨버터(ADC)는, 각 서브픽셀에서의 센싱 노드(SN)와 센싱라인(SL: Sensing Line)을 통해 전기적으로 연결될 수 있다. 아날로그 디지털 컨버터(ADC)는, 각 서브픽셀에서의 센싱 노드(SN)와 전기적으로 연결된 센싱라인(SL)을 통해, 센싱 노드(SN)의 센싱된 전압(Vsen)을 디지털 값으로 변환하여, 변환된 디지털 값들을 포함하는 토대로, 센싱데이터(Dsen)를 생성한다.

- [0043] 이러한 아날로그 디지털 컨버터(ADC)에 해당하는 센서(310)는, 다수 개가 있을 수 있으며, 하나의 센서(310), 즉 하나의 아날로그 디지털 컨버터(ADC)는 하나의 소스 드라이버 집적회로에 포함될 수 있다.

- [0044] 보상부(320)는, 수신된 센싱데이터(Dsen)를 토대로 보상 프로세스를 수행한다. 보상 프로세스는, 수신된 센싱데이터를 토대로, 다수의 서브픽셀 각각에 대한 데이터(Data)를 변경하기 위한 데이터 보상량(△Data)을 결정하여, 데이터 보상량을 메모리(미도시)에 저장하는 처리일 수 있다.

- [0045] 또한, 보상 프로세스는, 데이터 보상량(△Data)을 기초로, 호스트 시스템에서 출력된 데이터(Data)를 변경하는 처리를 포함할 수 있다. 이러한 데이터 변경 처리는, 호스트 시스템에서 출력된 데이터(Data)에 데이터 보상량 (△Data)을 더하여 변경 데이터(Data'=Data+△Data)로 변경할 수 있다.

- [0046] 보상부(320)는 타이밍 컨트롤러(140)의 내부에 포함될 수 있다.

- [0047] 유기발광표시패널(110) 상의 각 서브픽셀에서의 구동 트랜지스터(DRT)의 문턱전압을 센싱하는 기본적인 방법 및 원리에 대하여, 도 4 및 도 5를 참조하여 설명한다.

- [0048] 도 4는 본 실시예들에 따른 유기발광표시장치(100)의 센싱 모드 구간에서 센싱 동작 단계를 나타낸다. 도 5는 본 실시예들에 따른 유기발광표시장치(100)의 센싱 모드 구간에서, 구동전압 및 데이터 전압의 기본적인 신호 파형과, 센싱 노드의 전압 변화를 나타낸 도면이다.

- [0049] 도 4 및 도 5를 참조하면, 본 실시예들에 따른 유기발광표시장치(100)의 센싱 모드 구간에서 센싱 동작 단계는, 초기화 단계(STEP 1), 센싱 노드 플로팅 단계(STEP 2) 및 센싱 노드 센싱 단계(STEP 3)로 이루어진다.

- [0050] 초기화 단계(STEP 1)에서, 센싱 모드가 인에이블(Enable) 된 이후, 해당 서브픽셀 내 구동 트랜지스터(DRT)의 제1노드(N1) 및 제2노드(N2) 각각에 데이터 전압(Vdata) 및 기준전압(Vref)이 인가된다. 여기서, 구동 트랜지스터(DRT)의 제1노드(N1)는 구동 트랜지스터(DRT)의 게이트 노드이고, 구동 트랜지스터(DRT)의 제2노드(N2)는 구동 트랜지스터(DRT)의 소스 노드인 것으로 가정한다. 그리고, 구동 트랜지스터(DRT)의 소스 노드가 해당 서브픽셀에서의 센싱 노드인것으로 가정한다.

- [0051] 센싱 노드 플로팅 단계(STEP 2)에서, 구동 트랜지스터(DRT)의 제2노드(N2), 즉, 구동 트랜지스터(DRT)의 소스 노드가 Tr 시점에서 플로팅(Floating) 된다. 이때, 구동 트랜지스터(DRT)의 제1노드(N1)는, 초기화 전압에 해당하는 데이터 전압(Vdata)이 그대로 인가되어 있는 상태이다. 구동 트랜지스터(DRT)의 제2노드(N2), 즉, 구동 트랜지스터(DRT)의 소스 노드가 플로팅(Floating) 됨에 따라, 구동 트랜지스터(DRT)의 제2노드(N2)의 전압이 상승(Boosting) 된다.

- [0052] 이러한 구동 트랜지스터(DRT)의 소스 노드의 전압 상승은, 구동 트랜지스터(DRT)의 제1노드(N1)의 전압에 해당하는 데이터 전압(Vdata)을 향해 이루어지고, 구동 트랜지스터(DRT)의 제1노드(N1)의 전압에 해당하는 데이터 전압(Vdata)과 문턱전압(Vth)만큼 차이가 날 때까지 이루어진다.

- [0053] 이와 같이, 구동 트랜지스터(DRT)의 제2노드(N2), 즉, 구동 트랜지스터(DRT)의 소스 노드의 전압이 구동 트랜지스터(DRT)의 제1노드(N1)의 전압을 향해 상승(Boosting) 하는 것을 "소스 팔로윙(Source Following)"이라고 한다.

- [0054] 센싱 노드 센싱 단계(STEP 3)에서, 구동 트랜지스터(DRT)의 제2노드(N2)의 전압이 상승하다가 Tsat 시점에서 포화(Saturation) 하면, 구동 트랜지스터(DRT)의 제2노드(N2)의 포화된 전압이 센싱된다.

- [0055] 여기서, 구동 트랜지스터(DRT)의 제2노드(N2), 즉, 구동 트랜지스터(DRT)의 소스 노드의 포화된 전압은, 구동 트랜지스터(DRT)의 제1노드(N1)의 전압에 해당하는 데이터 전압(Vdata)에서 구동 트랜지스터(DRT)의 문턱전압 (Vth)을 뺀 전압(Vdata-Vth=Vd-Vth)이 된다. 단, 도 5에서, 구동 트랜지스터(DRT)의 문턱전압(Vth)이 포지티브 값인 경우를 도시한 것으로서, 구동 트랜지스터(DRT)의 문턱전압(Vth)이 네거티브 값일 수도 있다.

- [0056] 센싱 모드 구간에서, 데이터 전압(Vdata)은 일정한 전압(Vd)을 갖고, 구동전압(EVDD)도 일정한 전압(Ve)을 갖는다.

- [0057] 센싱 모드 구간에서, 구동 트랜지스터(DRT)의 문턱전압(Vth)을 정확하게 센싱하기 위해서는, 해당 서브픽셀에서의 센싱 노드(SN), 즉, 구동 트랜지스터(DRT)의 제2노드(N2)가 포화된 이후에, 구동 트랜지스터(DRT)의 제2노드(N2)의 전압이 센서(310)에 해당하는 아날로그 디지털 컨버터(ADC)에 의해 샘플링되어 센싱(측정) 되어야 한다.

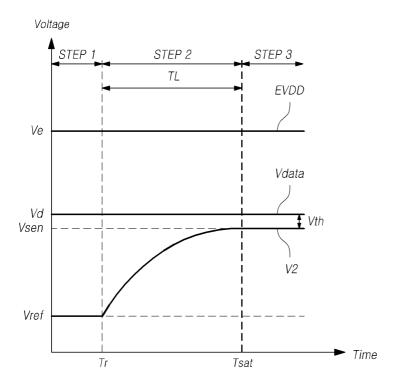

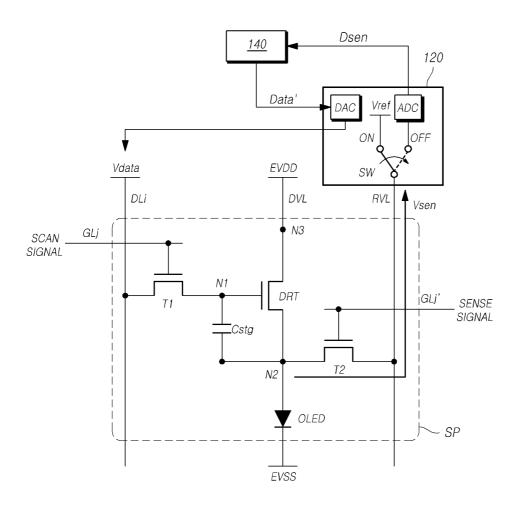

- [0058] 도 6은 본 실시예들에 따른 유기발광표시장치(100)의 서브픽셀의 센싱 및 보상 구성을 나타낸 도면이다.

- [0059] 도 6을 참조하면, 구동 트랜지스터(DRT)의 제2노드(N2)의 포화한 전압을 센싱하기 위한 구성으로서, 스위치(S W)를 통해 기준전압 라인(RVL)과 전기적으로 연결되고, 구동 트랜지스터(DRT)의 제2노드(N2)의 전압을 센싱하는 아날로그 디지털 컨버터(ADC)를 포함할 수 있다.

- [0060] 이러한 아날로그 디지털 컨버터(ADC)는, 다수의 기준전압 라인(RVL)과 전기적으로 연결되고, 하나의 소스 드라이버 집적회로들마다 하나씩 포함될 수 있다.

- [0061] 전술한 아날로그 디지털 컨버터(ADC)를 이용하면, 서브픽셀 내 구동 트랜지스터(DRT)의 문턱전압을 효율적이고 정확하게 센싱할 수 있다.

- [0062] 한편, 도 6을 참조하면, 아날로그 디지털 컨버터(ADC)는, 구동 트랜지스터(DRT)의 제2노드(N2)의 전압을 센싱하여, 센싱된 전압(Vsen)을 디지털 값으로 변환하고, 변환된 디지털 값들을 포함하는 센싱 데이터(Dsen)를 타이밍 컨트롤러(140)로 전송한다.

- [0063] 타이밍 컨트롤러(140)는, 센싱 데이터(Dsen)를 수신하고, 수신된 센싱 데이터(Dsen)를 토대로 서브픽셀들 각각 에 대한 데이터를 보상한다.

- [0064] 예를 들어, 타이밍 컨트롤러(140)는 센싱 데이터(Dsen)를 토대로 서브픽셀들 각각에 대한 데이터 보상량(△ Data)을 연산하여 이를 메모리(미도시)에 저장해두고, 서브픽셀들을 구동할 타이밍이 되면, 해당 서브픽셀에 대한 데이터(Data)에 데이터 보상량(△Data)을 더하고, 이렇게 얻어진 보상 데이터(Data'=Data+△Data)를 해당 데이터 구동부(120)로 공급해준다.

- [0065] 전술한 바에 따르면, 구동 트랜지스터(DRT) 간의 문턱전압 편차를 데이터 보상을 통해 보상해주어, 서브픽셀 간의 휘도 편차를 줄여주거나 제거하여, 화상 품질을 향상시킬 수 있다.

- [0066] 센싱 모드 구간에서, 소스 팔로윙(Source Following) 방식으로 구동 트랜지스터(DRT)의 문턱전압(Vth)을 센싱하고 구동 트랜지스터(DRT) 간의 문턱전압 편차를 데이터 보상을 통해 보상한 후 각 구동 트랜지스터(DRT)의 문턱전압의 변화량(ΔVth)를 업데이트 센싱하고 구동 트랜지스터(DRT) 간의 문턱전압 편차(Vth+ ΔVth)를 데이터 보

상을 통해 보상하여 보상 효율을 향상시키고 있다.

- [0067] 도 7은 본 실시예들에 따른 유기발광표시장치(100)의 서브픽셀의 센싱 단계를 나타낸 도면이다. 도 7은 본 실시 예들에 따른 유기발광표시장치(100)의 서브픽셀의 보상 단계를 나타낸 도면이다.

- [0068] 도 7을 참조하면, 서브픽셀 센싱 단계에서, 디지털 아날로그 컨버터(DAC)는 특정 데이터(Data)에 대응하는 데이터 전압(Vdata)를 구동 트랜지스터(DRT)의 게이트에 제공한다. 이때 데이터(Data)는 예를 들어 10비트의 영상 데이터일 수 있다. 예를 들어 데이터 전압(Vdata)은 5V로 고정될 수 있다. 또한 감마기준전압 공급부(750)는 10비트에 대응하는  $2^{10}(1024)$ 개의 감마기준전압들을 디지털 아날로그 컨버터(DAC)에 제공한다. 감마기준전압 공급부(750)는 도 1에 도시한 전원 컨트롤러(150) 내에 포함될 수 있다.

- [0069] 감마기준전압 공급부(750)는 최소 감마기준전압(GMAmin)과 최대 감마기준전압(GMAmax) 사이의 감마기준전압의 범위(△GMA)의 감마기준전압들을 공급한다.

- [0070] 예를 들어 문턱전압 센싱시 최대 감마기준전압(GMAmax)이 예를 들어 15V이고 최대 감마기준전압(GMAmin)은 0V일수 있다. 따라서, 디지털 아날로그 컨버터(DAC)는 10비트의 데이터(Data)를 타이밍 컨트롤러(140)으로부터 공급받아 1024개의 감마기준전압들을 감마기준전압 공급부(750)으로부터 공급받아 1024개의 데이터전압(Vdata)를 구동 트랜지스터(DRT)의 게이트에 제공한다. 따라서, 디지털 아날로그 컨버터(DAC)의 출력 전압 해상도는 15V/10비트로 1비트당 15mV를 표현할 수 있다.

- [0071] 본 실시예들에 따른 유기발광표시장치(100)의 서브픽셀의 문턱전압 센싱시 초기화 단계에서, 아날로그 디지털 컨버터(ADC)는 구동 트랜지스터(DRT)의 제2노드(N2)의 포화된 전압(Vg-Vth =Vdata-Vth)을 3mV 단위로 센싱할 수 있다. 아날로그 디지털 컨버터(ADC)의 센싱 전압(Vsen)을 문턱전압(Vth)만으로 표현하면 표 1과 같을 수 있다.

丑 1

| Vth(mV) |

|---------|

| 3       |

| 6       |

| 9       |

| 12      |

| 15      |

| 18      |

[0072]

- [0073] 타이밍 컨트롤러(140)는 문턱전압(Vth)을 서브픽셀들 각각에 대한 데이터 보상량(△Data(Vth))으로 연산하여 이를 메모리(760)에 저장해 둘 수 있다. 전술한 예와 동일하게 타이밍 컨트롤러(140)는 서브픽셀들 각각에 대한 문턱전압(Vth)을 아날로그 디지털 컨버터(ADC)의 센싱 전압 해상도와 동일한 전압 해상도, 즉 예를 들어 표 1와 같이 3V/10비트=3mV/비트 단위로 또는 아날로그 디지털 컨버터(ADC)의 센싱 전압 해상도보다 작은 전압 해상도, 예를 들어 표 2와 같이 6V/10비트=6mV/비트 단위로 문턱전압(Vth)에 대한 데이터 보상량(△Data(Vth))으로 연산하여 이를 메모리(760)에 저장해 둘 수 있다.

- [0074] 이하에서 타이밍 컨트롤러(140)는 서브픽셀들 각각에 대한 문턱전압(Vth)을 아날로그 디지털 컨버터(ADC)의 센싱 전압 해상도와 동일한 전압 해상도, 즉 예를 들어 표 1와 같이 3V/10비트=3mV/비트로 단위로 문턱전압(Vth)에 대한 데이터 보상량(△Data(Vth))으로 연산하여 이를 메모리(760)에 저장해 두는 것으로 예시적으로 설명하나 본 발명은 이에 제한되지 않는다.

- [0075] 도 8을 참조하면, 서브픽셀 보상 단계에서, 타이밍 컨트롤러(140)는 서브픽셀들을 구동할 타이밍이 되면, 메모리(760)에 저장해 둔 데이터 보상량(△Data(Vth))를 표 1과 같이 디지털 아날로그 컨버터(DAC)의 출력 전압 해상도(15mV/ 비트)에 맞게 환산하여 해당 서브픽셀의 데이터(Data)에 데이터 보상량(△Data(Vth))를 더한 보상데이터 (Data'=Data+△Data(Vth))를 해당 데이터 구동부(120)로 공급해준다. 예를 들어 데이터 전압(Vdata)은

각 서브픽셀의 데이터 전압이므로 보상 데이터 전압(Vdata=Vdata+Vth)은 표 2와 같을 수 있다.

### 丑 2

[0076]

| Vth | 인가전압        |

|-----|-------------|

| 3   | 데이터전압+15mV  |

| 6   | 데이터전압++15mV |

| 9   | 데이터전압++15mV |

| 12  | 데이터전압++15mV |

| 15  | 데이터전압++15mV |

| 18  | 데이터전압++18mV |

- [0077] 도 9는 데이터 전압(Vdata) 출력 전압 해상도에 따른 센싱 전압 오차 발생을 도시하고 있다.

- [0078] 도 9를 참조하면, 전술한 표시장치의 문턱전압 센싱 시, 데이터 구동부(120)의 디지털 아날로그 컨버터(DAC)은 최대감마기준전압을 10비트로 표현하여 나타낸다. 따라서, 각 서브픽셀의 구동 트랜지스터(DRT)의 게이트에 인가하는 데이터 전압(Vdata)은 데이터 구동부(120)의 디지털 아날로그 컨버터(DAC)의 출력 전압을 10비트로 나누어서 표현된다.

- [0079] 다시 말해 16V의 최대 감마기준전압을 10비트로 데이터(Data)를 환산하면 구동시 1LSB는 15mV이다. 한편, 서브 픽셀 센싱 범위는 3V이므로 10비트로 데이터(Data)를 환산하면 센싱시 1LSB는 3mv이다. 따라서, 데이터 구동부 (120)의 디지털 아날로그 컨버터(DAC)는 1비트에 해당되는 전압의 크기가 전술한 예에서 15mV/비트로 정해져 있기 때문에 각 서브픽셀의 구동 트랜지스터(DRT)의 게이트에 인가하는 데이터 전압(Vdata)을 세밀하게 출력하는 데 한계가 있다.

- [0080] 도 10은 저계조에서 보상 데이터(Data')을 반영할 때 구동과 센싱 사이 1LSB의 전압 편차로 인해 과보상이 되어 저계조에서 문턱전압 편차가 심하게 보이게 것을 도시하고 있다.

- [0081] 도 10을 참조하면, 저계조에서 보상 데이터(Data')을 반영할 때 구동과 센싱 사이 1LSB의 전압 편차로 인해 세 밀한 편차 보상이 되지 않아 저계조 얼룩 및 세로 블록 딤(Block Dim), 잔가로선 등 문제가 발생할 수 있다.

- [0082] 이하에서 도면들을 참조하여 구동과 센싱 사이 1LSB의 전압 편차가 없어 세밀한 편차 보상이 되어 저계조 얼룩 및 세로 블록 딤(Block Dim), 잔가로선 등 문제가 발생하지 않거나 취소화할 수 있는 실시예들을 설명한다.

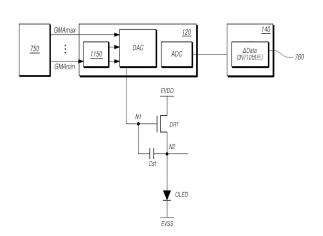

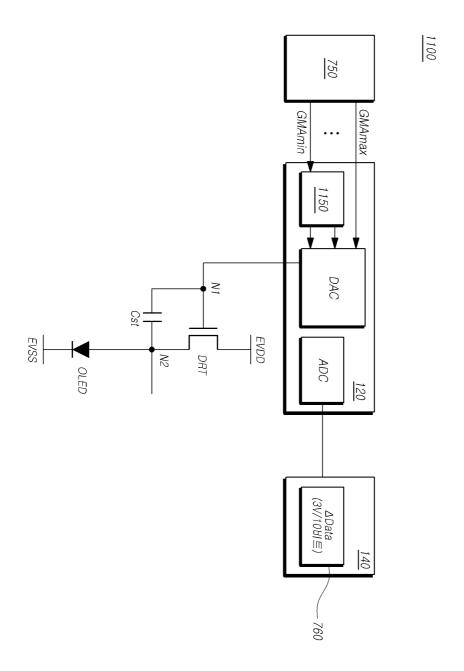

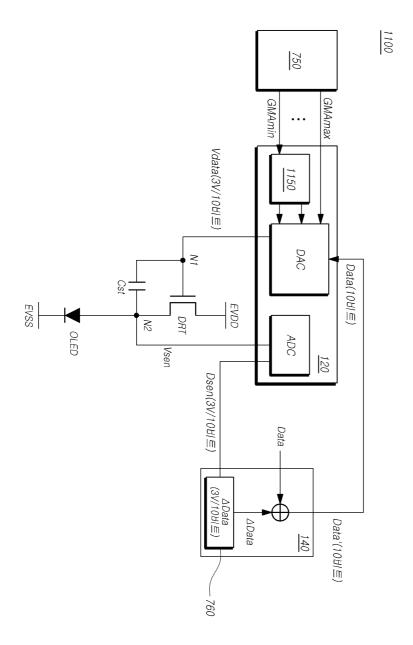

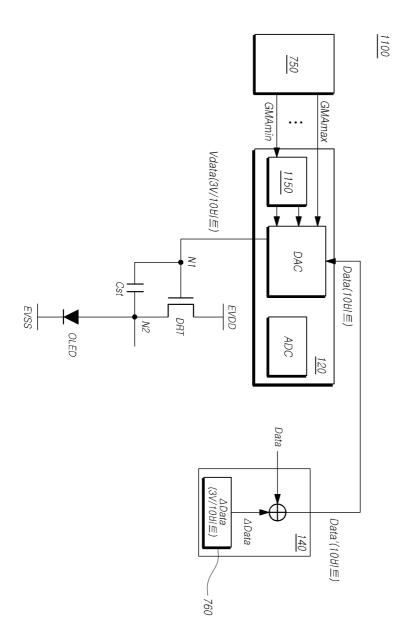

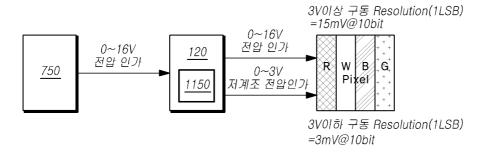

- [0083] 도 11은 다른 실시예에 따른 유기발광표시장치(1100)의 구성도이다.

- [0084] 다른 실시예에 따른 유기발광표시장치(1100)는 도 1 및 도 6에 도시한 바와 같이 유기발광표시패널(110), 데이터 구동부(120), 게이트 구동부(130), 타이밍 컨트롤러(140) 등을 포함한다. 또한 다른 실시예에 따른 유기발 광표시장치(1000)는 도 7에 도시한 바와 같이 감마기준전압 공급부(750)과 메모리(760)를 포함할 수 있다. 감마기준전압 공급부(750)는 도 1에 도시한 전원 컨트롤러(150) 내에 위치할 수 있다. 메모리(760)는 타이밍 컨트롤러(140) 내에 위치하는 프레임 버퍼(frame buffer)일 수 있으나 타이밍 컨트롤러(140)와 별도로 구현될 수 있다.

- [0085] 다른 실시예에 따른 유기발광표시장치(1000)는 도 11에 도시한 바와 같이 저계조 감마기준전압 공급부(1150)을 추가로 포함한다. 이때 저계조 감마기준전압 공급부(1150)는 데이터 구동부(120) 내에 위치할 수 있다.

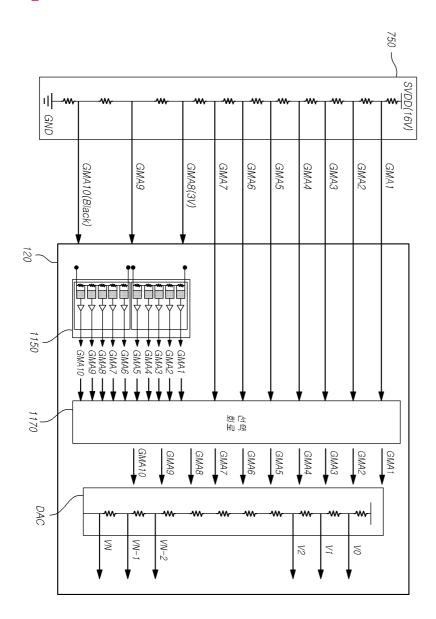

- [0086] 도 12는 데이터 구동부, 감마기준전압 공급부, 데이터 구동부 내에 위치하는 저계조 감마기준전압 공급부의 일부 구성도이다.

- [0087] 감마기준전압 공급부(750)는 최소 감마기준전압(GMAmin)과 최대 감마기준전압(GMAmax) 사이의 감마기준전압들 (GMA1~GMA10)을 공급한다. 감마기준전압 공급부(750)는 고전위전압(SVDD), 예를 들어 16V와 저전위전압(SVSS), 예를 들어 그라운드전압(GND) 사이 저항열들을 구성하고 저항열들 사이에서 최소 감마기준전압(GMAmin)과 최대 감마기준전압(GMAmax) 사이의 감마기준전압들(GMA1~GMA10)을 발생한다. 감마기준압 공급부(750)는 감마기준전 압들(GMA1~GMA10) 중 고전압의 일부 감마기준전압들(GMA1 내지 GMA7)을 데이터 구동부(120) 내 디지털 아날로그 컨버터(DAC)에 공급한다. 감마기준압 공급부(750)는 감마기준전압들(GMA1~GMA10) 중 저전압의 다른 일부 감마기준전압들(GMA8 내지 GMA10)을 데이터 구동부(120) 내 저계조 감마기준전압 공급부(1150)에 공급한다.

- [0088] 도 12에 도시한 바와 같이 데이터 구동부(120) 내 위치하는 저계조 감마기준전압 공급부(1150)는 데이터 구동부

(120)의 외부에 위치하는 감마기준전압 공급부(750)으로부터 공급된 일부 감마기준전압들, 예를 들어 3개의 감마기준전압들(GMA8(3V), GMA9(1.5V), GMA10(0V))를 입력받는다. 저계조 감마기준전압 공급부(1150)는 감마기준전압 공급부(750)으로부터 공급받은 3개의 감마기준전압들(GMA8(3V), GMA9(1.5V), GMA10(0V))을 이용하여 저전압의 감마기준전압들(GMA1' 내지 GMA10')을 데이터 구동부(120) 내 디지털 아날로그 컨버터(DAC)에 공급한다. 저계조 감마기준전압 공급부(1150)는 데이터 구동부 내 위치하는 패킷 감마기준전압 회로일 수 있다. 별도의 저계조 감마기준전압 공급부를 데이터 구동부 외부에 별도로 집적회로로 구현할 때 배선이 약 2배 증가하거나 집적회로 핀수 증가, PCB 레이어 증가가 필요한 반면, 저계조 감마기준전압 공급부를 데이터 구동부 내에 포함하여 별도로 독립된 저계조 감마기준전압들을 공급하므로 배선 증가나 집적회로 핀수 증가, PCB 레이어의 증가없이 데이터 전압의 해상도를 높일 수 있다.

- [0089] 선택회로(1170)는 감마기준전압 공급부(750)으로부터 공급된 고전압의 감마기준전압들(GMA1 내지 GMA7) 중 하나와 저계조 감마기준전압 공급부(1150)으로부터 공급된 저전압의 감마기준전압들((GMA1' 내지 GMA10') 중 하나를 선택하여 데이터 구동부(120) 내 디지털 아날로그 컨버터(DAC)에 공급한다. 도 13a에 도시한 바와 같이 선택회로(1170)는 제어신호의 제어에 따라 감마기준전압 공급부(750)으로부터 공급된 고전압의 하나의 감마기준전압 (GMAx, x=1 내지 7 중 하나)와 저계조 감마기준전압 공급부(1150)으로부터 공급된 저전압의 하나의 감마기준전압압들((GMAx')를 선택하여 하나의 감마기준전압을 디지털 아날로그 컨버터(DAC)에 공급한다.

- [0090] 타이밍 컨트롤러(140)는 선택회로(1170)에 제어신호를 공급한다. 또한 저전압의 일부 감마기준전압들(GMA8' 내지 GMA10')에 대응하는 고전압 감마기준전압들이 없으므로 선택회로(1170)는 저전압의 일부 감마기준전압들 (GMA8' 내지 GMA10')을 디지털 아날로그 컨버터(DAC)에 공급한다.

- [0091] 도 13b에 도시한 바와 같이 선택회로(1170)는 타이밍 컨트롤러(1140)으로부터 공급받은 제어신호의 제어에 따라 GMAx와 GMAx' 중 하나를 선택하는 멀티플레서(multiplexer, MUX)일 수 있다.

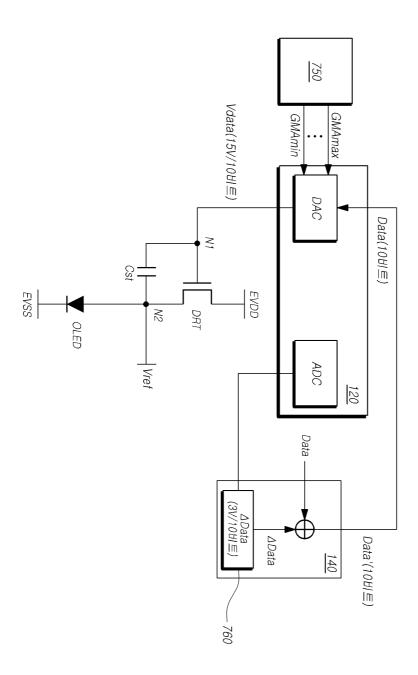

- [0092] 도 14는 본 실시예들에 따른 유기발광표시장치(100)의 서브픽셀의 센싱 단계를 나타낸 도면이다. 도 15는 본 실시예들에 따른 유기발광표시장치(100)의 서브픽셀의 보상 및 구동 단계를 나타낸 도면이다. 도 16은 서브픽셀의 세싱 및 구동시 해상도 관계를 도시하고 있다.

- [0093] 도 14 및 도 16을 참조하면, 서브픽셀 센싱 단계에서, 디지털 아날로그 컨버터(DAC)는 특정 데이터(Data)에 대응하는 데이터 전압(Vdata)를 구동 트랜지스터(DRT)의 게이트에 제공한다. 이때 데이터(Data)는 예를 들어 10 비트의 영상 데이터일 수 있다. 예를 들어 데이터 전압(Vdata)은 5V로 고정될 수 있다. 또한 저계조 감마기준전압 공급부(1150)는 저전압의 감마기준전압들(GMA1' 내지 GMA10')을 디지털 아날로그 컨버터(DAC)에 제공한다. 저계조 감마기준전압 공급부(750)는 도 11에 도시한 데이터 구동부(120) 내에 포함될 수 있다. 좀더 상세하게 도 12에 도시한 바와 같이 선택회로(1170)가 저계조 감마기준전압 공급부(1150)로부터 공급받은 저전압의 감마기준전압들(GMA1' 내지 GMA10')을 디지털 아날로그 컨버터(DAC)에 제공한다.

- [0094] 예를 들어 서브픽셀의 문턱전압 센싱시 최대 감마기준전압(GMAmax)이 예를 들어 3V이고 최대 감마기준전압 (GMAmin)은 0V일 수 있다. 따라서, 디지털 아날로그 컨버터(DAC)는 10비트의 데이터(Data)를 타이밍 컨트롤러 (140)으로부터 공급받아 감마기준전압들(GMA1' 내지 GMA10')을 저계조 감마기준전압 공급부(1150)으로부터 공급받아 데이터전압(Vdata)를 구동 트랜지스터(DRT)의 게이트에 제공한다. 따라서, 디지털 아날로그 컨버터(DAC)의 출력 전압 해상도는 3V/10비트로 1비트당 3mV를 표현할 수 있다.

- [0095] 본 실시예들에 따른 유기발광표시장치(100)의 서브픽셀의 문턱전압 센싱시 초기화 단계에서, 아날로그 디지털 컨버터(ADC)는 구동 트랜지스터(DRT)의 제2노드(N2)의 포화된 전압(Vg-Vth =Vdata-Vth)을 3mV 단위로 센싱할 수 있다. 아날로그 디지털 컨버터(ADC)의 센싱 전압(Vsen)을 문턱전압(Vth)만으로 표현하면 표 3과 같을 수 있다.

#### 丑 3

| Vth(mV) |

|---------|

| 3       |

| 6       |

| 9       |

| 12      |

| 15      |

| 18      |

[0096]

[0097] 타이밍 컨트롤러(140)는 문턱전압(Vth)을 서브픽셀들 각각에 대한 데이터 보상량(△Data(Vth))으로 연산하여 이를 메모리(760)에 저장해 둘 수 있다. 전술한 바와 동일하게 타이밍 컨트롤러(140)는 서브픽셀들 각각에 대한 문턱전압(Vth)을 아날로그 디지털 컨버터(ADC)의 센싱 전압 해상도와 동일한 전압 해상도, 즉 예를 들어 표 1와 같이 3V/10비트=3mV/비트로 단위로 문턱전압(Vth)에 대한 데이터 보상량(△Data(Vth))으로 연산하여 이를 메모리(760)에 저장해 두는 것으로 예시적으로 설명하나 본 발명은 이에 제한되지 않는다.

[0098] 도 15 및 도 16을 참조하면, 서브픽셀 보상 및 구동 단계에서, 데이터(Data)가 저계조인 경우 타이밍 컨트롤러 (140)는 메모리(760)에 저장해 둔 데이터 보상량(△Data(Vth))를 표 4와 같이 디지털 아날로그 컨버터(DAC)의 출력 전압 해상도(3mV/ 비트)에 맞게 환산하여 해당 서브픽셀의 데이터(Data)에 데이터 보상량(△Data(Vth))를 더한 보상 데이터 (Data'=Data+△Data(Vth))를 해당 데이터 구동부(120)로 공급해준다.

#### 丑 4

[0099]

| Vth | 인가전압       |

|-----|------------|

| 3   | 데이터전압+3mV  |

| 6   | 데이터전압+6mV  |

| 9   | 데이터전압+9mV  |

| 12  | 데이터전압+12mV |

| 15  | 데이터전압+15mV |

| 18  | 데이터전압+18mV |

[0100] 데이터 구동부(120)의 디지털 아날로그 컨버터(DAC)는 10비트의 저계조의 보상 데이터(Data'=Data+△Data(Vt h))를 감마기준전압들(GMA1' 내지 GMA10')을 저계조 감마기준전압 공급부(1150)으로부터 공급받아 보상 데이터 전압(Vdata'=Vdata+Vth)를 구동 트랜지스터(DRT)의 게이트에 제공한다. 따라서, 디지털 아날로그 컨버터(DAC)의 출력 전압 해상도는 3V/10비트로 1비트당 3mV를 표현할 수 있다.

[0101] 서브픽셀 보상 및 구동 단계에서, 영상 데이터가 고계조인 경우 타이밍 컨트롤러(140)는 메모리(760)에 저장해 둔 데이터 보상량(△Data(Vth))를 표 5과 같이 디지털 아날로그 컨버터(DAC)의 출력 전압 해상도(15mV/ 비트)에 맞게 환산하여 해당 서브픽셀의 데이터(Data)에 데이터 보상량(△Data(Vth))를 더한 보상 데이터 (Data'=Data+△Data(Vth))를 해당 데이터 구동부(120)로 공급해준다.

## 班 5

[0102]

| Vth | 인가전압       |

|-----|------------|

| 3   | 데이터전압+15mV |

| 6   | 데이터전압+15mV |

| 9   | 데이터전압+15mV |

| 12  | 데이터전압+15mV |

| 15  | 데이터전압+15mV |

- [0103] 데이터 구동부(120)의 디지털 아날로그 컨버터(DAC)는 10비트의 저계조의 보상 데이터(Data'=Data+△Data(Vt h))를 감마기준전압들(GMA1' 내지 GMA10')을 감마기준전압 공급부(750)으로부터 공급받아 보상 데이터전압 (Vdata'=Vdata+Vth)를 구동 트랜지스터(DRT)의 게이트에 제공한다. 따라서, 디지털 아날로그 컨버터(DAC)의 출력 전압 해상도는 3V/10비트로 1비트당 3mV를 표현할 수 있다.

- [0104] 도 17은 저계조에서 보상 데이터(Data')을 반영할 때 구동과 센싱 사이 1LSB의 전압 편차가 존재하지 않는 것을 도시하고 있다.

- [0105] 도 17을 참조하면, 저계조에서 보상 데이터(Data')을 반영할 때 구동과 센싱 사이 1LSB의 전압가 존재하지 않아 세밀한 문턱전압 보상이 되어 저계조 얼룩 및 세로 블록 딤(Block Dim), 잔가로선 등 문제가 발생하지 않을 수 있다.

- [0106] 전술한 표시장치의 문턱전압 센싱 및 구동 시, 문턱전압(Vth) 을 보다 정밀한 단위로 센싱하여 문턱전압(Vth) 보상이 보다 완벽하여 저계조의 휘도의 화면에서 얼룩이 나타나지 않는 효과가 있다.

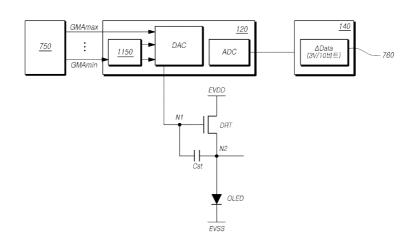

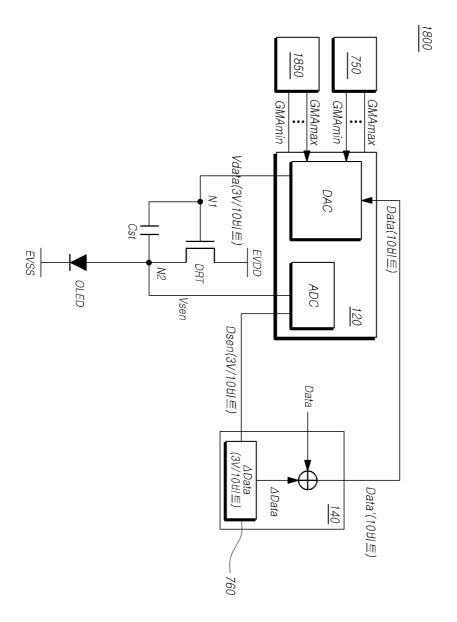

- [0107] 도 18은 다른 실시예에 따른 유기발광표시장치의 구성도이다.

- [0108] 다른 실시예에 따른 유기발광표시장치(1800)는 도 1 및 도 6에 도시한 바와 같이 유기발광표시패널(110), 데이터 구동부(120), 게이트 구동부(130), 타이밍 컨트롤러(140) 등을 포함한다. 또한 다른 실시예에 따른 유기발 광표시장치(1000)는 도 7에 도시한 바와 같이 감마기준전압 공급부(750)과 메모리(760)를 포함할 수 있다. 감마기준전압 공급부(750)는 도 1에 도시한 전원 컨트롤러(150) 내에 위치할 수 있다. 메모리(760)는 타이밍 컨트롤러(140) 내에 위치하는 프레임 버퍼(frame buffer)일 수 있으나 타이밍 컨트롤러(140)와 별도로 구현될 수 있다.

- [0109] 다른 실시예에 따른 유기발광표시장치(1800)는 도 18에 도시한 바와 같이 저계조 감마기준전압 공급부(1850)을 추가로 포함한다. 이때 저계조 감마기준전압 공급부(1850)는 데이터 구동부(120) 외부에 감마기준전압 공급부 (750)과 별도로 존재할 수 있다. 이때 저계조 감마기준전압 공급부(1850)는 데이터 구동부(120)의 외부에 존재하는 점을 제외하고 도 11을 참조하여 설명한 저계조 감마기준전압 공급부(1150)과 동일한 기능을 수행할 수 있다.

- [0110] 서브픽셀 보상 및 구동 단계에서, 데이터(Data)가 저계조인 경우 데이터 구동부(120)의 디지털 아날로그 컨버터 (DAC)는 10비트의 저계조의 보상 데이터(Data'=Data+△Data(Vth))를 감마기준전압들(GMA1' 내지 GMA10')을 저 계조 감마기준전압 공급부(1850)으로부터 공급받아 보상 데이터전압(Vdata'=Vdata+Vth)를 구동 트랜지스터(DR T)의 게이트에 제공한다. 따라서, 디지털 아날로그 컨버터(DAC)의 출력 전압 해상도는 3V/10비트로 1비트당 3mV를 표현할 수 있다.

- [0111] 반면에 서브픽셀 보상 및 구동 단계에서, 영상 데이터가 고계조인 경우 데이터 구동부(120)의 디지털 아날로그 컨버터(DAC)는 10비트의 저계조의 보상 데이터(Data'=Data+△Data(Vth))를 감마기준전압들(GMA1' 내지 GMA1 0')을 감마기준전압 공급부(750)으로부터 공급받아 보상 데이터전압(Vdata'=Vdata+Vth)를 구동 트랜지스터(DR T)의 게이트에 제공한다. 따라서, 디지털 아날로그 컨버터(DAC)의 출력 전압 해상도는 3V/10비트로 1비트당 3mV를 표현할 수 있다.

- [0112] 도 18을 참조하여 설명한 또다른 실시예에 따른 유기발광표시장치(1800)도 저계조 감마기준전압 공급부(1850)을 데이터 구동부의 외부에 별도의 독립된 집적회로로 구현할 경우 배선 증가 및 집적회로 핀수 증가, PCB 레이어 증가에도 불구하고 도 17에 도시한 바와 같이 저계조에서 보상 데이터(Data')을 반영할 때 구동과 센싱 사이 1LSB의 전압 편차가 존재하지 않아, 저계조에서 보상 데이터(Data')을 반영할 때 구동과 센싱 사이 1LSB의 전압 가 존재하지 않아 세밀한 문턱전압 보상이 되어 저계조 얼룩 및 세로 블록 딤(Block Dim), 잔가로선 등 문제가 발생하지 않을 수 있다.

- [0113] 이상에서의 설명 및 첨부된 도면은 본 발명의 기술 사상을 예시적으로 나타낸 것에 불과한 것으로서, 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자라면 본 발명의 본질적인 특성에서 벗어나지 않는 범위에서 구성의 결합, 분리, 치환 및 변경 등의 다양한 수정 및 변형이 가능할 것이다. 따라서, 본 발명에 개시된 실시예들은 본 발명의 기술 사상을 한정하기 위한 것이 아니라 설명하기 위한 것이고, 이러한 실시예에 의하여 본 발명의 기술 사상의 범위가 한정되는 것은 아니다. 본 발명의 보호 범위는 아래의 청구범위에 의하여 해석되어야 하며, 그와 동등한 범위 내에 있는 모든 기술 사상은 본 발명의 권리범위에 포함되는 것으로 해석되어야 할 것이다.

## 부호의 설명

[0114] 100: 유기발광표시장치

110: 유기발광표시패널

120: 데이터 구동부

130: 게이트 구동부

140: 타이밍 컨트롤러

750: 감마기준전압 공급부

1150: 저계조 감마기준전압 공급부1850: 저계조 감마기준전압 공급부

## 도면

## 도면1

## <u>100</u>

## 센싱시

보상전압 Resolution(1LSB)=3mV@ 10bit

## 구동시

보상전압 Resolution(1LSB)=15mV@ 10bit

도면11

## 도면13a

## 도면13b

## 센싱시

## 구동시

| 专利名称(译)        | 相关技术的描述                                      |         |            |  |  |

|----------------|----------------------------------------------|---------|------------|--|--|

| 公开(公告)号        | KR1020160083243A                             | 公开(公告)日 | 2016-07-12 |  |  |

| 申请号            | KR1020140193578                              | 申请日     | 2014-12-30 |  |  |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                     |         |            |  |  |

| 申请(专利权)人(译)    | LG显示器有限公司                                    |         |            |  |  |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                    |         |            |  |  |

| [标]发明人         | YOO SOCK JONG<br>유석종<br>SEONG NAK JIN<br>성낙진 |         |            |  |  |

| 发明人            | 유석종<br>성낙진                                   |         |            |  |  |

| IPC分类号         | H01L27/32                                    |         |            |  |  |

| CPC分类号         | H01L27/32 H01L27/3202 H01L27/3204            |         |            |  |  |

| 代理人(译)         | Gimeungu<br>宋.                               |         |            |  |  |

| 外部链接           | Espacenet                                    |         |            |  |  |

## 摘要(译)

本发明中,子像素被布置在有机发光显示面板,用于提供使用任何伽玛基准电压源,用于提供伽马参考电压的伽马参考电压,阈值电压的低电压伽马参考电压的低灰度级的伽马参考电压供应单元感应时间当感测子像素中的感测节点的电压时,当低灰度级是基于从所述低灰度级的伽马参考电压供给的伽马参考电压控制数据驱动器和用于供给数据电压施加到各子像素的数据驱动器和定时控制器,用于将数据驱动器的感测的电压的基础上执行补偿处理和有机发光二极管威尔。

1100