# (19) 대한민국특허청(KR)(12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

**G09G 3/3233** (2016.01) **H01L 27/12** (2006.01)

(52) CPC특허분류

*G09G 3/3233* (2013.01) *H01L 27/1225* (2013.01)

(21) 출원번호 **10-2017-0059310**

(22) 출원일자 2017년05월12일

심사청구일자 없음

(11) 공개번호 10-2018-0125101

(43) 공개일자 2018년11월22일

(71) 출원인

#### 엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

### 임병준

경기도 안산시 단원구 화정천동로5안길 2 (와동) 203호

#### 정화준

인천광역시 부평구 경원대로 1269 120동 1309호 (산곡동,현대1차아파트)

#### 우영빈

인천광역시 남동구 논현로 235 1005동 1901호 (논 현동,별빛마을웰카운티아파트)

(74) 대리인

특허법인로얄

전체 청구항 수 : 총 10 항

## (54) 발명의 명칭 **전계 발광 표시 장치**

#### (57) 요 약

본 발명은 전계 발광 표시 장치에 관한 것으로, 문턱 전압 샘플링 시간이 없는 내부 보상 방법으로 픽셀 회로에서 구동 소자의 이동도 편차와 온도 편차를 실시간 보상한다. 이 픽셀 회로의 구동 소자와 스위치 소자가 산화물 트랜지스터를 포함한다.

#### 대 표 도 - 도6

Oxide TFT

# (52) CPC특허분류

G09G 2230/00 (2013.01)

G09G 2300/043 (2013.01)

G09G 2300/0828 (2013.01)

G09G 2300/0842 (2013.01)

G09G 2320/0257 (2013.01)

G09G 2320/0626 (2013.01)

#### 명세서

#### 청구범위

#### 청구항 1

다수의 데이터 라인들과 다수의 게이트 라인들과 전기적으로 연결된 다수의 픽셀들이 배치된 표시패널을 구비하고,

상기 픽셀들 각각은

발광 소자의 전류를 게이트-소스간 전압으로 조절하는 구동 소자;

제1 스캔 신호에 응답하여 상기 구동 소자의 게이트에 제1 전압을 인가하는 제1 스위치 소자;

제2 스캔 신호에 응답하여 상기 구동 소자의 소스에 제2 전압을 인가하는 제2 스위치 소자; 및

발광 제어 신호에 응답하여 상기 구동 소자의 드레인에 고전위 전원 전압을 공급하는 제3 스위치 소자를 구비하고.

상기 제1 스위치 소자가 턴-온되고 상기 제2 스위치 소자가 턴-오프되는 실시간 보상 시간 동안 상기 구동 소자의 소스가 플로팅되어 상기 구동 소자의 소스 전압이 변하고.

상기 구동 소자와 상기 제1 스위치 소자 각각이 산화물 트랜지스터를 포함하는 전계 발광 표시장치.

#### 청구항 2

제 1 항에 있어서,

상기 제2 및 제3 스위치 소자들이 폴리 실리콘 트랜지스터를 포함하는 전계 발광 표시장치.

#### 청구항 3

제 2 항에 있어서,

상기 구동 소자와 상기 스위치 소자들이 백 플레인 상에 배치되고,

상기 산화물 트랜지스터의 반도체 패턴과 상기 백 플레인 사이의 절연층 두께가 상기 폴리 실리콘 트랜지스터의 반도체 패턴과 상기 백 플레인 사이의 절연층 두께 보다 큰 전계 발광 표시장치.

#### 청구항 4

제 3 항에 있어서.

상기 백 플레인은 폴리 이미드 필름(Polyimide Film)을 포함하는 전계 발광 표시장치.

#### 청구항 5

제 2 항 또는 제 3 항에 있어서,

상기 폴리 실리콘 트랜지스터는 폴리 실리콘 반도체 패턴 위에 게이트가 배치된 탑 게이트 구조의 n 타입 MOSFET를 포함하고,

상기 산화물 트랜지스터는 산화물 반도체 패턴 아래에 게이트가 배치된 바텀 게이트 구조의 n 타입 MOSFET와, 상기 산화물 반도체 패턴 위에 게이트가 배치된 탑 게이트 구조의 n 타입 MOSFET 중 어느 하나를 포함하는 전계 발광 표시장치.

## 청구항 6

제 1 항에 있어서,

상기 제2 및 제3 스위치 소자들 각각이 산화물 트랜지스터를 포함하는 전계 발광 표시장치.

#### 청구항 7

제 6 항에 있어서,

상기 스캔 신호들과 상기 발광 제어 신호를 발생하는 게이트 구동부를 더 구비하고,

상기 게이트 구동부는 상기 픽셀들과 함께 백 플레인 상에 배치되는 다수의 스위치 소자들을 포함하며,

상기 게이트 구동부의 스위치 소자들은 폴리 실리콘 트랜지스터들을 포함하는

전계 발광 표시장치.

#### 청구항 8

제 7 항에 있어서.

상기 산화물 트랜지스터의 반도체 패턴과 상기 백 플레인 사이의 절연층 두께가 상기 폴리 실리콘 트랜지스터의 반도체 패턴과 상기 백 플레인 사이의 절연층 두께 보다 큰 전계 발광 표시장치.

#### 청구항 9

제 8 항에 있어서,

상기 백 플레인은 폴리 이미드 필름(Polyimide Film)을 포함하는 전계 발광 표시장치.

#### 청구항 10

제 8 항 또는 제 9 항에 있어서,

상기 폴리 실리콘 트랜지스터는 반도체 패턴 위에 게이트가 배치된 탑 게이트 구조의 n 타입 MOSFET를 포함하고,

상기 산화물 트랜지스터는 산화물 반도체 패턴 아래에 게이트가 배치된 바텀 게이트 구조의 n 타입 MOSFET와, 상기 산화물 반도체 패턴 위에 게이트가 배치된 탑 게이트 구조의 n 타입 MOSFET 중 어느 하나를 포함하는 전계 발광 표시장치.

#### 발명의 설명

#### 기술분야

[0001] 본 발명은 산화물 트랜지스터와 폴리 실리콘 트랜지스터를 포함한 전계 발광 표시 장치에 관한 것이다.

#### 배경기술

- [0002] 전계 발광 표시장치는 발광층의 재료에 따라 무기발광 표시장치와 유기발광 표시장치로 대별된다. 이 중에서, 액티브 매트릭스 타입(active matrix type)의 유기발광 표시장치는 스스로 발광하는, 대표적인 전계 발광 다이오드(Organic Light Emitting Diode: 이하, "OLED"라 함)를 포함하며, 응답속도가 빠르고 발광효율, 휘도 및 시야각이 큰 장점이 있다.

- [0003] 자발광 소자인 OLED는 애노드전극 및 캐소드전극과, 이들 사이에 형성된 유기 화합물층을 포함한다. 유기 화합물층은 정공주입층(Hole Injection layer, HIL), 정공수송층(Hole transport layer, HTL), 발광층(Emission layer, EML), 전자수송층(Electron transport layer, ETL) 및 전자주입층(Electron Injection layer, EIL)으로 이루어진다. 애노드전극과 캐소드전극에 전원전압이 인가되면 정공수송층(HTL)을 통과한 정공과 전자수송층(ETL)을 통과한 전자가 발광층(EML)으로 이동되어 여기자를 형성하고, 그 결과 발광층(EML)이 가시광을 발생하게 된다.

- [0004] 유기발광 표시장치는 OLED와 구동 TFT(Thin Film Transistor)를 각각 포함한 픽셀들을 매트릭스 형태로 배열하고 영상 데이터의 계조에 따라 픽셀들에서 구현되는 영상의 휘도를 조절한다. 구동 TFT는 자신의 게이트전극과 소스전극 사이에 걸리는 전압(이하, "게이트-소스 간 전압"이라 함)에 따라 OLED에 흐르는 구동 전류를 제어한다. 구동 전류에 따라 OLED의 발광량과 휘도가 결정된다.

- [0005] 일반적으로 구동 TFT가 포화 영역에서 동작할 때, 구동 TFT의 드레인-소스 사이에 흐르는 구동 전류(Ids)는 아

래와 같이 표현된다.

- [0006] Ids =  $1/2*(u*C*W/L)*(Vgs-Vth)^2$

- [0007] 여기서, μ는 전자 이동도를, C는 게이트 절연막의 정전 용량을, W 는 구동 TFT의 채널 폭을, 그리고 L은 구동 TFT의 채널 길이를 각각 나타낸다. 그리고, Vgs는 구동 TFT의 게이트-소스 간 전압을 나타내고, Vth는 구동 TFT의 문턱전압(또는 임계전압)을 나타낸다. 픽셀 구조에 따라서, 구동 TFT의 게이트-소스 간 전압(Vgs)이 데이터 전압과 기준전압 간의 차 전압이 될 수 있다. 데이터전압은 영상 데이터의 계조에 대응되는 아날로그 전압이고 기준전압은 고정된 전압이므로, 데이터전압에 따라 구동 TFT의 게이트-소스 간 전압(Vgs)이 프로그래밍(또는 설정)된다. 프로그래밍된 게이트-소스 간 전압(Vgs)에 따라 구동 전류(Ids)가 결정된다.

- [0008] 구동 TFT의 문턱 전압(Vth), 구동 TFT의 전자 이동도(μ), 및 OLED의 문턱 전압 등과 같은 픽셀의 전기적 특성은 구동 전류(Ids)를 결정하는 팩터(factor)가 되므로 모든 픽셀들에서 동일해야 한다. 하지만, 공정 편차, 경시 변화 등 다양한 원인에 의해 픽셀들 간에 전기적 특성이 달라질 수 있다. 이러한 픽셀의 전기적 특성 편차는 화질 저하와 수명 단축을 초래한다.

- [0009] 구동 TFT의 전기적 특성 편차를 보상하기 위해 내부 보상 방법과 외부 보상 방법이 적용될 수 있다. 내부 보상 방법은 구동 TFT의 전기적 특성에 따라 변하는 구동 TFT의 게이트-소스 간 전압을 이용하여 픽셀들 간 구동 TFT의 전기적 특성 편차를 실시간 자동으로 보상한다. 외부 보상 방법은 구동 TFT들의 전기적 특성에 따라 변하는 픽셀의 전압을 센싱하고, 센싱된 전압을 바탕으로 외부 회로에서 입력 영상의 데이터를 변조함으로써 픽셀들 간 구동 TFT의 전기적 특성 편차를 보상한다.

#### 발명의 내용

#### 해결하려는 과제

[0010] 본 발명은 픽셀의 전기적 특성 변화를 실시간 보상하고 저속 구동시의 화질 저하를 방지할 수 있고 잔상을 방지할 수 있는 전계 발광 표시장치를 제공한다.

#### 과제의 해결 수단

- [0011] 본 발명의 전계 발광 표시장치는 문턱 전압 샘플링 시간이 없는 내부 보상 방법으로 픽셀 회로에서 구동 소자의 이동도 편차와 온도 편차를 실시간 보상한다. 이 픽셀 회로는 다수의 데이터 라인들과 다수의 게이트 라인들과 전기적으로 연결된 다수의 픽셀들이 배치된 표시패널을 구비한다.

- [0012] 상기 픽셀들 각각은 발광 소자의 전류를 게이트-소스간 전압으로 조절하는 구동 소자, 제1 스캔 신호에 응답하여 상기 구동 소자의 게이트에 제1 전압을 인가하는 제1 스위치 소자, 제2 스캔 신호에 응답하여 상기 구동 소자의 소스에 제2 전압을 인가하는 제2 스위치 소자, 및 발광 제어 신호에 응답하여 상기 구동 소자의 드레인에 고전위 전원 전압을 공급하는 제3 스위치 소자를 구비한다.

- [0013] 상기 제1 스위치 소자가 턴-온되고 상기 제2 스위치 소자가 턴-오프되는 실시간 보상 시간 동안 상기 구동 소자의 의 소스가 플로팅되어 상기 구동 소자의 소스 전압이 변한다. 상기 구동 소자와 상기 제1 스위치 소자 각각이 산화물 트랜지스터를 포함한다.

#### 발명의 효과

[0014] 본 발명은 픽셀 회로의 내부 보상 구동 방법에서 구동 소자의 문턱 전압 샘플링 시간이 필요 없기 때문에 고속 구동에 유리하다. 나아가, 본 발명은 오프 전류가 낮고 백 플레인 전하의 영향을 받지 않는 구조의 트랜지스터 소자를 이용하여 저속 구동시의 화질 저하를 방지할 수 있음은 물론, 픽셀 회로의 스위치 소자와 구동 소자를 구현함으로써 구동 소자의 문턱 전압 변화와 잔상을 방지할 수 있다.

#### 도면의 간단한 설명

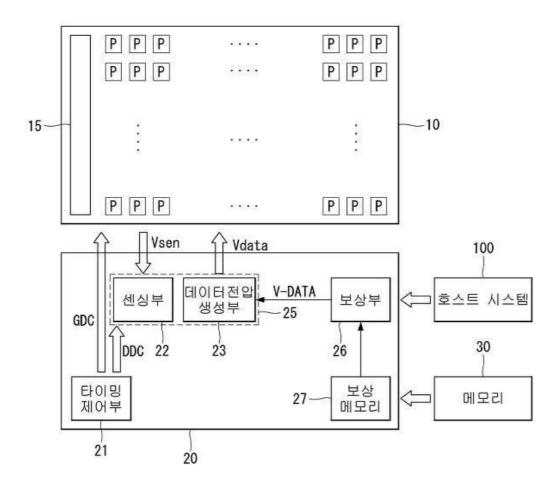

[0015] 도 1은 본 발명의 일 실시예에 따른 전계 발광 표시장치를 나타내는 블록도이다.

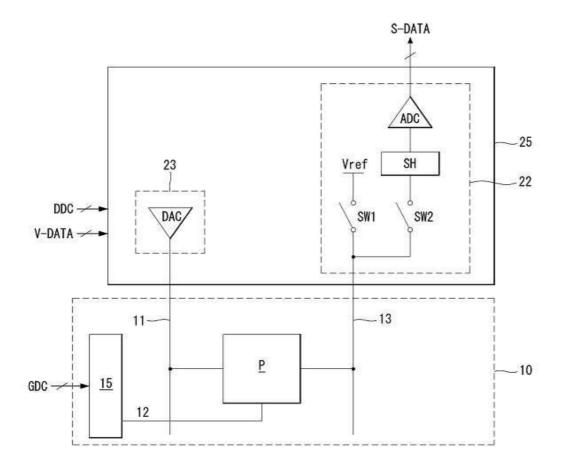

도 2는 센싱 회로의 일 예를 보여 주는 회로도이다.

도 3은 픽셀의 구동 특성 센싱 결과를 이용한 외부 보상 방법의 일 예를 보여 주는 흐름도이다.

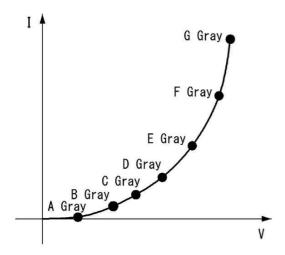

도 4a는 기준 커브를 도출하는 예를 보여 주는 도면이다.

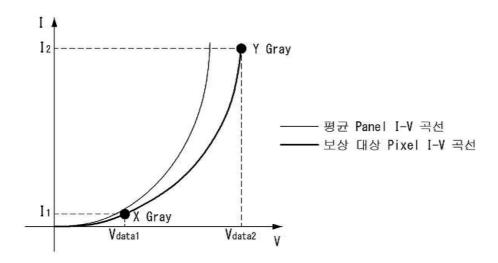

도 4b는 표시패널의 평균 I-V 곡선과 보상 대상 픽셀의 I-V 곡선을 보여주는 도면이다.

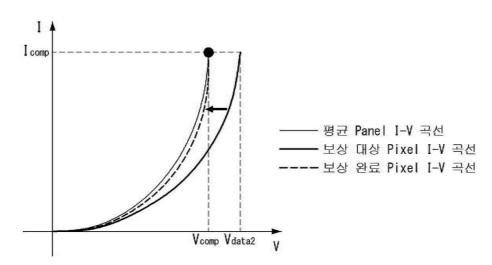

도 4c는 표시패널의 평균 I-V 곡선과 보상 대상 픽셀의 I-V 곡선과 보상 완료된 픽셀의 I-V 곡선을 보여주는 도면이다.

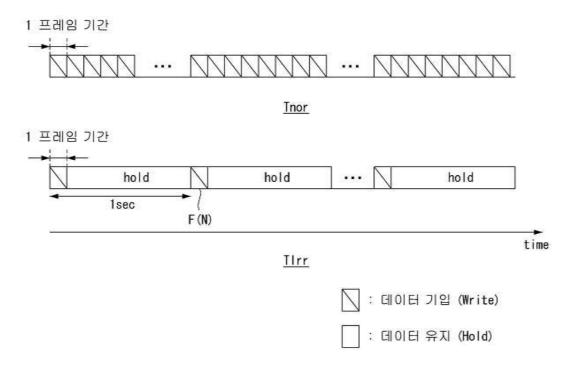

도 5는 노말 구동 모드와 저소비 전력 모드에서 픽셀들의 구동 주파수를 보여 주는 도면이다.

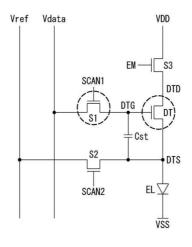

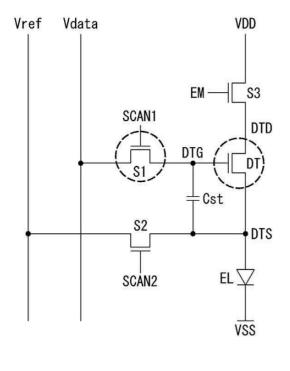

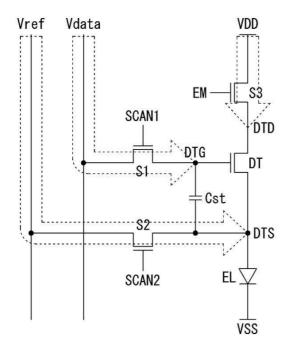

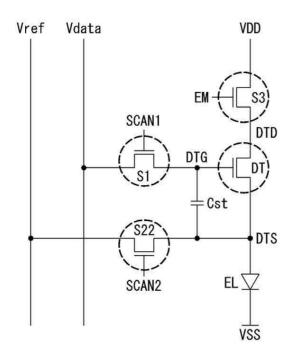

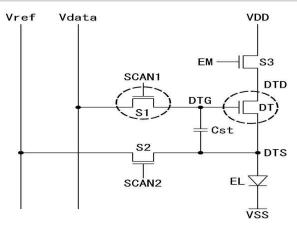

도 6은 본 발명의 제1 실시예에 따른 픽셀 회로를 보여 주는 도면이다.

도 7a 내지 도 7c는 도 6에 도시된 픽셀 회로의 동작을 단계적으로 보여 주는 도면들이다.

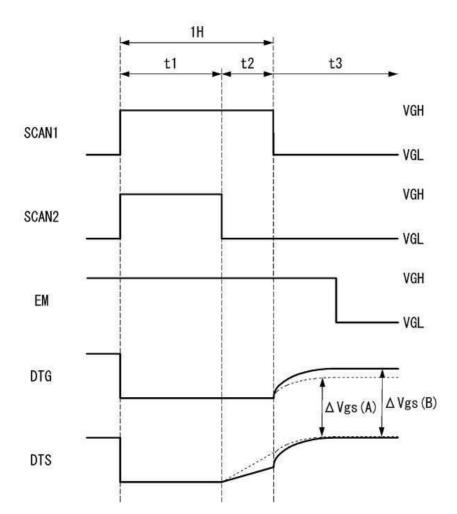

도 8은 도 6에 도시된 픽셀 회로의 구동 신호 파형을 보여 주는 도면이다.

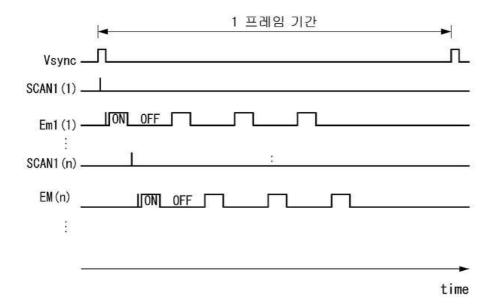

도 9는 픽셀의 발광 구동 시간 동안 미리 설정된 듀티비로 EM 신호가 온/오프 스위칭되는 예를 보여 주는 파형 도이다.

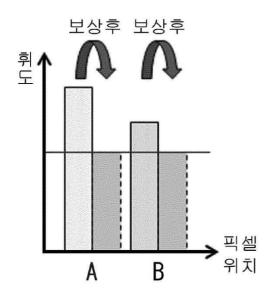

도 10은 이동도 편차에 따른 픽셀들 간의 휘도 차이와 실시간 보상 후 픽셀들 간의 휘도가 동일하게 보상되는 예를 보여 주는 도면이다.

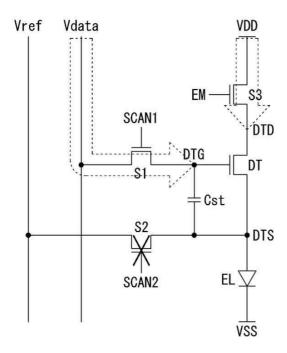

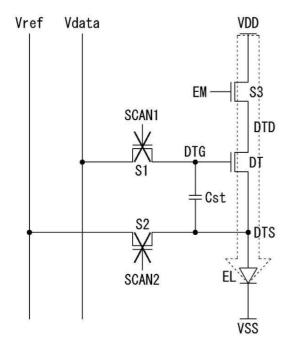

도 11은 본 발명의 제2 실시예에 따른 픽셀 회로를 보여 주는 도면이다.

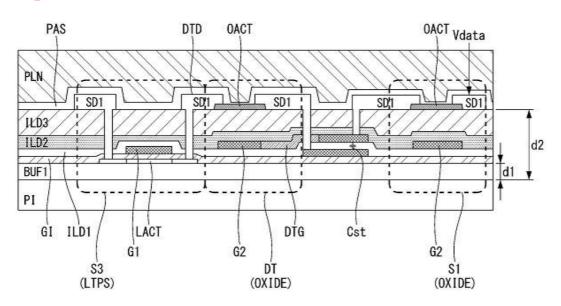

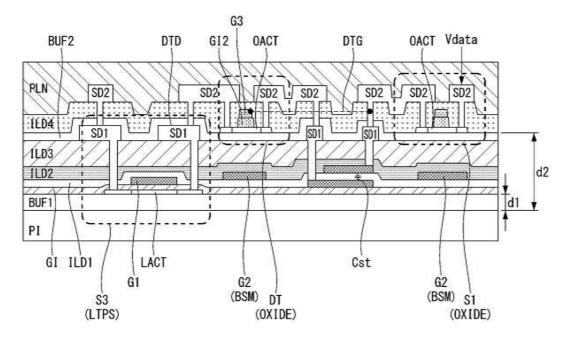

도 12 및 도 13은 본 발명의 실시예에 따른 픽셀 회로들의 단면 구조를 보여 주는 도면들이다.

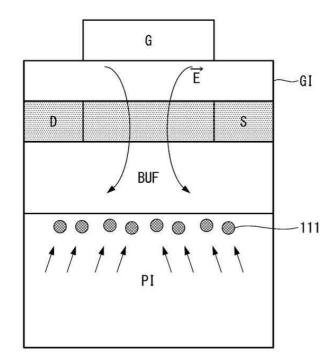

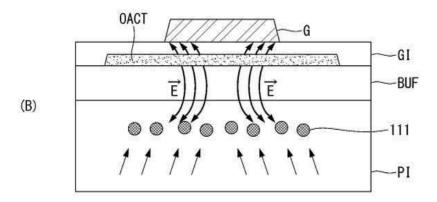

도 14는 TFT가 구동될 때 발생하는 전계에 의해 백 플레인으로부터의 전하가 TFT로 흐르는 현상을 개략적으로 보여 주는 도면이다.

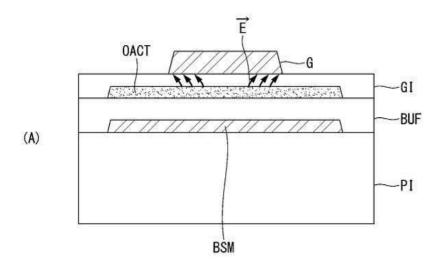

도 15는 차폐 금속층의 백 플레인 전하 차단 효과를 보여 주는 도면이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0016] 본 발명의 이점 및 특징, 그리고 그것들을 달성하는 방법은 첨부되는 도면과 함께 상세하게 후술되어 있는 실시 예들을 참조하면 명확해질 것이다. 그러나, 본 발명은 이하에서 개시되는 실시예들에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 것이며, 단지 본 실시예들은 본 발명의 개시가 완전하도록 하며, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 발명의 범주를 완전하게 알려주기 위해 제공되는 것이며, 본 발명은 청구항의 범주에 의해 정의될 뿐이다.

- [0017] 본 발명의 실시예를 설명하기 위한 도면에 개시된 형상, 크기, 비율, 각도, 개수 등은 예시적인 것이므로 본 발명이 도시된 사항에 한정되는 것은 아니다. 명세서 전체에 걸쳐 동일 참조 부호는 동일 구성 요소를 지칭한다. 또한, 본 발명을 설명함에 있어서, 관련된 공지 기술에 대한 구체적인 설명이 본 발명의 요지를 불필요하게 흐릴 수 있다고 판단되는 경우 그 상세한 설명은 생략한다. 본 명세서 상에서 언급된 '포함한다', '갖는다', '이루어진다' 등이 사용되는 경우 ' ~ 만'이 사용되지 않는 이상 다른 부분이 추가될 수 있다. 구성 요소를 단수로 표현한 경우에 특별히 명시적인 기재 사항이 없는 한 복수를 포함하는 경우를 포함한다.

- [0018] 구성 요소를 해석함에 있어서, 별도의 명시적 기재가 없더라도 오차 범위를 포함하는 것으로 해석한다.

- [0019] 위치 관계에 대한 설명일 경우, 예를 들어, '~ 상에', '~ 상부에', '~ 하부에', '~ 옆에' 등으로 두 부분의 위치 관계가 설명되는 경우, '바로' 또는 '직접'이 사용되지 않는 이상 두 부분 사이에 하나 이상의 다른 부분이 위치할 수도 있다.

- [0020] 제1, 제2 등이 다양한 구성요소들을 서술하기 위해서 사용될 수 있으나, 이 구성요소들은 이들 용어에 의해 제한되지 않는다. 이들 용어들은 단지 하나의 구성요소를 다른 구성요소와 구별하기 위하여 사용하는 것이다. 따라서, 이하에서 언급되는 제1 구성요소는 본 발명의 기술적 사상 내에서 제2 구성요소일 수도 있다.

- [0021] 명세서 전체에 걸쳐 동일 참조 부호는 실질적으로 동일 구성 요소를 지칭한다.

- [0022] 본 발명의 여러 실시예들의 특징들이 부분적으로 또는 전체적으로 서로 결합 또는 조합 가능하며, 기술적으로 다양한 연동 및 구동이 가능하며, 각 실시예들이 서로에 대하여 독립적으로 실시 가능할 수도 있고 연관 관계로함께 실시 가능할 수 있다.

- [0023] 본 발명에서 표시패널의 기판 상에 형성되는 픽셀 회로와 게이트 구동부는 n 타입 또는 p 타입 MOSFET(Metal

Oxide Semiconductor Field Effect Transistor) 구조의 TFT로 구현될 수 있다. 이하의 실시예에서 p 타입 TFT(PMOS)를 예시하였지만, 본 발명은 이에 한정되지 않는다는 것에 주의하여야 한다. TFT는 게이트(gate), 소스(source) 및 드레인(drain)을 포함한 3 전극 소자이다. 소스는 캐리어(carrier)를 트랜지스터에 공급하는 전 극이다. TFT 내에서 캐리어는 소스로부터 흐르기 시작한다. 드레인은 TFT에서 캐리어가 외부로 나가는 전극이다. 즉, MOSFET에서의 캐리어의 흐름은 소스로부터 드레인으로 흐른다. n 타입 TFT (NMOS)의 경우, 캐리어가 전자(electron)이기 때문에 소스에서 드레인으로 전자가 흐를 수 있도록 소스 전압이 드레인 전압보다 낮은 전압을 가진다. n 타입 TFT에서 전자가 소스로부터 드레인 쪽으로 흐르기 때문에 전류의 방향은 드레인으로 전공이 흐를 수 있도록 소스 전압이 드레인 전압보다 보다. p 타입 TFT에서 정공이 소스로부터 드레인 쪽으로 흐르기 때문에 전류가 소스로부터 드레인 쪽으로 흐르다. MOSFET의 소스와 드레인은 고정된 것이 아니라는 것에 주의하여야 한다. 예컨대, MOSFET의 소스와 드레인은 인가 전압에 따라 변경될 수 있다.

- [0024] 이하에서, 게이트 온 전압(Gate On Voltage)은 TFT가 턴-온(turn-on)될 수 있는 게이트 신호의 전압이다. 게이트 오프 전압(Gate Off Voltage)은 TFT가 턴-오프(turn-off)될 수 있는 전압이다. PMOS에서 게이트 온 전압은 게이트 로우 전압(VGL)이고, 게이트 오프 전압은 게이트 하이 전압(VGH)이다. NMOS에서 게이트 온 전압은 VGH 이고, 게이트 오프 전압은 VGL이다.

- [0025] 이하, 첨부된 도면을 참조하여 본 발명의 다양한 실시예들을 상세히 설명한다. 이하의 실시예들에서, 전계 발광 표시장치는 유기발광 물질을 포함한 유기발광 표시장치를 중심으로 설명한다. 하지만, 본 발명의 기술적 사상은 유기발광 표시장치에 국한되지 않고, 무기발광 물질을 포함한 무기발광 표시장치에 적용될 수 있음에 주의하여야 한다.

- [0026] 도 1 및 도 2를 참조하면, 본 발명의 전계 발광 표시장치는 표시패널(10), 드라이브 IC(Integrated Circuit)(20), 호스트 시스템(100), 메모리(30) 등을 구비한다.

- [0027] 표시패널(10)에서 입력 영상을 재현하는 화면은 신호 배선들에 연결된 복수의 픽셀들(pixel)(P)을 포함한다. 픽셀들(P) 각각은 컬러 구현을 위하여, 적색(R), 녹색(G), 및 청색(B) 서브 픽셀(sub-pixel)을 포함할 수 있다. 픽셀들 각각은 RGB 서브 픽셀들 이외에 백색(White, W) 서브 픽셀(sub-pixel)을 더 포함할 수 있다. 서브 픽셀들 각각은 도 6 및 도 11과 같은 픽셀 회로를 이용하여 픽셀의 전기적 특성 변화를 실시간 보상할 수 있다.

- [0028] 신호라인들은 픽셀들(P)에 아날로그 데이터전압(Vdata)을 공급하는 데이터라인들(11) 및 픽셀들(P)에 게이트 신호를 공급하는 게이트라인들(12)을 포함할 수 있다. 게이트 신호는 픽셀 회로의 구성에 따라 두 개 이상의 신호를 포함할 수 있다. 도 6 및 도 11에 도시된 픽셀 회로의 경우에 게이트 신호는 제1 스캔 신호(SCAN1), 제2 스캔 신호(SCAN2), 및 발광 제어 신호(이하, "EM 신호"라 함)(EM) 등을 포함한다. 신호 배선들은 픽셀들(P)의 전기적 특성을 센싱하는 데 이용되는 센싱 라인들(13)을 더 포함할 수 있다.

- [0029] 표시패널(10)의 픽셀들(P)은 매트릭스 형태로 배치되어 픽셀 어레이(Pixel array)를 구성한다. 각 픽셀(P)은 데이터라인들(11) 중 어느 하나에, 센싱 라인들(13) 중 어느 하나에, 그리고 게이트라인들(12) 중 적어도 어느 하나에 연결될 수 있다. 각 픽셀(P)은 전원생성부로부터 고전위 전원 전압(VDD)과 저전위 전원 전압(VSS)을 공급받도록 구성된다. 이를 위해, 전원생성부는 VDD 배선을 통해 고전위 전원 전압(VDD)을 픽셀들(P)에 공급할 수 있다. 전원생성부는 VSS 배선을 통해 저전위 전원 전압(VSS)을 픽셀들(P)에 공급할 수 있다.

- [0030] 드라이브 IC(20)는 데이터를 픽셀의 전기적 특성 센싱 결과를 바탕으로 미리 설정된 픽셀의 보상값으로 변조하고 데이터 전압을 발생하는 데이터 구동 회로(22, 23, 26, 27)와, 데이터 구동 회로(22, 23, 26, 27)와 게이트 구동부(15)의 동작 타이밍을 제어하는 타이밍 제어부(21)를 구비한다. 드라이브 IC(20)의 데이터 구동 회로(25, 26, 27)는 입력 영상의 데이터에 미리 설정된 보상값을 더하여 보상 데이터를 발생하고 그 보상 데이터를 데이터 전압으로 변환하여 데이터 라인들(11)에 공급한다. 데이터 구동 회로(25, 26, 27)는 데이터 구동부(25), 보상부(26) 및 보상 메모리(27) 등을 포함한다. 보상 메모리(27)와 메모리(30)는 하나의 메모리로 구현될 수 있다.

- [0031] 데이터 구동부(25)는 센싱부(22), 및 데이터전압 생성부(23)를 포함할 수 있으나, 이에 한정되지 않는다.

- [0032] 타이밍 제어부(21)는 호스트 시스템(100)으로부터 입력되는 영상 신호에서 타이밍 신호들, 예컨대 수직 동기신호(Vsync), 수평 동기신호(Hsync), 도트클럭신호(DCLK) 및 데이터 인에이블신호(DE) 등을 바탕으로 게이트 구동부(15)의 동작 타이밍을 제어하기 위한 게이트 타이밍 제어신호(GDC)와, 데이터 구동부(25)의 동작 타이밍을 제어하기 위한 데이터 타이밍 제어신호(DDC)를 생성할 수 있다.

- [0033] 데이터 타이밍 제어신호(DDC)는 소스 스타트 펄스(Source Start Pulse), 소스 샘플링 클럭(Source Sampling Clock), 및 소스 출력 인에이블신호(Source Output Enable) 등을 포함할 수 있으나 이에 한정되지 않는다. 소스 스타트 펄스는 데이터전압 생성부(23)의 데이터 샘플링 시작 타이밍을 제어한다. 소스 샘플링 클럭은 라이징 또는 폴링 에지에 기준하여 데이터의 샘플링 타이밍을 제어하는 클럭신호이다. 소스 출력 인에이블신호는 데이터 전압 생성부(23)의 출력 타이밍을 제어한다.

- [0034] 게이트 타이밍 제어신호(GDC)는 게이트 스타트 펄스(Gate Start Pulse), 게이트 시프트 클럭(Gate Shift Clock) 등을 포함할 수 있으나, 이에 한정되지 않는다. 게이트 스타트 펄스는 첫 번째 출력을 생성하는 스테이지에 인가되어 그 스테이지의 동작을 활성화한다. 게이트 시프트 클럭은 스테이지들에 공통으로 입력되는 클럭 신호로써 게이트 스타트 펄스를 시프트시키기 위한 클럭신호이다.

- [0035] 데이터전압 생성부(23)는 화면 상에 입력 영상을 재현하는 노말 구동 모드(normal driving mode)에서 디지털 신호를 아날로그 신호로 변환하는 디지털-아날로그 변환기(Digital to Analog converter, 이하 DAC라 함)를 이용하여 입력 영상의 데이터 전압(Vdata)을 발생하여 데이터 라인들(11)을 통해 픽셀들(P)에 공급한다.

- [0036] 제품 출하 전 또는 제품 구동 중 픽셀의 전기적 특성 편차를 측정하기 위한 센싱 모드에서, 데이터전압 생성부 (23)는 도시하지 않은 계조-휘도 측정 시스템으로부터 수신된 테스트 데이터를 변환하여 센싱용 데이터전압을 발생하고, 그 센싱용 데이터 전압을 데이터라인들(11)을 통해 표시패널(10)의 센싱 대상 픽셀들(P)에 공급한다. 계조-휘도 측정 시스템은 픽셀들 각각의 전기적 특성을 센싱하고 그 센싱 결과를 바탕으로 픽셀들 간의 전기적특성 편차 특히, 구동 TFT의 문턱 전압 편차를 보상하는 픽셀의 보상값(옵셋)을 도출하여 픽셀의 보상값을 메모리(30)에 저장하거나 또는 기 저장된 값을 갱신(update)한다. 메모리(30)는 플래시 메모리(flash memory)일 수 있으나 이에 한정되지 않는다.

- [0037] 센싱 모드에 사용되는 계조-휘도 측정 시스템은 센싱 모드 동작 시 메모리(30)와 전기적으로 연결될 수 있다.

- [0038] 노말 구동 모드에서, 전계 발광 표시장치에 전원이 인가되면 메모리(30)로부터의 보상값이 드라이브 IC(20)의 내부 보상 메모리(27)로 로딩된다. 드라이브 IC(20)의 보상 메모리(27)는 DDR SDRAM(Double Date Rate Synchronous Dynamic RAM) 또는 SRAM일 수 있으나 이에 한정되지 않는다.

- [0039] 센싱부(22)는 제품 출하전 에이징 공정에서 픽셀들 각각의 전기적 특성, 예컨대, 구동 TFT의 문턱 전압을 센싱하여 계조-휘도 측정 시스템으로 전송하도록 구성될 수 있다. 예시적으로, 텔레비전과 같은 어플리케이션의 경우에, 센싱부(22)는 제품 출하 후 노말 구동 모드에서 픽셀의 전기적 특성을 센싱하여 보상값을 실시간 업데이트(update)할 수도 있다. 단 어플리케이션에 제한되지 않는다.

- [0040] 센싱부(22)는 도 2에 도시된 바와 같이 샘플 앤 홀드 회로(SH)와 아날로그-디지털 변환기(Analog to Digital Convertor, 이하 "ADC"라 함), 및 제1 및 제2 스위치(SW1, SW2)를 포함한다. 센싱부(22)는 구동 TFT의 전류에 따른 구동 TFT의 소스 전압, 즉 센싱 라인(13)에 연결된 커패시터에 저장된 구동 TFT의 소스 전압을 샘플링하여 구동 TFT의 전기적 특성을 센싱할 수 있다. 제1 스위치(SW1)는 기준 전압(Vref)을 센싱 라인(13)에 공급한다. 제2 스위치(SW2)는 아날로그 센싱 전압(Vsen)의 샘플링 타이밍에 턴-온된다. ADC는 샘플 앤 홀드 회로(SH)에서 샘플링된 아날로그 센싱값들(Vsen)을 디지털 센싱 데이터(S-DATA)로 변환한다. 센싱부(22)는 도 2에 한정되지 않는다. 예컨대, 센싱부(22)는 공지된 전압 센싱 회로 또는 전류 센싱 회로로 구현될 수 있다.

- [0041] 보상부(26)는 보상 메모리(27)로부터 읽어 낸 보상값으로 입력 영상의 데이터(V-DATTA)를 변조하여 데이터 전압 생성부(23)로 전송한다.

- [0042] 호스트 시스템(100)은 텔레비전(Television) 시스템, 셋톱박스, 네비게이션 시스템, 개인용 컴퓨터(PC), 홈 시어터 시스템, 모바일 시스템, 웨어러블 시스템, 가상 현실 시스템(virtual reality system, VR) 중 어느 하나일수 있다. 도 1의 예는 모바일 시스템 구성을 예시한 것이다. 호스트 시스템(100)에 따라 표시패널의 구동 회로 구성이 달라질 수 있다. 호스트 시스템(100)은 모바일 시스템, 웨어러블 시스템, 가상 현실 시스템 등에서 어플리케이션 프로세서(Application Processor)로 구현될수 있다. 본 발명의 픽셀들은 구동 소자의 문턱 전압을 샘플링하여 문턱 전압을 보상하는 기간이 없이 구동 소자의 이동도와 온도 편차를 실시간으로 보상한다. 따라서, 본 발명은 120 Hz 이상의 프레임 레이트(frame rate)로 고속 구동이 필요한 어플리케이션 예를 들어, 가상 현실 시스템(VR)에 적용되기에 유리하다.

- [0043] 도 3 내지 도 4c를 결부하여 픽셀의 전기적 특성 편차를 보상하기 위한 보상값 산출 알고리즘에 대하여 설명하기로 한다. 도 4a 내지 도 4c에서 황축은 전압(V)이고, 종축은 전류(I)이다.

[0044] 도 3 및 도 4a를 참조하면, 미리 설정된 계조(A~G)에 대하여 픽셀의 전기적 특성을 센싱한 후에, 최소자승법[最小自乘法, least square method]을 바탕으로 평균 I-V 곡선을 수학식 1과 같이 도출한다(ST1). 단 본 발명에서 개시하는 최소자승법은 일 예시일 뿐이며, 본 발명은 최소자승법에 제한되지 않으며, 대안적인 회귀분석[回歸分析, regression analysis], 다항식근사[多項式近似, polynomial approximation] 등을 적용하는 것도 가능하다,

#### 수학식 1

$$[0045] I = a(V_{data} - b)^c$$

- [0046] 예시적인, 수학식 1에서, "a"는 구동 TFT의 전자 이동도이고, "b"는 구동 TFT의 문턱전압이며, "c"는 구동 TFT 의 물리적 특성치를 나타낸다.

- [0047] 도 3 및 도 4b를 참조하면, 저계조(X)와 고계조(Y) 2 포인트에서 측정된 전류(I1, I2)과 데이터 전압 (Vdata1,Vdata2))의 계조를 기준으로 아래의 수학식 2와 같이 센싱 대상 픽셀(P)의 파라미터값인 a'값, 및 b' 값을 계산한다(ST2).

# 수학식 2

[0048]

$$I_1 = a'(V_{data1} - b')^c$$

[0049]

$$I_2 = a'(V_{data2} - b')^c$$

- [0050] 예시적인, 수학식 2에서, 2차 방정식을 이용하여 기 센싱 픽셀(P)의 파라미터값인 a'값, 및 b'값을 산출할 수 있다.

- [0051] 도 3 및 도 4c와 같이 센싱 대상 픽셀(P)의 I-V 곡선이 전체 픽셀들(P)의 평균 I-V 곡선에 일치되도록 하기 위한 옵셋(Offset)과 게인(Gain) 등의 픽셀 보상값을 계산한다 (ST3). 옵셋(Offset)과 게인(Gain)은 수학식 3과

같다. 예시적인, 수학식 3에서, "Vcomp"는 보상 전압이다. 옵셋(Offset) **b'-b(♣)** 은 구동 TFT의 문턱 전

압 편차를 보상하기 위한 보상값이다. 게인(Gain) <sup>(출)</sup> 은 구동 TFT의 이동도 편차를 보상하기 위한 보상값이다.

#### 수학식 3

[0052]

$$V_{comp} = \left(\frac{a}{a'}\right)^{\frac{1}{c}} \times V_{data} + \left[b' - b\left(\frac{a}{a'}\right)^{\frac{1}{c}}\right]$$

- [0053] 보상부(26)는 입력 영상의 데이터(V-DATA)에 옵셋을 가산하여 픽셀들(P)의 구동 TFT 문턱 전압 편차를 보상한다. 구동 TFT의 이동도 편차와 온도 특성 차이는 서브 픽셀들 각각의 픽셀 회로 내에서 자동 보상된다. 따라서, 본 발명은 구동 TFT의 문턱전압을 외부 보상 방법으로 보상하고, 구동 TFT의 이동도 편차와 온도 편차를 외부 보상값을 이용하는 것이 아니라 픽셀 내에서 내부 보상 방법으로 실시간 보상한다(ST4).

- [0054] 본 발명은 구동 소자 즉, 구동 TFT의 이동도와 온도 편차를 실시간 보상하기 위하여 EM 신호(EM)의 게이트 온 전압에 따라 고전위 전원 전압(VDD)을 구동 소자에 공급하고, 미리 설정된 실시간 보상 시간 동안 EM 신호(EM)의 게이트 오프 전압에 따라 턴-오프되는 스위치 소자를 이용하여 구동 소자와 고전위 전원 전압 (VDD)사이의 경로를 차단한다. 실시간 보상 시간 동안 구동 소자의 소스 전압이 변하여 구동 소자의 이동도 편차와 온도 편차가 매 수평 기간 마다 실시간 보상된다.

- [0055] 게이트 구동부(15)는 게이트 신호를 생성하여 게이트라인들(12)에 순차적으로 공급한다. 게이트 구동부(15)는 픽셀 어레이의 신호 배선들 및 TFT 등과 함께 표시패널(10)의 기판 상에 직접 형성될 수 있다. 이 게이트 구동

부(15)는 레벨 시프터(level shifter)를 통해 입력된 게이트 타이밍 제어신호(GDC)에 응답하여 게이트 신호를 순차적으로 출력하는 시프트 레지스터(shift register)를 포함한다. 게이트 타이밍 제어 신호는 게이트 스타트 펄스(Gate Start Pulse), N상(N은 2이상의 정수) 게이트 시프트 클럭(Gate Shift Clock) 등을 포함한다. 레벨 시프터는 타이밍 제어부(21)로부터 수신된 게이트 타이밍 제어 신호(GDC)의 TTL(Transistor-Transistor-Logic) 전압 레벨을 TFT의 온/오프 스위칭이 가능한 전압 즉, 게이트 하이 전압과 게이트 로우 전압으로 변환한다.

- [0056] 본 발명의 전계 발광 표시장치는 저소비 전력 모드로 구동될 수 있다. 저소비 전력 모드는 화면 상에 영상을 재현하는 노말 구동 모드에 비하여 드라이브 IC(20)와 픽셀들의 구동 주파수를 낮춘다. 저소비 전력 구동 모드에서 픽셀(P)에 기입되는 영상 데이터는 노말 구동 모드에 비하여 낮은 주파수로 갱신(update)된다. 저소비 전력 구동 모드에서 프레임 레이트(frame rate)는 1 Hz로 낮아질 수 있다. 이 경우, 도 5의 예와 같이 드라이브 IC(20)는 60 프레임 기간 중에서 제1 프레임 기간(16.67ms)에 데이터를 픽셀들(P)에 기입하고 나머지 59 프레임 기간 동안 데이터를 출력하지 않는다. 픽셀들(P)은 저소비 전력 모드(Tlrr) 매 초마다 제1 프레임 기간(FR)에 데이터를 1차례 기입하고 나머지 대부분의 시간 동안 스토리지 커페시터(Cst)에 저장된 데이터 전압을 유지한다. 노말 구동 모드(Tnor)에서 프레임 레이트(frame rate)는 60 Hz로 설정될 수 있다. 드라이브 IC(20)는 노말 구동 모드(Tnor)에서 1 초에 60 개의 프레임 데이터를 픽셀들(P)에 기입한다.

- [0057] 본 발명의 전계 발광 표시장치에서 서브 픽셀들 각각은 도 6 및 도 11에 도시된 바와 같이 발광 소자(EL)의 전류를 게이트-소스간 전압(Vgs)으로 조절하는 구동 소자(DT), 및 EM 신호(EM)의 게이트 온 전압에 따라 고전위전원 전압(VDD)을 구동 소자(DT)에 공급하는 스위치 소자(S3)를 구비한다. 타이밍 제어부(21)는 1 수평 기간(1H) 내에서 구동 소자(DT)의 이동도를 실시간 보상하기 위한 실시간 이동도 보상 시간(t2)을 설정하고, 실시간이동도 보상 시간(t2) 동안 구동 소자(DT)의 소스 노드(DTS)을 플로팅하여 픽셀들(P) 간의 구동 소자 이동도 편차와 온도 편차를 실시간 보상한다.

- [0058] 도 6은 본 발명의 제1 실시예에 따른 픽셀 회로를 보여 주는 도면이다. 도 7a 내지 도 7c는 도 6에 도시된 픽셀 회로의 동작을 단계적으로 보여 주는 도면들이다. 도 8은 도 6에 도시된 픽셀 회로의 구동 신호 파형을 보여 주는 도면이다. 도 8에서 "lH"는 픽셀에 데이터가 기입(write)되는 1 수평 기간을 나타낸다.

- [0059] 도 6 내지 도 9를 참조하면, 픽셀 회로는 발광 소자(EL), 구동 TFT(DT), 스토리지 커패시터(Cst), 제1 스위치 TFT(S1), 제2 스위치 TFT(S2), 제3 스위치 TFT(S3)를 구비할 수 있다. 스위치 TFT들(S1~S3)과 구동 TFT(DT)는 n 타입 MOSFET로 구현될 수 있다.

- [0060] 구동 TFT(DT)와 제1 스위치 TFT(S1) 각각은 산화물 트랜지스터를 포함한다. 특히, 산화물 트랜지스터는 오프 전류(Off current)가 낮은 산화물 반도체를 포함한 NMOS(이하, "Oxide NMOS"라 함)로 구현될 수 있다. 오프 전류는 TFT의 오프 상태에서 TFT의 소스와 드레인 사이에 누설 전류이다. 오프 전류가 낮은 TFT 소자는 오프 상태가 길더라도 누설 전류가 없기 때문에 픽셀들을 저속 구동할 때 픽셀들의 휘도 변화를 최소화할 수 있다.

- [0061] 구동 TFT의 반도체 채널층이 백 플레인(Backplane)과 가까우면 구동 TFT에 인가된 전압에 따라 백 플레인에서 구동 TFT의 반도체 채널층에 유입되는 원치 않는 전하의 흐름이 발생된다. 이러한 백 플레인의 전하 거동은 구동 TFT의 문턱 전압(Vth)의 변화를 초래하고, 구동 TFT의 문턱 전압 변화는 발광 소자(EL)의 전류 및 휘도 변화를 초래하여 화면 상에서 잔상을 초래한다.

- [0062] 구동 TFT의 문턱 전압은 백 플레인(Backplane)으로부터 유입되는 원치 않는 전하(charge)에 의해 그 문턱 전압 (Vth)이 변할 수 있고, 그 결과 잔상이 초래될 수 있다. 이러한 잔상 문제를 방지하기 위하여, 구동 TFT(DT)와 제1 스위치 TFT(T2)에 적용되는 "Oxide TFT")는 도 12 및 도 13의 예와 같이 백 프레인으로부터 전하 유입을 방지할 수 있는 구조를 갖는 것이 바람직하다.

- [0063] 제2 스위치 TFT(S2)와 제3 스위치 TFT(S3)는 폴리 실리콘 트랜지스터를 포함한다. 폴리 실리콘 트랜지스터는 이동도가 높은 저온 폴리 실리콘(Low Temperature Poly Silicon, LTPS) NMOS(이하, "LTPS TFT"라 함)로 구현될 수 있다. 한편, LTPS TFT의 반도체 채널층은 도 12 및 도 13에 도시된 바와 같이 백 플레인과 가까운 구조이기 때문에 이러한 LTPS TFT로 구동 TFT를 구현하면 픽셀들이 잔상에 취약하게 된다.

- [0064] 본 발명의 전계 발광 표시장치는 정지 영상에서 소비 전력을 줄이기 위하여 도 5의 예와 같이 프레임 레이트 (frame rate)를 낮추어 픽셀들을 저속 구동할 수 있다. 이 경우, 데이터 업데이트 주기가 길어지기 때문에 픽셀에서 누설 전류가 발생되면 플리커(flicker)가 보일 수 있다. 오프 기간이 긴 제1 스위치(S1)를 오프 전류

(Off current)가 낮은 Oxide NMOS로 사용하면 저속 구동에서 누설 전류를 줄여 플리커(flicker) 현상을 줄일 수 있다. 픽셀들의 휘도가 주기적으로 변동될 때 사용자가 플리커를 느낄 수 있다.

- [0065] 이 픽셀 회로에는 제1 및 제2 스캔 신호(SCAN1, SCAN2), EM 신호(EM)가 인가된다. 이 신호들(SCAN1, SCAN2, EM) 각각은 VGH와 VGL 사이에서 스윙한다. 제1 스캔 신호(SCAN1)는 1 프레임 기간에서 t1 및 t2 시간 동안 게이트 온 전압(VGH)으로 발생되고, t3 기간과 그 이후에 게이트 오프 전압(VGL)으로 발생된다. 제2 스캔 신호(SCAN2)는 t1 시간 동안 게이트 온 전압(VGH)으로 발생되고, t2 기간과 그 이후에 게이트 오프 전압(VGL)으로 발생된다. EM 신호(EM)는 t1 및 t2 시간 동안 게이트 온 전압으로 발생되고, t3 기간 이후에 도 9에 도시된 바와 같이 미리 설정된 PWM(Pulse Width Modulation) 듀티비(duty ratio)로 픽셀들의 온/오프(On/Off)를 스위칭한다. 픽셀의 발광 구동 시간(t4) 동안 EM 신호에 의해 픽셀들이 20% 내지 90% 정도의 듀티비 범위내에서, 일예로, 50% 정도의 듀티비로 점등 및 소등을 반복하면 플리커와 잔상을 최소화할 수 있다. 본 발명은 특정 듀티비에 제한되지 않는다. 도 9에서, Vsync는 1 프레임 기간을 정의하는 수직 동기신호이다. 도 9에서, SCAN1(n) 및 Em1(n)는 표시패널(10)의 제n 라인에 배열된 픽셀들에 인가되는 제1 스캔 신호와 EM 신호이다. 도 9에서 제2 스캔 신호(SCAN2)는 생략되어 있다.

- [0066] 발광 소자(EL)는 애노드(Anode)와 캐소드(Cathode) 사이에 형성된 유기 화합물층을 포함한다. 유기 화합물층은 정공주입층(HIL), 정공수송층(HTL), 발광층(EML), 전자수송층(ETL) 및 전자주입층(EIL) 등을 포함할 수 있으나 이에 한정되지 않는다. 발광 소자(EL)의 캐소드(CAT)는 저전위 전원 전압(VSS)에 연결되고, 애노드(ANO)는 구동 TFT(DT)의 소스에 연결된다.

- [0067] 구동 TFT(DT)는 게이트-소스 간 전압(Vgs)에 따라 발광 소자(EL)에 흐르는 전류를 조절하는 구동 소자이다. 구동 TFT(DT)는 제1 노드(DTG)에 연결된 게이트, 제2 노드(DTS)에 연결된 소스, 및 제3 노드(DTD)에 연결된 드레인을 포함한다. 제1 노드(DTG)는 구동 TFT(DT)의 게이트, 스토리지 커패시터(Cst)의 일측 전극 및 제1 스위치TFT(S1)의 소스에 연결된다. 스토리지 커패시터(Cst)는 제1 노드(DTG)와 제2 노드(DTS) 사이에 연결된다. 고전위 전원 전압(VDD)은 제3 노드(DTD)를 통해 구동 TFT(DT)에 인가된다.

- [0068] 제1 스위치 TFT(S1)는 t1~t2 시간 동안 제1 스캔 신호(SCAN1)에 따라 턴-온되어 데이터 전압(Vdata)을 제1 노드 (DTG)에 공급한다. 제1 스위치 TFT(S1)는 제1 스캔 신호(SCAN1)가 인가되는 제1 게이트 라인에 연결된 게이트, 데이터 전압(Vdata)이 인가되는 데이터 라인(11)에 연결된 드레인, 및 제1 노드(DTG)를 통해 구동 TFT(DT)의 게이트에 연결된 소스를 포함한다.

- [0069] 제2 스위치 TFT(S2)는 t1 시간 동안 제2 스캔 신호(SCAN2)에 따라 턴-온되어 센싱 라인(13)과 제3 노드(DTD) 사이의 전류 경로(current path)를 형성한다. 제2 스위치 TFT(S2)는 제2 스캔 신호(SCAN2)가 인가되는 제2 게이트 라인에 연결된 게이트, 소정의 기준 전압(Vref)이 인가되는 센싱 라인(13)에 연결된 소스, 및 제2 노드(DT S)를 통해 구동 TFT(DT)의 소스와 발광 소자(EL)의 애노드(ANO) 그리고 스토리지 커패시터(Cst)의 타측 전극에 연결된 드레인을 포함한다. 기준 전압(Vref)은 고전위 전원 전압(VDD) 보다 낮은 전압이다.

- [0070] 제3 스위치 TFT(S3)는 VDD 배선과 구동 TFT(DT)의 드레인 사이에 배치되어 EM 신호(EM)에 응답하여 VDD 배선과 구동 TFT(DT) 사이의 전류 경로를 스위칭한다. 제3 스위치 TFT(S3)는 t1 및 t3 시간 동안 EM 신호(EM)의 게이트 온 전압(VGH)에 따라 턴-온되어 고전위 전원 저압(VDD)을 제3 노드(DTD)를 통해 구동 TFT(DT)의 드레인에 공급한다. 제3 스위치 TFT(S3)는 EM 신호(EM)가 인가되는 제3 게이트 라인에 연결된 게이트, 제3 노드(DTD)을 통해 구동 TFT(DT)의 드레인에 연결된 소스, 및 VDD 배선을 통해 고전위 전원 전압(VDD)이 인가되는 드레인을 포함한다.

- [0071] 이 픽셀 회로의 동작을 단계적으로 설명하기로 한다.

- [0072] 초기화 시간(t1) 동안, 제1 및 제2 스캔 신호(SCAN1, SCAN2)와 EM 신호(EM)의 게이트 온 전압(VGH)에 따라 스위치 TFT들(S1, S2, S3)이 모두 턴-온된다. 이 때, 도 7a에 도시된 바와 같이 제1 노드(DTG)에 데이터 전압 (Vdata)이 인가된다. 초기화 시간(t1) 동안 제2 노드(DTS)의 전압은 기준 전압(Vref)이고, 제3 노드(DTD)의 전압은 고전위 전원 전압(VDD)으로 초기화된다. 초기화 시간(t1) 동안, 구동 TFT(DT)는 게이트 전압이 소스 전압보다 문턱 전압(Vth) 이상 높기 때문에 턴-온된다.

- [0073] 이어서, 실시간 이동도 보상 시간(t2) 동안 제1 스위치 TFT(S1)는 제1 스캔 신호(SCAN1)가 게이트 온 전압(VGH)을 유지하여 온 상태를 유지하는 반면, 제2 스위치 TFT(S2)는 제2 스캔 신호(SCAN2)가 게이트 오프 전압(VGL)으로 반전되기 때문에 턴-오프된다. 이 때, 픽셀 회로의 전류 경로는 도 7b와 같다. 실시간 이동도 보상 시간(t2) 동안, 구동 TFT(DT)의 소스에 연결된 제2 노드(DTS)가 플로팅(floating)되어 구동 TFT(DT)의 이동도에

따라 구동 TFT(DT)의 소스 전압의 방전양이 달라진다.

- [0074] 픽셀들 간에 구동 TFT(DT)의 이동도 편차 또는 온도 편차가 있을 때 동일 계조에서 구동 TFT(DT)의 이동도가 높 은 픽셀(도 10에서 A 픽셀)은 밝게 보이는 반면, 구동 TFT(DT)의 이동도가 낮은 픽셀(도 10에서 B 픽셀)은 상대 적으로 어둡게 보인다. 한편, 픽셀의 온도가 높으면 구동 TFT(DT)의 I-V 전달 커브가 부극성(Negative) 쪽으로 시프트(shift)하여 구동 TFT(DT)의 전류가 높아진다. 따라서, 구동 TFT(DT)의 이동도가 높거나 온도가 높으면 픽셀의 휘도가 높아져 균일한 화질을 얻을 수 없다. 본 발명은 픽셀들(P) 각각에서 실시간 이동도 보상 시간 (t2)에 구동 TFT(DT)의 소스 전압을 구동 TFT(DT)의 이동도에 따라 변하게 함으로써 픽셀들 간에 구동 TFT의 이 동도 편차와 온도 편차를 실시간 보상한다. 실시간 이동도 보상 시간(t2) 동안 이동도가 높은 구동 TFT(DT)는 소스-드레인 간 전류양이 커서 소스 전압이 상대적으로 많이 방전되어 Vgs(ΔVgs(A))가 상대적으로 더 작아진다. 반면에, 실시간 이동도 보상 시간(t2) 동안 이동도가 낮은 구동 TFT(DT)는 소스-드레인간 전류양이 작아 소스 전압이 상대적으로 적게 방전되어 Vgs(ΔVgs(B))가 상대적으로 크다. 픽셀의 휘도는 구동 TFT(DT)의 Vgs에 따라 비례하는 발광 소자(EL)의 전류에 따라 결정된다. 따라서, 구동 TFT(DT)의 이동도가 높은 픽셀(A) 은 실시간 이동도 보상 시간(t2) 동안 구동 TFT(DT)의 Vgs가 큰 폭으로 감소되어 휘도가 감소되는 반면에, 구동 TFT(DT)의 이동도가 상대적으로 낮은 픽셀은 실시간 이동도 보상 시간(t2) 동안 구동 TFT(DT)의 Vgs 감소 폭이 작아 휘도가 감소가 상대적으로 작다. 따라서, 도 10에서 보상 전후의 픽셀 휘도에서 알 수 있는 바와 같이 화 면 전체에서 구동 TFT(DT)의 이동도 편차가 균일하게 보상되어 화면 전체에서 픽셀들의 휘도가 균일하게 제어될 수 있다.

- [0075] 구동 TFT(DT)의 전류는 픽셀의 온도에 비례한다. 이 때문에 실시간 이동도 보상 시간 동안 온도가 높은 픽셀에서 구동 TFT의 Vgs 감소폭이 온도가 낮은 픽셀 보다 커져 온도 차이에 따른 픽셀들의 휘도 편차도 보상된다.

- [0076] 발광 시간(t3) 동안, EM 신호(EM)는 도 9에 도시된 바와 같이 미리 설정된 PWM의 듀티비(%)로 게이트 온 전압과 게이트 오프 전압을 교번한다. EM 신호(EM)는 OLED의 전류 스위칭하여 발광 시간(t3) 동안 EP 신호(EM)의 PWM 듀티비로 픽셀이 점등 및 소등을 반복하게 한다. 이 때 발광 소자(EL)로 흐르는 전류 경로는 도 7c와 같다.

- [0077] 이러한 픽셀 회로는 구동 TFT(DT)의 문턱전압을 외부 보상 방법으로 보상하고, 구동 TFT(DT)의 이동도 편차와 온도 편차를 내부 보상 방법으로 매 프레임 기간 마다 실시간 보상한다.

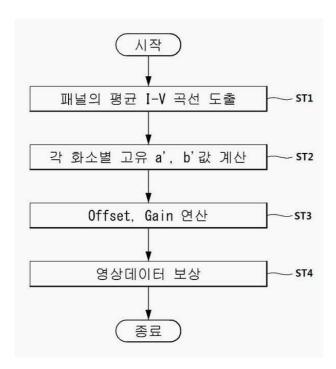

- [0078] 도 11은 본 발명의 제2 실시예에 따른 픽셀 회로를 보여 주는 도면이다.

- [0079] 도 11을 참조하면, 픽셀 회로는 발광 소자(EL), 구동 TFT(DT), 스토리지 커패시터(Cst), 제1 스위치 TFT(S1), 제2 스위치 TFT(S2), 제3 스위치 TFT(S3)를 구비할 수 있다. 스위치 TFT들(S1~S3)과 구동 TFT(DT)는 n 타입 MOSFET로 구현될 수 있다.

- [0080] 이 픽셀 회로는 픽셀 내의 모든 TFT들(S1~S3, DT)이 Oxide TFT로 구현된 것을 제외하면 전술한 제1 실시예와 실 질적으로 동일하다. 백 플레인의 전하 거동으로 인한 잔상 문제를 방지하기 위하여, 이 픽셀 회로의 TFT들 (S1~S3, DT)은 도 12 및 도 13과 같은 단면 구조로 구현되는 것이 바람직하다.

- [0081] 도 12 및 도 13은 본 발명의 실시예에 따른 픽셀 회로들의 단면 구조를 보여 주는 도면들이다. 도 12 및 도 13 에서 제2 스위치(S2)는 생략되어 있다.

- [0082] 도 12를 참조하면, 본 발명의 표시패널(10)은 백 플레인(PI) 위에 배치된 TFT들(S1, S3, DT)을 포함한다. 백 플레인(PI)은 플렉시블 디스플레이 구현이 가능한 PI 필름(Polyimide Film)와 같은 수지 기판으로 구현될 수 있으나 이에 한정되지 않는다.

- [0083] 백 플레인(PI) 위에 절연 물질의 버퍼충(BUF1)이 형성되고, 그 버퍼충(BUF1) 위에 픽셀 회로의 스위치 TFT들 (S1, S3)과 구동 TFT(DT)이 형성된다. 도 12는 제1 스위치 TFT(S1)와 구동 TFT(DT)가 Oxide TFT로 구현되고, 제3 스위치 TFT(S3)가 LTPS TFT로 구현된 예이나 이에 한정되지 않는다. 예컨대, 도 11에 도시된 바와 같이 픽셀 회로 내의 모든 TFT들(S1~S3, DT)이 Oxide TFT로 구현될 수 있다. 백 플레인(PI) 상에 픽셀 어레이와 함께 게이트 구동부(15)가 형성될 수 있다. 게이트 구동부(15)의 스위치 소자들은 도 12에 도시된 LTPS TFT와 실질적으로 동일한 구조로 구현될 수 있다.

- [0084] 도 12의 예에서, LTPS TFT는 반도체 패턴(LACT) 위에 게이트(G1)가 배치된 탑 게이트(top gate) 구조를 갖는다. Oxide TFT는 반도체 패턴(OACT) 아래에 게이트(G2)가 배치된 바텀 게이트(bottom gate) 구조를 갖는다. 반도체 패턴(LACT, OACT)의 소스 영역과 드레인 영역은 n+ 이온으로 도핑된다. 반도체 패턴(LACT, OACT)에서 소스 영역과 드레인 영역 사이의 반도체 채널층은 p+ 반도체이다.

- [0085] LTPS TFT에서, 반도체 패턴(LACT) 위에 게이트 절연막(GI)이 덮여 진다. LTPS TFT의 게이트(G1)는 게이트 절연막(GI) 상에 형성된 제1 금속 패턴(G1)으로 형성된다. 제1 층간 절연막(ILD1)은 게이트(G1)를 덮고, 제1 층간 절연막(ILD1) 상에 제2 및 제3 층간 절연막(ILD2, ILD3)가 적충된다. LTPS TFT의 소스 및 드레인(SD1)은 제3 층간 절연막(ILD3) 상의 제3 금속 패턴으로 형성된다. LTPS TFT의 소스(SD1)는 층간 절연막들(ILD1, ILD2, ILD3)를 관통하는 콘택홀(contact hole)을 통해 반도체 패턴(LACT)의 소스 영역에 접촉된다. 마찬가지로, LTPS TFT의 드레인(SD1)은 층간 절연막들(ILD1, ILD2, ILD3)를 관통하는 콘택홀을 통해 반도체 패턴(LACT)의 드레인 영역에 접촉된다. 제1 보호막(PAS)이 소스 및 드레인(SD1) 상에 덮여지고, 제1 보호막(PAS) 상에 제2 보호막 (PLN)이 형성된다.

- [0086] Oxide TFT는 제1 층간 절연막(ILD1) 상의 제2 금속 패턴으로 형성된 게이트(G2), 제2 및 제3 층간 절연막들 (ILD2, ILD3)를 사이에 두고 게이트(G2)와 중첩되는 반도체 패턴(OACT), 제3 금속 패턴으로 형성된 소스 및 드 레인(SD1) 등을 포함한다. 제1 금속 패턴(G1)과 제2 금속 패턴(G2) 사이에 스토리지 커패시터(Cst)가 형성될 수 있다.

- [0087] Oxide TFT는 백 플레인(PI)과 반도체 패턴(OACT) 사이에 게이트(G2)가 배치된다. 이 게이트(G2)는 백 플레인 (PI)으로부터 반도체 패턴(OACT)로 흐르는 전하를 차단한다. 따라서, Oxide TFT의 보텀 게이트 구조는 백 플레인(PI)의 전하 거동을 차폐하는 게이트를 이용하여 원치 않는 전하 유입으로 인한 문턱 전압(Vth) 변동을 방지함으로써 잔상을 방지할 수 있다. 나아가, Oxide TFT에서 백 플레인(PI)과 반도체 패턴(OACT) 사이의 절연막두께(d2)가 LTPS TFT의 그 것(d1) 보다 크기 때문에 전하 이동 경로가 길어 백 플레인(PI)으로부터 반도체 패턴 (OACT)로 전하가 유입되기가 더 어렵다.

- [0088] 도 13을 참조하면, 본 발명의 표시패널(10)은 백 플레인(PI) 위에 배치된 TFT들(S1, S3, DT)을 포함한다. 백 플레인(PI)은 플렉시블 디스플레이 구현이 가능한 PI 필름과 같은 수지 기판으로 구현될 수 있으나 이에 한정되지 않는다.

- [0089] 백 플레인(PI) 위에 절연 물질의 버퍼층(BUF1)이 형성되고, 그 버퍼층(BUF1) 위에 픽셀 회로의 스위치 TFT들 (S1, S3)과 구동 TFT(DT)이 형성된다. 도 13은 제1 스위치 TFT(S1)와 구동 TFT(DT)가 Oxide TFT로 구현되고, 제3 스위치 TFT(S3)가 LTPS TFT로 구현된 예이나 이에 한정되지 않는다. 예컨대, 도 11에 도시된 바와 같이 픽셀 회로 내의 모든 TFT들(S1~S3, DT)이 Oxide TFT로 구현될 수 있다. 백 플레인(PI) 상에 픽셀 어레이와 함께 게이트 구동부(15)가 형성될 수 있다. 게이트 구동부(15)의 스위치 소자들은 도 13에 도시된 LTPS TFT와 실질적으로 동일한 구조로 구현될 수 있다.

- [0090] 도 13의 예에서, LTPS TFT는 반도체 패턴(LACT) 위에 게이트(G1)가 배치된 탑 게이트(top gate) 구조를 갖는다. Oxide TFT 역시 반도체 패턴(OACT) 위에 게이트(G3)가 배치된 탑 게이트(top gate) 구조를 갖는다. Oxide TFT 의 반도체 패턴(OACT) 아래에 전하 유입을 차단하기 위한 차폐 금속층(Back shield metal layer, BSM)이 배치될 수 있으나 필수적이지 않다. 차폐 금속층(BSM)은 제1 층간 절연막(ILD1) 상의 제2 금속 패턴으로 형성될 수 있다. Oxide TFT에서 게이트(G3)와 반도체 패턴(OACT) 사이의 절연막 두께(d2)가 LTPS TFT의 그 것(d1) 보다충분히 크게 되면 전하 이동 경로가 길어 차폐 금속층(BSM) 없이 반도체 패턴(OACT)으로 유입되는 원치 않는 전하를 차단할 수 있다.

- [0091] LTPS TFT에서, 반도체 패턴(LACT) 위에 게이트 절연막(GI)이 덮여진다. LTPS TFT의 게이트(G1)는 게이트 절연막(GI) 상에 형성된 제1 금속 패턴(G1)으로 형성된다. 제1 층간 절연막(ILD1)은 게이트(G1)를 덮고, 제1 층간 절연막(ILD1) 상에 제2 및 제3 층간 절연막(ILD2, ILD3)가 적층된다. LTPS TFT의 소스 및 드레인(SD1, SD2)은 제3 층간 절연막(ILD3) 상의 제3 금속 패턴과, 제4 층간 절연막(ILD4) 상의 제5 금속 패턴으로 형성된다. LTPS TFT의 소스(SD1)는 층간 절연막들(ILD1, ILD2, ILD3)를 관통하는 콘택홀(contact hole)을 통해 반도체 패턴 (LACT)의 소스 영역에 접촉된다. 마찬가지로, LTPS TFT의 드레인(SD1)은 층간 절연막들(ILD1, ILD2, ILD3)를 관통하는 콘택홀을 통해 반도체 패턴(LACT)의 드레인 영역에 접촉된다. 제2 버퍼막(BUF2)이 소스 및 드레인(SD1) 상에 덮여지고, 제2 버퍼막(BUF2) 위에 제4 층간 절연막(ILD4)이 형성된다. 제4 층간 절연막(ILD4) 상의 제5 금속 패턴이 제2 버퍼막(BUF2)과 제4 층간 절연막(ILD4)을 관통하는 콘택홀을 통해 제3 금속 패턴에 연결된다. 보호막(PLN)은 제4 금속 패턴을 덮는다.

- [0092] Oxide TFT는 제2 버퍼막(BUF2) 상의 반도체 패턴(OACT), 반도체 패턴(OACT) 위에 배치된 게이트(G3), 제5 금속 패턴으로 형성된 소스 및 드레인(SD2) 등을 포함한다. 게이트(G3)는 제2 게이트 절연막(GI2) 상의 제4 금속 패턴으로 형성된다.

- [0093] 게이트(G3)는 제2 게이트 절연막(GI2)을 사이에 두고 반도체 패턴(OACT)과 중첩된다. 소스 및 드레인(SD2)은 제4 층간 절연막(ILD4) 상의 제5 금속 패턴으로 형성된다.

- [0094] Oxide TFT의 아래에 차폐 금속층(BSM)이 형성될 수 있다. 차폐 금속층(BSM)은 제1 층간 절연막(ILD2) 상의 제2 금속 패턴으로 형성될 수 있다. 제1 금속 패턴(G1)과 제2 금속 패턴(G2) 사이에 스토리지 커피시터(Cst)가 형성될 수 있다. 차폐 금속층(BSM)은 제2 및 제3 층간 절연막들(ILD2, ILD3)을 사이에 두고 반도체 패턴(OACT)과 중첩된다. 차폐 금속층(BSM)은 백 플레인(PI)으로부터 반도체 패턴(OACT)로 흐르는 전하를 차단한다. 따라서, 차폐 금속층(BSM)은 백 플레인(PI)으로부터 Oxide TFT로 유입되는 원치 않는 전하 유입을 차단하여 Oxide TFT의 문턱 전압(Vth) 변동을 방지함으로써 잔상을 방지할 수 있다. 나아가, Oxide TFT에서 백 플레인(PI)과 반도체 패턴(OACT) 사이의 절연막 두께(d2)가 LTPS TFT의 그 것(d1) 보다 크기 때문에 전하 이동 경로가 길어 백 플레인(PI)으로부터 반도체 패턴(OACT)로 전하가 유입되기가 더 어렵다.

- [0095] 도 14는 TFT가 구동될 때 발생하는 전계에 의해 백 플레인으로부터의 전하가 TFT로 흐르는 현상을 개략적으로 보여 주는 도면이다. 도 15는 차폐 금속층(BSM)의 백 플레인 전하 차단 효과를 보여 주는 도면이다.

- [0096] 도 14 및 도 15를 참조하면, 실험 결과에 의하면 TFT의 게이트에 화이트 계조의 전압이 30 분 이상 인가되면 그 TFT에서 발생되는 전계(E)로 인하여 백 플레인(PI)의 전하(111)가 TFT의 반도체 채널층으로 흘러 그 채널층 내의 전하양을 변동한다. 이러한 전하(111)는 전계의 극성에 따라 정공 또는 전하일 수 있다. 이러한 백 플레인 전하(111)는 TFT의 전류를 변화시켜 TFT의 문턱 전압 변화를 초래하고 나아가, 픽셀의 휘도 변화와 잔상을 초래한다. 백 플레인(PI)과 반도체 패턴(OACT) 사이의 두께(d2)를 충분히 길게 하거나 도 15의 (A)의 예와 같이 차폐 금속층(BSM)이 백 플레인(PI)과 반도체 패턴(OACT) 사이에 배치되면 백 플레인 전하(PI)의 흐름을 차단할 수있다. 도 15의 (B)는 차폐 금속층(BSM) 없이 백 플레인(PI)과 반도체 패턴(OACT) 사이의 두께(d2)가 작을 때반도체 패턴(OACT)으로 유입되는 백 플레인 전하(111)의 흐름을 보여 준다.

- [0097] 이상 설명한 내용을 통해 당업자라면 본 발명의 기술사상을 일탈하지 아니하는 범위에서 다양한 변경 및 수정이 가능함을 알 수 있을 것이다. 따라서, 본 발명의 기술적 범위는 명세서의 상세한 설명에 기재된 내용으로 한정되는 것이 아니라 특허 청구의 범위에 의해 정하여져야만 할 것이다.

#### 부호의 설명

[0098] 10 : 표시패널 20 : 드라이브 IC

22 : 센싱부 23 : 데이터전압 생성부

S1, S2, S3 : 픽셀 회로의 스위치 TFT PI : 백 플레인

DT : 픽셀 회로의 구동 TFT BSM : 차단 금속층

d1, d2 : 백 플레인과 반도체 패턴 사이의 절연층 두께

# 도면4a

# *도면4b*

# 도면4c

# 도면7a

# *도면7b*

# *도면7c*

도면11

Oxide TFT

도면14

| 专利名称(译)        | 电致发光显示装置                                                                                                |         |            |

|----------------|---------------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | KR1020180125101A                                                                                        | 公开(公告)日 | 2018-11-22 |

| 申请号            | KR1020170059310                                                                                         | 申请日     | 2017-05-12 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                                                               |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                                                                               |         |            |

| [标]发明人         | LIM BYUNG JUN<br>임병준<br>JUNG HWA JUN<br>정화준<br>WOO YOUNG BIN<br>우영빈                                     |         |            |

| 发明人            | 임병준<br>정화준<br>우영빈                                                                                       |         |            |

| IPC分类号         | G09G3/3233 H01L27/12                                                                                    |         |            |

| CPC分类号         | G09G3/3233 H01L27/1225 G09G2320/0257 G09G2300/043 G09G2300/0828 G09G2300/0842 G09G2230/00 G09G2320/0626 |         |            |

| 外部链接           | Espacenet                                                                                               |         |            |

# 摘要(译)

本发明涉及电致发光显示器,并且在没有阈值电压采样时间的内部补偿 方法中,像素电路,驱动器部件的运动实时补偿偏差和温度偏差。该像 素电路的驱动器组件和开关元件包括氧化物晶体管。

Oxide TFT