# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.) **G09G 3/3233** (2016.01)

(52) CPC특허분류

**G09G 3/3233** (2013.01) **G09G 2300/0426** (2013.01)

(21) 출원번호 10-2016-0067781

(22) 출원일자 **2016년05월31일**

심사청구일자 없음

(11) 공개번호 10-2017-0136153

(43) 공개일자 2017년12월11일

(71) 출원인

#### 엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

#### 조경현

전라북도 정읍시 금붕1길 1-1 102동 1405호 ( 상동,대림아파트)

#### 정일기

충청북도 청원군 옥산면 덕촌리 186(1/2)

#### 타니료스케

경기도 파주시 탄현면 엘씨디로241번길 30-15 40 4호 (금승리)

(74) 대리인

특허법인로얄

전체 청구항 수 : 총 6 항

(54) 발명의 명칭 유기발광 표시장치

#### (57) 요 약

본 발명의 유기발광 표시장치는 제1 방향을 따라 나란히 배치된 픽셀들을 각각 포함한 다수의 픽셀행들과, 제2 방향을 따라 나란히 배치된 픽셀들을 각각 포함하며 상기 다수의 픽셀행들과 교차되는 다수의 픽셀열들과, 상기 픽셀들에 고전위 픽셀전원을 공급하기 위해, 상기 제1 방향을 따라 이웃한 픽셀열들 사이에 배치되되, M(M은 2 이상의 양의 정수) 픽셀열마다 배치되는 제1 고전위 전원라인과, 상기 픽셀들에 고전위 픽셀전원을 공급하기 위해, 상기 제2 방향을 따라 각 픽셀행마다 배치되며, 상기 제1 고전위 전원라인과 교차되는 지점에서 상기 제1 고전위 전원라인에 연결되는 제2 고전위 전원라인과, 상기 제1 고전위 전원라인이 배치되어 있지 않은 이웃한 픽셀열들 사이에 상기 제1 고전위 전원라인과 나란히 배치되어 상기 제2 고전위 전원라인에 연결되는 스페어 바 패턴을 포함한다.

### 대 표 도 - 도6

# (52) CPC특허분류

G09G 2300/0452 (2013.01) G09G 2300/0465 (2013.01)

G09G 2300/0842 (2013.01)

### 명세서

### 청구범위

#### 청구항 1

제1 방향을 따라 나란히 배치된 픽셀들을 각각 포함한 다수의 픽셀행들;

제2 방향을 따라 나란히 배치된 픽셀들을 각각 포함하며 상기 다수의 픽셀행들과 교차되는 다수의 픽셀열들;

상기 픽셀들에 고전위 픽셀전원을 공급하기 위해, 상기 제1 방향을 따라 이웃한 픽셀열들 사이에 배치되되, M(M은 2 이상의 양의 정수) 픽셀열마다 배치되는 제1 고전위 전원라인;

상기 픽셀들에 고전위 픽셀전원을 공급하기 위해, 상기 제2 방향을 따라 각 픽셀행마다 배치되며, 상기 제1 고전위 전원라인과 교차되는 지점에서 상기 제1 고전위 전원라인에 연결되는 제2 고전위 전원라인; 및

상기 제1 고전위 전원라인이 배치되어 있지 않은 이웃한 픽셀열들 사이에 상기 제1 고전위 전원라인과 나란히 배치되어 상기 제2 고전위 전원라인에 연결되는 스페어 바 패턴을 포함하는 유기발광 표시장치.

#### 청구항 2

제 1 항에 있어서,

상기 스페어 바 패턴은 1 픽셀행 단위로 분리되는 유기발광 표시장치.

#### 청구항 3

제 1 항에 있어서,

상기 스페어 바 패턴은 상기 픽셀들에 연결되는 게이트라인들과 비 교차(Non-cross)되는 유기발광 표시장치.

### 청구항 4

제 1 항에 있어서,

상기 제1 고전위 전원라인과 상기 스페어 바 패턴은 제1 층에 위치하고,

상기 제2 고전위 전원라인은 제2 층에 위치하며,

상기 제1 층과 상기 제2 층 사이에는 적어도 하나 이상의 층간 절연막이 구비되는 유기발광 표시장치.

### 청구항 5

제 4 항에 있어서,

상기 제1 고전위 전원라인은 상기 층간 절연막을 관통하는 제1 콘택홀을 통해 상기 제2 고전위 전원라인에 접속되고.

상기 스페어 바 패턴은 상기 충간 절연막을 관통하는 제2 콘택홀을 통해 상기 제2 고전위 전원라인에 접속되는 유기발광 표시장치.

### 청구항 6

제 1 항에 있어서,

상기 픽셀들에 연결된 데이터라인들에 데이터전압을 공급하는 소스 드라이버 IC와, 상기 소스 드라이버 IC가 실장되는 필름 부재와, 상기 고전위 픽셀전원을 생성하는 전원 공급부를 더 포함하고,

상기 제1 고전위 전원라인, 상기 제2 고전위 전원라인, 및 상기 스페어 바 패턴 중에서, 상기 제1 고전위 전원라인만이 상기 소스 드라이버 IC와 상기 필름 부재를 경유하여 상기 전원 공급부에 직접 연결되는 유기발광 표시장치.

### 발명의 설명

#### 기술분야

[0001] 본 발명은 유기발광 표시장치에 관한 것으로, 특히 그물망 구조의 전원 라인을 갖는 유기발광 표시장치에 관한 것이다.

### 배경기술

- [0002] 액티브 매트릭스 타입의 유기발광 표시장치는 스스로 발광하는 유기발광다이오드(Organic Light Emitting Diode: 이하, "OLED"라 함)를 포함하며, 응답속도가 빠르고 발광효율, 휘도 및 시야각이 큰 장점이 있다.

- [0003] 자발광 소자인 OLED는 애노드전극 및 캐소드전극과, 이들 사이에 형성된 유기 화합물층을 포함한다. 유기 화합물층은 정공주입층(Hole Injection layer, HIL), 정공수송층(Hole transport layer, HTL), 발광층(Emission layer, EML), 전자수송층(Electron transport layer, ETL) 및 전자주입층(Electron Injection layer, EIL)으로 이루어진다. 애노드전극과 캐소드전극에 전원전압이 인가되면 정공수송층(HTL)을 통과한 정공과 전자수송층 (ETL)을 통과한 전자가 발광층(EML)으로 이동되어 여기자를 형성하고, 그 결과 발광층(EML)이 가시광을 발생하게 된다.

- [0004] 유기발광 표시장치는 OLED와 구동 TFT(Thin Film Transistor)를 포함한 픽셀들을 매트릭스 형태로 배열하고 영상 데이터의 계조에 따라 픽셀들에서 구현되는 영상의 휘도를 조절한다. 구동 TFT는 고전위 전원라인에 연결되어 고전위 픽셀 전원을 인가받고, 자신의 게이트전극과 소스전극 사이에 걸리는 전압에 따라 OLED에 흐르는 구동전류를 다르게 생성한다. 구동전류에 따라 OLED의 발광량과 영상의 휘도가 결정된다.

- [0005] 이러한 유기발광 표시장치에서는 고전위 전원라인의 배선저항에 의해 IR 드롭이 발생할 수 있다. IR 드롭이 생기면, 픽셀들에 인가되는 고전위 픽셀 전원의 크기가 달라져 픽셀들 간 휘도 편차가 발생된다. 고전위 전원라인에 생기는 IR 드롭을 최소화하기 위해, 고전위 전원라인을 그물망 구조로 형성하는 방안이 제안된 바 있다.

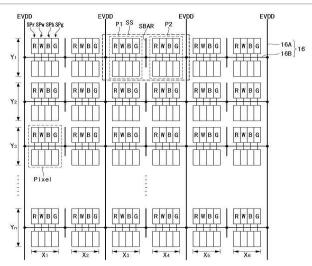

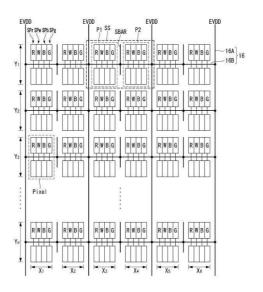

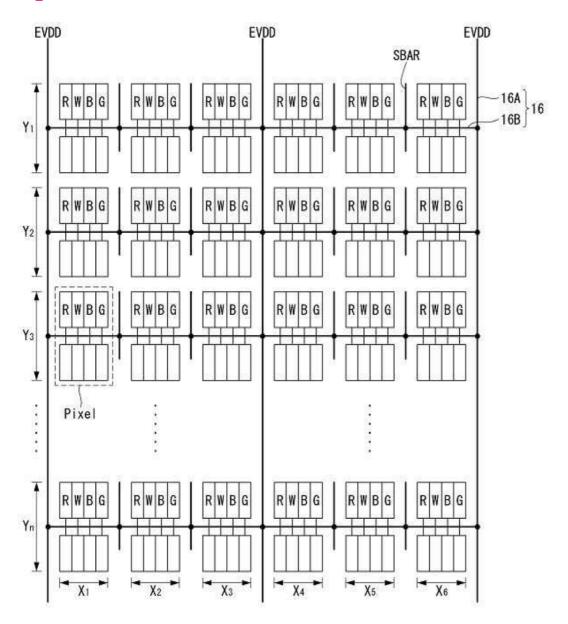

- [0006] 도 1은 종래 그물망 구조의 고전위 전원라인(VL)을 보여준다.

- [0007] 도 1을 참조하면, 종래 그물망 구조의 고전위 전원라인(VL)은 서로 교차하는 제1 고전위 전원라인(VVL)과 제2 고전위 전원라인(HVL)을 포함하여 이루어진다. 제1 고전위 전원라인(VVL)은 이웃한 픽셀열들(X1~X6) 사이에 배치되되, 개구율 저하를 줄이기 위해 2 픽셀열마다 배치된다. 제2 고전위 전원라인(HVL)은 각 픽셀행(Y1~Yn)마다 배치되며, 제1 고전위 전원라인(VVL)과 교차되는 지점에서 제1 고전위 전원라인(VVL)에 연결된다. 각 픽셀열 (X1~X6)은 제1 방향(수직 방향)을 따라 나란히 배치된 픽셀들을 포함하고, 각 픽셀행(Y1~Yn)은 제1 방향과 교차되는 제2 방향(수평 방향)을 따라 나란히 배치된 픽셀들을 포함한다.

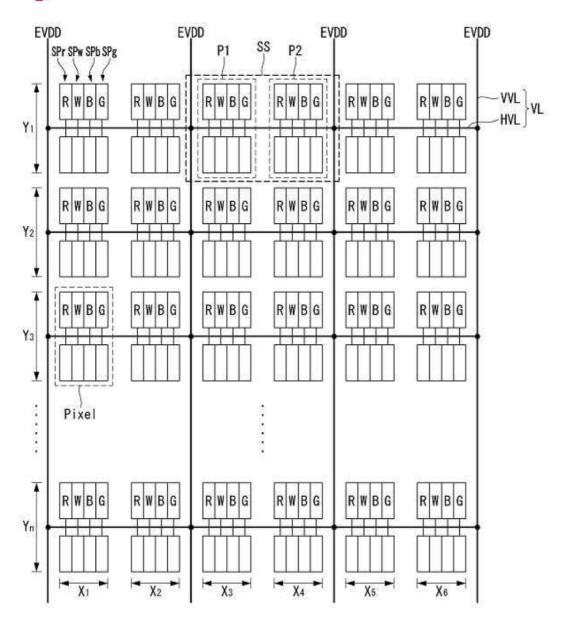

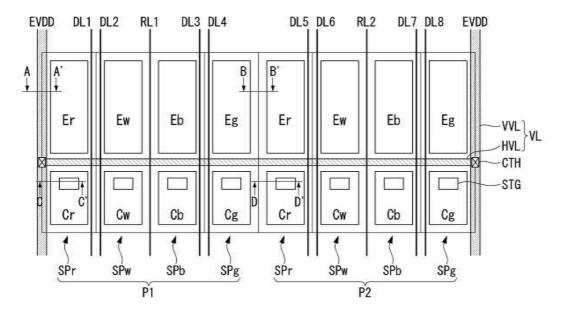

- [0008] 도 2는 도 1의 "SS" 영역을 구체적으로 보여주는 평면도이다.

- [0009] 도 2를 참조하면, "SS" 영역에는 고전위 전원라인(VL)으로부터 고전위 픽셀 전원(EVDD)을 입력 받아 동작하는 제1 픽셀(P1)과 제2 픽셀(P2)이 구비된다. 제1 픽셀(P1)과 제2 픽셀(P2)은 각각, 제1 색 서브픽셀(SPr), 제2 색 서브픽셀(SPw), 제3 색 서브픽셀(SPb), 및 제4 색 서브픽셀(SPg)을 포함할 수 있다. 여기서, 제1 내지 제4 색은 각각 적색(R), 백색(W), 청색(B), 및 녹색(G)일 수 있다. 제1 색 서브픽셀(SPr)은 OLED와 적색(R) 컬러필터를 포함한 제1 발광부(Er)와, 구동 TFT와 스토리지 커패시터(STG)를 포함한 제1 회로부(Cr)로 구성된다. 제2 색 서 브픽셀(SPw)은 OLED를 포함한 제2 발광부(Ew)와, 구동 TFT와 스토리지 커패시터(STG)를 포함한 제2 회로부(Cw)로 구성된다. 제3 색 서브픽셀(SPb)은 OLED와 청색(B) 컬러필터를 포함한 제3 발광부(Eb)와, 구동 TFT와 스토리지 커패시터(STG)를 포함한 제4 발광부(Eg)와, 구동 TFT와 스토리지 커패시터(STG)를 포함한 제4 발광부(Eg)와, 구동 TFT와 스토리지 커패시터(STG)를 포함한 제4 회로부(Cg)로 구성된다.

- [0010] 제1 픽셀(P1)에 속하는 4개의 서브 픽셀들(SPr, SPw, SPb, SPg)은 기준 전압이 공급되는 제1 기준 라인(RL1)에 공통으로 접속되고, 데이터전압이 공급되는 제1 내지 제4 데이터라인(DL1~DL4)에 개별적으로 접속된다. 제2 픽셀(P2)에 속하는 4개의 서브 픽셀들(SPr, SPw, SPb, SPg)은 기준 전압이 공급되는 제2 기준 라인(RL2)에 공통으로 접속되고, 데이터전압이 공급되는 제5 내지 제8 데이터라인(DL5~DL8)에 개별적으로 접속된다. 제1 픽셀(P1)과 제2 픽셀(P2)에 속하는 모든 서브 픽셀들(SPr, SPw, SPb, SPg)은 고전위 픽셀 전원(EVDD)이 공급되는 고전위 전원라인(VL)에 공통으로 접속된다. 제1 고전위 전원라인(VVL)과 제2 고전위 전원라인(HVL)은 콘택홀(CH)을 통해 서로 연결된다.

- [0011] 제1 고전위 전원라인(VVL)은 2 픽셀열마다 배치되기 때문에, 제1 픽셀(P1)의 좌측 및 제2 픽셀(P2)의 우측에 각각 배치되고, 제1 픽셀(P1)과 제2 픽셀(P2)의 사이에는 배치되지 않는다. 따라서, 제1 픽셀(P1)을 기준할 때 그 좌측에는 제1 고전위 전원라인(VVL)이 배치되지만 그 우측에는 제1 고전위 전원라인(VVL)이 없다. 또한, 제2 픽셀(P2)을 기준할 때 그 우측에는 제1 고전위 전원라인(VVL)이 배치되지만 그 좌측에는 제1 고전위 전원라인(VVL)이 없다. 이러한 제1 고전위 전원라인(VVL)의 배치 구조로 인해 종래 유기발광 표시장치는 다음과 같은 문제가 있다.

- [0012] 첫째, 상기한 전원라인 구조를 갖는 종래 유기발광 표시장치에서는 제1 고전위 전원라인(VVL)이 배치되지 않은 제1 픽셀(P1)과 제2 픽셀(P2)의 사이에서 혼색이 발생되는 문제가 있다.

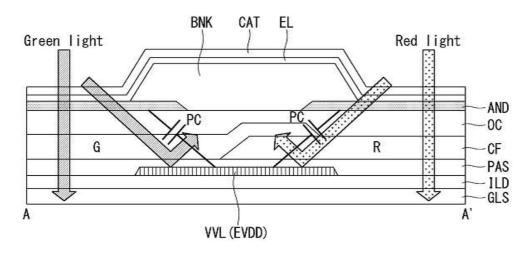

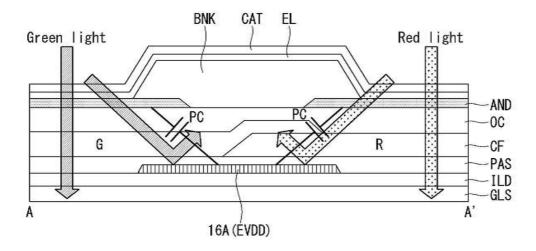

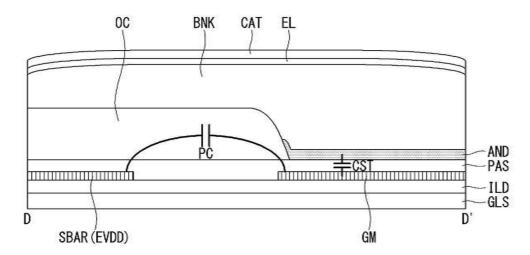

- [0013] 도 3a와 도 3b를 참조하여 구체적으로 설명하면 다음과 같다. 도 3a는 도 2의 A-A'를 따라 절취한 단면도로서, 제1 고전위 전원라인(VVL)을 사이에 두고 서로 이웃한 녹색 서브픽셀(SPg)의 발광부(Eg)와 적색 서브픽셀(SPr)의 발광부(Er)를 보여주고 있다. 그리고, 도 3b는 도 2의 B-B'를 따라 절취한 단면도로서, 제1 고전위 전원라인 (VVL)을 사이에 두지 않고 서로 이웃한 녹색 서브픽셀(SPg)의 발광부(Eg)와 적색 서브픽셀(SPr)의 발광부(Er)를 보여주고 있다.

- [0014] 영역 A-A'에는 제1 고전위 전원라인(VVL)이 배치되어 있기 때문에, 녹색 서브픽셀(SPg)의 발광부(Eg)에서 나오는 녹색 광과 적색 서브픽셀(SPr)의 발광부(Er)에서 나오는 적색 광이, 녹색 서브픽셀(SPg)과 적색 서브픽셀(SPr)의 경계부에서 섞이지 않는다.

- [0015] 하지만, 영역 B-B'에는 제1 고전위 전원라인(VVL)이 배치되어 있지 않기 때문에, 녹색 서브픽셀(SPg)의 발광부 (Eg)에서 나오는 녹색 광과 적색 서브픽셀(SPr)의 발광부(Er)에서 나오는 적색 광이, 녹색 서브픽셀(SPg)과 적 색 서브픽셀(SPr)의 경계부에서 섞이게 된다. 색 섞임이 발생되면, 색 시인성과 색 뎁스(color depth)가 떨어지는 문제가 있다.

- [0016] 둘째, 상기한 전원라인 구조를 갖는 종래 유기발광 표시장치에서는 제1 고전위 전원라인(VVL)이 2 픽셀열마다 배치되기 때문에, 동일 색을 구현하는 서브 픽셀들 간 기생 커패시턴스가 달라져 휘도 편차가 생기는 문제가 있다.

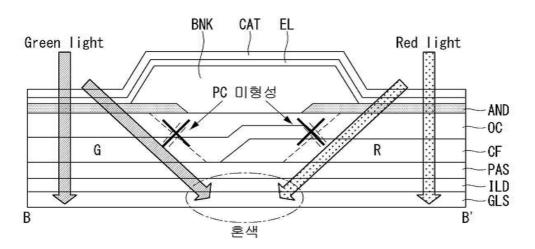

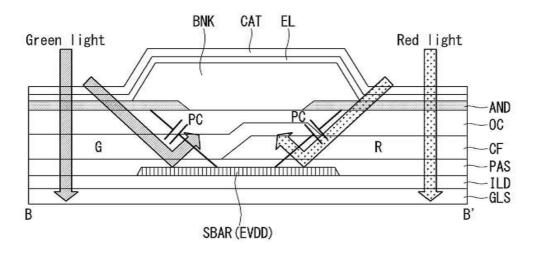

- [0017] 도 3a 및 도 3b와 함께, 도 4a와 도 4b를 참조하여 구체적으로 설명하면 다음과 같다. 도 4a는 도 2의 C-C'를 따라 절취한 단면도로서, 제1 고전위 전원라인(VVL)을 사이에 두고 서로 이웃한 녹색 서브픽셀(SPg)의 회로부 (Cg)와 적색 서브픽셀(SPr)의 회로부(Cr)를 보여주고 있다. 그리고, 도 4b는 도 2의 D-D'를 따라 절취한 단면도 로서, 제1 고전위 전원라인(VVL)을 사이에 두지 않고 서로 이웃한 녹색 서브픽셀(SPg)의 회로부(Cg)와 적색 서브픽셀(SPr)의 회로부(Cr)를 보여주고 있다.

- [0018] 도 3a의 영역 A-A'에서, 제1 픽셀(P1)에 속하는 적색 서브픽셀(SPr)의 애노드전극(AND)과 제1 고전위 전원라인 (WL) 사이에 기생 커패시터(PC)가 형성된다. 반면, 도 3b의 영역 B-B'에는 제1 고전위 전원라인(WL)이 없기 때문에, 제2 픽셀(P2)에 속하는 적색 서브픽셀(SPr)의 애노드전극(AND)에는 기생 커패시터(PC)가 형성되지 않는다. 그 결과, 제1 픽셀(P1)의 적색 서브픽셀(SPr)과 제2 픽셀(P2)의 적색 서브픽셀(SPr) 간에 기생 커패시턴스의 크기가 달라진다. 동일 색을 구현하는 서브픽셀들 간에 발광부의 기생 커패시턴스가 달라지면 휘도 편차가생기고, 그러한 휘도 편차가 표시 얼룩으로 시인될 수 있다. 이러한 문제점은 도 3a 및 도 3b에서와 같이 녹색서브픽셀들(SPg) 간에도 동일하게 생긴다.

- [0019] 도 4a의 영역 C-C'에서, 제1 픽셀(P1)에 속하는 적색 서브픽셀(SPr)의 게이트노드(GM)와 제1 고전위 전원라인 (WVL) 사이에 기생 커패시터(PC)가 형성된다. 반면, 도 4b의 영역 D-D'에는 제1 고전위 전원라인(WVL)이 없기 때문에, 제2 픽셀(P2)에 속하는 적색 서브픽셀(SPr)의 게이트노드(GM)에는 기생 커패시터(PC)가 형성되지 않는다. 그 결과, 제1 픽셀(P1)의 적색 서브픽셀(SPr)과 제2 픽셀(P2)의 적색 서브픽셀(SPr) 간에 기생 커패시턴스의 크기가 달라진다. 동일 색을 구현하는 서브픽셀들 간에 회로부의 기생 커패시턴스가 달라지면 휘도 편차가생기고, 그러한 휘도 편차가 표시 얼룩으로 시인될 수 있다. 게이트노드(GM)는 구동 TFT의 게이트전극에 연결된다. 이러한 문제점은 녹색 서브픽셀들(SPg) 간에도 동일하게 생긴다.

- [0020] 도 3a 내지 도 4b에서, CAT는 캐소드전극을, EL은 유기 화합물층을, BNK는 뱅크층을, AND는 애노드전극을, OC는 평탄화층을, CF는 컬러필터를, PAS와 ILD는 절연막을, GLS는 기판을, 그리고 CST는 스토리지 커패시터를 각각 지시한다.

- [0021] 이와 같이, 이웃한 서브 픽셀들 간에 생기는 혼색과, 동일 색을 구현하는 서브 픽셀들 간에 생기는 기생 커패시

턴스 편차로 인한 휘도 편차 등은 표시 품위를 떨어뜨리는 요인이 된다.

### 발명의 내용

#### 해결하려는 과제

[0022] 따라서, 본 발명의 목적은 그물망 구조의 고전위 전원라인을 갖는 유기발광 표시장치에서, 개구율 저하를 최소 화하면서도 표시 품위를 높일 수 있도록 한 유기발광 표시장치를 제공하는 데 있다.

#### 과제의 해결 수단

- [0023] 상기 목적을 달성하기 위하여, 본 발명의 유기발광 표시장치는 제1 방향을 따라 나란히 배치된 픽셀들을 각각 포함한 다수의 픽셀행들과, 제2 방향을 따라 나란히 배치된 픽셀들을 각각 포함하며 상기 다수의 픽셀행들과 교차되는 다수의 픽셀열들과, 상기 픽셀들에 고전위 픽셀전원을 공급하기 위해, 상기 제1 방향을 따라 이웃한 픽셀열들 사이에 배치되되, M(M은 2 이상의 양의 정수) 픽셀열마다 배치되는 제1 고전위 전원라인과, 상기 픽셀들에 고전위 픽셀전원을 공급하기 위해, 상기 제2 방향을 따라 각 픽셀행마다 배치되며, 상기 제1 고전위 전원라인과 교차되는 지점에서 상기 제1 고전위 전원라인에 연결되는 제2 고전위 전원라인과, 상기 제1 고전위 전원라인에 배치되어 있지 않은 이웃한 픽셀열들 사이에 상기 제1 고전위 전원라인과 나란히 배치되어 상기 제2 고전위 전원라인에 연결되는 스페어 바 패턴을 포함한다.

- [0024] 상기 스페어 바 패턴은 1 픽셀행 단위로 분리된다.

- [0025] 상기 스페어 바 패턴은 상기 픽셀들에 연결되는 게이트라인들과 비 교차된다.

- [0026] 상기 제1 고전위 전원라인과 상기 스페어 바 패턴은 제1 층에 위치하고, 상기 제2 고전위 전원라인은 제2 층에 위치하며, 상기 제1 층과 상기 제2 층 사이에는 적어도 하나 이상의 층간 절연막이 구비된다.

- [0027] 상기 제1 고전위 전원라인은 상기 충간 절연막을 관통하는 제1 콘택홀을 통해 상기 제2 고전위 전원라인에 접속되고, 상기 스페어 바 패턴은 상기 충간 절연막을 관통하는 제2 콘택홀을 통해 상기 제2 고전위 전원라인에 접속된다.

- [0028] 이 유기발광 표시장치는 상기 픽셀들에 연결된 데이터라인들에 데이터전압을 공급하는 소스 드라이버 IC와, 상기 소스 드라이버 IC가 실장되는 필름 부재와, 상기 고전위 픽셀전원을 생성하는 전원 공급부를 더 포함하고, 상기 제1 고전위 전원라인, 상기 제2 고전위 전원라인, 및 상기 스페어 바 패턴 중에서, 상기 제1 고전위 전원라인만이 상기 소스 드라이버 IC와 상기 필름 부재를 경유하여 상기 전원 공급부에 직접 연결된다.

### 발명의 효과

[0029] 본 발명은 전원 공급부에 직접 연결되는 제1 고전위 전원라인을 M 픽셀열마다 배치함으로써 개구율 저하를 최소화하면서도, 제1 고전위 전원라인이 결여된 픽셀열들 사이에 스페어 바 패턴을 배치하여 이웃한 서브 픽셀들 간에 생기는 혼색 문제와, 동일 색을 구현하는 서브 픽셀들 간에 생기는 기생 커패시턴스 편차로 인한 휘도 편차 문제를 해소할 수 있다. 다시 말해, 본 발명은 그물망 구조의 고전위 전원라인을 갖는 유기발광 표시장치에서, 개구율 저하를 최소화하면서도 표시 품위를 높일 수 있다.

#### 도면의 간단한 설명

[0030] 도 1은 종래 그물망 구조의 고전위 전원라인을 포함한 픽셀 어레이를 보여주는 평면도.

도 2는 도 1의 "SS" 영역을 구체적으로 보여주는 평면도.

도 3a는 도 2의 A-A'를 따라 절취한 단면도.

도 3b는 도 2의 B-B'를 따라 절취한 단면도.

도 4a는 도 2의 C-C'를 따라 절취한 단면도.

도 4b는 도 2의 D-D'를 따라 절취한 단면도.

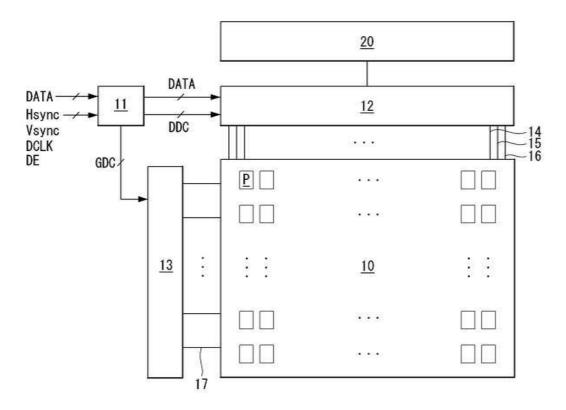

도 5는 본 발명의 실시예에 따른 유기발광 표시장치를 보여주는 블록도.

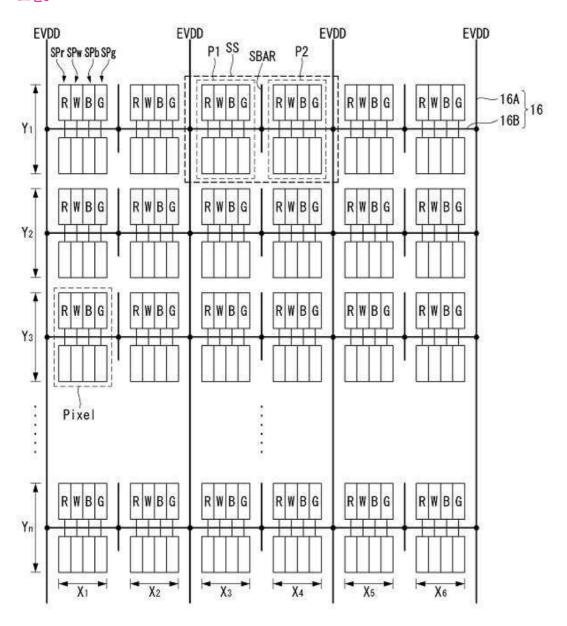

도 6은 본 발명의 제1 실시예에 따른 그물망 구조의 고전위 전원라인을 포함한 픽셀 어레이를 보여주는 평면도.

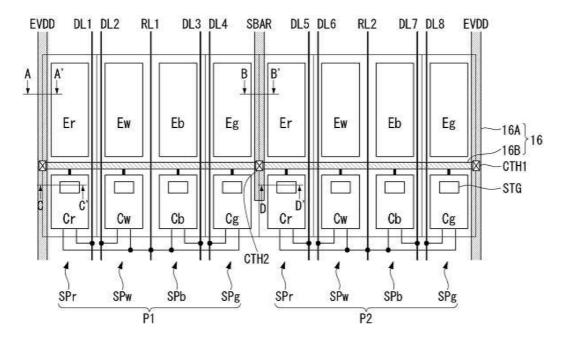

- 도 7은 도 6의 "SS" 영역을 구체적으로 보여주는 평면도.

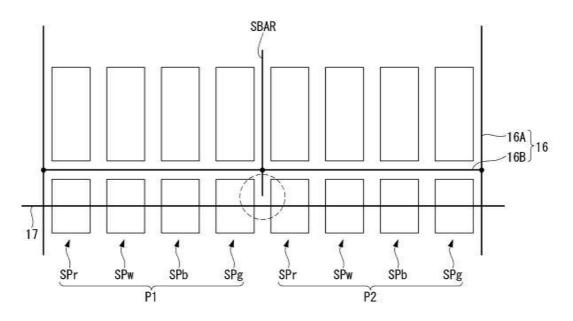

- 도 8은 스페어 바 패턴과 게이트라인 간의 비 교차 구조를 보여주는 도면.

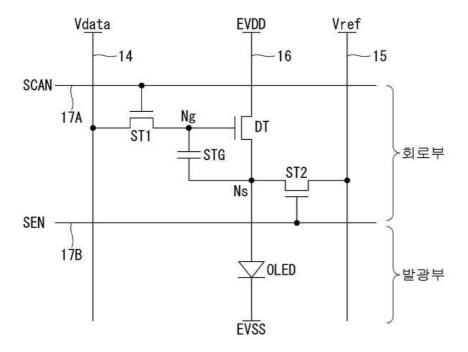

- 도 9는 본 발명에 따른 일 서브 픽셀의 등가 회로도.

- 도 10은 도 7의 A-A'를 따라 절취한 단면도.

- 도 11은 도 7의 B-B'를 따라 절취한 단면도.

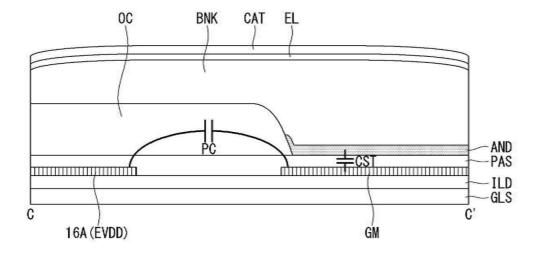

- 도 12는 도 7의 C-C'를 따라 절취한 단면도.

- 도 13은 도 7의 D-D'를 따라 절취한 단면도.

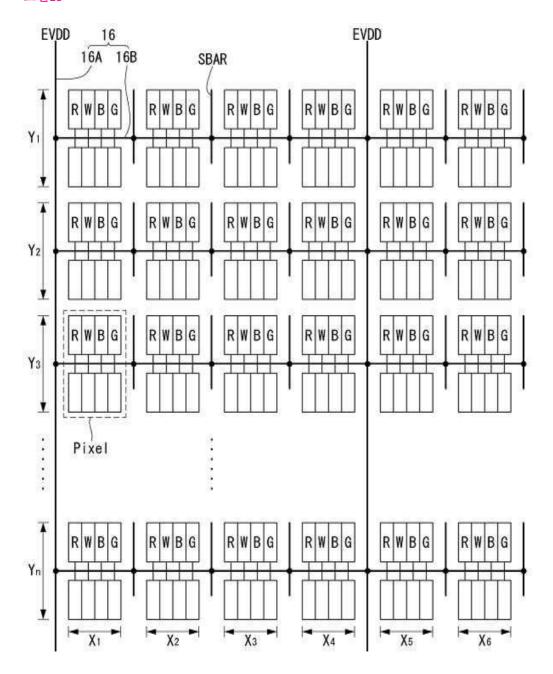

- 도 14는 본 발명의 제2 실시예에 따른 그물망 구조의 고전위 전원라인을 포함한 픽셀 어레이를 보여주는 평면도.

- 도 15는 본 발명의 제3 실시예에 따른 그물망 구조의 고전위 전원라인을 포함한 픽셀 어레이를 보여주는 평면도.

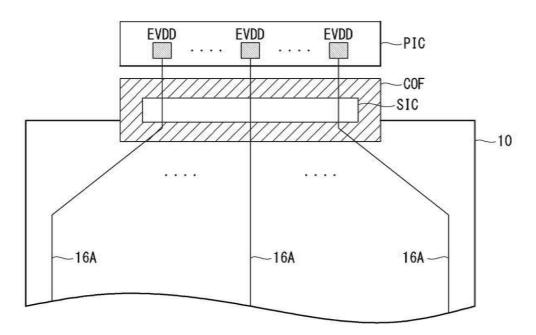

- 도 16은 필름 부재와 소스 드라이버 IC를 통해 전원 공급부에 연결되는 제1 고전위 전원라인을 보여주는 도면.

#### 발명을 실시하기 위한 구체적인 내용

- [0031] 본 발명의 이점 및 특징, 그리고 그것들을 달성하는 방법은 첨부되는 도면과 함께 상세하게 후술되어 있는 실시 예들을 참조하면 명확해질 것이다. 그러나, 본 발명은 이하에서 개시되는 실시예들에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 것이며, 단지 본 실시예들은 본 발명의 개시가 완전하도록 하며, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 발명의 범주를 완전하게 알려주기 위해 제공되는 것이며, 본 발명은 청구항의 범주에 의해 정의될 뿐이다.

- [0032] 본 발명의 실시예를 설명하기 위한 도면에 개시된 형상, 크기, 비율, 각도, 개수 등은 예시적인 것이므로 본 발명이 도시된 사항에 한정되는 것은 아니다. 명세서 전체에 걸쳐 동일 참조 부호는 동일 구성 요소를 지칭한다. 또한, 본 발명을 설명함에 있어서, 관련된 공지 기술에 대한 구체적인 설명이 본 발명의 요지를 불필요하게 흐릴 수 있다고 판단되는 경우 그 상세한 설명은 생략한다. 본 명세서 상에서 언급된 '포함한다', '갖는다', '이루어진다' 등이 사용되는 경우 ' ~ 만'이 사용되지 않는 이상 다른 부분이 추가될 수 있다. 구성 요소를 단수로 표현한 경우에 특별히 명시적인 기재 사항이 없는 한 복수를 포함하는 경우를 포함한다.

- [0033] 구성 요소를 해석함에 있어서, 별도의 명시적 기재가 없더라도 오차 범위를 포함하는 것으로 해석한다.

- [0034] 위치 관계에 대한 설명일 경우, 예를 들어, '~ 상에', '~ 상부에', '~ 하부에', '~ 옆에' 등으로 두 부분의 위치 관계가 설명되는 경우, '바로' 또는 '직접'이 사용되지 않는 이상 두 부분 사이에 하나 이상의 다른 부분이 위치할 수도 있다.

- [0035] 소자 또는 층이 다른 소자 또는 층 "위 (on)"로 지칭되는 것은 다른 소자 바로 위에 또는 중간에 다른 층 또는 다른 소자를 개재한 경우를 모두 포함한다.

- [0036] 비록 제1, 제2 등이 다양한 구성요소들을 서술하기 위해서 사용되나, 이들 구성요소들은 이들 용어에 의해 제한 되지 않는다. 이들 용어들은 단지 하나의 구성요소를 다른 구성요소와 구별하기 위하여 사용하는 것이다. 따라 서, 이하에서 언급되는 제1 구성요소는 본 발명의 기술적 사상 내에서 제2 구성요소일 수도 있다.

- [0037] 명세서 전체에 걸쳐 동일 참조 부호는 동일 구성 요소를 지칭한다.

- [0038] 도면에서 나타난 각 구성의 크기 및 두께는 설명의 편의를 위해 도시된 것이며, 본 발명이 도시된 구성의 크기 및 두께에 반드시 한정되는 것은 아니다.

- [0039] 본 발명의 여러 실시예들의 각각 특징들이 부분적으로 또는 전체적으로 서로 결합 또는 조합 가능하며, 기술적으로 다양한 연동 및 구동이 가능하며, 각 실시예들이 서로에 대하여 독립적으로 실시 가능할 수도 있고 연관관계로 함께 실시 가능할 수도 있다.

- [0040] 이하, 도 5 내지 도 16을 참조하여 본 발명의 다양한 실시예들을 상세히 설명한다.

- [0041] 도 5는 본 발명의 실시예에 따른 유기발광 표시장치를 보여주는 블록도이다.

- [0042] 도 5를 참조하면, 본 발명에 따른 유기발광 표시장치는 표시패널(10), 타이밍 콘트롤러(11), 데이터 구동회로 (12), 게이트 구동회로(13) 및 전원 공급회로(20)를 포함할 수 있다.

- [0043] 표시패널(10)에는 다수의 데이터라인들(14) 및 기준라인들(15)과, 다수의 게이트라인들(17)이 교차되고, 이 교차영역마다 픽셀들(P)이 매트릭스 형태로 배치되어 픽셀 어레이를 구성한다. 픽셀 어레이에는 픽셀들(P)에 고전위 픽셀 전원을 공급하기 위한 고전위 전원라인들(16)과, 픽셀들(P)에 저전위 픽셀 전원을 공급하기 위한 저전위 전원라인들(미도시)이 배치된다. 고전위 전원라인(16)에 생기는 IR 드롭을 최소화하기 위해, 고전위 전원라인들(16)은 픽셀 어레이에서 그물망 구조를 이루며 전기적으로 서로 쇼트된다. 저전위 전원라인들도 픽셀 어레이에서 전기적으로 서로 쇼트된다.

- [0044] 각 픽셀(P)은 다수의 서브 픽셀들을 포함할 수 있다. 일 서브 픽셀은 데이터전압이 공급되는 데이터라인들(14) 중 어느 하나에, 기준전압이 공급되는 기준라인들(15) 중 어느 하나에, 게이트신호가 공급되는 게이트라인들 (17) 중 어느 하나에, 고전위 픽셀 전원이 공급되는 고전위 전원라인들(16)에, 그리고, 저전위 픽셀 전원이 공급되는 저전위 전원라인들에 연결된다. 픽셀 어레이에서 개구율을 높이기 위해 다수의 픽셀들(P)이 하나의 기준라인(15)을 공유할 수 있다.

- [0045] 타이밍 콘트롤러(11)는 외부로부터 입력되는 디지털 영상 데이터(DATA)를 표시패널(10)의 해상도에 맞게 재정렬하여 데이터 구동회로(12)에 공급한다. 또한, 타이밍 콘트롤러(11)는 수직 동기신호(Vsync), 수평 동기신호(Hsync), 도트클럭신호(DCLK) 및 데이터 인에이블신호(DE) 등의 타이밍 신호들에 기초하여 데이터 구동회로(12)의 동작 타이밍을 제어하기 위한 데이터 제어신호(DDC)와, 게이트 구동회로(13)의 동작 타이밍을 제어하기 위한 게이트 제어신호(GDC)를 생성한다.

- [0046] 데이터 구동회로(12)는 데이터 제어신호(DDC)를 기반으로 타이밍 콘트롤러(11)로부터 입력되는 디지털 영상 데이터(RGB)를 아날로그 데이터전압으로 변환하여 데이터라인(14)들에 공급한다. 데이터 구동회로(12)는 적어도하나 이상의 소스 드라이버 IC(Integrated Circuit)를 포함한다. 소스 드라이버 IC는 칩 온 필름(Chip On Film, COF) 또는 테이프 캐리어 패키지(Tape Carrier Package, TCP) 등으로 구현되는 필름 부재에 실장된 후 표시패널(10)에 접합될 수 있다.

- [0047] 게이트 구동회로(13)는 게이트 제어신호(GDC)를 기반으로 게이트신호를 생성하여 게이트라인들(17)에 공급할 수 있다. 게이트신호는 적어도 하나 이상의 스캔신호를 포함할 수 있으며, 서브 픽셀 구조에 따라 발광제어신호를 더 포함할 수도 있다. 게이트 구동회로(13)는 GIP(Gate-driver In Panel) 방식에 따라 표시패널(10) 상에 직접 형성될 수 있다.

- [0048] 전원 공급회로(20)는 표시장치의 동작에 필요한 각종 전원들을 생성한다. 전원 공급회로(20)는 고전위 픽셀 전원을 생성하는 전원 공급부를 포함한다. 전원 공급부는 고전위 픽셀 전원을 생성한 후 고전위 전원라인들(16)에 공급한다.

- [0049] 이러한 그물망 구조의 고전위 전원라인을 갖는 유기발광 표시장치에서 개구율 저하를 최소화하면서도 표시 품위를 높이기 위해, 본 발명은 픽셀 어레이의 일 영역에 스페어 바 패턴(Spare Bar Pattern)을 형성한다. 이하에서 는 스페어 바 패턴을 갖는 픽셀 어레이의 다양한 실시예를 설명한다.

- [0050] 도 6은 본 발명의 제1 실시예에 따른 그물망 구조의 고전위 전원라인을 포함한 픽셀 어레이를 보여준다.

- [0051] 도 6을 참조하면, 본 발명의 실시예에 따른 픽셀 어레이는 서로 교차하는 다수의 픽셀행들(Y1~Yn)과 다수의 픽셀열들(X1~X6)을 포함한다. 픽셀행들(Y1~Yn)은 각각 제1 방향(예를 들어, 수평 방향)을 따라 나란히 배치된 픽셀들을 포함한다. 픽셀열들(X1~X6)은 각각 제2 방향(예를 들어, 수직 방향)을 따라 나란히 배치된 픽셀들을 포함하며 상기 다수의 픽셀행들과 교차된다.

- [0052] 본 발명의 제1 실시예에 따른 고전위 전원라인(16)은 픽셀들에 고전위 픽셀전원을 공급하기 위한 것으로, 제1 고전위 전원라인(16A), 제2 고전위 전원라인(16B), 및 스페어 바 패턴(SBAR)을 포함하여 그물망 구조를 갖는다. 제1 고전위 전원라인(16A)은 제1 방향을 따라 이웃한 픽셀열들(X1~X6) 사이에 배치되되, 개구율 확보를 위해 2 픽셀열마다 배치된다. 제2 고전위 전원라인(16B)은 제2 방향을 따라 각 픽셀행(Y1~Yn)마다 배치되며, 제1 고전위 전원라인(16A)과 교차되는 지점에서 제1 고전위 전원라인(16A)에 연결된다. 스페어 바 패턴(SBAR)은 제1 고전위 전원라인(16A)이 배치되어 있지 않은 이웃한 픽셀열들(X1~X6) 사이에 제1 고전위 전원라인(16A)과 나란히 배치되어 제2 고전위 전원라인(16B)에 연결된다. 본 발명은 스페어 바 패턴(SBAR)을 통해 중래 기술의 문제점들즉, 이웃한 서브 픽셀들 간에 생기는 혼색 문제와, 동일 색을 구현하는 서브 픽셀들 간에 생기는 기생 커패시턴

스 편차로 인한 휘도 편차 문제를 해결한다.

- [0053] 도 7은 도 6의 "SS" 영역을 구체적으로 보여준다.

- [0054] 도 7을 참조하면, "SS" 영역에는 고전위 전원라인(16)으로부터 고전위 픽셀 전원(EVDD)을 입력 받아 동작하는 제1 픽셀(P1)과 제2 픽셀(P2)이 구비된다. 제1 픽셀(P1)과 제2 픽셀(P2)은 각각, 제1 색 서브픽셀(SPr), 제2 색 서브픽셀(SPw), 제3 색 서브픽셀(SPb), 및 제4 색 서브픽셀(SPg)을 포함할 수 있다. 여기서, 제1 내지 제4 색은 각각 적색(R), 백색(W), 청색(B), 및 녹색(G)일 수 있다. 제1 색 서브픽셀(SPr)은 OLED와 적색(R) 컬러필터를 포함한 제1 발광부(Er)와, 구동 TFT와 스토리지 커패시터(STG)를 포함한 제1 회로부(Cr)로 구성된다. 제2 색 서브픽셀(SPw)은 OLED를 포함한 제2 발광부(Ew)와, 구동 TFT와 스토리지 커패시터(STG)를 포함한 제2 회로부(Cw)로 구성된다. 제3 색 서브픽셀(SPb)은 OLED와 청색(B) 컬러필터를 포함한 제3 발광부(Eb)와, 구동 TFT와 스토리지 커패시터(STG)를 포함한 제3 회로부(Cb)로 구성된다. 그리고, 제4 색 서브픽셀(SPg)은 OLED와 녹색(G) 컬러필터를 포함한 제4 발광부(Eg)와, 구동 TFT와 스토리지 커패시터(STG)를 포함한 제4 회로부(Cg)로 구성된다.

- [0055] 본 발명의 기술적 사상은 일 픽셀에 포함되는 서브 픽셀의 개수에 의해 제한되지 않는다. 예를 들어, 본 발명의 기술적 사상은 제1 픽셀(P1)과 제2 픽셀(P2)이 각각, 3개의 서브 픽셀들, 즉 제1 색 서브픽셀(SPr), 제3 색 서브픽셀(SPb), 및 제4 색 서브픽셀(SPg)로 구성되는 경우에도 그대로 적용된다. 이하에서는 설명의 편의상 일 픽셀의 구성이 도 7과 같이 4개의 서브 픽셀들로 구성되는 것으로 간주한다.

- [0056] 제1 픽셀(P1)에 속하는 4개의 서브 픽셀들(SPr, SPw, SPb, SPg)은 기준 전압이 공급되는 제1 기준 라인(RL1)에 공통으로 접속되고, 데이터전압이 공급되는 제1 내지 제4 데이터라인(DL1~DL4)에 개별적으로 접속된다. 제2 픽셀(P2)에 속하는 4개의 서브 픽셀들(SPr, SPw, SPb, SPg)은 기준 전압이 공급되는 제2 기준 라인(RL2)에 공통으로 접속되고, 데이터전압이 공급되는 제5 내지 제8 데이터라인(DL5~DL8)에 개별적으로 접속된다. 제1 픽셀(P1)과 제2 픽셀(P2)에 속하는 모든 서브 픽셀들(SPr, SPw, SPb, SPg)은 고전위 픽셀 전원(EVDD)이 공급되는 고전위 전원라인(16), 구체적으로 제2 고전위 전원라인(16B)에 공통으로 접속된다.

- [0057] 제1 고전위 전원라인(16A)은 2 픽셀열마다 배치되기 때문에, 제1 픽셀(P1)의 좌측 및 제2 픽셀(P2)의 우측에 각각 배치되고, 제1 픽셀(P1)과 제2 픽셀(P2)의 사이에는 배치되지 않는다. 그 대신 스페어 바 패턴(SBAR)이 제1 픽셀(P1)과 제2 픽셀(P2)의 사이에 배치된다.

- [0058] 제1 고전위 전원라인(16A)과 스페어 바 패턴(SBAR)은, 데이터라인들(DL1~DL8) 및 기준라인들(RL1,RL2)과 동일한 제1 마스크 공정을 통해 형성됨으로써, 공정의 편의성을 증대시킬 수 있다. 제1 고전위 전원라인(16A)과 스페어 바 패턴(SBAR)은 동일한 제1 층에 위치할 수 있다. 제2 고전위 전원라인(16B)은 데이터라인들(DL1~DL8), 및 기준라인들(RL1,RL2)과의 쇼트를 방지하기 위해 제1 마스크 공정과 다른 제2 마스크 공정을 통해 형성될 수 있다. 제2 고전위 전원라인(16B)은 제1 층과 다른 제2 층에 위치할 수 있다. 제1 층과 제2 층 사이에는 적어도 하나 이상의 층간 절연막이 위치할 수 있다.

- [0059] 제1 고전위 전원라인(16A)은 충간 절연막을 관통하는 제1 콘택홀(CH1)을 통해 제2 고전위 전원라인(16B)에 접속되고, 스페어 바 패턴(SBAR)은 충간 절연막을 관통하는 제2 콘택홀(CH2)을 통해 제2 고전위 전원라인(16B)에 접속됨으로써, 개구율 저하를 최소화하면서도 표시 품위 향상에 기여할 수 있는 개선된 그물망 구조가 완성될 수있다.

- [0060] 도 8은 스페어 바 패턴과 게이트라인 간의 비 교차 구조(Non-cross structure)를 보여준다.

- [0061] 도 8을 참조하면, 본 발명의 스페어 바 패턴(SBAR)은 1 픽셀행 단위로 분리됨으로써, 다수 픽셀행들을 가로질러 길게 연장되는 것에 비해 개구율 저하를 최소화할 수 있다. 특히, 본 발명의 스페어 바 패턴(SBAR)은 픽셀들에 연결되는 게이트라인들(17)과 비 교차(Non-cross)되도록 적절히 설계됨으로써, 게이트라인들(17)과 교차될 때생기는 불필요한 기생 커패시턴스를 미연에 방지할 수 있다.

- [0062] 도 9는 본 발명에 따른 일 서브 픽셀의 등가 회로도를 보여준다.

- [0063] 도 9를 참조하면, 본 발명에 따른 일 서브 픽셀은 OLED, 구동 TFT(DT), 제1 스위치 TFT(ST1), 제2 스위치 TFT(ST2), 및 스토리지 커패시터(Cst)를 포함한다. 이러한 일 서브 픽셀 구성은 일 예시에 불과하며, 본 발명의 기술적 사상은 서브 픽셀 구성에 한정되지 않는다.

- [0064] OLED는 컬러 필터 등과 함께 서브 픽셀의 발광부를 구성한다. 그리고, 구동 TFT(DT), 제1 스위치 TFT(ST1), 제2 스위치 TFT(ST2), 및 스토리지 커패시터(Cst) 등은 서브 픽셀의 회로부를 구성한다.

- [0065] OLED는 구동 TFT(DT)의 소스전극에 연결된 소스노드(Ns)와 저전위 픽셀전원(EVSS) 사이에 접속되며, 구동전류에 따라 발광하는 발광 소자이다. OLED는 애노드전극 및 캐소드전극과, 이들 사이에 형성된 유기 화합물층을 포함 한다.

- [0066] 구동 TFT(DT)는 게이트노드(Ng)에 연결된 게이트전극과, 고전위 픽셀전원(EVDD)에 연결된 드레인전극과, 소스노드(Ns)에 연결된 소스전극을 포함한다. 구동 TFT(DT)는 게이트-소스 간 전압에 따라 구동전류의 크기를 제어하는 구동 소자이다.

- [0067] 제1 스위치 TFT(ST1)는 제1 게이트라인(17A)에 접속되는 게이트전극과, 데이터라인(14)에 접속되는 드레인전극과, 소스노드(Ns)에 연결된 소스전극을 포함한다. 제1 스위치 TFT(ST1)는 제1 게이트라인(17A)으로부터의 제1 게이트신호(SCAN)에 응답하여 턴 온 되어 데이터라인(14)과 소스노드(Ns)를 전기적으로 연결함으로써, 데이터라인(14)에 충전되어 있는 데이터전압(Vdata)을 소스노드(Ns)에 인가한다.

- [0068] 제2 스위치 TFT(ST2)는 제2 게이트라인(17B)에 접속되는 게이트전극과, 기준라인(15)에 접속되는 소스전극과, 소스노드(Ns)에 연결된 드레인전극을 포함한다. 제2 스위치 TFT(ST2)는 제2 게이트라인(17B)으로부터의 제2 스캔 제어신호(SEN)에 응답하여 턴 온 되어 기준라인(15)과 소스노드(Ns)를 전기적으로 연결함으로써, 기준라인 (15)에 충전되어 있는 기준전압(Vref)을 소스노드(Ns)에 인가한다.

- [0069] 스토리지 커패시터(Cst)는 게이트노드(Ng)와 소스노드(Ns) 사이에 접속되어, 소정 기간 동안 구동 TFT(DT)의 게이트-소스 간 전압을 일정하게 유지시킨다.

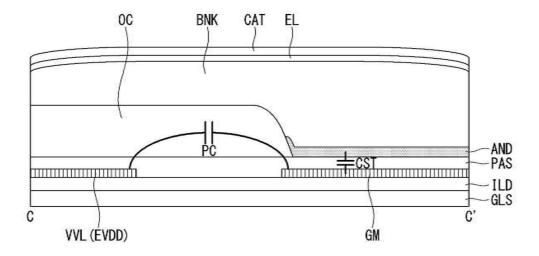

- [0070] 도 10은 도 7의 A-A'를 따라 절취한 단면도이고, 도 11은 도 7의 B-B'를 따라 절취한 단면도이다. 도 10 및 도 11을 참조하여, 제1 고전위 전원라인(16A)이 배치되지 않은 제1 픽셀(P1)과 제2 픽셀(P2)의 사이에서, 스페어바 패턴(SBAR)에 의해 혼색이 방지되는 작용/효과를 설명하면 다음과 같다.

- [0071] 도 10의 영역 A-A'는 제1 고전위 전원라인(16A)을 사이에 두고 서로 이웃한 녹색 서브픽셀(SPg)의 발광부(Eg)와 적색 서브픽셀(SPr)의 발광부(Er)를 보여주고 있다. 그리고, 도 11의 영역 B-B'는 스페어 바 패턴(SBAR)을 사이에 두고 서로 이웃한 녹색 서브픽셀(SPg)의 발광부(Eg)와 적색 서브픽셀(SPr)의 발광부(Er)를 보여주고 있다.

- [0072] 영역 A-A'에는 제1 고전위 전원라인(VVL)이 배치되어 있기 때문에, 녹색 서브픽셀(SPg)의 발광부(Eg)에서 나오는 녹색 광과 적색 서브픽셀(SPr)의 발광부(Er)에서 나오는 적색 광이, 녹색 서브픽셀(SPg)과 적색 서브픽셀(SPr)의 경계부에서 섞이지 않는다.

- [0073] 또한, 영역 B-B'에는 스페어 바 패턴(SBAR)이 배치되어 있기 때문에, 녹색 서브픽셀(SPg)의 발광부(Eg)에서 나오는 녹색 광과 적색 서브픽셀(SPr)의 발광부(Er)에서 나오는 적색 광이, 녹색 서브픽셀(SPg)과 적색 서브픽셀(SPr)의 경계부에서 섞이지 않는다. 스페어 바 패턴(SBAR)은 녹색 서브픽셀(SPg)과 적색 서브픽셀(SPr)의 경계부에서 색 섞임을 방지하여, 색 시인성과 색 뎁스(color depth)를 원하는 값으로 유지시킨다.

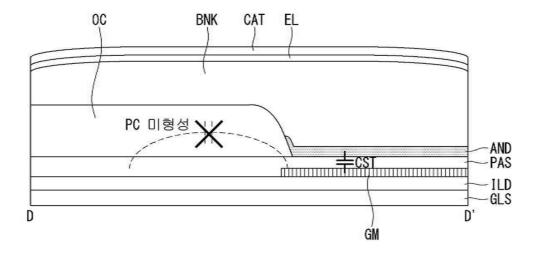

- [0074] 도 12는 도 7의 C-C'를 따라 절취한 단면도이고, 도 13은 도 7의 D-D'를 따라 절취한 단면도이다. 도 10 및 도 11과 함께 도 12 및 도 13을 참조하여, 동일 색을 구현하는 서브 픽셀들 간에 문제되던 기생 커패시턴스 차이를 스페어 바 패턴(SBAR)을 통해 방지하는 작용/효과를 설명하면 다음과 같다.

- [0075] 도 10의 영역 A-A'에서, 제1 픽셀(P1)에 속하는 적색 서브픽셀(SPr)의 애노드전극(AND)과 제1 고전위 전원라인 (16A) 사이에 기생 커패시터(PC)가 형성된다. 또한, 도 11의 영역 B-B'에는 스페어 바 패턴(SBAR)이 있기 때문에, 제2 픽셀(P2)에 속하는 적색 서브픽셀(SPr)의 애노드전극(AND)과 스페어 바 패턴(SBAR) 사이에는 기생 커패시터(PC)가 형성된다. 그 결과, 제1 픽셀(P1)의 적색 서브픽셀(SPr)과 제2 픽셀(P2)의 적색 서브픽셀(SPr) 간에 기생 커패시턴스의 크기 차이가 완화된다. 동일 색을 구현하는 서브픽셀들 간에 발광부의 기생 커패시턴스가 달라지면 휘도 편차가 생기고, 그러한 휘도 편차가 표시 얼룩으로 시인될 수 있는데, 본 발명은 스페어 바 패턴 (SBAR)을 추가 형성하여 이러한 문제를 최소화한다. 이러한 스페어 바 패턴(SBAR)에 따른 작용 효과는 녹색 서브픽셀들(SPg)에도 동일하게 적용된다.

- [0076] 도 12의 영역 C-C'는 제1 고전위 전원라인(16A)을 사이에 두고 서로 이웃한 녹색 서브픽셀(SPg)의 회로부(Cg)와 적색 서브픽셀(SPr)의 회로부(Cr)를 보여주고 있다. 그리고, 도 13의 영역 D-D'는 스페어 바 패턴(SBAR)을 사이에 두지 않고 서로 이웃한 녹색 서브픽셀(SPg)의 회로부(Cg)와 적색 서브픽셀(SPr)의 회로부(Cr)를 보여주고 있다.

- [0077] 도 12의 영역 C-C'에서, 제1 픽셀(P1)에 속하는 적색 서브픽셀(SPr)의 게이트노드(GM)와 제1 고전위 전원라인 (16A) 사이에 기생 커패시터(PC)가 형성된다. 또한, 도 13의 영역 D-D'에는 스페어 바 패턴(SBAR)이 있기 때문

에, 제2 픽셀(P2)에 속하는 적색 서브픽셀(SPr)의 게이트노드(GM)와 스페어 바 패턴(SBAR) 사이에도 기생 커패시터(PC)가 형성된다. 그 결과, 제1 픽셀(P1)의 적색 서브픽셀(SPr)과 제2 픽셀(P2)의 적색 서브픽셀(SPr) 간에 기생 커패시턴스 간에 기생 커패시턴스의 크기 차이가 완화된다. 동일 색을 구현하는 서브픽셀들 간에 회로부의 기생 커패시턴스가 달라지면 휘도 편차가 생기고, 그러한 휘도 편차가 표시 얼룩으로 시인될 수 있는데, 본 발명은 스페어 바 패턴(SBAR)을 추가 형성하여 이러한 문제를 최소화한다. 이러한 스페어 바 패턴(SBAR)에 따른 작용 효과는 녹색 서브픽셀들(SPg)에도 동일하게 적용된다. 게이트노드(GM)는 구동 TFT의 게이트전극에 연결되는 것으로, 일 예로 도 9의 Ng와 같다.

- [0078] 한편, 도 10 내지 도 13에서, CAT는 캐소드전극을, EL은 유기 화합물층을, BNK는 뱅크층을, AND는 애노드전극을, OC는 평탄화층을, CF는 컬러필터를, PAS와 ILD는 절연막을, GLS는 기판을, 그리고 CST는 스토리지 커패시터를 각각 지시한다.

- [0079] 도 14는 본 발명의 제2 실시예에 따른 그물망 구조의 고전위 전원라인을 포함한 픽셀 어레이를 보여준다.

- [0080] 도 14를 참조하면, 본 발명의 제2 실시예에 따른 고전위 전원라인(16)은 픽셀들에 고전위 픽셀전원을 공급하기 위한 것으로, 도 6과 비교하여, 제1 고전위 전원라인(16A)을 3 픽셀열마다 배치한다는 점에서 차이가 있다. 이 발명도 도 6과 마찬가지로 스페어 바 패턴(SBAR)을 통해 종래 기술의 문제점들 즉, 이웃한 서브 픽셀들 간에 생기는 혼색 문제와, 동일 색을 구현하는 서브 픽셀들 간에 생기는 기생 커패시턴스 편차로 인한 휘도 편차 문제를 해결한다. 나아가, 이 발명은 3 픽셀열마다 제1 고전위 전원라인(16A)을 배치하고, 제1 고전위 전원라인(16A)이 결여되어 있는 영역에 스페어 바 패턴(SBAR)을 배치하고 있기 때문에, 도 6에 비해 개구율 확보에 보다유리한 잇점이 있다.

- [0081] 도 15는 본 발명의 제3 실시예에 따른 그물망 구조의 고전위 전원라인을 포함한 픽셀 어레이를 보여준다.

- [0082] 도 15를 참조하면, 본 발명의 제3 실시예에 따른 고전위 전원라인(16)은 픽셀들에 고전위 픽셀전원을 공급하기 위한 것으로, 도 14와 비교하여, 제1 고전위 전원라인(16A)을 4 픽셀열마다 배치한다는 점에서 차이가 있다. 이 발명도 도 14와 마찬가지로 스페어 바 패턴(SBAR)을 통해 종래 기술의 문제점들 즉, 이웃한 서브 픽셀들 간에 생기는 혼색 문제와, 동일 색을 구현하는 서브 픽셀들 간에 생기는 기생 커패시턴스 편차로 인한 휘도 편차 문제를 해결한다. 나아가, 이 발명은 4 픽셀열마다 제1 고전위 전원라인(16A)을 배치하고, 제1 고전위 전원라인(16A)이 결여되어 있는 영역에 스페어 바 패턴(SBAR)을 배치하고 있기 때문에, 도 14에 비해 개구율 확보에 보다 유리한 잇점이 있다.

- [0083] 도 16은 필름 부재와 소스 드라이버 IC를 통해 전원 공급부에 연결되는 제1 고전위 전원라인을 보여준다.

- [0084] 도 16을 참조하면, 본 발명의 고전위 전원라인(16) 중에서, 제1 고전위 전원라인(16A) 만이 고전위 픽셀전원 (EVDD)을 생성하는 전원 공급부(PIC)에 직접 연결된다. 제2 고전위 전원라인(16B)과 스페어 바 패턴(SBAR)은 표시패널 상에서 제1 고전위 전원라인(16A)에 연결되어, 제1 고전위 전원라인(16A)으로부터 고전위 픽셀전원 (EVDD)을 전달 받는다.

- [0085] 제1 고전위 전원라인(16A)은 소스 드라이버 IC(SIC)와 필름 부재(COF)를 경유하여 전원 공급부(PIC)에 연결되기 때문에, 제1 고전위 전원라인(16A)의 개수에 따라 소스 드라이버 IC(SIC)와 필름 부재(COF)의 사이즈가 결정된다. 따라서, 제1 고전위 전원라인(16A)의 개수를 줄이면 그만큼 소스 드라이버 IC(SIC)와 필름 부재(COF)의 사이즈를 줄일 수 있어, 제조 비용면에서 유리한 효과가 있다. 예컨대, 제1 고전위 전원라인(16A)의 개수는 도 6,도 14,및도 15 순으로 점점 작아지기 때문에, 제조 비용도 동일 순으로 작아질 수 있다.

- [0086] 전술한 바와 같이, 본 발명은 전원 공급부에 직접 연결되는 제1 고전위 전원라인을 M 픽셀열마다 배치함으로써 개구율 저하를 최소화하면서도, 제1 고전위 전원라인이 결여된 픽셀열들 사이에 스페어 바 패턴을 배치하여 이 웃한 서브 픽셀들 간에 생기는 혼색 문제와, 동일 색을 구현하는 서브 픽셀들 간에 생기는 기생 커패시턴스 편차로 인한 휘도 편차 문제를 해소할 수 있다. 다시 말해, 본 발명은 그물망 구조의 고전위 전원라인을 갖는 유기발광 표시장치에서, 개구율 저하를 최소화하면서도 표시 품위를 높일 수 있다.

- [0087] 이상 설명한 내용을 통해 당업자라면 본 발명의 기술사상을 일탈하지 아니하는 범위에서 다양한 변경 및 수정이 가능함을 알 수 있을 것이다. 따라서, 본 발명의 기술적 범위는 명세서의 상세한 설명에 기재된 내용으로 한정되는 것이 아니라 특허 청구의 범위에 의해 정하여져야만 할 것이다.

#### 부호의 설명

[0088] 10 : 표시패널 11 : 타이밍 콘트롤러

12 : 데이터 구동회로 13 : 게이트 구동회로

14 : 데이터라인 15 : 기준 라인

16 : 고전위 전원라인 17 : 게이트라인

20 : 전원 공급회로

### 도면

# 도면3a

# 도면3b

도면4a

# 도면4b

도면9

도면10

도면11

도면12

| 专利名称(译)        | 有机发光显示器                                                            |         |            |  |

|----------------|--------------------------------------------------------------------|---------|------------|--|

| 公开(公告)号        | KR1020170136153A                                                   | 公开(公告)日 | 2017-12-11 |  |

| 申请号            | KR1020160067781                                                    | 申请日     | 2016-05-31 |  |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                           |         |            |  |

| 申请(专利权)人(译)    | LG显示器有限公司                                                          |         |            |  |

| [标]发明人         | CHO KYUNG HYUN<br>조경현<br>JUNG IL KI<br>정일기<br>TANIRYOSUKE<br>타니료스케 |         |            |  |

| 发明人            | 조경현<br>정일기<br>타니료스케                                                |         |            |  |

| IPC分类号         | G09G3/3233                                                         |         |            |  |

| CPC分类号         | G09G3/3233 G09G2300/0426 G09G2300/0465 G09G2300/0452 G09G2300/0842 |         |            |  |

| 外部链接           | Espacenet                                                          |         |            |  |

### 摘要(译)

本发明的有机发光显示装置的数目,其包括多个像素行和像素沿着由侧的第二方向上并排设置的第一,分别包括每个由像素的侧布置的侧的在第一方向上,的,并且相交与所述多个像素的行的为了提供高电势像素电源的像素列和像素,doedoe沿所述第一方向设置在相邻的像素列之间,M被设置为每个(M为2以上的正的整数)的像素列第一古典为电位侧电源线,并提供一个高电势像素电源的像素,被布置用于沿着所述第二方向上的每个像素线,其特征在于,所述第一1-1高电位侧电源线和在该点横经典以上在第二典型连接到所述电源线和所述电源线,所述第一高电位电源线被并排放置与不布置相邻的像素列和所述第二高电位电源