(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2014년07월03일

(11) 등록번호 10-1414501

(24) 등록일자 2014년06월26일

(51) 국제특허분류(Int. Cl.)

H01L 51/52 (2006.01) H05B 33/06 (2006.01)

(21) 출원번호 10-2012-0100011

(22) 출원일자 2012년09월10일

심사청구일자 2012년09월10일

(65) 공개번호 10-2014-0034380

(43) 공개일자 2014년03월20일

(56) 선행기술조사문현

KR1020060079020 A

JP2006309110 A

KR1020060047607 A

(73) 특허권자

네오뷰코오롱 주식회사

충남 홍성군 은하면 천광로 856-14,

(72) 발명자

경충현

경기 여주시 대신면 양촌로 174-10,

안희철

충남 보령시 한내로터리길 92, 306동 902호 (동대동, 동대휴먼시아3단지아파트)

(뒷면에 계속)

(74) 대리인

특허법인아이엠

전체 청구항 수 : 총 8 항

심사관 : 박성웅

(54) 발명의 명칭 OLED 소자용 COG 패널

**(57) 요약**

본 발명은 OLED 소자용 COG 패널에 관한 것으로, 구체적으로는 드라이버 IC로부터 기판 일측으로 연결된 데이터라인 및 스캔 라인과 연결되어 상기 기판의 일측 또는 타측으로 연결된 에이징 라인을 구비하여, 외부의 에이징 회로와 연결될 수 있게 한 OLED 소자용 COG 패널에 관한 것이다.

**대 표 도 - 도1**

(72) 발명자

김대용

서울 구로구 경인로65길 16-15, 1111동 2302호 (신

도림동, e편한세상대림4차아파트)

임우빈

충남 홍성군 홍성읍 충절로953번길 20, 109동 110

2호 (신동아파밀리에아파트)

## 특허청구의 범위

### 청구항 1

기판의 일정 부분에 드라이버 IC를 구비한 OLED 소자용 COG 패널로써,

상기 드라이버 IC에 연결되는 스캔 라인;

상기 스캔 라인과 겹치지 않게 배치되고, 상기 드라이버 IC에서 상기 기판의 일측 단부까지 연장되는 데이터 라인;

상기 스캔 라인 및 상기 데이터 라인의 상면에 형성되고, 상기 스캔 라인 및 상기 데이터 라인에 대응하는 소정의 위치에 복수의 컨택트 홀이 구비된 절연체;

상기 절연체 상면에 형성되며, 상기 복수의 컨택트 홀을 통해 특정 스캔 라인과 특정 데이터 라인을 전기적으로 연결하는 연결 라인;

상기 데이터 라인의 단부에 구비되거나 상기 기판의 일측 단부에서 외부로 더 연장형성되도록 구비되는 제 1ショート바;

상기 기판의 일측 단부에 구비되거나 기판의 외부로 더 연장형성된 제 2ショート바가 형성되며 상기 연결 라인을 통해 상기 스캔 라인에 연결되는 에이징 라인;을 포함하여 구성되고,

상기 제 1ショート바 및 상기 제 2ショート바를 통해 에이징 공정(aging process)을 위한 에이징 회로에 연결되고, 상기 에이징 공정이 완료된 후 상기 제 1ショート바 및 상기 제 2ショート바를 제거할 수 있게 한 것을 특징으로 하는 OLED 소자용 COG 패널.

### 청구항 2

삭제

### 청구항 3

제 1항에 있어서,

상기 제 1ショート바 및 상기 제 2ショート바는 특정 에이징 회로에 구비된 전선 또는 핀-프로브(Pin-Probe)와 연결되는 것을 특징으로 하는 OLED 소자용 COG 패널.

### 청구항 4

삭제

### 청구항 5

제 1항에 있어서,

상기 스캔 라인, 상기 데이터 라인, 상기 에이징 라인 및 상기 연결 라인은 ITO, Al, Cr 또는 Mo/Al/Mo로 이루어진 군에서 선택된 어느 하나로 이루어지는 전도성 금속인 것을 특징으로 하는 OLED 소자용 COG 패널.

### 청구항 6

제 5항에 있어서,

상기 스캔 라인, 상기 데이터 라인, 상기 에이징 라인 및 상기 연결 라인은 스퍼터링, 전자빔, 포토리소그래피 또는 실크스크린 인쇄법을 이용하여 형성되는 것을 특징으로 하는 OLED 소자용 COG 패널.

## 청구항 7

제 6항에 있어서,

상기 스캔 라인 및 상기 에이징 라인은 세퍼레이터(Separator) 또는 캐소드 증착 마스크를 이용하여, 서로 분리되게 증착한 것을 특징으로 하는 OLED 소자용 COG 패널.

## 청구항 8

제 6항에 있어서,

상기 에이징 라인은 상기 스캔 라인을 증착 시 동시에 증착된 것을 특징으로 하는 OLED 소자용 COG 패널.

## 청구항 9

제 6항에 있어서,

상기 에이징 라인은 상기 스캔 라인을 증착 이후에 증착된 것을 특징으로 하는 OLED 소자용 COG 패널.

## 청구항 10

제 6항에 있어서,

상기 스캔 라인, 상기 데이터 라인 및 상기 에이징 라인은 상기 드라이버 IC의 본딩 이전에 증착되는 것을 특징으로 하는 OLED 소자용 COG 패널.

## 명세서

### 기술 분야

[0001]

본 발명은 OLED 소자용 COG 패널에 관한 것으로, 구체적으로는 드라이버 IC로부터 기판 일측으로 연결된 데이터 라인 및 스캔 라인과 연결되어 상기 기판의 일측 또는 타측으로 연결된 에이징 라인을 구비하여, 외부의 에이징 회로와 연결될 수 있게 한 OLED 소자용 COG 패널에 관한 것이다.

### 배경 기술

[0002]

일반적으로, OLED 소자는 캐소드(cathode)에서 공급되는 전자(electron)와 애노드(anode)에서 공급되는 정공(hole)의 재결합에 의하여 빛을 발광하도록 이루어진 것으로, 평판 표시 장치(Flat Panel Display)로 사용되고 있으며, 특히, 얇은 두께, 넓은 시야각 및 빠른 응답속도 등의 장점을 가지므로 다양한 산업분야에서 폭넓게 활용되고 있다.

[0003]

또한, 상기 OLED 소자는 제조 공정 중에서 애노드와 캐소드 사이에 발생된 이물에 의해서 쇼트가(short)가 발생하여 암점(dark defect)을 유발시킬 수 있고, 유기막의 증착 이후에 바로 점등할 경우 초기 열화현상에 의해 상대적으로 휙도가 급격하게 감소될 수 있으므로, 일정 전압을 인가하여 초기 휙도 감소를 가속화하고 암점이 발생된 OLED 소자를 선별하기 위한 에이징(Aging) 공정을 실시하게 된다.

[0004]

또한, 상기 OLED 소자 중에서 TCP(Tape Carrier Package) 및 COF(Chip On Film)를 포함하는 TAB(Tape Automated Bonding) 형태의 실장방식을 사용한 경우에는, 캐소드 및 애노드를 포함하는 배선 라인이 서로 연결된 상태에서 외부로 연장되어 있으므로 상기 에이징 공정을 실시할 시 문제점이 없었다.

[0005]

한편, 상기 OLED 소자 중에서 COG(Chip On Glass) 형태의 실장방식을 사용한 경우에는 애노드 및 캐소드를 포함하는 배선 라인이 기판 상의 드라이버 IC에 연결되므로, 에이징 공정을 실시할 수 있는 배선 라인이 형성되지 못하는 문제점이 발생되었다.

[0006] 또한, 에이징 공정이 실시되지 않고 OLED 소자가 제작된 경우에는 암점이 지속적으로 발생하는 불량 제품이 발생하게 되고, 제품의 수명, 신뢰성 및 양품 수율을 저하시키는 문제점이 발생된다.

### 발명의 내용

#### 해결하려는 과제

[0007] 본 발명자들은 COG 형태의 실장방식을 사용한 COG 패널을 이용하여 OLED 소자를 제조하는 경우 COG 패널을 완제품으로 제조되기 이전에 에이징 공정을 실시할 수 있도록 애노드 및 캐소드를 포함하는 배선 라인을 설계하고자 연구 노력한 결과, OLED 소자용 COG 패널의 기술적 구성을 개발하게 되어 본 발명을 완성하게 되었다.

[0008] 따라서, 본 발명의 목적은 캐소드 라인 및 애노드 라인이 에이징 공정을 위한 에이징 회로와 용이하게 연결될 수 있는 OLED 소자용 COG 패널을 제공하는 것이다.

[0009] 본 발명의 목적들은 이상에서 언급한 목적들로 제한되지 않으며, 언급되지 않은 또 다른 목적들은 아래의 기재로부터 당업자에게 명확하게 이해될 수 있을 것이다.

#### 과제의 해결 수단

[0010] 상기의 목적을 달성하기 위하여 본 발명은 기판의 일정 부분에 드라이버 IC를 구비한 OLED 소자용 COG 패널로써, 상기 기판 상면의 일정 부분에서 상기 드라이버 IC까지 연결되는 스캔 라인; 상기 기판의 일측 단부에서 상기 드라이버 IC까지 연결되는 데이터 라인; 및 상기 스캔라인으로부터 상기 기판의 일측 또는 타측 단부로 연결되는 에이징 라인;을 포함하고, 상기 에이징 라인은 에이징 공정(aging process)을 위한 에이징 회로에 연결되는 것을 특징으로 하는 OLED 소자용 COG 패널을 제공한다.

[0011] 바람직한 실시예에 있어서, 상기 기판의 일측 단부에서 상기 데이터 라인과 연결되고, 상기 기판 외부로 연장된 제 1ショ트바; 및 상기 기판의 일측 또는 타측 단부에서 상기 에이징 라인과 연결되고, 상기 기판 외부로 연장된 제 2ショ트바;를 포함한다.

[0012] 바람직한 실시예에 있어서, 상기 제 1ショ트바 및 상기 제 2ショ트바는 특정 에이징 회로에 구비된 전선 또는 핀-프로브(Pin-Probe)와 연결된다.

[0013] 바람직한 실시예에 있어서, 상기 스캔 라인, 상기 데이터 라인 및 상기 에이징 라인 간의 연결을 차단하되, 소정 위치에는 전도성 금속이 충전된 컨택트 홀이 구비된 절연체; 및 상기 컨택트 홀을 통해 상기 데이터 라인과 상기 스캔 라인 및 상기 스캔 라인과 상기 에이징 라인을 서로 연결하는 연결 라인;을 더 포함한다.

[0014] 바람직한 실시예에 있어서, 상기 스캔 라인, 상기 데이터 라인, 상기 에이징 라인 및 상기 연결 라인은 ITO, Al, Cr 또는 Mo/AI/Mo로 이루어진 군에서 선택된 어느 하나로 이루어지는 전도성 금속이다.

[0015] 바람직한 실시예에 있어서, 상기 스캔 라인, 상기 데이터 라인, 상기 에이징 라인 및 상기 연결 라인은 스퍼터링, 전자빔, 포토리소그래피 또는 실크스크린 인쇄법을 이용하여 형성된다.

[0016] 바람직한 실시예에 있어서, 상기 스캔 라인 및 상기 에이징 라인은 세퍼레이터(Separator) 또는 캐소드 증착 마스크를 이용하여, 서로 분리되게 증착한다.

[0017] 바람직한 실시예에 있어서, 상기 에이징 라인은 상기 스캔 라인을 증착 시 동시에 증착된다.

[0018] 바람직한 실시예에 있어서, 상기 에이징 라인은 상기 스캔 라인을 증착 이후에 증착된다.

[0019] 바람직한 실시예에 있어서, 상기 스캔 라인, 상기 데이터 라인 및 상기 에이징 라인은 상기 드라이버 IC의 본딩 이전에 증착된다.

#### 발명의 효과

[0020] 본 발명은 다음과 같은 우수한 효과를 가진다.

[0021] 먼저, 본 발명의 일실시예에 따른 OLED 소자용 COG 패널에 의하면, 데이터 라인이 기판 일측까지 연결되고 스캔 라인과 연결된 에이징 라인이 상기 기판의 일측 또는 타측에 연결되는 구조를 가지므로, 외부의 에이징 회로가 상기 데이터 라인 및 상기 스캔 라인과 용이하게 연결될 수 있으며, 에이징 공정을 쉽고 효율적으로 실시할 수 있게 하는 효과를 얻을 수 있다.

## 도면의 간단한 설명

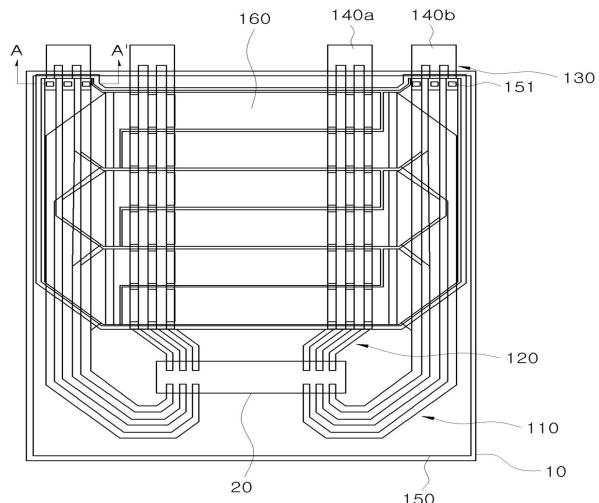

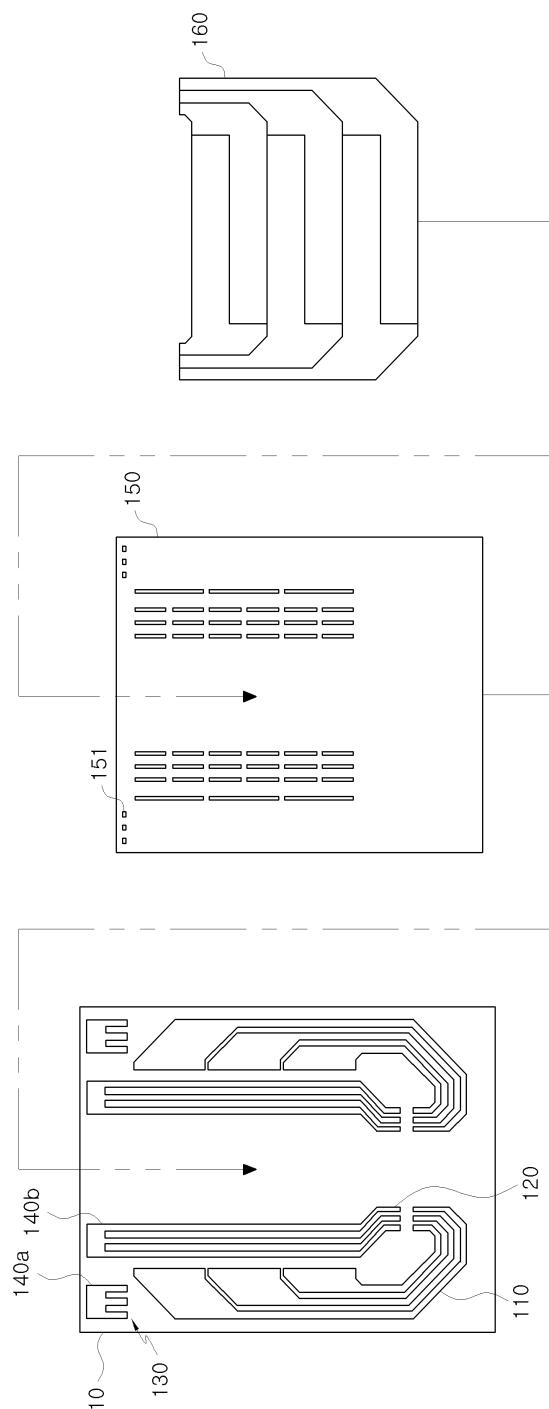

- [0022] 도 1은 본 발명의 일실시예에 따른 COG 패널을 나타내는 도면.

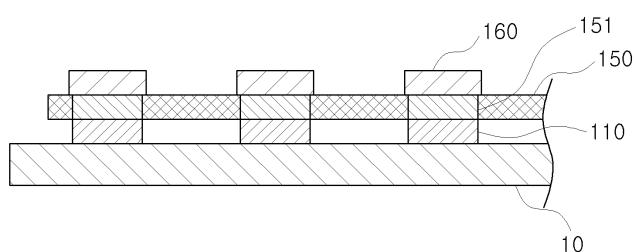

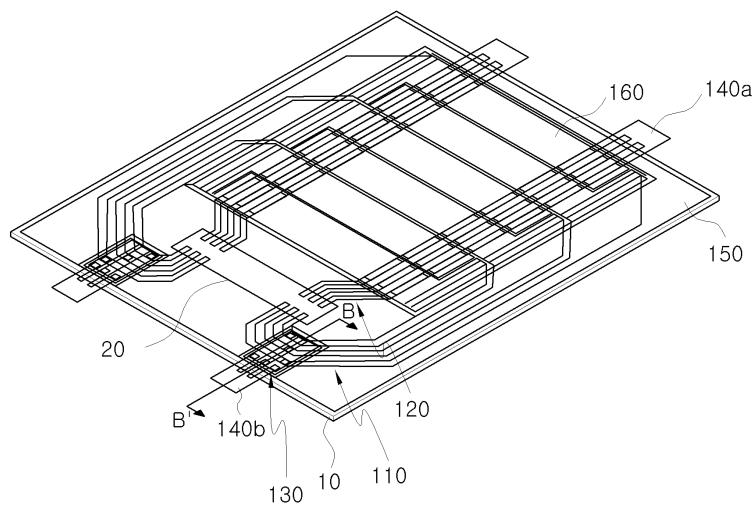

도 2은 도 1의 A-A' 단면을 나타내는 단면도.

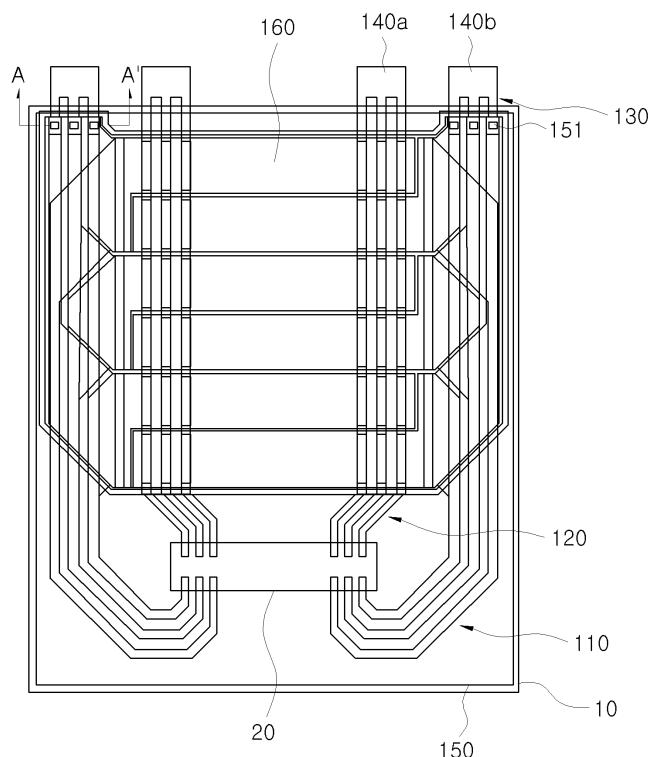

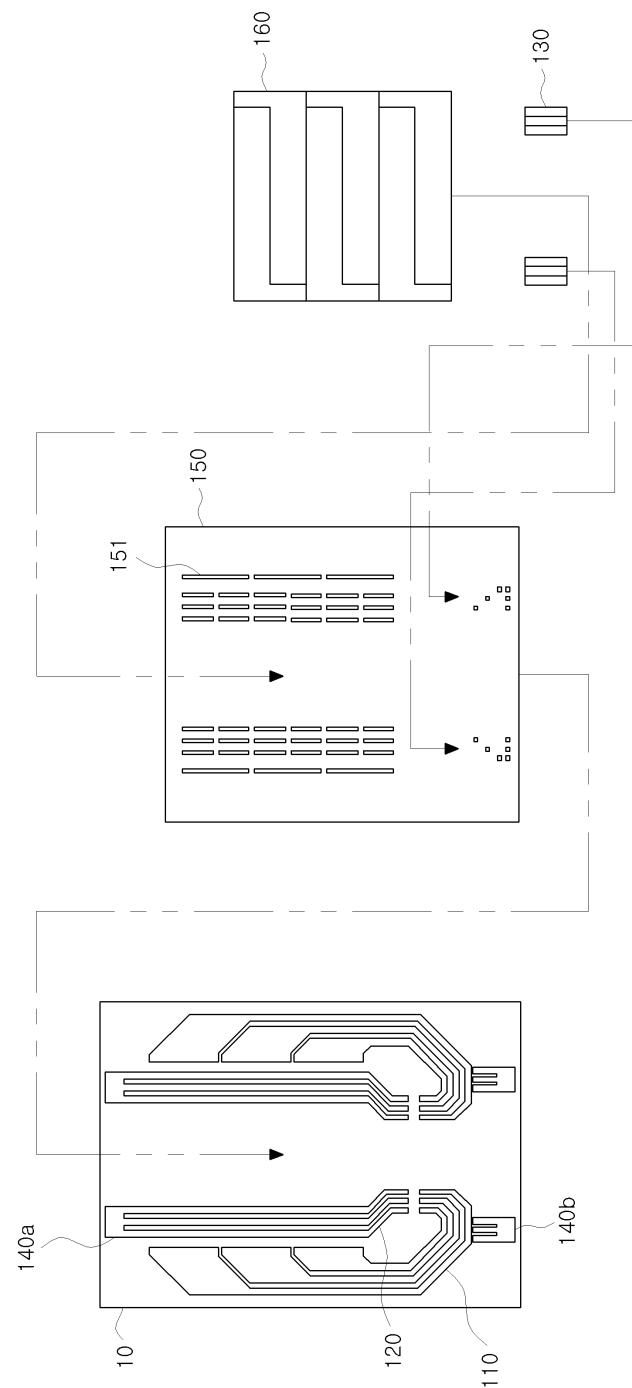

도 3은 본 발명의 일실시예에 따른 COG 패널의 분해도면.

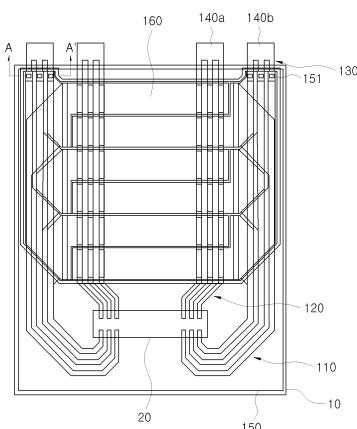

도 4는 본 발명의 다른 실시예에 따른 COG 패널을 나타내는 도면.

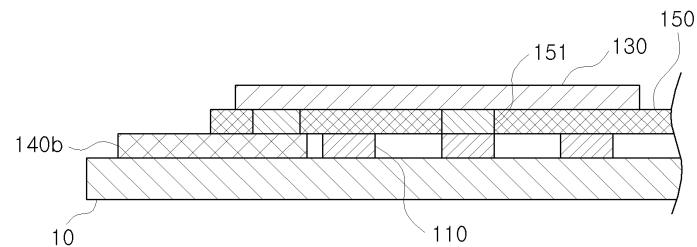

도 5는 도 4의 B-B' 단면을 나타내는 단면도.

도 6는 본 발명의 다른 실시예에 따른 COG 패널의 분해도면.

## 발명을 실시하기 위한 구체적인 내용

- [0023] 본 발명에서 사용되는 용어는 가능한 현재 널리 사용되는 일반적인 용어를 선택하였으나, 특정한 경우는 출원인이 임의로 선정한 용어도 있는데 이 경우에는 단순한 용어의 명칭이 아닌 발명의 상세한 설명 부분에 기재되어거나 사용된 의미를 고려하여 그 의미가 과악되어야 할 것이다.

- [0024] 이하, 첨부된 도면에 도시된 바람직한 실시예를 참조하여 본 발명의 기술적 구성을 상세하게 설명한다.

- [0025] 그러나, 본 발명은 여기서 설명되는 실시예에 한정되지 않고 다른 형태로 구체화될 수도 있다. 명세서 전체에 걸쳐 동일한 참조번호는 동일한 구성요소를 나타낸다.

- [0026] 도 1은 본 발명의 일실시예에 따른 COG 패널을 나타내는 도면이며, 도 2는 도 1의 A-A' 단면을 나타내는 단면도이다.

- [0027] 도 1 내지 도 2를 참조하면, 본 발명의 일실시예에 따른 COG 패널은, COG 실장방식을 사용하여 OLED 소자를 제조하는 경우에 에이징 공정을 실시할 수 있게 하기 위한 것으로, 에이징 공정을 위한 특정 에이징 회로와 연결되어 전압 또는 펄스를 인가받을 수 있게 구비되며, 스캔 라인(110), 데이터 라인(120), 에이징 라인(130), 제1ショ트바(140a), 제2ショ트바(140b), 절연체(150) 및 연결 라인(160)을 포함한다.

- [0028] 또한, 상기 COG 패널은 유리 또는 플라스틱 재질의 기판(10) 일정부분에 드라이버 IC(20)가 구비되는 것일 수 있으며, 상기 드라이버 IC(20)는 상기 에이징 공정 이후에 상기 기판(10)에 실장되게 된다. 즉, 후술될 스캔 라인(110), 데이터 라인(120) 및 에이징 라인(130)은 상기 드라이버 IC(20)의 본딩 이전에 증착되어 구비되고, 상기 드라이버 IC(20)가 가장 나중에 구비되는 것이다.

- [0029] 상기 스캔 라인(110)은 상기 COG 패널에 구비되는 캐소드 라인으로써, 상기 기판(10) 상면의 일정부분으로부터 상기 드라이버 IC(20)까지 연결되도록 구비되며, 실질적으로는 상기 드라이버 IC(20)의 범프(Bump)로 연결된다.

- [0030] 또한, 상기 스캔 라인(110)은 상기 기판(10)의 외부로 연장되지 않고 상기 기판(10) 내에서 상기 드라이버 IC(20)로만 연결되게 되며, 상기 드라이버 IC(20)로부터 상기 기판(10)의 일측 방향으로 연장되는 형태로 형성될 수 있다. 또한, 상기 기판(10)의 일측은 상기 기판(10)의 모서리들 중 하나의 모서리가 위치한 방향이거나, 상기 OLED 소자의 발광역역과 인접한 특정 모서리가 위치한 방향일 수 있다.

- [0031] 또한, 상기 스캔 라인(110)은 상기 드라이버 IC(20)가 실장되기 이전에 형성되므로, 실질적으로는 상기 드라이버 IC(20)가 실장될 위치 또는 상기 범프가 형성될 위치까지 연장되는 것이 바람직하다. 또한, 상기 스캔 라인(110)은 복수 개로 구비되게 되는데, 각 스캔 라인(110)은 서로 다른 스캔 라인(110)과는 겹치지 않도록 구비하게 된다.

- [0032] 또한, 상기 스캔 라인(110)은 ITO, Al, Cr 또는 Mo/Al/Mo으로 이루어진 전도성 물질로 구비할 수 있으며, 예컨대, 스퍼터링(sputtering), 전자빔(Electron beam processing), 포토리소그래피(Photolithography) 또는 실크스크린 인쇄법(serigraphy)을 포함하는 다양한 공정을 통해 상기 기판(10)에 형성할 수 있다.

- [0033] 또한, 상기 스캔 라인(110)은 세퍼레이터(Separator) 또는 캐소드 증착 마스크를 이용하여, 각 스캔 라인(110)이 서로 분리되도록 증착하여 형성할 수 있다.

- [0034] 상기 데이터 라인(120)은 상기 COG 패널에 구비되는 애노드 라인으로써, 상기 기판(10)의 일측 단부에서 상기 드라이버 IC(20)까지 연결되도록 구비되며, 실질적으로는 상기 스캔 라인(110)과 같이 상기 드라이버 IC(20)의 범프(Bump)로 연결된다.

- [0035] 또한, 상기 데이터 라인(120)은 상기 기판(10) 상면에 구비되어 상기 드라이버 IC(20)에서 연결되며 상기 기판(10)의 일측 단부로 연장되며, 또한, 상기 기판(10)의 일측 단부에서 외부로 더 연장된 구조를 갖도록 구비할 수도 있다.

- [0036] 또한, 상기 데이터 라인(120)은 복수 개로 구비되게 되는데, 각 데이터 라인(120)은 서로 다른 데이터 라인(120) 및 상기 스캔 라인(110)과 겹치지 않도록 구비하게 된다.

- [0037] 또한, 상기 데이터 라인(120)은 상기 스캔 라인(110)과 같이 ITO, Al, Cr 또는 Mo/Al/Mo으로 이루어진 전도성 물질로 구비할 수 있고, 스퍼터링(sputtering), 전자빔(Electron beam processing), 포토리소그래피(Photolithography) 또는 실크스크린 인쇄법(serigraphy)을 포함하는 다양한 공정을 통해 상기 기판(10)에 형성할 수 있으며, 상기 스캔 라인(110)과 동시에 상기 기판(10)에 형성될 수 있다.

- [0038] 상기 에이징 라인(130)은 상기 스캔 라인(110)과 연결되는 것으로, 상기 스캔 라인(110)을 상기 기판(10)의 일측 또는 타측 단부로 연결하게 된다.

- [0039] 또한, 상기 에이징 라인(130)은 복수 개로 구비할 수 있으며, 상기 스캔 라인(110)과 일대일로 연결되면서 상기 기판(10)의 일측 또는 타측 단부로 연결할 수 있다. 또한, 상기 에이징 라인(130)은 상기 기판(10)의 일측 단부 또는 타측 단부에서 상기 기판(10)의 외부로 더 연장된 구조를 갖도록 구비할 수도 있다.

- [0040] 또한, 상기 에이징 라인(130)은 실질적으로 상기 스캔 라인(110)과 직접 연결되지 않고, 후술될 연결 라인(160)을 통해 상기 스캔 라인(110)과 연결되게 된다. 또한, 상기 에이징 라인(130)은 상기 데이터 라인(120) 또는 상기 스캔 라인(110)과 같이 전도성 물질로 구비할 수 있다.

- [0041] 또한, 상기 에이징 라인(130)은 상기 스캔 라인(110)과 연결되면서 상기 기판(10)에서 외부로 더 연장되므로, 상기 기판(10) 내부에만 형성된 스캔 라인(110)을 외부의 회로장치와 연결될 수 있게 한다.

- [0042] 또한, 상기 에이징 라인(130)은 상기 스캔 라인(110) 또는 상기 데이터 라인(120)과 같이 ITO, Al, Cr 또는 Mo/Al/Mo으로 이루어진 전도성 물질로 구비할 수 있고, 스퍼터링(sputtering), 전자빔(Electron beam processing), 포토리소그래피(Photolithography) 또는 실크스크린 인쇄법(serigraphy)을 포함하는 다양한 공정을 통해 상기 기판(10)에 형성할 수 있다.

- [0043] 또한, 상기 에이징 라인(130)은 세퍼레이터(Separator) 또는 캐소드 증착 마스크를 이용하여, 각 에이징 라인(130)이 서로 분리되도록 증착하여 형성할 수 있다. 또한, 상기 에이징 라인(130)은 상기 스캔 라인(110)을 증착 시 동시에 증착될 수도 있고, 상기 스캔 라인(110)의 증착 이후에 증착하여 구비할 수도 있다.

- [0044] 상기 제 1ショート바(140a)는 상기 데이터 라인(120)의 단부에 형성된 것으로, 상기 데이터 라인(120)과 연결되고 상기 기판(10)의 외부로 연장되어 외부의 회로장치를 연결할 수 있게 구비된다.

- [0045] 또한, 상기 제 1ショート바(140a)는 특정 에이징 회로에 구비된 전선 또는 핀-프로브(Pin-Probe)와 연결되게 된다. 또한, 상기 제 1ショート바(140a)는 상기 데이터 라인(120)을 상기 기판(10)의 외부로 연장되게 하는 구조를 가지므로, 상기 데이터 라인(120)과 외부의 회로장치와의 연결이 쉽고 효율적으로 이루어질 수 있게 한다.

- [0046] 또한, 상기 제 1ショート바(140a)는 다양한 전도성 물질로 구비할 수 있으며, 예컨대, 금속 또는 전도성 필름 등으로 구비할 수 있다. 또한, 상기 제 1ショート바(140a)는 판 형태, 바(bar) 형태 또는 원통 형태 등의 다양한 형태로 구비할 수 있다. 또한, 상기 제 1ショート바(140a)는 상기 에이징 회로의 핀-프로브를 용이하게 연결할 수 있도록 관통홀이 구비될 수 있다.

- [0047] 상기 제 2ショート바(140b)는 상기 에이징 라인(130)의 단부에 형성된 것으로, 상기 에이징 라인(130) 및 상기 에이징 라인(130)과 연결된 스캔 라인(110)과 연결되며, 상기 기판(10)의 외부로 연장되어 외부의 회로 장치를 연결할 수 있게 구비된다.

- [0048] 또한, 상기 제 2ショート바(140b)는 특정 에이징 회로에 구비된 전선 또는 핀-프로브(Pin-Probe)와 연결된다. 또한, 상기 제 2ショート바(140b)는 상기 에이징 회로가 상기 기판(10)에 형성된 위치에 따라서 상기 기판(10)의 일측 또는 타측 단부에 형성될 수 있다.

- [0049] 또한, 상기 제 2ショート바(140b)는 상기 스캔 라인(110)과 연결된 에이징 라인(130)을 외부로 연장되게 하는 구조를 가지므로, 외부의 회로장치와의 연결을 쉽고 효율적으로 이루어지게 한다.

- [0050] 또한, 상기 제 2ショート바(140b)는 상기 제 1ショート바(140a)와 같이 전도성 물질로 구비할 수 있고, 판, 바(bar) 또

는 원통 형태 등의 다양한 형태로 구비할 수 있다. 또한, 상기 제 2쇼트바(140b)의 일정 부분에 에이징 회로의 핀-프로브를 연결할 수 있는 판통홀이 구비될 수 있다.

[0051] 상기 절연체(150)는 상기 기판(10) 상면에 구비되는 것으로, 상기 스캔 라인(110), 상기 데이터 라인(120) 및 상기 에이징 라인(130)의 상부를 덮을 수 있게 구비되며, 컨택트 홀(151)을 포함한다.

[0052] 또한, 상기 컨택트 홀(151)은 상기 절연체(150)에 구비되는 것으로, 상기 스캔 라인(110), 상기 데이터 라인(120) 및 상기 에이징 라인(130)이 후술될 연결 라인(160)을 통해 연결될 수 있게 하며 전도성 금속 또는 ITO를 포함하는 전도성 물질이 충전되게 된다.

[0053] 또한, 상기 컨택트 홀(151)은 복수 개로 구비되며, 상기 스캔 라인(110), 상기 데이터 라인(120) 및 상기 에이징 라인(130)에 대응하는 소정 위치에 구비될 수 있다. 또한, 상기 컨택트 홀(151)은 상기 절연체(150)에 미리 구비될 수 있으며, 상기 절연체(150)를 상기 기판(10)의 상면에 형성할 시 생성시킬 수도 있다.

[0054] 상기 연결 라인(160)은 각 컨택트 홀(151)을 통해 상기 데이터 라인(120)과 상기 스캔 라인(110) 및 상기 스캔 라인(110)과 상기 에이징 라인(130)을 서로 연결하기 위한 것으로, 전도성 금속 박막으로 구비될 수 있다.

[0055] 또한, 상기 연결 라인(160)은 ITO, Al, Cr 또는 Mo/AI/Mo로 이루어진 전도성 금속 박막일 수 있으며, 상기 절연체(150)의 상면에 구비되게 된다. 또한, 상기 연결 라인(160)은 실질적으로 일정 넓이를 갖는 판 형태로 구비될 수 있다.

[0056] 또한, 상기 연결 라인(160)은 스퍼터링(sputtering), 전자빔(Electron beam processing), 포토리소그래피(Photolithography) 또는 실크스크린 인쇄법(serigraphy)을 포함하는 다양한 공정을 통해 상기 절연체(150)의 상면에 형성할 수 있다.

[0057] 또한, 상기 연결 라인(160)을 통해 상기 데이터 라인(120)은 상기 스캔 라인(110)과 연결되게 되며, 상기 스캔 라인(110)은 상기 에이징 라인(130)과 연결되게 된다.

[0058] 또한, 상기 연결 라인(160)을 통해 상기 스캔 라인(110), 상기 데이터 라인(120) 및 상기 에이징 라인(130)이 서로 연결되므로, 특정 에이징 회로를 연결하여 전압 또는 펄스를 인가하는 에이징 공정을 실시할 수 있게 되는 것이다.

[0059] 도 3은 본 발명의 일실시예에 따른 COG 패널의 분해도면이다.

[0060] 도 3을 참조하면, 본 발명의 일실시예에 따른 COG 패널은, COG 실장방식을 사용한 OLED 소자이고, 먼저, 기판(10) 상면에 스캔 라인(110), 데이터 라인(120) 및 에이징 라인(130)을 ITO, Al, Cr 및 Mo/AI/Mo 중에서 어느 하나 이상의 전도성 물질로 형성할 수 있으며, 기판(10)은 유리 또는 플라스틱 재질로 구비될 수 있다.

[0061] 또한, 상기 스캔 라인(110)은 상기 기판(10)의 소정 위치에서 복수 개로 구비는 캐소드 라인이고 상기 데이터 라인(120)은 복수 개의 애노드 라인이며, 상기 스캔 라인(110)과 상기 데이터 라인(120)이 서로 겹치지 않게 형성되고 상기 기판(10)의 일측에서 타측 방향으로 연장된다.

[0062] 또한, 상기 에이징 라인(130)은 에이징 공정을 실시할 수 있게 하기 위한 것으로, 상기 스캔 라인(110)이 상기 기판(10)의 일측 일측 또는 타측 단부로 연결될 수 있게 한다. 실질적으로, 상기 에이징 라인(130)은 상기 스캔 라인(110)과 직접 연결되지 않고, 후술될 연결 라인(160)을 통해 상기 스캔 라인(110)과 연결된다.

[0063] 또한, 상기 스캔 라인(110), 상기 데이터 라인(120) 및 상기 에이징 라인(130)은 스퍼터링, 전자빔, 포토리소그래피 또는 실크스크린 인쇄법을 이용하여 상기 기판(10)에 형성할 수 있다. 또한, 복수 개의 라인으로 분리하기 위해서 세퍼레이터(Separator) 또는 캐소드 중착 마스크를 이용할 수 있다.

[0064] 한편, 상기 데이터 라인(120)의 단부는 제 1쇼트바(140a)로 기능하도록 구비되고 상기 에이징 라인(130)의 단부는 제 2쇼트바(140b)로 기능하도록 구비될 수 있으며, 상기 제 1쇼트바(140a) 및 상기 제 2쇼트바(140b)를 이용하여 외부의 회로장치를 연결할 수 있다.

[0065] 다음, 상기 기판(10) 상부 면에 절연체(150)를 형성하게 되는데, 상기 절연체(150)는 상기 스캔 라인(110), 상기 데이터 라인(120) 및 상기 에이징 라인(130)의 상부를 덮을 수 있게 형성된다. 또한, 상기 절연체에는 컨택트 홀(151)이 구비되어, 상기 스캔 라인(110), 상기 데이터 라인(120) 및 상기 에이징 라인(130)을 후술할 연결 라인(160)과 연결될 수 있게 한다.

[0066] 다음, 상기 절연체(150)의 상부 면에 연결 라인(160)을 형성하게 되는데, 상기 연결 라인(160)은 전도성 금속

박막으로 구비되고, 상기 컨택트 홀(151)을 통해서 상기 데이터 라인(120) 및 상기 스캔 라인(110)을 연결하며, 상기 스캔 라인(110) 및 상기 에이징 라인(130)을 연결한다.

[0067] 또한, 상기 연결 라인(160)의 경우에도 스퍼터링, 전자빔, 포토리소그래피 또는 실크스크린 인쇄법을 이용하여 형성할 수 있다.

[0068] 다음, 특정 에이징 회로를 연결하여 전압 또는 펄스를 인가하는 에이징 공정을 실시하게 되는데, 에이징 회로는 상기 제 1ショ트바(140a) 및 상기 제 2ショ트바(140b)로 연결되게 된다. 이때, 에이징 공정을 통해서 불량 제품을 선별하여 제거할 수 있다.

[0069] 다음, 상기 기판(10) 상부 면의 소정 위치에 드라이버 IC(미도시)를 설치할 수 있으며, 에이징 공정 이후에 불량 제품을 제거하고 드라이버 IC를 설치할 수 있어서 제품의 수명, 신뢰성 및 양품 수율이 향상되게 된다.

[0070] 도 4는 본 발명의 다른 실시예에 따른 COG 패널을 나타내는 도면이고, 도 5는 도 4의 B-B' 단면을 나타내는 단면도이며, 도 6는 본 발명의 다른 실시예에 따른 COG 패널의 분해도면이다.

[0071] 도 4 내지 도 6를 참조하면, 본 발명의 다른 실시예에 따른 COG 패널은, COG 설치방식을 사용하여 OLED 소자를 제조하는 경우에 에이징 공정을 실시할 수 있게 하기 위한 것이며, 스캔 라인(110), 데이터 라인(120), 에이징 라인(130), 제 1ショ트바(140a), 제 2ショ트바(140b), 절연체(150) 및 연결 라인(160)을 포함한다.

[0072] 또한, 본 발명의 다른 실시예에 따른 COG 패널은 실질적으로 본 발명의 일실시예에 따른 COG 패널과 동일한 구성요소를 갖도록 구비되지만, 상기 에이징 라인(130) 및 상기 제 2ショ트바(140b)의 배치가 상이한 차이가 있다.

[0073] 여기서, 상기 에이징 라인(130)은 상기 기판(10) 상에서 상기 드라이버 IC(20)의 반대 방향으로 연결되는 구조를 가지며, 상기 에이징 라인(130)에 상기 제 2ショ트바(140b)가 연결되어 기판(10)의 외부 방향으로 연장되게 된다.

[0074] 또한, 에이징 라인(130)과 기판(10) 사이에는 스캔 라인(110) 및 절연체(150)가 개재되게 되는데, 기판(10) 상부에 상기 스캔 라인(110)이 형성되고 상기 스캔 라인(110)과 이격되어 제 2ショ트바(140b)가 형성된다. 또한, 상기 스캔 라인(110) 및 상기 제 2ショ트바(140b)의 상부면에 상기 절연체(150) 및 컨택트 홀(151)이 형성되며, 상기 절연체(150)의 상부면에 상기 에이징 라인(130)이 형성되게 된다. 즉, 상기 에이징 라인(130)을 통해서 되어 상기 스캔 라인(110)이 외부의 특정 에이징 회로와 통전이 가능하게 되는 것이다.

[0075] 물론, 본 발명의 다른 실시예에 따른 COG 패널에서도 상기 스캔 라인(110) 및 상기 데이터 라인(120)이 연결 라인(160)을 통해 서로 연결되고, 상기 스캔 라인(110)이 상기 에이징 라인(130)을 통해 외부의 특정 에이징 회로에 연결되므로 전압 또는 펄스를 인가하는 에이징 공정을 실시할 수 있게 된다. 여기서, 상기 제 1ショ트바(140a) 및 상기 제 2ショ트바(140b)가 에이징 회로에 연결될 수 있으며, 에이징 공정을 통해서 불량 제품을 선별하여 제거할 수 있다. 또한, 에이징 공정 이후에 불량 제품을 제거하고 드라이버 IC를 설치할 수 있어서 제품의 수명, 신뢰성 및 양품 수율이 향상되게 된다.

[0076] 이상에서 살펴본 바와 같이 본 발명은 바람직한 실시예를 들어 도시하고 설명하였으나, 상기한 실시예에 한정되지 아니하며 본 발명의 정신을 벗어나지 않는 범위 내에서 당해 발명이 속하는 기술분야에서 통상의 지식을 가진 자에 의해 다양한 변경과 수정이 가능할 것이다.

## 부호의 설명

[0077] 110 : 스캔 라인 120 : 데이터 라인

130 : 에이징 라인 140a : 제 1ショット바

140b : 제 2ショット바 150 : 절연체

151 : 컨택트 홀 160 : 연결 라인

도면

도면1

도면2

도면3

도면4

도면5

도면6

|                |                                                                                             |         |            |

|----------------|---------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于OLED器件的COG面板                                                                              |         |            |

| 公开(公告)号        | <a href="#">KR101414501B1</a>                                                               | 公开(公告)日 | 2014-07-03 |

| 申请号            | KR1020120100011                                                                             | 申请日     | 2012-09-10 |

| [标]申请(专利权)人(译) | 娜我比可隆株式会社                                                                                   |         |            |

| 申请(专利权)人(译)    | Neoview的隆有限公司                                                                               |         |            |

| 当前申请(专利权)人(译)  | Neoview的隆有限公司                                                                               |         |            |

| [标]发明人         | GYOUNG CHUNG HYOUN<br>경충현<br>AN HUI CHUL<br>안희철<br>KIM DAE YONG<br>김대용<br>IM WOO BIN<br>임우빈 |         |            |

| 发明人            | 경충현<br>안희철<br>김대용<br>임우빈                                                                    |         |            |

| IPC分类号         | H01L51/52 H05B33/06                                                                         |         |            |

| CPC分类号         | G09G3/3233 H01L27/3276 H01L51/5203 H01L2251/56 H05B33/06                                    |         |            |

| 代理人(译)         | IAM专利和律师事务所                                                                                 |         |            |

| 其他公开文献         | KR1020140034380A                                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                   |         |            |

#### 摘要(译)

用于OLED器件的玻璃上芯片 ( COG ) 面板技术领域本发明涉及用于OLED器件的玻璃上芯片 ( COG ) 面板，更具体地，涉及通过包括连接到基板的一侧的数据线连接到外部老化电路的OLED器件的COG面板来自驱动器IC和通过连接到扫描线连接到基板的一侧或另一侧的老化线。