(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2017-0078075

(43) 공개일자 2017년07월07일

(51) 국제특허분류(Int. Cl.)

*H01L 27/32* (2006.01)

(52) CPC특허분류

*H01L 27/3265* (2013.01)

*H01L 27/3248* (2013.01)

(21) 출원번호 10-2015-0188214

(22) 출원일자 2015년12월29일

심사청구일자 없음

(71) 출원인

엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

이승민

서울특별시 강남구 강남대로 272, 102동 604호(도곡동, 도곡푸르지오)

오세훈터

서울특별시 영등포구 당산로 214, 405동 2302호(당산동5가, 당산 삼성 래미안)

(74) 대리인

박영복

전체 청구항 수 : 총 8 항

(54) 발명의 명칭 유기 발광 다이오드 표시 장치

### (57) 요 약

본 발명은 소비 전력을 저감함과 아울러 스토리지 커패시터 용량을 향상시킬 수 있는 OLED 표시 장치에 관한 것이다. 한 실시예에 따른 OLED 표시 장치에서 각 화소 회로는 구동 트랜지스터의 게이트 전극과 접속되는 게이트 절연층 상의 제1 스토리지 전극과, 구동 트랜지스터의 소스 전극과 접속되고 층간 절연층을 사이에 두고 제1 스토리지 전극과 오버랩하는 제2 스토리지 전극과, 제2 스토리지 전극과 접속되고 제1 스토리지 전극과 게이트 절연층을 사이에 두고 오버랩하거나, 게이트 절연층 및 베퍼층을 사이에 두고 오버랩하는 제3 스토리지 전극을 구비한다.

대 표 도 - 도3

(52) CPC특허분류

*H01L 27/3258* (2013.01)

*H01L 27/3262* (2013.01)

*H01L 27/3276* (2013.01)

*H01L 2227/32* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

버퍼층 상에 적층된 액티브층, 게이트 절연층, 게이트 전극 및 층간 절연층과, 그 층간 절연층 상에 위치하고 컨택홀을 통해 상기 액티브층과 접속된 소스 전극 및 드레인 전극을 포함하는 복수개의 박막 트랜지스터와,

상기 버퍼층 아래에서 상기 복수개의 박막 트랜지스터 중 적어도 하나의 액티브층과 오버랩하는 쉴드 금속층과,

상기 복수개의 박막 트랜지스터 중 구동 트랜지스터의 게이트 전극과 접속되는 상기 게이트 절연층 상의 제1 스토리지 전극과,

상기 구동 트랜지스터의 소스 전극과 접속되고 상기 층간 절연층을 사이에 두고 상기 제1 스토리지 전극과 오버랩하는 제2 스토리지 전극과,

상기 제2 스토리지 전극과 접속되고, 상기 제1 스토리지 전극과 상기 게이트 절연층을 사이에 두고 오버랩하거나, 상기 게이트 절연층 및 상기 버퍼층을 사이에 두고 오버랩하는 제3 스토리지 전극을 구비하는 각 화소 회로를 포함하는 유기 발광 다이오드 표시 장치.

#### 청구항 2

청구항 1에 있어서,

상기 제3 스토리지 전극은

상기 쉴드 금속층과 동일하게 상기 버퍼층 아래에 위치하고, 상기 쉴드 금속층과 동일 재료로 구성되고, 상기 버퍼층 및 층간 절연층을 관통하는 컨택홀을 통해 상기 제2 스토리지 전극과 접속되는 유기 발광 다이오드 표시 장치.

#### 청구항 3

청구항 2에 있어서,

상기 화소 회로를 포함하는 다수의 화소들이 위치하는 표시 영역과, 구동 회로를 연결하는 다수의 링크 배선들을 추가로 구비하고,

상기 다수의 링크 배선들은

상기 소스 전극 및 드레인 전극과 동일하게 상기 층간 절연층 상에 위치하고, 상기 소스 전극 및 드레인 전극과 동일 재료로 구성되는 제1 링크 배선과,

상기 쉴드 금속층 및 상기 제3 스토리지 전극과 동일하게 상기 버퍼층 아래에 위치하고, 상기 쉴드 금속층 및 제3 스토리지 전극과 동일 재료로 구성되는 제2 링크 배선을 구비하고,

비표시 영역에서 상기 제1 및 제2 링크 배선이 교번적으로 배치되는 유기 발광 다이오드 표시 장치.

#### 청구항 4

청구항 3에 있어서,

상기 표시 영역에서 상기 소스 전극 및 드레인 전극과 동일하게 상기 층간 절연층 상에 위치하고, 상기 소스 전극 및 드레인 전극과 동일 재료로 구성되는 제1 및 제2 데이터 라인이 교번적으로 배열되는 복수개의 데이터 라인들을 추가로 구비하고,

상기 제2 데이터 라인은 상기 제1 링크 배선과 직접 접속하고,

상기 제2 데이터 라인은 상기 층간 절연층 및 버퍼층을 관통하는 링크 컨택홀을 통해 상기 제2 링크 배선과 접속하는 유기 발광 다이오드 표시 장치.

## 청구항 5

청구항 1에 있어서,

상기 제3 스토리지 전극은

상기 액티브층과 동일하게 상기 베피층에 위치하고, 상기 액티브층과 다른 금속층으로 구성되고, 상기 층간 절연층을 관통하는 컨택홀을 통해 상기 제2 스토리지 전극과 접속되는 유기 발광 다이오드 표시 장치.

## 청구항 6

청구항 5에 있어서,

상기 화소 회로를 포함하는 다수의 화소들이 위치하는 표시 영역과, 구동 회로를 연결하는 다수의 링크 배선들을 추가로 구비하고,

상기 다수의 링크 배선들은

상기 소스 전극 및 드레인 전극과 동일하게 상기 층간 절연층 상에 위치하고, 상기 소스 전극 및 드레인 전극과 동일 재료로 구성되는 제1 링크 배선과,

상기 제3 스토리지 전극과 동일하게 상기 베피층 상에 위치하고, 상기 제3 스토리지 전극과 동일 재료로 구성되는 제2 링크 배선을 구비하고,

비표시 영역에서 상기 제1 및 제2 링크 배선이 교번적으로 배치되는 유기 발광 다이오드 표시 장치.

## 청구항 7

청구항 6에 있어서,

상기 표시 영역에서 상기 소스 전극 및 드레인 전극과 동일하게 상기 층간 절연층 상에 위치하고, 상기 소스 전극 및 드레인 전극과 동일 재료로 구성되는 제1 및 제2 데이터 라인이 교번적으로 배열되는 복수개의 데이터 라인들을 추가로 구비하고,

상기 제2 데이터 라인은 상기 제1 링크 배선과 직접 접속하고,

상기 제2 데이터 라인은 상기 층간 절연층을 관통하는 링크 컨택홀을 통해 상기 제2 링크 배선과 접속하는 유기 발광 다이오드 표시 장치.

## 청구항 8

청구항 1 내지 7 중 어느 한 청구항에 있어서,

상기 액티브층은 산화물 반도체층으로 구성되고,

상기 베피층 아래에 복수의 절연층이 적층된 멀티 배리어층을 추가로 구비하는 유기 발광 다이오드 표시 장치.

## 발명의 설명

### 기술 분야

[0001]

본 발명은 스토리지 커뮤니케이션 용량을 증가시킬 수 있음과 아울러 배선 간격을 충분히 확보할 수 있는 유기 발광 다이오드 표시 장치에 관한 것이다.

### 배경 기술

[0002]

표시 장치는 액정 표시 장치(Liquid Crystal Display; LCD), 유기 발광 다이오드(Organic Light Emitting Diode; OLED), 전기영동 표시 장치(ElectroPhoretic Display; EPD), 전기 습윤 표시 장치(Electro Wetting Display) 등이 있다.

[0003]

이들 중 OLED 표시 장치는 전자와 정공의 재결합으로 유기 발광층을 발광시키는 자발광 소자로 휘도가 높고 구동 전압이 낮으며 박막화가 가능하여 차세대 표시 장치로 기대되고 있다. OLED 표시 장치는 휴대 단말기, TV 세트, 플렉서블 디스플레이이나 투명 디스플레이 등과 같은 다양한 응용 제품에 적용 가능하다.

[0004] OLED 표시 장치를 구성하는 다수의 화소 각각은 애노드 및 캐소드 사이의 유기 발광층으로 구성된 OLED 소자와, OLED 소자를 독립적으로 구동하는 화소 회로를 구비한다. 화소 회로는 데이터 전압을 스토리지 커패시터에 공급하는 스위칭 박막 트랜지스터(Thin Film Transistor; TFT)와, 스토리지 커패시터에 충전된 구동 전압에 따라 구동 전류를 제어하여 OLED 소자로 공급하는 구동 TFT 등을 포함하고, OLED 소자는 구동 전류에 비례하는 광을 발생한다.

[0005] 최근 표시 장치에 적용되는 TFT로는 아몰퍼스 실리콘(Amorphous Silicon) TFT 보다 이동도가 높고, 폴리 실리콘(Poly-Silicon) TFT 보다 저온 공정으로 대면적 응용이 용이하고 극소 누설 전류 특징이 있는 산화물 반도체(Oxide Semiconductor) TFT(이하 산화물 TFT)가 각광받고 있다.

[0006] OLED 표시 장치는 해상도가 높아지면서 각 화소의 크기와 함께 각 화소에서 화소 회로 영역의 크기도 감소되고 있으므로 제한된 화소 회로 영역내에서 스토리지 커패시터의 용량을 증가시킬 수 있는 방안이 요구된다.

[0007] 또한, 중소형 플렉서블 표시 장치에 적용되는 OLED 표시 장치는 배선수가 증가함에 따라 제한된 비표시 영역에서 배선간 간격을 확보하기 위한 방안이 요구된다.

## 발명의 내용

### 해결하려는 과제

[0008] 본 발명은 스토리지 커패시터 용량을 증가시킬 수 있음과 아울러 배선 간격을 충분히 확보할 수 있는 OLED 표시 장치를 제공한다.

### 과제의 해결 수단

[0009] 본 발명의 한 실시예에 따른 OLED 표시 장치에서 각 화소 회로는 베퍼층 상에 적층된 액티브층, 게이트 절연층, 게이트 전극 및 충간 절연층과, 충간 절연층 상에 위치하고 컨택홀을 통해 액티브층과 접속된 소스 전극 및 드레인 전극을 포함하는 복수개의 박막 트랜지스터와, 베퍼층 아래에서 복수개의 박막 트랜지스터 중 어느 하나의 액티브층과 오버랩하는 쉴드 금속층을 구비한다.

[0010] 각 화소 회로는 구동 트랜지스터의 게이트 전극과 접속되는 게이트 절연층 상의 제1 스토리지 전극과, 구동 박막 트랜지스터의 소스 전극과 접속되고 충간 절연층을 사이에 두고 제1 스토리지 전극과 오버랩하는 제2 스토리지 전극과, 제2 스토리지 전극과 접속되고 제1 스토리지 전극과 게이트 절연층을 사이에 두고 오버랩하거나, 게이트 절연층 및 베퍼층을 사이에 두고 오버랩하는 제3 스토리지 전극을 구비한다.

[0011] 한 실시예에 따른 OLED 표시 장치는 표시 영역과, 구동 회로를 연결하는 다수의 링크 배선들을 추가로 구비한다. 다수의 링크 배선들은 소스 전극 및 드레인 전극과 동일하게 충간 절연층 상에 위치하고, 소스 전극 및 드레인 전극과 동일 재료로 구성되는 제1 링크 배선과, 제3 스토리지 전극과 동일층에 위치하고 제3 스토리지 전극과 동일 재료로 구성되는 제2 링크 배선을 구비한다.

[0012] 액티브층은 산화물 반도체층으로 구성되고, 베퍼층 아래에는 복수의 절연층이 적층된 멀티 배리어층과, 멀티 배리어층 아래의 플렉서블 기재가 추가로 구비될 수 있다.

## 발명의 효과

[0013] 본 발명의 한 실시예에 따른 OLED 표시 장치는 소비 전력을 저감할 수 있는 코플래너 구조의 산화물 TFT를 화소 회로의 스위칭 소자로 이용함과 아울러, 게이트 절연층 상의 제1 스토리지 전극이 충간 절연층 상의 제2 스토리지 전극과 오버랩하여 형성하는 제1 커패시터와, 제2 스토리지 전극과 접속되는 제3 스토리지 전극이 제1 스토리지 전극과 게이트 절연층을 사이에 두고 오버랩하거나, 게이트 절연층 및 베퍼층을 사이에 두고 오버랩하여 형성하는 제2 커패시터의 별도 구조로 스토리지 커패시터를 구비함으로써 제한된 화소 회로 영역내에서 면적 증가없이 스토리지 커패시터의 용량을 향상시킬 수 있다.

[0014] 본 발명의 한 실시예에 따른 OLED 표시 장치는 비표시 영역에는 데이터 라인과 동일층인 제1 링크 배선과, 제3 스토리지 전극과 동일층인 제2 링크 배선이 교번적으로 배치됨으로써 다수의 링크 배선들을 포함하는 제한된 비표시 영역에서 링크 배선간의 간격을 충분히 확보하여 신뢰성을 향상시킬 수 있다.

## 도면의 간단한 설명

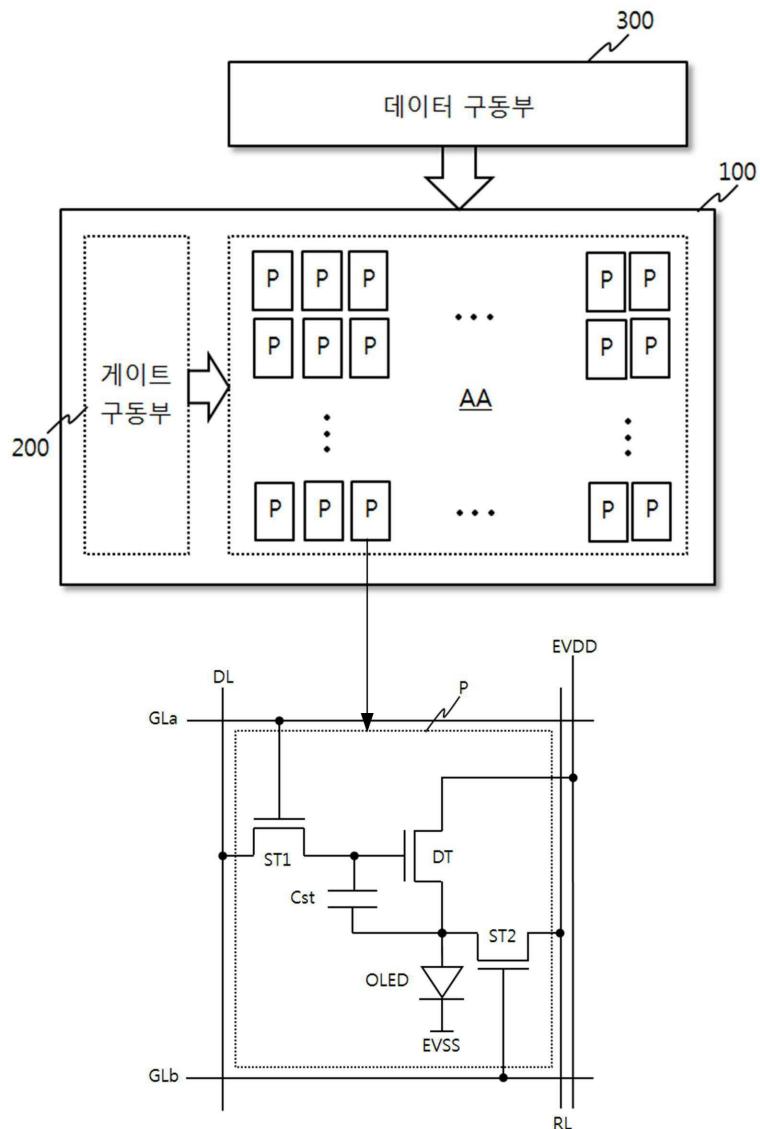

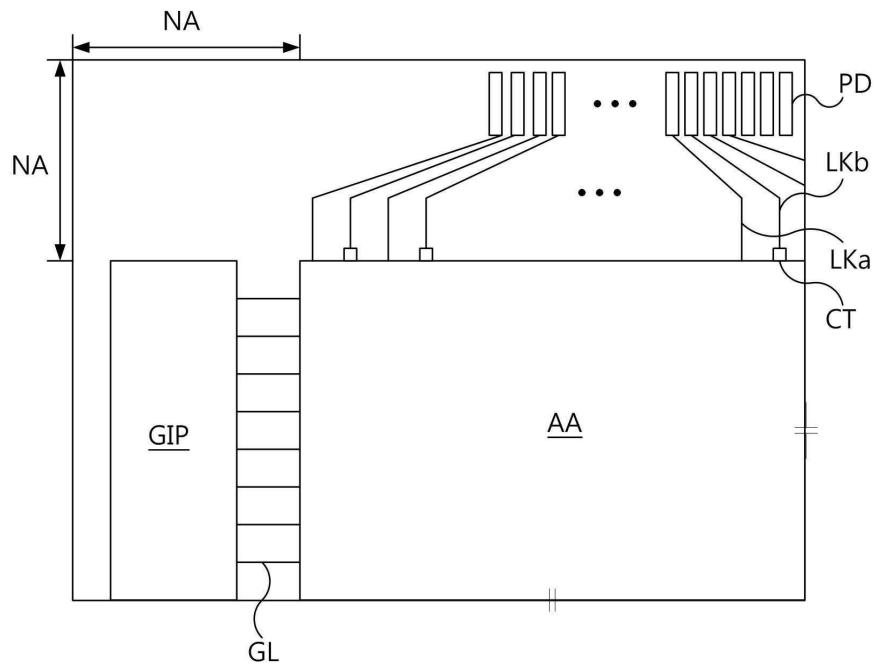

[0015] 도 1은 본 발명의 한 실시예에 따른 산화물 TFT를 이용하는 OLED 표시 장치 및 한 화소의 구성을 나타낸 도면이다.

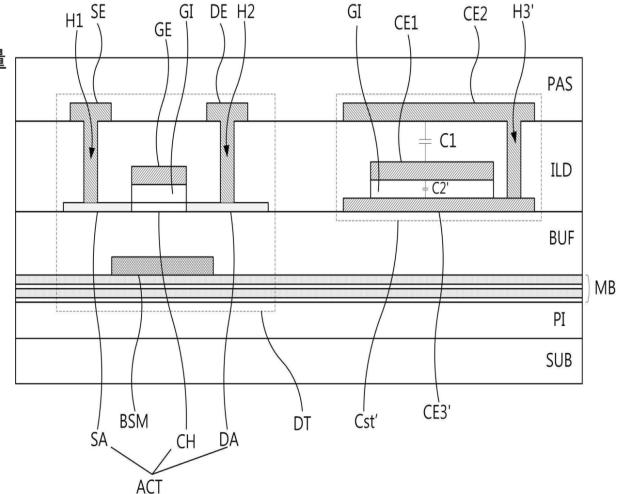

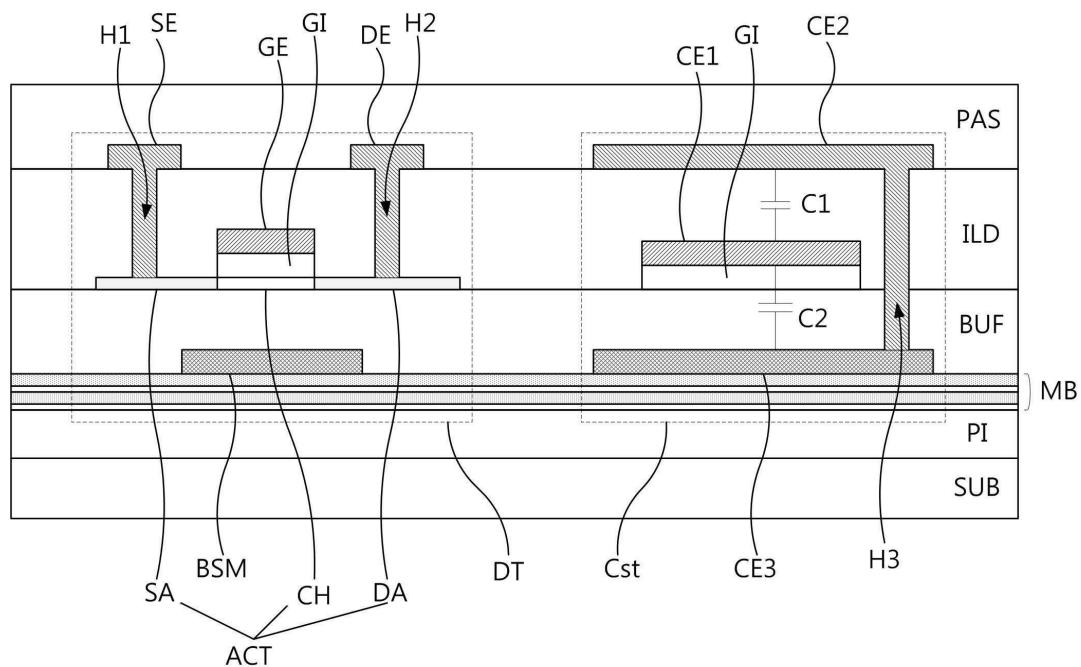

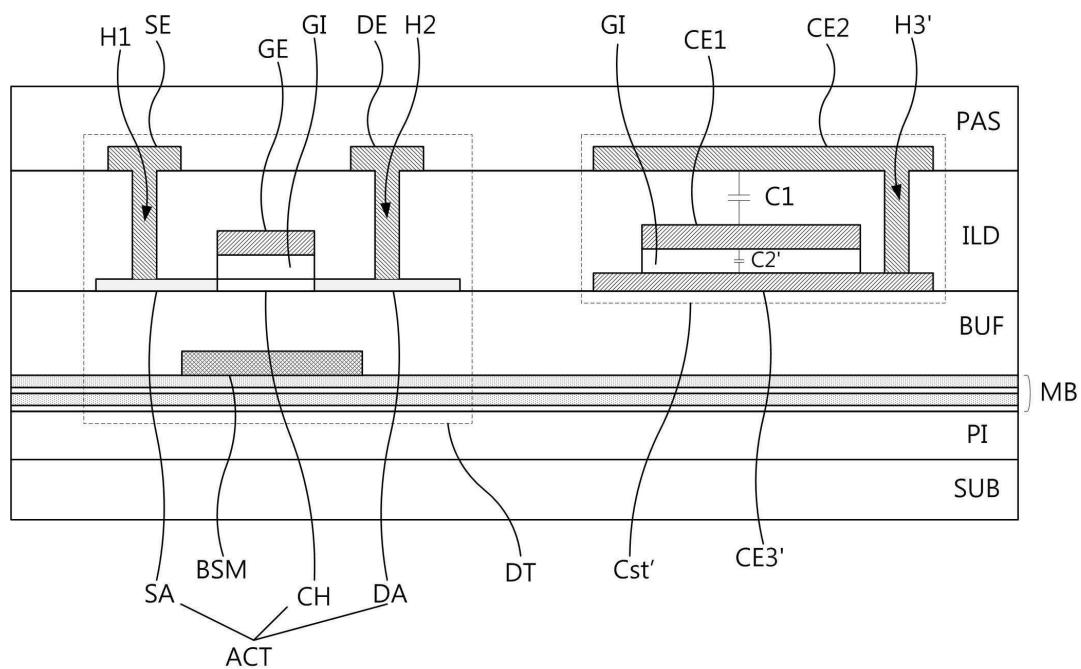

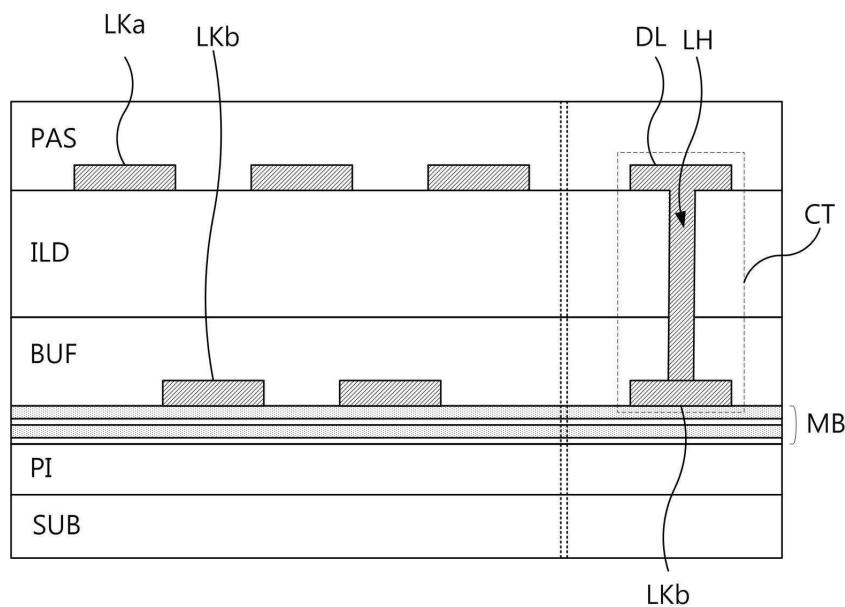

도 2는 본 발명의 한 실시예에 따른 화소 회로를 나타낸 단면도이다.

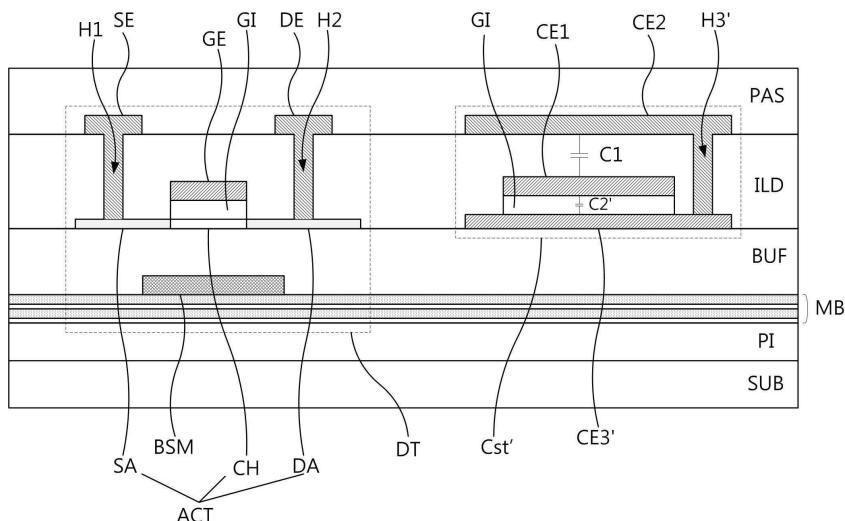

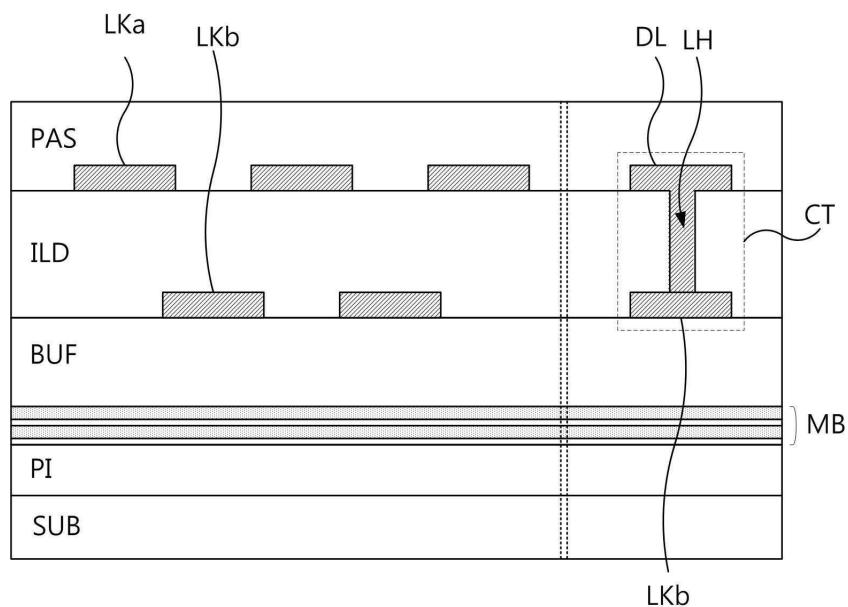

도 3은 본 발명의 다른 실시예에 따른 화소 회로를 나타낸 단면도이다.

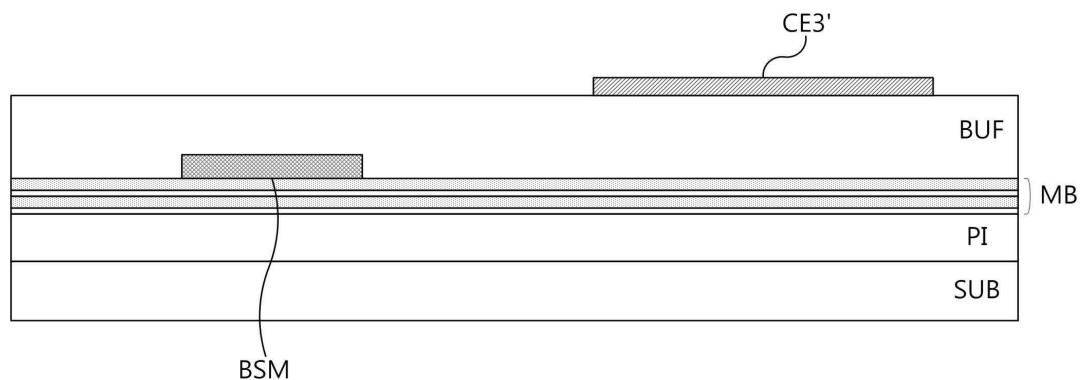

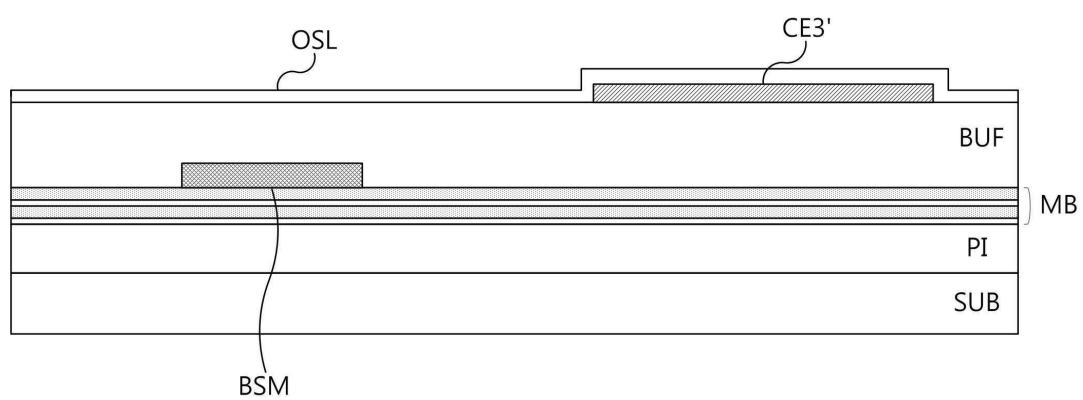

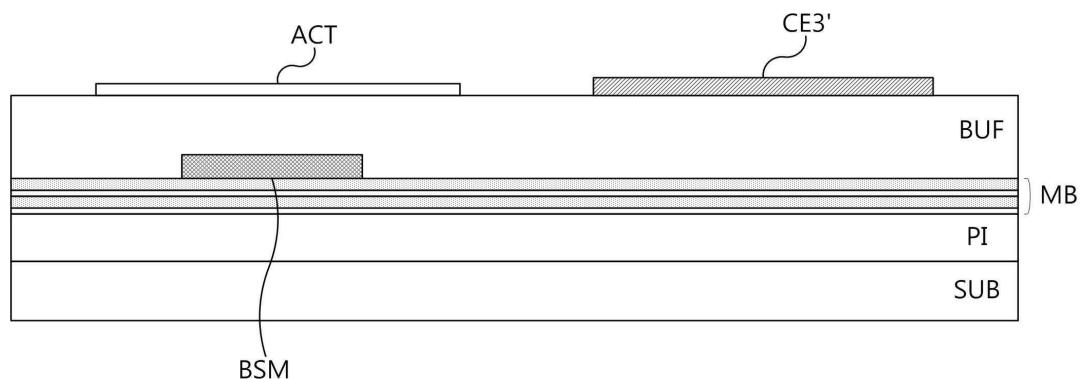

도 4a 내지 도 4c는 본 발명의 한 실시예에 따른 제3 스토리지 전극 및 액티브층 형성 방법을 순차적으로 나타낸 단면도들이다.

도 5는 본 발명의 한 실시예에 따른 OLED 표시 장치의 링크 배선들을 간략하게 나타낸 도면이다.

도 6은 본 발명의 한 실시예에 따른 링크 배선부를 나타낸 단면도이다.

도 7은 본 발명의 다른 실시예에 따른 링크 배선부를 나타낸 단면도이다.

**발명을 실시하기 위한 구체적인 내용**

[0016] 도 1은 본 발명의 한 실시예에 따른 산화물 TFT를 이용하는 OLED 표시 장치와 한 화소의 구성을 나타낸 도면이다.

[0017] 도 1를 참조하면, OLED 표시 장치는 표시 패널(100), 게이트 구동부(200), 데이터 구동부(300) 등을 포함한다.

[0018] 표시 패널(100)은 화소들이 매트릭스 형태로 배열된 화소 어레이(AA)를 통해 영상을 표시한다.

[0019] 각 화소(SP)은 고전위 전원(EVDD) 라인 및 저전위 전원(EVSS) 라인 사이에 접속된 OLED 소자와, OLED 소자를 독립적으로 구동하기 위하여 제1 및 제2 스위칭 TFT(ST1, ST2) 및 구동 TFT(DT)와 스토리지 커패시터(Cst)를 포함하는 화소 회로를 구비하며, 화소 회로 구성은 다양하므로 도 1의 구조로 한정되지 않는다. 각 화소(P)의 스위칭 TFT(ST1, ST2) 및 구동 TFT(DT)는 산화물 TFT를 이용한다. 산화물 TFT는 오프 전류가 작아 턴-온 시간이 짧고 턴-오프 시간을 길게 안정적으로 유지할 수 있으므로 저소비 전력 구동이 가능하다.

[0020] OLED 소자는 구동 TFT(DT)와 접속된 애노드와, 저전위 전압(EVSS)과 접속된 캐소드와, 애노드 및 캐소드 사이의 발광층을 구비하여, 구동 TFT(DT)로부터 공급된 전류량에 비례하는 광을 발생한다.

[0021] 제1 스위칭 TFT(ST1)는 한 게이트 라인(GLa)의 게이트 신호에 의해 구동되어 해당 데이터 라인(DL)으로부터의 데이터 전압을 구동 TFT(DT)의 게이트 노드에 공급하고, 제2 스위칭 TFT(ST2)는 다른 게이트 라인(GLb)의 게이트 신호에 의해 구동되어 레퍼런스 라인(RL)으로부터의 레퍼런스 전압을 구동 TFT(DT)의 소스 노드에 공급한다. 제2 스위칭 TFT(ST2)는 센싱 모드에서 구동 TFT(DT)로부터의 전류를 레퍼런스 라인(R)으로 출력하는 경로로 더 이용된다.

[0022] 구동 TFT(DT)의 게이트 전극 및 소스 전극 사이에 접속된 스토리지 커패시터(Cst)는 제1 스위칭 TFT(ST1)를 통해 구동 TFT(DT)의 게이트 전극으로 공급된 데이터 전압과, 제2 스위칭 TFT(ST2)를 통해 구동 TFT(DT)의 소스 전극으로 공급된 레퍼런스 전압의 차전압을 충전하고, 충전된 전압을 제1 및 제2 스위칭 TFT(ST1, ST2)가 턴-오프되는 구간에서 구동 TFT(DT)의 구동 전압으로 공급한다.

[0023] 구동 TFT(DT)는 고전위 전원(EVDD)으로부터 공급되는 전류를 스토리지 커패시터(Cst)로부터 공급된 구동 전압에 따라 제어함으로써 구동 전압에 비례하는 전류를 OLED 소자로 공급하여 OLED 소자를 발광시킨다.

[0024] 데이터 구동부(300)는 타이밍 컨트롤러(도시 생략)로부터의 영상 데이터를 감마 전압들을 이용하여 아날로그 데이터 신호로 변환하고, 아날로그 데이터 신호를 표시 패널(100)의 데이터 라인들(DL)로 각각 공급한다.

[0025] 게이트 구동부(200)는 표시 패널(100)의 다수의 게이트 라인을 각각 구동한다. 게이트 구동부(200)는 각 게이트 라인에 해당 스캔 기간에서 게이트 온 전압의 스캔 펄스를 공급하고, 나머지 기간에서는 게이트 오프 전압을 공급한다. 게이트 구동부(200)는 표시 패널(100)의 비표시 영역에서 화소 어레이(AA)의 각 화소(P)를 구성하는 박막 트랜지스터들과 함께 박막 트랜지스터 어레이 기판(백플레이트 기판)에 형성되어 표시 패널(100)에 내장될 수 있다. 표시 패널(100)에 내장된 게이트 구동부(200)를 구성하는 스위칭 소자들도 산화물 TFT가 적용될 수 있다.

[0026] 도 2는 본 발명의 한 실시예에 따른 화소 회로를 나타낸 단면도로써, 도 1에 도시된 화소 회로 중 구동 TFT(DT)와 스토리지 커패시터(Cst)의 구조를 나타낸 것이다.

도 2에 도시된 구동 TFT(DT)는 버퍼층(BUF) 아래 기판(SUB) 상의 쉴드 금속층(BSM), 버상에 적층된 액티브층

(ACT), 게이트 절연층(GI), 게이트 전극(GE)과, 버퍼층(BUF) 상에서 액티브층(ACT), 게이트 절연층(GI), 게이트 전극(GE)의 적층 구조를 덮는 충간 절연층(ILD)과, 충간 절연층(ILD)을 관통하는 컨택홀(H1, H2) 각각을 통해 액티브층(ACT)의 소스 영역(SA) 및 드레인 영역(DA)과 각각 접속하는 소스 전극(SE) 및 드레인 전극(DE)과, 충간 절연층(ILD) 상에서 소스 전극(SE) 및 드레인 전극(DE)를 덮는 폐시베이션층(PAS)을 구비한다.

[0028] 스토리지 커패시터(Cst)는 게이트 절연층(GI) 상의 제1 스토리지 전극(CE1)과, 제1 스토리지 전극(CE1)과 충간 절연층(ILD)을 사이에 두고 오버랩하여 제1 커패시터(C1)를 형성하는 충간 절연층(ILD) 상의 제2 스토리지 전극(CE2)과, 제1 스토리지 전극(CE1)과 게이트 절연층(GI) 및 버퍼층(BUF)을 사이에 두고 오버랩하여 제2 커패시터(C2)를 형성하고, 충간 절연층(ILD) 및 버퍼층(BUF)을 관통하는 컨택홀(H3)을 통해 제2 스토리지 전극(CE2)과 접속되는 버퍼층(BUF) 상의 제3 스토리지 전극(CE3)을 구비한다. 제1 및 제2 커패시터(C1, C2)가 서로 오버랩하면서 병렬로 접속된 구조를 갖으므로 제한된 화소 회로 영역내에서 스토리지 커패시터(Cst)의 용량을 증대시킬 수 있다.

[0029] 도 2에 도시된 화소 회로는 플렉서블 OLED 표시 장치에 적용되는 백플레인(Backplane) 기판 구조를 예시한 것으로, 유리 기판(SUB)과 버퍼층(BUF) 상에 적층되는 플렉서블 기재(P1) 및 멀티 배리어층(MB)를 더 구비하며, 유리 기판(SUB)은 제조 공정 동안 강성을 유지하기 위한 것으로 후속 공정에서 OLED 표시 장치가 완성되면 제거된다.

[0030] 플렉서블 기재(P1)는 플렉서블 플라스틱 필름으로, 폴리에스테르(polyester) 또는 폴리 에스테르를 포함하는 공중합체, 폴리이미드(polyimide) 또는 폴리 이미드를 포함하는 공중합체, 올레핀계 공중합체, 폴리아크릴산(polyacrylic acid) 또는 폴리아크릴산을 포함하는 공중합체, 폴리스티렌(polystyrene) 또는 폴리스테린을 포함하는 공중합체, 폴리설페이트(polysulfate) 또는 폴리설페이트를 포함하는 공중합체, 폴리카보네이트(polycarbonate) 또는 폴리 카보네이트를 포함하는 공중합체, 폴리아믹산(polyamic acid) 또는 폴리아믹산을 포함하는 공중합체, 폴리아민(polyamine) 및 폴리아믹산을 포함하는 공중합체, 폴리비닐 알콜(polyvinylalcohol), 폴리 알릴아민(polyallyamine)으로 이루어진 군에서 선택되는 하나 이상의 고분자 화합물을 포함할 수 있다.

[0031] 플렉서블 기재(PI) 상에 적층된 멀티 배리어층(MB)은 플렉서블 기재(PI)의 외부로부터 유입될 외부 수분이나 가스 등을 차단하기 위한 것으로, 유기 절연층과 무기 절연층이 교번적으로 적층된 구조나, 산화 실리콘(SiO<sub>x</sub>), 질화 실리콘(SiNx), 산화 알루미늄(AlO<sub>x</sub>) 등과 같은 무기 절연 물질이 적층된 구조로 형성될 수 있다.

[0032] 멀티 배리어층(MB) 상의 쉴드 금속층(BSM)은 산화물 액티브층(ACT)의 특성을 가변시키는 외부의 빛이 액티브층(ACT)으로 유입되는 것을 차단하기 위하여 차광 기능을 갖는 금속 재료로 형성되고, 제3 스토리지 전극(CE3)이 쉴드 금속층(BSM)과 함께 동일층에 동일 재료로 형성된다. 쉴드 금속층(BSM)은 몰리브덴(Mo), 알루미늄(Al), 크롬(Cr), 텉스텐(W), 티타늄(Ti), 니켈(Ni), 네오디뮴(Nd) 및 구리(Cu) 등의 금속 중 어느 하나 또는 이들의 합금으로 이루어진 단일층 또는 복층 구조로 형성될 수 있다. 쉴드 금속층(BSM)은 화소 회로를 구성하는 TFT를 중 적어도 하나의 액티브층과 오버랩할 수 있다.

[0033] 기판(SUB) 상에서 쉴드 금속층(BSM) 및 제3 스토리지 전극(CE3)을 덮는 버퍼층(BUF)은 멀티 배리어층(MB)으로부터 산화물 액티브층(ACT)으로 수소가 유입되는 것을 억제한다. 버퍼층(BUF)은 단일 절연층 또는 복수의 절연층이 적층된 구조로 형성되며, 액티브층(ACT)의 특성 변화를 방지하기 위하여 산화 실리콘(SiO<sub>x</sub>), 산화 알루미늄(AlO<sub>x</sub>) 등과 같은 산화물계 절연 물질로 형성된다.

[0034] 버퍼층(BUF) 상에 적층된 액티브층(ACT)은 채널 영역(CH)과, 옵셋 저항 감소를 위해 도체화 처리된 저저항의 소스 영역(SA) 및 드레인 영역(DA)을 구비한다. 액티브층(ACT)은 In, Ga, Zn, Al, Sn, Zr, Hf, Cd, Ni, Cu 중 적어도 하나의 금속을 포함하는 산화물 반도체로 형성된다. 액티브층(ACT)의 소스 영역(SA) 및 드레인 영역(DA)은 액티브층(ACT)이 후속 공정에서 플라즈마, 자외선(UV) 또는 에칠툰에 의해 노출되어 산소가 다소 제거되어 도체화된다.

[0035] 액티브층(ACT) 상에 채널 영역(CH)과 오버랩하는 게이트 절연층(GI) 및 게이트 전극(GE)이 적층 구조로 형성됨과 아울러 버퍼층(BUF) 상에 게이트 절연층(GI) 및 제1 스토리지 전극(CE1)이 적층 구조로 형성된다. 게이트 절연층(GI)은 산화 실리콘(SiO<sub>x</sub>), 질화 실리콘(SiNx), 산화 알루미늄(AlO<sub>x</sub>) 등과 같은 무기 절연 물질이 단층 또는 복층 구조로 형성될 수 있다. 게이트 절연층(GI)은 산화물 반도체를 이용하는 액티브층(ACT)의 특성 변화를 방지하기 위하여 산화물계 절연 물질로 형성될 수 있다. 게이트 전극(GE) 및 제1 스토리지 전극(CE1)으로 이용되는 게이트 금속층은 몰리브덴(Mo), 알루미늄(Al), 크롬(Cr), 텉스텐(W), 티타늄(Ti), 니켈(Ni), 네오디뮴(Nd) 및 구리(Cu) 등의 금속 중 어느 하나 또는 이들의 합금으로 이루어진 단일층 또는 복층 구조로 형성될 수 있다.

제1 스토리지 전극(CE1)은 베피층(BUF)을 사이에 두고 제3 스토리지 전극(CE3)과 오버랩하여 제2 커패시터(C2)를 형성한다.

[0036] 베피층(BUF) 상에 액티브층(ACT), 게이트 절연층(GI), 게이트 전극(GE) 및 제1 스토리지 전극(CE1)를 덮는 충간 절연층(ILD)이 형성되고, 충간 절연층(ILD)을 관통하는 컨택홀(H1, H2)과, 충간 절연층(ILD) 및 베피층(BUF)을 관통하는 컨택홀(H3)이 형성된다. 충간 절연층(ILD)은 산화 실리콘(SiO<sub>x</sub>), 질화 실리콘(SiNx), 산화 알루미늄(AlO<sub>x</sub>) 등과 같은 무기 절연 물질이 단층 또는 복층 구조로 형성되거나, 유기 절연 물질로 형성될 수 있다.

[0037] 충간 절연층(ILD) 상에 소스 전극(SE) 및 드레인 전극(DE)이 형성됨과 아울러 제1 스토리지 전극(CE1)과 오버랩하여 제1 커패시터(C1)를 형성하고, 제3 스토리지 전극(CE3)과 접속되는 제2 스토리지 전극(CE2)이 형성된다. 소스 전극(SE)은 컨택홀(H1)을 통해 액티브층(ACT)의 소스 영역(SA)과 접속되고, 드레인 전극(DE)은 컨택홀(H2)을 통해 액티브층(ACT)의 드레인 영역(DA)과 접속된다. 제2 스토리지 전극(CE2)은 컨택홀(H3)을 통해 제3 스토리지 전극(CE3)과 접속된다. 소스 전극(SE) 및 드레인 전극(DE)과 제2 스토리지 전극(CE2)으로 이용되는 소스/드레인 금속층은 몰리브덴(Mo), 알루미늄(Al), 크롬(Cr), 텅스텐(W), 티타늄(Ti), 니켈(Ni), 네오디뮴(Nd) 및 구리(Cu) 등의 금속 중 어느 하나 또는 이들의 합금으로 이루어진 단일층 또는 복층 구조로 형성될 수 있다.

[0038] 충간 절연층(ILD) 상에 소스 전극(SE) 및 드레인 전극(DE)과, 제2 스토리지 전극(CE2)을 덮는 폐시베이션층(PAS)이 형성된다. 충간 절연층(ILD)은 산화 실리콘(SiO<sub>x</sub>), 질화 실리콘(SiNx), 산화 알루미늄(AlO<sub>x</sub>) 등과 같은 무기 절연 물질이 단층 또는 복층 구조로 형성될 수 있다.

[0039] 본 발명의 한 실시예에 따른 스토리지 커패시터(Cst)는 게이트 절연층(GI) 상의 제1 스토리지 전극(CE1)과, 충간 절연층(ILD) 상의 제2 스토리지 전극(CE2)과, 베피층(BUF) 상의 제3 스토리지 전극(CE3)이 서로 오버랩함으로써 제1 및 제2 커패시터(C1, C2)가 서로 오버랩하면서 별도로 접속된 구조를 갖으므로 제한된 화소 회로 영역 내에서 스토리지 커패시터(Cst)의 용량을 증대시킬 수 있다. 이때, 제3 스토리지 전극(CE2)는 쉴드 금속층(BSM)과 동일층에 동일 재료로 형성되므로 이를 위한 별도의 제조 공정이 요구되지 않아 코스트 경쟁력을 강화할 수 있다.

[0040] 한편, 베피층(BUF)은 멀티 배리어층(MB)으로부터 산화물 액티브층(ACT)으로 수소가 유입되는 것을 억제하기 위하여 베피층(BUF)은 상대적으로 두껍게, 예를 들면 600nm 이상의 두께를 유지해야 한다. 이로 인하여, 제1 스토리지 전극(CE1) 및 제3 스토리지 전극(CE3) 사이의 거리는 베피층(BUF)과 게이트 절연층(GI)의 두께에 의해 700nm 이상이 되어야 하므로 스토리지 커패시터(Cst)의 용량 증가에 한계가 있다.

[0041] 이를 개선하기 위하여, 본 발명의 다른 실시예에 따른 화소 회로는 도 3에 도시된 바와 같이 제3 스토리지 전극(CE3')을 베피층(BUF) 상에 형성한 구조를 제안한다.

[0042] 도 3을 참조하면, 제3 스토리지 전극(CE3')은 베피층(BUF) 상에 위치함으로써 제1 스토리지 전극(CE1)과 제3 스토리지 전극(CE3')은 게이트 절연층(GI)을 사이에 두고 서로 오버랩하여 제2 커패시터(C2')를 형성한다. 이에 따라, 제3 스토리지 전극(CE3')이 베피층(BUF) 상에 형성된 도 2의 제2 커패시터(C2)와 대비하여, 도 3에 도시된 제2 커패시터(C2')는 제1 스토리지 전극(CE1)과 제3 스토리지 전극(CE3')간 간격이 게이트 절연층(GI)의 두께로 감소함으로써 스토리지 용량 증가를 극대화할 수 있다.

[0043] 제3 스토리지 전극(CE3')은 액티브층(ACT)과 동일층인 베피층(BUF) 상에 형성되지만 액티브층(ACT)과 다른 금속층으로 형성된다. 제3 스토리지 전극(CE3')은 액티브층(ACT)을 동일층에 형성하는 방법은 다음과 같다.

[0044] 도 4a에 도시된 바와 같이, 베피층(BUF) 상에 마스크 공정을 이용하여 제3 스토리지 전극(CE3')을 먼저 형성하고, 도 4b에 도시된 바와 같이 베피층(BUF) 상에 제3 스토리지 전극(CE3')을 덮는 산화물 반도체층(OSL)을 전면 증착한다. 이어서, 마스크를 이용한 포토리쏘그래피 공정 및 에칭 공정에 의해 산화물 반도체층(OSL)을 패터닝함으로써 액티브층(ACT)이 형성된다. 이때, 산화물 반도체층(OSL)의 에칭시 혼산과 OZ산을 모두 사용할 수 있으나, 금속층의 에чин트로 주로 이용되는 혼산이 아닌 ITO, IGZO 등의 에чин트로 주로 이용되는 OZ산을 이용함으로써 산화물 반도체층(OSL)의 에칭시 제3 스토리지 전극(CE3')이 에칭되는 것을 방지할 수 있다.

[0045] 도 5는 본 발명의 한 실시예에 따른 OLED 표시 장치의 링크 배선들을 간략하게 나타낸 도면이다.

[0046] 도 5를 참조하면, 표시 영역(AA)의 데이터 라인(도시 생략)은 비표시 영역에 형성된 데이터 링크(LKa, LKb)를 경유하여 패드 영역에 형성된 데이터 패드(PD)와 개별적으로 접속된다. 데이터 패드들(DP)은 구동 IC와 접속될 부분이다.

[0047] 데이터 링크(LKa, LKb)는 데이터 라인과 동일층에 동일한 소스/드레인 금속층으로 형성되어 제1 데이터 라인과

접속되는 제1 데이터 링크(LKa)와, 데이터 라인과 다른 배선층인 전술한 제3 스토리지 전극(CE3, CE')과 동일층에 동일한 금속층으로 형성되고 컨택부(CT)를 경유하여 제2 데이터 라인과 접속되는 제2 데이터 링크(LKb)를 구비한다. 비표시 영역에는 서로 다른 층에 형성되는 제1 데이터 링크(LKa)와 제2 데이터 링크(LKb)가 교번적으로 배치되고, 표시 영역에 교번적으로 배치된 제1 및 제2 데이터 라인과 개별적으로 접속된다. 이에 따라, 다수의 데이터 링크들(LKa, LKb)을 포함하는 제한된 비표시 영역에서 데이터 링크(LKa, LKb)간의 간격을 충분히 확보할 수 있으므로 신뢰성을 향상시킬 수 있다.

[0048] 도 6은 본 발명의 한 실시예에 따른 링크 배선부를 나타낸 단면도이고, 도 7은 본 발명의 다른 실시예에 따른 링크 배선부를 나타낸 단면도이다.

[0049] 도 6을 참조하면, 제1 데이터 링크(LKa)는 데이터 라인(DL)과 동일층인 층간 절연층(ILD) 상에 형성되고, 제2 데이터 링크(LKb)는 도 2에서 전술한 제3 스토리지 전극(CE3) 및 쉴드 금속층(BSM)과 동일층, 동일 재료로 멀티 배리어층(MB) 상에 형성된다. 멀티 배리어층(MB) 상의 제2 데이터 링크(LKb)는 컨택부(CT)에서 베퍼층(BUF) 및 층간 절연층(ILD)을 관통하는 컨택홀(LH)을 통해 데이터 라인(DL)과 접속된다. 이에 따라, 다수의 데이터 링크들(LKa, LKb)을 포함하는 제한된 비표시 영역에서 데이터 링크(LKa, LKb)간의 간격을 충분히 확보할 수 있으므로 신뢰성을 향상시킬 수 있음과 아울러 별도의 마스크 공정이 필요하지 않으므로 코스트 상승을 방지할 수 있다.

[0050] 도 7을 참조하면, 제1 데이터 링크(LKa)는 데이터 라인(DL)과 동일층인 층간 절연층(ILD) 상에 형성되고, 제2 데이터 링크(LKb)는 도 3에서 전술한 제3 스토리지 전극(CE3')과 동일층, 동일 재료로 베퍼층(BUF) 상에 형성된다. 베퍼층(BUF) 상의 제2 데이터 링크(LKb)는 컨택부(CT)에서 베퍼층(BUF)을 관통하는 컨택홀(LH)을 통해 데이터 라인(DL)과 접속된다. 이에 따라, 다수의 데이터 링크들(LKa, LKb)을 포함하는 제한된 비표시 영역에서 데이터 링크(LKa, LKb)간의 간격을 충분히 확보할 수 있으므로 신뢰성을 향상시킬 수 있음과 아울러 별도의 마스크 공정이 필요하지 않으므로 코스트 상승을 방지할 수 있다.

[0051] 전술한 바와 같이, 본 발명의 한 실시예에 따른 OLED 표시 장치는 소비 전력을 저감할 수 있는 코플래너 구조의 산화물 TFT를 화소 회로의 스위칭 소자로 이용함과 아울러, 게이트 절연층 상의 제1 스토리지 전극이 층간 절연층 상의 제2 스토리지 전극과 오버랩하여 형성하는 제1 커패시터와, 제2 스토리지 전극과 접속되는 제3 스토리지 전극이 제1 스토리지 전극과 게이트 절연층을 사이에 두고 오버랩하거나, 게이트 절연층 및 베퍼층을 사이에 두고 오버랩하여 형성하는 제2 커패시터의 별도 구조로 스토리지 커패시터를 구비함으로써 제한된 화소 회로 영역내에서 면적 증가없이 스토리지 커패시터의 용량을 향상시킬 수 있다.

[0052] 본 발명의 한 실시예에 따른 OLED 표시 장치는 비표시 영역에는 데이터 라인과 동일층인 제1 링크 배선과, 제3 스토리지 전극과 동일층인 제2 링크 배선이 교번적으로 배치됨으로써 다수의 링크 배선들을 포함하는 제한된 비표시 영역에서 링크 배선간의 간격을 충분히 확보하여 신뢰성을 향상시킬 수 있다.

[0053] 이상 설명한 내용을 통해 당업자라면 본 발명의 기술사상을 일탈하지 아니하는 범위에서 다양한 변경 및 수정이 가능함을 알 수 있을 것이다. 따라서, 본 발명의 기술적 범위는 명세서의 상세한 설명에 기재된 내용으로 한정되는 것이 아니라 특허 청구 범위에 의해 정하여져야만 할 것이다.

## 부호의 설명

|                              |             |

|------------------------------|-------------|

| [0054] SUB: 기판               | PI: 플렉서블 기재 |

| MB: 멀티 배리어층                  | BSM: 쉴드 금속층 |

| CE1, CE2, CE3, CE3': 스토리지 전극 | ACT: 액티브층   |

| CH: 채널 영역                    | SA: 소스 영역   |

| DA: 드레인 영역                   | GI: 게이트 절연층 |

| GE: 게이트 전극                   | SE: 소스 전극   |

| DE: 드레인 전극                   | PAS: 패시베이션층 |

| H1, H2, H3, H3', LH: 컨택홀     |             |

## 도면

## 도면1

## 도면2

## 도면3

도면4a

도면4b

도면4c

도면5

도면6

## 도면7

|                |                                                                         |         |            |

|----------------|-------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 标题 : OLED显示器件                                                           |         |            |

| 公开(公告)号        | <a href="#">KR1020170078075A</a>                                        | 公开(公告)日 | 2017-07-07 |

| 申请号            | KR1020150188214                                                         | 申请日     | 2015-12-29 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                               |         |            |

| [标]发明人         | LEE SEUNG MIN<br>이승민<br>OH SAEROONTER<br>오새룬터                           |         |            |

| 发明人            | 이승민<br>오새룬터                                                             |         |            |

| IPC分类号         | H01L27/32                                                               |         |            |

| CPC分类号         | H01L27/3265 H01L27/3262 H01L27/3258 H01L27/3276 H01L27/3248 H01L2227/32 |         |            |

| 代理人(译)         | Bakyoungbok                                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                               |         |            |

### 摘要(译)

OLED显示装置技术领域本发明涉及能够降低功耗并提高存储电容器容量的OLED显示装置。在根据实施例的OLED显示器中，每个像素电路包括在连接到驱动晶体管的栅极绝缘层上的第一存储电极，连接到驱动晶体管的源电极的第二存储电极，和第三存储电极，其连接到第二存储电极并与第一存储电极和栅极绝缘层重叠，或者与栅极绝缘层和插入其间的缓冲层重叠。