(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2018년07월26일

(11) 등록번호 10-1881853

(24) 등록일자 2018년07월19일

- (51) 국제특허분류(Int. Cl.)

*G09G 3/30* (2006.01) *H01L 51/50* (2006.01)

(21) 출원번호 10-2012-0021210

(22) 출원일자 2012년02월29일

심사청구일자 2017년02월27일

(65) 공개번호 10-2013-0099588

(43) 공개일자 2013년09월06일

(56) 선행기술조사문현

US20070052653 A1\*

(뒷면에 계속)

전체 청구항 수 : 총 20 항

심사관 : 진민숙

- (54) 발명의 명칭 **에미션 구동 유닛, 에미션 구동부 및 이를 포함하는 유기 발광 표시 장치**

**(57) 요 약**

에미션 구동 유닛은 입력 신호 생성 회로, 인버터 회로 및 출력 스위칭 회로를 포함한다. 입력 신호 생성 회로는 제 1 클락 신호에 응답하여 프레임 라인 마크(Frame Line Mark; FLM) 신호를 수신하고, 상기 FLM 신호에 응답하여 제 2 클락 신호를 수신하며, 순차 입력 신호를 출력한다. 인버터 회로는 제 1 클락 신호에 응답하여 FLM 신호를 수신하고, 상기 FLM 신호를 반전하여 인버터 출력 신호를 생성한다. 출력 스위칭 회로는 인버터 출력 신호에 응답하여 에미션(emission) 신호로서 하이 레벨의 제 1 전압 또는 로우 레벨의 제 2 전압을 출력한다. 입력 신호 생성 회로, 인버터 회로 및 출력 스위칭 회로는 동종의 단일형 트랜지스터들로 구현될 수 있다.

**대 표 도**

(56) 선행기술조사문현

US20090284454 A1\*

US20120038609 A1\*

US20110084947 A1\*

US20070132701 A1\*

US20060158394 A1\*

\*는 심사관에 의하여 인용된 문현

---

## 명세서

### 청구범위

#### 청구항 1

제 1 클락 신호에 응답하여 프레임 라인 마크(Frame Line Mark; FLM) 신호를 수신하고, 상기 FLM 신호에 응답하여 상기 제 1 클락 신호와 상이한 제 2 클락 신호를 수신하며, 순차 입력 신호를 출력하는 입력 신호 생성 회로;

상기 제 1 클락 신호에 응답하여 상기 FLM 신호를 수신하고, 상기 제 1 클락 신호 및 상기 제 2 클락 신호에 응답하여 상기 FLM 신호를 반전하여 인버터 출력 신호를 생성하는 인버터 회로; 및

상기 인버터 출력 신호에 응답하여 에미션(emission) 신호로서 하이 레벨의 제 1 전압 또는 로우 레벨의 제 2 전압을 출력하는 출력 스위칭 회로를 포함하고,

상기 입력 신호 생성 회로, 상기 인버터 회로 및 상기 출력 스위칭 회로는 동종의 단 일형 트랜지스터들로 구현되는 것을 특징으로 하는 에미션 구동 유닛.

#### 청구항 2

제 1 항에 있어서, 상기 에미션 신호는 상기 FLM 신호가 반전된(inverted) 형태를 가지는 것을 특징으로 하는 에미션 구동 유닛.

#### 청구항 3

제 2 항에 있어서, 상기 입력 신호 생성 회로, 상기 인버터 회로 및 상기 출력 스위칭 회로는 엔모스(N-channel Metal Oxide Semiconductor; NMOS) 트랜지스터들로 구현되는 것을 특징으로 하는 에미션 구동 유닛.

#### 청구항 4

제 3 항에 있어서, 상기 입력 신호 생성 회로는,

소스 전극, 상기 FLM 신호를 수신하는 드레인 전극, 및 상기 제 1 클락 신호를 수신하는 게이트 전극을 구비하고, 상기 제 1 클락 신호에 응답하여 상기 FLM 신호를 상기 드레인 전극에서 상기 소스 전극으로 인가하는 제 1 트랜지스터;

상기 제 2 클락 신호를 수신하는 드레인 전극, 상기 제 1 트랜지스터의 상기 소스 전극에 연결되는 게이트 전극, 및 상기 순차 입력 신호를 출력하는 소스 전극을 구비하는 제 2 트랜지스터; 및

상기 제 1 트랜지스터의 상기 소스 전극과 상기 제 2 트랜지스터의 상기 소스 전극 사이에 연결되는 제 1 커패시터를 포함하는 것을 특징으로 하는 에미션 구동 유닛.

#### 청구항 5

제 4 항에 있어서, 상기 인버터 회로는,

상기 제 1 클락 신호에 응답하여 상기 FLM 신호를 제 1 노드로 제공하는 제 3 트랜지스터;

상기 제 1 노드에 연결되는 게이트 전극, 제 2 전압 공급단에 연결되는 소스 전극, 및 제 2 노드에 연결되는 드레인 전극을 구비하는 제 4 트랜지스터;

상기 제 1 노드와 상기 제 2 전압 공급단 사이에 연결되는 제 2 커패시터;

상기 입력 신호 생성 회로의 상기 제 2 트랜지스터의 상기 소스 전극에 연결되는 드레인 전극, 상기 제 2 전압 공급단에 연결되는 소스 전극, 및 상기 제 2 노드에 연결되는 게이트 전극을 구비하는 제 5 트랜지스터;

상기 제 2 노드에 연결되는 소스 전극, 제 3 노드에 연결되는 드레인 전극, 및 상기 제 2 클락 신호를 수신하는 게이트 전극을 구비하는 제 6 트랜지스터;

상기 제 3 노드에 연결되는 소스 전극, 제 1 전압 공급단에 연결되는 드레인 전극, 및 상기 제 1 클락 신호를

수신하는 게이트 전극을 구비하는 제 7 트랜지스터;

상기 제 3 노드에 연결되는 게이트 전극, 상기 제 2 클락 신호를 수신하는 드레인 전극, 및 제 4 노드에 연결되는 소스 전극을 구비하는 제 8 트랜지스터; 및

상기 제 3 노드와 상기 제 4 노드 사이에 연결되는 제 3 커패시터를 포함하는 것을 특징으로 하는 에미션 구동 유닛.

#### 청구항 6

제 5 항에 있어서, 상기 출력 스위칭 회로는,

상기 에미션 신호를 출력하는 출력단;

상기 제 1 노드에 연결되는 게이트 전극, 상기 제 2 전압 공급단에 연결되는 소스 전극, 및 상기 출력단에 연결되는 드레인 전극을 구비하는 제 9 트랜지스터; 및

상기 제 2 노드에 연결되는 게이트 전극, 상기 출력단에 연결되는 소스 전극, 및 상기 제 1 전압 공급단에 연결되는 드레인 전극을 구비하는 제 10 트랜지스터를 포함하는 것을 특징으로 하는 에미션 구동 유닛.

#### 청구항 7

제 6 항에 있어서,

상기 제 1 전압 공급단과 상기 제 1 노드 사이에 연결되는 제 1 출력 제어 트랜지스터 및 상기 제 2 전압 공급단과 상기 제 2 노드 사이에 연결되는 제 2 출력 제어 트랜지스터를 구비하는 출력 제어 회로를 더 포함하는 것을 특징으로 하는 에미션 구동 유닛.

#### 청구항 8

제 7 항에 있어서, 상기 출력 제어 회로에 하이 레벨의 출력 제어 신호가 인가되는 경우, 상기 에미션 신호로 상기 제 2 전압이 DC 레벨로 출력되는 것을 특징으로 하는 에미션 구동 유닛.

#### 청구항 9

제 2 항에 있어서, 상기 입력 신호 생성 회로, 상기 인버터 회로 및 상기 출력 스위칭 회로는 퍼모스(P-channel Metal Oxide Semiconductor; PMOS) 트랜지스터들로 구현되는 것을 특징으로 하는 에미션 구동 유닛.

#### 청구항 10

제 9 항에 있어서, 상기 입력 신호 생성 회로는,

드레인 전극, 상기 FLM 신호를 수신하는 소스 전극, 및 상기 제 1 클락 신호를 수신하는 게이트 전극을 구비하고, 상기 제 1 클락 신호에 응답하여 상기 FLM 신호를 상기 소스 전극에서 상기 드레인 전극으로 인가하는 제 1 트랜지스터;

상기 제 2 클락 신호를 수신하는 소스 전극, 상기 제 1 트랜지스터의 상기 드레인 전극에 연결되는 게이트 전극, 및 상기 순차 입력 신호를 출력하는 드레인 전극을 구비하는 제 2 트랜지스터; 및

상기 제 1 트랜지스터의 상기 드레인 전극과 상기 제 2 트랜지스터의 상기 드레인 전극 사이에 연결되는 제 1 커패시터를 포함하는 것을 특징으로 하는 에미션 구동 유닛.

#### 청구항 11

제 10 항에 있어서, 상기 인버터 회로는,

상기 제 1 클락 신호에 응답하여 상기 FLM 신호를 제 1 노드로 제공하는 제 3 트랜지스터;

상기 제 1 노드에 연결되는 게이트 전극, 제 1 전압 공급단에 연결되는 소스 전극, 및 제 2 노드에 연결되는 드레인 전극을 구비하는 제 4 트랜지스터;

상기 제 1 노드와 상기 제 1 전압 공급단 사이에 연결되는 제 2 커패시터;

상기 입력 신호 생성 회로의 상기 제 2 트랜지스터의 상기 드레인 전극에 연결되는 드레인 전극, 상기 제 1 전

암 공급단에 연결되는 소스 전극, 및 상기 제 2 노드에 연결되는 게이트 전극을 구비하는 제 5 트랜지스터;

상기 제 2 노드에 연결되는 소스 전극, 제 3 노드에 연결되는 드레인 전극, 및 상기 제 2 클락 신호를 수신하는 게이트 전극을 구비하는 제 6 트랜지스터;

상기 제 3 노드에 연결되는 소스 전극, 제 2 전압 공급단에 연결되는 드레인 전극, 및 상기 제 1 클락 신호를 수신하는 게이트 전극을 구비하는 제 7 트랜지스터;

상기 제 3 노드에 연결되는 게이트 전극, 상기 제 2 클락 신호를 수신하는 소스 전극, 및 제 4 노드에 연결되는 드레인 전극을 구비하는 제 8 트랜지스터; 및

상기 제 3 노드와 상기 제 4 노드 사이에 연결되는 제 3 커패시터를 포함하는 것을 특징으로 하는 에미션 구동 유닛.

### 청구항 12

제 11 항에 있어서, 상기 출력 스위칭 회로는,

상기 에미션 신호를 출력하는 출력단;

상기 제 1 노드에 연결되는 게이트 전극, 상기 제 1 전압 공급단에 연결되는 소스 전극, 및 상기 출력단에 연결되는 드레인 전극을 구비하는 제 9 트랜지스터; 및

상기 제 2 노드에 연결되는 게이트 전극, 상기 출력단에 연결되는 소스 전극, 및 상기 제 2 전압 공급단에 연결되는 드레인 전극을 구비하는 제 10 트랜지스터를 포함하는 것을 특징으로 하는 에미션 구동 유닛.

### 청구항 13

제 12 항에 있어서,

상기 인버터 회로에 연결되고 출력 제어 신호에 의해 제어되는 출력 제어 회로를 더 포함하고,

상기 출력 제어 회로에 로우 레벨의 상기 출력 제어 신호가 인가되는 경우, 상기 에미션 신호로 상기 제 1 전압이 DC 레벨로 출력되는 것을 특징으로 하는 에미션 구동 유닛.

### 청구항 14

프레임 라인 마크(Frame Line Mark; FLM) 신호를 입력 신호로서 수신하고, 제 1 클락 신호 및 상기 제 1 클락 신호와 상이한 제 2 클락 신호에 의해 제어되며, 제 1 에미션(emission) 신호 및 제 1 순차 입력 신호를 출력하는 제 1 에미션 구동 유닛; 및

상기 제 1 클락 신호 및 상기 제 2 클락 신호에 의해 각각 제어되고, 제 2 내지 제 n(단, n은 3이상의 정수) 에미션 신호들을 각각 출력하는 제 2 내지 제 n 에미션 구동 유닛들을 포함하고,

상기 제 1 내지 제 (n-1) 에미션 구동 유닛들은 각각 상기 제 2 내지 제 n 에미션 구동 유닛들에 상기 제 1 순차 입력 신호 및 제 2 내지 제 (n-1) 순차 입력 신호들을 상기 입력 신호로서 순차적으로 제공하며,

상기 제 1 내지 제 n 에미션 구동 유닛들 각각은,

상기 제 1 클락 신호에 응답하여 상기 입력 신호를 수신하고, 상기 입력 신호에 응답하여 상기 제 2 클락 신호를 수신하며, 상기 제 1 내지 제 (n-1) 순차 입력 신호들 중 하나의 신호를 출력하는 입력 신호 생성 회로;

상기 제 1 클락 신호에 응답하여 상기 입력 신호를 수신하고, 상기 제 1 클락 신호 및 상기 제 2 클락 신호에 응답하여 상기 입력 신호를 반전하여 인버터 출력 신호를 생성하는 인버터 회로; 및

상기 인버터 출력 신호에 응답하여 상기 제 1 내지 제 n 에미션 신호들 중 하나의 신호로서 하이 레벨의 제 1 전압 또는 로우 레벨의 제 2 전압을 출력하는 출력 스위칭 회로를 포함하는 것을 특징으로 하는 에미션 구동부.

### 청구항 15

제 14 항에 있어서, 상기 제 1 내지 제 n 에미션 구동 유닛들 각각은 동종의 단일형 트랜지스터들로 구현되는 것을 특징으로 하는 에미션 구동부.

**청구항 16**

제 15 항에 있어서, 상기 제 1 내지 제 n 에미션 신호들은 상기 FLM 신호가 반전된(inverted) 형태를 가지는 것을 특징으로 하는 에미션 구동부.

**청구항 17**

유기 발광 다이오드를 각각 구비하는 복수의 화소 회로들을 포함하고, 제 1 전원 전압 및 제 2 전원 전압을 수신하는 표시 패널;

제 1 내지 제 n(단, n은 3 이상의 정수) 스캔 라인들을 통해 상기 화소 회로들에 순차적으로 제 1 내지 제 n 스캔 신호들을 제공하는 스캔 구동부;

상기 제 1 내지 제 n 스캔 신호들에 따라 복수의 데이터 라인들을 통해 상기 화소 회로들에 데이터 전압을 제공하는 데이터 구동부;

제 1 내지 제 n 에미션(emission) 제어 라인들을 통해 상기 화소 회로들에 순차적으로 제 1 내지 제 n 에미션 신호들을 제공하는 에미션 구동부; 및

상기 스캔 구동부, 상기 데이터 구동부 및 상기 에미션 구동부에 제 1 클락 신호 및 상기 제 1 클락 신호와 상이한 제 2 클락 신호를 제공하는 타이밍 컨트롤러를 포함하고,

상기 에미션 구동부는 상기 제 1 내지 제 n 에미션 신호들을 각각 생성하는 제 1 내지 제 n 에미션 구동 유닛들을 포함하며,

상기 제 1 내지 제 n 에미션 구동 유닛들 각각은

상기 제 1 클락 신호에 응답하여 입력 신호를 수신하고, 상기 입력 신호에 응답하여 상기 제 2 클락 신호를 수신하며, 제 1 내지 제 (n-1) 순차 입력 신호들 중 하나의 신호를 출력하는 입력 신호 생성 회로;

상기 제 1 클락 신호에 응답하여 상기 입력 신호를 수신하고, 상기 제 1 클락 신호 및 상기 제 2 클락 신호에 응답하여 상기 입력 신호를 반전하여 인버터 출력 신호를 생성하는 인버터 회로; 및

상기 인버터 출력 신호에 응답하여 상기 제 1 내지 제 n 에미션 신호들 중 하나의 신호로서 하이 레벨의 제 1 전압 또는 로우 레벨의 제 2 전압을 출력하는 출력 스위칭 회로를 포함하되,

상기 제 1 내지 제 n 에미션 구동 유닛들 각각은 동종의 단일형 트랜지스터들로 구현되는 것을 특징으로 하는 유기 발광 표시 장치.

**청구항 18**

제 17 항에 있어서, 상기 에미션 구동부가 엔모스(NMOS) 트랜지스터들로 구현될 때, 상기 제 1 내지 제 n 에미션 신호들이 로우 레벨인 구간은 상기 화소 회로들에서 데이터 프로그래밍이 수행되는 구간에 상응하고, 상기 제 1 내지 제 n 에미션 신호들이 하이 레벨인 구간은 상기 화소 회로들에 각각 포함되는 유기 발광 다이오드가 발광하는 구간에 상응하는 것을 특징으로 하는 유기 발광 표시 장치.

**청구항 19**

제 18 항에 있어서, 상기 에미션 구동부가 엔모스 트랜지스터들로 구현될 때, 상기 제 1 내지 제 n 에미션 신호들의 오프 드uty비(off duty ratio)를 제어함에 따라 상기 표시 패널이 블랙 이미지를 표시하는 구간의 길이가 제어되는 것을 특징으로 하는 유기 발광 표시 장치.

**청구항 20**

제 19 항에 있어서, 상기 에미션 구동부가 상기 화소 회로들에 순차적으로 상기 제 1 내지 제 n 에미션 신호들을 제공함에 따라, 상기 화소 회로들에 각각 포함되는 유기 발광 다이오드가 순차적으로 발광하는 것을 특징으로 하는 유기 발광 표시 장치.

**발명의 설명**

## 기술 분야

- [0001] 본 발명은 에미션 구동부(emission driver)에 관한 것으로, 보다 상세하게는 인버터 회로를 구비하여 n형 또는 p형의 단일형 트랜지스터로 구현되는 에미션 구동부에 관한 것이다.

## 배경 기술

- [0002] 유기 발광 표시 장치를 구동하는 방법 중 하나인 순차 발광 방식은 순차적으로 인가되는 스캔 신호에 따라 데이터를 스캔하고, 이어서 순차적으로 인가되는 에미션(emission) 신호에 따라 가장 먼저 스캔한 라인의 OLED 소자들부터 발광시키는 방식이다. 이때 에미션 신호가 인가되지 않는 구간의 길이, 즉 오프 뉴티비(off duty ratio)를 조절하여 연속적인 디밍(dimming) 효과를 얻을 수 있고, 더불어 블랙 띠를 삽입한 것과 같은 효과가 있으므로 모션 블러(motion blur)를 제거할 수 있다.

- [0003] 그런데 상기 에미션 신호를 제공하는 에미션 구동부를 씨모스(CMOS) 트랜지스터들로 구현할 경우 속도가 느리고 반전(inverted) 입력 신호가 추가적으로 필요하다는 문제가 있다.

## 발명의 내용

### 해결하려는 과제

- [0004] 본 발명의 일 목적은 인버터 회로를 구비하여 n형 또는 p형의 단일형 트랜지스터로 구현될 수 있는 에미션 구동 유닛을 제공하는 것이다.

- [0005] 본 발명의 다른 목적은 상기 에미션 구동 유닛을 구비하여 하나의 비반전 입력 신호로 제어 가능한 에미션 구동 부를 제공하는 것이다.

- [0006] 본 발명의 또 다른 목적은 상기 에미션 구동부를 구비하여 임펄스 구동이 가능한 유기 발광 표시 장치를 제공하는 것이다.

- [0007] 다만, 본 발명의 해결하고자 하는 과제는 이에 한정되는 것이 아니며, 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위에서 다양하게 확장될 수 있을 것이다.

### 과제의 해결 수단

- [0008] 본 발명의 일 목적을 달성하기 위하여, 본 발명의 실시예들에 따른 에미션 구동 유닛은 입력 신호 생성 회로, 인버터 회로 및 출력 스위칭 회로를 포함한다. 상기 입력 신호 생성 회로, 상기 인버터 회로 및 상기 출력 스위칭 회로는 동종의 단 일형 트랜지스터들로 구현된다.

- [0009] 상기 입력 신호 생성 회로는 제 1 클락 신호에 응답하여 프레임 라인 마크(Frame Line Mark; FLM) 신호를 수신하고, 상기 FLM 신호에 응답하여 제 2 클락 신호를 수신하며, 순차 입력 신호를 출력한다.

- [0010] 상기 인버터 회로는 상기 제 1 클락 신호에 응답하여 상기 FLM 신호를 수신하고, 상기 FLM 신호를 반전하여 인버터 출력 신호를 생성한다.

- [0011] 상기 출력 스위칭 회로는 상기 인버터 출력 신호에 응답하여 에미션(emission) 신호로서 하이 레벨의 제 1 전압 또는 로우 레벨의 제 2 전압을 출력한다.

- [0012] 일 실시예에 의하면, 상기 에미션 신호는 상기 FLM 신호가 반전된(inverted) 형태를 가질 수 있다.

- [0013] 일 실시예에 의하면, 상기 입력 신호 생성 회로, 상기 인버터 회로 및 상기 출력 스위칭 회로는 엔모스(N-channel Metal Oxide Semiconductor; NMOS) 트랜지스터들로 구현될 수 있다.

- [0014] 일 실시예에 의하면, 상기 입력 신호 생성 회로는 제 1 트랜지스터, 제 2 트랜지스터 및 제 1 커페시터를 포함할 수 있다. 상기 제 1 트랜지스터는 소스 전극, 상기 FLM 신호를 수신하는 드레인 전극, 및 상기 제 1 클락 신호를 수신하는 게이트 전극을 구비하고, 상기 제 1 클락 신호에 응답하여 상기 FLM 신호를 상기 드레인 전극에서 상기 소스 전극으로 인가할 수 있다. 상기 제 2 트랜지스터는 상기 제 2 클락 신호를 수신하는 드레인 전극, 상기 제 1 트랜지스터의 상기 소스 전극에 연결되는 게이트 전극, 및 상기 순차 입력 신호를 출력하는 소스 전극을 구비할 수 있다. 상기 제 1 커페시터는 상기 제 1 트랜지스터의 상기 소스 전극과 상기 제 2 트랜지스터의 상기 소스 전극 사이에 연결될 수 있다.

- [0015] 일 실시예에 의하면, 상기 인버터 회로는 제 3 내지 제 8 트랜지스터들, 제 2 커페시터 및 제 3 커페시터를 포함할 수 있다. 상기 제 3 트랜지스터는 상기 제 1 클락 신호에 응답하여 상기 FLM 신호를 제 1 노드로 제공할 수 있다. 상기 제 4 트랜지스터는 상기 제 1 노드에 연결되는 게이트 전극, 제 2 전압 공급단에 연결되는 소스 전극, 및 제 2 노드에 연결되는 드레인 전극을 구비할 수 있다. 상기 제 2 커페시터는 상기 제 1 노드와 상기 제 2 전압 공급단 사이에 연결될 수 있다. 상기 제 5 트랜지스터는 상기 입력 신호 생성 회로의 상기 제 2 트랜지스터의 상기 소스 전극에 연결되는 드레인 전극, 상기 제 2 전압 공급단에 연결되는 소스 전극, 및 상기 제 2 노드에 연결되는 게이트 전극을 구비할 수 있다. 상기 제 6 트랜지스터는 상기 제 2 노드에 연결되는 소스 전극, 제 3 노드에 연결되는 드레인 전극, 및 상기 제 2 클락 신호를 수신하는 게이트 전극을 구비할 수 있다. 상기 제 7 트랜지스터는 상기 제 3 노드에 연결되는 소스 전극, 제 1 전압 공급단에 연결되는 드레인 전극, 및 상기 제 1 클락 신호를 수신하는 게이트 전극을 구비할 수 있다. 상기 제 8 트랜지스터는 상기 제 3 노드에 연결되는 게이트 전극, 상기 제 2 클락 신호를 수신하는 드레인 전극, 및 제 4 노드에 연결되는 소스 전극을 구비할 수 있다. 상기 제 3 커페시터는 상기 제 3 노드와 상기 제 4 노드 사이에 연결되는 제 3 커페시터를 포함할 수 있다.

- [0016] 일 실시예에 의하면, 상기 출력 스위칭 회로는 출력단, 제 9 트랜지스터 및 제 10 트랜지스터를 포함할 수 있다. 상기 출력단은 상기 에미션 신호를 출력할 수 있다. 상기 제 9 트랜지스터는 상기 제 1 노드에 연결되는 게이트 전극, 상기 제 2 전압 공급단에 연결되는 소스 전극, 및 상기 출력단에 연결되는 드레인 전극을 구비할 수 있다. 상기 제 10 트랜지스터는 상기 제 2 노드에 연결되는 게이트 전극, 상기 출력단에 연결되는 소스 전극, 및 상기 제 1 전압 공급단에 연결되는 드레인 전극을 구비할 수 있다.

- [0017] 일 실시예에 의하면, 상기 에미션 구동 유닛은, 상기 제 1 전압 공급단과 상기 제 1 노드 사이에 연결되는 제 1 출력 제어 트랜지스터 및 상기 제 2 전압 공급단과 상기 제 2 노드 사이에 연결되는 제 2 출력 제어 트랜지스터를 구비하는 출력 제어 회로를 더 포함할 수 있다.

- [0018] 일 실시예에 의하면, 상기 출력 제어 회로에 하이 레벨의 출력 제어 신호가 인가되는 경우, 상기 에미션 신호로 상기 제 2 전압이 DC 레벨로 출력될 수 있다.

- [0019] 일 실시예에 의하면, 상기 입력 신호 생성 회로, 상기 인버터 회로 및 상기 출력 스위칭 회로는 퍼모스(P-channel Metal Oxide Semiconductor; PMOS) 트랜지스터들로 구현될 수 있다.

- [0020] 일 실시예에 의하면, 상기 에미션 구동 유닛이 퍼모스로 구현될 때, 상기 에미션 구동 유닛은 상기 인버터 회로에 연결되고 출력 제어 신호에 의해 제어되는 출력 제어 회로를 더 포함할 수 있다. 상기 출력 제어 회로에 로우 레벨의 상기 출력 제어 신호가 인가되는 경우, 상기 에미션 신호로 상기 제 1 전압이 DC 레벨로 출력될 수 있다.

- [0021] 본 발명의 다른 목적을 달성하기 위하여, 본 발명의 실시예들에 따른 에미션 구동부는, 프레임 라인 마크(Frame Line Mark; FLM) 신호를 입력 신호로서 수신하고, 제 1 클락 신호 및 제 2 클락 신호에 의해 제어되며, 제 1 에미션(emission) 신호 및 제 1 순차 입력 신호를 출력하는 제 1 에미션 구동 유닛, 및 상기 제 1 클락 신호 및 상기 제 2 클락 신호에 의해 각각 제어되고, 제 2 내지 제 n(단, n은 3이상의 정수) 에미션 신호들을 각각 출력하는 제 2 내지 제 n 에미션 구동 유닛들을 포함한다.

- [0022] 상기 제 1 내지 제 n 에미션 구동 유닛들 각각은, 상기 제 1 클락 신호에 응답하여 상기 입력 신호를 수신하고, 상기 입력 신호에 응답하여 상기 제 2 클락 신호를 수신하며, 상기 제 1 내지 제 (n-1) 순차 입력 신호들 중 하나의 신호를 출력하는 입력 신호 생성 회로, 상기 제 1 클락 신호에 응답하여 상기 입력 신호를 수신하고, 상기 입력 신호를 반전하여 인버터 출력 신호를 생성하는 인버터 회로, 및 상기 인버터 출력 신호에 응답하여 상기 제 1 내지 제 n 에미션 신호들 중 하나의 신호로서 하이 레벨의 제 1 전압 또는 로우 레벨의 제 2 전압을 출력하는 출력 스위칭 회로를 포함한다.

- [0023] 일 실시예에 의하면, 상기 제 1 내지 제 n 에미션 구동 유닛들 각각은 동종의 단일형 트랜지스터들로 구현될 수 있다.

- [0024] 일 실시예에 의하면, 상기 제 1 내지 제 n 에미션 신호들은 상기 FLM 신호가 반전된(inverted) 형태를 가질 수 있다.

- [0025] 본 발명의 또 다른 목적을 달성하기 위하여, 본 발명의 실시예들에 따른 유기 발광 표시 장치는, 유기 발광 다이오드를 각각 구비하는 복수의 화소 회로들을 포함하고 제 1 전원 전압 및 제 2 전원 전압을 수신하는 표시 패

널, 제 1 내지 제 n(단, n은 3 이상의 정수) 스캔 라인들을 통해 상기 화소 회로들에 순차적으로 제 1 내지 제 n 스캔 신호들을 제공하는 스캔 구동부, 상기 제 1 내지 제 n 스캔 신호들에 따라 복수의 데이터 라인들을 통해 상기 화소 회로들에 데이터 전압을 제공하는 데이터 구동부, 제 1 내지 제 n 에미션(emission) 제어 라인들을 통해 상기 화소 회로들에 순차적으로 제 1 내지 제 n 에미션 신호들을 제공하는 에미션 구동부, 및 상기 스캔 구동부, 상기 데이터 구동부 및 상기 에미션 구동부에 제 1 클락 신호 및 제 2 클락 신호를 제공하는 타이밍 컨트롤러를 포함한다.

[0026] 상기 에미션 구동부는 상기 제 1 내지 제 n 에미션 신호들을 각각 생성하는 제 1 내지 제 n 에미션 구동 유닛들을 포함한다. 상기 제 1 내지 제 n 에미션 구동 유닛들 각각은 상기 제 1 클락 신호 및 상기 제 2 클락 신호에 의해 제어되고, 프레임 라인 마크(Frame Line Mark; FLM) 신호 또는 제 1 내지 제 (n-1) 순차 입력 신호들을 입력 신호로서 수신하며, 동종의 단일형 트랜지스터들로 구현된다.

[0027] 일 실시예에 의하면, 상기 에미션 구동부가 엔모스(NMOS) 트랜지스터들로 구현될 때, 상기 제 1 내지 제 n 에미션 신호들이 로우 레벨인 구간은 상기 화소 회로들에서 데이터 프로그래밍이 수행되는 구간에 상응하고, 상기 제 1 내지 제 n 에미션 신호들이 하이 레벨인 구간은 상기 화소 회로들에 각각 포함되는 유기 발광 다이오드가 발광하는 구간에 상응할 수 있다.

[0028] 일 실시예에 의하면, 상기 에미션 구동부가 엔모스 트랜지스터들로 구현될 때, 상기 제 1 내지 제 n 에미션 신호들의 오프 듀티비(off duty ratio)를 제어함에 따라 상기 표시 패널이 블랙 이미지를 표시하는 구간의 길이가 제어될 수 있다.

[0029] 일 실시예에 의하면, 상기 에미션 구동부가 상기 화소 회로들에 순차적으로 상기 제 1 내지 제 n 에미션 신호들을 제공함에 따라, 상기 화소 회로들에 각각 포함되는 유기 발광 다이오드가 순차적으로 발광할 수 있다.

### 발명의 효과

[0030] 본 발명의 실시예들에 따른 에미션 구동 유닛은 내부에 인버터 회로를 구비함으로써 n형 또는 p형의 단일형 트랜지스터들로 구현될 수 있다.

[0031] 본 발명의 실시예들에 따른 에미션 구동부는 하나의 비반전 입력 신호로 제어될 수 있으며, 상기 입력 신호의 펄스 폭을 제어하여 에미션 신호의 펄스 폭을 조절할 수 있다.

[0032] 본 발명의 실시예들에 따른 유기 발광 표시 장치는 높은 속도로 임펄스 구동을 수행할 수 있다.

[0033] 다만, 본 발명의 효과는 이에 한정되는 것이 아니며, 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위에서 다양하게 확장될 수 있을 것이다.

### 도면의 간단한 설명

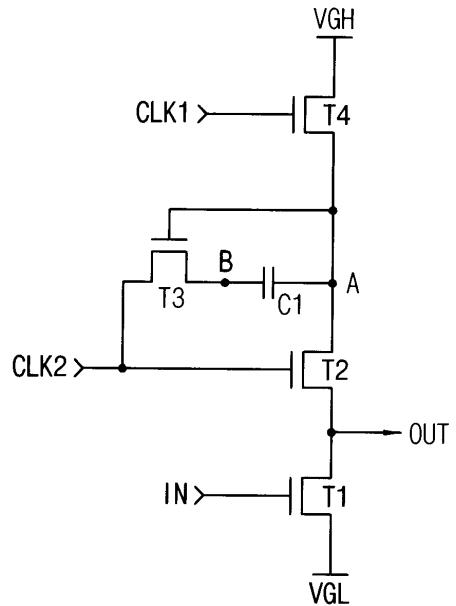

[0034] 도 1은 본 발명의 일 실시예에 따른 에미션 구동 유닛을 나타내는 회로도이다.

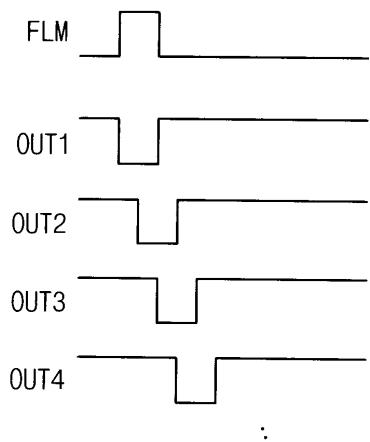

도 2a는 본 발명의 일 실시예에 따른 에미션 구동부를 나타내는 블록도이다.

도 2b는 도 2a의 에미션 구동부의 동작을 나타내는 타이밍도이다.

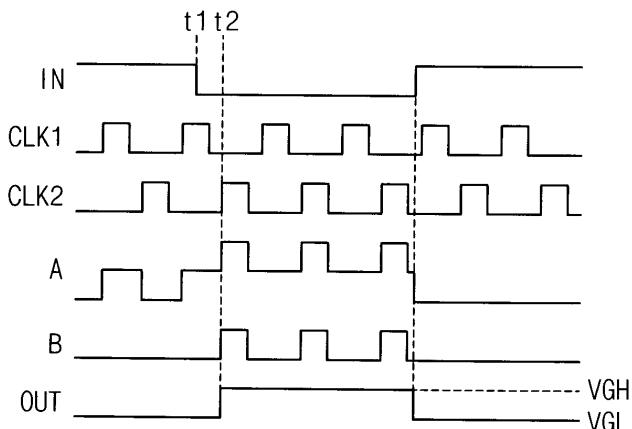

도 3a은 도 1의 에미션 구동 유닛에 포함되는 인버터 회로를 나타내는 회로도이다.

도 3b는 도 3a의 인버터 회로의 동작을 나타내는 타이밍도이다.

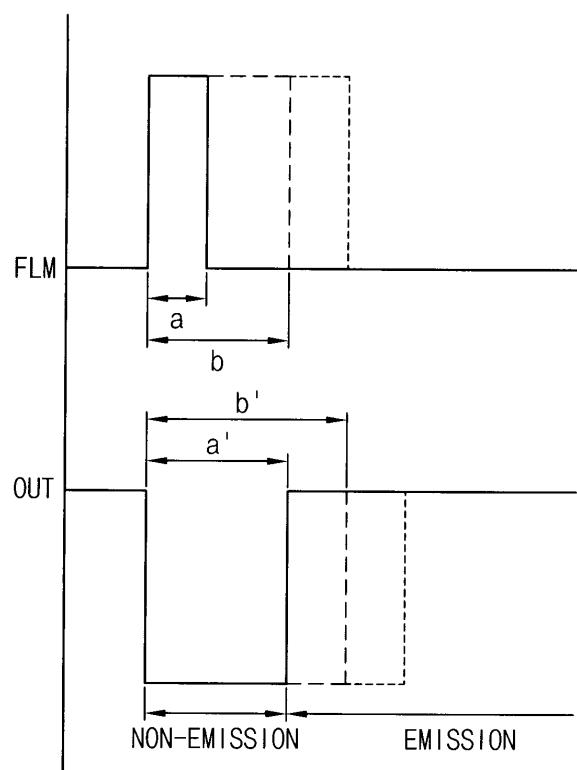

도 4는 도 1의 에미션 구동 유닛에서 입력과 출력의 관계를 나타내는 도면이다.

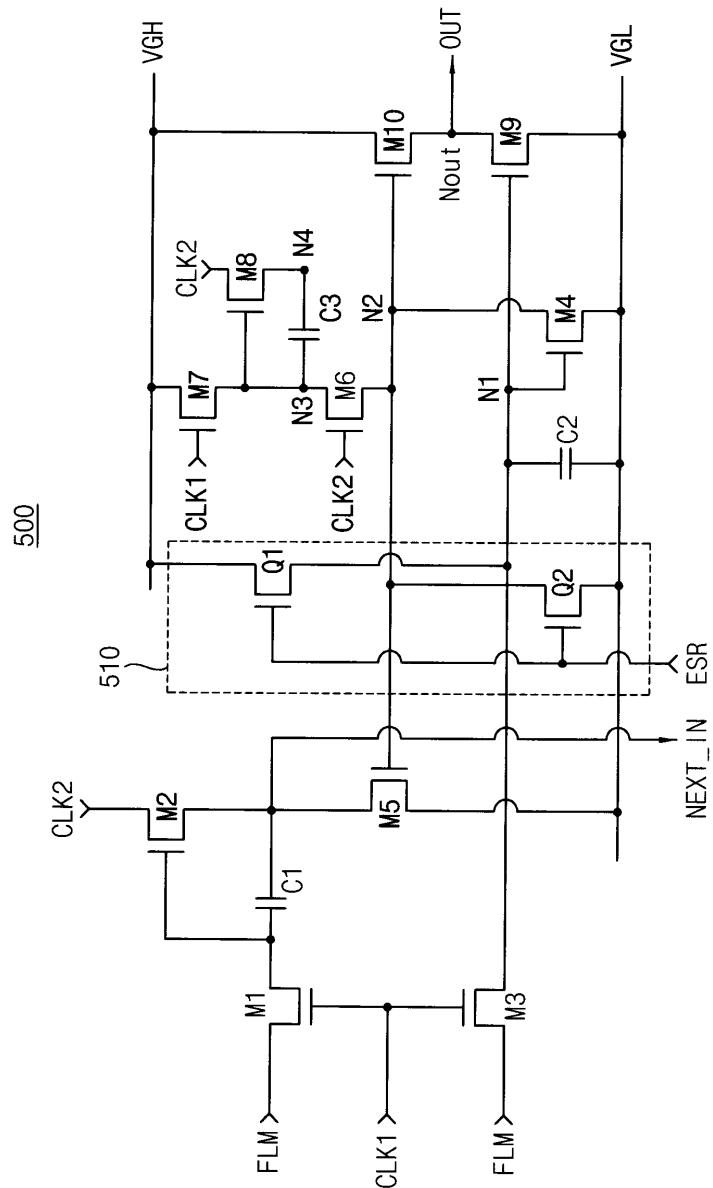

도 5는 본 발명의 다른 실시예에 따른 에미션 구동 유닛을 나타내는 회로도이다.

도 6은 본 발명의 또 다른 실시예에 따른 에미션 구동 유닛을 나타내는 회로도이다.

도 7은 도 6의 에미션 구동 유닛에 포함되는 인버터 회로를 나타내는 회로도이다.

도 8은 본 발명의 또 다른 실시예에 따른 에미션 구동 유닛을 나타내는 회로도이다.

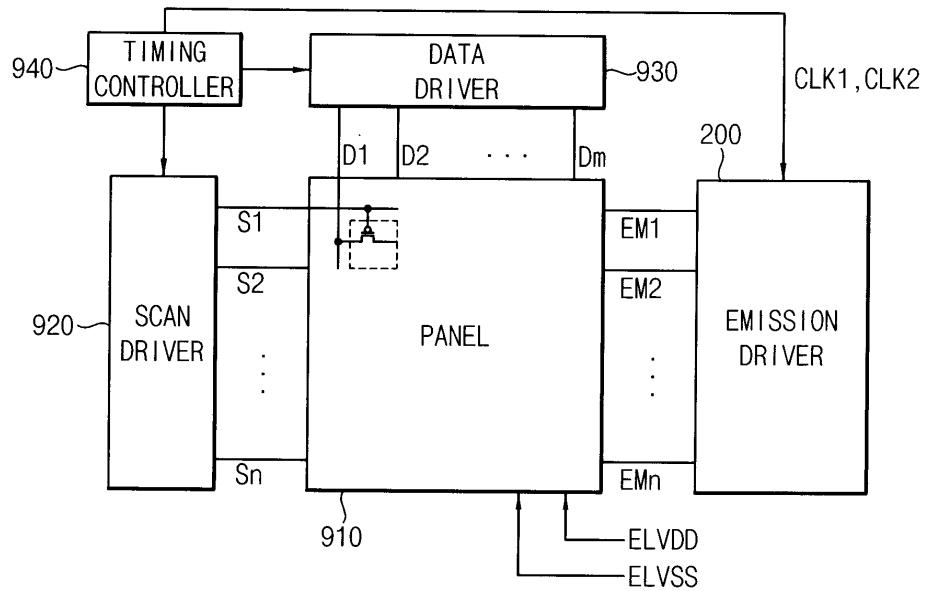

도 9는 본 발명의 일 실시예에 따른 유기 발광 표시 장치를 나타내는 블록도이다.

도 10은 도 9의 유기 발광 표시 장치를 포함하는 전자 기기를 나타내는 블록도이다.

## 발명을 실시하기 위한 구체적인 내용

- [0035] 본문에 개시되어 있는 본 발명의 실시예들에 대해서, 특정한 구조적 내지 기능적 설명들은 단지 본 발명의 실시예를 설명하기 위한 목적으로 예시된 것으로, 본 발명의 실시예들은 다양한 형태로 실시될 수 있으며 본문에 설명된 실시예들에 한정되는 것으로 해석되어서는 아니 된다.

- [0036] 본 발명은 다양한 변경을 가할 수 있고 여러 가지 형태를 가질 수 있는바, 특정 실시예들을 도면에 예시하고 본문에 상세하게 설명하고자 한다. 그러나 이는 본 발명을 특정한 개시 형태에 대해 한정하려는 것이 아니며, 본 발명의 사상 및 기술 범위에 포함되는 모든 변경, 균등물 내지 대체물을 포함하는 것으로 이해되어야 한다.

- [0037] 제1, 제2 등의 용어는 다양한 구성요소들을 설명하는데 사용될 수 있지만, 상기 구성요소들은 상기 용어들에 의해 한정되어서는 안 된다. 상기 용어들은 하나의 구성요소를 다른 구성요소로부터 구별하는 목적으로 사용될 수 있다. 예를 들어, 본 발명의 권리 범위로부터 이탈되지 않은 채 제1 구성요소는 제2 구성요소로 명명될 수 있고, 유사하게 제2 구성요소도 제1 구성요소로 명명될 수 있다.

- [0038] 어떤 구성요소가 다른 구성요소에 "연결되어" 있다거나 "접속되어" 있다고 언급된 때에는, 그 다른 구성요소에 직접적으로 연결되어 있거나 또는 접속되어 있을 수도 있지만, 중간에 다른 구성요소가 존재할 수도 있다고 이해되어야 할 것이다. 반면에, 어떤 구성요소가 다른 구성요소에 "직접 연결되어" 있다거나 "직접 접속되어" 있다고 언급된 때에는, 중간에 다른 구성요소가 존재하지 않는 것으로 이해되어야 할 것이다. 구성요소들 간의 관계를 설명하는 다른 표현들, 즉 "~사이에"와 "바로 ~사이에" 또는 "~에 이웃하는"과 "~에 직접 이웃하는" 등도 마찬가지로 해석되어야 한다.

- [0039] 본 출원에서 사용한 용어는 단지 특정한 실시예를 설명하기 위해 사용된 것으로, 본 발명을 한정하려는 의도가 아니다. 단수의 표현은 문맥상 명백하게 다르게 뜻하지 않는 한, 복수의 표현을 포함한다. 본 출원에서, "포함하다" 또는 "가지다" 등의 용어는 실시된 특징, 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것이 존재함을 지정하려는 것이지, 하나 또는 그 이상의 다른 특징들이나 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것들의 존재 또는 부가 가능성 미리 배제하지 않는 것으로 이해되어야 한다.

- [0040] 다르게 정의되지 않는 한, 기술적이거나 과학적인 용어를 포함해서 여기서 사용되는 모든 용어들은 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에 의해 일반적으로 이해되는 것과 동일한 의미이다. 일반적으로 사용되는 사전에 정의되어 있는 것과 같은 용어들은 관련 기술의 문맥상 가지는 의미와 일치하는 의미인 것으로 해석되어야 하며, 본 출원에서 명백하게 정의하지 않는 한, 이상적이거나 과도하게 형식적인 의미로 해석되지 않는다.

- [0041] 이하, 첨부한 도면들을 참조하여, 본 발명의 바람직한 실시예를 보다 상세하게 설명하고자 한다. 도면상의 동일한 구성요소에 대해서는 동일한 참조부호를 사용하고 동일한 구성요소에 대해서 중복된 설명은 생략한다.

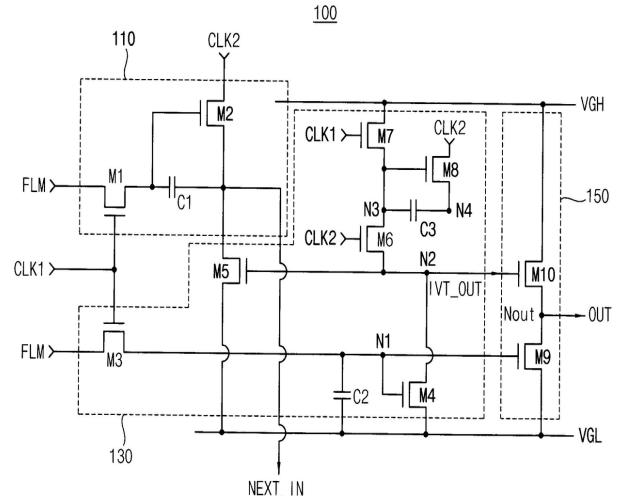

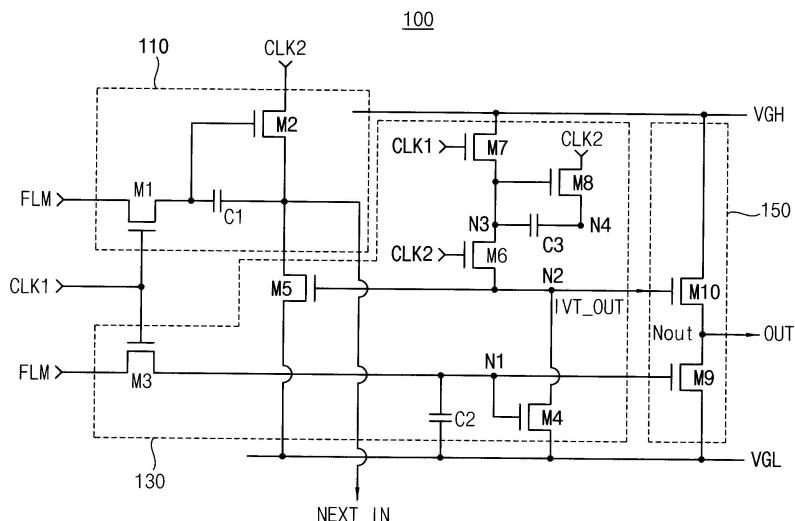

- [0042] 도 1은 본 발명의 일 실시예에 따른 에미션 구동 유닛을 나타내는 회로도이다.

- [0043] 일 실시예에서, 에미션 구동 유닛(100)은 엔모스(NMOS) 트랜지스터들로만 구현될 수 있다. 다른 실시예에서, 에미션 구동 유닛(100)은 피모스(PMOS) 트랜지스터들로만 구현될 수 있다. 종래의 에미션 구동부는 p-채널 트랜지스터와 n-채널 트랜지스터를 모두 구비하는 씨모스(CMOS) 트랜지스터로 구현된다. 따라서, 소비 전력은 작지만 동작 속도가 느리다는 단점이 있고, 특히 반전 입력 신호가 추가적으로 필요하게 된다는 문제가 있다. 본 발명의 실시예에 따른 에미션 구동부는 내부에 인버터 회로를 구비함으로써 n형 또는 p형의 단일형 트랜지스터로 구현될 수 있고, 하나의 비반전 입력 신호와 두 개의 클럭 신호만으로 제어될 수 있다.

- [0044] 도 1은 엔모스 트랜지스터로 구현된 에미션 구동 유닛(100)을 나타낸다. 이하, 엔모스 트랜지스터로 구현된 에미션 구동 유닛(100)의 구성 및 동작을 설명한다.

- [0045] 도 1을 참조하면, 에미션 구동 유닛(100)은 입력 신호 생성 회로(110), 인버터 회로(130) 및 출력 스위칭 회로(150)를 포함한다.

- [0046] 입력 신호 생성 회로(110)는 제 1 클락 신호(CLK1)에 응답하여 프레임 라인 마크(Frame Line Mark; FLM) 신호(FLM)를 수신하고, FLM 신호(FLM)에 응답하여 제 2 클락 신호(CLK2)를 수신하며, 순차 입력 신호(NEXT\_IN)를 출력한다. 일 실시예에서, 입력 신호 생성 회로(110)는 제 1 트랜지스터(M1), 제 2 트랜지스터(M2) 및 제 1 커판시터(C1)를 포함할 수 있다. 제 1 트랜지스터(M1)는 소스 전극, FLM 신호(FLM)를 수신하는 드레인 전극, 및 제 1 클락 신호(CLK1)에 응답하여 FLM 신호(FLM)를 상기 소스 전극으로 인가하는 게이트 전극을 구비한다. 제 2 트

랜지스터(M2)는 제 2 클락 신호(CLK2)를 수신하는 드레인 전극, 제 1 트랜지스터(M1)의 소스 전극에 연결되는 게이트 전극, 및 순차 입력 신호(NEXT\_IN)를 출력하는 소스 전극을 구비한다. 제 1 커패시터(C1)는 제 1 트랜지스터(M1)의 소스 전극과 제 2 트랜지스터(M2)의 소스 전극 사이에 연결된다.

[0047] 인버터 회로(130)는 제 1 클락 신호(CLK1)에 응답하여 FLM 신호(FLM)를 수신하고, FLM 신호(FLM)를 반전하여 인버터 출력 신호(IVT\_OUT)를 생성한다. 일 실시예에서, 인버터 회로(130)는 제 3 내지 제 8 트랜지스터들(M3~M8) 및 제 1 내지 제 3 커패시터들(C1~C3)을 포함할 수 있다.

[0048] 인버터 회로(130)에서, 제 3 트랜지스터(M3)는 제 1 클락 신호(CLK1)에 응답하여 FLM 신호(FLM)를 제 1 노드(N1)로 제공한다. 제 4 트랜지스터(M4)는 제 1 노드(N1)에 연결되는 게이트 전극, 제 2 전압 공급단(VGL)에 연결되는 소스 전극, 및 제 2 노드(N2)에 연결되는 드레인 전극을 구비한다. 제 2 커패시터(C2)는 제 1 노드(N1)와 제 2 전압 공급단(VGL) 사이에 연결된다. 제 5 트랜지스터(M5)는 입력 신호 생성 회로(110)의 제 2 트랜지스터(M2)의 소스 전극에 연결되는 드레인 전극, 제 2 전압 공급단(VGL)에 연결되는 소스 전극, 및 제 2 노드(N2)에 연결되는 게이트 전극을 구비한다. 제 6 트랜지스터(M6)는 제 2 노드(N2)에 연결되는 소스 전극, 제 3 노드(N3)에 연결되는 드레인 전극, 및 제 2 클락 신호(CLK2)를 수신하는 게이트 전극을 구비한다. 제 7 트랜지스터(M7)는 제 3 노드(N3)에 연결되는 소스 전극, 제 1 전압 공급단(VGH)에 연결되는 드레인 전극, 및 제 1 클락 신호(CLK1)를 수신하는 게이트 전극을 구비한다. 제 8 트랜지스터(M8)는 제 3 노드(N3)에 연결되는 게이트 전극, 제 2 클락 신호(CLK2)를 수신하는 드레인 전극, 및 제 4 노드(N4)에 연결되는 소스 전극을 구비한다. 제 3 커패시터(C3)는 제 3 노드(N3)와 제 4 노드(N4) 사이에 연결된다.

[0049] 인버터 회로(130)는 주기적으로 인가되는 클럭 신호에 응답하여 입력 신호를 반전하여 출력하는 기능을 수행한다. 그러므로, 인버터 회로(130)는 제 1 및 제 2 클락 신호들(CLK1, CLK2)에 응답하여 FLM 신호(FLM)를 반전함으로써 인버터 출력 신호(IVT\_OUT)를 생성할 수 있다. 인버터 회로(130)의 구체적인 동작에 관하여는 도 3a 및 도 3b를 참조하여 상세히 후술한다.

[0050] 출력 스위칭 회로(150)는 인버터 출력 신호(IVT\_OUT)에 응답하여 에미션(emission) 신호(OUT)로서 하이 레벨의 제 1 전압(VGH) 또는 로우 레벨의 제 2 전압(VGL)을 출력한다. 이에 따라, 에미션 구동 유닛(100)의 출력(OUT)은 펄스 형태를 가질 수 있다. 일 실시예에서, 출력 스위칭 회로(150)는 출력단(Nout), 제 9 트랜지스터(M9) 및 제 10 트랜지스터(M10)를 포함할 수 있다. 출력단(Nout)은 에미션 신호(OUT)를 출력한다. 제 9 트랜지스터(M9)는 제 1 노드(N1)에 연결되는 게이트 전극, 제 2 전압 공급단(VGL)에 연결되는 소스 전극, 및 출력단(Nout)에 연결되는 드레인 전극을 구비한다. 제 10 트랜지스터(M10)는 제 2 노드(N2)에 연결되는 게이트 전극, 출력단(Nout)에 연결되는 소스 전극, 및 제 1 전압 공급단(VGH)에 연결되는 드레인 전극을 구비한다.

[0051] 에미션 구동 유닛(100)에서, 에미션 신호(OUT)는 FLM 신호(FLM)가 반전된(inverted) 형태를 가질 수 있다. 일 실시예에서, FLM 신호(FLM)가 로우 레벨에서 하이 레벨로 상승하는 1회의 하이-펄스(hight-pulse)를 갖는 경우, 에미션 신호(OUT)는 하이 레벨에서 로우 레벨로 하강하는 1회의 로우-펄스(low-pulse)를 갖는다. 에미션 구동 유닛(100)에 따라화소 회로에 포함되는 에미션 트랜지스터도 엔모스 트랜지스터로 구현되므로, 에미션 신호(OUT)가 로우 레벨인 구간은 상기 에미션 트랜지스터가 턴-오프(turn-off)되고, 에미션 신호(OUT)가 하이 레벨인 구간은 상기 에미션 트랜지스터가 턴-온(turn-on)되어 이에 연결되는 유기 발광 다이오드가 발광하게 된다.

[0052] 일 실시예에서, 제 1 전압(OUT)은 엔모스 트랜지스터를 턴-온시킬 만큼 충분히 높은 전압 레벨을 가지고, 제 2 전압(OUT)은 엔모스 트랜지스터를 턴-오프시킬 만큼 충분히 낮은 전압 레벨을 가질 수 있다.

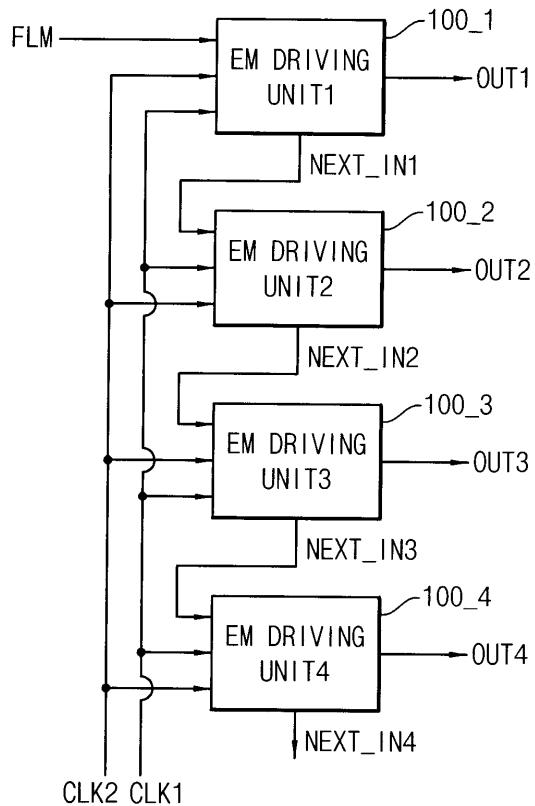

[0053] 도 2a는 본 발명의 일 실시예에 따른 에미션 구동부를 나타내는 블록도이다.

[0054] 도 2a를 참조하면, 에미션 구동부(200)는 표시 장치의 스캔 라인 수에 상응하는 복수의 에미션 구동 유닛들(100\_1 내지 100\_4)을 포함한다. 예를 들어, n개의 스캔 라인이 표시 패널과 스캔 구동부 사이에 존재하는 경우, n개의 에미션 구동 유닛들(100\_1 내지 100\_4)이 에미션 구동부(200)에 포함될 수 있다. 도 2a에는 네 개의 에미션 구동 유닛들(100\_1 내지 100\_4)만이 도시되어 있으나, 실시예에 따라 다양한 수의 에미션 구동 유닛들(100\_1 내지 100\_4)이 에미션 구동부(200)에 포함될 수 있다. 이하, 네 개의 에미션 구동 유닛들(100\_1 내지 100\_4)을 이용하여 에미션 구동부(200)의 동작을 설명한다.

[0055] 제 1 에미션 구동 유닛(100\_1)은 FLM 신호(FLM)를 입력 신호로서 수신하고, 제 1 클락 신호(CLK1) 및 제 2 클락 신호(CLK2)에 의해 제어되며, 제 1 에미션 신호(OUT1) 및 제 1 순차 입력 신호(NEXT\_IN1)를 출력한다. 제 1 에미션 신호(OUT1)는 제 1 에미션 라인을 통해 표시 패널에 인가되고, 제 1 순차 입력 신호(NEXT\_IN1)는 다음 단(100\_2)에 입력 신호로서 인가된다. 다시 말해, 이전 단에서 출력되는 순차 입력 신호가 인접한 다음 단에서 입

력 신호로 사용될 수 있다. 이에 따라, 제 1 에미션 구동 유닛(100\_1)에만 별도의 입력 신호(FLM)를 인가하면, 각각의 에미션 구동 유닛(100\_1 내지 100\_4)에서 생성된 순차 입력 신호(NEXT\_IN1 내지 NEXT\_IN3)가 다음 단의 에미션 구동 유닛(100\_1 내지 100\_4)에 순차적으로 인가될 수 있다.

[0056] 각각의 에미션 구동 유닛(100\_1 내지 100\_4)은 입력 신호 생성 회로, 인버터 회로 및 출력 스위칭 회로를 포함할 수 있다. 상기 입력 신호 생성 회로는 제 1 클락 신호(CLK1)에 응답하여 입력 신호(FLM, NEXT\_IN1 내지 NEXT\_IN3)를 수신하고, 입력 신호(FLM, NEXT\_IN1 내지 NEXT\_IN3)에 응답하여 제 2 클락 신호(CLK2)를 수신하며, 제 1 내지 제 4 순차 입력 신호들(NEXT\_IN1 내지 NEXT\_IN4) 중 하나의 신호를 출력한다. 상기 인버터 회로는 제 1 클락 신호(CLK1)에 응답하여 입력 신호(FLM, NEXT\_IN1 내지 NEXT\_IN3)를 수신하고, 입력 신호(FLM, NEXT\_IN1 내지 NEXT\_IN3)를 반전하여 인버터 출력 신호를 생성한다. 상기 출력 스위칭 회로는 상기 인버터 출력 신호에 응답하여 제 1 내지 제 4 에미션 신호들(OUT1 내지 OUT4) 중 하나의 신호로서 하이 레벨의 제 1 전압 또는 로우 레벨의 제 2 전압을 출력한다. 이와 같이 본 발명의 실시예들에 따른 에미션 구동부(200)는 별도의 반전 신호 없이 세 개의 신호(FLM, CLK1, CLK2)만으로 제어될 수 있다. 일 실시예에서, 제 1 내지 제 4 에미션 구동 유닛들(100\_1 내지 100\_4) 각각은 동종의 단일형 트랜지스터로 구현될 수 있다.

[0057] 도 2b는 도 2a의 에미션 구동부의 동작을 나타내는 타이밍도이다.

[0058] 도 2a 및 도 2b를 참조하면, 처음 FLM 신호(FLM)가 제 1 에미션 구동 유닛(100\_1)에 인가되고, 이후 제 1 내지 제 3 순차 입력 신호들(NEXT\_IN1, NEXT\_IN2, NEXT\_IN3)이 순차적으로 인가됨에 따라 제 1 내지 제 4 에미션 신호들(OUT1 내지 OUT4)이 순차적으로 출력된다. 즉, 에미션 신호(OUT1 내지 OUT4)의 로우-펄스가 일정한 시간 간격으로 시프트되면서 생성된다. 이에 따라, 에미션 신호(OUT1 내지 OUT4)를 수신하는 표시 패널은 라인 별로 순차적으로 발광할 수 있다. 일 실시예에서, 제 1 내지 제 4 에미션 신호들(OUT1 내지 OUT4)은 FLM 신호(FLM)가 반전된 형태를 가질 수 있다.

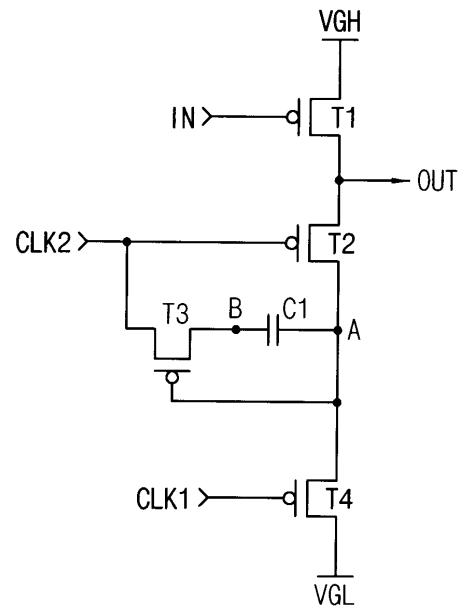

[0059] 도 3a은 도 1의 에미션 구동 유닛에 포함되는 인버터 회로를 나타내는 회로도이고, 도 3b는 도 3a의 인버터 회로의 동작을 나타내는 타이밍도이다.

[0060] 도 3a의 인버터 회로(300)는 도 1의 인버터 회로(130)에 실질적으로 상응한다. 구체적으로, 인버터 회로(300)의 입력 신호(IN), 출력 신호(OUT), 노드(A)는 각각 인버터 회로(130)의 FLM 신호(FLM), 인버터 출력 신호(IVT\_OUT), 제 3 노드(N3)에 상응한다. 도 3a에 도시된 바와 같이, 인버터 회로(300)는 엔모스 트랜지스터들로 구현된다. 이하 도 3a 및 도 3b를 참조하여 인버터 회로(300)의 동작을 설명한다.

[0061] 제 1 트랜지스터(T1)는 하이 레벨의 입력 신호(IN)에 응답하여 로우 레벨인 제 2 전압(VGL)을 출력 신호(OUT)로 출력한다. 다시 말해, 입력 신호(IN)가 하이 레벨일 때, 제 1 트랜지스터(T1)가 턴-온되고 제 2 전압(VGL)이 출력 신호(OUT)에 인가된다. 입력 신호(IN)가 로우 레벨인 경우, 제 1 트랜지스터(T1)는 턴-오프되고 제 1 클락 신호(CLK1) 및 제 2 클락 신호(CLK2)에 따라 하이 레벨인 제 1 전압(VGH)이 출력 신호(OUT)로서 출력된다. 구체적으로, 입력 신호(IN)가 하강하는 에지(edge; t1) 이후 처음으로 제 2 클락 신호(CLK2)가 상승하는 에지(t2)에서 출력 신호(OUT)도 하이 레벨(VGH)로 상승된다. 다시 말해, 지점(t2)에서 출력 신호(OUT)는 제 2 클락 신호(CLK2)에 동기화되어 하이 레벨(VGH)로 상승된다. 이러한 방식으로, 입력 신호(IN)는 인버터 회로(300)를 통과하면서 반전되어 출력 신호(OUT)로 출력될 수 있다.

[0062] 도 4는 도 1의 에미션 구동 유닛에서 입력과 출력의 관계를 나타내는 도면이다.

[0063] 도 1 및 도 4를 참조하면, 입력 신호(FLM)와 출력 신호(OUT)는 서로반전된 형태임을 알 수 있다. 입력 신호(FLM)는 도 1의 FLM 신호(FLM)에 상응하고, 출력 신호(OUT)는 도 1의 에미션 신호(OUT)에 상응할 수 있다. 일 실시예에서, 표시 장치가 엔모스 트랜지스터로 구현되는 경우, 하이 레벨의 에미션 신호가 인가될 때 상응하는 유기 발광 다이오드가 발광할 수 있다. 반대로, 로우 레벨의 에미션 신호가 인가되는 구간은 비 발광 구간에 해당할 수 있다.

[0064] 도 4에 도시된 바와 같이, 입력 신호(FLM)의 하이 레벨 펄스의 폭은 출력 신호(FLM)의 로우 레벨 펄스의 폭과 비례할 수 있다. 예를 들어, 입력 신호(FLM)의 하이 레벨 펄스의 폭이 a에서 b로 증가할 때, 출력 신호(OUT)의 로우레벨의 폭도 a'에서 b'로 증가한다. 이에 따라, 비 발광 구간(NON-EMISSION)의 길이도 증가할 수 있다. 본 발명의 실시예들에 따르면, 에미션 구동 유닛(100)에 입력되는 FLM 신호(FLM)의 하이 레벨 펄스의 폭을 조절하여 비 발광 구간(NON-EMISSION)의 길이를 조절할 수 있다. 비 발광 구간(NON-EMISSION) 동안 화소 회로에서 데이터 스캔 및 구동 트랜지스터의 문턱 전압 보상 등이 수행되므로 비 발광 구간(NON-EMISSION)의 길이를 제어함으로써 데이터 스캔 및 구동 트랜지스터의 문턱 전압 보상을 수행하기 위한 시간을 충분히 확보할 수 있다.

- [0065] 또한, 비 발광 구간(NON-EMISSION) 동안 유기 발광 다이오드가 발광하지 않으므로 비 발광 구간(NON-EMISSION)의 길이를 조절하여 연속적인 디밍(dimming) 효과를 얻을 수 있고, 블랙 띠를 삽입하는 효과가 있으므로 모션 블러(motion blur)를 제거할 수 있다. 따라서, 엔모스 트랜지스터로 구현된 에미션 구동 유닛(100)을 이용하여 임펄스 구동을 수행할 수 있다.

- [0066] 도 5는 본 발명의 다른 실시예에 따른 에미션 구동 유닛을 나타내는 회로도이다.

- [0067] 도 5를 참조하면, 도 5의 에미션 구동 유닛(500)은 출력 제어 회로(510)를 제외하고, 도 1의 에미션 구동 유닛(100)과 실질적으로 동일한 구성을 갖는다. 이하 도 1의 에미션 구동 유닛(100)과 중복되는 설명은 생략하고, 출력 제어 회로(510)의 기능을 중심으로 에미션 구동 유닛(500)의 동작을 설명한다.

- [0068] 출력 제어 회로(510)는 인버터 회로 내부에 연결되고 출력 제어 신호(ESR)에 의해 제어된다. 출력 제어 회로(510)는 제 1 출력 제어 트랜지스터(Q1) 및 제 2 출력 제어 트랜지스터(Q2)를 포함할 수 있다.

- [0069] 일 실시예에서, 출력 제어 회로(510)에 하이 레벨의 출력 제어 신호(ESR)가 인가되는 경우, 에미션 신호(OUT)로 제 2 전압(VGL)이 DC 레벨로 출력된다. 구체적으로, 하이 레벨의 출력 제어 신호(ESR)가 인가되면 제 1 및 제 2 출력 제어 트랜지스터들(Q1, Q2)은 턴-온된다. 그러면 하이 레벨인 제 1 전압(VGH)이 제 9 트랜지스터(M9)의 게이트 전극에 인가되어 제 9 트랜지스터(M9)가 턴-온되고, 로우 레벨인 제 2 전압(VGL)이 제 10 트랜지스터(M10)의 게이트 전극에 인가되어 제 10 트랜지스터(M10)가 턴-오프된다. 결과적으로 제 9 트랜지스터(M9)에 의해 제 2 전압(VGL)이 에미션 신호(OUT)로 출력될 수 있다. 이와 같이 출력 제어 회로(510)를 구비하는 에미션 구동 유닛(500)은 에미션 신호(OUT)를 DC 레벨로 제어할 수 있다. 예를 들어, 에미션 구동 유닛(500)과 같이 표시 장치가 엔모스 트랜지스터로 구현된 경우 에미션 신호(OUT)를 DC 로우 레벨로 제어할 수 있다. 반대로, 표시 장치가 피모스 트랜지스터로 구현된 경우 에미션 신호(OUT)를 DC 하이 레벨로 제어할 수 있다. 또한, 출력 제어 회로(510)에 로우 레벨의 출력 제어 신호(ESR)가 인가되는 경우, 제 1 및 제 2 출력 제어 트랜지스터들(Q1, Q2)이 턴-오프되므로 도 1의 에미션 구동 유닛(100)과 실질적으로 동일한 회로가 된다.

- [0070] 전술한 바와 같이, 출력 제어 회로(510)는 에미션 신호(OUT)를 하이 레벨 또는 로우 레벨의 DC 신호로 유지시켜 주는 기능을 수행한다. 일 실시예에서, 출력 제어 회로(510)를 구비하는 에미션 구동 유닛(500)은 표시 장치를 처음 구동할 때 유용하게 사용될 수 있다. 표시 장치를 처음 구동하면 정상 동작 모드로 가기 전에 소정의 준비 시간이 필요한데, 이때 원하지 않게 유기 발광 다이오드가 발광되는 것을 방지할 필요가 있다. 따라서, 표시 장치를 처음 구동할 때 로우 레벨의 출력 제어 신호(ESR)를 출력 제어 회로(510)에 인가하면 소정의 시간 동안 에미션 신호(OUT)를 DC 로우 레벨로 유지하여 유기 발광 다이오드를 오프 상태로 만들 수 있다.

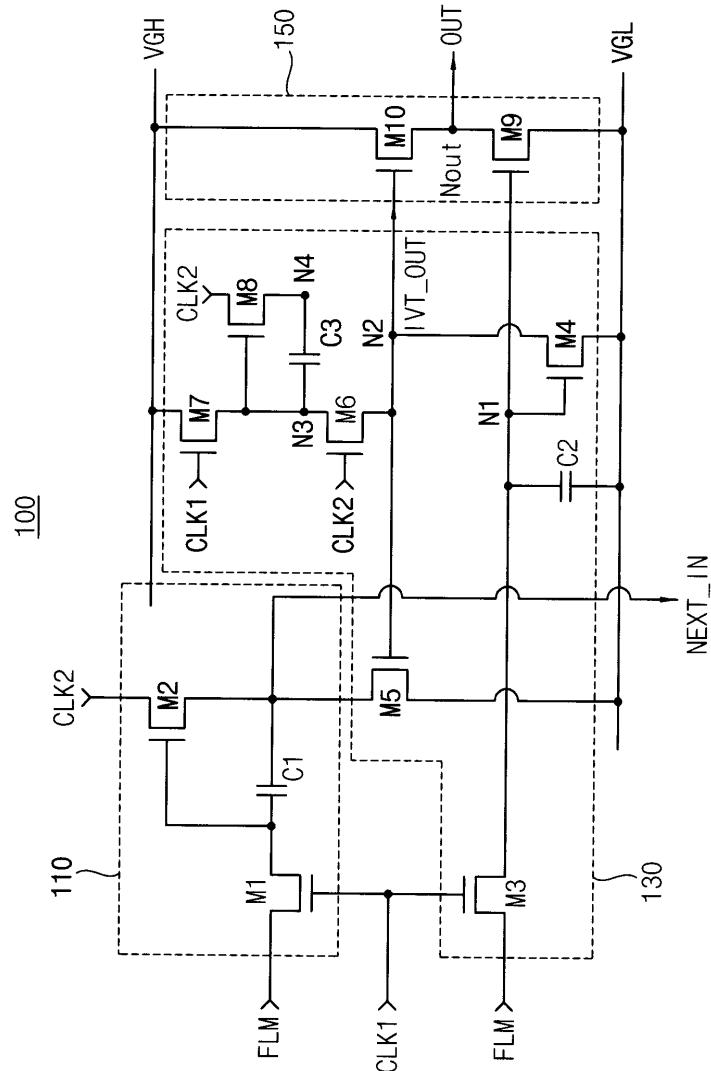

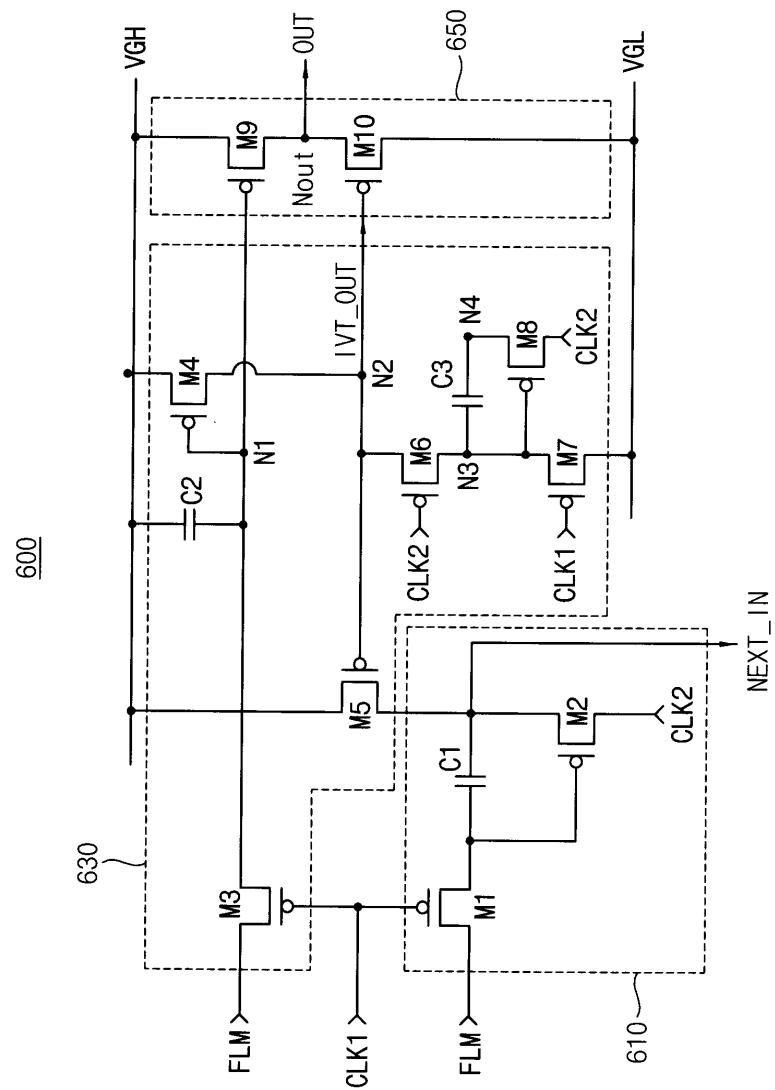

- [0071] 도 6은 본 발명의 또 다른 실시예에 따른 에미션 구동 유닛을 나타내는 회로도이다. 도 6은 피모스 트랜지스터로 구현된 에미션 구동 유닛(600)을 나타낸다.

- [0072] 도 6을 참조하면, 에미션 구동 유닛(600)은 입력 신호 생성 회로(610), 인버터 회로(630) 및 출력 스위칭 회로(650)를 포함한다.

- [0073] 입력 신호 생성 회로(610)는 제 1 클락 신호(CLK1)에 응답하여 FLM 신호(FLM)를 수신하고, FLM 신호(FLM)에 응답하여 제 2 클락 신호(CLK2)를 수신하며, 순차 입력 신호(NEXT\_IN)를 출력한다. 일 실시예에서, 입력 신호 생성 회로(610)는 제 1 트랜지스터(M1), 제 2 트랜지스터(M2) 및 제 1 커패시터(C1)를 포함할 수 있다. 제 1 트랜지스터(M1)는 드레인 전극, FLM 신호(FLM)를 수신하는 소스 전극, 및 제 1 클락 신호(CLK1)에 응답하여 FLM 신호(FLM)를 상기 드레인 전극으로 인가하는 게이트 전극을 구비한다. 제 2 트랜지스터(M2)는 제 2 클락 신호(CLK2)를 수신하는 소스 전극, 제 1 트랜지스터(M1)의 드레인 전극에 연결되는 게이트 전극, 및 순차 입력 신호(NEXT\_IN)를 출력하는 드레인 전극을 구비한다. 제 1 커패시터(C1)는 제 1 트랜지스터(M1)의 드레인 전극과 제 2 트랜지스터(M2)의 드레인 전극 사이에 연결된다.

- [0074] 인버터 회로(630)는 제 1 클락 신호(CLK1)에 응답하여 FLM 신호(FLM)를 수신하고, FLM 신호(FLM)를 반전하여 인버터 출력 신호(IVT\_OUT)를 생성한다. 일 실시예에서, 인버터 회로(630)는 제 3 내지 제 8 트랜지스터들(M3-M8) 및 제 1 내지 제 3 커패시터들(C1-C3)을 포함할 수 있다.

- [0075] 인버터 회로(630)에서, 제 3 트랜지스터(M3)는 제 1 클락 신호(CLK1)에 응답하여 FLM 신호(FLM)를 제 1 노드(N1)로 제공한다. 제 4 트랜지스터(M4)는 제 1 노드(N1)에 연결되는 게이트 전극, 제 1 전압 공급단(VGH)에 연결되는 소스 전극, 및 제 2 노드(N2)에 연결되는 드레인 전극을 구비한다. 제 2 커패시터(C2)는 제 1 노드(N1)와 제 1 전압 공급단(VGH) 사이에 연결된다. 제 5 트랜지스터(M5)는 입력 신호 생성 회로(610)의 제 2 트랜지스터

터(M2)의 드레인 전극에 연결되는 드레인 전극, 제 1 전압 공급단(VGH)에 연결되는 소스 전극, 및 제 2 노드(N2)에 연결되는 게이트 전극을 구비한다. 제 6 트랜지스터(M6)는 제 2 노드(N2)에 연결되는 소스 전극, 제 3 노드(N3)에 연결되는 드레인 전극, 및 제 2 클락 신호(CLK2)를 수신하는 게이트 전극을 구비한다. 제 7 트랜지스터(M7)는 제 3 노드(N3)에 연결되는 소스 전극, 제 2 전압 공급단(VGL)에 연결되는 드레인 전극, 및 제 1 클락 신호(CLK1)를 수신하는 게이트 전극을 구비한다. 제 8 트랜지스터(M8)는 제 3 노드(N3)에 연결되는 게이트 전극, 제 2 클락 신호(CLK2)를 수신하는 소스 전극, 및 제 4 노드(N4)에 연결되는 드레인 전극을 구비한다. 제 3 커패시터(C3)는 제 3 노드(N3)와 제 4 노드(N4) 사이에 연결된다. 인버터 회로(630)는 제 1 및 제 2 클락 신호들(CLK1, CLK2)에 응답하여 FLM 신호(FLM)를 반전함으로써 인버터 출력 신호(IVT\_OUT)를 생성할 수 있다.

[0076] 출력 스위칭 회로(650)는 인버터 출력 신호(IVT\_OUT)에 응답하여 에미션 신호(OUT)로서 하이 레벨인 제 1 전압(VGH) 또는 로우 레벨인 제 2 전압(VGL)을 출력한다. 이에 따라, 에미션 구동 유닛(600)의 출력(OUT)은 펄스 형태를 가질 수 있다. 일 실시예에서, 출력 스위칭 회로(650)는 출력단(Nout), 제 9 트랜지스터(M9) 및 제 10 트랜지스터(M10)를 포함할 수 있다. 출력단(Nout)은 에미션 신호(OUT)를 출력한다. 제 9 트랜지스터(M9)는 제 1 노드(N1)에 연결되는 게이트 전극, 제 1 전압 공급단(VGH)에 연결되는 소스 전극, 및 출력단(Nout)에 연결되는 드레인 전극을 구비한다. 제 10 트랜지스터(M10)는 제 2 노드(N2)에 연결되는 게이트 전극, 출력단(Nout)에 연결되는 소스 전극, 및 제 2 전압 공급단(VGL)에 연결되는 드레인 전극을 구비한다.

[0077] 에미션 구동 유닛(600)에서, 에미션 신호(OUT)는 FLM 신호(FLM)가 반전된 형태를 가질 수 있다. 일 실시예에서, FLM 신호(FLM)가 하이 레벨에서 로우 레벨로 하강하는 1회의 로우-펄스(low-pulse)를 갖는 경우, 에미션 신호(OUT)는 로우 레벨에서 하이 레벨로 상승하는 1회의 하이-펄스(high-pulse)를 갖는다. 에미션 구동 유닛(600)에 따라 화소 회로에 포함된 에미션 트랜지스터도 퍼모스 트랜지스터로 구현되므로, 에미션 신호(OUT)가 하이 레벨인 구간은 상기 에미션 트랜지스터가 턴-오프되고, 에미션 신호(OUT)가 로우 레벨인 구간은 상기 에미션 트랜지스터가 턴-온되어 이에 연결되는 유기 발광 다이오드가 발광하게 된다.

[0078] 일 실시예에서, 제 1 전압(OUT)은 퍼모스 트랜지스터를 턴-오프시킬 만큼 충분히 높은 전압 레벨을 가지고, 제 2 전압(OUT)은 퍼모스 트랜지스터를 턴-온시킬 만큼 충분히 낮은 전압 레벨을 가질 수 있다.

[0079] 도 7은 도 6의 에미션 구동 유닛에 포함되는 인버터 회로를 나타내는 회로도이다.

[0080] 도 7의 인버터 회로(700)는 도 6의 인버터 회로(630)에 실질적으로 상응한다. 구체적으로, 인버터 회로(700)의 입력 신호(IN), 출력 신호(OUT), 노드(A)는 각각 인버터 회로(630)의 FLM 신호(FLM), 인버터 출력 신호(IVT\_OUT), 제 3 노드(N3)에 상응한다. 도 7에 도시된 바와 같이, 인버터 회로(700)는 퍼모스 트랜지스터들로 구현된다. 제 1 트랜지스터(T1)는 로우 레벨의 입력 신호(IN)에 응답하여 하이 레벨인 제 1 전압(VGH)을 출력 신호(OUT)로 출력한다. 입력 신호(IN)가 하이 레벨인 경우 제 1 트랜지스터(T1)는 턴-오프되고 제 1 클락 신호(CLK1) 및 제 2 클락 신호(CLK2)에 따라 로우 레벨인 제 2 전압(VGL)이 출력 신호(OUT)로서 출력된다.

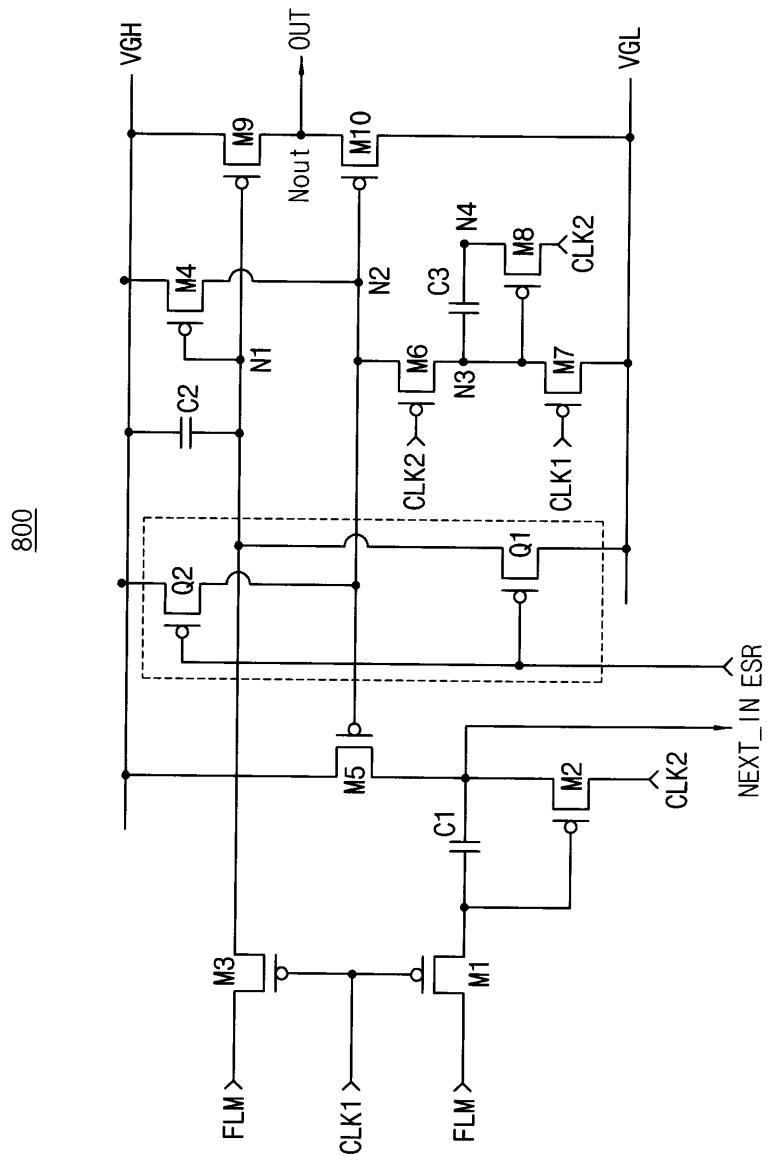

[0081] 도 8은 본 발명의 또 다른 실시예에 따른 에미션 구동 유닛을 나타내는 회로도이다.

[0082] 도 8을 참조하면, 도 8의 에미션 구동 유닛(800)은 출력 제어 회로(810)를 제외하고, 도 6의 에미션 구동 유닛(600)과 실질적으로 동일한 구성을 갖는다.

[0083] 출력 제어 회로(810)는 인버터 회로 내부에 연결되고 출력 제어 신호(ESR)에 의해 제어된다. 출력 제어 회로(810)는 제 1 출력 제어 트랜지스터(Q1) 및 제 2 출력 제어 트랜지스터(Q2)를 포함할 수 있다.

[0084] 일 실시예에서, 출력 제어 회로(810)에 로우 레벨의 출력 제어 신호(ESR)가 인가되는 경우, 에미션 신호(OUT)로 제 1 전압(VGH)이 DC 레벨로 출력된다. 보다 구체적으로, 로우 레벨의 출력 제어 신호(ESR)가 인가되면 제 1 및 제 2 출력 제어 트랜지스터들(Q1, Q2)은 턴-온된다. 그러면 로우 레벨인 제 2 전압(VGL)이 제 9 트랜지스터(M9)의 게이트 전극에 인가되어 제 9 트랜지스터(M9)가 턴-온되고, 하이 레벨인 제 1 전압(VGH)이 제 10 트랜지스터(M10)의 게이트 전극에 인가되어 제 10 트랜지스터(M10)가 턴-오프된다. 결과적으로 제 9 트랜지스터(M9)에 의해 제 1 전압(VGH)이 에미션 신호(OUT)로 출력될 수 있다. 이와 반대로, 출력 제어 회로(810)에 하이 레벨의 출력 제어 신호(ESR)가 인가되는 경우, 제 1 및 제 2 출력 제어 트랜지스터들(Q1, Q2)이 턴-오프되므로 도 6의 에미션 구동 유닛(600)과 실질적으로 동일한 회로가 된다.

[0085] 도 9는 본 발명의 일 실시예에 따른 유기 발광 표시 장치를 나타내는 블록도이다.

[0086] 도 9를 참조하면, 유기 발광 표시 장치(900)는 표시 패널(910), 스캔 구동부(920), 데이터 구동부(930), 에미션 구동부(200) 및 타이밍 컨트롤러(940)를 포함한다.

- [0087] 표시 패널(910)은 복수의 화소 회로들을 포함하고, 제 1 전원 전압(ELVDD) 및 제 2 전원 전압(ELVSS)을 수신한다. 상기 화소 회로들은 유기 발광 다이오드를 각각 구비한다. 스캔 구동부(920)는 제 1 내지 제 n(단, n은 3 이상의 정수) 스캔 라인들(S1-Sn)을 통해 상기 화소 회로들에 순차적으로 제 1 내지 제 n 스캔 신호들을 제공한다. 데이터 구동부(930)는 상기 제 1 내지 제 n 스캔 신호들에 따라 복수의 데이터 라인들(D1-Dm)을 통해 상기 화소 회로들에 데이터 전압을 제공한다. 에미션 구동부(200)는 제 1 내지 제 n 에미션(emission) 제어 라인들(EM1-EMn)을 통해 상기 화소 회로들에 순차적으로 제 1 내지 제 n 에미션 신호들을 제공한다. 타이밍 컨트롤러(940)는 스캔 구동부(920), 데이터 구동부(930) 및 에미션 구동부(200)에 제 1 클락 신호(CLK1) 및 제 2 클락 신호(CLK2)를 제공한다.

- [0088] 일 실시예에서, 에미션 구동부(200)는 상기 제 1 내지 제 n 에미션 신호들을 각각 생성하는 제 1 내지 제 n 에미션 구동 유닛들을 포함할 수 있다. 본 발명의 실시예들에 따르면, 상기 제 1 내지 제 n 에미션 구동 유닛들은 내부에 인버터 회로를 구비함으로써 엔모스 트랜지스터 또는 퍼모스 트랜지스터로만 구현될 수 있다. 상기 제 1 내지 제 n 에미션 구동 유닛들 각각은 제 1 클락 신호(CLK1) 및 제 2 클락 신호(CLK2)에 의해 제어되고, FLM 신호 또는 제 1 내지 제 (n-1) 순차 입력 신호들을 입력 신호로서 수신하며, 동종의 단일형 트랜지스터들로 구현될 수 있다.

- [0089] 실시예에 따라, 에미션 구동부(200)가 엔모스 트랜지스터로 구현될 때, 상기 제 1 내지 제 n 에미션 신호들이 모두 레벨인 구간은 상기 화소 회로들에서 데이터 프로그래밍이 수행되는 구간에 상응하고, 상기 제 1 내지 제 n 에미션 신호들이 하이 레벨인 구간은 상기 화소 회로들에 각각 포함되는 유기 발광 다이오드가 발광하는 구간에 상응할 수 있다.

- [0090] 또한, 에미션 구동부(200)가 퍼모스 트랜지스터로 구현될 때, 상기 제 1 내지 제 n 에미션 신호들의 오프 라티비(off duty ratio)를 제어함에 따라 표시 패널(910)이 블랙 이미지를 표시하는 구간의 길이를 제어할 수 있다. 이에 따라, 단일형 트랜지스터로 구현된 에미션 구동부(200)를 이용하여 임펄스 구동을 수행할 수 있다.

- [0091] 일 실시예에서, 에미션 구동부(200)가 상기 화소 회로들에 순차적으로 상기 제 1 내지 제 n 에미션 신호들을 제공함에 따라, 상기 화소 회로들에 각각 포함되는 OLED가 순차적으로 발광할 수 있다.

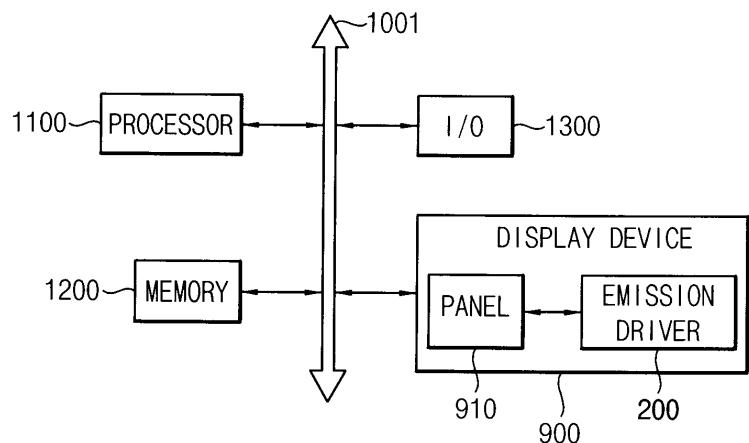

- [0092] 도 10은 도 9의 유기 발광 표시 장치를 포함하는 전자 기기를 나타내는 블록도이다.

- [0093] 도 10을 참조하면, 전자 기기(1000)는 프로세서(1100), 메모리 장치(1200), 입출력 장치(1300) 및 표시 장치(900)를 포함할 수 있다.

- [0094] 프로세서(1100)는 특정 계산들 또는 태스크(task)들을 수행하는 특정 소프트웨어를 실행하는 것과 같이 다양한 컴퓨팅 기능들을 실행할 수 있다. 예를 들어, 프로세서(1100)는 마이크로프로세서 또는 중앙 처리 장치(Central Processing Unit; CPU)일 수 있다. 프로세서(1100)는 버스(1001)를 통하여 메모리 장치(1200)에 연결될 수 있다. 프로세서(1100)는 어드레스 버스(address bus), 제어 버스(control bus) 및 데이터 버스(data bus) 등을 통하여 메모리 장치(1200) 및 표시 장치(900)에 연결되어 통신을 수행할 수 있다. 예시적인 실시예에 있어서, 프로세서(1100)는 주변 구성요소 상호연결(Peripheral Component Interconnect; PCI) 버스와 같은 확장 버스에도 연결될 수 있다.

- [0095] 메모리 장치(1200)는 예를 들어 동적 랜덤 액세스 메모리(Dynamic Random Access Memory; DRAM), 정적 랜덤 액세스 메모리(Static Random Access Memory; SRAM) 등과 같은 휘발성 메모리 장치 및 이피롬(Erasable Programmable Read-Only Memory; EPROM), 아이피롬(Electrically Erasable Programmable Read-Only Memory; EEPROM) 및 플래시 메모리 장치(flash memory device) 등과 같은 비휘발성 메모리 장치를 포함할 수 있다. 메모리 장치(1200)는 프로세서(1100)에 의해 실행되는 소프트웨어를 저장할 수 있다.

- [0096] 입출력 장치(1300)는 버스(1001)에 연결되며 키보드 또는 마우스와 같은 입력 수단 및 프린터와 같은 출력 수단을 포함할 수 있다. 프로세서(1100)는 입출력 장치(1300)의 동작을 제어할 수 있다.

- [0097] 표시 장치(900)는 버스(1001)를 통해 프로세서(1100)와 연결된다. 표시 장치(900)는 표시 패널(910) 및 에미션 구동부(200)를 포함할 수 있다. 전술한 바와 같이, 에미션 구동부(200)는 내부에 인버터 회로를 구비하여 단일형 트랜지스터로 구현될 수 있고, 입력 신호의 펄스 폭을 제어하여 에미션 신호의 펄스 폭을 자유롭게 조절할 수 있다.

- [0098] 전자 기기(1000)는 표시 장치(900)를 통해 사용자에게 화상을 제공하는 휴대폰, 스마트폰, 스마트패드, 텔레비전, PDA(Personal Digital Assistant), MP3 플레이어, 노트북 컴퓨터, 테스크톱 컴퓨터, 디지털 카메라 등을

포함하는 임의의 전자 장치일 수 있다.

### 산업상 이용가능성

[0099] 본 발명은 표시 장치를 포함하는 여러 응용분야에서 폭넓게 적용될 수 있다. 예를 들어, 표시 장치를 포함하는 모니터, 노트북, PDA, 스마트폰, 스마트패드, 중대형 표시 패널 등에 유용하게 이용될 수 있다.

[0100] 상기에서는 본 발명을 바람직한 실시예를 참조하여 설명하였지만, 해당 기술분야의 숙련된 당업자는 하기의 특허청구범위에 기재된 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 것이다.

### 도면

#### 도면1

## 도면2a

200

## 도면2b

도면3a

300

도면3b

도면4

도면5

도면6

도면7

700

도면8

## 도면9

900

## 도면10

1000

|                |                                                                         |         |            |

|----------------|-------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 发射驱动单元，发射驱动单元和包括其的有机发光显示器                                               |         |            |

| 公开(公告)号        | <a href="#">KR101881853B1</a>                                           | 公开(公告)日 | 2018-07-26 |

| 申请号            | KR1020120021210                                                         | 申请日     | 2012-02-29 |

| [标]申请(专利权)人(译) | 三星显示有限公司                                                                |         |            |

| 申请(专利权)人(译)    | 三星显示器有限公司                                                               |         |            |

| 当前申请(专利权)人(译)  | 三星显示器有限公司                                                               |         |            |

| [标]发明人         | JEONG JIN TAE<br>정진태                                                    |         |            |

| 发明人            | 정진태                                                                     |         |            |

| IPC分类号         | G09G3/30 H01L51/50                                                      |         |            |

| CPC分类号         | G09G3/3266 G11C19/184 G11C19/28 H01L21/02576 H01L21/02579 G09G2310/0286 |         |            |

| 代理人(译)         | 英西湖公园                                                                   |         |            |

| 其他公开文献         | <a href="#">KR1020130099588A</a>                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                               |         |            |

### 摘要(译)

发射驱动单元包括输入信号产生电路，反相器电路和输出开关电路。输入信号生成电路响应于第一时钟信号接收帧线标记 ( FLM ) 信号，响应于FLM信号接收第二时钟信号，并输出顺序输入信号。反相器电路响应于第一时钟信号接收FLM信号，并反转FLM信号以产生反相器输出信号。输出切换电路响应于逆变器输出信号输出高电平的第一电压或低电平的第二电压作为发射信号。输入信号生成电路，反相器电路和输出切换电路可以实现为相同类型的单类型晶体管。