공개특허 10-2020-0083736

(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2020-0083736

(43) 공개일자 2020년07월09일

(51) 국제특허분류(Int. Cl.)

*G09G 3/3208* (2016.01)

(52) CPC특허분류

*G09G 3/3208* (2013.01)

*G09G 2310/0221* (2013.01)

(21) 출원번호 10-2018-0171982

(22) 출원일자 2018년12월28일

심사청구일자 없음

(71) 출원인

삼성디스플레이 주식회사

경기도 용인시 기흥구 삼성로 1 (농서동)

(72) 발명자

전재현

서울특별시 종구 청구로1길 23(신당동, 신당동삼성아파트), 110동 2202호

김지혜

경기도 화성시 동탄순환대로21길 54(청계동, 동탄2신도시 센트럴 푸르지오), 1323동 1202호

(74) 대리인

박영우

전체 청구항 수 : 총 20 항

(54) 발명의 명칭 부분 구동 모드를 지원하는 유기 발광 표시 장치

**(57) 요 약**

유기 발광 표시 장치는 제1 부분 패널 영역 및 제2 부분 패널 영역을 포함하는 표시 패널, 제1 및 제2 부분 패널 영역들이 모두 구동되는 일반 구동 모드에서 제1 및 제2 부분 패널 영역들에 스캔 신호들을 순차적으로 인가하고, 제1 부분 패널 영역 또는 제2 부분 패널 영역 중 하나의 부분 패널 영역이 구동되고 다른 하나의 부분 패널 영역이 구동되지 않는 부분 구동 모드에서 구동되는 부분 패널 영역에 스캔 신호들을 순차적으로 인가하는 스캔 드라이버, 및 일반 구동 모드에서 제1 및 제2 부분 패널 영역들에 데이터 신호들을 인가하고, 부분 구동 모드에서 구동되는 부분 패널 영역에 데이터 신호들을 인가하는 데이터 드라이버를 포함한다. 부분 구동 모드에서, 스캔 드라이버는 구동되는 부분 패널 영역에 다이오드 초기화 신호들을 순차적으로 인가하고, 구동되지 않는 부분 패널 영역에 다이오드 초기화 신호들을 동시에 인가한다.

**대 표 도 - 도1**

(52) CPC특허분류

*G09G 2320/0214 (2013.01)*

*G09G 2320/0686 (2013.01)*

---

## 명세서

### 청구범위

#### 청구항 1

제1 부분 패널 영역 및 제2 부분 패널 영역을 포함하는 표시 패널;

상기 제1 및 제2 부분 패널 영역들이 모두 구동되는 일반 구동 모드에서 상기 제1 및 제2 부분 패널 영역들에 스캔 신호들을 순차적으로 인가하고, 상기 제1 부분 패널 영역 또는 상기 제2 부분 패널 영역 중 하나의 부분 패널 영역이 구동되고 다른 하나의 부분 패널 영역이 구동되지 않는 부분 구동 모드에서 상기 구동되는 부분 패널 영역에 상기 스캔 신호들을 순차적으로 인가하는 스캔 드라이버; 및

상기 일반 구동 모드에서 상기 제1 및 제2 부분 패널 영역들에 데이터 신호들을 인가하고, 상기 부분 구동 모드에서 상기 구동되는 부분 패널 영역에 상기 데이터 신호들을 인가하는 데이터 드라이버를 포함하고,

상기 부분 구동 모드에서, 상기 스캔 드라이버는 상기 구동되는 부분 패널 영역에 다이오드 초기화 신호들을 순차적으로 인가하고, 상기 구동되지 않는 부분 패널 영역에 상기 다이오드 초기화 신호들을 동시에 인가하는 것을 특징으로 하는 유기 발광 표시 장치.

#### 청구항 2

제1 항에 있어서, 상기 부분 구동 모드에서, 상기 구동되지 않는 부분 패널 영역에 포함되는 화소들의 유기 발광 다이오드들은 상기 동시에 인가되는 다이오드 초기화 신호들에 응답하여 초기화되는 것을 특징으로 하는 유기 발광 표시 장치.

#### 청구항 3

제1 항에 있어서, 상기 부분 구동 모드에서, 상기 구동되지 않는 부분 패널 영역에 포함되는 화소들은 상기 동시에 인가되는 다이오드 초기화 신호들에 응답하여 전원 전압 라인으로부터 초기화 전압 라인으로의 누설 전류 경로들을 형성하는 것을 특징으로 하는 유기 발광 표시 장치.

#### 청구항 4

제1 항에 있어서, 상기 제1 및 제2 부분 패널 영역들 각각은 복수의 화소들을 포함하고, 상기 복수의 화소들 각각은,

상기 다이오드 초기화 신호들 중 상응하는 하나를 수신하는 게이트, 초기화 전압 라인에 연결된 제1 단자, 및 유기 발광 다이오드의 애노드에 연결된 제2 단자를 포함하는 다이오드 초기화 트랜지스터를 포함하고,

상기 부분 구동 모드에서, 상기 구동되지 않는 부분 패널 영역에 포함되는 상기 복수의 화소들의 상기 다이오드 초기화 트랜지스터들은 상기 동시에 인가되는 다이오드 초기화 신호들에 응답하여 턴-온되는 것을 특징으로 하는 특징으로 하는 유기 발광 표시 장치.

#### 청구항 5

제4 항에 있어서, 상기 구동되지 않는 부분 패널 영역에 포함되는 상기 복수의 화소들의 상기 턴-온된 다이오드 초기화 트랜지스터들은 상기 유기 발광 다이오드들의 기생 커패시터들을 상기 초기화 전압 라인으로 방전시키는 방전 경로들을 형성하고, 구동 트랜지스터들의 누설 전류들이 상기 초기화 전압 라인으로 흐르게 하는 누설 전류 경로들을 형성하는 것을 특징으로 하는 유기 발광 표시 장치.

#### 청구항 6

제1 항에 있어서, 상기 부분 구동 모드에서, 상기 구동되지 않는 부분 패널 영역에 인가되는 상기 다이오드 초기화 신호들은 적어도 1 수평 시간 동안 온 레벨을 동시에 가지는 것을 특징으로 하는 유기 발광 표시 장치.

#### 청구항 7

제1 항에 있어서, 상기 부분 구동 모드에서, 상기 구동되지 않는 부분 패널 영역에 인가되는 상기 다이오드 초기화 신호들은 상기 부분 구동 모드의 첫 번째 프레임 구간에서 온 레벨을 순차적으로 가지고, 상기 일반 구동 모드로 전환될 때까지 상기 온 레벨로 유지되는 것을 특징으로 하는 유기 발광 표시 장치.

### 청구항 8

제1 항에 있어서, 상기 제1 부분 패널 영역은 제1 내지 제N 화소 행들(N은 2 이상의 정수)을 포함하고, 상기 제2 부분 패널 영역은 제N+1 내지 제N+M 화소 행들(M은 2 이상의 정수)을 포함하며, 상기 스캔 신호들은 제1 내지 제N+M 스캔 신호들을 포함하고, 상기 스캔 드라이버는,

제1 스캔 개시 신호에 응답하여 상기 제1 화소 행에 상기 제1 스캔 신호를 인가하는 제1 스캔 스테이지;

상기 제1 내지 제N-1 스캔 신호들에 응답하여 상기 제2 내지 제N 화소 행들에 상기 제2 내지 제N 스캔 신호들을 인가하는 제2 내지 제N 스캔 스테이지들;

모드 제어 신호에 응답하여 제2 스캔 개시 신호 또는 상기 제N 스캔 신호를 선택적으로 출력하는 스캔 입력 제어 회로;

상기 스캔 입력 제어 회로의 출력 신호에 응답하여 상기 제N+1 화소 행에 상기 제N+1 스캔 신호를 인가하는 제N+1 스캔 스테이지; 및

상기 제N+1 내지 제N+M-1 스캔 신호들에 응답하여 상기 제N+2 내지 제N+M 화소 행들에 상기 N+2 내지 제N+M 스캔 신호들을 인가하는 제N+2 내지 제N+M 스캔 스테이지들을 포함하는 것을 특징으로 하는 유기 발광 표시 장치.

### 청구항 9

제8 항에 있어서, 상기 스캔 입력 제어 회로는,

상기 일반 구동 모드에서 온 레벨을 가지는 상기 모드 제어 신호에 응답하여 상기 제N 스캔 스테이지로부터 출력된 상기 제N 스캔 신호를 출력하는 제1 스캔 입력 제어 트랜지스터; 및

상기 부분 구동 모드에서 상기 온 레벨을 가지는 반전된 모드 제어 신호에 응답하여 상기 제2 스캔 개시 신호를 출력하는 제2 스캔 입력 제어 트랜지스터를 포함하는 것을 특징으로 하는 유기 발광 표시 장치.

### 청구항 10

제8 항에 있어서,

상기 일반 구동 모드에서, 상기 모드 제어 신호는 온 레벨을 가지고, 상기 제1 스캔 개시 신호는 매 프레임 구간마다 스캔 시작 펄스를 포함하고, 상기 제2 스캔 개시 신호는 오프 레벨을 가지고,

상기 부분 구동 모드에서, 상기 제1 부분 패널 영역이 구동되고, 상기 제2 부분 패널 영역이 구동되지 않을 때, 상기 모드 제어 신호는 상기 오프 레벨을 가지고, 상기 제1 스캔 개시 신호는 매 프레임 구간마다 상기 스캔 시작 펄스를 포함하고, 상기 제2 스캔 개시 신호는 상기 오프 레벨을 가지고,

상기 부분 구동 모드에서, 상기 제1 부분 패널 영역이 구동되지 않고, 상기 제2 부분 패널 영역이 구동될 때, 상기 모드 제어 신호는 상기 오프 레벨을 가지고, 상기 제1 스캔 개시 신호는 상기 오프 레벨을 가지고, 상기 제2 스캔 개시 신호는 매 프레임 구간마다 상기 스캔 시작 펄스를 포함하는 것을 특징으로 하는 유기 발광 표시 장치.

### 청구항 11

제1 항에 있어서, 상기 제1 부분 패널 영역은 제1 내지 제N 화소 행들(N은 2 이상의 정수)을 포함하고, 상기 제2 부분 패널 영역은 제N+1 내지 제N+M 화소 행들(M은 2 이상의 정수)을 포함하며, 상기 다이오드 초기화 신호들은 제1 내지 제N+M 다이오드 초기화 신호들을 포함하고, 상기 스캔 드라이버는,

제1 다이오드 초기화 개시 신호에 응답하여 상기 제1 화소 행에 상기 제1 다이오드 초기화 신호를 인가하는 제1 다이오드 초기화 스테이지;

상기 제1 내지 제N-1 다이오드 초기화 신호들에 응답하여 상기 제2 내지 제N 화소 행들에 상기 제2 내지 제N 다이오드 초기화 신호들을 인가하는 제2 내지 제N 다이오드 초기화 스테이지들;

모드 제어 신호에 응답하여 제2 다이오드 초기화 개시 신호 또는 상기 제N 다이오드 초기화 신호를 선택적으로 출력하는 다이오드 초기화 입력 제어 회로;

상기 다이오드 초기화 입력 제어 회로의 출력 신호에 응답하여 상기 제N+1 화소 행에 상기 제N+1 다이오드 초기화 신호를 인가하는 제N+1 다이오드 초기화 스테이지; 및

상기 제N+1 내지 제N+M-1 다이오드 초기화 신호들에 응답하여 상기 제N+2 내지 제N+M 화소 행들에 상기 제N+2 내지 제N+M 다이오드 초기화 신호들을 인가하는 제N+2 내지 제N+M 다이오드 초기화 스테이지들을 포함하는 것을 특징으로 하는 유기 발광 표시 장치.

## 청구항 12

제11 항에 있어서, 상기 다이오드 초기화 입력 제어 회로는,

상기 일반 구동 모드에서 온 레벨을 가지는 상기 모드 제어 신호에 응답하여 상기 제N 다이오드 초기화 스테이지로부터 출력된 상기 제N 다이오드 초기화 신호를 출력하는 제1 다이오드 초기화 입력 제어 트랜지스터; 및

상기 부분 구동 모드에서 상기 온 레벨을 가지는 반전된 모드 제어 신호에 응답하여 상기 제2 다이오드 초기화 개시 신호를 출력하는 제2 다이오드 초기화 입력 제어 트랜지스터를 포함하는 것을 특징으로 하는 유기 발광 표시 장치.

## 청구항 13

제11 항에 있어서,

상기 일반 구동 모드에서, 상기 모드 제어 신호는 온 레벨을 가지고, 상기 제1 다이오드 초기화 개시 신호는 매 프레임 구간마다 다이오드 초기화 시작 펄스를 포함하고, 상기 제2 다이오드 초기화 개시 신호는 오프 레벨을 가지고,

상기 부분 구동 모드에서, 상기 제1 부분 패널 영역이 구동되고, 상기 제2 부분 패널 영역이 구동되지 않을 때, 상기 모드 제어 신호는 상기 오프 레벨을 가지고, 상기 제1 다이오드 초기화 개시 신호는 매 프레임 구간마다 상기 다이오드 초기화 시작 펄스를 포함하고, 상기 제2 다이오드 초기화 개시 신호는 상기 온 레벨을 가지고,

상기 부분 구동 모드에서, 상기 제1 부분 패널 영역이 구동되지 않고, 상기 제2 부분 패널 영역이 구동될 때, 상기 모드 제어 신호는 상기 오프 레벨을 가지고, 상기 제1 다이오드 초기화 개시 신호는 상기 온 레벨을 가지고, 상기 제2 다이오드 초기화 개시 신호는 매 프레임 구간마다 상기 다이오드 초기화 시작 펄스를 포함하는 것을 특징으로 하는 유기 발광 표시 장치.

## 청구항 14

제11 항에 있어서, 상기 제1 내지 제N 다이오드 초기화 스테이지들은 제1 및 제2 다이오드 초기화 클록 신호들에 응답하여 동작하고, 상기 제N+1 내지 제N+M 다이오드 초기화 스테이지들은 제3 및 제4 다이오드 초기화 클록 신호들에 응답하여 동작하고,

상기 일반 구동 모드에서, 상기 제1 및 제2 다이오드 초기화 클록 신호들은 상기 제3 및 제4 다이오드 초기화 클록 신호들과 각각 동일한 위상을 가지고,

상기 부분 구동 모드에서, 상기 제1 부분 패널 영역이 구동되고, 상기 제2 부분 패널 영역이 구동되지 않을 때, 상기 제1 및 제2 다이오드 초기화 클록 신호들은 온 레벨과 오프 레벨 사이에서 주기적으로 토클링하고, 상기 제3 및 제4 다이오드 초기화 클록 신호들은 상기 온 레벨과 오프 레벨 사이에서 주기적으로 토클링하고, 상기 제2 다이오드 초기화 개시 신호는 상기 부분 구동 모드의 첫 번째 프레임 구간에서 상기 다이오드 초기화 시작 펄스를 포함하고,

상기 부분 구동 모드에서, 상기 제1 부분 패널 영역이 구동되지 않고, 상기 제2 부분 패널 영역이 구동될 때, 상기 제1 및 제2 다이오드 초기화 클록 신호들은 상기 온 레벨을 가지고, 상기 제3 및 제4 다이오드 초기화 클록 신호들은 상기 온 레벨과 상기 오프 레벨 사이에서 주기적으로 토클링하고, 상기 제1 다이오드 초기화 개시 신호는 상기 부분 구동 모드의 상기 첫 번째 프레임 구간에서 상기 다이오드 초기화 시작 펄스를 포함하는 것을 특징으로 하는 유기 발광 표시 장치.

## 청구항 15

제1 내지 제N 화소 행들(N은 2 이상의 정수)을 포함하는 제1 부분 패널 영역 및 제N+1 내지 제N+M 화소 행들(M은 2 이상의 정수)을 포함하는 제2 부분 패널 영역을 포함하는 표시 패널;

상기 제1 및 제2 부분 패널 영역들이 모두 구동되는 일반 구동 모드에서 상기 제1 내지 제N+M 화소 행들에 스캔 신호들을 순차적으로 인가하고, 상기 제1 부분 패널 영역이 구동되지 않고 상기 제2 부분 패널 영역이 구동되는 부분 구동 모드에서 상기 제N+1 내지 제N+M 화소 행들에 상기 스캔 신호들을 순차적으로 인가하는 스캔 드라이버; 및

상기 일반 구동 모드에서 상기 제1 내지 제N+M 화소 행들에 데이터 신호들을 인가하고, 상기 제1 부분 패널 영역이 구동되지 않고 상기 제2 부분 패널 영역이 구동되는 상기 부분 구동 모드에서 상기 제N+1 내지 제N+M 화소 행들에 상기 데이터 신호들을 인가하는 데이터 드라이버를 포함하고,

상기 스캔 드라이버는 상기 일반 구동 모드에서 상기 제1 내지 제N+M 화소 행들에 다이오드 초기화 신호들을 순차적으로 인가하고, 상기 제1 부분 패널 영역이 구동되지 않고 상기 제2 부분 패널 영역이 구동되는 상기 부분 구동 모드에서 상기 제N+1 내지 제N+M 화소 행들에 상기 다이오드 초기화 신호들을 순차적으로 인가하고, 상기 제1 내지 제N 화소 행들에 상기 다이오드 초기화 신호들을 동시에 인가하는 것을 특징으로 하는 유기 발광 표시 장치.

#### 청구항 16

제15 항에 있어서, 상기 제1 부분 패널 영역이 구동되지 않고 상기 제2 부분 패널 영역이 구동되는 상기 부분 구동 모드에서, 상기 제1 내지 제N 화소 행들에 상기 스캔 신호들 및 상기 데이터 신호들이 인가되지 않는 것을 특징으로 하는 유기 발광 표시 장치.

#### 청구항 17

제15 항에 있어서, 상기 제1 부분 패널 영역이 구동되지 않고 상기 제2 부분 패널 영역이 구동되는 상기 부분 구동 모드에서, 상기 제1 부분 패널 영역에 포함되는 화소들의 유기 발광 다이오드들은 상기 동시에 인가되는 다이오드 초기화 신호들에 응답하여 초기화되는 것을 특징으로 하는 유기 발광 표시 장치.

#### 청구항 18

제15 항에 있어서, 상기 제1 부분 패널 영역이 구동되지 않고 상기 제2 부분 패널 영역이 구동되는 상기 부분 구동 모드에서, 상기 제1 부분 패널 영역에 포함되는 화소들은 상기 동시에 인가되는 다이오드 초기화 신호들에 응답하여 전원 전압 라인으로부터 초기화 전압 라인으로의 누설 전류 경로들을 형성하는 것을 특징으로 하는 유기 발광 표시 장치.

#### 청구항 19

제15 항에 있어서, 상기 제1 부분 패널 영역이 구동되지 않고 상기 제2 부분 패널 영역이 구동되는 상기 부분 구동 모드에서, 상기 제1 부분 패널 영역에 인가되는 상기 다이오드 초기화 신호들은 상기 부분 구동 모드의 첫 번째 프레임 구간에서 온 레벨을 순차적으로 가지고, 상기 일반 구동 모드로 전환될 때까지 상기 온 레벨로 유지되는 것을 특징으로 하는 유기 발광 표시 장치.

#### 청구항 20

제15 항에 있어서, 상기 제1 부분 패널 영역이 구동되고 상기 제2 부분 패널 영역이 구동되지 않는 상기 부분 구동 모드에서, 상기 스캔 드라이버는 상기 제1 내지 제N 화소 행들에 상기 다이오드 초기화 신호들을 순차적으로 인가하고, 상기 제N+1 내지 제N+M 화소 행들에 상기 다이오드 초기화 신호들을 동시에 인가하는 것을 특징으로 하는 유기 발광 표시 장치.

### 발명의 설명

#### 기술 분야

[0001] 본 발명은 표시 장치에 관한 것으로서, 더욱 상세하게는 부분 구동 모드를 지원하는 유기 발광 표시 장치에 관한 것이다.

## 배경 기술

[0002] 유기 발광 표시 장치는 백라이트 유닛이 불필요하고 뛰어난 유연성을 가지고 있어, 플렉서블(flexible) 표시 장치로 구현되기에 적합하다. 최근, 이러한 플렉서블 표시 장치로서, 폴더블(foldable) 표시 장치, 롤러블(rollable) 표시 장치, 스트레쳐블(stretchable) 표시 장치 등이 개발되고 있고, 이 중 폴더블 표시 장치는 화면을 접으면 휴대가 용이하고, 화면을 펼치면 대면적 표시 화면을 구현할 수 있다는 장점 때문에 차세대 표시 장치로 주목 받고 있다.

[0003] 이러한 폴더블 표시 장치에서, 특히 표시 패널의 일부가 배면에 위치하도록 표시 패널이 접히는 아웃-폴딩(Out-folding) 표시 장치에서는, 전면에 배치되는 일부 패널 영역만이 구동되고, 배면에 배치되는 나머지 패널 영역이 구동되지 않는 부분 구동 모드(Partial Driving Mode)가 채용될 수 있다. 다만, 부분 구동 모드에서 구동되지 않는 부분 패널 영역에 데이터 신호들이 인가되지 않더라도, 상기 구동되지 않는 부분 패널 영역이 잔류 전하들 또는 누설 전류들에 의해 원치 않게 발광할 수 있는 문제가 있다.

## 발명의 내용

### 해결하려는 과제

[0004] 본 발명의 일 목적은 부분 구동 모드에서 구동되지 않는 부분 패널 영역이 원치 않게 발광하는 것을 방지할 수 있는 유기 발광 표시 장치를 제공하는 것이다.

[0005] 다만, 본 발명의 해결하고자 하는 과제는 상기 언급된 과제에 한정되는 것이 아니며, 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위에서 다양하게 확장될 수 있을 것이다.

### 과제의 해결 수단

[0006] 본 발명의 일 목적을 달성하기 위하여, 본 발명의 실시예들에 따른 유기 발광 표시 장치는 제1 부분 패널 영역 및 제2 부분 패널 영역을 포함하는 표시 패널, 상기 제1 및 제2 부분 패널 영역들이 모두 구동되는 일반 구동 모드에서 상기 제1 및 제2 부분 패널 영역들에 스캔 신호들을 순차적으로 인가하고, 상기 제1 부분 패널 영역 또는 상기 제2 부분 패널 영역 중 하나의 부분 패널 영역이 구동되고 다른 하나의 부분 패널 영역이 구동되지 않는 부분 구동 모드에서 상기 구동되는 부분 패널 영역에 상기 스캔 신호들을 순차적으로 인가하는 스캔 드라이버, 및 상기 일반 구동 모드에서 상기 제1 및 제2 부분 패널 영역들에 데이터 신호들을 인가하고, 상기 부분 구동 모드에서 상기 구동되는 부분 패널 영역에 상기 데이터 신호들을 인가하는 데이터 드라이버를 포함한다. 상기 부분 구동 모드에서, 상기 스캔 드라이버는 상기 구동되는 부분 패널 영역에 다이오드 초기화 신호들을 순차적으로 인가하고, 상기 구동되지 않는 부분 패널 영역에 상기 다이오드 초기화 신호들을 동시에 인가한다.

[0007] 일 실시예에서, 상기 부분 구동 모드에서, 상기 구동되지 않는 부분 패널 영역에 포함되는 화소들의 유기 발광 다이오드들은 상기 동시에 인가되는 다이오드 초기화 신호들에 응답하여 초기화될 수 있다.

[0008] 일 실시예에서, 상기 부분 구동 모드에서, 상기 구동되지 않는 부분 패널 영역에 포함되는 화소들은 상기 동시에 인가되는 다이오드 초기화 신호들에 응답하여 전원 전압 라인으로부터 초기화 전압 라인으로의 누설 전류 경로들을 형성할 수 있다.

[0009] 일 실시예에서, 상기 제1 및 제2 부분 패널 영역들 각각은 복수의 화소들을 포함하고, 상기 복수의 화소들 각각은, 상기 다이오드 초기화 신호들 중 상응하는 하나를 수신하는 게이트, 초기화 전압 라인에 연결된 제1 단자, 및 유기 발광 다이오드의 애노드에 연결된 제2 단자를 포함하는 다이오드 초기화 트랜지스터를 포함하고, 상기 부분 구동 모드에서, 상기 구동되지 않는 부분 패널 영역에 포함되는 상기 복수의 화소들의 상기 다이오드 초기화 트랜지스터들은 상기 동시에 인가되는 다이오드 초기화 신호들에 응답하여 턴-온될 수 있다.

[0010] 일 실시예에서, 상기 구동되지 않는 부분 패널 영역에 포함되는 상기 복수의 화소들의 상기 턴-온된 다이오드 초기화 트랜지스터들은 상기 유기 발광 다이오드들의 기생 커패시터들을 상기 초기화 전압 라인으로 방전시키는 방전 경로들을 형성하고, 구동 트랜지스터들의 누설 전류들이 상기 초기화 전압 라인으로 흐르게 하는 누설 전류 경로들을 형성할 수 있다.

[0011] 일 실시예에서, 상기 부분 구동 모드에서, 상기 구동되지 않는 부분 패널 영역에 인가되는 상기 다이오드 초기화 신호들은 적어도 1 수평 시간 동안 온 레벨을 동시에 가질 수 있다.

- [0012] 일 실시예에서, 상기 부분 구동 모드에서, 상기 구동되지 않는 부분 패널 영역에 인가되는 상기 다이오드 초기화 신호들은 상기 부분 구동 모드의 첫 번째 프레임 구간에서 온 레벨을 순차적으로 가지고, 상기 일반 구동 모드로 전환될 때까지 상기 온 레벨로 유지될 수 있다.

- [0013] 일 실시예에서, 상기 제1 부분 패널 영역은 제1 내지 제N 화소 행들(N은 2 이상의 정수)을 포함하고, 상기 제2 부분 패널 영역은 제N+1 내지 제N+M 화소 행들(M은 2 이상의 정수)을 포함하며, 상기 스캔 신호들은 제1 내지 제N+M 스캔 신호들을 포함하고, 상기 스캔 드라이버는, 제1 스캔 개시 신호에 응답하여 상기 제1 화소 행에 상기 제1 스캔 신호를 인가하는 제1 스캔 스테이지, 상기 제1 내지 제N-1 스캔 신호들에 응답하여 상기 제2 내지 제N 화소 행들에 상기 제2 내지 제N 스캔 신호들을 인가하는 제2 내지 제N 스캔 스테이지들, 모드 제어 신호에 응답하여 제2 스캔 개시 신호 또는 상기 제N 스캔 신호를 선택적으로 출력하는 스캔 입력 제어 회로, 상기 스캔 입력 제어 회로의 출력 신호에 응답하여 상기 제N+1 화소 행에 상기 제N+1 스캔 신호를 인가하는 제N+1 스캔 스테이지, 및 상기 제N+1 내지 제N+M-1 스캔 신호들에 응답하여 상기 제N+2 내지 제N+M 화소 행들에 상기 N+2 내지 제N+M 스캔 신호들을 인가하는 제N+2 내지 제N+M 스캔 스테이지들을 포함할 수 있다.

- [0014] 일 실시예에서, 상기 스캔 입력 제어 회로는, 상기 일반 구동 모드에서 온 레벨을 가지는 상기 모드 제어 신호에 응답하여 상기 제N 스캔 스테이지로부터 출력된 상기 제N 스캔 신호를 출력하는 제1 스캔 입력 제어 트랜지스터, 및 상기 부분 구동 모드에서 상기 온 레벨을 가지는 반전된 모드 제어 신호에 응답하여 상기 제2 스캔 개시 신호를 출력하는 제2 스캔 입력 제어 트랜지스터를 포함할 수 있다.

- [0015] 일 실시예에서, 상기 일반 구동 모드에서, 상기 모드 제어 신호는 온 레벨을 가지고, 상기 제1 스캔 개시 신호는 매 프레임 구간마다 스캔 시작 펄스를 포함하고, 상기 제2 스캔 개시 신호는 오프 레벨을 가지고, 상기 부분 구동 모드에서, 상기 제1 부분 패널 영역이 구동되고, 상기 제2 부분 패널 영역이 구동되지 않을 때, 상기 모드 제어 신호는 상기 오프 레벨을 가지고, 상기 제1 스캔 개시 신호는 매 프레임 구간마다 상기 스캔 시작 펄스를 포함하고, 상기 제2 스캔 개시 신호는 상기 오프 레벨을 가지고, 상기 부분 구동 모드에서, 상기 제1 부분 패널 영역이 구동되지 않고, 상기 제2 부분 패널 영역이 구동될 때, 상기 모드 제어 신호는 상기 오프 레벨을 가지고, 상기 제1 스캔 개시 신호는 상기 오프 레벨을 가지고, 상기 제2 스캔 개시 신호는 매 프레임 구간마다 상기 스캔 시작 펄스를 포함할 수 있다.

- [0016] 일 실시예에서, 상기 제1 부분 패널 영역은 제1 내지 제N 화소 행들(N은 2 이상의 정수)을 포함하고, 상기 제2 부분 패널 영역은 제N+1 내지 제N+M 화소 행들(M은 2 이상의 정수)을 포함하며, 상기 다이오드 초기화 신호들은 제1 내지 제N+M 다이오드 초기화 신호들을 포함하고, 상기 스캔 드라이버는, 제1 다이오드 초기화 개시 신호에 응답하여 상기 제1 화소 행에 상기 제1 다이오드 초기화 신호를 인가하는 제1 다이오드 초기화 스테이지, 상기 제1 내지 제N-1 다이오드 초기화 신호들에 응답하여 상기 제2 내지 제N 화소 행들에 상기 제2 내지 제N 다이오드 초기화 신호들을 인가하는 제2 내지 제N 다이오드 초기화 스테이지들, 모드 제어 신호에 응답하여 제2 다이오드 초기화 개시 신호 또는 상기 제N 다이오드 초기화 신호를 선택적으로 출력하는 다이오드 초기화 입력 제어 회로, 상기 다이오드 초기화 입력 제어 회로의 출력 신호에 응답하여 상기 제N+1 화소 행에 상기 제N+1 다이오드 초기화 신호를 인가하는 제N+1 다이오드 초기화 스테이지, 및 상기 제N+1 내지 제N+M-1 다이오드 초기화 신호들에 응답하여 상기 제N+2 내지 제N+M 화소 행들에 상기 제N+2 내지 제N+M 다이오드 초기화 신호들을 인가하는 제N+2 내지 제N+M 다이오드 초기화 스테이지들을 포함할 수 있다.

- [0017] 일 실시예에서, 상기 다이오드 초기화 입력 제어 회로는, 상기 일반 구동 모드에서 온 레벨을 가지는 상기 모드 제어 신호에 응답하여 상기 제N 다이오드 초기화 스테이지로부터 출력된 상기 제N 다이오드 초기화 신호를 출력하는 제1 다이오드 초기화 입력 제어 트랜지스터, 및 상기 부분 구동 모드에서 상기 온 레벨을 가지는 반전된 모드 제어 신호에 응답하여 상기 제2 다이오드 초기화 개시 신호를 출력하는 제2 다이오드 초기화 입력 제어 트랜지스터를 포함할 수 있다.

- [0018] 일 실시예에서, 상기 일반 구동 모드에서, 상기 모드 제어 신호는 온 레벨을 가지고, 상기 제1 다이오드 초기화 개시 신호는 매 프레임 구간마다 다이오드 초기화 시작 펄스를 포함하고, 상기 제2 다이오드 초기화 개시 신호는 오프 레벨을 가지고, 상기 부분 구동 모드에서, 상기 제1 부분 패널 영역이 구동되고, 상기 제2 부분 패널 영역이 구동되지 않을 때, 상기 모드 제어 신호는 상기 오프 레벨을 가지고, 상기 제1 다이오드 초기화 개시 신호는 매 프레임 구간마다 상기 다이오드 초기화 시작 펄스를 포함하고, 상기 제2 다이오드 초기화 개시 신호는 상기 온 레벨을 가지고, 상기 부분 구동 모드에서, 상기 제1 부분 패널 영역이 구동되지 않고, 상기 제2 부분 패널 영역이 구동될 때, 상기 모드 제어 신호는 상기 오프 레벨을 가지고, 상기 제1 다이오드 초기화 개시 신호는 상기 온 레벨을 가지고, 상기 제2 다이오드 초기화 개시 신호는 매 프레임 구간마다 상기 다이오드 초기화

시작 펄스를 포함할 수 있다.

[0019] 일 실시예에서, 상기 제1 내지 제N 다이오드 초기화 스테이지들은 제1 및 제2 다이오드 초기화 클록 신호들에 응답하여 동작하고, 상기 제N+1 내지 제N+M 다이오드 초기화 스테이지들은 제3 및 제4 다이오드 초기화 클록 신호들에 응답하여 동작하고, 상기 일반 구동 모드에서, 상기 제1 및 제2 다이오드 초기화 클록 신호들은 상기 제3 및 제4 다이오드 초기화 클록 신호들과 각각 동일한 위상을 가지고, 상기 부분 구동 모드에서, 상기 제1 부분 패널 영역이 구동되고, 상기 제2 부분 패널 영역이 구동되지 않을 때, 상기 제1 및 제2 다이오드 초기화 클록 신호들은 온 레벨과 오프 레벨 사이에서 주기적으로 토클링하고, 상기 제3 및 제4 다이오드 초기화 클록 신호들은 상기 온 레벨을 가지고, 상기 제2 다이오드 초기화 개시 신호는 상기 부분 구동 모드의 첫 번째 프레임 구간에서 상기 다이오드 초기화 시작 펄스를 포함하고, 상기 부분 구동 모드에서, 상기 제1 부분 패널 영역이 구동되지 않고, 상기 제2 부분 패널 영역이 구동될 때, 상기 제1 및 제2 다이오드 초기화 클록 신호들은 상기 온 레벨을 가지고, 상기 제3 및 제4 다이오드 초기화 클록 신호들은 상기 온 레벨과 상기 오프 레벨 사이에서 주기적으로 토클링하고, 상기 제1 다이오드 초기화 개시 신호는 상기 부분 구동 모드의 상기 첫 번째 프레임 구간에서 상기 다이오드 초기화 시작 펄스를 포함할 수 있다.

[0020] 본 발명의 일 목적을 달성하기 위하여, 본 발명의 실시예들에 따른 유기 발광 표시 장치는 제1 내지 제N 화소 행들(N은 2 이상의 정수)을 포함하는 제1 부분 패널 영역 및 제N+1 내지 제N+M 화소 행들(M은 2 이상의 정수)을 포함하는 제2 부분 패널 영역을 포함하는 표시 패널, 상기 제1 및 제2 부분 패널 영역들이 모두 구동되는 일반 구동 모드에서 상기 제1 내지 제N+M 화소 행들에 스캔 신호들을 순차적으로 인가하고, 상기 제1 부분 패널 영역이 구동되지 않고 상기 제2 부분 패널 영역이 구동되는 부분 구동 모드에서 상기 제N+1 내지 제N+M 화소 행들에 상기 스캔 신호들을 순차적으로 인가하는 스캔 드라이버, 및 상기 일반 구동 모드에서 상기 제1 내지 제N+M 화소 행들에 데이터 신호들을 인가하고, 상기 제1 부분 패널 영역이 구동되지 않고 상기 제2 부분 패널 영역이 구동되는 상기 부분 구동 모드에서 상기 제N+1 내지 제N+M 화소 행들에 상기 데이터 신호들을 인가하는 데이터 드라이버를 포함한다. 상기 스캔 드라이버는 상기 일반 구동 모드에서 상기 제1 내지 제N+M 화소 행들에 다이오드 초기화 신호들을 순차적으로 인가하고, 상기 제1 부분 패널 영역이 구동되지 않고 상기 제2 부분 패널 영역이 구동되는 상기 부분 구동 모드에서 상기 제N+1 내지 제N+M 화소 행들에 상기 다이오드 초기화 신호들을 순차적으로 인가하고, 상기 제1 내지 제N 화소 행들에 상기 다이오드 초기화 신호들을 동시에 인가한다.

[0021] 일 실시예에서, 상기 제1 부분 패널 영역이 구동되지 않고 상기 제2 부분 패널 영역이 구동되는 상기 부분 구동 모드에서, 상기 제1 내지 제N 화소 행들에 상기 스캔 신호들 및 상기 데이터 신호들이 인가되지 않을 수 있다.

[0022] 일 실시예에서, 상기 제1 부분 패널 영역이 구동되지 않고 상기 제2 부분 패널 영역이 구동되는 상기 부분 구동 모드에서, 상기 제1 부분 패널 영역에 포함되는 화소들의 유기 발광 다이오드들은 상기 동시에 인가되는 다이오드 초기화 신호들에 응답하여 초기화될 수 있다.

[0023] 일 실시예에서, 상기 제1 부분 패널 영역이 구동되지 않고 상기 제2 부분 패널 영역이 구동되는 상기 부분 구동 모드에서, 상기 제1 부분 패널 영역에 포함되는 화소들은 상기 동시에 인가되는 다이오드 초기화 신호들에 응답하여 전원 전압 라인으로부터 초기화 전압 라인으로의 누설 전류 경로들을 형성할 수 있다.

[0024] 일 실시예에서, 상기 제1 부분 패널 영역이 구동되지 않고 상기 제2 부분 패널 영역이 구동되는 상기 부분 구동 모드에서, 상기 제1 부분 패널 영역에 인가되는 상기 다이오드 초기화 신호들은 상기 부분 구동 모드의 첫 번째 프레임 구간에서 온 레벨을 순차적으로 가지고, 상기 일반 구동 모드로 전환될 때까지 상기 온 레벨로 유지될 수 있다.

[0025] 일 실시예에서, 상기 제1 부분 패널 영역이 구동되고 상기 제2 부분 패널 영역이 구동되지 않는 상기 부분 구동 모드에서, 상기 스캔 드라이버는 상기 제1 내지 제N 화소 행들에 상기 다이오드 초기화 신호들을 순차적으로 인가하고, 상기 제N+1 내지 제N+M 화소 행들에 상기 다이오드 초기화 신호들을 동시에 인가할 수 있다.

### 발명의 효과

[0026] 본 발명의 실시예들에 따른 유기 발광 표시 장치는, 부분 구동 모드에서 구동되지 않는 부분 패널 영역에 다이오드 초기화 신호들을 동시에 인가함으로써, 상기 구동되지 않는 부분 패널 영역의 화소들에서 유기 발광 다이오드들의 기생 커패시터들을 방전시키는 방전 경로들 및 구동 트랜지스터들의 누설 전류들이 흐르는 누설 전류 경로들이 형성되게 할 수 있고, 이에 따라 상기 구동되지 않는 부분 패널 영역의 원치 않는 발광을 방지할 수 있다.

[0027] 다만, 본 발명의 효과는 상기 언급한 효과에 한정되는 것이 아니며, 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위에서 다양하게 확장될 수 있을 것이다.

### 도면의 간단한 설명

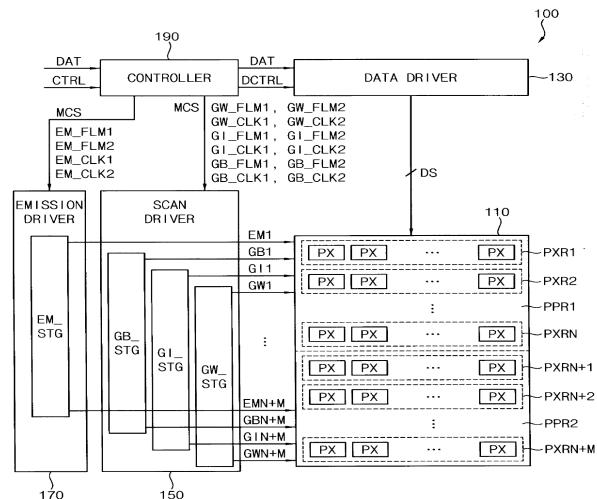

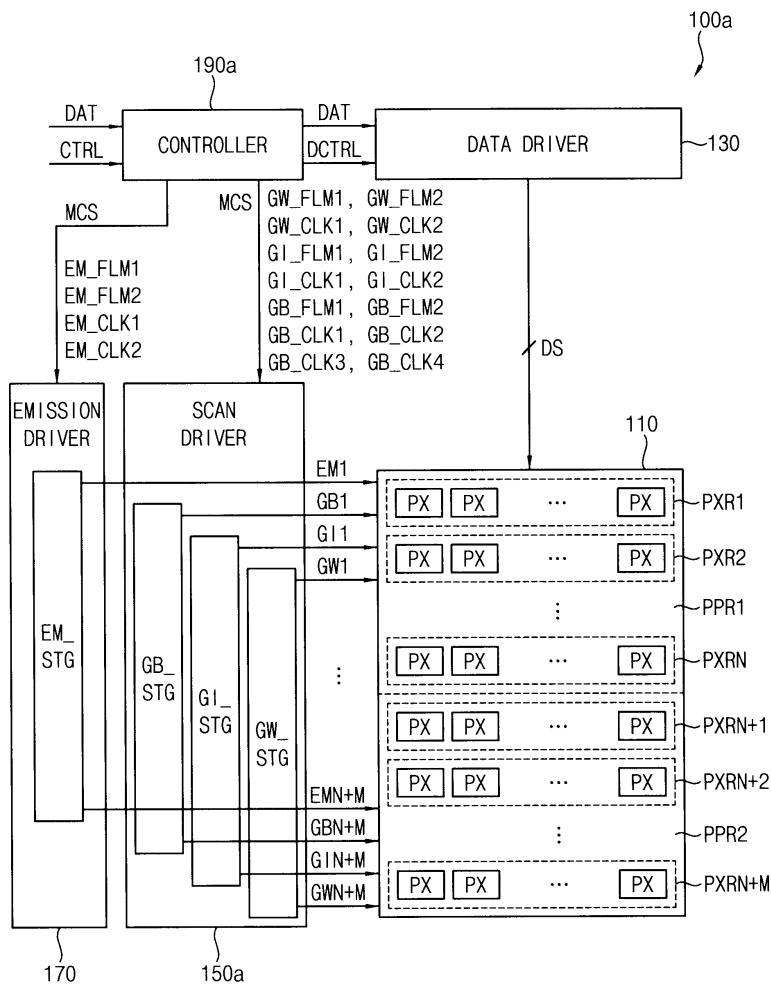

[0028] 도 1은 본 발명의 실시예들에 따른 유기 발광 표시 장치를 나타내는 블록도이다.

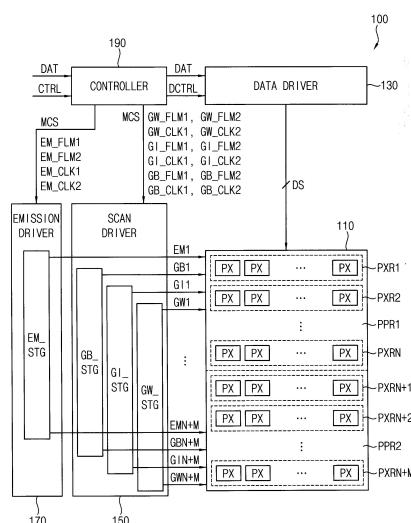

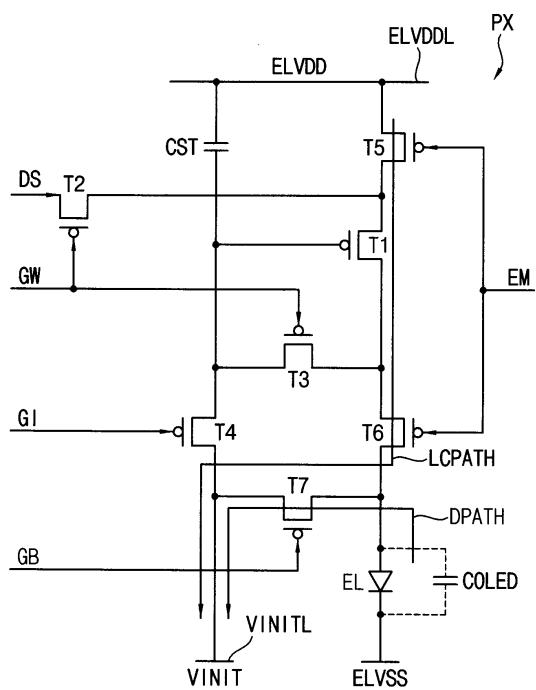

도 2는 도 1의 유기 발광 표시 장치에 포함된 화소의 일 예를 나타내는 회로도이다.

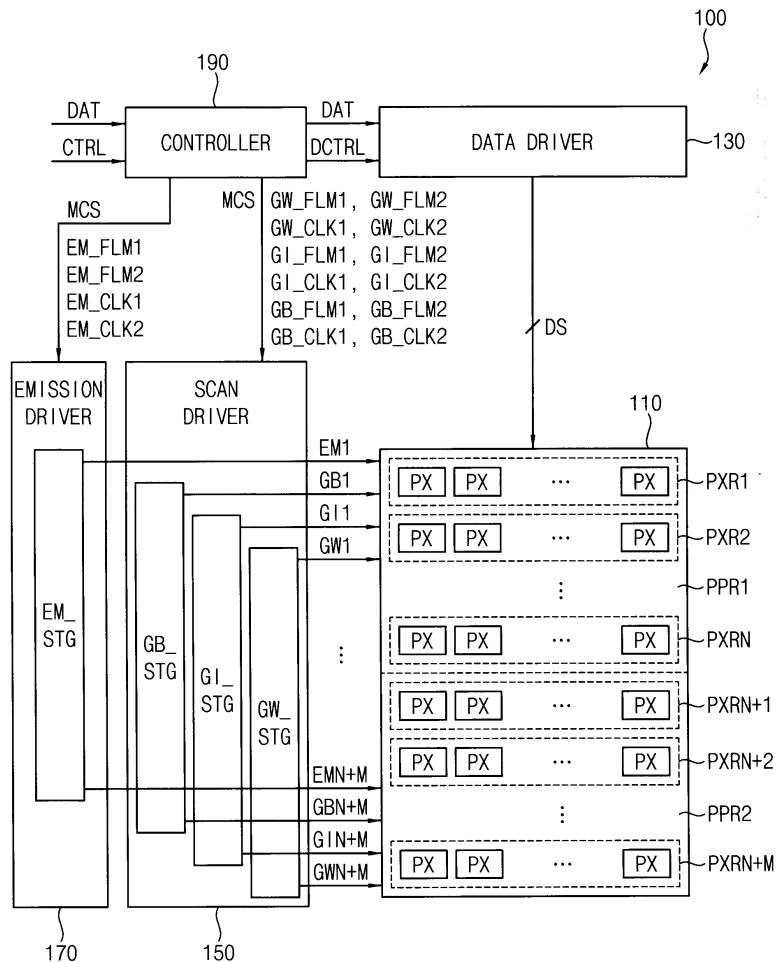

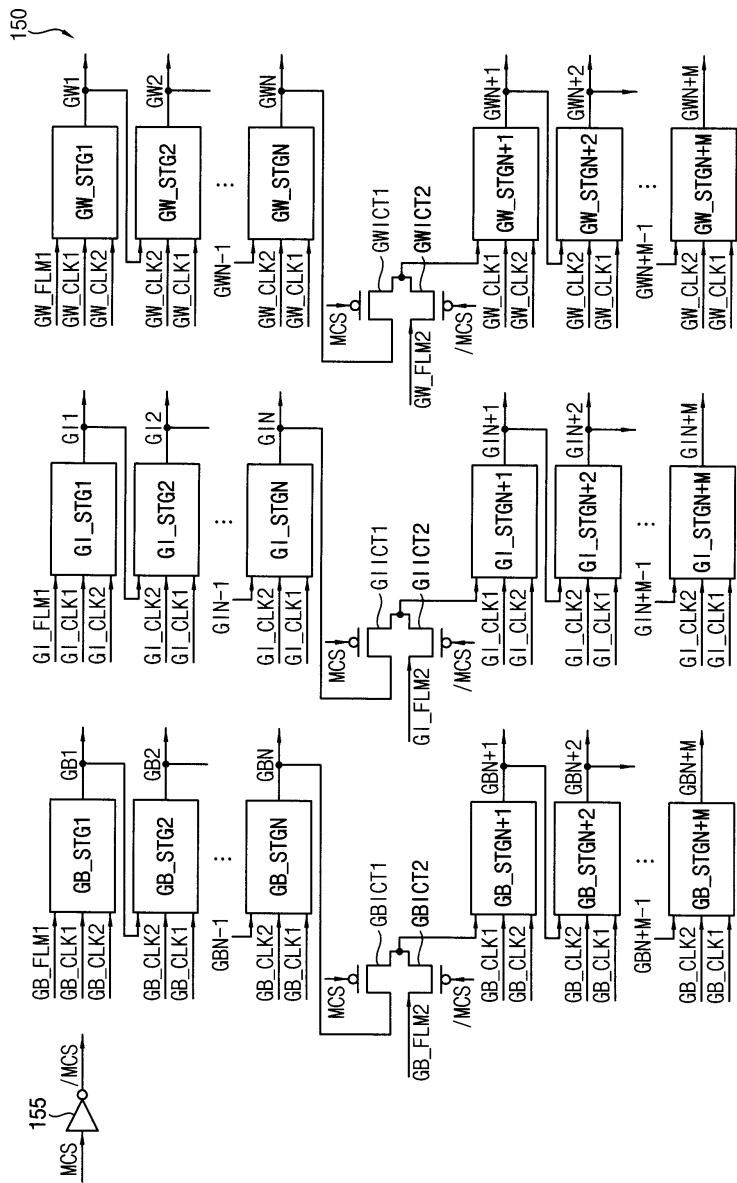

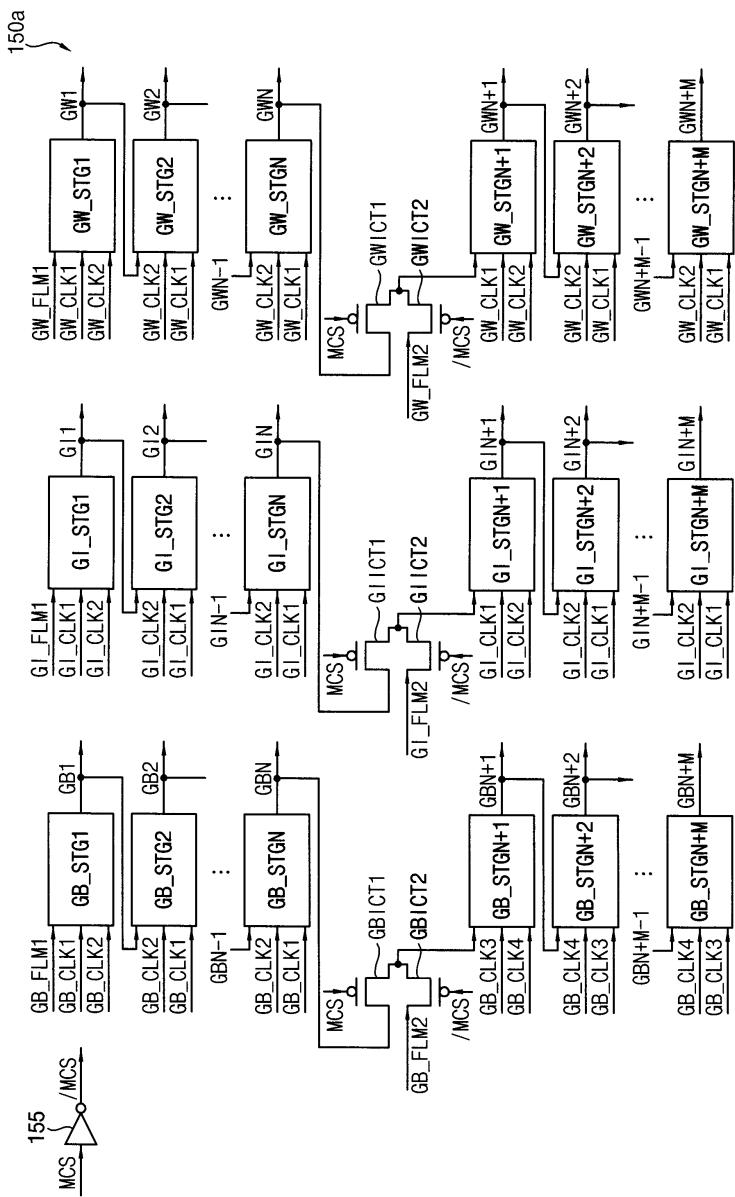

도 3은 도 1의 유기 발광 표시 장치에 포함된 스캔 드라이버의 일 예를 나타내는 블록도이다.

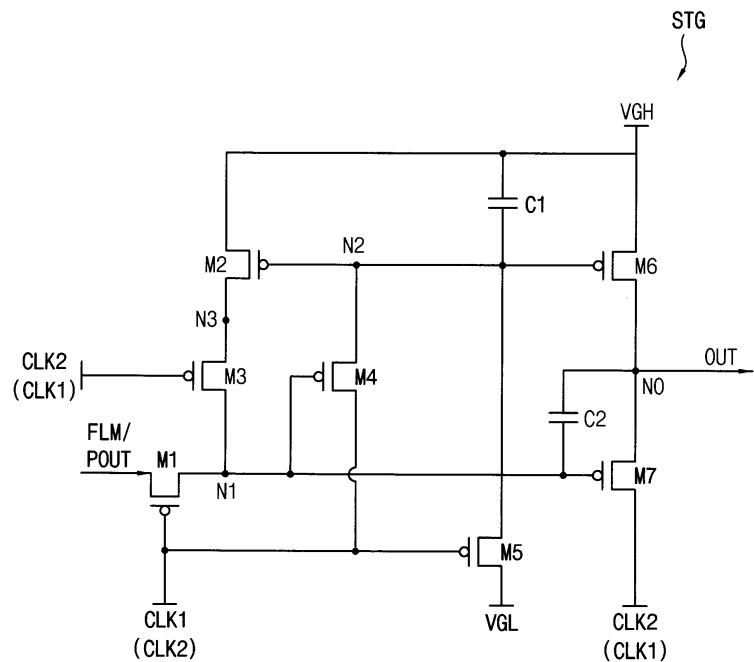

도 4는 도 3의 스캔 드라이버에 포함된 각 스테이지의 일 예를 나타내는 회로도이다.

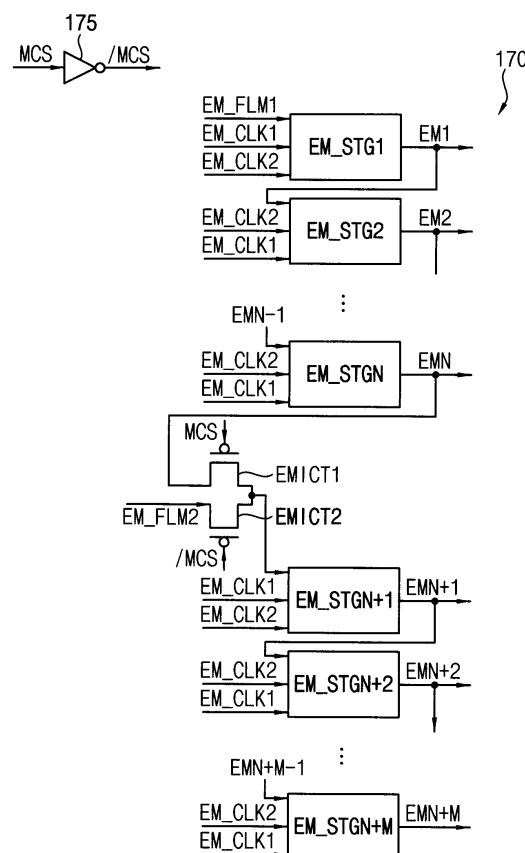

도 5는 도 1의 유기 발광 표시 장치에 포함된 발광 드라이버의 일 예를 나타내는 블록도이다.

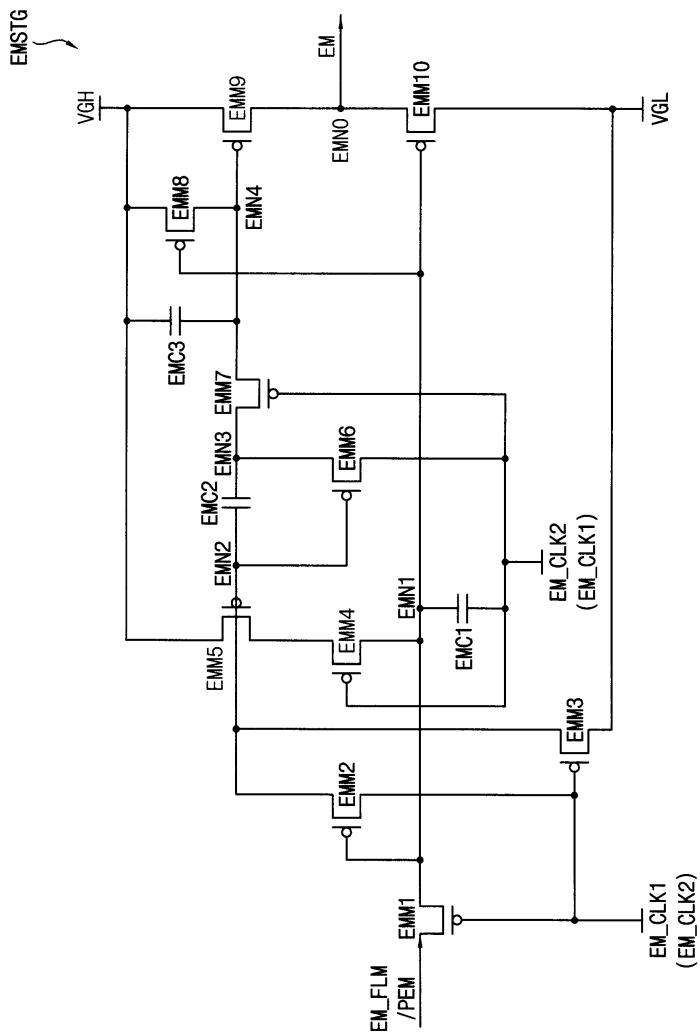

도 6은 도 5의 발광 드라이버에 포함된 각 스테이지의 일 예를 나타내는 회로도이다.

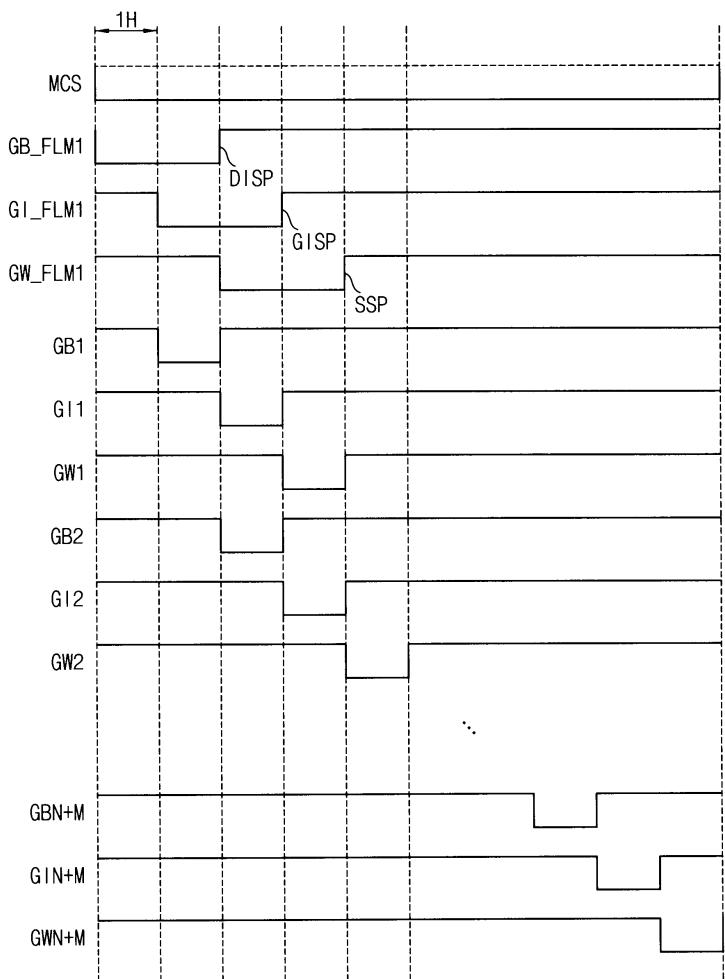

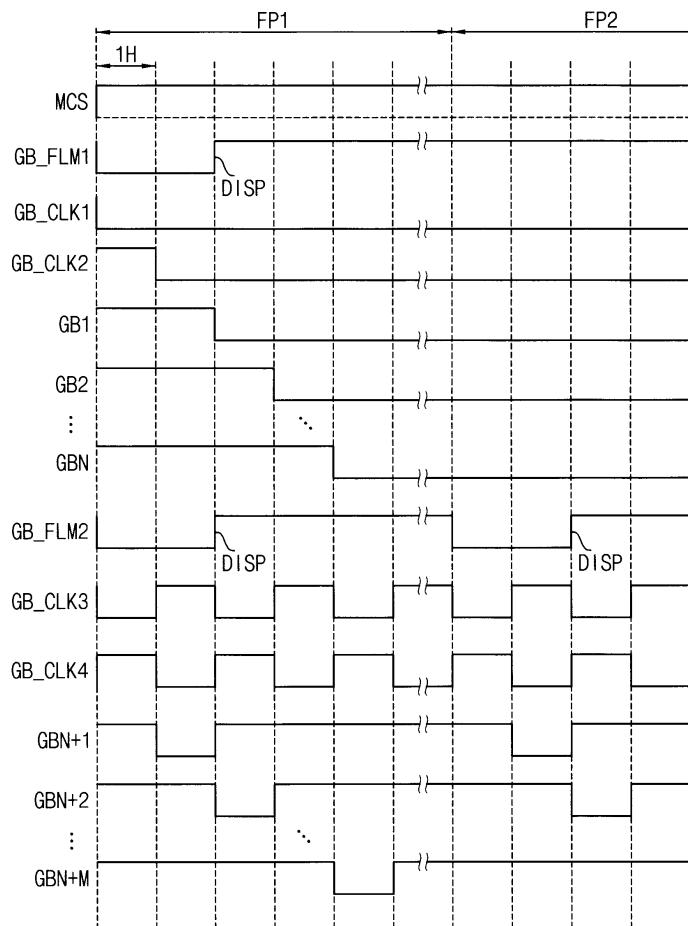

도 7은 일반 구동 모드에서의 도 1의 유기 발광 표시 장치의 동작의 일 예를 설명하기 위한 타이밍도이다.

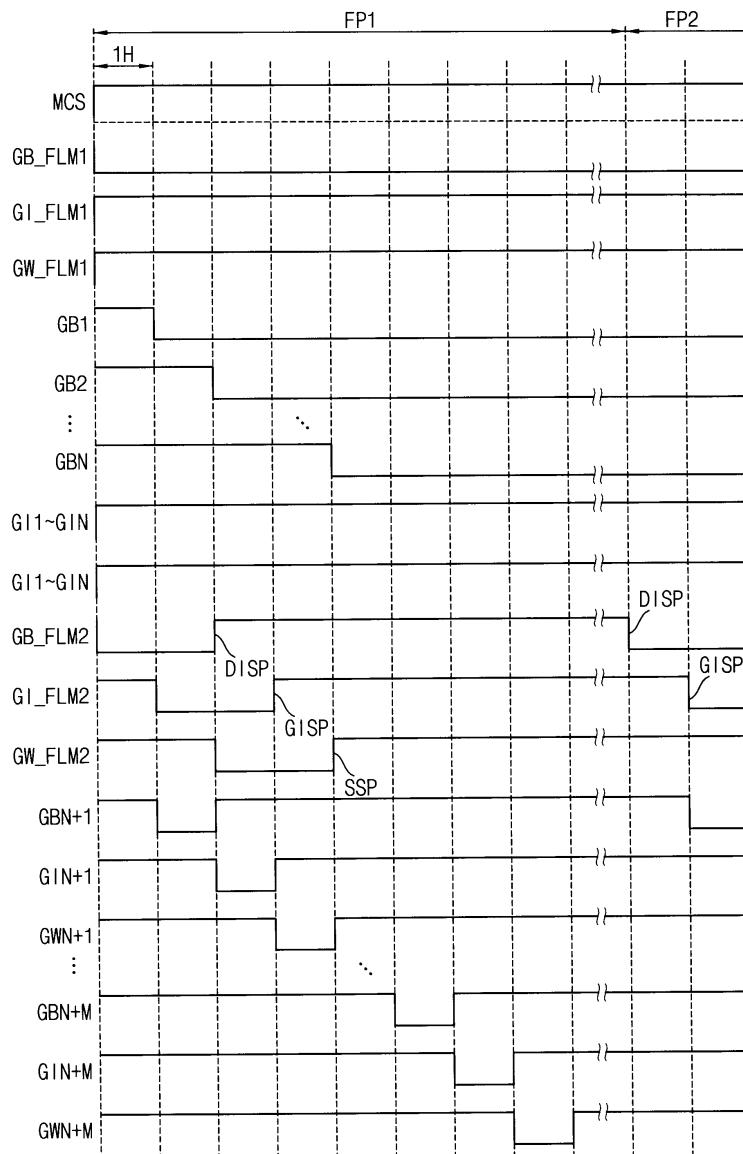

도 8은 부분 구동 모드에서의 도 1의 유기 발광 표시 장치의 동작의 일 예를 설명하기 위한 타이밍도이다.

도 9는 본 발명의 다른 실시예들에 따른 유기 발광 표시 장치를 나타내는 도면이다.

도 10은 도 9의 유기 발광 표시 장치에 포함된 스캔 드라이버의 일 예를 나타내는 블록도이다.

도 11은 부분 구동 모드에서의 도 9의 유기 발광 표시 장치의 동작의 일 예를 설명하기 위한 타이밍도이다.

도 12는 본 발명의 실시예들에 따른 유기 발광 표시 장치를 포함하는 전자 기기를 나타내는 블록도이다.

### 발명을 실시하기 위한 구체적인 내용

[0029] 이하, 첨부한 도면들을 참조하여, 본 발명의 바람직한 실시예를 보다 상세하게 설명하고자 한다. 도면상의 동일한 구성요소에 대해서는 동일한 참조부호를 사용하고 동일한 구성요소에 대해서 중복된 설명은 생략한다.

[0030] 도 1은 본 발명의 실시예들에 따른 유기 발광 표시 장치를 나타내는 블록도이다.

[0031] 도 1을 참조하면, 본 발명의 실시예들에 따른 유기 발광 표시 장치(100)는 표시 패널(110), 표시 패널(110)에 데이터 신호들(DS)을 제공하는 데이터 드라이버(130), 표시 패널(110)에 스캔 신호들(GW1 내지 GWN+M), 게이트 초기화 신호들(GI1 내지 GIN+M) 및 다이오드 초기화 신호들(GB1 내지 GBN+M)을 제공하는 스캔 드라이버(150), 표시 패널(110)에 발광 제어 신호들(EM1 내지 EMN+M)을 제공하는 발광 드라이버(170), 및 데이터 드라이버(130), 스캔 드라이버(150) 및 발광 드라이버(170)를 제어하는 컨트롤러(190)를 포함할 수 있다.

[0032] 표시 패널(110)은 복수의 데이터 라인들, 복수의 스캔 라인들, 복수의 게이트 초기화 라인들, 복수의 다이오드 초기화 라인들, 복수의 발광 제어 라인들, 및 이들에 연결된 복수의 화소들(PX)을 포함할 수 있다. 표시 패널(110)은 각 화소(PX)가 유기 발광 다이오드(Organic Light Emitting Diode; OLED)를 포함하는 OLED 표시 패널일 수 있다. 일 실시예에서, 표시 패널(110)은 폴더블(foldable) 표시 패널, 롤러블(rollable) 표시 패널, 스트레치블(stretchable) 표시 패널 등과 같은 플렉서블(flexible) 표시 패널일 수 있다.

[0033] 일 실시예에서, 각 화소(PX)는, 도 2에 도시된 바와 같이, 구동 트랜지스터(T1), 스위칭 트랜지스터(T2), 보상 트랜지스터(T3), 게이트 초기화 트랜지스터(T4), 제1 발광 트랜지스터(T5), 제2 발광 트랜지스터(T6), 다이오드 초기화 트랜지스터(T7), 저장 커패시터(CST) 및 유기 발광 다이오드(EL)를 포함할 수 있다. 구동 트랜지스터(T1)는 저장 커패시터(CST)에 저장된 전압에 기초하여 구동 전류를 생성할 수 있다. 스위칭 트랜지스터(T2)는 스캔 신호(GW)에 응답하여 데이터 신호(DS)를 구동 트랜지스터(T1)의 소스로 전달할 수 있다. 보상 트랜지스터(T3)는 스캔 신호(GW)에 응답하여 구동 트랜지스터(T1)를 다이오드-연결시킬 수 있다. 저장 커패시터(CST)는 구동 트랜지스터(T1)의 게이트와 제1 전원 전압(ELVDD)의 라인(ELVDDL) 사이에 연결될 수 있다. 예를 들어, 스캔 신호(GW)가 인가되는 동안, 저장 커패시터(CST)에는 보상 트랜지스터(T3)에 의해 다이오드-연결된 구동 트랜지스터(T1)를 통하여 데이터 신호(DS)에 구동 트랜지스터(T1)의 음의 문턱 전압이 가산된 보상 전압이 인가될 수 있다. 초기화 트랜지스터(T4)는 게이트 초기화 신호(GI)에 응답하여 초기화 전압(VINIT)을 구동 트랜지스터(T1)의 게이트 및 저장 커패시터(CST)에 인가할 수 있다. 초기화 트랜지스터(T4)를 통하여 인가되는 초기화 전압(VINIT)에 의해 구동 트랜지스터(T1)의 게이트 및 저장 커패시터(CST)가 초기화될 수 있다. 제1 발광 트랜지스터(T5)는 발광 제어 신호(EM)에 응답하여 제1 전원 전압 라인(ELVDDL)을 구동 트랜지스터(T1)의 소스에 연결하

고, 제2 발광 트랜지스터(T6)는 발광 제어 신호(EM)에 응답하여 구동 트랜지스터(T1)의 드레인을 유기 발광 다이오드(EL)에 연결할 수 있다. 예를 들어, 발광 제어 신호(EM)가 인가되는 동안, 제1 및 제2 발광 트랜지스터들(T5, T6)이 편-온되어, 제1 전원 전압 라인(ELVDDL)으로부터 제1 발광 트랜지스터(T5), 구동 트랜지스터(T1), 제2 발광 트랜지스터(T6) 및 유기 발광 다이오드(EL)를 통하여 제2 전원 전압(ELVSS)의 라인으로 상기 구동 전류가 흐르는 경로가 형성될 수 있다. 다이오드 초기화 트랜지스터(또는 바이패스 트랜지스터)(T7)는 다이오드 초기화 신호(또는 바이패스 신호)(GB)에 응답하여 초기화 전압(VINIT)의 라인(VINITL)을 유기 발광 다이오드(EL)의 애노드 및 제2 발광 트랜지스터(T6)의 드레인에 연결할 수 있다. 일 실시예에서, 다이오드 초기화 트랜지스터(T7)는 다이오드 초기화 신호(GB)를 수신하는 게이트, 초기화 전압 라인(VINITL)에 연결된 제1 단자, 및 유기 발광 다이오드(EL)의 애노드에 연결된 제2 단자를 포함할 수 있다. 유기 발광 다이오드(EL)는 제2 발광 트랜지스터(T6)와 제2 전원 전압(ELVSS)의 라인 사이에 연결될 수 있다. 한편, 도 2에는 각 화소(PX)가 7개의 트랜지스터들(T1 내지 T7) 및 하나의 커패시터(CST)를 포함하는 7T1C 구조를 가진 예가 도시되어 있으나, 본 발명의 실시예들에 따른 유기 발광 표시 장치(100)에 포함된 화소(PX)는 상기 7T1C 구조에 한정되지 않는다. 예를 들어, 본 발명의 실시예들에 따른 유기 발광 표시 장치(100)에 포함된 각 화소(PX)는 다이오드 초기화 신호(GB)에 응답하여 초기화 전압 라인(VINITL)을 유기 발광 다이오드(EL)의 애노드에 연결하는 다이오드 초기화 트랜지스터(T7)를 포함하는 임의의 구조를 가질 수 있다.

[0034] 표시 패널(110)은 복수의 부분 패널 영역들(PPR1, PPR2)을 포함할 수 있다. 일반 구동 모드에서 복수의 부분 패널 영역들(PPR1, PPR2)이 모두 구동되고, 부분 구동 모드(Partial Driving Mode)에서 복수의 부분 패널 영역들(PPR1, PPR2) 중 일부가 구동되고, 나머지가 구동되지 않을 수 있다. 일 실시예에서, 표시 패널(110)은 제1 내지 제N 화소 행들(PXR1, PXR2, …, PXRN)(N은 2 이상의 정수)을 포함하는 제1 부분 패널 영역(PPR1), 및 제N+1 내지 제N+M 화소 행들(PXRN+1, PXRN+2, …, PXRN+M)(M은 2 이상의 정수)을 포함하는 제2 부분 패널 영역(PPR2)을 포함할 수 있다. 여기서, 각 화소 행(PXR1 내지 PRXN+M)은 동일한 스캔 라인(또는 동일한 게이트/다이오드 초기화 라인)에 연결된 일련의 화소들(PX)로서, 실시예에 따라 상하 방향으로 동일한 위치에 배치되거나, 적어도 일부가 서로 다른 위치들에 배치될 수 있다. 예를 들어, 복수의 화소들(PX)이 다이아몬드 형태로 배치되는 경우, 동일한 화소 행의 인접한 두 개의 화소들(PX)이 일부가 상하 방향으로 서로 다른 위치들에 배치될 수 있다. 상기 부분 구동 모드에서, 제1 및 제2 부분 패널 영역들(PPR1, PPR2) 중 하나가 구동되고, 다른 하나가 구동되지 않을 수 있다.

[0035] 일 예에서, 표시 패널(110)이 폴더블 표시 패널이고, 제1 부분 패널 영역(PPR1)이 유기 발광 표시 장치(100)의 배면에 위치하도록 표시 패널(110)이 접힌 경우, 유기 발광 표시 장치(100)는, 제2 부분 패널 영역(PPR2)을 구동하고, 제1 부분 패널 영역(PPR1)을 구동하지 않는 상기 부분 구동 모드로 동작할 수 있다. 한편, 도 1에는 표시 패널(110)이 두 개의 부분 패널 영역들(PPR1, PPR2)로 구분되는 예가 도시되어 있으나, 본 발명의 실시예들은 이에 한정되지 않는다.

[0036] 데이터 드라이버(130)는 컨트롤러(190)로부터 수신된 영상 데이터(DAT) 및 데이터 제어 신호(DCTRL)에 기초하여 복수의 화소들(PX)에 데이터 신호들(DS)을 제공할 수 있다. 일 실시예에서, 데이터 제어 신호(DCTRL)는 수평 개시 신호 및 로드 신호를 포함할 수 있으나, 이에 한정되지 않는다. 한편, 제1 및 제2 부분 패널 영역들(PPR1, PPR2)이 모두 구동되는 일반 구동 모드에서, 데이터 드라이버(130)는 제1 및 제2 부분 패널 영역들(PPR1, PPR2)에 데이터 신호들(DS)을 인가할 수 있다. 또한, 제1 부분 패널 영역(PPR1) 또는 제2 부분 패널 영역(PPR2) 중 하나의 부분 패널 영역이 구동되고 다른 하나의 부분 패널 영역이 구동되지 않는 부분 구동 모드에서, 데이터 드라이버(130)는 상기 구동되는 부분 패널 영역에 데이터 신호들(DS)을 인가하고, 상기 구동되지 않는 부분 패널 영역에 데이터 신호들(DS)을 인가하지 않을 수 있다. 예를 들어, 제1 부분 패널 영역(PPR1)이 구동되지 않고 제2 부분 패널 영역(PPR2)이 구동되는 상기 부분 구동 모드에서, 데이터 드라이버(130)는 제1 내지 제N 화소 행들(PXR1 내지 PRXN)에 데이터 신호들(DS)을 인가하지 않고, 제N+1 내지 제N+M 화소 행들(PXRN+1 내지 PRXN+M)에 데이터 신호들(DS)을 인가할 수 있다.

[0037] 스캔 드라이버(150)는 컨트롤러(190)로부터 수신된 스캔 제어 신호에 기초하여 복수의 화소들(PX)에 스캔 신호들(GW1 내지 GWN+M), 게이트 초기화 신호들(GI1 내지 GIN+M) 및 다이오드 초기화 신호들(GB1 내지 GBN+M)을 화소 행 단위로 순차적으로 제공할 수 있다. 일 실시예에서, 상기 스캔 제어 신호는 모드 제어 신호(MCS), 제1 및 제2 스캔 개시 신호들(GW\_FLM1, GW\_FLM2), 제1 및 제2 스캔 클록 신호들(GW\_CLK1, GW\_CLK2), 제1 및 제2 게이트 초기화 개시 신호들(GI\_FLM1, GI\_FLM2), 제1 및 제2 게이트 초기화 클록 신호들(GI\_CLK1, GI\_CLK2), 제1 및 제2 다이오드 초기화 개시 신호들(GB\_FLM1, GB\_FLM2), 및 제1 및 제2 다이오드 초기화 클록 신호들(GB\_CLK1, GB\_CLK2)을 포함할 수 있으나, 이에 한정되지 않는다. 한편, 제1 및 제2 부분 패널 영역들(PPR1, PPR2)이 모두

구동되는 상기 일반 구동 모드에서, 스캔 드라이버(150)는 제1 및 제2 부분 패널 영역들(PPR1, PPR2)에 스캔 신호들(GW1 내지 GWN+M), 게이트 초기화 신호들(GI1 내지 GIN+M) 및 다이오드 초기화 신호들(GB1 내지 GBN+M)을 화소 행 단위로 순차적으로 인가할 수 있다. 또한, 제1 부분 패널 영역(PPR1) 또는 제2 부분 패널 영역(PPR2) 중 하나의 부분 패널 영역이 구동되고 다른 하나의 부분 패널 영역이 구동되지 않는 부분 구동 모드에서, 스캔 드라이버(150)는 상기 구동되는 부분 패널 영역(예를 들어, PPR2)에 스캔 신호들(예를 들어, GWN+1 내지 GWN+M), 게이트 초기화 신호들(예를 들어, GIN+1 내지 GIN+M) 및 다이오드 초기화 신호들(예를 들어, GBN+1 내지 GBN+M)을 화소 행 단위로 순차적으로 인가하고, 상기 구동되지 않는 부분 패널 영역(예를 들어, PPR1)에 스캔 신호들(예를 들어, GWW1 내지 GWN) 및 게이트 초기화 신호들(예를 들어, GI1 내지 GIN)을 인가하지 않을 수 있다. 한편, 스캔 드라이버(150)는, 상기 부분 구동 모드에서, 상기 구동되지 않는 부분 패널 영역(예를 들어, PPR1)에 다이오드 초기화 신호들(예를 들어, GB1 내지 GBN)을 실질적으로 동시에 인가할 수 있다.

[0038]

일 실시예에서, 도 1에 도시된 바와 같이, 스캔 드라이버(130)는 스캔 신호들(GW1 내지 GWN+M)을 순차적으로 출력하기 위한 복수의 스캔 스테이지들(GW\_STG), 게이트 초기화 신호들(GI1 내지 GIN+M)을 순차적으로 출력하기 위한 복수의 게이트 초기화 스테이지들(GI\_STG), 및 다이오드 초기화 신호들(GB1 내지 GBN+M)을 순차적으로 출력하기 위한 복수의 다이오드 초기화 스테이지들(GB\_STG)을 포함할 수 있다. 예를 들어, 복수의 스캔 스테이지들(GW\_STG)은, 모드 제어 신호(MCS), 제1 및 제2 스캔 개시 신호들(GW\_FLM1, GW\_FLM2) 및 제1 및 제2 스캔 클록 신호들(GW\_CLK1, GW\_CLK2)에 기초하여, 상기 일반 구동 모드에서 제1 내지 제N+M 화소 행들(PXR1 내지 PXN+M)에 제1 내지 제N+M 스캔 신호들(GW1 내지 GWN+M)을 순차적으로 출력할 수 있고, 상기 부분 구동 모드에서 제1 내지 제N+M 화소 행들(PXR1 내지 PXN+M) 중 일부(예를 들어, PXRN+1 내지 PXN+M)에 제1 내지 제N+M 스캔 신호들(GW1 내지 GWN+M)의 일부(예를 들어, GWN+1 내지 GWN+M)을 순차적으로 출력할 수 있다. 또한, 복수의 게이트 초기화 스테이지들(GI\_STG)은, 모드 제어 신호(MCS), 제1 및 제2 게이트 초기화 개시 신호들(GI\_FLM1, GI\_FLM2), 및 제1 및 제2 게이트 초기화 클록 신호들(GI\_CLK1, GI\_CLK2)에 기초하여, 상기 일반 구동 모드에서 제1 내지 제N+M 화소 행들(PXR1 내지 PXN+M)에 제1 내지 제N+M 게이트 초기화 신호들(GI1 내지 GIN+M)을 순차적으로 출력할 수 있고, 상기 부분 구동 모드에서 제1 내지 제N+M 화소 행들(PXR1 내지 PXN+M) 중 일부(예를 들어, PXRN+1 내지 PXN+M)에 제1 내지 제N+M 게이트 초기화 신호들(GI1 내지 GIN+M)의 일부(예를 들어, GIN+1 내지 GIN+M)을 순차적으로 출력할 수 있다. 복수의 다이오드 초기화 스테이지들(GB\_STG)은, 모드 제어 신호(MCS), 제1 및 제2 다이오드 초기화 개시 신호들(GB\_FLM1, GB\_FLM2), 및 제1 및 제2 다이오드 초기화 클록 신호들(GB\_CLK1, GB\_CLK2)에 기초하여, 상기 일반 구동 모드에서 제1 내지 제N+M 화소 행들(PXR1 내지 PXN+M)에 제1 내지 제N+M 다이오드 초기화 신호들(GB1 내지 GBN+M)을 순차적으로 출력할 수 있다. 한편, 복수의 다이오드 초기화 스테이지들(GB\_STG)은, 상기 부분 구동 모드에서, 상기 구동되는 부분 패널 영역(예를 들어, PPR2)에 상기 다이오드 초기화 신호들(예를 들어, GBN+1 내지 GBN+M)을 순차적으로 인가하고, 상기 구동되지 않는 부분 패널 영역(예를 들어, PPR1)에 상기 다이오드 초기화 신호들(예를 들어, GB1 내지 GBN)을 실질적으로 동시에 인가할 수 있다. 한편, 도 1에는 스캔 신호(GW), 게이트 초기화 신호(GI) 및 다이오드 초기화 신호(GB)가 서로 다른 스테이지들(GW\_STG, GI\_STG, GB\_STG)에 의해 출력되는 예가 도시되어 있으나, 실시예에 따라, 스캔 신호(GW), 게이트 초기화 신호(GI)와 다이오드 초기화 신호(GB) 중 적어도 일부는 동일한 스테이지에 의해 출력될 수 있다. 예를 들어, 각 화소 행의 게이트 초기화 신호(GI)로서 이전 화소 행에 대한 스캔 신호(GW)가 이용될 수 있다. 이 경우, 스캔 드라이버(130)는 스캔 스테이지들(GW\_STG) 및 다이오드 초기화 스테이지들(GB\_STG)만을 포함하고, 게이트 초기화 스테이지들(GI\_STG)을 포함하지 않을 수 있다.

[0039]

발광 드라이버(170)는 컨트롤러(190)로부터 수신된 발광 드라이버 제어 신호에 기초하여 복수의 화소들(PX)에 발광 제어 신호들(EM1 내지 EMN+M)을 순차적으로 제공할 수 있다. 일 실시예에서, 상기 발광 드라이버 제어 신호는 모드 제어 신호(MCS), 제1 및 제2 발광 제어 개시 신호들(EM\_FLM1, EM\_FLM2), 및 제1 및 제2 발광 제어 클록 신호들(EM\_CLK1, EM\_CLK2)을 포함할 수 있으나, 이에 한정되지 않는다. 상기 일반 구동 모드에서, 발광 드라이버(170)는 제1 및 제2 부분 패널 영역들(PPR1, PPR2)에 발광 제어 신호들(EM1 내지 EMN+M)을 화소 행 단위로 순차적으로 인가함으로써, 제1 내지 제N+M 화소 행들(PXR1 내지 PXRN+M)이 순차적으로 발광하게 할 수 있다. 또한, 상기 부분 구동 모드에서, 발광 드라이버(170)는 상기 구동되는 부분 패널 영역(예를 들어, PPR2)에 발광 제어 신호들(예를 들어, EMN+1 내지 EMN+M)을 화소 행 단위로 순차적으로 인가하고, 상기 구동되지 않는 부분 패널 영역(예를 들어, PPR1)에 발광 제어 신호들(예를 들어, EM1 내지 EMN)을 인가하지 않을 수 있다. 일 실시예에서, 발광 드라이버(170)는 발광 제어 신호들(EM1 내지 EMN+M)을 순차적으로 출력하기 위한 복수의 발광 제어 스테이지들(EM\_STG)을 포함할 수 있다.

[0040]

한편, 도 1에는 스캔 드라이버(150) 및 발광 드라이버(170)가 표시 패널(110)의 일 측에만 배치된 예가 도시되어 있으나, 실시예에 따라, 스캔 드라이버(150) 및 발광 드라이버(170)는 표시 패널(110)의 양 측 모두에 배치

될 수 있다.

[0041] 컨트롤러(예를 들어, 타이밍 컨트롤러(Timing Controller))(190)는 외부의 호스트(예를 들어, 그래픽 처리 유닛(Graphic Processing Unit; GPU) 또는 그래픽 카드(Graphic Card))로부터 영상 데이터(DAT) 및 제어 신호(CTRL)를 수신할 수 있다. 일 실시예에서, 제어 신호(CTRL)는 메인 클록 신호, 수직 동기 신호, 수평 동기 신호, 데이터 인에이블 신호 등을 포함할 수 있으나, 이에 한정되지 않는다. 컨트롤러(190)는 데이터 드라이버(130)에 영상 데이터(DAT) 및 데이터 제어 신호(DCTRL)를 제공하여 데이터 드라이버(130)를 제어할 수 있고, 스캔 드라이버(150)에 모드 제어 신호(MCS), 개시 신호들(GW\_FLM1, GW\_FLM2, GI\_FLM1, GI\_FLM2, GB\_FLM1, GB\_FLM2) 및 클록 신호들(GW\_CLK1, GW\_CLK2, GI\_CLK1, GI\_CLK2, GB\_CLK1, GB\_CLK2)을 제공하여 스캔 드라이버(150)를 제어할 수 있고, 발광 드라이버(170)에 모드 제어 신호(MCS), 발광 제어 개시 신호들(EM\_FLM1, EM\_FLM2) 및 발광 제어 클록 신호들(EM\_CLK1, EM\_CLK2)을 제공하여 발광 드라이버(170)를 제어할 수 있다.

[0042] 한편, 상기 부분 구동 모드에서, 상기 구동되지 않는 부분 패널 영역에 데이터 신호들(DS)이 인가되지 않더라도, 상기 구동되지 않는 부분 패널 영역이 잔류 전하들 또는 누설 전류들에 의해 원치 않게 발광할 수 있다. 예를 들어, 상기 구동되지 않는 부분 패널 영역의 어떠한 화소(PX)에서, 유기 발광 다이오드(EL)의 기생 커페시터(COLED)에는 이전 프레임 구간에서의 데이터 신호(DS)에 기초하여 잔류 전하들이 존재할 수 있고, 상기 화소(PX)가 구동되지 않더라도, 기생 커페시터(COLED)의 상기 잔류 전하들에 의해 상기 화소(PX)가 원치 않게 발광할 수 있다. 또한, 상기 화소(PX)가 구동되지 않더라도, 전원 전압 라인(ELVDDL)으로부터 구동 트랜지스터(T1)(및 발광 제어 트랜지스터들(T5, T6))의 누설 전류가 유기 발광 다이오드(EL)에 인가되어, 상기 누설 전류에 의해 상기 화소(PX)가 원치 않게 발광할 수 있다.

[0043] 그러나, 본 발명의 실시예들에 따른 유기 발광 표시 장치(100)에서는, 상기 부분 구동 모드에서, 스캔 드라이버(150)가 상기 구동되지 않는 부분 패널 영역(예를 들어, PPR1)에 상기 다이오드 초기화 신호들(예를 들어, GB1 내지 GBN)을 실질적으로 동시에 인가할 수 있다. 여기서, 스캔 드라이버(150)가 상기 구동되지 않는 부분 패널 영역(예를 들어, PPR1)에 상기 다이오드 초기화 신호들(예를 들어, GB1 내지 GBN)을 실질적으로 동시에 인가한다는 것은, 스캔 드라이버(150)가 상기 구동되지 않는 부분 패널 영역(예를 들어, PPR1)에 일정 시간 이상 온레벨(예를 들어, 로우 레벨)을 실질적으로 동시에 가지는 상기 다이오드 초기화 신호들(예를 들어, GB1 내지 GBN)을 인가하는 것을 의미할 수 있다. 일 실시예에서, 상기 부분 구동 모드에서, 상기 구동되지 않는 부분 패널 영역(예를 들어, PPR1)에 인가되는 상기 다이오드 초기화 신호들(예를 들어, GB1 내지 GBN)은 적어도 1 수평 시간 동안 상기 온레벨을 동시에 가질 수 있다. 또한, 일 실시예에서, 상기 부분 구동 모드에서, 상기 구동되지 않는 부분 패널 영역(예를 들어, PPR1)에 인가되는 상기 다이오드 초기화 신호들(예를 들어, GB1 내지 GBN)은 상기 부분 구동 모드의 첫 번째 프레임 구간에서 상기 온레벨을 순차적으로 가지고, 상기 일반 구동 모드로 전환될 때까지 상기 온레벨로 유지될 수 있다.

[0044] 상기 부분 구동 모드에서, 스캔 드라이버(150)가 상기 구동되지 않는 부분 패널 영역(예를 들어, PPR1)에 상기 다이오드 초기화 신호들(예를 들어, GB1 내지 GBN)을 실질적으로 동시에 인가하면, 상기 구동되지 않는 부분 패널 영역(예를 들어, PPR1)에 포함되는 화소들(PX)의 유기 발광 다이오드들(EL)은 상기 동시에 인가되는 다이오드 초기화 신호들(예를 들어, GB1 내지 GBN)에 응답하여 초기화될 수 있다. 또한, 상기 부분 구동 모드에서, 상기 구동되지 않는 부분 패널 영역(예를 들어, PPR1)에 포함되는 화소들(PX)은 상기 동시에 인가되는 다이오드 초기화 신호들(예를 들어, GB1 내지 GBN)에 응답하여 전원 전압 라인(ELVDD)으로부터 초기화 전압 라인(VINITL)으로의 누설 전류 경로들(LCPATH)을 형성할 수 있다. 예를 들어, 상기 부분 구동 모드에서, 상기 구동되지 않는 부분 패널 영역(예를 들어, PPR1)에 포함되는 화소들(PX)의 다이오드 초기화 트랜지스터들(T7)이 상기 동시에 인가되는 다이오드 초기화 신호들(예를 들어, GB1 내지 GBN)에 응답하여 턴-온되고, 상기 구동되지 않는 부분 패널 영역(예를 들어, PPR1)에 포함되는 화소들(PX)의 상기 턴-온된 다이오드 초기화 트랜지스터들(T7)은 유기 발광 다이오드들(EL)의 기생 커페시터들(COLED)을 초기화 전압 라인(VINITL)으로 방전시키는 방전 경로들(DPATH)을 형성하고, 구동 트랜지스터들(T1)(및 발광 제어 트랜지스터들(T5, T6))의 누설 전류들이 초기화 전압 라인(VINITL)으로 흐르게 하는 누설 전류 경로들(LCPATH)을 형성할 수 있다. 이에 따라, 방전 경로들(DPATH)을 통하여 유기 발광 다이오드들(EL)의 기생 커페시터들(COLED)의 잔류 전하들이 제거되고, 누설 전류 경로들(LCPATH)에 의해 전원 전압 라인(ELVDD)으로부터 구동 트랜지스터(T1)(및 발광 제어 트랜지스터들(T5, T6))의 누설 전류들이 유기 발광 다이오드(EL)에 인가되는 것이 감소 또는 방지됨으로써, 상기 잔류 전하들 및 상기 누설 전류들에 의해 상기 구동되지 않는 부분 패널 영역(예를 들어, PPR1)에 포함되는 화소들(PX)이 원치 않게 발광하는 것이 방지될 수 있다.

[0045] 상술한 바와 같이, 본 발명의 실시예들에 따른 유기 발광 표시 장치(100)는, 상기 부분 구동 모드에서 상기 구

동되지 않는 부분 패널 영역(예를 들어, PPR1)에 상기 다이오드 초기화 신호들(예를 들어, GB1 내지 GBN)을 동시에 인가함으로써, 상기 구동되지 않는 부분 패널 영역(예를 들어, PPR1)의 화소들(PX)에서 유기 발광 다이오드들(EL)의 기생 커패시터들(COLED)을 방전시키는 방전 경로들(DPATH) 및 구동 트랜지스터들(T1)의 누설 전류들이 흐르는 누설 전류 경로들(LCPATH)이 형성되게 할 수 있고, 이에 따라 상기 구동되지 않는 부분 패널 영역(예를 들어, PPR1)의 원치 않는 발광을 방지할 수 있다.

[0046] 도 3은 도 1의 유기 발광 표시 장치에 포함된 스캔 드라이버의 일 예를 나타내는 블록도이고, 도 4는 도 3의 스캔 드라이버에 포함된 각 스테이지의 일 예를 나타내는 회로도이다.

[0047] 도 1 및 도 3을 참조하면, 스캔 드라이버(150)는 제1 내지 제N+M 스캔 스테이지들(GW\_STG1 내지 GW\_STGN+M), 스캔 입력 제어 회로(GWICT1, GWICT2), 제1 내지 제N+M 게이트 초기화 스테이지들(GI\_STG1 내지 GI\_STGN+M), 게이트 초기화 입력 제어 회로(GIIC1, GIIC2), 제1 내지 제N+M 다이오드 초기화 스테이지들(GB\_STG1 내지 GB\_STGN+M), 다이오드 초기화 입력 제어 회로(GBICT1, GBICT2), 및 반전된 모드 제어 신호(/MCS)를 출력하는 인버터(155)를 포함할 수 있다.

[0048] 제1 내지 제N+M 스캔 스테이지들(GW\_STG1 내지 GW\_STGN+M)은 제1 및 제2 스캔 개시 신호들(GW\_FLM1, GW\_FLM2)과 제1 및 제2 스캔 클록 신호들(GW\_CLK1, GW\_CLK2)에 기초하여 제1 내지 제N+M 화소 행들(PXR1 내지 PXRN+M)에 제1 내지 제N+M 스캔 신호들(GW1 내지 GWN+M)을 순차적으로 인가할 수 있다. 일 실시예에서, 제1 및 제2 스캔 클록 신호들(GW\_CLK1, GW\_CLK2)은 서로 반전된 위상들을 가질 수 있다. 또한, 일 실시예에서, 홀수 번째 스캔 스테이지들(예를 들어, GW\_STG1, GW\_STGN+1 등)은 제2 스캔 클록 신호(GW\_CLK2)에 응답하여 스캔 신호들(예를 들어, GW1, GWN+1 등)을 출력하고, 짝수 번째 스캔 스테이지들(예를 들어, GW\_STG2, GW\_STGN, GW\_STGN+2, GW\_STGN+M 등)은 제1 스캔 클록 신호(GW\_CLK1)에 응답하여 스캔 신호들(예를 들어, GW2, GWN, GWN+2, GWN+M 등)을 출력할 수 있다. 일 실시예에서, 제1 내지 제N+M 스캔 스테이지들(GW\_STG1 내지 GW\_STGN+M) 각각(STG)은, 도 4에 도시된 바와 같이, 제1 내지 제7 트랜지스터들(M1 내지 M7), 및 제1 및 제2 커패시터들(C1, C2)을 포함할 수 있다. 도 4의 스테이지(STG)가 제1 내지 제N+M 스캔 스테이지들(GW\_STG1 내지 GW\_STGN+M) 중 하나인 경우, 개시 신호(FLM)은 제1 스캔 개시 신호(GW\_FLM1) 또는 제2 스캔 개시 신호(GW\_FLM2)이고, 이전 출력 신호(POUT)은 이전 스캔 신호이고, 출력 신호(OUT)는 스캔 신호이고, 제1 클록 신호(CLK1)는 제1 스캔 클록 신호(GW\_CLK1)이고, 제2 클록 신호(CLK2)는 제2 스캔 클록 신호(GW\_CLK2)일 수 있다.

[0049] 예를 들어, 제1 내지 제N+M 스캔 스테이지들(GW\_STG1 내지 GW\_STGN+M) 각각(STG)에서, 제1 트랜지스터(M1)는 제1 클록 신호(CLK1)(짝수 번째 스테이지의 경우, 제2 클록 신호(CLK2))에 응답하여 개시 신호(FLM) 또는 이전 출력 신호(POUT)를 제1 노드(N1)에 전송하고, 제2 트랜지스터(M2)는 제2 노드(N2)의 전압에 응답하여 하이 게이트 전압(VGH)을 제3 노드(N3)에 전송하고, 제3 트랜지스터(M3)는 제2 클록 신호(CLK2)(짝수 번째 스테이지의 경우, 제1 클록 신호(CLK1))에 응답하여 제3 노드(N3)의 전압을 제1 노드(N1)에 전송하고, 제4 트랜지스터(M4)는 제1 노드(N1)의 전압에 응답하여 제1 클록 신호(CLK1)(짝수 번째 스테이지의 경우, 제2 클록 신호(CLK2))를 제2 노드(N2)에 전송하고, 제5 트랜지스터(M5)는 제1 클록 신호(CLK1)(짝수 번째 스테이지의 경우, 제2 클록 신호(CLK2))에 응답하여 로우 게이트 전압(VGL)을 제2 노드(N2)에 전송하고, 제6 트랜지스터(M6)는 제2 노드(N2)의 전압에 응답하여 출력 노드(No)에 출력 신호(OUT)로서 하이 게이트 전압(VGH)을 출력하고, 제7 트랜지스터(M7)는 제1 노드(N1)의 전압에 응답하여 출력 노드(No)에 출력 신호(OUT)로서 제2 클록 신호(CLK2)(짝수 번째 스테이지의 경우, 제1 클록 신호(CLK1))를 출력할 수 있다. 또한, 제1 커패시터(C1)는 하이 게이트 전압(VGH)과 제2 노드(N2) 사이에 연결되고, 제2 커패시터(C2)는 제1 노드(N1)와 출력 노드(No) 사이에 연결될 수 있다. 다만, 도 4의 각 스테이지(STG)의 회로 구성은 예시적인 것으로서 본 발명의 실시예들에 따른 스캔 드라이버(150)의 각 스캔 스테이지(GW\_STG1 내지 GW\_STGN+M)의 구성은 이에 한정되지 않는다.

[0050] 또한, 일 실시예에서, 제1 스캔 스테이지(GW\_STG1)는 제1 스캔 개시 신호(GW\_FLM1)에 응답하여 제1 화소 행(PXR1)에 제1 스캔 신호(GW1)를 인가하고, 제2 내지 제N 스캔 스테이지들(GW\_STG2 내지 GW\_STGN)은 이전 스캔 신호들, 즉 제1 내지 제N-1 스캔 신호들(GW1 내지 GWN-1)에 응답하여 제2 내지 제N 화소 행들(PXR2 내지 PXRN)에 제2 내지 제N 스캔 신호들(GW2 내지 GWN)을 인가할 수 있다.

[0051] 스캔 입력 제어 회로(GWICT1, GWICT2)는 모드 제어 신호(MCS)에 응답하여 제2 스캔 개시 신호(GW\_FLM2) 또는 제N 스캔 신호(GWN)를 선택적으로 출력할 수 있다. 스캔 입력 제어 회로(GWICT1, GWICT2)는 모드 제어 신호(MCS)가 일반 구동 모드를 나타낼 때, 예를 들어 모드 제어 신호(MCS)가 온 레벨을 가질 때 제N 스캔 신호(GWN)를 출력하고, 모드 제어 신호(MCS)가 부분 구동 모드를 나타낼 때, 예를 들어 모드 제어 신호(MCS)가 오프 레벨을 가질 때 제2 스캔 개시 신호(GW\_FLM2)를 출력할 수 있다. 일 실시예에서, 스캔 입력 제어 회로(GWICT1, GWICT2)는

상기 일반 구동 모드에서 상기 온 레벨을 가지는 모드 제어 신호(MCS)에 응답하여 제N 스캔 스테이지(GW\_STGN)로부터 출력된 제N 스캔 신호(GWN)를 출력하는 제1 스캔 입력 제어 트랜지스터(GWICT1), 및 상기 부분 구동 모드에서 상기 온 레벨을 가지는 반전된 모드 제어 신호(/MCS)에 응답하여 제2 스캔 개시 신호(GW\_FLM2)를 출력하는 제2 스캔 입력 제어 트랜지스터(GWICT2)를 포함할 수 있다.

[0052] 제N+1 스캔 스테이지(GW\_STGN+1)는 스캔 입력 제어 회로(GWICT1, GWICT2)의 출력 신호(즉, 제2 스캔 개시 신호(GW\_FLM2) 또는 제N 스캔 신호(GWN))에 응답하여 제N+1 화소 행(PXRN+1)에 제N+1 스캔 신호(GWN+1)를 인가할 수 있다. 제N+2 내지 제N+M 스캔 스테이지들(GW\_STGN+2 내지 GW\_STGN+M)은 이전 스캔 신호들, 즉 제N+1 내지 제N+M-1 스캔 신호들(GWN+1 내지 GWN+M-1)에 응답하여 제N+2 내지 제N+M 화소 행들(PXRN+2 내지 PXRN+M)에 제N+2 내지 제N+M 스캔 신호들(GWN+2 내지 GWN+M)을 인가할 수 있다.

[0053] 한편, 상기 일반 구동 모드에서, 모드 제어 신호(MCS)는 상기 온 레벨을 가지고, 제1 스캔 개시 신호(GW\_FLM1)는 매 프레임 구간마다 스캔 시작 펄스를 포함하고, 제2 스캔 개시 신호(GW\_FLM2)는 오프 레벨을 가질 수 있다. 이에 따라, 스캔 입력 제어 회로(GWICT1, GWICT2)는 제N 스캔 신호(GWN)를 출력하고, 제1 내지 제N+M 스캔 스테이지들(GW\_STG1 내지 GW\_STGN+M)은 제1 내지 제N+M 화소 행들(PXR1 내지 PXRN+M)에 제1 내지 제N+M 스캔 신호들(GW1 내지 GWN+M)을 순차적으로 인가할 수 있다.

[0054] 상기 부분 구동 모드에서, 제1 부분 패널 영역(PPR1)이 구동되고, 제2 부분 패널 영역(PPR2)이 구동되지 않는 경우, 모드 제어 신호(MCS)는 상기 오프 레벨을 가지고, 제1 스캔 개시 신호(GW\_FLM1)는 매 프레임 구간마다 상기 스캔 시작 펄스를 포함하고, 제2 스캔 개시 신호(GW\_FLM2)는 상기 오프 레벨을 가질 수 있다. 이 경우, 제1 내지 제N 스캔 스테이지들(GW\_STG1 내지 GW\_STGN)은 제1 스캔 개시 신호(GW\_FLM1)에 응답하여 매 프레임 구간마다 제1 내지 제N 화소 행들(PXR1 내지 PXRN)에 제1 내지 제N 스캔 신호들(GW1 내지 GWN)을 순차적으로 인가할 수 있다. 한편, 스캔 입력 제어 회로(GWICT1, GWICT2)는 제2 스캔 개시 신호(GW\_FLM2)를 출력하나, 제2 스캔 개시 신호(GW\_FLM2)가 상기 오프 레벨을 가지므로, 제N+1 내지 제N+M 스캔 스테이지들(GW\_STGN+1 내지 GW\_STGN+M)은 제N+1 내지 제N+M 화소 행들(PXRN+1 내지 PXRN+M)에 제N+1 내지 제N+M 스캔 신호들(GWN+1 내지 GWN+M)을 인가하지 않을 수 있다.

[0055] 상기 부분 구동 모드에서, 제1 부분 패널 영역(PPR1)이 구동되지 않고, 제2 부분 패널 영역(PPR2)이 구동되는 경우, 모드 제어 신호(MCS)는 상기 오프 레벨을 가지고, 제1 스캔 개시 신호(GW\_FLM1)는 상기 오프 레벨을 가지고, 제2 스캔 개시 신호(GW\_FLM2)는 매 프레임 구간마다 상기 스캔 시작 펄스를 포함할 수 있다. 이 경우, 제1 스캔 개시 신호(GW\_FLM1)가 상기 오프 레벨을 가지므로, 제1 내지 제N 스캔 스테이지들(GW\_STG1 내지 GW\_STGN)은 제1 내지 제N 화소 행들(PXR1 내지 PXRN)에 제1 내지 제N 스캔 신호들(GW1 내지 GWN)을 인가하지 않을 수 있다. 한편, 스캔 입력 제어 회로(GWICT1, GWICT2)는 제2 스캔 개시 신호(GW\_FLM2)를 출력하고, 제N+1 내지 제N+M 스캔 스테이지들(GW\_STGN+1 내지 GW\_STGN+M)은 제2 스캔 개시 신호(GW\_FLM2)에 응답하여 매 프레임 구간마다 제N+1 내지 제N+M 화소 행들(PXRN+1 내지 PXRN+M)에 제N+1 내지 제N+M 스캔 신호들(GWN+1 내지 GWN+M)을 순차적으로 인가할 수 있다.

[0056] 제1 내지 제N+M 게이트 초기화 스테이지들(GI\_STG1 내지 GI\_STGN+M)은 제1 및 제2 게이트 초기화 개시 신호들(GI\_FLM1, GI\_FLM2)과 제1 및 제2 게이트 초기화 클록 신호들(GI\_CLK1, GI\_CLK2)에 기초하여 제1 내지 제N+M 화소 행들(PXR1 내지 PXRN+M)에 제1 내지 제N+M 게이트 초기화 신호들(GI1 내지 GIN+M)을 순차적으로 인가할 수 있다. 일 실시예에서, 제1 및 제2 게이트 초기화 클록 신호들(GI\_CLK1, GI\_CLK2)은 서로 반전된 위상들을 가질 수 있다. 또한, 일 실시예에서, 홀수 번째 게이트 초기화 스테이지들(예를 들어, GI\_STG1, GI\_STGN+1 등)은 제2 게이트 초기화 클록 신호(GI\_CLK2)에 응답하여 게이트 초기화 신호들(예를 들어, GI1, GIN+1 등)을 출력하고, 짝수 번째 게이트 초기화 스테이지들(예를 들어, GI\_STG2, GI\_STGN, GI\_STGN+2, GI\_STGN+M 등)은 제1 게이트 초기화 클록 신호(GI\_CLK1)에 응답하여 게이트 초기화 신호들(예를 들어, GI2, GIN, GIN+2, GIN+M 등)을 출력할 수 있다. 일 실시예에서, 제1 내지 제N+M 게이트 초기화 스테이지들(GI\_STG1 내지 GI\_STGN+M) 각각(STG)은, 도 4에 도시된 바와 같이, 제1 내지 제7 트랜지스터들(M1 내지 M7), 및 제1 및 제2 커패시터들(C1, C2)을 포함할 수 있으나, 이에 한정되지 않는다.

[0057] 게이트 초기화 입력 제어 회로(GIICT1, GIICT2)는 상기 일반 구동 모드에서 상기 온 레벨을 가지는 모드 제어 신호(MCS)에 응답하여 제N 게이트 초기화 스테이지(GI\_STGN)로부터 출력된 제N 게이트 초기화 신호(GIN)를 출력하는 제1 게이트 초기화 입력 제어 트랜지스터(GIICT1), 및 상기 부분 구동 모드에서 상기 온 레벨을 가지는 반전된 모드 제어 신호(/MCS)에 응답하여 제2 게이트 초기화 개시 신호(GI\_FLM2)를 출력하는 제2 게이트 초기화 입력 제어 트랜지스터(GIICT2)를 포함할 수 있다.

- [0058] 상기 일반 구동 모드에서, 모드 제어 신호(MCS)는 상기 온 레벨을 가지고, 제1 게이트 초기화 개시 신호(GI\_FLM1)는 매 프레임 구간마다 게이트 초기화 시작 펄스를 포함하고, 제2 게이트 초기화 개시 신호(GI\_FLM2)는 오프 레벨을 가질 수 있다. 이에 따라, 게이트 초기화 입력 제어 회로(GIICT1, GIICT2)는 제N 게이트 초기화 신호(GIN)를 출력하고, 제1 내지 제N+M 게이트 초기화 스테이지들(GI\_STG1 내지 GI\_STGN+M)은 제1 내지 제N+M 화소 행들(PXR1 내지 PXRN+M)에 제1 내지 제N+M 게이트 초기화 신호들(GI1 내지 GIN+M)을 순차적으로 인가할 수 있다.

- [0059] 상기 부분 구동 모드에서, 제1 부분 패널 영역(PPR1)이 구동되고, 제2 부분 패널 영역(PPR2)이 구동되지 않는 경우, 모드 제어 신호(MCS)는 상기 오프 레벨을 가지고, 제1 게이트 초기화 개시 신호(GI\_FLM1)는 매 프레임 구간마다 상기 게이트 초기화 시작 펄스를 포함하고, 제2 게이트 초기화 개시 신호(GI\_FLM2)는 상기 오프 레벨을 가질 수 있다. 이 경우, 제1 내지 제N 게이트 초기화 스테이지들(GI\_STG1 내지 GI\_STGN)은 매 프레임 구간마다 제1 내지 제N 화소 행들(PXR1 내지 PXRN)에 제1 내지 제N 게이트 초기화 신호들(GI1 내지 GIN)을 순차적으로 인가하고, 제N+1 내지 제N+M 게이트 초기화 스테이지들(GI\_STGN+1 내지 GI\_STGN+M)은 제N+1 내지 제N+M 화소 행들(PXR1+1 내지 PXRN+M)에 제N+1 내지 제N+M 게이트 초기화 신호들(GIN+1 내지 GIN+M)을 인가하지 않을 수 있다.

- [0060] 상기 부분 구동 모드에서, 제1 부분 패널 영역(PPR1)이 구동되지 않고, 제2 부분 패널 영역(PPR2)이 구동되는 경우, 모드 제어 신호(MCS)는 상기 오프 레벨을 가지고, 제1 게이트 초기화 개시 신호(GI\_FLM1)는 상기 오프 레벨을 가지고, 제2 게이트 초기화 개시 신호(GI\_FLM2)는 매 프레임 구간마다 상기 게이트 초기화 시작 펄스를 포함할 수 있다. 이 경우, 제1 내지 제N 게이트 초기화 스테이지들(GI\_STG1 내지 GI\_STGN)은 제1 내지 제N 화소 행들(PXR1 내지 PXRN)에 제1 내지 제N 게이트 초기화 신호들(GI1 내지 GIN)을 인가하지 않을 수 있고, 제N+1 내지 제N+M 게이트 초기화 스테이지들(GI\_STGN+1 내지 GI\_STGN+M)은 매 프레임 구간마다 제N+1 내지 제N+M 화소 행들(PXR1+1 내지 PXRN+M)에 제N+1 내지 제N+M 게이트 초기화 신호들(GIN+1 내지 GIN+M)을 순차적으로 인가할 수 있다.

- [0061] 제1 내지 제N+M 다이오드 초기화 스테이지들(GB\_STG1 내지 GB\_STGN+M)은 제1 및 제2 다이오드 초기화 개시 신호들(GB\_FLM1, GB\_FLM2)과 제1 및 제2 다이오드 초기화 클록 신호들(GB\_CLK1, GB\_CLK2)에 기초하여 제1 내지 제N+M 화소 행들(PXR1 내지 PXRN+M)에 제1 내지 제N+M 다이오드 초기화 신호들(GB1 내지 GBN+M)을 순차적으로 인가할 수 있다. 일 실시예에서, 제1 및 제2 다이오드 초기화 클록 신호들(GB\_CLK1, GB\_CLK2)은 서로 반전된 위상들을 가질 수 있다. 또한, 일 실시예에서, 홀수 번째 다이오드 초기화 스테이지들(예를 들어, GB\_STG1, GB\_STGN+1 등)은 제2 다이오드 초기화 클록 신호(GB\_CLK2)에 응답하여 다이오드 초기화 신호들(예를 들어, GB1, GBN+1 등)을 출력하고, 짝수 번째 다이오드 초기화 스테이지들(예를 들어, GB\_STG2, GB\_STGN, GB\_STGN+2, GB\_STGN+M 등)은 제1 다이오드 초기화 클록 신호(GB\_CLK1)에 응답하여 다이오드 초기화 신호들(예를 들어, GB2, GBN, GBN+2, GBN+M 등)을 출력할 수 있다. 일 실시예에서, 제1 내지 제N+M 다이오드 초기화 스테이지들(GB\_STG1 내지 GB\_STGN+M) 각각(STG)은, 도 4에 도시된 바와 같이, 제1 내지 제7 트랜지스터들(M1 내지 M7), 및 제1 및 제2 커패시터들(C1, C2)을 포함할 수 있으나, 이에 한정되지 않는다.

- [0062] 다이오드 초기화 입력 제어 회로(GBICT1, GBICT2)는 상기 일반 구동 모드에서 상기 온 레벨을 가지는 모드 제어 신호(MCS)에 응답하여 제N 다이오드 초기화 스테이지(GB\_STGN)로부터 출력된 제N 다이오드 초기화 신호(GBN)를 출력하는 제1 다이오드 초기화 입력 제어 트랜지스터(GBICT1), 및 상기 부분 구동 모드에서 상기 온 레벨을 가지는 반전된 모드 제어 신호(/MCS)에 응답하여 제2 다이오드 초기화 개시 신호(GB\_FLM2)를 출력하는 제2 다이오드 초기화 입력 제어 트랜지스터(GBICT2)를 포함할 수 있다.

- [0063] 상기 일반 구동 모드에서, 모드 제어 신호(MCS)는 상기 온 레벨을 가지고, 제1 다이오드 초기화 개시 신호(GB\_FLM1)는 매 프레임 구간마다 다이오드 초기화 시작 펄스를 포함하고, 제2 다이오드 초기화 개시 신호(GB\_FLM2)는 오프 레벨을 가질 수 있다. 이에 따라, 다이오드 초기화 입력 제어 회로(GBICT1, GBICT2)는 제N 다이오드 초기화 신호(GBN)를 출력하고, 제1 내지 제N+M 다이오드 초기화 스테이지들(GB\_STG1 내지 GB\_STGN+M)은 제1 내지 제N+M 화소 행들(PXR1 내지 PXRN+M)에 제1 내지 제N+M 다이오드 초기화 신호들(GB1 내지 GBN+M)을 순차적으로 인가할 수 있다.

- [0064] 상기 부분 구동 모드에서, 제1 부분 패널 영역(PPR1)이 구동되고, 제2 부분 패널 영역(PPR2)이 구동되지 않는 경우, 모드 제어 신호(MCS)는 상기 오프 레벨을 가지고, 제1 다이오드 초기화 개시 신호(GB\_FLM1)는 매 프레임 구간마다 상기 다이오드 초기화 시작 펄스를 포함하고, 제2 다이오드 초기화 개시 신호(GB\_FLM2)는 상기 온 레벨을 가질 수 있다. 이 경우, 제1 내지 제N 다이오드 초기화 스테이지들(GB\_STG1 내지 GB\_STGN)은 매 프레임 구

간마다 제1 내지 제N 화소 행들(PXR1 내지 PXRN)에 제1 내지 제N 다이오드 초기화 신호들(GB1 내지 GBN)을 순차적으로 인가할 수 있다. 한편, 다이오드 초기화 입력 제어 회로(GBICT1, GBICT2)가 제2 다이오드 초기화 개시 신호(GB\_FLM2)를 출력하고, 제2 다이오드 초기화 개시 신호(GB\_FLM2)가 상기 온 레벨을 가지므로, 제N+1 내지 제N+M 다이오드 초기화 스테이지들(GB\_STGN+1 내지 GB\_STGN+M)은 제N+1 내지 제N+M 화소 행들(PXRN+1 내지 PXRN+M)에, 상기 부분 구동 모드의 첫 번째 프레임 구간에서 상기 온 레벨을 순차적으로 가지고, 상기 일반 구동 모드로 전환될 때까지 상기 온 레벨로 유지되는 제N+1 내지 제N+M 다이오드 초기화 신호들(GBN+1 내지 GBN+M)을 인가할 수 있다.

[0065] 또한, 상기 부분 구동 모드에서, 제1 부분 패널 영역(PPR1)이 구동되지 않고, 제2 부분 패널 영역(PPR2)이 구동되는 경우, 모드 제어 신호(MCS)는 상기 오프 레벨을 가지고, 제1 다이오드 초기화 개시 신호(GB\_FLM1)는 상기 온 레벨을 가지고, 제2 다이오드 초기화 개시 신호(GB\_FLM2)는 매 프레임 구간마다 상기 다이오드 초기화 시작 폴스를 포함할 수 있다. 이 경우, 제1 내지 제N 게이트 초기화 스테이지들(GI\_STG1 내지 GI\_STGN)은 제1 내지 제N 화소 행들(PXR1 내지 PXRN)에, 상기 부분 구동 모드의 첫 번째 프레임 구간에서 상기 온 레벨을 순차적으로 가지고, 상기 일반 구동 모드로 전환될 때까지 상기 온 레벨로 유지되는 제1 내지 제N 다이오드 초기화 신호들(GB1 내지 GBN)을 인가할 수 있다. 또한, 제N+1 내지 제N+M 다이오드 초기화 스테이지들(GB\_STGN+1 내지 GB\_STGN+M)은 매 프레임 구간마다 제N+1 내지 제N+M 화소 행들(PXRN+1 내지 PXRN+M)에 제N+1 내지 제N+M 다이오드 초기화 신호들(GBN+1 내지 GBN+M)을 순차적으로 인가할 수 있다.

[0066] 도 5는 도 1의 유기 발광 표시 장치에 포함된 발광 드라이버의 일 예를 나타내는 블록도이고, 도 6은 도 5의 발광 드라이버에 포함된 각 스테이지의 일 예를 나타내는 회로도이다.

[0067] 도 1 및 도 5를 참조하면, 발광 드라이버(170)는 제1 내지 제N+M 발광 제어 스테이지들(EM\_STG1 내지 EM\_STGN+M), 발광 제어 입력 제어 회로(EMICT1, EMICT2), 및 반전된 모드 제어 신호(/MCS)를 출력하는 인버터(175)를 포함할 수 있다.

[0068] 제1 내지 제N+M 발광 제어 스테이지들(EM\_STG1 내지 EM\_STGN+M)은 제1 및 제2 발광 제어 개시 신호들(EM\_FLM1, EM\_FLM2)과 제1 및 제2 발광 제어 클록 신호들(EM\_CLK1, EM\_CLK2)에 기초하여 제1 내지 제N+M 화소 행들(PXR1 내지 PXRN+M)에 제1 내지 제N+M 발광 제어 신호들(EM1 내지 EMN+M)을 순차적으로 인가할 수 있다. 일 실시예에서, 제1 및 제2 발광 제어 클록 신호들(EM\_CLK1, EM\_CLK2)은 서로 반전된 위상들을 가질 수 있다. 또한, 일 실시예에서, 홀수 번째 발광 제어 스테이지들(예를 들어, EM\_STG1, EM\_STGN+1 등) 각각은 제1 및 제2 클록 입력들에서 제1 및 제2 발광 제어 클록 신호들(EM\_CLK1, EM\_CLK2)을 각각 수신하고, 짝수 번째 발광 제어 스테이지들(예를 들어, EM\_STG2, EM\_STGN, EM\_STGN+2, EM\_STGN+M 등)은 상기 제1 및 제2 클록 입력들에서 제2 및 제1 발광 제어 클록 신호들(EM\_CLK2, EM\_CLK1)을 각각 수신할 수 있다.

[0069] 일 실시예에서, 제1 내지 제N+M 발광 제어 스테이지들(EM\_STG1 내지 EM\_STGN+M) 각각(EMSTG)은, 도 6에 도시된 바와 같이, 제1 내지 제10 트랜지스터들(EMM1 내지 EMM10) 및 3개의 커패시터들(EMC1 내지 EMC3)을 포함할 수 있다. 제1 트랜지스터(EMM1)는 제1 발광 제어 클록 신호(EM\_CLK1)에 응답하여 발광 제어 개시 신호(EM\_FLM) 또는 이전 발광 제어 신호(PEM)를 제1 노드(EMN1)에 전송할 수 있다. 제2 트랜지스터(EMM2)는 제1 노드(EMN1)의 전압에 응답하여 제1 발광 제어 클록 신호(EM\_CLK1)를 제2 노드(EMN2)에 전송할 수 있다. 제3 트랜지스터(EMM3)는 제1 발광 제어 클록 신호(EM\_CLK1)에 응답하여 로우 게이트 전압(VGL)을 제2 노드(EMN2)에 전송할 수 있다. 제4 및 제5 트랜지스터들(EMM4, EMM5)은 제2 발광 제어 클록 신호(EM\_CLK2) 및 제2 노드(EMN2)의 전압에 응답하여 하이 게이트 전압(VGH)을 제1 노드(EMN1)에 전송할 수 있다. 제6 트랜지스터(EMM6)는 제2 노드(EMN2)의 전압에 응답하여 제2 발광 제어 클록 신호(EM\_CLK2)를 제3 노드(EMN3)에 전송할 수 있다. 제7 트랜지스터(EMM7)는 제2 발광 제어 클록 신호(EM\_CLK2)에 응답하여 제3 노드(EMN3)와 제4 노드(EMN4)를 연결할 수 있다. 제8 트랜지스터(EMM8)는 제1 노드(EMN1)의 전압에 응답하여 하이 게이트 전압(VGH)을 제4 노드(EMN4)에 전송할 수 있다. 제9 트랜지스터(EMM9)는 제4 노드(EMN4)의 전압에 응답하여 하이 게이트 전압(VGH)을 출력 노드(EMN0)에 전송할 수 있다. 제10 트랜지스터(EMM10)는 제1 노드(EMN1)의 전압에 응답하여 발광 제어 신호(EM)로서 로우 게이트 전압(VGL)을 출력 노드(EMN0)에 전송할 수 있다. 제1 커패시터(EMC1)는 제1 노드(EMN1)와 제2 발광 제어 클록 신호(EM\_CLK2)의 라인 사이에 연결되고, 제2 커패시터(EMC2)는 제2 노드(EMN2)와 제3 노드(EMN3) 사이에 연결되고, 제3 커패시터(EMC3)는 하이 게이트 전압(VGH)의 라인과 제4 노드(EMN4) 사이에 연결될 수 있다.

[0070] 도 7은 일반 구동 모드에서의 도 1의 유기 발광 표시 장치의 동작의 일 예를 설명하기 위한 타이밍도이고, 도 8은 부분 구동 모드에서의 도 1의 유기 발광 표시 장치의 동작의 일 예를 설명하기 위한 타이밍도이다.

[0071] 도 1, 도 3 및 도 7을 참조하면, 제1 및 제2 부분 패널 영역들(PPR1, PPR2)이 모두 구동되는 일반 구동 모드에

서, 모드 제어 신호(MCS)는 상기 일반 구동 모드를 나타내는 온 레벨(예를 들어, 로우 레벨)을 가지고, 제1 다이오드 초기화 개시 신호(GB\_FLM1)는 매 프레임 구간마다 다이오드 초기화 시작 펄스(DISP)를 가지고, 제1 게이트 초기화 개시 신호(GI\_FLM1)는 매 프레임 구간마다 게이트 초기화 시작 펄스(GISP)를 가지고, 제1 스캔 개시 신호(GW\_FLM1)는 매 프레임 구간마다 스캔 시작 펄스(SSP)를 가질 수 있다. 이에 따라, 제1 내지 제N+M 다이오드 초기화 신호들(GB1, GB2, …, GBN+M)이 1 수평 시간(1H)마다 순차적으로 출력되고, 제1 내지 제N+M 게이트 초기화 신호들(GI1, GI2, …, GIN+M)이 1 수평 시간(1H)마다 순차적으로 출력되며, 제1 내지 제N+M 스캔 신호들(GW1, GW2, …, GWN+M)이 1 수평 시간(1H)마다 순차적으로 출력될 수 있다. 한편, 도 7에는 각 화소 행(예를 들어, PXR1)에 대하여 다이오드 초기화 신호(예를 들어, GB1), 게이트 초기화 신호(예를 들어, GI1) 및 스캔 신호(예를 들어, GW1)가 순차적으로 출력되는 예가 도시되어 있으나, 본 발명의 실시예들은 이에 한정되지 않는다.

[0072] 도 1, 도 3 및 도 8을 참조하면, 제1 부분 패널 영역(PPR1)이 구동되지 않고 제2 부분 패널 영역(PPR2)이 구동되는 부분 구동 모드에서, 모드 제어 신호(MCS)는 상기 부분 구동 모드를 나타내는 오프 레벨(예를 들어, 하이 레벨)을 가지고, 제1 다이오드 초기화 개시 신호(GB\_FLM1)는 온 레벨을 가지고, 제1 게이트 초기화 개시 신호(GI\_FLM1) 및 제1 스캔 개시 신호(GW\_FLM1)는 오프 레벨을 가질 수 있다. 상기 온 레벨을 가지는 제1 다이오드 초기화 개시 신호(GB\_FLM1)에 기초하여, 제1 내지 제N 다이오드 초기화 신호들(GB1, GB2, …, GBN)은 상기 부분 구동 모드의 첫 번째 프레임 구간(FP1)에서 상기 온 레벨을 순차적으로 가지고, 상기 일반 구동 모드로 전환될 때까지, 예를 들어 두 번째 프레임 구간(FP2)으로부터 마지막 프레임 구간까지 상기 온 레벨로 유지될 수 있다. 한편, 제1 내지 제N 게이트 초기화 신호들(GI1 내지 GIN) 및 제1 내지 제N 스캔 신호들(GW1 내지 GWN)은 오프 레벨을 가질 수 있다.

[0073] 제2 다이오드 초기화 개시 신호(GB\_FLM2)는 매 프레임 구간마다 다이오드 초기화 시작 펄스(DISP)를 가지고, 제2 게이트 초기화 개시 신호(GI\_FLM2)는 매 프레임 구간마다 게이트 초기화 시작 펄스(GISP)를 가지고, 제2 스캔 개시 신호(GW\_FLM2)는 매 프레임 구간마다 스캔 시작 펄스(SSP)를 가질 수 있다. 이에 따라, 제N+1 내지 제N+M 다이오드 초기화 신호들(GBN+1 내지 GBN+M)이 1 수평 시간(1H)마다 순차적으로 출력되고, 제N+1 내지 제N+M 게이트 초기화 신호들(GIN+1 내지 GIN+M)이 1 수평 시간(1H)마다 순차적으로 출력되며, 제N+1 내지 제N+M 스캔 신호들(GWN+1 내지 GWN+M)이 1 수평 시간(1H)마다 순차적으로 출력될 수 있다.

[0074] 도 9는 본 발명의 다른 실시예들에 따른 유기 발광 표시 장치를 나타내는 도면이고, 도 10은 도 9의 유기 발광 표시 장치에 포함된 스캔 드라이버의 일 예를 나타내는 블록도이며, 도 11은 부분 구동 모드에서의 도 9의 유기 발광 표시 장치의 동작의 일 예를 설명하기 위한 타이밍도이다.

[0075] 도 9의 유기 발광 표시 장치(100a)는, 컨트롤러(190a)가 스캔 드라이버(150a)에 제3 및 제4 다이오드 초기화 클록 신호들(GB\_CLK3, GB\_CLK4)을 더욱 제공하는 것을 제외하고, 도 1의 유기 발광 표시 장치(100)와 유사한 구성 및 동작을 가질 수 있다.

[0076] 도 9 및 도 10을 참조하면, 제1 내지 제N 다이오드 초기화 스테이지들(GB\_STG1 내지 GB\_STGN)은 제1 및 제2 다이오드 초기화 클록 신호들(GB\_CLK1, GB\_CLK2)에 응답하여 동작하고, 제N+1 내지 제N+M 다이오드 초기화 스테이지들(GB\_STGN+1 내지 GB\_STGN+M)은 제3 및 제4 다이오드 초기화 클록 신호들(GB\_CLK3, GB\_CLK4)에 응답하여 동작할 수 있다.

[0077] 일반 구동 모드에서, 제3 다이오드 초기화 클록 신호(GB\_CLK3)는 제1 다이오드 초기화 클록 신호(GB\_CLK1)와 동일한 위상을 가지고, 제4 다이오드 초기화 클록 신호(GB\_CLK4)는 제2 다이오드 초기화 클록 신호(GB\_CLK2)와 동일한 위상을 가질 수 있다. 이에 따라, 제1 내지 제N+M 다이오드 초기화 스테이지들(GB\_STG1 내지 GB\_STGN+M)은 제1 내지 제N+M 화소 행들(PXR1 내지 PXRN+M)에 제1 내지 제N+M 다이오드 초기화 신호들(GB1 내지 GBN+M)을 순차적으로 출력할 수 있다.

[0078] 제1 부분 패널 영역(PPR1)이 구동되지 않고, 제2 부분 패널 영역(PPR2)이 구동되는 부분 구동 모드에서, 도 11에 도시된 바와 같이, 제1 및 제2 다이오드 초기화 클록 신호들(GB\_CLK1, GB\_CLK2)은 상기 온 레벨을 가지고, 제1 다이오드 초기화 개시 신호(GB\_FLM1)는 상기 부분 구동 모드의 첫 번째 프레임 구간(FP1)에서 다이오드 초기화 시작 펄스(DISP)를 포함할 수 있다. 제1 내지 제N 다이오드 초기화 스테이지들(GB\_STG1 내지 GB\_STGN)은, 제1 다이오드 초기화 개시 신호(GB\_FLM1)와 상기 온 레벨을 가지는 제1 및 제2 다이오드 초기화 클록 신호들(GB\_CLK1, GB\_CLK2)에 응답하여, 상기 부분 구동 모드의 첫 번째 프레임 구간(FP1)에서 상기 온 레벨을 순차적으로 가지고 상기 일반 구동 모드로 전환될 때까지 상기 온 레벨로 유지되는 제1 내지 제N 다이오드 초기화 신호들(GB1, GB2, …, GBN)을 제1 내지 제N 화소 행들(PXR1 내지 PXRN)에 인가할 수 있다.

- [0079] 한편, 제3 및 제4 다이오드 초기화 클록 신호들(GB\_CLK3, GB\_CLK4)은 상기 온 레벨과 상기 오프 레벨 사이에서 주기적으로 토클링하고, 제2 다이오드 초기화 개시 신호(GB\_FLM2)는 매 프레임 구간마다 다이오드 초기화 시작 펄스(DISP)를 포함할 수 있다. 이에 따라, 제N+1 내지 제N+M 다이오드 초기화 스테이지들(GB\_STGN+1 내지 GB\_STGN+M)은 제N+1 내지 제N+M 화소 행들(PXRN+1 내지 PXRN+M)에 제N+1 내지 제N+M 다이오드 초기화 신호들(GBN+1, GBN+2, …, GBN+M)을 순차적으로 출력할 수 있다.

- [0080] 또한, 제1 부분 패널 영역(PPR1)이 구동되고, 제2 부분 패널 영역(PPR2)이 구동되지 않는 부분 구동 모드에서, 제1 및 제2 다이오드 초기화 클록 신호들(GB\_CLK1, GB\_CLK2)은 온 레벨과 오프 레벨 사이에서 주기적으로 토클링하고, 제3 및 제4 다이오드 초기화 클록 신호들(GB\_CLK3, GB\_CLK4)은 상기 온 레벨을 가지고, 제1 다이오드 초기화 개시 신호(GB\_FLM1)는 매 프레임 구간마다 다이오드 초기화 시작 펄스(DISP)를 포함하고, 제2 다이오드 초기화 개시 신호(GB\_FLM2)는 상기 부분 구동 모드의 첫 번째 프레임 구간(FP1)에서 다이오드 초기화 시작 펄스(DISP)를 포함할 수 있다. 이에 따라, 제1 내지 제N 다이오드 초기화 스테이지들(GB\_STG1 내지 GB\_STGN)은 제1 내지 제N 화소 행들(PXR1 내지 PXRN+M)에 제1 내지 제N 다이오드 초기화 신호들(GB1 내지 GBN)을 순차적으로 출력하고, 제N+1 내지 제N+M 다이오드 초기화 스테이지들(GB\_STGN+1 내지 GB\_STGN+M)은 상기 부분 구동 모드의 첫 번째 프레임 구간(FP1)에서 상기 온 레벨을 순차적으로 가지고 상기 일반 구동 모드로 전환될 때까지 상기 온 레벨로 유지되는 제N+1 내지 제N+M 다이오드 초기화 신호들(GBN+1 내지 GBN+M)을 제N+1 내지 제N+M 화소 행들(PXRN+1 내지 PXRN+M)에 인가할 수 있다.

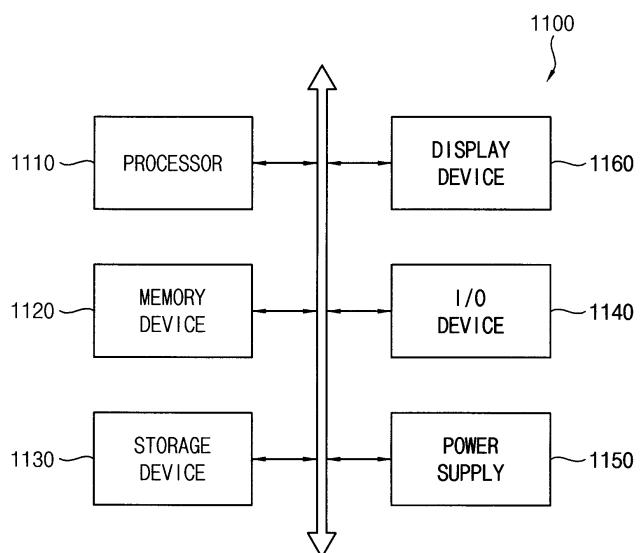

- [0081] 도 12는 본 발명의 실시예들에 따른 유기 발광 표시 장치를 포함하는 전자 기기를 나타내는 블록도이다.

- [0082] 도 12를 참조하면, 전자 기기(1100)는 프로세서(1110), 메모리 장치(1120), 저장 장치(1130), 입출력 장치(1140), 파워 서플라이(1150) 및 유기 발광 표시 장치(1160)를 포함할 수 있다. 전자 기기(1100)는 비디오 카드, 사운드 카드, 메모리 카드, USB 장치 등과 통신하거나, 또는 다른 시스템들과 통신할 수 있는 여러 포트(port)들을 더 포함할 수 있다.

- [0083] 프로세서(1110)는 특정 계산들 또는 태스크(task)들을 수행할 수 있다. 실시예에 따라, 프로세서(1110)는 마이크로프로세서(microprocessor), 중앙 처리 장치(CPU) 등일 수 있다. 프로세서(1110)는 어드레스 버스(address bus), 제어 버스(control bus) 및 데이터 버스(data bus) 등을 통하여 다른 구성 요소들에 연결될 수 있다. 실시예에 따라서, 프로세서(1110)는 주변 구성요소 상호연결(Peripheral Component Interconnect; PCI) 버스와 같은 확장 버스에도 연결될 수 있다.

- [0084] 메모리 장치(1120)는 전자 기기(1100)의 동작에 필요한 데이터들을 저장할 수 있다. 예를 들어, 메모리 장치(1120)는 EPROM(Erasable Programmable Read-Only Memory), EEPROM(Electrically Erasable Programmable Read-Only Memory), 플래시 메모리(Flash Memory), PRAM(Phase Change Random Access Memory), RRAM(Resistance Random Access Memory), NFGM(Nano Floating Gate Memory), PoRAM(Polymer Random Access Memory), MRAM(Magnetic Random Access Memory), FRAM(Ferroelectric Random Access Memory) 등과 같은 비휘발성 메모리 장치 및/또는 DRAM(Dynamic Random Access Memory), SRAM(Static Random Access Memory), 모바일 DRAM 등과 같은 휘발성 메모리 장치를 포함할 수 있다.

- [0085] 저장 장치(1130)는 솔리드 스테이트 드라이브(Solid State Drive; SSD), 하드 디스크 드라이브(Hard Disk Drive; HDD), 씬디롬(CD-ROM) 등을 포함할 수 있다. 입출력 장치(1140)는 키보드, 키패드, 터치패드, 터치스크린, 마우스 등과 같은 입력 수단, 및 스피커, 프린터 등과 같은 출력 수단을 포함할 수 있다. 파워 서플라이(1150)는 전자 기기(1100)의 동작에 필요한 파워를 공급할 수 있다. 유기 발광 표시 장치(1160)는 상기 버스들 또는 다른 통신 링크를 통해서 다른 구성 요소들에 연결될 수 있다.

- [0086] 유기 발광 표시 장치(1160)는, 부분 구동 모드에서 구동되지 않는 부분 패널 영역에 다이오드 초기화 신호들을 동시에 인가함으로써, 상기 구동되지 않는 부분 패널 영역의 화소들에서 유기 발광 다이오드들의 기생 커패시터들을 방전시키는 방전 경로들 및 구동 트랜지스터들의 누설 전류들이 흐르는 누설 전류 경로들이 형성되게 할 수 있고, 이에 따라 상기 구동되지 않는 부분 패널 영역의 원치 않는 발광을 방지할 수 있다.

- [0087] 실시예에 따라, 전자 기기(1100)는 휴대폰(Mobile Phone), 스마트 폰(Smart Phone), 태블릿 컴퓨터(Table Computer), 디지털 TV(Digital Television), 3D TV, 개인용 컴퓨터(Personal Computer; PC), 가정용 전자기기, 노트북 컴퓨터(Laptop Computer), 개인 정보 단말기(personal digital assistant; PDA), 휴대형 멀티미디어 플레이어(portable multimedia player; PMP), 디지털 카메라(Digital Camera), 음악 재생기(Music Player), 휴대용 게임 콘솔(portable game console), 내비게이션(Navigation) 등과 같은 유기 발광 표시 장치(1160)를 포함

하는 임의의 전자 기기일 수 있다.

### 산업상 이용가능성

[0088] 본 발명은 임의의 유기 발광 표시 장치 및 이를 포함하는 전자 기기에 적용될 수 있다. 예를 들어, 본 발명은 휴대폰, 스마트 폰, 태블릿 컴퓨터, TV, 디지털 TV, 3D TV, PC, 가정용 전자기기, 노트북 컴퓨터, PDA, PMP, 디지털 카메라, 음악 재생기, 휴대용 게임 콘솔, 내비게이션 등에 적용될 수 있다.

[0089] 이상에서는 본 발명의 실시예들을 참조하여 설명하였지만, 해당 기술 분야의 숙련된 당업자는 하기의 특허 청구의 범위에 기재된 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다.

### 부호의 설명

[0090] 100: 유기 발광 표시 장치

110: 표시 패널

130: 데이터 드라이버

150: 스캔 드라이버

170: 발광 드라이버

190: 컨트롤러

GW\_STG: 스캔 스테이지

GI\_STG: 게이트 초기화 스테이지

GB\_STG: 다이오드 초기화 스테이지

EM\_STG: 발광 제어 스테이지

## 도면

## 도면1

## 도면2

도면3

## 도면4

## 도면5

## 도면6

## 도면7

## 도면8

## 도면9

## 도면10

도면11

도면12

|                |                                                      |         |            |

|----------------|------------------------------------------------------|---------|------------|

| 专利名称(译)        | 支持部分驱动模式的有机发光显示装置                                    |         |            |

| 公开(公告)号        | <a href="#">KR1020200083736A</a>                     | 公开(公告)日 | 2020-07-09 |

| 申请号            | KR1020180171982                                      | 申请日     | 2018-12-28 |

| [标]申请(专利权)人(译) | 三星显示有限公司                                             |         |            |

| 申请(专利权)人(译)    | 三星显示器有限公司                                            |         |            |

| [标]发明人         | 전재현<br>김지혜                                           |         |            |

| 发明人            | 전재현<br>김지혜                                           |         |            |

| IPC分类号         | G09G3/3208                                           |         |            |

| CPC分类号         | G09G3/3208 G09G2310/0221 G09G2320/0214 G09G2320/0686 |         |            |

| 代理人(译)         | 英西湖公园                                                |         |            |

## 摘要(译)

有机发光显示装置包括:显示面板,其包括第一部分面板区域和第二部分面板区域;以及在其中驱动第一部分面板区域和第二部分面板区域两者的正常驱动模式下,扫描信号到第一部分面板区域和第二部分面板区域。并且将扫描信号顺序地施加到以部分驱动模式驱动的部分面板区域,在该部分驱动模式中,第一子面板区域或第二子面板区域的一个子面板区域被驱动,而另一子面板区域未被驱动。并且数据驱动器在正常驱动模式下将数据信号施加到第一和第二部分面板区域,并且将数据信号施加在以部分驱动模式驱动的部分面板区域。在部分驱动模式下,扫描驱动器顺序地将二极管初始化信号施加到被驱动的部分面板区域,同时将二极管初始化信号施加到未驱动的部分面板区域。