(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2019-0030964

(43) 공개일자 2019년03월25일

(51) 국제특허분류(Int. Cl.)

*G09G 3/3233* (2016.01)

(52) CPC특허분류

*G09G 3/3233* (2013.01)

*G09G 2230/00* (2013.01)

(21) 출원번호 10-2017-0118677

(22) 출원일자 2017년09월15일

심사청구일자 없음

(71) 출원인

엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

홍준환

경기도 파주시 월롱면 엘지로 245

이철환

경기도 파주시 월롱면 엘지로 245

(뒷면에 계속)

(74) 대리인

특허법인로얄

전체 청구항 수 : 총 9 항

(54) 발명의 명칭 유기발광 표시장치

### (57) 요 약

본 발명의 유기발광 표시장치는 유기발광 다이오드의 구동전류를 제어하는 구동 트랜지스터, 커패시터, 제1 내지 제3 제어부를 포함한다. 구동 트랜지스터는 제1 노드에 연결된 게이트전극, 제2 노드에 연결된 소스전극, 제3 노드에 연결된 드레인전극을 포함한다. 커패시터는 제1 노드와 공유노드 사이에 접속된다. 제1 제어부는 초기화 기간 동안, 공유노드와 고전위전압라인을 연결시킨다. 제2 제어부는 초기화 기간에 이어지는 센싱 기간 동안, 공유노드와 초기화전압라인을 연결시킨다. 제3 제어부는 센싱 기간에 이어지는 발광 기간 동안, 공유노드와 고전위전압라인을 연결시킨다.

**대 표 도** - 도4

(52) CPC특허분류

G09G 2320/0233 (2013.01)

(72) 발명자

**문선지**

경기도 파주시 월롱면 엘지로 245

---

**이주연**

경기도 파주시 월롱면 엘지로 245

## 명세서

### 청구범위

#### 청구항 1

유기발광 다이오드의 구동전류를 제어하며, 제1 노드에 연결된 게이트전극, 제2 노드에 연결된 소스전극, 제3 노드에 연결된 드레인전극을 포함하는 구동 트랜지스터;

상기 제1 노드와 공유노드 사이에 접속된 커패시터;

초기화 기간 동안, 상기 공유노드와 고전위전압라인을 연결시키는 제1 제어부;

상기 초기화 기간에 이어지는 센싱 기간 동안, 상기 공유노드와 초기화전압라인을 연결시키는 제2 제어부; 및

상기 센싱 기간에 이어지는 발광 기간 동안, 상기 공유노드와 상기 고전위전압라인을 연결시키는 제3 제어부를 포함하는 유기발광 표시장치.

#### 청구항 2

제 1 항에 있어서,

상기 센싱 기간 동안,

상기 제1 노드 및 제3 노드를 연결시키는 제1 트랜지스터; 및

상기 제2 노드 및 데이터라인을 연결시키는 제2 트랜지스터를 더 포함하는 유기발광 표시장치.

#### 청구항 3

제 2 항에 있어서,

상기 초기화 기간 동안,

상기 초기화전압라인과 상기 제1 노드를 연결시키는 제3 트랜지스터를 더 포함하는 유기발광 표시장치.

#### 청구항 4

제 3 항에 있어서,

상기 발광 기간 동안 상기 고전위전압라인과 상기 제2 노드를 연결시키는 제4 트랜지스터를 더 포함하는 유기발광 표시장치.

#### 청구항 5

제 3 항에 있어서,

$n$ ( $n$ 은 자연수) 번째 픽셀라인에 배치된 픽셀들에서,

상기 제1 제어부 및 상기 제3 트랜지스터들 각각의 게이트전극은 제 $(n-1)$  스캔신호를 입력받고,

상기 제2 제어부, 상기 제1 및 제2 트랜지스터들 각각의 게이트 전극은 제 $n$  스캔신호를 입력받으며,

상기 제 $(n-1)$  스캔신호는  $(n-1)$  번째 픽셀라인에 배치된 상기 제2 노드제어 트랜지스터, 상기 제1 및 제2 트랜지스터들 각각의 게이트 전극에 인가되는 유기발광 표시장치.

#### 청구항 6

공유노드의 전압을 제어하는 공유노드 제어부; 및

상기 공유노드를 공유하는 다수의 단위 픽셀들을 포함하고,

상기 단위 픽셀들 각각은

소스전극을 통해서 고전위전압을 인가받아 유기발광 다이오드를 구동하는 구동 트랜지스터; 및

상기 구동 트랜지스터의 게이트전극에 연결되는 커패시터를 포함하고,

상기 공유노드 제어부는

상기 공유노드의 전압을 제어하여, 상기 커패시터와 커플링되는 상기 구동 트랜지스터의 게이트전압을

제어하되, 상기 픽셀들에 데이터를 기입하는 센싱 기간 동안 상기 공유노드에 상기 고전위전압을 인가하는 유기

발광 표시장치.

### 청구항 7

제 6 항에 있어서,

스캔라인 방향을 따라서 배열되는 픽셀라인에 위치한 상기 단위 픽셀들 각각의 상기 커패시터는 상기 공유노드

에 연결되어서, 상기 공유노드 전압에 따라 상기 단위 픽셀들에 각각의 상기 구동 트랜지스터의 게이트전압은

동일하게 제어되는 유기발광 표시장치.

### 청구항 8

제 7 항에 있어서,

상기 공유노드 제어부는

상기 공유노드와 고전위전압라인 사이에 접속된 제1 제어부;

상기 공유노드와 초기화전압라인 사이에 접속된 제2 제어부; 및

상기 공유노드와 상기 고전위전압라인에 접속된 제3 제어부를 포함하는 유기발광 표시장치.

### 청구항 9

제 7 항에 있어서,

상기 구동 트랜지스터는 제1 노드에 연결된 게이트전극, 제2 노드에 연결된 소스전극, 제3 노드에 연결된 드레

인전극을 포함하고,

상기 단위 픽셀들 각각은

상기 제1 노드 및 제3 노드 사이에 접속된 제1 트랜지스터;

상기 제2 노드 및 데이터라인 사이에 접속된 제2 트랜지스터;

상기 초기화전압라인과 상기 제1 노드 사이에 접속된 제3 트랜지스터; 및

상기 고전위전압라인과 상기 제2 노드 사이에 접속된 제4 트랜지스터를 더 포함하는 유기발광 표시장치.

## 발명의 설명

### 기술 분야

[0001]

본 발명은 유기발광 표시장치에 관한 것이다.

### 배경 기술

[0002]

평판 표시장치(Flat Panel Display; FPD)는 소형화 및 경량화에 유리한 장점으로 인해서 테스크탑 컴퓨터의 모

니터뿐만 아니라, 노트북컴퓨터, 태블릿 등의 휴대용 컴퓨터나 휴대 전화 단말기 등에 폭넓게 이용되고 있다.

현재는 평판 표시장치뿐만 아니라 커브드 표시장치(Curved Display), 플렉서블 표시장치(Flexible Display), 롤

러블 표시장치(Rollable Display), 및 웨어러블 표시장치(Wearable Display) 등 다양한 형태의 표시장치가 개

발되고 있다. 이러한 표시장치들은 액정표시장치(Liquid Crystal Display; LCD), 플라즈마 표시장치(Plasma

Display Panel; PDP), 전계 방출표시장치(Field Emission Display; FED), 유기발광 표시장치(Organic Light

Emitting diode Display; 이하, OLED), 및 양자점 표시장치(Quantum Dot Display; QD) 등이 있다.

[0003]

이 중에서 유기발광 표시장치는 응답속도가 빠르고, 발광효율이 높은 휘도를 표현할 수 있으며 시야각이 큰 장

점이 있다. 일반적으로 유기발광 표시장치는 스캔신호에 의해서 턴-온 되는 트랜지스터를 이용하여 데이터전압을 구동트랜지스터의 게이트 전극에 인가하고, 구동트랜지스터에 공급되는 데이터전압을 스토리지 커패시터에 충전한다. 그리고 발광제어신호를 이용하여 스토리지 커패시터에 충전된 데이터전압을 출력함으로써 유기발광 다이오드를 발광시킨다.

- [0004] 유기발광 표시장치는 공정 편차 또는 구동 특성에 의해서 휘도 불균일이 발생하기도 한다. 휘도 불균일의 원인 중 하나로 구동 트랜지스터의 전기적 특성을 보상하기 위한 내부 보상 방법들이 알려져 있다.

- [0005] 하지만, 유기발광 표시장치는 구동 트랜지스터의 전기적 특성이 이외에도 고전위전압의 전압 강하에 의해서 유기발광 다이오드에 인가되는 구동전류의 크기가 달라지기도 한다. 고전위전압의 전압 강하에 의한 휘도 불균일은 표시패널의 사이즈가 커지고 해상도가 높아지면서 더욱 큰 문제로 나타나고 있다.

- [0006] 또한, 내부 보상을 위해서는 다수의 트랜지스터들이 요구되기 때문에 픽셀들의 사이즈가 커지고 제조비용이 증가하는 단점이 있다.

### 발명의 내용

#### 해결하려는 과제

- [0007] 본 발명은 고전위전압의 전압 강하로 인해서 픽셀들이 발광하는 휘도가 달라지는 것을 개선할 수 있는 유기발광 표시장치를 제공하기 위한 것이다.

- [0008] 본 발명은 픽셀의 사이즈를 줄여서 제조비용을 줄이면서 고해상도에 적합한 유기발광 표시장치를 제공하기 위한 것이다.

#### 과제의 해결 수단

- [0009] 본 발명의 유기발광 표시장치는 유기발광 다이오드의 구동전류를 제어하는 구동 트랜지스터, 커패시터, 제1 내지 제3 제어부를 포함한다. 구동 트랜지스터는 제1 노드에 연결된 게이트전극, 제2 노드에 연결된 소스전극, 제3 노드에 연결된 드레인전극을 포함한다. 커패시터는 제1 노드와 공유노드 사이에 접속된다. 제1 제어부는 초기화 기간 동안, 공유노드와 고전위전압라인을 연결시킨다. 제2 제어부는 초기화 기간에 이어지는 센싱 기간 동안, 공유노드와 초기화전압라인을 연결시킨다. 제3 제어부는 센싱 기간에 이어지는 발광 기간 동안, 공유노드와 고전위전압라인을 연결시킨다.

#### 발명의 효과

- [0010] 본 발명에 의한 유기발광 표시장치는 발광 기간 동안 구동 트랜지스터의 게이트전극과 소스전극 간의 전압 차이가 고전위전압의 파라미터에 영향을 받지 않도록 하여, 고전위전압 편차에 의해서 휘도 편차가 발생하는 것을 개선할 수 있다.

- [0011] 또한, 본 발명에 의한 유기발광 표시장치는 픽셀라인에 배치된 다수의 픽셀들이 구동 트랜지스터의 게이트전극 전압을 제어하는 공유노드 제어부를 공유함으로써, 픽셀들 각각의 사이즈를 줄일 수 있다.

#### 도면의 간단한 설명

- [0012] 도 1은 본 발명에 의한 유기발광 표시장치의 구성을 나타내는 블록도이다.

도 2는 쉬프트레지스터의 구성을 나타내는 블록도이다.

도 3은 제1 실시 예에 의한 픽셀 어레이의 일부를 나타내는 도면이다.

도 4는 도 3에 도시된 하나의 픽셀을 나타내는 도면이다.

도 5는 도 4에 도시된 픽셀을 구동하기 위한 게이트신호들 및 주요 노드의 전압 변화를 나타내는 타이밍도이다.

도 6 내지 도 8은 동작 타이밍에 따라 픽셀의 구동을 설명하는 도면들이다.

도 9는 제2 실시 예에 의한 픽셀 어레이의 일부를 나타내는 도면이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0013] 본 명세서의 이점 및 특징, 그리고 그것들을 달성하는 방법은 첨부되는 도면과 함께 상세하게 후술되어 있는 실시예들을 참조하면 명확해질 것이다. 그러나 본 명세서는 이하에서 개시되는 실시예들에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 것이며, 단지 본 실시예들은 본 명세서의 개시가 완전하도록 하며, 본 명세서가 속하는 기술 분야에서 통상의 지식을 가진 자에게 발명의 범주를 완전하게 알려주기 위해 제공되는 것이며, 본 명세서는 청구항의 범주에 의해 정의될 뿐이다.

- [0014] 본 명세서의 실시예를 설명하기 위한 도면에 개시된 형상, 크기, 비율, 각도, 개수 등은 예시적인 것이므로 본 명세서가 도시된 사항에 한정되는 것은 아니다. 명세서 전체에 걸쳐 동일 참조 부호는 동일 구성 요소를 지칭한다. 또한, 본 명세서를 설명함에 있어서, 관련된 공지 기술에 대한 구체적인 설명이 본 명세서의 요지를 불필요하게 흐릴 수 있다고 판단되는 경우 그 상세한 설명은 생략한다. 본 명세서 상에서 언급한 '포함한다', '갖는다', '이루어진다' 등이 사용되는 경우 '~만'이 사용되지 않는 이상 다른 부분이 추가될 수 있다. 구성 요소를 단수로 표현한 경우에 특별히 명시적인 기재 사항이 없는 한 복수를 포함하는 경우를 포함한다.

- [0015] 구성 요소를 해석함에 있어서, 별도의 명시적 기재가 없더라도 오차 범위를 포함하는 것으로 해석한다.

- [0016] 위치 관계에 대한 설명일 경우, 예를 들어, '~상에', '~상부에', '~하부에', '~옆에' 등으로 두 부분의 위치 관계가 설명되는 경우, '바로' 또는 '직접'이 사용되지 않는 이상 두 부분 사이에 하나 이상의 다른 부분이 위치할 수도 있다.

- [0017] 시간 관계에 대한 설명일 경우, 예를 들어, '~후에', '~에 이어서', '~다음에', '~전에' 등으로 시간적 선후 관계가 설명되는 경우, '바로' 또는 '직접'이 사용되지 않는 이상 연속적이지 않은 경우도 포함할 수 있다.

- [0018] 제1, 제2 등이 다양한 구성요소들을 서술하기 위해서 사용되나, 이들 구성요소들은 이를 용어에 의해 제한되지 않는다. 이들 용어들은 단지 하나의 구성 요소를 다른 구성요소와 구별하기 위하여 사용하는 것이다. 따라서, 이하에서 언급되는 제1 구성요소는 본 명세서의 기술적 사상 내에서 제2 구성요소일 수도 있다.

- [0019] 본 명세서의 여러 실시예들의 각각 특징들이 부분적으로 또는 전체적으로 서로 결합 또는 조합 가능하고, 기술적으로 다양한 연동 및 구동이 가능하며, 각 실시예들이 서로에 대하여 독립적으로 실시 가능할 수도 있고 연관 관계로 함께 실시할 수도 있다.

- [0020] 본 명세서의 게이트 구동회로에서 스위치 소자들은 n 타입 또는 p 타입 MOSFET(Metal Oxide Semiconductor Field Effect Transistor) 구조의 트랜지스터로 구현될 수 있다. 이하의 실시예에서 p 타입 트랜지스터를 예시하였지만, 본 명세서는 이에 한정되지 않는다. 트랜지스터는 게이트(gate), 소스(source) 및 드레인(drain)을 포함한 3 전극 소자이다. 소스는 캐리어(carrier)를 트랜지스터에 공급하는 전극이다. 트랜지스터 내에서 캐리어는 소스로부터 흐르기 시작한다. 드레인은 트랜지스터에서 캐리어가 외부로 나가는 전극이다. 즉, MOSFET에서의 캐리어의 흐름은 소스로부터 드레인으로 흐른다. n 타입 MOSFET(NMOS)의 경우, 캐리어가 전자(electron)이기 때문에 소스에서 드레인으로 전자가 흐를 수 있도록 소스 전압이 드레인 전압보다 낮은 전압을 가진다. n 타입 MOSFET에서 전자가 소스로부터 드레인 쪽으로 흐르기 때문에 전류의 방향은 드레인으로부터 소스 쪽으로 흐른다. p 타입 MOSFET(PMOS)의 경우, 캐리어가 정공(hole)이기 때문에 소스로부터 드레인으로 정공이 흐를 수 있도록 소스 전압이 드레인 전압보다 높다. p 타입 MOSFET에서 정공이 소스로부터 드레인 쪽으로 흐르기 때문에 전류가 소스로부터 드레인 쪽으로 흐른다. MOSFET의 소스와 드레인은 고정된 것은 아니다. 예컨대, MOSFET의 소스와 드레인은 인가 전압에 따라 변경될 수 있다. 이하의 실시예에서 트랜지스터의 소스와 드레인으로 인하여 발명이 제한되지 않는다.

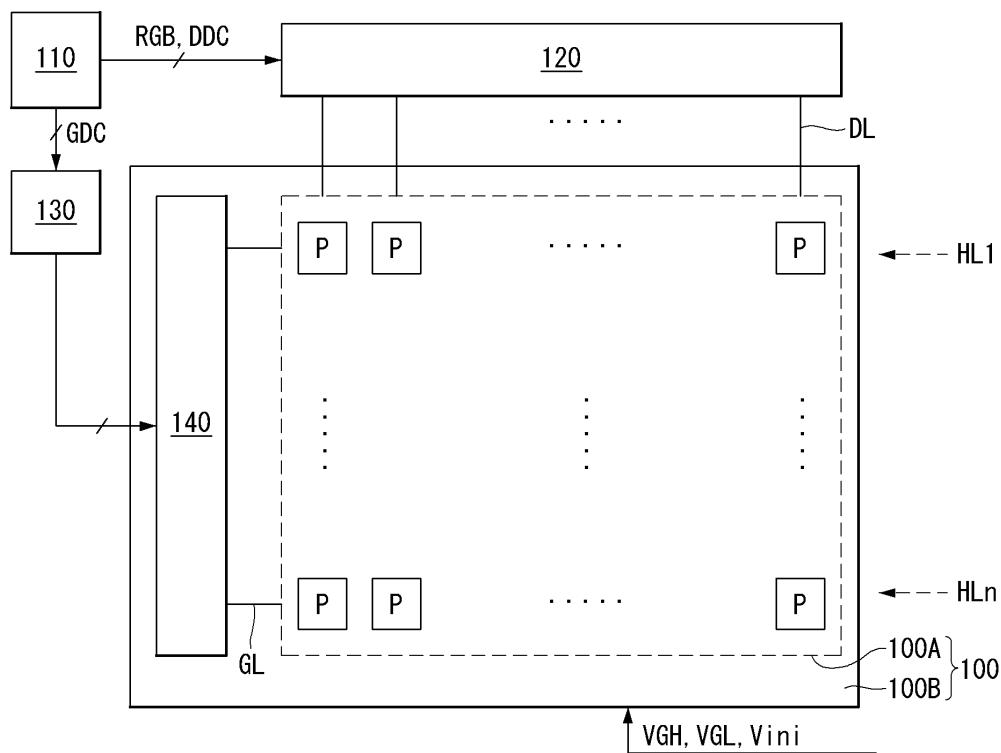

- [0021] 도 1은 본 명세서에 의한 표시장치의 구성을 나타내는 도면이다.

- [0022] 도 1을 참조하면, 본 명세서에 의한 유기발광 표시장치는 픽셀들(P)이 매트릭스 형태로 배열되는 표시패널(100), 데이터 구동부(120), 게이트 구동부(130, 140) 및 타이밍 콘트롤러(110)를 구비한다.

- [0023] 표시패널(100)은 픽셀(P)들이 배치되어 영상을 표시하는 픽셀 어레이(100A) 및 게이트 구동회로(140)가 배치되고 영상을 표시하지 않는 비표시부(100B)를 포함한다.

- [0024] 픽셀 어레이(100A)는 복수 개의 픽셀(P)을 포함하고, 각각의 픽셀(P)들이 표시하는 계조를 기반으로 영상을 표시한다. 픽셀(P)들은 제1 내지 제n 픽셀라인(HL1 내지 HL<sub>n</sub>)들을 따라 배열된다. 각각의 픽셀(P)은 컬럼라인(Column Line)을 따라 배열되는 데이터라인(DL)과 연결되고, 픽셀라인(HL)을 따라 배열되는 게이트라인(GL)에 연결된다. 즉, 동일한 픽셀라인에 배치된 픽셀들은 동일한 게이트라인(GL)을 공유하여 동시에 구동된다. 그리고 제1 픽셀라인(HL1)에 배치된 픽셀들을 제1 픽셀(P1)들이라 정의하고, 제n 픽셀라인(HLn)에 배치된 픽셀들을

제n 픽셀(Pn)들이라고 정의할 때, 제1 픽셀(P1)들부터 제n 픽셀(Pn)들은 순차적으로 구동된다. 그리고, 하나의 스캔라인에 데이터를 기입하는 샘플링 기간을 1수평기간(1H)이라고 정의할 수 있다.

[0025] 게이트라인(GL)은 픽셀 구조에 따라 에미션라인과 복수의 스캔라인을 포함할 수 있다.

[0026] 타이밍 콘트롤러(110)는 데이터 구동부(120) 및 게이트 구동부(130, 140)의 구동 타이밍을 제어하기 위한 것이다. 타이밍 콘트롤러(110)는 외부로부터 입력되는 디지털 비디오 데이터(RGB)를 표시패널(100)의 해상도에 맞게 재정렬하여 데이터 구동부(120)에 공급한다. 또한, 타이밍 콘트롤러(110)는 수직 동기신호(Vsync), 수평 동기신호(Hsync), 도트클럭신호(DCLK) 및 데이터 인에이블신호(DE) 등의 타이밍 신호들에 기초하여 데이터 구동부(120)의 동작 타이밍을 제어하기 위한 데이터 제어신호(DDC)와, 게이트 구동부의 동작 타이밍을 제어하기 위한 게이트 제어신호(GDC)를 발생한다.

[0027] 데이터 구동부(120)는 데이터라인부(DL)를 구동하기 위한 것이다. 이를 위해서 데이터 구동부(120)는 데이터 제어신호(DDC)를 기반으로 타이밍 콘트롤러(110)로부터 입력되는 디지털 비디오 데이터(RGB)를 아날로그 데이터 전압으로 변환하여 데이터라인(DL)들에 공급한다.

[0028] 게이트 구동부(130, 140)는 레벨 시프터(130) 및 시프트레지스터(140)를 포함한다. 레벨 시프터(130)는 IC 형태로 표시패널(100)에 접속되는 인쇄회로기판(미도시)에 형성되고, 게이트 구동회로(140)는 표시패널(100)의 비표시영역(100B)에 GIP 회로로 형성될 수 있다.

[0029] 레벨 시프터(130)는 타이밍 콘트롤러(110)의 제어하에 클럭신호들 및 스타트신호(VST)를 레벨 쉬프팅한 후 시프트레지스터(140)에 공급한다. 게이트 구동회로(140)는 GIP 방식에 의해 표시패널(100)의 비표시영역(100B)에서 다수의 박막 트랜지스터(이하 트랜지스터)조합으로 형성된다.

[0030] 시프트레지스터(140)는 스캔신호를 출력하기 위한 스캔신호 생성부 및 에미션 신호를 출력하기 위한 에미션신호 생성부를 포함할 수 있다. 스캔신호 생성부 및 에미션신호 생성부는 서로 종속적으로 접속되는 다수의 스테이지를 포함하는 시프트레지스터의 구성으로 형성될 수 있다.

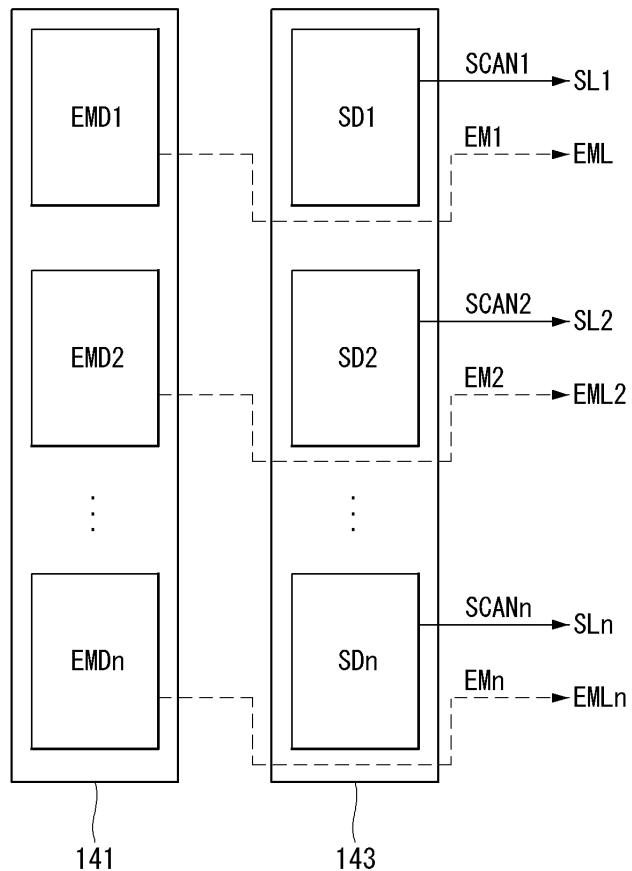

[0031] 도 2는 시프트레지스터의 구성을 나타내는 블록도이다.

[0032] 도 2를 참조하면, 쉬프트 레지스터(140)는 에미션신호 생성부(141) 및 스캔신호 생성부(143)를 포함한다.

[0033] 에미션신호 생성부(141)는 서로 종속적으로 연결되는 제1 내지 제n 에미션 드라이버(EMD1~EMDn)를 포함한다. 제1 에미션 드라이버(EMD1)는 제1 에미션신호(EM1)를 생성하여, 제1 에미션신호(EM1)를 제1 픽셀라인(HL1)의 에미션 라인에 인가한다. 제2 에미션 드라이버(EMD2)는 제2 에미션신호(EM2)를 생성하고, 제2 에미션신호(EM2)를 제2 픽셀라인(HL2)의 에미션 라인에 인가한다. 제n 에미션 드라이버(EMDn)는 제n 에미션신호(EMn)를 생성하고, 제n 에미션신호(EMn)를 제n 픽셀라인(HLn)의 에미션 라인에 인가한다.

[0034] 제1 에미션 드라이버(EMD1)는 스타트신호를 입력받아 동작을 하고, 제2 에미션 드라이버(EMD2) 내지 제n 에미션 드라이버(EMD(n))은 이전 에미션 드라이버의 출력신호, 즉 에미션신호를 캐리신호로 인가받음으로써 동작한다.

[0035] 스캔신호 생성부(143)는 서로 종속적으로 연결되는 제1 내지 제n 스캔 드라이버(SD1~SDn)를 포함한다. 제1 스캔 드라이버(SD1)는 제1 스캔신호(SCAN1)를 생성하고, 제1 스캔신호(SCAN1)를 제1 픽셀라인(HL1)의 스캔라인에 인가한다. 제2 스캔 드라이버(SD2)는 제2 스캔신호(SCAN2)를 생성하여, 제2 스캔신호(SCAN2)를 제2 픽셀라인(HL2)의 스캔라인에 인가한다. 마찬가지로, 제n 스캔 드라이버(SDn)는 제n 스캔신호(SCAN(n))를 생성하여, 제n 스캔신호(SCAN(n))를 제n 픽셀라인(HLn)의 스캔라인에 인가한다.

[0036] 제1 스캔 드라이버(SD1)는 스타트신호를 입력받아 동작을 하고, 제2 스캔 드라이버(SD2) 내지 제n 스캔 드라이버(SD(n))은 이전 스캔 드라이버의 출력신호, 즉 스캔신호를 캐리신호로 인가받음으로써 동작한다.

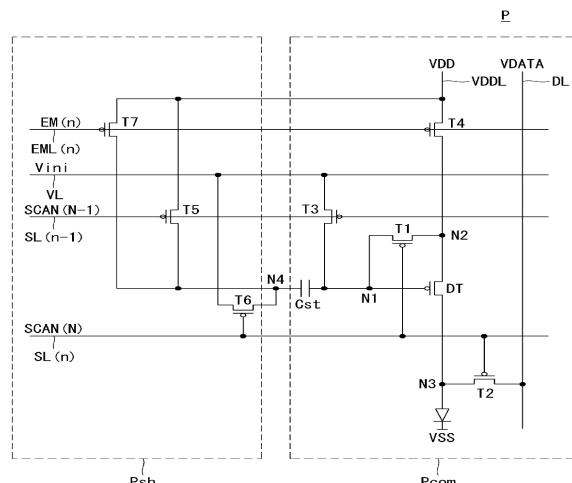

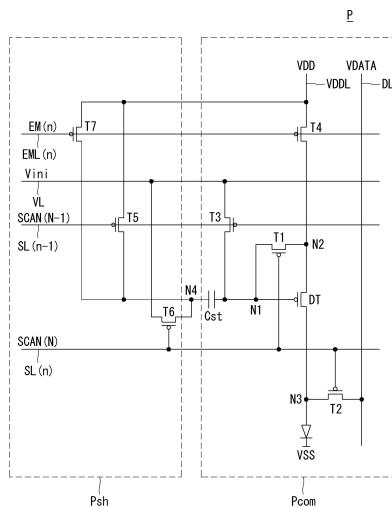

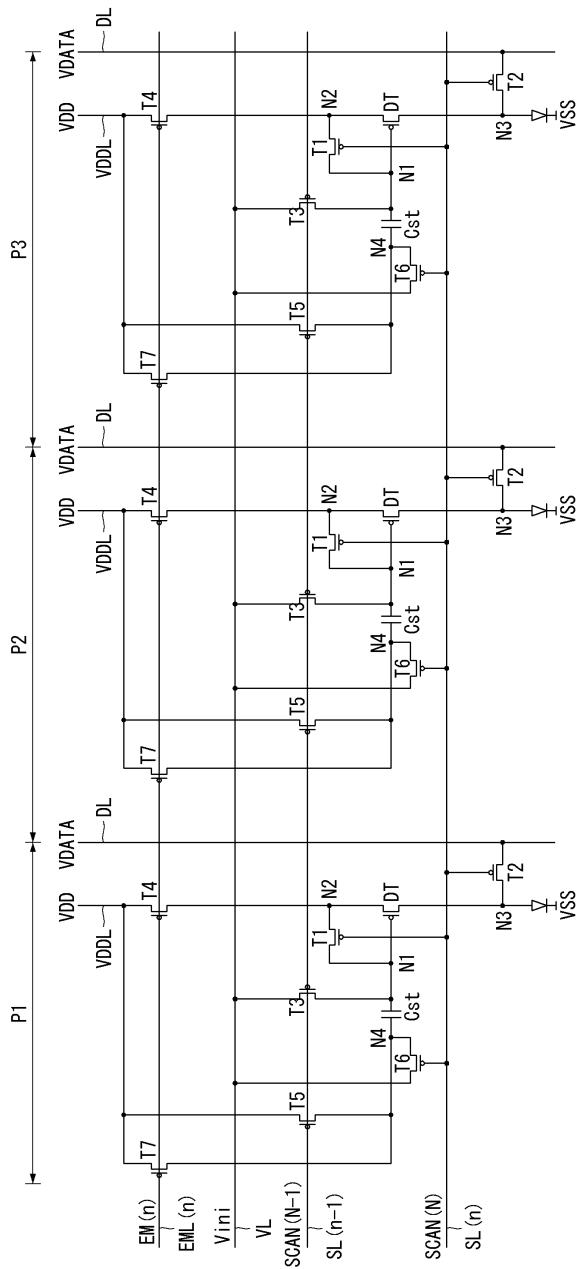

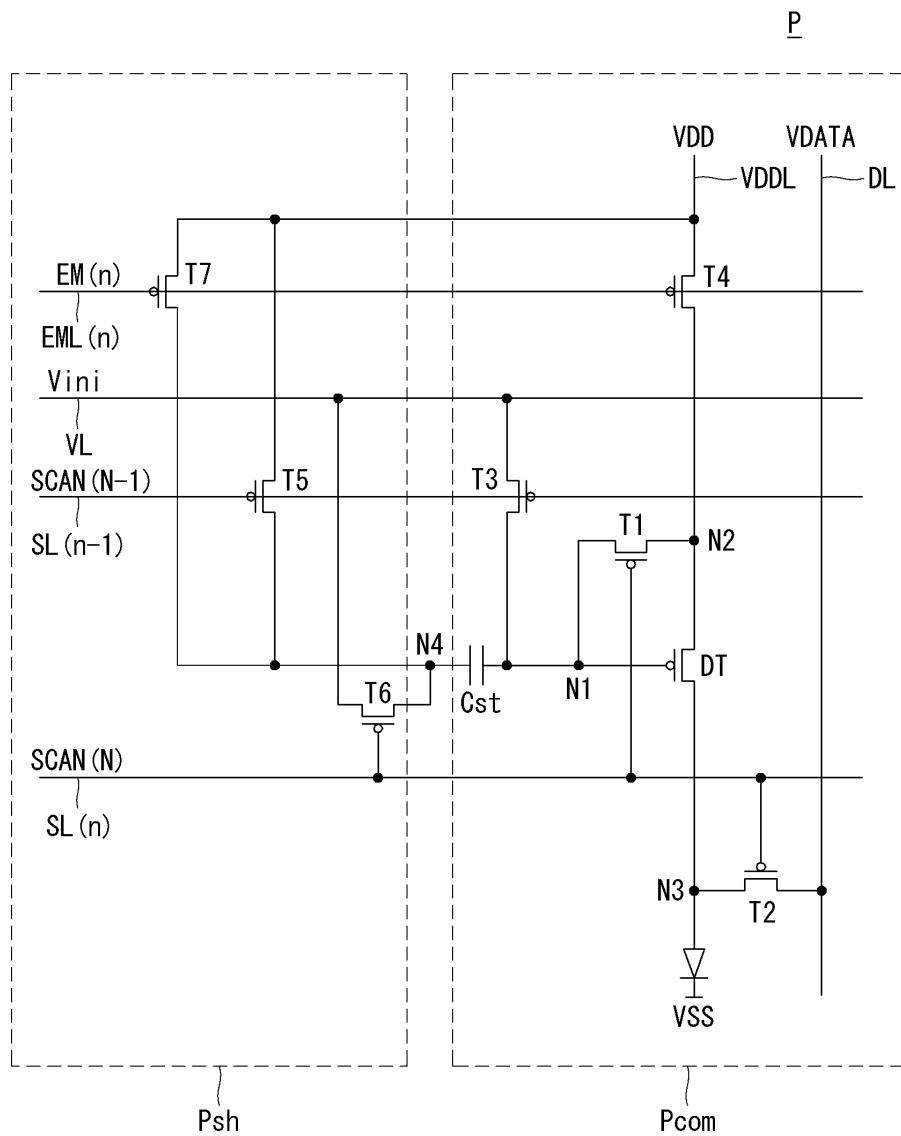

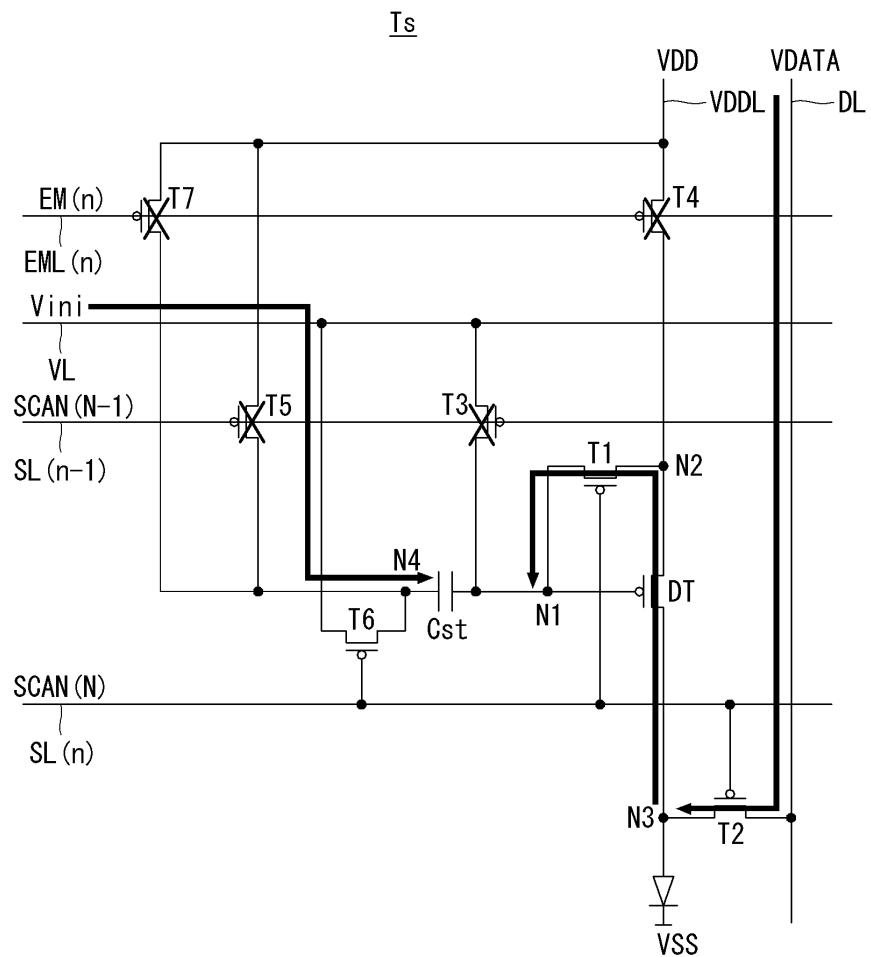

[0037] 도 3은 제1 실시 예에 의한 픽셀 어레이의 일부를 도시한 도면이다. 도 4는 도 3에 도시된 하나의 픽셀을 도시한 도면이다.

[0038] 도 3 및 도 4를 참조하면, 동일한 픽셀라인에 배치된 제1 내지 제3 픽셀들(P1,P2,P3)은 이웃하게 배치된다. 제1 내지 제3 픽셀들(P1,P2,P3) 각각은 공유노드 제어부(Psh) 및 단위 픽셀(Pcom)을 포함한다. 공유노드 제어부(Psh)는 제1 내지 제3 제어부(T5,T6,T7)를 포함한다. 단위 픽셀(Pcom)은 유기발광 다이오드(OLED), 구동 트랜지스터(DT), 제1 내지 제4 트랜지스터(T1,T2,T3,T4) 및 커페시터(Cst)를 포함한다.

[0039] 구동 트랜지스터(DT)는 자신의 소스-게이트 간 전압(Vsg)에 따라 유기발광소자(OLED)에 인가되는 구동전류를 제

어한다. 구동 트랜지스터(DT)의 게이트전극은 제1 노드(N1)에 접속되고, 소스전극은 제2 노드(N2)에 접속되며, 드레인전극은 제3 노드(N3)에 접속된다. 제1 트랜지스터(T1)는 제n 스캔신호(SCAN(n))에 응답하여, 제1 노드(N1)와 제2 노드(N2)를 연결시킨다. 제2 트랜지스터(T2)는 제n 스캔신호(SCAN(n))에 응답하여, 데이터라인(DL)과 제3 노드(N3)를 연결시킨다. 제3 트랜지스터(T3)는 제(n-1) 스캔신호(SCAN(n-1))에 응답하여, 초기화전압라인(VL)과 제1 노드(N1)를 연결시킨다. 제4 트랜지스터(T4)는 제n 에미션신호(EM(n))에 응답하여, 제2 노드(N2)와 고전위 구동전압(VDD)의 입력단을 연결시킨다. 커페시터(Cst)는 제1 노드(N1)와 공유노드(N4)(이하, 제4 노드) 사이에 접속된다.

[0040] 제1 제어부(T5)(이하, 제5 트랜지스터)는 제(n-1) 스캔신호(SCAN(n-1))에 응답하여, 제4 노드(N4)와 고전위전압라인(VDDL)을 연결시킨다. 제2 제어부(T6)(이하, 제6 트랜지스터)는 제n 스캔신호(SCAN(n))에 응답하여, 제4 노드(N4)와 초기화전압라인(VL)을 연결시킨다. 제3 제어부(T7)(이하, 제7 트랜지스터)는 제n 에미션신호(EM(n))에 응답하여, 제4 노드(N4)와 고전위전압라인(VDDL)을 연결시킨다.

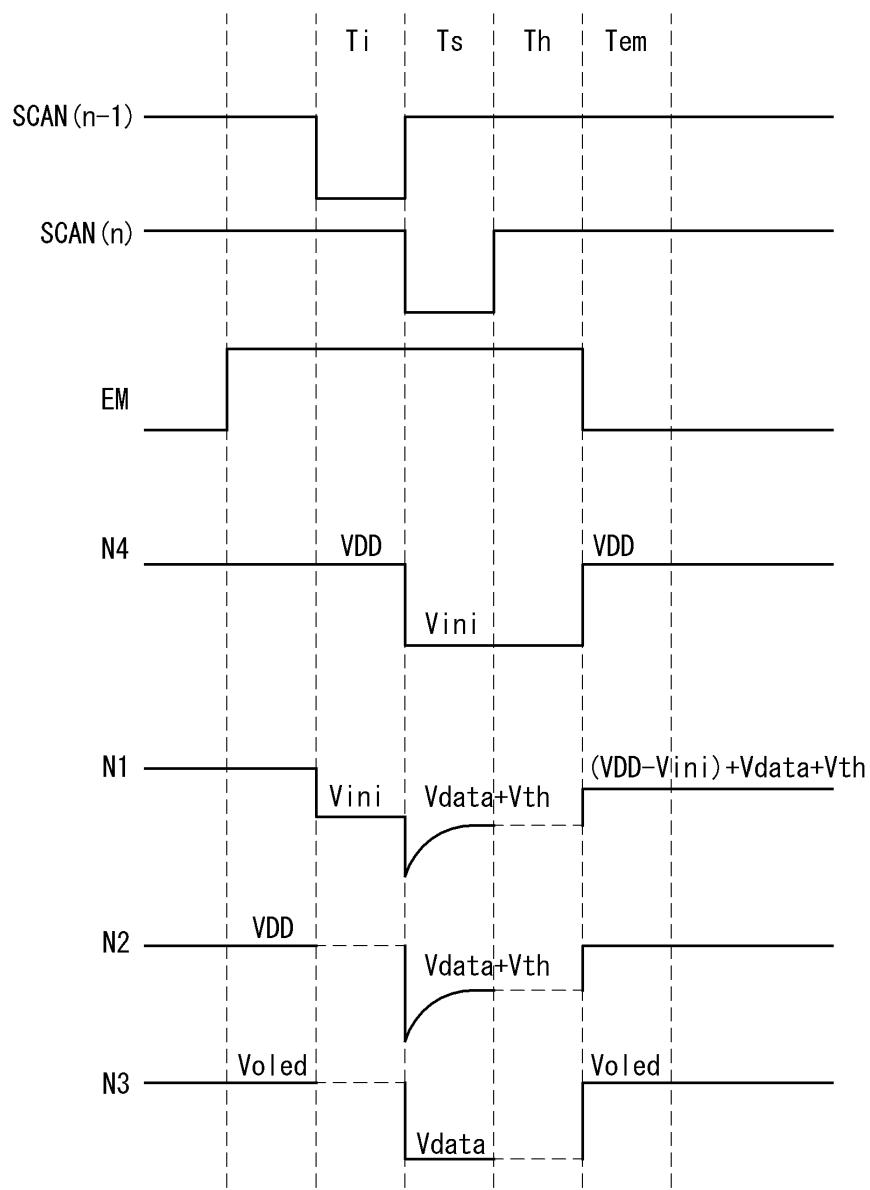

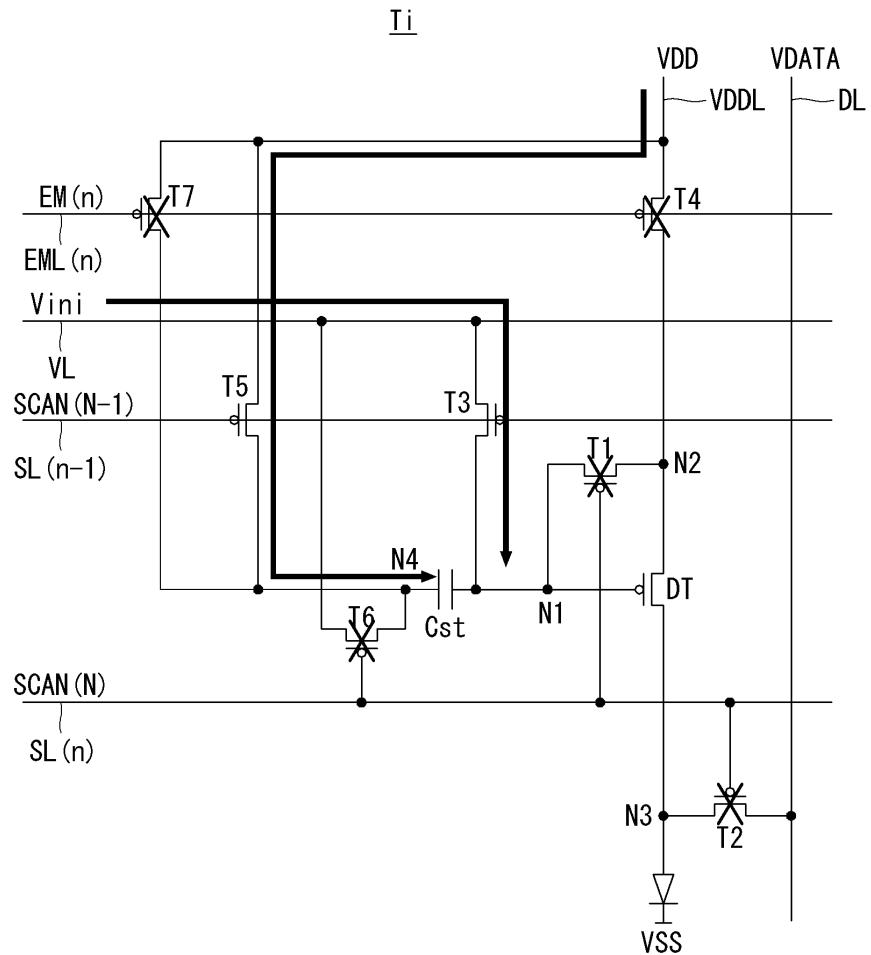

[0041] 도 5는 도 4에 도시된 픽셀에 인가되는 게이트신호들 및 주요 노드의 전압 변화를 나타내는 도면이다. 도 6은 이니셜 기간에서 픽셀의 동작을 도시한 도면이고, 도 7은 센싱 기간에서 픽셀의 동작을 도시한 도면이며, 도 8은 발광 기간에서 픽셀의 동작을 도시한 도면이다.

[0042] 도 4 내지 도 6을 참조하면, 초기화 기간(Ti)에서, 제(n-1) 스캔신호(SCAN(n-1))는 턴-온 전압이 된다.

[0043] 제3 트랜지스터(T3)는 제(n-1) 스캔신호(SCAN(n-1))에 응답하여, 제1 노드(N1)에 초기화전압(Vini)을 인가한다. 제5 트랜지스터(T5)는 제(n-1) 스캔신호(SCAN(n-1))에 응답하여, 제4 노드(N4)에 고전위전압(VDD)을 인가한다.

[0044] 도 4, 도 5 및 도 7을 참조하면, 센싱 기간(Ts)에서 제n 스캔신호(SCAN(n))는 턴-온 전압이 된다.

[0045] 제n 스캔신호(SCAN(n))에 응답하여, 제1 트랜지스터(T1), 제2 트랜지스터(T2) 및 제6 트랜지스터는 턴-온된다.

[0046] 제6 트랜지스터(T6)는 제n 스캔신호(SCAN(n))에 응답하여, 제4 노드(N4)에 초기화전압(Vini)을 인가한다. 제4 노드(N4)의 전압은 고전위전압(VDD)에서 초기화전압(Vini)으로 감소하여, 제4 노드(N4)의 전압 변화량은 "VDD-Vini"이 된다.

[0047] 커페시터(Cst)의 커플링 현상에 의해서, 제4 노드(N4)의 전압 변화량만큼 제1 노드(N1)의 전압은 변한다. 즉, 제1 노드(N1)의 전압은 초기화 전압(Vini)에서 "VDD-Vini"의 전압만큼 감소하기 때문에, "Vini-(VDD-Vini)"의 전압이 된다. 센싱 기간(Ts)의 시작 시점에서 제1 노드(N1)의 전압레벨인 "2Vini-VDD"는 턴-온 전압이 되도록 설정된다. 그 결과 구동 트랜지스터(DT)는 턴-온 된다.

[0048] 제2 트랜지스터(T2)는 제n 스캔신호(SCAN(n))에 응답하여, 제3 노드(N3)에 데이터전압(Vdata)을 인가한다. 제3 노드(N3)의 전압은 데이터전압(Vdata)이 된다.

[0049] 제4 트랜지스터(T4)가 턴-오프 상태여서 제2 노드(N2)는 플로팅 상태가 되고, 제2 노드(N2)를 경유하는 전류에 의해서 제2 노드(N2)의 전압레벨은 점차적으로 상승한다. 제n 스캔신호(SCAN(n))에 응답하여 제1 트랜지스터(T1)는 턴-온 되기 때문에, 제2 노드(N2)를 경유하여 제1 노드(N1)로 전류가 흐른다. 이에 따라, 제1 노드(N1)는 전압이 점차적으로 상승한다. 제1 노드(N1)의 전압은 데이터전압(Vdata)과 구동 트랜지스터 문턱전압(Vth)을 합한 값 "Vdata+Vth"이 될 때까지 상승한다.

[0050] 센싱 기간(Ts)에서, 유기발광 디이이오드(OLED)의 애노드 전극과 접속하는 제3 노드(N3)는 데이터전압(Vdata)으로 초기화된다.

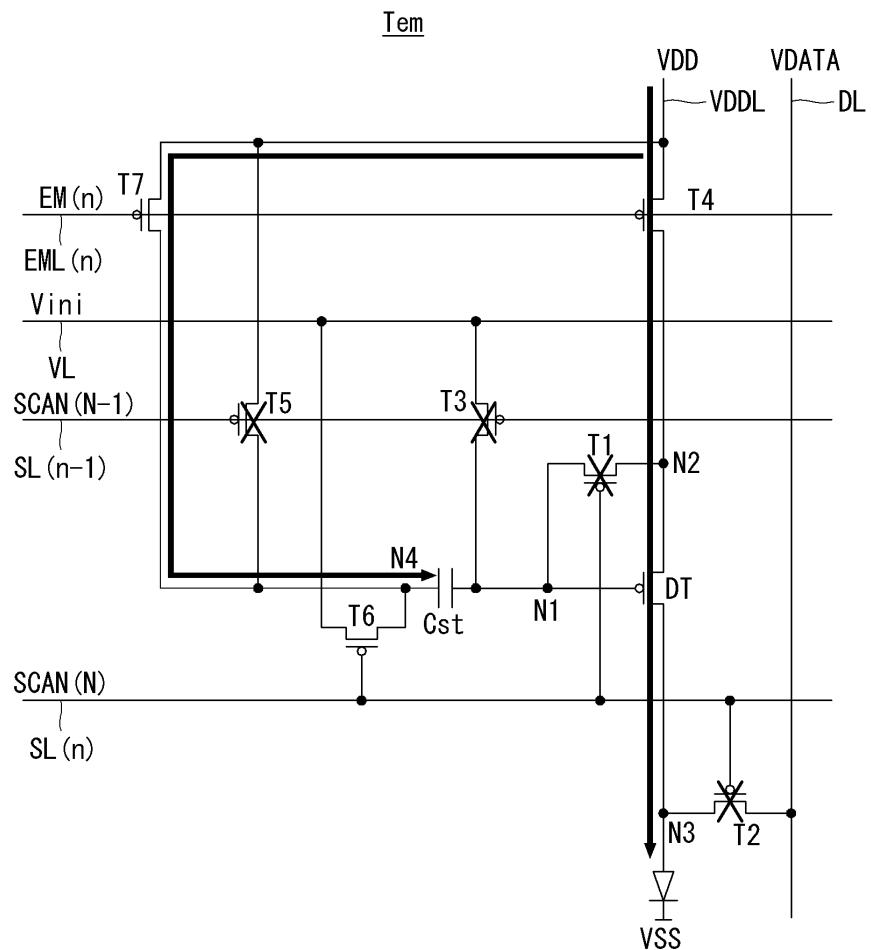

[0051] 도 4, 도 5 및 도 8을 참조하면, 발광기간(Tem)에서, 제n 에미션신호(EM(n))는 턴-온 전압이 된다.

[0052] 제7 트랜지스터(T7)는 제n 에미션신호(EM(n))에 응답하여, 제4 노드(N4)에 고전위전압(VDD)을 인가한다. 센싱 기간(Ts)에서 초기화전압(Vini)이었던 제4 노드(N4)의 전압은 고전위전압(VDD)으로 상승한다. 즉, 발광 기간(Tem)의 시작 시점에서, 제4 노드(N4)의 전압은 "VDD-Vini"만큼 변한다.

[0053] 커플링 현상에 의해서, 제1 노드(N1)의 전압은 제4 노드(N4)의 전압 변화량만큼 변한다. 즉, 제1 노드(N1)의 전압은 "Vdata+Vth+VDD-Vini"가 된다.

[0054] 제4 트랜지스터(T4)는 제n 에미션신호(EM(n))에 응답하여, 고전위전압라인(VDDL)과 제2 노드(N2)를 연결시킨다. 그 결과 구동 트랜지스터(DT)의 소스 전압은 고전위전압(VDD)이 된다. 발광 기간(Tem)에서 구동 트랜지스터

(DT)의 게이트-소스 전압은 턴-온 전압이 되고, 제2 노드(N2)에서 제3 노드(N3)를 경유하는 구동전류(Ioled)가 발생한다.

[0055] 발광기간(Pem)에서 유기발광 다이오드(OLED)에 흐르는 구동전류(Ioled)에 대한 관계식은 하기 수학식 1과 같다.

[0056] [수학식 1]

$$I_{\text{OLED}} = k/2(V_{\text{gs}} - V_{\text{th}})^2 = k/2(V_{\text{g}} - V_{\text{s}} - V_{\text{th}})^2$$

$$= k/2\{(V_{\text{data}} + V_{\text{th}} + V_{\text{DD}} - V_{\text{ini}}) - V_{\text{DD}} - V_{\text{th}}\}^2$$

$$= k/2(V_{\text{data}} - V_{\text{ini}})^2$$

[0060] 수학식 1에서,  $k/2$ 는 구동트랜지스터(DT)의 전자 이동도, 기생 커패시턴스 및 채널 용량 등에 의해 결정되는 비례 상수를 나타낸다. 결국 발광 기간(Te) 동안, 유기발광다이오드(OLED)에 흐르는 구동전류(Ioled)는 구동 트랜지스터(DT)의 문턱전압( $V_{\text{th}}$ )뿐만 아니라 고전위전압( $V_{\text{DD}}$ )의 영향을 받지 않는다.

[0061] 내부보상 방식의 일반적인 유기발광 표시장치는 구동 트랜지스터(DT)의 문턱전압 편차를 개선하지만 고전위전압( $V_{\text{DD}}$ )의 편차는 보상하지 못하였다. 고전위전압( $V_{\text{DD}}$ )은 정전위전압이기 때문에 픽셀 어레이(100A)의 픽셀(P)들은 모두 동일한 전압을 제공받아야 한다.

[0062] 하지만, 고전위전압라인(VDDL)에는 다수의 픽셀들이 연결되고, 각 픽셀들은 초기화 기간( $T_i$ )과 센싱 기간( $T_s$ ) 정도를 제외하는 대부분의 기간 동안 턴-온 상태이다. 따라서, 고전위전압라인(VDDL)으로부터 각 픽셀(P)들에 전류가 흐르게 되고, 고전위전압라인(VDDL)의 위치에 따라 'IR 드롭(drop)'으로 인한 고전위전압( $V_{\text{DD}}$ )의 전압 강하가 발생한다. 그 결과 픽셀(P)들에 인가되는 고전위전압( $V_{\text{DD}}$ )은 다소 상이해지고, 유기발광 다이오드(OLED)에 흐르는 구동전류의 크기도 달라진다. 결국, 고전위전압( $V_{\text{DD}}$ )의 편차로 인한 휘도가 달라지는 문제점이 나타나기도 한다.

[0063] 이에 반해서, 본원발명은 구동 트랜지스터(DT)의 게이트전극에 연결되는 커패시터(Cst)의 커플링 현상을 이용하여, 구동 트랜지스터(DT)의 게이트전극의 전압을 제어하여 발광 기간(Tem)에서는 구동전류가 고전위전압( $V_{\text{DD}}$ )의 영향을 받지 않도록 한다. 그 결과, 고전위전압( $V_{\text{DD}}$ )의 편차로 인해서 휘도가 달라지는 것을 방지할 수 있다. 고전위전압( $V_{\text{DD}}$ )의 'IR 드롭' 현상은 대면적, 고해상도 표시패널에 심하기 때문에, 본 발명은 대면적, 고해상도 표시패널에 적용하기에 유리하다.

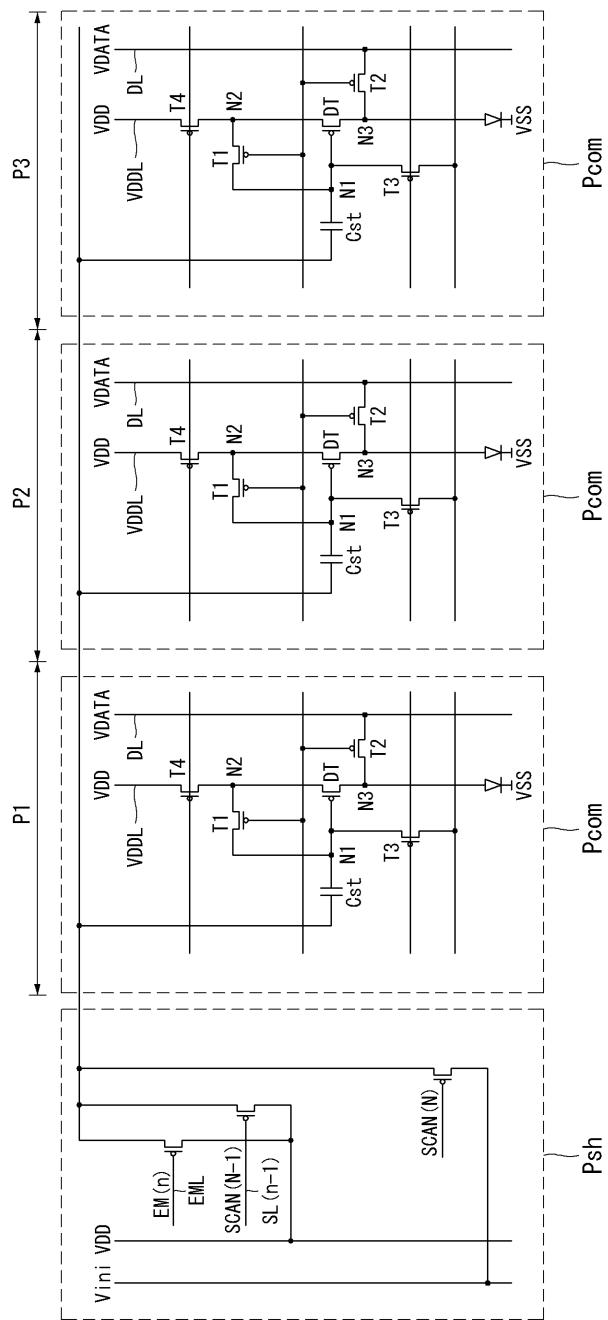

[0064] 도 9는 제2 실시 예에 의한 픽셀 어레이를 도시한 도면이다.

[0065] 도 9를 참조하면, 하나의 픽셀 어레이는 공유노드 제어부(Psh) 및 다수의 단위 픽셀(Pcom)들을 포함한다. 다수의 단위 픽셀(Pcom)들은 공유노드 제어부(Psh)를 공유한다. 공유노드 제어부(Psh)는 제5 내지 제7 트랜지스터(T7)를 포함한다. 단위 픽셀(Pcom)은 유기발광 다이오드(OLED), 구동 트랜지스터(DT), 제1 내지 제4 트랜지스터(T4) 및 커패시터(Cst)를 포함한다. 공유노드 제어부(Psh) 및 단위 픽셀(Pcom)에 포함되는 구성들은 도 4에 도시된 픽셀들의 구성과 동일하고 동일한 게이트신호를 바탕으로 동일한 동작을 수행하기 때문에 자세한 설명은 생략하기로 한다.

[0066] 공유노드 제어부(Psh)에 속하는 제5 내지 제7 트랜지스터들(T5, T6, T7)은 제4 노드(N4)를 제어하기 위한 것으로, 각각 제4 노드(N4)와 정전압원들을 스위칭한다. 즉, 제4 노드(N4)를 제어하는 제5 내지 제7 트랜지스터들(T5, T6, T7)의 동작에는 데이터전압( $V_{\text{data}}$ )이 개입되지 않기 때문에, 동일한 픽셀라인에 배치된 픽셀들의 제4 노드(N4)는 동일한 전압으로 제어된다. 따라서, 제2 실시 예는 제4 노드(N4)를 제어하는 공유노드 제어부(Psh)를 픽셀라인에 1개 배치하고, 단위 픽셀(Pcom)들 각각의 커패시터(Cst)를 제4 노드(N4)에 연결시켜서, 공유노드 제어부(Psh)를 공유할 수 있다.

[0067] 제2 실시 예에 의한 픽셀 어레이는 유기발광 다이오드(OLED)를 포함하는 단위 픽셀(Pcom)이 하나의 픽셀에 해당한다. 따라서, 제2 실시 예는 제1 실시 예에 비하여, 픽셀(P)에 포함되는 트랜지스터의 개수를 줄일 수 있다.

[0068] 제2 실시 예는 픽셀의 사이즈를 줄일 수 있기 때문에, 고해상도의 표시장치에 적용하기에 유리하다. 또는 픽셀의 사이즈를 줄이지 않으면서 제2 실시 예를 적용할 경우에는 발광영역을 크게 할 수 있어서 휘도를 높일 수도

있다.

[0069]

이상 설명한 내용을 통해 당업자라면 본 명세서의 기술사상을 일탈하지 아니하는 범위에서 다양한 변경 및 수정이 가능함을 알 수 있을 것이다. 따라서, 본 명세서의 기술적 범위는 명세서의 상세한 설명에 기재된 내용으로 한정되는 것이 아니라 특히 청구의 범위에 의해 정하여져야만 할 것이다.

### 부호의 설명

[0070]

100: 표시패널 110: 타이밍 콘트롤러

120: 데이터 구동부 130, 140: 게이트 구동부

Psh: 공유노드 제어부 Pcom: 단위 픽셀

### 도면

#### 도면1

## 도면2

140

## 도면3

## 도면4

## 도면5

도면6

## 도면7

## 도면8

## 도면9

|                |                                      |         |            |

|----------------|--------------------------------------|---------|------------|

| 专利名称(译)        | 有机发光显示器                              |         |            |

| 公开(公告)号        | <a href="#">KR1020190030964A</a>     | 公开(公告)日 | 2019-03-25 |

| 申请号            | KR1020170118677                      | 申请日     | 2017-09-15 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                             |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                            |         |            |

| [标]发明人         | 홍순환<br>이철환<br>문선지<br>이주연             |         |            |

| 发明人            | 홍순환<br>이철환<br>문선지<br>이주연             |         |            |

| IPC分类号         | G09G3/3233                           |         |            |

| CPC分类号         | G09G3/3233 G09G2230/00 G09G2320/0233 |         |            |

| 外部链接           | <a href="#">Espacenet</a>            |         |            |

### 摘要(译)

本发明的有机发光二极管显示器包括驱动晶体管，电容器以及用于控制有机发光二极管的驱动电流的第一至第三控制器。驱动晶体管包括连接到第一节点的栅极，连接到第二节点的源极和连接到第三节点的漏极。电容器连接在第一节点和共享节点之间。在初始化期间，第一控制器连接共享节点和高电位电压线。第二控制器在初始化时段之后的感测时段期间将共享节点和初始化电压线连接。第三控制器在感测时段之后的发光时段期间连接共享节点和高电位电压线。