(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2017-0044167

(43) 공개일자 2017년04월24일

- (51) 국제특허분류(Int. Cl.)

*H01L 27/32* (2006.01) *H01L 27/12* (2006.01)

- (52) CPC특허분류

*H01L 27/3262* (2013.01)

*H01L 27/1225* (2013.01)

- (21) 출원번호 10-2017-7007597

- (22) 출원일자(국제) 2014년10월09일

심사청구일자 2017년03월20일

- (85) 번역문제출일자 2017년03월20일

- (86) 국제출원번호 PCT/US2014/059936

- (87) 국제공개번호 WO 2016/048385

국제공개일자 2016년03월31일

- (30) 우선권주장

14/494,931 2014년09월24일 미국(US)

- (71) 출원인

애플 인크.

미합중국 95014 캘리포니아 쿠퍼티노 인피니트 루프 1

- (72) 발명자

차이, 쟁-팅

대만 타이페이 시티 신이 디스트릭트 쟽즈 로드 넘버 1 19에이 메일 스탬 706-알이

굽타, 바수다

미국 95014 캘리포니아주 쿠퍼티노 엠/에스 83-오

인피니트 루프 1

린, 친-웨이

미국 95014 캘리포니아주 쿠퍼티노 엠/에스 83-오

인피니트 루프 1

- (74) 대리인

장덕순, 백만기

전체 청구항 수 : 총 20 항

(54) 발명의 명칭 규소 및 반도체 산화물 박막 트랜지스터 디스플레이

### (57) 요 약

전자 디바이스 디스플레이에는 픽셀 회로들의 어레이를 가질 수 있다. 각각의 픽셀 회로는 유기발광 다이오드 및 구동 트랜지스터를 포함할 수 있다. 각각의 구동 트랜지스터를 조정하여 얼마나 많은 전류가 유기발광 다이오드를 통해 흐를지 제어할 수 있다. 각각의 픽셀 회로는 스위칭 트랜지스터들과 같은 하나 이상의 추가 트랜지스터 및 저장 커패시터를 포함할 수 있다. 반도체 산화물 트랜지스터들 및 규소 트랜지스터들은 픽셀 회로들의 트랜지스터들을 형성하는 데 사용될 수 있다. 저장 커패시터들 및 트랜지스터들은 금속층들, 반도체 구조체들, 및 유전체층들을 이용하여 형성될 수 있다. 디스플레이의 에지를 따라 층들의 일부를 제거하여 용이하게 구부러지게 할 수 있다. 유전체층들은 어레이의 데이터 라인들이 비활성 에지 영역 안으로 연장됨에 따라 데이터 라인들이 기판의 표면을 향해 단계적으로 내려가도록 하는 계단형 프로파일을 가질 수 있다.

### 대 표 도 - 도3

(52) CPC특허분류

*H01L 27/1251* (2013.01)

*H01L 27/1255* (2013.01)

*H01L 27/3258* (2013.01)

*H01L 27/3265* (2013.01)

*H01L 27/3276* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

유기발광 다이오드 디스플레이로서,

기판;

상기 기판의 활성 영역을 형성하는 픽셀 회로들의 어레이; 및

상기 기판의 비활성 영역에 있는 회로부

를 포함하고, 각각의 픽셀 회로는:

유기발광 다이오드;

상기 유기발광 다이오드와 직렬로 결합된 규소 트랜지스터;

상기 규소 트랜지스터에 결합된 저장 커패시터; 및

상기 저장 커패시터에 결합된 반도체 산화물 트랜지스터

를 포함하는, 유기발광 다이오드 디스플레이.

#### 청구항 2

제1항에 있어서, 상기 기판은 상기 비활성 영역에서 구부러진, 유기발광 다이오드 디스플레이.

#### 청구항 3

제2항에 있어서, 유전체층들을 추가로 포함하고, 상기 유전체층들은 상기 활성 영역에 존재하고 상기 유전체층들의 적어도 일부는 상기 비활성 영역에 존재하지 않는, 유기발광 다이오드 디스플레이.

#### 청구항 4

제3항에 있어서, 각각의 픽셀 회로의 상기 규소 트랜지스터는 규소 채널을 포함하고, 상기 유전체층들은 상기 기판과 상기 규소 채널 사이의 베퍼층을 포함하고, 상기 베퍼층은 상기 비활성 영역에 존재하지 않는, 유기발광 다이오드 디스플레이.

#### 청구항 5

제4항에 있어서, 상기 활성 영역에 제1 금속층을 추가로 포함하고, 상기 제1 금속층의 일부는 각각의 픽셀 회로에서 상기 규소 트랜지스터를 위한 게이트를 형성하는, 유기발광 다이오드 디스플레이.

#### 청구항 6

제5항에 있어서, 상기 제1 금속층의 일부는 각각의 픽셀 회로에서 상기 반도체 산화물 트랜지스터를 위한 게이트를 형성하는, 유기발광 다이오드 디스플레이.

#### 청구항 7

제5항에 있어서, 제2 금속층을 추가로 포함하고, 상기 제2 금속층은 상기 활성 영역에서 패터닝되어 상기 규소 트랜지스터 및 상기 반도체 산화물 트랜지스터를 위한 소스-드레인 단자들을 형성하는, 유기발광 다이오드 디스플레이.

#### 청구항 8

제7항에 있어서, 상기 제2 금속층은 상기 비활성 영역에서 패터닝되어 상기 픽셀 회로들의 어레이와 상기 비활성 영역 내의 상기 회로부 사이에 결합되는 데이터 라인들을 형성하는, 유기발광 다이오드 디스플레이.

**청구항 9**

제8항에 있어서, 상기 기판은 구부러진 가요성 기판이고, 상기 데이터 라인들은 구부러지고 상기 기판의 표면 상에 형성되어 상기 유전체층들 중 어느 것도 상기 데이터 라인들과 상기 기판 사이에 개재되지 않도록 하는, 유기발광 다이오드 디스플레이.

**청구항 10**

제9항에 있어서, 각각의 픽셀의 상기 반도체 산화물 트랜지스터는 반도체 산화물 채널을 포함하는, 유기발광 다이오드 디스플레이.

**청구항 11**

제10항에 있어서, 상기 유전체층들은 각각의 픽셀 회로에서 상기 규소 트랜지스터의 상기 규소 채널과 중첩되고 각각의 픽셀 회로에서 상기 반도체 산화물 트랜지스터의 상기 반도체 산화물 채널과 중첩되지 않는 규소 질화물 층을 포함하는, 유기발광 다이오드 디스플레이.

**청구항 12**

제11항에 있어서, 상기 저장 커패시터는 상기 제2 금속의 층으로 형성된 제1 전극을 가지며 제2 전극을 가지는, 유기발광 다이오드 디스플레이.

**청구항 13**

제12항에 있어서, 상기 유전체층들은 추가 규소 질화물층을 포함하고, 상기 추가 규소 질화물층은 각각의 픽셀 회로에서 상기 저장 커패시터의 상기 제1 및 제2 전극 사이에 개재되는, 유기발광 다이오드 디스플레이.

**청구항 14**

제13항에 있어서, 규소 산화물층을 추가로 포함하고, 상기 규소 산화물층은 각각의 픽셀 회로에서 상기 반도체 산화물 채널과 중첩되고 각각의 픽셀 회로의 상기 저장 커패시터에서 국부적으로 제거되어 상기 규소 산화물층 중 어느 것도 상기 저장 커패시터의 상기 제1 및 제2 전극 사이에 개재되지 않도록 하는, 유기발광 다이오드 디스플레이.

**청구항 15**

제3항에 있어서, 상기 활성 영역으로부터 상기 비활성 영역으로 연장되는 데이터 라인들을 추가로 포함하고, 상기 유전체층들은 상기 활성 영역으로부터 상기 비활성 영역으로 전이될 때 높이가 감소하는 계단형 프로파일을 가지며, 상기 데이터 라인들은 상기 계단형 프로파일을 갖는 상기 유전체층들 상에 형성되는, 유기발광 다이오드 디스플레이.

**청구항 16**

제1항에 있어서, 각각의 픽셀 회로의 상기 반도체 산화물 트랜지스터는 구동 트랜지스터를 포함하고 각각의 픽셀 회로의 상기 규소 트랜지스터는 스위칭 트랜지스터를 포함하는, 유기발광 다이오드 디스플레이.

**청구항 17**

유기발광 다이오드 디스플레이로서,

유기발광 다이오드들의 어레이;

상기 유기발광 다이오드들의 각각의 유기발광 다이오드와 직렬로 각각 결합된 규소 구동 트랜지스터들; 및

상기 규소 트랜지스터들에 결합된 반도체 산화물 스위칭 트랜지스터들

을 포함하는, 유기발광 다이오드 디스플레이.

**청구항 18**

제17항에 있어서, 상기 반도체 산화물 스위칭 트랜지스터들은 각각 반도체 산화물 채널을 가지며, 상기 유기발

광 다이오드 디스플레이는 상기 규소 구동 트랜지스터들과 중첩되고 상기 반도체 산화물 채널들과 중첩되지 않는 규소 질화물층을 추가로 포함하는, 유기발광 다이오드 디스플레이.

### 청구항 19

제18항에 있어서,

상기 반도체 산화물 스위칭 트랜지스터들에 결합된 저장 커패시터들; 및

상기 반도체 산화물 채널과 중첩되고 상기 저장 커패시터들과 중첩되지 않는 규소 산화물층을 추가로 포함하는, 유기발광 다이오드 디스플레이.

### 청구항 20

유기발광 다이오드 디스플레이로서,

가요성 중합체 기판;

상기 기판 상의 픽셀 회로들의 어레이 - 각각의 픽셀 회로는 유기발광 다이오드, 각각 반도체 산화물 채널을 갖는 적어도 2개의 반도체 산화물 트랜지스터, 상기 유기발광 다이오드와 직렬로 결합된 적어도 하나의 규소 트랜지스터, 및 적어도 하나의 저장 커패시터를 포함함 -;

상기 픽셀 회로들의 어레이로부터 상기 픽셀 회로들의 어레이에 인접한 비활성 영역으로 전이될 때 높이가 감소하는 계단형 프로파일을 갖는 상기 가요성 중합체 기판 상의 유전체층들; 및

상기 계단형 프로파일을 따르는 상기 유전체층들 상의 데이터 라인들 - 상기 유전체층들은 상기 규소 트랜지스터들과 중첩되고 상기 반도체 산화물 채널들과 중첩되지 않는 유전체층을 포함함 -

을 포함하는, 유기발광 다이오드 디스플레이.

## 발명의 설명

### 기술 분야

[0001] 본 출원은 본 명세서에 전체적으로 참조로서 포함되는, 2014년 9월 24일자로 출원된, 미국 특허 출원 제 14/494,931호에 대하여 우선권을 주장한다.

### 배경 기술

[0002] 이는 일반적으로 전자 디바이스에 관한 것이고, 더 구체적으로, 박막 트랜지스터들을 갖는 디스플레이를 구비한 전자 디바이스에 관한 것이다.

[0003] 전자 디바이스들은 종종 디스플레이를 포함한다. 예를 들어, 셀룰러 전화기 및 휴대용 컴퓨터는 사용자에게 정보를 제시하기 위한 디스플레이들을 포함한다.

[0004] 유기발광 다이오드 디스플레이와 같은 디스플레이에는 발광 다이오드에 기초한 픽셀들의 어레이를 가진다. 이러한 유형의 디스플레이에서, 각각의 픽셀은 발광 다이오드 및 발광 다이오드에 대한 신호의 적용을 제어하기 위한 박막 트랜지스터들을 포함한다.

[0005] 주의를 기울이지 않는 경우, 디스플레이의 박막 트랜지스터 회로부는 과도한 트랜지스터 누설 전류, 불충분한 트랜지스터 구동 강도, 열악한 면적 효율성, 히스테리시스, 불균일성, 및 기타 이슈들을 나타낼 수 있다. 따라서, 개선된 전자 디바이스 디스플레이를 제공할 수 있는 것이 바람직할 것이다.

### 발명의 내용

[0006] 전자 디바이스는 디스플레이를 포함할 수 있다. 디스플레이에는 활성 영역을 형성하는 픽셀들을 가질 수 있다. 비활성 경계 영역은 활성 영역의 에지 부분을 따라 연장될 수 있다. 픽셀들은 기판 상에서 픽셀 회로들의 어레이로부터 형성될 수 있다. 기판은 경성 재료로 형성될 수 있거나 또는 비활성 영역에서 구부러지는 가요성 재료로 형성될 수 있다.

[0007] 각각의 픽셀 회로는 유기발광 다이오드 및 그 유기발광 다이오드에 결합된 구동 트랜지스터를 포함할 수 있다.

각각의 구동 트랜지스터를 조정하여 그것이 결합된 유기발광 다이오드를 통해 얼마나 많은 전류가 흐르는지 그리고 그럼으로써 그 다이오드에 의해 얼마나 많은 빛이 생성되는지 제어할 수 있다. 각각의 픽셀 회로는 스위칭 트랜지스터들과 같은 하나 이상의 추가 트랜지스터를 포함할 수 있고, 저장 커패시터를 포함할 수 있다.

[0008] 반도체 산화물 트랜지스터들 및 규소 트랜지스터들은 픽셀 회로들의 트랜지스터들을 형성하는 데 사용될 수 있다. 예를 들어, 반도체 산화물 트랜지스터들은 스위칭 트랜지스터들로서 사용될 수 있고, 규소 트랜지스터들은 구동 트랜지스터들로서 사용될 수 있다. 픽셀 회로 당 단일 구동 트랜지스터 및 하나 이상의 추가 트랜지스터가 있을 수 있다.

[0009] 저장 커패시터들 및 트랜지스터들은 금속층들, 반도체 구조체들, 및 유전체층들을 이용하여 형성될 수 있다. 유전체층들은 픽셀 회로들의 어레이의 데이터 라인들이 디스플레이의 비활성 구부러진 에지 영역 안으로 연장됨에 따라 데이터 라인들이 기판의 표면을 향해 점진적으로 단계적으로 내려가도록 하는 계단형 프로파일을 가질 수 있다. 유전체층들의 일부 또는 전부는 비활성 에지 영역에서 제거되어 쉽게 구부러지도록 할 수 있다.

### 도면의 간단한 설명

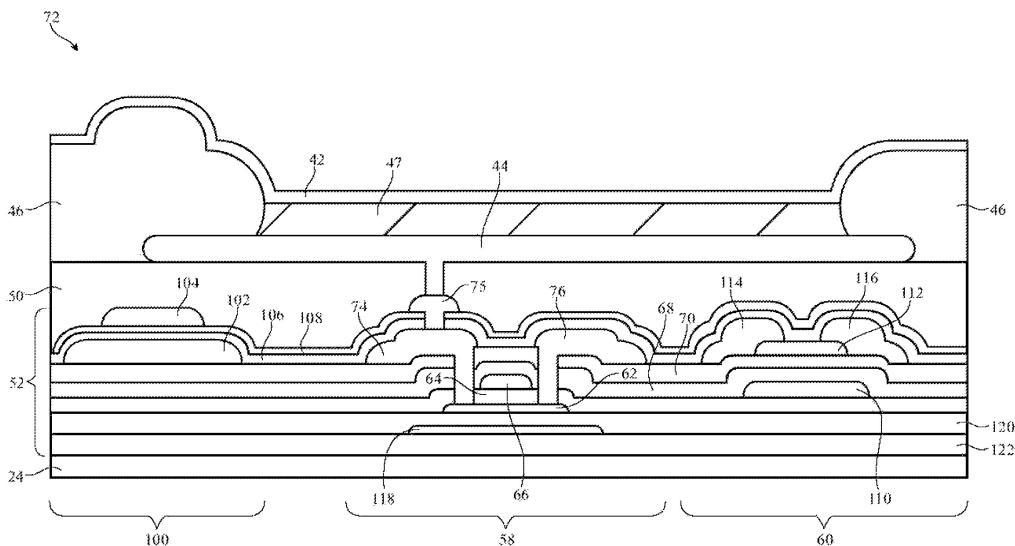

[0010] 도 1은 실시예에 따른 유기발광 다이오드 픽셀들의 어레이를 갖는 유기발광 다이오드 디스플레이와 같은 예시적인 디스플레이의 다이어그램이다.

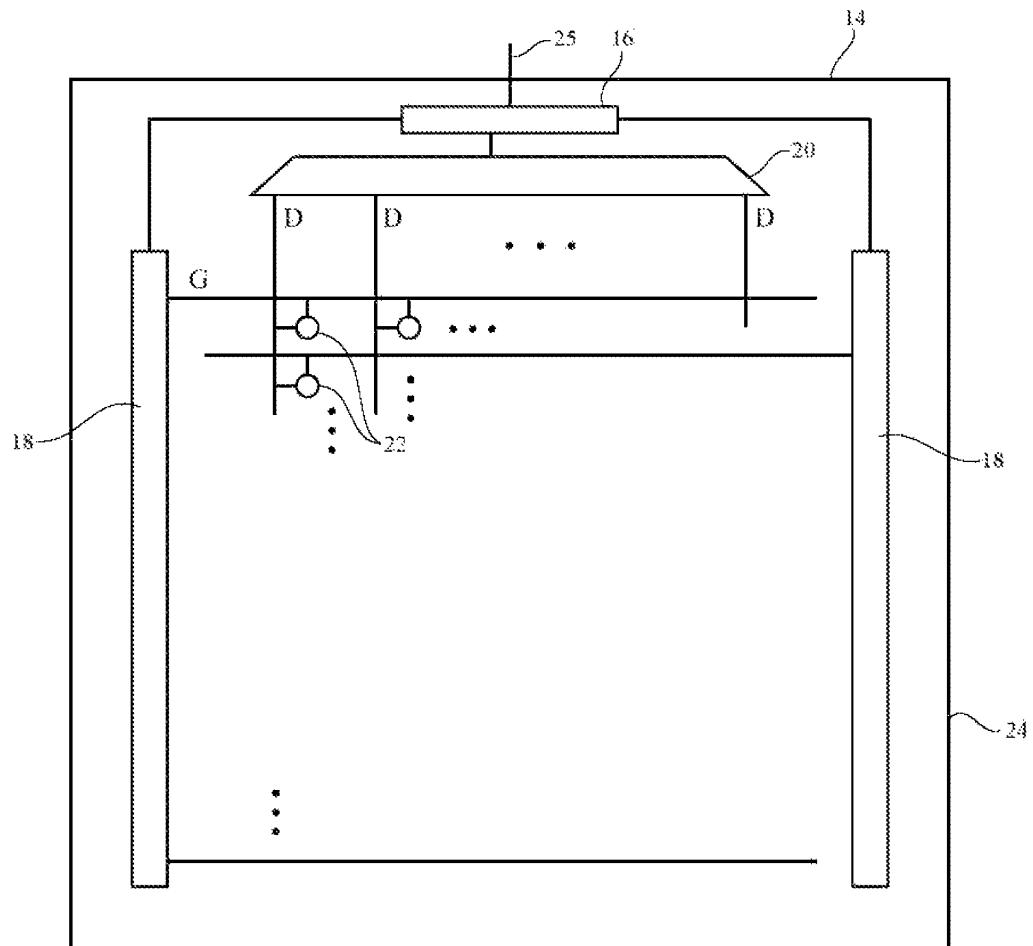

도 2는 실시예에 따른 반도체 산화물 박막 트랜지스터들 및 규소 박막 트랜지스터들을 구비한 유기발광 다이오드에 사용될 수 있는 유형의 예시적인 유기발광 다이오드 디스플레이 픽셀의 다이어그램이다.

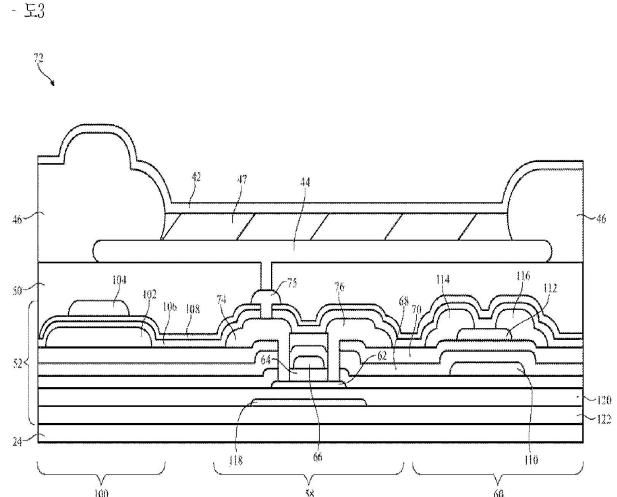

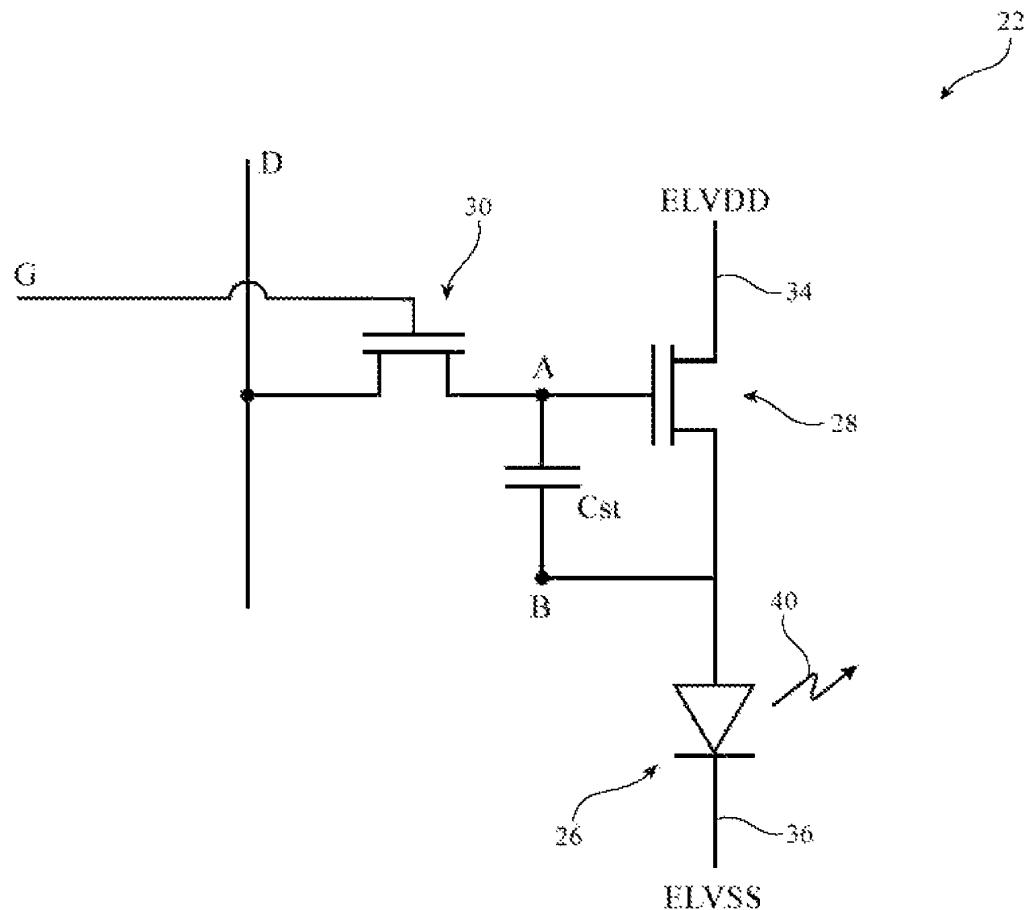

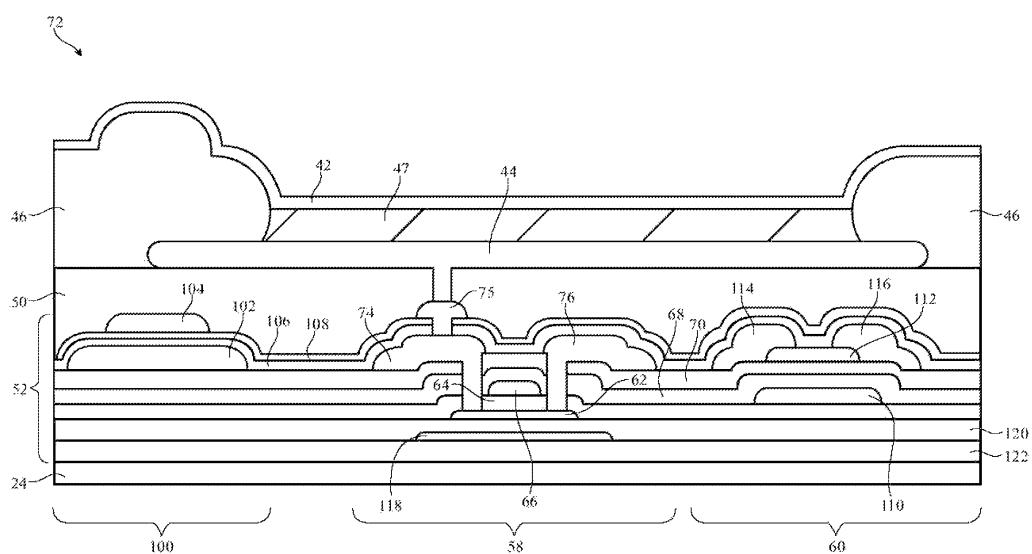

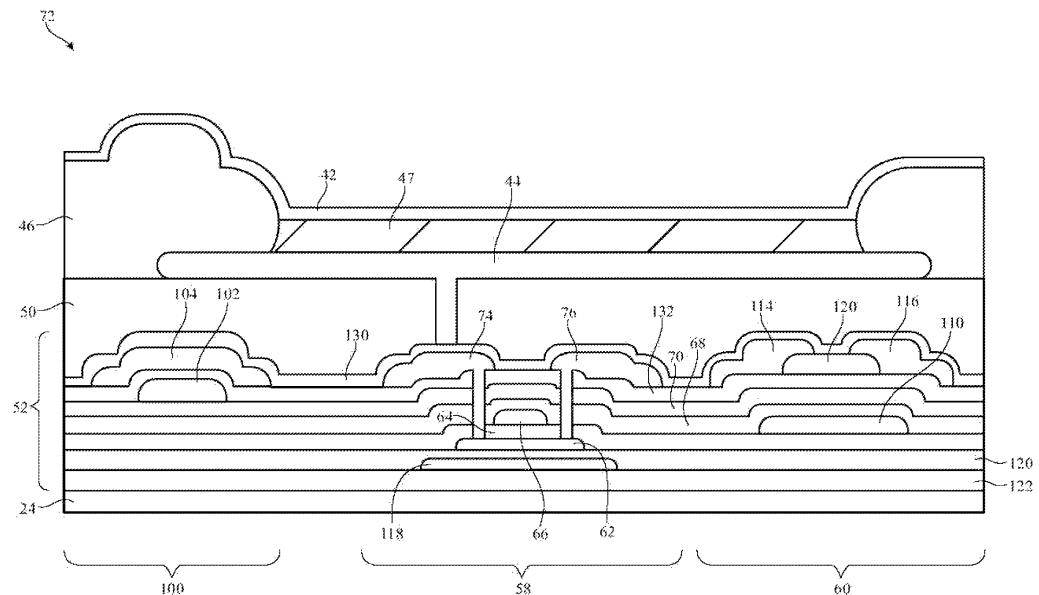

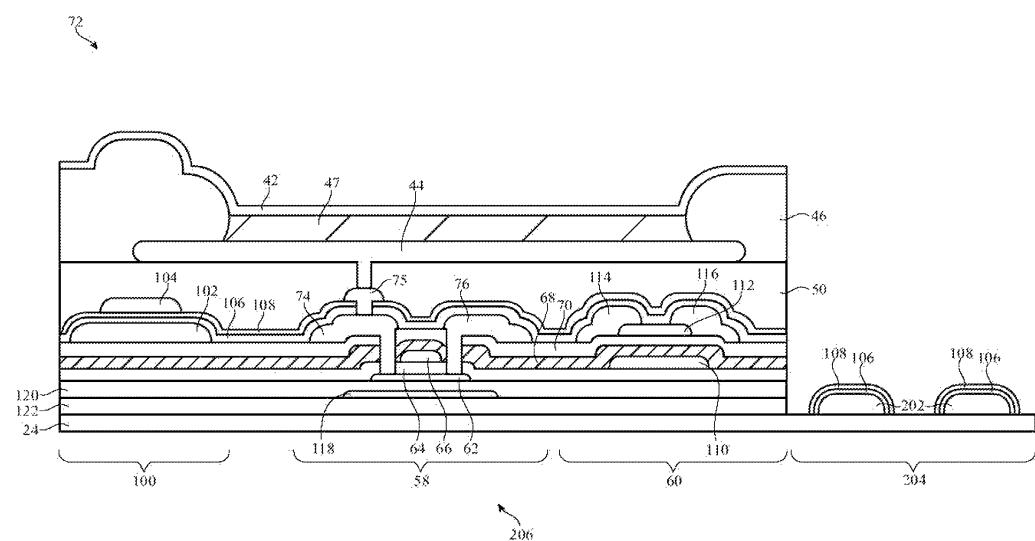

도 3은 실시예에 따른 반도체 산화물 박막 트랜지스터가 저부 게이트 배열을 이용하여 형성된 구성의 디스플레이 픽셀을 위한 예시적인 박막 트랜지스터 구조체들의 측단면도이다.

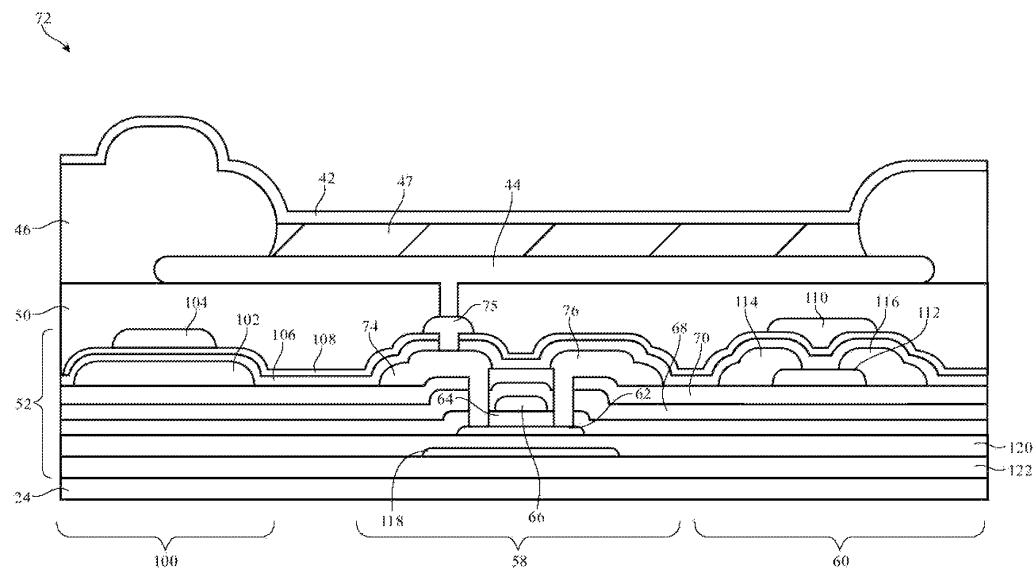

도 4는 실시예에 따른 반도체 산화물 박막 트랜지스터가 상부 게이트 배열을 이용하여 형성된 구성의 디스플레이 픽셀을 위한 예시적인 박막 트랜지스터 구조체들의 측단면도이다.

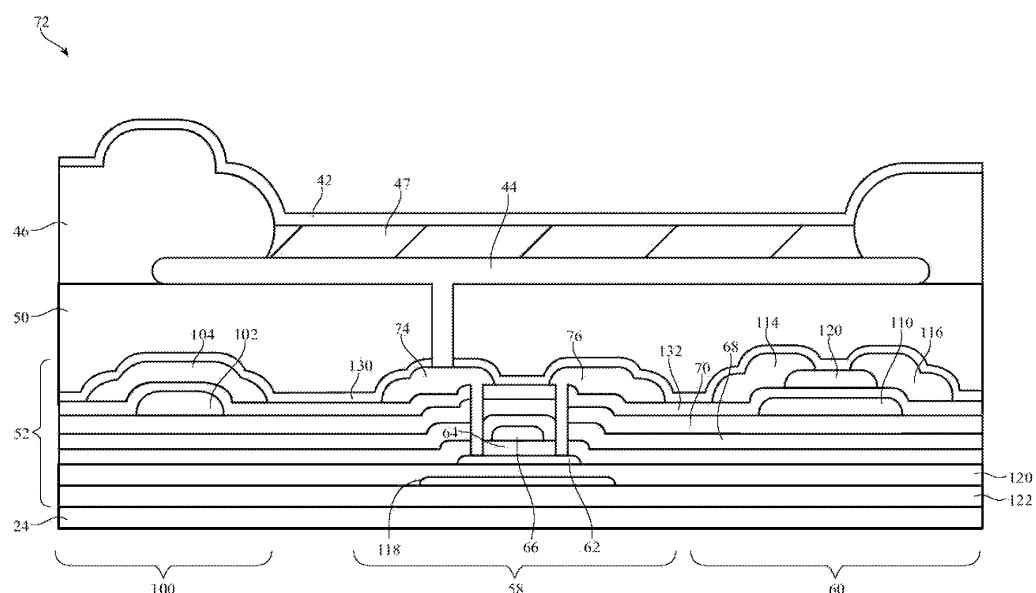

도 5는 실시예에 따른 반도체 산화물 박막 트랜지스터가 저부 게이트 배열을 이용하여 형성되고, 저장 커패시터가 반도체 산화물 박막 트랜지스터의 게이트와 동일한 금속층으로부터 패터닝된 제1 전극 및 트랜지스터 소스-드레인 전극을 또한 형성하는 제2 전극을 가지는 구성의 디스플레이 픽셀을 위한 예시적인 박막 트랜지스터 구조체들의 측단면도이다.

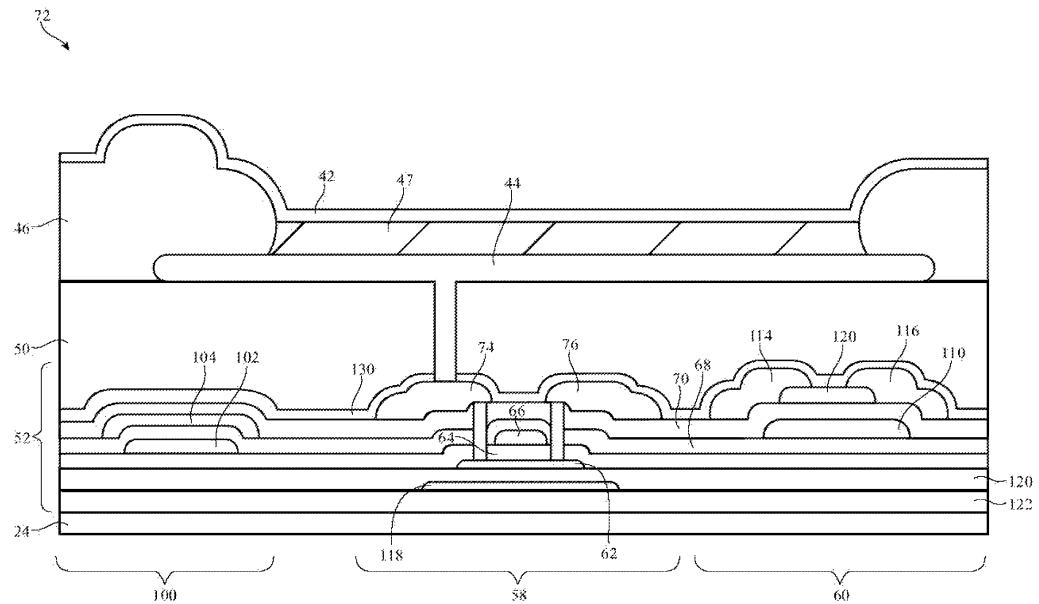

도 6은 실시예에 따른 반도체 산화물 박막 트랜지스터가 저부 게이트 배열을 이용하여 형성되고 저장 커패시터가 또한 규소 트랜지스터에서 박막 트랜지스터 게이트 금속의 역할을 하는 금속의 층으로부터 패터닝된 하위 전극을 이용하여 형성된 구성의 디스플레이 픽셀을 위한 예시적인 박막 트랜지스터 구조체들의 측단면도이다.

도 7은 실시예에 따른 반도체 산화물 박막 트랜지스터가 그것의 게이트와 그것의 채널 사이에 개재된 3개의 층 간 유전체의 층을 갖는 저부 게이트 배열을 이용하여 형성된 구성의 디스플레이 픽셀을 위한 예시적인 박막 트랜지스터 구조체들의 측단면도이다.

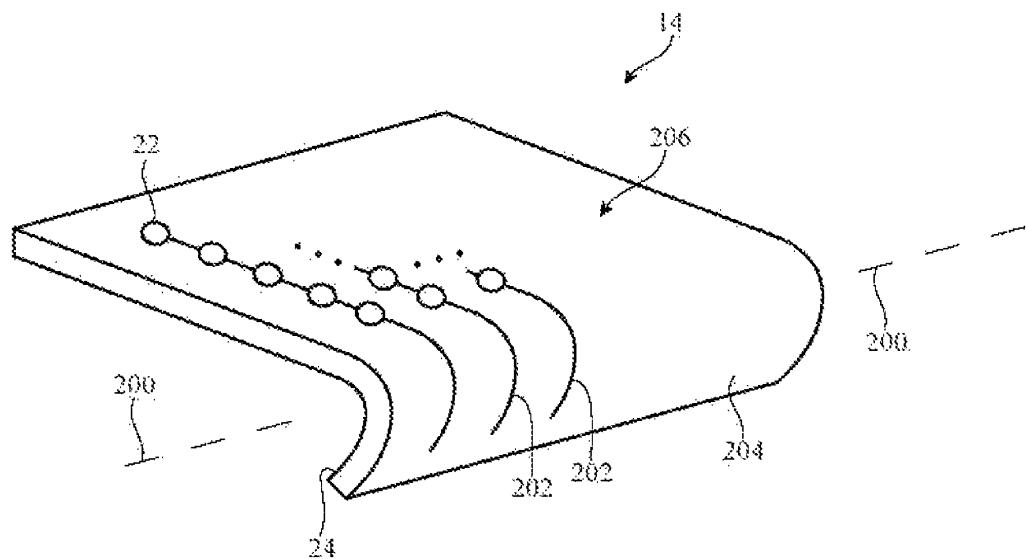

도 8은 실시예에 따른 구부러진 에지를 구비한 예시적인 디스플레이의 사시도이다.

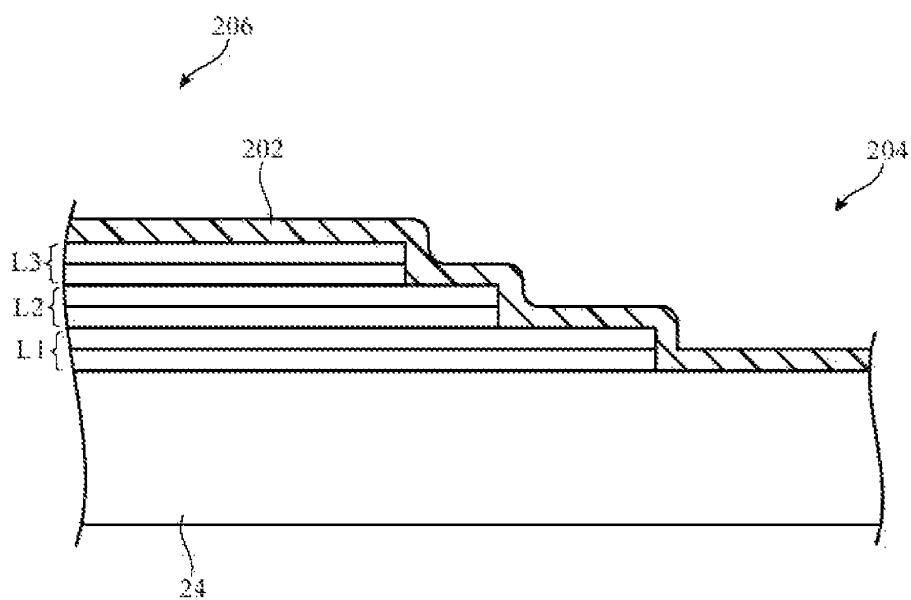

도 9는 실시예에 따른 구부러진 에지를 구비한 디스플레이를 위한 예시적인 계단형 유전체층들의 측단면도이다.

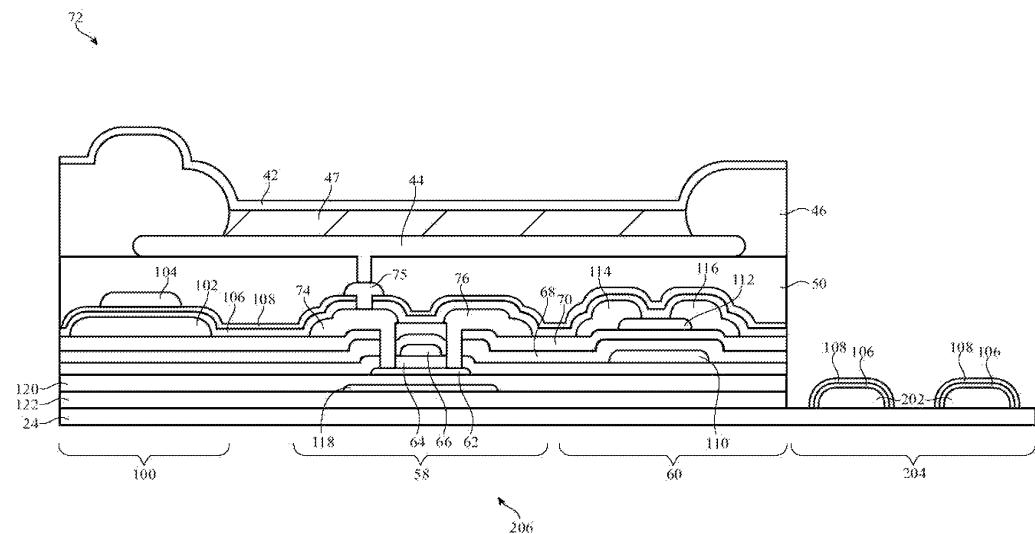

도 10은 실시예에 따른 재료의 상위 층들이 디스플레이로부터 제거되어 디스플레이의 에지를 따라 비활성 영역에서 디스플레이가 용이하게 구부러지는 구성의 디스플레이를 위한 예시적인 박막 트랜지스터 구조체들의 측단면도이다.

도 11은 실시예에 따른 재료의 상위 층들이 디스플레이로부터 제거되어 디스플레이의 에지를 따라 만곡 영역에서 디스플레이가 용이하게 구부러지고, 반도체 산화물 트랜지스터 구조체들이 어떠한 수소 풍부 규소 질화물과도 중첩되지 않는 구성의 디스플레이를 위한 예시적인 박막 트랜지스터 구조체들의 측단면도이다.

### 발명을 실시하기 위한 구체적인 내용

[0011] 전자 디바이스의 디스플레이에는 픽셀들의 어레이 상에 이미지들을 표시하기 위한 구동 회로부가 제공될 수 있다. 예시적인 디스플레이가 도 1에 도시된다. 도 1에 도시된 바와 같이, 디스플레이(14)는 기판(24)과 같은 하나 이상의 층을 가질 수 있다. 기판(24)과 같은 층들은 유리, 플라스틱, 세라믹, 및/또는 기타 유전체들과 같은 절연 재료들로 형성될 수 있다. 기판(24)은 직사각형일 수 있거나 또는 다른 형상들을 가질 수 있다. 경성 기

판 재료(예컨대, 유리) 또는 가요성 기판 재료(예컨대, 폴리이미드의 층과 같은 중합체 또는 기타 재료들의 가요성 시트)가 기판(24)을 형성하는 데 사용될 수 있다.

[0012] 디스플레이(14)는 사용자를 위하여 이미지를 표시하기 위한 픽셀들(22)의 어레이(종종 픽셀 회로들로 지칭됨)를 가질 수 있다. 픽셀들(22)의 어레이는 기판(24) 상에 픽셀 구조체들의 행과 열로 형성될 수 있다. 픽셀들(22)의 어레이에 임의의 적합한 수의 행과 열이 있을 수 있다(예컨대, 10개 이상, 100개 이상, 또는 1000개 이상).

[0013] 디스플레이 구동 접적회로(16)와 같은 디스플레이 구동 회로부는 솔더 또는 전도성 접착제를 이용하여 기판(24) 상에 금속 트레이스와 같은 전도성 경로들에 결합될 수 있다. 디스플레이 구동 접적회로(16)(종종 타이밍 제어 칩으로 지칭됨)는 경로(25)를 통해 시스템 제어 회로부와 통신하기 위한 통신 회로부를 포함할 수 있다. 경로(25)는 가요성 인쇄 회로 상의 트레이스들 또는 기타 케이블로 형성될 수 있다. 제어 회로부는 전자 디바이스, 예컨대, 셀룰러 전화기, 컴퓨터, 셋톱박스, 미디어 플레이어, 휴대용 전자 디바이스, 손목시계 디바이스, 태블릿 컴퓨터, 또는 디스플레이(14)가 사용되고 있는 기타 전자 장비의 메인 로직 보드 상에 위치할 수 있다. 동작 동안, 제어 회로부는 디스플레이 구동 접적회로(16)에 디스플레이(14) 상에서 표시될 이미지들에 관한 정보를 공급할 수 있다. 디스플레이 픽셀들(22) 상에 이미지들을 표시하기 위하여, 디스플레이 구동 접적회로(16)는 게이트 구동 회로부(18) 및 디멀티플렉싱 회로부(20)와 같은 지원 박막 트랜지스터 디스플레이 구동 회로부에 클록 신호들 및 기타 제어 신호들을 발행하면서 대응하는 이미지 데이터를 데이터 라인들(D)에 공급할 수 있다.

[0014] 게이트 구동 회로부(18)는 기판(24) 상에(예컨대, 디스플레이(14)의 좌측 및 우측 에지 상에, 디스플레이(14)의 단일 에지 상에만, 또는 디스플레이(14)의 어느 곳이든) 형성될 수 있다. 디멀티플렉서 회로부(20)는 데이터 신호들을 디스플레이 구동 접적회로(16)로부터 복수의 대응하는 데이터 라인들(D)로 디멀티플렉싱하는 데 사용될 수 있다. 도 1의 예시적인 배열에 따라, 데이터 라인들(D)은 디스플레이(14)에 걸쳐 수직으로 연장된다. 각각의 데이터 라인(D)은 디스플레이 픽셀들(22)의 각각의 열과 연관된다. 게이트 라인들(G)은 디스플레이(14)에 걸쳐 수평으로 연장된다. 각각의 게이트 라인(G)은 디스플레이 픽셀들(22)의 각각의 행과 연관된다. 게이트 구동 회로부(18)는 디스플레이(14)의 좌측, 디스플레이(14)의 우측, 또는 디스플레이(14)의 우측 및 좌측 둘 모두에 위치할 수 있고, 이는 도 1에 도시된 바와 같다.

[0015] 게이트 구동 회로부(18)는 디스플레이(14)의 게이트 라인들(G) 상에 게이트 신호들(종종 스캔 신호들로서 지칭됨)을 활성설정할 수 있다. 예를 들어, 게이트 구동 회로부(18)는 디스플레이 구동 접적회로(16)로부터 클록 신호들 및 기타 제어 신호들을 수신할 수 있고, 수신된 신호들에 응답하여, 디스플레이 픽셀들(22)의 제1 행에서의 게이트 라인 신호(G)를 시작으로, 순서대로 게이트 라인들(G) 상의 게이트 신호를 활성설정할 수 있다. 각각의 게이트 라인이 활성설정되면, 게이트 라인이 활성설정된 행의 대응하는 디스플레이 픽셀들은 데이터 라인들(D) 상에 나타나는 디스플레이 데이터를 표시할 것이다.

[0016] 디스플레이 구동 회로부(16)는 하나 이상의 접적회로를 이용하여 구현될 수 있다. 디멀티플렉서 회로부(20) 및 게이트 구동 회로부(18)와 같은 디스플레이 구동 회로부는 기판(24) 상의 하나 이상의 접적회로 및/또는 박막 트랜지스터 회로부를 이용하여 구현될 수 있다. 박막 트랜지스터들은 디스플레이 픽셀들(22)에 회로부를 형성하는 데 사용될 수 있다. 디스플레이 성능을 강화하기 위하여, 누설 전류, 스위칭 속도, 구동 강도, 균일성 등과 같은 바람직한 기준을 충족하는 디스플레이(14)의 박막 트랜지스터 구조체들이 사용될 수 있다. 디스플레이(14)의 박막 트랜지스터들은, 일반적으로, 임의의 적합한 유형의 박막 트랜지스터 기술(예컨대, 규소기반, 반도체 산화물기반 등)을 이용하여 형성될 수 있다.

[0017] 종종 본 명세서에서 예로서 기재되는 하나의 적합한 배열을 이용하여, 디스플레이(14) 상의 일부 박막 트랜지스터들의 채널 영역(활성 영역)이 규소(예컨대, 종종 LTPS 또는 저온 폴리실리콘으로 지칭되는 저온 공정을 이용하여 침착된 폴리실리콘과 같은 규소)로 형성되고 디스플레이(14) 상의 다른 박막 트랜지스터들의 채널 영역은 반도체 산화물 재료(예컨대, 비정질 인듐 갈륨 아연 산화물, 종종 IGZO로 지칭됨)로 형성된다. 바람직한 경우, 비정질 규소, IGZO 이외의 반도체 산화물 등과 같은 다른 유형들의 반도체가 박막 트랜지스터들을 형성하는 데 사용될 수 있다. 이러한 유형의 하이브리드 디스플레이 구성에서, 스위칭 속도 및 우수한 신뢰성과 같은 속성들이 요구되는 곳에(예컨대, 픽셀들의 유기발광 다이오드를 통해 전류를 구동하기 위한 구동 트랜지스터들에) 규소 트랜지스터들(예컨대, LTPS 트랜지스터)이 사용될 수 있는 반면, (예컨대, 가변적인 리프레시 레이트 스Kim 또는 낮은 누설 전류가 요구되는 기타 시나리오를 구현하는 디스플레이에서의 디스플레이 픽셀 스위칭 트랜지스터들과 같은) 낮은 누설 전류가 요구되는 곳에는 산화물 트랜지스터들(예컨대, IGZO 트랜지스터들)이 사용될 수

있다. 다른 고려사항들(예컨대, 전력 소모, 실제 차지하는 면적, 히스테리시스, 트랜지스터 균일성 등과 관련된 고려사항들)이 또한 고려될 수 있다.

[0018] IGZO 박막 트랜지스터들과 같은 산화물 트랜지스터들은 일반적으로 n-채널 디바이스(즉, NMOS 트랜지스터들)이지만, 바람직한 경우 PMOS 디바이스가 산화물 트랜지스터에 사용될 수 있다. 규소 트랜지스터들은 또한 p-채널 또는 n-채널 설계(즉, LTPS 디바이스는 PMOS 또는 NMOS일 수 있음)를 이용하여 제조될 수 있다. 이러한 박막 트랜지스터 구조체들의 조합은 유기발광 다이오드 디스플레이에 최적의 성능을 제공할 수 있다.

[0019] 유기발광 다이오드 디스플레이에서, 각각의 픽셀은 각각의 유기발광 다이오드를 포함한다. 예시적인 유기발광 다이오드 디스플레이 픽셀의 개략적인 다이어그램이 도 2에 도시된다. 도 2에 도시된 바와 같이, 픽셀(22)은 발광 다이오드(26)를 포함할 수 있다. 양극 전력공급 전압(ELVDD)이 양극 전력공급 단자(34)에 공급될 수 있고 접지 전력공급 전압(ELVSS)이 접지 전력공급 단자(36)에 공급될 수 있다. 구동 트랜지스터(28)의 상태는 다이오드(26)를 통해 흐르는 전류량을 제어함으로써 디스플레이 픽셀(22)로부터 방출되는 광(40)의 양을 제어한다.

[0020] 트랜지스터(28)가 연속적인 데이터의 프레임들 사이에서 바람직한 상태로 유지되도록 보장하기 위하여, 디스플레이 픽셀(22)은 저장 커패시터(Cst)와 같은 저장 커패시터를 포함할 수 있다. 트랜지스터(28)를 제어하기 위하여 저장 커패시터(Cst)의 전압이 노드(A)에서 트랜지스터(28)의 게이트에 인가된다. 데이터는 스위칭 트랜지스터(30)와 같은 하나 이상의 스위칭 트랜지스터를 이용하여 저장 커패시터(Cst)에 로딩될 수 있다. 스위칭 트랜지스터(30)가 꺼지면, 데이터 라인(D)은 저장 커패시터(Cst)로부터 격리되고, 단자(A)의 게이트 전압은 저장 커패시터(Cst)에 저장된 데이터 값(즉, 디스플레이(14) 상에 표시되고 있는 이전 프레임의 디스플레이 데이터로부터의 데이터 값)과 동일하다. 픽셀(22)과 연관된 행의 게이트 라인(G)(종종 스캔 라인으로 지칭됨)이 활성설정되면, 스위칭 트랜지스터(30)는 켜질 것이고, 데이터 라인(D) 상의 새로운 데이터 신호가 저장 커패시터(Cst)에 로딩될 것이다. 커패시터(Cst) 상의 새로운 신호가 노드(A)에서 트랜지스터(28)의 게이트에 인가됨으로써, 트랜지스터(28)의 상태를 조정하고 대응하는 발광 다이오드(26)에 의해 방출되는 광(40)의 양을 조정한다.

[0021] 도 2의 예시적인 픽셀 회로는 단지 디스플레이(14)의 픽셀들의 어레이에 사용될 수 있는 회로부의 일례이다. 예를 들어, 각각의 픽셀 회로는 임의의 적합한 수의 스위칭 트랜지스터들(하나 이상, 2개 이상, 3개 이상 등)을 포함할 수 있다. 바람직한 경우, 유기발광 다이오드 디스플레이 픽셀(22)은 추가적인 컴포넌트들(예컨대, 임계전압 보상 등과 같은 기능들을 구현하도록 돋기 위하여 구동 트랜지스터와 직렬로 결합된 하나 또는 2개의 방출인에이블 트랜지스터)을 가질 수 있다. 일반적으로, 본 명세서에 기재된 박막 트랜지스터 구조체들은 도 2의 픽셀 회로 또는 임의의 기타 적합한 픽셀 회로들에 사용될 수 있다. 예를 들어, 본 명세서에 기재된 박막 트랜지스터 구조체들은, 2개의 상이한 스캔 라인에 의해 제어되는 3개의 스위칭 트랜지스터, 유기발광 다이오드와 직렬로 결합된 하나의 구동 트랜지스터, 및 2개의 각각의 방출 라인들에 의해 제어되고 구동 트랜지스터 및 발광 다이오드와 직렬로 결합되어 임계전압 보상 기능들을 구현하는 2개의 방출 인에이블 트랜지스터를 갖는 6 트랜지스터 픽셀 회로들에 사용될 수 있다. 디스플레이(14)의 픽셀을 위한 박막 트랜지스터 회로들은 또한 다른 수의 스위칭 트랜지스터들(예컨대, 하나 이상, 2개 이상, 3개 이상, 4개 이상 등) 또는 다른 수의 방출 트랜지스터들(방출 트랜지스터 없음, 하나 이상의 방출 트랜지스터, 2개 이상의 방출 트랜지스터, 3개 이상의 방출 트랜지스터, 4개 이상의 방출 트랜지스터 등)을 가질 수 있다. 각각의 픽셀 회로의 트랜지스터들은 규소 및 규소산화물 트랜지스터들의 임의의 적합한 조합 및 NMOS 및 PMOS 트랜지스터들의 임의의 적합한 조합으로 형성될 수 있다. 도 2의 픽셀 회로부는 단지 예시일 뿐이다.

[0022] 도 2의 픽셀(22)과 같은 유기발광 다이오드 픽셀들 또는 디스플레이(14)를 위한 임의의 기타 적합한 픽셀 회로들은 도 3에 도시된 유형의 박막 트랜지스터 구조체들을 이용할 수 있다. 이러한 유형의 구조체에서, 2개의 상이한 유형의 반도체가 사용된다. 도 3에 도시된 바와 같이, 픽셀 회로부(72)는 발광 다이오드 캐소드 단자(42) 및 발광 다이오드 애노드 단자(44)와 같은 픽셀 구조체들을 포함할 수 있다. 캐소드(42)와 애노드(44) 사이에 유기발광 다이오드 방출 재료(47)가 개재됨으로써, 도 2의 발광 다이오드(26)를 형성할 수 있다. 유전체층(46)은 픽셀의 레이아웃(예컨대, 애노드(44)에 대한 방출 재료(47)의 정렬)을 정의하는 역할을 할 수 있고 종종 픽셀 정의층으로 지칭될 수 있다. 평탄화층(50)(예컨대, 중합체층)은 박막 트랜지스터 구조체들(52)의 상부 상에 형성될 수 있다. 박막 트랜지스터 구조체들(52)은 기판(24) 상에 형성될 수 있다. 기판(24)은 경성 또는 가요성일 수 있고 유리, 세라믹, 사파이어와 같은 결정질 재료, 중합체(예컨대, 폴리이미드의 가요성층 또는 기타 중합체 재료의 가요성 층) 등으로 형성될 수 있다.

[0023] 박막 트랜지스터 구조체들(52)은 규소 트랜지스터(58)와 같은 규소 트랜지스터들을 포함할 수 있다. 트랜지스

터(58)는 "상부 게이트" 설계를 이용하여 형성된 LTPS 트랜지스터일 수 있고 광센(22)의 트랜지스터들 중 임의 것을 형성하는 데 사용될 수 있다(예컨대, 트랜지스터(58)는 도 2의 광센(22)에서 구동 트랜지스터(28)와 같은 구동 트랜지스터의 역할을 할 수 있음). 트랜지스터(58)는 게이트 절연층(64)(예컨대, 규소 산화물의 층 또는 기타 무기층)에 의해 커버되는 폴리실리콘 채널(62)을 가질 수 있다. 게이트(66)는 패터닝된 금속(예컨대, 예를 들어, 몰리브덴)으로 형성될 수 있다. 게이트(66)는 층간 유전체의 층(예컨대, 규소 질화물층(68) 및 규소 산화물층(70) 또는 기타 무기층 또는 유기 재료)에 의해 커버될 수 있다. 소스-드레인 컨택들(74, 76)은 폴리실리콘층(62)의 양측에 접촉하여 규소 박막 트랜지스터(58)를 형성할 수 있다.

[0024] 게이트(66)는 금속층(GATE)으로 형성될 수 있고, 소스-드레인 단자들(74, 76)은 금속층(SD)으로 형성될 수 있고, 추가 금속층(M3)은 금속 비아(75)를 형성하여 소스-드레인 전극(74)을 애노드(44)에 결합하는 데 사용될 수 있다.

[0025] 회로부(72)는 또한 커패시터 구조체(100)와 같은 커패시터 구조체들(예컨대, 도 2의 커패시터(Cst))을 포함할 수 있다. 커패시터 구조체(100)는 전극(102)과 같은 하위 전극 및 전극(104)과 같은 상위 전극을 가질 수 있다. 하위 전극(102)은 금속층(SD)의 패터닝된 부분으로 형성될 수 있다. 상위 전극(104)은 금속층(M3)의 패터닝된 부분으로 형성될 수 있다. 유전체층은 상위 전극(104)과 하위 전극(102)을 분리할 수 있다. 유전체층은 하프늄 산화물 또는 알루미늄 산화물과 같은 높은 유전상수 재료로 형성될 수 있거나 또는 하나 이상의 다른 층으로 형성될 수 있다. 도 3의 예에서, 전극들(102, 104)을 분리하는 유전체층은 2개의 패시베이션층(106, 108)을 포함한다. 층들(106, 108)은 각각 규소 산화물 및 규소 질화물로 형성될 수 있다. 바람직한 경우, 기타 무기층들 및/또는 유기층들은 층들(106, 108)을 형성하는 데 사용될 수 있다(예컨대, 산화물층, 질화물층, 중합체층 등).

[0026] 박막 트랜지스터 구조체들(52)은 반도체 산화물 트랜지스터(60)와 같은 반도체 산화물 트랜지스터들을 포함할 수 있다. 구조체들(60)의 박막 트랜지스터는 "저부 게이트" 산화물 트랜지스터일 수 있다. 트랜지스터(60)의 게이트(110)는 금속층(GATE)의 일부분으로 형성될 수 있다. 트랜지스터(60)의 반도체 산화물 채널 영역(채널(112))은 IGZO와 같은 반도체 산화물로 형성될 수 있다. 층간 유전체(예컨대, 층들(68, 70))은 게이트(110)와 반도체 산화물 채널(112) 사이에 개재될 수 있고, 트랜지스터(60)를 위한 게이트 절연층의 역할을 할 수 있다. 산화물 트랜지스터(60)는 금속층(SD)의 패터닝된 부분들로 형성된 소스-드레인 단자들(114, 116)을 가질 수 있다.

[0027] 기판(24) 상의 베퍼층(122)은 폴리아미드 또는 기타 유전체의 층으로 형성될 수 있다. 베퍼층(122)의 전하로부터 트랜지스터(58)를 보호하기 위하여 트랜지스터(58) 아래에 배면 금속층(118)이 형성될 수 있다. 실드층(118) 위에 베퍼층(120)이 형성될 수 있고 유전체로 형성될 수 있다(예컨대, 중합체층 또는 기타 절연층과 같은 유기층).

[0028] 광센 회로(22)를 위한 추가 예시적인 박막 트랜지스터 회로부(72)가 도 4에 도시된다. 도 4의 예에서, 산화물 트랜지스터(60)는 "상부 게이트" 배열을 이용하여 형성되었다. 이러한 접근법으로, 트랜지스터(60)를 위한 게이트(110)는 금속층(M3)의 패터닝된 부분으로 형성된다. 금속층(M3)은 또한 (예를 들어) 커패시터(100)의 전극(104)을 형성하는 데 사용될 수 있다. 금속층(SD)은 전극(102), 소스-드레인 단자들(74, 76), 및 소스-드레인 단자들(114, 116)을 형성하는 데 사용될 수 있다. 산화물 트랜지스터(60)는 반도체 산화물 채널(112)을 가질 수 있다. 유전체(예컨대, 패시베이션층들(106, 108) 및/또는 높은 유전상수 재료 또는 기타 절연 재료)가 채널(112)과 게이트(110) 사이에 개재될 수 있다.

[0029] 도 5의 예에서, 회로부(72)의 트랜지스터(60)는 저부 게이트 산화물 트랜지스터이다. 유전체층(132)이 커패시터(100)의 상위 전극(104)과 하위 전극(102) 사이에 개재될 수 있다. 유전체층(132)은 무기 절연체(예컨대, 규소 산화물, 규소 질화물 등)로 형성될 수 있거나 또는 중합체층으로 형성될 수 있다. 층(132)은 종종 층간 유전체층으로 지칭될 수 있고, 층간 유전체층들(68, 70)의 상부 상에 형성될 수 있다. 커패시터(100)에서, 층(132)은 서로 전극들(102, 104)을 분리한다. 상위 전극(104)은 금속층(SD)으로 형성될 수 있다. 금속층(SD)은 또한 규소 트랜지스터(58)를 위한 소스-드레인 전극들(74, 76) 및 산화물 트랜지스터(60)를 위한 소스-드레인 전극들(114, 116)을 형성하는 데 사용될 수 있다. 하위 전극(102)은 게이트(66)를 위한 게이트 금속(GATE)과 금속층(SD) 사이에서 침착되고 패터닝된 금속층으로 형성될 수 있다. 도 5의 하위 전극(102)을 형성하는 데 사용되는 금속층은 종종 금속층(M2S)으로 지칭될 수 있다. 금속층(M2S)은 커패시터(100)의 하위 전극(102)을 형성하는 데 사용되는 것뿐만 아니라, 트랜지스터(60)의 게이트(110)를 형성하는 데 사용될 수 있다.

[0030] 도 5의 구성에서, 금속층(M2S)은 유전체층들(68, 70) 상에 형성되었다. 유전체층(132)은 게이트(110)와 반도체

산화물 채널(120) 사이에 개재되고 트랜지스터(60)를 위한 게이트 절연체의 역할을 한다. 채널(120)의 반도체 산화물 인터페이스를 보호하기 위하여 채널(120) 위에 유전체층(130)과 같은 패시베이션층이 형성될 수 있다. 유전체층(130) 및 유전체층(132)은 각각 규소 산화물, 규소 질화물, 알루미늄 산화물, 하프늄 산화물, 단일층, 다중 서브층들, 또는 기타 절연 재료들로 형성될 수 있다.

[0031] 도 6은 트랜지스터 회로부(74)에 대한 다른 예시적인 구성을 도시한다. 도 6의 배열에서, 회로부(74)는 3개의 금속층을 가진다. 금속층(GATE)은 커패시터(100)를 위한 하위 전극(102)을 형성하는 데 사용되고 규소 트랜지스터(58)를 위한 게이트(66)를 형성하는 데 사용된다. 금속층(SD)은 소스-드레인 단자들(74, 76, 114, 116)을 형성하는 데 사용된다. 종종 금속층(G2)으로 지칭되는, 추가적인 금속층이 금속층(SD)과 금속층(GATE) 사이에 개재된다. 금속층(G2)은 커패시터(100)의 상위 전극(104)을 형성하는 데 사용될 수 있고 산화물 트랜지스터(60)의 게이트(110)를 형성하는 데 사용될 수 있다. 도 6의 산화물 트랜지스터(60)는 저부 게이트 트랜지스터이다. 유전체층(70)은 트랜지스터(60)를 위한 게이트 절연체의 역할을 하고, 게이트(110)와 반도체 산화물 채널(120) 사이에 개재된다. 패시베이션층(130)은 채널 영역(120)을 보호할 수 있다. 커패시터(100)에서, 유전체층(68)은 상위 전극(104)과 하위 전극(102) 사이에 개재된다.

[0032] 도 7에 도시된 회로부(72)에 대한 예시적인 구성에서, 커패시터(100)의 상위 전극(104)은 금속층(SD)으로 형성된다. 금속층(SD)은 또한 규소 트랜지스터(58)의 소스-드레인 전극들(74, 76) 및 산화물 트랜지스터(60)의 소스-드레인 전극들(114, 116)을 형성하는 데 사용될 수 있다. 산화물 트랜지스터(60)는 저부 게이트 구성을 가질 수 있다. 산화물 트랜지스터(60)의 게이트(110) 및 규소 트랜지스터(58)의 게이트(66)는 동일한 금속층(즉, 금속층(GATE))의 각각의 부분들로 형성될 수 있다. 추가적인 금속층(금속층(M2S))이 금속층(GATE)과 금속층(SD) 사이에 형성될 수 있다. 금속층(M2S)은 커패시터(100)의 하위 전극(102)을 형성하는 데 사용될 수 있다. 유전체층(132)이 하위 전극(102)과 상위 전극(104) 사이에 개재될 수 있다. 패시베이션층(130)은 산화물 트랜지스터(60)에서 반도체 산화물층(120)의 인터페이스를 보호하는 데 사용될 수 있다.

[0033] 디스플레이(14)의 비활성 경계 영역을 최소화하는 것이 바람직할 수 있다. 픽셀들(22)은 사용자를 위한 이미지를 표시하여, 픽셀들(22)의 어레이에 의해 점유되는 디스플레이(14) 부분이 디스플레이(14)의 활성 영역을 형성한다. 활성 영역을 둘러싼 디스플레이(14)의 부분들은 사용자를 위한 이미지를 표시하지 않고 따라서 비활성이다. 사용자에게 보이는 비활성 영역의 양은 활성 영역의 평면으로부터 (예컨대, 직각 또는 기타 적합한 각도로) 아래로 기판(24)의 부분들을 구부림으로써 최소화 또는 제거될 수 있다. 구부리는 동안 디스플레이(14)가 손상되지 않도록 보장하기 위하여, 기판(24) 상의 구조체들은 비활성 영역의 구부러지는 부분들에서 디스플레이(14)의 가요성을 강화하도록 구성될 수 있다. 예를 들어, 무기 유전체층들과 같은 절연층들 및 디스플레이(14)의 다른 층들(예컨대, 금속층들 중 일부)이 부분적으로 또는 완전히 비활성 영역에서 제거되어 구부리는 동안 스트레스성 크래킹 또는 기타 손상(특히 금속 신호 라인들)을 방지할 수 있다.

[0034] 예를 들어, 도 8의 디스플레이(14)를 고려해본다. 도 8에 도시된 바와 같이, 비활성 에지 영역(204)이 구부리는 축(200)을 중심으로 활성 영역(206)으로부터 아래로 구부러졌다. 라인들(202)(예컨대, 디스플레이(14)의 데이터 라인들 또는 기타 금속 신호 트레이스들)이 축(200)에서 구부러지는 부분을 횡단한다. 크랙의 형성 및 디스플레이(14)의 구조체들에 대한 기타 손상을 방지하기 위하여, 라인들(202) 이외의 디스플레이(14)의 구조체들의 일부 또는 전부가 비활성 영역(204)에서 선택적으로 제거될 수 있다(반면 도 3, 도 4, 도 5, 도 6 및 도 7의 회로부(72)와 같은 박막 트랜지스터 회로부(72)를 형성하도록 활성 영역(206)에서 유지됨). 이러한 접근법으로, 라인들(202)을 형성하는 금속층은 비활성 영역(204)에서보다 활성 영역(206)에서 기판(24) 위에서 더 먼 거리에 위치할 수 있다.

[0035] 활성 영역(206)과 비활성 영역(204)의 층들 사이의 높이의 격차를 수용하기 위하여, 일련의 계단들이 디스플레이(14)의 유전체층들에 형성될 수 있다. 계단들은 유전체층들 상에 지지되는 금속 트레이스들의 높이를 천천히 낮출 수 있어서, 금속 트레이스들은 높이를 점진적으로 변경할 수 있고 유전체의 급격한 높이 불연속으로 인해 단절되지 않는다.

[0036] 금속 라인들(202)이 활성 영역(206)과 비활성 영역(204) 사이에서 연속적으로 전이될 수 있도록 계단형 프로파일을 갖는 유전체층들의 예시적인 세트가 도 9에 도시된다. 도 9에 도시된 바와 같이, 디스플레이(14)는 층들(L1, L2, L3)과 같은 유전체층들을 가질 수 있다(예컨대, 도 3, 도 4, 도 5, 및 도 6의 회로부(72)의 유전체층들 참조). 층들(L1, L2, L3)은 중합체의 하나 이상의 서브층 및/또는 무기층들로 형성될 수 있다(예컨대, 규소 산화물, 규소 질화물, 하프늄 산화물, 알루미늄 산화물 등). 도 9의 예에 3개의 유전체층(L1, L2, L3)이 있지만, 이는 단지 예시일 뿐이다. 활성 영역(206)인 도 9의 좌측에, 모든 유전체층(L1, L2, L3)이 존재하고, 따라

서 금속 라인(202)이 기판(24)으로부터 그것의 최대 거리에 위치한다. 활성 영역(206)으로부터 연속적으로 더 큰 측방향 거리에서 층들(L3, L2, L1)을 선택적으로 제거함으로써 계단(계단형) 유전체 프로파일이 생성된다. 유전체층들에 형성된 높이의 계단들은 금속 라인(202)이 그것의 최대 높이(활성 영역(206))로부터 비활성 영역(204)에서의 그것의 최소 높이로 부드럽게 전이되도록 한다. 라인(202)은, 예를 들어, 비활성 영역(204)에서 기판(24)의 표면 상에 또는 그 근처에 놓일 수 있다.

[0037] 도 10은 재료의 상위 층들이 디스플레이로부터 제거되어 디스플레이가 구부러지는 영역에서 디스플레이의 비활성 에지를 따라 용이하게 구부러지게 하는 구성의 디스플레이(14)를 위한 예시적인 박막 트랜지스터 회로부(72)의 측단면도이다. 도 10의 예에서, 패시베이션층들(106, 108)을 제외한 모든 유전체층들이 영역(204)에서 기판(24)으로부터 제거되었고, 따라서 금속 라인들(202)(예컨대, 디스플레이(14)의 데이터 라인들 및/또는 기타 신호 라인들)은 기판(24)의 표면 상에 놓인다. 이는 영역(204)에서 기판(24)이 용이하게 구부러지게 한다. 일반적으로, 임의의 적합한 박막 트랜지스터 회로부(72)는 도 10의 비활성 영역 재료 제거 스킴에 이용될 수 있다(예컨대, 도 3, 도 4, 도 5, 도 6, 도 7 및 도 8 등의 회로부(72)와 같은 회로부). 도 10의 회로부는 단지 예시일 뿐이다.

[0038] 도 10의 예시적인 구성에서, 상위 커패시터 전극(104)은 금속층(M3)으로 형성되었다. 금속층(M3)은 또한 소스-드레인 단자(74)를 애노드(44)에 결합하는 비아(74)를 형성하는 데 사용될 수 있다. 하위 커패시터 전극(102)은 금속층(SD)으로 형성될 수 있다. 금속층(SD)은 또한 소스-드레인 단자들(74, 76, 114, 116)을 형성하는 데 사용될 수 있다. 패시베이션층들(106, 108)(예컨대, 각각 규소 질화물 및 규소 산화물층들) 또는 다른 적합한 유전체층(들)은 반도체 산화물 채널(112)의 상부 상에 형성될 수 있다. 커패시터(100)에서, 층들(106, 108) 중 하나를 국부적으로 제거하여 유전체 두께를 줄임으로써 커패시터(100)의 커패시턴스 값을 증가시킬 수 있다. 도 10에 도시된 바와 같이, 예를 들어, 층(106)이 전극(104) 아래에서 제거되어, 층(106)이 커패시터(100)와 중첩되지 않도록 하고 유전체층(108)만이 커패시터(100)의 상위 전극(104)과 하위 전극(102) 사이에 개재되도록 할 수 있다. 유전체층(108)은 규소 질화물로 형성될 수 있고, 이는 규소 산화물보다 큰 유전상수를 가지므로, 유전체층(108)을 전극들(102, 104) 사이에서 배타적인 절연층으로서 사용하는 것은 커패시터(100)의 커패시턴스를 증가시키는 것을 도울 수 있다. 규소 산화물 층(106)을 선택적으로 제거하기 위하여 추가적인 포토리소그래픽 마스크가 사용될 수 있다. 마스크는 또한 금속 라인들(202)을 위한 유전체 계단을 형성하는 데 사용될 수 있다(예컨대, 도 9의 유전체 계단들 참조). 금속 라인들(202)은 금속층(SD)으로 형성될 수 있다. 디스플레이(14)의 활성 영역(206)에서, 금속 라인들(202)은 층들(122, 120, 64, 68, 70)(즉, 도 9의 예시적인 층들(L1, L2, L3)을 형성할 수 있는 유형의 층들)과 같은 유전체층들에 의해 지지되는 금속층(SD)의 부분들로 형성될 수 있다. 도 9의 예에서 3개의 높이 계단이 있지만, 1개의 계단, 2개의 계단, 3개의 계단, 또는 3개 초과의 계단이 형성될 수 있다.

[0039] 도 11의 예시적인 구성은 도 10의 구성과 유사하지만, 국부적으로 제거된 규소 질화물 패시베이션층을 구비한 산화물 트랜지스터를 가진다. 도 10의 패시베이션층(106)은 규소 질화물층일 수 있다. 규소 질화물층(106)은 규소 트랜지스터(58)의 폴리실리콘층(62)에서 댕글링 본드를 부동태화하기 위하여 고농도의 수소를 가질 수 있다. 효과적인 패시베이션을 위하여, 규소 질화물층(106)은 트랜지스터(58) 및 규소 채널(62)과 중첩될 수 있다. 규소 질화물층(106)으로부터 수소가 반도체 산화물 채널(112)에 도달하는 것을 방지하는 것이 바람직할 수 있다. 이는 질화물층(106)을 트랜지스터(60)로부터 제거함으로써 성취될 수 있다. 예를 들어, 규소 질화물층(106)이 반도체 산화물(112) 아래에 없도록(즉, 트랜지스터(60)와 중첩되는 질화물층(106) 부분이 없도록) 규소 질화물층(106)을 패터닝하는 데 포토리소그래픽 마스크가 사용될 수 있다. 규소 질화물이 게이트(110)와 산화물(112) 사이에 없도록 보장함으로써, 트랜지스터(60)의 성능은 층(106)으로부터의 수소로 인해 떨어지지 않을 것이다.

[0040] 실시예에 따른, 기판, 기판의 활성 영역을 형성하는 픽셀 회로들의 어레이, 및 기판의 비활성 영역에 있는 회로부를 포함하는 유기발광 다이오드 디스플레이가 제공되고, 각각의 픽셀 회로는 유기발광 다이오드, 유기발광 다이오드와 직렬로 결합된 규소 트랜지스터, 규소 트랜지스터에 결합된 저장 커패시터, 및 저장 커패시터에 결합된 반도체 산화물 트랜지스터를 포함한다.

[0041] 다른 실시예에 따라, 기판은 비활성 영역에서 구부러진다.

[0042] 다른 실시예에 따라, 유기발광 다이오드 디스플레이의 유전체층들을 포함하고, 유전체층들은 활성 영역에 존재하고 유전체층들의 적어도 일부는 비활성 영역에 존재하지 않는다.

[0043] 다른 실시예에 따라, 각각의 픽셀 회로의 규소 트랜지스터는 규소 채널을 포함하고, 유전체층들은 기판과 규소

채널 사이의 베피충을 포함하고, 베피충은 비활성 영역에 존재하지 않는다.

[0044] 다른 실시예에 따라, 유기발광 다이오드 디스플레이의 활성 영역에 제1 금속층을 포함하고, 제1 금속층의 일부는 각각의 픽셀 회로에서 규소 트랜지스터를 위한 게이트를 형성한다.

[0045] 다른 실시예에 따라, 제1 금속층의 일부는 각각의 픽셀 회로에서 반도체 산화물 트랜지스터를 위한 게이트를 형성한다.

[0046] 다른 실시예에 따라, 유기발광 다이오드 디스플레이의 제2 금속층을 포함하고, 제2 금속층을 활성 영역에서 패터닝하여 규소 트랜지스터 및 반도체 산화물 트랜지스터를 위한 소스-드레인 단자들을 형성한다.

[0047] 다른 실시예에 따라, 제2 금속층을 비활성 영역에서 패터닝하여 픽셀 회로들의 어레이와 비활성 영역의 회로부 사이에 결합되는 데이터 라인들을 형성한다.

[0048] 다른 실시예에 따라, 기판은 구부러진 가요성 기판이고 데이터 라인들은 구부러지고 기판의 표면 상에 형성되어 유전체층들 중 어느 것도 데이터 라인들과 기판 사이에 개재되지 않도록 한다.

[0049] 다른 실시예에 따라, 각각의 픽셀의 반도체 산화물 트랜지스터는 반도체 산화물 채널을 포함한다.

[0050] 다른 실시예에 따라, 유전체층들은 각각의 픽셀 회로에서 규소 트랜지스터의 규소 채널과 중첩되고 각각의 픽셀 회로에서 반도체 산화물 트랜지스터의 반도체 산화물 채널과 중첩되지 않는 규소 질화물층을 포함한다.

[0051] 다른 실시예에 따라, 저장 커패시터는 제2 금속의 층으로 형성된 제1 전극을 가지며, 제2 전극을 가진다.

[0052] 다른 실시예에 따라, 유전체층들은 추가 규소 질화물층을 포함하고, 추가 규소 질화물층은 각각의 픽셀 회로에서 저장 커패시터의 제1 및 제2 전극 사이에 개재된다.

[0053] 다른 실시예에 따라, 유기발광 다이오드 디스플레이의 각각의 픽셀 회로에서 반도체 산화물 채널과 중첩되고 각각의 픽셀 회로의 저장 커패시터에서 국부적으로 제거되어 규소 산화물층 중 어느 것도 저장 커패시터의 제1 및 제2 전극 사이에 개재되지 않도록 하는, 규소 산화물층을 포함한다.

[0054] 다른 실시예에 따라, 유기발광 다이오드 디스플레이의 활성 영역에서 비활성 영역으로 연장되는 데이터 라인들을 포함하고, 유전체층들은 활성 영역에서 비활성 영역으로 전이될 때 높이가 감소하는 계단형 프로파일을 가지고, 데이터 라인들은 계단형 프로파일을 구비한 유전체층들 상에 형성된다.

[0055] 다른 실시예에 따라, 각각의 픽셀 회로의 반도체 산화물 트랜지스터는 구동 트랜지스터를 포함하고 각각의 픽셀 회로의 규소 트랜지스터는 스위칭 트랜지스터를 포함한다.

[0056] 실시예들에 따른, 유기발광 다이오드들의 어레이, 유기발광 다이오드들의 각각의 유기발광 다이오드에 직렬로 각각 결합된 규소 구동 트랜지스터들, 및 규소 트랜지스터들에 결합된 반도체 산화물 스위칭 트랜지스터들을 포함하는 유기발광 다이오드 디스플레이가 제공된다.

[0057] 다른 실시예에 따라, 반도체 산화물 스위칭 트랜지스터들은 각각 반도체 산화물 채널을 갖고, 유기발광 다이오드 디스플레이의 규소 구동 트랜지스터들과 중첩되고 반도체 산화물 채널들과 중첩되지 않는 규소 질화물층을 포함한다.

[0058] 다른 실시예에 따라, 유기발광 다이오드 디스플레이의 반도체 산화물 스위칭 트랜지스터들에 결합된 저장 커패시터들, 및 반도체 산화물 채널과 중첩되고 저장 커패시터들과 중첩되지 않는 규소 산화물층을 포함한다.

[0059] 실시예들에 따른, 가요성 중합체 기판, 기판 상의 픽셀 회로들의 어레이 - 각각의 픽셀 회로는 유기발광 다이오드, 각각 반도체 산화물 채널을 갖는 적어도 2개의 반도체 산화물 트랜지스터, 유기발광 다이오드와 직렬로 결합된 적어도 하나의 규소 트랜지스터, 및 적어도 하나의 저장 커패시터를 포함함 -, 픽셀 회로들의 어레이로부터 픽셀 회로들의 어레이에 인접한 비활성 영역으로 전이될 때 높이가 감소하는 계단형 프로파일을 갖는 가요성 중합체 기판 상의 유전체층들, 및 계단형 프로파일을 따르는 유전체층들 상의 데이터 라인들 - 유전체층들은 규소 트랜지스터들과 중첩되고 반도체 산화물 채널들과 중첩되지 않는 유전체층을 포함함 -을 포함하는 유기발광 다이오드 디스플레이가 제공된다.

[0060] 전술한 사항은 단지 예시적인 것이며, 기술된 실시예들의 범주 및 사상으로부터 벗어남이 없이 본 발명이 속한 기술분야에서 통상의 지식을 가진 자들에 의해 다양한 수정들이 이루어질 수 있다. 상기의 실시예들은 개별적으로 또는 임의의 조합으로 구현될 수 있다.

도면

도면1

## 도면2

## 도면3

## 도면4

## 도면5

## 도면6

## 도면7

도면8

도면9

## 도면10

## 도면11

|                |                                                                                                                                                                   |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 硅和半导体氧化物薄膜晶体管显示器                                                                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">KR1020170044167A</a>                                                                                                                                  | 公开(公告)日 | 2017-04-24 |

| 申请号            | KR1020177007597                                                                                                                                                   | 申请日     | 2014-10-09 |

| [标]申请(专利权)人(译) | 苹果公司                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 苹果公司                                                                                                                                                              |         |            |

| 当前申请(专利权)人(译)  | 苹果公司                                                                                                                                                              |         |            |

| [标]发明人         | TSAI TSUNG TING<br>차이충팅<br>GUPTA VASUDHA<br>굽타바수다<br>LIN CHIN WEI<br>린진웨이                                                                                         |         |            |

| 发明人            | 차이,충 텡<br>굽타,바수다<br>린,친 웨이                                                                                                                                        |         |            |

| IPC分类号         | H01L27/32 H01L27/12                                                                                                                                               |         |            |

| CPC分类号         | H01L27/3262 H01L27/3265 H01L27/1225 H01L27/1251 H01L27/3258 H01L27/3276 H01L27/1255<br>H01L51/0097 H01L2251/5338 Y02E10/549 H01L29/78651 H01L29/78672 H01L29/7869 |         |            |

| 代理人(译)         | Jangdeoksun<br>Baekmangi                                                                                                                                          |         |            |

| 优先权            | 14/494931 2014-09-24 US                                                                                                                                           |         |            |

| 其他公开文献         | KR101963522B1                                                                                                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                         |         |            |

#### 摘要(译)

电子设备显示器可以具有像素电路阵列。每个像素电路可以包括有机发光二极管和驱动晶体管。可以调节每个驱动晶体管以控制流过有机发光二极管的电流量。每个像素电路可以包括一个或多个附加晶体管，例如开关晶体管和存储电容器。半导体氧化物晶体管和硅晶体管可用于形成像素电路的晶体管。可以使用金属层，半导体结构和介电层来形成存储电容器和晶体管。可以沿着显示器的边缘去除一些层以便于弯曲。介电层可以具有阶梯式轮廓，当阵列的数据线延伸到无效边缘区域时，该阶梯式轮廓允许数据线向下朝向基板的表面逐步降低。