(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2017-0015700

(43) 공개일자 2017년02월09일

(51) 국제특허분류(Int. Cl.)

*H01L 51/52* (2006.01) *H01L 27/32* (2006.01)

*H01L 51/56* (2006.01)

(52) CPC특허분류

*H01L 51/5203* (2013.01)

*H01L 27/3225* (2013.01)

(21) 출원번호 10-2015-0108133

(22) 출원일자 2015년07월30일

심사청구일자 없음

(71) 출원인

엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

박경진

경기도 파주시 문산읍 독서울1길 21 410동 1102호

(선유리, 문산선유4단지)

강병권

경상북도 구미시 인동19길 10-11, 명품명가 야구

202호(인의동)

(74) 대리인

특허법인네이트

전체 청구항 수 : 총 14 항

(54) 발명의 명칭 유기발광다이오드 표시장치 및 그 제조방법

### (57) 요 약

본 발명은 유기발광다이오드의 제1전극에 대한 플라즈마 처리 공정에 의해 소수성 뱅크층이 친수화되는 것을 개선할 수 있는 방안을 제공하는 것에 과제가 있다.

이를 위해, 본 발명에서는, 화소영역의 경계를 따라 형성된 소수성의 뱅크층의 표면 일부에 이온차폐전극을 형성(뒷면에 계속)

대 표 도 - 도4

하며, 제1전극에 대한 플라즈마 처리 공정시 이온차폐전극에 양전하를 인가하게 된다. 이에 따라, 이온차폐전극은 플라즈마 처리 공정시 발생된 양이온 플라즈마에 대해 척력을 발생시켜, 양이온 플라즈마가 뱅크층 표면에 충돌되는 것을 방지하게 됨으로써, 소수성의 뱅크층이 친수화되는 것을 방지할 수 있는 효과가 발생하게 된다.

더욱이, 뱅크층을 포함하는 적어도 하나의 절연막을 사이에 두고 이온차폐전극에 대향하는 대향전극을 하부에 형성하며, 유기발광다이오드 구동시 이온차폐전극과 대향전극 사이에 전압을 인가하여 유기발광다이오드 내에 순방향을 따라 전기장을 발생시키게 된다. 이에 따라, 유기발광다이오드의 적층막 사이의 에너지 배리어를 낮춤과 동시에 에너지 레벨에 테이퍼를 형성하게 된다. 이로 인해, 캐리어의 주입 및 수송 효율이 향상되는 효과가 발생하게 된다.

(52) CPC특허분류

*H01L 27/3246* (2013.01)

*H01L 27/3248* (2013.01)

*H01L 27/3274* (2013.01)

*H01L 51/56* (2013.01)

*H01L 2227/32* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

기판 상의 화소영역에 위치하고, 보호막 상의 제1전극과, 상기 제1전극 상의 유기발광층과, 상기 유기발광층 상의 제2전극을 포함하는 유기발광다이오드와;

상기 화소영역의 경계에 위치하는 소수성의 뱅크층과;

상기 뱅크층의 표면 일부에 위치하는 이온차폐전극

을 포함하는 유기발광다이오드 표시장치.

#### 청구항 2

제 1 항에 있어서,

상기 유기발광층은 상기 화소영역 내에 위치하는 발광물질층과, 상기 발광물질층과 이온차폐전극을 덮으며 상기 제2전극 하부에 위치하는 제2유기막을 포함하는

유기발광다이오드 표시장치.

#### 청구항 3

제 2 항에 있어서,

상기 유기발광층은 상기 발광물질층 하부에 위치하는 제1유기막을 포함하는

유기발광다이오드 표시장치.

#### 청구항 4

제 1 항에 있어서,

상기 뱅크층을 사이에 두고 상기 이온차폐전극과 대향하며 상기 발광다이오드의 순방향으로 전기장을 발생시키는 대향전극

을 포함하는 유기발광다이오드 표시장치.

#### 청구항 5

제 4 항에 있어서,

상기 대향전극은 상기 제1전극과 동일물질로 동일층에 위치하는

유기발광다이오드 표시장치.

#### 청구항 6

제 4 항에 있어서,

상기 대향전극은 상기 유기발광다이오드와 연결되는 구동 박막트랜지스터 상의 절연막과, 상기 절연막 상의 상

기 보호막 사이에 위치하는

유기발광다이오드 표시장치.

#### 청구항 7

제 1 항에 있어서,

상기 뱅크층 하부에 위치하는 친수성의 제2뱅크층

을 포함하는 유기발광다이오드 표시장치.

#### 청구항 8

제 1 항에 있어서,

상기 뱅크층 하부의 상기 보호막 부분은 상기 기판 방향으로 요입된 형태를 갖는

유기발광다이오드 표시장치.

#### 청구항 9

제 8 항에 있어서,

상기 뱅크층 하부의 상기 보호막 부분은 전체 또는 일부가 제거되어 요입된 형태를 갖게 되는

유기발광다이오드 표시장치.

#### 청구항 10

기판 상의 보호막 상부에 제1전극을 화소영역에 형성하는 단계와;

상기 화소영역의 경계에 소수성의 뱅크층을 형성하는 단계와;

상기 뱅크층의 표면 일부에 이온차폐전극을 형성하는 단계와;

상기 이온차폐전극에 양전하를 인가한 상태에서, 상기 제1전극에 대한 플라즈마 처리를 수행하는 단계와;

상기 플라즈마 처리를 수행한 후, 유기발광층과 제2전극을 형성하는 단계

를 포함하는 유기발광다이오드 표시장치 제조방법.

#### 청구항 11

제 10 항에 있어서,

상기 유기발광층을 형성하는 단계는,

제1유기막과 그 상부의 발광물질층을 용액 공정을 이용하여 상기 제1전극 상에 형성하는 단계와;

상기 발광물질층 상의 제2유기막을 증착 공정을 이용하여 상기 기판 전면에 형성하는 단계

를 포함하는 유기발광다이오드 표시장치 제조방법.

#### 청구항 12

제 10 항에 있어서,

상기 뱅크층을 사이에 두고 상기 이온차폐전극과 대향하는 대향전극을 형성하는 단계

를 포함하는 유기발광다이오드 표시장치 제조방법.

### 청구항 13

제 12 항에 있어서,

상기 대향전극은 상기 제1전극과 동일공정에서 형성되는

유기발광다이오드 표시장치 제조방법.

### 청구항 14

제 12 항에 있어서,

상기 대향전극은 상기 유기발광다이오드와 연결되는 구동 박막트랜지스터 상의 절연막과, 상기 절연막 상의 상기 보호막 사이에 형성되는

유기발광다이오드 표시장치 제조방법.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 유기발광다이오드 표시장치에 관한 것으로서, 보다 상세하게는, 유기발광다이오드의 제1전극에 대한 플라즈마 처리 공정에 의해 소수성 뱅크층이 친수화되는 것을 개선할 수 있는 유기발광다이오드 표시장치 그 제조방법에 대한 것이다.

### 배경 기술

[0002] 최근, 박형화, 경량화, 저 소비전력화 등의 우수한 특성을 가지는 평판표시장치(flat panel display)가 널리 개발되어 다양한 분야에 적용되고 있다.

[0003] 평판표시장치 중에서, 유기 전계발광 표시장치 또는 유기 전기발광 표시장치(organic electroluminescent display device)라고도 불리는 유기발광다이오드 표시장치(organic light emitting diode display device: OLED display device)는, 전자 주입 전극인 음극과 정공 주입 전극인 양극 사이에 형성된 발광층에 전하를 주입하여 전자와 정공이 쌍을 이룬 후 소멸하면서 빛을 내는 소자이다.

[0004] 이러한 유기발광다이오드 표시장치는 플라스틱과 같은 유연한 기판(flexible substrate) 위에도 형성할 수 있을 뿐 아니라, 자체 발광형이기 때문에 대조비(contrast ratio)가 크며, 응답시간이 수 마이크로초( $\mu$ s) 정도이므로 동화상 구현이 쉽고, 시야각의 제한이 없으며 저온에서도 안정적이고, 직류 5V 내지 15V의 비교적 낮은 전압으로 구동이 가능하므로 구동회로의 제작 및 설계가 용이하다.

[0005] 유기발광다이오드는 하부전극인 제1전극과, 상부전극인 제2전극과, 제1전극 및 제2전극 사이에 다수의 유기막을 갖는 유기발광층으로 구성된다. 여기서, 유기발광층을 구성하는 유기막을 화소영역 단위로 형성함에 있어, 기존에는 증착 공정(deposition process)을 이용하였다. 이에 따라, 마스크 공정이 증가하고 공정비용이 상승하는 문제가 발생하게 되었다.

[0006] 이를 개선하기 위해, 최근에 용액 공정(solution process)이 제안된바 있다. 이 용액 공정에서는 용액 상태의 유기물질을 인쇄법이나 코팅법을 이용하여 기판에 도포하고 건조하는 과정을 통해 화소영역 단위로 유기막을 형성하게 된다.

[0007] 이처럼, 용액 공정은 별도의 마스크 공정을 요구하지 않게 되므로, 증착 공정 이용에 따른 마스크 공정 증가 및 공정비용 상승을 개선할 수 있게 된다.

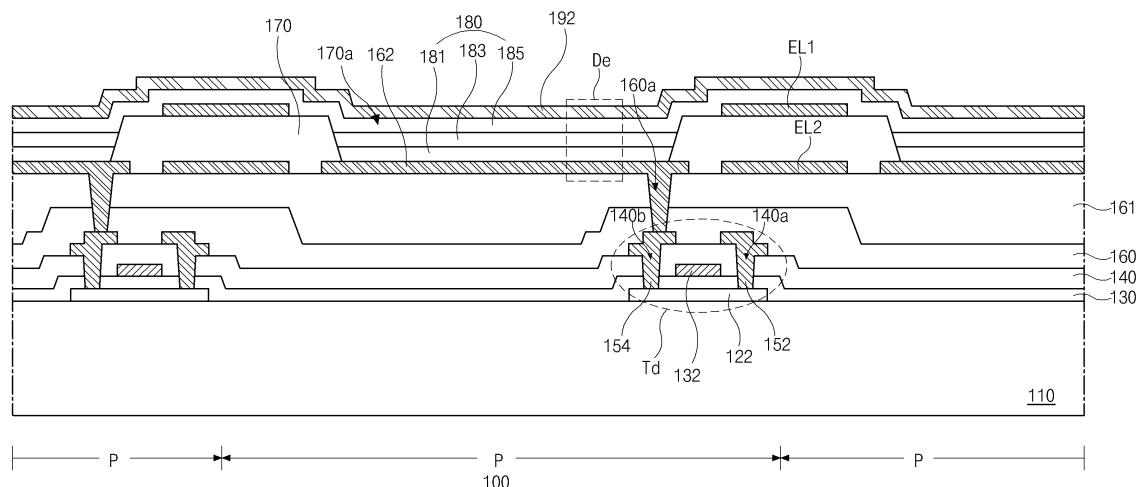

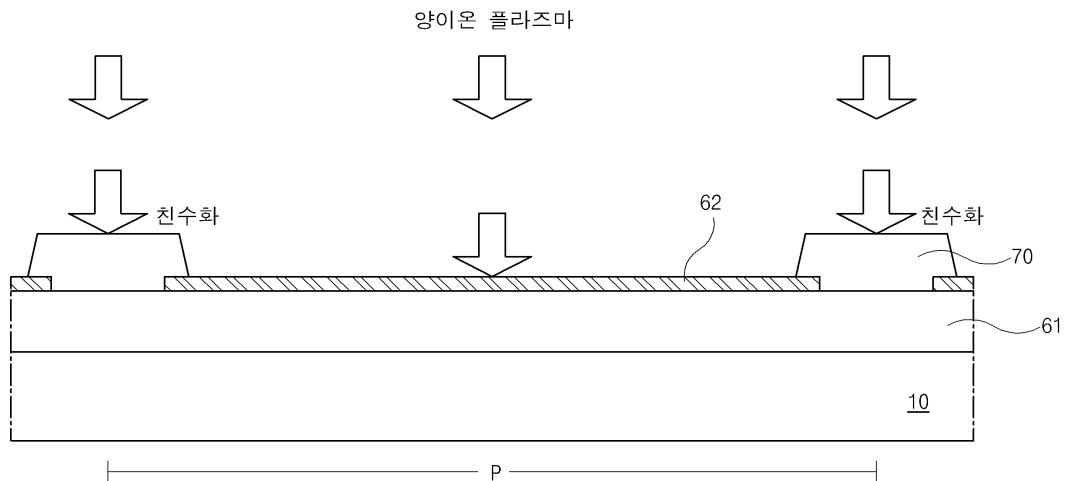

- [0008] 도 1은 종래의 유기발광다이오드 표시장치의 제1전극에 대해 플라즈마 처리 공정을 진행하는 모습을 개략적으로 도시한 단면도로서, 설명의 편의를 위해, 일부 구성만을 도시하였다.

- [0009] 도 1을 참조하면, 기판(10) 상의 보호막(61) 상부에는 화소영역(P) 단위로 제1전극(62)과, 제1전극(62) 가장자리를 덮으며 이웃하는 화소영역(P)의 경계를 따라 배치되어 화소영역(P)을 구분하도록 뱅크층(70)이 형성된다.

- [0010] 구체적으로 도시하지는 않았지만, 뱅크층(70) 형성 후에는 용액 공정을 통해 적어도 일부 유기막을 기판(10) 상에 도포하게 된다. 이때, 유기막을 화소영역(P) 단위로 구분하여 형성하기 위해, 뱅크층(70)의 표면은 소수성을 갖도록 구성된다.

- [0011] 한편, 용액 공정을 통한 유기막 형성 전에, 제1전극(62)에 대한 표면 개질 및 이물 세정을 위해 플라즈마를 사용한 전처리 공정이 진행된다. 즉, 제1전극(62)의 일함수(work function)를 낮추고 표면 상에 존재하는 이물 제거를 위해 플라즈마 처리 공정이 진행된다.

- [0012] 그런데, 제1전극(62)에 대한 플라즈마 처리 공정을 진행함에 있어, 플라즈마 상태의 양이온 즉 양이온 플라즈마는 제1전극(62) 표면 뿐만 아니라 뱅크층(70) 표면에도 충돌하게 되어 소수성의 뱅크층(70)이 친수화되는 문제가 발생하게 된다. 이에 따라, 후속하는 용액 공정에서 유기막이 화소영역(P) 단위로 구분되어 형성될 수 없게 됨으로써 소자 불량이 발생하게 된다.

## 발명의 내용

### 해결하려는 과제

- [0013] 본 발명은 유기발광다이오드의 제1전극에 대한 플라즈마 처리 공정에 의해 소수성 뱅크층이 친수화되는 것을 개선할 수 있는 방안을 제공하는 것에 과제가 있다.

### 과제의 해결 수단

- [0014] 전술한 바와 같은 과제를 달성하기 위해, 본 발명은 기판 상의 화소영역에 위치하고, 보호막 상의 제1전극과, 상기 제1전극 상의 유기발광층과, 상기 유기발광층 상의 제2전극을 포함하는 유기발광다이오드와, 상기 화소영역의 경계에 위치하는 소수성의 뱅크층과, 상기 뱅크층의 표면 일부에 위치하는 이온차폐전극을 포함하는 유기발광다이오드 표시장치를 제공한다.

- [0015] 여기서, 상기 유기발광층은 상기 화소영역 내에 위치하는 발광물질층과, 상기 발광물질층과 이온차폐전극을 덮으며 상기 제2전극 하부에 위치하는 제2유기막을 포함할 수 있다.

- [0016] 상기 유기발광층은 상기 발광물질층 하부에 위치하는 제1유기막을 포함할 수 있다.

- [0017] 상기 뱅크층을 사이에 두고 상기 이온차폐전극과 대향하며 상기 발광다이오드의 순방향으로 전기장을 발생시키는 대향전극을 포함할 수 있다.

- [0018] 상기 대향전극은 상기 제1전극과 동일물질로 동일층에 위치할 수 있다.

- [0019] 상기 대향전극은 상기 유기발광다이오드와 연결되는 구동 박막트랜지스터 상의 절연막과, 상기 절연막 상의 상기 보호막 사이에 위치할 수 있다.

- [0020] 상기 뱅크층 하부에 위치하는 친수성의 제2뱅크층을 포함할 수 있다.

- [0021] 상기 뱅크층 하부의 상기 보호막 부분은 상기 기판 방향으로 요입된 형태를 가질 수 있다.

- [0022] 상기 뱅크층 하부의 상기 보호막 부분은 전체 또는 일부가 제거되어 요입된 형태를 가질 수 있다.

- [0023] 다른 측면에서, 본 발명은 기판 상의 보호막 상부에 제1전극을 화소영역에 형성하는 단계와, 상기 화소영역의 경계에 소수성의 뱅크층을 형성하는 단계와, 상기 뱅크층의 표면 일부에 이온차폐전극을 형성하는 단계와, 상기 이온차폐전극에 양전하를 인가한 상태에서, 상기 제1전극에 대한 플라즈마 처리를 수행하는 단계와, 상기 플라즈마 처리를 수행한 후, 유기발광층과 제2전극을 형성하는 단계를 포함하는 유기발광다이오드 표시장치 제조방법을 제공한다.

- [0024] 여기서, 상기 유기발광층을 형성하는 단계는, 제1유기막과 그 상부의 발광물질층을 용액 공정을 이용하여 상기 제1전극 상에 형성하는 단계와, 상기 발광물질층 상의 제2유기막을 증착 공정을 이용하여 상기 기판 전면에 형

성하는 단계를 포함할 수 있다.

[0025] 상기 뱅크층을 사이에 두고 상기 이온차폐전극과 대향하는 대향전극을 형성하는 단계를 포함할 수 있다.

[0026] 상기 대향전극은 상기 제1전극과 동일공정에서 형성될 수 있다.

[0027] 상기 대향전극은 상기 유기발광다이오드와 연결되는 구동 박막트랜지스터 상의 절연막과, 상기 절연막 상의 상기 보호막 사이에 형성될 수 있다.

### 발명의 효과

[0028] 본 발명에서는, 화소영역의 경계를 따라 형성된 소수성의 뱅크층의 표면 일부에 이온차폐전극을 형성하며, 제1전극에 대한 플라즈마 처리 공정시 이온차폐전극에 양전하를 인가하게 된다. 이에 따라, 이온차폐전극은 플라즈마 처리 공정시 발생된 양이온 플라즈마에 대해 척력을 발생시키며, 양이온 플라즈마가 뱅크층 표면에 충돌되는 것을 방지하게 됨으로써, 소수성의 뱅크층이 친수화되는 것을 방지할 수 있는 효과가 발생하게 된다.

[0029] 더욱이, 뱅크층을 포함하는 적어도 하나의 절연막을 사이에 두고 이온차폐전극에 대향하는 대향전극을 하부에 형성하며, 유기발광다이오드 구동시 이온차폐전극과 대향전극 사이에 전압을 인가하여 유기발광다이오드 내에 순방향을 따라 전기장을 발생시키게 된다. 이에 따라, 유기발광다이오드의 적층막 사이의 에너지 배리어를 낮춤과 동시에 에너지 레벨에 테이퍼를 형성하게 된다. 이로 인해, 캐리어의 주입 및 수송 효율이 향상되는 효과가 발생하게 된다.

### 도면의 간단한 설명

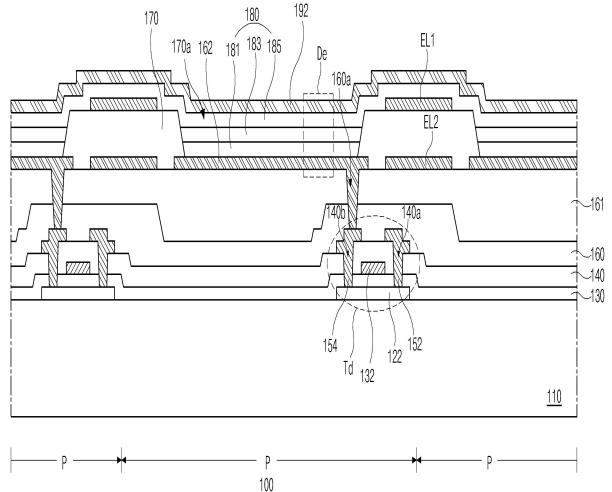

[0030] 도 1은 종래의 용액 공정을 이용한 유기발광다이오드 표시장치의 화소영역을 개략적으로 도시한 도면.

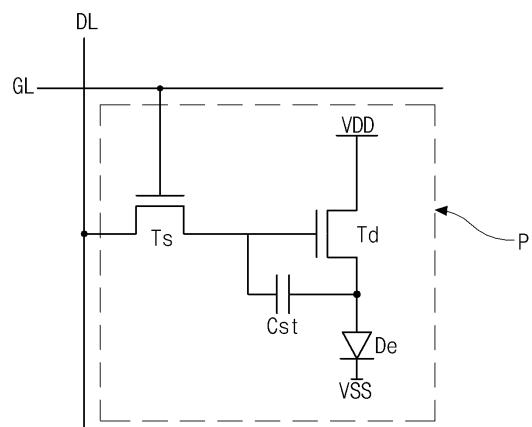

도 2는 본 발명의 제1실시예에 따른 유기발광다이오드 표시장치의 하나의 화소영역에 대한 회로도.

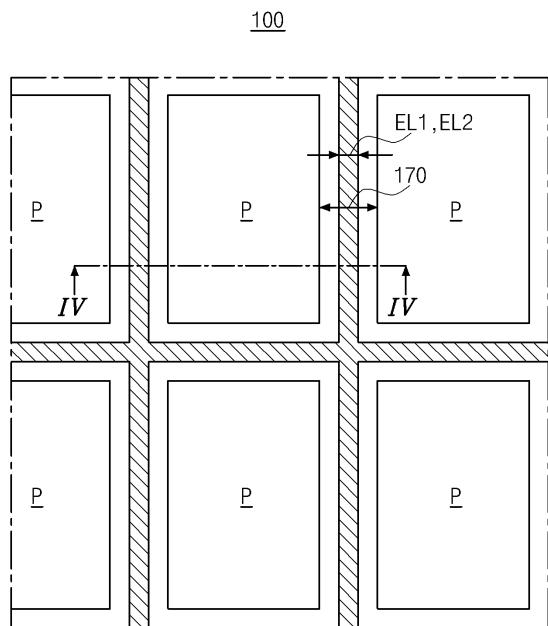

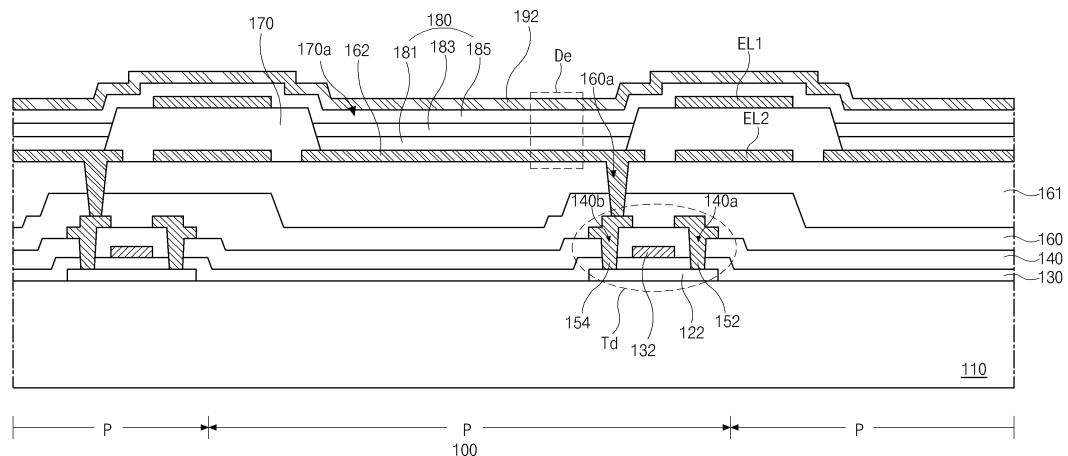

도 3은 본 발명의 제1실시예에 따른 유기발광다이오드 표시장치의 일부를 개략적으로 도시한 평면도.

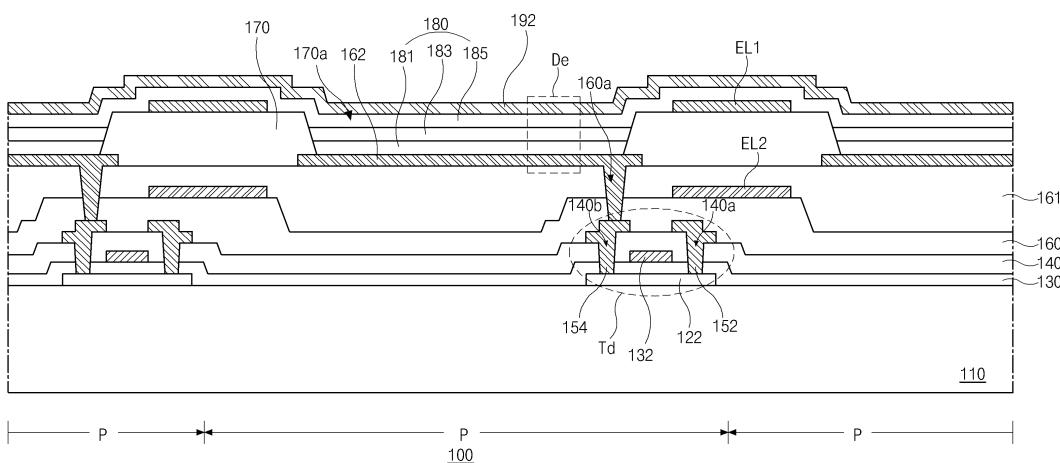

도 4는 도 3의 절단선 III-III을 따라 도시한 단면도.

도 5는 본 발명의 제1실시예에 따른 이온차폐전극과 대향전극에 의해 발생되는 전기장의 모습을 개략적으로 도시한 도면.

도 6은 본 발명의 제1실시예에 따른 유기발광다이오드 표시장치의 제1전극을 플라즈마 처리하는 플라즈마 처리장치를 개략적으로 도시한 도면.

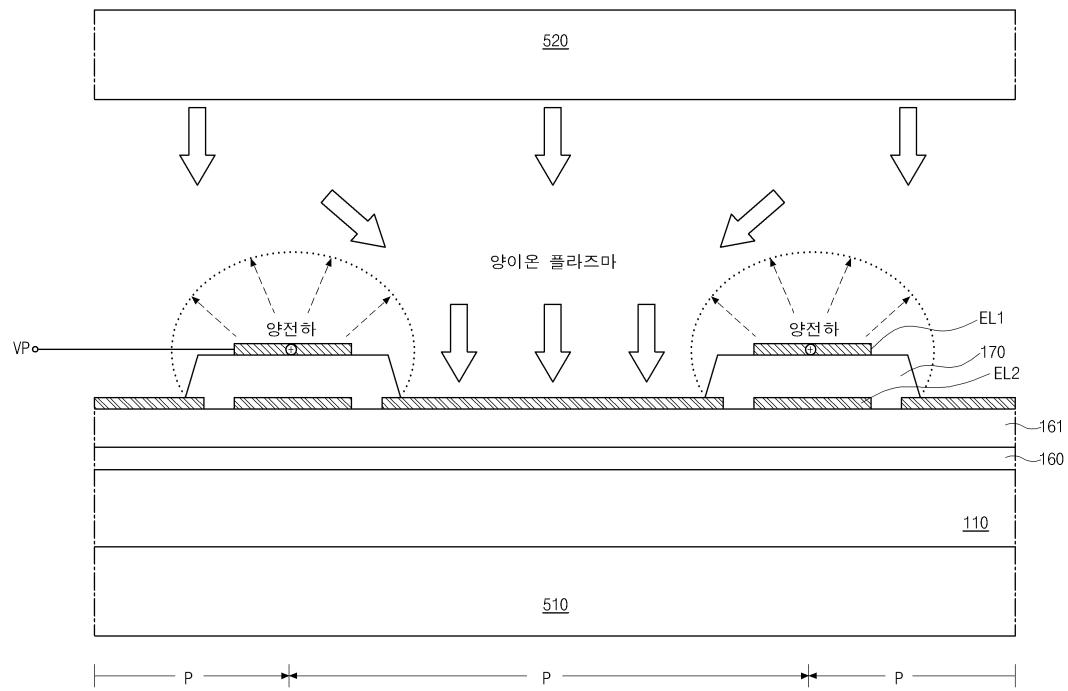

도 7은 도 6의 플라즈마 처리 장치를 사용한 플라즈마 처리 공정 시의 유기발광다이오드 표시장치의 모습을 개략적으로 도시한 도면.

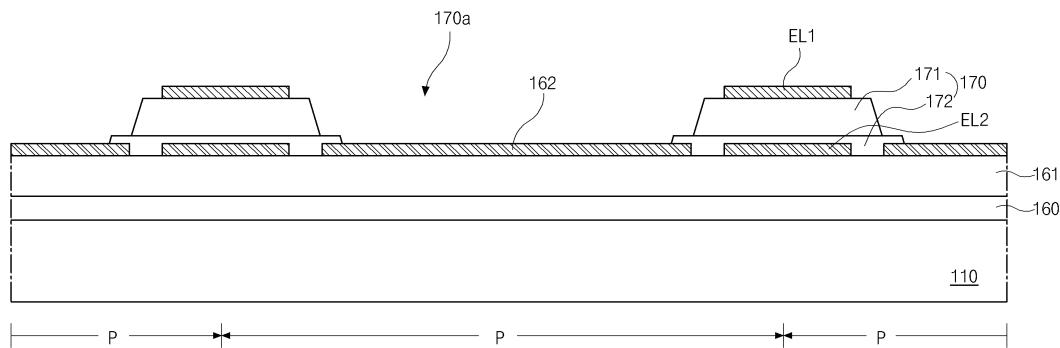

도 8은 본 발명의 제1실시예에 따른 유기발광다이오드 표시장치에서 2중층 구조의 뱅크층이 구비된 예를 개략적으로 도시한 단면도.

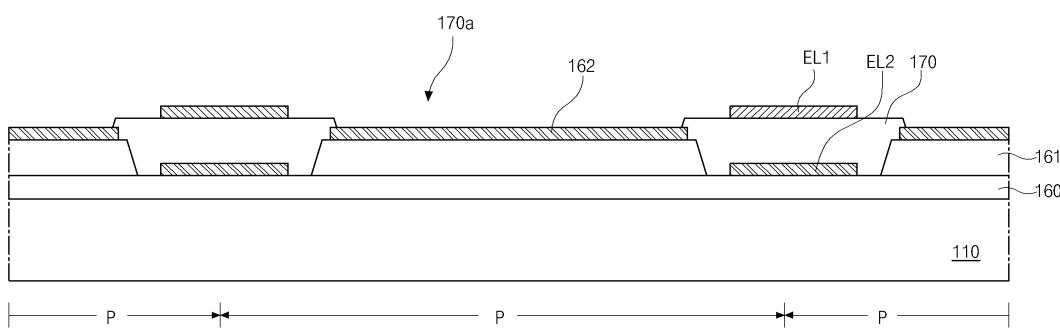

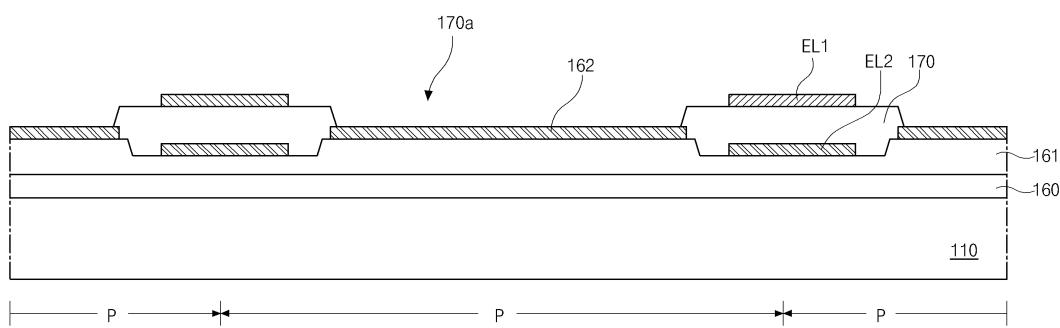

도 9 및 10은 본 발명의 제1실시예에 따른 유기발광다이오드 표시장치에서 뱅크층 하부의 제2보호막 부분이 요입된 형태로 형성된 예들을 개략적으로 도시한 단면도.

도 11은 본 발명의 제2실시예에 따른 유기발광다이오드 표시장치를 개략적으로 도시한 단면도.

도 12는 본 발명의 제2실시예에 따른 유기발광다이오드 표시장치에서 2중층 구조의 뱅크층이 구비된 예를 개략적으로 도시한 단면도.

도 13 및 14는 본 발명의 제2실시예에 따른 유기발광다이오드 표시장치에서 뱅크층 하부의 제2보호막 부분이 요입된 형태로 형성된 예들을 개략적으로 도시한 단면도.

### 발명을 실시하기 위한 구체적인 내용

[0031] 이하, 도면을 참조하여 본 발명의 실시예를 상세하게 설명한다. 한편, 이하의 실시예에서는 동일 유사한 구성에 대해서는 동일 유사한 도면번호가 부여되고, 그 구체적인 설명은 생략될 수도 있다.

[0032] 본 발명의 실시예에 따른 유기발광다이오드 표시장치에서는, 화소영역의 경계를 따라 형성된 소수성의 뱅크층의 표면에 이온차폐전극을 형성하며, 제1전극에 대한 플라즈마 처리 공정시 이온차폐전극에 양전하를 인가하게 된

다. 이에 따라, 이온차폐전극은 플라즈마 처리 공정시 발생된 양이온 플라즈마에 대해 척력을 발생시켜, 양이온 플라즈마가 뱅크층 표면에 충돌되는 것을 방지하게 됨으로써, 소수성의 뱅크층이 친수화되는 것을 방지할 수 있는 효과가 발생하게 된다.

[0033] 더욱이, 본 발명의 실시예에서는, 뱅크층 하부에 이온차폐전극에 대향하는 대향전극을 형성하며, 유기발광다이오드 구동시 이온차폐전극과 대향전극 사이에 전압을 인가하여 유기발광다이오드 내에 전기장을 발생시키게 된다. 이에 따라, 유기발광다이오드의 적층막 사이의 에너지 배리어를 낮춤과 동시에 에너지 레벨에 테이퍼(taper)를 형성하게 된다. 이로 인해, 캐리어의 주입 및 수송 효율이 향상되는 효과가 발생하게 된다.

[0034] 이하에서는, 이온차폐전극을 구비한 유기발광다이오드 표시장치의 다양한 실시예에 대해 보다 상세하게 설명한다.

[0035] <제1실시예>

[0036] 도 2는 본 발명의 제1실시예에 따른 유기발광다이오드 표시장치의 하나의 화소영역에 대한 회로도이다.

[0037] 도 2에 도시한 바와 같이, 본 발명의 제1실시예에 따른 유기발광다이오드 표시장치는 서로 교차하여 화소영역(P)을 정의하는 게이트배선(GL)과 데이터배선(DL)을 포함하고, 각각의 화소영역(P)에는 스위칭 박막트랜지스터(Ts)와 구동 박막트랜지스터(Td), 스토리지 커패시터(Cst), 그리고 유기발광다이오드(De)가 형성된다.

[0038] 스위칭 박막트랜지스터(Ts)의 게이트전극은 게이트배선(GL)에 연결되고 소스전극은 데이터배선(DL)에 연결된다. 구동 박막트랜지스터(Td)의 게이트전극은 스위칭 박막트랜지스터(Ts)의 드레인전극에 연결되고, 소스전극은 고전위 전원전압(VDD)에 연결될 수 있다. 유기발광다이오드(De)의 제1전극으로서 예를 들어 애노드(anode)는 구동 박막트랜지스터(Td)의 드레인전극에 연결되고, 제2전극으로서 예를 들어 캐소드(cathode)는 저전위 전원전압(VSS)에 연결된다. 스토리지 커패시터(Cst)는 구동 박막트랜지스터(Td)의 게이트전극과 드레인전극에 연결된다.

[0039] 이러한 유기발광다이오드 표시장치의 영상표시 동작을 살펴보면, 게이트배선(GL)을 통해 인가된 게이트신호에 따라 스위칭 박막트랜지스터(Ts)가 턠-온(turn-on) 되고, 이에 동기하여 데이터배선(DL)으로 인가된 데이터신호가 스위칭 박막트랜지스터(Ts)를 통해 구동 박막트랜지스터(Td)의 게이트전극에 인가된다.

[0040] 구동 박막트랜지스터(Td)는 데이터신호에 따라 턠-온 되어 유기발광다이오드(De)를 흐르는 전류를 제어하여 빛을 방출함으로써 영상을 표시하게 된다.

[0041] 여기서, 유기발광다이오드(De)를 흐르는 전류의 양은 데이터신호의 크기에 비례하고, 유기발광다이오드(De)가 방출하는 빛의 세기는 유기발광다이오드(De)를 흐르는 전류의 양에 비례하므로, 화소영역(P)은 데이터신호의 크기에 따라 상이한 계조를 표시하고, 그 결과 유기발광다이오드 표시장치는 영상을 표시한다.

[0042] 스토리지 커패시터(Cst)는 구동 박막트랜지스터(Td)의 게이트전극에 인가된 데이터신호를 하나의 프레임(frame) 동안 유지하는 역할을 한다.

[0043] 도 3은 본 발명의 제1실시예에 따른 유기발광다이오드 표시장치의 일부를 개략적으로 도시한 평면도이고, 도 4는 도 3의 절단선 III-III을 따라 도시한 단면도이다. 도 3에서는, 설명의 편의를 위해, 뱅크층(170)과 이온차폐전극(EL1)과 대향전극(EL2)의 배치를 개략적으로 도시하였다.

[0044] 도 3 및 4를 참조하면, 본 발명의 제1실시예에 따른 유기발광다이오드 표시장치(100)는, 기판(110) 상의 각 화소영역(P)에 형성된 스위칭 박막트랜지스터(도 2의 Ts 참조) 및 구동 박막트랜지스터(Td)와, 이 박막트랜지스터들 상에 위치하고 구동 박막트랜지스터(Td)와 연결된 유기발광다이오드(De)를 포함할 수 있다.

[0045] 특히, 본 실시예에 따른 유기발광다이오드 표시장치(100)는 뱅크층(170)의 표면 일부에 형성되며 유기막에 대한 용액 공정시 양전하가 인가되어 양이온 플라즈마를 차폐하도록 하는 이온차폐전극(EL1)이 구비된다.

[0046] 더욱이, 뱅크층(170) 하부에 이온차폐전극(EL1)과 전기장을 유발하는 대향전극(EL2)을 구비할 수 있다.

[0047] 이와 같은 구성을 갖는 유기발광다이오드 표시장치(100)의 단면 구조에 대해 보다 상세하게 설명하면, 기판(110) 상부에는 패터닝된 반도체층(122)이 형성된다.

[0048] 여기서, 기판(110)은 유리기판이나 플라스틱기판일 수 있다. 반도체층(122)은 산화물 반도체 물질로 이루어질 수 있는데, 이 경우 반도체층(122) 하부에는 차광패턴(미도시)과 베퍼층(미도시)이 형성될 수 있으며, 차광패턴은 반도체층(122)으로 빛이 입사되는 것을 방지하여 반도체층(122)이 빛에 의해 열화되는 것을 방지한다. 다른 예로서, 반도체층(122)은 다결정 실리콘으로 이루어질 수도 있으며, 이 경우 반도체층(122)의 양 가장자리에 불

순물이 도핑될 수 있다.

- [0049] 반도체층(122) 상부에는 절연물질로 이루어진 절연막으로서 게이트 절연막(130)이 기판(110) 전면에 형성될 수 있다. 게이트 절연막(130)은 산화실리콘(SiO<sub>2</sub>)과 같은 무기절연물질로 형성될 수 있다. 한편, 반도체층(122)이 다결정 실리콘으로 이루어지는 경우, 게이트 절연막(130)은 산화 실리콘(SiO<sub>2</sub>)이나 질화 실리콘(SiNx)으로 형성될 수 있다.

- [0050] 게이트 절연막(130) 상부에는 금속과 같은 도전성 물질로 이루어진 게이트전극(132)이 반도체층(122)의 중앙에 대응하여 형성된다. 또한, 게이트 절연막(130) 상부에는 게이트배선(도 2의 GL 참조)과 제1커패시터전극(미도시)이 형성될 수 있다. 게이트배선은 제1방향을 따라 연장되고, 제1커패시터 전극은 게이트전극(132)에 연결된다.

- [0051] 한편, 본 실시예에서는 게이트 절연막(130)이 기판(110) 전면에 형성된 경우를 예로 들고 있으나, 게이트 절연막(130)은 게이트전극(132)과 동일한 모양으로 패터닝될 수도 있다.

- [0052] 게이트전극(132) 상부에는 절연물질로 이루어진 절연막으로서 충간 절연막(140)이 기판(110) 전면에 형성될 수 있다. 충간 절연막(140)은 산화 실리콘(SiO<sub>2</sub>)이나 질화 실리콘(SiNx)과 같은 무기절연물질로 형성되거나, 벤조사이클로부텐(benzocyclobutene)이나 포토 아크릴(photo acryl)과 같은 유기절연물질로 형성될 수 있다.

- [0053] 충간 절연막(140)은 반도체층(122)의 양측을 노출하는 제1 및 2콘택홀(140a, 140b)을 구비할 수 있다. 제1 및 2콘택홀(140a, 140b)은 게이트전극(132)의 양측에 게이트전극(132)과 이격되어 위치한다. 더욱이, 제1 및 2콘택홀(140a, 140b)은 게이트 절연막(130) 내에도 형성될 수 있다. 이와 달리, 게이트 절연막(130)이 게이트전극(132)과 동일한 모양으로 패터닝될 경우, 제1 및 2콘택홀(140a, 140b)은 충간 절연막(140) 내에 형성되도록 구성된다.

- [0054] 충간 절연막(140) 상부에는 금속과 같은 도전성 물질로 소스전극 및 드레인전극(152, 154)이 형성된다. 또한, 충간 절연막(140) 상부에는 제2방향을 따라 연장되는 데이터배선(도 2의 DL 참조)과 전원배선(미도시) 및 제2커패시터 전극(미도시)이 형성될 수 있다.

- [0055] 소스 및 드레인전극(152, 154)은 게이트전극(132)을 중심으로 이격되어 위치하며, 각각 제1 및 2콘택홀(140a, 140b)을 통해 반도체층(122)의 양측과 접촉한다. 도시하지 않았지만, 데이터배선은 제2방향을 따라 연장되고 게이트배선과 교차하여 화소영역(P)을 정의하며, 고전위 전원전압(도 2의 VDD 참조)을 전송하는 전원배선은 데이터배선과 이격되어 위치한다. 제2커패시터 전극은 드레인전극(154)과 연결되고 제1커패시터 전극과 중첩하며 이들 두 전극 사이의 충간 절연막(140)을 유전체로 하여 스토리지 커패시터를 이룬다.

- [0056] 한편, 반도체층(122)과, 게이트전극(132), 그리고 소스전극 및 드레인전극(152, 154)은 구동 박막트랜지스터(Td)를 이룬다. 여기서, 구동 박막트랜지스터(Td)는 반도체층(122)의 일측, 즉 반도체층(122)의 상부에 게이트전극(132)과 소스전극 및 드레인전극(152, 154)이 위치하는 코플라나(coplanar) 구조를 갖도록 구성될 수 있다.

- [0057] 다른 예로서, 구동 박막트랜지스터(Td)는 반도체층의 하부에 게이트전극이 위치하고 반도체층의 상부에 소스전극 및 드레인전극이 위치하는 역 스탠더드(inverted staggered) 구조를 가질 수 있다. 이 경우, 반도체층은 비정질 실리콘으로 이루어질 수 있다.

- [0058] 한편, 도시하지는 않았지만, 구동 박막트랜지스터(Td)와 동일한 구조의 스위칭 박막트랜지스터(도 2의 Ts 참조)가 기판(110) 상에 형성된다. 구동 박막트랜지스터(Td)의 게이트 전극(132)은 스위칭 박막트랜지스터의 드레인전극에 전기적으로 연결되고 구동 박막트랜지스터(Td)의 소스전극(152)은 전원배선에 연결된다. 또한, 스위칭 박막트랜지스터의 게이트전극과 소스전극은 게이트 배선 및 데이터 배선과 각각 연결된다.

- [0059] 소스전극 및 드레인전극(152, 154) 상부에는 절연물질로 이루어진 절연막으로서 제1보호막(160)이 기판(110) 전면에 형성될 수 있다. 제1보호막(160)은 산화 실리콘(SiO<sub>2</sub>)이나 질화 실리콘(SiNx)과 같은 무기절연물질로 형성될 수 있다.

- [0060] 제1보호막(160) 상에는 절연물질로 이루어진 절연막으로서 제2보호막(161)이 기판(110) 전면에 형성될 수 있다. 제2보호막(161)은 벤조사이클로부텐이나 포토 아크릴과 같은 유기절연물질로 형성될 수 있다. 이와 같은 제2보호막(161)은 평탄화층으로서 기능하여 그 상면은 실질적으로 평탄하게 된다.

- [0061] 이처럼, 본 실시예에서는, 구동 박막트랜지스터(Td) 상에 2중층 구조의 보호막(160, 161)이 형성될 수 있다. 이

와 같은 제1 및 2보호막(160, 161)은 드레인전극(154)을 노출하는 드레인 콘택홀(160a)을 가진다. 다른 예로서, 구동 박막트랜지스터(Td) 상에는 단일층 구조의 보호막이 형성될 수도 있다.

[0062] 제2보호막(161) 상부에는 각 화소영역(P)마다 패터닝된 형태의 제1전극(162)이 형성될 수 있다. 제1전극(162)은 드레인 콘택홀(160a)을 통해 드레인전극(154)과 접촉한다. 제1전극(162)은 비교적 일함수가 높은 도전성 물질로 형성될 수 있는데, 예를 들면, ITO(indium tin oxide)나 IZO(indium zinc oxide)와 같은 투명 도전성 물질로 형성될 수 있다.

[0063] 제1전극(162) 상부에는 절연물질로 이루어진 절연막으로서 뱅크층(170)이 형성된다. 이와 같은 뱅크층(170)은 이웃하는 화소영역(P)의 경계를 따라 각 화소영역(P)을 둘러싸도록 배치된다. 뱅크층(170)은 각 화소영역(P)의 제1전극(162)을 노출하는 투과홀(170a)을 가지며, 제1전극(162)의 가장자리를 덮는다.

[0064] 이와 같은 뱅크층(170)은 소수성의 특성을 갖도록 형성된다. 이와 관련하여 예를 들면, 뱅크층(170)에는 소수성을 갖는 폴리머 등의 첨가제 즉 소수첨가제가 함유되며, 이 소수첨가제는 뱅크층(170) 형성을 위한 경화 공정(예를 들어, 소프트 베이킹 공정)에서 표면으로 이동하게 되어, 뱅크층(170)의 표면은 소수성을 갖게 된다.

[0065] 이처럼, 뱅크층(170)이 소수성 특성을 갖게 됨으로써, 후속하는 용액 공정을 이용한 유기막 형성시에 해당 유기막이 화소영역(P) 단위로 분할되어 형성될 수 있게 된다.

[0066] 뱅크층(170)의 투과홀(170a)을 통해 노출된 제1전극(162) 상부에는 유기발광층(180)이 형성된다. 유기발광층(180)은 발광물질층(183)을 포함하는 다수의 유기막으로 구성된 다층 구조로 형성된다.

[0067] 이와 관련하여 예를 들면, 제1전극(162)이 애노드이고 제2전극(192)이 캐소드인 경우에, 제1전극(162)과 발광물질층(183) 사이에는 정공주입층과 정공수송층이 순차적으로 배치될 수 있고, 발광물질층(183)과 제2전극(192) 사이에는 전자수송층과 전자주입층이 순차적으로 배치될 수 있다. 본 실시예에서는, 설명의 편의를 위해, 발광물질층(183) 하부의 유기막으로서 정공주입층 및 정공수송층을 단일층의 유기막(181)으로 도시하였고, 발광물질층(183) 상부의 유기막으로서 전자주입층과 전자수송층을 단일층의 유기막(185)으로 도시하였다.

[0068] 한편, 경우에 따라, 정공주입층과 정공수송층 중 적어도 하나는 생략될 수 있으며, 전자주입층과 전자수송층 중 적어도 하나는 생략될 수 있다.

[0069] 이처럼, 유기발광층(180)을 구성하는 다수의 유기막은 다양한 형태로 배치될 수 있다.

[0070] 이때, 본 실시예에서의 유기발광층(180)을 형성함에 있어, 상대적으로 하부에 배치된 일부 유기막은 용액 공정으로 화소영역(P) 단위로 형성되고, 상대적으로 상부에 배치된 나머지 유기막은 증착 공정으로 실질적으로 기판 전면에 형성되는 것이 바람직하다. 여기서, 용액 공정으로는 인쇄법이나 코팅법이 이용될 수 있으며, 인쇄법으로는 잉크젯 인쇄법(inkjet printing) 또는 노즐 인쇄법(nozzle printing)이 이용될 수 있다. 한편, 증착 공정으로는 PECVD 방법 등으로 형성될 수 있다.

[0071] 이와 관련하여 예를 들면, 발광물질층(183) 하부에 위치하는 단일층 또는 다층 구조의 유기막(181)인 제1유기막(181)에 대해서는 용액 공정이 적용되며, 소수성의 뱅크층(170)에 의해 화소영역(P) 단위로 제1유기막(181)이 분할되어 형성될 수 있다.

[0072] 그리고, 발광물질층(183) 또한 용액 공정에 의해 화소영역(P) 단위로 형성될 수 있다. 한편, 적색, 녹색, 청색 화소영역을 갖는 컬러 표시장치의 경우에, 발광물질층(183)을 형성함에 있어, 예를 들면, 적색 및 녹색 화소영역에 각각 형성되는 적색 및 녹색 발광물질층은 용액 공정으로 형성되고, 이에 대한 후속 공정에서 청색 발광물질층을 기판 전면에 증착 공정으로 형성할 수 있다. 물론, 청색 발광물질층 또한 용액 공정을 적용하여 청색 화소영역에 형성되도록 할 수도 있다.

[0073] 한편, 발광물질층(183) 상부에 위치하는 단일층 또는 다층 구조의 유기막(185)인 제2유기막(185)에 대해서는 증착 공정이 적용되며, 실질적으로 기판 상의 표시영역 전체를 덮도록 형성될 수 있다. 즉, 제2유기막(185)은 화소영역(P) 뿐만 아니라 그 경계의 뱅크층(170)을 덮도록 형성될 수 있다.

[0074] 위와 같이 유기발광층(180)을 구성하는 일부 유기막에 대해 용액 공정을 적용하여 형성하게 되면, 해당 유기막들에 대한 마스크 공정이 저감되어 공정 효율성이 향상되는 효과가 있다.

[0075] 위와 같이 구성된 유기발광층(180) 상부에는 비교적 일함수가 낮은 도전성 물질로 제2전극(192)이 기판(110) 전면에 형성될 수 있다. 즉, 제2전극(192)은 유기발광층(180)의 제2유기막(185) 표면을 따라 형성될 수 있다.

- [0076] 여기서, 제2전극(192)은 알루미늄(aluminum)이나 마그네슘(magnesium), 은(silver) 또는 이들의 합금으로 형성될 수 있다.

- [0077] 제1전극(162)과 유기발광층(180) 및 제2전극(192)은 유기발광다이오드(De)를 이루게 된다. 여기서, 제1 및 2전극(162, 192) 중 하나는 애노드로 역할하고, 나머지 하나는 캐소드로 역할하게 된다.

- [0078] 한편, 본 실시예에 따른 유기발광다이오드 표시장치(100)는 유기발광층(180)으로부터 방출된 빛이 제2전극(192)을 통해 외부로 출력되는 상부발광방식(top emission type)으로 구성될 수 있다. 이 경우에, 제1전극(162)은 불투명 도전성 물질로 이루어진 반사층(도시하지 않음)을 더 포함한 다층 구조로 구성될 수 있다. 일례로, 반사층은 알루미늄-팔라듐-구리(aluminum-paladium-copper: APC) 합금으로 형성될 수 있으며, 제1전극(162)은 ITO/APC/ITO의 3중층 구조를 가질 수 있다. 또한, 제2전극(192)은 빛이 투과되도록 비교적 얇은 두께를 가지며, 제2전극(192)의 빛 투과도는 약 45-50%일 수 있다.

- [0079] 다른 예로서, 유기발광다이오드 표시장치(100)는 유기발광층(180)으로부터 방출된 빛이 제1전극(162)을 통해 외부로 출력되는 하부발광방식(bottom emission type)으로 구성될 수 있다.

- [0080] 또한, 본 실시예에 따른 유기발광다이오드 표시장치(100)는 각 화소영역(P)에 대응되는 컬러필터를 구비할 수 있다. 이 경우에, 컬러필터는 발광방향 측으로서, 예를 들면, 하부발광방식의 경우에는 유기발광다이오드(De) 하부측에, 상부발광방식의 경우에는 유기발광다이오드(De) 상부측에 배치될 수 있다. 이처럼, 컬러필터를 사용하게 되면 색재현율이 향상되는 장점이 발생할 수 있게 된다.

- [0081] 한편, 본 실시예에서는, 소수성의 뱅크층(170) 표면에 이온차폐전극(EL1)을 형성하는 것을 특징으로 한다. 이와 같은 이온차폐전극(EL1)은 소수성의 뱅크층(170)의 표면이 친수화되는 것을 방지하는 기능을 수행하게 되는 것으로서, 평면적으로 볼 때 실질적으로 뱅크층(170)과 동일한 형태로 형성된다. 즉, 이온차폐전극(EL1)은 이웃하는 화소영역(P)의 경계를 따라 각 화소영역(P) 주변을 둘러싸도록 형성된다.

- [0082] 한편, 이온차폐전극(EL1) 상에는 실질적으로 절연막으로서 기능하는 제2유기막(185)이 위치하여, 유기발광다이오드(De) 구동시 그 상부에 위치하는 제2전극(192)과 전기적으로 단락되는 것이 방지될 수 있다. 이처럼, 제2유기막(185)은 제2전극(192)으로부터 유입되는 캐리어의 수송 기능뿐만 아니라, 이온차폐전극(EL1)과 제2전극(192) 간의 전기적 단락을 방지하는 기능 또한 수행할 수 있게 된다.

- [0083] 그리고, 이온차폐전극(EL1)은 제1전극(162)과 이격되도록 뱅크층(170)의 표면 일부로서 상면에 형성되어, 실질적으로 제1전극(162)과도 전기적으로 단선된 상태를 갖게 된다. 이온차폐전극(EL1)은, 예를 들면, 은(Ag), ITO, 구리(Cu)와 같은 금속물질들 중 적어도 하나로 형성될 수 있다.

- [0084] 이와 같은 이온차폐전극(EL1)을 뱅크층(170) 상에 형성한 후 제1전극(162)에 대한 플라즈마 처리를 수행하게 되는데, 이 공정 진행시 이온차폐전극(EL1)에는 양전하가 인가되도록 한다. 즉, 이온차폐전극(EL1)에 대해 정극성 전압을 인가함으로써, 이온차폐전극(EL1)에는 정극성의 양전하가 유입되어, 이온차폐전극(EL1)은 정극성을 갖게 된다. 이에 따라, 플라즈마 처리를 위해 발생된 양이온 플라즈마가, 이온차폐전극(EL1)에 충전된 양전하의 영향으로 인해, 뱅크층(170) 표면과 충돌하는 것을 방지하는 효과가 발생하게 된다. 또한, 이온차폐전극(EL1)은 마치 가이드링의 역할을 하여 양이온 플라즈마가 뱅크층(170) 사이의 노출된 제1전극(162) 표면으로 집중되도록 함으로써, 제1전극(162)에 대한 플라즈마 처리 효율이 향상되는 효과 또한 발생하게 된다.

- [0085] 또한, 본 실시예에 따르면, 뱅크층(170) 하부로서 예를 들면 제2보호막(161) 상부에 대향전극(EL2)이 형성될 수 있는데, 대향전극(EL2)은 뱅크층(170)을 사이에 두고 이온차폐전극(EL1)과 마주보도록 배치될 수 있다.

- [0086] 이와 같은 대향전극(EL2)은 제1전극(162)과 동일 공정을 통해 동일층에 동일물질로 형성될 수 있게 된다. 이에 따라, 대향전극(EL2)을 형성하기 위한 별도의 마스크 공정이 생략될 수 있는 장점이 있다.

- [0087] 유기발광다이오드(De) 구동시에는, 대향전극(EL2)은 이온차폐전극(EL1)과 함께 유기발광다이오드(De) 내부에 전기장을 발생시키도록 동작하게 되는데, 이에 대해 5를 더욱 참조하여 설명한다.

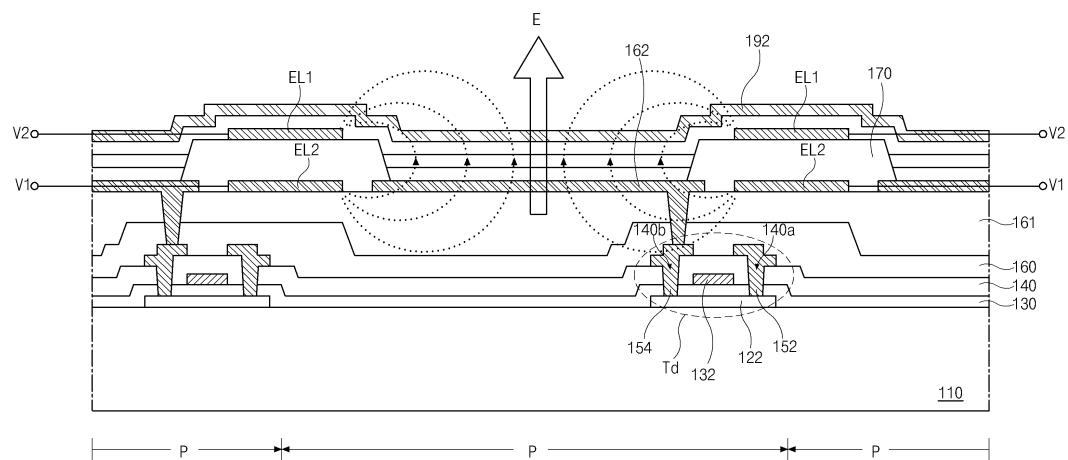

- [0088] 도 5는 본 발명의 제1실시예에 따른 이온차폐전극과 대향전극에 의해 발생되는 전기장의 모습을 개략적으로 도시한 도면으로서, 설명의 편의를 위해, 관련된 주요 구성을 위주로 도시하였다.

- [0089] 도 5를 참조하면, 대향전극(EL2)과 이온차폐전극(EL1)을 통해 발생되는 전기장(E)은 유기발광다이오드(De) 내부를 통과하게 되는데, 유기발광다이오드(De)에 작용하는 전기장(E)의 방향이 유기발광다이오드(De)의 순방향이 되도록 한다.

- [0090] 이와 관련하여, 유기발광다이오드(De)에 대해 발광전류가 흐르는 순방향을 따라 전기장(E)을 발생시키게 되면, 적층막 간의 에너지 배리어가 낮아짐과 동시에 적층막의 에너지 레벨에 테이퍼가 발생하게 되어, 캐리어의 주입 및 수송 효율이 향상된다.

- [0091] 본 실시예에서는 이 점을 반영하여, 이온차폐전극(EL1) 및 대향전극(EL2)에 의해 발생되는 전기장(E)이 유기발광다이오드(De)의 순방향을 따르도록 구성하게 된다. 이에 따라, 에너지 배리어가 낮아지고 또한 에너지 레벨에 테이퍼가 발생하게 됨으로써, 캐리어의 주입 및 수송 효율이 향상될 수 있게 된다.

- [0092] 이로 인해, 캐리어 주입 및 수송 효율 향상을 위해 제1 및 2전극(162, 192)에 높은 전압을 인가함으로써 유기막이 열화되어 유기발광다이오드(De)의 수명이 저하되는 문제를 개선할 수 있는 장점을 갖게 된다.

- [0093] 따라서, 본 실시예에서는 유기발광다이오드(De)의 순방향으로 전기장(E)이 유도되도록 하는 구동전압을 이온차폐전극(EL1) 및 대향전극(EL2)에 인가하게 된다.

- [0094] 이와 관련하여 예를 들면, 유기발광다이오드(De)의 제1전극(162)이 애노드이고 제2전극(192)이 캐소드인 경우에, 발광전류의 순방향은 제1전극(162)에서 제2전극(192) 방향이므로, 하부에 위치하는 대향전극(EL2)에 상대적으로 높은 제1구동전압(V1)을 인가하고, 상부에 위치하는 이온차폐전극(EL1)에 상대적으로 낮은 제2구동전압(V2)를 인가하게 된다 (즉, V1>V2). 이에 따라, 유기발광다이오드(De)의 순방향을 따라 전기장(E)이 유도된다.

- [0095] 다른 예로서, 유기발광다이오드(De)의 제1전극(162)이 캐소드이고 제2전극(192)이 애노드인 경우에, 발광전류의 순방향은 제2전극(192)에서 제1전극(162) 방향이므로, 상부에 위치하는 이온차폐전극(EL1)에 상대적으로 높은 제1구동전압(V1)을 인가하고, 하부에 위치하는 대향전극(EL2)에 상대적으로 낮은 제2구동전압(V2)를 인가하게 된다. 이에 따라, 유기발광다이오드(De)의 순방향을 따라 전기장(E)이 유도된다.

- [0096] 한편, 유기발광다이오드 표시장치(100)를 구동하는 동안에는 지속적으로 전기장(E)이 인가되도록 구동전압(V1, V2)을 인가하는 것이 바람직하다.

- [0097] 이하, 도면을 참조하여, 본 발명의 제1실시예에 따른 유기발광다이오드 표시장치의 제조방법에 대해 설명한다.

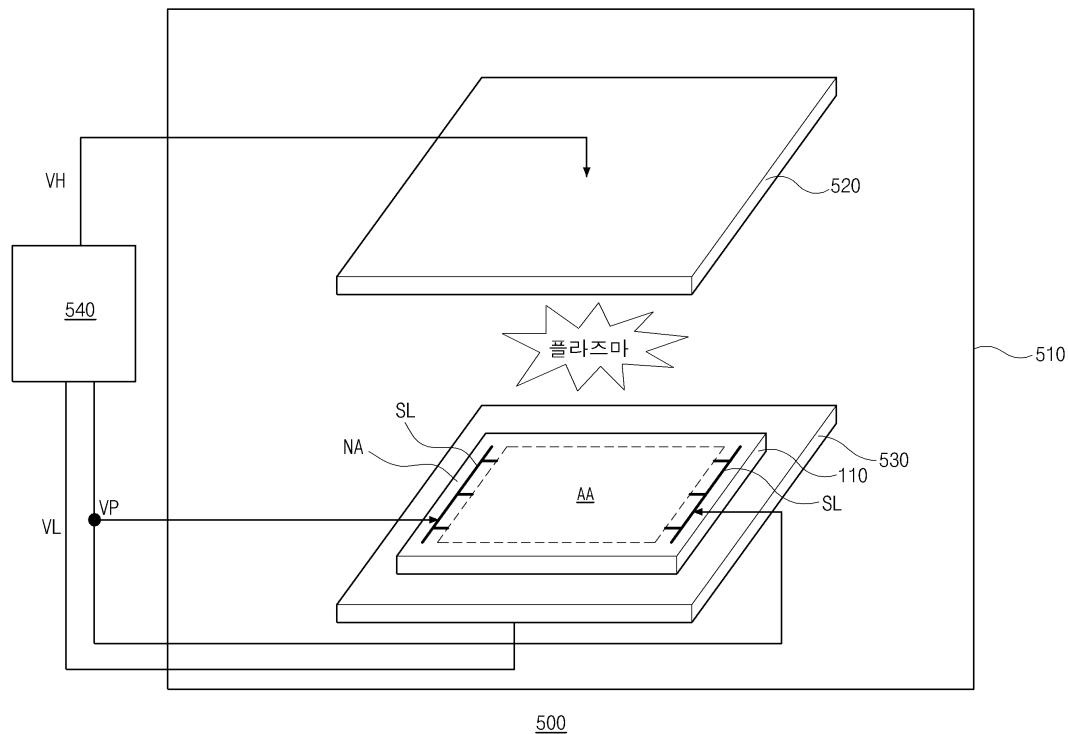

- [0098] 도 6은 본 발명의 제1실시예에 따른 유기발광다이오드 표시장치의 제1전극을 플라즈마 처리하는 플라즈마 처리장치를 개략적으로 도시한 도면이고, 도 7은 도 6의 플라즈마 처리 장치를 사용한 플라즈마 처리 공정 시의 유기발광다이오드 표시장치의 모습을 개략적으로 도시한 도면이다. 도 6 및 7에서는, 설명의 편의를 위해, 관련된 주요 구성을 위주로 도시하였다.

- [0099] 도 6 및 7을 참조하면, 본 실시예에 따른 제1전극(162)을 플라즈마 처리하는 플라즈마 처리장치(500)는 챔버(510) 내에 위치하는 상부의 제1전극 플레이트(520)와 제1전극 플레이트(520)와 마주보는 하부의 제2전극 플레이트(530)를 포함한다. 여기서, 제2전극 플레이트(520)의 상면에는 제1전극(162)과 뱅크층(170)과 이온차폐전극(EL1)이 형성된 상태의 기판(110)이 놓여진다.

- [0100] 플라즈마 처리 공정을 수행함에 있어, 예를 들면, 전원공급부(540)는 제1전극 플레이트(520)에 고전위 전압(VH)을 인가하고 제2전극 플레이트(530)에 저전위 전압(VL)을 인가하며, 이에 따라 챔버(510) 내부의 반영영역에 플라즈마가 생성된다.

- [0101] 한편, 도 6을 참조하면, 기판(110)의 주변영역으로서, 다수의 화소영역(P)이 구성되어 영상을 표시하는 표시영역(AA) 주변의 비표시영역(NA)에는 표시영역(AA) 내에 구성된 이온차폐전극(EL1)에 정극성의 차폐전압(VP)을 전달하기 위한 전송배선패턴(SL)이 형성될 수 있다. 전송배선패턴(SL)에는 핀(pin)과 같은 전압 인가 수단이 접속되어 전원공급부(540)로부터 차폐전압(VP)이 인가되고, 인가된 차폐전압(VP)은 전송배선패턴(SL)을 경유하여 표시영역(AA) 내부의 이온차폐전극(EL1)으로 전달된다. 이처럼, 비표시영역(NA)에 전송배선패턴(SL)을 형성함으로써, 차폐전압(VP)을 이온차폐전극(EL1)에 용이하게 공급할 수 있다.

- [0102] 이처럼, 차폐전압(VP)이 이온차폐전극(EL1)에 인가되면, 이온차폐전극(EL1)은 양전하를 띠게 된다. 이에 따라, 제1전극(162)을 플라즈마 처리하는 양이온 플라즈마가, 이온차폐전극(EL1)의 양전하의 영향으로 인해, 뱅크층(170) 표면과 충돌하는 것이 방지된다. 또한, 이온차폐전극(EL1)은 마치 가이드링의 역할을 하여 양이온 플라즈마가 제1전극(162) 표면으로 집중되도록 함으로써, 제1전극(162)에 대한 플라즈마 처리 효율이 향상되는 효과 또한 발생하게 된다.

- [0103] 위와 같이 제1전극(162)에 대한 플라즈마 처리 수행 후, 용액 공정을 통해 유기막을 형성하게 된다. 이때, 이온

차폐전극(EL1)에 의해 뱅크층(170)은 소수성을 유지하게 되므로, 해당 유기막은 원하는 바와 같이 화소영역(P) 단위로 분할되어 형성될 수 있게 된다.

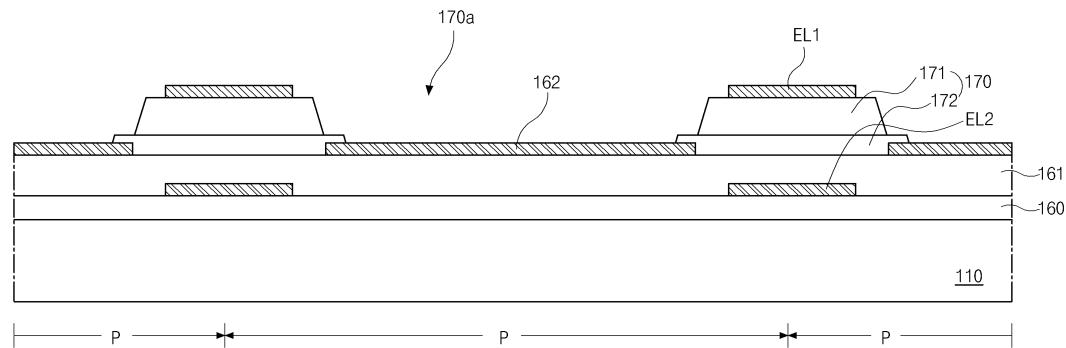

[0104] 한편, 전술한 바에서는 단일층 구조의 뱅크층(170)을 구비한 경우를 예로 들어 설명하였는데, 이와 다른 예로서 2중층 구조의 뱅크층이 사용될 수 있다. 이와 관련하여 도 8을 참조할 수 있는데, 뱅크층(170)은 상부에 위치하는 제1뱅크층(171)과 하부에 위치하는 제2뱅크층(172)으로 구성될 수 있다. 도 8에서는 설명의 편의를 위해, 관련 구성을 위주로 하여 도시하였다.

[0105] 이 경우에, 상부에 위치하는 제1뱅크층(171)은 전술한 예와 마찬가지로 소수성을 갖도록 구성된다. 한편, 하부에 위치하는 제2뱅크층(172)은 친수성을 갖도록 구성될 수 있으며, 제2뱅크층(172)은 제1뱅크층(171)에 비해 넓은 폭으로 형성될 수 있다.

[0106] 이와 같이 2중층 구조의 뱅크층(170)을 형성하게 되면, 용액 공정에 의해 형성되는 유기막의 화소영역 내에서의 두께 균일도를 향상시킬 수 있는 장점이 발생하게 된다.

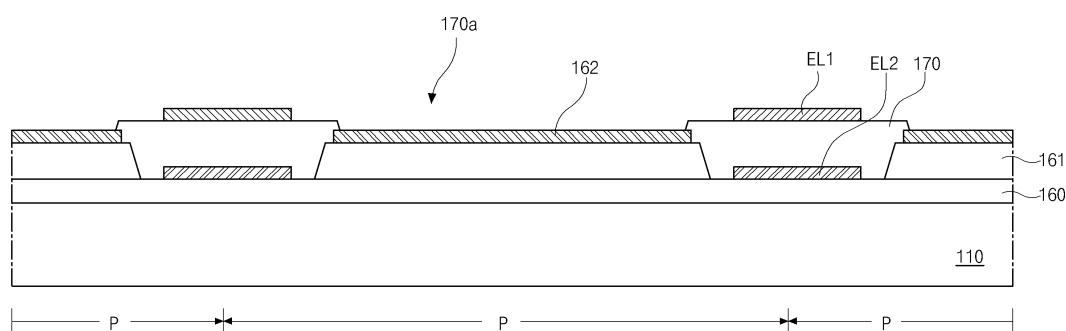

[0107] 또한, 전술한 바에서는 평탄화 기능을 갖는 제2보호막(161)이 기판 전면을 따라 형성된 경우를 예로 들어 설명하였는데, 이와 다른 예로서 뱅크층(170)에 대응되는 제2보호막(161) 부분이 기판 방향으로 요입된 형태를 갖도록 제거되어 구성될 수 있다. 이와 관련하여 도 9 및 10을 참조할 수 있다. 도 9 및 10에서는 설명의 편의를 위해, 관련 구성을 위주로 하여 도시하였다.

[0108] 도 9에서는, 제2보호막(161)이 뱅크층(170)에 대응되는 부분이 완전히 제거되어 요입되고, 뱅크층(170)이 노출된 제1보호막(160) 상면에 형성된 경우가 도시되어 있다.

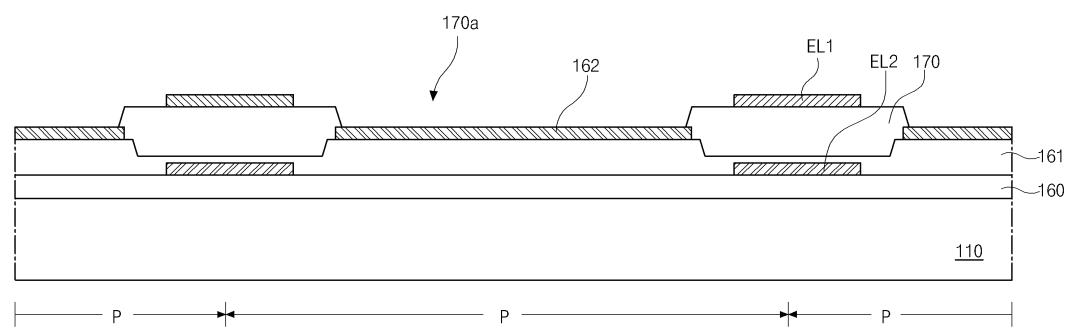

[0109] 그리고, 도 10에서는, 제2보호막(161)이 일부 제거 즉 두께 방향으로 일부 제거되어 요입되고, 이 부분의 제2보호막(161) 상면에 뱅크층(170)이 형성되도록 구성될 수도 있다. 이와 같이 일부 제거된 제2보호막(161)을 형성함에 있어서는, 예를 들면, 반투과부를 갖는 하프톤 마스크를 사용할 수 있다.

[0110] 한편, 도 9 및 10의 경우에 있어, 도 8에 도시한 바와 같이 2중층 구조의 뱅크층(170)이 사용될 수 있다.

[0111] 이와 같이 제2보호막(161)이 제거되어 요입된 형태로 형성된 경우에, 요입된 부분에 뱅크층(170)이 형성된 상태에서 기판 면의 단차가 전체적으로 완화될 수 있다. 즉, 뱅크층(170)은 어느 정도 두께를 갖게 되므로, 뱅크층(170)에 의해 기판 면이 단차가 발생하게 된다. 이와 같은 단차에 의해, 이후에 기판 전면에 적층막을 형성하는 경우에 해당 적층막이 단차에 의해 연결이 끊어지는 문제가 발생할 수 있는데, 제2보호막(161)을 제거함으로써 뱅크층(170)의 단차에 기인한 문제를 개선할 수 있는 효과가 있다.

[0112] 특히, 2중층 구조의 뱅크층(170)을 사용하는 경우에 단차가 더욱 커지게 되므로, 제2보호막(161) 제거에 따른 효과는 2중층 구조의 뱅크층(170)을 사용하는 경우에 더욱 효과적일 수 있다.

[0113] <제2실시예>

[0114] 도 11은 본 발명의 제2실시예에 따른 유기발광다이오드 표시장치를 개략적으로 도시한 단면도이다.

[0115] 제2실시예의 유기발광다이오드 표시장치는, 대향전극의 배치를 제외하고는, 제1실시예의 유기발광다이오드 표시장치와 실질적으로 동일 유사하다. 설명의 편의를 위해, 동일 유사한 구성에 대한 구체적인 설명을 생략할 수 있다.

[0116] 도 11을 참조하면, 본 발명의 제2실시예에 따른 유기발광다이오드 표시장치(100)는, 기판(110) 상의 각 화소영역(P)에 형성된 스위칭 박막트랜지스터(도 2의 Ts 참조) 및 구동 박막트랜지스터(Td)와, 이 박막트랜지스터들 상에 위치하고 구동 박막트랜지스터(Td)와 연결된 유기발광다이오드(De)를 포함할 수 있다.

[0117] 특히, 본 실시예에 따른 유기발광다이오드 표시장치(100)는 뱅크층(170)의 표면에 형성되며 유기막에 대한 용액 공정시 양전하가 인가되어 양이온 플라즈마를 차폐하도록 하는 이온차폐전극(EL1)이 구비된다.

[0118] 더욱이, 뱅크층(170) 하부에 이온차폐전극(EL1)과 전기장을 유발하는 대향전극(EL2)을 구비할 수 있는데, 본 실시예의 대향전극(EL2)은 제1보호막(160) 및 제2보호막(161) 사이에 배치될 수 있다.

[0119] 이와 같은 구성을 갖는 유기발광다이오드 표시장치(100)의 단면 구조에 대해 보다 상세하게 설명하면, 기판(110) 상부에는 패터닝된 반도체층(122)이 형성된다.

[0120] 여기서, 기판(110)은 유리기판이나 플라스틱기판일 수 있다. 반도체층(122)은 산화물 반도체 물질로 이루어질 수 있는데, 이 경우 반도체층(122) 하부에는 차광패턴(미도시)과 베피층(미도시)이 형성될 수 있으며, 차광패턴

은 반도체층(122)으로 빛이 입사되는 것을 방지하여 반도체층(122)이 빛에 의해 열화되는 것을 방지한다. 다른 예로서, 반도체층(122)은 다결정 실리콘으로 이루어질 수도 있으며, 이 경우 반도체층(122)의 양 가장자리에 불순물이 도핑될 수 있다.

[0121] 반도체층(122) 상부에는 절연물질로 이루어진 절연막으로서 게이트 절연막(130)이 기판(110) 전면에 형성될 수 있다. 게이트 절연막(130)은 산화실리콘( $SiO_2$ )과 같은 무기절연물질로 형성될 수 있다. 한편, 반도체층(122)이 다결정 실리콘으로 이루어지는 경우, 게이트 절연막(130)은 산화 실리콘( $SiO_2$ )이나 질화 실리콘( $SiNx$ )으로 형성될 수 있다.

[0122] 게이트 절연막(130) 상부에는 금속과 같은 도전성 물질로 이루어진 게이트전극(132)이 반도체층(122)의 중앙에 대응하여 형성된다. 또한, 게이트 절연막(130) 상부에는 게이트배선(도 2의 GL 참조)과 제1커패시터전극(미도시)이 형성될 수 있다. 게이트배선은 제1방향을 따라 연장되고, 제1커패시터 전극은 게이트전극(132)에 연결된다.

[0123] 한편, 본 실시예에서는 게이트 절연막(130)이 기판(110) 전면에 형성된 경우를 예로 들고 있으나, 게이트 절연막(130)은 게이트전극(132)과 동일한 모양으로 패터닝될 수도 있다.

[0124] 게이트전극(132) 상부에는 절연물질로 이루어진 절연막으로서 층간 절연막(140)이 기판(110) 전면에 형성될 수 있다. 층간 절연막(140)은 산화 실리콘( $SiO_2$ )이나 질화 실리콘( $SiNx$ )과 같은 무기절연물질로 형성되거나, 벤조사이클로부텐(benzocyclobutene)이나 포토 아크릴(photo acryl)과 같은 유기절연물질로 형성될 수 있다.

[0125] 층간 절연막(140)은 반도체층(122)의 양측을 노출하는 제1 및 2콘택홀(140a, 140b)을 구비할 수 있다. 제1 및 2콘택홀(140a, 140b)은 게이트전극(132)의 양측에 게이트전극(132)과 이격되어 위치한다. 더욱이, 제1 및 2콘택홀(140a, 140b)은 게이트 절연막(130) 내에도 형성될 수 있다. 이와 달리, 게이트 절연막(130)이 게이트전극(132)과 동일한 모양으로 패터닝될 경우, 제1 및 2콘택홀(140a, 140b)은 층간 절연막(140) 내에 형성되도록 구성된다.

[0126] 층간 절연막(140) 상부에는 금속과 같은 도전성 물질로 소스전극 및 드레인전극(152, 154)이 형성된다. 또한, 층간 절연막(140) 상부에는 제2방향을 따라 연장되는 데이터배선(도 2의 DL 참조)과 전원배선(미도시) 및 제2커패시터 전극(미도시)이 형성될 수 있다.

[0127] 소스 및 드레인전극(152, 154)은 게이트전극(132)을 중심으로 이격되어 위치하며, 각각 제1 및 2콘택홀(140a, 140b)을 통해 반도체층(122)의 양측과 접촉한다. 도시하지 않았지만, 데이터배선은 제2방향을 따라 연장되고 게이트배선과 교차하여 화소영역(P)을 정의하며, 고전위 전원전압(도 2의 VDD 참조)을 전송하는 전원배선은 데이터배선과 이격되어 위치한다. 제2커패시터 전극은 드레인전극(154)과 연결되고 제1커패시터 전극과 중첩하며 이들 두 전극 사이의 층간 절연막(140)을 유전체로 하여 스토리지 커패시터를 이룬다.

[0128] 한편, 반도체층(122)과, 게이트전극(132), 그리고 소스전극 및 드레인전극(152, 154)은 구동 박막트랜지스터(Td)를 이룬다. 여기서, 구동 박막트랜지스터(Td)는 반도체층(122)의 일측, 즉 반도체층(122)의 상부에 게이트전극(132)과 소스전극 및 드레인전극(152, 154)이 위치하는 코플라나(coplanar) 구조를 갖도록 구성될 수 있다.

[0129] 다른 예로서, 구동 박막트랜지스터(Td)는 반도체층의 하부에 게이트전극이 위치하고 반도체층의 상부에 소스전극 및 드레인전극이 위치하는 역 스태거드(inverted staggered) 구조를 가질 수 있다. 이 경우, 반도체층은 비정질 실리콘으로 이루어질 수 있다.

[0130] 한편, 도시하지는 않았지만, 구동 박막트랜지스터(Td)와 동일한 구조의 스위칭 박막트랜지스터(도 2의 Ts 참조)가 기판(110) 상에 형성된다. 구동 박막트랜지스터(Td)의 게이트 전극(132)은 스위칭 박막트랜지스터의 드레인전극에 전기적으로 연결되고 구동 박막트랜지스터(Td)의 소스전극(152)은 전원배선에 연결된다. 또한, 스위칭 박막트랜지스터의 게이트전극과 소스전극은 게이트 배선 및 데이터 배선과 각각 연결된다.

[0131] 소스전극 및 드레인전극(152, 154) 상부에는 절연물질로 이루어진 절연막으로서 제1보호막(160)이 기판(110) 전면에 형성될 수 있다. 제1보호막(160)은 산화 실리콘( $SiO_2$ )이나 질화 실리콘( $SiNx$ )과 같은 무기절연물질로 형성될 수 있다.

[0132] 제1보호막(160) 상에는 절연물질로 이루어진 절연막으로서 제2보호막(161)이 기판(110) 전면에 형성될 수 있다. 제2보호막(161)은 벤조사이클로부텐이나 포토 아크릴과 같은 유기절연물질로 형성될 수 있다. 이와 같은 제2보

호막(161)은 평탄화층으로서 기능하여 그 상면은 실질적으로 평탄하게 된다.

[0133] 이처럼, 본 실시예에서는, 구동 박막트랜지스터(Td) 상에 2층층 구조의 보호막(160, 161)이 형성될 수 있다. 이와 같은 제1 및 2보호막(160, 161)은 드레인전극(154)을 노출하는 드레인 콘택홀(160a)을 가진다.

[0134] 제2보호막(161) 상부에는 각 화소영역(P)마다 패터닝된 형태의 제1전극(162)이 형성될 수 있다. 제1전극(162)은 드레인 콘택홀(160a)을 통해 드레인전극(154)과 접촉한다. 제1전극(162)은 비교적 일함수가 높은 도전성 물질로 형성될 수 있는데, 예를 들면, ITO(indium tin oxide)나 IZO(indium zinc oxide)와 같은 투명 도전성 물질로 형성될 수 있다.

[0135] 제1전극(162) 상부에는 절연물질로 이루어진 절연막으로서 뱅크층(170)이 형성된다. 이와 같은 뱅크층(170)은 이웃하는 화소영역(P)의 경계를 따라 각 화소영역(P)을 둘러싸도록 배치된다. 뱅크층(170)은 각 화소영역(P)의 제1전극(162)을 노출하는 투과홀(170a)을 가지며, 제1전극(162)의 가장자리를 덮는다.

[0136] 이와 같은 뱅크층(170)은 소수성의 특성을 갖도록 형성된다. 이와 관련하여 예를 들면, 뱅크층(170)에는 소수성을 갖는 폴리머 등의 첨가제 즉 소수첨가제가 함유되며, 이 소수첨가제는 뱅크층(170) 형성을 위한 경화 공정(예를 들어, 소프트 베이킹 공정)에서 표면으로 이동하게 되어, 뱅크층(170)의 표면은 소수성을 갖게 된다.

[0137] 이처럼, 뱅크층(170)이 소수성 특성을 갖게 됨으로써, 후속하는 용액 공정을 이용한 유기막 형성시에 해당 유기막이 화소영역(P) 단위로 분할되어 형성될 수 있게 된다.

[0138] 뱅크층(170)의 투과홀(170a)을 통해 노출된 제1전극(162) 상부에는 유기발광층(180)이 형성된다. 유기발광층(180)은 발광물질층(183)을 포함하는 다수의 유기막으로 구성된 다층 구조로 형성된다.

[0139] 이와 관련하여 예를 들면, 제1전극(162)이 애노드이고 제2전극(192)이 캐소드인 경우에, 제1전극(162)과 발광물질층(183) 사이에는 정공주입층과 정공수송층이 순차적으로 배치될 수 있고, 발광물질층(183)과 제2전극(192) 사이에는 전자수송층과 전자주입층이 순차적으로 배치될 수 있다. 본 실시예에서는, 설명의 편의를 위해, 발광물질층(183) 하부의 유기막으로서 정공주입층 및 정공수송층을 단일층의 유기막(181)으로 도시하였고, 발광물질층(183) 상부의 유기막으로서 전자주입층과 전자수송층을 단일층의 유기막(185)으로 도시하였다.

[0140] 한편, 경우에 따라, 정공주입층과 정공수송층 중 적어도 하나는 생략될 수 있으며, 전자주입층과 전자수송층 중 적어도 하나는 생략될 수 있다.

[0141] 이처럼, 유기발광층(180)을 구성하는 다수의 유기막은 다양한 형태로 배치될 수 있다.

[0142] 이때, 본 실시예에서의 유기발광층(180)을 형성함에 있어, 상대적으로 하부에 배치된 일부 유기막은 용액 공정으로 화소영역(P) 단위로 형성되고, 상대적으로 상부에 배치된 나머지 유기막은 증착 공정으로 실질적으로 기판 전면에 형성되는 것이 바람직하다. 여기서, 용액 공정으로는 인쇄법이나 코팅법이 이용될 수 있으며, 인쇄법으로는 잉크젯 인쇄법(inkjet printing) 또는 노즐 인쇄법(nozzle printing)이 이용될 수 있다. 한편, 증착 공정으로는 PECVD 방법 등으로 형성될 수 있다.

[0143] 이와 관련하여 예를 들면, 발광물질층(183) 하부에 위치하는 단일층 또는 다층 구조의 유기막(181)인 제1유기막(181)에 대해서는 용액 공정이 적용되며, 소수성의 뱅크층(170)에 의해 화소영역(P) 단위로 제1유기막(181)이 분할되어 형성될 수 있다.

[0144] 그리고, 발광물질층(183) 또한 용액 공정에 의해 화소영역(P) 단위로 형성될 수 있다. 한편, 적색, 녹색, 청색 화소영역을 갖는 컬러 표시장치의 경우에, 발광물질층(183)을 형성함에 있어, 예를 들면, 적색 및 녹색 화소영역에 각각 형성되는 적색 및 녹색 발광물질층은 용액 공정으로 형성되고, 이에 대한 후속 공정에서 청색 발광물질층을 기판 전면에 증착 공정으로 형성할 수 있다. 물론, 청색 발광물질층 또한 용액 공정을 적용하여 청색 화소영역에 형성되도록 할 수도 있다.

[0145] 한편, 발광물질층(183) 상부에 위치하는 단일층 또는 다층 구조의 유기막(185)인 제2유기막(185)에 대해서는 증착 공정이 적용되며, 실질적으로 기판 상의 표시영역 전체를 덮도록 형성될 수 있다. 즉, 제2유기막(185)은 화소영역(P) 뿐만 아니라 그 경계의 뱅크층(170)을 덮도록 형성될 수 있다.

[0146] 위와 같이 유기발광층(180)을 구성하는 일부 유기막에 대해 용액 공정을 적용하여 형성하게 되면, 해당 유기막들에 대한 마스크 공정이 저감되어 공정 효율성이 향상되는 효과가 있다.

[0147] 위와 같이 구성된 유기발광층(180) 상부에는 비교적 일함수가 낮은 도전성 물질로 제2전극(192)이 기판(110) 전

면에 형성될 수 있다. 즉, 제2전극(192)은 유기발광층(180)의 제2유기막(185) 표면에 형성될 수 있다.

[0148] 여기서, 제2전극(192)은 알루미늄(aluminum)이나 마그네슘(magnesium), 은(silver) 또는 이들의 합금으로 형성될 수 있다.

[0149] 제1전극(162)과 유기발광층(180) 및 제2전극(192)은 유기발광다이오드(De)를 이루게 된다. 여기서, 제1 및 2전극(162, 192) 중 하나는 애노드로 역할하고, 나머지 하나는 캐소드로 역할하게 된다.

[0150] 한편, 본 실시예에 따른 유기발광다이오드 표시장치(100)는 유기발광층(180)으로부터 방출된 빛이 제2전극(192)을 통해 외부로 출력되는 상부발광방식(top emission type)으로 구성될 수 있다. 이 경우에, 제1전극(162)은 불투명 도전성 물질로 이루어진 반사층(도시하지 않음)을 더 포함한 다층 구조로 구성될 수 있다. 일례로, 반사층은 알루미늄-팔라듐-구리(aluminum-palladium-copper: APC) 합금으로 형성될 수 있으며, 제1전극(162)은 ITO/APC/ITO의 3중층 구조를 가질 수 있다. 또한, 제2전극(192)은 빛이 투과되도록 비교적 얇은 두께를 가지며, 제2전극(192)의 빛 투과도는 약 45-50%일 수 있다.

[0151] 다른 예로서, 유기발광다이오드 표시장치(100)는 유기발광층(180)으로부터 방출된 빛이 제1전극(162)을 통해 외부로 출력되는 하부발광방식(bottom emission type)으로 구성될 수 있다.

[0152] 또한, 본 실시예에 따른 유기발광다이오드 표시장치(100)는 각 화소영역(P)에 대응되는 컬러필터를 구비할 수 있다. 이 경우에, 컬러필터는 발광방향 측으로서, 예를 들면, 하부발광방식의 경우에는 유기발광다이오드(De) 하부측에, 상부발광방식의 경우에는 유기발광다이오드(De) 상부측에 배치될 수 있다. 이처럼, 컬러필터를 사용하게 되면 색재현율이 향상되는 장점이 발생할 수 있게 된다.

[0153] 한편, 본 실시예에서는, 소수성의 뱅크층(170)의 표면에 이온차폐전극(EL1)을 형성하는 것을 특징으로 한다. 이와 같은 이온차폐전극(EL1)은 소수성의 뱅크층(170)의 표면이 친수화되는 것을 방지하는 기능을 수행하게 되는 것으로서, 평면적으로 볼 때 실질적으로 뱅크층(170)과 동일한 형태로 형성된다. 즉, 이온차폐전극(EL1)은 이웃하는 화소영역(P)의 경계를 따라 각 화소영역(P) 주변을 둘러싸도록 형성된다.

[0154] 한편, 이온차폐전극(EL1) 상에는 실질적으로 절연막으로서 기능하는 제2유기막(185)이 위치하여, 유기발광다이오드(De) 구동시 그 상부에 위치하는 제2전극(192)과 전기적으로 단락되는 것이 방지될 수 있다. 이처럼, 제2유기막(185)은 제2전극(192)으로부터 유입되는 캐리어의 수송 기능뿐만 아니라, 이온차폐전극(EL1)과 제2전극(192)의 전기적 단락을 방지하는 기능 또한 수행할 수 있게 된다.

[0155] 그리고, 이온차폐전극(EL1)은 제1전극(162)과 이격되도록 뱅크층(170)의 표면 일부로서 상면에 형성되어, 실질적으로 제1전극(162)과도 전기적으로 단선된 상태를 갖게 된다. 이온차폐전극(EL1)은, 예를 들면, 은(Ag), ITO, 구리(Cu)와 같은 금속물질들 중 적어도 하나로 형성될 수 있다.

[0156] 이와 같은 이온차폐전극(EL1)을 뱅크층(170) 상에 형성한 후 제1전극(162)에 대한 플라즈마 처리를 수행하게 되는데, 이 공정 진행시 이온차폐전극(EL1)에는 양전하가 인가되도록 한다. 즉, 이온차폐전극(EL1)에 대해 정극성 전압을 인가함으로써, 이온차폐전극(EL1)에는 정극성의 양전하가 유입되어, 이온차폐전극(EL1)은 정극성을 갖게 된다. 이에 따라, 플라즈마 처리를 위해 발생된 양이온 플라즈마가, 이온차폐전극(EL1)에 충전된 양전하의 영향으로 인해, 뱅크층(170) 표면과 충돌하는 것을 방지하는 효과가 발생하게 된다. 또한, 이온차폐전극(EL1)은 마치 가이드링의 역할을 하여 양이온 플라즈마가 제1전극(162) 표면으로 집중되도록 함으로써, 제1전극(162)에 대한 플라즈마 처리 효율이 향상되는 효과 또한 발생하게 된다.

[0157] 또한, 본 실시예에 따르면, 뱅크층(170) 하부로서 예를 들면 제1보호막(160) 상에 대향전극(EL2)이 형성될 수 있다. 즉, 대향전극(EL2)은 뱅크층(170)과 제2보호막(161)을 사이에 두고 이온차폐전극(EL1)과 마주보도록 배치될 수 있다.

[0158] 이와 같은 대향전극(EL2)을 형성하기 위해 별도의 마스크 공정이 추가로 진행될 수 있다.

[0159] 유기발광다이오드(De) 구동시에는, 대향전극(EL2)은 이온차폐전극(EL1)과 함께 유기발광다이오드(De) 내부에 전기장을 발생시키도록 동작하게 된다.

[0160] 이때, 대향전극(EL2)과 이온차폐전극(EL1)을 통해 발생되는 전기장은 유기발광다이오드(De) 내부를 통과하게 되는데, 유기발광다이오드(De)에 작용하는 전기장의 방향이 유기발광다이오드(De)의 순방향이 되도록 한다.

[0161] 이에 따라, 에너지 배리어가 낮아지고 또한 에너지 레벨에 테이퍼가 발생하게 됨으로써, 캐리어의 주입 및 수송 효율이 향상될 수 있게 된다.

- [0162] 이로 인해, 캐리어 주입 및 수송 효율 향상을 위해 제1 및 2전극(162, 192)에 높은 전압을 인가함으로써 유기막이 열화되어 유기발광다이오드(De)의 수명이 저하되는 문제를 개선할 수 있는 장점을 갖게 된다.

- [0163] 따라서, 본 실시예에서는 유기발광다이오드(De)의 순방향으로 전기장(E)이 유도되도록 하는 구동전압을 이온차폐전극(EL1) 및 대향전극(EL2)에 인가하게 된다.

- [0164] 이와 관련하여 전술한 제1실시예의 도 5를 참조할 수 있다. 즉, 유기발광다이오드(De)의 제1전극(162)이 애노드이고 제2전극(192)이 캐소드인 경우에, 발광전류의 순방향은 제1전극(162)에서 제2전극(192) 방향이므로, 대향전극(EL2)에 상대적으로 높은 제1구동전압(도 5의 V1 참조)을 인가하고, 이온차폐전극(EL1)에 상대적으로 낮은 제2구동전압(도 5의 V2 참조)을 인가하게 된다. 이에 따라, 유기발광다이오드(De)의 순방향을 따라 전기장이 유도된다.

- [0165] 다른 예로서, 유기발광다이오드(De)의 제1전극(162)이 캐소드이고 제2전극(192)이 애노드인 경우에, 이온차폐전극(EL1)에 상대적으로 높은 제1구동전압을 인가하고, 대향전극(EL2)에 상대적으로 낮은 제2구동전압을 인가하게 된다. 이에 따라, 유기발광다이오드(De)의 순방향을 따라 전기장이 유도된다.

- [0166] 한편, 유기발광다이오드 표시장치(100)를 구동하는 동안에는 지속적으로 전기장(E)이 인가되도록 구동전압을 인가하는 것이 바람직하다.

- [0167] 본 발명의 제2실시예에 따른 유기발광다이오드 표시장치의 제조방법에 대해서는, 전술한 제1실시예의 도 6 및 7을 참조할 수 있다.

- [0168] 즉, 제1전극(162)에 대한 플라즈마 처리 공정시, 차폐전압(도 6의 VP 참조)이 이온차폐전극(EL1)에 인가되면, 이온차폐전극(EL1)은 양전하를 띠게 된다. 이에 따라, 제1전극(162)을 플라즈마 처리하는 양이온 플라즈마가, 이온차폐전극(EL1)의 양전하의 영향으로 인해, 뱅크층(170) 표면과 충돌하는 것이 방지된다. 또한, 이온차폐전극(EL1)은 마치 가이드링의 역할을 하여 양이온 플라즈마가 제1전극(162) 표면으로 집중되도록 함으로써, 제1전극(162)에 대한 플라즈마 처리 효율이 향상되는 효과 또한 발생하게 된다.

- [0169] 위와 같이 제1전극(162)에 대한 플라즈마 처리 수행후, 용액 공정을 통해 유기막을 형성하게 된다. 이때, 이온차폐전극(EL1)에 의해 뱅크층(170)은 소수성을 유지하게 되므로, 해당 유기막은 원하는 바와 같이 화소영역 단위로 분할되어 형성될 수 있게 된다.

- [0170] 한편, 전술한 바에서는 단일층 구조의 뱅크층(170)을 구비한 경우를 예로 들어 설명하였는데, 이와 다른 예로서 2중층 구조의 뱅크층이 사용될 수 있다. 이와 관련하여 도 12를 참조할 수 있는데, 뱅크층(170)은 상부에 위치하는 제1뱅크층(171)과 하부에 위치하는 제2뱅크층(172)으로 구성될 수 있다.

- [0171] 이 경우에, 상부에 위치하는 제1뱅크층(171)은 전술한 예와 마찬가지로 소수성을 갖도록 구성된다. 한편, 하부에 위치하는 제2뱅크층(172)은 친수성을 갖도록 구성될 수 있으며, 이는 제1뱅크층(171)에 비해 넓은 폭으로 형성될 수 있다.

- [0172] 이와 같이 2중층 구조의 뱅크층(170)을 형성하게 되면, 용액 공정에 의해 형성되는 유기막의 화소영역 내에서의 두께 균일도를 향상시킬 수 있는 장점이 발생하게 된다.

- [0173] 또한, 전술한 바에서는 평탄화 기능을 갖는 제2보호막(161)이 기판 전면을 따라 형성된 경우를 예로 들어 설명하였는데, 이와 다른 예로서 뱅크층(170)에 대응되는 제2보호막(161) 부분이 기판 방향으로 요입된 형태를 갖도록 제거되어 구성될 수 있다. 이와 관련하여 도 13 및 14를 참조할 수 있다. 도 13 및 14에서는 설명의 편의를 위해, 관련 구성을 위주로 하여 도시하였다.

- [0174] 도 13에서는, 제2보호막(161)이 뱅크층(170)에 대응되는 부분이 완전히 제거되어 요입되고, 뱅크층(170)이 노출된 제1보호막(160) 상면에 형성된 경우가 도시되어 있다.

- [0175] 그리고, 도 14에서는, 제2보호막(161)이 일부 제거 즉 두께 방향으로 일부 제거되어 요입되고, 이 부분의 제2보호막(161) 상면에 뱅크층(170)이 형성되도록 구성될 수도 있다. 이와 같이 일부 제거된 제2보호막(161)을 형성함에 있어서는, 예를 들면, 반투과부를 갖는 하프톤 마스크를 사용할 수 있다.

- [0176] 한편, 도 13 및 14의 경우에 있어, 도 12에 도시한 바와 같이 2중층 구조의 뱅크층(170)이 사용될 수 있다.

- [0177] 이와 같이 제2보호막(161)이 제거되어 요입된 형태로 형성된 경우에, 요입된 부분에 뱅크층(170)이 형성된 상태에서 기판 면의 단차가 전체적으로 완화될 수 있다. 즉, 뱅크층(170)은 어느 정도 두께를 갖게 되므로, 뱅크층

(170)에 의해 기판 면에 단차가 발생하게 된다. 이와 같은 단차에 의해, 이후에 기판 전면에 적층막을 형성하는 경우에 해당 적층막이 단차에 의해 연결이 끊어지는 문제가 발생할 수 있는데, 제2보호막(161)을 제거함으로써 뱅크층(170)의 단차에 기인한 문제를 개선할 수 있는 효과가 있다.

[0178] 특히, 2중층 구조의 뱅크층(170)을 사용하는 경우에 단차가 더욱 커지게 되므로, 제2보호막(161) 제거에 따른 효과는 2중층 구조의 뱅크층(170)을 사용하는 경우에 더욱 효과적일 수 있다.

[0179] 전술한 바와 같이, 본 발명의 실시예에 따른 유기발광다이오드 표시장치에서는, 화소영역의 경계를 따라 형성된 소수성의 뱅크층의 표면 일부에 이온차폐전극을 형성하며, 제1전극에 대한 플라즈마 처리 공정시 이온차폐전극에 양전하를 인가하게 된다. 이에 따라, 이온차폐전극은 플라즈마 처리 공정시 발생된 양이온 플라즈마에 대해 척력을 발생시켜, 양이온 플라즈마가 뱅크층 표면에 충돌되는 것을 방지하게 됨으로써, 소수성의 뱅크층이 친수화되는 것을 방지할 수 있는 효과가 발생하게 된다.

[0180] 더욱이, 뱅크층을 포함하는 적어도 하나의 절연막을 사이에 두고 이온차폐전극에 대향하는 대향전극을 하부에 형성하며, 유기발광다이오드 구동시 이온차폐전극과 대향전극 사이에 전압을 인가하여 유기발광다이오드 내에 순방향을 따라 전기장을 발생시키게 된다. 이에 따라, 유기발광다이오드의 적층막 사이의 에너지 배리어를 낮춤과 동시에 에너지 레벨에 테이퍼를 형성하게 된다. 이로 인해, 캐리어의 주입 및 수송 효율이 향상되는 효과가 발생하게 된다.

[0181] 전술한 본 발명의 실시예는 본 발명의 일예로서, 본 발명의 정신에 포함되는 범위 내에서 자유로운 변형이 가능하다. 따라서, 본 발명은, 첨부된 특허청구범위 및 이와 등가되는 범위 내에서의 본 발명의 변형을 포함한다.

### 부호의 설명

[0182] 100: 액정표시장치 110: 기판

122: 반도체층 130: 게이트 절연막

132: 게이트전극 140: 충간 절연막

140a: 제1콘택홀 140b: 제2콘택홀

152: 소스전극 154: 드레인전극

160: 제1보호막 161: 제2보호막

160a: 드레인 콘택홀 162: 제1전극

170: 뱅크층 171: 제1뱅크층

172: 제2뱅크층 180: 유기발광층

181: 제1유기막 183: 발광물질층

185: 제2유기막 192: 제2전극

EL1: 이온차폐전극 EL2: 대향전극

## 도면

## 도면1

## 도면2

## 도면3

## 도면4

## 도면5

## 도면6

## 도면7

## 도면8

## 도면9

## 도면10

## 도면11

도면12

도면13

도면14

|                |                                                                                   |         |            |

|----------------|-----------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 标题 : OLED显示装置及其制造方法                                                               |         |            |

| 公开(公告)号        | <a href="#">KR1020170015700A</a>                                                  | 公开(公告)日 | 2017-02-09 |

| 申请号            | KR1020150108133                                                                   | 申请日     | 2015-07-30 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                          |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                                         |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                                                         |         |            |

| [标]发明人         | PARK KYOUNG JIN<br>박경진<br>KANG BYUNG KWUN<br>강병권                                  |         |            |

| 发明人            | 박경진<br>강병권                                                                        |         |            |

| IPC分类号         | H01L51/52 H01L27/32 H01L51/56                                                     |         |            |

| CPC分类号         | H01L51/5203 H01L27/3246 H01L27/3225 H01L27/3274 H01L27/3248 H01L51/56 H01L2227/32 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                         |         |            |

### 摘要(译)

本发明具有提供一种方法，以改善在任务由用于有机发光二极管的第一电极的等离子体处理工序中的亲水化的疏水性堤层。为此，根据本发明，形成沿所述像素区域的边界形成的堤层的疏水部分的表面上的离子屏蔽电极，并且在第一电极的等离子体处理工序的正电荷被施加到离子屏蔽电极。因此，离子屏蔽电极产生针对在等离子体处理过程中产生的阳离子等离子体的排斥力，使得阳离子等离子体可从撞击堤层表面上，从而防止堤层的亲水疏水性可以防止由此影响它产生。此外，与之间的至少一个绝缘膜含有堤层，以形成面向离子CHAPE电极到下一个反电极，将电压施加在有机发光离子期间的发光二极管驱动器的屏蔽电极和所述有机发光二极管的对电极之间施加沿前向产生电场。结果，有机发光二极管的层压膜之间的能垒降低，并且在能级上形成锥形。结果，改善了载体的注入和输送效率。