(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2014년06월02일

(11) 등록번호 10-1401606

(24) 등록일자 2014년05월23일

(51) 국제특허분류(Int. Cl.)

G09G 3/30 (2006.01)

(21) 출원번호 10-2012-0050404

(22) 출원일자 2012년05월11일

심사청구일자 2012년05월11일

(65) 공개번호 10-2012-0127315

(43) 공개일자 2012년11월21일

(30) 우선권주장

201110124714.X 2011년05월13일 중국(CN)

(56) 선행기술조사문헌

US20090284511 A1\*

JP2005258427 A

JP2004302211 A

JP2003330418 A

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

보에 테크놀로지 그룹 컴퍼니 리미티드

중국 베이징 100016, 차오양 디스트릭트, 지우시

양치아오 로드 10호

(72) 발명자

우 종위엔

중국 베이징 100176 비디에이 시환중로 8호

두안 리예

중국 베이징 100176 비디에이 시환중로 8호

위엔 광카이

중국 베이징 100176 비디에이 시환중로 8호

(74) 대리인

리엔목특허법인

전체 청구항 수 : 총 12 항

심사관 : 양성지

(54) 발명의 명칭 화소 유닛 회로, 화소 어레이, 패널 및 패널 구동방법

**(57) 요약**

일종의 화소회로어레이는 프리차지회로, 보상회로, 유지회로, 구동회로, 제1 전원단자, 제2 전원단자, 제3 전원단자, 스캔 제어단, 제1 제어단 및 제2 제어단을 구비하는 화소 유닛 회로를 포함하며; 그 중, 프리차지회로의 입력단은 제1 전원단자와 연결되고, 제1 출력단은 유지회로의 입력단과 연결되며, 제2 출력단은 보상회로의 입력단 및 구동회로의 제어단과 연결되고, 제어단은 스캔 제어단과 연결되며; 보상회로의 출력단은 구동회로의 출력단 및 발광회로의 입력단과 연결되고, 제어단은 제2 제어단과 연결되며; 유지회로의 출력단은 구동회로의 입력단 및 제2 전원단자와 연결되고, 제어단은 제1 제어단과 연결된다.

**대 표 도** - 도6b

## 특허청구의 범위

### 청구항 1

스캔라인;

데이터라인; 및

상기 스캔라인과 상기 데이터라인이 교차하면서 한정하는 화소 유닛 회로를 포함하며, 각 화소 유닛 회로는, 발광을 위한 발광회로;

상기 발광회로의 구동을 위한 구동회로;

상기 구동회로가 정상적으로 동작하도록 하기 위한 프리차지회로;

상기 구동회로의 역치전압을 보상하기 위한 보상회로;

상기 구동회로의 제어단 및 입력단의 전압을 유지하기 위한 유지회로;

상기 프리차지 회로에 전압을 제공하기 위한 제1 전원단자;

상기 구동회로에 전압을 제공하기 위한 제2 전원단자;

상기 발광회로에 전압을 제공하기 위한 제3 전원단자;

상기 프리차지회로를 제어하여 작동하게 하거나 차단하기 위한 스캔 제어단;

상기 유지회로를 제어하여 작동하게 하거나 차단하기 위한 제1 제어단 및 상기 보상회로를 제어하여 작동하게 하거나 차단하기 위한 제2 제어단을 포함하며;

상기 프리차지회로의 입력단은 상기 제1 전원단자와 연결되고, 그 제1 출력단은 상기 유지회로의 입력단과 연결되며, 그 제2 출력단은 상기 보상회로의 입력단 및 상기 구동회로의 제어단과 연결되고, 그 제어단은 상기 스캔 제어단과 연결되며;

상기 보상회로의 출력단은 상기 구동회로의 출력단 및 상기 발광회로의 입력단과 연결되고, 그 제어단은 상기 제2 제어단과 연결되며;

상기 유지회로의 출력단은 상기 구동회로의 입력단 및 상기 제2 전원단자와 연결되고, 그 제어단은 상기 제1 제어단과 연결되는 것을 특징으로 하는 화소 회로 어레이.

### 청구항 2

제1 항에 있어서,

상기 프리차지회로는 제4 트랜지스터 및 제1 커패시터를 포함하고; 상기 보상회로는 제2 트랜지스터를 포함하며; 상기 유지회로는 제3 트랜지스터를 포함하고; 상기 구동회로는 제1 트랜지스터를 포함하며; 상기 발광회로는 유기 발광다이오드(OELD)를 포함하며;

상기 제1 트랜지스터의 게이트는 상기 제1 커패시터의 일단 및 상기 제2 트랜지스터의 소스와 연결되고;

상기 제1 트랜지스터의 소스는 상기 제3 트랜지스터의 드레인 및 상기 제2 전원단자와 연결되며;

상기 제1 트랜지스터의 드레인은 상기 제2 트랜지스터의 드레인 및 상기 OLED의 애노드와 연결되고;

상기 제2 트랜지스터의 게이트는 상기 제2 제어단과 연결되며;

상기 제3 트랜지스터의 소스는 상기 제1 커패시터의 타단 및 상기 제4 트랜지스터의 드레인과 연결되고, 게이트는 상기 제1 제어단과 연결되며;

상기 제4 트랜지스터의 게이트는 상기 스캔 제어단과 연결되고, 소스는 상기 제1 전원단자와 연결되는 것을 특징으로 하는 화소 회로 어레이.

**청구항 3**

제2 항에 있어서,

상기 제1 트랜지스터, 제2 트랜지스터, 제3 트랜지스터 및 제4 트랜지스터는 모두 박막트랜지스터(TFT)인 것을 특징으로 하는 화소 회로 어레이.

**청구항 4**

청구항 1의 화소 회로 어레이를 포함하는 OLED 패널.

**청구항 5**

청구항 4의 OLED 패널에 응용되는 OLED 패널의 구동방법으로서,

화소 유닛 회로 중의 프리차지회로는 제4 트랜지스터 및 제1 커패시터를 포함하고; 보상회로는 제2 트랜지스터를 포함하며; 유지회로는 제3 트랜지스터를 포함하고; 구동회로는 제1 트랜지스터를 포함하며; 발광회로는 유기 발광다이오드(OLED)를 포함하며; 상기 방법은

상기 스캔라인이 스캔 제어단을 통해 유효신호를 출력하여 상기 제4 트랜지스터를 온시키고, 상기 제1 제어단 및 상기 제2 제어단이 무효신호를 출력하여, 상기 제2 트랜지스터 및 상기 제3 트랜지스터를 컷오프시키는 단계;

제1 트랜지스터의 게이트에게 유효신호를 입력하여 상기 제1 트랜지스터를 온시키는 단계;

제2 전원단자가 출력하는 제1 레벨신호를 상기 제1 트랜지스터를 통해 상기 OLED의 애노드로 전송하는 단계;

를 포함하는 것을 특징으로 하는 OLED 패널 구동 방법.

**청구항 6**

제5 항에 있어서,

제2 전원단자가 출력한 제1 레벨신호를 상기 제1 트랜지스터를 통해 상기 OLED의 애노드로 전송하기 전에,

제1 전원단자 및 제2 전원단자가 모두 제1 레벨신호를 출력하고, 제3 전원단자가 제2 레벨신호를 출력하는 단계를 더 포함하는 것을 특징으로 하는 OLED 패널 구동 방법.

**청구항 7**

제6 항에 있어서,

상기 제2 제어단이 유효신호를 출력하여 상기 제2 트랜지스터를 온시키고, 상기 제1 트랜지스터의 드레인전압과 게이트전압이 같아지도록 하는 단계를 더 포함하는 것을 특징으로 하는 OLED 패널 구동 방법.

**청구항 8**

제7 항에 있어서,

상기 제2 트랜지스터가 온되기 전에,

상기 제1 전원단자의 출력전압을 현재 프레임의 데이터전압으로 변환하는 단계를 더 포함하는 것을 특징으로 하는 OLED 패널 구동 방법.

**청구항 9**

제7 항에 있어서,

상기 제1 트랜지스터의 드레인전압과 게이트전압은 모두 상기 제2 전원단자의 출력전압과 같은 것을 특징으로 하는 OLED 패널 구동 방법.

**청구항 10**

제8 항에 있어서,

상기 제2 전원단자가 유효신호를 출력하여 상기 제2 트랜지스터를 온시키고, 상기 제1 트랜지스터의 드레인전압이 게이트전압과 같아지도록 한 후,

제2 전원단자가 직류 참고전압을 출력하는 단계를 더 포함하는 것을 특징으로 하는 OLED 패널 구동 방법.

## 청구항 11

제6 항에 있어서,

상기 제1 트랜지스터의 게이트로 유효신호를 출력하여 상기 제1 트랜지스터를 온시키고, 상기 제1 제어단이 유효신호를 출력하여 상기 제3 트랜지스터를 온시키는 단계와;

상기 제2 제어단 및 상기 스캔 제어단이 무효신호를 출력하여 상기 제2 트랜지스터 및 상기 제4 트랜지스터를 컷오프시키고, 상기 제1 트랜지스터의 드레인을 통해 데이터전류를 상기 OLED로 전송하는 단계를 더 포함하는 것을 특징으로 하는 OLED 패널 구동 방법.

## 청구항 12

제11 항에 있어서,

상기 제1 트랜지스터의 게이트로 유효신호를 출력하여 상기 제1 트랜지스터를 온시키고, 상기 제1 제어단이 유효신호를 출력하여 상기 제3 트랜지스터를 온시키기 전에,

상기 제2 전원단자가 제2 레벨신호를 출력하고, 상기 제3 전원단자가 제1 레벨신호를 출력하는 단계를 더 포함하는 것을 특징으로 하는 OLED 패널 구동 방법.

## 명세서

### 기술 분야

[0001] 본 발명의 실시예는 일종의 화소 유닛 회로, 화소 어레이, 패널 및 패널 구동방법에 관한 것이다.

### 배경 기술

[0002] 일종의 전류형 발광소자로서의 유기 발광 다이오드(OLED)는 이미 고성능 디스플레이 장치에 갈수록 많이 응용되고 있다. 종래의 수동 매트릭스 유기 발광 디스플레이(Passive Matrix OLED)는 디스플레이 사이즈가 커짐에 따라 개별 화소의 구동시간이 더욱 짧아져야 하기 때문에 과도전류가 증가되어 소비전력이 늘어난다. 이와 동시에 고전류의 응용은 ITO(인듐 주석 산화물) 라인의 전압 강하가 지나치게 커지게 하고, 또한 OLED 동작전압을 과도하게 높여 효율을 떨어진다. 그러나 능동 매트릭스 유기 발광 디스플레이(Active Matrix OLED, AMOLED)는 스위칭 소자를 이용하여 순차주사를 통해 OLED 전류를 입력하므로, 이러한 문제를 매우 잘 해결할 수 있다.

[0003] AMOLED 화소회로는 작동 과정에서, 스위칭 소자로서의 TFT의 역치전압의 비균일성, OLED의 비균일성 또는 전압 강하(IR Drop, 즉 백패널 중 ARVDD 전원 공급 위치에 가까운 전압이 전원 공급 위치에서 비교적 먼 영역의 전압 보다 높은 현상) 등이 회로의 불안정을 초래하여 OLED 휙도가 균일하지 않게 됨으로써 전체 화소 회로 어레이에 영향을 미친다. 따라서 관련 기술은 OLED 구동회로가 화소 보상을 실행할 수 있도록 OLED 구동회로를 개선하였다.

[0004] AMOLED는 구동 유형에 따라 디지털 방식, 전류 방식과 전압 방식의 세 종류로 구분할 수 있다. 전압 방식의 구동방법은 종래의 AMLCD 구동방법과 유사하며, 구동 접적칩을 통해 화소에 대하여 그레이 스케일을 나타내는 하나의 전압신호를 제공한다. 상기 전압신호는 화소 회로 내부에서 전류신호로 변환되어 OLED를 구동시킨다. 이러한 방법은 구동속도가 빠르고 실현이 간단한 장점을 지녀 대형 사이즈의 패널을 구동시키기에 적합하며 업계에서 광범위하게 채택되는 방식이다.

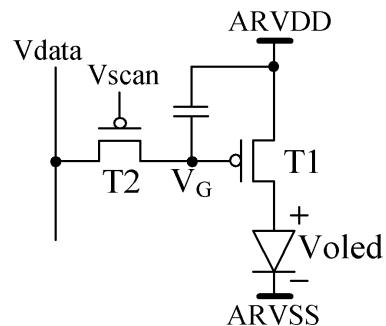

[0005] 도 1은 관련 기술 중 OLED를 구동시키기 위한 첫 번째 종류의 전압식 구동회로이다. 각 화소에 있어서 T2가 데이터라인 상의 전압신호를 T1의 게이트로 전송하면, T1은 수신된 데이터 전압신호를 상용하는 데이터 전류신호로 변환하여 OLED에게 제공한다. 정상 작동 시, T1은 포화상태에 놓이며, 그 전류는 다음과 같이 나타낼 수 있다:

$$I_{OLED} = \frac{1}{2} \mu_p \cdot Cox \cdot \frac{W}{L} \cdot (Vdata - ARVDD - Vthp)^2 \quad (1)$$

[0006]

[0007] 그 중  $\mu_p$ 는 전하 캐리어 유동도이고,  $C_{ox}$ 는 게이트 산화층 커패시터이며, W/L은 TFT 채널의 폭길이비이고,  $Vdata$ 는 데이터 전압이며,  $ARVDD$ 는 AMOLED 백패널 전원으로서 모든 화소 유닛 회로에 의해 공유되며,  $Vthp$ 는 T1의 역치전압이다. 상기 식으로부터 알 수 있듯이, 만약 각기 다른 화소 유닛 회로 사이의 구동 TFT(즉 도 1 중의 T1)의  $Vthp$ 가 다르면, 설사 전송되는 데이터 전압이 같더라도, OLED에 입력되는 전류에 차이가 존재하게 된다. 이와 동시에 만약 각 화소에 실제로 인가되는  $ARVDD$ 가 다를 경우, OLED에 전송되는 전류 역시 차이가 존재할 수 있다.

[0008]

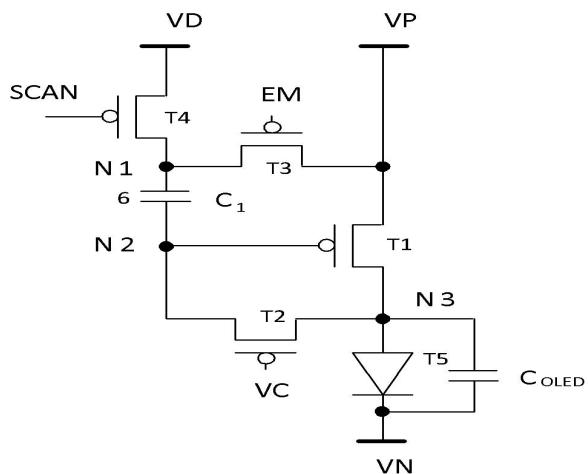

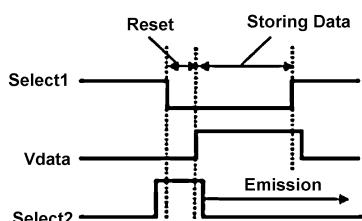

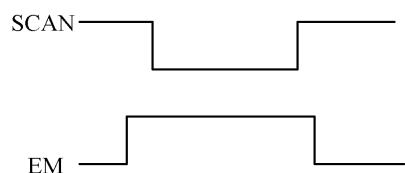

도 2a는 관련 기술 중 OLED 구동을 위한 두 번째 종류의 전압 방식의 구동회로이고, 도 2b는 상기 전압 방식의 구동회로의 시퀀스 제어도이다. 이 회로에서, T2 게이트에 인가되는 전압은  $Vdata + Vthp$ 로서, 전원전압(VDD)과 무관하며, 따라서 상기 회로는 IR Drop은 보상할 수 있으나 TFT의 비균일성은 보상할 수 없다.

[0009]

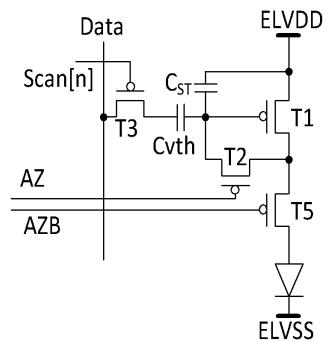

도 3a는 관련 기술 중 OLED 구동을 위한 세 번째 종류의 전압 방식의 구동회로도이고, 도 3b는 상기 전압 방식의 구동회로의 시퀀스 제어도이다. 이러한 회로구조는 실제로 T1 튜브 게이트에 인가되는 전압이 T1의 역치전압( $Vth$ ) 및 전원전압(ELVDD)과 모두 무관하여 구동튜브(T1)의 역치전압 비균일성과 IR Drop을 보상할 수 있다. 그러나 이러한 회로는 4개의 TFT와 2개의 커패시터가 필요하며, 또한 실제로 T1 튜브 게이트에 인가되는 전압은 두 커패시터의 비율과 관련이 있는데, 이 회로 중 두 개의 커패시터의 크기는 서로 차이가 많지 않고, 입력 전압의 동적범위가 비교적 작다.

[0010]

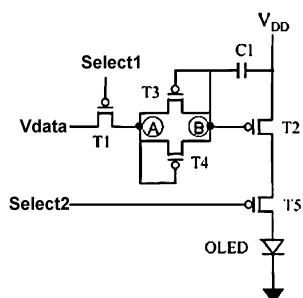

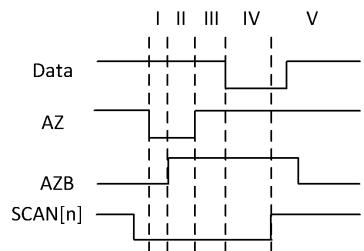

도 4a는 관련 기술 중 OLED 구동을 위한 네 번째 종류의 전압식 구동회로도이고, 도 4b는 상기 전압식 구동회로의 시퀀스 제어도이다. 이러한 회로 중 OLED에 입력되는 전류는 일정하여 OLED의 비균일성을 보상할 수는 있으나, T1 튜브에 인가되는 게이트전압이 T1의 역치전압( $Vth$ ) 및 전원전압(ELVDD)과 모두 관련이 있어, 구동튜브(T1)의 역치전압의 비균일성과 IR Drop을 보상할 수 없다.

## 발명의 내용

### 해결하려는 과제

[0011]

본 발명이 해결하고자 하는 과제는, 상기 종래 기술의 문제점을 해결하기 위한 것으로서, TFT의 역치전압의 비균일성, OLED 비균일성 및 IR Drop을 보상할 수 있으며, 개구율을 효과적으로 높일 수 있는 화소 유닛 회로, 화소 어레이, 패널 및 패널 구동방법을 제공하는 데 있다.

### 과제의 해결 수단

[0012]

본 발명의 일 실시예에서는 스캔라인과; 데이터라인과; 상기 스캔라인 및 상기 데이터라인이 교차하면서 한정하는 화소 유닛 회로를 포함하는 일종의 화소 회로 어레이를 제공한다. 각 화소 유닛 회로는 발광을 위한 발광회로, 상기 발광회로를 구동하기 위한 구동회로, 상기 구동회로가 정상적으로 동작하도록 하기 위한 프리차지 회로, 상기 구동회로의 역치전압을 보상하기 위한 보상회로, 상기 구동회로의 제어단 및 입력단의 전압을 유지하기 위한 유지회로, 상기 프리차지 회로에게 전압을 제공하기 위한 제1 전원단자, 상기 구동회로에게 전압을 제공하기 위한 제2 전원단자, 상기 발광회로에게 전압을 제공하기 위한 제3 전원단자, 상기 프리차지 회로를 제어하여 동작하게 하거나 차단하기 위한 스캔 제어단, 상기 유지회로를 제어하여 동작하게 하거나 차단하기 위한 제1 제어단 및 상기 보상회로를 제어하여 동작하게 하거나 차단하기 위한 제2 제어단을 포함하며; 그 중 상기 프리차지 회로의 입력단은 상기 제1 전원단자와 연결되고, 그 제 1 출력단은 상기 유지회로의 입력단과 연결되며, 제2 출력단은 상기 보상회로의 입력단 및 상기 구동회로의 제어단과 연결되고, 그 제어단은 상기 스캔 제어단과 연결되며; 상기 보상회로의 출력단은 상기 구동회로의 출력단 및 상기 발광회로의 입력단과 연결되고, 그 제어단은 상기 제2 제어단과 연결되며; 상기 유지회로의 출력단은 상기 구동회로의 입력단 및 상기 제2 전원단자와 연결되고, 그 제어단은 상기 제1 제어단과 연결된다.

[0013]

본 발명의 다른 일 실시예에서 제공하는 일종의 OLED 패널은 상기한 화소 회로 어레이를 포함한다.

[0014]

본 발명의 또 다른 일 실시예에서 제공하는 일종의 OLED 패널 구동방법은 상기한 OLED 패널에 응용되며, 화소 유닛 회로 중의 프리차지 회로는 제4 트랜지스터 및 제1 커패시터를 포함하고; 보상회로는 제2 트랜지스터를 포함하며; 유지회로는 제3 트랜지스터를 포함하고; 구동회로는 제1 트랜지스터를 포함하며; 발광회로는 유기 발광

다이오드 OLED를 포함한다. 상기 방법은 상기 스캔라인이 스캔 제어단을 통해 유효신호를 출력하여 상기 제4 트랜지스터를 온시키고, 상기 제1 제어단 및 상기 제2 제어단이 무효신호를 출력하여, 상기 제2 트랜지스터 및 상기 제3 트랜지스터를 컷오프시키는 단계와; 제1 트랜지스터의 게이트에 유효신호를 입력함으로써 상기 제1 트랜지스터를 온시키는 단계와; 제2 전원단자가 출력한 제1 레벨신호를 상기 제1 트랜지스터를 통해 상기 OLED의 애노드로 전송하는 단계를 포함한다.

### 발명의 효과

[0015] 본 발명에 따른 화소 유닛 회로를 채택할 경우, OLED에 입력되는 전류가 TFT의 역치전압 및 전원전압과 모두 무관하게 되므로, TFT의 역치전압의 비균일성, OLED 비균일성 및 IR Drop을 보상할 수 있다. 또한 본 실시예에서 사용되는 소자가 비교적 적기 때문에 개구율을 효과적으로 높일 수 있다.

### 도면의 간단한 설명

[0016] 도 1은 관련기술 중 OLED를 구동시키기 위한 첫 번째 종류의 전압식 구동회로이다.

도 2a는 관련 기술 중 OLED 구동을 위한 두 번째 종류의 전압식 구동회로이다.

도 2b는 관련 기술 중 OLED 구동을 위한 두 번째 종류의 전압식 구동회로의 시퀀스 제어도이다.

도 3a는 관련 기술 중 OLED 구동을 위한 세 번째 종류의 전압식 구동회로도이다.

도 3b는 관련 기술 중 OLED 구동을 위한 세 번째 종류의 전압식 구동회로의 시퀀스 제어도이다.

도 4a는 관련 기술 중 OLED 구동을 위한 네 번째 종류의 전압식 구동회로도이다.

도 4b는 관련 기술 중 OLED 구동을 위한 네 번째 종류의 전압식 구동회로의 시퀀스 제어도이다.

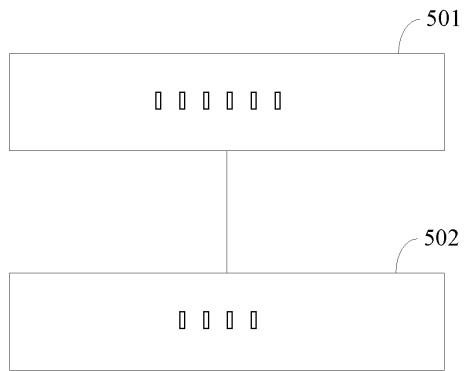

도 5는 본 발명의 실시예 중 OLED 패널의 주요 구조도이다.

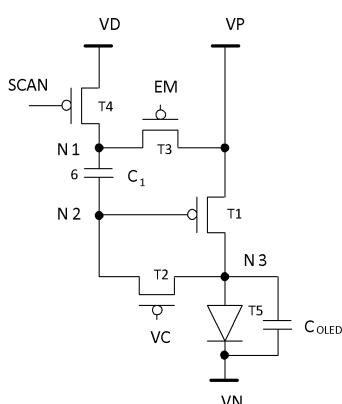

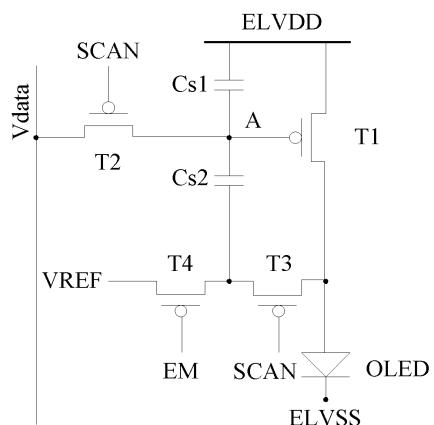

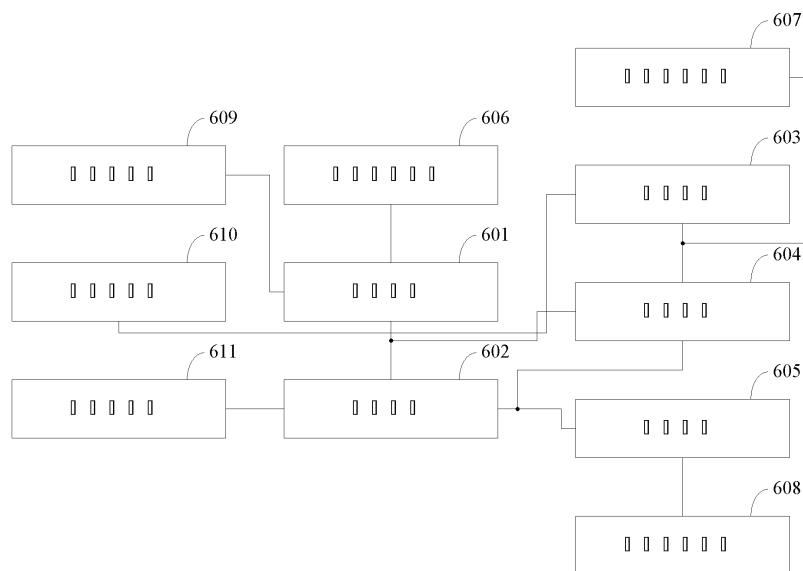

도 6a는 본 발명의 실시예 중 화소 유닛 회로의 주요 구조도이다.

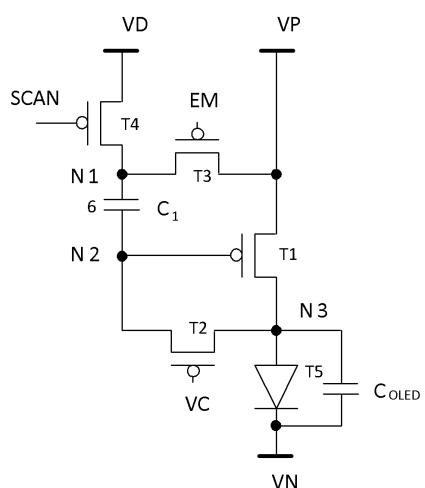

도 6b는 본 발명의 실시예 중 화소 유닛 회로의 상세 구조도이다.

### 발명을 실시하기 위한 구체적인 내용

[0017] 본 발명의 실시예 중 OLED 패널은 제1 전원단자, 제2 전원단자, 제3 전원단자 및 화소 회로 어레이를 포함한다. 상기 화소 회로 어레이에는 다수의 화소 유닛 회로로 구성된다. 상기 화소 회로 어레이에는 스캔라인과 데이터라인을 더 포함한다. 상기 화소 유닛 회로는 매 회로마다 제1 트랜지스터, 제2 트랜지스터, 제3 트랜지스터, 제4 트랜지스터, 제1 커패시터 및 유기발광다이오드(OLED)를 포함한다. 상기 제1 트랜지스터의 게이트는 상기 제1 커패시터의 일단 및 상기 제2 트랜지스터의 소스와 연결된다. 상기 제1 트랜지스터의 소스는 상기 제3 트랜지스터의 드레인 및 상기 제2 전원단자와 연결된다. 상기 제1 트랜지스터의 드레인은 상기 제2 트랜지스터의 드레인 및 상기 OLED의 애노드와 연결된다. 상기 제3 트랜지스터의 소스는 상기 제1 커패시터의 타단 및 상기 제4 트랜지스터의 드레인과 연결된다. 상기 제4 트랜지스터의 게이트는 상기 스캔라인과 연결된다. 상기 제4 트랜지스터의 소스는 상기 제1 커패시터의 전원단자와 연결된다.

[0018] 본 발명의 실시예에서 제공하는 화소 유닛 회로를 채택할 경우, OLED에 입력되는 전류가 TFT의 역치전압 및 전원전압과 모두 무관하므로, TFT의 역치전압의 비균일성, OLED 비균일성 및 IR Drop을 보상할 수 있다. 또한 본 실시예에서 사용되는 소자가 비교적 적기 때문에 개구율을 효과적으로 높일 수 있다.

[0019] 도 5를 참조하면, 본 발명의 실시예 중의 패널은 화소 회로 어레이(501)를 포함한다. 상기 OLED 패널은 화소 회로 어레이(501)에 제어신호를 제공하기 위한 제어 유닛(502)을 더 포함한다.

[0020] 화소 회로 어레이(501)는 스캔라인, 데이터라인과 화소 유닛 회로를 포함하며, 화소 회로 어레이(501)는 스캔라인과 데이터라인이 교차되면서 한정하는 화소 유닛 회로로 구성된다.

[0021] 도 6a를 참조하면, 본 발명의 실시예 중 화소 유닛 회로는 발광을 위한 발광회로(605), 발광회로(605)를 구동하기 위한 구동회로(604), 상기 구동회로(604)가 정상적으로 동작하도록 하기 위한 프리차지회로(601), 구동회로(604)의 역치전압을 보상하기 위한 보상회로(602), 상기 구동회로(604)의 제어단 및 입력단의 전압을 유지하기 위한 유지회로(603), 프리차지회로(601)에 전압을 제공하기 위한 제1 전원단자(606), 구동회로(604)에 전압을 제공하기 위한 제2 전원단자(607), 발광회로(605)에 전압을 제공하기 위한 제3 전원단자(608), 프리차지회로

(601)를 제어하여 동작하게 하거나 차단하기 위한 스캔 제어단(609), 유지회로(603)를 제어하여 동작하게 하거나 차단하기 위한 제1 제어단(610) 및 보상회로(602)를 제어하여 동작하게 하거나 차단하기 위한 제2 제어단(611)을 포함한다. 프리차지회로(601)의 입력단은 제1 전원단자(606)와 연결되고, 프리차지회로(601)의 제1 출력단은 유지회로(602)의 입력단과 연결되며, 프리차지회로(601)의 제2 출력단은 보상회로(602)의 입력단 및 구동회로(604)의 제어단과 연결되고, 프리차지회로(601)의 제어단은 스캔 제어단(609)과 연결되며, 보상회로(602)의 출력단은 구동회로(604)의 출력단 및 발광회로(605)의 입력단과 연결되고, 보상회로(602)의 제어단은 제2 제어단(611)과 연결되며, 유지회로(603)의 출력단은 구동회로(604)의 입력단 및 제2 전원단자(607)와 연결되고, 유지회로(603)의 제어단은 제1 제어단(610)과 연결되며, 발광회로(605)의 출력단은 제3 전원단자(608)와 연결된다. 제1 제어단(601)과 제2 제어단(611)은 모두 제어유닛(502)에 연결되며, 제어유닛(502)에 의해 제1 제어단(601)과 제2 제어단(611)을 통해 각기 다른 제어신호를 출력한다. 스캔 제어단(609)은 화소 회로 어레이 중의 스캔라인과 연결되며, 스캔라인은 스캔라인 제어단(609)을 통해 프리차지 회로(601)에 제어신호를 제공한다. 제1 전원단자(606)는 화소 회로 어레이(501) 중의 데이터라인과 연결된다. 제2 전원단자(607) 및 제3 전원단자(608)는 각각 다른 전원전압단에 연결된다.

[0022] 제1 전원단자(606), 제2 전원단자(607) 및 제3 전원단자(608)는 각각 다른 전원전압단과 연결되어, 화소 회로 어레이(601)에 전원전압을 제공한다.

[0023] 도 6b를 참조하면, 프리차지회로(601)는 제4 트랜지스터(이하 T4로 약칭) 및 제1 커패시터(이하 C1으로 약칭)를 포함한다. 프리차지회로(601)의 제1 출력단은 도 6b 중의 N1단이며, 제2 출력단은 도 6b 중의 N2단이다. 보상회로(602)는 제2 트랜지스터(이하 T2로 약칭)를 포함하며; 유지회로(603)는 제3 트랜지스터(이하 T3로 약칭)를 포함하고; 구동회로(604)는 제1 트랜지스터(이하 T1으로 약칭)를 포함하며; 발광회로(605)는 OLED를 포함한다. 프리차지회로(601)의 입력단은 T4의 소스단을 지칭하고, 출력단은 T4의 드레인단을 지칭하며, 보상회로(602)의 입력단은 T2의 소스단을 지칭하고, 출력단은 T2의 드레인단을 지칭하며, 유지회로(603)의 입력단은 T3의 소스단을 지칭하고, 출력단은 T3의 드레인단을 지칭하며, 구동회로(604)의 입력단은 T1의 소스단을 지칭하고, 출력단은 T1의 드레인단을 지칭하며, 발광회로(605)의 입력단은 발광다이오드(T5)의 애노드단을 지칭한다. T4가 온되면, 즉 프리차지회로(601)가 동작하고, T4가 컷오프되면 프리차지회로(601)가 차단되며; T3가 온되면 유지회로(603)가 동작하고, T3가 컷오프되면 유지회로(603)가 차단되며; T2가 온되면 보상회로(602)가 동작하고, T2가 컷오프되면 보상회로(602)가 차단된다.

[0024] T1의 게이트는 C1의 일단 및 T2의 소스와 연결되고; T1의 소스는 상기 T3의 드레인 및 제2 전원단자(607)(제2 전원단자(607)의 출력단은 즉 도 6b 중의 VP단임)와 연결되며; T1의 드레인은 T2의 드레인 및 OLED의 애노드와 연결되고; T3의 소스는 C1의 타단 및 T4의 드레인과 연결되고, T3의 게이트는 제1 제어단(610)과 연결되며; T4의 게이트는 스캔제어단(609)과 연결되고; T4의 소스는 제1 전원단자(606)(제1 전원단자(606)의 출력단은 즉 도 6b 중의 VD단임)에 연결된다. T2의 게이트는 제2 제어단(611)(즉 도 6B 중의 VC단)에 연결되어, 제2 제어단(611)이 T2에게 제2 제어신호를 제공하고, T3의 게이트는 제1 제어단(610)(즉 도 6B중의 EM단)에 연결되어, 제1 제어단(610)이 T3에게 제1 제어신호를 제공한다. 그 중, OLED는 하나의 발광다이오드(T5)와 하나의 커패시터( $C_{OLED}$ )의 병렬과 등가적이며, OLED의 애노드는 즉 발광다이오드(T5)의 애노드로서, 즉 도 6b 중의 N3점, 즉 발광회로(608)의 입력단이고, 발광회로(608)의 출력단은 즉 발광다이오드(T5)의 캐소드단이다. 발광다이오드(T5)의 캐소드는 제3 전원단자(608)와 연결된다. 상기 제1 제어신호 및 제2 제어신호는 모두 OLED 패널 상의 제어유닛(502)에 의해 제공되며, 제어유닛(502)은 제1 제어신호 및 제2 제어신호를 제어하기 위한 것으로서, 즉 제어유닛(502)은 각각 제2 제어단(611)과 제1 제어단(610)을 통해 T2와 T3의 게이트전압을 제어한다.

[0025] 본 발명의 실시예 중 제1 트랜지스터, 제2 트랜지스터, 제3 트랜지스터 및 제4 트랜지스터는 모두 TFT일 수 있으며, 본 발명의 실시예에서는 모든 TFT는 P형 TFT를 예로 들었다. 본 분야의 기술자라면 본 발명의 실시예에 대하여 변형을 실시할 수 있다. 예를 들어 본 발명의 실시예 중 TFT는 N형 TFT를 사용할 수 있으며, 따라서 회로구조와 제어신호의 시퀀스 역시 이에 상응하도록 변경해야 하며, 그 작동원리 역시 P형 TFT로 구성된 화소 회로와 유사하므로, 본 분야의 기술자라면 본 발명의 실시예의 교시에 따라 어떻게 N형 TFT를 사용하여 본 발명의 기타 실시예를 구현할 수 있는지 자연적으로 알 수 있을 것이다.

[0026] 본 발명의 실시예 중 OLED의 구동에 대하여 초기화단계, 보상단계 및 유지단계의 3 단계로 구분할 수 있다.

[0027] < 초기화 단계 >

[0028] 제1 전원단자(606)(VD) 및 제2 전원단자(607)(VP)는 로우 전원레벨(ARVSS)을 출력하고, 제3 전원단자(608)(VN)는 하이 전원레벨(ARVDD)을 출력한다. OLED는 전기학 성능 상 하나의 발광다이오드(T5)와 제2 커패시터(이하

$C_{OLED}$ 로 약칭)의 병렬과 등가적이기 때문에, OLED는 역방향 컷오프된다. 도 6b중 N1점의 이전 단계에서 저장된 전압이 ARVDD이고, N2점의 이전 단계에서 저장된 전압이  $ARVDD - V_{DATA}(n-1) + VREF + Vthp$ 으로, C1의 전압 강하는  $-V_{DATA}(n-1) + VREF + Vthp$ 임을 알 수 있다. 그 중,  $V_{DATA}(n-1)$ 은 이전 프레임에서 입력된 데이터 전압이고, VREF는 직류 참고전압이며,  $Vthp$ 는 T1의 역치전압( $Vthp < 0$ )이다. 이때 스캔라인은 로우 전원레벨(VGL)을 출력하여 EM과 VC가 하이 전원레벨(VGH)이 되도록 제어한다. T1, T4를 온시키고, T2, T3를 오프시켜, T4를 거쳐 로우 전원레벨(ARVSS)을 N1점에 전송하면, C1의 부트스트랩 효과에 의해, N2점의 전압이  $ARVSS - V_{DATA}(n-1) + VREF + Vthp$ 로 변환되며, 즉 N1점의 전압에서 C1의 전압 강하를 뺀 것이다. 본 발명의 실시예는 합리적으로 VREF를 선택하여,  $-V_{DATA}(n-1) + VREF < 0$ 이 되도록 하면, 즉 N2점의 전압이 로우 레벨로 변환되어, T1은 온되고, N3점의 전압 역시 ARVSS가 된다.

[0029] 그 다음, VD단의 출력전압은 ARVSS로부터 현재 프레임의 데이터전압  $V_{DATA}(n)$ 으로 변환되고, VP는 로우 전원레벨(ARVSS)을 유지하며, VN은 하이 전원레벨(ARVDD)을 유지한다. 이때 N2점의 전압은  $V_{DATA}(n) - V_{DATA}(n-1) + VREF + Vthp$ 로 변환되는데, 즉 N1점 전압에서 C1의 전압 강하를 뺀 것이다. N3점의 전압은 ARVSS를 유지한다. VC가 로우 전원레벨(VGL)이 되도록 제어하여, T2를 온시키고, C1과 OLED 등가회로 중의 커패시터( $C_{OLED}$ )를 직렬 연결시키면, N2, N3점의 최종전압을 전하보존의 원리에 따라 얻을 수 있다(그 중 T2가 온된 후에는, N2점을  $V_{INIT}$ 점이라고도 칭한다)

$$[-V_{DATA}(n-1) + VREF + Vthp] \cdot C_6 + (ARVSS - ARVDD) \cdot C_{OLED} = V_{INIT} \cdot (C_6 + C_{OLED}) \quad (1)$$

[0030] 따라서,

$$V_{INIT} = \frac{[-V_{DATA}(n-1) + VREF + Vthp] \cdot C_6 + (ARVSS - ARVDD) \cdot C_{OLED}}{C_6 + C_{OLED}} \quad (2)$$

[0031] 이며,

[0032] ARVSS-ARVDD<0이고, 또한 통상적으로  $C_{OLED} \gg C_6$ 이므로, 즉

$$V_{INIT} \approx ARVSS - ARVDD \quad (3)$$

[0033] 이다.

[0034] N2점과 N3점의 전압이 같아  $V_{INIT}$ 이다. 즉 본 단계에서 N2와 N3점 전압의 프리차지를 완료한다.

[0035] < 보상단계 >

[0036] VD단이 현재 프레임의 데이터전압( $V_{DATA}(n)$ )을 출력하고, VP단이 직류 참고전압(VREF)을 출력하며, VN단이 하이 전원레벨신호(ARVDD)를 출력하면, OLED는 역방향 컷오프를 유지한다. 스캔라인(SCAN단)과 VC가 로우 전원레벨(VGL)이 되도록, EM은 하이 전원레벨(VGH)이 되도록 제어한다. 이 단계에서, VREF>0이고, 또한 N2, N3점의 시작 전압이  $V_{INIT} < 0$ 이기 때문에, 이때 T1은 통전되어 하나의 디오드에 해당하며, 전류가 VREF단으로부터 N3점으로 흐르면서 N3점의 전압이  $VREF + Vthp$ (즉 VREF에 T1의 역치 전압을 더한 것)에 이를 때까지 N3에 충전을 실행한 후, T1을 컷오프시킨다. 보상단계가 종료될 때, C1 양단에 저장된 전하는  $(VREF + Vthp - V_{DATA}(n)) \cdot C_6$ 이며, T4가 리니어 영역에서 작동하기 때문에 역치전압의 소모가 없다.

[0037] < 유지단계 >

[0038] VP단이 하이 전원레벨(ARVDD)을 출력하고, VN단이 로우 전원레벨(ARVSS)을 출력하면, OLED가 순방향으로 온된다. SCAN, VC는 하이 전원레벨(VGH)이 되도록, EM은 로우 전원레벨(VGL)이 되도록 제어하고, T1, T3를 온시키고, T2, T4는 컷오프시키며, C1은 T1의 게이트 소스 사이에 연결하여, T1의  $V_{GS}$ (즉 게이스 소스 전압)를 유지시키고, 저장된 전하가 불변하도록 유지시킨다. N1점을 T3을 통해 ARVDD에 연결하면, C1의 부트스트랩 효과에 의해 N2점의 전압이  $ARVDD - V_{DATA}(n) + VREF + Vthp$ (즉 N1점의 전압에서 C1의 전압 강하를 뺀 것)로 변환된다. T1의  $V_{GS}$ 는  $VREF + Vthp - V_{DATA}(n)$ (즉 ARVDD에서 N2점 전압을 뺀 것)를 유지한다. 이때 T1에 흐르는 전류는

[0042]  $I_{OLED} = \frac{1}{2} \cdot \mu_p \cdot Cox \cdot \frac{W}{L} \cdot [VREF + Vthp - V_{DATA}(n) - Vthp]^2 \quad (4)$

[0043] 이며, 따라서

[0044]  $I_{OLED} = \frac{1}{2} \cdot \mu_p \cdot Cox \cdot \frac{W}{L} \cdot [VREF - V_{DATA}(n)]^2 \quad (5)$

[0045] 이다.

[0046] 공식(5)로부터 알 수 있듯이, T1을 흐르는 전류는 T1의 역치전압 및 전원전압(ARVDD)과 모두 무관하며, 따라서 이상의 세 단계를 통해 기본적으로 TFT의 역치전압의 비균일성 및 IR Drop에 대한 보상을 실현하게 된다. 입력된 직류 참고전압(VREF) 및 데이터전압( $V_{DATA}(n)$ )이 일정하기만 하면, T1을 흐르는 전류가 일정하게 되어 OLED의 비균일성을 효과적으로 보상하게 된다.

[0047] 이하 플로우를 통하여 본 발명의 실시예 중의 OLED 패널 구동방법을 상세히 소개하며, 이는 다음 단계를 포함한다.

[0048] 단계 701: 스캔 제어단(609)이 유효신호를 출력하여 상기 제4 트랜지스터를 온시키고, 상기 제1 제어단(610) 및 상기 제2 제어단(611)이 무효신호를 출력하여, 상기 제2 트랜지스터 및 상기 제3 트랜지스터를 컷오프시키는 단계. 본 발명의 실시예는 도 6b와 결합하여 설명하겠다.

[0049] 단계 702: 제1 트랜지스터의 게이트에게 유효신호를 입력하여, 상기 제1 트랜지스터를 온시키는 단계.

[0050] 단계 703: 제2 전원단자(607)가 출력한 제1 레벨신호를 상기 제1 트랜지스터를 통해 상기 OLED의 애노드로 전송하는 단계.

[0051] 제1 전원단자(606) 및 제2 전원단자(607)는 모두 제1 레벨신호를 출력하고, 스캔라인은 스캔 제어단(609)을 통해 유효신호를 출력하며, 제3 전원단자(608)는 제2 레벨신호를 출력한다. 그 중 본 발명의 실시예에서 제1 레벨신호는 로우 전원레벨신호(ARVSS)일 수 있고, 제2 레벨신호는 하이 전원레벨신호(ARVDD)일 수 있으며, 본 발명의 실시예에서 유효신호는 로우 레벨신호일 수 있다. 이와 동시에 제1 제어신호 및 제2 제어신호는 모두 무효신호이다. 화소 유닛 회로 중 OLED의 애노드는 즉 도 6b 중의 N3점이다.

[0052] 그 다음, 제1 전원단자(606)의 출력전압을 현재 프레임의 데이터전압으로 변환하고, 제어유닛(502)이 제2 제어단(611)을 통해 유효신호를 출력하여 제2 트랜지스터를 온시키고, 또한 제1 트랜지스터의 드레인전압을 게이트전압과 같아지게 하면, 모두 제2 전원단자(607)의 출력전압과 같아지게 된다. 본 발명의 실시예에서 유효신호는 로우 레벨신호일 수 있다. 제2 제어단(611)을 제2 트랜지스터의 게이트와 연결하고, 제어유닛(502)이 제2 제어단(611)을 통해 제2 트랜지스터의 게이트에 유효신호를 출력하면, 즉 제2 트랜지스터가 온된다. 제2 전원단자(607)는 직류 참고전압을 출력한다.

[0053] 제2 전원단자(607)는 제2 레벨신호를 출력하고, 제3 전원단자(608)는 제1 레벨신호를 출력한다. 제1 트랜지스터의 게이트로 유효신호를 출력하여 제1 트랜지스터를 온시키고, 제1 제어단(610)은 유효신호를 출력하여 제3 트랜지스터를 온시킨다. 제2 제어단(611) 및 스캔제어단(609)은 무효신호를 출력하여 제2 트랜지스터 및 제4 트랜지스터를 컷오프시키며, 제1 트랜지스터의 드레인을 통하여 데이터 전류를 OLED로 전송한다.

[0054] 본 발명의 실시예 중 OLED 패널은 제1 전원단자(606), 제2 전원단자(607), 제3 전원단자(608) 및 화소 회로 어레이(501)를 포함한다. 상기 화소 회로 어레이(501)는 화소 유닛 회로로 구성되며; 상기 화소 회로 어레이(501)는 스캔라인을 더 포함한다. 상기 화소 유닛 회로는 제1 트랜지스터, 제2 트랜지스터, 제3 트랜지스터, 제4 트랜지스터, 제1 커패시터 및 OLED를 포함한다. 상기 제1 트랜지스터의 게이트는 상기 제1 커패시터의 일단 및 상기 제2 트랜지스터의 소스와 연결되고; 상기 제1 트랜지스터의 소스는 상기 제3 트랜지스터의 드레인 및 상기 제2 전원단자와 연결되며; 상기 제1 트랜지스터의 드레인은 상기 제2 트랜지스터의 드레인 및 상기 OLED의 애노드와 연결되고; 상기 제3 트랜지스터의 소스는 상기 제1 커패시터의 타단 및 상기 제4 트랜지스터의 드레인과 연결되며; 상기 제4 트랜지스터의 게이트는 상기 스캔제어단과 연결되고; 상기 제4 트랜지스터의 소스는 상기 제1 전원단자(606)와 연결된다.

[0055] 본 발명의 실시예에서 제공하는 화소 유닛 회로를 채택할 경우, 입력된 직류 참고전압과 데이터전압의 신호가 불변하기만 하다면 OLED에 전송된 전류가 일정함을 유지하기 때문에, OLED의 비균일성을 보상할 수 있다. 또한 OLED에 전송된 전류는 TFT의 역치전압 및 OLED 패널의 전원전압과 모두 무관하기 때문에, TFT의 역치전압의 비

균일성 및 IR Drop을 보상할 수 있으며, 제어방법이 간단하고 실현이 용이하다. 본 발명의 실시예 중의 화소 유닛 회로는 구조가 간단하고 사용하는 부품 소자가 비교적 적어 개구율을 효과적으로 향상시킬 수 있다.

[0056]

물론, 본 분야의 통상의 기술자라면 본 발명의 실시예에 대하여 각종 변동과 변형을 실시하되 본 발명의 정신과 범위를 벗어나지 않도록 하여야 한다. 이와 같이, 만약 본 발명의 이러한 보정과 변형이 본 발명의 청구항 및 그와 동등한 기술의 범위에 속하는 경우, 본 발명은 또한 이러한 변동과 변형을 포함할 수 있다.

## 도면

### 도면1

### 도면2a

### 도면2b

도면3a

도면3b

도면4a

도면4b

## 도면5

## 도면6a

## 도면6b

|                |                                                            |         |            |

|----------------|------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 标题 : 像素单元电路 , 僧素阵列 , 面板和面板驱动方法                             |         |            |

| 公开(公告)号        | <a href="#">KR101401606B1</a>                              | 公开(公告)日 | 2014-06-02 |

| 申请号            | KR1020120050404                                            | 申请日     | 2012-05-11 |

| [标]申请(专利权)人(译) | 京东方科技股份有限公司                                                |         |            |

| 申请(专利权)人(译)    | 博科技集团股份有限公司                                                |         |            |

| 当前申请(专利权)人(译)  | 博科技集团股份有限公司                                                |         |            |

| [标]发明人         | WU ZHONGYUAN<br>우종위엔<br>DUAN LIYE<br>두안리예<br>YUAN GUANGCAI |         |            |

| 发明人            | 우종위엔<br>두안리예<br>위엔광카이                                      |         |            |

| IPC分类号         | G09G3/30                                                   |         |            |

| CPC分类号         | G09G3/3233 G09G2300/0866 G09G2300/0842 G09G2320/045        |         |            |

| 优先权            | 201110124714.X 2011-05-13 CN                               |         |            |

| 其他公开文献         | KR1020120127315A                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                  |         |            |

### 摘要(译)

所公开的技术涉及像素单元电路，像素阵列，显示面板和显示面板驱动方法。像素电路阵列包括像素单元电路，每个像素单元电路包括预充电电路，补偿电路，保持电路，驱动电路，发光电路，第一电源端子，第二电源端子，第三电源端子，扫描控制端子，第一控制端子和第二控制端子。利用像素单元电路，只要输入的直流参考电压和数据电压信号不变，输送到OLED的电流保持恒定，因此可以补偿OLED的均匀性。