(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2015-0124659

(43) 공개일자 2015년11월06일

(51) 국제특허분류(Int. Cl.)

*H01L 51/52* (2006.01) *H01L 51/56* (2006.01)

(21) 출원번호 10-2014-0051418

(22) 출원일자 2014년04월29일

심사청구일자 없음

(71) 출원인

엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

오금미

서울특별시 서대문구 세무서2가길 47 (홍제동)

이석우

경기도 부천시 원미구 장말로 71, 1512동 1203호

(상동, 한아름아파트)

(74) 대리인

박영복

전체 청구항 수 : 총 13 항

(54) 발명의 명칭 유기 발광 다이오드 표시 장치 및 이의 제조 방법

### (57) 요 약

본 발명은 박막 트랜지스터의 면적을 증가시키지 않고 칸크(kink) 현상을 방지할 수 있는 유기 발광 다이오드 표시 장치 및 이의 제조 방법에 관한 것으로, 본 발명의 유기 발광 다이오드 표시 장치는 기판 상에 형성되어 복수 개의 게이트 배선 및 복수개의 데이터 배선과 각각 접속된 제 1 박막 트랜지스터; 상기 제 1 박막 트랜지스터와 (뒷면에 계속)

**대 표 도** - 도3b

T2

접속된 제 2 박막 트랜지스터; 및 상기 제 2 박막 트랜지스터와 접속된 유기 발광 소자를 포함하며, 상기 제 1, 제 2 박막 트랜지스터는 각각 채널 영역, 소스 영역 및 드레인 영역을 포함하는 반도체층, 게이트 절연막, 게이트 전극, 소스 콘택홀을 통해 상기 소스 영역과 접속된 소스 전극 및 드레인 콘택홀을 통해 상기 드레인 영역과 접속된 드레인 전극을 포함하며, 상기 제 2 박막 트랜지스터의 반도체층은 바디 영역을 더 포함하여 이루어져, 상기 소스 영역과 드레인 영역은 제 1 불순물이 도핑되고, 상기 바디 영역은 상기 제 1 불순물과 상이한 제 2 불순물이 도핑되며, 상기 바디 영역과 상기 소스 영역은 상기 소스 콘택홀을 공유하여 상기 바디 영역이 상기 소스 전극과 접속된다.

---

## 명세서

### 청구범위

#### 청구항 1

기판 상에 형성되어 복수 개의 게이트 배선 및 복수개의 데이터 배선과 각각 접속된 제 1 박막 트랜지스터;

상기 제 1 박막 트랜지스터와 접속된 제 2 박막 트랜지스터; 및

상기 제 2 박막 트랜지스터와 접속된 유기 발광 소자를 포함하며,

상기 제 1, 제 2 박막 트랜지스터는 각각 채널 영역, 소스 영역 및 드레인 영역을 포함하는 반도체층, 게이트 절연막, 게이트 전극, 소스 콘택홀을 통해 상기 소스 영역과 접속된 소스 전극 및 드레인 콘택홀을 통해 상기 드레인 영역과 접속된 드레인 전극을 포함하며,

상기 제 2 박막 트랜지스터의 반도체층은 바디 영역을 더 포함하여 이루어져, 상기 소스 영역과 드레인 영역은 제 1 불순물이 도핑되고, 상기 바디 영역은 상기 제 1 불순물과 상이한 제 2 불순물이 도핑되며, 상기 바디 영역과 상기 소스 영역은 상기 소스 콘택홀을 공유하여 상기 바디 영역이 상기 소스 전극과 접속된 것을 특징으로 하는 유기 발광 다이오드 표시 장치.

#### 청구항 2

제 1 항에 있어서,

상기 제 1 불순물은 n형 불순물이며, 상기 제 2 불순물은 p형 불순물인 것을 특징으로 하는 유기 발광 다이오드 표시 장치.

#### 청구항 3

제 1 항에 있어서,

상기 바디 영역은 상기 채널 영역에 인접하도록 형성되는 것을 특징으로 하는 유기 발광 다이오드 표시 장치.

#### 청구항 4

제 1 항에 있어서,

상기 바디 영역은 상기 소스 영역 상에 형성되어 상기 바디 영역의 두께가 상기 소스 영역의 두께보다 얇고, 상기 바디 영역 하부에도 상기 소스 영역이 위치하는 것을 특징으로 하는 유기 발광 다이오드 표시 장치.

#### 청구항 5

제 1 항에 있어서,

상기 바디 영역과 상기 소스 영역은 동일 평면 상에 위치하여, 상기 바디 영역과 상기 소스 영역의 두께가 동일한 것을 특징으로 하는 유기 발광 다이오드 표시 장치.

#### 청구항 6

제 1 항에 있어서,

상기 제 1 박막 트랜지스터의 드레인 전극과 상기 제 2 박막 트랜지스터의 게이트 전극이 접속된 것을 특징으로 하는 유기 발광 다이오드 표시 장치.

#### 청구항 7

제 1 항에 있어서,

상기 데이터 배선과 평행한 기준 전압 배선과 전원 배선을 더 포함하여,

상기 기준 전압 배선과 상기 게이트 배선이 교차하는 영역에 형성된 제 3 박막 트랜지스터 및 일측이 상기 제 2

박막 트랜지스터와 접속되고 타측이 상기 제 3 박막 트랜지스터와 접속된 커패시터를 더 포함하는 것을 특징으로 하는 유기 발광 다이오드 표시 장치.

#### 청구항 8

기판 상에 복수 개의 게이트 배선 및 복수 개의 데이터 배선과 각각 접속된 제 1 박막 트랜지스터와 상기 제 1 박막 트랜지스터와 접속된 제 2 박막 트랜지스터를 형성하는 단계; 및

상기 제 2 박막 트랜지스터와 접속된 유기 발광 소자를 형성하는 단계를 포함하며,

상기 제 1, 제 2 박막 트랜지스터를 형성하는 단계는 반도체층을 형성하는 단계; 상기 반도체층 상에 게이트 절연막과 게이트 전극을 형성하는 단계; 상기 반도체층에 제 1 불순물을 도핑하여 채널 영역, 소스 영역 및 드레인 영역을 정의하는 단계; 및 소스 콘택홀을 통해 상기 소스 영역과 접속된 소스 전극 및 드레인 콘택홀을 통해 상기 드레인 영역과 접속된 드레인 전극을 형성하는 단계를 포함하며,

상기 제 2 박막 트랜지스터는 제 1 불순물과 다른 제 2 불순물을 도핑하여 반도체층에 바디 영역을 정의하는 단계를 더 포함하여 이루어져, 상기 바디 영역과 상기 소스 영역은 상기 소스 콘택홀을 공유하여 상기 바디 영역이 상기 소스 전극과 접속된 것을 특징으로 하는 유기 발광 다이오드 표시 장치의 제조 방법.

#### 청구항 9

제 8 항에 있어서,

상기 반도체층을 형성하는 단계는 상기 기판 상에 비정질 실리콘을 증착하고 상기 비정질 실리콘을 결정화하여 저온 폴리 실리콘막을 형성하는 단계;

상기 저온 폴리 실리콘막을 패터닝하는 단계를 포함하는 것을 특징으로 하는 유기 발광 다이오드 표시 장치의 제조 방법.

#### 청구항 10

제 8 항에 있어서,

상기 제 1 불순물은 n형 불순물이며, 상기 제 2 불순물은 p형 불순물인 것을 특징으로 하는 유기 발광 다이오드 표시 장치의 제조 방법.

#### 청구항 11

제 8 항에 있어서,

상기 바디 영역을 상기 채널 영역에 인접하도록 형성하는 것을 특징으로 하는 유기 발광 다이오드 표시 장치의 제조 방법.

#### 청구항 12

제 8 항에 있어서,

상기 바디 영역을 상기 소스 영역 상에 형성하여 상기 바디 영역의 두께가 상기 소스 영역의 두께보다 얇고, 상기 바디 영역 하부에도 상기 소스 영역이 위치하는 것을 특징으로 하는 유기 발광 다이오드 표시 장치의 제조 방법.

#### 청구항 13

제 8 항에 있어서,

상기 바디 영역과 상기 소스 영역을 동일 평면 상에 형성하여, 상기 바디 영역과 상기 소스 영역의 두께가 동일한 것을 특징으로 하는 유기 발광 다이오드 표시 장치의 제조 방법.

### 발명의 설명

### 기술 분야

[0001] 본 발명은 유기 발광 다이오드 표시 장치에 관한 것으로, 박막 트랜지스터의 킨크(Kink) 현상을 방지하여 신뢰성이 향상된 유기 발광 다이오드 표시 장치 및 이의 제조 방법에 관한 것이다.

### 배경기술

[0002] 다양한 정보를 화면으로 구현하는 영상 표시 장치는 정보 통신 시대의 핵심 기술로, 더 얇고 더 가볍고 휴대가 가능하면서도 고성능의 방향으로 발전하고 있다. 공간성, 편리성의 추구로 구부릴 수 있는 플렉시블 디스플레이가 요구되면서 평판 표시 장치로 유기 발광층의 발광량을 제어하는 유기 발광 다이오드 표시 장치가 근래에 각광받고 있다.

[0003] 유기 발광 표시 장치는 기판 상에 형성된 박막 트랜지스터와 커패시터에 저장된 데이터에 의해 구동되어 영상을 표현한다. 박막 트랜지스터는 스위칭 박막 트랜지스터와 구동용 박막 트랜지스터를 포함하며, 구동용 박막 트랜지스터와 유기 발광 다이오드가 접속된다.

[0004] 박막 트랜지스터와 유기 발광 다이오드는 서브 화소마다 형성된다. 유기 발광 다이오드는 제 1 전극, 제 2 전극 및 제 1 전극과 제 2 전극 사이에 형성된 유기 발광층을 포함하여 이루어져, 제 1 전극 및 제 2 전극에 전류를 가하여 발광층 내에 전자와 정공을 주입 및 전달시켜 발광층에서 쌍을 이룬 전자와 정공은 여기상태로부터 기저상태로 떨어지면서 발광한다.

[0005] 그런데, 박막 트랜지스터가 저온 폴리 실리콘(Low Temperature Polycrystalline Silicon; LTPS)을 이용하여 형성된 반도체층을 포함하는 경우, 박막 트랜지스터의 크기가 축소됨에 따라 드레인 영역에서 강한 횡방향 전계가 발생하고, 이에 따라 드레인 영역에 강한 횡방향 전계에 의해 야기된 정공을 방전시키기 위한 통로가 없어 킨크(Kink) 현상이 발생되었다. 킨크 현상은 게이트 전압의 증가에 따라 드레인 전류가 포화(saturation)되지 못하고 계속적으로 증가하는 현상으로, 킨크 현상에 의해 유기 발광 다이오드 표시 장치의 신뢰성이 저하된다.

[0006] 상기와 같은 킨크 현상을 방지하기 위해, 박막 트랜지스터가 소스 단자, 드레인 단자, 게이트 단자 및 바디 단자의 총 4개의 터미널(Terminal)을 갖도록 형성하고, 소스 단자와 바디 단자를 접속시켜 소스 영역에 과잉된 정공을 바디 단자를 통해 방출시키는 방법이 개발되었다.

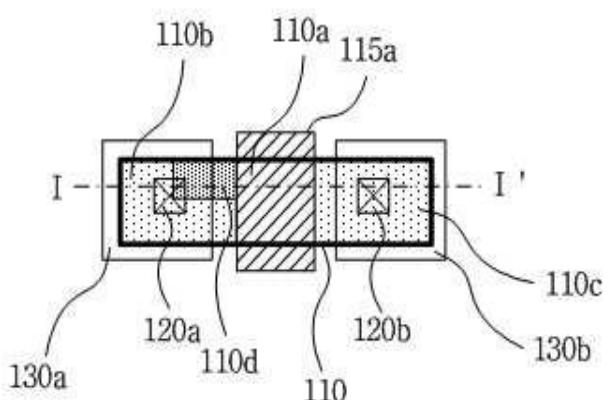

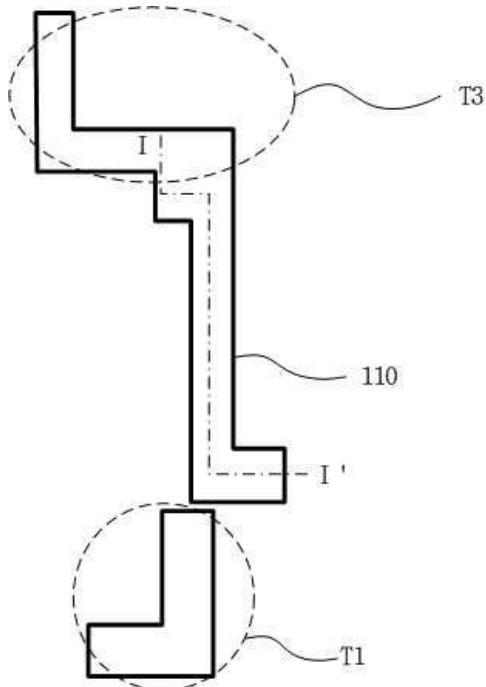

[0007] 도 1은 4개의 터미널(Terminal)을 갖는 일반적인 박막 트랜지스터의 반도체층의 평면도이다.

[0008] 도 1과 같이, 일반적인 박막 트랜지스터의 반도체층(10)은 채널 영역(10a), 소스 영역(10b), 드레인 영역(10c) 및 채널 영역(10a)과 연결된 바디 영역(10d)을 포함하여 이루어진다. 일반적으로, 바디 영역(10d)은 채널 영역(10a)에서 돌출된 구조로 형성되므로, 바디 영역(10d)을 포함하는 반도체층을 구비한 박막 트랜지스터는 소스 영역, 드레인 영역 및 채널 영역만을 갖는 3개의 터미널을 갖는 박막 트랜지스터보다 면적이 넓다. 특히, 소스 영역(10b)과 바디 영역(10d)을 접속시키기 위한 연결부(15)를 더 구비함에 따라 박막 트랜지스터의 면적이 현저히 증가한다.

### 발명의 내용

#### 해결하려는 과제

[0009] 본 발명은 상기와 같은 문제점을 해결하기 위한 것으로, 박막 트랜지스터의 면적을 증가시키지 않고 킨크(kink) 현상을 방지할 수 있는 유기 발광 다이오드 표시 장치 및 이의 제조 방법을 제공하는데, 그 목적이 있다.

#### 과제의 해결 수단

[0010] 상기와 같은 목적을 달성하기 위한 본 발명의 유기 발광 다이오드 표시 장치는 기판 상에 형성되어 복수 개의 게이트 배선 및 복수개의 데이터 배선과 각각 접속된 제 1 박막 트랜지스터; 상기 제 1 박막 트랜지스터와 접속된 제 2 박막 트랜지스터; 및 상기 제 2 박막 트랜지스터와 접속된 유기 발광 소자를 포함하며, 상기 제 1, 제 2 박막 트랜지스터는 각각 채널 영역, 소스 영역 및 드레인 영역을 포함하는 반도체층, 게이트 절연막, 게이트 전극, 소스 콘택홀을 통해 상기 소스 영역과 접속된 소스 전극 및 드레인 콘택홀을 통해 상기 드레인 영역과 접속된 드레인 전극을 포함하며, 상기 제 2 박막 트랜지스터의 반도체층은 바디 영역을 더 포함하여 이루어져, 상기 소스 영역과 드레인 영역은 제 1 불순물이 도핑되고, 상기 바디 영역은 상기 제 1 불순물과 상이한 제 2 불순물이 도핑되며, 상기 바디 영역과 상기 소스 영역은 상기 소스 콘택홀을 공유하여 상기 바디 영역이 상기 소스 전극과 접속된다.

- [0011] 상기 제 1 박막 트랜지스터의 드레인 전극과 상기 제 2 박막 트랜지스터의 게이트 전극이 접속된다.

- [0012] 상기 기준 전압 배선과 상기 게이트 배선이 교차하는 영역에 형성된 제 3 박막 트랜지스터 및 일측이 상기 제 2 박막 트랜지스터와 접속되고 타측이 상기 제 3 박막 트랜지스터와 접속된 커패시터를 더 포함한다.

- [0013] 또한, 동일 목적을 달성하기 위한 본 발명의 유기 발광 다이오드 표시 장치의 제조 방법은 기판 상에 게이트 배선 및 데이터 배선과 접속된 제 1 박막 트랜지스터와 상기 제 1 박막 트랜지스터와 접속된 제 2 박막 트랜지스터를 형성하는 단계; 및 상기 제 2 박막 트랜지스터와 접속된 유기 발광 소자를 형성하는 단계를 포함하며, 상기 제 1, 제 2 박막 트랜지스터를 형성하는 단계는 반도체층을 형성하는 단계; 상기 반도체층 상에 게이트 절연막과 게이트 전극을 형성하는 단계; 상기 반도체층에 제 1 불순물을 도핑하여 채널 영역, 소스 영역 및 드레인 영역을 정의하는 단계; 및 소스 콘택홀을 통해 상기 소스 영역과 접속된 소스 전극 및 드레인 콘택홀을 통해 상기 드레인 영역과 접속된 드레인 전극을 형성하는 단계를 포함하며, 상기 제 2 박막 트랜지스터는 제 1 불순물과 다른 제 2 불순물을 도핑하여 반도체층에 바디 영역을 정의하는 단계를 더 포함하여 이루어져, 상기 바디 영역과 상기 소스 영역은 상기 소스 콘택홀을 공유하여 상기 바디 영역이 상기 소스 전극과 접속된다.

- [0014] 상기 반도체층을 형성하는 단계는 상기 기판 상에 비정질 실리콘을 증착하고 상기 비정질 실리콘을 결정화하여 저온 폴리 실리콘막을 형성하는 단계; 상기 저온 폴리 실리콘막을 패터닝하는 단계를 포함한다.

- [0015] 상기 제 1 불순물은 n형 불순물이며, 상기 제 2 불순물은 p형 불순물이다.

- [0016] 상기 바디 영역을 상기 채널 영역에 인접하도록 형성한다.

- [0017] 상기 바디 영역을 상기 소스 영역 상에 형성하여 상기 바디 영역의 두께가 상기 소스 영역의 두께보다 얇고, 상기 바디 영역 하부에도 상기 소스 영역이 위치한다.

- [0018] 상기 바디 영역과 상기 소스 영역을 동일 평면 상에 형성하여, 상기 바디 영역과 상기 소스 영역의 두께가 동일하다.

### 발명의 효과

- [0019] 상기와 같은 본 발명의 유기 발광 다이오드 표시 장치 및 이의 제조 방법은 추가적으로 반도체층의 면적을 증가시키지 않고 반도체층에 바디 영역을 구비하여, 바디 영역과 소스 영역이 소스 콘택홀을 공유함으로써, 채널 영역에서 핫캐리어(hot carrier)가 발생하면, 정공이 p 바디 영역을 통해서 소스 전극으로 빠져 나가므로, 친크 현상을 방지하여 표시 장치의 신뢰성을 향상시킬 수 있다.

### 도면의 간단한 설명

- [0020] 도 1은 4개의 터미널(Terminal)을 갖는 일반적인 박막 트랜지스터의 반도체층의 평면도이다.

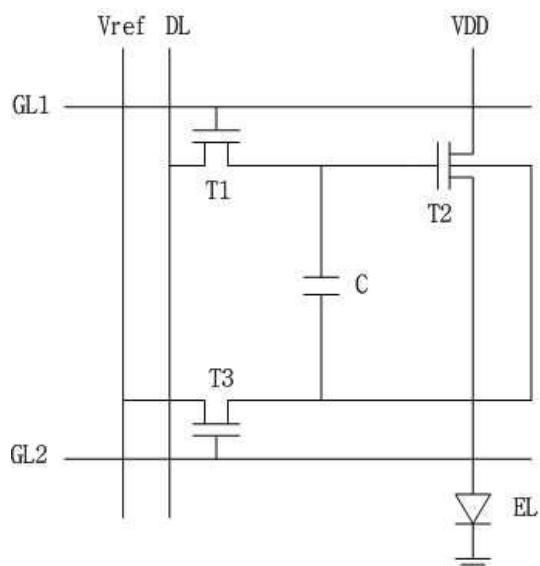

- 도 2a는 본 발명의 유기 발광 다이오드 표시 장치의 회로도이다.

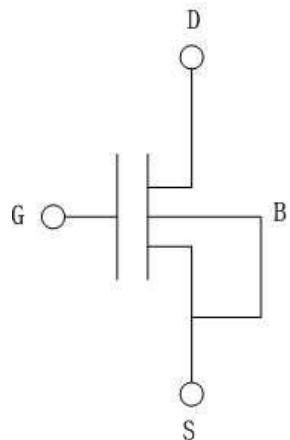

- 도 2b는 제 2 박막 트랜지스터의 회로도이다.

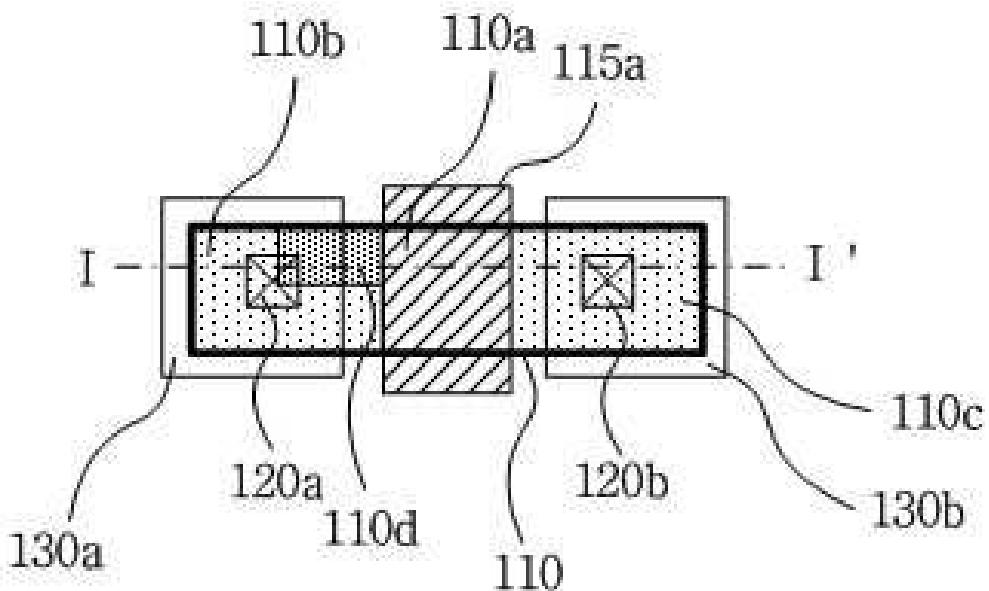

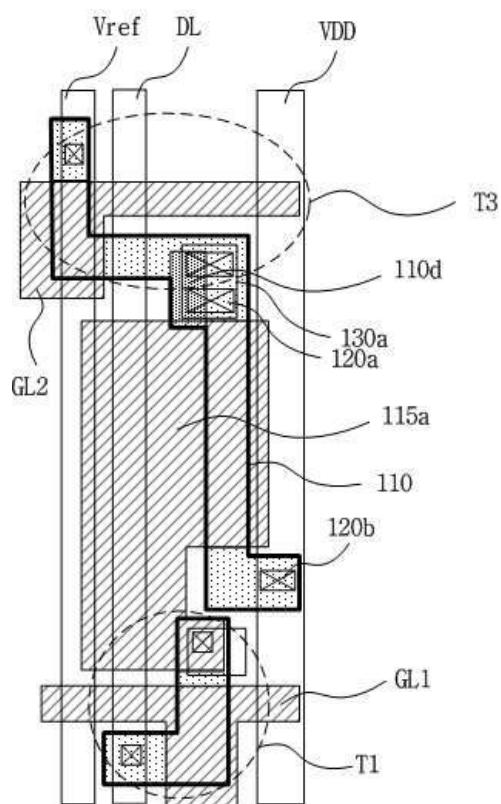

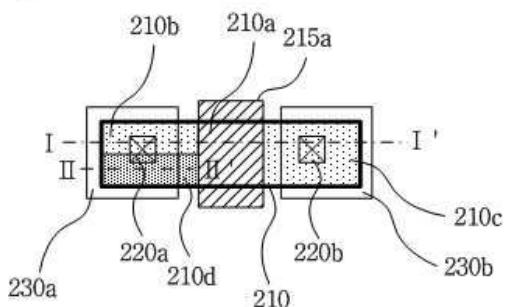

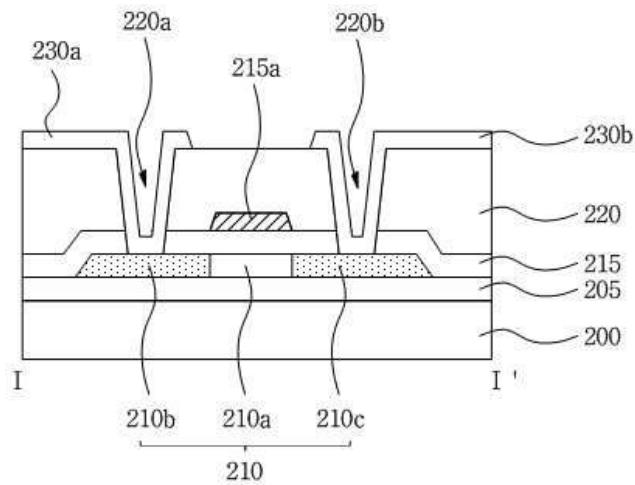

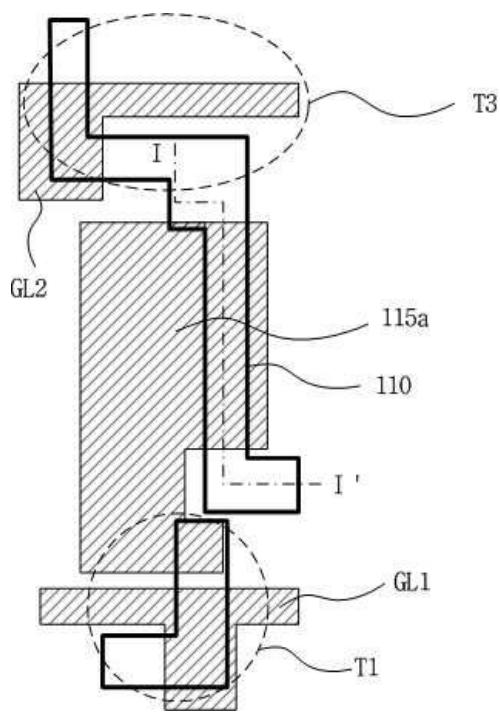

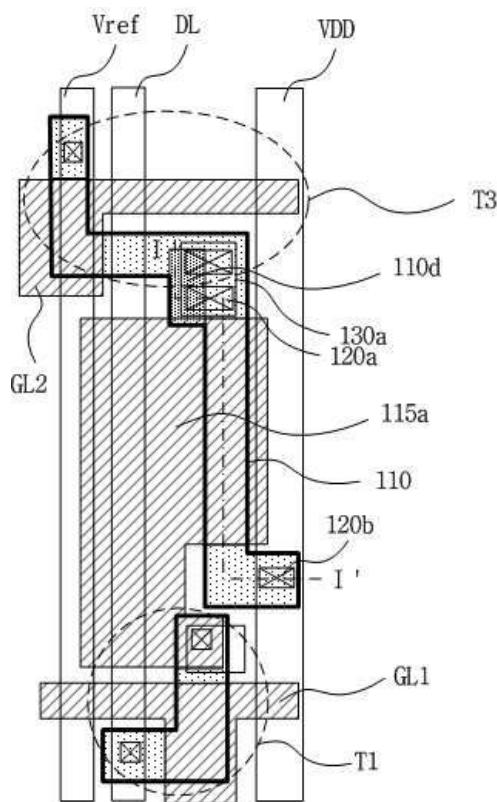

- 도 3a는 본 발명의 유기 발광 다이오드 표시 장치의 회로부의 평면도이다.

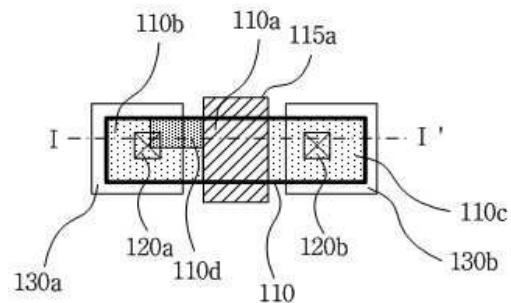

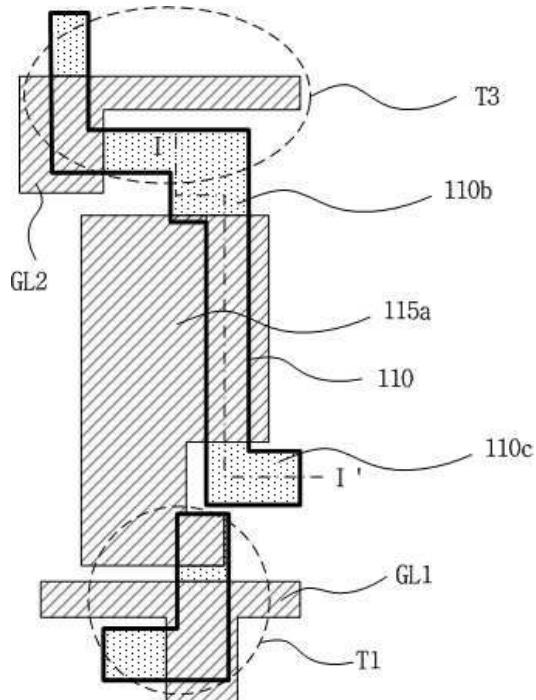

- 도 3b는 도 3a의 제 2 박막 트랜지스터의 확대 평면도이다.

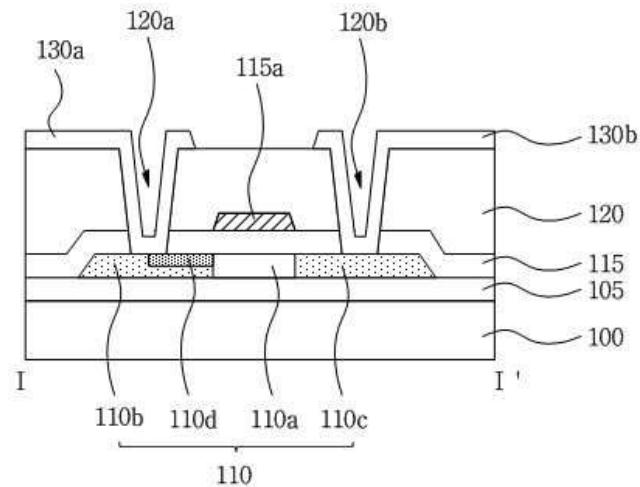

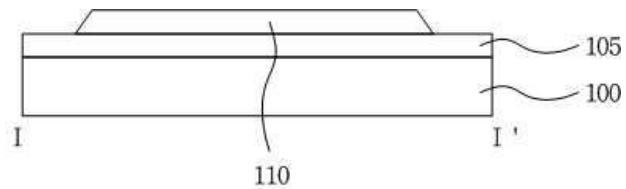

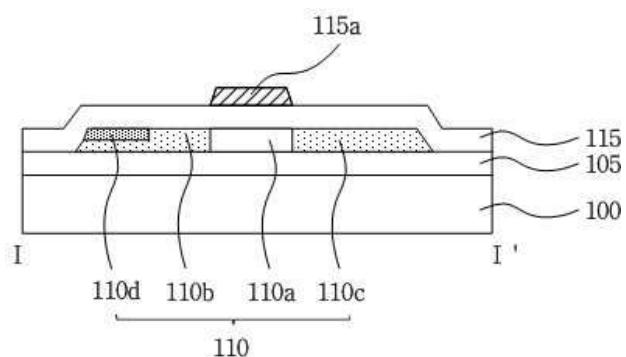

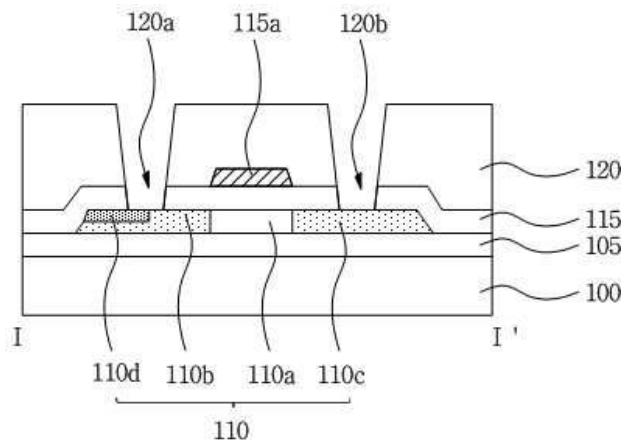

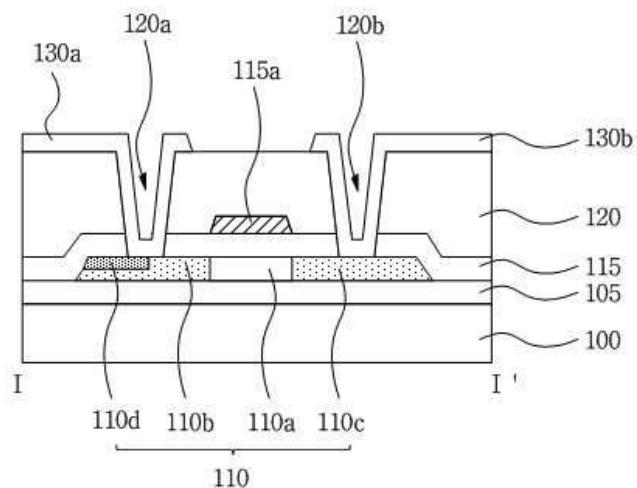

- 도 3c는 도 3b의 I - I '의 단면도이다.

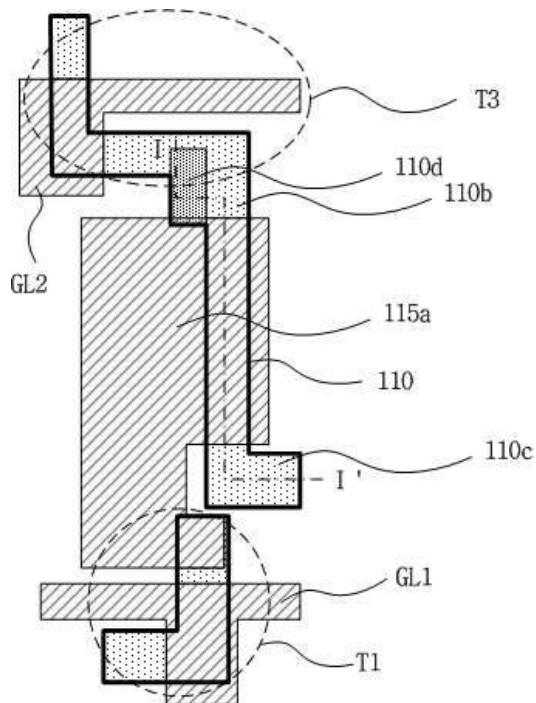

- 도 4a는 다른 실시 예에 따른 제 2 박막 트랜지스터의 평면도이다.

- 도 4b는 도 4a의 I - I '의 단면도이다.

- 도 4c는 도 4a의 II - II '의 단면도이다.

- 도 5a 내지 도 5f는 본 발명의 유기 발광 다이오드 표시 장치의 회로부의 제조 방법을 나타낸 공정 평면도이다.

- 도 6a 내지 도 6f는 도 5a 내지 도 5f의 I - I '의 단면도이다.

### 발명을 실시하기 위한 구체적인 내용

- [0021] 이하, 첨부된 도면을 참조하여 본 발명의 유기 발광 다이오드 표시 장치를 상세히 설명하면 다음과 같다.

- [0022] 도 2a는 본 발명의 유기 발광 다이오드 표시 장치의 회로도이다. 도 2b는 제 2 박막 트랜지스터의 회로도이다.

- [0023] 도 2a와 같이, 본 발명의 유기 발광 다이오드 표시 장치는 제 1 박막 트랜지스터(T1), 제 1 박막 트랜지스터(T1)와 접속된 제 2 박막 트랜지스터(T2) 및 제 2 박막 트랜지스터(T2)와 접속된 유기 발광 소자(EL)를 포함한다. 특히, 구동 안정성을 향상시키기 위해 제 3 박막 트랜지스터(T3)를 더 포함하여 이루어질 수 있다.

- [0024] 제 1 박막 트랜지스터(T1)는 스위칭 박막 트랜지스터로, 제 1 게이트 배선(GL1)의 제 1 스캔 신호에 응답하여 구동 박막 트랜지스터인 제 2 박막 트랜지스터(T2) 및 커패시터(C)의 일측 단자에 데이터 배선(DL)의 데이터 신호를 전달한다. 이 때, 제 1 박막 트랜지스터(T1)의 드레인 전극이 제 2 박막 트랜지스터(T2)의 게이트 전극과 접속되어 제 1, 제 2 박막 트랜지스터(T1, T2)가 연결된다.

- [0025] 제 2 박막 트랜지스터(T2)는 제 1 박막 트랜지스터(T1)를 통해 전달된 데이터 신호에 대응되는 전류를 유기 발광 소자(EL)로 출력한다. 유기 발광 소자(EL)는 제 1 전극, 제 2 전극 및 제 1 전극과 제 2 전극 사이에 구비된 유기 발광층을 포함하여 이루어진다. 제 1 전극은 제 2 박막 트랜지스터(T2)를 통해 데이터 배선(DL)과 평행한 전원 배선(VDD)과 접속되어 제 2 박막 트랜지스터(T2)에 흐르는 전류에 대응되는 광을 방출한다.

- [0026] 제 3 박막 트랜지스터(T3)는 유기 발광 다이오드 표시 장치의 구동 안정성을 향상시키기 위한 것으로, 데이터 배선(DL)과 평행한 기준 전압 배선(Vref)과 접속되어 제 2 게이트 배선(GL2)과 기준 전압 배선(Vref)가 교차하는 영역에 구비된다. 상기와 같은 제 3 박막 트랜지스터(T3)는 제 2 게이트 배선(GL2)의 제 2 스캔 신호에 응답하여 커패시터(C)의 타측 단자에 기준 전압을 공급한다.

- [0027] 제 1 내지 제 3 박막 트랜지스터는 채널 영역, 소스 영역 및 드레인 영역을 포함하는 반도체층, 게이트 절연막, 게이트 전극, 소스 콘택홀을 통해 소스 영역과 접속된 소스 전극 및 드레인 콘택홀을 통해 드레인 영역과 접속된 드레인 전극을 포함한다. 특히, 제 2 박막 트랜지스터(T2)의 반도체층은 바디 영역을 더 포함하여 이루어져, 소스 영역과 드레인 영역은 제 1 불순물이 도핑되고, 바디 영역은 제 1 불순물과 상이한 제 2 불순물이 도핑되며, 바디 영역과 소스 영역은 소스 콘택홀을 공유하여 바디 영역이 소스 전극과 접속된다.

- [0028] 상기와 같은 제 2 박막 트랜지스터(T2)는 도 2b와 같이, 게이트 단자(G), 소스 단자(S), 드레인 단자(D) 및 바디 단자(B)를 포함하여 이루어진다. 이 때, 바디 단자(B)는 소스 단자(S)와 접속되어 제 2 박막 트랜지스터(T2)를 구동할 때 소스 영역(110b)에 정공 농도가 증가하여 플로팅 바디 효과(floating body effect)에 의한 친크 현상이 발생하는 것을 방지한다.

- [0029] 도 3a는 본 발명의 유기 발광 다이오드 표시 장치의 회로부의 평면도로, 게이트 배선, 데이터 배선, 전원 배선, 기준 전압 배선 및 제 1 내지 제 3 박막 트랜지스터만 도시하였다. 도 3b는 도 3a의 제 2 박막 트랜지스터의 확대 평면도이며, 도 3c는 도 3b의 I - I '의 단면도이다.

- [0030] 도 3a 내지 도 3c와 같이, 본 발명의 제 2 박막 트랜지스터는 채널 영역(110a), 소스 영역(110b), 드레인 영역(110c) 및 바디 영역(110d)을 구비한 반도체층(110), 채널 영역(110a)과 중첩되는 게이트 전극(115a), 소스 콘택홀(120a)을 통해 소스 영역(110b) 및 바디 영역(110d)과 접속된 소스 전극(130a) 및 드레인 콘택홀(120b)을 통해 드레인 영역(110c)과 접속된 드레인 전극(130b)을 포함한다. 특히, 바디 영역(110d)의 두께가 소스 영역(110b)의 두께보다 얇고, 바디 영역(110d)이 소스 영역(110b)의 일부 영역 상에 구비되어, 바디 영역(110d) 하부에도 소스 영역(110b)이 위치한다. 즉, 바디 영역(110d)과 소스 영역(110b)이 중첩되도록 구비되어 바디 영역(110d)과 소스 영역(110b)이 소스 콘택홀(120a)을 공유한다.

- [0031] 구체적으로, 채널 영역(110a)은 소스 영역(110b)과 드레인 영역(110c) 사이에 형성되며, 바디 영역(110d)은 채널 영역(110a)에 인접하도록 형성된다. 채널 영역(110a)은 불순물이 도핑되지 않은 진성 영역이며, 소스 영역(110b)과 드레인 영역(110c) 사이에 구비되어 소스 영역(110b) 및 드레인 영역(110c)은 제 1 불순물로 도핑되어 형성된다. 그리고, 바디 영역(110d)은 제 1 불순물과 상이한 제 2 불순물로 도핑되어 형성된다.

- [0032] 반도체층(110)은 기판(100) 상에 형성된 베퍼층(105) 상에 형성되며, 반도체층(110)을 덮도록 게이트 절연막(115)이 형성된다. 게이트 절연막(115) 상에는 채널 영역(110a)과 중첩되도록 게이트 전극(115a)이 구비되며, 게이트 전극(115a)을 덮도록 기판(100) 상에 층간 절연막(120)이 형성된다. 그리고, 게이트 절연막(115) 및 층간 절연막(120)을 선택적으로 제거하여 소스 영역(110b)과 바디 영역(110d)을 노출시키는 소스 콘택홀(120a)과 드레인 영역(110c)을 노출시키는 드레인 콘택홀(120b)이 형성된다.

- [0033] 소스 콘택홀(120a)을 통해 전원 배선(VDD)과 연결된 소스 전극(130a)이 소스 영역(110b) 및 바디 영역(110d)과 접속되며, 드레인 콘택홀(120b)을 통해 드레인 전극(130b)이 드레인 영역(110c)과 접속된다.

[0034] 예를 들어, 제 2 박막 트랜지스터가 n형 박막 트랜지스터인 경우, 제 1 불순물은 n형 불순물이며, 제 2 불순물은 p형 불순물이다. 채널 영역(110a)에서 핫캐리어(hot carrier)가 발생하면, 전자는 n형 불순물로 도핑된 드레인 영역(110c)을 통해서 드레인 전극(130b)으로 빠져 나간다. 그리고, 정공은 p형 불순물로 도핑된 바디 영역(110d)을 통해서 소스 전극(130a)으로 빠져 나갈 수 있으므로, 정공이 소스 영역(110b)으로 이동하는 것을 효과적으로 억제하여 친크 현상을 방지함으로써, 구동 박막 트랜지스터의 신뢰성이 향상된다.

[0035] 반대로, 제 2 박막 트랜지스터가 p형 박막 트랜지스터인 경우에는 제 1 불순물은 p형 불순물이며, 제 2 불순물은 n형 불순물이다. 채널 영역(110a)에서 핫캐리어(hot carrier)가 발생하면, 전자는 p형 불순물로 도핑된 드레인 영역(110c)을 통해서 드레인 전극(130b)으로 빠져 나간다. 그리고, 정공은 n형 불순물로 도핑된 바디 영역(110d)을 통해서 소스 전극(130a)으로 빠져 나갈 수 있으므로, 정공이 소스 영역(110b)으로 이동하는 것을 효과적으로 억제할 수 있다.

[0036] 즉, 상기와 같은 본 발명의 유기 발광 다이오드 표시 장치는 구동 박막 트랜지스터인 제 2 박막 트랜지스터의 면적을 증가시키지 않고도 친크 효과를 효율적으로 방지하여 표시 장치의 신뢰성을 향상시킬 수 있다.

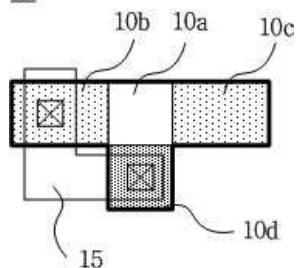

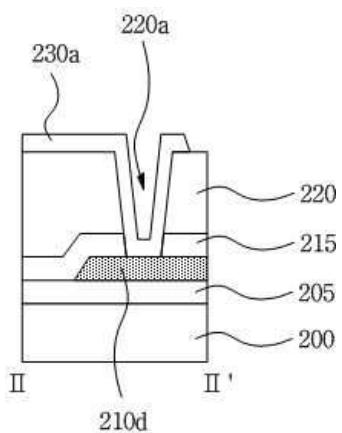

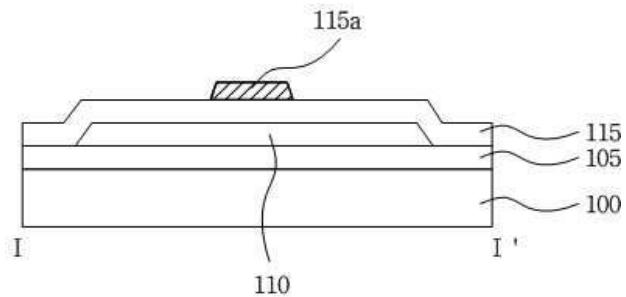

[0037] 도 4a는 다른 실시 예에 따른 제 2 박막 트랜지스터의 평면도이다. 도 4b는 도 4a의 I-I'의 단면도이며, 도 4c는 도 4a의 II-II'의 단면도이다.

[0038] 도 4a 내지 도 4c와 같이, 본 발명의 다른 실시 예에 따른 제 2 박막 트랜지스터는 반도체층(210)의 바디 영역(210d)과 소스 영역(210b)의 두께가 동일하다. 이 때, 바디 영역(210d)은 소스 영역(210b)과 중첩되는 것이 아니라, 바디 영역(210d)과 소스 영역(210b)은 동일 평면 상에 형성된다.

[0039] 바디 영역(210d)은 소스 영역(210b)의 일부 영역에 제 1 불순물을 도핑하지 않고 제 1 불순물이 도핑되지 않은 영역에만 제 2 불순물을 도핑하여 형성되며, 바디 영역(210d)과 소스 영역(210b)이 소스 콘택홀(220a)을 공유하여 바디 영역(210d)과 소스 영역(210b)이 소스 콘택홀(220a)을 통해 소스 전극(230a)과 접속된다.

[0040] 이하, 본 발명의 유기 발광 다이오드 표시 장치의 제조 방법을 구체적으로 설명하면 다음과 같다.

[0041] 도 5a 내지 도 5f는 본 발명의 유기 발광 다이오드 표시 장치의 회로부의 제조 방법을 나타낸 공정 평면도이며, 도 6a 내지 도 6f는 도 5a 내지 도 5f의 I-I'의 단면도이다.

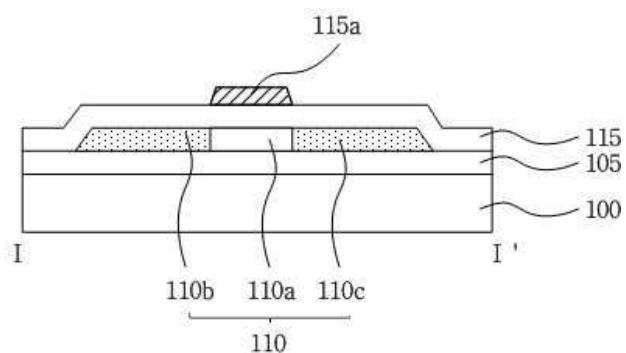

[0042] 먼저, 도 5a 및 도 6a와 같이, 기판(100) 상에 베퍼층(105)을 형성하고, 베퍼층(105) 상에 비정질 실리콘을 증착하고 이를 결정화하여 저온 폴리 실리콘막을 형성한다. 그리고, 저온 폴리 실리콘막을 패터닝하여 반도체층(110)을 형성한다. 이 때, 반도체층(110)은 제 1, 제 3 박막 트랜지스터(T1, T3) 및 구동 박막 트랜지스터인 제 2 박막 트랜지스터(T2)가 형성될 영역에 형성된다.

[0043] 도 5b 및 도 6b와 같이, 반도체층(110)을 덮도록 기판(100) 전면에 게이트 절연막(115)을 형성하고, 게이트 절연막(115) 상에 반도체층(110)의 일부 영역과 중첩되도록 게이트 전극(115a), 게이트 배선(GL1, GL2)을 형성한다. 이 때, 제 1 박막 트랜지스터(T1) 및 제 3 박막 트랜지스터는 각각 반도체층과 제 1 게이트 배선(GL1) 및 제 2 게이트 배선(GL2)이 중첩되는 영역이 게이트 전극으로 정의된다. 그리고, 제 2 박막 트랜지스터의 게이트 전극(115a)은 제 2 박막 트랜지스터(T1)의 반도체층(110)의 일부 영역과 중첩된다.

[0044] 이어, 도 5c 및 도 6c와 같이, 게이트 전극(115), 게이트 배선(GL1, GL2)을 마스크로 이용하여 노출된 반도체층(110)의 양측에 제 1 불순물을 도핑하여, 각 반도체층(110)에 소스 영역(110b)과 드레인 영역(110c)을 형성한다. 제 1 불순물은 n형 불순물이다. 게이트 전극(115)과 중첩되는 영역의 반도체층(110)은 제 1 불순물이 도핑되지 않은 진성 영역으로, 채널 영역(110a)으로 정의된다.

[0045] 그리고, 도 5d 및 도 6d와 같이, 제 2 박막 트랜지스터의 소스 영역(110b)의 일부 영역에 부분적으로 제 2 불순물을 도핑한다. 제 1 불순물은 n형 불순물이며, 제 2 불순물은 p형 불순물이다. 제 2 불순물이 도핑된 영역은 바디 영역(110d)으로 정의되며, 바디 영역(110d)은 드레인 영역(110c)과 채널 영역(110a)의 경계 부분에서 발생되는 핫캐리어(hot carrier)가 바디 영역을 빠져 나가 친크 현상을 방지한다.

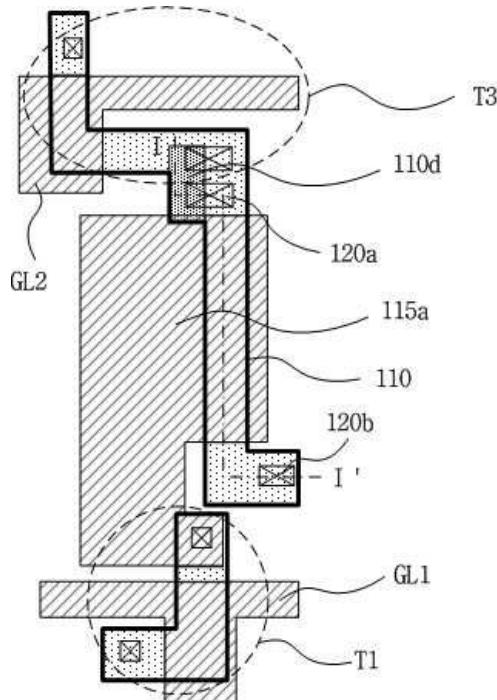

[0046] 바디 영역(110d)은 제 1 불순물이 형성된 영역에 제 2 불순물을 카운터 도핑하여 제 1 불순물이 도핑된 소스 영역(110b)의 일부 영역이 p형 불순물로 도핑되어 정의되며, 이 경우, 바디 영역(110d)은 소스 영역(110b) 상에 부분적으로 형성된다. 또한, 게이트 전극(115a)에 의해 노출된 영역 중 일부 영역에 제 1 불순물을 도핑하지 않고, 제 1 불순물이 도핑되지 않은 영역에 제 2 불순물을 도핑하여 바디 영역(110d)을 형성할 수도 있다. 이 경우에는 바디 영역(110d)과 소스 영역(110b)의 두께가 동일하다.

[0047] 이어, 도 5e 및 도 6e와 같이, 게이트 전극(115a)을 덮도록 중간 절연막(120)을 형성하고, 중간 절연막(120)과 게이트 절연막(115)을 선택적으로 제거하여 소스 콘택홀(120a)과 드레인 콘택홀(120b)을 형성한다. 이 때, 소스 콘택홀(120a)은 소스 영역(110b)과 바디 영역(110d)을 노출시키도록 형성되어, 소스 영역(110b)과 바디 영역(110d)은 소스 콘택홀(120a)을 공유하며, 드레인 콘택홀(120b)은 드레인 영역(110c)을 노출시키도록 형성된다.

[0048] 그리고, 도 5f 및 도 6f와 같이, 전원 배선(VDD), 기준 전압 배선(Vref) 및 데이터 배선(DL)을 형성한다. 이 때, 데이터 배선(DL)은 제 1 박막 트랜지스터(T1)와 접속되며, 기준 전압 배선(Vref)은 제 3 박막 트랜지스터(T3)와 접속된다. 그리고, 전원 배선(VDD)는 제 2 박막 트랜지스터의 드레인 콘택홀(120b)을 통해 드레인 영역(110c)과 접속되어 드레인 전극(130b)이 형성되며, 동시에 제 2 박막 트랜지스터의 소스 영역(110b) 및 바디 영역(110d)과 접속되는 소스 전극(130a)이 형성된다.

[0049] 그리고, 도시하지는 않았으나, 제 2 박막 트랜지스터와 접속되도록 제 1 전극, 유기 발광층 및 제 2 전극을 포함하는 유기 발광 소자(EL)를 형성한다. 먼저, 제 2 박막 트랜지스터와 접속되도록 애노드(Anode)인 제 1 전극을 형성한다. 그리고, 제 1 전극 상에 유기 발광층을 형성하고, 유기 발광층을 덮도록 캐소드(Cathode)인 제 2 전극을 형성한다. 또한, 도시하지는 않았으나, 제 2 박막 트랜지스터의 게이트 전극(115a)과 중첩되는 커페시터를 형성한다. 이 때, 커페시터의 일측 단자는 제 1 박막 트랜지스터(T1)와 접속되며, 타측 단자는 제 3 박막 트랜지스터(T3)와 접속된다.

[0050] 상기와 같은 본 발명의 유기 발광 다이오드 표시 장치는 유기 발광 소자(EL)과 접속되어 구동 박막 트랜지스터로 기능하는 제 2 박막 트랜지스터(T2)의 반도체층(110)이 채널 영역(110a) 소스 영역(110b), 드레인 영역(110c), 바디 영역(110d)을 포함하며, 바디 영역(110d)에는 소스 영역(110b) 및 드레인 영역(110c)에 도핑되는 불순물과 다른 불순물이 도핑된다.

[0051] 소스 영역(110b) 및 드레인 영역(110c)이 제 1 불순물로 도핑되는 경우, 바디 영역은 제 1 불순물과 상이한 제 2 불순물이 도핑되고, 채널 영역(110a)은 제 1, 제 2 불순물이 도핑되지 않은 진성 영역이다. 제 1 불순물은 n형 불순물이고 제 2 불순물은 p형 불순물이다.

[0052] 따라서, 본 발명의 유기 발광 다이오드 표시 장치는 제 2 박막 트랜지스터(T2)의 동작 중에 드레인 영역(110c)의 횡방향 전계에 의해 드레인 영역(110c)과 채널 영역(110a)의 경계 부분에서 발생되는 핫캐리어(hot carrier)가 바디 영역(110d)을 통해 빠져 나갈 수 있으므로, 핫캐리어가 소스 영역(110b)으로 이동하는 것을 방지하여 표시 장치의 신뢰성이 향상된다. 더욱이, 상술한 바와 같이 일반적인 4개의 터미널의 박막 트랜지스터는 바디 영역 및 연결부를 추가로 구비함에 따라 소자의 면적이 현저히 증가하나, 본 발명은 소자의 면적 증가 없이 키크 현상을 방지할 수 있다.

[0053] 특히, 본 발명은 3개의 박막 트랜지스터와 1개의 커페시터가 하나의 화소 영역에 구비된 유기 발광 다이오드 표시 장치를 개시하였으나, 소스 영역과 바디 영역이 연결된 구동 박막 트랜지스터를 포함하는 어떠한 유기 발광 다이오드 표시 장치에 적용 가능하다.

[0054] 한편, 이상에서 설명한 본 발명은 상술한 실시 예 및 첨부된 도면에 한정되는 것이 아니고, 본 발명의 기술적 사상을 벗어나지 않는 범위 내에서 여러 가지 치환, 변형 및 변경이 가능하다는 것이 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 있어 명백할 것이다.

## 부호의 설명

[0055] DL: 데이터 배선 GL1: 제 1 게이트 배선

GL2: 제 2 게이트 배선 T1: 제 1 박막 트랜지스터

T2: 제 2 박막 트랜지스터 T3: 제 3 박막 트랜지스터

VDD: 전원 배선 Vref: 기준 전압 배선

100: 기판 105: 벼파층

110: 반도체층 110a: 채널 영역

110b: 소스 영역 110c: 드레인 영역

110d: 바디 영역 115: 게이트 절연막

115a: 게이트 전극 120: 층간 절연막

120a: 소스 콘택홀 120b: 드레인 콘택홀

130a: 소스 전극 130b: 드레인 전극

## 도면

### 도면1

10

### 도면2a

도면2b

T2

도면3a

도면3b

T2

도면3c

도면4a

T2

도면4b

도면4c

도면5a

도면5b

도면5c

도면5d

도면5e

도면5f

도면6a

도면6b

도면6c

도면6d

도면6e

도면6f

|                |                                         |         |            |

|----------------|-----------------------------------------|---------|------------|

| 专利名称(译)        | 标题 : OLED显示器及其制造方法                      |         |            |

| 公开(公告)号        | <a href="#">KR1020150124659A</a>        | 公开(公告)日 | 2015-11-06 |

| 申请号            | KR1020140051418                         | 申请日     | 2014-04-29 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                               |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                               |         |            |

| [标]发明人         | OH KUM MI<br>오금미<br>LEE SEOK WOO<br>이석우 |         |            |

| 发明人            | 오금미<br>이석우                              |         |            |

| IPC分类号         | H01L51/52 H01L51/56                     |         |            |

| CPC分类号         | H01L51/5296 H01L51/5203                 |         |            |

| 代理人(译)         | PARK , YOUNG BOK                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>               |         |            |

## 摘要(译)

T2

本发明涉及到，在不增加薄膜晶体管kinkeu ( 扭结 ) 有机发光二极管，可以防止显示装置及其制造方法，本发明的有机发光二极管显示装置的多个形成在基板上的区域第一薄膜晶体管分别连接到栅极布线和多条数据线;第二薄膜晶体管，连接到第一薄膜晶体管;以及连接到第二薄膜晶体管的有机发光装置，其中第一和第二薄膜晶体管中的每一个包括包括沟道区，源区和漏区的半导体层，栅极绝缘膜，栅电极，源极连接到源极区，漏极通过漏极接触孔连接到漏极区，其中第二薄膜晶体管的半导体层还包括体区，其中，体区掺杂有不同于第一杂质的第二杂质，体区和源区共用源极接触孔，使得体区连接到源极。