공개특허 10-2020-0005347

(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2020-0005347

(43) 공개일자 2020년01월15일

(51) 국제특허분류(Int. Cl.)

*G09G 3/3233* (2016.01) *G09G 3/00* (2006.01)

*G09G 3/20* (2006.01) *G09G 3/3275* (2016.01)

(52) CPC특허분류

*G09G 3/3233* (2013.01)

*G09G 3/006* (2013.01)

(21) 출원번호 10-2018-0078969

(22) 출원일자 2018년07월06일

심사청구일자 없음

(71) 출원인

엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

박준민

경기도 파주시 월롱면 엘지로 245

(74) 대리인

특허법인(유한)유일하이스트

전체 청구항 수 : 총 21 항

(54) 발명의 명칭 유기발광표시장치, 데이터구동회로, 컨트롤러 및 구동방법

### (57) 요 약

본 발명은 유기발광표시장치, 데이터구동회로, 컨트롤러 및 구동방법에 관한 것으로서, 더욱 상세하게는, 검은색의 디 형태의 블록이 보이는 라인 결함을 발생시키는 불량 서브픽셀을 검출하고, 검출된 불량 서브픽셀의 구동이 다른 서브픽셀에 영향을 주지 않도록 하는 데이터전압을 불량 서브픽셀에 공급함으로써, 라인 결함을 방지하여 화상 품질을 향상시켜줄 수 있는 유기발광표시장치, 데이터구동회로, 컨트롤러 및 구동방법에 관한 것이다.

대 표 도 - 도1

(52) CPC특허분류

*G09G 3/2074* (2013.01)

*G09G 3/3275* (2013.01)

*G09G 2230/00* (2013.01)

*G09G 2300/0842* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

다수의 데이터라인, 다수의 게이트라인 및 다수의 기준전압라인이 배치되고, 상기 다수의 데이터라인과 상기 다수의 게이트라인에 의해 정의되는 다수의 서브픽셀이 매트릭스 타입으로 배열된 유기발광표시장치;

상기 다수의 데이터라인을 구동하는 데이터구동회로;

상기 다수의 게이트라인을 구동하는 게이트구동회로; 및

상기 데이터구동회로 및 상기 게이트구동회로를 제어하는 컨트롤러를 포함하고,

상기 다수의 서브픽셀 각각은,

유기발광다이오드와, 상기 유기발광다이오드를 구동하는 구동 트랜지스터와, 제1 스캔신호에 의해 제어되며 상기 구동 트랜지스터의 제1 노드와 상기 다수의 데이터라인 중 하나의 데이터라인 사이에 전기적으로 연결된 제1 트랜지스터와, 제2 스캔신호에 의해 제어되며 상기 구동 트랜지스터의 제2 노드와 상기 다수의 기준전압라인 중 하나의 기준전압라인 사이에 전기적으로 연결된 제2 트랜지스터와, 상기 제1 노드와 상기 제2 노드 사이에 전기적으로 연결된 캐패시터를 포함하고,

상기 다수의 기준전압라인의 개수는 상기 다수의 데이터라인의 개수보다 적고, 상기 다수의 기준전압라인 각각은 둘 이상의 서브픽셀에 포함된 제2 트랜지스터들의 소스 노드 또는 드레인 노드와 공통으로 연결되고,

상기 다수의 기준전압라인 각각과 기준전압이 공급되는 기준전압 공급 노드 간의 연결을 제어하는 기준 스위치와, 상기 다수의 기준전압라인 각각과 아날로그 디지털 컨버터 간의 연결을 제어하는 샘플링 스위치를 더 포함하고,

제1 기준전압라인을 통해 기준전압을 공통으로 공급받는 둘 이상의 서브픽셀 중 제1 서브픽셀 내 제2 트랜지스터가 단락이 된 경우, 상기 데이터구동회로는,

상기 제1 서브픽셀의 구동 기간에, 상기 제1 서브픽셀 내 구동 트랜지스터가 턴-오프 되도록 하는 제1 특정 데이터전압을 제1 데이터라인을 통해 상기 제1 서브픽셀로 공급하는 유기발광표시장치.

#### 청구항 2

제1항에 있어서,

상기 제1 서브픽셀의 구동 기간에,

상기 제1 서브픽셀과 함께 상기 제1 기준전압라인에 연결된 제2 서브픽셀 내 구동 트랜지스터의 이동도 센싱이 진행되는 유기발광표시장치의 컨트롤러.

#### 청구항 3

제1항에 있어서,

미리 정의된 불량 서브픽셀 검출 기간 동안 상기 다수의 서브픽셀 중 확인 대상 서브픽셀 내 제2 트랜지스터의 단락 여부에 따라, 상기 확인 대상 서브픽셀을 불량 서브픽셀로서 검출하는 불량 서브픽셀 검출 회로를 더 포함하고,

상기 불량 서브픽셀 검출 회로는,

상기 확인 대상 서브픽셀 내 제2 트랜지스터의 게이트 노드에 턴-오프 레벨 전압의 제2 스캔신호가 인가되고 있는 동안,

상기 확인 대상 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 기준전압라인의 전압 변화 여부 또는 전압 변화 크기에 기초하여, 상기 확인 대상 서브픽셀 내 제2 트랜지스터의 단락 여부를 판단하는 유기발광표시장치.

#### 청구항 4

제3항에 있어서,

상기 불량 서브픽셀 검출 회로는,

상기 제1 서브픽셀의 구동 기간 전에 상기 확인 대상 서브픽셀로서 상기 제1 서브픽셀 내 제2 트랜지스터의 단락 여부를 판단하되,

상기 제1 서브픽셀 내 제2 트랜지스터의 게이트 노드에 턴-오프 레벨 전압의 제2 스캔신호가 인가되고 있는 동안, 상기 제1 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 상기 제1 기준전압라인의 전압이 상승한 것으로 확인되면, 상기 제1 서브픽셀 내 제2 트랜지스터가 단락이 된 것으로 판단하여, 상기 제1 서브픽셀을 불량 서브픽셀로서 검출하는 유기발광표시장치.

#### 청구항 5

제3항에 있어서,

상기 불량 서브픽셀 검출 회로는,

상기 제1 서브픽셀과 함께 상기 제1 기준전압라인에 연결된 제2 서브픽셀이 상기 확인 대상 서브픽셀인 경우, 상기 제2 서브픽셀 내 제2 트랜지스터의 게이트 노드에 턴-오프 레벨 전압의 제2 스캔신호가 인가되고 있는 동안,

상기 제2 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 상기 제1 기준전압라인의 전압변화가 없거나 전압 변화 크기가 미리 정해진 임계 수준 이하인 것으로 확인되면,

상기 제2 서브픽셀 내 제2 트랜지스터가 미 단락이 된 것으로 판단하여, 상기 제2 서브픽셀을 정상 서브픽셀로서 검출하는 유기발광표시장치.

#### 청구항 6

제5항에 있어서,

상기 데이터구동회로는,

상기 제2 서브픽셀이 구동될 때, 상기 제1 서브픽셀 내 구동 트랜지스터가 턴-오프 되도록 하는 제1 특정 데이터전압을 상기 제1 데이터라인을 통해 상기 제1 서브픽셀로 공급하는 유기발광표시장치.

#### 청구항 7

제3항에 있어서,

상기 불량 서브픽셀 검출 기간은,

파워 온 신호가 발생하고 디스플레이 구동이 시작되기 전에 진행되거나,

파워 오프 신호가 발생한 이후에 진행되거나,

디스플레이 구동 중 실시간으로 진행되는 유기발광표시장치.

**청구항 8**

제1항에 있어서,

상기 제1 서브픽셀과 함께 상기 제1 기준전압라인에 연결된 제2 서브픽셀은 구동 기간에 구동 트랜지스터가 턴-온 되도록 하는 데이터전압이 인가되고,

상기 제2 서브픽셀은 상기 제1 서브픽셀과 동일한 서브픽셀 행에 배치되는 유기발광표시장치.

**청구항 9**

제1항에 있어서,

상기 제1 서브픽셀과 함께 상기 제1 기준전압라인에 연결된 제2 서브픽셀은 구동 기간에 구동 트랜지스터가 턴-온 되도록 하는 데이터전압이 인가되고,

상기 제2 서브픽셀은 상기 제1 서브픽셀과 다른 서브픽셀 행에 배치되는 유기발광표시장치.

**청구항 10**

제1항에 있어서,

상기 제2 트랜지스터가 단락이 된 불량 서브픽셀의 위치정보를 저장하는 메모리를 더 포함하고,

상기 컨트롤러는,

상기 메모리를 참조하여, 상기 불량 서브픽셀에 공급해야 하는 영상데이터를 상기 불량 서브픽셀 내 구동 트랜지스터를 턴-오프 시키는 특정 영상데이터로 교체하여 상기 데이터구동회로로 출력하는 유기발광표시장치.

**청구항 11**

제1항에 있어서,

상기 제1 특정 데이터전압은 시간경과에 따라 변화되는 유기발광표시장치.

**청구항 12**

유기발광다이오드와, 상기 유기발광다이오드를 구동하는 구동 트랜지스터와, 제1 스캔신호에 의해 제어되며 상기 구동 트랜지스터의 제1 노드와 상기 다수의 데이터라인 중 하나의 데이터라인 사이에 전기적으로 연결된 제1 트랜지스터와, 제2 스캔신호에 의해 제어되며 상기 구동 트랜지스터의 제2 노드와 상기 다수의 기준전압라인 중 하나의 기준전압라인 사이에 전기적으로 연결된 제2 트랜지스터와, 상기 제1 노드와 상기 제2 노드 사이에 전기적으로 연결된 캐패시터를 포함하는 다수의 서브픽셀이 배열된 유기발광표시패널과 전기적으로 연결된 데이터구동회로에 있어서,

입력된 영상데이터를 저장하는 래치회로;

상기 영상데이터를 아날로그 신호들로 변환하는 디지털 아날로그 변환회로;

상기 아날로그 신호들에 대응되는 데이터전압들을  $n$ 개의 데이터라인과 대응되는  $n$ ( $n$ 은 2 이상의 자연수)개의 데이터채널로 출력하는 출력회로;

$m$ ( $m$ 은 1 이상의 자연수)개의 기준전압라인의 전압을 디지털 값으로 변환하여 출력하는 아날로그 디지털 변환회로; 및

상기  $m$ 개의 기준전압라인에 대응되는  $m$ 개의 기준채널과 상기 아날로그 디지털 변환회로 사이에 연결된 스위치회로를 포함하고,

상기  $n$ 은 상기  $m$ 의 2 이상의 정수 배이고,

상기  $m$ 개의 기준전압라인 각각은, 둘 이상의 서브픽셀에 포함된 제2 트랜지스터들의 소스 노드 또는 드레인 노드와 공통으로 연결되고,

상기 다수의 서브픽셀은 상기  $m$ 개의 기준전압라인 중 제1 기준전압라인을 통해 기준전압을 공통으로 공급받는 둘 이상의 서브픽셀 중에서 제1 서브픽셀 내 제2 트랜지스터가 단락이 된 경우,

상기 제1 서브픽셀의 구동 기간에, 상기 제1 서브픽셀 내 구동 트랜지스터가 턴-오프 되도록 하는 제1 특정 데이터전압이 제1 데이터라인으로 출력되어 상기 제1 서브픽셀로 공급되는 데이터구동회로.

### 청구항 13

제12항에 있어서,

상기 제1 서브픽셀의 구동 기간에, 상기 아날로그 디지털 변환회로는,

상기 제1 서브픽셀과 함께 상기 제1 기준전압라인에 연결된 제2 서브픽셀 내 구동 트랜지스터의 제2 노드의 상승된 전압을 상기 제1 기준전압라인을 통해 센싱하는 데이터구동회로.

### 청구항 14

제12항에 있어서,

상기 제1 서브픽셀과 함께 상기 제1 기준전압라인에 연결된 제2 서브픽셀 내 제2 트랜지스터는 미 단락되어 있고, 상기 제2 서브픽셀이 구동될 때,

상기 제1 서브픽셀 내 구동 트랜지스터가 턴-오프 되도록 하는 제1 특정 데이터전압이 상기 제1 데이터라인을 통해 상기 제1 서브픽셀로 공급되는 데이터구동회로.

### 청구항 15

다수의 데이터라인, 다수의 게이트라인 및 다수의 기준전압라인이 배치되고, 상기 다수의 데이터라인과 상기 다수의 게이트라인에 의해 정의되는 다수의 서브픽셀이 매트릭스 타입으로 배열되며, 상기 다수의 서브픽셀 각각은 유기발광다이오드와, 상기 유기발광다이오드를 구동하는 구동 트랜지스터와, 제1 스캔신호에 의해 제어되며 상기 구동 트랜지스터의 제1 노드와 상기 다수의 데이터라인 중 하나의 데이터라인 사이에 전기적으로 연결된 제1 트랜지스터와, 제2 스캔신호에 의해 제어되며 상기 구동 트랜지스터의 제2 노드와 상기 다수의 기준전압라인 중 하나의 기준전압라인 사이에 전기적으로 연결된 제2 트랜지스터와, 상기 제1 노드와 상기 제2 노드 사이에 전기적으로 연결된 캐패시터가 배치되어 있는 유기발광표시패널을 포함하는 유기발광표시장치의 구동방법에 있어서,

상기 다수의 서브픽셀 중 제1 기준전압라인을 통해 기준전압을 공통으로 공급받는 둘 이상의 서브픽셀 중 제1 서브픽셀의 구동 기간에, 영상 구동을 위한 데이터전압을 제1 데이터라인을 통해 상기 제1 서브픽셀로 공급하는 정상 구동 단계; 및

상기 제1 서브픽셀 내 제2 트랜지스터가 단락이 된 경우, 상기 제1 서브픽셀의 구동 기간에, 상기 제1 서브픽셀 내 구동 트랜지스터가 턴-오프 되도록 하는 제1 특정 데이터전압을 제1 데이터라인을 통해 상기 제1 서브픽셀로 공급하는 라인 결합 방지 단계를 포함하는 유기발광표시장치의 구동방법.

### 청구항 16

제15항에 있어서,

상기 라인 결합 방지 단계에서,

상기 제1 서브픽셀과 함께 상기 제1 기준전압라인에 연결된 제2 서브픽셀 내 구동 트랜지스터의 이동도 센싱이 진행되는 유기발광표시장치의 구동방법.

### 청구항 17

제15항에 있어서,

상기 정상 구동 단계와 상기 라인 결합 방지 단계 사이에,

상기 다수의 서브픽셀 중 확인 대상 서브픽셀인 상기 제1 서브픽셀 내 제2 트랜지스터의 단락 여부를 판단하여 상기 확인 대상 서브픽셀인 상기 제1 서브픽셀이 불량 서브픽셀인지 아닌지를 검출하는 불량 서브픽셀 검출 단계를 더 포함하고,

상기 불량 서브픽셀 검출 단계는,

상기 제1 서브픽셀 내 제2 트랜지스터의 게이트 노드에 턴-오프 레벨 전압의 제2 스캔신호가 인가되고 있는 동안, 상기 제1 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 제1 기준전압라인의 전압 변화 여부 또는 전압 변화 크기에 기초하여, 상기 확인 대상 서브픽셀 내 제2 트랜지스터의 단락 여부를 판단하되,

상기 제1 서브픽셀 내 제2 트랜지스터의 게이트 노드에 턴-오프 레벨 전압의 제2 스캔신호가 인가되고 있는 동안, 상기 제1 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 상기 제1 기준전압라인의 전압이 상승한 것으로 확인되면, 상기 제1 서브픽셀 내 제2 트랜지스터의 단락이 된 것으로 판단되어, 상기 제1 서브픽셀을 불량 서브픽셀로서 검출하는 유기발광표시장치의 구동방법.

### 청구항 18

제17항에 있어서,

상기 불량 서브픽셀 검출 단계는,

상기 제1 서브픽셀 내 제1 트랜지스터의 게이트 노드로 턴-온 레벨 전압의 제1 스캔신호를 공급하고, 상기 제1 서브픽셀 내 제2 트랜지스터의 게이트 노드로 턴-온 레벨 전압의 제2 스캔신호를 공급하고, 상기 제1 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 제1 기준전압라인에 연결된 기준 스위치를 턴-온 시키고, 상기 제1 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 제1 기준전압라인에 연결된 샘플링 스위치를 턴-오프 시키는 제1 단계;

상기 제1 단계 이후, 상기 제1 서브픽셀 내 제1 트랜지스터의 게이트 노드로 턴-오프 레벨 전압의 제1 스캔신호를 공급하고, 상기 제1 서브픽셀 내 제2 트랜지스터의 게이트 노드로 턴-오프 레벨 전압의 제2 스캔신호를 공급하고, 상기 제1 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 제1 기준전압라인에 연결된 기준 스위치를 턴-오프 시키고, 상기 제1 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 샘플링 스위치를 턴-오프 시키는 제2 단계;

상기 제2 단계 이후, 상기 제1 서브픽셀 내 제1 트랜지스터의 게이트 노드로 턴-오프 레벨 전압의 제1 스캔신호를 공급하고, 상기 제1 서브픽셀 내 제2 트랜지스터의 게이트 노드로 턴-오프 레벨 전압의 제2 스캔신호를 공급하고, 상기 제1 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 제1 기준전압라인에 연결된 기준 스위치를 턴-오프 시키고, 상기 제1 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 샘플링 스위치를 턴-온 시키는 제3 단계;

상기 샘플링 스위치가 턴-온 됨에 따라, 상기 아날로그 디지털 컨버터가 상기 샘플링 스위치를 통해 전기적으로 연결된 제1 기준전압라인의 전압을 센싱하여 센싱된 전압을 디지털 값에 해당하는 센싱값으로 변환하는 제4 단계; 및

상기 센싱값을 토대로, 제1 기준전압라인의 전압 변화 여부 또는 전압 변화 크기를 확인하여 제2 트랜지스터의 단락 여부를 판단하여, 상기 제1 서브픽셀이 불량 서브픽셀인지 아닌지를 검출하는 제5 단계를 포함하는 유기발광표시장치의 구동방법.

## 청구항 19

다수의 데이터라인, 다수의 게이트라인 및 다수의 기준전압라인이 배치되고, 상기 다수의 데이터라인과 상기 다수의 게이트라인에 의해 정의되는 다수의 서브픽셀이 매트릭스 타입으로 배열되며, 상기 다수의 서브픽셀 각각은 유기발광다이오드와, 상기 유기발광다이오드를 구동하는 구동 트랜지스터와, 제1 스캔신호에 의해 제어되며 상기 구동 트랜지스터의 제1 노드와 상기 다수의 데이터라인 중 하나의 데이터라인 사이에 전기적으로 연결된 제1 트랜지스터와, 제2 스캔신호에 의해 제어되며 상기 구동 트랜지스터의 제2 노드와 상기 다수의 기준전압라인 중 하나의 기준전압라인 사이에 전기적으로 연결된 제2 트랜지스터와, 상기 제1 노드와 상기 제2 노드 사이에 전기적으로 연결된 캐패시터가 배치되어 있는 유기발광표시장치의 컨트롤러에 있어서,

상기 다수의 기준전압라인 중 제1 기준전압라인을 통해 기준전압을 공통으로 공급받는 둘 이상의 서브픽셀 중 제1 서브픽셀 내 제2 트랜지스터가 단락 된 정보 또는 상기 제1 서브픽셀의 위치정보를 저장하는 메모리; 및 상기 메모리를 참조하여, 상기 제1 서브픽셀 내 제2 트랜지스터가 단락이 된 경우, 상기 제1 서브픽셀의 구동기간에, 상기 제1 서브픽셀에 공급해야 하는 영상데이터를 상기 제1 서브픽셀 내 구동 트랜지스터가 턴-오프 되도록 하는 제1 특정 영상데이터로 교체하여 데이터구동회로로 출력하는 영상데이터 공급기를 포함하는 유기발광표시장치의 컨트롤러.

## 청구항 20

제19항에 있어서,

상기 제1 서브픽셀의 구동 기간에, 상기 제1 서브픽셀과 함께 상기 제1 기준전압라인에 연결된 제2 서브픽셀 내 구동 트랜지스터의 이동도 센싱이 진행되는 유기발광표시장치의 컨트롤러.

## 청구항 21

제19항에 있어서,

불량 서브픽셀 검출 기간 동안 상기 다수의 서브픽셀 중 확인 대상 서브픽셀 내 제2 트랜지스터의 단락 여부에 따라 상기 확인 대상 서브픽셀이 불량 서브픽셀인지 아닌지를 검출하는 불량 서브픽셀 검출 회로를 더 포함하고,

상기 불량 서브픽셀 검출 회로는,

상기 확인 대상 서브픽셀 내 제2 트랜지스터의 게이트 노드에 턴-오프 레벨 전압의 제2 스캔신호가 인가되고 있는 동안,

상기 확인 대상 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 기준전압라인의 전압 변화 여부 또는 전압 변화 크기에 기초하여, 상기 확인 대상 서브픽셀 내 제2 트랜지스터의 단락 여부를 판단하는 유기발광표시장치의 컨트롤러.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 유기발광표시장치, 데이터구동회로, 컨트롤러 및 구동방법에 관한 것이다.

### 배경 기술

[0002] 최근, 표시장치로서 각광받고 있는 유기발광표시장치는 스스로 발광하는 유기발광다이오드(OLED: Organic Light Emitting Diode)를 이용함으로써 응답속도가 빠르고, 발광효율, 휘도 및 시야각 등이 크다는 장점이 있다.

[0003] 유기발광표시장치는 유기발광다이오드와 이를 구동하기 위한 구동 트랜지스터가 포함된 서브픽셀을 매트릭스 형태로 배열하고 스캔 신호에 의해 선택된 서브픽셀들의 밝기를 데이터의 계조에 따라 제어한다.

[0004] 종래의 유기발광표시장치는 검은색의 띠 형태의 블록이 보이는 화면 이상 현상이 발생하는 문제점이 발생하고 있는 실정이다. 이러한 라인 결함은 그 원인 및 최초 발생 위치 등을 알아내기가 어려운 문제점이며, 유기발광표시장치의 품질에 큰 영향을 끼칠 수 있다.

### 발명의 내용

#### 해결하려는 과제

[0005] 이러한 배경에서, 본 발명의 실시예들의 목적은, 검은색의 띠 형태의 블록이 보이는 라인 결함을 방지하여 화상 품질을 향상시켜줄 수 있는 유기발광표시장치, 데이터구동회로, 컨트롤러 및 구동방법을 제공하는데 있다.

[0006] 본 발명의 실시예들의 다른 목적은, 라인 결함을 발생시키는 불량 서브픽셀을 검출할 수 있는 유기발광표시장치, 데이터구동회로, 컨트롤러 및 구동방법을 제공하는데 있다.

[0007] 본 발명의 실시예들의 또 다른 목적은, 불량 서브픽셀의 구동에 의해 다른 정상 서브픽셀의 센싱 및 보상 오류가 발생하지 않도록 해줌으로써, 영상 품질을 향상시켜줄 수 있는 유기발광표시장치, 데이터구동회로, 컨트롤러 및 구동방법을 제공하는데 있다.

#### 과제의 해결 수단

[0008] 일 측면에서, 본 발명의 실시예들은 라인 결함을 방지할 수 있는 유기발광표시장치, 데이터구동회로, 컨트롤러 및 구동방법을 제공할 수 있다.

[0009] 다른 측면에서, 본 발명의 실시예들은, 다수의 데이터라인, 다수의 게이트라인 및 다수의 기준전압라인이 배치되고, 다수의 데이터라인과 다수의 게이트라인에 의해 정의되는 다수의 서브픽셀이 매트릭스 타입으로 배열된 유기발광표시패널과, 다수의 데이터라인을 구동하는 데이터구동회로와, 다수의 게이트라인을 구동하는 게이트구동회로와, 데이터구동회로 및 게이트구동회로를 제어하는 컨트롤러를 포함하는 유기발광표시장치를 제공할 수 있다.

[0010] 다수의 서브픽셀 각각은, 유기발광다이오드와, 유기발광다이오드를 구동하는 구동 트랜지스터와, 제1 스캔신호에 의해 제어되며 구동 트랜지스터의 제1 노드와 다수의 데이터라인 중 하나의 데이터라인 사이에 전기적으로 연결된 제1 트랜지스터와, 제2 스캔신호에 의해 제어되며 구동 트랜지스터의 제2 노드와 다수의 기준전압라인 중 하나의 기준전압라인 사이에 전기적으로 연결된 제2 트랜지스터와, 제1 노드와 제2 노드 사이에 전기적으로 연결된 캐패시터를 포함할 수 있다.

[0011] 다수의 기준전압라인의 개수는 다수의 데이터라인의 개수보다 적을 수 있다.

[0012] 다수의 기준전압라인 각각은 둘 이상의 서브픽셀에 포함된 제2 트랜지스터들의 소스 노드 또는 드레인 노드와 공통으로 연결될 수 있다.

[0013] 유기발광표시장치는, 다수의 기준전압라인 각각과 기준전압이 공급되는 기준전압 공급 노드 간의 연결을 제어하는 기준 스위치와, 다수의 기준전압라인 각각과 아날로그 디지털 컨버터 간의 연결을 제어하는 샘플링 스위치를 더 포함할 수 있다.

[0014] 제1 기준전압라인을 통해 기준전압을 공통으로 공급받는 둘 이상의 서브픽셀 중에서, 제1 서브픽셀 내 제2 트랜지스터가 단락이 된 경우, 데이터구동회로는, 제1 서브픽셀의 구동 기간에, 제1 서브픽셀 내 구동 트랜지스터가 턠-오프 되도록 하는 제1 특정 데이터전압을 제1 데이터라인을 통해 제1 서브픽셀로 공급할 수 있다.

[0015] 제1 서브픽셀의 구동 기간에, 제1 서브픽셀과 함께 제1 기준전압라인에 연결된 제2 서브픽셀 내 구동 트랜지스터의 이동도 센싱이 진행될 수 있다.

[0016] 유기발광표시장치는, 미리 정의된 불량 서브픽셀 검출 기간 동안 다수의 서브픽셀 중 확인 대상 서브픽셀 내 제2 트랜지스터의 단락 여부에 따라, 확인 대상 서브픽셀을 불량 서브픽셀로서 검출하는 불량 서브픽셀 검출 회로를 더 포함할 수 있다.

[0017] 불량 서브픽셀 검출 회로는, 확인 대상 서브픽셀 내 제2 트랜지스터의 게이트 노드에 턠-오프 레벨 전압의 제2 스캔신호가 인가되고 있는 동안, 확인 대상 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 기준전압라인의 전압 변화 여부 또는 전압 변화 크기에 기초하여, 확인 대상 서브픽셀 내 제2 트랜지스터의 단락 여부를 판단할 수 있다.

- [0018] 불량 서브픽셀 검출 회로는, 제1 서브픽셀의 구동 기간 전에 확인 대상 서브픽셀로서 제1 서브픽셀 내 제2 트랜지스터의 단락 여부를 판단하되, 제1 서브픽셀 내 제2 트랜지스터의 게이트 노드에 턴-오프 레벨 전압의 제2 스캔신호가 인가되고 있는 동안, 제1 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 제1 기준전압라인의 전압이 상승한 것으로 확인되면, 제1 서브픽셀 내 제2 트랜지스터가 단락이 된 것으로 판단하여, 제1 서브픽셀을 불량 서브픽셀로서 검출할 수 있다.

- [0019] 불량 서브픽셀 검출 회로는, 제1 서브픽셀과 함께 제1 기준전압라인에 연결된 제2 서브픽셀이 확인 대상 서브픽셀인 경우, 제2 서브픽셀 내 제2 트랜지스터의 게이트 노드에 턴-오프 레벨 전압의 제2 스캔신호가 인가되고 있는 동안, 제2 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 제1 기준전압라인의 전압변화가 없거나 전압 변화 크기가 미리 정해진 임계 수준 이하인 것으로 확인되면, 제2 서브픽셀 내 제2 트랜지스터가 미 단락이 된 것으로 판단하여, 제2 서브픽셀을 정상 서브픽셀로서 검출할 수 있다.

- [0020] 데이터구동회로는, 제2 서브픽셀이 구동될 때, 제1 서브픽셀 내 구동 트랜지스터가 턴-오프 되도록 하는 제1 특정 데이터전압을 제1 데이터라인을 통해 제1 서브픽셀로 공급할 수 있다.

- [0021] 불량 서브픽셀 검출 기간은, 파워 온 신호가 발생하고 디스플레이 구동이 시작되기 전에 진행되거나, 파워 오프 신호가 발생한 이후에 진행되거나, 디스플레이 구동 중 실시간으로 진행될 수 있다.

- [0022] 제1 서브픽셀과 함께 제1 기준전압라인에 연결된 제2 서브픽셀은, 정상 서브픽셀인 경우, 구동 기간에 구동 트랜지스터가 턴-온 되도록 하는 데이터전압이 인가될 수 있다.

- [0023] 이러한 정상 서브픽셀인 제2 서브픽셀은 불량 서브픽셀인 제1 서브픽셀과 동일한 서브픽셀 행에 배치될 수도 있고, 다른 서브픽셀 행에 배치될 수도 있다.

- [0024] 유기발광표시장치는, 제2 트랜지스터가 단락이 된 불량 서브픽셀의 위치정보를 저장하는 메모리를 더 포함할 수 있다.

- [0025] 컨트롤러는, 메모리를 참조하여, 불량 서브픽셀에 공급해야 하는 영상데이터를 불량 서브픽셀 내 구동 트랜지스터를 턴-오프 시키는 특정 영상데이터로 교체하여 데이터구동회로로 출력할 수 있다.

- [0026] 다른 측면에서, 본 발명의 실시예들은, 라인 결함을 방지할 수 있는 데이터구동회로를 제공할 수 있다.

- [0027] 데이터구동회로는, 입력된 영상데이터를 저장하는 래치회로와, 영상데이터를 아날로그 신호들로 변환하는 디지털 아날로그 변환회로와, 아날로그 신호들에 대응되는 데이터전압들을  $n$ 개의 데이터라인과 대응되는  $n$ ( $n$ 은 2 이상의 자연수)개의 데이터채널로 출력하는 출력회로와,  $m$ ( $m$ 은 1 이상의 자연수)개의 기준전압라인의 전압을 디지털 값으로 변환하여 출력하는 아날로그 디지털 변환회로와,  $m$ 개의 기준전압라인에 대응되는  $m$ 개의 기준채널과 아날로그 디지털 변환회로 사이에 연결된 스위치 회로를 포함할 수 있다.

- [0028]  $n$ 은  $m$ 의 2 이상의 정수 배일 수 있다.

- [0029]  $m$ 개의 기준전압라인 각각은, 둘 이상의 서브픽셀에 포함된 제2 트랜지스터들의 소스 노드 또는 드레인 노드와 공통으로 연결될 수 있다.

- [0030] 다수의 서브픽셀은  $m$ 개의 기준전압라인 중 제1 기준전압라인을 통해 기준전압을 공통으로 공급받는 둘 이상의 서브픽셀 중에서 제1 서브픽셀 내 제2 트랜지스터가 단락이 된 경우, 제1 서브픽셀의 구동 기간에, 제1 서브픽셀 내 구동 트랜지스터가 턴-오프 되도록 하는 제1 특정 데이터전압이 제1 데이터라인으로 출력되어 제1 서브픽셀로 공급될 수 있다.

- [0031] 제1 서브픽셀의 구동 기간에, 아날로그 디지털 변환회로는, 제1 서브픽셀과 함께 제1 기준전압라인에 연결된 제2 서브픽셀 내 구동 트랜지스터의 제2 노드의 상승된 전압을 제1 기준전압라인을 통해 센싱할 수 있다.

- [0032] 제1 서브픽셀과 함께 제1 기준전압라인에 연결된 제2 서브픽셀 내 제2 트랜지스터는 미 단락 되어 있고, 제2 서브픽셀이 구동될 때, 제1 서브픽셀 내 구동 트랜지스터가 턴-오프 되도록 하는 제1 특정 데이터전압이 제1 데이터라인을 통해 제1 서브픽셀로 공급될 수 있다.

- [0033] 또 다른 측면에서, 본 발명의 실시예들은, 라인 결함을 방지할 수 있는 유기발광표시장치의 구동방법을 제공할 수 있다.

- [0034] 구동방법은, 다수의 서브픽셀 중 제1 기준전압라인을 통해 기준전압을 공통으로 공급받는 둘 이상의 서브픽셀 중 제1 서브픽셀의 구동 기간에, 영상 구동을 위한 데이터전압을 제1 데이터라인을 통해 제1 서브픽셀로 공급하

는 정상 구동 단계와, 제1 서브픽셀 내 제2 트랜지스터가 단락이 된 경우, 제1 서브픽셀의 구동 기간에, 제1 서브픽셀 내 구동 트랜지스터가 턴-오프 되도록 하는 제1 특정 데이터전압을 제1 데이터라인을 통해 제1 서브픽셀로 공급하는 라인 결합 방지 단계를 포함할 수 있다.

[0035] 라인 결합 방지 단계에서, 제1 서브픽셀과 함께 제1 기준전압라인에 연결된 제2 서브픽셀 내 구동 트랜지스터의 이동도 센싱이 진행될 수 있다.

[0036] 구동방법은, 정상 구동 단계와 라인 결합 방지 단계 사이에, 다수의 서브픽셀 중 확인 대상 서브픽셀인 제1 서브픽셀 내 제2 트랜지스터의 단락 여부를 판단하여 확인 대상 서브픽셀인 제1 서브픽셀이 불량 서브픽셀인지 아닌지를 검출하는 불량 서브픽셀 검출 단계를 더 포함할 수 있다.

[0037] 불량 서브픽셀 검출 단계는, 제1 서브픽셀 내 제2 트랜지스터의 게이트 노드에 턴-오프 레벨 전압의 제2 스캔신호가 인가되고 있는 동안, 제1 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 제1 기준전압라인의 전압 변화 여부 또는 전압 변화 크기에 기초하여, 확인 대상 서브픽셀 내 제2 트랜지스터의 단락 여부를 판단할 수 있다.

[0038] 불량 서브픽셀 검출 단계는, 제1 서브픽셀 내 제2 트랜지스터의 게이트 노드에 턴-오프 레벨 전압의 제2 스캔신호가 인가되고 있는 동안, 제1 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 제1 기준전압라인의 전압이 상승한 것으로 확인되면, 제1 서브픽셀 내 제2 트랜지스터의 단락이 된 것으로 판단되어, 제1 서브픽셀을 불량 서브픽셀로서 검출할 수 있다.

[0039] 불량 서브픽셀 검출 단계는, 제1 서브픽셀 내 제1 트랜지스터의 게이트 노드로 턴-온 레벨 전압의 제1 스캔신호를 공급하고, 제1 서브픽셀 내 제2 트랜지스터의 게이트 노드로 턴-온 레벨 전압의 제2 스캔신호를 공급하고, 제1 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 제1 기준전압라인에 연결된 기준 스위치를 턴-온 시키고, 제1 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 제1 기준전압라인에 연결된 기준 스위치를 턴-오프 시키고, 제1 서브픽셀 내 제1 트랜지스터의 게이트 노드로 턴-오프 레벨 전압의 제1 스캔신호를 공급하고, 제1 서브픽셀 내 제2 트랜지스터의 게이트 노드로 턴-오프 레벨 전압의 제2 스캔신호를 공급하고, 제1 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 제1 기준전압라인에 연결된 기준 스위치를 턴-오프 시키고, 제1 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 제1 기준전압라인에 연결된 기준 스위치를 턴-온 시키고, 제1 서브픽셀 내 제2 트랜지스터의 게이트 노드로 턴-오프 레벨 전압의 제1 스캔신호를 공급하고, 제1 서브픽셀 내 제2 트랜지스터의 게이트 노드로 턴-오프 레벨 전압의 제2 스캔신호를 공급하고, 제1 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 제1 기준전압라인에 연결된 기준 스위치를 턴-온 시키고, 제1 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 제1 기준전압라인에 연결된 기준 스위치를 턴-오프 시키고, 제1 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 제1 기준전압라인에 연결된 기준 스위치를 턴-온 시키는 제3 단계; 및 섬플링 스위치가 턴-온 됨에 따라, 아날로그 디지털 컨버터가 섬플링 스위치를 통해 전기적으로 연결된 제1 기준전압라인의 전압을 센싱하여 센싱된 전압을 디지털 값에 해당하는 센싱값으로 변환하는 제4 단계; 및 센싱값을 토대로, 제1 기준전압라인의 전압 변화 여부 또는 전압 변화 크기를 확인하여 제2 트랜지스터의 단락 여부를 판단하여, 제1 서브픽셀이 불량 서브픽셀인지 아닌지를 검출하는 제5 단계를 포함할 수 있다.

[0040] 또 다른 측면에서, 본 발명의 실시예들은, 라인 결함을 방지할 수 있는 유기발광표시장치의 컨트롤러를 제공할 수 있다.

[0041] 컨트롤러는, 다수의 기준전압라인 중 제1 기준전압라인을 통해 기준전압을 공통으로 공급받는 둘 이상의 서브픽셀 중 제1 서브픽셀 내 제2 트랜지스터가 단락 된 정보 또는 제1 서브픽셀의 위치정보를 저장하는 메모리와, 메모리를 참조하여, 제1 서브픽셀 내 제2 트랜지스터가 단락이 된 경우, 제1 서브픽셀의 구동 기간에, 제1 서브픽셀에 공급해야 하는 영상데이터를 제1 서브픽셀 내 구동 트랜지스터가 턴-오프 되도록 하는 제1 특정 영상데이터로 교체하여 데이터구동회로로 출력하는 영상데이터 공급기를 포함할 수 있다.

[0042] 제1 서브픽셀의 구동 기간에, 제1 서브픽셀과 함께 제1 기준전압라인에 연결된 제2 서브픽셀 내 구동 트랜지스터의 이동도 센싱이 진행될 수 있다.

[0043] 컨트롤러는 불량 서브픽셀 검출 기간 동안 다수의 서브픽셀 중 확인 대상 서브픽셀 내 제2 트랜지스터의 단락 여부에 따라 확인 대상 서브픽셀이 불량 서브픽셀인지 아닌지를 검출하는 불량 서브픽셀 검출 회로를 더 포함할 수 있다.

[0044] 불량 서브픽셀 검출 회로는, 확인 대상 서브픽셀 내 제2 트랜지스터의 게이트 노드에 턴-오프 레벨 전압의 제2

스캔신호가 인가되고 있는 동안, 확인 대상 서브픽셀 내 제2 트랜지스터의 소스 노드 또는 드레인 노드와 전기적으로 연결된 기준전압라인의 전압 변화 여부 또는 전압 변화 크기에 기초하여, 확인 대상 서브픽셀 내 제2 트랜지스터의 단락 여부를 판단할 수 있다.

### 발명의 효과

- [0045] 이상에서 설명한 본 발명의 실시예들에 의하면, 라인 결함을 방지하여 화상 품질을 향상시켜줄 수 있는 유기발광표시장치, 데이터구동회로, 컨트롤러 및 구동방법을 제공할 수 있다.

- [0046] 본 발명의 실시예들에 의하면, 라인 결함을 발생시키는 불량 서브픽셀을 검출할 수 있는 유기발광표시장치, 데이터구동회로, 컨트롤러 및 구동방법을 제공할 수 있다.

- [0047] 본 발명의 실시예들에 의하면, 불량 서브픽셀의 구동에 의해 다른 정상 서브픽셀의 센싱 및 보상 오류가 발생하지 않도록 해줌으로써, 영상 품질을 향상시켜줄 수 있는 유기발광표시장치, 데이터구동회로, 컨트롤러 및 구동방법을 제공할 수 있다.

### 도면의 간단한 설명

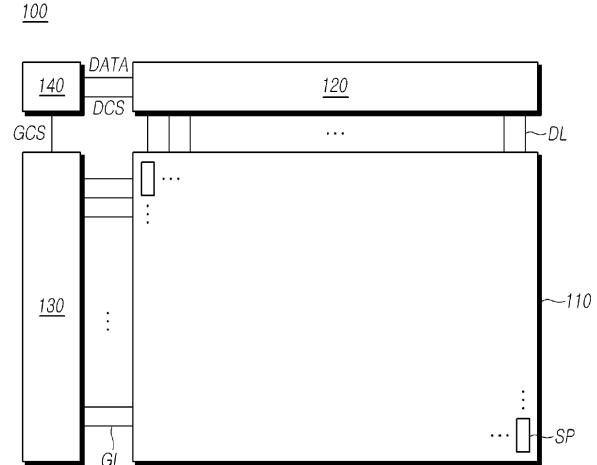

- [0048] 도 1은 본 발명의 실시예들에 따른 유기발광표시장치의 개략적인 시스템 구성도이다.

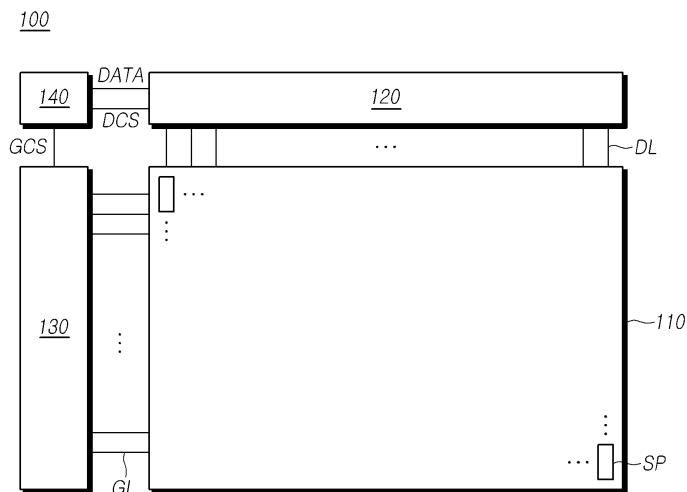

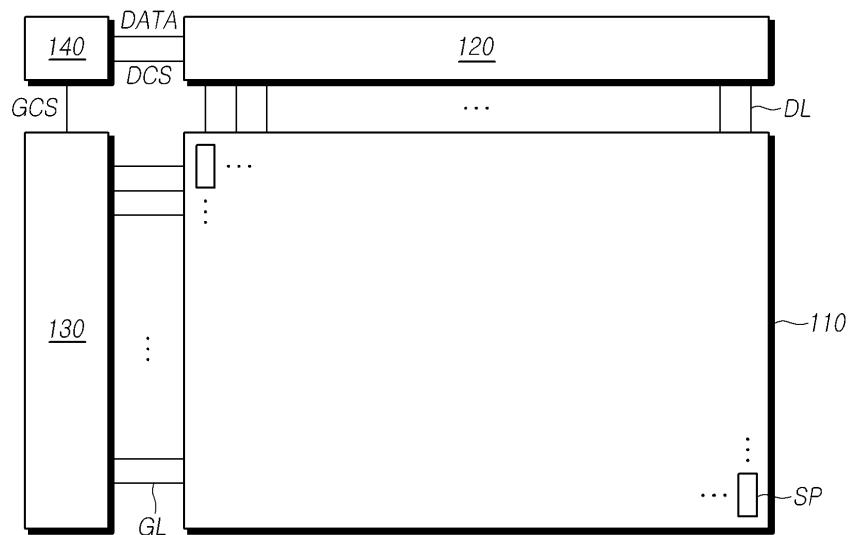

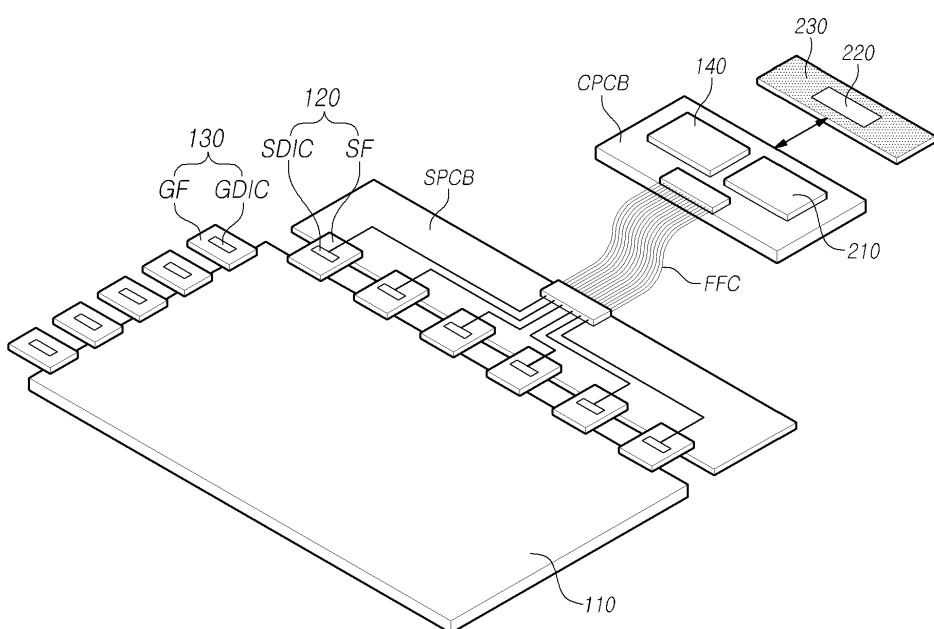

- 도 2는 본 발명의 실시예들에 따른 유기발광표시장치의 시스템 구현 예시도이다.

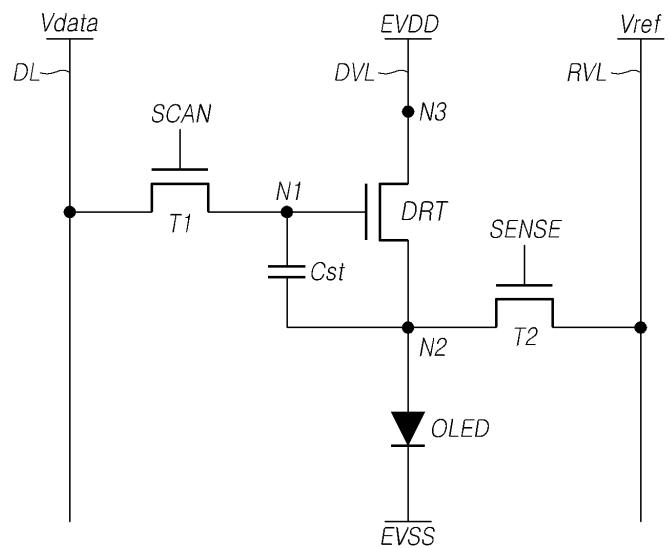

- 도 3은 본 발명의 실시예들에 따른 유기발광표시장치의 서브픽셀의 회로이다.

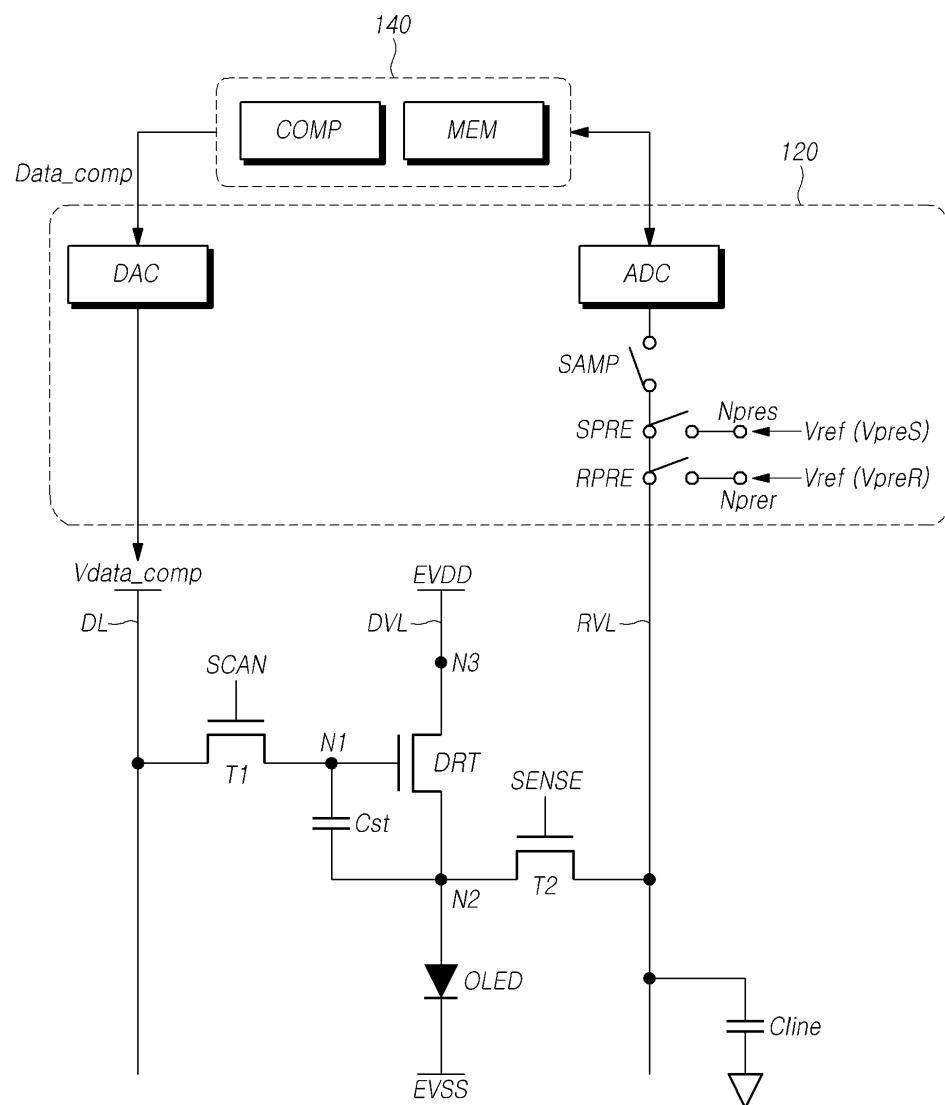

- 도 4는 본 발명의 실시예들에 따른 유기발광표시장치의 보상 회로이다.

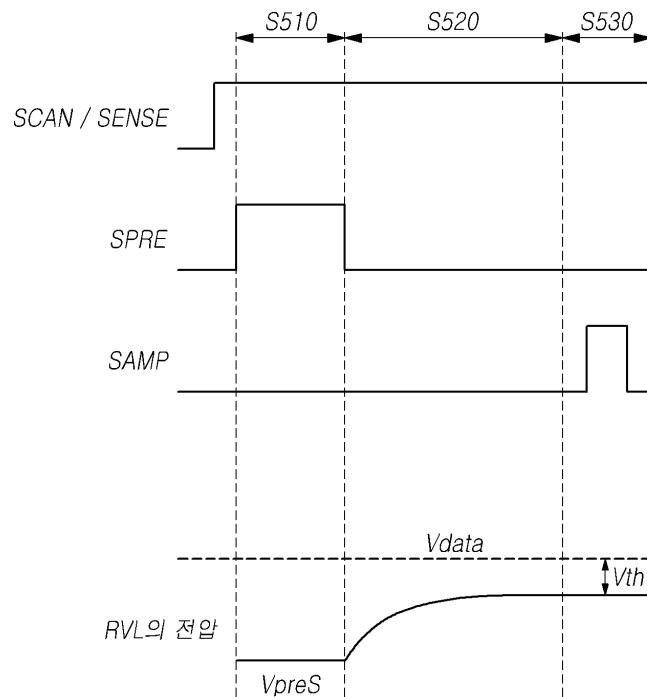

- 도 5는 본 발명의 실시예들에 따른 유기발광표시장치의 문턱전압 센싱을 위한 구동 타이밍 다이어그램이다.

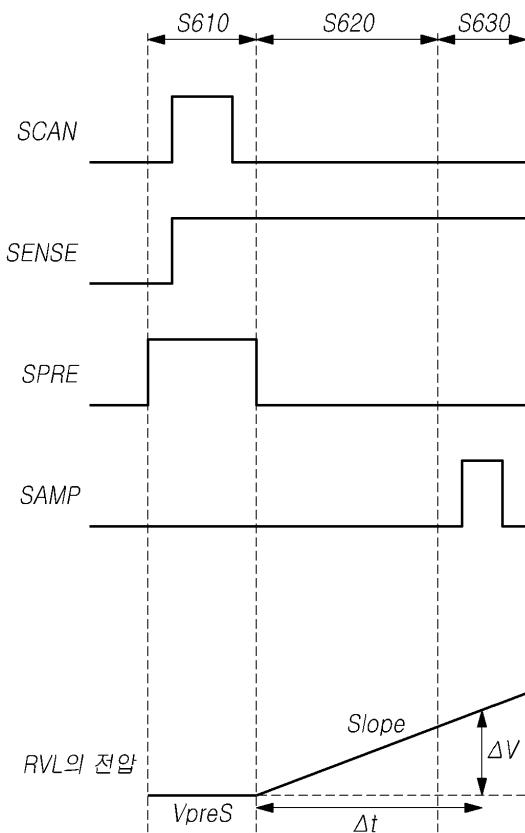

- 도 6은 본 발명의 실시예들에 따른 유기발광표시장치의 이동도 센싱을 위한 구동 타이밍 다이어그램이다.

- 도 7은 본 발명의 실시예들에 따른 유기발광표시장치의 센싱 프로세스를 나타낸 도면이다.

- 도 8은 본 발명의 실시예들에 따른 유기발광표시장치에서, 4개의 서브픽셀과 연결되는 배선들에 대한 배치도이다.

- 도 9는 본 발명의 실시예들에 따른 유기발광표시장치에서, 제2 트랜지스터가 단락이 된 서브픽셀 (불량 서브픽셀)의 회로이다.

- 도 10은 본 발명의 실시예들에 따른 유기발광표시장치에서, 하나의 기준전압라인을 공유하는 4개의 서브픽셀 중 불량 서브픽셀이 존재하는 경우, 4개의 서브픽셀에 대한 등가 회로이다.

- 도 11 및 도 12는 본 발명의 실시예들에 따른 유기발광표시장치에서, 하나의 기준전압라인을 공유하는 4개의 서브픽셀 중 불량 서브픽셀이 존재하는 경우, 불량 서브픽셀의 구동에 의해 발생되는 센싱 및 보상 오류와, 이에 따라 발생하는 라인 결함 현상을 설명하기 위한 도면들이다.

- 도 13은 본 발명의 실시예들에 따른 유기발광표시장치에서, 정상 서브픽셀과 불량 서브픽셀에 대한 문턱전압 센싱을 위한 구동 타이밍 다이어그램이다.

- 도 14는 본 발명의 실시예들에 따른 유기발광표시장치에서, 정상 서브픽셀과 불량 서브픽셀에 대한 이동도 센싱을 위한 구동 타이밍 다이어그램이다.

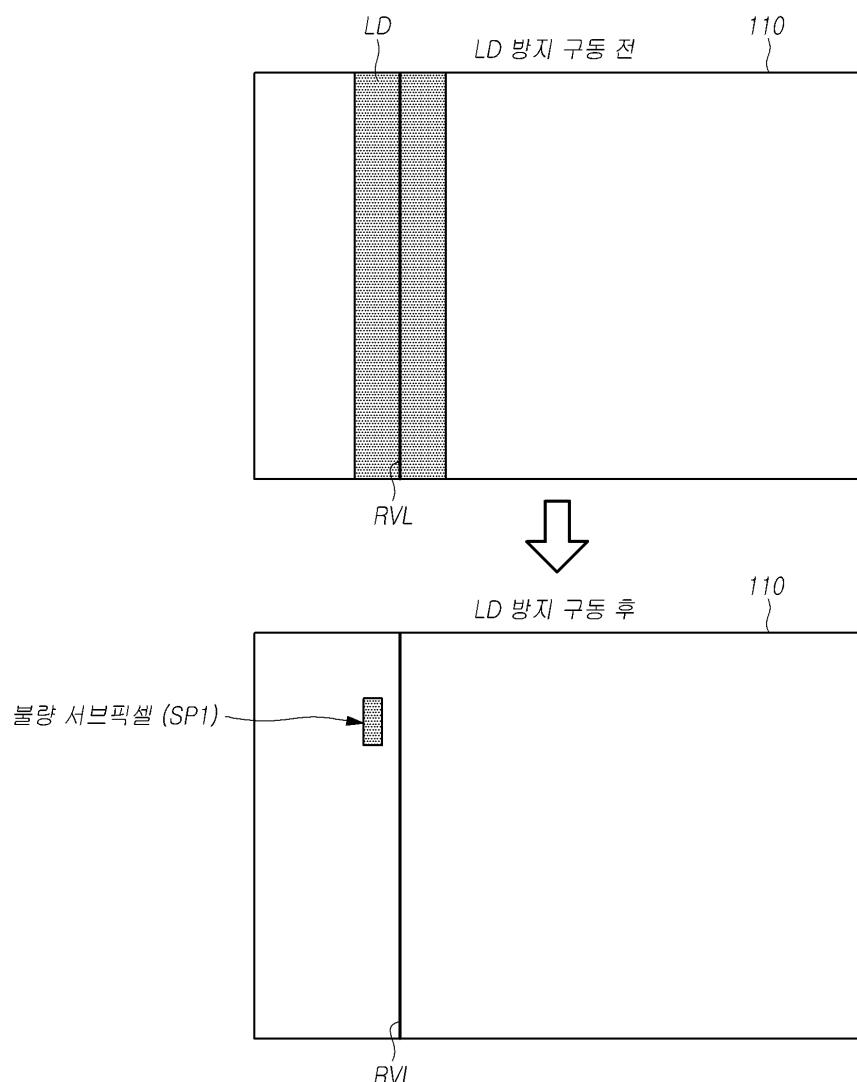

- 도 15는 본 발명의 실시예들에 따른 유기발광표시장치의 라인 결함 방지 회로이다.

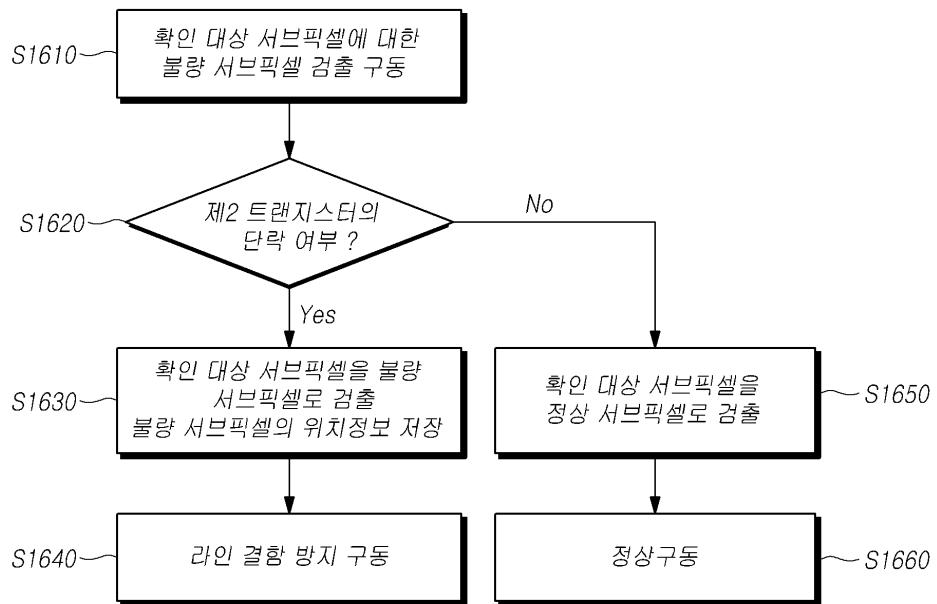

- 도 16은 본 발명의 실시예들에 따른 유기발광표시장치의 라인 결함 방지 방법의 흐름도이다.

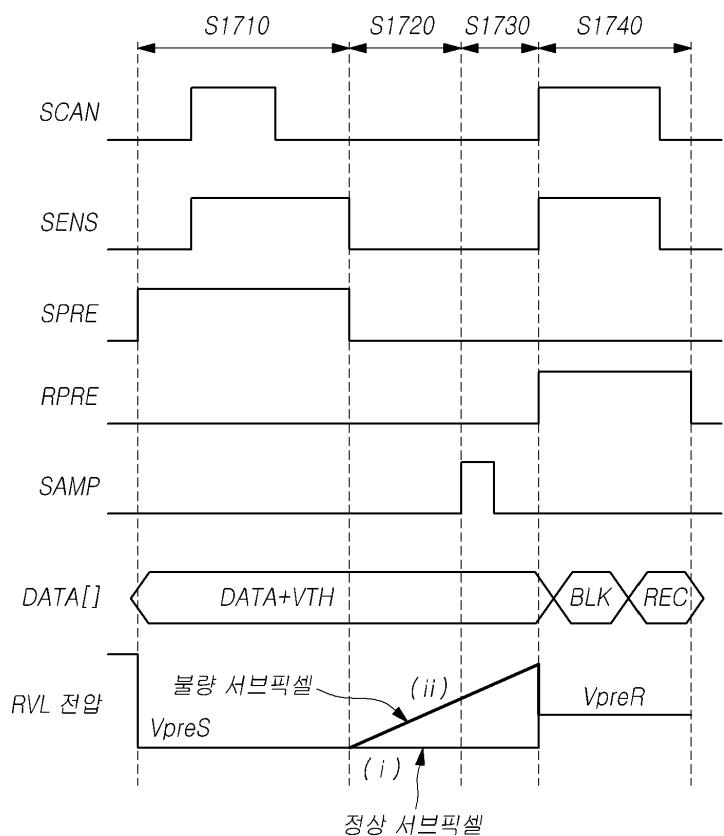

- 도 17은 본 발명의 실시예들에 따른 유기발광표시장치의 불량 서브픽셀 검출을 위한 구동 타이밍 다이어그램이다.

- 도 18 및 도 19는 본 발명의 실시예들에 따른 유기발광표시장치에서, 하나의 기준전압라인을 공유하는 4개의 서브픽셀 중 제1 서브픽셀이 불량 서브픽셀인 경우, 라인 결함 방지 동작과 이에 따른 효과를 설명하기 위한 도면들이다.

- 도 20 및 도 21은 본 발명의 실시예들에 따른 데이터구동회로를 나타낸 도면이다.

도 22는 본 발명의 실시예들에 따른 컨트롤러를 나타낸 도면이다.

도 23 및 도 24는 본 발명의 실시예들에 따른 유기발광표시장치의 구동방법에 대한 흐름도이다.

### 발명을 실시하기 위한 구체적인 내용

- [0049] 이하, 본 발명의 일부 실시예들을 예시적인 도면을 참조하여 상세하게 설명한다. 각 도면의 구성요소들에 참조부호를 부가함에 있어서, 동일한 구성요소들에 대해서는 비록 다른 도면상에 표시되더라도 가능한 한 동일한 부호를 가질 수 있다. 또한, 본 발명을 설명함에 있어, 관련된 공지 구성 또는 기능에 대한 구체적인 설명이 본 발명의 요지를 흐릴 수 있다고 판단되는 경우에는 그 상세한 설명은 생략할 수 있다.

- [0050] 또한, 본 발명의 구성 요소를 설명하는 데 있어서, 제 1, 제 2, A, B, (a), (b) 등의 용어를 사용할 수 있다. 이러한 용어는 그 구성 요소를 다른 구성 요소와 구별하기 위한 것일 뿐, 그 용어에 의해 해당 구성 요소의 본질, 차례, 순서 또는 개수 등이 한정되지 않는다. 어떤 구성 요소가 다른 구성요소에 "연결", "결합" 또는 "접속"된다고 기재된 경우, 그 구성 요소는 그 다른 구성요소에 직접적으로 연결되거나 또는 접속될 수 있지만, 각 구성 요소 사이에 다른 구성 요소가 "개재"되거나, 각 구성 요소가 다른 구성 요소를 통해 "연결", "결합" 또는 "접속"될 수도 있다고 이해되어야 할 것이다.

- [0051] 도 1은 본 발명의 실시예들에 따른 유기발광표시장치(100)의 개략적인 시스템 구성도이다.

- [0052] 도 1을 참조하면, 본 실시예들에 따른 유기발광표시장치(100)는, 다수의 데이터라인(DL) 및 다수의 게이트라인(GL)이 배치되고, 다수의 데이터라인(DL) 및 다수의 게이트라인(GL)에 의해 정의되는 다수의 서브픽셀(SP)이 매트릭스 타입으로 배열된 유기발광표시패널(110)과, 유기발광표시패널(110)을 구동하기 위한 구동회로를 포함할 수 있다.

- [0053] 구동회로는, 기능적으로 볼 때, 다수의 데이터라인(DL)을 구동하는 데이터구동회로(120)와, 다수의 게이트라인(GL)을 구동하는 게이트구동회로(130)와, 데이터구동회로(120) 및 게이트구동회로(130)를 제어하는 컨트롤러(140) 등을 포함할 수 있다.

- [0054] 유기발광표시패널(110)에서 다수의 데이터라인(DL) 및 다수의 게이트라인(GL)은 서로 교차하여 배치될 수 있다. 예를 들어, 다수의 게이트라인(GL)은 행(Row) 또는 열(Column)으로 배열될 수 있고, 다수의 데이터라인(DL)은 열(Column) 또는 행(Row)으로 배열될 수 있다. 아래에서는, 설명의 편의를 위하여, 다수의 게이트라인(GL)은 행(Row)으로 배치되고, 다수의 데이터라인(DL)은 열(Column)으로 배치되는 것으로 가정한다.

- [0055] 유기발광표시패널(110)에는, 다수의 데이터라인(DL) 및 다수의 게이트라인(GL) 이외에, 다른 종류의 배선들이 배치될 수 있다.

- [0056] 컨트롤러(140)는, 데이터구동회로(120)로 영상데이터(DATA)를 공급할 수 있다.

- [0057] 또한, 컨트롤러(140)는, 데이터구동회로(120) 및 게이트구동회로(130)의 구동 동작에 필요한 각종 제어신호(DCS, GCS)를 공급하여 데이터구동회로(120) 및 게이트구동회로(130)의 동작을 제어할 수 있다.

- [0058] 컨트롤러(140)는, 각 프레임에서 구현하는 타이밍에 따라 스캔을 시작하고, 외부에서 입력되는 입력 영상데이터를 데이터구동회로(120)에서 사용하는 데이터 신호 형식에 맞게 전환하여 전환된 영상데이터(DATA)를 출력하고, 스캔에 맞춰 적당한 시간에 데이터 구동을 통제한다.

- [0059] 컨트롤러(140)는, 데이터구동회로(120) 및 게이트구동회로(130)를 제어하기 위하여, 수직 동기 신호(Vsync), 수평 동기 신호(Hsync), 입력 데이터 인에이블(DE: Data Enable) 신호, 클럭 신호(CLK) 등의 타이밍 신호를 외부(예: 호스트 시스템)로부터 입력 받아, 각종 제어 신호들을 생성하여 데이터구동회로(120) 및 게이트구동회로(130)로 출력한다.

- [0060] 예를 들어, 컨트롤러(140)는, 게이트구동회로(130)를 제어하기 위하여, 게이트 스타트 펄스(GSP: Gate Start Pulse), 게이트 쉬프트 클럭(GSC: Gate Shift Clock), 게이트 출력 인에이블 신호(GOE: Gate Output Enable) 등을 포함하는 각종 게이트 제어 신호(GCS: Gate Control Signal)를 출력한다.

- [0061] 또한, 컨트롤러(140)는, 데이터구동회로(120)를 제어하기 위하여, 소스 스타트 펄스(SSP: Source Start Pulse), 소스 샘플링 클럭(SSC: Source Sampling Clock), 소스 출력 인에이블 신호(SOE: Source Output Enable) 등을 포함하는 각종 데이터 제어 신호(DCS: Data Control Signal)를 출력한다.

- [0062] 컨트롤러(140)는, 통상의 디스플레이 기술에서 이용되는 타이밍 컨트롤러(Timing Controller)이거나, 타이밍 컨

트롤러(Timing Controller)를 포함하여 다른 제어 기능도 더 수행할 수 있는 제어장치일 수 있다.

[0063] 컨트롤러(140)는, 데이터구동회로(120)와 별도의 부품으로 구현될 수도 있고, 데이터구동회로(120)와 함께 통합되어 접적회로로 구현될 수 있다.

[0064] 데이터구동회로(120)는, 컨트롤러(140)로부터 영상데이터(DATA)를 입력 받아 다수의 데이터라인(DL)로 데이터 전압을 공급함으로써, 다수의 데이터라인(DL)을 구동한다. 여기서, 데이터구동회로(120)는 소스 구동회로라고도 한다.

[0065] 데이터구동회로(120)는 시프트 레지스터(Shift Register), 래치 회로(Latch Circuit), 디지털 아날로그 컨버터(DAC: Digital to Analog Converter), 출력 버퍼(Output Buffer) 등을 포함할 수 있다.

[0066] 데이터구동회로(120)는, 경우에 따라서, 하나 이상의 아날로그 디지털 컨버터(ADC: Analog to Digital Converter)를 더 포함할 수 있다.

[0067] 게이트구동회로(130)는, 다수의 게이트라인(GL)로 스캔신호를 순차적으로 공급함으로써, 다수의 게이트라인(GL)을 순차적으로 구동한다. 여기서, 게이트구동회로(130)는 스캔 구동회로라고도 한다.

[0068] 게이트구동회로(130)는 시프트 레지스터(Shift Register), 레벨 시프터(Level Shifter) 등을 포함할 수 있다.

[0069] 게이트구동회로(130)는, 컨트롤러(140)의 제어에 따라, 온(On) 전압 또는 오프(Off) 전압의 스캔신호를 다수의 게이트라인(GL)로 순차적으로 공급한다.

[0070] 데이터구동회로(120)는, 게이트구동회로(130)에 의해 특정 게이트라인이 열리면, 컨트롤러(140)로부터 수신한 영상데이터(DATA)를 아날로그 형태의 데이터 전압으로 변환하여 다수의 데이터라인(DL)로 공급한다.

[0071] 데이터구동회로(120)는, 유기발광표시패널(110)의 일 측(예: 상측 또는 하측)에만 위치할 수도 있고, 경우에 따라서는, 구동 방식, 패널 설계 방식 등에 따라 유기발광표시패널(110)의 양측(예: 상 측과 하 측)에 모두 위치할 수도 있다.

[0072] 게이트구동회로(130)는, 유기발광표시패널(110)의 일 측(예: 좌측 또는 우측)에만 위치할 수도 있고, 경우에 따라서는, 구동 방식, 패널 설계 방식 등에 따라 유기발광표시패널(110)의 양측(예: 좌 측과 우 측)에 모두 위치할 수도 있다.

[0073] 데이터구동회로(120)는 적어도 하나의 소스 드라이버 접적회로(SDIC: Source Driver Integrated Circuit)를 포함하여 구현될 수 있다.

[0074] 각 소스 드라이버 접적회로(SDIC)는, TAB (Tape Automated Bonding) 방식 또는 COG (Chip On Glass) 방식으로 유기발광표시패널(110)의 본딩 패드(Bonding Pad)에 연결되거나 유기발광표시패널(110) 상에 직접 배치될 수도 있다. 경우에 따라서, 각 소스 드라이버 접적회로(SDIC)는 유기발광표시패널(110)에 접착화되어 배치될 수도 있다. 또한, 각 소스 드라이버 접적회로(SDIC)는 COF (Chip On Film) 방식으로 구현될 수 있다. 이 경우, 각 소스 드라이버 접적회로(SDIC)는 회로필름 상에 실장 되어, 회로필름을 통해 유기발광표시패널(110)에서의 데이터라인들(DL)과 전기적으로 연결될 수 있다.

[0075] 게이트구동회로(130)는 하나 이상의 게이트 드라이버 접적회로(GDIC: Gate Driver IC)가 TAB 방식 또는 COG 방식으로 유기발광표시패널(110)의 본딩 패드(Bonding Pad)에 연결될 수 있다. 또한, 게이트구동회로(130)는 GIP(Gate In Panel) 타입으로 구현되어 유기발광표시패널(110) 상에 직접 배치될 수도 있다. 또한, 게이트구동회로(130)는 COF (Chip On Film) 방식으로 구현될 수 있다. 이 경우, 게이트구동회로(130)에 포함된 각 게이트 드라이버 접적회로(GDIC)는 회로필름 상에 실장 되어, 회로필름을 통해 유기발광표시패널(110)에서의 게이트라인들(GL)과 전기적으로 연결될 수 있다..

[0076] 도 2는 본 발명의 실시예들에 따른 유기발광표시장치(100)의 시스템 구현 예시도이다.

[0077] 도 2의 예시는, 데이터구동회로(120)에서 포함된 각 소스 드라이버 접적회로(SDIC)가 다양한 방식들(TAB, COG, COF 등) 중 COF (Chip On Film) 방식으로 구현되고, 게이트구동회로(130)가 다양한 방식들(TAB, COG, COF, GIP 등) 중 GIP (Gate In Panel) 타입으로 구현된 경우이다.

[0078] 데이터구동회로(120)에 포함된 다수의 소스 드라이버 접적회로(SDIC) 각각은, 소스 측 회로필름(SF) 상에 실장될 수 있다.

- [0079] 소스 측 회로필름(SF)의 일 측은 유기발광표시패널(110)과 전기적으로 연결될 수 있다.

- [0080] 소스 측 회로필름(SF) 상에는, 소스 드라이버 집적회로(SDIC)과 유기발광표시패널(110)을 전기적으로 연결해주기 위한 배선들이 배치될 수 있다.

- [0081] 유기발광표시장치(100)는, 다수의 소스 드라이버 집적회로(SDIC)와 다른 장치들 간의 회로적인 연결을 위해, 적어도 하나의 소스 인쇄회로기판(SPCB)과, 제어 부품들과 각종 전기 장치들을 실장 하기 위한 컨트롤 인쇄회로기판(CPCB)을 포함할 수 있다.

- [0082] 적어도 하나의 소스 인쇄회로기판(SPCB)에는 소스 드라이버 집적회로(SDIC)가 실장 된 소스 측 회로필름(SF)의 타 측이 연결될 수 있다.

- [0083] 즉, 소스 드라이버 집적회로(SDIC)가 실장 된 소스 측 회로필름(SF)은 일 측이 유기발광표시패널(110)과 전기적으로 연결되고, 타 측이 소스 인쇄회로기판(SPCB)과 전기적으로 연결될 수 있다.

- [0084] 컨트롤 인쇄회로기판(CPCB)에는, 데이터 구동회로(120) 및 게이트 구동회로(130) 등의 동작을 제어하는 컨트롤러(140)와, 유기발광표시패널(110), 데이터구동회로(120) 및 게이트구동회로(130) 등으로 각종 진압 또는 전류를 공급해주거나 공급할 각종 전압 또는 전류를 제어하는 파워 관리 집적회로(PMIC: Power Management IC, 210) 등이 실장될 수 있다.

- [0085] 적어도 하나의 소스 인쇄회로기판(SPCB)과 컨트롤 인쇄회로기판(CPCB)은 적어도 하나의 연결 부재를 통해 회로적으로 연결될 수 있다. 여기서, 연결 부재는, 일 예로, 가요성 인쇄 회로(FPC: Flexible Printed Circuit), 가요성 플랫 케이블(FFC: Flexible Flat Cable) 등일 수 있다.

- [0086] 적어도 하나의 소스 인쇄회로기판(SPCB)과 컨트롤 인쇄회로기판(CPCB)은 하나의 인쇄회로기판으로 통합되어 구현될 수도 있다.

- [0087] 유기발광표시장치(100)는, 컨트롤 인쇄회로기판(CPCB)과 전기적으로 연결된 세트보드(Set Board, 230)를 더 포함할 수 있다. 이러한 세트 보드(230)는 파워 보드(Power Board)라고도 할 수 있다.

- [0088] 이러한 세트보드(230)에는 유기발광표시장치(100)의 전체적인 파워를 관리하는 메인 파워 관리 회로(220, MPC: Main Power Management Circuit)가 존재할 수 있다.

- [0089] 파워 관리 집적회로(210)는 유기발광표시패널(110)과 그 구동 회로(120, 130, 140) 등을 포함하는 표시모듈에 대한 파워를 관리하는 회로이고, 메인 파워 관리 회로(220)는 표시모듈을 포함한 전체적인 파워를 관리하는 회로이고, 파워 관리 집적회로(210)와 연동할 수 있다.

- [0090] 본 실시예들에 따른 유기발광표시장치(100)에 포함된 유기발광표시패널(110)에 배열된 각 서브픽셀(SP)은 자발광 소자인 유기발광다이오드(OLED: Organic Light Emitting Diode)와, 유기발광다이오드(OLED)를 구동하기 위한 구동 트랜지스터(Driving Transistor) 등의 회로 소자로 구성될 수 있다.

- [0091] 각 서브픽셀(SP)을 구성하는 회로 소자의 종류 및 개수는, 제공 기능 및 설계 방식 등에 따라 다양하게 정해질 수 있다.

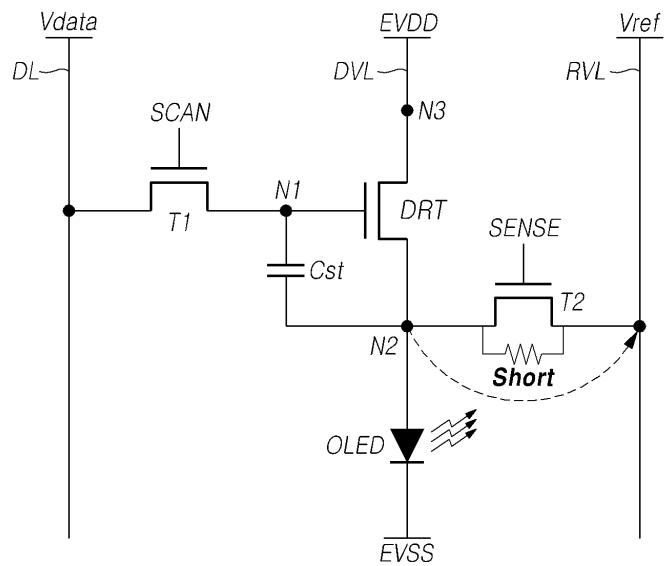

- [0092] 도 3은 본 발명의 실시예들에 따른 유기발광표시장치(100)의 서브픽셀의 회로이다.

- [0093] 본 발명의 실시예들에 따른 유기발광표시패널(110)에는, 다수의 데이터라인(DL), 다수의 게이트라인(GL), 다수의 구동전압라인(DVL) 및 다수의 기준전압라인(RVL) 등이 배치될 수 있다.

- [0094] 유기발광표시패널(110)에서의 각 서브픽셀(SP)은, 유기발광다이오드(OLED)와, 유기발광다이오드(OLED)를 구동하는 구동 트랜지스터(DRT)와, 구동 트랜지스터(DRT)의 제1 노드(N1)와 다수의 데이터라인(DL) 중 해당 데이터라인(DL) 사이에 전기적으로 연결된 제1 트랜지스터(T1)와, 구동 트랜지스터(DRT)의 제2 노드(N2)와 다수의 기준전압라인(RVL) 중 해당 기준전압라인(RVL) 사이에 전기적으로 연결된 제2 트랜지스터(T2)와, 구동 트랜지스터(DRT)의 제1 노드(N1)와 제2 노드(N2) 사이에 전기적으로 연결된 스토리지 캐패시터(Cst) 등을 포함하여 구현될 수 있다.

- [0095] 유기발광다이오드(OLED)는 애노드 전극, 유기 발광층 및 캐소드 전극 등으로 이루어질 수 있다.

- [0096] 도 3의 회로 예시에 따르면, 유기발광다이오드(OLED)의 애노드 전극은 구동 트랜지스터(DRT)의 제2 노드(N2)와 전기적으로 연결될 수 있다. 유기발광다이오드(OLED)의 캐소드 전극에는 기저전압(EVSS)이 인가될 수 있다. 여

기서, 기저전압(EVSS)은, 일 예로, 그라운드 전압이거나 그라운드 전압보다 높거나 낮은 전압일 수 있다. 또한, 기전전압(EVSS)은 구동상태에 따라 가변될 수 있다. 예를 들어, 영상 구동 시 기저전압(EVSS)과 센싱 구동 시 기저전압(EVSS)은 서로 다르게 설정될 수 있다.

- [0097] 구동 트랜지스터(DRT)는 유기발광다이오드(OLED)로 구동전류를 공급해줌으로써 유기발광다이오드(OLED)를 구동해준다.

- [0098] 구동 트랜지스터(DRT)는 제1 노드(N1), 제2 노드(N2) 및 제3 노드(N3) 등을 포함할 수 있다. 구동 트랜지스터(DRT)의 제1 노드(N1)는 게이트 노드에 해당하는 노드이다. 구동 트랜지스터(DRT)의 제1 노드(N1)는 제1 트랜지스터(T1)의 소스 노드 또는 드레인 노드와 전기적으로 연결될 수 있다. 구동 트랜지스터(DRT)의 제2 노드(N2)는 소스 노드 또는 드레인 노드일 수 있다. 구동 트랜지스터(DRT)의 제2 노드(N2)는 유기발광다이오드(OLED)의 애노드 전극(또는 캐소드 전극)과 전기적으로 연결될 수 있고, 제2 트랜지스터(T2)의 소스 노드 또는 드레인 노드와 전기적으로 연결될 수 있다. 구동 트랜지스터(DRT)의 제3 노드(N3)는 드레인 노드 또는 소스 노드일 수 있다. 구동 트랜지스터(DRT)의 제3 노드(N3)는 구동전압(EVDD)이 인가되는 노드로서, 구동전압(EVDD)을 공급하는 구동전압 라인(DVL: Driving Voltage Line)과 전기적으로 연결될 수 있다.

- [0099] 아래에서는, 설명의 편의를 위하여, 구동 트랜지스터(DRT)의 제2 노드(N2)는 소스 노드이고, 제3노드(N3)는 드레인 노드인 것을 예로 들어 설명할 수 있다.

- [0100] 스토리지 캐패시터(Cst)는 구동 트랜지스터(DRT)의 제1 노드(N1)와 제2 노드(N2) 사이에 전기적으로 연결되어, 영상 신호 전압에 해당하는 데이터전압(Vdata) 또는 이에 대응되는 전압을 한 프레임 시간 동안 유지해줄 수 있다.

- [0101] 제1 트랜지스터(T1)의 드레인 노드 또는 소스 노드는 해당 데이터라인(DL)에 전기적으로 연결되고, 제1 트랜지스터(T1)의 소스 노드 또는 드레인 노드는 구동 트랜지스터(DRT)의 제1 노드(N1)에 전기적으로 연결되고, 제1 트랜지스터(T1)의 게이트 노드는 해당 게이트 라인과 전기적으로 연결되어 제1 스캔신호(SCAN1)를 인가 받을 수 있다.

- [0102] 제1 트랜지스터(T1)는 해당 게이트 라인을 통해 제1 스캔신호(SCAN1)를 게이트 노드로 인가 받아 온-오프가 제어될 수 있다.

- [0103] 이러한 제1 트랜지스터(T1)는 제1 스캔신호(SCAN1)에 의해 턴-온 되어 해당 데이터라인(DL)으로부터 공급된 데이터전압(Vdata)을 구동 트랜지스터(DRT)의 제1 노드(N1)로 전달해줄 수 있다.

- [0104] 제2 트랜지스터(T2)의 드레인 노드 또는 소스 노드는 기준전압라인(RVL)에 전기적으로 연결되고, 제2 트랜지스터(T2)의 소스 노드 또는 드레인 노드는 구동 트랜지스터(DRT)의 제2 노드(N2)에 전기적으로 연결될 수 있다. 제2 트랜지스터(T2)의 게이트 노드는 해당 게이트 라인과 전기적으로 연결되어 제2 스캔신호(SCAN2)를 인가 받을 수 있다.

- [0105] 제2 트랜지스터(T2)는 해당 게이트 라인을 통해 제2 스캔신호(SCAN2)를 게이트 노드로 인가 받아 온-오프가 제어될 수 있다.

- [0106] 제2 트랜지스터(T2)는 제2 스캔신호(SCAN2)에 의해 턴-온 되어 해당 기준전압라인(RVL)으로부터 공급된 기준전압(Vref)을 구동 트랜지스터(DRT)의 제2 노드(N2)로 전달해줄 수 있다.

- [0107] 한편, 스토리지 캐패시터(Cst)는, 구동 트랜지스터(DRT)의 제1 노드(N1)와 제2 노드(N2) 사이에 존재하는 내부 캐패시터(Internal Capacitor)인 기생 캐패시터(예: Cgs, Cgd)가 아니라, 구동 트랜지스터(DRT)의 외부에 의도적으로 설계한 외부 캐패시터(External Capacitor)일 수 있다.

- [0108] 구동 트랜지스터(DRT), 제1 트랜지스터(T1) 및 제2 트랜지스터(T2) 각각은 n 타입 트랜지스터이거나 p 타입 트랜지스터일 수 있다.

- [0109] 한편, 제1 스캔신호(SCAN1) 및 제2 스캔신호(SCAN2)는 별개의 게이트 신호일 수 있다. 이 경우, 제1 스캔신호(SCAN1) 및 제2 스캔신호(SCAN2)는 서로 다른 게이트 라인을 통해, 제1 트랜지스터(T1)의 게이트 노드 및 제2 트랜지스터(T2)의 게이트 노드로 각각 인가될 수도 있다.

- [0110] 경우에 따라서는, 제1 스캔신호(SCAN1) 및 제2 스캔신호(SCAN2)는 동일한 게이트 신호일 수도 있다. 이 경우, 제1 스캔신호(SCAN1) 및 제2 스캔신호(SCAN2)는 동일한 게이트 라인을 통해 제1 트랜지스터(T1)의 게이트 노드 및 제2 트랜지스터(T2)의 게이트 노드에 공통으로 인가될 수도 있다.

- [0111] 도 3에 예시된 각 서브픽셀 구조는 3T(Transistor) 1C (Capacitor) 구조로서, 설명을 위한 예시일 뿐, 1개 이상의 트랜지스터를 더 포함하거나, 경우에 따라서는, 1개 이상의 캐패시터를 더 포함할 수도 있다. 또는, 다수의 서브픽셀들 각각이 동일한 구조로 되어 있을 수도 있고, 다수의 서브픽셀들 중 일부는 다른 구조로 되어 있을 수도 있다.

- [0112] 아래에서는, 각 서브픽셀(SP)의 영상 구동 동작을 간단하게 예를 들어 설명한다.

- [0113] 각 서브픽셀(SP)의 영상 구동 동작은 영상 데이터 기록 단계, 부스팅 단계 및 발광 단계로 진행될 수 있다.

- [0114] 영상 데이터 기록 단계에서, 구동 트랜지스터(DRT)의 제1 노드(N1)에 영상신호에 해당하는 데이터전압(Vdata)이 인가하고, 구동 트랜지스터(DRT)의 제2 노드(N2)에 기준전압(Vref)이 인가될 수 있다. 여기서, 구동 트랜지스터(DRT)의 제2 노드(N2)과 기준전압 라인(RVL) 사이의 저항성분 등으로 인해, 구동 트랜지스터(DRT)의 제2 노드(N2)에 기준전압(Vref)과 유사한 전압(Vref+ $\Delta$  V)이 인가될 수 있다.

- [0115] 영상 구동을 위한 기준전압(Vref)을 VpreR이라고도 한다.

- [0116] 영상 데이터 기록 단계에서, 제1 트랜지스터(T1) 및 제2 트랜지스터(T2)는 동시에 또는 약간의 시간 차를 갖고 턴-온 될 수 있다.

- [0117] 영상 데이터 기록 단계에서, 스토리지 캐패시터(Cst)는 양단 전위차 (Vdata-Vref 또는 Vdata-(Vref+ $\Delta$  V))에 대응되는 전하가 충전될 수 있다.

- [0118] 구동 트랜지스터(DRT)의 제1 노드(N1)에 영상 데이터전압(Vdata)이 인가되는 것을 영상 데이터 기록(Data Writing)이라고 한다.

- [0119] 영상 데이터 기록 단계에 이어서 진행되는 부스팅 단계에서, 구동 트랜지스터(DRT)의 제1 노드(N1) 및 제2 노드(N2)는 동시에 또는 약간의 시간 차를 갖고 전기적으로 플로팅(Floating) 될 수 있다.

- [0120] 이를 위해, 제1 스캔신호(SCAN1)의 턴-오프 레벨 전압에 의해 제1 트랜지스터(T1)가 턴-오프 될 수 있다. 또한, 제2 스캔신호(SCAN2)의 턴-오프 레벨 전압에 의해 제2 트랜지스터(T2)가 턴-오프 될 수 있다.

- [0121] 부스팅 단계에서, 구동 트랜지스터(DRT)의 제1 노드(N1) 및 제2 노드(N2) 간의 전압 차이는 유지되면서, 구동 트랜지스터(DRT)의 제1 노드(N1) 및 제2 노드(N2)는 전압이 부스팅(Boosting) 될 수 있다.

- [0122] 부스팅 단계 동안, 구동 트랜지스터(DRT)의 제1 노드(N1) 및 제2 노드(N2)는 전압이 부스팅(Boosting)되다가, 구동 트랜지스터(DRT)의 제2 노드(N2)이 상승된 전압이 일정 전압 이상이 되면, 발광 단계로 진입된다.

- [0123] 이러한 발광 단계에서는, 유기발광다이오드(OLED)로 구동 전류가 흐르게 된다. 이에 따라, 유기발광다이오드(OLED)가 발광할 수 있다.

- [0124] 본 발명의 실시예들에 따른 유기발광표시패널(110)에 배열된 다수의 서브픽셀(SP) 각각에 배치된 구동 트랜지스터(DRT)는 문턱전압, 이동도 등의 고유한 특성치를 갖는다.

- [0125] 구동 트랜지스터(DRT)는 구동시간에 따라 열화가 발생할 수 있다. 이에 따라, 구동 트랜지스터(DRT)의 고유한 특성치는 구동시간에 따라 변할 수 있다.

- [0126] 구동 트랜지스터(DRT)는 특성치 변화에 따라 온-오프 타이밍이 달라지거나 유기발광다이오드(OLED)의 구동 능력이 달라질 수 있다. 즉, 구동 트랜지스터(DRT)는 특성치 변화에 따라 유기발광다이오드(OLED)로 전류를 공급하는 타이밍과, 유기발광다이오드(OLED)로 공급하는 전류량이 달라질 수 있다. 이러한 구동 트랜지스터(DRT)의 특성치 변화에 따라, 해당 서브픽셀(SP)의 휘도는 원하는 휘도와 달라질 수 있다.

- [0127] 또한, 유기발광표시패널(110)에 배열된 다수의 서브픽셀(SP)은 각기 구동 시간이 서로 다를 수 있다. 따라서, 각 서브픽셀(SP) 내 구동 트랜지스터(DRT) 간의 특성치 편차가 발생할 수 있다.

- [0128] 이러한 구동 트랜지스터(DRT) 간의 특성치 편차는 서브픽셀(SP) 간의 휘도 편차를 발생시킬 수 있다. 따라서, 유기발광표시패널(110)의 휘도 균일도도 나빠질 수 있으며, 결국, 화상 품질 저하로 이어질 수 있다.

- [0129] 따라서, 본 발명의 실시예들에 따른 유기발광표시장치(100)는, 구동 트랜지스터(DRT) 간의 특성치 편차를 보상해줄 수 있는 보상회로를 포함하고, 이를 이용한 보상 방법을 제공할 수 있다. 이에 대하여, 도 4 내지 도 7을 참조하여 더욱 상세하게 설명한다.

- [0130] 도 4는 본 발명의 실시예들에 따른 유기발광표시장치(100)의 보상 회로이다.

- [0131] 본 발명의 실시예들에 따른 유기발광표시장치(100)는, 구동 트랜지스터(DRT) 간의 특성치 편차를 보상하기 위하여, 각 구동 트랜지스터(DRT)의 특성치 또는 특성치 변화를 센싱해야 한다.

- [0132] 본 발명의 실시예들에 따른 유기발광표시장치(100)의 보상회로는, 3T1C 구조 또는 이에 기반하여 변형된 구조를 갖는 서브픽셀(SP)을 구동(센싱 구동)하여 서브픽셀(SP) 내 구동 트랜지스터(DRT)의 특성치 또는 특성치 변화를 센싱하기 위한 구성을 포함할 수 있다.

- [0133] 본 발명의 실시예들에 따른 유기발광표시장치(100)의 센싱 구동에 따라, 서브픽셀(SP) 내 구동 트랜지스터(DRT)의 특성치 또는 그 변화는, 기준전압라인(RVL)의 전압으로 표현될 수 있다.

- [0134] 보다 구체적으로, 본 발명의 실시예들에 따른 유기발광표시장치(100)의 센싱 구동에 따라, 구동 트랜지스터(DRT)의 특성치 또는 그 변화는 구동 트랜지스터(DRT)의 제2 노드(N2)의 전압(예:  $V_{data}-V_{th}$ )으로 반영된다.

- [0135] 구동 트랜지스터(DRT)의 제2 노드(N2)의 전압은, 제2 트랜지스터(T2)가 턠-온 상태인 경우, 기준전압라인(RVL)의 전압과 대응될 수 있다. 구동 트랜지스터(DRT)의 제2 노드(N2)의 전압에 의해, 기준전압라인(RVL) 상의 라인 캐패시터(Cline)가 충전될 수 있다. 충전된 라인 캐패시터(Cline)에 의해 기준전압라인(RVL)은 구동 트랜지스터(DRT)의 제2 노드(N2)의 전압과 대응되는 전압을 가질 수 있다.

- [0136] 본 발명의 실시예들에 따른 유기발광표시장치(100)의 보상회로는, 구동 트랜지스터(DRT)의 제2 노드(N2)가 특성치를 반영하는 전압 상태가 되도록 구동하여, 특성치를 반영하는 전압 상태가 구동 트랜지스터(DRT)의 제2 노드(N2)의 전압을 센싱하기 위하여, 기준전압라인(RVL)의 전압을 측정하여 디지털 값에 해당하는 센싱값으로 변환하는 아날로그 디지털 컨버터(ADC)와, 센싱 구동을 위한 스위치 회로를 포함할 수 있다.

- [0137] 센싱 구동을 위한 스위치 회로는, 각 기준전압라인(RVL)과 기준전압(Vref)이 공급되는 센싱 구동용 기준전압 공급 노드(Npres) 간의 연결을 제어하는 센싱 구동용 기준 스위치(SPRE)와, 각 기준전압라인(RVL)과 아날로그 디지털 컨버터(ADC) 간의 연결을 제어하는 샘플링 스위치(SAMP)를 포함할 수 있다.

- [0138] 위에서 언급한 센싱 구동용 기준 스위치(SPRE)는 센싱 구동 시 이용되는 스위치이다. 센싱 구동용 기준 스위치(SPRE)에 의해 기준전압라인(RVL)으로 공급되는 기준전압(Vref)은 센싱 구동용 기준전압(VpreS)이다.

- [0139] 한편, 도 4를 참조하면, 스위치 회로는, 영상 구동 시 이용되는 영상 구동용 기준 스위치(RPRE)를 포함할 수 있다.

- [0140] 영상 구동용 기준 스위치(RPRE)는, 각 기준전압라인(RVL)과 기준전압(Vref)이 공급되는 영상 구동용 기준전압 공급 노드(Nprer) 간의 연결을 제어할 수 있다.

- [0141] 위에서 언급한 영상 구동용 기준 스위치(RPRE)는 영상 구동 시 이용되는 스위치이다. 영상 구동용 기준 스위치(SPRE)에 의해 기준전압라인(RVL)에 공급되는 기준전압(Vref)은 영상 구동용 기준전압(VpreR)이다.

- [0142] 센싱 구동용 기준 스위치(SPRE)와 영상 구동용 기준 스위치(RPRE)는 별도로 구비될 수도 있고, 하나로 통합되어 구현될 수도 있다. 센싱 구동용 기준전압(VpreS)과 영상 구동용 기준전압(VpreR)은 동일한 전압 값일 수도 있고, 다른 전압 값일 수도 있다.

- [0143] 본 발명의 실시예들에 따른 유기발광표시장치(100)의 보상회로는, 아날로그 디지털 컨버터(ADC)에서 출력되는 센싱값을 저장하거나 기준 센싱값을 미리 저장하고 있는 메모리(MEM)와, 메모리(MEM)에 저장된 센싱값과 기준 센싱값을 비교하여 특성치 편차를 보상해주는 보상값을 산출하는 보상기(COMP)를 더 포함할 수 있다.

- [0144] 보상기(COMP)에 의해 산출된 보상값은 메모리(MEM)에 저장될 수 있다.

- [0145] 컨트롤러(140)는 보상기(COM)에 의해 산출된 보상값을 이용하여 데이터구동회로(120)에 공급할 영상데이터(Data)를 변경하고, 변경된 영상데이터(Data\_comp)를 데이터구동회로(120)로 출력할 수 있다.

- [0146] 이에 따라, 데이터구동회로(120)는 디지털 아날로그 컨버터(DAC)를 통해 변경된 영상데이터(Data\_comp)를 아날로그 신호 형태의 데이터전압( $V_{data\_comp}$ )으로 변환하여 해당 서브픽셀(SP)에 공급할 수 있다. 이에 따라, 해당 서브픽셀(SP)의 구동 트랜지스터(DRT)에 대한 특성치 편차(문턱전압 편차, 이동도 편차)가 보상될 수 있다.

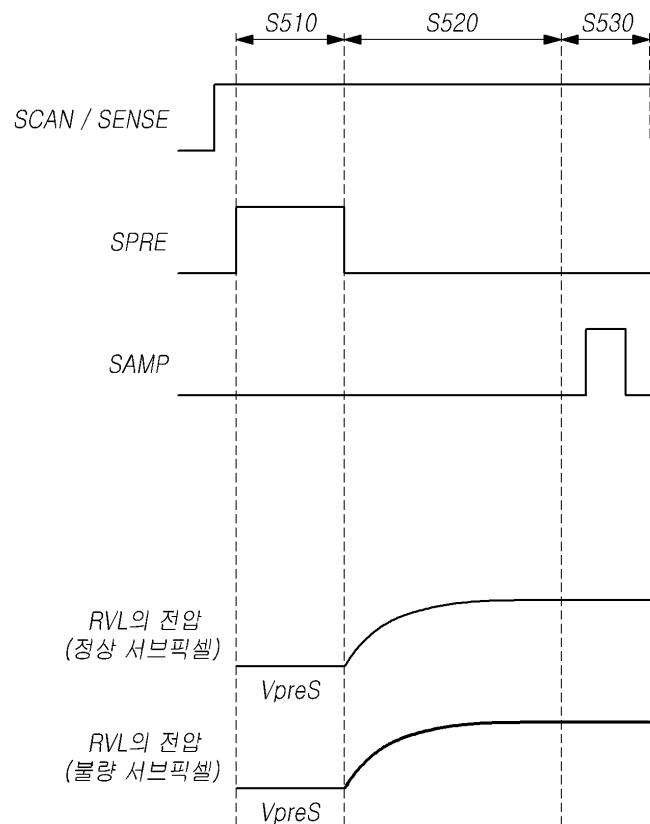

- [0147] 도 5는 본 발명의 실시예들에 따른 유기발광표시장치(100)의 문턱전압 센싱을 위한 구동 타이밍 다이어그램이다.

- [0148] 도 5를 참조하면, 문턱전압 센싱 구동은, 초기화 단계(S510), 트래킹 단계(S520) 및 샘플링 단계(S530)로 진행될 수 있다.

- [0149] 초기화 단계(S510)에서, 턴-온 레벨 전압의 제1 스캔신호(SCAN)에 의해, 제1 트랜지스터(T1)가 턴-온 상태가 된다. 이에 따라, 구동 트랜지스터(DRT)의 제1 노드(N1)는 문턱전압 센싱 구동용 데이터전압(Vdata)으로 초기화된다.

- [0150] 초기화 단계(S510)에서, 턴-온 레벨 전압의 제2 스캔신호(SENSE)에 의해, 제2 트랜지스터(T2)가 턴-온 상태가 되고, 센싱 구동용 기준 스위치(SPRE)가 턴-온 된다. 이에 따라, 구동 트랜지스터(DRT)의 제2 노드(N2)는 센싱 구동용 기준전압(VpreS)으로 초기화 된다.

- [0151] 트래킹 단계(S520)는 구동 트랜지스터(DRT)의 문턱전압(Vth)을 트래킹하는 단계이다.

- [0152] 트래킹 단계(S520)에서는, 제1 트랜지스터(T1) 및 제2 트랜지스터(T2)는 턴-온 상태를 유지하고, 센싱 구동용 기준 스위치(SPRE)가 턴-오프 된다. 이에 따라, 구동 트랜지스터(DRT)의 제2 노드(N2)는 플로팅 되고, 구동 트랜지스터(DRT)의 제2 노드(N2)의 전압이 센싱 구동용 기준전압(VpreS)에서부터 상승하기 시작한다.

- [0153] 제2 트랜지스터(T2)가 턴-온 되어 있기 때문에, 구동 트랜지스터(DRT)의 제2 노드(N2)의 전압 상승은 기준전압라인(RVL)의 전압 상승으로 이어진다.

- [0154] 구동 트랜지스터(DRT)의 제2 노드(N2)의 전압은 상승하다가 포화(Saturation)가 된다. 구동 트랜지스터(DRT)의 제2 노드(N2)의 포화된 전압은, 문턱전압 센싱 구동용 데이터전압(Vdata)에서 구동 트랜지스터(DRT)의 문턱전압(Vth)의 전압 차이(Vdata-Vth)와 대응된다.

- [0155] 따라서, 구동 트랜지스터(DRT)의 제2 노드(N2)의 전압이 포화되었을 때, 기준전압라인(RVL)의 전압은 문턱전압 센싱 구동용 데이터전압에서 구동 트랜지스터(DRT)의 문턱전압의 전압 차이(Vdata-Vth)와 대응된다.

- [0156] 구동 트랜지스터(DRT)의 제2 노드(N2)의 전압이 포화(Saturation)가 되면, 샘플링 스위치(SAMP)가 턴-온 되어, 샘플링 단계(S530)가 진행된다.

- [0157] 샘플링 단계(S530)에서는, 아날로그 디지털 컨버터(ADC)는, 샘플링 스위치(SAMP)에 의해 기준전압라인(RVL)의 전압을 센싱하고 센싱된 전압을 디지털 값에 해당하는 센싱값으로 변환할 수 있다. 여기서, 아날로그 디지털 컨버터(ADC)에 의해 센싱된 전압은 Vdata-Vth에 해당한다.

- [0158] 보상기(COMP)는, 아날로그 디지털 컨버터(ADC)에서 출력된 센싱값을 토대로 해당 서브픽셀(SP)의 구동 트랜지스터(DRT)의 문턱전압을 파악할 수 있고, 구동 트랜지스터(DRT)의 파악된 문턱전압을 보상해 수 있다.

- [0159] 보상기(COMP)는, 센싱 구동을 통해 측정된 센싱값(Vdata-Vth와 대응되는 디지털 값)과, 이미 알고 있는 문턱전압 센싱 구동용 데이터(Vdata와 대응되는 디지털 값)으로부터 구동 트랜지스터(DRT)의 문턱전압(Vth)을 파악할 수 있다.

- [0160] 보상기(COMP)는, 해당 구동 트랜지스터(DRT)에 대하여 파악된 문턱전압(Vth)을 기준 문턱전압 또는 다른 구동 트랜지스터(DRT)의 문턱전압과 비교하여, 구동 트랜지스터(DRT) 간의 문턱전압 편차를 보상해줄 수 있다. 여기서, 문턱전압 편차 보상은 영상데이터 변경 처리(영상데이터에 보상값(오프셋)을 가감하는 처리)를 의미할 수 있다.

- [0161] 도 6은 본 발명의 실시예들에 따른 유기발광표시장치(100)의 이동도 센싱을 위한 구동 타이밍 다이어그램이다.

- [0162] 도 6을 참조하면, 이동도 센싱 구동은, 초기화 단계(S610), 트래킹 단계(S620) 및 샘플링 단계(S630)로 진행될 수 있다.

- [0163] 초기화 단계(S610)에서, 턴-온 레벨 전압의 제1 스캔신호(SCAN)에 의해, 제1 트랜지스터(T1)가 턴-온 상태가 된다. 이에 따라, 구동 트랜지스터(DRT)의 제1 노드(N1)는 이동도 센싱 구동용 데이터전압(Vdata)으로 초기화 된다.

- [0164] 초기화 단계(S610)에서, 턴-온 레벨 전압의 제2 스캔신호(SENSE)에 의해, 제2 트랜지스터(T2)가 턴-온 상태가 되고, 센싱 구동용 기준 스위치(SPRE)가 턴-온 된다. 이에 따라, 구동 트랜지스터(DRT)의 제2 노드(N2)는 센싱 구동용 기준전압(VpreS)으로 초기화 된다.

- [0165] 트래킹 단계(S620)는 구동 트랜지스터(DRT)의 이동도를 트래킹하는 단계이다. 구동 트랜지스터(DRT)의 이동도는

구동 트랜지스터(DRT)의 전류구동능력을 나타낼 수 있다.

[0166] 트래킹 단계(S620)에서는, 턴-오프 레벨 전압의 제1 스캔신호(SCAN)에 의해 제1 트랜지스터(T1)가 턴-오프 되고, 센싱 구동용 기준 스위치(SPRE)가 턴-오프 된다. 이에 따라, 구동 트랜지스터(DRT)의 제1 노드(N1) 및 제2 노드(N2)는 모두 플로팅 된다. 이에 따라, 구동 트랜지스터(DRT)의 제1 노드(N1) 및 제2 노드(N2)의 전압이 모두 상승하게 된다. 특히, 구동 트랜지스터(DRT)의 제2 노드(N2)의 전압은 센싱 구동용 기준전압(VpreS)에서부터 상승하기 시작한다.

[0167] 제2 트랜지스터(T2)가 턴-온 되어 있기 때문에, 구동 트랜지스터(DRT)의 제2 노드(N2)의 전압 상승은 기준전압라인(RVL)의 전압 상승으로 이어진다.

[0168] 구동 트랜지스터(DRT)의 제2 노드(N2)의 전압이 상승하기 시작한 시점으로부터 일정 시간( $\Delta t$ )이 경과되면, 샘플링 스위치(SAMP)가 턴-온 되어, 샘플링 단계(S630)가 진행된다.

[0169] 샘플링 단계(S630)에서는, 아날로그 디지털 컨버터(ADC)는, 샘플링 스위치(SAMP)에 의해 기준전압라인(RVL)의 전압을 센싱하고 센싱된 전압을 디지털 값에 해당하는 센싱값으로 변환할 수 있다. 여기서, 아날로그 디지털 컨버터(ADC)에 의해 센싱된 전압은 센싱 구동용 기준전압(VpreS)에서 일정 전압( $\Delta V$ )만큼 상승된 전압( $VpreS + \Delta V$ )에 해당한다.

[0170] 보상기(COMP)는, 아날로그 디지털 컨버터(ADC)에서 출력된 센싱값을 토대로 해당 서브픽셀(SP)의 구동 트랜지스터(DRT)의 이동도를 파악할 수 있고, 구동 트랜지스터(DRT)의 파악된 이동도를 보상해 수 있다.

[0171] 보상기(COMP)는, 센싱 구동을 통해 측정된 센싱값( $VpreS + \Delta V$ 와 대응되는 디지털 값)과, 이미 알고 있는 센싱 구동용 기준전압(VpreS)과 경과시간( $\Delta t$ )으로부터 구동 트랜지스터(DRT)의 이동도를 파악할 수 있다.

[0172] 구동 트랜지스터(DRT)의 이동도는 트래킹 단계(S620)에서 기준전압라인(RVL)의 단위 시간 당 전압 변동량 ( $\Delta V / \Delta t$ )과 비례한다. 즉, 구동 트랜지스터(DRT)의 이동도는 도 6에서 기준전압라인(RVL)의 전압 과형에서 기울기 (Slope)와 비례한다.

[0173] 보상기(COMP)는, 해당 구동 트랜지스터(DRT)에 대하여 파악된 이동도를 기준 이동도 또는 다른 구동 트랜지스터(DRT)의 이동도와 비교하여, 구동 트랜지스터(DRT) 간의 이동도 편차를 보상해줄 수 있다. 여기서, 이동도 편차 보상은 영상데이터 변경 처리(영상데이터에 보상값(계인)을 곱하는 연산처리)를 의미할 수 있다.

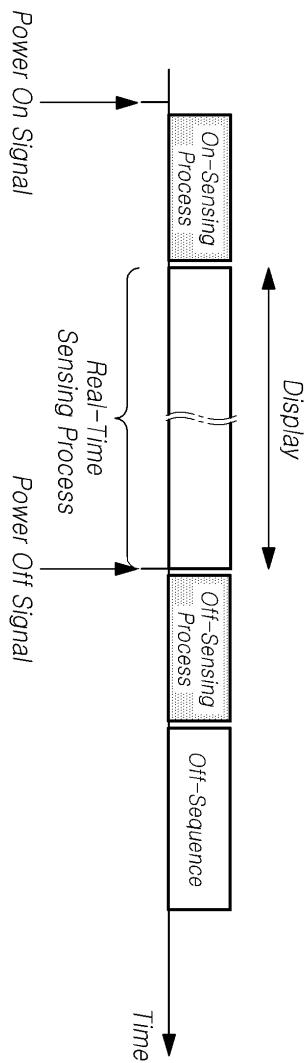

[0174] 도 7은 본 발명의 실시예들에 따른 유기발광표시장치(100)의 센싱 프로세스를 나타낸 도면이다.

[0175] 도 7을 참조하면, 유기발광표시장치(100)는, 파워 온 신호가 발생하면, 디스플레이 구동을 시작하기 위한 정해진 온 시퀀스 처리를 수행하고, 온 시퀀스 처리가 완료되면, 정상적인 디스플레이 구동이 시작된다.

[0176] 유기발광표시장치(100)는, 파워 오프 신호가 발생하면, 진행 중이던 디스플레이 구동을 중지하고 정해진 오프 시퀀스 처리를 수행하고, 오프 시퀀스 처리가 완료되면, 완전한 오프 상태가 된다.

[0177] 이러한 전원 처리 타이밍과 관련하여 센싱 구동 (문턱전압 센싱 구동, 이동도 센싱 구동)이 진행될 수 있다.

[0178] 센싱 구동은, 파워 온 신호의 발생 이후 디스플레이 구동이 시작하기 전에 진행될 수 있다. 이러한 센싱 및 센싱 프로세스를 온-센싱(On-Sensing) 및 온-센싱 프로세스(On-Sensing Process)라고 한다.

[0179] 또한, 센싱 구동은, 파워 오프 신호의 발생 이후 진행될 수 있다. 이러한 센싱 및 센싱 프로세스를 오프-센싱(Off-Sensing) 및 오프-센싱 프로세스(Off-Sensing Process)라고 한다.

[0180] 또한, 센싱 구동은, 디스플레이 구동 중에서 실시간으로 진행될 수도 있다. 이러한 센싱 및 센싱 프로세스를 실시간(RT: Real-Time) 센싱 및 실시간 센싱 프로세스(RT Sensing Process)라고 한다.

[0181] 실시간 센싱 프로세스의 경우, 디스플레이 구동 중에서 블랭크 시간마다 하나 이상의 서브픽셀 라인(서브픽셀 행)에서 하나 이상의 서브픽셀(SP)에 대하여 센싱 구동이 진행될 수 있다. 여기서, 블랭크 시간마다 센싱 구동이 되는 서브픽셀 라인(서브픽셀 행)은 랜덤하게 선택될 수 있다. 이에 따라, 블랭크 시간에서의 센싱 구동 후 액티브 시간에 센싱 구동이 된 서브픽셀 라인에서의 화상 이상 현상이 완화될 수 있다. 또한, 블랭크 시간에서의 센싱 구동 후 액티브 시간에 센싱 구동이 된 서브픽셀에 센싱 구동 이전의 데이터전압과 대응되는 회복 데이터전압을 공급해줄 수 있다. 이에 따라, 블랭크 시간에서의 센싱 구동 후 액티브 시간에 센싱 구동이 된 서브픽셀 라인에서의 화상 이상 현상이 더욱더 완화될 수 있다.

[0182] 한편, 문턱전압 센싱 구동의 경우, 구동 트랜지스터(DRT)의 제2 노드(N2)의 전압 포화에 많은 시간이 걸릴 수

있기 때문에, 다소 긴 시간 동안 진행될 수 있는 오프-센싱 프로세스로 진행될 수 있다.

[0183] 이동도 센싱 구동의 경우, 문턱전압 센싱 구동에 비해 상대적으로 짧은 시간만을 필요로 하기 때문에, 짧은 시간 동안 진행되는 온-센싱 프로세스 및/또는 실시간 센싱 프로세스로 진행될 수 있다.

[0184] 한편, 하나의 서브픽셀(SP)에는 1개의 데이터전압(Vdata), 2개의 스캔신호(SCAN, SENSE), 기준전압(Vref), 구동전압(EVDD) 등이 공급되어야 한다. 따라서, 하나의 서브픽셀(SP)은 1개의 데이터라인(DL), 1개 또는 2개의 게이트라인(GL), 1개의 기준전압(RVL), 1개의 구동전압라인(DVL)과 전기적으로 연결되어야 한다(도 3 참조).

[0185] 하나의 서브픽셀 행을 온-오프 시키기 위하여, 1개 또는 2개의 게이트라인(GL)이 하나의 서브픽셀 행마다 배치되어야 한다. 그리고, 각 서브픽셀(SP)마다 데이터전압(Vdata)이 공급되어야 하기 때문에, 1개의 데이터라인(DL)이 하나의 서브픽셀 열마다 배치될 수 있다. 경우에 따라서, 1개의 데이터라인(DL)이 2개의 서브픽셀 열마다 공통으로 배치될 수도 있다.

[0186] 구동전압(EVDD)은 공통전압일 수 있기 때문에, 1개의 서브픽셀 열(또는 1개의 서브픽셀 행)마다 1개의 구동전압라인(DVL)이 배치될 수도 있고, 2개 이상의 서브픽셀 열(또는 2개 이상의 서브픽셀 열)마다 1개의 구동전압라인(DVL)이 배치될 수 있다.

[0187] 마찬가지로, 기준전압(Vref)은 공통전압일 수 있기 때문에, 1개의 서브픽셀 열(또는 1개의 서브픽셀 행)마다 1개의 기준전압라인(RVL)이 배치될 수도 있고, 2개 이상의 서브픽셀 열(또는 2개 이상의 서브픽셀 열)마다 1개의 기준전압라인(RVL)이 배치될 수 있다.

[0188] 2개 이상의 서브픽셀 열(또는 2개 이상의 서브픽셀 열)마다 1개의 구동전압라인(DVL) 및/또는 1개의 기준전압라인(RVL)이 배치되는 경우, 유기발광표시패널(110)의 개구율을 높여줄 수 있다.

[0189] 아래에서는, 유기발광표시패널(110)의 개구율을 높여주기 위하여, 4개 이상의 서브픽셀 열마다 1개의 구동전압라인(DVL)이 데이터라인(DL)과 평행하게 배치되고, 4개 이상의 서브픽셀 열마다 1개의 기준전압라인(RVL)이 데이터라인(DL)과 평행하게 배치되는 구조를 도 8을 참조하여 설명한다.

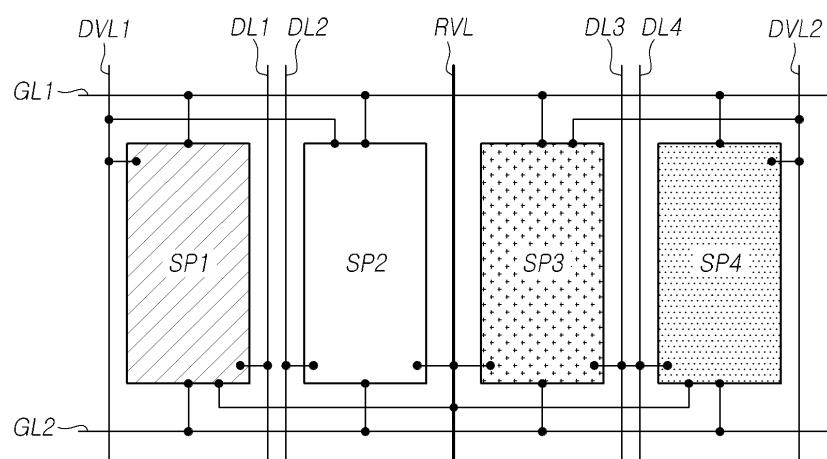

[0190] 도 8은 본 발명의 실시예들에 따른 유기발광표시장치(100)에서, 4개의 서브픽셀(SP1, SP2, SP3, SP4)과 연결되는 배선들(DL1~DL2, GL1~GL2, DVL1~DVL2, RVL)에 대한 배치도이다.

[0191] 4개의 서브픽셀(SP1, SP2, SP3, SP4)은, 일 예로, 적색 빛을 발광하는 서브픽셀, 흰색 빛을 발광하는 서브픽셀, 녹색 빛을 발광하는 서브픽셀 및 청색 빛을 발광하는 서브픽셀일 수 있다.

[0192] 전술한 바와 같이, 제1 스캔신호(SCAN)와 제2 스캔신호(SENSE)는 동일한 게이트라인을 통해 공급될 수도 있지만, 서로 다른 게이트라인들(GL1, GL2)에 의해 공급될 수 있다.

[0193] 도 8의 예시는, 제1 스캔신호(SCAN)와 제2 스캔신호(SENSE)가 서로 다른 게이트라인들(GL1, GL2)을 통해 공급되는 경우로서, 이 경우, 4개의 서브픽셀(SP1, SP2, SP3, SP4)이 배열된 서브픽셀 행에는, 제1 트랜지스터(T1)의 게이트 노드에 제1 스캔신호(SCAN)를 공급하기 위한 제1 게이트라인(GL1)과, 제2 트랜지스터(T2)의 게이트 노드에 제2 스캔신호(SENSE)를 공급하기 위한 제2 게이트라인(GL2)이 배치될 수 있다.

[0194] 도 8을 참조하면, 4개의 서브픽셀(SP1, SP2, SP3, SP4)이 행 방향으로 배열된 경우, 4개의 서브픽셀(SP1, SP2, SP3, SP4) 각각에 데이터전압을 공급하기 위한 4개의 데이터라인(DL1, DL2, DL3, DL4)이 열 방향으로 배치될 수 있다.

[0195] 도 8을 참조하면, 유기발광표시패널(110)의 개구율을 높여주기 위하여, 제1 서브픽셀(SP1) 및 제2 서브픽셀(SP2)은 제1 구동전압라인(DVL1)을 통해 구동전압(EVDD)을 공통으로 공급받을 수 있다. 제3 서브픽셀(SP3) 및 제4 서브픽셀(SP4)은 제2 구동전압라인(DVL2)을 통해 구동전압(EVDD)을 공통으로 공급받을 수 있다.

[0196] 제1 서브픽셀(SP1)과 동일한 열에 배열된 서브픽셀들과, 제2 서브픽셀(SP2)과 동일한 열에 배열된 서브픽셀들 모두는, 제1 구동전압라인(DVL1)을 통해 구동전압(EVDD)을 공통으로 공급받을 수 있다. 제3 서브픽셀(SP3)과 동일한 열에 배열된 서브픽셀들과, 제4 서브픽셀(SP4)과 동일한 열에 배열된 서브픽셀들 모두는, 제2 구동전압라인(DVL2)을 통해 구동전압(EVDD)을 공통으로 공급받을 수 있다.

[0197] 도 8을 참조하면, 유기발광표시패널(110)의 개구율을 높여주기 위하여, 4개의 서브픽셀(SP1, SP2, SP3, SP4)은 1개의 기준전압라인(RVL)을 통해 기준전압(Vref)을 공통으로 공급받을 수 있다.

[0198] 제1 서브픽셀(SP1)과 동일한 열에 배열된 서브픽셀들과, 제2 서브픽셀(SP2)과 동일한 열에 배열된

서브픽셀들과, 제3 서브픽셀(SP3)과 동일한 열에 배열된 서브픽셀들과, 제4 서브픽셀(SP4)과 동일한 열에 배열된 서브픽셀들 모두는, 1개의 기준전압라인(RVL)을 통해 기준전압(Vref)을 공통으로 공급받을 수 있다.

[0199] 다시 말해, 제1 서브픽셀(SP1)과 동일한 열에 배열된 서브픽셀들과, 제2 서브픽셀(SP2)과 동일한 열에 배열된 서브픽셀들과, 제3 서브픽셀(SP3)과 동일한 열에 배열된 서브픽셀들과, 제4 서브픽셀(SP4)과 동일한 열에 배열된 서브픽셀들 모두는, 1개의 기준전압라인(RVL)을 공유한다.

[0200] 여기서, 제1 서브픽셀(SP1)과 동일한 열에 배열된 서브픽셀들과, 제2 서브픽셀(SP2)과 동일한 열에 배열된 서브픽셀들과, 제3 서브픽셀(SP3)과 동일한 열에 배열된 서브픽셀들과, 제4 서브픽셀(SP4)과 동일한 열에 배열된 서브픽셀들은, 1개의 기준전압라인(RVL)이 공유되는 서브픽셀 그룹이다.

[0201] 1개의 기준전압라인(RVL)이 공유되는 서브픽셀 그룹 중 어느 하나의 서브픽셀에서 이상 현상이 발생하면, 발생된 이상 현상은 1개의 기준전압라인(RVL)을 통해 서브픽셀 그룹 전체로 전파될 수 있다.

[0202] 도 9는 본 발명의 실시예들에 따른 유기발광표시장치(100)에서, 제2 트랜지스터(T2)가 단락이 된 서브픽셀(불량 서브픽셀)의 회로이다.

[0203] 패널 제작 공정 시, 유기발광표시장치(100)의 제2 트랜지스터(T2)의 근처에 이물이 발생하는 경우, 제2 트랜지스터(T2)가 단락이 될 수 있다. 이뿐만 아니라, 제품 출하 후 내부 또는 외부 충격 등의 다양한 요인에 의해, 제2 트랜지스터(T2)가 단락이 될 수 있다.

[0204] 제2 트랜지스터(T2)의 단락은, 제2 트랜지스터(T2)의 소스 노드와 드레인 노드 간의 단락을 의미할 수 있다.

[0205] 이뿐만 아니라, 제2 트랜지스터(T2)의 단락은, 제2 트랜지스터(T2)가 턴-오프 되어야 하는 상황에서 제2 트랜지스터(T2)가 비정상적으로 턴-온 되는 상황을 모두 의미할 수 있다.

[0206] 예를 들어, 게이트구동회로(130)가 제2 트랜지스터(T2)의 게이트 노드와 연결된 제2 게이트라인(GL2)으로 턴-오프 레벨 전압의 제2 스캔신호(SENSE)를 출력함에도 불구하고, 제2 게이트라인(GL2)이 턴-온 레벨 전압과 유사한 전압 값을 갖는 다른 배선들과 단락이 되어, 제2 트랜지스터(T2)가 비정상적으로 턴-온 될 수도 있다.

[0207] 아래에서는, 제2 트랜지스터(T2)가 단락이 된 서브픽셀(SP)을 불량 서브픽셀이라고 한다. 제2 트랜지스터(T2)가 단락이 되지 않은 서브픽셀(SP)을 정상 서브픽셀이라고 한다.

[0208] 정상 서브픽셀이 영상 구동 될 때, 영상 데이터 기록 단계 이후 진행되는 부스팅 단계에서 플로팅 되는 구동 트랜지스터(DRT)의 제2 노드(N2)의 전압은, 단락 되지 않은 제2 트랜지스터(T2)의 턴-오프에 따라, 기준전압라인(RVL)으로 전달되지 않는다.

[0209] 하지만, 불량 서브픽셀이 영상 구동 될 때, 영상 데이터 기록 단계 이후 진행되는 부스팅 단계에서 플로팅 되는 구동 트랜지스터(DRT)의 제2 노드(N2)의 전압은, 턴-오프 되어야 하는 제2 트랜지스터(T2)의 단락에 의해서, 기준전압라인(RVL)으로 전달될 수 있다.

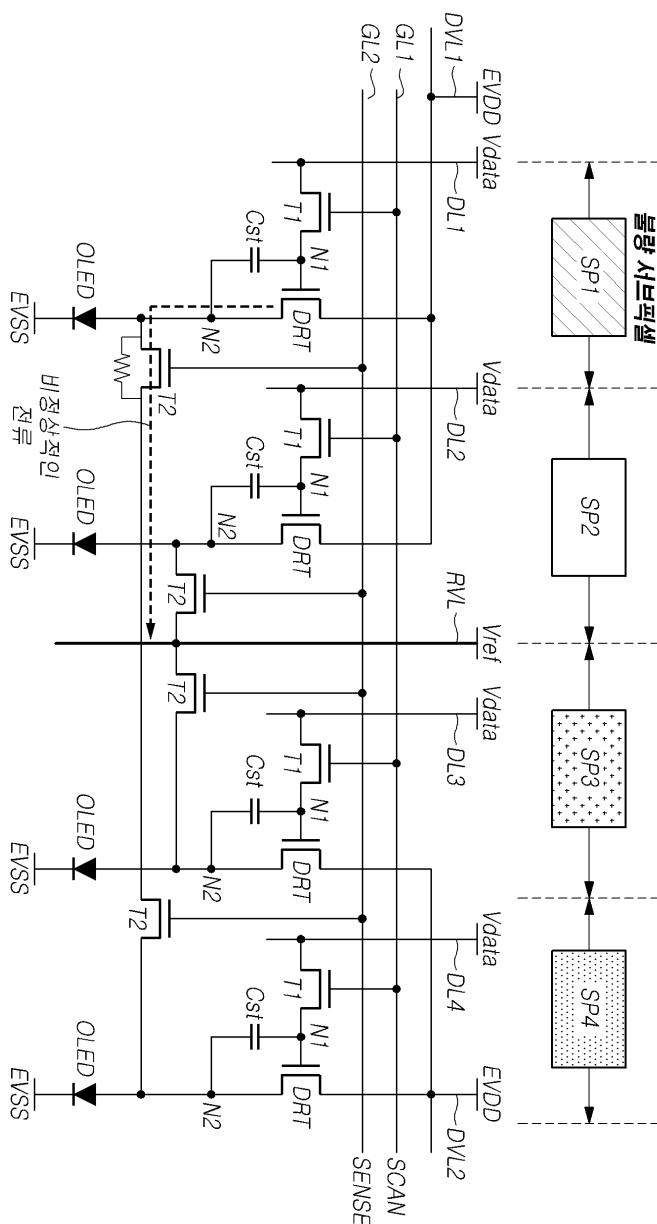

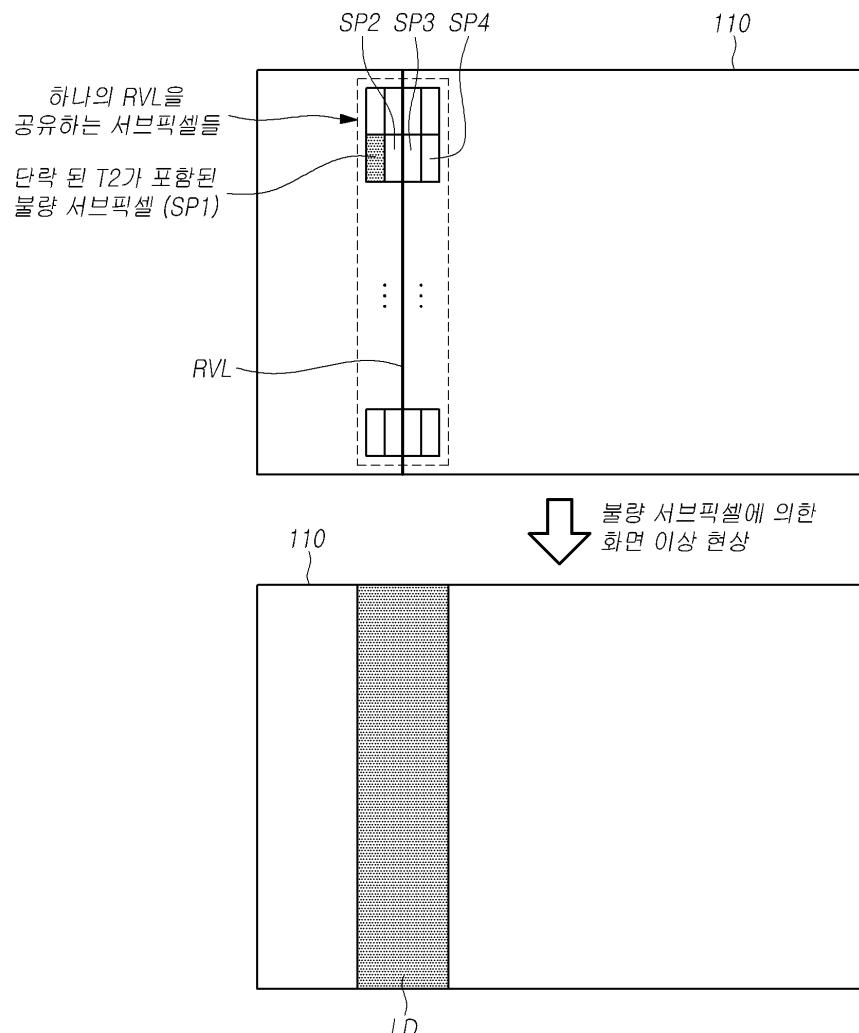

[0210] 도 10은 본 발명의 실시예들에 따른 유기발광표시장치(100)에서, 하나의 기준전압라인(RVL)을 공유하는 4개의 서브픽셀(SP1, SP2, SP3, SP4) 중 불량 서브픽셀이 존재하는 경우, 4개의 서브픽셀(SP1, SP2, SP3, SP4)에 대한 등가 회로이고, 도 11 및 도 12는 본 발명의 실시예들에 따른 유기발광표시장치(100)에서, 하나의 기준전압라인(RVL)을 공유하는 4개의 서브픽셀(SP1, SP2, SP3, SP4) 중 불량 서브픽셀이 존재하는 경우, 불량 서브픽셀의 구동에 의해 발생되는 센싱 및 보상 오류와, 이에 따라 발생하는 라인 결함 현상을 설명하기 위한 도면들이다.

[0211] 하나의 기준전압라인(RVL)을 공유하는 4개의 서브픽셀(SP1, SP2, SP3, SP4) 중 하나 또는 둘 이상이 불량 서브픽셀일 수 있다.

[0212] 도 10의 예시에서는, 하나의 기준전압라인(RVL)을 공유하는 4개의 서브픽셀(SP1, SP2, SP3, SP4) 중 제1 서브픽셀(SP1)이 제2 트랜지스터(T2)가 단락이 된 불량 서브픽셀이다.

[0213] 만약, 하나의 기준전압라인(RVL)을 공유하는 4개의 서브픽셀(SP1, SP2, SP3, SP4)이 모두 정상 서브픽셀이라면, 정상 서브픽셀인 제1 서브픽셀(SP1)이 구동될 때, 영상 구동 시 부스팅 단계 및 발광 단계에서 제2 트랜지스터(T2)가 턴-오프 상태이기 때문에, 제1 서브픽셀(SP1)에서 기준전압라인(RVL)으로 전류가 흐르지 않는다.

[0214] 하지만, 하나의 기준전압라인(RVL)을 공유하는 4개의 서브픽셀(SP1, SP2, SP3, SP4) 중 제1 서브픽셀(SP1)이 제2 트랜지스터(T2)가 단락이 된 불량 서브픽셀인 경우, 불량 서브픽셀인 제1 서브픽셀(SP1)이 구동될 때, 제1 서

브피셀(SP1)에서 기준전압라인(RVL)으로 전류가 흘러서는 안 되는 상황에서도, 단락이 의해 턴-온 된 것과 유사한 제2 트랜지스터(T2)를 통해서, 제1 서브피셀(SP1)에서 기준전압라인(RVL)으로 비정상적인 전류가 흐르게 된다.

[0215] 도 10에 도시된 바와 같이, 기준전압라인(RVL)을 공유하는 4개의 서브피셀(SP1, SP2, SP3, SP4)이 포함된 서브피셀 라인(서브피셀 행)은 불량 서브피셀 라인(불량 서브피셀 행)이다. 기준전압라인(RVL)을 공유하는 모든 서브피셀 라인 중에서 불량 서브피셀 라인(불량 서브피셀 행)을 제외한 나머지 서브피셀 라인들(서브피셀 행들)은 정상 서브피셀 라인(정상 서브피셀 행)인 것으로 가정한다. 즉, 유기발광표시패널(110)에서, 기준전압라인(RVL)을 공유하는 모든 서브피셀들 중에서 도 10의 제1 서브피셀(SP1)만 불량 서브피셀인 것으로 가정한다.

[0216] 한편, 도 10에 도시된 4개의 서브피셀(SP1, SP2, SP3, SP4)이 디스플레이 구동(영상 구동)이 되는 동안, 하나의 서브피셀 라인(서브피셀 행)에 포함된 서브피셀들의 전체 또는 일부가 실시간 센싱(RT 센싱)이 될 수 있다.

[0217] 실시간 센싱(RT 센싱)이 되는 하나의 서브피셀 라인(서브피셀 행)은, 도 10에 도시된 4개의 서브피셀(SP1, SP2, SP3, SP4)과 기준전압라인(RVL)을 공유할 수 있으며, 도 10에 도시된 4개의 서브피셀(SP1, SP2, SP3, SP4)이 포함된 불량 서브피셀 라인(불량 서브피셀 행)일 수도 있고, 도 10에 도시된 4개의 서브피셀(SP1, SP2, SP3, SP4)이 포함된 불량 서브피셀 라인(불량 서브피셀 행)과 다른 정상 서브피셀 라인(정상 서브피셀 행)일 수도 있다.

[0218] 4개의 서브피셀(SP1, SP2, SP3, SP4) 중 불량 서브피셀인 제1 서브피셀(SP1)의 구동에 따라, 제1 서브피셀(SP1) 내 단락이 된 제2 트랜지스터(T2)를 통해, 기준전압라인(RVL)으로 비정상적인 전류가 흐르게 된다.

[0219] 이에 따라, 실시간 센싱(RT 센싱)이 되는 하나의 서브피셀 라인(서브피셀 행)에서의 서브피셀에 대한 센싱값이 영향을 받게 된다.

[0220] 보다 구체적으로, 실시간 센싱(RT 센싱)이 이동도 센싱인 경우, 이동도 센싱이 되는 서브피셀에서 기준전압라인(RVL)으로 정상적인 전류가 흐를 때, 제1 서브피셀(SP1)의 구동에 의해 비정상적인 전류가 기준전압라인(RVL)으로 더 흐르게 되어, 이동도 센싱이 되는 서브피셀에 대한 이동도 센싱을 위한 센싱값 (RT 센싱값)이 높아지게 된다.

[0221] 따라서, 비정상적으로 높아진 센싱값(RT 센싱값)에 의해, 보상값이 낮은 값으로 결정된다. 이에 따라, 불량 서브피셀의 구동에 의해 영향을 받은 서브피셀은 영상 구동 시 검게 보인 암점(온암, 약암)으로 보이게 된다. 여기서, 온암인 서브피셀은 완전하게 블랙으로 보이고, 약암인 서브피셀은 거의 완전한 블랙으로 보이게 된다.

[0222] 전술한 바와 같이, 불량 서브피셀(SP1)의 구동에 의해 기준전압라인(RVL)을 공유하는 모든 서브피셀들에 대한 센싱 오류가 발생하고, 이 센싱 오류(이동도 센싱 오류)는 보상 오류(이동도 보상 오류)로 이어져, 결국에는 기준전압라인(RVL)을 공유하는 모든 서브피셀들이 블랙으로 보이는 라인 결함(LD: Line Defect)을 발생시킬 수 있다.

[0223] 라인 결함(LD)은 검은색의 띠 형태의 블록이 보이는 현상을 의미할 수 있다. 라인 결함(LD)은 기준전압라인(RVL)이 배치되는 열 방향(세로 방향)으로 생긴다. 라인 결함(LD)에 해당하는 블록의 폭(행 방향 길이)은 하나의 서브피셀 행에서 기준전압라인(RVL)을 공유하는 서브피셀들의 개수에 비례할 수 있다. 라인 결함(LD)에 해당하는 블록의 길이(열 방향 길이)는 기준전압라인(RVL)의 길이에 비례하거나 기준전압라인(RVL)을 공유하는 서브피셀 행의 개수와 비례할 수 있다.

[0224] 도 12를 참조하여 다시 설명하면, 하나의 기준전압라인(RVL)을 공유하는 모든 서브피셀 라인(모든 서브피셀 행) 중에서 일부의 2번째 서브피셀 라인(2번째 서브피셀 행)에서 속하는 제1 서브피셀(SP1)만 불량 서브피셀이더라도, 제1 서브피셀(SP1)의 구동 영향이 제1 서브피셀(SP1)과 함께 기준전압라인(RVL)을 공유하는 모든 서브피셀들로 전파될 수 있다.

[0225] 즉, 하나의 기준전압라인(RVL)을 공유하는 모든 서브피셀 라인(모든 서브피셀 행) 중에서 일부의 2번째 서브피셀 라인(2번째 서브피셀 행)에서 속하는 제1 서브피셀(SP1)만 불량 서브피셀이더라도, 제1 서브피셀(SP1)에서의 단락이 된 제2 트랜지스터(T2)에 의해, 불량 서브피셀인 제1 서브피셀(SP1)이 연결된 기준전압라인(RVL)을 함께 공유하고 있는 모든 서브피셀 라인(모든 서브피셀 행)에 포함된 서브피셀들의 센싱값 (이동도 센싱값)과 보상값 (이동도 보상값)에 오류를 발생시키고, 결국에는, 불량 서브피셀인 제1 서브피셀(SP1)이 연결된 기준전압라인(RVL)을 함께 공유하고 있는 모든 서브피셀 라인(모든 서브피셀 행)에 포함된 서브피셀들이 암점(온점 또는 약점)으로 보이는 라인 결함(LD)이 발생할 수 있다.

- [0226] 참고로, 불량 서브픽셀에 의해, 문턱전압에 대한 센싱 오류 및 보상 오류는 발생하지 않을 수 있다. 이는 문턱 전압 센싱 구동 시 트래킹 단계(S520)에서 제1 트랜지스터(T1)가 터-온 되어 있기 때문이다.

- [0227] 도 13은 본 발명의 실시예들에 따른 유기발광표시장치(100)에서, 정상 서브픽셀과 불량 서브픽셀에 대한 문턱전 압 센싱을 위한 구동 타이밍 다이어그램이다.

- [0228] 도 13을 참조하면, 문턱전압 센싱 구동 시, 트래킹 단계(S520)에서 제2 트랜지스터(T2)가 터-온 되어 있기 때문에, 제2 트랜지스터(T2)의 단락 유무와 관계 없이 구동 트랜지스터(DRT)의 제2 노드(N2)와 기준전압라인(RVL)은 전기적으로 연결될 수 있다.

- [0229] 따라서, 제2 트랜지스터(T2)가 단락이 되지 않은 정상 서브픽셀에 대한 문턱전압 센싱 시 기준전압라인(RVL)의 전압 변화와, 제2 트랜지스터(T2)가 단락이 된 불량 서브픽셀에 대한 문턱전압 센싱 시 기준전압라인(RVL)의 전압 변화는 동일하다.

- [0230] 따라서, 문턱전압 센싱 구동 방식을 이용하여, 제2 트랜지스터(T2)가 단락이 되지 않은 정상 서브픽셀과 제2 트랜지스터(T2)가 단락이 된 불량 서브픽셀을 구별할 수 없다. 즉, 불량 서브픽셀 검출 방법으로 문턱전압 센싱 구동을 활용할 수 없다.

- [0231] 도 14는 본 발명의 실시예들에 따른 유기발광표시장치(100)에서, 정상 서브픽셀과 불량 서브픽셀에 대한 이동도 센싱을 위한 구동 타이밍 다이어그램이다.

- [0232] 도 14를 참조하면, 이동도 센싱 구동 시, 트래킹 단계(S620)에서 제2 트랜지스터(T2)가 터-온 되어 있기 때문에, 제2 트랜지스터(T2)의 단락 유무와 관계 없이 구동 트랜지스터(DRT)의 제2 노드(N2)와 기준전압라인(RVL)은 전기적으로 연결될 수 있다.

- [0233] 따라서, 제2 트랜지스터(T2)가 단락이 되지 않은 정상 서브픽셀에 대한 이동도 센싱 시 기준전압라인(RVL)의 전압 변화와, 제2 트랜지스터(T2)가 단락이 된 불량 서브픽셀에 대한 이동도 센싱 시 기준전압라인(RVL)의 전압 변화는 동일하다.

- [0234] 따라서, 이동도 센싱 구동 방식을 이용하여, 제2 트랜지스터(T2)가 단락이 되지 않은 정상 서브픽셀과 제2 트랜지스터(T2)가 단락이 된 불량 서브픽셀을 구별할 수 없다. 즉, 불량 서브픽셀 검출 방법으로 이동도 센싱 구동을 활용할 수 없다.

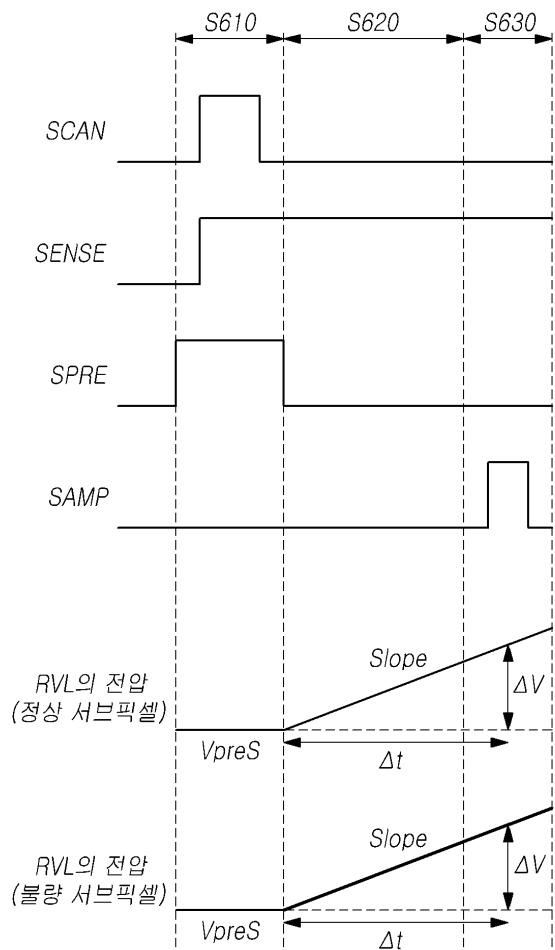

- [0235] 도 15는 본 발명의 실시예들에 따른 유기발광표시장치(100)의 라인 결함 방지 회로이고, 도 16은 본 발명의 실시예들에 따른 유기발광표시장치(100)의 라인 결함 방지 방법의 흐름도이고, 도 17은 본 발명의 실시예들에 따른 유기발광표시장치(100)의 불량 서브픽셀 검출을 위한 구동 타이밍 다이어그램이며, 도 18 및 도 19는 본 발명의 실시예들에 따른 유기발광표시장치(100)에서, 하나의 기준전압라인(RVL)을 공유하는 4개의 서브픽셀 중 제1 서브픽셀(SP1)이 불량 서브픽셀인 경우, 라인 결함 방지 동작과 이에 따른 효과를 설명하기 위한 도면들이다.

- [0236] 유기발광표시패널(110)은 도 15에 도시된 4개의 서브픽셀(SP1, SP2, SP3, SP4)과 그 영역에서의 배선들(DL1~DL4, GL1~GL2, DVL1~DVL2, RVL)의 배치 패턴이 반복되어 구성될 수 있다.

- [0237] 유기발광표시패널(110)의 개구율 향상을 위해, 둘 이상의 서브픽셀 열마다 1개의 기준전압라인(RVL)이 배치되는 경우, 유기발광표시패널(110)에 배치되는 다수의 기준전압라인(RVL)의 개수는 다수의 데이터라인(DL)의 개수보다 적을 수 있다.

- [0238] 이 경우, 각 기준전압라인(RVL)은 둘 이상의 서브픽셀에 포함된 제2 트랜지스터들(T2)의 소스 노드 또는 드레인 노드와 공통으로 연결될 수 있다.

- [0239] 도 15의 예시에 따르면, 4개의 서브픽셀 열에 1개의 기준전압라인(RVL)이 배치된다. 이 경우, 유기발광표시패널(110)에서, 다수의 기준전압라인(RVL)의 개수는 다수의 데이터라인(DL)의 개수의 1/4이다.

- [0240] 각 기준전압라인(RVL)은 4개의 서브픽셀(SP1, SP2, SP3, SP4)에 포함된 제2 트랜지스터들(T2)의 소스 노드 또는 드레인 노드와 공통으로 연결될 수 있다.

- [0241] 도 15를 참조하면, 본 발명의 실시예들에 따른 유기발광표시장치(100)는, 하나의 기준전압라인(RVL)과 전기적으로 연결되는 스위치 회로를 포함할 수 있다.

- [0242] 스위치 회로는, 각 기준전압라인(RVL)과 기준전압(Vref)이 공급되는 센싱 구동용 기준전압 공급 노드(Npres) 간의 연결을 제어하는 센싱 구동용 기준 스위치(SPRE)와, 각 기준전압라인(RVL)과 아날로그 디지털 컨버터(ADC)

간의 연결을 제어하는 샘플링 스위치(SAMP)를 포함할 수 있다.

[0243] 스위치 회로는, 각 기준전압라인(RVL)과 기준전압(Vref)이 공급되는 영상 구동용 기준전압 공급 노드(Nprer) 간의 연결을 제어하는 영상 구동용 기준 스위치(RPRE)를 더 포함할 수 있다.

[0244] 센싱 구동용 기준 스위치(SPRE)는 센싱 구동 시 이용되는 스위치이다. 센싱 구동용 기준 스위치(SPRE)에 의해 기준전압라인(RVL)으로 공급되는 기준전압(Vref)은 센싱 구동용 기준전압(VpreS)이다. 영상 구동용 기준 스위치(RPRE)는 영상 구동 시 이용되는 스위치이다. 영상 구동용 기준 스위치(SPRE)에 의해 기준전압라인(RVL)에 공급되는 기준전압(Vref)은 영상 구동용 기준전압(VpreR)이다.

[0245] 센싱 구동용 기준 스위치(SPRE)와 영상 구동용 기준 스위치(RPRE)는 별도로 구비될 수도 있고, 하나로 통합되어 구현될 수도 있다. 센싱 구동용 기준전압(VpreS)과 영상 구동용 기준전압(VpreR)은 동일한 전압 값일 수도 있고, 다른 전압 값일 수도 있다.

[0246] 도 15를 참조하면, 유기발광표시패널(110)에 배치된 다수의 서브픽셀(SP)은, 제1 기준전압라인(RVL)을 통해 기준전압(Vref)을 공통으로 공급받는 제1 서브픽셀(SP1), 제2 서브픽셀(SP2), 제3 서브픽셀(SP3) 및 제4 서브픽셀(SP4)을 포함할 수 있다. 여기서, 제1 서브픽셀(SP1)은 제1 서브픽셀 열을 대표하고, 제2 서브픽셀(SP2)은 제2 서브픽셀 열을 대표하고, 제3 서브픽셀(SP3)은 제3 서브픽셀 열을 대표하고, 제4 서브픽셀(SP4)은 제4 서브픽셀 열을 대표한다.

[0247] 제1 서브픽셀(SP1) 내 제2 트랜지스터(T2)가 단락이 된 경우, 데이터구동회로(DDC)는, 제1 서브픽셀(SP1)의 구동 기간(예: 영상 구동 기간)에, 제1 서브픽셀(SP1) 내 구동 트랜지스터(DRT)가 터-오프 되도록 하는 제1 특정 데이터전압(OFF\_Vdata)을 제1 데이터라인(DL)을 통해 제1 서브픽셀(SP1)로 공급할 수 있다.

[0248] 이에 따라, 불량 서브픽셀인 제1 서브픽셀(SP1)이 구동되더라도, 제1 서브픽셀(SP1)에서 기준전압라인(RVL)으로 전류가 흐르지 않아, 불량 서브픽셀인 제1 서브픽셀(SP1)과 함께 기준전압라인(RVL)에 연결된 서브픽셀들(SP2, SP3, SP4)은, 불량 서브픽셀인 제1 서브픽셀(SP1)의 구동 영향을 받지 않는다. 따라서, 라인 결합(LD)이 발생하지 않을 수 있다.

[0249] 제1 서브픽셀(SP1)의 구동 기간에, 제1 서브픽셀(SP1)과 함께 제1 기준전압라인(RVL)에 연결된 제2 서브픽셀(SP2), 제3 서브픽셀(SP3) 및 제4 서브픽셀(SP4) 중 하나에 포함된 구동 트랜지스터(DRT)의 이동도 센싱이 진행될 수 있다.

[0250] 또한, 제1 서브픽셀(SP1)의 구동 기간에, 제1 서브픽셀(SP1)과 함께 제1 기준전압라인(RVL)에 연결되어 제1 내지 제4 서브픽셀(SP1~SP4)와 다른 서브픽셀 행에 포함되는 서브픽셀 내 구동 트랜지스터(DRT)의 이동도 센싱이 진행될 수도 있다.

[0251] 이와 같이, 불량 서브픽셀인 제1 서브픽셀(SP1)의 구동 기간 동안, 제1 서브픽셀(SP1) 내 구동 트랜지스터(DRT)가 터-오프 시킬 수 있는 특정 데이터전압(OFF\_Vdata)이 제1 데이터라인(DL1)을 통해 제1 서브픽셀(SP1)에 공급됨으로써, 제1 서브픽셀(SP1)의 구동 기간 동안, 제1 서브픽셀(SP1)과 함께 기준전압라인(RVL)에 연결된 다른 서브픽셀에 대한 이동도 센싱이 센싱 오류 없이 진행될 수 있다.

[0252] 도 15를 참조하면, 본 발명의 실시예들에 따른 유기발광표시장치(100)는, 불량 서브픽셀 검출 기간 동안 다수의 서브픽셀(SP) 중 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 단락 여부에 따라, 확인 대상 서브픽셀을 불량 서브픽셀로서 검출하는 불량 서브픽셀 검출 회로(DPDC)를 더 포함할 수 있다.

[0253] 불량 서브픽셀 검출 회로(DPDC)는, 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 게이트 노드에 터-오프 레벨 전압의 제2 스캔신호(SENSE)가 인가되고 있는 동안, 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 소스 노드 또는 드레인 노드와 전기적으로 연결된 기준전압라인(RVL)의 전압 변화 여부 또는 전압 변화 크기에 기초하여, 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 단락 여부를 판단할 수 있다.

[0254] 불량 서브픽셀 검출 회로(DPDC)는 제2 트랜지스터(T2)가 단락이 된 불량 서브픽셀이 검출되면, 불량 서브픽셀의 위치정보를 메모리(MEM)에 저장할 수 있다.

[0255] 컨트롤러(140)는, 메모리(MEM)를 참조하여, 불량 서브픽셀에 공급해야 하는 영상데이터(DATA)를 불량 서브픽셀 내 구동 트랜지스터(DRT)를 터-오프 시키는 특정 영상데이터(OFF\_DATA)로 교체하여 데이터구동회로(120)로 출력할 수 있다.

[0256] 이에 따라, 데이터구동회로(120)는, 디지털 아날로그 컨버터(DAC)를 통해 특정 영상데이터(OFF\_DATA)를 특정 데

이터전압(OFF\_Vdata)로 변환하여 출력할 수 있다. 여기서, 특정 데이터전압(OFF\_Vdata)은 불량 서브픽셀 내 구동 트랜지스터(DRT)가 턴-오프 되도록 하는 데이터전압이다.

[0257] 불량 서브픽셀 검출 회로(DPDC)는 컨트롤러(140)의 내부에 포함될 수 있다. 메모리(MEM)는 컨트롤러(140)의 내부에 포함되는 레지스터일 수 있다.

[0258] 불량 서브픽셀 내 구동 트랜지스터(DRT)가 턴-오프 되도록 하는 특정 데이터전압(OFF\_Vdata)은 불량 서브픽셀이 구동되는 시간 경과에 따라 변화될 수 있다. 불량 서브픽셀 내 구동 트랜지스터(DRT)의 문턱전압 또는 이동도 등이 변화되는 경우, 구동 트랜지스터(DRT)를 턴-오프 시킬 수 있는 특정 데이터전압(OFF\_Vdata)도 변할 수 있다.

[0259] 도 16을 참조하면, 본 발명의 실시예들에 따른 유기발광표시장치(100)는 라인 결합 방지 방법을 제공할 수 있다.

[0260] 이를 위해, 유기발광표시장치(100)는 확인 대상 서브픽셀이 불량 서브픽셀인지 아닌지를 검출하기 위한 구동을 수행한다(S1610).

[0261] 유기발광표시장치(100)는 불량 서브픽셀의 검출을 위한 구동 수행 결과에 따라 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 단락 여부를 판단한다(S1620).

[0262] 유기발광표시장치(100)는, S1620 단계에서의 판단 결과, 확인 대상 서브픽셀 내 제2 트랜지스터(T2)가 단락이 된 것으로 판단되면, 확인 대상 서브픽셀을 불량 서브픽셀로 검출하고, 검출된 불량 서브픽셀의 위치정보를 메모리(MEM)에 저장하고(S1630), 불량 서브픽셀에 대한 구동 시, 라인 결합 방지를 위한 특정 데이터전압(OFF\_Vdata)을 불량 서브픽셀로 공급함으로써 라인 결합 방지 구동을 수행할 수 있다(S1640).

[0263] 유기발광표시장치(100)는, S1620 단계에서의 판단 결과, 확인 대상 서브픽셀 내 제2 트랜지스터(T2)가 단락이 되지 않은 것으로 판단되면, 확인 대상 서브픽셀을 정상 서브픽셀로 검출하고(S1650), 정상 서브픽셀에 대한 구동 시, 정상적인 구동을 수행할 수 있다(S1660).

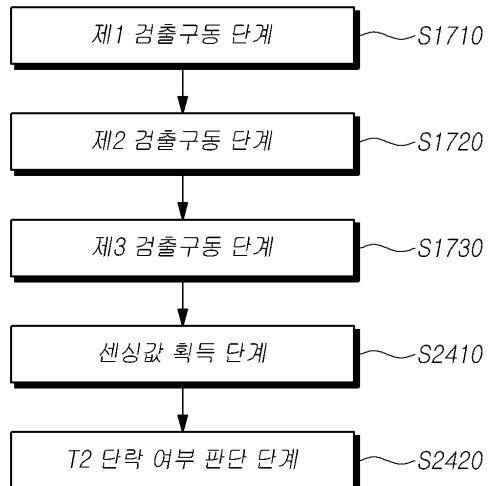

[0264] 도 17을 참조하면, 유기발광표시장치(100)는, 불량 서브픽셀 검출 기간 동안 다수의 서브픽셀(SP) 중 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 단락 여부에 따라 확인 대상 서브픽셀을 불량 서브픽셀로서 검출한다.

[0265] 따라서, 유기발광표시장치(100)는, 확인 대상 서브픽셀을 불량 서브픽셀인지 아닌지를 구별하기 위해서는, 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 단락 여부를 판단해야만 한다.

[0266] 게이트구동회로(130)는, 제2 게이트라인(GL2)를 통해, 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 게이트 노드에 턴-오프 레벨 전압의 제2 스캔신호(SENSE)를 인가한다(S1720).

[0267] 이때, 아날로그 디지털 컨버터(ADC)는, 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 소스 노드 또는 드레인 노드와 전기적으로 연결된 기준전압라인(RVL)의 전압을 센싱하고, 센싱된 전압을 디지털 값인 센싱값으로 변환하여 출력한다(S1730).

[0268] 불량 서브픽셀 검출회로(DPDC)는, 아날로그 디지털 컨버터(ADC)에 출력된 센싱값을 토대로, 기준전압라인(RVL)의 전압 변화 여부 또는 전압 변화 크기를 파악하고, 이에 기초하여, 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 단락 여부를 판단할 수 있다.

[0269] 도 17을 참조하면, 불량 서브픽셀 검출 기간 동안, 제1 검출 구동 단계(S1710), 제2 검출 구동 단계(S1720), 제3 검출 구동 단계(S1730) 등을 포함할 수 있다.

[0270] 제1 검출 구동 단계(S1710)에서, 게이트구동회로(130)는, 확인 대상 서브픽셀 내 제1 트랜지스터(T1)의 게이트 노드에 턴-온 레벨 전압의 제1 스캔신호(SCAN)를 공급한다. 이에 따라, 구동 트랜지스터(DRT)의 제1 노드(N1)에 검출 구동용 데이터전압이 인가된다. 여기서, 검출 구동용 데이터전압은 문턱전압(Vth)이 보상된 데이터(DATA+VTH)에 해당하는 데이터전압일 수 있다.

[0271] 제1 검출 구동 단계(S1710)에서, 게이트구동회로(130)는, 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 게이트 노드에 턴-온 레벨 전압의 제2 스캔신호(SENSE)를 공급한다. 센싱 구동용 기준 스위칭(SPRE)는 턴-온 상태이다. 이에 따라, 구동 트랜지스터(DRT)의 제2 노드(N2)에 센싱 구동용 기준전압(VpreS)이 인가된다.

[0272] 제1 검출 구동 단계(S1710)에서, 샘플링 스위치(SAMP)는 턴-오프 상태이다.

[0273] 제2 검출 구동 단계(S1720)에서, 게이트구동회로(130)는, 확인 대상 서브픽셀 내 제1 트랜지스터(T1)의 게이트

노드에 턴-오프 레벨 전압의 제1 스캔신호(SCAN)를 공급한다. 이에 따라, 구동 트랜지스터(DRT)의 제1 노드(N1)에 검출 구동용 데이터전압이 인가되지 못하고, 구동 트랜지스터(DRT)의 제1 노드(N1)는 플로팅 상태가 된다.

[0274] 제2 검출 구동 단계(S1720)에서, 센싱 구동용 기준 스위칭(SPRE)는 턴-오프 상태이다. 이에 따라, 센싱 구동용 기준전압(VpreS)은 기준전압라인(RVL)에도 인가되지 못한다. 그리고, 구동 트랜지스터(DRT)의 제2 노드(N2)는 플로팅 상태가 된다.

[0275] 또한, 제2 검출 구동 단계(S1720)에서, 게이트구동회로(130)는 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 게이트 노드에 턴-오프 레벨 전압의 제2 스캔신호(SENSE)를 공급한다.

[0276] 제2 검출 구동 단계(S1720)에서, 샘플링 스위치(SAMP)는 턴-오프 상태이다.

[0277] 제2 검출 구동 단계(S1720) 동안, 구동 트랜지스터(DRT)의 제1 노드(N1) 및 제2 노드(N2) 모두는 플로팅 상태이다. 그리고, 구동 트랜지스터(DRT)의 제1 노드(N1) 및 제2 노드(N2) 각각의 전압은 상승하게 된다.

[0278] 만약, 확인 대상 서브픽셀이 제2 트랜지스터(T2)이 단락 되지 않은 정상 서브픽셀이라면, 제2 검출 구동 단계(S1720) 동안, 제2 트랜지스터(T2)는 게이트 노드에 인가된 턴-오프 레벨 전압의 제2 스캔신호(SENSE)에 의해 턴-오프 상태이기 때문에, 구동 트랜지스터(DRT)의 제2 노드(N2)의 상승되는 전압이 기준전압라인(RVL)에 전달되지 못한다.

[0279] 이에 따라, 확인 대상 서브픽셀이 정상 서브픽셀인 경우, 기준전압라인(RVL)의 전압은 변동이 없다.

[0280] 만약, 확인 대상 서브픽셀이 제2 트랜지스터(T2)가 단락이 된 불량 서브픽셀이라면, 제2 검출 구동 단계(S1720) 동안, 제2 트랜지스터(T2)는 턴-오프 레벨 전압의 제2 스캔신호(SENSE)가 게이트 노드에 인가되더라도, 단락에 의해 비정상적인 턴-온 상태이다. 따라서, 구동 트랜지스터(DRT)의 제2 노드(N2)의 상승되는 전압은 제2 트랜지스터(T2)를 통해 기준전압라인(RVL)에 전달된다.

[0281] 이에 따라, 확인 대상 서브픽셀이 불량 서브픽셀인 경우, 기준전압라인(RVL)은 전압 변동이 발생할 수 있다.

[0282] 제2 검출 구동 단계(S1720)가 일정 시간 경과한 이후, 제3 검출 구동 단계(S1730)가 진행될 수 있다.

[0283] 제3 검출 구동 단계(S1730)에서는, 샘플링 스위치(SAMP)만 턴-온 된다.

[0284] 이에 따라, 아날로그 디지털 컨버터(ADC)는 턴-온 된 샘플링 스위치(SAMP)를 통해 기준전압라인(RVL)과 연결된다.

[0285] 따라서, 아날로그 디지털 컨버터(ADC)는, 기준전압라인(RVL)의 전압을 센싱하여 센싱된 전압을 디지털 값에 해당하는 센싱값으로 변환하여 출력한다.

[0286] 불량 서브픽셀 검출 회로(DPDC)는, 센싱값을 토대로, 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 소스 노드 또는 드레인 노드와 전기적으로 연결된 기준전압라인(RVL)의 전압 변화 여부 또는 전압 변화 크기를 확인하여 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 단락 여부를 판단할 수 있다.

[0287] 도 15의 예시를 참조하면, 불량 서브픽셀 검출 회로(DPDC)는, 제1 서브픽셀(SP1)의 구동 기간 전에 확인 대상 서브픽셀로서 제1 서브픽셀(SP1) 내 제2 트랜지스터(T2)의 단락 여부를 판단하되, 제1 서브픽셀(SP1) 내 제2 트랜지스터(T2)의 게이트 노드에 턴-오프 레벨 전압의 제2 스캔신호(SENSE)가 인가되고 있는 동안(S1720~S1730), 제1 서브픽셀(SP1) 내 제2 트랜지스터(T2)의 소스 노드 또는 드레인 노드와 전기적으로 연결된 제1 기준전압라인(RVL)의 전압이 상승한 것으로 확인되면, 제1 서브픽셀(SP1) 내 제2 트랜지스터(T2)가 단락이 된 것으로 판단하여, 제1 서브픽셀(SP1)을 불량 서브픽셀로서 검출할 수 있다.

[0288] 도 15의 예시를 참조하면, 불량 서브픽셀 검출 회로(DPDC)는, 확인 대상 서브픽셀로서 제2 서브픽셀(SP2) 내 제2 트랜지스터(T2)의 게이트 노드에 턴-오프 레벨 전압의 제2 스캔신호(SENSE)가 인가되고 있는 동안(S1720~S1730), 제2 서브픽셀(SP2) 내 제2 트랜지스터(T2)의 소스 노드 또는 드레인 노드와 전기적으로 연결된 제1 기준전압라인(RVL)의 전압변화가 없거나 전압 변화 크기가 미리 정해진 임계 수준 이하인 것으로 확인되면, 제2 서브픽셀(SP2) 내 제2 트랜지스터(T2)가 미 단락이 된 것으로 판단하여, 제2 서브픽셀(SP2)을 정상 서브픽셀로서 검출할 수 있다.

[0289] 이 경우, 데이터구동회로(120)는, 제2 서브픽셀(SP2)이 구동(센싱 구동 또는 영상 구동)될 때, 제1 서브픽셀(SP1) 내 구동 트랜지스터(DRT)가 턴-오프 되도록 하는 제1 특정 데이터전압(OFF\_Vdata)을 제1 데이터라인(DL1)을 통해 제1 서브픽셀(SP1)로 공급할 수 있다. 이에 따라, 제2 서브픽셀(SP2)은 불량 서브픽셀인 제1 서브픽

셀(SP1)의 구동 영향을 받지 않는다.

[0290] 도 18을 참조하면, 전술한 라인 결합 방지 구동에 따르면, 불량 서브픽셀인 제1 서브픽셀(SP1) 내 구동 트랜지스터(DRT)가 턴-오프 되도록 하는 제1 특정 데이터전압(OFF\_Vdata)이 제1 서브픽셀(SP1)로 공급될 때, 제1 서브픽셀(SP1)과 함께 기준전압라인(RVL)에 연결된 다른 서브픽셀들(SP2, SP3, SP4)이 센싱 구동이 되더라도, 센싱 값 및 보상값이 정상적으로 얻어질 수 있고, 이에 따라, 제1 서브픽셀(SP1)과 함께 기준전압라인(RVL)에 연결된 다른 서브픽셀들(SP2, SP3, SP4)의 영상 구동도 정상적으로 진행될 수 있다.

[0291] 도 17 및 18을 참조하면, 불량 서브픽셀인 제1 서브픽셀(SP1)과 함께 기준전압라인(RVL)에 연결된 다른 서브픽셀들(SP2, SP3, SP4)은, 불량 서브픽셀인 제1 서브픽셀(SP1)이 포함된 불량 서브픽셀 라인일 수도 있고, 포함된 불량 서브픽셀 라인과 다른 정상 서브픽셀 라인일 수도 있다.

[0292] 예를 들어, 제1 기준전압라인(RVL)과 공통으로 연결 가능한 제1 서브픽셀(SP1)과 제2 서브픽셀(SP2)이 있다고 하고, 제1 서브픽셀(SP1)은 불량 서브픽셀이고, 제2 서브픽셀(SP2)은 정상 서브픽셀일 때, 제1 서브픽셀(SP1)과 제2 서브픽셀(SP2)은 동일한 서브픽셀 행 (동일한 서브픽셀 라인)에 배치될 수 있고, 서로 다른 서브픽셀 행 (서로 다른 서브픽셀 라인)에 배치될 수 있다.

[0293] 도 17 및 18을 참조하면, 라인 결합 방지 구동에 따라, 불량 서브픽셀인 제1 서브픽셀(SP1)의 구동 트랜지스터(DRT)가 턴-오프 되도록 하는 제1 특정 데이터전압(OFF\_Vdata)이 제1 서브픽셀(SP1)으로 공급되기 때문에, 제1 서브픽셀(SP1)은 암점(온점)으로 보인다. 하지만, 도 11과 비교해볼 때, 제1 서브픽셀(SP1)과 함께 기준전압라인(RVL)에 연결된 다른 모든 서브픽셀들(SP2, SP3, SP4)은 암점으로 보이지 않고 정상적으로 보이게 된다.

[0294] 한편, 불량 서브픽셀 검출 기간은, 파워 온 신호가 발생하고 디스플레이 구동이 시작되기 전에 진행되거나, 파워 오프 신호가 발생한 이후에 진행되거나, 디스플레이 구동 중 실시간으로 진행될 수 있다.

[0295] 다시 말해, 도 7을 참조하면, 불량 서브픽셀 검출 동작은 온-센싱 프로세스로 진행될 수도 있고, 오프-센싱 프로세스로 진행될 수도 있고, 실시간 센싱 프로세스로 진행될 수도 있다.

[0296] 불량 서브픽셀 검출 동작이 온-센싱 프로세스로 진행되는 경우, 유기발광표시장치(100)는 불량 서브픽셀에 의한 영향 없이 디스플레이 구동을 정상적으로 새롭게 시작할 수 있다.

[0297] 불량 서브픽셀 검출 동작이 오프-센싱 프로세스로 진행되는 경우, 유기발광표시장치(100)는 디스플레이에 영향을 끼치지 않고 불량 서브픽셀 검출 동작을 수행할 수 있고, 시간적인 여유가 있기 때문에, 모든 서브픽셀들에 대하여 검출 동작을 수행할 수 있는 이점이 있다.

[0298] 불량 서브픽셀 검출 동작이 실시간 센싱 프로세스로 진행되는 경우, 불량 서브픽셀이 발생하는 즉시, 신속하게 대처할 수 있는 이점이 있다.

[0299] 한편, 도 15를 참조하면, 불량 서브픽셀 검출 기간에서 제3 검출 구동 단계(S1730)가 진행된 이후 회복(Recovery) 단계(S1740)가 진행될 수도 있다.

[0300] 회복 단계(S1740)에서는, 턴-온 레벨 전압의 제1 스캔신호(SCAN)에 의해 제1 트랜지스터(T1)가 턴-온 되어, 데이터전압(Vdata)이 구동 트랜지스터(DRT)의 제1 노드(N1)에 전달된다.

[0301] 회복 단계(S1740)에서, 구동 트랜지스터(DRT)의 제1 노드(N1)에 전달되는 데이터전압(Vdata)은 블랙 데이터(BLK)가 변환된 데이터전압일 수 있다.

[0302] 회복 단계(S1740)에서, 구동 트랜지스터(DRT)의 제1 노드(N1)에는, 블랙 데이터(BLK)가 변환된 데이터전압이 인가되다가, 회복 데이터(REC)가 변환된 데이터전압이 인가될 수도 있다. 회복 데이터(REC)는 불량 서브픽셀 검출 동작 전에 해당 서브픽셀(SP)에 공급된 영상데이터(DATA)와 대응되는 데이터일 수 있다.

[0303] 회복 단계(S1740)에서, 턴-온 레벨 전압의 제2 스캔신호(SENSE)에 의해 제2 트랜지스터(T2)가 턴-온 된다. 그리고, 영상 구동용 기준 스위치(RPRE)가 턴-온 된다. 이에 따라, 기준전압라인(RVL)에 공급된 기준전압(VpreR)이 제2 트랜지스터(T2)를 통해 구동 트랜지스터(DRT)의 제2 노드(N2)에 인가된다.

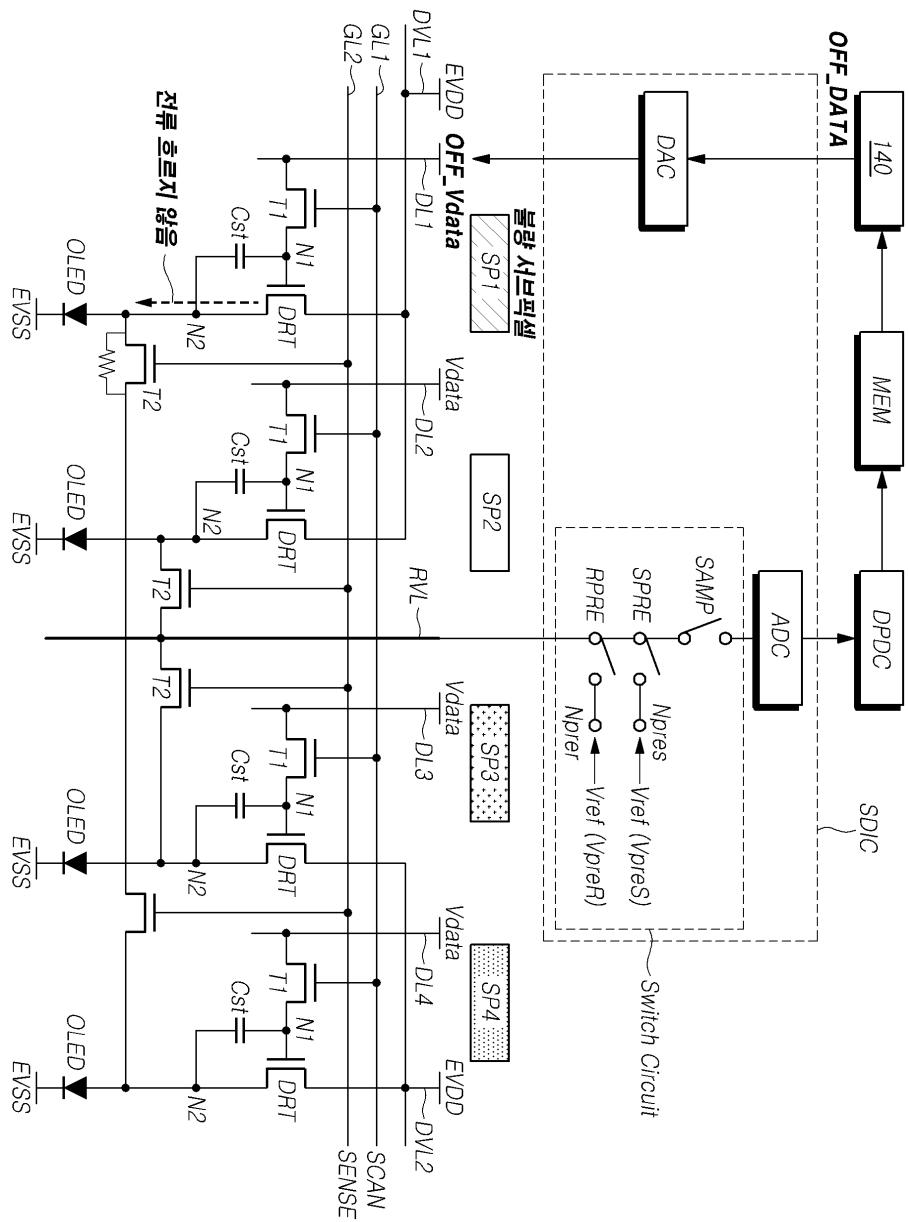

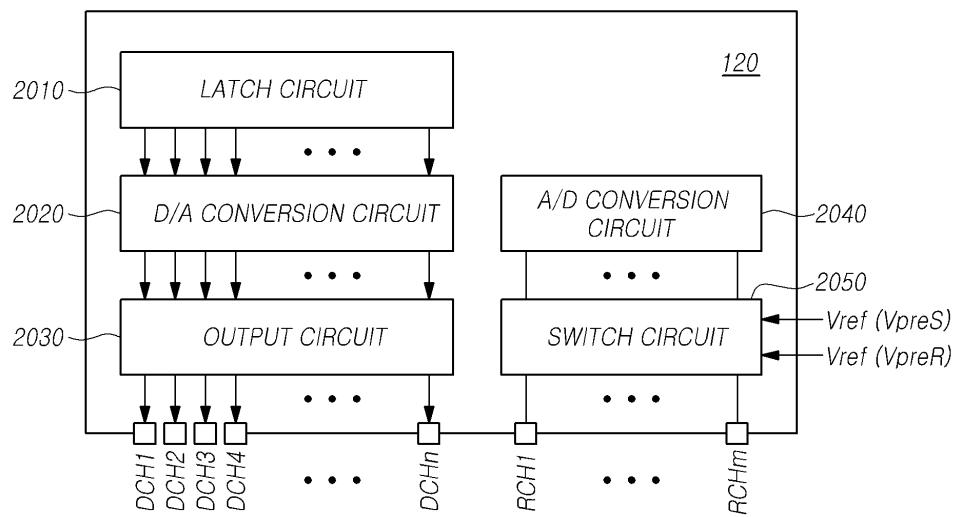

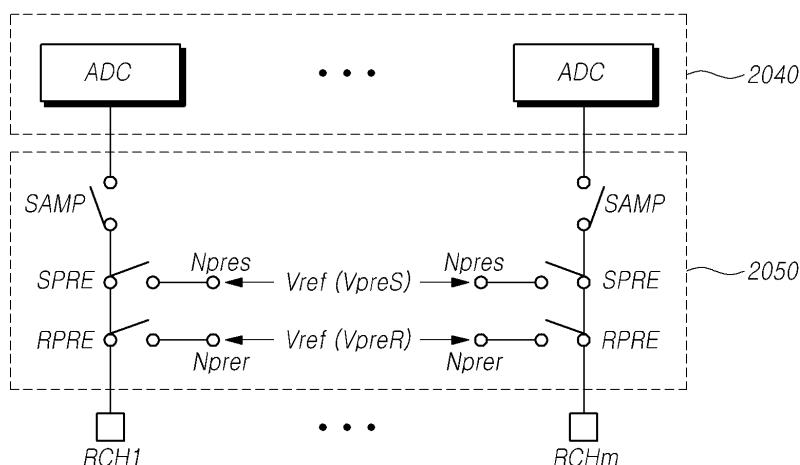

[0304] 도 20 및 도 21은 본 발명의 실시예들에 따른 데이터구동회로(120)를 나타낸 도면이다.

[0305] 도 20을 참조하면, 본 발명의 실시예들에 따른 데이터구동회로(120)는, 입력된 영상데이터(DATA)를 저장하는 래치회로(2010)와, 영상데이터(DATA)를 아날로그 신호들로 변환하는 디지털 아날로그 변환회로(2020)와, 아날로그 신호들에 대응되는 데이터전압들(Vdata)을 n(n은 4 이상의 자연수)개의 데이터라인(DL)과 대응되는 n개의 데이터

터채널(DCH1~DChn)로 출력하는 출력회로(2030) 등을 포함할 수 있다.

[0306] 래치회로(2010)는 n개 또는 2n개 이상의 래치를 포함할 수 있다. n개의 데이터채널(DCH1~DChn) 각각에 하나 또는 둘 이상의 래치(Latch)가 대응될 수 있다.

[0307] 디지털 아날로그 변환회로(2020)는 n개의 데이터채널(DCH1~DChn)과 대응되는 n개의 디지털 아날로그 컨버터(DAC)를 포함할 수 있다.

[0308] 출력회로(2030)는 n개의 데이터채널(DCH1~DChn)과 대응되는 n개의 출력버퍼를 포함할 수 있다.

[0309] 도 20을 참조하면, 본 발명의 실시예들에 따른 데이터구동회로(120)는,  $m$ ( $m$ 은 1이상의 자연수)개의 기준전압라인(RVL)의 전압을 디지털 값으로 변환하여 출력하는 아날로그 디지털 변환회로(2040)와,  $m$ 개의 기준전압라인(RVL)에 대응되는  $m$ 개의 기준채널(RCH1~RChm)과 아날로그 디지털 변환회로(2040) 사이에 연결된 스위치 회로(2050)를 포함할 수 있다.

[0310] 도 21을 참조하면, 아날로그 디지털 변환회로(2040)는  $m$ 개의 기준채널(RCH1~RChm)에 대응되는  $m$ 개의 아날로그 디지털 컨버터(ADC)를 포함할 수 있다.

[0311] 도 21을 참조하면, 스위치 회로(2050)는, 각 기준전압라인(RVL)과 기준전압(Vref)이 공급되는 센싱 구동용 기준전압 공급 노드(Npres) 간의 연결을 제어하는 센싱 구동용 기준 스위치(SPRE)와, 각 기준전압라인(RVL)과 아날로그 디지털 컨버터(ADC) 간의 연결을 제어하는 샘플링 스위치(SAMP)를 포함할 수 있다.

[0312] 스위치 회로(2050)는, 각 기준전압라인(RVL)과 기준전압(Vref)이 공급되는 영상 구동용 기준전압 공급 노드(Npres) 간의 연결을 제어하는 영상 구동용 기준 스위치(RPRE)를 더 포함할 수 있다.

[0313] 센싱 구동용 기준 스위치(SPRE)는 센싱 구동 시 이용되는 스위치이다. 센싱 구동용 기준 스위치(SPRE)에 의해 기준전압라인(RVL)으로 공급되는 기준전압(Vref)은 센싱 구동용 기준전압(VpreS)이다. 영상 구동용 기준 스위치(RPRE)는 영상 구동 시 이용되는 스위치이다. 영상 구동용 기준 스위치(SPRE)에 의해 기준전압라인(RVL)에 공급되는 기준전압(Vref)은 영상 구동용 기준전압(VpreR)이다.

[0314] 센싱 구동용 기준 스위치(SPRE)와 영상 구동용 기준 스위치(RPRE)는 별도로 구비될 수도 있고, 하나로 통합되어 구현될 수도 있다. 센싱 구동용 기준전압(VpreS)과 영상 구동용 기준전압(VpreR)은 동일한 전압 값일 수도 있고, 다른 전압 값일 수도 있다.

[0315] 기준채널 개수( $m$ )는 데이터채널 개수( $n$ )보다 적을 수 있다. 예를 들어, 데이터채널 개수( $n$ )는 기준채널 개수( $m$ )의 2 이상의 정수 배일 수 있다. 즉,  $n=k*m$  ( $k$ 는 2 이상의 자연수)이다.

[0316]  $m$ 개의 기준전압라인(RVL) 각각은 둘 이상의 서브픽셀(SP)에 포함된 제2 트랜지스터들(T2)의 소스 노드 또는 드레인 노드와 공통으로 연결될 수 있다.

[0317] 다수의 서브픽셀(SP)은  $m$ 개의 기준전압라인(RVL) 중 제1 기준전압라인(RVL)을 통해 기준전압(Vref)을 공통으로 공급받는 제1 서브픽셀(SP1)과 제2 서브픽셀(SP2)을 포함할 수 있다.

[0318] 제1 서브픽셀(SP1) 내 제2 트랜지스터(T2)가 단락이 된 경우, 제1 서브픽셀(SP1)의 구동 기간에, 제1 서브픽셀(SP1) 내 구동 트랜지스터(DRT)가 턴-오프 되도록 하는 제1 특정 데이터전압(OFF\_Vdata)이 제1 데이터라인(DL1)으로 출력되어 제1 서브픽셀(SP1)로 공급될 수 있다.

[0319] 제1 서브픽셀(SP1)의 구동 기간 (영상 구동 기간 또는 센싱 구동 기간)에, 아날로그 디지털 변환회로(2040)는, 제1 서브픽셀(SP1)과 함께 제1 기준전압라인(RVL)에 연결된 제2 서브픽셀(SP2) 내 구동 트랜지스터(DRT)의 제2 노드(N2)의 상승된 전압을 제1 기준전압라인(RVL)을 통해 센싱할 수 있다. 여기서, 센싱된 전압은 이동도를 반영하는 전압일 수 있다(도 6 참조).

[0320] 제2 서브픽셀(SP2) 내 제2 트랜지스터(T2)는 미 단락 되어 있고, 제2 서브픽셀(SP2)이 구동(센싱 구동 또는 영상 구동)될 때, 제1 서브픽셀(SP1) 내 구동 트랜지스터(DRT)가 턴-오프 되도록 하는 제1 특정 데이터전압(OFF\_Vdata)이 제1 데이터라인(DL1)을 통해 제1 서브픽셀(SP1)로 공급될 수 있다.

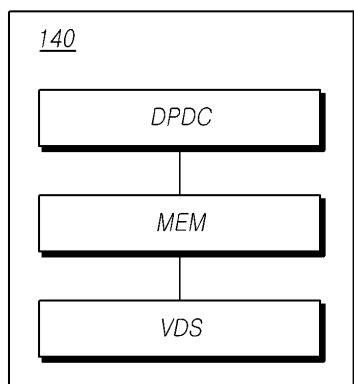

[0321] 도 22는 본 발명의 실시예들에 따른 컨트롤러(140)를 나타낸 도면이다.

[0322] 도 22를 참조하면, 본 발명의 실시예들에 따른 컨트롤러(140)는, 다수의 서브픽셀(SP) 중 제1 기준전압라인(RVL)을 통해 기준전압(Vref)을 공통으로 공급받는 제1 서브픽셀(SP1)과 제2 서브픽셀(SP2) 중 제1 서브픽셀(SP1) 내 제2 트랜지스터(T2)가 단락 된 정보 또는 제1 서브픽셀(SP1)의 위치정보를 저장하는 메모리(MEM)와,

메모리(MEM)를 참조하여, 제1 서브픽셀(SP1) 내 제2 트랜지스터(T2)가 단락이 된 경우, 제1 서브픽셀(SP1)의 구동 기간에, 제1 서브픽셀(SP1)에 공급해야 하는 영상데이터(DATA)를 제1 서브픽셀(SP1) 내 구동 트랜지스터(DRT)가 턴-오프 되도록 하는 제1 특정 영상데이터(OFF\_DATA)로 교체하여 데이터구동회로(120)로 출력하는 영상데이터 공급기(VDS) 등을 포함할 수 있다.

[0323] 제1 서브픽셀(SP1)의 구동 기간에, 제1 서브픽셀(SP1)과 함께 제1 기준전압라인(RVL)에 연결된 제2 서브픽셀(SP2) 내 구동 트랜지스터(DRT)의 이동도 센싱이 진행될 수 있다.

[0324] 도 22를 참조하면, 본 발명의 실시예들에 따른 컨트롤러(140)는, 불량 서브픽셀 검출 기간 동안 다수의 서브픽셀(SP) 중 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 단락 여부에 따라 확인 대상 서브픽셀이 불량 서브픽셀인지 아닌지를 검출하는 불량 서브픽셀 검출 회로(DPDC)를 더 포함할 수 있다.

[0325] 불량 서브픽셀 검출 회로(DPDC)는, 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 게이트 노드에 턴-오프 레벨 전압의 제2 스캔신호(SENSE)가 인가되고 있는 동안, 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 소스 노드 또는 드레인 노드와 전기적으로 연결된 기준전압라인(RVL)의 전압 변화 여부 또는 전압 변화 크기에 기초하여, 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 단락 여부를 판단할 수 있다.

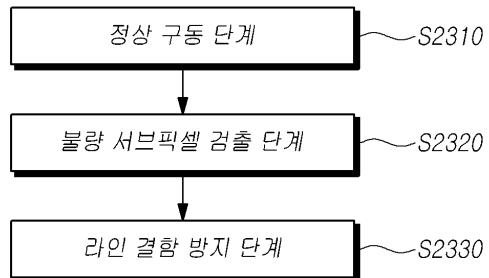

[0326] 도 23 및 도 24는 본 발명의 실시예들에 따른 유기발광표시장치(100)의 구동방법에 대한 흐름도이다.

[0327] 도 23을 참조하면, 본 발명의 실시예들에 따른 유기발광표시장치(100)의 구동방법은 정상 구동 단계(S2310) 및 라인 결합 방지 단계(S2330) 등을 포함할 수 있다.

[0328] 정상 구동 단계(S2310)에서, 유기발광표시장치(100)의 데이터구동회로(120)는, 다수의 서브픽셀(SP) 중 제1 기준전압라인(RVL)을 통해 기준전압(Vref)을 공통으로 공급받는 제1 서브픽셀(SP1)과 제2 서브픽셀(SP2) 중 제1 서브픽셀(SP1)의 구동 기간에, 영상 구동을 위한 데이터전압(Vdata)을 제1 데이터라인(DL1)을 통해 제1 서브픽셀(SP1)로 공급할 수 있다.

[0329] 라인 결합 방지 단계(S2330)에서, 유기발광표시장치(100)의 데이터구동회로(120)는, 제1 서브픽셀(SP1) 내 제2 트랜지스터(T2)가 단락이 된 경우, 제1 서브픽셀(SP1)의 구동 기간에, 제1 서브픽셀(SP1) 내 구동 트랜지스터(DRT)가 턴-오프 되도록 하는 제1 특정 데이터전압(OFF\_Vdata)을 제1 데이터라인(DL1)을 통해 제1 서브픽셀(SP1)로 공급할 수 있다.

[0330] 라인 결합 방지 단계(S2330)에서, 제1 서브픽셀(SP1)과 함께 제1 기준전압라인(RVL)에 연결된 제2 서브픽셀(SP2) 내 구동 트랜지스터(DRT)의 이동도 센싱이 진행될 수 있다.

[0331] 도 23을 참조하면, 본 발명의 실시예들에 따른 유기발광표시장치(100)의 구동방법은, 정상 구동 단계(S2310)와 라인 결합 방지 단계(S2330) 사이에, 다수의 서브픽셀(SP) 중 확인 대상 서브픽셀인 제1 서브픽셀(SP1) 내 제2 트랜지스터(T2)의 단락 여부를 판단하여 확인 대상 서브픽셀인 제1 서브픽셀(SP1)이 불량 서브픽셀인지 아닌지를 검출하는 불량 서브픽셀 검출 단계(S2320)를 더 포함할 수 있다.

[0332] 불량 서브픽셀 검출 단계(S2320)에서, 불량 서브픽셀 검출회로(DPDC)는, 제1 서브픽셀(SP1) 내 제2 트랜지스터(T2)의 게이트 노드에 턴-오프 레벨 전압의 제2 스캔신호(SENSE)가 인가되고 있는 동안, 제1 서브픽셀(SP1) 내 제2 트랜지스터(T2)의 소스 노드 또는 드레인 노드와 전기적으로 연결된 제1 기준전압라인(RVL)의 전압 변화 여부 또는 전압 변화 크기에 기초하여, 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 단락 여부를 판단할 수 있다.

[0333] 불량 서브픽셀 검출회로(DPDC)는, 제1 서브픽셀(SP1) 내 제2 트랜지스터(T2)의 게이트 노드에 턴-오프 레벨 전압의 제2 스캔신호(SENSE)가 인가되고 있는 동안, 제1 서브픽셀(SP1) 내 제2 트랜지스터(T2)의 소스 노드 또는 드레인 노드와 전기적으로 연결된 제1 기준전압라인(RVL)의 전압이 상승한 것으로 확인되면, 제1 서브픽셀(SP1) 내 제2 트랜지스터(T2)의 단락이 된 것으로 판단되어, 제1 서브픽셀(SP1)을 불량 서브픽셀로서 검출할 수 있다.

[0334] 도 24를 참조하면, 불량 서브픽셀 검출 단계(S2320)는, 제1 검출 구동 단계(S1710), 제2 검출 구동 단계(S1720), 제3 검출 구동 단계(S1730), 센싱값 획득 단계(S2410) 및 제2 트랜지스터(T2)의 단락 여부 판단 단계(S2420) 등을 포함할 수 있다.

[0335] 제1 검출 구동 단계(S1710)에서, 게이트구동회로(130)는, 확인 대상 서브픽셀 내 제1 트랜지스터(T1)의 게이트 노드에 턴-온 레벨 전압의 제1 스캔신호(SCAN)를 공급한다. 게이트구동회로(130)는, 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 게이트 노드에 턴-온 레벨 전압의 제2 스캔신호(SENSE)를 공급한다. 센싱 구동용 기준 스위칭

(SPRE)는 턴-온 상태이다. 샘플링 스위치(SAMP)는 턴-오프 상태이다.

- [0336] 여기서, 센싱 구동용 기준 스위칭(SPRE) 및 샘플링 스위치(SAMP)는 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 소스 노드 또는 드레인 노드와 전기적으로 연결된 기준전압라인(RVL)에 연결될 수 있다.

- [0337] 제2 검출 구동 단계(S1720)에서, 게이트구동회로(130)는, 확인 대상 서브픽셀 내 제1 트랜지스터(T1)의 게이트 노드에 턴-오프 레벨 전압의 제1 스캔신호(SCAN)를 공급한다. 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 게이트 노드에 턴-오프 레벨 전압의 제2 스캔신호(SENSE)를 공급한다. 센싱 구동용 기준 스위칭(SPRE)는 턴-오프 상태이고, 샘플링 스위치(SAMP)는 턴-오프 상태이다.

- [0338] 제3 검출 구동 단계(S1730)에서, 게이트구동회로(130)는, 확인 대상 서브픽셀 내 제1 트랜지스터(T1)의 게이트 노드에 턴-오프 레벨 전압의 제1 스캔신호(SCAN)를 공급한다. 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 게이트 노드에 턴-오프 레벨 전압의 제2 스캔신호(SENSE)를 공급한다. 센싱 구동용 기준 스위칭(SPRE)는 턴-오프 상태이고, 샘플링 스위치(SAMP)는 턴-온 된다.

- [0339] 센싱값 획득 단계(S2410)에서, 아날로그 디지털 컨버터(ADC)는 턴-온 된 샘플링 스위치(SAMP)를 통해 기준전압라인(RVL)과 연결되어, 기준전압라인(RVL)의 전압을 센싱하여 센싱된 전압을 디지털 값에 해당하는 센싱값으로 변환하여 출력한다.

- [0340] 제2 트랜지스터(T2)의 단락 여부 판단 단계(S2420)에서, 불량 서브픽셀 검출 회로(DPDC)는, 센싱값을 토대로, 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 소스 노드 또는 드레인 노드와 전기적으로 연결된 기준전압라인(RVL)의 전압 변화 여부 또는 전압 변화 크기를 확인하여 확인 대상 서브픽셀 내 제2 트랜지스터(T2)의 단락 여부를 판단할 수 있다.

- [0341] 불량 서브픽셀 검출 회로(DPDC)는, 확인 대상 서브픽셀 내 제2 트랜지스터(T2)가 단락이 된 것으로 판단되면, 확인 대상 서브픽셀을 불량 서브픽셀로서 검출할 수 있다.

- [0342] 불량 서브픽셀 검출 회로(DPDC)는, 확인 대상 서브픽셀 내 제2 트랜지스터(T2)가 단락이 되지 않은 것으로 판단되면, 확인 대상 서브픽셀을 정상 서브픽셀로서 검출할 수 있다.

- [0343] 이상에서 설명한 본 발명의 실시예들에 의하면, 라인 결합(LD)을 방지하여 화상 품질을 향상시켜줄 수 있는 유기발광표시장치(100), 데이터구동회로(120), 컨트롤러(140) 및 구동방법을 제공할 수 있다.

- [0344] 본 발명의 실시예들에 의하면, 라인 결합(LD)을 발생시키는 불량 서브픽셀을 검출할 수 있는 유기발광표시장치(100), 데이터구동회로(120), 컨트롤러(140) 및 구동방법을 제공할 수 있다.

- [0345] 본 발명의 실시예들에 의하면, 불량 서브픽셀의 구동에 의해 다른 정상 서브픽셀의 센싱 및 보상 오류가 발생하지 않도록 해줌으로써, 영상 품질을 향상시켜줄 수 있는 유기발광표시장치(100), 데이터구동회로(120), 컨트롤러(140) 및 구동방법을 제공할 수 있다.

- [0346] 이상에서의 설명 및 첨부된 도면은 본 발명의 기술 사상을 예시적으로 나타낸 것에 불과한 것으로서, 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자라면 본 발명의 본질적인 특성에서 벗어나지 않는 범위에서 구성의 결합, 분리, 치환 및 변경 등의 다양한 수정 및 변형이 가능할 것이다. 따라서, 본 발명에 개시된 실시예들은 본 발명의 기술 사상을 한정하기 위한 것이 아니라 설명하기 위한 것이고, 이러한 실시예에 의하여 본 발명의 기술 사상의 범위가 한정되는 것은 아니다. 본 발명의 보호 범위는 아래의 청구범위에 의하여 해석되어야 하며, 그와 동등한 범위 내에 있는 모든 기술 사상은 본 발명의 권리범위에 포함되는 것으로 해석되어야 할 것이다.

## 부호의 설명

- [0347] 100: 유기발광표시장치

110: 유기발광표시패널

120: 데이터구동회로

130: 게이트구동회로

140: 컨트롤러

## 도면

## 도면1

100

## 도면2

## 도면3

## 도면4

## 도면5

## 도면6

도면7

도면8

도면9

도면10

도면11

| SP1 구동 시                             |        | SP1  | SP2 | SP3 | SP4 |

|--------------------------------------|--------|------|-----|-----|-----|

| 화<br>랑<br>서<br>브<br>피<br>셀<br>라<br>인 | RT 센싱값 | 정상   | 높아짐 | 높아짐 | 높아짐 |

|                                      | 보상값    | 정상   | 낮아짐 | 낮아짐 | 낮아짐 |

|                                      | 구동 시   | 온/악암 | 악암  | 악암  | 악암  |

| 정<br>상<br>서<br>브<br>피<br>셀<br>라<br>인 | RT 센싱값 | 정상   | 높아짐 | 높아짐 | 높아짐 |

|                                      | 보상값    | 정상   | 낮아짐 | 낮아짐 | 낮아짐 |

|                                      | 구동 시   | 정상   | 악암  | 악암  | 악암  |

## 도면12

## 도면13

도면14

## 도면15

## 도면16

## 도면17

## 도면18

| SP1 구동 시      | SP1    | SP2 | SP3 | SP4 |

|---------------|--------|-----|-----|-----|

| 불량 서브픽셀<br>라인 | RT 센싱값 | 정상  | 정상  | 정상  |

|               | 보상값    | 정상  | 정상  | 정상  |

|               | 구동 시   | 온암  | 정상  | 정상  |

| 정상 서브픽셀<br>라인 | RT 센싱값 | 정상  | 정상  | 정상  |

|               | 보상값    | 정상  | 정상  | 정상  |

|               | 구동 시   | 정상  | 정상  | 정상  |

## 도면19

도면20

도면21

도면22

**도면23****도면24**S2320

|                |                                                                      |         |            |

|----------------|----------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机发光显示装置，数据驱动电路，控制器和驱动方法                                             |         |            |

| 公开(公告)号        | <a href="#">KR1020200005347A</a>                                     | 公开(公告)日 | 2020-01-15 |

| 申请号            | KR1020180078969                                                      | 申请日     | 2018-07-06 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                             |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                            |         |            |

| [标]发明人         | 박준민                                                                  |         |            |

| 发明人            | 박준민                                                                  |         |            |

| IPC分类号         | G09G3/3233 G09G3/00 G09G3/20 G09G3/3275                              |         |            |

| CPC分类号         | G09G3/3233 G09G3/006 G09G3/2074 G09G3/3275 G09G2230/00 G09G2300/0842 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                            |         |            |

### 摘要(译)

有机发光显示装置，数据驱动电路，控制器和驱动方法技术领域本发明涉及有机发光显示装置，数据驱动电路，控制器和驱动方法。更具体地，本发明涉及一种有机发光显示装置，数据驱动电路，控制器和驱动方法，该有机发光显示装置，数据驱动电路，控制器和驱动方法能够通过检测不良的子像素而产生不良的像素以防止线路故障并改善图像质量。黑条形可见并且提供数据电压，这使得驱动检测到的坏子像素不影响其他子像素到坏子像素。该有机发光显示装置包括：有机发光显示面板；以及有机发光显示面板。数据驱动电路；栅极驱动电路；和一个控制器。