(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2015년05월29일

(11) 등록번호 10-1524084

(24) 등록일자 2015년05월22일

(51) 국제특허분류(Int. Cl.)

G09G 3/30 (2006.01) G09G 3/20 (2006.01)

G09G 3/32 (2006.01) H01L 51/50 (2006.01)

(21) 출원번호 10-2008-0103142

(22) 출원일자 2008년10월21일

심사청구일자 2013년10월01일

(65) 공개번호 10-2009-0041331

(43) 공개일자 2009년04월28일

(30) 우선권주장

JP-P-2007-274753 2007년10월23일 일본(JP)

(56) 선행기술조사문헌

JP2006003744 A\*

KR1020030032530 A\*

KR1020060088828 A\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

소니 주식회사

일본국 도쿄도 미나토구 코난 1-7-1

(72) 발명자

야마시타 준이치

일본국 도쿄도 미나토구 코난 1-7-1 소니 가부시

끼 가이샤 나이

우치노 카쓰히데

일본국 도쿄도 미나토구 코난 1-7-1 소니 가부시

끼 가이샤 나이

(74) 대리인

이화의

전체 청구항 수 : 총 3 항

심사관 : 조기덕

(54) 발명의 명칭 표시장치 및 전자기기

**(57) 요약**

복수행에 속하는 인접하는 복수의 서브 퍽셀에 의해 단위화소를 구성하는 동시에, 발광 기간/비발광 기간을 제어하는 기능을 구동 트랜지스터에 갖게 하는 화소구성을 채용하는 경우에 있어서, 표시 패널의 고선명화 및 협테두리화를 가능하게 한다. 상하 2행에 속하는 서로 인접하는 4개의 서브 퍽셀(20W, 20R, 20G, 20B)에 의해 단위화소(20b)을 구성하는 동시에, 유기 EL 소자(21)의 발광 기간/비발광 기간을 제어하는 기능을 구동 트랜지스터에 갖게 하는 화소구성을 취하는 액티브 매트릭스형 유기 EL 표시장치(10B)에 있어서, 전원 공급선(32)(32-1~32-m)을 1행마다 1개씩 배선하고, 해당 1개의 전원 공급선(32)을 동일한 단위화소(20b)을 구성하는 상하 2행에 속하는 4개의 서브 퍽셀(20W, 20R, 20G, 20B)에 대하여 공통화한다.

**대표도**

## 명세서

### 청구범위

#### 청구항 1

전기광학소자와, 영상신호를 기록하는 기록 트랜지스터와, 상기 기록 트랜지스터에 의해 기록된 상기 영상신호를 유지하는 유지용량과, 상기 유지용량에 유지된 상기 영상신호에 의거하여 상기 전기광학소자를 구동하는 구동 트랜지스터를 포함하는 서브 픽셀이 행렬 모양으로 배치되고, 복수행에 속하는 인접하는 복수의 상기 서브 픽셀에 의해 단위화소가 구성된 화소 어레이부와,

상기 구동 트랜지스터에 대하여 전위가 다른 전원전위를 선택적으로 공급하는 전원 공급선을 구비하고,

상기 전원 공급선은, 상기 복수행마다 1개씩 배선되어 있으며,

상기 서브 픽셀은, 상기 구동 트랜지스터의 임계전압의 서브 픽셀마다의 격차를 보정하는 임계값 보정동작이 가능하고, 상기 단위화소를 구성하는 동일 열에 속하는 서브 픽셀에 있어서 상기 임계값 보정동작의 보정기간을 동일하게 하며,

상기 서브 픽셀은, 상기 구동 트랜지스터의 이동도의 화소마다의 격차를 보정하는 이동도 보정동작이 가능하고, 상기 단위화소를 구성하는 동일 열에 속하는 서브 픽셀에 있어서 상기 기록 트랜지스터에 의한 상기 영상신호의 기록 동작 및 상기 이동도 보정동작을 상기 임계값 보정동작후에 1수평기간 내에서 시간을 늦추어 행하는 것을 특징으로 하는 표시장치.

#### 청구항 2

삭제

#### 청구항 3

삭제

#### 청구항 4

제 1항에 있어서,

상기 복수행이 2행이며,

상기 2행에 속하는 상하의 서브 픽셀에 있어서, 상기 기록 트랜지스터, 상기 유지용량 및 상기 구동 트랜지스터가 상기 2행의 경계선에 관해서 상하 대칭으로 배치되어 있는 것을 특징으로 하는 표시장치.

#### 청구항 5

전기광학소자와, 영상신호를 기록하는 기록 트랜지스터와, 상기 기록 트랜지스터에 의해 기록된 상기 영상신호를 유지하는 유지용량과, 상기 유지용량에 유지된 상기 영상신호에 의거하여 상기 전기광학소자를 구동하는 구동 트랜지스터를 포함하는 서브 픽셀이 행렬 모양으로 배치되고, 복수행에 속하는 인접하는 복수의 상기 서브 픽셀에 의해 단위화소가 구성된 화소 어레이부와,

상기 구동 트랜지스터에 대하여 전위가 다른 전원전위를 선택적으로 공급하는 전원 공급선을 구비한 표시장치를 가지는 전자기기로서,

상기 전원 공급선은, 상기 복수행마다 1개씩 배선되어 있으며,

상기 서브 픽셀은, 상기 구동 트랜지스터의 임계전압의 서브 픽셀마다의 격차를 보정하는 임계값 보정동작이 가능하고, 상기 단위화소를 구성하는 동일 열에 속하는 서브 픽셀에 있어서 상기 임계값 보정동작의 보정기간을 동일하게 하며,

상기 서브 픽셀은, 상기 구동 트랜지스터의 이동도의 화소마다의 격차를 보정하는 이동도 보정동작이 가능하고,

상기 단위화소를 구성하는 동일 열에 속하는 서브 픽셀에 있어서 상기 기록 트랜지스터에 의한 상기 영상신호의 기록 동작 및 상기 이동도 보정동작을 상기 임계값 보정동작후에 1수평기간 내에서 시간을 늦추어 행하는 것을 특징으로 하는 전자기기.

## 발명의 설명

### 발명의 상세한 설명

#### 기술 분야

[0001] 본 발명은, 표시장치 및 전자기기에 관한 것으로서, 특히 전기광학소자를 포함하는 화소가 행렬 형태(매트릭스 형태)에 배치되어 이루어진 평면형(플랫 패널형)의 표시장치 및 해당 표시장치를 가지는 전자기기에 관한 것이다.

#### 배경기술

[0002] 최근, 화상표시를 행하는 표시장치의 분야에서는, 발광소자를 포함하는 화소(화소회로)가 행렬 모양으로 배치되어 이루어진 평면형의 표시장치가 급속하게 보급되고 있다. 평면형의 표시장치로서는, 화소의 발광소자로서, 디바이스에 흐르는 전류값에 따라 발광 휘도가 변화되는 소위 전류구동형의 전기광학소자, 예를 들면 유기 박막에 전계를 걸면 발광하는 현상을 이용한 유기 EL(Electro Luminescence)소자를 사용한 유기 EL 표시장치가 개발되어, 상품화가 진행되고 있다.

[0003] 유기 EL 표시장치는 다음과 같은 특징을 가지고 있다. 즉, 유기 EL 소자가 10V 이하의 인가전압에서 구동할 수 있기 때문에 저소비 전력이며, 또한 자발광 소자이기 때문에, 액정 셀을 포함하는 화소마다 해당 액정 셀에서 광원(백라이트)으로부터의 광강도를 제어함으로써 화상을 표시하는 액정표시장치에 비해, 화상의 시인성이 높고, 게다가 액정표시장치에는 필수적인 백라이트 등의 조명부재를 필요로 하지 않기 때문에 경량화 및 초박형화가 용이하다. 더구나, 유기 EL 소자의 응답 속도가 수  $\mu\text{sec}$ 정도로 대단히 고속이기 때문에 동영상 표시 시의 잔상이 발생하지 않는다.

[0004] 유기 EL 표시장치에서는, 액정표시장치와 마찬가지로, 그것의 구동방식으로서 단순(패시브) 매트릭스 방식과 액티브 매트릭스 방식을 채용할 수 있다. 다만, 단순 매트릭스 방식의 표시장치는, 구조가 간단하지만, 전기광학소자의 발광 기간이 주사선(즉, 화소수)의 증가에 의해 감소하기 때문에, 대형이고 고세밀한 표시장치의 실현이 어려운 것 등의 문제가 있다.

[0005] 그 때문에, 최근, 전기광학소자에 흐르는 전류를, 해당 전기광학소자와 같은 화소회로 내에 설치한 능동소자, 예를 들면 절연 게이트형 전계효과트랜지스터(일반적으로는, TFT(Thin Film Transistor; 박막트랜지스터))에 의해 제어하는 액티브 매트릭스 방식의 표시장치의 개발이 활발히 행해지고 있다. 액티브 매트릭스 방식의 표시장치는, 전기광학소자가 1프레임의 기간에 걸쳐서 발광을 지속하기 때문에, 대형이고 고세밀한 표시장치의 실현이 용이하다.

[0006] 그런데, 일반적으로, 유기 EL 소자의 I-V특성(전류-전압특성)은, 시간이 경과하면 열화(소위, 경시 열화)하는 것이 알려져 있다. 유기 EL 소자를 전류구동하는 트랜지스터(이하, 「구동 트랜지스터」라고 기술한다)로서 N채널형의 TFT를 사용한 화소회로에서는, 구동 트랜지스터의 소스측에 유기 EL 소자가 접속되게 되기 때문에, 유기 EL 소자의 I-V특성이 경시 열화하면, 구동 트랜지스터의 게이트-소스간 전압  $V_{gs}$ 가 변화하고, 그 결과, 유기 EL 소자의 발광 휘도도 변화된다.

[0007] 이것에 대해서 더 구체적으로 설명한다. 구동 트랜지스터의 소스 전위는, 해당 구동 트랜지스터와 유기 EL 소자의 동작점에서 결정된다. 그리고, 유기 EL 소자의 I-V특성이 열화하면, 구동 트랜지스터와 유기 EL 소자의 동작점이 변동해 버리기 때문에, 구동 트랜지스터의 게이트에 같은 전압을 인가했다고 하더라도 구동 트랜지스터의 소스 전위가 변화된다. 이에 따라, 구동 트랜지스터의 소스-게이트간 전압  $V_{gs}$ 가 변화되기 때문에, 해당 구동 트랜지스터에 흐르는 전류값이 변화된다. 그 결과, 유기 EL 소자에 흐르는 전류값도 변화하기 때문에, 유기 EL 소자의 발광 휘도가 변화되게 된다.

[0008] 또한, 폴리실리콘 TFT를 사용한 화소회로에서는, 유기 EL 소자의 I-V 특성의 시간 경과열화에 덧붙여, 구동 트랜지스터의 임계전압  $V_{th}$ , 구동 트랜지스터의 채널을 구성하는 반도체 박막의 이동도(이하, 「구동 트

랜지스터의 이동도」라고 기술한다)  $\mu$  가 경시적으로 변화되거나, 제조 프로세스의 격차에 의해 임계전압  $V_{th}$ 나 이동도  $\mu$  가 화소마다 다르거나 한다(개개의 트랜지스터 특성에 격차가 있다).

[0009] 구동 트랜지스터의 임계전압  $V_{th}$ 나 이동도  $\mu$  가 화소마다 다르면, 화소마다 구동 트랜지스터에 흐르는 전류값에 격차가 생기기 때문에, 구동 트랜지스터의 게이트에 화소 사이에서 같은 전압을 인가해도, 유기 EL 소자의 발광 휘도에 화소 사이에서 격차가 생기고, 그 결과, 화면의 균일성(유니포머티)이 손상된다.

[0010] 따라서, 유기 EL 소자의 I-V 특성이 경시 열화하거나, 구동 트랜지스터의 임계전압  $V_{th}$ 나 이동도  $\mu$  가 경시 변화하여도, 그것들의 영향을 받지 않고, 유기 EL 소자의 발광 휘도를 일정하게 유지하도록 하기 위해서, 유기 EL 소자의 특성변동에 대한 보상 기능, 더구나 구동 트랜지스터의 임계전압  $V_{th}$ 의 변동에 대한 보정(이하, 「임계값 보정」이라고 기술한다)이나, 구동 트랜지스터의 이동도  $\mu$ 의 변동에 대한 보정(이하, 「이동도 보정」이라고 기술한다)의 각 보정기능을 화소회로의 각각에 갖게 하는 구성을 채용하고 있다(예를 들면 특허문현 1 참조).

[0011] [특허문현 1] 일본국 특개 2006-215213호 공보

## 발명의 내용

### 해결 하고자하는 과제

[0012] 특허문현 1 기재의 종래기술에서는, 화소회로의 각각에, 유기 EL 소자의 특성변동에 대한 보상 기능 및 구동 트랜지스터의 임계전압  $V_{th}$ 나 이동도  $\mu$ 의 변동에 대한 보정기능을 갖게 함으로써 유기 EL 소자의 I-V 특성이 경시 열화하거나, 구동 트랜지스터의 임계전압  $V_{th}$ 나 이동도  $\mu$ 가 경시 변화하거나 하더라도, 그것들의 영향을 받지 않고, 유기 EL 소자의 발광휘도를 일정하게 유지할 수 있지만, 그 반면, 화소회로를 구성하는 소자수가 많아, 화소 사이즈의 미세화의 방해가 된다.

[0013] 이에 대하여, 화소회로를 구성하는 소자수나 배선수의 삽감을 피하기 위해서, 예를 들면 화소회로의 구동 트랜지스터에 공급하는 전원전위를 전환가능한 구성으로 하고, 해당 전원전위의 전환에 의해 유기 EL 소자의 발광 기간/비발광 기간을 제어하는 기능을 구동 트랜지스터에 갖게 하고, 발광/비발광을 제어하는 전용의 트랜지스터를 생략하는 수법을 채용하는 것이 생각된다.

[0014] 이러한 수법을 채용하는 것에 의해, 영상신호를 샘플링해서 화소내에 기록하는 기록 트랜지스터와, 이 기록 트랜지스터에 의해 기록된 영상신호에 의거하여 유기 EL 소자를 구동하는 구동 트랜지스터의 필요 최소한의 2개의 트랜지스터(용량소자를 제외한다)에 의해 화소회로를 구성할 수 있다(그 상세에 관해서는 후술한다).

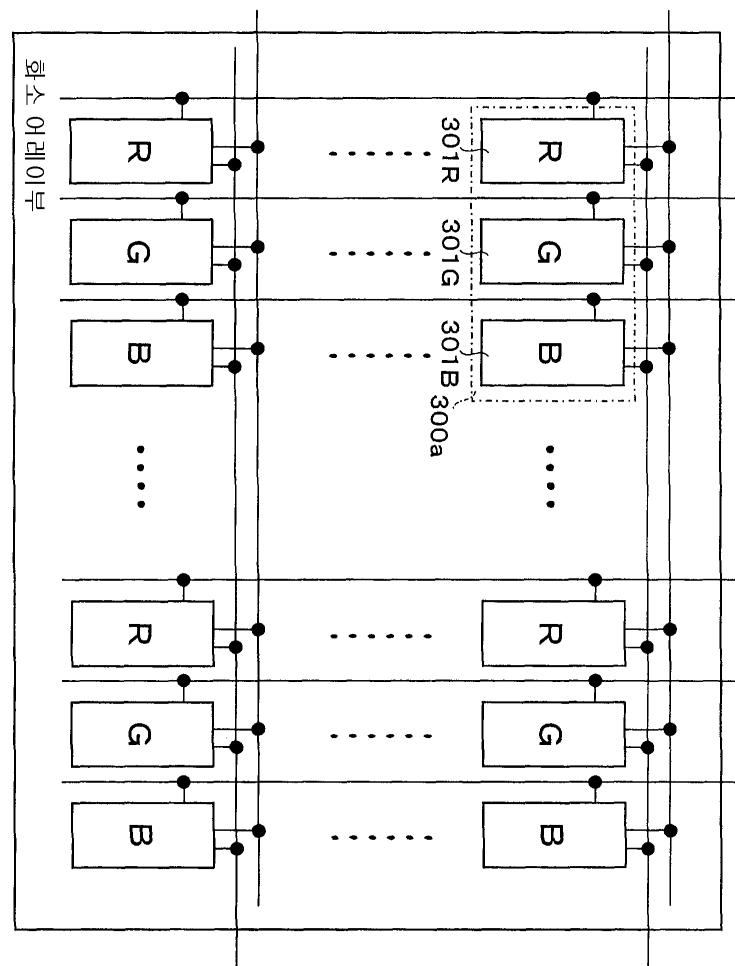

[0015] 그런데, 컬러 방식의 표시장치에 있어서, 단위화소(1 화소)(300a)는, 도20에 도시된 것과 같이 동일한 행에 속하는 인접하는 R(적색) G(녹색) B(청색)의 삼원색의 서브 픽셀(301R, 301G, 301B)에 의해 구성되어 있는 것이 일반적이다.

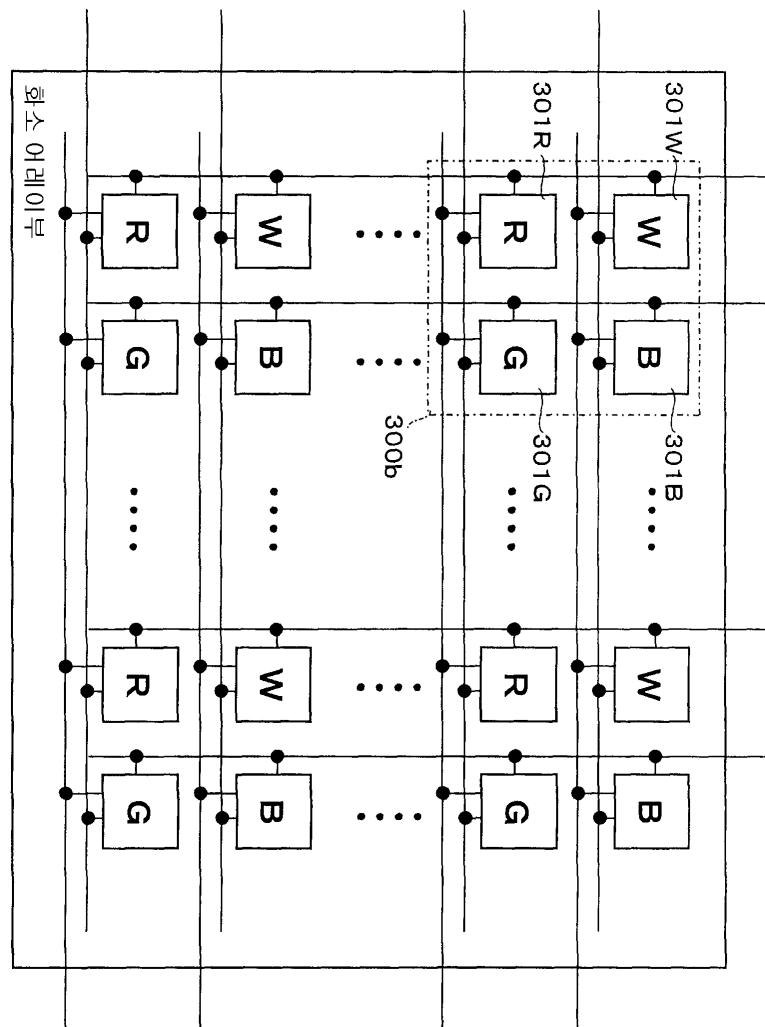

[0016] 이에 대하여, 고화도화나 저소비 전력화 등을 도모하기 위해서, 도21에 도시된 것과 같이 RGB의 서브 픽셀(301R, 301G, 301B)에 덧붙여 사용 빈도가 높은 백색(W)의 서브 픽셀(301W)을 사용하여, WRGB의 4종의 서브 픽셀(301W, 301R, 301G, 201B)로 단위화소(300b)을 구성할 경우도 있다.

[0017] 이렇게, 단위화소(300b)을 4종의 서브 픽셀(301W, 301R, 301G, 301B)로 구성할 경우, 일반적으로는, 도20에 도시된 것과 같이, 정방형의 서브 픽셀(301W, 301R, 301G, 301B)을 복수행, 예를 들면 2행에 걸쳐서 상하 좌우로 균등하게 레이아웃하게 된다. 이 경우, 단위화소당의 신호선의 개수를, RGB의 경우의 3개로부터 2개로 삽감할 수 있다.

[0018] 그렇지만, 단위화소(300b)가 2행을 단위로 하고 있기 때문에, 유기 EL 소자의 발광 기간/비발광 기간을 제어하는 기능을 구동 트랜지스터에 갖게 하는 화소구성을 채용할 경우, 구동 트랜지스터에 전원전위를 공급하는 전원 공급선으로서 RGB의 경우의 2배의 개수가 필요하게 된다.

[0019] 전원 공급선의 개수가 2배가 되면, 해당 전원 공급선은 화소면적에서 차지하는 비율이 크기 때문에, 화소의 고선명도가 저하해 버린다. 또한, 전원 공급선의 개수가 2배가 되면, 해당 전원 공급선을 구동하는 전원공급 주사 회로의 단수도 2배가 되기 때문에, 해당 전원공급 주사 회로의 규모가 증대하여, 표시 패널 상의 소위 테두리로 불리는 화소 어레이부의 주변부의 협테두리화가 곤란해진다.

[0020]

따라서, 본 발명은, 복수행에 속하는 인접하는 복수의 서브 팩셀에 의해 단위화소를 구성하는 동시에, 발광 기간/비발광 기간을 제어하는 기능을 구동 트랜지스터에 갖게 하는 화소구성을 채용할 경우에 있어서, 표시 패널의 고선명화 및 협테두리화를 가능하게 한 표시장치 및 해당 표시장치를 가지는 전자기기를 제공하는 것을 목적으로 한다.

### 과제 해결수단

[0021]

상기 목적을 달성하기 위하여, 본 발명은, 전기광학소자와, 영상신호를 기록하는 기록 트랜지스터와, 상기 기록 트랜지스터에 의해 기록된 상기 영상신호를 유지하는 유지용량과, 상기 유지용량에 유지된 상기 영상 신호에 의거하여 상기 전기광학소자를 구동하는 구동 트랜지스터를 포함하는 서브 팩셀이 행렬 모양으로 배치되고, 복수행에 속하는 인접하는 복수의 상기 서브 팩셀에 의해 단위화소가 구성된 화소 어레이부와, 상기 구동 트랜지스터에 대하여 전위가 다른 전원전위를 선택적으로 공급하는 전원 공급선을 구비한 표시장치에 있어서, 상기 전원 공급선을 상기 복수행마다, 즉 단위화소마다 1개씩 배선하는 구성을 채용하고 있다.

[0022]

상기 구성의 표시장치 및 해당 표시장치를 사용한 전자기기에 있어서, 동일한 단위화소를 구성하는 복수행에 속하는 복수의 서브 팩셀에 대하여, 1개의 전원 공급선을 공통화함으로써, 복수행을 예를 들면 2행으로 했을 경우, 즉 2행을 단위로서 단위화소를 구성한 경우에 전원 공급선의 개수가 2배로 늘리지 않으면 안되는 좀 을 늘리지 않아도 되며, 전원 공급선을 구동하는 전원공급 주사 회로의 회로 구성도 그대로 되기 때문에, 표시 패널의 협테두리화가 가능하게 된다. 또한, 서브 팩셀 개개의 사이즈의 축소화를 피할 수 있기 때문에, 표시 패널의 고선명화를 피하는 것이 가능하게 된다.

### 효과

[0023]

본 발명에 따르면, 복수행에 속하는 인접하는 복수의 서브 팩셀에 의해 단위화소를 구성하는 동시에, 발광 기간/비발광 기간을 제어하는 기능을 구동 트랜지스터에 갖게 하는 화소구성을 채용할 경우에 있어서, 전원 공급선을 상기 복수행마다(단위화소마다) 1개씩 배선함으로써, 표시 패널의 고선명화 및 협테두리가 가능하게 된다.

### 발명의 실시를 위한 구체적인 내용

[0024]

이하, 본 발명의 실시예에 대해서 도면을 참조해서 상세하게 설명한다.

[0025]

[참고예에 관련되는 유기 EL 표시장치]

[0026]

우선, 본 발명의 이해를 쉽게 하기 위해서, 본 발명의 전제가 되는 액티브 매트릭스형 표시장치에 대해서 참고예로서 설명한다. 이 참고예에 관련되는 액티브 매트릭스형 표시장치는, 본출원인에 의해 특원 2006-141836호 명세서에서 제안된 표시장치이다.

[0027]

도 1은, 참고예에 관련되는 액티브 매트릭스형 표시장치의 구성의 개략을 나타낸 시스템 구성도이다. 여기에서는, 일례로서, 디바이스에 흐르는 전류값에 따라 발광 휘도가 변화되는 전류구동형의 전기광학소자, 예를 들면 유기 EL 소자(유기전계발광소자)을 서브 팩셀(서브 화소)의 발광소자로서 사용한 액티브 매트릭스형 유기 EL 표시장치의 경우를 예로 들어 설명하는 것으로 한다.

[0028]

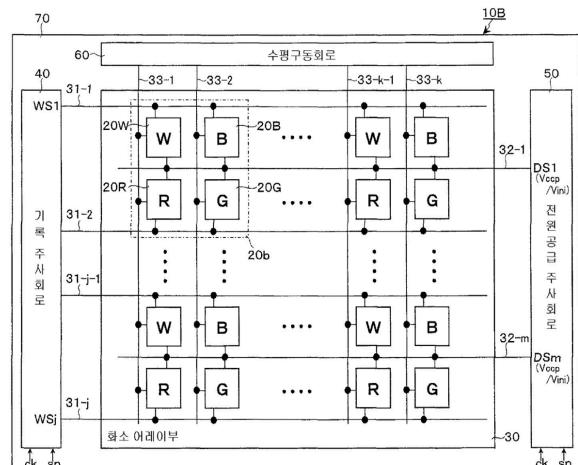

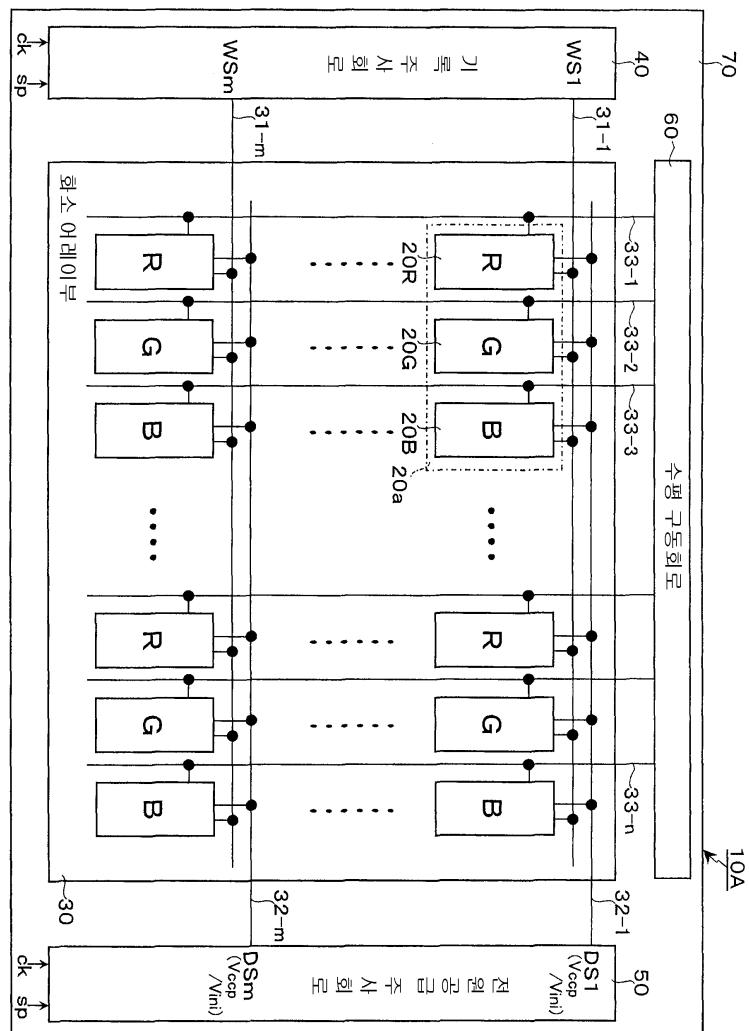

도 1에 도시된 것과 같이 참고예에 관련되는 유기 EL 표시장치(10A)는, 동일한 행에 속하는 인접하는 RGB의 서브 팩셀(20R, 20G, 20B)로 이루어지는 단위화소(20a)가 행렬 형태(매트릭스 형태)로 2차원 배치되어서 이루어진 화소 어레이부(30)와, 해당 화소 어레이부(30)의 주변부(테두리)에 배치되고, 각 단위화소(1팩셀)(20a)를 구동하는 구동부를 가지는 시스템 구성으로 되어 있다. 단위화소(20a)를 구동하는 구동부로서는, 예를 들면 기록 주사 회로(40), 전원공급 주사 회로(50) 및 수평구동회로(60)가 설치되어 있다.

[0029]

화소 어레이부(30)에는,  $m$ 행  $n$ 열의 서브 팩셀 배열에 대하여, 행마다 주사선(31-1~31- $m$ )과 전원 공급 선(32-1~32- $m$ )이 배선되고, 열마다 신호선(33-1~33- $n$ )이 배선되어 있다.

[0030] 화소 어레이부(30)은, 통상, 유리 기판 등의 투명 절연 기판 위에 형성되고, 평면형(플랫형)의 패널 구조로 되어 있다. 화소 어레이부(30)의 각 서브 팩셀(20R, 20G, 20B)은, 아모페스 실리콘 TFT(Thin Film Transistor; 박막트랜지스터) 또는 저온 폴리실리콘 TFT를 사용해서 형성할 수 있다. 저온 폴리실리콘 TFT를 사용할 경우에는, 기록 주사 회로(40), 전원공급 주사 회로(50) 및 수평구동회로(60)에 대해서도, 화소 어레이부(30)을 형성하는 표시 패널(기판)(70) 위에 설치할 수 있다.

[0031] 기록 주사 회로(40)은, 클록펄스 ck에 동기해서 스타트펄스 sp을 순차적으로 시프트(전송)하는 시프트 레지스터 등으로 구성되고, 화소 어레이부(30)의 각 서브 팩셀(20R, 20G, 20B)에의 영상신호의 기록에 있어서, 주사선(31-1~31-m)에 순차 기록 주사 신호(WS1~WSm)을 공급함으로써 화소 어레이부(30)의 각 서브 팩셀(20R, 20G, 20B)을 행단위로 순서대로 주사(선 순차 주사)한다.

[0032] 전원공급 주사 회로(50)은, 클록펄스 ck에 동기해서 스타트펄스 sp을 순차적으로 시프트하는 시프트 레지스터 등으로 구성되고, 기록 주사 회로(40)에 의한 선 순차 주사에 동기하여, 제1전위 Vccp과 해당 제1전위 Vccp보다도 낮은 제2전위 Vini로 전환하는 전원 공급선 전위 DS1~DSm을 전원 공급선(32-1~32-m)에 공급함으로써, 서브 팩셀(20R, 20G, 20B)의 발광/비발광의 제어를 행한다.

[0033] 즉, 전원 공급선(32-1~32-m)의 전위 DS1~DSm은, 서브 팩셀(20R, 20G, 20B)의 발광/비발광의 제어를 행하는 발광 제어신호로서의 기능을 가지고 있다. 또한, 전원공급 주사 회로(50)은, 서브 팩셀(20R, 20G, 20B)의 발광 구동의 제어를 행하는 발광 구동주사 회로로서의 기능을 가지고 있다.

[0034] 수평구동회로(60)은, 신호 공급원(도시 생략)으로부터 공급되는 휘도정보에 따른 영상신호의 신호 전압(이하, 간단히 「신호 전압」이라고 기술할 경우도 있다) Vsig과 오프셋 전압 Vofs의 어느 한쪽을 적당하게 선택하고, 신호선(33-1~33-n)을 거쳐서 화소 어레이부(30)의 각 서브 팩셀(20R, 20G, 20B)에 대하여 예를 들면 행단위로 기록한다. 즉, 수평구동회로(60)은, 영상신호의 신호 전압 Vsig을 행(라인)단위로 기록하는 선 순차 기록의 구동형태를 취하는 신호 공급부이다.

[0035] 여기에서, 오프셋 전압 Vofs는, 영상신호의 신호 전압 Vsig의 기준이 되는 기준전압(예를 들면 흑 레벨에 해당하는 전압)이다. 또한, 제2전위 Vini는, 오프셋 전압 Vofs보다도 낮은 전위, 예를 들면 구동 트랜지스터(22)의 임계전압을 Vth로 할 때 Vofs-Vth보다도 낮은 전위, 바람직하게는 Vofs-Vth보다도 충분하게 낮은 전위로 설정된다.

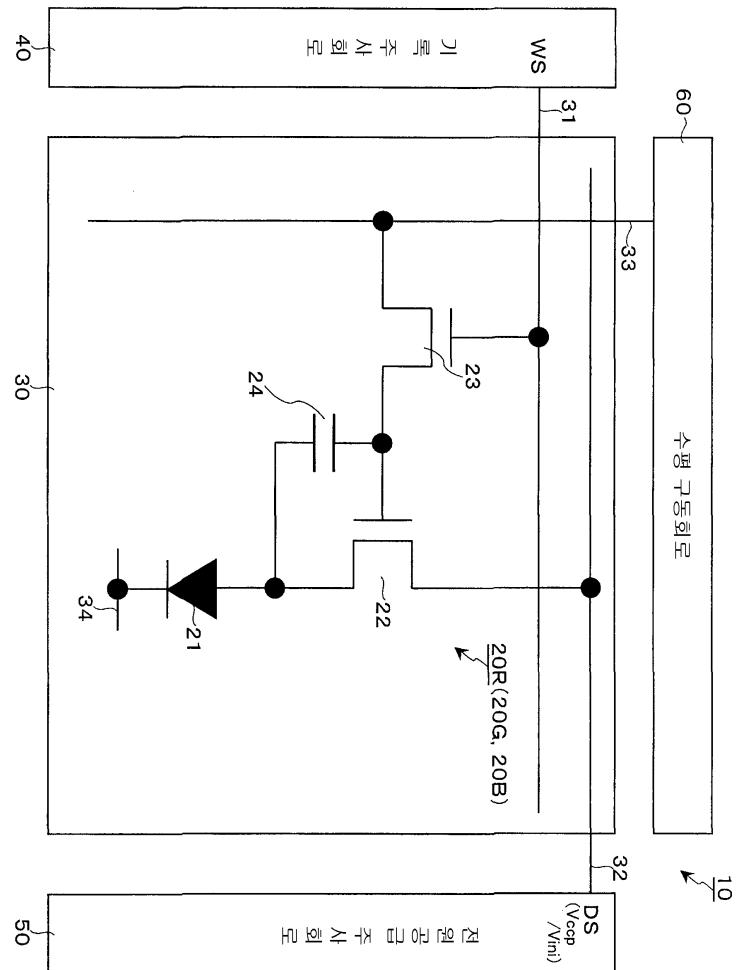

[0036] (서브 팩셀의 화소회로)

[0037] 도 2는, 참고예에 관련되는 유기 EL 표시장치(10A)에 있어서의 서브 팩셀(20R, 20G, 20B)의 화소회로의 구체적인 구성예를 나타낸 회로도다.

[0038] 도 2에 도시된 것과 같이 서브 팩셀(20R, 20G, 20B)은, 디바이스에 흐르는 전류값에 따라 발광 휘도가 변화되는 전류구동형의 전기광학소자, 예를 들면 유기 EL 소자(21)을 발광소자로서 가지고, 해당 유기 EL 소자(21)에 덧붙여, 구동 트랜지스터(22), 기록 트랜지스터(23) 및 유지용량(24)을 가지는 화소구성으로 되어 있다.

[0039] 여기에서, 구동 트랜지스터(22) 및 기록 트랜지스터(23)로서 N채널형의 TFT를 사용하고 있다. 다만, 여기에서의 구동 트랜지스터(22) 및 기록 트랜지스터(23)의 도전형의 조합은 일례에 지나지 않고, 이를 조합에 한정되는 것은 아니다.

[0040] 유기 EL 소자(21)은, 모든 서브 팩셀(20R, 20G, 20B)에 대하여 공통적으로 배선된 공통 전원 공급선(34)에 캐소드 전극이 접속되어 있다. 구동 트랜지스터(22)은, 소스 전극이 유기 EL 소자(21)의 애노드 전극에 접속되고, 드레인 전극이 전원 공급선(32)(32-1~32-m)에 접속되어 있다.

[0041] 기록 트랜지스터(23)은, 게이트 전극이 주사선(31)(31-1~31-m)에 접속되고, 한쪽의 전극(소스 전극/드레인 전극)이 신호선(33)(33-1~33-n)에 접속되고, 다른 쪽의 전극(드레인 전극/소스 전극)이 구동 트랜지스터(22)의 게이트 전극에 접속되어 있다.

[0042] 유지용량(24)은, 한쪽의 전극이 구동 트랜지스터(22)의 게이트 전극에 접속되고, 다른 쪽의 전극이 구동 트랜지스터(22)의 소스 전극(유기 EL 소자(21)의 애노드 전극)에 접속되어 있다. 이때, 유기 EL 소자(21)의 애노드 전극과 고정 전위 사이에 보조 용량을 접속해서 유기 EL 소자(21)의 용량 부족분을 보충하는 구성을 채용하는 경우도 있다.

[0043] 상기 구성의 서브 팩셀(20R,20G,20B)에 있어서, 기록 트랜지스터(23)은, 기록 주사 회로(40)로부터 주사선(31)을 통해서 게이트 전극에 인가되는 기록 주사 신호 WS에 응답해서 도통상태가 되는 것에 의해, 신호선(33)을 통과시켜서 수평구동회로(60)로부터 공급되는 휘도정보에 따른 영상신호의 신호 전압 Vsig 또는 오프셋 전압 Vofs를 샘플링해서 서브 팩셀(20R,20G,20B) 내에 기록한다.

[0044] 이 기록된 신호 전압 Vsig 또는 오프셋 전압 Vofs는, 구동 트랜지스터(22)의 게이트 전극에 인가되는 동시에 유지용량(24)에 유지된다. 구동 트랜지스터(22)은, 전원 공급선(32)(32-1~32-m)의 전위 DS가 제1전위 Vccp에 있으면, 전원 공급선(32)으로부터 전류의 공급을 받고, 유지용량(24)에 유지된 신호 전압 Vsig의 전압값에 따른 전류값의 구동전류를 유기 EL 소자(21)에 공급하여, 해당 유기 EL 소자(21)을 전류 구동함으로써 발광시킨다.

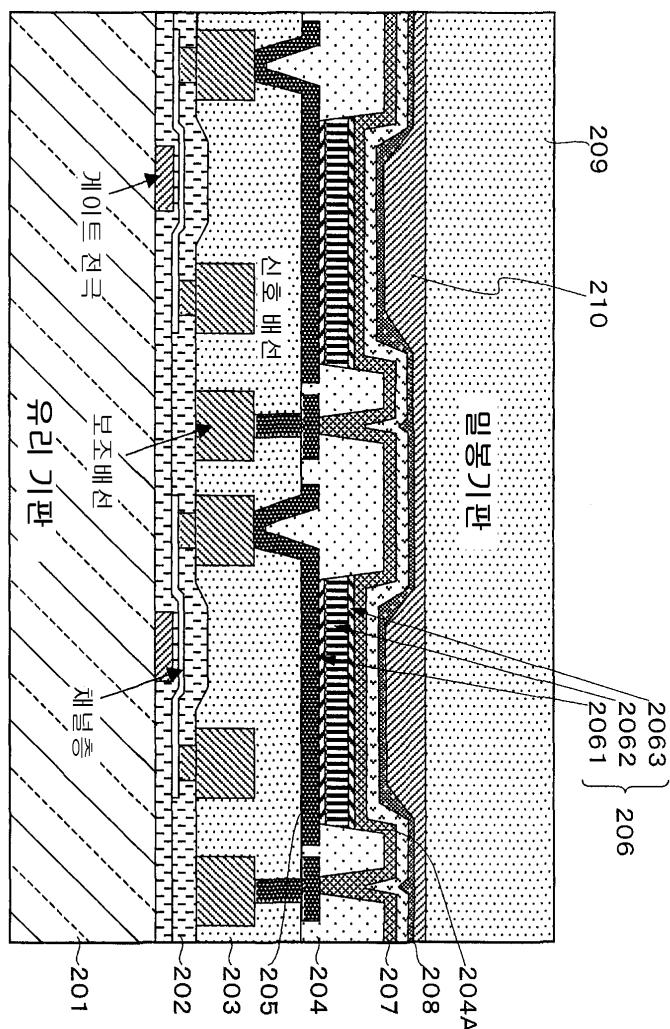

#### (서브 팩셀의 구조)

[0046] 도 3은, 서브 팩셀(20R,20G,20B)의 단면구조의 일례를 나타낸 단면도이다. 도 3에 도시된 것과 같이 서브 팩셀(20R,20G,20B)은, 구동 트랜지스터(22), 기록 트랜지스터(23) 등의 화소회로가 형성된 유리 기판(201) 위에 절연막(202), 절연 평탄화막(203) 및 윈도우 절연막(204)이 순차적으로 형성되고, 해당 윈도우 절연막(204)의 오목부(204A)에 유기 EL 소자(21)가 설치된 구성으로 되어 있다.

[0047] 유기 EL 소자(21)은, 상기 윈도우 절연막(204)의 오목부(204A)의 저부에 형성된 금속 등으로 이루어진 애노드 전극(205)과, 해당 애노드 전극(205) 위에 형성된 유기층(전자수송층, 발광층, 홀 수송층/홀 주입층)(206)과, 해당 유기층(206) 위에 전체 화소 공통으로 형성된 투명도전막 등으로 이루어지는 캐소드 전극(207)으로 구성되어 있다.

[0048] 이 유기 EL 소자(21)에 있어서, 유기층(206)은, 애노드 전극(205) 위에 홀 수송층/홀 주입층(2061), 발광층(2062), 전자수송층(2063) 및 전자주입층(도시 생략)이 순차 퇴적됨으로써 형성된다. 그리고, 도 2의 구동 트랜지스터(22)에 의한 전류구동하에서, 구동 트랜지스터(22)로부터 애노드 전극(205)을 통해서 유기층(206)에 전류가 흐름으로써 해당 유기층(206) 내부의 발광층(2062)에 있어서 전자와 정공이 재결합할 때에 발광하도록 되어 있다.

[0049] 도 3에 도시된 것과 같이, 화소회로가 형성된 유리 기판(201) 위에, 절연막(202), 절연 평탄화막(203) 및 윈도우 절연막(204)을 통해 유기 EL 소자(21)가 서브 팩셀 단위로 형성된 후에는, 패시베이션 막(208)을 통해 밀봉기판(209)이 접착제(210)에 의해 접합되고, 해당 밀봉기판(209)에 의해 유기 EL 소자(21)이 밀봉됨으로써, 표시 패널(70)이 형성된다.

#### (참고예에 관련되는 유기 EL 표시장치의 회로 동작)

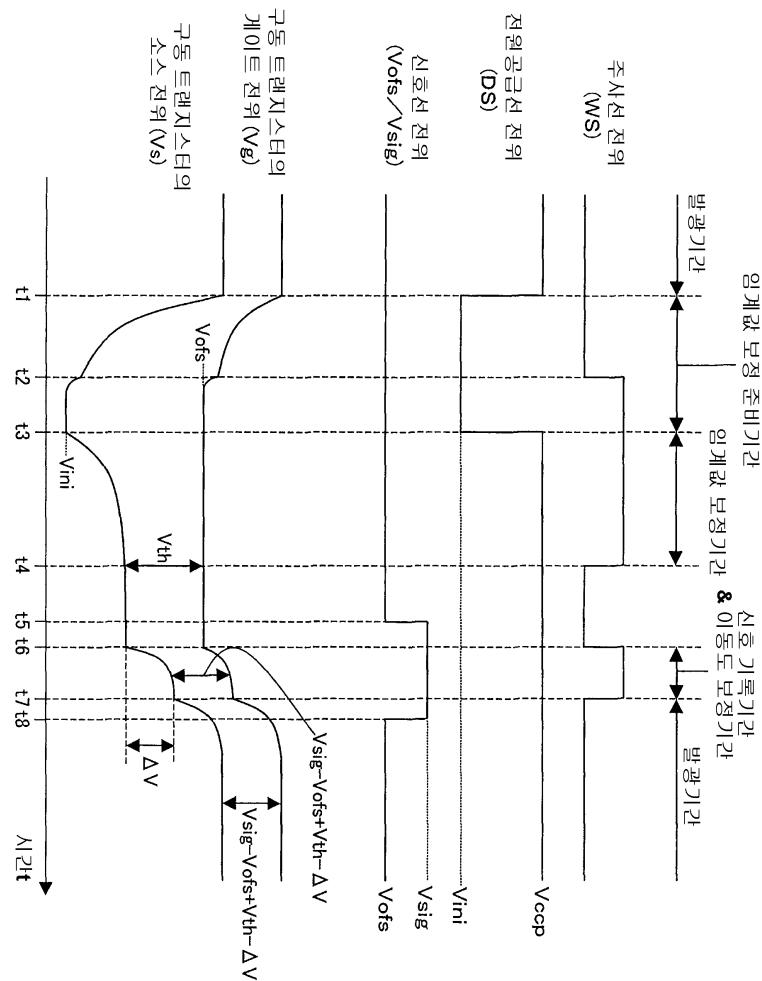

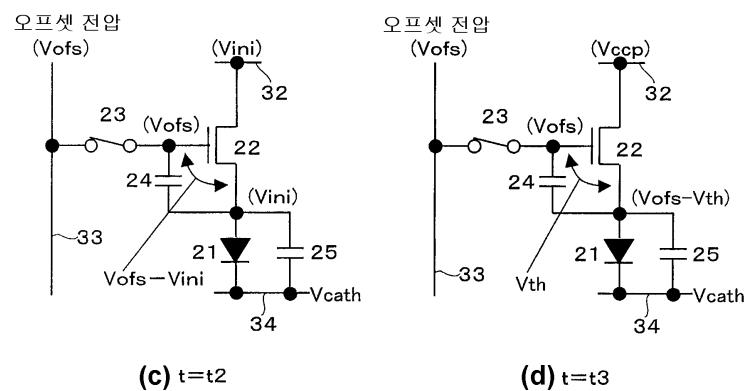

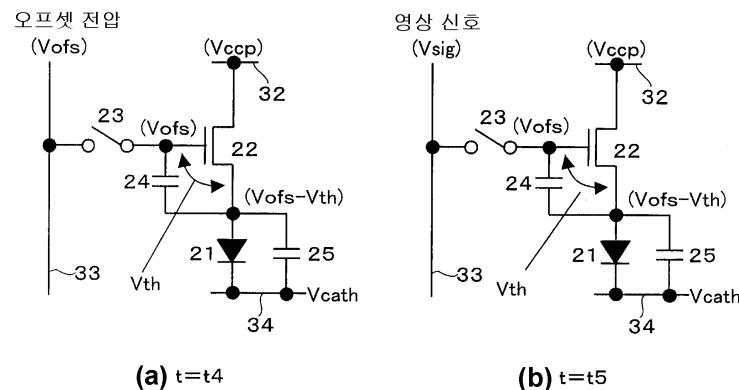

[0051] 다음에, 참고예에 관련되는 유기 EL 표시장치(10A)의 기본적인 회로 동작에 대해서, 도 4의 타이밍 파형도를 기초로, 도 5 및 도 6의 동작 설명도를 사용하여 설명한다. 이때, 도 5 및 도 6의 동작 설명도에서는, 도면의 간략화를 위해, 기록 트랜지스터(23)을 스위치의 심별로 도시하고 있다. 유기 EL 소자(21)의 용량성분(EL용량(25))에 대해서도 도시하고 있다.

[0052] 도 4의 타이밍 파형도에 있어서는, 1H(H는 수평기간)에 있어서의 주사선(31)(31-1~31-m)의 전위(기록 주사 신호) WS의 변화, 전원 공급선(32)(32-1~32-m)의 전위 DS의 변화, 신호선(33)(33-1~33-n)의 전위(Vofs/Vsig)의 변화, 구동 트랜지스터(22)의 게이트 전위Vg 및 소스 전위 Vs의 변화를 나타내고 있다.

#### <발광 기간>

[0054] 도 4의 타이밍 차트에 있어서, 시간 t1 이전은 유기 EL 소자(21)가 발광 상태에 있다(발광 기간). 이 발광 기간에서는, 전원 공급선(32)의 전위 DS가 제1전위 Vccp에 있고, 또한, 기록 트랜지스터(23)이 비도통상태에 있다. 이때, 구동 트랜지스터(22)은 포화 영역에서 동작하도록 설정되어 있기 때문에에, 도5a에 도시된 것과 같이 전원 공급선(32)으로부터 구동 트랜지스터(22)을 통해서 해당 구동 트랜지스터(22)의 게이트-소스간 전압 Vgs에 따른 구동전류(드레인-소스간 전류) Ids가 유기 EL 소자(21)에 공급된다. 따라서, 유기 EL 소자(21)이 구

동전류  $Ids$ 의 전류값에 따른 휘도로 발광한다.

#### [0055] <임계값 보정준비 기간>

[0056] 그리고, 시간  $t_1$ 이 되면, 선 순차 주사의 새로운 필드에 들어가, 도 5b에 도시된 것과 같이 전원 공급선(32)의 전위  $DS$ 가 제1전위(이하, 「고전위」라고 기술한다)  $V_{CCP}$ 로부터, 신호선(33)의 오프셋 전압  $V_{ofs-V}$ 보다도 충분하게 낮은 제2전위(이하, 「저전위」라고 기술한다)  $V_{ini}$ 로 바뀐다.

[0057] 여기에서, 유기 EL 소자(21)의 임계전압을  $V_{el}$ , 공통 전원 공급선(34)의 전위를  $V_{cath}$ 라고 할 때, 저전위  $V_{ini}$ 를  $V_{ini} < V_{el} + V_{cath}$ 라고 하면, 구동 트랜지스터(22)의 소스 전위  $V_s$ 가 저전위  $V_{ini}$ 에 거의 같아지기 때문에, 유기 EL 소자(21)은 역바이어스 상태가 되어 소광한다.

[0058] 다음에 시간  $t_2$ 에서 주사선(31)의 전위  $WS$ 가 저전위측에서 고전위측으로 천이함으로써 도 5c에 도시된 것과 같이 기록 트랜지스터(23)이 도통상태가 된다. 이 때, 수평구동회로(60)로부터 신호선(33)에 대하여 오프셋 전압  $V_{ofs-V}$ 가 공급되고 있기 때문에, 구동 트랜지스터(22)의 게이트 전위  $V_g$ 가 오프셋 전압  $V_{ofs-V}$ 가 된다. 또한, 구동 트랜지스터(22)의 소스 전위  $V_s$ 는, 오프셋 전압  $V_{ofs-V}$ 보다도 충분하게 낮은 전위  $V_{ini}$ 에 있다.

[0059] 이때, 구동 트랜지스터(22)의 게이트-소스간 전압  $V_{gs}$ 는  $V_{ofs-V} - V_{ini}$ 가 된다. 여기에서,  $V_{ofs-V} - V_{ini}$ 가 구동 트랜지스터(22)의 임계전압  $V_{th}$ 보다도 크지 않으면, 후술하는 임계값 보정동작을 행할 수 없기 때문에,  $V_{ofs-V} - V_{ini} > V_{th}$ 가 되는 전위관계로 설정할 필요가 있다. 이렇게, 구동 트랜지스터(22)의 게이트 전위  $V_g$ 을 오프셋 전압  $V_{ofs-V}$ 로, 소스 전위  $V_s$ 를 저전위  $V_{ini}$ 로 각각 고정해서(확정시켜서) 초기화하는 동작이 임계값 보정준비의 동작이다.

#### [0060] <임계값 보정기간>

[0061] 다음에 시간  $t_3$ 에서, 도 5d에 도시된 것과 같이 전원 공급선(32)의 전위  $DS$ 가 저전위  $V_{ini}$ 로부터 고전위  $V_{CCP}$ 로 바뀌면, 구동 트랜지스터(22)의 소스 전위  $V_s$ 가 상승을 시작한다. 드디어, 구동 트랜지스터(22)의 게이트-소스간 전압  $V_{gs}$ 가 해당 구동 트랜지스터(22)의 임계전압  $V_{th}$ 로 수속하여, 해당 임계전압  $V_{th}$ 에 해당하는 전압이 유지용량(24)에 유지된다.

[0062] 여기에서는, 편의상, 구동 트랜지스터(22)의 임계전압  $V_{th}$ 로 수속한 게이트-소스간 전압  $V_{gs}$ 를 검출해서 해당 임계전압  $V_{th}$ 에 해당하는 전압을 유지용량(24)에 유지하는 기간을 임계값 보정기간으로 부르고 있다. 이때, 이 임계값 보정기간에 있어서, 전류가 단지 유지용량(24)측에만 흘르고, 유기 EL 소자(21)측에는 흘르지 않도록 하기 위해서, 유기 EL 소자(21)가 컷오프 상태가 되도록 공통 전원 공급선(34)의 전위  $V_{cath}$ 를 설정해두는 것으로 한다.

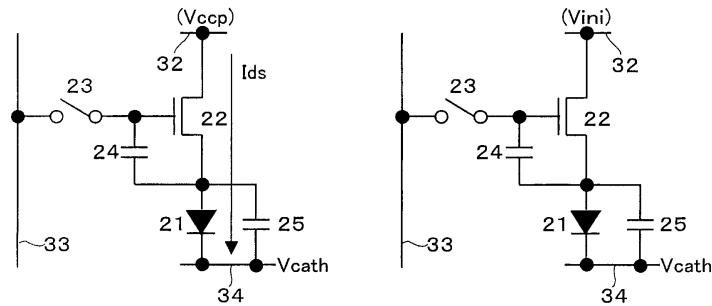

[0063] 다음에, 시간  $t_4$ 에서 주사선(31)의 전위  $WS$ 가 저전위측에 천이함으로써 도 6a에 도시된 것과 같이 기록 트랜지스터(23)가 비도통상태가 된다. 이때, 구동 트랜지스터(22)의 게이트 전극이 플로팅 상태가 되지만, 게이트-소스간 전압  $V_{gs}$ 가 구동 트랜지스터(22)의 임계전압  $V_{th}$ 와 같기 때문에, 해당 구동 트랜지스터(22)은 컷오프 상태에 있다. 따라서, 구동 트랜지스터(22)에 드레인-소스간 전류  $Ids$ 는 흘르지 않는다.

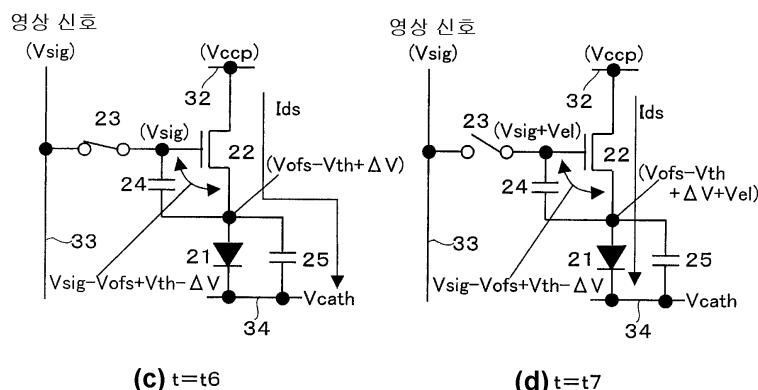

#### [0064] <기록 기간/이동도 보정기간>

[0065] 다음에, 시간  $t_5$ 에서, 도 6b에 도시된 것과 같이 신호선(33)의 전위가 오프셋 전압  $V_{ofs}$ 부터 영상신호의 신호 전압  $V_{sig}$ 로 바뀐다. 이어서, 시간  $t_6$ 에서, 주사선(31)의 전위  $WS$ 가 고전위측으로 천이함으로써 도 6c에 도시된 것과 같이 기록 트랜지스터(23)가 도통상태가 되어서 영상신호의 신호 전압  $V_{sig}$ 을 샘플링해서 기록한다.

[0066] 이 기록 트랜지스터(23)에 의한 신호 전압  $V_{sig}$ 의 기록에 의해, 구동 트랜지스터(22)의 게이트 전위  $V_g$ 가 신호 전압  $V_{sig}$ 가 된다. 그리고, 영상신호의 신호 전압  $V_{sig}$ 에 의한 구동 트랜지스터(22)의 구동시에에, 해당 구동 트랜지스터(22)의 임계전압  $V_{th}$ 가 유지용량(24)에 유지된 임계전압  $V_{th}$ 에 해당하는 전압과 상쇄됨으로써 임계값 보정이 행해진다. 임계값 보정의 원리에 관해서는 후술한다.

[0067] 이때, 유기 EL 소자(21)은 처음에 역바이어스 상태에 있음으로써 컷오프 상태(하이 임피던스 상태)에

있다. 유기 EL 소자(21)은 역바이어스 상태에 있을 때에는 용량성을 나타낸다. 따라서, 영상신호의 신호 전압  $V_{sig}$ 에 따라 전원 공급선(32)으로부터 구동 트랜지스터(22)에 흐르는 전류(드레인-소스간 전류  $I_{ds}$ )은 유기 EL 소자(21)의 EL용량(25)에 흘러 들어 와, 해당 EL용량(25)의 충전이 개시된다.

[0068] 이 EL용량(25)의 충전에 의해, 구동 트랜지스터(22)의 소스 전위  $V_s$ 가 시간의 경과와 함께 상승해 간다. 이때 이미, 구동 트랜지스터(22)의 임계전압  $V_{th}$ 의 격차는 보정되고 있고, 구동 트랜지스터(22)의 드레인-소스간 전류  $I_{ds}$ 는 해당 구동 트랜지스터(22)의 이동도  $\mu$ 에 의존하게 된다.

[0069] 여기에서, 기록 계인(영상신호의 신호 전압  $V_{sig}$ 에 대한 유지용량(24)의 유지 전압  $V_{gs}$ 의 비율)이 1(이상값)이라고 가정하면, 구동 트랜지스터(22)의 소스 전위  $V_s$ 가  $V_{ofs} - V_{th} + \Delta V$ 의 전위까지 상승함으로써 구동 트랜지스터(22)의 게이트-소스간 전압  $V_{gs}$ 는  $V_{sig} - V_{ofs} + V_{th} - \Delta V$ 가 된다.

[0070] 즉, 구동 트랜지스터(22)의 소스 전위  $V_s$ 의 상승분  $\Delta V$ 는, 유지용량(24)에 유지된 전압( $V_{sig} - V_{ofs} + V_{th}$ )에서 빼지도록, 바꾸어 말하면, 유지용량(24)의 충전 전하를 방전하도록 작용하여, 부귀환이 걸리게 된다. 따라서, 소스 전위  $V_s$ 의 상승 분  $\Delta V$ 는 부귀환의 귀환량이 된다.

[0071] 이렇게, 구동 트랜지스터(22)에 흐르는 드레인-소스간 전류  $I_{ds}$ 를 해당 구동 트랜지스터(22)의 게이트 입력에, 즉 게이트-소스간 전압  $V_{gs}$ 에 부귀환함에 의해, 구동 트랜지스터(22)의 드레인-소스간 전류  $I_{ds}$ 의 이동도  $\mu$ 에 대한 의존성을 상쇄한다. 즉 이동도  $\mu$ 의 화소마다의 격차를 보정하는 이동도 보정이 행해진다.

[0072] 보다 구체적으로는, 영상신호의 신호 전압  $V_{sig}$ 이 높을수록 드레인-소스간 전류  $I_{ds}$ 가 커지기 때문에, 부귀환의 귀환량(보정량)  $\Delta V$ 의 절대값도 커진다. 따라서, 발광 휘도 레벨에 따른 이동도 보정이 행해진다. 또한, 영상신호의 신호 전압  $V_{sig}$ 을 일정하게 했을 경우, 구동 트랜지스터(22)의 이동도  $\mu$ 이 클수록 부귀환의 귀환량  $\Delta V$ 의 절대값도 커지기 때문에, 화소(서브 픽셀)마다의 이동도  $\mu$ 의 격차를 제거할 수 있다. 이동도 보정의 원리에 관해서는 후술한다.

#### <발광 기간>

[0073] 다음에 시간  $t_7$ 에서 주사선(31)의 전위  $W_S$ 가 저전위측으로 천이함으로써 도 6d에 도시된 것과 같이 기록 트랜지스터(23)가 비도통상태가 된다. 이에 따라 구동 트랜지스터(22)의 게이트 전극은 신호선(33)로부터 분리되어 플로팅 상태가 된다.

[0074] 여기에서, 구동 트랜지스터(22)의 게이트 전극이 플로팅 상태에 있을 때에는, 구동 트랜지스터(22)의 게이트-소스간에 유지용량(24)이 접속되어 있는 것에 의해, 구동 트랜지스터(22)의 소스 전위  $V_s$ 가 변동하면, 해당 소스 전위  $V_s$ 의 변동에 연동해서(추종해서) 구동 트랜지스터(22)의 게이트 전위  $V_g$ 도 변동한다. 이것이 유지용량(24)에 의한 부트스트랩 동작이다.

[0075] 구동 트랜지스터(22)의 게이트 전극이 플로팅 상태가 되고, 그것과 동시에, 구동 트랜지스터(22)의 드레인-소스간 전류  $I_{ds}$ 가 유기 EL 소자(21)에 흐르기 시작하는 것에 의해, 유기 EL 소자(21)의 애노드 전위는, 구동 트랜지스터(22)의 드레인-소스간 전류  $I_{ds}$ 에 따라 상승한다.

[0076] 유기 EL 소자(21)의 애노드 전위의 상승은, 즉 구동 트랜지스터(22)의 소스 전위  $V_s$ 의 상승 이외는 다른 것은 없다. 구동 트랜지스터(22)의 소스 전위  $V_s$ 가 상승하면, 유지용량(24)의 부트스트랩 동작에 의해, 구동 트랜지스터(22)의 게이트 전위  $V_g$ 도 연동해서 상승한다.

[0077] 이때, 부트스트랩 계인(1(이상값))이라고 가정했을 경우, 게이트 전위  $V_g$ 의 상승량은 소스 전위  $V_s$ 의 상승량과 같아진다. 그러므로, 발광 기간 동안 구동 트랜지스터(22)의 게이트-소스간 전압  $V_{gs}$ 는  $V_{sig} - V_{ofs} + V_{th} - \Delta V$ 로 일정하게 유지된다.

[0078] 그리고, 구동 트랜지스터(22)의 소스 전위  $V_s$ 의 상승에 따라, 유기 EL 소자(21)의 역바이어스 상태가 해소되고, 순바이어스 상태가 되면, 구동 트랜지스터(22)로부터 유기 EL 소자(21)에 구동전류가 공급되기 때문에, 유기 EL 소자(21)가 실제로 발광을 시작한다. 그후에 시간  $t_8$ 에서 신호선(33)의 전위가 영상신호의 신호 전압  $V_{sig}$ 으로부터 오프셋 전압  $V_{ofs}$ 로 바뀐다.

#### (임계값 보정의 원리)

[0081] 여기에서, 구동 트랜지스터(22)의 임계값 보정의 원리에 관하여 설명한다. 구동 트랜지스터(22)은, 포화 영역에서 동작하도록 설계되어 있기 때문에 정전류원으로서 동작한다. 이에 따라 유기 EL 소자(21)에는 구동 트랜지스터(22)로부터, 다음 식 (1)로 주어지는 일정한 드레인-소스간 전류(구동전류)  $Ids$ 가 공급된다.

$$Ids = \frac{1}{2} \cdot \mu (\frac{W}{L}) Cox (V_{gs} - V_{th})^2 \quad \dots\dots(1)$$

[0082] 여기에서,  $W$ 는 구동 트랜지스터(22)의 채널 폭,  $L$ 은 채널길이,  $Cox$ 는 단위면적당의 게이트 용량이다.

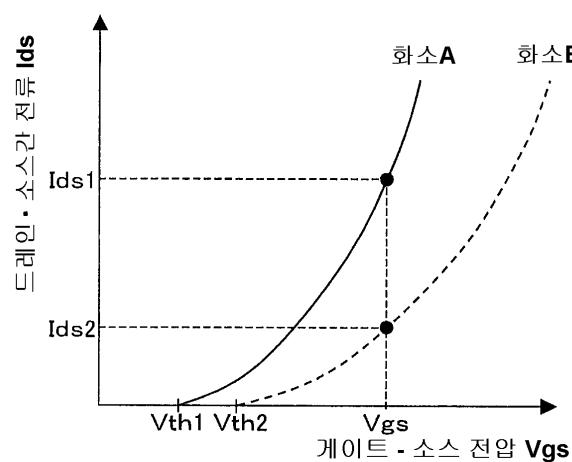

[0083] 도 7에, 구동 트랜지스터(22)의 드레인-소스간 전류  $Ids$  대 게이트-소스간 전압  $V_{gs}$ 의 특성을 나타낸다.

[0084] 이 특성 도면에 도시된 것과 같이 구동 트랜지스터(22)의 임계전압  $V_{th}$ 의 화소(서브 픽셀)마다의 격차에 대한 보정을 행하지 않으면, 임계전압  $V_{th}$ 가  $V_{th1}$ 일 때, 게이트-소스간 전압  $V_{gs}$ 에 대응하는 드레인-소스간 전류  $Ids$ 가  $Ids1$ 이 된다.

[0085] 이에 대하여, 임계전압  $V_{th}$ 가  $V_{th2}$ ( $V_{th2} > V_{th1}$ )일 때, 같은 게이트-소스간 전압  $V_{gs}$ 에 대응하는 드레인-소스간 전류  $Ids$ 가  $Ids2$ ( $Ids2 < Ids1$ )가 된다. 즉, 구동 트랜지스터(22)의 임계전압  $V_{th}$ 가 변동하면, 게이트-소스간 전압  $V_{gs}$ 가 일정하여도 드레인-소스간 전류  $Ids$ 가 변동한다.

[0086] 한편, 상기 구성의 화소회로에서는, 전술한 것 같이, 발광시의 구동 트랜지스터(22)의 게이트-소스간 전압  $V_{gs}$ 가  $V_{sig} - V_{ofs} + V_{th} - \Delta V$ 이기 때문에, 이것을 식(1)에 대입하면, 드레인-소스간 전류  $Ids$ 는,

$$Ids = \frac{1}{2} \cdot \mu (\frac{W}{L}) Cox (V_{sig} - V_{ofs} - \Delta V)^2 \quad \dots\dots(2) \text{로 나타낸다.}$$

[0087] 즉, 구동 트랜지스터(22)의 임계전압  $V_{th}$ 의 향이 캔슬되어 있어, 구동 트랜지스터(22)로부터 유기 EL 소자(21)에 공급되는 드레인-소스간 전류  $Ids$ 는, 구동 트랜지스터(22)의 임계전압  $V_{th}$ 에 의존하지 않는다. 그 결과, 구동 트랜지스터(22)의 제조 프로세스의 격차나 시간에 따른 변화에 의해, 구동 트랜지스터(22)의 임계전압  $V_{th}$ 가 화소마다 변동해도, 드레인-소스간 전류  $Ids$ 가 변동하지 않기 때문에, 유기 EL 소자(21)의 발광 휘도를 일정하게 유지할 수 있다.

[0088] (이동도 보정의 원리)

[0089] 다음에 구동 트랜지스터(22)의 이동도 보정의 원리에 관하여 설명한다. 여기에서는, 설명의 사정상, 「서브 픽셀」을 「화소」라고 기술하는 것으로 한다.

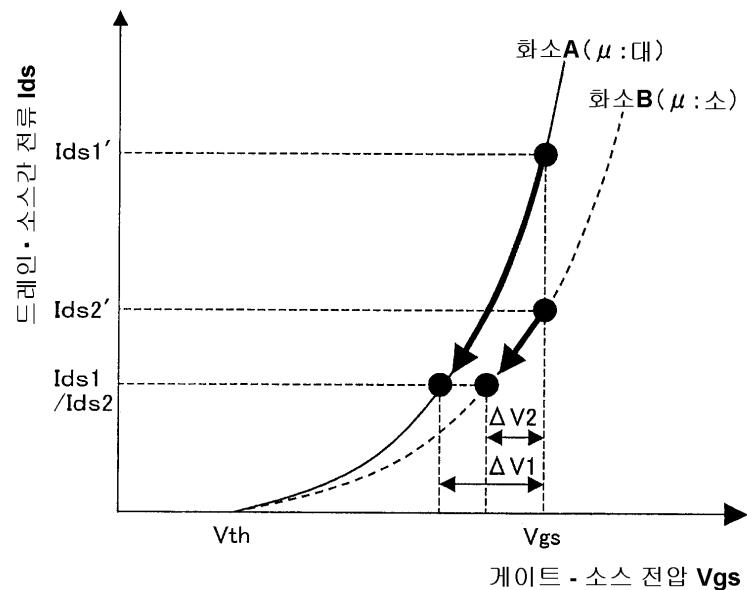

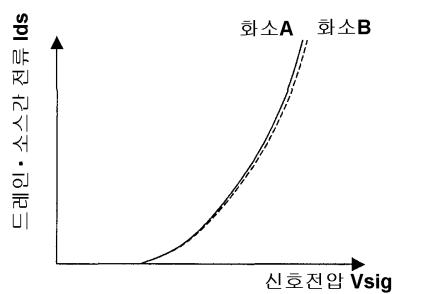

[0090] 도 8에, 구동 트랜지스터(22)의 이동도  $\mu$ 가 상대적으로 큰 화소 A와, 구동 트랜지스터(22)의 이동도  $\mu$ 가 상대적으로 작은 화소 B를 비교한 상태에서 특성 커브를 나타낸다. 구동 트랜지스터(22)을 폴리실리콘 박막트랜지스터 등으로 구성했을 경우, 화소 A나 화소 B과 같이, 화소 사이에서 이동도  $\mu$ 가 변동하는 것은 피할 수 없다.

[0091] 화소 A와 화소 B에서 이동도  $\mu$ 에 격차가 있는 상태에서, 예를 들면 양쪽 화소 A, B에 같은 레벨의 영상신호의 신호 전압  $V_{sig}$ 을 기록했을 경우에, 아무런 이동도  $\mu$ 의 보정을 행하지 않으면, 이동도  $\mu$ 가 큰 화소 A에 흐르는 드레인-소스간 전류  $Ids1'$ 과 이동도  $\mu$ 가 작은 화소 B에 흐르는 드레인-소스간 전류  $Ids2'$  사이에는 큰 차이가 생겨 버린다. 이렇게, 이동도  $\mu$ 의 화소마다의 격차에 기인해서 드레인-소스간 전류  $Ids$ 에 화소 사이에서 큰 차이가 생기면, 화면의 유티포머티가 손상되게 된다.

[0092] 여기에서, 전술한 식(1)의 트랜지스터 특성식으로부터 명확한 것과 같이, 이동도  $\mu$ 가 크면 드레인-소스간 전류  $Ids$ 가 커진다. 따라서, 부귀환에 있어서의 귀환량  $\Delta V$ 는 이동도  $\mu$ 가 커질수록 커진다. 도 8에 도시된 것과 같이 이동도  $\mu$ 가 큰 화소 A의 귀환량  $\Delta V1$ 은, 이동도가 작은 화소 B의 귀환량  $\Delta V2$ 에 비해 크다.

[0093] 따라서, 이동도 보정동작에 의해 구동 트랜지스터(22)의 드레인-소스간 전류  $Ids$ 를 영상신호의 신호 전압  $V_{sig}$ 으로 부귀환시킴으로써, 이동도  $\mu$ 가 클수록 부귀환이 크게 걸리게 되기 때문에, 이동도  $\mu$ 의 화소마다의 격차를 억제할 수 있다.

[0094] 구체적으로는, 이동도  $\mu$ 가 큰 화소 A에서 귀환량  $\Delta V1$ 의 보정을 걸면, 드레인-소스간 전류  $Ids$ 는  $Ids1'$ 로부터  $Ids1$ 까지 크게 하강한다. 한편, 이동도  $\mu$ 가 작은 화소 B의 귀환량  $\Delta V2$ 은 작기 때문에, 드레인-소스간 전류  $Ids$ 는  $Ids2'$ 로부터  $Ids2$ 까지 하강하게 되고, 그만큼 크게 하강하지 않는다. 결과적으로, 화소 A의 드

레인-소스간 전류  $Ids_1$ 과 화소 B의 드레인-소스간 전류  $Ids_2$ 는 거의 같아지기 때문에, 이동도  $\mu$ 의 화소마다의 격차가 보정된다.

[0097] 이상을 정리하면, 이동도  $\mu$ 가 다른 화소 A와 화소 B가 있었을 경우, 이동도  $\mu$ 가 큰 화소 A의 귀환량  $\Delta V_1$ 은 이동도  $\mu$ 가 작은 화소 B의 귀환량  $\Delta V_2$ 에 비해서 커진다. 즉, 이동도  $\mu$ 가 큰 화소일수록 귀환량  $\Delta V$ 가 크고, 드레인-소스간 전류  $Ids$ 의 감소량이 커진다.

[0098] 따라서, 구동 트랜지스터(22)의 드레인-소스간 전류  $Ids$ 를 영상신호의 신호 전압  $V_{sig}$ 측에 부귀환시킴으로써, 이동도  $\mu$ 가 다른 화소의 드레인-소스간 전류  $Ids$ 의 전류값이 균일화된다. 그 결과, 이동도  $\mu$ 의 화소마다의 격차를 보정할 수 있다.

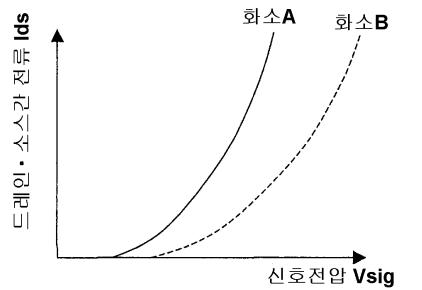

[0099] 여기에서, 도 2에 나타낸 화소회로에 있어서, 임계값 보정, 이동도 보정의 유무에 의한 영상신호의 신호 전위(샘플링 전위)  $V_{sig}$ 과 구동 트랜지스터(22)의 드레인 · 소스간 전류  $Ids$ 의 관계에 대해서 도 9을 사용하여 설명한다.

[0100] 도 9에 있어서, (a)은 임계값 보정 및 이동도 보정을 모두 행하지 않을 경우, (b)은 이동도 보정을 행하지 않고, 임계값 보정만을 행했을 경우, (c)은 임계값 보정 및 이동도 보정을 모두 행한 경우를 각각 보이고 있다. 도9a에 도시된 것과 같이 임계값 보정 및 이동도 보정을 모두 행하지 않을 경우에는, 임계전압  $V_{th}$  및 이동도  $\mu$ 의 화소 A, B마다의 격차에 기인해서 드레인 · 소스간 전류  $Ids$ 에 화소A, B 사이에서 큰 차이가 생기게 된다.

[0101] 이에 대하여 임계값 보정만을 행한 경우에는, 도 9b에 도시된 것과 같이 해당 임계값 보정에 의해 드레인-소스간 전류  $Ids$ 의 격차를 어느 정도 저감할 수 있지만, 이동도  $\mu$ 의 화소 A, B마다의 격차에 기인하는 화소 A, B 사이에서의 드레인-소스간 전류  $Ids$ 의 차이는 남는다.

[0102] 그리고, 임계값 보정 및 이동도 보정을 모두 행함으로써, 도 9c에 도시된 것과 같이 임계전압  $V_{th}$  및 이동도  $\mu$ 의 화소 A, B마다의 격차에 기인하는 화소 A, B 사이에서의 드레인-소스간 전류  $Ids$ 의 차이를 거의 없앨 수 있기 때문에, 어느 계조에 있어서도 유기 EL 소자(21)의 휘도 격차는 발생하지 않아, 양호한 화질의 표시화상을 얻을 수 있다.

[0103] 또한, 도 2에 나타낸 화소(20)는, 임계값 보정 및 이동도 보정의 각 보정기능에 덧붙여, 전술한 부트스트랩 기능을 갖추고 있음으로써 다음과 같은 작용 효과를 얻을 수 있다.

[0104] 즉, 유기 EL 소자(21)의 I-V 특성이 경시 변화되고, 이것에 따라 구동 트랜지스터(22)의 소스 전위  $V_s$ 가 변화되었다고 하더라도, 유지용량(24)에 의한 부트스트랩 동작에 의해, 구동 트랜지스터(22)의 게이트-소스간 전위  $V_{gs}$ 가 일정하게 유지되기 때문에, 유기 EL 소자(21)에 흐르는 전류는 변화되지 않는다. 따라서, 유기 EL 소자(21)의 발광 휘도도 일정하게 유지되기 때문에, 유기 EL 소자(21)의 I-V 특성이 경시 변화되어도, 거기에 따르는 휘도열화가 없는 화상표시를 실현할 수 있다.

[0105] 이상 설명한 것으로부터 명백한 것과 같이, 참고예에 관련되는 유기 EL 표시장치(10A)는, 서브 팩셀(20R, 20G, 20B)이, 구동 트랜지스터(22) 및 기록 트랜지스터(23)의 2개의 트랜지스터를 가지는 화소구성에서, 이를 트랜지스터에 덧붙여 몇 개의 트랜지스터를 가지는 화소구성의 특허문현 1 기재의 유기 EL 표시장치와 동등하게, 유기 EL 소자(21)의 특성변동에 대한 보상 기능이나, 임계값 보정 및 이동도 보정의 각 보정기능을 실현 할 수 있는 동시에, 화소회로의 구성 소자가 적을수록 화소 사이즈를 미세화할 수 있어, 표시 패널(70)의 고선 명화를 피할 수 있다.

#### [0106] [본 실시예에 따른 유기 EL 표시장치]

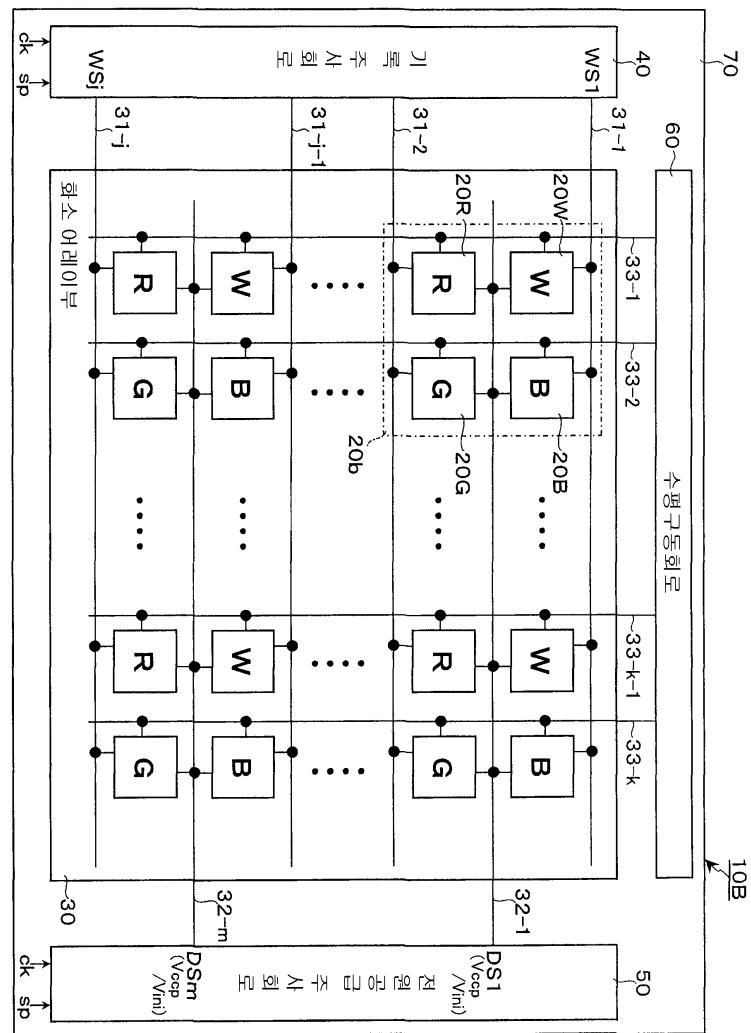

[0107] 도10은, 본 발명의 일 실시 형태에 따른 액티브 매트릭스형 표시장치의 구성의 개략을 나타낸 시스템 구성도로서, 도면 중, 도 1과 동등 부분에는 동일한 부호를 붙여 나타내고 있다.

[0108] 본 실시예에 있어서도, 일례로서, 디바이스에 흐르는 전류값에 따라 발광 휘도가 변화되는 전류구동형의 전기광학소자, 예를 들면 유기 EL 소자를 서브 팩셀의 발광소자로서 사용한 액티브 매트릭스형 유기 EL 표시장치의 경우를 예로 들어 설명하기로 한다.

[0109] 도 10에 도시된 것과 같이 본 실시예에 따른 유기 EL 표시장치(10B)은, 단위화소(20b)가 행렬 모양으로 2차원 배치되어 이루어진 화소 어레이부(30)과, 해당 화소 어레이부(30)의 주변부(테두리)에 배치되어, 각 단위

화소(20b)을 구동하는 구동부, 예를 들면 기록 주사 회로(40), 전원공급 주사 회로(50) 및 수평구동회로(60)를 가지고, 기본적으로는, 참고예에 관련되는 유기 EL 표시장치(10A)와 같은 시스템 구성으로 되어 있다.

[0110] 그리고, 본 실시예에 따른 유기 EL 표시장치(10B)은, 단위화소(20b)의 구성과 그것에 따르는 구동계의 구성의 점에서 참고예에 관련되는 유기 EL 표시장치(10A)와 다르다. 구체적으로는, 참고예에 관련되는 유기 EL 표시장치(10A)에서는, 단위화소(20a)가 동일한 행에 속하는 서브 픽셀(20R, 20G, 20B)로 구성되어 있는 것에 대해서, 본 실시예에 따른 유기 EL 표시장치(10B)에서는 단위화소(20b)가 복수행, 예를 들면 상하 2행에 속하는 인접하는 복수의 서브 픽셀로 구성되어 있다.

[0111] 그리고, 본 예에 관련되는 단위화소(20b)은, 고휘도화나 저소비 전력화 등을 목적으로 하여, RGB의 서브 픽셀(20R, 20G, 20B)에 덧붙여 사용 빈도가 높은 W(백색)의 서브 픽셀(20W)을 가지는 4종의 서브 픽셀(20W, 20R, 20G, 20B)에 의해, 2행 2열을 단위로서 구성되어 있다.

[0112] 4종의 서브 픽셀(20W, 20R, 20G, 20B) 중, 예를 들면 서브 픽셀 20W와 20B이 상부의 행에 속하고, 서브 픽셀 20R와 20G이 하부의 행에 속하고 있다. 또한, 서브 픽셀 20W와 20R가 좌측의 열에 속하고, 서브 픽셀 20B과 20G가 우측의 열에 속하고 있다. 4종의 서브 픽셀(20W, 20R, 20G, 20B)의 개개의 화소회로는, 도 2에 나타낸 화소회로와 같다.

[0113] 이렇게, 단위화소(20b)가 2행 2열을 단위로 하고 있기 때문에, 1행 3열을 단위로 하는 단위화소(20a)의 경우(참고예에 관련되는 유기 EL 표시장치(10A)의 경우)에 비교하여, 화소 어레이부(30)의 행수가 2배가 되고, 열수가 2/3이 된다. 따라서, 화소 어레이부(30)의 서브 픽셀의 배열은, j행( $j=2m$ ) k열( $k=(2/3) \times n$ )이 된다.

[0114] 이  $j$ 행 $k$ 열의 서브 픽셀 배열에 대하여 행마다 주사선(31-1~31- $j$ )이 배선되고, 열마다 신호선(33-1~33- $k$ )이 배선되어 있다. 즉, 1행 3열을 단위로 하는 단위화소(20a)의 경우에 대하여, 주사선(31-1~31- $j$ )의 개수가 2배로 증가하지만, 신호선(33-1~33- $k$ )에 대해서는, 단위화소당 3개로부터 2개에 삭감할 수 있다.

[0115] 통상은, 전원 공급선(32)에 대해서도, 주사선(31)과 마찬가지로 행마다 배선되게 되지만, 본 실시예에 따른 유기 EL 표시장치(10B)에 있어서는, 단위화소(20b)(4개의 서브 픽셀(20W, 20R, 20G, 20B))당 1개씩, 즉 2행에 1개씩 전원 공급선(32-1~32- $m$ )이 배선되어 있다. 즉, 본 실시예에 따른 유기 EL 표시장치(10B)에서는 동일한 단위화소(20b)을 구성하는 4개의 서브 픽셀(20W, 20R, 20G, 20B) 사이에서 1개의 전원 공급선(32)(32-1~32- $m$ )을 공용하는 구성을 채용하고 있다.

[0116] 이렇게, 동일한 단위화소(20b)을 구성하는 상하 2행에 속하는 4개의 서브 픽셀(20W, 20R, 20G, 20B)에 대하여, 1개의 전원 공급선(32)(32-1~32- $m$ )을 공통화하도록 한 점이 본 실시예의 특징으로 하는 점이다. 1개의 전원 공급선(32)(32-1~32- $m$ )을 거쳐서 전원공급 주사 회로(50)에 의해 4개의 서브 픽셀(20W, 20R, 20G, 20B)을 구동할 경우의 구체적인 회로 동작 등에 관해서는 후술한다.

[0117] 단위화소(20b)을 구성하는 4개의 서브 픽셀(20W, 20R, 20G, 20B)에 대하여, 1개의 전원 공급선(32)을 공통화한 것에 의해, 1행 3열을 단위로 하는 단위화소(20a)의 경우에 대하여 행수가 2배로 증가하지만, 전원공급 주사 회로(50)로서는, 1행 3열을 단위로 하는 단위화소(20a)의 경우와 같은  $m$ 단의 회로 구성인 상태로도 된다.

[0118] 기록 주사 회로(40)에 대해서는, 행수만큼의  $j$ 개의 기록 주사 신호를 출력하는 회로 구성의 것이 아니면 안되지만, 후술하는 이유에 의해, 시프트 레지스터의 단수로서는  $m$ 단의 회로 구성의 것으로 된다. 그리고,  $m$ 단의 시프트 레지스터로부터 출력되는  $m$ 개의 기록 주사 신호를 기초로, 시프트 레지스터의 후단의 로직 회로에 있어서, 2배의  $j$ 개의 기록 주사 신호를 생성하도록 하면 좋다(그것의 상세에 관해서는 후술한다).

[0119] 또한, 수평구동회로(60)에 대해서는, 1행3열을 단위로 하는 단위화소(20a)의 경우에 대하여 열수가 2/3로 줄어들기 때문에, 거기에 대응해서 수평구동회로(60)의 회로 규모의 축소화를 피할 수 있다.

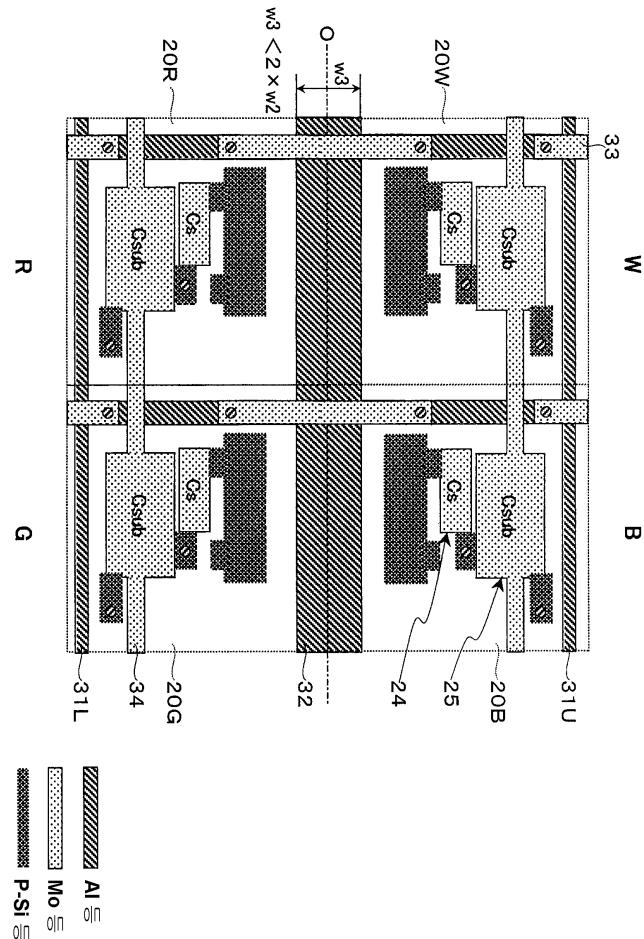

[0120] (단위 화소의 배치)

[0121] 여기에서, 단위화소(20b)의 각 서브 픽셀의 구성 소자와 주사선(31) 및 전원 공급선(32)의 배치 관계에 대하여 설명한다. 여기에서는, 유지용량(Cs)(24)에 덧붙여, 유기 EL 소자(21)의 용량부족을 보충하기 위한 보조 용량(Csub)(25)가 설정되었을 경우를 예로 들어 보이고 있다. 이때, 보조 용량(Csub)(25)의 사이즈가 발광 색에 따라 다른 것은 다음의 이유에 따른다.

[0122] 즉, 유기 EL 소자(21)은 발광 색에 의해 발광 효율이 다르다. 그 때문에, 유기 EL 소자(21)를 전류구동

하는 구동 트랜지스터(22)의 사이즈는 유기 EL 소자(21)의 발광색에 따라 다르다. 구동 트랜지스터(22)의 사이즈가 유기 EL 소자(21)의 발광색에 따라 다르면, 이동도 보정을 행할 때의 보정시간에, 유기 EL 소자(21)의 발광색에 의해 차이가 생기게 된다.

[0123] 이동도 보정시간은, 유기 EL 소자(21)가 가지는 용량성분(EL 용량)로 의해 결정된다. 따라서, 이동도 보정시간을 유기 EL 소자(21)의 발광색에 관계없이 일정하게 하기 위해서는, 구동 트랜지스터(22)의 사이즈에 따라 유기 EL 소자(21)의 사이즈를 변화시킴으로써, 유기 EL 소자(21)의 발광색 사이에서 EL 용량에 차이를 가지게 하도록 하면 된다. 그렇지만, 화소의 개구율 등의 관계에서, 유기 EL 소자(21)의 사이즈를 크게 하는 것에도 한계가 있다.

[0124] 이 때문에, 보조 용량(Csub)(25)을 사용해서 그것의 한쪽의 전극을 유기 EL 소자(21)의 애노드 전극에, 다른 쪽의 전극을 고정 전위, 예를 들면 공통 전원 공급선(34)에 접속하고, 해당 보조 용량(25)의 사이즈를 유기 EL 소자(21)의 발광색마다 변하게 함으로써 EL 용량의 용량부족을 보충하면서, 이동도 보정시간을 유기 EL 소자(21)의 발광색에 관계없이 일정하게 하도록 하고 있기 때문이다.

#### <참고예>

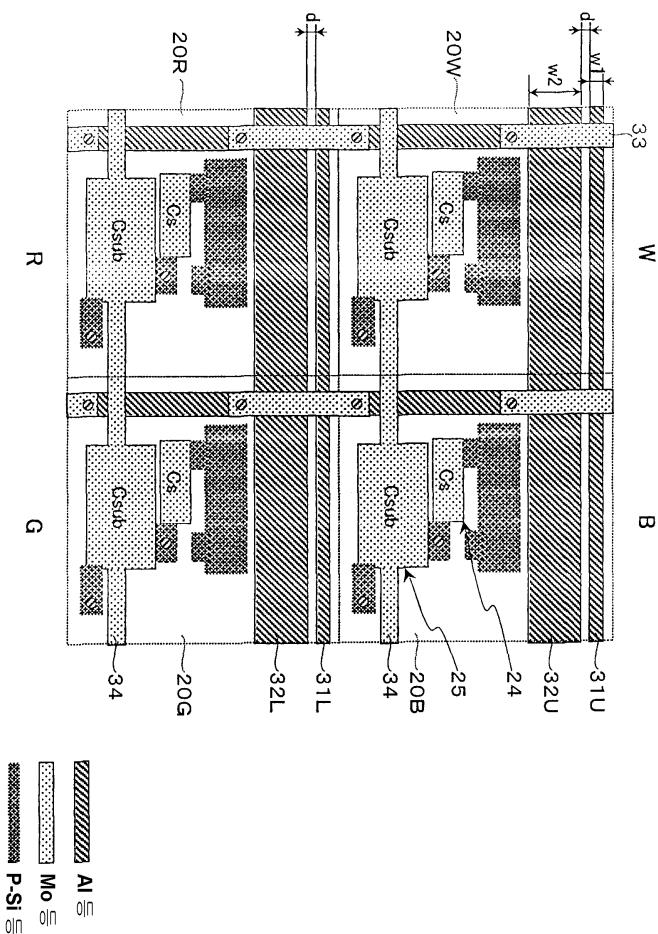

[0126] 우선, 전원 공급선(32)을 1행에 대해서 1개씩 배선했을 경우의 단위화소(20a)의 각 서브 픽셀의 구성 소자와 주사선(31) 및 전원 공급선(32)의 배치 관계에 대해서 참고예로서, 도 11을 사용하여 설명한다.

[0127] 도 11에 도시된 것과 같이 WRGB의 4종의 서브 픽셀(20W, 20R, 20G, 20B) 중에서, 예를 들면 서브 픽셀 20W와 20B가 상부의 행에 속하고, 서브 픽셀 20R와 20G가 하부의 행에 속해 있다. 또한, 서브 픽셀 20W와 20R가 좌측의 열에 속하고, 서브 픽셀 20B와 20G가 우측의 열에 속해 있다.

[0128] 이들 서브 픽셀(20W, 20R, 20G, 20B)은 모두, 상측부분이 배선 영역으로 되어 있고, 중앙부로부터 하측으로 유지용량(Cs)(24)과 보조 용량(Csub)(25)을 포함하는 구성 소자가 형성되어 있다.

[0129] 그리고, 서브 픽셀 20W, 20B의 배선 영역에는, 상측의 행의 주사선(31U)과 전원 공급선(32U)이 소정의 간격 d를 갖고 행 방향(행의 서브 픽셀 배열 방향)을 따라 배선되어 있다. 마찬가지로, 서브 픽셀 20R, 20G의 배선 영역에는, 하측의 행의 주사선(31L)과 전원 공급선(32L)이 소정의 간격 d를 갖고 행방향을 따라 배선되어 있다.

[0130] 여기에서, 전원 공급선 32U, 32L은, 구동 트랜지스터(22)에 구동전류를 공급하고, 또한 유기 EL 소자(21)의 발광/비발광을 제어하기 위한 배선이다. 따라서, 전원 공급선 32U, 32L의 배선 폭 w2은, 기록 주사 신호를 전송하는 주사 신호 31U, 31L의 배선 폭 w1에 비해 넓어져 있다.

[0131] 전술한 바와 같이, 전원 공급선(32)(32U, 32L)을 1행에 대해서 1개씩 배선했는 구성을 채용하는 경우에는, 전술한 것으로부터 알 수 있는 것 같이, 해당 전원 공급선(32)은 화소면적에서 차지하는 비율이 크기 때문에, 화소(서브 픽셀)의 고선명도가 저하해 버린다.

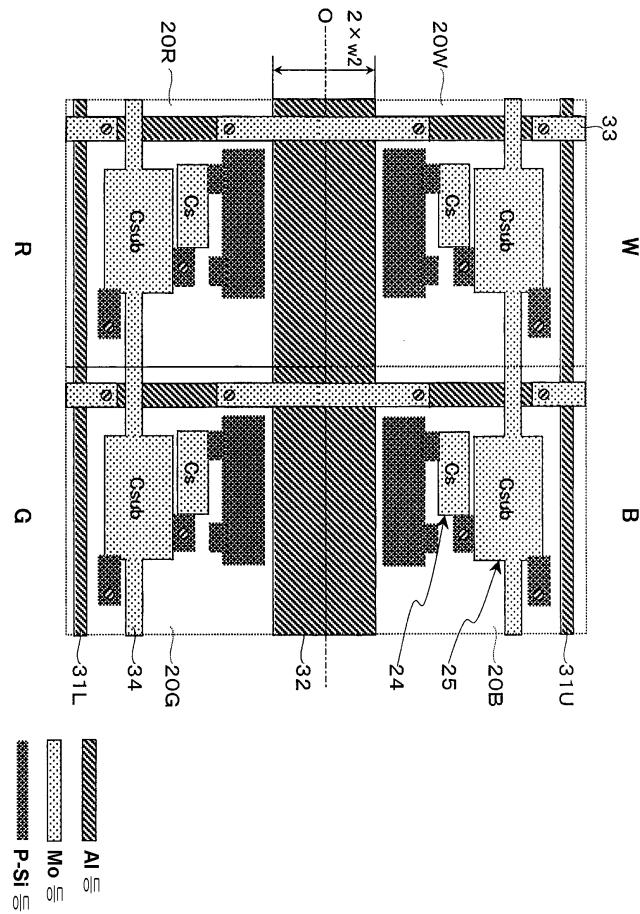

#### <제1예>

[0133] 도 12은, 전원 공급선(32)을 2행에 대해서 1개씩 배선했을 경우의 단위화소(20b)의 각 서브 픽셀의 구성 소자와 주사선(31) 및 전원 공급선(32)의 배치 관계의 제1 예를 나타낸 배치도이다. 도면 중, 도 11과 동등 부분에는 동일한 부호를 붙여 보이고 있다.

[0134] 도 12에 도시된 것과 같이 WRGB의 4종의 서브 픽셀(20W, 20R, 20G, 20B) 중에서, 예를 들면 서브 픽셀 20W와 20B가 상부의 행에 속하고, 서브 픽셀 20R와 20G가 하부의 행에 속해 있다. 또한, 서브 픽셀 20W와 20R가 좌측의 열에 속하고, 서브 픽셀 20B와 20G가 우측의 열에 속해 있다.

[0135] 또한, 도 12에서 명백한 것과 같이, 상부의 행에 속하는 서브 픽셀 20W, 20B와 하부의 행에 속하는 서브 픽셀 20R, 20G는, 유지용량(Cs)(24)과 보조 용량(Csub)(25)을 포함하는 구성 소자의 배치에 대해서, 상부의 행과 하부의 행의 경계선 0에 관해서 상하 대칭한 관계로 되어 있다. 이에 따라 서브 픽셀 20W, 20B의 하단 부분과 서브 픽셀 20R, 20G의 상단 부분의 사이에 넓은 배선 영역을 확보할 수 있다.

[0136] 그리고, 상측의 행의 주사선 31U이 서브 픽셀 20W, 20B의 상단의 배선 영역에 행방향을 따라 배선되고,

하측의 행의 주사선 31L이 서브 팩셀 20R, 20G의 하단의 배선 영역에 행방향을 따라 배선되어 있다. 또한, 상하 2행에 공통인 전원 공급선(32)이 서브 팩셀 20W, 20B의 하단의 배선 영역 및 서브 팩셀 20R, 20G의 상단의 배선 영역에 배선폭 2w2로 행방향을 따라 배선되어 있다.

[0137] 이렇게, 상부의 행에 속하는 서브 팩셀 20W, 20B과 하부의 행에 속하는 서브 팩셀 20R, 20G의 각 구성 소자가 경계선 0에 관해서 상하 대칭한 배치 관계에 있어, 이들 상하의 서브 팩셀의 각 구성 소자 사이의 배선 영역에 전원 공급선(32)을 배선함에 의해, 해당 전원 공급선(32)과 상하의 서브 팩셀의 각 구동 트랜지스터(22)의 드레인 전극 사이의 거리가 가까워지기 때문에, 양자간의 전기적 접속이 간단해진다고 하는 이점이 있다.

[0138] 이렇게, 전원 공급선(32)을 2행에 대해서 1개씩, 다시 말해 동일한 단위화소(20)의 4개의 서브 팩셀(20W, 20R, 20G, 20B)에 대해서 1개씩 배선하는 구성을 채용하는 것에 의해, 도 12에 있어서의 상측의 행의 주사선 31U-전원 공급선 32U 사이의 간격 d 및 하측의 행의 주사선 31L-전원 공급선 32L 사이의 간격 d를 확보할 필요가 없어지기 때문에, 그만큼 화소(서브 팩셀)의 고선명도를 상승시킬 수 있는 동시에, 배치의 자유도를 상승시킬 수 있다.

[0139] 또한, 전원 공급선(32)의 배선폭 2w2이, 전원 공급선(32)을 1행에 대해서 1개씩 배선하는 경우의 배선 폭 w2의 2배가 되는 것에 의해, 단색발광의 경우, 구체적으로는 서브 팩셀(20R, 20G, 20B)이 단독으로 발광하는 경우의 1서브 팩셀당의 배선 저항을 작게 할 수 있기 때문에, 전원공급 주사 회로(50)로부터 면 서브 팩셀과 가까운 서브 팩셀 사이에서의 전파 지연의 차이를 작게 할 수 있다.

#### [0140] <제2예>

[0141] 도13은, 전원 공급선(32)을 2행에 대해서 1개씩 배선했을 경우의 단위화소(20b)의 각 서브 팩셀의 구성 소자와 주사선(31) 및 전원 공급선(32)의 배치 관계의 제2 예를 나타낸 배치도이다. 도면 중, 도 12과 동등 부분에는 동일한 부호를 붙여 나타내고 있다.

[0142] 제1예에서는, 전원 공급선(32)의 배선 폭 2w2을, 전원 공급선(32)을 1행에 대해서 1개씩 배선할 경우의 배선 폭 w2의 2배로 설정한 구성을 채용하고 있는 것에 대해서, 제2예에서는, 도 13에서 알 수 있는 것과 같이 전원 공급선(32)의 배선 폭 w3을 배선 폭 2w2보다도 좁게 설정한 구성을 채용하고 있다.

[0143] 이렇게, 전원 공급선(32)의 배선 폭 w3을 배선 폭 2w2보다도 좁게 설정함에 의해, 단색발광의 경우의 1서브 팩셀당의 배선 저항이 상승하기는 하지만, 서브 팩셀(20W, 20R, 20G, 20B) 각각의 소자의 배치 스페이스를 충분하게 취할 수 있기 때문에, 그 만큼 화소회로의 구성 소자수를 늘리는 것이 가능하게 된다. 또한, 서브 팩셀(20W, 20R, 20G, 20B) 각각의 사이즈의 축소화를 피할 수 있기 때문에, 표시 패널(70)의 고선명화를 피하는 것이 가능하게 된다.

#### [0144] (회로 동작)

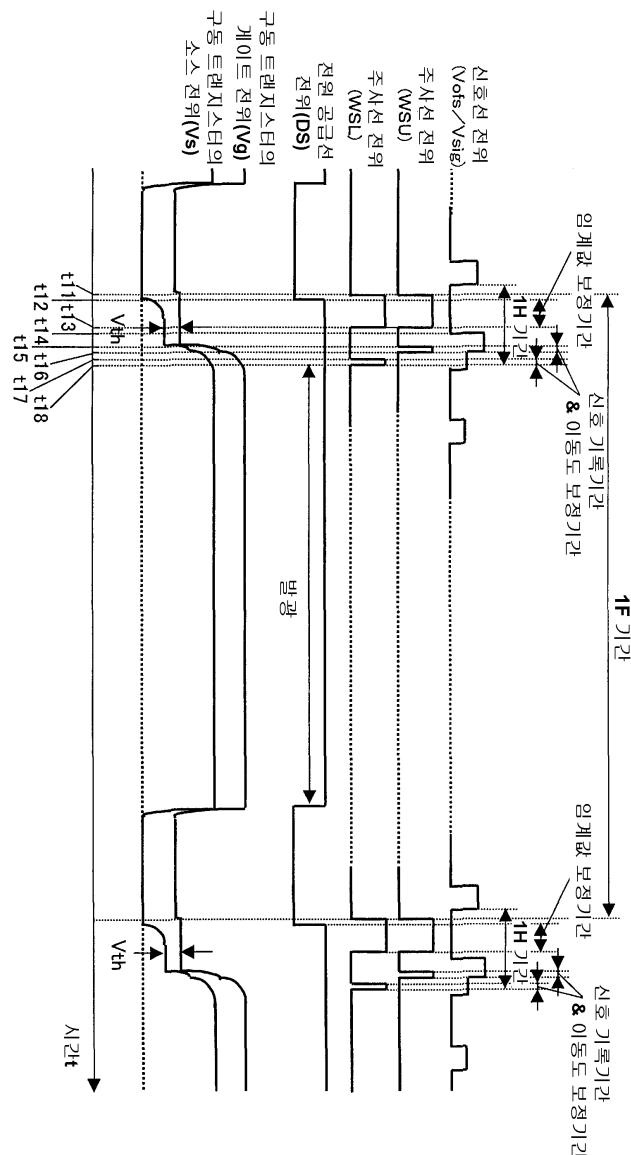

[0145] 이어서, 본 실시예에 따른 유기 EL 표시장치(10B)의 회로 동작에 대해서, 도 14의 타이밍 파형도를 사용하여 설명한다.

[0146] 도 14에는, 1F(F는 필드/프레임 기간)에 있어서의 신호선(33)의 전위(Vofs/Vsig)의 변화, 상하 2행의 주사선(31U, 31L)의 전위(기록 주사 신호) WSU, WSL의 변화, 전원 공급선(32)의 전위 DS의 변화, 구동 트랜지스터(22)의 게이트 전위 Vg 및 소스 전위 Vs의 변화를 나타내고 있다.

[0147] 이때, 4종의 서브 팩셀(20W, 20R, 20G, 20B)에 있어서의 임계값 보정 준비, 임계값 보정, 신호 기록 & 이동도 보정 및 발광의 각 구체적인 동작에 대해서는, 전술한 참고예에 관련되는 유기 EL 표시장치(10A)의 회로 동작의 경우와 기본적으로 동일하다.

[0148] 비발광의 상태에 있어서, 시간 t11에서 상하 2행의 주사선(31U, 31L)의 전위 WSU, WSL이 모두 저전위측으로부터 고전위측으로 천이한다. 시간 t11은, 도 4의 타이밍 파형도에 있어서의 시간 t2에 해당한다. 이때, 신호선(33)의 전위가 오프셋 전압 Vofs의 상태에 있고, 상하 2행의 서브 팩셀(20W, 20R, 20G, 20B)에 있어서, 오프셋 전압 Vofs가 기록 트랜지스터(23)에 의해 구동 트랜지스터(22)의 게이트 전극에 기록된다.

[0149] 다음에, 시간 t12에서 전원 공급선(32)의 전위 DS가 저전위 Vini로부터 고전위 Vccp로 전환함으로써,

상하 2행의 서브 팩셀(20W,20R,20G,20B)에 있어서, 임계값 보정 동작이 개시된다. 시간 t12은, 도 4의 타이밍 파형도에 있어서의 시간 t3에 해당한다. 임계값 보정동작은, 시간 t12로부터 주사선(31U,31L)의 전위 WSU, WSL가 함께 고전위측으로부터 저전위측으로 천이하는 시간 t13까지의 기간(임계값 보정기간)에서 행해진다.

[0150] 다음에, 시간 t14에서 수평구동회로(60)로부터 신호선(33)에 대하여 상부의 행에 관한 영상신호의 신호 전압 Vsig가 공급되고, 이어서, 시간 t15에서 상부의 행의 주사선(31U)의 전위 WSU가 다시 저전위측으로부터 고전위측으로 천이함에 의해, 상부의 행의 서브 팩셀(20W,20B)에 있어서, 기록 트랜지스터(23)에 의해 영상신호의 신호 전압 Vsig이 구동 트랜지스터(22)의 게이트 전극에 기록된다. 시간 t14, t15은, 도 4의 타이밍 파형도에 있어서의 시간 t5, t6에 해당한다.

[0151] 다음에, 시간 t16에서 상부의 행의 주사선(31U)의 전위 WSU가 고전위측에서 저전위측으로 천이하는 동시에, 수평구동회로(60)로부터 신호선(33)에 대하여 하부의 행에 관한 영상신호의 신호 전압 Vsig이 공급되고, 이어서, 시간 t17에서 하부의 행의 주사선(31L)의 전위 WSL이 다시 저전위측으로부터 고전위측으로 천이함에 의해, 하부의 행의 서브 팩셀(20R,20G)에 있어서, 기록 트랜지스터(23)에 의해 영상신호의 신호 전압 Vsig이 구동 트랜지스터(22)의 게이트 전극에 기록된다. 그리고, 시간 t18에서 하부의 행의 주사선(31L)의 전위 WSL이 고전위측으로부터 저전위측으로 천이함으로써 발광 기간에 들어간다.

[0152] 전술한 일련의 동작 설명으로부터 알 수 있는 것 같이, 전원 공급선(32)을 2행에 대해서 1개씩 배선하고, 해당 전원 공급선(32)을 통해 전원공급 주사 회로(50)로부터 주어지고, 유기 EL 소자(21)의 발광 기간을 제어하는 전원전위 DS(Vccp/Vini)을 동일한 단위화소(20b)의 4개의 서브 팩셀(20W,20R,20G,20B)에서 공통화할 경우, 전원전위 DS의 저전위 Vini로부터 고전위 Vccp으로의 천이 타이밍으로 결정되는 임계값 보정기간이 상부의 행의 서브 팩셀(20W,20B)과 하부의 행의 서브 팩셀(20R,20G)과 동일해진다. 임계값 보정동작에 대해서는, 상하 2행 사이에서 동시에 실행되어도 회로 동작상 아무런 문제가 되는 일은 없다.

[0153] 한편, 신호 기록 & 이동도 보정의 동작에 대해서는, 임계값 보정기간을 포함하는 1H 기간 내에 있어서, 상부의 행의 서브 팩셀(20W,20B)과 하부의 행의 서브 팩셀(20R,20G)에서 일정시간(t16-t17), 예를 들면 수  $\mu$  sec의 시간의 차이를 갖고 실행한다. 이들 동작에 의해, 상부의 행의 서브 팩셀(20W,20B)과 하부의 행의 서브 팩셀(20R,20G)에서 발광 기간에 차이가 생기지만, 그 차이는 수  $\mu$  sec의 값이며, 발광 휴드 차이로서는 시인되지 않는 레벨이기 때문에, 아무런 문제가 되는 일은 없다.

[0154] 또한, 상부의 행의 서브 팩셀(20W,20B)과 하부의 행의 서브 팩셀(20R,20G)에서 신호 기록 & 이동도 보정의 동작을 1H 기간내에 시간을 늦추어 행함으로써, 수직주사의 주사 주기로서는, 행수가 m인 경우와 동일한 1H 주기로 되는 것으로 되기 때문에, 전술한 것 같이, 기록 주사 신호를 발생하는 기록 주사 회로(40)을 구성하는 시프트 레지스터의 단수를, 행수 j(j=2m)의 절반 정도에 해당하는 m단으로 할 수 있다.

[0155] 그리고, m단의 시프트 레지스터로부터 출력되는 m개의 기록 주사 신호를 기초로, 시프트 레지스터의 후단의 로직 회로에 있어서, 2배의 j개의 기록 주사 신호를 생성하도록 하면 된다. 더욱 구체적으로는, 로직 회로에 있어서, 예를 들면 시프트 레지스터로부터 출력되는 기록 주사 신호를 상부의 행의 기록 주사 신호로서 사용하는 한편, 해당 상부의 행의 기록 주사 신호를 기초로 상기 일정시간만큼 늦추어진 기록 주사 신호를 생성하고, 해당 기록 주사 신호를 하부의 행의 기록 주사 신호로서 사용하도록 하면 된다.

#### [0156] (본 실시예의 작용 효과)

[0157] 이상에서 설명한 바와 같이, 복수행, 예를 들면 상하 2행에 속하는 서로 인접하는 4개의 서브 팩셀(20W,20R,20G,20B)에 의해 단위화소(20b)을 구성하는 동시에, 유기 EL 소자(21)의 발광 기간/비발광 기간을 제어하는 기능을 구동 트랜지스터(22)에 갖게 하는 화소구성을 채용하는 액티브 매트릭스형 유기 EL 표시장치(10B)에 있어서, 동일한 단위화소(20b)을 구성하는 상하 2행에 속하는 4개의 서브 팩셀(20W,20R,20G,20B)에 대하여, 1개의 전원 공급선(32)(32-1~32-m)을 공통화함으로써, 기록 주사 회로(40)의 시프트 레지스터 및 전원공급 주사 회로(50)로서는 m단의 회로 구성인 상태로 되며, 기록 주사 회로(40)에 대해서는 회로 규모를 삭감할 수 있기 때문에, 표시 패널(70)의 협테두리화를 피할 수 있다.

[0158] 또한, 동일한 단위화소(20b)을 구성하는 상하 2행에 속하는 4개의 서브 팩셀(20W,20R,20G,20B)에 대하여, 1개의 전원 공급선(32)(32-1~32-m)을 공통화함으로써, 서브 팩셀(20W,20R,20G,20B) 각각의 면적을 충분하게 취할 수 있기 때문에, 그 만큼 화소회로의 구성 소자수를 늘리는 것이 가능하게 되고, 또한, 서브 팩셀(20W,20R,20G,20B) 개개의 사이즈의 축소화를 피할 수 있기 때문에, 표시 패널(70)의 고선명화를 피하는 것이

가능하게 된다.

[0159] [변형예]

상기 실시예에서는 서브 퍽셀(20W, 20R, 20G, 20B)의 전기광학소자로서, 유기 EL 소자를 사용한 유기 EL 표시장치에 적용한 경우를 예로 들어 설명했지만, 본 발명은 이 적용예에 한정되는 것은 아니고, 복수의 행에 속하는 복수의 서브 퍽셀로 이루어지는 단위화소가 행렬 모양으로 2차원 배치되어 이루어진 평면형(플랫 패널형)의 표시장치 전반에 대하여 적용가능하다.

[0161] [적용예]

이상 설명한 본 발명에 의한 표시장치는, 일례로서, 도 15~도 19에 나타낸 여러가지 전자기기, 예를 들면 디지털 카메라, 노트북형 퍼스널컴퓨터, 휴대전화 등의 휴대 단말장치, 비디오카메라 등, 전자기기에 입력된 영상신호, 혹은, 전자기기 내에서 생성한 영상신호를, 화상 혹은 영상으로서 표시하는 모든 분야의 전자기기의 표시장치에 적용하는 것이 가능하다.

이렇게, 모든 분야의 전자기기의 표시장치료서 본 발명에 의한 표시장치를 사용함으로써, 전술한 실시예의 설명으로부터 알 수 있는 것과 같이, 본 발명에 의한 표시장치는, 표시 패널(70)의 협테두리화 및 고선명화를 꾀할 수 있기 때문에, 각종의 전자기기에 있어서, 기기 본체의 소형화에 기여할 수 있는 동시에, 고세밀한 화상표시를 실현할 수 있다.

이때, 본 발명에 의한 표시장치는, 봉지된 구성의 모듈 형상의 것도 포함한다. 예를 들면 화소 어레이부(30)에 투명한 유리 등의 대향부에 부착되어 형성된 표시 모듈이 해당한다. 이 투명한 대향부에는, 칼라필터, 보호막 등, 더구나, 상기 한 차광막이 설치되어도 된다. 한편, 표시 모듈에는, 외부로부터 화소 어레이부에의 신호 등을 입출력하기 위한 회로부나 FPC(플렉시블 프린트 서킷) 등이 설치되어 있어도 된다.

이하에서, 본 발명이 적용되는 전자기기의 구체적인 예에 관하여 설명한다.

도 15은, 본 발명이 적용되는 텔레비전 세트의 외관을 나타낸 사시도이다. 본 적용예에 관련되는 텔레비전 세트는, 프런트 패널(102)과 필터 유리(103) 등으로 구성된 영상표시 화면부(101)을 포함하고, 그 영상표시 화면부(101)로서 본 발명에 의한 표시장치를 사용함으로써 작성된다.

도 16은, 본 발명이 적용되는 디지털 카메라의 외관을 나타낸 사시도이며, (a)은 표면측에서 본 사시도, (b)은 이면측에서 본 사시도이다. 본 적용예에 관련되는 디지털 카메라는, 플래쉬용의 발광부(111), 표시부(112), 메뉴 스위치(113), 셔터 버튼(114) 등을 포함하고, 그 표시부(112)로서 본 발명에 의한 표시장치를 사용함으로써 제작된다.

도 17은, 본 발명이 적용되는 노트북형 퍼스널컴퓨터의 외관을 나타낸 사시도이다. 본 적용예에 관련되는 노트북형 퍼스널컴퓨터는, 본체(121)에, 문자 등을 입력할 때 조작되는 키보드(122), 화상을 표시하는 표시부(123) 등을 포함하고, 그 표시부(123)로서 본 발명에 의한 표시장치를 사용함으로써 제작된다.

도 18은, 본 발명이 적용되는 비디오카메라의 외관을 나타낸 사시도이다. 본 적용예에 관련되는 비디오 카메라는, 본체부(131), 전방을 향한 측면에 피사체 촬영용의 렌즈(132), 촬영시의 스타트/스톱 스위치(133), 표시부(134) 등을 포함하고, 그 표시부(134)로서 본 발명에 의한 표시장치를 사용함으로써 제작된다.

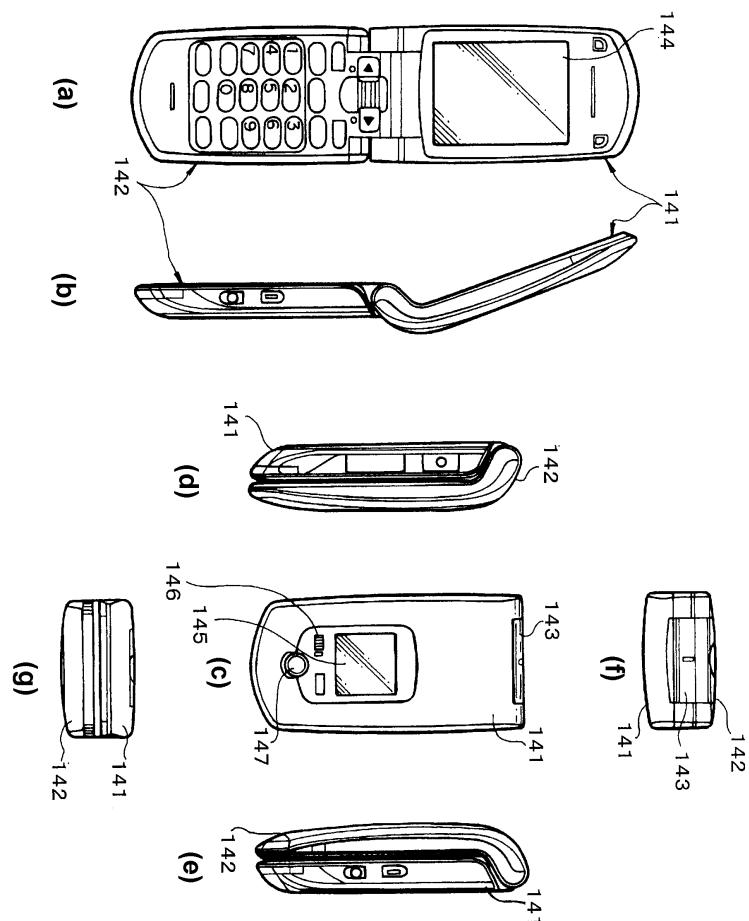

도 19은, 본 발명이 적용되는 휴대 단말장치, 예를 들면 휴대전화기를 나타낸 외관도이며, (a)은 연 상태에서의 정면도, (b)은 그 측면도, (c)은 닫은 상태에서의 정면도, (d)은 좌측면도, (e)은 우측면도, (f)은 평면도, (g)은 하면도이다. 본 적용예에 관련되는 휴대전화기는, 상측케이싱(141), 하측케이싱(142), 연결부(여기에서는 힌지)(143), 디스플레이(144), 서브 디스플레이(145), 퍽처 라이트(146), 카메라(147) 등을 포함하고, 그 디스플레이(144)나 서브 디스플레이(145)로서 본 발명에 의한 표시장치를 사용함으로써 제작된다.

### 도면의 간단한 설명

도 1은 본 발명의 참고예에 관련되는 유기 EL 표시장치의 구성의 개략을 나타낸 시스템 구성도이다.

도 2는 화소(화소회로)의 회로 구성의 일례를 나타낸 회로도이다.

- [0173] 도 3은 화소의 단면구조의 일례를 나타낸 단면도이다.

- [0174] 도 4는 본 발명의 참고예에 관련되는 유기 EL 표시장치의 동작 설명에 제공하는 타이밍 파형도이다.

- [0175] 도 5는 본 발명의 참고예에 관련되는 유기 EL 표시장치의 회로 동작의 설명도(그것의 1)이다.

- [0176] 도 6은 본 발명의 참고예에 관련되는 유기 EL 표시장치의 회로 동작의 설명도(그것의 2)이다.

- [0177] 구동 트랜지스터의 임계전압  $V_{th}$ 의 격차에 기인하는 과제의 설명에 제공하는 특성도이다.

- [0178] 도 8은 구동 트랜지스터의 이동도  $\mu$ 의 격차에 기인하는 과제의 설명에 제공하는 특성도이다.

- [0179] 도 9는 임계값 보정, 이동도 보정의 유무에 의한 영상신호의 신호 전압  $V_{sig}$ 과 구동 트랜지스터의 드레인 · 소스간 전류  $Ids$ 의 관계의 설명에 제공하는 특성도이다.

- [0180] 도 10은 본 발명의 일 실시예에 따른 유기 EL 표시장치의 구성의 개략을 나타낸 시스템 구성도이다.

- [0181] 도 11은 전원 공급선을 1행에 대해서 1개씩 배선했을 경우의 단위화소의 각 서브 픽셀의 구성 소자와 주사선 및 전원 공급선의 배치 관계를 나타낸 배치도이다.

- [0182] 도 12는 전원 공급선을 2행에 대해서 1개씩 배선했을 경우의 단위화소의 각 서브 픽셀의 구성 소자와 주사선 및 전원 공급선의 배치 관계의 제1예를 나타낸 배치도이다.

- [0183] 도 13은 전원 공급선을 2행에 대해서 1개씩 배선했을 경우의 단위화소의 각 서브 픽셀의 구성 소자와 주사선 및 전원 공급선의 배치 관계의 제2 예를 나타낸 배치도이다.

- [0184] 도 14는 본 실시예에 따른 유기 EL 표시장치의 동작 설명에 제공하는 타이밍 파형도이다.

- [0185] 도 15는 본 발명이 적용되는 텔레비전 세트의 외관을 나타낸 사시도이다.

- [0186] 도 16은 본 발명이 적용되는 디지털 카메라의 외관을 나타낸 사시도이며, (a)은 표면측에서 본 사시도, (b)은 이면측에서 본 사시도이다.

- [0187] 도 17은 본 발명이 적용되는 노트북형 퍼스널컴퓨터의 외관을 나타낸 사시도다.

- [0188] 도 18은 본 발명이 적용되는 비디오카메라의 외관을 나타낸 사시도다.

- [0189] 도 19는 본 발명이 적용되는 휴대전화기를 나타낸 외관도이며, (a)은 연 상태에서의 정면도, (b)은 그 측면도, (c)은 닫은 상태에서의 정면도, (d)은 좌측면도, (e)은 우측면도, (f)은 평면도, (g)은 하면도이다.

- [0190] 도 20은 동일 행에 속하는 인접하는 RGB의 삼원색의 서브 픽셀로 구성된 단위화소를 가지는 컬러 표시장치를 나타낸 시스템 구성도이다.

- [0191] 도 21은 상하 2행에 속하는 인접하는 WRGB의 4종의 서브 픽셀로 구성된 단위화소를 가지는 컬러 표시장치를 나타낸 시스템 구성도이다.

- [0192] \* 도면의 주요부분에 대한 부호의 설명 \*

- |                                     |             |

|-------------------------------------|-------------|

| [0193] 10A, 10B…유기 EL 표시장치          | 20…단위화소     |

| [0194] 20W, 20R, 20G, 20B…서브 픽셀     | 21…유기 EL 소자 |

| [0195] 22…구동 트랜지스터                  | 23…기록 트랜지스터 |

| [0196] 24…유지용량                      | 25…보조 용량    |

| [0197] 30…화소 어레이부                   |             |

| [0198] 31(31-1~31-j, 31-1~31-m)…주사선 |             |

| [0199] 32(32-1~32-m)…전원 공급선         |             |

| [0200] 33(33-1~33-k, 33-1~33-n)…신호선 |             |

| [0201] 34…공통 전원 공급선                 | 40…기록 주사 회로 |

| [0202] 50…전원공급 주사 회로                | 60…수평구동회로   |

[0203]

70…표시 패널

## 도면

도면1

도면2

도면3

## 도면4

## 도면5

## 도면6

## 도면7

## 도면8

## 도면9

(a) 임계값 보정 : 없음, 이동도 보정 : 없음

(b) 임계값 보정 : 있음, 이동도 보정 : 없음

(c) 임계값 보정 : 있음, 이동도 보정 : 있음

도면10

도면11

도면12

도면13

도면14

도면15

도면16

도면17

도면18

도면19

도면20

도면21

|                |                                                                                                  |         |            |

|----------------|--------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置和电子设备                                                                                        |         |            |

| 公开(公告)号        | <a href="#">KR101524084B1</a>                                                                    | 公开(公告)日 | 2015-05-29 |

| 申请号            | KR1020080103142                                                                                  | 申请日     | 2008-10-21 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                             |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                             |         |            |

| 当前申请(专利权)人(译)  | 索尼公司                                                                                             |         |            |

| [标]发明人         | YAMASHITA JUNICHI<br>야마시타준이치<br>UCHINO KATSUHIDE<br>우치노카쓰히데                                      |         |            |

| 发明人            | 야마시타준이치<br>우치노카쓰히데                                                                               |         |            |

| IPC分类号         | G09G3/30 G09G3/20 G09G3/32 H01L51/50                                                             |         |            |

| CPC分类号         | G09G2300/0426 G09G2320/043 G09G2300/0842 G09G2300/0819 G09G2300/0866 G09G2300/0452<br>G09G3/3233 |         |            |

| 代理人(译)         | LEE HWA我                                                                                         |         |            |

| 优先权            | 2007274753 2007-10-23 JP                                                                         |         |            |

| 其他公开文献         | KR1020090041331A                                                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                        |         |            |

### 摘要(译)

在采用像素结构的情况下，其中单位像素由属于多次驱动的多个相邻子像素构成，并且驱动晶体管具有控制发光时段/非发光时段的功能，它可以实现窄边框。单位像素20b由在上下两行中彼此相邻的四个子像素20W，20R，20G和20B构成，并且具有控制有机EL元件21的发光时段/非发光时段的功能。在具有其中驱动晶体管具有驱动晶体管32B的像素结构的有源矩阵有机EL显示装置10B中，电源线32(32-1至32-m)对于每行逐个布线，供电线32与属于构成相同单位像素20b的上下两行的四个子像素20W，20R，20G和20B共用。