(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2013년04월12일

(11) 등록번호 10-1253717

(24) 등록일자 2013년04월05일

- (51) 국제특허분류(Int. Cl.)

*G09G 3/30* (2006.01)

(21) 출원번호 10-2010-7016388

(22) 출원일자(국제) 2008년12월11일

심사청구일자 2012년08월13일

(85) 번역문제출일자 2010년07월21일

(65) 공개번호 10-2010-0105732

(43) 공개일자 2010년09월29일

(86) 국제출원번호 PCT/US2008/013573

(87) 국제공개번호 WO 2009/085113

국제공개일자 2009년07월09일

(30) 우선권주장

11/962,182 2007년12월21일 미국(US)

(56) 선행기술조사문헌

JP2003195813 A\*

JP2007017198 A\*

W02005071649 A1

US20060007248 A1

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 11 항

심사관 : 조기덕

(54) 발명의 명칭 구동 트랜지스터를 활성하기 위한 보상된 아날로그 신호를 가지는 전계발광 디스플레이

**(57) 요 약**

EL 디바이스에 전류를 인가하는 구동 회로에서의 구동 트랜지스터의 게이트 전극에 아날로그 구동 트랜지스터 제어 신호를 제공하는 장치가 제공되어 있으며, 구동 회로는 구동 트랜지스터의 제 2 공급 전극에 전기적으로 연결된 EL 디바이스 및 구동 트랜지스터의 제 1 공급 전극에 전기적으로 연결된 전압 공급기를 포함하며, 시간에 걸쳐 구동 트랜지스터 및 EL 디바이스의 동작에 의해 유발된 구동 트랜지스터 및 EL 디바이스의 특성에서의 변화를 나타내는 노화 신호를 제공하기 위해 다른 시간들에서의 제 1 및 제 2 공급 전극을 관통하는 전류를 측정하기 위한 측정 회로; 선형 코드 값을 제공하기 위한 수단; 구동 트랜지스터 및 EL 디바이스의 특성에서의 변화를 보상하기 위해 노화 신호에 응답하여 선형 코드 값을 변경시키기 위한 보상기; 및 구동 트랜지스터의 게이트 전극을 구동하기 위한 변경된 선형 코드 값에 응답하여 아날로그 구동 트랜지스터 제어 신호를 발생하기 위한 선형 소스 드라이버를 포함한다.

**대 표 도** - 도2

(72) 발명자

페럿 게리

미국 뉴욕 14650 로체스터 343 스테이트 스트리트

**프리미라노 브루노**

미국 뉴욕 14650 로체스터 343 스테이트 스트리트

---

## 특허청구의 범위

### 청구항 1

EL 디바이스에 전류를 인가하는 구동 회로에서 구동 트랜지스터의 게이트 전극에 아날로그 구동 트랜지스터 제어 신호를 제공하는 장치로서,

상기 구동 회로는 상기 구동 트랜지스터의 제 1 공급 전극에 전기적으로 연결된 전압 공급기 및 상기 구동 트랜지스터의 제 2 공급 전극에 전기적으로 연결된 EL 디바이스를 포함하며,

a) 시간에 따라 구동 트랜지스터 및 EL 디바이스의 동작에 의해 유발된 구동 트랜지스터 및 EL 디바이스의 특성에서의 변화를 나타내는 개별 노화 신호들을 제공하기 위해 제 1 및 제 2 시간에서 제 1 및 제 2 공급 전극을 통과하는 전류를 측정하기 위한 측정 회로;

b) 명령된 구동 전압 또는 명령된 광 세기를 나타내는 선형 코드 값을 제공하기 위한 수단;

c) 구동 트랜지스터 및 EL 디바이스의 특성에서의 변화를 보상하기 위해 노화 신호에 응답하여 선형 코드 값을 변경시키기 위한 보상기;

d) 구동 트랜지스터의 게이트 전극을 구동하기 위한 변경된 선형 코드 값에 응답하여 아날로그 구동 트랜지스터 제어 신호를 발생하기 위하여, 입력 코드 값 대 아날로그 전압이 선형 관계를 갖는 선형 소스 드라이버; 및

e) 상기 제 1 및 제 2 공급 전극을 통한 전류 흐름에 측정 회로를 선택적으로 전기적으로 연결하기 위한 스위치를 포함하며,

상기 측정 회로는 상기 제 1 시간에서 측정된 전류를 저장하기 위한 메모리를 구비하며,

상기 보상기는 변경된 선형 코드 값을 제공하기 위하여 상기 제 1 및 제 2 시간에서 노화 신호 값으로부터 전류변경을 계산하고, 전류 손실을 역치 전압 이동에 맵핑하며, 맵핑된 역치 전압 이동을 선형 코드 값에 추가하도록 설계되는, 아날로그 구동 트랜지스터 제어 신호의 제공 장치.

### 청구항 2

제 1 항에 있어서,

상기 EL 디바이스는 OLED 디바이스인 아날로그 구동 트랜지스터 제어 신호의 제공 장치.

### 청구항 3

제 1 항에 있어서,

상기 구동 트랜지스터는 비결정 실리콘 트랜지스터인 아날로그 구동 트랜지스터 제어 신호의 제공 장치.

### 청구항 4

삭제

### 청구항 5

제 1 항에 있어서,

상기 측정 회로는 제 1 및 제 2 공급 전극을 통과하는 구동 전류의 함수인 미러된 전류를 발생하기 위한 제 1 전류 미러 및 상기 제 1 전류 미러에서 전압 변화를 감소시키기 위해 제 1 전류 미러에 바이어스 전류를 인가하기 위한 제 2 전류 미러를 포함하는 아날로그 구동 트랜지스터 제어 신호의 제공 장치.

### 청구항 6

제 5 항에 있어서,

상기 측정 회로는 전압 신호를 발생하기 위해 상기 미러된 전류에 응답하는 전류-전압 컨버터 및 상기 보상기에 노화 신호를 제공하기 위해 전압 신호에 응답하는 수단을 더 포함하는 아날로그 구동 트랜지스터 제어 신호의

제공 장치.

### 청구항 7

제 1 항에 있어서,

비선형 입력 신호를 수신하고 상기 비선형 입력 신호를 선형 코드 값으로 전환하기 위한 전환 수단을 더 포함하는 아날로그 구동 트랜지스터 제어 신호의 제공 장치.

### 청구항 8

제 7 항에 있어서,

상기 전환 수단은 투엽 테이블을 포함하는 아날로그 구동 트랜지스터 제어 신호의 제공 장치.

### 청구항 9

제 1 항에 있어서,

상기 보상기는 EL 디바이스의 효율성-보상 수단 및 전압-보상 수단을 포함하는 아날로그 구동 트랜지스터 제어 신호의 제공 장치.

### 청구항 10

제 1 항에 있어서,

상기 보상기는 기준 노화 신호 측정 및 가장 최근 노화 신호 측정을 저장하기 위한 메모리를 더 포함하는 아날로그 구동 트랜지스터 제어 신호의 제공 장치.

### 청구항 11

제 1 항에 있어서,

상기 보상기는 EL 디바이스의 효율성 보상 및 전압 보상 모두를 수행하도록 설계된 아날로그 구동 트랜지스터 제어 신호의 제공 장치.

### 청구항 12

제 11 항에 있어서,

상기 전압 보상은 역치 전압( $V_{th}$ ) 이동 및 순방향 전압( $V_{oled}$ ) 상승 모두에 대한 보상을 포함하는 것을 특징으로 하는 아날로그 구동 트랜지스터 제어 신호의 제공 장치.

### 청구항 13

삭제

### 청구항 14

삭제

### 청구항 15

삭제

### 청구항 16

삭제

### 청구항 17

삭제

### 청구항 18

삭제

청구항 19

삭제

청구항 20

삭제

청구항 21

삭제

청구항 22

삭제

청구항 23

삭제

청구항 24

삭제

## 명세서

### 기술 분야

[0001]

본 발명은 전계발광 디바이스를 통해 전류를 공급하기 위한 구동 트랜지스터에 인가된 아날로그 신호의 제어에 관한 것이다.

### 배경 기술

[0002]

평패널 디스플레이는 정보가 컴퓨팅, 오락 및 통신을 위해 디스플레이 함에 따라 더 관심을 끈다. 유기 발광 다이오드(OLED) 기술과 같은 전계발광(EL) 평패널 디스플레이 기술은 액정 디스플레이(LCD) 및 플라즈마 디스플레이 패널(PDP)와 같은 다른 기술에 대해 색역(color gamut), 휘도 및 전력 소모에서의 이점을 제공한다. 그러나, EL 디스플레이는 시간에 걸쳐 성능 저하를 겪는다. 디스플레이의 수명 상의 높은-품질 이미지를 제공하기 위해, 이 저하는 보상되어야 한다.

[0003]

EL 디스플레이는 전형적으로 동일한 서브픽셀의 어레이를 포함한다. 각각의 서브픽셀은 구동 트랜지스터(전형적으로 박막, TFT) 및 EL 디바이스를 포함하고, 유기 다이오드는 실제로 광을 방출한다. EL 디바이스의 광 출력은 디바이스를 통한 전류와 대략 비례하며, 그래서 구동 트랜지스터는 게이트-소스 전압( $V_{gs}$ )에 응답하여 전압-제어된 전류원으로서 구성된다. LCD 디스플레이에 사용된 것과 유사한 소스 드라이버는 구동 트랜지스터로 제어 전압을 제공한다. 소스 드라이버는 구동 트랜지스터를 제어하기 위해 바람직한 코드 값 단계(74)를 아날로그 전압 단계(75)로 전환한다. 더 높은 비트 깊이를 가지는 선형 소스 드라이버가 이용 가능하게 되더라도, 코드 값과 전압 사이의 관계는 전형적으로 비선형이다. 비선형 코드 값-대-전압 관계가 (예를 들어 US 특허 4,896,947에 도시된) 특정 LCD S-형태보다 OLED에 대한 다른 형태를 가지더라도, 필요한 소스 드라이버 전자제품은 2 가지의 기술 사이에서 매우 유사하다. LCD와 EL 소스 드라이버 사이의 유사성 이외에, LCD 디스플레이 및 EL 디스플레이는 전형적으로 동일한 기판, 즉 다나카(Tanaka) 등에 의한 US 특허 5,034,340에 개시된 바와 같이, 비결정 실리콘(a-Si) 상에서 제조된다. 비결정 Si는 값이 싸며 큰 디스플레이로 처리하기에 쉽다.

[0004]

### 저하 모드

[0005]

그러나, 비결정 실리콘은 준안정성이다: 시간에 걸쳐, 전압 바이어스가 a-Si TFT의 게이트에 인가됨에 따라, 이의 역치 전압( $V_{th}$ )은 이동하고, 따라서 I-V 곡선을 이동시킨다(Kagan & Andry, ed. *Thin-Film Transistors*. New York: Marcel Dekker, 2003. Sec. 3.5, pp. 121-131).  $V_{th}$ 은 전형적으로 순방향 바이어스 하에서 시간에 걸쳐

증가하며, 그래서, 시간에 걸쳐,  $V_{th}$  이동은 평균적으로, 디스플레이가 어두워지도록 할 것이다.

[0006] a-Si TFT 불안정 이외에, 현재 EL 디바이스는 이들의 자신의 불안정성을 가진다. 예를 들어, OLED 디바이스에서, 시간에 걸쳐, 전류가 OLED 디바이스를 관통함에 따라, 이의 순방향 전압( $V_{oled}$ )은 증가하고 이의 효율성(전형적으로는 cd/A로 측정됨)은 감소한다(Shinar, ed. *Organic Light-Emitting Devices: a survey*. New York: Springer-Verlag, 2004. Sec.3.4, pp. 95-97). 일정 전류로 구동되는 경우에 조차, 효율성의 손실은 디스플레이가 시간에 걸쳐 평균하여 어두워지게 한다. 또한, 전형적 OLED 디스플레이 구성에서, OLED는 구동 트랜지스터의 소스에 부착된다. 이 구성에서,  $V_{oled}$ 에서의 증가는 트랜지스터의 소스 전압을 증가하며,  $V_{gs}$ 를 낮추며 따라서 OLED 디바이스를 통한 전류( $I_{oled}$ )를 낮춰, 시간에 걸쳐 어두워지는 것을 유발한다.

[0007] 이들 3 개의 영향( $V_{th}$  이동, OLED 효율성 손실, 및  $V_{oled}$  상승)은 각각의 개별적인 OLED 서브픽셀이 OLED 디바이스를 관통하는 전류에 비례하는 비율로 시간에 걸쳐 휘도를 손실하게 한다. ( $V_{th}$  이동이 주된 영향이고,  $V_{oled}$  이동은 2 차 영향이며, OLED 효율성 손실은 3차 영향이다) 그러므로, 디스플레이가 시간에 걸쳐 어두워짐에 따라, 더 많은 전류로 구동되는 이들 서브픽셀은 더 빠르게 페이딩될 것이다. 이 차등 노화는 디스플레이 상에서 불쾌한 가시적 변인을 유발한다. 차등 노화는 예를 들어, 더 많은 방송사가 고정된 위치에서 이들 콘텐츠 상에 이들의 로고를 연속하여 덧붙임에 따라, 오늘날 더 증가하는 문제점이다. 전형적으로, 로고는 이 주변의 콘텐츠보다 밝아, 로고에서의 픽셀들은, 로고를 포함하지 않은 콘텐츠를 보는 경우 가시적인 로고의 음의 카피(copy)를 형성하는, 주변 콘텐츠보다 더 빠르게 노화한다. 로고가 전형적으로 높은 공간-주파수 콘텐츠(예를 들어, AT&T 글러브)를 포함하기 때문에, 하나의 서브픽셀은 인접한 서브픽셀만이 약하게 노화되는 동안 더 많이 노화될 수 있다. 그러므로, 각각의 서브픽셀은 불쾌한 가시적 변인(burn-in)을 제거하기 위해 노화를 독립하여 보상해야 한다.

## 종래 기술

[0009] 이들 3 개의 영향 중 하나 이상을 보상하는 것이 공지되어 있다.  $V_{th}$  이동, 주된 영향 및 인가된 바이어스와 역 전될 수 있는 것(Mohan 등, "Stability issue in digital circuits in amorphous silicon technology," Electrical and Computer Engineering, 2001, Vol.1, pp. 583-588)을 고려하여, 보상 방식들은 일반적으로 4 개의 그룹, 즉 인-픽셀 보상, 인-픽셀 측정, 인-패널 측정 및 역 바이어스로 나눠진다.

[0010] 인-픽셀  $V_{th}$  보상 방식은 일어나는 경우  $V_{th}$  이동을 보상하기 위해 각각의 서브픽셀에 추가 회로소자를 추가한다. 예를 들어, 이(Lee) 등에 의한, "A New a-Si:H TFT Pixel Design Compensating Threshold Voltage Degradation of TFT and OLED", SID 2004 Digest, pp. 264-274는 바람직한 데이터 전압을 인가하기 전에 서브픽셀의 저장 커퍼시터 상에 각각이 서브픽셀의  $V_{th}$ 를 저장함으로써  $V_{th}$  이동을 보상하는 7-트랜지스터, 1-커퍼시터(7T1C) 서브픽셀 회로를 개시하고 있다. 이와 같은 방법은  $V_{th}$  이동을 보상하지만, 그러나 이들은  $V_{oled}$  이동 또는 OLED 효율성 손실을 보상할 수 없다. 이들 방법은 통상적인 2T1C 전압-구동 서브픽셀 회로와 비교하여 증가된 서브픽셀 복잡성 및 증가된 서브픽셀 전자제품 크기를 요구한다. 요구된 더 미세한 피처가 제조 오류에서 더 취약하기 때문에, 증가된 서브픽셀 복잡성은 산출량을 감소시킨다. 구체적으로 전형적 하부-발광 구성에서, 서브픽셀 전자제품의 증가된 전체 크기는 개구율(aperture ratio), 광을 방출하는 각각의 서브픽셀의 백분율을 감소시키기 때문에, 전력 소모를 증가시킨다. OLED 광 방출은 고정 전류로 영역에 비례하여, 더 작은 개구율을 가지는 OLED 디바이스는 더 큰 개구율을 가지는 OLED로 동일한 휘도를 발생하기 위해 더 많은 전류를 필요로 한다. 또한, 더 작은 영역에서의 더 높은 전류는 OLED 디바이스에서의 전류 밀도를 증가시키며, 이는  $V_{oled}$  이동 또는 OLED 효율성 손실을 가속화한다.

[0011] 인-픽셀 측정  $V_{th}$  보상 방식은  $V_{th}$  이동을 나타내는 값들이 측정되도록 각각이 서브픽셀에 추가 회로소자를 추가한다. 오프-패널 회로소자는 이후 측정을 처리하며  $V_{th}$  이동을 보상하기 위해 각각의 서브픽셀의 구동을 조절한다. 예를 들어, 나탄(Nathan) 등에 의한, US 2006/0273997(A1)은 TFT 저하 데이터가 주어진 전압 조건 하의 전류 또는 주어진 전류 조건 하의 전압으로서 측정되도록 하는 4-트랜지스터 픽셀 회로를 개시하고 있다. 나라(Nara) 등에 의한, US 특허 7,199,602는 디스플레이에 검사 상호연결을 추가하는 것, 및 검사 상호연결에 연결하기 위해 디스플레이의 각각의 픽셀에 스위칭 트랜지스터를 추가하는 것을 개시하고 있다. 키무라(Kimura) 등에 의한 US 특허 6,518,962는 EL 저하를 보상하기 위해 디스플레이의 각각의 픽셀에 정정 TFT를 추가하는 것을 개

시하고 있다. 이를 방법은 인-픽셀  $V_{th}$  보상 방식의 단점을 공유하지만, 그러나 몇 가지의 방법은 추가로  $V_{oled}$  이동 또는 OLED 효율성 손실을 보상할 수 있다.

[0012] 역-바이어스  $V_{th}$  보상 방식은 몇 가지의 시작 포인트로 다시  $V_{th}$ 를 이동하기 위해 역 전압 바이어스의 소정의 형태를 사용한다. 이를 방법은  $V_{oled}$  이동 또는 OLED 효율성 손실을 보상할 수 없다. 예를 들어, 로(Lo) 등에 의한, US 특허 7,116,058은 각각의 프레임 사이의 역-바이어스 구동 트랜지스터로 액티브-매트릭스 픽셀 회로에서의 저장 커패시터의 기준 전압을 변조하는 것을 개시하고 있다. 프레임들 사이 또는 프레임들 내에 역-바이어스를 인가하는 것은 가시적 아티팩트를 방지하지만, 그러나 듀티 사이클(duty cycle)을 감소시키고 따라서 피트 밝기를 감소시킨다. 역-바이어스 방법들은 인-픽셀 보상 방법보다 전력 소모에서 덜 증가로 패널의 평균  $V_{th}$  이동을 보상할 수 있지만, 그러나 이들은 더 복잡한 외부 전원을 필요로 하고, 추가 픽셀 회로소자 또는 신호 라인을 요구할 수 있으며, 다른 것들보다 더 많이 페이딩되는 개별 서브픽셀을 보상할 수 없다.

[0013]  $V_{oled}$  이동 또는 OLED 효율성 손실을 고려하여, 아놀드(Arnold) 등에 의한, US 특허 6,995,519는 OLED 디바이스의 노화를 보상하는 방법의 일 예이다. 이 방법은 디바이스 회로에서의 전체 변경이 OLED 에미터에서의 변경에 의해 유발된다고 가정한다. 그러나, 회로에서의 구동 트랜지스터가 a-Si로부터 형성되는 경우, 트랜지스터의 역 치 전압이 사용함에 따라 변하므로, 이 가정은 유효하지 않다. 아놀드의 방법은 따라서 트랜지스터가 노화 영향을 나타내는 회로에서 서브픽셀 노화의 완전한 보상을 제공하지 않는다. 추가로, 역 바이어스와 같은 방법이 a-Si 트랜지스터 역 치 전압 이동을 완화시키기 위해 사용되는 경우, OLED 효율성 손실의 보상은 적절한 역 바이어스 영향의 추적/예상, 또는 OLED 전압 변화 또는 트랜지스터 역 치 전압 변화의 직접적 측정 없이 신뢰성이 없게 될 수 있다.

[0014] 보상을 위한 대안의 방법은 영(Young) 등에 의한, 미국 특허 6,489,631에 나타난 바와 같이, 직접적으로 각각의 서브픽셀의 광 출력력을 측정한다. 이와 같은 방법은 모든 3 개의 노화 요인들에서의 변화를 보상할 수 있지만, 그러나 각각의 서브픽셀에서의 통합 광 센서 또는 매우 높은-정밀한 외부 광 센서를 필요로 한다. 외부 광 센서는 디바이스의 복잡성 및 비용을 추가하는 반면, 통합된 광 센서는 수반되는 성능 감소를 가지는, 서브픽셀 복잡성 및 전자제품 크기를 증가시킨다.

[0015] 현존하는  $V_{th}$  보상 방식은 결함이 없지 않으며, 이들 중 소수의 방식이  $V_{oled}$  상승 또는 OLED 효율성 손실을 보상한다.  $V_{th}$  이동에 대한 각각의 서브픽셀을 보상하는 방식은 낮은 산출량 및 패널 복잡성의 비용에서 이와 같다. 그러므로, EL 디스플레이 패널의 전체 수명에 걸쳐 불쾌한 가시적 번인(burn-in)을 방지하고 EL 패널 저하를 보상하기 위해 이들의 단점을 극복하는 것이 보상을 개선하는데 대한 요구가 계속되었다.

## 발명의 내용

### 해결하려는 과제

[0016] 본 발명의 내용에 포함되어 있음.

### 과제의 해결 수단

[0017] 본 발명에 따르면, EL 디바이스에 전류를 인가하는 구동 회로에서의 구동 트랜지스터의 게이트 전극에 아날로그 구동 트랜지스터 제어 신호를 제공하는 장치가 제공되어 있으며, 구동 회로는 구동 트랜지스터의 제 1 공급 전극에 전기적으로 연결된 전압 공급기 및 구동 트랜지스터의 제 2 공급 전극에 전기적으로 연결된 EL 디바이스를 포함하고:

[0018] a) 시간에 걸쳐 구동 트랜지스터 및 EL 디바이스의 동작에 의해 유발된 구동 트랜지스터 및 EL 디바이스의 특성에서의 변화를 나타내는 노화 신호를 제공하기 위해 다른 시간들에서의 제 1 및 제 2 공급 전극을 관통하는 전류를 측정하기 위한 측정 회로;

[0019] b) 선형 코드 값을 제공하기 위한 수단;

[0020] c) 구동 트랜지스터 및 EL 디바이스의 특성에서의 변화를 보상하기 위해 노화 신호에 응답하여 선형 코드 값을 변경시키기 위한 보상기; 및

[0021] d) 구동 트랜지스터의 게이트 전극을 구동하기 위한 변경된 선형 코드 값에 응답하여 아날로그 구동 트랜지스터

제어 신호를 발생하기 위한 선형 소스 드라이버를 포함한다.

[0022] 또한 EL 디바이스에 전류를 인가하는 구동 회로에서의 구동 트랜지스터의 게이트 전극에 아날로그 구동 트랜지스터 제어 신호를 제공하는 방법이 제공되어 있으며, 구동 회로는 구동 트랜지스터의 제 1 공급 전극에 전기적으로 연결된 전압 공급기 및 구동 트랜지스터의 제 2 공급 전극에 전기적으로 연결된 EL 디바이스를 포함하고:

[0023] a) 시간에 걸쳐 구동 트랜지스터 및 EL 디바이스의 동작에 의해 유발된 구동 트랜지스터 및 EL 디바이스의 특성에서의 변화를 나타내는 노화 신호를 제공하기 위해 다른 시간들에서의 제 1 및 제 2 공급 전극을 관통하는 전류를 측정하는 단계;

[0024] b) 선형 코드 값을 제공하는 단계;

[0025] c) 구동 트랜지스터 및 EL 디바이스의 특성에서의 변화를 보상하기 위해 노화 신호에 응답하여 선형 코드 값을 변경시키는 단계; 및

[0026] d) 구동 트랜지스터의 게이트 전극을 구동하기 위한 변경된 선형 코드 값에 응답하여 아날로그 구동 트랜지스터 제어 신호를 발생하기 위한 선형 소스 드라이버를 제공하는 단계를 포함한다.

[0027] 또한 EL 패널에서의 복수의 EL 서브픽셀에서의 구동 트랜지스터의 게이트 전극에 아날로그 구동 트랜지스터 제어 신호를 제공하는 장치가 제공되어 있으며, 제 1 전압 공급기, 제 2 전압 공급기 및 EL 패널에서의 복수의 EL 서브픽셀; 각각의 EL 서브픽셀에서의 EL 다비아이스로의 전류를 인가하기 위한 구동 회로에서의 EL 디바이스; EL 디바이스의 제 1 전극에 전기적으로 연결되어 있는 제 2 공급 전극 및 제 1 전압 공급기에 전기적으로 연결되어 있는 제 1 공급 전극을 가지는 구동 트랜지스터를 포함하는 각각의 구동 회로; 및 제 2 전압 공급기에 전기적으로 연결되어 있는 제 2 전극을 포함하는 각각의 EL 디바이스를 포함하며,

[0028] a) 시간에 걸쳐 구동 트랜지스터 및 EL 디바이스의 동작에 의해 유발된 구동 트랜지스터 및 EL 디바이스의 특성에서의 변화를 나타내는 노화 신호를 제공하기 위해 다른 시간들에서의 제 1 및 제 2 전압 공급기를 관통하는 전류를 측정하기 위한 측정 회로;

[0029] b) 선형 코드 값을 제공하기 위한 수단;

[0030] c) 구동 트랜지스터 및 EL 디바이스의 특성에서의 변화를 보상하기 위해 노화 신호에 응답하여 선형 코드 값을 변경시키기 위한 보상기; 및

[0031] d) 구동 트랜지스터의 게이트 전극을 구동하기 위한 변경된 선형 코드 값에 응답하여 아날로그 구동 트랜지스터 제어 신호를 발생하기 위한 선형 소스 드라이버를 포함한다.

### 발명의 효과

[0032] 본 발명은 아날로그 구동 트랜지스터 제어 신호를 제공하는 효율적 방법을 제공한다. 보상을 수행하기 위해 하나의 측정만을 요구한다. 임의 액티브-매트릭스 백플레인(backplane)에 적용될 수 있다. 제어 신호의 보상은 비선형에서 선형으로 신호를 변경시키기 위해 룩-업 테이블을 사용함으로써 간소화되며, 그래서 보상은 선형 전압 도메인(domain)에 있을 수 있다. 외부 측정 디바이스 또는 복잡한 픽셀 회로소자를 요구하지 않고  $V_{th}$  이동(shift),  $V_{oled}$  이동, 및 OLED 효율성 손실을 보상한다. 서브픽셀의 개구율을 감소시키기 않는다. 패널의 정상 동작 상에 어떠한 영향도 미치지 않는다.

### 도면의 간단한 설명

[0033] 본 발명의 전술한 그리고 다른 목적, 특징 및 이점은 가능하다면, 도면에 공통되는 동일한 특징으로 가리키기 위해, 동일한 참조 번호가 사용되는 다음의 도면 및 설명으로 더 명백하게 될 것이다.

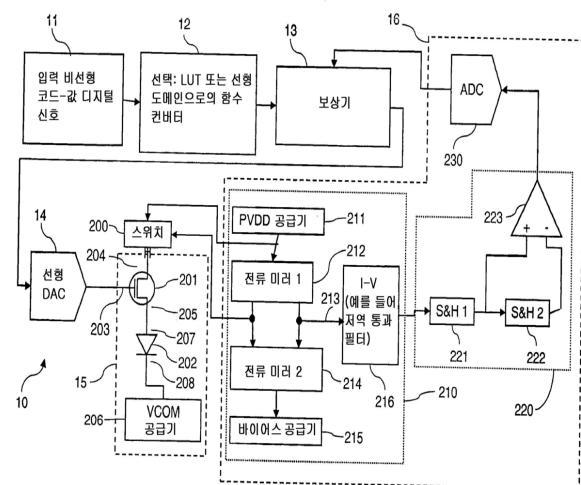

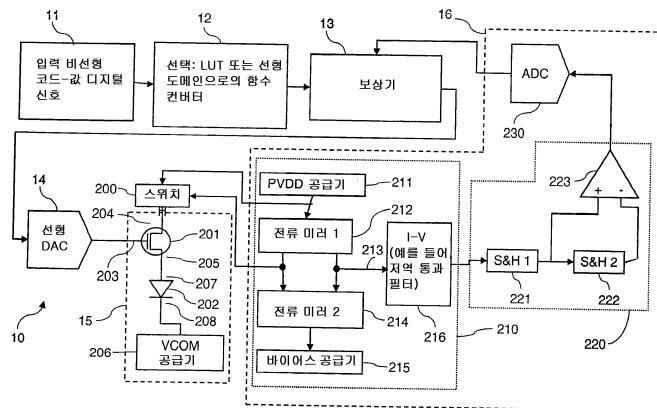

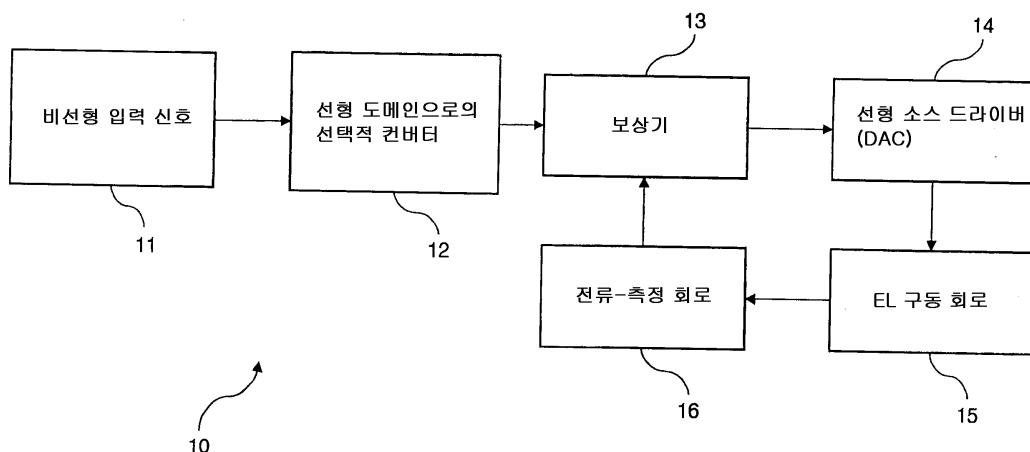

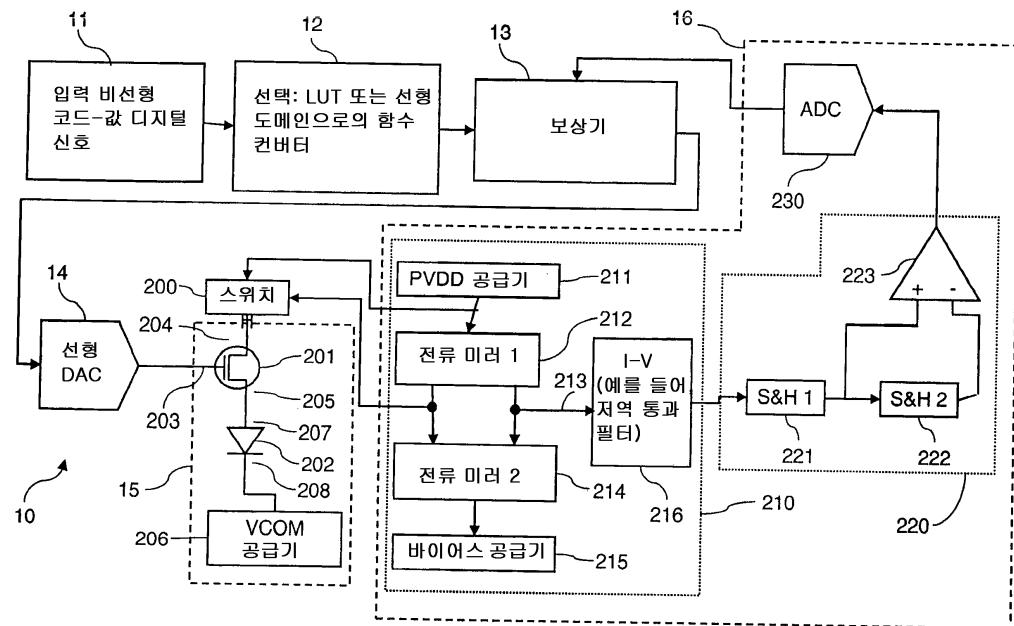

도 1은 본 발명을 실행하기 위한 제어 시스템의 블록도이다;

도 2는 개략적인 더 상세한 버전의 도 1의 블록도이다;

도 3은 전형적인 OLED 패널의 다이어그램이다;

도 4a는 이상적 조건하에서 도 2의 측정 회로를 동작하기 위한 타이밍도이다;

도 4b는 서브픽셀의 자기-가열에 기인한 오류를 포함하는 도 2의 측정 회로를 동작하기 위한 타이밍도이다;

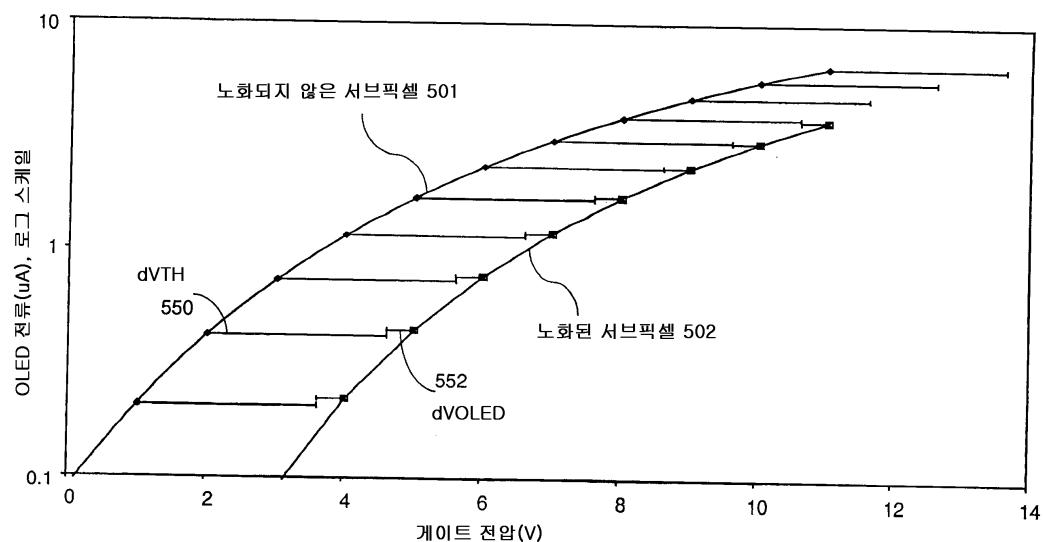

도 5a는  $V_{th}$  이동을 나타내는, 노화되지 않은 서브픽셀 및 노화된 서브픽셀의 대표적 I-V 특성 곡선이다;

도 5b는  $V_{th}$  및  $V_{oled}$  이동을 나타내는, 노화되지 않은 서브픽셀 및 노화된 서브픽셀의 대표적 I-V 특성 곡선이다;

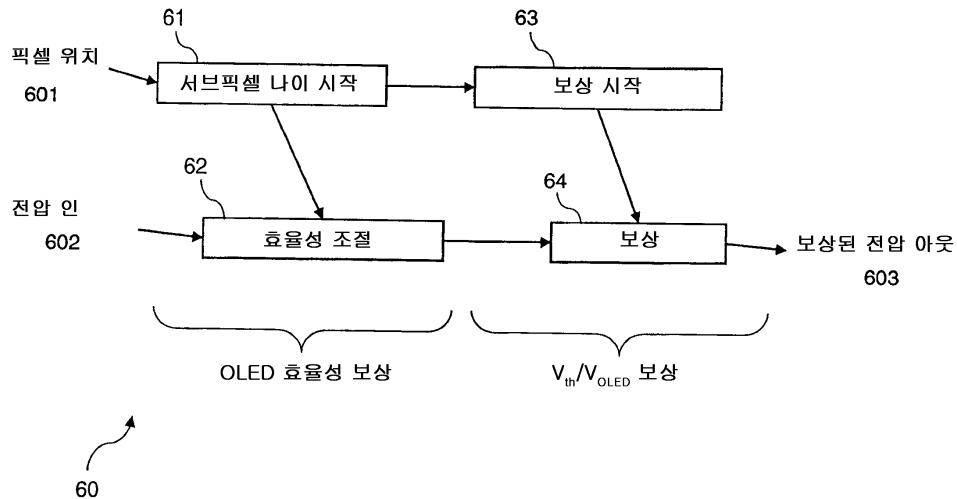

도 6a는 도 1의 보상기의 높은 레벨의 데이터흐름도이다;

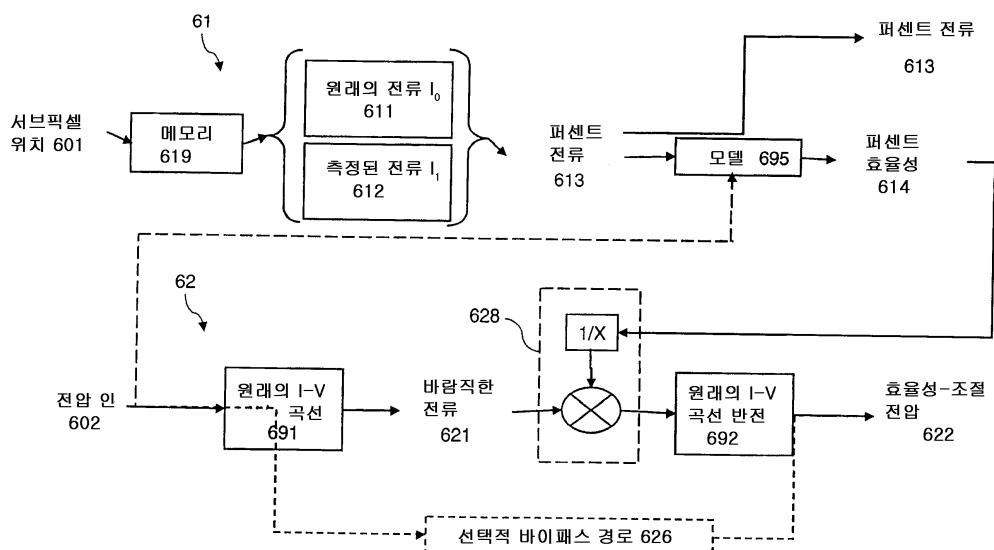

도 6b는 보상기의 상세한 데이터흐름도의 (2 개 중) 제 1 부분이다;

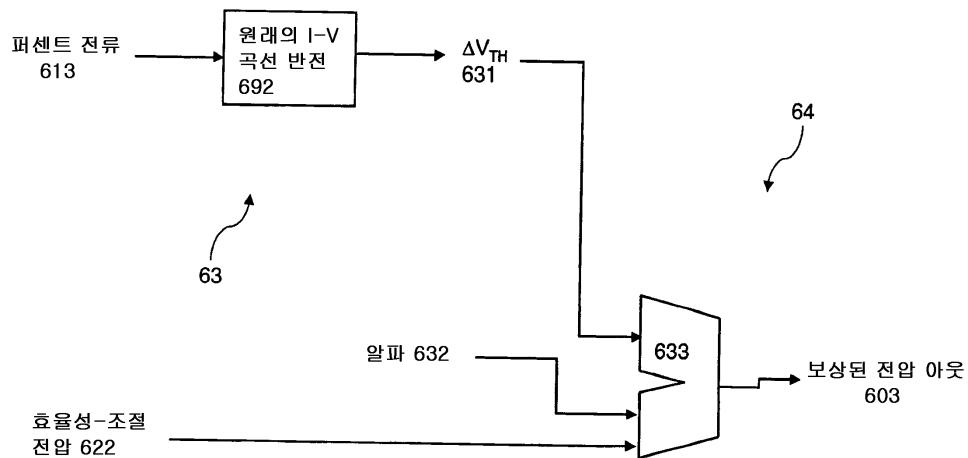

도 6c는 보상기의 상세한 데이터흐름도의 (2 개 중) 제 2 부분이다;

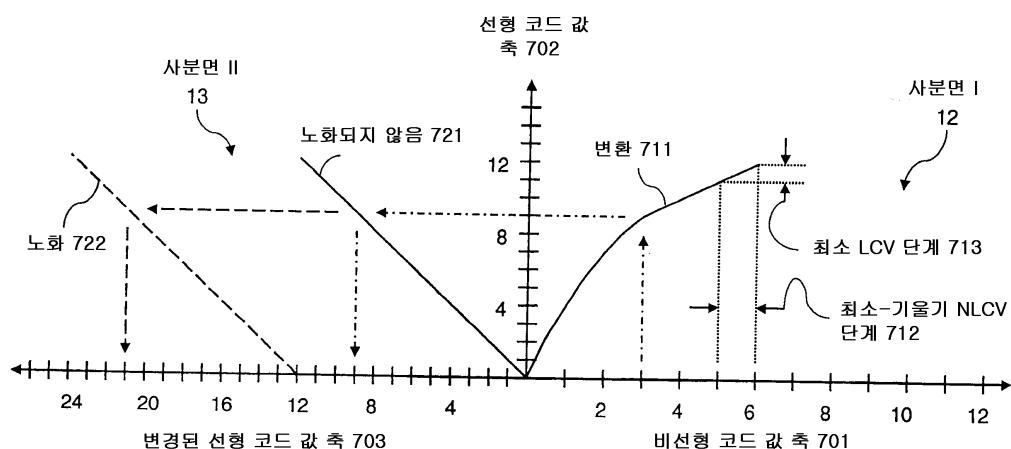

도 7은 보상기 및 도메인-전환 유닛의 효과의 존스-다이어그램이다;

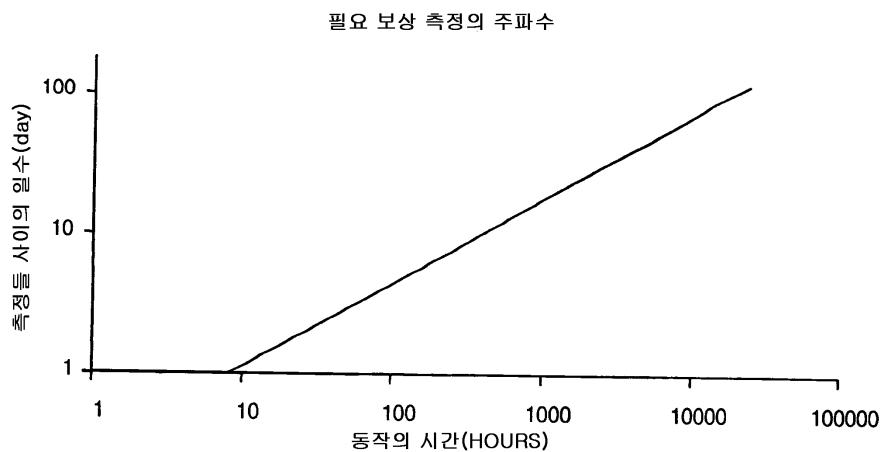

도 8은 시간에 걸쳐 보상 측정의 주파수를 나타내는 대표적 플롯이다;

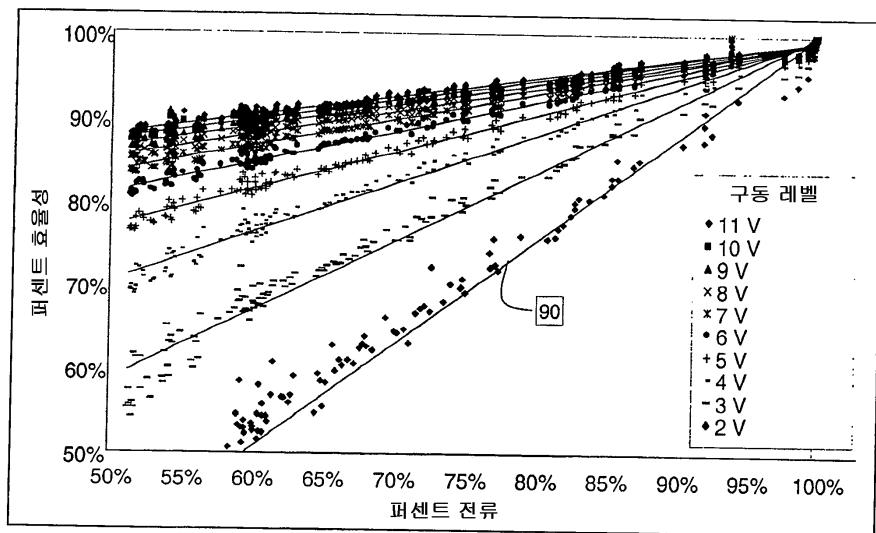

도 9는 퍼센트 전류의 함수로서 퍼센트 효율성을 나타내는 대표적 플롯이다; 그리고

도 10은 본 발명에 따른 상세한 구동 회로이다.

### 발명을 실시하기 위한 구체적인 내용

[0034]

본 발명은 액티브-매트릭스 EL 디스플레이 패널 상의 EL 디바이스 및 구동 트랜지스터에서의 저하를 보상한다. 일 실시예에서, 액티브-매트릭스 OLED 패널 위의 모든 서브픽셀의  $V_{th}$  이동,  $V_{oled}$  이동, 및 OLED 효율성 손실을 보상한다. 패널은 하나 이상의 서브픽셀을 각각 포함하는, 복수의 픽셀들을 포함한다. 예를 들어, 각각의 픽셀은 적색, 녹색 및 청색 서브픽셀을 포함할 수 있다. 각각의 서브픽셀은 둘러싼 전자제품 및 광을 방출하는 EL 디바이스를 포함한다. 서브픽셀은 패널의 최소의 어드레스가능한 소자이다. EL 디바이스는 OLED 디바이스일 수 있다.

[0035]

이하 설명은 전체로서 시스템을 먼저 고려한다. 서브픽셀의 전기적 세부사항에 이어서, 하나의 서브픽셀을 측정하기 위한 전기적 세부사항 및 다수의 서브픽셀을 측정하기 위한 타이밍으로 진행된다. 다음으로 보상기가 어떻게 측정을 사용하는지를 포함한다. 마지막으로, 공장에서 수명종료시까지, 일 실시예에서, 예를 들어 소비자 제품에서, 이 시스템이 어떻게 이행되는지를 설명한다.

[0036]

### 개요

[0037]

도 1은 본 발명의 전체 시스템(10)의 블록도를 나타낸다. 비선형 입력 신호(11)는 EL 서브픽셀에서 EL 디바이스로부터 특정 광의 세기를 명령하며(command), 이는 EL 패널 상의 많은 서브픽셀 중 하나 일 수 있다. 이 신호(11)는 비디오 디코더, 이미지 처리 경로, 또는 또 다른 신호원로부터 오며, 디지털 또는 아날로그일 수 있고, 비선형적으로, 또는 선형적으로 코딩될 수 있다. 예를 들어, 비선형 입력 신호는 sRGB 코드 값 단계 74 또는 NTSC 루마(luma) 전압 단계 75일 수 있다. 소스 및 포맷이 무엇이든지 간에, 신호는 컨버터(12)에 의해, 선형 전압과 같이, 디지털 형태 및 선형 도메인으로 우선하여 전환될 수 있고, 이는 이하, "크로스-도메인 처리, 및 비트 깊이(bit depth)"에서 더 설명될 것이다. 룩-업 테이블 또는 LCD 소스 드라이버와 유사한 기능은 이 전환을 수행할 수 있다. 전환의 결과는 선형 코드 값일 것이며, 이는 명령된 구동 전압을 나타낼 수 있다.

[0038]

보상기(13)는 EL 서브픽셀로부터 명령된 특정 광 세기에 대응할 수 있는 선형 코드 값을 포함한다. 시간에 걸쳐 EL 서브픽셀에서의 EL 디바이스 및 구동 트랜지스터의 동작에 의해 야기된 EL 디바이스 및 구동 트랜지스터에서의 변화는, EL 서브픽셀이 일반적으로 선형 코드 값에 응답하여 명령된 광 세기를 생산하지 않을 것을 의미한다. 보상기(13)는 EL 서브픽셀이 명령된 세기를 발생하도록 하는 변경된 선형 코드 값을 출력한다. 보상기의 동작은 이하 "이행"에서 더 상세히 설명될 것이다.

[0039]

보상기(13)로부터의 변경된 선형 코드 값은 디지털-아날로그 컨버터일 수 있는 선형 소스 드라이버(14)로 보내진다. 선형 소스 드라이버(14)는 아날로그 구동 트랜지스터 제어 신호를 발생하며, 이는 변경된 선형 코드 값에 응답하는, 전압일 수 있다. 선형 소스 드라이버(14)는 선형으로 설계된 소스 드라이버, 또는 대략 선형의 출력을 발생하기 위해 감마 전압 세트를 가지는 통상적인 LCD 또는 OLED 소스 드라이버일 수 있다. 후자의 경우에, 선형성에서의 임의 편차는 결과들의 품질에 영향을 미칠 것이다. 선형 소스 드라이버(14)는 또한 예를 들어, 가와베(Kawabe)에 의한 WO 2005/116971 A1에 개시된 바와 같이, 시-분할 (디지털-구동) 소스 드라이버일 수 있다. 이 경우에, 소스 드라이버로부터의 아날로그 전압은 보상기로부터의 출력 신호에 좌우하는 시간의 양에 대한 광 출력을 명령하는 기결정된 레벨에서 설정된다. 그에 반하여, 통상적 선형 소스 드라이버는 (일반적으로 전체 프

레임) 고정된 시간의 양 동안 보상기로부터의 출력 신호에 좌우되는 레벨에서 아날로그 전압을 제공한다. 선형 소스 드라이버는 하나 이상의 아날로그 구동 트랜지스터 제어 신호를 동시에 출력할 수 있다. 본 발명의 일 실시예에서, EL 패널은 하나 이상의 마이크로칩을 포함하는 선형의 소스 드라이버를 가질 수 있고 각각의 마이크로칩은 하나 이상의 아날로그 구동 트랜지스터 제어 신호를 출력할 수 있어, EL 패널에서의 EL 서브픽셀의 열(column)의 개수와 동일한 많은 아날로그 구동 트랜지스터 제어 신호를 동시에 발생한다.

[0040] 선형 소스 드라이버(14)에 의해 발생된 아날로그 구동 트랜지스터 제어 신호는 EL 서브픽셀일 수 있는, EL 구동 회로(15)에 제공된다. 이 회로는 이하, "디스플레이 소자 설명"에 설명되어 있는 바와 같이, EL 디바이스 및 구동 트랜지스터를 포함한다. 아날로그 전압이 구동 트랜지스터의 게이트 전극에 제공되는 경우, 전류는 EL 디바이스가 광을 방출하게 하며, 구동 트랜지스터 및 EL 디바이스를 통해 흐른다. 일반적으로 출력 디바이스의 회도와 EL 디바이스를 통한 전류 사이의 선형 관계, 및 EL 디바이스를 통한 전류와 구동 트랜지스터에 인가된 전압 사이의 비선형 관계가 존재한다. 따라서 한 프레임 동안 EL 디바이스에 의해 방출된 광의 전체 양은 선형 소스 드라이버(14)로부터 전압의 비선형 함수일 수 있다.

[0041] EL 구동 회로를 통해 흐르는 전류는 이하, "데이터 수집"에서 더 설명된 바와 같이, 전류-측정 회로(16)에 의해 특정 구동 조건들 하에서 측정된다. EL 서브픽셀에 대해 측정된 전류는 보상기에 명령된 구동 신호를 조절하는데 필요한 정보를 제공한다. 이는 이하 "알고리즘"에서 더 설명될 것이다.

[0042] 이 시스템은 이하, "동작의 순서"에서 더 설명되어 있는 바와 같이, EL 패널의 동작 수명 상의 EL 패널에서의 EL 디바이스 및 구동 트랜지스터에서의 변화를 보상할 수 있다.

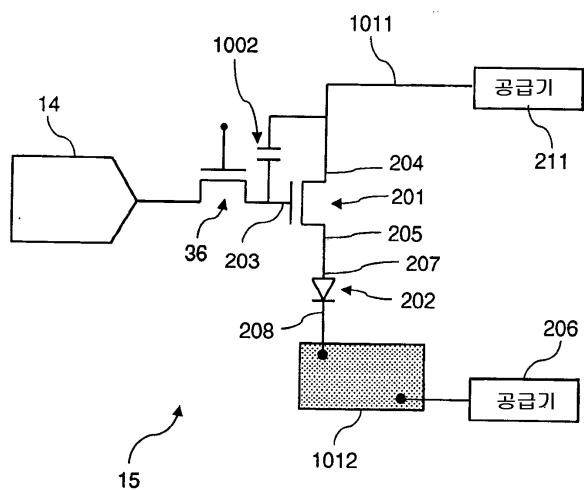

#### 디스플레이 소자 설명

[0044] 도 10은 OLED 디바이스와 같은, EL 디바이스로 전류를 인가하는 구동 회로(15)를 도시하고 있다. 구동 회로(15)는 비결정 실리콘 트랜지스터일 수 있는 구동 트랜지스터(201), EL 디바이스(202), 양일 수 있는 제 1 전압 공급기(211)("PVDD"), 및 음일 수 있는 제 2 전압 공급기(206)("Vcom")를 포함한다. EL 디바이스(202)는 제 1 전극(207) 및 제 2 전극(208)을 가진다. 구동 트랜지스터는 게이트 전극(203), 구동 트랜지스터의 드레인일 수 있는 제 1 공급 전극(204), 및 구동 트랜지스터의 소스일 수 있는 제 2 공급 전극(205)을 가진다. 아날로그 구동 트랜지스터 제어 신호는 선택 트랜지스터(36)를 통해 선택적으로, 게이트 전극(203)에 제공될 수 있다. 아날로그 구동 트랜지스터 제어 신호는 저장 커패시터(1002)에 저장될 수 있다. 제 1 공급 전극(204)은 제 1 전압 공급기(211)에 전기적으로 연결되어 있다. 제 2 공급 전극은 EL 디바이스(202)의 제 1 전극(207)에 전기적으로 연결되어 있다. EL 디바이스의 제 2 전극(208)은 제 2 전압 공급기(206)에 전기적으로 연결되어 있다. 옵션으로 선택 트랜지스터(36) 및 저장 커패시터(1002)와 함께, 구동 트랜지스터(201) 및 EL 디바이스(202)는 전형적으로 EL 패널 상에 존재하는 구동 회로의 일부, EL 서브픽셀을 구성한다. 전원은 전형적으로 EL 패널을 벗어나 위치하고 있다. 전기적 연결은 스위치, 버스 라인, 도전성 트랜지스터, 또는 전류용 경로를 제공할 수 있는 다른 디바이스 또는 구조를 통해 형성될 수 있다.

[0045] 본 발명의 일 실시예에서, 제 1 공급 전극(204)은 PVDD 버스 라인(1011)을 통해 제 1 전압 공급기(211)에 전기적으로 연결되어 있고, 제 2 전극(208)은 시트(sheet) 캐소드(1012)를 통해 제 2 전압 공급기(206)에 전기적으로 연결되어 있으며, 아날로그 구동 트랜지스터 제어 신호는 선형 소스 드라이버(14)에 의해 게이트 전극(203)에 제공된다.

[0046] 본 발명은 구동 트랜지스터의 게이트 전극에 아날로그 구동 트랜지스터 제어 신호를 제공한다. 시간에 걸쳐 EL 디바이스 및 구동 트랜지스터의 동작에 의해 야기된 EL 디바이스 및 구동 트랜지스터의 특성에서의 변화를 보상하는, 제어 신호를 제공하기 위해, 이 변화를 알아야 한다. 변화는 변화를 나타내는 노화 신호를 제공하기 위해 다른 시간들에서 구동 트랜지스터의 제 1 및 제 2 공급 전극을 관통하는 전류를 측정함으로써 결정된다. 이는 "알고리즘"에서, 이하 상세히 설명될 것이다. 노화 신호는 디지털 또는 아날로그일 수 있다. 전압 또는 전류를 나타낼 수 있다.

[0047] 도 2는 도 1에 도시된 바와 같이, 비선형 입력 신호(11), 컨버터(12), 보상기(13) 및 선형 소스 드라이버(14)를 포함하는 전체 시스템의 맥락에서 구동 회로(15)를 나타낸다. 전술한 바와 같이, 구동 트랜지스터(201)는 게이트 전극(203), 제 1 공급 전극(204) 및 제 2 공급 전극(205)을 가진다. EL 디바이스(202)는 제 1 전극(207) 및 제 2 전극(208)을 가진다. 시스템은 전압 공급기(211, 206)를 가진다. 제 1 전압 공급기(211)가 이하, 전류 미러 유닛(210)의 설명에서 명료함을 위해 구동 회로(15) 밖에 도시되어 있음을 유의한다.

[0048] 일반적으로 FET인 구동 트랜지스터(201), 및 EL 디바이스(202)의 움직임은 제 1 전압 공급기(211)로부터, 제 2

전압 공급기(206)로, EL 디바이스 전극(207 및 208)을 통해, 제 2 공급 전극(205) 및 제 1 공급 전극(204)을 통해 본질적으로 동일한 전류가 통과하도록 한다. 그러므로, 전류는 이 사슬에서 임의 지점에서 측정될 수 있다. 전류는 EL 서브픽셀의 복잡도를 감소시키기 위해 제 1 전압 공급기(211)에서 EL 패널에서 떨어져 측정될 수 있다. 일 실시예에서, 본 발명은 전류 미러 유닛(210), 상관 이중-샘플링 유닛(220) 및 아날로그-디지털 컨버터(230)를 사용한다. 이들은 이하 "데이터 수집"에서 설명될 것이다.

[0049] 도 2에 도시된 구동 회로(15)는 N-채널 구동 트랜지스터 및 비-반전 EL 구조를 위한 것이다. 이 경우에, EL 디바이스(202)는 구동 트랜지스터(201)의 소스(205)에 뮤여 있고, 게이트 전극(203) 상의 더 높은 전압이 더 많은 광 출력을 명령하며, 전압 공급기(211)는 제 2 전압 공급기(206)보다 양(positive)이어서, 전류는 211에서 206으로 흐른다. 그러나, 본 발명은 P- 또는 N-채널 구동 트랜지스터 및 비-반전 또는 반전 EL 디바이스의 임의 조합에 적용가능하다. 본 발명은 또한 LTPS 또는 a-Si 구동 트랜지스터에 적용가능하다.

#### [0050] 데이터 수집

##### [0051] 하드웨어

[0052] 도 2를 참고하면, 패널 상의 임의 특수 전자제품에 좌우되지 않고 각각의 EL 서브픽셀의 전류를 측정하기 위해, 본 발명은 전류 미러 유닛(210), 상관 이중-샘플링(CDS) 유닛(220), 및 아날로그-디지털 컨버터(ADC)(230)을 포함하는 측정 회로(16)를 이용한다.

[0053] 전류 미러 유닛(210)은, 전압 공급기(211), 전압 공급기(206), 또는 구동 트랜지스터의 제 1 및 제 2 공급 전극 및 EL 디바이스를 관통하는 전류 경로 어디든 부착될 수 있더라도, 전압 공급기(211)에 부착되어 있다. 이는 EL 디바이스가 광을 방출하도록 하는 구동 전류의 경로이다. 제 1 전류 미러(212)는 스위치(200)를 통해 EL 구동 회로(15)에 구동 전류를 공급하고, 이의 출력(213) 상에 미러된 전류를 발생한다. 미러된 전류는 구동 전류와 동일할 수 있다. 일반적으로, 구동 전류의 함수일 수 있다. 예를 들어, 미러된 전류는 추가 측정-시스템 이득을 제공하기 위해 구동 전류의 배수일 수 있다. 제 2 전류 미러(214) 및 바이어스 공급기(215)는 제 1 전류 미러에서의 전압 변화를 감소시키기 위해 제 1 전류 미러(212)로 바이어스 전류를 인가하여, 측정은 회로에서 기생 임피던스에 의해 영향받지 않는다. 이 회로는 또한 측정 회로의 전류 인출(current draw)로부터의 결과인 전류 미러에서의 전압 변경 때문에 측정되는 EL 서브픽셀을 통해 전류에서의 변경을 감소한다. 유리하게는 이는 단순한 센스 저항과 같은, 다른 전류-측정 선택 상에서 신호대 잡음 비를 개선하며, 이는 전류에 따라 구동 트랜지스터 단자들에서의 전압을 변경시킬 수 있다. 마지막으로, 전류-전압(I-to-V) 컨버터(216)는 또 다른 처리 동안 전압 신호로 제 1 전류 미러로부터의 미러된 전류를 전환한다. 전류-전압 컨버터(216)는 트랜스임피던스 증폭기 또는 저역 통과 필터를 포함할 수 있다. 하나의 EL 서브픽셀의 경우, 전류-전압 컨버터의 출력은 이 서브픽셀에 대한 노화 신호일 수 있다. 이하 설명되어 있는 바와 같이, 다수의 서브픽셀의 측정의 경우, 측정 회로소자는 노화 신호를 발생하기 위해 전압 신호에 응답하는 또 다른 회로소자를 포함할 수 있다. 구동 트랜지스터 및 EL 디바이스의 특성이 시간에 걸쳐 EL 디바이스 및 구동 트랜지스터의 동작에 기인하여 변함에 따라, 전술한 바와 같이,  $V_{th}$  및  $V_{oled}$ 는 변할 것이다. 따라서, 측정된 전류, 및 노화 신호는 이를 변화에 응답하여 변할 것이다. 이는 "알고리즘"에서 이하 설명될 것이다.

[0054] 일 실시예에서, 제 1 전압 공급기(211)는 +15 VDC의 전위를 가질 수 있고, 제 2 전압 공급기(206)는 -5 VDC의 전위를 가질 수 있고, 바이어스 공급기(215)는 -16 VDC의 전위를 가질 수 있다. 바이어스 공급기(215)의 전위는 모든 측정 전류 레벨에서 안정한 바이어스 전류를 제공하기 위해 제 1 전압 공급기(211)의 전위에 기초하여 선택될 수 있다.

[0055] EL 서브픽셀이 측정되지 않는 경우, 전류 미러는 릴레이(relay) 또는 FET일 수 있는, 스위치(200)에 의해 패널로부터 전기적으로 연결해제될 수 있다. 스위치는 구동 트랜지스터(201)의 제 1 및 제 2 전극을 통해 구동 전류 흐름에 측정 회로를 선택적으로 전기적으로 연결할 수 있다. 측정 동안, 스위치(200)는 측정을 허용하기 위해 제 1 전류 미러(212)로 제 1 전압 공급기(211)를 전기적으로 연결할 수 있다. 정상 동작 동안, 스위치(200)는 제 1 전류 미러(212)보다는 차라리 제 2 공급 전극(204)에 바로 제 1 전압 공급기(211)를 전기적으로 연결할 수 있어, 따라서 구동 전류 흐름으로부터 측정 회로를 제거한다. 이는 측정 회로소자가 패널의 정상 동작에 어떠한 영향도 미치지 않도록 한다. 또한 유리하게는 전류 미러(212, 및 214)에서의 트랜지스터와 같은, 측정 회로의 소자들이, 작동 전류가 아닌 측정 전류에 대해서만 크기가 변경될 수 있도록 한다. 정상 동작이 일반적으로 측정보다 훨씬 많은 전류를 인출함에 따라, 이는 측정 회로의 비용 및 크기에서의 실질적 감소를 허용한다.

#### [0056] 샘플링

[0057]

전류 미러 유닛(210)은 하나의 EL 서브픽셀에 대한 전류의 측정을 허용한다. 다수의 서브픽셀에 대한 전류를 측정하기 위해, 일 실시예에서 본 발명은 표준 OLED 소스 드라이버와 이용가능한 타이밍 방식으로, 상관 이중-샘플링을 사용한다.

[0058]

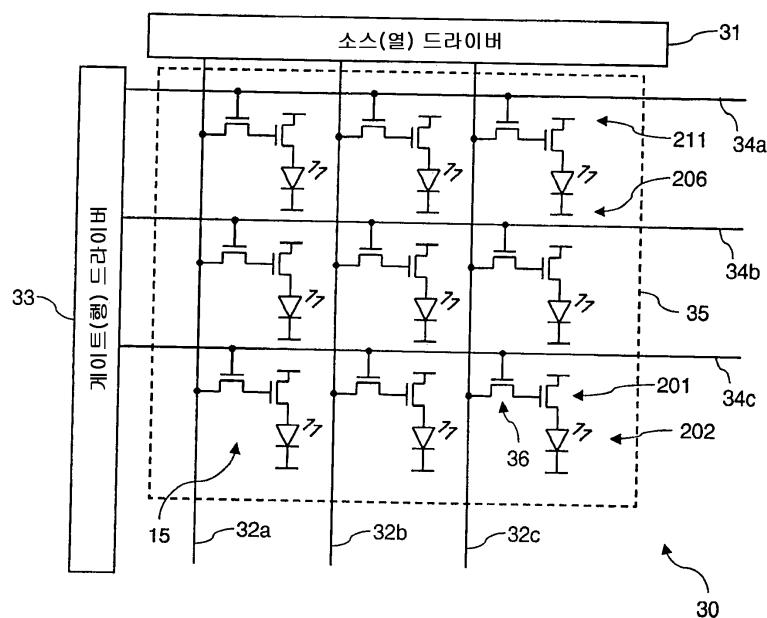

도 3을 참고하면, 본 발명에서 유용한 EL 패널(30)은 3 개의 주요 소자: 열 라인(32a, 32b, 32c)을 구동하는 소스 드라이버(31); 행 라인(34a, 34b, 34c)을 구동하는 게이트 드라이버(33); 및 서브픽셀 매트릭스(35)를 가진다. 본 발명의 일 실시예에서, 소스 드라이버(31)는 선형 소스 드라이버(14)일 수 있다. 소스 및 게이트 드라이버가 하나 이상의 마이크로칩을 포함할 수 있음을 유의한다. 또한, "행" 및 "열"이란 용어가 EL 패널의 어떤 특정 방향도 암시하지 않음을 유의한다. 서브픽셀 매트릭스는 행 및 열의 어레이에 일반적으로 배열되어 있으며, 일반적으로 동일한, 복수의 서브픽셀을 포함한다. 각각의 EL 서브픽셀은 EL 디바이스(202)를 포함하는 구동 회로(15)를 포함한다. 각각의 구동 회로는 EL 디바이스에 전류를 인가하며, 구동 트랜지스터(201) 및 선택 트랜지스터(36)를 포함한다. 스위치로서 동작하는 선택 트랜지스터(36)는 구동 트랜지스터(201)에 행 및 열 라인들을 전기적으로 연결한다. 선택 트랜지스터의 게이트는 적당한 행 라인(34)에 전기적으로 연결되고, 이의 소스 및 드레인 전극 중, 하나는 적당한 열 라인(32)에 연결되며, 하나는 구동 트랜지스터의 게이트 전극에 연결된다. 소스가 행 라인 또는 구동 트랜지스터 게이트 전극에 연결되는지 여부는 선택 트랜지스터의 동작에 영향을 미치지 않는다. 본 발명의 일 실시예에서, 서브픽셀 매트릭스(35)에서의 각각의 EL 디바이스(202)는 OLED 디바이스일 수 있고, 서브픽셀 매트릭스(35)에서의 각각의 구동 트랜지스터(201)는 비결정 실리콘 트랜지스터일 수 있다.

[0059]

EL 패널은 또한 제 1 전압 공급기(211) 및 제 2 전압 공급기(206)를 포함한다. 도 10을 참고하면, 전류는 제 1 전압 공급기(211)와 구동 트랜지스터의 제 1 공급 전극(204)을 전기적으로 연결하는 PVDD 버스 라인, 예를 들어(1011)에 의해 구동 트랜지스터(201)에 공급될 수 있다. 제 2 전압 공급기(206)와 EL 디바이스(202)의 제 2 전극(208)을 전기적으로 연결하는 시트 캐소드(1012)는 전류 경로를 완성할 수 있다. 도 3을 참고하면, 명료함을 위해, 본 발명을 서브픽셀과 공급기들을 연결하기 위해 다양한 방식으로 이용할 수 있는 경우, 각각의 서브픽셀에 연결하는 전압 공급기(211, 206)는 도 3에 표시되어 있다. 각각의 구동 트랜지스터의 제 2 공급 전극(205)은 대응하는 EL 디바이스의 제 1 전극(207)에 전기적으로 연결될 수 있다.

[0060]

도 2에 도시된 바와 같이, EL 패널은 제 1 전압 공급기(211)에 전기적으로 연결된 측정 회로(16)를 포함할 수 있다. 이 회로는 키리아호프 전류 법칙에 의해 동일한, 제 1 및 제 2 전압 공급기를 관통하는 전류를 측정한다.

[0061]

이 패널의 전형적 동작에서, 소스 드라이버(31)는 열 라인(32) 상의 적당한 아날로그 구동 트랜지스터 제어 신호를 구동한다. 게이트 드라이버(33)는 트랜지스터들이 부착된 EL 디바이스(202)에 전류를 인가하게 하기 위해 적당한 제어 신호들이 적절한 구동 트랜지스터(201)의 게이트 전극들에 선택 트랜지스터(36)를 관통하게 하는, 제 1 행 라인(34a)을 활성시킨다. 게이트 드라이버는 다른 행들에 대한 제어 신호가 선택 트랜지스터를 관통한 값에 오류를 일으키는 것을 방지하는, 제 1 행 라인(34a)을 불활성시킨다. 소스 드라이버는 열 라인들 상의 다음 행에 대한 제어 신호를 구동하고, 게이트 드라이버는 다음 행(34b)을 활성시킨다. 이 과정은 모든 행에 반복된다. 이 방식으로 패널 상의 모든 서브픽셀은 한번에 하나의 행, 적절한 제어 신호를 수신하다. 행 시간은 하나의 행 라인(예를 들어, 34a)을 활성시키는 것과 다음 행 라인(예를 들어, 34b)을 활성시키는 것 사이의 시간이다. 이 시간은 일반적으로 모든 행에 대해 일정하다.

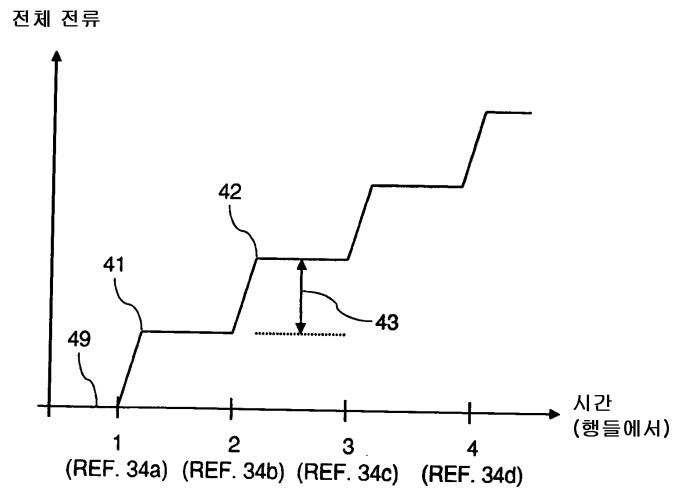

[0062]

본 발명에 따르면, 이 행 스텝핑(stepping)은 유리하게는, 열을 아래로 동작하며, 한번에 하나의 서브픽셀만을 활성시키는 데 사용된다. 도 3을 참고하면, 모든 서브픽셀을 오프로 시작하여, 하나의 열(32a)만이 구동된다고 가정한다. 열 라인(32a)은 부착되어 있는 서브픽셀들이 광을 방출하게 하는, 높은 전압과 같은 아날로그 구동 트랜지스터 제어 신호를 가질 것이다; 모든 다른 열 라인(32b, ... 32c)은 이에 부착된 서브픽셀이 광을 방출하지 않도록 하는, 저 전압과 같은, 제어 신호를 가질 것이다. 모든 서브픽셀이 오프이기 때문에, 패널은 어떠한 전류도 인출할 수 없다(이하, "잡음의 근원" 참고). 최상부 열에서 시작하여, 행은 시간 축 상의 체크표시(tick)에 의해 표시된 지점들에서 활성된다. 행이 활성됨에 따라, 열(32a)에 부착된 서브픽셀은 켜지고, 그래서 패널에 의해 인출된 전체 전류는 상승한다. 도 4a를 참고하면, 시간 1에서, 서브픽셀이 활성되고(예를 들어, 행 라인(34a)으로) 이의 전류(41)는 측정 회로(16)로 측정된다. 구체적으로는, 측정되는 것은 전술한 바와 같이 제 1 및 제 2 전압 공급기를 통한 전류를 나타내는, 전류-측정 회로로부터 전압 신호이고; 전류를 나타내는 전압 신호를 측정하는 것은 명료함을 위해 "측정 전류"로서 언급된다. 시간 2에서, 다음 서브픽셀은 활성되고(예를 들어, 행 라인(34b)로) 전류(42)가 측정된다. 전류(42)는 제 1 서브픽셀로부터의 전류 및 제 2 서브픽셀로부터의 전류의 합이다. 제 2 측정(42)과 제 1 측정(41) 사이의 차는 제 2 서브픽셀에 의해 인출된 전류(43)이다. 이렇게 하여 과정은 각각의 서브픽셀의 전류를 측정하며, 제 1 열 아래로 진행한다. 제 2 열, 제 3 열, 등 패널의

나머지 열이 측정된다. 각각의 측정(예를 들어, 41, 42)이 가능한한 서브픽셀을 활성화 하자마자 얻어짐을 유의 한다. 이상적 상황에서, 각각의 측정은 다음 서브픽셀을 활성시키기 전에 임의 시간에 행해질 수 있지만, 이하 설명된 바와 같이, 서브픽셀을 활성시킨 후 바로 측정을 하는 것은 자기-가열 영향에 기인하여 오류를 제거하는 것을 협조할 수 있다. 이 방법은 측정이, 서브픽셀의 정착 시간(settling time)이 허용되는 만큼 빨리 행해지도록 한다.

[0063] 상관 이중-샘플링 유닛(220)은 노화 신호를 발생하기 위해 측정된 전류를 샘플링한다. 하드웨어에서, 전류는 도 2의 샘플-및-유지(sample and hold) 유닛(221, 222)로 전류 미러 유닛(210)으로부터의 대응하는 전압 신호를 래치(latch)함으로써 측정된다. 전압 신호는 전류-전압 컨버터(216)에 의해 발생된 것일 수 있다. 차동 증폭기(223)는 연속하는 서브픽셀 측정 사이의 차를 가진다. 샘플-및-유지 유닛(221)의 출력은 차동 증폭기(223)의 양의 단자에 전기적으로 연결되고 유닛(222)이 출력은 증폭기(223)의 음의 단자에 전기적으로 연결된다. 예를 들어, 전류(41)가 측정되는 경우, 측정은 샘플-및-유지 유닛(221)으로 래치된다. 이때, 전류(42)가 측정되기 전에 (유닛(221)으로 래치되기 전에), 유닛(221)의 출력은 제 2 샘플-및-유지 유닛(222)으로 래치된다. 전류(42)가 이때 측정된다. 이는 유닛(222)에서의 전류(41) 및 유닛(221)에서의 전류(42)를 남긴다. 차동 증폭기의 출력, 즉 유닛(222)에서의 값 빼기 유닛(222)에서의 값은 따라서 전류(42)(를 나타내는 전압 신호) 빼기 전류(41)(를 나타내는 전압 신호), 또는 차(43)이다. 각각의 전류 차, 예를 들어 43은 대응하는 서브픽셀에 대한 노화 신호일 수 있다. 예를 들어, 전류 차(43)는 행 라인(34b) 및 열 라인(32a)에 부착된 서브픽셀에 대한 노화 신호일 수 있다. 이 방식으로, 행 아래로 기르고 열을 가로지르는 스테핑은 각각의 서브픽셀로 취해질 수 있고 노화 신호는 각각의 서브픽셀에 제공된다.

#### 잡음의 균원

[0065] 실제로, 전류 파형은 클린 단계 이외일 수 있어, 측정은 정착하기 위해 파형에 대한 대기 이후에만 행해질 수 있다. 각각의 서브픽셀의 다수의 측정이 또한 행해질 수 있으며 함께 평균된다. 이와 같은 측정은 다음 서브픽셀로 진행하기 전에 연이어 행해질 수 있다. 이와 같은 측정은 또한 개별 측정 패스(pass)에서 행해질 수 있으며, 패널 상의 각각의 서브픽셀은 각각이 패스에서 측정된다. 전압 공급기(206)와 전압 공급기(211) 사이의 커페시턴스가 정착 시간에 더해질 수 있다. 이 커페시턴스는 정상 동작에서 일반적임에 따라, 외부 커페시터에 의해 제공되거나 또는 패널에 고유하다. 측정하는 동안 외부 커페시터를 전기적으로 연결해제하는데 사용될 수 있는 스위치를 제공하는 것이 유리할 수 있다. 이는 정착 시간을 감소시킬 것이다.

[0066] 모든 전원은 가능한한 깨끗하게 유지되어야 한다. 임의 전원 상의 잡음은 전류 측정에 영향을 미칠 것이다. 예를 들어, (종종 VGL 또는 Voff라 불리고 전형적으로 대략 -8VDC인) 게이트 드라이버가 행들을 불활성시키는 데 사용하는 전원 상의 잡음은 구동 트랜지스터로 선택 트랜지스터를 가로질러 용량성으로 결합할 수 있고 전류에 영향을 미칠 수 있어, 전류 측정을 더 잡음으로 한다. 패널이 다수의 전원 영역, 예를 들어 분할 공급 면(split supply plane)을 가진다면, 이들 영역은 동시에 측정될 수 있다. 이와 같은 측정은 영역들 사이의 잡음을 격리 할 수 있고 측정 시간을 감소시킬 수 있다.

[0067] 잡음의 하나의 주요 근원은 소스 드라이버 자체일 수 있다. 소스 드라이버가 스위칭할 때마다, 잡음 과도현상(noise transient)은 측정 잡음을 유발하는, 전원 면 및 개별 서브픽셀로 결합할 수 있다. 이 잡음을 감소시키기 위해, 소스 드라이버 밖의 제어 신호는 열을 아래로 스테핑하는 동안 일정하게 유지될 수 있다. 예를 들어, RGB 줄무늬 패널 상의 적색 서브픽셀의 열을 측정하는 경우, 이 열에 대한 소스 드라이버에 인가된 적색 코드값은 전체 열에 일정할 수 있다. 이는 소스-드라이버 과도현상 잡음을 제거할 것이다.

[0068] 소스 드라이버가 현재의 열(예를 들어, 32a)을 활성시키는 것으로부터 다음 열(예를 들어, 32b)을 활성시키는 것으로 변해야 하는 경우, 소스 드라이버 과도현상은 열의 시작 및 끝에서 불가피할 수 있다. 따라서, 임의 열에서의 처음 및 마지막 하나 이상의 서브픽셀에 대한 측정은 과도현상에 기인한 잡음에 영향을 받는다. 일 실시 예에서, EL 패널은 가시적인 행 위 및 아래에, 사용자에 보이지 않는 여분의 행을 가질 수 있다. 이들 여분의 행들에서만 소스 드라이버 과도현상이 일어나는 충분한 여분의 행들이 존재할 수 있어, 가시적 서브픽셀의 측정은 악화되지 않는다. 또 다른 실시 예에서, 지연은 열의 시작에서의 소스 드라이버 과도현상과 이 열에서의 제 1 행의 측정 사이에, 그리고 이 열에서의 마지막 행의 측정과 열의 끝에서의 소스 드라이버 과도현상 사이에 삽입될 수 있다.

[0069] 패널은 모든 서브픽셀이 꺼진 경우에 조차 약간의 전류를 인출할 수 있다. 이 "다크 전류(dark current)"는 컷 오프에서 구동 트랜지스터 누설에 기인할 수 있다. 다크 전류는 측정된 전류에 DC 바이어스 잡음을 추가한다. 도 4a 상의 지점(49)에 의해 도시된 바와 같이, 제 1 서브픽셀을 활성시키기 전에 오프인 모든 서브픽셀들과의

측정을 행함으로써 제거될 수 있다. 이 경우에, 서브픽셀(1)에 의해 인출한 전류는 측정(41)보다는 차라리, 측정(49) 빼기 측정(41)일 수 있다.

#### [0070] 전류 안정성

[0071] 이 설명은 하나의 서브픽셀이 켜지고 소정의 전류로 정착된다면, 열의 나머지에 대한 전류에 남아 있다고 가정한다. 상기 가정을 위반할 수 있는 2 개의 영향은 저장-커패시터 누설 및 내부-서브픽셀(within-subpixel) 영향이다.

[0072] 당해 기술에 공지된 바와 같이, 저장 커패시터는 모든 서브픽셀의 일부일 수 있으며, 기준 전압과 구동 트랜지스터 사이에 전기적으로 연결될 수 있다. 서브픽셀에서의 선택 트랜지스터의 누설 전류는, 구동 트랜지스터의 게이트 전압 및 이에 의해 인출된 전류를 변경시키며, 저장 커패시터 상의 전하를 점진적으로 빼낼 수 있다. 또한, 서브픽셀에 부착된 열 라인이 시간에 걸쳐 값을 변경한다면, AC 성분을 가지고, 그러므로 저장 커패시터의 값 및 서브픽셀에 의해 인출된 전류를 변경하며, 저장 커패시터 상으로 선택 트랜지스터의 기생 커패시턴스를 통해 결합할 수 있다.

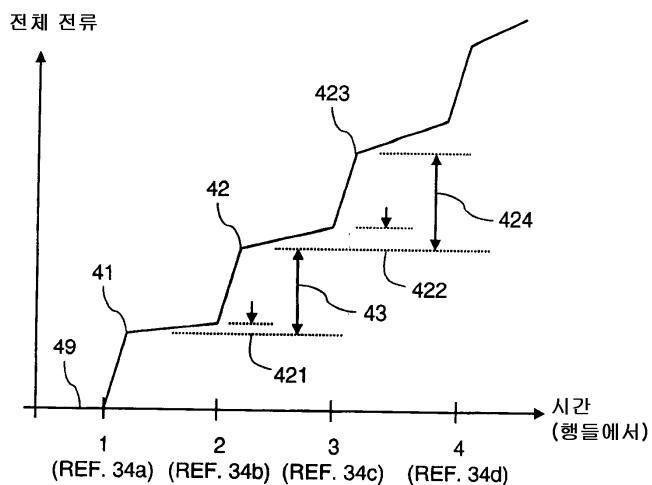

[0073] 저장 커패시터의 값이 안정적인 경우에 조차, 내부-서브픽셀 영향은 측정에 오류를 일으킬 수 있다. 공통의 내부-서브픽셀 영향은 서브픽셀의 자기-가열이며, 이는 시간에 걸쳐 서브픽셀에 의해 인출된 전류를 변경할 수 있다. a-Si TFT의 드리프트 이동도(drift mobility)는 온도의 함수이다; 온도를 증가시키는 것은 이동도를 증가시킨다(Kagan & Andry, op., cit., sec. 2.2.2, pp. 42-43). 전류가 구동 트랜지스터를 통해 흐름에 따라, 구동 트랜지스터 및 EL 디바이스에서의 전력 손실(power dissipation)은 서브픽셀을 가열시킬 것이며, 트랜지스터의 온도 및 이에 의해 이동도를 증가시킬 것이다. 또한, 열은  $V_{oled}$ 를 낮춘다; OLED가 구동 트랜지스터의 소스 단자에 부착되는 경우에는, 이는 구동 트랜지스터의  $V_{gs}$ 를 증가시킬 수 있다. 이들 영향은 트랜지스터를 통해 흐르는 전류의 양을 증가시킨다. 정상 동작 하에서, 패널이 디스플레이하고 있는 이미지의 평균 콘텐츠에 기초하여 평균 온도로 안정할 수 있음에 따라, 자기-가열은 부 영향일 수 있다. 그러나, 서브픽셀 전류를 측정하는 경우, 자기-가열은 측정에 오류를 일으킬 수 있다. 도 4b를 참고하면, 측정(41)은 서브픽셀(1)을 활성시킨 후 가능하다면 바로 행해진다. 서브픽셀(1)의 자기가열은 이 측정에 영향을 미치지 않는다. 그러나, 측정(41)과 측정(42) 사이의 시간에서, 서브픽셀(1)은 양(amount)(421) 만큼 전류를 증가시키며, 자기-가열할 것이다. 그러므로, 서브픽셀(2)의 전류를 나타내는 계산된 차(43)는 오류가 있을 것이다; 양(421) 만큼 너무 클 것이다. 양(421)은 행 시간마다 서브픽셀 당 전류에서의 상승이다.

[0074] 유사한 잡음 서명(noise signature)을 발생하는 임의 다른 내부-서브픽셀 영향 및 자기-가열 영향을 수정하기 위해, 자기-가열은 특징지를 수 있고 각각의 서브픽셀의 공지된 자기-가열 성분을 뺀다. 각각의 서브픽셀은 일 반적으로 각각의 행 시간 동안 동일한 양만큼 전류를 증가시켜, 각각의 다음 서브픽셀에 의해 모든 활성 서브픽셀에 대한 자기-가열을 뺄 수 있다. 예를 들어, 서브픽셀 3의 전류(424)를 얻기 위해, 측정(423)은 2 배의 성분(421)인, 자기-가열 성분(422) 만큼 감소될 수 있다: 서브픽셀 당 성분(421)은, 2 개의 서브픽셀이 이미 활성으로 시간을 맞춘다. 자기-가열은 수십 또는 수백의 행 시간 동안 하나의 서브픽셀을 켜고 켜져 있는 동안 주기적으로 이의 전류를 측정함으로써 특징지어질 수 있다. 시간에 대한 전류의 평균 기울기는 행 시간(421)마다 서브픽셀마다 상승을 계산하기 위해 하나의 행 시간에 의해 곱해질 수 있다.

[0075] 자기-가열, 및 전력 손실에 기인한 오류는 낮은 측정 기준 게이트 전압(도 5a, 510)을 선택함으로써 감소될 수 있지만, 그러나 더 높은 전압은 신호대잡음 비를 개선시킨다. 측정 기준 게이트 전압은 이들 요인들의 균형을 이루도록 각각의 패널 설계를 위해 선택될 수 있다.

#### [0076] 알고리즘

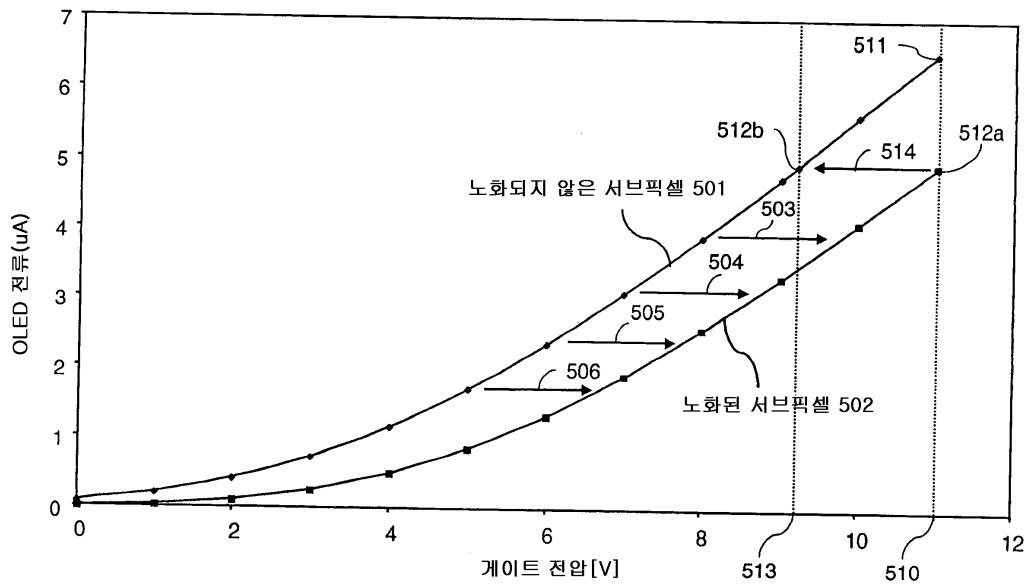

[0077] 도 5a를 참고하면, I-V 곡선(501)은 노화되기 전의 서브픽셀의 측정된 특성이다. I-V 곡선(502)은 노화된 후의 이 서브픽셀의 측정된 특성이다. 곡선(501) 및 곡선(502)은 다른 전류 레벨에서의 동일한 전압차(503, 504, 505 및 506)로 도시된 바와 같이, 주로 수평 이동인 것에 의해 떨어져 있다. 즉, 노화의 주된 영향은 일정한 양만큼 게이트 전압 축 상으로 I-V 곡선을 이동시키는 것이다. 이는 MOSFET 포화-영역 구동 트랜지스터 방정식,  $I_d = K(V_{gs} - V_{th})^2$ 과 일치한다(Lursh, N. *Fundamentals of electronics*, 2e. New York: John Wiley & Sons, 1971, pg.110): 구동 트랜지스터는 동작되고,  $V_{th}$ 는 증가하며;  $V_{th}$ 가 증가함에 따라,  $V_{gs}$ 는  $I_d$ 를 일정하게 유지하기 위해 증가해야 한다. 그러므로 일정한  $V_{gs}$ 는  $V_{th}$ 가 증가함에 따라 낮은  $I_d$ 를 가져온다.

- [0078] 도 5a의 예에서, 측정 기준 게이트 전압(510)에서, 노화되지 않은 서브픽셀은 지점(511)에서 나타난 전류를 발생하였다. 전류는 이 서브픽셀에 대한 노화 신호이다. 그러나, 노화된 서브픽셀은 지점(512a)에서 나타난 전류의 낮은 양을 게이트 전압에서 발생한다. 지점(511, 512a)은 다른 시간에 취해진 동일한 서브픽셀의 2 개의 측정일 수 있다. 예를 들어, 지점(511)은 제조 시간에서의 측정일 수 있으며, 지점(512a)은 소비자에 의해 약간의 사용 후 측정일 수 있다. 지점(512a)에서 나타난 전류는 전압(513)(지점(512b))으로 구동되는 경우 노화되지 않은 서브픽셀에 의해 발생될 수 있어, 전압 이동  $\Delta V_{th}(514)$ 은 전압(510)과 전압(513) 사이의 전압 차로서 계산된다. 전압 이동(514)은 노화되지 않은 곡선으로 다시 노화된 곡선을 가져가기 위해 필요한 이동이다. 이 예에서,  $\Delta V_{th}(514)$ 은 2 볼트 아래에 있다. 이후,  $\Delta V_{th}$  이동을 보상하기 위해, 그리고 노화되지 않은 픽셀이 가지는 것과 동일한 전류로 노화된 서브픽셀을 구동하기 위해, 전압차(514)는 (선행 코드 값) 모든 명령된 구동 전압에 추가된다. 또 다른 처리를 위해, 퍼센트 전류가 또한 전류(511)에 의해 나눠진 전류(512a)로서 계산된다. 노화되지 않은 서브픽셀이 따라서 100% 전류를 가질 것이다. 퍼센트 전류는 본 발명에 따라 여러 알고리즘으로 사용된다. 극도의 환경 잡음에 의해 유발되는 것과 같이, 임의 음 전류 판독(511)은 0으로 고정될 수 있거나, 또는 무시될 수 있다. 퍼센트 전류가 항상 측정 기준 게이트 전압(510)에서 계산됨을 유의한다.

- [0079] 일반적으로, 노화된 서브픽셀의 전류는 노화되지 않은 서브픽셀의 전류보다 더 크거나 또는 낮을 수 있다. 예를 들어, 더 높은 온도는 더 많은 전류가 흐르게 하여, 뜨거운 환경에서의 약간 노화된 서브픽셀은 차가운 환경에서의 노화되지 않은 서브픽셀보다 더 많은 전류를 얻을 수 있다. 본 발명의 보상 알고리즘은  $\Delta V_{th}(514)$ 가 양 또는 음(또는 노화되지 않은 픽셀의 경우 0)일 수 있는 각 경우를 다룰 수 있다. 마찬가지로, 퍼센트 전류는 100 % 보다 크거나 또는 작을 수 있다(또는 노화되지 않은 픽셀의 경우 정확하게는 100%).

- [0080]  $V_{th}$  이동에 기인한 전압차가 모든 전류에서 동일하기 때문에, I-V 곡선 상의 임의 하나의 포인트는 상기 차를 결정하기 위해 측정될 수 있다. 일 실시예에서, 측정은 측정의 신호대잡음비를 유리하게 증가시키며, 높은 게이트 전압에서 행해지지만, 곡선 상의 임의 게이트 전압이 사용될 수 있다.

- [0081]  $V_{oled}$  이동은 2차 노화 영향이다. EL 디바이스가 동작되는 경우, 노화된 I-V 곡선이 더이상 노화되지 않은 곡선의 단순한 이동이 아니게 하며,  $V_{oled}$ 가 이동한다. 이는  $V_{oled}$ 가 전류와 비선형으로 상승하기 때문이며, 그래서  $V_{oled}$  이동은 낮은 전류와 다르게 높은 전류에 영향을 미칠 것이다. 이 영향은 I-V 곡선이 이동과 마찬가지로 수평으로 뻗도록 한다.  $V_{oled}$  이동을 보상하기 위해, 다른 구동 레벨에서의 2 개의 측정은 얼마나 많이 곡선이 뻗는지를 결정하기 위해 행해질 수 있거나, 또는 로드 하의 OLED의 전형적  $V_{oled}$  이동은 개루프 방식으로  $V_{oled}$  기여의 추정을 허용하기 위해 특징될 수 있다. 반로그(semilog) 스케일 상의 I-V 곡선, 도 5b를 참고하면, 성분(550)은  $V_{th}$  이동 때문이며, 성분(552)은  $V_{oled}$  이동 때문이다.  $V_{oled}$  이동은 시간의 긴 주기 동안 전형적 입력 신호로 계기(instrumented) OLED 서브픽셀을 구동하고, 주기적으로  $V_{th}$  및  $V_{oled}$ 를 측정함으로써 특징지어질 수 있다. 2 개의 측정은 트랜지스터와 OLED 사이의 계기 서브픽셀 상의 프로브 포인트를 제공함으로써 개별적으로 행해질 수 있다. 이 특성을 사용하여, 퍼센트 전류는  $V_{th}$  이동만으로보다는 차라리, 적절한  $\Delta V_{th}$  및  $\Delta V_{oled}$ 로 매핑될 수 있다.

- [0082] OLED 효율성 손실은 3차 노화 영향이다. OLED가 노화함에 따라, 이의 효율성이 감소하고, 더이상 전류의 동일한 양이 광의 동일한 양을 발생하지 않는다. 광학 센서 또는 추가 전자제품을 요구하지 않고 이를 보상하기 위해,  $V_{th}$  이동의 함수로서 OLED 효율성 손실은, 이전 레벨로 광 출력을 반환하기 위해 필요한 여분의 전류의 양의 추정을 허용하여, 특징지어질 수 있다. OLED 효율성 손실은 시간의 긴 주기 동안 전형적 입력 신호로 계기된 OLED 서브픽셀을 구동하고, 다양한 구동 레벨에서 주기적으로  $V_{th}$ ,  $V_{oled}$  및  $I_{oled}$ 를 측정함으로써 특징지어질 수 있다. 효율성은  $I_{oled}/V_{oled}$ 로서 계산될 수 있고 계산은  $V_{th}$  또는 퍼센트 전류와 상관될 수 있다.  $V_{th}$  이동이 쉽게 역전될 수 있지만 OLED 효율성 손실이 아니기 때문에, 이 특성화는,  $V_{th}$  이동이 항상 순방향인 경우 가장 효과적은 결과를 달성할 수 있음을 유의한다.  $V_{th}$  이동이 역전된다면,  $V_{th}$  이동과 OLED 효율성 손실의 상관은 복잡하게 될 수 있다. 또 다른 처리를 위해, 퍼센트 효율성은 전술한 바와 같이 퍼센트 효율성의 계산과 유사한, 새로운 효율성으로 나눠진 노화된 효율성으로서 계산될 수 있다.

- [0083] 도 9를 참고하면, 실험 데이터로 예를 들어 90인 선형 팅(fit)으로, 다양한 구동 레벨에서 퍼센트 전류의 함수로서 퍼센트 효율성의 실험적 플롯이 도시되어 있다. 플롯이 임의 주어진 구동 레벨에서, 나타냄에 따라, 효율

성은 퍼센트 전류에 선형으로 관련되어 있다. 이 선형 모델은 효율적 개루프 효율성 보상을 허용한다. 유사한 결과는 파커 등에 의한, "Lifetime and degradation effects in polymer light-emitting diodes", *J. App. Phys.* 85.4(1999): 2441-2447, 구체적으로, p.2445, 도 12에 도시된 바와 같이, 보고되어 있다. 파커 등은 또한 단일 메커니즘이 효율성 손실(휘도 감소) 및  $V_{oled}$  상승(전압 증가) 모두에 책임이 있음을 제안한다.

[0084]  $V_{th}$  및  $V_{oled}$ 를 포함하는, 구동 트랜지스터 및 EL 디바이스의 특성은 시간에 걸쳐 EL 디바이스 및 구동 트랜지스터의 동작에 기인하여 시간에 걸쳐 변한다. 퍼센트 전류는 이를 변화에 대한 보상을 나타내며 가능하게 하는, 노화 신호로서 사용될 수 있다.

[0085] 이 알고리즘이 OLED 디바이스의 맥락에서 설명되어 있더라도, 다른 EL 디바이스가 또한 당업자에 명백한 바와 같이, 이를 분석을 적용하기 위해 보상될 수 있다.

#### 이행

[0087] 도 6a를 참고하면, 선형 코드 값이 명령된 구동 전압이고 변경된 선형 코드 값이 보상된 전압인 보상기의 이행이 도시되어 있다. 보상기는 한번에 하나의 픽셀 상에서 동작하며; 다수의 서브픽셀은 순차적으로 처리될 수 있다. 예를 들어, 보상은 선형 코드 값이 통상적으로 좌측에서 우측으로, 상부에서 하부로 스캔 순서로 신호원으로부터 도달함에 따라 각각의 서브픽셀에 대해 수행될 수 있다. 보상은 보상기의 파이프라인(pipelining)에 의해 또는 보상 회로소자의 다수의 카피(copy)의 파이프라인에 의해 동시에 다수의 픽셀 상에서 수행될 수 있다; 이들 기술은 당업자에 명백할 것이다.

[0088] 보상기(60)의 입력은 명령된 구동 전압을 나타낼 수 있는, 서브픽셀(602)의 선형 코드 값 및 서브픽셀(601)의 위치이다. 보상기는 예를 들어, 보상된 전압 아웃(voltage out)(603)일 수 있는, 선형 소스 드라이버에 대해 변경된 선형 코드 값을 발생하기 위해 선형 코드 값을 변경한다. 보상기는 4 개의 주요 블록: 서브픽셀의 나이 결정(61), OLED 효율성에 대한 선택적 보상(62), 나이에 기초한 보상의 결정(63) 및 보상(64)을 포함할 수 있다. 블록 61 및 62는 OLED 효율성 보상에 주로 관련하며, 블록(63, 64)은 전압 보상, 구체적으로는  $V_{th}/V_{oled}$  보상에 주로 관련한다.

[0089] 도 6b는 블록(61 및 62)의 확대도이다. 서브픽셀의 위치(601)는 제조에서 취해진 저장된 기준 노화 신호( $i_0$ )(611) 및 가장 최근에 저장된 노화 신호 측정( $i_1$ )(612)을 검색하는데 사용된다. 노화 신호 측정은 위에서 "데이터 수집"에서 설명된 측정 회로에 의해 출력된 노화 신호일 수 있다. 측정은 다른 시간에서 위치(601)에서의 서브픽셀의 노화 신호의 측정일 수 있다. 이들 측정은 메모리(619)에 저장될 수 있으며, 이는 플래시 메모리와 같은 비휘발성 RAM, 및 EEPROM과 같은 ROM을 포함한다.  $i_0$  측정은 NVRAM 또는 ROM에 저장될 수 있다;  $i_1$  측정은 NVRAM에 저장될 수 있다. 측정(612)은 단일 측정, 다수의 측정의 평균, 시간에 걸쳐 측정의 지수적으로 가중된 이동 평균, 또는 당업자에 명백한 다른 평활화(smoothing) 방법의 결과일 수 있다.

[0090] 퍼센트 전류(613)는 전술한 바와 같이  $i_1/i_0$ 로서, 계산될 수 있고, 1보다 크거나(전류 이득), 1 보다 작거나(전류 손실), 1 이거나(변화 없음), 또는 0(데드 픽셀)일 수 있다. 가장 최근 노화 신호 측정이 제조-시간 측정보다 더 낮기 때문에, 일반적으로는 0과 1 사이일 것이다. 개별 측정  $i_1$  및  $i_0$ 로서 전류에서의 변화를 나타내는 경우, 퍼센트 전류는 자체로 노화 신호일 수 있고, 이 경우에 바로 메모리(619)에 저장될 수 있다.

[0091] 퍼센트 전류(613)는 다음 처리 단계(63)로 전송되며, 또한 퍼센트 OLED 효율성(614)을 결정하기 위해 모델(695)로 입력된다. 모델(695)은 제조 시간에 전류에 대해 방출된 광의 양으로 나눠진, 가장 최근 측정의 시간에서의 주어진 전류에 대해 방출된 광의 양인 효율성(614)을 출력한다. 효율성 손실이 수득된 전류를 가지는 픽셀에 대해 계산하기 어렵기 때문에, 1보다 큰 임의 퍼센트 전류는 1의 효율성을 낼 수 있거나 또는 어떠한 손실도 없다. 모델(695)은 또한 점선의 화살표로 나타난 바와 같이, 선형 코드 값(602)의 함수일 수 있고, 이 경우 OLED 효율성은 명령된 전류에 의존한다. 모델(695)로의 입력으로서 선형 코드 값(602)을 포함하는지 여부는 패널 설계의 수명 검사 및 모델링에 의해 결정될 수 있다.

[0092] 동시에, 보상기는 선형 코드 값, 예를 들어 명령된 전압 인(voltage in)(602)을 수신한다. 이 선형 코드 값은 바람직한 전류(621)를 결정하기 위해 제조 시간에서 측정된 패널의 원래의 I-V 곡선(691)을 통해 통과된다. 이는 제조 시간 값으로 바람직한 전류에 대한 광 출력을 반환하기 위해 연산(628)에서의 퍼센트 효율성(614)에 의해 나눠진다. 결과의 부스팅(boosted)된 전류는 어떤 명령된 전압이 효율성 손실이 존재시 원하는 광의 양을 발생하는지를 결정하기 위해, 곡선(692), 곡선(691)의 역을 통해 통과된다. 곡선(692)의 밖의 값은 효율성-조절

전압(622)으로서 다음 단계로 진행된다.

[0093] 효율성 보상을 원하지 않는다면, 입력 전압(602)은 선택적 바이패스 경로(626)로 표시된 바와 같이, 효율성-조절 전압(622)으로서 다음 단계로 변경되지 않은채 전송된다. 이 경우에, 퍼센트 전류(613)는 여전히 계산되어야 하지만, 그러나 퍼센트 효율성(614)은 필요하지 않다.

[0094] 도 6c는 도 6a의 블록(63, 64)의 확대도이다. 이전 단계로부터 퍼센트 전류(613) 및 효율성-조절 전압(622)을 수신한다. 블록(63), "보상 시작(get compensation)"은 반전 I-V 곡선(692)을 통해 전류 손실(623)을 매핑하고  $V_{th}$  이동  $\Delta V_{th}$ (631)를 발견하기 위해 측정 기준 게이트 전압(510)으로부터 결과(513)를 빼는 것을 포함한다. 블록(64), "보상"은 방정식 1에 주어진 바와 같이 보상된 전압 아웃(603)을 계산하는, 연산(633)을 포함한다:

$$V_{out} = V_{in} + \Delta V_{th}(1 + a(V_{g,ref} - V_{in})) \quad (\text{방정식 } 1)$$

[0095] 여기서,  $V_{out}$ 은 603이고,  $\Delta V_{th}$ 는 631이며,  $a$ 는 알파 값 632이고,  $V_{g,ref}$ 는 측정 기준 게이트 전압(510)이고,  $V_{in}$ 은 효율성-조절 전압(622)이다. 보상된 전압 아웃은 선형 소스 드라이버에 대한 변경된 선형 코드 값으로 표현될 수 있고, 구동 트랜지스터 및 EL 디바이스의 특성에서의 변화를 보상한다.

[0097] 직선의  $V_{th}$  이동의 경우에,  $a$ 는 0일 것이며, 연산(633)은 효율성-조절 전압(622)에  $V_{th}$  이동 양을 추가하는 것으로 감소할 것이다. 임의 특정 서브픽셀의 경우, 추가하기 위한 양은 새로운 측정이 취해질 때까지 일정하다. 그러므로, 이 경우에, 연산(633)에 추가하기 위한 양은, 블록(63, 64)이 저장된 값을 찾고 이를 추가하는 것을 무너뜨리도록(collapse) 하는, 측정이 취해진 이후 사전-계산될 수 있다. 이는 상당한 로직을 절약할 수 있다.

### 크로스-도메인 처리, 및 비트 깊이

[0099] 당해 기술에 공지된 이미지-처리 경로는 비선형 코드 값(NLCV), 즉, 휘도와의 비선형 관계를 가지는 디지털 값을 전형적으로 발생한다(Giorigianni & Madden. Digital Color Management: encoding solutions. Reading, Mass.: Addison-Wesley, 1998. Ch. 13, pp.283-295). 비선형 출력을 사용하는 것은 전형적 소스 드라이버의 입력 도메인과 일치하고, 사람의 눈의 정확도 범위에 대한 코드 값 정확도 범위와 일치한다. 그러나,  $V_{th}$  이동은 전압-도메인 동작이고, 따라서 선형-전압 공간에서 가장 쉽게 이행된다. 선형 소스 드라이버는 사용될 수 있고, 선형-도메인 보상기와 비선형-도메인 이미지-처리 경로를 효과적으로 통합하기 위해, 소스 드라이버 전에 도메인 전환이 수행된다. 이 논의가 디지털 처리와 관련하는 반면, 아날로그 처리가 아날로그 또는 혼합된 디지털/아날로그 시스템에서 수행될 수 있음을 유의한다. 또한 보상기가 전압 이외의 선형 공간에서 동작할 수 있음을 유의한다. 예를 들어, 보상기는 선형 전류 공간에서 동작할 수 있다.

[0100] 도 7을 참고하면, 도메인 전환 유닛(12) 및 보상기(13)의 영향의 존스-다이어그램 표현이 도시되어 있다. 이 도면은 이들 유닛이 어떻게 이행되는 지가 아니라, 이들 유닛의 수학적 영향을 나타낸다. 이들 유닛의 이행은 아날로그 또는 디지털일 수 있다. 사분면 I는 도메인-전환 유닛(12)의 동작을 나타내고: 축(701) 상의, 비선형 코드 값(NLCV)일 수 있는 비선형 입력 신호들은 축(702) 상의 비선형 코드 값(LCV)을 형성하기 위해 변환(711)을 통해 이들을 매핑함으로써 전환된다. 사분면 II는 보상기(13)의 동작을 나타내고: 축(702) 상의 LCV는 축(703)의 전환된 선형 코드 값(CLVC)을 형성하기 위해 721 및 722와 같은 변환을 통해 매핑된다.

[0101] 사분면 I를 참고하면, 도메인-전환 유닛(12)은 비선형 입력 신호, 예를 들어 NLCV를 수신하고, 이를 LCV로 전환한다. 이 전환은 윤곽(contouring) 및 뭉개진 여백(crushed blank)과 같은 불쾌한 가시적 아티팩트를 피하기 위해 충분한 해결방법으로 수행되어야 한다. 디지털 시스템에서, 도 7에 나타난 바와 같이, NLCV 축(701)은 양자화될 수 있다. 이 경우에, LCV 축(702)은 2 개의 인접한 NLCV 사이의 변환(711)에서의 최소의 변화를 나타내는데 충분한 해상도를 가져야 한다. 이는 NLCV 단계(712) 및 대응하는 LCV 단계(713)로서 도시된다. LCV가 선명도 (definition)에 의해 선형임에 따라, 전체 LCV 축(702)의 해상도는 단계(713)를 나타내는 데 충분해야 한다. 따라서, LCV는 이미지 정보의 손실을 피하기 위해 NLCV 보다 더 미세한 해상도로 정의될 수 있다. 해상도는 나이퀴스트(Nyquist) 샘플링으로 유추에 의해 단계 713의 해상도의 2배일 수 있다.

[0102] 변환(711)은 노화되지 않은 서브픽셀에 대한 이상적 변환이다. 전체로서 패널 또는 임의 서브픽셀의 노화와의 어떠한 관계도 가지지 않는다. 구체적으로는, 변환(711)은 임의  $V_{th}$ ,  $V_{oled}$ , 또는 OLED 효율성 변화 때문에 수정되지 않는다. 각각의 색상에 대한 하나의 변환 또는 모든 색상에 대한 하나의 변환이 존재할 수 있다. 변환(711)을 통해, 도메인-전환 유닛은 유리하게는, 2 개가 정보를 공유하지 않고 함께 동작하도록 하는, 보상기로부터 이미지-처리 경로를 결합해제한다. 이는 이들 모드의 이행을 단순화한다.

- [0103] 사분면 II를 참고하면, 보상기(13)는 서브픽셀마다 기초하여 변경된 선형 코드 값(CLKV)으로 LCV를 변경한다. 도 7은 일반성을 잃지 않고, 직선의  $V_{th}$  이동에 대한 정정을 나타낸다. 직선의  $V_{th}$  이동은 LCV에서 CLKV로의 직선의 전압 이동에 의해 수정될 수 있다. 다른 노화 영향은 "이행"에서 전술된 바와 같이 처리될 수 있다.

- [0104] 곡선(721)은 노화되지 않은 서브픽셀에 대한 보상기의 움직임을 나타낸다. 이 경우에, CLKV는 LCV와 동일할 수 있다. 곡선(722)은 노화된 서브픽셀에 대한 보상기의 움직임을 나타낸다. 이 경우에, CLKV는 당해 서브픽셀의  $V_{th}$  이동을 나타내는 오프셋에 더해진 LCV일 수 있다. 따라서, CLKV는 일반적으로 보상에 헤드룸(headroom)을 제공하기 위해 LCV 보다 큰 범위를 필요로 할 것이다. 예를 들어, 서브픽셀이 새거인 경우 256 개의 LCV를 필요로 하고, 이이 수명에 걸쳐 최대 이동이 128 개의 LCV라면, CLKV는 매우-노화된 서브픽셀의 보상을 클리핑하는 것을 피하기 위해  $384=256+128$ 에 달하는 값들을 나타내는 것이 필요할 것이다.

- [0105] 도 7은 보상기 및 도메인-전환 유닛의 영향의 복잡한 예를 나타낸다. 도 7 상의 점선 화살표를 따르면, 3의 NLCV은 사분면 I에 나타난 바와 같이, 9의 LCV로 변환(711)을 통해 도메인-전환 유닛(12)에 의해 변환된다. 노화된 서브픽셀에 대해, 보상기(13)는 사분면 II에 나타난 바와 같이, 9의 CLKV로서 곡선(721)을 통과할 것이다. 12 개의 CLKV와 유사한  $V_{th}$  이동을 가지는 노화된 서브픽셀에 대해, 9의 LCV는  $9+12=21$ 의 CLKV로 곡선(722)을 통해 전환될 것이다.

- [0106] 실제로, NLCV는 이미지-처리 경로로부터의 코드 값일 수 있으며 8 비트 이상을 가질 수 있다. 각각의 프레임에 대해, 패널 상의 각각의 서브픽셀에 대한 NLCV가 있을 수 있다. LCV는 소스 드라이버에 의해 구동되도록 전압을 나타내는 선형 값일 수 있으며, 전술한 바와 같이, 충분한 해상도를 가지기 위해, NLCV 보다 많은 비트를 가질 수 있다. CLKV는 또한 소스 드라이버에 의해 구동되기 위해 전압을 나타내는 선형 값일 수 있다. 이들은 전술한 바와 같이, 보상을 위해 헤드룸을 제공하기 위해 LCV보다 많은 비트를 가질 수 있다. 설명된 바와 같이 입력 NLCV로부터 각각 발생된, 각각의 서브픽셀에 대해 LCV 및 CLKV가 존재할 수 있다.

- [0107] 일 실시예에서, 코드 값(NLCV), 또는 이미지 처리 경로로부터의 비선형 입력 신호는 9 비트 와이드이다. 비선형 입력 신호에서 선형 코드 값으로의 변환은 LUT 또는 함수에 의해 수행될 수 있다. 보상기는 바람직한 전압을 나타내는 11-비트 선형 코드 값에서 취할 수 있으며 선형 소스 드라이버(14)로 전송하기 위해 12-비트 변경된 선형 코드 값을 발생한다. 선형 소스 드라이버는 변경된 선형 코드 값에 응답하여 부착된 EL 서브픽셀의 구동 트랜지스터의 게이트 전극을 구동할 수 있다. 보상기는 보상을 위한 헤드룸을 제공하기 위해, 즉 최소 선형 코드 값 단계(74)에 필요한 경우, 새로운 확장된 범위를 가로질러 동일한 해상도를 유지하는 동안 전압 범위(79)로 전압 범위(78)를 확장하기 위해, 입력보다 출력 상의 더 큰 비트 깊이를 가질 수 있다. 보상기 출력 범위는 곡선(71)의 범위의 위로뿐만 아니라 아래로 확장할 수 있다.

- [0108] 각각의 패널 설계는 최대  $V_{th}$  이동(73),  $V_{oled}$  상승 및 효율성 손실이 패널의 설계 수명 상의 무엇인지를 결정하기 위해 특정될 수 있으며, 보상기 및 소스 드라이버는 보상하기에 충분한 범위를 가질 수 있다. 이 특성은 필요한 전류로부터 표준 트랜지스터 포화-영역  $Ids$  방정식을 통해 필요한 게이트 바이어스 및 트랜지스터 치수로, 이후 시간에 걸쳐 a-Si 저하에 대해 당해 기술에 공지된 다양한 모델을 통해 시간에 걸쳐  $V_{th}$  이동으로 나아갈 수 있다.

- [0109] 동작의 순서

- [0110] 패널 설계 특성화

- [0111] 이 부분은 특정 OLED 패널 설계의 대량 생산의 맥락에서 쓰여졌다. 대량 생산의 시작 전에, 이 설계는 특징될 수 있다: 가속 수명 검사가 수행될 수 있고, 그리고 I-V 곡선은 다양한 레벨로 노화된 다양한 샘플 패널들 상의 다양한 색상의 다양한 서브픽셀에 대해 측정된다. 필요한 측정의 유형 및 횟수, 및 노화 레벨의 유형 및 개수는 특정 패널의 특성에 좌우된다. 이들 측정으로, 값 알파( $\alpha$ )는 계산될 수 있으며 측정 기준 게이트 전압은 선택될 수 있다. 알파(도 6c, 항목 634)는 시간에 걸쳐 직선의 이동으로부터의 편차를 나타내는 값이다. 예를 들어, 단독으로  $V_{th}$  이동에 대한 케이스의 경우, 모든 노화를 나타내는 0의  $\alpha$  값은 전압 축 상의 직선 이동이다. 측정 기준 게이트 전압(도 5a 310)은 보상을 위해 노화 신호 측정을 하는 전압이며, 전력 손실을 낮게 유지하는 동안 양호한 S/N 비를 제공하도록 선택된다.

- [0112]  $\alpha$  값은 최적화에 의해 계산될 수 있다. 일 예가 표 1에 주어진다.  $\Delta V_{th}$ 는 다수의 노화 조건들 하에서, 다수의 게이트 전압들에서 측정될 수 있다.  $\Delta V_{th}$  차는 측정 기준 게이트 전압(310)에서의  $\Delta V_{th}$ 와 각각의  $\Delta V_{th}$  사이에

서 계산될 수 있다. 측정 기준 게이트 전압(310)과 각각의 게이트 전압 사이의  $V_g$  차가 계산될 수 있다. 방정식 1의 내부 항, 즉  $\Delta V_{th} \cdot a \cdot (V_{g,ref} - V_{in})$ 은, 방정식에서의  $\Delta V_{th}$ 로서 측정 기준 게이트 전압(310)에서의 적절한  $\Delta V_{th}$ 를 사용하고,  $(V_{g,ref} - V_{in})$ 로서 적당한 계산된 게이트 전압 차를 사용하여, 예상된  $\Delta V_{th}$  차를 내기 위해 각각의 측정에 대해 계산될 수 있다.  $a$  값은 예상된  $\Delta V_{th}$  차와 계산된  $\Delta V_{th}$  차 사이의 오류를, 감소시키고, 바람직하게는 수학적으로 최소화하도록 선택될 수 있다. 오류는 RMS 차 또는 최대 차로서 표현될 수 있다.  $V_g$  차의 함수로서  $\Delta V_{th}$  차의 최소 자승법(least squares fitting)과 같은 당해 기술에 공지된 대안의 방법이 또한 사용될 수 있다.

## 표 1

[0113]

### a 계산의 예

| $V_g$                | $\Delta V_{th}$ |      | $V_g$ 차 | $\Delta V_{th}$ 차 |      | 예상된 $\Delta V_{th}$ 차 | 오류   |      |

|----------------------|-----------------|------|---------|-------------------|------|-----------------------|------|------|

|                      | 1일              | 8일   |         | 1일                | 8일   |                       | 1일   | 8일   |

| 기준= 13.35            | 0.96            | 2.07 | 0       | 0                 | 0    | 0.00                  | 0.00 | 0.00 |

| 12.54                | 1.05            | 2.17 | 0.81    | 0.09              | 0.1  | 0.04                  | 0.08 | 0.05 |

| 11.72                | 1.1             | 2.23 | 1.63    | 0.14              | 0.16 | 0.08                  | 0.17 | 0.06 |

| 10.06                | 1.2             | 2.32 | 3.29    | 0.24              | 0.25 | 0.16                  | 0.33 | 0.08 |

| $V_{g,ref} - V_{in}$ |                 |      |         | $a = 0.0491$      |      | 최대=0.08               |      |      |

[0114]

$a$  및 측정 기준 게이트 전압 이외에, 특성화는 또한 전술한 바와 같이,  $V_{th}$  이동의 함수로서  $V_{oled}$  이동,  $V_{th}$  이동의 함수로서 효율성 손실, 서브픽셀당 자기-가열 성분, 최대  $V_{th}$  이동,  $V_{oled}$  이동 및 효율성 손실, 및 보상기와 비선형-선형 변환(transform)에 필요한 해상도를 결정할 수 있다. 요구된 해상도는 본 발명에 참조로 통합되어 있는, 2007/4/13 날짜의 알레시(Alessi) 등에 의한, "Calibrating RGBW Displays"란 명칭의, 동시 계류중인 USSN 11/734,934와 같은 패널 교정 절차와 함께 특징지어질 수 있다. 특성화는 또한, 아래의 "이 필드에서" 더 설명되어 있는 바와 같이, 필드에서의 특성 측정을 하기 위한 조건을 결정한다. 모든 이런 결정은 당업자에 의해 이뤄질 수 있다.

[0115]

### 대량 생산

[0116]

설계가 일단 특정된다면, 대량 생산이 시작할 수 있다. 제조 시에, 하나 이상의 I-V 곡선은 생산된 각각의 패널에 대해 측정된다. 이를 패널 곡선은 다수의 서브픽셀에 대한 곡선들의 평균일 수 있다. 다른 색상, 또는 패널의 다른 영역에 대한 개별 곡선들이 존재할 수 있다. 전류는 현실적 I-V 곡선을 형성하기 위해 충분한 구동 전압으로 측정될 수 있다; I-V 곡선에서의 임의 오류가 결과에 영향을 미칠 수 있다. 또한 제조 시에, 기준 전류, 측정 기준 게이트 전압에서의 전류는 패널 상의 모든 서브픽셀에 대해 측정될 수 있다. I-V 곡선 및 기준 전류는 패널과 함께 저장되고 이는 이 필드로 전송된다.

[0117]

### 이 필드에서

[0118]

이 필드에서 일단, 패널 상의 서브픽셀은 이들이 얼마나 세게 구동되는지에 따라 다른 비율로 노화한다. 약간의 시간 이후, 하나 이상의 픽셀은 이들이 보상될 필요가 있는데 충분히 멀리 이동된다. 이 시간을 결정하는 방법이 이하 고려된다.

[0119]

보상하기 위해, 보상 측정이 행해지고 적용된다. 보상 측정은 측정 기준 게이트 전압에서 각각의 픽셀의 전류를 가진다. 측정은 위의 "알고리즘"에 설명되어 있는 바와 같이 적용된다. 측정은 저장되어, 측정되는 다음 시간까지, 서브픽셀이 구동될 때마다 적용될 수 있다. 전체 패널 또는 이의 임의 서브세트는 보상 측정을 한 경우 측정될 수 있다; 임의 서브픽셀을 구동하는 하는 경우, 이 서브픽셀에 대한 가장 최근 측정이 보상에 사용될 수 있다. 이는 또한 모든 서브픽셀이 가장 최근 패스에서 측정되지 않더라도 패널 전체의 보상을 허용하는, 서브픽셀의 제 1 서브세트가 한 번에 측정될 수 있고, 제 2 서브세트는 다른 시간에 측정될 수 있음을 의미한다. 하나의 서브픽셀 보다 많은 블록들이 또한 측정될 수 있고, 동일한 보상이 블록에서의 모든 서브픽셀에 적용되지만, 그러나 이는 블록-경계 아티팩트(Artifact)를 도입하는 것을 방지하기 위한 주의를 필요로 한다. 또한, 하나의 서브픽셀보다 많은 블록을 측정하는 것은 높은 공간-주파수 패턴의 가시적 번-인에 취약성(vulnerability)을 도

입한다; 이와 같은 패턴은 블록 크기보다 작은 피처를 가질 수 있다. 이 취약성은 개별 서브픽셀과 비교하여 다수-서브픽셀 블록들을 측정하는데 필요한 감소된 시간에 대해 균형이 유지될 수 있다.

[0120] 자주 또는 원한다면 드물게 보상 측정을 할 수 있고; 전형적 범위는 8시간마다 한번에서 4 주마다 한번일 수 있다. 도 8은 패널이 얼마나 활성하는지의 함수로서 보상 측정을 얼마나 자주 할 수 있는지의 일 예를 나타낸다. 이 곡선은 일 예일뿐이며, 실제로 이 곡선은 임이 특정 패널 설계의 가속된 수명 검사를 통해 이 설계에 대해 결정될 수 있다. 측정 주파수는 시간에 걸쳐 EL 디바이스 및 구동 트랜지스터의 특성에서의 변화율에 기초하여 선택될 수 있다; 패널이 새것인 경우, 이동이 빠르며, 그래서 패널이 오래된 것보다는 새것인 경우 자주 더 보상 측정을 할 수 있다. 언제 보상 측정을 하는지를 결정하기 위한 다양한 방법이 존재한다. 예를 들어, 주어진 소정의 구동 전압에서 활성인 전체 패널에 의해 얻어진 전체 전류가 측정될 수 있고 동일한 측정의 이전 결과와 비교될 수 있다. 또 다른 예에서, 온도 및 주위 광과 같은, 패널에 영향을 미치는 환경 요인들은 측정될 수 있고, 예를 들어, 주위 온도가 소정의 역치보다 많이 변한다면, 보상 측정을 한다. 대안으로는, 개별 서브픽셀의 전류가 패널의 이미지 영역 안에서 또는 밖에서 측정될 수 있다. 패널의 이미지 영역 밖이라면, 서브픽셀들은 측정 목적을 위해 제공된 기준 서브픽셀일 수 있다. 서브픽셀은 필요한 주변 조건의 일부가 무엇이든지 간에 노출될 수 있다. 예를 들어, 서브픽셀은 주위 광이 아니라 주위 온도에 응답하도록 하기 위해 불투명한 물질로 덮어질 수 있다.

[0121] 구동 회로에서의 트랜지스터가 n-채널 트랜지스터인 상기 실시예들을 구성하였다. 트랜지스터가 p-채널 트랜지스터이거나, n-채널 및 p-채널의 소정의 조합인 실시예들이, 회로에 대한 적절히 주지된 수정으로, 본 발명에서 또한 유용할 수 있음을 당업자는 이해할 것이다. 또한, 전술한 실시예는 비-반전(공통-캐소드)에서의 OLED를 나타낸다; 본 발명은 또한 반전(공통-애노드) 구성에 적용된다. 구동 회로에서의 트랜지스터가 a-Si 트랜지스터인 상기 실시예들을 더 구성하였다. 상기 실시예들은 시간의 함수로서 안정적이지 않은 임의 액티브 매트릭스 백플레이에 적용할 수 있다. 예를 들어, 유기 반도체 물질 및 아연 산화물로부터 형성된 트랜지스터는 시간의 함수로서 변한다고 알려져 있으며 그러므로 이 동일한 접근은 이를 트랜지스터에 적용될 수 있다. 또한, 본 발명이 트랜지스터 노화에 상관 없이 EL 디바이스 노화를 보상할 수 있음에 따라, 본 발명은 또한 LTPS TFT와 같은, 노화하지 않은 트랜지스터를 가지는 액티브-매트릭스 백플레이에 적용될 수 있다. 본 발명은 또한 OLED 이외의 EL 디바이스에 적용된다. 다른 EL 디바이스 유형의 저하 모드가 전술한 저하 모드와 다를 수 있더라도, 본 발명의 측정, 모델링 및 보상 기술은 여전히 적용될 수 있다.

## 부호의 설명

[0122] 10 전체 시스템

11 비선형 입력 신호

12 전압 도메인으로의 컨버터

13 보상기

14 선형 소스 드라이버

15 OLED 구동 회로

16 전류-측정 회로

30 OLED 패널

31 소스 드라이버

32a 열 라인

32b 열 라인

32c 열 라인

33 게이트 드라이버

34a 행 라인

34b 행 라인

- 34c 행 라인

- 35 서브픽셀 매트릭스

- 36 선택 트랜지스터

- 41 측정

- 42 측정

- 43 차

- 49 측정

- 60 보상기

- 61 블록

- 62 블록

- 63 블록

- 64 블록

- 71 I-V 곡선

- 73 전압 이동

- 74 코드 값 단계

- 75 전압 단계

- 76 전압 단계

- 78 전압 범위

- 79 전압 범위

- 90 선형 팻

- 200 스위치

- 201 구동 트랜지스터

- 202 OLED 디바이스

- 203 게이트 전극

- 204 제 1 공급 전극

- 205 제 2 공급 전극

- 206 전압 공급기

- 207 제 1 전극

- 208 제 2 전극

- 210 전류 미러 유닛

- 211 전압 공급기

- 212 제 1 전류 미러

- 213 제 1 전류 미러 출력

- 214 제 2 전류 미러

- 215 바이어스 공급기

- 216 전류-전압 컨버터

220 상관 이중-샘플링 유닛

221 샘플-및-유지 유닛

222 샘플-및-유지 유닛

223 차동 증폭기

230 아날로그-디지털 컨버터

421 자기-가열 량

422 자기-가열 량

424 차

501 노화되지 않은 I-V 곡선

502 노화된 I-V 곡선

503 전압차

504 전압차

505 전압차

506 전압차

510 측정 기준 케이트 전압

511 전류

512a 전류

512b 전류

513 전압

514 전압 이동

550 전압 이동

552 전압 이동

601 서브픽셀 위치

602 명령된 전압

603 보상된 전압

611 전류

612 전류

613 퍼센트 전류

614 퍼센트 효율성

619 메모리

621 전류

622 전압

626 블록

628 연산

631 전압 이동

632 알파 값

633 연산

691 I-V 곡선

692 I-V 곡선의 역

695 모델

701 측

702 측

703 측

711 변환에서의 최소 변화

712 단계

713 단계

721 변환

722 변환

1002 저장 커패시터

1011 버스 라인

1012 시트 캐소드

## 도면

### 도면1

## 도면2

## 도면3

## 도면4a

## 도면4b

도면5a

도면5b

## 도면6a

## 도면6b

## 도면6c

## 도면7

## 도면8

도면9

도면10

|                |                                                                                                                                  |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种电致发光显示器，具有用于激活驱动晶体管的补偿模拟信号                                                                                                     |         |            |

| 公开(公告)号        | KR101253717B1                                                                                                                    | 公开(公告)日 | 2013-04-12 |

| 申请号            | KR1020107016388                                                                                                                  | 申请日     | 2008-12-11 |

| [标]申请(专利权)人(译) | 全球OLED TECH                                                                                                                      |         |            |

| 申请(专利权)人(译)    | 글로벌오엘아이디테크놀러지엘엘씨                                                                                                                 |         |            |

| 当前申请(专利权)人(译)  | 글로벌오엘아이디테크놀러지엘엘씨                                                                                                                 |         |            |

| [标]发明人         | LEON FELIPE ANTONIO<br>레온펠립안토니오<br>WHITE CHRISTOPHER JASON<br>화이트크리스토퍼제이슨<br>PARRETT GARY<br>파럿게리<br>PRIMERANO BRUNO<br>프리마라노브루노 |         |            |

| 发明人            | 레온펠립안토니오<br>화이트크리스토퍼제이슨<br>파럿게리<br>프리마라노브루노                                                                                      |         |            |

| IPC分类号         | G09G3/30                                                                                                                         |         |            |

| CPC分类号         | G09G3/3291 G09G3/3233 G09G2300/0417 G09G2320/029 G09G2320/043 G09G2320/045                                                       |         |            |

| 代理人(译)         | Gimyongin                                                                                                                        |         |            |

| 优先权            | 11/962182 2007-12-21 US                                                                                                          |         |            |

| 其他公开文献         | KR1020100105732A                                                                                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                        |         |            |

### 摘要(译)

提供了用于在EL器件中施加电流的驱动电路处向驱动晶体管的栅极提供模拟驱动晶体管控制信号的装置，并且驱动电路包括线性源极驱动器，其包括电连接到的电源供应器。驱动晶体管的第一馈电电极和EL器件电连接到驱动晶体管的第二馈电电极，并且响应于改变的线性码值产生模拟驱动晶体管控制信号，用于操作栅极电极。驱动晶体管和补偿器，用于响应老化信号改变线性码值，以补偿由EL器件和驱动晶体管的工作时间和测试电路引起的驱动晶体管特性的变化：装置：用于提供线性码值的驱动晶体管和用于mea的EL器件在另一时间确定通过第一和第二馈电电极的电流，以便提供表示EL器件性能变化的老化信号。