(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(51) Int. Cl.

H05B 33/00 (2006.01)

(45) 공고일자

2007년08월09일

(11) 등록번호

10-0747418

(24) 등록일자

2007년08월02일

(21) 출원번호 10-2000-0057639

(22) 출원일자 2000년09월30일

심사청구일자 2005년09월30일

(65) 공개번호 10-2001-0039961

(43) 공개일자 2001년05월15일

(30) 우선권주장 99-279870 1999년09월30일 일본(JP)

(73) 특허권자 가부시키가이샤 한도오따이 에네루기 켄큐쇼

일본국 가나가와肯 아쓰기시 하세 398

(72) 발명자 야마자키순페이

일본가나가와켄아쓰기시하세398가부시키가이샤한도오따이에네루기켄

큐쇼내

아라이야스유키

일본가나가와켄아쓰기시하세398가부시키가이샤한도오따이에네루기켄

큐쇼내

(74) 대리인 이병호

장훈

(56) 선행기술조사문현

EP0886329 EP0350907

JP11040347 JP12030871

심사관 : 김창균

전체 청구항 수 : 총 16 항

(54) 유기 이엘 표시 장치 및 전자 장치

(57) 요약

단결정 반도체 기판 위에 형성된 절연 게이트 전계 효과 트랜지스터들이 유기 EL 층으로 덮이는 액티브 매트릭스형의 유기 EL 표시 장치는, 상기 단결정 반도체 기판(도4의 413)이, 절연 재료로 형성된 받침판(401) 및 덮개판(405)과, 상기 받침판 및 상기 덮개판을 결합시키는 패킹 재료(404)에 의해 규정되는 빈 공간(414) 내에서 유지되며, 상기 빈 공간(414)은 불활성 가스 및 건조제로 채워지는 것을 특징으로 하며, 이에 의해 상기 유기 EL 층의 산화가 방지된다.

대표도

도 1

### 특허청구의 범위

#### 청구항 1.

액티브 매트릭스형 유기 EL 표시 장치에 있어서,

단결정 반도체 기판 위에 제공된 절연 게이트 전계 효과 트랜지스터;

상기 절연 게이트 전계 효과 트랜지스터 위에 제공된 유기 재료를 포함하는 EL 층;

절연 재료로 형성된 받침판(bed plate) 및 덮개판(cover plate); 및

상기 받침판 및 덮개판을 결합시키는 패킹 재료를 포함하며,

상기 단결정 반도체 기판은 상기 받침판, 상기 덮개판 및 상기 패킹 재료에 의해 규정된 공간 내에 유지되며,

상기 공간은 불활성 가스 및 건조제로 채워지며,

상기 단결정 반도체 기판은 상기 받침판 위에 고정되는, 액티브 매트릭스형 유기 EL 표시 장치.

#### 청구항 2.

액티브 매트릭스형 유기 EL 표시 장치에 있어서,

단결정 반도체 기판 위의 화소부에 제공된 절연 게이트 전계 효과 트랜지스터;

상기 절연 게이트 전계 효과 트랜지스터 위에 제공된 유기 재료를 포함하는 EL 층;

절연 재료로 형성된 받침판 및 덮개판; 및

상기 받침판과 덮개판을 결합시키는 패킹 재료를 포함하며,

상기 단결정 반도체 기판은 상기 받침판, 상기 덮개판 및 상기 패킹 재료에 의해 규정된 공간 내에 유지되며,

상기 덮개판은 상기 화소부와 겹치는 상기 덮개판의 영역에서 투광성 재료를 포함하며,

상기 공간은 불활성 가스와 건조제로 채워지며,

상기 단결정 반도체 기판은 상기 받침판 위에 고정되는, 액티브 매트릭스형 유기 EL 표시 장치.

#### 청구항 3.

액티브 매트릭스형 유기 EL 표시 장치에 있어서,

단결정 반도체 기판 위의 화소부에 제공된 절연 게이트 전계 효과 트랜지스터;

상기 절연 게이트 전계 효과 트랜지스터 위에 제공된 유기 재료를 포함하는 EL 층;

세라믹 재료로 형성된 받침판 및 덮개판; 및

상기 반침판 및 덮개판을 결합시키는 패킹 재료를 포함하며,

상기 단결정 반도체 기판은 상기 반침판, 상기 덮개판 및 상기 패킹 재료에 의해 규정된 공간 내에 유지되며,

상기 덮개판은 상기 화소부와 겹치는 상기 덮개판의 영역에서 투광성 재료를 포함하며,

상기 공간은 헬륨, 아르곤, 크립톤(kryton), 크세논 및 질소로 구성되는 그룹으로부터 선택된 불활성 가스와, 산화 바륨 및 실리카 젤로 구성되는 그룹으로부터 선택된 건조제로 채워지며,

상기 단결정 반도체 기판은 상기 반침판 위에 고정되는, 액티브 매트릭스형 유기 EL 표시 장치.

#### 청구항 4.

액티브 매트릭스형 유기 EL 표시 장치에 있어서,

단결정 반도체 기판 위에 제공된 절연 게이트 전계 효과 트랜지스터;

상기 절연 게이트 전계 효과 트랜지스터 위에 제공된 유기 재료를 포함하는 EL 층;

절연 재료로 형성된 반침판 및 덮개판; 및

상기 반침판 및 덮개판을 결합시키는 바인더 층을 포함하며,

상기 단결정 반도체 기판은 상기 반침판, 상기 덮개판 및 상기 바인더 층에 의해 규정된 공간 내에 유지되며,

상기 공간은 불활성 가스 및 건조제로 채워지며,

상기 단결정 반도체 기판은 상기 반침판 위에 고정되는, 액티브 매트릭스형 유기 EL 표시 장치.

#### 청구항 5.

액티브 매트릭스형 유기 EL 표시 장치에 있어서,

단결정 반도체 기판 위의 화소부에 제공된 절연 게이트 전계 효과 트랜지스터;

상기 절연 게이트 전계 효과 트랜지스터 위에 제공된 유기 재료를 포함하는 EL 층;

절연 재료로 형성된 반침판 및 덮개판; 및

상기 반침판 및 덮개판을 결합시키는 바인더 층을 포함하며,

상기 단결정 반도체 기판은 상기 반침판, 상기 덮개판 및 상기 바인더 층에 의해 규정된 공간 내에 유지되며,

상기 덮개판은 상기 화소부와 겹치는 상기 덮개판의 영역에서 투광성 재료를 포함하며,

상기 공간은 불활성 가스 및 건조제로 채워지며,

상기 단결정 반도체 기판은 상기 반침판 위에 고정되는, 액티브 매트릭스형 유기 EL 표시 장치.

## 청구항 6.

액티브 매트릭스형 유기 EL 표시 장치에 있어서,

단결정 반도체 기판 위의 화소부에 제공된 절연 게이트 전계 효과 트랜지스터;

상기 절연 게이트 전계 효과 트랜지스터 위에 제공된 유기 재료를 포함하는 EL 층;

세라믹 재료로 형성된 받침판 및 덮개판; 및

상기 받침판 및 덮개판을 결합시키는 바인더 층을 포함하며,

상기 단결정 반도체 기판은 상기 받침판, 상기 덮개판 및 상기 바인더 층에 의해 규정된 공간 내에 유지되며,

상기 덮개판은 상기 화소부와 겹치는 상기 덮개판의 영역에서 투광성 재료를 포함하며,

상기 공간은 헬륨, 아르곤, 크립톤, 크세논 및 질소로 구성되는 그룹으로부터 선택된 불활성 가스와, 산화 바륨 및 실리카겔로 구성되는 그룹으로부터 선택된 건조제로 채워지며,

상기 단결정 반도체 기판은 상기 받침판 위에 고정되는, 액티브 매트릭스형 유기 EL 표시 장치.

## 청구항 7.

제 1 항 내지 제 6 항 중 어느 한 항에 있어서,

상기 유기 EL 표시 장치는 고글형 표시 장치의 표시부로 사용되는, 액티브 매트릭스형 유기 EL 표시 장치.

## 청구항 8.

전자 장치에 있어서,

단결정 반도체 기판을 갖는 적어도 하나의 디스플레이;

상기 단결정 반도체 기판 위에 제공된 절연 게이트 전계 효과 트랜지스터;

상기 절연 게이트 전계 효과 트랜지스터 위에 제공된 유기 재료를 포함하는 EL 층;

절연 재료로 형성된 받침판 및 덮개판; 및

상기 받침판 및 덮개판을 결합시키는 패킹 재료를 포함하며,

상기 단결정 반도체 기판은 상기 받침판, 상기 덮개판 및 상기 패킹 재료에 의해 규정된 공간 내에 유지되며,

상기 공간은 불활성 가스 및 건조제로 채워지며,

상기 단결정 반도체 기판은 상기 받침판 위에 고정되는, 전자 장치.

## 청구항 9.

전자 장치에 있어서,

단결정 반도체 기판을 갖는 적어도 하나의 디스플레이;

상기 단결정 반도체 기판 위의 화소부에 제공된 절연 게이트 전계 효과 트랜지스터;

상기 절연 게이트 전계 효과 트랜지스터 위에 제공된 유기 재료를 포함하는 EL 층;

절연 재료로 형성된 반침판 및 덮개판; 및

상기 반침판 및 덮개판을 결합시키는 패킹 재료를 포함하며,

상기 단결정 반도체 기판은 상기 반침판, 상기 덮개판 및 상기 패킹 재료에 의해 규정된 공간 내에 유지되며,

상기 덮개판은 상기 화소부와 겹치는 상기 덮개판의 영역에서 투광성 재료를 포함하며,

상기 공간은 불활성 가스 및 건조제로 채워지며,

상기 단결정 반도체 기판은 상기 반침판 위에 고정되는, 전자 장치.

## 청구항 10.

전자 장치에 있어서,

단결정 반도체 기판을 갖는 적어도 하나의 디스플레이;

상기 단결정 반도체 기판 위의 화소부에 제공된 절연 게이트 전계 효과 트랜지스터;

상기 절연 게이트 전계 효과 트랜지스터 위에 제공된 유기 재료를 포함하는 EL 층;

세라믹 재료로 형성된 반침판 및 덮개판; 및

상기 반침판 및 덮개판을 결합시키는 패킹 재료를 포함하며,

상기 단결정 반도체 기판은 상기 반침판, 상기 덮개판 및 상기 패킹 재료에 의해 규정된 공간 내에 유지되며,

상기 덮개판은 상기 화소부와 겹치는 상기 덮개판의 영역에서 투광성 재료를 포함하며,

상기 공간은 헬륨, 아르곤, 크립톤, 크세논 및 질소로 구성되는 그룹으로부터 선택된 불활성 가스와, 산화 바륨 및 실리카겔로 구성되는 그룹으로부터 선택된 건조제로 채워지며,

상기 단결정 반도체 기판은 상기 반침판 위에 고정되는, 전자 장치.

## 청구항 11.

전자 장치에 있어서,

단결정 반도체 기판을 갖는 적어도 하나의 디스플레이;

상기 단결정 반도체 기판 위의 화소부에 제공된 절연 게이트 전계 효과 트랜지스터;

상기 절연 게이트 전계 효과 트랜지스터 위에 제공된 유기 재료를 포함하는 EL 층;

절연 재료로 형성된 반침판 및 덮개판; 및

상기 반침판 및 덮개판을 결합시키는 바인더 층을 포함하며,

상기 단결정 반도체 기판은 상기 반침판, 상기 덮개판 및 상기 바인더 층에 의해 규정된 공간 내에 유지되며,

상기 공간은 불활성 가스 및 건조제로 채워지며,

상기 단결정 반도체 기판은 상기 반침판 위에 고정되는, 전자 장치.

## 청구항 12.

전자 장치에 있어서,

단결정 반도체 기판을 갖는 적어도 하나의 디스플레이;

상기 단결정 반도체 기판 위의 화소부에 제공된 절연 게이트 전계 효과 트랜지스터;

상기 절연 게이트 전계 효과 트랜지스터 위에 제공된 유기 재료를 포함하는 EL 층;

절연 재료로 형성된 반침판 및 덮개판; 및

상기 반침판 및 덮개판을 결합시키는 바인더 층을 포함하며,

상기 단결정 반도체 기판은 상기 반침판, 상기 덮개판 및 상기 바인더 층에 의해 규정된 공간 내에 유지되며,

상기 덮개판은 상기 화소부와 겹치는 상기 덮개판의 영역에서 투광성 재료를 포함하며,

상기 공간은 불활성 가스 및 건조제로 채워지며,

상기 단결정 반도체 기판은 상기 반침판 위에 고정되는, 전자 장치.

## 청구항 13.

전자 장치에 있어서,

단결정 반도체 기판을 갖는 적어도 하나의 디스플레이;

상기 단결정 반도체 기판 위의 화소부에 제공된 절연 게이트 전계 효과 트랜지스터;

상기 절연 게이트 전계 효과 트랜지스터 위에 제공된 유기 재료를 포함하는 EL 층;

세라믹 재료로 형성된 반침판 및 덮개판; 및

상기 반침판 및 덮개판을 결합시키는 바인더 층을 포함하며,

상기 단결정 반도체 기판은 상기 반침판, 상기 덮개판 및 상기 바인더 층에 의해 규정된 공간 내에 유지되며,

상기 덮개판은 상기 화소부와 겹치는 상기 덮개판의 영역에서 투광성 재료를 포함하며,

상기 공간은 헬륨, 아르곤, 크립톤, 크세논 및 질소로 구성되는 그룹으로부터 선택된 불활성 가스와, 산화 바륨 및 실리카겔로 구성되는 그룹으로부터 선택된 건조제로 채워지며,

상기 단결정 반도체 기판은 상기 반침판 위에 고정되는, 전자 장치.

#### 청구항 14.

제 8 항 내지 제 13 항 중 어느 한 항에 있어서,

상기 디스플레이에는 렌즈 상에 장착되는, 전자 장치.

#### 청구항 15.

제 8 항 내지 제 13 항 중 어느 한 항에 있어서,

상기 전자 장치에는 좌 및 우 표시 유닛들 2개가 설치되는, 전자 장치.

#### 청구항 16.

제 8 항 내지 제 13 항 중 어느 한 항에 있어서,

상기 디스플레이에는 고글형 표시 장치의 표시부로 사용되는, 전자 장치.

명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 단결정 반도체를 활성층으로 사용하는 절연 게이트 전계 효과 트랜지스터들에 기초한 회로를 갖는 반도체 장치 및 상기 반도체 장치의 제조 방법에 관한 것이다. 보다 구체적으로, 본 발명은, 동일 기판이 화소부 및 상기 화소부 주위에 배치된 구동 회로들로 덮여지는 유기 일렉트로루미니센트 표시 장치(organic electroluminescent display device)로 대표되는 전기 광학 장치 및 상기 전기 광학 장치가 설치되는 전자 장치의 애플리케이션에 매우 적합하다. 부언하여, 본 명세서에서 "반도체 장치(semiconductor device)"란 반도체 특성을 활용하여 기능하는 전반적인 장치들을 가리키며, 상기 전기 광학 장치 및 전기 광학 장치를 탑재하는 전자 장비를 그 범주 내에 포함한다.

액정 표시 장치 및 유기 EL(ElectroLuminescent) 표시 장치 등으로 대표되는 평면 표시 장치(평면 패널 디스플레이들) 분야에서, 단결정 반도체 기판 위에 형성된 절연 게이트 전계 효과 트랜지스터들(이후 "전계 효과 트랜지스터들(field effect transistors)"을 간단히 "FETs"라 한다)을 사용하여 액티브 매트릭스형 표시 장치를 제조하는 기술이 공지되어 있다. 유기 기판 또는 석영 기판 위에 박막 트랜지스터들(이후 간단히 "TFTs"라 한다)을 형성하여 액티브 매트릭스형 표시 장치를 제조하는 경우와는 달리, 상기 기술에서는, 대규모 집적 회로들(LSIs)의 분야에서 사용된 기술을 그대로 적용할 수 있고, 고속에서 저전압 구동이 가능한 고성능의 TFTs를 기판 위에 고밀도로 집적하여 형성할 수 있다는 이점이 있다. 그렇지만 다른 한편, 기판이 가시광을 통과시키지 못하기 때문에 상기 표시 장치는 반사형 또는 자체 발광형에 제한되거나, 단결정 반도체 기판이 시장에서 이용 가능한 크기에 대해 제한된다는 단점이 고려되어 왔다.

표시 장치들의 분야에서 고화질화 및 완전 디지털화로의 기술 지향에 있어서, 상기 액티브 매트릭스형 표시 장치에 요구되는 성능 향상은 피할 수 없게 높아지고 있다. 그래서 화상을 표시하는데 하나의 화소부에 수십 내지 수백만 개의 트랜지스

터(예를 들어 TFTs 또는 FETs)를 배열하고, 상기 트랜지스터들에 화소 전극들을 각각 접속시켜 상기 액티브 매트릭스형 표시 장치를 제조한다. 동작에 있어서, 각각의 화소들에 인가되는 전압들을 대응하는 트랜지스터들의 스위칭 기능에 의해 제어하고, 이에 의해 몇몇 EL 소자들을 발광하게 하는 방식으로 해서 화상을 표시한다. 유기 EL 표시 장치에 있어서, 각각의 화소들에 배치된 스위칭 트랜지스터들이 ON으로 터되면, 화상 데이터에 따라 발생된 신호들에 의해 전류 제어 트랜지스터들에 전류들이 흐르게 되고, 이에 의해 EL 소자들이 자기 발광한다.

그렇지만, 상기 유기 EL 표시 장치의 기본 부분의 역할을 하는 유기 EL 층이 산화에 대해 매우 약하여, 소량의 산소만 있어도 쉽게 저하된다. 이 이외에도, 열에 약하며 이것도 또한 산화를 조장하는 요인이다. 산화에 대해 약하다는 결점은 유기 EL 소자의 수명을 단축시키는 원인이 되며, 상기 소자를 실제로 사용하는데 있어서 중대한 장애로 된다.

### 발명이 이루고자 하는 기술적 과제

본 발명의 목적은 위에서 언급한 문제를 극복하여 고신뢰성의 유기 EL 표시 장치를 제공하는 것이다.

본 발명의 다른 목적은 그러한 유기 EL 표시 장치를 표시부에 적용하여 상기 표시부의 신뢰성이 높은 전자 장치를 제공하는 것이다.

상기 목적들을 달성하기 위한 본 발명의 구성은, 액티브 매트릭스형 유기 EL 표시 장치에 있어서, 단결정 반도체 기판 위에 형성된 절연 게이트 전계 효과 트랜지스터들 위에 유기 EL 층이 형성되며, 상기 단결정 반도체 기판은 절연 재료로 형성된 반침판 및 덮개판과, 상기 반침판 및 덮개판들을 결합시키는 패킹 재료에 의해 규정되는 빈 공간 내에서 유지되며, 상기 빈 공간은 불활성 가스 및 건조제로 채워지는 것을 특징으로 한다.

또한, 본 발명의 구성은, 화소부를 갖는 액티브 매트릭스형 유기 EL 표시 장치에 있어서, 단결정 반도체 기판 위에 형성된 절연 게이트 전계 효과 트랜지스터들 위에 유기 EL 층이 형성되며, 상기 단결정 반도체 기판은 절연 재료로 형성된 반침판 및 덮개판과, 상기 반침판 및 덮개판들을 결합시키는 패킹 재료에 의해 규정되는 빈 공간 내에서 유지되며, 상기 덮개판은 상기 화소부와 겹치는 영역에서 투명성 부재로 형성되며, 상기 빈 영역은 불활성 가스 및 건조제로 채워지는 것을 특징으로 한다.

단결정 실리콘 기판은 단결정 반도체 기판으로 양호하게 사용될 수 있다. 이 이외에도, 상기 빈 영역은 헬륨, 아르곤, 크립톤, 크세논 및 질소로 구성되는 그룹으로부터 선택된 불활성 가스와, 산화 바륨 및 실리카 젤로 구성되는 그룹으로부터 선택된 건조제로 양호하게 채워진다.

### 발명의 구성

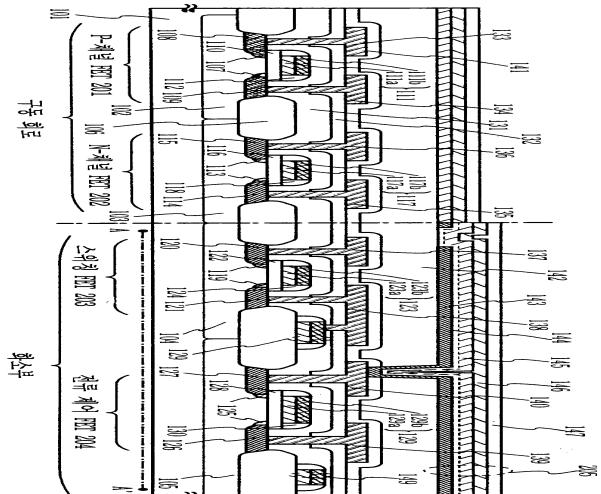

먼저, 본 발명에 따른 유기 EL 표시 장치에 대해 도 1을 참조해서 설명한다. 본 발명에 따른 상기 유기 EL 표시 장치는 화소부와 상기 화소부 주위의 구동 회로들이 단결정 반도체 기판(예를 들어, 단결정 실리콘 기판) 위에 형성되는 절연 게이트 형의 전계 효과 트랜지스터(FETs)를 사용해서 배치되는 구조를 갖는다.

기판(101)은 비교적 높은 저항(예를 들어, n형에서 약  $10[\Omega\text{cm}]$ )을 갖는 단결정 실리콘으로 이루어지며, 그 내부에 p 웨일(102) 및 n 웨일(103 내지 105)이 자기 정렬된다. 이웃하는 FET들은 웨일 산화막(106)에 의해 격리된다. 상기 웨일 산화막(106)의 형성에 있어서, 상기 기판(101)의 선택된 부분들에 봉소(B)를 이온 주입에 따라 주입해서 채널 스토퍼를 형성할 수 있다.

게이트 절연막(110, 116, 122 및 128)을 열 산화법으로 형성한다. 게이트들(111, 117, 123 및 129)은 다결정 실리콘 막으로부터 100 내지 300[nm]의 두께로 CVD에 의해 형성된 다결정 실리콘 층(111a, 117a, 123a 및 129a)로 구성되며, 그 위에 실리사이드 층들(111b, 117b, 123b, 및 129b)이 50 내지 300[nm]의 두께로 각각 형성된다. 상기 다결정 실리콘 층들은 저항을 낮추기 위해 사전에  $10^{21}[\text{cm}^3]$ 의 농도에서 인(P)으로 도핑될 수 있거나, 상기 다결정 실리콘 막이 형성된 후 고농도의 n형 불순물이 확산될 수 있다. 상기 실리사이드 층들의 재료로는 몰리드데늄 실리사이드( $\text{MoSi}_X$ ), 텅스텐 실리사이드( $\text{WSi}_X$ ), 탄탈륨 실리사이드( $\text{TaSi}_X$ ), 티타늄 실리사이드( $\text{TiSi}_X$ ) 등을 사용할 수 있으며, 상기 실리사이드 층들은 공지의 방법으로 잘 형성될 수 있다.

p 채널 FET(210)의 저농도 드레인(LDD) 영역들(107)은  $1 \times 10^{13}$  내지  $1 \times 10^{14} / \text{cm}^2$ 의 도즈량으로 불순물 원소로서 봉소(B)로 도핑되며, 상기 불순물 원소는 p형의 전도성을 제공한다. 한 편, n 채널 FET(202)의 LDD 영역들(113)과, 스위칭 FET(203)의 LDD 영역들(119 및 125)과, n 채널 FET들로 이루어진 전류 제어 FET(204)는 p형의 도즈량과 유사한 도즈량으로 불순물 원소로서 인(P) 또는 비소(As)로 도핑되며, 상기 불순물 원소는 n형의 전도성을 제공한다. 이들 LDD 영역들은 대응하는 게이트들을 마스크들로서 사용하여 이온 주입법 또는 이온 도핑법에 따라 자기 정합으로 각각 형성된다.

상기 LDD 영역들을 형성한 후, 실리콘 산화막 또는 실리콘 질화막과 같은 절연막이 결과적인 기판위 전체 표면 상에 CVD 법에 의해 형성되고, 상기 절연막이 이방성 드라이 에칭법에 의해 그 전체 영역에 대해 불균일하게 에칭되어, 대응하는 게이트들의 측벽들 위에 남겨지게 되는 방식으로 측벽 스페이서들(112, 118, 124, 및 130)이 형성된다. 상기 대응하는 측벽 스페이서들을 마스크들로서 사용함으로써 각각의 FETs의 소스 영역들과 드레인 영역들을 형성한다. 보다 구체적으로, p 채널 FET(201)의 소스 영역(108) 및 드레인 영역(109)을  $5 \times 10^{14}$  내지  $1 \times 10^{16} / \text{cm}^2$ 의 도즈량으로 봉소(B)를 이온 주입함으로써 형성한다. n채널 FET(202), 및 상기 n 채널 FET들로 이루어진 스위칭 FET(203) 및 전류 제어 FET(204)는, 소스 영역들(114, 120 및 126), 및 드레인 영역들(115, 121 및 127)에  $5 \times 10^{14}$  내지  $1 \times 10^{16} / \text{cm}^2$ 의 도즈량으로 비소(As)를 이온 주입함으로써 각각 형성된다.

플라즈마 CVD 법 또는 감압(low-pressure) CVD 법에 의해 양호하게 제조된 실리콘 산화막, 산화 실리콘 질화막 등에 100 내지 2000 nm의 두께로 제 1 층간 절연막을 형성한다. 또한, 상기 제 1 층간 절연막 위에 인규산염 유리(PSG), 봉소 규산염 유리(BSG), 또는 인봉소규산염 유리(PBSG)로 이루어진 제 2 층간 절연막(132)이 형성된다. 상기 제 2 층간 절연막(132)은 스픬 코팅법 또는 정상 압력 CVD법으로 제조된다. 상기 제조된 막은, 700 내지 900[°C]에서 열활성화 처리에 의해 리플로우(reflow)되고, 이것은 제조 후 실행되면서 열처리로도 가능하며, 이에 의해 상기 제 2 층간 절연막의 표면은 평탄화된다.

상기 대응하는 FETs의 소스 영역들과 드레인 영역들에 도달하는 접촉 구멍들을 상기 제 1 층간 절연막(131)과 상기 평탄화된 막(132)에 형성한 후, 소스 배선들(133, 135, 137 및 139) 및 드레인 배선들(134, 136, 138 및 140)을 각각 형성한다. 통상적으로 저저항 재료로서 종종 사용하는 알루미늄(Al)을 상기 배선들에 사용한다. 대안으로, Al 층과 티타늄(Ti) 층으로 구성되는 다층 구조체를 상기 배선들 각각에 사용할 수도 있다.

폐시베이션 막(141)을 플라스마 CVD 법에 의해 실리콘 질화막, 실리콘 산화막 또는 질화 실리콘 산화막으로 형성한다. 또한, 제 3 층간 절연막(142)을 유기 수지 재료로 1 [ $\mu\text{m}$ ] 내지 2 [ $\mu\text{m}$ ]의 두께로 형성한다. 상기 유기 수지 재료로서는, 폴리 이미드 수지, 폴리아미드 수지, 아크릴 수지, 벤젠-시클로-부탄(BCB) 중 임의의 것이 될 수 있다. 상기 유기 수지 재료를 사용하는 장점들은, 막을 형성하는 방법이 간단하다는 것과, 비교적 낮은 절연 상수로 인해 기생 용량이 낮아질 수 있다는 것과, 상기 재료가 평탄화에 적합하다는 것이다. 물론, 위에서 언급한 것과는 다른 유기 수지 막이 사용될 수도 있다. 본 문현에서는, 결과적인 기판상에 적용되어 열 중합에 의해 처리되는 형태의 폴리이미드 수지를 사용하여 클린 오븐(clean oven)에서 300[°C]에서 굽는다.

상기 전류 제어 FET(204)의 드레인 배선에 화소 전극(143)이 접속된다. 상기 화소 전극(143)은 Al로 대표되는 저저항 재료로 형성된다. Al 막은 공지의 막 형성 방법, 예를 들어 진공 증착법 또는 스팍터링법으로 쉽게 형성될 수 있다. 콘트라스트를 향상시키기 위해, 상기 화소 전극(143)의 표면을 거칠게 하여 확산 반사 표면(diffusing reflective surface)으로 한다.

상기 화소 전극들(143)을 형성한 후, 모든 화소 전극들 위에 일함수(work function)가 낮은 금속을 포함하는 음극층들(144)을 형성한다. 상기 음극층(144)은 수 nm으로 얇기 때문에, 층이 진짜로 형성되느지 또는 층이 산발적으로 섬 모양으로 형성되는지가 불명확하며, 그래서 그 윤곽을 점선으로 표시한다.

일함수가 낮은 금속을 포함하는 음극층(144)으로서 사용가능한 재료로서는, 리튬 불화물(LiF), 리튬 산화물( $\text{Li}_2\text{O}$ ), 바륨 불화물( $\text{BaF}_2$ ), 바륨 산화물( $\text{BaO}$ ), 칼슘 불화물( $\text{CaF}_2$ ), 칼슘 산화물( $\text{CaO}$ ), 스트론튬 산화물( $\text{SrO}$ ) 또는 세슘 산화물( $\text{Cs}_2\text{O}$ )이 있다. 상기 재료는 절연성이기 때문에, 상기 음극층(144)이 접속층일지라도 화소 전극들간에 단락 회로가 발생하지 않는다. 물론, MgAg 전극과 같은 전도성을 갖는 공지의 재료로 이루어진 음극층이 상기 음극층으로서 사용될 수 있다. 그렇지만, 선택적으로 음극들을 형성하거나 패턴화를 실행하여, 상기 화소 전극들이 단락 회로가 되는 것을 방지할 필요가 있다.

일 함수가 낮은 금속을 포함하는 음극층(144) 위에 유기 EL(ElectroLuminescent) 층(145)을 형성한다. 공지의 재료 또는 구조체를 상기 유기 EL 층(145)을 형성하는데 사용할지라도, 백색 발광이 가능한 재료가 본 발명에 사용된다. 구조적으로, 상기 유기 EL 층(145)을 재결합 위치를 제공하는 발광층으로만 형성할 수 있다. 필요하다면, 그 위에 전자 주입층, 전자 수송층, 정공 수송층, 전자 차단층, 정공 차단층 또는 정공 주입층을 적층하는 것도 가능하다. 본 명세서에 있어서, 캐리어가 주입, 수송 또는 재결합되는 모든 층을 "유기 EL 층(organic EL layer)"으로 칭한다.

또한, 유기 EL 층(145)에 사용되는 유기 EL 재료는 중합체에 기초한 고분자계 유기 EL 재료이다. 예를 들어, PVK(폴리비닐 카바졸), Bu-PBD(2-(4'-tert-부틸페닐)-5-(4"-비페닐)-1, 3, 4-옥사디아졸), 커마린 6, DCM 1(4-디시아노메틸렌-2-메틸-6-p-디메틸아미노스티릴-4H-피란), TPB(테트라페닐부타디엔) 및 나일 레드(Nile red)를 1,2-디클로로메탄 또는 클로로포름에 용해하고 그래서 얻어진 용액에 스펀 코팅법을 적용한다. 상기 용액으로 코팅된 기판 구조체를 약 500 내지 1000[rpm]의 회전 주파수에서 20 내지 60[초]동안 회전시켜 균일한 코팅막을 형성한다.

물론, 상기 코팅막은 상기 유기 EL 층이 적어도 3회, 양호하게는 5회 이상 (통상적으로, 투근법(dialyzing)으로) 정제된 후 형성되며, 이에 의해 상기 재료의 소듐 농도(sodium content)가 0.1[ppm] 이하(양호하게는, 0.01[ppm] 이하)로 낮아진다. 그래서, 상기 유기 EL 층(349)의 소듐 농도는 0.1[ppm] 이하(양호하게는, 0.01[ppm]이하)로 되며, 그 체적 저항은  $1 \times 10^{11}$  내지  $1 \times 10^{12} [\Omega\text{cm}]$ (양호하게는,  $1 \times 10^{12}$  내지  $1 \times 10^{13} [\Omega\text{cm}]$ )으로 된다.

이 방법으로 형성된 유기 EL 표시 장치 위에 투명 전도막이 양극층(146)으로서 형성된다. 상기 투명 전도막으로서는, 인듐 산화물 및 주석 산화물로부터 생성된 화합물(ITO라 칭함), 인듐 산화물 및 아연 산화물로부터 생성된 화합물, 주석 산화물( $\text{SnO}_2$ ), 아연 산화물( $\text{ZnO}$ )이 사용 가능하다.

또한, 상기 양극층(146) 위에 절연막이 패시베이션 막(147)으로서 형성된다. 상기 패시베이션 막(147)으로서는 실리콘 질화막 또는 질화 실리콘 산화막("SiO<sub>x</sub>N<sub>y</sub>"으로 표시함)이 가능하다.

본 명세서에서는 이때까지 완성된 기판 구조체를 "액티브 매트릭스 기판(active matrix substrate)"이라 칭한다. 즉, "액티브 매트릭스 기판"은, FETs, 상기 FETs에 전기적으로 접속된 화소 전극들, 및 화소 전극들을 음극들로서 포함하는 유기 EL 소자(음극층들, 상기 유기 EL 층 및 양극들로 구성되는 캐패시터들)로 형성되는 기판이다.

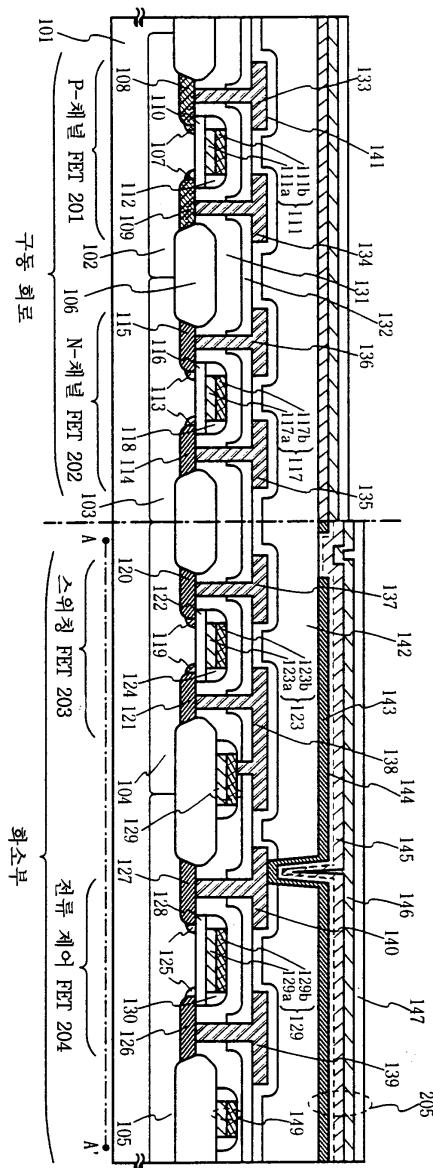

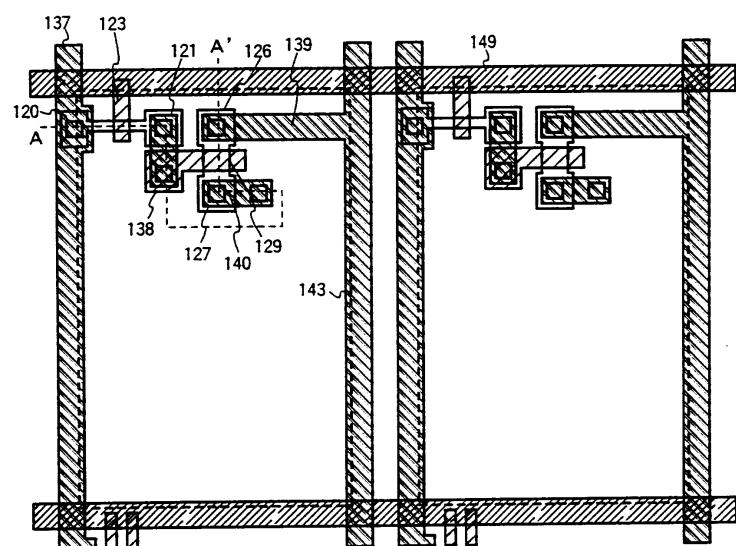

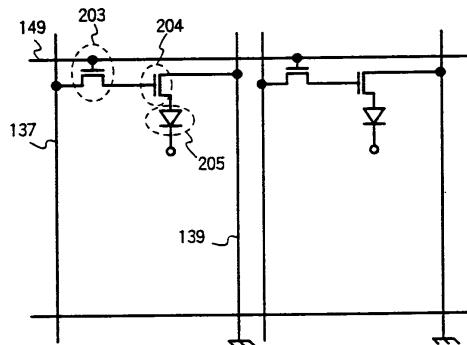

도 2(a)는 상기 액티브 매트릭스 기판의 화소부에 대한 평면도이며, 도 2(b)는 상기 화소부의 회로 배열에 대한 접속도이다. 실제로, 상기 화소부(화상 표시부)는 복수의 화소들이 매트릭스 모양으로 배열되도록 구성된다. 또한, 도 2(a)에서 A-A'를 따라 절취한 단면도가 도 1의 화소부의 단면도와 대응한다. 따라서, 도 1 및 도 2(a)에서 공통의 도면 부호가 사용되며, 두 도면을 양호하게 참조한다. 또한, 도 2(a)의 평면도에 두 개의 화소들이 도시되며, 이 두 개의 화소는 동일한 구조를 갖는다. 도 2(b)에 도시된 바와 같이, 화소 당 두 개의 FETs가 유기 EL 소자(205)에 설치된다. 상기 두 개의 FETs는 n 채널형이며, 스위칭 FET(203) 및 전류 제어 FET(204)로서 기능한다.

상기 방법에서, 상기 단결정 실리콘 기판 위에는, p 채널 FET(201) 및 n 채널 FET(202)로 구성되는 CMOS 회로를 각각 기본으로 하는 구동 회로들과, n 채널 FET로 형성된 스위칭 FET(203) 및 전류 제어 FET(204)를 각각 구비하는 화소부들이 형성된다. 상기 CMOS 회로를 기본으로 한 구동 회로들은 예를 들어 시프트 레지스터 회로, 버퍼 회로, 샘플링 회로, D/A 변환기 및 래치 회로를 형성할 수 있다. 그러한 회로들은, 액티브 층들이 단결정 실리콘으로 이루어지는 절연 게이트 FETs로 구성되기 때문에, 고속 동작이 가능하며, 구동 전압들을 3 내지 5[V]로 설정함으로써 낮은 전원 소비를 달성할 수 있다. 이 방법에서, 본 실시예에서 설명된 FETs의 구조체는 단순히 예에 지나지 않으며, 상기 FETs는 도 1에 도시된 구조체들에 제한되지 않는다.

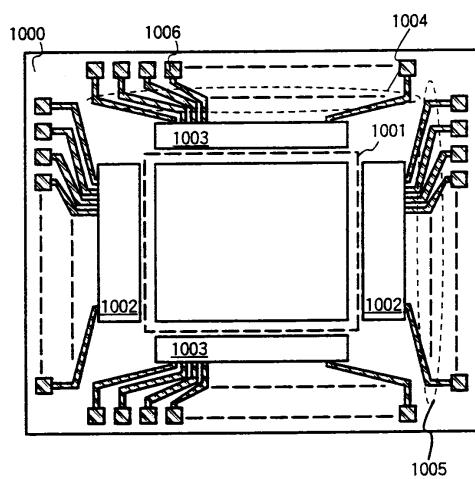

도 3은 액티브 매트릭스 기판을 도시하는 평면도이다. 도면을 참조하면, 액티브 매트릭스 기판은 기판(1000), 화소부(1001), 데이터 라인측 구동 회로들(1003), 및 주사 라인측 구동 회로들(1002)을 포함한다. 각각의 구동 회로에 대한 입력 단자들은 기판(1000)의 가장자리들에 설치된 와이어 본딩용 패드(1006)들이며, 이 패드들은 리드들(1004 내지 1005)을 통해 구동 회로들에 접속된다. 화소부의 크기는 0.5 인치 클래스 내지 2.5 인치 클래스가 제조에 적합하다.

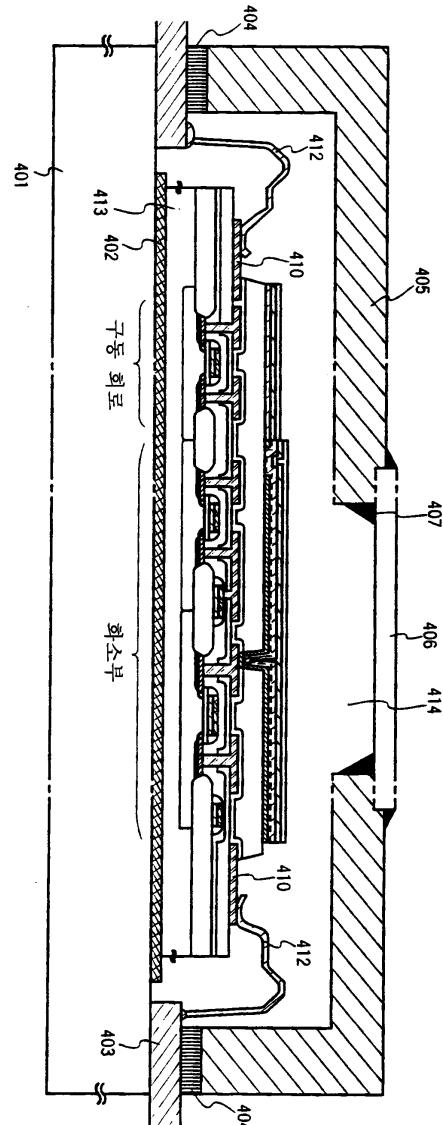

상기 유기 EL 층으로 형성된 액티브 매트릭스 기판은 패키지로 봉해져서 외부 충격 및 먼지나 습기와 같은 환경 상태들로부터 차단된다. 패키지의 모양이나 방식은 도 4에 예시되어 있다. 세라믹과 같은 절연 재료로 받침판(bed plate)(401)을

형성하고, 그 위에 저용점 유리 또는 금속화층(402)에 의해 상기 유기 EL 층이 형성된 액티브 매트릭스 기판(413)이 고정된다. 상기 액티브 매트릭스 기판(413)은 리드 프레임(404)에 의해 외부 회로와 접속되며, 상기 리드 프레임은 와이어 본딩용 패드(410)들을 통해 금(Au)으로 형성된 와이어들(412)에 의해 상기 액티브 매트릭스 기판(413)과 접속된다.

상기 액티브 매트릭스 기판(413)은 세라믹 덮개판(cover ceramic plate)(405)으로 봉해진다. 상기 세라믹 덮개판(405)은 바인더 층(404)에 의해 상기 받침판(401)과 결합된다. 상기 바인더 층(404)으로서는, 파이로세람 시멘트(pyroceram cement), 산화 비스무쓰계 유리(bismuth oxide-based glass), 산화 납계 유리(lead oxide-based glass) 등이 사용된다. 상기 액티브 매트릭스 기판(413)의 화소부 위에 상기 받침판(401)과 유사하게, 세라믹 등의 절연 재료로 이루어진 상기 덮개판(405)이 형성되는 영역에, 투명 석영판, 투명 유리판 등으로 이루어진 창 부재(406)가 접착제(407)로 장착되어 고정된다. 이 방법에서, 상기 유기 EL 층이 형성된 상기 액티브 매트릭스 기판(413)이 밀폐되어, 빈 공간(414)이 형성된다. 또한, 상기 빈 공간(414)은 불활성 가스(예를 들어, 아르곤, 헬륨, 크립톤, 크세논 또는 질소)가 채워지거나, 건조제(예를 들어, 바륨 산화물)가 그 안에 채워진다. 이 방법에서, 습기 등에 의한 상기 EL 소자의 저하를 방지할 수 있다.

본 실시예에서는 설명하지는 않았지만, 상기 액티브 매트릭스 기판의 유기 EL 층으로부터 형성된 개개의 화소에 대응하여 상기 유기 EL 층 위에 칼라 필터 또는 흑색 매트릭스 층들(광 차단층들)을 설치함으로써 칼라 표시도 구성할 수 있다. 대안으로, 도 4에 도시된 창(406)에 칼라 필터를 설치할 수도 있다.

위에서 서술한 바와 같이 도 4에 도시된 상태에서, 상기 리드 프레임(403)은 외부 장비의 단자에 접속되며, 이에 의해 화상 신호 등이 상기 화소부 상에 화상을 표시하기 위해 입력될 수 있다. 본 명세서에서는, 리드 프레임을 외부 회로에 부착시킴으로써, 화상이 표시 가능한 상태로 되는 물품을 "유기 EL 표시 장치(organic EL display device)"로서 규정된다.

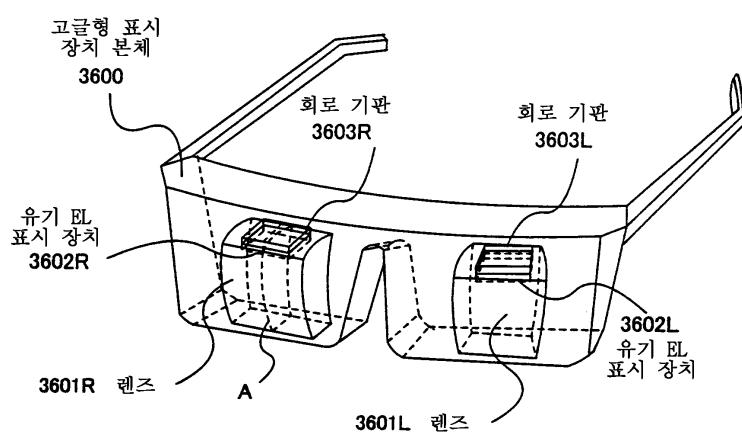

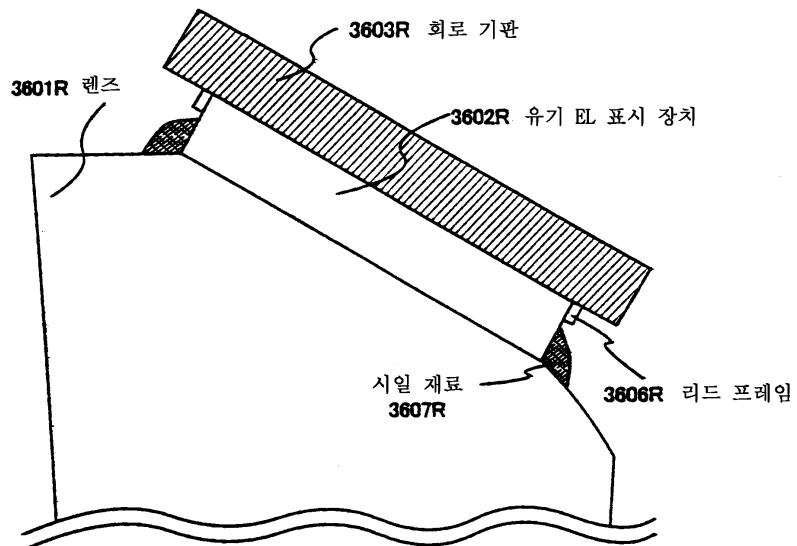

이제, 액티브 매트릭스형 유기 EL 표시 장치가 고글형 표시 장치로 사용되는 실제의 예에 대해 설명한다. 도 5는 본 예에서 고글형 표시 장치의 개략도를 도시한다. 상기 고글형 표시 장치의 본체(3600)는 두 개, 즉 좌우 표시부들을 가지며, 이 표시부들은 유기 EL 표시 장치들(3602R, 3602L), 회로 기판들(3603R, 3603L) 및 렌즈들(3601R, 3601L)로 구성된다.

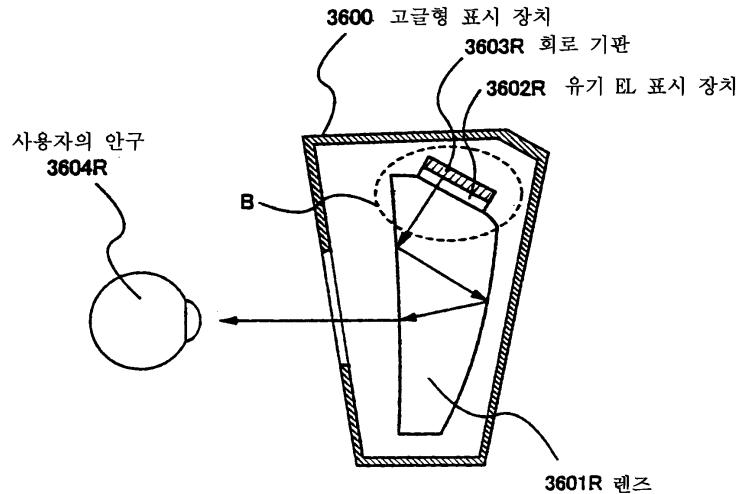

도 6(a)는 도 5에 표시된 부분 A의 단면도이고, 도 6(b)는 도 6(a)에 도시된 부분 B의 확대도이다. 도 6(a) 및 도 6(b)에 도시된 바와 같이, 본 예에서는, 상기 고글형 표시 장치(3600)에서, 상기 렌즈(3601R) 위에 장착된 유기 EL 표시 장치(3602R)가 리드 프레임(3606R)을 통해, 신호 제어 회로 등을 구비한 회로 기판(3603R)에 접속된다. 상기 유기 EL 표시 장치(3602R)로부터 발광하는 광은 도 6(a)의 화살표로 지시된 광 경로를 통해 사용자의 안구(3604R)에 도착하고, 이에 의해 사용자는 화상을 인식할 수 있다.

상기 유기 EL 표시 장치는 그 자체적인 발광에 의해 넓은 시야 각을 갖는다. 상기 고글형 표시 장치에 적용될 때, 상기 유기 EL 표시는, 상기 표시 장치와 관찰자의 눈이 상대적으로 어긋나는 경우에도 나빠지지 않는다.

### 발명의 효과

본 발명은 다음과 같은 효과를 갖는다.

절연 게이트 전계 효과 트랜지스터 및 EL 층이 형성된 단결정 반도체 기판이, 절연 재료로 형성된 받침판 및 덮개판과, 상기 받침판 및 덮개판들을 결합시키는 패킹 재료에 의해 규정되는 빈 공간에서 유지되고, 상기 빈 공간은 불활성 가스 및 전조제로 채워지며, 이에 의해 상기 EL 층의 산화는 고신뢰성의 유기 EL 표시 장치를 제공함으로써 방지된다.

### 도면의 간단한 설명

도 1은 액티브 매트릭스형의 유기 EL 표시 장치의 단면도.

도 2(a) 및 2(b)는 각각 유기 EL 표시 장치의 화소부의 평면도 및 회로 구성도.

도 3은 액티브 매트릭스형 유기 EL 표시 장치의 평면도.

도 4는 유기 EL 표시 장치의 내부 구조 단면도.

도 5는 유기 EL 표시 장치가 설치된 고글형 표시 장치의 구조를 도시하는 투시도.

도 6(a) 및 6(b)는 유기 EL 표시 장치가 설치된 고글형 표시 장치의 단면도.

\*도면의 주요 부호에 대한 설명

101 : 기판 102 : p 웨

103 내지 105 : n 웨 106 : 필드 산화막

107 : LDD(p) 108 : 소스(p)

109 : 드레인(p) 113, 119, 125 : LDD(n)

114, 120, 126 : 소스(n) 115, 121, 127 : 드레인(n)

110, 116, 122, 128 : 게이트 절연막

111, 117, 123, 129 : 게이트

112, 118, 124, 130 : 측벽

131 : 제 1 층간 절연막 132 : 제 2 층간 절연막

133, 135, 137, 139 : 소스 전극

134, 136, 138, 140 : 드레인 전극

141 : 패시베이션 막 142 : 제 3 층간 절연막

143 : 화소 전극 144 : 음극층

145 : EL 층 146 : 양극층

**도면**

도면1

도면2a

도면2b

도면3

도면4

도면5

도면6a

도면6b

|                |                                                                                                   |         |            |

|----------------|---------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机EL显示器和电子设备                                                                                      |         |            |

| 公开(公告)号        | <a href="#">KR100747418B1</a>                                                                     | 公开(公告)日 | 2007-08-09 |

| 申请号            | KR1020000057639                                                                                   | 申请日     | 2000-09-30 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                                                                      |         |            |

| 申请(专利权)人(译)    | 株式会社绒布器肯kyusyo极限戴哦                                                                                |         |            |

| 当前申请(专利权)人(译)  | 株式会社绒布器肯kyusyo极限戴哦                                                                                |         |            |

| [标]发明人         | YAMAZAKI SHUNPEI<br>아마자키순페이<br>ARAI YASUYUKI<br>아라이야스유키                                           |         |            |

| 发明人            | 아마자키순페이<br>아라이야스유키                                                                                |         |            |

| IPC分类号         | H05B33/00 H01L27/32 H01L51/52 H05B33/04                                                           |         |            |

| CPC分类号         | H01L51/5281 H01L51/524 H01L2251/5315 H01L27/3244 H01L51/5275 H05B33/04 H01L51/5259<br>H01L51/5237 |         |            |

| 代理人(译)         | 李，何炳<br>李昌勋                                                                                       |         |            |

| 优先权            | 1999279870 1999-09-30 JP                                                                          |         |            |

| 其他公开文献         | KR1020010039961A                                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                         |         |            |

## 摘要(译)

一种有源矩阵型有机EL显示装置，其中在单晶半导体衬底上形成的绝缘栅场效应晶体管覆盖有有机EL层；其特征在于，单晶半导体衬底（图4中的413）被保持在由床板（401）和由绝缘材料形成的盖板（405）限定的空余空间（414）中，并且用于粘合床和盖板的包装材料（404）；并且空余空间（414）填充有惰性气体和干燥剂，从而防止有机EL层氧化。