## (19) 대한민국특허청(KR)

### (12) 공개특허공보(A)

(51) Int. Cl.

G09G 3/30 (2006.01)

H05B 33/12 (2006.01)

(11) 공개번호

10-2006-0064534

(43) 공개일자

2006년06월13일

(21) 출원번호 10-2005-0118083

(22) 출원일자 2005년12월06일

(30) 우선권주장 JP-P-2004-00355401 2004년12월08일 일본(JP)

(71) 출원인 가부시키가이샤 히타치 디스플레이즈

일본국 치바켄 모바라시 하야노 3300(72) 발명자 다나카 마사히로

일본국 치바켄 치바시 미도리쿠 오유미노미나미 6-45-31

마츠우라 토시유키

일본국 치바켄 모바라시 시모나가요시 460

무라카미 하지메

일본국 도쿄도 신쥬쿠구 나카이 2-29-8

아키모토 하지메

일본국 도쿄도 코쿠분지시 나이토 1-2-7-703

(74) 대리인 특허법인 원전

심사청구 : 있음

## (54) 표시장치 및 그 구동방법

## 요약

표시장치의 표시 품위를 향상하는 것이 과제이다.

그 해결 수단으로서, 화소에, 빌광 소자, 스위칭 소자를 구비하고, 상기 스위칭 소자는, 상기 빌광 소자에 전원을 공급시키는 것으로서, 제1 스위칭 소자와 제2 스위칭 소자로 구성되며, 이들의 제1 및 제2 스위칭 소자는, 화소 내로의 데이터 신호의 입력에 따라, 한쪽이 정(正)바이어스 상태로 다른쪽이 역(逆)바이어스 상태로 되는 동시에, 상기 바이어스 상태는 상기 데이터 신호의 시계열적인 입력에 따라서 상기 제1 스위칭 소자와 제2 스위칭 소자의 사이에서 교대로 전환되어 동작되고, 상기 빌광 소자로의 전원의 공급은 제1 또는 제2 스위칭 소자를 통하는 것이 있다.

## 대표도

도 1

## 색인어

표시장치, 구동방법, 화소, 빌광, 소자, 스위칭, 바이어스, 전환, 전원, 데이터

## 명세서

### 도면의 간단한 설명

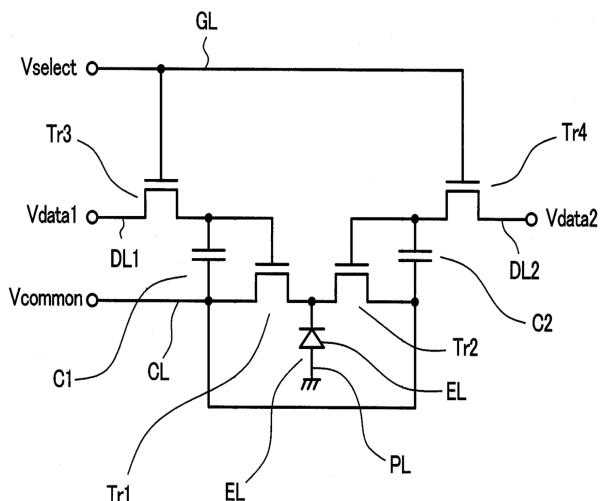

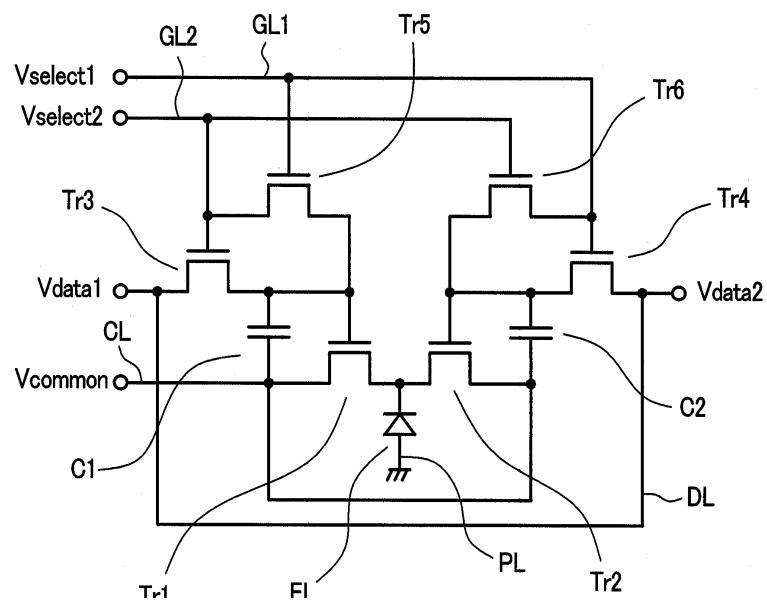

도 1은, 본 발명에 의한 표시장치의 화소 구성의 일실시예를 나타내는 등가회로도이다.

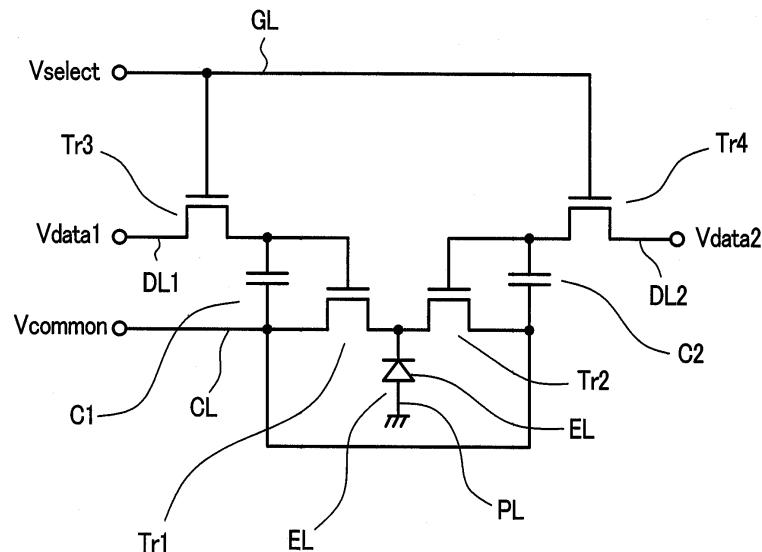

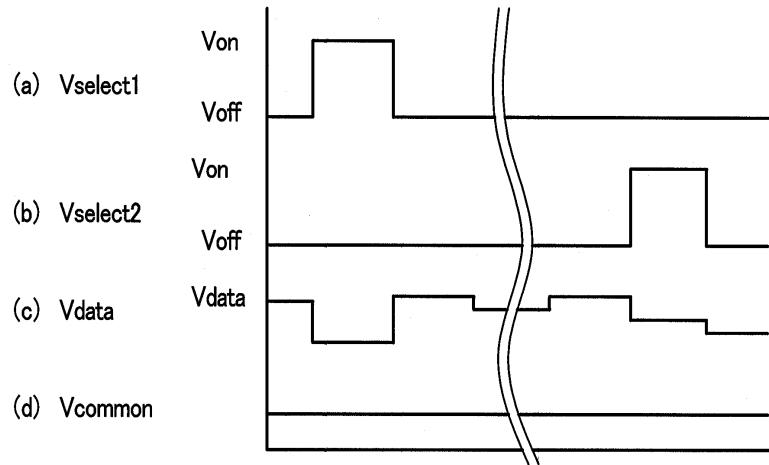

도 2는, 도 1에 나타낸 등가회로도에서의 동작 타이밍도이다.

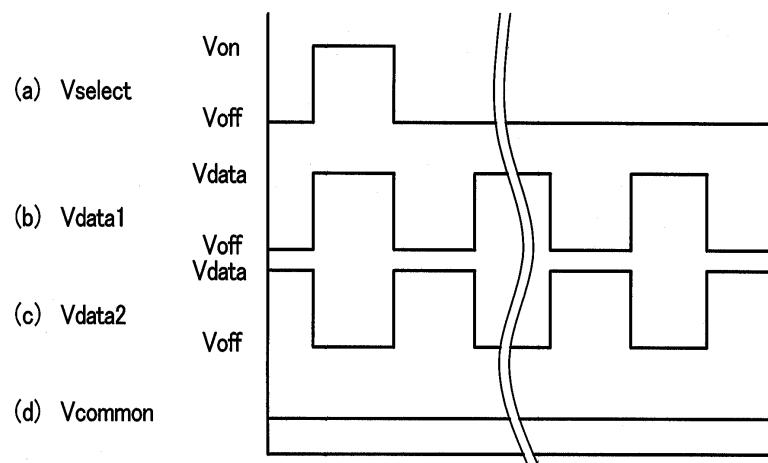

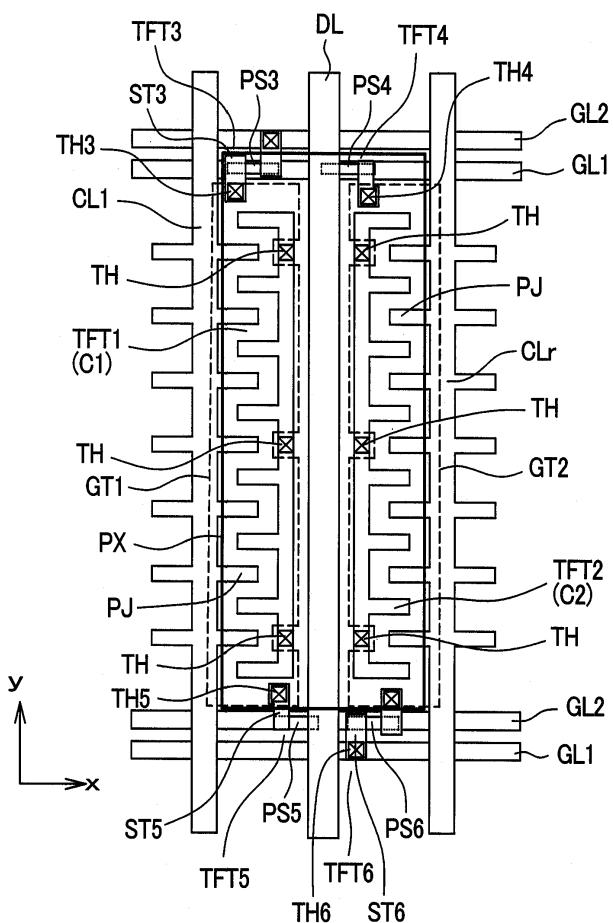

도 3은, 도 1에 나타낸 등가회로를 구비하는 화소 구성의 일실시예를 나타내는 평면도이다.

도 4는, 본 발명에 의한 표시장치의 화소 구성의 다른 실시예를 나타내는 등가회로도이다.

도 5는, 도 4에 나타낸 등가회로도에서의 동작 타이밍도이다.

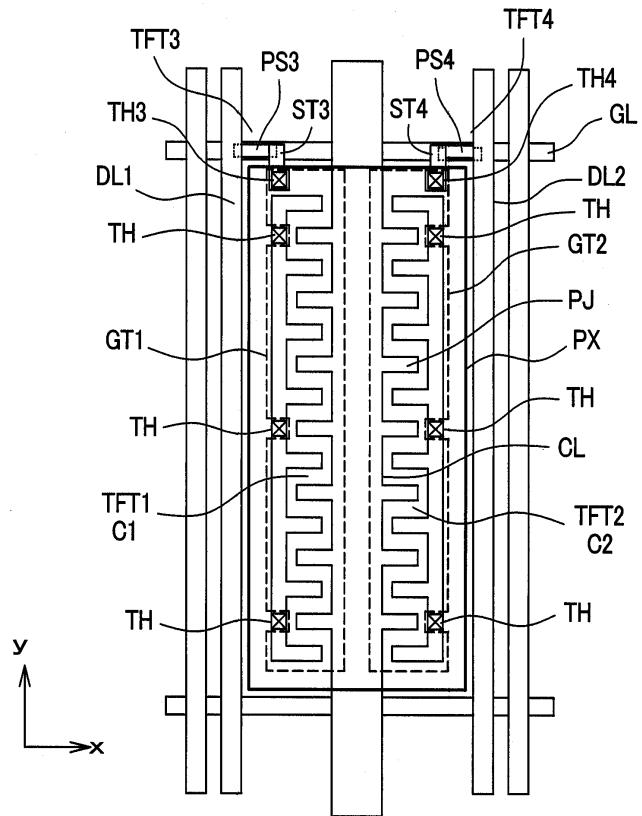

도 6은, 도 4에 나타낸 등가회로를 구비하는 화소 구성의 일실시예를 나타내는 평면도이다.

### [도면의 주요 부분에 대한 간단한 부호의 설명]

GL 게이트 신호선, GL1 제1 게이트 신호선,

GL2 제2 게이트 신호선, DL1 제1 데이터 신호선,

DL2 제2 데이터 신호선, Tr1 제1 스위칭 소자,

Tr2 제2 스위칭 소자, Tr3 제3 스위칭 소자,

Tr4 제4 스위칭 소자, Tr5 제5 스위칭 소자,

Tr6 제6 스위칭 소자, CL 공통전압 신호선,

C1 제1 용량소자, C2 제2 용량소자,

EL 유기 EL 소자, Vselect 주사신호,

Vdata 1 제1 데이터 신호, Vdata 1 제2 데이터 신호,

Vcommon 공통전압, TFT 박막 트랜지스터.

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 표시장치 및 그 구동방법에 관한 것으로서, 예를들면 유기 EL 표시장치 및 그 구동방법에 관한 것이다.

액티브 · 매트릭스형의 유기 EL 표시장치는, 예를들면 x방향으로 병설된 각 화소를 주사신호에 의해 선택하고, 그 선택 타이밍에 맞추어 상기 각 화소에 데이터 신호를 공급하도록 되어 있다.

그리고, 데이터 신호가 공급된 화소에서는, 상기 데이터 신호를 용량소자에 의해 축적시켜, 그 축적된 전하에 의해 스위칭 소자(구동 스위칭 소자)을 구동시키고, 이 구동 스위칭 소자를 통해서 유기 EL 소자에 전원을 공급하도록 구성되어 있다.

이 스위칭 소자는, 통상, 1개의 화소에 1개 이용되지만, 예를들면 하기의 각 특허문헌에 나타내는 바와 같이, 복수 이용한 것도 알려지는데 이르고 있다.

여기에서, 특허문헌1에는 화소의 휘도의 균일화를 도모한 취지의 개시가 이루어져 있다. 특허문헌2에는 복수 화소를 1화소로 간주해서 이용하는 것에 의한 용장성을 도모한 취지의 개시가 이루어져 있다. 특허문헌3에는 얼라인먼트 어긋남을 일으켜도 기생 용량의 합계를 일정하게 하는 취지의 개시가 이루어져 있다.

[특허문헌1] 일본특허공개 2003-84689호 공보

[특허문헌2] 일본특허공개 2001-202032호 공보

[특허문헌3] 일본특허공개 평8-328038호 공보

그러나, 상술한 바와 같이 구성된 표시장치는, 그 동작 중에 있어서 구동 스위칭 소자가 상시 구동되고 있기 때문에, 그 Vth(문턱치전압)가 변화하여 버린다는 소위 Vth 시프트가 생기는 것이 발견되었다.

특히, 구동 스위칭 소자로서 N채널형의 것을 이용한 경우에, 이 Vth 시프트에 의한 부적합이 현저해지는 것이 분명해지고 있다.

게다가, 이 Vth 시프트가 액티브 매트릭스형의 유기 EL 표시장치의 각 화소를 구성하는 유기 EL 소자를 구동하는 구동 스위칭 소자인 경우, 흐르는 전류의 크기나 흐르는 시간이 변화하게 되므로, 소망의 휘도가 얻어지도록 발광하지 않을 가능성이 있었다.

또한, 이 구동 스위칭 소자에 있어서는, 화소 영역의 일부에 형성하는 것이 통상이며, 충분한 광량을 확보하기 위해서 구동 스위칭 소자를 형성하는 영역이 제한되어, 그 이동도를 충분히 확보할 수 없었다.

특히, 구동 스위칭 소자의 반도체층으로서 예를들면 아모르퍼스 실리콘을 이용한 경우에, 폴리실리콘을 사용한 경우에 비해서 이동도가 낮기 때문에, 이 이동도의 향상의 대책을 필요로 하는 것이 분명해지고 있다.

### 발명이 이루고자 하는 기술적 과제

본 발명의 목적은, 이러한 사정에 의거해서 이루어진 것으로, 그 목적은, 구동 스위칭 소자의 Vth 시프트를 억제함으로써, 각 화소로부터 소망의 광을 방출시키는 표시장치를 제공하는데 있다.

또한, 본 발명의 다른 목적은, 구동 스위칭 소자에 있어서, 유기 EL 소자를 구동하여 소정의 발광량을 얻는데 충분한 전류량을 확보하고, 화면 전체에서의 휘도 불균일을 억제한 표시장치를 제공하는데 있다.

### 발명의 구성 및 작용

본원에 있어서 개시되는 발명 중, 대표적인 것의 개요를 간단히 설명하면, 이하와 같다.

(1) 본 발명에 의한 표시장치는, 예를들면, 화소에, 발광 소자, 스위칭 소자를 적어도 구비하고,

상기 스위칭 소자는, 이 스위칭 소자를 통해서 상기 발광 소자에 전원을 공급시키는 것으로서, 제1 스위칭 소자와 제2 스위칭 소자로 구성되며,

상기 제1 스위칭 소자와 제2 스위칭 소자는, 화소 내로의 데이터 신호의 입력에 따라, 한쪽이 정(正) 바이어스 상태로 다른 쪽이 역(逆) 바이어스 상태로 되는 동시에, 상기 바이어스 상태는 상기 데이터 신호의 시계열적인 입력에 따라서 상기 제1 스위칭 소자와 제2 스위칭 소자의 사이에서 교대로 전환되어 동작되고,

상기 발광 소자로의 전원의 공급은 제1 스위칭 소자 및 제2 스위칭 소자 중 어느 것인가 한쪽의 스위칭 소자를 통해서 이루어지는 것을 특징으로 한다.

(2) 본 발명에 의한 표시장치는, 예를들면, (1)의 구성을 전제로 해서, 상기 제1 스위칭 소자와 제2 스위칭 소자의 바이어스 상태의 전환은 순차 입력되는 데이터 신호마다 이루어지는 것을 특징으로 한다.

(3) 본 발명에 의한 표시장치는, 예를들면, 화소에 순차 입력되는 데이터 신호로서 제1 데이터 신호와 제2 데이터 신호를 갖고, 상기 제1 데이터 신호와 제2 데이터 신호는, 서로 반전된 관계를 갖는 동시에, 시계열적으로 반전을 교환하는 것이며,

상기 화소에는, 게이트 신호선으로부터의 신호에 의해 구동되는 제3 스위칭 소자와 제4 스위칭 소자와,

제3 스위칭 소자를 통해서 상기 제1 데이터 신호에 대응하는 전하가 축적되는 제1 용량소자와, 제4 스위칭 소자를 통해서 상기 제2 데이터 신호에 대응하는 전하가 축적되는 제2 용량소자와,

제1 용량소자에 축적된 전하에 의해 구동하는 제1 스위칭 소자와, 제2 용량소자에 축적된 전하에 의해 구동하는 제2 스위칭 소자와,

제1 스위칭 소자 혹은 제2 스위칭 소자를 통해서 전원이 공급되는 발광 소자를 적어도 구비하는 것을 특징으로 한다.

(4) 본 발명에 의한 표시장치는, 예를들면, (3)의 구성을 전제로 해서, 제1 데이터 신호는 제1 데이터 신호선을 통해서 입력되고, 제2 데이터 신호는 제2 데이터 신호선을 통해서 입력되는 것을 특징으로 한다.

(5) 본 발명에 의한 표시장치는, 예를들면, (3)의 구성을 전제로 해서, 상기 제1 데이터 신호와 제2 데이터 신호의 반전은 순차 입력되는 각 데이터 신호마다 반전하는 것을 특징으로 한다.

(6) 본 발명에 의한 표시장치는, 예를들면, 화소에 순차 입력되는 주사신호로서 제1 주사신호와 제2 주사신호를 갖고, 제1 주사신호와 제2 주사신호는, 한쪽에서 온(on) 신호가 입력될 때 다른쪽은 오프(off) 신호가 입력되는 관계를 갖는 동시에, 주사(走査)과정에서 그들이 전환되는 것이며,

상기 화소에는, 발광 소자와, 이 발광 소자에 전원을 어느 것인가의 스위칭 소자를 통해서 공급하는 제1 스위칭 소자 및 제2 스위칭 소자와,

상기 제1 주사신호의 온 신호에 의해 구동되는 동시에 제2 주사신호의 오프 신호를 제1 스위칭 소자의 게이트 전극에 공급하는 제5 스위칭 소자와, 제2 주사신호의 온 신호에 의해 구동되는 동시에 제1 주사신호의 오프 전류를 제2 스위칭 소자의 게이트 전극에 공급하는 제6 스위칭 소자와,

제2 주사신호의 온 신호에 의해 구동되는 제3 스위칭 소자와, 제1 주사신호의 온 신호에 의해 구동되는 제4 스위칭 소자와,

제3 스위칭 소자를 통해서 데이터 신호에 대응하는 전하를 축적시키는 동시에 상기 제1 스위칭 소자를 구동시키는 제1 용량소자와, 제4 스위칭 소자를 통해서 상기 데이터 신호에 대응하는 전하를 축적시키는 동시에 상기 제2 스위칭 소자를 구동시키는 제2 용량소자를 적어도 구비하는 것을 특징으로 한다.

(7) 본 발명에 의한 표시장치는, 예를들면, (6)의 구성을 전제로 해서, 제1 주사신호는 제1 게이트 신호선을 통해서 입력되고, 제2 주사신호는 제2 게이트 신호선을 통해서 입력되는 것을 특징으로 한다.

(8) 본 발명에 의한 표시장치는, 예를들면, (6)의 구성을 전제로 해서, 제1 주사신호와 제2 주사신호의 온 · 오프의 전환은 프레임마다 이루어지는 것을 특징으로 한다.

(9) 본 발명에 의한 표시장치의 구동방법은, 예를들면, 화소에, 발광 소자와, 이 발광 소자에 전원을 어느 것인가의 스위칭 소자를 통해서 공급하는 제1 스위칭 소자 및 제2 스위칭 소자를 구비하고,

화소 내로의 데이터 신호의 순차 입력의 과정에서,

제1 스위칭 소자 및 제2 스위칭 소자를, 그 한쪽에서 정 바이어스 상태로 다른쪽에서 역 바이어스 상태로 하는 동시에, 상기 바이어스 상태를 상기 제1 스위칭 소자와 제2 스위칭 소자의 사이에서 교대로 전환되도록 동작하는 것을 특징으로 한다.

(10) 본 발명에 의한 표시장치의 구동방법은, 예를들면, (9)의 구성을 전제로 해서, 제1 스위칭 소자 및 제2 스위칭 소자의 바이어스 상태의 교대의 전환은, 화소 내로 입력되는 데이터 신호마다 행하는 것을 특징으로 한다.

(11) 본 발명에 의한 표시장치는, 예를들면, (1), (2), (3), (6)의 어느 것인가의 구성을 전제로 해서, 제1 스위칭 소자 및 제2 스위칭 소자는, 각각 그 채널영역이 사행(蛇行) 모양의 패턴으로 형성되어 있는 것을 특징으로 한다.

(12) 본 발명에 의한 표시장치는, 예를들면, (1), (2), (3), (6)의 어느 것인가의 구성을 전제로 해서, 제1 스위칭 소자 및 제2 스위칭 소자는, 발광층의 하층(下層) 층에 형성되어 있는 동시에, 상기 발광층의 상층(上層)에 형성되는 한쪽 전극은 투광성의 도전층으로 형성되어 있는 것을 특징으로 한다.

(13) 본 발명에 의한 표시장치는, 예를들면, (1), (2), (3), (6), (11), (12)의 어느 것인가의 구성을 전제로 해서, 제1 스위칭 소자 및 제2 스위칭 소자는, 어느 것이나 N채널형인 것을 특징으로 한다.

(14) 본 발명에 의한 표시장치는, 예를들면, (1), (2), (3), (6), (11), (12)의 어느 것인가의 구성을 전제로 해서, 제1 스위칭 소자 및 제2 스위칭 소자는, 어느 것이나 그 반도체층이 아모르페스 실리콘으로 형성되어 있는 것을 특징으로 한다.

또, 본 발명은 이상의 구성에 한정되지 않고, 본 발명의 기술사상을 이탈하지 않는 범위에서 여러 가지 변경이 가능하다.

이하, 본 발명에 의한 표시장치 및 그 구동방법의 실시예를 도면을 이용해서 설명을 한다.

#### 실시예1.

도 1은, 본 발명에 의한 표시장치의 화소(畫素) 구성의 일실시예를 나타내는 등가회로도이다. 표시장치의 일실시예로서 예를들면 액티브 · 매트릭스형의 유기 EL 표시장치를 내세우고 있다.

따라서, 각 화소는 매트릭스 모양으로 배치되며, 그 x방향으로 병설되는 각 화소의 화소군은 후술의 게이트 신호선(GL)을 공통으로 하고, y 방향으로 병설되는 각 화소의 화소군은 후술의 제1 데이터 신호선(DL1) 및 제2 데이터 신호선(DL2)을 공통으로 하고 있다.

또, 등가회로에 이용되는 제1 스위칭 소자(Tr1)로부터 제4 스위칭 소자(Tr4)는 예를들면 N채널형의 MIS(Metal Insulator Semiconductor) 트랜ジ스터로 구성되어 있다.

도 1에 있어서, 우선, 제3 스위칭 소자(Tr3)가 구비되고, 이 제3 스위칭 소자(Tr3)는 게이트 신호선(화소 선택신호선) (GL)으로부터의 주사신호(Vselect)의 공급에 의해 온 동작하도록 되어 있다.

제3 스위칭 소자(Tr3)에는 제1 데이터 신호선(DL1)을 통해서 제1 데이터 신호(Vdata1)가 공급되고, 이 제1 데이터 신호(Vdata1)는, 상기 제3 스위칭 소자(Tr3)의 온에 의해, 일단(一端)에서 공통전압 신호선(CL)에 접속된 제1 용량소자(C1)에 축적되도록 되어 있다.

또한, 상기 제1 용량소자(C1)에 축적되는 전하에 의해 온 동작하는 제1 스위칭 소자(Tr1)가 있고, 이 제1 스위칭 소자(Tr1)를 통해서, 일단에 전원공급 신호선(PL)에 접속된 유기 EL 소자(EL)에 전류가 흐르며, 이 전류는 상기 공통전압 신호선(CL)으로 인도되도록 되어 있다. 또, 상기 공통전압 신호선(CL)에는 공통전압(Vcommon)이 공급되도록 되어 있다.

한편, 상기 게이트 신호선(GL)로부터 신호의 공급에 의해 온 동작하는 제4 스위칭 소자(Tr4)가 있고, 이 제4 스위칭 소자(Tr4)에는 제2 데이터 신호선(DL2)을 통해서 제2 데이터 신호(Vdata2)가 공급되도록 되어 있다.

이 제2 데이터 신호(Vdata2)는, 상기 제4 스위칭 소자(Tr4)의 온에 의해, 일단에서 상기 공통전압 신호선(CL)에 접속된 제2 용량소자(C2)에 축적되도록 되어 있다.

그리고, 상기 제2 용량소자(C2)에 축적되는 전하에 의해 온 동작하는 제2 스위칭 소자(Tr2)가 있고, 이 제2 스위칭 소자(Tr2)를 통해서, 상기 유기 EL 소자(EL)에 흐르고, 이 전류는 상기 공통 신호선(CL)으로 인도되도록 되어 있다.

여기에서, 제1 스위칭 소자(Tr1) 및 제2 스위칭 소자(Tr2)는 소위 구동 스위칭 소자라고 칭해지는 것이다.

도 2는, 상술한 등가(等價)회로의 동작을 나타내는 신호 타이밍도이다.

도 2에 있어서, 그 (a)에는 주사신호(Vselect)의 파형을, (b)에는 제1 데이터 신호(Vdata1)의 파형을, (c)에는 제2 데이터 신호(Vdata2)의 파형을, (d)에는 공통전압(Vcommon)을 나타내고 있다.

주사신호(Vselect)가 그 Von에 의해 입력되면, 제3 스위칭 소자(Tr3) 및 제4 스위칭 소자(Tr4)가 동시에 온 한다.

온 된 제3 스위칭 소자(Tr3)에는 제1 데이터 신호(Vdata1)가 공급되고, 이 제1 데이터 신호(Vdata1)는 제1 용량소자(C1)에 축적(기록)되며, 온 된 제4 스위칭 소자(Tr4)에는 제2 데이터 신호(Vdata2)가 공급되고, 이 제2 데이터 신호(Vdata2)는 제2 용량소자(C2)에 축적(기록)된다.

이 경우 제1 데이터 신호(Vdata1)와 제2 데이터 신호(Vdata2)는, 도 2의 (b) 및 (c)에 나타내는 바와 같이, 예를들면 1프레임째에 있어서, 제1 데이터 신호(Vdata1)가 공통전압(Vcommon)에 대해서 정(正)인 경우, 제2 데이터 신호(Vdata2)는 상기 공통전압(Vcommon)에 대해서 부(負)가 되도록, 그들은 반전된 관계로 되어 있다.

그리고, 상기 제1 데이터 신호(Vdata1)와 제2 데이터 신호(Vdata2)는, 다음의 프레임에 있어서, 제1 데이터 신호(Vdata1)는 공통전압(Vcommon)에 대해서 부가 되고, 제2 데이터 신호(Vdata2)는 상기 공통전압(Vcommon)에 대해서 정이 되도록, 또 다음의 프레임에 있어서, 제1 데이터 신호(Vdata1)는 공통전압(Vcommon)에 대해서 정이 되고, 제2 데이터 신호(Vdata2)는 상기 공통전압(Vcommon)에 대해서 부(負)가 되도록, 그들은 이하의 프레임에 있어서 순차 반전이 교환되도록 되어 있다.

그리고, 예를들면 1프레임째에 있어서 상술한 제1 데이터 신호(Vdata1)와 제2 데이터 신호(Vdata2)가 입력된 경우, 공통전압(Vcommon)에 대해서 정(正)인 제1 데이터 신호(Vdata1)가 유기 EL 소자(EL)를 구동시키는 화소 정보로서 기여하고, 공통전압(Vcommon)에 대해서 부(負)인 제2 데이터 신호(Vdata2)는 화소 정보로서 기여하지 않는 것이 된다.

이 때문에, 다음의 프레임에 있어서는, 공통전압(Vcommon)에 대해서 부인 제1 데이터 신호(Vdata1)는 화소 정보로서 기여하지 않고, 공통전압(Vcommon)에 대해서 정인 제2 데이터 신호(Vdata2)가 화소 정보로서 기여하게 된다.

이것은, 예를들면 제1 데이터 신호(Vdata1)가 공통전압(Vcommon)에 대해서 정인 경우, 제1 용량소자(C1)를 통해서 전하가 인가되는 제1 스위칭 소자(Tr1)는 정(正) 바이어스 상태가 되고, 제2 데이터 신호(Vdata2)가 공통전압(Vcommon)에 대해서 부가 되며, 제2 용량소자(C2)를 통해서 전하가 인가되는 제2 스위칭 소자(Tr2)는 부(역)바이어스 상태가 되고, 이들은 프레임 주기마다 교대로 교체되게 된다.

여기에서, 제1 스위칭 소자(Tr1)가 정(正) 바이어스 상태란, 상기 제1 스위칭 소자(Tr1)의 공통전압 신호선(CL)에 접속된 전극에 인가되는 전압에 대해서 게이트 전극에 인가되는 전압이 정(正)이며, 제2 스위칭 소자(Tr2)가 부(負) 바이어스 상태란, 상기 제2 스위칭 소자(Tr2)의 공통전압 신호선(CL)에 접속된 전극에 인가되는 전압에 대해서 게이트 전극에 인가되는 전압이 부(負)인 것을 의미한다.

따라서, 정 바이어스 상태의 스위칭 소자(Tr)에 있어서 유기 EL 소자(EL)에 전류를 흘리도록 구동하는 것에 대해서, 부 바이어스 상태의 스위칭 소자(Tr)에 있어서는, 그 구동이 휴지(休止) 상태가 되고, 이 사이에, 1프레임 전의 단계에서 구동하고 있었을 때의 Vth 시프트를 역 바이어스 인가로 취소하는 것이 된다. 그리고, 이 공정은 프레임의 전환마다 교대로 반복되게 된다.

이 때문에, 제1 스위칭 소자(Tr1) 및 제2 스위칭 소자(Tr2)에 있어서 각각 Vth 시프트가 생기는 것을 대폭 억제할 수 있게 된다.

이것으로, 제1 스위칭 소자(Tr1)와 제2 스위칭 소자(Tr2)의 각각 바이어스 상태의 전환은 1프레임마다 한정되는 것은 아니고, 복수 프레임마다 라도 같은 효과가 얻어지는 것은 말할 것도 없게 된다.

요점은, 화소 내로의 데이터 신호(Vdata1 및 Vdata2)의 순차(順次) 입력의 과정에서 제1 스위칭 소자(Tr1)와 제2 스위칭 소자(Tr2)의 각각 바이어스 상태의 전환이 이루어지면 좋다.

도 3은, 도 1에 나타낸 등가회로가 구비되는 화소의 구체적인 구성의 일실시예를 나타내는 평면도이다. 또, 이 도 3에 있어서 1개의 화소는, x방향으로 연재(延在)하여 y방향으로 병설되는 한쌍의 게이트 신호선(GL)과 y방향으로 연재하여 x방향으로 병설되는 제1 데이터 신호선(DL1) 및 제2 데이터 신호선(DL2)에 의해 둘러싸여진 영역 내에 구성되도록 되어 있다.

또한, 도 3에 나타내는 박막 트랜지스터(TFT1에서 TFT4)의 각 반도체층(PS1에서 PS4)은 각각 예를들면 폴리실리콘을 사용한 것으로 되어 있다.

또, 유기 EL층(유기 EL 소자)(EL)과 전원공급 신호선(PL)은 생략해서 묘사하고 있다. 도면이 복잡화하는 것을 회피하기 위함이다.

또한, 도 3중, 박막 트랜지스터(TFT1)는 도 1에 나타낸 제1 스위칭 소자(Tr1)에, 박막 트랜지스터(TFT2)는 도 1에 나타낸 제2 스위칭 소자(Tr2)에, 박막 트랜지스터(TFT3)는 도 1에 나타낸 제3 스위칭 소자(Tr3)에, 박막 트랜지스터(TFT4)는 도 1에 나타낸 제4 스위칭 소자(Tr4)에 대응하는 것이다.

도 3에 있어서, 예를들면 유리 등의 절연 기판의 주(主)표면에, 우선, 도면 중 x방향으로 연재해서 게이트 신호선(GL)이 형성되어 있다.

또한, 이 게이트 신호선(GL)을 덮어 절연 기판의 표면에는 제1 절연막(도시하지 않음)이 형성되어 있다. 이 제1 절연막은 후술하는 박막 트랜지스터(TFT3, TFT4)의 게이트 절연막으로서 기능하는 것이므로, 그것에 맞추어 막 두께가 설정되어 있다.

상기 제1 절연막의 상면에서 상기 게이트 신호선(GL)의 일부에 중첩하도록 하여 반도체층(PS3 및 PS4)이 형성되어 있다. 후술하는 제1 데이터 신호선(DL1)에 근접되는 측에서 반도체층(PS3)이, 후술하는 제2 데이터 신호선(DL2)에 근접되는 측에서 반도체층(PS4)이 형성되어 있다.

반도체층(PS3)은 후술하는 박막 트랜지스터(TFT3)의 반도체층으로 구성되고, 반도체층(PS4)은 후술하는 박막 트랜지스터(TFT4)의 반도체층으로 구성되기 때문이다.

그리고, 제1 데이터 신호선(DL1) 및 제2 데이터 신호선(DL2)이 형성되어 있다. 제1 데이터 신호선(DL1)은 상기 반도체층(PS3)의 일부에 중첩되어 형성되고, 그 중첩부에 있어서 상기 제1 데이터 신호선(DL1)은 박막 트랜지스터(TFT3)의 드레인 전극을 구성하도록 되어 있다. 또한, 제2 데이터 신호선(DL2)은 상기 반도체층(PS4)의 일부에 중첩되어 형성되고, 그 중첩부에 있어서 상기 제2 데이터 신호선(DL2)은 박막 트랜지스터(TFT4)의 드레인 전극을 구성하도록 되어 있다.

또한, 예를들면 제1 데이터 신호선(DL1) 및 제2 데이터 신호선(DL2)의 형성과 동시에 설치되는 박막 트랜지스터(TFT3)의 소스 전극(ST3) 및 박막 트랜지스터(TFT4)의 소스 전극(ST4)이 형성되어 있다. 이들 각 소스 전극(ST3, ST4)은 각각 후술하는 박막 트랜지스터(TFT1)의 게이트 전극(GT1)과 박막 트랜지스터(TFT2)의 게이트 전극(GT2)과 스루홀을 통해서 접속하도록 하기 위해서, 화소 영역의 중앙측으로 약간 연재되어 형성되도록 되어 있다.

또한, 예를들면 제1 데이터 신호선(DL1) 및 제2 데이터 신호선(DL2)의 형성과 동시에 설치되는 공통전압 신호선(CL)이 형성되어 있다. 이 공통전압 신호선(CL)은 화소 영역의 거의 중앙을 통해서 y방향으로 연재되어 형성되어 있다.

또한, 이 공통전압 신호선(CL)은, 화소의 영역 내에 있어서, 그 양측 변(邊)에서 신장(伸張) 방향에 교차하는 방향으로 연재하는 돌출부(PJ)가 상기 신장 방향으로 병설되어 형성된 패턴(파쉬본 패턴)으로서 형성되어 있다. 이들 돌출부(PJ)는, 도면 중 우측에서는 후술하는 박막 트랜지스터(TFT1)의 한쪽 전극(전극군)으로서, 도면 중 좌측에서는 후술하는 박막 트랜지스터(TFT2)의 한쪽 전극(전극군)으로 구성되게 된다.

계다가, 박막 트랜지스터(TFT1 및 TFT2)의 다른쪽 전극은 예를들면 상기 제1 데이터 신호선(DL1) 및 제2 데이터 신호선(DL2)의 형성과 동시에 형성되도록 되어 있다. 박막 트랜지스터(TFT1)의 다른쪽 전극은, 상기 박막 트랜지스터(TFT1)의 상기 한쪽 전극군의 각 전극(상기 돌출부(PJ))을 간격으로 해서 각 전극이 배치된 전극군으로서 구성되고, 또한,

그들을 전기적으로 접속시키기 위해서 빗살 모양의 패턴을 이루어 형성되어 있다. 마찬가지로, 박막 트랜지스터(TFT2)의 다른쪽 전극은, 상기 박막 트랜지스터(TFT2)의 상기 한쪽 전극군의 각 전극(상기 돌출부(PJ))을 간격으로 해서 각 전극이 배치된 전극군으로서 구성되고, 또한, 그들을 전기적으로 접속시키기 위해서 빗살 모양의 패턴을 이루어 형성되어 있다.

1화소의 영역 내에 있어서, 그 중앙을 통해서 y방향으로 신장하는 가상의 선분을 경계로 하여, 그 좌측의 영역에는 반도체층(PS1)이, 오른쪽의 영역에는 반도체층(PS2)가 각각 서로 분리되어 형성되어 있다.

이 반도체층(PS1) 및 반도체층(PS2)은, 도시되어 있지 않지만, 예를들면, 각각 후술하는 게이트 전극(GT1) 및 게이트 전극(GT2)에서 나타내는 영역(도면 중, 점선으로 둘러싸여지는 영역)에 상당하는 부분에 형성되어 있다.

반도체층(PS1)은 후술하는 박막 트랜지스터(TFT1)의 반도체층으로서 구성되고, 반도체층(PS2)은 후술하는 박막 트랜지스터(TFT2)의 반도체층으로서 구성되기 때문이다.

또한, 이들 각 반도체층(PS1 및 PS2)도 덮어 절연 기판의 표면에는 제2 절연막(도시하지 않음)이 형성되어 있다. 이 제2 절연막은 박막 트랜지스터(TFT1 및 TFT2)의 게이트 절연막으로서 기능하는 것이므로, 그것에 맞추어 막 두께가 설정되어 있다.

제2 절연막의 표면에는, 박막 트랜지스터(TFT1)의 게이트 전극(GT1)이, 박막 트랜지스터(TFT2)의 게이트 전극(GT2)이 형성되어 있다. 박막 트랜지스터(TFT1)의 게이트 전극(GT1)은 상기 반도체층(PS1)이 형성된 영역에 중첩되어 형성되고, 그 연재된 일부에 있어서 하층(下層)의 제2 절연막에 형성된 스루홀(TH3)을 통해서 박막 트랜지스터(TFT3)의 소스 전극(ST3)과 접속되어 있다. 마찬가지로, 박막 트랜지스터(TFT2)의 게이트 전극(GT2)은 상기 반도체층(PS2)이 형성된 영역에 중첩되어 형성되고, 그 연재된 일부에 있어서 하층의 제2 절연막에 형성된 스루홀(TH4)을 통해서 박막 트랜지스터(TFT4)의 소스 전극(ST4)과 접속되어 있다.

각 게이트 전극(GT1 및 GT2)도 덮어 절연 기판의 표면에는 제3 절연막(도시하지 않음)을 통해서 화소 전극(PX)이 형성되어 있다. 이 화소 전극(PX)은 소위 화소의 개구율을 향상시키기 위해서 화소 영역의 거의 전체 영역에 형성되고, 그 하층의 제3 절연막 및 제2 절연막을 관통해서 형성된 스루홀(TH)을 통해서 박막 트랜지스터(TFT1, TFT2)의 다른쪽 전극(공통 전압 신호선(CL)과 일체에 형성된 전극과는 다른 전극)에 접속되어 있다. 이 경우, 상기 스루홀(TH)의 각 형성 개소에는 게이트 전극(GT1 및 GT2)이 노출되는 것을 회피하기 위해서, 상기 게이트 전극(GT1 및 GT2)의 상기 개소에 있어서 미리 노치가 형성된 패턴으로 되어 있다. 화소 전극(PX)과 각 게이트 전극(GT1 및 GT2)의 전기적 접속이 이루어지는 것을 회피하기 위함이다. 또한, 본 실시예의 액티브·매트릭스형의 유기 EL 표시장치는, 액티브 소자를 형성한 기판의 형성면(상면)에서 광을 방출하는 텁 애미션 구조를 채용하고 있으므로, 이 화소 전극(PX)은, 금속 전극 또는, 금속 전극 상에 IZO나 ITO란 투명도전막을 형성한 적층막으로 되어 있다.

또, 화소 전극(PX)과 박막 트랜지스터(TFT1 및 TFT2)의 한쪽 전극(공통전압 신호선(CL)과 일체로 형성된 전극)과의 사이에는 제2 절연막과 제3 절연막을 유전체막으로 하는 용량소자(C1 및 C2)가 형성되게 된다.

화소 전극(PX)의 상면에는 그 전체 영역에 걸쳐 유기 EL층(도시하지 않음)이 형성되어 있다. 이 경우, 유기 EL층을 포함해서 전하 수송층 혹은 전자 수송층 등을 적층시켜 형성해도 좋다. 즉, 유기 EL층만, 유기 EL층과 전하 수송층과의 적층체, 유기 EL층과 전자 수송층과의 적층체, 유기 EL층과 전하 수송층과 전자 수송층과의 적층체로 구성하도록 해도 좋다. 또, 본 명세서에서는 이러한 구성을 총칭해서 발광층이라고 칭하는 경우가 있다.

그리고, 이 발광층의 상면에 전원공급 신호선(PL)이 형성되어 있다. 이 전원공급 신호선(PL)은 각 화소의 영역에 있어서 공통으로, 즉, 각 화소의 집합체에서 구성되는 표시부의 전체 영역에 걸쳐 형성되어 있다. 또, 이 전원공급 신호선(PL)은 그 재료로서 예를들면 ITO(Indium Tin Oxide)이나 IZO(Indium Zinc Oxide) 등으로 이루어지는 투광성의 도전층으로서 형성된 것으로 되어 있다. 이것은 전술한 바와 같이, 본 실시예가, 상기 발광층으로부터 광을 도면의 지면(紙面)의 표면 측에 조사시키도록 되어 있는 구조(텅 애미션 구조)였기 때문이다.

또한, 이렇게, 전원공급 신호선(PL)을 층(層)구조에 있어서 상층에 형성하는 구조는 소위 텁 애노드 구조라 칭해지며, 소위 화소의 개구율(1화소의 면적에 차지하는 발광 면적의 비율)을 향상시키기 쉬운 구조으로 되어 있다.

또, 상술한 구조에 있어서, 박막 트랜지스터(TFT3, TFT4)는, 그 반도체층(PS3, PS4)에 대해서 게이트 전극(게이트 신호선(GL))을 하층으로 하는 소위 역(逆)스태커 구조로 한 것이지만, 이것에 한정되는 것은 아니고, 상기 게이트 전극을 반도체층(PS3, PS4)의 상층에 형성하는 스태커 구조로 하도록 하여도 좋은 것은 말할 필요도 없다.

마찬가지로, 박막 트랜지스터(TFT1, TFT2)를 스태커 구조로서 구성한 것이지만, 역 스태커 구조로서 구성해도 좋은 것은 물론이다.

또한, 박막 트랜지스터(TFT1, TFT2)는, 화소 내의 발광 영역, 즉, 유기 EL층이 형성된 영역에 중첩되어 형성한 것이지만, 이것에 한정되는 것은 아니고, 평면적으로 보았을 경우, 발광 영역과 구별되는 다른 영역 내에 형성하도록 구성해도 좋은 것은 말할 필요도 없다.

또, 박막 트랜지스터(TFT1 및 TFT2)는, 각각, 화소 영역의 약 절반을 차지해서 형성되어 있으므로, 대형화되어 있다. 또한, 그들의 채널영역(한쌍의 전극 사이의 영역)이 사행 모양의 패턴으로서 형성되는 것에 의해, 채널 폭이 크게 구성된 것으로 되어 있다. 이들의 사항으로부터, 이동도를 크게 하고, 온 전류를 대폭 향상시키게 되어 있다.

특히, 그들의 반도체층(PS1 및 PS2)로서 예를들면 아모르페스 실리콘을 이용한 경우, 상기 아모르페스 실리콘은 이동도가 작은 것이므로, 상술한 구성으로 함으로써, 그 부적합을 해소할 수 있게 된다.

통상, 구동 스위칭 소자에 흘리는 전류는  $200\sim300\text{A}/\text{m}^2$ 이며, 예를들면  $100\times300\mu\text{m}^2$ 의 화소당으로 하면  $7.5\mu\text{A}$  정도가 되고, 상기 구동 스위칭 소자의 반도체층이 아모르페스 실리콘으로 이루어지는 경우, 이동도가 0.5 정도가 된다.

따라서, 게이트 전극에 인가하는 전압이 15V, 소스 · 드레인 전극간의 전압이 10V 정도이고 상기  $7.5\mu\text{A}$ 의 전류를 흘리기 위해서는, 구동 스위칭 소자인 박막 트랜지스터(TFT1 및 TFT2)의 각각은, 그 채널 폭 대 채널 길이의 비(比)가 50정도라면 충분해진다.

채널 길이가  $6\mu\text{m}$ 의 경우, 박막 트랜지스터(TFT1 및 TFT2)의 반도체층(PS1, PS2)의 폭은 약  $300\mu\text{m}$ 로 하면 좋고, 이것은 그 길이는 화소의 그것에 거의 상당하게 된다.

상기 실시예에서 나타낸 화소 구성은 톱 애노드 구조로 되어 있으므로, 박막 트랜지스터(TFT1 및 TFT2)는 화소의 거의 전체 영역에 걸쳐 형성할 수 있고, 가령 상기 박막 트랜지스터(TFT1 및 TFT2)의 반도체층이 아모르페스 실리콘이라도, 충분한 구동 전류를 흘릴 수 있게 된다.

덧붙여서 말하면, N채널형이고 반도체층이 폴리실리콘인 경우의 구동 스위칭 소자의 경우, 이동도는 100 정도가 되는 것 이므로, 상기 소자의 크기를 작게 할 수 있다.

실시예2.

도 4는, 본 발명에 의한 표시장치의 화소 구성의 다른 실시예를 나타내는 등가회로도이며, 도 1과 대응한 도면으로 되어 있다.

도 1의 경우와 비교해서 다른 구성은, 우선, 각 화소에 있어서, 데이터 신호선(DL)을 1개로 하고, 대신에 게이트 신호선(GL)을 2개로 한 것에 있다.

컬러 표시의 경우, 예를들면 게이트 신호선(GL)의 주행방향에 인접하는 3개의 화소를, 빨강(R), 초록(G), 파랑(B)의 각색을 발광시키도록 하고, 이들 각 화소를 컬러 표시의 단위 화소로서 구성하게 되지만, 도 1의 등가회로에서는 이 단위 화소당 함께 6개의 데이터 신호선(DL)을 필요로 하게 된다. 그러나, 상기 각 화소에 공통에 형성되는 게이트 신호선(GL)을 1개 증가시키는 쪽이 전체로서 신호선의 수를 대폭 저감시키는 효과를 이루게 된다.

도 4에 나타내는 바와 같이, 2개의 게이트 신호선(GL) 중 한쪽의 게이트 신호선을 제1 게이트 신호선(GL1), 다른쪽의 게이트 신호선을 제2 게이트 신호선(GL2)으로 하면, 제1 게이트 신호선(GL1)로부터의 주사신호(Vselect1)에 의해 온 되는 제5 스위칭 소자(Tr5), 제2 게이트 신호선(GL2)로부터의 주사신호(Vselect2)에 의해 온 되는 제6 스위칭 소자(Tr6)가 새롭게 설치된 구성으로 되어 있다.

또한, 도 1의 경우와 달리, 제3 스위칭 소자(Tr3)는 제2 게이트 신호선(GL2)으로부터의 주사신호(Vselect2)에 의해 온 되고, 제4 스위칭 소자(Tr4)는 제1 게이트 신호선(GL1)으로부터의 주사신호(Vselect1)에 의해 온 되도록 되어 있다.

상기 제5 스위칭 소자(Tr5)는, 그 일단이 제3 스위칭 소자(Tr3)의 게이트 전극(제2 게이트 신호선(GL2)으로부터의 주사신호(Vselect2)가 공급되는 전극)에 접속되고, 타단이 제1 스위칭 소자(Tr1)의 게이트 전극(제1 용량소자(C1)의 전하가 인가되는 전극)에 접속되어 있다. 제6 스위칭 소자(Tr6)는, 그 일단이 제4 스위칭 소자(Tr4)의 게이트 전극(제1 게이트 신호선(GL1)로부터의 주사신호(Vselect1)가 공급되는 전극)에 접속되고, 타단이 제2 스위칭 소자(Tr2)의 게이트 전극(제2 용량소자(C2)의 전하가 인가되는 전극)에 접속되어 있다.

또, 제1 용량소자(C1), 제1 스위칭 소자(Tr1), 제2 용량소자(C2), 제2 스위칭 소자(Tr2), 유기 EL 소자(EL) 및 공통전압(Vcommon)이 공급되는 단자의 각각의 접속관계는 도 1의 경우와 같은 형태로 되어 있다.

여기에서, 도 1의 경우, 화소에 입력되는 데이터 신호는 서로 반전된 제1 데이터 신호(Vdata1) 및 제2 데이터 신호(Vdata2)를 갖는 것이었지만, 본 실시예에서는, 하나의 데이터 신호(Vdata)만을 갖고, 상기 데이터 신호(Vdata)는 제3 스위칭 소자(Tr3)를 통해서 제1 용량소자(C1)에 축적되는 동시에, 제4 스위칭 소자(Tr4)를 통해서 제2 용량소자(C2)에 축적되게 되어 있다.

도 5는, 상술한 등가회로의 동작을 나타내는 신호 타이밍도이다.

도 5에 있어서, 그 (a)에는 제1 주사신호(Vselect1)의 파형을, (b)에는 제2 주사신호(Vselect2)의 파형을, (c)에는 데이터 신호(Vdata)의 파형을, (d)에는 공통전압(Vcommon)을 나타내고 있다.

또, 이 타이밍도는, 예를들면 최초의 프레임에 있어서 제1 게이트 신호선(GL1)에 주사신호(Vselect1)의 온 신호(Von)를 공급하고(이때, 제2 게이트 신호선(GL2)에는 주사신호(Vselect2)의 온 신호(Von)는 공급되지 않는다), 다음의 프레임에 있어서 제2 게이트 신호선(GL2)에 주사신호(Vselect2)의 온 신호(Von)를 공급하게(이때, 제1 게이트 신호선(GL1)에는 주사신호(Vselect1)의 온 신호(Von)는 공급되지 않는다) 되어 있는 것을 예로 든 것이다.

최초의 프레임에 있어서, 주사신호(Vselect1)가 그 온 신호(Von)에 의해 입력되면, 제4 스위칭 소자(Tr4), 제5 스위칭 소자(Tr5)가 온 한다.

이 중 제4 스위칭 소자(Tr4)에는 데이터 신호(Vdata)가 공급되고, 이 데이터 신호(Vdata)는 제2 용량소자(C2)에 축적(기록)된다.

제2 용량소자(C2)에 축적된 전하는 제2 스위칭 소자(Tr2)를 온으로 하고, 이 제2 스위칭 소자(Tr2)를 통해서 공통전압(Vcommon)이 유기 EL 소자(EL)에 공급되며, 상기 유기 EL 소자(EL)에는 전원공급 신호선(PL)으로부터 전류가 흐르게 된다.

이 동작 중, 제2 게이트 신호선(GL2)에는 주사신호(Vselect2)의 온 신호(Von)가 공급되고 있지 않고, 이때의 오프 신호(Voff)는, 상기 주사신호(Vselect1)에 의해 온 된 제5 스위칭 소자(Tr5)를 통해서 제1 스위칭 소자(Tr1)의 게이트 전극으로 인가되게 된다.

또, 이 제1 스위칭 소자(Tr1)의 게이트 전극에는 데이터 신호(Vdata)에 대응하는 제1 용량소자(C1)의 전하가 인가되는 일은 없다. 제3 스위칭 소자(Tr3)의 게이트 전극에는 오프 신호(Voff)로 이루어지는 제2 주사신호(Vselect2)가 공급되고 있기 때문이다.

다음의 프레임에 있어서, 주사신호(Vselect2)가 그 온 신호(Von)에 의해 입력되면, 제3 스위칭 소자(Tr3), 제6 스위칭 소자(Tr6)가 온 한다.

이 중 제3 스위칭 소자(Tr3)에는 데이터 신호(Vdata)가 공급되고, 이 데이터 신호(Vdata)는 제1 용량소자(C1)에 축적(기록)된다.

제1 용량소자(C1)에 축적된 전하는 제1 스위칭 소자(Tr1)를 온으로 하고, 이 제1 스위칭 소자(Tr1)를 통해서 공통전압(Vcommon)이 유기 EL 소자(EL)에 공급되며, 상기 유기 EL 소자(EL)에는 전원공급 신호선(PL)으로부터 전류가 흐르게 된다.

이 동작 중, 제1 게이트 신호선(GL1)에는 주사신호(Vselect1)의 온 신호(Von)가 공급되고 있지 않고, 이때의 오프 신호(Voff)는, 상기 주사신호(Vselect2)에 의해 온 된 제6 스위칭 소자(Tr6)를 통해서 제2 스위칭 소자(Tr2)의 게이트 전극에 인가되게 된다.

또, 이 제2 스위칭 소자(Tr2)의 게이트 전극에는 데이터 신호(Vdata)에 대응하는 제2 용량소자(C2)의 전하가 인가되는 일은 없다. 제4 스위칭 소자(Tr4)의 게이트 전극에는 오프 신호(Voff)로 이루어지는 제1 주사신호(Vselect1)가 공급되고 있기 때문이다.

본 실시예의 경우에 있어서도, 제1 스위칭 소자(Tr1)와 제2 스위칭 소자(Tr2)의 사이에 있어서, 한쪽이 동작 중일 때는 다른쪽이 휴지(休止) 중으로 되어 있고, 휴지 중인 측의 스위칭 소자는, 그때까지 동작해서 Vth가 시프트해도 휴지 중인 동안에 본래 상태로 되돌아가는 효과를 이루게 된다.

도 6은, 도 4에 나타낸 등가회로가 구비되는 화소의 구체적인 구성의 일실시예를 나타내는 평면도이다. 또, 이 도 6에 있어서 1개의 화소는, x방향으로 연재하고 y방향으로 병설되는 제1 게이트 신호선(GL1) 및 제2 게이트 신호선(GL2)과 y방향으로 연재하고 x방향으로 병설되는 한쌍의 공통전압 신호선(CL)에 의해 둘러싸여진 영역 내에 구성되게 되어 있다.

그리고, 유기 EL층(EL)과 전원공급 신호선(PL)을 생략해서 묘사하고 있다. 도면이 복잡화하는 것을 회피하기 위함이다.

또한, 도 6중, 박막 트랜지스터(TFT1)로부터 박막 트랜지스터(TFT6)는, 각각 도 4에 나타낸 제1 트랜지스터 소자(Tr1)로부터 제6 트랜지스터 소자(Tr6)에 대응하는 것이다.

그리고, 실시예1의 경우와 같이 박막 트랜지스터(TFT1로부터 TFT6)의 각 반도체층은 예를들면 폴리실리콘을 사용하고 있다.

도 3에 있어서, 예를들면 유리 등의 절연 기판의 주(主)표면에, 우선, 도면 중 x방향으로 연재하고 y방향으로 병설되는 제1 게이트 신호선(GL1), 제2 게이트 신호선(GL2)이 형성되어 있다.

또한, 이들 제1 게이트 신호선(GL1), 제2 게이트 신호선(GL2)도 덮어 절연 기판의 표면에는 제1 절연막(도시하지 않음)이 형성되어 있다. 이 제1 절연막은 후술하는 박막 트랜지스터(TFT4로부터 TFT6)의 게이트 절연막으로서 기능하는 것으로, 그것에 맞추어 막 두께가 설정되어 있다.

상기 절연막의 상면에서 상기 제1 게이트 신호선(GL1), 제2 게이트 신호선(GL2)의 일부에 중첩하도록 해서 각각 반도체층(PS4 및 PS5)이 형성되어 있다. 이 반도체층(PS4 및 PS5)은 각각 박막 트랜지스터(TFT4, TFT5)의 반도체층으로서 구성되는 것이다. 그리고, 이들은 어느 것이나 화소의 중앙을 y방향으로 연재해서 형성되는 후술의 데이터 신호선(DL)에 대하여 다른 측에 형성되고, 또 상기 데이터 신호선(DL)의 형성 영역에 도달해서 형성되어 있다. 이들 반도체층(PS4 및 PS5)의 일단에서 상기 데이터 신호선(DL)과 접속을 도모하기 위함이다.

또한, 제1 절연막 상에는, 게이트 신호선(GL1)과 중첩되어 반도체층(PS3)이, 게이트 신호선(GL2)과 중첩되어 반도체층(PS6)이 형성되어 있다. 이 반도체층(PS3 및 PS6)은 각각 박막 트랜지스터(TFT3, TFT6)의 반도체층으로서 구성되는 것이다. 반도체층(PS3)은 상기 반도체층(PS4)과는 후술의 데이터 신호선(DL)을 간격으로 해서 다른 측에 형성되고, 반도체층(PS4)은 상기 반도체층(PS5)과는 상기 데이터 신호선(DL)을 간격으로 해서 다른 측에 형성되어 있다.

반도체층(PS3), 반도체층(PS6)은, 예를들면 상기 반도체층(4), 반도체층(5)의 형성시에 동시에 형성되도록 되어 있다.

그리고, 데이터 신호선(DL) 및 공통전압 신호선(CL)이 형성되어 있다. 데이터 신호선(DL)은 화소의 중앙을 y방향으로 연재해서 형성되고, 공통전압 신호선(CL)은 상기 화소를 인접하는 화소와 구획하도록 해서 상기 데이터 신호선(DL)의 양 옆에 각각 형성되어 있다. 도 6에 있어서는 데이터 신호선(DL)의 좌측에 위치하는 공통전압 신호선(CL)을 공통전압 신호선(CLl)과 데이터 신호선(DL)의 오른쪽에 위치하는 공통전압 신호선(CL)을 공통전압 신호선(CLr)으로 나타내고 있다. 그러나, 이들 공통전압 신호선(CLl)과 공통전압 신호선(CLr)은 별개의 신호선으로 나타내는 것은 아니고, 화소의 집합인 표시부의 외측의 영역에 있어서 서로 접속되는 것으로서 구성되어 있다.

이 경우, 데이터 신호선(DL)은 그 형성에 의해 상기 반도체층(PS4, PS5)의 각 일단 변과 포개지도록 해서 형성된다. 상기 데이터 신호선(DL)의 겹침 부분을 박막 트랜지스터(TFT4, TFT5)의 한쪽 전극(드레인 전극)으로서 구성하지 않게 하기 위함이다.

또, 박막 트랜지스터(TFT4, TFT5)의 다른쪽 전극은 예를들면 상기 데이터 신호선(DL)의 형성시에 동시에 형성되도록 되어 있고, 상기 다른쪽 전극은 화소의 영역으로 약간 연재된 패턴으로 형성되어 있다. 박막 트랜지스터(TFT4)의 다른쪽 전극은 후술의 박막 트랜지스터(TFT2)의 게이트 전극(GT2)과 스루홀을 통해서 접속시키기 위함이며, 박막 트랜지스터(TFT5)의 다른쪽 전극은 후술의 박막 트랜지스터(TFT1)의 게이트 전극(GT1)과 스루홀을 통해서 접속시키기 위함이다.

또한, 데이터 신호선(DL)의 형성시에는, 동시에 박막 트랜지스터(TFT3, TFT6)의 각 전극이 형성되도록 되어 있다. 즉, 박막 트랜지스터(TFT3)의 한쪽 전극은 화소의 영역으로 약간 연재된 패턴으로 형성되어 있다. 후술하는 박막 트랜지스터(TFT1)의 게이트 전극(GT1)과 스루홀을 통해서 접속시키기 위함이다. 박막 트랜지스터(TFT3)의 다른쪽 전극은 상기 화소와 인접하는 다른 화소에서의 제2 게이트 신호선(GL2)(상기 화소의 제1 게이트 전극(GL1)에 인접한다)에 중첩하는데 이르기까지 연재하고, 이 연재단에 있어서 하층의 제1 절연막에 미리 형성된 스루홀을 통해서 상기 제2 게이트 신호선(GL2)에 접속되어 있다.

또한, 박막 트랜지스터(TFT6)의 한쪽 전극은 화소의 영역으로 약간 연재된 패턴으로 형성되어 있다. 후술하는 박막 트랜지스터(TFT2)의 게이트 전극(GT2)과 스루홀을 통해서 접속시키기 위함이다. 박막 트랜지스터(TFT6)의 다른쪽 전극은 상기 화소와 인접하는 다른 화소에서의 제1 게이트 신호선(GL1)(상기 화소의 제2 게이트 전극(GL2)에 인접한다)에 중첩하는데 이르기까지 연재하고, 이 연재단에 있어서 하층의 제1 절연막에 미리 형성된 스루홀을 통해서 상기 제1 게이트 신호선(GL1)에 접속되어 있다.

또한, 공통전압 신호선(CLl)과 공통전압 신호선(CLr)은 그 어느 것에 있어서도, 화소 영역 내에 있어서, 신장 방향에 교차하는 방향으로 연재하는 돌출부(PJ)가 상기 신장 방향으로 병설되어 형성되어 있다. 이 돌기부(PJ)는 인접하는 화소의 영역 내에 있어서도 같은 형태로 형성되어 있으므로 전체로서 소위 피쉬본 패턴으로서 형성되어 있다. 이 돌기부(PJ)는 공통전압 신호선(CLl)측에서는 박막 트랜지스터(TFT1)의 한쪽 전극(전극군)으로서, 공통전압 신호선(CLr)측에서는 박막 트랜지스터(TFT2)의 한쪽 전극(전극군)으로서 구성된다.

또한, 박막 트랜지스터(TFT1, TFT2)의 다른쪽 전극은 예를들면 공통전압 신호선(CL)의 형성과 동시에 형성되도록 되어 있다. 박막 트랜지스터(TFT1)의 다른쪽 전극은, 상기 박막 트랜지스터(TFT1)의 상기 한쪽 전극군의 각 전극(상기 돌출부(PJ))을 간격으로 해서 각 전극이 배치된 전극군으로서 구성되고, 또한, 그들을 전기적으로 접속시키기 위해서 빗살 모양의 패턴을 이루어 형성되어 있다. 마찬가지로, 박막 트랜지스터(TFT2)의 다른쪽 전극은, 상기 박막 트랜지스터(TFT2)의 상기 한쪽 전극군의 각 전극(상기 돌출부(PJ))을 간격으로 해서 각 전극이 배치된 전극군으로서 구성되고, 또한, 그들을 전기적으로 접속시키기 위해서 빗살 모양의 패턴을 이루어 형성되어 있다.

화소 내에 있어서, 상기 데이터 신호선(DL)을 경계로 해서 그 좌측의 영역에는 반도체층(PS1)이, 오른쪽의 영역에는 반도체층(PS2)이 각각 서로 분리되어 형성되어 있다.

이 반도체층(PS1) 및 반도체층(PS2)은, 도시되어 있지 않지만, 예를들면, 각각 후술하는 게이트 전극(GT1) 및 게이트 전극(GT2)으로 나타내는 영역(도면 중, 점선으로 둘러싸여지는 영역)에 상당하는 부분에 형성되어 있다.

반도체층(PS1)은 후술하는 박막 트랜지스터(TFT1)의 반도체층으로 구성되고, 반도체층(PS2)은 후술하는 박막 트랜지스터(TFT2)의 반도체층으로 구성되기 때문이다.

또한, 이들 각 반도체층(PS1 및 PS2)도 덮어 절연 기판의 표면에는 제2 절연막(도시하지 않음)이 형성되어 있다. 이 제2 절연막은 박막 트랜지스터(TFT1 및 TFT2)의 게이트 절연막으로서 기능하는 것이므로, 그것에 맞추어 막 두께가 설정되어 있다.

제2 절연막의 표면에는, 박막 트랜지스터(TFT1)의 게이트 전극(GT1)이, 박막 트랜지스터(TFT2)의 게이트 전극(GT2)이 형성되어 있다. 박막 트랜지스터(TFT1)의 게이트 전극(GT1)은 상기 반도체층(PS1)이 형성된 영역에 중첩되어 형성되고, 그 연재된 일부에 있어서 하층의 제2 절연막에 형성된 스루홀(TH3)을 통해서 박막 트랜지스터(TFT3)의 소스 전극(ST3)과 접속되며, 또한, 스루홀(TH5)을 통해서 박막 트랜지스터(TFT5)의 소스 전극(ST5)과 접속되어 있다. 마찬가지로, 박

막 트랜지스터(TFT2)의 게이트 전극(GT2)은 상기 반도체층(PS2)이 형성된 영역에 중첩되어 형성되고, 그 연재된 일부에 있어서 하층의 제2 절연막에 형성된 스루홀(TH4)을 통해서 박막 트랜지스터(TFT4)의 소스 전극(ST4)과 접속되며, 또한, 스루홀(TH6)을 통해서 박막 트랜지스터(TFT4)의 소스 전극(ST6)과 접속되어 있다.

각 게이트 전극(GT1 및 GT2)도 덮어 절연 기판의 표면에는 제3 절연막(도시하지 않음)을 통해서 화소 전극(PX)이 형성되어 있다. 이 화소 전극(PX)은 소위 화소의 개구율을 향상시키기 위해서 화소 영역의 거의 전체 영역에 형성되고, 그 하층의 제3 절연막 및 제2 절연막을 관통해서 형성된 스루홀(TH)를 통해서 박막 트랜지스터(TFT1, TFT2)의 다른쪽 전극(공통 전압 신호선(CL)과 일체로 형성된 전극과는 다른 전극)에 접속되어 있다. 이 경우, 상기 스루홀(TH)의 각 형성 개소에는 게이트 전극(GT1 및 GT2)이 노출되는 것을 회피하기 위해서, 상기 게이트 전극(GT1 및 GT2)의 상기 개소에 있어서 미리 노치가 형성된 패턴으로 되어 있다. 화소 전극(PX)과 각 게이트 전극(GT1 및 GT2)의 전기적 접속이 이루어지는 것을 회피하기 위함이다.

또, 화소 전극(PX)과 박막 트랜지스터(TFT1 및 TFT2)의 한쪽 전극(공통전압 신호선(CL)과 일체로 형성된 전극)과의 사이에는 제2 절연막과 제3 절연막을 유전체막으로 하는 용량(C1 및 C2)이 형성되게 된다.

화소 전극(PX)의 상면에는 그 전체 영역에 걸쳐 유기 EL층(EL)(도시하지 않음)이 형성되어 있다. 이 경우, 유기 EL층(EL)을 포함해서 전하 수송층 혹은 전자수송층 등을 적층시켜 형성해도 좋은 것은 실시예1의 경우와 같다.

그리고, 이 발광층의 상면에 전원공급 신호선(PL)이 형성되어 있다. 이 전원공급 신호선(PL)은 각 화소의 영역에 있어서 공통으로, 즉, 각 화소의 집합체로 구성되는 표시부의 전체 영역에 걸쳐 형성되어 있다. 또, 이 전원공급 신호선(PL)은 그 재료로서 예를들면 ITO(Indium Tin Oxide)이나 IZO(Indium Zinc Oxide) 등등으로 이루어지는 투광성의 도전층으로서 형성된 것으로 되어 있다. 상기 발광층으로부터의 광을 도면의 지면의 표면측으로 조사시키도록 되어 있기 때문이다.

또, 상술한 구성에 있어서, 박막 트랜지스터(TFT3로부터 TFT6)는, 그들 반도체층에 대해서 게이트 전극(게이트 신호선(GL))을 하층으로 하는 소위 역스태커 구조로 한 것이지만, 이것에 한정되는 일 없이, 상기 게이트 전극을 반도체층의 상층에 형성하는 스태커 구조로 하도록 해도 좋은 것은 실시예1의 경우와 같다.

마찬가지로, 박막 트랜지스터(TFT1, TFT2)를 스태커 구조로 구성한 것이지만, 역스태커 구조로 구성해도 좋은 것은 실시예1의 경우와 같다.

또한, 박막 트랜지스터(TFT1, TFT2)는, 화소 내의 발광 영역, 즉, 유기 EL층(EL)이 형성된 영역에 중첩되어 형성한 것이지만, 이것에 한정되는 것은 아니고, 평면적으로 보았을 경우, 발광 영역과 구별되는 다른 영역 내에 형성하도록 구성해도 좋은 것은 실시예1의 경우와 같다.

게다가, 박막 트랜지스터(TFT1 및 TFT2)는, 온 전류를 대폭 향상시킬 수 있고, 그들의 반도체층(PS1 및 PS2)으로서 예를들면 아모르퍼스 실리콘을 이용한 경우, 상기 아모르퍼스 실리콘은 비교적 이동도가 작은 것으로, 상술한 구성으로 함으로써, 그 부적합을 해소할 수 있게 되는 것도 실시예1의 경우와 같다.

상술한 각 실시예에서는, 구동 스위칭 소자(TFT1 및 TFT2)의 소스 전극과 드레인 전극의 한쪽이 되는 공통전압 신호선의 돌출부 선단(先端)이 구형(矩形)의 볼록(凸), 돌출부의 사이가 구형의 오목(凹)으로 되고, 다른쪽 전극이 되는 빗살 전극의 선단이 구형의 볼록(凸), 그 사이가 구형의 오목(凹)으로 되어 있기 때문에, 염밀하게는, 한쪽 전극(凸)의 각(角)과 다른쪽 전극간의 웅덩이(凹))의 구석과의 거리와, 공통전압 신호선과 빗살 전극간이 실질적으로 평행하게 되어 있는 영역에서의 전극간의 거리와는, 다르다(단순 계산으로 폭이  $\sqrt{2}$ 배 넓게 된다). 즉, 채널 폭은 넓어졌지만, 특히, 전극 폭이 넓은 경우, 채널 길이가 일정하다고는 말할 수 없게 된다.

그래서, 이들의 오목(凹)의 바닥 형상과 볼록(凸)의 선단 형상을 대응(엄밀하게는 테두리 형상의 동일화)한 곡선 형상(볼록(凸) 반원의 선단 형상과, 오목(凹) 반원의 움덩이 형상 등)으로 하는 것으로, 전극간, 즉, 채널 길이를 일정하게 할 수 있게 된다.

또, 요철(凹凸) 쌍방을 반드시 곡선 모양으로 가공하지 않으면 안되는 것은 아니고, 볼록(凸)의 선단의 폭이 가는 경우에는, 그 선단은 점으로 간주할 수 있고, 그 염밀한 형상에 관계없이, 오목(凹)의 형상을 반원이나 부분 타원과 같은 곡선 형상이 되도록 하는 것만으로도, TFT의 구동 특성을 크게 개선할 수 있다.

## 발명의 효과

상술한 각 실시예는 각각 단독으로 혹은 조합해서 이용해도 좋다. 각각의 실시예에서의 효과를 단독 혹은 상승해서 이룰 수 있기 때문이다.

#### (57) 청구의 범위

##### 청구항 1.

화소에, 발광 소자, 스위칭 소자를 적어도 구비하고,

상기 스위칭 소자는, 이 스위칭 소자를 통해서 상기 발광 소자에 전원을 공급시키는 것으로서, 제1 스위칭 소자와 제2 스위칭 소자로 구성되며,

상기 제1 스위칭 소자와 제2 스위칭 소자는, 화소 내로의 데이터 신호의 입력에 따라, 한쪽이 정(正)바이어스 상태로 다른 쪽이 역(逆)바이어스 상태로 되는 동시에, 상기 바이어스 상태는 상기 데이터 신호의 시계열적인 입력에 따라 상기 제1 스위칭 소자와 제2 스위칭 소자의 사이에서 교대로 전환되어 동작되고,

1개의 프레임 내에서의 상기 발광 소자로의 전원의 공급은 제1 스위칭 소자 및 제2 스위칭 소자 중 어느 것인가 한쪽의 스위칭 소자를 통해서 이루어지는 것을 특징으로 하는 표시장치.

##### 청구항 2.

제 1 항에 있어서,

상기 제1 스위칭 소자와 제2 스위칭 소자의 바이어스 상태의 전환은 순차 입력되는 데이터 신호마다 이루어지는 것을 특징으로 하는 표시장치.

##### 청구항 3.

제 1 항에 있어서,

제1 스위칭 소자 및 제2 스위칭 소자는, 각각 그 채널영역이 사행(蛇行) 모양의 패턴으로 형성되어 있는 것을 특징으로 하는 표시장치.

##### 청구항 4.

제 1 항에 있어서,

제1 스위칭 소자 및 제2 스위칭 소자는, 발광층의 하층(下層) 측에 형성되어 있는 동시에, 상기 발광층의 상층(上層)에 형성되는 한쪽 전극은 투광성의 도전층으로 형성되어 있는 것을 특징으로 하는 표시장치.

##### 청구항 5.

제 1 항에 있어서,

제1 스위칭 소자 및 제2 스위칭 소자는, 어느 것이나 N채널형인 것을 특징으로 하는 표시장치.

**청구항 6.**

제 1 항에 있어서,

제1 스위칭 소자 및 제2 스위칭 소자는, 어느 것이나 그 반도체층이 아모르페스 실리콘으로 형성되어 있는 것을 특징으로 하는 표시장치.

**청구항 7.**

화소에 순차 입력되는 데이터 신호로서 제1 데이터 신호와 제2 데이터 신호를 갖고, 상기 제1 데이터 신호와 제2 데이터 신호는, 서로 반전된 관계를 갖는 동시에, 시계열적으로 반전을 교환하는 것이며,

상기 화소에는, 게이트 신호선으로부터의 신호에 의해 구동되는 제3 스위칭 소자와 제4 스위칭 소자와,

제3 스위칭 소자를 통해서 상기 제1 데이터 신호에 대응하는 전하가 축적되는 제1 용량소자와, 제4 스위칭 소자를 통해서 상기 제2 데이터 신호에 대응하는 전하가 축적되는 제2 용량소자와,

제1 용량소자에 축적된 전하에 의해 구동하는 제1 스위칭 소자와, 제2 용량소자에 축적된 전하에 의해 구동하는 제2 스위칭 소자와,

제1 스위칭 소자 혹은 제2 스위칭 소자를 통해서 전원이 공급되는 발광 소자를 적어도 구비하는 것을 특징으로 하는 표시장치.

**청구항 8.**

제 7 항에 있어서,

제1 데이터 신호는 제1 데이터 신호선을 통해서 입력되고, 제2 데이터 신호는 제2 데이터 신호선을 통해서 입력되는 것을 특징으로 하는 표시장치.

**청구항 9.**

제 7 항에 있어서,

상기 제1 데이터 신호와 제2 데이터 신호의 반전은, 순차 입력되는 각 데이터 신호마다 반전하는 것을 특징으로 하는 표시장치.

**청구항 10.**

제 7 항에 있어서,

제1 스위칭 소자 및 제2 스위칭 소자는, 각각 그 채널영역이 사행 모양의 패턴으로 형성되어 있는 것을 특징으로 하는 표시장치.

**청구항 11.**

제 7 항에 있어서,

제1 스위칭 소자 및 제2 스위칭 소자는, 발광층의 하층 측에 형성되어 있는 동시에, 상기 발광층의 상층에 형성되는 한쪽 전극은 투광성의 도전층으로 형성되어 있는 것을 특징으로 하는 표시장치.

### 청구항 12.

제 7 항에 있어서,

제1 스위칭 소자 및 제2 스위칭 소자는, 어느 것이나 N채널형인 것을 특징으로 하는 표시장치.

### 청구항 13.

제 7 항에 있어서,

제1 스위칭 소자 및 제2 스위칭 소자는, 어느 것이나 그 반도체층이 아모르퍼스 실리콘으로 형성되어 있는 것을 특징으로 하는 표시장치.

### 청구항 14.

화소에 순차 입력되는 주사신호로서 제1 주사신호와 제2 주사신호를 갖고, 제1 주사신호와 제2 주사신호는, 한쪽에서 온(on) 신호가 입력될 때에 다른쪽은 오프(off) 신호가 입력되는 관계를 갖는 동시에, 주사(走査)과정에서 그들이 전환되는 것이며,

상기 화소에는, 발광 소자와, 이 발광 소자에 전원을 어느 것인가의 스위칭 소자를 통해서 공급하는 제1 스위칭 소자 및 제2 스위칭 소자와,

상기 제1 주사신호의 온 신호에 의해 구동되는 동시에 제2 주사신호의 오프 신호를 제1 스위칭 소자의 게이트 전극에 공급하는 제5 스위칭 소자와, 제2 주사신호의 온 신호에 의해 구동되는 동시에 제1 주사신호의 오프 전류를 제2 스위칭 소자의 게이트 전극에 공급시키는 제6 스위칭 소자와,

제2 주사신호의 온 신호에 의해 구동되는 제3 스위칭 소자와, 제1 주사신호의 온 신호에 의해 구동되는 제4 스위칭 소자와,

제3 스위칭 소자를 통해서 데이터 신호에 대응하는 전하를 축적시키는 동시에 상기 제1 스위칭 소자를 구동시키는 제1 용량소자와, 제4 스위칭 소자를 통해서 상기 데이터 신호에 대응하는 전하를 축적시키는 동시에 상기 제2 스위칭 소자를 구동시키는 제2 용량소자를 적어도 구비하는 것을 특징으로 하는 표시장치.

### 청구항 15.

제 14 항에 있어서,

제1 주사신호는 제1 게이트 신호선을 통해서 입력되고, 제2 주사신호는 제2 게이트 신호선을 통해서 입력되는 것을 특징으로 하는 표시장치.

### 청구항 16.

제 14 항에 있어서,

제1 주사신호와 제2 주사신호의 온·오프의 전환은, 프레임마다 이루어지는 것을 특징으로 하는 표시장치.

### 청구항 17.

제 14 항에 있어서,

제1 스위칭 소자 및 제2 스위칭 소자는, 각각 그 채널영역이 사행 모양의 패턴으로 형성되어 있는 것을 특징으로 하는 표시장치.

### 청구항 18.

제 14 항에 있어서,

제1 스위칭 소자 및 제2 스위칭 소자는, 발광층의 하층 측에 형성되어 있는 동시에, 상기 발광층의 상층에 형성되는 한쪽 전극은 투광성의 도전층으로 형성되어 있는 것을 특징으로 하는 표시장치.

### 청구항 19.

제 14 항에 있어서,

제1 스위칭 소자 및 제2 스위칭 소자는, 어느 것이나 N채널형인 것을 특징으로 하는 표시장치.

### 청구항 20.

제 14 항에 있어서,

제1 스위칭 소자 및 제2 스위칭 소자는, 어느 것이나 그 반도체층이 아모르페스 실리콘으로 형성되어 있는 것을 특징으로 하는 표시장치.

### 청구항 21.

화소에, 발광 소자와, 이 발광 소자에 전원을 어느 것인가의 스위칭 소자를 통해서 공급하는 제1 스위칭 소자 및 제2 스위칭 소자를 구비하고,

화소 내로의 데이터 신호의 순차 입력의 과정에서,

제1 스위칭 소자 및 제2 스위칭 소자를, 그 한쪽에서 정(正) 바이어스 상태로 다른쪽에서 역(逆) 바이어스 상태로 하는 동시에, 상기 바이어스 상태를 상기 제1 스위칭 소자와 제2 스위칭 소자의 사이에서 교대로 전환되도록 동작시키는 것을 특징으로 하는 표시장치의 구동방법.

### 청구항 22.

제 21 항에 있어서,

제1 스위칭 소자 및 제2 스위칭 소자의 바이어스 상태의 교대 전환은, 화소 내로 입력되는 데이터 신호마다 행하는 것을 특징으로 하는 표시장치의 구동방법.

도면

도면1

도면2

### 도면3

## 도면4

도면5

도면6

|                |                                                                                                                         |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置及其驱动方法                                                                                                              |         |            |

| 公开(公告)号        | <a href="#">KR1020060064534A</a>                                                                                        | 公开(公告)日 | 2006-06-13 |

| 申请号            | KR1020050118083                                                                                                         | 申请日     | 2005-12-06 |

| [标]申请(专利权)人(译) | 株式会社日本显示器                                                                                                               |         |            |

| 申请(专利权)人(译)    | 株式会社日本排气量                                                                                                               |         |            |

| 当前申请(专利权)人(译)  | 株式会社日本排气量                                                                                                               |         |            |

| [标]发明人         | TANAKA MASAHIRO<br>다나카마사히로<br>MATSUURA TOSHIYUKI<br>마츠우라토시유키<br>MURAKAMI HAJIME<br>무라카미하지메<br>AKIMOTO HAJIME<br>아키모토하지메 |         |            |

| 发明人            | 다나카마사히로<br>마츠우라토시유키<br>무라카미하지메<br>아키모토하지메                                                                               |         |            |

| IPC分类号         | G09G3/30 H05B33/12                                                                                                      |         |            |

| CPC分类号         | G09G2320/043 G09G2300/0823 G09G2320/0233 G09G3/3233                                                                     |         |            |

| 优先权            | 2004355401 2004-12-08 JP                                                                                                |         |            |

| 其他公开文献         | <a href="#">KR100695770B1</a>                                                                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                               |         |            |

### 摘要(译)

改善显示装置的显示质量是一个问题。作为解决该问题的手段，像素包括发光元件和开关元件，并且开关元件向发光元件供电，并且由第一开关元件和第二开关元件构成，在第二开关元件中，第一开关元件和第二开关元件中的一个处于正偏置状态而另一个根据数据信号输入到像素中而处于反向偏置状态，因此，第一开关元件和第二开关元件交替地切换和操作，并且通过第一或第二开关元件对发光元件供电。1指教方面显示装置，驱动方法，像素，发光，元件，开关，偏置，开关，电源，数据