(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2014년08월18일

(11) 등록번호 10-1431408

(24) 등록일자 2014년08월11일

(51) 국제특허분류(Int. Cl.)

H01L 27/32 (2006.01) H01L 51/00 (2006.01)

(21) 출원번호 10-2013-7014519(분할)

(22) 출원일자(국제) 2006년08월22일

심사청구일자 2013년06월05일

(85) 번역문제출일자 2013년06월05일

(65) 공개번호 10-2013-0079634

(43) 공개일자 2013년07월10일

(62) 원출원 특허 10-2008-7006960

원출원일자(국제) 2006년08월22일

심사청구일자 2011년08월22일

(86) 국제출원번호 PCT/GB2006/003135

(87) 국제공개번호 WO 2007/023272

국제공개일자 2007년03월01일

(30) 우선권주장

0517195.4 2005년08월23일 영국(GB)

0605128.8 2006년03월15일 영국(GB)

(56) 선행기술조사문현

EP00993235 A2

WO1999048338 A1

WO2001041229 A1

전체 청구항 수 : 총 15 항

심사관 : 박성호

(54) 발명의 명칭 유기 전자 디바이스 구조체, O L E D 디스플레이 디바이스, 유기 전자 디바이스 제조 방법, 액정 증착 웰 형성 방법 및 유기 전자 디바이스

**(57) 요 약**

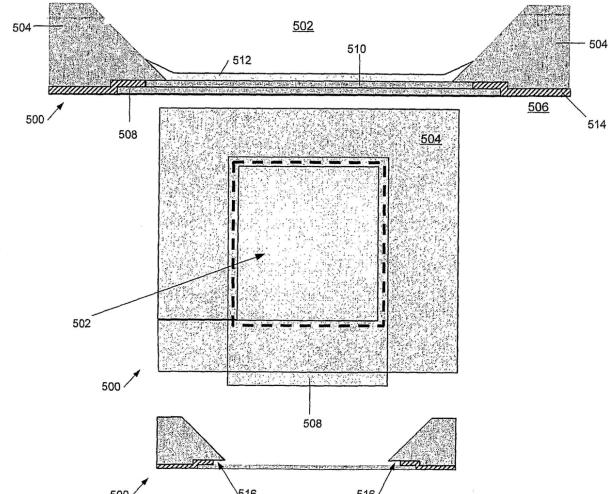

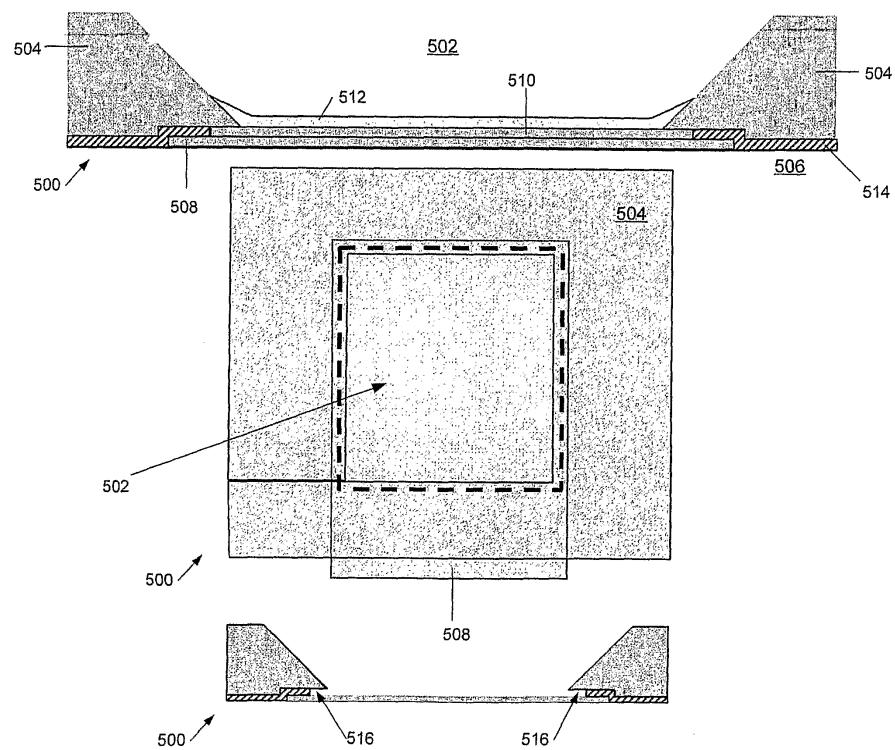

본 발명은 유기 전자 디바이스, 특히 유기 발광 다이오드(OLED)의 구조체 및 제조 방법에 관한 것이다. 유기 전자 디바이스 구조체(500)는 기판(506)과, 이 기판(506)에 의해 지지되고 유기 전자 물질(510, 512)의 용매 기반 증착을 위한 웰의 기저를 정의하는 기저 층(508)과, 기저 층(508) 위에 형성된 하나 이상의 스페이서 층(514)과, 웰(502)의 측면을 정의하도록 스페이서 층(514) 위에 형성된 벙크 층(504)을 포함하되, 기저 층(508)에 인접한 웰(502)의 에지는 언더컷되어 기저 층(508) 위에 유기 전자 물질(510)을 수용하는 리세스를 정의하는 쉘프(516)를 정의한다.

**대 표 도 - 도5**

## 특허청구의 범위

### 청구항 1

유기 전자 디바이스 구조체에 있어서,

기판과,

상기 기판에 의해 지지되고 유기 전자 물질의 용매 기반 증착을 위한 웰을 정의하는 소수성 뱅크 층을 포함하되,

상기 소수성 뱅크 층은 상기 기판쪽으로 점점 가늘어지는(taper) 두께를 가지며,

상기 구조체는 상기 웰의 내부 에지 및 상기 웰의 기저에서 필렛(a fillet)을 정의하도록 패터닝된 필렛 층을 더 포함하는

유기 전자 디바이스 구조체.

### 청구항 2

제 1 항에 있어서,

상기 필렛은 친수성 물질을 포함하는

유기 전자 디바이스 구조체.

### 청구항 3

제 1 항에 있어서,

상기 필렛은 실리콘의 산화물과 실리콘의 질화물 중 적어도 하나를 포함하는

유기 전자 디바이스 구조체.

### 청구항 4

제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 필렛은 상기 웰의 측면에 가까워짐에 따라 상기 기판 쪽으로 점점 가늘어지는 상기 소수성 뱅크 층의 부분을 덮는

유기 전자 디바이스 구조체.

### 청구항 5

제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 웰의 상기 내부 에지에서 단부(a step)를 정의하도록 패터닝된 하나 이상의 단부 층을 더 포함하되,

상기 필렛은 상기 단부에 접하는 것인

유기 전자 디바이스 구조체.

### 청구항 6

제 5 항에 있어서,

상기 기판에 의해 지지되고 상기 웰의 상기 기저를 정의하는 기저 층을 더 포함하되,

상기 단부 층은 상기 기저 층과 상기 기판 사이에 위치하고,

상기 단부는 상기 기판으로부터 상기 기저 층까지의 단부 변경 거리를 포함하며,

상기 필릿은 상기 기저 층에 접하는 것인

유기 전자 디바이스 구조체.

## 청구항 7

제 6 항에 있어서,

상기 하나 이상의 단부 층은 적어도 2 개의 단부 층을 포함하되,

상기 적어도 2 개의 단부 층은 상기 필릿에 대한 상기 웰의 상기 내부 에지에서 이중 단부(a double step)를 정의하도록 패터닝되는

유기 전자 디바이스 구조체.

## 청구항 8

제 6 항에 있어서,

상기 소수성 맹크 층의 두께는 상기 웰의 측면에 가까워짐에 따라 상기 기판 쪽으로 점점 가늘어져서, 상기 기저 층의 위치와 상기 웰의 상기 내부 에지의 둘레의 상기 유기 전자 물질 사이의 접촉을 허용하는

유기 전자 디바이스 구조체.

## 청구항 9

제 5 항에 있어서,

상기 하나 이상의 단부 층은 상기 유기 전자 디바이스 구조체의 능동 부분에 대한 금속층과 실리콘층 중 적어도 하나를 포함하는

유기 전자 디바이스 구조체.

## 청구항 10

OLED 디스플레이 디바이스에 있어서,

상기 OLED 디스플레이 디바이스는 제 1 항 내지 제 3 항 중 어느 한 항의 유기 전자 디바이스 구조체를 포함하되,

상기 소수성 맹크 층은 양성 포토레지스트를 포함하고,

상기 유기 전자 물질은 제 1 도전성 물질 층 및 제 2 발광 물질 층을 포함하는

OLED 디스플레이 디바이스.

## 청구항 11

삭제

### 청구항 12

유기 전자 디바이스의 액적 증착 기반 제조를 위한 구조체 내에 액적 증착 웰을 형성하는 방법에 있어서,

기판 상에 친수성 물질 층을 증착하는 단계와,

상기 친수성 물질 층 위에 소수성 레지스트 물질 층을 증착하는 단계와,

하나 이상의 상기 액적 증착 웰을 형성하는 뱅크를 정의하도록 상기 소수성 레지스트 물질 층을 패터닝하는 단계와,

상기 하나 이상의 액적 증착 웰의 기저 영역의 적어도 일부로부터 친수성 물질을 제거하도록 상기 친수성 물질 층을 패터닝하는 단계와,

상기 하나 이상의 액적 증착 웰을 형성하는 상기 뱅크의 기저에 인접한 상기 패터닝된 친수성 물질 층의 상부면의 일부를 노광시키도록 레지스트 제거 처리를 이용하는 단계를 포함하는

액적 증착 웰 형성 방법.

### 청구항 13

제 12 항에 있어서,

상기 레지스트 제거 처리는 플라즈마 애싱(plasma ashing)을 포함하는

액적 증착 웰 형성 방법.

### 청구항 14

제 12 항 또는 제 13 항에 있어서,

액적 증착 공정을 사용하여 상기 액적 증착 웰 내로 용해된 유기 전자 물질을 증착함으로써 상기 유기 전자 디바이스를 제조하는 단계를 더 포함하는

액적 증착 웰 형성 방법.

### 청구항 15

제 14 항에 있어서,

상기 유기 전자 디바이스는 OLED 디바이스를 포함하고,

상기 용해된 유기 전자 물질은 PEDOT의 친수성 용액을 포함하는

액적 증착 웰 형성 방법.

### 청구항 16

유기 전자 물질로 충진된 복수의 액적 증착 웰 아래에 패터닝된 친수성 물질 층을 구비하는 기판을 포함하는 유기 전자 디바이스에 있어서,

상기 복수의 액적 증착 웰 중 하나 이상의 액적 증착 웰을 형성하는 뱅크의 소수성 기저에 인접하는 상기 패터닝된 친수성 물질 층의 상부면의 일부는 상기 유기 전자 물질에 노광되는

유기 전자 디바이스.

## 명세서

## 기술 분야

[0001] 본 발명은 유기 전자 디바이스, 특히, 유기 발광 다이오드(OLED)의 구조체 및 제조 방법에 관한 것이다.

## 배경 기술

[0002] 본 발명의 이해를 돋기 위해, 우선 OLED 디스플레이의 몇몇 특징 및 이들의 제조에 관한 몇몇 문제점을 설명하는 것이 도움이 된다. 그러나, 특히 OLED 디스플레이를 참조하여 본 발명의 실시예를 설명할 것이지만 본 기술이 유기 전자 디바이스의 제조에 보다 통상적으로 적용가능함이 명백할 것이다.

[0003] 유기 발광 다이오드(OLED)는 특히 이로운 전자 디스플레이 형태이다. OLED는 빛나고, 색상이 다채로우며, 고속 스위칭하고, 얕은 시야각을 제공하며, 다양한 기판 상에 제조하기 쉽고 저가이다. (본 명세서에서 유기금속을 포함하는) 유기 LED는 사용된 물질에 따라, 색상 범위 (또는 다색 디스플레이)에서 폴리머 또는 저분자를 사용하여 제조될 수 있다. 전형적인 OLED 디바이스는 2 개의 유기 물질 층을 포함하는데, 한 층은 발광 폴리머 (LEP), 올리고머(oligomer) 또는 발광 저분자량 물질과 같은 발광 물질 층이고, 다른 층은 폴리티오펜 유도체 (polythiophene derivative) 또는 폴리아닐린 유도체(polyaniline derivative)와 같은 정공 전달 물질 층이다.

[0004] 유기 LED는 픽셀 행렬로 기판 상에 증착되어 단일 또는 다색 픽셀화 디스플레이를 형성할 수 있다. 다색 디스플레이에는 적색, 녹색 및 청색의 방출 픽셀 그룹을 사용하여 구성될 수 있다. 소위 능동 매트릭스 디스플레이에는 각 픽셀과 관련된 메모리 소자, 전형적으로 저장 캐패시터 및 트랜지스터를 구비하지만, 수동 매트릭스 디스플레이에는 이러한 메모리 소자를 구비하지 않는 대신에 안정된 영상을 프린트하도록 반복하여 스캐닝된다.

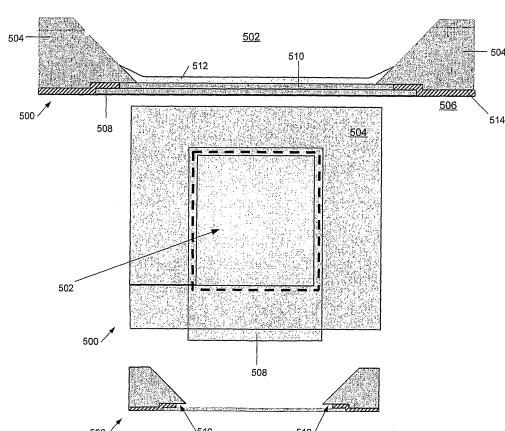

[0005] 도 1은 일례의 OLED 디바이스(100)의 종단면도를 도시한다. 픽셀 영역의 능동 매트릭스 디스플레이부는 관련된 드라이브 회로(도 1에 도시 생략)에 의해 점유된다. 디바이스의 구조는 도시를 위해 다소 간단해진다.

[0006] OLED(100)는 다른 층이 증착되는 기판(102) -전형적으로 0.7mm 또는 1.1mm의 유리이지만 선택적으로 투명한 플라스틱임-을 포함한다. 애노드 층은 전형적으로 상부에 때로는 애노드 금속으로 지칭되는 약 500nm 두께의 알루미늄인 금속 접촉 층이 제공되는 약 150nm 두께의 ITO(indium tin oxide)를 포함한다. ITO 및 접촉 금속으로 코팅된 유리 기판은 미국 코닝으로부터 구매할 수 있다. 접촉 금속(및 선택적으로 ITO)은 종래의 포토리소그래피 공정에 의해 디스플레이를 어렵게 하지 않도록 원하는 만큼 패터닝되고 이어서 에칭된다.

[0007] 실질적으로 투명한 정공 전달 층(108a)은 애노드 금속 위에 제공되고 그 위에 전계발광 층(108b)이 제공된다. 뱅크(112)는 예컨대, 양성 또는 음성의 포토레지스트 물질로부터 기판 상에 형성되어, 예컨대, 액적(droplet) 증착 또는 잉크젯 프린트 기술에 의해 이들 능동 유기층이 선택적으로 증착될 수 있는 웨(114)을 정의할 수 있다. 따라서, 웨는 디스플레이의 발광 영역 또는 픽셀을 정의한다.

[0008] 이어서 캐소드 층(110)은 물리적 기상 증착에 의해 적용된다. 캐소드 층은 전형적으로 전자 에너지 레벨 정합을 개선하기 위해 더 두꺼운 알루미늄 캐핑 층으로 덮이고 플루오르화 리튬 층과 같이 전계발광 층에 바로 인접한 다른 층을 선택적으로 포함하는 칼슘 또는 바륨과 같은 저농도의 금속을 포함한다. 캐소드 라인의 상호 전기적 절연은 캐소드 분리기(도 3b의 소자(302))를 사용하여 달성될 수 있다. 전형적으로 다수의 디스플레이에는 단일 기판 상에 제조되고, 제조 공정의 마지막에 기판이 스크라이빙되며, 캡슐화 전에 분리된 디스플레이는 각각에 접착되어 산화 및 습기 유입을 억제한다.

[0009] 이러한 일반적인 유형의 유기 LED는 폴리머, 덴드리머(dendrimer) 및 소위 저분자를 포함하는 다양한 물질을 사용하여 제조되어, 가변하는 드라이브 전압 및 효율에서 광장 범위 이상으로 방출한다. 폴리머 기반 OLED 물질의 예는 WO 90/13148, WO 95/06400 및 WO 99/48160에 설명되고, 덴드리머 기반 물질은 WO 99/21935 및 WO 02/067343에 설명되며, 저분자 OLED 물질의 예는 US 4,539,507에 설명된다. 상술한 폴리머, 덴드리머 및 저분자는 단일 여기자(형광)의 방사 감쇠에 의해 발광한다. 그러나, 여기자 중 75 %는 통상적으로 무방사 감쇠되는 삼중향 여기자이다. 삼중향 여기자의 무방사 감쇠에 의한 전계발광(인광)은 예컨대, 1999년 7월 5일, Applied Physics Letters, vol. 75(1) pp.4-6, M.A. Baldo, S. Lamansky, P.E. Burrows, M.E. Thompson 및 S.R. Forrest의 "Very high-efficiency green organic light-emitting devices based on electrophosphorescence"에 개시된다. 폴리머 기반 OLED 층(108)은 정공 전달 층(108a)과 발광 폴리머(LEP) 전계발광 층(108b)을 포함한다. 전계발광 층은 예컨대, 약 70nm (건성) 두께의 PPV(poly(p-phenylenevinylene))를 포함할 수 있고, 애노드 층과 전계발광 층의 정공 에너지 레벨 정합을 지원하는 정공 전달 층은 예컨대, 약 50-200nm, 바람직하게

는 약 150nm (건성) 두께의 PEDOT:PSS(polystyrene-sulphonate-doped polyethylene-dioxythiophene)를 포함할 수 있다.

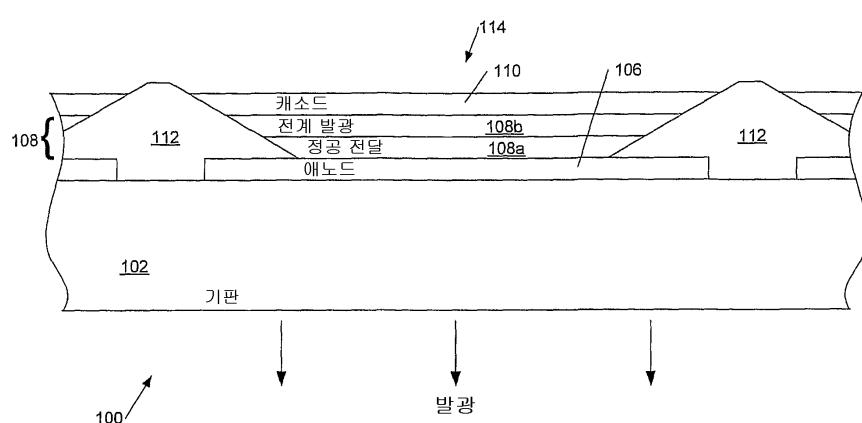

[0010] 도 2는 능동 색상 층들 중 하나의 증착 이후의 삼색 능동 매트릭스 픽셀화 OLED 디스플레이(200)의 일부분을 위에서 바라본(즉, 기판을 통과하지 않은) 도면을 도시한다. 도면은 디스플레이의 픽셀을 정의하는 뱅크(112) 및 웨(114) 어레이를 도시한다.

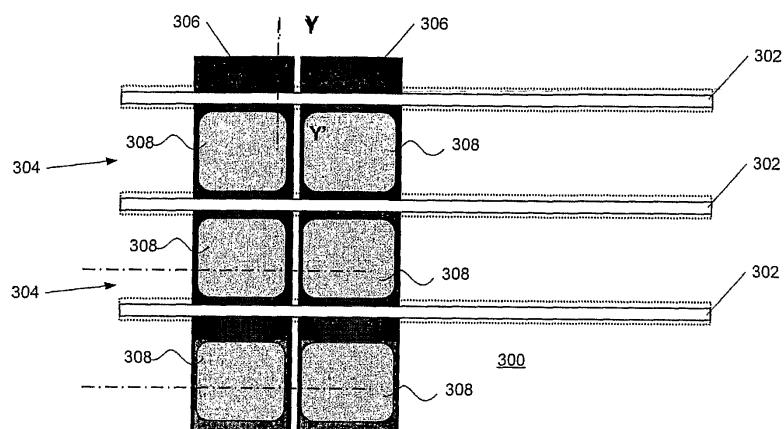

[0011] 도 3a는 수동 매트릭스 OLED 디스플레이를 잉크젯 프린트하는 기판(300)을 위에서 바라본 도면을 도시한다. 도 3b는 도 3a의 기판을 선 Y-Y'를 따라 자른 단면도를 도시한다.

[0012] 도 3a 및 도 3b를 참조하면, 기판은 (영역(304) 내에 증착될) 인접한 캐소드 라인들을 분리하는 복수의 캐소드 언더컷 분리기(302)를 구비한다. 복수의 웨(308)은 각 웨(308)의 주변에 구성되고 애노드 층(306)이 웨의 기저에서 노광되게 하는 뱅크(310)에 의해 정의된다. 뱅크의 에지 또는 표면은 도시된 바와 같이 기판의 표면 상에 전형적으로 10° 내지 40°로 점점 가늘어진다. 뱅크는 증착된 유기 물질의 용해에 의해 습윤되지 않으므로 웨 내에 증착된 물질을 포함하는 것을 지원하도록 소수성 표면을 나타낸다(극성 또는 무극성 용매가 이용될 수 있지만 사용된 용매는 소정의 극성을 가짐). 이는 EP 0989778에 개시된  $O_2/CF_4$  플라즈마를 가진 폴리아미드와 같은 뱅크 물질의 처리에 의해 달성된다. 이와 달리, 플라즈마 처리 단계는 WO 03/083960에 개시된 플루오르화 폴리아미드와 같은 플루오르화 물질을 사용함으로써 방지될 수 있다.

[0013] 이전에 설명한 바와 같이, 뱅크 및 분리기 구조는 예컨대, 뱅크에 양성(또는 음성) 레지스트를 사용하고 분리기에 음성(또는 양성) 레지스트를 사용하는 레지스트 물질로부터 형성될 수 있는데, 이를 레지스트 양자 모두 폴리아미드에 기반하고 기판 상에 스펀 코팅될 수 있거나, 플루오르화 또는 플루오르화형 포토레지스트가 이용될 수 있다. 도시된 예에서 캐소드 분리기의 높이는 약 5  $\mu m$ 이고 폭은 대략 20  $\mu m$ 이다. 일반적으로 뱅크의 폭은 20  $\mu m$  내지 100  $\mu m$ 이며, 이 예에서는 각 에지에서 4  $\mu m$  테이퍼를 가지는 것으로 도시되었다(이로써 뱅크의 높이는 약 1  $\mu m$ 임). 도 3a의 픽셀은 대략 300  $\mu m^2$ 이지만, 이후 설명되는 바와 같이, 픽셀의 크기는 애플리케이션에 따라 상당히 변할 수 있다.

[0014] 잉크젯 프린트 기법을 사용하는 유기 발광 다이오드(OLED) 물질의 증착 기술은 예컨대, Applied Physics Letters, Vol. 72, No. 5, pp. 519-521, 1998, T.R. Hebner, C.C. Wu, D. Marcy, M.H. Lu 및 J.C. Stum의 "Ink-jet Printing of doped Polymers for Organic Light Emitting Devices"와, SPIE Photonics West: Optoelectronics '98, Conf. 3279, San Jose, Jan., 1998, Y. Yang의 "Review of Recent Progress on Polymer Electroluminescent Devices"와, EP 0 880 303 및 Proceedings of SPIE Vol. 4464 (2002), Organic Light-Emitting Materials and Devices V, Zakra H. Kafafi, Editor, Paul C. Duineveld, Margreet M. de Kok, Michael Buechel, Aad H. Sempel, Kees A.H. Mutsaers, Peter van de Weijer, Ivo G.J. Camps, Ton J.M. van den Biiggelaar, Jan-Eric J.M. Rubingh 및 Eliav I. Haskal의 "Ink-Jet Printing of Polymer Light-Emitting Devices"와 같은 다수의 문서에 개시되어 있다. 잉크젯 기법은 저분자와 폴리머 LED 양자 모두에 대한 물질을 증착하는 데 사용될 수 있다.

[0015] 휘발성 용매는 일반적으로 유기 전자 물질을 증착하는 데 이용된다. 수 초 내지 수 분 동안 건조하는 데 어떠한 것도 사용될 수 있고, 초기 "잉크" 용량에 비해 박막이 된다. 흔히 바람직하게는 건조가 시작되기 전에 다수의 방울이 증착되어 충분한 두께의 건성 물질을 제공한다. 사용될 수 있는 용매는 사이클로헥실벤젠(cyclohexylbenzene) 및 알킬화 벤젠(alkylated benzenes), 특히 톨루엔(toluene) 또는 자일렌(xylene)을 포함하는데, 다른 것은 WO 00/59267, WO 01/16251 및 WO 02/18513에 설명되고, 이들의 혼합물을 포함하는 용매도 이용될 수 있다. 미국 캘리포니아주 라이트렉스사의 기계와 같은 정밀한 잉크젯 프린터가 이용되는데, 적합한 프린트 헤드는 영국 캠프리지 자아 및 미국 뉴햄프셔주 스펙트라사로부터 이용가능하다. 몇몇 특히 이로운 프린트 방법은 2002년 11월 28일에 출원된 출원인의 영국 특허 출원 번호 제 0227778.8 호 (및 대응 PCT 공보 WO 2004/049466)에 설명되어 있다.

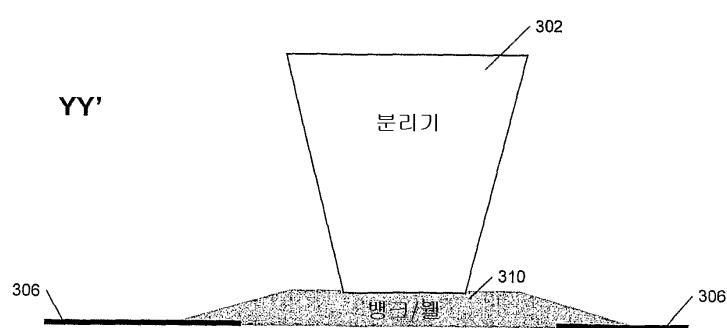

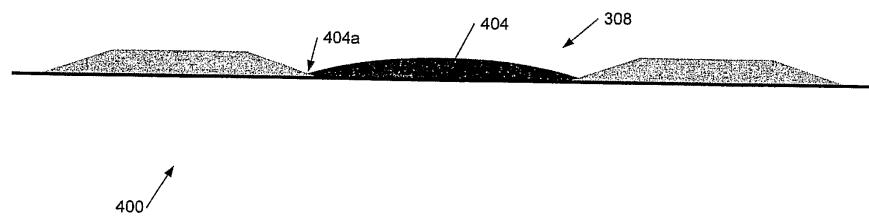

[0016] 잉크젯 프린팅은 유기 전자 디바이스의 물질의 증착에 관하여 다수의 장점이 있지만, 이 기법에 관련된 몇몇 단점도 있다. 그러나, 에지가 좁은 웨 내부로 증착된 용해된 유기 전자 물질이 건조되어 비교적 에지가 좁은 막을 형성한다는 것을 알게 되었다. 도 4a 및 도 4b는 이러한 공정을 도시한다.

[0017] 도 4a는 용해된 물질(402)로 충진된 웨(308)을 통과한 간략한 단면도(400)를 도시하고, 도 4b는 단단한 막(404)을 형성하도록 물질이 건조된 이후의 동일한 웨를 도시한다. 이 예에서 뱅크 각도는 대략 15°이고 뱅크의 높이는 대략 1.5  $\mu m$ 이다. 알 수 있듯이, 웨는 일반적으로 가득 찰 때까지 충진된다. 용액(402)은 플라즈마 처

리된 뱅크 물질과 전형적으로  $30^\circ$  내지  $40^\circ$ , 예컨대, 약  $35^\circ$  의 접촉 각도  $\theta_c$ 를 갖는데, 이는 예컨대, 도 4a의 각도(402a)와 같이, 용해된 물질(402)의 표면이 이에 접촉하는 (뱅크) 물질과 이루는 각도이다. 용매가 증발함에 따라 용액은 더 농축되고 용액의 표면은 기판 쪽으로 뱅크의 점점 가늘어진 표면 아래로 이동하는데, 건성 에지의 고정(pinning)은 초기에 배치된 습성 에지와 기판 상의 뱅크(웰의 기저)의 풋(foot) 사이의 지점에서 발생할 수 있다. 도 4b에 도시된 결과는 건성 물질(404)의 막이 뱅크의 표면과 만나는 영역(404a)에서, 예컨대, 10nm 이하 정도로 상당히 얇아질 수 있다.

[0018] WO 2005/076386으로 공개되고, 2004년 2월 5일에 출원된 영국 특허 출원 번호 제 0402559.9 호에서, 웰의 에지 쪽으로 용액을 끌어당기는 언더컷 뱅크의 사용은 보다 균일한 충진을 달성하는 것을 지원한다고 전술하였다. 그러나, 이러한 뱅크는 제조하기 어려울 수 있고 일반적으로 공정 조건에 고가이고 민감한 음성 포토레지스트를 사용할 수 있다. 따라서 양성 포토레지스트 사용에 보다 적합한 보다 개선된 기술이 필요하다.

[0019] 예컨대, 300  $\mu\text{m}$  픽셀 피치를 제공하는 데 사용된 240  $\mu\text{m}$  내지 260  $\mu\text{m}$ 의 개구부를 가진 웰과 같은 보다 큰 픽셀(웰)로 인한 다른 어려움이 발생한다. 잉크 방울의 용량은 방울에 대한 특성 길이의 세제곱에 비례하지만, 표면 커버리지는 픽셀 넓이의 제곱에 비례하며, 이로 인해 주어진 잉크 회석에 있어서 큰 픽셀 내에 너무 많은 물질이 증착되어 더 회석된 잉크가 필요하게 된다. 예컨대, 큰 픽셀 및 바람직한 80nm 두께의 PED(O)T 막에 있어서 대략 1 %의 잉크 농도가 이용될 수 있지만, 1 %의 잉크가 큰 픽셀을 확산하고 습윤하며 충진하게 하기 어렵다. 이는  $500\mu\text{m}^2$  이상의 픽셀의 제조를 어렵게 하는데, 완전히 가득 찬 픽셀이 120nm 두께의 막이 되기 때문이다. 또한 제조 공정에서 잉크 회석을 변경하는 것은 고가이다.

[0020] 일반적으로 픽셀 웰의 기저는 전형적으로  $10^\circ$  미만(예컨대,  $5^\circ$  내지  $10^\circ$ )의 저접촉 각도를 가진 ITO를 포함하므로, 비교적 양호한 친수성 습윤을 제공한다. 그러나, 특히 보다 큰 픽셀에 있어서, 습윤은 결코 원형의 증착된 액적(droplet)보다 완벽하지 않은데, 증착된 액적은 일반적으로 용매가 웰 기저 내의 지점에서 고정되기 쉬우므로 보다 불완전한 에지를 갖는다. 전술한 바와 같이, 다량의 용매가 웰에 첨가됨에 따라 뱅크 상의 용매의 접촉 에지는 비교적 높으므로, 액적 높이는 뱅크까지 이동하는 용매보다 증가하기 쉽고, 표면 에너지는 웰의 에지로부터 멀리 용매를 끌어당기기 쉽다. 이는 특히 얇은 에지가 픽셀 효율이 불완전해지거나 감소하게 되는 상부 발광 폴리머(LEP)와 캐소드(ITO) 사이에서 직접 접촉할 수 있는 PEDOT 증착과 관련된 문제이다. EP 0993235에서 세이코 엡손은 픽셀 웰의 기저의 내부 에지에서 애노드 위에 유전체 층을 증착함으로써 이러한 문제를 해결하려 하지만, 정렬 허용오차에 대한 필요성이 고려되는 경우에 효율적인 픽셀 영역이 20 % 까지 감소한다는 단점이 있다.

[0021] 따라서 이들 문제점을 해결하고 특히, 용매 기반 증착 공정에서 유기 전자 물질을 확산하는 것을 지원하는 개선된 유기 전자 디바이스 구조체 및 제조 기술이 필요하다.

## 발명의 내용

### 과제의 해결 수단

[0022] 본 발명의 제 1 측면에 따르면, 유기 전자 디바이스 구조체가 제공되는데, 이 구조체는 기판과, 기판에 의해 지지되고 유기 전자 물질의 용매 기반 증착에 대한 웰의 기저를 정의하는 기저 층과, 기판 위에 형성된 하나 이상의 스페이서 층과, 웰의 측면을 정의하도록 스페이서 층 위에 형성된 뱅크 층을 포함하되, 기저 층에 인접한 웰의 에지는 언더컷되어 기판 위에 유기 전자 물질을 수용하는 리세스를 정의하는 쉘프를 정의한다.

[0023] 바람직하게 쉘프의 밑면은 실질적으로 수평이고 하나 이상의 스페이서 층에 의해 정의된 거리만큼 기판으로부터 이격된다. 쉘프는 뱅크에 의해 정의될 수 있고 또는 쉘프를 정의하도록 하나 이상의 쉘프 층이 스페이서 층과 뱅크 층 사이의 구조체 내에 포함될 수 있다. 바람직하게 쉘프 층은 유전체 층을 포함하지만, 실시예에서, 쉘프 층은 금속 층을 포함할 수 있다. 후술되는 실시예로부터, 쉘프 및/또는 스페이서 층이 일반적으로 금속, 산화물 및/또는 도핑 또는 무도핑 실리콘층과 같이 디바이스의 제조용으로 이미 존재하는 층에 의해 제공됨을 알 것이다. 능동 매트릭스 디스플레이 디바이스에 있어서, 막막 트랜지스터(TFT)는 각 픽셀과 관련되고 이어서 TFT의 제조에 사용된 도핑 및/또는 무도핑 비결정질 실리콘층 또는 산화물층의 일부에 의해 스페이서 층이 형성될 수 있다. 마찬가지로 쉘프 층도 실리콘 질화물 유전체 및/또는 패시베이션 층과 같이 TFT의 제조 동안 증착된 임의의 경우에 존재하는 층들 중 하나에 의해 형성될 수 있다.

- [0024] 바람직하게 웰프 아래의 리세스는 스페이서 층과 유기 전자 물질 사이의 접촉을 허용하도록 -즉, 리세스가 스페이서 층의 에지를 노광시킴- 구성된다. 이는 웰의 에지에 용매를 고정하는 것을 지원한다. 따라서 (용매가 적어도 일부분 극성인) 바람직한 실시예에서, 스페이서 층은 실리콘, 실리콘 일산화물(silicon monoxide), 실리콘 이산화물(silicon dioxide), 실리콘 산질화물(silicon oxynitride) 등과 같은 친수성 물질을 포함한다. 선택적으로 스페이서 층은 보다 친수성이 되도록 처리될 수 있다.

- [0025] 실시예에서, 친수성 물질을 사용하는 것은 PEDOT 및 LEP 습윤에 대한 바람직한 속성을 분리하는 것을 지원하는데, (PEDOT 습윤이 친수성 물질에 의해 좌우되기 때문에) PEDOT가 친수성 스페이서 층을 습윤시킴에 따라 뱅크 상의 LEP의 습윤 각도가 실질적으로 독립적으로 조정되게 하기 때문이다. 예컨대, 일반적으로 뱅크 레지스트는 LEP 용매에 대한 습윤 각도가  $90^\circ$  이상인 소수성이지만, 예컨대, 뱅크 물질에 대한 LEP의 습윤을 개선하도록  $90^\circ$ ,  $60^\circ$  또는 심지어  $30^\circ$  미만까지 감소할 수 있다. PEDOT 용매가 웰프 아래에서 작용하고 친수성 층에 의해 고정되므로, PEDOT 층을 통한 단락의 위험은 상당히 감소한다. 일반적으로 PEDOT 용매 고정에 친구성 에지를 제공하는 스페이서 층을 참조하였지만, (소정의 극성을 가진 용매가 이용되는 경향이 있으므로) 예컨대,  $15^\circ$ ,  $10^\circ$  또는 그 미만과 같은 낮은 접촉 각도에 의해 정의된 바와 같이 노광된 스페이서 층 에지에 대한 용매의 보다 일반적으로 양호한 습윤이 바람직함을 알 것이다.

- [0026] 이상의 구조체의 실시예에서 뱅크 층은 (웰 측면에 가까워짐에 따라 기판 쪽으로 점점 가늘어지는) 통상적인 방향으로 기판 쪽으로 점점 가늘어질 수 있으므로 뱅크는 양성 포토레지스트를 사용하여 정의될 수 있음을 알 것이다.

- [0027] 일부 바람직한 실시예에서, 구조체는 능동 매트릭스 디스플레이 패셀과 같은 OLED 디스플레이 디바이스의 일부를 형성한다. 이 경우에 기저 층은 일반적으로 ITO와 같은 투명한 애노드 층을 포함하고, 웰 내로 증착되는 유기 전자 물질은 PEDOT와 같은 제 1 (정공) 전달 물질 층과 이 위를 덮는 예컨대, 발광 폴리머, 저분자 물질, 텐드리머 기반 물질 등과 같은 제 2 발광 물질 층을 포함한다. 이어서 웰프 아래의 리세스는 제 1 유기 전자 물질 층(예컨대, PEDOT)에 의해 점유되며, 바람직하게는 이 물질에 의해 실질적으로 완전히 점유되고, 제 2 발광 층은 제 1 층을 덮고 일부분은 뱅크에도 도달할 수 있다. 다른 실시예에서, 발광 층은 웰프 아래에도 위치할 수 있고, 예컨대, 양호한 습윤을 제공하도록 발광 층을 증착하는 데 사용된 용매에 따라 튜닝될 수 있는 제 2 스페이서 층에 의해 웰 에지에 고정될 수 있다. 이러한 실시예에서, 제 1 스페이서 층은 무도핑 (비결정질) 실리콘을 포함하고 제 2 스페이서 층은 도핑 (비결정질) 실리콘을 포함하는데, 양자 모두 능동 매트릭스 TFT 트랜지스터의 제조에 사용되므로 웰 에지에 고정하도록 증착하기에 편리하다.

- [0028] 이와 관련된 측면에서 본 발명은 기판 상에 유기 전자 디바이스를 제조하는 방법을 제공하는데, 이 방법은 기판 상에 하나 이상의 기저 층을 제조하는 단계와, 하나 이상의 기저 층 상에 하나 이상의 스페이서 층을 제조하는 단계와, 하나 이상의 스페이서 층 위에 뱅크 물질을 증착하는 단계와, 기저에서 리세스를 정의하는 언더컷 웰프를 가진 웰을 정의하도록 기판을 에칭하는 단계와, 웰 내로 유기 전자 물질을 증착하는 단계를 포함한다.

- [0029] 바람직하게 에칭 단계는 적어도 일부분 자기정렬된 에칭을 포함한다. 이러한 방식으로 뱅크를 정의하는 데 사용된 마스크는 언더컷 웰프를 에칭하여 부분적으로 자기정렬된 디바이스에서 웰프 층을 에칭하도록 스페이서 층을 노광하는 데에도 사용될 수 있다.

- [0030] 다른 측면에서 본 발명은 유기 전자 디바이스의 액적 증착 기반 제조를 위한 구조체 내에 액적 증착 웰을 형성하는 방법을 제공하는데, 이 방법은 기판 상에 친수성 물질 층을 증착하는 단계와, 친수성 물질 층 위에 뱅크 물질 층을 증착하는 단계와, 하나 이상의 액적 증착 웰을 형성하는 뱅크를 정의하도록 뱅크 물질 층을 패터닝하는 단계와, 패터닝된 뱅크 물질 층을 레지스트로서 사용하여 자기정렬된 공정으로 친수성 물질 층을 에칭하는 단계를 포함한다.

- [0031] 실시예에서 본 방법은 하나는 뱅크 물질용이고 다른 하나는 친수성(또는 스페이서) 층용인 2 개의 개별 마스크 스텝을 필요로 하지 않는다. 당업자는 일반적으로 방법이 적용되는 기판이 ITO와 같은 초기의 투명한 기저 도전체 층으로 구매되고 준비됨을 알 것이다. 본 방법의 일부 바람직한 실시예에서 뱅크 물질은 레지스트, 바람직하게는 양성 레지스트를 포함한다. 바람직하게 뱅크는 (소수성인 것이 바람직한) 하나의 뱅크 물질 층 및 (산화물과 같은) 하나의 친수성 물질 층만을 갖는다.

- [0032] 본 방법의 일부 바람직한 실시예에서 친수성 물질은 유전체 물질, 특히,  $\text{SiO}_2$ 를 포함하지만, 실리콘 질화물 및 실리콘 산질화물과 같은 다른 유전체 물질 또는 레지스트도 이용될 수 있다. 다른 실시예에서 친수성 물질은 알루미늄, 크롬 또는 몰리크롬과 같은 친수성 금속을 포함한다. 이러한 실시예에서 금속은 예컨대, 애노드 트

랙 저항을 감소시키기 위해 ITO 위에 형성된 애노드 금속일 수 있다. 이러한 방법을 사용하여 제조된 OLED 디바이스의 실시예에서 금속은 이후에 웰 내에 증착되는 유기 전자 물질, 특히, PEDOT에 노광될 수 있다. 그러나 금속이 관련된 물질에 대해 좋지 않은 전자 주사기(높은 일함수를 가짐)이면 사실상 그것이 실질적으로 절연체로서 작용하므로 이러한 접촉은 디바이스의 동작에 중요하지 않다.

[0033] 뱅크 레지스트가 마스크로서 작용하는 쉘프 정렬 에칭 단계는 등방성 또는 이방성일 수 있다. 바람직한 실시예에서 에칭은 플라즈마 에칭을 포함한다. 등방성 에칭은 친수성 층을 언더컷하고 (따라서 기판과 상부 뱅크 층 사이의 스페이서로서 작용함), 이방성 에칭은 (일반적으로 가늘어지는) 뱅크 에지가 끝나는 친수성 층의 양단을 실질적으로 수직으로 식각한다. 등방성 에칭의 경우에, 건식 에칭, 특히, 언더컷 내에서 자기제어하는 플라즈마 가스 에칭이 이용되어 언더컷의 깊이가 조절되게 한다. 이와 달리, 에칭액이 존재하는 한 계속해서 에칭하는 습식 에칭이 이용될 수 있다. 이방성 에칭의 경우에 건식 플라즈마 에칭이 바람직하다.

[0034] 디바이스 구조체의 언더컷 실시예에 있어서, 친수성 (스페이서) 층의 두께는 500nm 미만, 예컨대, 50nm 내지 200nm일 수 있으며 일부 실시예에서는 대략 100nm일 수 있다. 다른 실시예에서, 친수성 층이 (증착된 유기 전자 물질은 용매 기반 효과 때문에 얇아지기 쉬운) 뱅크 에지의 기저에서의 단력을 감소시키도록 돋기 위해 효율적인 절연을 제공하는 경우에, 친수성 층은 예컨대, 100nm, 50nm, 10nm 또는 5nm 미만으로 얇아질 수 있다. 제한 두께는 연속적인 절연막을 형성하려는 소망에 의해 결정되고, SiO<sub>2</sub>의 경우에 대략 2nm일 수 있다. 이방성 에칭은 실질적으로 언더컷을 방지하므로 웰의 기저에 절연 쉘프를 생성함으로써 이러한 쉘프를 남기기 위해 제거되는 뱅크 물질의 양을 감소시키는 방법의 실시예에 바람직하다.

[0035] 일부 특히 바람직한 실시예에서, 에칭 이후에, 레지스트 제거 처리, 바람직하게는 O<sub>2</sub> 플라즈마 애싱과 같은 플라즈마 애싱 처리가 수행된다. 이는 웰의 기저에 인접하는 (가장 얇은 부분인) 가늘어진 뱅크의 기저의 일부를 제거하여(뱅크의 전체 두께도 감소시킴), 웰의 기저에 인접한 친수성 물질을 노광한다. 이는 뱅크 물질의 개구부를 친수성 층의 개구부보다 크도록 확장한다. 전술한 바와 같이, 친수성 층의 노광된 부분은 절연 스페이서로서 작용하여 웰 기저의 에지에서의 단력을 방지한다. 특히, 이러한 물질의 노광된 부분에 효율적으로 부착되며 이러한 증착된 물질의 액적의 에지를 고정하는 친수성 PEDOT 용액을 끌어당긴다. 또한, PEDOT 용액은 이러한 방식으로 제한되므로, 뱅크 물질 층의 표면 에너지 특성은 발광 폴리머(LEP) 층과 같이 이후에 증착되는 물질 층에 바람직한 특성 쪽으로 개별적으로 튜닝될 수 있다. 뱅크 레지스트의 경우에, 예컨대, 이는 더 나은 LEP 제한을 위해, CF<sub>4</sub> 플라즈마를 사용하여 뱅크 물질이 소수성이 되도록 처리함으로써 수행될 수 있다. (이러한 "튜닝"은 하부 산화물의 친수성 특성에 영향을 주지 않지만, 적은 "오염 효과"가 존재한다.) 이와 달리, "테플론화" 또는 플루오르화 레지스트가 이용되어 소수성 뱅크 특성을 얻을 수 있다. 따라서 본 방법의 이들 실시예는 대체로, 예를 들면, PEDOT 및 LEP의 용액 증착을 위한 상이한 표면 에너지 처리(친수성 또는 소수성)가 분리되게 한다. 또한, 예컨대, 90° 내지 110° 일 수 있는, 물 내 PEDOT의 용액의 높은 뱅크 접촉 각도는 뱅크와 PEDOT를 분리시키는 것을 도우므로 이 물질을 포함한다.

[0036] 따라서, 다른 측면에서 본 발명은 유기 전자 디바이스의 액적 증착 기반 제조를 위한 구조체 내에 액적 증착 웰을 형성하는 방법을 제공하는데, 이 방법은 기판 상에 친수성 물질 층을 증착하는 단계와, 친수성 물질 층 위에 레지스트 물질 층을 증착하는 단계와, 하나 이상의 액적 증착 웰을 형성하는 뱅크를 정의하도록 레지스트 물질 층을 패터닝하는 단계와, 하나 이상의 액적 증착 웰의 기저 영역의 적어도 일부로부터 친수성 물질을 제거하도록 친수성 물질 층을 패터닝하는 단계와, 하나 이상의 액적 증착 웰을 형성하는 뱅크의 기저에 인접한 패터닝된 친수성 물질 층의 상부면의 일부를 노광시키도록 레지스트 제거 처리를 이용하는 단계를 포함한다.

[0037] 실시예에서, 뱅크 위로 돌출되고 하부 ITO와 유사한 표면 에너지를 갖는 낮은 층을 제공함으로써 비용 및 개구부 비율에 상당한 영향을 주지 않으면서 균일성을 산출할 수 있다. 레지스트 제거(애싱)되기 쉬운 구조체는 자기정렬된 공정으로 형성될 필요는 없지만, 예컨대, 2-마스크 공정을 사용하여 형성될 수 있다.

[0038] 관련된 측면에서, 본 발명은 전술한 방법을 사용하여 제조된 유기 전자 디바이스를 제공한다. 특히, 이러한 디바이스는 유기 전자 물질로 충진된 복수의 액적 증착 웰 아래에 패터닝된 친수성 물질 층을 구비하는 기판을 포함하는데, 하나 이상의 액적 증착 웰을 형성하는 뱅크의 기저에 인접하는 패터닝된 친수성 물질 층의 상부면의 일부는 유기 전자 물질에 노광된다.

[0039] 또 다른 측면에서, 본 발명은 유기 전자 디바이스 구조체를 제공하는데, 이 구조체는 기판과, 기판에 의해 지지되고 유기 전자 물질의 용매 기반 증착을 위한 웰을 정의하는 뱅크 층을 포함하되, 이 구조체는 웰의 내부 에지 및 웰의 기저에서 필럿을 정의하도록 패터닝된 필럿 층을 더 포함한다.

[0040] 바람직하게, 필럿은 실리콘 산화물 및/또는 실리콘 질화물과 같은 친수성 물질을 포함한다. 필럿 층은 디바이스와 관련되거나 디바이스의 일부를 형성하는 박막 트랜지스터의 산화물층과 같은 유기 전자 디바이스의 다른 부분도 형성하는 층을 편리하게 포함할 수 있다.

[0041] 일 실시예에서, 필럿은 기판 쪽으로 가늘어지는 뱅크의 일부를 덮는데, 다른 실시예에서, 하나 이상의 층은 웰의 내부 에지에서 단부를 정의하도록 패터닝되고 필럿은 그 단부에 인접한다. 예컨대, 바람직한 실시예에서, 웰은 애노드 또는 ITO 층과 같은 기저 층을 구비하고, 기저 층과 기판 사이에 (디바이스의 기준 층을 "재사용" 함으로써 제공될 수 있는) 단부 층이 제공되어, 웰의 내부 에지에 인접한 기저 층에서 단부의 높이 변화를 제공한다. 이러한 경우에 필럿은 기저 층 내의 이러한 단부에 인접한다. 일부 실시예에서, 기저 층 내에 2 개(또는 그 이상)의 하부 "단부" 층을 사용하는 이중 단부가 정의되어 ITO 아래에 높은 스페이서 층을 제공하므로 웰의 에지에 대한 개선된 용매 고정을 위한 넓은 필럿 영역도 제공한다. 실시예에서, 하나 이상의 단부 층은 금속층, 무도핑 실리콘층, 도핑 실리콘층 및 제 2 금속층 중 하나 이상을 포함할 수 있다. 이들 층은 예컨대, OLED 디스플레이 디바이스의 픽셀과 관련된 박막 트랜지스터에 대한 기준의 제조 공정의 일부로서 이미 존재할 수 있다. 바람직하게, 이러한 디바이스에서 뱅크 층은 양성 포토레지스트를 포함하고 통상적으로 기판 쪽으로 가늘어진다. 이러한 경우에 증착된 유기 전자 물질 층은 도전성 (정공 전달) 층 및 상부 발광 층을 포함할 수 있다.

[0042] 다른 측면에서 본 발명은 유기 전자 물질의 용매 기반 증착을 위한 적어도 하나의 웰을 구비하는 기판 상에 유기 전자 디바이스를 제조하는 방법을 제공하는데, 이 방법은 디바이스를 제조하는 유기 전자 물질의 용매 기반 증착 이전에 웰의 내부 에지에서 필럿을 정의하도록 필럿 층을 증착하고 이 필럿 층을 이방성 에칭하는 단계를 포함한다.

[0043] 바람직하게 필럿 물질은 유기 전자 물질을 증착하는 데 사용된 용매 또는 용매 혼합물에 의해 습윤되도록 선택되거나 처리된다. 바람직하게 이러한 습윤은 15° 미만, 보다 바람직하게는 10° 미만인 필럿과 용매 또는 용매 혼합물 간의 접촉 각도를 제공한다.

[0044] 본 발명은 또한 유기 전자 디바이스, 특히, 본 발명의 측면의 방법에 따라 제조된 능동 또는 수동 OLED 디스플레이 디바이스를 제공한다. 이제 첨부하는 도면을 예로써만 참조하여 본 발명의 이들 및 다른 측면을 설명할 것이다.

## 도면의 간단한 설명

[0045] 도 1은 일례의 OLED 디바이스를 통과한 종단면도를 도시한다.

도 2는 삼색 광셀화 OLED 디바이스의 일부분을 위에서 바라본 도면을 도시한다.

도 3a 및 도 3b는 각각 수동 매트릭스 OLED 디스플레이의 단면도 및 상부도를 도시한다.

도 4a 및 도 4b는 각각 용해된 물질 및 건성 물질로 충진된 OLED 디스플레이 기판의 웰의 단면도를 간략하게 도시한다.

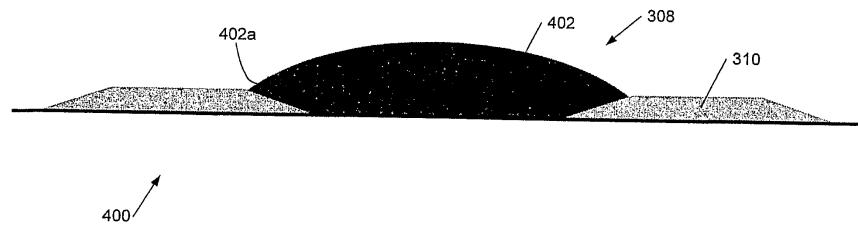

도 5는 본 발명의 제 1 측면의 제 1 실시예에 따른 유기 전자 디바이스 구조체를 도시한다.

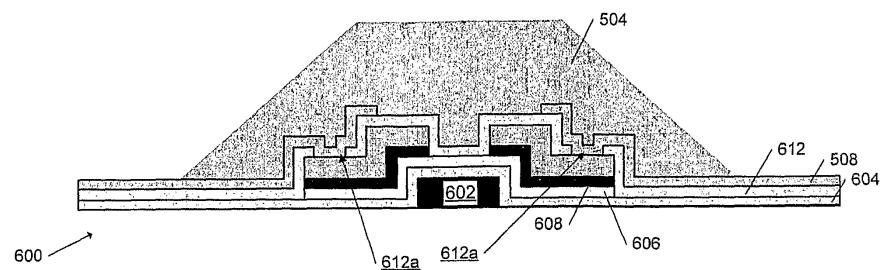

도 6은 본 발명의 측면을 구현하는 구조체와 함께 제조에 적합한 하부 게이트 박막 트랜지스터(TFT) 구조체를 도시한다.

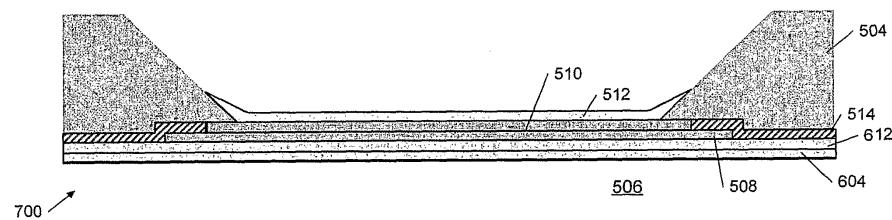

도 7은 본 발명의 제 1 측면의 제 2 실시예에 따른 유기 전자 디바이스 구조체를 도시한다.

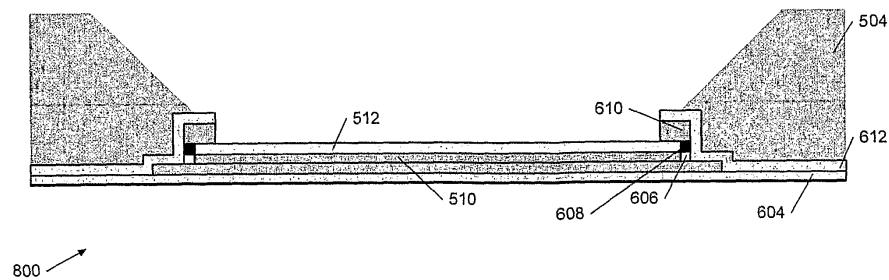

도 8은 본 발명의 제 1 측면의 제 3 실시예에 따른 유기 전자 디바이스 구조체를 도시한다.

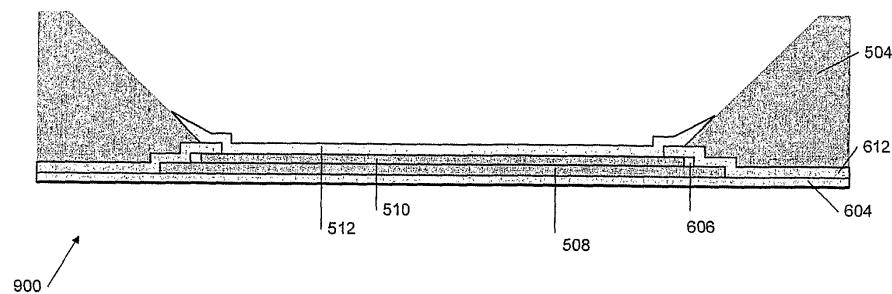

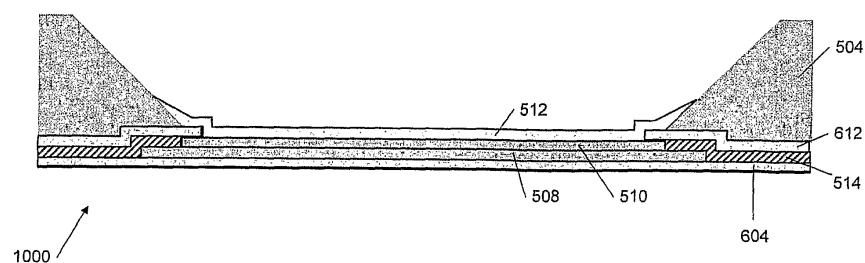

도 9는 본 발명의 제 1 측면의 제 4 실시예에 따른 유기 전자 디바이스 구조체를 도시한다.

도 10은 본 발명의 제 1 측면의 제 5 실시예에 따른 유기 전자 디바이스 구조체를 도시한다.

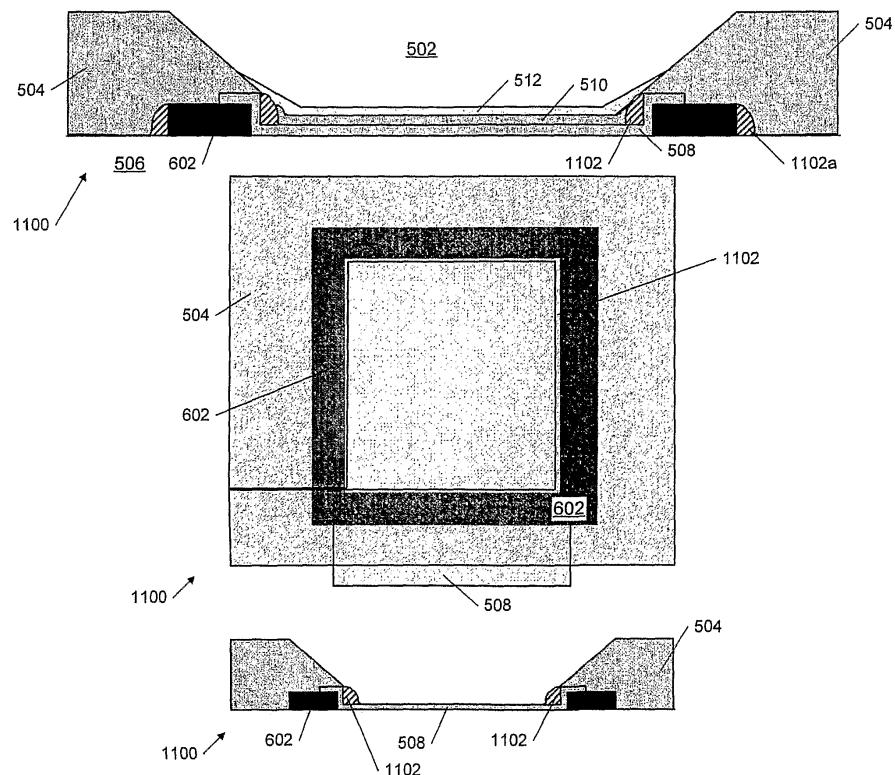

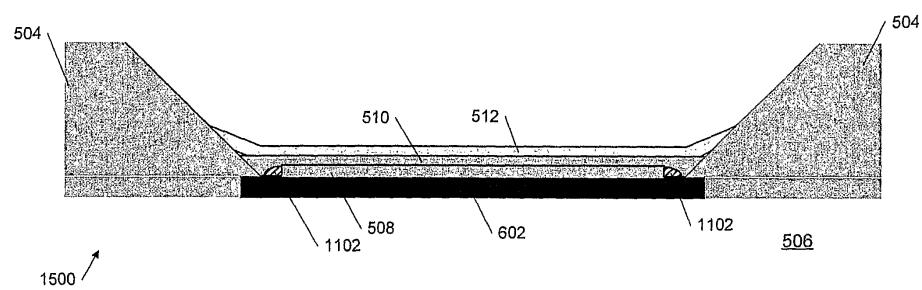

도 11은 본 발명의 제 2 측면의 제 1 실시예에 따른 유기 전자 디바이스 구조체를 도시한다.

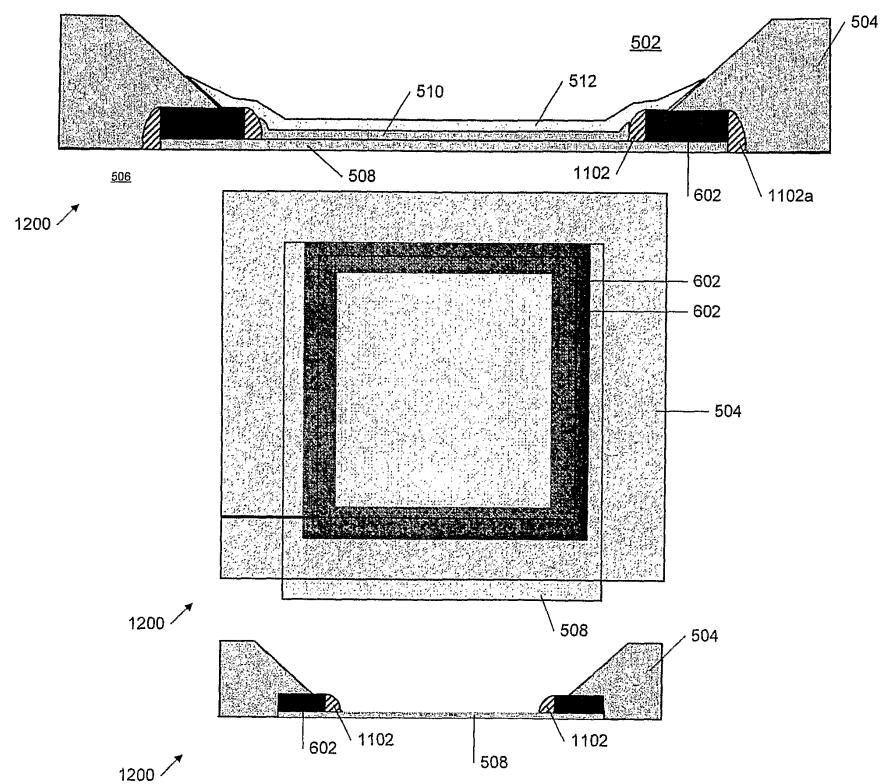

도 12는 본 발명의 제 2 측면의 제 2 실시예에 따른 유기 전자 디바이스 구조체를 도시한다.

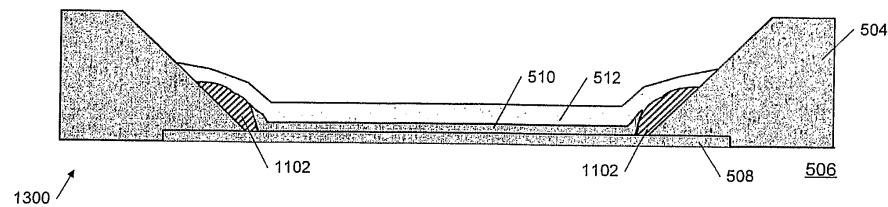

도 13은 본 발명의 제 2 측면의 제 3 실시예에 따른 유기 전자 디바이스 구조체를 도시한다.

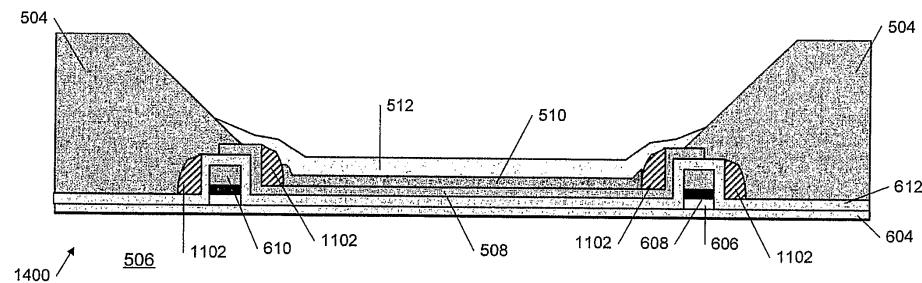

도 14는 본 발명의 제 2 측면의 제 4 실시예에 따른 유기 전자 디바이스 구조체를 도시한다.

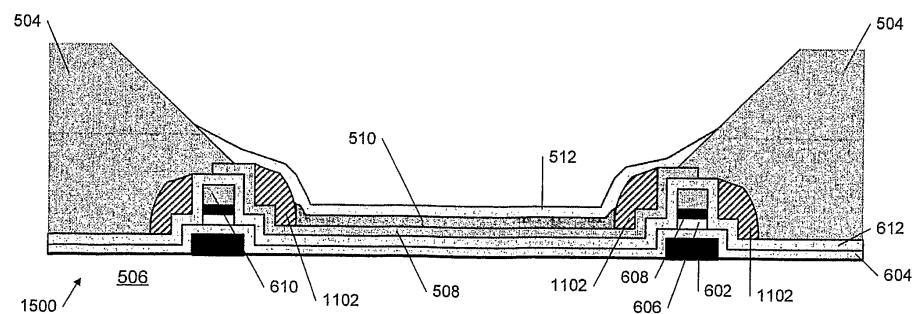

도 15는 본 발명의 제 2 측면의 제 5 실시예에 따른 유기 전자 디바이스 구조체를 도시한다.

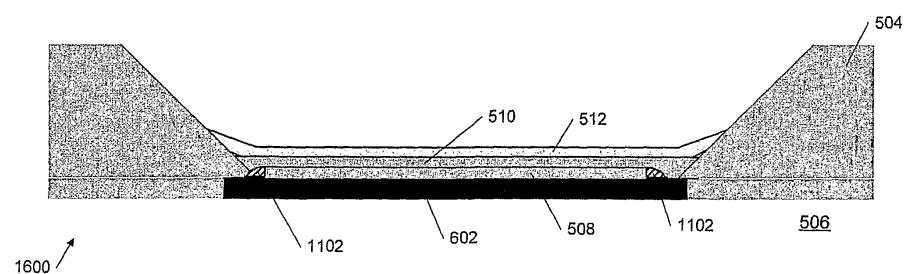

도 16은 본 발명의 제 2 측면의 제 6 실시예에 따른 유기 전자 디바이스 구조체를 도시한다.

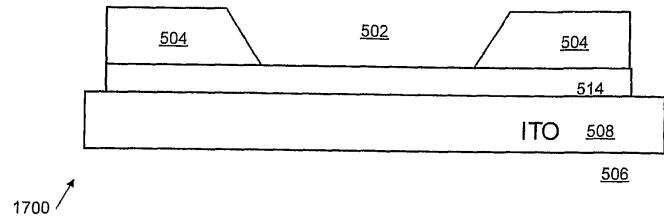

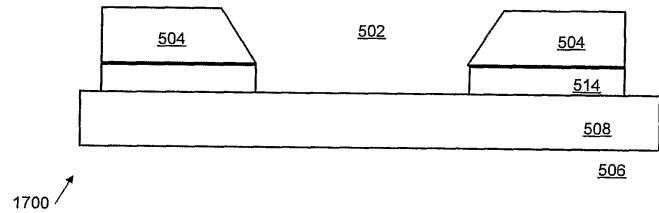

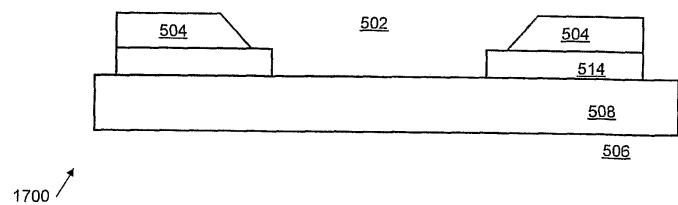

도 17은 본 발명의 측면의 실시예에 따른 유기 전자 디바이스의 제조를 도시한다.

### 발명을 실시하기 위한 구체적인 내용

[0046]

우선 능동 매트릭스 OLED 디스플레이의 픽셀의 웰(502)에 대한 제 1 구조체(500)의 종단면도 및 상부도를 도시하는 도 5를 참조한다. 웰(502)은 픽셀에 애노드를 제공하는 ITO 층(508)이 상부에 위치하는 기판(506) 쪽으로 점점 가늘어지는 뱅크(504)에 의해 정의된다. 웰(502) 내에 PEDOT 층(510)이 증착되고, 이 위에 발광 폴리미(LEP) 층(512)이 위치한다. 도 5는 PEDOT 층 및 LEP 층의 증착 이전의 구조체의 단면도도 도시한다.

[0047]

ITO 층(508) 위에 및 뱅크 층(504) 아래에 산화물 스페이서 층(514)이 제공된다. 이것은 양성 뱅크 프토레지스트의 패터닝 이후에 종래의 습식 또는 건식 등방성 에칭 공정을 사용하여 에칭된다. 이러한 에칭 공정은 웰(502)의 내부 에지 둘레에 돌출 쉘프(516)(상부도에서 점선으로 도시됨)를 초래하여, 용해된 PEDOT를 함유하는 용매가 증착 공정 동안 흐를 수 있는 리세스(a recess)를 제공하게 된다. PEDOT 용액은 모세관 작용에 의해 자연히 리세스 내에 포함되지만, 산화물 스페이서(514)가 친수성이므로 용매는 쉘프(516) 아래에 층(514)의 노출된 내부 에지에도 귀속될 것이다. 실시예에서 이들 2 가지 결과의 조합은 확실한 PEDOT 에지 두께 특징을 제공한다. PEDOT는 이러한 리세스 에지에 귀속된 채로 있지만, 건조중인 (소수성) 뱅크에 귀속되는 것은 아니다. 예컨대, 뱅크는 CF<sub>4</sub>에 의해 처리되어 PEDOT 용액 요구조건과 상당히 무관한 LEP(바람직한 정도까지 소수성임)의 증착에 특히 알맞은 표면을 제공할 수 있는데, 이는 PEDOT 용액이 친수성 층(514)의 노출된 에지 및/또는 리세스의 모세관 인력에 의해 효과적으로 고정되기 때문이다.

[0048]

간단한 예시적인 제조 공정에서, ITO 코팅된 표면은 다양한 공급원 중 임의의 공급원으로부터 구매되고 패터닝된 후 실리콘 이산화물, 실리콘 일산화물 또는 실리콘 산질화물과 같은 블랭킷 산화물로 코팅되어 친수성 층을 제공한다. 이 블랭킷 산화물은 예컨대, 스핀 온 글래스(spin-on-glass)를 포함할 수 있다. 이어서 양성 포토레지스트 층(504)은 포토리소그래피에 의해 스핀 온 및 패터닝(노광, 현상 및 세정)된다. 그 다음에 다른 마스크 필요 없이 산화물 스페이서 층(514)의 등방성 에칭백에 의해 리세스가 형성되는데, 이 공정은 뱅크가 산화물 층에 에칭 마스크를 효율적으로 자기정렬된다.

[0049]

도 6은 도 5의 픽셀 구조체(500) 및/또는 나중에 설명되는 본 발명의 제 1 및 제 2 측면 양자 모두의 다른 실시예와 함께 제조될 수 있는 하부 게이트 TFT 구조체(600)를 통과한 종단면도를 도시한다. 도 6에서 도 5의 구성 요소와 동일한 구성요소는 동일한 참조번호로 나타낸다. 이 예에서 기판은 아직 ITO로 패터닝되지 않았고, 대신에, 우선 비교적 두꺼운 금속층(602)이 유리 기판(506) 상에 증착되고 패터닝되어 TFT에 게이트 금속을 제공한다. 예컨대, 실리콘 질화물을 포함하는 게이트 유전체 층(604)은 게이트 금속(602) 위에 증착되고, 그 다음에 각각 TFT의 채널 및 드레인/소스 영역을 형성하는 무도핑 비결정질 실리콘층(606) 및 도핑 비결정질 실리콘층(608)이 증착 및 패터닝된다. 이어서 제 2 금속층(610)이 증착 및 패터닝되어 트랜지스터에 소스 및 드레인 도전체를 제공하고, 그 다음에 예컨대, 실리콘 질화물로 이루어진 패시베이션 층(612)이 구조체 위에 증착되며 소스 및 드레인 접촉 윈도우(612a)가 에칭된다. 이어서 소스 및 드레인 전극에 대한 접속부가 하나 이상의 인접하는 픽셀에 이들 소스 및 드레인 전극을 연결하게 하는 ITO 층(508)이 증착된다. 종래의 공정에서 이러한 ITO 층은 뱅크 포토레지스트 층(504)이 증착되기 이전의 마지막 층이지만, 이러한 TFT 구조체가 예컨대, 도 5의 개선된 웰 구조체와 함께 사용되는 경우에는 뱅크 층(504)의 증착 및 패터닝 이전에 ITO 층 위에 다른 산화물 층(도 6에 도시 생략)이 증착된다.

[0050]

이제, 도 5에 도시된 원리를 이용하는 보다 전형적인 "실재의" 웰 구조체를 도시하는 도 7을 참조한다.

[0051]

도 7 및 후속하는 도면에서, 도 5 및 도 6의 구성요소와 동일한 구성요소는 동일한 참조번호로 나타낸다.

[0052]

도 7에 도시된 웰 구조체(700)의 실시예에서, 2 개의 하부 실리콘 질화물 층(유전체 층(604) 및 패시베이션 층(612))이 도시된다.

[0053]

도 8은 패시베이션 층(612)과 제 2 금속 층(610)의 결합에 의해 쉘프가 제공되는 웰 구조체(800)의 다른 실시예를 도시한다. 이전의 2 개의 실시예와 달리, 이 실시예는 부분적으로만 자기정렬되고, 또한, 임의의 실리콘층이전에 ITO 층(508)의 증착을 수반한다. 이는 능동 매트릭스 디스플레이에서 가능한데, TFT 구조체가 픽셀의

능동 영역에서만 사용되기 때문이다. 그러나 이 실시예에서 층 순서는 다르지만, 동일한 원리가 이용된다.

[0054] 개략적으로, 실리콘층(606, 608), 금속층(610) 및 질화물(612) 층은 뱅크 에지 내에 정렬되고, 이어서 (실리콘 에지가 금속을 침범하지 않으므로) 금속 에지 아래에 등방성 에칭백이 이용되어 구조체를 생성한다. 금속층 및 /또는 질화물 층은 동시에 패터닝된다.

[0055] 웰 구조체(800)에서 헬프 아래의 공간은 이전 실시예의 공간보다 깊을 가능성이 있는데, (도시된) 실시예에서 이 깊이는 PEDOT 층에 의해 완전히 충진되지 않을 수도 있다. 이러한 경우에 전계발광 층도 헬프 아래로 확장 한다. PEDOT 층 및 전계발광 층은 각각 예컨대, 도시된 무도핑 및 도핑 실리콘(양자 모두 친수성)과 같은 상이 한 개별 스페이서 층과 관련될 수 있다. 유기 물질 층의 두께는 500nm까지일 수 있지만, 일반적으로 두께는 그 미만, 예컨대, 50nm 내지 200nm일 것이며, 도 8의 실시예에서 헬프 아래 리세스의 층 높이는 500nm(또는 그 이상)까지일 수 있다.

[0056] 다음으로 실리콘 증착 이전에 ITO 증착을 가진 부분적으로 자기정렬된 에칭 공정을 사용하는 웰 구조체(900)의 다른 실시예를 도시하는 도 9를 참조한다. 개략적으로, 실리콘층 및 질화물 층은 뱅크 에지와 정렬되고 이어서 실리콘층이 질화물 에지 아래에서 등방성 에칭백된다. 이는 TFT를 통합하는 구조체에서 가능한데, 도핑층 및 무도핑층이 상이한 스텝에서 에칭되기 때문이다.

[0057] 도 10은 ITO 층(508) 이후이지만 (실리콘질화물) 패시베이션 층(612) 이전에 산화물 스페이서 층(514)이 증착되는 웰 구조체(1000)의 또 다른 실시예를 도시한다. 리세스가 산화물층의 등방성 에칭백에 의해 형성됨에 따라 구조체의 제조는 부분적으로 자기정렬된다. 다시 PEDOT 용액이 리세스 내에 포함되고 친수성 및/또는 모세관 작용에 의해 웰의 에지에서 고정되어 확실한 PEDOT 에지 두께 특성을 제공하는 것을 지원한다.

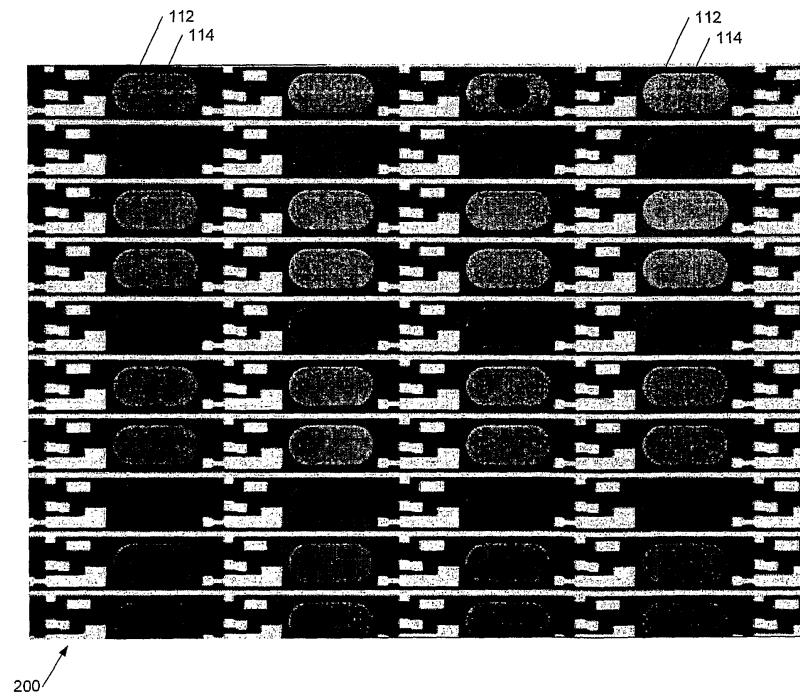

[0058] 이제 본 발명의 제 2 측면에 따른 웰 구조체(1100)의 제 1 실시예의 (용매 기반 유기 물질 증착 이전 및 이후의) 종단면도 및 상부도를 도시하는 도 11을 참조한다.

[0059] 다시, 이 실시예 및 후속하는 실시예에서, 전술한 층과 동일한 층은 동일한 참조번호로 나타낸다.

[0060] 도 11에서 제 1 금속층(602)은 패터닝되어 내부 에지 바로 바깥쪽의 웰 주변에 "화상 프레임"을 제공한다. 이는 상부 ITO(508) 내에 단부를 생성한다. 이어서 블랭킷 산화물층은 당업자에게 잘 알려져 있는 방식으로 증착 및 등방성(수직) 에칭되어 수직 에지 상의 물질의 필릿(fillet)(1102, 1102a)을 생성한다. 이들 산화물 필릿은 친수성 물질을 포함하므로 웰의 에지에 PEDOT 함유 용매를 고정하는 것을 돋는다(그러나 이러한 용매는 소수성 뱅크 에지에 도달하지 않으려는 경향이 있음). 따라서 소수성 CF<sub>4</sub> 표면 처리는, PEDOT 용매가 전부는 아니지만 뱅크 위로 단거리만 흐르므로 PEDOT 증착과 상당히 무관한 LEP 용매에 따라 적합해질 수 있다. 따라서 뱅크 물질, 처리 및/또는 LEP 용매는 예컨대, LEP 용매가 뱅크를 어느 정도까지 습윤하도록 조정될 수 있으므로, 도시된 바와 같이 LEP의 말단이 뱅크에 도달하게 된다. 도 11은 필릿을 가진 뱅크 에지의 정확한 정렬을 도시하지만, 실제로 이는 발생하지 않을 수도 있음을 알 것이며, 구조체가 (특히 점점 가늘어지는 뱅크 에지에 관하여 발생할 수 있는) 뱅크 에지 정렬의 근소한 변경에 소정의 허용오차를 제공함도 알 것이다.

[0061] 도 12는 본 발명의 제 2 측면에 따른 웰 구조체(1200)의 제 2 실시예를 도시한다. 도 11에 도시된 실시예와 마찬가지로, 이는 어느 정도 이상적인 구조체를 나타낸다. 또 필릿(1102)이 형성되지만, 이 경우에 ITO 층(508)의 아래보다는 위에 금속층이 위치한다. 이전과 같이 필릿(1102)은 웰(502)의 기저에서 내부 에지 주변에 "화상 프레임"을 제공한다. 도 12의 실시예에서 주목해야 할 특징은 금속(602)과 LEP 층(512) 사이의 직접 접촉이다. 작용 기능의 차이 때문에 금속과 LEP 사이의 직접 접촉 영역으로부터 발광되는 광이 거의 없거나 전혀 없으므로, 이러한 정렬은 뱅크 정렬에 개선된 강건성을 제공한다. 금속(602)은 (나타낸) PEDOT와 같은 정공 전달 층과 접촉하지 않아야 하므로 애노드로서의 효율이 감소하고/하거나, 실질적으로 불투명할 정도로 충분히 두꺼워서 금속(602)과 LEP 층 사이의 접촉 영역에서 방출되는 어떠한 광도 보이지 않게 하고/하거나 일함수가 낮아야 한다. 불투명한 금속(602)의 두께는 30nm(불투명에 필요한 정밀한 두께는 서로 다른 물질마다 상이함)보다 두꺼운 것이 바람직하다.

[0062] 도 13은 필릿(1102)이 웰 뱅크 층(504)의 경사진 벽에 도달하는 웰 구조체(1300)의 제 3의 (이상적인) 예를 도시한다. 구조체(1300)는 예컨대, 양성 뱅크 포토레지스트 층(504)이 스피닝 및 포토리소그래픽적으로 패터닝된 후 스픈 온 글래스의 블랭킷 증착에 의해 제조될 수 있다. 이어서 스픈 온 글래스는 필릿이 남겨진 스픈 온 글래스를 제거하는 이방성, 바람직하게는 건식 에칭 공정을 사용하여 블랭킷 (비마스킹) 에칭될 수 있다. 보다 일반적으로 다른 저온 또는 스픈 온 물질이 증착되고 이어서 이방성 에칭백되어 뱅크 레지스트 에지 내부에 친수성 공간을 형성할 수 있다. 도 13의 실시예는 보다 높은 필릿의 장점을 가지므로 개선된 용매 고정을 제공할

가능성이 있다.

[0063] 도 14는 단부 층이, 이 예에서, 실리콘질화물 패시베이션 층(612)의 아래 및 ITO 층(508)의 아래에 무도핑 및 도핑 비결정질 실리콘층(606, 608) 및 제 2 금속층(610)을 포함하는 웰 구조체(1400)의 또 다른 실시예를 도시한다. ITO 층(508) 아래에 스페이서 층을 가진 이 구조체는 높은 단부 에지를 제공할 가능성이 있으므로, 필럿 표면이 커지고 PEDOT 뱅크 분리가 개선된다.

[0064] 도 15는 도 14에 도시된 것과 유사하지만, 실리콘 질화물 유전체 층(604) 아래에, 제 1 금속층(602)에 의해 제 공된 다른 단부가 추가된 도 14의 실시예와 동일한 층 세트에 의해 형성된 이중 단부를 가진 웰 구조체(1500)의 또 다른 실시예를 도시한다. 이는 ITO 층(508) 아래에 더 높은 스페이서 층을 제공하므로, 필럿(1102)의 표면 영역이 더 커질 가능성이 있다.

[0065] 도 16은 정렬 허용오차를 도시하는, 구조체 내의 점점 가늘어지는 뱅크(504) 에지의 2 개의 서로 다른 상대적 정렬을 도시하는 웰 구조체(1600)의 또 다른 실시예를 도시한다.

[0066] 도 16의 구조체에서 ITO 층(508)은 금속층들 중 하나, 도시된 예에서, 제 1 금속층(602) 위에 증착되고 이어서 (패터닝된) ITO 층(508)의 에지 주변에 자기정렬된 스페이서 필럿(1102)이 형성된다. 점점 가늘어지는 뱅크층(504)의 에지는 하부 금속층에 정렬되지만, 하부 금속층(602)이 일함수의 부정합 때문에 노광되더라도 형성된 다이오드가 발광에 비효율적이므로 ITO 층(508)에 정확하게 정렬될 필요는 없다. 따라서 도 16의 구조체(1600) 내의 픽셀의 방사는 본질적으로 ITO 층(508)의 영역에 의해 결정되어 정렬 허용 구조체를 제공한다. 그럼에도 불구하고, 이전과 같이, 필럿은 PEDOT 함유 용매를 웰 측면의 기저 쪽으로 끌어당긴다(그리고 이것이 ITO를 덮을 것이므로 습윤된 정도는 본질적으로 중요하지 않으며 또는 이와 달리 뱅크 에지의 바로 옆에 어떠한 효율적인 디바이스도 존재하지 않으므로 뱅크 에지의 정도는 본질적으로 중요하지 않다).

[0067] 원리는 도 12 실시예와 유사한 몇몇 방식에 존재하지만, 이 실시예에서 픽셀 영역의 (주변)은 사실상 정렬된 허용오차와 교환된다. 도시된 바와 같이, 도 16의 제 1 실시예에서, 금속은 투명하지만 PEDOT와 접촉하고 있지 않으므로, 높은 일함수 금속일 수 있다. 도 16의 제 2 실시예에서, 금속은 투명하고 뱅크 오정렬 때문에 PEDOT와 접촉하고 있을 수 있는데, 이는 이 실시예에서 금속층이 PEDOT와의 오정렬을 제공하도록 낮은 일함수를 갖는 것이 바람직함을 의미한다.

[0068] "잉크 방울" 증착 웰의 기저에 친수성 물질의 얇은 돌출 헬프를 포함하는 디바이스를 제조하는 방법을 설명하는, OLED 디바이스를 제조하는 방법의 실시예를 도시하는 도 17을 참조한다. 이 방법은 이와 달리 언더컷 뱅크를 가진 디바이스도 제조할 수 있다.

[0069] 보다 상세하게 도 17a 내지 도 17c는 이전에 이용된 참조 번호를 사용하여, OLED 디스플레이의 픽셀에 대한 웰(502)이 기판(506) 상의 뱅크(504)에 의해 정의되는 웰 구조체(1700)를 제조하는 연속 단계를 도시한다. 기판(506)은 픽셀에 대한 애노드 접속부를 제공하도록 ITO 층(508)을 지지하되, 이 ITO 층(508) 위에 산화물 스페이서 층(514)이 증착되고, 이어서 도 17a에 도시된 바와 같이 기판 쪽으로 점점 가늘어지는 뱅크(504)를 형성하도록 종래의 방식으로 패터닝되는 양성 포토레지스트와 같은 유기 물질로 정의되는 것이 바람직한 뱅크 물질이 증착된다.

[0070] 도 17b에서 자기정렬된 에칭 마스크 처리를 제공하도록 뱅크(504)를 마스크로서 사용하여 SiO<sub>2</sub> 층(514)의 이방성 전식 (플라즈마 가스) 에칭이 수행된다. 이는 도 17c에 도시된 바와 같이, 돌출 단부의 제조를 위한 준비이다. 이는 뱅크 물질에 의해 정의된 개구부와 실질적으로 동일한 개구부를 생성한다. 이와 달리 도 17b에 도시된 일직선의 수직 에지를 제공하는 것보다 산화물 층(514)을 언더컷하는 습식 (또는 전식, 플라즈마) 이방성 에칭이 수행되어 도 5에 도시된 전형적인 유형의 구조체를 제공할 수 있다. 또한 이와 달리 습식 (또는 전식, 플라즈마) 이방성 에칭이 수행될 수 있고, 도 17c에 도시된 돌출 단부도 제거하도록 후속 스텝에서 뱅크 물질이 충분히 제거된다.

[0071] 도 17c는 픽셀 에지에서의 세선화(thinning)가 단화(shorting)를 발생시키지 않도록, 도시된 바와 같이 SiO<sub>2</sub> 층의 에지를 노광시키도록 개구부를 넓히는 뱅크(504)의 두께를 감소시키는 O<sub>2</sub> 플라즈마 애칭 레지스트 제거 스텝 이후의 구조체를 도시한다. 이 스텝은 또한 PEDOT 용액 증착 및 이어서 LEP 증착에 대비하여, 웰을 습윤하도록 산화물 및 하부 ITO를 세정한다.

[0072] 이 방법의 실시예는 레지스트 뱅크 픽셀 웰의 에지에서의 친수성 작용을 제공하고, 산화물층에 별도의 마스크를 사용하지 않으면서 자기정렬 또는 부분적으로 자기정렬 방식으로 구현되게 한다. 또한, 에지(돌출 단부 또는

언더컷) 구조체가 알루미늄과 같은 층의 측면 상에 형성되면 이 층은 능동 픽셀의 자연 증착도 제공할 수 있는 데, 애노드 접촉부가 낮은 일함수 금속(일반적으로 애노드는 ITO와 같은 높은 일함수 금속임)을 사용하여 형성되는 경우에 다이오드 구조체가 비효율적이기 때문이다. 이 방법의 실시예는 (픽셀 뱅크 에지를 통과한 캐소드 금속화에 대한 양호한 스텝 커버리지를 유지하기 위해) 표준 양성 레지스트가 사용되게 한다. 따라서 LEP 잉크는 표면 에너지 변경 처리 공정(예컨대, 전술한 바와 같이 CF4 플라즈마 처리)에 기초하여 (선택적으로) 제한될 수 있는 한편, PEDT 습윤 및 LEP 습윤 공정의 분리를 가능하게 한다. 이는 표면 조절 공정이 LEP에 대해 튜닝되게(픽셀 레지스트 내에서 더 나은 제한을 허용할 가능성이 있음) 하는 한편, 현재 자기정렬된 픽셀 에지(돌출단부 또는 언더컷) 구조체의 친수성 또는 모세관 작용에 많이 또는 실질적으로 완전히 의존해야 하므로 PEDT 습윤이 레지스트 상의 PEDT 접촉 각도에 덜 민감해질 수 있다.

[0073] 본 발명의 실시예는 양성 뱅크 레지스트의 사용을 가능하게 하고 (본 명세서에) 전술한 구조체의 장점, 특히, 픽셀 에지에 걸쳐 불연속성 없이 양호한 금속 캐소드 접촉을 제조하고 PEDOT 및 LEP (또는 다른 발광 물질) 증착의 개별 단계에 대한 구조체의 적합화(예컨대, 표면 조절)를 용이하게 하도록 PEDOT 및 LEP 습윤 공정을 실질적으로 분리한다는 장점을 제공한다. 또한 전술하였던 구조체의 실시예는 예컨대, 추가적인 마스크/패터닝 스텝 필요 없이 자기정렬된 또는 부분적으로 자기정렬된 공정을 사용하여 제조될 수 있다. 다른 실시예는 애노드 접촉이 예컨대, 4 eV 미만과 같은 낮은 일함수 금속으로 형성되는 경우에 발광 다이오드 구조체의 고유한 비효율성을 이용함으로써 및/또는 사이에 정공 전달층 없이 정렬 허용오차를 획득한다. 대체로, 본 발명의 실시예는 물질이 증착되는 웨의 측면에서 PEDOT (및 LEP) 용매의 습윤/고정을 용이하게 하는 기술에 관련된 표면 에너지에 좌우된다.

[0074] 전술한 웨 구조체는 광범위한 용액 증착형 유기 전자 디바이스에서 이용될 수 있다. 웨 구조체는 이러한 디바이스가 가령, 뱅크 층 및/또는 유기 전자 물질의 증착을 용이하게 하기 위해 능동 또는 수동 매트릭스 전계발광 디스플레이 디바이스 또는 예컨대, TFT 기반 능동 매트릭스 후면 내로 통합될 수 있다.

[0075] 당업자에게 다수의 다른 효율적인 대안이 발생할 것임은 확실하다. 본 발명이 설명된 실시예로 제한되지 않으며, 본 명세서에 첨부되는 특허청구범위의 사상 및 범주 내에 존재하는 당업자에게 자명한 변경을 포함함을 알 것이다.

## 도면

### 도면1

#### (종래기술)

도면2

도면3a

도면3b

도면4a

도면4b

도면5

도면6

도면7

도면8

도면9

도면10

## 도면11

## 도면12

도면13

도면14

도면15

도면16

도면17a

도면17b

도면17c

|                |                                                                                   |         |            |

|----------------|-----------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 标题 : 有机电子器件结构 , OLED显示器件 , 有机电子器件制造方法 ,                                           |         |            |

| 公开(公告)号        | <a href="#">KR101431408B1</a>                                                     | 公开(公告)日 | 2014-08-18 |

| 申请号            | KR1020137014519                                                                   | 申请日     | 2006-08-22 |

| [标]申请(专利权)人(译) | 剑桥显示技术有限公司                                                                        |         |            |

| 申请(专利权)人(译)    | 剑桥显示科技有限公司                                                                        |         |            |

| 当前申请(专利权)人(译)  | 剑桥显示科技有限公司                                                                        |         |            |

| [标]发明人         | GREGORY HAYDN<br>그레고리하이든<br>CARTER JULIAN<br>카터줄리안                                |         |            |

| 发明人            | 그레고리하이든<br>카터줄리안                                                                  |         |            |

| IPC分类号         | H01L27/32 H01L51/00                                                               |         |            |

| CPC分类号         | H01L51/5253 H01L27/3246 H01L27/3283 H01L51/0005 H01L51/0012 H01L51/0037 H01L51/56 |         |            |

| 优先权            | 2005017195 2005-08-23 GB<br>2006005128 2006-03-15 GB                              |         |            |

| 其他公开文献         | KR1020130079634A                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                         |         |            |

### 摘要(译)

有机电子器件技术领域本发明涉及有机电子器件，特别涉及有机发光二极管 (OLED) 的结构和制造方法。有机电子器件结构500包括衬底506 和基层508，基层508由衬底506支撑并限定用于有机电子材料510和512 的溶剂基沉积的阱基，并且在间隔层514上方形成堤层504以限定阱502 的侧面，其中至少一个间隔层514形成在与基层508相邻的阱502上方。堤层504形成在间隔层514上方，限定搁架516，搁架516限定凹槽底切以容纳下层508上的有机电子材料510。