**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

|                                             |                          |

|---------------------------------------------|--------------------------|

| (51) Int. Cl.<br><i>G09G 3/30</i> (2006.01) | (45) 공고일자<br>2006년10월31일 |

|                                             | (11) 등록번호<br>10-0641443  |

|                                             | (24) 등록일자<br>2006년10월25일 |

|                              |                              |

|------------------------------|------------------------------|

| (21) 출원번호<br>10-2005-0043555 | (65) 공개번호<br>10-2006-0046154 |

| (22) 출원일자<br>2005년05월24일     | (43) 공개일자<br>2006년05월17일     |

(30) 우선권주장      JP-P-2004-00152749      2004년05월24일      일본(JP)

(73) 특허권자      로무 가부시키가이샤

일본 교토시 우교구 사이잉 미조사카쵸 21

(72) 발명자      야구마 히로시

일본국 교토후 교토시 우교구 사이잉 미조사카쵸 21

코바야시 마사토

일본국 교토후 교토시 우교구 사이잉 미조사카쵸 21

(74) 대리인      특허법인태평양

심사관 : 최정윤

---

**(54) 유기 EL 구동 회로 및 이를 이용한 유기 EL 디스플레이장치**

---

**요약**

본 발명은 유기 EL 소자 또는 캐패시터를 리셋하는데 필요한 소정의 정전압을 생성하는 증폭 회로가 제공되고, 동작 전류 스위칭 회로가 상기 증폭 회로의 동작 전류를 디스플레이 기간에는 아이들링(idling) 전류로 스위칭하며, 또한 리셋 기간에는 리셋 동작을 실행하는데 필요한 안정한 동작 전류로 스위칭함으로써, 아이들링 상태에서부터 안정한 동작 상태로의 증폭 회로의 시프트 시간이 단축될 수 있으며, 유기 EL 소자 또는 캐패시터를 리셋하기 위한 제어 정전압(constant control voltage)이 리셋 기간의 초기에 생성될 수 있다.

**대표도**

도 1

**명세서**

**도면의 간단한 설명**

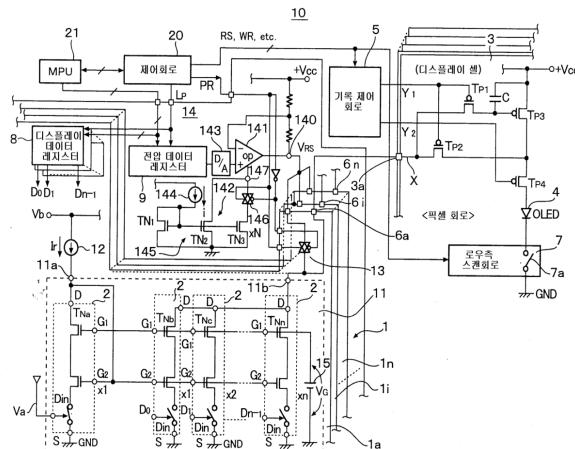

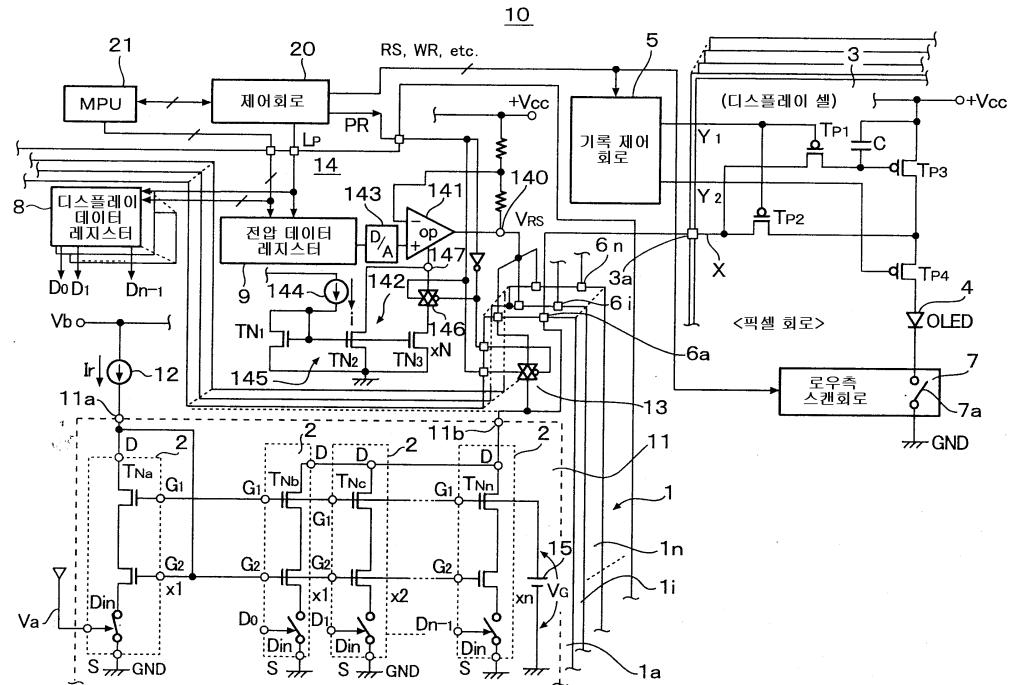

도 1은 본 발명의 한 실시형태에 따른 액티브 매트릭스형 유기 EL 디스플레이 패널의 유기 EL 구동 회로의 블록 회로도.

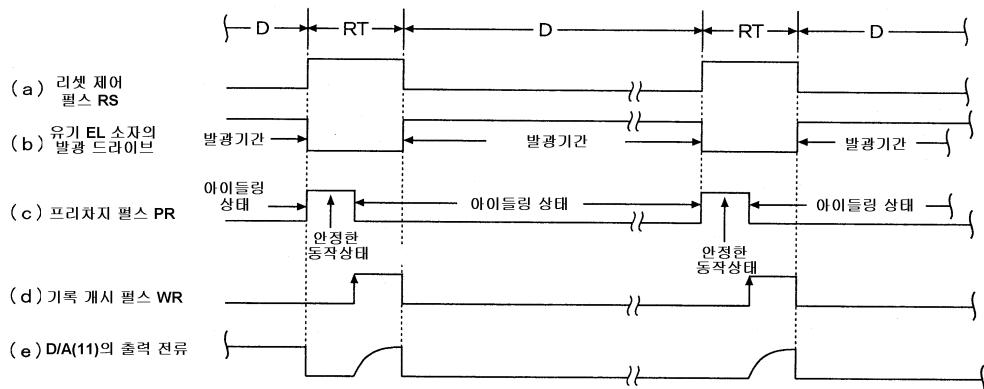

도 2(a) 내지 도 2(e)는 리셋 동작의 타이밍 차트.

## 발명의 상세한 설명

### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 유기 EL 구동 회로 및 이 유기 EL 구동 회로를 이용한 유기 EL 디스플레이 장치에 관한 것이다. 보다 구체적으로, 본 발명은 액티브 매트릭스형 유기 EL 디스플레이 패널의 픽셀 회로의 캐패시터의 정전압을 리셋하기 위한 리셋 회로의 소비 전력을 감소시킴으로써 장치의 소비 전력을 감소시킬 수 있으며 픽셀 회로의 캐패시터를 리셋하는데 필요한 시간을 단축할 수 있는 유기 EL 구동 회로 및 이러한 유기 EL 구동 회로를 이용한 유기 EL 디스플레이 장치에 관한 것이다.

폐시브 매트릭스형 유기 EL 소자를 구동하고, 또 유기 EL 소자의 애노드(anode)와 캐소드(cathode)를 접지시킴으로써 유기 EL 소자를 리셋하는 구동 회로가 JPH9-232074A에 기술되어 있다.

한편, D/A 변환 회로에 의해 데이터 라인을 구동하는 액정 디스플레이 장치가 공지되어 있다. 이러한 액정 디스플레이 장치의 구동 회로는 액티브 매트릭스형 유기 EL 디스플레이 패널의 픽셀 회로에 적용되는 것으로서, 상기 유기 EL 디스플레이 패널을 소형화하는 것이 어렵다. 이러한 문제점이 JP2000-276108A에 기재되어 있다.

그러나, 액티브 매트릭스형 유기 EL 디스플레이 패널을 구동하는 유기 EL 구동 회로가 디스플레이 패널의 외부에 공급되는 경우에, 유기 EL 디스플레이 패널을 소형화하는 것이 실현될 수 있다. 이러한 경우에, 구동 전류값의 기록은 일반적으로 수백 pF의 픽셀 회로의 캐패시터 각각을  $0.1\mu A$  내지  $10\mu A$  정도의 전류를 이용하여 충전함으로써 실행된다. 그러나, 상기 액티브 매트릭스형 유기 EL 디스플레이 패널의 회도가 점진적으로 제어되는 것인 경우에, 약  $1nA$  내지  $30nA$ 의 최소 전류값을 갖는 고정밀도의 구동 전류값이 요구된다. 구동 전류가 흐르는 방향은 싱크(sink)형과 소스(source)형이 있다. 전원 라인 + Vcc의 전압은 상기 유기 EL 디스플레이 패널이 폐시브 매트릭스형 또는 액티브 매트릭스형인지의 여부와는 관계없이 통상 약 10V 내지 20V 정도이다.

싱크형 전류에서, 유기 EL 디스플레이 패널의 픽셀 회로의 캐패시터를 리셋하는 전압이 전원 라인 + Vcc의 전압 또는 그 전후이기 때문에, 비교적 높은 브레이크다운(breakdown) 전압을 갖는 유기 EL 소자로 D/A 변환 회로를 구성하는 것이 필수적이다. 그러므로, 각 유기 EL 소자의 점유 면적이 커지게 되고, 이에 따라 유기 EL 디스플레이 패널의 단자 핀 또는 컬럼 핀에 대응하여 제공된 D/A 변환 회로 각각의 점유 면적이 상당히 증가된다.

회도를 유지하기 위하여, 유기 EL 소자의 발광 기간이 가능한 한 길어야 하며, 이에 따라 수평 스캔의 귀선(retrace) 시간에 상당하는 유기 EL 소자의 리셋 기간이 가능한 한 짧아야 한다. 그러므로, 상기 리셋 회로의 고속 동작이 요구된다. 또한, 수평 스캔 방향에서 하나의 수평 디스플레이 라인에 대한 픽셀 회로의 캐패시터 또는 복수의 픽셀 회로의 캐패시터를 동시에 리셋해야 한다. 복수의 컬럼 드라이버가 하나의 수평 디스플레이 라인을 맡는 후자의 경우에, 각 컬럼 드라이버가 맡는 단자 핀 수 또는 컬러 디스플레이인 경우에는 R, G, B 컬러 각각에 대한 단자 핀 수에 상당하는 복수의 픽셀 회로의 캐패시터를 동시에 리셋한다. 그러므로, 대형의 구동 전류가 각 리셋 회로에 필요하게 된다.

이러한 리셋 회로를 동작시키기 위하여 리셋 회로가 리셋 동작으로 진입하기 전에 시간이 소요되므로 리셋 기간이 연장된다. 이러한 문제를 피하기 위하여, 상기 리셋 회로는 일반적으로 디스플레이 기간에도 동작 상태로 된다. 그 결과, 상기 리셋 회로의 소비 전력은 동시에 리셋되는 대상인 유기 EL 소자 또는 픽셀 회로의 캐패시터 수가 늘어남에 따라 증가한다.

#### 발명이 이루고자 하는 기술적 과제

본 발명의 목적은 이러한 문제점을 해결하기 위한 것이며, 리셋 회로의 소비 전력을 경감시켜서 유기 EL 회로의 소비 전력을 감소시킬 수 있고, 단시간내에 픽셀 회로의 캐패시터 또는 유기 EL 소자를 리셋할 수 있는 유기 EL 구동 회로를 제공하는 것이다.

본 발명의 다른 목적은 상기 유기 EL 구동 회로를 이용한 유기 EL 디스플레이 장치를 제공하는 것이다.

### 발명의 구성 및 작용

이러한 목적을 달성하기 위한 본 발명에 따라, 소정 주파수를 갖는 타이밍 제어 신호의 리셋 기간에서 유기 EL 디스플레이 패널의 단자 핀을 통해 유기 EL 디스플레이 패널의 픽셀 회로의 유기 EL 소자 또는 캐패시터의 정전압을 리셋하고, 하나의 수평 스캔 라인에 대한 스캔 기간에 상응하는 디스플레이 기간으로부터 수평 스캔의 귀선 기간에 상응하는 리셋 기간을 분리하는 유기 EL 구동 회로에 있어서, 유기 EL 소자 또는 캐패시터를 리셋하는 소정의 정전압을 생성하는 증폭 회로와, 상기 증폭 회로의 출력 단자와 단자 핀과의 사이에 제공되며, 상기 타이밍 제어 신호, 상기 타이밍 제어 신호와 동일한 리셋 제어 전압 신호, 리셋 펄스, 및 상기 신호들 또는 상기 리셋 펄스와 동기하여 리셋 기간에 생성된 그외 펄스 중 한 신호에 의해 온/오프 동작되는 리셋 스위치와, 디스플레이 기간에 증폭 회로의 동작 전류를 아이들링(idling) 상태의 전류값으로 하고, 상기 증폭 회로의 동작 전류를 상기 리셋 기간 또는 상기 리셋 펄스나 그외 펄스가 생성된 기간에서 리셋 동작에 필요한 값으로 하는 동작 전류 스위칭 회로를 구비하여 구성된다.

본 발명에서, 유기 EL 소자 또는 캐패시터를 리셋하는 소정 정전압을 생성하는 증폭 회로가 제공된다. 상기 동작 전류 스위칭 회로는 상기 증폭 회로의 동작 전류를 상기 디스플레이 기간에서 아이들링 전류값으로 설정하고, 상기 아이들링 전류를 리셋 기간에서 리셋 동작을 실행하는데 필요한 전류로 스위칭한다. 상기 리셋 동작에 필요한 전류는 이하 "안정한 상태의 전류"로 참조될 것이다. 그러므로, 아이들링 상태가 안정한 동작 상태로 스위칭되는 입상(rising) 시간이 짧아지게 됨으로써, 유기 EL 소자 또는 캐패시터를 리셋하는 정전압이 리셋 기간의 초기 시점에 발생될 수 있다.

그 결과, 하나의 수평 라인에 대한 유기 EL 소자 또는 캐패시터가 리셋되거나 또는 하나의 수평 디스플레이 라인이 복수의 컬럼 드라이버에 의해 처리되는 경우에, 각각의 컬럼 드라이버에 의해 처리된 단자 핀(컬러 디스플레이의 R, G, B 컬러에 대한 단자 핀) 수에 상응하는 픽셀 회로의 복수 유기 EL 소자 또는 캐패시터의 리셋이 동시에 고속으로 완료될 수 있다.

아이들링 전류만이 디스플레이 기간에서 상기 증폭 회로에 흐르기 때문에, 리셋 회로의 소비 전력을 억제하여 유기 EL 회로의 소지 전력을 감소시킬 수 있다.

도 1에서, 참조 부호 10은 액티브 매트릭스형 유기 EL 디스플레이 패널을 나타내고, 유기 EL 구동 회로(1)는 집적된 회로 드라이버로 형성된다. 상기 유기 EL 구성 회로(1)는 유기 EL 디스플레이 패널의 데이터 라인에 대응하여 제공된 전류 구동 회로(1a 내지 1n)를 구비한다. 참조 부호 2는 트랜지스터 셀(cell) 회로를 나타낸다. 상기 트랜지스터 셀 회로(2)는 D/A 컨버터 회로(11)를 구성한다.

참조 부호 3은 유기 EL 디스플레이 패널(10)에 매트릭스-배열된 픽셀 회로(디스플레이 셀)를 나타내고, 참조 부호 4는 픽셀 회로(3)에 제공된 유기 EL 소자를 각각 나타내고, 참조 부호 5는 기록 제어 회로를 나타낸다. 참조 부호 6a 내지 6n은 각각 전류 구동 회로(1a 내지 1n)의 출력 단자를 나타낸다. 참조 부호 7은 로우측 스캔 회로를 나타내고, 참조 부호 7a는 상기 로우측 스캔 회로(7)의 스위치 회로를 나타낸다. 참조 부호 8은 상기 전류 구동 회로(1a 내지 1n)에 대응하여 제공되며, 디스플레이 데이터를 저장하는 디스플레이 데이터 레지스터를 나타낸다. 참조 부호 9는 전압 데이터 레지스터를 나타낸다. 참조 부호 20은 유기 EL 구동 회로(1)의 외부에 설치된 제어 회로를 나타낸다. 참조 부호 21은 유기 EL 구동 회로(1)의 외부에 설치된 MPU를 나타낸다.

상기 유기 EL 구동 회로 IC(1)에 내장된 전류 구동 회로(1a 내지 1n)는 구성이 동일하다. 각각의 전류 구동 회로는 D/A 컨버터 회로(11), 기준 구동 전류 Ir을 생성하는 정전류원(12), 리셋 스위치(13)를 포함한다. 유기 EL 구동 회로(1)의 리셋 전압 발생 회로(14)는 전류 구동 회로(1a 내지 1n)에 공통 회로로서 제공된다.

상기 정전압 리셋 회로는 리셋 전압 발생 회로(14), 리셋 스위치(13)로 구성되고, 상기 제어 회로(20)로부터 공급된 프리차지(precharge) 펄스 PR에 응답하여 동작한다. 상기 전류 구동 회로(1a 내지 1n)의 리셋 스위치(13)는 각각 높은 브레이크다운 전압 아날로그 스위치로 구성된다. 그러므로, D/A 컨버터 회로(11)는 낮은 브레이크다운 전압의 트랜지스터로 구성될 수 있다.

상기 전류 구동 회로는 동일한 구성으로 동일하게 동작하므로, 상기 전류 구동 회로(1a)만이 기술될 것이다.

상기 D/A 컨버터 회로(11)는 입력측 트랜지스터 셀 회로 TN<sub>a</sub>와, 출력측 트랜지스터 셀 회로 TN<sub>b</sub> 내지 TN<sub>n</sub>으로 구성된 커런트 미러 회로로 이루어진다.

상기 출력측 트랜지스터 셀 회로 TNb 내지 TNn 각각은 직렬로 접속되며 전원 라인과 접지 라인 사이에 제공된 3개의 N채널 MOS 트랜지스터를 구비하고, 드레인 단자 D와 게이트 단자 G1 및 G2와 입력 단자 Din과 소스 단자 S를 갖는다. 또한, 트랜지스터 셀 회로(2)를 구성하는 3개의 직렬 접속된 트랜지스터의 접지측 트랜지스터는 도 1에 도시된 바와 같이 스위치 회로 SW를 구성한다.

상기 트랜지스터 셀 회로(2)의 소스 단자 S는 공통으로 접지된다. 상기 입력측 트랜지스터 셀 회로 TNa의 입력 단자 Din은 바이어스 라인 Va에 접속되어서 스위치가 일반적으로 온 상태를 지속하도록 한다. 상기 D/A 컨버터 회로(11)의 출력측 트랜지스터 셀 회로 TNb 내지 TNn의 입력 단자 Din은 각각의 전류 구동 회로(1a 내지 1n)에 대응하여 공급된 디스플레이 데이터 레지스터(8)로부터 디스플레이 데이터 D0 내지 Dn-1을 공급받는다. 상기 출력측 트랜지스터 셀 회로 TNb 내지 TNn의 스위치 회로 SW는 각각 상기 디스플레이 데이터 D0 내지 Dn-1에 따라 온/오프 제어된다. 상기 MPU(21)로부터의 디스플레이 데이터 D0 내지 Dn-1은 각각 상기 제어 회로(20)의 래치(latch) 펄스 LP에 따라 디스플레이 데이터 레지스터(8)에 설정된다.

상기 트랜지스터 셀 회로 TNa 내지 TNn 각각의 게이트 단자 G1 및 G2는 공통적으로 접속된다. 또, 상기 입력측 트랜지스터 셀 회로 TNa의 드레인 D와 게이트 단자 G2는 D/A 컨버터 회로(11)의 입력 단자(11a)에 접속된다. 그러므로, 3개의 N채널 MOS 트랜지스터 셀 회로 TNa 중 중앙 트랜지스터는 다이오드-접속되고, 커런트 미러 회로의 입력측 트랜지스터로서 정전류원(12)으로부터 구동 전류 Ir을 공급받는다.

상기 정전류원(12)은 바이어스 라인 Vb에 접속되고, 기준 전류 분배 회로의 출력 전류원으로서 작동한다. 상기 기준 전류 분배 회로의 입력측 트랜지스터에 공급된 기준 전류에 응답하여, 상기 유기 EL 구동 회로(컬럼 드라이버)(1)의 출력 단자(6a 내지 6n)에 대응하여 별별로 공급된 복수의 출력측 트랜지스터에서 미러 전류로서 기준 전류를 복제한다. 그러므로, 상기 기준 전류 또는 기준 구동 전류는 상기 유기 EL 디스플레이 패널의 출력 단자 핀(컬럼 핀)에 분배된다.

상기 출력측 트랜지스터 셀 회로로서 트랜지스터 셀 회로 TNb 내지 TNn의 드레인 단자 D는 상기 D/A 컨버터 회로(11)의 출력 단자(11b)에 접속된다. 상기 출력 단자(11b)는 유기 EL 디스플레이 패널의 컬럼 핀에 접속된 출력 단자(6a)에 접속된다. 상기 출력 단자(6a)는 리셋 스위치(13)를 통해 리셋 전압 발생 회로(14)의 출력 단자(140)에도 접속된다.

상기 리셋 전압 발생 회로(14)는 도 2(a)에 도시된 리셋 제어 펄스 RS의 디스플레이 기간 D에 대하여 아이들링 상태로 있으며, 리셋 기간 RT에서 아이들링 상태에서부터 안정한 동작 상태로 복귀하여 정전압 리셋하는 전압 VRS를 생성한다. 그러므로, 리셋 전압 발생 회로(14)는 하나의 수평 스캔 라인에 상당하는 유기 EL 구동 회로(컬럼 드라이버)(1) 또는 캐페시터의 단자(6a 내지 6n)에 접속된 캐페시터를 동시에 리셋한다. 상기 리셋 기간 RT에서의 유기 EL 구동 회로의 동작이 종료되고, 그 다음의 디스플레이 기간 D로 진입하는 경우에, 상기 리셋 전압 발생 회로(14)는 아이들링 상태로 돌아간다. 또한, 리셋 제어 펄스 RS는 소정의 주파수를 갖는 타이밍 제어 신호에 대응하여, 하나의 수평 라인의 스캔 기간에 따른 디스플레이 기간과 수평 스캔의 귀선 기간에 따른 리셋 기간을 분리한다.

그러므로, 상기 리셋 제어 펄스 RS는 타이밍 제어 신호일 수도 있다. 상기 타이밍 제어 신호가 패시브 매트릭스형 유기 EL 구동 회로에서 리셋 제어 펄스 RS이기 때문에, 유기 EL 구동 회로의 동작은 타이밍 제어 신호가 아닌 리셋 제어 펄스 RS를 이용하여 설명될 것이다.

상기 리셋 전압 발생 회로(14)는 증폭 회로로서의 OP 앰프(operational amplifier)(141)와, 상기 OP 앰프(141)의 동작 전류를 스위칭하는 동작 전류 스위칭 회로(142), D/A 변환 회로(143), 그리고 정전류원(144)으로 구성된다.

상기 OP 앰프(141)는 전원 라인 +Vcc로부터의 전력에 의해 구동된 비-변환형의 증폭기이다. 상기 OP 앰프(141)는 상기 D/A 변환 회로(143)로부터 공급된 출력 전압을 (+)입력 단자에 소정의 증폭율로 증폭하고, 증폭된 전압을 출력 정전압 VRS로서 출력 단자(140)에 출력한다. 전원 라인 +Vcc의 전압은 5V 내지 20V 정도이고, 상기 소정 전압 VRS는 전원 라인 +Vcc의 전압보다 수 V 만큼 낮다. 또한, 도 1에 도시된 바와 같이, 상기 OP 앰프(141)의 기준 저항과 피드백 저항의 직렬 회로는 전원 라인 +Vcc에 접속된다. 또, 동작 기준 전위는 접지 전위가 아닌 전원 라인 +Vcc의 전압이다.

상기 D/A 컨버터 회로(143)는 래치 펄스 LP에 따라 MPU(21)로부터 전압 데이터 레지스터(9)에 설정된 데이터를 받고, 상기 데이터를 아날로그 데이터로 변환하여 OP 앰프(141)의 (+)입력에 공급되는 대상인 출력 전압을 생성한다. 그 결과, 상기 OP 앰프(141)가 리셋 동작에 필요한 출력 전압 VRS를 생성하기 때문에, 상기 출력 정전압 VRS는 프로그램형이다.

또한, MPU(21)는 전원 스위치가 온으로 된 경우에 전압 데이터 레지스터(9)에서 리셋 데이터를 설정한다. 상기 리셋 데이터는 MPU(21)의 비휘발성 메모리에 저장되어 있다. 또, 상기 리셋 제어 펄스 RS의 리셋 기간 RT(도 2(a))에서, 리셋되는 대상인 유기 EL 소자의 캐소드측은 로우측 스캔 라인의 스캔에 대응하여 접지된다.

상기 동작 전류 스위칭 회로(142)는 정전류원(144)으로부터 출력측 트랜지스터 TN2 및 TN3와 함께 커런트 미러 회로를 구성하는 입력측 트랜지스터 TN1로 공급된 아이들링 전류 i에 상당하는 정전류 i에 응답하여 OP 앰프(141)의 동작 전류를 생성한다. 상기 동작 전류 스위칭 회로(142)에 의해 생성된 전류는 아이들링 상태의 커런트 미러 회로의 출력측 트랜지스터 TN2에서 생성된 정전류 i, 또는 안정한 동작 상태의 커런트 미러 회로의 출력측 트랜지스터 TN3에서 생성된 전류  $N \times i$ 이다. 상기 동작 전류 스위칭 회로(142)는 아이들링 상태에서의 전류 i로부터 리셋 제어 펄스 RS(도 2(a))의 라이징 엣지(rising edge)에 동기하여 생성된 (상기 리셋 펄스에 상응하는) 프리차지 펄스 PR에 따라 안정한 동작 상태에서의 전류  $N \times i$ 로 OP 앰프(141)의 동작 전류를 스위칭하거나 또는, 리셋 제어 펄스 RS의 폴링 엣지(falling edge)에 동기하여 아이들링 상태의 전류로 상기 안정한 상태의 전류를 스위칭한다. 즉, 상기 OP 앰프(141)의 동작 전류는 프리차지 펄스 PR이 "H" (하이 레벨)가 아닌 경우에 아이들링 상태에서의 전류 i이고, 이에 따라 리셋 전압 발생 회로(14)는 아이들링 상태로 된다.

또한, 액티브 매트릭스형의 유기 EL 디스플레이 패널의 구동 상태에서, 상기 프리차지 펄스 PR은 도 2(c)에 나타낸 바와 같이, 리셋 제어 펄스 RS의 상승과 함께 상승하며 리셋 제어 펄스의 "H" 기간보다 짧은 시간 주기동안 "H"인 상태로 유지되는 리셋 펄스이다. 상기 리셋 기간 RT에서, 광셀 회로(3)의 캐패시터 C에 구동 전류를 기록하는 기록 개시 펄스(또는 기록 펄스) WR은 도 2(d)에 나타낸 바와 같이, 상기 프리차지 펄스 PR이 하강할 때에 이와 동시에 생성되고, 상기 캐패시터 C는 상기 기록 개시 펄스 WR로 인한 구동 전류로 기록된다. 상기 리셋 기간 RT는 상기 기록 동작이 완료될 때에 종료된다.

또한, 패시브 매트릭스형의 유기 EL 디스플레이 패널에서, 상기 구동 전류의 기록은 불필요하다. 그러므로, 상기 리셋 제어 펄스 RS는 리셋 펄스로서 이용된다. 이 경우에, 상기 리셋 스위치(13)는 상기 리셋 제어 펄스 RS에 따른 리셋 기간 RT 동안에 일관적으로 온으로 되고, 상기 각각의 유기 EL 소자를 통해 출력 단자를 리셋한다. 상기 리셋 전압 발생 회로(14)는 리셋 기간 RT 동안에 안정한 동작 상태에서 전류  $N \times i$ 에 의해 동작하고, 상기 디스플레이 기간 D 동안에 아이들링 상태에서 전류 i에 의해 동작한다.

상기 동작 전류 스위칭 회로(142)는 커런트 미러 회로(145)와 아날로그 스위치(146)로 구성된다. 상기 커런트 미러 회로(145)는 입력측 N채널 MOS 트랜지스터 TN1과 출력측 트랜지스터 TN2 및 TN3으로 구성되고, OP 앰프(141)의 동작 전류원으로 작동한다. 또한, 상기 커런트 미러 회로(145)는 상기 정전류원(144)에서부터 상기 입력측 트랜지스터 TN1로 공급된 정전류에 의해 정전류 회로로서 작동한다. 상기 커런트 미러 회로(145)를 구성하는 상기 트랜지스터의 소스는 접지된다. 상기 입력측 트랜지스터 TN1은 다이오드-접속되며 상기 정전류원(144)으로부터 그 드레인에 공급된 전류 i에 의해 구동된다.

상기 출력측 트랜지스터 TN2의 드레인은 상기 동작 전류 스위칭 회로(142)의 출력 단자(147)에 접속되고, 상기 출력측 트랜지스터 TN3의 드레인은 상기 아날로그 스위치(146)를 통해 상기 동작 전류 스위칭 회로(142)의 전류 출력 단자(147)에 접속된다. 상기 전류 출력 단자(147)는 OP 앰프(141)의 동작 전류(접지 전류)를 접지로 방전한다.

상기 아날로그 스위치(146)는 제어 회로(20)로부터의 프리차지 펄스 PR이 "L"(로우 레벨)에서 "H"로 변경되는 경우에 온으로 되고, "H" 기간 동안에 온 상태를 유지한다. 또한, 프리차지 펄스 PR이 "H"에서 "L"로 변경되는 경우에 오프로 된다. 그러므로, 상기 리셋 기간 RT의 기록 기간과 디스플레이 기간 D에서 오프 상태로 있다.

상기 입력측 트랜지스터 TN1과 출력측 트랜지스터 TN2의 채널폭(게이트폭)비는 1:1이고, 상기 입력측 트랜지스터 TN1과 출력측 트랜지스터 TN3의 비는 1:N이다. 여기서 N은 2 이상의 정수이다. 그러므로, 상기 입력측 트랜지스터 TN1과 출력측 트랜지스터 TN3의 동작 전류비는 1:N이 된다. 또한, 이 경우의 N은 병렬로 셀 트랜지스터를 접속하여 실현된다.

그 결과, 상기 OP 앰프(141)의 동작 전류는 아날로그 스위치(146)가 오프로 되는 디스플레이 기간 D에서 i로 되고, 이에 따라 상기 OP 앰프(141)는 아이들링 상태로 된다. 상기 아날로그 스위치(146)가 온으로 있는 리셋 기간 RT(적어도 프리차지 기간)에서, 상기 OP 앰프(141)의 동작 전류는 프리차지 펄스 PR의 "H" 기간 동안에 안정한 동작 상태에서 동작 전류로서 흐르는  $(N+1) \times i$ 로 된다.

상술한 동작은 상기 리셋 전압 발생 회로(14)가 정전류원(144)으로부터의 아이들링 전류 i에 상응하는 정전류 i로 동작하는 경우의 예시이다. 그러나, 상기 정전류원(144)의 전류는 안정한 동작 기간에서의 동작 전류  $N \times i$ 일 수도 있다. 후자의

경우에, 상기 입력측 트랜지스터 TN1과 출력측 트랜지스터 TN3의 채널폭(게이트폭)비를 1:1로 하고, 상기 입력측 트랜지스터 TN1과 출력측 트랜지스터 TN2의 비는 1:1/N으로 한다. 또한, 상기 안정한 동작 상태의 전류는  $(N \times i) + i/N$ 으로 된다.

그러므로, 상기 OP 앰프(141)는 상기 디스플레이 기간 D 동안에 아이들링 전류로 동작하기 때문에 OP 앰프(141)는 소비 전력이 감소되고, 상기 동작이 리셋 기간 RT로 진입하는 경우에 즉시 동작 상태로 진입할 수 있다.

도 1에서, 상기 출력 전압 VRS를 출력 단자(6a)와 아날로그 스위치(146)에 공급하는 리셋 스위치(13)는 제어 회로(20)로부터 프리차지 펄스 PR를 받는다. 상기 리셋 스위치(13)는 상기 프리차지 펄스 PR의 상태가 "L"에서 "H"로 변경되는 경우에 온으로 되며, "H"인 동안에 온 상태로, 또는 상기 리셋 제어 펄스 RS를 받는 경우에 리셋 기간 RT로도 유지된다. 상기 프리차지 펄스 PR이 "H"에서 "L"로 변경되는 경우에, 스위치(13)는 오프로 되고, 이 오프 상태는 디스플레이 기간 D 동안 유지된다.

이와 같이, 상기 OP 앰프의 동작은 아이들링 상태에서부터 안정한 동작 상태로 이동되며, 하나의 수평 로우측 스캔 라인의 스캔 기간(디스플레이 기간 D)이 종료되는 동시에, 상기 리셋 기간 RT로 진입함으로써, 상기 OP 앰프의 아이들링 상태에서부터 안정한 동작 상태로의 고속 입상(rising)이 달성된다. 상기 OP 앰프(141)가 디스플레이 기간 D에서 아이들링 상태 이기 때문에, 아이들링 전류 i만으로 동작할 수 있으며, 이에 따라 소비 전력이 경감된다.

도 2(a) 내지 도 2(e)를 참조하면 유기 EL 구동 회로의 리셋 동작의 타이밍 차트이며, 도 2(a)는 상기 제어 회로(20)로부터 출력된 리셋 제어 펄스 RS(타이밍 제어 신호를 나타낸다. 도 2(b)는 리셋 제어 펄스 RS에 의해 규정되는 유기 EL 소자(4)의 발광 기간을 나타낸다. 도 2(c)는 제어 회로(20)로부터의 프리차지 펄스 PR을 나타낸다. 도 2(d)는 프리차지 펄스 PR에 따른 전압 리셋이 종료된 후에 상기 제어 회로(20)로부터 기록 제어 회로(5)에 공급된 기록 개시 펄스 WR을 나타낸다. 상기 스캔 라인 Y1은 상기 기록 개시 펄스 WR에 따른 기록 제어 회로(5)에 의해 "L" 레벨로 설정된다. 이는 후술될 것이다. 도 2(e)는 상기 D/A 컨버터 회로(11)의 구동 전류(싱크 출력 전류)를 나타낸다.

도 1을 참조하면, 상기 D/A 컨버터 회로(11)의 트랜지스터 셀 회로 TN<sub>a</sub> 내지 TN<sub>n</sub>의 공통 접속된 게이트 단자 G1은 정전압 바이어스 회로(15)에 접속된다. 소정 저항값을 갖는 상기 트랜지스터 셀 회로(2)의 상부 트랜지스터는 상기 정전압 바이어스 회로(15)에 의해 설정된 게이트 전압 VG에 의해 온 상태로 설정된다. 그러므로, 상기 트랜지스터 셀 회로 TN<sub>a</sub> 내지 TN<sub>n</sub>의 드레인 단자 D에서 전압을 실질적으로 동일한 값으로 설정할 수 있고, 이에 따라 D/A 변환의 정밀도를 향상시킬 수 있다.

그 결과, 유기 EL 구동 회로(컬럼 드라이버)(1)의 D/A의 변환 특성의 불균일이 감소하고, 이에 따라 상기 컬럼 핀에서의 출력 전류의 불균일이 경감된다.

또한, 병렬로 접속되는 트랜지스터 셀 회로(2)에서 3개의 트랜지스터의 직렬 접속의 수 각각은  $\times 1, \times 2, \dots, \times n$ 으로 나타낸다. 상기 트랜지스터 셀 회로(2)의 수가  $\times 1$ 인 경우에 병렬 접속은 없다. 상기 출력측 트랜지스터 셀 회로 TN<sub>b</sub> 내지 TN<sub>n</sub>의 출력은 병렬 접속되는 대상인 트랜지스터 셀 회로에서 직렬 접속의 수에 대응하여 중량된다.

상기 광셀 회로(디스플레이 셀)(3)는 유기 EL 디스플레이 패널의 각 광셀에 대응하여 제공된다. 상기 광셀 회로(3) 중 하나는 데이터 라인 X와 접속 단자(3a)를 통해 커런트 구동 회로(1a)의 출력 단자(6a)에 접속된다. 상기 출력 단자(6a)는 D/A 컨버터 회로(11)의 출력 단자(11b)와 리셋 스위치(13)를 통해 상기 리셋 전압 발생 회로(14)의 출력 단자(140)에 접속된다. 상기 광셀 회로(3)는 X 및 Y 매트릭스 와이어링 라인(데이터 라인 X 및 스캔 라인 Y<sub>1</sub>, Y<sub>2</sub>, ...)의 교점에 각각 배열된다. 상기 광셀 회로(3)에서, 상기 데이터 라인 X에 접속된 드레인과 상기 스캔 라인 X<sub>1</sub>에 접속된 게이트를 갖는 P채널 MOS 트랜지스터 TP<sub>1</sub> 및 TP<sub>2</sub>가 배열된다. 상기 유기 EL 소자(4)는 광셀 회로(3)에 제공된 P채널 MOS 트랜지스터 TP<sub>3</sub> 및 TP<sub>4</sub>에 의해 구동된다. 캐패시터 C는 상기 트랜지스터 TP<sub>3</sub>의 소스와 게이트 사이에 접속된다.

상기 트랜지스터 TP<sub>1</sub>의 소스는 트랜지스터 TP<sub>3</sub>의 게이트에 접속되고, 상기 트랜지스터 TP<sub>2</sub>의 소스는 트랜지스터 TP<sub>3</sub>의 드레인에 접속된다. 상기 트랜지스터 TP<sub>1</sub> 및 TP<sub>2</sub>가 기록 개시 펄스 WR에 의해 온으로 된 경우에, 상기 트랜지스터 TP<sub>3</sub>의 게이트와 소스는 다이오드-접속되고, 이에 따라 상기 D/A 컨버터 회로(11)로부터의 구동 전류(싱크 전류)는 트랜지스터 TP<sub>3</sub>으로 흐르고, 상기 캐패시터 C는 구동 전류에 대응하는 전압으로 충전된다.

상기 트랜지스터 TP<sub>3</sub>의 소스는 전원 라인 +V<sub>cc</sub>에 접속되고, 그 드레인은 트랜지스터 TP<sub>4</sub>의 소스-드레인 회로를 통해 유기 EL 소자(4)의 애노드에 접속된다.

상기 리셋 기간 RT에서, 로우측상에서 스캔되는 대상인 상기 유기 EL 소자(4)의 캐소드는 로우측 스캔 회로(7)의 스위치 회로(7a)에 접속되고, 이 스위치 회로(7a)를 통해 접지된다.

상기 트랜지스터 TP1 및 TP2의 게이트는 스캔 라인(기록 라인) Y1을 통해 기록 제어 회로(5)에 접속된다. 그러므로, 상기 트랜지스터 TP1 및 TP2는 게이트가 도 2(d)에 도시된 기록 개시 펄스 WR에 따른 기록 제어 회로(5)에 의해 스캔되는 경우에 온으로 된다. 이에 따라, 상기 스캔 라인 Y1이 "L" 레벨로 된다. 그러므로, D/A 변환 회로(11)로부터의 소정 구동 전류는 상기 트랜지스터 TP3, 캐패시터 C, 트랜지스터 TP1 및 TP2, 데이터 라인 X, 단자(3a), 출력 단자(6a)를 통해 전원 라인 + Vcc로부터 흐른다. 그러므로, 상기 구동 전류에 상응하는 전압은 캐패시터 C에 정확히 기록된다. 그리고, 스캔 라인 Y1은 "H"로 되고, 상기 트랜지스터 TP1 및 TP2는 오프로 된다.

상기 트랜지스터 TP4의 게이트는 스캔 라인 Y2를 통해 기록 제어 회로(5)에 접속된다. 상기 게이트는 기록 제어 회로(5)에 의해 스캔된다. 상기 트랜지스터 T4는 상기 스캔 라인 Y2(구동 라인)가 "L"로 되는 경우에 온으로 된다. 상기 트랜지스터 TP3 및 TP4의 온 상태는 상기 기록 개시 펄스 WR의 하강으로 인해 지속되고, 이에 따라 구동 회로가 상기 유기 EL 소자(4)의 애노드에 공급된다. 상기 스캔 라인 Y2의 전위는 발광 기간 D에서 "H"로 되는 도 2(b)에 도시된 펄스 신호에 대응한다. 또한 이 경우에 상기 스캔 라인 Y1은 "H"임에 따라, 상기 트랜지스터 TP1 및 TP2는 오프 상태로 있다.

상기 트랜지스터 TP3 및 TP4의 구동이 종료되는 시점에서, 상기 스캔 라인 Y2가 "H"로 되고, 이에 따라 상기 트랜지스터 TP4가 오프로 된다. 이러한 타이밍으로 상기 스캔 라인 Y1은 "L"로 된다. 그러므로, 상기 출력 단자(140)는 온으로 된 상기 트랜지스터 TP1 및 TP2와 프리차지 펄스 PR에 의해 온으로 된 리셋 스위치(13)에 의해 리셋 전압 발생 회로(14)의 출력 전압 VRS를 통해 설정된다. 그러므로, 상기 캐패시터 C의 전압은 출력 단자(6a)를 통해 트랜지스터 TPa에 의해 출력 정전압 VRS로 설정된다.

또한, 이 경우에 상기 프리차지 펄스 PR에 의해 온으로 되는 리셋 스위치(13)는 유기 EL 디스플레이 패널(10)의 각 단자 핀에 대응하는 전류 구동 회로(1a 내지 1n) 각각에 공급된다. 그러므로, 리셋되는 대상인 캐패시터 C는 하나의 수평 라인에 대하여 있거나 또는 하나의 수평 디스플레이 라인이 복수의 컬럼 드라이버에 의해 처리되는 경우에 복수의 컬럼 드라이버에 의해 처리된 단자 핀의 수에 대응한다. 컬러 디스플레이의 경우에, 상기 리셋 전압 발생 회로(14)는 각 R, G, B 컬러에 대응하여 제공된다. 이러한 경우에, 각 컬럼 드라이버에 의해 리셋되는 대상인 단자 핀의 수는 30 이상으로 된다.

상기 로우측 스캔 회로(7)의 하나의 스위치 회로(7a)만이 도 1에 도시되어 있으나, 복수의 스위치 회로(7a)가 제공되며, 실질적으로 각 로우측 수평 라인의 스캔에 대응하여 온/오프 제어된다. 상기 로우측 스캔 회로(7)는 패시브 매트릭스형 유기 EL 구동 회로에 필요하다. 그러나, 액티브 매트릭스형 유기 EL 구동 회로에서, 도 1에 도시된 광 셀 회로(3)의 구동 트랜지스터 TP4를 스위치 회로(7a)로 대체하고, 상기 로우측 스캔 회로(7)의 스위치 회로(7a)를 제거하는 것이 가능하다. 그 이유는 상기 구동 트랜지스터 TP4가 유기 EL 소자(4)의 상류측 또는 하류측상에 제공되며, 직렬로 유기 EL 소자(4)에 접속되기 때문이다. 또한, 상기 트랜지스터 TP4는 스위치 회로(7a)의 동작과 같이 상기 디스플레이 기간에서 온으로 되며, 리셋 기간 RT에서 오프로 된다.

또한, 도 1에 도시하지 않았으나, 상기 D/A 컨버터 회로(11)의 입력측 트랜지스터 셀 회로 TNa의 스위치 회로 SW는 캐패시터 C가 리셋인 리셋 기간에 오프로 변경될 수 있다. 이는 바이어스 전압 Va를 공급받아서 입력 단자를 "L"로 하는 입력 측 트랜지스터 셀 회로 TNa의 입력 단자 Din에 리셋 제어 펄스 RS의 반전된 펄스를 공급함으로써 실현될 수 있다. 그러므로, 상기 스위치 회로 SW가 오프로 되는 경우에, 상기 출력측 트랜지스터 셀 회로 TNb 내지 TNn은 오프로 된다. 이에 따라, 상기 리셋 스위치(13)가 리셋 제어 펄스 RS에 의해 온으로 되는 경우에, 상기 D/A 컨버터 회로(11)의 출력측 트랜지스터 셀 회로 TNb 내지 TNn에서 흐르는 전류가 블로킹되고, 그 결과 소비 전력이 감소된다.

상술한 바와 같이, 상기 실시형태에서, 아이들링 상태로부터 안정한 동작 상태로의 스위칭은 상기 리셋 기간의 개시 타이밍을 이용하여 실행된다. 그러나, 상기 리셋 전압 발생 회로(14)의 개시 동작을 고려하여 상기 리셋 기간의 개시 전에 잠시의 타이밍으로 상태를 스위칭할 수 있다. 이러한 경우에, 상기 리셋 전압 발생 회로(14)는 상기 리셋 기간 RT가 개시되는 경우에 안정한 동작 상태로 된다.

상술한 바와 같이, 상기 OP 앰프의 동작은 상기 리셋 제어 펄스 RS가 "H"로 되는 경우에 아이들링 상태에서부터 안정한 동작 상태로 이동된다. 그러나, 상기 리셋 제어 펄스 RS가 "L" 상태로 있을 때에 상기 동작이 리셋 기간 RT로 진입하는 경우에, 상기 아이들링 상태에서부터 안정한 동작 상태로의 이동은 상기 리셋 제어 펄스 RS가 "L"일 때에 일어난다. 상기 리셋

제어 펄스 RS의 "H" 및 "L"은 상기 동작 타이밍을 나타내는 로직 신호이며, 상기 아이들링 상태에서부터 안정한 동작 상태로의 이동을 실현하기 위한 조건은 아니다. 상기 리셋 기간 RT의 개시 또는 그 이전에 상기 상태를 스위칭하는데 충분하다.

상술한 실시형태에서는 상기 액티브 매트릭스형 유기 EL 디스플레이 패널에서 픽셀 회로의 캐패시터의 리셋이 행해진다. 그러나, 본 발명은 패시브 매트릭스형 유기 EL 디스플레이 패널의 유기 EL 소자의 단자 전압의 리셋에 적용될 수 있다. 이 경우에, 상기 리셋 전압 발생 회로(14)는 접지 전위보다 높은, 예를 들어 수 V 높은 정전압을 생성한다.

또한, 상술한 실시형태에서, 상기 정전압은 소정 증폭율을 갖는 OP 앰프를 이용하여 생성된다. 그러나, OP 앰프 대신에 일반 증폭기가 사용되기도 한다. 예를 들면, 증폭율이 1인 전압 팔로워 앰프가 사용되어도 된다.

또한, 상술한 실시형태에서, 상기 D/A 컨버터 회로는 출력단 전류원으로서 사용된다. 그러나, 커런트 미러 회로와 같은 전류원을 출력단으로서 추가로 공급하는 것이 가능하다. 이 경우에, 상기 D/A 컨버터 회로의 출력에 의해 출력단 전류원을 구동할 수 있다. 이 경우에, 픽셀 회로 또는 유기 EL 소자는 상기 출력단 전류원으로부터의 방전 전류에 의해 구동된다.

또한, 상술한 실시형태에서, 전체의 구동 회로가 주로 N채널 MOS 트랜지스터로 구성된다. 그러나, 상기 회로는 P채널 MOS 트랜지스터 또는 N채널 MOS 트랜지스터와 P채널 MOS 트랜지스터의 조합형으로 구성되어도 된다.

### 발명의 효과

본 발명에 따르면, 리셋 회로의 소비 전력을 경감하여 유기 EL 회로의 소비 전력을 감소시킬 수 있고, 단시간내에 픽셀 회로의 캐패시터 또는 유기 EL 소자를 리셋할 수 있는 유기 EL 구동 회로 및 이 유기 EL 구동 회로를 이용한 유기 EL 디스플레이 장치를 제공할 수 있다.

### (57) 청구의 범위

#### 청구항 1.

소정 주파수를 갖는 타이밍 제어 신호의 리셋 기간에서 유기 EL 디스플레이 패널의 단자 핀을 통해 유기 EL 디스플레이 패널의 픽셀 회로의 유기 EL 소자 또는 캐패시터를 리셋하고, 하나의 수평 라인의 스캔 기간에 상응하는 디스플레이 기간과 상기 수평 스캔의 귀선(retrace) 기간에 상응하는 리셋 기간을 분리하기 위한 유기 EL 구동 회로에 있어서,

상기 유기 EL 소자 또는 캐패시터를 리셋하기 위한 소정의 정전압을 생성하는 증폭 회로;

상기 증폭 회로의 출력 단자와 단자 핀 중 하나와의 사이에 제공되며, 상기 타이밍 제어 신호, 상기 타이밍 제어 신호와 동일한 리셋 제어 신호, 리셋 펄스, 및 상기 신호들 중 하나와 또는 상기 리셋 펄스와 동기하여 리셋 기간에 생성된 그외 펄스 중 한 신호에 의해 온/오프 동작되는 리셋 스위치;

상기 한 신호에 응답하며, 디스플레이 기간에 상기 증폭 회로의 동작 전류를 아이들링(idling) 상태의 전류로 설정하고, 또 상기 리셋 기간 또는 상기 리셋 펄스나 그외 펄스가 생성된 기간에서 리셋 동작에 필요한 리셋 전류로 설정하기 위한 동작 전류 스위칭 회로를 구비하는 것을 특징으로 하는 유기 EL 구동 회로.

#### 청구항 2.

제1항에 있어서,

상기 동작 전류 스위칭 회로는 상기 동작 전류를 생성하기 위한 정전류 회로를 포함하고,

상기 정전류 회로의 전류는 상기 한 신호에 따라 아이들링 상태와 안정한 동작 상태와의 사이에서 스위칭되는 것을 특징으로 하는 유기 EL 구동 회로.

### 청구항 3.

제2항에 있어서,

상기 한 신호는 레벨이 로우(LOW)로부터 하이(HIGH)를 거쳐서 로우로 또는 하이로부터 로우를 거쳐서 하이로 변경되고,

상기 동작 전류 스위칭 회로는 아이들링 상태의 전류와, 상기 한 신호가 하이에서 로우로 레벨 변경하는 타이밍이나 또는 상기 레벨 변경 이전의 타이밍에서의 안정한 동작 상태의 전류와, 로우에서 하이로의 레벨 변경의 타이밍이나 또는, 상기 레벨 변경 이전의 타이밍에서의 다른 상태의 전류 중 하나를 선택하는 것을 특징으로 하는 유기 EL 구동 회로.

### 청구항 4.

제3항에 있어서,

상기 유기 EL 디스플레이 패널은 다수의 상기 단자 펈을 갖고,

상기 증폭 회로는 상기 정전류 회로의 전류에 의해 규정된 동작 전류를 갖는 OP 앰프(operational amplifier)이고,

상기 복수의 리셋 스위치는 상기 단자 펈 수 중 적어도 복수의 단자 펈에 대응하여 각각 제공되고,

상기 복수의 리셋 스위치는 동시에 온으로 되는 것을 특징으로 하는 유기 EL 구동 회로.

### 청구항 5.

제4항에 있어서,

상기 리셋 스위치는 출력 단자와 상기 각각의 단자 펈과의 사이에 제공되고,

상기 정전류 회로는 상기 OP 앰프의 동작 전류원으로서의 복수의 출력측 트랜지스터를 갖는 커런트 미러 회로와, 상기 복수의 출력측 트랜지스터 중 적어도 하나에 대응하여 제공된 스위치 회로를 구비하고,

상기 OP 앰프의 동작 전류는 상기 한 신호에 따라 상기 스위치 회로의 온/오프 동작에 상응하여 아이들링 상태의 전류와 안정한 동작 상태의 전류 중 하나로 스위칭되는 것을 특징으로 하는 유기 EL 구동 회로.

### 청구항 6.

제5항에 있어서,

상기 한 신호는 프리차지(preecharge) 펄스이고,

상기 커런트 미러 회로의 상기 복수의 출력측 트랜지스터 중 하나는 상기 커런트 미러 회로의 입력측 트랜지스터에 대하여 1:N(N은 1 이상의 수)의 동작 전류비를 갖고,

상기 스위치 회로는 상기 하나의 출력측 트랜지스터에 직렬로 접속되며, 상기 프리차지 펄스를 따른 상기 리셋 스위치와 함께 온으로 되는 것을 특징으로 하는 유기 EL 구동 회로.

### 청구항 7.

제6항에 있어서,

제1 D/A 변환 회로와 제2 D/A 변환 회로를 추가로 구비하고,

상기 제1 D/A 변환 회로, 상기 OP 앰프, 상기 동작 전류 스위칭 회로는 리셋 전압 발생 회로를 구성하고,

상기 OP 앰프는 상기 제1 D/A 변환 회로에 의해 변환된 전압을 입력 전압으로서 공급받고,

상기 리셋 전압 발생 회로는 상기 픽셀 회로의 유기 EL 소자 또는 캐패시터를 리셋하기 위한 소정의 정전압을 리셋 전압으로서 생성하고,

상기 제2 D/A 변환 회로는 상기 단자 핀에 접속되며, 디스플레이 데이터를 상기 D/A 변환함으로써 상기 픽셀 회로의 유기 EL 소자 또는 캐패시터에 구동 전류를 출력하는 것을 특징으로 하는 유기 EL 구동 회로.

### 청구항 8.

제5항에 있어서,

상기 한 신호는 프리차지 펄스이고,

상기 커런트 미러 회로의 상기 복수의 출력측 트랜지스터 중 하나는 상기 커런트 미러 회로의 입력측 트랜지스터에 대하여 1:1/N(N은 1 이상의 수)의 동작 전류비를 갖고,

상기 다른 출력측 트랜지스터는 상기 입력측 트랜지스터에 대하여 1:1의 동작 전류비를 갖고,

상기 스위치 회로는 상기 커런트 미러 회로의 다른 출력측 트랜지스터에 직렬로 접속되며, 상기 프리차지 펄스를 따른 상기 리셋 스위치와 함께 온으로 되는 것을 특징으로 하는 유기 EL 구동 회로.

### 청구항 9.

제7항에 있어서,

상기 유기 EL 디스플레이 패널은 액티브 매트릭스형이고,

상기 리셋 전압 발생 회로는 상기 픽셀 회로의 캐패시터의 전압을 리셋하는 것을 특징으로 하는 유기 EL 구동 회로.

### 청구항 10.

제7항에 있어서,

상기 유기 EL 디스플레이 패널은 패시브 매트릭스형이고,

상기 리셋 전압 발생 회로는 상기 유기 EL 소자의 단자 전압을 리셋하는 것을 특징으로 하는 유기 EL 구동 회로.

### 청구항 11.

소정 주파수를 갖는 타이밍 제어 신호의 리셋 기간에서 유기 EL 디스플레이 패널의 단자 핀을 통해 유기 EL 디스플레이 패널의 광센 회로의 유기 EL 소자 또는 캐패시터를 리셋하고, 하나의 수평 라인의 스캔 기간에 상응하는 디스플레이 기간과 상기 수평 스캔의 귀선 기간에 상응하는 리셋 기간을 분리하기 위한 유기 EL 구동 회로를 구비하는 유기 EL 디스플레이 장치에 있어서,

상기 유기 EL 소자 또는 캐패시터를 리셋하기 위한 소정의 정전압을 생성하는 증폭 회로;

상기 증폭 회로의 출력 단자와 단자 핀 중 하나와의 사이에 제공되며, 상기 타이밍 제어 신호, 상기 타이밍 제어 신호와 동일한 리셋 제어 신호, 리셋 펄스, 및 상기 신호들 중 하나 또는 상기 리셋 펄스와 동기하여 리셋 기간에 생성된 그외 펄스 중 한 신호에 의해 온/오프 동작되는 리셋 스위치;

상기 한 신호에 응답하며, 디스플레이 기간에 상기 증폭 회로의 동작 전류를 아이들링 상태의 전류로 설정하고, 또 상기 리셋 기간 또는 상기 리셋 펄스나 그외 펄스가 생성된 기간에서 리셋 동작에 필요한 리셋 전류로 설정하기 위한 동작 전류 스위칭 회로를 구비하는 것을 특징으로 하는 유기 EL 디스플레이 장치.

## 청구항 12.

제11항에 있어서,

상기 동작 전류 스위칭 회로는 상기 동작 전류를 생성하기 위한 정전류 회로를 포함하고,

상기 정전류 회로의 전류는 상기 한 신호에 따라 아이들링 상태와 안정한 동작 상태와의 사이에서 스위칭되는 것을 특징으로 하는 유기 EL 디스플레이 장치.

## 청구항 13.

제12항에 있어서,

상기 한 신호는 레벨이 로우로부터 하이를 거쳐서 로우로 또는 하이로부터 로우를 거쳐서 하이로 변경되고,

상기 동작 전류 스위칭 회로는 아이들링 상태의 전류와, 상기 한 신호가 하이에서 로우로 레벨 변경하는 타이밍이나 또는 상기 레벨 변경 이전의 타이밍에서의 안정한 동작 상태의 전류와, 로우에서 하이로의 레벨 변경의 타이밍이나 또는 상기 레벨 변경 이전의 타이밍에서의 다른 상태의 전류 중 하나를 선택하는 것을 특징으로 하는 유기 EL 디스플레이 장치.

## 청구항 14.

제13항에 있어서,

상기 유기 EL 디스플레이 패널은 다수의 상기 단자 핀을 갖고,

상기 증폭 회로는 상기 정전류 회로의 전류에 의해 규정된 동작 전류를 갖는 OP 앰프이고,

상기 복수의 리셋 스위치는 상기 단자 핀 수 중 적어도 복수의 단자 핀에 대응하여 각각 제공되고,

상기 복수의 리셋 스위치는 동시에 온으로 되는 것을 특징으로 하는 유기 EL 디스플레이 장치.

## 도면

도면1

도면2

|                |                                                               |         |            |

|----------------|---------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机EL驱动电路和使用其的有机EL显示装置                                         |         |            |

| 公开(公告)号        | <a href="#">KR100641443B1</a>                                 | 公开(公告)日 | 2006-10-31 |

| 申请号            | KR1020050043555                                               | 申请日     | 2005-05-24 |

| [标]申请(专利权)人(译) | 罗姆股份有限公司<br>罗穆亚尔德是部分株式会社                                      |         |            |

| 申请(专利权)人(译)    | 罗穆亚尔德株式会社                                                     |         |            |

| 当前申请(专利权)人(译)  | 罗穆亚尔德株式会社                                                     |         |            |

| [标]发明人         | YAGUMA HIROSHI<br>야구마 히로시<br>KOBAYASHI MASATO<br>코바야시 마사토     |         |            |

| 发明人            | 야구마 히로시<br>코바야시 마사토                                           |         |            |

| IPC分类号         | G09G3/30 G09G3/32                                             |         |            |

| CPC分类号         | G09G2300/0861 G09G3/325 G09G2330/021 G09G3/3283 G09G2310/0248 |         |            |

| 优先权            | 2004152749 2004-05-24 JP                                      |         |            |

| 其他公开文献         | KR1020060046154A                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                     |         |            |

## 摘要(译)

另外，本发明切换到有机EL元件或用于产生被提供给复位的电容器所需的预定的恒定电压的放大器电路，所述周期，其中所述开关电路的工作电流显示放大器电路空转（空转）电流的工作电流，和复位在重置期间，通过切换到所需要的工作电流，可以是放大电路的较短切换时间从急速状态到稳定操作状态中，用于复位的有机EL元件或电容器（恒定control voltage）在重置时段的开始时产生的控制电压，可以。1