(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2008-0037538

(43) 공개일자 2008년04월30일

(51) Int. Cl.

H05B 33/10 (2006.01)

(21) 출원번호 10-2007-0107021

(22) 출원일자 2007년10월24일

심사청구일자 없음(30) 우선권주장

JP-P-2006-00291147 2006년10월26일 일본(JP)

(71) 출원인

가부시키가이샤 한도오따이 에네루기 켄큐쇼

일본국 가나가와Ken 아쓰기시 하세 398

(72) 발명자

키무라 하지메

일본국 가나가와Ken 아쓰기시 하세 398 가부시키가

이샤 한도오따이에네루기 켄큐쇼 나이

야마다 토모코일본국 가나가와Ken 아쓰기시 하세 398 가부시키가

이샤 한도오따이에네루기 켄큐쇼 나이(74) 대리인

이화의, 권태복

전체 청구항 수 : 총 94 항

**(54) 전자기기, 표시장치, 반도체 장치 및 그 구동방법****(57) 요 약**

본 발명은, 부하에 공급하는 전류값을 제어하는 트랜지스터와, 제 1 유지용량과, 제 2 유지용량과, 제 1 스위치 내지 제 4 스위치를 포함하는 화소를 가지고, 상기 제 2 유지용량에 상기 트랜지스터의 임계값 전압을 유지시킨 후, 비디오 신호에 따른 전위를 상기 화소에 입력한다. 이와 같이, 상기 제 2 유지용량에, 상기 임계값 전압에 상기 비디오 신호에 따른 전위 중의 상기 제 1 유지용량과 용량분할된 전위가 가산된 전압을 유지시킴으로써, 트랜지스터의 임계값 전압의 편차에 의거한 전류값의 편차를 억제한다. 따라서, 발광소자를 비롯한 부하에 원하는 전류를 공급할 수 있다. 또한, 비디오 신호에 따라, 지정된 휘도로부터의 차이가 적은 표시장치를 제공할 수 있다.

**대표도** - 도1

## 특허청구의 범위

### 청구항 1

반도체 장치에 있어서,

트랜지스터와;

유지용량과;

제 1 스위치와;

제 2 스위치와;

제 3 스위치와;

제 4 스위치를 포함하고,

상기 트랜지스터의 제 1 전극은 화소전극에 전기적으로 접속되고,

상기 트랜지스터의 제 2 전극은 상기 제 2 스위치를 통하여 제 1 배선에 전기적으로 접속되고,

상기 트랜지스터의 제 2 전극은 상기 제 3 스위치를 통하여 상기 트랜지스터의 게이트 전극에 전기적으로 접속되고,

상기 트랜지스터의 게이트 전극은 상기 유지용량과 상기 제 4 스위치를 통하여 제 2 배선에 전기적으로 접속되고,

상기 트랜지스터의 게이트 전극은 상기 유지용량과 상기 제 1 스위치를 통하여 제 3 배선에 전기적으로 접속되는, 반도체 장치.

### 청구항 2

제 1 항에 있어서,

상기 제 2 배선은 상기 제 1 스위치를 제어하는 배선과 동일한, 반도체 장치.

### 청구항 3

제 1 항에 있어서,

상기 제 2 배선은 전행 또는 다음 행의 제 1 스위치 내지 제 4 스위치의 하나를 제어하는 주사선의 어느 하나인, 반도체 장치.

### 청구항 4

제 1 항에 있어서,

상기 트랜지스터는 박막 트랜지스터인, 반도체 장치.

### 청구항 5

제 1 항에 있어서,

상기 트랜지스터는 N채널형 트랜지스터인, 반도체 장치.

### 청구항 6

제 1 항에 있어서,

상기 트랜지스터의 반도체 층은 비정질 반도체 막으로 되는, 반도체 장치.

### 청구항 7

제 1 항에 있어서,

상기 트랜지스터의 반도체 층은 비정질 규소로 되는, 반도체 장치.

**청구항 8**

제 1 항에 있어서,

상기 트랜지스터의 반도체 층은 결정성 반도체 막으로 되는, 반도체 장치.

**청구항 9**

제 1 항에 있어서,

상기 제 1 배선의 전위는 상기 화소전극의 전위에 상기 트랜지스터의 임계값 전압을 가한 값보다 높은, 반도체 장치.

**청구항 10**

제 1 항에 있어서,

상기 트랜지스터는 P채널형 트랜지스터인, 반도체 장치.

**청구항 11**

제 1 항에 있어서,

상기 제 1 배선의 전위는 상기 화소전극의 전위로부터 상기 트랜지스터의 임계값 전압을 뺀 값보다 낮은, 반도체 장치.

**청구항 12**

제 1 항에 있어서,

상기 제 1 스위치 내지 제 4 스위치는 트랜지스터인, 반도체 장치.

**청구항 13**

청구항 1에 따른 반도체 장치를 포함하는, 표시장치.

**청구항 14**

청구항 13에 따른 상기 표시장치를 표시부에 가지는, 전자기기.

**청구항 15**

반도체 장치에 있어서,

트랜지스터와;

제 1 유지용량과;

제 2 유지용량과;

제 1 스위치와;

제 2 스위치와;

제 3 스위치와;

제 4 스위치를 포함하고,

상기 트랜지스터의 제 1 전극은 화소전극에 전기적으로 접속되고,

상기 트랜지스터의 제 1 전극은 상기 제 2 유지용량을 통하여 상기 트랜지스터의 게이트 전극에 전기적으로 접속되고,

상기 트랜지스터의 제 2 전극은 상기 제 2 스위치를 통하여 제 1 배선에 전기적으로 접속되고,

상기 트랜지스터의 제 2 전극은 상기 제 3 스위치를 통하여 상기 트랜지스터의 게이트 전극에 전기적으로 접속되고,

상기 트랜지스터의 게이트 전극은 상기 제 1 유지용량과 상기 제 4 스위치를 통하여 제 2 배선에 전기적으로 접속되고,

상기 트랜지스터의 게이트 전극은 상기 제 1 유지용량과 상기 제 1 스위치를 통하여 제 3 배선에 전기적으로 접속되는, 반도체 장치.

#### 청구항 16

제 15 항에 있어서,

상기 제 2 배선은 상기 제 1 스위치를 제어하는 배선과 동일한, 반도체 장치.

#### 청구항 17

제 15 항에 있어서,

상기 제 2 배선은 전행 또는 다음 행의 제 1 스위치 내지 제 4 스위치의 하나를 제어하는 주사선의 어느 하나인, 반도체 장치.

#### 청구항 18

제 15 항에 있어서,

상기 트랜지스터는 박막 트랜지스터인, 반도체 장치.

#### 청구항 19

제 15 항에 있어서,

상기 트랜지스터는 N채널형 트랜지스터인, 반도체 장치.

#### 청구항 20

제 15 항에 있어서,

상기 트랜지스터의 반도체 층은 비정질 반도체 막으로 되는, 반도체 장치.

#### 청구항 21

제 15 항에 있어서,

상기 트랜지스터의 반도체 층은 비정질 규소로 되는, 반도체 장치.

#### 청구항 22

제 15 항에 있어서,

상기 트랜지스터의 반도체 층은 결정성 반도체 막으로 되는, 반도체 장치.

#### 청구항 23

제 15 항에 있어서,

상기 제 1 배선의 전위는 상기 화소전극의 전위에 상기 트랜지스터의 임계값 전압을 가한 값보다 높은, 반도체 장치.

#### 청구항 24

제 15 항에 있어서,

상기 트랜지스터는 P채널형 트랜지스터인, 반도체 장치.

청구항 25

제 15 항에 있어서,

상기 제 1 배선의 전위는 상기 화소전극의 전위로부터 상기 트랜지스터의 임계값 전압을 뺀 값보다 낮은, 반도체 장치.

청구항 26

제 15 항에 있어서,

상기 제 1 스위치 내지 제 4 스위치는 트랜지스터인, 반도체 장치.

청구항 27

청구항 15에 따른 반도체 장치를 포함하는, 표시장치.

청구항 28

청구항 27에 따른 상기 표시장치를 표시부에 가지는, 전자기기.

청구항 29

반도체 장치에 있어서,

트랜지스터와;

제 1 유지용량과;

제 2 유지용량과;

제 1 스위치와;

제 2 스위치와;

제 3 스위치와;

제 4 스위치와;

제 5 스위치를 포함하고,

상기 트랜지스터의 제 1 전극은 화소전극에 전기적으로 접속되고,

상기 트랜지스터의 제 1 전극은 상기 제 2 유지용량을 통하여 상기 트랜지스터의 게이트 전극에 전기적으로 접속되고,

상기 트랜지스터의 제 1 전극은 상기 제 5 스위치를 통하여 제 4 배선에 전기적으로 접속되고,

상기 트랜지스터의 제 2 전극은 상기 제 2 스위치를 통하여 제 1 배선에 전기적으로 접속되고,

상기 트랜지스터의 제 2 전극은 상기 제 3 스위치를 통하여 상기 트랜지스터의 게이트 전극에 전기적으로 접속되고,

상기 트랜지스터의 게이트 전극은 상기 제 1 유지용량과 상기 제 4 스위치를 통하여 제 2 배선에 전기적으로 접속되고,

상기 트랜지스터의 게이트 전극은 상기 제 1 유지용량과 상기 제 1 스위치를 통하여 제 3 배선에 전기적으로 접속되는, 반도체 장치.

청구항 30

제 29 항에 있어서,

상기 제 2 배선은 상기 제 1 스위치를 제어하는 배선과 동일한, 반도체 장치.

청구항 31

제 29 항에 있어서,

상기 제 2 배선은 전행 또는 다음 행의 제 1 스위치 내지 제 4 스위치의 하나를 제어하는 주사선의 어느 하나인, 반도체 장치.

### 청구항 32

제 29 항에 있어서,

상기 트랜ジ스터는 박막 트랜지스터인, 반도체 장치.

### 청구항 33

제 29 항에 있어서,

상기 트랜ジ스터는 N채널형 트랜지스터인, 반도체 장치.

### 청구항 34

제 29 항에 있어서,

상기 트랜ジ스터의 반도체 층은 비정질 반도체 막으로 되는, 반도체 장치.

### 청구항 35

제 29 항에 있어서,

상기 트랜ジ스터의 반도체 층은 비정질 규소로 되는, 반도체 장치.

### 청구항 36

제 29 항에 있어서,

상기 트랜ジ스터의 반도체 층은 결정성 반도체 막으로 되는, 반도체 장치.

### 청구항 37

제 29 항에 있어서,

상기 제 1 배선의 전위는 상기 화소전극의 전위에 상기 트랜ジ스터의 임계값 전압을 가한 값보다 높은, 반도체 장치.

### 청구항 38

제 29 항에 있어서,

상기 트랜ジ스터는 P채널형 트랜지스터인, 반도체 장치.

### 청구항 39

제 29 항에 있어서,

상기 제 1 배선의 전위는 상기 화소전극의 전위로부터 상기 트랜ジ스터의 임계값 전압을 뺀 값보다 낮은, 반도체 장치.

### 청구항 40

제 29 항에 있어서,

상기 제 1 스위치 내지 제 4 스위치는 트랜지스터인, 반도체 장치.

### 청구항 41

청구항 29에 따른 반도체 장치를 포함하는, 표시장치.

**청구항 42**

청구항 41에 따른 상기 표시장치를 표시부에 가지는, 전자기기.

**청구항 43**

반도체 장치에 있어서,

트랜지스터와;

제 1 유지용량과;

제 2 유지용량과;

제 1 스위치와;

제 2 스위치와;

제 3 스위치와;

제 4 스위치를 포함하고,

상기 트랜지스터의 제 1 전극은 화소전극에 전기적으로 접속되고,

상기 트랜지스터의 제 1 전극은 상기 제 2 유지용량을 통하여 상기 트랜지스터의 게이트 전극에 전기적으로 접속되고,

상기 트랜지스터의 제 2 전극은 상기 제 2 스위치를 통하여 제 1 배선에 전기적으로 접속되고,

상기 트랜지스터의 제 2 전극은 상기 제 3 스위치를 통하여 상기 트랜지스터의 게이트 전극에 전기적으로 접속되고,

상기 트랜지스터의 게이트 전극은 상기 제 1 유지용량과 상기 제 4 스위치를 통하여 제 1 배선에 전기적으로 접속되고,

상기 트랜지스터의 게이트 전극은 상기 제 1 유지용량과 상기 제 1 스위치를 통하여 제 2 배선에 전기적으로 접속되는, 반도체 장치.

**청구항 44**

제 43 항에 있어서,

상기 트랜지스터는 박막 트랜지스터인, 반도체 장치.

**청구항 45**

제 43 항에 있어서,

상기 트랜지스터는 N채널형 트랜지스터인, 반도체 장치.

**청구항 46**

제 43 항에 있어서,

상기 트랜지스터의 반도체 층은 비정질 반도체 막으로 되는, 반도체 장치.

**청구항 47**

제 43 항에 있어서,

상기 트랜지스터의 반도체 층은 비정질 규소로 되는, 반도체 장치.

**청구항 48**

제 43 항에 있어서,

상기 트랜지스터의 반도체 층은 결정성 반도체 막으로 되는, 반도체 장치.

#### 청구항 49

제 43 항에 있어서,

상기 제 1 배선의 전위는 상기 화소전극의 전위에 상기 트랜지스터의 임계값 전압을 가한 값보다 높은, 반도체 장치.

#### 청구항 50

제 43 항에 있어서,

상기 트랜지스터는 P채널형 트랜지스터인, 반도체 장치.

#### 청구항 51

제 43 항에 있어서,

상기 제 1 배선의 전위는 상기 화소전극의 전위로부터 상기 트랜지스터의 임계값 전압을 뺀 값보다 낮은, 반도체 장치.

#### 청구항 52

제 43 항에 있어서,

상기 제 1 스위치 내지 제 4 스위치는 트랜지스터인, 반도체 장치.

#### 청구항 53

청구항 43에 따른 반도체 장치를 포함하는, 표시장치.

#### 청구항 54

청구항 53에 따른 상기 표시장치를 표시부에 가지는, 전자기기.

#### 청구항 55

반도체 장치에 있어서,

트랜지스터와;

제 1 유지용량과;

제 2 유지용량과;

제 1 스위치와;

제 2 스위치와;

제 3 스위치와;

정류소자를 포함하고,

상기 트랜지스터의 제 1 전극은 화소전극에 전기적으로 접속되고,

상기 트랜지스터의 제 1 전극은 상기 제 2 유지용량을 통하여 상기 트랜지스터의 게이트 전극에 전기적으로 접속되고,

상기 트랜지스터의 제 2 전극은 상기 제 2 스위치를 통하여 제 1 배선에 전기적으로 접속되고,

상기 트랜지스터의 제 2 전극은 상기 제 3 스위치를 통하여 상기 트랜지스터의 게이트 전극에 전기적으로 접속되고,

상기 트랜지스터의 게이트 전극은 상기 제 1 유지용량과 상기 정류소자를 통하여 제 2 배선에 전기적으로 접속되고,

상기 트랜지스터의 게이트 전극은 상기 제 1 유지용량과 상기 제 1 스위치를 통하여 제 3 배선에 전기적으로 접속되는, 반도체 장치.

#### 청구항 56

제 55 항에 있어서,

상기 트랜지스터는 박막 트랜지스터인, 반도체 장치.

#### 청구항 57

제 55 항에 있어서,

상기 트랜지스터는 N채널형 트랜지스터인, 반도체 장치.

#### 청구항 58

제 55 항에 있어서,

상기 트랜지스터의 반도체 층은 비정질 반도체 막으로 되는, 반도체 장치.

#### 청구항 59

제 55 항에 있어서,

상기 트랜지스터의 반도체 층은 비정질 규소로 되는, 반도체 장치.

#### 청구항 60

제 55 항에 있어서,

상기 트랜지스터의 반도체 층은 결정성 반도체 막으로 되는, 반도체 장치.

#### 청구항 61

제 55 항에 있어서,

상기 제 1 배선의 전위는 상기 화소전극의 전위에 상기 트랜지스터의 임계값 전압을 가한 값보다 높은, 반도체 장치.

#### 청구항 62

제 55 항에 있어서,

상기 트랜지스터는 P채널형 트랜지스터인, 반도체 장치.

#### 청구항 63

제 55 항에 있어서,

상기 제 1 배선의 전위는 상기 화소전극의 전위로부터 상기 트랜지스터의 임계값 전압을 뺀 값보다 낮은, 반도체 장치.

#### 청구항 64

제 55 항에 있어서,

상기 제 1 스위치 내지 제 3 스위치는 트랜지스터인, 반도체 장치.

#### 청구항 65

청구항 55에 따른 반도체 장치를 포함하는, 표시장치.

#### 청구항 66

청구항 65에 따른 상기 표시장치를 표시부에 가지는, 전자기기.

#### 청구항 67

반도체 장치에 있어서,

트랜지스터와;

제 1 유지용량과;

제 2 유지용량과;

제 1 스위치와;

제 2 스위치와;

제 3 스위치와;

제 4 스위치를 포함하고,

상기 트랜지스터의 제 1 전극은 화소전극에 전기적으로 접속되고,

상기 트랜지스터의 제 1 전극은 상기 제 2 유지용량을 통하여 상기 트랜지스터의 게이트 전극에 전기적으로 접속되고,

상기 트랜지스터의 제 2 전극은 상기 제 2 스위치를 통하여 제 1 배선에 전기적으로 접속되고,

상기 트랜지스터의 제 2 전극은 상기 제 3 스위치를 통하여 상기 트랜지스터의 게이트 전극에 전기적으로 접속되고,

상기 트랜지스터의 게이트 전극은 상기 제 1 유지용량과 상기 제 1 스위치를 통하여 제 2 배선에 전기적으로 접속되고,

상기 제 4 스위치는 평행으로 상기 제 1 유지용량에 전기적으로 접속되고, 상기 제 1 스위치를 통하여 상기 제 2 배선에 전기적으로 접속되는, 반도체 장치.

#### 청구항 68

제 67 항에 있어서,

상기 트랜지스터는 박막 트랜지스터인, 반도체 장치.

#### 청구항 69

제 67 항에 있어서,

상기 트랜지스터는 N채널형 트랜지스터인, 반도체 장치.

#### 청구항 70

제 67 항에 있어서,

상기 트랜지스터의 반도체 층은 비정질 반도체 막으로 되는, 반도체 장치.

#### 청구항 71

제 67 항에 있어서,

상기 트랜지스터의 반도체 층은 비정질 규소로 되는, 반도체 장치.

#### 청구항 72

제 67 항에 있어서,

상기 트랜지스터의 반도체 층은 결정성 반도체 막으로 되는, 반도체 장치.

**청구항 73**

제 67 항에 있어서,

상기 제 1 배선의 전위는 상기 화소전극의 전위에 상기 트랜지스터의 임계값 전압을 가한 값보다 높은, 반도체 장치.

**청구항 74**

제 67 항에 있어서,

상기 트랜지스터는 P채널형 트랜지스터인, 반도체 장치.

**청구항 75**

제 67 항에 있어서,

상기 제 1 배선의 전위는 상기 화소전극의 전위로부터 상기 트랜지스터의 임계값 전압을 뺀 값보다 낮은, 반도체 장치.

**청구항 76**

제 67 항에 있어서,

상기 제 1 스위치 내지 제 4 스위치는 트랜지스터인, 반도체 장치.

**청구항 77**

청구항 67에 따른 반도체 장치를 포함하는, 표시장치.

**청구항 78**

청구항 77에 따른 상기 표시장치를 표시부에 가지는, 전자기기.

**청구항 79**

반도체 장치에 있어서,

트랜지스터와;

제 1 유지용량과;

부하와;

상기 트랜지스터의 게이트-소스간 전압을 유지하는 제 2 유지용량과;

상기 제 1 유지용량의 전극과 제 2 배선의 사이에 전기적으로 접속되는 제 1 스위치와;

상기 트랜지스터의 제 1 전극과 제 1 배선의 사이에 전기적으로 접속되는 제 2 스위치를 포함하고,

회로는:

상기 제 1 스위치가 온되고, 상기 제 2 스위치가 오프될 때, 제 1 전압은 상기 제 1 유지용량에서 유지되고, 제 2 전압은 상기 제 2 유지용량에서 유지되고,

상기 제 1 스위치가 온되고, 상기 제 2 스위치가 온될 때, 상기 제 2 유지용량의 전압이 상기 제 2 전압으로부터 상기 트랜지스터의 임계값 전압까지 변화하도록 상기 제 2 유지용량은 방전되고,

상기 제 1 스위치가 오프되고, 상기 제 2 스위치가 온될 때, 비디오 신호에 따른 전위는 상기 제 2 배선으로부터 상기 제 1 유지용량에 입력되고,

상기 제 1 스위치가 온되고, 상기 제 2 스위치가 오프될 때, 상기 트랜지스터에 설정된 전류는 상기 제 1 배선으로부터 상기 부하에 공급되는, 반도체 장치.

**청구항 80**

제 79 항에 있어서,

상기 트랜지스터는 박막 트랜지스터인, 반도체 장치.

#### 청구항 81

제 79 항에 있어서,

상기 트랜지스터는 N채널형 트랜지스터인, 반도체 장치.

#### 청구항 82

제 79 항에 있어서,

상기 트랜지스터의 반도체 층은 비정질 반도체 막으로 되는, 반도체 장치.

#### 청구항 83

제 79 항에 있어서,

상기 트랜지스터의 반도체 층은 비정질 규소로 되는, 반도체 장치.

#### 청구항 84

제 79 항에 있어서,

상기 트랜지스터의 반도체 층은 결정성 반도체 막으로 되는, 반도체 장치.

#### 청구항 85

제 79 항에 있어서,

상기 트랜지스터는 P채널형 트랜지스터인, 반도체 장치.

#### 청구항 86

청구항 79에 따른 반도체 장치를 포함하는, 표시장치.

#### 청구항 87

청구항 86에 따른 상기 표시장치를 표시부에 가지는, 전자기기.

#### 청구항 88

반도체 장치의 구동방법에 있어서, 상기 반도체 장치는,

트랜지스터와;

상기 제 1 유지용량의 제 2 전극은 상기 트랜지스터의 게이트 전극에 전기적으로 접속되는 제 1 유지용량과;

상기 트랜지스터의 소스 전극에 전기적으로 접속되는 부하와;

상기 트랜지스터의 게이트-소스간 전압을 유지하는 제 2 유지용량과;

상기 제 1 유지용량의 제 1 전극과 제 2 배선의 사이에 전기적으로 접속되는 제 1 스위치와;

상기 트랜지스터의 드레인 전극과 제 1 배선의 사이에 전기적으로 접속되는 제 2 스위치를 포함하는 반도체 장치의 구동방법에 있어서,

제 1 기간에 있어서 제 1 유지용량에서 제 1 전압을 유지하고, 제 2 유지용량에서 제 2 전압을 유지하는 공정과;

상기 제 1 기간 후의 제 2 기간에 있어서 상기 제 2 유지용량의 전압이 상기 제 2 전압으로부터 상기 트랜지스터의 임계값 전압에 상당하는 제 3 전압으로 변화하도록 상기 제 2 유지용량을 방전하는 공정과;

상기 제 2 기간 후의 제 3 기간에 있어서 상기 비디오 신호에 따른 제 4 전압과 상기 트랜지스터의 제 3 전압이 상기 트랜지스터의 게이트 전압에 인가되도록 비디오 신호를 상기 제 2 배선에 공급하는 공정과;

상기 제 3 기간 후의 제 4 기간에 있어서 적어도 상기 제 4 전압에 따른 상기 트랜지스터를 통하여 상기 부하에 전류를 공급하는 공정을 포함한, 반도체 장치의 구동방법.

#### 청구항 89

제 88 항에 있어서,

상기 트랜지스터는 박막 트랜지스터인, 반도체 장치의 구동방법.

#### 청구항 90

제 88 항에 있어서,

상기 트랜지스터는 N채널형 트랜지스터인, 반도체 장치의 구동방법.

#### 청구항 91

제 88 항에 있어서,

상기 트랜지스터의 반도체 층은 비정질 반도체 막으로 되는, 반도체 장치의 구동방법.

#### 청구항 92

제 88 항에 있어서,

상기 트랜지스터의 반도체 층은 비정질 규소로 되는, 반도체 장치의 구동방법.

#### 청구항 93

제 88 항에 있어서,

상기 트랜지스터의 반도체 층은 결정성 반도체 막으로 되는, 반도체 장치의 구동방법.

#### 청구항 94

제 88 항에 있어서,

상기 트랜지스터는 P채널형 트랜지스터인, 반도체 장치의 구동방법.

### 명세서

#### 발명의 상세한 설명

##### 기술분야

&lt;1&gt;

본 발명은 부하에 공급하는 전류를 트랜지스터로 제어하는 기능을 설치한 반도체 장치에 관한 것이며, 신호에 의해 휘도가 변화하는 표시소자로 형성된 화소나, 그 화소를 구동시키는 신호선 구동회로나 주사선 구동회로를 포함하는 표시장치에 관한 것이다. 또한, 그 구동방법에 관한 것이다. 또한, 그 표시장치를 표시부에 가지는 전자기기에 관한 것이다.

##### 배경기술

&lt;2&gt;

근년, 화소를 일렉트로루미네스نس(EL: Electro Luminescence) 등의 발광소자를 사용한 자발광형 표시장치, 소위 발광장치가 주목을 받고 있다. 이러한 자발광형 표시장치에 사용되는 발광소자로서는, 유기발광 다이오드(OLED(Organic Light Emitting Diode))나, EL소자가 주목을 받고 있으며, EL 디스플레이 등에 사용되어 왔다. 이들의 발광소자는 스스로 발광하므로, 액정 장치에 비해 화소의 시인성이 높고, 백 라이트가 필요하지 않다. 또한, 응답 속도가 빠른 등의 이점이 있다. 또한, 발광소자의 휘도는, 그 발광소자에 흐르는 전류값에 의해 제어되는 것이 많다.

&lt;3&gt;

또한, 발광소자의 발광을 제어하는 트랜지스터가 각 화소에 설치된 액티브 매트릭스형 표시장치의 개발

이 진행되어 있다. 액티브 매트릭스형 표시장치는, 패시브 매트릭스형 표시장치에서는 달성이 곤란한 고정세한 표시나 대화면의 표시를 가능하게 할 뿐만 아니라, 패시브 매트릭스형 표시장치보다 낮은 소비전력으로 동작하므로 실용화가 기대되고 있다.

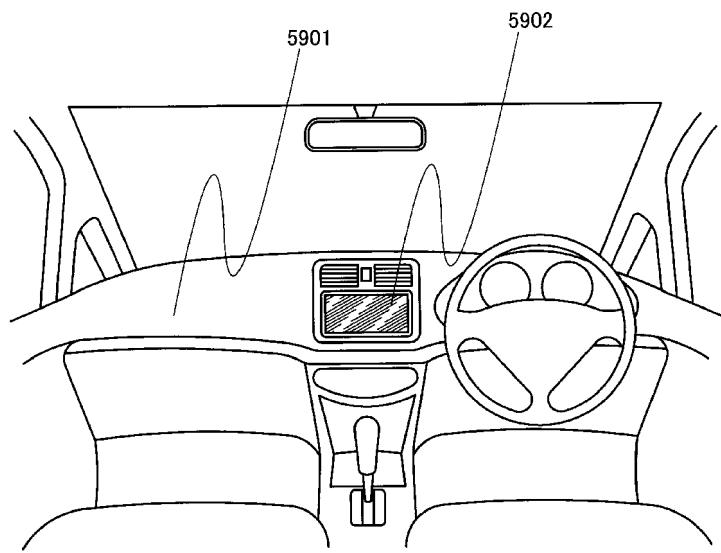

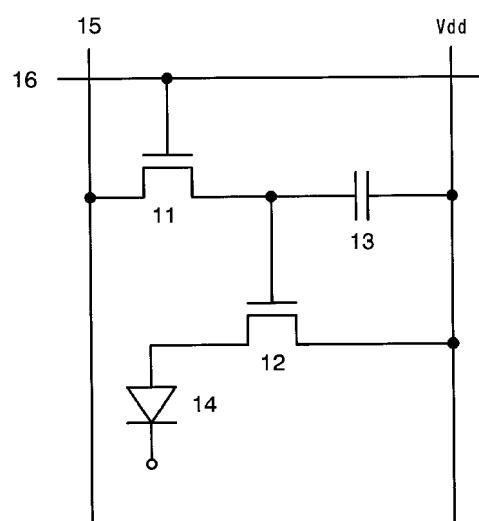

<4> 종래의 액티브 매트릭스형 표시장치의 화소구성을 도 62에 도시한다.(특허문헌 1). 도 62에 도시한 화소는, 박막 트랜지스터(Thin Film Transistor: TFT)(11), TFT(12), 용량소자(13), 발광소자(14)를 가지고, 신호선(15) 및 주사선(16)에 접속된다. 또한, TFT(12)의 소스 전극 혹은 드레인 전극의 어느 한쪽 및 용량소자(13)의 한쪽 전극에는 전원전위 Vdd가 공급되고, 발광소자(14)의 대향전극에는 그라운드 전위가 공급된다.

<5> 이때, 발광소자(14)에 공급하는 전류값을 제어하는 TFT(12), 즉, 구동용 TFT의 반도체층에 아모퍼스 실리콘을 사용한 경우, 열화 등에 의해 임계값 전압(Vth)에 변동이 생긴다. 이 경우, 다른 화소에 신호선(15)으로부터 동일의 전위를 인가했는데도 불구하고, 발광소자(14)에 흐르는 전류는 화소마다 다르고, 표시되는 휘도가 화소에 따라 불균일해진다. 이때, 구동용 TFT의 반도체층에 폴리실리콘을 사용한 경우에 있어서도, 트랜지스터의 특성이 열화하거나, 변동한다.

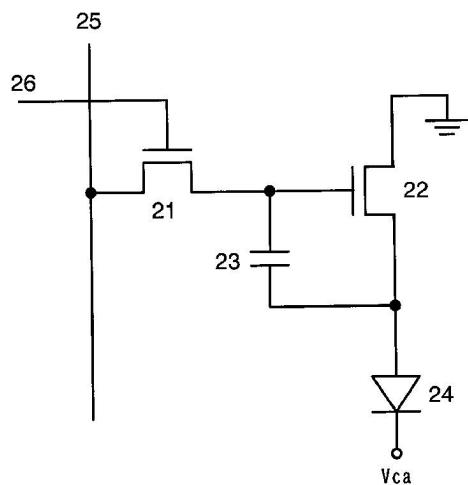

<6> 이 문제를 개선하기 위해, 특허문헌 2에 있어서, 도 63의 화소를 사용한 동작 방법이 제안된다. 도 63에 나타낸 화소는, 트랜지스터(21), 발광소자(24)에 공급하는 전류값을 제어하는 구동용 트랜지스터(22), 용량소자(23), 발광소자(24)를 가지고, 화소는 신호선(25), 주사선(26)에 접속된다. 이때, 구동용 트랜지스터(22)는 NMOS트랜지스터이며, 구동용 트랜지스터(22)의 소스 전극 혹은 드레인 전극의 어느 한쪽에는 그라운드 전위가 공급되고, 발광소자(24)의 대향전극에는 Vca가 공급된다.

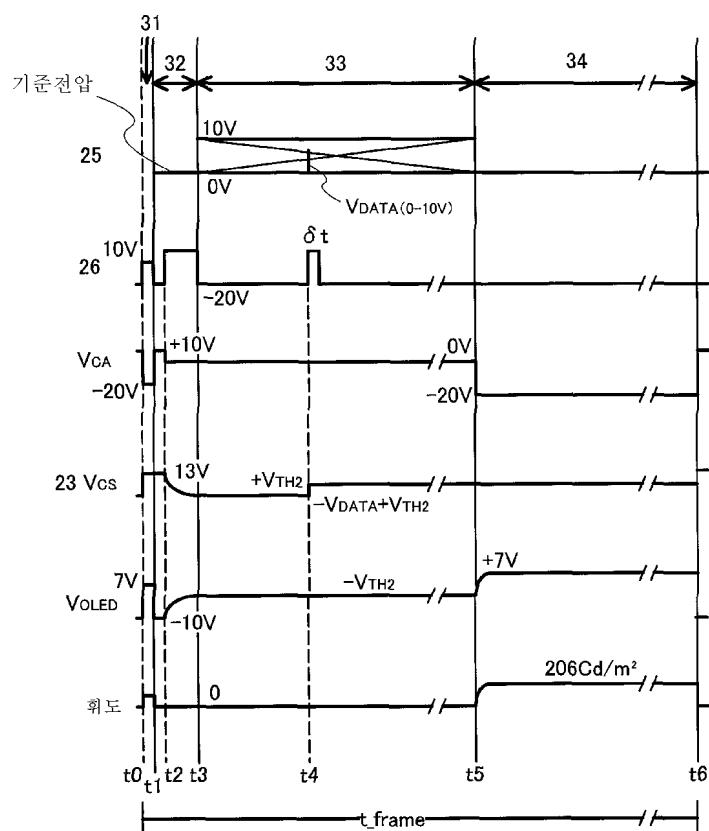

<7> 이 화소의 동작에 있어서의 타이밍 차트를 도 64에 도시한다. 도 64에 있어서, 1프레임 기간은, 초기화 기간(31), 임계값 전압(Vth) 기록 기간(32), 데이터 기록 기간(33) 및 발광 기간(34)으로 분할된다. 이때, 1프레임 기간은 1화면의 화상을 표시하는 기간에 해당하고, 초기화 기간, 임계값 전압(Vth) 기록 기간 및 데이터 기록 기간을 통틀어 어드레스 기간이라고 부른다.

<8> 우선, 임계값 전압 기록 기간(32)에 있어서, 구동용 트랜지스터(22)의 임계값 전압이 용량소자(23)에 기록된다. 그 후, 데이터 기록 기간(33)에, 화소의 휘도를 나타내는 데이터 전압(Vdata)이 용량소자(23)에 기록되고, Vdata + Vth가 용량소자(23)에 측정된다. 그리고, 발광 기간(34)에 구동용 트랜지스터(22)는 온 상태가 되어, Vca를 변화시킴으로써 데이터 전압에 의해 지정된 휘도로 발광소자(24)가 발광한다. 이러한 동작에 의해, 구동용 트랜지스터(22)의 임계값 전압의 변동에 의한 휘도의 편차를 저감한다.

<9> 특허문헌 3에 있어서도, 구동용 TFT의 임계값 전압에 데이터 전위를 가한 전압이 게이트-소스간 전압이 되고, TFT의 임계값 전압이 변동한 경우에도 흐르는 전류는 변화하지 않는 것이 공개되어 있다.

<10> 상술한 바와 같이, 표시장치에서는, 구동용 TFT의 임계값 전압의 편차에 기인하는 전류값의 편차를 억제하는 기술이 요구되고 있다.

<11> [특허문헌 1] 특개평8-234683호 공보

<12> [특허문헌 2] 특개2004-295131호 공보

<13> [특허문헌 3] 특개2004-280059호 공보

## 발명의 내용

### 해결 하고자하는 과제

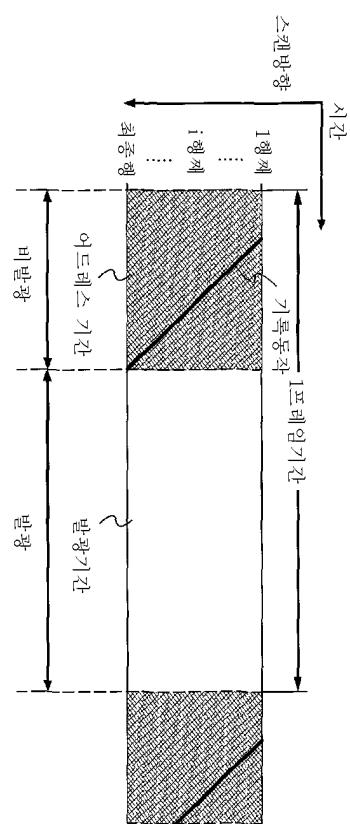

<14> 특허문헌 2 및 특허문헌 3에 기재되는 각각의 동작 방법에서는, Vca의 전위를 1프레임 기간당 수차례 변화시킴으로써 상술한 초기화, 임계값 전압의 기록, 발광을 실행한다. 특허문헌 2 및 특허문헌 3에 기재되는 화소에 있어서, Vca가 공급되어 있는 발광소자의 한쪽 전극, 즉, 그 대향전극은 화소영역 전체에 형성되므로, 초기화 및 임계값 전압의 기록 이외에 데이터의 기록 동작을 행하고 있는 화소가 한 개라도 있으면, 발광소자를 발광시킬 수 없다. 따라서, 도 65에 도시하는 바와 같이, 1프레임 기간에 있어서의 발광 기간의 비율(즉, 뉴터비)이 낮아진다.

<15> 뉴터비가 낮으면, 발광소자나 구동용 트랜지스터에 공급하는 전류값을 크게 해야 하므로, 발광소자에 걸리는 전압이 높아지고 소비전력이 크게 된다. 또한, 발광소자나 구동용 트랜지스터가 쉽게 열화하므로, 화면에 번인(Burn-in)이 생기거나, 열화전과 동등한 휘도를 얻기 위해 더욱 큰 전력을 필요로 하게 된다.

<16> 또한 대향전극은 전체 화소에 접속되어 있으므로, 발광소자는 용량이 큰 소자로서 기능한다. 따라서, 대향전극의 전위를 변화시키기 위해서는, 높은 소비 전력이 요구된다.

<17> 상기 문제를 감안하여, 본 발명은, 소비전력이 낮고, 밝은 표시장치를 제공하는 것을 과제로 한다. 또한, 데이터 전위에 의해 지정된 휘도로부터의 차이가 적은 화소 구성, 반도체 장치, 및 표시장치를 얻는 것을 과제로 한다. 또한, 발광소자를 가지는 표시장치만을 대상으로 하는 것이 아니라, 본 발명은 트랜지스터의 임계값 전압의 편차에 기인하는 전류값의 편차를 억제하는 것을 과제로 한다.

### 과제 해결수단

<18> 본 발명의 일형태는, 부하에 공급하는 전류값을 제어하는 트랜지스터와, 제 1 유지용량과, 제 2 유지용량과, 제 1 스위치 내지 제 4 스위치를 포함하는 화소를 가지고, 상기 제 2 유지용량에 상기 트랜지스터의 임계값 전압을 유지시킨 후, 비디오 신호에 따른 전위를 상기 화소에 입력한다. 이렇게 해서, 상기 제 2 유지용량에, 상기 임계값 전압에 상기 비디오 신호에 따른 전위 중 상기 제 1 유지용량과, 용량분할된 전위가 가산된 전압을 유지시킴으로써, 트랜지스터의 임계값 전압의 편차에 기인한 전류값의 편차를 억제한다. 따라서, 발광소자를 비롯한 부하에 원하는 전류를 공급할 수 있다. 또한, 비디오 신호에 따라, 지정된 휘도로부터의 차이가 적은 표시장치를 제공할 수 있다.

<19> 본 발명의 일형태는, 트랜지스터와, 유지용량과, 제 1 스위치와, 제 2 스위치와, 제 3 스위치와, 제 4 스위치를 가지고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 한쪽은 화소전극과 전기적으로 접속되고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 다른 쪽은 상기 제 2 스위치를 통하여 제 1 배선과 전기적으로 접속되고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 다른 쪽은 상기 제 3 스위치를 통하여 상기 트랜지스터의 게이트 전극과 전기적으로 접속되고, 상기 트랜지스터의 게이트 전극은, 상기 유지용량 및 상기 제 4 스위치를 통하여 제 2 배선에 전기적으로 접속하여, 상기 트랜지스터의 게이트 전극은, 상기 유지용량 및 상기 제 1 스위치를 통하여 제 3 배선에 전기적으로 접속되는 반도체 장치이다.

<20> 본 발명의 일형태는, 트랜지스터와, 제 1 유지용량과, 제 2 유지용량과, 제 1 스위치와, 제 2 스위치와, 제 3 스위치와, 제 4 스위치를 가지고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 한쪽은 화소전극과 전기적으로 접속되고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 한쪽은 상기 제 2 유지용량을 통하여 상기 트랜지스터의 게이트 전극과 전기적으로 접속되고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 다른 쪽은 상기 제 2 스위치를 통하여, 제 1 배선과 전기적으로 접속되고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 다른 쪽은 상기 제 3 스위치를 통하여 상기 트랜지스터의 게이트 전극과 전기적으로 접속되고, 상기 트랜지스터의 게이트 전극은, 상기 제 1 유지용량 및 상기 제 4 스위치를 통하여 제 2 배선과 전기적으로 접속되고, 상기 트랜지스터의 게이트 전극은, 상기 제 1 유지용량 및 상기 제 1 스위치를 통하여 제 3 배선과 전기적으로 접속되는 반도체 장치이다.

<21> 본 발명의 일형태는, 트랜지스터와, 제 1 유지용량과, 제 2 유지용량과, 제 1 스위치와, 제 2 스위치와, 제 3 스위치와, 제 4 스위치와, 제 5 스위치를 가지고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 한쪽은 화소전극과 전기적으로 접속되고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 한쪽은 화소전극과 전기적으로 접속되고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 다른 쪽은 상기 제 2 유지용량을 통하여 상기 트랜지스터의 게이트 전극 및 드레인 전극과 전기적으로 접속되고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 한쪽은 제 5 스위치를 통하여 제 4 배선과 전기적으로 접속되고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 다른 쪽은 상기 제 2 스위치를 통하여 제 1 배선과 전기적으로 접속되고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 다른 쪽은 상기 제 3 스위치를 통하여 상기 트랜지스터의 게이트 전극과 전기적으로 접속되고, 상기 트랜지스터의 게이트 전극은, 상기 제 1 유지용량 및 상기 제 4 스위치를 통하여 제 2 배선에 전기적으로 접속되고, 상기 트랜지스터의 게이트 전극은, 상기 제 1 유지용량 및 상기 제 1 스위치를 통하여 제 3 배선에 전기적으로 접속되는 반도체 장치이다.

<22> 상기 구성에 있어서, 상기 제 2 배선은 제 1 스위치를 제어하는 배선과 동일한 것을 특징으로 하여도 좋다. 또한, 상기 제 2 배선은 전행(前行) 또는 차행(次行)의 제 1 스위치 내지 제 4 스위치를 제어하는 주사선의 어느 것이라도 좋다.

<23> 본 발명의 일형태는, 트랜지스터와, 제 1 유지용량과, 제 2 유지용량과, 제 1 스위치와, 제 2 스위치와, 제 3 스위치와, 제 4 스위치를 가지고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 한쪽은 화소전극과 전기적으로 접속되고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 한쪽은 상기 제 2 유지용량을 통

하여 상기 트랜지스터의 게이트 전극과 전기적으로 접속되고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 다른 쪽은 상기 제 2 스위치를 통하여 제 1 배선과 전기적으로 접속되고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 다른 쪽은 상기 제 3 스위치를 통하여 상기 트랜지스터의 게이트 전극과 전기적으로 접속되고, 상기 트랜지스터의 게이트 전극은, 상기 제 1 유지용량 및 상기 제 4 스위치를 통하여 상기 제 1 배선과 전기적으로 접속되고, 상기 트랜지스터의 게이트 전극은, 상기 제 1 유지용량 및 상기 제 1 스위치를 통하여 제 3 배선과 전기적으로 접속되는 반도체 장치이다.

<24> 본 발명의 일형태는, 트랜지스터와, 제 1 유지용량과, 제 2 유지용량과, 제 1 스위치와, 제 2 스위치와, 제 3 스위치와, 정류소자를 가지고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 한쪽은 화소전극과 전기적으로 접속되고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 한쪽은 상기 제 2 유지용량을 통하여 상기 트랜지스터의 게이트 전극과 전기적으로 접속되고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 다른 쪽은 상기 제 2 스위치를 통하여 제 1 배선과 전기적으로 접속되고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 다른 쪽은 상기 제 3 스위치를 통하여 상기 트랜지스터의 게이트 전극과 전기적으로 접속되고, 상기 트랜지스터의 게이트 전극은, 상기 제 1 유지용량 및 상기 정류소자를 통하여 제 2 배선에 전기적으로 접속되고, 상기 트랜지스터의 게이트 전극은, 상기 제 1 유지용량 및 상기 제 1 스위치를 통하여 제 3 배선에 전기적으로 접속되는 반도체 장치이다.

<25> 본 발명의 일형태는, 트랜지스터와, 제 1 유지용량과, 제 2 유지용량과, 제 1 스위치와, 제 2 스위치와, 제 3 스위치와, 제 4 스위치를 가지고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 한쪽은 화소전극과 전기적으로 접속되고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 한쪽은 상기 제 2 유지용량을 통하여 상기 트랜지스터의 게이트 전극과 전기적으로 접속되고, 상기 트랜지스터의 소스 전극 및 드레인 전극의 다른 쪽은 상기 제 2 스위치를 통하여 제 1 배선과 전기적으로 접속되고, 상기 트랜지스터의 게이트 전극 및 드레인 전극의 다른 쪽은 상기 제 3 스위치를 통하여 상기 트랜지스터의 게이트 전극과 전기적으로 접속되고, 상기 트랜지스터의 게이트 전극은, 상기 제 1 유지용량 및 상기 제 1 스위치를 통하여 제 3 배선에 전기적으로 접속되고, 상기 제 4 스위치는 상기 제 1 유지용량과 병렬으로 전기적으로 접속되고, 또한, 상기 제 1 스위치를 통하여 상기 제 3 배선에 전기적으로 접속되는 반도체 장치이다.

<26> 상기 트랜지스터는, N채널형 트랜지스터이라도 좋다. 또한, 상기 트랜지스터의 반도체 층은, 비정질 반도체 막으로 되는 것을 특징으로 하여도 좋다. 또한, 상기 트랜지스터의 반도체 층은, 아모퍼스 실리콘으로 되는 것을 특징으로 하여도 좋다.

<27> 또한, 상기 트랜지스터의 반도체 층은, 결정성 반도체 막으로 되는 것을 특징으로 하여도 좋다.

<28> 상기 발명에 있어서, 상기 제 1 배선의 전위는, 상기 화소전극의 전위에 상기 트랜지스터의 임계값 전압을 가산한 값보다 높은 것을 특징으로 하여도 좋다.

<29> 또한, 상기 트랜지스터는, P채널형 트랜지스터이어도 좋다. 그 경우, 상기 발명에 있어서, 상기 제 1 배선의 전위는, 상기 화소전극의 전위에서 상기 트랜지스터의 임계값 전압을 뺀 값보다 낮은 것을 특징으로 하여도 좋다.

<30> 본 발명의 일형태는, 제 1 유지용량과, 소스 전극 및 드레인 전극의 한쪽이 부하에 전기적으로 접속되고, 소스 전극 및 드레인 전극의 다른 쪽이 제 1 배선에 전기적으로 접속되고, 게이트 전극이 상기 제 1 유지용량을 통하여 제 2 배선과 전기적으로 접속되는 트랜지스터와, 상기 트랜지스터의 게이트-소스간 전압을 유지하는 제 2 유지용량과, 상기 제 1 유지용량에 제 1 전압을, 상기 제 2 유지용량에 제 2 전압을 유지시키는 수단과, 상기 제 2 유지용량의 제 2 전압을 상기 트랜지스터의 임계값 전압까지 방전시키는 수단과, 상기 제 2 배선으로부터 비디오 신호에 따른 전위를 상기 제 1 유지용량에 입력함으로써 상기 트랜지스터에 설정된 전류를 상기 부하에 공급하는 수단을 가지는 것을 특징으로 하는 반도체 장치이다.

<31> 상기 트랜지스터는, N채널형 트랜지스터이라도 좋다. 또한, 상기 트랜지스터의 반도체 층은, 비정질 반도체 막으로 되는 것을 특징으로 하여도 좋다. 또한, 상기 트랜지스터의 반도체 층은, 아모퍼스 실리콘으로 되는 것을 특징으로 하여도 좋다.

<32> 또한, 상기 트랜지스터의 반도체 층은, 결정성 반도체 막으로 되는 것을 특징으로 하여도 좋다.

<33> 또한, 상기 트랜지스터는, P채널형 트랜지스터이라도 좋다.

<34> 또한, 본 발명의 일형태는, 상술한 반도체 장치를 가지는 표시장치이다. 또한, 상기 표시장치를 가지

는 전자기기이다.

<35> 또한, 명세서에 나타내는 스위치는, 여러가지 형태의 스위치를 사용할 수 있다. 예로서는, 전기적 스위치나, 기계적인 스위치 등이 있다. 즉, 전류의 흐름을 제어할 수 있는 것이면 좋고, 특정의 것으로 한정되지 않는다. 예를 들면, 스위치로서, 트랜지스터(예를 들면, 바이폴라 트랜지스터, MOS 트랜지스터 등), 다이오드(예를 들면, PN 다이오드, PIN 다이오드, 쇼트키 다이오드, MIM(Metal Insulator Metal) 다이오드, MIS(Metal Insulator Semiconductor) 다이오드, 다이오드 접속의 트랜지스터 등), 사이리스터(thyristor) 등을 사용할 수 있다. 또한, 이들을 조합한 논리회로를 스위치로서 사용할 수도 있다.

<36> 스위치로서 트랜지스터를 사용하는 경우, 그 트랜지스터는, 단순한 스위치로서 동작하기 때문에, 트랜지스터의 극성(도전형)은 특히 한정되지 않는다. 다만, 오프 전류가 적은 쪽의 극성의 트랜지스터를 사용하는 것이 바람직하다. 오프 전류가 적은 트랜지스터로서는, LDD영역을 가지는 트랜지스터나 멀티 게이트 구조를 가지는 트랜지스터 등이 있다. 또한, 스위치로서 동작시키는 트랜지스터의 소스 전극의 전위가, 저전위측 전원(Vss, GND, OV)에 가까운 상태로 동작하는 경우는 N채널형을, 반대로, 소스 전극의 전위가 고전위측 전원(Vdd 등)에 가까운 상태로 동작하는 경우는, P채널형의 트랜지스터를 사용하는 것이 바람직하다. 이렇게 동작시킴으로써, 게이트-소스간 전압의 절대값을 크게 할 수 있기 때문에, 스위치로서의 동작이 보다 쉽게 된다. 또한, 소스 폴로워(source follower)동작을 하는 것이 적기 때문에, 출력전압의 크기가 작게 되는 것을 방지할 수 있다.

<37> 또한, N채널형 트랜지스터와 P채널형 트랜지스터의 양쪽 모두를 사용하여, CMOS형의 스위치를 스위치로서 사용하여도 좋다. CMOS형의 스위치로 하면, 여러가지 입력전압에 대해서 출력전압을 제어하기 쉽기 때문에, 적절한 동작을 할 수 있다. 또한, 스위치를 온/오프 시키기 위한 신호의 전압진폭값을 작게 할 수 있기 때문에, 소비전력을 저감할 수도 있다.

<38> 또한, 스위치로서 트랜지스터를 사용하는 경우, 소스 전극 및 드레인 전극의 한쪽이 스위치의 입력단자로서, 소스 전극 및 드레인 전극의 다른 쪽이 출력단자로서, 게이트 전극이 스위치의 도통을 제어하는 단자로서 기능한다. 한편, 스위치로서 다이오드를 사용하는 경우, 스위치는, 도통을 제어하는 단자를 가지지 않는 경우가 있다. 따라서, 스위치로서 트랜지스터보다 다이오드를 사용하면, 단자를 제어하기 위한 배선이 불필요하기 때문에, 배선수를 적게 할 수 있다.

<39> 또한, 본 발명에 있어서, 접속된다는 말은, 전기적으로 접속되는 것과 동일한 의미이다. 따라서, 본 발명이 개시하는 구성에 있어서, 소정의 접속관계, 예를 들면, 도면 또는 문장에 나타내진 접속관계, 또는 그 사이에 전기적인 접속을 할 수 있는 다른 소자(예를 들면, 스위치나 트랜지스터나 용량소자나 인덕터나 저항소자나 다이오드 등)가 배치되어도 좋다. 물론, 사이에 다른 소자를 통하지 않고서 배치되어도 좋고, 전기적으로 접속된다는 말은, 직접적으로 접속되는 경우를 포함하는 것으로 한다.

<40> 또한, 부하는 일렉트로 루미네센스(EL) 소자로 대표되는 발광소자에 한정되지 않고, 전류가 흐르는 것에 의해 밝기, 색조, 편광 등이 변화되는 표시 매체를 적용할 수 있다. 원하는 전류를 부하에 공급할 수 있으면 좋기 때문에, 부하에는, 예를 들면, 전자방출소자, 액정소자, 전자잉크, 전기영동(泳動)소자, 그레이팅 라이트밸브(GLV), 플라즈마 디스플레이(PDP), 디지털 마이크로미러 디바이스(DMD) 등 자기적 작용에 의해 콘트라스트가 변화되는 표시 매체 등도 적용할 수 있다. 또한, 전자방출소자에 카본나노튜브를 이용할 수도 있다. 또한, EL소자를 사용한 표시장치로서는, EL디스플레이, 전자방출소자를 사용한 표시장치로서는 필드 이미션 디스플레이(FED)나 SED방식 평면형 디스플레이(SED: Surface-conduction Electron-emitter Display) 등을 들 수 있다. 또한, 액정소자를 사용한 표시장치로서는 액정 디스플레이, 투과형 액정 디스플레이, 반투과형 액정 디스플레이나, 반사형 액정 디스플레이가, 전자 잉크를 사용한 표시장치로서는 전자 페이퍼가 있다.

<41> 또한, 트랜지스터는, 게이트 전극과, 드레인 영역과, 소스 영역을 포함하는 적어도 세 개의 단자를 가지는 소자이며, 드레인 영역과 소스 영역 사이에 채널 형성 영역을 가진다. 여기서, 소스 영역과 드레인 영역은, 트랜지스터의 구조나 동작조건 등에 따라 변화하므로, 소스 영역 또는 드레인 영역의 범위를 정확히 한정하기 어렵다. 따라서, 트랜지스터의 접속 관계를 설명할 때에는, 드레인 영역과 소스 영역의 두 단자에 대해서는, 이들의 영역에 접속된 전극 중 한쪽은 제 1 전극, 다른 쪽은 제 2 전극으로 표기하여 설명한다.

<42> 또한, 트랜지스터는, 베이스와 에미터와 컬렉터를 포함하는 적어도 세 개의 단자를 가지는 소자라도 좋고, 에미터와 컬렉터의 어느 한쪽이 제 1 전극, 다른 쪽이 제 2 전극에 상당한다.

<43> 본 발명에 있어서, 트랜지스터는, 여러가지 형태의 트랜지스터를 적용시킬 수 있고, 종류는 특별히 한

정되지 않는다. 예를 들면, 비정질 실리콘, 다결정 실리콘, 미결정(micro crystal, 세미 아모퍼스라고도 한다)실리콘 등으로 대표되는 비단결정 반도체막을 가지는 박막 트랜지스터(TFT) 등을 사용할 수 있다. TFT를 사용하는 경우, 여러가지 메리트가 있다. 예를 들면, 단결정 실리콘의 경우보다 낮은 온도로 제조할 수 있기 때문에, 제조비용의 삭감이나, 제조 장치의 대형화를 도모할 수 있다. 제조장치의 대형화가 가능하게 되는 것으로써, 대형 기판 위에 제조할 수 있고, 동시에 다수의 표시장치를 제조할 수 있다. 따라서, 보다 저비용으로 제조할 수 있다. 또한, 제조온도가 낮기 때문에, 내열성이 약한 기판을 사용할 수도 있고, 예를 들면, 유리 기판 등의 투광성을 가지는 기판 위에 트랜지스터를 제조할 수 있다.

<44> 또한, 다결정 실리콘을 제조할 때, 촉매(니켈 등)를 사용함으로써, 결정성을 보다 향상시켜, 전기특성이 좋은 트랜지스터를 제조할 수 있다. 그 결과, 게이트 드라이버회로(주사선 구동회로)나 소스 드라이버회로(신호선 구동회로), 신호처리회로(신호생성회로, 감마보정회로, DA변환회로 등)를 기판 위에 일체 형성할 수 있다. 또한, 반드시 촉매를 사용할 필요는 없다.

<45> 또한, 미결정 실리콘을 사용한 경우에도, 게이트 드라이버 회로(주사선 구동회로)나 소스 드라이버회로의 일부(아날로그 스위치 등)를 기판 위에 일체 형성할 수 있다.

<46> 또한, 반도체 기판이나 SOI 기판 등을 사용하여 트랜지스터를 형성할 수 있다. 그 경우, MOS형 트랜지스터, 접합형 트랜지스터, 바이폴라 트랜지스터 등을 트랜지스터로서 사용할 수 있다. 이들에 의하여, 특성, 사이즈나 형상 등의 편차가 적고, 전류공급능력이 높은 트랜지스터를 제조할 수 있다. 따라서, 회로의 저소비전력화, 회로의 고집적화 등을 도모할 수 있다.

<47> 또한, ZnO, a-InGaZnO, SiGe, GaAs, IZO, ITO, SnO 등의 화합물 반도체 또는 산화물 반도체를 가지는 트랜지스터나, 덧붙여 이들의 화합물 반도체 또는 산화물 반도체를 박막화한 박막 트랜지스터 등을 사용할 수 있다. 이들에 의하여, 제조온도를 낮게 할 수 있고, 예를 들면, 실온에서 트랜지스터를 제조할 수 있다. 그 결과, 내열성이 낮은 기판, 예를 들면, 플라스틱 기판이나 필름 기판에 직접 트랜지스터를 형성할 수 있다. 또한, 이들의 화합물 반도체 또는 산화물 반도체를, 트랜지스터의 채널부분에 사용하는 것뿐만 아니라, 그 이외의 용도로 사용할 수도 있다. 예를 들면, 이들의 화합물 반도체 또는 산화물 반도체를 저항소자, 화소전극, 투광성을 가지는 전극으로서 사용할 수 있다. 또한, 이들을 트랜지스터와 동시에 성막 또는 형성할 수 있기 때문에, 비용을 저감할 수 있다.

<48> 또한, 잉크젯법이나 인쇄법을 사용하여 형성한 트랜지스터 등도 사용할 수 있다. 이것에 의하여, 실온에서 제조, 저진공도로 제조, 또는 대형 기판 위에 제조할 수 있다. 또한, 마스크(레티클)를 사용하지 않고 제조할 수 있기 때문에, 트랜지스터의 레이아웃을 용이하게 변경할 수 있다. 또한, 레지스트를 사용할 필요가 없기 때문에, 공정수가 삭감되고, 제조비용을 저감할 수 있다. 또한, 필요한 부분만 성막하기 위하여, 전면에 성막한 후에 에칭하는 경우에 비하여 재료를 낭비하지 않고, 저비용으로 제작할 수 있다.

<49> 또한, 유기 반도체나 카본 나노튜브를 가지는 트랜지스터 등을 사용할 수 있다. 이러한 트랜지스터는, 플렉시블 기판에도 형성할 수 있기 때문에, 충격내성이 뛰어나다. 이것으로 한정되지 않고, 그 이외에도 여러가지 트랜지스터를 사용할 수 있다.

<50> 또한, 트랜지스터가 형성되는 기판의 종류에 있어서도 여러가지 기판을 사용할 수 있고, 특별히 한정되지 않는다. 기판으로서는, 예를 들면, 단결정 기판, SOI기판, 유리 기판, 석영 기판, 플라스틱 기판, 종이기판, 셀로판 기판, 석재기판, 목재 기판, 직물 기판(천연섬유(비단, 면, 삼), 합성섬유(나일론, 폴리우레탄, 폴리에스테르) 또는, 재생섬유(아세테이트, 큐프라, 레이온, 재생 폴리에스테르) 등을 포함한다), 피혁 기판, 고무 기판, 스테인리스 스틸 기판, 스테인리스 스틸 포일을 가지는 기판 등을 사용할 수 있다. 또한, 어느 기판에 트랜지스터를 형성하고, 그 후, 다른 기판에 트랜지스터를 전치하고, 다른 기판에 트랜지스터를 배치하여도 좋다. 트랜지스터가 전치되는 기판으로서는, 단결정 기판, SOI기판, 유리 기판, 석영 기판, 플라스틱 기판, 종이기판, 셀로판 기판, 석재기판, 목재 기판, 직물 기판(천연섬유(명종, 면, 삼), 합성섬유(나일론, 폴리우레탄, 폴리에스테르) 또는, 재생섬유(아세테이트, 큐프라, 레이온, 재생 폴리에스테르) 등을 포함한다), 피혁 기판, 고무 기판, 스테인리스 스틸 기판, 스테인리스 스틸 포일을 가지는 기판 등을 사용할 수 있다. 이들의 기판을 사용함으로써, 보다 특성이 높은 트랜지스터의 형성, 내열성의 향상이나 경량화를 도모할 수 있다.

<51> 또한, 트랜지스터의 구성은, 여러가지 형태를 선택할 수 있고, 특정의 구성에 한정되지 않는다. 예를 들면, 게이트 전극이 2개 이상인 멀티 게이트 구조를 이용하여도 좋다. 멀티 게이트 구조로 하면, 채널영역이 직렬로 접속되기 때문에, 복수의 트랜지스터가 직렬로 접속된 구성으로 된다. 이러한 멀티 게이트 구조에 의하

여, 오프 전류의 저감, 및 트랜지스터의 내압향상에 의하여, 트랜지스터의 신뢰성을 보다 좋게 할 수 있다. 또한, 멀티 게이트 구조에 의하여, 포화영역에서 동작할 때에 드레인-소스간 전압이 변화해도, 드레인-소스간 전류가 거의 변화하지 않고, 기울기가 플랫한 전압-전류 특성을 얻을 수 있다. 기울기가 플랫한 전압-전류 특성을 이용하면, 이상적인 전류원 회로나, 매우 높은 저항값을 가지는 능동부하를 실현할 수 있다. 그 결과, 특성이 좋은 차동회로나 커런트 미러 회로를 실현할 수 있다. 또한, 채널영역의 상하에 게이트 전극이 배치되는 구조라도 좋다. 채널영역의 상하에 게이트 전극을 배치되는 것에 의하여, 실효적인 채널영역이 증가하기 때문에, 전류량의 증가나 공핍증이 쉽게 형성되므로 S값의 저감을 도모할 수 있다. 또한, 채널영역의 상하에 게이트 전극을 배치한 경우, 복수의 트랜지스터가 병렬로 접속되는 구성이 된다.

&lt;52&gt;

또한 채널영역 위에 게이트 전극이 배치되어 있는 구조라도 좋고, 채널영역 아래에 게이트 전극이 배치되어 있는 구조라도 좋다. 또한, 정스태거 구조, 또는, 역스태거 구조라도 좋다. 또한, 채널영역이 복수의 영역에 분할되거나, 채널영역이 병렬 또는 직렬로 접속되어도 좋다. 또한, 채널영역(또는 그 일부)에 소스 전극이나 드레인 전극이 겹치는 구조로 하는 것으로써, 채널영역의 일부에 전하가 축적하여, 동작이 불안정하게 되는 것을 방지할 수 있다. 또한, LDD영역을 형성하여도 좋다. LDD영역을 형성함으로써, 오프 전류의 저감 및 트랜지스터의 내압향상에 의하여 트랜지스터의 신뢰성을 보다 좋은 것으로 할 수 있다. 또는, LDD영역을 형성함으로써, 포화영역에서 동작할 때, 드레인-소스간 전압이 변화해도, 드레인-소스간 전류가 거의 변화하지 않고 기울기가 플랫한 전압-전류 특성을 얻을 수 있다.

&lt;53&gt;

또한, 상술한 바와 같이, 본 발명에 있어서의 트랜지스터는, 여러가지 타입의 트랜지스터를 사용할 수 있고, 덧붙여, 여러가지 기판에 형성시킬 수 있다. 따라서, 소정의 기능을 실현시키기 위해서 필요한 회로의 모두가, 동일한 기판에 형성되어도 좋다. 예를 들면, 소정의 기능을 실현시키기 위해서 필요한 회로의 모두가 유리기판, 플라스틱 기판, 단결정 기판, 또는 SOI 기판에 형성되어도 좋다. 이와 같이, 소정의 기능을 실현시키기 위해서 필요한 회로의 모두를 같은 기판에 형성함으로써, 부품점수의 삭감에 의한 비용의 저감이나 회로부품과의 접속점수의 저감에 의한 신뢰성의 향상을 도모할 수 있다. 한편, 소정의 기능을 실현시키기 위해서 필요한 회로의 일부를 어느 기판에, 소정의 기능을 실현시키기 위해서 필요한 회로의 다른 일부를 다른 기판에 형성하여도 좋다. 즉, 소정의 기능을 실현시키기 위해서 필요한 회로의 모두가 같은 기판에 형성할 필요는 없다.

&lt;54&gt;

예를 들면, 소정의 기능을 실현시키기 위해서 필요한 회로의 일부를 유리 기판 위에, 다른 일부를 단결정 기판에 형성하고, 단결정 기판의 트랜지스터로 구성된 IC칩을 COG(Chip On Glass)로 유리 기판에 접속하여 유리 기판 위에 배치하여도 좋다. 또는, 그 IC칩을 TAB(Tape Automated Bonding)나 프린트 기판을 사용하여 유리 기판과 접속하여도 좋다. 이와 같이, 회로의 일부가 동일한 기판에 형성됨으로써, 부품점수의 삭감에 의한 비용의 저감이나 회로부품과의 접속점수의 저감에 의한 신뢰성의 향상을 도모할 수 있다. 또한, 구동전압이 높은 부분이나 구동 주파수가 높은 부분의 회로는 소비전력이 크기 때문에, 이러한 부분의 회로는 다른 회로와 동일한 기판에 형성하지 않고, 예를 들면, 단결정 기판에 형성한 IC칩을 사용함으로써, 소비전력의 증가를 방지할 수 있다.

&lt;55&gt;

또한, 본 명세서에 있어서, 1화소는 밝기를 제어할 수 있는 요소 하나를 나타내는 것이다. 일례로서는, 1화소는, 하나의 색 요소를 나타내는 것으로 하고, 그 색 요소 하나로 밝기를 표현한다. 따라서, 그때는, R(적색) G(녹색) B(청색)의 색 요소로 이루어지는 컬러 표시 장치의 경우에는, 화상의 최소단위는, R의 화소와 G의 화소와 B의 화소의 3화소로 구성되는 것으로 한다. 또한, 색 요소는, 3색에 한정되지 않고, 그 이상의 수를 사용하여도 좋고, RGB 이외의 색을 사용하여도 좋다. 예를 들면, RGBW(W는 백색)나 RGB에, 예를 들면, 황색, 시안색, 진홍색, 에메랄드 그린, 주홍색 등을 1색 이상 추가한 것도 있다. 또한, RGB 중의 적어도 1색에 관해서, 유사한 색을 RGB에 추가하여도 좋다. 예를 들면, R, G, B1, B2로 하여도 좋다. B1과 B2는, 어느 쪽이나 청색이지만, 약간 주파수가 다르다. 마찬가지로, R1, R2, G, B나 R, G1, G2, B로 하여도 좋다. 이러한 색 요소를 사용함으로써, 더욱 실물에 가까운 표시를 할 수 있다. 또한, 이러한 색 요소를 사용함으로써, 소비전력을 저감할 수 있다. 또한, 다른 예로서는, 1개의 색 요소에 관해서, 복수의 영역을 사용하여 밝기를 제어하는 경우는, 그 영역 하나를 1화소로 하여도 좋다. 일례로서는, 면적 계조를 하는 경우, 또는 부화소(서브 화소)를 가지는 경우를 들 수 있다. 이러한 경우, 하나의 색 요소에 관하여, 밝기를 제어하는 영역이 복수 있고, 그 전체로 계조를 표현하는 것이지만, 밝기를 제어하는 영역의 하나를 1화소로 하여도 좋고, 이 경우는, 하나의 색 요소는, 복수의 화소로 구성된다. 또한, 밝기를 제어하는 영역이 하나의 색 요소 중에 복수 있어도, 그들을 종합하여 하나의 색 요소를 1화소로 하여도 좋다. 또한, 그 경우에는, 하나의 색 요소로 1화소를 구성한다. 또한, 하나의 색 요소에 대해서, 복수의 영역을 사용하여 밝기를 제어할 경우, 화소에 따라 표시에 기여하는 영역의 크기가 다른 경우가 있다. 또한, 하나의 색 요소에 대해 복수 있는, 밝기를 제어하는 영역에 있어서, 각

각에 공급하는 신호를 약간 다르도록 하고, 시야각을 확대하도록 하여도 좋다. 즉, 하나의 색 요소에 대해서 복수 있는 영역이 가지는 화소전극의 전위를 각각 다른 것으로 함으로써, 액정분자에 가해지는 전압을 다르게 하고, 시야각을 향상시킬 수 있다.

<56> 또한, 본 명세서에 있어서, 반도체 장치는 반도체 소자(트랜지스터나 다이오드 등)를 포함하는 회로를 가지는 장치를 의미한다. 또한, 반도체 특성을 이용함으로써 기능할 수 있는 장치 전반이라도 좋다. 또한, 표시장치는, 기판 위에 부하를 포함하는 복수의 화소나 그들의 화소를 구동시키는 주변구동회로가 형성된 표시패널 본체뿐만 아니라, 표시패널 본체에 Flexible Printed Circuit(FPC)나, 프린트 배선 기판(PWB)이 설치된 것도 포함한다.

<57> 또한, 본 발명에 있어서, “어느 물체 위에 형성된다”, 또는, “무엇무엇 위에 형성된다”고 하는 표현과 같이, “무엇무엇의 위에”, 또는 “무엇무엇 위에”라고 하는 기재는 어느 물체 위에 직접 접하는 경우에 한정되지 않는다. 직접 접하지 않는 경우, 즉, 사이에 다른 것이 끼워지는 경우도 포함한다. 따라서, 예를 들면, “층 A 위에(또는 층 A 위에) 층 B가 형성되어 있다”고 기재된 경우에는, 층 A 위에 직접 접해서 층 B이 형성되어 있는 경우와, 층 A의 위에 다른 층(예를 들면 층 C나 층 D 등)이 형성되고, 그 위에 층 B가 형성되는 경우를 포함하는 것으로 한다. 또한, “무엇무엇의 상방에”라고 하는 기재도 같으며, 어느 것의 위에 직접 접하는 것으로 한정되지 않고, 사이에 다른 것이 끼워지는 경우도 포함한다. 따라서, 예를 들면, “층 A의 상방에 층 B가 형성된다”고 하는 경우는, 층 A의 위에 직접 접하여 층 B가 형성된 경우와, 층 A의 위에 다른 층(예를 들면, 층 C나 층 D 등)이 형성되어, 그 위에 층 B가 형성되는 경우를 포함한다. 또한, “무엇무엇의 아래, 또는 무엇무엇의 하방에”라고 하는 기재에 대해서도, 마찬가지로 직접 접하는 경우와, 접하지 않는 경우를 포함한다.

## 효과

<58> 본 발명에 의하여, 트랜지스터의 임계값 전압의 편차에 기인한 전류값의 편차를 억제할 수 있다. 따라서, 발광소자를 비롯한 부하에 원하는 전류를 공급할 수 있다. 특히, 부하로서 발광소자를 사용하는 경우, 휘도의 편차가 적고 1프레임 기간에 있어서의 발광기간의 비율이 높은 표시장치를 제공할 수 있다.

## 발명의 실시를 위한 구체적인 내용

<59> 이하, 본 발명의 형태에 관하여 설명한다. 단, 본 발명은 다양한 형태로 실시할 수 있으며, 본 발명의 취지 및 그 범위에서 벗어남이 없이 그 형태 및 상세한 내용을 다양하게 변경할 수 있다는 것은 당업자라면 용이하게 이해된다. 따라서, 본 형태의 기재 내용에 한정해서 해석되지 않는다. 이때, 이하에 설명하는 본 발명의 구성에 있어서, 동일한 부분을 가리키는 부호는 다른 도면간에서 공통으로 사용한다.

<60> (실시형태 1)

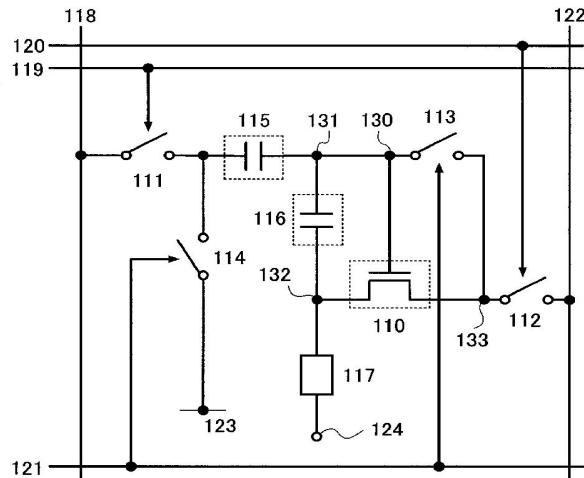

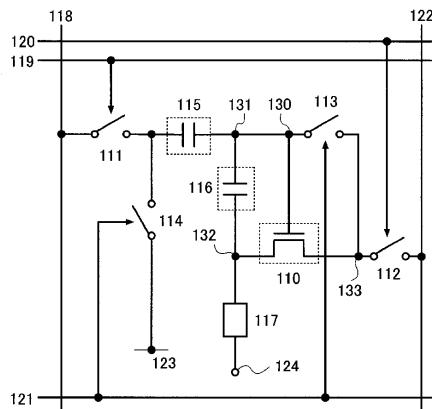

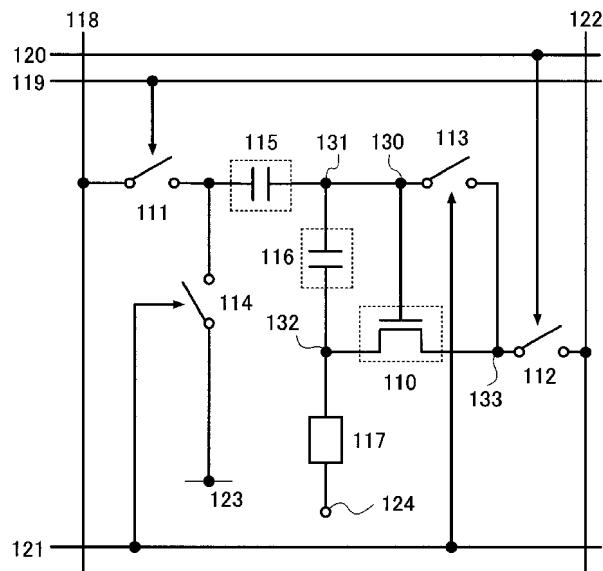

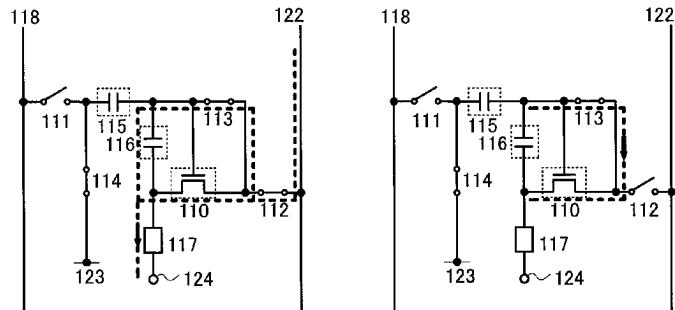

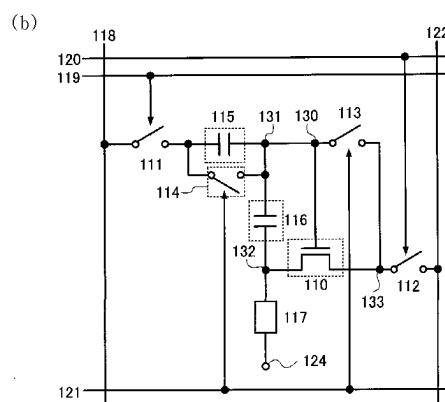

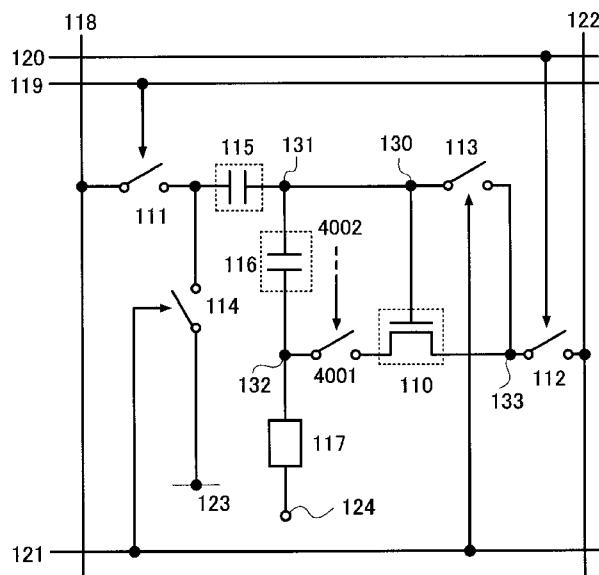

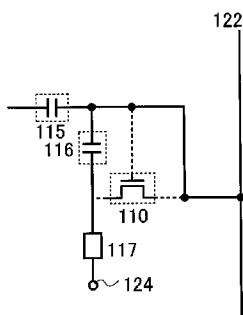

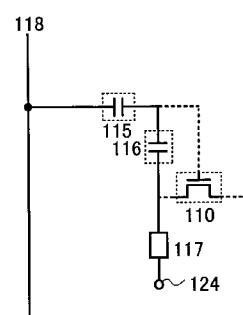

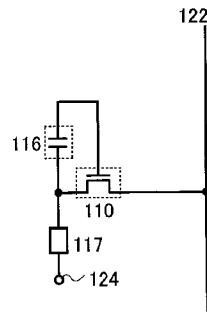

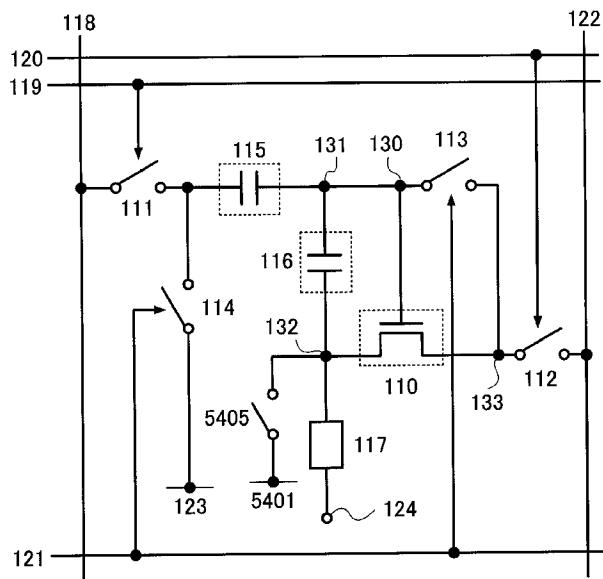

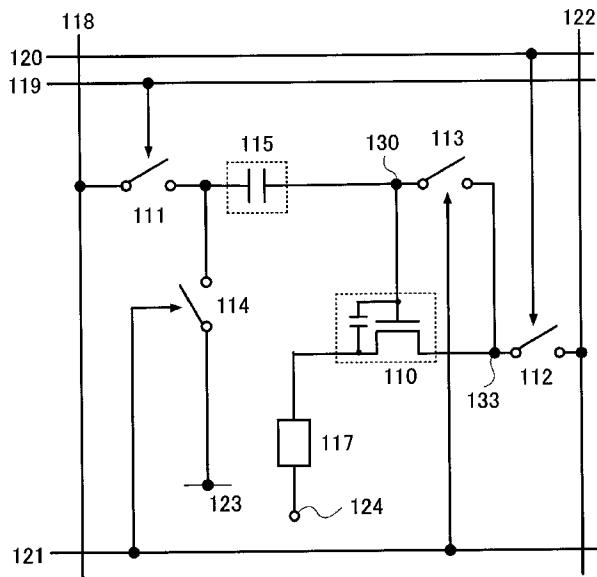

<61> 본 발명의 화소의 기본 구성에 대해서, 도 1을 참조하여 설명한다. 도 1에 도시하는 화소는, 트랜지스터(110), 제 1 스위치(111), 제 2 스위치(112), 제 3 스위치(113), 제 4 스위치(114), 제 1 용량소자(115), 제 2 용량소자(116), 발광소자(117)를 가진다. 또한, 화소는, 신호선(118), 제 1 주사선(119), 제 2 주사선(120), 제 3 주사선(121), 전원선(122), 및 전위공급선(123)에 접속되어 있다. 본 실시형태에 있어서, 트랜지스터(110)는 N채널형 트랜지스터로 하고, 그 게이트-소스간 전압( $V_{gs}$ )이 임계값 전압( $V_{th}$ )을 초과하면, 도통상태가 되는 것으로 한다. 또한 발광소자(117)의 화소전극은 양극, 대향전극(124)은 음극으로서 기능한다. 또한, 트랜지스터의, 게이트-소스간 전압은  $V_{gs}$ , 드레인-소스간 전압은  $V_{ds}$ , 임계값 전압은  $V_{th}$ , 제 1 용량소자(115) 및 제 2 용량소자(116)에 축적된 전압은 각각  $V_{c1}$ ,  $V_{c2}$ 로 기재하고, 전원선(122), 전위공급선(123) 및 신호선(118)을 각각의 제 1 배선, 제 2 배선, 제 3 배선이라고도 부른다. 또한, 제 1 주사선(119), 제 2 주사선(120), 및 제 3 주사선(121)을 각각 제 4 배선, 제 5 배선, 제 6 배선이라고 불러도 좋다.

<62> 트랜지스터(110)의 제 1 전극(소스 전극 및 드레인 전극의 한쪽)은, 발광소자(117)의 화소전극에 접속되고, 제 2 전극(소스 전극 및 드레인 전극의 다른 쪽)은 제 2 스위치(112)를 통하여 전원선(122)에 접속되고, 게이트 전극은 제 3 스위치(113) 및 제 2 스위치(112)를 통하여 전원선(122)과 접속되어 있다. 또한, 제 3 스위치(113)는, 트랜지스터(110)의 게이트 전극과 제 2 스위치(112) 사이에 접속되어 있다.

<63> 또한, 트랜지스터(110)의 게이트 전극과 제 3 스위치(113)의 접속개소를 노드(130)로 하면, 노드(130)는 제 1 용량소자(115) 및 제 1 스위치(111)를 통하여 신호선(118)과 접속된다. 즉, 제 1 용량소자(115)의 제 1 전극이 제 1 스위치(111)를 통하여 신호선(118)에, 제 2 전극이 트랜지스터(110)의 게이트 전극에 접속된다.

또한, 제 1 용량소자(115)의 제 1 전극은 제 4 스위치(114)를 통하여 전위공급선(123)과도 접속된다. 노드(130)는 덧붙여 제 2 용량소자(116)를 통하여 트랜지스터(110)의 제 1 전극과도 접속된다. 즉, 제 2 용량소자(116)의 제 1 전극이 트랜지스터(110)의 게이트 전극과, 제 2 전극이 트랜지스터(110)의 제 1 전극에 접속된다. 이들의 용량소자는, 배선, 반도체 층이나 전극에 의하여 절연막을 끼워으로써 형성하여도 좋고, 경우에 따라, 도 55에 도시하는 바와 같이, 트랜지스터(110)의 게이트 용량을 사용하여 제 2 용량소자(116)를 생략할 수도 있다. 이들의 전압을 유지하는 수단을 유지용량이라고 한다. 또한, 노드(130)와, 제 1 용량소자(115)의 제 2 전극과 제 2 용량소자(116)의 제 1 전극이 접속되는 배선과의 접속개소를 노드 131, 트랜지스터(110)의 제 1 전극과, 제 2 용량소자(116)의 제 2 전극과 발광소자(117)의 화소전극이 접속되는 배선과의 접속개소를 노드 132, 및 트랜지스터(110)의 제 2 전극과, 제 2 스위치(112)와 제 3 스위치(113)가 접속되는 배선과의 접속개소를 노드 133으로 한다.

<64> 또한, 제 1 주사선(119), 제 2 주사선(120), 제 3 주사선(121)에 신호를 입력함으로써, 각각 제 1 스위치(111), 제 2 스위치(112), 제 3 스위치(113) 및 제 4 스위치(114)의 온(ON)/오프(OFF)가 제어된다.

<65> 신호선(118)에는, 비디오 신호에 상당하는 화소의 계조에 따른 신호, 즉, 휘도 데이터에 따른 전위가 입력된다.

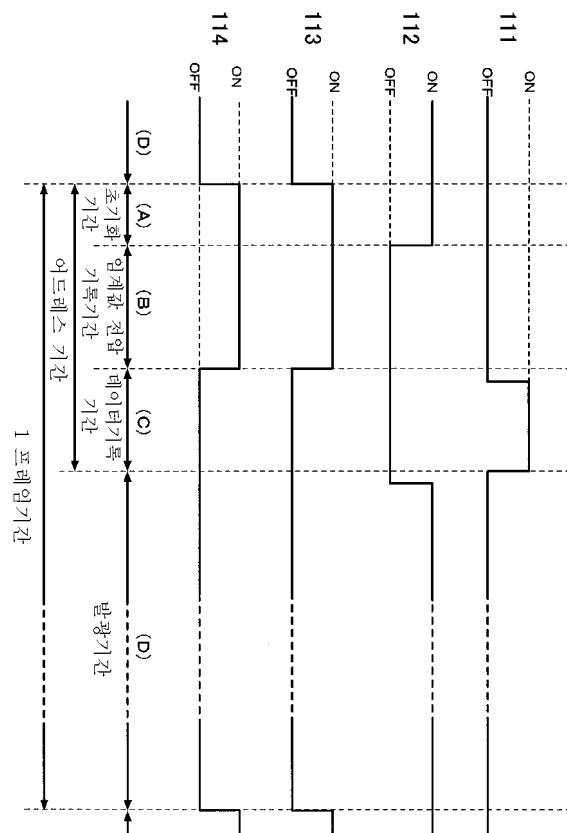

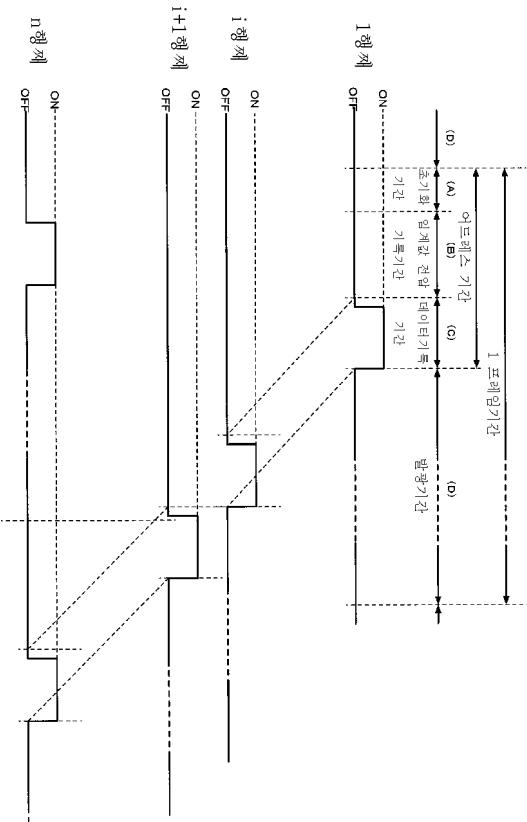

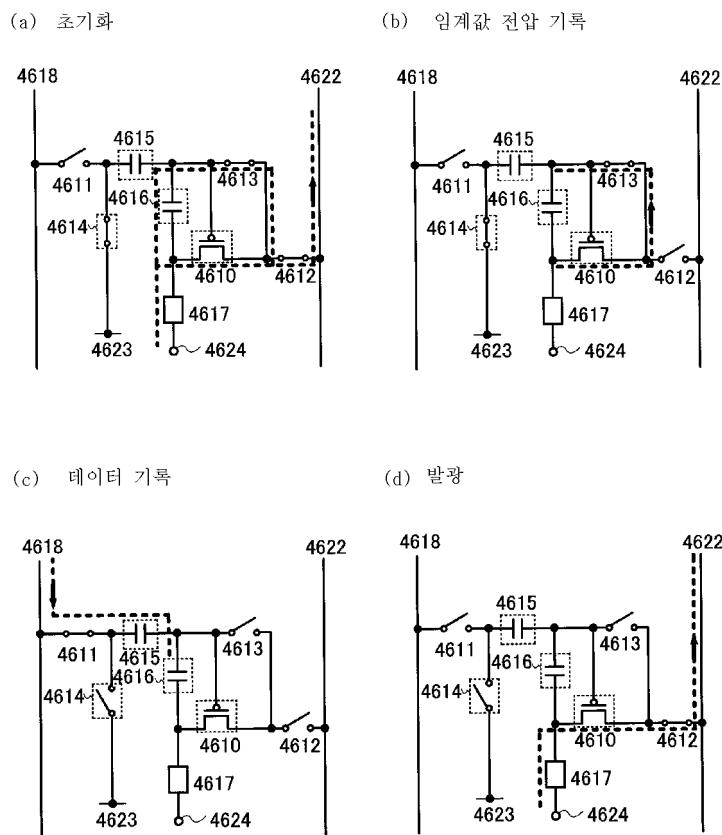

<66> 다음, 도 1에서 도시하는 화소의 동작에 대해서 도 2의 타이밍 차트 및 도 3a 내지 도 3d를 사용하여 설명한다. 또한, 도 2에 있어서 1화면분의 화상을 표시하는 기간에 상당하는 1프레임 기간은, 초기화 기간, 임계값 전압 기록 기간, 데이터 기록 기간, 및 발광기간으로 분할된다. 또한, 초기화 기간, 임계값 전압 기록 기간, 데이터 기록 기간을 종합하여 어드레스 기간이라고 부른다. 1프레임 기간은 특별히 한정되지 않지만, 화상을 보는 사람이 깜박거림(flicker)을 느끼지 않도록 1/60초 이하로 하는 것이 바람직하다.

<67> 또한, 발광소자(117)의 대향전극(124)에는 V1의 전위(V1: 임의의 수)가 입력된다. 또한, 발광소자(117)가 발광하기 위해서 적어도 필요로 하는 전위차를  $V_{EL}$ 로 하면, 전원선(122)에는,  $V1+V_{EL}+V_{th}+a$  ( $a$ : 임의의 양수)의 전위가 입력된다. 즉, 전원선(122)의 전위는  $V1+V_{EL}+V_{th}+a$  이상이면 좋다. 전위공급선(123)의 전위는 특별히 한정되지 않지만, 화소가 형성된 패널에 입력되는 전위의 범위내인 것이 바람직하다. 이렇게 하면, 전원을 별도 제작할 필요가 없어진다. 또한, 여기서는 전위공급선(123)의 전위를 V2로 한다.

<68> 우선, 도 2의 기간(A) 및 도 3a에 도시하는 초기화기간에서는, 제 1 스위치(111)를 오프로 하여, 제 2 스위치(112), 제 3 스위치(113) 및 제 4 스위치(114)를 온으로 한다. 이 때, 트랜지스터(110)는 도통상태이며, 제 1 용량소자(115)에는  $V1+V_{EL}+V_{th}+a-V2$ 가, 제 2 용량소자(116)에는  $V_{th}+a$ 가 유지된다. 또한, 초기화 기간에서는, 제 1 용량소자(115)에는 소정의 전압이, 제 2 용량소자(116)에는 적어도  $V_{th}$ 보다 높은 전압이 유지되면 좋다.

<69> 도 2의 기간(B) 및 도 3b에 도시하는 임계값 전압 기록 기간에서는, 제 2 스위치(112)를 오프로 한다. 따라서, 트랜지스터(110)의 제 1 전극 즉, 소스 전극의 전위는 점점 상승하고, 트랜지스터(110)의 게이트-소스 간 전압  $V_{gs}$ 가 임계값 전압( $V_{th}$ )으로 되면, 트랜지스터(110)는 비도통 상태가 된다. 따라서, 제 2 용량소자(116)에 유지되는 전압  $V_{c2}$ 는 대체로  $V_{th}$ 가 된다.

<70> 그 후의 도 2의 기간(C) 및 도 3c에 도시하는 데이터 기록 기간에 있어서는, 제 3 스위치(113) 및 제 4 스위치(114)를 오프로 한 후, 제 1 스위치(111)를 온으로 하고, 신호선(118)보다 휘도 데이터에 따른 전위( $V2+V_{data}$ )를 입력한다. 이 때, 제 2 용량소자(116)에 유지되는 전압  $V_{c2}$ 는, 제 1 용량소자(115), 제 2 용량소자(116) 및 발광소자(117)의 정전용량을 각각 C1, C2, C3로 하면,  $C3 \gg C1, C2$ 로부터 수식(1)과 같이 나타낼 수 있다.

<71> [수식 1]

$$V_{c2} = V_{th} + V_{data} \times \frac{C1}{C1+C2} \quad \dots (1)$$

<72>

<73> 또한, C1과 C2는 신호선(118)으로부터 공급하는 전위를 결정할 때에 필요하지만, 이들의 관계는 특별히 한정되지 않는다. 또한,  $C1 > C2$ 의 경우에는, 휘도변화에 따른  $V_{data}$ 의 진폭을 적게 할 수 있기 때문에, 소비전력을 저감할 수 있다. 한편,  $C2 > C1$ 의 경우에는, 주위의 스위치의 온, 오프나 오프 전류에 의한  $V_{c2}$ 의 변화를

억제할 수 있다. 이들의 상반되는 효과에 의거하여 C1과 C2는 동일이며, 제 1 용량소자(115)와 제 2 용량소자(116)의 크기는 동일한 것이 바람직하다.

<74> 또한, 다음 발광기간에 있어서, 발광소자(117)를 비발광으로 하고 싶은 경우는,  $V_{data} \leq 0$ 의 전위를 입력하면 좋다.

<75> 다음, 도 2의 기간(D) 및 도 3d에 도시하는 발광기간에서는, 제 1 스위치(111)를 오프로 한 후, 제 2 스위치(112)를 온으로 한다. 이 때, 트랜지스터(110)의 게이트-소스간 전압은  $V_{gs}=V_{th}+V_{data} \times (C_1/(C_1+C_2))$ 이고, 휘도 데이터에 따른 전류가 트랜지스터(110) 및 발광소자(117)에 흘러, 발광소자(117)가 발광한다. 물론, 신호선(118)으로부터 입력되는 휘도 데이터에 따른 전위에 대해서는, 트랜지스터(110)의 게이트-소스간 전압이  $V_{gs}=V_{th}+V_{data} \times (C_1/(C_1+C_2))$ 로 되는 것을 고려하여  $V_{data}$ 를 결정한다.

<76> 또한, 발광소자(117)에 흐르는 전류 I는, 트랜지스터(110)를 포화영역에서 동작시킨 경우, 수식 (2)로 나타내진다.

<77> [수식 2]

$$\begin{aligned} I &= \frac{1}{2} \left( \frac{W}{L} \right) \mu C_{ox} ( V_{gs} - V_{th} )^2 \\ &= \frac{1}{2} \left( \frac{W}{L} \right) \mu C_{ox} ( V_{th} + V_{data} \times \frac{C_1}{C_1+C_2} - V_{th} )^2 \\ &= \frac{1}{2} \left( \frac{W}{L} \right) \mu C_{ox} ( V_{data} \times \frac{C_1}{C_1+C_2} )^2 \dots (2) \end{aligned}$$

<78>

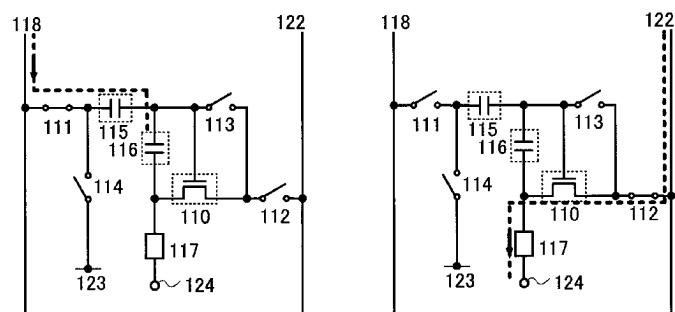

<79> 또한, 트랜지스터(110)를 선형영역에서 동작시킨 경우, 발광소자(117)에 흐르는 전류 I는 수식(3)로 나타내진다.

<80> [수식 3]

$$\begin{aligned} I &= \left( \frac{W}{L} \right) \mu C_{ox} [ ( V_{gs} - V_{th} ) V_{ds} - \frac{1}{2} V_{ds}^2 ] \\ &= \left( \frac{W}{L} \right) \mu C_{ox} [ ( V_{th} + V_{data} \times \frac{C_1}{C_1+C_2} - V_{th} ) V_{ds} - \frac{1}{2} V_{ds}^2 ] \\ &= \left( \frac{W}{L} \right) \mu C_{ox} [ ( V_{data} \times \frac{C_1}{C_1+C_2} ) V_{ds} - \frac{1}{2} V_{ds}^2 ] \dots (3) \end{aligned}$$

<81>

<82> 여기서, W는 트랜지스터(110)의 채널 폭, L는 채널 길이,  $\mu$ 는 이동도,  $C_{ox}$ 는 측적용량을 가리킨다.

<83> 수식(2) 및 수식(3)으로부터, 트랜지스터(110)의 동작영역이 포화영역, 선형영역의 어느 경우에 있어서도, 발광소자(117)에 흐르는 전류는, 트랜지스터(110)의 임계값 전압( $V_{th}$ )에 의존하지 않는다. 따라서, 트랜지스터(110)의 임계값 전압의 편차에 기인한 전류값의 편차를 억제하고, 휘도 데이터에 대응한 전류를 발광소자(117)에 공급할 수 있다.

<84> 상술한 바와 같이, 트랜지스터(110)의 임계값 전압의 편차에 기인한 휘도의 편차를 억제할 수 있다. 또한, 대향전극(124)의 전위를 일정하게 동작시키기 때문에, 소비전력을 낮게 할 수 있다.

<85> 또한, 트랜지스터(110)를 포화영역에서 동작시킨 경우에 있어서는, 발광소자(117)의 열화에 의한 휘도의 편차도 억제할 수 있다. 또한, 발광소자(117)의 열화는, 그 전류전압특성이 열화 전에 비하여 평행으로 시프트한 경우에 한정되지 않는다. 예를 들면, 특성의 기울기나 특성이 곡선으로 나타내지는 경우에는, 그 미분값이 열화전과 비하여 다른 경우도 포함된다. 발광소자(117)가 열화하면, 발광소자(117)의  $V_{EL}$ 는 증가하고, 트랜지스터(110)의 제 1 전극, 즉 소스 전극의 전위는 상승한다. 이 때, 트랜지스터(110)의 소스 전극은 제 2 용량소자(116)의 제 2 전극에 트랜지스터(110)의 게이트 전극은 제 2 용량소자(116)의 제 1 전극에 접속되어, 게이트 전극은 부유 상태로 된다. 따라서, 소스 전위의 상승에 따라, 동일한 전위분 트랜지스터(110)의 게이트 전위도 상승한다. 따라서, 트랜지스터(110)의  $V_{gs}$ 는 변화하지 않기 때문에, 혹시 발광소자가 열화해도 트랜지

스터(110) 및 발광소자(117)에 흐르는 전류에 영향을 미치지 않는다. 또한, 수식(2)에 있어서도, 발광소자(117)에 흐르는 전류 I는 소스 전위나 드레인 전위에 의존하지 않는 것을 알 수 있다.

<86> 따라서, 트랜지스터(110)를 포화영역에서 동작시킨 경우에 있어서는, 트랜지스터(110)의 임계값 전압의 편차 및 발광소자(117)의 열화에 기인한 트랜지스터(110)에 흐르는 전류의 편차를 억제할 수 있다.

<87> 또한, 트랜지스터(110)를 포화영역에서 동작시킨 경우, 채널 길이 L가 짧을수록, 항복현상에 의하여 드레인 전압을 현저히 증가시키면 전류가 대량으로 흐르기 쉽다.

<88> 또한, 드레인 전압을 핀치-오프(pinch-off) 전압보다 증가시키면, 핀치-오프점이 소스측에 이동하여, 실질 채널로서 기능하는 실효적인 채널 길이는 감소한다. 따라서, 전류값이 증가한다. 이 현상을 채널 길이 변조라고 부른다. 또한, 핀치-오프점은, 채널이 소멸해 가 게이트 아래에 있어서 채널의 두께가 0으로 되는 경계 개소이며, 핀치-오프 전압은 핀치-오프점이 드레인 단으로 되는 경우의 전압을 가리킨다. 이 현상도, 채널 길이 L가 짧을수록 생기기 쉽다. 예를 들면, 채널 길이 변조에 의한 전압-전류특성의 모델 도면을 도 4에 도시 한다. 또한, 도 4에 있어서, 트랜지스터의 채널 길이 L는 (a)>(b)>(c)이다.

<89> 이상으로부터, 트랜지스터(110)를 포화영역에서 동작시키는 경우, 드레인-소스간 전압 V<sub>ds</sub>에 대한 전류 I는 보다 일정에 가까운 것이 바람직하다. 따라서, 트랜지스터(110)의 채널 길이 L는 긴 것이 바람직하다. 예를 들면, 트랜지스터의 채널 길이 L는 채널 폭 W보다 큰 것이 바람직하다. 또한, 채널 길이 L는 10μm 이상 50 μm 이하, 보다 바람직하게는, 15μm 이상 40μm 이하이다. 다만, 채널 길이 L 및 채널 폭 W는 이것에 한정되지 않는다.

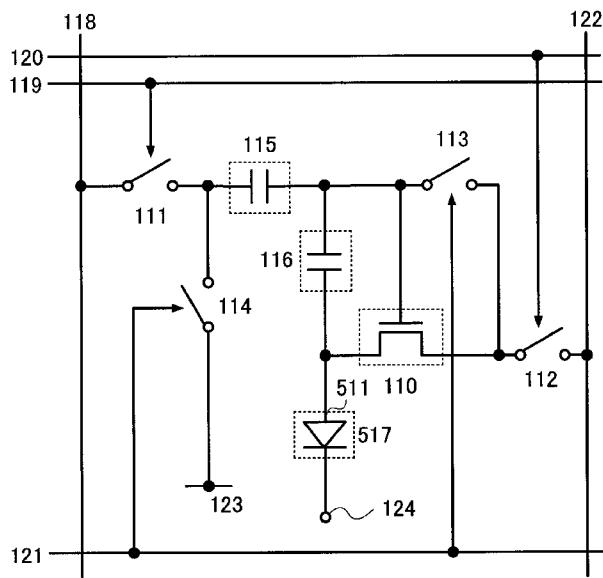

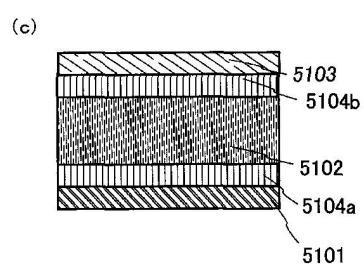

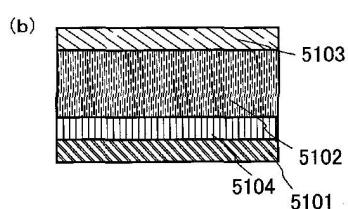

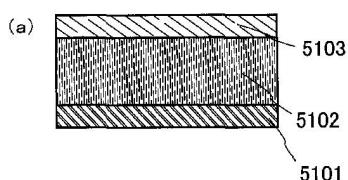

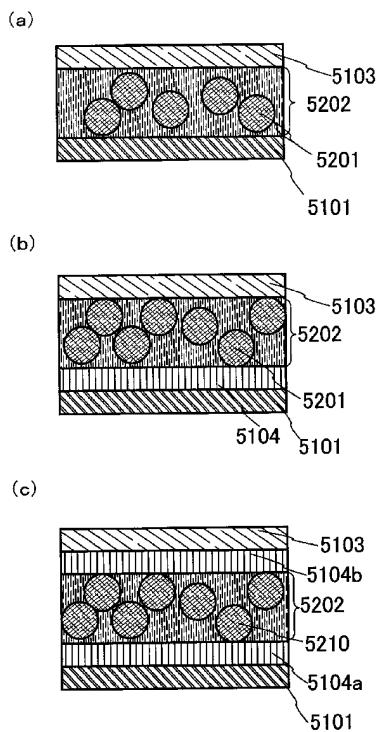

<90> 이상과 같이, 트랜지스터의 임계값 전압의 편차에 기인한 전류값의 편차를 억제할 수 있기 때문에, 본 발명에 있어서 그 트랜지스터에 의하여 제어된 전류가 공급되는 지점은 특별히 한정되지 않는다. 따라서, 도 1에 나타낸 발광소자(117)는, 대표적으로는, EL소자(유기 EL 소자, 무기 EL 소자 또는 유기물 및 무기물을 포함하는 EL소자)를 적용할 수 있다. 또한, 발광소자(117) 대신에, 잠자방출소자, 액정소자, 전자잉크 등을 적용할 수도 있다. 도 5에 발광소자(117)에 EL소자(517)를 사용한 예를 나타낸다. 또한, 도 5는 화소전극(511)으로부터 대향전극(124)에 전류가 흐르는 상태를 나타낸다.

<91> 또한, 트랜지스터(110)는 발광소자(117)에 공급하는 전류를 제어하는 기능을 가지면 좋기 때문에, 트랜지스터의 종류는 특별히 한정되지 않고, 다양한 형태의 것을 사용할 수 있다. 예를 들면, 결정성 반도체막을 사용한 박막 트랜지스터(TFT), 비정질 실리콘이나 다결정 실리콘으로 대표되는 비결정성 반도체막을 사용한 박막 트랜지스터, 반도체 기판이나 SOI기판을 사용하여 형성되는 트랜지스터, MOS형 트랜지스터, 접합형 트랜지스터, 바이폴러 트랜지스터, ZnO나 a-InGaZnO 등의 화합물 반도체를 사용한 트랜지스터, 유기반도체나 카본나노튜브를 사용한 트랜지스터, 그 이외의 트랜지스터를 트랜지스터(110)에 적용할 수 있다.

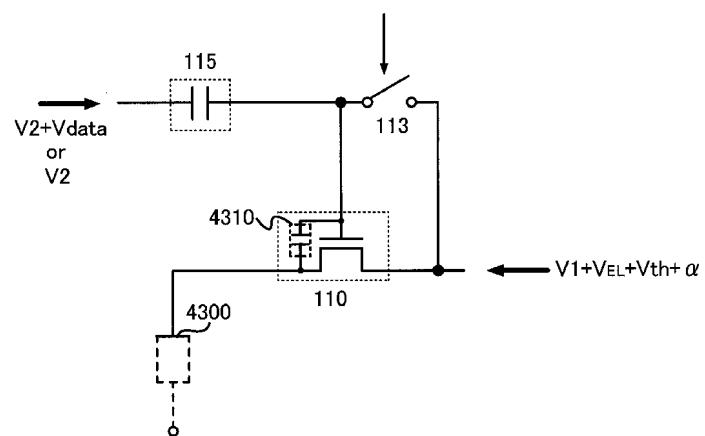

<92> 제 1 스위치(111)는 휘도 데이터에 따른 전위, 즉 비디오 신호를 신호선(118)으로부터 화소에 입력하는 타이밍을 선택하여, 주로 제 1 용량소자(115)에 유지되는 전압, 및 제 2 용량소자(116)에 유지되는 전압 즉 트랜지스터(110)의 게이트-소스간 전압을 변화시키는 것이다. 또한, 제 2 스위치(112)는 트랜지스터(110)의 제 2 전극에 소정의 전위를 공급하는 타이밍을 선택하는 것이다. 또한, 경우에 따라, 제 1 용량소자(115)의 제 2 전극 및 제 2 용량소자(116)의 제 1 전극에도 상기 소정의 전위를 공급한다. 제 3 스위치(113)는, 트랜지스터(110)의 게이트 전극과 제 2 전극과의 접속을 제어하는 것이며, 제 4 스위치(114)는 프레임 기간마다 제 1 용량소자(115)에 소정의 전압을 유지시키는 타이밍을 선택하여, 제 1 용량소자(115)의 제 1 전극에 소정의 전위를 공급하는지 아닌지를 제어하는 것이다. 따라서, 제 1 스위치(111), 제 2 스위치(112), 제 3 스위치(113), 제 4 스위치(114)는, 상기 기능을 가지면 특별히 한정되지 않는다. 예를 들면, 트랜지스터나 다이오드라도 좋고, 그들을 조합한 논리회로라도 좋다. 또한, 제 1 스위치(111), 제 2 스위치(112) 및 제 4 스위치(114)는, 상기 타이밍으로 신호 또는 전위를 화소에 줄 수 있으면 특별히 필요는 없다. 또한, 제 3 스위치(113)에 있어서도, 상기 기능을 실현할 수 있으면, 특별히 필요는 없다.

<93> 예를 들면, 초기화 기간 및 임계값 전압 기록 기간에 있어서 제 1 용량소자(115)에 소정의 전압을 유지시킬 수 있고, 덧붙여, 화소의 계조에 따른 신호를 데이터 기록 기간에 화소에 입력할 수 있는 경우는, 화소내에 제 1 스위치(111) 및 제 4 스위치(114)를 형성하지 않아도 좋다. 또한, 화소에 초기기간 및 발광기간에 있어서  $V_1 + V_{EL} + V_{th} + \alpha$  ( $\alpha > 0$ )를 공급하는 것이 가능하면, 도 43에 도시하는 바와 같이, 제 2 스위치(112)를 특별히 형성하지 않아도 좋다. 도 43에 도시하는 화소는, 트랜지스터(110), 제 1 용량소자(115), 제 3 스위치(113), 화소전극(4300)을 가진다. 그리고, 트랜지스터(110)의 제 1 전극(소스 전극 및 드레인 전극의 한쪽)은 화소전

극(4300)에 접속되고, 게이트 전극은 제 3 스위치(113)를 통하여 트랜지스터(110)의 제 2 전극과 접속된다. 또한, 트랜지스터(110)의 게이트 전극은 제 1 용량소자(115)의 제 2 전극과도 접속된다. 또한, 제 1 용량소자(115)의 제 1 전극에는 계조에 따른 신호, 즉 휘도 데이터에 따른 전위(즉, V<sub>2</sub>+V<sub>data</sub>) 및 제 1 용량소자(115)에 소정의 전압을 유지시키기 위한 임의의 전위(즉, V<sub>2</sub>)가 소정의 기간에 공급된다. 또한, 트랜지스터(110)의 게이트 용량(4310)을 유지용량으로서 이용하기 때문에, 도 1에 있어서의 제 2 용량소자(116)를 특별히 형성할 필요는 없다. 이러한 화소에 있어서도, 도 2a 내지 도 2d에 도시하는 타이밍 차트와 유사하게 각각의 전극에 원하는 전위를 공급함으로써, 트랜지스터(110)의 임계값 전압의 편차에 기인한 전류값의 편차를 억제할 수 있다. 따라서, 화소전극(4300)에 원하는 전류를 공급할 수 있다. 물론, 도 1에 있어서의 제 2 용량소자(116)에 있어서도 트랜지스터(110)의 게이트 용량을 이용하여, 생략하는 것도 가능하다.

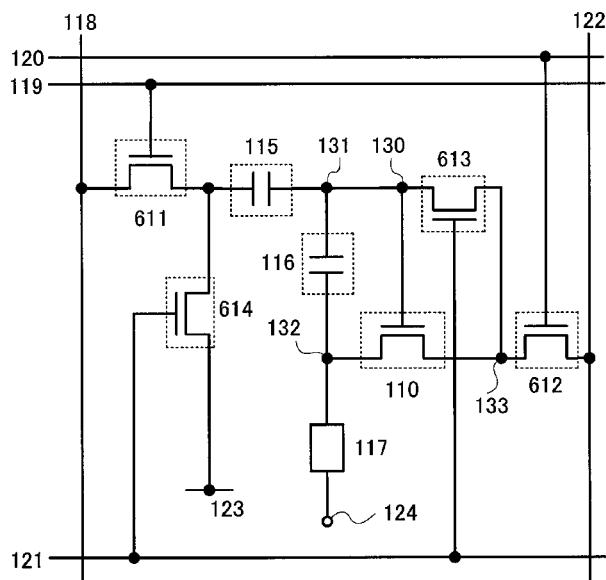

<94> 다음, 도 6에 제 1 스위치(111), 제 2 스위치(112), 제 3 스위치(113) 및 제 4 스위치(114)에 N채널형의 트랜지스터를 적용한 경우에 대해서 나타낸다. 또한, 도 1의 구성과 공통하는 부분은, 공통의 부호를 사용하여 그 설명을 생략한다.

<95> 제 1 스위칭 트랜지스터(611)가 도 1에 있어서의 제 1 스위치(111)에 상당하고, 제 2 스위칭 트랜지스터(612)가 제 2 스위치(112)에 상당하고, 제 3 스위칭 트랜지스터(613)가 제 3 스위치(113)에 상당하고, 제 4 스위칭 트랜지스터(614)가 제 4 스위치(114)에 상당한다. 또한, 트랜지스터(110)의 채널 길이는, 제 1 스위칭 트랜지스터(611), 제 2 스위칭 트랜지스터(612), 제 3 스위칭 트랜지스터(613) 및 제 4 스위칭 트랜지스터(614) 중의 어느 트랜지스터의 채널 길이보다 긴 것이 바람직하다.

<96> 제 1 스위칭 트랜지스터(611)는, 게이트 전극이 제 1 주사선(119)에, 제 1 전극이 신호선(118)에, 제 2 전극이 제 1 용량소자(115)의 제 1 전극에 접속된다.

<97> 또한, 제 2 스위칭 트랜지스터(612)는 게이트 전극이 제 2 주사선(120)에 접속되고, 제 1 전극이 노드(133)에 접속되고, 제 2 전극이 전원선(122)에 접속된다.

<98> 제 3 스위칭 트랜지스터(613)는 게이트 전극이 제 3 주사선(121)에 접속되고, 제 1 전극이 노드(130)에 접속되고, 제 2 전극이 노드(133)에 접속된다.

<99> 또한, 제 4 스위칭 트랜지스터(614)는 게이트 전극이 제 3 주사선(121)에 접속되고, 제 1 전극이 제 1 용량소자(115)의 제 1 전극에 접속되고, 제 2 전극이 전위공급선(123)에 접속된다.

<100> 각각의 스위칭 트랜지스터는, 각각의 주사선에 입력되는 신호가 H레벨 때에 온이 되고, 입력되는 신호가 L레벨 때에 오프가 된다.

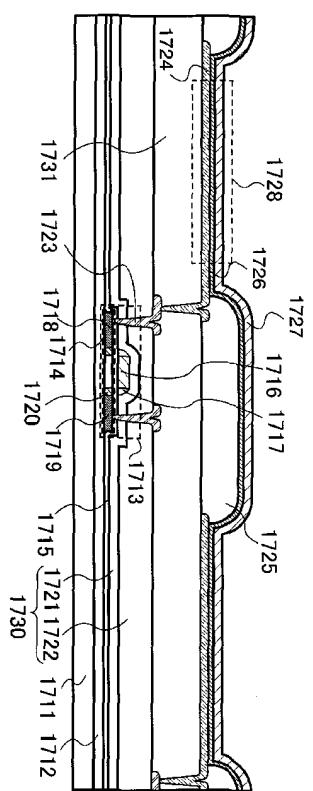

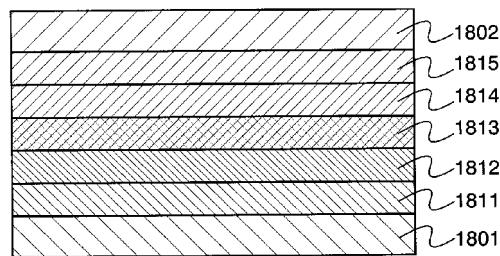

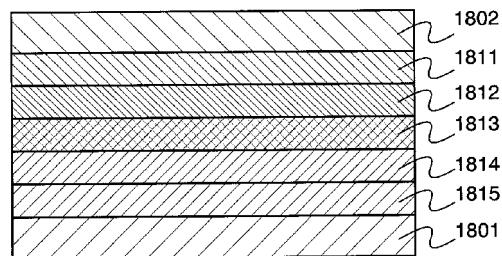

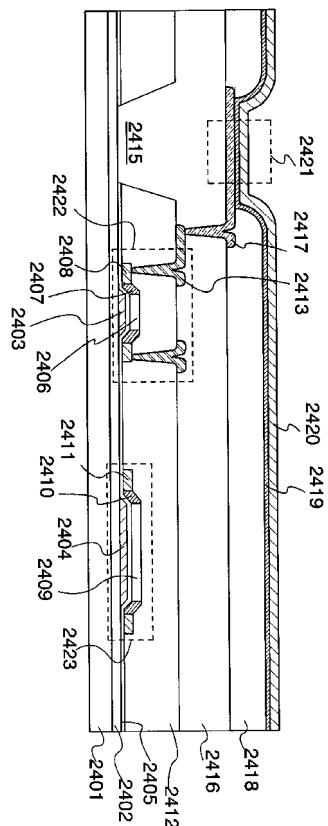

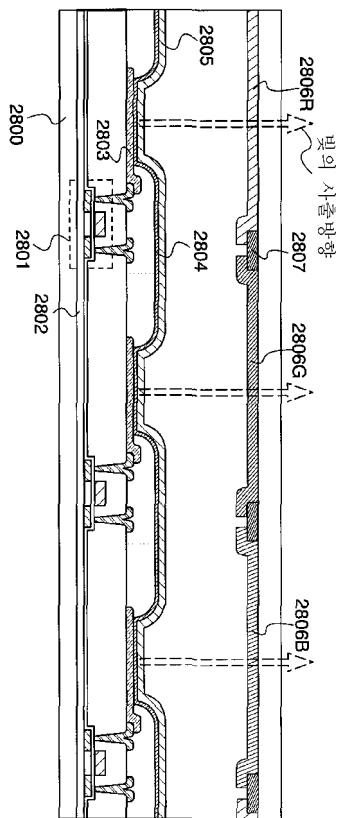

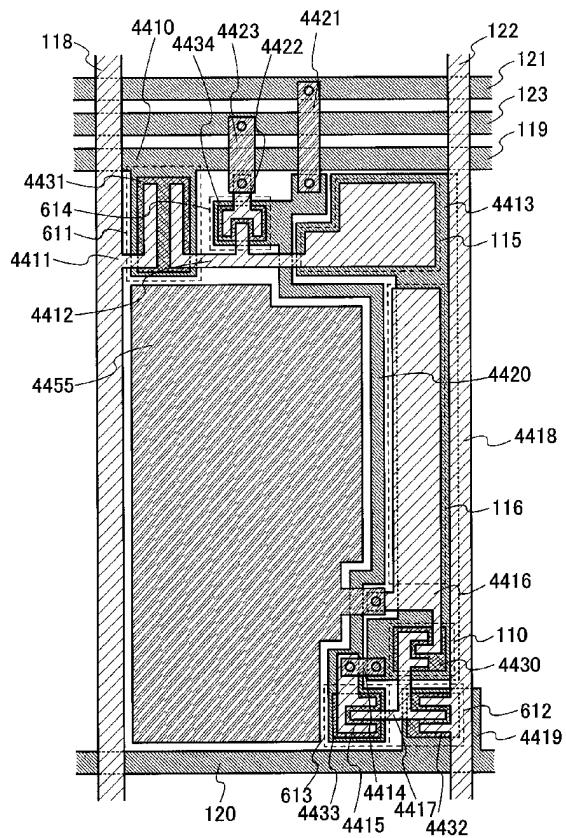

<101> 도 6에 도시한 화소의 레이아웃의 일형태를 상면도를 사용하여 도 44에 도시한다. 또한, 트랜지스터나 용량소자, 발광소자 등의 구성에 대해서는, 후술의 실시형태에서 설명하기 때문에, 여기서는 레이아웃에 대해서만 설명한다. 또한, 도 44에 도시하는 트랜지스터(110) 및 제 1 스위칭 트랜지스터(611) 내지 제 4 스위칭 트랜지스터(614)에는, 반도체 층의 아래에 게이트 전극이 위치하는 보텀 게이트형의 트랜지스터를 사용한다.

<102> 도 44에 도시하는 도전층(4410)은, 제 1 주사선(119)과 제 1 스위칭 트랜지스터(611)의 게이트 전극으로서 기능하는 부분을 포함하고, 도전층(4411)은 신호선(118)과 제 1 스위칭 트랜지스터(611)의 제 1 전극으로서 기능하는 부분을 포함한다. 또한, 도전층(4412)은, 제 1 스위칭 트랜지스터(611)의 제 2 전극과, 제 1 용량소자(115)의 제 1 전극과, 제 4 스위칭 트랜지스터(614)의 제 1 전극으로서 기능하는 부분을 포함한다. 도전층(4413)은, 제 1 용량소자(115)의 제 2 전극과, 제 2 용량소자(116)의 제 1 전극과, 트랜지스터(110)의 게이트 전극으로서 기능하는 부분을 포함한다. 또한, 이 도전층(4413)은, 배선(4414)을 통하여 제 3 스위칭 트랜지스터(613)의 제 1 전극으로서 기능하는 부분을 포함하는 도전층(4415)과 접속된다. 도전층(4416)은, 제 2 용량소자(116)의 제 2 전극과, 트랜지스터(110)의 제 1 전극으로서 기능하는 부분을 포함하고, 콘택트 홀을 통하여 발광소자의 화소전극(4455)과 접속된다. 또한, 도전층(4417)은, 트랜지스터(110)의 제 2 전극과, 제 3 스위칭 트랜지스터(613)의 제 2 전극과, 제 2 스위칭 트랜지스터(612)의 제 1 전극으로서 기능하는 부분을 포함하고, 도전층(4418)은, 전원선(122)과, 제 2 스위칭 트랜지스터(612)의 제 2 전극으로서 기능하는 부분을 포함한다. 도전층(4419)은, 제 2 주사선(120)과, 제 2 스위칭 트랜지스터(612)의 게이트 전극으로서 기능하는 부분을 포함한다. 도전층(4420)은, 제 3 스위칭 트랜지스터(613)의 게이트 전극과, 제 4 스위칭 트랜지스터(614)의 게이트 전극으로서 기능하는 부분을 포함하고, 배선(4421)을 통하여 제 3 주사선(121)과 접속된다. 또한, 제 4 스위칭 트랜지스터(614)의 제 2 전극으로서 기능하는 부분을 포함하는 도전층(4422)은, 배선(4423)을 통하여 전위공급선(123)과 접속된다.

<103> 또한, 각각 도전층 중, 제 1 스위칭 트랜지스터(611)의 게이트 전극, 제 1 전극 및 제 2 전극으로서 기능하는 부분은, 각각을 포함하는 도전층과 반도체 층(4431)이 겹치는 부분이며, 제 2 스위칭 트랜지스터(612)의 게이트 전극, 제 1 전극 및 제 2 전극으로서 기능하는 부분은, 각각을 포함하는 도전층과 반도체 층(4432)이 겹치는 부분이다. 또한, 각각의 도전층 중, 제 3 스위칭 트랜지스터(613)의 게이트 전극, 제 1 전극 및 제 2 전극으로서 기능하는 부분은, 각각을 포함하는 도전층과 반도체 층(4433)과 겹치는 부분이며, 제 4 스위칭 트랜지스터(614)의 게이트 전극, 제 1 전극 및 제 2 전극으로서 기능하는 부분은, 각각을 포함하는 도전층과 반도체 층(4434)이 겹치는 부분이다. 마찬가지로, 트랜지스터(110)에 있어서도, 게이트 전극, 제 1 전극 및 제 2 전극으로서 기능하는 부분은, 각각을 포함하는 도전층과 반도체 층(4430)과 겹치는 부분이다. 또한, 제 1 용량소자(115)는, 도전층(4412)과 도전층(4413)이 겹치는 부분에, 제 2 용량소자(116)는 도전층(4413)과 도전층(4416)이 겹치는 부분에 형성된다.

<104> 또한, 도전층(4410, 4413, 4419, 4420), 제 3 주사선(121) 및 전위공급선(123)은, 동일한 재료로 동일한 층을 사용하여 제작할 수 있다. 반도체 층(4430, 4431, 4432, 4433) 및 반도체 층(4434)이나 도전층(4411, 4412, 4415, 4416, 4417, 4418, 4422)은, 각각 동일한 재료로 동일한 층을 사용하여 제작할 수 있다. 또한, 화소전극(4455)과 동일한 재료로 동일한 층을 사용하여 배선(4414, 4421, 4423)을 제작할 수 있다.

<105> 도 44에 도시하는 바와 같이, 제 1 스위칭 트랜지스터(611)이외의 각각의 트랜지스터에 있어서, 소스 전극 및 드레인 전극의 한쪽이 다른 쪽의 전극을 둘러싸는 구조로 함으로써, 채널 폭을 넓게 할 수 있다. 따라서, 화소를 구성하는 트랜지스터의 반도체 층에 결정성 반도체 층보다 이동도의 낮은 비정질 반도체 층을 사용한 경우에는, 특히 유효하다. 물론, 제 1 스위칭 트랜지스터(611)에 있어서도, 소스 전극 및 드레인 전극의 한쪽이 다른 쪽의 전극을 둘러싸는 구조로 하여도 좋다.

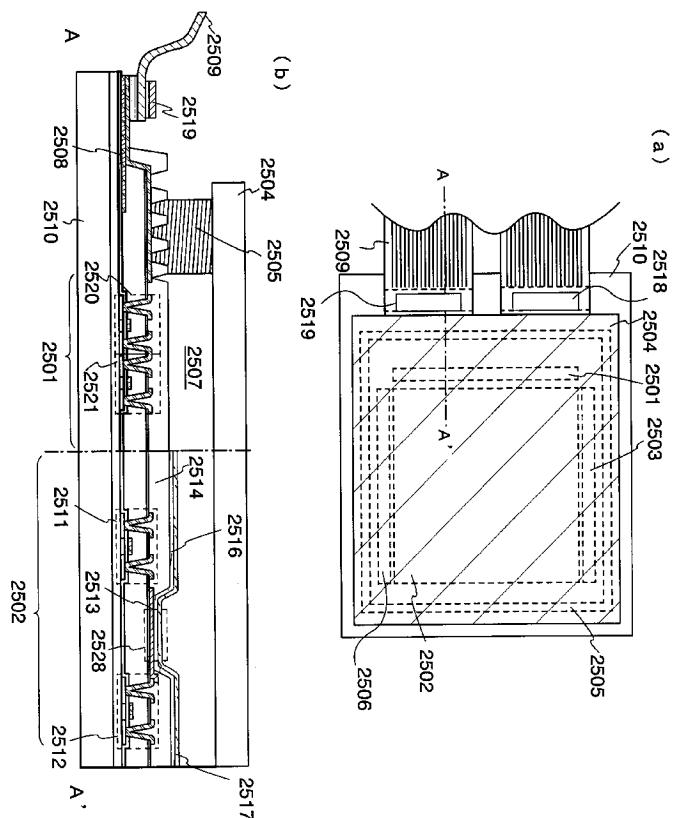

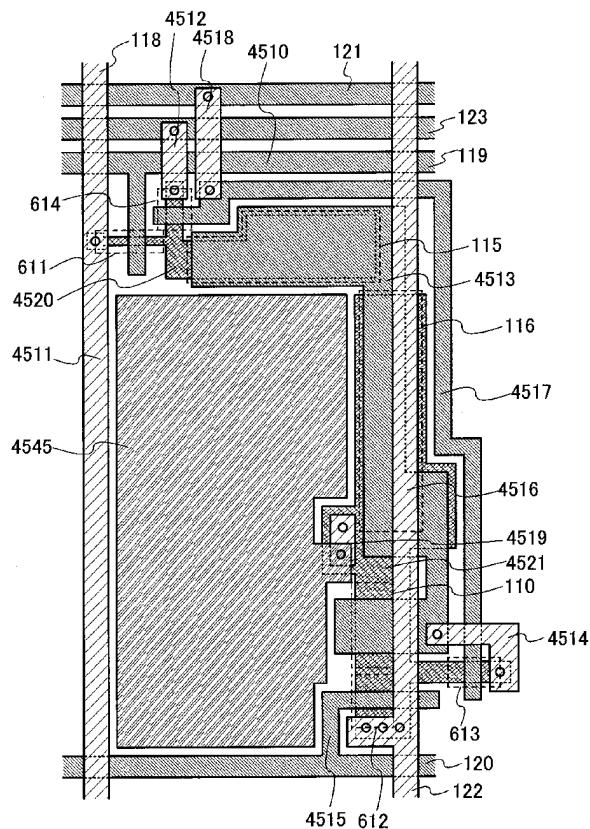

<106> 다음, 도 6에 나타내는 화소의 도 44와 다른 레이아웃의 일형태를 상면도를 사용하여 도 45에 도시한다. 또한, 도 45에 도시하는 트랜지스터(110) 및 제 1 스위칭 트랜지스터(611) 내지 제 4 스위칭 트랜지스터(614)에는, 반도체 층 위에 게이트 전극이 위치하는 순 스태거형 등의 톱 게이트형 트랜지스터를 사용한다.

<107> 도 45에 있어서, 도전층(4510)은, 제 1 주사선(119)과 제 1 스위칭 트랜지스터(611)의 게이트 전극으로서 기능하는 부분을 포함하고, 도전층(4511)은 신호선(118)과 제 1 스위칭 트랜지스터(611)의 제 1 전극으로서 기능하는 부분을 포함한다. 반도체 막(4520)은, 제 1 스위칭 트랜지스터(611)의 반도체 층 및 제 2 전극으로서 기능하는 부분, 제 4 스위칭 트랜지스터(614)의 제 1 전극 및 반도체 층으로서 기능하는 부분, 제 1 용량소자(115)의 제 1 전극으로서 기능하는 부분을 포함한다. 또한, 반도체 막(4520)은 배선(4512)을 통하여 전위공급선(123)과 접속되고, 배선(4512)은 제 4 스위칭 트랜지스터(614)의 제 2 전극으로서 기능한다. 또한, 도전층(4513)은, 제 1 용량소자(115)의 제 2 전극과, 제 2 용량소자(116)의 제 1 전극과 트랜지스터(110)의 게이트 전극으로서 기능하는 부분을 포함한다. 또한, 도전층(4513)은 제 3 스위칭 트랜지스터(613)의 제 1 전극으로서 기능하는 배선(4514)을 통하여 반도체 막(4521)과 접속된다. 이 반도체 막(4521)은, 제 3 스위칭 트랜지스터(613)의 반도체 층 및 제 2 전극으로서 기능하는 부분, 제 2 스위칭 트랜지스터(612)의 제 1 전극 및 반도체 층으로서 기능하는 부분, 트랜지스터(110)의 제 1 전극, 반도체 및 제 2 전극으로서 기능하는 부분, 덧붙여, 제 2 용량소자(116)의 제 2 전극으로서 기능하는 부분을 포함한다. 도전층(4515)은, 제 2 주사선(120)과 제 2 스위칭 트랜지스터(612)의 게이트 전극으로서 기능하는 부분을 포함한다. 도전층(4516)은, 전원선(122)과, 제 2 스위칭 트랜지스터(612)의 제 2 전극으로서 기능하는 부분을 포함한다. 도전층(4517)은, 제 3 스위칭 트랜지스터(613)의 게이트 전극으로서 기능하는 부분, 및 제 4 스위칭 트랜지스터(614)의 게이트 전극으로서 기능하는 부분을 포함하고, 배선(4518)을 통하여 제 3 주사선(121)과 접속된다. 또한, 발광소자의 화소전극(4545)은 배선(4519)을 통하여 반도체 막(4521)과 접속된다.

<108> 또한, 제 1 용량소자(115)는, 반도체 막(4520)과 도전층(4513)이 겹치는 부분에, 제 2 용량소자(116)는 반도체 막(4521)과 도전층(4513)이 겹치는 부분에 형성된다.

<109> 또한, 도전층(4510, 4513, 4515, 4517), 제 3 주사선(121) 및 전위 공급선(123)은, 동일한 재료로 동일한 층을 사용하여 제작할 수 있다. 반도체 막(4520, 4521)도 동일한 재료로 동일한 층을 사용하여 제작할 수 있다. 또한, 도전층(4511)과 동일한 재료로 동일한 층을 사용하여, 배선(4512, 4514), 도전층(4516), 배선(4518)을 제작할 수 있다.

<110> 또한, 화소의 레이아웃은 상기에 한정되지 않는다.

<111> 도 6의 화소구성에 있어서도, 도 1과 같은 동작방법에 의하여 트랜지스터(110)의 임계값 전압의 편차에

기인한 전류값의 편차를 억제할 수 있다. 따라서, 휘도 데이터에 대응한 전류를 발광소자(117)에 공급할 수 있고, 휘도의 편차를 억제할 수 있다. 또한, 트랜지스터(110)를 포화영역에서 동작시킨 경우에 있어서는, 발광소자(117)의 열화에 기인한 휘도의 편차도 억제할 수 있다.

<112> 또한, N채널형의 트랜지스터만으로 화소를 구성할 수 있기 때문에, 제조공정의 간략화를 도모할 수 있다. 또한, 화소를 구성하는 트랜지스터의 반도체 층에 비정질 반도체, 세미 아모퍼스 반도체 등을 사용할 수 있다. 예를 들면, 비정질 반도체로서, 아모퍼스 실리콘(a-Si: H)을 들 수 있다. 이들의 반도체를 사용함으로써, 보다 제조공정의 간략화가 가능하다. 따라서, 제조비용의 삭감이나 수율의 향상을 도모할 수 있다.

<113> 또한, 제 1 스위칭 트랜지스터(611), 제 2 스위칭 트랜지스터(612), 제 3 스위칭 트랜지스터(613) 및 제 4 스위칭 트랜지스터(614)는, 단순히 스위치로서 동작시키기 때문에, 트랜지스터의 극성(도전형)은 특별히 한정되지 않는다. 다만, 오프 전류가 적은 트랜지스터를 사용하는 것이 바람직하다. 오프 전류가 적은 트랜지스터로서는, LDD영역을 형성하는 것이나, 멀티 게이트 구조로 하는 것 등이 있다. 또한, N채널형과 P채널형의 양쪽 모두를 사용하여, CMOS형의 스위치로 하여도 좋다.

<114> 또한, 도 1과 같은 동작을 행하는 것이면, 스위치의 접속은 다양한 구성을 취할 수 있으며, 도 1에 한정되지 않는다. 도 1의 화소구성의 동작을 설명한 도 3a 내지 도 3d로부터 알 수 있는 바와 같이, 본 발명에서는, 초기화 기간, 임계값 전압 기록 기간, 데이터 기록 기간 및 발광기간은, 각각 도 53a 내지 도 53d에 도시하는 실선과 같이, 도통 상태이면 좋다. 따라서, 이것을 충족시킬도록 스위치 등을 배치하여 동작시킬 수 있는 구성이면 좋다.

<115> 또한, 초기화 기간에서는, 제 1 용량소자(115)에 소정의 전압이, 제 2 용량소자(116)에는 적어도 트랜지스터(110)의 임계값 전압  $V_{th}$ 보다 높은 전압이 유지되면 좋기 때문에, 도 54에 나타내는 바와 같이, 노드(132)는 제 5 스위치(5405)를 통하여 전위공급선(5401)과 접속되어도 좋다. 이 제 5 스위치(5405)는 초기화 기간만 온하여, 도 54에서는, 제 5 스위치(5405)의 온/오프를 제어하는 제어하는 주사선은 도시하지 않는다. 또한, 전위공급선(5401)의 전위는,  $V_1 + V_{EL}$ 보다 낮은 전위라면 좋다. 보다 바람직하게는,  $V_1$ 이하의 전위이며, 이러한 전위로 함으로써, 발광소자(117)에 반대방향의 바이어스 전압을 인가할 수 있기 때문에, 발광소자에 있어서의 단락개소를 절연화하거나, 발광소자의 열화를 억제할 수 있다. 따라서, 발광소자의 수명을 연장시킬 수 있다.

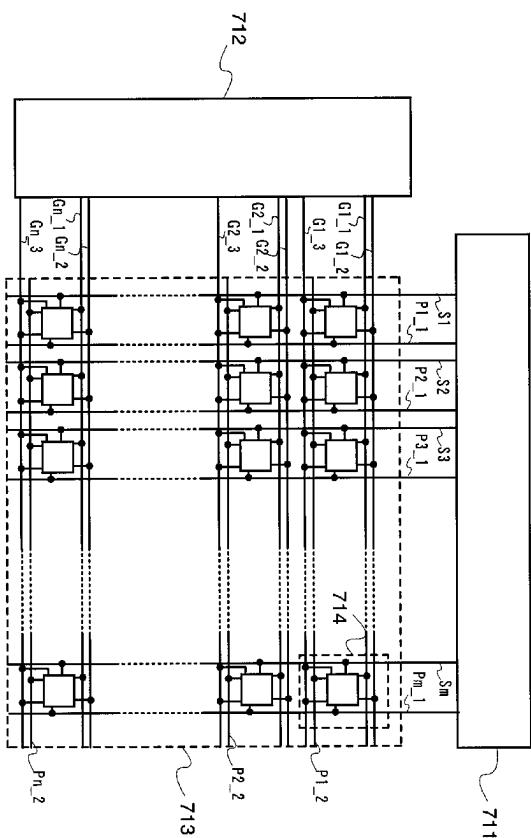

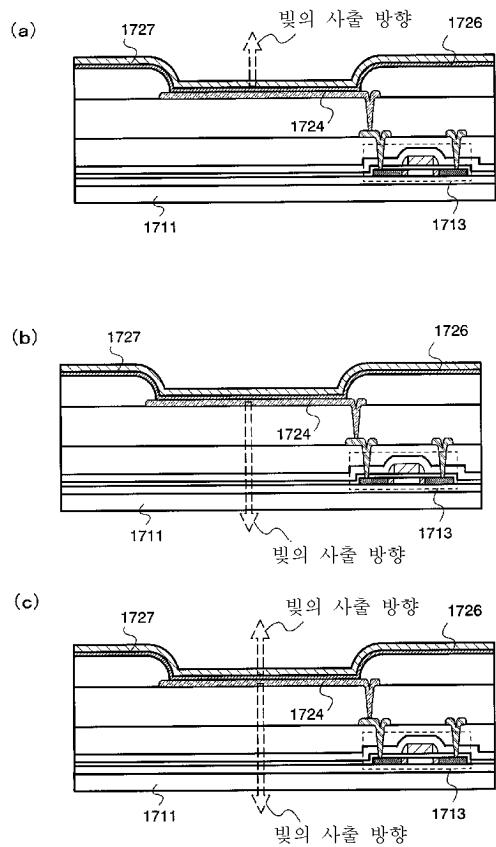

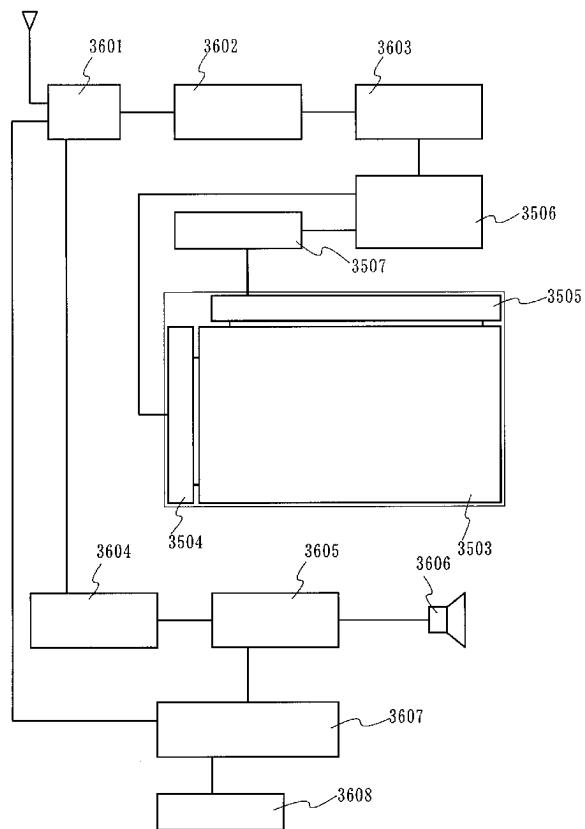

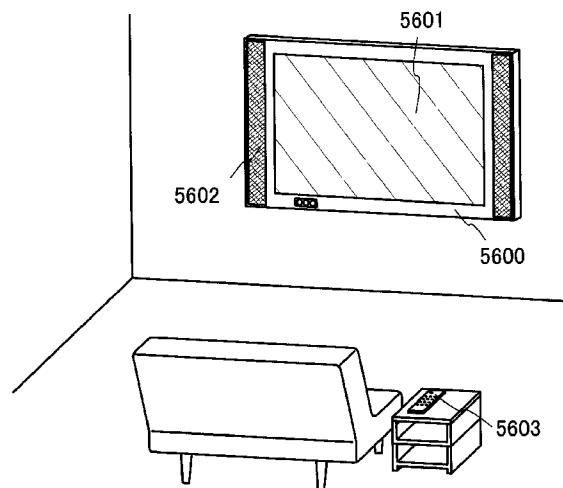

<116> 계속해서, 상술한 본 발명의 화소를 가지는 표시장치에 대해서 도 7을 사용하여 설명한다.

<117> 표시장치에는, 신호선 구동회로(711), 주사선 구동회로(712) 및 화소부(713)가 포함된다. 화소부(713)는, 신호선 구동회로(711)로부터 열 방향으로 신장해서 배치된 복수의 신호선 S1 내지 Sm, 및 전원선 P1\_1 내지 Pm\_1, 주사선 구동회로(712)로부터 행 방향으로 신장해서 배치된 복수의 제 1 주사선 G1\_1 내지 Gn\_1, 제 2 주사선 G1\_2 내지 Gn\_2, 제 3 주사선 G1\_3 내지 Gn\_3, 및 전위공급선 P1\_2 내지 Pn\_2, 및 신호선 S1 내지 Sm에 대응해서 매트릭스 형상으로 배치된 복수의 화소(714)를 가진다. 그리고, 각 화소(714)는, 신호선 Sj(신호선 S1 내지 Sm 중 어느 하나), 전원선 Pj\_1, 제 1 주사선 Gi\_1(주사선 G1\_1 내지 Gn\_1 중 어느 하나), 제 2 주사선 Gi\_2, 제 3 주사선 Gi\_3, 및 전위공급선 Pi\_2에 접속된다.

<118> 또한, 신호선 Sj, 전원선 Pj\_1, 제 1 주사선 Gi\_1, 제 2 주사선 Gi\_2, 제 3 주사선 Gi\_3, 전위공급선 Pi\_2는, 각각 도 1의 신호선(118), 전원선(122), 제 1 주사선(119), 제 2 주사선(120), 제 3 주사선(121), 전위공급선(123)에 해당한다.

<119> 주사선 구동회로(712)로부터 출력되는 신호에 따라, 동작시키는 화소의 행을 선택하는 것과 동시에 동일한 행에 속하는 각각의 화소에 대해서 동시에 도 2a 내지 도 2d에 도시한 동작을 행한다. 또한, 도 2a 내지 도 2d의 데이터 기록 기간에는, 선택된 행의 화소에 신호선 구동회로(711)로부터 출력된 비디오 신호를 기록한다. 이 때, 각각의 화소의 휘도 데이터에 따른 전위가 각 신호선 S1 내지 Sm에 입력된다.

<120> 도 8에 나타낸 바와 같이, 예를 들면 i번째 행의 데이터 기록 기간을 종료하면 i + 1번째 행에 속하는 화소에 신호의 기록을 행한다. 또한, 도 8에는, 각 행에 있어서의 데이터 기록 기간을 나타내기 위해서, 이 기간을 충실하게 나타낼 수 있는 도 2a 내지 도 2d의 제 1 스위치(111)의 동작을 발췌하여 기재한다. 그리고, i 번째 행에 있어서의 데이터 기록 기간을 종료한 화소는, 발광 기간으로 이동하여, 그 화소에 기록된 신호에 따라 발광한다.

<121> 따라서, 각 행에 있어서의 데이터 기록 기간만 중복되지 않으면, 각 행에서 자유롭게 초기화 개시 시기

를 설정할 수 있다. 또한, 각 화소는 자신의 어드레스 기간을 제외하고 발광할 수 있으므로, 1프레임 기간에 있어서의 발광 기간의 비율(즉, 듀티비)을 매우 크게 할 수 있고, 대략 100%로 할 수도 있다. 따라서, 휘도의 편차가 적고 듀티비가 높은 표시장치를 얻을 수 있다.

<122> 또한, 임계값 전압 기록 기간을 길게 설정할 수도 있으므로, 트랜지스터의 임계값 전압을 보다 정확하게 용량소자에 기록할 수 있다. 따라서, 표시장치로서의 신뢰성을 향상시킬 수 있다.

<123> 이때, 도 7에 나타낸 표시장치의 구성은 일례이며, 본 발명은 이것에 한정되지 않는다. 예를 들면, 전위공급선 P1\_2 내지 Pn\_2는 제 1 주사선 G1\_1 내지 Gn\_1과 평행하게 배치되어 있을 필요는 없고, 신호선 S1 내지 Sm과 평행하게 배치되어 있어도 된다. 또한, 전원선 P1\_1 내지 Pm\_1에 있어서도 신호선 S1 내지 Sm과 평행으로 배치되는 필요는 없고, 제 1 주사선 G1\_1 내지 Gn\_1과 평행으로 배치되어도 좋다.

<124> 본 실시형태에서는, 제 3 스위치(113) 및 제 4 스위치(114)의 온/오프는 동일한 주사선, 즉 제 3 주사선(121)을 사용하여 제어하는 경우에 대해서 나타내지만, 각각 다른 주사선을 사용하여 도 2a 내지 도 2d의 타이밍 차트에 따라 각각 스위치를 제어하여도 좋다.

<125> 또한, 임계값 전압의 편차에는, 화소간에 있어서의 각 트랜지스터의 임계값 전압의 차이 이외에도, 1개의 트랜지스터에 주목한 경우에 있어서 경시적인 임계값 전압의 변화도 포함한다. 또한, 각 트랜지스터의 임계값 전압의 차이는, 트랜지스터의 제작시의 트랜지스터 특성의 차이에 의한 것도 포함한다. 또한, 여기서 말하는 트랜지스터는 발광소자 등의 부하에 전류를 공급하는 기능을 가지는 트랜지스터를 가리킨다.

<126> (실시형태 2)

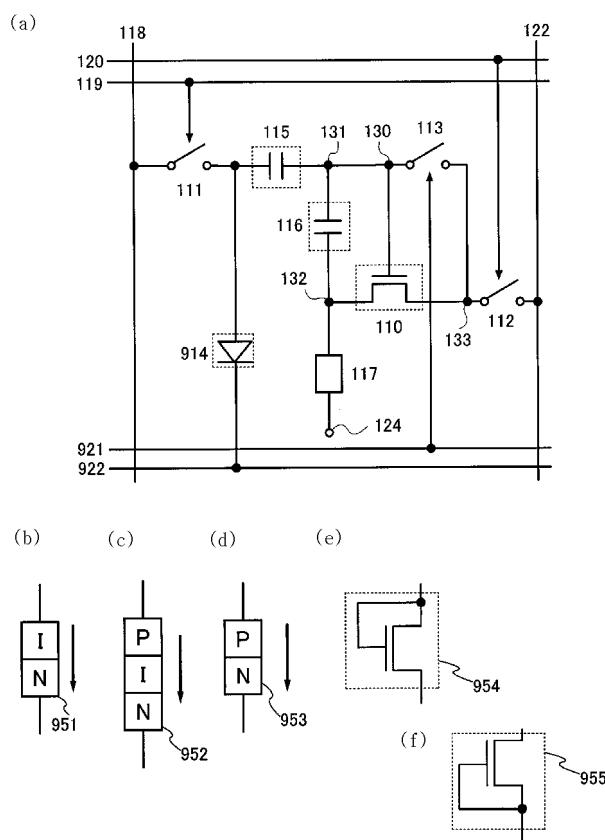

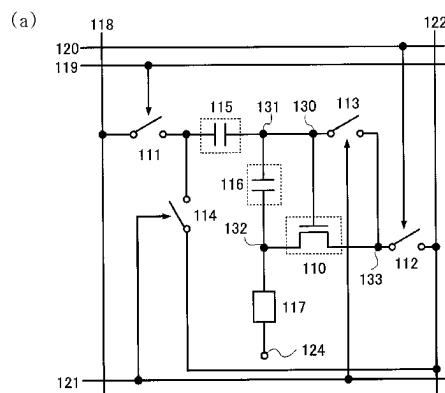

<127> 본 실시형태에서는, 실시형태 1과 다른 구성의 화소를 도 9a에 도시한다. 또한, 실시형태 1과 같은 것에 대해서는, 공통의 부호를 사용하여 나타내고, 동일부분 또는 동일한 기능을 가지는 부분의 자세한 설명은 생략한다.

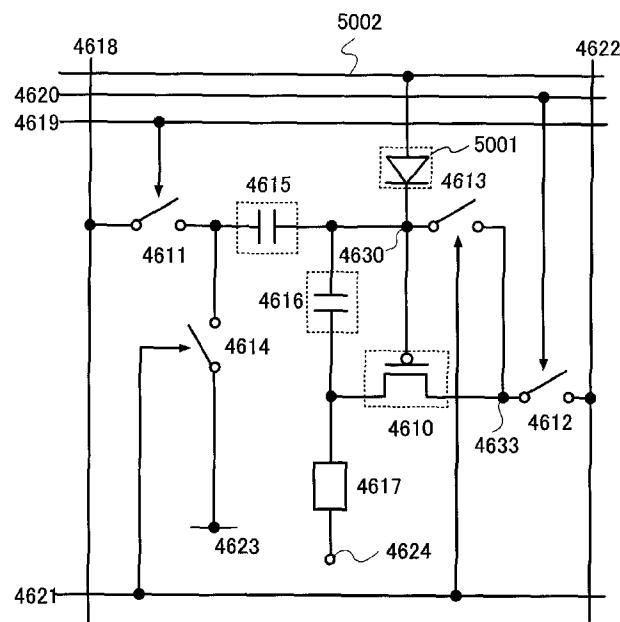

<128> 도 9a에 도시하는 화소는, 트랜지스터(110), 제 1 스위치(111), 제 2 스위치(112), 제 3 스위치(113), 정류소자(115), 제 1 용량소자(115), 제 2 용량소자(116), 발광소자(117)를 가진다. 또한, 화소는, 신호선(118), 제 1 주사선(119), 제 2 주사선(120), 제 3 주사선(921), 제 4 주사선(922) 및 전원선(122)에 접속되어 있다. 도 9a에 도시한 화소는, 도 1에 있어서의 제 4 스위치(114)에 정류소자(914)를 사용한 구성이며, 제 1 용량소자(115)의 제 1 전극은, 정류소자(914)를 통하여 제 4 주사선(922)과 접속된다. 즉, 정류소자(914)는 제 1 용량소자(115)의 제 1 전극으로부터 제 4 주사선(922)에 전류가 흐르도록 접속된다. 물론, 실시형태 1에 도시하는 바와 같이, 제 1 스위치(111), 제 2 스위치(112) 및 제 4 스위치(114)는, 트랜지스터 등을 사용하여도 좋다. 또한, 정류소자(914)에는, 도 9b 내지 도 9d에 나타내는 쇼트키 배리어형(951), PIN형(952), PN형(953) 등의 다이오드 이외에도, 도 9e 및 도 9f에 도시한 다이오드 접속되는 트랜지스터(954, 955) 등을 사용할 수 있다. 다만, 트랜지스터 954 및 트랜지스터 955는, 전류가 흐르는 방향에 따라 트랜지스터의 극성을 적절히 선택할 필요가 있다.

<129> 정류소자(914)는, 제 4 주사선(922)에 H레벨의 신호가 입력된 경우에는, 전류가 흐르지 않고, L레벨의 신호가 입력된 경우에는 정류소자(914)에 전류가 흐른다. 따라서, 도 9a 내지 도 9f의 화소를 도 1에 도시한 화소와 동일하게 동작시킬 때는, 초기화 기간 및 임계값 전압 기록 기간에 있어서 제 4 주사선(922)에 L레벨의 신호를 입력하여, 그 이외의 간격에 있어서는 H레벨의 신호를 입력한다. L레벨의 신호는 정류소자(914)에 단순히 전류가 흐를뿐만 아니라, 실시형태 1과 같이, 화소에 입력되는 휘도 데이터에 따른 전위를 ( $V2+Vdata$ )로 하면, 제 2 용량소자(116)의 제 1 전극의 전위를 V2까지 낮출 필요가 있으므로, V2에서 정류소자(914)의 순 방향에 있어서의 임계값 전압을 뺀 전위로 한다. 다만, V2는 임의의 값이며, 발광기간에 있어서, 발광소자(117)를 비발광시키고 싶은 경우에는,  $Vdata=0$ 의 전위를 입력하면 좋다. 또한, H레벨의 신호는, 상술한 바와 같이, 정류소자(914)에 전류가 흐르지 않으면 좋으므로, V2에서 정류소자(914)의 순 방향에 있어서의 임계값 전압을 감산한 값보다 크면 좋다.

<130> 상기 사항을 고려하여, 도 9a 내지 도 9f의 화소 구성에 있어서도 도 1과 같이 동작시킴으로써, 트랜지스터(110)의 임계값 전압의 편차에 기인한 전류치의 편차를 억제할 수 있다. 따라서, 휘도 데이터에 대응한 전류를 발광소자(117)에 공급할 수 있어, 휘도의 편차를 억제할 수 있다. 또한, 트랜지스터(110)를 포화영역에서 동작시키는 경우에는, 발광소자(117)의 열화에 기인한 휘도의 편차도 억제할 수 있다.

<131> 또한, 본 실시형태에 나타낸 화소를 도 7의 표시장치에 적용할 수 있다. 실시형태 1과 같이, 각 행에 있어서의 데이터 기록 기간만 중복되지 않으면, 각 행에서 자유롭게 초기화 개시 시기를 설정할 수 있다.

또한, 각 화소는 자신의 어드레스 기간을 제외하고 발광할 수 있으므로, 1프레임 기간에 있어서의 발광 기간의 비율(즉, 뉴티비)을 매우 크게 할 수 있고, 대략 100%로 할 수도 있다. 따라서, 휙도의 편차가 적고 뉴티비가 높은 표시장치를 얻을 수 있다.

<132> 또한, 임계값 전압 기록 기간을 길게 설정할 수도 있으므로, 발광소자에 흐르는 전류치를 제어하는 트랜지스터의 임계값 전압을 보다 정확하게 용량소자에 기록할 수 있다. 따라서, 표시장치로서의 신뢰성이 향상된다.

<133> 본 실시형태는, 상술한 도 1 이외에도, 기타 실시형태에 나타낸 화소 구성과도 자유롭게 조합할 수 있다. 즉, 정류소자(914)는, 다른 실시형태에서 나타내는 화소에도 적용할 수 있다.

<134> (실시형태 3)

<135> 본 실시형태에서는, 실시형태 1 및 실시형태 2와는 다른 구성의 화소를 도 10a 내지 도 11에 나타낸다. 구체적으로는, 도 1에서 도시한 전위공급선(123)을 다른 배선으로 대용하는 구성의 화소에 대해서 설명한다. 또한, 제 1 용량소자(115)의 제 1 전극에 임의의 전위를 공급할 수 있으면 좋으므로 이러한 구성을 취할 수 있다. 실시형태 1과 같은 것에 대해서는 공통의 부호를 사용하여 나타내고, 동일부분 또는 같은 기능을 가지는 부분의 자세한 설명은 생략한다.

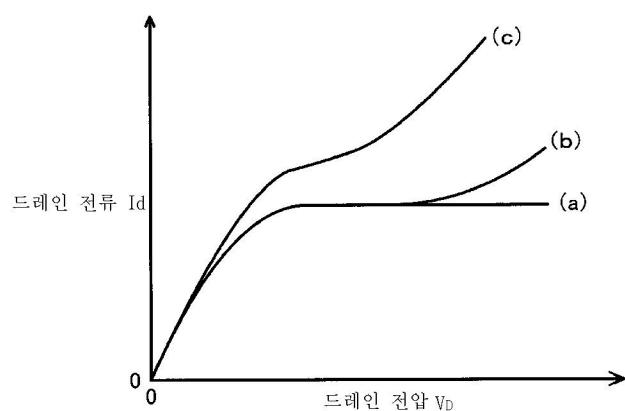

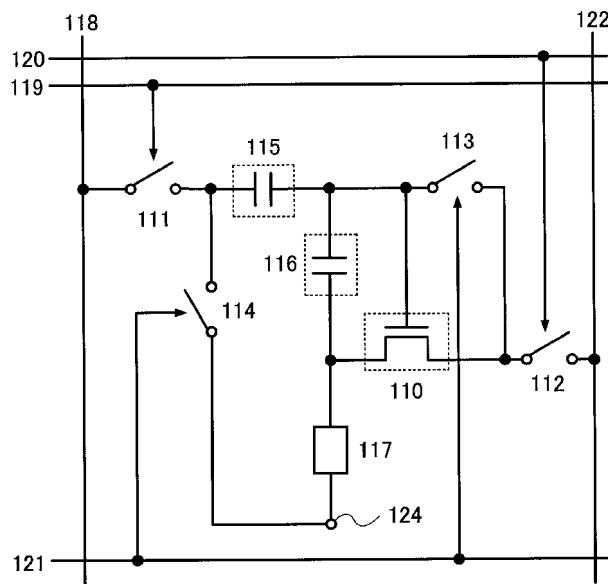

<136> 도 10a에 나타내는 화소는 트랜지스터(110), 제 1 스위치(111), 제 2 스위치(112), 제 3 스위치(113), 제 4 스위치(114), 제 1 용량소자(115), 제 2 용량소자(116), 발광소자(117)를 가진다. 또한, 화소는 신호선(118), 제 1 주사선(119), 제 2 주사선(120), 제 3 주사선(121), 및 전원선(122)에 접속된다.

<137> 실시형태 1에 나타낸 도 1의 화소에서는 용량소자(115)의 제 1 전극이 제 4 스위치(114)를 통하여 전위 공급선(123)에 접속되지만, 도 10a에서는 전원선(122)에 접속할 수 있다. 이는, 전위공급선(123)에 한정되지 않고, 초기화 기간에 및 임계값 전압 기록 기간에 있어서 제 1 용량소자(115)의 소정의 전압이 유지되도록 제 1 전극에 전위를 공급할 수 있으면 좋기 때문이다. 따라서, 전위공급선(123) 대신에 전원선(122)을 사용할 수 있다. 이와 같이, 제 1 용량소자(115)의 제 1 전극에 전위를 공급하는 배선을 전원선(122)으로 대용함으로써, 배선 수를 줄일 수 있어, 개구율을 향상시킬 수 있다.

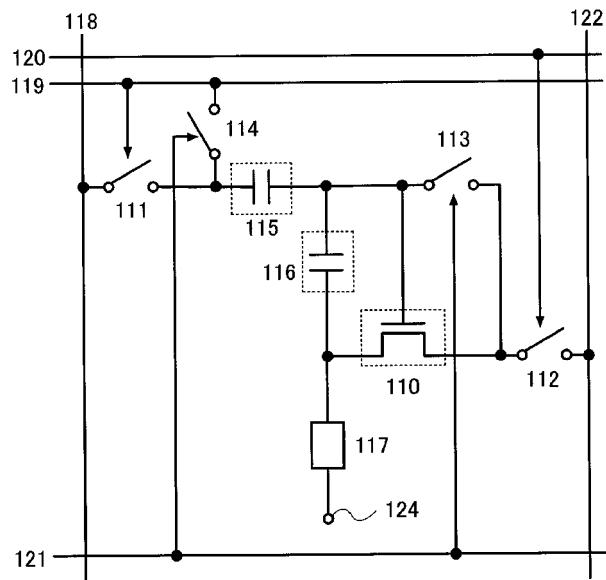

<138> 또한, 도 10b에 도시하는 바와 같이, 제 4 스위치(114)를 제 1 용량소자(115)와 병렬로 접속하여도 좋다. 즉, 제 1 용량소자(115)의 제 1 전극은 제 4 스위치(114)를 통하여 노드(131)에 접속하여도 좋다. 이러한 구성에 있어서도, 초기화 기간 및 임계값 전압 기록 기간에 있어서 제 1 용량소자(115)에 소정의 전압이 유지되도록 제 1 전극에 전위를 공급할 수 있다.

<139> 또한, 도 11의 화소에 나타내는 바와 같이, 제 1 용량소자(115)의 제 1 전극을 발광소자(117)의 대향전극(124) 또는 대향전극(124)에 소정의 전위를 공급하는 배선에 제 4 스위치(114)를 통하여 접속하여도 좋다. 즉, 도 1에 있어서의 전위공급선(123)으로부터 공급되는 전위 대신에, 대향전극(124)에 공급되는, 소정의 전위를 사용하여도 좋다. 이상과 같이 해서, 배선 수를 줄일 수 있어, 개구율을 향상시킬 수 있다.

<140> 또한, 제 1 용량소자(115)의 제 1 전극과 발광소자(117)의 대향전극(124)을 접속하는 배선을, 대향전극(124)과 접속할 뿐만 아니라, 대향전극(124)에 접하고 병렬로 연장시킴으로써, 대향전극(124)에 있어서의 보조배선으로서 이용하여도 좋다. 물론, 보조배선은 1화소 내뿐만 아니라, 인접하는 화소나 화소영역 전체로 배치되어도 좋다. 이러한 보조배선에 의하여, 대향전극(124)의 저저항화를 도모할 수 있다. 그렇기 때문에, 대향전극(124)을 박막화한 경우에는, 저항값은 증가를 방지할 수 있다. 특히, 대향전극(124)에 투광성을 가지는 전극을 사용한 경우에 있어서 효과적이다. 또한, 대향전극(124)의 저항값이 높아지는 경우에, 전압항하에 의한 대향전극(124)의 불균일한 면내전위분포에 의하여 생기는 발광소자(117)의 휙도의 편차를 억제할 수 있다. 따라서, 보다 신뢰성을 향상시킬 수 있다.

<141> 이때, 도 10a 내지 도 11에 도시한 화소 구성에 있어서도, 실시형태 1과 같이 동작을 시킴으로써, 트랜지스터(110)의 임계값 전압의 편차에 기인한 전류치의 편차를 억제할 수 있다. 따라서, 휙도 데이터에 대응한 전류를 발광소자(117)에 공급할 수 있어, 휙도의 편차를 억제할 수 있다. 또한, 대향전극의 전위를 일정하게 고정하여 동작시키므로, 소비 전력을 낮게 할 수 있다. 또한, 트랜지스터(110)의 동작 영역은 특별히 한정되지 않지만, 포화영역에서 동작시키는 경우에는, 발광소자(117)의 열화에 기인한 트랜지스터(110)에 흐르는 전류의 편차에 있어서도 억제할 수 있다.

<142> 또한, 도 1에 있어서의 전위공급선(123)은, 초기화 기간 및 임계값 기록 전압 기간에 있어서 제 1 용량

소자(115)의 제 1 전극에 임의의 전위를 공급하여, 제 1 용량소자(115)에 소정의 전압이 유지되면 좋다. 따라서, 전위공급선에 대용하는 배선은 상기에 한정되지 않고, 초기화 기간 및 임계값 전압 기록 기간에 전위가 변화하지 않는 배선이면 좋다. 예를 들면, 도 12에 나타내는 바와 같이, 제 1 주사선(119)이나, 제 3 주사선(121)을 사용할 수도 있다. 다만, 제 3 주사선(121)을 사용하는 경우에는, 제 4 스위치(114)는 실시형태 2에서 나타낸 정류소자로서 기능하는 경우가 있는 것에 유의하여, 스위치의 종류를 선택할 필요가 있다.

<143> 또한, 본 실시형태에서 나타낸 화소를 도 7의 표시장치에 적용할 수 있다. 실시형태 1과 같이, 각 행에 있어서의 데이터 기록 기간만 중복되지 않으면, 각 행에서 자유롭게 초기화 개시 시기를 설정할 수 있다. 또한, 각 화소는 자신의 어드레스 기간을 제외하고 발광할 수 있으므로, 1프레임 기간에 있어서의 발광 기간의 비율(즉, 듀티비)을 매우 크게 할 수 있고, 대략 100%로 할 수도 있다. 따라서, 휙도의 편차가 적고 듀티비가 높은 표시장치를 얻을 수 있다.

<144> 또한, 임계값 전압 기록 기간을 길게 설정할 수도 있으므로, 발광소자에 흐르는 전류값을 제어하는 트랜지스터의 임계값 전압을 보다 정확하게 용량소자에 기록할 수 있다. 따라서, 표시장치로서의 신뢰성이 향상된다.

<145> 상기에 한정되지 않고, 본 실시형태는, 다른 실시형태에 나타낸 화소구성과도 자유롭게 조합할 수 있다.

<146> (실시형태 4)

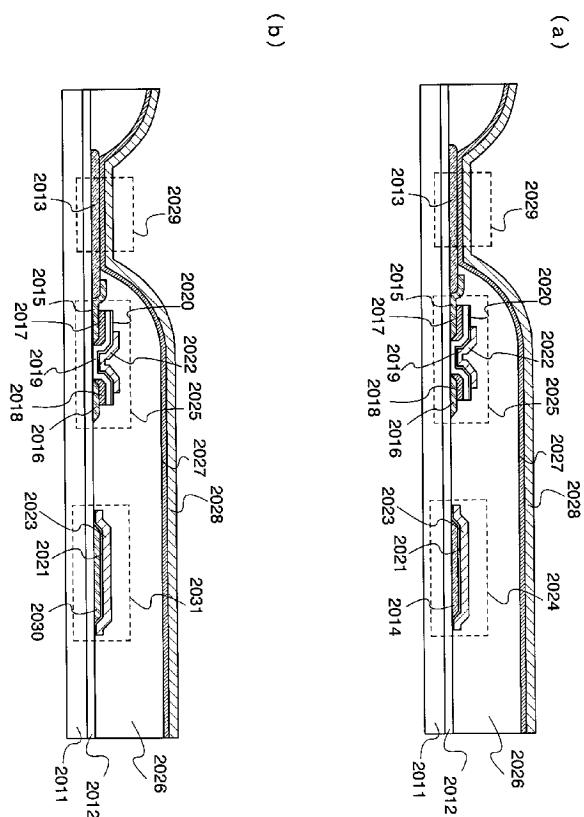

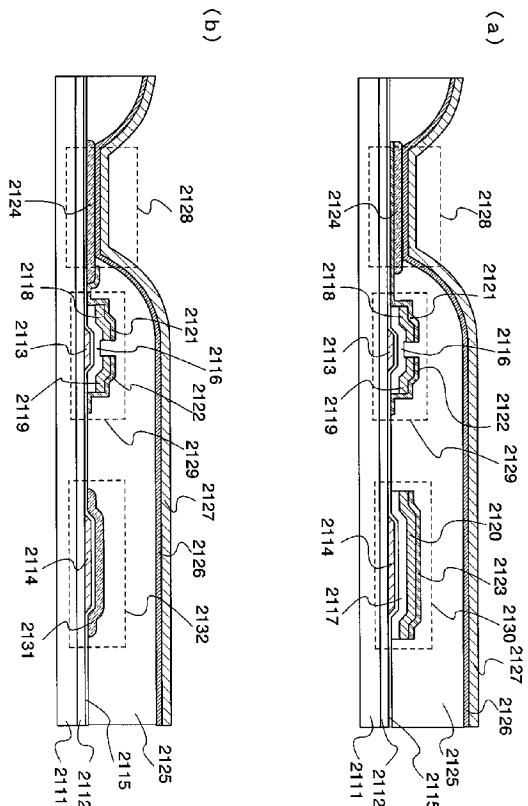

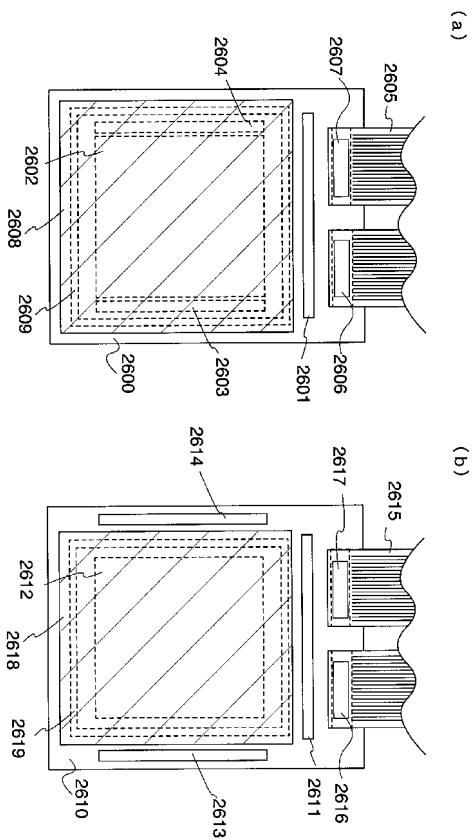

<147> 본 실시형태에서는, 실시형태 1 내지 실시형태 3과는 다른 구성의 화소를 도 13 내지 도 16에 나타낸다. 또한, 실시형태 3에 있어서는, 1화소에 주목하여 설명했지만, 각 화소에 접속된 배선을 화소간에서 공유하여 사용함으로써, 배선 수를 줄일 수도 있다. 이 경우, 정상으로 동작시키면 다양한 배선을 화소간에서 공유할 수 있다. 예를 들면, 이웃 화소와 배선을 공유할 수 있고, 그 경우의 일례에 대해서 본 실시형태에서 나타낸다. 또한, 실시형태 1과 같은 것에는 공통의 부호를 사용하여 나타내고, 동일한 부분 또는 유사한 기능을 가지는 부분의 상세한 설명은 생략한다.

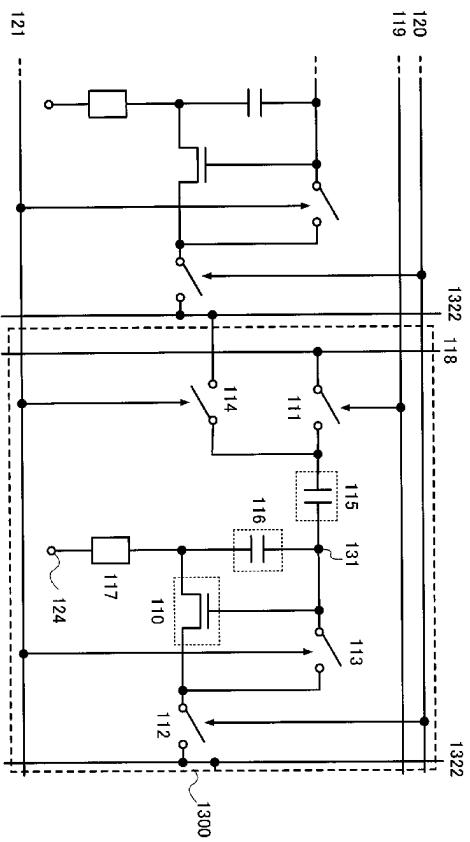

<148> 도 13에 나타내는 화소(1300)는 트랜지스터(110), 제 1 스위치(111), 제 2 스위치(112), 제 3 스위치(113), 제 4 스위치(114), 제 1 용량소자(115), 제 2 용량소자(116), 발광소자(117)를 가진다. 또한, 화소(1300)는, 신호선(118), 제 1 주사선(119), 제 2 주사선(120), 제 3 주사선(121), 및 전열의 전원선(1322)에 접속된다.

<149> 실시형태 1에서 나타낸 도 1의 화소에서는, 제 1 용량소자(115)의 제 1 전극은 제 4 스위치(114)를 통하여 전위공급선(123)에 접속되지만, 도 13에서는, 전열의 전원선(1322)에 접속할 수 있다. 이는, 전위공급선(123)에 한정 되지 않고, 초기화 기간 및 임계값 전압 기록 기간에 있어서 제 1 용량소자(115)에 소정의 전압이 유지되도록 제 1 용량소자(115)의 제 1 전극에 전위를 공급될 수 있으면 좋기 때문이다. 따라서 전위공급선(123) 대신에 전열의 전원선(1322)을 사용할 수 있다. 이와 같이, 화소(1300)는 전열의 화소와 배선을 공유함으로써 배선 수를 줄일 수도 있고, 개구율을 향상시킬 수 있다.

<150> 또한, 도 13에 나타낸 화소구성에 있어서도, 실시형태 1과 같은 동작을 시킴으로써 트랜지스터(110)의 임계값 전압의 편차에 기인한 전류값의 편차를 억제할 수 있다. 따라서, 휙도 데이터에 대응한 전류를 발광소자(117)에 공급할 수 있고, 휙도의 편차를 억제할 수 있다. 또한, 대향전극의 전위를 일정하게 고정하여 동작시키므로 소비전력을 낮게 할 수 있다. 또한, 트랜지스터(110)의 동작영역은 특별히 한정되지 않지만, 포화영역에서 동작시킨 경우에 있어서는, 발광소자(117)의 열화에 기인한 트랜지스터(110)에 흐르는 전류의 편차에 있어서도 억제할 수 있다.

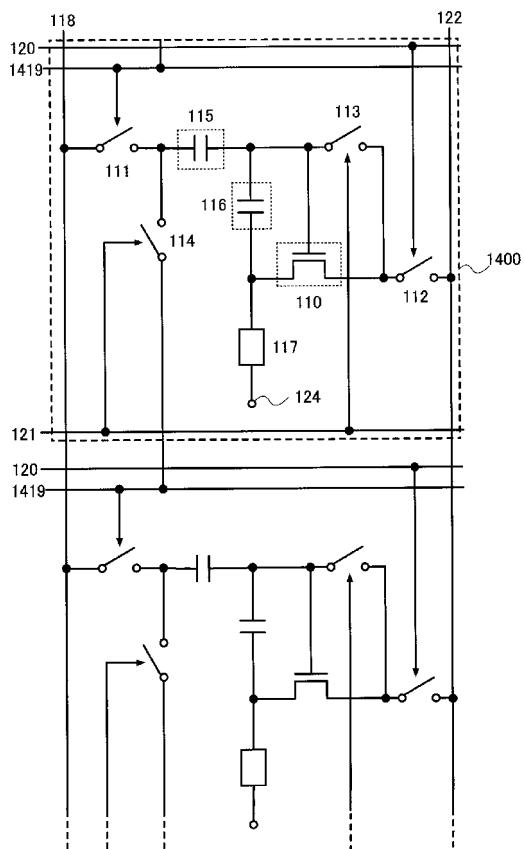

<151> 또한, 도 14의 화소(1400)에 나타내는 바와 같이, 도 1 전위공급선(123)을 다음 행의 제 1 주사선(1419)과 공유하여도 좋다. 화소(1400)에 있어서도, 실시형태 1과 같은 동작을 시킬 수 있다. 다만, 화소(1400)가 속하는 행의 초기화 기간 및 임계값 전압 기록 기간은 배선을 공유한 행의 데이터 기록 기간과 겹치지 않도록 동작시킬 필요가 있다.

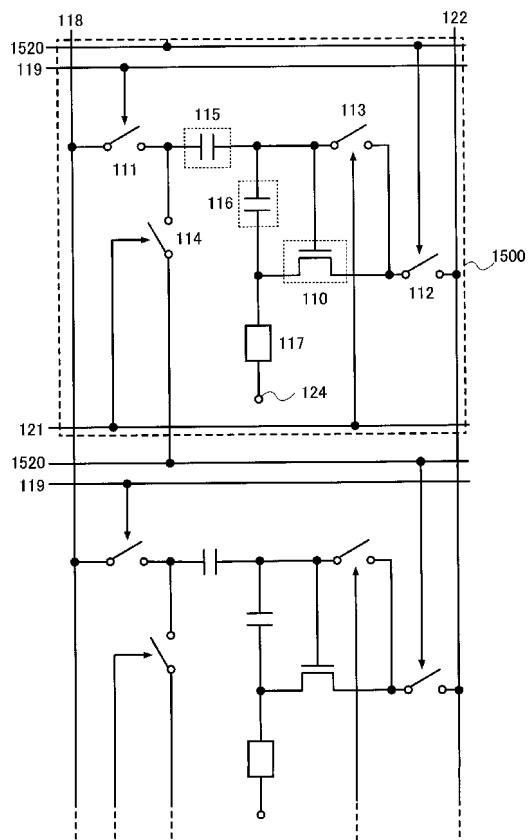

<152> 또한, 도 15의 화소(1500)에 나타내는 바와 같이, 도 1 전위공급선(123)을 다음 행의 제 2 주사선(1520)과 공유하여도 좋다. 화소(1500)에 있어서도, 실시형태 1과 같은 동작을 시킬 수 있다. 다만, 화소(1500)가 속하는 행의 초기화 기간 및 임계값 기록 기간은 배선을 공유한 행의 임계값 전압 기록 기간 및 데이터 기록 기간과 겹치도록 동작시키거나, 전혀 이들과 겹치지 않도록 동작시킬 필요가 있다. 즉, 제 1 용량소자(115)의 제 1 전극에 공급하는 전위를 제 2 스위치(112)를 온시키는 신호 또는 오프시키는 신호의 어느 한쪽에

사용한다.

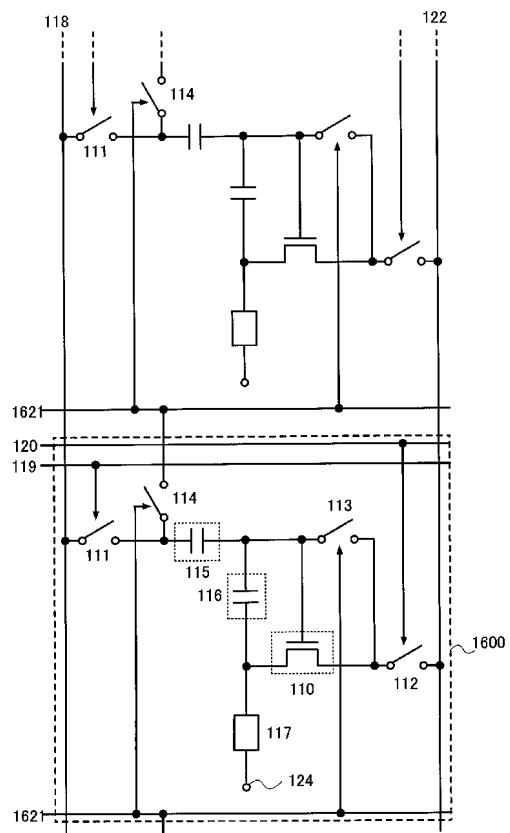

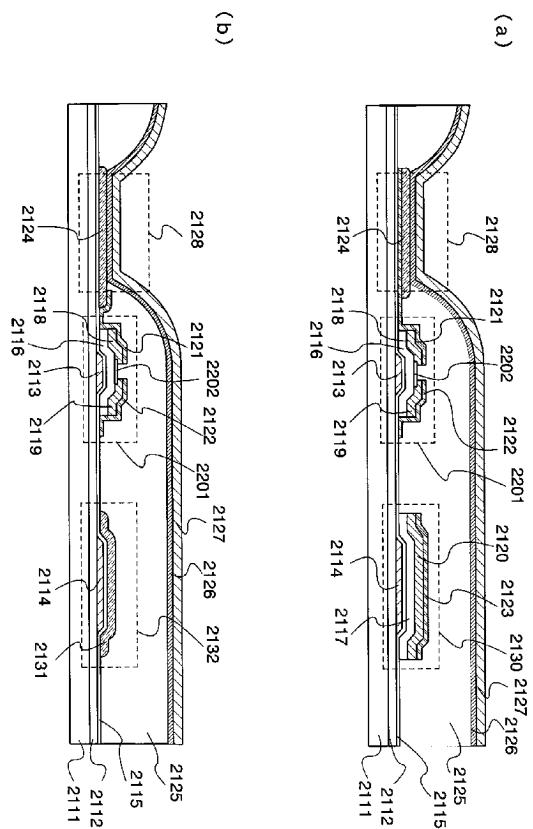

<153> 또한, 상기 이외에도, 도 1의 전위 공급선(123)을 도 16에 나타내는 바와 같이, 전행의 제 3 주사선(1621)과 공유하여도 좋다. 다만, 화소(1600)가 속하는 행의 초기화 기간 및 임계값 전압 기록 기간은 배선을 공유한 행의 임계값 전압 기록 기간 및 데이터 기록기간과 겹치지 않도록 동작시킬 필요가 있다.

<154> 또한, 본 실시형태에서는, 도 1 전위공급선(123)이 전열의 전원선, 또는 다음 행 또는 전행의 주사선과 공유하는 경우에 대해서 나타내지만, 초기화 기간 및 임계값 전압 기록 기간에 있어서 제 1 용량소자(115)에 소정의 전압이 유지되도록 제 1 전극에 전위를 공급할 수 있는 배선이면 그 이외에도 좋다.

<155> 또한, 본 실시형태에서 나타낸 화소를 도 7의 표시장치에 적용할 수 있다. 또한, 표시장치에 있어서, 도 13 내지 도 16에 기재한 화소마다의 동작의 제약 및 각 행에 있어서의 데이터 기록 기간이 중복하지 않는 범위 내로, 각 행 자유롭게 초기화 개시 시기를 설정할 수 있다. 또한, 각 화소는 자신의 어드레스 기간을 제거하고 발광할 수 있기 때문에, 1프레임 기간에 있어서의 발광기간의 비율(즉, 듀티비)을 매우 크게 할 수 있고, 대략 100%로 할 수도 있다. 따라서, 휙도의 편차가 적고 듀티비가 높은 표시장치를 얻을 수 있다.

<156> 또한, 임계값 전압 기록 기간을 길게 설정할 수도 있기 때문에, 발광소자에 흐르는 전류값을 제어하는 트랜지스터의 임계값 전압을 보다 정확하게 용량소자에 기록할 수 있다. 따라서, 표시장치로서의 신뢰성이 향상된다.

<157> 상기에 한정되지 않고, 본 실시형태는, 다른 실시형태에 나타낸 화소구성과도 자유롭게 조합할 수 있다.

<158> (실시형태 5)

<159> 본 실시형태에서는, 실시형태 1과는 다른 구성의 화소에 대해서 도 29에 나타낸다. 또한, 실시형태 1과 같은 것에는 공통의 부호를 사용하여 나타내고, 동일한 부분 또는 유사한 기능을 가지는 부분의 상세한 설명은 생략한다.

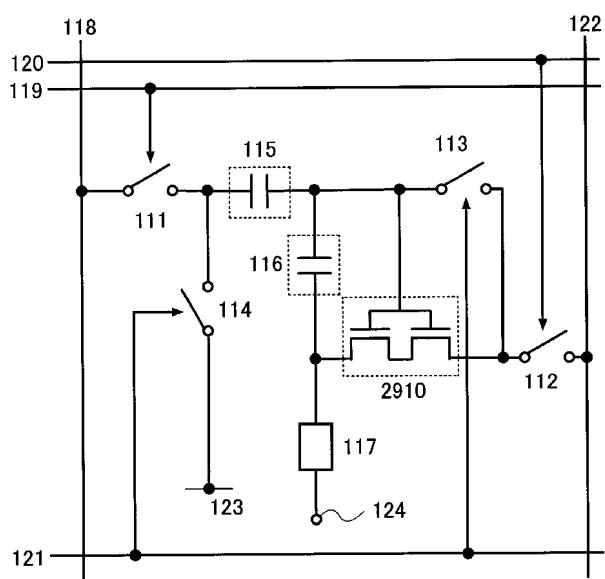

<160> 도 29에 도시하는 화소는, 트랜지스터(2910), 제 1 스위치(111), 제 2 스위치(112), 제 3 스위치(113), 제 4 스위치(114), 제 1 용량소자(115), 제 2 용량소자(116), 발광소자(117)를 가진다. 또한, 화소는, 신호선(118), 제 1 주사선(119), 제 2 주사선(120), 제 3 주사선(121), 및 전원선(122), 및 전위공급선(123)에 접속된다.

<161> 본 실시형태에 있어서의 트랜지스터(2910)는, 트랜지스터를 2개 직렬로 접속한 멀티 게이트형 트랜지스터이며, 실시형태 1의 트랜지스터(110)와 동일한 위치에 형성된다. 다만, 직렬로 접속되는 트랜지스터의 수는 특별히 한정되지 않는다.

<162> 도 1의 화소와 마찬가지로, 도 29에 도시한 화소를 동작시킴으로써, 트랜지스터(2910)의 임계값 전압의 편차에 기인한 전류치의 편차를 억제할 수 있다. 따라서, 휙도 데이터에 대응한 전류를 발광소자(117)에 공급할 수 있어, 휙도의 편차를 억제할 수 있다. 또한, 대향전극의 전위를 일정하게 고정하여 동작시키므로 소비전력을 낮게 할 수 있다. 또한, 트랜지스터(2910)의 동작 영역은 특별히 한정되지 않지만, 포화영역에서 동작시키는 경우에는, 발광소자(117)의 열화에 기인한 트랜지스터(2910)에 흐르는 전류의 편차에 있어서도 억제할 수 있다.

<163> 본 실시형태에 있어서의 트랜지스터(2910)의 채널 길이 L는, 직렬로 접속된 2개의 트랜지스터의 채널 폭이 동일한 경우, 각 트랜지스터의 채널 길이의 합계로서 작용한다. 따라서, 포화영역에 있어서 드레인-소스간 전압 Vds에 관계없이, 보다 일정치에 가까운 전류치를 용이하게 얻을 수 있다. 특히, 트랜지스터(2910)는 긴 채널 길이 L를 가지는 트랜지스터의 제작이 곤란할 경우에 효과적이다. 이 때, 2개의 트랜지스터의 접속부는 저항으로서 기능한다.

<164> 이 때, 트랜지스터(2910)는 발광소자(117)에 공급하는 전류치를 제어하는 기능을 가지면 되고, 트랜지스터의 종류는 특별히 한정되지 않는다. 따라서, 결정성 반도체막을 사용한 박막 트랜지스터(TFT), 아모퍼스 실리콘이나 다결정 실리콘으로 대표되는 비단결정성 반도체막을 사용한 박막 트랜지스터, 반도체 기판이나 SOI 기판을 사용해서 형성되는 MOS형 트랜지스터, 접합형 트랜지스터, 바이폴러 트랜지스터, ZnO나 a-InGaZnO 등의 화합물 반도체를 사용한 트랜지스터, 유기 반도체나 카본나노튜브를 사용한 트랜지스터, 또는 그 외의 트랜지스터를 적용할 수 있다.

<165> 또한 도 29에 도시한 화소는, 도 1에 도시한 화소와 같이, 제 1 스위치(111), 제 2 스위치(112), 제 3 스위치(113), 제 4 스위치(114)는 트랜지스터 등을 사용할 수 있다.

<166> 또한, 도 7의 표시장치에 본 실시형태에 나타낸 화소를 적용할 수 있다. 실시형태 1과 같이, 각 행에 있어서의 데이터 기록 기간만 중복되지 않으면, 각 행에서 자유롭게 초기화 개시 시기를 설정할 수 있다. 또한, 각 화소는 자신의 어드레스 기간을 제외하고 발광할 수 있으므로, 1프레임 기간에 있어서의 발광 기간의 비율(즉, 듀티비)을 매우 크게 할 수 있고, 대략 100%로 할 수도 있다. 따라서, 휴도의 편차가 적고 듀티비가 높은 표시장치를 얻을 수 있다.

<167> 또한, 임계값 전압 기록 기간을 길게 설정할 수도 있으므로, 발광소자에 흐르는 전류치를 제어하는 트랜지스터의 임계값 전압을 보다 정확하게 용량소자에 기록할 수 있다. 따라서, 표시장치로서의 신뢰성이 향상된다.

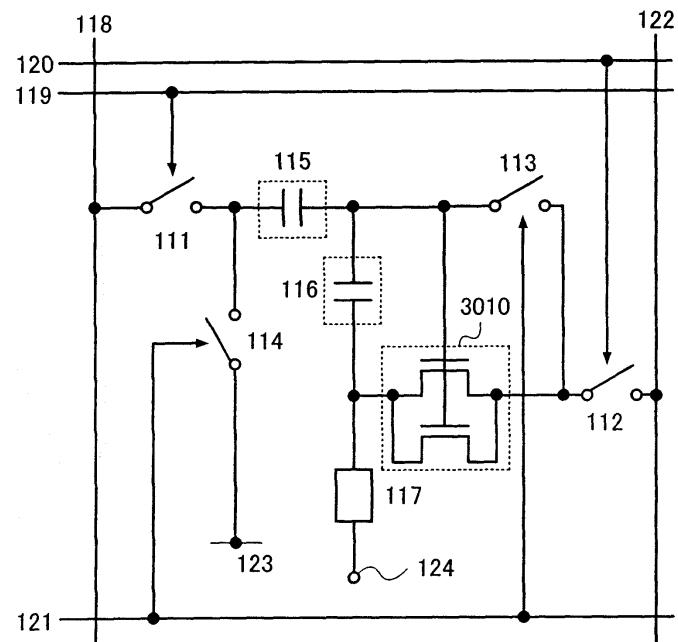

<168> 또한, 트랜지스터(2910)는 트랜지스터가 직렬로 접속된 구성에 한정되지 않고, 도 30에 도시하는 트랜지스터(3010)와 같이, 병렬로 트랜지스터가 접속된 구성이라도 좋다. 트랜지스터(3010)에 의해, 보다 큰 전류를 발광소자(117)에 공급할 수 있다. 또한, 병렬로 접속한 2개의 트랜지스터에 의해 트랜지스터의 특성이 평균화되므로, 트랜지스터(3010)를 구성하는 트랜지스터 본래의 특성 편차를 더욱 작게 할 수 있다. 따라서, 편차가 작으면, 트랜지스터의 임계값 전압의 편차에 기인하는 전류치의 편차를 보다 쉽게 억제할 수 있다.

<169> 또한 트랜지스터(3010)에 나타낸 병렬로 접속된 각각의 트랜지스터를 도 29에 나타낸 트랜지스터(2910)와 같이 직렬로 접속해도 된다.

<170> 상기에 한정되지 않고, 본 실시형태는, 다른 실시형태에 나타낸 화소구성과도 자유롭게 조합할 수 있다. 즉, 트랜지스터 2910 또는 트랜지스터 3010은, 다른 실시형태에 나타낸 화소 구성에도 적용할 수 있다.

<171> (실시형태 6)

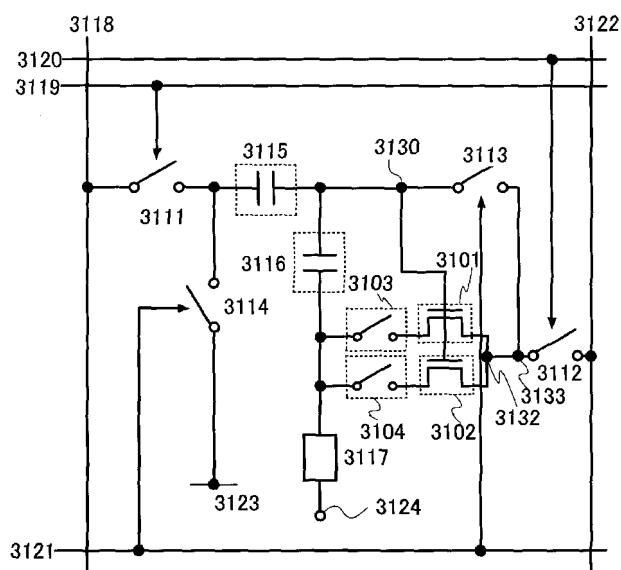

<172> 본 실시형태에서는 본 발명의 화소에 있어서, 발광소자에 공급하는 전류치를 제어하는 트랜지스터를 각각의 기간마다 전환함으로써, 트랜지스터의 경시적인 열화를 평균화하는 화소 구성에 대해서 도 31을 사용하여 설명한다.

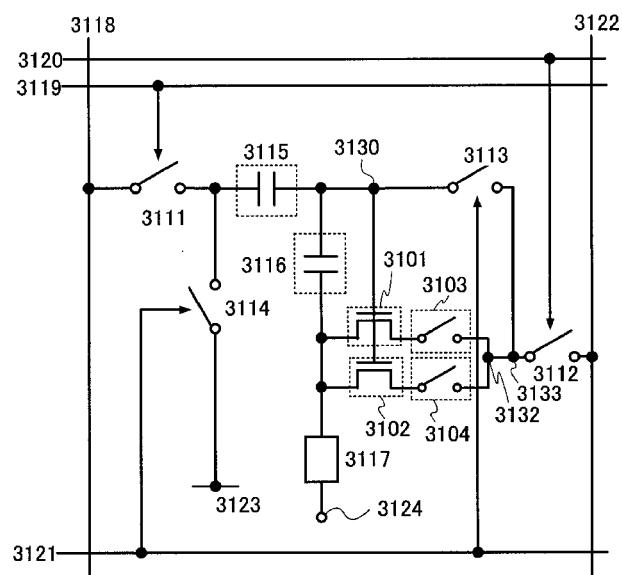

<173> 도 31에 나타내는 화소는, 제 1 트랜지스터(3101), 제 2 트랜지스터(3102), 제 1 스위치(3111), 제 2 스위치(3112), 제 3 스위치(3113), 제 4 스위치(3114), 제 5 스위치(3103), 제 6 스위치(3104), 제 1 용량소자(3115), 제 2 용량소자(3116), 발광소자(3117)를 가진다. 또한, 화소는, 신호선(3118), 제 1 주사선(3119), 제 2 주사선(3120), 제 3 주사선(3121), 전원선(3122), 및 전위공급선(3123)에 접속된다. 또한, 도 31에는 도시하지 않지만, 제 5 스위치(3103) 및 제 6 스위치(3104)의 온/오프를 각각 제어하는 제 4 주사선 및 제 5 주사선에도 접속되어 있다. 본 실시형태에 있어서, 제 1 트랜지스터(3101) 및 제 2 트랜지스터(3102)는 N채널형 트랜지스터로 하고, 각각의 트랜지스터는 게이트-소스간 전압( $V_{gs}$ )이 임계값 전압을 초과했을 때, 도통 상태가 되는 것으로 한다. 또한, 발광소자(3117)의 화소전극은 양극, 대향전극(3124)은 음극으로 한다. 또한, 트랜지스터의 게이트-소스간 전압은  $V_{gs}$ , 제 1 용량소자(3115) 및 제 2 용량소자(3116)에 축적된 전압은 각각  $V_{c1}$ ,  $V_{c2}$ 라고 기재한다. 또한, 제 1 트랜지스터(3101)의 임계값 전압을  $V_{th1}$ , 제 2 트랜지스터(3102)의 임계값 전압을  $V_{th2}$ 라고 기재하고, 전원선(3122), 전위공급선(3123) 및 신호선(3118)을 각각 제 1 배선, 제 2 배선, 제 3 배선이라고도 부른다.

<174> 제 1 트랜지스터(3101)의 제 1 전극(소스 전극 및 드레인 전극의 한쪽)은, 제 5 스위치(3103)를 통하여 발광소자(3117)의 화소전극에 접속되고, 제 2 전극(소스 전극 및 드레인 전극의 다른 쪽)은 제 2 스위치(3112)를 통하여 전원선(3122)에 접속된다. 또한, 제 1 트랜지스터(3101)의 게이트 전극도 제 3 스위치(3113) 및 제 2 스위치(3112)를 통하여 전원선(3122)과 접속되어 있다. 또한, 제 3 스위치(3113)는, 제 1 트랜지스터(3101)의 게이트 전극과 제 2 스위치(3112) 사이에 접속되어 있고, 제 1 트랜지스터(3101)의 제 2 전극과, 제 2 스위치(3112)와 제 3 스위치(3113)가 접속되는 배선과의 접속개소를 노드(3133)로 한다.

<175> 제 2 트랜지스터(3102)의 제 1 전극(소스 전극 및 드레인 전극의 한쪽)은, 제 6 스위치(3104)를 통하여 발광소자(3117)의 화소전극에 접속되고, 제 2 전극(소스 전극 및 드레인 전극의 다른 쪽)은 제 1 트랜지스터(3101)의 제 2 전극과 접속된다. 또한, 제 1 트랜지스터(3101)의 제 2 전극과 제 2 트랜지스터(3102)의 제 2 전극과의 접속개소를 노드 3132로 하면, 노드 3132는 노드 3133과 접속된다. 또한, 제 2 트랜지스터(3102)의 게이트 전극은 제 3 스위치(3113)를 통하여 노드(3133)에 접속된다. 또한, 제 1 트랜지스터(3101)의 게이트 전

극과 제 2 트랜지스터(3102)의 게이트 전극은 접속된다.

<176> 또한, 제 1 트랜지스터(3101) 및 제 2 트랜지스터(3102)의 게이트 전극과, 제 3 스위치(3113)와의 접속 개소를 노드 3130으로 하면, 노드 3130은 제 1 용량소자(3115) 및 제 1 스위치(3111)를 통하여 신호선(3118)과 접속된다. 즉, 제 1 용량소자(3115)의 제 1 전극이 제 1 스위치(3111)를 통하여 신호선(3118)에, 제 2 전극이 제 1 트랜지스터(3101) 및 제 2 트랜지스터(3102)의 게이트 전극에 접속된다. 또한, 제 1 용량소자(3115)의 제 1 전극은 제 4 스위치(3114)를 통하여 전위공급선(3123)과도 접속된다. 노드(3130)는 또 제 2 용량소자(3116)를 통하여 발광소자(3117)의 화소전극과도 접속된다. 즉, 제 2 용량소자(3116)의 제 1 전극이 제 1 트랜지스터(3101) 및 제 2 트랜지스터(3102)의 게이트 전극과, 제 2 전극이 제 5 스위치(3103) 및 제 6 스위치(3104)를 통하여 제 1 트랜지스터(3101) 및 제 2 트랜지스터(3102)의 제 1 전극에 접속된다. 이들 용량소자는, 배선, 반도체 층이나 전극으로 절연막을 끼우는 것으로 형성하여도 좋고, 경우에 따라, 제 1 트랜지스터(3101) 및 제 2 트랜지스터(3102)의 게이트 용량을 사용하여 제 2 용량소자(3116)를 생략할 수도 있다.

<177> 또한, 제 1 주사선(3119), 제 2 주사선(3120), 제 3 주사선(3121)에 신호를 입력함으로써, 각각의 제 1 스위치(3111), 제 2 스위치(3112), 제 3 스위치(3113) 및 제 4 스위치(3114)의 온/오프가 제어된다. 상술한 바와 같이, 도 31에서, 제 5 스위치(3103) 및 제 6 스위치(3104)의 온/오프를 제어하는 주사선은 생략한다.

<178> 신호선(3118)에는, 비디오신호에 해당하는 화소의 계조에 따른 신호, 즉 휘도 데이터에 따른 전위가 입력된다.

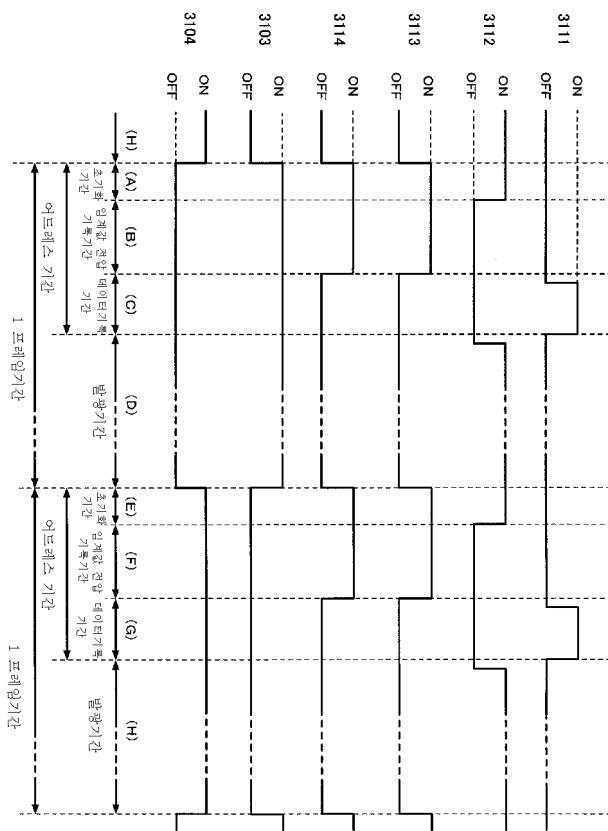

<179> 다음으로, 도 31에서 나타낸 화소의 동작에 대해서 도 32의 타이밍 차트를 참조하여 설명한다. 또한, 도 32a 내지 도 32h에 있어서 1화면분의 화상을 표시하는 기간에 해당하는 1프레임 기간은, 초기화 기간, 임계값 전압 기록 기간, 데이터 기록 기간 및 발광 기간으로 분할된다.

<180> 또한, 발광소자(3117)의 대향전극(3124)에는 V1의 전위(V1: 임의의 수)가 입력된다. 또한, 발광소자(3117)가 발광하기 위하여 적어도 필요로 하는 전위차를  $V_{EL}$ 로 하면, 전원선(3122)에는  $V1+V_{EL}+Vth+\alpha$  ( $\alpha$ : 임의의 양수)의 전위가 입력된다. 즉, 전원선(3122)은  $V1+V_{EL}+Vth+\alpha$  이상의 전위이면 좋다. 또한,  $Vth$ 는  $Vth1$  또는  $Vth2$ 의 큰 쪽의 값으로 한다. 전위공급선(3123)의 전위는 특별히 한정되지 않지만, 화소가 형성된 패널에 입력되는 전위의 범위 내인 것이 바람직하다. 이렇게 하면, 전원을 별도 제작할 필요가 없어진다. 또한, 여기서는 전위공급선(3123)의 전위를  $V2$ 로 한다.

<181> 우선, 도 32의 기간(A)에 나타내는 초기화기간에서는, 제 1 스위치(3111) 및 제 6 스위치(3104)를 오프로 하여, 제 2 스위치(3112), 제 3 스위치(3113) 및 제 4 스위치(3114) 및 제 5 스위치(3103)를 온으로 한다. 이 때, 제 1 트랜지스터(3101)는 도통상태이며, 제 1 용량소자(3115)에는  $V1+V_{EL}+Vth+\alpha-V2$ 가, 제 2 용량소자(3116)에는  $Vth+\alpha$ 가 유지된다. 또한, 초기화 기간에서는, 제 1 용량소자(3115)에는 소정의 전압이, 제 2 용량소자(3116)에는 적어도  $Vth1$ 보다 높은 전압이 유지되면 좋다.

<182> 도 32의 기간(B)에 나타내는 임계값 전압 기록 기간에서는, 제 2 스위치(3112)를 오프로 한다. 따라서, 트랜지스터(3101)의 제 1 전극 즉, 소스 전극의 전위는 점점 상승하고, 제 1 트랜지스터(3101)의 게이트-소스간 전압  $Vgs$ 가 임계값 전압( $Vth1$ )으로 되면, 제 1 트랜지스터(3101)는 비도통 상태가 된다. 따라서, 제 2 용량소자(3116)에 유지되는 전압  $Vc2$ 는 대체로  $Vth1$ 가 된다.

<183> 그 후의 도 32의 기간(C)에 나타내는 데이터 기록 기간에 있어서는, 제 3 스위치(3113) 및 제 4 스위치(3114)를 오프로 한 후, 제 1 스위치(3111)를 온으로 하고, 신호선(3118)보다 휘도 데이터에 따른 전위( $V2+Vdata$ )를 입력한다. 이 때, 제 2 용량소자(3116)에 유지되는 전압  $Vc2$ 는, 제 1 용량소자(3115), 제 2 용량소자(3116) 및 발광소자(3117)의 정전용량을 각각  $C1$ ,  $C2$ ,  $C3$ 로 하면,  $C3>>C1$ ,  $C2$ 로부터  $Vth1+Vdata \times (C1/(C1+C2))$ 로 된다.

<184> 또한,  $C1$ 과  $C2$ 는 신호선(3118)으로부터 공급하는 전위를 결정할 때에 필요하지만, 이들의 관계는 특별히 한정되지 않는다. 또한,  $C1>C2$ 의 경우에는, 휘도변화에 따른  $Vdata$ 의 진폭을 적게 할 수 있기 때문에, 소비전력을 저감할 수 있다. 한편,  $C2>C1$ 의 경우에는, 주위의 스위치의 온, 오프나 오프 전류에 의한  $Vc2$ 의 변화를 억제할 수 있다. 이들의 상반되는 효과에 의거하여  $C1$ 과  $C2$ 는 동일하며, 제 1 용량소자(3115)와 제 2 용량소자(3116)의 크기는 동일한 것이 바람직하다.

<185> 또한, 다음 발광기간에 있어서, 발광소자(3117)를 비발광으로 하고 싶은 경우는,  $Vdata \leq 0$ 의 전위를 입력하면 좋다.

- <186> 다음, 도 32의 기간(D)에 나타내는 발광기간에서는, 제 1 스위치(3111)를 오프로 한 후, 제 2 스위치(3112)를 온으로 한다. 이 때, 트랜지스터(3101)의 게이트-소스간 전압  $V_{gs}$ 는  $V_{th1}+V_{data}\times(C1/(C1+C2))$ 로 되고, 휘도 데이터에 따른 전류가 제 1 트랜지스터(3101) 및 발광소자(3117)에 흐르고, 발광소자(3117)가 발광한다.

- <187> 이러한 동작에 의해, 발광소자(3117)에 흐르는 전류는, 제 1 트랜지스터(3101)의 동작영역이 포화영역, 선형영역 중 어느 경우에도, 제 1 트랜지스터(3101)의 임계값 전압( $V_{th1}$ )에 의존하지 않는다.

- <188> 또한, 도 32의 기간(E)에 나타내는 다음 1프레임 기간에 있어서의 초기화 기간에는, 제 5 스위치(3103)를 오프 상태로 하고, 제 3 스위치(3113), 제 4 스위치(3114) 및 제 6 스위치(3104)를 온 상태로 한다. 제 2 트랜지스터(3102)는 도통상태로 되고, 제 1 용량소자(3115)에는  $V_1+V_{EL}+V_{th1} \alpha - V_2$ 가, 제 2 용량소자(3116)에는  $V_{th1} \alpha$ 가 유지된다. 또한, 이 초기화 기간에서는, 제 1 용량소자(3115)에는 소정의 전압이, 제 2 용량소자(3116)에는 적어도  $V_{th2}$ 보다 높은 전압이 유지되면 좋다.

- <189> 도 32의 기간(F)에 도시하는 임계값 전압 기록 기간에서는, 제 2 스위치(3112)를 오프로 한다. 따라서, 제 2 트랜지스터(3102)의 제 1 전극 즉, 소스 전극의 전위는 점점 상승하고, 제 2 트랜지스터(3102)의 게이트-소스간 전압  $V_{gs}$ 가 임계값 전압( $V_{th2}$ )으로 되면, 제 1 트랜지스터(3102)는 비도통 상태가 된다. 따라서, 제 2 용량소자(3116)에 유지되는 전압  $V_{c2}$ 는 대체로  $V_{th2}$ 가 된다.

- <190> 그 후의 도 32의 기간(G)에 나타내는 데이터 기록 기간에 있어서는, 제 3 스위치(3113) 및 제 4 스위치(3114)를 오프로 한 후, 제 1 스위치(3111)를 온으로 하고, 신호선(3118)보다 휘도 데이터에 따른 전위( $V_2+V_{data}$ )를 입력한다. 이 때, 제 2 용량소자(3116)에 유지되는 전압  $V_{c2}$ 는,  $V_{th2}+V_{data}\times(C1/(C1+C2))$ 로 된다.

- <191> 다음, 도 32의 기간(H)에 도시하는 발광기간에서는, 제 1 스위치(3111)를 오프로 한 후, 제 2 스위치(3112)를 온으로 한다. 이 때, 제 2 트랜지스터(3102)의 게이트-소스간 전압  $V_{gs}$ 는  $V_{th2}+V_{data}\times(C1/(C1+C2))$ 로 되고, 휘도 데이터에 따른 전류가 제 2 트랜지스터(3102) 및 발광소자(3117)에 흐르고, 발광소자(3117)가 발광한다.

- <192> 또한, 제 2 트랜지스터(3102)의 동작영역이 포화영역, 선형영역 중의 어느 경우에 있어서도, 발광소자(3117)에 흐르는 전류는 임계값 전압( $V_{th1}$ )에 의존하지 않는다.

- <193> 따라서, 제 1 트랜지스터(3101), 또는 제 2 트랜지스터(3102) 중의 어느 트랜지스터를 사용하여 발광소자에 공급하는 전류를 제어하더라도, 트랜지스터의 임계값 전압의 편차에 기인한 전류치의 편차를 억제하여, 휘도 데이터에 대응한 전류치를 발광소자(3117)에 공급할 수 있다. 이 때, 제 1 트랜지스터(3101)와, 제 2 트랜지스터(3102)를 전환하여 사용함으로써, 하나의 트랜지스터에 가해지는 부하를 경감함으로써, 트랜지스터의 경시적인 임계값 전압의 변화를 작게 할 수 있다.

- <194> 이상에 따라, 제 1 트랜지스터(3101), 제 2 트랜지스터(3102)의 임계값 전압에 기인한 휘도의 편차를 억제할 수 있다. 또한, 대향전극(3124)의 전위를 일정한 전위로 고정하므로, 소비 전력을 낮출 수 있다.

- <195> 또한, 제 1 트랜지스터(3101)와, 제 2 트랜지스터(3102)를 포화영역에서 동작시키는 경우에는, 발광소자(3116)의 열화에 의한 각각의 트랜지스터에 흐르는 전류의 편차도 억제할 수 있다.

- <196> 또한, 제 1 트랜지스터(3101), 제 2 트랜지스터(3102)를 포화영역에서 동작시키는 경우, 이들의 트랜지스터의 채널 길이  $L$ 은 긴 것이 바람직하다.

- <197> 또한, 본 발명에서는, 트랜지스터의 임계값 전압의 편차에 기인하는 전류치의 편차를 억제할 수 있으므로, 그 트랜지스터에 의해 제어된 전류가 공급되는 곳은 특별히 한정되지 않는다. 따라서, 도 31에 나타낸 발광소자(3117)에는, 대표적으로는 EL소자(유기 EL소자, 무기 EL소자 또는 유기물 및 무기물을 포함한 EL소자)를 적용할 수 있다. 또한, 발광소자(3117) 대신에, 전자방출소자, 액정소자, 전자 잉크 등을 적용할 수도 있다.

- <198> 제 1 트랜지스터(3101), 제 2 트랜지스터(3102)는 발광소자(3117)에 공급하는 전류치를 제어하는 기능을 가지면 좋으므로, 트랜지스터의 종류는 특별히 한정되지 않는다. 따라서, 결정성 반도체막을 사용한 박막 트랜지스터(TFT), 비정질 실리콘이나 다결정 실리콘으로 대표되는 비결정성 반도체막을 사용한 박막 트랜지스터, 반도체기판이나 SOI기판을 사용해서 형성되는 트랜지스터, MOS형 트랜지스터, 접합형 트랜지스터, 바이폴러 트랜지스터, ZnO나 a-InGaZnO 등의 화합물 반도체를 사용한 트랜지스터, 유기반도체나 카본나노튜브를

사용한 트랜지스터, 그 이외의 트랜지스터를 적용할 수 있다.

<199> 제 1 스위치(3111)는 휘도 데이터에 따른 전위, 즉, 신호를 신호선(3118)으로부터 화소에 입력하는 타이밍을 선택하여, 주로 제 1 용량소자(3115)에 유지되는 전압, 및 제 2 용량소자(3116)에 유지되는 전압, 즉 제 1 트랜지스터(3101) 또는 제 2 트랜지스터(3102)의 게이트-소스간 전압을 변화시키는 것이다. 또한, 제 2 스위치(3112)는 제 1 트랜지스터(3101) 또는 제 2 트랜지스터(3102)의 제 2 전극에 소정의 전위를 공급하는 타이밍을 선택하는 것이다. 또한, 경우에 따라, 제 1 용량소자(3115)의 제 2 전극 및 제 2 용량소자(3116)의 제 1 전극에도 상기 소정의 전위를 공급한다. 제 3 스위치(3113)는 제 1 트랜지스터(3101) 또는 제 2 트랜지스터(3102)의 게이트 전극과 각각의 트랜지스터의 제 2 전극과의 접속을 제어하는 것이며, 제 4 스위치(3114)는 프레임 기간마다 제 1 용량소자(3115)에 소정의 전압을 유지시키는 타이밍을 선택하여, 제 1 용량소자(3115)의 제 1 전극에 소정의 전위를 공급하는지 아닌지를 제어하는 것이다. 따라서, 제 1 스위치(3111), 제 2 스위치(3112), 제 3 스위치(3113), 제 4 스위치(3114)는, 상기 기능을 가지면 특별히 한정되지 않는다. 예를 들면, 트랜지스터나 다이오드라도 좋고, 그들을 조합한 논리회로라도 좋다. 또한, 제 1 스위치(3111), 제 2 스위치(3112) 및 제 4 스위치(3114)는, 상기 타이밍으로 신호 또는 전위를 화소에 줄 수 있으면, 특별히 필요는 없다. 또한, 제 3 스위치(3113)에 있어서도 상기 기능을 실현할 수 있으면, 특별히 필요는 없다.

<200> 예를 들면, 제 1 스위치(3111), 제 2 스위치(3112), 제 3 스위치(3113), 제 4 스위치(3114), 제 5 스위치(3103), 제 6 스위치(3104)에 N채널형 트랜지스터를 사용한 경우, 화소를 N채널형 트랜지스터만으로 구성할 수 있으므로, 제조 공정의 간략화를 도모할 수 있다. 또한, 화소를 구성하는 트랜지스터의 반도체층에 아모포스 반도체나 세미 아모포스 반도체 등을 사용할 수 있다. 예를 들면, 아모포스 반도체로서 아모퍼스 실리콘(a-Si:H)을 들 수 있다. 이들의 비결정 반도체를 사용함으로써, 더욱 제조 공정의 간략화가 가능하다. 따라서, 제조비용의 삭감이나 수율의 향상을 도모할 수 있다.

<201> 또한, 제 1 스위치(3111), 제 2 스위치(3112), 제 3 스위치(3113), 제 4 스위치(3114), 제 5 스위치(3103), 제 6 스위치(3104)에 트랜지스터를 사용한 경우, 트랜지스터의 극성(도전형)은 특별히 한정되지 않는다. 다만, 오프 전류가 적은 트랜지스터를 사용하는 것이 바람직하다.

<202> 또한, 제 1 트랜지스터(3101) 및 제 5 스위치(3103)와 제 2 트랜지스터(3102) 및 제 6 스위치(3104)는, 도 37에 도시하는 바와 같이, 각각 위치를 바꾸어도 된다. 즉, 제 1 트랜지스터(3101) 및 제 2 트랜지스터(3102)의 제 1 전극은 제 2 용량소자(3116)를 통하여 제 1 트랜지스터(3101) 및 제 2 트랜지스터(3102)의 게이트 전극에 접속되어 있다. 또한, 제 1 트랜지스터(3101)의 제 2 전극은 제 5 스위치(3103)를 통하여 노드3132와 접속되고, 제 2 트랜지스터(3102)의 제 2 전극은 제 6 스위치(3104)를 통하여 노드 3132와 접속된다.

<203> 또한, 도 31 및 도 37에서는 트랜지스터와 스위치를 세트로 해서, 즉 제 1 트랜지스터(3101)와 제 5 스위치(3103), 제 2 트랜지스터(3102)와 제 6 스위치(3104)를 세트로 해서 병렬 수가 2인 경우에 대해서 기재했지만, 병렬로 배치하는 수는 특별히 한정되지 않는다.

<204> 또한 도 7의 표시장치에 본 실시형태에서 나타낸 화소를 적용함으로써, 실시형태 1과 유사하게, 각 행에 있어서의 데이터 기록 기간만 중복되지 않으면, 각 행에서 자유롭게 초기화 개시 시기를 설정할 수 있다. 또한, 각 화소는 자신의 어드레스 기간을 제외하고 발광할 수 있으므로, 1프레임 기간에 있어서의 발광 기간의 비율(즉, 뉴티비)을 상당히 크게 할 수 있고, 대략 100%로 할 수도 있다. 따라서, 휘도의 편차가 적고 뉴티비가 높은 표시장치를 얻을 수 있다.

<205> 또한 임계값 전압 기록 기간을 길게 설정할 수도 있으므로, 발광소자에 흐르는 전류치를 제어하는 트랜지스터의 임계값 전압을 더 정확하게 용량소자에 기록할 수 있다. 따라서, 표시장치로서의 신뢰성이 향상된다.

<206> 또한, 본 실시형태에 있어서도, 실시형태 3에서 나타내는 바와 같이, 전위공급선(3123)을 동일 화소 내의 배선으로 대용하거나, 실시형태 4와 같이, 다른 행의 배선과 공유하여도 좋다. 또한, 제 1 트랜지스터(3101) 및 제 2 트랜지스터(3102)의 각각에 트랜지스터가 직렬로 접속된 멀티 게이트형 트랜지스터나 병렬로 배치된 트랜지스터를 사용하여도 좋다. 이것들에 한정되지 않고, 본 실시형태는, 실시형태 1 내지 실시형태 5에 나타낸 화소 구성에 적용할 수 있다.

<207> (실시형태 7)

<208> 본 실시형태에서는, 실시형태 1과는 다른 구성의 화소를 나타낸다. 실시형태 1과 같은 것에는 공통의 부호로 나타내고, 동일 부분 또는 같은 기능을 가지는 부분의 상세한 설명은 생략한다. 또한, 이들은 실시형태

1과 마찬가지로 동작시키는 것으로 한다.

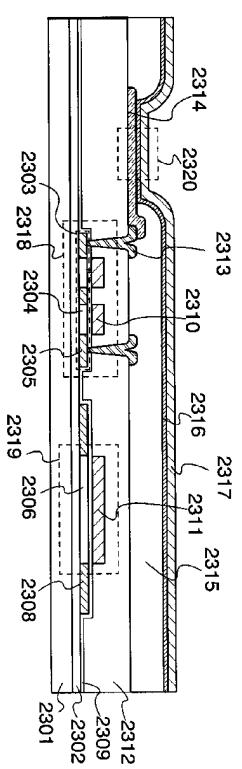

<209> 본 실시형태에서는 발광소자(117)에 강제적으로 전류가 흐르지 않도록 하는 화소 구성에 관하여 설명한다. 즉, 비발광 상태를 강제적으로 만드는 것으로써, 잔상이 거의 나타나지 않고, 동영상 특성이 뛰어난 표시장치를 얻는 것을 목적으로 한다.

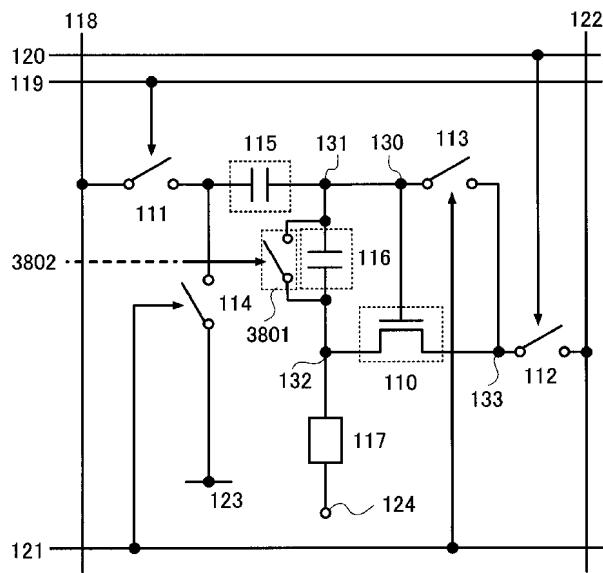

<210> 이러한 화소 구성의 하나를 도 38에 도시한다. 도 38에 도시하는 화소에는, 트랜지스터(110), 제 1 스위치(111), 제 2 스위치(112), 제 3 스위치(113), 제 4 스위치(114), 제 1 용량소자(115), 제 2 용량소자(116), 발광소자(117) 이외에도, 제 5 스위치(3801)를 가진다. 또한, 화소는 신호선(118), 제 1 주사선(119), 제 2 주사선(120), 제 3 주사선(121), 전원선(122) 및 전위공급선(123) 이외에도, 제 4 주사선(3802)에도 접속된다.

<211> 도 38에 있어서, 제 5 스위치(3801)는, 제 2 용량소자(116)와 병렬로 접속된다. 따라서, 제 5 스위치(3801)가 온 상태가 되면 트랜지스터(110)의 게이트 전극과 제 1 전극간이 단락된다. 따라서, 용량소자(116)에 유지된 트랜지스터(110)의 게이트-소스간 전압을 0V로 할 수 있으므로, 트랜지스터(110)는 오프 상태가 되고, 발광소자(117)를 비발광으로 할 수 있다. 또한, 제 5 스위치(3801)의 온/오프의 제어는, 제 4 주사선(3802)에 입력되는 신호에 의해 화소 1 행씩 주사함으로써 행해진다.

<212> 이러한 동작에 의하여, 화소에 기록된 신호를 소거한다. 따라서, 다음 초기화 기간까지는 강제적으로 비발광 상태가 되는 소거 기간을 설정할 수 있다. 즉, 흑색 표시가 삽입된다. 따라서, 잔상이 거의 나타나지 않고, 동영상 특성의 향상을 도모할 수 있다.

<213> 한편, 표시장치의 계조를 표현하는 구동방식에는, 아날로그 계조방식과 디지털 계조방식이 있다. 아날로그 계조방식에는, 발광소자의 발광 강도를 아날로그로 제어하는 방식과, 발광소자의 발광 시간을 아날로그로 제어하는 방식이 있다. 아날로그 계조방식에 있어서는 발광소자의 발광 강도를 아날로그로 제어하는 방식이 주로 이용되고 있다. 한편, 디지털 계조방식에서는 디지털 제어로 발광소자를 온/오프시켜, 계조를 표현하고 있다. 디지털 계조방식의 경우, 디지털 신호로 처리할 수 있으므로 노이즈에 강하다는 장점이 있다. 그러나, 발광상태와 비발광 상태의 2 상태밖에 없으므로, 이 상태대로는 2계조밖에 표현할 수 없다. 그래서, 별도의 방법을 조합하여, 다계조화를 도모하고 있다. 다계조화를 위한 방법으로서는, 화소의 발광 면적에 비중을 두고 그 선택에 의해 계조표시를 행하는 면적계조방식과, 발광 시간에 비중을 두고 그 선택에 의해 계조표시를 행하는 시간계조방식이 있다.

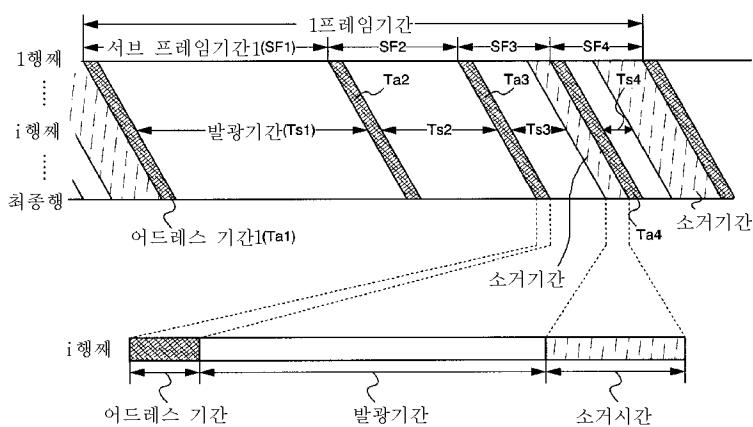

<214> 이 디지털 계조방식과 시간계조방식을 조합하는 경우, 도 39에 도시한 바와 같이, 1프레임 기간을 복수의 서브 프레임 기간(SFn)으로 분할한다. 각 서브 프레임 기간은, 초기화 기간, 임계값 전압 기록 기간 및 데이터 기록 기간을 포함하는 어드레스 기간(Ta)과, 발광 기간(Ts)을 포함한다. 또한, 서브 프레임 기간은 표시비트수 n에 따른 수를 1프레임 기간에 설정한다. 또한, 각 서브 프레임 기간에 있어서 발광 기간의 길이의 비를  $2^{(n-1)}:2^{(n-2)}:\dots:2:1$ 로 하고, 각 발광 기간에서 발광소자의 발광, 혹은 비발광을 선택하고, 발광소자가 발광하고 있는 1프레임 기간 동안의 합계 시간의 차이를 이용하여 계조표현을 행한다. 1프레임 기간에 있어서, 발광하는 합계 시간이 길면 휘도가 높고, 짧으면 휘도가 낮다. 또한, 도 39에 있어서는 4비트 계조의 예를 나타내는데, 1프레임 기간은 4개의 서브 프레임 기간으로 분할되어, 발광 기간의 조합에 의해,  $2^4 = 16$ 계조를 표현할 수 있다. 이때, 발광 기간의 길이의 비는, 특히 2의 거듭제곱의 비로 하지 않아도, 계조표현은 가능하다. 또한, 어느 서브 프레임 기간을 더 분할해도 좋다.

<215> 또한, 상기한 바와 같이, 시간계조방식을 사용하여 다계조화를 도모할 경우, 하위 비트의 발광 기간의 길이는 짧기 때문에, 발광 기간의 종료 후 즉시 다음 서브 프레임 기간의 데이터 기록 동작을 시작하려고 하면, 이전의 서브 프레임 기간의 데이터 기록 동작과 중복하여, 정상적인 동작을 할 수 없게 된다. 따라서, 서브 프레임 기간 내에 상기와 같이 소거 기간을 설정함으로써, 모든 행에 필요한 데이터 기록 기간보다 짧은 발광도 표현할 수 있다. 즉, 발광 기간을 자유롭게 설정할 수 있다.

<216> 본 발명은 아날로그 계조방식에 있어서 특히 효과적이다. 또한, 디지털 계조방식과 시간계조방식을 조합한 방식에 있어서도, 발광 기간을 자유롭게 설정할 수 있으므로, 소거 기간을 설정하는 것은 효과적이다.

<217> 또한, 전원선(122)으로부터 트랜지스터(110)를 통하여 발광소자(117)의 화소전극까지의 전류의 경로를 차단함으로써, 소거 기간을 설정하여도 좋다. 예를 들면, 전원선(122)으로부터 트랜지스터(110)를 통하여 발광소자(117)의 화소전극까지의 사이의 전류경로에 새로 스위치를 형성하여, 1 행마다 화소를 주사하여 그 스위치

를 오프로 함으로써 소거 기간을 형성할 수 있다.

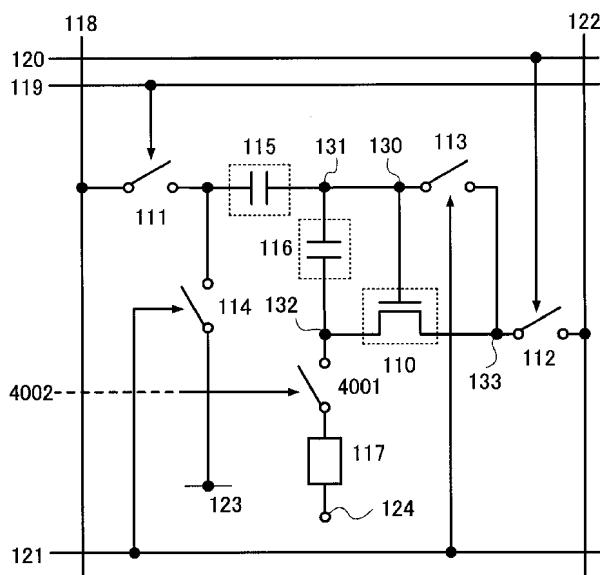

<218> 이러한 구성의 하나를 도 40에 도시한다. 도 40의 구성은, 도 1의 화소 구성에 추가로, 제 5 스위치(3001)가 트랜지스터(110)의 제 1 전극과 노드(132)의 사이에 접속된다. 그리고, 제 5 스위치(4001)의 온/오프는, 제 4 주사선(4002)에 입력되는 신호에 의하여 제어된다. 이 제 5 스위치(4001)를 오프로 함으로써, 소거기간을 형성할 수 있다.

<219> 또한, 트랜지스터(110)의 제 2 전극과 노드 133의 사이나, 도 41에 도시하는 바와 같이, 발광소자(117)의 화소전극과 노드 132의 사이에 제 5 스위치(4001)를 접속하여 소거기간을 형성하여도 좋다.

<220> 물론, 도 1에 있어서의 화소에 있어서 제 2 스위치(112)를 오프로 하여, 전원선(122)으로부터 발광소자(117)에의 전류경로를 차단함으로써, 새로운 스위치를 형성하지 않고 소거 기간을 형성하여도 좋다.

<221> 또한, 트랜지스터(110)의 게이트 전극의 전위를 변화시킴으로써, 강제적으로 소거 기간을 설정할 수도 있다.

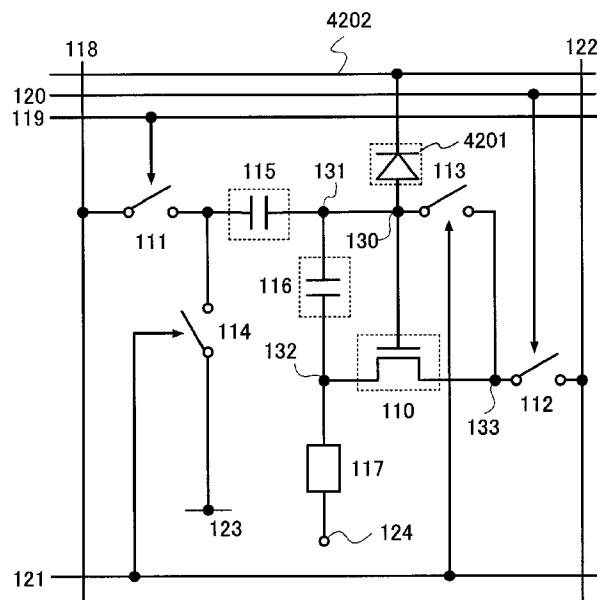

<222> 이러한 구성의 하나를 도 42에 도시한다. 도 42의 구성은, 도 1의 화소 구성에 대하여 정류소자(420 1)를 가지고, 그 정류소자(4201)를 통하여 트랜지스터(110)의 게이트 전극과 제 4 주사선(4202)이 접속된다. 또한, 트랜지스터(110)가 N채널형 트랜지스터이면, 정류소자(4201)는 트랜지스터(110)의 게이트 전극으로부터 제 4 주사선(4202)에 전류가 흐르도록 접속된다. 제 4 주사선(4202)은, 트랜지스터(110)를 강제적으로 오프 상태로 할 때에만 L레벨의 신호가 입력되고, 그 이외는 H레벨의 신호가 입력된다. 제 4 주사선(4202)이 H레벨일 때에는, 정류소자(4201)에는 전류가 흐르지 않고, L레벨이 되면 트랜지스터(110)의 게이트 전극으로부터 제 4 주사선(4202)에 전류가 흐른다. 이와 같이, 제 4 주사선(4202)에 전류를 흘려보냄으로써, 트랜지스터(110)의 게이트-소스간 전압을 임계값 전압( $V_{th}$ )이하로 하여, 트랜지스터(110)를 강제적으로 오프로 한다. 또한, L레벨의 전위는 트랜지스터(110)의 게이트 전극의 전위가 L레벨의 전위는, 트랜지스터(110)의 게이트 전극의 전위가 L레벨의 전위에 정류소자(4201)의 순 방향에 있어서의 임계값 전압을 가산한 전위이하로 되지 않는 것을 고려하여 결정해야 한다.

<223> 또한, 정류소자(4201)에는, 도 9b 내지 도 9d에 나타낸 쇼트키-배리어형 다이오드, PIN형 다이오드, PN형 다이오드, 이외에도, 도 9e 및 도 9f에 나타낸 다이오드 접속되어 있는 트랜지스터 등을 사용할 수 있다.

<224> 또한, 화소 구성은 강제적으로 비발광으로 하는 수단을 가지면 흑색 표시의 삽입에 의하여 잔상을 나타낼 수 없으므로, 상기의 구성에 특별히 한정되지 않는다.

<225> 본 실시형태에 나타낸 소거 기간을 설정하기 위한 스위치 등은, 상술한 도 1의 화소구성에 한정되지 않고, 그 이외의 실시형태에 나타낸 화소 구성에도 적용할 수 있다.

<226> 또한, 이러한 스위치를 설치하지 않아도 초기화 기간을 길게 설정함으로써 초기화 기간은 소거 기간을 겹힐 수 있다. 따라서, 실시형태 1 내지 실시형태 6에 기재한 화소를 동작할 때, 잔상을 보기 어렵게 하기 위하여 흑색 표시시키고자 하는 기간을 초기화 기간의 길이로 설정함으로써 동영상 특성의 향상을 도모할 수도 있다. 또한, 발광 기간에 있어서 전원선(122)의 전위를 대향전극(124)의 전위와 동일하게 함으로써 흑색 표시를 삽입해도 좋다.

<227> 또한, 본 실시형태에 나타낸 화소는, 실시형태 1에서 나타낸 표시장치에 적용할 수 있다. 이上面에 따라, 휴대의 편차가 적고, 동영상 특성이 뛰어난 표시장치를 얻을 수 있다.

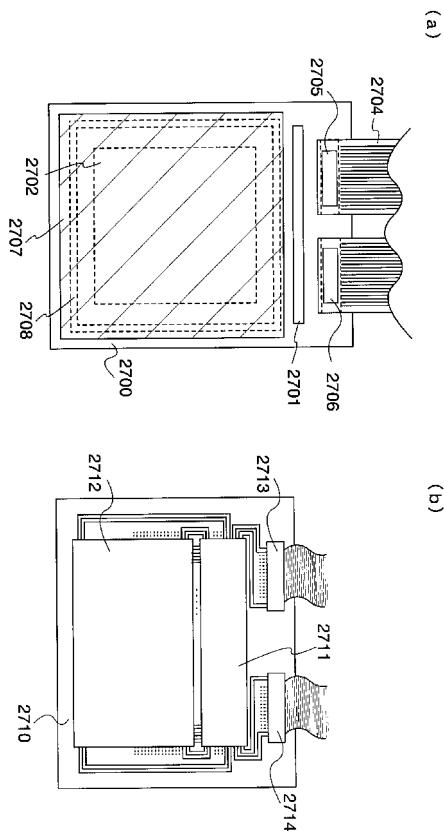

<228> (실시형태 8)

<229> 본 실시형태에서는, 발광소자에 공급하는 전류치를 제어하는 트랜지스터에 P채널형 트랜지스터를 적용한 경우에 대해서 도 46을 참조하여 설명한다.

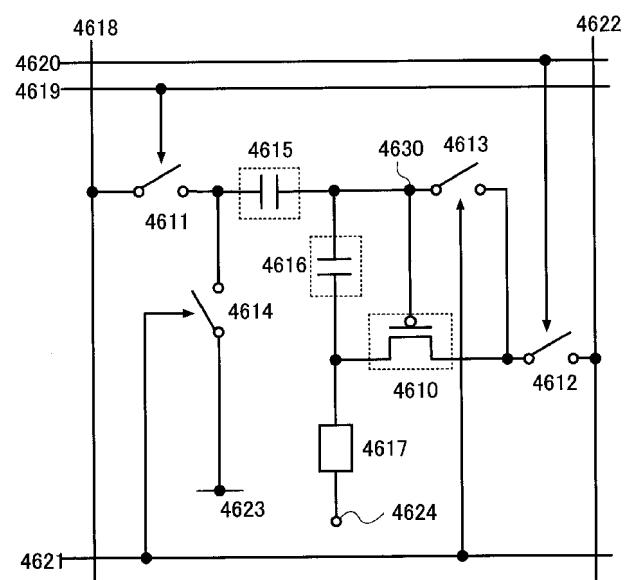

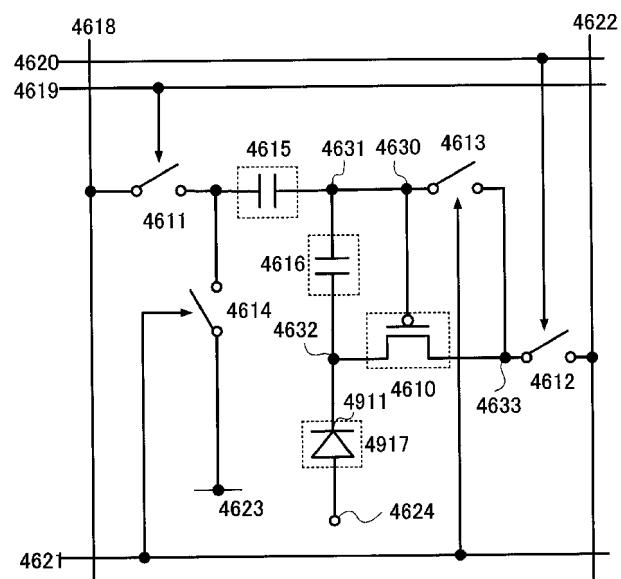

<230> 도 46에 도시하는 화소는, 트랜지스터(4610), 제 1 스위치(4611), 제 2 스위치(4612), 제 3 스위치(4613), 제 4 스위치(4614), 제 1 용량소자(4615), 제 2 용량소자(4616), 발광소자(4617)를 가진다. 화소는, 신호선(4618), 제 1 주사선(4619), 제 2 주사선(4620), 제 3 주사선(4621), 전원선(4622) 및 전위공급선(462 3)에 접속된다. 본 실시형태에 있어서, 트랜지스터(4610)는 P채널형 트랜지스터로 하고, 그 게이트-소스 전압의 절대치( $|V_{gs}|$ )가 임계값 전압( $|V_{th}|$ )을 초과했을 때(즉,  $V_{gs}$ 가  $V_{th}$  미만일 때) 도통 상태로 되는 것이다. 또한, 발광소자(4617)의 화소전극은 음극, 대향전극(4624)은 양극으로서 기능한다. 또한, 트랜지스터의 게이트-소스간 전압의 절대치를  $|V_{gs}|$ , 임계값 전압의 절대치를  $|V_{th}|$ , 제 1 용량소자(4615) 및 제 2 용량소자(4616)

에 축적된 전압을 각각  $V_{c1}$ ,  $V_{c2}$ 로 기재한다. 또한, 전원선(4622), 전위공급선(4623) 및 신호선(4618)을 각각 제 1 배선, 제 2 배선, 제 3 배선이라고도 부른다. 또한, 제 1 주사선(4619), 제 2 주사선(4620), 및 제 3 주사선(4621)을 각각 제 4 배선, 제 5 배선, 제 6 배선이라고 불러도 좋다.

<231> 트랜지스터(4610)의 제 1 전극(소스 전극 및 드레인 전극의 한쪽)은, 발광소자(4617)의 화소전극에 접속되고, 제 2 전극(소스 전극 및 드레인 전극의 다른 쪽)은 제 2 스위치(4612)를 통하여 전원선(4622)에 접속되며, 게이트 전극은 제 3 스위치(4613) 및 제 2 스위치(4612)를 통하여 전원선(4622)과 접속된다. 또한, 제 3 스위치(4613)는, 트랜지스터(4610)의 게이트 전극과 제 2 스위치(4612)의 사이에 접속된다.

<232> 또한, 트랜지스터(4610)의 게이트 전극과 제 3 스위치(4613)의 접속개소를 노드(4630)로 하면, 노드(4630)는 제 1 용량소자(4615) 및 제 1 스위치(4611)를 통하여 신호선(4618)과 접속된다. 즉, 제 1 용량소자(4615)의 제 1 전극이 제 1 스위치(4611)를 통하여 신호선(4618)에, 제 2 전극이 트랜지스터(4610)의 게이트 전극에 접속된다. 또한, 제 1 용량소자(4615)의 제 1 전극은 제 4 스위치(4614)를 통하여 전위공급선(4623)과도 접속된다. 노드(4630)는, 덧붙여 제 2 용량소자(4616)를 통하여 트랜지스터(4610)의 제 1 전극과도 접속된다. 즉, 제 2 용량소자(4616)의 제 1 전극이 트랜지스터(4610)의 게이트 전극과, 제 2 전극이 트랜지스터(4610)의 제 1 전극에 접속된다. 이를 용량소자는, 배선, 반도체 층이나 전극에 의하여 절연막을 끼우는 것으로 형성하여도 좋고, 경우에 따라, 트랜지스터(4610)의 게이트 용량을 사용하여 제 2 용량소자(4616)를 생략하는 것도 가능하다.

<233> 또한, 제 1 주사선(4619), 제 2 주사선(4620), 제 3 주사선(4621)에 신호를 입력함으로써, 각각 제 1 스위치(4611), 제 2 스위치(4612), 제 3 스위치(4613) 및 제 4 스위치(4614)의 온/오프가 제어된다.

<234> 신호선(4618)에는, 비디오신호에 해당하는 화소의 계조에 따른 신호, 즉 휘도 데이터에 따른 전위가 입력된다.

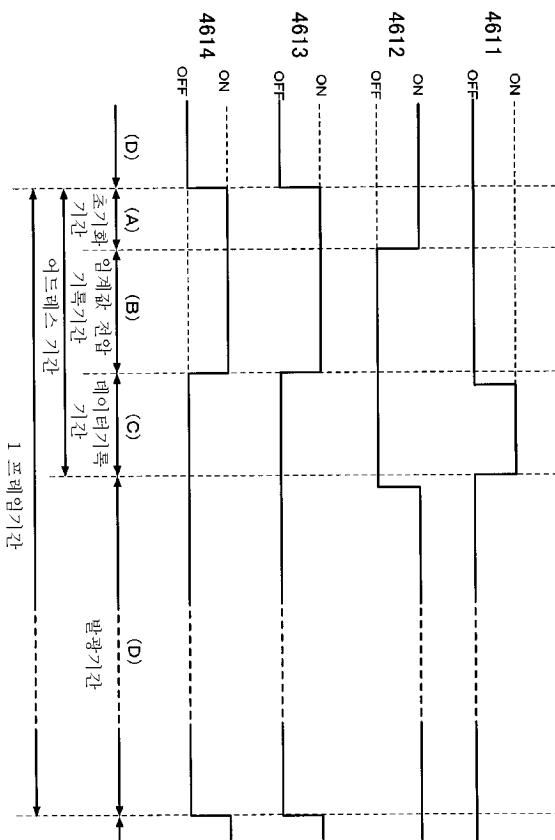

<235> 다음으로, 도 46에 나타낸 화소의 동작에 대해서 도 47a 내지 도 47d의 타이밍 차트 및 도 48a 내지 도 48d를 사용하여 설명한다. 또한, 도 47a 내지 도 47d에 있어서, 1화면분의 화상을 표시하는 시간에 해당하는 1프레임 기간은, 초기화 기간, 임계값 기록 기간, 데이터 기록 기간 및 발광 기간으로 분할된다. 또한, 초기화 기간, 임계값 기록 기간, 데이터 기록 기간을 종합하여 어드레스 기간이라고 부른다. 1프레임 기간은 특별히 한정되지 않지만, 화상을 보는 사람이 깜박거림(flicker)을 느끼지 않도록 1/60초 이하로 하는 것이 바람직하다.

<236> 또한, 발광소자(4617)의 대향전극(4624)에는,  $V_1$ 의 전위( $V_1$ : 임의의 수)가 입력된다. 또한, 발광소자(4617)가 발광하기 위하여 적어도 필요로 하는 전위차를  $V_{EL}$ 로 하면, 전원선(4622)에는  $V_1 - V_{EL} - |V_{th}| - \alpha$  ( $\alpha$ : 임의의 양수)의 전위가 입력된다. 즉, 전원선(4622)에는  $V_1 - V_{EL} - |V_{th}| - \alpha$  이하의 전위라면 좋다. 전위공급선(4623)의 전위는 특별히 한정되지 않지만, 화소가 형성된 패널에 입력하는 전위의 범위 내인 것이 바람직하다. 이렇게 함으로써, 전원을 별도 제작할 필요가 없다. 또한, 여기서는 전위공급선(4623)의 전위를  $V_2$ 로 한다.

<237> 우선, 도 47의 기간(A) 및 도 48a에 도시한 바와 같이, 초기화 기간에서는, 제 1 스위치(4611)를 오프 상태로 하고, 제 2 스위치(4612), 제 3 스위치(4613) 및 제 4 스위치(4614)를 온 상태로 한다. 이 때, 트랜지스터(4610)는 도통상태이며, 제 1 용량소자(4615)에는  $V_1 - V_{EL} - |V_{th}| - \alpha - V_2$ , 제 2 용량소자(4616)에는  $|V_{th}| + \alpha$ 가 유지된다. 또한, 초기화 기간에서는, 제 1 용량소자(4615)에는 소정의 전압이, 제 2 용량소자(4616)에는 적어도  $|V_{th}|$ 보다 높은 절대치의 전압이 유지되면 좋다.

<238> 도 47의 기간(B) 및 도 48b에 나타내는 임계값 전압 기록 기간에는, 제 2 스위치(4612)를 오프 상태로 한다. 따라서, 트랜지스터(4610)의 게이트 전극은 점점 상승하고, 트랜지스터(4610)의 게이트-소스간 전압  $V_{gs}$ 가 임계값 전압  $|V_{th}|$ 로 되면 트랜지스터(4610)는 비도통 상태가 된다. 따라서, 제 2 용량소자(4616)에 유지되는 전압  $V_{c2}$ 는 대략  $|V_{th}|$ 가 된다.

<239> 그 후의 도 47의 기간(C) 및 도 48c에 도시하는 데이터 기록 기간에 있어서는, 제 3 스위치(4613) 및 제 4 스위치(4614)를 오프 상태로 한 후, 제 1 스위치(4611)를 온 상태로 하여 신호선(4618)으로부터 휘도 데이터에 따른 전위( $V_2 - V_{data}$ )를 입력한다. 이 때, 제 2 용량소자(4616)에 보유되는 전압  $V_{c2}$ 는, 제 1 용량소자(4615) 및 제 2 용량소자(4616) 및 발광소자(4617)의 정전용량을 각각  $C_1$ ,  $C_2$ ,  $C_3$ 이라고 하면  $C_3 >> C_1, C_2$ 로부터 수식 (4)와 같이 나타낼 수 있다.

&lt;240&gt;

[수식 4]

$$V_{C2} = \left| -|V_{th}| - V_{data} \times \frac{C1}{C1+C2} \right| \dots (4)$$

&lt;241&gt;

&lt;242&gt;

또한, C1과 C2는 신호선(4618)으로부터 공급하는 전위를 결정할 때에 필요하지만, 이들의 관계는 특별히 한정되지 않는다. 또한, C1>C2의 경우에는, 휘도변화에 따른 Vdata의 진폭을 적게 할 수 있기 때문에, 소비전력을 저감할 수 있다. 한편, C2>C1의 경우에는, 주위의 스위치의 온, 오프나 오프 전류에 의한 Vc2의 변화를 억제할 수 있다. 이들의 상반되는 효과에 의거하여 C1과 C2는 동일이며, 제 1 용량소자(4615)와 제 2 용량소자(4616)의 크기는 동일한 것이 바람직하다.

&lt;243&gt;

또한, 다음 발광기간에 있어서, 발광소자(4617)를 비발광으로 하고 싶은 경우는,  $V_{data} \leq 0$ 의 전위를 입력하면 좋다.

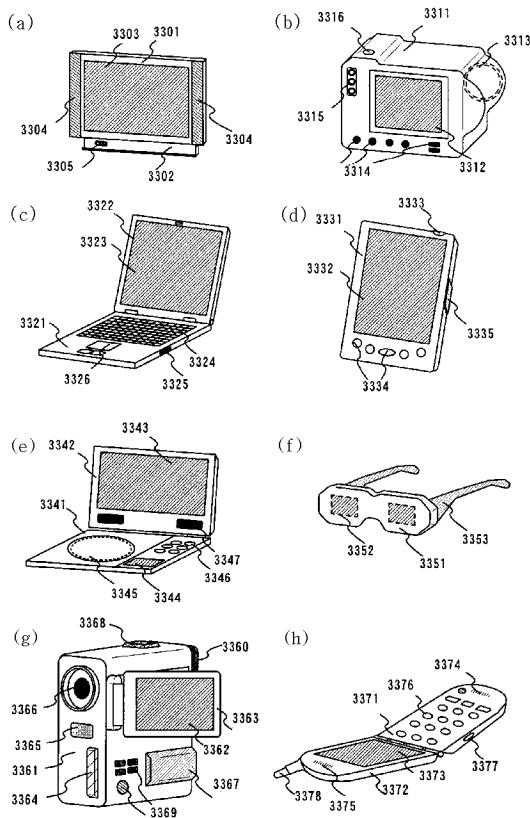

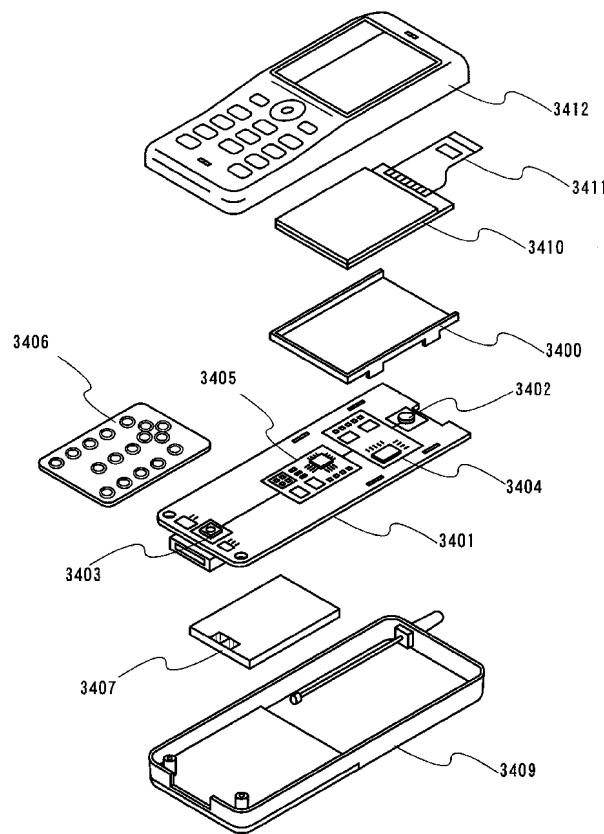

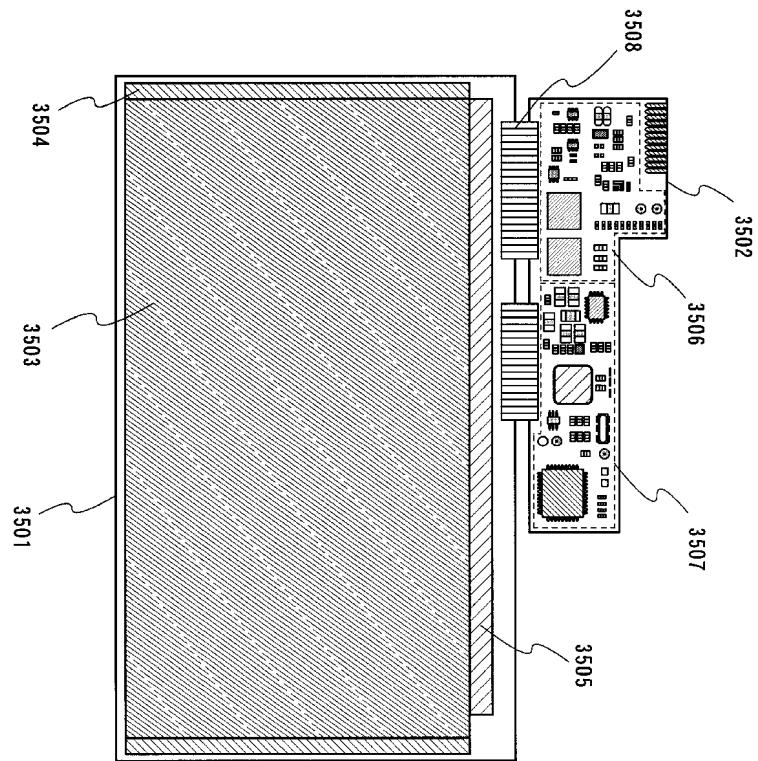

&lt;244&gt;