## (19) 대한민국특허청(KR)

### (12) 공개특허공보(A)

(51) Int. Cl.

G09G 3/30 (2006.01)

G09G 3/20 (2006.01)

(11) 공개번호 10-2006-0107345

(43) 공개일자 2006년10월13일

(21) 출원번호 10-2006-0031017

(22) 출원일자 2006년04월05일

(30) 우선권주장 JP-P-2005-00109708 2005년04월06일 일본(JP)

(71) 출원인 가부시끼가이샤 르네사스 테크놀로지

일본 100-6334 도쿄도 지요다구 마루노우찌 2-조메 4-1

(72) 발명자 오가따 야스히로

일본 도쿄도 지요다구 마루노우찌 2조메 4-1 가부시끼가이샤르네사스

테크놀로지 지적재산권 총괄 내

게이즈 다까유끼

일본 도쿄도 지요다구 마루노우찌 2조메 4-1 가부시끼가이샤르네사스

테크놀로지 지적재산권 총괄 내

(74) 대리인 장수길

이중희

구영창

심사청구 : 없음

#### (54) 표시 구동용 반도체 집적 회로 및 자발광형 표시 장치를포함한 전자 기기

#### 요약

주위의 밝기 및 사용하는 표시 장치의 사양에 따라 계조 전압 및 감마 커브 특성을 변경하여 최적의 화질로 표시를 행할 수 있는 유기 EL 패널 등의 자발광 패널의 표시 구동용 반도체 집적 회로를 제공한다. 표시 구동용 반도체 집적 회로에, 계조 전압의 진폭을 변경하기 위한 복수의 값을 저장하는 레지스터(KAOR)나 ROM 등의 기억 회로와, 감마 커브 특성을 변경하기 위한 복수의 값을 저장하는 레지스터(KCOR)나 ROM 등의 기억 회로를 형성한다. 그리고, 포토 센서의 출력에 따라 상기 기억 회로 내의 복수의 값으로부터 어느 하나의 값을 선택하여 계조 전압 생성 회로에 공급시킴으로써, 동적으로 계조 전압 및 감마 커브 특성을 변경할 수 있도록 구성하였다.

#### 대표도

도 5

#### 색인어

히스테리시스 특성, 감마 커브, 래더 저항, 유기 EL 패널

## 명세서

### 도면의 간단한 설명

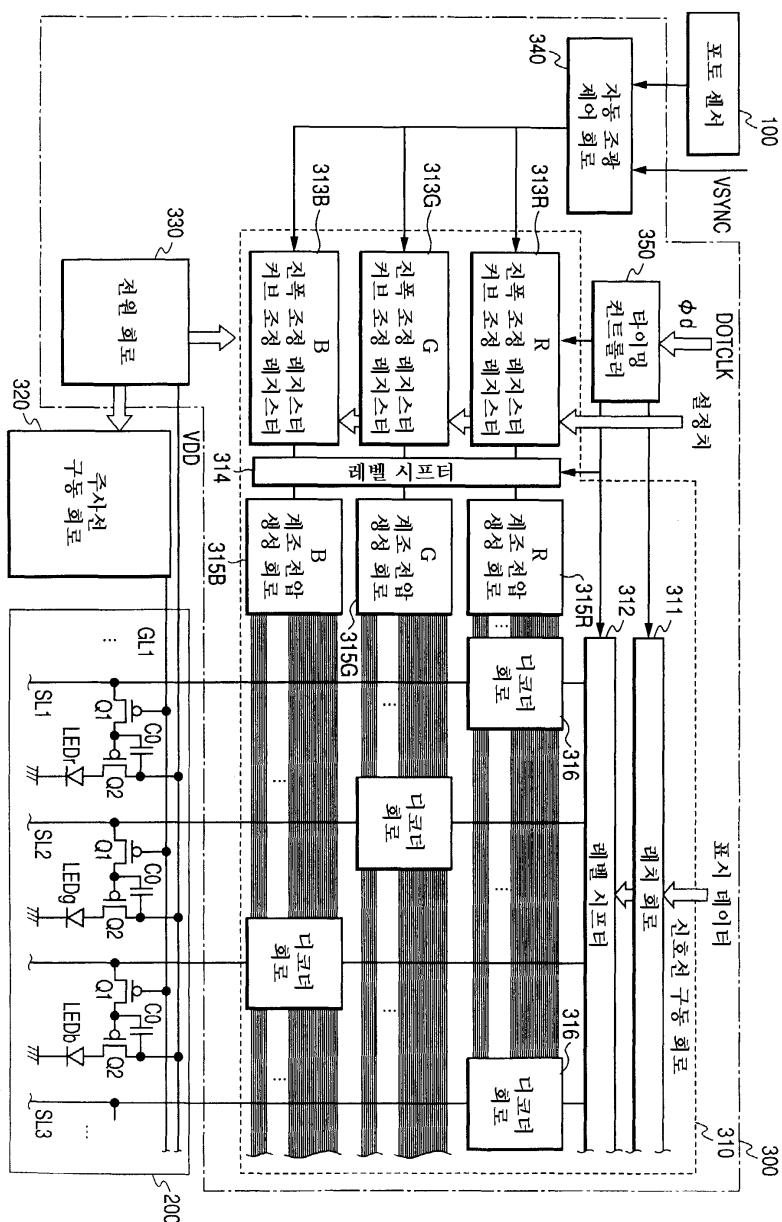

도 1은 본 발명을 적용하기에 유효한 유기 EL 패널의 신호선 구동 회로를 내장한 유기 EL 패널 드라이버 IC와 이 드라이버 IC에 의해 구동되는 유기 EL 패널로 이루어지는 유기 EL 표시 장치의 구성예를 도시하는 블록도.

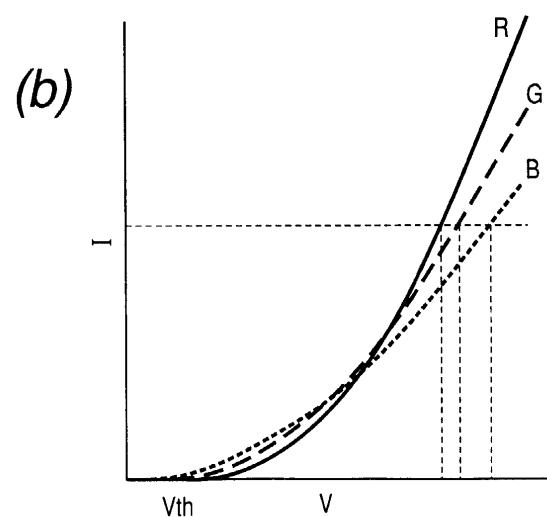

도 2는 본 발명에 따른 유기 EL 발광 소자의 RGB 사이의 특성 변동을 설명하기 위한 특성도로서, (a)는 RGB 사이의 V-I 특성 변동을 도시하는 도면이며, (b)는 RGB 사이의 I-B 특성 변동을 도시하는 도면.

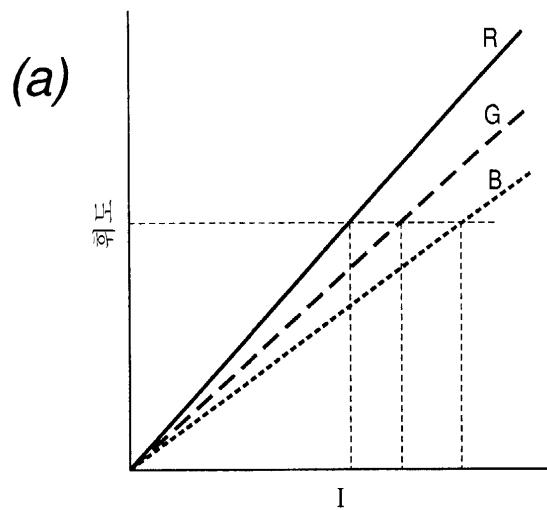

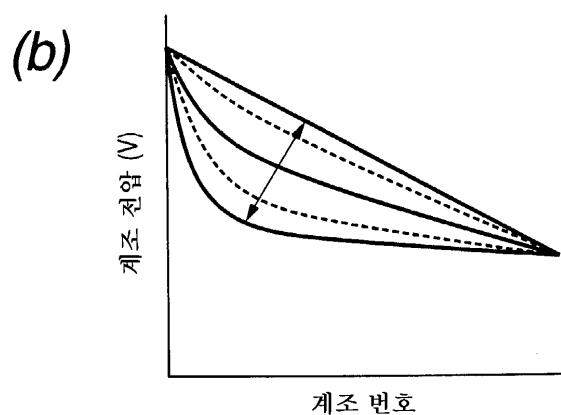

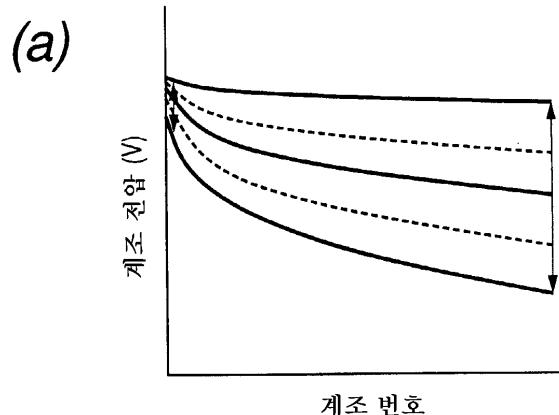

도 3은 본 발명에 따른 감마 특성 조정 내용을 도시하는 도면으로서, (a)는 계조 전압 진폭 조정을 도시하는 도면이고, (b)는 계조 전압 커브 조정을 도시하는 도면.

도 4는 본 발명에 따른 유기 EL 패널 드라이버 IC에서의 신호선 구동 회로 내의 계조 전압 생성 회로의 구체예를 도시하는 회로 구성도.

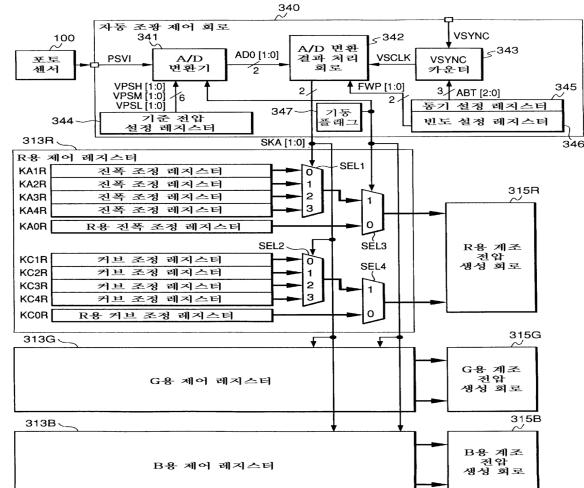

도 5는 본 발명에 따른 유기 EL 패널 드라이버 IC에서의 자동 조광 제어 회로와 제어 레지스터의 구체예를 도시하는 회로 구성도.

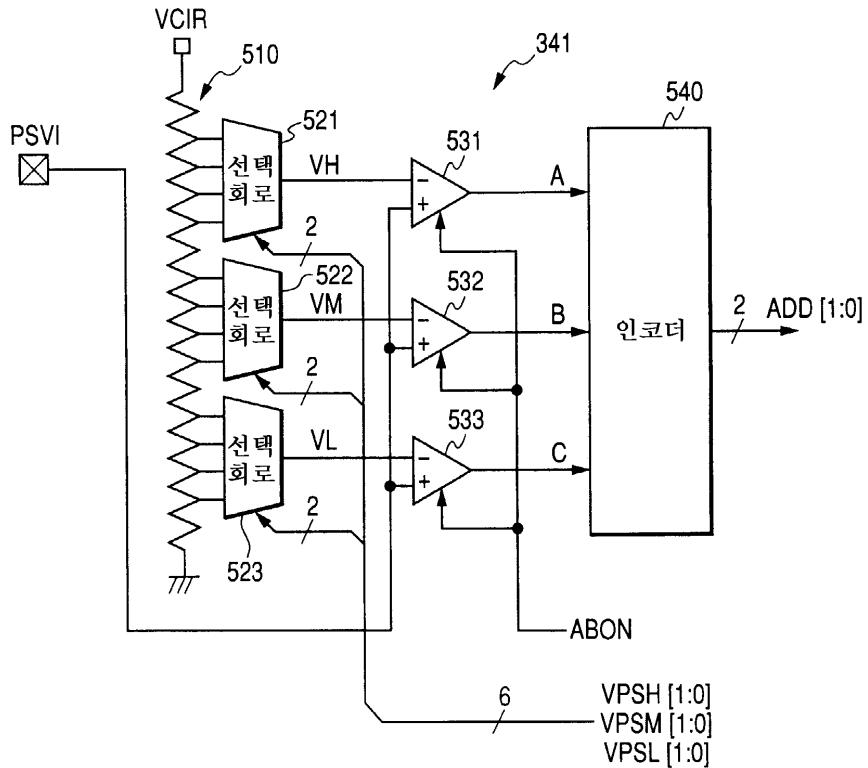

도 6은 자동 조광 제어 회로를 구성하는 A/D 변환 회로의 제1 실시예를 도시하는 회로 구성도.

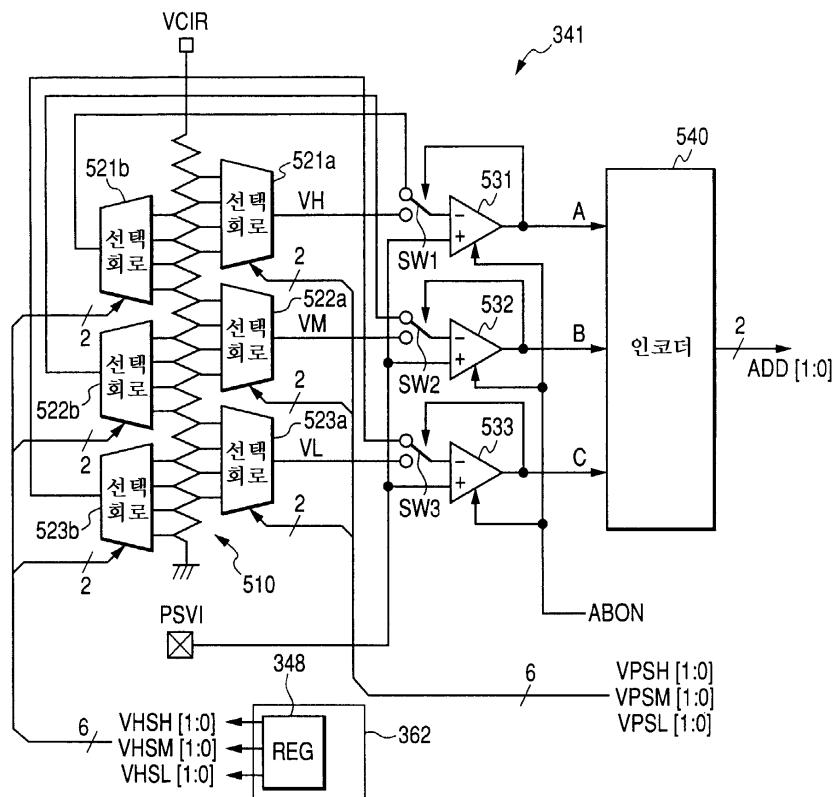

도 7은 자동 조광 제어 회로를 구성하는 A/D 변환 회로의 제2 실시예를 도시하는 회로 구성도.

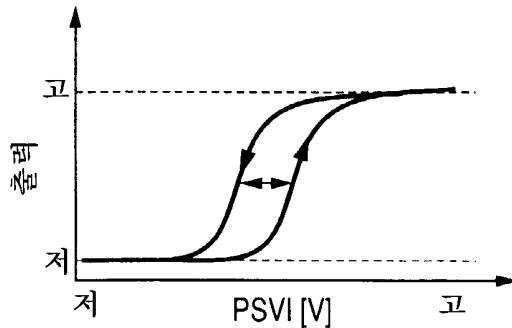

도 8은 제2 실시예의 A/D 변환 회로 내의 콤퍼레이터의 히스테리시스 특성을 도시하는 특성도.

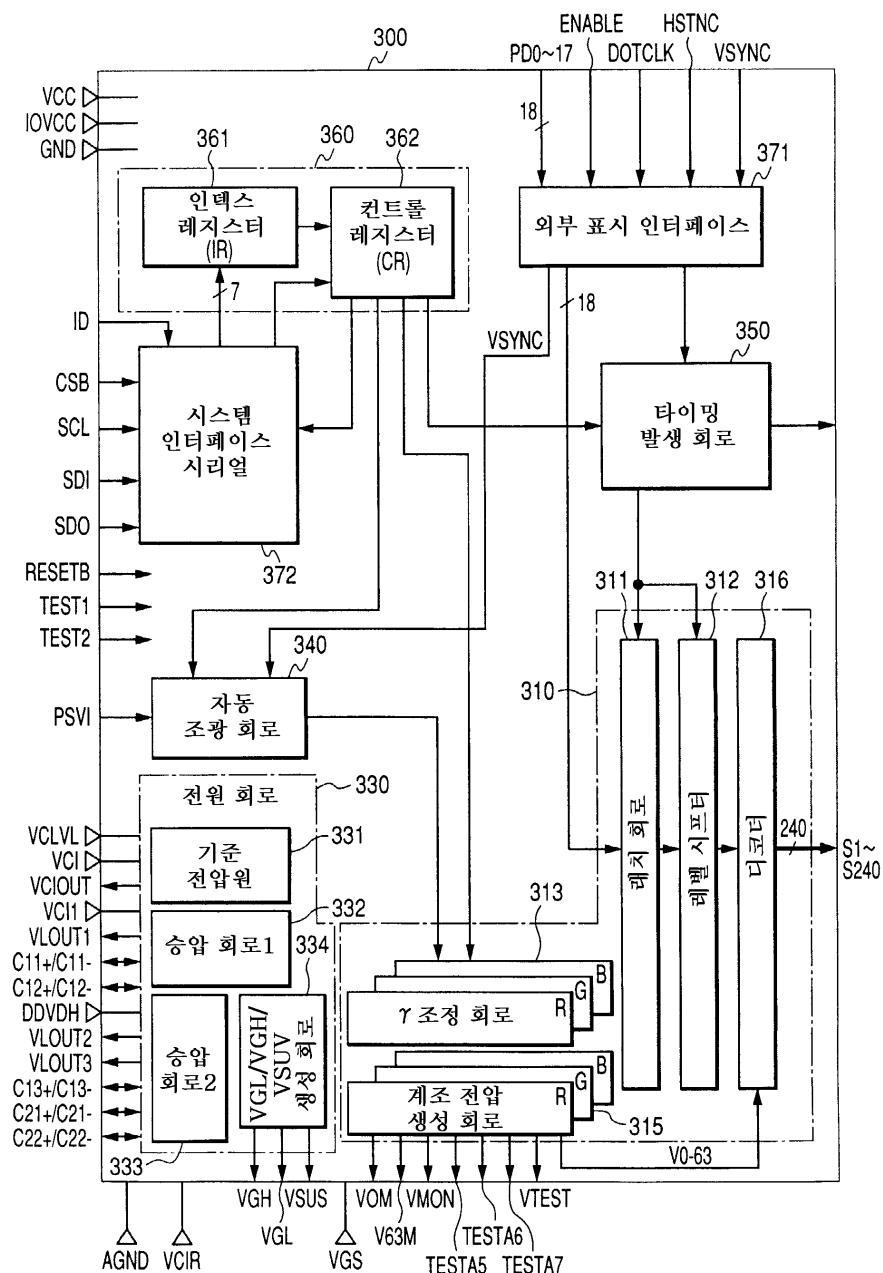

도 9는 본 발명을 적용하기에 유효한 유기 EL 패널의 신호선 구동 회로를 내장한 유기 EL 패널 드라이버 IC 전체의 구성예를 도시하는 블록도.

### <도면의 주요부분에 대한 부호의 설명>

100: 포토 센서

200: 유기 EL 패널

300: 유기 EL 패널 드라이버 IC

310: 신호선 구동 회로

313: 제어 레지스터

315: 계조 전압 생성 회로

320: 주사선 구동 회로

330: 전원 회로

340: 자동 조광 제어 회로

350: 타이밍 제어 회로(타이밍 컨트롤러)

410, 460, 510: 저항 분할 회로

531~533: 콤퍼레이터

## 발명의 상세한 설명

### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은, 표시 데이터에 따른 계조(階調) 전압을 생성하고, 유기 EL 패널 등의 자발광 패널에 출력하는 자발광 표시용 구동 장치에 관한 것으로, 특히, 감마 특성(계조 번호-휘도 특성)의 조정이 가능한 유기 EL 표시 장치 등의 자발광형 표시 장치의 표시 구동용 반도체 집적 회로 및 이들을 포함한 전자 기기에 이용하기에 유효한 기술에 관한 것이다.

최근, 휴대 전화기나 디지털 카메라, PDA(Personal Digital Assistants) 등의 휴대용 전자 기기의 표시 장치로서, 복수의 표시 화소가 매트릭스 형상으로 2차원 배열된 유기 EL 패널 등의 자발광 패널이나 백라이트를 사용하는 액정 표시 패널이 이용되고 있다. 이러한 표시 패널을 탑재한 기기 내부에는 패널의 표시 구동을 행하는 반도체 집적 회로화된 표시용 구동 장치가 탑재되어 있다.

그런데, 유기 EL 패널이나 액정 표시 패널의 표시용 구동 장치는 사용하는 패널의 종류나 구동 방식에 의해, 감마 특성이거나 구동 전압(계조 전압), 동작 클록의 주파수 등 사양이 서로 다르고, 표시용 구동 장치를 제공하는 메이커는 사양이 서로 다른 표시 패널이어도 적용할 수 있도록, 감마 특성이나 계조 전압을 조정 가능하게 구성되어 있다. 유기 EL 패널 개개의 특성에 따라 원하는 감마 특성이나 계조 전압을 조정하는 것이 가능한 회로에 관한 발명으로서는, 예를 들면 특히 문헌 1에 개시되어 있는 것이 있다.

#### 발명이 이루고자 하는 기술적 과제

상기 선원(先願) 발명은, 유기 EL 등의 자발광 표시 장치에서, RGB의 각 색마다 감마 특성의 변동이 서로 다른 것에 주목하여, R, G, B 각각의 색마다 특성 변동에 맞춘 계조 전압의 양단의 전압을 선택하는 레지스터와, 감마 커브 특성을 선택하는 레지스터를 형성하고, 특성 변동에 따라 레지스터 값을 설정함으로써, 계조 전압과 감마 특성을 각각 조정할 수 있도록 하고 있다.

그런데, 유기 EL 패널은 자발광형 표시 장치이기 때문에, 동일한 휘도라도 기기 주위의 밝기에 의해 표시가 보기 편하거나, 보기 힘들거나 하는 과제가 있다. 이러한 과제를 해결하기 위해, 주위의 밝기를 검출하는 수광 소자를 형성하고, 주위의 밝기에 따라 유기 EL 소자의 휘도를 변화시키도록 한 발명이 제안되어 있다(특히 문헌 2).

그러나, 주위의 밝기에 따라 유기 EL 소자의 휘도를 변화시키는 상기 선원 발명은, 주위의 밝기에 따라 감마 특성을 조정하도록 하지는 않을 뿐만 아니라, 유기 EL 소자의 휘도를 변화시키는 구체적인 구조에 대해서는 어떠한 개시도 하지 않고 있다.

본 발명의 목적은, 주위의 밝기에 따라 자동적으로 휘도를 변화시킴으로써 어떠한 환경 하에서도 표시가 보기 편한 유기 EL 패널 등의 자발광 패널의 표시 구동용 반도체 집적 회로를 제공하는 데 있다.

본 발명의 다른 목적은, 주위의 밝기 및 사용하는 표시 장치의 사양에 따라 계조 전압 및 감마 커브 특성을 변경하여 최적의 화질로 표시를 행할 수 있는 유기 EL 패널 등의 자발광 패널의 표시 구동용 반도체 집적 회로를 제공하는 데 있다.

본 발명의 상기 및 그 밖의 목적과 신규의 특징에 대해서는, 본 명세서의 기술 및 첨부 도면으로부터 명백해질 것이다.

### 발명의 구성 및 작용

본원에서 개시되는 발명 중 대표적인 것의 개요를 설명하면, 하기와 같다.

즉, 표시 구동용 반도체 집적 회로에, 계조 전압의 진폭을 변경하기 위한 복수의 값을 저장하는 레지스터나 ROM 등의 기억 회로와, 감마 커브 특성을 변경하기 위한 복수의 값을 저장하는 레지스터나 ROM 등의 기억 회로를 형성한다. 그리고, 포토 센서의 출력에 따라 상기 기억 회로 내의 복수의 값을 선택하여 계조 전압 생성 회로에 공급 시킴으로써, 동적으로 계조 전압 및 감마 커브 특성을 변경할 수 있도록 구성한 것이다.

상기한 수단에 따르면, 주위의 밝기에 따라 자동적으로 휘도가 변화되기 때문에, 어떠한 환경 하에서도 자발광 패널에 보기 편한 상태에서 표시를 행할 수 있다. 여기서, 바람직하게는, 포토 센서의 출력을 디지털 신호로 변환하는 A/D 변환 회로를 형성하고, 그 A/D 변환 회로를 구성하는 콤퍼레이터(comparator)에 히스테리시스 특성을 갖게 하도록 한다. 또한, 포토 센서의 출력을 관정하는 타이밍을 조정하는 타이밍 조정 회로를 형성한다. 이것에 의해, 주위의 밝기가 변화했을 때에 회로가 과민하게 반응하여 표시의 휘도가 빈번하게 변화하여 표시가 보기 힘들게 되는 것을 회피할 수 있다.

이하, 본 발명의 적합한 실시 형태를 도면에 기초하여 설명한다.

도 1은, 본 발명을 적용하기에 유효한 유기 EL 패널의 신호선 구동 회로를 내장한 유기 EL 패널 표시 구동용 반도체 집적 회로(유기 EL 패널 드라이버 IC)와 이 드라이버 IC에 의해 구동되는 유기 EL 패널로 이루어지는 유기 EL 표시 장치의 구성을 도시한 것이다. 도 1에서, 참조 부호 200은 유기 EL 소자가 매트릭스 형상으로 배치되어 이루어지는 유기 EL 패널이고, 참조 부호 300은 이 유기 EL 패널(200)을 구동하여 표시를 행하는 유기 EL 패널 드라이버 IC이다.

유기 EL 패널(300)은, 화상 신호가 인가되는 복수의 신호선으로서의 소스선(소스 전극)(SL1, SL2, ...)과 소정의 주기로 순차적으로 선택 구동되는 복수의 주사선으로서의 게이트선(게이트 전극)(GL1, ...)이 직교하는 방향으로 배치되어 있다. 그리고, 소스선(SL1, SL2,...)과 게이트선(GL1,...)의 각 교차점에 화소가 배치되고, 액티브 매트릭스형 패널로서 구성되어 있다. 각 화소는, 어느 하나의 주사선(GL)에 게이트 단자가, 또한 어느 하나의 신호선(SL)에 소스 단자가 접속된 선택 소자로서의 TFT(박막 트랜지스터)(Q1)와, 스위칭 소자로서의 TFT(Q2)와, 전원 라인(VDL)과 접지점 사이에 TFT(Q2)와 직렬로 접속된 자발광 소자로서의 유기 EL 소자 LED로 이루어진다. TFT(Q2)는, 상기 선택용 TFT(Q1)의 드레인 단자에 게이트 단자가, 또한 전원 전압(VDD)을 공급하는 전원 라인(VDL)에 소스 단자가 접속되어 있다.

유기 EL 소자 LED에는, R(적)용 소자(LEDr)와, G(녹)용 소자(LEDg)와, B(청)용 소자(LEDb)가 있고, 이들의 소자를 갖는 화소가 R, G, B와 같은 순서로 배치되어 있다. 이와 함께, 스위칭용의 TFT(Q2)의 게이트 단자와 소스 단자 사이에는, 신호선(SL)을 통하여 공급되는 화상 신호를 선택용 TFT(Q1)가 오프되어 있는 동안에도 유지하는 용량 소자(C0)가 형성되어 있다. 여기서, 상기 선택용 TFT(Q1)를 통하여 TFT(Q2)의 게이트 단자에 인가된 계조 전압에 의해, 유기 EL 소자(LEDr, LEDg, LEDb)에 흐르는 전류량이 변화하여, 각 화소의 휘도가 제어된다.

유기 EL 패널 드라이버 IC(300)는, 상기 유기 EL 패널(200)의 신호선(SL1, SL2,...)을 구동하는 신호선 구동 회로(310)와, 구동 회로에 필요한 전압을 공급하는 전원 회로(330)를 포함하고 있다. 또한, 이 드라이버 IC(300)는, 외부의 포토 센서(100)로부터의 신호와 수직 동기 신호(VSYNC)에 기초하여 신호선 구동 회로(310)에 보내는 제어 신호를 생성하는 자동 조광 제어 회로(340)와, 칩 내부의 회로의 동작 타이밍 신호를 생성하는 타이밍 컨트롤러(350)를 포함하고 있다. 참조 부호 320은 상기 유기 EL 패널(200)의 주사선(GL1, ...)을 구동하는 주사선 구동 회로이며, 전원 회로(330)는 주사선 구동 회로(320)에 필요한 전압도 생성한다.

신호선 구동 회로(310)는, CPU로부터 전송되는 표시 데이터에 기초하여, 유기 EL 패널(300)의 신호선(SL1, SL2,...)에 인가되는 화상 신호의 계조 전압을 제어한다. 신호선 구동 회로(310)는, 표시 데이터를 래치하는 래치 회로(311), 표시 데이터 신호의 레벨을 변환하는 레벨 시프터(312), 제어 레지스터(313), 그 제어 레지스터(313)의 출력 신호의 레벨을 변환하는 레벨 시프터(314), 계조 전압 생성 회로(315), 디코더 회로(316) 등으로 구성된다. 계조 전압 생성 회로(315)는, 유기 EL 패널(200)의 신호선(SL1, SL2,...)의 계조 전압 제어에 필요한 복수의 계조 전압을 생성한다. 디코더 회로(316)는, 표시 데이터에 따라 복수의 계조 전압 중에서 하나를 선택한다. 상기 래치 회로(311)나 제어 레지스터(313), 레벨 시프터(312, 314)는, 타이밍 컨트롤러(350)에 의해 생성되는 동작 타이밍 신호에 의해 제어된다.

제어 레지스터(313) 및 계조 전압 생성 회로(315)는, R, G, B의 각 색에 대응하여 각각 R용의 제어 레지스터(313R) 및 계조 전압 생성 회로(315R), G용의 제어 레지스터(313G) 및 계조 전압 생성 회로(315G), B용의 제어 레지스터(313G) 및 계조 전압 생성 회로(315G)가 형성되어 있다. 또한, 제어 레지스터(313R, 313G, 313B)는, 각 색마다 또한 계조 전압의 최대 전압과 최소 전압을 지정하는 값을 저장하는 진폭 조정 레지스터와 감마 커브의 특성을 지정하는 값을 저장하는 커브 조정 레지스터의 두 가지의 레지스터를 포함하고 있다. 이것은, R, G, B의 각 화소의 유기 EL 소자는, 도 2의 (a)에 도시하는 바와 같이, 소자가 흘리는 전류와 발광 휘도의 관계를 나타내는 I-B(전류-휘도) 특성이 색마다 서로 다를 뿐만 아니라, 도 2의 (b)에 도시하는 바와 같이, 소자에 인가하는 전압과 소자에 흐르는 전류와의 관계를 나타내는 V-I(전압-전류) 특성이 색마다 서로 다르기 때문이다.

진폭 조정 레지스터에는, 사용하는 유기 EL 패널의 유기 EL 소자의 특성에 따라 도 3의 (a)에 도시하는 바와 같이, 계조 전압의 특성을 바꾸기 위한 값이 저장된다. 한편, 커브 조정 레지스터에는, 사용하는 유기 EL 패널의 유기 EL 소자의 특성에 따라 도 3의 (b)에 도시하는 바와 같이, 감마 커브의 특성을 바꾸기 위한 값이 저장된다. 본 실시예에서는, 이러한 계조 전압의 특성과 감마 커브의 특성을 R, G, B의 각 색마다 개별적으로 설정할 수 있도록 되어 있다.

타이밍 컨트롤러(317)는, 클록을 계수하는 카운터를 갖고 있고, 외부로부터 입력되는 도트 클록( $\Phi_d$ )을 카운트하고, 라인 클록( $\Phi_1$ )을 생성한다. 래치 회로(311)는, 도트 클록( $\Phi_d$ )에 동기하여 예를 들면 18 비트와 같은 단위의 표시 데이터를 순차적으로 취득하여, 라인 클록( $\Phi_1$ )의 하강 타이밍에 동작하고, 1 라인분의 표시 데이터를 통합하여 레벨 시프터(312)에 전송한다.

레벨 시프터(312)는, 래치 회로(311)로부터 전송되는 표시 데이터를 로직 회로의 전원 전압인 Vcc-GND 레벨로부터, 계조 전압 생성 회로(315R, 315G, 315B) 및 디코더 회로(313)의 동작 전원인 VDD-VSS 레벨로 변환한다. 또한, 이 레벨 변환을 행하는 이유는, 각 블록의 제어를 이들의 동작 전원에 따른 전압 레벨로 행할 필요가 있기 때문이다.

RGB 개별의 제어 레지스터(313R, 313G, 313B)는 각각 래치 회로를 내장하고 있고, 전원 투입 시 등에 외부의 CPU로부터 공급되는 레지스터 설정치를 취득하여, 타이밍 컨트롤러(316)로부터의 라인 클록( $\Phi_1$ )의 하강 타이밍에서, 레지스터 설정치를 레벨 시프터(314)에 전송한다. 레벨 시프터(314)는, 각 제어 레지스터(313R, 313G, 313B)로부터 공급되는 레지스터 설정치 신호를 Vcc-GND 레벨로부터 VDD-GND 레벨로 변환하여, 계조 전압 생성 회로(315R, 315G, 315B)에 전송한다.

RGB 개별의 계조 전압 생성 회로(315R, 315G, 315B)는, 레벨 시프터(314)를 통하여 입력되는 레지스터 설정치에 따라 복수의 계조 전압을 생성한다. 디코더 회로(313)는, 계조 전압 생성 회로(315R, 315G, 315B)에서 생성된 아날로그의 계조 전압 중에서 레벨 시프터(312)로부터의 표시 데이터의 비트 코드에 대응된 전압을 선택함으로써, 디지털의 표시 데이터를 아날로그의 계조 전압으로 변환하는 DA 컨버터의 역할을 한다.

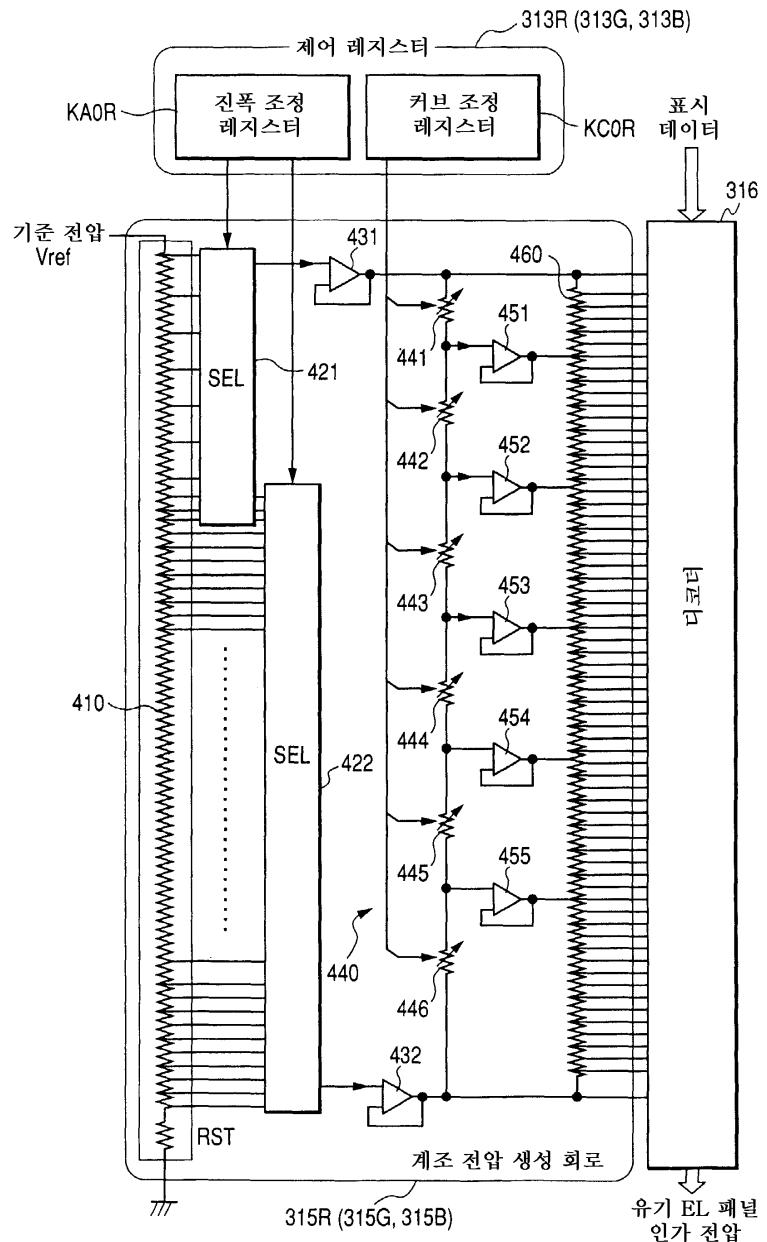

다음으로, 도 4를 이용하여, 본 발명에 따른 RGB 개별의 계조 전압 생성 회로(315R, 315G, 315B)의 구체적인 구성과 동작을 설명한다. 또한, 계조 전압 생성 회로(315R, 315G, 315B)는 각각 동일한 구성이므로, 대표로서, R용의 제어 레지스터(313R)와 계조 전압 생성 회로(315R)에 대해 설명하고, 다른 색의 회로의 도시와 설명은 생략한다. 또한, 도시의 사정상, 도 4에서는, 레벨 시프터(312 및 314)를 생략하고 있다.

도 4에 도시되어 있는 바와 같이, 제어 레지스터(313R)에는, 진폭 조정 레지스터(KA0R)와 커브 조정 레지스터(KC0R)가 형성되어 있다. 계조 전압 생성 회로(315R)는, 외부로부터 공급되는 기준 전압(Vref)과 접지점(GND) 사이에 형성된 래더 저항을 포함하는 저항 분할 회로(410), 그 저항 분할 회로(410)에 의해 생성된 복수의 전압 레벨 중에서 어느 하나의 전압을 계조 전압으로서 선택하는 셀렉터 회로(421, 422)를 포함한다. 또한, 그 셀렉터 회로(421, 422)에 의해 선택된 전압을 임피던스 변환하는 오피 앰프로 이루어지는 볼티지 팔로워(voltage follower)(431, 432), 및 그 볼티지 팔로워(431, 432)의 출력 전압을 저항 분할하기 위한 가변 저항(441~446)으로 이루어지는 저항 분할 회로(440)를 포함한다. 또한, 계조 전압 생성 회로(315R)는, 그 저항 분할 회로(440)에서 분할된 전압을 임피던스 변환하는 오피 앰프로 이루어지는 볼티지 팔로워(451~455), 볼티지 팔로워(431, 432 및 451~455)의 출력 전압을 저항 분할하여 원하는 계조 수만큼(여기서는 예를 들면 64 계조)의 계조 전압을 생성하는 래더 저항으로 이루어지는 저항 분할 회로(460)를 포함한다.

상기 셀렉터 회로(421, 422) 중 전압이 높은 측에 형성된 셀렉터 회로(421)는 진폭 조정 레지스터(KA0R)의 최대 계조 전압 설정치에 따른 전압을 선택하고, 전압이 낮은 측에 형성된 셀렉터 회로(422)는 진폭 조정 레지스터(KA0R)의 최소 계조 전압 설정치에 따른 전압을 선택할 수 있는 구성으로 된다. 그리고, 이들의 셀렉터 회로(421, 422)에 의해 선택된 전압이 계조 번호의 최소치와 최대치에 대응한 계조 전압으로서, 볼티지 팔로워(431, 432)를 통하여 저항 분할 회로(440)에 공급된다.

또한, 저항 분할 회로(440)의 가변 저항(441~446)은, 커브 조정 레지스터(KC0R)의 설정치에 기초하여, 그 저항치를 변경할 수 있도록 구성되어 있다. 이러한 가변 저항으로서는, 예를 들면 MOSFET와 같이 전압에 따라 저항치가 아날로그적으로 변화하는 소자 이외에, 복수의 직렬 저항과 이들의 각 저항과 병렬로 형성된 복수의 스위치 소자로 이루어져 온되는 스위치 소자의 수에 따라 저항치가 변화하도록 된 저항 회로에 의해 구성해도 된다.

본 실시예의 계조 전압 생성 회로(315R)는, 이상의 회로 구성으로, 우선은, 가변 저항(441~446)의 저항 분할에 의해, 원하는 계조 번호-계조 전압 특성을 얻는 데에 있어서 기준으로 되는 계조 전압(기준 계조 전압)을 생성한다. 또한, 전술에

의해 생성되는 각 계조 전압은 후단의 볼티지 팔로워(451~455)에서 버퍼링되고, 래더 저항으로 이루어지는 저항 분할 회로(460)에서 상기 기준 계조 전압 사이를 전압 관계가 선형이 되도록 저항 분할하고, 계조 번호가 대응하는 예를 들면 64 계조분의 계조 전압을 생성한다. 계조 전압 생성 회로(315R)에서 생성된 64 계조의 계조 전압은, 디코드 회로(316)에서 표시 데이터에 맞춘 계조 전압으로 디코드하고(변환하고), 유기 EL 패널(200)의 대응하는 신호선에의 인가 전압(출력 전압)으로서 출력된다. 다른 계조 전압 생성 회로(315G, 315B)도 마찬가지로 구성되어 있다.

이상과 같은 회로 구성에 의해, 감마 특성의 조정에서, 진폭 조정 레지스터(KA0R) 및 커브 조정 레지스터(KC0R) 등에의 설정으로, 계조 전압의 진폭 전압 및 중간 계조부의 커브의 조정이 가능해지고, 고화질의 표시를 기대할 수 있는 계조 전압 생성 회로를 실현할 수 있다.

다음으로, 도 1에 도시되어 있는 포토 센서로부터의 신호에 기초하여 유기 EL 소자의 휘도를 조정하는 자동 조광 제어 회로(340)와 제어 레지스터(313)의 구성예와 동작에 대해 설명한다.

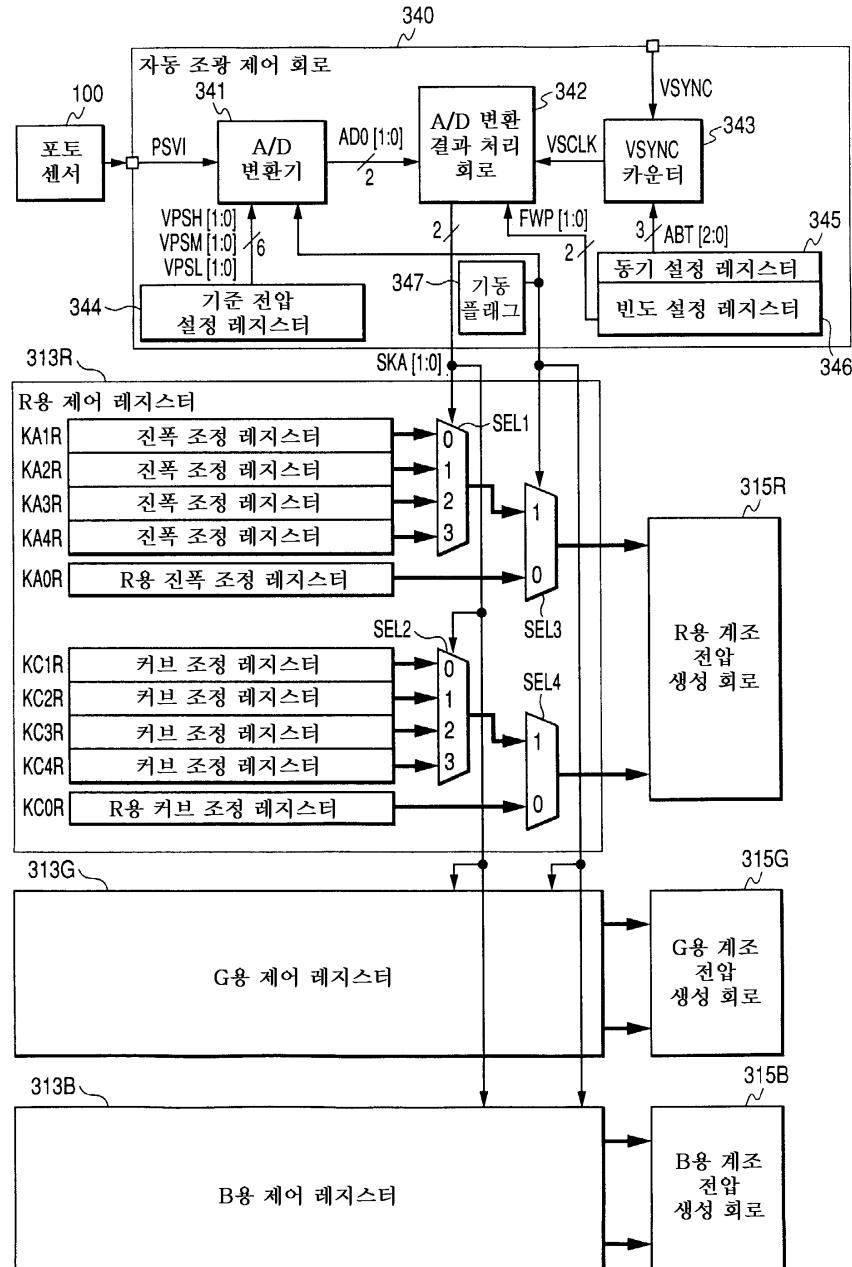

도 5에 감마 특성을 조정하기 위한 자동 조광 기능 구성도를 도시한다. 이 실시예의 자동 조광 기능은, 자동 조광 제어 회로(340)와, R용의 제어 레지스터(313R), R용의 계조 전압 생성 회로(315R), G용의 제어 레지스터(313G), G용의 계조 전압 생성 회로(315G), B용의 제어 레지스터(313B), B용의 계조 전압 생성 회로(315B)로 이루어진다. 자동 조광 제어 회로(340)는, 외부의 포토 센서(100)로부터 입력된 PSVI 신호를 디지털 신호로 변환하는 A/D 변환 회로(341), A/D 변환 결과를 설정된 주기로 R용의 제어 레지스터(313R)에 공급하여 계조 전압의 조정 타이밍을 부여하는 A/D 변환 결과 처리 회로(342), 주기 신호를 생성하는 VSYNC 카운터(343)를 포함한다. 또한, 자동 조광 제어 회로(340)는, A/D 변환 회로(341)에서 이용되는 기준 전압을 설정하는 기준 전압 설정 레지스터(344), A/D 변환 결과를 반영하는 주기를 설정하는 주기 설정 레지스터(345), A/D 변환 결과를 반영하는 빈도를 설정하는 빈도 설정 레지스터(346), 자동 조광 기능의 유효/무효를 설정하는 기동 설정 플래그(347)를 포함한다.

R용의 제어 레지스터(313R)는, 도 4에 도시되어 있는 본래의 R용 진폭 조정 레지스터(KA0R)와 커브 조정 레지스터(KC0R) 이외에, 4개의 자동 조광용 진폭 조정 레지스터(KA1R, KA2R, KA3R, KA4R)를 포함한다. 또한, 레지스터(313R)는, 이들 4개의 자동 조광용 진폭 조정 레지스터로부터 하나를 선택하는 선택 회로(SEL1), R용 진폭 조정 레지스터(KA0R) 또는 자동 조광용 진폭 조정 레지스터(KA1R~KA4R) 중 어느 하나의 출력을 선택하는 선택 회로(SEL2)를 포함한다. 또한, 레지스터(313R)는, 4개의 자동 조광용 커브 조정 레지스터(KC1R, KC2R, KC3R, KC4R), 이들 4개의 자동 조광용 커브 조정 레지스터(KC1R~KC4R) 중 어느 하나의 출력을 선택하는 선택 회로(SEL3), 본래의 R용 커브 조정 레지스터(KC0R)와 자동 조광용 커브 조정 레지스터(KC1R~KC4R) 중 어느 하나의 출력을 선택하는 선택 회로(SEL4)를 포함한다. G용 제어 레지스터(313G) 및 B용 제어 레지스터(313B)도, R용 제어 레지스터(313R)와 마찬가지의 회로 구성을 갖기 때문에, 이하 R용의 제어 레지스터(313R)에 대해 설명하고, G용 제어 레지스터(313G) 및 B용 제어 레지스터(313B)에 대해서는, 자세한 구성의 도시 및 설명은 생략한다.

도 6에는 A/D 변환 회로(341)의 상세한 구성예가 도시되어 있다. 이 실시예의 A/D 변환 회로(341)는, 래더 저항으로 이루어지는 저항 분할 회로(510)와, 그 저항 분할 회로(510)에서 정전압(VCIR)을 분할함으로써 생성된 전압 중에서 적당한 것을 선택하는 선택 회로(셀렉터)(521, 522, 523)를 포함한다. 또한, A/D 변환 회로(341)는, 선택 회로(셀렉터)(521, 522, 523)에서 선택된 전압이 각각 반전 입력 단자에 인가되고, 비반전 입력 단자에 외부의 포토 센서(100)로부터의 신호 PSVI가 입력되는 콤퍼레이터(531, 532, 533)와, 그 콤퍼레이터(531, 532, 533)를 인코드하여 2 비트의 신호로서 출력하는 인코더(540)를 포함한다.

콤퍼레이터(531, 532, 533)는, 기동 설정 플래그(346)의 상태에 의해, 활성화 또는 비활성화된다. 선택 회로(셀렉터)(521, 522, 523)는, 기준 전압 설정 레지스터(344)의 각 2 비트의 설정치 VPSH[1:0], VPSM[1:0], VPSL[1:0]에 따라 각각 저항 분할 회로(510)에서 생성된 전압 중에서 적당한 것을 선택한다. 표 1~표 3에, 설정치 VPSH[1:0], VPSM[1:0], VPSL[1:0]과, 선택 회로(셀렉터)(521, 522, 523)에 의해 선택되는 기준 전압과의 관계의 일례가 나타나 있다. 또한, 표 4에는, 인코더(540)의 입력과 출력, 즉 콤퍼레이터(531, 532, 533)의 출력과 A/D 변환 결과 ADO[1:0] 및 주위의 밝기의 정도와의 관계가 나타나 있다.

[표 1]

| 레지스터 값<br>VPSH[1:0] | 기준 전압 VH[V]<br>(VCIR=2.5V) |

|---------------------|----------------------------|

| 0 0                 | VCIR × 0.35                |

| 0 1                 | VCIR × 0.45                |

| 1 0                 | VCIR × 0.55                |

| 1 1                 | VCIR × 0.65                |

[표 2]

| 레지스터 값<br>VPSM[1:0] | 기준 전압 VM[V]<br>(VCIR=2.5V) |

|---------------------|----------------------------|

| 0 0                 | VCIR × 0.20                |

| 0 1                 | VCIR × 0.25                |

| 1 0                 | VCIR × 0.30                |

| 1 1                 | VCIR × 0.35                |

[표 3]

| 레지스터 값<br>VPSL[1:0] | 기준 전압 VL[V]<br>(VCIR=2.5V) |

|---------------------|----------------------------|

| 0 0                 | VCIR × 0.05                |

| 0 1                 | VCIR × 0.10                |

| 1 0                 | VCIR × 0.15                |

| 1 1                 | VCIR × 0.20                |

[표 4]

| 입력 A,B,C | A/D 변환 결과<br>ADO[1:0] | 밝기의 정도      |

|----------|-----------------------|-------------|

| 0 0 0    | 0 0                   | 가장 어두운 환경   |

| 0 0 1    | 0 1                   | 2번째로 어두운 환경 |

| 0 1 1    | 1 0                   | 2번째로 밝은 환경  |

| 1 1 1    | 1 1                   | 가장 밝은 환경    |

표 4에 도시하는 바와 같이, 입력 A, B, C=000의 경우가 가장 어두운 환경인 것을 나타내고, ADO[1:0]=00을 출력한다. 입력 A, B, C=001의 경우가 2번째로 어두운 환경인 것을 나타내고, ADO[1:0]=01을 출력한다. 입력 A, B, C=011이 2번째로 밝은 환경인 것을 나타내고, ADO[1:0]=10을 출력한다. 입력 A, B, C=111이 가장 밝은 환경인 것을 나타내고, ADO[1:0]=11을 출력한다. 외부의 포토 센서(100)로부터의 신호 PSVI가 A/D 변환 회로(341)에 입력되면, A/D 변환 회로(341)에서는, PSVI 신호를 표 4에 나타내는 바와 같은 주위의 밝기의 정도를 나타내는 2 비트의 디지털 신호 ADO[1:0]로 변환한다.

VSYNC 카운터(343)는, 외부로부터 입력되는 수직 동기 신호(VSYNC)와 주기 설정 레지스터(345)의 3 비트의 설정치 ABT[2:0]로부터, A/D 변환 결과 ADO[1:0]을 반영시키기 위한 주기를 결정하는 신호(VSCLK)를 생성한다. A/D 변환 결과 처리 회로(342)는, VSCLK 신호와 빈도 설정 레지스터(346)의 2 비트의 설정치 FWP[1:0]로부터, 실제로 계조 전압을 조정하는 주기를 결정하고, 그 주기에 따른 타이밍에서 A/D 변환 결과 ADO[1:0]을 조정 제어 신호 SKA[1:0]로 하여, 각 제어 레지스터(313R, 313G, 313B)에 공통으로 출력한다.

R용 제어 레지스터(313R)에서는, SKA[1:0]을 선택 신호로 하여, 셀렉터(SEL1, SEL2)가 진폭 조정 레지스터(KA1R, KA2R, KA3R, KA4R) 및 커브 조정 레지스터(KC1R, KC2R, KC3R, KC4R) 중에서 각각 사용하는 레지스터를 하나 선택

한다. 후단의 셀렉터(SEL3, SEL4)는, 기동 설정 플래그(347)의 상태에 따라, 선택된 레지스터 또는 본래의 R용 진폭 조정 레지스터(KA0R) 및 R용 커브 조정 레지스터(KC0R) 중 어느 하나를 선택하고, 그 레지스터의 값을 후단의 R용 계조 전압 생성 회로(314R)에 입력 한다. G용(313G) 및 B용 제어 레지스터(313B)도 마찬가지로 동작한다. 계조 전압 생성 회로(314R)는, R용 제어 레지스터(313R)로부터의 입력에 따른 계조 전압을 출력한다. 기동 설정 플래그(347)는, IC 전체를 제어하는 제어 회로에 형성되는 컨트롤 레지스터 내의 1 비트이어도 된다.

표 5에는, 도 5의 주기 설정 레지스터(345)의 설정치 ABT[2:0]와, VSYNC 카운터(343)로부터 출력하는 VSCLK 신호의 샘플링 주기와의 관계의 일례를 나타낸다. VSYNC 카운터(343)는, 주기 설정 레지스터(345)의 설정치 ABT[2:0]에 따라 PSVI 신호의 샘플링 주기를 표 5에 나타내는 바와 같이 결정하고, 결정한 주기에 대응한 타이밍에서 VSCLK 신호를 출력 한다.

[표 5]

| 레지스터 값<br>ABT[2:0] | 샘플링 주기<br>VSCLK |

|--------------------|-----------------|

| 0 0 0              | 1/fvSYNC        |

| 0 0 1              | 2/fvSYNC        |

| 0 1 0              | 4/fvSYNC        |

| 0 1 1              | 8/fvSYNC        |

| 1 0 0              | 16/fvSYNC       |

| 1 0 1              | 32/fvSYNC       |

| 1 1 0              | 64/fvSYNC       |

| 1 1 1              | 설정 금지           |

표 6에는, 빈도 설정 레지스터(346)의 설정치 FWP[1:0]와, 도 5의 A/D 변환 결과 처리 회로(342)에 입력된 A/D 변환 결과 ADO[1:0]을 출력 SKA[1:0]에 반영시키기 위한 조건(반영 빈도)과의 관계를 나타낸다. 구체적으로는, VSCLK 신호로 나타내는 현 주기의 ADO[1:0]의 값과, VSCLK로 나타내는 하나 전의 주기의 ADO[1:0]의 값을 비교하여, 반영 조건을 결정한다.

[표 6]

| 레지스터 값<br>FWP[1:0] | 샘플링한 A/D<br>변환 결과의 반영 조건 |

|--------------------|--------------------------|

| 0 0                | 무조건(매회)                  |

| 0 1                | 연속 2회 일치                 |

| 1 0                | 연속 3회 일치                 |

| 1 1                | 연속 4회 일치                 |

표 6에 나타내는 바와 같이, 이 실시예에서는, 빈도 설정 레지스터(346)의 설정치 FWP[1:0]=00일 때에는, 매 VSCLK 주기마다 A/D 변환 결과 ADO[1:0]의 값을 SKA[1:0]로서 출력한다. 또한, FWP[1:0]=01일 때에는, 연속하는 VSCLK 주기 2회의 A/D 변환 결과 ADO[1:0]의 값이 일치했을 때에 ADO[1:0]의 값을 SKA[1:0]로서 출력한다. FWP[1:0]=10일 때에는, 연속하는 VSCLK 주기 3회의 ADO[1:0]의 값이 일치했을 때에 ADO[1:0]의 값을 SKA[1:0]로서 출력한다. 또한, FWP[1:0]=11일 때에는, 연속하는 VSCLK 주기 4회의 ADO[1:0]의 값이 일치했을 때에, ADO[1:0]의 값을 SKA[1:0]로서 출력한다. 이와 같이 하여, 본 실시예에서는, 미리 레지스터(345, 346)의 설정치에 의해 조광 제어 회로의 반영 조건을 결정함으로써, 적절한 주기로 외부의 포토 센서로부터 입력되는 PSVI 신호의 레벨 변화량에 따른 감마 특성 조정이 행할 수 있도록 하고 있다.

표 7에는, A/D 변환 결과 처리 회로(342)의 출력 신호 SKA[1:0]에 의해 선택되는 진폭 조정 레지스터 및 커브 조정 레지스터를 나타낸다.

[표 7]

| A/D변환 결과<br>처리 회로<br>출력 SKA[1:0] | 주위의 밝기         | 대응하는 레지스터     | 비고                                              |

|----------------------------------|----------------|---------------|-------------------------------------------------|

| 0 0                              | 가장 어두운 환경      | 진폭 조정<br>레지스터 | KA1R[6:0] R 용<br>KA1G[6:0] G 용<br>KA1B[6:0] B 용 |

|                                  |                | 커브 조정<br>레지스터 | KC1R[3:0] R 용<br>KC1G[3:0] G 용<br>KC1B[3:0] B 용 |

|                                  |                | 진폭 조정<br>레지스터 | KA2R[6:0] R 용<br>KA2G[6:0] G 용<br>KA2B[6:0] B 용 |

|                                  |                | 커브 조정<br>레지스터 | KC2R[3:0] R 용<br>KC2G[3:0] G 용<br>KC2B[3:0] B 용 |

|                                  |                | 진폭 조정<br>레지스터 | KA3R[6:0] R 용<br>KA3G[6:0] G 용<br>KA3B[6:0] B 용 |

|                                  |                | 커브 조정<br>레지스터 | KC3R[3:0] R 용<br>KC3G[3:0] G 용<br>KC3B[3:0] B 용 |

| 0 1                              | 2번째로<br>어두운 환경 | 진폭 조정<br>레지스터 | KA4R[6:0] R 용<br>KA4G[6:0] G 용<br>KA4B[6:0] B 용 |

|                                  |                | 커브 조정<br>레지스터 | KC4R[3:0] R 용<br>KC4G[3:0] G 용<br>KC4B[3:0] B 용 |

|                                  |                | 진폭 조정<br>레지스터 | KA1R[6:0] R 용<br>KA1G[6:0] G 용<br>KA1B[6:0] B 용 |

|                                  |                | 커브 조정<br>레지스터 | KC1R[3:0] R 용<br>KC1G[3:0] G 용<br>KC1B[3:0] B 용 |

|                                  |                | 진폭 조정<br>레지스터 | KA2R[6:0] R 용<br>KA2G[6:0] G 용<br>KA2B[6:0] B 용 |

|                                  |                | 커브 조정<br>레지스터 | KC2R[3:0] R 용<br>KC2G[3:0] G 용<br>KC2B[3:0] B 용 |

| 1 0                              | 2번째로<br>밝은 환경  | 진폭 조정<br>레지스터 | KA3R[6:0] R 용<br>KA3G[6:0] G 용<br>KA3B[6:0] B 용 |

|                                  |                | 커브 조정<br>레지스터 | KC3R[3:0] R 용<br>KC3G[3:0] G 용<br>KC3B[3:0] B 용 |

|                                  |                | 진폭 조정<br>레지스터 | KA4R[6:0] R 용<br>KA4G[6:0] G 용<br>KA4B[6:0] B 용 |

|                                  |                | 커브 조정<br>레지스터 | KC4R[3:0] R 용<br>KC4G[3:0] G 용<br>KC4B[3:0] B 용 |

|                                  |                | 진폭 조정<br>레지스터 | KA1R[6:0] R 용<br>KA1G[6:0] G 용<br>KA1B[6:0] B 용 |

|                                  |                | 커브 조정<br>레지스터 | KC1R[3:0] R 용<br>KC1G[3:0] G 용<br>KC1B[3:0] B 용 |

| 1 1                              | 가장 밝은 환경       | 진폭 조정<br>레지스터 | KA2R[6:0] R 용<br>KA2G[6:0] G 용<br>KA2B[6:0] B 용 |

|                                  |                | 커브 조정<br>레지스터 | KC2R[3:0] R 용<br>KC2G[3:0] G 용<br>KC2B[3:0] B 용 |

|                                  |                | 진폭 조정<br>레지스터 | KA3R[6:0] R 용<br>KA3G[6:0] G 용<br>KA3B[6:0] B 용 |

|                                  |                | 커브 조정<br>레지스터 | KC3R[3:0] R 용<br>KC3G[3:0] G 용<br>KC3B[3:0] B 용 |

|                                  |                | 진폭 조정<br>레지스터 | KA4R[6:0] R 용<br>KA4G[6:0] G 용<br>KA4B[6:0] B 용 |

|                                  |                | 커브 조정<br>레지스터 | KC4R[3:0] R 용<br>KC4G[3:0] G 용<br>KC4B[3:0] B 용 |

표 7에 나타난 바와 같이, 이 실시예에서는, 가장 어두운 환경인 SKA[1:0]=00의 경우에는, 진폭 조정 레지스터는 R, G, B 각각 KA1R, KA1G, KA1B를, 커브 조정 레지스터는 R, G, B 각각 KC1R, KC1G, KC1B를 선택한다. 2번째로 어두운 환경인 SKA[1:0]=01의 경우에는, 진폭 조정 레지스터는 KA2R, KA2G, KA2B를, 커브 조정 레지스터는 R, G, B 각각 KC2R, KC2G, KC2B를 선택한다. 2번째로 밝은 환경인 SKA[1:0]=10의 경우에는, 진폭 조정 레지스터는 R, G, B 각각 KA3R, KA3G, KA3B를, 커브 조정 레지스터는 R, G, B 각각 KC3R, KC3G, KC3B를 선택한다. 가장 밝은 환경인 SKA[1:0]=11의 경우에는, 진폭 조정 레지스터는 R, G, B 각각 KA4R, KA4G, KA4B를, 커브 조정 레지스터는 R, G, B 각각 KC4R, KC4G, KC4B를 선택한다. 선택된 각각 RGB 개별의 레지스터 값을, 각각의 계조 전압 생성 회로(314R, 314G, 314B)에 입력함으로써, 원하는 계조 전압 레벨 및 감마 커브를 생성한다. 또한 각 레지스터에는, 각각의 밝기에 대응하는 계조 전압을 생성하기 위한 값이 설정되어 있다.

전술한 바와 같이, 이 실시예의 유기 EL 패널의 표시용 구동 회로에서는, 외부의 포토 센서(100)로부터의 입력 신호(PSVI)에 기초하여, 임의의 결정된 주기마다 주위의 밝기(어둡기)를 검지하여 각각 RGB 개별의 계조 전압의 조정과 감마 커브의 조정을 행하도록 하고 있기 때문에, 보다 고화질의 표시 구동을 행할 수 있다.

도 7에는 A/D 변환 회로(341)의 다른 실시예가 도시되어 있다.

이 실시예의 A/D 변환 회로(341)는, 히스테리시스 특성을 갖게 한 것이다. 구체적으로는, A/D 변환 회로(341)에는, 래더 저항으로 이루어지는 저항 분할 회로(510)에 의해 생성된 전압 중에서 적당한 것을 선택하는 1조의 선택 회로(셀렉터)(521a, 522a, 523a)가 형성되어 있다. 그 밖에, A/D 변환 회로(341)에는, 이들의 선택 회로(셀렉터)(521a, 522a, 523a)에서 선택되는 전압보다도 약간 낮은 전압을 선택하는 선택 회로(셀렉터)(521b, 522b, 523b)가 1조 더 형성되어 있다.

이와 함께, 한 쪽의 조의 선택 회로(셀렉터)(521a, 522a, 523a)에 의해 선택되는 전압과 다른 쪽의 조의 선택 회로(셀렉터)(521b, 522b, 523b)에 의해 선택되는 전압을 절환하여, 콤퍼레이터(531, 532, 533)의 반전 입력 단자(-)에 인가시키는 절환 스위치(SW1~SW3)가 형성되어 있다. 콤퍼레이터(531, 532, 533)의 비반전 입력 단자(+)에는, 외부의 포토 센서(100)로부터의 입력 신호(PSVI)가 공급된다. 선택 회로(셀렉터)(521b, 522b, 523b)는, 각각 예를 들면 4개의 전압 중에

서 1개를 선택할 수 있도록 되어, 히스테리시스 설정 레지스터(348)의 설정치 VHSH[1:0], VHSM[1:0], VHSL[1:0]에 의해 원하는 전압을 선택하여 콤퍼레이터(531, 532, 533)에 공급하도록 구성된다. 또한, 히스테리시스 설정 레지스터(348)는, 후술되는 도 9의 컨트롤 레지스터(CR)(362)에 형성된다.

절환 스위치(SW1~SW3)는, 콤퍼레이터(531, 532, 533)의 출력에 의해, 그 출력이 로우 레벨로부터 하이 레벨로 변화하면 반전 입력 단자에 입력되는 전압을, 선택 회로(셀렉터)(521b, 522b, 523b)에 의해 선택되는 낮은 쪽의 전압으로 절환한다. 또한, SW1~SW3은, 콤퍼레이터(531, 532, 533)의 출력이 하이 레벨로부터 로우 레벨로 변화하면 반전 입력 단자에 입력되는 전압을, 선택 회로(셀렉터)(521a, 522a, 523a)에 의해 선택되는 높은 쪽의 전압으로 절환하도록 제어가 행해진다. 이와 같이 구성됨으로써, 이 실시예의 A/D 변환 회로(341)는, 포토 센서(100)로부터의 입력 신호(PSVI)에 대하여, 도 8에 도시하는 바와 같은 히스테리시스 특성을 갖게 된다. 그 결과, 주위의 밝기의 미묘한 변동 즉 외란(外亂)(disturbance) 노이즈에 대한 반응을 둔하게 하여, 유기 EL 패널의 휘도가 빈번하게 변화하여 표시가 보기 힘들게 되는 것을 회피할 수 있다.

또한, 저항 분할 회로(510)에 의해 생성된 전압을 선택하는 선택 회로(셀렉터)를 2조 형성하는 대신에, 콤퍼레이터(531, 532, 533)로서, 히스테리시스 특성을 갖는 타입의 콤퍼레이터를 사용하도록 해도 된다. 히스테리시스 특성을 갖는 콤퍼레이터는 공지된 것으로서, 이 실시예에서는 공지의 히스테리시스 콤퍼레이터를 사용할 수 있으므로, 구체적인 예시는 생략한다.

단, 본 실시예와 같이, 콤퍼레이터의 참조 전압을 절환함으로써 히스테리시스를 갖게 하도록 구성하면, 본 실시예를 적용한 드라이버 IC가 사용되는 기기에 따라, 히스테리시스의 정도(폭)를 조정할 수 있다. 이것에 의해, 기기에 최적의 표시를 행할 수 있음과 함께, 사용 중에도, 예를 들면 포토 센서(100)로부터의 신호의 강도 등에 따라 다이내믹하게 히스테리시스를 변화시킬 수 있다. 그 때문에, 실내에서 사용하는 경우와 실외에서 사용하는 경우에 의해 히스테리시스의 정도(폭)를 바꿔, 사용 환경에 따라 너무 빈번하게 기동이 변화하지 않도록 제어할 수 있다고 하는 이점이 있다.

다음으로, 도 9를 이용하여 도 1의 신호선 구동 회로(310)를 내장하는 유기 EL 패널 드라이버 IC 전체의 구성을 설명한다. 도 9에서, 도 1에 도시되어 있는 회로와 동일한 회로에는 동일한 부호를 부여하고 중복된 설명은 생략한다.

이 실시예의 유기 EL 패널 드라이버 IC(300)는, 외부의 마이크로프로세서 혹은 마이크로 컴퓨터(이하, CPU라고 함) 등으로부터의 명령에 기초하여 칩 내부 전체를 제어하는 제어부(360)를 포함한다. 또한, 드라이버 IC(300)는, 도시하지 않은 표시 데이터 버스를 통하여 주로 애플리케이션 프로세서 등으로부터의 동화상 데이터나 수평·수직 동기 신호(HSYNC, VSYNC), 도트 클록(DOTCLK) 등의 동기 신호, 인에이블 신호와 같은 외부 제어 신호를 받는 외부 표시 인터페이스(371)를 포함한다. 또한, 드라이버 IC(300)는, 도시하지 않은 시스템 버스를 통하여 CPU 등 사이에서 주로 인스트럭션 코드 등의 데이터의 송수신을 행하는 시스템 인터페이스(372)를 포함한다.

칩 내부의 다양한 회로의 동작 타이밍을 부여하는 타이밍 신호를 발생하는 타이밍 제어 회로(350)는, 외부 표시 인터페이스(371)를 통하여 외부로부터 수취한 동기 신호에 기초하여 타이밍 신호를 생성한다. 상기 애플리케이션 프로세서로부터의 동화상 데이터는, 도트 클록 신호(DOTCLK)에 동기하여 공급된다. 시스템 인터페이스(372)는, 칩 셀렉트 신호(CSB)가 유효 레벨로 되는 것을 조건으로 CPU 등으로부터 공급되는 클록(SCL)에 동기하여 시리얼로 데이터의 입출력을 행한다. 신호선 구동 회로(310)의 래치 회로(311)에는, 외부 표시 인터페이스(371)로부터 표시 데이터가 18 비트 혹은 6 비트와 같은 단위로 전송된다.

제어부(360)에는, 해당 드라이버 IC(300)의 동작 모드 등 칩 전체의 동작 상태를 제어하기 위한 컨트롤 레지스터(CR)(362)나, 그 컨트롤 레지스터(362)의 참조를 위한 인덱스 정보를 기억하는 인덱스(IR)(361) 등의 레지스터가 형성되어 있다. 컨트롤 레지스터(CR)(362)에는, 도 1 및 도 4의 참조 부호 313R, 313G, 313B, 도 5의 참조 부호 344, 345, KA0R-KA4R, KC0R-KC4R 등의 레지스터가 포함된다. 그리고, 외부의 CPU 등이 인덱스 레지스터(362)에 기입을 행함으로써 실행하는 인스트럭션을 지정하면, 제어부(360)가 지정된 인스트럭션에 대응한 제어 신호를 생성하여 출력하는 제어 방식을 채용하고 있다. 제어부(360)의 제어 방식으로서, 외부의 CPU 등으로부터 커맨드 코드를 받으면, 이 커맨드를 디코드하여 제어 신호를 생성하는 방식을 채용해도 된다.

전원 회로(330)는, 기준 전압 발생 회로(331)나 외부로부터 공급되는 전원 전압 Vcc를 승압하여 Vcc보다 높은 전압을 생성하는 승압 회로(332, 333), 주사선 구동 회로(320)에 필요한 전압 VGH, VGL, VSUS를 생성하는 주사선 구동용 전압 생성 회로(334) 등으로 구성된다. 이 전원 회로(330)는, 유기 EL 패널을 구동하는 계조 전압을 생성하는 계조 전압 생성

회로(315)나 칩 외부의 주사선 구동 회로(320)에 필요한 전압을 생성한다. 특별히 제한되는 것은 아니지만, 이 실시예의 드라이버 IC(300)의 신호선 구동 회로(310)는, 유기 EL 패널의 240개의 신호선에 인가되는 전압 S1~S240을 생성하여 출력할 수 있도록 구성되어 있다.

이 실시예의 드라이버 IC(300)에 입력되는 신호로서는, 상기 이외에, 전술한 포토 센서로부터의 신호 PSVI나 칩 내부를 초기 상태로 하는 리셋 신호(RESET), 내부 회로의 시험을 위한 테스트 신호(TEST1, TEST2) 등이 있다. 또한, 이 실시예의 드라이버 IC(300)의 칩에는, 이들의 신호의 입출력 단자 외에, 승압 회로(332, 333)에 이용되는 용량 소자가 접속되는 단자, 승압 회로(332, 333)나 계조 전압 생성 회로(315)에 의해 생성된 전압을 출력하기 위한 단자 등이 형성되어 있지만, 이들은 본 발명에 직접 관계하지 않으므로 설명은 생략한다.

이상 본 발명자에 의해 이루어진 발명을 실시예에 기초하여 구체적으로 설명하였지만, 본 발명은 상기 실시 형태에 한정되는 것이 아니라, 그 요지를 일탈하지 않는 범위에서 다양하게 변경 가능한 것은 물론이다. 예를 들면, 상기 실시예에서는, 감마 특성을 조정하는 값을 유지하는 진폭 조정 레지스터 및 커브 조정 레지스터를 형성하고 있지만, 레지스터 대신에 불휘발성 메모리 소자로 이루어지는 설정 수단(ROM)을 이용하도록 해도 된다. 또한, 그 경우, ROM 내의 어느 하나의 진폭 조정치가 선택되었다면 그 진폭 조정치에 최적의 커브 조정치를 자동적으로 ROM으로부터 판독하도록 구성해도 된다.

또한, 상기 실시예의 유기 EL 패널 드라이버 IC(300)는, 유기 EL 패널(200)의 주사선을 구동하는 주사선 구동 회로(320)를 IC 외부의 회로로 하고 있지만, 주사선 구동 회로(320)도 내장한 드라이버 IC로서 구성하도록 해도 된다. 또한, 상기 실시예에서는, 주위의 밝기를 나타내는 신호로서 포토 센서의 검출 신호가 그대로 사용되고 있지만, 다른 회로로부터 공급되는 신호를 이용하도록 해도 된다. 즉, 주위의 밝기를 나타내는 신호이면 포토 센서로부터의 신호에 한정되지 않고 어떠한 것이어도 된다.

### 발명의 효과

본원에서 개시되는 발명 중 대표적인 것에 의해 얻어지는 효과를 간단히 설명하면 하기와 같다.

즉, 본 발명에 따르면, 주위의 밝기에 따라 자동적으로 회도를 변화시킴으로써 어떠한 환경 하에서도 표시가 보기 편한 EL 패널 등의 자발광 패널의 표시 구동용 반도체 집적 회로를 실현할 수 있다.

또한, 본 발명에 따르면, 주위의 밝기 및 사용하는 표시 장치의 사양에 따라 계조 전압 및 감마 커브 특성을 변경하여 최적의 화질로 표시를 행할 수 있는 유기 EL 패널 등의 자발광 패널의 표시 구동용 반도체 집적 회로를 실현할 수 있다고 하는 효과가 있다.

### <산업상의 이용 가능성>

이상의 설명에서는 주로 본 발명자에 의해 이루어진 발명을 그 배경으로 된 이용 분야인 유기 EL 패널을 구동하는 드라이버에 대해 설명하였지만, 본 발명은 그것에 한정되는 것은 아니고, 예를 들면, 유기 EL 패널 이외의 자발광 패널을 표시 구동하는 드라이버에 적용할 수 있다.

### (57) 청구의 범위

#### 청구항 1.

표시 데이터에 따라 자발광형 표시 패널의 신호선에 인가되는 구동 전압을 생성하여 출력함과 함께, 주위의 밝기에 따른 입력 신호에 응답하여 상기 구동 전압에 부여되는 계조(階調) 전압을 변경 가능한 표시 구동용 반도체 집적 회로로서,

상기 계조 전압의 최대치 및 최소치를 규정하기 위한 복수의 설정치를 저장하는 기억 회로와,

상기 입력 신호에 따라 상기 기억 회로 내의 어느 하나의 설정치를 지정하는 신호를 출력하는 제어 회로와,

해당 제어 회로의 출력에 의해 상기 기억 회로로부터 상기 입력 신호에 대응한 설정치를 선택하는 선택 회로와,

해당 선택 회로의 출력을 받아 상기 구동 전압에 부여되는 계조 전압을 생성하는 계조 전압 생성 회로를 포함하는 것을 특징으로 하는 표시 구동용 반도체 집적 회로.

## 청구항 2.

제1항에 있어서,

상기 계조 전압의 변화 특성을 규정하기 위한 복수의 설정치를 저장하는 제2 기억 회로를 더 포함하는 것을 특징으로 하는 표시 구동용 반도체 집적 회로.

## 청구항 3.

제2항에 있어서,

상기 기억 회로 및 제2 기억 회로는, 저장되는 설정치가 재기입 가능한 레지스터인 것을 특징으로 하는 표시 구동용 반도체 집적 회로.

## 청구항 4.

제1항에 있어서,

상기 계조 전압 생성 회로는 적, 청, 뉴의 3원색의 각 색에 대응하여 각각 형성되고, 상기 구동 전압은 3원색의 각 색에 대응한 신호로서 별개로 생성되고, 상기 기억 회로에 저장되는 설정치는 3원색의 각 색에 대응하여 저장되는 것을 특징으로 하는 표시 구동용 반도체 집적 회로.

## 청구항 5.

제1항 내지 제4항 중 어느 한 항에 있어서,

상기 제어 회로는 상기 입력 신호를 디지털 신호로 변환하는 A/D 변환 회로를 포함하고, 상기 A/D 변환 회로의 출력에 따라 상기 선택 회로에 의해 상기 기억 회로로부터 선택되는 설정치가 변경되는 것을 특징으로 하는 표시 구동용 반도체 집적 회로.

## 청구항 6.

제5항에 있어서,

상기 제어 회로는 상기 A/D 변환 회로의 출력의 유효·무효를 제어하는 유효화 제어 회로를 포함하고, 해당 유효화 제어 회로가 유효화된 경우에 상기 선택 회로에 의해 상기 기억 회로로부터 선택되는 설정치가 변경되는 것을 특징으로 하는 표시 구동용 반도체 집적 회로.

## 청구항 7.

제6항에 있어서,

상기 제어 회로는 상기 A/D 변환 회로의 출력의 유효화의 빈도를 지정하는 설정치를 저장하는 레지스터를 포함하고, 상기 유효화 제어 회로는 해당 레지스터의 설정치에 따라 상기 A/D 변환 회로의 출력의 유효/무효를 제어하는 것을 특징으로 하는 표시 구동용 반도체 집적 회로.

### 청구항 8.

제5항 내지 제7항 중 어느 한 항에 있어서,

상기 A/D 변환 회로는 입력에 대하여 히스테리시스 특성을 갖도록 구성되어 있는 것을 특징으로 하는 표시 구동용 반도체 집적 회로.

### 청구항 9.

제8항에 있어서,

상기 A/D 변환 회로는, 상기 입력 신호와 소정의 참조 전압을 비교하는 복수의 콤퍼레이터(comparator)를 포함하고, 상기 참조 전압이 각 콤퍼레이터의 출력의 변화에 따라 절환됨으로써 히스테리시스 특성을 갖도록 구성되어 있는 것을 특징으로 하는 표시 구동용 반도체 집적 회로.

### 청구항 10.

제1항 내지 제9항 중 어느 한 항의 표시 구동용 반도체 집적 회로와, 해당 표시 구동용 반도체 집적 회로에 의해 구동되는 자발광형 표시 장치와, 기기 주위의 밝기를 검출하는 광량 검출 수단을 포함하는 전자 기기로서,

상기 광량 검출 수단의 검출 신호가 상기 입력 신호로서 상기 표시 구동용 반도체 집적 회로에 입력되도록 구성되어 있는 것을 특징으로 하는 전자 기기.

도면

도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

|                |                                                                             |         |            |

|----------------|-----------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 电子设备包括显示驱动半导体集成电路和自发光显示设备                                                   |         |            |

| 公开(公告)号        | <a href="#">KR1020060107345A</a>                                            | 公开(公告)日 | 2006-10-13 |

| 申请号            | KR1020060031017                                                             | 申请日     | 2006-04-05 |

| [标]申请(专利权)人(译) | 株式会社瑞萨科技<br>Sikki瑞萨科技有限公司                                                   |         |            |

| 申请(专利权)人(译)    | Sikki瑞萨科技有限公司                                                               |         |            |

| 当前申请(专利权)人(译)  | Sikki瑞萨科技有限公司                                                               |         |            |

| [标]发明人         | OGATA YASUHIRO<br>오가따야스히로<br>KEICHO TAKAYUKI<br>게이쪼다까유끼                     |         |            |

| 发明人            | 오가따야스히로<br>게이쪼다까유끼                                                          |         |            |

| IPC分类号         | G09G3/30 G09G3/20                                                           |         |            |

| CPC分类号         | G09G2320/0242 G09G2310/027 G09G3/3233 G09G3/3291 G09G2320/0673 G09G2360/144 |         |            |

| 代理人(译)         | CHANG, SOO KIL<br>LEE , JUNG HEE                                            |         |            |

| 优先权            | 2005109708 2005-04-06 JP                                                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                   |         |            |

### 摘要(译)

一种自发光面板的显示驱动半导体集成电路，例如有机EL面板，其能够根据周围环境的亮度改变灰度电压和伽马曲线特性，以及用于执行具有最佳图像质量的显示装置的规格。显示驱动半导体集成电路具有存储电路，例如寄存器 (KA0R) 或ROM，用于存储用于改变灰度电压的幅度的多个值;以及寄存器 (KC0R)，用于存储用于改变伽马曲线特性的多个值。或者诸如ROM的存储电路。通过根据光电传感器的输出选择存储电路中的多个值之一并将其提供给灰度电压产生电路，可以动态地改变灰度电压和伽马曲线特性。五指数组方面磁滞特性，伽玛曲线，梯形电阻，有机EL面板