**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

|                                             |                          |

|---------------------------------------------|--------------------------|

| (51) Int. Cl.<br><i>G09G 3/30</i> (2006.01) | (45) 공고일자<br>2006년04월18일 |

|                                             | (11) 등록번호<br>10-0572428  |

|                                             | (24) 등록일자<br>2006년04월12일 |

---

|                            |                   |                          |                               |

|----------------------------|-------------------|--------------------------|-------------------------------|

| (21) 출원번호<br>2004년03월05일   | 10-2004-7003328   | (65) 공개번호<br>2004년04월09일 | 10-2004-0031055               |

| 번역문 제출일자<br>2004년03월05일    |                   | (43) 공개일자<br>2004년04월09일 |                               |

| (86) 국제출원번호<br>2002년09월06일 | PCT/JP2002/009111 | (87) 국제공개번호<br>국제공개일자    | WO 2003/023750<br>2003년03월20일 |

---

|            |                    |             |        |

|------------|--------------------|-------------|--------|

| (30) 우선권주장 | JP-P-2001-00271311 | 2001년09월07일 | 일본(JP) |

|            | JP-P-2001-00291598 | 2001년09월25일 | 일본(JP) |

|            | JP-P-2001-00347014 | 2001년11월13일 | 일본(JP) |

|            | JP-P-2002-00136117 | 2002년05월10일 | 일본(JP) |

|           |                                                   |

|-----------|---------------------------------------------------|

| (73) 특허권자 | 마츠시타 덴끼 산교 가부시키가이샤<br>일본 오오사카후 가도마시 오오아자 가도마 1006 |

|-----------|---------------------------------------------------|

|          |                                                                                          |

|----------|------------------------------------------------------------------------------------------|

| (72) 발명자 | 다카하라 히로시<br>일본오사카후네야가와시오아자우즈마사 1011-1-345-씨-345<br><br>츠게히토시<br>일본오사카후가도마시미야마에쵸 16-1-314 |

|----------|------------------------------------------------------------------------------------------|

|          |     |

|----------|-----|

| (74) 대리인 | 김창세 |

|----------|-----|

**심사관 : 천대식**

---

**(54) EL 표시 패널, 그 구동 방법 및 EL 표시 장치**

---

**요약**

본 발명의 EL 표시 장치는, 공급되는 전류에 따른 회도로 발광하는 EL 소자(15)를 구비하고 있고, 이 EL 소자(15)에 대해, 화상 신호에 따른 전류보다도 큰 전류가 소스 신호선(18)을 거쳐서 소스 드라이버(14)로부터 출력된다. 이에 따라, 소스 신호선(18)에 존재하는 기생 용량의 충/방전이 이루어진다. 또한, EL 소자(15)와 소스 드라이버(14) 사이에 형성된 트랜지스터(11d)의 동작에 의해, 1 프레임 기간중의 일부의 기간만 EL 소자(15)에 대해 상기 전류가 공급된다. 그 결과, EL 소자(15)는 상기 일부의 기간만 발광한다.

**대표도**

12 ... 게이트 드라이버(회로)

14 ... 소스 드라이버(회로)

15 ... EL(소자)

16 ... 화소

17 ... 게이트 신호선

18 ... 소스 신호선

19 ... 저장 용량(부가 용량)

## 명세서

### 기술분야

본 발명은, 유기 또는 무기 일렉트로루미네슨스(전계 발광 : (EL)) 소자를 이용한 EL 표시 장치에 관한 것으로, 특히 소망하는 전류를 EL 소자에 대해 공급할 수 있는 EL 표시 장치, 그 구동 방법 및 그 EL 표시 장치를 구비한 전자 기기에 관한 것이다.

### 배경기술

일반적으로, 액티브 매트릭스형 표시 장치에서는, 다수의 화소를 매트릭스 형상으로 배열하여, 인가된 화상 신호에 따라 화소마다 광 강도를 제어함으로써 화상을 표시한다. 예를 들면, 전기 광학 물질로서 액정을 이용한 경우는, 각 화소에 기입되는 전압에 따라 화소의 투과율이 변화한다. 전기 광학 변환 물질로서 유기 일렉트로루미네슨스(EL) 재료를 이용한 액티브 매트릭스형의 화상 표시 장치에서도, 기본적인 동작은 액정을 이용한 경우와 마찬가지이다.

액정 표시 패널에서는, 각 화소는 셀터로서 동작하여, 백 라이트로부터의 광을 화소인 셀터로 온/오프시킴으로써 화상을 표시한다. 유기 EL 표시 패널은 각 화소에 발광 소자를 갖는 자발광형의 표시 패널이다. 이러한 자발광형의 표시 패널은, 액정 표시 패널에 비해서 화상의 시인성이 높고, 백 라이트가 불필요하며, 응답 속도가 빠른 등의 이점을 갖고 있다.

유기 EL 표시 패널은 각 발광 소자(화소)의 휘도를 전류량에 의해서 제어한다. 이와 같이, 발광 소자가 전류 구동형 혹은 전류 제어형이라고 하는 점에서 액정 표시 패널과는 크게 상이하다.

유기 EL 표시 패널에 있어서도, 액정 표시 패널과 마찬가지로, 단순 매트릭스 방식 및 액티브 매트릭스 방식의 구성이 가능하다. 전자는 구조가 단순하지만 대형이고 또한 고 선명의 표시 패널의 실현이 곤란하다. 그러나, 염가이다. 후자는 대형이며, 고 선명 표시 패널을 실현할 수 있다. 그러나, 제어 방법이 기술적으로 어렵고, 비교적 고가라고 하는 문제가 있다. 현재에는, 액티브 매트릭스 방식의 개발이 한창 행해지고 있다. 액티브 매트릭스 방식은, 각 화소에 마련한 발광 소자에 흐르는 전류를 화소 내부에 마련한 박막 트랜지스터(TFT)에 의해서 제어한다.

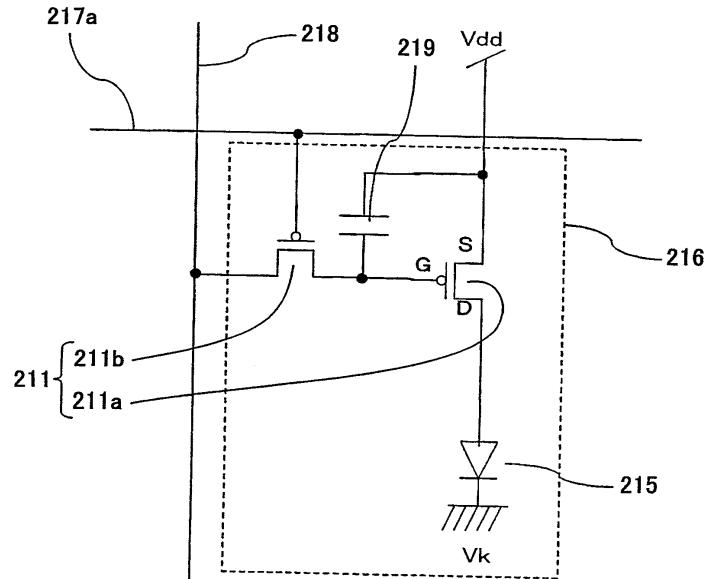

이 액티브 매트릭스 방식의 유기 EL 표시 패널은, 예컨대 일본 특허 공개 평성 제 8-234683 호 공보에 개시되어 있다. 이 표시 패널의 1 화소분의 등가 회로를 도 62에 나타낸다. 화소(216)는 발광 소자인 EL 소자(215), 제 1 트랜지스터(211a), 제 2 트랜지스터(211b) 및 축적 용량(219)으로 이루어진다. 여기서 EL 소자(215)는 유기 일렉트로루미네스نس(EL) 소자이다.

또, 본 명세서에서는, EL 소자에 전류를 공급(제어)하는 트랜지스터를 구동용 트랜지스터라고 부른다. 또한, 도 62에 있어서의 트랜지스터(211b)와 같이, 스위치로서 동작하는 트랜지스터를 스위치용 트랜지스터라고 부른다.

EL 소자(215)는 대부분의 경우, 정류성이 있기 때문에, OLED(유기 발광 다이오드)라고 불리는 경우가 있다. 그 때문에, 도 62에서는 EL 소자(215)를 OLED로서 다이오드의 기호를 이용하고 있다.

도 62의 예에서는, P 채널형의 트랜지스터(211a)의 소스 단자(S)를 Vdd(전원 전위)로 하고, EL 소자(215)의 캐소드(음극)는 접지 전위(Vk)에 접속된다. 한편, 애노드(양극)는 트랜지스터(211b)의 드레인 단자(D)에 접속되어 있다. 한편, P 채널형의 트랜지스터(211b)의 게이트 단자는 게이트 신호선(217a)에 접속되고, 소스 단자는 소스 신호선(218)에 접속되며, 드레인 단자는 축적 용량(219) 및 트랜지스터(211a)의 게이트 단자(G)에 접속되어 있다.

화소(216)를 동작시키기 위해서, 우선, 게이트 신호선(217a)을 선택 상태로 하여, 소스 신호선(218)에 휘도 정보를 나타내는 화상 신호를 인가한다. 그러면, 트랜지스터(211b)가 도통하여, 축적 용량(219)이 충전 또는 방전되어, 트랜지스터(211a)의 게이트 전위는 화상 신호의 전위에 일치한다. 게이트 신호선(217a)을 비 선택 상태로 하면, 트랜지스터(211a)가 오프로 되어, 트랜지스터(211a)는 전기적으로 소스 신호선(218)으로부터 분리된다. 그러나, 트랜지스터(211a)의 게이트 전위는 축적 용량(219)에 의해서 안정적으로 유지된다. 트랜지스터(211a)를 거쳐서 EL 소자(215)에 흐르는 전류는, 트랜지스터(211a)의 게이트/소스 단자간 전압 Vgs에 따른 값으로 되어, EL 소자(215)는 트랜지스터(211a)를 통해 공급되는 전류량에 따른 휘도로 발광을 계속한다.

이상과 같이, 도 62에 나타낸 종래 예는, 1 화소가, 하나의 선택 트랜지스터 (스위칭 소자)와, 하나의 구동용 트랜지스터로 구성된 것이다. 그 밖의 종래 예는, 예컨대, 특허 출원 평성 제 11-327637 호 공보에 개시되어 있다. 이 공보에는, 화소가 커런트 미러 회로로 구성된 실시예가 도시되어 있다.

그런데, 유기 EL 표시 패널은, 통상, 저온 폴리실리콘 트랜지스터 어레이를 이용하여 패널을 구성하고 있다. 그러나, 유기 EL 소자는, 전류에 근거하여 발광하기 때문에, 트랜지스터의 특성에 편차가 있으면, 표시 얼룩이 발생한다고 하는 문제가 있었다.

또한, 소스 신호선(18)에는 기생 용량이 존재하지만, 종래의 EL 표시 패널에서는 이 기생 용량을 충분히 충/방전할 수 없었다. 그 때문에, 화소(16)에 소망하는 전류를 공급할 수 없는 경우가 발생한다고 하는 문제가 있었다.

### 발명의 개시

본 발명은 이러한 사정을 감안하여 이루어진 것으로서, 그 목적은, 소스 신호선에 존재하는 기생 용량을 충분히 충/방전함으로써, 양호한 화상 표시를 실현할 수 있는 EL 표시 장치를 제공하는 것에 있다.

그리고, 이러한 목적을 달성하기 위해서, 본 발명에 따른 EL 표시 장치는, 서로 교차하도록 배열된 복수의 게이트 신호선 및 복수의 소스 신호선과, 매트릭스 형상으로 배치되어, 공급되는 전류에 따른 휘도로 발광하는 EL 소자와, 상기 게이트 신호선에 대해 게이트 신호를 출력하는 게이트 드라이버와, 상기 소스 신호선에 대해 외부로부터 입력되는 화상 신호에 따른 전류보다도 큰 전류를 출력하는 소스 드라이버와, 상기 EL 소자의 각각에 대응하여 마련되어, 상기 소스 드라이버로부터 출력된 전류를 상기 EL 소자에 대해 출력하는 트랜지스터와, 상기 게이트 신호선을 거쳐서 공급되는 게이트 신호에 따라 상기 EL 소자와 상기 트랜지스터 사이의 도통/비도통을 전환하는 것에 의해, 상기 소스 드라이버로부터 출력된 전류를 상기 EL 소자에 공급할 수 있는 제 1 스위칭 소자를 구비하며, 상기 게이트 드라이버는, 상기 EL 소자와 상기 트랜지스터 사이가 1 프레임 기간에 있어서 적어도 한 번은 도통 및 비도통으로 되도록 상기 게이트 신호선에 대해 게이트 신호를 출력하도록 구성되어 있다.

이와 같이 구성하면, 화상 신호에 따른 전류보다도 큰 전류가 소스 드라이버로부터 소스 신호선에 대해 출력되기 때문에, 소스 신호선에 기생 용량이 존재하는 경우더라도 그 기생 용량을 충/방전할 수 있다. 또한, 이와 같이 큰 전류를 EL 소자

에 공급한 경우, EL 소자가 화상 신호에 따른 휘도보다도 높은 휘도로 발광하는 것으로 되지만, EL 소자에 전류를 공급하는 시간을 1 프레임 기간보다도 짧은 기간으로 함으로써, EL 소자의 발광 시간을 단축화하는 것이 가능해지고, 그 결과 화상 신호에 따른 휘도에 상당하는 휘도에서의 화상 표시를 실현한다.

또한, 상기 발명에 따른 EL 표시 장치에 있어서, 상기 게이트 드라이버는, 상기 EL 소자와 상기 트랜지스터 사이의 1 프레임 기간에 있어서 주기적으로 복수회 도통 및 비도통으로 되도록 상기 게이트 신호선에 게이트 신호를 출력하도록 구성되어 있더라도 좋다.

이와 같이 구성하면, 이른바 인터레이스 구동을 실현할 수 있으므로, 보다 양호한 화상 표시를 행할 수 있다.

또한, 상기 발명에 따른 EL 표시 장치에 있어서, 상기 게이트 신호선을 거쳐서 공급되는 게이트 신호에 따라 상기 소스 드라이버와 상기 트랜지스터 사이의 도통/비도통을 전환하는 것에 의해, 상기 소스 드라이버로부터 출력된 전류를 상기 트랜지스터에 공급할 수 있는 제 2 스위칭 소자를 더 구비하며, 상기 게이트 드라이버는, 상기 EL 소자와 상기 트랜지스터 사이를 비도통으로 한 상태에서 상기 소스 드라이버와 상기 트랜지스터 사이를 도통으로 하여 상기 소스 드라이버로부터 출력되는 전류를 상기 트랜지스터에 프로그램한 후, 상기 EL 소자와 상기 트랜지스터 사이가 1 프레임 기간에 있어서 적어도 한 번은 도통 및 비도통으로 되도록 상기 게이트 신호선에 대해 게이트 신호를 출력하도록 구성되어 있더라도 좋다.

이와 같이 구성하면, 트랜지스터의 특성 편차에 의한 표시 얼룩 등을 방지할 수 있어, 양호한 화상 표시를 실현할 수 있다.

또한, 상기 발명에 따른 EL 표시 장치에 있어서, 상기 게이트 드라이버와 상기 트랜지스터가 동일 프로세스로 형성되어 있더라도 좋다. 즉, 예컨대, 저온 폴리실리콘 기술을 이용하여 게이트 드라이버와 드라이버가 형성되어 있더라도 좋다. 이와 같이 형성하는 것에 의해 협베젤(bezel)화를 실현할 수 있다.

또한, 상기 발명에 따른 EL 표시 장치에 있어서, 상기 소스 드라이버는, 반도체 칩으로 형성되어 있더라도 좋다.

또한, 본 발명에 따른 EL 표시 장치는, 서로 교차하도록 배열된 복수의 게이트 신호선 및 복수의 소스 신호선과, 매트릭스 형상으로 배치되어, 공급되는 전류에 따른 휘도로 발광하는 EL 소자와, 상기 게이트 신호선에 대해 게이트 신호를 출력하는 게이트 드라이버와, 상기 소스 신호선에 대해 외부로부터 입력되는 화상 신호에 따른 전류보다도 큰 전류를 출력하는 소스 드라이버와, 상기 EL 소자의 각각에 대응하여 마련되어, 상기 게이트 신호선을 거쳐서 공급되는 게이트 신호에 따라 상기 EL 소자와 상기 소스 신호선 사이의 도통/비도통을 전환하는 것에 의해, 상기 소스 신호선을 거쳐서 공급되는 전류를 상기 EL 소자에 공급할 수 있는 스위칭 소자와, 상기 EL 소자가 형성된 영역과는 상이한 영역에 마련되어, 화상 표시에 실질적으로 이용되지 않는 복수의 더미 소자와, 상기 더미 소자의 각각에 대응하여 마련되어, 상기 게이트 신호선을 거쳐서 공급되는 게이트 신호에 따라 상기 더미 소자와 상기 소스 신호선 사이의 도통/비도통을 전환하는 것에 의해, 상기 소스 신호선을 거쳐서 공급되는 전류를 상기 더미 소자에 공급할 수 있는 제 2 스위칭 소자를 구비하며, 상기 게이트 드라이버가 상기 EL 소자에 관한 게이트 신호선 및 상기 더미 소자에 관한 게이트 신호선에 대해 대략 동일한 타이밍에서 게이트 신호를 출력함으로써, 상기 소스 신호선을 거쳐서 공급되는 전류를 상기 EL 소자 및 상기 더미 소자의 각각에 분할하여 공급하도록 구성되어 있다.

이와 같이 구성하면, 화상 신호에 따른 전류보다도 큰 전류가 소스 드라이버로부터 소스 신호선에 대해 출력되기 때문에, 소스 신호선에 기생 용량이 존재하는 경우더라도 그 기생 용량을 충/방전할 수 있다. 또한, 소스 드라이버로부터 화상 신호에 따른 전류보다도 큰 전류가 출력된 경우더라도, 그 전류는 EL 소자 및 더미 소자로 분할하여 공급되기 때문에, EL 소자가 필요 이상으로 높은 휘도로 발광하는 것을 방지할 수 있다.

또한, 상기 발명에 따른 EL 표시 장치에 있어서, 상기 더미 소자에 관한 게이트 신호선은, 제 1 행 또는 최종 행의 상기 EL 소자에 관한 게이트 신호선과 이웃하도록 하여 형성되어 있고, 상기 게이트 드라이버가 이웃하는 복수 행의 게이트 신호선에 대해 대략 동일한 타이밍에서 순차적으로 게이트 신호를 출력함으로써, 복수의 상기 EL 소자의 각각 또는 상기 EL 소자 및 상기 더미 소자의 각각에 상기 소스 신호선을 거쳐서 공급되는 전류를 분할하여 공급하도록 구성되어 있더라도 좋다.

또한, 본 발명의 EL 표시 장치의 구동 방법은, 공급되는 전류에 따른 휘도로 발광하는 EL 소자와, 소스 신호선을 거쳐서 상기 EL 소자에 전류를 출력하는 소스 드라이버를 구비하는 EL 표시 장치의 구동 방법에 있어서, 외부로부터 입력된 화상 신호에 따른 전류보다도 큰 전류를 상기 소스 드라이버가 상기 소스 신호선에 출력하는 단계와, 1 프레임 기간의 일부의 기간에 걸쳐 상기 소스 신호선에 출력된 전류를 상기 EL 소자에 공급함으로써, 상기 일부의 기간에 있어서 상기 소스 신호선에 출력된 전류에 따른 휘도로 상기 EL 소자를 발광시키는 단계를 포함하고 있다.

또한, 상기 발명에 따른 EL 표시 장치의 구동 방법에 있어서, 상기 일부의 기간은, 복수의 기간으로 분할되어 있더라도 좋다.

또한, 본 발명의 전자 기기는, 청구항 1에 기재된 EL 표시 장치를 구비하며, 상기 EL 표시 장치에 대해 화상 신호를 출력하도록 구성되어 있다.

또한, 본 발명에 따른 EL 표시 장치는, 매트릭스 형상으로 배치된 EL 소자와, 상기 EL 소자에 흐르는 전류를 공급하는 구동용 트랜지스터와, 상기 EL 소자와 상기 구동용 트랜지스터 사이에 배치된 제 1 스위칭 소자와, 상기 제 1 스위칭 소자를 온/오프 제어하는 게이트 드라이버를 구비하며, 상기 게이트 드라이버는, 상기 제 1 스위칭 소자를, 1 프레임 기간에 있어서, 적어도 한 번 이상 오프 상태로 제어하는 것을 특징으로 한다.

또한, 상기 발명에 따른 EL 표시 장치에 있어서, 상기 제 1 스위칭 소자는, 1 프레임 기간에 있어서, 주기적으로 또한 복수회 오프 상태로 제어되더라도 좋다.

또한, 본 발명에 따른 EL 표시 장치는, 프로그램 전류를 출력하는 소스 드라이버 회로와, 매트릭스 형상으로 배치된 EL 소자와, 상기 EL 소자에 흐르는 전류를 공급하는 구동용 트랜지스터와, 상기 EL 소자와 상기 구동용 트랜지스터 사이에 배치된 제 1 스위칭 소자와, 상기 구동용 트랜지스터에 상기 프로그램 전류를 전달하는 경로를 구성하는 제 2 스위칭 소자와, 상기 제 1 및 제 2 스위칭 소자를 온/오프 제어하는 게이트 드라이버 회로를 구비하며, 상기 게이트 드라이버 회로는, 상기 제 1 스위칭 소자를, 1 프레임 기간에 있어서, 적어도 한 번 이상 온 상태로 하고, 또한 한 번 이상 오프 상태로 제어하는 것을 특징으로 한다.

또한, 상기 발명에 따른 EL 표시 장치에 있어서, 상기 게이트 드라이버는, 상기 구동용 트랜지스터와 동일 프로세스로 형성되고, 상기 소스 드라이버는, 반도체 칩으로 형성되어 있더라도 좋다.

또, 본 발명에 따른 EL 표시 장치는, 게이트 신호선과, 소스 신호선과, 프로그램 전류를 출력하는 소스 드라이버와, 게이트 드라이버와, 매트릭스 형상으로 배치된 EL 소자와, 상기 EL 소자에 흐르는 전류를 공급하는 구동용 트랜지스터와, 상기 EL 소자와 상기 구동용 트랜지스터 사이에 배치된 제 1 트랜지스터와, 상기 구동용 트랜지스터에 상기 프로그램 전류를 전달하는 경로를 구성하는 제 2 트랜지스터를 구비하며, 상기 소스 드라이버는, 상기 소스 신호선에 프로그램 전류를 출력하고, 상기 게이트 드라이버는, 게이트 신호선에 접속되고, 상기 제 2 트랜지스터의 게이트 단자는, 상기 게이트 신호선에 접속되며, 상기 제 2 트랜지스터의 소스 단자는, 상기 소스 신호선에 접속되고, 상기 제 2 트랜지스터의 드레인 단자는, 상기 구동용 트랜지스터의 드레인 단자와 접속되며, 상기 게이트 드라이버는, 복수의 게이트 신호선을 선택하여, 상기 프로그램 전류를 복수의 화소의 상기 구동용 트랜지스터에 공급하고, 상기 게이트 드라이버는, 상기 제 1 트랜지스터를, 1 프레임 기간에 있어서, 적어도 한 번 이상 온 상태로 하고, 또한 한 번 이상 오프 상태로 제어하는 것을 특징으로 한다.

또한, 상기 발명에 따른 EL 표시 장치에 있어서, 상기 게이트 드라이버는, 상기 구동용 트랜지스터와 동일 프로세스로 형성되고, 상기 소스 드라이버는, 반도체 칩으로 형성되어 있더라도 좋다.

또한, 본 발명에 따른 EL 표시 장치는, I(I는 2 이상의 정수) 화소 행, J(J는 2 이상의 정수) 화소 열로 이루어지는 표시 영역을 갖고, 상기 표시 영역의 소스 신호선에 영상 신호를 인가하는 소스 드라이버와, 상기 표시 영역의 게이트 신호선에 온전압 또는 오프 전압을 인가하는 게이트 드라이버와, 상기 표시 영역 이외의 개소에 형성된 더미 화소 행을 구비하며, 상기 표시 영역에는 EL 소자가 매트릭스 형상으로 형성되어, 상기 소스 드라이버로부터의 영상 신호에 근거하여 발광하고, 상기 더미 화소 행은, 발광하지 않거나, 또는 발광 상태가 시각적으로 보이지 않도록 구성되어 있는 것을 특징으로 한다.

또한, 상기 발명에 따른 EL 표시 장치에 있어서, 상기 게이트 드라이버는, 복수 화소 행을 동시에 선택하고, 상기 소스 드라이버로부터의 영상 신호를 상기 복수의 화소 행에 인가하여, 제 1 행의 화소 행 또는 I 화소 행이 선택될 때에는, 더미 화소 행이 선택되도록 구성되어 있더라도 좋다.

또한, 본 발명에 따른 EL 표시 장치의 구동 방법은, EL 소자를 소정 휘도보다도 고 휘도로 발광하는 전류를 상기 EL 소자에 공급하고, 1 프레임의 1/N(N은 1보다 작음)의 기간, 상기 EL 소자를 발광시키는 것을 특징으로 한다.

또한, 상기 발명에 따른 EL 표시 장치의 구동 방법에 있어서, 1 프레임의 1/N의 기간은, 복수 기간으로 분할되어 있더라도 좋다.

또한, 본 발명에 따른 EL 표시 장치의 구동 방법은, 전류에 의해 EL 소자에 흐르는 전류를 프로그램하는 EL 표시 장치의 구동 방법으로서, 소정 휘도보다도 높은 휘도로 상기 EL 소자를 발광시켜, 1/N(N>1)의 표시 영역을 표시하고, 상기 1/N의 표시 영역을 순차적으로 시프트하여 전체 화면을 표시하는 것을 특징으로 한다.

또한, 본 발명의 전자 기기는, 청구항 11에 기재된 EL 표시 장치와, 수화기와, 스피커를 구비하는 것을 특징으로 한다.

본 발명의 상기 목적, 다른 목적, 특징, 및 이점은, 첨부 도면을 참조하여, 이하의 바람직한 실시예의 상세한 설명으로부터 명백하게 된다.

### 도면의 간단한 설명

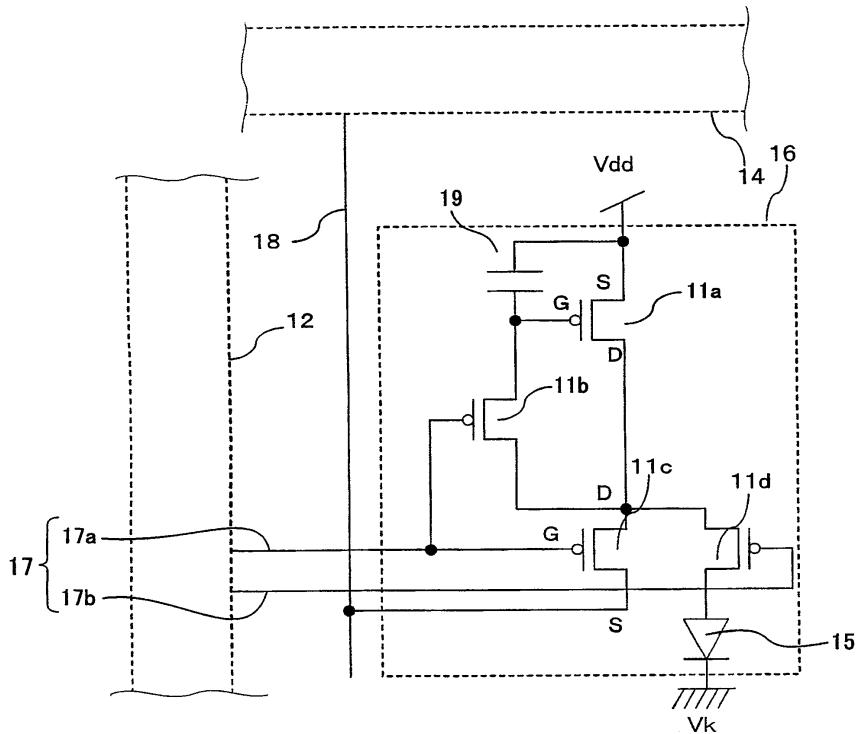

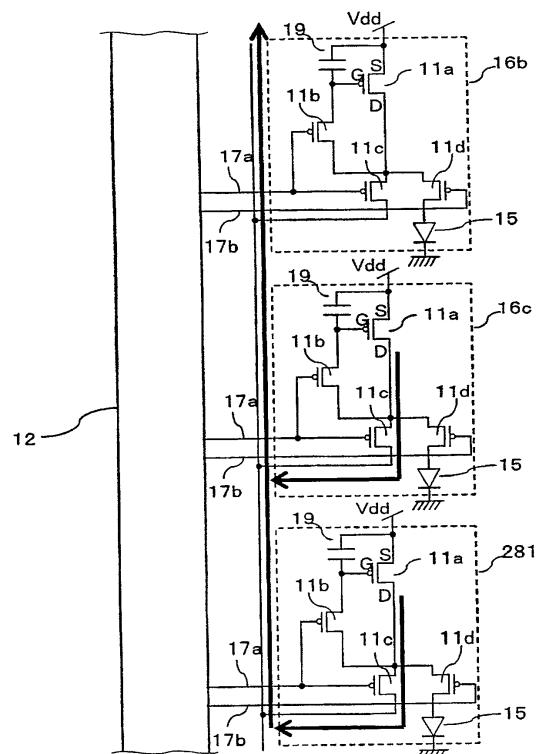

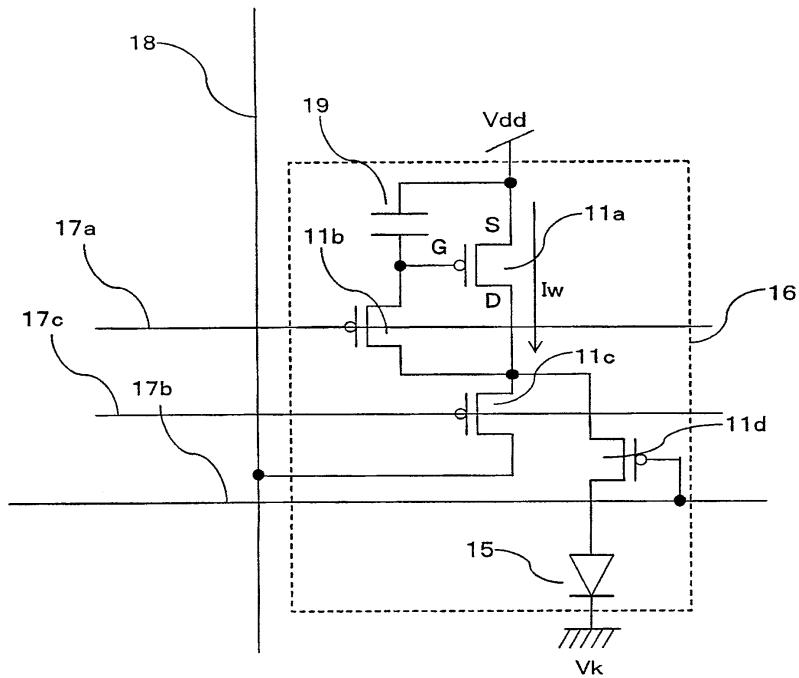

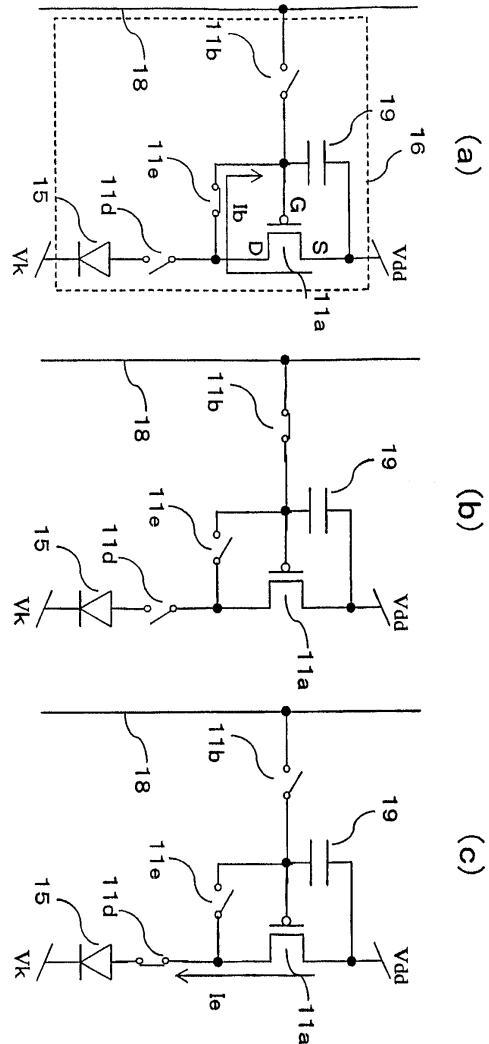

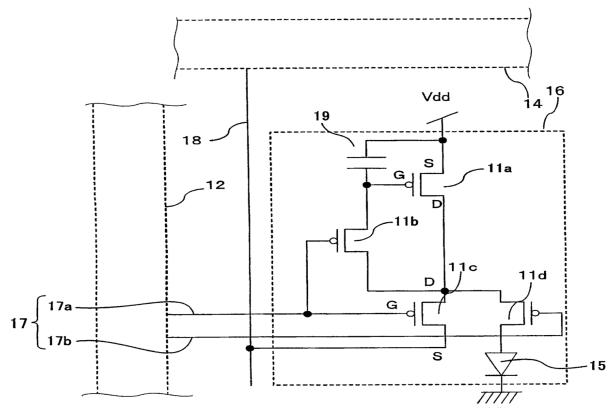

도 1은, 본 발명의 EL 표시 패널의 화소 구성도이다.

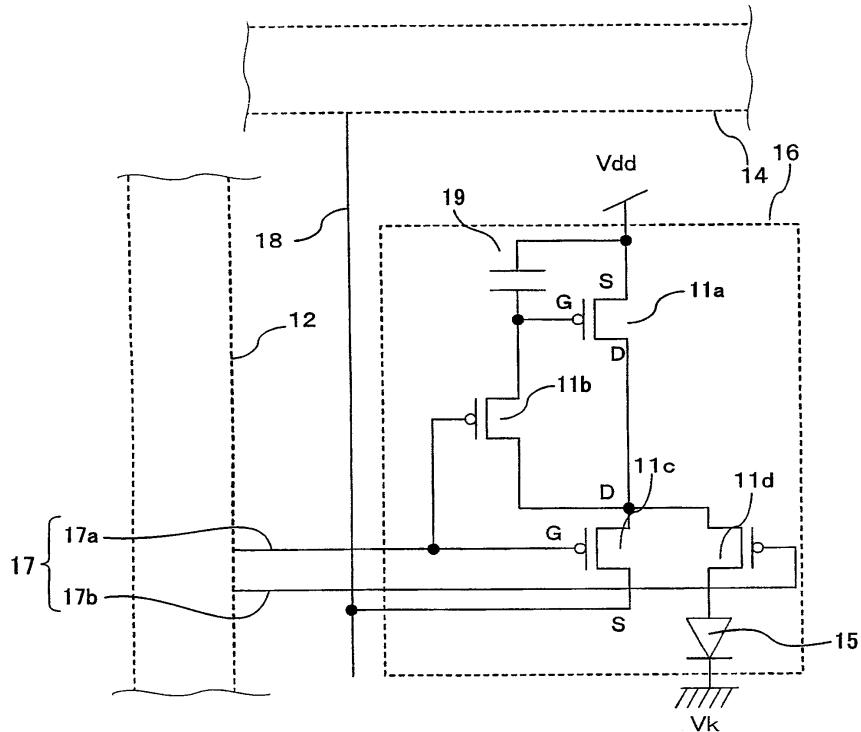

도 2는, 본 발명의 EL 표시 패널의 화소 구성도이다.

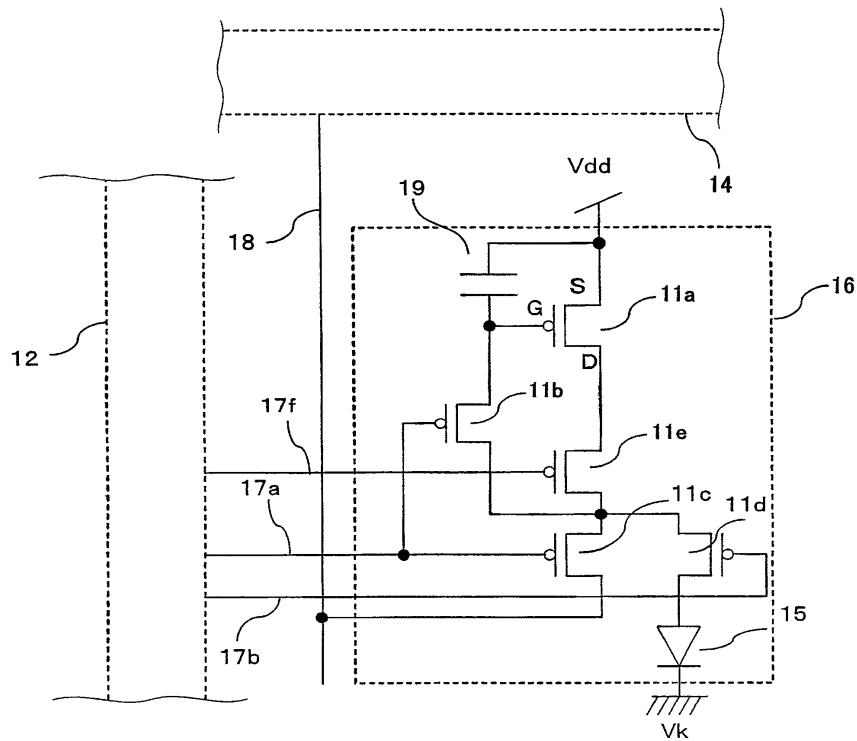

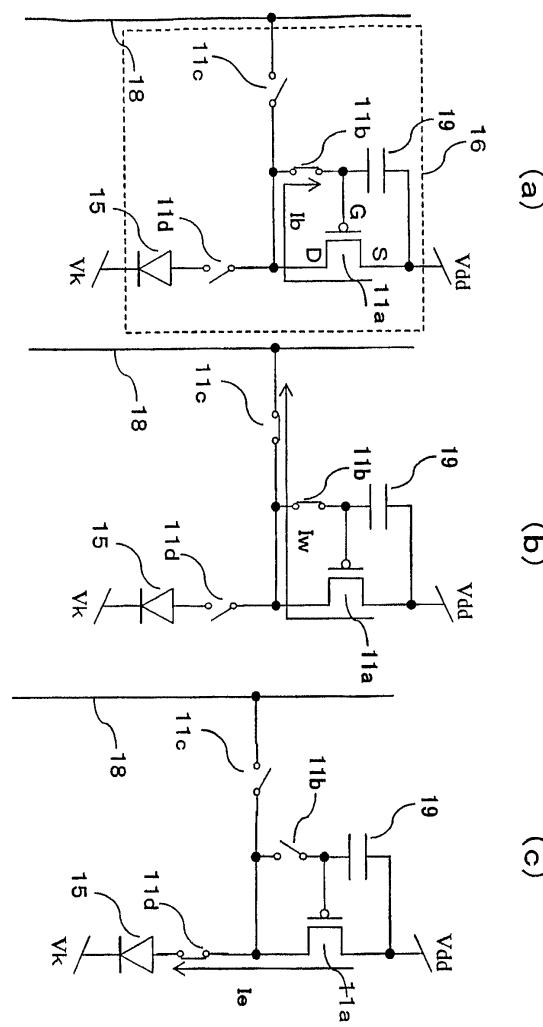

도 3은, 본 발명의 EL 표시 패널의 동작 설명도이다.

도 4는, 본 발명의 EL 표시 패널의 동작 설명도이다.

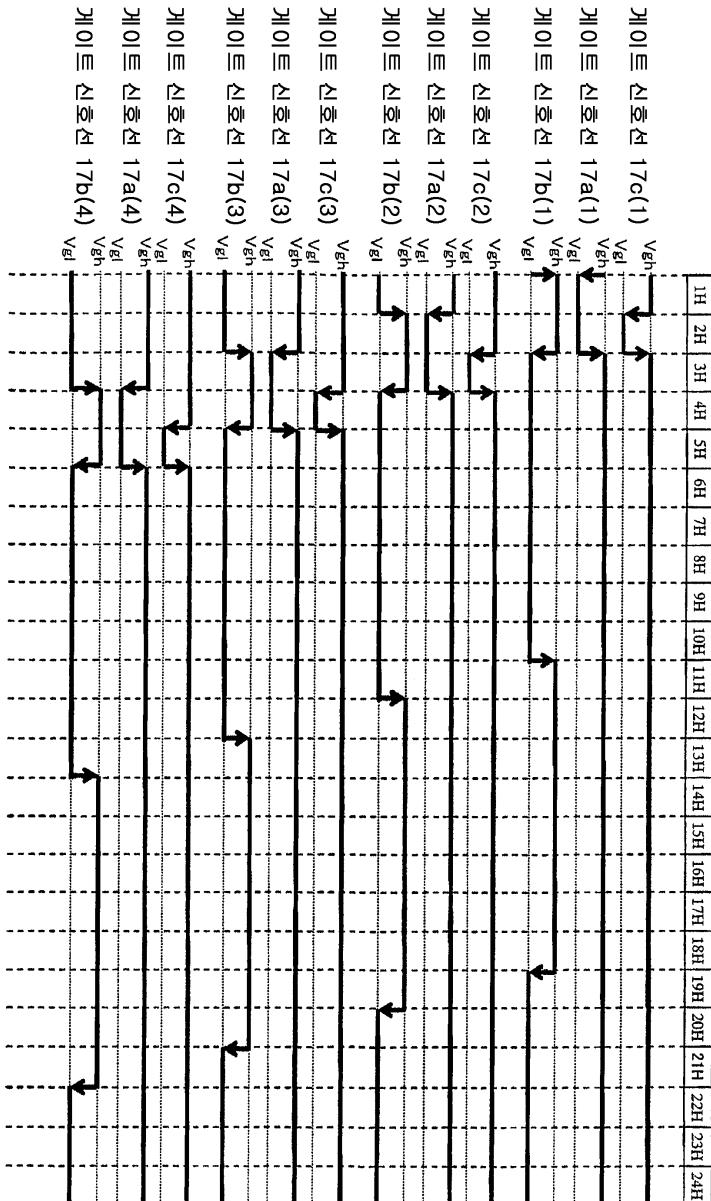

도 5는, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

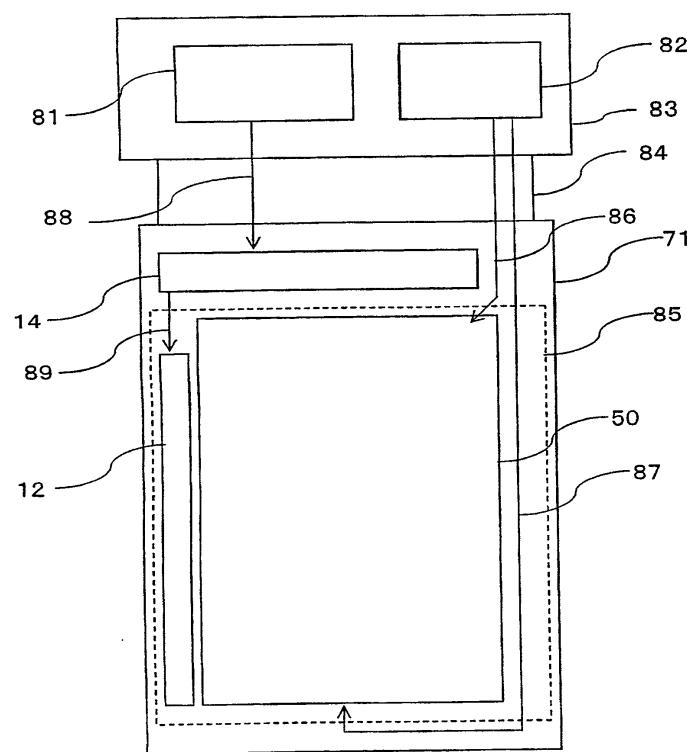

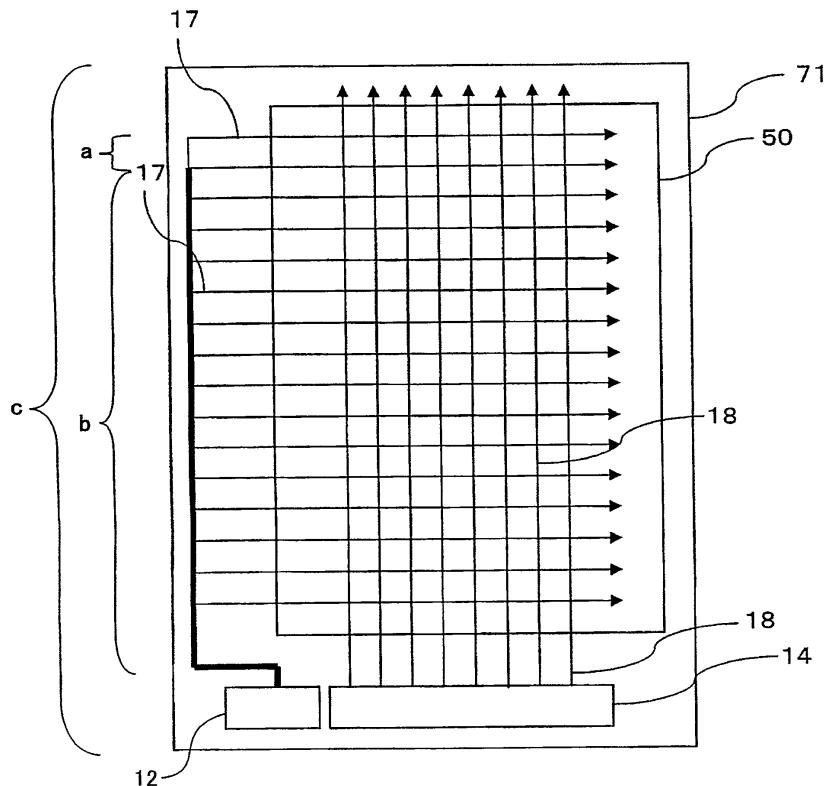

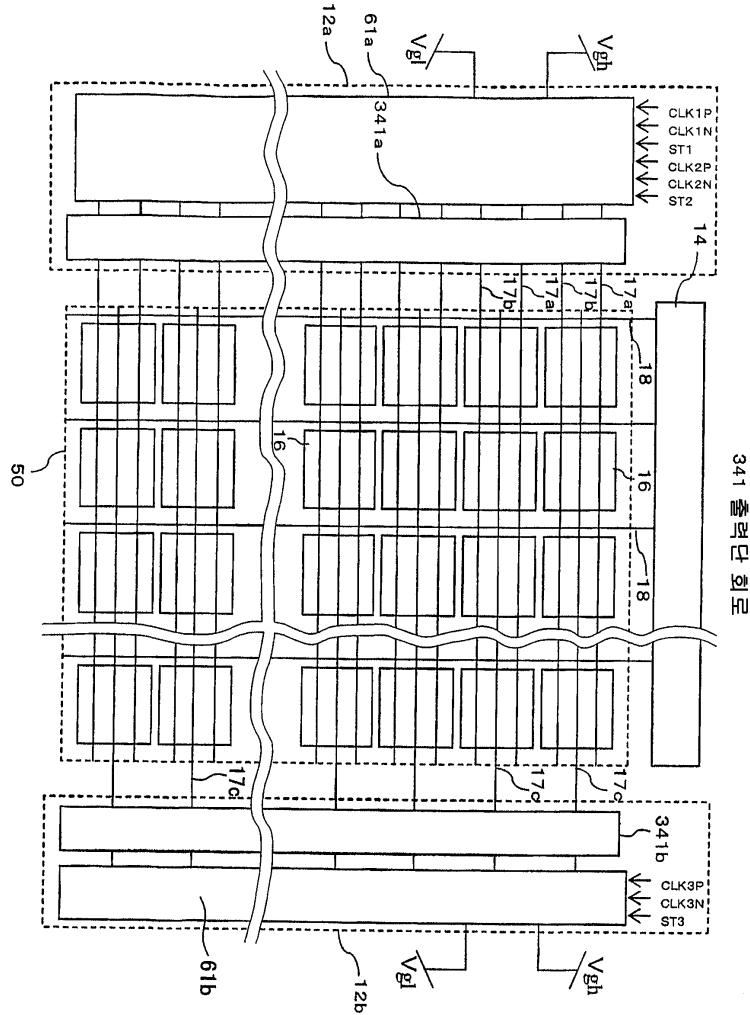

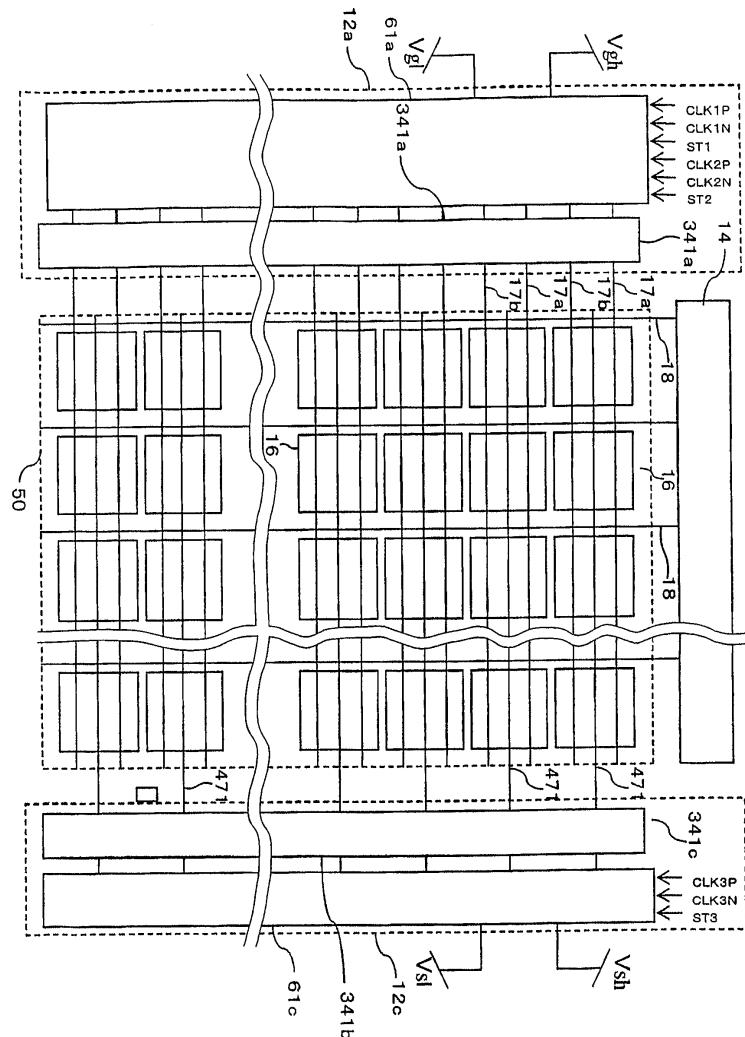

도 6은, 본 발명의 EL 표시 장치의 구성도이다.

도 7은, 본 발명의 EL 표시 패널의 제조 방법의 설명도이다.

도 8은, 본 발명의 EL 표시 장치의 구성도이다.

도 9는, 본 발명의 EL 표시 장치의 구성도이다.

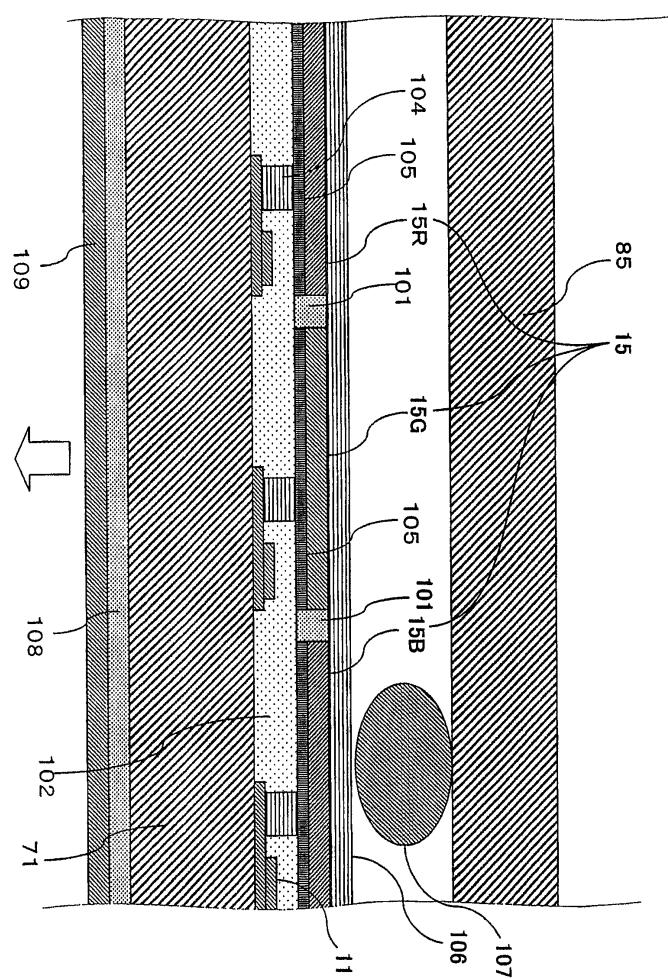

도 10은, 본 발명의 EL 표시 패널의 단면도이다.

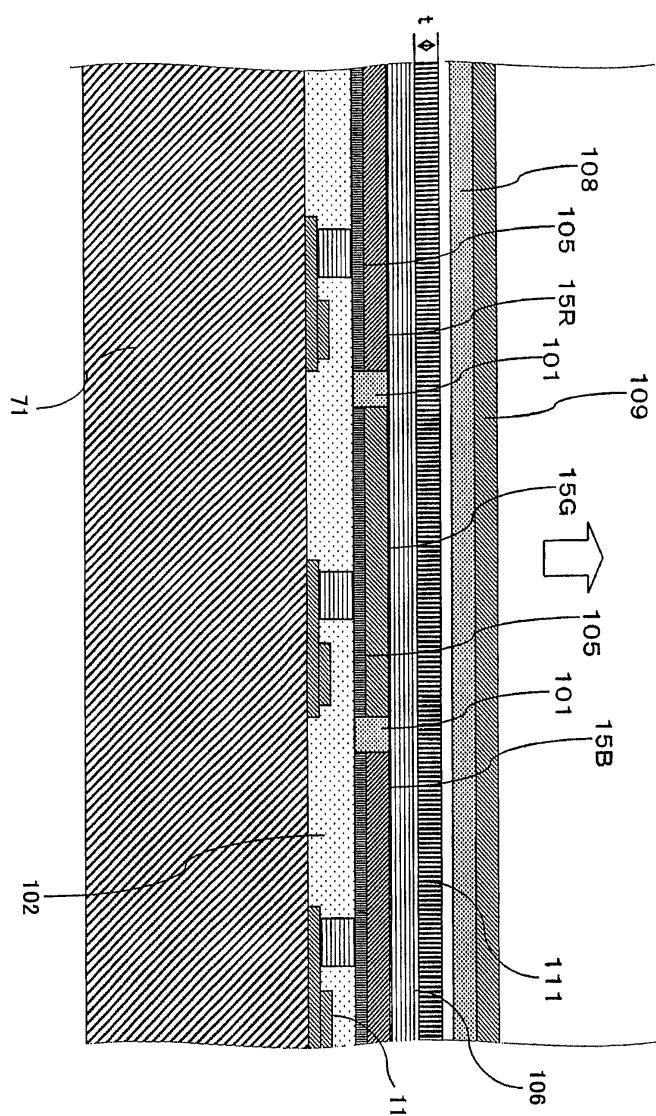

도 11은, 본 발명의 EL 표시 패널의 단면도이다.

도 12는, 본 발명의 EL 표시 패널의 설명도이다.

도 13은, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 14는, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 15는, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 16은, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 17은, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 18은, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 19는, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 20은, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 21은, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 22는, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 23은, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 24는, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 25는, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 26은, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 27은, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 28은, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 29는, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 30은, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 31은, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 32는, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 33은, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 34는, 본 발명의 EL 표시 장치의 구성도이다.

도 35는, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 36은, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 37은, 본 발명의 EL 표시 장치의 구성도이다.

도 38은, 본 발명의 EL 표시 장치의 구성도이다.

도 39는, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 40은, 본 발명의 EL 표시 장치의 구성도이다.

도 41은, 본 발명의 EL 표시 장치의 구성도이다.

도 42는, 본 발명의 EL 표시 패널의 화소 구성도이다.

도 43은, 본 발명의 EL 표시 패널의 화소 구성도이다.

도 44는, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 45는, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 46은, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 47은, 본 발명의 EL 표시 패널의 화소 구성도이다.

도 48은, 본 발명의 EL 표시 장치의 구성도이다.

도 49는, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 50은, 본 발명의 EL 표시 패널의 화소 구성도이다.

도 51은, 본 발명의 EL 표시 패널의 화소도이다.

도 52는, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 53은, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 54는, 본 발명의 EL 표시 패널의 화소 구성도이다.

도 55는, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

도 56은, 본 발명의 EL 표시 장치의 구동 방법의 설명도이다.

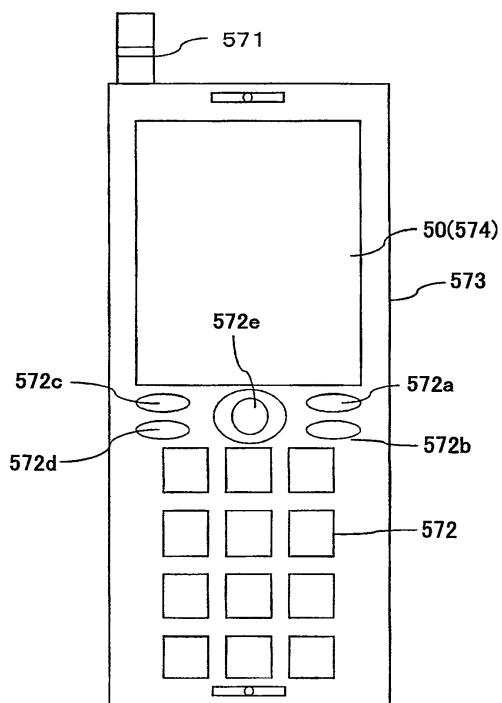

도 57은, 본 발명의 휴대형 전화기의 설명도이다.

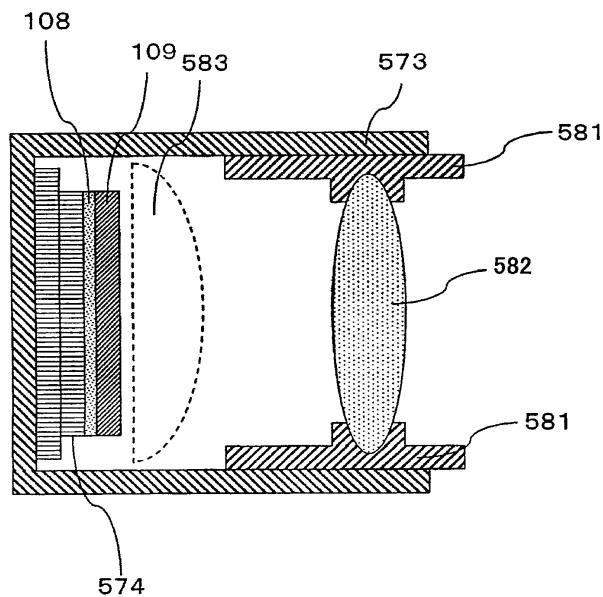

도 58은, 본 발명의 뷰 파인더(view Finder)의 설명도이다.

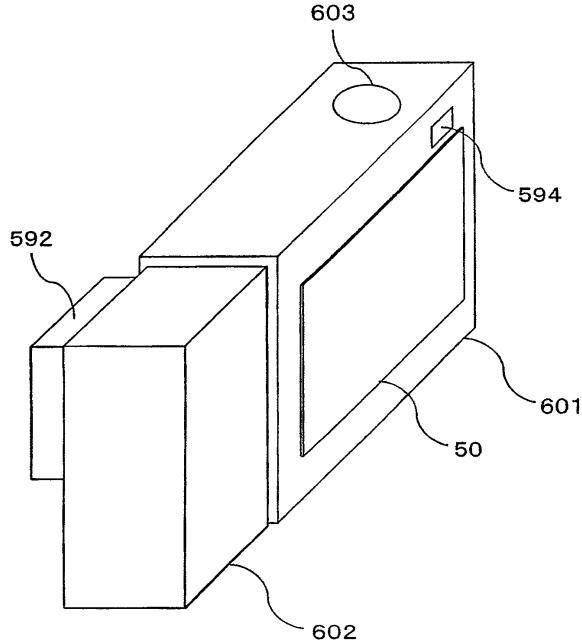

도 59는, 본 발명의 디지털 비디오 카메라의 설명도이다.

도 60은, 본 발명의 디지털 스틸 카메라의 설명도이다.

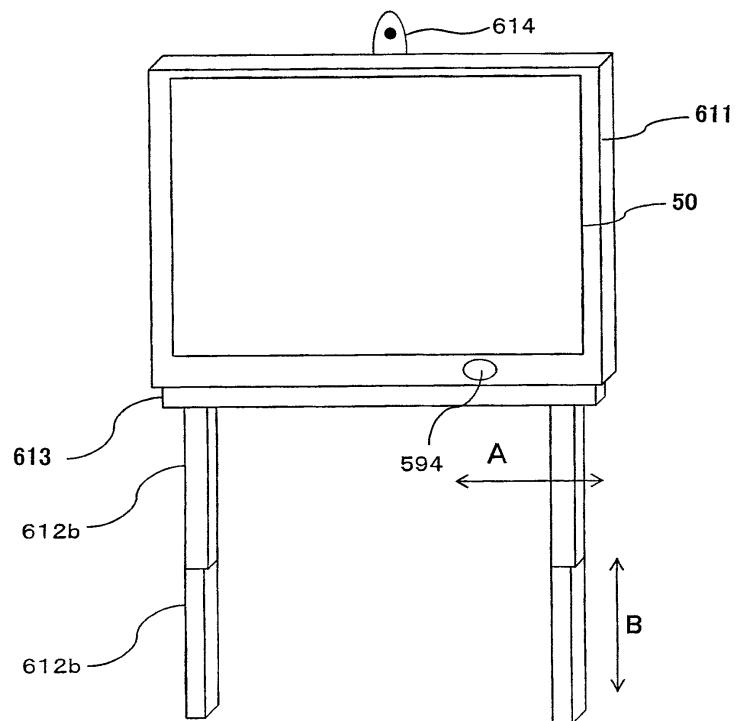

도 61은, 본 발명의 텔레비전(모니터)의 설명도이다.

도 62는, 종래의 EL 표시 패널의 화소 구성도이다.

#### 발명을 실시하기 위한 최선의 형태

이하, 본 발명의 실시예에 대해, 도면을 참조하면서 설명한다.

본 명세서에 있어서 각 도면은 이해를 용이하게 또는/및 작도를 용이하게 하기 위해서, 생략 또는/및 확대 축소한 개소가 있다. 예를 들면, 도 11에 도시하는 표시 패널의 단면도에서는 봉지막(111) 등을 충분히 두껍게 도시하고 있다. 한편, 도 10에 있어서, 봉지덮개(85)는 얇게 도시하고 있다. 또한, 생략한 개소도 있다. 예를 들면, 본 발명의 표시 패널 등에서는, 반사 방지를 위해서 원편광판 등의 위상필름이 필요하다. 그러나, 본 명세서의 각 도면에서는 생략하고 있다. 이상의 것은 이하의 도면에 대해서도 마찬가지이다. 또한, 동일 번호 또는, 기호 등을 부여한 개소는 동일 또는 유사의 형태, 재료, 기능 또는 동작을 나타내고 있다.

또, 각 도면 등에서 설명한 내용은 특별한 설명이 없더라도, 다른 실시예 등과 조합할 수 있다. 예를 들면, 도 8의 표시 패널에 터치 패널 등을 부가하여, 도 19, 도 59 내지 도 61에 도시하는 정보 표시 장치로 할 수 있다. 또한, 확대 렌즈(582)를 부착하여, 비디오 카메라(도 59 등의 것 참조) 등에 이용하는 뷰 파인더(도 58의 것을 참조)를 구성할 수도 있다. 또한, 도 4, 도 15, 도 18, 도 21, 도 23 등에서 설명한 본 발명의 구동 방법은, 어느 쪽의 본 발명의 표시 장치 또는 표시 패널에 적용하는 것이 가능하다.

또, 본 명세서에서는, 구동용 트랜지스터(11), 스위칭용 트랜지스터(11)는 박막 트랜지스터로서 설명하지만, 이것에 한정하는 것은 아니다. 박막 다이오드(TFD), 링 다이오드 등으로도 구성할 수 있다. 또한, 박막 소자에 한정하는 것은 아니고, 실리콘 웨이퍼에 형성한 것이라도 좋다. 물론, FET, MOS-FET, MOS 트랜지스터, 바이폴라 트랜지스터이더라도 좋다. 이들도 기본적으로 박막 트랜지스터이다. 그 외에, 배리스터, 사이리스터, 링 다이오드, 포토다이오드, 핫 트랜지스터, PLZT 소자 등이더라도 되는 것은 말할 필요도 없다. 즉, 스위치 소자(11), 구동용 소자(11)는 이들 중 어느 하나로 구성되어 있더라도 좋다.

유기 EL 표시 패널은, 도 10에 도시하는 바와 같이, 화소 전극으로서의 투명 전극(105)이 형성된 유리판(71)(어레이 기판) 상에, 전자 수송층, 발광층, 정공 수송층 등으로 이루어지는 적어도 한 층의 유기 기능층(EL 층)(15)(15R, 15G, 15B), 및 금속 전극(반사막)(캐소드)(106)이 적층된 것이다. 투명 전극(화소 전극)(105)인 양극(애노드)에 플러스, 금속 전극(반사 전극)(106)의 음극(캐소드)에 마이너스의 전압을 각각 가하여, 즉, 투명 전극(105) 및 금속 전극(106) 사이에 전류를 인가함으로써, 유기 기능층(EL 층)(15)이 발광한다.

애노드 혹은 캐소드에 전류를 공급하는 배선(도 8의 캐소드 배선(86), 애노드 배선(87))에는 큰 전류가 흐른다. 예를 들면, EL 표시 장치의 화면 사이즈가 40 인치로 되면 100(A) 정도의 전류가 흐른다. 따라서, 이들 배선의 저항치는 충분히 낮게 제작할 필요가 있다. 이 과제에 대해, 본 발명에서는, 우선, 애노드 등의 배선(EL 소자에 발광 전류를 공급하는 배선)을 박막으로 형성한다. 그리고, 이 박막 배선에 전해 도금 기술 혹은 무전해 도금 기술로 배선의 두께를 두껍게 형성하고 있다.

도금 금속으로서는, 크롬, 니켈, 금, 동, 알루미늄 혹은 이들의 합금, 아만감 또는 적층 구조 등이 예시된다. 또한, 필요에 따라서, 배선 그 자체, 혹은 배선에 동박으로 이루어지는 금속 배선을 부가하고 있다. 또한, 배선 위에 동 페이스트 등을 스크린 인쇄하여, 페이스트 등을 적층시킴으로써 배선의 두께를 두껍게 하여, 배선 저항을 저하시킨다. 또한, 본딩 기술로 배선을 중복하여 형성함으로써 배선을 보강하더라도 좋다. 또한, 필요에 따라서, 배선에 적층하여 그라운드 패턴을 형성하여, 배선과의 사이에 콘텐서(용량)를 형성하더라도 좋다.

또한, 애노드 혹은 캐소드 배선에 큰 전류를 공급하기 때문에, 전류 공급 수단으로부터 고 전압이며 소 전류의 전력 배선으로, 상기 애노드 배선 등의 근방까지 배선하고, DCDC 컨버터 등을 이용하여 저 전압, 고 전류로 전력 변환하여 공급하고 있다. 즉, 전원으로부터 고 전압, 소 전류 배선으로 전력 소비 대상까지 배선하여, 전력 소비 대상의 근방에서 대 전류, 저 전압으로 변환한다. 이러한 것으로 하여, DCDC 컨버터, 트랜스포머 등이 예시된다.

금속 전극(106)에는, 리튬, 은, 알루미늄, 마그네슘, 인듐, 구리 또는 각각의 합금 등의 일 함수가 작은 것을 이용하는 것이 바람직하다. 특히, 예컨대, A1-Li 합금을 이용하는 것이 바람직하다. 또한, 투명 전극(105)에는, ITO 등의 일 함수가 큰 도전성 재료 또는 금 등을 이용할 수 있다. 또, 금을 전극 재료로서 이용한 경우, 전극은 반투명의 상태로 된다. 또, ITO는 IZO 등의 다른 재료라도 좋다. 이 사항은 다른 화소 전극(105)에 대해서도 마찬가지이다.

또, 화소 전극(105) 등에 박막을 증착할 때에는, 아르곤 분위기 중에서 유기 EL 막(15)을 성막하면 좋다. 또한, 화소 전극(105)으로서의 ITO 상에 카본막을 20 이상 50nm 이하로 성막함으로써, 계면의 안정성이 향상하고, 발광 휘도 및 발광 효율도 양호한 것으로 된다. 또한, EL 막(15)은 증착으로 형성하는 것에 한정하는 것은 아니고, 잉크젯으로 형성하더라도 되는 것은 말할 필요도 없다.

또, 봉지덮개(85)와 어레이 기판(71)과의 공간에는 건조제(107)를 배치한다. 이것은, 유기 EL 막(15)은 습도에 약하기 때문이다. 건조제(107)에 밀봉제를 침투하는 수분을 흡수하여 유기 EL 막(15)의 열화를 방지한다.

도 10은 유리의 덮개(85)를 이용하여 봉지하는 구성이지만, 도 11과 같이 필름(박막이어도 좋음. 즉, 박막 봉지막임)(111)을 이용한 봉지이더라도 좋다. 예를 들면, 봉지필름(박막 봉지막)(111)으로서는 전해 콘텐서의 필름에 DLC(diamond like carbon : 다이아몬드 라이크 카본)를 증착한 것을 이용하는 것이 예시된다. 이 필름은 수분 침투성이 극히 불량하다(방습 성능이 높음). 그 때문에, 이 필름을 봉지막(111)으로서 이용한다. 또한, DLC 막 등을 전극(106)의 표면에 직접 증착하는 구성이라도 됨은 말할 필요도 없다. 그 외에, 수지 박막과 금속 박막을 다층으로 적층하여, 박막 봉지막을 구성하더라도 좋다.

박막의 막 두께는  $n \cdot d$  ( $n$ 은 박막의 굴절율, 복수의 박막이 적층되어 있는 경우는 그들의 굴절율을 종합(각 박막의  $n \cdot d$ 를 계산)하여 계산함.  $d$ 는 박막의 막 두께, 복수의 박막이 적층되어 있는 경우는 그들의 굴절율을 종합하여 계산함)가, EL 소자(15)의 발광 주파장  $\lambda$  이하로 되도록 하면 좋다. 이 조건을 만족시킴으로써, EL 소자(15)로부터의 광 취출 효율이, 유리 기판으로 봉지한 경우와 비교하여 2배 이상으로 된다. 또한, 알루미늄과 은의 합금 혹은 혼합물 혹은 적층물을 형성하더라도 좋다.

이상과 같이 덮개(85)를 이용하지 않고, 봉지막(111)으로 봉지하는 구성을 박막 봉지라고 부른다. 기판(71) 측으로부터 광을 취출하는 「하측 취출(도 10을 참조, 광 취출 방향은 도 10의 화살표 방향임)」인 경우의 박막 봉지는, EL 막을 형성한 후, EL 막 상에 캐소드로 되는 알루미늄 전극을 형성한다. 다음에 이 알루미늄막 상에 완충층으로서의 수지층을 형성한다. 완충층으로서는, 아크릴, 에폭시 등의 유기 재료가 예시된다. 또한, 막 두께는  $1\mu\text{m}$  이상  $10\mu\text{m}$  이하의 두께가 적합하다. 더욱 바람직하게는, 막 두께는  $2\mu\text{m}$  이상  $6\mu\text{m}$  이하의 두께가 적합하다. 이 완충막 상의 봉지막(74)을 형성한다. 완충막이 없으

면, 응력에 의해 EL 막의 구조가 붕괴되어, 줄무늬 형상으로 결함이 발생한다. 봉지막(111)은 상술한 바와 같이, DLC(다아몬드 라이크 카본), 혹은 전계 콘텐서의 층 구조(유전체 박막과 알루미늄 박막을 교대로 다층 증착한 구조)가 예시된다.

EL 층(15) 측으로부터 광을 취출하는 「상측 취출(도 11을 참조, 광 취출 방향은 도 11의 화살표 방향임)」 인 경우의 박막 봉지는, EL 막(15)을 형성한 후, EL 막(15) 상에 캐소드(애노드)로 되는 Ag-Mg막을 20Å 이상 300Å 이하의 막 두께로 형성한다. 그 위에, ITO 등의 투명 전극을 형성하여 저 저항화한다. 다음에 이 전극막 상에 완충층으로서의 수지층을 형성한다. 이 완충막 상에 봉지막(111)을 형성한다.

유기 EL 층(15)으로부터 발생한 광의 절반은, 반사막(106)에서 반사되어, 어레이 기판(71)을 투과하여 출사된다. 그러나, 반사막(106)에 외광이 반사함으로써 편광 반사가 발생하여 표시 콘트라스트가 저하한다. 이 대책을 위해, 어레이 기판(71)에  $\lambda/4$ 판(108) 및 편광판(편광 필름)(109)을 배치하고 있다. 이들은 일반적으로 원편광판(원편광 시트)이라고 불린다.

또, 화소가 반사 전극인 경우는 EL 층(15)으로부터 발생한 광은 상 방향으로 출사된다. 따라서, 위상판(108) 및 편광판(109)은 광 출사 측에 배치하는 것은 말할 필요도 없다. 또, 반사형 화소는, 화소 전극(105)을, 알루미늄, 크롬, 은 등으로 구성될 수 있다. 또한, 화소 전극(105)의 표면에, 볼록부(또는 요철부)를 마련함으로써 유기 EL 층(15)과의 계면이 넓게 되어 발광 면적이 커지고, 또한, 발광 효율이 향상한다. 또, 캐소드(106)(애노드(105))로 되는 반사막을 투명 전극에 형성하거나, 혹은 반사율을 30% 이하로 저감할 수 있는 경우는, 원편광판은 불필요하다. 편광 반사가 대폭 감소하기 때문이다. 또한, 광의 간섭도 저감하는 것으로 되기 때문에 바람직하다.

트랜지스터(11)는 LDD(로우 도핑 드레인) 구조를 채용하는 것이 바람직하다. 또한, 본 명세서에서는 EL 소자로서 유기 EL 소자(OEL, PEL, PLED, OLED 등 다종 다양한 약칭으로 기술됨)(15)를 예로 들어 설명하지만 이것에 한정하는 것은 아니고, 무기 EL 소자에도 적용되는 것은 말할 필요도 없다.

우선, 유기 EL 표시 패널에 이용되는 액티브 매트릭스 방식은,

(1) 특정한 화소를 선택하여, 필요한 표시 정보를 인가되는 것

(2) 1 프레임 기간을 통하여 EL 소자에 전류를 흘릴 수 있는 것이라고 하는 2개의 조건을 만족시키지 않으면 안 된다.

이 2개의 조건을 만족시키기 위해서, 도 62에 도시하는 종래의 유기 EL의 화소 구성에서는, 제 1 트랜지스터(211b)는 화소를 선택하기 위한 스위칭용 트랜지스터, 제 2 트랜지스터(211a)는 EL 소자(EL 막)(215)에 전류를 공급하기 위한 구동용 트랜지스터로 한다.

이 구성을 이용하여 계조를 표시시키는 경우, 구동용 트랜지스터(211a)의 게이트 전압으로서 계조에 따른 전압을 인가할 필요가 있다. 따라서, 구동용 트랜지스터(211a)의 온 전류의 편차가 그대로 표시에 나타난다.

트랜지스터의 온 전류는 단결정으로 형성된 트랜지스터이면, 매우 균일하지만, 염가인 유리 기판에 형성할 수 있는 형성 온도가 450도 이하의 저온 폴리실리콘 기술로 형성한 저온 다결정 트랜지스터에서는, 그 임계값에  $\pm 0.2V \sim 0.5V$ 의 범위에서 편차가 있다. 그 때문에, 구동용 트랜지스터(211a)를 흐르는 온 전류가 이에 대응하여 편차, 표시에 얼룩이 발생한다. 이들의 얼룩은, 임계값 전압의 편차 뿐만 아니라, 트랜지스터의 이동도, 게이트 절연막의 두께 등에서도 발생한다. 또한, 트랜지스터(211)의 열화에 의해서도 특성은 변화한다.

이 현상은, 저온 폴리실리콘 기술에 한정되는 것이 아니라, 프로세스 온도가 450도(섭씨) 이상의 고온 폴리실리콘 기술에서도, 고상(CGS) 성장시킨 반도체막을 이용하여 트랜지스터 등을 형성한 것에서도 발생한다. 그 외에, 유기 트랜지스터에서도 발생한다. 비정질 실리콘 트랜지스터에서도 발생한다. 따라서, 이하에 설명하는 본 발명은, 이들의 기술에 대응하여, 대책 할 수 있는 구성 혹은 방식이다. 또, 본 명세서에서는 저온 폴리실리콘 기술로 형성한 트랜지스터를 주로 설명한다.

도 62와 같이, 전압을 기입하는 것에 의해, 계조를 표시시키는 방법에서는, 균일한 표시를 얻기 위해서, 장치의 특성을 염밀하게 제어할 필요가 있다. 그러나, 현상의 저온 다결정 폴리실리콘 트랜지스터 등에서는 이 편차를 소정 범위 이내로 억제한다고 하는 요구를 만족할 수 없다.

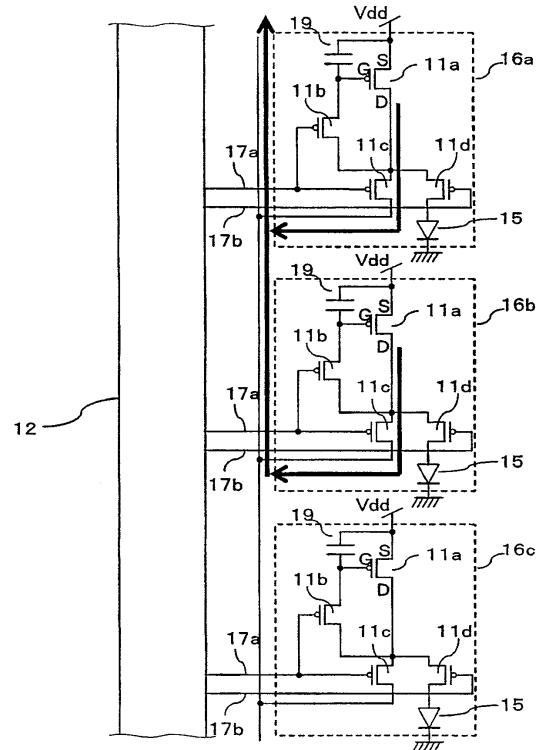

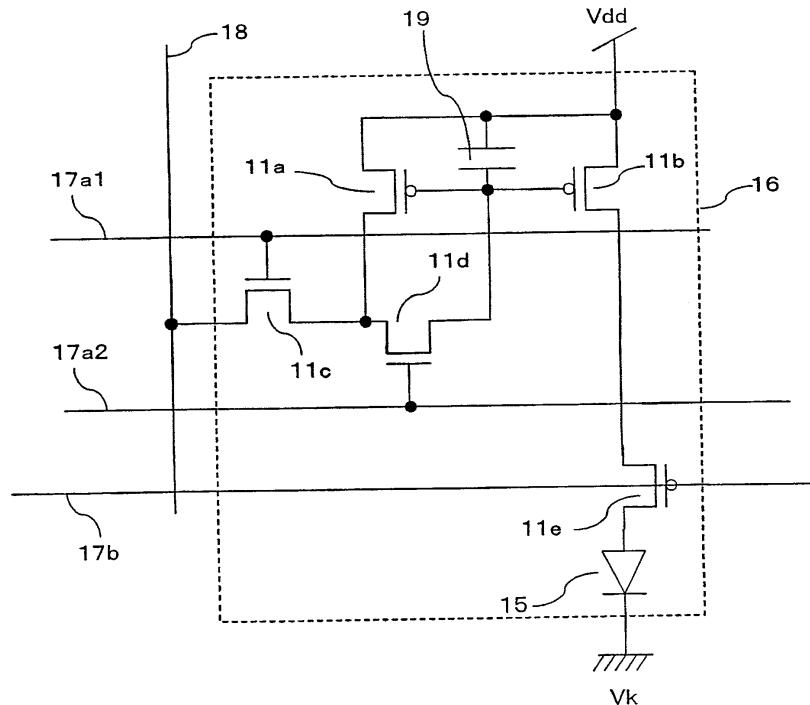

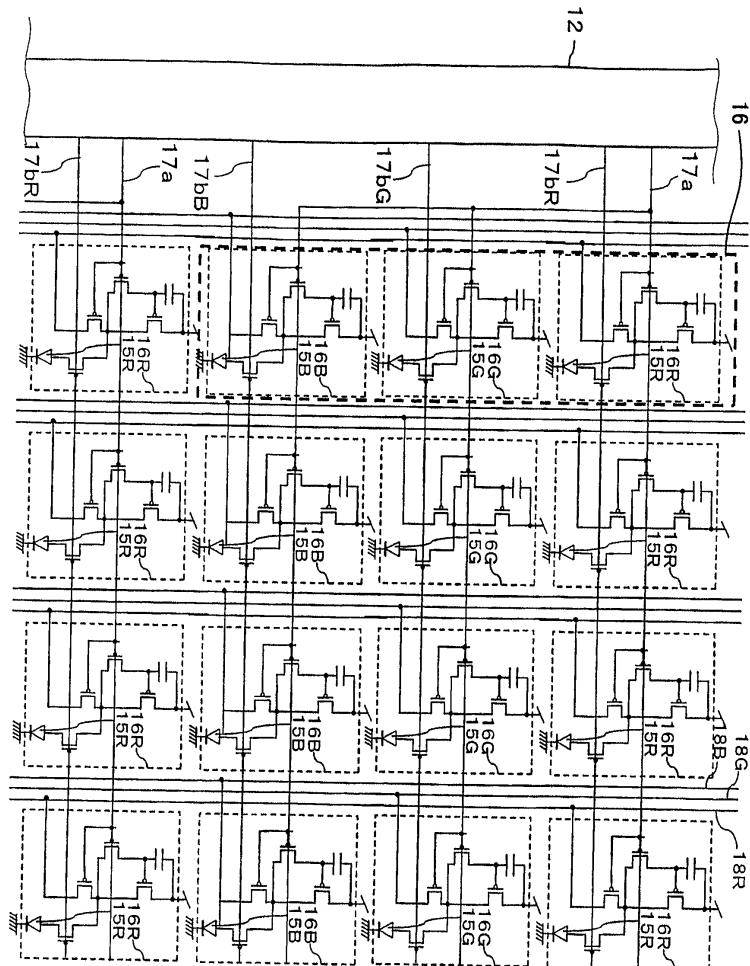

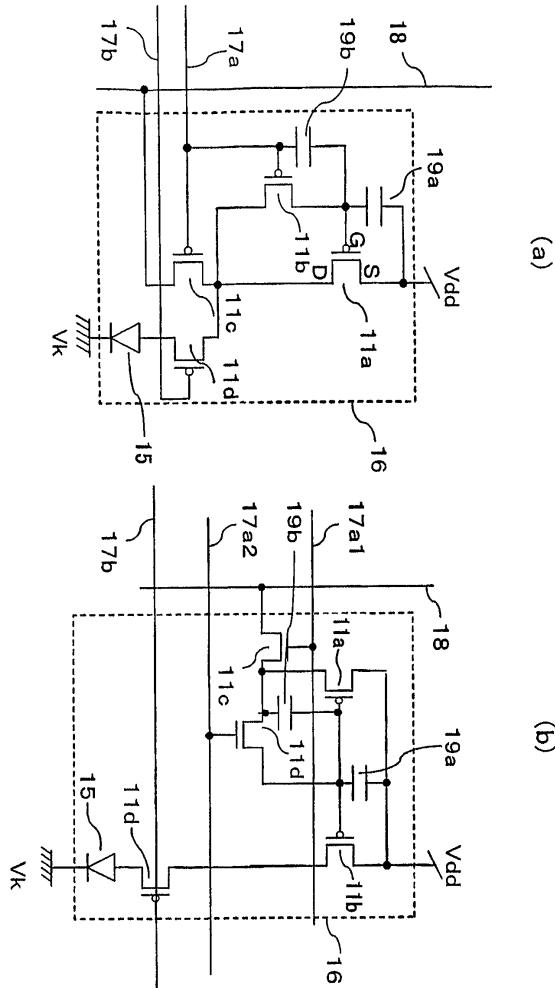

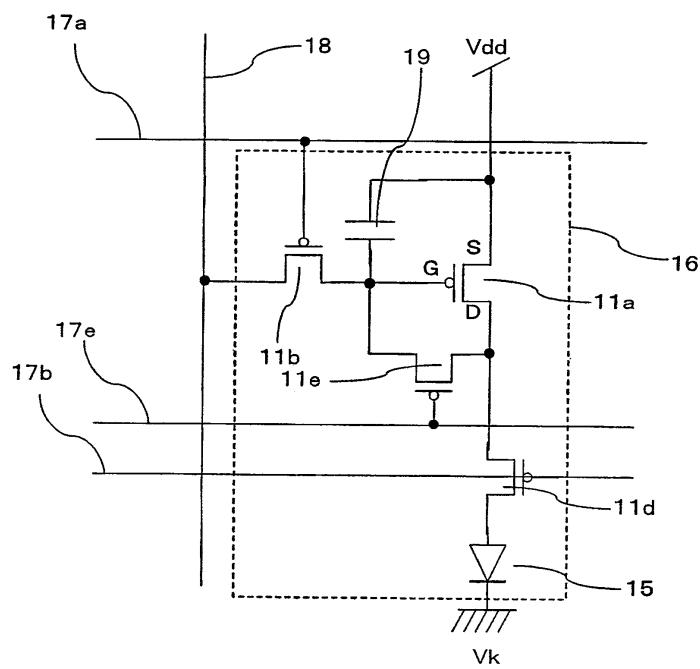

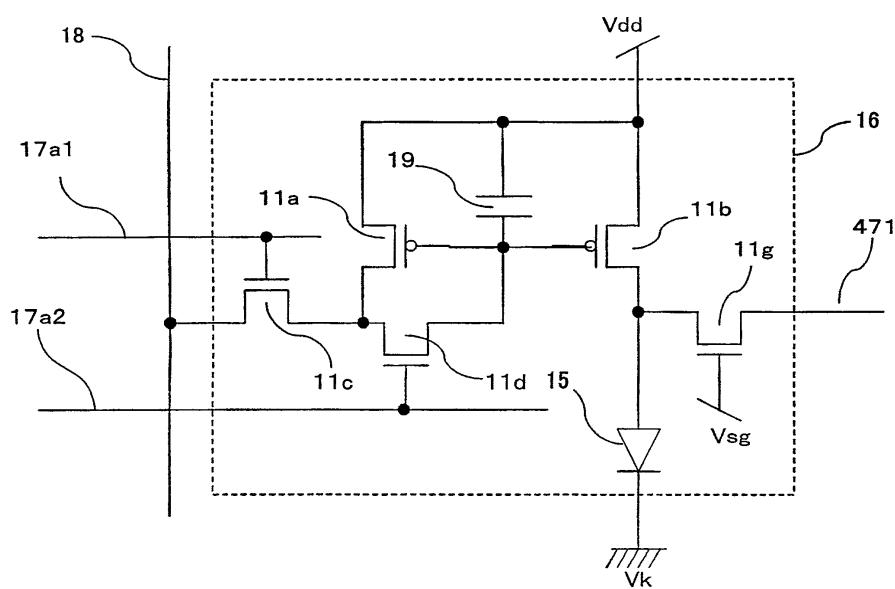

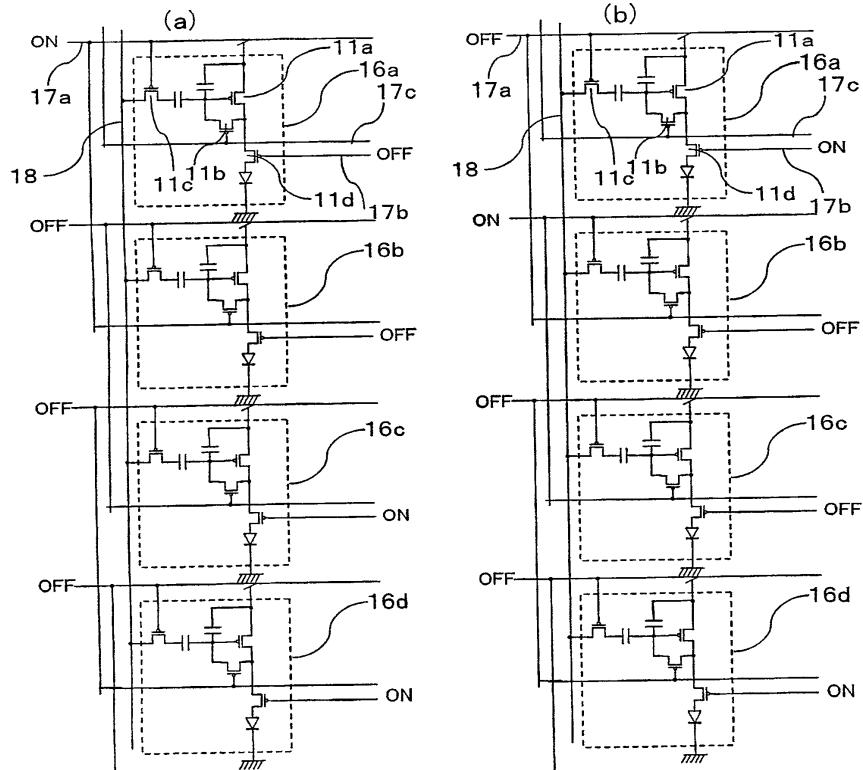

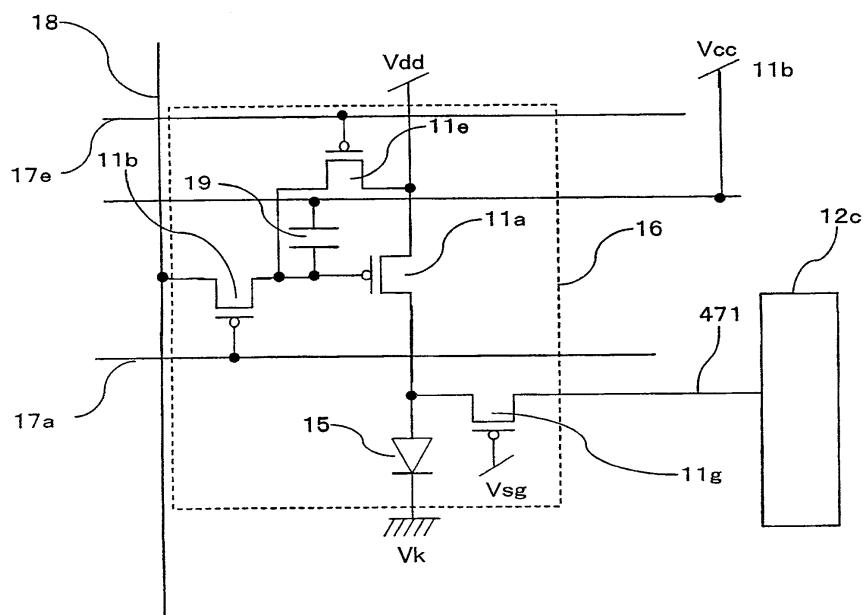

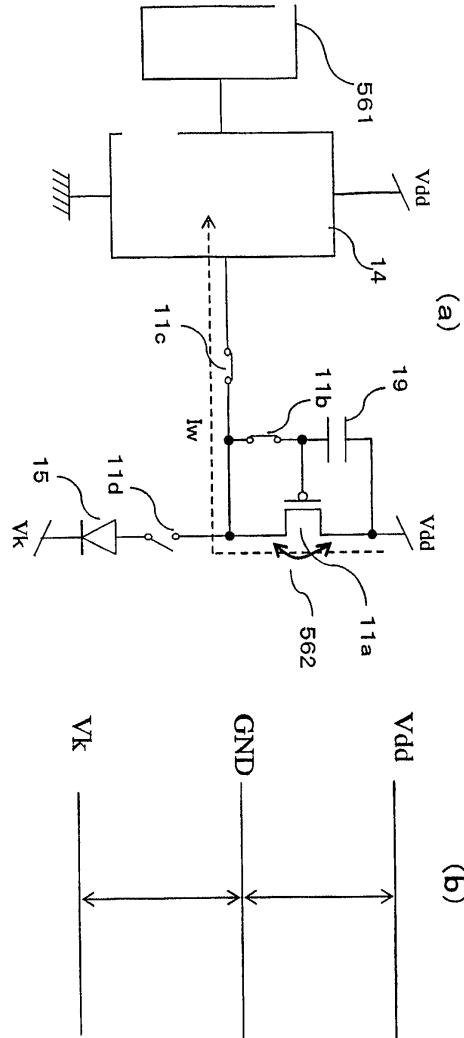

본 발명의 EL 표시 장치의 화소 구조는, 구체적으로는 도 1에 도시하는 바와 같이, 단위 화소가 4개의 트랜지스터(11) 및 EL 소자에 의해 형성된다. 화소 전극은 소스 신호선과 겹치도록 구성한다. 즉, 소스 신호선(18) 상에 절연막 혹은 아크릴

재료로 이루어지는 평탄화막을 형성하여 절연하고, 이 절연막상에 화소 전극(105)을 형성한다. 이와 같이 소스 신호선(18)상의 적어도 일부에 화소 전극을 포개는 구성을 하이 애퍼처(hight aperture : HA) 구조라고 부른다. 불필요한 간섭 광 등이 저감하여, 양호한 발광 상태를 기대할 수 있다.

게이트 신호선(제 1 주사선)(17a)에 대해 게이트 신호를 출력하여 액티브(ON 전압을 인가)로 하는 것에 의해 EL 소자(15)의 구동용의 트랜지스터(11a) 및 스위치용 트랜지스터(11c)를 통해서, 상기 EL 소자(15)에 흐르게 할 전류값을 소스드라이버(14)로부터 흐른다. 또한, 트랜지스터(11a)의 게이트와 드레인 사이를 단락하도록, 게이트 신호선(17a)을 액티브(ON 전압을 인가)로 하는 것에 의해 트랜지스터(11b)를 개방함과 동시에, 트랜지스터(11a)의 게이트와 소스 사이에 접속된 콘덴서(캐패시터, 축적 용량, 부가 용량)(19)에 트랜지스터(11a)의 게이트 전압(혹은 드레인 전압)을 기억한다(도 3의 (a)의 것을 참조).

또, 트랜지스터(11a)의 소스(S)-게이트(G)간의 용량(콘덴서)(19)은  $0.2\text{pF}$  이상의 용량으로 하는 것이 바람직하다. 다른 구성으로서, 별도, 콘덴서(19)를 형성하는 구성도 예시된다. 즉, 콘덴서 전극충과 게이트 절연막 및 게이트 금속으로 축적 용량을 형성하는 구성이다. 트랜지스터(11c)의 리크에 의한 휘도 저하를 방지하는 관점, 표시 동작을 안정화시키기 위한 관점으로부터는 이와 같이 별도의 콘덴서를 구성하는 쪽이 바람직하다.

또한, 콘덴서(축적 용량)(19)의 크기는,  $0.2\text{pF}$  이상  $2\text{pF}$  이하로 하는 것이 바람직하고, 그 중에서도 콘덴서(축적 용량)(19)의 크기는,  $0.4\text{pF}$  이상  $1.2\text{pF}$  이하로 하는 것이 바람직하다. 화소 사이즈를 고려하여 콘덴서(19)의 용량을 결정한다. 1 화소에 필요한 용량을  $C_s(\text{pF})$ 로 하고, 1 화소가 차지하는 면적(개구율은 아님)을  $S_p(\text{평방 }\mu\text{m})$ 로 하면,  $500/S \leq C_s \leq 20000/S$ 로 하고, 더욱 바람직하게는,  $1000/S_p \leq C_s \leq 10000/S_p$ 로 되도록 한다. 또, 트랜지스터의 게이트 용량은 작기 때문에, 여기서 말하는 Q란, 축적 용량(콘덴서)(19) 단독의 용량이다.

콘덴서(19)는 인접하는 화소간의 비표시 영역에 대략 형성하는 것이 바람직하다. 일반적으로, 풀 컬러 유기 EL 소자(15)를 작성하는 경우, 유기 EL 층(15)을 금속 마스크에 의한 마스크 증착으로 형성하기 때문에 마스크 위치 어긋남에 의한 EL 층의 형성 위치가 발생한다. 위치 어긋남이 발생하면 각 색의 유기 EL 층(15R, 15G, 15B)가 겹칠 위험성이 있다. 그 때문에, 각 색의 인접하는 화소간의 비표시 영역은  $10\mu\text{m}$  이상 떨어지지 않으면 안 된다. 이 부분은 발광에 기여하지 않는 부분으로 된다. 따라서, 축적 용량(19)을 이 영역에 형성하는 것은 개구율 향상을 위해 유효한 수단으로 된다.

다음에, 게이트 신호선(17a)을 비액티브(OFF 전압을 인가), 게이트 신호선(17b)을 액티브로 하여, 전류가 흐르는 경로를 상기 제 1 트랜지스터(11a) 및 EL 소자(15)에 접속된 트랜지스터(11d) 및 EL 소자(15)를 포함하는 경로로 전환하여, 상술한 바와 같이 하여 기억한 전류를 상기 EL 소자(15)에 흘리도록 동작한다(도 3의 (b)의 것을 참조).

이 회로는 1 화소 내에 4개의 트랜지스터(11)를 갖고 있고, 트랜지스터(11a)의 게이트는 트랜지스터(11b)의 소스에 접속되어 있다. 또한, 트랜지스터(11b) 및 트랜지스터(11c)의 게이트는 게이트 신호선(17a)에 접속되어 있다. 트랜지스터(11b)의 드레인은 트랜지스터(11c)의 드레인 및 트랜지스터(11d)의 소스에 접속되고, 트랜지스터(11c)의 소스는 소스 신호선(18)에 접속되어 있다. 트랜지스터(11d)의 게이트는 게이트 신호선(17b)에 접속되고, 트랜지스터(11d)의 드레인은 EL 소자(15)의 애노드 전극에 접속되어 있다.

또, 도 1에서는 모든 트랜지스터가 P 채널로 구성되어 있다. P 채널은 N 채널의 트랜지스터에 비교하여 다소 모빌리티(mobility)가 낮지만, 내압이 크고 또한 열화도 발생하기 어렵기 때문에 바람직하다. 그러나, 본 발명은 EL 소자 구성은 P 채널로 구성하는 것에만 한정하는 것은 아니다. N 채널만으로 구성하더라도 좋다. 또한, N 채널과 P 채널의 양쪽을 이용하여 구성하더라도 좋다.

또한, 도 1에 있어서 트랜지스터(11c, 11b)는 동일한 극성으로 구성하고, 또한 N 채널로 구성하며, 트랜지스터(11a, 11d)는 P 채널로 구성하는 것이 바람직하다. 일반적으로 P 채널 트랜지스터는 N 채널 트랜지스터와 비교하여, 신뢰성이 높고, 킹크(kink) 전류가 적은 등의 특징이 있어, 전류를 제어함으로써 목적으로 하는 발광 강도를 얻는 EL 소자(15)에 대해서는, 트랜지스터(11a)를 P 채널로 하는 효과가 크다.

최적으로는 화소를 구성하는 트랜지스터(11)를 모두 P 채널로 형성하고, 내장 게이트 드라이버(12)도 P 채널로 형성하는 것이 바람직하다. 이와 같이 어레이를 P 채널만의 트랜지스터로 형성함으로써, 마스크 매수가 5매로 되어, 저 비용화, 고 양품율화를 실현할 수 있다.

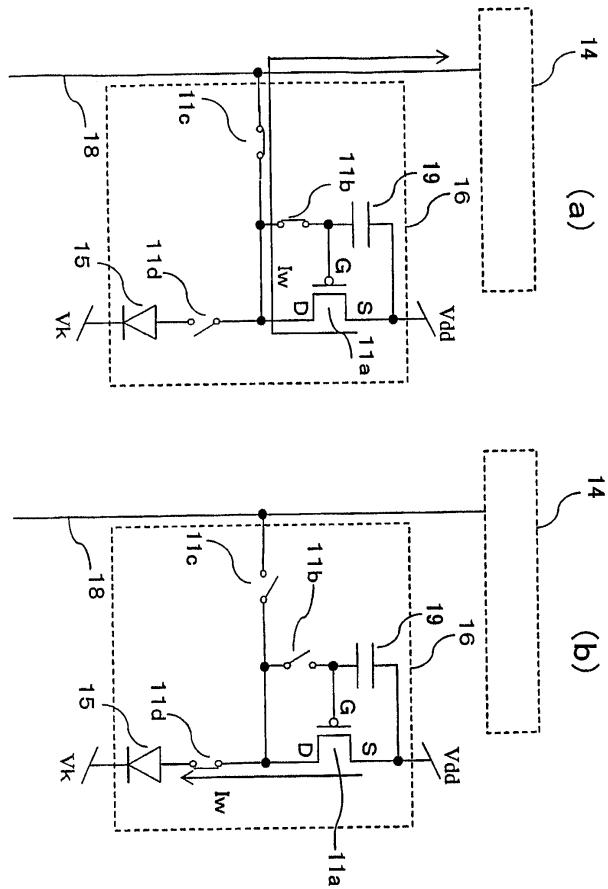

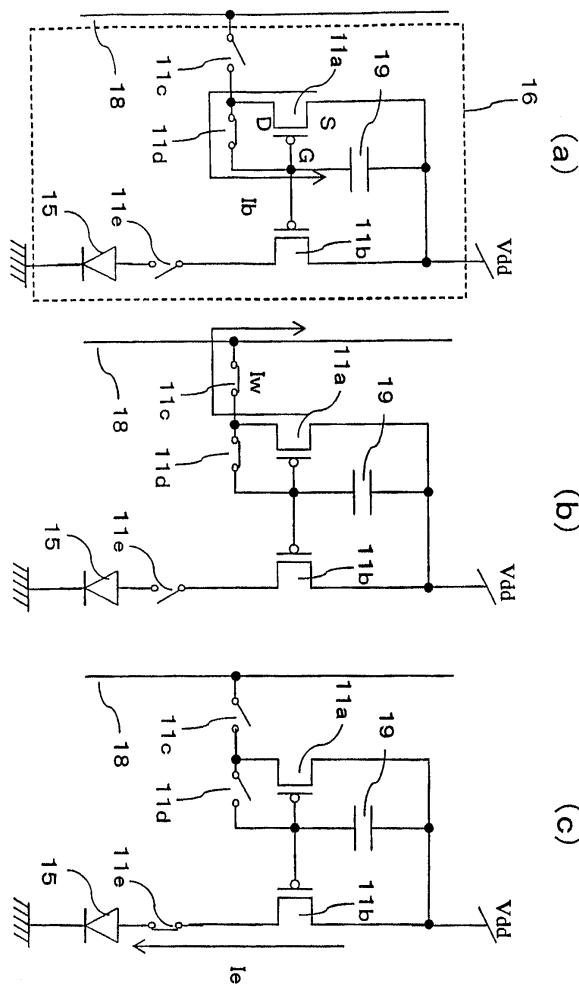

이하, 또한 본 발명의 이해를 용이하게 하기 위해서, 본 발명의 EL 소자 구성에 대해 도 3을 이용하여 설명한다. 본 발명의 EL 소자 구성은 2개의 타이밍에 의해 제어된다. 제 1 타이밍은 필요한 전류값을 기억시키는 타이밍이다. 이 타이밍에서 트

랜지스터(11b) 및 트랜지스터(11c)를 ON으로 하는 것에 의해, 등가 회로로서 도 3의 (a)로 된다. 여기서, 신호선으로부터 소정의 전류  $I_w$ 가 기입된다. 이에 따라 트랜지스터(11a)는 게이트와 드레인의 접속된 상태로 되어, 이 트랜지스터(11a)와 트랜지스터(11c)를 통하여 전류  $I_w$ 가 흐른다. 따라서, 트랜지스터(11a)의 게이트-소스간의 전압은 전류  $I_w$ 가 흐르는 것과 같은 전압으로 된다.

제 2 타이밍은 트랜지스터(11b)와 트랜지스터(11c)가 폐쇄되고, 트랜지스터(11d)가 개방하는 타이밍이며, 그 때의 등가 회로는 도 3의 (b)로 된다. 트랜지스터(11a)의 소스-게이트간의 전압은 유지된 채로 된다. 이 경우, 트랜지스터(11a)는 항상 포화 영역에서 동작하기 때문에,  $I_w$ 의 전류는 일정하게 된다.

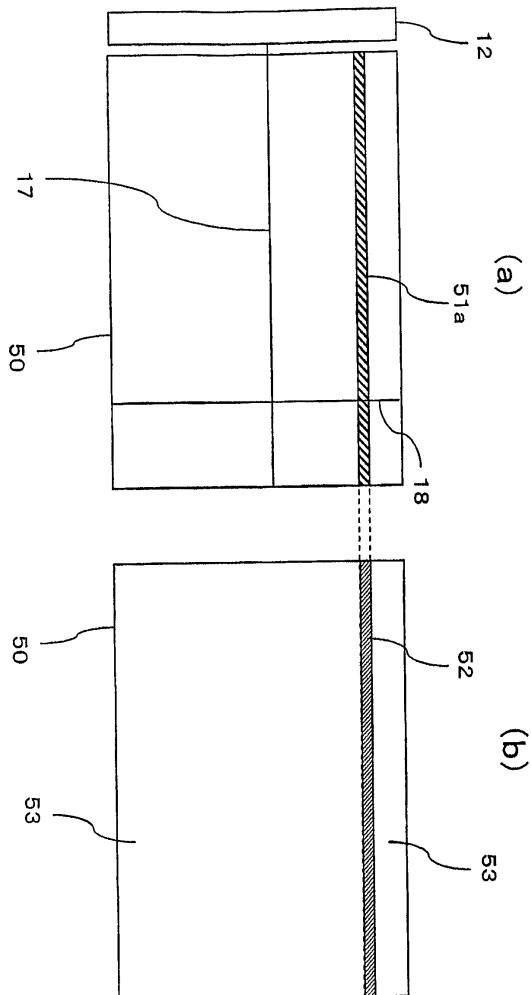

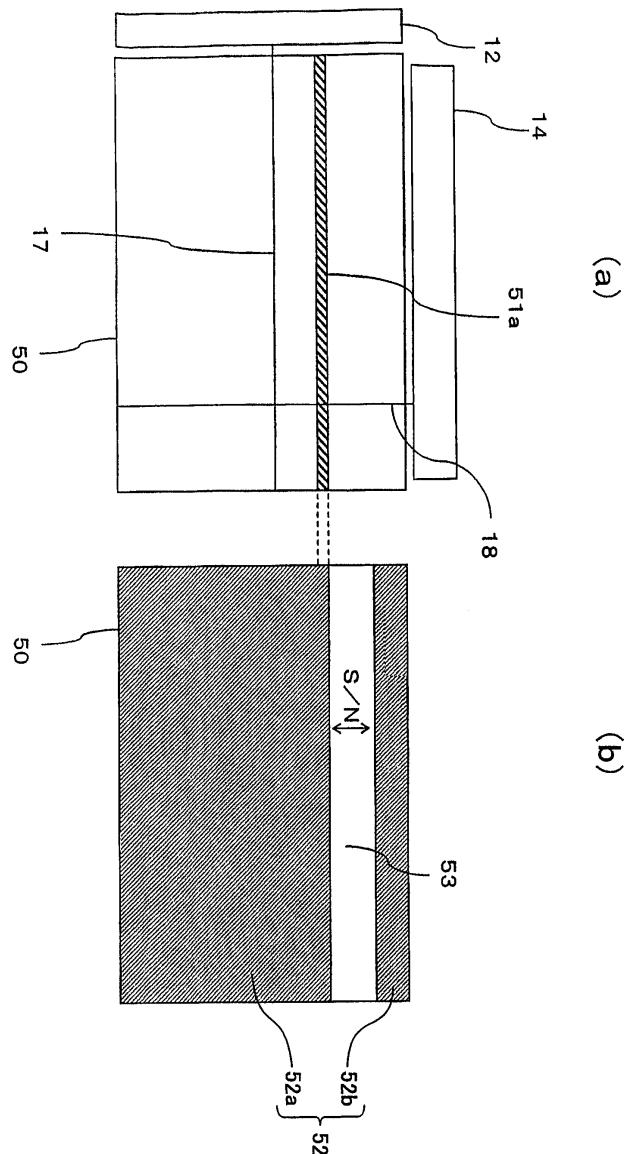

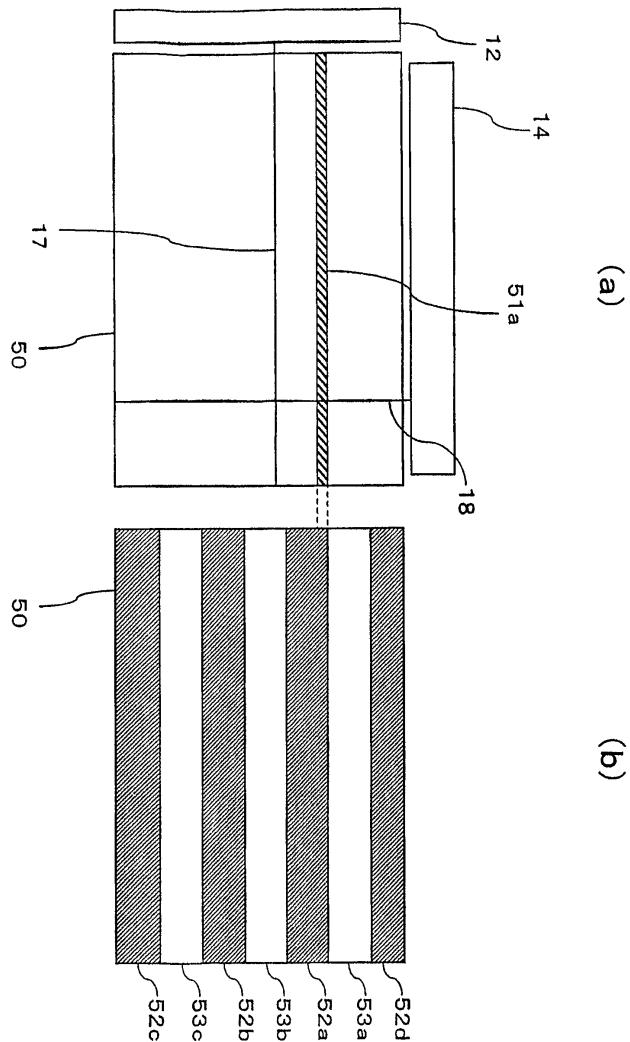

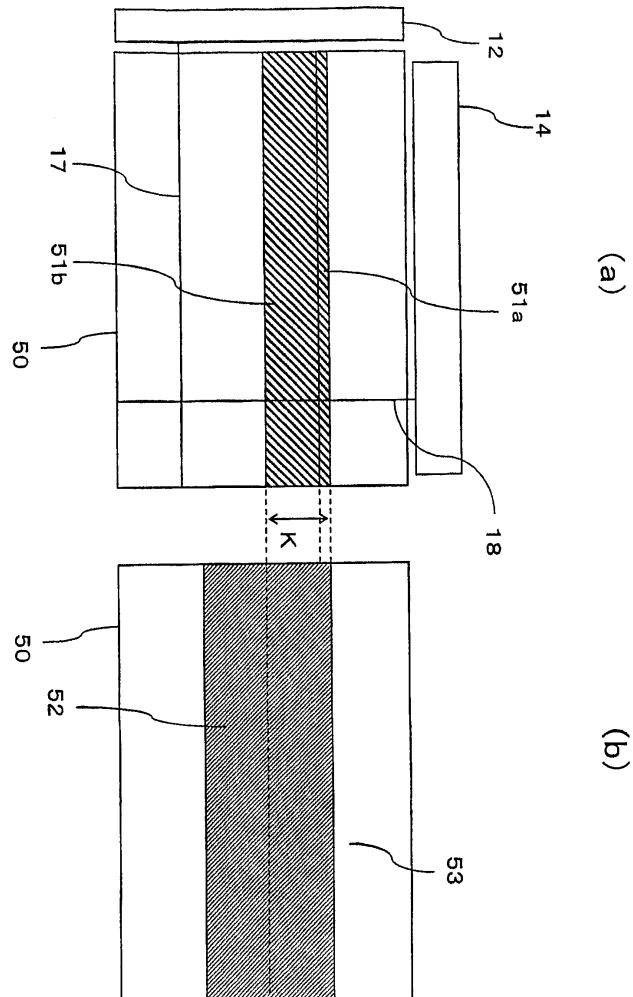

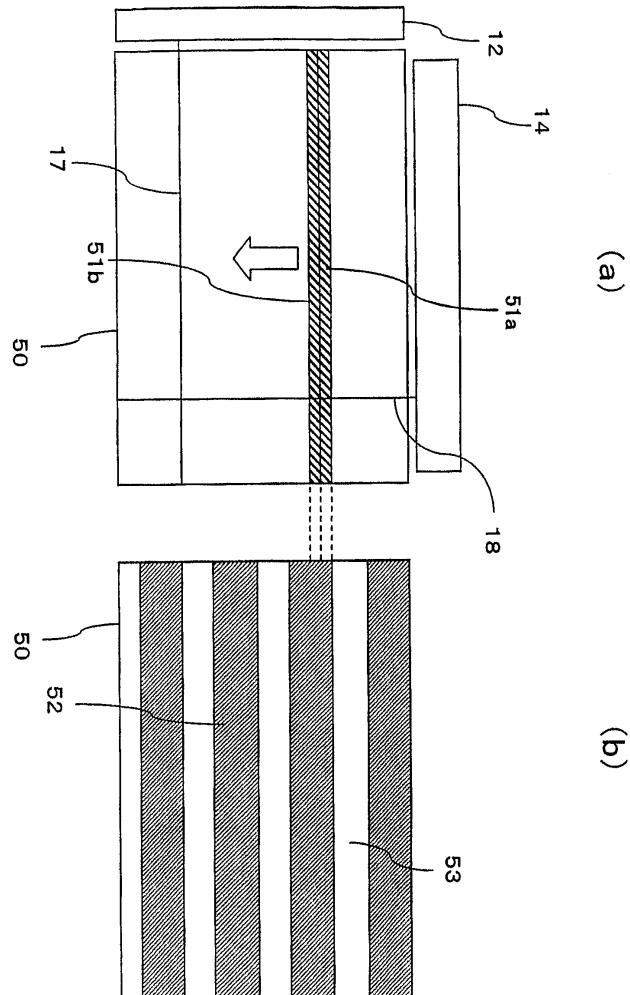

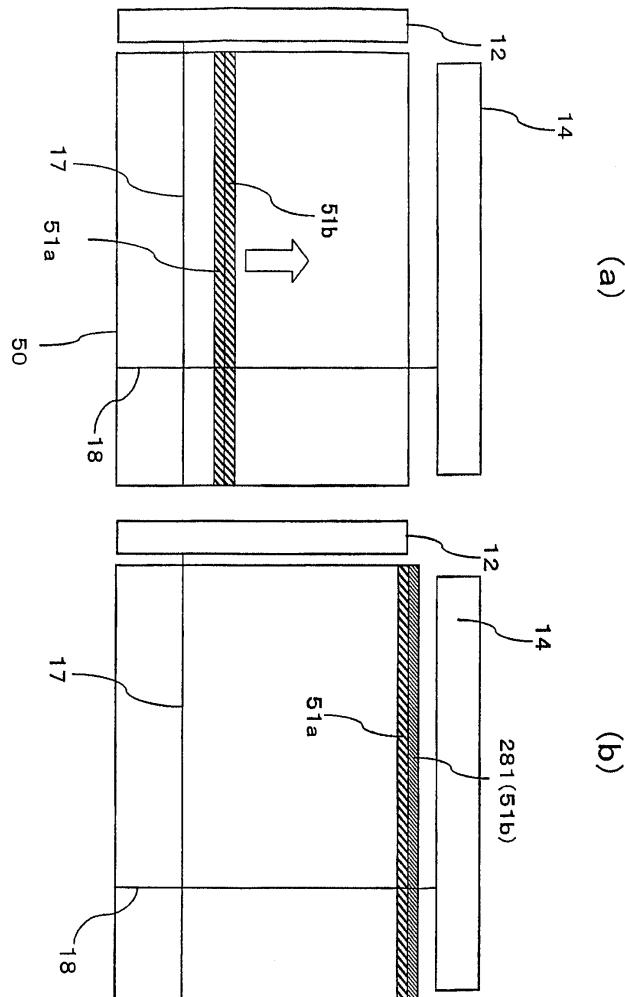

이와 같이 동작시키면, 도 5에 도시하는 바와 같이 된다. 도 5의 (a)의 (51a)는 표시 화면(50)에 있어서의, 소정의 시각에서의 전류 프로그램되어 있는 화소(행)(기입 화소(행))를 나타내고 있다. 이 화소(행)(51a)는, 도 5의 (b)에 도시하는 바와 같이, 비접등(비표시 화소(행))으로 한다. 다른 화소(행)는 표시 화소(행)(53)로 한다(표시 화소(행)(53)의 EL 소자(15)에는 전류가 흘러, EL 소자(15)가 발광하고 있음).

도 1의 화소 구성의 경우, 도 3의 (a)에 도시하는 바와 같이, 전류 프로그램 시에는, 프로그램 전류  $I_w$ 가 소스 신호선(18)에 흐른다. 이 전류  $I_w$ 가 트랜지스터(11a)를 흘려, 전류  $I_w$ 를 흐르는 전압이 유지되도록, 콘덴서(19)에 전압 설정(프로그램)된다. 이 때, 트랜지스터(11d)는 오픈 상태(오프 상태)이다.

다음에, EL 소자(15)에 전류를 흘리는 기간은 도 3의 (b)와 같이, 트랜지스터(11c, 11b)가 오프하고, 트랜지스터(11d)가 온 한다. 즉, 게이트 신호선(17a)에 오프 전압( $V_{gh}$ )이 인가되어, 트랜지스터(11b, 11c)가 오프한다. 한편, 게이트 신호선(17d)에 온 전압( $V_{g1}$ )이 인가되어, 트랜지스터(11d)가 온한다.

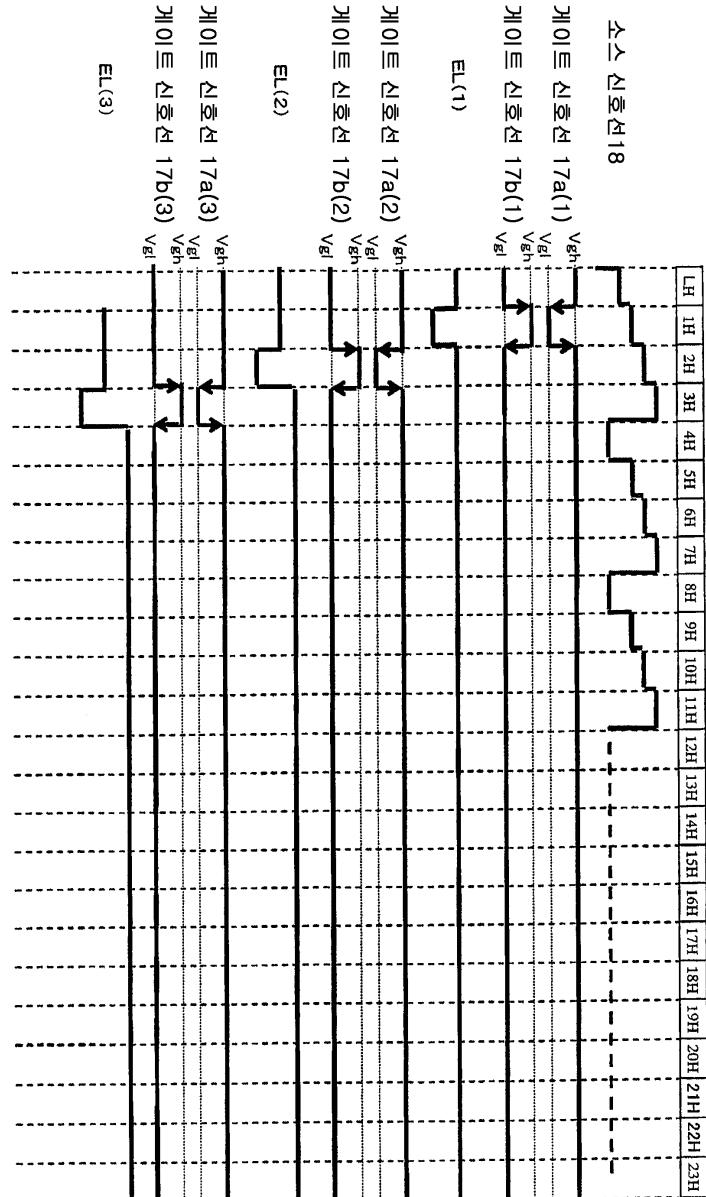

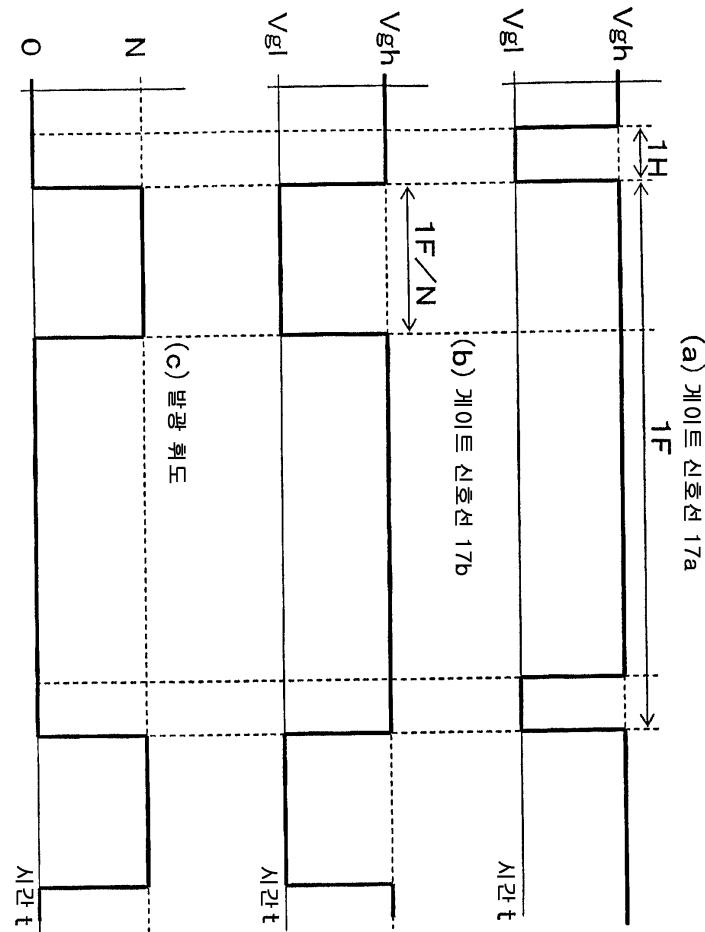

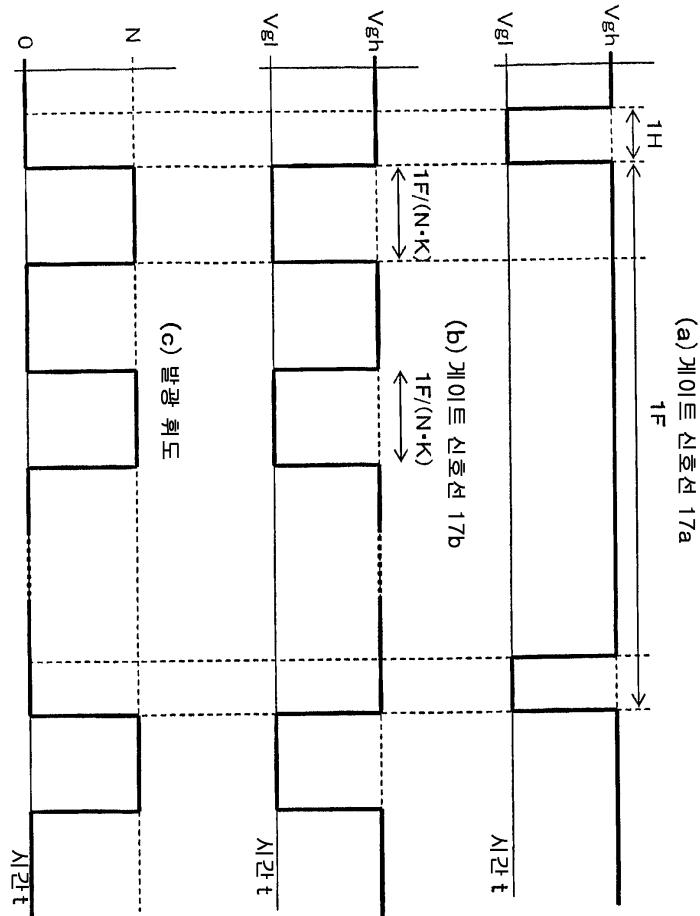

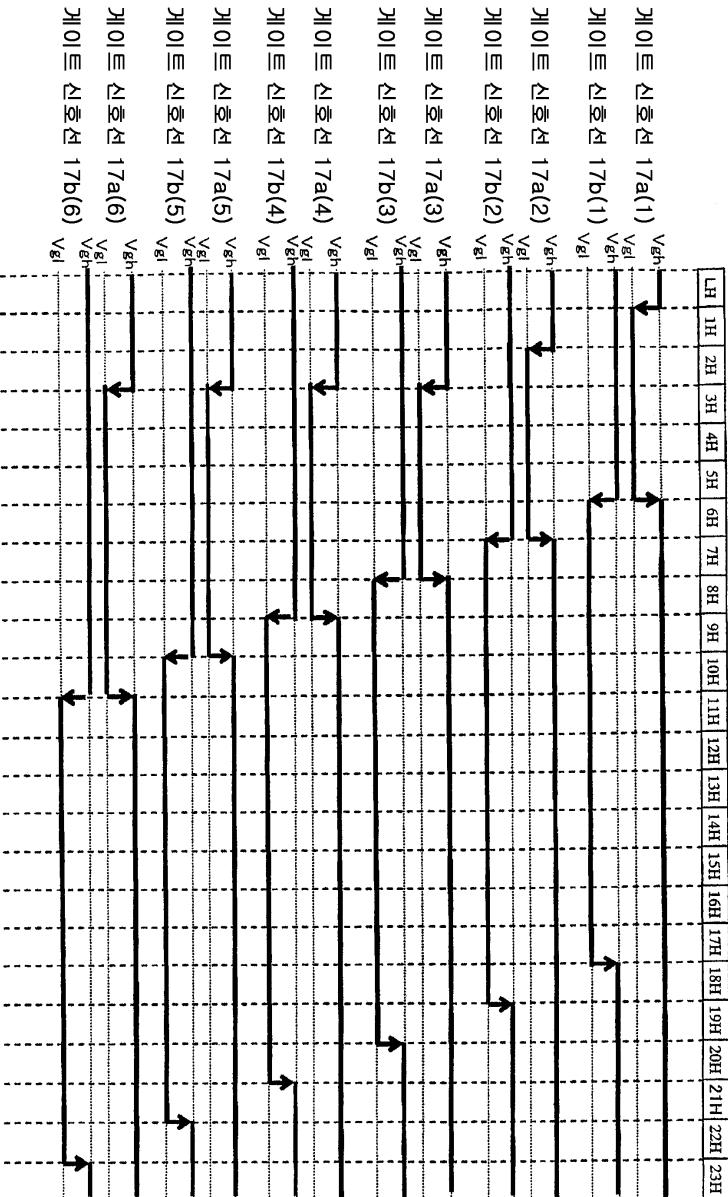

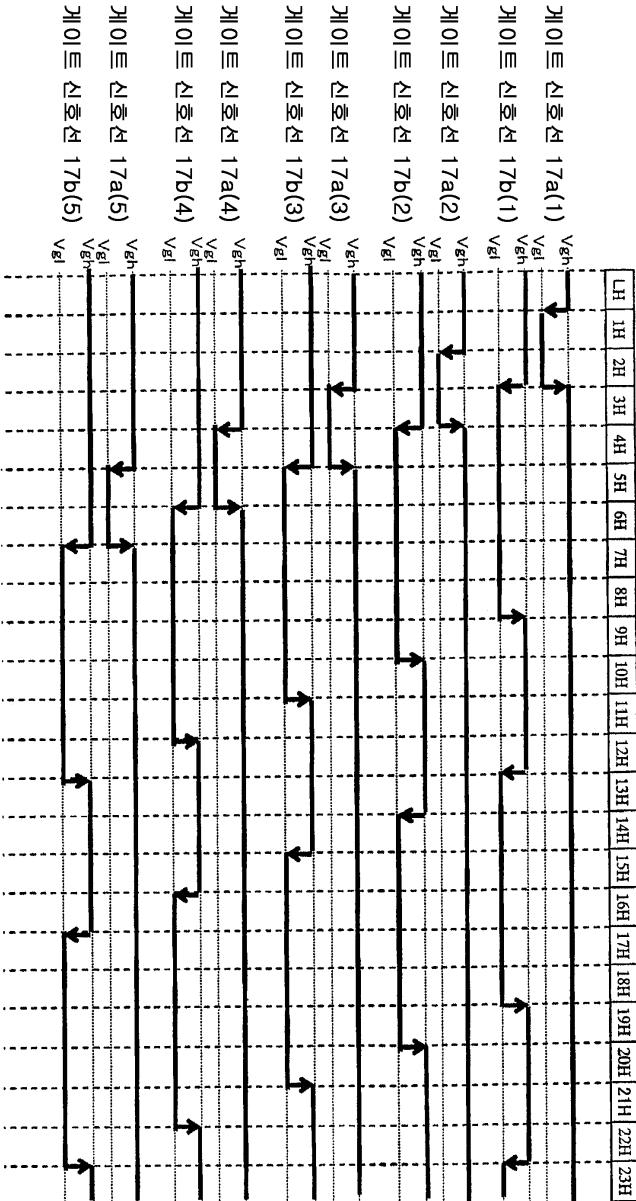

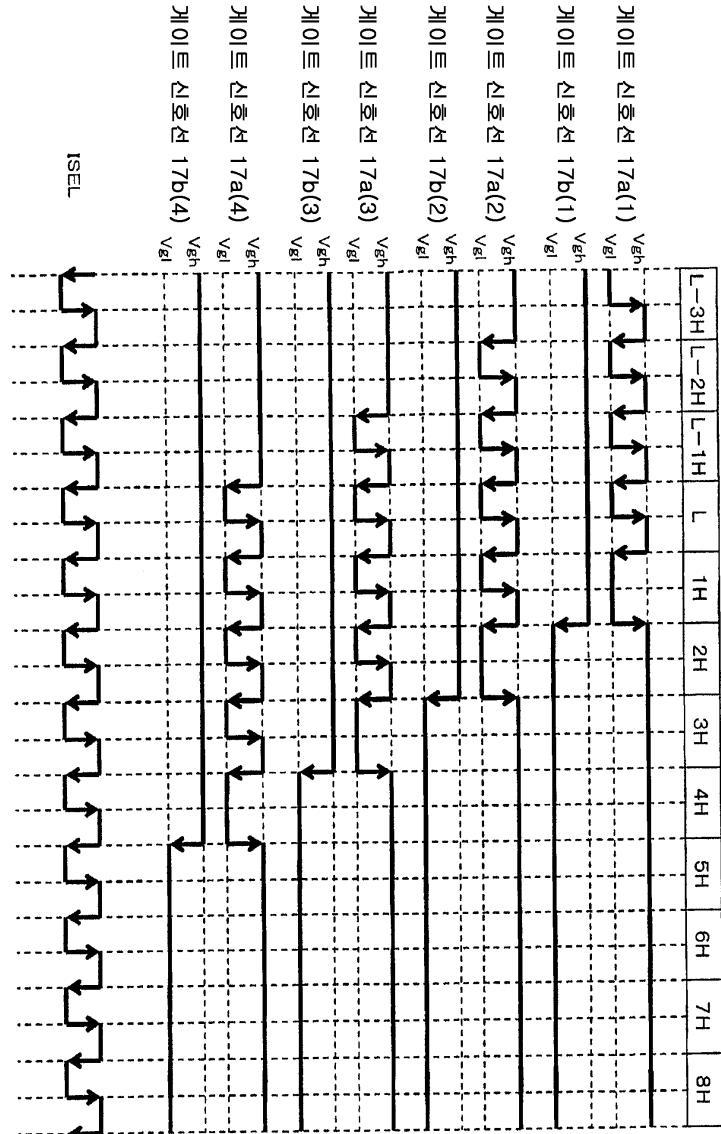

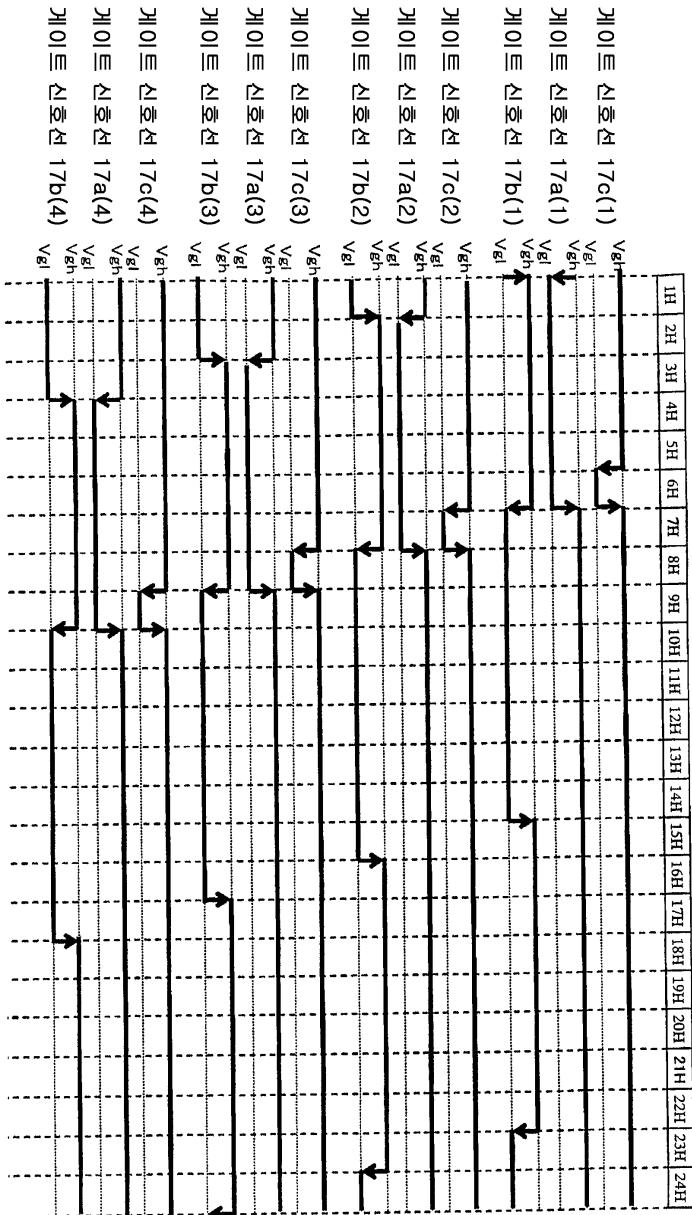

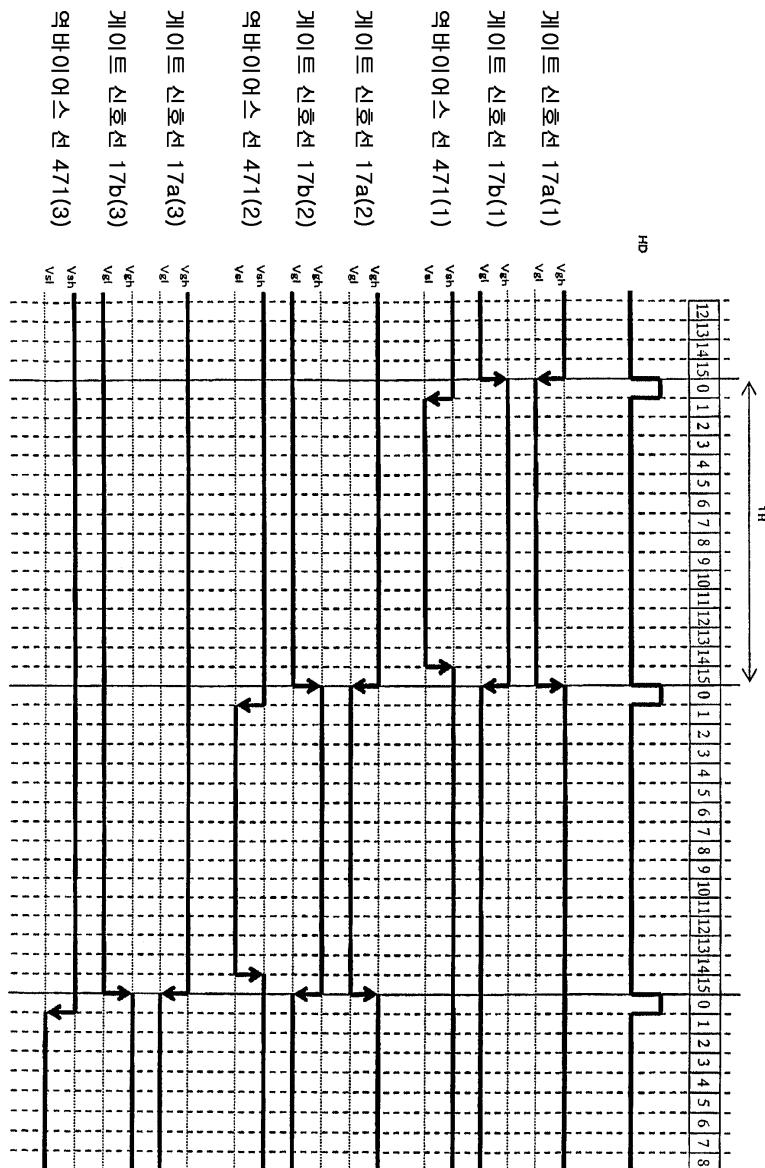

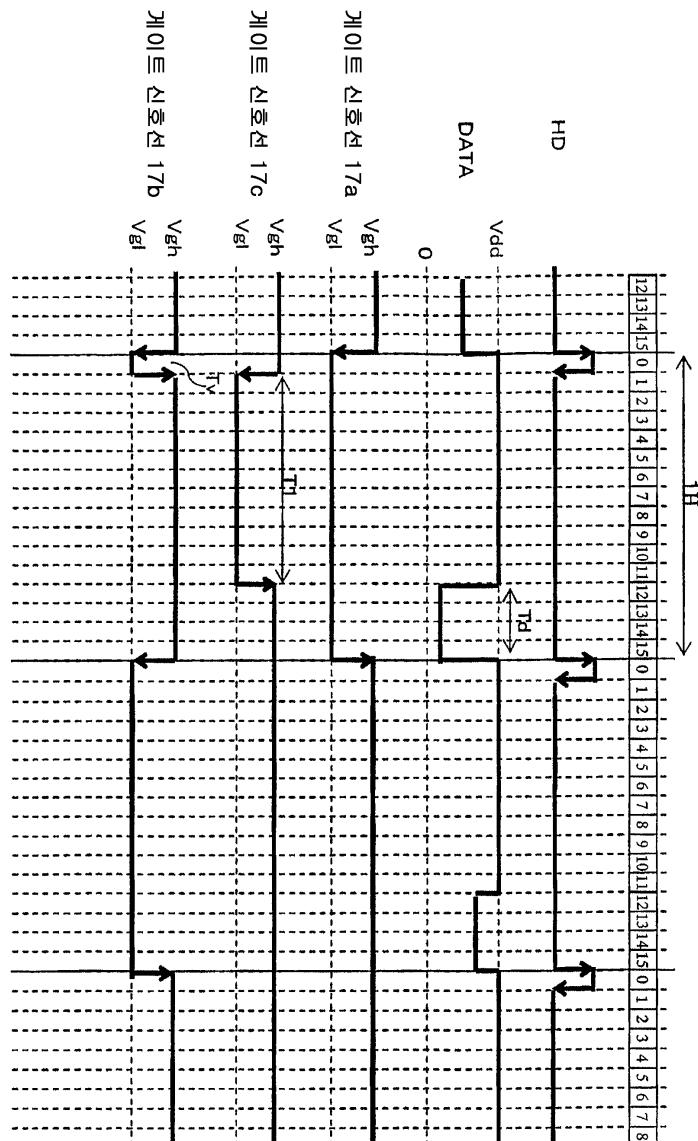

이 타이밍차트를 도 4에 나타낸다. 또, 도 4 등에 있어서, 괄호 내의 첨자(예를 들면, (1) 등)는 화소 행의 행 번호를 나타내고 있다. 즉, 게이트 신호선(17a)(1)이란, 화소 행(1)의 게이트 신호선(17a)을 나타내고 있다. 또한, 도 4의 상단의 \*H ('\*'에는 임의의 기호, 수치가 적합하며, 수평 주사선의 번호를 나타냄)이란, 수평 주사 기간을 나타내고 있다. 즉, 1H란 제 1 번째의 수평 주사 기간이다. 또, 이상의 사항은, 설명을 용이하게 하기 위한 것으로서, 1H의 번호, 1H 주기, 화소 행의 행 번호의 순서 등을 한정하는 것은 아니다.

도 4에서 알 수 있는 바와 같이, 각 선택된 화소 행(선택 기간은, 1H로 하고 있음)에 있어서, 게이트 신호선(17a)에 온 전압이 인가되어 있는 때에는, 게이트 신호선(17b)에는 오프 전압이 인가되어 있다. 이 기간은, EL 소자(15)에는 전류가 흐르고 있지 않다(비접등 상태). 한편, 선택되어 있지 않은 화소 행에 있어서, 게이트 신호선(17a)에 오프 전압이 인가되고, 게이트 신호선(17b)에는 온 전압이 인가되어 있다. 이 기간은, EL 소자(15)에 전류가 흐르고 있다(점등 상태).

또, 트랜지스터(11b)의 게이트와 트랜지스터(11c)의 게이트는 동일한 게이트 신호선(17a)에 접속하고 있다. 그러나, 트랜지스터(11b)의 게이트와 트랜지스터(11c)의 게이트를 상이한 게이트 신호선(도 32에 있어서의 게이트 신호선(17a, 17c)에 각각 접속하더라도 좋음. 이 경우, 1 화소의 게이트 신호선은 3개로 된다(도 1의 구성은 2개임). 트랜지스터(11b)의 게이트의 ON/OFF 타이밍과 트랜지스터(11c)의 게이트의 ON/OFF 타이밍을 개별적으로 제어함으로써, 트랜지스터(11a)의 편차에 의한 EL 소자(15)의 전류값 편차를 더 저감할 수 있다.

게이트 신호선(17a)과 게이트 신호선(17b)을 공통으로 하여, 트랜지스터(11c와 11d)를 상이한 도전형(N 채널과 P 채널)으로 하면, 구동 회로의 간략화를 도모할 수 있어, 화소의 개구율을 향상시킬 수 있다.

이와 같이 구성하면 본 발명의 동작 타이밍으로서는 신호선으로부터의 기입 경로가 오프로 된다. 즉, 소정의 전류가 기억될 때에, 전류가 흐르는 경로에 분기가 있으면 정확한 전류값이 트랜지스터(11a)의 소스(S)-게이트(G)간의 용량(콘덴서)에 기억되지 않는다. 트랜지스터(11c)와 트랜지스터(11d)를 상이한 도전형으로 한 경우, 서로의 임계값을 제어함으로써 주사선이 전환되는 타이밍에서 반드시 트랜지스터(11c)가 오프한 후에, 트랜지스터(11d)가 온한다고 하는 동작이 가능하게 된다.

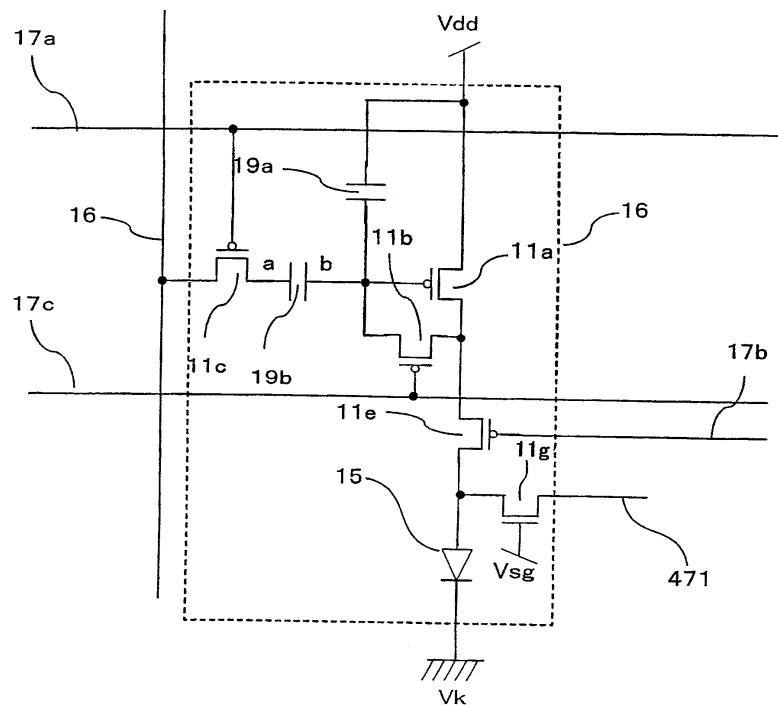

단, 이 경우 서로의 임계값을 정확하게 제어할 필요가 있기 때문에 프로세스에는 충분한 주의를 할 필요가 있다. 또, 이상 서술한 회로는 최저 4개의 트랜지스터로 실현 가능하지만, 보다 정확한 타이밍 제어를 실현하기 위해서, 또는 후술하는 바와 같이 미러 효과 저감을 위해서, 트랜지스터(11e)를 도 2에 도시하는 바와 같이, 캐소드 접속하는 구성으로 하여 트랜지스터의 총수가 4 이상으로 되더라도 동작 원리는 동일하다. 이와 같이 트랜지스터(11e)를 부가한 구성으로 하는 것에 의해, 트랜지스터(11c)를 거쳐서 프로그램한 전류를 보다 정밀하게 EL 소자(15)에 흐를 수 있게 된다.

트랜지스터(11a)의 특성의 편차는 트랜지스터 사이즈에 상관이 있다. 특성편차를 작게 하기 위해서, 제 1 트랜지스터(11a)의 채널 길이가  $5\mu m$  이상  $100\mu m$  이하로 하는 것이 바람직하다. 더욱 바람직하게는, 제 1 트랜지스터(11a)의 채널 길이가  $10\mu m$  이상  $50\mu m$  이하로 하는 것이 바람직하다. 이것은, 채널 길이 L을 길게 한 경우, 채널에 포함되는 임계가 증대하는 것에 의해서 전계가 완화되어 킹크 효과가 낮게 억제되기 때문이라고 생각된다.

또한, 화소를 구성하는 트랜지스터(11)가, 레이저 재결정화 방법(레이저 어닐링)에 의해 형성된 폴리실리콘 트랜지스터로 형성되고, 모든 트랜지스터에 있어서의 채널 방향이 레이저의 조사 방향에 대해 동일한 방향인 것이 바람직하다. 또한, 레이저는 동일 개소를 2회 이상 스캔하여 반도체막을 형성하는 것이 바람직하다.

본 발명의 목적은, 트랜지스터 특성의 편차가 표시에 영향을 부여하지 않는 회로 구성을 제안하는 것으로, 그 때문에 4 이상의 트랜지스터가 필요하게 된다. 이들 트랜지스터의 특성에 의해 회로 정수를 결정하는 경우, 4개의 트랜지스터의 특성이 갖추어지지 않으면, 적절한 회로 정수를 구하기 어렵다. 레이저 조사의 긴 축 방향에 대해, 채널 방향이 수평의 경우와 수직의 경우에는, 트랜지스터 특성의 임계값과 이동도가 상이하게 형성된다. 또, 어느 쪽의 경우에도 편차의 정도는 동일하다. 수평 방향과, 수직 방향에서는 이동도, 임계값의 평균치가 상이하다. 따라서, 화소를 구성하는 모든 트랜지스터의 채널 방향은 동일한 쪽이 바람직하다.

또한, 축적 용량(19)의 용량값을  $C_s$ , 제 2 트랜지스터(11b)의 오프 전류값을  $I_{off}$ 로 한 경우, 다음 식을 만족시키는 것이 바람직하다.

$$3 < C_s/I_{off} < 24$$

또한, 다음 식을 만족시키는 것이 보다 바람직하다.

$$6 < C_s/I_{off} < 18$$

트랜지스터(11b)의 오프 전류를  $5pA$  이하로 하는 것에 의해, EL을 흐르는 전류값의 변화를 2% 이하로 억제하는 것이 가능하다. 이것은 리크 전류가 증가하면, 전압 비기입 상태에 있어서 게이트-소스간(콘덴서의 양단)에 축적된 전하를 1 펠드간 유지할 수 없기 때문이다. 따라서, 콘덴서(19)의 축적용 용량이 크면 오프 전류의 허용량도 커진다. 상기 식을 만족하는 것에 대해서 인접 화소간의 전류값의 변동을 2% 이하로 억제할 수 있다.

또한, 액티브 매트릭스를 구성하는 트랜지스터가 p-ch 폴리실리콘 박막 트랜지스터로 구성되고, 트랜지스터(11b)를 듀얼 게이트 이상인 멀티 게이트 구조로 하는 것이 바람직하다. 트랜지스터(11b)는, 트랜지스터(11a)의 소스-드레인간의 스위치로서 작용하기 때문에, 가능한 한 ON/OFF 비가 높은 특성이 요구된다. 트랜지스터(11b)의 게이트 구조를 듀얼 게이트 구조 이상의 멀티 게이트 구조로 하는 것에 의해 ON/OFF 비가 높은 특성을 실현할 수 있다.

화소(16)의 트랜지스터(11)를 구성하는 반도체막은, 저온 폴리실리콘 기술에 있어서, 레이저 어닐링에 의해 형성하는 것이 일반적이다. 이 레이저 어닐링의 조건의 편차가 트랜지스터(11)의 특성의 편차로 된다. 그러나, 1 화소(16) 내의 트랜지스터(11)의 특성이 일치하고 있으면, 도 1 등의 전류 프로그램을 행하는 방식에서는, 소정의 전류가 EL 소자(15)에 흐르도록 구동할 수 있다. 이 점은, 전압 프로그램에 없는 이점이다. 여기서 레이저로서는 엑시머 레이저를 이용하는 것이 바람직하다.

또, 본 발명에 있어서, 반도체막의 형성은, 레이저 어닐링 방법에 한정하는 것은 아니고, 열 어닐링 방법, 고상(CGS) 성장에 의한 방법이라도 좋다. 그 외에, 저온 폴리실리콘 기술에 한정하는 것은 아니고, 고온 폴리실리콘 기술을 이용해도 좋은 것은 말할 필요도 없다.

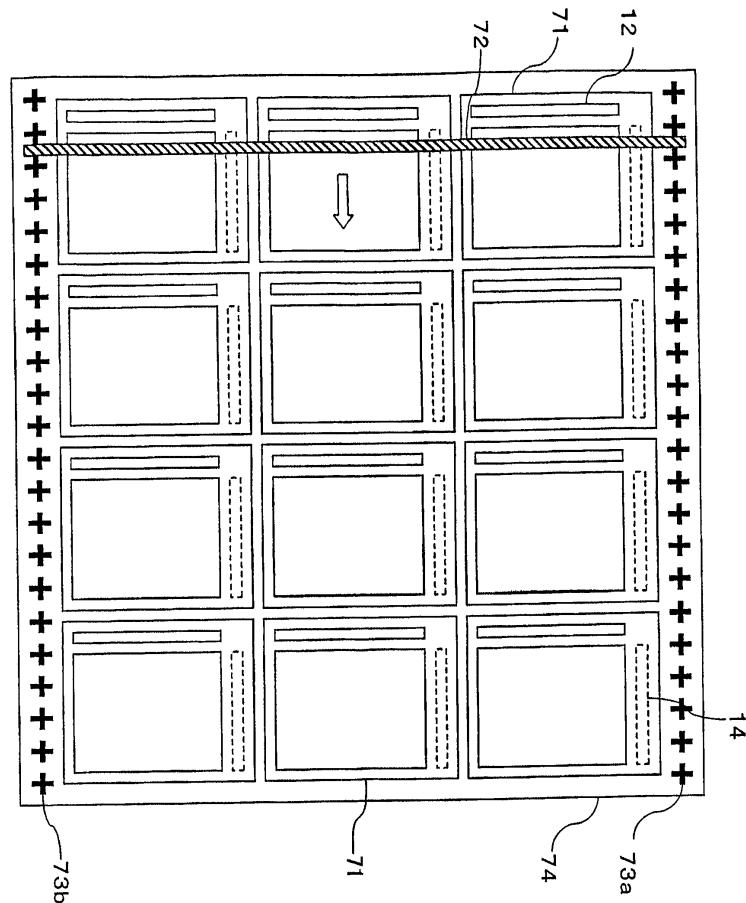

이 과제에 대해, 본 발명에서는 도 7에 도시하는 바와 같이, 어닐링 시의 레이저 조사 스폿(레이저 조사 범위)(72)을 소스 신호선(18)에 평행하게 조사한다. 또한, 1 화소 열에 일치하도록 레이저 조사 스폿(72)을 이동시킨다. 물론, 1 화소 열에 한정하는 것은 아니고, 예를 들면, RGB를 1 화소(16)라는 단위로 레이저를 조사하더라도 좋다(이 경우는, 3 화소 열이라는 것으로 됨). 또한, 복수의 화소에 동시에 조사하더라도 좋다. 또한, 레이저 조사 범위의 이동이 오버랩하더라도 되는 것은 말할 필요도 없다(통상, 이동하는 레이저광의 조사 범위는 오버랩하는 것이 보통임).

화소는 RGB의 3 화소로 정방형의 형상으로 되도록 제작되어 있다. 따라서, R, G, B의 각 화소는 세로 길이의 화소 형상으로 된다. 따라서, 레이저 조사 스폿(72)을 세로 길이로 하여 어닐링함으로써, 1 화소 내에서는 트랜지스터(11)의 특성 편차

가 발생하지 않도록 할 수 있다. 또한, 하나의 소스 신호선(18)에 접속된 트랜지스터(11)의 특성(모빌리티,  $V_t$ ,  $S_{\text{값}}$  등)을 균일하게 할 수 있다(즉, 인접한 소스 신호선(18)의 트랜지스터(11)와는 특성이 상이한 경우가 있지만, 하나의 소스 신호선(18)에 접속된 트랜지스터(11)의 특성은 거의 동등하게 할 수 있음).

일반적으로 레이저 조사 스폟(72)의 길이는 10인치 등과 같이 고정값이다. 이 레이저 조사 스폟(72)을 이동시키는 것이기 때문에, 하나의 레이저 조사 스폟(72)을 이동할 수 있는 범위 내에 수용되도록 패널을 배치할 필요가 있다(즉, 패널의 표시 영역(50)의 중앙부에서 레이저 조사 스폟(72)이 겹치지 않도록 함).

도 7에 나타내는 구성에서는, 레이저 조사 스폟(72)의 길이의 범위 내에 3개의 패널이 세로로 배치되도록 형성되어 있다. 레이저 조사 스폟(72)을 조사하는 어닐링 장치는 유리 기판(74)의 위치 결정 마커(73a, 73b)를 인식(패턴 인식에 의한 자동 위치 결정)하여 레이저 조사 스폟(72)을 이동시킨다. 위치 결정 마커(73)의 인식은 패턴 인식 장치에서 실행한다. 어닐링 장치(도시하지 않음)는 위치 결정 마커(73)를 인식하여, 화소 열의 위치를 산출해 낸다(레이저 조사 범위(72)가 소스 신호선(18)과 평행하게 되도록 함). 화소 열 위치에 겹치도록 레이저 조사 스폟(72)을 조사하여 어닐링을 순차적으로 실행한다.

도 7에서 설명한 레이저 어닐링 방법(소스 신호선(18)에 평행하게 라인 형상의 레이저 스폟을 조사하는 방식)은, 유기 EL 표시 패널의 전류 프로그램 방식 시에 채용하는 것이 특히 바람직하다. 왜냐하면, 소스 신호선에 평행 방향으로 트랜지스터(11)의 특성이 일치하고 있기 때문이다(세로 방향으로 인접한 화소 트랜지스터의 특성이 근사하고 있음). 그 때문에, 전류 구동 시에 소스 신호선의 전압 레벨의 변화가 적고, 전류 기입 부족이 발생하기 어렵다.

예를 들면, 백 래스터(raster) 표시이면, 인접한 각 화소의 트랜지스터(11a)에 흐르는 전류는 거의 동일하므로, 소스 드라이버(14)로부터 출력하는 전류 진폭의 변화가 적다. 만약, 도 1의 트랜지스터(11a)의 특성이 동일하며, 각 화소에 전류 프로그램하는 전류값이 화소 열에서 동등한 것이면, 전류 프로그램 시의 소스 신호선(18)의 전위는 일정하다. 따라서, 소스 신호선(18)의 전위 변동은 발생하지 않는다. 하나의 소스 신호선(18)에 접속된 트랜지스터(11a)의 특성이 거의 동일하면, 소스 신호선(18)의 전위 변동은 작은 것으로 된다. 이 것은, 도 38 등의 다른 전류 프로그램 방식의 화소 구성이라도 동일하다(즉, 도 7의 제조 방법을 적용하는 것이 바람직함).

또한, 도 27, 도 30 등에서 설명하는 복수의 화소 행을 동시 기입하는 방식으로 균일한 화상 표시를 실현할 수 있다. 이것은, 주로 트랜지스터 특성의 편차에 기인하는 표시 얼룩이 발생하기 어렵기 때문이다. 도 27 등은 복수 화소 행은 동시에 선택하기 때문에, 인접한 화소 행의 트랜지스터가 균일하면, 세로 방향의 트랜지스터 특성 얼룩은 드라이버 회로(14)에서 흡수할 수 있다.

또, 도 7에 나타내는 바와 같이, 소스 드라이버(14)는, IC 칩을 적재하여 형성되어 있지만, 이것에 한정하는 것은 아니고, 소스 드라이버(14)를 화소(16)와 동일 프로세스로 형성하더라도 되는 것은 말할 필요도 없다.

본 발명에서는 특히, 트랜지스터(11b)의 임계 전압  $V_{th2}$ 가 화소 내에서 대응하는 트랜지스터(11a)의 임계 전압  $V_{th1}$ 보다 낮게 되지 않도록 설정되어 있다. 예컨대, 트랜지스터(11b)의 게이트 길이  $L_2$ 를 트랜지스터(11a)의 게이트 길이  $L_1$ 보다도 길게 하고, 이들의 박막 트랜지스터의 프로그램 파라미터가 변동하더라도,  $V_{th2}$ 가  $V_{th1}$ 보다도 낮게 되지 않도록 한다. 이에 따라, 미소한 전류 리크를 억제하는 것이 가능하다.

또, 이상의 사항은, 도 38에 도시하는 커런트 미러의 화소 구성에도 적용할 수 있다. 도 38에서는, 신호 전류가 흐르는 구동 용 트랜지스터(11a), EL 소자(15) 등으로 이루어지는 발광 소자에 흐르는 구동 전류를 제어하는 구동용 트랜지스터(11b) 이외에, 게이트 신호선(17a1)의 제어에 의해서 화소 회로와 데이터선 data를 접속 또는 차단하는 취입용 트랜지스터(11c), 게이트 신호선(17a2)의 제어에 의해서 기입 기간 동안에 트랜지스터(11a)의 게이트·드레인을 단락하는 스위치용 트랜지스터(11d), 트랜지스터(11a)의 게이트-소스간의 전압의 기입 종료 후에도 유지하기 위한 축적 용량(19) 및 발광 소자로서의 EL 소자(15) 등으로 구성된다.

도 38에서 트랜지스터(11c, 11d)는 N 채널 트랜지스터로, 그 밖의 트랜지스터는 P 채널 트랜지스터로 각각 구성하고 있지만, 이것은 일례로서, 반드시 이와 같을 필요는 없다. 축적 용량(19)은, 그 한쪽의 단자가 트랜지스터(11a)의 게이트에 접속되고, 다른쪽의 단자가 Vdd(전원 전위)에 접속되어 있지만, Vdd에 한하지 않고 임의의 일정 전위라도 좋다. EL 소자(15)의 캐소드(음극)는 접지 전위에 접속되어 있다.

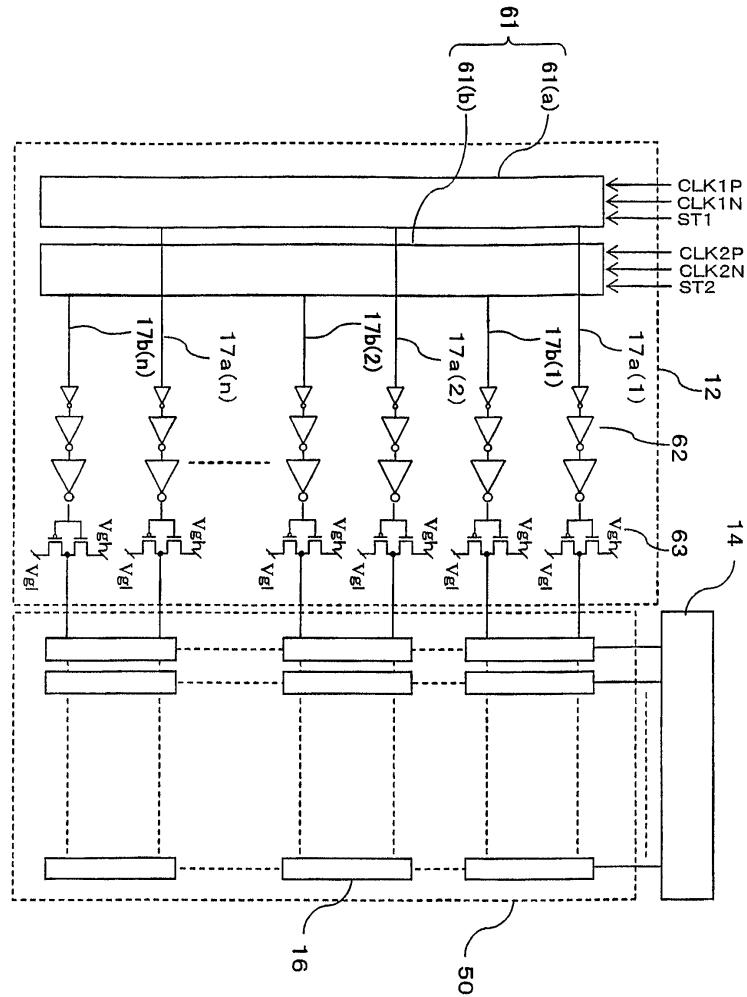

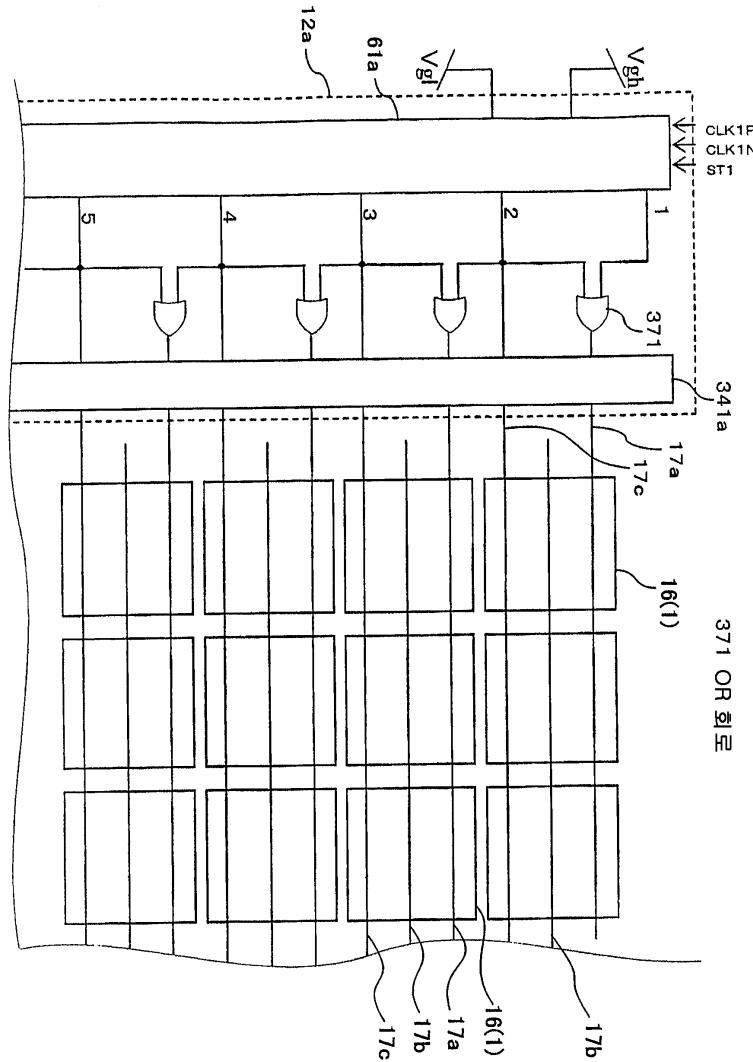

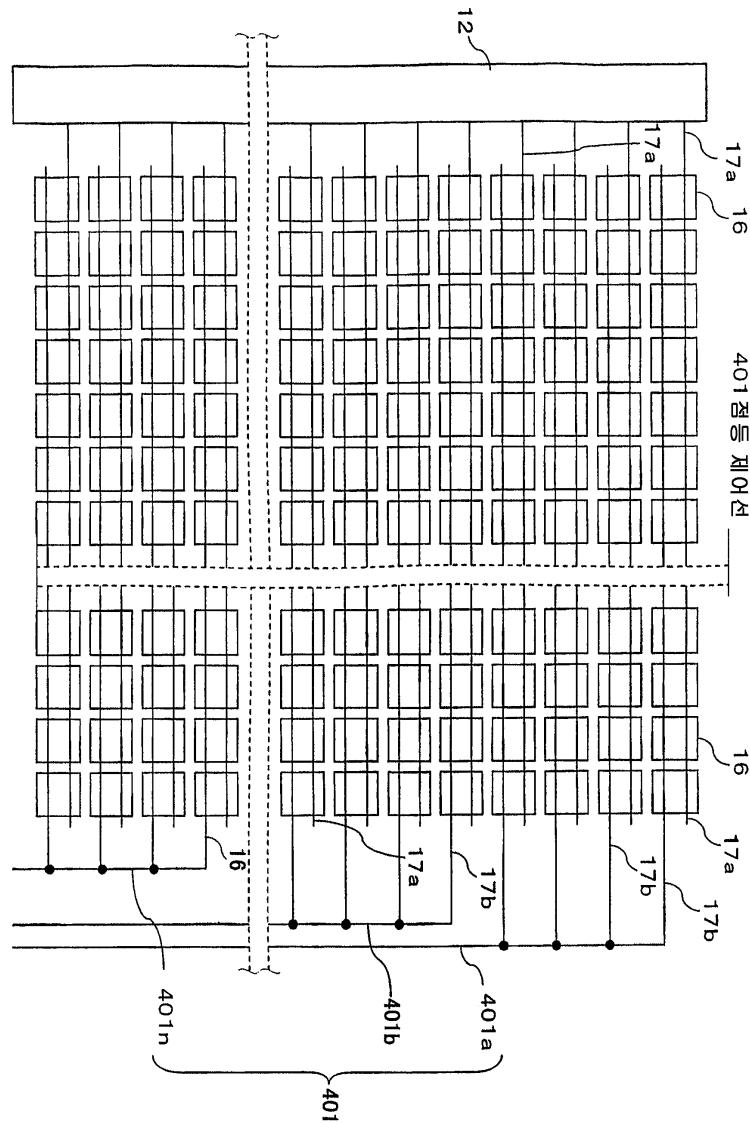

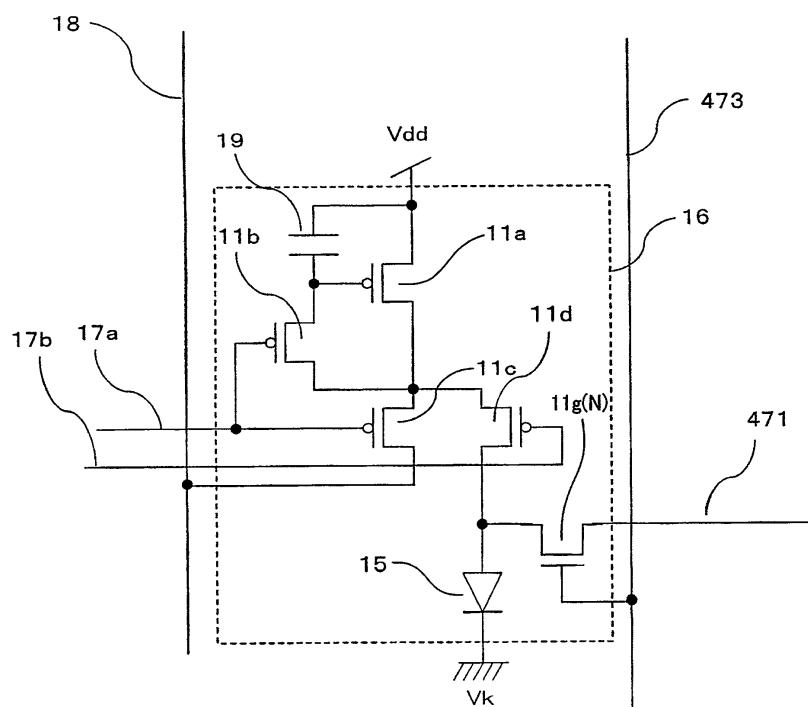

다음에, 본 발명의 EL 표시 패널 및 EL 표시 장치에 대해 설명을 한다. 도 6은 EL 표시 장치의 회로를 중심으로 한 설명도이다. 화소(16)가 매트릭스 형상으로 배치 또는 형성되어 있다. 각 화소(16)에는 각 화소의 전류 프로그램을 행하는 전류를

출력하는 소스 드라이버(14)가 접속되어 있다. 소스 드라이버(14)의 출력단은 계조 데이터인 화상 신호의 비트 수에 대응한 커런트 미러 회로가 형성되어 있다(이후에 설명함). 예를 들어, 64 계조이면, 63개의 커런트 미러 회로가 각 소스 신호 선에 형성되고, 이들의 커런트 미러 회로의 개수를 선택함으로써 소망하는 전류를 소스 신호선(18)에 인가할 수 있도록 구성되어 있다.

또, 하나의 커런트 미러 회로의 최소 출력 전류는 10nA 이상 50nA 이하로 하고 있다. 특히, 커런트 미러 회로의 최소 출력 전류는 15nA 이상 35nA 이하로 하는 것이 바람직하다. 소스 드라이버(14) 내의 커런트 미러 회로를 구성하는 트랜지스터의 정밀도를 확보하기 위해서이다.

또한, 소스 드라이버(14)는, 소스 신호선(18)의 전하를 강제적으로 방출 또는 충전하는 프리차지 또는 방전 회로를 내장한다. 소스 신호선(18)의 전하를 강제적으로 방출 또는 충전하는 프리차지 또는 방전 회로의 전압(전류) 출력값은, R, G, B에서 독립적으로 설정할 수 있도록 구성되어 있는 것이 바람직하다. EL 소자(15)의 임계값이 RGB에서 상이하기 때문이다.

유기 EL 소자는 큰 온도 의존성 특성이 있는 것으로 알려져 있다. 이 온도 특성에 의한 발광 휘도 변화를 조정하기 위해서, 커런트 미러 회로에 출력 전류를 변화시키는 서비스터 혹은 포지스터 등의 비직선 소자를 부가하여, 온도 의존성 특성에 의한 변화를 상기 서비스터 등으로 조정함으로써 아날로그적으로 기준 전류를 작성한다.

본 발명에 있어서, 소스 드라이버(14)는 반도체 칩으로 형성되어 있고, 클래스 온칩(COG) 기술로 기판(71)의 소스 신호선(18)의 단자와 접속되어 있다. 소스 신호선(18) 등의 신호선의 배선은 크롬, 동, 알루미늄, 은 등의 금속 배선이 이용된다. 가는 배선 폭으로 저 저항의 배선을 얻을 수 있기 때문이다. 배선은 화소가 반사형인 경우는 화소의 반사막을 구성하는 재료로, 반사막과 동시에 형성하는 것이 바람직하다. 공정을 간략화할 수 있기 때문이다.

소스 드라이버(14)의 실장은, COG 기술에 한정하는 것은 아니고, 칩온필름(COF) 기술에 전술한 소스 드라이버(14) 등을 적재하여, 표시 패널의 신호선과 접속한 구성으로 해도 좋다. 또한, 드라이브 IC는 전원 IC(82)를 별도 제작하고, 3 칩 구성으로 해도 좋다.

한편, 게이트 드라이버(12)는 저온 폴리실리콘 기술로 형성되어 있다. 즉, 화소의 트랜지스터와 동일한 프로세스로 형성하고 있다. 이것은, 소스 드라이버(14)와 비교하여 내부의 구조가 용이하고, 동작 주파수도 낮기 때문이다. 따라서, 저온 폴리실리콘 기술을 이용해도 용이하게 게이트 드라이버(12)를 형성할 수 있고, 이것에 의해 협베젤화를 실현할 수 있다. 물론, 게이트 드라이버(12)를 실리콘 텁으로 형성하여, COG 기술 등을 이용하여 기판(71) 상에 실장하더라도 되는 것은 말할 필요도 없다. 또한, 화소 트랜지스터 등의 스위칭 소자, 게이트 드라이버 등은 고온 폴리실리콘 기술로 형성하더라도 좋고, 유기 재료로 형성(유기 트랜지스터)하더라도 좋다.

게이트 드라이버(12)는 게이트 신호선(17a)용의 시프트 레지스터 회로(61a)와, 게이트 신호선(17b)용의 시프트 레지스터 회로(61b)를 내장한다. 각 시프트 레지스터 회로(61)는 정상(正相) 및 부상(負相)의 클럭 신호(CLKxP, CLKxN), 스타트 펄스(start pulse)(STx)로 제어된다. 그 외에, 게이트 신호선의 출력, 비(非)출력을 제어하는 인에이블(ENABL) 신호, 시프트 방향을 상하 역전하는 업 다운(up down)(UPDWM) 신호를 부가하는 것이 바람직하다. 그 외에, 스타트 펄스가 시프트 레지스터에 시프트되고, 그리고 출력되고 있는 것을 확인하는 출력 단자 등을 마련하는 것이 바람직하다. 또, 시프트 레지스터의 시프트 타이밍은 콘트롤 IC(81)로부터의 제어 신호로 제어된다. 또한, 외부 데이터의 레벨 시프트를 행하는 레벨 시프트 회로를 내장한다. 또한, 검사 회로를 내장한다.

시프트 레지스터 회로(61)의 버퍼 용량은 작기 때문에, 직접적으로는 게이트 신호선(17)을 구동할 수 없다. 그 때문에, 시프트 레지스터 회로(61)의 출력과 게이트 신호선(17)을 구동하는 출력 게이트(63) 사이에는 적어도 2개 이상의 인버터 회로(62)가 형성되어 있다.

소스 드라이버(14)를 저온 폴리실리콘 등의 폴리실리콘 기술로 기판(71) 상에 직접 형성하는 경우도 마찬가지이며, 소스 신호선(18)을 구동하는 트랜스퍼 게이트 등의 아날로그 스위치의 게이트와 소스 드라이버(14)의 시프트 레지스터 사이에는 복수의 인버터 회로가 형성된다. 이하의 사항(시프트 레지스터의 출력과, 신호선을 구동하는 출력단(출력 게이트 혹은 트랜스퍼 게이트 등의 출력단) 사이에 배치되는 인버터 회로에 관한 사항)은, 소스 드라이버 및 게이트 드라이버에 공통의 사항이다.

예를 들면, 도 6에서는 소스 드라이버(14)의 출력이 직접 소스 신호선(18)에 접속되어 있는 바와 같이 도시하였지만, 실제로는, 소스 드라이버의 시프트 레지스터의 출력은 다단의 인버터 회로에 접속되고, 인버터의 출력이 트랜스퍼 게이트 등의 아날로그 스위치의 게이트에 접속되어 있다.

인버터 회로(62)는 P 채널의 MOS 트랜지스터와 N 채널의 MOS 트랜지스터로 구성된다. 앞에서도 설명한 바와 같이 게이트 드라이버(12)의 시프트 레지스터 회로(61)의 출력단에는 인버터 회로(62)가 다단으로 접속되어 있고, 그 최종 출력이 출력 게이트 회로(63)에 접속되어 있다. 또, 인버터 회로(62)는 P 채널만으로 구성하더라도 좋다. 단, 이 경우는, 인버터가 아니라 단순한 게이트 회로로서 구성하더라도 좋다.

도 8은 본 발명의 표시 장치의 신호, 전압의 공급의 구성도 혹은 표시 장치의 구성도이다. 콘트롤 IC(81)로부터 소스 드라이버(14a)에 공급하는 신호(전원 배선, 데이터 배선 등)는 플렉서블 기판(84)을 거쳐서 공급한다.

도 8에서는 게이트 드라이버(12)의 제어 신호는 콘트롤 IC(81)에서 발생시키고, 소스 드라이버(14)에서, 레벨 시프트를 행한 후, 게이트 드라이버(12)에 인가하고 있다. 소스 드라이버(14)의 구동 전압은 4~8(V)이므로, 콘트롤 IC(81)로부터 출력된 3.3(V) 진폭의 제어 신호를, 게이트 드라이버(12)가 수취하는 것이 가능한 5(V) 진폭으로 변환할 수 있다.

소스 드라이버(14) 내에는 화상 메모리를 마련하는 것이 바람직하다. 화상 메모리의 화상 데이터는 오차 확산 처리 혹은 디서(dither) 처리를 행한 후의 데이터를 메모리하더라도 좋다. 오차 확산 처리, 디서 처리 등을 행하는 것에 의해, 26만색 표시 데이터를 4096색 등으로 변환할 수 있어, 화상 메모리의 용량을 작게 할 수 있다. 오차 확산 처리 등은 오차 확산 콘트롤러(81)로 실행할 수 있다. 또한, 디서 처리를 행한 후, 오차 확산 처리를 더 행하더라도 좋다. 이상의 사항은, 역오차 확산 처리에도 적용된다.

또, 도 8 등에 있어서 (14)를 소스 드라이버로 기재하였지만, 간단한 드라이버 뿐만 아니라, 전원 회로, 버퍼 회로(시프트 레지스터 등의 회로를 포함함), 데이터 변환 회로, 래치 회로, 커맨드 디코더, 시프트 회로, 어드레스 변환 회로, 화상 메모리 등을 내장시키더라도 좋다. 또, 도 8 등에서 설명하는 구성에 있어서도, 도 9 등에서 설명하는 3변 프리 구성(구조), 구동 방식 등을 적용할 수 있는 것은 말할 필요도 없다.

표시 패널을 휴대형 전화기 등의 정보 표시 장치에 사용하는 경우, 소스 드라이버(회로)(14), 게이트 드라이버(회로)(12)를 도 9에 도시하는 바와 같이, 표시 패널의 한 변에 실장(형성)하는 것이 바람직하다(또, 이와 같이 한 변에 드라이버 IC(회로)를 실장(형성)하는 형태를 3변 프리 구성(구조)이라고 부름. 종래에는, 표시 영역의 X 변에 게이트 드라이버(12)가 실장되고, Y 변에 소스 드라이버(14)가 실장되어 있었음). 화면(50)의 중심선이 표시 장치의 중심으로 되도록 설계하기 용이하고, 또한, 드라이버 IC의 실장도 용이하게 되기 때문이다. 또, 게이트 드라이버를 고온 폴리실리콘 혹은 저온 폴리실리콘 기술 등으로 3변 프리 구성으로 제조하더라도 좋다(즉, 도 9의 소스 드라이버(14) 및 게이트 드라이버(12)중, 적어도 한쪽을 폴리실리콘 기술로 기판(71)에 직접 형성함).

또, 3변 프리 구성이란, 기판(71)에 직접 IC을 적재 혹은 형성한 구성 뿐만 아니라, 소스 드라이버(회로)(14), 게이트 드라이버(회로)(12) 등을 부착한 필름(TCP, TAB 기술 등)을 기판(71)의 한 변(또는 거의 한 변)에 부착한 구성도 포함한다. 즉, 2변에 IC가 실장 혹은 부착되어 있지 않은 구성, 배치 혹은 그것에 유사한 전부를 의미한다.

도 9와 같이 게이트 드라이버(12)를 소스 드라이버(14)의 옆에 배치하면, 게이트 신호선(17)은 변 C를 따라서 형성할 필요가 있다.

또, 도 9 등에 있어서 굵은 실선으로 도시한 개소는 게이트 신호선(17)이 병렬하여 형성되어 있는 개소를 나타내고 있다. 따라서, b의 부분(화면 하부)은 게이트 신호선의 개수분의 게이트 신호선(17)이 병렬하여 형성되고, a의 부분(화면 상부)은 게이트 신호선(17)이 1개 형성되어 있다.

C 변에 형성하는 게이트 신호선(17)의 피치는  $5\mu m$  이상  $12\mu m$  이하로 한다.  $5\mu m$  미만에서는 인접 게이트 신호선에 기생 용량의 영향에 의해 노이즈가 더해지게 된다. 실험에 의하면  $7\mu m$  이하에서 기생 용량의 영향이 현저하게 발생한다. 또한  $5\mu m$  미만에서는 표시 화면에 페트 형상 등의 화상 노이즈가 심하게 발생한다. 특히 노이즈의 발생은 화면의 좌우에서 상이하고, 이 페트 형상 등의 화상 노이즈를 저감하는 것은 곤란하다. 또한, 저감  $12\mu m$ 을 초과하면 표시 패널의 베젤폭 D가 너무 크게 되어 실용적이지 않다.

전술한 화상 노이즈를 저감하기 위해서는, 게이트 신호선(17)을 형성한 부분의 하층 혹은 상층에, 그라운드 패턴(일정 전압으로 전압 고정 혹은 전체로서 안정한 전위로 설정되고 있는 도전 패턴)을 배치함으로써 저감할 수 있다. 또한, 별도 마련한 쉴드판(쉴드박(일정 전압으로 전압 고정 혹은 전체로서 안정한 전위로 설정되어 있는 도전 패턴))을 게이트 신호선(17) 상에 배치하면 좋다.

도 9의 C 변의 게이트 신호선(17)은 ITO 전극으로 형성하더라도 좋지만, 저 저항화하기 때문에, ITO와 금속 박막을 적층하여 형성하는 것이 바람직하다. 또한, 금속막으로 형성하는 것이 바람직하다. ITO와 적층하는 경우에는, ITO 상에 티탄막을 형성하여, 그 위에 알루미늄 혹은 알루미늄과 몰리브덴의 합금 박막을 형성한다. 또는 ITO 상에 크롬막을 형성한다. 금속막의 경우에는, 알루미늄 박막, 크롬 박막으로 형성한다. 이상의 사항은 본 발명의 다른 실시예에서도 마찬가지이다.

또, 도 9 등에 있어서, 게이트 신호선(17) 등은 표시 영역의 한 쪽에 배치한다고 하였지만 이것에 한정되는 것은 아니고, 양쪽에 배치하더라도 좋다. 예를 들면, 게이트 신호선(17a)을 표시 영역(50)의 우측에 배치(형성)하고, 게이트 신호선(17b)을 표시 영역(50)의 좌측에 배치(형성)하더라도 좋다. 이상의 사항은 다른 실시예에서도 마찬가지이다.

또한, 소스 드라이버(14)와 게이트 드라이버(12)를 1칩화하더라도 좋다. 1칩화하면, 표시 패널로의 IC 칩의 실장이 1개로도 된다. 따라서, 실장 비용도 저감할 수 있다. 또한, 1칩 드라이버 IC 내에서 사용하는 각종 전압도 동시에 발생할 수 있다.

또, 소스 드라이버(14), 게이트 드라이버(12)는 실리콘 등의 반도체 웨이퍼로 제작하여, 표시 패널에 실장한다고 하였지만 이것에 한정하는 것은 아니며, 저온 폴리실리콘 기술, 고온 폴리실리콘 기술에 의해 표시 패널(82)에 직접 형성하더라도 되는 것은 말할 필요도 없다.

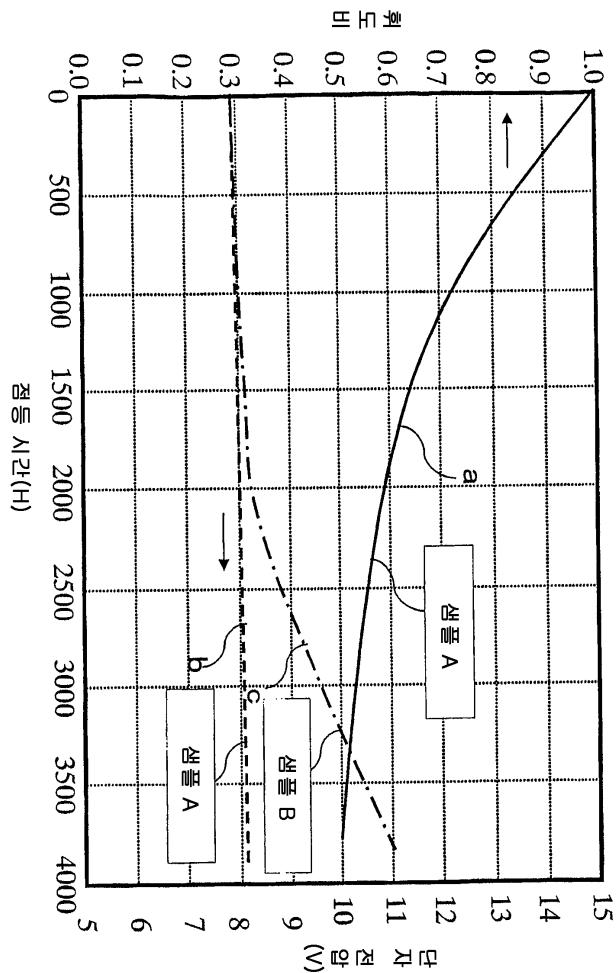

도 1 등에서 나타낸 구성에서는 EL 소자(15)는 트랜지스터(11a)를 거쳐서 Vdd 전위에 접속되어 있다. 그러나, 각 색을 구성하는 유기 EL(20)의 구동 전압이 상이하다고 하는 문제가 있다. 예를 들면, 단위 평방 센티미터 당 0.01(A)의 전류를 흘린 경우, 파랑(B)에서는 EL 소자의 단자 전압은 5(V)이지만, 초록(G) 및 빨강(R)에서는 9(V)이다. 즉, 단자 전압이 B와 G, R에서 상이하다. 따라서, B와 G 및 R에서는 유지하는 트랜지스터(11a)의 소스-드레인(in) 전압(SD 전압)이 상이하다. 그 때문에, 각 색에서 트랜지스터의 소스-드레인(in) 전압(SD 전압)간의 오프 리크 전류가 상이한 것으로 된다. 오프 리크 전류가 발생하고, 또한 오프 리크 특성이 각 색에서 상이하면, 색 밸런스가 어긋난 상태에서 플리커(flicker)가 발생한다, 발광 색에 상관하여 감마 특성이 어긋난다고 하는 복잡한 표시 상태로 된다.

이 과제에 대응하기 위해서, 적어도 R, G, B 색 중, 하나의 캐소드 전극의 전위를 다른 색의 캐소드 전극의 전위와 상이하게 하도록 구성하고 있다. 또는 R, G, B 색 중, 하나의 Vdd의 전위를 다른 색의 Vdd의 전위와 상이하게 하도록 구성하고 있다.

R, G, B의 EL 소자(15)의 단자 전압은 매우 일치시키는 것이 바람직한 것은 말할 필요도 없다. 적어도, 백 피크 휘도를 표시하고 있고, 색 온도가 7000K 이상 12000K 이하의 범위에서, R, G, B의 EL 소자의 단자 전압은 10(V) 이하로 되도록 재료 혹은 구조의 선정을 할 필요가 있다. 또한, R, G, B 중, EL 소자의 최대의 단자 전압과 최소의 단자 전압의 차는, 2.5(V) 이내로 할 필요가 있다. 더욱 바람직하게는 이 차를 1.5(V) 이하로 할 필요가 있다. 또, 이상의 실시예에서는, 색은 RGB로 하였지만 이것에 한정하는 것은 아니다. 이것은 이후에 설명한다.

또, 화소는, R, G, B의 3원색으로 하였지만 이것에 한정하는 것은 아니고, 시안, 황색, 마젠타의 3색이라도 좋다. 또한, B와 황색의 2색이라도 좋다. 물론, 단색이라도 좋다. 또한, R, G, B, 시안, 황색, 마젠타의 6색이라도 좋다. R: G, B, 시안, 마젠타의 5색이라도 좋다. 이들은 천연색(natural color)으로서 색 재현범위가 확대하여 양호한 표시를 실현할 수 있다. 그 외에, R, G, B, 백의 4색이라도 좋다. R, G, B, 시안, 황색, 마젠타, 흑, 백의 7색이라도 좋다. 또한, 백색 발광의 화소를 표시 영역(50) 전체에 형성(제작)하여, RGB 등의 컬러 필터로 3원색 표시로 해도 좋다. 이 경우는, EL 층에 각 색의 발광 재료를 적층하여 형성하면 좋다. 또한, 1 화소를 B 및 황색과 같이 나누어 칠하더라도 좋다. 이상과 같이 본 발명의 EL 표시 장치는, RGB의 3원색으로 컬러 표시를 행하는 것에 한정되는 것은 아니다.

유기 EL 표시 패널의 컬러화에는 주로 3개의 방식이 있고, 색 변환 방식은 이 중 하나이다. 발광층으로서 청색만의 단층을 형성하면 좋고, 풀 컬러화에 필요한 나머지의 녹색과 적색은, 청색광으로부터 색 변환에 의해서 만들어낸다. 따라서, RGB의 각 층을 나누어 칠할 필요가 없고, RGB의 각 색의 유기 EL 재료를 구비할 필요가 없다고 하는 이점이 있다. 색 변환 방식은, 나누어 칠하는 방식과 같이 양품을 저하가 없다. 본 발명의 EL 표시 패널 등은 이 어느 쪽의 방식도 적용 가능하다.

또한, 3원색 이외에, 백색 발광의 화소를 형성하더라도 좋다. 백색 발광의 화소는 R, G, B 발광의 구조를 적층함으로써 제작(형성 또는 구성)함으로써 실현할 수 있다. 1 세트의 화소는, RGB의 3원색과, 백색 발광의 화소(16W)로 이루어진다. 백색 발광의 화소를 형성함으로써, 백색의 피크 휘도가 표현하기 용이하게 된다. 따라서, 밝기가 선명한 화상 표시를 실현할 수 있다.

RGB 등의 3원색을 1 세트의 화소를 하는 경우이더라도, 각 색의 화소 전극의 면적을 상이하게 한 것이 바람직하다. 물론, 각 색의 발광 효율이 벨런스 좋고, 색 순도도 벨런스가 좋으면, 동일 면적이라도 무방하다. 그러나, 하나 또는 복수의 색의 벨런스가 나쁘면, 화소 전극의 발광 면적을 조정하는 것이 바람직하다. 각 색의 전극 면적은 전류 밀도를 기준으로 결정하면 좋다. 즉, 색 온도가 7000 K(켈빈) 이상 12000K 이하의 범위에서, 화이트 벨런스를 조정하였을 때, 각 색의 전류 밀도의 차가 ±30% 이내로 되도록 한다. 더욱 바람직하게는 ±15% 이내로 되도록 한다. 예를 들면, 전류 밀도가 100A/평방미터라고 하면, 3원색이 모두 70A/평방미터 이상 130A/평방미터 이하로 되도록 한다. 더욱 바람직하게는, 3원색이 모두 85 A/평방미터 이상 115A/평방미터 이하로 되도록 한다.

유기 EL(15)은 자기 발광 소자이다. 이 발광에 의한 광이 스위칭 소자로서의 트랜지스터에 입사하면 핫 컨덕터(hot conductor) 현상이 발생한다. 핫 컨덕터란, 광 여기에 의해 트랜지스터 등의 스위칭 소자의 오프 시에서의 리크(오프 리크)가 증대하는 현상을 말한다.

이 과제에 대처하기 위해서, 본 발명에서는 게이트 드라이버(12)(경우에 따라서는 소스 드라이버(14))의 하층, 화소 트랜지스터(11)의 하층에 차광막을 형성하고 있다. 차광막은 크롬 등의 금속 박막으로 형성하여, 그 막 두께는 50nm 이상 150nm 이하로 한다. 막 두께가 얇으면 차광 효과가 모자라고, 두꺼우면 요철이 발생하여 상층의 트랜지스터(11a)의 패터닝이 곤란하게 된다.

차광막 상에 20nm 이상 100nm 이하의 무기 재료로 이루어지는 평활화막을 형성한다. 이 차광막의 레이어(layer)를 이용하여 축적 용량(19)의 한쪽 전극을 형성하더라도 좋다. 이 경우, 평활막은 매우 얇게 하여 축적 용량의 용량값을 크게 하는 것이 바람직하다. 또한, 차광막을 알루미늄으로 형성하고, 양극 산화 기술을 이용하여 산화 실리콘막을 차광막의 표면에 형성하며, 이 산화 실리콘막을 축적 용량(19)의 유전체막으로서 이용하더라도 좋다. 평활화막 상에는 하이 애피치(HA) 구조의 화소 전극이 형성된다.

드라이버 회로(12) 등은 이면 뿐만 아니라, 표면으로부터의 광의 진입도 억제해야 한다. 핫 컨덕터 현상의 영향에 의해 오동작하기 때문이다. 따라서, 본 발명에서는, 캐소드 전극이 금속막의 경우에는, 드라이버(12) 등의 표면에도 캐소드 전극을 형성하여, 이 전극을 차광막으로서 이용하고 있다.

그러나, 드라이버(12)의 위에 캐소드 전극을 형성하면, 이 캐소드 전극부터의 전계에 의한 드라이버의 오동작 혹은 캐소드 전극과 드라이버 회로의 전기적 접촉이 발생할 가능성이 있다. 이 과제에 대처하기 위해서, 본 발명에서는 드라이버 회로(12) 등의 위에 적어도 1층, 바람직하게는 복수 층의 유기 EL 막을 화소 전극상의 유기 EL 막 형성과 동시에 형성한다.

기본적으로 유기 EL 막은 절연물이므로, 드라이버 상에 유기 EL 막을 형성함으로써, 캐소드와 드라이버 사이가 격리된다. 따라서, 전술의 과제를 해소할 수 있다.

화소의 1개 이상의 트랜지스터(11)의 단자간 혹은 트랜지스터(11)와 신호선이 단락하면, EL 소자(15)가 상시, 점등하는 것으로 되어, 이러한 화소가 휘점으로 되는 경우가 있다. 이 휘점은 시각적으로 눈에 띄기 때문에 흑점화(비점등)할 필요가 있다. 휘점에 대해서는, 해당 화소(16)를 검출하여, 콘덴서(19)에 레이저 광을 조사하여 콘덴서의 단자간을 단락시킨다. 따라서, 콘덴서(19)에는 전하를 유지할 수 없게 되므로, 트랜지스터(11a)는 전류를 흘리지 않게 할 수 있다.

또, 레이저 광을 조사하는 위치에 상당하는 캐소드막을 제거해 놓는 것이 바람직하다. 레이저 조사에 의해, 콘덴서(19)의 단자 전극과 캐소드막이 쇼트하는 것을 방지하기 위해서이다.

화소(16)의 트랜지스터(11)의 결합은, 드라이버 회로(14) 등에도 영향을 준다. 예컨대, 도 56에서는 구동용 트랜지스터(11a)에 소스-드레인(SD) 쇼트(562)가 발생하고 있으면, 패널의 Vdd 전압이 소스 드라이버(14)에 인가된다. 따라서, 소스 드라이버(14)의 전원 잔압은, 패널의 전원 전압 Vdd와 동일하거나 또는 높게 해 놓는 것이 바람직하다. 또, 소스 드라이버(14)에서 사용하는 기준 전류는 전자 불륨(561)에서 조정할 수 있도록 구성해 놓은 것이 바람직하다.

트랜지스터(11a)에 SD 쇼트(562)가 발생하고 있으면, EL 소자(15)에 과대한 전류가 흐른다. 즉, EL 소자(15)가 상시 점등 상태(휘점)로 된다. 휘점은 결합으로서 눈에 띄기 쉽다. 예를 들면, 도 56에 있어서, 트랜지스터(11a)의 소스-드레인(SD) 쇼트가 발생하고 있으면, 트랜지스터(11a)의 게이트(G) 단자 전위의 대소에 관계없이, Vdd 전압으로부터 EL 소자(15)에 전류가 상시 흐른다(트랜지스터(11d)가 온인 때). 따라서, EL 소자(15)가 휘점으로 된다.

또한, 트랜지스터(11a)에 SD 셀트가 발생하고 있으면, 트랜지스터(11c)가 온 상태인 때, Vdd 전압이 소스 신호선(18)에 인가되어 소스 드라이버(14)에 Vdd 전압이 인가된다. 만약 소스 드라이버(14)의 전원 전압이 Vdd 이하이면, 내압을 초과하여, 소스 드라이버(14)가 파괴될 우려가 있다. 그 때문에, 소스 드라이버(14)의 전원 전압은 Vdd 전압(패널이 높은 쪽의 전압) 이상으로 하는 것이 바람직하다.

트랜지스터(11a)의 SD 셀트 등은, 점 결합으로 머물지 않고, 패널의 소스 드라이버의 파괴로 이어질 우려가 있고, 또한, 휘점은 눈에 띄기 때문에 패널로서는 불량으로 된다. 따라서, 트랜지스터(11a)와 EL 소자(15) 사이를 접속하는 배선을 절단하여, 휘점을 흑점 결합으로 할 필요가 있다. 이 절단에는, 레이저 광 등의 광학 수단을 이용하여 절단하면 좋다.

또, 이상의 실시예는 배선을 절단시킨다고 하였지만, 흑 표시하기 위해서는 이것에 한정되는 것은 아니다. 예를 들면, 도 1에서도 알 수 있는 바와 같이, 트랜지스터(11a)의 전원 Vdd가, 트랜지스터(11a)의 게이트(G) 단자에 상시 인가되도록 수정하더라도 좋다. 예를 들면, 콘덴서(19)의 2개의 전극간을 셀트시키면, Vdd 전압이 트랜지스터(11a)의 게이트(G) 단자에 인가되게 된다. 따라서, 트랜지스터(11a)는 완전히 오프 상태로 되어, EL 소자(15)에 전류를 흘리지 않게 할 수 있다. 이것은, 콘덴서(19)에 레이저 광을 조사함으로써 콘덴서 전극을 셀트할 수 있기 때문에, 용이하게 실현할 수 있다.

또한, 실제로는, 화소 전극의 하층에 Vdd 배선이 배치되어 있으므로, Vdd 배선과 화소 전극에 레이저 광을 조사함으로써, 화소의 표시 상태를 제어(수정)할 수 있다.

그 외에, 트랜지스터(11a)의 SD간(채널)을 오픈으로 하는 것도 실현할 수 있다. 간단하게는 트랜지스터(11a)에 레이저 광을 조사하여, 트랜지스터(11a)의 채널을 오픈으로 한다. 마찬가지로, 트랜지스터(11d)의 채널을 오픈으로 해도 좋다. 물론, 트랜지스터(11b)의 채널을 오픈으로 한 경우, 해당 화소(16)가 선택되지 않기 때문에, 흑 표시로 된다.

화소(16)를 흑 표시로 하기 위해서는, EL 소자(15)를 열화시키더라도 좋다. 예를 들면, 레이저 광을 EL 층(15)에 조사하여, EL 층(15)을 물리적으로 혹은 화학적으로 열화시켜, 발광하지 않도록 한다(상시 흑 표시). 레이저 광의 조사에 의해 EL 층(15)을 가열하여, 용이하게 열화시킬 수 있다. 또한, 엑시머 레이저를 이용하면, EL 막(15)의 화학적 변화를 용이하게 실행할 수 있다.

또, 이상의 실시예는, 도 1에 도시한 화소 구성을 예시하였지만, 본 발명은 이것에 한정하는 것은 아니다. 레이저 광을 이용하여 배선 혹은 전극을 오픈 혹은 셀트시키는 것은, 커런트 미러 등의 다른 전류 구동의 화소 구성 혹은 도 62, 도 51 등에 도시되어 있는 전압 구동의 화소 구성으로서도 적용할 수 있는 것은 말할 필요도 없다.

이하, 도 1에 나타내는 화소 구성에 대해, 그 구동 방법에 대해 설명을 한다. 도 1에 도시하는 바와 같이, 게이트 신호선(17a)은 행 선택 기간에 도통 상태(여기서는 도 1의 트랜지스터(11)가 p 채널 트랜지스터이기 때문에 로우 레벨로 도통으로 됨)로 되고, 게이트 신호선(17b)은 비선택 기간 시에 도통 상태로 한다.

소스 신호선(18)에는 기생 용량(도시하지 않음)이 존재한다. 기생 용량은, 소스 신호선(18)과 게이트 신호선(17)의 크로스 부의 용량, 트랜지스터(11b, 11c)의 채널 용량 등에 의해 발생한다.

소스 신호선(18)의 전류값 변화에 요하는 시간  $t$ 는, 기생 용량의 크기를  $C$ , 소스 신호선(18)의 전압을  $V$ , 소스 신호선(18)에 흐르는 전류를  $I$ 라고 하면  $t = C \cdot V / I$ 이다. 그 때문에, 전류값을 10배 크게 하는 것에 의해 전류값 변화에 요하는 시간을 10분의 1 가까이까지 짧게 할 수 있다. 또는 소스 신호선(18)의 기생 용량이 10배로 되어도 소정의 전류값으로 변화시킬 수 있다는 것을 나타내고 있다. 따라서, 짧은 수평 주사 기간 내에 소정의 전류값을 기입하기 위해서는 전류값을 증가시키는 것이 유효하다.

또, 소스 신호선(18)의 기생 용량의 총/방전을 행하기 위해서는,  $I > (C \cdot V) / t$ 의 관계를 충족하는 전류값  $I$ 를 소스 신호선(18)에 흘리게 하면 좋다.

그런데, 입력 전류를 10배로 하면 출력 전류도 10배로 된다. 그러나, 이 경우, EL의 휘도도 10배로 되기 때문에, 소정의 휘도를 얻을 수 없다. 그래서, 본 발명에서는, 도 1의 트랜지스터(17d)의 도통 기간을 종래의 10분의 1로 하고, EL 소자(15)의 발광 기간을 10분의 1로 함으로써, 소정의 휘도를 실현하도록 하였다.

즉, 소스 신호선(18)의 기생 용량의 총/방전을 충분히 실행하여, 소정의 전류값을 화소(16)의 트랜지스터(11a)에 프로그램하기 위해서는, 소스 드라이버(14)로부터 비교적 큰 전류를 출력할 필요가 있다. 그러나, 이와 같이 큰 전류를 소스 신호선

(18)에 훌리면 이 전류값이 화소에 프로그램되게 되어, 소정의 전류에 대해 큰 전류가 EL 소자(15)에 흐른다. 예를 들면, 10배의 전류로 프로그램하면, 당연, 10배의 전류가 EL 소자(15)에 흘러, EL 소자(15)는 10배의 휘도로 발광한다. 소정의 발광 휘도로 하기 위해서는, EL 소자(15)에 흐르는 시간을 1/10으로 하면 좋다. 이와 같이 구동함으로써, 소스 신호선(18)의 기생 용량을 충분히 충/방전할 수 있어, 소정의 발광 휘도를 얻을 수 있다.

또, 10배의 전류값을 화소의 트랜지스터(11a)(정확하게는 콘덴서(19)의 단자 전압을 설정하고 있음)에 기입하여, EL 소자(15)의 온 시간을 1/10으로 한다고 하였지만 이것은 일례이다. 경우에 따라서는, 10배의 전류값을 화소의 트랜지스터(11a)에 기입하여, EL 소자(15)의 온 시간을 1/5로 해도 좋다. 또한, 10배의 전류값을 화소의 트랜지스터(11a)에 기입하여, EL 소자(15)의 온 시간을 1/2배로 하는 경우도 있을 것이다.

본 발명은, 화소로의 기입 전류를 소정값 이외의 값으로 하여, EL 소자(15)에 흐르는 전류를 간헐 상태로 하여 구동하는 것에 특징이 있다. 본 명세서에서는 설명을 용이하게 하기 위해서, 소정의 전류의 N배의 전류를 화소의 트랜지스터(11)에 기입하여, EL 소자(15)의 온 시간을 1/N배로 하는 것으로 하여 설명한다. 그러나, 이것에 한정하는 것은 아니고, N배의 전류를 화소의 트랜지스터(11)에 기입하여, EL 소자(15)의 온 시간을 1/(N2)배(N과 N2는 상이함)로도 되는 것은 말할 필요도 없다.

여기서, 상기 소정의 전류란, 화상 신호가 나타내는 계조 표시를 실현하기 위해서 필요하게 되는 전류이다. 이 소정의 전류의 전류값은, EL 표시 장치의 사양 등에 따라서 상이하지만, 예컨대 휘도 150nt를 실현하는 경우에는 0.25~0.75 $\mu$ A 정도이다. 따라서, N=4의 경우이면, 트랜지스터(11)에 기입되는 전류값은 1~3 $\mu$ A 정도로 된다. 마찬가지로 해서, N=8의 경우이면 상기 전류값은 2~6 $\mu$ A로 되고, N=2의 경우이면 상기 전류값은 0.5~1.5 $\mu$ A로 된다.

또, 간헐하는 간격은 등간격으로 한정하는 것은 아니다. 예를 들면, 랜덤하게 해도 좋다(전체로서, 표시 기간 또는 비표시 기간이 소정값(일정 비율)으로 되면 좋음). 또한, RGB에서 상이하더라도 좋다. 즉, 백(화이트) 밸런스가 최적으로 되도록, R, G, B 표시 기간 또는 비표시 기간이 소정값(일정 비율)으로 되도록 조정(설정)하면 좋다.

또한, 설명을 용이하게 하기 위해서, 1/N이란, 1F(1 필드 또는 1 프레임 기간)를 기준으로 하여 이 1F를 1/N으로 하는 것으로 하여 설명한다. 그러나, 1 화소 행이 선택되어, 전류값이 프로그램되는 시간(통상, 1 수평 주사 기간(IH))이 있고, 또한, 주사 상태에 따라서는 오차도 발생한다. 따라서, 이상의 설명은 어디까지나 설명을 용이하게 하기 위한 편의상의 문제일 뿐이며, 이것에 한정하는 것은 아니다.

예를 들면, N=10배의 전류로 화소(16)에 전류를 프로그램하여, 1/5의 기간 동안, EL 소자(15)를 점등시키더라도 좋다. EL 소자(15)는, 10/5=2배의 휘도로 점등한다. 반대로, N=2배의 전류로 화소(16)에 전류를 프로그램하여, 1/4의 기간 동안, EL 소자(15)를 점등시켜도 좋다. EL 소자(15)는, 2/4=0.5배의 휘도로 점등한다. 즉, 본 발명은, N=1배가 아닌 전류로 프로그램하고, 또한, 상시 점등(1/1, 즉, 간헐 구동이 아님) 상태 이외의 표시를 실시하는 것이다. 또한, 넓은 의미로는, EL 소자(15)에 공급하는 전류를 1 프레임(혹은 1 필드)의 기간에 있어서, 적어도 1회, 오프로 하는 구동 방식이다. 또한, 소정값보다도 큰 전류를 화소(16)에 프로그램하여, 적어도, 간헐 표시를 실시하는 구동 방식이다.

유기(무기) EL 표시 장치는, CRT와 같이 전자총으로 선 표시의 집합으로서 화상을 표시하는 디스플레이와는 표시 방법이 기본적으로 상이한 점에도 문제가 있다. 즉, EL 표시 장치에서는, 1F(1 필드 혹은 1 프레임)의 기간의 사이는, 화소에 기입한 전류(전압)를 유지한다. 그 때문에, 동화상 표시를 행하면 표시 화상의 흐릿한 윤곽이 발생한다고 하는 과제가 발생한다.

본 발명에서는, 1F/N의 기간의 동안만, EL 소자(15)에 전류를 훌리고, 다른 기간(IF(N-1)/N)에는 전류를 훌리지 않는다. 이 구동 방식을 실시하여 화면의 일점을 관측한 경우를 생각한다. 이 표시 상태에서는 1F마다 화상 데이터 표시, 혹은 표시(비점등)가 반복하여 표시된다. 즉, 화상 데이터의 표시 상태가 시간적으로 띄엄띄엄 표시(간헐 표시) 상태로 된다. 동화상 데이터 표시를, 이 간헐 표시 상태에서 보면 화상의 흐릿한 윤곽이 없어져 양호한 표시 상태를 실현할 수 있다. 즉, CRT에 가까운 동화상 표시를 실현할 수 있다. 또한, 간헐 표시를 실현하지만, 회로의 메인 클럭은 종래와 변함이 없다. 따라서, 회로의 소비 전력이 증가하는 것도 없다.

액정 표시 패널의 경우는, 광 변조를 하는 화상 데이터(전압)는 액정층에 유지된다. 따라서, 흑 삽입 표시를 실시하고자 하면 액정층에 인가하고 있는 데이터를 리라이트할 필요가 있다. 그 때문에, 소스 드라이버(14)의 동작 클럭을 높게 하여, 화상 데이터와 흑 표시 데이터를 교대로 소스 신호선(18)에 인가할 필요가 있다. 따라서, 흑 삽입(흑 표시 등의 간헐 표시)을 실현하고자 하면 회로의 메인 클럭을 높일 필요가 있다. 또한, 시간축 신장을 실시하기 위한 화상 메모리도 필요하게 된다.

도 1, 도 2, 및 도 38 등에 나타내는 본 발명의 EL 표시 패널의 화소 구성에서는, 화상 데이터는 콘텐서(19)에 유지되어 있다. 이 콘텐서(19)의 단자 전압에 대응하는 전류를 EL 소자(15)에 흘린다. 따라서, 화상 데이터는 액정 표시 패널과 같이 광변조층에 유지되어 있는 것은 아니다.

본 발명은 스위칭의 트랜지스터(11d), 혹은 트랜지스터(11e) 등을 온/오프시키는 것만으로 EL 소자(15)에 흘리는 전류를 제어한다. 즉, EL 소자(15)에 흐르는 전류  $I_w$ 를 오프로 하더라도, 화상 데이터는 그대로 콘텐서(19)에 유지되어 있다. 따라서, 다음 타이밍에서 스위칭 소자(11d) 등을 온시켜, EL 소자(15)에 전류를 흘리면, 그 흐르는 전류는 전에 흐르고 있던 전류값과 동일하다. 본 발명에서는 흑 삽입(흑 표시 등의 간헐 표시)을 실현할 때에 있어서도, 회로의 메인 클럭을 올릴 필요가 없다. 또한, 시간축 신장을 실시할 필요도 없기 때문에 화상 메모리도 불필요하다. 또한, 유기 EL 소자(15)는 전류를 공급하고 나서 발광하기까지의 시간이 짧고, 고속으로 응답한다. 그 때문에, 동화상 표시에 적합하고, 또한 간헐 표시를 실시함으로써, 종래의 데이터 유지형의 표시 패널(액정 표시 패널, EL 표시 패널 등)의 문제인 동화상 표시의 문제를 해결할 수 있다.

또한, 대형의 표시 장치에서 소스 용량이 커지는 경우는 소스 전류를 10배 이상으로 해 주면 좋다. 일반적으로 소스 전류값을  $N$ 배로 한 경우, 게이트 신호선(17b)(트랜지스터(11d))의 도통 기간을 1F/N으로 하면 좋다. 이에 따라 텔레비전, 모니터용의 표시 장치 등에도 적용이 가능하다.

이하, 도면을 참조하면서, 본 발명의 구동 방법에 대해 더 상세하게 설명을 한다. 소스 신호선(18)의 기생 용량은, 이웃하는 소스 신호선(18) 사이의 결합 용량, 소스 드라이브 IC(회로)(14)의 버퍼 출력 용량, 게이트 신호선(17)과 소스 신호선(18)의 크로스 용량 등에 의해 발생한다. 이 기생 용량은 통상  $10\text{pF}$  이상으로 된다. 전압 구동의 경우는, 드라이버 IC(14)로부터는 저 임피던스로 전압이 소스 신호선(18)에 인가되기 때문에, 기생 용량이 다소 크더라도 구동에는 문제로 되지 않는다.

그러나, 전류 구동에서는 특히 흑 레벨의 화상 표시에서는  $20\text{nA}$  이하의 미소 전류로 화소의 콘텐서(19)를 프로그램할 필요가 있다. 따라서, 기생 용량이 소정값 이상의 크기로 발생하면, 1 화소 행에 프로그램하는 시간(통상, 1H 이내, 단, 2 화소 행을 동시에 기입하는 경우도 있으므로 1H 이내에 한정되는 것이 아님) 내에 기생 용량을 충/방전할 수 없다. 그러나, 1H 기간에서 충/방전할 수 있게 되면, 화소로의 기입 부족으로 되어, 소망하는 해상도에서의 표시를 실현할 수 없다.

도 1의 화소 구성의 경우, 도 3의 (a)에 도시하는 바와 같이, 전류 프로그램 시는, 프로그램 전류  $I_w$ 가 소스 신호선(18)에 흐른다. 이 전류  $I_w$ 가 트랜지스터(11a)를 흘려, 전류  $I_w$ 를 흐르는 전압이 유지되도록, 콘텐서(19)에 전압 설정(프로그램)된다. 이 때, 트랜지스터(11d)는 오픈 상태(오프 상태)이다.

다음에, EL 소자(15)에 전류를 흘리는 기간은 도 3의 (b)와 같이, 트랜지스터(11c, 11b)가 오프하여, 트랜지스터(11d)가 동작한다. 즉, 게이트 신호선(17a)에 오프 전압( $V_{gh}$ )이 인가되어, 트랜지스터(11b, 11c)가 오프한다. 한편, 게이트 신호선(17b)에 온 전압( $V_{gl}$ )이 인가되어, 트랜지스터(11d)가 온한다.

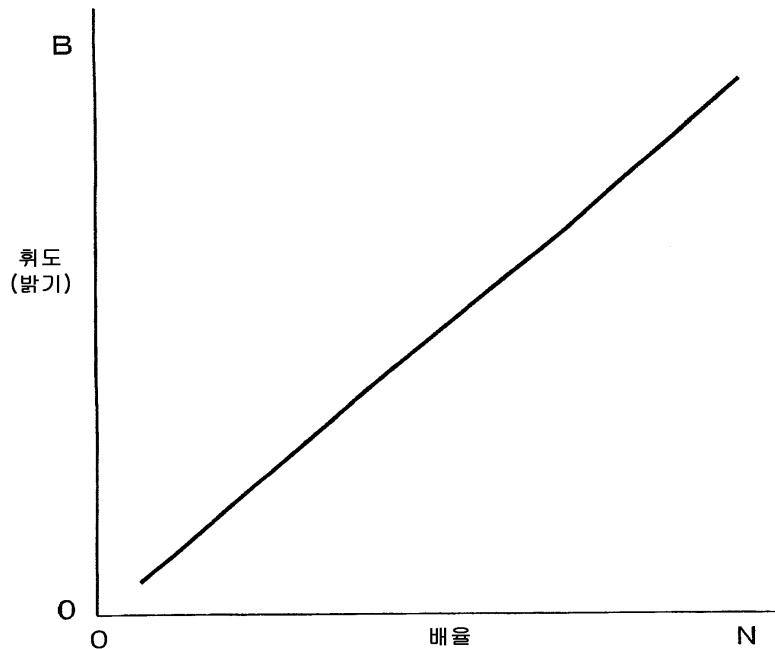

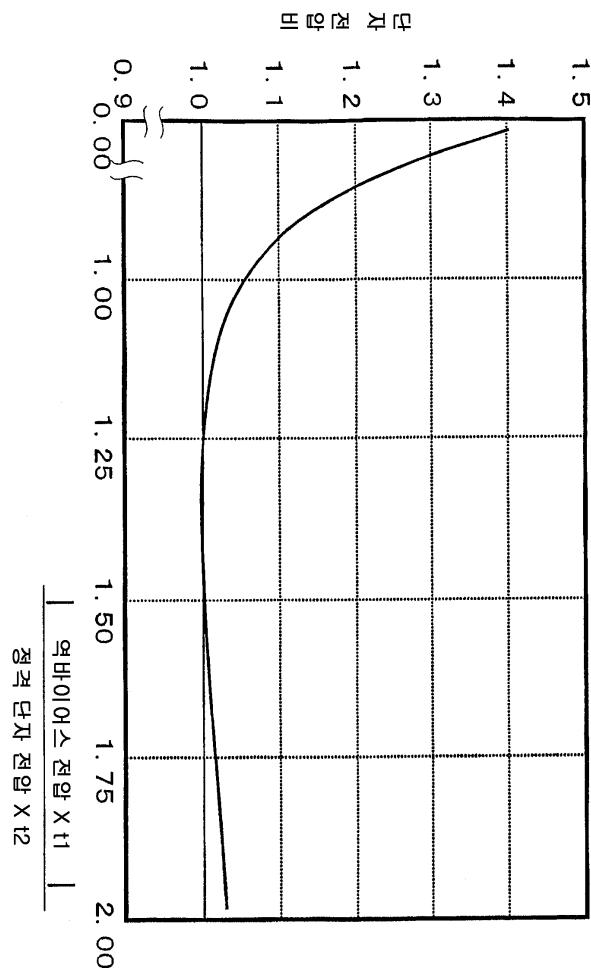

현재, 전류  $I_w$ 가 본래 흐를 전류(소정값)의 10배라고 하면, 도 3의 (b)의 EL 소자(15)에 흐르는 전류도 소정값의 10배로 된다. 따라서, 소정값의 10배의 휘도로 EL 소자(15)는 발광하는 것으로 된다. 즉, 도 12에 도시하는 바와 같이, 배율  $N$ 을 높게 할수록, 표시 패널의 표시 휘도  $B$ 도 높게 된다. 따라서, 휘도와 배율이란 비례 관계로 된다. 한편,  $1/N$ 로 구동함으로써, 휘도와 배율은 반비례의 관계로 된다.

그래서, 트랜지스터(11d)를 본래 온하는 시간(약 1F)의  $1/N$ 의 기간만큼 온시키고, 다른 기간 ( $(N-1)/N$ ) 기간은 오프시키면, 1F 전체의 평균 휘도는 소정의 휘도로 된다. 이 표시 상태는, CRT가 전자총으로 화면을 주사하고 있는 것에 근사한다. 상이한 점은, 화상을 표시하고 있는 범위가 화면 전체의  $1/N$ (전체 화면을 1로 한함이 점등하고 있는 점이다(CRT에서는, 점등하고 있는 범위는 1 화소 행(엄밀하게는 1 화소)임).

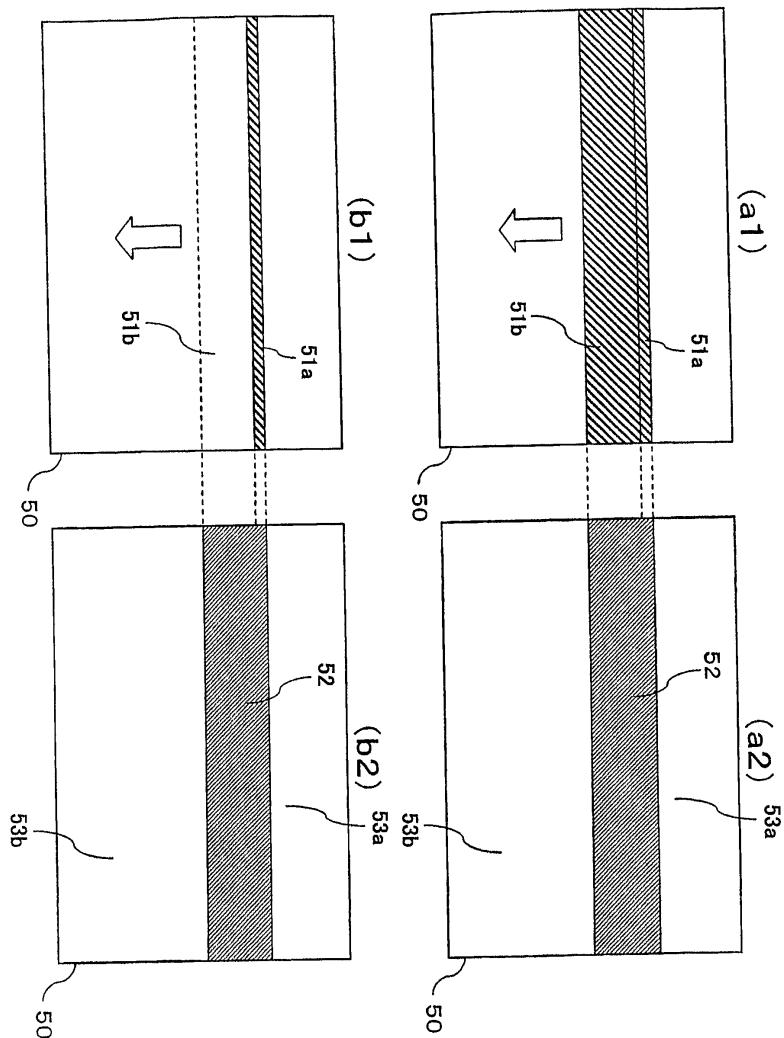

본 발명에서는, 이  $1/N$ 의 화상 표시 영역(53)이 도 13의 (b)에 도시하는 바와 같이 화면(50)의 위로부터 밑으로 이동한다. 본 발명에서는, 1F/N의 기간 동안에만, EL 소자(15)에 전류가 흐르고, 다른 기간 ( $(1F \cdot (N-1))/N$ )은 전류가 흐르지 않는다. 따라서, 각 화소는 간헐 표시로 된다. 그러나, 인간의 눈에는 잔상에 의해 화상이 유지된 상태로 되기 때문에, 전체 화면이 균일하게 표시되어 있는 것과 같이 보인다.

또, 도 13에 도시하는 바와 같이, 기입 화소 행(51a)은 비점등 표시(52a)로 한다. 그러나, 이것은, 도 1, 도 2 등의 화소 구성의 경우이다. 도 38 등에서 도시하는 커런트 미러의 화소 구성에서는, 기입 화소 행(51a)은 점등 상태로 해도 좋다. 그러나, 본 명세서에서는, 설명을 용이하게 하기 위해서, 주로, 도 1의 화소 구성을 예시하여 설명을 한다. 또한, 도 13, 도 16 등의 소정 구동 전류 Iw보다도 큰 전류로 프로그램하여, 간헐 구동하는 구동 방법을 N배 펠스 구동이라고 부른다.

이 표시 상태에서는 1F마다 화상 데이터 표시, 혹 표시(비점등)가 반복 표시된다. 즉, 화상 데이터의 표시 상태가 시간적으로 띄엄띄엄 표시(간헐 표시) 상태로 된다. 액정 표시 패널(및 본 발명 이외의 EL 표시 패널)에서는, 1F의 기간, 화소에 데이터가 유지되어 있기 때문에, 동화상 표시의 경우는 화상 데이터가 변화하더라도 그 변화에 추종할 수 없고, 흐릿한 동화상으로 되어 있었다(화상의 흐릿한 윤곽). 그러나, 본 발명에서는 화상을 간헐 표시하기 위해서, 화상의 흐릿한 윤곽이 없어져 양호한 표시 상태를 실현할 수 있다. 즉, CRT에 가까운 동화상 표시를 실현할 수 있다.

이 타이밍차트를 도 14에 나타낸다. 또, 본 발명 등에 있어서, 특히 설명을 하지 않을 때의 화소 구성은 도 1에 나타낸 것이다. 도 14에서 알 수 있는 바와 같이, 각 선택된 화소 행(선택 기간은, 1H로 하고 있음)에 있어서, 게이트 신호선(17a)에 온 전압(Vgl)이 인가되어 있는 때(도 14의 (a)를 참조)에는, 게이트 신호선(17b)에는 오프 전압(Vgh)이 인가되어 있다(도 14의 (b)를 참조). 이 기간은, EL 소자(15)에는 전류가 흐르고 있지 않다(점등 상태). 한편, 선택되어 있지 않은 화소 행에 있어서는, 게이트 신호선(17a)에 오프 전압(Vgh)이 인가되고, 게이트 신호선(17b)에는 온 전압(Vgl)이 인가되어 있다. 이 기간은, EL 소자(15)에 전류가 흐르고 있다(점등 상태). 또한, 점등 상태에서는, EL 소자(15)는 소정의 N배의 휘도(N·B)로 점등하고, 그 점등 기간은 1F/N이다. 따라서, 1F를 평균한 표시 패널의 표시 휘도는,  $(N \cdot B) \times (1/N) = B$ (소정 휘도)로 된다.

도 15는, 도 14의 동작을 각 화소 행에 적용한 실시예이다. 게이트 신호선(17)에 인가하는 전압 파형을 나타내고 있다. 전압 파형은 오프 전압을 Vgh(H 레벨)로 하고, 온 전압을 Vgl(L 레벨)로 하고 있다. (1), (2) 등의 첨자는 선택하고 있는 화소 행의 행 번호를 나타내고 있다.

도 15에 있어서, 게이트 신호선(17a)(1)가 선택되고(Vgl 전압), 선택된 화소 행의 트랜지스터(11a)로부터 소스 드라이버(14)로 향하여 소스 신호선(18)에 프로그램 전류가 흐른다. 이 프로그램 전류는 소정값의 N배(설명을 용이하게 하기 위해서, N=10으로 하여 설명함. 물론, 소정값이란 화상을 표시하는 데이터 전류이므로, 백 래스터 표시 등이 아닌 한 고정값이 아님)이다. 따라서, 콘덴서(19)에는 10배의 전류가 트랜지스터(11a)에 흐르도록 프로그램된다. 화소 행(1)이 선택되어 있을 때에는, 도 1의 화소 구성에서는 게이트 신호선(17b)(1)은 오프 전압(V9h)이 인가되어, EL 소자(15)에는 전류가 흐르지 않는다.

1H 후에는, 게이트 신호선(17a)(2)가 선택되어(Vgl 전압), 선택된 화소 행의 트랜지스터(11a)로부터 소스 드라이버(14)로 향하여 소스 신호선(18)에 프로그램 전류가 흐른다. 이 프로그램 전류는 소정값의 N배(설명을 용이하게 하기 위해서, N=10으로서 설명함)이다. 따라서, 콘덴서(19)에는 10배의 전류가 트랜지스터(11a)에 흐르도록 프로그램된다. 화소 행(2)이 선택되어 있는 때에는, 도 1의 화소 구성에서는 게이트 신호선(17b)(2)은 오프 전압(V9h)이 인가되어, EL 소자(15)에는 전류가 흐르지 않는다. 그러나, 전면의 화소 행(1)의 게이트 신호선(17a)(1)에는 오프 전압(Vgh)이 인가되고, 게이트 신호선(17b)(1)에는 온 전압(Vgl)이 인가되기 때문에, 점등 상태로 되어 있다.

다음의 1H 후에는, 게이트 신호선(17a)(3)이 선택되어, 게이트 신호선(17b)(3)은 오프 전압(Vgh)이 인가되어, 화소 행(3)의 EL 소자(15)에는 전류가 흐르지 않는다. 그러나, 이전의 화소 행(1)(2)의 게이트 신호선(17a)(1)(2)에는 오프 전압(V9h)이 인가되어, 게이트 신호선(17b)(1)(2)에는 온 전압(Vgl)이 인가되기 때문에, 점등 상태로 되어 있다.

이상의 동작을 1H의 동기 신호에 동기하여 화상을 표시하여 간다. 그러나, 도 15의 구동 방식에서는, EL 소자(15)에는 10배의 전류가 흐른다. 따라서, 표시 화면(50)은 약 10배의 휘도로 표시된다. 물론, 이 상태에서 소정의 휘도 표시를 행하기 위해서는, 프로그램 전류를 1/10으로 해 두면 되는 것은 말할 필요도 없다. 그러나, 1/10의 전류이면 기생 용량 등에 의해 기입 부족이 발생하기 때문에, 높은 전류로 프로그램하여, 혹 화면(52)의 삽입에 의해 소정의 휘도를 얻는 것이 본 발명의 기본적인 주지이다.

그런데, 본 발명의 구동 방법에 있어서는, 소정 전류보다도 높은 전류가 EL 소자(15)에 흐르도록 하고, 소스 신호선(18)의 기생 용량을 충분히 충/방전하는 것이 요점이다. 따라서, EL 소자(15)에 소정 전류의 N배의 전류를 흘리지 않더라도 좋다. 예를 들면, EL 소자(15)에 병렬로 전류 경로를 형성하여(더미의 EL 소자를 형성하고, 이 EL 소자는 차광막을 형성하여 발광시키지 않는 등의 처리를 실시함), 더미 EL 소자와 EL 소자(15)로 나누어 전류를 흘리더라도 좋다. 예를 들면, 신호 전류가  $0.2\mu A$ 인 때, 프로그램 전류를  $2.2\mu A$ 로 하여, 트랜지스터(11a)에는  $2.2\mu A$ 를 흘린다. 이 전류 중, 신호 전류  $0.2\mu A$ 를 EL

소자(15)에 흘려,  $2\mu\text{A}$ 를 더미의 EL 소자에 흘리는 등의 방식이 예시된다. 즉, 도 27의 더미 화소 행(281)을 상시 선택 상태로 한다. 또, 더미 화소 행은 발광시키지 않거나, 또는 차광막 등을 형성하여, 발광하고 있더라도 시각적으로 보이지 않도록 구성한다.

이상과 같이 구성함으로써, 소스 신호선(18)에 흘리는 전류를 N배로 증가시킴으로써, 구동용 트랜지스터(11a)에 소정 전류의 N배의 전류가 흐르도록 프로그램할 수 있고, 또한, EL 소자(15)에는, 상기 N배의 전류보다는 충분히 작은 전류를 흘릴 수 있는 것으로 된다. 이상의 방법에서는, 도 5에 도시하는 바와 같이, 비점등 영역(52)을 마련하는 일없이, 전체 표시 영역(50)을 화상 표시 영역(53)으로 할 수 있다.

도 13의 (a)는 표시 화면(50)로의 기입 상태를 도시하고 있다. 도 13의 (a)에 있어서, (51a)는 기입 화소 행이다. 소스 드라이버(14)로부터 각 소스 신호선(18)에 프로그램 전류가 공급된다. 또, 도 13 등에서는 1H 기간에 기입하는 화소 행은 1행이다. 그러나, 어느 것도 1H에 한정하는 것은 아니고, 0.5H이어도 좋고, 2H 기간이어도 좋다. 또한, 소스 신호선(18)에 프로그램 전류를 기입한다고 하였지만, 본 발명은 전류 프로그램 방식으로 한정하는 것은 아니고, 소스 신호선(18)에 기입되는 것이 전압인 전압 프로그램 방식(도 62 등)이어도 좋다.

도 13의 (a)에 있어서, 게이트 신호선(17a)이 선택되면 소스 신호선(18)에 흐르는 전류가 트랜지스터(11a)에 프로그램된다. 이 때, 게이트 신호선(17b)에는 오프 전압이 인가되고, 그 결과 EL 소자(15)에는 전류가 흐르지 않는다. 이것은, 트랜지스터(11d)가 온 상태이면, 소스 신호선(18)으로부터 EL 소자(15)의 용량 성분이 나타나고, 이 용량에 영향받아 콘덴서(19)에 충분히 정확한 전류 프로그램을 할 수 없게 되기 때문이다. 따라서, 도 1에 나타내는 구성을 예로 하면, 도 13의 (b)에서 도시하는 바와 같이, 전류가 기입되어 있는 화소 행은 비점등 영역(52)으로 된다.

지금, N(여기서는, 앞서 서술한 바와 같이 N=10으로 함)배의 전류로 프로그램한 것으로 하면, 화면의 휙도는 10배로 된다. 따라서, 표시 영역(50)의 90%의 범위를 비점등 영역(52)으로 하면 좋다. 따라서, 화상 표시 영역의 수평 주사선이 QCIF (Quarter Common Intermediate Format)의 220개(S= 220)로 하면, 22개를 표시 영역(53)으로 하고, 220-22=198개를 비표시 영역(52)으로 하면 좋다. 일반적으로 서술하면, 수평 주사선의 개수(화소 행 수)를 S라고 하면, S/N의 영역을 표시 영역(53)으로 하여, 이 표시 영역(53)을 N배의 휙도로 발광시킨다. 그리고, 이 표시 영역(53)을 화면의 상하 방향으로 주사한다. 따라서, S(N-1)/N의 영역은 비점등 영역(52)으로 한다. 이 비점등 영역은 흑 표시(비발광)이다. 또한, 이 비발광 영역(52)은 트랜지스터(11d)를 오프시킴으로써 실현한다. 또, N배의 휙도로 점등시킨다고 하였지만, 당연한 것이지만 밝기 조정, 감마 조정에 의해 N배의 값으로 조정하는 것은 말할 필요도 없다.

또한, 이전의 실시예에서, 10배의 전류로 프로그램한 것으로 하면, 화면의 휙도는 10배로 되기 때문에, 표시 영역(50)의 90%의 범위를 비점등 영역(52)으로 하면 좋은 것으로 했다. 그러나, 이것은, RGB의 화소를 공통으로 비점등 영역(52)으로 하는 것에 한정하는 것은 아니다. 예컨대, R의 화소는, 1/8을 비점등 영역(52)으로 하고, G의 화소는, 1/6을 비점등 영역(52)으로 하며, B의 화소는, 1/10을 비점등 영역(52)과, 각각의 색에 의해 변화시키더라도 좋다. 또한, RGB의 색으로 개별적으로 비점등 영역(52)(혹은 점등 영역(53))을 조정할 수 있도록 하더라도 좋다. 이들을 실현하기 위해서는, R, G, B에서 개별의 게이트 신호선(17b)이 필요하게 된다. 그러나, 이상의 RGB의 개별 조정을 가능하게 하는 것에 의해, 화이트 밸런스를 조정하는 것이 가능하게 되어, 각 계조에 있어서 색의 밸런스 조정이 용이하게 된다(도 41의 것을 참조).

도 13의 (b)에 도시하는 바와 같이, 기입 화소 행(51a)을 포함하는 화소 행을 비점등 영역(52)으로 하고, 기입 화소 행(51a)보다도 상측 화면의 S/N(시간적으로는 1F/N)의 범위를 표시 영역(53)으로 한다(화면을 아래로부터 위로 주사하는 경우에는, 그 반대로 됨). 화상 표시 상태는, 표시 영역(53)이 띠 형상으로 되어, 화면의 위로부터 아래로 이동한다.

도 13의 표시에서는, 하나의 표시 영역(53)이 화면의 상 방향으로부터 하 방향으로 이동한다. 프레임 레이트가 낮으면, 표시 영역(53)이 이동하는 것이 시각적으로 인식된다. 특히, 눈꺼풀을 닫았을 때, 혹은 얼굴을 상하로 이동시켰을 때 등에 인식되기 쉽게 된다.

이 과제에 대해서는, 도 16에 도시하는 바와 같이, 표시 영역(53)을 복수로 분할하면 좋다. 이 분할된 총합이 S(N-1)/N의 면적으로 되면, 도 13의 밝기와 동등하게 된다. 또, 분할된 표시 영역(53)은 동등하게(등분으로) 할 필요는 없다. 또한, 마찬가지로 분할된 비표시 영역(52)도 동등하게 할 필요는 없다.

이상과 같이, 표시 영역(53)을 복수로 분할함으로써 화면의 깜빡거림은 감소한다. 따라서, 플리커의 발생은 없고, 양호한 화상 표시를 실현할 수 있다. 또, 분할은 더 잘게 하더라도 좋다. 그러나, 분할할수록 동화상 표시 성능은 저하하는 것으로 된다.

도 17은 게이트 신호선(17)의 전압 파형 및 EL의 발광 휘도를 도시하고 있다. 도 17에서 명백한 바와 같이, 게이트 신호선(17b)을 Vg1로 하는 기간(IF/N)을 복수로 분할(분할 수 K)하고 있다. 즉, Vg1로 하는 기간은 1F/(K/N)의 기간을 K회 실시한다. 이와 같이 제어하면, 플리커의 발생을 억제할 수 있어, 저 프레임 레이트의 화상 표시를 실현할 수 있다. 또한, 이 화상의 분할 수도 가변할 수 있도록 구성하는 것이 바람직하다. 예를 들면, 사용자가 밝기 조정 스위치를 누르는 것에 의해, 혹은 밝기 조정 볼륨을 높이는 것에 의해, 이 변화를 검출하여 K의 값을 변경하더라도 좋다. 또한, 사용자가 휘도를 조정하도록 구성하더라도 좋다. 표시할 화상의 내용, 데이터에 의해 수동으로, 혹은 자동적으로 변화시키도록 구성하더라도 좋다.

또, 도 17 등에 있어서, 게이트 신호선(17b)을 Vgl로 하는 기간 (IF/N)을 복수로 분할(분할 수 K)하여, 1F/(K/N)의 기간을 K회 실시하는 것으로 하였지만 이것에 한정되는 것은 아니다. 1F/(K/N)의 기간을 L(L≠K)회 실시하더라도 좋다. 즉, 본 발명은, EL 소자(15)에 흘리는 기간(시간)을 제어함으로써 화상을 표시하는 것이다. 따라서, 1F/(K/N)의 기간을 L(L≠K)회 실시하는 것은 본 발명의 기술적 사상에 포함된다. 또한, L의 값을 변화시킴으로써, 화상(50)의 휘도를 디지털적으로 변경할 수 있다. 예를 들면, L=2와 L=3에서는 50%의 휘도(콘트라스트) 변화로 된다. 또한, 화상의 표시 영역(53)을 분할할 때, 게이트 신호선(17b)을 Vg1로 하는 기간은 동일 기간에 한정하는 것은 아니다.

이상의 실시예는, EL 소자(15)에 흘리는 전류를 차단하고, 또한, EL 소자에 흘리는 전류를 접속함으로써, 표시 화면(50)을 온/오프(점등, 비점등)하는 것이었다. 즉, 콘덴서(19)에 유지된 전하에 의해 트랜지스터(11a)에 복수회, 대략 동일한 전류를 흘리는 것이다. 그러나, 본 발명은 이것에 한정하는 것은 아니다. 예를 들면, 콘덴서(19)에 유지된 전하를 충/방전시킴으로써, 표시 화면(50)을 온/오프(점등, 비점등)하는 방식이라도 좋다.

도 18은 도 16의 화상 표시 상태를 실현하기 위한 게이트 신호선(17)에 인가하는 전압 파형을 나타내고 있다. 도 18과 도 15의 차이는, 게이트 신호선(17b)의 동작이다. 게이트 신호선(17b)은 화면을 분할하는 개수에 대응하여, 그 개수만큼 온/오프(Vg1와 Vgh) 동작한다. 다른 점은 도 15와 동일하기 때문에 설명을 생략한다.

EL 표시 장치에서는 흑 표시는 완전히 비점등이므로, 액정 표시 패널을 간헐 표시한 경우와 같이, 콘트라스트의 저하는 없다. 또한, 도 1에 나타내는 구성에 있어서는, 트랜지스터(11d)를 온/오프 조작하는 것만으로 간헐 표시를 실현할 수 있다. 또한, 도 38, 도 51의 구성에 있어서는, 트랜지스터 소자(11e)를 온/오프 조작하는 것만으로, 간헐 표시를 실현할 수 있다. 이것은, 콘덴서(19)에 화상 데이터가 메모리(아날로그값이므로 계조 수는 무한대)되어 있기 때문이다. 즉, 각 화소(16)에, 화상 데이터는 1F의 기간 동안은 유지되어 있다. 이 유지되어 있는 화상 데이터에 상당하는 전류를 EL 소자(15)에 흘리는지 여부를 트랜지스터(11d, 11e)의 제어에 의해 실현하고 있는 것이다. 따라서, 이상의 구동 방법은, 전류 구동 방식에 한정되는 것이 아니라, 전압 구동 방식에도 적용할 수 있는 것이다. 즉, EL 소자(15)에 흘리는 전류가 각 화소 내에서 보존하고 있는 구성에 있어서, EL 소자(15)간의 전류 경로에 있어서 구동용 트랜지스터(11)를 온/오프함으로써, 간헐 구동을 실현하는 것이다.

콘덴서(19)의 단자 전압을 유지하는 것은 중요하다. 1 필드(프레임) 기간에서 콘덴서(19)의 단자 전압이 변화(충/방전)하면, 화면 휘도가 변화하여, 프레임 레이트가 저하하였을 때에 깜빡거림(플리커 등)이 발생하기 때문이다. 트랜지스터(11a)가 1 프레임(1 필드) 기간에서 EL 소자(15)에 흘리는 전류는, 적어도 65% 이하로 저하하지 않도록 할 필요가 있다. 이 65%란, 화소(16)에 기입하여, EL 소자(15)에 흘리는 전류의 최초가 100%로 하였을 때, 다음 프레임(필드)에서 상기 화소(16)에 기입하기 직전의 EL 소자(15)에 흘리는 전류를 65% 이상으로 하는 것이다.

도 1의 화소 구성에서는, 간헐 표시를 실현하는 경우로 하지 않는 경우에는, 1 화소를 구성하는 트랜지스터(11)의 개수에 변화는 없다. 즉, 화소 구성은 그대로, 소스 신호선(18)의 기생 용량의 영향을 제거하여, 양호한 전류 프로그램을 실현하고 있다. 더욱이, CRT에 가까운 동화상 표시를 실현하고 있는 것이다.

또한, 게이트 드라이버(12)의 동작 클럭은 소스 드라이버(14)의 동작 클럭과 비교하여 충분히 느리기 때문에, 회로의 메인 클럭이 높게 되지는 않는다. 또한, N의 값의 변경도 용이하다.

또, 화상 표시 방향(화상 기입 방향)은, 1 필드(1 프레임)째에서는 화면의 상 방향으로부터 하 방향으로 하고, 다음의 제 2 필드(프레임)째에서는 화면의 하 방향으로부터 상 방향으로 해도 좋다. 즉, 상 방향으로부터 하 방향과, 하 방향으로부터 상 방향을 교대로 반복하도록 하더라도 좋다.

또한, 1 필드(1 프레임)째에서는 화면의 상 방향으로부터 하 방향으로 하여, 일단, 전체 화면을 흑 표시(비표시)로 한 후, 다음의 제 2 필드(프레임)째에서는 화면의 하 방향으로부터 상 방향으로 해도 좋다. 또한, 일단, 전체 화면을 흑 표시(비표시)로 해도 좋다.

또, 이상의 구동 방법의 설명에서는, 화면의 기입 방법을 화면의 위로부터 아래로 혹은 아래로부터 위로하였지만, 이것에 한정하는 것은 아니다. 화면의 기입 방향은 중단 없이, 화면의 위로부터 아래로 혹은 아래로부터 위로 고정하여, 비표시 영역(52)의 동작 방향을 1 필드째에서는 화면의 상 방향으로부터 하 방향으로 하고, 다음의 제 2 필드째에서는 화면의 하 방향으로부터 상 방향으로 해도 좋다. 또한, 1 프레임을 3 필드로 분할하여, 제 1 필드에서는 R, 제 2 필드에서는 G, 제 3 필드에서는 B로 하여, 3 필드로 1 프레임을 형성하는 것으로 해도 좋다. 또한, 1 수평 주사 기간(IH)마다, R, G, B를 전환하여 표시하더라도 좋다. 이상의 사항은 본 발명의 다른 실시예에서도 마찬가지이다.

비표시 영역(52)은 완전히 비점등 상태일 필요는 없다. 미약한 발광 혹은 희미하게 한 화상 표시가 있더라도 실용상은 문제없다. 즉, 화상 표시 영역(53)보다도 표시 휘도가 낮은 영역으로 해석해야 한다. 또한, 비표시 영역(52)이란, R, G, B 화상 표시 중, 1색 또는 2색(25)만이 비표시 상태라고 하는 경우도 포함된다.

기본적으로는 표시 영역(53)의 휘도(밝기)가 소정값으로 유지되는 경우, 표시 영역(53)의 면적이 넓게 될수록, 화면(50)의 휘도는 높게 된다. 예를 들면, 표시 영역(53)의 휘도가 100(nt)의 경우, 표시 영역(53)이 전체 화면(50)에 차지하는 비율이 10% 내지 20%로 하면, 화면의 휘도는 2배로 된다. 따라서, 전체 화면(50)에 차지하는 표시 영역(53)의 면적을 변화시킴으로써, 화면의 표시 휘도를 변화할 수 있다.

표시 영역(53)의 면적은 시프트 레지스터(61)로의 데이터 펄스(ST2)를 제어함으로써, 임의로 설정할 수 있다. 또한, 데이터 펄스의 입력 타이밍, 주기를 변화시킴으로써, 도 16의 표시 상태와 도 13의 표시 상태를 전환할 수 있다. 1F 주기에서의 데이터 펄스 수를 많게 하면, 화면(50)은 밝아지고, 적게 하면, 화면(50)은 어둡게 된다. 또한, 연속하여 데이터 펄스를 인가하면 도 13의 표시 상태로 되어, 간헐적으로 데이터 펄스를 입력하면 도 16의 표시 상태로 된다.

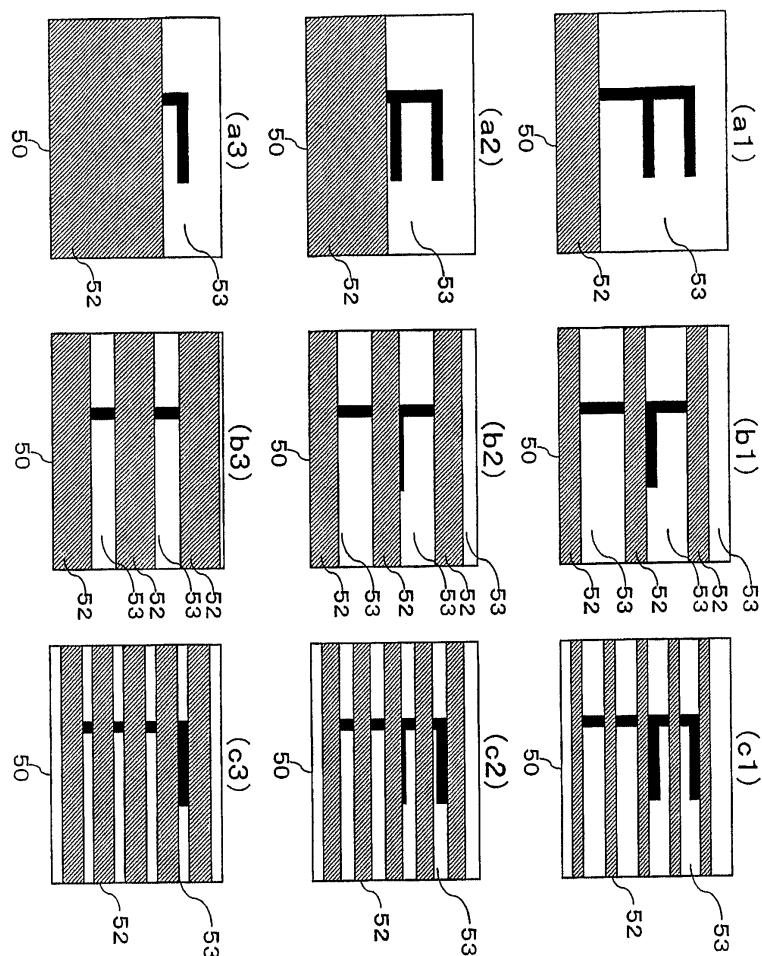

도 19의 (a)는 도 13과 같이 표시 영역(53)이 연속하고 있는 경우의 밝기 조정 방식을 설명하고 있다. 도 19(a1)의 화면(50)의 표시 휘도가 가장 밝다. 도 19(a2)의 화면(50)의 표시 휘도가 다음으로 밝고, 도 19(a3)의 화면(50)의 표시 휘도가 가장 어둡다. 도 19(a1)로부터 도 19(a3)로의 변화(혹은 그 반대)는, 앞에서도 기재한 바와 같이 게이트 드라이버(12)의 시프트 레지스터 회로(61) 등의 제어에 의해, 용이하게 실현할 수 있다. 이 때, 도 1의 Vdd 전압은 변화시킬 필요가 없다. 즉, 전원 전압을 변화시키지 않고 표시 화면(50)의 휘도 변화를 실시할 수 있다. 또한, 도 19(a1)로부터 도 19(a3)로의 변화인 때, 화면의 감마 특성은 전혀 변화하지 않는다. 따라서, 화면(50)의 휘도에 의하지 않고, 표시 화상의 콘트라스트, 계조 특성이 유지된다. 이것은 본 발명의 효과가 있는 특징이다. 종래의 화면의 휘도 조정에서는, 화면(50)의 휘도가 낮을 때에는, 계조 성능이 저하한다. 즉, 고 휘도 표시인 때에는 64 계조 표시를 실현할 수 있더라도, 저 휘도 표시인 때에는, 절반 이하의 계조 수밖에 표시할 수 없는 경우가 대부분이다. 이것과 비교하여, 본 발명의 구동 방법에서는, 화면의 표시 휘도에 의존하지 않고, 최고의 64 계조 표시를 실현할 수 있다.

도 19의 (b)는 도 16과 같이 표시 영역(53)이 분산하고 있는 경우의 밝기 조정 방식을 설명하고 있다. 도 19(b1)의 화면(50)의 표시 휘도가 가장 밝다. 도 19(b2)의 화면(50)의 표시 휘도가 다음으로 밝고, 도 19(b3)의 화면(50)의 표시 휘도가 가장 어둡다. 도 19(b)로부터 도 19(b3)로의 변화(혹은 그 반대)는, 앞에서도 기재한 바와 같이 게이트 드라이버(12)의 시프트 레지스터 회로(61) 등의 제어에 의해, 용이하게 실현할 수 있다. 도 19의 (b)와 같이 표시 영역(53)을 분산시키면, 저 프레임 레이트에서도 플리커가 발생하지 않는다.

또한, 저 프레임 레이트에서도, 플리커가 발생하지 않도록 하기 위해서는, 도 19의 (c)와 같이 표시 영역(53)을 잘게 분산시키면 좋다. 그러나, 동화상의 표시 성능은 저하한다. 따라서, 동화상을 표시하기 위해서는, 도 19의 (a)의 구동 방법이 적합하다. 정지 화상을 표시하여, 저 소비 전력화를 요망하는 때에는, 도 19의 (c)의 구동 방법이 적합하다. 도 19의 (a)로부터 도 19의 (c)의 구동 방법의 전환도, 시프트 레지스터(61)의 제어에 의해 용이하게 실현할 수 있다.

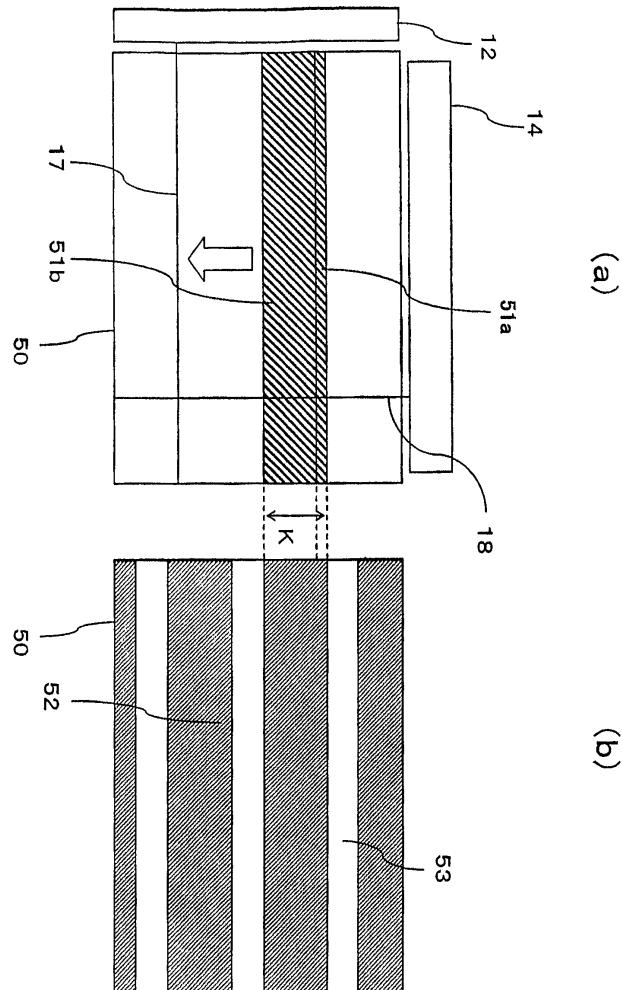

도 20은 소스 신호선(18)에 흐르는 전류를 증대시키는 다른 실시예의 설명도이다. 기본적으로 복수의 화소 행을 동시에 선택하여, 복수의 화소 행을 합한 전류로 소스 신호선(18)의 기생 용량 등을 충/방전하여 전류 기입 부족을 대폭 개선하는 방식이다. 단, 복수의 화소 행을 동시에 선택하기 때문에, 1 화소 당의 구동하는 전류를 감소시킬 수 있다. 따라서, EL 소자(15)에 흐르는 전류를 감소시킬 수 있다. 여기서, 설명을 용이하게 하기 위해서, 일례로서, N=10으로 하여 설명한다(소스 신호선(18)에 흘리는 전류를 10배로 함).

도 20에 도시하는 바와 같이, 본 발명에서는, K행의 화소 행을 동시에 선택한다. 소스 드라이버(14)로부터는 소정 전류의 N배 전류를 소스 신호선(18)에 인가한다. 각 화소에는 EL 소자(15)에 흘리는 전류의 N/K배의 전류가 프로그램된다. EL 소자(15)를 소정의 발광 휘도로 하기 위해서, EL 소자(15)에 흐르는 시간을 1 프레임(1 필드)의 K/N 시간으로 한다. 이와 같이 구동함으로써, 소스 신호선(18)의 기생 용량을 충분히 충/방전할 수 있어, 양호한 해상도로 소정의 발광 휘도를 얻을 수 있다.

즉, 1 프레임(1 필드)의 K/N의 기간 동안만, EL 소자(15)에 전류를 흘리고, 다른 기간(1F(N-1)K/N)은 전류를 흘리지 않는다. 이 표시 상태에서는 1F마다 화상 데이터 표시, 흑 표시(비점등)이 반복하여 표시된다. 즉, 화상 데이터의 표시 상태가 시간적으로 띄엄띄엄 표시(간헐 표시) 상태로 된다. 따라서, 화상의 흐릿한 윤곽이 없어져 양호한 동화상 표시를 실현할 수 있다. 또한, 소스 신호선(18)에는 N배의 전류로 구동하기 때문에, 기생 용량의 영향을 받지 않고, 고 선명 표시 패널에도 대응할 수 있다.

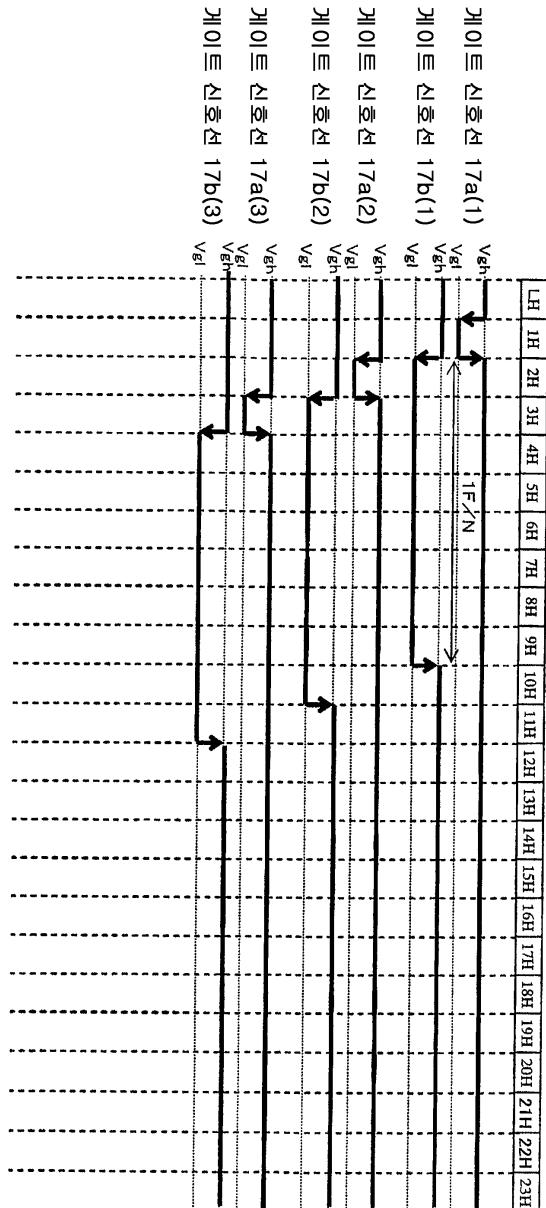

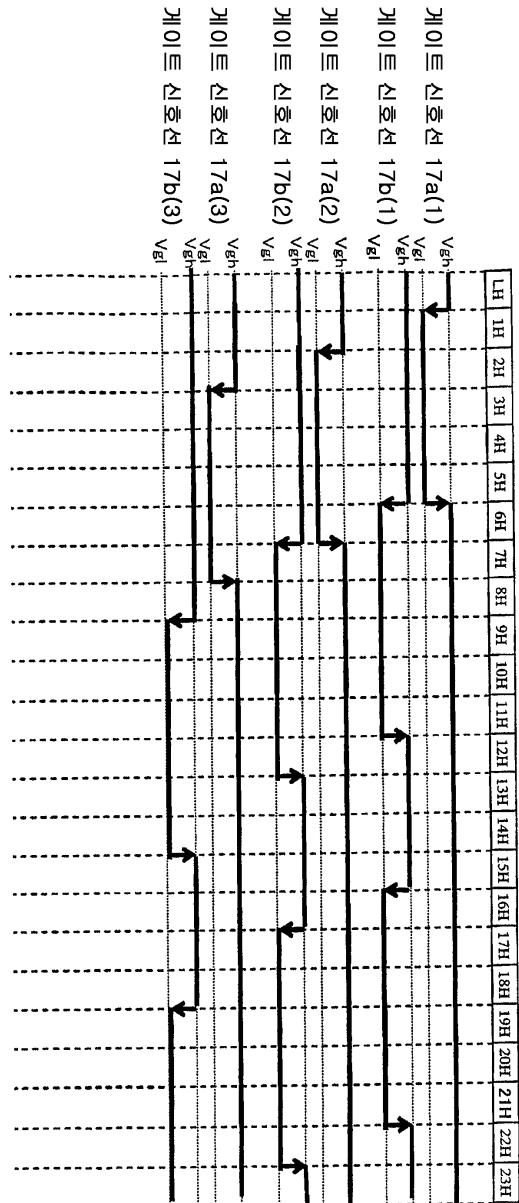

도 21은, 도 20의 구동 방법을 실현하기 위한 구동 파형의 설명도이다. 신호 파형은 오프 전압을  $V_{gh}$ (H 레벨)로 하고, 온 전압을  $V_{gl}$ (L 레벨)로 하고 있다. 각 신호선의 첨자는 화소 행의 행 번호((1)(2)(3) 등)를 기재하고 있다. 또, 행수는 QCIF 표시 패널의 경우는 220개이며, VGA 패널에서는 480개이다.

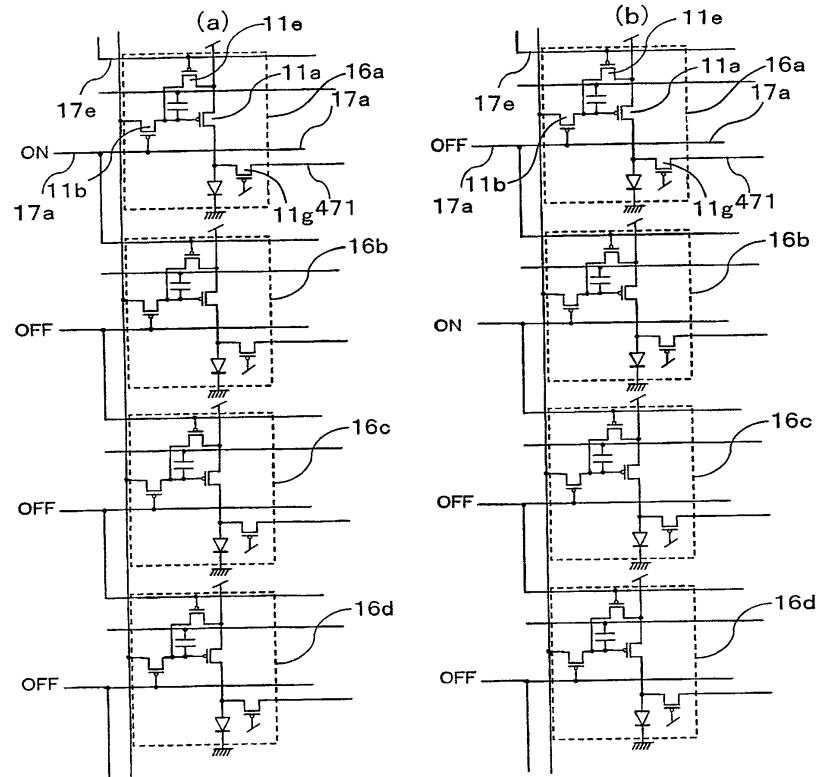

도 21에 있어서, 게이트 신호선(17a)(1)이 선택되어( $V_{gl}$  전압), 선택된 화소 행의 트랜지스터(11a)로부터 소스 드라이버(14)로 향하여 소스 신호선(18)에 프로그램 전류가 흐른다. 여기서는 설명을 용이하게 하기 위해서, 우선, 기입 화소 행(51a)이 제 1 행의 화소 행인 것으로 하여 설명한다.

또한, 소스 신호선(18)에 흐르는 프로그램 전류는 소정값의 N배(설명을 용이하게 하기 위해서,  $N=10$ 으로 하여 설명함. 물론, 소정값이란 화상을 표시하는 데이터 전류이므로, 백 래스터 표시 등이 아닌 한 고정값이 아님.)이다. 또한, 5 화소 행이 동시에 선택( $K=5$ )으로 하여 설명을 한다. 따라서, 이상적으로는 하나의 화소의 콘덴서(19)에는 2배( $N/K=10/5=2$ )로 전류가 트랜지스터(11a)에 흐르도록 프로그램된다.

기입 화소 행이 (1) 화소 행째인 때, 도 21에서 도시한 바와 같이, 게이트 신호선(17a)은 (1)(2)(3)(4)(5)가 선택되어 있다. 즉, 화소 행 (1)(2)(3)(4)(5)의 스위칭 트랜지스터(11b), 트랜지스터(11c)가 온 상태이다. 또한, 게이트 신호선(17b)은 게이트 신호선(17a)의 반대 위상으로 되어 있다. 따라서, 화소 행 (1)(2)(3)(4)(5)의 스위칭 트랜지스터(11d)가 오프 상태이며, 대응하는 화소 행의 EL 소자(15)에는 전류가 흐르고 있지 않다. 즉, 비점등 상태(52)이다.

이상적으로는, 5 화소의 트랜지스터(11a)가, 각각  $I_w \times 2$ 의 전류를 소스 신호선(18)에 흘린다(즉, 소스 신호선(18)에는  $I_w \times 2 \times N = I_w \times 2 \times 5 = I_w \times 10$ . 따라서, 본 발명의 N배 펄스 구동을 실시하지 않는 경우가 소정 전류  $I_w$ 라고 하면,  $I_w$ 의 10 배의 전류가 소스 신호선(18)에 흐름).

이상의 동작(구동 방법)에 의해, 각 화소(16)의 콘덴서(19)에는, 2배의 전류가 프로그램된다. 여기서는, 이해를 용이하게 하기 위해서, 각 트랜지스터(11a)는 특성( $V_t$ ,  $S$ 값)이 일치하고 있는 것으로 설명을 한다.

동시에 선택하는 화소 행이 5 화소 행( $K=5$ )이므로, 5개의 구동용 트랜지스터(11a)가 동작한다. 즉, 1 화소 당,  $10/5=2$ 배의 전류가 트랜지스터(11a)에 흐른다. 소스 신호선(18)에는, 5개의 트랜지스터(11a)의 프로그램 전류를 부가한 전류가 흐른다. 예를 들면, 기입 화소 행(51a)에, 본래, 기입하는 전류  $I_w$ 로 하여, 소스 신호선(18)에는,  $I_w \times 10$ 의 전류를 흘린다. 기입 화소 행(1)보다 이후에 화상 데이터를 기입하는 기입 화소 행(51b)은, 소스 신호선(18)으로의 전류량을 증가시키기 때문에, 보조적으로 이용하는 화소 행이다. 그러나, 기입 화소 행(51b)은 이후에 정규의 화상 데이터가 기입되기 때문에 문제가 없다.

따라서, 4 화소 행(51b)에 있어서, 1H 기간 동안은 (51a)와 동일 표시이다. 그 때문에, 기입 화소 행(51a)과 전류를 증가시키기 위해서 선택한 화소 행(51b)을 적어도 비표시 상태(52)로 하는 것이다. 단, 도 38과 같은 커런트 미러의 화소 구성, 그 밖의 전압 프로그램 방식의 화소 구성에서는 표시 상태로 해도 좋다.

1H 후에는, 게이트 신호선(17a)(1)은 비선택으로 되어, 게이트 신호선(17b)에는 온 전압( $V_{gl}$ )이 인가된다. 또한, 동시에, 게이트 신호선(17a)(6)이 선택되어 ( $V_{gl}$  전압), 선택된 화소 행(6)의 트랜지스터(11a)로부터 소스 드라이버(14)로 향하여 소스 신호선(18)에 프로그램 전류가 흐른다. 이와 같이 동작함으로써, 화소 행(1)에는 정규의 화상 데이터가 유지된다.

다음의, 1H 후에는, 게이트 신호선(17a)(2)은 비선택으로 되어, 게이트 신호선(17b)에는 온 전압(Vgl)이 인가된다. 또한, 동시에, 게이트 신호선(17a)(7)이 선택되어(Vgl 전압), 선택된 화소 행(7)의 트랜지스터(11a)로부터 소스 드라이버(14)로 향하여 소스 신호선(18)에 프로그램 전류가 흐른다. 이와 같이 동작함으로써, 화소 행(2)에는 정규의 화상 데이터가 유지된다. 1 화소 행씩 시프트하면서 주사하여 이상의 동작을 행하는 것에 의해 1 화면이 리라이트된다.

도 20의 구동 방법에서는, 각 화소에 있어서 2배의 전류(전압)가 프로그램되기 때문에, 각 화소의 EL 소자(15)의 발광 휘도는 이상적으로는 2배로 된다. 따라서, 표시 화면의 휘도는 소정 값보다도 2배로 된다. 이것을 소정의 휘도로 하기 위해서는, 도 16에 도시하는 바와 같이, 기입 화소 행(51)을 포함하고, 또한 표시 영역(50)의 1/2의 범위를 비표시 영역(52)으로 하면 좋다.

도 13과 마찬가지로, 도 20과 같이 하나의 표시 영역(53)이 화면의 상 방향으로부터 하 방향으로 이동한 경우, 프레임 레이트가 낮으면, 표시 영역(53)이 이동하는 형태가 시각적으로 인식된다. 특히, 눈꺼풀을 닫았을 때, 혹은 얼굴을 상하로 이동시켰을 때 등에 인식되기 쉽게 된다.

이 과제에 대해서는, 도 22에 도시하는 바와 같이, 표시 영역(53)을 복수로 분할하면 좋다. 분할된 비표시 영역(52)을 부가한 부분이 S(N-1)/N의 면적으로 되면, 분할하지 않는 경우와 동일하게 된다.

도 23은 게이트 신호선(17)에 인가하는 전압 파형이다. 도 21과 도 23의 차이는, 기본적으로는 게이트 신호선(17b)의 동작이다. 게이트 신호선(17b)은 화면을 분할하는 개수에 대응하여, 그 개수만큼 온/오프(Vg1과 Vgh) 동작한다. 다른 점은 도 21과 거의 동일 혹은 유추할 수 있기 때문에 설명을 생략한다.

이상과 같이, 표시 영역(53)을 복수로 분할함으로써 화면의 깜박거림은 감소한다. 따라서, 플리커의 발생은 없고, 양호한 화상 표시를 실현할 수 있다. 또, 분할은 더 잘게 하더라도 좋다. 분할하면 할수록 플리커는 경감한다. 특히 EL 소자(15)의 응답성은 빠르기 때문에, 5 $\mu$ sec보다도 작은 시간으로 온/오프하더라도, 표시 휘도의 저하는 없다.

본 발명의 구동 방법에 있어서, EL 소자(15)의 온/오프는, 게이트 신호선(17b)에 인가하는 신호의 온/오프로 제어할 수 있다. 그 때문에, 클럭 주파수는 KHz 정도의 저 주파수로 제어가 가능하다. 또한, 혹 화면 삽입(비표시 영역(52) 삽입)을 실현하는 데에는, 화상 메모리 등을 필요로 하지 않는다. 따라서, 저 비용으로 본 발명의 구동 회로 혹은 방법을 실현할 수 있다.

도 24는 동시에 선택하는 화소 행이 2 화소 행의 경우이다. 발명자 등이 검토한 결과에 의하면, 저온 폴리실리콘 기술로 형성한 표시 패널에서는, 2 화소 행을 동시에 선택하는 방법은 표시 균일성이 실용적이었다. 이것은, 인접하는 화소의 구동 용 트랜지스터(11a)의 특성이 매우 일치하고 있기 때문에 추정된다. 또한, 레이저 어닐링할 때에, 스트라이프 형상의 레이저의 조사 방향은 소스 신호선(18)과 평행하게 조사함으로써 양호한 결과를 얻을 수 있었다.

이것은 동일 시간에 어닐링되는 범위의 반도체막은, 그 특성이 균일하게 되기 때문이다. 즉, 스트라이프 형상의 레이저 조사 범위 내에서는 반도체막이 균일하게 제작되어, 이 반도체막을 이용한 트랜지스터의 Vt, 모빌리티가 거의 동등하게 되기 때문이다. 따라서, 소스 신호선(18)의 형성 방향과 평행하게 스트라이프 형상의 레이저 샷을 조사하여, 이 조사 위치를 이동시키는 것에 의해, 소스 신호선(18)에 따른 화소(화소 열, 화면의 상하 방향의 화소)의 특성은 거의 동등하게 제작된다. 따라서, 복수의 화소 행을 동시에 온시켜 전류 프로그램을 행한 경우, 동시에 선택된 복수의 화소 행에는, 프로그램 전류를 선택된 화소 행수로 분할한 전류가, 거의 동일하게 프로그램된다. 따라서, 목표값에 가까운 전류 프로그램을 실시할 수 있어, 균일 표시를 실현할 수 있다. 따라서, 레이저 샷 방향과 도 24 등에서 설명하는 구동 방식은 상승 효과가 있다.

이상과 같이, 레이저 샷의 방향을 소스 신호선(18)의 형성 방향과 대략 일치시킴으로써, 화소의 상하 방향의 트랜지스터(11a)의 특성이 거의 동일하게 되어, 양호한 전류 프로그램을 실시할 수 있다(화소의 좌우 방향의 트랜지스터(11a)의 특성이 일치하지 않고 있더라도). 이상의 동작은, 1H(1 수평 주사 기간)에 동기하여, 1 화소 행 혹은 복수 화소 행씩 선택 화소 행의 위치를 어긋나게 하여 실시한다. 또, 본 발명은, 레이저 샷의 방향을 소스 신호선(18)과 평행으로 한다고 하였지만, 반드시 평행이 아니더라도 좋다. 소스 신호선(18)에 대해 경사 방향으로 레이저 샷을 조사하더라도 하나의 소스 신호선(18)에 따른 화소의 상하 방향의 트랜지스터(11a)의 특성은 거의 일치하여 형성되기 때문이다. 따라서, 소스 신호선에 평행하게 레이저 샷을 조사한다는 것은, 소스 신호선(18)의 배선 방향(상하 방향)에 인접한 임의의 화소를, 하나의 레이저 조사 범위에 들어가도록 형성한다고 하는 것이다. 또한, 소스 신호선(18)이란 일반적으로는, 화상 신호로 되는 프로그램 전류 혹은 전압을 전달하는 배선이다.

또, 본 발명의 실시예에서는 1H마다, 기입 화소 행 위치를 시프트시키는 것으로 하였지만, 이것에 한정되는 것은 아니고, 2H마다 시프트하더라도 좋고, 또한, 그 이상의 화소 행마다 시프트시키더라도 좋다. 또한, 임의의 시간 단위로 시프트하더라도 좋다. 또한, 화면 위치에 따라서, 시프트하는 시간을 변화시키더라도 좋다. 예를 들면, 화면의 중앙부에서의 시프트 시간을 짧게 하고, 화면의 상하부에서 시프트 시간을 길게 하더라도 좋다. 또한, 프레임마다 시프트 시간을 변화시키더라도 좋다. 또한, 연속한 복수 화소 행을 선택하는 것에 한정하는 것은 아니다. 예컨대, 1 화소 행으로 세운 화소 행을 선택하더라도 좋다. 즉, 제 1 번째의 수평 주사 기간에 제 1 번째의 화소 행과 제 3 번째의 화소 행을 선택하고, 제 2 번째의 수평 주사 기간에 제 2 번째의 화소 행과 제 4 번째의 화소 행을 선택하며, 제 3 번째의 수평 주사 기간에 제 3 번째의 화소 행과 제 5 번째의 화소 행을 선택하고, 제 4 번째의 수평 주사 기간에 제 4 번째의 화소 행과 제 6 번째의 화소 행을 선택한다고 한 구동 방법이다. 물론, 제 1 번째의 수평 주사 기간에 제 1 번째의 화소 행과 제 3 번째의 화소 행과 제 5 번째의 화소 행을 선택한다고 하는 구동 방법도 기술적 범주이다. 물론, 복수 화소 행으로 세운 화소 행 위치를 선택하더라도 좋다.

또, 이상의 레이저 샷 방향과, 복수 라인의 화소 행을 동시에 선택한다고 하는 조합은, 도 1, 도 2, 도 32의 화소 구성에만 한정되는 것이 아니라, 커런트 미러의 화소 구성인 도 38, 도 42, 도 50 등의 다른 전류 구동 방식의 화소 구성에도 적용할 수 있는 것은 말할 필요도 없다. 또한, 도 43, 도 51, 도 54, 도 62 등의 전압 구동의 화소 구성에도 적용할 수 있다. 왜냐하면, 상하 방향으로 인접하는 화소의 트랜지스터의 특성이 일치하고 있으면, 동일한 소스 신호선(18)에 인가한 전압값에 의해 양호한 전압 프로그램을 실시할 수 있기 때문이다.

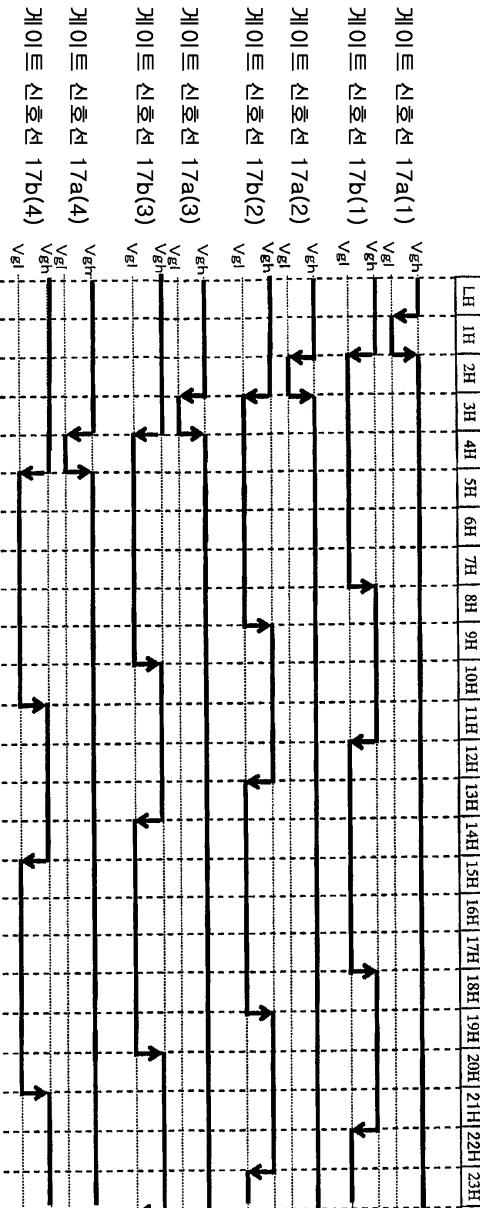

도 24에 있어서, 기입 화소 행이 제 1 행인 경우, 게이트 신호선(17a)은 (1)(2)이 선택되어 있다(도 25의 것을 참조). 즉, 화소 행 (1)(2)의 스위칭 트랜지스터(11b), 트랜지스터(11c)가 온 상태이다. 또한, 게이트 신호선(17b)은 게이트 신호선(17a)의 반대 위상으로 되어 있다. 따라서, 적어도 화소 행 (1)(2)의 스위칭 트랜지스터(11d)가 오프 상태이며, 대응하는 화소 행의 EL 소자(15)에는 전류가 흐르고 있지 않다. 따라서, 이러한 화소 행은 비점등 상태(52)로 된다. 또, 도 24에서는, 플리커의 발생을 저감하기 때문에, 표시 영역(53)을 5 분할하고 있다.

이상적으로는, 2 화소(행)의 트랜지스터(11a)가, 각각  $I_w \times 5$ ( $N=10$ 인 경우. 즉,  $K=2$ 이므로, 소스 신호선(18)에 흐르는 전류는  $I_w \times K \times 5 = I_w \times 10$ 으로 됨)의 전류를 소스 신호선(18)에 흘린다. 그리고, 각 화소(16)의 콘텐서(19)에는, 5배의 전류가 프로그램된다.

동시에 선택하는 화소 행이 2 화소 행( $K=2$ )이므로, 2개의 구동용 트랜지스터(11a)가 동작한다. 즉, 1 화소 당,  $10/2=5$ 배의 전류가 트랜지스터(11a)에 흐른다. 소스 신호선(18)에는, 2개의 트랜지스터(11a)의 프로그램 전류를 부가한 전류가 흐른다.

예를 들면, 기입 화소 행(51a)에, 본래, 기입하는 전류  $I_d$ 를 흘리고, 소스 신호선(18)에는,  $I_w \times 10$ 의 전류를 흘린다. 기입 화소 행(51b)은 이후에 정규의 화상 데이터가 기입되기 때문에 문제가 없다. 화소 행(51b)은, 1H 기간 동안은 (51a)와 동일 표시이다. 그 때문에, 기입 화소 행(51a)과 전류를 증가시키기 위해서 선택한 화소 행(51b)을 적어도 비표시 상태(52)로 하는 것이다.

다음, 1H 후에는, 게이트 신호선(17a)(1)은 비선택으로 되어, 게이트 신호선(17b)에는 온 전압(Vg1)이 인가된다. 또한, 동시에, 게이트 신호선(17a)(3)이 선택되어(Vg1 전압), 선택된 화소 행(3)의 트랜지스터(11a)로부터 소스 드라이버(14)로 향하여 소스 신호선(18)에 프로그램 전류가 흐른다. 이와 같이 동작함으로써, 화소 행(1)에는 정규의 화상 데이터가 유지된다.

다음, 1H 후에는, 게이트 신호선(17a)(2)은 비선택으로 되어, 게이트 신호선(17b)에는 온 전압(Vg1)이 인가된다. 또한, 동시에, 게이트 신호선(17a)(4)이 선택되어(Vg1 전압), 선택된 화소 행(4)의 트랜지스터(11a)로부터 소스 드라이버(14)를 향해서 소스 신호선(18)에 프로그램 전류가 흐른다. 이와 같이 동작함으로써, 화소 행(2)에는 정규의 화상 데이터가 유지된다. 1 화소 행씩 시프트(물론, 복수 화소 행씩 시프트하더라도 좋음. 예를 들면, 유사 인터레이스 구동이면, 2행씩 시프트 할 것임. 또한, 화상 표시의 관점에서, 복수의 화소 행에 동일 화상을 기입하는 경우도 있음)하면서 주사하여 이상의 동작을 행하는 것에 의해 1 화면이 리라이트된다.

도 16과 마찬가지이지만, 도 24의 구동 방법에서는, 각 화소에는 5배의 전류(전압)로 프로그램을 행하기 때문에, 각 화소의 EL 소자(15)의 발광 휙도는 이상적으로는 5배로 된다. 따라서, 표시 영역(53)의 휙도는 소정값의 5배로 된다. 이것을 소정의 휙도로 하기 위해서는, 도 16 등에 도시하는 바와 같이, 기입 화소 행(51)을 포함하고, 또한 표시 화면(50)의 1/5의 범위를 비표시 영역(52)으로 하면 좋다.

도 27에 도시하는 바와 같이, 2개의 기입 화소 행(51)(51a, 51b)이 선택되고, 화면(50)의 상변으로부터 하변으로 순차적으로 선택되어 간다(도 26의 것도 참조. 도 26에서는 화소 행(16a와 16b)이 선택되어 있음). 그러나, 도 27의 b)와 같이, 화면의 하변까지 오면 기입 화소 행(51a)은 존재하지만, (51b)는 없어진다. 즉, 선택하는 20 화소 행이 1개밖에 없어진다. 그 때문에, 소스 신호선(18)에 인가된 전류는, 전부 화소 행(51a)에 기입된다. 따라서, 화소 행(51a)과 비교하여, 2배의 전류가 화소에 프로그램되게 된다.

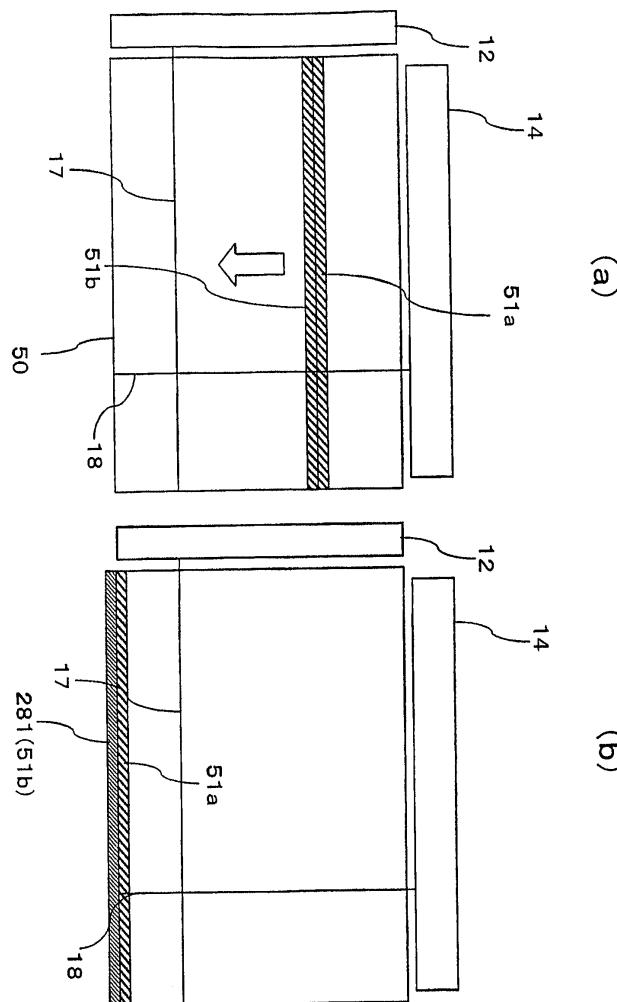

이 과제에 대해, 본 발명은, 도 27의 (b)에 도시하는 바와 같이 화면(50)의 하변에 더미 화소 행(281)을 형성(배치)하고 있다. 따라서, 선택 화소 행이 화면(50)의 하변까지 선택된 경우에는, 화면(50)의 최종 화소 행과 더미 화소 행(281)이 선택된다. 그 때문에, 도 27의 (b)의 기입 화소 행에는, 규정대로의 전류가 기입된다. 또, 더미 화소 행(281)은 표시 영역(50)의 상단 혹은 하단에 인접하여 형성한 바와 같이 도시하였지만, 이것에 한정하는 것은 아니다. 표시 영역(50)으로부터 떨어진 위치에 형성되어 있더라도 좋다. 또한, 더미 화소 행(281)은, 도 1의 스위칭 트랜지스터(11d), EL 소자(15) 등은 형성할 필요는 없다. 이들을 형성하지 않는 것에 의해, 더미 화소 행(281)의 사이즈를 작게 할 수 있다.

도 28은 도 27의 (b)의 상태를 나타내고 있다. 도 28에서 명백한 바와 같이, 선택 화소 행이 화면(50)의 하변의 화소(16c) 행까지 선택된 경우에는, 화면(50)의 최종 화소 행(281)이 선택된다. 더미 화소 행(281)은 표시 영역(50) 밖에 배치한다. 즉, 더미 화소 행(281)은 점등하지 않거나, 혹은 점등시키지 않는다, 또는 점등하더라도 표시로서 보이지 않도록 구성한다. 예를 들면, 화소 전극과 트랜지스터(11)의 콘택트 홀을 없애든지, 더미 화소 행에는 EL 막을 형성하지 않는 등이다.

도 27에서는, 화면(50)의 하변에 더미 화소(행)(281)을 마련하는(형성하는, 배치하는) 것으로 하였지만, 이것에 한정하는 것은 아니다. 예를 들면, 도 29의 (a)에 도시하는 바와 같이, 화면의 하변으로부터 상변으로 주사하는(상하 역전 주사)하는 경우에는, 도 29의 (b)에 도시하는 바와 같이 화면(50)의 상변에도 더미 화소 행(281)을 형성해야 한다. 즉, 화면(50)의 상변 및 하변의 각각 더미 화소 행(281)을 형성(배치)한다. 이상과 같이 구성함으로써, 화면의 상하 반전 주사에도 대응할 수 있도록 된다.

이상의 실시예는, 2 화소 행을 동시에 선택하는 경우이었다. 그러나, 본 발명은 이것에 한정되는 것이 아니라, 예를 들면, 5 화소 행을 동시에 선택하는 방식(도 23의 것을 참조)이어도 좋다. 즉, 5 화소 행 동시 구동의 경우는, 더미 화소 행(281)은 4 행분 형성하면 좋다. 본 발명의 더미 화소 행 구성 혹은 더미 화소 행 구동은, 적어도 하나 이상의 더미 화소 행을 이용하는 방식이다. 물론, 더미 화소 행 구동 방법과 N배 펠스 구동을 조합하여 이용하는 것이 바람직하다.

복수개의 화소 행을 동시에 선택하는 구동 방법에서는, 동시에 선택하는 화소 행수가 증가할수록, 트랜지스터(11a)의 특성 편차를 흡수하는 것이 곤란하게 된다. 그러나, 선택 개수가 저하하면, 1 화소에 프로그램하는 전류가 커져, EL 소자(15)에 큰 전류를 흘리는 것으로 된다. EL 소자(15)에 흘리는 전류가 크면 EL 소자(15)가 열화하기 쉽게 된다.

도 30은 이 과제를 해결하는 것이다. 도 30에 나타낸 본 발명의 기본 개념은, 1/2H(수평 주사 기간의 1/2)는, 도 22, 도 29에서 설명한 바와 같이, 복수의 화소 행을 동시에 선택하는 방법이다. 그 후의 1/2H(수평 주사 기간의 1/2)는 도 5, 도 13 등에서 설명한 바와 같이, 1 화소 행을 선택하는 방법을 조합한 것이다. 이와 같이 조합한 경우, 트랜지스터(11a)의 특성 편차가 흡수되기 때문에, 고속이고 또한 면내 균일성을 양호하게 할 수 있다.

도 30에 있어서, 설명을 용이하게 하기 위해서, 제 1 기간에서는 5 화소 행을 동시에 선택하고, 제 2 기간에서는 1 화소 행을 선택하는 것으로 해서 설명을 한다. 우선, 제 1 기간(전반의 1/2H)에서는, 도 30(a1)에 도시하는 바와 같이, 5 화소 행을 동시에 선택한다. 이 동작은 도 22를 이용하여 설명하였기 때문에 생략한다. 일례로서 소스 신호선(18)에 흘리는 전류는 소정값의 25배로 한다. 따라서, 각 화소(16)의 트랜지스터(11a)(도 1의 화소 구성의 경우)에는 5배의 전류(25/5 화소 행=5)가 프로그램된다. 25배의 전류이므로, 소스 신호선(18) 등에 발생하는 기생 용량은 매우 단 기간에 충/방전된다. 따라서, 소스 신호선(18)의 전위는, 단 시간에서 목표의 전위로 되어, 각 화소(16)의 콘덴서(19)의 단자 전압도 5배 전류를 흘리도록 프로그램된다. 이 25배 전류의 인가 시간은 전반의 1/2H(1 수평 주사 기간의 1/2)로 한다.

당연한 것이지만, 기입 화소 행의 5 화소 행은 동일 화상 데이터가 기입되기 때문에, 표시를 행하지 않도록 5 화소 행의 트랜지스터(11d)는 오프 상태로 된다. 따라서, 표시 상태는 도 30(a2)에 도시하는 바와 같이 된다.

다음 후반의 1/2H 기간은, 1 화소 행을 선택하여, 전류(전압) 프로그램을 행한다. 이 상태를 도 30(b1)에 도시하고 있다. 기입 화소 행(51a)은 이전과 마찬가지로 5배의 전류를 흘리도록 전류(전압) 프로그램된다. 도 30(a1)과 도 30(b1)에서 각 화소에 흘리는 전류를 동일하게 하는 것은, 프로그램된 콘덴서(19)의 단자 전압의 변화를 작게 하여, 보다 고속으로 목표의 전류를 흘릴 수 있도록 하기 위해서이다.

즉, 도 30(a1)에서, 복수의 화소에 전류를 흘려, 고속으로 개략의 전류가 흐르는 값까지 접근시킨다. 이 제 1 단계에서는, 복수의 트랜지스터(11a)에서 프로그램하고 있기 때문에, 목표값에 대해 트랜지스터의 편차에 의한 오차가 발생하고 있다. 다음의 제 2 단계에서, 데이터를 기입하고 또한 유지하는 화소 행만을 선택하여, 개략의 목표값으로부터, 소정의 목표값까지 완전한 프로그램을 행하는 것이다.

또, 비점등 영역(52)을 화면의 상 방향으로부터 하 방향으로 주사하고, 또한, 기입 화소 행(51a)도 화면의 상 방향으로부터 하 방향으로 주사하는 것은 도 13 등의 실시예와 마찬가지이기 때문에 설명을 생략한다.

도 31은 도 30의 구동 방법을 실현하기 위한 구동 파형이다. 도 31에서 알 수 있는 바와 같이, 1H(1 수평 주사 기간)는 2개의 단계로 구성되어 있다. 이 2개의 단계는 ISEL 신호로 전환한다. ISEL 신호는 도 31에 도시하고 있다.

우선, ISEL 신호에 대해 설명을 해 놓는다. 도 30을 실시하는 드라이버 회로(14)는, 제 1 전류 출력 회로와 제 2 전류 출력 회로를 구비하고 있다. 이들 제 1 및 제 2 전류 출력 회로는, 8 비트의 계조 데이터를 DA 변환하는 DA 회로 및 연산 증폭기 등으로 구성된다. 도 30의 실시예에서는, 제 1 전류 출력 회로는 25배의 전류를 출력하도록 구성되어 있다. 한편, 제 2 전류 출력 회로는 5배의 전류를 출력하도록 구성되어 있다. 제 1 전류 출력 회로 및 제 2 전류 출력 회로의 출력은 ISEL 신호에 의해 전류 출력부에 형성(배치)된 스위치 회로가 제어되어, 소스 신호선(18)에 인가된다. 이들 제 1 및 제 2 전류 출력 회로는 각 소스 신호선에 배치되어 있다.

ISEL 신호는, L 레벨인 때, 25배 전류를 출력하는 제 1 전류 출력 회로가 선택되어 소스 신호선(18)로부터의 전류를 소스 드라이버(14)가 흡수한다(보다 적절하게는, 소스 드라이버(14) 내에 형성된 제 1 전류 출력 회로가 흡수함). 25배, 5배 등의 제 1 및 제 2 전류 출력 회로 전류의 크기 조정은 용이하다. 복수의 저항과 아날로그 스위치로 용이하게 구성할 수 있기 때문이다.

도 30에 도시하는 바와 같이 기입 화소 행이 제 1 행인 때(도 30의 1H의 란을 참조), 게이트 신호선(17a)은 (1)(2)(3)(4)(5)이 선택되어 있다(도 1의 화소 구성의 경우). 즉, 화소 행 (1)(2)(3)(4)(5)의 스위치 트랜지스터(11b), 트랜지스터(11c)가 온 상태이다. 또한, ISEL이 L 레벨이므로, 25배 전류를 출력하는 제 1 전류 출력 회로가 선택되고, 소스 신호선(18)과 접속되어 있다. 또한, 게이트 신호선(17b)에는, 오프 전압(Vgh)이 인가되어 있다. 따라서, 화소 행 (1)(2)(3)(4)(5)의 스위칭 트랜지스터(11d)가 오프 상태이며, 대응하는 화소 행의 EL 소자(15)에는 전류가 흐르고 있지 않다. 즉, 비점등 상태(52)이다.

이상적으로는, 5 화소의 트랜지스터(11a)가, 각각  $I_w \times 2$ 의 전류를 소스 신호선(18)에 흘린다. 그리고, 각 화소(16)의 콘덴서(19)에는, 5배의 전류가 프로그램된다. 여기서는, 이해를 용이하게 하기 위해서, 각 트랜지스터(11a)는 특성( $V_t$ ,  $S$ 값)이 일치하고 있는 것으로 해서 설명을 한다.

동시에 선택하는 화소 행이 5 화소 행( $K=5$ )이므로, 5개의 구동용 트랜지스터(11a)가 동작한다. 즉, 1 화소 당,  $25/5=5$ 배의 전류가 트랜지스터(11a)에 흐른다. 소스 신호선(18)에는, 5개의 트랜지스터(11a)의 프로그램 전류를 가한 전류가 흐른다. 예를 들면, 기입 화소 행(51a)에, 종래의 구동 방법에서 화소에 기입하는 전류  $I_w$ 로 할 때, 소스 신호선(18)에는,  $I_w \times 25$ 의 전류를 흘린다. 기입 화소 행(1)보다 이후에 화상 데이터를 기입하는 기입 화소 행(51b)의 소스 신호선(18)으로의 전류량을 증가시키기 위해서, 보조적으로 이용하는 화소 행이다. 그러나, 기입 화소 행(51b)은 이후에 정규의 화상 데이터가 기입되기 때문에 문제가 없다.

따라서, 화소 행(51b)은, 1H 기간 동안은 기입 화소 행(51a)과 동일 표시이다. 그 때문에, 기입 화소 행(51a)과 전류를 증가시키기 위해서 선택한 화소 행(51b)을 적어도 비표시 상태(52)로 하는 것이다.

다음의 1/2H(수평 주사 기간의 1/2)에서는, 기입 화소 행(51a)L0만을 선택한다. 즉, 제 1 행만을 선택한다. 도 31에서 명백한 바와 같이, 게이트 신호선(17a)(1)만이, 온 전압(Vgl)이 인가되고, 게이트 신호선(17a)(2)(3)(4)(5)는 오프(Vgh)가 인가되어 있다. 따라서, 화소 행(1)의 트랜지스터(11a)는 동작 상태(소스 신호선(18)에 전류를 공급하고 있는 상태)이지만, 화소 행(2)(3)(4)(5)의 스위칭 트랜지스터(11b), 트랜지스터(11c)가 오프 상태이다. 즉, 비선택 상태이다. 또한, ISEL이 H 레벨이므로, 5배 전류를 출력하는 전류 출력 회로 B가 선택되고, 이 전류 출력 회로 B와 소스 신호선(18)이 접속되어 있다. 또한, 게이트 신호선(17b)의 상태는 이전의 1/2H의 상태와 변화가 없고, 오프 전압(Vgh)이 인가되어 있다. 따라서, 화소 행(1)(2)(3)(4)(5)의 스위칭 트랜지스터(11d)가 오프 상태이며, 대응하는 화소 행의 EL 소자(15)에는 전류가 흐르고 있지 않다. 따라서, 이러한 화소 행은 비점등 상태(52)로 된다.

이상의 것으로부터, 화소 행(1)의 트랜지스터(11a)가, 각각  $Iw \times 5$ 의 전류를 소스 신호선(18)에 흘린다. 그리고, 각 화소 행(1)의 콘덴서(19)에는, 5배의 전류가 프로그램된다.

다음의 수평 주사 기간에서는 1 화소 행, 기입 화소 행이 시프트한다. 즉, 이번에는 기입 화소 행이 (2)이다. 최초의 1/2H의 기간에서는, 도 31에 도시하는 바와 같이 기입 화소 행이 2 행째인 경우, 게이트 신호선(17a)은 (2)(3)(4)(5)(6)이 선택되어 있다. 즉, 화소 행(2)(3)(4)(5)(6)의 스위칭 트랜지스터(11b), 트랜지스터(11c)가 온 상태이다. 또한, ISEL이 L 레벨이므로, 25배 전류를 출력하는 제 1 전류 출력 회로가 선택되어, 소스 신호선(18)과 접속되어 있다. 또한, 게이트 신호선(17b)에는, 오프 전압(Vgh)이 인가되어 있다. 따라서, 화소 행(2)(3)(4)(5)(6)의 스위칭 트랜지스터(11d)가 오프 상태이며, 대응하는 화소 행의 EL 소자(15)에는 전류가 흐르고 있지 않다. 따라서, 이러한 화소 행은 비점등 상태(52)로 된다. 한편, 화소 행(1)의 게이트 신호선(17b)(1)은 Vg1 전압이 인가되어 있으므로, 트랜지스터(11d)는 온 상태이며, 화소 행(1)의 EL 소자(15)는 점등한다.

동시에 선택하는 화소 행이 5 화소 행( $K=5$ )이므로, 5개의 구동용 트랜지스터(11a)가 동작한다. 즉, 1 화소 당,  $25/5=5$ 배의 전류가 트랜지스터(11a)에 흐른다. 소스 신호선(18)에는, 5개의 트랜지스터(11a)의 프로그램 전류를 가한 전류가 흐른다.

다음의 1/2H(수평 주사 기간의 1/2)에서는, 기입 화소 행(51a)만을 선택한다. 즉, 2 행째만을 선택한다. 도 31에서 명백한 바와 같이, 게이트 신호선(17a)(2)만이, 온 전압(Vgl)이 인가되고, 게이트 신호선(17a)(3)(4)(5)(6)는 오프(Vgh)가 인가되어 있다. 따라서, 화소 행(1)(2)의 트랜지스터(11a)는 동작 상태(화소 행(1)은 EL 소자(15)에 전류를 흘리고, 화소 행(2)은 소스 신호선(18)에 전류를 공급하고 있는 상태)이지만, 화소 행(3)(4)(5)(6)의 스위칭 트랜지스터(11b), 트랜지스터(25)(11c)가 오프 상태이다. 즉, 비선택 상태이다. 또한, ISEL이 H 레벨이므로, 5배 전류를 출력하는 제 2 전류 출력 회로가 선택된다. 또한, 게이트 신호선(17b)의 상태는 이전의 1/2H의 상태와 변화가 없고, 오프 전압(Vgh)이 인가되어 있다. 따라서, 화소 행(2)(3)(4)(5)(6)의 스위칭 트랜지스터(11d)가 오프 상태이며, 대응하는 화소 행의 EL 소자(15)에는 전류가 흐르고 있지 않다. 따라서, 이러한 화소 행은 비점등 상태(52)로 된다.

이상의 것으로부터, 화소 행(2)의 트랜지스터(11a)가, 각각  $I5w \times 5$ 의 전류를 소스 신호선(18)에 흘린다. 그리고, 각 화소 행(2)의 콘덴서(19)에는, 5배의 전류가 프로그램된다. 이상의 동작을 순차적으로, 실시하는 것에 의해 1 화면을 표시할 수 있다.

도 30에서 설명한 구동 방법은, 제 1 기간에서 G 화소 행(G는 2 이상)을 선택하여, 각 화소 행에는 N배의 전류를 흘리도록 프로그램한다. 제 1 기간 후의 제 2 기간에서는 B 화소 행(B는 G보다도 작고, 1 이상)을 선택하여, 화소에는 N배의 전류를 흘리도록 프로그램하는 방식이다.

그러나, 다른 방책도 있다. 제 1 기간에서 G 화소 행(G는 2 이상)을 선택하여, 각 화소 행의 총합 전류가 N배의 전류가 되도록 프로그램한다. 제 1 기간 후의 제 2 기간에서는 B 화소 행(B는 G보다도 작고, 1 이상)을 선택하여, 선택된 화소 행의 총합의 전류(단, 선택 화소 행이 1인 때에는, 1 화소 행의 전류)가 N배가 되도록 프로그램하는 방식이다. 예를 들면, 도 30(a1)에 있어서, 5 화소 행을 동시에 선택하여, 각 화소의 트랜지스터(11a)에는 2배의 전류를 흘린다. 이에 따라, 소스 신호선(18)에는  $5 \times 2 = 10$ 배의 전류가 흐른다. 다음의 제 2 기간에서는 도 30(b1)에 있어서, 1 화소 행을 선택한다. 이 1 화소의 트랜지스터(11a)에는 10배의 전류를 흘린다.

또, 도 31에 있어서, 복수의 화소 행을 동시에 선택하는 기간을 1/2H로 하고, 1 화소 행을 선택하는 기간을 1/2H로 하였지만 이것에 한정하는 것은 아니다. 복수의 화소 행을 동시에 선택하는 기간을 1/4H로 하고, 1 화소 행을 선택하는 기간을 3/4H로 해도 좋다. 또한, 복수의 화소 행을 동시에 선택하는 기간과, 1 화소 행을 선택하는 기간을 가한 기간은 1H로 하였지만 이것에 한정하는 것은 아니다. 예를 들면, 2H 기간에서도, 1.5H 기간이더라도 좋다.

또한, 도 30에 있어서, 5 화소 행을 동시에 선택하는 기간을 1/2H로 하고, 다음의 제 2 기간에서는 2 화소 행을 동시에 선택하는 것으로 해도 좋다. 이 경우에도 실용상, 지장이 없는 화상 표시를 실현할 수 있다.

또한, 도 30에 있어서, 5 화소 행을 동시에 선택하는 제 1 기간을 1/2H로 하고, 1 화소 행을 선택하는 제 2 기간을 1/2H로 하는 2단계로 하였지만 이것에 한정하는 것은 아니다. 예를 들면, 제 1 단계는, 5 화소 행을 동시에 선택하고, 제 2 기간은 상기 5 화소 행 중, 2 화소 행을 선택하며, 마지막으로, 1 화소 행을 선택하는 3개의 단계로 해도 좋다. 즉, 복수의 단계에서 화소 행에 화상 데이터를 기입하더라도 좋다.