(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2009-0013811

(43) 공개일자 2009년02월05일

(51) Int. Cl.<sup>9</sup>

G09G 3/30 (2006.01) G09G 3/32 (2006.01)

G09G 3/20 (2006.01) H01L 51/50 (2006.01)

(21) 출원번호 10-2008-7029124

(22) 출원일자 2008년11월27일

심사청구일자 2008년11월27일

번역문제출일자 2008년11월27일

(86) 국제출원번호 PCT/JP2007/066953

국제출원일자 2007년08월24일

(87) 국제공개번호 WO 2008/029717

국제공개일자 2008년03월13일

(30) 우선권주장

JP-P-2006-240257 2006년09월05일 일본(JP)

(71) 출원인

캐논 가부시끼가이샤

일본 도쿄도 오오따꾸 시모마루코 3조메 30방 2고

(72) 발명자

아베, 가쓰미

일본 146-8501 도쿄도 오오따꾸 시모마루코 3조메

30-2 캐논 가부시끼가이샤 내

(74) 대리인

장수길, 박충범

전체 청구항 수 : 총 17 항

#### (54) 유기 발광 표시 디바이스

#### (57) 요 약

트랜지스터들의 특성 시프트의 영향을 억제하고 대형 고해상도의 발광 디스플레이에 적용할 수 있는, 단극성 박막 트랜지스터들로만 형성된 구동 회로를 이용하는 발광 표시 디바이스가 제공된다. 이 디바이스는, 유기 EL 디바이스(LED) 및 그에 대한 구동 회로를 갖는 화소를 포함한다. 전류 기입 기간 동안, 구동 회로는 TFT3, TFT4 및 TFT5를 온으로 설정하고, TFT3를 통해 접지선 및 LED의 일 단을 동일한 전압으로 설정한다. 데이터선으로부터의 전류는, TFT4 및 TFT5를 통해, 커런트 미러 회로를 형성하는 트랜지스터들 L-TFT 및 D-TFT에 공급되며 L-TFT 및 D-TFT의 게이트 및 소스 단자를 간의 전압은 캐패시터에 유지된다. LED 구동 기간 동안, TFT3, TFT4 및 TFT5는 차단되며, D-TFT의 소스와 드레인 간에 흐르는 전류는, 유지 전압에 따라서 LED에 공급된다.

**대 표 도** - 도1

## 특허청구의 범위

### 청구항 1

발광 디바이스와, 상기 발광 디바이스를 구동하기 위한 구동 회로를 갖는 화소를 포함하는 발광 표시 디바이스로서,

상기 구동 회로는,

동일한 극성을 갖는 제1 박막 트랜지스터 및 제2 박막 트랜지스터 - 상기 제1 박막 트랜지스터의 게이트 단자는 상기 제2 박막 트랜지스터의 게이트 단자에 접속되고, 상기 제1 박막 트랜지스터의 소스 단자는 상기 제2 박막 트랜지스터의 소스 단자에 접속되고, 상기 제1 박막 트랜지스터 및 상기 제2 박막 트랜지스터의 소스 단자들은 상기 발광 디바이스의 일 단에 접속되어 있음 -;

일 단이 상기 제1 박막 트랜지스터 및 상기 제2 박막 트랜지스터의 소스 단자들과 상기 발광 디바이스의 일 단에 접속되어 있고, 타 단이 제1 배선에 접속되어 있는 제1 스위치; 및

일 단이 상기 제1 박막 트랜지스터 및 상기 제2 박막 트랜지스터의 게이트 단자들에 접속되어 있고, 타 단이 상기 제1 박막 트랜지스터 및 상기 제2 박막 트랜지스터의 소스 단자들에 접속되어 있는 캐패시터

를 포함하며,

상기 구동 회로는, 구동 신호를 기입하기 위한 제1 기간과, 상기 제1 기간 후에 상기 발광 디바이스를 구동하기 위한 제2 기간을 적어도 가지며,

상기 제1 기간은, 상기 제1 스위치를 통해 상기 제1 배선과 상기 발광 디바이스의 상기 일 단이 동일한 전압으로 설정되고, 상기 발광 디바이스의 구동 신호를 공급하기 위한 제2 배선이 상기 제1 박막 트랜지스터의 드레인 단자와 상기 제1 박막 트랜지스터 및 상기 제2 박막 트랜지스터의 게이트 단자들에 전기적으로 접속되어, 상기 제2 배선으로부터 상기 제1 박막 트랜지스터에 전류를 공급하는 기간을 포함하며,

상기 제2 기간은, 상기 제2 배선과 상기 제1 박막 트랜지스터 간의 접속, 상기 제2 배선과 상기 제2 박막 트랜지스터 간의 접속, 및 상기 제1 스위치가 차단되는 기간을 포함하는 발광 표시 디바이스.

### 청구항 2

발광 디바이스와, 상기 발광 디바이스를 구동하기 위한 구동 회로를 갖는 화소를 포함하는 발광 표시 디바이스로서,

상기 구동 회로는,

동일한 극성을 갖는 제1 박막 트랜지스터 및 제2 박막 트랜지스터 - 상기 제1 박막 트랜지스터의 게이트 단자는 상기 제2 박막 트랜지스터의 게이트 단자에 접속되고, 상기 제1 박막 트랜지스터의 소스 단자는 상기 제2 박막 트랜지스터의 소스 단자에 접속되고, 상기 제1 박막 트랜지스터 및 상기 제2 박막 트랜지스터의 소스 단자들은 상기 발광 디바이스의 일 단에 접속되어 있음 -;

일 단이 상기 제1 박막 트랜지스터 및 상기 제2 박막 트랜지스터의 소스 단자들과 상기 발광 디바이스의 일 단에 접속되어 있고, 타 단이 제1 배선에 접속되어 있는 제1 스위치; 및

일 단이 상기 제1 박막 트랜지스터 및 상기 제2 박막 트랜지스터의 게이트 단자들에 접속되어 있고, 타 단이 상기 제1 박막 트랜지스터 및 상기 제2 박막 트랜지스터의 소스 단자들에 접속되어 있는 캐패시터

를 포함하며,

상기 구동 회로는, 구동 신호를 기입하기 위한 제1 기간과, 상기 제1 기간 후에 상기 발광 디바이스를 구동하기 위한 제2 기간을 적어도 가지며,

상기 제1 기간 동안, 상기 제1 스위치를 통해 상기 제1 배선과 상기 발광 디바이스의 일 단이 동일한 전압으로 설정되고, 상기 발광 디바이스의 구동 신호를 공급하기 위한 제2 배선으로부터의 전류가, 상기 제1 박막 트랜지스터의 드레인 단자와 상기 제1 박막 트랜지스터 및 상기 제2 박막 트랜지스터의 게이트 단자들에 공급되어, 상기 제1 박막 트랜지스터의 드레인 단자와 소스 단자 사이에 흐르는 전류에 기초하여 결정되는, 상기 제2 박막

트랜지스터의 게이트 단자와 소스 단자 간의 전압을 상기 캐패시터에 유지하고,

상기 제2 기간 동안, 상기 캐패시터의 유지 전압에 따라 상기 제2 박막 트랜지스터의 소스 단자와 드레인 단자 사이에 흐르는 전류가 상기 발광 디바이스에 공급되는 발광 표시 디바이스.

### 청구항 3

제2항에 있어서,

상기 구동 회로는,

일 단이 상기 제2 배선에 접속되고, 타 단이 상기 제1 박막 트랜지스터의 드레인 단자에 접속되는 제2 스위치; 및

일 단이 상기 제1 박막 트랜지스터의 드레인 단자에 접속되고, 타 단이 상기 제1 박막 트랜지스터의 게이트 단자에 접속되는 제3 스위치

를 더 포함하며,

상기 제2 배선으로부터의 전류는, 상기 제2 및 제3 스위치들을 통해 상기 제1 박막 트랜지스터의 드레인 단자, 및 상기 제1 박막 트랜지스터 및 상기 제2 박막 트랜지스터의 게이트 단자들에 공급되는 발광 표시 디바이스.

### 청구항 4

제1항에 있어서,

상기 제1 박막 트랜지스터의 채널 폭을 그것의 채널 길이로 나눔으로써 얻어진 값이, 상기 제2 박막 트랜지스터의 채널 폭을 그것의 채널 길이로 나눔으로써 얻어진 값보다 크거나 같은 발광 표시 디바이스.

### 청구항 5

제1항에 있어서,

상기 구동 회로는, 제3 배선과 상기 제2 박막 트랜지스터의 드레인 단자 사이에 제4 스위치를 더 포함하는 발광 표시 디바이스.

### 청구항 6

제1항에 있어서,

상기 캐패시터는, 상기 제1 박막 트랜지스터의 채널 용량 및 게이트와 드레인 오버랩 용량과, 상기 제2 박막 트랜지스터의 채널 용량 및 게이트와 드레인 오버랩 용량을 합함으로써 얻어진 총 용량값의 3배 이상인 용량값을 갖는 발광 표시 디바이스.

### 청구항 7

제1항에 있어서,

상기 제1 박막 트랜지스터 및 상기 제2 박막 트랜지스터는 각각 p형 박막 트랜지스터로 구성되며; 상기 발광 디바이스의 캐소드 단자가, 상기 제1 p형 박막 트랜지스터 및 상기 제2 p형 박막 트랜지스터의 소스 단자들에 접속되는 발광 표시 디바이스.

### 청구항 8

제1항에 있어서,

상기 제1 박막 트랜지스터 및 상기 제2 박막 트랜지스터는 각각 n형 박막 트랜지스터로 구성되며; 상기 발광 디바이스의 애노드 단자가, 상기 제1 박막 트랜지스터 및 상기 제2 박막 트랜지스터의 소스 단자들에 접속되는 발광 표시 디바이스.

### 청구항 9

제8항에 있어서,

상기 제1 스위치, 상기 제2 스위치, 상기 제3 스위치, 및 상기 제4 스위치는, 제3 박막 트랜지스터, 제4 박막 트랜지스터, 제5 박막 트랜지스터, 및 제6 박막 트랜지스터로 각각 구성되며; 상기 제3 박막 트랜지스터, 상기 제4 박막 트랜지스터, 상기 제5 박막 트랜지스터, 및 상기 제6 박막 트랜지스터는, 상기 제1 박막 트랜지스터 및 상기 제2 박막 트랜지스터와 동일한 극성을 갖는 발광 표시 디바이스.

#### 청구항 10

제9항에 있어서,

상기 제1 스위치, 상기 제2 스위치, 및 상기 제3 스위치에 각각 대응하는 상기 제3 박막 트랜지스터, 상기 제4 박막 트랜지스터, 및 상기 제5 박막 트랜지스터는 각각 제4 배선에 접속되는 게이트 단자를 갖는 발광 표시 디바이스.

#### 청구항 11

제1항에 있어서,

상기 발광 디바이스의 동작 전압보다 낮거나 같은 전압이 상기 제1 배선에 인가되는 발광 표시 디바이스.

#### 청구항 12

제1항에 있어서,

상기 구동 회로는, 상기 제1 기간 및 상기 제2 기간 중 적어도 한쪽의 일부 기간에, 상기 제2 박막 트랜지스터의 소스 단자와 드레인 단자 사이에 전류가 흐르지 않도록 하는 전류 차단기를 더 포함하는 발광 표시 디바이스.

#### 청구항 13

제12항에 있어서,

상기 전류 차단기는, 상기 제2 박막 트랜지스터의 드레인 단자에서의 전압을, 상기 제1 배선의 전압과 동일한 전위로 설정하는 발광 표시 디바이스.

#### 청구항 14

제12항에 있어서,

상기 전류 차단기는, 상기 제4 스위치에 의해 상기 제2 박막 트랜지스터의 전류 경로를 차단하는 발광 표시 디바이스.

#### 청구항 15

제1항에 있어서,

상기 발광 디바이스는 유기 EL 디바이스인 발광 표시 디바이스.

#### 청구항 16

제8항에 있어서,

상기 구동 회로의 n형 박막 트랜지스터는,  $10^{18} [\text{cm}^{-3}]$  이하의 캐리어 밀도를 갖는 비정질 금속 산화물로 이루어진 n형 반도체 막을, 상기 n형 박막 트랜지스터의 채널 막으로서 이용하고,  $1 [\text{cm}^2/\text{Vs}]$  이상의 이동도와,  $10^6$  이상의 온/오프 비를 갖는 발광 표시 디바이스.

#### 청구항 17

제1항에 있어서,

복수의 화소들이 매트릭스 형상으로 기판 상에 배치되어 있는 발광 표시 디바이스.

## 명세서

### 기술분야

<1> 본 발명은 공급될 전류에 따라 그 기능을 달성하는 전류 부하 디바이스에 관한 것이며, 보다 구체적으로는 전류 부하로서 발광 디바이스를 이용하는 발광 표시 디바이스에 관한 것이다. 특히, 본 발명은 매트릭스 형상으로 형성된 복수의 화소를 포함하는 발광 표시 디바이스에 관한 것이며, 그 화소들 각각은 발광 디바이스로서 기능하는 유기 전계 발광(electro-luminescence)(이하, "EL"로 칭함) 디바이스와, 유기 EL 디바이스에 전류를 공급하기 위한 구동 회로로 구성된다.

### 배경기술

<2> 유기 EL 디바이스는, 발광 다이오드(LED; light emitting diode)에서처럼 전류가 통과될 때 발광하는 발광 디바이스이며, OLED(organic LED)로도 칭해진다. 매트릭스 형상으로 형성된 복수의 화소를 포함하는 발광 표시 디바이스로서 - 그 화소들 각각은 유기 EL 디바이스와 이 유기 EL 디바이스를 구동하기 위한 구동 회로로 구성됨 -, 액티브 매트릭스(active-matrix, 이하 AM으로 칭함)형 유기 EL 디스플레이가 검토되었다.

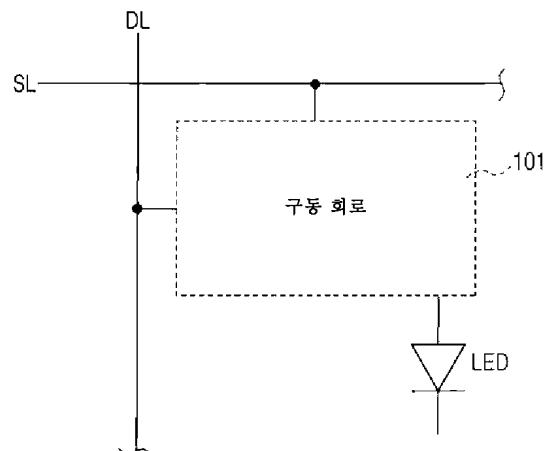

<3> 도 6은 AM형 유기 EL 디스플레이의 화소의 구성 예를 나타낸다. 도 6에서, 참조 부호 LED는 유기 EL 디바이스를 나타내며, 참조 번호 101은 구동 회로를 나타내며, 참조 부호 DL은 데이터선을 나타내며, 참조 부호 SL은 주사선을 나타낸다. 도 7은 복수 개의 화소가 매트릭스 형상( $n$ 열  $\times$   $m$ 행)으로 배열되어 있는 AM형 유기 EL 디스플레이의 구성 예를 나타낸다. 도 7에서, 참조 부호 SL<sub>1</sub> 내지 SL<sub>m</sub> 각각은 첫 번째 행에서  $m$ 번째 행까지의 행마다 배치되는 주사선을 나타내며, 참조 부호 DL<sub>1</sub> 내지 DL<sub>n</sub> 각각은 첫 번째 열에서  $n$ 번째 열까지의 열마다 배치되는 데이터선을 나타낸다. 도 7에 도시된 AM형 유기 EL 디스플레이(100)는, 화소마다, 각 행에 대한 주사선 SL의 신호(H 레벨 또는 L 레벨)에 응답하여, 각 열에 대한 데이터선 DL을 통해 구동 회로(101)로부터 유기 EL 디바이스 LED에 공급될 전압 및 전류, 시간 등을 제어한다. 이러한 제어를 통해, 유기 EL 디바이스 LED의 휘도가 조정되며, 그 계조 표시가 행해진다.

<4> 전술한 바와 같은 AM형 유기 EL 디스플레이에서, 유기 EL 디바이스의 전압-휘도 특성이 시간에 따라 변화하는 경우, 표시 품질에 영향을 미친다. 이는 또한 구동 회로의 구성 요소인 박막 트랜ジ스터(thin film transistor; 이하 TFT라 칭함)의 특성에 변동이 있는 경우와, 인가되는 전기적 스트레스로 인해 TFT의 특성이 변화하는 경우에도 적용된다. 따라서, 불균일성이 없는 고품질의 표시를 달성하기 위해서는, 유기 EL 디바이스 특성의 시간적 변화, 또는 TFT의 특성 변동 및 변화에 의한 영향을 받기 어려운 구동 회로 및 구동 방법을 개발할 필요가 있다.

<5> (종래 기술 1)

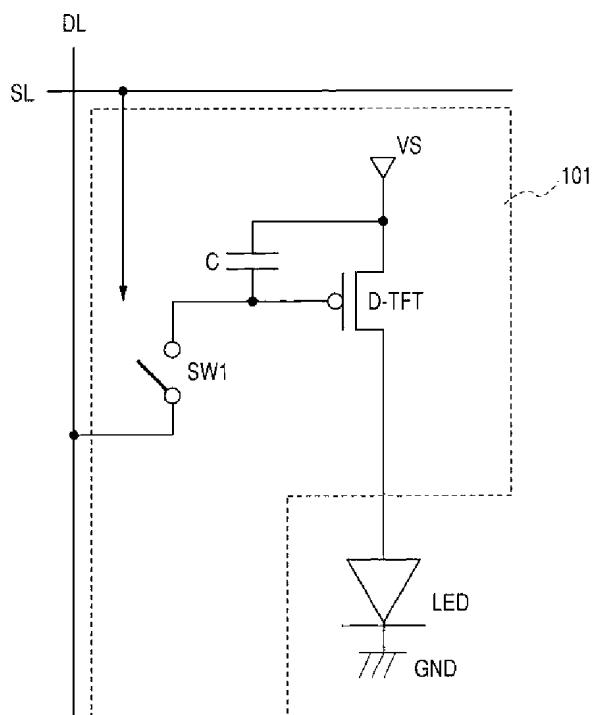

<6> 도 8은 제1 종래 기술로서 가장 간단한 구동 회로를 나타내고 있다. 도 8에서, 참조 부호 LED는 유기 EL 디바이스를 나타내며, 참조 번호 101은 구동 회로를 나타내며, 참조 부호 DL은 데이터선을 나타내며, 참조 부호 SL은 주사선을 나타내며, 참조 부호 VS는 전원선을 나타내며, 참조 부호 GND는 접지선을 나타내며, 참조 부호 D-TFT는 구동 p형 TFT를 나타내며, 참조 부호 C는 캐패시터를 나타낸다. 스위치(스위칭 소자) SW1의 온/오프 동작은 주사선 SL의 신호에 응답하여 제어된다.

<7> 이 종래 기술에서, 스위치 SW1은 주사선 SL의 신호에 응답하여 턴 온되며, 데이터선 DL로부터의 전압은, 스위치 SW1을 통해, 구동 회로(101) 내에 제공되는 TFT(D-TFT)의 게이트 단자에 인가되며, 이에 따라 게이트 단자와 소스 단자 간의 전압을 캐패시터 C에 유지한다. TFT는, 게이트 단자에 인가된 전압에 따라 유기 EL 디바이스 LED에 전류를 공급한다. 이 종래 기술에서는, OLED 디바이스의 전류-휘도 특성의 시간 변동이 전압-휘도 특성보다 작기 때문에, OLED 발광의 변화가 작다. 한편, TFT의 특성에 변동이 있으면, 유기 EL 디바이스 LED에 공급되는 전류가 변동되어, 표시 불균일이 나타난다. 종래 기술에서는, 전술한 문제점을 해결하기 위해 몇몇 구동 회로들이 제안되었다. 이하의 설명에서는, 이를 구동 회로들의 종래 기술의 예에 대해 기술할 것이다.

<8> (종래 기술 2)

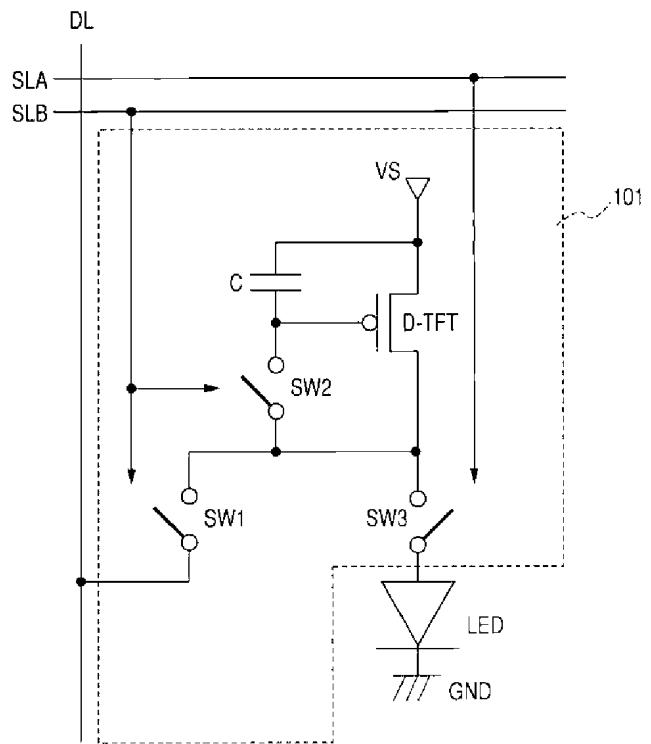

<9> 도 9는 제2 종래 기술로서 미국특허 제6,373,454호에 개시된 구동 회로를 도시한다. 도 9에서, 참조 부호 LED는 유기 EL 디바이스를 나타내며, 참조 번호 101은 구동 회로를 나타내며, 참조 부호 DL은 데이터선을 나타내며, 참조 부호 SLA 및 SLB 각각은 주사선을 나타내며, 참조 부호 VS는 전원선을 나타내며, 참조 부호 GND는 접지선을 나타내며, 참조 부호 D-TFT는 구동 p형 TFT를 나타내며, 참조 부호 C는 캐패시터를 나타낸다. 스

위치(스위칭 소자) SW1, SW2 및 SW3 각각의 온/오프 동작은, 주사선 SL의 신호에 응답하여 제어된다.

<10> 이 종래 기술에서, 스위치들 SW1 및 SW2는, 주사선 SLA의 신호에 응답하여 턴 온되며, 구동 회로(101) 내에 제 공되는, 게이트 단자와 드레인 단자 사이에 스위치 SW2를 통해 단락이 형성된 TFT(D-TFT)에, 스위치 SW1을 통해 외부(데이터선 DL)로부터 전류가 공급된다. 이에 따라, TFT의 게이트 단자에서의 전압이, TFT의 임계치와 이동 도에 따라 외부로부터 전류가 흐르는 전압으로서 설정될 수 있다. 그러면, 스위치 SW3이 주사선 SLB의 신호에 응답하여 턴 온되면, TFT는 전류원으로서 기능하며, 외부로부터의 전류와 동일한 강도의 전류를 스위치 SW3을 통해 유기 EL 디바이스 LED에 전달할 수 있다. 따라서, 외부로부터의 전류가 변동하지 않는 경우, 본 종래 기술에 따르면, TFT의 특성 변동에 관계없이, 유기 EL 디바이스를 통해 일정한 전류가 흐르게 할 수 있으며 불균 일 없이 표시를 행할 수 있다.

<11> (종래 기술 3)

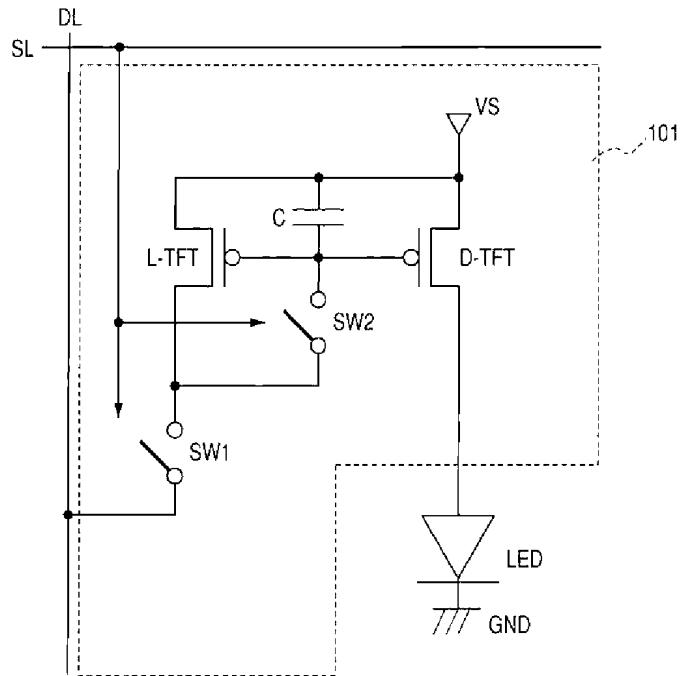

<12> 도 10은 제3 종래 기술로서 미국특허 제6,501,466호에 개시된 구동 회로를 나타낸다. 도 10에서, 참조 부호 LED는 유기 EL 디바이스를 나타내며, 참조 번호 101은 구동 회로를 나타내며, 참조 부호 DL은 데이터선을 나타 내며, 참조 부호 SL은 주사선을 나타내며, 참조 부호 VS는 전원선을 나타내며, 참조 부호 GND는 접지선을 나타 내며, 참조 부호 L-TFT 및 D-TFT는 커런트 미러 회로를 형성하는 한 쌍의 p형 TFT를 나타내며, 참조 부호 C는 캐패시터를 나타낸다. 스위치(스위칭 소자) SW1 및 SW2 각각의 온/오프 동작은, 주사선 SL의 신호에 응답하여 제어된다.

<13> 이 종래 기술에 따르면, 스위치들 SW1 및 SW2는 주사선 SL의 신호에 응답하여 턴 온되며, 하나의 TFT(L-TFT)의 게이트 단자와 드레인 단자는 스위치 SW2를 통해 단락되며, 외부(데이터선 DL)로부터 스위치 SW1을 통해 전류가 공급된다. 이에 따라, L-TFT의 게이트 단자에서의 전압은, 전류가 외부로부터 흐르는 전압으로서 설정될 수 있다. 이러한 구성에 의해, 종래 기술의 TFT들 중 다른 TFT(D-TFT)가 전압에 따라 유기 EL 디바이스 LED에 전류를 공급한다. 커런트 미러 회로를 형성하는 두 개의 TFT는 서로 근접하여 위치되며, 그 사이의 특성 변동이 작기 때문에, 유기 EL 디바이스 LED에 공급된 전류는, 외부로부터의 전류 및 L-TFT와 D-TFT 간의 전류 능력비 (current capability ratio)에 기초하여 결정된다. 따라서, 외부로부터의 전류가 변동하지 않는 경우, 본 종래 기술에 따르면, TFT의 특성 변동에 관계없이, 유기 EL 디바이스를 통해 일정한 전류가 흐르도록 할 수 있으며, 불균일 없이 표시를 행할 수 있다.

<14> 전술한 회로의 경우, 다결정 실리콘(polycrystal-Si, 이하 "p-Si"라 칭함), 비정질 실리콘(amorphous silicon, 이하 "a-Si"라 칭함), 유기 반도체(organic semiconductor, 이하 "OS"라 칭함) 등으로 이루어진 채널 층을 갖는 TFT가 검토되었다. p-Si TFT는 낮은 동작 전압에서 높은 이동도를 갖도록 제조될 수 있지만, 그 제조 코스트가 높다. 한편, a-Si TFT 또는 OS TFT는 제조 공정수가 적어 낮은 코스트로 제조될 수 있지만, a-Si 및 OS TFT는 p-Si TFT보다 낮은 이동도를 갖기 때문에 높은 동작 전압과 큰 전력 소비를 요구한다. 또한, ZnO 등의 금속 산화물 반도체를 채널 층으로서 이용하는 TFT가 최근에 개발되었으며, 이러한 TFT는 a-Si TFT 및 OS TFT보다 높은 이동도를 갖는 것으로 보고되어 있다.

<15> a-Si, OS, 또는 금속 산화물 반도체로 이루어진 채널 층을 갖는 TFT는, n형 TFT와 p형 TFT가 동일한 기판 상에 형성되는 상보형 TFT로 되는 것이 어렵다. 예를 들면, 높은 이동도를 갖는 p형 반도체는 a-Si 또는 금속 산화물을 이용하여 얻어지지 않았기 때문에, p형 TFT를 형성하는 것은 어렵다. 또한, OS에 관해서는, 높은 이동도를 갖는 n형 반도체와 p형 반도체는 서로 다른 재료로 이루어지며, 이로 인해 공정이 2배로 되며, 이 TFT를 낮은 코스트로 제조하는 것이 어렵게 된다. 따라서, 이들 TFT를 이용하는 구동 회로가 n형 TFT 혹은 p형 TFT만으로 형성될 필요가 있다.

<16> 또한, a-Si, OS, 혹은 금속 산화물로 이루어진 채널 층을 갖는 TFT는, 게이트 단자와 소스 단자 사이에 인가될 전압에 따라 시프트될 수 있는 전류-전압 특성을 갖는다는 것이 알려져 있다.

<17> 전술한 설명에서, a-Si TFT는 AM형 액정 디스플레이(이하, "LCD"라 칭함)의 화소에 이용되고 있으며, 그에 대한 수십 인치의 대각 사이즈를 갖는 생산 기술이 확립되어 있다. 이러한 이유 때문에, a-Si TFT는, 10인치 이상의 대각 사이즈를 갖는 대형 AM형 유기 EL 디스플레이의 구동 회로를 위한 유망한 TFT로서 간주되며, 기술 개발이 촉진되고 있다(후술하는 도 11에 도시된 제4 종래 기술 참조).

<18> 한편, 유기 EL 디바이스는, 일반적으로, 애노드 전극과 캐소드 전극 사이에, 적어도 유기 재료로 이루어진 발광 층이 끼어져 있는 구조를 갖는다. 유기 재료는 열, 전자파, 수분 등에 영향을 받으므로 그 특성이 변화되기 쉽다. 이 때문에, 유기 EL 디바이스를 이용하는 발광 표시 디바이스의 경우, 구동 회로 및 애노드 전극의 형성

후에, 유기 재료로 이루어지는 발광층이 형성되고, 그 후 손상이 적은 진공 성막 등에 의해 캐소드 전극이 형성되는 제조 프로세스를 이용하는 것이 바람직하다.

<19> 전술한 프로세스에 따르면, AM형 유기 EL 디스플레이의 각 화소가, n형 TFT로 형성되는 구동 회로와, 아래로부터 애노드 전극, 유기 발광층, 및 캐소드 전극의 순서로 형성되는 유기 EL 디바이스를 포함하는 경우가 고려된다. 이 경우, 미국특허 제6,373,454호 및 미국특허 제6,501,466호에 개시된 기능은 p형 TFT를 n형 TFT로 치환하는 것만으로는 달성될 수 없다. 이는, 미국특허 제6,373,454호 및 미국특허 제6,501,466호에서는, p형 TFT의 소스 단자 전압은 전원에 의해 고정되며, 게이트 단자 전압은 외부로부터의 전류에 기초하여 결정되기 때문이다. 이 때문에, 유기 EL 디바이스 구동시에는, 게이트 단자와 소스 단자 간의 전압차가 고정되어 있으며, 이는 유기 EL 디바이스에 대하여, 정전류원으로서 기능한다. 이 경우, p형 TFT가 n형 TFT로 치환되면, 게이트 단자와 드레인 단자 간의 전압이 고정되며, 이는 정전류원으로서 기능하지 않는다. 또한, 전술한 바와 같이, 인가되는 전압에 의한 특성 시프트(characteristic shift)가 야기되므로, 특성 시프트의 영향을 억제할 필요가 있다.

<20> (종래 기술 4)

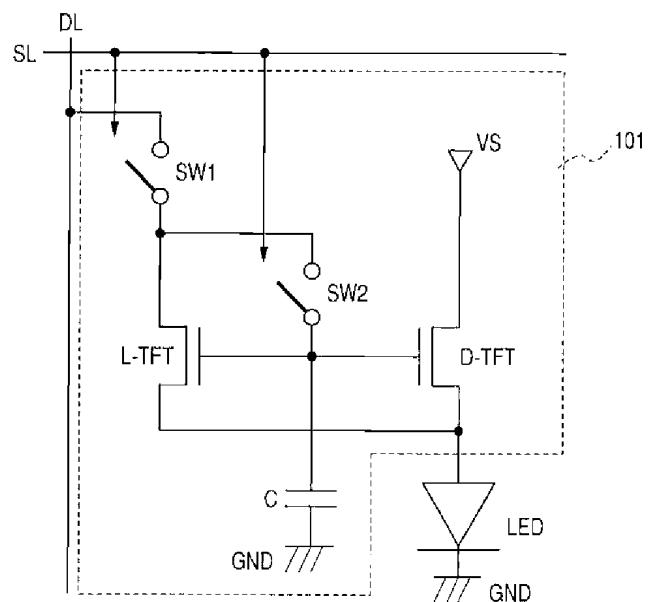

<21> 제4 종래 기술은 a-Si TFT를 이용한 구동 회로에 의한 상기 언급된 문제점을 해결하기 위한 종래 기술이다. 도 11은 A.Nathan 등(SID 05 DIGEST, p.26, 도 3) 및 A.Nathan 등(SID 06 DIGEST, 46.1, 도 1)에 개시된 구동 회로를 나타낸다. 도 11에서, 참조 부호 LED는 유기 EL 디바이스를 나타내며, 참조 번호 101은 구동 회로를 나타내며, 참조 부호 DL은 데이터선을 나타내며, 참조 부호 SL은 주사선을 나타내며, 참조 부호 VS는 전원선을 나타내며, 참조 부호 GND는 접지선을 나타내며, 참조 부호 L-TFT 및 D-TFT는 커런트 미러 회로를 형성하는 한 쌍의 n형 TFT를 나타내며, 참조 부호 C는 캐패시터를 나타낸다. 스위치(스위칭 소자) SW1 및 SW2 각각의 온/오프 동작은, 주사선 SL의 신호에 응답하여 제어된다.

<22> 이 종래 기술에서는, 미국특허 제6,501,466호에 개시된 커런트 미러 회로가 적용된다. 이 종래 기술에 따르면, 스위치들 SW1 및 SW2는, 주사선 SL의 신호에 응답하여 턴 온되며, L-TFT의 게이트 단자와 드레인 단자는 스위치 SW2를 통해 서로 접속되어 있으며, 스위치 SW1을 통해 외부(데이터선 DL)로부터 전류가 공급된다. 그러면, 공급된 전류는, L-TFT의 드레인 단자로부터 그 소스 단자, 또한 유기 EL 디바이스 LED에 흐른다. 따라서, L-TFT의 게이트 단자와 소스 단자에서의 전압은, 전류가 외부로부터 흐르게 되는 전압으로 된다. 또한, D-TFT는 L-TFT와 공통인 게이트 단자와 소스 단자를 갖기 때문에, L-TFT의 게이트 단자 전압 및 소스 단자 전압에 따라 D-TFT는 유기 EL 디바이스 LED에 전류를 공급한다. 이 게이트 단자 전압을 캐패시터 C에 유지함으로써, 외부로부터의 전류가 중단된 기간에도, D-TFT는, 외부로부터 전류가 공급되는 기간 동안 얻어지는 전류와 동일한 전류를 공급할 수 있다.

<23> 또한, 동작 동안에는, D-TFT와 L-TFT의 게이트 단자들 및 소스 단자들에는 동일한 전압이 공급되며, TFT들의 특성 시프트는 동등하게 된다. 이 때, D-TFT와 L-TFT 간의 전류 능력비가 유지된다. 이 경우, 특성 시프트가 유발되는 경우에도, 이를 TFT를 통해 흐르는 전류는, 특성 시프트가 유발되기 전에 얻어진 전류와 동등하게 될 수 있다.

<24> 이 종래 기술에서는, L-TFT가, D-TFT에 비해, 전류를 흘리는 능력이 충분히 낮을 필요가 있음에 주목한다. 이는, 유기 EL 디바이스에는, 외부로부터 전류가 공급되고 있는 기간 동안에는 L-TFT와 D-TFT로부터 전류가 공급되는 한편, 외부로부터의 전류가 중단되는 기간 동안에는 유기 EL 디바이스에 D-TFT로부터만 전류가 공급되기 때문이다. 따라서, 두 기간에서, 유기 EL 디바이스의 전류 능력에 기초하여 결정되는 L-TFT와 D-TFT의 소스 전압들은, L-TFT의 전류값이 D-TFT의 전류값보다 큰 경우에는 서로 일치하지 않는다. 이 경우, 외부로부터의 전류가 공급되는 기간 동안 설정된 전류는, 외부로부터의 전류가 중단되는 기간 동안에는 흐를 수 없게 된다. 이에 따라, 외부로부터 L-TFT에 공급되는 전류는, D-TFT에 의해 유기 EL 디바이스에 공급되는 전류보다 작게 될 필요가 있다.

<25> 한편, 최근에, 유기 EL 디바이스의 전류-회로 특성이 개선되었으며, 유기 EL 디바이스로 공급되는 전류가 저하되었다. 또한, 보다 대형이며 보다 높은 선명도를 갖는 유기 EL 디스플레이에 대한 요구가 존재하며, 배선 부하가 증가하는 경향에 있다. 따라서, 종래 기술에서, 특히, 낮은 제조에 대응하는 낮은 전류를 외부로부터 공급하는 경우, 배선 부하를 충전하기 위해서는 긴 시간이 필요하게 된다. 이 경우, 구동 회로 내에 제공되는 TFT의 게이트 단자에서의 전압을, TFT의 임계치와 이동도에 따라, 외부로부터 전류가 흐르는 전압과 동일하게 설정하는 동작을 수행하는 데에는 긴 시간이 걸리게 되며, 이는 높은 해상도 및 큰 화면을 갖는 표시 디바이스에 유기 EL 디바이스를 적용하는 것을 어렵게 만든다. 이러한 어려움을 극복하기 위해, 외부로부터의 전류를

증가시키기 위한 유닛을 이용할 수도 있지만, 이 유닛은 전술한 바와 같이, 제4 종래 기술에는 적용될 수 없다.

### 발명의 상세한 설명

&lt;26&gt;

<발명의 개시>

&lt;27&gt;

본 발명의 목적은, 인가되는 전압에 기인한 박막 트랜지스터의 특성 시프트의 영향을 억제할 수 있으며, 대형 고해상도의 발광 표시 디바이스에 적용될 수 있는, 단극성의 박막 트랜지스터들만으로 구성되는 구동 회로를 이용하는 발광 표시 디바이스를 제공하는 것이다.

&lt;28&gt;

전술한 목적을 달성하기 위해, 본 발명의 제1 양태에 따르면, 발광 디바이스와, 이 발광 디바이스를 구동하기 위한 구동 회로를 갖는 화소를 포함하는 발광 표시 디바이스가 제공된다. 구동 회로는, 제1 박막 트랜지스터, 제2 박막 트랜지스터, 제1 스위치, 및 캐패시터를 포함한다.

&lt;29&gt;

제1 박막 트랜지스터의 게이트 단자는 제2 박막 트랜지스터의 게이트 단자에 접속되고, 제1 박막 트랜지스터의 소스 단자는 제2 박막 트랜지스터의 소스 단자에 접속된다. 소스 단자들은 발광 디바이스의 일 단에 접속되며, 제1 박막 트랜지스터 및 제2 박막 트랜지스터는 동일한 극성을 갖는다. 또한, 제1 스위치는, 일 단이 제1 박막 트랜지스터 및 제2 박막 트랜지스터의 소스 단자들과 발광 디바이스의 일 단에 접속되어 있고, 타 단이 제1 배선에 접속되어 있다. 또한, 캐패시터는, 일 단이 제1 박막 트랜지스터 및 제2 박막 트랜지스터의 게이트 단자들에 접속되어 있고, 타 단이 제1 박막 트랜지스터 및 제2 박막 트랜지스터의 소스 단자들에 접속되어 있다. 제2 배선은 구동 신호를 발광 디바이스에 공급한다.

&lt;30&gt;

구동 회로는, 구동 신호를 기입하기 위한 제1 기간과, 제1 기간 후에, 발광 디바이스를 구동하기 위한 제2 기간을 적어도 갖는다.

&lt;31&gt;

제1 기간은, 제1 스위치를 통해 제1 배선과 발광 디바이스의 일 단이 동일한 전압으로 설정되고, 제2 배선이, 제1 박막 트랜지스터의 드레인 단자와 제1 박막 트랜지스터 및 제2 박막 트랜지스터의 게이트 단자들에 전기적으로 접속되어, 제2 배선으로부터 제1 박막 트랜지스터에 전류를 공급하는 기간을 포함한다.

&lt;32&gt;

제2 기간은, 제2 배선과 제1 박막 트랜지스터 간의 접속, 제2 배선과 제2 박막 트랜지스터 간의 접속, 및 제1 스위치가 차단되는 기간을 포함한다.

&lt;33&gt;

또한, 전술한 목적을 달성하기 위해, 본 발명의 제2 양태에 따르면, 발광 디바이스와, 이 발광 디바이스를 구동하기 위한 구동 회로를 갖는 화소를 포함하는 발광 표시 디바이스가 제공된다. 구동 회로는, 제1 박막 트랜지스터, 제2 박막 트랜지스터, 제1 스위치, 및 캐패시터를 포함한다.

&lt;34&gt;

제1 박막 트랜지스터의 게이트 단자는 제2 박막 트랜지스터의 게이트 단자에 접속되고, 제1 박막 트랜지스터의 소스 단자는 제2 박막 트랜지스터의 소스 단자에 접속된다. 소스 단자들은, 발광 디바이스의 일 단에 접속되며, 제1 박막 트랜지스터 및 제2 박막 트랜지스터는 동일한 극성을 갖는다. 또한, 제1 스위치는, 일 단이 제1 박막 트랜지스터 및 제2 박막 트랜지스터의 소스 단자들과 발광 디바이스의 일 단에 접속되어 있고, 타 단이 제1 배선에 접속되어 있다. 또한, 캐패시터는, 일 단이 제1 박막 트랜지스터 및 제2 박막 트랜지스터의 게이트 단자들에 접속되어 있고, 타 단이 제1 박막 트랜지스터 및 제2 박막 트랜지스터의 소스 단자들에 접속되어 있다. 제2 배선은 구동 신호를 발광 디바이스에 공급한다.

&lt;35&gt;

구동 회로는 구동 신호를 기입하기 위한 제1 기간과, 제1 기간 후에, 발광 디바이스를 구동하기 위한 제2 기간을 적어도 갖는다.

&lt;36&gt;

제1 기간 동안, 구동 회로는, 제1 스위치를 통해 제1 배선과 발광 디바이스의 일 단을 동일한 전압으로 설정하고, 제2 배선으로부터의 전류를, 제1 박막 트랜지스터의 드레인 단자와 제1 박막 트랜지스터 및 제2 박막 트랜지스터의 게이트 단자들에 공급하여, 제1 박막 트랜지스터의 드레인 단자와 소스 단자 사이에 흐르는 전류에 기초하여 결정되는, 제2 박막 트랜지스터의 게이트 단자와 소스 단자 간의 전압을 캐패시터에 유지시킨다.

&lt;37&gt;

또한, 제2 기간 동안, 구동 회로는, 캐패시터의 유지 전압에 따라, 제2 박막 트랜지스터의 소스 단자와 드레인 단자 사이에 흐르는 전류를 발광 디바이스에 공급한다.

&lt;38&gt;

본 발명에 따르면, 각 화소는, 동일한 극성을 갖는 한 쌍의 박막 트랜지스터들로 형성되는 커런트 미러 회로를 포함하는 구동 회로를 갖는다. 이 한 쌍의 박막 트랜지스터들은, 제1 스위치를 통해 발광 디바이스의 일 단과 제1 배선에 접속되는 공통의 소스 단자를 가지며, 게이트 단자와 소스 단자 사이에는 캐패시터가 제공된다. 이

러한 구성에 의해, 인가되는 전압에 의한 박막 트랜지스터들의 특성 시프트의 효과를 억제할 수 있으며 대형 고해상도의 발광 표시 디바이스에 적용될 수 있는, 단극성 박막 트랜지스터들만으로 구성되는 구동 회로를 이용하는 발광 표시 디바이스를 제공할 수 있다.

<39> 본 발명의 또 다른 특성들은, 첨부된 도면을 참조하여 이하의 예시적인 실시예들로부터 명백하게 될 것이다.

### 실시예

<51> 이하, 본 발명의 실시예를 도면을 참조하여 설명한다.

<52> 본 발명의 일 실시예에서는, 유기 EL 디바이스를 이용하는 발광 표시 디바이스를 설명하지만, 본 발명은 유기 EL 디바이스 외의, 공급되는 전류에 의해 발광하는 발광 표시 디바이스, 및 공급되는 전류에 대해 임의의 기능을 나타내는 일반적인 전류 부하를 이용하는 전류 부하 디바이스에도 적용할 수 있다. 또한, 본 실시예에서는, n형 TFT를 설명한다. 대안으로는, 후술하는 바와 같이, n형 TFT 대신에 p형 TFT를 이용하고, 유기 EL 디바이스의 애노드 단자를 캐소드 단자로 교체할 수 있다.

<53> 본 실시예에 따른 발광 디바이스는, 공급되는 전류에 기초하여 휙도가 결정되는 유기 EL 디바이스와, 이 유기 EL 디바이스에 일정한 전류를 공급하는 구동 회로를 적어도 포함하는 화소를 갖는다.

<54> 유기 EL 디바이스는 또한 전술한 바와 같이 "OLED"로도 칭해지며, 고휙도의 발광이 가능한 면 형상의 자발광 (planar self-emitting)을 제공할 수 있다. 유기 EL 디바이스는, 애노드 전극 및 캐소드 전극 사이에 발광층으로서 기능하는 유기 층들을 그 기능에 따라 적층하고, 그 유기 층들의 기능적 적층 수를 증가시킴으로써, 저전압으로 고효율의 발광을 가능하게 한다. 유기 EL 디바이스의 기본 구성은, 유기 EL 디바이스가, 애노드 전극과 캐소드 전극 사이에, 유기층으로 이루어지는 EL 발광층 및 정공 수송층을 포함하여, 애노드 전극/정공 수송층/EL 발광층/캐소드 전극의 적층 구조를 형성하는 것이다. 발광 디바이스로서 유기 EL 디바이스를 이용하는 발광 표시 디바이스에서는, 발광층 내에 정공과 전자의 주입을 통해 발광 휙도가 제어된다. 유기 EL 디바이스는 공지된 사항이기 때문에, 그 상세한 설명은 생략함에 주목한다.

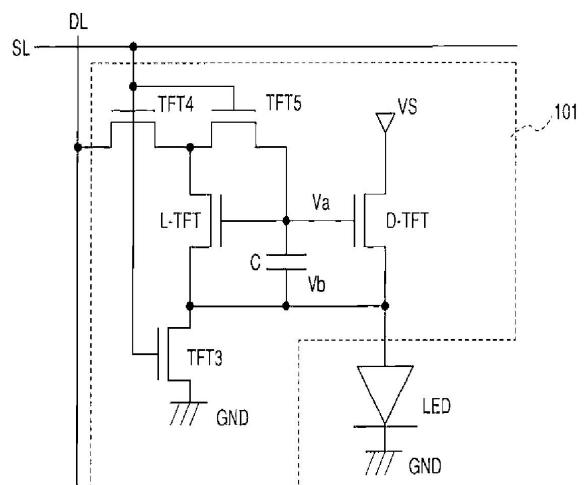

<55> 본 발명에 따른 발광 표시 디바이스를 도 1 및 도 2를 참조하여 설명할 것이다.

<56> 본 발명에 따른 발광 표시 디바이스는, 발광 디바이스와, 이 발광 디바이스를 구동하기 위한 구동 회로(101)를 포함하는 화소를 갖는다. 구동 회로(101)는 제1 박막 트랜지스터 L-TFT, 제2 박막 트랜지스터 D-TFT, 제1 스위치 TFT3, 캐패시터 C, 및 제1 배선 GND를 포함한다.

<57> 제1 박막 트랜지스터 및 제2 박막 트랜지스터(L-TFT 및 D-TFT)는, 서로 접속되어 있는 게이트 단자들과 서로 접속되어 있는 소스 단자들을 가지며, 소스 단자들은 발광 디바이스의 일 단(애노드 단자)에 접속되어 있다. 이 경우, 제1 박막 트랜지스터 및 제2 박막 트랜지스터(L-TFT 및 D-TFT)는 동일한 극성을 갖는다.

<58> 또한, 제1 스위치 TFT3은, 일 단이 제1 박막 트랜지스터 및 제2 박막 트랜지스터(L-TFT 및 D-TFT)의 소스 단자들 및 발광 디바이스의 일 단(애노드 단자)에 접속되어 있고, 타 단이 제1 배선 GND에 접속되어 있다.

<59> 또한, 캐패시터 C는, 일 단이 제1 박막 트랜지스터 및 제2 박막 트랜지스터(L-TFT 및 D-TFT)의 게이트 단자들에 접속되어 있고, 타 단이 제1 박막 트랜지스터 및 제2 박막 트랜지스터의 소스 단자들에 접속되어 있다. 제2 배선 DL은 발광 디바이스의 구동 신호를 공급한다.

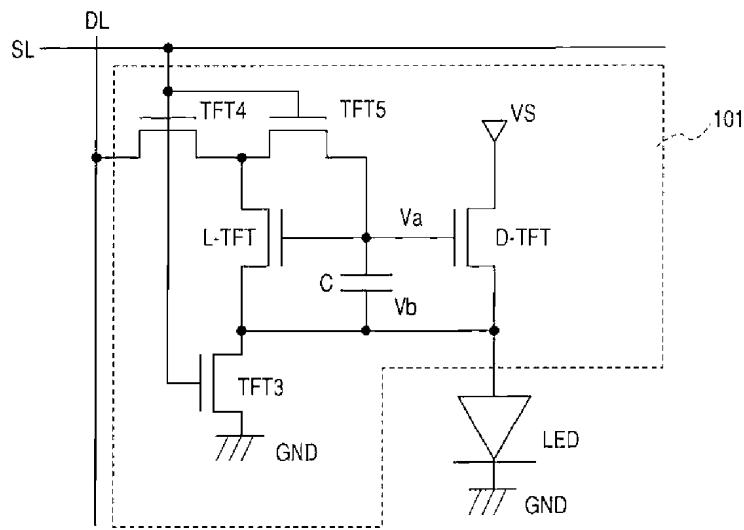

<60> 그러면, 본 발명에 따른 구동 회로는, 구동 신호를 기입하기 위한 제1 기간(도 2의 T1)과, 제1 기간 후에, 발광 디바이스를 구동하기 위한 제2 기간(도 2의 T2)을 적어도 갖는다.

<61> 제1 기간(T1) 동안, 구동 회로는 제1 스위치 TFT3를 통해 제1 배선과 발광 디바이스의 일 단(애노드 단자)을 동일 전압으로 설정한다. 또한, 제1 기간(T1) 동안, 구동 회로는, 제2 배선 DL을, 제1 박막 트랜지스터의 드레인 단자와 제1 박막 트랜지스터 및 제2 박막 트랜지스터의 게이트 단자들에 전기적으로 접속시켜서 제2 배선으로부터 제1 박막 트랜지스터에 전류를 공급한다. 제1 기간(T1)은 전술한 동작을 행하기 위한 기간을 포함한다.

<62> 이 경우, 제2 배선을, 제1 박막 트랜지스터의 드레인 단자와 제1 박막 트랜지스터 및 제2 박막 트랜지스터의 게이트 단자들에 접속시킬 때, 제2 스위치 TFT4 및 제3 스위치 TFT5는 도 1에 도시된 바와 같이 이용될 수 있다.

<63> 즉, 일 단이 제2 배선에 접속되며, 타 단이 L-TFT의 드레인 단자에 접속되는 제2 스위치 TFT4와, 일 단이 L-TFT의 드레인 단자에 접속되며, 타 단이 L-TFT의 게이트 단자에 접속되는 제3 스위치 TFT5를 이용하는 것이 가능하다.

- <64> 또한, 이 경우, 제3 스위치 TFT5의 드레인 단자는 제2 배선 DL에 직접 접속될 수 있다.

- <65> 제2 기간(T2)은, 제2 배선과 제1 박막 트랜지스터 간의 접속, 제2 배선과 제2 박막 트랜지스터 간의 접속, 및 제1 스위치를 차단하는 기간을 포함한다.

- <66> 전술한 제1 기간 및 제2 기간 동안의 동작에 의해, 구동 회로는 이하의 동작을 행한다.

- <67> 제1 기간(T1) 동안, 구동 회로는, 제1 스위치 TFT3를 통해 제1 배선과 발광 디바이스의 일 단을 동일한 전압으로 설정한다. 또한, 구동 회로는, 제2 배선 DL로부터의 전류를, 제1 박막 트랜지스터의 드레인 단자와, 제1 박막 트랜지스터 및 제2 박막 트랜지스터의 게이트 단자들에 공급한다. 이에 의해, 제1 박막 트랜지스터의 드레인 단자와 소스 단자 사이에 흐르는 전류에 기초하여 결정되는, 제2 박막 트랜지스터의 게이트 단자와 소스 단자 간의 전압을 캐패시터 C에 유지할 수 있게 된다.

- <68> 또한, 제2 기간(T2) 동안, 구동 회로는, 캐패시터의 유지 전압에 따라, 제2 박막 트랜지스터의 소스 단자와 드레인 단자 사이를 흐르는 전류를 발광 디바이스에 공급한다. 이 경우, 캐패시터의 유지 전압은 Va와 Vb 간의 전위 차에 대응한다. 또한, 발광 디바이스에 공급되는 전류는 전원선 VS로부터 공급된다.

- <69> 보다 바람직하게는, 본 실시예에 따른 발광 표시 디바이스에서, L-TFT의 채널 폭을 그 채널 길이로 나눔으로써 얻어진 값(W/L)이, D-TFT의 값 W/L과 동일하거나, 혹은, L-TFT의 값 W/L이 D-TFT의 값 W/L보다 크다. 이에 따라, 커런트 미러 회로를 형성하는 한 쌍의 L-TFT 및 D-TFT 간의 사이즈 비율을 규정하는 것이 가능하게 된다.

- <70> 보다 바람직하게는, 본 실시예에 따른 발광 표시 디바이스에서, 캐패시터의 용량값은, L-TFT의 채널 용량 및 게이트-드레인 오버랩 용량과, D-TFT의 채널 용량 및 게이트-드레인 오버랩 용량을 합함으로써 얻어지는 전체 용량값의 3배 이상이다. 이에 따라, 용량의 사이즈를 규정하는 것이 가능하다.

- <71> 보다 바람직하게는, 본 실시예에 따른 발광 표시 디바이스에서, 제1 배선의 전압은, 유기 EL 디바이스의 동작 전압보다 낮거나 같다. 이에 따라, 전류 기입 시에 유기 EL 디바이스에 구동 전류가 흐르는 것을 중단시킬 수 있다.

- <72> 보다 바람직하게는, 본 실시예에 따른 발광 표시 디바이스는, 적어도 제1 내지 제3 스위치가 도통되는 기간(ON 기간: 제1 기간) 동안, D-TFT의 소스와 드레인 사이에 전류가 흐르지 않게 하는 구동 회로를 포함한다. 이에 따라, 전류 기입 시에 유기 EL 디바이스를 통해 구동 전류가 흐르는 것을 중단시킬 수 있다.

- <73> 보다 바람직하게는, 본 실시예에 따른 발광 표시 디바이스는, D-TFT의 소스와 드레인 사이에 전류가 흐르지 않게 하는 구동 회로로서, 제1 내지 제3 스위치가 ON 상태에 있는 기간 동안, D-TFT의 드레인 단자 전압을, 제1 배선의 전압으로 설정하는 회로를 포함한다. 이에 따라, 유기 EL 디바이스를 통해 흐르는 구동 전류는, D-TFT의 드레인 단자 전압에 대응하는 전원 전압의 변동에 의해 중단된다. 대안으로는, 본 실시예에 따른 발광 표시 디바이스는, D-TFT의 드레인 단자와 제3 배선(혹은 전원) 사이에 제4 스위치를 포함한다. 제4 스위치는, 적어도 제1 내지 제3 스위치가 ON 상태에 있는 기간 동안, 차단 혹은 턴 오프하는 구동 회로(전류 차단기)를 적어도 포함한다. 제4 스위치를 통해, 구동 전류가 유기 EL 디바이스를 통해 흐르는 것을 중단시킬 수 있다.

- <74> 보다 바람직하게는, 본 실시예에 따른 발광 표시 디바이스는, 제1 내지 제3 스위치가 차단되는 기간(OFF 기간 : 제2 기간)의 적어도 일부 동안, D-TFT의 소스와 드레인 사이에 전류가 흐르지 않도록 하는 기간(제3 기간)을 제공하는 구동 회로를 포함한다. 구동 회로는, 전원 전압의 변동, 혹은 제4 스위치를 이용하는 것을 특징으로 한다. 이에 따라, 제3 기간 동안 구동 전류가 유기 EL 디바이스에 흐르는 것을 중단시킬 수 있다.

- <75> 보다 바람직하게는, 본 실시예에 따른 발광 표시 디바이스에서, 제1 내지 제3 스위치가 각각, L-TFT 및 D-TFT와 동일한 구성을 갖는 n형 TFT(이하에서는 제3 내지 제5 n형 TFT라 칭함)로 형성된다. 제3 내지 제5 n형 TFT에서는, 그 소스 단자와 드레인 단자 중 하나가 각 스위치의 일 단으로서 기능하며, 소스 단자와 드레인 단자 중 다른 하나가 각 스위치의 타 단으로서 기능한다. 이에 따라, 제1 내지 제3 스위치들은, L-TFT 및 D-TFT와 동일한 구성을 갖는 TFT로 형성될 수 있다.

- <76> 보다 바람직하게는, 본 실시예에 따른 발광 표시 디바이스는, 제3 내지 제5 n형 TFT의 게이트 단자들이 제4 배선에 접속되어 있는 것을 특징으로 한다. 이에 따라, 스위치들을 형성하는 TFT들의 공통 제어를 수행하는 것이 가능하게 된다.

- <77> 보다 바람직하게는, 본 실시예에 따른 발광 표시 디바이스에서는, 제4 스위치가, L-TFT, D-TFT, 및 제3 내지 제5 n형 TFT와 동일한 구성을 갖는 n형 TFT(이하, "제6 n형 TFT"라 칭함)로 형성된다. 제6 n형 TFT에서는, 소스

단자와 드레인 단자 중 하나가 스위치의 일 단으로서 기능하며, 소스 단자와 드레인 단자 중 다른 하나가 스위치의 타 단으로서 기능한다. 이에 따라, 제4 스위치는, L-TFT, D-TFT, 제1 내지 제3 스위치와 동일한 구성을 갖는 TFT로 형성된다.

<78> 보다 바람직하게는, 본 실시예에 따른 발광 표시 디바이스에서는, 구동 회로를 구성하는 TFT 각각이,  $10^{18} [\text{cm}^{-3}]$  이하의 캐리어 밀도를 갖는 비정질 금속 산화물로 이루어진 n형 반도체 막을, n형 TFT의 n형 TFT 채널 막으로서 갖는다. 이 막은  $1[\text{cm}^2/\text{Vs}]$  이상의 이동도와,  $10^6$  이상의 온/오프 비를 갖는다. 이에 따라, 구동 회로를 형성하는 TFT로서, 산화물 반도체를 채널 막으로서 이용하는 TFT가 이용될 수 있다.

<79> 보다 바람직하게는, 본 실시예에 따른 발광 표시 디바이스에서, 전술한 구동 회로들 중 임의의 하나가 구동 회로로서 이용되며, 복수의 구동 회로들이 기판 상에 매트릭스 형상으로 형성된다.

<80> 본 실시예의 구동 회로에 따르면, 외부로부터 전류가 공급되고 커런트 미러 회로를 형성하는 한 쌍의 n형 TFT(L-TFT 및 D-TFT)를 통해 흐르게 되는 전류가 설정되는 기간 동안에는, 유기 EL 디바이스의 캐소드 단자와 애노드 단자 간의 전압이 동작 전압보다 낮거나 같아지기 때문에 전류가 흐르지 않는다. 또한, 외부로부터 공급되는 전류가 흐르는, 게이트 단자와 소스 단자 간의 전압은 L-TFT와 D-TFT에서 유지된다. 따라서, D-TFT는, D-TFT가 포화 영역에서 동작하는 한, 정전류원으로서 기능한다. 또한, 용량은, 오버랩 용량 등의 기생 용량보다 충분히 크기 때문에, 소스 단자, 드레인 단자 등에서의 전압이 변동할 때에도, 기생 용량의 효과를 무시할 수 있다.

<81> 또한, 본 실시예에 따르면, 유기 EL 디바이스에 전류를 공급하는 기간 동안에는, L-TFT의 드레인 단자 및 소스 단자에서의 전압은, D-TFT의 소스 단자의 전압과 동일하게 되며, L-TFT 및 D-TFT 각각의 게이트 단자 및 소스 단자에서의 전압은 서로 동일하다. 따라서, 인가되는 전압에 의한 특성 변화를, L-TFT와 D-TFT 간에 동일하게 되도록 설정할 수 있다.

<82> 또한, 본 실시예에 따르면, L-TFT의 전류 능력을 D-TFT의 전류 능력보다 크게 설정함으로써, 외부로부터 L-TFT에 공급되는 전류를, D-TFT에 의해 유기 EL 디바이스에 공급되는 전류보다 크게 할 수 있다. 따라서, 본 발명은 또한 대형 고해상도의 디스플레이에도 또한 적용될 수 있다. 또한, 본 실시예에 따르면, 전술한 바와 같이, 전류를 설정하는 기간 동안에는, 전류가 유기 EL 디바이스를 통해 흐르지 않게 된다. 따라서, 외부로부터 공급되는 전류가 클 경우에도, 유기 EL 디바이스를 통해 큰 전류가 흐르지 않게 된다. 이에 따라, 전류 설정 기간 동안, 큰 전류에 의한 유기 EL 디바이스의 열화가 억제될 수 있으며, 전류 설정 시에 필요한 전압을 더 높게 설정할 필요가 없어지게 된다.

<83> 또한, 본 실시예에 따르면, 전류가 외부로부터 공급되고 커런트 미러 n형 TFT(L-TFT 및 D-TFT)를 통해 흐르게 되는 전류가 설정되는 기간 동안에는, D-TFT를 통해 흐르는 전류가 중단될 수 있다. 또한, 이 기능이, 유기 EL 디바이스에 전류가 공급되는 기간, 즉 유기 EL 디바이스가 발광하는 기간의 전후, 혹은 그 기간 전에만, 혹은 그 기간 후에만 이용되는 경우, D-TFT를 통해 전류가 흐르지 않고, 유기 EL 디바이스의 발광을 중단시키는 기간을 제공할 수 있다. 이러한 방식으로 발광을 중단시키는 기간이 제공되면, 발광을 중단시키는 기간이 제공되지 않는 경우와 동일한 시간-평균 휘도를 달성하기 위해서는, 유기 EL 디바이스에 공급되는 전류가 증가하게 된다. 이는, 외부로부터 공급되는 전류를 증가시키는 것에 대응하므로, 본 발명은 대형 고해상도의 디스플레이에도 또한 적용될 수 있다. 또한, 발광을 중단시키는 기간을 제공함으로써, CRT(Cathode Ray Tube)와 유사한 기능이 얻어지며, 잔상이 적은 고품질의 동화상 표시를 실현할 수 있다.

<84> 또한, 본 실시예에 따르면, n형 TFT로서,  $10^{18} [\text{cm}^{-3}]$  이하의 캐리어 밀도와  $1[\text{cm}^2/\text{Vs}]$  이상의 전계 효과 이동도를 갖는 비정질 금속 산화물로 이루어진 반도체 층을 채널 층으로서 이용하는 n형 TFT가 이용된다. 이에 따라, a-Si TFT 또는 OS TFT를 이용하는 발광 표시 디바이스를 구성하는 경우에 비해, 전력 소모가 적으며 실내 온도에서 형성될 수 있는 TFT를 이용하는 발광 표시 디바이스가 제조될 수 있다. 또한, 발광 디바이스는 높은 이동도를 가지기 때문에, 고해상도 및 대형 화면을 달성할 수 있다.

<85> 전술한 바와 같이, 본 실시예에 따르면, 유기 EL 디바이스를 이용하는 발광 표시 디바이스에서, 구동 회로 상에, 아래로부터, 애노드 전극, 유기 재료 발광층, 및 캐소드 전극의 순서로 적층되어 있는 유기 EL 디바이스에 대한 구동 회로를 제공할 수 있다. 구동 회로는, a-Si, OS, 또는 금속 산화물 반도체를 채널 층으로서 이용하는 n형 TFT로 구성될 수 있다. 또한, 인가되는 전압에 의해 유발되는, TFT의 특성 시프트의 영향을 억제할 수 있는 구동 회로를 제공할 수 있다. 또한, 대형 고해상도의 발광 표시 디바이스에 적용될 수 있는 구동 회로

를 제공할 수 있다.

<86> 이하, 유기 EL 디바이스를 이용한 발광 표시 디바이스의 각종 예를 설명할 것이다. 그러나, 본 발명은, 유기 EL 디바이스에 한정되지 않으며, 다른 전류 부하에도 적용될 수 있다. 또한, 이하의 설명에서는, 비정질 금속 산화물 반도체를 채널 층으로서 이용하는 n형 TFT가 이용되지만, 본 발명은 a-Si TFT 및 OS TFT에도 적용될 수 있다. 또한, 본 발명은, 다른 반도체 재료로 이루어진 채널 층을 갖는 n형 TFT만으로 형성되는 발광 표시 디바이스에도 적용될 수 있다.

<87> (예 1)

<88> 우선, 본 발명의 예 1을 설명할 것이다.

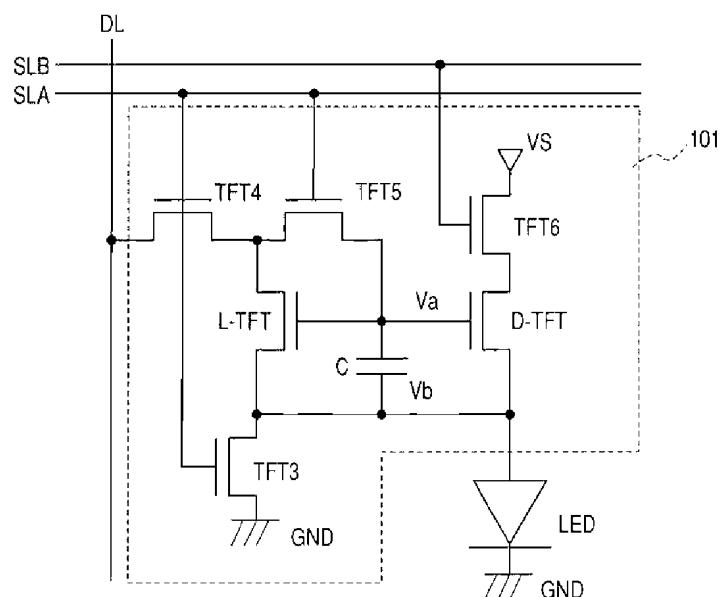

<89> 이 예의 구성은 도 1에 도시되어 있다. 도 1에 도시된 발광 표시 디바이스는, 접지선 GND에 접속(접지)되어 있는 캐소드 단자를 갖는 유기 EL 디바이스 LED와, 이 유기 EL 디바이스 LED를 구동하기 위한 구동 회로(101)를 각각 갖는 화소들을 포함하는 유기 EL 표시 디바이스(AM형 유기 EL 디스플레이)이다.

<90> 유기 EL 디바이스 LED는, 아래로부터, 애노드 전극, 유기 재료 발광 층, 및 캐소드 전극이 이 순서대로 적층되어 있다.

<91> 구동 회로(101)는 제1 n형 TFT(이하, "L-TFT"라 칭함), 제2 n형 TFT(이하, "D-TFT"라 칭함), 제3 n형 TFT(이하, "TFT3"이라 칭함), 제4 n형 TFT(이하, "TFT4"라 칭함), 제5 n형 TFT(이하, "TFT5"라 칭함), 및 캐패시터 C를 포함한다. L-TFT 및 D-TFT는 각각, 커런트 미러 회로(n형 커런트 미러 TFT)를 형성하는 n형 TFT로 형성되며, TFT3, TFT4, 및 TFT5는 각각, 스위치(스위칭 소자)를 형성하는 n형 TFT(n형 스위칭 TFT)로 형성된다.

<92> 구동 회로(101)에서는, 화소의 표시 계조에 대응하는 전류를 L-TFT에 공급하기 위한 데이터선 DL과, TFT3, TFT4, 및 TFT5의 각 게이트 단자에 접속되는 주사선 SL과, 전원선 VS와, 접지선 GND 등의 배선들이 배치되어 있다. 접지선 GND는 본 발명의 제1 배선에 대응하며, 데이터선 DL은 본 발명의 제2 배선에 대응하며, 전원선 VS는 본 발명의 제3 배선에 대응하며, 주사선 SL은 본 발명의 제4 배선에 각각 대응한다.

<93> L-TFT는, 유기 EL 디바이스 LED의 애노드 단자에 접속된 소스 단자와, 캐패시터 C의 일 단에 접속된 게이트 단자를 갖는다. L-TFT는, 본 발명의 커런트 미러 회로를 형성하는 제1 박막 트랜지스터에 대응한다.

<94> D-TFT는 유기 EL 디바이스 LED의 애노드 단자에 접속된 소스 단자와, 캐패시터 C의 일 단에 접속된 게이트 단자와, 전원선 VS에 접속된 드레인 단자를 갖는다. D-TFT는, 본 발명의 커런트 미러 회로를 형성하는 제2 박막 트랜지스터에 대응한다.

<95> TFT3은, 소스 및 드레인 단자들을 갖는데, 이를 소스 및 드레인 단자들 중 하나가 유기 EL 디바이스 LED의 애노드 단자에 접속되어 있으며, 이를 소스 및 드레인 단자들 중 다른 하나가 접지선 GND에 접속(접지)되어 있다. TFT3은 본 발명의 제1 스위치에 대응한다.

<96> TFT4는 소스 및 드레인 단자들을 갖는데, 이를 소스 및 드레인 단자들 중 하나가 데이터선 DL에 접속되어 있으며, 이를 소스 및 드레인 단자들 중 다른 하나가 L-TFT의 드레인 단자에 접속되어 있다. TFT4는 본 발명의 제2 스위치에 대응한다.

<97> TFT5는 소스 및 드레인 단자들을 갖는데, 이를 소스 및 드레인 단자들 중 하나가 L-TFT의 드레인 단자에 접속되어 있으며, 이를 소스 및 드레인 단자들 중 다른 하나가 L-TFT의 게이트 단자에 접속되어 있다. TFT5는 본 발명의 제3 스위치에 대응한다.

<98> 캐패시터 C는, 일 단이 L-TFT 및 D-TFT의 게이트 단자들에 접속되어 있고, 타 단이 L-TFT 및 D-TFT의 소스 단자들에 접속되어 있다. 또한, 캐패시터 C의 타 단은 유기 EL 디바이스 LED의 애노드 단자에 접속되어 있다.

<99> 이 경우, 전원선 VS의 전압은, 후술하는 전류 기입 기간 동안 설정되는 전류가, D-TFT와 유기 EL 디바이스 LED를 통해 흐르게 되는 경우에도, D-TFT가 포화 영역에서 동작하는 전압 VD로 설정된다.

<100> 또한, L-TFT의 전류 능력은, D-TFT의 4배인 것으로 가정한다. 이는, L-TFT의 채널 길이가 D-TFT의 채널 길이와 동일하게 되도록 설정하고 L-TFT의 채널 폭이 D-TFT의 채널 폭의 4배로 되도록 설정함으로써 실현될 수 있다.

<101> 또한, 캐패시터 C의 용량값은, L-TFT 및 D-TFT에 관한 오버랩 용량 등의 기생 용량의 총합보다 3배 이상 크게 설정된다.

- <102> 다음으로, 도 2에 도시된 타이밍차트에 관하여, 이 예에 따른 동작을 설명할 것이다.

- <103> 우선, 주사선 SL의 신호가 H 레벨로 설정되는 기간 T1(전류 기입 기간 : 제1 기간) 동안, TFT3, TFT4, 및 TFT5가 턴 온된다. 기간 T1 동안, TFT3이 턴 온되면, L-TFT 및 D-TFT의 소스 단자들에서의 전압 및, 유기 EL 디바이스 LED의 애노드 단자에서의 전압 Vb가, TFT3을 통해 접지선 GND의 전압과 동일하게 된다. 한편, TFT4 및 TFT5가 턴 온되면, 유기 EL 디바이스 LED에 공급될 전류의 4배인 전류가, 데이터선 DL로부터 TFT4를 통해 L-TFT의 드레인 단자에 공급된다. 이에 따라, 게이트 단자에서의 전압 Va는, L-TFT의 드레인 단자와 소스 단자 사이에 유기 EL 디바이스 LED에 공급될 전류의 4배인 전류가 흐르게 되는 전압으로 설정된다. 이와 동시에, D-TFT의 드레인 단자와 소스 단자 사이에는, 데이터선 DL로부터의 전류의 1/4, 즉 유기 EL 디바이스에 LED에 공급될 전류가 흐른다. 한편, 유기 EL 디바이스 LED의 애노드 단자에서의 전압 Vb는, 접지선 GND의 전압과 동일한 전위에 있다. 따라서, D-TFT를 통해 흐르는 전류는, 유기 EL 디바이스 LED를 통해 흐르지 않지만, 모두 TFT3을 통해 접지선 GND를 향해 흐른다.

- <104> 다음으로, 주사선 SL의 신호가 L 레벨로 설정되는 기간 T2(발광 기간에 대응하는 LED 구동 기간: 제2 기간) 동안, TFT3, TFT4, 및 TFT5는 턴 오프된다. 기간 T2 동안, 캐패시터 C를 통해, D-TFT의 게이트 단자와 소스 단자 간의 전압 차는, 전류 기입 기간 T1 동안 설정된 전압 차로 된다. 즉, D-TFT는, D-TFT가 포화 동작을 행하는 한, D-TFT로부터 유기 EL 디바이스 LED를 통해 전류 기입 기간 T1 동안 설정된 전류를 공급하기 위한 전류원으로 된다. 따라서, D-TFT의 소스 단자 전압은, 전류 기입 기간 T1 동안 설정된 전류가 유기 EL 디바이스 LED를 통해 흐르게 되는 애노드 단자 전압으로 된다. 그러면, D-TFT의 게이트 단자 전압은, 유기 EL 디바이스 LED의 애노드 단자 전압에, 전류 기입 기간 T1 동안 설정되는, 게이트 단자와 소스 단자 간의 전압 차를 합함으로써 얻어지는 전압으로 된다. 이에 따라, 유기 EL 디바이스 LED는 공급되는 전류에 따라 발광한다.

- <105> 한편, L-TFT의 게이트 단자는, D-TFT의 게이트 단자와 동일한 전압이므로, L-TFT의 소스 단자 및 드레인 단자의 전압은, D-TFT의 소스 단자와 동일한 전압으로 된다.

- <106> 이 후, 유기 EL 디스플레이에서는, 전술한 동작들이 각 배선에 대해 반복되어서, 디스플레이 상에 화상을 표시하게 된다.

- <107> 따라서, 이 예에 따르면, 데이터선으로부터 L-TFT에 전류를 공급하기 위한 전류 기입 기간 동안, 유기 EL 디바이스 LED의 캐소드 단자 및 애노드 단자에서의 전압은 동일하게 되므로, 이들을 통해 전류가 흐르지 않게 된다. 또한, 데이터선으로부터 공급되는 전류가 흐르는 게이트 단자와 소스 단자 간의 전압은, L-TFT와 D-TFT에 대해 캐패시터 C에 유지된다. 또한 LED 구동 기간 동안에도, D-TFT가 포화 영역에서 동작하는 한, D-TFT는 정전류원으로서 기능한다. 또한, 캐패시터 C는, L-TFT 및 D-TFT에 관한 오버랩 용량 등의 기생 용량의 총 합보다 충분히 크다. 따라서, 소스 단자, 드레인 단자 등의 전압이 변동될 때에도, 기생 용량의 효과를 무시할 수 있다.

- <108> 또한, 본 예에 따르면, LED 구동 기간 동안, L-TFT의 드레인 단자와 소스 단자 간의 전압은, D-TFT의 소스 단자에서의 전압과 동일하게 되며, L-TFT 및 D-TFT의 게이트 단자들 및 소스 단자들 간의 전압들은 서로 동일하게 되도록 설정될 수 있다. 따라서, 인가되는 전압에 의해 유발되는 동일한 특성 변화가 L-TFT 및 D-TFT에서 얻어질 수 있다. 이에 의해, L-TFT와 D-TFT 간의 전류 능력비의 변화가 나타나지 않으며, 데이터선으로부터 전류가 기입되는 한, L-TFT 및 D-TFT의 특성 변화의 영향은 억제될 수 있다.

- <109> 또한, 본 예에 따르면, L-TFT의 전류 능력을 D-TFT의 전류 능력보다 크게 설정함으로써, 데이터선으로부터 L-TFT에 공급될 전류를, D-TFT에 의해 유기 EL 디바이스 LED에 공급되는 전류보다 크게 할 수 있다. 이에 의해, 전류 기입 기간이 단축될 수 있으며, 대형 고해상도의 디스플레이에 적용할 수 있다.

- <110> 또한, 본 예에 따르면, 전류 기입 기간 동안에는 유기 EL 디바이스를 통해 전류가 흐르지 않는다. 따라서, 전술한 바와 같이, 외부로부터 공급되는 전류가 클 경우에도, 유기 EL 디바이스를 통해 큰 전류가 흐르지 않는다. 이 경우, 유기 EL 디바이스의 열화를 억제할 수 있으며, 유기 EL 디바이스의 애노드 단자 전압의 상승을 보상하기 위해 데이터선의 전압을 높일 필요가 없다.

- <111> 또한, 본 예에 따르면, L-TFT 및 D-TFT로서,  $10^{18} [\text{cm}^{-3}]$  이하의 캐리어 밀도와  $1[\text{cm}^2/\text{Vs}]$  이상의 전계 효과 이동도를 갖는 비정질 금속 산화물로 이루어진 반도체 층을 채널 층으로서 이용하는 n형 TFT가 이용된다. 이에 따라, a-Si TFT 또는 OS TFT를 이용하는 발광 디바이스를 구성하는 경우에 비해, 전력 소모가 적으며 실내 온도에서 형성될 수 있는 TFT를 이용하는 발광 표시 디바이스가 제조될 수 있다. 또한, 발광 디바이스는 높은 이동도를 가지므로, 고해상도의 대형 디스플레이를 실현할 수 있다.

&lt;112&gt; (예 2)

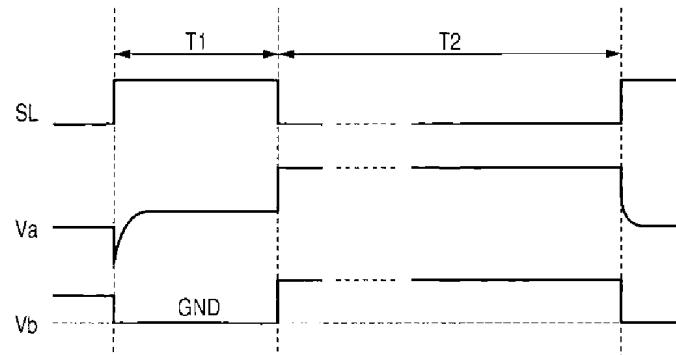

<113> 다음으로, 본 발명의 예 2를 설명할 것이다. 본 예에 따른 발광 표시 디바이스의 구성은 예 1의 구성과 동일하다. 본 예는, 전원선 VS의 전압이 변동된다는 것을 특징으로 한다.

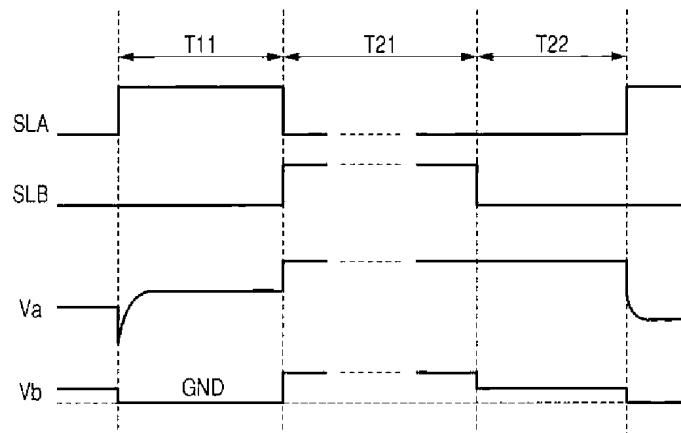

<114> 이하, 도 3에 도시된 타이밍차트를 참조하여, 본 예에 따른 동작을 설명할 것이다.

<115> 우선, 주사선 SL의 신호가 H 레벨로 설정되고 전원선 VS의 전압이 접지선 GND의 전압과 동일한 전위(이하, "GND"라 칭함)에 있도록 설정되는 기간 T11(전류 기입 기간)에서, TFT3, TFT4, 및 TFT5가 턴 온된다. 기간 T11 동안, TFT3가 턴 온되면, L-TFT 및 D-TFT의 소스 단자들의 전압과, 유기 EL 디바이스 LED의 애노드 단자의 전압 Vb는, TFT3을 통해 접지선 GND의 전압과 동일한 전위로 된다. 한편, TFT4 및 TFT5가 턴 온되면, 유기 EL 디바이스 LED에 공급될 전류의 16배의 전류가 데이터선 DL로부터 L-TFT의 드레인 단자에 공급된다. 이에 따라, 게이트 단자의 전압 Va는, 유기 EL 디바이스 LED에 공급될 전류의 16배의 전류가 L-TFT의 드레인 단자와 소스 단자 사이에 흐르게 되는 전압으로 설정된다. 한편, 전원선 VS의 전압은 GND와 동일하므로, D-TFT의 드레인 단자와 소스 단자 사이에는 전류가 흐르지 않는다. 또한, 유기 EL 디바이스 LED의 애노드 단자에서의 전압 Vb는 접지선 GND의 전압과 동일한 전위이므로, 유기 EL 디바이스 LED를 통해 전류가 흐르지 않는다.

<116> 그러면, 주사선 SL의 신호가 L 레벨로 설정되고 전원선 VS의 전압 VD에 설정되는 기간 T21(발광 기간에 대응하는 LED 구동 기간)이 제공된다. 기간 T21은 예 1의 LED 구동 기간 T2의 1/4로 설정됨에 유의한다. 기간 T21 동안, TFT3, TFT4, 및 TFT5가 턴 오프된다. 또한, 캐패시터 C를 통해, D-TFT의 게이트 단자와 소스 단자 간의 전압 차는, 전류 기입 기간 T11 동안 설정되는 전압 차로 된다. 구체적으로는, D-TFT가 포화 동작을 행하는 한, D-TFT는, D-TFT로부터 유기 EL 디바이스 LED를 향해 전류 기입 기간 T11 동안 설정된 전류, 즉 유기 EL 디바이스 LED에 공급될 전류의 4배의 전류를 공급하기 위한 전류원으로 된다. 따라서, D-TFT의 소스 단자 전압은, 전류 기입 기간 T11 동안 설정된 전류가 유기 EL 디바이스 LED를 통해 흐르게 되는 애노드 단자 전압으로 된다. 그러면, D-TFT의 게이트 단자 전압은, 유기 EL 디바이스 LED의 애노드 단자 전압에, 전류 기입 기간 T1 동안 설정되는, 게이트 단자와 소스 단자 간의 전압차를 더함으로써 얻어지는 전압으로 된다. 이에 따라, 유기 EL 디바이스 LED는, 공급되는 전류에 따라 발광하게 된다.

<117> 또한, 주사선 SL의 신호가 L 레벨로 설정되고 전원선 VS의 전압이 GND로 설정되는 기간 T22(혹 표시 기간)가 제공된다. 기간 T22 동안, D-TFT로부터 전류가 흐르지 않으므로, 유기 EL 디바이스 LED는 발광하지 않는다.

<118> 이 후, 유기 EL 디스플레이에서는, 전술한 동작이 각 배선에서 반복되어 디스플레이 상에 화상을 표시하게 된다.

<119> 따라서, 본 예에 따르면, 예 1과 동일한 효과가 얻어질 수 있다. 또한, 본 예에서는, 후 표시 기간이 제공되며, LED 구동 기간이 예 1의 1/4로 설정되며, 유기 EL 디바이스 LED를 통해 흐르는 전류가 예 1의 전류의 4배로 설정된다. 이에 따라, 시간 평균 휘도가 예 1의 시간 평균 휘도와 실질적으로 동일하게 되도록 설정될 수 있다. 한편, 데이터선으로부터 공급되는 전류는, 예 1의 4배가 되므로, 전류 기입 기간이 단축될 수 있으며, 예 1에 비해 더 크고 더 높은 선명도의 디스플레이에 적용할 수 있다.

&lt;120&gt; (예 3)

<121> 다음으로, 본 발명의 예 3에 대해 설명한다.

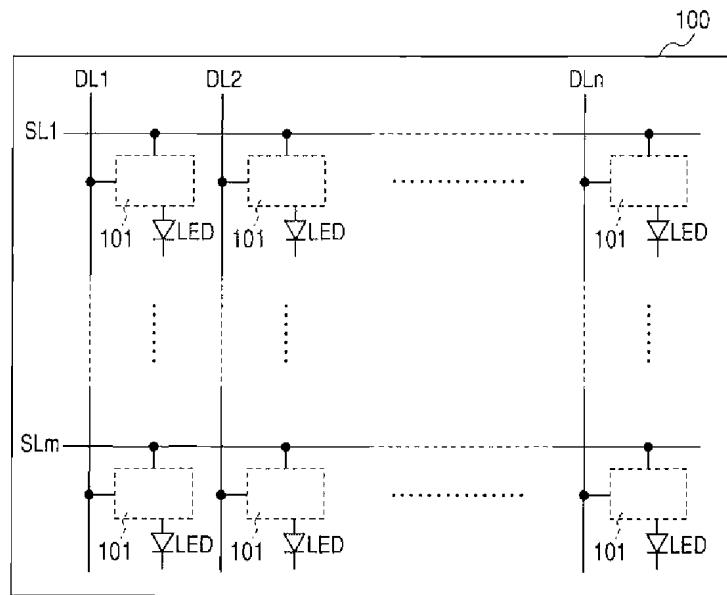

<122> 이 예의 구성은 도 4에 도시되어 있다. 도 4에 도시된 발광 표시 디바이스는, 접지선 GND에 접속(접지)되어 있는 캐소드 단자를 갖는 유기 EL 디바이스 LED와, 이 유기 EL 디바이스 LED를 구동하기 위한 구동 회로(101)를 각각이 구비하는 화소들을 포함하는 유기 EL 표시 디바이스(AM형 유기 디스플레이)이다.

<123> 이 유기 EL 디바이스 LED에서는, 아래로부터, 애노드 전극, 유기 재료 발광 층, 및 캐소드 전극이 이 순서대로 적층되어 있다.

<124> 구동 회로(101)는 제1 n형 TFT(이하, "L-TFT"라 칭함), 제2 n형 TFT(이하, "D-TFT"라 칭함), 제3 n형 TFT(이하, "TFT3"이라 칭함), 제4 n형 TFT(이하, "TFT4"라 칭함), 제5 n형 TFT(이하, "TFT5"라 칭함)를 포함한다. 또한, 구동 회로(101)는 제6 n형 TFT(이는 제6 박막 트랜지스터에 대응하며; "TFT6"이라 칭함) 및 캐패시터 C를 포함한다. L-TFT 및 D-TFT는 각각, 커런트 미러를 형성하는 n형 TFT(n형 커런트 미러 TFT)로 형성되며, TFT3, TFT4, TFT5, 및 TFT6는 각각, 스위칭 소자(스위치)를 형성하는 n형 TFT(n형 스위칭 TFT)로 형성된다.

<125> 구동 회로(101)에서는, 화소의 표시 계조에 대응하는 전류를 L-TFT에 공급하기 위한 데이터선 DL과, TFT3,

TFT4, 및 TFT5의 각 게이트 단자에 접속되는 제1 주사선 SLA가 배치되어 있다. 또한, 구동 회로(101)에서는, TFT6의 게이트 단자에 접속되어 있는 제2 주사선 SLB와, 전원선 VS와, 접지선 GND 등의 배선들이 제공되어 있다. 접지선 GND는 본 발명의 제1 배선에 대응하며, 데이터선 DL은 본 발명의 제2 배선에 대응하며, 전원선 VS는 본 발명의 제3 배선에 대응하며, 제1 주사선 SLA 및 제2 주사선 SLB는 본 발명의 제4 및 제5 배선에 각각 대응한다.

<126> L-TFT는, 유기 EL 디바이스 LED의 애노드 단자에 접속된 소스 단자와, 캐패시터 C의 일 단에 접속된 게이트 단자를 갖는다. L-TFT는, 본 발명의 커런트 미러 회로를 형성하는 제1 박막 트랜지스터에 대응한다.

<127> D-TFT는 유기 EL 디바이스 LED의 애노드 단자에 접속된 소스 단자와, 캐패시터 C의 일 단에 접속된 게이트 단자를 갖는다. D-TFT는, 본 발명의 커런트 미러 회로를 형성하는 제2 박막 트랜지스터에 대응한다.

<128> TFT3은, 소스 및 드레인 단자들을 갖는데, 이들 소스 및 드레인 단자들 중 하나가 유기 EL 디바이스 LED의 애노드 단자에 접속되어 있으며, 이들 소스 및 드레인 단자들 중 다른 하나가 접지선 GND에 접속(접지)되어 있다. TFT3은 본 발명의 제1 스위치에 대응한다.

<129> TFT4는 소스 및 드레인 단자들을 갖는데, 이들 소스 및 드레인 단자들 중 하나가 데이터선 DL에 접속되어 있으며, 이들 소스 및 드레인 단자들 중 다른 하나가 L-TFT의 드레인 단자에 접속되어 있다. TFT4는 본 발명의 제2 스위치에 대응한다.

<130> TFT5는 소스 및 드레인 단자들을 갖는데, 이들 소스 및 드레인 단자들 중 하나가 L-TFT의 드레인 단자에 접속되어 있으며, 이들 소스 및 드레인 단자들 중 다른 하나가 L-TFT의 게이트 단자에 접속되어 있다. TFT5는 본 발명의 제3 스위치에 대응한다.

<131> TFT6는 소스 및 드레인 단자들을 갖는데, 이들 소스 및 드레인 단자들 중 하나가 D-TFT의 드레인 단자에 접속되어 있으며, 이들 소스 및 드레인 단자들 중 다른 하나가 전원선 VS에 접속되어 있다. TFT6는 본 발명의 제4 스위치에 대응한다.

<132> 캐패시터 C는, 일 단이 L-TFT 및 D-TFT의 게이트 단자들에 접속되어 있고, 타 단이 L-TFT 및 D-TFT의 소스 단자들에 접속되어 있다. 또한, 캐패시터 C의 타단은 유기 EL 디바이스 LED의 애노드 단자에 접속되어 있다.

<133> 이 경우, 전원선 VS의 전압은, 후술하는 전류 기입 기간 동안 기입되는 전류가, D-TFT와 유기 EL 디바이스 LED를 통해 흐르게 되는 경우에도, D-TFT가 포화 영역에서 동작하는 전압 VD로 설정된다.

<134> 또한, L-TFT의 전류 능력은, D-TFT의 4배인 것으로 가정하며, 이는, L-TFT의 채널 길이가 D-TFT의 채널 길이와 동일하게 되도록 설정하고 L-TFT의 채널 폭이 D-TFT의 채널 폭의 4배로 되도록 설정함으로써 실현될 수 있다.

<135> 또한, 캐패시터 C의 용량값은, L-TFT 및 D-TFT에 관한 오버랩 용량 등의 기생 용량의 총합보다 3배 이상 크게 설정된다.

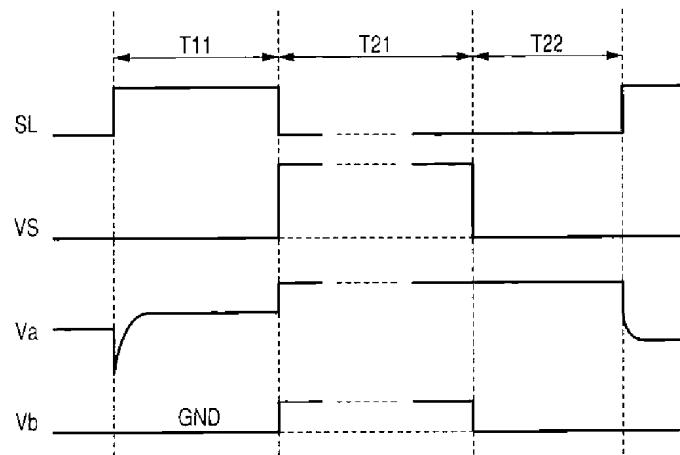

<136> 다음으로, 도 5에 도시된 타이밍차트를 참조하여, 이 예에 따른 동작을 설명할 것이다.

<137> 우선, 주사선 SLA의 신호가 H 레벨로 설정되고 제2 주사선 SLB의 신호가 L 레벨로 설정되는 기간 T11(전류 기입 기간) 동안, TFT3, TFT4, 및 TFT5가 턴 온되고 TFT6은 턴 오프된다. 기간 T11 동안, TFT3이 턴 온되어서, L-TFT 및 D-TFT의 소스 단자들의 전압 및, 유기 EL 디바이스 LED의 애노드 단자의 전압 Vb가, 접지선 GND의 전압과 동일한 전위로 된다. 한편, TFT4 및 TFT5가 턴 온되어서, 유기 EL 디바이스 LED에 공급될 전류의 16배의 전류가, 데이터선 DL로부터 L-TFT의 드레인 단자에 공급된다. 이에 따라, 게이트 단자의 전압 Va는, L-TFT의 드레인 단자와 소스 단자 사이에, 유기 EL 디바이스 LED에 공급될 전류의 4배의 전류가 흐르도록 하는 전압으로 설정된다. 한편, D-TFT의 드레인 단자와 소스 단자 사이에서는, TFT6가 턴 오프되므로, 전원선 VS와의 사이의 전류 경로가 차단되어, 전류가 흐르지 않는다. 또한, 유기 EL 디바이스 LED의 애노드 단자의 전압과, 접지선 GND의 전압은 동일한 전위이므로, 유기 EL 디바이스 LED를 통해 전류가 흐르지 않는다.

<138> 다음으로, 제1 주사선 SLA의 신호가 L 레벨로 설정되며 제2 주사선 SLB의 신호가 H 레벨로 설정되는 기간 T21(발광 기간에 대응하는 LED 구동 기간)이 제공된다. 기간 T21은 예 1의 LED 구동 기간 T2의 1/4로 설정되어 있음에 유의한다. 기간 T21 동안, TFT3, TFT4, TFT5는 턴 오프되며, TFT6는 턴 온된다. 또한, 캐패시터 C를 통해, D-TFT의 게이트 단자와 소스 단자 사이의 전압 차는, 전류 기입 기간 T11 동안 설정된 전압 차로 된다. 즉, D-TFT가 포화 동작을 행하는 한, D-TFT는, D-TFT로부터 유기 EL 디바이스 LED를 향해 전류 기입 기간 T11 동안 설정된 전류, 즉 유기 EL 디바이스 LED에 공급될 전류의 4배의 전류를 공급하기 위한 전류원으로 된다.

따라서, D-TFT의 소스 단자 전압은, 전류 기입 기간 T11 동안 설정된 전류가 유기 EL 디바이스 LED를 통해 흐르게 되는 애노드 단자 전압으로 된다. 그러면, D-TFT의 게이트 단자 전압은, 유기 EL 디바이스 LED의 애노드 단자 전압에, 전류 기입 기간 T1 동안 설정되는, 게이트 단자와 소스 단자 간의 전압 차를 가함으로써 얻어지는 전압으로 된다. 이에 따라, 유기 EL 디바이스 LED는 공급되는 전류에 따라 발광한다.

<139> 또한, 제1 주사선 SLA의 신호가 L 레벨로 설정되고 제2 주사선 SLB의 신호가 L 레벨로 설정되는 기간 T22(혹 표시 기간)가 제공된다. 기간 T22 동안, TFT6이 턴 오프되며, 전원선 VS와 D-TFT의 드레인 단자 간의 전류 경로가 차단되므로, D-TFT로부터 전류가 흐르지 않아서, 유기 EL 디바이스 LED가 발광하지 않는다.

<140> 이 후, 유기 EL 디스플레이에서, 전술한 동작이 각 배선에 대해 반복되어서 디스플레이 상에 화상을 표시하게 된다.

<141> 이 예에서는, 신호선 SLB 및 TFT6를 추가함으로써, 전원 VS를 변동시키지 않고 예 2의 효과를 달성할 수 있다.

<142> 예 1 내지 예 3에서는, L-TFT와 D-TFT 간의 전류 능력비가 '4'로 설정되지만, L-TFT와 D-TFT 간의 전류 능력비는, 유기 EL 디바이스 LED의 전류-휘도 특성과, 데이터선 DL의 부하 용량에 따라 설정될 수 있음에 유의해야 한다.

<143> 또한, 예 2 및 예 3에서, LED 구동 기간은 예 1의 LED 구동 기간의 1/4로 설정된다. 예 1의 LED 구동 기간이 단축되지만, 효과의 정도가 다소 변할지라도 동일한 효과를 얻을 수 있다.

<144> 또한, 예 1 내지 예 3에서, 유기 EL 디바이스 LED는 접지된 캐소드 단자를 가지며, 모든 TFT가 n형 TFT(n형 박막 트랜지스터)로 형성된다. p형 TFT(p형 박막 트랜지스터)만으로 유기 EL 디바이스 LED를 구성하는 경우, 이하의 구성이 채택될 수 있다.

<145> 유기 EL 디바이스 LED의 애노드 단자는 전원선 VS에 접속되며, p형 커런트 미러 TFT들(L-TFT 및 D-TFT의 제1 및 제2 p형 박막 트랜지스터들)의 소스 단자들이 유기 EL 디바이스 LED의 캐소드 단자에 접속되어 있다. L-TFT 및 D-TFT의 소스 단자들과 전원선 VS 사이에 p형 TFT(TFT3)가 제공된다. L-TFT의 드레인 단자와, 계조에 대응하는 전류를 공급하기 위한 배선 DL 사이에, p형 TFT(TFT4)가 제공된다. L-TFT의 드레인 단자와 게이트 단자 사이에 p형 TFT(TFT5)가 제공된다. D-TFT의 드레인 단자는, 전압 GND가 인가되는 전원선에 접속되어 있다. 대안으로는, D-TFT의 드레인 단자는, LED 구동 기간 동안에는 전압 GND가 인가될 수 있으며 그 외의 기간 동안에는 전압 VS가 인가될 수 있는 전원에 접속되어 있다. 또한 대안으로는, D-TFT의 드레인 단자는, 전압 GND가 p형 TFT(TFT6)를 통해 인가되는 전원선에 접속되어 있다. 그러면, 주사선들 SL, SLA, 및 SLB의 신호들은 반전된다. 그러므로, 예 1 내지 예 3과 동일한 구성이 실현될 수 있으며, 동일한 효과가 얻어질 수 있다.

<146> 또한, 예 1 내지 예 3에서 주사선을 추가함으로써, 제1 기간의 종료시에, 스위칭 기능을 완수한 TFT들 중, TFT5가 가장 빨리 ON 상태에서 OFF 상태로 동작하게 된다. 이에 따라, 스위칭 동작을 완수한 다른 TFT들의 동작과 연관되어 유발되는 노이즈가 억제될 수 있으며, 높은 정확성으로 구동이 수행될 수 있다.

<147> 본 발명은 유기 EL 디바이스를 이용하는 발광 표시 디바이스 뿐만 아니라, 유기 EL 디바이스 이외의, 공급되는 전류에 의해 발광하는 발광 디바이스를 이용하는 발광 표시 디바이스, 및 공급되는 전류에 의해 임의의 기능을 나타내는 전류 부하를 이용하는 통상의 전류 부하 디바이스에도 적용될 수 있다.

<148> 본 발명이 예시적인 실시예들을 참조하여 설명되었지만, 본 발명은 개시된 예시적인 실시예들에 제한되는 것이 아님을 이해해야 한다. 이하의 특허청구범위의 범주는 이러한 모든 변경들 및 등가적인 구조들 및 기능들을 포함하도록 하는 가장 넓은 해석에 따른 것이다.

<149> 본 출원은, 그 전체가 참조로 본원에 포함되는, 2006년 9월 5일에 출원된 일본특허출원 제2006-240257호의 이익을 주장한다.

### 도면의 간단한 설명

<40> 도 1은 본 발명의 예 1에 따른 발광 표시 디바이스의 화소의 구성을 나타낸 회로도.

<41> 도 2는 예 1에 따른 발광 표시 디바이스의 동작을 나타낸 타이밍차트.

<42> 도 3은 본 발명의 예 2에 따른 발광 표시 디바이스의 동작을 나타낸 타이밍차트.

<43> 도 4는 본 발명의 예 3에 따른 발광 표시 디바이스의 화소의 구성을 나타낸 회로도.

- <44> 도 5는 예 3에 따른 발광 표시 디바이스의 동작을 나타낸 타이밍차트.

- <45> 도 6은 화소의 구성을 나타낸 도면.

- <46> 도 7은 유기 EL 표시 디바이스의 구성을 나타낸 도면.

- <47> 도 8은 제1 종래 기술 예에 따른 화소의 구성을 나타낸 회로도.

- <48> 도 9는 제2 종래 기술 예에 따른 화소의 구성을 나타낸 회로도.

- <49> 도 10은 제3 종래 기술 예에 따른 화소의 구성을 나타낸 회로도.

- <50> 도 11은 제4 종래 기술 예에 따른 화소의 구성을 나타낸 회로도.

## 도면

### 도면1

### 도면2

T1 : 전류 기입 시간

T2 : LED 구동(발광) 시간

## 도면3

T11 ; 전류 기입 기간

T21 ; LED 구동(발광) 기간

T22 ; 흑 표시 기간

## 도면4

도면5

T11 ; 전류 기입 시간

T21 ; LED 구동(발광) 시간

T22 ; 측 표시 시간

도면6

**도면7****도면8**

(종래 기술)

도면9

(종래 기술)

**도면10**

(종래 기술)

**도면11**

(종래 기술)

|                |                                                                                                                                                                             |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机发光显示装置                                                                                                                                                                    |         |            |

| 公开(公告)号        | <a href="#">KR1020090013811A</a>                                                                                                                                            | 公开(公告)日 | 2009-02-05 |

| 申请号            | KR1020087029124                                                                                                                                                             | 申请日     | 2007-08-24 |

| [标]申请(专利权)人(译) | 佳能株式会社                                                                                                                                                                      |         |            |

| 申请(专利权)人(译)    | 佳能sikki有限公司                                                                                                                                                                 |         |            |

| 当前申请(专利权)人(译)  | 佳能sikki有限公司                                                                                                                                                                 |         |            |

| [标]发明人         | ABE KATSUMI<br>아베가쯔미                                                                                                                                                        |         |            |

| 发明人            | 아베, 가쯔미                                                                                                                                                                     |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50 G09G3/32                                                                                                                                        |         |            |

| CPC分类号         | G09G3/3241 G09G3/2011 H01L51/5262 G09G2300/0417 G09G2300/0842 G09G2300/0861 G09G2300/0866 G09G2310/0251 G09G2310/061 G09G2320/0223 G09G2320/0233 G09G2320/0238 G09G2330/025 |         |            |

| 代理人(译)         | Jangsugil<br>Bakchungbeom                                                                                                                                                   |         |            |

| 优先权            | 2006240257 2006-09-05 JP                                                                                                                                                    |         |            |

| 其他公开文献         | <a href="#">KR101014899B1</a>                                                                                                                                               |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                   |         |            |

## 摘要(译)

OKIPO0026 #WIPO 2009