**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

(51) Int. Cl.

*H05B 33/10* (2006.01)

*H05B 33/22* (2006.01)

(11) 공개번호 10-2006-0044531

(43) 공개일자 2006년05월16일

(21) 출원번호 10-2005-0023527

(22) 출원일자 2005년03월22일

(30) 우선권주장 JP-P-2004-00082477 2004년03월22일 일본(JP)

(71) 출원인 소니 가부시끼 가이샤

일본국 도쿄도 시나가와쿠 키타시나가와 6쵸메 7반 35고

(72) 발명자 시바사끼 다까노리

일본 도쿄도 시나가와구 기따시나가와 6쵸메 7-35 소니 가부시끼가이

샤내

아사노 미쓰루

일본 도쿄도 시나가와구 기따시나가와 6쵸메 7-35 소니 가부시끼가이

샤내

(74) 대리인 장수길

이중희

구영창

심사청구 : 없음

**(54) 표시 장치 및 그의 제조 방법**

**요약**

구동 전압이 낮은 상태에서, 각 유기 EL 소자에 있어서의 비발광 결함이 적고, 발광 수명이 길며, 생산성도 우수한 표시 장치의 제조 방법 및 표시 장치를 제공한다.

표시 장치 제조 방법은, 기판 상에 제1 절연막을 형성하는 제1 단계와, 화소 영역 내의 제1 절연막 상에, 각 화소에 대응하는 복수의 하부 전극을 형성하고, 화소 영역의 외측의 제1 절연막 상에 도전막을 형성하며, 도전막을 통해 제1 절연막까지 훌을 형성하는 제2 단계와, 하부 전극 및 도전막이 제공된 상기 기판을 베이킹하는 제3 단계를 포함한다.

**대표도**

도 1a

**색인어**

기판, 하부 전극, 상부 전극, 화소 영역, 절연막, 표시 장치

## 명세서

### 도면의 간단한 설명

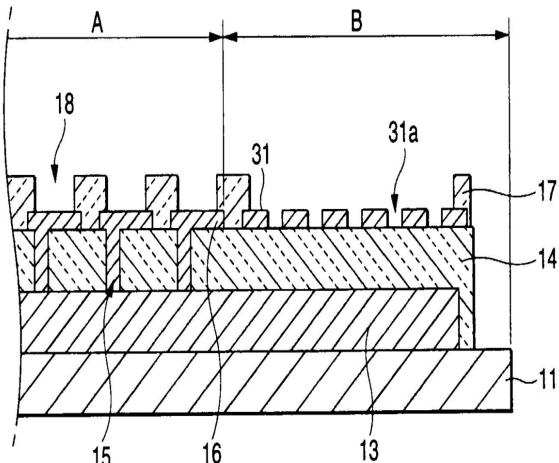

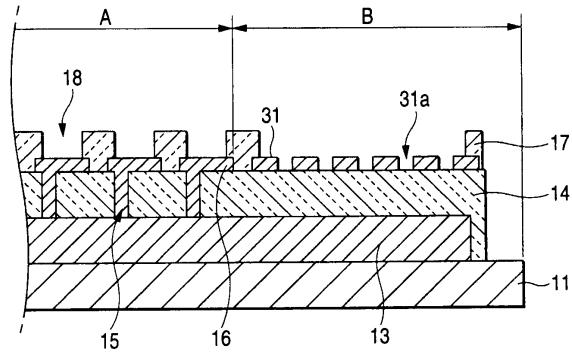

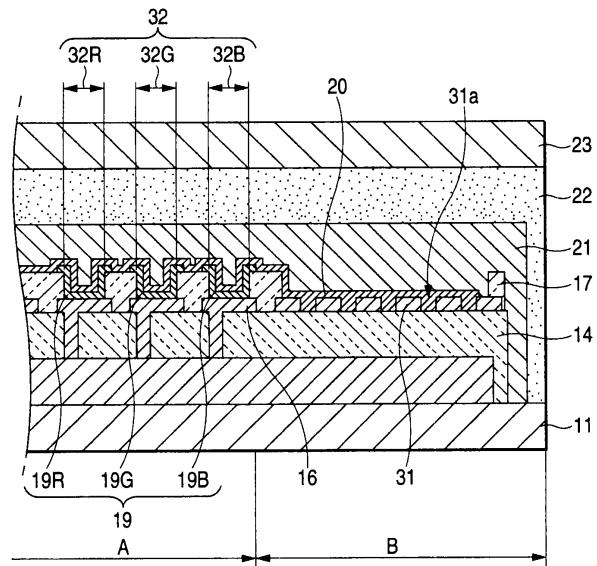

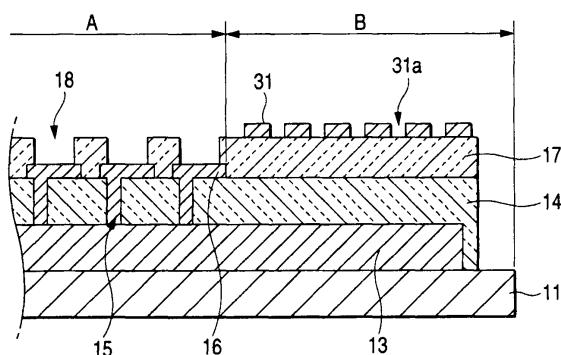

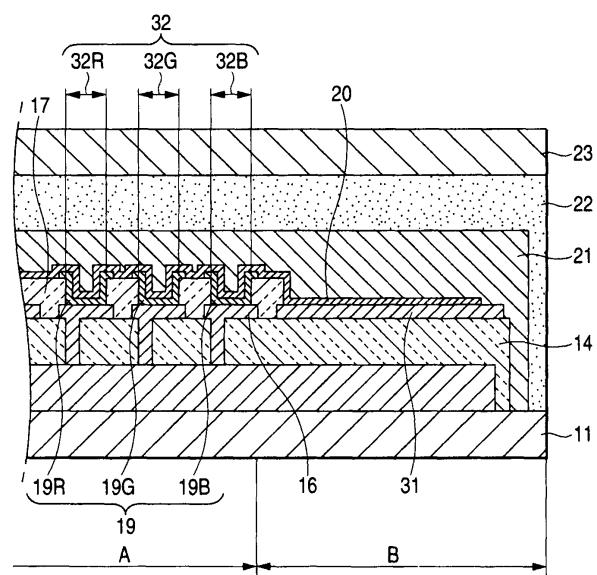

도 1a 및 도 1b는 본 발명의 표시 장치의 제조 방법에 따른 제1 실시 형태를 설명하기 위한 단면도 및 상면도이다.

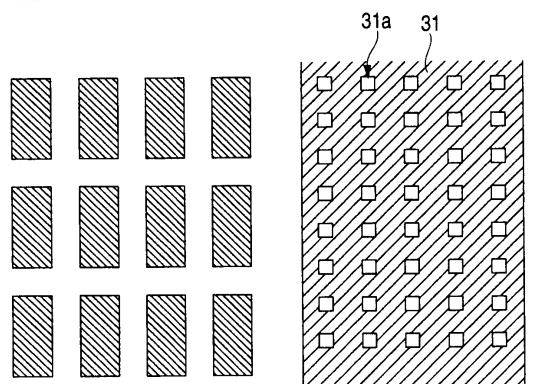

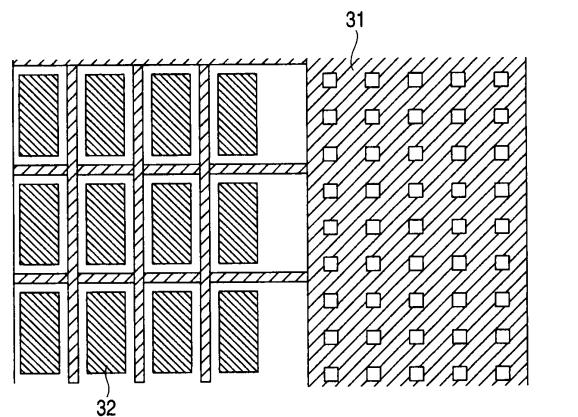

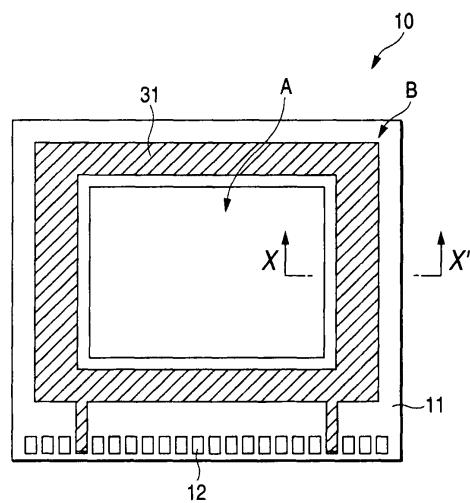

도 2는 본 발명의 표시 장치의 제조 방법에 따른 제1 실시 형태를 설명하기 위한 상면도이다.

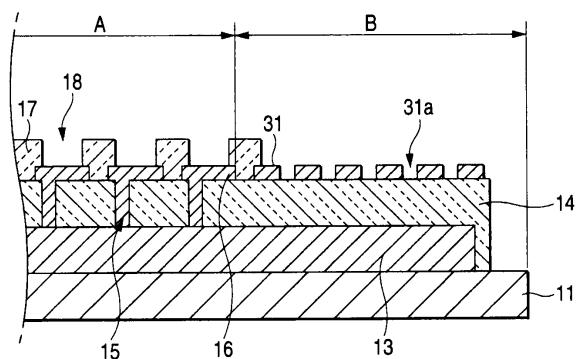

도 3은 본 발명의 표시 장치의 제조 방법에 따른 제1 실시 형태를 설명하기 위한 단면도이다.

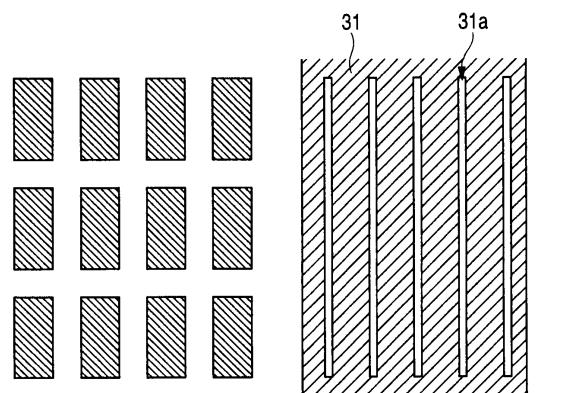

도 4는 본 발명의 표시 장치의 제조 방법에 따른 제1 실시 형태를 설명하기 위한 상면도이다.

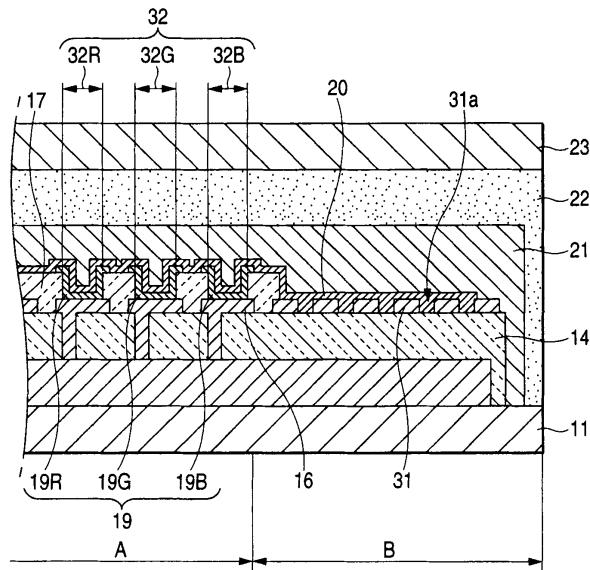

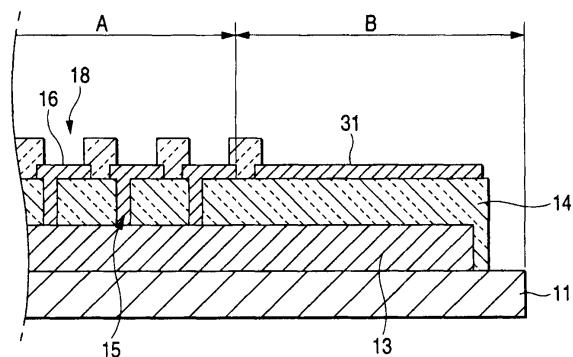

도 5는 본 발명의 표시 장치의 제조 방법에 따른 제2 실시 형태를 설명하기 위한 단면도이다.

도 6은 본 발명의 표시 장치의 제조 방법에 따른 제2 실시 형태의 변형 예를 설명하기 위한 단면도이다.

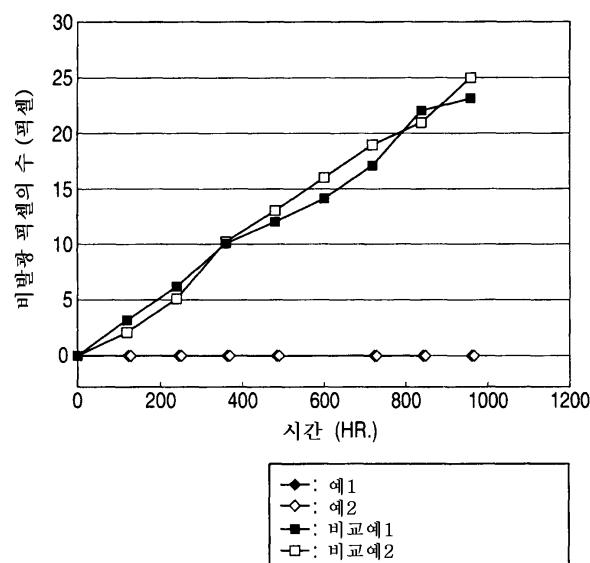

도 7은 본 발명의 실시 예 및 비교예에 있어서의 비접등 화소수의 시간의 경과에 따른 변화를 나타내는 그래프이다.

도 8은 종래의 표시 장치의 제조 방법을 설명하기 위한 상면도이다.

도 9는 종래의 표시 장치의 제조 방법을 설명하기 위한 단면도이다.

### <도면의 주요부분에 대한 부호의 설명>

11: 기판 14: 제1 절연막

16: 하부 전극 17: 제2 절연막

19: 유기층 20: 상부 전극

31: 도전막 31a: 홀

32: 유기 EL 소자

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은, 표시 장치의 제조 방법 및 이에 의한 표시 장치에 관한 것으로, 특히, 유기 전계 발광 소자(유기 EL 소자)를 구비한 표시 장치의 제조 방법 및 표시 장치에 관한 것이다.

유기 EL 소자는, 하부 전극과 상부 전극과의 사이에, 발광층을 포함하는 유기층이 개재되어 있으며, 저전압 직류 구동에 의한 고화도 발광이 가능한 발광 소자로서 주목받고 있다.

이러한 유기 EL 소자를 구비한 액티브 매트릭스형의 표시 장치(즉, 유기 EL 디스플레이)는, 기판 위의 각 화소에 TFT (Thin Film Transistor)를 구비하고 있다. 그리고, 각 화소가 되는 유기 EL 소자는, 이 TFT에 접속된 상태에서 화소마다 패턴 형성된 하부 전극과, 하부 전극 상에 형성된 유기층과, 이 유기층을 피복하도록 형성된 상부 전극으로 구성되어 있다. 이들 중 상부 전극은, 예를 들면, 복수의 화소를 피복하는 전면막(an allover film)으로서 형성되어, 복수의 화소 간에 공통의 상부 전극으로서 이용되고 있다.

이러한 액티브 매트릭스형의 표시 장치에 있어서는, 유기 EL 소자의 개구율을 확보하기 위해, 기판의 반대측으로부터 광을 추출하는 상면 발광형으로서 구성하는 것이 유효하게 된다. 이 때문에, 상부 전극은, 광 투과성을 확보하기 위해, ITO (Indium Tin Oxide), IZO(Indium Zinc Oxide) 등의 투명 도전성 산화물 혹은 Al, MgAg 등을 광 투과성을 가질 정도로 박막화한 것이 이용되지만, 이들은 시트 저항이 높기 때문에 전압 강하가 증가한다. 또한, 유기 EL 디스플레이의 대형화, 고화도화를 도모하기 위한 구동 전류의 증가에 의해서도, 전압 강하가 증가하기 쉬운 경향이 있다.

전술한 바와 같은 전압 강하의 증가에 의한, 유기 EL 디스플레이의 휘도의 저하나 표시 얼룩짐 등의 면내 휘도의 불균일을 방지하기 위해서, 화소 개구 사이의 절연막 상 및 화소 영역의 외측의 절연막 상에 금속 재료로 이루어지는 보조 전극을 형성하여, 이 보조 전극에 상부 전극을 접속시키는 표시 장치의 예가 보고되어 있다.

이러한 보조 전극이 설치된 표시 장치의 예를 도 8에 도시한다. 이 표시 장치(10)는, 상면 발광형 유기 EL 디스플레이이고, 기판(11)상에 화소, 즉 유기 EL 소자(도시 생략)가 배열된 화소 영역 A를 갖고 있다. 여기서는, 보조 전극으로서, 이 화소 영역 A의 외측의 주변 영역 B에, 화소 영역 A를 둘러싸는 프레임 형상으로 도전막(31)이 배치된 예에 대하여 설명한다. 이 도전막(31)은, 기판(11)의 단부에 설치된 구동 회로(12)에 접속되며, 화소 공통의 상부 전극(도시 생략)과도 접속되는 것이다. 도 9(a) 및 도 9(b)각각은 도 8의 X-X'를 따라 자른 단면도이다.

통상적으로, 전술한 바와 같은 구성을 갖는 표시 장치의 제조 방법에 있어서, 제1 절연막(14) 및 제2 절연막(17)은, 보통, 예를 들어, 폴리벤족사졸로 만들어진 유기 절연막에 의해 각각 형성되며, 수분 등을 갖는 경향이 있다. 따라서, 상기 형성 후, 막 상에 베이크 처리를 수행하여, 막이 경화되며 내부에 포함된 수분 등이 제거된다. 그러나, 기판(11)의 주변 영역 내의 제1 절연막 상에 보조 전극으로서의 도전막(31)이 형성된 경우에는, 이후 제2 절연막 상에 베이트 처리를 수행할 때, 도전막(31)이 제1 절연막(14)을 피복한 상태가 된다. 이로 인해, 제1 절연막(14) 내에 남아 있는 수분 등을 제거하는 것이 충분히 수행되지 않는다.

따라서, 이로 인한 영향은 유기 EL 소자(32)에 대한 열화로 점점 진행되어 비발광 결점이 생성되거나 휘도 수명 시간이 줄어들게 된다.

또한, 유기 EL 소자(32)의 열화에 따라, 드라이브 전압도 높아진다.

도전막(31)에 의해 피복된 제1 절연막(14)에서 수분 등을 확실한 방법으로 제거하기 위해서는 고온 뜬느 장시간 베이크 처리를 해야 할 필요가 있는데, 이는 수율을 떨어뜨리는 원인이 된다.

### 발명이 이루고자 하는 기술적 과제

전술한 바와 같은 과제를 해결하기 위해, 본 발명에 있어서의 표시 장치의 제1 제조 방법은, 기판 상에 하부 전극과 상부 전극 사이에 개재된 유기층을 각각 구비한 복수의 화소를 배열하여 화소 영역이 형성된 표시 장치의 제조 방법으로서, 다음과 같은 공정을 순차적으로 행하는 것을 특징으로 한다. 우선, 기판 상에 절연막을 형성하는 공정을 행한다. 다음으로, 화소 영역 내의 절연막 위에 각 화소에 대응하는 복수의 하부 전극을 형성함과 동시에, 화소 영역의 외측의 절연막 위에 도전막을 형성하여, 이 도전막에 절연막까지 연장되는 홀을 형성하는 공정을 행한다. 그 후, 하부 전극 및 도전막이 설치된 기판에 베이크 처리를 행한다.

또한, 이러한 제조 방법에 의해 얻어지는 본 발명의 제1 표시 장치는, 기판 상에 하부 전극과 상부 전극 사이에 개재된 유기층을 각각 구비한 복수의 화소를 배열하여 화소 영역이 형성된 표시 장치로서, 기판 상에 설치된 절연막과, 화소 영역 내의 절연막 위에 설치된 각 화소에 대응하는 복수의 하부 전극과, 화소 영역의 외측의 절연막 위에 설치됨과 동시에, 절연막까지 연장되는 홀이 형성된 도전막을 구비한 것을 특징으로 한다.

이러한 표시 장치의 제1 제조 방법 및 이에 의한 제1 표시 장치에 따르면, 도전막에 절연막까지 연장되는 홀을 형성한 후, 베이크 처리를 행함으로써, 베이크 처리시에, 이 홀에서, 도전막의 하층의 절연막에 함유되는 수분 등이 방출되어 제거된다. 이 때문에, 예를 들어 상기 도전막이 보조 전극으로서 설치되어 있고, 이 도전막이 넓은 면적을 갖도록 형성되었을 경우에도, 도전막의 하층의 절연막에 수분 등이 잔존하는 것이 방지되어, 이 수분 등에 기인하는 화소, 즉 유기 EL 소자의 열화가 방지된다.

또한, 본 발명에 있어서의 표시 장치의 제2 제조 방법은, 기판 상에 하부 전극과 상부 전극 사이에 개재된 유기층을 각각 구비한 복수의 화소를 배열하여 화소 영역이 형성된 표시 장치의 제조 방법으로서, 다음과 같은 공정을 순차적으로 행하는

것을 특징으로 한다. 우선, 화소 영역 내의 기판 상에, 각 화소에 대응하는 복수의 하부 전극을 형성하는 공정을 행한다. 다음으로, 이 하부 전극을 피복한 상태에서, 기판 상에 절연막을 형성하고, 절연막에 하부 전극의 표면을 노출하는 화소 개구를 형성하는 공정을 행한다. 계속해서, 화소 영역의 외측의 절연막 위에 도전막을 형성함과 함께, 도전막에 절연막까지 연장되는 홀을 형성하는 공정을 행한다. 그 후, 도전막이 설치된 기판에 베이크 처리를 행한다.

또한, 이러한 제조 방법에 의해 얻어지는 본 발명의 제2 표시 장치는, 기판 상에 하부 전극과 상부 전극 사이에 개재된 유기 층을 각각 구비한 복수의 화소를 배열하여 화소 영역이 형성된 표시 장치로서, 화소 영역 내의 기판 상에 설치된 각 화소에 대응하는 복수의 하부 전극과, 기판 상에 설치됨과 동시에, 하부 전극을 노출하는 화소 개구가 설치된 절연막과, 화소 영역의 외측의 절연막 위에 설치됨과 동시에, 절연막까지 연장되는 홀이 형성된 도전막을 구비한 것을 특징으로 한다.

이러한 표시 장치의 제2 제조 방법 및 이것에 의해서 얻어지는 제2 표시 장치에 따르면, 도전막에 절연막까지 연장되는 홀을 형성한 후, 베이크 처리를 행함으로써, 베이크 처리시에, 도전막의 하층의 절연막에 함유되는 수분 등이 이 홀을 통해 제거된다. 이 때문에, 예를 들면 상기 도전막이 보조 전극으로서 설치되어 있고, 이 도전막이 넓은 면적을 갖는 경우에서 도, 도전막의 하층의 절연막에 수분 등이 잔존하는 것이 방지되어, 이 수분 등에 기인하는 유기 EL 소자의 열화가 방지된다.

### 발명의 구성 및 작용

이하, 본 발명의 실시 형태를 도면에 기초하여 상세히 설명한다.

#### (제1 실시 형태)

여기서는, 상면 발광형의 유기 EL 디스플레이를 예로 들어, 각 부재의 상세한 구성을 제조 공정순으로 설명한다. 또한, 본 발명의 배경 기술에서 설명한 것과 동일한 구성에는 동일한 번호 및 부호를 붙이고 설명한다.

우선, 도 1(a)에 도시한 바와 같이 예를 들면 글래스 등의 절연 재료로 이루어지는 기판(11) 상에, 복수의 TFT가 배열 형성된 TFT 어레이(13)를 형성한다. 다음으로, 이 TFT 어레이(13)가 형성된 기판(11)상에, 예를 들면 스판 코팅법에 의해 포지티브형 감광성 폴리벤족사졸(photosensitive polybenzoxazole)로 이루어지는 제1 절연막(14)을 도포 형성한다. 이와 같이 형성된 제1 절연막(14)은, 기판(11)의 표면측에 발생한 요철을 평탄화하는 평탄화막으로서 기능한다. 또한, 여기서는 제1 절연막(14)으로 폴리벤족사졸을 사용했지만, 그 외에도 포지티브형 감광성 폴리아미드 등의 절연 재료가 사용가능하다.

그 후, 이 제1 절연막(14)을 노광 및 현상함으로써, 제1 절연막(14)에 TFT와 접속하기 위한 컨택트홀(15)을 형성한다. 계속해서, 이 상태의 기판(11)에, N<sub>2</sub> 등의 불활성 가스 분위기 하에서 베이크 처리를 행함으로써, 폴리벤족사졸로 이루어지는 제1 절연막(14)을 경화시키고 제1 절연막(14) 내에 포함된 수분 등을 제거한다.

계속해서, 컨택트홀(15)을 매립하는 방식으로, 제1 절연막(14) 상에, ITO막, Ag 합금막, ITO막을 기판(11)측으로부터 순차적으로 적층한 도전 재료층(도시 생략)을 성막한다. 이 도전 재료층의 막 두께는, 예를 들면 기판(11)측으로부터, ITO막/Ag 합금막/ITO막이 약 30nm/약 100nm/약 10nm인 것으로 한다. 여기서, Ag 합금막은, 후공정에서, 상기 도전 재료층을 패터닝하여 형성하는 하부 전극의 반사층으로 된다.

계속해서, 통상의 리소그래피 기술에 의해서 형성한 레지스트 패턴(도시 생략)을 마스크로 이용한 에칭에 의해, 상기 도전 재료층을 패터닝한다. 이에 의해, 도전 재료층이 컨택트홀(15)을 통하여 화소 영역 A 내의 제1 절연막(14) 상의 TFT에 접속되어, 각 화소에 대응하는 하부 전극(16)을 배열 형성하며, 화소 영역 A의 외측의 주변 영역 B의 제1 절연막(14)상에 도전막(31)을 형성한다. 이 도전막(31)은 약 3mm의 폭으로 화소 영역 A를 둘러싸는 프레임 형상으로 형성하며, 구동 회로(도시 생략)와 접속시킨다. 여기서, 이 도전막(31)은, 보조 전극으로서 기능하며, 후공정으로 형성하는 상부 전극과 접속되어 배선 저항을 저하시킴으로써, 휘도를 향상시키고, 양호한 면내 휘도 분포를 얻기 위해서 설치된다. 이 때문에, 도전성이 우수한 재료로 형성되는 것이 바람직하며, 그 폭은 넓은 것이 바람직하다.

그리고, 이 도전막(31)에, 제1 절연막(14)까지 연장되는 복수의 홀(31a)을 형성한다. 여기서는, 도 1(b)에 도시한 바와 같이 도전막(31)에, 예를 들면 20μm x 20μm의 직사각형 홀(31a)을 폭 방향 및 길이 방향으로 각각 100μm의 간격을 두고 형성하는 것으로 한다.

여기서, 홀(31a)은, 후공정으로 제1 절연막(14)(상기 도면1(a) 참조) 상에 패턴 형성되는 제2 절연막(17)(상기 도면1(a) 참조)에 베이크 처리를 행할 때, 도전막(31) 하층의 제1 절연막(14)에 잔존하는 수분 등을 제거하기 위한 것이다. 여기서는, 복수의 홀(31a)이 도전막(31)에 배열 형성되는 것으로 했지만, 예를 들면 20 $\mu$ m x 20 $\mu$ m의 직사각형 홀(31a)이 1개여도, 그 홀(31a) 주위의 제1 절연막(14) 내의 수분 등을 제거된다. 단, 제1 절연막(14)에 잔존하는 수분 등을 확실하게 제거하기 위해선, 후공정으로 형성하는 상부 전극과 도전막(31)을 접속시킨 후의 전압 강하가 억제되는 허용 범위 내에서, 홀(31a)의 개구 면적을 넓히고 그 수를 많이 하는 것이 바람직하다. 또한, 도전막(31)의 전역에 걸쳐, 홀(31a)이 균등한 간격으로 배치되는 것이 바람직하다. 또한, 홀(31a)의 형상은 특별한 형상에 한정되지 않으며, 도 2에 도시한 바와 같이, 도전막(31)에 슬릿 형 홀(31a)을 형성해도 된다.

다음으로, 도 1(a)에 도시한 바와 같이, 하부 전극(16) 및 도전막(31)이 설치된 제1 절연막(14)상에, 예를 들면 다시 스펀 코팅법에 의해 포지티브형 감광성 폴리벤족사졸로 이루어지는 제2 절연막(17)을 도포 형성한다. 그 후, 제2 절연막(17)을 노광, 현상 및 경화시키고, 화소 영역 A 내에 각 화소, 즉, 유기 EL 소자를 형성하기 위한 화소 개구(18)를 형성하여, 하부 전극(16)의 표면을 노출하며, 주변 영역 B의 도전막(31)의 표면도 노출시킨다. 이 때, 도전막(31)의 단부는, 제2 절연막(17)으로 괴복된 상태로 남겨둔다. 이에 의해, 제2 절연막(17)은 화소간을 분리하기 위한 소자 분리막으로서 기능하며, 도전막(31)의 단부를 괴복하는 보호막으로서도 기능한다. 또한, 여기서는 제2 절연막(17)으로 폴리벤족사졸을 사용했지만, 그 외에 포지티브형 감광성 폴리이미드 등의 절연 재료를 사용해도 된다.

여기서, 도전막(31)이 산화하여 쉬운 재료로 형성되어 있는 경우에는, 도전막(31)의 단부의 산화를 방지하기 위해서는, 제2 절연막(17)으로 도전막(31)의 단부를 괴복하는 것이 바람직하다. 본 실시 형태에서는, 도전막(31)이 ITO막/Ag 합금막/ITO막으로 이루어지는 적층막으로 형성되어 있기 때문에, 도전막(31)의 단부가 괴복되는 것에 의해, 산화되어 쉬운 Ag 합금막의 산화가 방지된다. 단, 도전막(31)이 산화되기 어려운 재료인 경우에는 이 도전막(31)의 단부가 노출되어 있더라도 상관 없다.

계속해서, 이 상태의 기판(11)에, N<sub>2</sub> 등의 불활성 가스 분위기하에서 베이크 처리를 행함으로써, 폴리벤족사졸을 경화시키고, 제1 절연막(14) 및 제2 절연막(17)에 포함되는 수분 등을 제거한다. 이 때, 주변 영역 B의 제1 절연막(14) 상을 괴복하는 도전막(31)에는, 복수의 홀(31a)이 설치되어 있기 때문에, 이들 홀(31a)에서, 제1 절연막(14)에 잔존하는 수분 등이 방출되어 제거된다.

이 후, 미소 이물을 제거하기 위해 순수로 스펀 세정을 행한 후, 진공 분위기 하에서 베이크 처리를 행한다. 이에 의해, 제1 절연막(14) 및 제2 절연막(17)에 흡착된 수분이 제거된다. 계속해서, 진공 분위기를 유지한 상태에서 전처리실에 반송하여, O<sub>2</sub> 플라즈마로 기판(11)의 전처리를 행하고, 다음으로, 진공 분위기를 유지한 상태에서, 후술하는 바와 같이 다음의 공정인 유기층을 증착한다. 상기한 바와 같은 공정에 따르면, 베이크 처리 후의 공정은 진공 분위기에 유지되고, 따라서 대기 중의 수분 등이 기판(11) 상에 흡착되는 것이 방지되기 때문에 바람직하다.

다음으로, 진공 분위기를 유지한 상태에서, 도 3에 도시한 바와 같이 화소 개구(18)(상기 도면1(a) 참조) 내의 하부 전극(16)상에, 다양한 색의 유기 EL 소자(32)(적색 유기 EL 소자(32R), 녹색 유기 EL 소자(32G), 청색 유기 EL 소자(32B))에 있어서의 유기층(19), 즉, 적색 유기층(19R), 녹색 유기층(19G), 청색 유기층(19B)를 각각 형성한다.

이 경우에는, 예를 들어, 진공 분위기 하에서, 청색 유기층(19B)을 증착하기 위한 챔버에 기판(11)을 반송하여, 기판(11) 상에 증착 마스크(도시 생략)를 얼라인먼트하고, 정공 주입층, 정공 수송층, 발광층, 전자 수송층을 순차적으로 증착함으로써, 바닥부에 하부 전극(16)이 노출된 화소 개구(18)의 내벽을 괴복하여, 약 200nm의 막 두께로 청색 유기층(19B)를 형성한다.

계속해서, 진공 분위기를 유지한 상태에서, 적색 유기층(19R)을 증착하기 위한 챔버에 기판(11)을 반송하여, 기판(11)상에 증착 마스크(도시 생략)를 얼라인먼트하고, 청색의 유기층(19B)에서와 같은 방식으로, 적색 유기층(19R)을 약 150nm의 막 두께로 형성한다.

그 후, 진공 분위기를 유지한 상태에서, 녹색 유기층(19G)을 증착하기 위한 챔버에 기판(11)을 반송하고, 기판(11)상에 증착 마스크(도시 생략)를 얼라인먼트하여, 청색 유기층(19B)에서와 같은 방식으로, 녹색 유기층(19G)을 약 100nm의 막 두께로 형성한다.

이상과 같이, 각 유기층(19)을 형성한 후, 진공 분위기를 유지한 상태에서, 기판(11) 상에 증착 마스크(도시 생략)를 열라인먼트하고, 가령, 증착법에 의해, 유기층(19) 상, 제2 절연막(17) 상 및 도전막(31) 상에, 가령 LiF로 이루어지는 전자 주입층(도시 생략)을 약 1nm의 막 두께로 형성한다. 그 후, 증착 마스크를 이용한 진공 증착법에 의해, 전자 주입층 상에, 예를 들어 반 투과성의 MgAg 합금으로 이루어지는 상부 전극(20)을 약 10nm의 막 두께로 형성한다. 이에 따라, 전자 주입층이 개재하여 도전막(31)과 상부 전극(20)이 접속된다.

계속해서, 예를 들면 스퍼터법에 의해, 상부 전극(20)을 증착할 때에 이용한 증착 마스크를 기판(11) 상에 열라인먼트하여, 상부 전극(20) 상에, 예를 들면 IZO로 이루어지는 투명 도전층(도시 생략)을 100nm의 막 두께로 형성한다.

그 후, CVD법에 의해, 마스크를 열라인먼트한 상태에서, 투명 도전층 상에 질화 실리콘(SiNx)으로 이루어진 보호막(21)을 1μm의 막 두께로 형성한다. 다음으로, 보호막(21) 상 및 기판(11)의 주변부 상에, 열 경화성의 수지(22)를 도포하고, 이 수지(22)상에, 예를 들면 글래스로 이루어지는 기판(23)을 접합시킨 상태로 가열함으로써 수지 밀봉을 행한다.

이상과 같은 제조 방법에 의해, 유기층(19)의 발광층에서 발생한 광을, Ag 합금막을 포함하는 하부 전극(16)측에서 반사시켜, 반 투과성의 MgAg 합금으로 형성된 상부 전극(20)측으로부터 추출한다. 이에 따라, 상면 발광형의 유기 EL 디스플레이를 얻을 수 있다.

이러한 표시 장치의 제조 방법 및 이에 따라 얻어지는 표시 장치에 따르면, 화소 영역 A의 외측의 주변 영역 B에 배치되는 도전막(31)에, 제1 절연막(14)까지 연장되는 홀(31a)을 형성한 후, 베이크 처리를 행함으로써, 상기 홀(31a)에서 제1 절연막(14)에 함유되는 수분 등이 방출되어 제거된다. 이 때문에, 제1 절연막(14)에 수분 등이 잔존하는 것이 방지되어, 수분 등에 기인하는 유기 EL 소자(32)의 열화가 방지된다.

따라서, 유기 EL 소자(32)의 비발광 결함을 저감할 수 있음과 동시에 발광 수명을 향상시킬 수 있고, 구동 전압을 낮게 유지할 수 있다. 또한, 고온 또는 장시간의 베이크 처리를 행하지 않더라도, 제1 절연막(14)에 포함되는 수분 등이 확실하게 제거되기 때문에, 생산성을 향상시킬 수 있다.

또한, 본 실시 형태에서는, 하부 전극(16)과 도전막(31)이 동일 재료로 형성되기 때문에, 하부 전극(16) 및 도전막(31)을 동일 공정에서 형성할 수 있고, 도전막(31)에 형성하는 홀(31a)도 동일 공정에서 형성하기 때문에 제조 공정이 증가되지 않으며 생산성도 높아진다.

또한, 여기서는, 도전막(31)이 화소 영역 A를 둘러싸는 프레임 형상으로 형성되는 예에 대하여 설명했지만, 도전막(31)의 형상은 상기에 한정되는 것은 아니며, 예를 들어 주변 영역 B에서, 화소 영역 A가 둘러싸인 상태로, 소정의 폭을 갖는 긴 스트라이프형 도전막(31)이 구동 회로와 접속되도록 배치되었던 것과 같은 구성이어도 된다.

또한, 주변 영역 B에만 도전막(31)이 설치된 예에 대하여 설명했지만, 도 4에 도시한 바와 같이 배열 형성된 유기 EL 소자(32)로 이루어진 각 화소간의 제1 절연막(14)상에 격자 형상으로 도전막(31)이 설치된 구성이어도 무방하다. 이 경우에는, 도 1(a)을 이용하여 설명한 바와 같이, 제1 절연막(14) 상에 도전 재료층을 성막하여, 화소 영역 A에 하부 전극(16)을 배열 형성함과 동시에, 주변 영역 B에 도전막(31)을 형성할 때에, 각 화소간에 격자 형상으로 배치되는 상태로, 주변 영역 B의 도전막(31)과 접속되도록 도전 재료층을 패터닝한다.

## (제2 실시 형태)

제1 실시 형태에서는, 상면 발광형의 유기 EL 디스플레이를 예로 들어 설명했지만, 본 실시 형태에서는, 유기층에서 발생한 광을 하부 전극측으로부터 추출하는 하면 발광형의 유기 EL 디스플레이에 대하여도 5(a) 및 5(b)을 이용하여 설명한다. 또한, 제1 실시 형태와 동일한 구성에는 동일한 참조 번호를 붙이고 설명하는 것으로 한다.

또한, 도 5(a)에 도시한 바와 같이 TFT 어레이(13)가 형성된 기판(11) 상에, 제1 절연막(14)을 도포 형성하여, 제1 절연막(14)에 TFT와 접속하기 위한 컨택트홀(15)을 형성한 후, 기판(11)에 베이크 처리를 행하기까지의 공정은, 제1 실시 형태와 동일한 것으로 한다.

다음으로, 예를 들면 스퍼터법에 의해, 컨택트홀(15)을 매립한 상태에서, 제1 절연막(14) 상에, 예를 들면 ITO 막으로 이루어지는 도전 재료층(도시 생략)을, 약 100nm의 막 두께로 성막한다. 계속해서, 통상의 리소그래피 기술에 의해서 형성한 레지스트 패턴(도시 생략)을 마스크로 이용한 에칭으로, 이 도전 재료층을 패터닝한다. 이에 의해, 화소 영역 A 내의 제1 절연막(14) 상에, 컨택트홀(15)을 통해 TFT에 접속되어, 각 화소에 대응하는 하부 전극(16)을 배열 형성한다.

계속해서, 예를 들면 스퍼터법에 의해, 이 하부 전극(16)을 피복한 상태에서, 제1 절연막(14) 상에, 하부 전극(16)을 형성하는 ITO보다도 도전성이 양호한 알루미늄네오디뮴(AlNd)으로 이루어진 도전 재료층(도시 생략)을, 약 300nm의 막 두께로 성막한다. 계속해서, 통상의 리소그래피 기술에 의해서 형성한 레지스트 패턴(도시 생략)을 마스크로 이용한 에칭으로, 이 도전 재료층을 패터닝한다. 이 때, 하부 전극(16) 상에도 도전 재료층이 성막되지만, AlNd는 ITO에 대하여 충분히 에칭 선택비가 있는 재료이기 때문에 문제 없다.

이에 의해, 화소 영역 A의 외측의 주변 영역 B에, 제1 실시 형태와 같이, 화소 영역 A를 둘러싸는 형상으로, 약 3mm의 폭의 도전막(31)을 형성함과 함께, 이 도전막(31)에, 제1 절연막(14)까지 연장되는 복수의 홀(31a)을 형성한다.

다음으로, 하부 전극(16)이 설치된 제1 절연막(14) 상에, 예를 들면 다시 스픬 코팅법에 의해 포지티브형 감광성 폴리벤족 사졸로 이루어지는 제2 절연막(17)을 도포 형성하고, 그 후, 노광 및 현상함으로써, 화소 영역 A 내에 각 화소, 즉, 유기 EL 소자를 형성하기 위한 화소 개구(18)를 형성하여, 하부 전극(16)의 표면을 노출함과 동시에 주변 영역 B의 도전막(31)의 표면도 노출한다. 이 때, 제1 실시 형태에서는, 도전막(31)의 단부를 제2 절연막(17)으로 피복하는 것으로 했지만, 본 실시 형태에서는 도전막(31)에 이용되는 AlNd는 산화하여 쉬운 재료가 아니기 때문에, 도전막(31)의 단부는 노출된 상태로 둔다. 또한, 여기서는 제2 절연막(17)으로 폴리벤족사졸을 사용했지만, 그 외에도 포지티브형 감광성 폴리이미드 등의 절연 재료를 사용해도 무방하다.

계속해서, 이 상태의 기판(11)에, 제1 실시 형태와 같이,  $N_2$  등의 불활성 가스 분위기 하에서 베이크 처리를 행함으로써, 폴리벤족사졸을 경화시키고, 제1 절연막(14) 및 제2 절연막(17)에 포함되는 수분 등을 제거한다. 이 때, 주변 영역 B의 제1 절연막(14)상을 피복하는 도전막(31)에는, 복수의 홀(31a)이 설치되어 있기 때문에, 이들의 홀(31a)에서, 제1 절연막(14)에 잔존하는 수분 등이 방출되어 제거된다.

이 후, 미소 이물을 제거하기 위해 순수로 스픬 세정을 행한 후, 진공 분위기 하에서 베이크 처리를 행한다. 이에 의해, 제1 절연막(14) 및 제2 절연막(17)에 흡착된 수분이 제거된다. 계속해서, 진공 분위기를 유지한 상태에서, 전처리실로 반송하여,  $O_2$  플라즈마에 의한 기판(11)의 전처리를 행하고, 다음으로, 진공 분위기를 유지한 상태에서, 후술하는 바와 같이, 다음의 공정인 유기층의 증착을 행한다. 상기한 바와 같은 공정을 수행하면, 베이크 처리 후의 공정은 진공 분위기에 유지되기 때문에, 대기 중의 수분 등이 기판(11) 상에 흡착되는 것이 방지되기 때문에 바람직하다.

다음으로, 진공 분위기를 유지한 상태에서, 도 5(b)에 도시한 바와 같이 제1 실시 형태와 동일한 방법으로, 화소 개구(18) 내의 하부 전극(16)상에, 다양한 색의 유기 EL 소자(32)(적색 유기 EL 소자(32R), 녹색 유기 EL 소자(32G), 청색 유기 EL 소자(32B))에 있어서의 유기층(19)(적색 유기층(19R), 녹색 유기층(19G), 청색 유기층(19B))을 각각 형성한다.

계속해서, 진공 분위기를 유지한 상태에서, 기판(11)상에 증착 마스크(도시 생략)을 열라인먼트하고, 예를 들면 증착법에 의해, 각 유기층(19) 상, 제2 절연막(17) 상 및 도전막(31) 상에, 예를 들면 LiF로 이루어지는 전자 주입층(도시 생략)을 약 1nm의 막 두께로 형성한다. 그 후, 이 증착 마스크를 이용한 진공 증착법에 의해, 전자 주입층 상에, 예를 들면 알루미늄(Al)으로 이루어지는 반사성 상부 전극(20)을 약 100nm의 막 두께로 형성한다. 이에 의해, 전자 주입층이 개재되어 도전막(31)과 상부 전극(20)이 접속된다. 그 후, CVD법에 의해, 마스크를 열라인먼트한 상태에서, 상부 전극(20) 상에 SiNx로 이루어지는 보호막(21)을 1 $\mu$ m의 막 두께로 형성한다. 다음으로, 보호막(21) 상 및 기판(11)의 주변부 상에, 열 경화성의 수지(22)를 도포하고, 상기 수지(22)상에, 예를 들면 글래스로 이루어진 기판(23)을 접합시킨 상태에서, 가열함으로써 수지 밀봉을 행한다.

이상과 같은 제조 방법에 의해, 유기층(19)의 발광층에서 발생한 광을, Al로 이루어지는 상부 전극(20)측에서 반사시켜, 투과성의 ITO 막으로 이루어지는 하부 전극(16)측으로부터 추출하는 유기 EL 디스플레이를 얻을 수 있다.

이러한 제조 방법 및 이에 의해 제조된 표시 장치에서도, 화소 영역 A의 외측의 주변 영역 B에 배치되는 도전막(31)에, 제1 절연막(14)에 달하는 홀(31a)을 형성함으로써, 제1 실시 형태와 마찬가지의 효과를 얻을 수 있다.

또한, 본 실시 형태에 따르면, 도전막(31)을 하부 전극(16)보다도 도전성이 양호한 재료로 형성하고, 이 도전막(31)을 상부 전극(20)과 접속시켜 배선 저항을 저하시킴으로써, 휘도를 향상시킴과 동시에 양호한 면내 휘도 분포를 얻을 수 있다.

또한, 본 실시 형태와 같이, 도전막(31)을 하부 전극(16)과는 다른 재료로 형성하는 제조 방법은, 제1 실시 형태에서 설명한 상면 발광형의 표시 장치에서도 적용 가능하다. 단, 특히, 하면 발광형의 표시 장치이고, 하부 전극(16)이 양극이 되는 구성인 경우에는, 하부 전극(16)으로 투과성을 갖는 ITO 막이 이용되는 경우가 많은데, ITO 막은 비교적 저항이 높은 재료이기 때문에, 하부 전극(16)보다도 높은 도전성을 갖는 재료로 도전막(31)을 형성하는 것이 바람직하다.

(변형 예)

전술한 바와 같이, 하부 전극(16)보다도 높은 도전성을 갖는 재료로 도전막(31)을 형성하는 경우에는, 제2 절연막(17) 상에 도전막(31)을 형성해도 된다. 이 경우의 표시 장치의 제조 방법에 대하여, 제2 실시 형태와 같이, 하면 발광형의 표시 장치를 예로 들어 도 6을 이용하여 설명한다. 여기서, TFT 어레이(13)가 형성된 기판(11)상에, 제1 절연막(14)을 도포 형성하고, 제1 절연막(14)에 TFT와 접속하기 위한 컨택트홀(15)을 형성한 후, 기판(11)에 베이크 처리를 행하기까지의 공정은, 도 5(a)을 이용하여 설명한 제2 실시 형태와 동일한 방법으로 행하는 것으로 한다. 또한, 여기까지의 구성이, 청구항 11 및 청구항 14의 기판에 상당한다.

다음으로, 도 6에 도시한 바와 같이 제2 실시 형태와 동일한 방법으로, 화소 영역 A 내의 제1 절연막(14) 상에, 컨택트홀(15)을 통하여 TFT에 접속되어, 각 화소에 대응하는 하부 전극(16)을 배열 형성한다. 계속해서, 하부 전극(16)이 설치된 제1 절연막(14) 상에, 예를 들면 스픬 코팅법에 의해 포지티브형 감광성 폴리벤족사졸로 이루어지는 제2 절연막(17)을 도포 형성한다. 이 제2 절연막(17)이, 청구항 11 및 청구항 14의 절연막에 상당한다. 또한, 여기서는 제2 절연막(17)에 폴리벤족사졸을 사용했지만, 그 외에도 포지티브형 감광성 폴리아미드 등의 절연 재료를 사용해도 된다.

그 후, 노광 및 현상을 통해, 화소 영역 A 내에 각 화소, 즉, 유기 EL 소자(32)를 형성하기 위한 화소 개구(18)를 형성하여, 하부 전극(16)의 표면을 노출한다. 계속해서, 이 상태의 기판(11)에, N<sub>2</sub> 등의 불활성 가스 분위기 하에서 베이크 처리를 행함으로써, 폴리벤족사졸을 경화시킴과 동시에, 제1 절연막(14) 및 제2 절연막(17)에 포함된 수분 등을 제거한다.

다음으로, 예를 들어 스퍼터법을 이용하여, 하부 전극(16) 상 및 제2 절연막(17) 상에, 하부 전극(16)을 형성하는 ITO보다도 도전성이 양호한 AlNd로 이루어진 도전 재료층(도시 생략)을, 약 300nm의 막 두께로 성막한다. 이 때, 화소 개구(18) 내에 노출된 하부 전극(16) 상에도 도전 재료층이 성막되지만, AlNd는 ITO에 대하여 충분히 애칭 선택비 있는 재료이기 때문에 문제없다.

계속해서, 통상의 리소그래피 기술에 의해서 형성한 레지스트 패턴(도시 생략)을 마스크에 이용한 애칭으로, 이 도전 재료층을 패터닝한다. 이에 의해, 화소 영역 A의 외측의 주변 영역 B에, 화소 영역 A를 둘러싸는 형상으로, 약 3mm의 폭의 도전막(31)을 형성함과 동시에, 이 도전막(31)에, 제2 절연막(14)에 달하는 상태의 복수의 홀(31a)을 형성한다. 여기서는, 제1 실시 형태와 같이, 이 도전막(31)에, 예를 들면 20μm x 20μm의 구형의 홀(31a)을 폭 방향 및 길이 방향으로 각각 100μm의 간격을 두고 형성하는 것으로 한다. 그 후, 레지스트 패턴을 제거한다.

이후, 미소 이물을 제거하기 위해 순수로 스픬 세정을 행한 후, 진공 분위기 하에서 이 상태의 기판(11)에 베이크 처리를 행한다. 이에 의해, 제1 절연막(14) 및 제2 절연막(17)에 흡착된 수분이 제거된다. 이 때, 주변 영역 B의 제2 절연막(17) 상을 피복하는 도전막(31)에는, 복수의 홀(31a)이 제공되어 있기 때문에, 이들의 홀(31a)에서 제1 절연막(14) 및 제2 절연막(17)에 잔존하는 수분 등이 방출되어 제거된다. 계속해서, 진공 분위기를 유지한 상태에서 기판(11)을 전처리실로 반송하여, O<sub>2</sub> 플라즈마에 의해 기판(11)의 전처리를 행한다. 다음으로, 진공 분위기를 유지한 상태에서, 후술하는 바와 같이 다음의 공정인 유기층의 증착을 행한다. 상기한 바와 같은 공정에 의하면, 베이크 처리 후의 공정은 진공 분위기에 유지되기 때문에, 대기 중의 수분 등이 기판(11) 상에 흡착되는 것이 방지되기 때문에 바람직하다.

이후의 공정은, 진공 분위기를 유지한 상태에서, 도 3(b)를 이용하여 설명한 제2 실시 형태와 마찬가지의 방법으로 행하는 것으로 한다.

이러한 표시 장치의 제조 방법 및 이것에 의해서 얻어지는 표시 장치에서도, 화소 영역 A의 외측의 주변 영역 B에 배치되는 도전막(31)에, 제2 절연막(17)까지 연장되는 홀(31a)을 형성한 후, 이 상태의 기판(11)에 베이크 처리를 행하기 때문에, 제1 실시 형태와 마찬가지의 효과를 얻을 수 있다.

또한, 전술한 바와 같은 제2 절연막(17) 상에 도전막(31)이 배치된 구성의 변형예에 대해서는, 제1 실시 형태로 설명한 상면 발광형의 표시 장치에 있어서도 적용 가능하다. 또한, 이러한 구성의 표시 장치에 있어서, 도 4를 이용하여 설명한 바와 같이 화소간에 보조 전극이 형성된 구성을 취하는 경우에는, 제2 절연막(14) 상에 도전 재료층을 성막 및 패터닝하여, 주변 영역 B에 화소 영역 A를 둘러싸는 상태의 도전막(31)을 형성할 때에, 각 화소간에 격자 형상으로 배치되는 상태로, 주변 영역 B의 도전막(31)과 접속되도록, 도전 재료층을 패터닝한다.

이상 설명한 표시 장치에 대해서는, 하부 전극(16)을 양극으로 하고, 상부 전극(20)을 음극으로 한 구성에 대하여 설명했지만, 하부 전극(16)이 음극이고, 상부 전극(20)이 양극이어도 된다. 이 경우에는, 전자 주입층을 통해 하부 전극(16)이 노출되는 화소 개구(18) 내에, 전자 수송층, 발광층, 정공 수송층, 정공 주입층의 순으로 적층된 유기층(19)을 형성하여, 이 상태의 기판(11)의 전면을 피복하는 상태가 되도록, 상부 전극(20)을 형성한다.

또한, 제1 실시 형태로서는 상면 발광형의 표시 장치, 제2 실시 형태로서는 하면 발광형의 표시 장치에 대하여 설명했으며, 이 경우, 하부 전극(16)과 상부 전극(20)을 반투과성의 재료로 형성했다. 양면에서 발광된 광을 추출하는 것과 같은 양면 발광형 표시 장치에서도 본 발명은 적용 가능하다.

계속하여, 본 발명의 구체적인 예에 대하여 설명한다.

#### (제1 예)

상기 제1 실시 형태와 동일한 방법에 의해, 도 3에 도시하는 상면 발광형의 표시 장치를 제조하였다. 또한, 이것에 대한 비교예로서, 제1 절연막(14)의 주변 영역 B에, 홀(31a)이 설치되어 있지 않는 상태의 도전막(31)을, 화소 영역 A를 둘러싸는 형상으로 약 3mm의 폭으로 형성한 표시 장치를 제조하였다.

이들의 표시 장치에 대하여, 80°C의 항온기 내에 약 1000 시간 보존한 경우의 비점등 화소 수의 시간에 따른 변화를 도 7의 그래프에 도시한다. 이 그래프는, 횡축에 보존 시간, 종축에 비점등 화소 수를 나타내고 있다. 이 그래프에 도시한 바와 같이 제1 예의 표시 장치에 대해서는, 약 1000 시간 경과한 후도 비점등 화소 수가 증가하지 않고 양호한 화상 표시가 얻어졌지만, 비교예 1의 표시 장치는, 시간에 따라 비점등 화소 수가 증가하여, 화상 표시가 악화하는 것이 확인되었다.

#### (제2 예)

상기 제2 실시 형태와 동일한 방법에 의해, 도 5(b)에 도시하는 하면 발광형의 표시 장치를 제조하였다. 또한, 이것에 대한 비교예 2로서, 제1 절연막(14)의 주변 영역 B에, 홀(31a)이 설치되어 있지 않는 상태의 도전막(31)을, 화소 영역 A를 둘러싸는 형상으로 약 3mm의 폭으로 형성한 표시 장치를 제조하였다.

이들의 표시 장치에 대하여, 80°C의 항온기 내에 약 1000 시간 보존한 경우의 비점등 화소 수의 시간에 따른 변화를 도 7의 그래프에 도시한다. 이 그래프에 도시한 바와 같이, 제2 예의 표시 장치에 대해서는, 약 1000 시간 경과 후도 비점등 화소 수가 증가하지 않고 양호한 화상 표시가 얻어졌지만, 비교예 2의 표시 장치는, 시간에 따라 비점등 화소 수가 증가하여, 화상 표시가 악화하는 것이 확인되었다.

이들의 결과로부터, 제1 예 및 제2 예의 표시 장치는 비교예 1 및 비교예 2의 표시 장치와 비교하여, 비점등 화소 수의 증가가 방지되기 때문에, 비발광 결합이 적고 발광 수명도 긴 것이 시사되었다.

#### 발명의 효과

이상 설명한 바와 같이, 본 발명에 있어서의 표시 장치의 제조 방법 및 이에 따른 표시 장치에 따르면, 절연막에 잔존한 수분 등에 기인하는 유기 EL 소자의 열화가 방지되기 때문에, 유기 EL 소자의 비발광 결함을 저감할 수 있음과 동시에 발광 수명을 향상시킬 수 있고 구동 전압을 낮게 유지할 수 있다. 또한, 고온 또는 장시간의 베이크 처리를 행하지 않더라도, 절연막에 포함되는 수분 등이 확실하게 제거되기 때문에 생산성을 향상시킬 수 있다.

#### (57) 청구의 범위

## 청구항 1.

기판 상에 하부 전극과 상부 전극 사이에 개재된 유기층을 각각 구비한 복수의 화소를 배열하여 화소 영역이 형성된 표시 장치의 제조 방법에 있어서,

상기 기판 상에 제1 절연막을 형성하는 제1 단계와,

상기 화소 영역 내의 상기 제1 절연막 상에, 상기 각 화소에 대응하는 복수의 상기 하부 전극을 형성하고, 상기 화소 영역의 외측의 상기 제1 절연막 상에 도전막을 형성하며, 상기 도전막을 통해 상기 제1 절연막까지 훌을 형성하는 제2 단계와,

상기 하부 전극 및 상기 도전막이 제공된 상기 기판을 베이킹하는 제3 단계를 포함하는 표시 장치의 제조 방법.

## 청구항 2.

제1항에 있어서,

상기 하부 전극과 상기 도전막을 동일 재료로 형성하는 표시 장치의 제조 방법.

## 청구항 3.

제1항에 있어서,

상기 제2 단계에서, 복수의 상기 훌을 상기 도전막의 전역에 걸쳐 대략 균등한 간격으로 형성하는 표시 장치의 제조 방법.

## 청구항 4.

제1항에 있어서,

상기 제2 단계와 상기 제3 단계 사이에, 상기 제1 절연막 상에 상기 하부 전극 및 상기 도전막을 피복하는 제2 절연막을 형성하고, 상기 제2 절연막 상에 각각의 상기 하부 전극 표면을 노출시키는 화소 개구를 형성하며, 상기 도전막 상의 상기 제2 절연막을 제거하여 상기 도전막의 표면을 노출시키는 단계를 포함하고,

상기 제3 단계 후, 상기 하부 전극 상에 유기층을 형성하고, 상기 유기층, 상기 제2 절연막 및 상기 도전막을 피복하는 상부 전극을 형성하여 상기 상부 전극과 상기 도전막이 상호 접속되도록 하는 표시 장치의 제조 방법.

## 청구항 5.

제4항에 있어서,

상기 도전막의 표면 노출 단계에서, 상기 도전막의 단부 상에 상기 제2 절연막의 일부가 남도록 상기 도전막 상의 상기 제2 절연막을 제거하는 표시 장치의 제조 방법.

## 청구항 6.

기판 상에 하부 전극과 상부 전극 사이에 개재된 유기층을 각각 구비한 복수의 화소를 배열하여 형성된 화소 영역을 구비한 표시 장치에 있어서,

상기 기판 상에 제공된 제1 절연막과,

상기 화소 영역 내의 상기 절연막 상에 제공된 각 상기 화소에 각각 대응하는 복수의 하부 전극과,

상기 화소 영역 외측의 상기 제1 절연막 상에 제공되며, 홀이 상기 제1 절연막까지 제공된 도전막을 포함하는 표시 장치.

#### 청구항 7.

제6항에 있어서,

상기 하부 전극과 상기 도전막은 동일 재료로 형성된 표시 장치.

#### 청구항 8.

제6항에 있어서,

복수의 상기 홀은 상기 도전막의 전역에 걸쳐 대략 균등한 간격으로 형성되어 있는 표시 장치.

#### 청구항 9.

제6항에 있어서,

상기 제1 절연막 상에 제공되고, 상기 각각의 하부 전극이 노출되도록 하는 화소 개구가 제공된 제2 절연막과,

상기 하부 전극 상에 제공된 유기층과,

상기 유기층, 상기 제2 절연막 및 상기 도전막을 피복한 상부 전극을 더 포함하고,

상기 상부 전극 및 상기 도전막은 상호 접속되어 있는 표시 장치.

#### 청구항 10.

제9항에 있어서,

상기 도전막의 단부는 상기 제2 절연막에 의해 피복된 표시 장치.

#### 청구항 11.

기판 상에 하부 전극과 상부 전극 사이에 개재된 유기층을 각각 구비한 복수의 화소를 배열하여 화소 영역이 형성된 표시 장치의 제조 방법에 있어서,

상기 기판 상에 각 상기 화소에 각각 대응하는 복수의 상기 하부 전극을 형성하는 제1 단계와,

상기 기판 상에 상기 하부 전극을 피복하는 제1 절연막을 형성하고, 상기 제1 절연막 상에 상기 각 하부 전극의 표면을 노출시키는 화소 개구를 형성하는 제2 단계와,

상기 화소 영역의 외측의 상기 제1 절연막 상에 도전막을 형성하고, 상기 도전막을 통해 상기 절연막까지 홀을 형성하는 제3 단계와,

상기 도전막이 제공된 상기 기판을 베이킹하는 제4 단계를 포함하는 표시 장치의 제조 방법.

### 청구항 12.

제11항에 있어서,

상기 제3 단계에서, 복수의 상기 홀을 상기 도전막의 전역에 걸쳐 대략 균등한 간격으로 형성하는 표시 장치의 제조 방법.

### 청구항 13.

제11항에 있어서,

상기 제4 단계 후, 상기 유기층을 상기 하부 전극상에 형성하고, 상기 제1 절연층 및 상기 도전층을 피복하는 상기 상부 전극을 형성하여 상기 상부 전극 및 상기 도전막이 상호 접속되도록 하는 표시 장치의 제조 방법.

### 청구항 14.

기판 상에 하부 전극과 상부 전극 사이에 개재된 유기층을 각각 구비한 복수의 화소를 배열하여 형성된 화소 영역을 구비한 표시 장치에 있어서,

상기 화소 영역 내의 기판 상에 제공되는 각 상기 화소에 각각이 대응하는 복수의 하부 전극과,

기판 상에 제공되고, 각 상기 하부 전극이 노출되도록 하는 화소 개구가 제공된 제1 절연막과,

상기 화소 영역의 외측의 상기 제1 절연막 상에 제공되며, 상기 홀이 상기 제1 절연막까지 제공된 도전막을 포함하는 표시 장치.

### 청구항 15.

제14항에 있어서,

복수의 상기 홀은 상기 도전막의 전역에 걸쳐 대략 균등한 간격으로 형성되어 있는 표시 장치.

### 청구항 16.

제14항에 있어서,

상기 하부 전극상에 제공된 유기층과,

상기 유기층, 상기 절연막 및 상기 도전막을 피복하도록 제공된 상부 전극을 더 포함하며,

상기 상부 전극과 상기 도전막은 상호 접속된 하는 표시 장치.

도면

도면1a

도면1b

도면2

도면3

도면4

도면5a

도면5b

도면6

도면7

도면8

도면9a

도면9b

|                |                                                                                        |         |            |

|----------------|----------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置及其制造方法                                                                             |         |            |

| 公开(公告)号        | <a href="#">KR1020060044531A</a>                                                       | 公开(公告)日 | 2006-05-16 |

| 申请号            | KR1020050023527                                                                        | 申请日     | 2005-03-22 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                   |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                   |         |            |

| 当前申请(专利权)人(译)  | 索尼公司                                                                                   |         |            |

| [标]发明人         | SHIBASAKI TAKANORI<br>시바사끼다까노리<br>ASANO MITSURU<br>아사노미쓰루                              |         |            |

| 发明人            | 시바사끼다까노리<br>아사노미쓰루                                                                     |         |            |

| IPC分类号         | H05B33/10 H05B33/22 H05B33/06 G09F9/00 G09F9/30 H01J1/62 H01L27/32 H01L51/50 H05B33/14 |         |            |

| CPC分类号         | H01L27/3276 H01L51/5237 H01L27/3258 H01L27/3246 H01L51/524 H01L51/5253                 |         |            |

| 代理人(译)         | CHANG, SOO KIL<br>LEE, JUNG HEE                                                        |         |            |

| 优先权            | 2004082477 2004-03-22 JP                                                               |         |            |

| 其他公开文献         | KR101161443B1                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                              |         |            |

### 摘要(译)

在具有低驱动电压的状态下，每个有机电致发光显示器中的不发光畸形的变色和发光寿命长。并且生产率提供了优秀的显示装置制造方法和显示装置。显示装置的制造方法包括第一步骤在基板上形成第一绝缘层，第二步骤通过导电膜形成孔直到第一绝缘层，导电膜形成在像素区域外侧的第一绝缘层上底部电极由与第一绝缘层上的每个像素相对应的多个，在像素区域和底部电极内形成，以及第三步骤，其中烘培其中设置有导电膜的基板。基板，下电极，上电极，像素区域，绝缘层，显示装置。