(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2013년11월04일

(11) 등록번호 10-1322195

(24) 등록일자 2013년10월21일

- (51) 국제특허분류(Int. C1.)

*G09G 3/30* (2006.01) *G09G 3/32* (2006.01)

*G09G 3/20* (2006.01) *H01L 51/50* (2006.01)

- (21) 출원번호 10-2008-7008960

- (22) 출원일자(국제) 2006년09월06일

심사청구일자 2011년09월06일

- (85) 번역문제출일자 2008년04월15일

- (65) 공개번호 10-2008-0051175

- (43) 공개일자 2008년06월10일

- (86) 국제출원번호 PCT/JP2006/318097

- (87) 국제공개번호 WO 2007/032361

국제공개일자 2007년03월22일

- (30) 우선권주장

JP-P-2005-00269013 2005년09월15일 일본(JP)

- (56) 선행기술조사문헌

KR1020040085653 A

JP2005181920 A

JP2004280059 A

US20040174349 A1

- 전체 청구항 수 : 총 31 항

- 심사관 : 양성지

(54) 발명의 명칭 표시 장치 및 이의 구동 방법

**(57) 요 약**

EL 소자를 포함하는 표시 장치의 문제인 프로그램 시간의 부족을 해결하고, 고 애퍼처 비를 갖는 화소 회로를 포함하는 표시 장치 및 이의 구동 방법을 제공한다. 구동 트랜ジ스터, 용량소자, 용량소자로서 사용될 수 있는 표시 소자, 제1 전원선 및 제2 전원선을 포함하는 회로에서, 제1 전원선 및 제2 전원선의 전위들은 거의 동일하게 되게 설정되고, 그럼으로써 구동 트랜지스터의 임계 전압이 표시 소자에서 유지되고, 그 후에, 전하는 표시 소자 및 용량소자에 분배된다.

**대 표 도 - 도1**

## 특허청구의 범위

### 청구항 1

데이터 전류를 공급하기 위한 복수의 데이터선들;

선택 신호를 전송하기 위한 복수의 주사선들; 및

상기 복수의 데이터선들 및 상기 복수의 주사선들에 접속된 복수의 화소 회로들을 포함하는 화소부를 포함하고, 상기 복수의 화소 회로들의 각각은,

상기 데이터 전류에 대응하는 휘도에서 발광하는 표시 소자;

소스 전극, 드레인 전극, 및 게이트 전극을 포함하고 상기 데이터 전류를 상기 표시 소자에 공급하는 제1 트랜지스터;

상기 제1 트랜지스터에 접속된 제1 전원선;

상기 표시 소자에 접속된 제2 전원선;

상기 제1 트랜지스터의 상기 소스 전극과 상기 제1 트랜지스터의 상기 게이트 전극간에 전압을 유지하는 제1 용량소자;

상기 제1 트랜지스터의 상기 드레인 전극과 상기 제1 트랜지스터의 상기 게이트 전극간에 접속을 선택하는 제1 스위치 소자;

상기 복수의 데이터선들 중 하나와 상기 표시 소자간에 접속을 선택하는 제2 스위치 소자;

상기 제1 트랜지스터와 상기 표시 소자간에 접속을 선택하는 제3 스위치 소자; 및

상기 제1 용량소자와 상기 표시 소자간에 접속을 선택하는 제4 스위치 소자를 포함하고,

상기 표시 소자는 제2 용량소자로서 기능하는, 표시 장치.

### 청구항 2

삭제

### 청구항 3

삭제

### 청구항 4

삭제

### 청구항 5

삭제

### 청구항 6

삭제

### 청구항 7

삭제

### 청구항 8

삭제

### 청구항 9

삭제

**청구항 10**

삭제

**청구항 11**

데이터 전류를 공급하기 위한 복수의 데이터선들;

선택 신호를 전송하기 위한 복수의 주사선들; 및

상기 복수의 데이터선들 및 상기 복수의 주사선들에 접속된 복수의 화소 회로들을 포함하는 화소부를 포함하고,

상기 복수의 화소 회로들의 각각은,

상기 데이터 전류에 대응하는 회도에서 발광하는 표시 소자;

소스 전극, 드레인 전극, 및 게이트 전극을 포함하고 상기 데이터 전류를 상기 표시 소자에 공급하는

제1 트랜지스터;

상기 제1 트랜지스터에 접속된 제1 전원선;

상기 표시 소자에 접속된 제2 전원선;

상기 제1 트랜지스터의 상기 소스 전극과 상기 제1 트랜지스터의 상기 게이트 전극간에 접속을 유지하

는 제1 용량소자;

상기 제1 트랜지스터의 상기 드레인 전극과 상기 제1 트랜지스터의 상기 게이트 전극간에 접속을 선택

하는 제2 트랜지스터;

상기 복수의 데이터선들 중 하나와 상기 표시 소자간에 접속을 선택하는 제3 트랜지스터;

상기 제1 트랜지스터와 상기 표시 소자간에 접속을 선택하는 제4 트랜지스터; 및

상기 제1 용량소자와 상기 표시 소자간에 접속을 선택하는 제5 트랜지스터를 포함하고,

상기 표시 소자는 제2 용량소자로서 기능하는, 표시 장치.

**청구항 12**

제 1 항 또는 제 11 항에 있어서,

상기 복수의 데이터선들에 접속된 데이터선 구동 회로; 및

상기 복수의 주사선들에 접속된 주사선 구동 회로를 더 포함하는, 표시 장치.

**청구항 13**

제 1 항 또는 제 11 항에 있어서,

상기 제1 전원선의 전위는 상기 표시 소자의 양극과 동일 전위인, 표시 장치.

**청구항 14**

제 1 항 또는 제 11 항에 있어서,

상기 제2 전원선의 전위는 상기 표시 소자의 음극과 동일 전위인, 표시 장치.

**청구항 15**

제 1 항 또는 제 11 항에 있어서,

상기 제1 전원선의 전위 또는 상기 제2 전원선의 전위는 변경되는, 표시 장치.

**청구항 16**

삭제

**청구항 17**

삭제

**청구항 18**

삭제

**청구항 19**

삭제

**청구항 20**

삭제

**청구항 21**

삭제

**청구항 22**

제1 및 제2 배선들;

용량소자;

표시 소자;

트랜지스터; 및

제1 내지 제4 스위치 소자들을 포함하고,

상기 트랜지스터의 게이트 전극은 상기 용량소자를 통해 상기 제1 배선에 전기적으로 접속되고,

상기 트랜지스터의 제1 단자는 상기 제1 배선에 전기적으로 접속되고,

상기 트랜지스터의 제2 단자는 상기 제1 스위치 소자를 통해 상기 게이트 전극에 전기적으로 접속되고 상기 제2 스위치 소자를 통해 상기 제2 배선에 전기적으로 접속되고,

상기 표시 소자의 제1 전극은 상기 제3 스위치 소자를 통해 상기 트랜지스터의 상기 제2 단자에 전기적으로 접속되고 상기 제4 스위치 소자를 통해 상기 용량소자의 한 전극에 전기적으로 접속되는, 표시 장치.

**청구항 23**

삭제

**청구항 24**

제 22 항에 있어서,

상기 트랜지스터는 p채널 트랜지스터인, 표시 장치.

**청구항 25**

제 22 항에 있어서,

상기 트랜지스터는 n채널 트랜지스터인, 표시 장치.

**청구항 26**

제 22 항에 있어서,

상기 트랜지스터는 구동 트랜지스터인, 표시 장치.

**청구항 27**

삭제

### 청구항 28

삭제

### 청구항 29

삭제

### 청구항 30

삭제

### 청구항 31

제1 및 제2 배선들;

용량소자;

표시 소자; 및

제1 내지 제5 트랜지스터들을 포함하고,

상기 제1 트랜지스터의 게이트 전극은 상기 용량소자를 통해 상기 제1 배선에 전기적으로 접속되고,

상기 제1 트랜지스터의 제1 단자는 상기 제1 배선에 전기적으로 접속되고,

상기 제1 트랜지스터의 제2 단자는 상기 제2 트랜지스터를 통해 상기 게이트 전극에 전기적으로 접속되고 상기 제3 트랜지스터를 통해 상기 제2 배선에 전기적으로 접속되고,

상기 표시 소자의 제1 전극은 상기 제4 트랜지스터를 통해 상기 제1 트랜지스터의 상기 제2 단자에 전기적으로 접속되고 상기 제5 트랜지스터를 통해 상기 용량소자의 한 전극에 전기적으로 접속되는, 표시 장치.

### 청구항 32

제 22 항 또는 제 31 항에 있어서,

상기 표시 소자는 용량소자로서 기능하는, 표시 장치.

### 청구항 33

제 1 항, 제 11 항, 및 제 31 항 중 어느 한 항에 있어서,

상기 제1 트랜지스터는 p채널 트랜지스터인, 표시 장치.

### 청구항 34

제 1 항, 제 11 항, 및 제 31 항 중 어느 한 항에 있어서,

상기 제1 트랜지스터는 n채널 트랜지스터인, 표시 장치.

### 청구항 35

제 1 항, 제 11 항, 및 제 31 항 중 어느 한 항에 있어서,

상기 제1 트랜지스터는 구동 트랜지스터인, 표시 장치.

### 청구항 36

제 1 항, 제 11 항, 제 22 항, 및 제 31 항 중 어느 한 항에 있어서,

상기 표시 소자는 EL 소자인, 표시 장치.

### 청구항 37

제 1 항, 제 11 항, 제 22 항, 및 제 31 항 중 어느 한 항에 따른 표시 장치를 구비하는 전자 기기에 있어서, 상기 전자 기기는 텔레비전 장치, 디지털 카메라와 같은 카메라, 디지털 비디오 카메라, 휴대 전화 장치, PDA와 같은 휴대 정보 단말, 휴대형 게임기, 모니터, 컴퓨터, 카 오디오와 같은 음향 재생 장치, 가정용 게임기와 같은 기록 매체가 구비된 화상 재생 장치로 구성되는 그룹에서 선택되는 것인, 전자 기기.

#### 청구항 38

제 22 항 또는 제 31 항에 있어서,

상기 제1 배선은 전원선인, 표시 장치.

#### 청구항 39

제 22 항 또는 제 31 항에 있어서,

상기 제2 배선은 데이터선인, 표시 장치.

#### 청구항 40

제 11 항 또는 제 31 항에 있어서,

상기 제1 내지 제5 트랜ジ스터들은 동일 극성을 갖는, 표시 장치.

#### 청구항 41

제1 트랜ジ스터를 턴 온(turn on) 하고, 제2 트랜ジ스터를 턴 온 하고, 제3 트랜ジ스터를 턴 오프(turn off) 하고, 제4 트랜ジ스터를 턴 오프 하고, 제5 트랜ジ스터를 턴 온 함으로써 임계 기입 기간에 표시 소자에 전하를 저장하는 공정; 및

상기 임계 기입 기간 후에, 상기 제2 트랜ジ스터를 턴 오프 하고, 상기 제3 트랜ジ스터를 턴 오프 하고, 상기 제4 트랜ジ스터를 턴 온 하고, 상기 제5 트랜ジ스터를 턴 오프 함으로써 발광 기간에 상기 표시 소자로부터 발광하는 공정을 포함하고,

상기 제2 트랜ジ스터는 상기 제1 트랜ジ스터의 드레인 전극과 상기 제1 트랜ジ스터의 게이트 전극간에 접속을 선택하고,

상기 제3 트랜ジ스터는 상기 제1 트랜ジ스터와 전류원 사이에 설치되고,

상기 제4 트랜ジ스터는 상기 제1 트랜ジ스터의 상기 드레인 전극과 상기 표시 소자간에 접속을 선택하고,

상기 제5 트랜ジ스터는 상기 표시 소자와 상기 제1 트랜ジ스터 사이에 설치되고 상기 제1 트랜ジ스터의 상기 게이트 전극과 상기 표시 소자간에 접속을 선택하는, 표시 장치의 구동 방법.

#### 청구항 42

제 41 항에 있어서,

상기 임계 기입 기간에, 상기 표시 소자의 음극 측 상의 전원선의 전위는 상기 표시 소자의 양극 측 상의 전원선의 전위와 동일하고,

상기 발광 기간에, 상기 표시 소자의 상기 음극 측 상의 전원선의 전위는 상기 표시 소자의 양극 측 상의 전원선의 전위보다 낮은, 표시 장치의 구동 방법.

#### 청구항 43

제 41 항에 있어서,

상기 표시 소자는 용량소자로서 기능하는, 표시 장치의 구동 방법.

#### 청구항 44

삭제

**청구항 45**

삭제

**청구항 46**

삭제

**청구항 47**

삭제

**청구항 48**

삭제

**청구항 49**

제2 트랜지스터를 턴 오프 하고, 제3 트랜지스터를 턴 오프 하고, 제4 트랜지스터를 턴 오프 하고, 제5 트랜지스터를 턴 온 함으로써 Cs 재기입 기간에 전하를 표시 소자 및 용량소자에 분배하는 공정; 및

상기 Cs 재기입 기간 후에, 제1 트랜지스터를 턴 온 하고, 상기 제2 트랜지스터를 턴 오프 하고, 상기 제3 트랜지스터를 턴 오프 하고, 상기 제4 트랜지스터를 턴 온 하고, 상기 제5 트랜지스터를 턴 오프함으로써 발광 기간에 상기 표시 소자로부터 발광하는 공정을 포함하고,

상기 제2 트랜지스터는 상기 제1 트랜지스터의 드레인 전극과 상기 제1 트랜지스터의 게이트 전극간에 접속을 선택하고,

상기 제3 트랜지스터는 상기 제1 트랜지스터와 전류원 사이에 설치되고,

상기 제4 트랜지스터는 상기 제1 트랜지스터의 상기 드레인 전극과 상기 표시 소자간에 접속을 선택하고,

상기 제5 트랜지스터는 상기 표시 소자와 상기 제1 트랜지스터 사이에 설치되고, 상기 제1 트랜지스터의 상기 게이트 전극과 상기 표시 소자간에 접속을 선택하는, 표시 장치의 구동 방법.

**청구항 50**

제 49 항에 있어서,

상기 Cs 재기입 기간에, 상기 표시 소자의 음극 측 상의 전원선의 전위는 상기 표시 소자의 양극 측 상의 전원선의 전위와 동일하거나 실질적으로 동일하고,

상기 발광 기간에, 상기 표시 소자의 상기 음극 측 상의 상기 전원선의 상기 전위는 상기 표시 소자의 상기 양극 측 상의 상기 전원선의 상기 전위보다 낮은, 표시 장치의 구동 방법.

**청구항 51**

삭제

**청구항 52**

제 41 항 또는 제 49 항에 있어서,

상기 제1 트랜지스터는 p채널 트랜지스터인, 표시 장치의 구동 방법.

**청구항 53**

제 41 항 또는 제 49 항에 있어서,

상기 제1 트랜지스터는 n채널 트랜지스터인, 표시 장치의 구동 방법.

**청구항 54**

제 41 항 또는 제 49 항에 있어서,

상기 제1 트랜지스터는 구동 트랜지스터인, 표시 장치의 구동 방법.

#### 청구항 55

삭제

#### 청구항 56

제 41 항 또는 제 49 항에 있어서,

상기 제1 내지 제5 트랜지스터들은 동일 극성을 갖는, 표시 장치의 구동 방법.

#### 청구항 57

삭제

#### 청구항 58

제 49 항에 있어서,

상기 표시 소자는 제2 용량소자로서 기능하는, 표시 장치의 구동 방법.

#### 청구항 59

삭제

#### 청구항 60

삭제

#### 청구항 61

삭제

#### 청구항 62

제 41 항 또는 제 49 항에 있어서,

상기 표시 소자는 EL 소자인, 표시 장치의 구동 방법.

### 명세서

#### 기술 분야

[0001] 본 발명은 자기발광형 표시 소자가 적용되는 표시 장치 및 이의 구동 방법에 관한 것이다.

#### 배경 기술

[0002] 표시 장치의 구동 방법에는 주로 능동 매트릭스 구동 및 수동 매트릭스 구동이 있다. 수동 매트릭스 구동은 저 비용으로 제조될 수 있는, 매트릭스로 배열된 전극들 사이에 표시 소자가 개재된 구조를 갖는다. 그러나, 한 화소가 구동될 때, 다른 화소들은 구동될 수 없으므로 대면적 또는 고 상세 표시 장치용으로는 좋지 않다. 한편, 능동 매트릭스 구동은 능동소자 및 각 화소에서 휴도 데이터를 유지하기 위한 유닛을 구비하며, 따라서 제조비용이 수동 매트릭스 구동보다 높다. 그러나, 한 화소가 구동될 때, 다른 화소들이 휴도 데이터를 유지하는 광을 방출할 수 있다. 그러므로, 능동 매트릭스 구동 방법이 대부분의 대면적 또는 고 상세 표시 장치들용으로 사용된다.

[0003] 능동 매트릭스 표시 장치는 위에 기술된 바와 같이 각 화소에서 휴도 데이터를 유지하기 위한 유닛을 구비한다. 표시 장치는 휴도 데이터가 디지털 값을 갖는지 아니면 아날로그 값을 갖는지 여부에 의해 분류될 수 있다. 휴도 데이터가 디지털 값을 가질 때, 발광소자는 온 또는 오프의 바이너리 값만을 가지며, 그럼으로써 표시 화상은 단지 2개의 계조들만을 갖는다. 바이너리 값들의 화상을 신속하고 반복적으로 표시함으로써 복수의 계조를 표현하는 방법이 널리 사용된다(시간 계조 방법). 또한, 휴도 데이터가 아날로그 값을 가질 때, 표시 소자의 휴도는 중간 값으로 제어될 수 있고, 따라서 복수 계조를 표현하기 위해서 시간 계조 방법이 향시 요구되는 것은

아니다.

- [0004] 아날로그 값은 휘도 데이터를 사용하는 능동 매트릭스 구동 표시 장치는 주로 예를 들면 액정 디스플레이이다. 액정 디스플레이는 널리 퍼져 있으나, 느린 응답 속도에 기인한 동화상을 표시하는데 있어 부적당성, 및 시야각에의 의존성과 같은 문제들이 있다. 또한, 표시 소자는 자기발광형이 아니며, 따라서 백 라이트가 요구되므로 전력소비가 높다. 그러므로, 액정 디스플레이를 대체하는 새로운 디스플레이의 개발이 기대된다.

- [0005] 한편, 화소가 발광 다이오드(LED)와 같은 발광소자로 형성되는 소위 자기발광형의 표시 장치가 주목을 끈다. 자기발광형의 표시 장치용으로 채용되는 발광소자로서, 유기 발광 다이오드(OLED(Organic Light Emitting Diode)라고도 함), 유기 EL 소자, 전장발광(EL) 소자, 등이 주목을 끌고 있고 EL 디스플레이 등용으로 사용이 되고 있다. OLED와 같은 발광소자는 자기발광형이기 때문에, 화소는 보다 큰 가시도를 가지며, 백 라이트는 요구되지 않으며, 응답속도는 액정 디스플레이에 비해 더 빠르다. 그러므로, 표시 소자로서 유기 EL 소자를 채용하는 능동 매트릭스 구동 표시 장치가 활발하게 개발되었다.

- [0006] 여기에서는 유기 EL 소자에 대해 기술한다. 유기 EL 소자의 휘도는 흐르는 전류값에 의해 결정된다. 이러한 특징은 주로 능동 매트릭스 구동에 의해 구동되는 유기 EL 소자의 문제를 야기한다. 즉, 아날로그 값의 전압이 액정 디스플레이처럼 화소의 휘도 데이터 유지 유닛(예를 들면, 용량소자)에 기입될 때, 표시 소자에 흐르는 전류를 제어하는 능동소자는 표시 소자에 인가되는 전압이 아날로그 방식으로 제어되는 액정 디스플레이와는 달리, 아날로그 방식으로 제어된다. 능동 소자는 각 EL 소자에 제공되며, 따라서 각 화소에 능동소자의 전기적 특성을 변동은 직접 휘도의 변동을 야기한다.

- [0007] 따라서, 유기 EL 소자와 같은 전류 구동형 표시 소자가 아날로그 값에 의해 능동 매트릭스 구동에 의해 구동될 때, 표시 소자를 구동하는 능동소자의 특성 변동을 보상하는 것이 중요하다. 이에 대한 방법으로서 예를 들면, 화소 회로의 구조가 안출되는 전류 입력형 표시 소자가 채용된다.

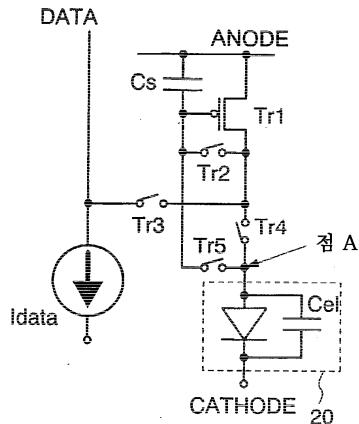

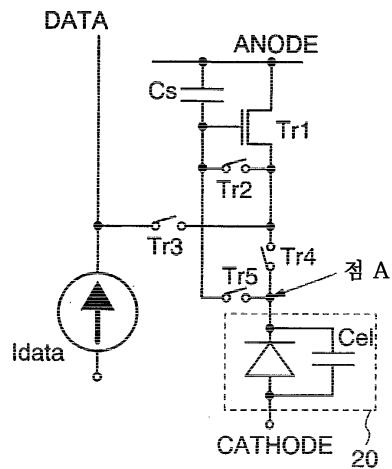

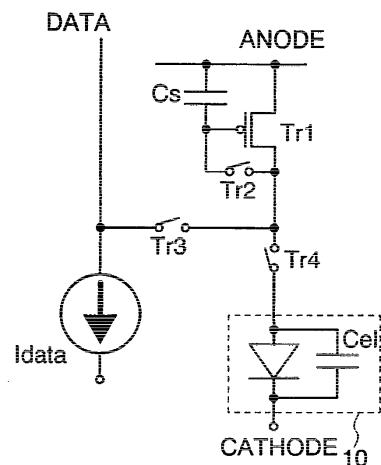

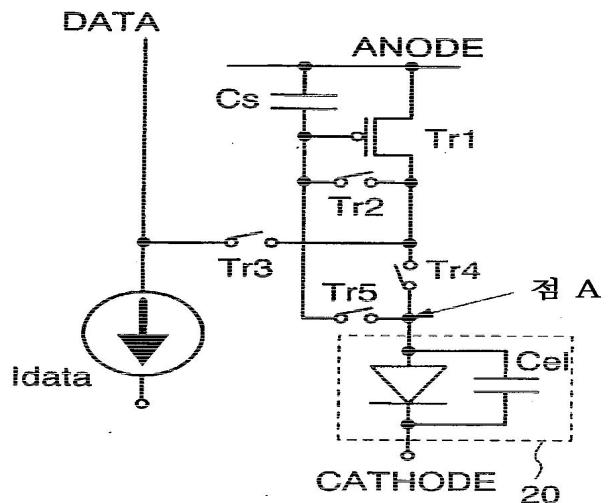

- [0008] 전류 입력형 화소 회로에서는 화소에 입력되는 휘도 데이터로서 아날로그 전류가 채용된다. 아날로그 전류는 여기에서는 복수 레벨에 의해 전류값을 제어할 수 있는 회로로부터 출력되는 전류를 지칭하는 것에 유의한다. 표시 소자의 휘도에 대응하는 이러한 주변 구동 회로에 의해 나오는 아날로그 전류(데이터 전류(Idata)라고도 함)는 각 화소의 능동소자에 공급되고, 이때 능동소자에 인가되는 전압이 유지된다. 결과적으로, 전류값이 유지되고 데이터 전류의 공급이 중지된 후에라도 표시 소자에 공급이 계속 유지될 수 있다. 도 8은 이러한 화소 회로의 예를 도시한 것이다. 도 8에 도시된 회로는 제1 전원선(ANODE), 제2 전원선(CATHODE), 데이터 전류(Idata)를 공급하기 위한 전류원, 데이터 전류(Idata)가 흐르는 배선(DATA), 표시 소자(10), 구동 트랜지스터(Tr1), 휘도 데이터 유지 유닛으로서의 용량소자(Cs), 구동 트랜지스터(Tr1)의 게이트 전극과 드레인 전극간을 접속 및 단절시키기 위한 스위치(Tr2), Idata가 구동 트랜지스터(Tr1)에 공급되는 화소를 선택하기 위한 스위치(Tr3), 표시 소자(10)와 구동 트랜지스터(Tr1)의 드레인 전극간을 접속 및 단절시키기 위한 스위치(Tr4)를 포함한다.

- [0009] 전류 입력형 화소 회로는 능동소자의 특성에 관계없이 데이터 전류를 그대로 계속 공급할 수 있고, 그럼으로써 능동 매트릭스 구동에 의해 전류 구동형 표시 소자를 구동하는데 적합하다. 그러나, 유기 EL 소자와 같은 표시 소자가 구동될 때 표시 소자의 전류값이 매우 작을 때, 데이터 전류는 도 8에 도시된 회로로 구동될 때 표시 소자(10)의 전류값에 1 대 1로 대응하므로 용량소자(Cs)를 충전하기 위한 시간(프로그램 시간이라고도 함)이 매우 길어지게 되는 문제가 있다.

- [0010] 그러므로, 화소 회로에 용량소자를 추가함으로써 표시 소자가 구동될 때 전류값에 대해 데이터 전류가 증가될 수 있는 전류 입력형 화소 회로가 암시된다(특허문헌 1 참조).

- [0011] [특허문헌 1]

- [0012] 일본 특허공개 번호 2004-310006

### 발명의 상세한 설명

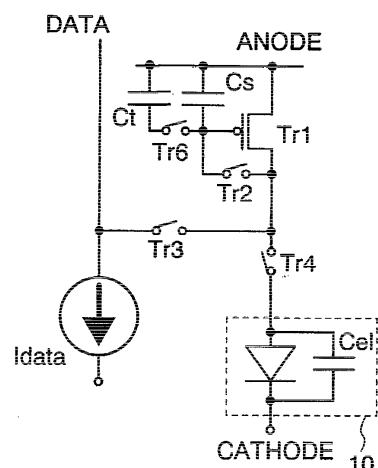

- [0013] 종래의 화소 회로의 예로서, 특허문헌 1의 도 5에 대응하는 화소 회로가 도 9에 도시되었다(참조부호는 특허문헌 1의 참조부호들과는 다른 것에 유의한다). 도 9의 회로 구조는, 임계값을 유지하기 위한 용량소자(Ct) 및 용량소자를 접속하기 위한 스위치(Tr6)- 이들은 직렬로 접속되어 있다 -가 도 8에 화소 회로에 추가되는 화소 회로에 대응한다.

- [0014] 특허문헌 1에서, 구동 트랜지스터(Tr1)의 임계전압은 데이터 전류에 대응하는 전압(Vgs(data)라고도 함)이 임계

값을 유지하기 위한 용량소자(Cs)에 유지되기 전에 용량소자(Ct)에 유지되고, Ct 및 Cs는 Cs에 Vgs(data)를 유지한 후에 접속되고, 그럼으로써 데이터 전류는 표시 소자가 구동될 때 전류값보다 더 커질 수 있다. 또한, 이의 차이는 Cs의 용량에 응하여 Ct의 용량값이 커짐에 따라 더 커지게 된다. 프로그램 시간은 데이터 전류를 증가시킴으로써 짧아질 수 있다. 표시 소자가 구동될 때 전류값(Ioled)과 데이터 전류(Idata)와의 관계가 식(1)로 나타나는 것에 유의한다.

[0015] [식 1]

$$[0016] I_{oled} = \left( \frac{Cs}{(Ct+Cs)} \right)^2 \times I_{data}$$

[0017] 한 화소에 데이터 전류를 기입하는 시간은 한 프레임 기간(약 1/60초)을 주사선 수로 나눔으로써 얻어지는 값이며, 320 주사선들을 가진 표시 장치에 있어서의 시간은 약 50μs이다. 한편, 표시 소자(예를 들면, EL 소자)가 약 수십 nA의 구동전류를 갖고 있고 데이터 전류도 약 수십 nA일 때 데이터선의 기생용량을 충분히 충전시키기 위해서는 수 ms가 걸린다. 충전시간은 전류값에 비례하며, 따라서 계산들에 의해서, 데이터 전류는 수십 μs 이내에 화소에 데이터 전류를 기입하기 위해 표시 소자에 공급되는 전류값에 약 100배만큼 클 필요가 있다. 즉, 데이터 전류가 특허문헌 1에 기술된 방식으로 기입되는 경우에, 임계 유지 용량소자(Ct)의 용량값은 Vgs(data) 유지 용량소자(Cs)의 용량값에 약 10배일 것이 요구된다. Cs는 Vgs(data)를 유지하기 위해서 어떤 량의 용량을 가질 것이 요구되며, 따라서 Ct의 면적은 데이터 전류를 증가시키기 위해서 더 크게 할 것이 요구된다.

[0018] 그러나, 화소 면적 대 Ct 면적의 비는 Ct의 면적이 커짐에 따라 커지게 되고, 표시 소자의 발광면적이 화소면적에서 점유하는 면적(애피쳐 비라 함)이 감소된다. Ct가 Cs의 약 10배일 것이 요구된다면, 애피쳐 비의 감소는 심각한 문제이다. 휙도는 애피쳐 비가 클 때와 동일한 전류밀도의 동일 전압 및 전류가 표시 소자에 공급될지라도 애피쳐 비의 감소 때문에 낮아지게 된다. 동일 휙도를 얻기 위해서, 표시 소자에 더 높은 전압이 인가될 것이 요구되고 따라서 더 높은 전류밀도의 전류가 표시 소자에 공급되어 더 높은 전력소비를 야기한다. 또한, 보다 높은 전류밀도의 전류가 표시 소자에 공급될 때 표시 소자의 신뢰성 및 수명에 문제가 있다.

[0019] 위에 기술된 바와 같이, 특허문헌 1의 화소 구조를 사용함으로써 프로그램 시간이 정규 프로그램 시간 이내가 되게 단축될 때, Ct는 더 클 것이 요구되며, 따라서 화소의 애피쳐 비의 감소가 발생된다. 애피쳐 비에 감소는 휙도, 전력소비, 신뢰성, 및 수명과 같은 문제를 야기한다.

[0020] 전술한 문제들에 비추어, 본 발명은 보다 짧은 프로그램 시간 및 화소의 큰 애피쳐 비를 갖는 전류 입력형 화소 회로를 제공한다.

[0021] 발명에서 전술한 과제에 비추어, 표시 소자는 용량소자로서 기능한다. 표시 소자를 구동하는 트랜지스터의 임계 전압이 용량소자에 기입될 수 있다. 그러므로, 트랜지스터의 임계 전압은 임계값을 유지하기 위한 용량소자를 제공함이 없이도 기입될 수 있다.

[0022] 이하, 발명의 구체적인 구조에 대해 기술한다.

[0023] 발명의 한 형태는 데이터 전류를 공급하기 위한 복수의 데이터선들, 선택 신호를 전송하기 위한 복수의 주사선들, 및 데이터선들 및 주사선들에 접속된 복수의 화소 회로들을 포함하는 화소부를 포함하는 표시 장치이다. 화소 회로 각각은, 데이터 전류에 대응하는 휙도에서 발광하는 표시 소자; 데이터 전류를 표시 소자에 공급하며 소스 전극, 드레인 전극 및 게이트 전극을 포함하는 제1 트랜지스터; 표시 소자의 양극과 동일한 전위인 하이 전위측에 제1 전원선; 표시 소자의 음극과 동일한 전위인 로우 전위측에 제2 전원선; 제1 트랜지스터의 소스 전극과 게이트 전극간에 전압을 유지하는 제1 용량소자; 제1 트랜지스터의 드레인 전극과 게이트 전극간에 접속을 선택하기 위한 제2 트랜지스터; 데이터선과 화소 회로간에 접속을 선택함으로써 데이터 전류가 기입되는 화소 회로를 선택하기 위한 제3 트랜지스터; 제1 트랜지스터와 표시 소자간에 접속을 선택하기 위한 제4 트랜지스터; 및 용량소자와 표시 소자간에 접속을 선택하는 제5 트랜지스터를 포함한다. 표시 소자는 제2 용량소자로서 기능한다.

[0024] 발명의 또 다른 형태는 데이터 전류를 공급하기 위한 복수의 데이터선들; 선택 신호를 전송하기 위한 복수의 주사선들; 및 데이터선들 및 주사선들에 접속된 복수의 화소 회로들을 포함하는 화소부를 포함하는 표시 장치이다. 화소 회로 각각은, 데이터 전류에 대응하는 휙도에서 발광하는 표시 소자; 데이터 전류를 표시 소자에 공급하며 소스 전극, 드레인 전극 및 게이트 전극을 구비하는 제1 트랜지스터; 제1 전원선 및 제2 전원선, 이중 어느 하나에서 전위는 변하며; 제1 트랜지스터의 소스 전극과 게이트 전극간에 전압을 유지하는 제1 용량소자; 제1 트랜지스터의 드레인 전극과 게이트 전극간에 접속을 선택하기 위한 제2 트랜지스터; 데이터선과 화

소 회로간 접속을 선택함으로써 데이터 전류가 기입되는 화소 회로를 선택하기 위한 제3 트랜지스터; 제1 트랜지스터와 표시 소자간에 접속을 선택하기 위한 제4 트랜지스터; 및 제1 용량소자와 표시 소자간에 접속을 선택하는 제5 트랜지스터를 포함한다. 표시 소자는 제2 용량소자로서 기능한다.

[0025] 발명의 또 다른 형태는 데이터선 구동 회로, 데이터선 구동 회로에 접속된 복수의 데이터선들, 주사선 구동 회로, 주사선 구동 회로에 접속된 복수의 주사선들, 데이터선들 및 주사선들에 접속된 복수의 화소 회로들을 포함하는 화소부를 포함하는 표시 장치이다. 화소 회로 각각은, 데이터선들로부터 공급되는 데이터 전류에 대응하는 회도에서 발광하는 표시 소자; 데이터 전류를 표시 소자에 공급하며 소스 전극, 드레인 전극 및 게이트 전극을 구비하는 제1 트랜지스터; 제1 전원선 및 제2 전원선, 이중 어느 하나에서 전위는 변하며; 제1 트랜지스터의 소스 전극과 게이트 전극간에 전압을 유지하는 제1 용량소자; 주사선 구동 회로에 의해 제어되며 제1 트랜지스터의 드레인 전극과 게이트 전극간에 접속을 선택하는 제2 트랜지스터; 데이터선과 화소 회로간 접속을 선택함으로써 데이터 전류가 기입되는 화소 회로를 선택하기 위한 제3 트랜지스터; 제1 트랜지스터와 표시 소자간에 접속을 선택하기 위한 제4 트랜지스터; 및 제1 용량소자와 표시 소자간에 접속을 선택하는 제5 트랜지스터를 포함한다. 표시 소자는 제2 용량소자로서 기능한다.

[0026] 발명의 또 다른 형태는 제1 트랜지스터, 제1 트랜지스터에 접속된 제2 트랜지스터, 제1 트랜지스터와 전류원 사이에 제공된 제3 트랜지스터, 표시 소자, 표시 소자와 제1 트랜지스터 사이에 제공된 제4 트랜지스터 및 제5 트랜지스터를 포함하는, 표시 장치의 구동 방법이다. 표시 소자에 전하를 저장하기 위한 임계 기입 기간 후에 표시 소자가 방출되는 발광기간은 한 프레임 기간 내에 제공된다. 임계 기입 기간에서, 제1 트랜지스터가 턴 온 되고, 제2 트랜지스터가 턴 온 되고, 제3 트랜지스터가 턴 오프 되고, 제4 트랜지스터가 턴 오프 되고, 제5 트랜지스터가 턴 온 된다. 발광기간에서, 제2 트랜지스터가 턴 오프 되고, 제3 트랜지스터가 턴 오프 되고, 제4 트랜지스터가 턴 온 되고, 제5 트랜지스터가 턴 오프 된다.

[0027] 발명의 또 다른 형태는 제1 트랜지스터, 제1 트랜지스터에 접속된 제2 트랜지스터, 제1 트랜지스터와 전원선에 접속된 용량소자, 제1 트랜지스터와 전류원간에 접속된 제3 트랜지스터, 표시 소자, 표시 소자와 제1 트랜지스터 사이에 제공된 제4 트랜지스터 및 제5 트랜지스터를 포함하는, 표시 장치의 구동 방법이다. 표시 소자가 방출되는 발광기간은 한 프레임 기간 내에 표시 소자에 전하를 저장하기 위한 임계 기입 기간 후에 제공된다. Cs 재기입 기간에, 제2 트랜지스터가 턴 오프 되고, 제3 트랜지스터가 턴 오프 되고, 제4 트랜지스터가 턴 오프 되고, 제5 트랜지스터가 턴 온 된다. 발광기간에, 제2 트랜지스터가 턴 오프 되고, 제3 트랜지스터가 턴 오프 되고, 제4 트랜지스터가 턴 오프 되고, 제5 트랜지스터가 턴 온 된다.

[0028] 발명의 또 다른 형태는 제1 트랜지스터, 제1 트랜지스터에 접속된 제2 트랜지스터, 제1 트랜지스터와 전류원간에 제공된 제3 트랜지스터, 표시 소자, 표시 소자와 제1 트랜지스터 사이에 제공된 제4 트랜지스터 및 제5 트랜지스터를 포함하는, 표시 장치의 구동 방법이다. 표시 소자가 방출되는 발광기간은 한 프레임 기간 내에 표시 소자에 전하를 저장하기 위한 임계 기입 기간 후에 제공된다. 임계 기입 기간에, 제1 트랜지스터가 턴 온 되고, 제2 트랜지스터가 턴 온 되고, 제3 트랜지스터가 턴 오프 되고, 제4 트랜지스터가 턴 오프 되고, 제5 트랜지스터가 턴 온 되고, 표시 소자의 음극 측에 전원선의 전위는 표시 소자의 양극 측에 전원선의 전위와 같거나 거의 같다. 발광기간에, 제1 트랜지스터가 턴 온 되고, 제2 트랜지스터가 턴 오프 되고, 제3 트랜지스터가 턴 오프 되고, 제4 트랜지스터가 턴 온 되고, 제5 트랜지스터가 턴 오프 되고, 표시 소자의 음극 측에 전원선의 전위는 표시 소자의 양극 측에 전원선의 전위보다 낮다.

[0029] 발명의 또 다른 형태는 제1 트랜지스터, 제1 트랜지스터에 접속된 제2 트랜지스터, 제1 트랜지스터와 전원선에 접속된 용량소자, 제1 트랜지스터와 전류원간에 접속된 제3 트랜지스터, 표시 소자, 표시 소자와 제1 트랜지스터 사이에 제공된 제4 트랜지스터 및 제5 트랜지스터를 포함하는, 표시 장치의 구동 방법이다. 표시 소자가 방출되는 발광기간은 한 프레임 기간 내에 표시 소자 및 용량소자에 전하를 분배하기 위한 Cs 재기입 기간 후에 제공된다. Cs 재기입 기간에, 제2 트랜지스터가 턴 오프 되고, 제3 트랜지스터가 턴 오프 되고, 제4 트랜지스터가 턴 오프 되고, 제5 트랜지스터가 턴 온 되고, 표시 소자의 음극 측에 전원선의 전위는 표시 소자의 양극 측에 전원선의 전위와 같거나 거의 같다. Cs 재기입 기간 후에 오는 발광기간에, 제2 트랜지스터가 턴 오프 되고, 제3 트랜지스터가 턴 오프 되고, 제4 트랜지스터가 턴 온 되고, 제5 트랜지스터가 턴 오프 되고, 표시 소자의 음극 측에 전원선의 전위는 표시 소자의 양극 측에 전원선의 전위보다 낮다.

[0030] 발명에서, 표시 장치의 구동 방법은 동일 극성을 갖는 제1 내지 제5 트랜지스터들을 포함한다.

[0031] 발명에서, 제1 트랜지스터는 p채널 트랜지스터이며, 표시 소자가 발광할 때 더 높은 전위를 갖는, 제1 트랜지스터의 소스 전극 및 드레인 전극 중 하나는 제1 전원선에 접속될 수 있다.

- [0032] 발명에서, 제1 트랜지스터는 n채널 트랜지스터이며, 표시 소자가 발광할 때 더 낮은 전위를 갖는, 제1 트랜지스터의 소스 전극 및 드레인 전극 중 하나는 제1 전원선에 접속될 수 있다.

- [0033] 발명의 또 다른 형태는 제1, 제2 및 제3 배선들; 제1 용량소자; 표시 소자; 제1 내지 제5 트랜지스터들을 포함하는 표시 장치이다. 제1 트랜지스터의 게이트 전극은 제1 용량소자를 통해 제1 배선에 접속된다. 제1 트랜지스터의 제1 단자는 제1 배선에 접속된다. 제1 트랜지스터의 제2 단자는 제2 트랜지스터를 통해 제2 트랜지스터의 게이트 전극에 접속되고 제3 트랜지스터를 통해 제3 배선에 접속된다. 표시 소자의 제1 전극은 제4 트랜지스터를 통해 제1 트랜지스터의 제2 단자에 접속되고 제5 스위치 소자를 통해 제1 용량소자의 한 전극에 접속된다.

- [0034] 발명의 또 다른 형태는 한 프레임 기간 내에 제1 내지 제4 기간들을 갖는 표시 장치의 구동 방법이다. 표시 장치는 제1 용량소자, 표시 소자, 제1 내지 제5 트랜지스터들, 및 제1 및 제2 배선들을 포함한다. 제1 기간에, 표시 소자에 전하가 축적된다. 제2 기간에, 용량소자에 전하가 축적된다. 제3 기간에, 제1 용량소자의 한 전극 및 제1 배선은 전기적으로 접속되고, 제1 용량소자의 다른 전극 및 제5 트랜지스터의 제1 단자가 전기적으로 접속되고, 제5 트랜지스터의 제2 단자 및 표시 소자의 한 전극이 전기적으로 접속되고, 표시 소자의 다른 전극 및 제2 배선이 전기적으로 접속되고, 제5 트랜지스터가 턴 온 되고, 그럼으로써 표시 소자에 축적된 전하 및 제1 용량소자에 축적된 전하는 표시 소자 및 제1 용량소자에 분배된다. 제4 기간에, 제1 트랜지스터의 제1 단자 및 제1 배선이 전기적으로 접속되고, 제1 트랜지스터의 제2 단자 및 제4 트랜지스터의 제1 단자가 전기적으로 접속되고, 제4 트랜지스터 및 표시 소자의 한 전극이 전기적으로 접속되고, 표시 소자의 다른 전극 및 제2 배선이 전기적으로 접속되고, 제1 및 제4 트랜지스터들이 턴 온 되고, 그럼으로써 표시 소자가 발광한다.

- [0035] 발명에서, 표시 소자의 음극 측에 접속된 제1 배선의 전위는 제1 내지 제3 기간들에서 표시 소자의 양극 측에 접속된 제2 배선의 전위와 같거나 거의 같다. 제4 기간에, 표시 소자의 음극 측에 접속된 제1 배선의 전위는 표시 소자의 양극 측에 접속된 제2 배선의 전위보다 낮다.

- [0036] 발명에서, 표시 소자는 제2 용량소자로서도 기능한다.

- [0037] 발명에서, 제1 및 제2 배선들 중 한 배선의 전위는 변한다.

- [0038] 발명에서, 제1 내지 제5 트랜지스터들은 동일 극성을 가질 수 있다.

- [0039] 발명에서, 제1 트랜지스터는 p채널 트랜지스터이다.

- [0040] 발명에서, 제1 트랜지스터는 n채널 트랜지스터이다.

- [0041] 위에 기술된 바와 같이, 임계 유지 용량소자(Ct)는 표시 소자의 용량(Cel)에 의해 대체되고, 따라서, Ct를 제공함이 없이 표시 소자의 구동전류에 비해 데이터 전류가 증가될 수 있다. 또한, Ct가 화소에 제공되지 않기 때문에 애피쳐 비가 증가될 수 있다. 애피쳐 비가 클 때, 표시 소자의 용량(Cel)은 커지게 되고, 따라서, 데이터 전류가 더 증가될 수 있다. 따라서, 애피쳐 비의 증가는 데이터 전류의 증가로 이어지며, 이것은 상승적인 혈저한 효과를 발생한다.

## 실시예

- [0062] 발명이 첨부한 도면들을 참조하여 실시형태들로서 완전히 기술될지라도, 다양한 변경들 및 수정들이 당업자들에게 명백할 것임을 알 것이다. 그러므로, 이러한 변경들 및 수정들이 본 발명의 범위에 있는 한, 이들은 이에 포함되는 것으로서 파악되어야 할 것이다.

- [0063] 명세서에서, 구체적으로 기술되는 않는 한 접속은 전기적으로 접속됨을 의미하는 것에 유의한다. 단절(disconnection)은 접속되지 않고 전기적으로 분리된 것을 의미한다.

[0064] [실시형태 1]

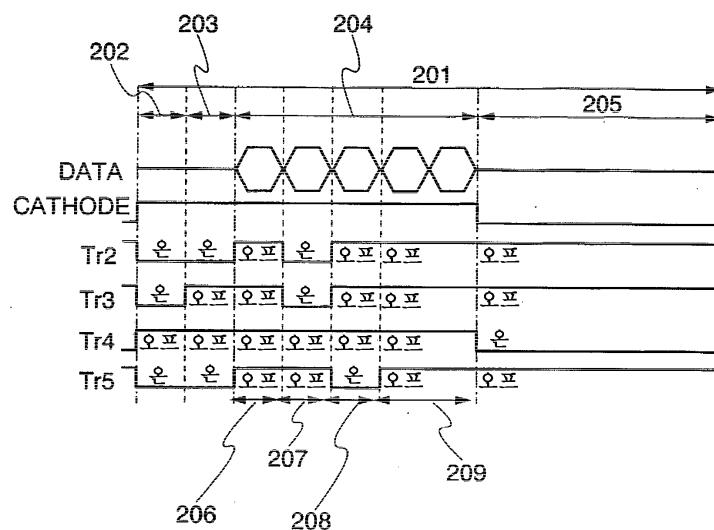

- [0065] 이 실시형태에서, 먼저, 도 3을 참조하여 발명의 표시 장치에 대해 기술한다. 발명의 표시 소자는, 주변 구동 회로로서 데이터선 구동 회로(302), 주사선 구동 회로(303), 주사선 구동 회로(302)에 의해 구동되는 n 주사선들(X<sub>1</sub> 내지 X<sub>n</sub>)(n은 정수), 주사선 구동 회로(303)에 의해 구동되는 m 주사선들(Y<sub>1</sub> 내지 Y<sub>m</sub>)(m은 정수), m 주사선들(m은 2이상) 및 n 데이터선들이 교차하는 위치에 배열된 복수의 화소 회로들(304), 및 복수의 화소 회로들(304)을 포함하는 화소부(301)를 포함한다. 선택 신호가 주사선들에 의해 전송되며 화상 신호를 나타내기 위한 데이터 전류는 데이터선들을 통해 흐른다. 도 3이 화소 회로(304)에 하나의 데이터선과 하나의 주사선이 제공된

경우를 보이고 있을지라도, 발명은 이것으로 제한되는 것은 아니며 한 화소 회로(304)에 복수의 주사선들 및 데이터선들이 제공될 수 있음에 유의한다. 위에 기술된 바와 같이, 데이터 전류가 동시에 기입되는 화소들의 수가 증가될 수 있고, 기입시간이 감소될 수 있다. 또한, 구동 회로들의 수는 발명에서 제한되지 않으며 복수의 데이터선 구동 회로들 및 주사선 구동 회로들이 제공될 수도 있다.

[0066] 다음에, 도 1을 참조하여 화소 회로(304)의 구조에 대해 기술한다. 복수의 화소 회로들(304) 각각은 제1 전원선(ANODE), 제2 전원선(CATHODE), 데이터 전류(Idata)를 공급하기 위한 데이터선(DATA), 용량소자(Cel)로서도 기능하는 표시 소자, Idata가 기입되는 화소를 선택하기 위한 스위치 소자(Tr3), 직렬로 표시 소자에 접속되고 표시 소자에 흐르는 전류를 제어하는 제1 트랜지스터(구동 트랜지스터라고도 함)(Tr1), 구동 트랜지스터(Tr1)의 게이트 전극에 접속되고 Idata가 구동 트랜지스터(tr1)에 공급될 때 게이트와 소스간의 전압(게이트-소스 전압)  $V_{gs}(data)$ 을 Idata의 전류값을 공급하기에 충분히 높게 유지하는 용량소자(Cs), 구동 트랜지스터(Tr1)의 게이트 전극과 드레인 전극간을 접속 또는 단절시키는 스위치 소자(Tr2), 직렬로 표시 소자에 접속되고 표시 소자와 구동 트랜지스터(Tr1)간을 접속 또는 단절시키는 스위치 소자(Tr4), 용량소자(Cs)와 표시 소자간을 접속하고 단절시키는 스위치 소자(Tr5)를 포함한다. 회로도는 표시 소자로서 제공된 EL 소자(20), 발광 다이오드 및 용량소자가 제공된 회로를 보이고 있으나, EL 소자는 발광소자 및 용량소자 둘 다로서 기능한다. 발명의 화소 회로는 EL 소자의 용량소자(Cel)를 사용함으로써 임계 유지 용량소자(Ct)를 제공함이 없이 구동 트랜지스터(Tr1)의 임계전압을 저장할 수 있다. 화소 회로(304)에서, 표시 소자는 제1 전원선(ANODE)의 전위 및 제2 전원선(CATHODE)의 전위를 변경시킴으로써 구동될 수 있는 것에 유의한다. 또한, 제2 전원선(CATHODE)은 모든 화소 회로들에 공통으로 접속될 수도 있다.

[0067] 다양한 형태들의 소자는 전기적 스위치 및 기계적 스위치와 같은 스위치로서 기능하는 소자로서 채용될 수도 있다. 즉, 전류의 흐름이 제어될 수 있는 한, 특정 형태의 스위치로 제한되는 것은 아니며 다양한 소자들이 사용될 수도 있다. 예를 들면, 트랜지스터, 다이오드(PN 다이오드, PIN 다이오드, 쇼트키 다이오드, 다이오드 접속 트랜지스터, 등), 또는 이들의 조합의 논리 회로가 채용될 수도 있다. 트랜지스터가 스위치로서 사용될 때, 박막 트랜지스터(TFT라고도 함)가 채용될 수도 있다. 박막 트랜지스터가 구동 트랜지스터로서 채용될 수도 있다. 트랜지스터가 스위치로서 사용되는 경우에, 이의 극성(도전형)은 p채널이거나 n채널일 수 있고, 모든 트랜지스터들은 동일 극성을 가질 수도 있다. 일반적으로, p채널 트랜지스터는 고 신뢰성을 가지며, n채널 트랜지스터는 보다 큰 온 전류를 갖는다. 전술한 바에 기인하여, 어느 한 극성이 선택된다. 그러나, 오프 전류가 보다 작은 것이 바람직할 때 보다 작은 오프 전류를 갖는 트랜지스터가 채용되는 것이 바람직하다. 작은 오프 전류를 갖는 트랜지스터에 관하여, LDD 영역이 제공된 트랜지스터, 복수-게이트 구조를 갖는 트랜지스터, 등이 사용될 수도 있다. 또한, 트랜지스터의 소스 단자의 전위가 하이 전위측 전원(Vdd 등)에 가까운 상태에서 동작할 때 p채널 트랜지스터를 채용하는 것이 바람직한 반면, 스위치로서 동작하는 트랜지스터의 소스단자의 전위가 로우 전위측 전원(Vss, GND, OV, 등)에 가까운 상태에서 동작할 때 n채널 트랜지스터를 채용하는 것이 바람직하다. 이것은 트랜지스터의 게이트-소스 전압의 절대값이 크게 설정될 수 있기 때문에, 이 트랜지스터가 스위치로서 쉽게 동작될 수 있기 때문이다. n채널 및 p채널 트랜지스터들 둘 다를 사용함으로써 CMOS 스위치가 적용될 수도 있는 것에 유의한다. CMOS 스위치가 채용되는 경우에, 스위치는 스위치를 통해 입력되는 전압(즉, 입력전압)이 출력전압보다 크거나 낮게 되도록 상황들이 변경될 때라도 적합하게 동작될 수 있다.

[0068] 그러나, EL 소자에 흐르는 전류를 제어하는 구동 트랜지스터(Tr1)의 극성은 EL 소자(20)가 발광할 때 구동 트랜지스터(Tr1)에 접속되는 제1 전원선(ANODE)의 전위에 의해 결정된다. 예를 들면, EL 소자(20)의 양극이 도 1에 도시된 바와 같이 구동 트랜지스터(Tr1)에 접속되는 경우에, 전류는 EL 소자(20)가 발광할 때 제1 전원선(ANODE), 구동 트랜지스터(TR1), 및 EL 소자(20)를 이 순서로 통과한다. 이때, 구동 트랜지스터(Tr1)에 접속된 제1 전원선(ANODE)은 이 전류경로에서 가장 큰 전위를 갖는다. 구동 트랜지스터(Tr1)는 제1 전원선(ANODE)이 하이 전위를 갖는 경우 p채널 트랜지스터이고, 구동 트랜지스터(Tr1)는 제1 전원선(ANODE)이 로우 전위를 갖는 경우 n채널 트랜지스터이다. 이것은 포화영역에서 동작하는 트랜지스터에 공급되는 전류값이 이 트랜지스터의 게이트-소스 전압에 따라 변하기 때문이며, 따라서 전류값이 일정하게 유지된다면 전력공급에 소스 전극이 접속될 때 전류값을 제어하기가 더 쉽다. 소스 전극 및 드레인 전극 중 하나인 소스 전극은 p채널 트랜지스터의 경우 하이 전위측에 전극이며 n채널 트랜지스터의 경우 로우 전위측에 전극임에 유의한다.

[0069] 구동 트랜지스터(Tr1)의 극성 및 각 스위칭 트랜지스터는 반드시 동일한 것은 아니다. 그러나, 트랜지스터들의 극성이 모두 같다면, 트랜지스터들을 제조하기 위한 공정들의 수가 감소되기 때문에 비용감축에 유리하다.

[0070] 또한, 대면적 및 저 비용으로 제조될 수 있는 비정질 실리콘 TFT가 구동 트랜지스터(Tr1) 및 각각의 스위치 소자로서 채용될 수 있기 때문에 비용감축에 더 유리하다. 비정질 실리콘 TFT를 사용하는 경우에, 트랜지스터들의

극성은 모드 n채널형인 것이 바람직하다. 도 7은 도 1에 화소 회로에서 모드 n채널 트랜지스터들을 사용한 화소 회로를 도시한 것이다.

- [0071] 이 실시형태에서, 스위칭 트랜지스터 및 구동 트랜지스터의 극성이 모드 p채널형인 것에 대해 기술한다.

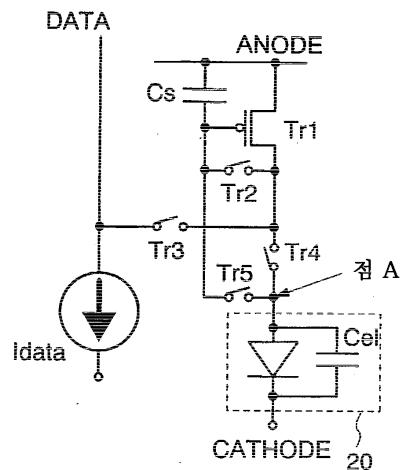

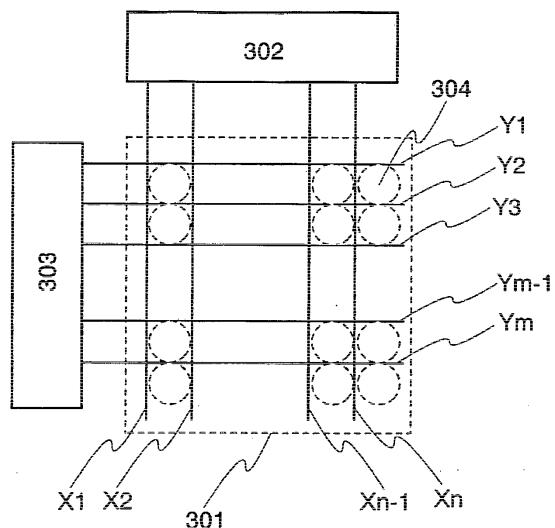

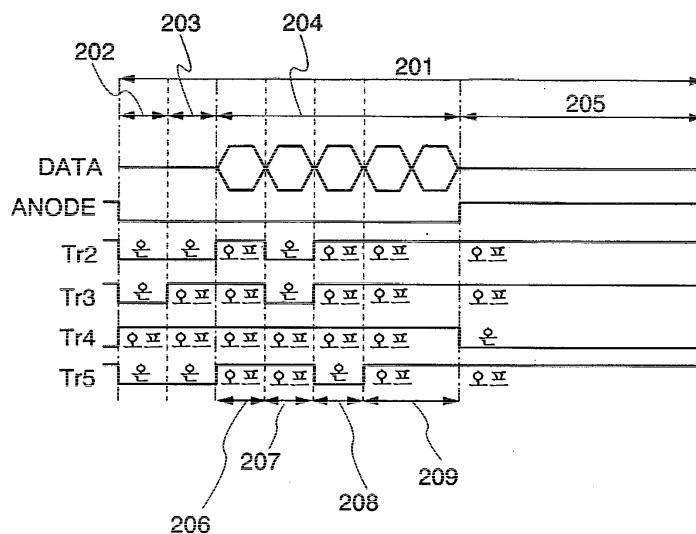

- [0072] 다음에, 도 1에 도시된 이 실시형태의 화소 회로의 구동 방법이 도 2를 참조로 기술된다. 도 2는 수평축이 시간을 나타내는 것으로 하여 데이터선(DATA), 제2 전원선(CATHODE), 스위칭 트랜지스터들(Tr2, Tr3, Tr4, Tr5)의 각각의 게이트 전극의 전위의 변화를 나타내는 타이밍도이다.

- [0073] 이 실시형태의 표시 장치의 구동은 초기화 기간(202)을 갖는 한 프레임 기간(201), 임계 기입 기간(203), 어드레스 기간(204), 및 한 프레임 기간(201)을 한 단위로서 갖는 발광기간(205)을 포함한다. 여기에서, 초기화 기간(202)은 임계 기입 기간(203)에서 적합하게 임계 기입 동작이 수행되는 기간이다. 임계 기입 기간(203)은 구동 트랜지스터(Tr1)의 임계전압을 EL 소자(20)의 용량소자(Ce1)에 기입하기 위한 기간이다. 어드레스 기간(204)은 데이터 전류를 모든 화소들에 기입하기 위한 기간이다. 구동 트랜지스터(Tr1)의 임계 전압이 기입되는 EL 소자(20)의 용량소자(Ce1)을, 구동 트랜지스터(Tr1)의 게이트와 소스간 전압(Vgs(data))(게이트-소스 전압이라 함)이 데이터 전류(Idata)에 대응하여 기입된 용량소자(Cs)에 접속하고 이들간에 전하를 분배함으로써, 큰 데이터 전류를 갖는 화소에 데이터 전류가 기입될 수 있는 것에 유의한다. 발광기간(205)은 EL 소자(20)가 어드레스 기간(204)에 기입된 데이터 전류에 따라 발광하는 기간이다.

- [0074] 먼저, 각 신호선의 전위가 기술된다. 데이터선(DATA)의 전위는 초기화 기간(202)에서 구동 트랜지스터(Tr1)의 임계전압의 절대값만큼 제1 전원선(ANODE)의 전위보다 낮을 수도 있다. 이 상태가 만족되지 않는다면, 구동 트랜지스터(Tr1)는 이의 게이트-소스 전압이 임계 기입 기간(203)에서 임계전압과 같거나 이보다 높아지지 않기 때문에 턴 온 되지 않으며, 임계전압은 전류가 EL 소자(20)의 용량소자(Ce1)에 흐르지 않기 때문에 기입될 수 없다. n채널 트랜지스터를 구동 트랜지스터(Tr1)로서 사용하는 경우에, 초기화 기간(202)에서 데이터선(DATA)의 전위는 구동 트랜지스터(Tr1)의 임계전압의 절대값만큼 제1 전원선(ANODE)의 전위와 같거나 이보다 커질 수 있는 것에 유의한다.

- [0075] 어드레스 기간(204)에서, 데이터선(DATA)의 전위는 화상 데이터로부터의 휘도 데이터에 따라 주변 구동 회로에서 발생되는 전류값과 구동 트랜지스터(Tr1)의 전기적 특성에 의해 결정된다. 즉, 데이터선(DATA)의 전위는 시간에 따라 다르며, 따라서 값은 도 2에서 결정되지 않는다. 또한, 발광기간(205)에 데이터선(DATA)의 전위는 EL 소자(20)의 상태가 영향받지 않기 때문에 임의이다. 즉, 데이터선(DATA)의 전기적 상태가 전위에 의해 결정되는 것은 초기화 기간(202)에서만일 수 있다.

- [0076] 초기화 기간(202), 임계 기입 기간(203) 및 어드레스 기간(204)에서, 제2 전원선(CATHODE)의 전위는 하이일 수 있고, 제1 전원선(ANODE)의 전위가 같거나 거의 같을 수 있다. 발광기간(205)에서, 제2 전원선(CATHODE)의 전위는 로우이고 제1 전원선(ANODE)의 전위보다 낮으며, 스위치(Tr4)가 턴 온 될 때 구동 트랜지스터(Tr1)가 포화영역에서 동작하게 하는 전위일 수도 있다.

- [0077] 제1 전원선(ANODE)의 전위가 도 2에 도시되지 않았을지라도, 전력소비 및 잡음 감소를 고려하여 어떤 전위를 갖는 것이 바람직하다.

- [0078] 스위칭 트랜지스터들(Tr2, Tr3, Tr4, Tr5)에 입력되는 신호의 전위에 관하여, 스위치 소자가 충분히 턴 온 또는 오프 되는 전위(포화영역에서 동작하는 전위)일 수 있다. 게이트 전극에 입력되는 신호의 진폭은 전력소비 및 잡음 감소를 고려하여 스위치로서의 기능이 손상되지 않을 정도로 더 작은 것이 바람직하다.

- [0079] 도 1에서 화소는 이하 기술되는 바와 같이 도 2의 타이밍도에서 보인 입력신호에 의해 동작된다. 먼저, 이전 프레임의 발광기간(205A)은 관계된 프레임의 초기화 기간(202)으로 이동된다. 이때, 제2 전원선(CATHODE)의 전위는 제1 전원선(ANODE)의 전위까지 상승된다. 또한, 거의 동시에, 스위치 소자는 점(A), 데이터선(DATA), 구동 트랜지스터(Tr1)의 게이트 전극 및 드레인 전극이 전기적으로 접속되도록 전환되고, 데이터선(DATA)의 전위는 구동 트랜지스터(Tr1)의 임계전압의 절대값만큼 제1 전원선(ANODE)의 전위보다 낮게 설정된다. 이 상태를 실현하기 위해서 각 스위치 소자의 상태는 임의이며, 도 2에서 초기화 기간(202)에 의해 보인 바와 같이, 예를 들면, 스위치 소자들(Tr2, Tr3, Tr5)이 턴 온 될 수 있고 Tr4는 턴 오프 될 수 있다. 이러한 상태를 실현함에 있어, 점(A)의 전위, 구동 트랜지스터(Tr1)의 게이트 전극 및 드레인 전극은 구동 트랜지스터(Tr1)의 임계전압의 절대값만큼 제1 전원선(ANODE)의 전위보다 낮은 값으로 초기화된다.

- [0080] 제2 전원선(CATHODE)의 전위는 초기화 기간(202)에서 점(A)의 전위보다 낮으며(역 바이어스라고도 함), 따라서 EL 소자(20)에 순방향 전류가 인가되지 않아 발광하지 않는 것에 유의한다. 또한, EL 소자(20)는 역 바이어스

전압을 인가함으로써 더 긴 수명과 더 높은 신뢰성을 얻을 수 있다.

- [0081] 역 바이어스 전압을 EL 소자(20)에 인가함으로써, EL 소자(20)의 결함 및 신뢰성이 향상될 수 있다. EL 소자(20)는 이물질들의 부착, 양극 또는 음극의 작은 돌기에 의해 야기되는 편홀, 또는 전장발광 물질의 피착의 비균질성에 기인하여 양극과 음극간에 단락회로의 초기 결함을 종종 야기한다. 이러한 초기 결함이 발생할 때, 신호에 따른 점등 및 점멸은 수행되지 않으며, 대부분의 전류는 단락회로가 된 소자에 흐른다. 결국, 화상의 표시는 잘 수행되지 않는다. 결함은 임의의 화소에서 발생할 수도 있다.

- [0082] 결국, 이 실시형태에서와 같이 역 바이어스 전압이 EL 소자(20)에 인가될 때, 단락회로가 된 부분에 국부적인 전류가 공급되고, 단락회로가 된 부분은 열을 발생하고 산화 또는 탄화될 수 있다. 그러므로, 단락회로가 된 부분은 절연될 수 있고, 전류는 단락회로가 된 부분을 제외한 영역에 공급되며, 그럼으로써 EL 소자(20)는 정상적으로 동작될 수 있다. 위에 기술된 바와 같이, 초기 결함이 일어난다면, 역 바이어스 전압을 인가함으로써 해결될 수 있다. 이러한 단락회로가 된 부분은 출하전에 절연될 수 있는 것에 유의한다. 예를 들면, 모든 화소들의 스위치 소자들(Tr3, Tr4)은 턴 온 되고, 데이터선(DATA)의 전위는 제2 전원선(CATHODE)의 전위보다 낮아지게 되고, 그러므로, 역 바이어스가 출하전에 공급될 수 있다.

- [0083] 양극과 음극간에 단락회로는 초기 결함 외에도 시간이 지남에 따라 발생할 수도 있다. 이러한 결함은 점진적 결함이라고도 한다. 이 실시형태에서와 같이 EL 소자에 역 바이어스 전압을 인가함으로써, 점진적 결함은 이것이 발생할지라도 해결될 수 있고, EL 소자(20)는 정상적으로 동작될 수 있다.

- [0084] 또한, 역 바이어스 전압을 인가함으로써 화상 번-인(burn-in)이 방지될 수 있다. EL 소자(20)의 열화상태에 따라 화상 번-인이 발생한다. 열화상태는 역 바이어스 전압을 인가함으로써 감소될 수 있고, 따라서, 화상 번-인이 방지될 수 있다.

- [0085] 일반적으로, EL 소자(20)의 열화는 초기 단계에서 진행되며, 열화의 진행은 시간이 지남에 따라 줄어든다. 즉, 한번 열화된 EL 소자(20)는 더 열화되지는 않게 될 것이다. 결국, EL 소자(20)의 열화 상태는 변한다. 이것을 해결하기 위해서, 모든 EL 소자(20)는 출하전에 또는 화상이 표시되지 않을 때 발광할 수도 있다. 이 때, 열화되지 않는 소자에서도 열화가 야기될 수 있고, 모든 EL 소자(20)의 열화상태는 평균이 될 수 있다.

- [0086] 제2 전원선(CATHODE)의 전위를 상승시키는 타이밍 및 각 스위치 소자를 전환시키기 위한 타이밍은 전위(A)의 전위를 많이 변경하지 않기 위해서 제2 전원선(CATHODE)의 전위가 상승된 후에 각 스위치 소자가 스위칭될 것인지 아니면 제2 전원선(CATHODE)의 전위가 상승되기 전에 각 스위치 소자가 스위칭될 것인지 여부일 수 있음에 유의한다. 이것은 제2 전원선(CATHODE)에 접속된 기생용량이 크기 때문에 전위를 안정화하기 위한 시간이 고려되기 때문이다. 초기화 기간(202)을 제공하기 위한 목적은 이하 기술되는 임계 기입 기간(203)에서 임계 기입 동작을 확실하게 수행하는 것이며 이에 따라 임계 기입 동작이 확실히 수행된다면 초기화 기간(202)을 제공할 것이 항상 요구되지 않는 것에 유의한다. 그러나, 제2 전원선(CATHODE)의 전위가 상승될 때 점(A)의 전위가 변경되기 때문에 임계 기입 동작을 확실히 수행하기 위해 초기화 기간(202)이 제공되는 것이 바람직하다. 이 실시형태에서, 초기화를 위해 데이터선(DATA)이 채용되는 경우가 기술되었을지라도, 데이터선(DATA) 대신 전용의 전원선 또는 주사선과 같은 또 다른 배선이 초기화를 위해 채용될 수도 있다.

- [0087] 다음에, 점(A)의 전위가 구동 트랜지스터(Tr1)의 임계전압의 절대값만큼 제1 전원선(ANODE)의 전위보다 낮게 설정된 후에, 기간은, 용량소자(Ce1)의 전극들의 양단들에 공급되는 전압을 구동 트랜지스터(Tr1)의 임계전압으로 변경하기 위한 기간으로(임계 기입 기간(203)에 대응하는) 이동된다. 이때, 점(A), 구동 트랜지스터(Tr1)의 게이트 전극 및 드레인 전극이 전기적으로 접속되고 플로팅 상태가 되도록 스위치 소자가 스위칭된다. 이 상태를 실현하기 위한 각 스위치 소자의 상태는 임의이다. 예를 들면, 도 2의 임계 기입 기간(203)에 나타낸 바와 같이 스위치 소자들(Tr2, Tr5)은 턴 온 되고, 스위치 소자들(Tr3, Tr4)은 턴 오프 된다. 이러한 상태를 실현함으로써, 제1 전원선(ANODE)에서 구동 트랜지스터(Tr1)를 통해 용량소자(Cs)로 전류가 흐른다. 구동 트랜지스터(Tr1)는 턴 오프 되고 구동 트랜지스터(Tr1)의 게이트-소스 전압이 이 트랜지스터의 임계 전압이 될 때 전류는 흐름을 멈춘다.

- [0088] 이때, 점(A), 구동 트랜지스터(Tr1)의 게이트 전극 및 드레인 전극은 전기적으로 접속되고, 따라서 점(A)의 전위는 구동 트랜지스터(Tr1)의 임계전압의 절대값만큼 제1 전원선(ANODE)의 전위보다 낮다. 이때 용량소자(Cs)의 두 전극들에 인가하는 전압은 구동 트랜지스터(Tr1)의 임계전압이 된다. 한편, 점(A)의 전위는 제2 전원선(CATHODE)의 전위에 관계없이 구동 트랜지스터(Tr1)의 임계 전압의 절대값만큼 제1 전원선(ANODE)의 전위보다 낮으며, 따라서 용량소자(Ce1)의 두 전극들에 인가하는 전압은 제2 전원선(CATHODE)의 전위가 제1 전원선

(ANODE)의 전위와 같거나 거의 같은 경우에 구동 트랜지스터(Tr1)의 임계전압이 된다. 또한, 제2 전원선(CATHODE)의 전위가 변함에 따라 점(A)의 전위도 변하기 때문에 제2 전원선(CATHODE)의 전위를 초기화 기간(202)에서의 전위로부터 변하지 않는 것이 바람직하다.

[0089] 다음에, 기간은 각 주사선에 의해 데이터 전류를 기입하기 위한 기간을 포함하는 어드레스 기간(204)으로 이동된다. 어드레스 기간(204)에서, 화소를 선택하기 전에 기간은 기입전 기간(206)이라 하며, 데이터 전류를 화소에 기입하기 위한 기간은 데이터 기입 기간(207)이라 하며, 용량(Cel)에 유지된 전압에 의해 화소의 용량소자(Cs)에 인가되는 전압을 재기입하기 위한 기간은 Cs 재기입 기간(208)이라 하며, Cs 재기입 기간(208)이 종료된 후에 기간은 재기입 후 기간(209)이라 한다. 발명의 화소 회로에서, EL 소자(20)의 용량(Cel)은 임계 유지 용량소자(Ct)를 제공함이 없이 인가되며, 용량(Cel)에 유지하는 전압에 의해 화소의 용량소자(Cs)에 인가되는 전압을 재기입하기 위해 Cs 재기입 기간(208)이 제공된다. 각 주사선(Y1 내지 Ym)에 접속된 각 화소에 데이터 전류가 기입될 때, 도 2에 도시된 어드레스 기간(204)에 각 기간의 타이밍 및 길이는 일 예인 것에 유의한다. 데이터 기입 기간(207)을 위한 타이밍, 및 기입전 기간(206)의 길이 및 재기입 후 기간(209)의 길이는, 각 주사선(Y1 내지 Ym)에 접속된 각 화소에 따라 다르다. 어드레스 기간(204)에서, 제2 전원선(CATHODE)의 전위로서, 점(A)의 전위도 변화되고, 따라서, 구동 트랜지스터(Tr1)의 정확한 게이트-소스 전압은 Cs 재기입 기간(208)에서 얻어질 수 없고 제2 전원선(CATHODE)의 전위는 초기화 기간(202) 및 임계 기입 기간(203)에서의 전위로부터 변경되지 않는 것이 바람직함에 유의한다.

[0090] 기입 전 기간(206)에서, 점(A)은 언급된 임계 기입 기간(203)에서 얻어진 구동 트랜지스터(Tr1)의 임계전압이 용량소자(Cel)에 유지되도록 플로팅 상태가 되게 설정한다. 화소 내 스위치 소자를 제외한 각 소자(특히, 용량소자(Cs), 구동 트랜지스터(Tr1), 및 EL 소자(20)) 및 데이터선(DATA)은 관계된 화소에 접속된 주사선 이외의 선택된 주사선에 접속된 화소에 기입하는 것을 방지하지 않기 위해서 전기적으로 접속되지 않게 설정된다. 이러한 상태를 실현하기 위한 각 스위치 소자의 상태는 임의이며, 예를 들면, 도 2의 기입 전 기간(206)에서 보인 바와 같이 스위치 소자들(Tr2, Tr3, Tr4, Tr5)은 턴 오프 된다.

[0091] 데이터 기입 기간(207)에서, 점(A)은 언급된 임계 기입 기간(203)에서 얻어진 구동 트랜지스터(Tr1)의 임계전압을 용량소자(Cel)가 유지하도록 플로팅 상태가 되게 설정한다. 데이터선(DATA) 및 구동 트랜지스터(Tr1)의 게이트 및 드레인 전극들은 서로 전기적으로 접속되며, 이들은 스위치 소자를 제외한 다른 소자들에 전기적으로 접속되는 것으로부터 방지된다. 이러한 상태를 실현하기 위한 각 스위치 소자의 상태는 임의이며, 예를 들면, 도 2에 임계 기입 기간(203)에 보인 바와 같이 스위치 소자들(Tr2, Tr3)은 턴 온 되고, 스위치 소자들(Tr4, Tr5)은 턴 오프 된다. 이러한 상태를 실현함으로써, 데이터 전류(Idata)는 구동 트랜지스터(Tr1)에 흐르며, 구동 트랜지스터(Tr1)가 데이터 전류(Idata)를 공급할 만큼 충분히 하이인 게이트-소스 전압(Vga(data))이 용량소자(Cs)에 공급된다.

[0092] Cs 재기입 기간(208)에, 언급된 임계 기입 기간(203)에 얻어진 구동 트랜지스터(Tr1)의 임계 전압을 유지하는 용량소자(Cel)는 구동 트랜지스터(Tr1)가 데이터 전류(Idata)를 공급하는데 충분히 하이인 게이트-소스 전압을 유지하는 용량소자(Cs)에 전기적으로 접속되며, 점(A)는 스위치 소자(구동 트랜지스터(Tr1)의 게이트 전극을 제외한)를 제외한 다른 소자들에 전기적으로 접속되는 것으로부터 방지된다. 이러한 상태를 실현하기 위한 각 스위치 소자의 상태는, 예를 들면, 도 2의 Cs 재기입 기간(208)에 보인 바와 같이 스위치 소자들(Tr2, Tr3, Tr4)이 턴 오프 되고, 스위치 소자(Tr5)가 턴 온 된다는 것이다. 이러한 상태를 실현함으로써, 식2를 만족하는 전류(Ioled)를 공급하기에 충분히 하이인 게이트-소스 전압(Vgs(oled)라고도 함)은 용량소자(Cs)에 공급된다. 전류(Ioled)는 다음 식에 의해 기술된다.

[0093] [식2]

$$I_{oled} = (Cs/(Cel + Cs))^2 \times I_{data}$$

[0095] 재기입 후 기간(209)에서, 구동 트랜지스터(Tr1)의 게이트 전극은 Cs 재기입 기간(208)에서 용량소자(Cs)에 인가되는 전압(Vgs(oled))가 유지될 수 있도록 플로팅 상태가 되게 설정되며, 화소 내 스위치 소자를 제외한 각 소자(특히, 용량소자(Cs), 구동 트랜지스터(Tr1), 및 EL 소자(20)) 및 데이터선(DATA)은 화소에 접속된 주사선 이외의 선택된 주사선에 접속된 화소에 기입하는 것을 방지하지 않도록 전기적으로 접속되지 않게 설정된다. 이러한 상태를 실현하기 위한 각 스위치 소자의 상태는 임의이며, 예를 들면 도 2의 재기입 후 기간(209)에 보인 바와 같이 스위치 소자들(Tr2, Tr3, Tr4, Tr5)이 턴 오프 된다.

[0096] 위에 기술된 바와 같이, 어드레스 기간(204)에서, 각 회로에 대응하는 전류(Ioled)를 공급하기에 충분히 하이인

게이트-소스 전압은 각 주사선(Y1 내지 Ym)에 순차로 데이터를 기입함으로써 모든 화소들에 용량소자(Cs)에 기입된다. 이어서, 전압은 다음 한 프레임 기간(201)에서 이동되고 용량소자(Cs)에 유지된다. 도 2에 어드레스 기간(204)을 분할하는 수의 서술은 일 예이고, 이 실시형태는 이것으로 제한되는 것은 아닌 것에 유의한다. 예를 들면, 어드레스 기간(204)을 분할하는 수는 주사선들의 수와 같거나 거의 같다. 또한, 복수의 주사선들은 어드레스 기간(204)을 단축시키기 위해서 복수의 데이터선 구동 회로들(302)을 사용하여 구동될 수도 있다. 예를 들면, 2개의 주사선들이 2개의 데이터선 구동 회로들(302)을 사용함으로써 구동되는 경우에, 어드레스 기간(204)을 분할하는 수는 주사선들의 수의 반이다.

[0097] 다음에, 기간은 발광기간(205)으로 이동되며, 여기서 EL 소자(20)는 언급한 어드레스 기간(204)에서 구동 트랜지스터(Tr1)의 게이트-소스 전압(Vgsoled))에 따라 발광한다. 이때, 구동 트랜지스터(Tr1) 및 EL 소자(20)는 직렬로 접속되고, 언급한 어드레스 기간(204)에 유지하는 구동 트랜지스터(Tr1)의 게이트-소스 전압(Vgs(ole d))이 유지되며, 따라서, 구동 트랜지스터(Tr1)의 게이트 전극은 플로팅 상태가 되게 설정되며, 각 화소 내 각 스위치 소자를 제외한 소자 및 데이터선(DATA)은 전기적으로 접속되지 않게 설정된다. 각 스위치 소자의 상태는 예를 들면 도 2의 발광기간(205)에 보인 바와 같이 스위치 소자(Tr4)가 턴 온 되고, 스위치 소자들(Tr2, Tr3, Tr5)가 턴 오프 된다는 것이다. 이러한 상태를 실현함으로써, 식2를 만족시키는 전류(Ioled)는 구동 트랜지스터(Tr1) 및 EL 소자(20)에 흐르며, EL 소자(20)는 데이터 전류(Idata)에 따른 휙도로 발광한다.

[0098] 이 실시형태에서 화소 회로 및 이의 구동 방법으로서, 임계 유지 용량소자(Ct)는 EL 소자의 용량(Cel)에 의해 대체된다. 결과적으로, 데이터 전류는 Ct를 제공함이 없이도 EL 소자의 구동 전류에 응하여 증가될 수 있다. 또한, 이것은 이 실시형태에서 화소 회로 및 이의 구동 방법을 도 9에 도시된 종래의 화소 회로 및 EL 소자(20)에 흐르는 전류를 나타내는 식1과 비교로부터 이해될 수 있다.

[0099] 이 실시형태에서, 애퍼처 비는 Ct가 화소에 제공되지 않기 때문에 증가될 수 있다. 애퍼처 비의 증가는 EL 소자의 용량(Cel)의 증가로 이어지고, 따라서, 데이터 전류는 더 증가될 수 있다. 이에 따라, 애퍼처 비의 증가는 데이터 전류의 증가로 이어져 상승적이고 현저한 효과를 발생한다.

#### [0100] [실시형태 2]

[0101] 다음에, 도 4a, 도 4b, 도 5를 참조하여 발명의 표시 장치의 제2 형태에 대해 기술한다.

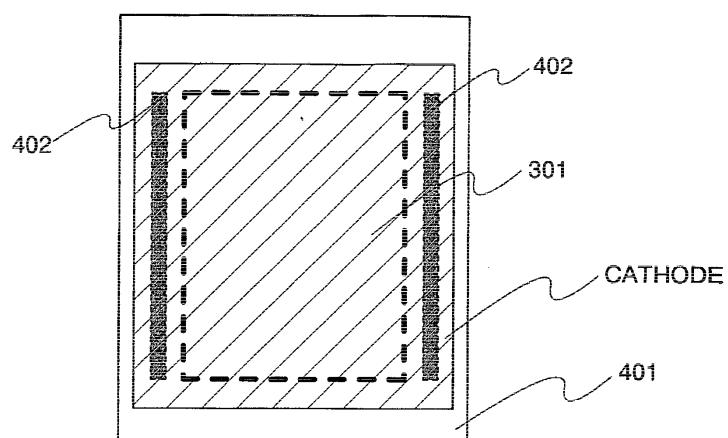

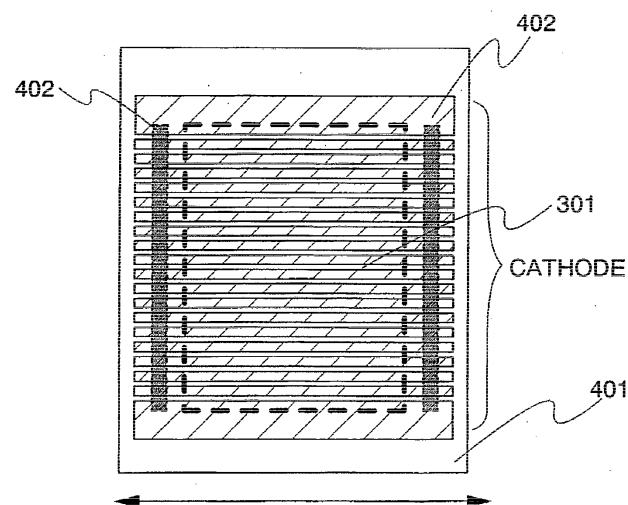

[0102] 이 실시형태에서 화소 회로는 실시형태 1에서 설명된 도 1에 적용될 수도 있다. 이 실시형태에서 제2 전원선(CATHODE)의 제조방법은 실시형태 1에서 설명된 형태와는 다르고 특정 효과를 발생할 수 있는 것에 유의한다. 도 4a 및 도 4b를 참조하여 제2 전원선(CATHODE)의 형태에 대해 기술한다.

[0103] 도 4a는 전술한 실시형태 1에서 설명된 표시 장치에서 제2 전원선(CATHODE)의 개략도이다. 도 4a에서 제2 전원선(CATHODE)은 실시형태 1에서 이미 기술된 바와 같이 모든 화소 회로들에 공통으로 접속되는 형태를 갖는다. 화소부(301)는 기판(401) 상에 형성되고, 이 위에 EL 소자가 표시 소자로서 형성되고, 이 위에 하측 전극을 갖는 접촉영역(402)이 형성되며, 이 위에 제2 전원선(CATHODE)이, 공통전극에 직접 적용될 수 있는 증기증착에 의해 전체 영역 상에 형성된다.

[0104] 표시 소자로서 EL 소자를 사용하는 경우에, 제2 전원선(CATHODE)은 포토리소그래피에 의해 형상대로 가공될 수 있으나, 그러나 공정에 의한 EL 소자에의 손상이 클 것으로 생각되는 것에 유의한다. 제2 전원선(CATHODE)이 증기증착 마스크를 사용하여 증기증착에 의해 형성되는 경우에, 제2 전원선(CATHODE)은 EL 소자에 큰 손상을 주지 않고 형상되로 가공될 수 있다. 이 실시형태에서, 도 4b에 도시된 화살표로 나타낸 주사선들(Y1 내지 Ym)에 별별로 제2 전원선(CATHODE)이 형상대로 가공되는 경우에 대해 기술한다. 형상을 가공함으로써 제2 전원선(CATHODE)을 분할하는 수는 주사선과 별별인 한 화소 행 당 한선인 주사선들의 수와 동일한 것이 바람직한 것에 유의한다. 그러나, 분할들 자체의 수는 임의이며, 가공될 제2 전원선(CATHODE)의 수는 자유롭게 결정될 수 있다.

[0105] 제2 전원선과 접촉하는 영역(402)으로서, 제2 전원선(CATHODE)는 제2 전원선(CATHODE)에 또는 하측 전극에 접속되는 회로에서 개별적으로 제어되는 것이 바람직하다.

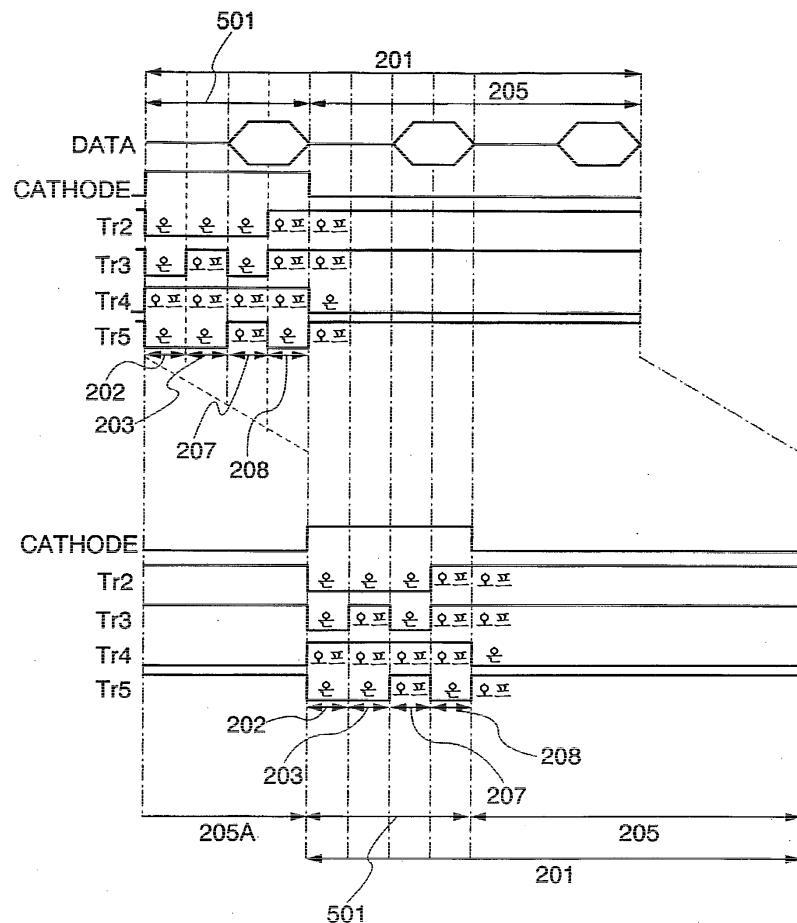

[0106] 이 실시형태에서 화소 회로(304)의 동작이며 제2 전원선(CATHODE)를 각 주사선에 특유하게 함으로써 실현될 수 있는 구동 방법을 도 5를 참조하여 기술한다. 도 5는 관계된 선의 타이밍도 및 다음 선의 타이밍도를 도시한 것이다. 선은 동일 주사선에 접속된 화소 그룹을 의미한다.

- [0107] 이 실시형태에서, 화소 회로(304)의 구조는 실시형태 1에서와 같이 도 1의 구조에 채용할 수 있다.

- [0108] 도 5는 수평축이 시간을 나타내는 것으로 하여 데이터선(DATA), 제2 전원선(CATHODE), 스위칭 트랜지스터들(Tr2, Tr3, Tr4, Tr5)의 각각의 게이트 전극의 전위의 변화를 나타내는 타이밍도이다. 이 실시형태의 표시 장치의 구동에서, 한 프레임(201)은 한 주사선 기입 기간(501) 및 발광기간(205)을 한 단위로서 포함한다. 한 주사선 기입 기간(501)은 초기화 기간(202), 임계 기입 기간(203), 데이터 기입 기간(207), Cs 재기입 기간(208)을 포함한다.

- [0109] 관계된 선이 이전 프레임에서 광 방출을 종료하고 한 주사선 기입 기간(501)으로 이동할 때, 선은, 이전 선의 Vgs에서, 초기화 기간(202), 임계 기입 기간(203), 데이터 기입 기간(207) 및 Cs 재기입 기간(208)의 상태를 통해 데이터 전류에 대응하는 관계된 선의 Vgs(oled)로 재기입되며, 다시 발광상태로 이동될 수 있다.

- [0110] 여기에서, 각 상태에 상세한 설명은 실시형태 1에 이미 기술되었으므로 생략된다. 그러나, 데이터선(DATA)에의 입력신호는 실시형태 1의 입력신호와는 다르며 각 선에 데이터를 기입하기 전에 각 선에 의해 개별적으로 초기화되도록 구동 트랜지스터(Tr1)의 임계전압의 절대값만큼 제1 전원선(ANODE)보다 낮은 값이 될 것이 요구된다. 도 5에서 초기화 기간(202)은 임계 기입 기간(203) 바로 전이지만, 그러나 특히 임계 기입 기간(203) 바로 전일 필요는 없으며 초기화는 임계 기입 기간(203) 전에 수행될 수도 있는 것에 유의한다. 예를 들면, 관계된 선은 데이터선(DATA)이 관계된 선들 전의 2개의 선들에서 구동 트랜지스터(Tr1)의 임계 전압의 절대값만큼 제1 전원선(ANODE)보다 낮은 값을 가질 때 초기화될 수 있다. 초기화 후에, Tr3는 턴 오프 되고, 임계전압이 EL 소자의 용량소자(Ce1)에 기입된다. 이어서, 데이터 기입 등이 선택기간에 수행된다. 위에 기술된 바와 같이 수행함에 있어, 임계 기입 기간(203)은 충분히 길게 설정될 수 있다.

- [0111] 도 5에 도시된 수평축의 길이가 거의 같아 이격되어 있을지라도, 이 실시형태는 이것으로 제한되지 않으며, 각 기간의 길이는 필요할 때 적합하게 결정될 수 있는 것에 유의한다.

- [0112] 도 5에 도시된 이 실시형태의 구동 방법은 주사선들과 별별로 제2 전원선(CATHODE)를 형성함으로써 특징화된다. 관계된 선에 기입되기 위해서, 관계된 선의 제2 전원선(CATHODE)가 변경되는 경우에, 관계된 선 이외의 선들의 동작은 영향을 받지 않는다. 그러므로, 선이 선택되어 데이터 전류가 이에 기입되는 동안, 다른 선들은 이전 선의 데이터 전류에 따라 Vgs(oled)가 유지되어 광을 계속하여 방출할 수 있다. 즉, 한 프레임 기간(201) 내에서 발광기간의 비(듀티 비)가 실질적으로 개선된다. 듀티 비가 클 때, 발광소자의 순간 휘도는 보다 작은 듀티 비에서보단 더 작더라도, 동일 휘도로서 인지된다. 그러므로, 실시형태 1에서의 효과를 외에도, 구동전압은 더 작을 수 있고, 전력소비가 감소될 수 있고, 신뢰성이 향상될 수 있다.

- [0113] [실시형태 3]

- [0114] 다음에, 도 6을 참조하여 발명의 표시 장치의 제3 형태에 대해 기술한다. 이 실시형태에서, 제1 전원선(ANODE)를 교번시킴으로써 표시 장치의 구동 방법이 기술된다. 이 실시형태에서, 제2 전원선(CATHODE)은 모든 화소들에 공통으로 접속될 수 있고, 이것이 이 실시형태에서 기술된다. 그러나, 제2 전원선(CATHODE)이 이 실시형태에서 형상대로 가공될 수도 있다.

- [0115] 도 6에서, 모든 트랜지스터의 극성을 p채널로 하여 제1 전원선(ANODE)을 교번시킴으로써 발명의 표시 장치가 구동되는 경우에 입력신호가 기술된다. 한 프레임은 실시형태 1에 보인 구동과 동일하게 초기화 기간(202), 임계 기입 기간(203), 어드레스 기간(204), 발광기간(205)을 포함하고, 각 기간에서 회로들의 수행도 거의 동일하다. 그러므로, 이 실시형태에서, 실시형태 1과 다른 점들에 대해 주로 기술한다.

- [0116] 먼저, 각 신호선의 전위가 기술된다. 초기화 기간(202), 임계 기입 기간(203), 및 어드레스 기간(204)에서, 제1 전원선(ANODE)의 전위는 로우일 수 있고 제2 전원선(CATHODE)의 전위와 같거나 거의 같을 수 있다. 발광기간(205)에서, 제1 전원선(ANODE)의 전위는 하이일 수 있고 이 때 제2 전원선(CATHODE)의 전위보다 클 수 있고, 스위치 소자(Tr4)가 턴 온 될 때 구동 트랜지스터(Tr1)가 포화영역에서 동작하는 전위일 수 있다.

- [0117] 제2 전원선(CATHODE)의 전위는 도 6에 도시되지 않았으나, 전력소비 및 잡음 감소를 고려하여 일정한 전위인 것이 바람직하다.

- [0118] 초기화 기간(202)에서 데이터선(DATA)의 전위는 구동 트랜지스터(Tr1)의 임계전압의 절대값만큼 제1 전원선(ANODE)의 전위보다 낮을 수 있다. 이 상태가 만족되지 않는다면, 구동 트랜지스터(Tr1)는 임계 기입 기간(203)에서 이 트랜지스터의 게이트-소스 전압이 임계전압보다 크지 않기 때문에 턴 온 되지 않으며 임계 전압은 전

류가 EL 소자(20)의 용량소자(Cs1)에 흐르지 않기 때문에 EL 소자(20)에 기입될 수 없다. 구동 트랜지스터(Tr1)로서 n 채널 트랜지스터를 사용하는 경우, 초기화 기간(202)에서 데이터선(DATA)의 전위는 구동 트랜지스터(Tr1)의 임계 트랜지스터의 절대값만큼 제1 전원선(ANODE)의 전위와 같거나 이보다 높을 수 있는 것에 유의한다.

[0119] 어드레스 기간(204)에서 데이터선(DATA)의 전위는 화상 데이터로부터의 회도 데이터에 따라 주변 구동 회로에서 발생되는 데이터 전류의 값과 구동 트랜지스터(Tr1)의 전기적 특성에 의해 결정된다. 즉, 데이터선(DATA)의 전위는 시간에 따라 다르며, 따라서 값은 도 6에서 결정되지 않는다. 또한, 발광기간(205)에 데이터선(DATA)의 전위는 EL 소자(20)의 상태가 영향받지 않기 때문에 임의이다. 즉, 데이터선(DATA)의 전기적 상태가 전위에 의해 결정되는 것은 초기화 기간(202)에서만일 수 있다.

[0120] 스위칭 트랜지스터들(Tr2, Tr3, Tr4, Tr5)에 입력되는 신호의 전위는 스위치 소자가 충분히 턴 온 또는 오프 되는 전위일 수 있다(선형영역에서 동작하는 전위). 게이트 전극에 입력되는 신호의 진폭은 전력소비 및 잡음 감소를 고려하여 스위치로서의 기능이 손상되지 않을 정도로 더 작은 것이 바람직하다.

[0121] 이 실시형태에서, 실시형태 1과는 다른 동작 부분은 제2 전원선(CATHODE)의 전위가 변하지 않고 제2 전원선(CATHODE)의 전위와 함께 되도록 제1 전원선(ANODE)의 전위가 변한다는 것이다. 구체적으로 다음의 3가지 차이점들이 있다. 먼저, 발광기간(205)이 초기화 기간(202)으로 이동될 때, 제1 전원선(ANODE)의 전위가 낮아진다. 두 번째로, 어드레스 기간(204)이 발광기간(205)으로 이동될 때, 제1 전원선(ANODE)의 전위는 상승된다. 세 번째로, 초기화 기간(202), 임계 기입 기간(203), 및 어드레스 기간(204)에서, 제1 전원선(ANODE)의 전위는 전위가 로우인 제2 전원선(CATHODE)의 전위와 같게 되거나 거의 같게 되도록 설정된다. 그러나, 위에 기술된 세 번째 차이점은 회로 동작에 영향을 미치지 않으며, 따라서, 이 실시형태 및 실시형태 1에서 회로동작들은 다르지 않다. 그러므로, 회로동작의 설명은 실시형태 1에서와 동일하므로 생략된다.

[0122] 이전 프레임의 발광기간(205A)이 관계된 프레임의 초기화 기간(202)으로 이동될 때 제1 전원선(ANODE)의 전위가 낮아지는 제1 점에 관한 동작에 대해 기술한다. 이전 프레임의 발광기간(205A)이 관계된 프레임의 초기화 기간(202)으로 이동될 때, 오프인 스위치 소자들(Tr2, Tr3, Tr5)은 턴 온 되고, 온인 Tr4는 턴 오프 된다. 그리고, 거의 동시에, 제1 전원선(ANODE)의 전위는 제2 전원선(CATHODE)의 전위와 거의 같게 되도록 낮아지며, 데이터선(DATA)의 전위는 구동 트랜지스터(Tr1)의 임계전압의 절대값만큼 제1 전원선(ANODE)의 보다 낮은 전위(로우상태)보다 낮아진다. 실시형태 1에서, 초기화에서 데이터선(DATA)의 전위는 구동 트랜지스터(Tr1)의 임계전압의 절대값만큼 제2 전원선(CATHODE)의 하이 전위(하이 상태)보다 낮아지며, 이것은 이 실시형태와는 다르다. 구동 트랜지스터(Tr1)가 n채널 트랜지스터인 경우에, 데이터선(DATA)의 전위는 이 실시형태에서 구동 트랜지스터(Tr1)의 임계전압의 절대값만큼 제1 전원선(ANODE)의 보다 낮은 전위보다 상승되는 것에 유의한다. 실시형태 1에서, 구동 트랜지스터(Tr1)가 n채널 트랜지스터인 경우에, 데이터선(DATA)의 전위는 구동 트랜지스터(Tr1)의 임계전압의 절대값만큼 제2 전원선(CATHODE)의 보다 높은 전위보다 상승되며, 이것은 이 실시형태와는 다르다.

[0123] 어드레스 기간(204)이 발광기간(205)으로 이동될 때 제1 전원선(ANODE)의 전위가 상승되는 제2 점에 관한 동작에 대해 기술한다. 어드레스 기간(204)이 발광기간(205)으로 이동될 때, 스위치 소자(Tr2, Tr3)는 오프 된 상태에 있으며, 온인 Tr4는 턴 오프 되고, Tr5는 오프인 상태에 있거나 턴 오프 된다. 스위치 소자(Tr5)가 정확하게 턴 오프되어 용량소자(Cs)의 한 전극이 플로팅 상태에 있게 된 후에, 제1 전원선(ANODE)의 전위는 더 높은 전위가 되게 상승된다. 스위치 소자(Tr5)가 정확하게 턴 오프 되지 않고 용량소자(Cs)의 전극이 플로팅 상태에 있지 않다면, 전압은 제1 전원선(ANODE)의 전위가 상승될 때 용량소자(Cs)에 유지될 수 없고, 이것은 실시형태 1과 같다.

[0124] 이 실시형태에서, 제1 전원선(ANODE)의 전위를 교번시킴으로써 발명의 표시 장치가 구동되는 경우에 잇점들이 이하 기술된다. 먼저, 구동에서 전력소비는 큰 용량에 접속된 제2 전원선(CATHODE)가 변경되지 않기 때문에 감소될 수 있다. 또한, 제1 전원선(ANODE)가 기관측 상에 형성될 수 있기 때문에 독립적으로 각 주사선을 구동하게 가공하는 것이 쉽다. 즉, 고 뉴티 비로 구동은 제조시 마스크 피착과 같은 단계를 추가함이 없이 실현될 수 있다.

[0125] [실시형태 4]

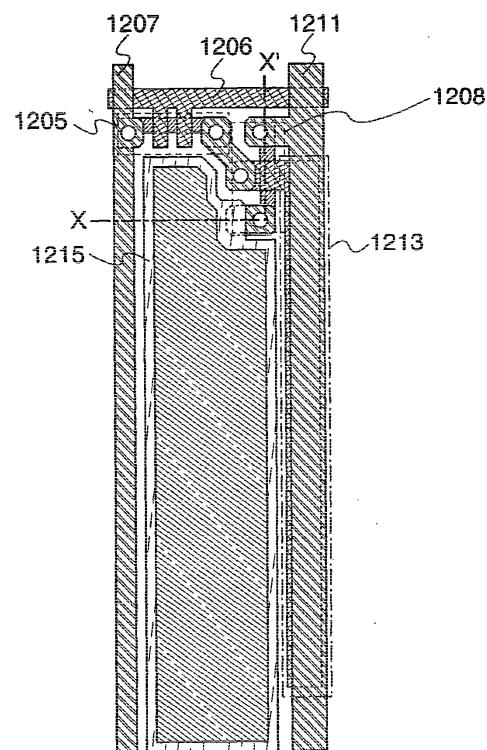

[0126] 도 12a는 한 화소당 두 TFT들을 포함하는 화소 내 소자의 레이아웃 예를 도시한 것이다. 도 12b는 도 12a에 도

시된 선 X-X'을 따라 취한 단면도이다.

- [0127] 도 12a에 도시된 바와 같은 발명의 화소는 제1 TFT(1205), 제1 배선(1206), 제2 배선(1207), 제2 TFT(1208), 제3 배선(1211), 대향 전극(1212), 용량소자(1213), 화소 전극(1215), 격벽(1216), 유기 도전막(1217), 유기 박막(1218), 및 기판(1219)을 포함할 수 있다. 제1 TFT(1205)는 스위칭 TFT로서 기능하며, 제1 배선(1206)은 게이트 신호선으로서 기능하며, 제2 배선(1207)은 소스 신호선으로서 기능하며, 제2 TFT(1208)은 구동 TFT로서 기능하며, 제3 배선(1211)은 전원선으로서 기능하는 것이 바람직함에 유의한다.

- [0128] 도 12a에 도시된 바와 같이, 제1 TFT(1205)의 게이트 전극은 제1 배선(1206)에 전기적으로 접속되고, 제1 TFT(1205)의 소스 및 드레인 전극들 중 하나가 제2 배선(1207)에 전기적으로 접속되고, 이 제1 TFT의 소스 및 드레인 전극들 중 다른 하나는 제2 TFT(1208)의 게이트 전극 및 용량소자(1213)의 한 전극에 전기적으로 접속되는 것이 바람직하다. 제1 TFT(1205)의 게이트 전극은 도 12a에 도시된 바와 같이 복수의 게이트 전극들을 포함할 수 있는 것에 유의한다. 결과적으로, 제1 TFT(1205)의 오프 상태에서 누설전류가 감소될 수 있다.

- [0129] 또한, 제2 TFT(1208)의 소스 및 드레인 전극들 중 하나는 제3 배선(1211)에 전기적으로 접속되고 제2 TFT(1208)의 소스 및 드레인 전극들 중 다른 하나는 화소 전극(1215)에 전기적으로 접속되는 것이 바람직하다. 결국, 화소전극(1215)에 흐르는 전류는 제2 TFT(1208)에 의해 제어될 수 있다.

- [0130] 유기 도전막(1217)은 화소전극(1215) 상에 형성될 수 있고, 이 위에 유기 박막(유기 복합층)(1218)이 형성될 수 있다. 대향 전극(1212)은 유기 박막(유기 복합층)(1218) 상에 형성될 수 있다. 대향 전극(1212)은 모든 화소들에 공통으로 접속되기 위해서 형성될 수 있고 새도우 마스크 등을 사용하여 패터닝될 수 있는 것에 유의한다.

- [0131] 유기 박막(유기 복합층)(1218)으로부터의 광은 방출되기 위해서 화소전극(1215) 및 대향 전극(1212) 중 하나를 통해 투과된다. 이 때, 도 12b에서, 광이 화소 전극 측, 즉, TFT 등이 형성된 측으로 방출되는 경우, 화소전극(1215)은 광 투과 도전막으로 형성되는 것이 바람직하다. 광이 대향 전극 측으로 방출되는 경우에, 대향 전극(1212)은 광 투과 도전막으로 형성되는 것이 바람직하다.

- [0132] 또한, 컬러 디스플레이용 발광 장치로서, R, G, 또는 B의 각각의 광 방출 색을 갖는 EL 소자가 개별적으로 피착될 수도 있고, 또는 RGB의 광 방출은 컬러 필터를 통해 얻어질 수도 있다.

- [0133] 도 12a 및 도 12b에 도시된 구조들은 단지 예들이며, 화소 레이아웃, 단면구조, EL 소자의 전극들의 접촉 순서 등은 도 12a 및 도 12b에 도시된 것들 이외의 다양한 구조들을 구비할 수도 있는 것에 유의한다. 발광층에 대하여, 도면들에 도시된 유기 박막을 포함하는 소자 외에, 결정질 소자와 같은 다양한 소자들, 예를 들면 LED, 또는 무기 박막을 포함하는 소자가 채용될 수도 있다.

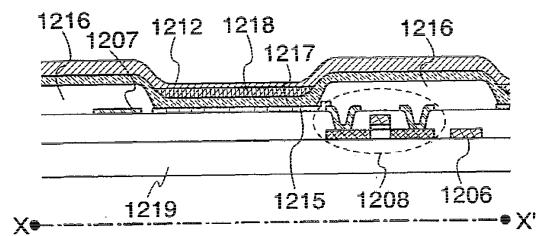

- [0134] 다음에, 도 13a를 참조하여 3개의 TFT들을 포함하는 화소에 소자의 레이아웃 예에 대해 기술된다. 도 13b는 도 13a에 도시된 선 X-X'를 따라 취한 단면도이다.

- [0135] 도 13a에 도시된 바와 같이, 발명의 화소는 기판(1300), 제1 배선(1301), 제2 배선(1302), 제3 배선(1303), 제4 배선(1304), 제1 TFT(1305), 제2 TFT(1306), 제3 TFT(1307), 화소전극(1308), 격벽(1311), 유기 도전막(1312), 유기 박막(1313), 및 대향전극(1314)을 포함할 수 있다. 제1 배선(1301)은 소스 신호선으로서 기능하고, 제2 배선(1302)은 기입 게이트 신호선으로서 기능하고, 제3 배선(1303)은 소거 게이트 신호선으로서 기능하고, 제4 배선(1304)은 전원선으로서 기능하고, 제1 TFT(1305)는 스위칭 TFT로서 기능하고, 제2 TFT(1306)은 구동 TFT로서 기능하는 것이 바람직한 것에 유의한다.

- [0136] 도 13a에 도시된 바와 같이, 제1 TFT(1305)의 게이트 전극은 제2 배선(1302)에 전기적으로 접속되며, 제1 TFT(1305)의 소스 및 드레인 전극들 중 하나는 제1 배선(1301)에 전기적으로 접속되며, 이 제1 TFT의 소스 및 드레인 전극들 중 다른 하나는 제3 TFT(1307)의 게이트 전극에 전기적으로 접속되는 것이 바람직하다. 제1 TFT(1305)의 게이트 전극은 도 13a에 도시된 바와 같이 복수의 게이트 전극들을 포함할 수 있고, 이는 제1 TFT(1305)의 오프 상태에서 누설 전류를 감소시킬 수 있는 것에 유의한다.

- [0137] 또한, 제2 TFT(1306)의 게이트 전극은 제3 배선(1303)에 전기적으로 접속되고, 제2 TFT(1306)의 소스 및 드레인 전극들 중 하나는 제4 배선(1304)에 전기적으로 접속되고, 이 제2 TFT의 소스 및 드레인 전극들 중 다른 하나는 제3 TFT(1307)의 게이트 전극에 전기적으로 접속되는 것에 바람직하다. 제2 TFT(1306)의 게이트 전극은 도 13a에 도시된 바와 같이 복수의 게이트 전극들을 포함할 수 있고, 이는 제2 TFT(1306)의 오프 상태에서 누설 전류를 감소시킬 수 있는 것에 유의한다.

- [0138] 또한, 제3 TFT(1307)의 소스 및 드레인 전극들 중 하나는 제4 배선(1304)에 전기적으로 접속되고 이 제3 TFT의

소스 및 드레인 전극들 중 다른 하나는 화소 전극(1308)에 전기적으로 접속되는 것이 바람직하고, 이는 제3 TFT(1307)에 의해 화소전극(1308)에 흐르는 전류를 제어할 수 있다.

[0139] 유기 도전막(1312)은 화소전극(1308) 상에 형성될 수 있고, 이 위에 유기 박막(유기 복합층)(1313)이 형성될 수 있다. 대향 전극(1314)은 유기 박막(유기 복합층)(1313) 상에 형성될 수 있다. 대향 전극(1314)은 모든 화소들에 공통으로 접속되기 위해 형성될 수 있고 새도우 마스크 등을 사용하여 패터닝될 수도 있는 것에 유의한다.

[0140] 유기 박막(유기 복합층)(1313)으로부터의 광은 방출되기 위해 화소전극(1308) 및 대향전극(1314) 중 하나를 통해 투과된다. 이때, 도 13b에서, 광이 화소 전극 측, 즉, TFT 등이 형성된 측으로 방출되는 경우, 화소전극(1308)은 광 투과 도전막으로 형성되는 것이 바람직하다. 광이 대향 전극 측으로 방출되는 경우에, 대향 전극(1314)은 광 투과 도전막으로 형성되는 것이 바람직하다.

[0141] 또한, 컬러 디스플레이용 발광 장치로서, R, G, 또는 B의 각각의 광 방출 색을 갖는 EL 소자가 개별적으로 피착될 수도 있고, 또는 RGB의 광 방출은 컬러 필터를 통해 얻어질 수도 있다.

[0142] 도 13a 및 도 13b에 도시된 구조들은 예들이며, 화소 레이아웃, 단면구조, EL 소자의 전극들의 적층 순서 등은 도 13a 및 도 13b에 도시된 것들 이외의 다양한 구조들을 구비할 수도 있는 것에 유의한다. 발광층에 대하여, 도면들에 도시된 유기 박막을 포함하는 소자 외에, 결정질 소자와 같은 다양한 소자들, 예를 들면 LED, 또는 무기 박막을 포함하는 소자가 채용될 수도 있다.

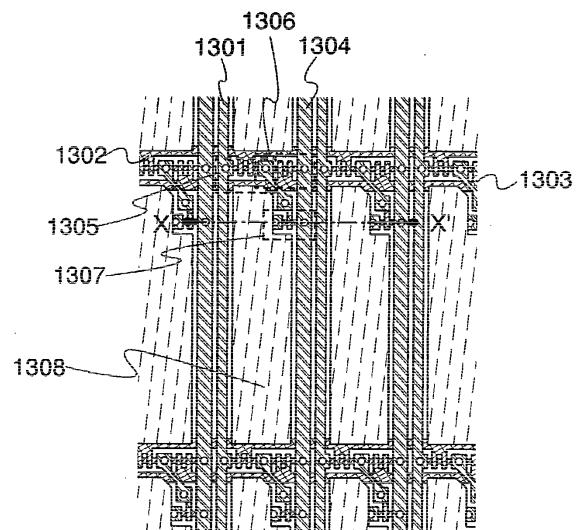

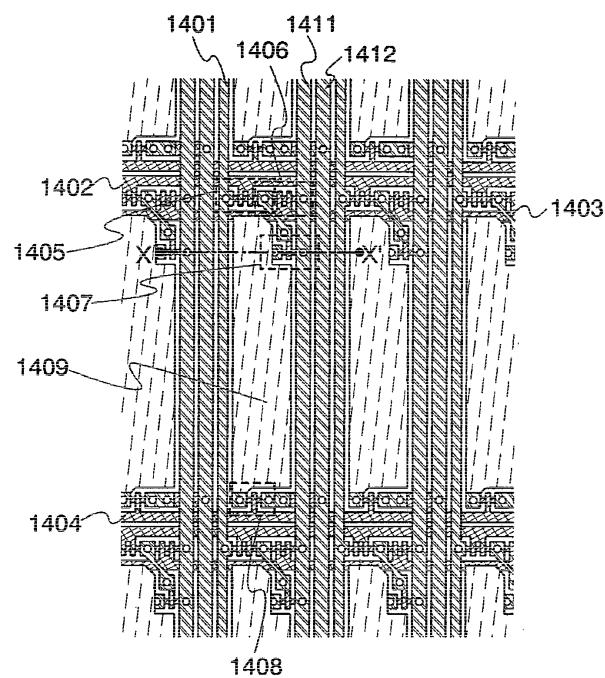

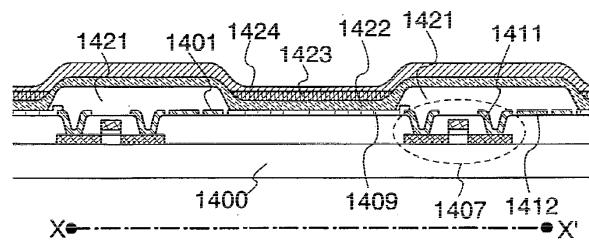

[0143] 다음에, 도 14a를 참조하여 4개의 TFT들을 포함하는 화소에 소자의 레이아웃 예에 대해 기술된다. 도 14b는 도 14a에 도시된 선 X-X'를 따라 취한 단면도이다.

[0144] 도 14a에 도시된 바와 같이, 발명의 화소는 기판(1400), 제1 배선(1401), 제2 배선(1402), 제3 배선(1403), 제4 배선(1404), 제1 TFT(1405), 제2 TFT(1406), 제3 TFT(1407), 제4 TFT(1408), 화소전극(1409), 제4 배선(1411), 제6 배선(1412), 격벽(1421), 유기 도전막(1422), 유기 박막(1423), 및 대향전극(1424)을 포함할 수 있다. 제1 배선(1401)은 소스 신호선으로서 기능하고, 제2 배선(1402)은 기입 게이트 신호선으로서 기능하고, 제3 배선(1403)은 소거 게이트 신호선으로서 기능하고, 제4 배선(1404)은 역 바이어스 공급 신호선으로서 기능하고, 제1 TFT(1405)는 스위칭 TFT로서 기능하고, 제2 TFT(1406)는 소거 TFT로서 기능하고, 제3 TFT(1407)은 구동 TFT로서 기능하고, 제4 TFT(1408)은 역 바이어스 공급 TFT로서 기능하고, 제5 배선(1411)은 전원선으로서 기능하고, 제6 배선(1412)은 역 바이어스 전원선으로서 기능하는 것이 바람직한 것에 유의한다.

[0145] 도 14a에 도시된 바와 같이, 제1 TFT(1405)의 게이트 전극은 제2 배선(1402)에 전기적으로 접속되며, 제1 TFT(1405)의 소스 및 드레인 전극들 중 다른 하나는 제1 배선(1401)에 전기적으로 접속되며, 이 제1 TFT의 소스 및 드레인 전극들 중 다른 하나는 제3 TFT(1407)의 게이트 전극에 전기적으로 접속되는 것이 바람직하다. 제1 TFT(1405)의 게이트 전극은 도 14a에 도시된 바와 같이 복수의 게이트 전극들을 포함할 수 있고, 이는 제1 TFT(1405)의 오프 상태에서 누설 전류를 감소시킬 수 있는 것에 유의한다.

[0146] 또한, 제2 TFT(1406)의 게이트 전극은 제3 배선(1403)에 전기적으로 접속되고, 제2 TFT(1406)의 소스 및 드레인 전극들 중 하나는 제5 배선(1411)에 전기적으로 접속되고, 이 제2 TFT의 소스 및 드레인 전극들 중 다른 하나는 제3 TFT(1407)의 게이트 전극에 전기적으로 접속되는 것에 바람직하다. 제2 TFT(1406)의 게이트 전극은 도 14a에 도시된 바와 같이 복수의 게이트 전극들을 포함할 수 있고, 이는 제2 TFT(1406)의 오프 상태에서 누설 전류를 감소시킬 수 있는 것에 유의한다.

[0147] 또한, 제3 TFT(1406)의 소스 및 드레인 전극들 중 하나는 제5 배선(1411)에 전기적으로 접속되고 이 제3 TFT의 소스 및 드레인 전극들 중 다른 하나는 화소 전극(1409)에 전기적으로 접속되는 것이 바람직하고, 이는 제3 TFT(1407)에 의해 화소전극(1409)에 흐르는 전류를 제어할 수 있다.

[0148] 또한, 제4 TFT(1408)의 게이트 전극은 제4 배선(1404)에 전기적으로 접속되고, 제4 TFT(1408)의 소스 및 드레인 전극들 중 하나는 제6 배선(1412)에 전기적으로 접속되고, 이 제4 TFT의 소스 및 드레인 전극들 중 다른 하나는 화소전극(1409)에 전기적으로 접속되는 것에 바람직하다. 결국, 화소전극(1409)의 전위는 제4 TFT(1408)에 의해 제어될 수 있고, 따라서, 역 바이어스 전압이 유기 도전막(1422) 및 유기 박막(1423)에 인가될 수 있다. 역 바이어스 전압은 유기 도전막(1422), 유기 박막(1423) 등을 포함하는 발광소자에 인가되며, 이는 발광소자의 신뢰성을 현저하게 향상시킬 수 있다.

[0149] 예를 들면, DC 전압(3.65V)으로 구동될 때 휘도의 반 감쇠(decay) 시간이 약 400시간인 발광소자가 AC 전압으로 구동되는 경우(순방향 바이어스:3.7V, 역 바이어스:1.7V, 듀티 비:50%, 및 AC 주파수:60Hz), 이의 휘도의 반 감

최 시간은 700 시간 이상인 것으로 알려져 있다.

- [0150] 유기 도전막(1422)은 화소전극(1409) 상에 형성될 수 있고, 이 위에 유기 박막(유기 복합층)(1423)이 형성될 수 있다. 대향 전극(1424)은 유기 박막(유기 복합층)(1423) 상에 형성될 수 있다. 대향 전극(1424)은 모든 화소들에 공통으로 접속되기 위해 형성될 수 있고 새도우 마스크 등을 사용하여 패터닝될 수도 있는 것에 유의한다.

- [0151] 유기 박막(유기 복합층)(1423)으로부터의 광은 방출되기 위해 화소전극(1409) 및 대향전극(1424) 중 하나를 통해 투과된다. 이때, 도 14b에서, 광이 화소 전극 측, 즉, TFT 등이 형성된 측으로 방출되는 경우, 화소전극(1409)은 광 투과 도전막으로 형성되는 것이 바람직하다. 광이 대향 전극 측으로 방출되는 경우에, 대향 전극(1424)은 광 투과 도전막으로 형성되는 것이 바람직하다.

- [0152] 또한, 컬러 디스플레이용 발광 장치로서, R, G, 또는 B의 각각의 광 방출 색을 갖는 EL 소자가 개별적으로 퍼착될 수도 있고, 또는 RGB의 광 방출은 컬러 필터를 통해 얻어질 수도 있다.

- [0153] 도 14a 및 도 14b에 도시된 구조들은 예들이며, 화소 레이아웃, 단면구조, EL 소자의 전극들의 적층 순서 등은 도 14a 및 도 14b에 도시된 것들 이외의 다양한 구조들을 구비할 수도 있는 것에 유의한다. 발광층에 대하여, 도면들에 도시된 유기 박막을 포함하는 소자 외에, 결정질 소자와 같은 다양한 소자들, 예를 들면 LED, 또는 무기 박막을 포함하는 소자가 채용될 수도 있다.

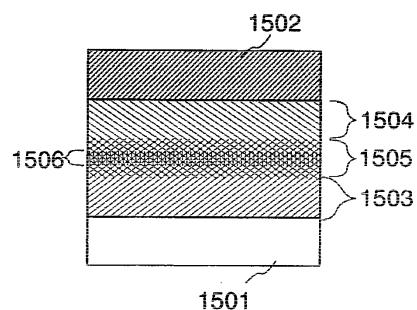

- [0154] 다음에, 발명에 적용될 수 있는 EL 소자의 구조에 대해 기술한다.

- [0155] 대신에 발명에 적용될 수 있는 EL 소자는 정공 주입재료, 정공 수송재료, 발광재료, 전자 수송재료, 및 전자 주입재료가 혼합된 층(혼합층)을 포함하는 구조(이하 혼합 접합형 EL소자), 및 명백하게 구별되는, 정공 주입재료로 형성된 정공 주입층, 정공 수송재료로 형성된 정공 수송층, 발광재료로 형성된 발광층, 전자 수송재료로 형성된 전자 수송층, 전자 주입재료로 형성된 전자 주입층의 적층구조를 구비할 수도 있다.

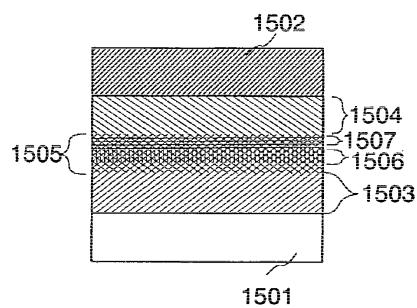

- [0156] 도 15a 내지 도 15e는 혼합 접합형 EL 소자의 구조들의 개략도들이다. 도 15a 내지 도 15e에서, 참조부호 1501은 EL 소자의 양극을 나타내며 1502는 EL 소자의 음극을 나타낸다. 양극(1501)과 음극(1502)간에 개재된 층은 EL 층에 대응한다.

- [0157] 도 15a에서, EL 층은 정공 수송재료로 형성된 정공 수송영역(1503) 및 전자 수송재료로 형성된 전자 수송영역(1504)을 포함할 수 있고, 여기서 정공 수송영역(1503)은 전자 수송영역(1504)보다는 양극 측에 더 가까우며, 정공 수송재료 및 전자 수송재료 둘 다를 포함하는 혼합영역(1505)은 정공 수송영역(1503)과 전자 수송영역(1504) 사이에 제공된다.

- [0158] 이때, 혼합영역(1505)에서 전자 수송재료의 농도가 증가하는 반면, 혼합영역(1505)에서 정공 수송재료의 농도는 양극(1501)에서 음극(1502)으로의 방향으로 감소하는 것이 특징일 수 있는 것에 유의한다.

- [0159] 위의 구조에서, 정공 수송재료로만으로 구성된 정공 수송영역(1503)은 존재하지 않을 수 있고, 각 기능성 재료의 농도의 비는 정공 수송재료 및 전자 수송재료 둘 다를 포함하는 혼합영역(1505)(즉, 농도 기울기를 갖는 구조)에서 변하는 것에 유의한다. 또한, 정공 수송재료로만으로 구성된 정공 수송영역(1503) 및 전자 수송재료로만으로 구성된 전자 수송영역이 존재하지 않고, 각 기능성 재료의 농도의 비가 정공 수송재료 및 전자 수송재료 둘 다를 포함하는 혼합영역(1505)에서 변하는 구조(즉, 농도 기울기를 갖는 구조)를 구비할 수도 있다. 농도의 비는 양극 또는 음극으로부터의 거리에 따라 변할 수 있다. 또한, 농도의 비는 연속적으로 변할 수도 있다. 농도 기울기는 자유롭게 설정될 수 있다.

- [0160] 발광재료가 첨가되는 영역(1506)은 혼합영역(1505)에 제공된다. EL 소자의 광 방출 색은 발광재료에 의해 제어될 수 있다. 또한, 캐리어가 발광재료에 의해 트랩될 수 있다. 발광재료에 대해서, 다양한 형광염료들 뿐만 아니라, 퀴놀린 골격을 포함하는 금속착물, 벤조옥사졸 골격을 포함하는 금속착물, 벤조티아졸 골격을 포함하는 금속착물, 등이 채용될 수 있다. EL 소자의 광 방출 색은 이를 발광재료들을 첨가함으로써 제어될 수 있다.

- [0161] 양극(1501)에 대해서, 정공을 효과적으로 주입하기 위해서 고 일함수를 갖는 전극재료가 채용되는 것이 바람직하다. 예를 들면, 주석이 도핑된 인듐 산화물(ITO), 아연이 도핑된 인듐 산화물(IZO), ZnO, SnO<sub>2</sub>, 및 In<sub>2</sub>O<sub>3</sub>와 같은 광 투과성 전극이 채용될 수도 있다. 투명성이 요구되지 않는다면, 양극(1501)은 불투명한 금속재료로 형성될 수도 있다.

- [0162] 정공 수송재료에 대해서, 방향족 아민기 등의 화합물이 채용될 수도 있다.

- [0163] 전자 수성재료에 대해서, 퀴놀린 유도체, 리간드로서 8-퀴놀리놀 또는 이의 유도체를 포함하는 금속착물(특히

- 트리스(8-퀴놀리노라토)알루미늄) 등이 채용될 수도 있다.

- [0164] 음극(1502)에 대해서, 전자를 효과적으로 주입하기 위해서 낮은 일함수를 갖는 전극재료가 채용되는 것이 바람직하다. 알루미늄, 인듐, 마그네슘, 은, 칼슘, 바륨, 및 리튬과 같은 금속이 단일 재료로서 채용될 수도 있다. 또한, 이들의 합금이, 위에 언급된 금속 및 다른 금속의 합금 외에도, 채용될 수 있다.

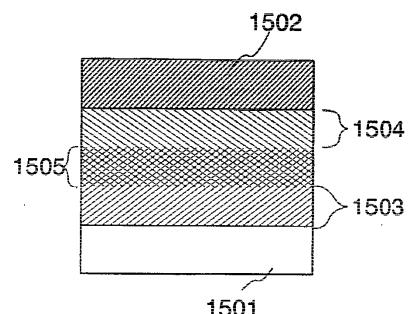

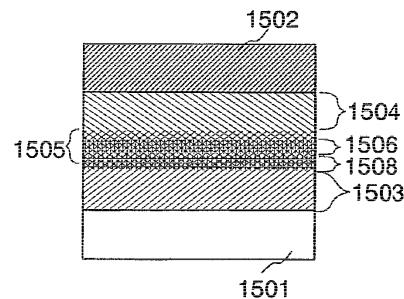

- [0165] 도 15b는 도 15a에 도시된 것 이외의 EL 소자의 구조의 개략도이다. 도 15a에 것들과 동일한 부분들은 동일 참조부호로 기술되고 이들의 설명은 여기에서는 생략되는 것에 유의한다.

- [0166] 도 15b에서, 발광재료가 첨가되는 영역은 포함되지 않는다. 그러나, 전자 수송영역(1504)에 첨가되는 재료에 대해서, 전자 수송특성 및 발광특성 둘 다를 포함하는 재료(전자-수송 발광재료), 예를 들면, 트리스(8-퀴놀리노라토)알루미늄이 채용될 수 있으며, 이것은 광 방출을 수행할 수 있다.

- [0167] 대안적으로, 정공 수송영역(1503)에 첨가되는 재료에 대해서, 정공 수송특성 및 발광특성 둘 다를 포함하는 재료(정공-수송 발광재료)가 채용될 수도 있다.

- [0168] 도 15c는 도 15a 및 도 15b에 구조들과는 다른 EL 소자의 구조의 개략도이다. 도 15a 및 도 15b에 것들과 동일한 부분들은 동일 참조부호로 기술되고 이들의 설명은 여기에서는 생략되는 것에 유의한다.

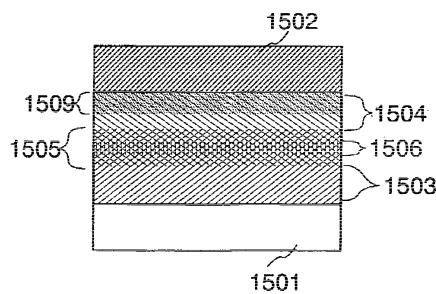

- [0169] 도 15c는 최고 점유 분자 궤도와 최저 점유 분자 궤도간의 에너지 차가 정공 수송재료의 차보다 더 넓은 정공 차단재료가 첨가되는 혼합영역(1505)을 포함하는 영역(1507)을 포함한다. 정공 차단재료가 첨가되는 영역(1507)은 혼합영역(1505)에서 발광재료가 첨가되는 영역(1506)보다는 음극(1502) 측에 놓여지고, 그럼으로써 캐리어의 재결합율 및 광 방출효율이 증가될 수 있다. 위에 기술된 바와 같이 정공 차단재료가 첨가되는 영역(1507)이 제공된 구조는 트리플렛 여기에 의한 광 방출(인광)을 이용하는 EL 소자에서 특히 효과적이다.

- [0170] 도 15d는 도 15a, 도 15b, 도 15c에 구조들과는 다른 EL 소자의 구조의 개략도이다. 도 15a 및 도 15b에 것들과 동일한 부분들은 동일 참조부호로 기술되고 이들의 설명은 여기에서는 생략되는 것에 유의한다.

- [0171] 도 15d는 최고 점유 분자 궤도와 최저 점유 분자 궤도간의 에너지 차가 전자 수송재료의 차보다 더 넓은 전자 차단재료가 첨가되는 혼합영역(1505)을 포함하는 영역(1508)을 포함한다. 전자 차단재료가 첨가되는 영역(1508)은 혼합영역(1505)에서 발광재료가 첨가되는 영역(1506)보다는 양극(1501) 측에 놓여지고, 그럼으로써 캐리어의 재결합율 및 광 방출효율이 증가될 수 있다. 위에 기술된 바와 같이 전자 차단재료가 첨가되는 영역(1508)이 제공된 구조는 트리플렛 여기에 의한 광 방출(인광)을 이용하는 EL 소자에서 특히 효과적이다.

- [0172] 도 15e는 도 15a 내지 도 15d에 구조들과는 다른 혼합 접합형 EL 소자의 구조의 개략도이다. 도 15e는 EL 소자의 전극과 접촉된 EL 층의 부분에 금속재료가 첨가되는 영역(1509)을 포함하는 구조의 예를 도시한 것이다. 도 15e에서, 도 15a 내지 도 15d에 것들과 동일한 부분들은 동일 참조부호로 기술되고 이들의 설명은 여기에서는 생략된다. 도 15e에 도시된 구조는 예를 들면 음극(1502)으로서 MgAg(Mg-Ag 합금)을 채용할 수 있으며 전자 수송재료가 첨가되는 영역(1504)의 음극(1502)과 접촉되는 영역에서 Al(알루미늄)이 첨가되는 영역(1509)을 포함할 수 있다. 위에 언급된 구조에 의해서, 음극의 산화가 방지될 수도 있고, 음극으로부터 전자의 주입 효율이 증가될 수 있다. 그러므로, 혼합 접합형 EL 소자의 수명은 더 길 수 있고 구동전압은 낮아질 수 있다.

- [0173] 위에 기술된 혼합 접합형 EL 소자를 제공하는 방법은 공-증기증착(co-vapor deposition) 등일 수도 있다.

- [0174] 도 15a 내지 도 15e에 도시된 것들과 같은 혼합 접합형 EL 소자는 충돌간 명확한 계면을 가질 필요는 없으며, 전하 축적이 감소될 수 있다. 따라서, EL 소자의 수명은 확장될 수 있고, 구동전압은 낮아질 수 있다.

- [0175] 도 15a 내지 도 15e에 도시된 구조들은 서로 조합하여 자유롭게 구현될 수 있음을 유의한다.

- [0176] 혼합 접합형 EL 소자의 구조는 위에 기술된 것들로 제한되지 않음에 유의한다. 공지의 구조가 자유롭게 채용될 수도 있다.

- [0177] EL 소자의 EL 층을 형성하는 유기 재료는 저 분자 재료, 고 분자 재료, 또는 이들 둘 다인 재료일 수 있음을 유의한다. 유기 복합 재료로서 저 분자 재료가 채용되는 경우에, 증기 증착에 의해 막이 형성될 수 있다. 한편, 고 분자 재료가 EL 층으로서 채용되는 경우에, 고 분자 재료가 용매에 용해되고 스펀 코팅 방법 또는 잉크젯 방법에 의해 막이 형성될 수 있다.

- [0178] 또한, EL 층은 중간 분자 재료로 형성될 수 있다. 이 명세서에서, 중간 분자 유기 발광재료는 승화 특성은 없고 약 20도 이하의 중합도를 갖는 유기 발광재료를 나타낸다. 중간 분자 재료가 EL 층으로서 채용되는 경우에, 막

- 은 잉크젯 방법 등에 의해 형성될 수 있다.

- [0179] 저 분자 재료, 고 분자 재료 및 중간 분자 재료는 조합하여 사용될 수도 있는 것에 유의한다.

- [0180] 또한, EL 소자는 싱글렛 여기의 광 방출(형광) 또는 트리플렛 여기의 광 방출(인광)을 이용할 수 있다.

- [0181] 다음에, 도면들을 참조하여 발명이 적용될 수 있는 표시 장치를 제조하기 위한 증기증착 장치를 기술한다.

- [0182] 발명이 적용될 수 있는 표시 장치는 EL 층을 형성함으로써 제조될 수 있다. EL 층은 적어도 일부에서 전장발광을 나타내는 재료를 포함하여 형성된다. EL 층은 서로 다른 기능들을 갖는 복수의 층들로 형성될 수 있다. 이 경우, EL 층은 정공 주입 수송층, 발광층, 전자 주입 수송층, 등이라 하는 서로 다른 기능들을 갖는 층들의 조합으로 형성될 수 있다.

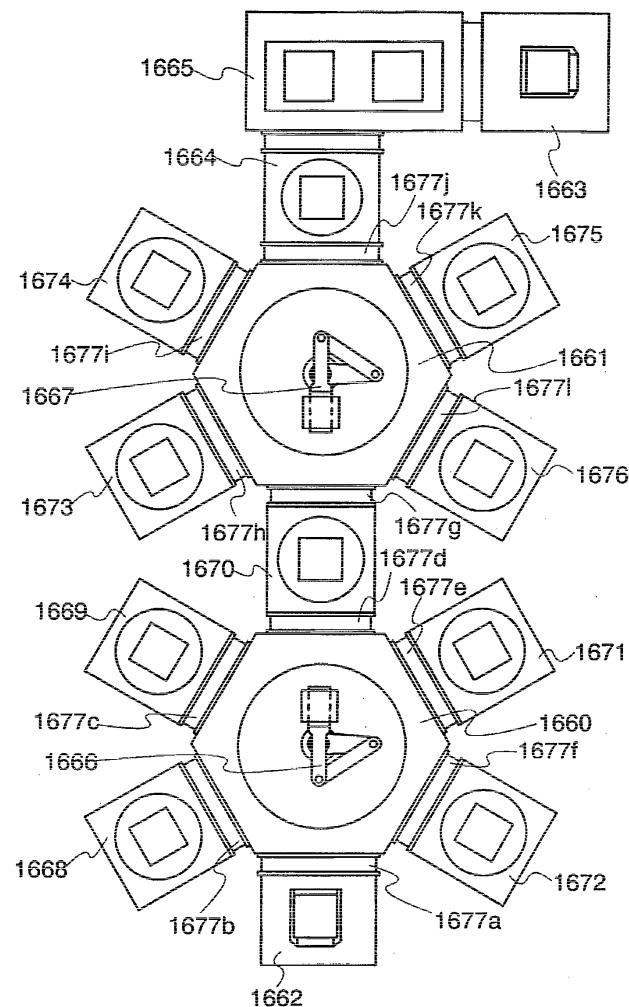

- [0183] 도 16은 트랜지스터가 형성되는 소자 기판 상에 EL 층을 형성하기 위한 증기증착 장치의 구조를 도시한 것이다. 증기 증착 장치에서, 이송 챔버들(1660, 1661)이 복수의 처리 챔버들에 접속된다. 각 처리 챔버는 기판을 공급하기 위한 로딩 챔버(1662), 기판을 모으기 위한 언로딩 챔버(1663), 열 처리 챔버(1668), 플라즈마 처리 챔버(1672), EL 재료를 증착하기 위한 증착 처리 챔버들(1669 내지 1671, 1673 내지 1675), 알루미늄으로 형성된 도전막을 형성하거나 주성분으로 알루미늄을 EL 소자의 한 전극으로서 사용하기 위한 증착 처리 챔버(1676)를 포함한다. 또한, 게이트 밸브들(1677a 내지 16771)은 이송 챔버들과 각각의 처리 챔버 사이에 제공되고, 그럼으로써 각 처리 챔버에 압력을 독립적으로 제어될 수 있으며, 처리 챔버들간에 교차 오염이 방지된다.

- [0184] 로딩 챔버(1662)로부터 이송 챔버(1660)에 도입된 기판은 암 형 이송유닛(1666)에 의해 소정의 처리 챔버에 회전적으로 전송된다. 또한, 기판은 이송유닛(1666)에 의해 어떤 처리 챔버로부터 또 다른 처리 챔버로 이송된다. 이송 챔버들(1660, 1661)은 증착 처리 챔버(1670)에 의해 접속되고, 여기서 기판은 전송유닛(1666) 및 이송유닛(1667)에 의해 운반되고 수용된다.

- [0185] 이송 챔버들(1660, 1661)에 접속된 각 처리 챔버는 감소된 압력 하에 유지된다. 그러므로, 증기증착 장치에서, 기판의 막 형성 공정은 투의 공기에 직접 접촉함이 없이 연속적으로 수행된다. EL 층을 형성하기 위해 완성된 표시 패널은 습기 등에 기인하여 열화될 수 있으며, 그러므로, 이 증기증착 장치에서, 공기에 노출 전에 질을 유지하기 위해 시일링 처리를 수행하는 시일링 처리 챔버(1665)는 이송 챔버(1661)에 접속된다. 시일링 처리 챔버(1665)가 대기압 또는 이와 유사한 감압 하에 있을 때, 이송 챔버(1661)와 시일링 처리 챔버(1665) 사이에 중간 챔버(1664)가 제공된다. 중간 챔버(1664)는 기판을 운반하고 수용하며 챔버 내 압력을 완충하기 위해 제공된다.

- [0186] 배기유닛은 챔버 내 감소된 압력을 유지하기 위해서 로딩 챔버, 언로딩 챔버, 및 증착처리 챔버에 제공된다. 배기 유닛에 대해서, 건식 펌프, 터보-분자 펌프, 확산 펌프와 같은 다양한 진공펌프들이 채용될 수도 있다.

- [0187] 도 16의 증기증착 장치에서, 이송 챔버들(1660, 1661) 및 이의 구조에 접속되는 처리 챔버들의 수는 적합하게 EL 소자의 적층 구조에 따라 서로 조합될 수 있다. 조합의 예가 이하 기술된다.

- [0188] 열 처리 챔버(1668)는 하측 전극, 및 절연 격벽, 등이 주로 형성되는 기판을 가열함으로써 탈기(degasification)를 수행한다. 플라즈마 처리 챔버(1672)에서, 하측 전극의 표면은 불활성 기체 또는 산소 플라즈마로 처리된다. 플라즈마 처리는 표면을 세정하고, 표면상태를 안정화하고, 표면의 물리적 또는 화학적 상태(예를 들면, 일함수 등)를 안정화하기 위해 수행된다.

- [0189] 증착 처리 챔버(1669)는 EL 소자의 한 전극에 접속되는 전극 베퍼층을 형성하기 위한 처리 챔버이다. 전극 베퍼층은 캐리어 주입 특성(정공 주입 또는 전자 주입)을 구비하며 EL 소자의 단락회로 또는 흑점 결함의 발생을 제어한다. 통상적으로, 전극 베퍼층은 30 내지 300nm의 두께를 갖기 위해서, 저항률이  $5 \times 10^4$  내지  $1 \times 10^6 \Omega\text{cm}$  인 유기 무기 혼성 재료로 형성된다. 또한, 증착 처리 챔버(1671)는 정공 수송층을 형성하기 위한 처리 챔버이다.

- [0190] EL 소자에 발광층은 단색 광을 방출하는 경우와 백색 광을 방출하는 경우간에 상이한 구조를 갖는다. 증착 처리 챔버는 이에 따라 증기증착 장치에 제공되는 것이 바람직하다. 예를 들면, 표시 패널에 다른 광 방출 색을 갖는 3종류의 EL 소자들을 형성하는 경우에, 각 광 방출 색에 대응하는 발광층을 형성할 것이 요구된다. 이 경우, 제1 발광층을 형성하기 위해 증착 처리 챔버(1670)가 사용될 수 있고, 제2 발광층을 형성하기 위해 증착 처리 챔버(1673)가 사용될 수 있고, 제3 발광층을 형성하기 위해 증착 처리 챔버(1674)가 사용될 수 있다. 각 발광층에 대해 증착 처리 챔버들을 분리함으로써, 서로 다른 발광재료들에 기인한 교차 오염이 방지될 수 있고, 증착 처

리의 수율이 향상될 수 있다.

- [0191] 또한, 서로 다른 광 방출 색들을 갖는 3종류의 EL 소자들이 증착 처리 챔버들(1670, 1673, 1674) 각각에 순차로 증착될 수 있다. 이 경우, 증착될 영역에 따라 세도우 마스크를 이동시킴으로써 증착이 수행된다.

- [0192] 백색광을 방출하는 EL 소자를 형성하는 경우에, EL 소자는 서로 다른 광 방출 색들의 발광층들을 수직으로 적층 시킴으로써 형성된다. 이 경우에, 소자 기판은 각 발광층을 위한 막을 형성하기 위해서 순차로 증착 처리 챔버들을 통해 이송될 수 있다. 또한, 서로 다른 발광층들이 동일 증착 처리 챔버에서 연속적으로 형성될 수 있다.

- [0193] 증착 처리 챔버(1676)에서, 전극이 EL층 상에 형성된다. 전극은 전자 빔 증기 증착 또는 스퍼터링 방법에 의해 형성될 수 있으나, 저항 가열 증기 증착이 채용되는 것이 바람직하다.

- [0194] 전극까지 형성되는 소자 기판은 중간 챔버(1664)를 통해 시일링 처리 챔버(1665)에 이송된다. 시일링 처리 챔버(1665)는 헬륨, 아르곤, 네온, 또는 질소와 같은 불활성 가스로 채워지며, 시일링 기판은 소자 기판의 EL 층이 분위기 하에 형성되는 측에 부착되고 시일링된다. 시일링된 상태에서, 소자 기판과 시일링 기판간에 공간은 불활성 가스 또는 수지 물질로 채워질 수 있다. 시일링 처리 챔버(1665)에는 실란트를 인출하는 디스펜서, 소자 기판에 면하게 시일링 기판을 고정시키는 암 및 고정 스테이지와 같은 기계요소, 챔버를 수지 물질로 채우는 디스펜서 또는 스픈 코터가 제공된다.

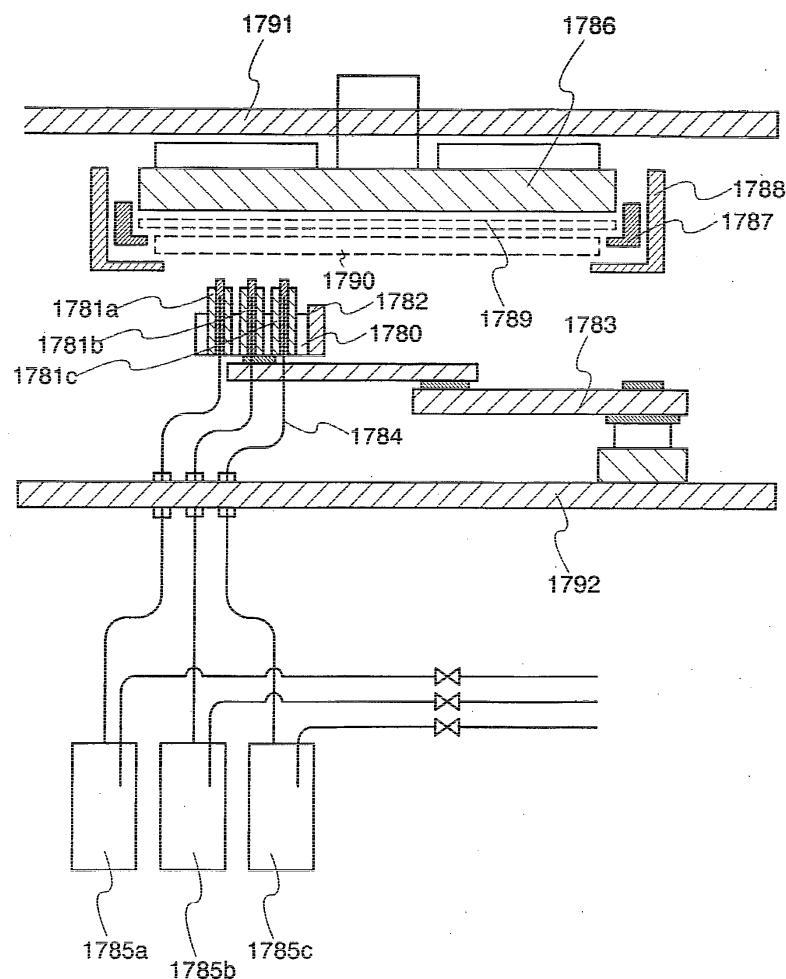

- [0195] 도 17은 증착 처리 챔버의 내부 구조를 도시한 것이다. 감소된 압력이 증착 처리 챔버에 유지된다. 도 17에서, 상측 판(1791)과 하측 판(1792) 사이에 개재된 내측이 내측 챔버이며, 이 챔버는 감소된 압력 하에 유지된다.

- [0196] 처리 챔버에 하나 또는 복수의 증발원들이 제공된다. 이것은 서로 다른 조성들을 갖는 복수의 층들을 형성하는 경우 또는 서로 다른 재료들을 공-증발(co-evaporating)하는 경우에 복수의 증발원들을 제공하는 것이 바람직하기 때문이다. 도 17에서, 증발원들(1781a, 1781b, 1781c)이 증발원 홀더(1780)에 장착된다. 증발원 홀더(1780)는 다관절 암(1783)에 의해 유지된다. 다관절 암(1783)은 관절을 뻗음으로써 이의 이동범위 내에서 증발원 홀더(1780)를 자유롭게 이동시킬 수 있다. 또한, 증발원 홀더(1780)에는 증발원들(1781a 내지 1781c)과 기판(1789)간 거리를 모니터하기 위해 거리 센서(1782)가 제공될 수 있고, 따라서 증착을 위한 최적의 거리가 제어될 수 있다. 이 경우, 상측 및 하측 방향(Z 방향)으로도 변위되는 다관절 암이 다관절 암(1783)으로서 채용될 수도 있다.

- [0197] 기판(1789)은 기판 스테이지(1786) 및 기판 척(1787)에 의해 고정된다. 기판 스테이지(1786)는 기판(1789)이 가열될 수 있도록 히터가 탑재되는 구조를 구비할 수 있다. 기판(1789)은 기판 스테이지(1786)에 고정되며 기판 척(1787)을 조이고 느슨하게 함으로써 반입 반출된다. 증착시에, 증착 플랫폼에 대응하여 개구를 포함하는 세도우 마스크(1790)가 필요시 채용될 수도 있다. 이 경우, 기판(1789)과 증발원들(1781a 내지 1781c) 사이에 세도우 마스크(1790)가 제공된다. 세도우 마스크(1790)는 마스크 척(1788)에 의해 밀접하여 접촉하거나 어떤 간격으로 기판(1789)에 고정된다. 세도우 마스크(1790)의 정렬이 요구될 때, 처리 챔버에 카메라를 배치하고 마스크 척(1788)에 X-Y-Θ 방향으로 약간 이동하는 위치설정 유닛을 제공함으로써 정렬이 수행된다.

- [0198] 증발원들(1781a 내지 1781c)은 증발원들에 증발물질을 연속적으로 공급하는 증발물질 공급유닛을 포함한다. 증발물질 공급유닛은 증발원들(1781a 내지 1781c)로부터 떨어져 배치되는 증발물질 공급원들(1785a, 1785b, 1785c), 및 이들간을 접속하는 물질 공급관(1784)을 포함한다. 통상적으로, 물질 공급원들(1785a 내지 1785c)은 증발원들(1781a 내지 1781c)에 대응하여 제공된다. 도 17에서, 물질 공급원(1785a)은 증발원(1781a)에 대응한다. 동일하게 물질공급원(1785b) 및 증발원(1781b), 물질공급원(1785c) 및 증발원(1781c)에 적용된다.

- [0199] 증발물질을 공급하기 위한 방법으로서, 기류 이송 방법, 에어로졸 방법, 등이 적용될 수 있다. 기류 이송 방법에 의해서, 증발물질의 무형의 분말이 기류로 이송되며, 이를 위해서 불활성 가스 등이 증발원들(1781a 내지 1781c)에 이송하기 위해서 사용된다. 에어로졸 방법에 의해서, 기상증착은, 증발물질이 분무기에 의해 에어로졸화된 용매에 용해 또는 분해되고 에오로졸 내 용매가 증감되는 재료액을 이송시킴으로써 수행된다. 이 경우, 증발원들(1781a 내지 1781c)은 가열유닛을 구비하고 이에 이송된 증발물질을 증발시킴으로써 기판(1789) 상에 막을 형성한다. 도 17에서, 물질 공급관(1784)은 유연하게 구부러질 수 있고 감소된 압력 하에서도 변형되기 않을 만큼 충분한 강성을 갖는 얇은 판으로 형성된다.

- [0200] 기류 이송 방법 및 에어로졸 방법의 경우에, 증기증착은 증착 처리 챔버에서 대기압 또는 이보다 낮은 압력 하에서 수행될 수 있고, 바람직하게는 133 내지 13300Pa의 감소된 압력 하에서 수행된다. 증착 처리 챔버 내 압력은 증착 처리 챔버에서 헬륨, 아르곤, 네온, 크립톤, 크세논, 또는 질소와 같은 불활성 기체를 채우고, 기체를 공급함으로써(아울러 동시에 기체를 배기함으로써) 조정될 수 있다. 또한, 산화막이 형성되는 증착 처리 챔버에

산소 또는 이산화질소와 같은 기체를 도입함으로써 산화 분위기가 형성될 수 있다. 또한, 유기 재료가 증착되는 증착 처리 챔버에 수소와 같은 기체를 도입함으로써 감압 분위기가 형성될 수도 있다.

[0201] 증발 재료를 공급하기 위한 또 다른 방법에 대해서, 재료 공급관(1784)에 스크류를 제공함으로써 증발재료가 연속적으로 증발원 쪽으로 넣어지는 구조가 채용될 수도 있다.

[0202] 도 16의 기상 증착 장치를 사용함으로써, 대형 표시 패널의 경우에도 고 균일성으로 막이 연속적으로 형성될 수 있다. 또한, 증발재료가 증발원으로부터 끊길 때마다 증발원에 증발재료를 공급할 것이 요구되지 않으며, 따라서 수율이 향상될 수 있다.

[0203] 이 실시형태는 다른 실시형태들과 조합하여 자유롭게 구현될 수 있는 것에 유의한다.

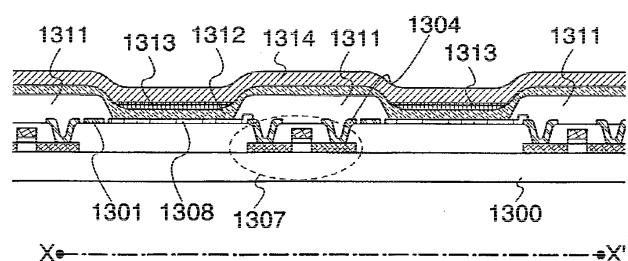

[0204] [실시형태 5]

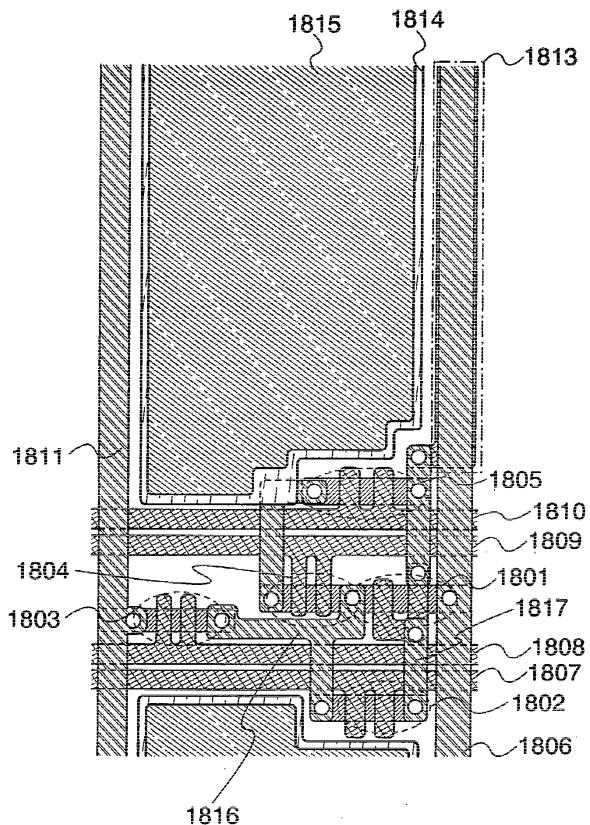

[0205] 도 18은 발명이 적용될 수 있는 화소의 레이아웃 예를 도시한 것이다.

[0206] 도 18에 도시된 바와 같이, 발명의 화소는 제1 TFT(1801), 제2 TFT(1802), 제3 TFT(1803), 제4 TFT(1804), 제5 TFT(1805), 제1 배선(1806), 제2 배선(1807), 제3 배선(1808), 제4 배선(1809), 제5 배선(1810), 제6 배선(1811), 용량소자(1813), 화소전극(1814), 격벽 개구(1815), 격벽 개구(1815)에 제공된 발광소자, 전극(1816) 및 전극(1817)을 포함할 수 있다. 제1 TFT(1801)은 구동 TFT로서 채용되는 것이 바람직하며, 제2 TFT(1802), 제3 TFT(1803), 제4 TFT(1804) 및 제5 TFT(1805)는 스위칭 TFT들로서 채용되는 것이 바람직한 것에 유의한다. 또한, 제1 배선(1806)은 전원선으로서 채용되는 것이 바람직하다. 제2 배선(1807), 제3 배선(1808), 제4 배선(1809) 및 제5 배선(1810)은 제2 TFT(1802), 제3 TFT(1803), 제4 TFT(1804), 및 제5 TFT(1805)을 턴 온 또는 오프하기 위한 신호선으로서 채용되는 것이 바람직하다. 제6 배선(1811)은 소스 신호선으로서 채용되는 것이 바람직하다.

[0207] 도 18에 도시된 바와 같이, 제1 TFT(1801)의 게이트 전극은 전극(1817)에 전기적으로 접속될 수 있고, 제1 TFT(1801)의 소스 및 드레인 전극들 중 하나는 제1 배선(1806)에 전기적으로 접속될 수 있고, 제1 TFT(1801)의 소스 및 드레인 전극들 중 다른 하나는 전극(1816)에 전기적으로 접속될 수 있다. 제1 TFT(1801)은 도 18에 도시된 바와 같이 복수의 채널 영역들을 갖는 구조로 형성되는 것이 바람직하며, 이것은 제1 TFT(1801)이 오프 될 때 누설전류에 의해 발광소자의 광 방출을 방지할 수 있는 것에 유의한다.

[0208] 또한, 제2 TFT(1802)의 게이트 전극은 제2 배선(1807)에 전기적으로 접속될 수 있고, 제2 TFT(1802)의 소스 및 드레인 전극들 중 하나는 전극(1816)에 전기적으로 접속될 수 있고, 제2 TFT(1802)의 소스 및 드레인 전극들 중 다른 하나는 전극(1817)에 전기적으로 접속될 수 있다. 제2 TFT(1802)는 도 18에 도시된 바와 같이 복수의 채널 영역들을 갖는 구조로 형성되는 것이 바람직하며, 이것은 제2 TFT(1802)이 오프 될 때 용량소자(1813)에 저장된 전하가 누설전류에 의해 누설되는 것을 방지할 수 있는 것에 유의한다.

[0209] 또한, 제3 TFT(1803)의 게이트 전극은 제3 배선(1808)에 전기적으로 접속될 수 있고, 제3 TFT(1803)의 소스 및 드레인 전극들 중 하나는 제6 배선(1811)에 전기적으로 접속될 수 있고, 제3 TFT(1803)의 소스 및 드레인 전극들 중 다른 하나는 전극(1816)에 전기적으로 접속될 수 있다. 제3 TFT(1803)는 도 18에 도시된 바와 같이 복수의 채널 영역들을 갖는 구조로 형성되는 것이 바람직하며, 이것은 제3 TFT(1803)이 오프 될 때 발광소자에 흐르는 전류가 누설전류에 의해 변하는 것을 방지할 수 있는 것에 유의한다.

[0210] 또한, 제4 TFT(1804)의 게이트 전극은 제4 배선(1809)에 전기적으로 접속될 수 있고, 제4 TFT(1804)의 소스 및 드레인 전극들 중 하나는 화소전극(1814)에 전기적으로 접속될 수 있고, 제4 TFT(1804)의 소스 및 드레인 전극들 중 다른 하나는 전극(1816)에 전기적으로 접속될 수 있다. 제4 TFT(1804)는 도 18에 도시된 바와 같이 복수의 채널 영역들을 갖는 구조로 형성되는 것이 바람직하며, 이것은 제4 TFT(1804)이 오프 될 때 누설전류에 의해 발광소자에 공급되는 전류에 의한 발광소자의 광 방출을 방지할 수 있는 것에 유의한다.

[0211] 또한, 제5 TFT(1805)의 게이트 전극은 제5 배선(1810)에 전기적으로 접속될 수 있고, 제5 TFT(1805)의 소스 및 드레인 전극들 중 하나는 화소전극(1814)에 전기적으로 접속될 수 있고, 제5 TFT(1805)의 소스 및 드레인 전극들 중 다른 하나는 전극(1817)에 전기적으로 접속될 수 있다. 제5 TFT(1805)는 도 18에 도시된 바와 같이 복수의 채널 영역들을 갖는 구조로 형성되는 것이 바람직하며, 이것은 제5 TFT(1805)이 오프될 때 용량소자(1813)에 저장된 전하가 누설전류에 의해 누설되는 것을 방지할 수 있는 것에 유의한다.

[0212] 복수의 TFT들이 전류흐름의 방향이 도 18에 도시된 방향과 거의 동일한 구조를 구비하는 것이 바람직한 것에 유의한다. 여기에서, 전류흐름의 방향은 수직방향 및 수평방향과 같은 각을 의미하며, 전류흐름의 바이어스에 의존하지 않는다. 즉, 수직방향은 전류가 우에서 좌로 흐르는 경우와 전류가 좌에서 우로 흐르는 경우 둘 다를 포함한다. 위에 기술된 바와 같이, 전류의 방향이 복수의 TFT들과 거의 동일한 구조에 의해, TFT 특징들은 균일할 수 있고, 표시 장치의 회도 변화들이 감소될 수 있다.

[0213] 화소전극(1814)은 유기 도전막을 포함할 수 있고 유기 박막(유기 복합층)을 더 포함할 수 있는 것에 유의한다. 대향 전극이 유기 박막(유기 복합층)에 제공될 수도 있다. 또한, 대향전극은 모든 화소들에 공통으로 접속되기 위해 형성될 수 있고 새도우 마스크 등을 사용하여 패터닝될 수도 있다.

[0214] 또한, 컬러 디스플레이용 발광 장치로서, R, G, 또는 B의 각각의 광 방출 색을 갖는 EL 소자가 개별적으로 피착될 수도 있고, 또는 RGB의 광 방출은 컬러 필터를 통해 얻어질 수도 있다.

[0215] 도 18에 도시된 구조는 단지 예들이며, 화소 레이아웃, 단면구조, EL 소자의 전극들의 적층 순서 등은 도 18에 도시된 것들 이외의 다양한 구조들을 구비할 수도 있는 것에 유의한다. 발광층에 대하여, 도면들에 도시된 유기 박막을 포함하는 소자 외에, 결정질 소자와 같은 다양한 소자들, 예를 들면 LED, 또는 무기 박막을 포함하는 소자가 채용될 수도 있다.

#### [0216] [실시형태 6]

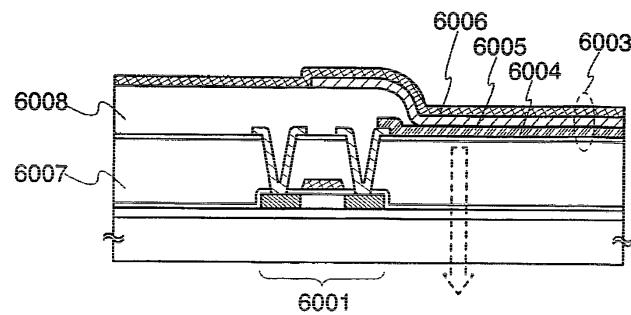

[0217] 이 실시형태에서, 도 10a 내지 도 10c를 참조하여 구동 트랜지스터로서 p채널형 박막 트랜지스터(TFT)가 채용되는 경우에 화소 회로의 단면 구조에 대해 기술한다. 이 실시형태에서, EL 소자의 한 전극은 제1 전극이라 하고 이의 다른 전극은 제2 전극이라 하는 것에 유의한다.

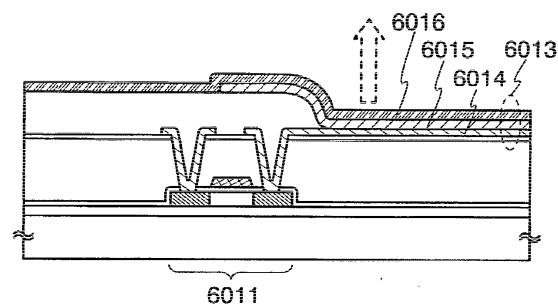

[0218] 도 10a는 EL 소자(6003)로부터 방출되는 광이 제1 전극(6004) 측으로부터 추출되는 경우에 화소 회로의 단면도를 도시한 것이다. 도 10a에서, EL 소자(6003)의 제1 전극(6004)은 TFT(6001)에 전기적으로 접속된다. TFT(6001)은 p채널형 트랜지스터이며, 그러므로 제1 전극(6004)은 양극이다.

[0219] TFT(6001)은 결정질 반도체막 또는 비정질 반도체막을 포함하는 공자의 구조를 구비할 수 있으며, 소스 전극, 드레인 전극, 및 게이트 전극을 포함한다. TFT(6001)는 중간 절연막(6007)으로 피복되고, 이 위에 개구를 포함하는 격벽(6008)이 형성된다. 격벽(6008)의 개구에서 소스 및 드레인 전극들 중 하나에 접속되는 제1 전극(6004)은 부분적으로 노출되고, 제1 전극(6004), 전장발광층(6005), 및 제2 전극(6006)은 개구 위에 이 순서로 적층된다.

[0220] 중간 절연막(6007)은 유기재료 또는 무기재료를 사용하여 형성될 수 있고, 단일층 구조 또는 적층 구조를 구비할 수 있다. 무기재료에 대해서, 산화실리콘 또는 질화실리콘이 채용될 수 있다. 유기재료에 대해서, 폴리아미드, 아크릴, 실록산, 또는 폴리실라잔이 채용될 수도 있다. 실록산은 실리콘(Si) 및 산소(O)의 본드에 의해 형성되는 골격구조를 갖는 것에 유의한다. 치환분으로서, 적어도 수소를 내포하는 유기기(organic group)(예를 들면, 알킬기 및 방향족 탄화소수)가 사용된다. 플루오로기가 치환분으로서 채용될 수도 있다. 또한, 적어도 수소를 내포하는 유기기 및 폴루오로기가 치환분으로서 채용될 수도 있다. 폴리실라잔은 출발재료로서 실리콘(Si) 및 질소(N)의 본드를 갖는 폴리머 재료로 형성된다. 또한, 저 유전상수 재료(저-k 재료)라 하는 재료가 중간 절연막(6007)으로서 채용될 수도 있다.

[0221] 격벽(6008)은 중간 절연막(6007) 뿐만 아니라 유기 재료 또는 무기 재료를 사용하여 형성될 수 있다. 감광성 유기재료가 격벽(6008)으로서 채용되는 경우에, 제1 전극(6004) 상에 개구의 측벽은 연속한 곡률을 갖는 경사된 표면을 갖는다. 이러한 형상은 전장발광층(6005)이 파손되지 않는 것, 및 제1 전극(6004)과 제2 전극(6006)간에 단락회로를 방지할 수 있다.

[0222] 제1 전극(6004)은 양극에 적합한 재료로 형성된다. 양극에 적합한 재료는 금속, 합금, 전기적 도전성의 화합물, 및 낮은 일함수를 갖는 이들의 조성물을 포함한다. 제1 전극(6004) 측으로부터 광을 추출하기 위해서, 제1 전극(6004)은 광 투과성 재료로 형성되거나 광을 투과시키기에 충분한 두께를 갖는다. 구체적으로, 인듐 주석 산화물(ITO), 아연 산화물(ZnO), 인듐 아연 산화물(IZO), 또는 갈륨이 도핑된 아연 산화물(GZO)와 같은 광 투과 도전성 재료가 채용될 수도 있다. 또한, 산화실리콘을 함유하는 인듐 주석 산화물(이하 ITSO라 함), 아연 산화물(ZnO)이 혼합된 ITO, 및 아연 산화물(ZnO)이 혼합된 ITSO가 채용될 수도 있다. 비-광 투과 도전성 재료로서, 예를 들면, 주성분으로서 알루미늄을 포함하는 막 및 질화티탄막의 적층구조, 질화티탄막, 주성분으로서 알루미늄

을 포함하는 막, 질화티탄막의 3층 구조 등뿐만 아니라, TiN, ZrN, Ti, W, Ni, Pt, Ci, Ag, Al, 등 중 하나 이상에서 선택된 단일층 막이 채용될 수도 있다. 그러나, 비-광투과 도전성 재료를 사용하는 경우에, 제1 전극(6004)은 발광하기에 충분한 두께를 갖게 형성된다(대략 바람직하게 5nm 내지 30nm).

[0223] 제2 전극(6006)은 음극에 적합한 재료로 형성된다. 음극에 적합한 재료는 금속, 합금, 전기적 도전성 복합물, 및 낮은 일함수를 갖는 이들의 조성물을 포함한다. 제2 전극(6004) 측으로부터만 광을 추출하기 위해서, 광을 반사 또는 차폐하는 재료가 채용될 수도 있다. 구체적으로, Li, Cs, Mg, Ca 및 Sr과 같은 금속, 이들의 합금(Mg:Ag, Al:Li, Mg:In, 등), 이들의 복합물(플루오르화 칼슘 및 질화칼슘), Yb 및 Er과 같은 희토류 금속, 등이 채용될 수도 있다.

[0224] 전장발광층(6005)은 단일층 또는 복수층들로 형성된다. 전장발광층(6005)이 복수의 층들로 형성되는 경우에, 복수의 층들은 정공 주입층, 정공 수송층, 발광층, 전자 수송층, 전자 주입층, 등으로 분할된다. 제1 전극(6004)이 양극이기 때문에, 정공 주입층, 정공 수송층, 발광층, 전자 수송층, 및 전자 주입층은 이 순서로 적층된다. 층들간에 경계는 명확할 필요는 없고 각 층을 형성하는 재료의 부분이 혼합되는 경우가 있을 수 있고 이들의 경계가 불명료할 수 있는 것에 유의한다. 각 층은 유기재료 또는 무기재료로 형성될 수 있다. 유기재료에 대해서, 고 분자 재료, 중간 분자 재료, 및 저 분자 재료가 채용될 수도 있다. 중간 분자 재료는 구조 단위(중합도)의 반복 수가 대략 2 내지 20인 저 폴리머에 대응하는 것에 유의한다. 정공 주입층과 정공 수송층 간에 구별은 항상 명확하지 않으며, 이것은 정공 수송특성(정공 이동도)이 특히 중요한 특성인 점에서 동일하다. 양극과 접촉한 층 상에 층인 정공 주입층과 정공 주입층과 접촉한 층인 정공 수송층간에 구별이 될 수 있다. 전자 수송층과 전자 주입층에 유사한 설명이 적용될 수 있다. 음극과 접촉한 층은 전자 주입층이라 하며 전자 주입층과 접촉한 층은 전자 수송층이라 한다. 발광층은 전자 수송층으로서 작용할 수도 있다.

[0225] 도 10a에 도시된 위에 기술된 화소에서, EL 소자(6003)로부터 방출되는 광은 점선 화살표로 나타낸 바와 같이 제1 전극(6004)으로부터 추출될 수 있다.

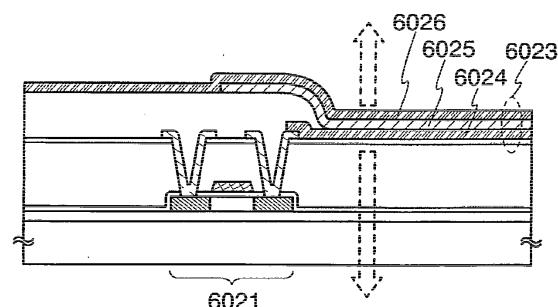

[0226] 다음에, 도 10b는 EL 소자(6013)로부터 방출되는 광이 제2 전극(6016) 측으로부터 추출되는 화소 회로의 단면도이다. 도 10b에서, EL 소자(6013)의 제1 전극(6014)은 TFT(6011)에 전기적으로 접속된다. TFT(6011)은 p채널형 트랜지스터이며, 따라서 제1 전극(6014)은 양극이다. 전장발광층(6015) 및 제2 전극(6016)은 이 순서로 제1 전극(6014) 상에 적층된다.

[0227] 제1 전극(6014)은 양극에 적합한 재료로 형성되며 제2 전극(6016)으로부터만 광을 추출하기 위해서 광 반사 또는 차폐재료로 형성된다. 예를 들면, 제1 전극(6014)에 대해, 질화티탄막 및 주성분으로서 알루미늄을 포함하는 막의 적층구조, 질화티탄막, 주성분으로서 알루미늄을 포함하는 막, 질화티탄막의 3층 구조 등뿐만 아니라, TiN, ZrN, Ti, W, Ni, Pt, Cr, Ag, Al, 등 중 하나 이상으로부터 선택되는 단일층 막이 채용될 수 있다.

[0228] 제2 전극(6016)은 음극에 적합한 재료로 형성되며, 광 투과 재료로 형성되고 제2 전극(6016) 측으로부터 광을 추출하기 위해서 발광하기 충분한 두께를 갖도록 형성된다. 구체적으로, Li, Cs, Mg, Ca 및 Sr과 같은 금속, 이들의 합금(Mg:Ag, Al:Li, Mg:In, 등), 이들의 복합물(플루오르화 칼슘 및 질화칼슘), Yb 및 Er과 같은 희토류 금속, 등이 채용될 수도 있고, 발광하기 위한 두께(대략 바람직하게는 5 내지 30nm)를 갖도록 막이 형성된다. 인듐 주석 산화물(ITO), 아연 산화물(ZnO), 인듐 아연 산화물(IZO), 또는 갈륨이 도핑된 아연 산화물(GZO)과 같은 광 투과 도전성 재료가 채용될 수도 있는 것에 유의한다. 또한, 산화실리콘을 함유하는 인듐 주석 산화물(이하 ITSO라 함), 아연 산화물(ZnO)이 혼합된 ITO, 및 아연 산화물(ZnO)이 혼합된 ITSO가 채용될 수도 있다. 이러한 광 투과 도전성 막을 사용하는 경우, 전자 주입층이 전자발광층(6015)에 형성되는 것이 바람직하다.

[0229] 전장발광층(6015)은 도 10a에서 전장발광층(6005)과 동일한 방식으로 형성될 수도 있다.

[0230] 도 10b에 도시된 위에 기술된 화소에서, EL 소자(6013)로부터 방출되는 광은 점선 화살표로 나타낸 바와 같이 제2 전극(6016) 측으로부터 추출될 수 있다.

[0231] 다음에, 도 10c는 EL 소자(6023)로부터 방출되는 광이 제1 전극(6024) 측 및 제2 전극(6026) 측 둘 다로부터 추출되는 경우에 화소 회로의 단면 구성을 도시한 것이다. 도 10c에서, EL 소자(6023)의 제1 전극(6024)은 TFT(6021)에 전기적으로 접속되고, TFT(6021)은 p채널형 트랜지스터이며, 따라서, 제1 전극(6024)은 양극이다. 전장발광층(6025) 및 제2 전극(6026)은 이 순서로 제1 전극(6024) 상에 적층된다.

[0232] 제1 전극(6024)은 제1 전극(6024)으로부터 광을 추출하기 위해 도 10a에서 제1 전극(6004)과 유사하게 형성될 수 있다. 제2 전극(6026)도 제2 전극(6026)으로부터 광을 추출하기 위해 도 10b에서 제2 전극(6016)과 유사하게

형성될 수 있다. 전장발광층(6025)은 도 10a에서 전장발광층(6005)과 유사하게 형성될 수 있다.

- [0233] 도 10c에 도시된 위에 기술된 화소에서, EL 소자(6023)로부터 방출되는 광은 점선 화살표로 나타낸 바와 같이 제1 전극(6024) 및 제2 전극(6026) 둘 다로부터 추출될 수 있다.

- [0234] 이 실시형태에서, 제1 전극이 양극이고 제2 전극이 음극인 경우에 대해 기술되었을지라도, 제1 전극이 음극이고 제2 전극이 양극일 수도 있다. 제1 전극이 음극이고 제2 전극이 양극인 경우에, n채널형 박막 트랜지스터는 구동 트랜지스터로서 채용되는 것이 바람직하다.

- [0235] 이 실시형태는 다른 실시형태들과 조합하여 자유롭게 구현될 수 있는 것에 유의한다.

#### [0236] [실시형태 7]

- [0237] 발명의 표시 장치를 포함하는 전자 기기는 텔레비전 장치(텔레비전 또는 텔레비전 수신기), 디지털 카메라와 같은 카메라, 디지털 비디오 카메라, 휴대 전화 장치(휴대전화기), PDA와 같은 휴대 정보 단말, 휴대형 게임기, 모니터, 컴퓨터, 카 오디오와 같은 음향 재생 장치, 가정용 게임기와 같은 기록 매체가 구비된 화상 재생 장치를 포함한다. 도 11a 내지 도 11f를 참조하여 구체적인 예들에 대해 기술한다.

- [0238] 도 11a에 도시된 발명의 표시 장치를 사용한 휴대 정보 단말은 본체(9201), 표시부(9202), 등을 포함한다. 큰 애피처 비를 가진 휴대 정보 단말이 발명에 의해 제공될 수 있다.

- [0239] 도 11b에 도시된 발명의 표시 장치를 사용한 디지털 비디오 카메라(9701)는 표시부(9702) 등을 포함한다. 큰 애피처 비를 가진 디지털 비디오 카메라가 발명에 의해 제공될 수 있다.

- [0240] 도 11c에 도시된 발명의 표시 장치를 사용한 휴대전화는 본체(9101), 표시부(9102) 등을 포함한다. 큰 애피처 비를 가진 휴대전화가 발명에 의해 제공될 수 있다.

- [0241] 도 11d에 도시된 발명의 표시 장치를 사용한 휴대 텔레비전은 본체(9301), 표시부(9302) 등을 포함한다. 큰 애피처 비를 가진 휴대 텔레비전이 발명에 의해 제공될 수 있다.

- [0242] 도 11e에 도시된 발명의 표시 장치를 사용한 휴대 컴퓨터는 본체(9401), 표시부(9402), 등을 포함한다. 큰 애피처 비를 가진 휴대 컴퓨터가 발명에 의해 제공될 수 있다.

- [0243] 도 11f에 도시된 발명의 표시 장치를 사용한 텔레비전은 본체(9501), 표시부(9502), 등을 포함한다. 큰 애피처 비를 가진 텔레비전이 발명에 의해 제공될 수 있다.

- [0244] 위에 기술된 바와 같이, 발명의 표시 장치는 다양한 전자 기기들에 적용될 수 있다.

- [0245] 이 출원은 전체 내용을 참조로 여기 포함시키는 2005년 9월 15일 일본특허청에 출원된 일본 특허출원 번호 2005-269013에 기초한다.

### 도면의 간단한 설명

- [0042] 도 1은 발명의 표시 장치의 화소 회로를 도시한 도면이다.

- [0043] 도 2는 발명의 표시 장치의 화소 회로의 구동 방법을 도시한 도면이다.

- [0044] 도 3은 발명의 표시 장치의 구조를 도시한 도면이다.

- [0045] 도 4a 및 도 4b는 각각 발명의 표시 장치의 전극의 형상을 도시한 도면들이다.

- [0046] 도 5는 발명의 표시 장치의 화소 회로의 구동 방법을 도시한 도면이다.

- [0047] 도 6은 발명의 표시 장치의 화소 회로의 구동 방법을 도시한 도면이다.

- [0048] 도 7은 발명의 표시 장치의 화소 회로를 도시한 도면이다.

- [0049] 도 8은 표시 장치의 화소 회로를 도시한 도면이다.

- [0050] 도 9는 표시 장치의 화소 회로를 도시한 도면이다.

- [0051] 도 10a 내지 도 10c는 각각 발명의 표시 장치의 제조단계를 도시한 도면들이다.

- [0052] 도 11a 내지 11f는 각각 발명의 전자 기기를 도시한 도면들이다.

- [0053] 도 12a 및 도 12b는 각각 발명의 화소를 도시한 도면들이다.

- [0054] 도 13a 및 도 13b는 각각 발명의 화소를 도시한 도면들이다.

- [0055] 도 14a 및 도 14b는 각각 발명의 화소를 도시한 도면들이다.

- [0056] 도 15a 내지 도 15e는 각각 발명의 EL 소자의 구조들을 도시한 도면들이다.

- [0057] 도 16은 발명의 표시 소자를 제조하기 위한 증기 증착장치를 도시한 도면이다.

- [0058] 도 17은 발명의 증기 증착장치의 증착 가공 챔버를 도시한 도면이다.

- [0059] 도 18은 발명의 화소를 도시한 도면이다.

[0060] <도면의 주요 부분에 대한 부호의 설명>

[0061] ANODE: 제1 전원선, CATHODE: 제2 전원선, DATA: 데이터선, X1 내지 Xn: 데이터선들, Y1 내지 Ym: 주사선들, Tr1: 제1 트랜ジ스터, Tr2: 제2 트랜ジ스터, Tr3: 제3 트랜ジ스터, Tr4: 제4 트랜ジ스터, Tr5: 제5 트랜ジ스터, Idata: 데이터 전류, 10: EL 소자, 20: EL 소자, 201: 한 프레임 기간, 202: 초기화 기간, 203: 임계 기입 기간, 204: 어드레스 기간, 205: 발광기간, 205A: 발광기간(이전 프레임), 206: 기입전 기간, 207: 데이터 기입 기간, 208: Cs 재기입 기간, 209: 기입후 기간, 301: 화소부, 302: 데이터선 구동 회로, 303: 주사선 구동 회로, 304: 화소 회로, 401: 기판, 402: 접촉영역, 501: 한 주사선 기입 기간, 6001: TFT, 6003: EL 소자, 6004: 전극, 6005: 전장발광층, 6006: 전극, 6007: 충간 절연막, 6008: 격벽, 6011: TFT, 6013: EL 소자, 6014: 전극, 6015: 전장발광층, 6016: 전극, 6021:TFT, 6023: EL 소자, 6024: 전극, 6025: 전장발광층, 6026: 전극, 9101: 휴대 전화 장치전화의 본체, 9102: 표시부, 9201: 휴대 전화 장치 정보 단말의 본체, 9202: 표시부, 9301: 휴대 전화 장치 텔레비전의 본체, 9302: 표시부, 9401: 휴대 컴퓨터의 본체, 9402: 표시부, 9501: 텔레비전의 본체, 9502: 표시부, 9701: 디지털 비디오 카메라의 본체, 9702: 표시부, 1205: 제1 TFT, 1206: 제1 배선, 1207: 제2 배선, 1208: 제2 TFT, 1211: 제3 배선, 1212: 대향 전극, 1213: 용량소자, 1215: 화소 전극, 1216: 격벽, 1217: 유기 도전막, 1218: 유기 박막, 1219: 기판, 1300: 기판, 1301: 제1 배선, 1302: 제2 배선, 1303: 제3 배선, 1304: 제4 배선, 1305: 제1 TFT, 1306: 제2 TFT, 1307: 제3 TFT, 1308: 화소 전극, 1311: 격벽, 1312: 유기 도전막, 1313: 유기 박막(발광층), 1314: 대향전극, 1400: 기판, 1401: 제1 배선, 1402: 제2 배선, 제3 배선, 1404: 제4 배선, 1405: 제1 TFT, 1406: 제2 TFT, 1407: 제3 TFT, 1408: 제4 TFT, 1409: 화소전극, 1411: 제4 배선, 1412: 제6 배선, 1421: 격벽, 1422: 유기 도전막, 1423: 유기 박막(발광층), 1424: 대향전극, 1501: 양극, 1502: 음극, 1503: 정공 수송영역, 1504: 전자 수송영역, 1505: 혼합영역, 1506: 발광재료가 첨가되는 영역, 1507: 정공 차단재료가 첨가되는 영역, 1508: 전자 차단재료가 첨가되는 영역, 1509: 금속재료가 첨가되는 영역, 1660: 이송 챔버, 1661: 이송 챔버, 1662: 로딩 챔버, 1663: 언로딩 챔버, 1664: 중간 챔버, 1665: 시일링 처리 챔버, 1666: 이송 유닛, 1667: 이송 유닛, 1668: 열 처리 챔버, 1669: 증착 처리 챔버, 1670: 증착 처리 챔버, 1671: 증착 처리 챔버, 1672: 증착 처리 챔버, 1673: 증착 처리 챔버, 1674: 증착 처리 챔버, 1675: 증착 처리 챔버, 1676: 증착 처리 챔버, 1677a 내지 1677m: 게이트 밸브들, 1780: 증발원 홀더, 1781a 내지 1781c: 증발원들, 1782: 거리 센서, 1783: 다관절 암, 1784: 물질 공급관, 1785a 내지 1785c: 물질 공급원들, 1786: 기판 스테이지, 1787: 기판 척, 1788: 마스크 척, 1789: 기판, 1790: 세도우 마스크, 1791: 상측 판, 1792: 하측 판, 1801: 제1 TFT, 1802: 제2 TFT, 1803: 제3 TFT, 1804: 제4 TFT, 1805: 제5 TFT, 1806: 제1 배선, 1807: 제2 배선, 1808: 제3 배선, 1809: 제4 배선, 1810: 제5 배선, 1811: 제6 배선, 1813: 전기 콘덴서, 1814: 화소 전극, 1815: 격벽 개구, 1816: 전극, 1817: 전극

도면

도면1

도면2

도면3

도면4a

도면4b

도면5

도면6

도면7

도면8

도면9

도면10a

도면10b

도면10c

도면11a

도면11b

도면11c

도면11d

도면11e

도면11f

도면12a

도면12b

도면13a

도면13b

도면14a

도면14b

도면15a

도면15b

도면15c

도면15d

도면15e

## 도면16

## 도면17

## 도면18

【심사관 직권보정사항】

【직권보정 1】

【보정항목】 청구범위

【보정세부항목】 청구항 제50항 3째 줄

【변경전】

거의 동일하고

【변경후】

실질적으로 동일하고

|                |                                                                                                                                                                                        |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 标题显示装置及其驱动方法                                                                                                                                                                           |         |            |

| 公开(公告)号        | <a href="#">KR101322195B1</a>                                                                                                                                                          | 公开(公告)日 | 2013-11-04 |

| 申请号            | KR1020087008960                                                                                                                                                                        | 申请日     | 2006-09-06 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                                                                                                                                                           |         |            |

| 申请(专利权)人(译)    | 株式会社绒布器肯kyusyo极限戴哦                                                                                                                                                                     |         |            |

| 当前申请(专利权)人(译)  | 株式会社绒布器肯kyusyo极限戴哦                                                                                                                                                                     |         |            |

| [标]发明人         | YOSHIDA YASUNORI                                                                                                                                                                       |         |            |

| 发明人            | YOSHIDA, YASUNORI                                                                                                                                                                      |         |            |

| IPC分类号         | G09G3/30 G09G3/32 H01L51/50 G09G3/20                                                                                                                                                   |         |            |

| CPC分类号         | H01L51/0011 G09G2320/043 H01L27/3211 H01L2251/5323 G09G3/325 G09G2300/0417 G09G2300/0809 G09G2300/0866 G09G2320/0223 G09G2300/0465 H01L27/3244 G09G2300/0852 G09G2330/08 G09G2310/0256 |         |            |

| 代理人(译)         | 李昌勋                                                                                                                                                                                    |         |            |

| 优先权            | 2005269013 2005-09-15 JP                                                                                                                                                               |         |            |

| 其他公开文献         | KR1020080051175A                                                                                                                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                              |         |            |

## 摘要(译)

提供一种包括具有高孔径比的像素电路的显示装置及其驱动方法，其克服了编程时间的不足，这是包括EL元件的显示装置的问题。在包括可用作驱动晶体管的显示元件，电容器元件，电容器元件，第一电源线和第二电源线的电路中，第一电源线和第二电源线的电位设定为彼此基本相等，驱动晶体管的阈值电压保持在显示元件中，然后电荷被分配到显示元件和电容器元件。

20