# (19)대한민국특허청(KR) (12) 등록특허공보(B1)

(51) 。Int. Cl.<sup>7</sup> H05B 33/00

(45) 공고일자 2005년04월15일 (11) 등록번호 10-0483311 (24) 등록일자 2005년04월06일

(21) 출원번호10-2002-0040201(분할)(65) 공개번호(22) 출원일자2002년07월11일(43) 공개일자(62) 원출원특허10-1997-0033088

62) 년월년 국어10 1997-0033086 원출원일자 : 1997년07월16일 심사청구일자 2002년07월11일

(30) 우선권주장 JP-P-1996-00205417 1996년07월16일 일본(JP)

(73) 특허권자 가부시키가이샤 한도오따이 에네루기 켄큐쇼 일본국 가나가와켄 아쓰기시 하세 398

(72) 발명자 야마자끼순페이

일본국가나가와켄아쓰기시하세398가부시키가이샤한도오따이에네루기

켄큐쇼내

데라모토사토시

일본국가나가와켄아쓰기시하세398가부시키가이샤한도오따이에네루기

켄큐쇼내

(74) 대리인 황의만

심사관: 박재훈

## (54) EL 표시장치

#### 요약

힐록 또는 휘스커의 발생을 방지하기 위해 알루미늄으로 된 배선을 사용한 반도체장치가 제공된다. 그 배선은  $8\times10^{18}$  원자·cm $^{-3}$ 이하의 농도의 산소 원자와,  $5\times10^{18}$  원자·cm $^{-3}$ 이하의 농도의 탄소 원자, 및  $7\times10^{17}$  원자·cm $^{-3}$ 이하의 농도의 질소 원자를 함유하며, 알루미늄 게이트 상에 질화규소막이 형성되고, 그의 측면에 양극산화막이 형성된다.

## 대표도

도 1

## 명세서

## 도면의 간단한 설명

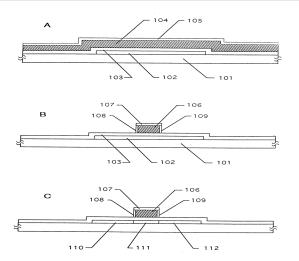

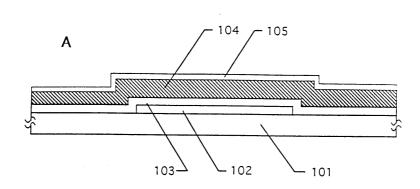

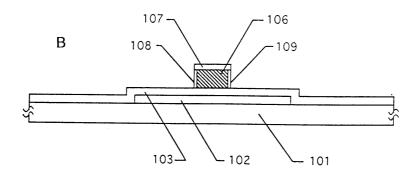

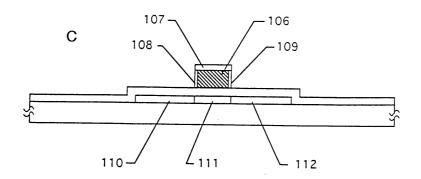

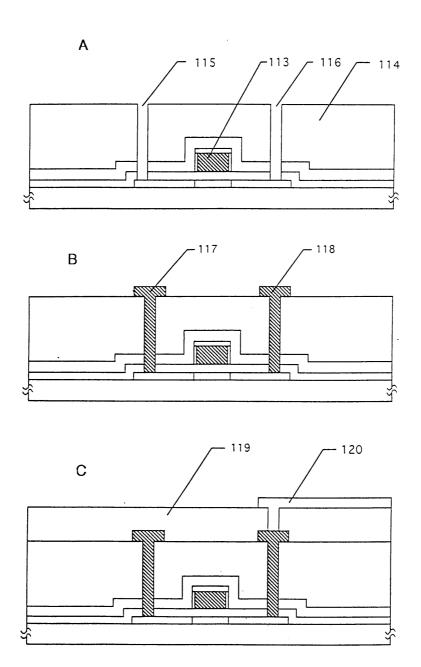

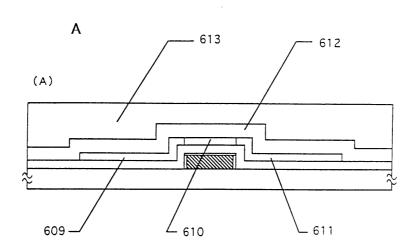

도 1(A)~도 1(C)는 실시예 1에 따른 박막트랜지스터의 제작공정을 나타내는 도면,

도 2(A)~도 2(C)는 실시예 1에 따른 박막트랜지스터의 제작공정을 나타내는 도면.

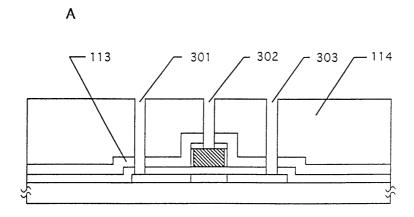

도 3(A) 및 도 3(B)는 실시예 2에 따른 박막트랜지스터의 제작공정을 나타내는 도면.

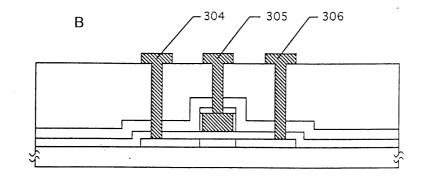

도 4(A)~도 4(C)는 실시예 3에 따른 박막트랜지스터의 제작공정을 나타내는 도면.

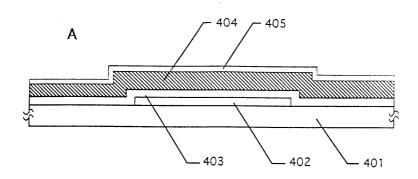

도 5(A)~도 5(C)는 실시예 3에 따른 박막트랜지스터의 제작공정을 나타내는 도면.

도 6(A)~도 6(D)는 실시예 4에 따른 박막트랜지스터의 제작공정을 나타내는 도면.

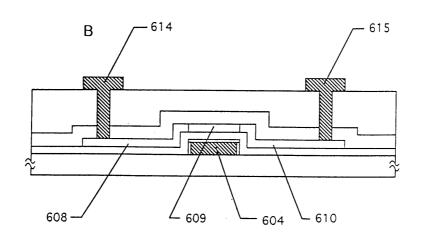

도 7(A) 및 도 7(B)는 실시예 4에 따른 박막트랜지스터의 제작공정을 나타내는 도면.

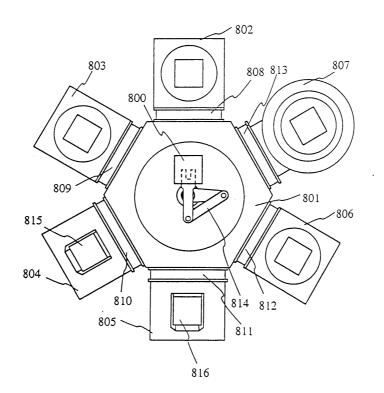

도 8은 성막(成膜)장치의 개략도.

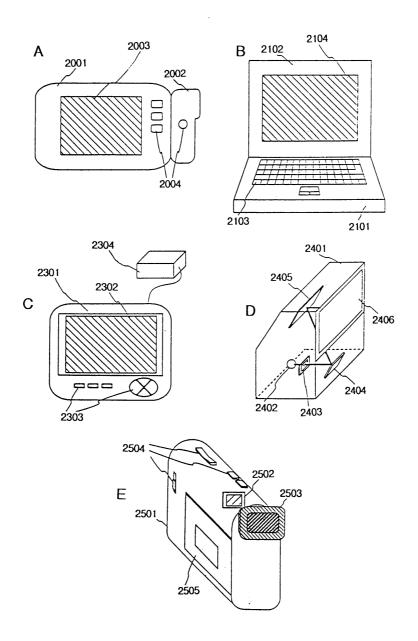

도 9(A)~도 9(E)는 액정 패널을 이용한 장치를 개략적으로 나타내는 도면.

\* 도면의 주요 부분에 대한 부호의 설명

101: 유리 기판 102: 활성층 103: 산화규소막

104: 알루미늄막 105: 질화규소막

106: 패터닝된 알루미늄막(게이트 전극) 107: 질화규소막

108, 109: 양극산화막 110: 소스 영역 111: 채널 영역

113: 드레인 영역 113: 질화규소막(제1 층간절연막)

114: 폴리이미드막(제2 층간절연막) 115, 116: 콘택트 홀

117: 소스 전극 118: 드레인 전극 119: 제3 층간절연막

120: 화소전극

### 발명의 상세한 설명

## 발명의 목적

## 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은, 전극과 배선이 알루미늄 또는 알루미늄을 주성분으로 하는 재료로 구성된 반도체장치를 포함하는 EL 표시장치에 관한 것이다.

최근, 대면적의 화면을 가진 액티브 매트릭스형 액정 표시장치가 많은 관심을 끌고 있다. 그러한 액티브 매트릭스형 액정 표시장치는 대면적의 화면을 요구할 뿐 아니라, 미세한 패터닝도 필요로 한다.

상기한 요구를 충족시키기 위해서는, 배선 재료로서 전기 저항이 낮은 재료를 사용하는 것이 필요한데, 그 이유는  $10 \times 10$  인치<sup>2</sup> 이상의 사이즈를 가지는 장치에서는 배선에서 전파(傳播)하는 신호의 지연이 문제로 되기 때문이다.

전기 저항이 낮은 배선 재료로서는 알루미늄이 가장 바람직한 재료이다. 그러나, 알루미늄을 사용하는 경우에는, 제작공정에 있어서의 내열성에 문제가 있다(이 점에 관해서는, Science Communication International 발행 "Display and Imaging" 제4권(1996), 199-206 페이지에 기재된 해설논문 참조).

구체적으로는, 박막트랜지스터의 제작공정에 있어서의 각종 박막의 성막(成膜)이나 어닐, 또는 레이저광의 조사 및 불순물이온의 주입 공정에서, 알루미늄의 이상(異常) 성장이 일어나, 힐록 또는 휘스커라 불리는 돌기물이 형성되는 문제가 있다. 이들 힐록 및 휘스커는 알루미늄의 불량한 내열성에 기인하는 것으로 믿어진다.

혈록 또는 휘스커로 알려진 이들 돌기물은 종종 1 ﷺ 이상 성장하기도 한다. 이러한 현상은 배선들 사이의 단락(短絡)의 원인이 된다.

상기 문제는 알루미늄 배선의 표면에 양극산화막을 형성함으로써 방지될 수 있다(상기 참고문헌 참조).

## 발명이 이루고자 하는 기술적 과제

본 발명자들의 연구에 따르면, 양극산화막( $Al_2O_3$ 를 주성분으로 하는 것으로 고려된다)은 막질(膜質)이 강하고, 힐록이나 휘스커의 발생을 방지하는데 효과적이지만, 한편으로는, 그러한 강한 재료는 알루미늄 배선에 대하여 콘택트 홀을 형성하는 것을 어렵게 하는 것으로 밝혀졌다.

상기한 상황에 비추어, 본 발명의 목적은, 알루미늄 배선의 내열성의 문제를 극복하고, 양극산화막이 형성된 알루미늄 배선에 콘택트 홀을 형성하는데 있어서의 어려움을 해결하는 기술을 제공하는데 있다.

## 발명의 구성 및 작용

본 발명의 일 양태에 따르면, 알루미늄 또는 알루미늄을 주성분으로 하는 재료로 된 막 패턴을 포함하는 반도체장치로서, 알루미늄 또는 알루미늄을 주성분으로 하는 재료로 된 막이  $8\times10^{18}$  원자·cm $^{-3}$  이하의 농도의 산소 원자와,  $5\times10^{18}$  원자·cm $^{-3}$  이하의 농도의 탄소 원자, 및  $7\times10^{17}$  원자·cm $^{-3}$  이하의 농도의 질소 원자를 함유하는 것을 특징으로 하는 반도체 장치가 제공된다.

상기 구성을 이용함으로써, 힐록 및 휘스커와 같은 돌기물의 최대 높이가 500 Å 이하로 억제될 수 있다.

본 발명의 다른 양태에 따르면, 알루미늄 또는 알루미늄을 주성분으로 하는 재료로 된 막 패턴을 포함하는 반도체장치를 제작하는 방법으로서, 알루미늄 또는 알루미늄을 주성분으로 하는 재료로 된 막이  $8\times10^{18}$  원자·cm $^{-3}$  이하의 농도의 산소 원자와,  $5\times10^{18}$  원자·cm $^{-3}$  이하의 농도의 탄소 원자, 및  $7\times10^{17}$  원자·cm $^{-3}$  이하의 농도의 질소 원자를 함유하고, 제조 공정 중에 상기 막 패턴에 가해지는 공정 온도가 400℃ 이하인 것을 특징으로 하는 반도체장치 제조방법을 제공한다..

공정 온도를 400℃ 이하로 제어함으로써, 산소 원자, 탄소 원자 및 질소 원자의 농도를 소망의 낮은 수준으로 제어하는 효과를 최대한 얻는 것이 가능하다.

도 1(B)에 나타낸 바와 같이, 본 발명의 일 실시형태는,  $8\times10^{18}$  원자·cm $^{-3}$  이하의 농도의 산소 원자와,  $5\times10^{18}$  원자·cm $^{-3}$  이하의 농도의 탄소 원자, 및  $7\times10^{17}$  원자·cm $^{-3}$  이하의 농도의 질소 원자를 함유하는 패터닝된 알루미늄막(106)의 상면에 질화규소막(107)을 형성하고, 패터닝된 알루미늄 막(106)의 측면에는 양극산화막(산화막)(108, 109)을 형성하는 것을 포함한다.

상기 구성을 이용함으로써, 힐록 및 휘스커와 같은 돌기물의 형성이 억제될 수 있고, 콘택트가 보다 쉽게 형성될 수 있다.

본 발명의 바람직한 실시예를 상세히 설명한다. 그러나, 본 발명이 하기 실시예에 한정되는 것은 아니다.

#### [실시예 1]

도 1(A)~도 1(C)는 본 실시예의 제작공정을 개략적으로 나타내는 단면도이다. 본 실시예에서는, 액티브 매트릭스형 액정 표시장치의 화소 매트릭스부에 배치되는 박막트랜지스터(일반적으로 "화소 트랜지스터"로 불림)의 제작공정을 나타낸다.

먼저, 도 1(A)에 나타낸 바와 같이, 유리 기판(101)의 표면에 하지막(下地膜)(도시되지 않음)을 형성한다. 본 실시예에서 사용되는 하지막으로서는, 두꼐 3000 Å의 산화규소막을 스퍼터링법에 의해 형성한다.

그 하지막은 유리 기판으로부터 확산되는 불순물 및 유리 기판의 표면의 미세한 요철의 영향을 완화시키는 기능을 한다. 본 실시예에서는 유리 기판이 사용되었지만, 석영 기판이 대신 사용될 수도 있다.

유리 기판(101)상에 하지막을 형성한 후, 박막트랜지스터의 활성층(102)을 구성하는 반도체막의 출발막이 되는 비정질 규소막(도시되지 않음)을 플라즈마 CVD법에 의해 500 Å의 두께로 형성한다.

그 다음, 그 비정질 규소막에 레이저광을 조사하여 결정성 규소막(도시되지 않음)을 얻고, 그 결정성 규소막을 패터닝하여 활성층(102)을 형성한다.

그 다음, 게이트 절연막으로서 기능하는 산화규소막(103)을 플라즈마 CVD법에 의해 1000 Å의 두께로 형성한다.

산화규소막(103)을 성막한 후, 스퍼터링법에 의해 알루미늄막(104)을 4000 Å의 두께로 형성한다. 그리하여, 도 1(A)에 나타낸 상태가 얻어진다.

본 실시예에서는, 알루미늄막에 0.18 중량%의 농도로 스칸듐이 첨가되었다.

스칸듐의 첨가는 후의 공정에서의 힐록과 휘스커의 발생을 억제한다. 스칸듐은 알루미늄의 이상(異常) 성장을 억제하기 때문에 힐록과 휘스커의 발생의 방지에 효과적이다.

그 다음, 알루미늄막(104)과 질화규소막(105)의 적층 막을 패터닝하여, 부호 106으로 나타낸 패터닝된 알루미늄막을 얻는다. 그 패터닝된 알루미늄막(106)상에는, 부호 107로 나타낸 질화규소막이 잔존한다. 즉, 패터닝된 알루미늄막(106)은 게이트 전극이 된다. 그 게이트 전극(106)으로부터 게이트 선이 연장한다.

화소 매트릭스부에서는, 게이트 전극(106)들로부터 연장한 게이트 선들이 소스 선들과 함께 격자로 배열되어 매트릭스를 형성한다. 그 후, 게이트 전극(106)을 양극으로 한 양극산화를 행하여, 알루미늄막의 노출된 측면에 양극산화막(108, 109)을 형성한다. 이들 양극산화막은 각각 500 Å의 두께로 제공된다.

상기 양극산화 공정에서는, 3% 주석산을 함유한 에틸렌 글리콜 용액을 암모니아수로 중화한 것이 전해용액으로 사용되었고, 그 전해용액 내에서, 백금을 음극으로 그리고 알루미늄막을 양극으로 하여, 양 전극 사이에 전류를 흘려보냄으로써 양극산화막이 형성된다.

그렇게 하여 얻어진 양극산화막은 치밀하고 강하다. 이 양극산화 공정에서 얻어진 막의 두께는 인가 전압을 조정함으로써 제어될 수 있다.

상기 공정에서는, 전해용액이 게이트 전극(106)의 측면에만 접촉하기 때문에, 게이트 전극(106)의 상면에는 양극산화막이 형성되지 않는다. 그리하여, 도 1(B)에 나타낸 상태가 얻어진다.

그 후, 인(P)을 도핑함으로써 소스 영역(110), 채널 영역(111), 드레인 영역(112)이 형성된다. 본 실시예에서는, 도핑 수단으로서 플라즈마 도핑법이 사용되었다. 그리하여, 도 1(C)에 나타낸 상태가 얻어진다.

여기서는, N채널형 박막트랜지스터를 제작하기 위해 인(P)의 도핑이 행해졌지만, P채널형 박막트랜지스터를 제작하는 경우에는 붕소(B)를 도핑한다.

도핑 공정에서는, 시료를 가열 또는 불가피하게 가열하는 상황이 생기는데, 알루미늄의 내열성의 관점에서, 시료를 400℃이하의 온도로 유지하는 것이 중요하다. 가열 온도가 400℃를 넘을 경우에는, 힐록(또는 휘스커)(이들은 명확하게 서로 구분되지 않는다)의 발생이 분명해지기 때문에 주의를 해야 한다.

도핑 공정의 완료 후, 레이저광 조사를 행하여, 도펀트와 도핑된 영역을 동시에 활성화한다.

그 후, 플라즈마 CVD법에 의해 두께 2000 Å의 질화규소막(113)을 형성하여 제1 층간절연막을 제공한다.(도 2(A))

그 후, 스핀 코팅법에 의해 폴리이미드막(114)을 형성하여 제2 층간절연막을 제공한다. 층간절연막으로서 폴리이미드를 사용하는 경우, 평탄한 표면이 얻어질 수 있다.

그 후, 소스 영역 및 드레인 영역에 대한 콘택트 홀(115, 116)을 형성한다. 그리하여, 도 2(A)에 나타낸 상태가 얻어진다.

그 다음, 티탄막, 알루미늄막, 티탄막의 순서로 이루어진 적층 막을 스퍼터링법에 의해 형성하고, 이것을 패터닝하여 소스전극(117) 및 드레인 전극(118)을 얻는다. 그리하여, 도 2(B)에 나타낸 상태가 얻어진다.

그 다음, 폴리이미드를 사용하여 제3 층간절연막(119)을 형성하고, 드레인 전극(118)에 대하여 콘택트 홀을 형성한 후, ITO로 된 화소전극(120)을 형성한다. 그렇게 하여 얻어진 상태가 도 2(C)에 도시되어 있다.

마지막으로, 활성층 내에 존재하는 결함을 보상하기 위해 수소 분위기 중에서 가열처리를 행함으로써, 박막트랜지스터를 완성한다.

#### [실시예 2]

본 실시예는 실시예 1에서 설명된 제작공정과 동시에 행해지는 공정을 나타낸다. 구체적으로는, 화소 매트릭스부의 주변에 형성되는 주변 구동회로에 설치되는 박막트랜지스터의 제작공정을 나타낸다. 본 실시예에서도, N채널형 박막트랜지스터를 제작하는 공정을 설명한다.

본 실시예에서 나타내는 박막트랜지스터의 제작공정은 도  $1(A)\sim$ 도 1(C)에 의거하여 실시예 1에서 설명된 것과 동일하다 (물론, 배선 패턴 및 활성층 패턴의 크기에 다소 차이가 있다).

먼저, 실시예 1에서 설명된 공정들에 따라, 도 1(C)에 나타낸 상태를 얻는다. 그 다음, 도 3(A)에 나타낸 바와 같이, 제1 층 간절연막으로서 질화규소막(113)을 형성한다.

그 다음, 제2 층간절연막으로서 폴리이미드막(114)을 형성한 후, 콘택트 홀(301, 302, 303)을 형성한다.

게이트 전극(106)의 상면에는 양극산화막이 아니라 질화규소막이 형성되어 있기 때문에, 콘택트 홀(302)이 쉽게 형성될 수 있다.

본 실시예에 따른 구성에서는, 건식 에칭법을 사용하여 콘택트 홀(301, 302, 303)이 동시에 형성된다. 그리하여, 도 3(A) 에 나타낸 상태가 얻어진다.

그 다음, 티탄막, 알루미늄막, 티탄막으로 이루어진 3층 막을 스퍼터링법에 의해 형성한 후, 그 3층 막을 패터닝하여 소스전극(304), 게이트 인출 전극(305), 드레인 전극(306)을 형성한다. 그리하여, 도 3(B)에 나타낸 상태가 얻어진다.

그 다음, 실시예 1에서 설명된 것과 유사한 수소화 공정을 행하여, 박막트랜지스터를 완성한다.

상기 설명에서는 N채널형 박막트랜지스터를 제작하는 공정을 설명하였다. 일반적으로 주변 구동회로에는, N채널형 박막트랜지스터와 P채널형 박막트랜지스터가 상보형으로 구성된 것이 배치된다.

#### [실시예 3]

본 실시예는 채널 영역과 드레인 영역 사이에 저농도 불순물 영역이 배치된 박막트랜지스터를 제작하는 공정을 나타낸다.

도 4(A)~도 4(C) 및 도 5(A)~도 5(C)에 본 실시예의 박막트랜지스터 제작공정을 나타낸다. 먼저, 유리 기판(401)의 표면에 하지막(도시되지 않음)을 형성한 다음, 비정질 규소막을 형성하고, 레이저광 조사에 의해 결정화시킨다. 그리하여, 결정성 규소막이 얻어진다. 그 다음, 그 결정성 규소막을 패터닝하여 박막트랜지스터의 활성층(402)을 형성한다.

그 다음, 게이트 절연막으로서 기능하는 산화규소막(403)을 형성한 후, 그 위에 알루미늄막(404)을 형성한다.

그리고, 그 알루미늄막 상에 질화규소막(405)을 형성한다. 그리하여, 도 4(A)에 나타낸 상태가 얻어진다.

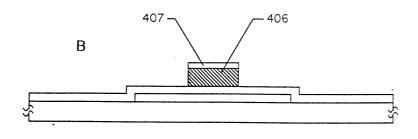

도 4(A)에 나타낸 구조에 대하여 패터닝을 행하여 알루미늄 패턴(406)을 얻는다. 그 알루미늄 패턴은 나중에 형성될 게이트 전극의 기초 패턴이 된다. 잔존하는 질화규소막 패턴이 부호 407로 나타내어져 있다. 그리하여, 도 4(B)에 나타낸 상태가 얻어진다.

그 후, 알루미늄 패턴(406)을 양극으로 하여 양극산화를 행하여, 양극산화막(409, 410)을 형성한다.

본 실시예에서는, 3% 수산 수용액이 전해용액으로서 사용되었다. 이 공정에서 형성된 양극산화막은 다공질이고 수 마이크로미터의 길이로 성장할 수 있다. 이 성장 길이는 양극산화 시간을 조정함으로써 제어될 수 있다. 그리하여, 도 4(C)에 나타낸 상태가 얻어진다. 이 상태에서, 잔존한 패턴(408)이 게이트 전극으로 된다.

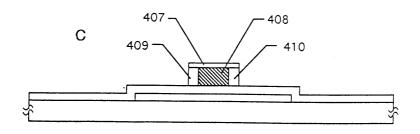

그 다음, 양극산화를 다시 행한다. 이 경우, 양극산화는 실시예 1에서 치밀한 양극산화막을 형성하는데 이용된 것과 동일한 조건 하에 행해진다. 그리하여, 도 5(A)에 나타낸 것과 같은 치밀한 양극산화막(411, 412)이 얻어진다.

그 치밀한 양극산화막(411, 412)은 500 Å의 두께로 형성된다. 그 치밀한 양극산화막은 질화규소막(407)이 게이트 전극(408)의 상면에 미리 형성되어 있기 때문에 게이트 전극(408)의 측면에 선택적으로 형성된다. 또한, 다공질 양극산화막(409, 410)의 내부에 전해용액이 침투하기 때문에, 치밀한 양극산화막(411, 412)이 도 5(A)에 나타낸 바와 같이 형성된다

그 후, 본 실시예에서는 플라즈마 도핑법을 이용하여 인(P) 원자를 주입한다. 그리하여, 도 5(B)에 나타낸 바와 같이, 소스 영역(413), I형 영역(414) 및 드레인 영역(415)이 자기정합적으로 형성된다.

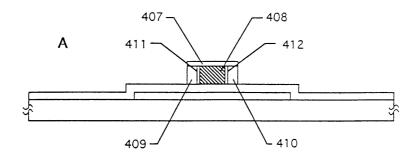

그 다음, 다공질 양극산화막(409, 410)을 선택적으로 제거한다. 이 공정에서는, 도 5(C)에 도시된 바와 같이, 양극산화막(409, 410)의 상부의 질화규소막(407)의 일부가 그 양극산화막과 함께 제거된다.

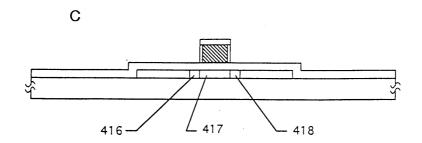

이어서, 인(P) 원자의 도핑을 다시 행한다. 이 공정에서, 도핑이 이전의 도핑 공정에서 이용된 것보다 낮은 도즈량으로 행해진다. 이 공정에서, 저농도 불순물 영역(416, 418)이 자기정합적으로 형성되고, 또한, 채널 형성 영역(417)이 자기정합적으로 형성된다.

저농도 불순물 영역(416, 418)은 소스 영역(413) 또는 드레인 영역(415)에서의 것보다 낮은 농도로 인(P)을 함유한다.

일반적으로, 드레인 영역 측의 저농도 불순물 영역(418)이 "LDD 영역"(저농도로 도핑된 드레인 영역)으로 불린다.

도 5(C)에 나타낸 상태가 얻어진 후, 레이저광을 조사하여, 도핑된 영역을 어닐한다.

본 실시예에서 설명된 구성에서는, 게이트 전극(및 그로부터 연장하는 게이트 선)의 상면은 질화규소막으로 덮여 있고, 측면은 치밀한 양극산화막으로 덮여 있다. 그러한 구성으로 함으로써, 불순물 도핑 공정 및 레이저광 조사 공정 중에 게이트 전극의 표면에서의 힐록이나 휘스커의 발생이 억제될 수 있다. 또한, 그러한 구성에서는, 게이트 전극(또는 게이트 선)에 대한 콘택트가 보다 쉽게 형성될 수 있다.

## [실시예 4]

본 실시예는 게이트 전극이 활성층과 기판 사이에 제공된 소위 보텀 게이트형의 박막트랜지스터를 나타낸다.

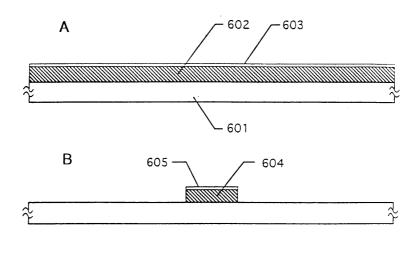

도 6(A)~도 6(D), 도 7(A) 및 도 7(B)는 본 실시예를 따른 박막트랜지스터 제작공정을 나타낸다. 먼저, 유리 기판(601)의 표면에 알루미늄막(602)을 스퍼터링법에 의해 3000 Å의 두께로 형성한다. 이 알루미늄막은 후의 공정에서 게이트 전극을 구성한다.

알루미늄막(602)이 형성된 후, 그 위에 질화규소막(603)을 플라즈마 CVD법에 의해 500 Å의 두께로 형성한다. 그리하여, 도 6(A)에 나타낸 상태가 얻어진다.

그 후, 패터닝에 의해 게이트 전극(604)을 형성한다. 질화규소막(605)이 게이트 전극(604)상에 잔존한다. 이렇게 하여, 도 6(B)에 나타낸 상태가 얻어진다.

다음에, 게이트 전극(604)을 양극으로 하여 양극산화를 행함으로써, 치밀한 양극산화막(606, 607)을 각각 500 Å의 두께로 형성한다.

이 공정에서는 질화규소막(605)이 여전히 잔존하기 때문에, 양극산화막이 게이트 전극(604)의 측면에만 형성된다. 그리하여, 도 6(C)에 나타낸 상태가 얻어진다.

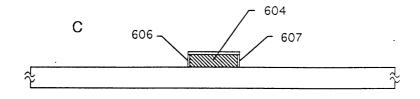

그 후, 게이트 절연막으로서 기능하는 산화규소막(608)을 플라즈마 CVD법에 의해 1000 Å의 두께로 형성한다. 그 다음, 활성층을 형성하기 위해, 두께 500 Å의 비정질 규소막(도시되지 않음)을 플라즈마 CVD법으로 형성한 다음, 그 비정질 규소막에 레이저광을 조사하여 결정성 규소막(도시되지 않음)을 얻는다.

결정성 규소막(도시되지 않음)이 얻어진 후, 그것을 패터닝하여, 영역(609, 610, 611)으로 된 활성층 패턴을 형성한다.

그 다음, 게이트 전극(604)을 마스크로 하여 기판(601)의 뒷쪽에서 노광을 행함으로써 레지스트 마스크(612)를 형성한다.(도 6(D) 참조)

이 상태에서, 플라즈마 도핑을 행하여 인(P) 원자를 도핑한다. 그리하여, 이 도핑 공정에서 소스 영역(609), 드레인 영역(611), 채널영 역(610)이 자기정합적으로 형성된다. 그리하여, 도 6(D)에 나타낸 상태가 얻어진다.

상기 도핑 공정의 완료 후, 레이저광 조사를 행하여, 도핑된 원자를 활성화하고 도핑된 영역을 어닐한다.

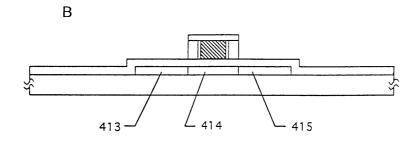

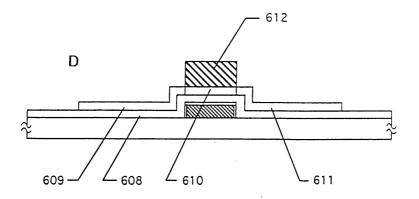

그 다음, 플라즈마 CVD법에 의해 두께 2000 Å의 질화규소막을 형성하여 제1 층간절연막(612)을 제공하고, 그 후, 폴리이미드막을 형성하여 제2 층간절연막(613)을 제공한다. 그리하여, 도 7(A)에 나타낸 상태가 얻어진다.

콘택트 홀을 형성한 후, 소스 전극(614) 및 드레인 전극(615)을 형성한다. 마지막으로, 수소화를 행하여 트랜지스터를 완성한다.

도시되지 않았지만, 다른 부분에서 게이트 전극(604)으로부터 연장한 배선의 상부에 콘택트 홀을 형성함으로써 게이트 전극(604)에 대한 콘택트가 형성된다. 그리하여, 도 7(B)에 나타낸 상태가 얻어진다.

또한, 본 실시예의 구성에서는, 게이트 전극(604)의 측면에 양극산화막이 형성되고 게이트 전극(604)의 상면에 질화규소 막이 형성되어 있기 때문에, 전체적으로 힐록 및 휘스커의 발생이 방지될 수 있다. 또한, 게이트 전극의 상면에 질화규소막 이 형성되어 있기 때문에, 콘택트 홀의 형성이 용이하게 된다.

#### [실시예 5]

본 실시예에서는 스칸듐을 0.18 중량% 함유한 알루미늄막 중의 불순물 농도와 힐록 발생의 관계를 나타낸다. 스퍼터링법에 의해 두께 3000 Å의 알루미늄막을 형성하고, 수소 분위기에서 350℃로 1시간 가열처리를 행하였다. 표 1은 그렇게 하여 얻어진 막 중의 불순물 농도와 관찰된 힐록의 높이의 관계를 나타낸다.

#### 丑 1

| No. | 막 중의 불순물 농도(원자·cm <sup>-3</sup> )(최대치) |                    |                    |                  |  |

|-----|----------------------------------------|--------------------|--------------------|------------------|--|

|     | 산소 농도                                  | 탄소 농도              | 질소 농도              | 힐록의 최대 높이<br>(Å) |  |

| 1   | $2 \times 10^{20}$                     | $9 \times 10^{19}$ | $1 \times 10^{19}$ | 1552             |  |

| 2   | $7 \times 10^{19}$                     | $4 \times 10^{19}$ | $7 \times 10^{18}$ | 1627             |  |

| 3   | $7 \times 10^{19}$                     | $2 \times 10^{19}$ | $5 \times 10^{18}$ | 2472             |  |

| 4   | $1 \times 10^{19}$                     | $8 \times 10^{18}$ | $2 \times 10^{18}$ | 837              |  |

| 5   | $8 \times 10^{18}$                     | $4 \times 10^{18}$ | $6 \times 10^{17}$ | 322              |  |

| 6   | $7 \times 10^{18}$                     | $4 \times 10^{18}$ | $7 \times 10^{17}$ | 481              |  |

| 7   | $7 \times 10^{18}$                     | $5 \times 10^{18}$ | $7 \times 10^{17}$ | 373              |  |

표 1에서, 불순물의 농도는 시료마다 다르다. 이 차이는 스퍼터링 시에 있어서의 배기 시간의 차이, 스퍼터링 장치의 체임 버의 세정 유무, 배기 펌프의 정비(maintenance) 차이와 같은 인자에 기인하여 일어난다. 여기서, 힐록의 높이는 단면 SEM(주사형 전자현미경) 관찰 및 AFM(원자간력 현미경) 관찰에 의해 측정된 것이다. 또한, 불순물 원소의 농도는 SIMS법(이차 이온 질량 분석법)에 의해 측정된 최대 값이다.

막 중에 함유된 산소(O), 탄소(C), 질소(N)의 농도를 감소시킴으로써 힐록의 발생이 억제될 수 있다는 것이 표 1로부터 명백하다.

충간절연막의 막 두께 등의 막 두께를 고려하면, 500 Å 이하의 높이를 가지는 힐록은 실용상 허용 가능하다. 표 1에 의하면, 이 값을 만족시키는 조건으로서, 불순물의 허용 가능한 농도는 산소에 대해서는  $8\times10^{18}$  원자·cm $^{-3}$  이하이고, 탄소에 대해서는  $5\times10^{18}$  원자·cm $^{-3}$  이하이고, 질소에 대해서는  $7\times10^{17}$  원자·cm $^{-3}$  이하이면 되는 것으로 결론지어진다.

불순물 농도의 측정을 위해 SIMS법을 사용할 경우에는, 막의 계면 부근에서 실제와 다른 값이 측정되는 일이 있으므로 주 의해야 한다.

#### (장치의 설명)

이하, 본 발명의 실시예에서 이용되는 장치에 대하여 설명한다. 도 8은 이 장치를 개략적으로 나타낸다. 도 8에 도시된 장치는, 시료를 대기에 노출시키지 않고 다수의 공정을 연속적으로 행할 수 있는 멀티체임버형으로 되어 있다. 각 체임버는 필요로 하는 배기장치를 구비하고 있고, 기밀(氣密) 환경을 유지할 수 있도록 구성되어 있다.

도 8에 도시된 장치는 기판 반입실(804)과 기판 반출실(805)을 포함한다. 카세트(815)내에 수납된 다수의 기판(시료)이 외부로부터 기판 반입실(804)내로 반입된다. 처리가 종료된 기판들은 카세트(816)내에 다시 수납되고, 소정 수의 기판에 대한 공정이 완료된 후, 그러한 기판들을 수납한 카세트(816)가 기판 반출실(805)로부터 외부로 반출된다.

기판 운반실(801)에서는 로봇 팔(814)에 의해 기판(800)을 필요로 하는 체임버로 운반한다.

스퍼터링법에 의해 알루미늄막을 성막하기 위한 알루미늄막 성막실(803)이 제공되어 있고, 이 알루미늄막 성막실(803)은 알루미늄막 중의 불순물 농도를 소정의 수준 이하로 제어하기 위해 크라이오(cryo) 펌프를 구비하고 있다.

콘택트를 형성하는데 있어서 양호한 전기적 콘택트를 실현하기 위해 이용되는 게르마늄(또는 은) 막을 형성하기 위한 스퍼터링실(802)이 제공되어 있다. 이 스퍼터링실(802)도 불순물의 혼입을 최대한 방지하기 위해 크라이오 펌프를 구비하고 있다.

가열처리를 행하기 위한 가열처리실(807)이 제공되어 있고, 이 가열처리실에서는, 램프로부터 방사된 광을 조사함으로써 가열이 행해진다.

플라즈마 CVD법에 의해 질화규소막을 성막하기 위한 질화규소막 성막실(806)도 제공되어 있다.

기판 운반실(801)과 각종 공정을 행하기 위한 각각의 주변 체임버 사이에는, 개폐식의 격벽 또는 칸막이인 게이트 밸브 (810, 809, 808, 813, 812, 811)들이 제공되어 있다.

이하, 도 8에 도시된 장치의 작동 예를 설명한다. 이 장치에서는, 알루미늄막을 성막하는 공정, 게르마늄막을 성막하는 공정, 가열처리 공정, 및 질화규소막을 성막하는 공정을 연속적으로 행한다.

상기 공정들에서, 시료가 통과하는 게이트 밸브만을 제외하고 게이트 밸브들이 모두 폐쇄된다. 먼저, 알루미늄막을 형성하기 위한 다수의 기판(시료)이 카세트(815)내에 수납되어, 기판 반입실(804)내로 반입된다. 그 다음, 로봇 팔(814)에 의해기판이 하나씩 알루미늄막 성막실(803) 내로 운반된다.

알루미늄막 성막실(803) 내에서의 알루미늄막의 성막이 완료된 후, 기판은 그 위에 질화규소막을 형성하기 위해 질화규소막 성막실(806)로 운반된다. 그 다음, 기판이 기판 반출실(805)의 카세트(816)내에 수납되어 일련의 공정이 완료된다.

콘택트 홀의 형성 후 콘택트로서 사용하기 위한 알루미늄막을 형성하는 경우에는, 알루미늄막 성막실(803)에서의 알루미늄막의 성막 후에 스퍼터링실(802)에서 게르마늄막이 성막된 후, 가열처리실(807)에서 가열처리가 행해져, 리플로우 (reflow) 처리, 즉, 콘택트를 형성하기 위한 어닐을 행한다.

리플로우 처리는 알루미늄과 그와 접촉할 전극(즉, 콘택트 홀의 바닥에서 노출된 전극) 사이의 양호한 전기적 콘택트를 제공하는데, 그 이유는 알루미늄과 게르마늄 사이의 접촉부에서 융점이 저하하여, 가열처리에 의해 게르마늄이 알루미늄막속으로 확산하기 때문이다.

### [실시예 6]

본 실시예는 양극산화 대신에, 알루미늄의 표면에 금속 산화막을 형성하기 위해 플라즈마 산화를 이용하는 경우에 관한 것이다. 플라즈마 산화는 감압 산화 분위기에서 고주파 방전을 행함으로써 실시될 수 있다.

## [실시예 7]

본 명세서에 개시된 발명은 액티브 매트릭스형 전기광학장치에 응용될 수 있다. 전기광학장치로서는, 예를 들어, 액정 표시장치, EL(전계 발광) 표시장치 및 EC(일렉트로크로믹) 표시장치를 들 수 있다.

응용되는 제품으로서는, TV 카메라, 퍼스널 컴퓨터, 자동차 네비게이션 시스템, TV 프로젝션 시스템, 비디오 카메라 등을 들 수 있다. 이하, 도 9(A)~도 9(E)에 의거하여 이들 제품에 대하여 간단히 설명한다.

도 9(A)는 본체(2001), 카메라(2002), 표시장치(2003) 및 조작 스위치(2004)를 포함하는 TV 카메라를 나타낸다. 표시장치(2003)는 뷰 파인더로도 사용된다.

도 9(B)는 본체(2101), 커버(2102), 키보드(2103) 및 표시장치(2104)를 포함하는 퍼스널 컴퓨터를 나타낸다. 표시장치(2104)가 모니터로 사용되고, 수 십 인치의 대각선 크기가 요구된다.

도 9(C)는 본체(2301), 표시장치(2302), 조작 스위치(2303) 및 안테나(2304)를 포함하는 자동차 네비게이션 시스템을 나타낸다. 표시장치(2302)가 모니터로 사용되지만, 그의 주 용도는 지도를 나타내는 것이다. 따라서, 해상도의 허용 범위는 비교적 넓다.

도 9(D)는 본체(2401), 광원(2402), 표시장치(2403), 거울(2404, 2405) 및 스크린(2406)을 포함하는 TV 프로젝션 시스템을 나타낸다. 표시장치(2403)에 표시된 화상이 스크린(2406)에 투영되기 때문에, 표시장치(2403)는 높은 해상도를 가져야 한다.

도 9(E)는 본체(2501), 표시장치(2502), 접안부(2503), 조작 스위치(2504) 및 테이프 홀더(2505)를 포함하는 비디오 카메라를 나타낸다. 촬영된 화상이 실시간으로 접안부(2503)를 통해 보여질 수 있기 때문에, 사용자는 화상을 보면서 사진을 찍을 수 있다.

#### 발명의 효과

상기한 바와 같이, 본 발명을 이용함으로써, 알루미늄 배선의 내열성에 관한 문제가 해결될 뿐만 아니라, 양극산화막이 형 성된 경우에 문제가 되는 콘택트의 형성이 용이하게 된다.

상기한 실시예들에서는 게이트 전극과 게이트 선에 알루미늄이 사용되었지만, 본 발명은 알루미늄 대신에 탄탈과 같은 양 극산화 가능한 금속에도 적용될 수 있다.

## (57) 청구의 범위

## 청구항 1.

기판;

상기 기판 위에 형성된 다수의 게이트 선;

상기 기판 위에 형성되고, 상기 다수의 게이트 선과 함께 매트릭스를 형성하는 다수의 소스 선;

상기 게이트 선들 중 하나와 상기 소스 선들 중 하나에 전기적으로 접속된 적어도 하나의 박막트랜지스터; 및

상기 적어도 하나의 박막트랜지스터에 전기적으로 접속된 적어도 하나의 화소전극을 포함하고;

상기 게이트 선들 중 적어도 하나가 알루미늄을 포함하고,  $8\times10^{18}$  원자·cm $^{-3}$  이하의 농도의 산소 원자와,  $5\times10^{18}$  원자·cm $^{-3}$  이하의 농도의 탄소 원자와,  $7\times10^{17}$  원자·cm $^{-3}$  이하의 농도의 질소 원자를 함유하는 것을 특징으로 하는 EL 표시 장치.

## 청구항 2.

기판;

상기 기판 위에 형성된 적어도 하나의 박막트랜지스터;

상기 박막트랜지스터 위에 형성된 층간절연막;

상기 층간절연막 위에 형성되고, 상기 층간절연막의 콘택트 홀을 통해 상기 상기 박막트랜지스터의 소스 또는 드레인에 전 기적으로 접속되어 있으며, 티탄으로 이루어진 제1 막과 알루미늄으로 이루어진 제2 막과 티탄으로 이루어진 제3 막의 적 층 막으로 이루어진 적어도 하나의 전극; 및 상기 적어도 하나의 전극에 전기적으로 접속된 적어도 하나의 화소전극을 포함하고;

상기 박막트랜지스터의 게이트 전극이 알루미늄을 포함하고,  $8\times10^{18}$  원자·cm $^{-3}$  이하의 농도의 산소 원자와,  $5\times10^{18}$  원자·cm $^{-3}$  이하의 농도의 탄소 원자와,  $7\times10^{17}$  원자·cm $^{-3}$  이하의 농도의 질소 원자를 함유하는 것을 특징으로 하는 EL 표시장치.

## 청구항 3.

기판;

상기 기판 위에 형성된 다수의 게이트 선;

상기 기판 위에 형성되고, 상기 다수의 게이트 선과 함께 매트릭스를 형성하는 다수의 소스 선;

상기 게이트 선들 중 하나와 상기 소스 선들 중 하나에 전기적으로 접속된 적어도 하나의 박막트랜지스터; 및

상기 적어도 하나의 박막트랜지스터에 전기적으로 접속된 적어도 하나의 화소전극을 포함하고;

상기 소스 선들 중 적어도 하나가 알루미늄을 포함하고,  $8 \times 10^{18}$  원자·cm $^{-3}$  이하의 농도의 산소 원자와,  $5 \times 10^{18}$  원자·cm $^{-3}$  이하의 농도의 탄소 원자와,  $7 \times 10^{17}$  원자·cm $^{-3}$  이하의 농도의 질소 원자를 함유하는 것을 특징으로 하는 EL 표시 장치.

## 청구항 4.

기판;

상기 기판 위에 형성된 적어도 하나의 박막트랜지스터;

상기 박막트랜지스터 위에 형성된 충간절연막;

상기 충간절연막 위에 형성되고, 상기 충간절연막의 콘택트 홀을 통해 상기 상기 박막트랜지스터의 소스 또는 드레인에 전 기적으로 접속되어 있으며, 한 쌍의 티탄막과 그 티탄막들 사이에 끼어진 알루미늄막으로 이루어진 적어도 하나의 전극; 및

상기 적어도 하나의 전극에 전기적으로 접속된 적어도 하나의 화소전극을 포함하고;

상기 알루미늄막이  $8 \times 10^{18}$  원자·cm $^{-3}$  이하의 농도의 산소 원자와,  $5 \times 10^{18}$  원자·cm $^{-3}$  이하의 농도의 탄소 원자와,  $7 \times 10^{17}$  원자·cm $^{-3}$  이하의 농도의 질소 원자를 함유하는 것을 특징으로 하는 EL 표시장치.

## 청구항 5.

기판;

알루미늄층으로 이루어진 게이트 전극;

상기 게이트 전극 위에 형성된 게이트 절연막; 및

상기 게이트 절연막을 사이에 두고 상기 게이트 전극 위에 위치된 채널영역을 적어도 가지는 반도체층을 포함하고;

상기 알루미늄층이  $8 \times 10^{18}$  원자·cm $^{-3}$  이하의 농도의 산소 원자와,  $5 \times 10^{18}$  원자·cm $^{-3}$  이하의 농도의 탄소 원자와,  $7 \times 10^{17}$  원자·cm $^{-3}$  이하의 농도의 질소 원자를 함유하는 것을 특징으로 하는 EL 표시장치.

## 청구항 6.

기판;

알루미늄층으로 이루어진 게이트 전극;

상기 게이트 전극 위에 형성되고 질화규소로 이루어진 제1 절연막;

상기 제1 절연막 위에 형성된 제2 절연막; 및

상기 제1 및 제2 절연막을 사이에 두고 상기 게이트 전극 위에 위치된 채널영역을 적어도 가지는 반도체층을 포함하고;

상기 알루미늄층이  $8\times10^{18}$  원자·cm $^{-3}$  이하의 농도의 산소 원자와,  $5\times10^{18}$  원자·cm $^{-3}$  이하의 농도의 탄소 원자와,  $7\times10^{17}$  원자·cm $^{-3}$  이하의 농도의 질소 원자를 함유하는 것을 특징으로 하는 EL 표시장치.

## 도면

도면5

도면7

| 专利名称(译)        | EL显示器件                                                                                               |         |            |  |  |

|----------------|------------------------------------------------------------------------------------------------------|---------|------------|--|--|

| 公开(公告)号        | KR100483311B1                                                                                        | 公开(公告)日 | 2005-04-06 |  |  |

| 申请号            | KR1020020040201                                                                                      | 申请日     | 2002-07-11 |  |  |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                                                                         |         |            |  |  |

| 申请(专利权)人(译)    | 株式会社绒布器肯kyusyo极限戴哦                                                                                   |         |            |  |  |

| 当前申请(专利权)人(译)  | 株式会社绒布器肯kyusyo极限戴哦                                                                                   |         |            |  |  |

| [标]发明人         | YAMAZAKI SHUNPEI<br>야마자끼순페이<br>TERAMOTO SATOSHI<br>데라모토사토시                                           |         |            |  |  |

| 发明人            | 야마자끼순페이<br>데라모토사토시                                                                                   |         |            |  |  |

| IPC分类号         | H05B33/00                                                                                            |         |            |  |  |

| CPC分类号         | H01L23/53214 H01L27/1214 H01L29/458 H01L29/4908 H01L29/66757 H01L29/66765 H01L29/78621 H01L2924/0002 |         |            |  |  |

| 优先权            | 1996205417 1996-07-16 JP                                                                             |         |            |  |  |

| 外部链接           | <u>Espacenet</u>                                                                                     |         |            |  |  |

|                |                                                                                                      |         |            |  |  |

## 摘要(译)

提供一种EL显示器件,包括其电极和导线由铝或以铝为主要成分的材料制成的半导体器件,从而解决了与铝导线的耐热性能有关的问题,同时易于形成接触。在基板(101)上形成多条栅极线。多个源极线形成在基板(101)上,并配置具有多条栅极线的矩阵。至少一个TFT(薄膜晶体管)电连接到栅极线之一和源极线之一。至少一个像素电极电连接到至少一个TFT。至少一条栅极线包括铝。