**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl.

H01L 27/115 (2006.01)

(45) 공고일자

2007년07월24일

(11) 등록번호

10-0742369

(24) 등록일자

2007년07월18일

(21) 출원번호 10-2005-0109256

(22) 출원일자 2005년11월15일

심사청구일자 2005년11월15일

(65) 공개번호

10-2007-0051548

(43) 공개일자

2007년05월18일

(73) 특허권자 삼성에스디아이 주식회사

경기 수원시 영통구 신동 575

(72) 발명자 최대철

경기 용인시 기흥읍 공세리 삼성SDI중앙연구소

최병덕

경기 용인시 기흥읍 공세리 삼성SDI중앙연구소

박혜향

경기 용인시 기흥읍 공세리 삼성SDI중앙연구소

정주연

경기 용인시 기흥읍 공세리 삼성SDI중앙연구소

박현선

경기 용인시 기흥읍 공세리 삼성SDI중앙연구소

(74) 대리인 박상수

(56) 선행기술조사문헌

|                   |                   |

|-------------------|-------------------|

| US 5962891        | KR1020000004233 A |

| KR1020030054684 A | KR1020040054143 A |

| KR1020040059382 A |                   |

**심사관 : 홍경희**

전체 청구항 수 : 총 9 항

**(54) 비휘발성 메모리 소자 및 이를 포함하는 유기 전계 발광표시 장치****(57) 요약**

본 발명은 기판상에 소오스 영역에 비해 불순물이 도핑된 영역이 얇은 드레인 영역을 포함하는 반도체층과 드레인 영역과 가까운 영역의 두께가 얇은 제1게이트 절연막을 포함하는 비휘발성 메모리 소자가 형성되어 있고, 상기 비휘발성 메모리 소자를 포함하는 유기 전계 발광 표시 장치를 포함하고 있는 비휘발성 메모리 소자 및 이를 포함하는 유기 전계 발광 표시 장치에 관한 것이다.

**대표도**

도 1

**특허청구의 범위****청구항 1.**

기판;

상기 기판상에 위치하고, 소오스 영역, 상기 소오스 영역에 비해 불순물 주입 영역의 깊이가 상대적으로 얕은 드레인 영역 및 상기 소오스 영역과 드레인 영역 사이에 위치한 채널 영역을 포함하는 반도체층;

상기 반도체층상에 위치하고, 상기 드레인 영역에 가까운 영역이 상기 소오스 영역에 가까운 영역에 비해 두께가 얕은 제1 게이트 절연막; 및

상기 제1게이트 절연막상에 위치한 제1게이트 전극, 제2게이트 절연막 및 제2게이트 전극

을 포함하는 것을 특징으로 하는 비휘발성 메모리 소자.

**청구항 2.**

제 1 항에 있어서,

상기 반도체층은 다결정 실리콘층인 것을 특징으로 하는 비휘발성 메모리 소자.

**청구항 3.**

제 2 항에 있어서,

상기 다결정 실리콘층은 RTA법, SPC법, MIC법, MILC법, SGS법, ELA법 및 SLS법 중 어느 하나를 이용하여 형성된 다결정 실리콘층인 것을 특징으로 하는 비휘발성 메모리 소자.

**청구항 4.**

제 1 항에 있어서,

상기 제1게이트 전극은 플로팅 게이트인 것을 특징으로 하는 비휘발성 메모리 소자.

**청구항 5.**

제 1 항에 있어서,

상기 제2게이트 전극은 컨트롤 게이트인 것을 특징으로 하는 비휘발성 메모리 소자.

## 청구항 6.

기판;

상기 기판상에 위치하고, 제1전극, 유기 발광층을 포함하는 유기막층 및 제2전극을 포함하는 표시 영역; 및

상기 표시 영역의 제1전극 또는 제2전극과 전기적으로 연결되고, 상기 표시 영역과 이격된 영역상에 위치하는 비휘발성 메모리 소자를 포함하며,

상기 비휘발성 메모리 소자는 소오스 영역, 상기 소오스 영역에 의해 불순물 주입 영역의 깊이가 상대적으로 얇은 드레인 영역 및 상기 소오스 영역과 드레인 영역 사이에 위치한 채널 영역을 포함하는 반도체층;

상기 반도체층상에 위치하고, 상기 드레인 영역에 가까운 영역이 상기 소오스 영역에 가까운 영역에 의해 두께가 얇은 제1 게이트 절연막; 및

상기 제1게이트 절연막상에 위치한 제1게이트 전극, 제2게이트 절연막 및 제2게이트 전극을 포함하여 이루어져 있는 것을 특징으로 하는 비휘발성 메모리 소자를 포함하는 유기 전계 발광 표시 장치.

## 청구항 7.

제 6 항에 있어서,

상기 표시 영역에는 상기 표시 영역의 제1전극과 상기 비휘발성 메모리 소자 사이에 연결되고, 반도체층, 게이트 절연막, 게이트 전극, 충간절연막 및 소오스/드레인 전극을 포함하는 박막트랜지스터를 더 포함하는 것을 특징으로 하는 비휘발성 메모리 소자를 포함하는 유기 전계 발광 표시 장치.

## 청구항 8.

제 7 항에 있어서,

상기 박막트랜지스터의 반도체층은 상기 비휘발성 메모리 소자의 반도체층과 동일한 결정화법으로 결정화된 반도체층인 것을 특징으로 하는 비휘발성 메모리 소자를 포함하는 유기 전계 발광 표시 장치.

## 청구항 9.

제 7 항에 있어서,

상기 박막트랜지스터의 게이트 전극은 상기 비휘발성 메모리 소자의 제2게이트 전극과 동일한 물질로 이루어져 있는 것을 특징으로 하는 비휘발성 메모리 소자를 포함하는 유기 전계 발광 표시 장치.

**명세서**

### 발명의 상세한 설명

#### 발명의 목적

발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 비휘발성 메모리 소자 및 이를 포함하는 유기 전계 발광 표시 장치에 관한 것으로, 보다 자세하게는 기판상에 소오스 영역에 의해 불순물이 도핑된 영역이 얇은 드레인 영역을 포함하는 반도체층과 드레인 영역과 가까운 영역의 두께가 얇은 제1게이트 절연막을 포함하는 비휘발성 메모리 소자 및 상기 비휘발성 메모리 소자를 포함하고 있는 유기 전계 발광 표시 장치에 관한 것이다.

일반적으로, 메모리 소자는 전원이 끊어졌을 때, 정보가 사라지는 휘발성 메모리 소자(Volatile memory device)와 전원이 끊어져도 정보가 남아 있는 비휘발성 메모리 소자(Nonvolatile memory device)로 구분할 수 있다. 이때, 상기 휘발성 메모리 소자는 대표적으로 DRAM(Dynamic Random Access Memory)과 SRAM(Static Random Access Memory)가 있고, 상기 비휘발성 메모리 소자는 대표적으로 플래시 메모리(Flash Memory)가 있다.

이때, 상기 플래시 메모리는 반도체 기판 상에 터널 산화막(Tunnel Oxide), 플로팅 게이트(Floating Gate), 상부 게이트 절연막, 컨트롤 게이트(Control Gate)를 순차적으로 적층한 후 식각하여 형성한다.

이때, 상기 플로팅 게이트는 상기 터널 산화막과 상부 게이트 절연막 사이에서 고립된 상태로 존재하게 되고, 상기 컨트롤 게이트에 인가되는 전압에 따라 정보를 저장하거나 지우거나 읽을 수 있게 된다.

그러나, 상기의 플래시 메모리는 단결정 실리콘으로 이루어진 웨이퍼 기판상에 형성됨으로서 메모리의 특성은 우수하나, 다른 장치, 예를 들어, 표시 장치와 결합되기 위해서는 별도의 연결장치 또는 구성이 필요하다는 단점이 있다.

또한, 종래의 플래시 메모리는 쓰기(Programming) 시 터널 산화막과 반도체층의 계면에 손상이 발생하기 쉬울 뿐만 아니라 지우기(Erasing) 시 컨트롤 게이트에 쓰기 또는 읽기(Reading) 시 보다 상대적으로 고전압을 인가해야 하는 문제점이 있다.

### 발명이 이루고자 하는 기술적 과제

따라서, 본 발명은 상기와 같은 종래 기술의 제반 단점과 문제점을 해결하기 위한 것으로, 비휘발성 메모리 소자를 유기 전계 발광 소자와 같은 평판 표시 장치가 형성되는 기판상에 형성하고, 소오스 영역이 드레인 영역 보다 불순물 주입 영역이 깊게 되도록 형성하고, 드레인 영역과 가까운 터널 산화막을 다른 영역에 의해 얕게 형성함으로서 평판 표시 장치에 직접 메모리 소자를 직접 구현할 수 있을 뿐만 아니라 쓰기 및 지우기 동작을 용이하게 할 수 있는 비휘발성 메모리 및 이를 포함하는 유기 전계 발광 소자를 제공함에 본 발명의 목적이 있다.

### 발명의 구성

본 발명의 상기 목적은 기판; 상기 기판상에 위치하고, 소오스 영역, 상기 소오스 영역에 의해 불순물 주입 영역의 깊이가 상대적으로 얕은 드레인 영역 및 상기 소오스 영역과 드레인 영역 사이에 위치한 채널 영역을 포함하는 반도체층; 상기 반도체층상에 위치하고, 상기 드레인 영역에 가까운 영역이 상기 소오스 영역에 가까운 영역에 의해 두께가 얇은 제1게이트 절연막; 및 상기 제1게이트 절연막상에 위치한 제1게이트 전극, 제2게이트 절연막 및 제2게이트 전극으로 이루어진 비휘발성 메모리 소자에 의해 달성된다.

또한, 본 발명의 상기 목적은 기판; 상기 기판상에 위치하고, 제1전극, 적어도 유기 발광층을 포함하는 유기막층 및 제2전극을 포함하는 표시 영역; 및 상기 표시 영역의 제1전극 또는 제2전극과 전기적으로 연결되고, 상기 표시 영역과 이격된 영역상에 위치하는 비휘발성 메모리 소자를 포함하며, 상기 비휘발성 메모리 소자는 소오스 영역, 상기 소오스 영역에 의해 불순물 주입 영역의 깊이가 상대적으로 얕은 드레인 영역 및 상기 소오스 영역과 드레인 영역 사이에 위치한 채널 영역을 포함하는 반도체층; 상기 반도체층상에 위치하고, 상기 드레인 영역에 가까운 영역이 상기 소오스 영역에 가까운 영역에 의해 두께가 얇은 제1게이트 절연막; 및 상기 제1게이트 절연막상에 위치한 제1게이트 전극, 제2게이트 절연막 및 제2게이트 전극으로 이루어진 비휘발성 메모리 소자를 포함하는 유기 전계 발광 표시 장치에 의해서도 달성된다.

본 발명의 상기 목적과 기술적 구성 및 그에 따른 작용효과에 관한 자세한 사항은 본 발명의 바람직한 실시예를 도시하고 있는 도면을 참조한 이하 상세한 설명에 의해 보다 명확하게 이해될 것이다. 또한 도면들에 있어서, 층 및 영역의 길이, 두께등은 편의를 위하여 과장되어 표현될 수도 있다. 명세서 전체에 걸쳐서 동일한 참조번호들은 동일한 구성요소들을 나타낸다.

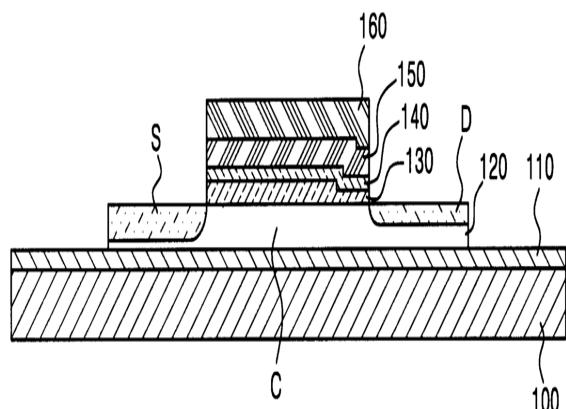

도 1은 본 발명의 일 실시 예에 따른 비휘발성 메모리 소자의 단면도이다.

도 1을 참조하여 설명하면, 유리 또는 플라스틱과 같은 투명한 기판(100)상에 베피층(110)이 위치한다.

상기 베피층(110)상에 소오스 영역(S), 드레인 영역(D) 및 채널 영역(C)을 포함하는 반도체층(120)이 위치한다.

또한, 상기 반도체층(120)상에 터널 산화막의 역할을 하는 제1게이트 절연막(130), 플로팅 게이트의 역할을 하는 제1게이트 전극(140), 상부 게이트 절연막의 역할을 하는 제2게이트 절연막(150) 및 컨트롤 게이트의 역할을 하는 제2게이트 전극(160)이 위치한다.

이때, 상기 반도체층(120)의 소오스 영역(S)의 불순물 주입 영역은 상기 드레인 영역(D)의 불순물 주입 영역에 비해 깊게 형성, 즉, 상기 드레인 영역(D)이 상기 소오스(S)에 비해 상대적으로 얕게 형성되어 있어 쓰기(즉, 프로그래밍) 시 소오스 영역(S)과 채널 영역(C)의 접합(Junction) 영역과 상기 제1게이트 절연막(130)과 채널 영역(C)의 계면(Interface) 사이에 발생하는 손상을 줄일 수 있다.

이때, 상기 제1게이트 절연막(130)은 실리콘 산화막을 사용하는 것이 바람직하며, 두께는 50 내지 300 Å의 두께로 형성 한다. 상기 제1 게이트 절연막의 두께가 50 Å이면, 제 1 게이트 절연막의 열화가 너무 빨리 일어나서 소자 수명이 짧게 되고, 두께가 300 Å보다 크게 되면 전자의 이동이 방지되어 쓰기 효율이 떨어진다는 문제점이 있다.

또한, 상기 제1게이트 절연막(130)은 도 1에서 도시된 바와 같이 드레인 영역(D)에 가까운 영역에서는 다른 영역에 비해 두께가 얕게 형성되어 있다. 이는 지우기 동작 시 컨트롤 게이트(160)에 가장 높은 전압이 걸리게 되는데, 상기 컨트롤 게이트(160)에 인가되는 전압의 크기는 상기 제1게이트 절연막(130)의 특성(특히, 드레인 영역(D)에 가까운 제1게이트 절연막의 두께)에 영향을 받게 된다. 즉, 상기 제1게이트 절연막(130)의 두께가 얇을수록 지우기 동작시 입력되는 전압의 크기는 작아지게 된다.

한편, 상기 제2게이트 절연막(150)은 컨트롤 옥사이드로 작용하며, 두께는 절연성을 만족하면서 공정 조건을 고려하여 50 내지 1,000 Å의 두께로 형성하는 것이 바람직하다. 상기 제2게이트 절연막 역시 실리콘 산화막으로 형성될 수 있다.

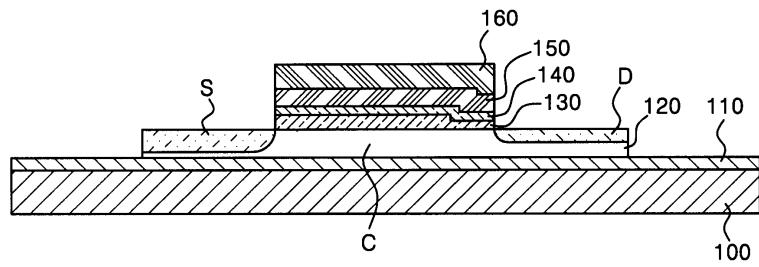

도 2는 본 발명의 일 실시 예에 따른 비휘발성 메모리 소자의 전기적인 특성을 나타내는 그래프이다.

도 2를 참조하여 설명하면, 상기 비휘발성 메모리 소자에 아무런 정보를 저장하고 있지 않은 경우, 즉, 초기 상태(Initial State)이거나 지우기 동작을 실행한 경우의 I-V 곡선(E)에 비해 정보를 저장하고 있는 경우, 즉, 쓰기 동작을 실행한 경우의 I-V 곡선(P)이 오른쪽으로 이동(Shift)되어 있는 것을 볼 수 있다.

이는 상기 비휘발성 메모리 소자가 정보를 저장하고 있는 경우에는 같은 전압이 컨트롤 게이트상에 인가되었을 때, 정보를 저장하고 있지 않은 경우에 비해 낮은 전류 값을 나타낸다는 뜻이다. 반대로, 동일한 전류 값을 얻기 위해서 정보를 저장하고 있는 경우에는 더 높은 전압이 인가되어야 한다는 것을 의미한다.

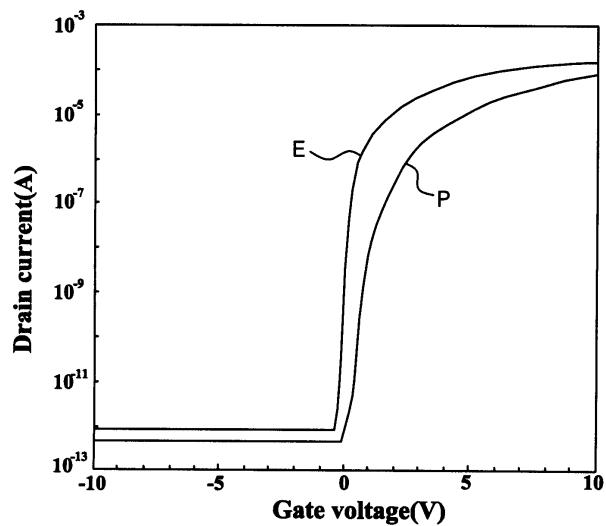

도 3은 본 발명의 일 실시 예에 따른 비휘발성 메모리 소자를 포함하는 유기 전계 발광 소자의 단면도이다.

도 3을 참조하여 설명하면, 유리 또는 플라스틱과 같은 투명한 기판(200)상에 베피층(210)이 위치한다.

이때, 상기 베피층(210)은 상기 기판(200)에서 발생하는 수분 또는 불순물의 확산을 방지하거나, 결정화 시 열의 전달의 속도를 조절함으로서, 반도체층의 결정화가 잘 이루어질 수 있도록 하는 역할을 한다.

상기 베피층(210)상에 표시 영역(300) 및 메모리 영역(400)상에 각각 박막트랜지스터의 반도체층(310) 및 메모리 영역의 반도체층(410)이 위치한다.

이때, 상기 표시 영역(300)의 반도체층(310)은 불순물 주입 영역의 깊이가 거의 동일한 소오스/드레인 영역(312,314)가 형성되어 있는 반면, 메모리 영역(400)의 반도체층(410)의 소오스/드레인 영역(412,414)은 소오스 영역(412)가 드레인 영역(414)보다 깊게 형성되어 있다.

또한, 상기 표시 영역(300)의 소오스/드레인 영역(312,314)의 불순물 주입 영역의 깊이는 상기 메모리 영역(400)의 소오스 영역(412) 또는 드레인 영역(414) 중 어느 하나와 동일한 깊이일 수 있다.

또한, 상기 표시 영역(300)의 반도체층(310) 및 메모리 영역(400)의 반도체층(410)은 RTA법(Rapid Thermal Annealing), SPC법(Solid Phase Crystallization), ELA법(Excimer Laser Crystallization), MIC법(Metal Induced Crystallization), MILC법(Metal Induced Lateral Crystallization), SGS법(Super Grain Silicon) 및 SLS법(Sequential Lateral Solidification) 중 어느 하나의 결정화법을 이용하여 형성된 다결정 실리콘층을 각각 패터닝하여 형성함으로서 동일한 결정성 및 특성을 나타낼 수 있다.

이때, 상기 SGS법은 비정질 실리콘층상에 금속 촉매가 확산할 수 있는 절연막으로 캡핑층을 형성하고, 상기 캡핑층상에 Ni 등과 같이 비정질 실리콘을 결정화할 수 있는 금속 촉매로 금속 촉매층을 형성한 후, 열처리함으로써, 캡핑층상에 위치한 금속 촉매가 비정질 실리콘층으로 확산하고, 확산된 금속 촉매에 의해 비정질 실리콘층이 다결정 실리콘층으로 결정화되는 결정화법을 말한다.

상기 표시 영역(300)의 반도체층(310)상에 게이트 절연막(320) 및 상기 반도체층(310)의 채널 영역(316)에 대응하는 위치에 게이트 전극(330)이 위치하고 있는 반면, 상기 메모리 영역(400)상의 반도체층(410)의 채널 영역(416)에 대응하는 위치에 제1게이트 절연막(422), 제1게이트 전극(424), 제2게이트 절연막(426) 및 제2게이트 전극(428)이 위치하고, 상기 제1게이트 절연막(422), 제1게이트 전극(424), 제2게이트 절연막(426) 및 제2게이트 전극(428)의 측면상에 이들을 보호하는 스페이서(430)가 위치한다.

이때, 상기 표시 영역(300)의 게이트 절연막(320)과 상기 메모리 영역(400)의 제1게이트 절연막(422)은 동일한 물질로 동시에 형성될 수도 있다.

또한, 상기 표시 영역(300)의 게이트 전극(330)과 상기 메모리 영역(400)의 제2게이트 전극(428)은 동일한 물질로 동시에 형성될 수도 있다.

상기 표시 영역(300)의 게이트 전극(330) 및 상기 메모리 영역(400)의 제2게이트 전극(428)상에 충간절연막(340,440)이 위치할 수 있다.

이때, 상기 충간절연막(340,440)은 같은 물질로 한번에 형성될 수 도 있고, 각기 다른 물질로 형성할 수도 있다.

상기 충간절연막(340,440)상에 각각 상기 표시 영역(300)의 충간절연막(340) 및 게이트 절연막(320)의 소정 영역이 식각되어 노출된 반도체층(310)의 소오스/드레인 영역(312,314)과 콘택하는 소오스/드레인 전극(350) 및 상기 메모리 영역(400)의 충간절연막(340)의 소정 영역이 식각되어 노출된 반도체층(410)의 소오스/드레인 영역(412,414)과 콘택하는 소오스/드레인 전극(450)이 위치한다.

이때, 상기 표시 영역(300)의 소오스/드레인 전극(350)과 메모리 영역(400)의 소오스/드레인 전극(450)은 동일한 물질로 동시에 형성될 수 있다.

따라서, 상기 표시 영역(300)상에는 박막트랜지스터가 위치하게 되고, 메모리 영역(400)상에는 비휘발성 메모리가 위치하게 된다.

상기 소오스/드레인 전극(350,450)들이 위치하는 기판상에 평탄화층(360,460)이 위치할 수 있다.

상기 표시 영역(300)의 상기 평탄화층(360)의 일부를 식각하여 노출된 상기 소오스/드레인 전극(350)과 콘택하는 제1전극(370)이 위치하고, 상기 제1전극(370)의 소정 영역을 노출시키는 화소 정의막(380,480)이 상기 평탄화층(360,460)상에 위치할 수 있다.

이때, 도에서는 도시하지 않았지만, 상기 표시 영역(300)의 상기 제1전극(370)상에 적어도 유기 발광층을 포함하는 유기 막층 및 제2전극이 위치할 수 있다.

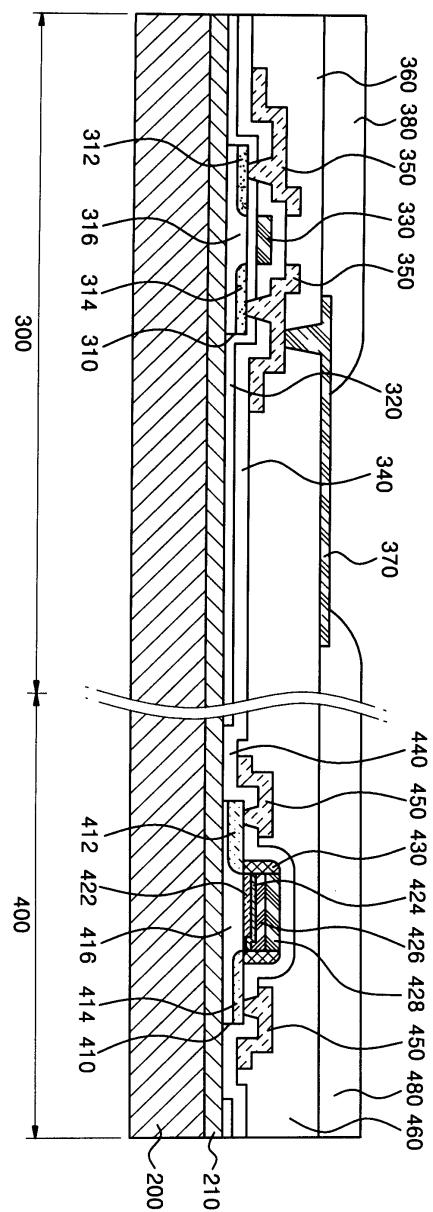

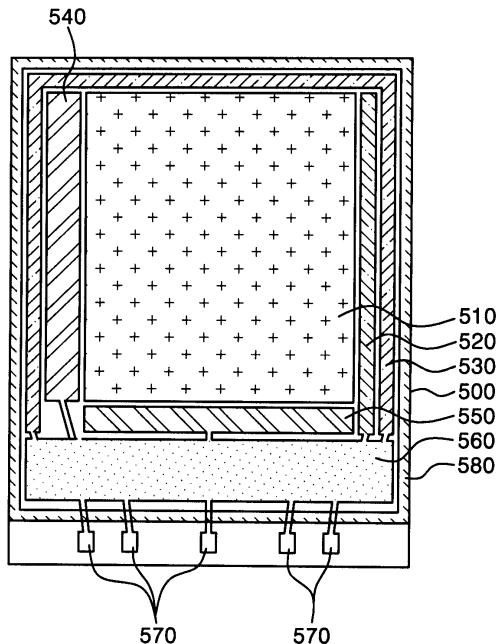

도 4는 본 발명의 일 실시 예에 따른 비휘발성 메모리 소자를 포함하는 유기 전계 발광 소자의 평면도이다.

도 4을 참조하여 설명하면, 유리 또는 플라스틱과 같은 절연 기판(500)상에 제1전극, 적어도 유기 발광층을 포함하는 유기 막층 및 제2전극을 포함하고 있는 표시 영역(510)이 위치한다.

상기 표시 영역(510) 외각에는 표시 영역(510)에 전원을 공급하기 위한 공통전원 버스 라인(520) 및 캐소드 버스 라인(530)과 표시 영역(510)에 신호를 공급하기 위한 스캔 드라이버(540) 및 데이터 드라이버(550)이 위치하고 있다.

또한, 상기 표시 영역(510)에 전원 또는 신호를 공급하는 공통전원 버스 라인(520), 캐소드 버스 라인(530), 스캔 드라이버(540) 및 데이터 드라이버(550)와 연결된 플래시 메모리와 같은 비휘발성 메모리를 포함하는 메모리 영역(560)이 상기 표시 영역(510)의 외각에 위치하고 있다.

또한, 외부 장치에서 상기 공통전원 버스 라인(520), 캐소드 버스 라인(530), 스캔 드라이버(540), 데이터 드라이버(550) 또는 메모리 영역(560)에 신호 또는 전원을 공급하기 위한 접촉부인 패드(570)가 가장 외각에 위치하고 있다.

또한, 상기 표시 영역(510), 공통전원 버스 라인(520), 캐소드 버스 라인(530), 스캔 드라이버(540), 데이터 드라이버(550) 및 메모리 영역(560)을 감싸도록 위치하고, 봉지 기판(도시 안함)을 봉지하기 위한 실링부(580)가 기판의 가장자리에 위치하고 있다.

따라서, 상기 표시 영역(510), 공통전원 버스 라인(520), 캐소드 버스 라인(530), 스캔 드라이버(540) 및 데이터 드라이버(550) 등의 유기 전계 발광 표시 장치와 패드(570) 사이에 위치한 메모리 영역(560)에는 비휘발성 메모리 소자가 위치하고 있어, 상기 패드(570)를 통해 입력되는 신호 또는 전원 등의 신호를 저장하거나, 상기 패드(570)를 통해 입력되는 신호 또는 전원 등에 의해 비휘발성 메모리 소자에 저장되어 있는 신호 등을 전기적으로 연결되어 있는 상기 공통전원 버스 라인(520), 캐소드 버스 라인(530), 스캔 드라이버(540) 및 데이터 드라이버(550) 등을 통해 상기 표시 영역(510)의 박막트랜지스터, 제1전극 또는 제2전극으로 전달할 수 있다.

본 발명은 이상에서 살펴본 바와 같이 바람직한 실시예를 들어 도시하고 설명하였으나, 상기한 실시 예에 한정되지 아니하며 본 발명의 정신을 벗어나지 않는 범위 내에서 당해 발명이 속하는 기술분야에서 통상의 지식을 가진 자에 의해 다양한 변경과 수정이 가능할 것이다.

### 발명의 효과

따라서, 본 발명의 비휘발성 메모리 소자 및 이를 포함하는 유기 전계 발광 표시 장치는 평판 표시 장치에 직접 비휘발성 메모리 소자를 직접 구현할 수 있을 뿐만 아니라 쓰기 및 지우기 동작을 용이하게 할 수 있는 효과가 있다.

### 도면의 간단한 설명

도 1은 본 발명의 일 실시 예에 따른 비휘발성 메모리 소자의 단면도이다.

도 2는 본 발명의 일 실시 예에 따른 비휘발성 메모리 소자의 전기적인 특성을 나타내는 그래프이다.

도 3은 본 발명의 일 실시 예에 따른 비휘발성 메모리 소자를 포함하는 유기 전계 발광 소자의 단면도이다.

도 4는 본 발명의 일 실시 예에 따른 비휘발성 메모리 소자를 포함하는 유기 전계 발광 소자의 평면도이다.

<도면의 주요부분에 대한 부호의 설명>

100 : 기판 120 : 반도체층

130 : 제1게이트 절연막 140 : 제1게이트 전극

150 : 제2게이트 절연막 160 : 제2게이트 전극

### 도면

도면1

도면2

도면3

도면4

|               |                                                                                                                         |         |            |

|---------------|-------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)       | 非易失性存储器件和包括其的有机发光显示器件                                                                                                   |         |            |

| 公开(公告)号       | <a href="#">KR100742369B1</a>                                                                                           | 公开(公告)日 | 2007-07-24 |

| 申请号           | KR1020050109256                                                                                                         | 申请日     | 2005-11-15 |

| 申请(专利权)人(译)   | 三星SD眼有限公司                                                                                                               |         |            |

| 当前申请(专利权)人(译) | 三星SD眼有限公司                                                                                                               |         |            |

| [标]发明人        | CHOI DAE CHUL<br>최대철<br>CHOI BYOUNG DEOG<br>최병덕<br>PARK HYE HYANG<br>박혜향<br>JUNG JU YEUN<br>정주연<br>PARK HYUN SUN<br>박현선 |         |            |

| 发明人           | 최대철<br>최병덕<br>박혜향<br>정주연<br>박현선                                                                                         |         |            |

| IPC分类号        | H01L27/115                                                                                                              |         |            |

| 代理人(译)        | PARK , 常树                                                                                                               |         |            |

| 其他公开文献        | KR1020070051548A                                                                                                        |         |            |

| 外部链接          | <a href="#">Espacenet</a>                                                                                               |         |            |

### 摘要(译)

目的：提供一种非易失性存储器件和具有该非易失性存储器件的有机电致发光显示器件，以将存储器件直接体现在平板显示器件中，并通过使用半导体层的不均匀掺杂结构和不均匀厚度来执行容易的写入和读取操作。第一栅极绝缘层的一部分。