## 특허청구의 범위

### 청구항 1

흐르는 전류에 의해 회도가 변화되는 전기 광학 소자를 구동하는 화소 회로로서,

회도 정보에 따른 데이터 신호가 공급되는 데이터선과,

제1, 제2, 제3, 및 제4 노드와,

제1 및 제2 기준 전위와,

소정의 기준 전류를 공급하는 기준 전류 공급 수단과,

상기 제2 노드에 접속된 전기적 접속 수단과,

상기 제1 노드와 상기 제2 노드 사이에 접속된 화소 용량 소자와,

상기 전기적 접속 수단과 상기 제4 노드 사이에 접속된 결합 용량 소자와,

제1 단자와 제2 단자간에서 전류 공급 라인을 형성하고, 상기 제2 노드에 접속된 제어 단자의 전위에 따라 상기 전류 공급 라인에서 흐르는 전류를 제어하는 구동 트랜지스터와,

상기 제1 노드와 상기 제3 노드 사이에 접속된 제1 스위치와,

상기 제3 노드와 상기 제4 노드 사이에 접속된 제2 스위치와,

상기 제1 노드와 고정 전위 사이에 접속된 제3 스위치와,

상기 제2 노드와 소정의 전위선 사이에 접속된 제4 스위치와,

상기 데이터선과 상기 제4 노드 사이에 접속된 제5 스위치와,

상기 제3 노드와 상기 기준 전류 공급 수단 사이에 접속된 제6 스위치를 포함하고,

상기 제1 기준 전위와 제2 기준 전위 사이에, 상기 구동 트랜지스터의 전류 공급 라인, 상기 제3 노드, 상기 제1 스위치, 상기 제1 노드 및 상기 전기 광학 소자가 직렬로 접속되어 있는 화소 회로.

### 청구항 2

제1항에 있어서,

상기 전기적 접속 수단은 상기 제2 노드와 상기 결합 용량 소자를 직접 접속하는 배선을 포함하는 화소 회로.

### 청구항 3

제1항에 있어서,

상기 전기적 접속 수단은 상기 제2 노드와 상기 결합 용량 소자를 선택적으로 접속하는 제7 스위치를 포함하는 화소 회로.

### 청구항 4

제1항에 있어서,

상기 제1 노드와 상기 전기 광학 소자 사이에 접속된 제7 스위치와,

상기 제1 노드와 상기 데이터선 사이에 접속된 제8 스위치를 포함하는 화소 회로.

### 청구항 5

제1항에 있어서,

상기 제1 노드와 상기 전기 광학 소자 사이에 접속된 제7 스위치와,

상기 제1 노드와 상기 제4 노드 사이에 접속된 제8 스위치를 포함하는 화소 회로.

#### 청구항 6

제3항에 있어서,

상기 제1 노드와 상기 전기 광학 소자 사이에 접속된 제8 스위치와,

상기 제1 노드와 상기 데이터선 사이에 접속된 제9 스위치를 포함하는 화소 회로.

#### 청구항 7

제3항에 있어서,

상기 제1 노드와 상기 전기 광학 소자 사이에 접속된 제8 스위치와,

상기 제1 노드와 상기 제4 노드 사이에 접속된 제9 스위치를 포함하는 화소 회로.

#### 청구항 8

제1항에 있어서,

상기 소정의 전위선은 상기 데이터선과 공용되어 있는 화소 회로.

#### 청구항 9

제1항에 있어서,

상기 구동 트랜지스터가 전계 효과 트랜지스터이며, 소스가 상기 제3 노드에 접속되고, 드레인이 상기 제1 기준 전위에 접속되어 있는 화소 회로.

#### 청구항 10

제2항에 있어서,

상기 전기 광학 소자를 구동하는 경우,

제1 스테이지로서, 상기 제1, 제2, 제4, 제5 및 제6 스위치가 비도통 상태로 유지된 상태에서, 상기 제3 스위치가 도통 상태로 유지되어, 상기 제1 노드가 고정 전위에 접속되며,

제2 스테이지로서, 상기 제2, 제4, 및 상기 제6 스위치가 도통 상태로 유지되어, 소정 전위를 상기 제2 노드에 입력시켜, 기준 전류를 상기 제3 노드에 흘려, 화소 용량 소자에 소정 전위를 충전하며,

제3 스테이지로서, 상기 제2 및 제6 스위치가 비도통 상태로 유지되고, 또한 제4 스위치가 비도통 상태로 유지되고, 상기 제5 스위치가 도통 상태로 유지되어 상기 데이터선에서 전파되는 데이터가 상기 제2 노드에 입력된 후, 상기 제5 스위치가 비도통 상태로 유지되며,

제4 스테이지로서, 상기 제1 스위치가 도통 상태로 유지되고, 상기 제3 스위치가 비도통 상태로 유지되는 화소 회로.

#### 청구항 11

제3항에 있어서,

상기 전기 광학 소자를 구동하는 경우,

제1 스테이지로서, 상기 제1, 제2, 제4, 제5, 제6, 및 제7 스위치가 비도통 상태로 유지된 상태에서, 상기 제3 스위치가 도통 상태로 유지되어, 상기 제1 노드가 고정 전위에 접속되며,

제2 스테이지로서, 상기 제2, 제4, 제6, 및 제7 스위치가 도통 상태로 유지되어, 상기 데이터선에서 전파되는 데이터 전위를 상기 제2 노드에 입력시켜, 기준 전류를 상기 제3 노드에 흘려, 화소 용량 소자에 소정 전위를 충전하며,

제3 스테이지로서, 상기 제2 및 제6 스위치가 비도통 상태로 유지되고, 또한 제4 스위치가 비도통 상태로 유지되고, 상기 제5 스위치가 도통 상태로 유지되어 상기 데이터선에서 전파되는 데이터가 상기 제4 노드를 통하여

제2 노드에 입력된 후, 상기 제5 및 제7 스위치가 비도통 상태로 유지되며,

제4 스테이지로서, 상기 제1 스위치가 도통 상태로 유지되고, 상기 제3 스위치가 비도통 상태로 유지되는 화소 회로.

### 청구항 12

매트릭스 형상으로 복수 배열된 화소 회로와,

상기 화소 회로의 매트릭스 배열에 대해 열마다 배선되며, 휘도 정보에 따른 데이터 신호가 공급되는 데이터선과,

제1 및 제2 기준 전위와,

소정의 기준 전류를 공급하는 기준 전류 공급 수단을 포함하고,

상기 화소 회로는,

흐르는 전류에 의해 휘도가 변화되는 전기 광학 소자와,

제1, 제2, 제3, 및 제4 노드와,

상기 제2 노드에 접속된 전기적 접속 수단과,

상기 제1 노드와 상기 제2 노드 사이에 접속된 화소 용량 소자와,

상기 전기적 접속 수단과 상기 제4 노드 사이에 접속된 결합 용량 소자와,

제1 단자와 제2 단자간에서 전류 공급 라인을 형성하고, 상기 제2 노드에 접속된 제어 단자의 전위에 따라 상기 전류 공급 라인에서 흐르는 전류를 제어하는 구동 트랜지스터와,

상기 제1 노드와 상기 제3 노드 사이에 접속된 제1 스위치와,

상기 제3 노드와 상기 제4 노드 사이에 접속된 제2 스위치와,

상기 제1 노드와 고정 전위 사이에 접속된 제3 스위치와,

상기 제2 노드와 소정의 전위선 사이에 접속된 제4 스위치와,

상기 데이터선과 상기 제4 노드 사이에 접속된 제5 스위치와,

상기 제3 노드와 상기 기준 전류 공급 수단 사이에 접속된 제6 스위치를 포함하고,

상기 제1 기준 전위와 제2 기준 전위 사이에, 상기 구동 트랜지스터의 전류 공급 라인, 상기 제3 노드, 상기 제1 스위치, 상기 제1 노드 및 상기 전기 광학 소자가 직렬로 접속되어 있는 표시 장치.

### 청구항 13

흐르는 전류에 의해 휘도가 변화되는 전기 광학 소자와,

휘도 정보에 따른 데이터 신호가 공급되는 데이터선과,

제1, 제2, 제3, 및 제4 노드와,

제1 및 제2 기준 전위와,

소정의 기준 전류를 공급하는 기준 전류 공급 수단과,

상기 제2 노드에 접속된 전기적 접속 수단과,

상기 제1 노드와 상기 제2 노드 사이에 접속된 화소 용량 소자와,

상기 전기적 접속 수단과 상기 제4 노드 사이에 접속된 결합 용량 소자와,

제1 단자와 제2 단자간에서 전류 공급 라인을 형성하고, 상기 제2 노드에 접속된 제어 단자의 전위에 따라 상기 전류 공급 라인에서 흐르는 전류를 제어하는 구동 트랜지스터와,

상기 제1 노드와 상기 제3 노드 사이에 접속된 제1 스위치와,

상기 제3 노드와 상기 제4 노드 사이에 접속된 제2 스위치와,

상기 제1 노드와 고정 전위 사이에 접속된 제3 스위치와,

상기 제2 노드와 소정의 전위선 사이에 접속된 제4 스위치와,

상기 데이터선과 상기 제4 노드 사이에 접속된 제5 스위치와,

상기 제3 노드와 상기 기준 전류 공급 수단 사이에 접속된 제6 스위치를 포함하고,

상기 제1 기준 전위와 제2 기준 전위 사이에, 상기 구동 트랜지스터의 전류 공급 라인, 상기 제3 노드, 상기 제1 스위치, 상기 제1 노드 및 상기 전기 광학 소자가 직렬로 접속되어 있는 화소 회로의 구동 방법으로서,

상기 제1, 제2, 제4, 제5, 및 제6 스위치를 비도통 상태로 유지한 상태에서, 상기 제3 스위치를 도통 상태로 유지시켜, 상기 제1 노드를 고정 전위에 접속하며,

상기 제2, 제4, 및 상기 제6 스위치를 도통 상태로 유지하여, 소정 전위를 상기 제2 노드에 입력시키고, 기준 전류를 상기 제3 노드에 흘려, 화소 용량 소자에 소정 전위를 충전하며,

상기 제2 및 제6 스위치를 비도통 상태로 유지하고, 또한 제4 스위치를 비도통 상태로 유지하고, 상기 제5 스위치를 도통 상태로 유지하여 상기 데이터선에서 전파되는 데이터를 상기 제2 노드에 입력시킨 후, 상기 제5 스위치를 비도통 상태로 유지하며,

상기 제1 스위치를 도통 상태로 유지하고, 상기 제3 스위치를 비도통 상태로 유지하는 화소 회로의 구동 방법.

## 명세서

### 기술분야

[0001]

본 발명은 유기 EL(Electroluminescence) 디스플레이 등의, 전류치에 의해 휙도가 제어되는 전기 광학 소자를 갖는 화소 회로, 및 이 화소 회로가 매트릭스 형상으로 배열된 화상 표시 장치 중, 특히 각 화소 회로 내부에 설치된 절연 게이트형 전계 효과 트랜지스터에 의해 전기 광학 소자에 흐르는 전류치가 제어되는, 소위 액티브 매트릭스형 화상 표시 장치 및 화소 회로의 구동 방법에 관한 것이다.

### 배경기술

[0002]

화상 표시 장치, 예를 들어 액정 디스플레이 등에서는, 다수의 화소를 매트릭스 형상으로 배열하고, 표시할 화상 정보에 따라 화소마다 광 강도를 제어함으로써 화상을 표시한다.

[0003]

이것은 유기 EL 디스플레이 등에서도 마찬가지이지만, 유기 EL 디스플레이에는 각 화소 회로에 발광 소자를 갖는, 소위 자발광형의 디스플레이로서, 액정 디스플레이에 비해 화상의 시인성이 높고, 백라이트가 불필요하며, 응답 속도가 빠른 등의 이점을 갖는다.

[0004]

또한, 각 발광 소자의 휙도는 그것에 흐르는 전류치에 의해 제어함으로써 발색의 계조를 얻는, 즉 발광 소자가 전류 제어형이라는 점에서 액정 디스플레이 등과는 크게 상이하다.

[0005]

유기 EL 디스플레이에서는, 액정 디스플레이와 마찬가지로, 그 구동 방식으로서 단순 매트릭스 방식과 액티브 매트릭스 방식이 가능하지만, 전자는 구조가 단순하지만, 대형이며 또한 고선명의 디스플레이의 실현이 어려운 등의 문제가 있기 때문에, 각 화소 회로 내부의 발광 소자에 흐르는 전류를, 화소 회로 내부에 설치한 능동 소자, 일반적으로는 TFT(Thin Film Transistor, 박막 트랜지스터)에 의해 제어하는, 액티브 매트릭스의 개발이 활발히 행해지고 있다.

[0006]

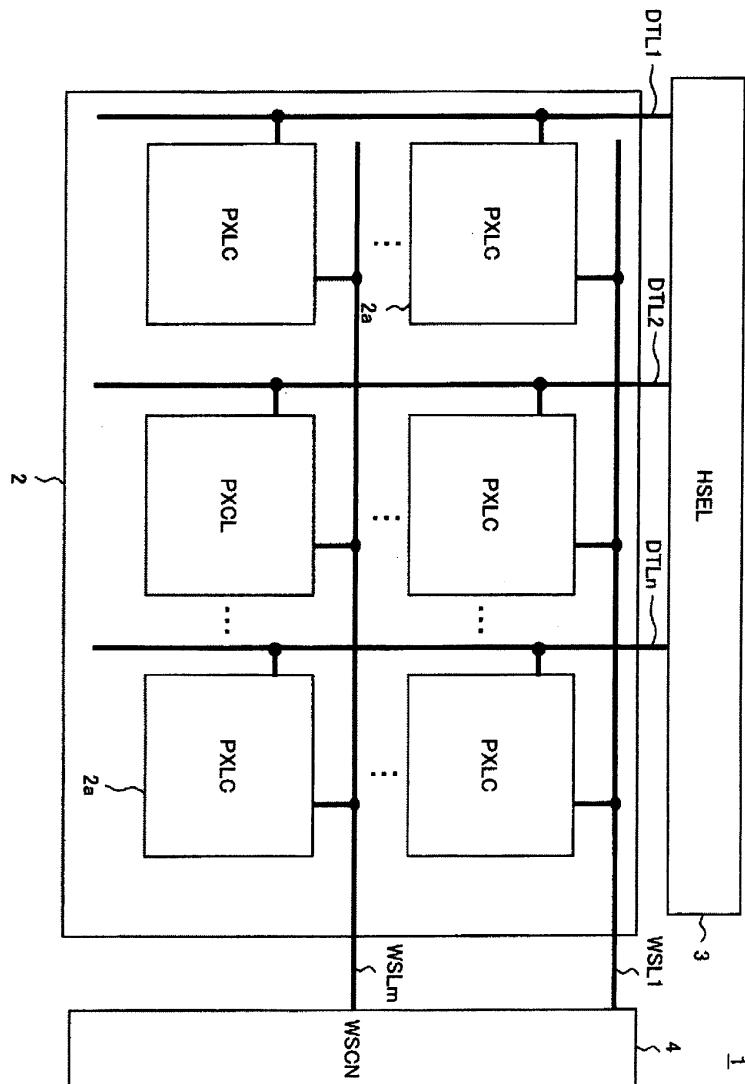

도 1은, 일반적인 유기 EL 표시 장치의 구성을 도시하는 블록도이다.

[0007]

이 표시 장치(1)는, 도 1에 도시하는 바와 같이, 화소 회로(PXLC)(2a)가  $m \times n$ 의 매트릭스 형상으로 배열된 화소 어레이부(2), 수평 셀렉터(HSEL)(3), 라이트 스캐너(WSCN)(4), 수평 셀렉터(3)에 의해 선택되어 휙도 정보에 따른 데이터 신호가 공급되는 데이터선 DTL1~DTLn, 및 라이트 스캐너(4)에 의해 선택 구동되는 주사선 WSL1~WSLm을 갖는다.

[0008]

또한, 수평 셀렉터(3), 라이트 스캐너(4)에 관해서는, 다결정 실리콘 상에 형성하는 경우나, MOSIC 등에서 화소의 주변에 형성하는 경우도 있다.

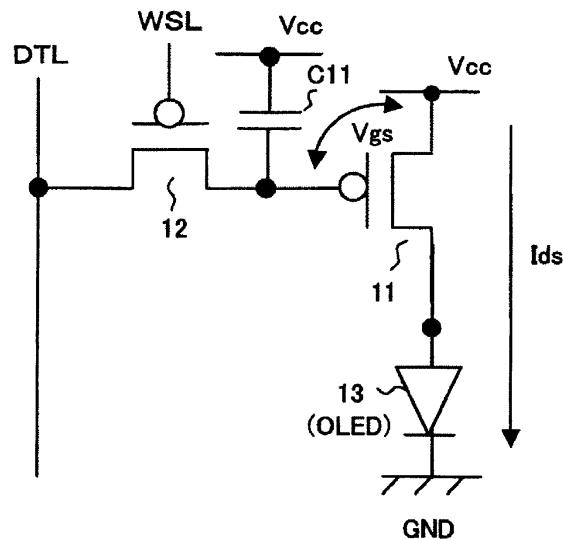

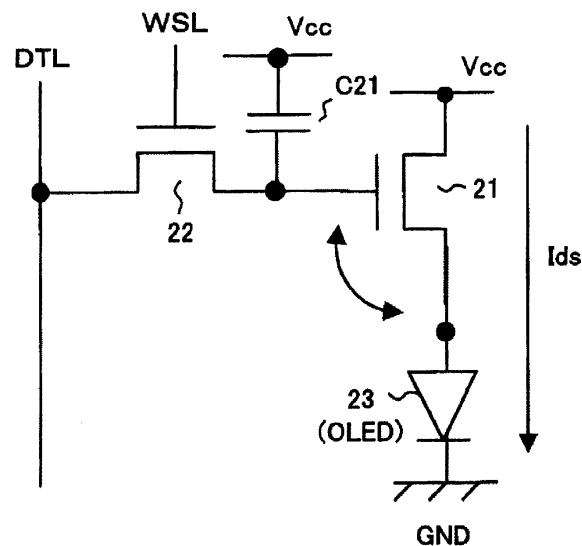

- [0009] 도 2는, 도 1의 화소 회로(2a)의 일 구성예를 도시하는 회로도이다(예를 들어 특히 문현 1, 2 참조).

- [0010] 도 2의 화소 회로는, 다수 제안되어 있는 회로 중에서 가장 단순한 회로 구성으로서, 소위 2 트랜지스터 구동 방식의 회로이다.

- [0011] 도 2의 화소 회로(2a)는, p채널 박막 전계 효과 트랜지스터(이하, TFT라고 함)(11) 및 TFT(12), 캐패시터 C11, 발광 소자인 유기 EL 소자(OLED)(13)를 갖는다. 또한, 도 42에서, DTL은 데이터선을, WSL은 주사선을 각각 나타내고 있다.

- [0012] 유기 EL 소자는 대부분의 경우 정류성이 있기 때문에, OLED(Organic Light Emitting Diode)로 불리는 경우가 있고, 도 2 그 외에서는 발광 소자로서 다이오드의 기호를 이용하고 있지만, 이하의 설명에서 OLED에는 반드시 정류성을 요구하는 것은 아니다.

- [0013] 도 2에서는 TFT(11)의 소스가 전원 전위 VCC에 접속되고, 발광 소자(13)의 캐소드(음극)는 접지 전위 GND에 접속되어 있다. 도 2의 화소 회로(2a)의 동작은 이하와 같다.

- [0014] 스텝 ST1:

- [0015] 주사선 WSL을 선택 상태(여기에서는 저레벨)로 하고, 데이터선 DTL에 기입 전위 Vdata를 인가하면, TFT(12)가 도통하여 캐패시터 C11이 충전 또는 방전되어, TFT(11)의 게이트 전위는 Vdata로 된다.

- [0016] 스텝 ST2:

- [0017] 주사선 WSL을 비선택 상태(여기에서는 고레벨)로 하면, 데이터선 DTL과 TFT(11)는 전기적으로 분리되지만, TFT(11)의 게이트 전위는 캐패시터 C11에 의해 안정적으로 유지된다.

- [0018] 스텝 ST3:

- [0019] TFT(11) 및 발광 소자(13)에 흐르는 전류는, TFT(11)의 게이트 · 소스간 전압 Vgs에 따른 값으로 되며, 발광 소자(13)는 그 전류치에 따른 휘도로 계속해서 발광한다.

- [0020] 상기 스텝 ST1과 같이, 주사선 WSL을 선택하여 데이터선에 제공된 휘도 정보를 화소 내부에 전달하는 조작을, 이하 「기입」이라고 부른다.

- [0021] 상술한 바와 같이, 도 2의 화소 회로(2a)에서는, 한번 Vdata의 기입을 행하면, 다음에 재기입될 때까지의 동안, 발광 소자(13)는 일정한 휘도로 발광을 계속한다.

- [0022] 상술한 바와 같이, 화소 회로(2a)에서는, 드라이브 트랜지스터인 TFT(11)의 게이트 인가 전압을 변화시킴으로써, EL 발광 소자(13)에 흐르는 전류치를 제어하고 있다.

- [0023] 이 때, p채널의 드라이브 트랜지스터의 소스는 전원 전위 VCC에 접속되어 있고, 이 TFT(11)는 항상 포화 영역에서 동작하고 있다. 따라서, 하기의 수학식 1에 나타낸 값을 갖는 정전류원으로 되어 있다.

## 수학식 1

$$I_{DS} = 1/2 \cdot \mu (W/L) C_{ox} (V_{GS} - |V_{TH}|)^2$$

- [0024] 여기에서,  $\mu$ 는 캐리어의 이동도를,  $C_{ox}$ 는 단위 면적당의 게이트 용량을,  $W$ 는 게이트 폭을,  $L$ 은 게이트 길이를,  $V_{GS}$ 는 TFT(11)의 게이트 · 소스간 전압을,  $V_{TH}$ 는 TFT(11)의 임계치를 각각 나타내고 있다.

- [0025] 단순 매트릭스형 화상 표시 장치에서는, 각 발광 소자는, 선택된 순간에만 발광하는 데 비해, 액티브 매트릭스에서는, 상술한 바와 같이, 기입 종료 후에도 발광 소자가 발광을 계속하기 때문에, 단순 매트릭스에 비해 발광 소자의 피크 휘도, 피크 전류를 낮출 수 있는 등의 점에서, 특히 대형 · 고선명의 디스플레이에서는 유리하게 된다.

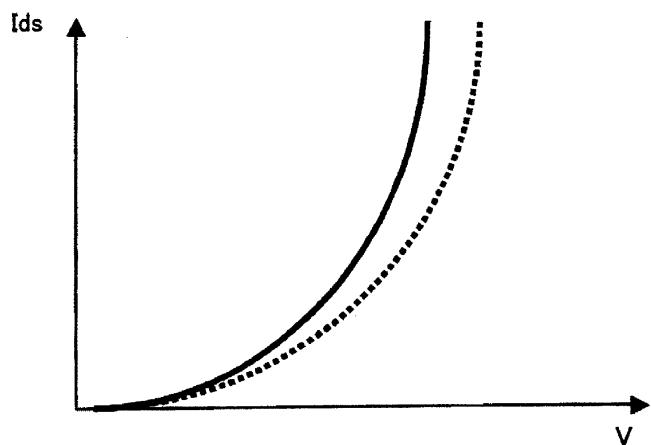

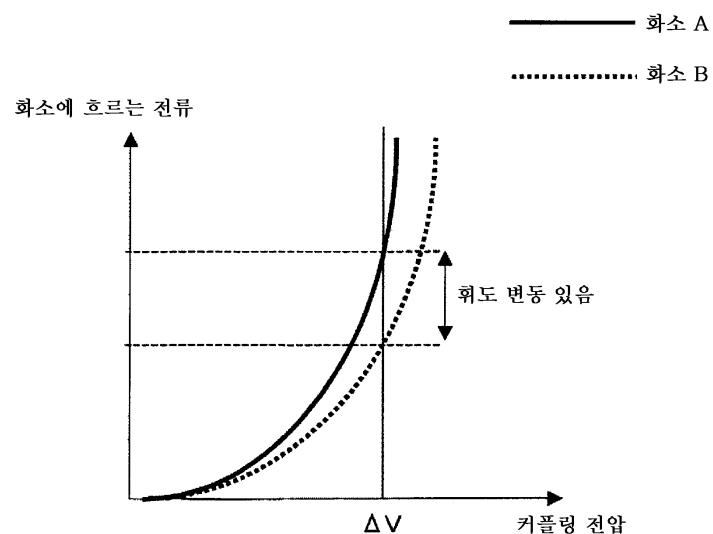

- [0026] 도 3은, 유기 EL 소자의 전류-전압(I-V) 특성의 경시 변화를 도시하는 도면이다. 도 3에서, 실선으로 나타내는 곡선이 초기 상태시의 특성을 나타내고, 파선으로 나타내는 곡선이 경시 변화 후의 특성을 나타내고 있다.

- [0027] 일반적으로, 유기 EL 소자의 I-V 특성은, 도 3에 도시하는 바와 같이, 시간이 경과하면 열화되게 된다.

- [0028] 그러나, 도 2의 2 트랜지스터 구동은 정전류 구동이기 때문에 유기 EL 소자에는 상술한 바와 같이 정전류가 계속해서 흘러, 유기 EL 소자의 I-V 특성이 열화되어도 그 발광 휘도는 경시 열화되지 않는다.

- [0030] 그런데, 도 2의 화소 회로(2a)는, p채널의 TFT에 의해 구성되어 있지만, n채널의 TFT에 의해 구성할 수 있으면, TFT 제작에서 종래의 아몰퍼스 실리콘(a-Si) 프로세스를 이용할 수 있게 된다. 이에 의해, TFT 기판의 저코스트화가 가능해진다.

- [0031] 다음으로, 트랜지스터를 n채널 TFT로 치환한 화소 회로에 대해 고찰한다.

- [0032] 도 4는, 도 2의 회로의 p채널 TFT를 n채널 TFT로 치환한 화소 회로를 도시하는 회로도이다.

- [0033] 도 4의 화소 회로(2b)는, n채널 TFT(21) 및 TFT(22), 캐패시터 C21, 발광 소자인 유기 EL 소자(OLED)(23)를 갖는다. 또한, 도 4에서, DTL은 데이터선을, WSL은 주사선을 각각 나타내고 있다.

- [0034] 이 화소 회로(2b)에서는, 드라이브 트랜지스터로서 TFT(21)의 드레인측이 전원 전위 VCC에 접속되고, 소스는 EL 소자(23)의 애노드에 접속되고 있어, 소스 팔로워 회로를 형성하고 있다.

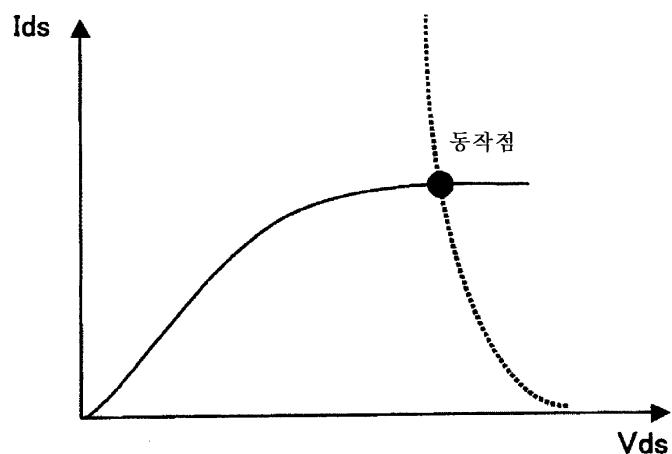

- [0035] 도 5는, 초기 상태에서의 드라이브 트랜지스터로서의 TFT(21)와 EL 소자(23)의 동작점을 도시하는 도면이다. 도 5에서, 횡축은 TFT(21)의 드레인 · 소스간 전압 Vds를, 종축은 드레인 · 소스간 전류 Ids를 각각 나타내고 있다.

- [0036] 도 5에 도시하는 바와 같이, 소스 전압은 드라이브 트랜지스터인 TFT(21)와 EL 소자(23)의 동작점에서 정해지고, 그 전압은 게이트 전압에 따라 상이한 값을 갖는다.

- [0037] 이 TFT(21)는 포화 영역에서 구동되므로, 동작점의 소스 전압에 대한 Vgs에 관하여 상기 수학식 1에 나타낸 방정식의 전류치의 전류 Ids를 흘린다.

- [0038] 특허 문헌 1: USP5,684,365

- [0039] 특허 문헌 2: 일본 특허공개 평8-234683호 공보

- [0040] <발명의 개시>

- [0041] <발명이 해결하고자 하는 과제>

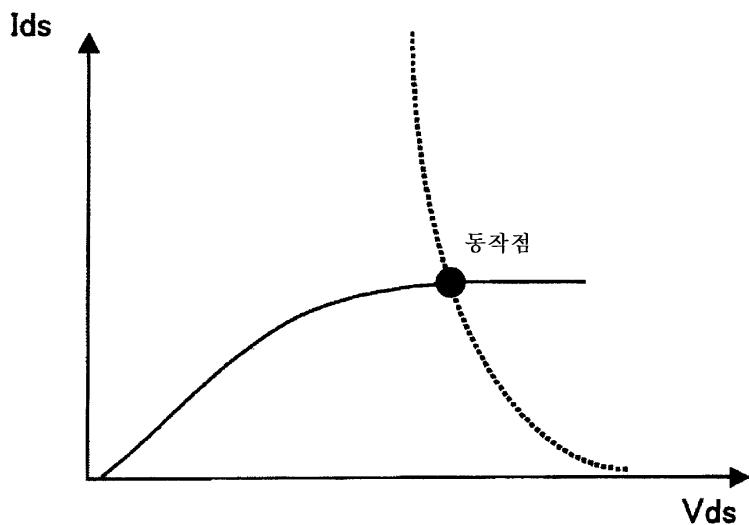

- [0042] 그러나, 여기에서도 마찬가지로 EL 소자의 I-V 특성은 경시 열화되게 된다. 도 6에 도시하는 바와 같이, 이 경시 열화에 의해 동작점이 변동되게 되어, 동일한 게이트 전압을 인가하고 있어도 그 소스 전압은 변동된다.

- [0043] 이에 의해, 드라이브 트랜지스터인 TFT(21)의 게이트 · 소스간 전압 Vgs가 변화되게 되어, 흐르는 전류치가 변동된다. 동시에 EL 소자(23)에 흐르는 전류치도 변화되므로, EL 소자(23)의 I-V 특성이 열화되면, 도 4의 소스 팔로워 회로에서는 그 발광 회도는 경시 변화되게 된다.

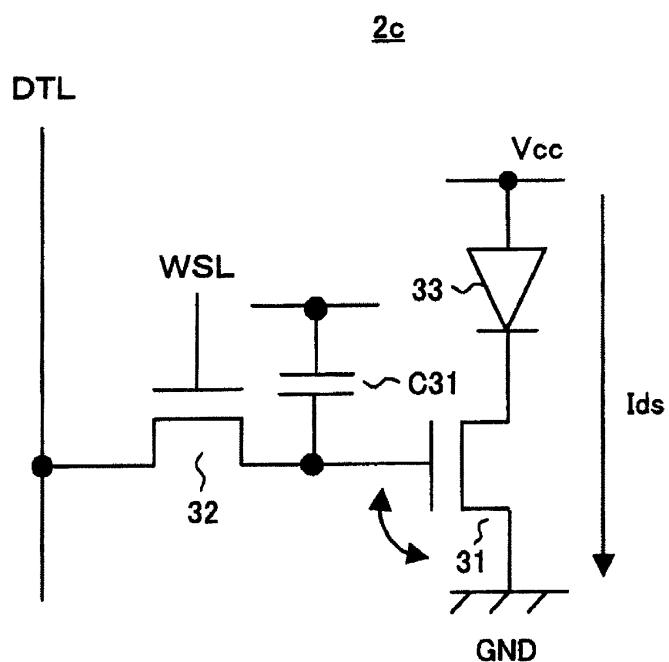

- [0044] 또한, 도 7에 도시하는 바와 같이, 드라이브 트랜지스터로서의 n채널 TFT(31)의 소스를 접지 전위 GND에 접속하고, 드레인을 EL 소자(33)의 캐소드에 접속하고, EL 소자(33)의 애노드를 전원 전위 VCC에 접속하는 회로 구성도 고려할 수 있다.

- [0045] 이 방식에서는, 도 2의 p채널 TFT에 의한 구동과 마찬가지로, 소스의 전위가 고정되어 있어, 드라이브 트랜지스터로서 TFT(31)는 정전류원으로서 동작하여, EL 소자(33)의 I-V 특성의 열화에 의한 회도 변화도 방지할 수 있다.

- [0046] 그러나, 이 방식에서는 드라이브 트랜지스터를 EL 소자의 캐소드측에 접속할 필요가 있고, 이 캐소드 접속은 신규로 애노드 · 캐소드의 전극의 개발이 필요하여, 현상의 기술로는 매우 곤란하게 되어 있다.

- [0047] 이상으로부터, 종래 방식에서는 회도 변화가 없는, n채널 트랜지스터 사용의 유기 EL 소자의 개발은 이루어져 있지 않았다.

- [0048] 또한, 비록, 회도 변화가 없는, n채널 트랜지스터 사용의 유기 EL 소자의 개발이 이루어졌다고 하여도, TFT 트랜지스터는 일반적으로 이동도  $\mu$ 나 임계치 Vth의 변동이 큰 것이 특징이기 때문에, 구동 트랜지스터의 게이트에 동일한 값의 전압이 인가되어도, 화소마다 전류치는 구동 트랜지스터의 이동도  $\mu$ 나 임계치 Vth에 의해 변동되게 되어, 균일한 화질을 얻을 수 없다.

- [0049] 본 발명의 목적은, 발광 소자의 전류-전압 특성이 경시 변화되어도, 회도 열화가 없는 소스 팔로워 출력을 행할 수 있어, n채널 트랜지스터의 소스 팔로워 회로가 가능해져, 현상의 애노드 · 캐소드 전극을 이용한 채로, n채널 트랜지스터를 전기 광학 소자의 구동 소자로서 이용할 수 있고, 또한, 화소 내부의 능동 소자의 임계치나 이동도의 변동에 상관없이 균일하며 고품위의 화상을 표시할 수 있는 화소 회로, 표시 장치, 및 화소 회로의 구동

방법을 제공하는 것에 있다.

[0050] <과제를 해결하기 위한 수단>

상기 목적을 달성하기 위해, 본 발명의 제1 관점은, 흐르는 전류에 의해 휘도가 변화되는 전기 광학 소자를 구동하는 화소 회로로서, 휘도 정보에 따른 데이터 신호가 공급되는 데이터선과, 제1, 제2, 제3, 및 제4 노드와, 제1 및 제2 기준 전위와, 소정의 기준 전류를 공급하는 기준 전류 공급 수단과, 상기 제2 노드에 접속된 전기적 접속 수단과, 상기 제1 노드와 상기 제2 노드 사이에 접속된 화소 용량 소자와, 상기 전기적 접속 수단과 상기 제4 노드 사이에 접속된 결합 용량 소자와, 제1 단자와 제2 단자간에서 전류 공급 라인을 형성하고, 상기 제2 노드에 접속된 제어 단자의 전위에 따라 상기 전류 공급 라인에서 흐르는 전류를 제어하는 구동 트랜지스터와, 상기 제1 노드와 상기 제3 노드 사이에 접속된 제1 스위치와, 상기 제3 노드와 상기 제4 노드 사이에 접속된 제2 스위치와, 상기 제1 노드와 고정 전위 사이에 접속된 제3 스위치와, 상기 제2 노드와 소정의 전위선 사이에 접속된 제4 스위치와, 상기 데이터선과 상기 제4 노드 사이에 접속된 제5 스위치와, 상기 제3 노드와 상기 기준 전류 공급 수단 사이에 접속된 제6 스위치를 포함하고, 상기 제1 기준 전위와 제2 기준 전위 사이에, 상기 구동 트랜지스터의 전류 공급 라인, 상기 제3 노드, 상기 제1 스위치, 상기 제1 노드 및 상기 전기 광학 소자가 직렬로 접속되어 있다.

[0052] 바람직하게는, 상기 전기적 접속 수단은, 상기 제2 노드와 상기 결합 용량 소자를 직접 접속하는 배선을 포함한다.

[0053] 바람직하게는, 상기 전기적 접속 수단은, 상기 제2 노드와 상기 결합 용량 소자를 선택적으로 접속하는 제7 스위치를 포함한다.

[0054] 바람직하게는, 상기 제1 노드와 상기 전기 광학 소자 사이에 접속된 제7 스위치와, 상기 제1 노드와 상기 데이터선 사이에 접속된 제8 스위치를 포함한다.

[0055] 또한, 상기 제1 노드와 상기 전기 광학 소자 사이에 접속된 제7 스위치와, 상기 제1 노드와 상기 제4 노드 사이에 접속된 제8 스위치를 포함한다.

[0056] 바람직하게는, 상기 소정의 전위선은 상기 데이터선과 공용되어 있다.

[0057] 또한, 상기 구동 트랜지스터가 전계 효과 트랜지스터이며, 소스가 상기 제3 노드에 접속되고, 드레인은 상기 제1 기준 전위에 접속되어 있다.

[0058] 바람직하게는, 상기 전기 광학 소자를 구동하는 경우, 제1 스테이지로서, 상기 제1, 제2, 제4, 제5 및 제6 스위치가 비도통 상태로 유지된 상태에서, 상기 제3 스위치가 도통 상태로 유지되어, 상기 제1 노드가 고정 전위에 접속되고, 제2 스테이지로서 상기 제2, 제4, 및 상기 제6 스위치가 도통 상태로 유지되어, 소정 전위를 상기 제2 노드에 입력시켜, 기준 전류를 상기 제3 노드에 흘리어, 화소 용량 소자에 소정 전위를 충전하며, 제3 스테이지로서 상기 제2 및 제6 스위치가 비도통 상태로 유지되고, 또한 제4 스위치가 비도통 상태로 유지되며, 상기 제5 스위치가 도통 상태로 유지되어 상기 데이터선에서 전파되는 데이터가 상기 제2 노드에 입력된 후, 상기 제5 스위치가 비도통 상태로 유지되며, 제4 스테이지로서 상기 제1 스위치가 도통 상태로 유지되고, 상기 제3 스위치가 비도통 상태로 유지된다.

[0059] 또한, 바람직하게는, 상기 전기 광학 소자를 구동하는 경우, 제1 스테이지로서, 상기 제1, 제2, 제4, 제5, 제6 및 제7 스위치가 비도통 상태로 유지된 상태에서, 상기 제3 스위치가 도통 상태로 유지되어, 상기 제1 노드가 고정 전위에 접속되며, 제2 스테이지로서 상기 제2, 제4, 제6 및 제7 스위치가 도통 상태로 유지되어, 상기 데이터선에서 전파되는 데이터 전위를 상기 제2 노드에 입력시켜, 기준 전류를 상기 제3 노드에 흘려, 화소 용량 소자에 소정 전위를 충전하며, 제3 스테이지로서 상기 제2 및 제6 스위치가 비도통 상태로 유지되고, 또한 제4 스위치가 비도통 상태로 유지되며, 상기 제5 스위치가 도통 상태로 유지되어 상기 데이터선에서 전파되는 데이터가 상기 제4 노드를 통해 제2 노드에 입력된 후, 상기 제5 및 제7 스위치가 비도통 상태로 유지되며, 제4 스테이지로서 상기 제1 스위치가 도통 상태로 유지되고, 상기 제3 스위치가 비도통 상태로 유지된다.

[0060] 본 발명의 제2 관점은, 복수 배열된 화소 회로와, 상기 화소 회로의 매트릭스 배열에 대해 열마다 배선되며, 휘도 정보에 따른 데이터 신호가 공급되는 데이터선과, 제1 및 제2 기준 전위와, 소정의 기준 전류를 공급하는 기준 전류 공급 수단을 포함하고, 상기 화소 회로는, 흐르는 전류에 의해 휘도가 변화되는 전기 광학 소자와, 제1, 제2, 제3, 및 제4 노드와, 상기 제2 노드에 접속된 전기적 접속 수단과, 상기 제1 노드와 상기 제2 노드 사이에 접속된 화소 용량 소자와, 상기 전기적 접속 수단과 상기 제4 노드 사이에 접속된 결합

용량 소자와, 제1 단자와 제2 단자간에서 전류 공급 라인을 형성하고, 상기 제2 노드에 접속된 제어 단자의 전위에 따라 상기 전류 공급 라인에서 흐르는 전류를 제어하는 구동 트랜지스터와, 상기 제1 노드와 상기 제3 노드 사이에 접속된 제1 스위치와, 상기 제3 노드와 상기 제4 노드 사이에 접속된 제2 스위치와, 상기 제1 노드와 고정 전위 사이에 접속된 제3 스위치와, 상기 제2 노드와 소정의 전위선 사이에 접속된 제4 스위치와, 상기 데이터선과 상기 제4 노드 사이에 접속된 제5 스위치와, 상기 제3 노드와 상기 기준 전류 공급 수단 사이에 접속된 제6 스위치를 포함하고, 상기 제1 기준 전위와 제2 기준 전위 사이에, 상기 구동 트랜지스터의 전류 공급 라인, 상기 제3 노드, 상기 제1 스위치, 상기 제1 노드 및 상기 전기 광학 소자가 직렬로 접속되어 있는 표시 장치를 제공한다.

[0061] 본 발명의 제3 관점은, 흐르는 전류에 의해 회도가 변화되는 전기 광학 소자와, 회도 정보에 따른 데이터 신호가 공급되는 데이터선과, 제1, 제2, 제3, 및 제4 노드와, 제1 및 제2 기준 전위와, 소정의 기준 전류를 공급하는 기준 전류 공급 수단과, 상기 제2 노드에 접속된 전기적 접속 수단과, 상기 제1 노드와 상기 제2 노드 사이에 접속된 화소 용량 소자와, 상기 전기적 접속 수단과 상기 제4 노드 사이에 접속된 결합 용량 소자와, 제1 단자와 제2 단자간에서 전류 공급 라인을 형성하고, 상기 제2 노드에 접속된 제어 단자의 전위에 따라 상기 전류 공급 라인에서 흐르는 전류를 제어하는 구동 트랜지스터와, 상기 제1 노드와 상기 제3 노드 사이에 접속된 제1 스위치와, 상기 제3 노드와 상기 제4 노드 사이에 접속된 제2 스위치와, 상기 제1 노드와 고정 전위 사이에 접속된 제3 스위치와, 상기 제2 노드와 소정의 전위선 사이에 접속된 제4 스위치와, 상기 데이터선과 상기 제4 노드 사이에 접속된 제5 스위치와, 상기 제3 노드와 상기 기준 전류 공급 수단 사이에 접속된 제6 스위치를 포함하고, 상기 제1 기준 전위와 제2 기준 전위 사이에, 상기 구동 트랜지스터의 전류 공급 라인, 상기 제3 노드, 상기 제1 스위치, 상기 제1 노드 및 상기 전기 광학 소자가 직렬로 접속되어 있는 화소 회로의 구동 방법으로서, 상기 제1, 제2, 제4, 제5, 및 제6 스위치를 비도통 상태로 유지한 상태에서, 상기 제3 스위치를 도통 상태로 유지시켜, 상기 제1 노드를 고정 전위에 접속하여, 상기 제2, 제4, 및 상기 제6 스위치를 도통 상태로 유지하여, 소정 전위를 상기 제2 노드에 입력시키고, 기준 전류를 상기 제3 노드에 흘려, 화소 용량 소자에 소정 전위를 충전하며, 상기 제2 및 제6 스위치를 비도통 상태로 유지하고, 또한 제4 스위치를 비도통 상태로 유지하고, 상기 제5 스위치를 도통 상태로 유지하여 상기 데이터선에서 전파되는 데이터를 상기 제2 노드에 입력시킨 후, 상기 제5 스위치를 비도통 상태로 유지하며, 상기 제1 스위치를 도통 상태로 유지하고, 상기 제3 스위치를 비도통 상태로 유지한다.

[0062] 본 발명에 따르면, 예를 들면 전기 광학 소자의 발광 상태 시에는, 제1 스위치가 온 상태(도통 상태)로 유지되고, 제2 내지 제7 스위치가 오프 상태(비도통 상태)로 유지된다.

[0063] 드라이브(구동) 트랜지스터는 포화 영역에서 동작하도록 설계되어 있어, 전기 광학 소자에 흐르는 전류  $Ids$ 는 상기 수학식 1로 나타내는 값을 취한다.

[0064] 다음으로, 제1 스위치가 오프로 되고, 제2, 제4 내지 제7 스위치는 오프 상태로 유지된 채로, 제3 스위치가 온 한다.

[0065] 이 때, 제3 스위치를 통하여 전류가 흘러 제1 노드의 전위는 접지 전위 GND까지 하강한다. 그 때문에, 전기 광학 소자에 인가되는 전압도 0V가 되어, 전기 광학 소자는 발광하지 않게 된다.

[0066] 다음으로, 제3 스위치가 온 상태, 제1 및 제5 스위치가 오프 상태로 유지된 채로, 제2, 제4, 제6, 제7 스위치가 온한다.

[0067] 이에 의해, 예를 들어 소정 전위  $V0$  혹은 데이터선을 전파된 입력 전압  $Vin$ 이 제2 노드에 입력되고, 이것과 병행하여, 기준 전류 공급 수단에 의해 기준 전류가 제3 노드에 흐른다. 그 결과, 구동 트랜지스터의 게이트 · 소스간 전압  $Vgs$ 가, 결합 용량 소자에 충전된다.

[0068] 이 때, 구동 트랜지스터는 포화 영역에서 동작하기 때문에, 구동 트랜지스터의 게이트 · 소스간 전압  $Vgs$ 는, 이동도  $\mu$  및 임계치  $Vth$ 를 포함한 항으로 된다. 또한, 이 때, 화소 용량 소자에는  $V0$  또는  $Vin$ 이 충전된다.

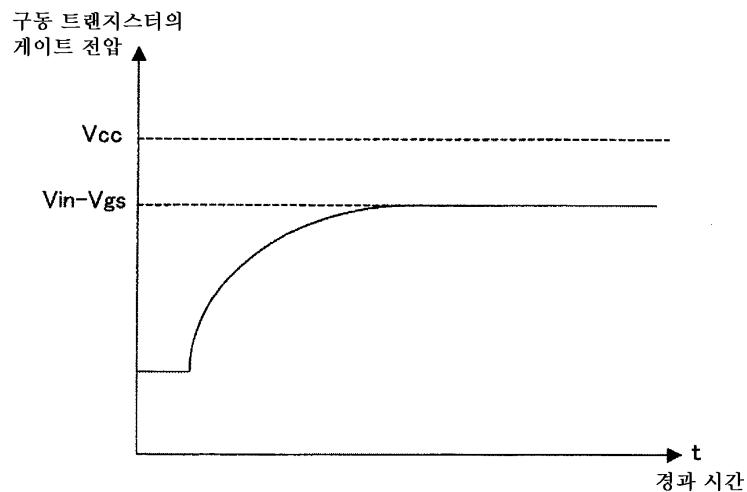

[0069] 다음으로, 제2 및 제6 스위치가 오프한다. 이에 의해, 구동 트랜지스터의 소스 전위(제3 노드의 전위)는, 예를 들어 ( $V0$  또는  $Vin-Vth$ )까지 상승한다.

[0070] 그리고, 또한, 제3 및 제7 스위치가 온 상태, 제1, 제2, 제6 스위치가 오프 상태로 유지된 채로, 제5 스위치가 온하고, 제4 스위치가 오프한다. 제5 스위치가 온함으로써, 제5 스위치를 통하여 데이터선을 전파된 입력 전압  $Vin$ 이 결합 용량 소자를 통하여 구동 트랜지스터의 게이트에 전압  $\Delta V$ 를 커플링시킨다.

- [0071] 이 커플링량  $\Delta V$ 는, 제1 노드와 제2 노드간의 전압 변화량(구동 트랜지스터의  $V_{gs}$ )과, 화소 용량 소자, 결합 용량 소자 및 구동 트랜지스터의 기생 용량에 의해 정해지며, 화소 용량 소자와 기생 용량에 비해 결합 용량 소자의 용량을 크게 하면 변화량의 거의 전부가 구동 트랜지스터의 게이트에 커플링되어, 구동 트랜지스터의 게이트 전위는 ( $V_0$  또는  $V_{in}+V_{gs}$ )로 된다.

- [0072] 기입 종료 후, 제5 및 제7 스위치가 오프하고, 또한, 제1 스위치가 온하며, 제3 스위치가 오프한다.

- [0073] 이에 의해, 구동 트랜지스터의 소스 전위는 일단 접지 전위 GND로 강하, 그 후 상승하고, 전기 광학 소자에도 전류가 흐르기 시작한다. 구동 트랜지스터의 소스 전위는 변동됨에도 불구하고, 그 게이트 · 소스간에는 화소 용량 소자가 있고, 또한, 화소 용량 소자의 용량을 구동 트랜지스터의 기생 용량보다 크게 함으로써 게이트 · 소스 전위는 항상 ( $V_{in}+V_{gs}$ )의 일정치로 유지된다.

- [0074] 이 때, 구동 트랜지스터는 포화 영역에서 구동하므로, 구동 트랜지스터에 흐르는 전류치  $I_{ds}$ 는 수학식 1로 나타낸 값을 취하고, 그것은 게이트 · 소스간 전압에 의해 결정된다. 이  $I_{ds}$ 는 전기 광학 소자에도 마찬가지로 흘러 전기 광학 소자가 발광한다.

- [0075] <발명의 효과>

- [0076] 본 발명에 따르면, EL 발광 소자의 I-V 특성이 경시 변화되어도, 휘도 열화가 없는 소스 팔로워 출력을 행할 수 있다.

- [0077] n채널 트랜지스터의 소스 팔로워 회로가 가능해져, 현상의 애노드 · 캐소드 전극을 이용한 채로, n채널 트랜지스터를 EL 발광 소자의 구동 소자로서 이용할 수 있다.

- [0078] 또한, 구동 트랜지스터의 임계치의 변동뿐만 아니라, 이동도의 변동도 대폭 억제할 수 있어 유니포미티가 균일한 화질을 얻을 수 있다.

- [0079] 또한, 기준 전류를 흘려 구동 트랜지스터의 임계치의 변동의 캔슬을 행하고 있기 때문에, 패널마다 스위치의 온, 오프의 타이밍의 설정으로 임계치를 캔슬할 필요가 없으므로, 타이밍을 설정하는 공수의 증가를 억제할 수 있다.

- [0080] 또한, 화소 내의 용량 설계를 용이하게 행할 수 있고 또한 용량은 작게 할 수 있으므로, 화소 면적을 축소할 수 있어, 패널의 고선명화가 가능해진다.

- [0081] 또한, 입력 전압을 입력할 때에 전압 변화량의 거의 전부를 구동 트랜지스터의 게이트에 커플링시킬 수 있으므로, 화소마다의 전류치의 변동을 저감할 수 있어, 균일한 화질을 얻을 수 있다.

- [0082] 또한, 구동 트랜지스터의 게이트에 고정 전위를 입력하여 기준 전류  $I_{ref}$ 를 흘림으로써 화소 내에 신호선으로부터의 입력 전압이 입력되어 있는 시간을 짧게 할 수 있어, 화소에 고속으로 기입할 수 있으며, 3회 기입 방식과 같이 1H를 수분할하여 화소에 기입하는 구동 방식에도 대응할 수 있다.

- [0083] 또한, n채널만으로 화소 회로의 트랜지스터를 구성할 수 있어, TFT 작성에서 a-Si 프로세스를 이용할 수 있게 된다. 이에 의해, TFT 기판의 저코스트화가 가능해진다.

### 산업상 이용 가능성

- [0307] 본 발명의 화소 회로, 표시 장치, 및 화소 회로의 구동 방법은, 발광 소자의 전류-전압 특성이 경시 변화되어도, 휘도 열화가 없는 소스 팔로워 출력을 행할 수 있어, n채널 트랜지스터의 소스 팔로워 회로가 가능하게 되고, 또한, 화소 내부의 능동 소자의 임계치나 이동도의 변동에 상관없이 균일하며 고품위의 화상을 표시하는 것이 가능하기 때문에, 휴대 정보 단말기(Personal Digital Assistant), 퍼스널 컴퓨터, 카 네비게이션용의 표시 장치, 휴대 전화, 디지털 카메라, 비디오 카메라 등의 전자 기기에 적용 가능하다.

### 도면의 간단한 설명

- [0084] 도 1은 일반적인 유기 EL 표시 장치의 구성을 도시하는 블록도.

- [0085] 도 2는 도 1의 화소 회로의 일 구성예를 도시하는 회로도.

- [0086] 도 3은 유기 EL 소자의 전류-전압(I-V) 특성의 경시 변화를 도시하는 도면.

- [0087] 도 4는 도 2의 회로의 p채널 TFT를 n채널 TFT로 치환한 화소 회로를 도시하는 회로도.

- [0088] 도 5는 초기 상태에서의 드라이브 트랜지스터로서의 TFT와 EL 소자의 동작점을 도시하는 도면.

- [0089] 도 6은 경시 변화 후의 드라이브 트랜지스터로서의 TFT와 EL 소자의 동작점을 도시하는 도면.

- [0090] 도 7은 드라이브 트랜지스터로서의 n채널 TFT의 소스를 접지 전위에 접속한 화소 회로를 도시하는 회로도.

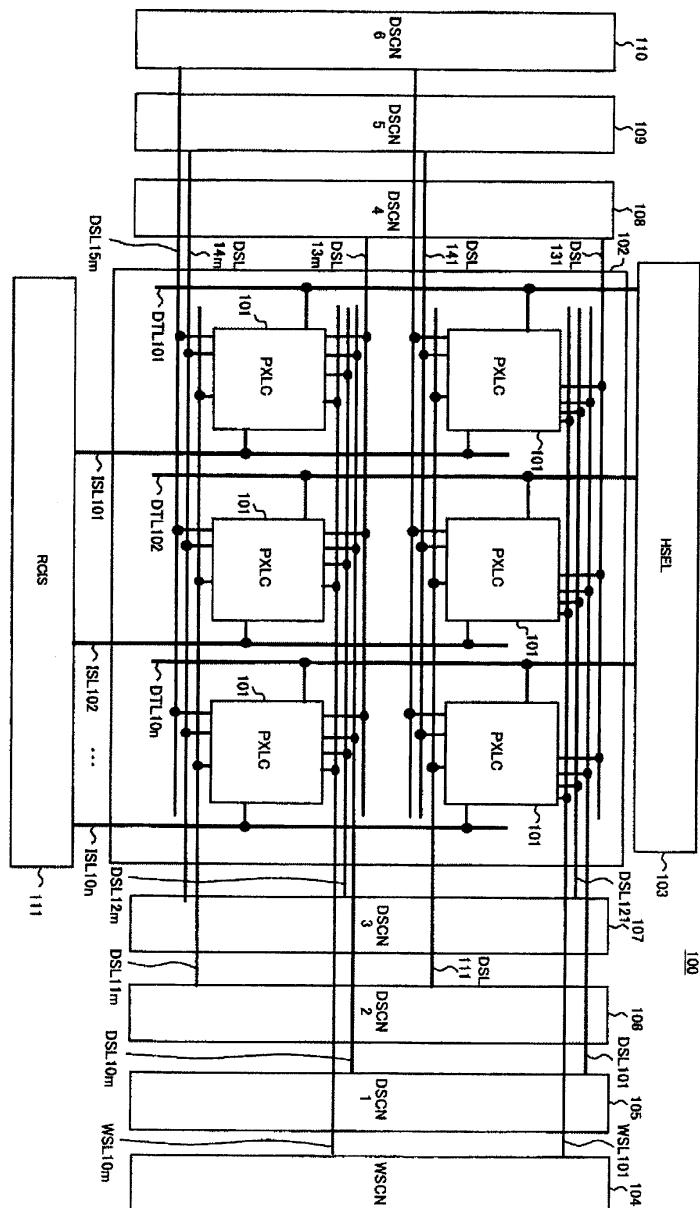

- [0091] 도 8은 제1 실시 형태에 따른 화소 회로를 채용한 유기 EL 표시 장치의 구성을 도시하는 블록도.

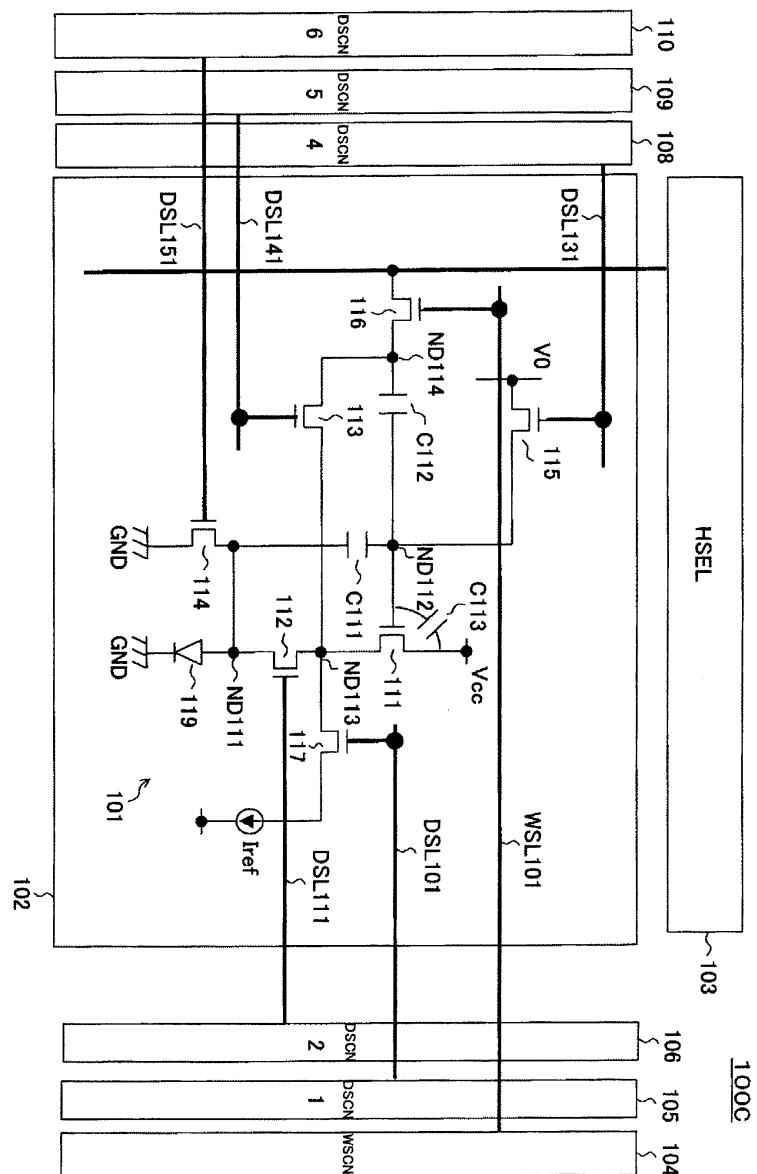

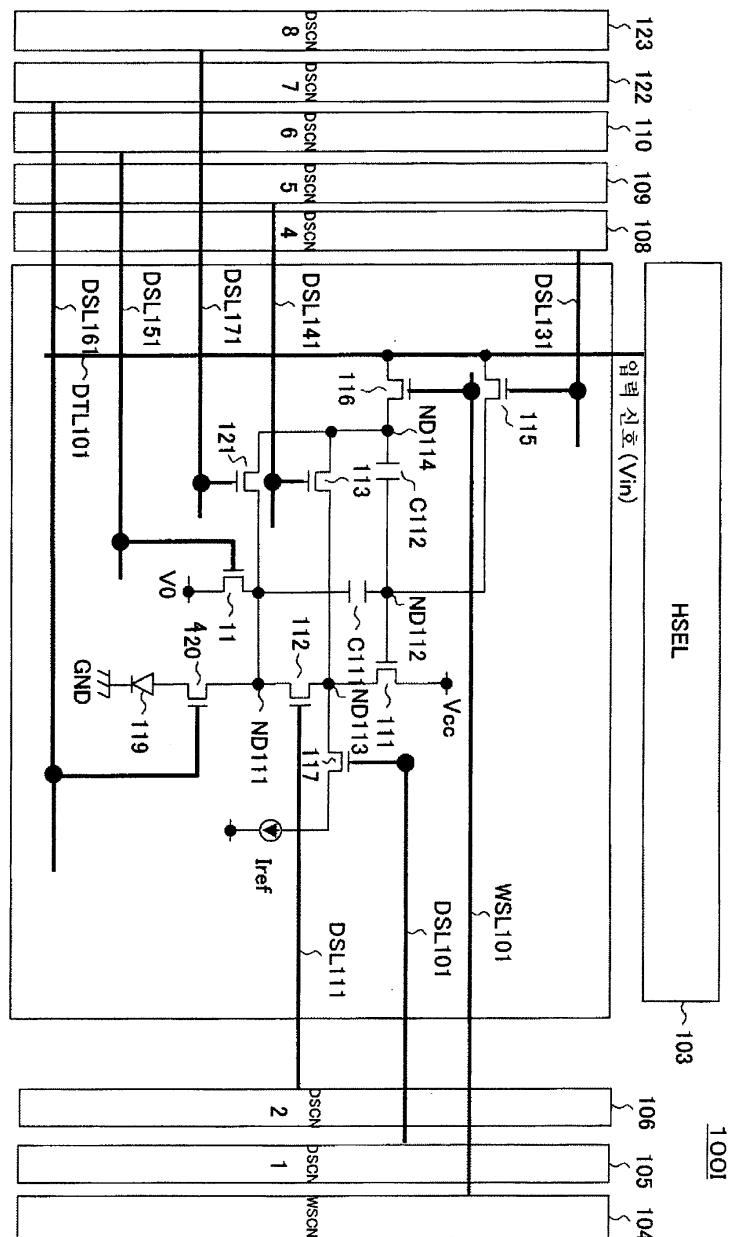

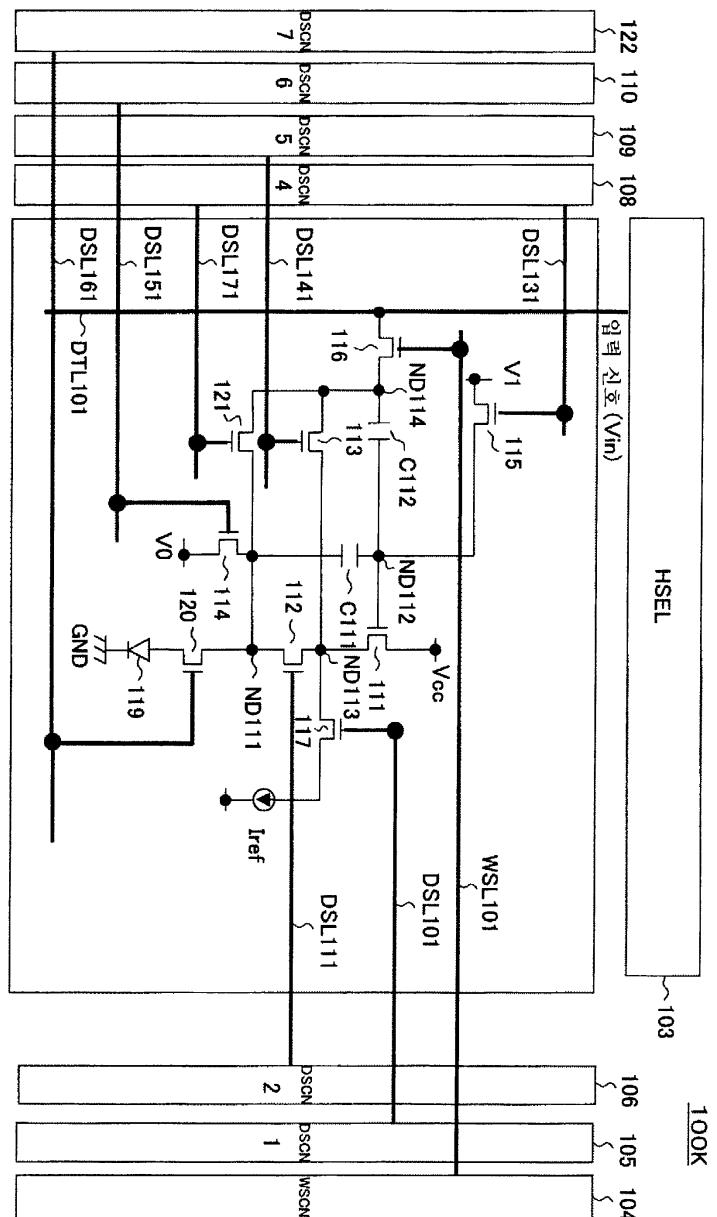

- [0092] 도 9는 도 8의 유기 EL 표시 장치에서 제1 실시 형태에 따른 화소 회로의 구체적인 구성을 도시하는 회로도.

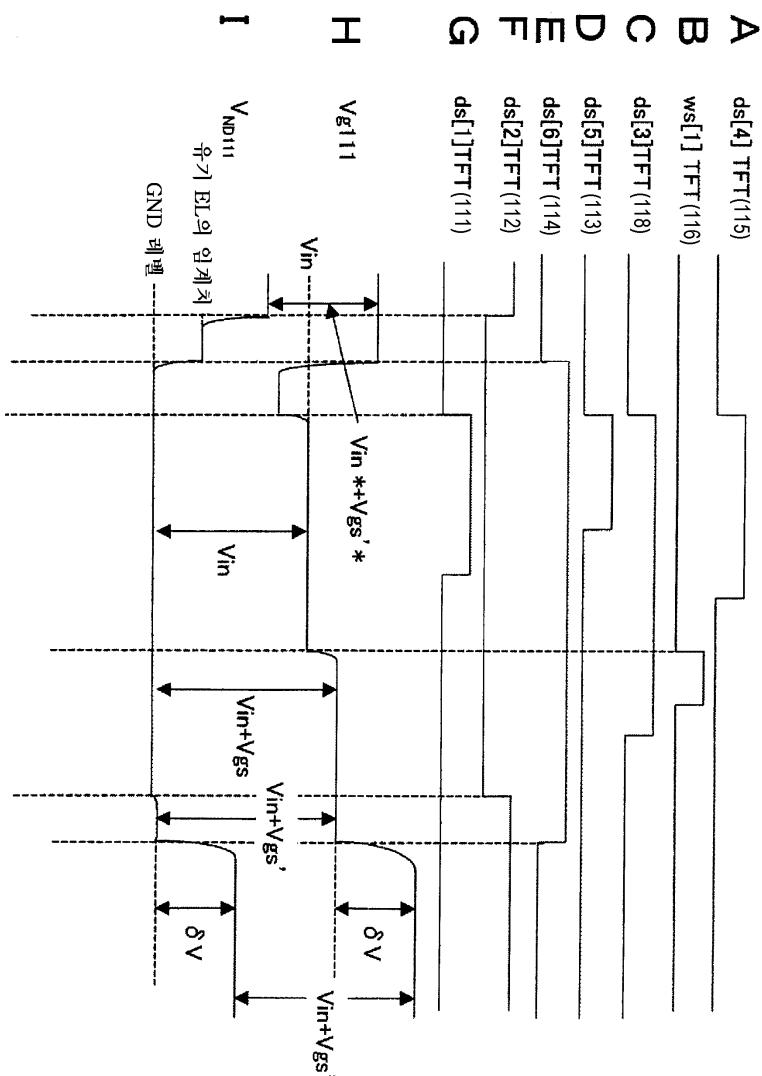

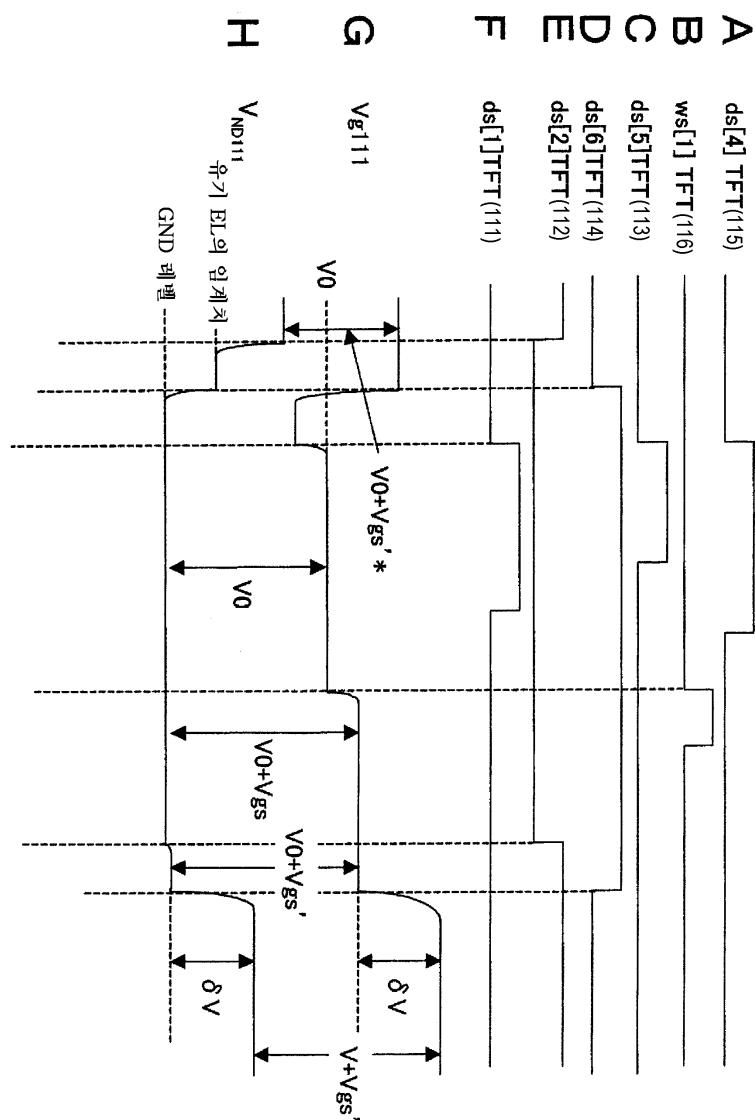

- [0093] 도 10의 (A) 내지 도 10의 (I)는 도 9의 회로의 구동 방법을 설명하기 위한 타이밍차트.

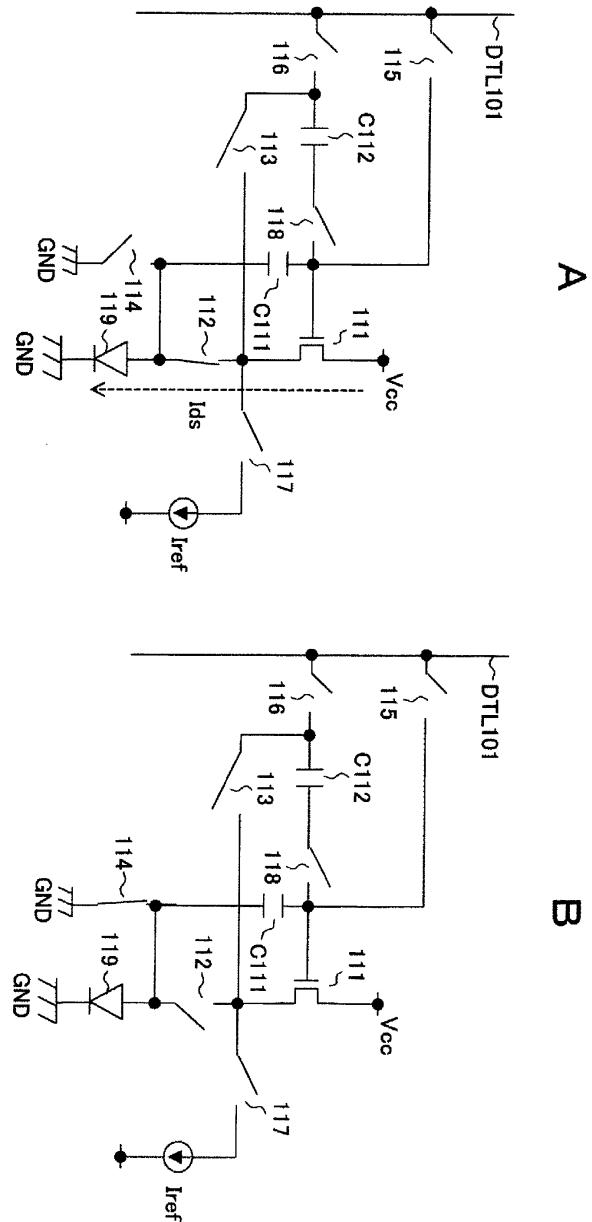

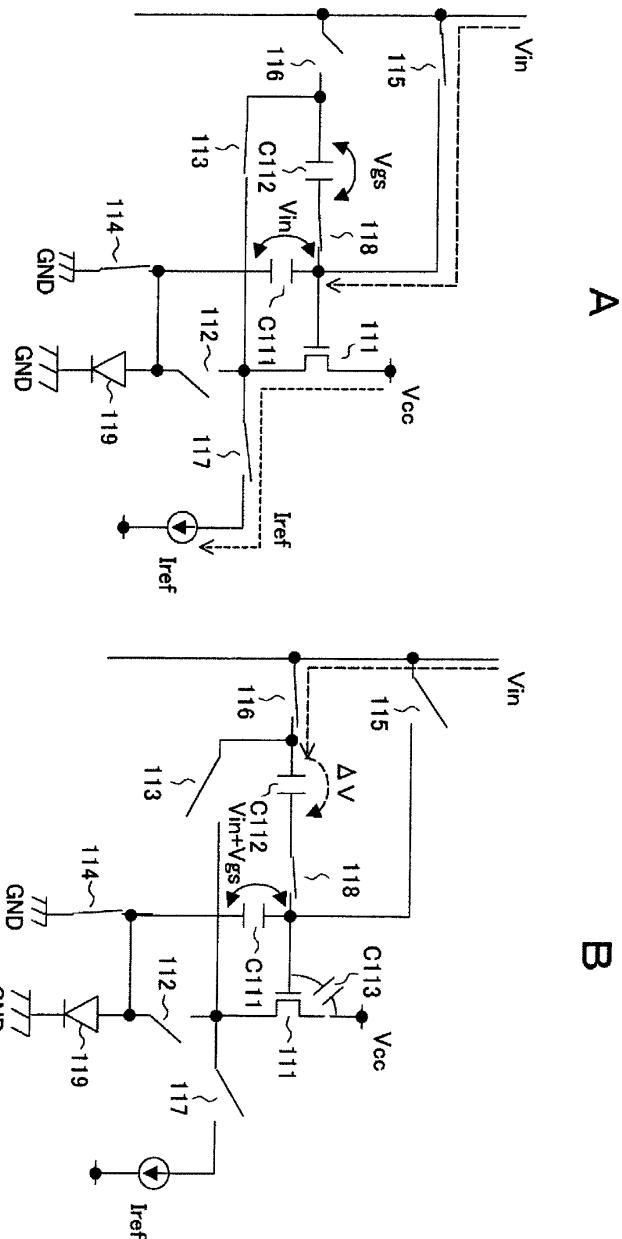

- [0094] 도 11의 (A) 및 도 11의 (B)는 도 9의 회로의 구동 방법에 따른 동작을 설명하기 위한 도면.

- [0095] 도 12의 (A) 및 도 12의 (B)는 도 9의 회로의 구동 방법에 따른 동작을 설명하기 위한 도면.

- [0096] 도 13은 도 9의 회로의 구동 방법에 따른 동작을 설명하기 위한 도면.

- [0097] 도 14는 도 9의 회로의 구동 방법에 따른 동작을 설명하기 위한 도면.

- [0098] 도 15는 기준 전류를 구동 트랜지스터의 소스에 공급하는 이유를 설명하기 위한 도면.

- [0099] 도 16은 기준 전류를 구동 트랜지스터의 소스에 공급하는 이유를 설명하기 위한 도면.

- [0100] 도 17은 기준 전류를 구동 트랜지스터의 소스에 공급하는 이유를 설명하기 위한 도면.

- [0101] 도 18은 기준 전류를 구동 트랜지스터의 소스에 공급하는 이유를 설명하기 위한 도면.

- [0102] 도 19는 제2 실시 형태에 따른 화소 회로의 구체적인 구성을 도시하는 회로도.

- [0103] 도 20의 (A) 내지 도 20의 (I)는 도 19의 회로의 구동 방법을 설명하기 위한 타이밍차트.

- [0104] 도 21은 제3 실시 형태에 따른 화소 회로를 채용한 유기 EL 표시 장치의 구성을 도시하는 블록도.

- [0105] 도 22는 도 21의 유기 EL 표시 장치에서 제3 실시 형태에 따른 화소 회로의 구체적인 구성을 도시하는 회로도.

- [0106] 도 23의 (A) 내지 도 23의 (H)는 도 22의 회로의 구동 방법을 설명하기 위한 타이밍차트.

- [0107] 도 24는 제4 실시 형태에 따른 화소 회로의 구체적인 구성을 도시하는 회로도.

- [0108] 도 25의 (A) 내지 도 25의 (H)는 도 24의 회로의 구동 방법을 설명하기 위한 타이밍차트.

- [0109] 도 26은 제5 실시 형태에 따른 화소 회로의 구체적인 구성을 도시하는 회로도.

- [0110] 도 27은 제6 실시 형태에 따른 화소 회로의 구체적인 구성을 도시하는 회로도.

- [0111] 도 28의 (A) 내지 도 28의 (K)는 도 26의 회로의 동작을 설명하기 위한 타이밍차트.

- [0112] 도 29의 (A) 내지 도 29의 (K)는 도 27의 회로의 타이밍차트.

- [0113] 도 30의 (A) 및 도 30의 (B)는 도 26의 회로의 동작을 설명하기 위한 도면.

- [0114] 도 31의 (A) 및 도 31의 (B)는 도 26의 회로의 동작을 설명하기 위한 도면.

- [0115] 도 32의 (A) 및 도 32의 (B)는 도 26의 회로의 동작을 설명하기 위한 도면.

- [0116] 도 33의 (A) 및 도 33의 (B)는 도 26의 회로의 동작을 설명하기 위한 도면.

- [0117] 도 34는 도 26의 회로에서 기준 전류를 구동 트랜지스터의 소스에 공급하는 이유를 설명하기 위한 도면.

- [0118] 도 35는 도 26의 회로에서 기준 전류를 구동 트랜지스터의 소스에 공급하는 이유를 설명하기 위한 도면.

- [0119] 도 36은 제7 실시 형태에 따른 화소 회로의 구체적인 구성을 도시하는 회로도.

- [0120] 도 37은 제8 실시 형태에 따른 화소 회로의 구체적인 구성을 도시하는 회로도.

- [0121] 도 38의 (A) 내지 도 38의 (K)는 도 36의 회로의 동작을 설명하기 위한 타이밍차트.

- [0122] 도 39의 (A) 내지 도 39의 (K)는 도 37의 회로의 동작을 설명하기 위한 타이밍차트.

- [0123] 도 40은 제9 실시 형태에 따른 화소 회로의 구체적인 구성을 도시하는 회로도.

- [0124] 도 41은 제10 실시 형태에 따른 화소 회로의 구체적인 구성을 도시하는 회로도.

- [0125] 도 42의 (A) 내지 도 42의 (J)는 도 40의 회로의 동작을 설명하기 위한 타이밍차트.

- [0126] 도 43의 (A) 내지 도 43의 (J)는 도 41의 회로의 동작을 설명하기 위한 타이밍차트.

- [0127] 도 44는 제11 실시 형태에 따른 화소 회로의 구체적인 구성을 도시하는 회로도.

- [0128] 도 45는 제12 실시 형태에 따른 화소 회로의 구체적인 구성을 도시하는 회로도.

- [0129] 도 46의 (A) 내지 도 46의 (J)는 도 44의 회로의 동작을 설명하기 위한 타이밍차트.

- [0130] 도 47의 (A) 내지 도 47의 (J)는 도 45의 회로의 동작을 설명하기 위한 타이밍차트.

- [0131] <부호의 설명>

- [0132] 100, 100A~100J : 표시 장치

- [0133] 101 : 화소 회로(PXLC)

- [0134] 102 : 화소 어레이부

- [0135] 103 : 수평 셀렉터(HSEL)

- [0136] 104 : 라이트 스캐너(WSCN)

- [0137] 105 : 제1 드라이브 스캐너(DSCN1)

- [0138] 106 : 제2 드라이브 스캐너(DSCN2)

- [0139] 107 : 제3 드라이브 스캐너(DSCN3)

- [0140] 108 : 제4 드라이브 스캐너(DSCN4)

- [0141] 109 : 제5 드라이브 스캐너(DSCN5)

- [0142] 110 : 제6 드라이브 스캐너(DSCN6)

- [0143] DTL101~DTL10n : 데이터선

- [0144] WSL101~WSL10m : 주사선

- [0145] DSL101~DSL10m, DSL111~DSL11m, DSL121~DSL12m, DSL131~DSL13m, DSL141~DSL14m, DSL151~DSL15m, DSL161~DSL16m : 구동선

- [0146] 111 : 드라이브(구동) 트랜지스터로서의 TFT

- [0147] 112 : 제1 스위치로서의 TFT

- [0148] 113 : 제2 스위치로서의 TFT

- [0149] 114 : 제3 스위치로서의 TFT

- [0150] 115 : 제4 스위치로서의 TFT

- [0151] 116 : 제5 스위치로서의 TFT

- [0152] 117 : 제6 스위치로서의 TFT

- [0153] 118 : 제7 스위치로서의 TFT

- [0154] 119 : 발광 소자

- [0155] 120 : 제7 또는 제8 스위치로서의 TFT

- [0156] 121 : 제8 또는 제9 스위치로서의 TFT

- [0157] ND111 : 제1 노드

- [0158] ND112 : 제2 노드

- [0159] ND113 : 제3 노드

- [0160] ND114 : 제4 노드

- [0161] <발명을 실시하기 위한 최량의 형태>

- [0162] 이하, 본 발명의 실시 형태를 첨부 도면에 관련지어 설명한다.

- [0163] <제1 실시 형태>

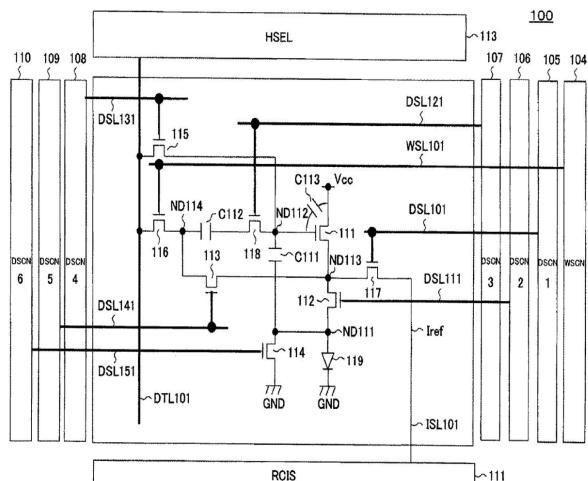

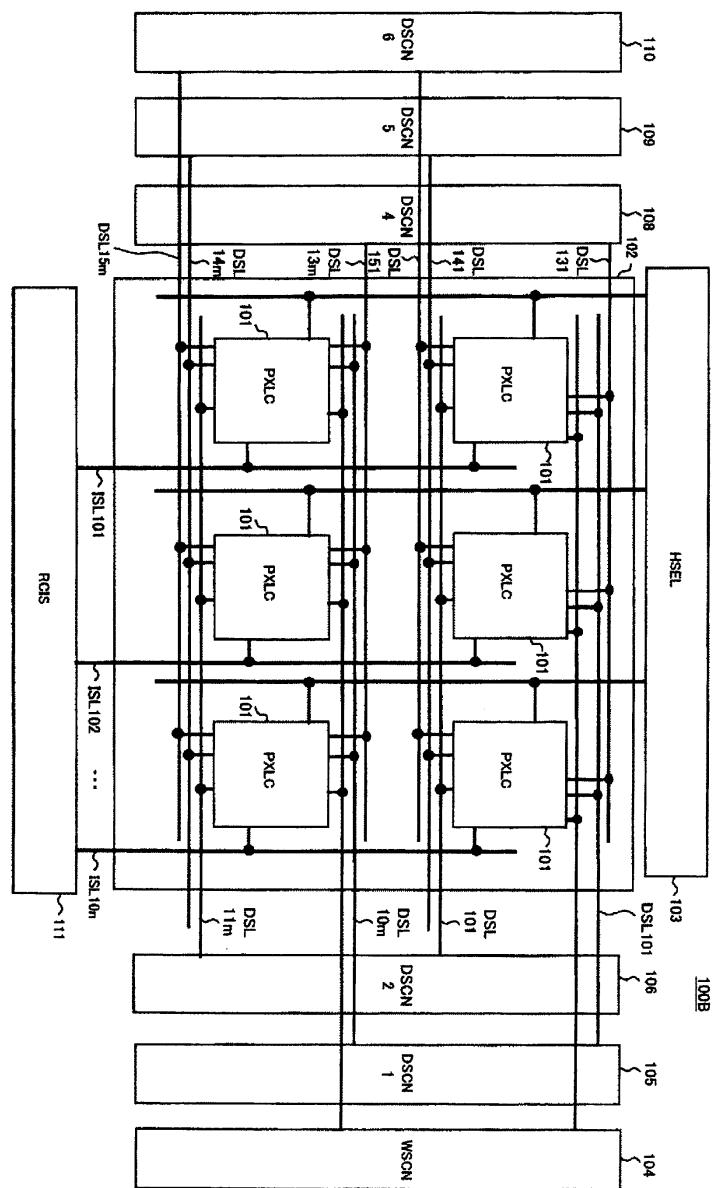

- [0164] 도 8은, 본 제1 실시 형태에 따른 화소 회로를 채용한 유기 EL 표시 장치의 구성을 도시하는 블록도이다.

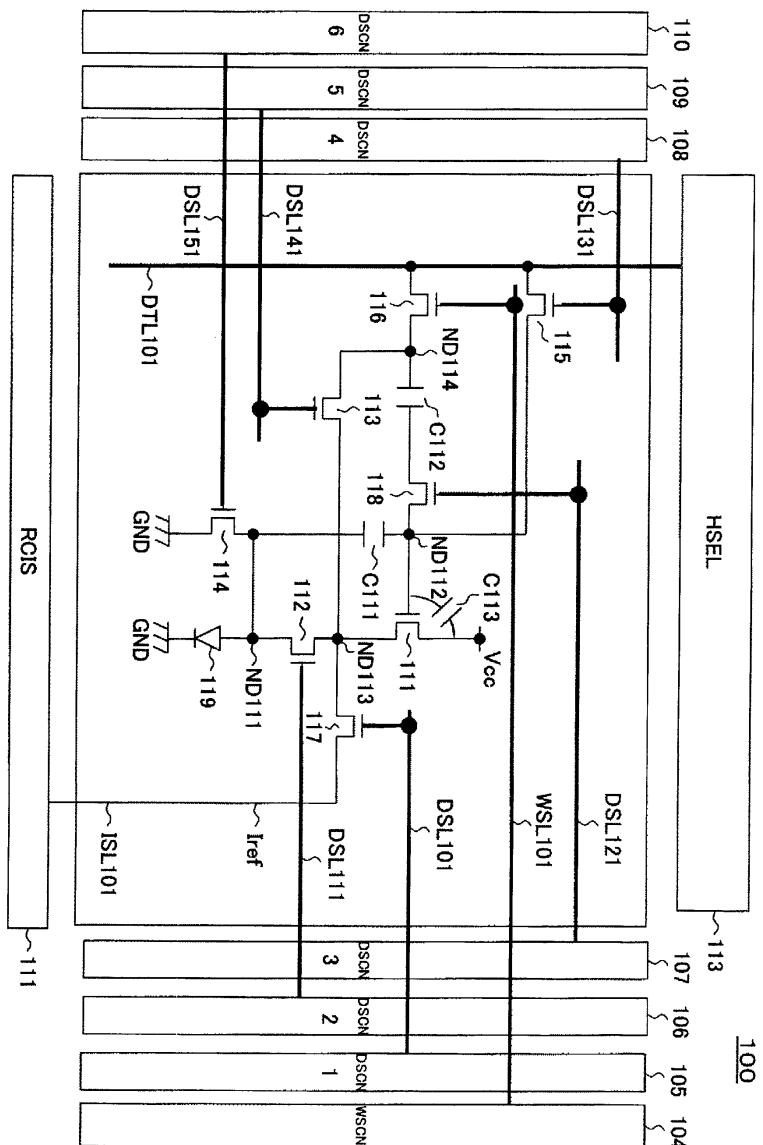

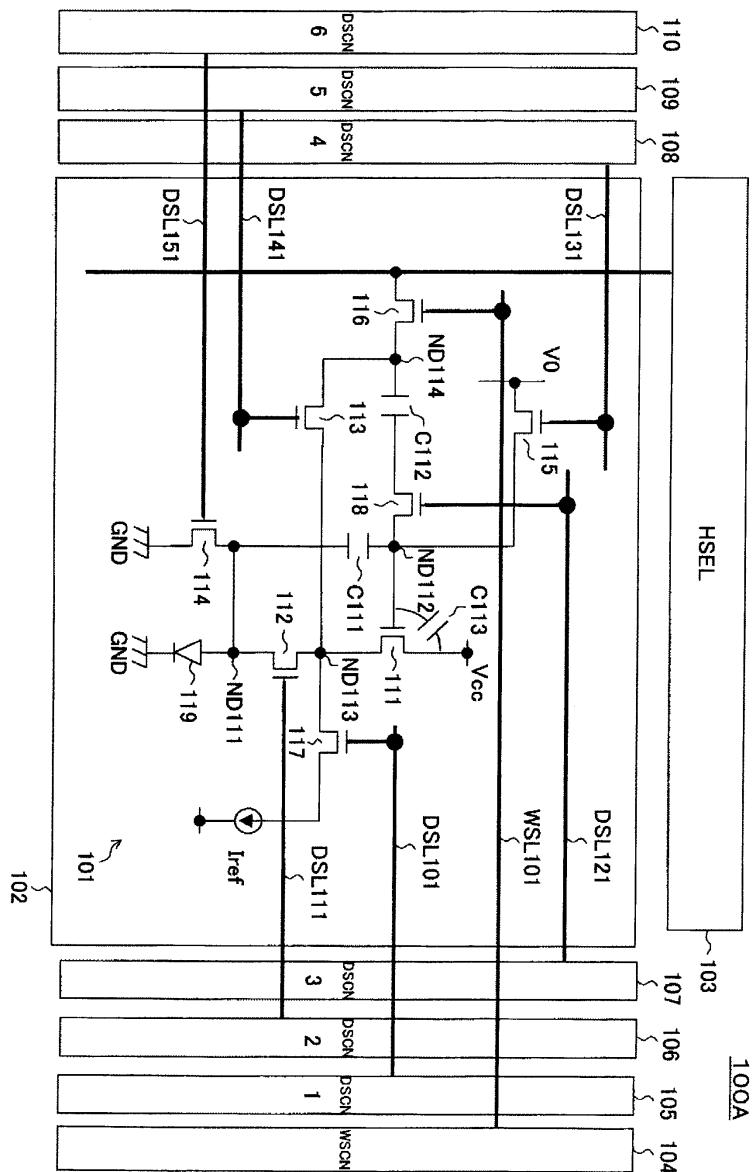

- [0165] 도 9는, 도 8의 유기 EL 표시 장치에서 본 제1 실시 형태에 따른 화소 회로의 구체적인 구성을 도시하는 회로도이다.

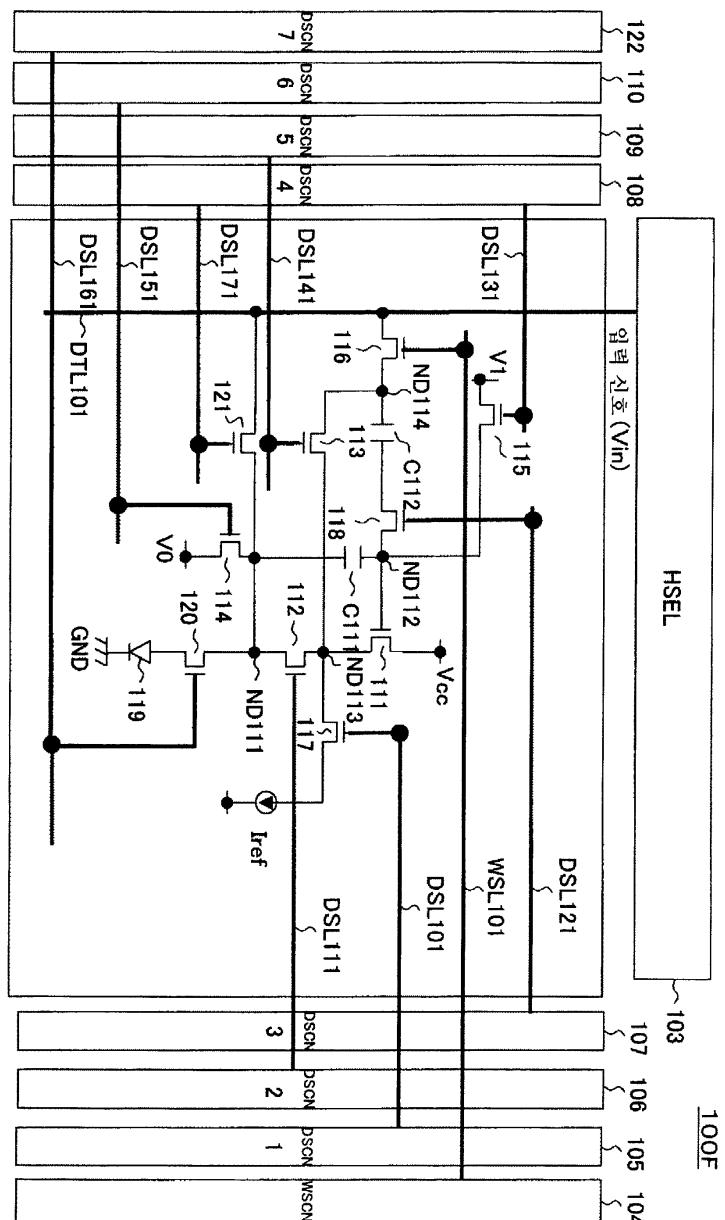

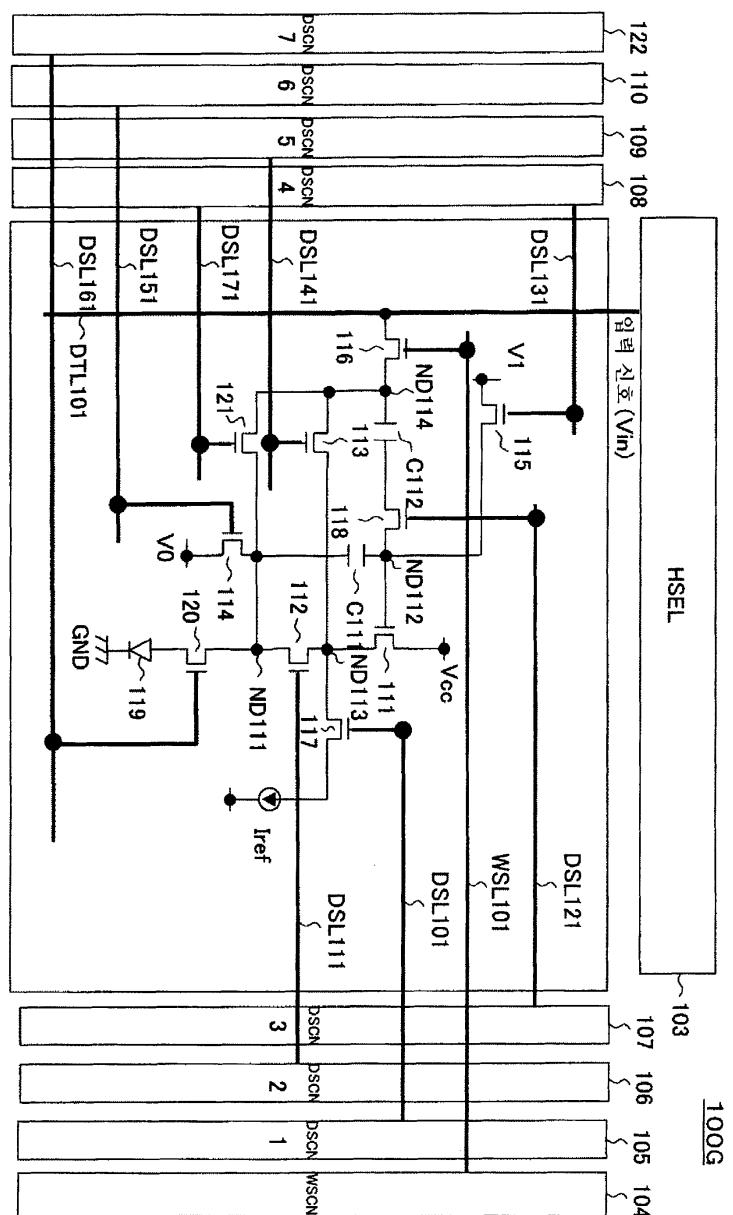

- [0166] 이 표시 장치(100)는, 도 8 및 도 9에 도시하는 바와 같이, 화소 회로(PXLC)(101)가  $m \times n$ 의 매트릭스 형상으로 배열된 화소 어레이부(102), 수평 셀렉터(HSEL)(103), 라이트 스캐너(WSCN)(104), 제1 드라이브 스캐너(DSCN1)(105), 제2 드라이브 스캐너(DSCN2)(106), 제3 드라이브 스캐너(DSCN3)(107), 제4 드라이브 스캐너(DSCN4)(108), 제5 드라이브 스캐너(DSCN5)(109), 제6 드라이브 스캐너(DSCN6)(110), 레퍼런스 정전류원(RCIS)(111), 수평 셀렉터(103)에 의해 선택되어 회로 정보에 따른 데이터 신호가 공급되는 데이터선 DTL101~DTL10n, 라이트 스캐너(104)에 의해 선택 구동되는 주사선 WSL101~WSL10m, 제1 드라이브 스캐너(105)에 의해 선택 구동되는 구동선 DSL101~DSL10m, 제2 드라이브 스캐너(106)에 의해 선택 구동되는 구동선 DSL111~DSL11m, 제3 드라이브 스캐너(107)에 의해 선택 구동되는 구동선 DSL121~DSL12m, 제4 드라이브 스캐너(108)에 의해 선택 구동되는 구동선 DSL131~DSL13m, 제5 드라이브 스캐너(109)에 의해 선택 구동되는 구동선 DSL151~DSL15m, 및 정전류원(111)에 의한 기준 전류  $I_{ref}$ 가 공급되는 기준 전류 공급선 ISL101~ISL10n을 갖는다.

- [0167] 또한, 화소 어레이부(102)에서, 화소 회로(101)는  $m \times n$ 의 매트릭스 형상으로 배열되지만, 도 8에서는 도면의 간단화를 위해  $2(=m) \times 3(=n)$ 의 매트릭스 형상으로 배열한 예를 나타내고 있다.

- [0168] 또한, 도 9에서도, 도면의 간단화를 위해 하나의 화소 회로의 구체적인 구성을 나타내고 있다.

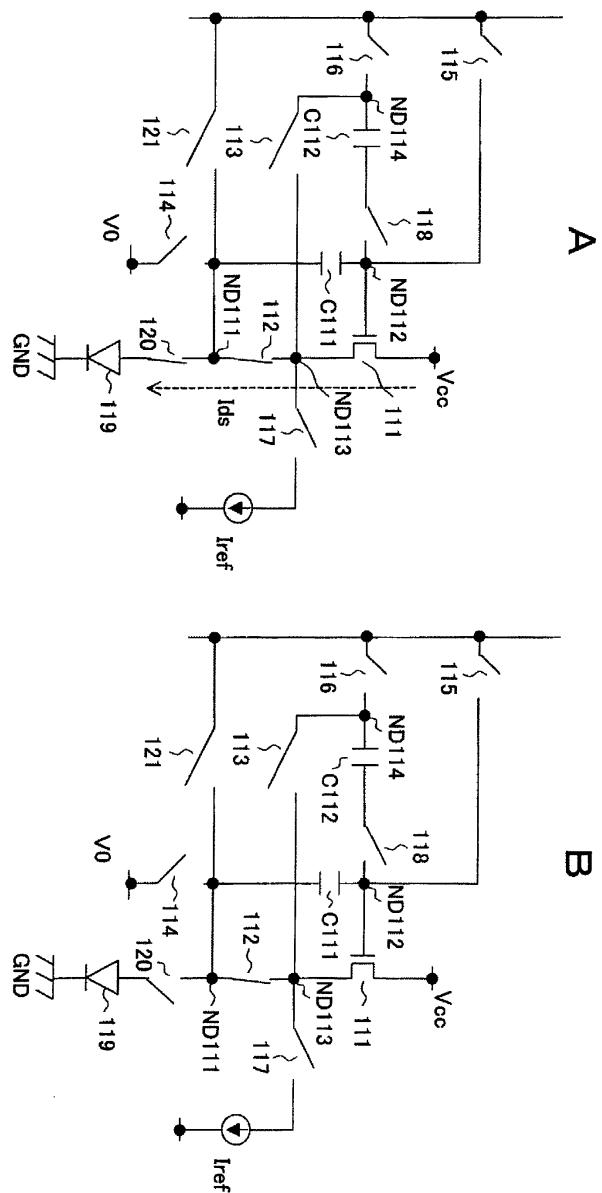

- [0169] 본 제1 실시 형태에 따른 화소 회로(101)는, 도 9에 도시하는 바와 같이, n채널 TFT(111)~TFT(118), 캐패시터 C111, C112, 유기 EL 소자(OLED: 전기 광학 소자)를 포함하는 발광 소자(119), 제1 노드 ND111, 제2 노드 ND112, 제3 노드 ND113 및 제4 노드 ND114를 갖는다.

- [0170] 또한, 도 9에서, DTL101은 데이터선을, WSL101은 주사선을, DSL101, DSL111, DSL121, DSL131, DSL141, DSL151은 구동선을 각각 나타내고 있다.

- [0171] 이들 구성 요소 중, TFT(111)가 본 발명에 따른 전계 효과 트랜지스터(드라이브(구동) 트랜지스터)를 구성하고, TFT(112)가 제1 스위치를 구성하고, TFT(113)가 제2 스위치를 구성하고, TFT(114)가 제3 스위치를 구성하고, TFT(115)가 제4 스위치를 구성하고, TFT(116)가 제5 스위치를 구성하고, TFT(117)가 제6 스위치를 구성하고, TFT(118)가 전기적 접속 수단으로서의 제7 스위치를 구성하며, 캐패시터 C111이 본 발명에 따른 화소 용량 소자를 구성하고, 캐패시터 C112가 본 발명에 따른 결합 용량 소자를 구성하고 있다.

- [0172] 또한, 전원 전압 VCC의 공급 라인(전원 전위)이 제1 기준 전위에 상당하고, 접지 전위 GND가 제2 기준 전위에 상당하고 있다.

- [0173] 또한, 본 제1 실시 형태에서는, 데이터선과 소정 전위선이 공용되어 있다.

- [0174] 화소 회로(101)에서, 제1 기준 전위(본 실시 형태에서는 전원 전위 VCC)와 제2 기준 전위(본 실시 형태에서는 접지 전위 GND) 사이에, 드라이브 트랜지스터로서의 TFT(111), 제3 노드 ND113, 제1 스위치로서의 TFT(112), 제1 노드 ND111 및 발광 소자(OLED)(119)가 직렬로 접속되어 있다.

- [0175] 구체적으로는, 발광 소자(119)의 캐소드가 접지 전위 GND에 접속되고, 애노드가 제1 노드 ND111에 접속되고, TFT(112)의 소스가 제1 노드 ND111에 접속되고, 제1 노드 ND111과 제3 노드 ND113 사이에 TFT(112)의 소스·드레인이 접속되고, TFT(111)의 소스가 제3 노드 ND113에 접속되고, TFT(111)의 드레인이 전원 전위 VCC에 접속되어 있다.

- [0176] 그리고, TFT(111)의 게이트가 제2 노드 ND112에 접속되고, TFT(112)의 게이트가 제2 드라이브 스캐너(106)에 의

해 구동되는 구동선 DSL111에 접속되어 있다.

[0177] 제3 노드 ND113과 제4 노드 ND114 사이에 제2 스위치로서의 TFT(113)의 소스·드레인이 접속되고, TFT(113)의 게이트가 제5 드라이브 스캐너(109)에 의해 구동되는 구동선 DSL141에 접속되어 있다.

[0178] 제3 스위치로서의 TFT(114)의 드레인이 제1 노드 ND111 및 캐패시터 C111의 제1 전극에 접속되고, 소스가 고정 전위(본 실시 형태에서는 접지 전위 GND)에 접속되고, TFT(114)의 게이트가 제6 드라이브 스캐너에 의해 구동되는 구동선 DSL151에 접속되어 있다. 또한, 캐패시터 C111의 제2 전극이 제2 노드 ND112에 접속되어 있다.

[0179] 제2 노드 ND112와 캐패시터 C112의 제1 전극에 제7 스위치로서의 TFT(118)의 소스·드레인이 접속되고, TFT(118)의 제3 드라이브 스캐너에 의해 구동되는 게이트가 구동선 DLS121에 접속되어 있다.

[0180] 데이터선(소정 전위선) DTL101과 제2 노드 ND112에 제4 스위치로서의 TFT(115)의 소스·드레인이 각각 접속되고, TFT(115)의 게이트가 제4 드라이브 스캐너(108)에 구동되는 구동선 DSL131에 접속되어 있다.

[0181] 데이터선 DTL101과 제4 노드 ND114에 제5 스위치로서의 TFT(116)의 소스·드레인이 각각 접속되어 있다. 그리고, TFT(116)의 게이트가 라이트 스캐너(104)에 의해 구동되는 주사선 WSL101에 접속되어 있다.

[0182] 또한, 제3 노드 ND113과 기준 전류 공급선 ISL101 사이에 제6 스위치로서의 TFT(117)의 소스·드레인이 각각 접속되어 있다. 그리고, TFT(117)의 게이트가 제1 드라이브 스캐너(105)에 의해 구동되는 구동선 DSL101에 접속되어 있다.

[0183] 이와 같이, 본 실시 형태에 따른 화소 회로(101)는, 드라이브 트랜지스터로서의 TFT(111)의 게이트·소스간에 화소 용량으로서의 캐패시터 C111이 접속되고, 비발광 기간에 TFT(111)의 소스측 전위를 스위치 트랜지스터로서의 TFT(114)를 통하여 고정 전위에 접속하고, 또한, TFT(111)의 소스(제3 노드 ND113)에 소정의 기준 전류(예를 들어  $2\mu\text{A}$ ) Iref를 소정의 타이밍에서 공급하여, 기준 전류 Iref에 상당하는 전압을 유지하고, 그 전압을 중심으로 하여 입력 신호 전압을 커플링시킴으로써, 이동도의 변동의 센터치를 중심으로 EL 발광 소자(119)를 구동하고, 드라이브 트랜지스터로서의 TFT(111)의 이동도 변동에 의해 유니포미터 변동을 억제한 화질을 얻도록 구성되어 있다.

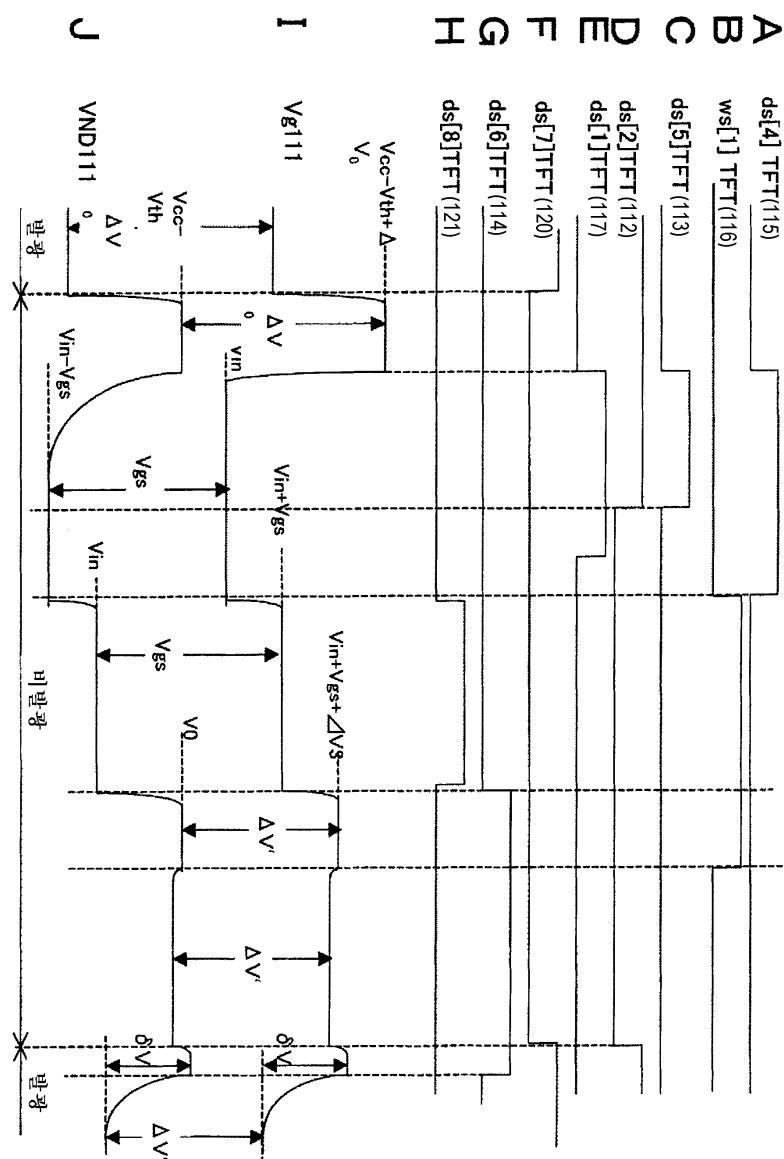

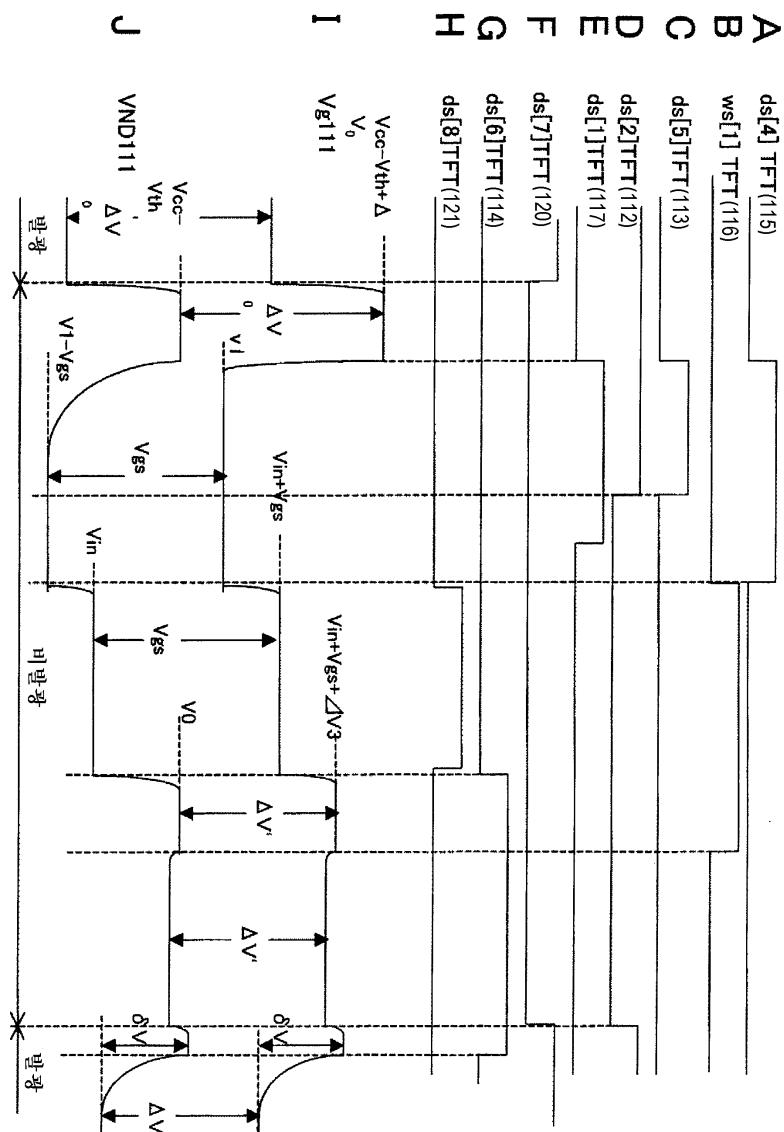

[0184] 다음으로, 상기 구성의 동작을, 화소 회로의 동작을 중심으로, 도 10의 (A) 내지 도 10의 (I) 및 도 11, 도 12의 (A), 도 12의 (B), 및 도 13, 도 14에 관련지어 설명한다.

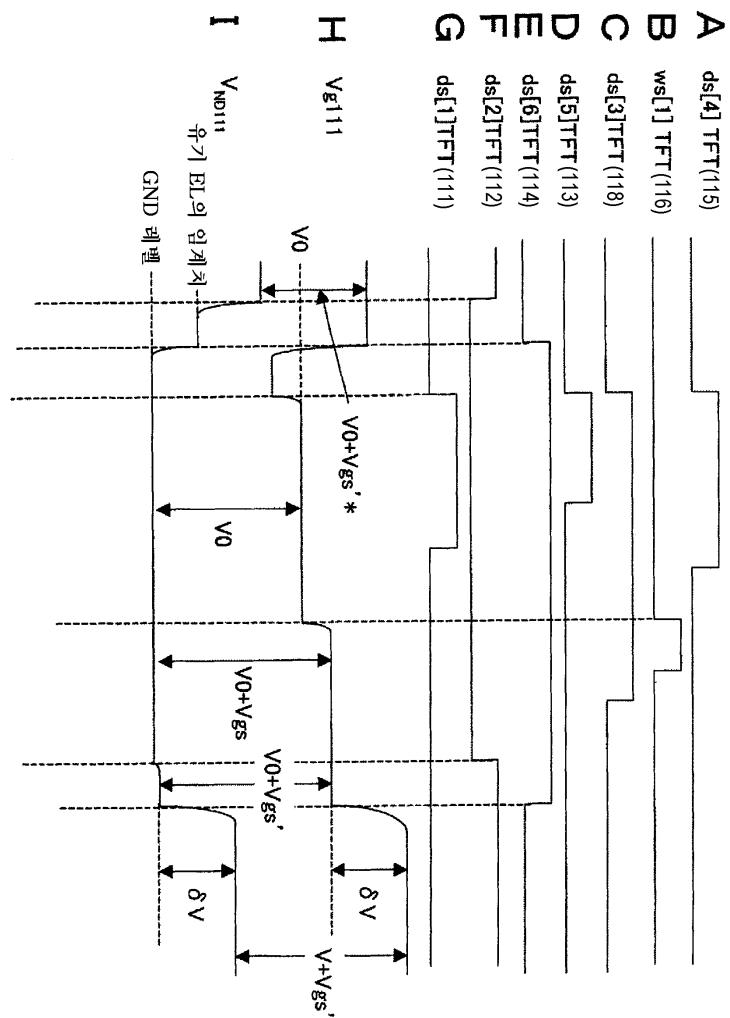

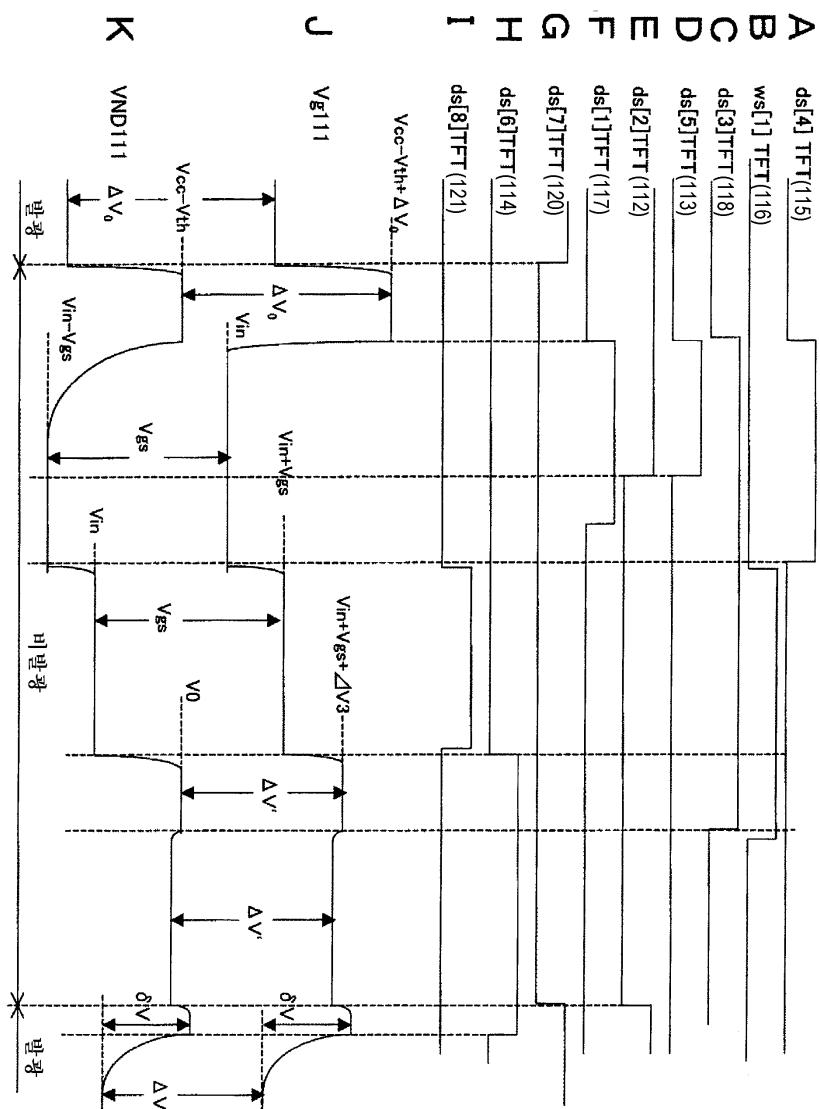

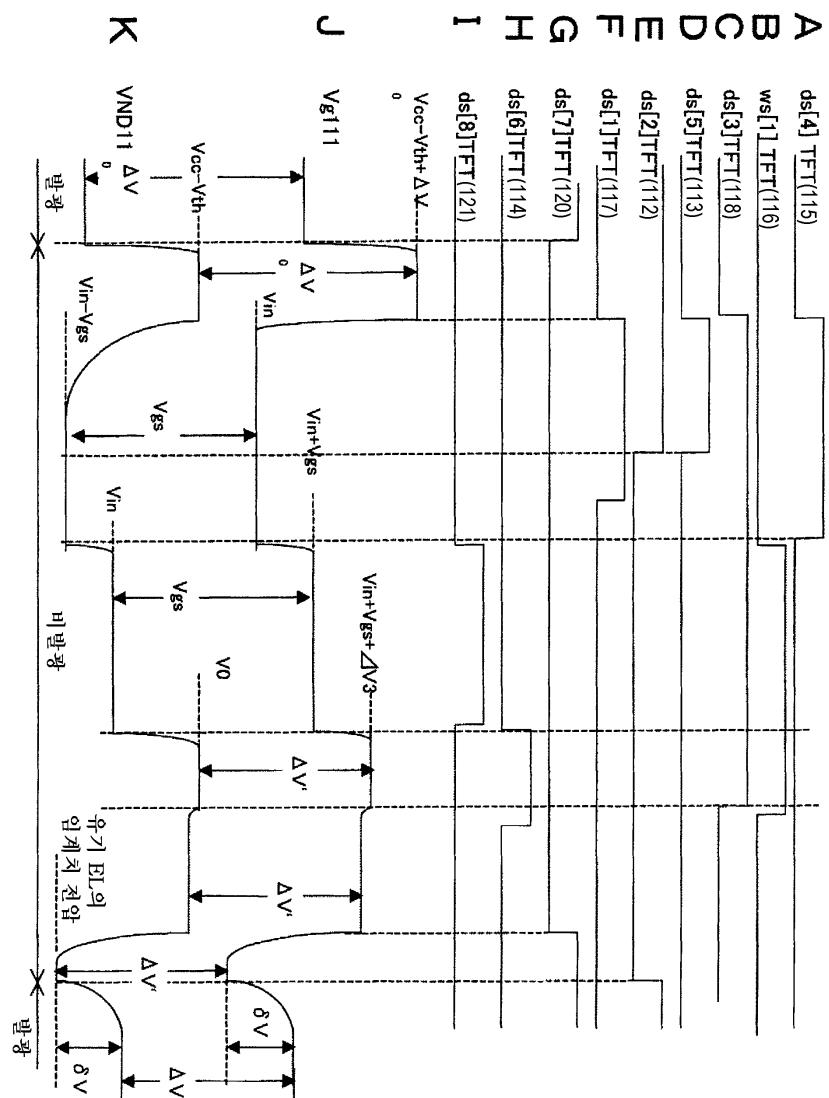

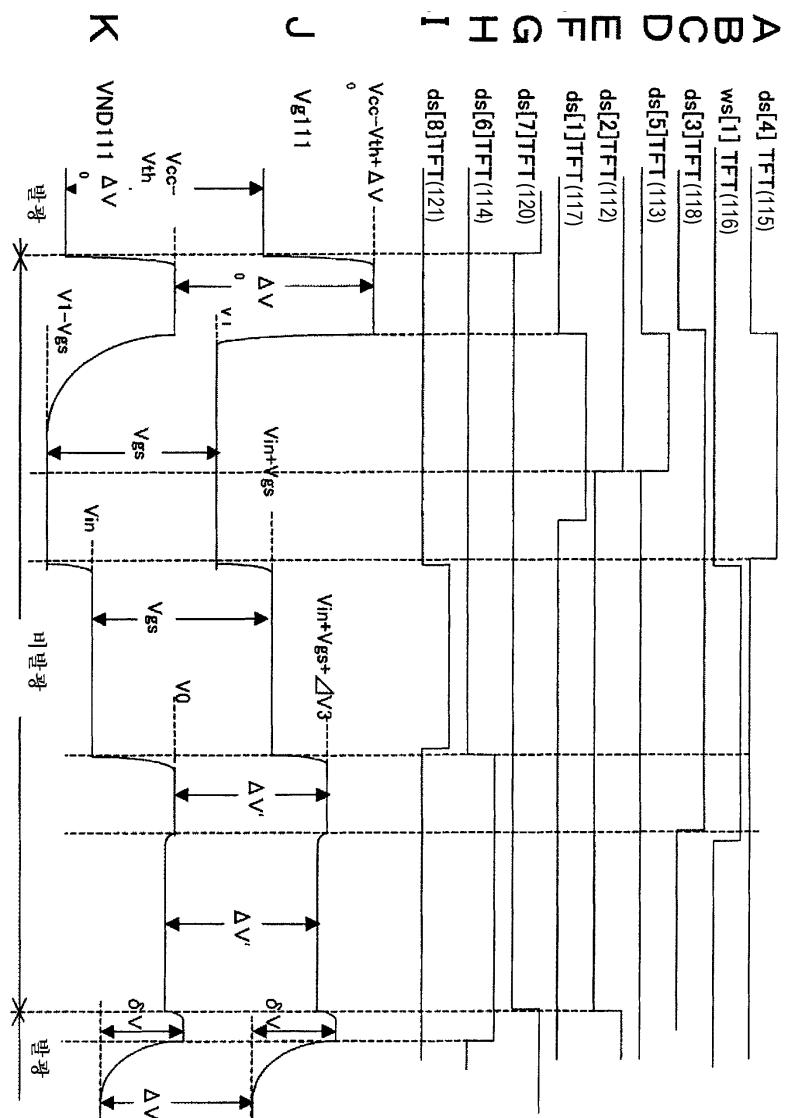

[0185] 또한, 도 10의 (A)는 화소 배열의 제1행째의 구동선 DSL131에 인가되는 구동 신호 ds[4]를, 도 10의 (B)는 화소 배열의 제1행째의 조작선 WSL101에 인가되는 주사 신호 ws[1]을, 도 10의 (C)는 화소 배열의 제1행째의 구동선 DSL121에 인가되는 구동 신호 ds[3]을, 도 10의 (D)는 화소 배열의 제1행째의 구동선 DSL141에 인가되는 구동 신호 ds[5]를, 도 10E는 화소 배열의 제1행째의 구동선 DSL151에 인가되는 구동 신호 ds[6]을, 도 10의 (F)는 화소 배열의 제1행째의 구동선 DSL111에 인가되는 구동 신호 ds[2]를, 도 10의 (G)는 화소 배열의 제1행째의 구동선 DSL101에 인가되는 구동 신호 ds[1]을, 도 10의 (H)는 드라이브 트랜지스터로서의 TFT(111)의 게이트 전위 Vg111을, 도 10의 (I)는 제1 노드 ND111의 전위 VND111을 각각 나타내고 있다.

[0186] 우선, 통상의 EL 발광 소자(119)의 발광 상태 시에는, 도 10의 (A)~도 10의 (G)에 도시하는 바와 같이, 라이트 스캐너(104)에 의해 주사선 WSL101에의 주사 신호 ws[1]이 로우 레벨로 설정되고, 드라이브 스캐너(105)에 의해 구동선 DSL101에의 구동 신호 ds[1]이 로우 레벨로 설정되고, 드라이브 스캐너(107)에 의해 구동선 DSL121에의 구동 신호 ds[4]가 로우 레벨로 설정되고, 드라이브 스캐너(108)에 의해 구동선 DSL131에의 구동 신호 ds[3]이 로우 레벨로 설정되고, 드라이브 스캐너(109)에 의해 구동선 DSL141에의 구동 신호 ds[5]가 로우 레벨로 설정되고, 드라이브 스캐너(110)에 의해 구동선 DSL151에의 구동 신호 ds[6]이 로우 레벨로 설정되며, 드라이브 스캐너(106)에 의해 구동선 DSL111에의 구동 신호 ds[2]만이 선택적으로 하이 레벨로 설정된다.

[0187] 그 결과, 화소 회로(101)에서는, 도 11의 (A)에 도시하는 바와 같이, TFT(112)가 온 상태(도통 상태)로 유지되고, TFT(113)~TFT(118)가 오프 상태(비도통 상태)로 유지된다.

[0188] 드라이브 트랜지스터(111)는 포화 영역에서 동작하도록 설계되어 있어, EL 발광 소자(119)에 흐르는 전류 Ids는, 상기 수학식 1로 나타내는 값을 취한다.

[0189] 다음으로, EL 발광 소자(119)의 비발광 기간에서, 도 10의 (A)~도 10의 (G)에 도시하는 바와 같이, 라이트 스캐너(104)에 의해 주사선 WSL101에의 주사 신호 ws[1]이 로우 레벨로 유지되고, 드라이브 스캐너(105)에 의해 구동선 DSL101에의 구동 신호 ds[1]이 로우 레벨로 유지되고, 드라이브 스캐너(106)에 의해 구동선 DSL111에의

구동 신호 ds[2]가 로우 레벨로 전환되고, 드라이브 스캐너(107)에 의해 구동선 DSL121에의 구동 신호 ds[3]이 로우 레벨로 유지되고, 드라이브 스캐너(108)에 의해 구동선 DSL131에의 구동 신호 ds[4]가 로우 레벨로 유지되고, 드라이브 스캐너(109)에 의해 구동선 DSL141에의 구동 신호 ds[5]가 로우 레벨로 유지되며, 드라이브 스캐너(110)에 의해 구동선 DSL151에의 구동 신호 ds[6]이 선택적으로 하이 레벨로 설정된다.

[0190] 그 결과, 화소 회로(101)에서는, 도 11의 (B)에 도시하는 바와 같이, TFT(112)가 오프하고, TFT(113), TFT(115)~TFT(118)는 오프 상태로 유지된 채로, TFT(114)가 온한다.

[0191] 이 때, TFT(114)를 통하여 전류가 흘러 도 10의 (H), 도 10의 (I)에 도시하는 바와 같이, 제1 노드 ND111의 전위 VND111은 접지 전위 GND까지 하강한다. 그 때문에, EL 발광 소자(119)에 인가되는 전압도 0V로 되어, EL 발광 소자(119)는 발광하지 않게 된다.

[0192] 다음으로, 도 10의 (A)~도 10의 (G)에 도시하는 바와 같이, 라이트 스캐너(104)에 의해 주사선 WSL101에의 주사 신호 ws[1]이 로우 레벨로 유지되고, 드라이브 스캐너(106)에 의해 구동선 DSL111에의 구동 신호 ds[2]가 로우 레벨로 유지되고, 드라이브 스캐너(110)에 의해 구동선 DSL151에의 구동 신호 ds[6]이 하이 레벨로 유지된 상태에서, 드라이브 스캐너(105)에 의한 구동선 DSL101에의 구동 신호 ds[1], 드라이브 스캐너(107)에 의한 구동선 DSL121에의 구동 신호 ds[3], 드라이브 스캐너(108)에 의한 구동선 DSL131에의 구동 신호 ds[4], 드라이브 스캐너(109)에 의해 구동선 DSL141에의 구동 신호 ds[5]가 각각 선택적으로 하이 레벨로 설정된다.

[0193] 그 결과, 화소 회로(101)에서는, 도 12의 (A)에 도시하는 바와 같이, TFT(114)가 온 상태, TFT(112), TFT(116)가 오프 상태로 유지된 채로, TFT(113), TFT(115), TFT(117), TFT(118)가 온한다.

[0194] 이에 의해, TFT(115)를 통하여 데이터선 DTL101에서 전파된 입력 전압 Vin이 제2 노드 ND112에 입력되고, 이와 병행하여, 정전류원(111)에 의해 기준 전류 공급선 ISL101에 공급된 기준 전류 Iref(예를 들어  $2\mu\text{A}$ )가 제3 노드 ND113에 흐른다. 그 결과, 드라이브 트랜지스터로서의 TFT(111)의 게이트·소스간 전압 Vgs가 캐패시터 C112에 충전된다.

[0195] 이 때, TFT(111)는 포화 영역에서 동작하기 때문에, 하기의 수학식 2로 나타내는 바와 같이, TFT(111)의 게이트·소스간 전압 Vgs는, 이동도  $\mu$  및 임계치 Vth를 포함한 항으로 된다. 또한, 이 때, 캐패시터 C111에는 Vin이 충전된다.

## 수학식 2

$$V_{gs} = V_{th} + \{ 2I_{ds}/(\mu(W/L)C_{ox}) \}^2$$

[0196] 다음으로, 캐패시터 C111에는 Vin이 충전된 후, 도 10의 (A)~도 10의 (G)에 도시하는 바와 같이, 라이트 스캐너(104)에 의해 주사선 WSL101에의 주사 신호 ws[1]이 로우 레벨로 유지되고, 드라이브 스캐너(106)에 의해 구동선 DSL111에의 구동 신호 ds[2]가 로우 레벨로 유지되고, 드라이브 스캐너(107)에 의해 구동선 DSL121에의 구동 신호 ds[3]이 하이 레벨로 유지되고, 드라이브 스캐너(108)에 의해 구동선 DSL131에의 구동 신호 ds[4]가 하이 레벨로 유지되고, 드라이브 스캐너(110)에 의해 구동선 DSL151에의 구동 신호 ds[6]이 하이 레벨로 유지된 상태에서, 드라이브 스캐너(105)에 의해 구동선 DSL101에의 구동 신호 ds[1]이 로우 레벨로, 드라이브 스캐너(109)에 의해 구동선 DSL141에의 구동 신호 ds[5]가 로우 레벨로 각각 선택적으로 설정된다.

[0197] 그 결과, 화소 회로(101)에서는, 도 12의 (A)의 상태로부터, TFT(113), TFT(117)가 오프한다. 이에 의해, TFT(111)의 소스 전위(제3 노드 ND113의 전위)는 (Vin-Vth)까지 상승한다.

[0198] 그리고, 또한, 라이트 스캐너(104)에 의해 주사선 WSL101에의 주사 신호 ws[1]이 하이 레벨로 전환되고, 드라이브 스캐너(108)에 의해 구동선 DSL131에의 구동 신호 ds[4]가 로우 레벨로 전환된다.

[0199] 그 결과, 화소 회로(101)에서는, 도 12의 (B)에 도시하는 바와 같이, TFT(114), TFT(118)가 온 상태, TFT(112), TFT(113), TFT(117)가 오프 상태로 유지된 채로, TFT(116)가 온하고, TFT(115)가 오프한다.

[0200] TFT(116)가 온함으로써, TFT(116)를 통하여 데이터선 DTL101을 전파된 입력 전압 Vin이 캐패시터 C112를 통하여 TFT(111)의 게이트에 전압  $\Delta V$ 를 커플링시킨다.

[0201] 이 커플링량  $\Delta V$ 는, 제1 노드 ND111과 제2 노드 ND112간의 전압 변화량(TFT(111)의 Vgs)과 캐패시터 C111, C112, 및 TFT(111)의 기생 용량 C113에 의해 정해지며, 캐패시터 C111과 기생 용량 C113에 비해 캐패시터 C112의 용량을 크게 하면 변화량의 거의 전부가 TFT(111)의 게이트에 커플링되어, TFT(111)의 게이트 전위는

( $V_{in}+V_{gs}$ )로 된다.

[0203] 기입 종료 후, 도 10의 (A)~도 10의 (G)에 도시하는 바와 같이, 라이트 스캐너(104)에 의해 주사선 WSL101에의 주사 신호  $ws[1]$ 이 로우 레벨로 전환되고, 드라이브 스캐너(107)에 의해 구동선 DSL121에의 구동 신호  $ds[3]$ 이 로우 레벨로 전환되고, 또한, 드라이브 스캐너(106)에 의해 구동선 DSL111에의 구동 신호  $ds[2]$ 가 하이 레벨로 전환되고, 드라이브 스캐너(110)에 의해 구동선 DSL151에의 구동 신호  $ds[6]$ 이 로우 레벨로 전환된다.

[0204] 이에 의해, 화소 회로(101)에서는, 도 13에 도시하는 바와 같이, TFT(116), TFT(118)가 오프하고, 또한 TFT(112)가 온하며, TFT(114)가 오프한다.

[0205] 이에 의해, TFT(111)의 소스 전위는 일단 접지 전위 GND로 강하, 그 후 상승하고, EL 발광 소자(119)에도 전류가 흐르기 시작한다. TFT(111)의 소스 전위는 변동됨에도 불구하고, 그 게이트 · 소스간에는 캐패시터 C111이 있고, 또한, 캐패시터 C111의 용량을 TFT(111)의 기생 용량 C113보다 크게 함으로써 게이트 · 소스 전위는 항상 ( $V_{in}+V_{gs}$ )의 일정치로 유지된다.

[0206] 이 때, TFT(111)는 포화 영역에서 구동하므로, TFT(111)에 흐르는 전류치  $Ids$ 는 수학식 1로 나타낸 값으로 되고, 그것은 게이트 · 소스간 전압에 의해 결정된다. 이  $Ids$ 는 EL 발광 소자(119)에도 마찬가지로 흘러 EL 발광 소자(119)는 발광한다.

[0207] 이 EL 발광 소자(119)를 포함하는 화소 회로(101)의 등가 회로는 도 14에 도시하는 바와 같이 되어 있기 때문에, TFT(111)의 소스 전위는 EL 발광 소자(119)에 전류  $Ids$ 가 흐르는 게이트 전위까지 상승한다. 이 전위 상승에 수반하여, 캐패시터 C111을 통하여 TFT(111)의 게이트 전위도 마찬가지로 상승한다.

[0208] 이에 의해, 상술한 바와 같이 TFT(111)의 게이트 · 소스간 전위는 일정하게 유지된다.

[0209] 여기에서, 기준 전류  $I_{ref}$ 에 대하여 고려한다.

[0210] 상술한 바와 같이, 기준 전류  $I_{ref}$ 를 흘림으로써, TFT(111)의 게이트 · 소스간 전압을 수학식 2로 나타낸 값으로 한다.

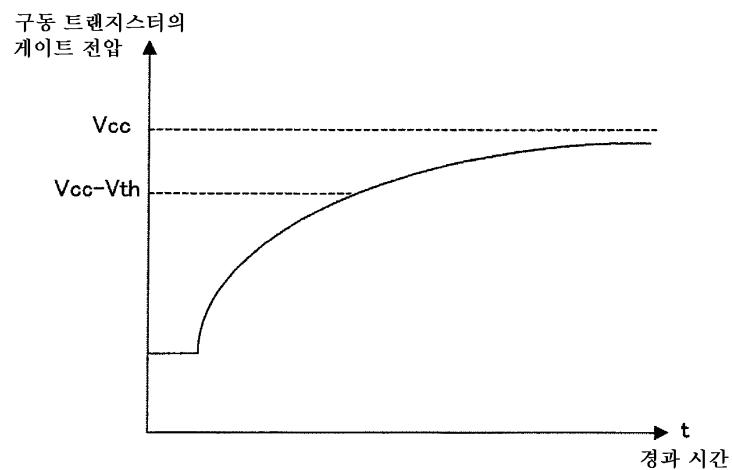

[0211] 그러나,  $I_{ref}=0$ 일 때에는, 게이트 · 소스간 전압은  $V_{th}$ 로 되지 않는다. 왜냐하면, 게이트 · 소스간 전압이  $V_{th}$ 가 되어도, TFT(111)에는 소량에 리크 전류가 흐르게 되므로, 도 15에 도시하는 바와 같이, TFT(111)의 소스 전압은  $V_{cc}$ 까지 상승하게 되기 때문이다.

[0212] TFT(111)의 게이트 · 소스간 전압을  $V_{th}$ 로 하기 위해서는, TFT(113)가 온하고 있는 기간을 조절하여 게이트 · 소스간 전압이  $V_{th}$ 로 된 부분에서 오프해야만 하므로, 실디바이스에서 이 타이밍은 패널마다 조절해야만 한다.

[0213] 본 실시 형태와 같이, 기준 전류  $I_{ref}$ 를 흘리지 않는 경우에는, TFT(113)의 타이밍을 조절하여, 게이트 · 소스간 전압을  $V_{th}$ 로 설정할 수 있다고 하여도, 예를 들면 이동도가 서로 다른 화소 A와 B에서, 동일한 입력 전압  $V_{in}$ 이 인가되어 있을 때에도, 수학식 1에 따라 이동도  $\mu$ 에 의해, 도 16에 도시하는 바와 같이, 전류  $Ids$ 의 변동이 발생하여 그 화소의 휘도가 서로 달라지게 된다. 즉, 전류치가 많게 흘러 밝아짐에 따라 전류치는 이동도의 변동을 받게 되어, 유니포미티는 변동되게 되며, 화질은 악화되게 된다.

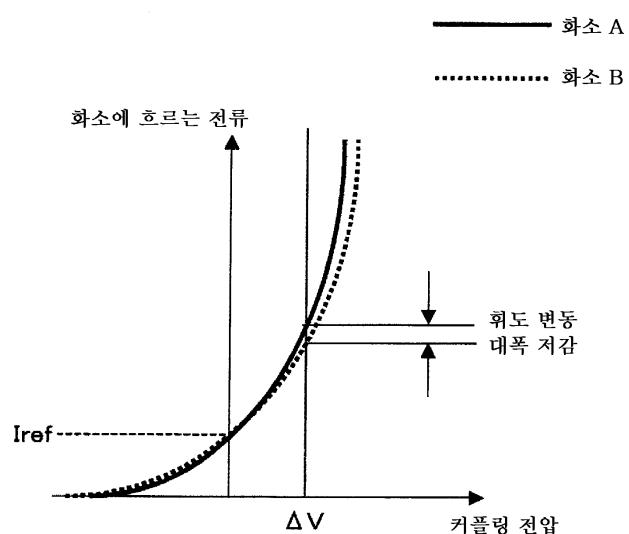

[0214] 그러나, 본 실시 형태와 같이, 일정량의 기준 전류  $I_{ref}$ 를 흘림으로써, 도 17에 도시하는 바와 같이, TFT(113)의 온 · 오프의 타이밍에 상관없이 TFT(111)의 게이트 · 소스간 전압을 수학식 2로 나타내는 일정치로 결정할 수 있어, 이동도가 서로 다른 화소 A와 B에서도, 도 18에 도시하는 바와 같이, 전류  $Ids$ 의 변동을 작게 억제할 수 있으므로, 유니포미티의 변동도 억제할 수 있다.

[0215] 또한, 종래의 소스 팔로워의 문제점에 근거하여 본 실시 형태의 회로에 대해 고려한다. 본 회로에서도, EL 발광 소자(119)는 발광 시간이 길어짐에 따라, 그 I-V 특성은 열화된다. 그 때문에 TFT(111)가 동일한 전류치를 흘렸다고 해도, EL 발광 소자(119)에 인가되는 전위는 변화되어, 제1 노드 ND111의 전위 VND111은 하강한다.

[0216] 그러나, 본 회로에서는, TFT(111)의 게이트 · 소스간 전위가 일정하게 유지된 채로 제1 노드 ND111의 전위 VND111은 하강하므로, TFT(111)에 흐르는 전류는 변화되지 않는다.

[0217] 따라서, EL 발광 소자(119)에 흐르는 전류도 변화되지 않아, EL 발광 소자(119)의 I-V 특성이 열화되어도, 게이트 · 소스간 전압에 상당하는 전류가 항상 흘러, 종래의 문제를 해결할 수 있다.

[0218] 이상 설명한 바와 같이, 본 제1 실시 형태에 따르면, 전압 구동형 TFT 액티브 매트릭스 유기 EL 디스플레이에서, 드라이브 트랜지스터로서의 TFT(111)의 게이트와 소스간에 캐패시터 C111을 접속하고,

TFT(111)의 소스측(제1 노드 ND111)을 TFT(114)를 통하여 고정 전위(본 실시 형태에서는 GND)에 접속하도록 하고, 또한, TFT(111)의 소스(제3 노드 ND113)에 소정의 기준 전류(예를 들어  $2\mu\text{A}$ )  $I_{ref}$ 를 소정의 타이밍에서 공급하여, 기준 전류  $I_{ref}$ 에 상당하는 전압을 유지하고, 그 전압을 중심으로 하여 입력 신호 전압을 커플링시킴으로써, 이동도의 변동의 센터치를 중심으로 EL 발광 소자(119)를 구동하도록 구성하였기 때문에, 이하의 효과를 얻을 수 있다.

[0219] 즉, EL 발광 소자의 I-V 특성이 경시 변화되어도, 회도 열화가 없는 소스 팔로워 출력을 행할 수 있다.

[0220] n채널 트랜지스터의 소스 팔로워 회로가 가능해져서, 현상의 애노드 · 캐소드 전극을 이용한 채로, n채널 트랜지스터를 EL 발광 소자의 구동 소자로서 이용할 수 있다.

[0221] 또한, 구동 트랜지스터의 임계치의 변동뿐만 아니라, 이동도의 변동도 대폭 억제할 수 있어, 유니포미티가 균일한 화질을 얻을 수 있다.

[0222] 또한, 기준 전류를 훌려 구동 트랜지스터의 임계치 변동의 캔슬을 행하고 있기 때문에, 패널마다 스위치의 온, 오프의 타이밍의 설정으로 임계치를 캔슬할 필요가 없기 때문에, 타이밍을 설정하는 공수의 증가를 억제할 수 있다.

[0223] 또한, n채널만으로 화소 회로의 트랜지스터를 구성할 수 있어, TFT 작성에서 a-Si 프로세스를 이용할 수 있게 된다. 이에 의해, TFT 기판의 저코스트화가 가능해진다.

[0224] <제2 실시 형태>

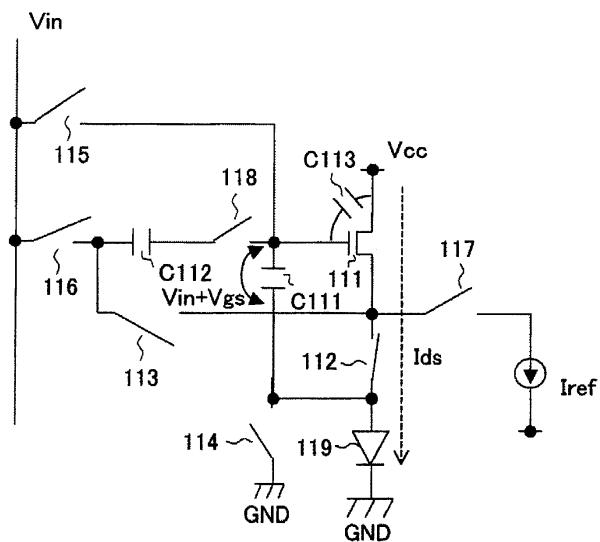

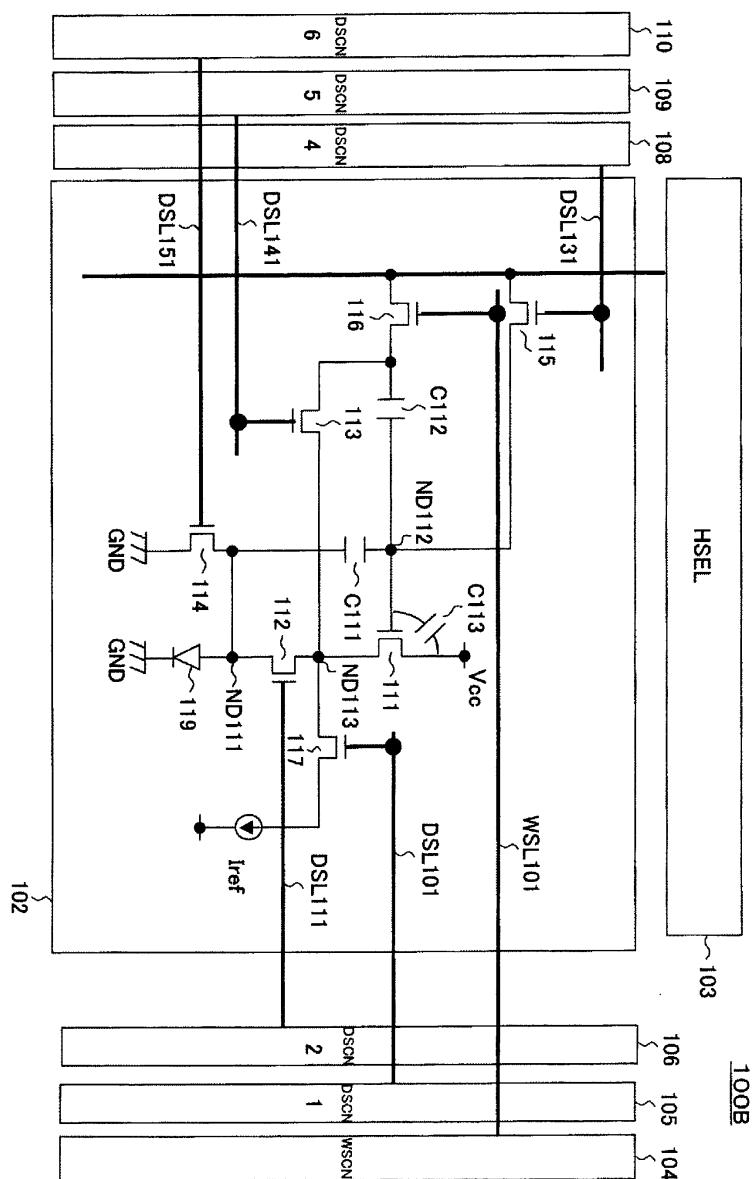

[0225] 도 19는, 본 제2 실시 형태에 따른 화소 회로의 구체적인 구성을 도시하는 회로도이다. 또한, 도 20은, 도 19의 회로의 타이밍차트이다.

[0226] 본 제2 실시 형태가 상술한 제1 실시 형태와 다른 점은, 제4 스위치로서의 TFT(115)가 접속되는 소정의 전위선을 데이터선 DTL과 공용하지 않고, 별도로 설치한 것에 있다.

[0227] 그 외의 구성은 제1 실시 형태와 마찬가지이며, 여기에서는, 구성 및 기능에 관한 상세한 설명은 생략한다.

[0228] 본 제2 실시 형태에서는, 드라이버 트랜지스터로서의 TFT(111)의 소스에 기준 전류  $I_{ref}$ 를 훌릴 때에 TFT(111)의 게이트 전압에 입력 전압  $V_{in}$ 을 입력하는 것이 아니라, 고정 전위  $V_0$ 을 입력한다. 고정 전위  $V_0$ 을 입력하여 기준 전류  $I_{ref}$ 를 훌림으로써 화소 내에  $V_{in}$ 이 입력되어 있는 시간을 짧게 할 수 있어, 화소에 고속으로 기입할 수 있다.

[0229] 이 때문에, 예를 들어 3회 기입 방식과 같이 1H를 수분할하여 화소에 기입하는 구동 방식에도 대응할 수 있게 된다.

[0230] <제3 실시 형태>

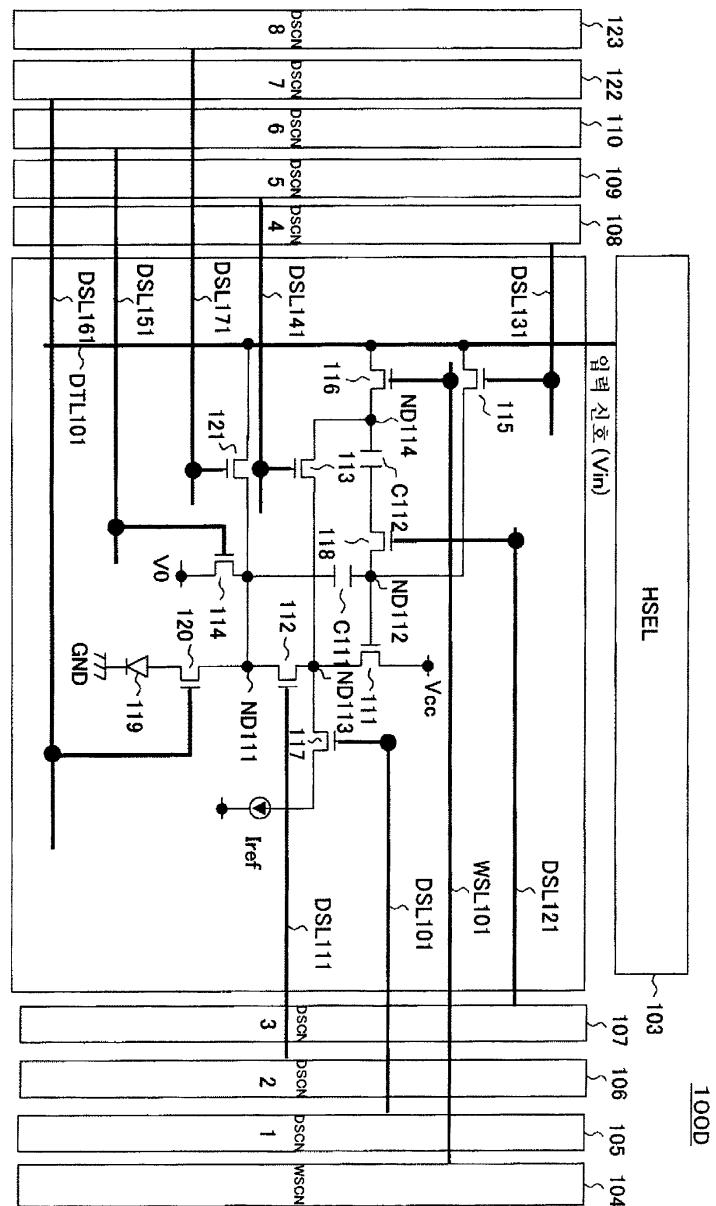

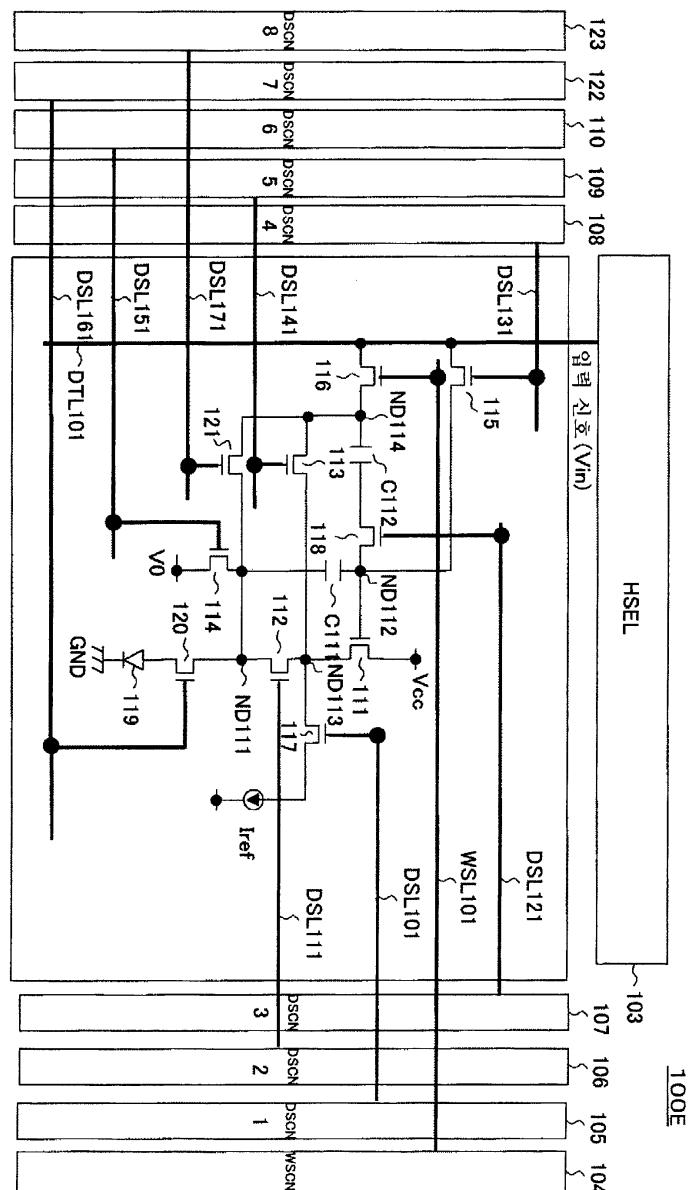

[0231] 도 21은, 본 제3 실시 형태에 따른 화소 회로를 채용한 유기 EL 표시 장치의 구성을 도시하는 블록도이다.

[0232] 도 22는, 도 21의 유기 EL 표시 장치에서 본 제3 실시 형태에 따른 화소 회로의 구체적인 구성을 도시하는 회로도이다. 또한, 도 23의 (A)~도 23의 (H)는, 도 22의 회로의 타이밍차트이다.

[0233] 본 제3 실시 형태가 제1 실시 형태와 다른 점은, 캐패시터 C112의 제1 전극과 제2 노드 ND112를 접속하는 전기적 접속 수단을, 양자간을 선택적으로 접속하는 스위치(118)에 의해 구성하는 대신에, 전기 배선에 의해 직접 접속하도록 한 것에 있다.

[0234] 그 결과, 제3 드라이브 스캐너(107)와 구동선 DSL121이 불필요하게 되어 있다.

[0235] 그 외의 구성은, 상술한 제2 실시 형태와 마찬가지이다.

[0236] 본 제3 실시 형태에 따르면, 상술한 제1 실시 형태의 효과 외에, 화소 회로 내의 소자수를 저감할 수 있어, 회로 구성을 간단화할 수 있는 이점이 있다.

[0237] <제4 실시 형태>

[0238] 도 24는, 본 제4 실시 형태에 따른 화소 회로의 구체적인 구성을 도시하는 회로도이다. 또한, 도 25의 (A)~도 25의 (H)는, 도 24의 회로의 타이밍차트이다.

[0239] 본 제4 실시 형태가 상술한 제3 실시 형태와 다른 점은, 제4 스위치로서의 TFT(115)가 접속되는 소정의 전위선

을 데이터선 DTL과 공용하지 않고, 별도로 설치한 것에 있다.

[0240] 그 외의 구성은 제1 실시 형태와 마찬가지이고, 여기에서는, 구성 및 기능에 관한 상세한 설명은 생략한다.

[0241] 본 제4 실시 형태에서는, 드라이버 트랜지스터로서의 TFT(111)의 소스에 기준 전류  $I_{ref}$ 를 흘릴 때에 TFT(111)의 게이트 전압에 입력 전압  $V_{in}$ 을 입력하는 것이 아니라, 고정 전위  $V_0$ 을 입력한다. 고정 전위  $V_0$ 을 입력하여 기준 전류  $I_{ref}$ 를 흘림으로써 화소 내에  $V_{in}$ 이 입력되어 있는 시간을 짧게 할 수 있어, 화소에 고속으로 기입할 수 있다.

[0242] 이 때문에, 예를 들어 3회 기입 방식과 같이 1H를 수분할하여 화소에 기입하는 구동 방식에도 대응할 수 있게 된다.

[0243] 〈제5 실시 형태 및 제6 실시 형태〉

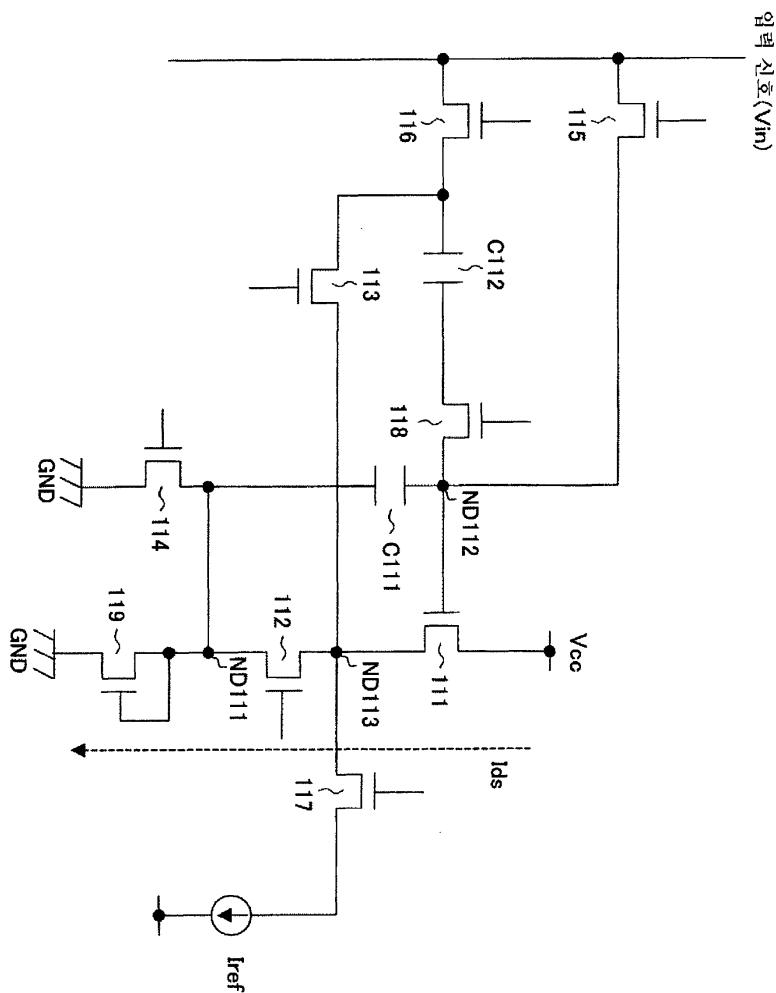

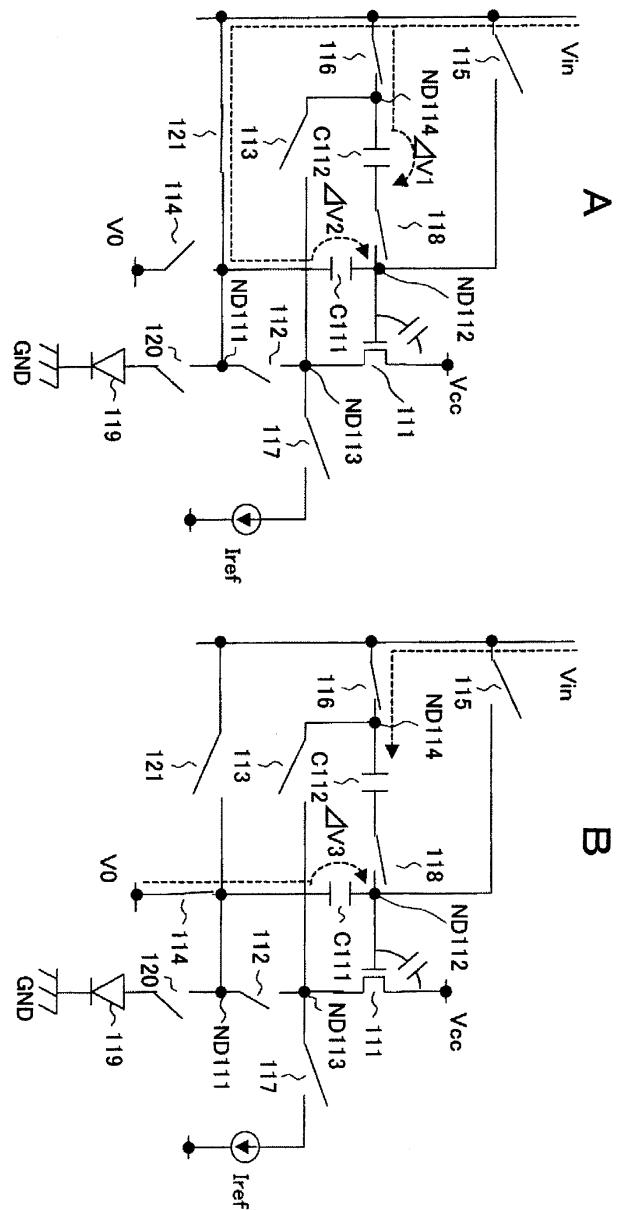

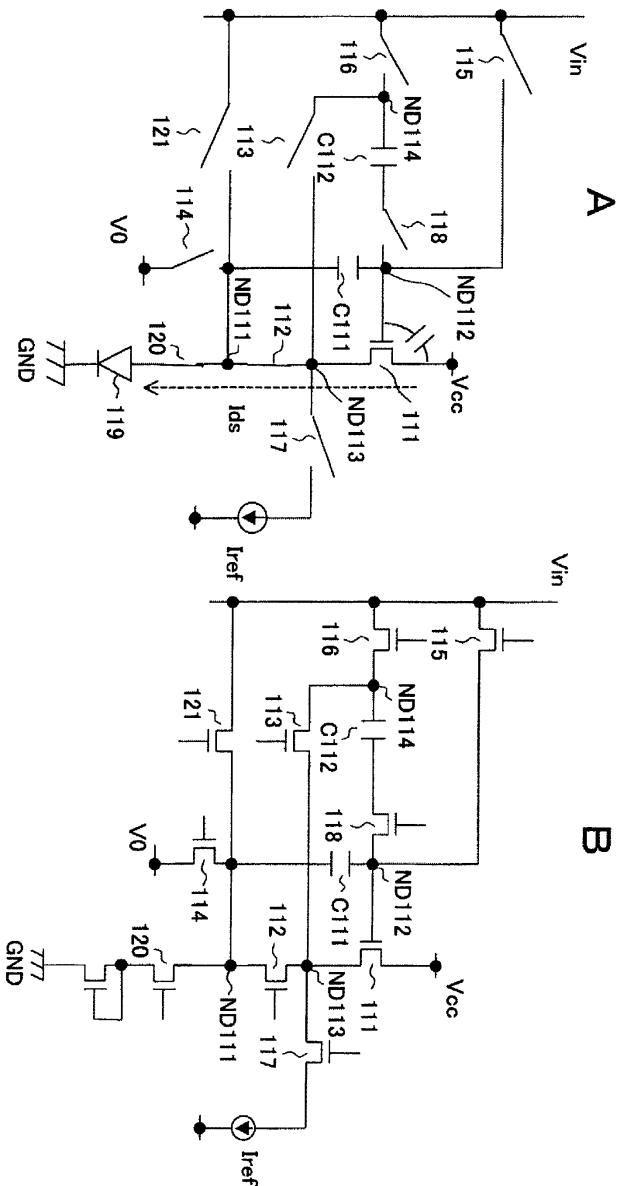

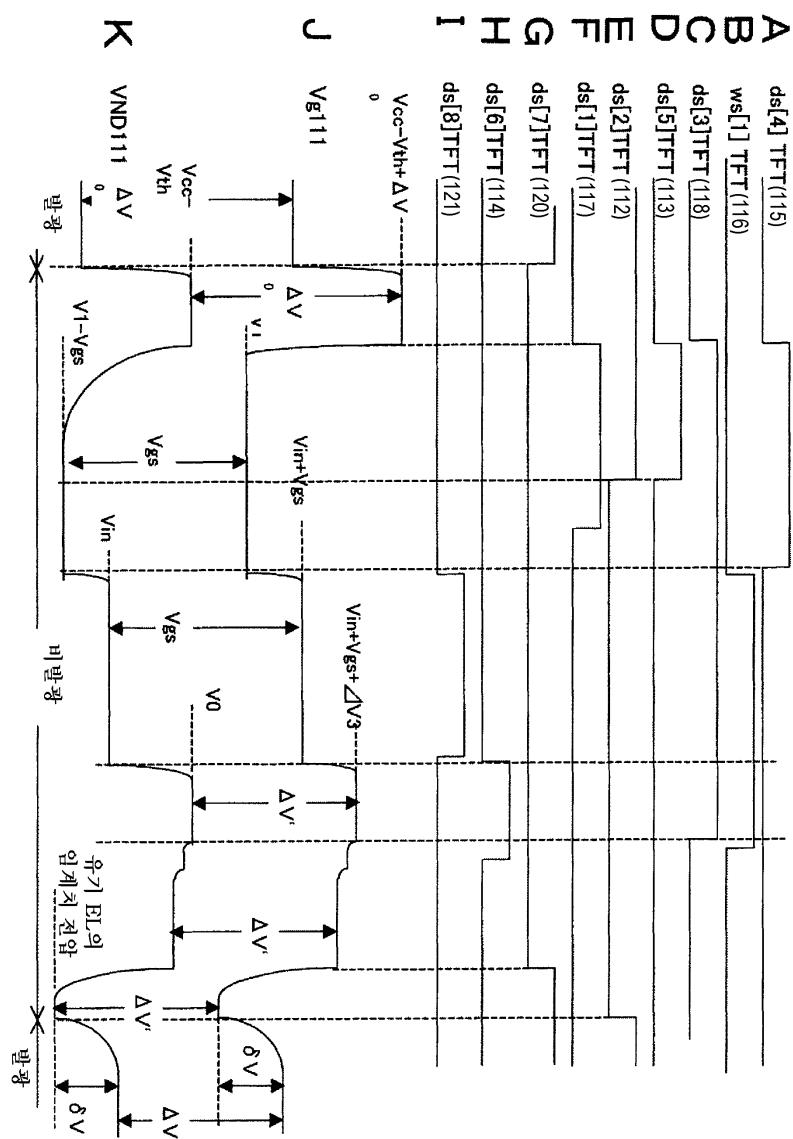

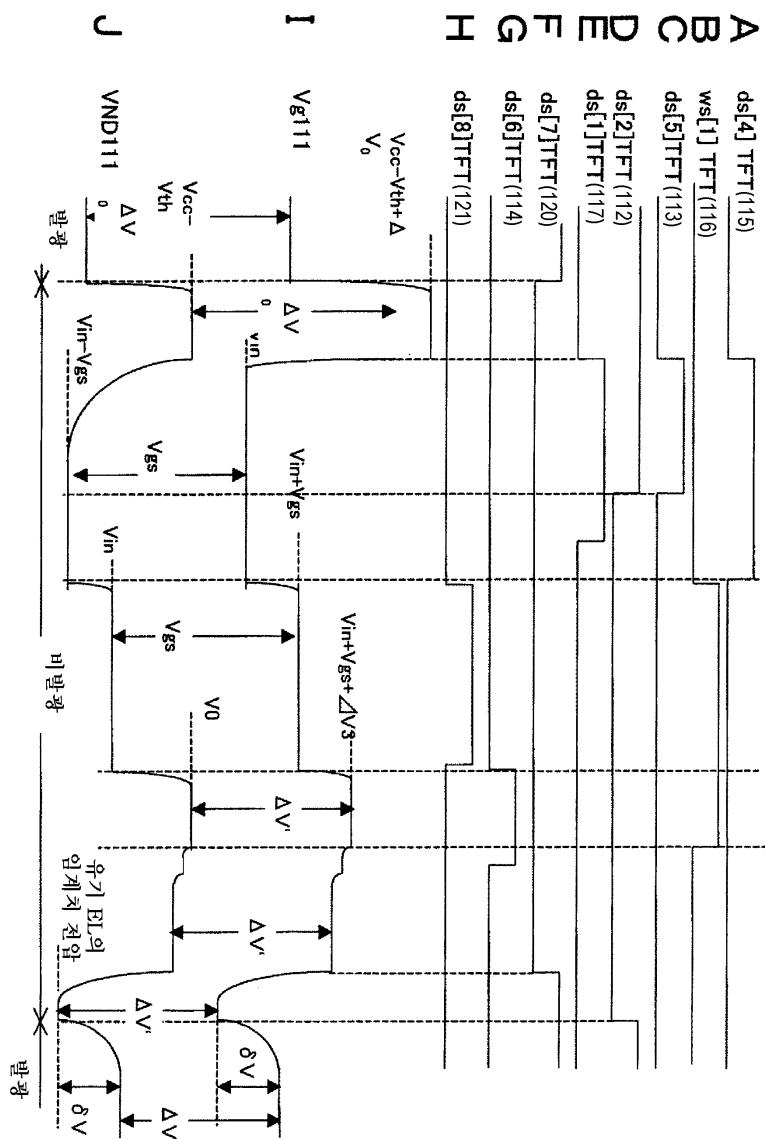

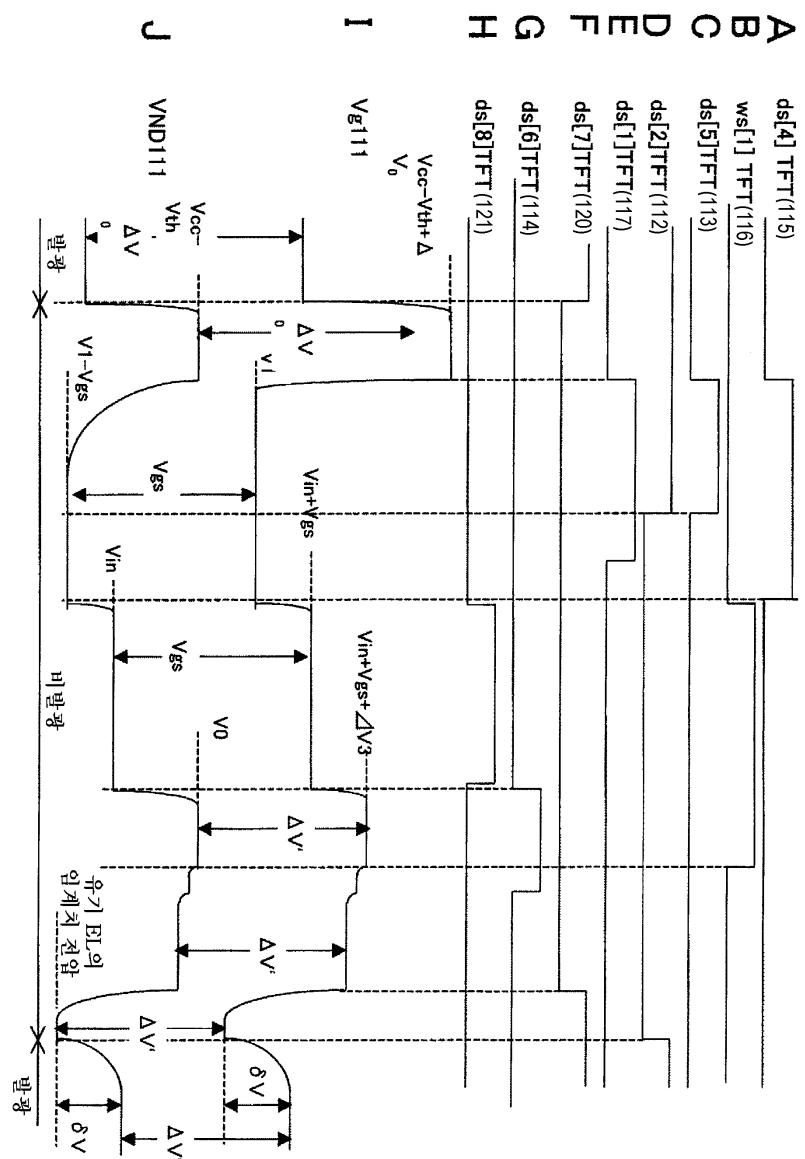

[0244] 도 26은, 본 제5 실시 형태에 따른 화소 회로의 구체적인構成을 도시하는 회로도이다. 또한, 도 27은, 본 제6 실시 형태에 따른 화소 회로의 구체적인構成을 도시하는 회로도이다.

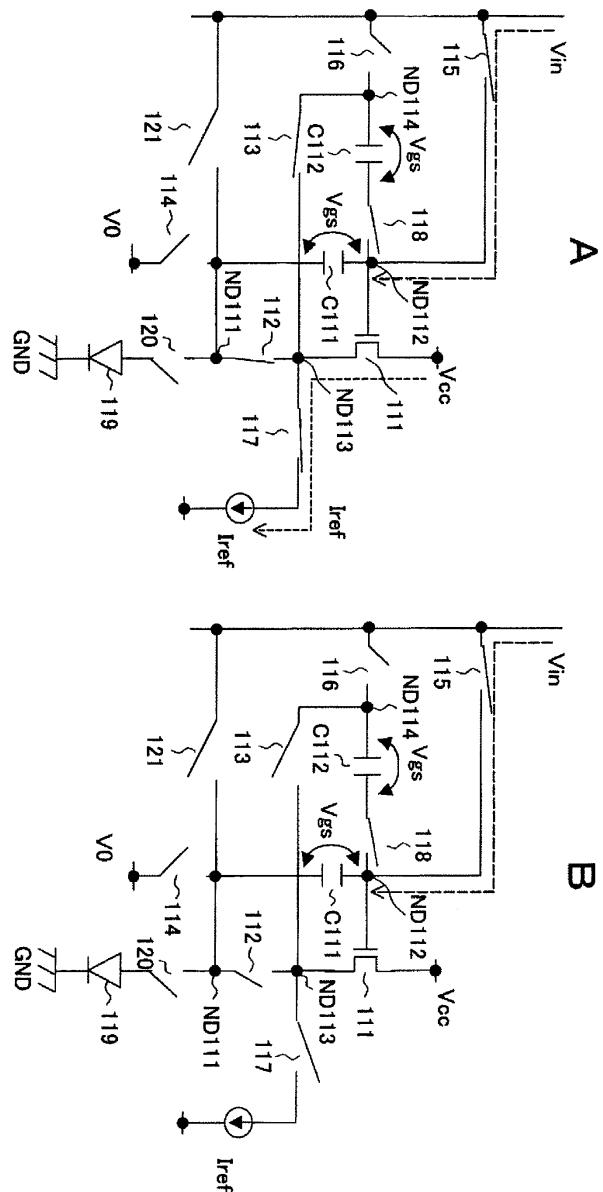

[0245] 본 제5 실시 형태가 상술한 제1 실시 형태와 다른 점은, 제1 노드 ND111과 발광 소자(119)의 애노드 사이에 제8 스위치로서의 TFT(120)를 삽입하고, 또한, 제1 노드 ND111과 데이터선 DTL101을 제9 스위치로서의 TFT(121)에 의해 접속하고, TFT(114)의 소스를 고정 전위  $V_0$ 에 접속한 것에 있다.

[0246] 그리고, TFT(120)의 게이트가 제7 드라이브 스캐너(DSCN7)(122)에 의해 구동되는 구동선 DSL161(~16m)에 접속되고, TFT(121)의 게이트가 제8 드라이브 스캐너(DSCN8)(123)에 의해 구동되는 구동선 DSL171(~17m)에 접속되어 있다.

[0247] 또한, 제6 실시 형태와 제5 실시 형태가 다른 점은, TFT(121)가 제1 노드 ND111을 데이터선 DTL101과 선택적으로 접속하는 대신에, 제1 노드 ND111을 제4 노드 ND114와 선택적으로 접속하도록 한 것에 있다.

[0248] 제5 및 제6 실시 형태는 기본적으로는 마찬가지로 동작한다.

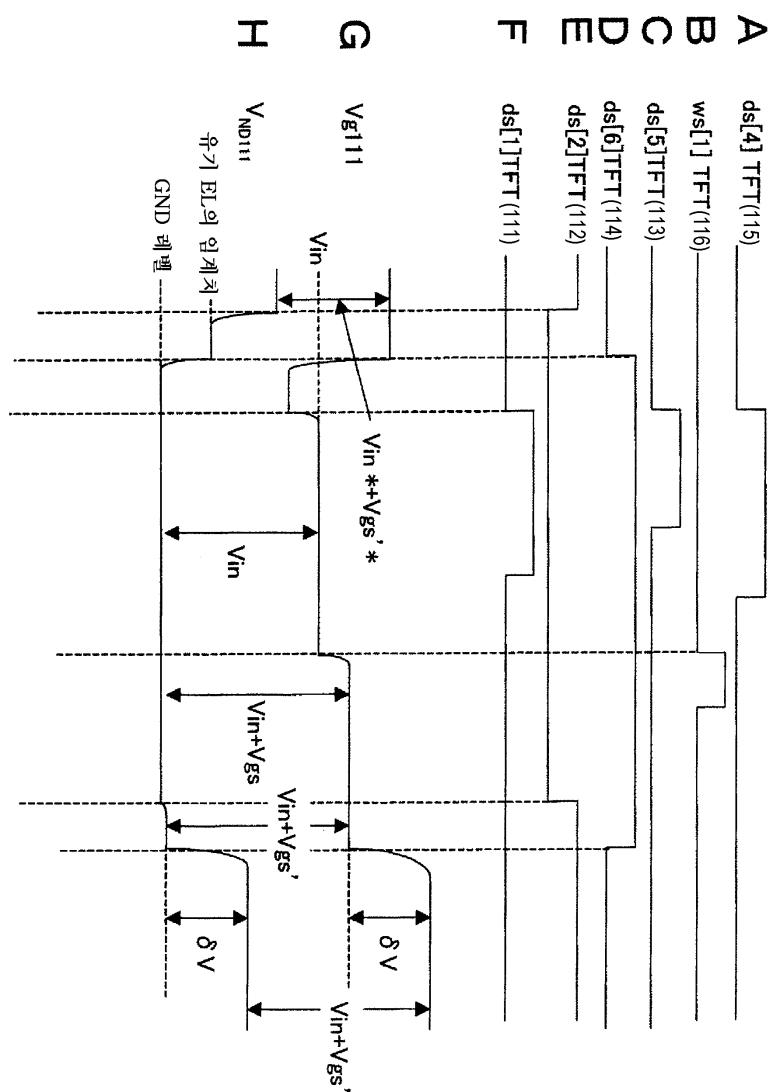

[0249] 도 28의 (A)~도 28의 (K) 및 도 29의 (A)~도 29의 (K)에 그 동작예의 타이밍차트를 도시한다.

[0250] 또한, 도 28의 (A), 도 29의 (A)는 화소 배열의 제1행째의 구동선 DSL131에 인가되는 구동 신호  $ds[4]$ 를, 도 28의 (B), 도 29의 (B)는 화소 배열의 제1행째의 조작선 WSL101에 인가되는 주사 신호  $ws[1]$ 을, 도 28의 (C), 도 29의 (C)는 화소 배열의 제1행째의 구동선 DSL121에 인가되는 구동 신호  $ds[3]$ 을, 도 28의 (D), 도 29의 (D)는 화소 배열의 제1행째의 구동선 DSL141에 인가되는 구동 신호  $ds[5]$ 를, 도 28의 (E), 도 29의 (E)는 화소 배열의 제1행째의 구동선 DSL111에 인가되는 구동 신호  $ds[2]$ 를, 도 28의 (F), 도 29의 (F)는 화소 배열의 제1행째의 구동선 DSL101에 인가되는 구동 신호  $ds[1]$ 을, 도 28의 (G), 도 29의 (G)는 화소 배열의 제1행째의 구동선 DSL161에 인가되는 구동 신호  $ds[7]$ 을, 도 28의 (H), 도 29의 (H)는 화소 배열의 제1행째의 구동선 DSL141에 인가되는 구동 신호  $ds[6]$ 을, 도 28의 (I), 도 29의 (I)는 화소 배열의 제1행째의 구동선 DSL171에 인가되는 구동 신호  $ds[8]$ 을, 도 28의 (J), 도 29의 (J)는 드라이브 트랜지스터로서의 TFT(111)의 게이트 전위  $V_{g111}$ 을, 도 28의 (K), 도 29의 (K)는 제1 노드 ND111의 전위  $V_{ND111}$ 을 각각 나타내고 있다.

[0251] 이하에, 도 26의 회로의 동작을 도 30의 (A), 도 30의 (B), 도 31의 (A), 도 31의 (B), 도 32의 (A), 도 32의 (B), 및 도 33의 (A), 도 33의 (B)에 관련지어 설명한다.

[0252] 우선, 통상의 EL 발광 소자(119)의 발광 상태는 도 30의 (A)에 도시하는 바와 같이, TFT(112)와 TFT(120)가 온한 상태이다.

[0253] 다음으로, EL 발광 소자(119)의 비발광 기간에서, 도 30의 (B)에 도시하는 바와 같이, TFT(112)를 온한 채로 TFT(120)를 오프한다.

[0254] 이 때, EL 발광 소자(119)에는 전류가 공급되지 않게 되어, 발광하지 않게 된다.

[0255] 다음으로, 도 31의 (A)에 도시하는 바와 같이, TFT(115), TFT(118), TFT(113) 및 TFT(117)를 온하여 구동 트랜지스터인 TFT(111)의 게이트에 입력 전압( $V_{in}$ )을 입력하고, 전류원으로부터 전류  $I_{ref}$ 를 흘림으로써, 구동 트랜지스터의 게이트 소스간 전압  $V_{gs}$ 를 캐패시터 C111, C112에 충전한다. 이 때, TFT(114)는 포화 영역에서 동작하므로,  $V_{gs}$ 는 수학식 3으로 나타내는 바와 같이  $\mu$ ,  $V_{th}$ 를 포함한 항으로 된다.

### 수학식 3

$$V_{gs} = V_{th} + [2I/(\mu(W/L)C_{ox})]^{1/2}$$

[0256] 캐패시터 C111, C112에 V<sub>gs</sub>가 충전된 후에 TFT(113), TFT(112)를 오프한다. 이에 의해 캐패시터 C111, C112에 충전되어 있는 전압을 V<sub>gs</sub>로 확정시킨다.

[0257] 그 후, 도 31의 (B)에 도시하는 바와 같이, TFT(117)를 오프하여 전류의 공급을 멈춤으로써 TFT(111)의 소스 전위는 V<sub>in</sub>-V<sub>th</sub>까지 상승한다.

[0258] 또한, 도 32의 (A)에 도시하는 바와 같이, TFT(115)를 오프하고 TFT(116)와 TFT(121)를 온한다. TFT(116)와 TFT(121)를 온함으로써 V<sub>in</sub>을 캐패시터 C111, C112를 통하여 구동 트랜지스터인 TFT(111)의 게이트에 전압  $\Delta V$ 를 커플링시킨다. 이 커플링량  $\Delta V$ 는 도면에서 A점, B점의 전압 변화량 V<sub>gs</sub>와 캐패시터 C111, C112의 용량 C<sub>1</sub>, C<sub>2</sub>의 합, TFT(111)의 기생 용량 C<sub>3</sub>의 비에 의해 정해지고 수학식 4, C<sub>3</sub>에 비하여 C<sub>1</sub>, C<sub>2</sub>의 합을 크게 하면 변화량의 거의 전부가 TFT(111)의 게이트에 커플링되어, TFT(111)의 게이트 전위는 V<sub>in</sub>+V<sub>gs</sub>로 된다.

### 수학식 4

$$\Delta V = \Delta V_1 + \Delta V_2 = \{ (C_1 + C_2) / (C_1 + C_2 + C_3) \} \cdot V_{gs}$$

[0260] 기입이 종료된 후에, 도 32의 (B)에 도시하는 바와 같이, TFT(121)를 오프하고, TFT(114)를 온한다.

[0261] TFT(114)는 V<sub>0</sub>이라는 고정 전위에 접속되어 있어, 온함으로써 노드 ND112의 전압 변화량(V<sub>0</sub>-V<sub>in</sub>)을 캐패시터 C111을 통하여 TFT(11)의 게이트에 다시 커플링시킨다. 이 커플링량  $\Delta V_3$ 은 노드 ND112의 전압 변화량과 C<sub>1</sub>과 C<sub>3</sub>의 합과 C<sub>2</sub>의 비에 의해 정해진다(식 5). 이 비를  $\alpha$ 로 하면, TFT(111)의 게이트 전위는  $(1 - \alpha)V_{in} + V_{gs} + \alpha V_0$ 으로 되어, 캐패시터 C111에 유지되어 있는 전압은 V<sub>gs</sub>로부터  $(1 - \alpha)(V_{in} - V_0)$ 만큼 증가한다.

### 수학식 5

$$\Delta V = \{ C_1 / (C_1 + C_2 + C_3) \} \cdot (V_0 - V_{in}) = \alpha$$

[0262] 그 후, 도 33의 (A)에 도시하는 바와 같이, TFT(116), TFT(118)를 오프하고, TFT(112), TFT(120)를 온, TFT(114)를 오프한다. 이에 의해 TFT(111)의 소스 전위는 일단 V<sub>0</sub> 레벨로 되고, 그 후 EL 발광 소자(119)에 전류가 흐르기 시작한다. TFT(111)의 소스 전위는 변동됨에도 불구하고, 게이트 소스간에는 캐패시터 C111이 있어, 캐패시터 C111의 용량 C<sub>1</sub>을 기생 용량 C<sub>3</sub>보다 크게 함으로써 게이트 소스 전압은 항상 일정치로 유지된다.

[0263] 이 때, TFT(111)는 포화 영역에서 구동하므로, TFT(111)에 흐르는 전류치 I<sub>ds</sub>는 수학식 1로 나타낸 값으로 되고, 그것은 게이트 소스간 전압에 의해 결정된다. 이 I<sub>ds</sub>는 EL 발광 소자(119)에도 마찬가지로 흘러 EL 발광 소자(119)가 발광한다.

[0264] 소자의 등가 회로는 도 33의 (B)에 도시하는 바와 같이 되어 있기 때문에, TFT(111)의 소스 전압은 EL 발광 소자(119)에 전류 I<sub>ds</sub>가 흐르는 게이트 전위까지 상승한다. 이 전위 상승에 수반하여, 캐패시터 C111을 통하여 TFT(111)의 게이트 전위도 마찬가지로 상승한다. 이에 의해, 상술한 바와 같이 TFT(111)의 게이트 소스 전위는 일정하게 유지되게 되어, EL 발광 소자(119)가 경시 열화되어 TFT(111)의 소스 전위가 변화되어도 게이트 소스간 전압은 일정한 상태 그대로로 EL 발광 소자(119)에 흐르는 전류치가 변화되지 않는다.

[0265] 여기에서, 캐패시터 C111, C112의 용량 C<sub>1</sub>, C<sub>2</sub>에 대해 고려한다.

[0266] 우선 C<sub>1</sub>과 C<sub>2</sub>의 합은, C<sub>1</sub>+C<sub>2</sub>»C<sub>3</sub>으로 해야만 한다. C<sub>3</sub>에 비해 매우 크게 함으로써 노드 ND111, ND112의 전위 변화량의 전부를 TFT(111)의 게이트에 커플링시킬 수 있다.

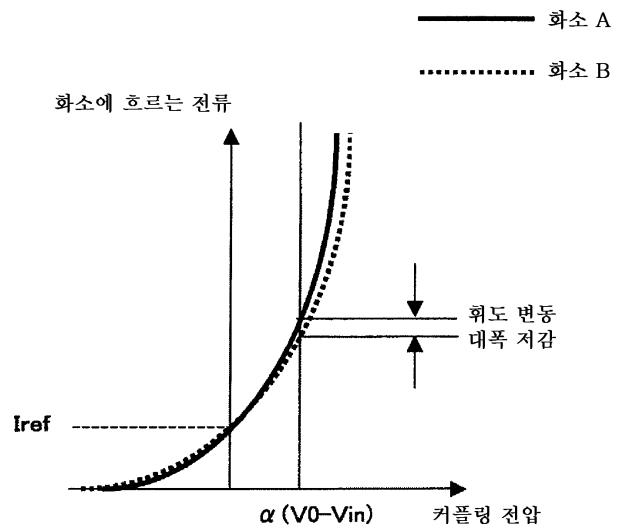

[0267] 이 때, TFT(111)에 흐르는 전류치는 수학식 1로 나타내는 값으로 되어, 도 34와 같이 TFT(111)의 게이트 소스간 전압은 I<sub>ref</sub>를 흘리는 전압으로부터  $\alpha(V_0 - V_{in})$ 의 일정치만큼 커져, 이동도가 서로 다른 화소 A와 B에서도, I<sub>ds</sub>의 변동을 작게 억제할 수 있으므로, 유니포미터의 변동도 억제할 수 있다.

[0268] 그러나, C<sub>1</sub>+C<sub>2</sub>를 작게 하면, 노드 ND111, ND112의 전압 변화량은 전부 커플링되지 않아, 게인을 갖게 된다. 이 게인을  $\beta$ 로 하면, TFT(111)에 흐르는 전류량은 수학식 6으로 표현되며, T10의 게이트 소스간 전압은 I<sub>ref</sub>를 흘

리는 전압으로부터  $V_{in} + (\beta-1)V_{gs}$ 라는 값만큼 커지지만,  $V_{gs}$ 는 화소마다 다른 값이기 때문에,  $I_{ds}$ 의 변동을 작게 억제할 수 없게 된다(도 35). 이에 의해,  $C1+C2$ 는  $C3$ 에 비해 크게 취해야만 한다.

## 수학식 6

$$\Delta V = \{C1/(C1+C2+C3)\} \cdot V_{gs}$$

[0271] 다음으로  $C1$ 의 크기에 대해 고려한다.

[0273]  $C1$ 은 TFT(111)의 기생 용량  $C3$ 에 비해 매우 커야만 한다. 만약  $C1$ 이  $C3$ 과 동일한 레벨이라면, TFT(114)의 소스 전위의 변동이 캐패시터  $C111$ 을 통해 TFT(114)의 게이트에 커플링되게 되어, 캐패시터  $C111$ 에 유지되어 있는 전압이 변동되게 된다. 이 때문에, TFT(111)는 일정량의 전류를 흘릴 수 없게 되어, 화소마다 변동이 생기게 된다. 이 때문에,  $C1$ 은 TFT(111)의 기생 용량  $C3$ 에 비해 매우 크게 취해야만 한다.

[0274] 또한,  $C2$ 에 대해 고려한다.  $C2 \gg C1$ 인 것으로 하면, TFT(114)를 온하여  $V_0 - V_{in}$ 의 전압 변화를 캐패시터  $C111$ 을 통하여 TFT(111)의 게이트에 커플링시킬 때에, 캐패시터  $C111$ 에 유지되어 있는 전위차는  $I_{ref}$ 를 TFT(111)에 흘려 유지된  $V_{gs}$ 라는 전위로부터  $V_{in} - V_0$ 의 일정치만큼 증가하므로, 이동도가 서로 다른 화소 A와 B에서도,  $I_{ds}$ 의 변동을 작게 억제할 수 있어, 유니포미터의 변동도 억제할 수 있다.

[0275] 그러나,  $C2 \ll C1$ 로 하면,  $I_{ds}$ 의 변동을 작게 억제할 수 없어, 유니포미터의 변동도 억제할 수 없다.

[0276] 다음으로,  $C2 \ll C1$ 로 하면 TFT(114)를 온 상태로 했을 때에,  $V_0 - V_{in}$ 이라는 전압 변화가 전부 캐패시터  $C111$ 을 통하여 TFT(111)의 게이트에 커플링되므로, 캐패시터  $C111$ 에 유지되어 있는 전압은  $V_{gs}$ 로부터 전혀 변화되지 않는다. 이에 의해, EL 발광 소자(119)에는 입력 전압에 관계없이  $I_{ref}$ 라는 일정 전류밖에 흘릴 수 없기 때문에 화소는 래스터 표시밖에 할 수 없다.

[0277] 이상으로부터,  $C1$ 과  $C2$ 의 크기는 동일 레벨로 설정하고, TFT(114)를 온함으로써 커플링에서 일정한 개인을 갖게 할 필요가 있다.

[0278] 여기에서 상술한 바와 같이  $C3$ 은 TFT(114)의 기생 용량이며, 그 크기는 수10 내지 수100fF의 오더이지만,  $C1$ ,  $C2$ ,  $C3$ 의 관계는,  $C2 \gg C3$ ,  $C1 \gg C3$ 이며, 또한  $C1$ 과  $C2$ 는 동일 레벨이어야 하므로  $C1$ ,  $C2$ 는 각각 수 100fF 내지 수 pF의 크기이어도 된다. 이에 의해, 화소 내라는 한정된 크기 중에 용량을 용이하게 설정할 수 있어, 종래의 문제점이었던 화소마다 전류치가 변동되게 되어 화소 얼룩으로 되게 되는 문제점도 극복할 수 있다.

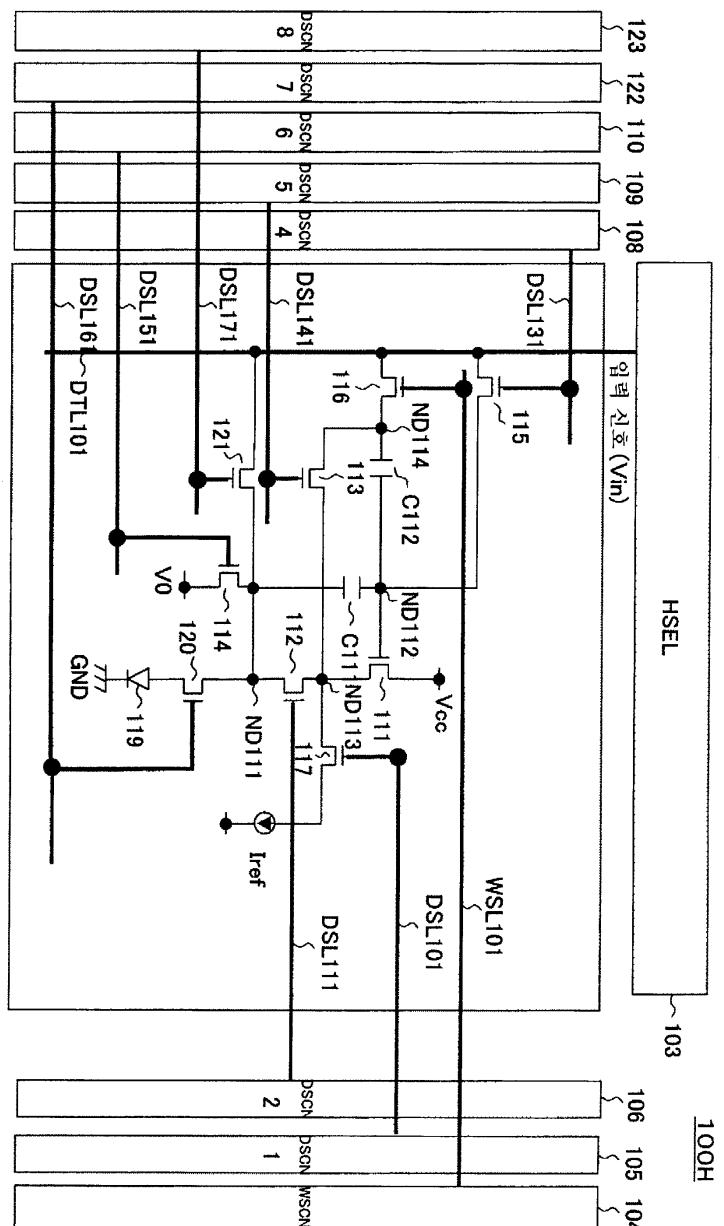

[0279] <제7 실시 형태 및 제8 실시 형태>

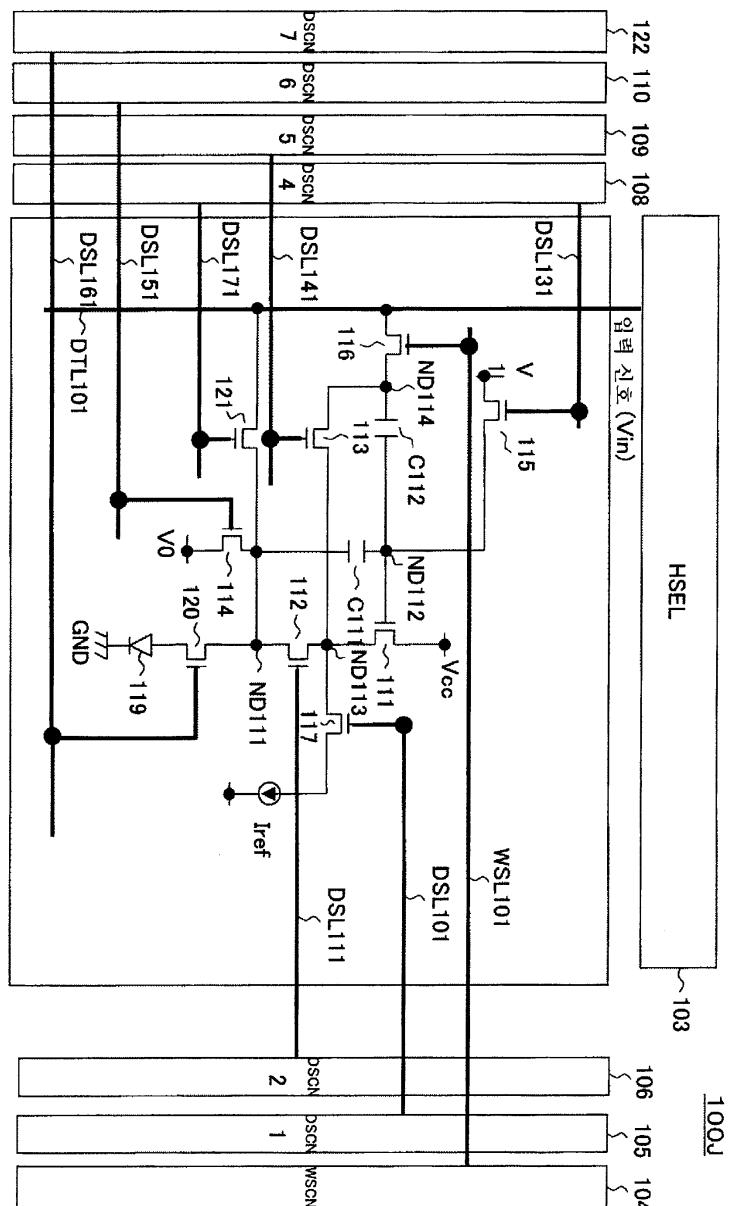

[0280] 도 36은, 본 제7 실시 형태에 따른 화소 회로의 구체적인 구성을 도시하는 회로도이다. 도 37은, 본 제8 실시 형태에 따른 화소 회로의 구체적인 구성을 도시하는 회로도이다.

[0281] 본 제7 실시 형태가 상술한 제5 실시 형태와 다른 점은, 제4 스위치로서의 TFT(115)가 접속되는 소정의 전위선을 데이터선 DTL과 공용하지 않고, 별도로 설치한 것이다.

[0282] 마찬가지로, 본 제8 실시 형태가 상술한 제6 실시 형태와 다른 점은, 제4 스위치로서의 TFT(115)가 접속되는 소정의 전위선을 데이터선 DTL과 공용하지 않고, 별도로 설치한 것이다.

[0283] 그 외의 구성은 제5 및 제6 실시 형태와 마찬가지이고, 여기에서는, 구성 및 기능에 관한 상세한 설명은 생략한다.

[0284] 제7 및 제8 실시 형태는 기본적으로는 마찬가지로 동작한다.

[0285] 도 38의 (A)~도 38의 (K) 및 도 39의 (A)~도 39의 (K)에 그 동작예의 타이밍차트를 도시한다.

[0286] 본 제4 실시 형태에서는, 드라이버 트랜지스터로서의 TFT(111)의 소스에 기준 전류  $I_{ref}$ 를 흘릴 때에 TFT(111)의 게이트 전압에 입력 전압  $V_{in}$ 을 입력하는 것이 아니라, 고정 전위  $V_0$ 을 입력한다. 고정 전위  $V_0$ 을 입력하여 기준 전류  $I_{ref}$ 를 흘림으로써 화소 내에  $V_{in}$ 이 입력되어 있는 시간을 짧게 할 수 있어, 화소에 고속으로 기입할 수 있다.

[0287] 이 때문에, 예를 들어 3회 기입 방식과 같이 1H를 수분할하여 화소에 기입하는 구동 방식에도 대응할 수 있게 된다.

[0288] <제9 실시 형태 및 제10 실시 형태>

- [0289] 도 40은, 본 제9 실시 형태에 따른 화소 회로의 구체적인 구성을 도시하는 회로도이다. 도 41은, 본 제10 실시 형태에 따른 화소 회로의 구체적인 구성을 도시하는 회로도이다.

- [0290] 본 제9 실시 형태가 제5 실시 형태와 다른 점은, 캐페시터 C112의 제1 전극과 제2 노드 ND112를 접속하는 전기적 접속 수단을, 양자간을 선택적으로 접속하는 스위치(118)에 의해 구성하는 대신에, 전기 배선에 의해 직접 접속하도록 한 것에 있다.

- [0291] 본 제10 실시 형태가 제6 실시 형태와 다른 점은, 캐페시터 C112의 제1 전극과 제2 노드 ND112를 접속하는 전기적 접속 수단을, 양자간을 선택적으로 접속하는 스위치(118)에 의해 구성하는 대신에, 전기 배선에 의해 직접 접속하도록 한 것에 있다.

- [0292] 그 결과, 제3 드라이브 스캐너(107)와 구동선 DSL121이 불필요하게 되어 있다.

- [0293] 그 외의 구성은, 상술한 제5 및 제6 실시 형태와 마찬가지이다.

- [0294] 제9 및 제10 실시 형태는 기본적으로는 마찬가지로 동작한다.

- [0295] 도 42의 (A)~도 42의 (J) 및 도 43의 (A)~도 43의 (J)에 그 동작예의 타이밍차트를 도시한다.

- [0296] 본 제9 및 제10 실시 형태에 따르면, 상술한 제5 및 제6 실시 형태의 효과 외에, 화소 회로 내의 소자수를 저감할 수 있어 회로 구성을 간단화할 수 있는 이점이 있다.

- [0297] <제11 실시 형태 및 제12 실시 형태>

- [0298] 도 44는, 본 제11 실시 형태에 따른 화소 회로의 구체적인 구성을 도시하는 회로도이다. 도 45는, 본 제12 실시 형태에 따른 화소 회로의 구체적인 구성을 도시하는 회로도이다.

- [0299] 본 제11 실시 형태가 제7 실시 형태와 다른 점은, 캐페시터 C112의 제1 전극과 제2 노드 ND112를 접속하는 전기적 접속 수단을, 양자간을 선택적으로 접속하는 스위치(118)에 의해 구성하는 대신에, 전기 배선에 의해 직접 접속하도록 한 것에 있다.

- [0300] 본 제12 실시 형태가 제8 실시 형태와 다른 점은, 캐페시터 C112의 제1 전극과 제2 노드 ND112를 접속하는 전기적 접속 수단을, 양자간을 선택적으로 접속하는 스위치(118)에 의해 구성하는 대신에, 전기 배선에 의해 직접 접속하도록 한 것에 있다.

- [0301] 그 결과, 제3 드라이브 스캐너(107)와 구동선 DSL121이 불필요하게 되어 있다.

- [0302] 그 외의 구성은, 상술한 제7 및 제8 실시 형태와 마찬가지이다.

- [0303] 삭제

- [0304] 제11 및 제12 실시 형태는 기본적으로는 마찬가지로 동작한다.

- [0305] 도 46의 (A)~도 46의 (J) 및 도 47의 (A)~도 47의 (J)에 그 동작예의 타이밍차트를 도시한다.

- [0306] 본 제11 및 제12 실시 형태에 따르면, 상술한 제7 및 제8 실시 형태의 효과 외에, 화소 회로 내의 소자수를 저감할 수 있어, 회로 구성을 간단화할 수 있는 이점이 있다.

도면

도면1

도면2

2a

도면3

도면4

2b

도면5

도면6

도면7

도면8

## 도면9

도면10

도면11

## 도면12

도면13

도면14

도면15

도면16

도면17

도면18

### 도면19

## 도면20

도면21

도면22

도면23

도면24

도면25

## 도면26

## 도면27

도면28

## 도면29

દોર્ય 30

도면31

### 도면32

### 도면33

도면34

도면35

## 도면36

### 도면37

## 도면38

## 도면39

## 도면40

도면41

도면42

### 도면43

도면44

도면45

## 도면46

도면47

|                |                                                                                            |         |            |

|----------------|--------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 像素电路，显示装置和像素电路的驱动方法                                                                        |         |            |

| 公开(公告)号        | <a href="#">KR101065950B1</a>                                                              | 公开(公告)日 | 2011-09-19 |

| 申请号            | KR1020067008943                                                                            | 申请日     | 2004-11-10 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                       |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                       |         |            |

| 当前申请(专利权)人(译)  | 索尼公司                                                                                       |         |            |

| [标]发明人         | UCHINO KATSUHIDE<br>우찌노가쓰히데<br>YAMASHITA JUNICHI<br>야마시따준이찌<br>YAMAMOTO TETSURO<br>야마모또데쓰로 |         |            |

| 发明人            | 우찌노, 가쓰히데<br>야마시따, 준이찌<br>야마모또, 데쓰로                                                        |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50 G09F9/30 G09G3/32 G09G5/10 H01L29/786 H05B33/00 H05B33/14      |         |            |

| CPC分类号         | G09G3/3233 G09G2300/0819 G09G2300/0852 G09G2300/0861 G09G2310/0262 G09G2320/043            |         |            |

| 代理人(译)         | Jangsugil<br>Yijunghui                                                                     |         |            |

| 优先权            | 2003380171 2003-11-10 JP                                                                   |         |            |

| 其他公开文献         | KR1020060120083A                                                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                  |         |            |

## 摘要(译)

一种像素电路，显示装置和用于驱动像素电路的方法，其中即使发光元件的电流/电压特性老化，也可以在不降低亮度的情况下实现源极跟随器输出，并且源-可以实现n沟道晶体管的跟随器电路，并且其中可以显示均匀的高质量图像，而不管像素中的有源元件的迁移率和阈值的变化。电容器（C111）连接在TFT（111）的栅极和源极之间，TFT（111）的源极通过TFT（114）连接到固定电位（GND）。在预定定时将预定参考电流（Iref）提供给TFT（111）的源极，以保持对应于参考电流（Iref）的电压，使得输入信号电压耦合到该电压附近，从而驱动EL。发光元件（19），其中心值以移动性的变化为中心。©KIP&WIPO 2007