(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2007-0095620

(43) 공개일자 2007년10월01일

(51) Int. Cl.

*H01L 29/786*(2006.01) *H01L 51/50*(2006.01)

*H01L 51/52*(2006.01)

(21) 출원번호 10-2006-0026031

(22) 출원일자 2006년03월22일

심사청구일자 **없음**

(71) 출원인

## 삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자

최재범

경기 수원시 영통구 영통동 황골마을2단지 벽산아파트 222동 1801호

장영진

경기 용인시 기흥구 서천동 서그네마을 SK아파트

104동 506호

(뒷면에 계속)

(74) 대리인

박영우

전체 청구항 수 : 총 33 항

#### (54) 표시 장치 및 그 제조 방법

### (57) 요약

본 발명은 기판, 상기 기판 상에 형성되고 채널 영역을 포함하는 제 1 반도체 층을 포함하는 구동 박막 트랜지스터, 상기 구동 박막 트랜지스터 상에 형성된 절연막 및 상기 절연막 상에 형성된 채널 영역을 포함하는 제 2 반도체 층을 포함하는 스위칭 박막 트랜지스터를 포함하고, 상기 구동 박막 트랜지스터 및 스위칭 박막 트랜지스터 중 적어도 하나의 소스 전극 및 드레인 전극 전체가 채널 영역을 제외한 반도체 층 상부에 형성된 소스 전극 및 드레인 전극을 포함하는 표시 장치 및 그 제조 방법을 제공한다.

본 발명은 유기 발광 표시 장치의 스위칭 박막 트랜지스터 및 구동 박막 트랜지스터에 요구되는 특성을 동시에 충족한 표시 장치의 구조 및 그 제조 방법을 제공한다.

## 대표도 - 도2

(72) 발명자

**정관옥**

경기 수원시 영통구 영통동 벽적골9단지 벽적골 주

공아파트 909동802호

**심승환**

경기 성남시 분당구 수내동 두산위브 센티움 102동

710호

## 특허청구의 범위

### 청구항 1

기판;

상기 기판 상에 형성되고 채널 영역을 포함하는 제 1 반도체 층을 포함하는 구동 박막 트랜지스터;

상기 구동 박막 트랜지스터 상에 형성된 절연막; 및

상기 절연막 상에 형성된 채널 영역을 포함하는 제 2 반도체 층을 포함하는 스위칭 박막 트랜지스터를 포함하고,

상기 구동 박막 트랜지스터 및 스위칭 박막 트랜지스터 중 적어도 하나의 소스 전극 및 드레인 전극 전체가 채널 영역을 제외한 반도체 층 상부에 형성된 것을 특징으로 하는 표시 장치.

### 청구항 2

제 1 항에 있어서,

상기 구동 박막 트랜지스터는 구동 전압이 인가되는 제 1 신호선에 연결되고,

상기 스위칭 박막 트랜지스터는 데이터 신호가 인가되는 제 2 신호선에 연결된 것을 특징으로 하는 표시 장치.

### 청구항 3

제 2 항에 있어서,

상기 제 1 신호선 및 제 2 신호선 중 적어도 하나는 반도체 층 상부에 형성된 표시 장치.

### 청구항 4

제 2 항에 있어서,

제 1 반도체 층 및 제 2 반도체 층은 서로 다른 결정구조로 형성된 것을 특징으로 하는 표시 장치.

### 청구항 5

제 4 항에 있어서,

제 1 반도체 층은 다결정 실리콘 및 미세 결정질 실리콘 중 어느 하나를 포함하고, 제 2 반도체 층은 비정질 실리콘을 포함하는 것을 특징으로 하는 표시 장치.

### 청구항 6

제 2 항에 있어서,

상기 구동 박막 트랜지스터는 게이트 전극, 제 1 신호선과 전기적으로 연결되는 소스 전극 및 화소 전극과 전기적으로 연결되는 드레인 전극을 포함하는 표시 장치.

### 청구항 7

제 6 항에 있어서,

상기 스위칭 박막 트랜지스터는 제 3신호선과 전기적으로 연결되는 게이트 전극, 제 2 신호선과 전기적으로 연결되는 소스 전극 및 상기 구동 박막 트랜지스터와 전기적으로 연결되는 드레인 전극을 포함하는 표시 장치.

### 청구항 8

제 7 항에 있어서,

상기 화소 전극과 대향하는 공통 전극 및

상기 화소 전극과 공통 전극 사이에 개재된 발광 물질을 더 포함하는 표시 장치.

### 청구항 9

제 7 항에 있어서,

상기 구동 박막 트랜지스터의 게이트 전극은 제 1 반도체 층 하부에 형성된 바텀 게이트 구조인 표시 장치.

### 청구항 10

제 9 항에 있어서,

상기 구동 박막 트랜지스터의 게이트 전극과 상기 스위칭 박막 트랜지스터의 게이트 전극은 동일한 층 위에 형성된 것을 특징으로 하는 표시 장치

### 청구항 11

제 10 항에 있어서,

상기 스위칭 박막 트랜지스터의 게이트 전극과 제 2 반도체 층 사이에는 두 층의 절연막이 개재된 표시 장치.

### 청구항 12

제 7 항에 있어서,

상기 구동 박막 트랜지스터의 게이트 전극은 제 1 반도체 층 상부에 형성된 텁 게이트 구조인 표시 장치.

### 청구항 13

제 12 항에 있어서, 상기 스위칭 박막 트랜지스터의 게이트 전극과 제 2 반도체 층 사이에는 한 층의 절연막이 개재된 표시 장치.

### 청구항 14

기판;

상기 기판 상에 형성되고, 채널 영역을 포함하는 제 1 반도체 층 및 구동 전압을 전달하는 제 1 신호선을 포함하는 제 1 박막 트랜지스터;

제 1 박막 트랜지스터 상에 형성된 절연막; 및

상기 절연막 상에 형성된, 채널 영역을 포함하는 제 2 반도체 층 및 데이터 신호를 전달하는 제 2 신호선을 포함하는 제 2 박막 트랜지스터를 포함하고,

제 1 신호선 및 제 2 신호선 중 적어도 하나는 하부에 상기 신호선의 폭보다 넓거나 동일한 폭을 갖는 반도체 층이 형성된 표시 장치.

### 청구항 15

제 14 항에 있어서,

제 1 반도체 층 및 제 2 반도체 층은 서로 다른 결정구조로 형성된 것을 특징으로 하는 표시 장치.

### 청구항 16

제 15 항에 있어서,

제 1 반도체 층은 다결정 실리콘 및 미세 결정질 실리콘 중 어느 하나를 포함하고, 제 2 반도체 층은 비정질 실리콘을 포함하는 표시 장치.

### 청구항 17

제 14 항에 있어서,

제 1 박막 트랜지스터는 게이트 전극, 제 1 신호선과 전기적으로 연결되는 소스 전극 및 화소 전극과 전기적으로 연결되는 드레인 전극을 포함하는 표시 장치.

### 청구항 18

제 17 항에 있어서,

제 2 박막 트랜지스터는 주사 신호를 제공하는 제 3 신호선과 전기적으로 연결되는 게이트 전극, 데이터 신호를 제공하는 제 2 신호선과 전기적으로 연결되는 소스 전극 및 제 1 박막 트랜지스터의 게이트 전극과 전기적으로 연결되는 드레인 전극을 포함하는 표시 장치.

### 청구항 19

제 18 항에 있어서,

상기 화소 전극과 대향하는 공통 전극; 및

상기 화소 전극과 공통 전극 사이에 개재된 발광 물질을 더 포함하는 표시 장치.

### 청구항 20

제 18 항에 있어서,

제 1 박막 트랜지스터의 게이트 전극은 제 1 반도체 층 하부에 형성된 바텀 게이트 구조인 표시 장치.

### 청구항 21

제 18 항에 있어서,

제 1 박막 트랜지스터의 게이트 전극은 제 1 반도체 층 상부에 형성된 탑 게이트 구조인 표시 장치.

### 청구항 22

기판;

상기 기판 상에 형성되고 채널 영역을 포함하는 제 1 반도체 층을 포함하는 구동 박막 트랜지스터;

상기 구동 박막 트랜지스터 상에 형성된 절연막;

상기 절연막 상에 형성된 채널 영역을 포함하는 제 2 반도체 층을 포함하는 스위칭 박막 트랜지스터;

상기 구동 박막 트랜지스터와 연결되어 있는 제 1 전극;

상기 제 1 전극과 마주보는 제 2 전극; 및

상기 제 1 전극과 상기 제 2 전극 사이에 형성되어 있는 발광 부재를 포함하고,

구동 박막 트랜지스터의 게이트 전극과 스위칭 박막 트랜지스터의 게이트 전극은 동일한 층 위에 형성되어 있는 표시 장치.

### 청구항 23

제 22 항에 있어서,

상기 스위칭 박막 트랜지스터 및 구동 박막 트랜지스터 중 적어도 하나의 소스 전극과 드레인 전극 전체가 채널 영역을 제외한 반도체층 상부에 형성된 표시 장치.

### 청구항 24

제 23 항에 있어서,

상기 제 1 반도체 층은 다결정 실리콘 층을 포함하고, 상기 제 2 반도체 층은 비정질 실리콘 층을 포함하는 표시 장치.

### 청구항 25

기판;

상기 기판 상에 형성된 구동 반도체 층, 상기 구동 반도체 층 상부에 형성된 구동 입력 전극 및 구동 출력

전극;

상기 구동 입력 전극 및 구동 출력 전극 상에 형성된 제 1 절연막;

제 1 절연막 상에 형성되고, 상기 구동 반도체 층과 일부 중첩되는 구동 제어 전극;

상기 구동 제어 전극과 동일 층에 형성된 스위칭 제어 전극;

상기 구동 제어 전극과 스위칭 제어 전극 상에 형성된 제 2 절연막;

제 2 절연막 상에 형성되고, 상기 스위칭 제어 전극과 일부 중첩하는 스위칭 반도체 층, 상기 스위칭 반도체 층 상부에 형성된 스위칭 입력 전극 및 스위칭 출력 전극;

상기 스위칭 출력 전극과 구동 제어 전극과 전기적으로 연결된 연결 부재;

상기 연결 부재와 동일한 층에 형성되고, 구동 출력 전극과 전기적으로 연결된 화소 전극; 및

상기 화소 전극 상부에 형성된 유기 발광 재료를 포함하는 표시 장치.

### 청구항 26

제 25 항에 있어서,

상기 스위칭 박막 트랜지스터 및 구동 박막 트랜지스터 중 적어도 하나의 입력 전극과 출력 전극 전체가 채널 영역을 제외한 반도체층 상부에 형성된 표시 장치.

### 청구항 27

제 26 항에 있어서,

상기 구동 반도체 층은 다결정 실리콘 층을 포함하고, 상기 스위칭 반도체 층은 비정질 실리콘 층을 포함하는 표시 장치.

### 청구항 28

기판 상에 구동 제어 전극 및 스위칭 제어 전극을 형성하는 단계;

상기 구동 제어 전극 및 스위칭 제어 전극 상에 제 1 절연막을 형성하는 단계;

제 1 절연막 상에 구동 반도체 층을 적층하는 단계;

상기 구동 반도체 층을 결정화하는 단계;

상기 결정화된 구동 반도체 층 상에 제 1 도전층을 적층하는 단계;

동일한 마스크를 사용하여 상기 결정화된 구동 반도체 층 및 제 1 도전층을 식각하여 구동 박막 트랜지스터를 형성하는 단계;

상기 구동 박막 트랜지스터 상에 제 2 절연막을 형성하는 단계;

제 2 절연막 상에 스위칭 반도체 층 및 제 2 도전층을 적층하는 단계; 및

동일한 마스크를 사용하여 상기 스위칭 반도체 층 및 제 2 도전층을 식각하여 스위칭 박막 트랜지스터를 형성하는 단계를 포함하는 표시 장치의 제조 방법.

### 청구항 29

제 28 항에 있어서,

상기 스위칭 박막 트랜지스터 상에 상기 구동 제어 전극 및 상기 구동 박막 트랜지스터 및 스위칭 박막 트랜지스터의 출력 전극을 외부에 노출시키는 컨택홀을 포함하는 패시베이션 층을 형성하는 단계;

상기 패시베이션 층 상에 상기 컨택홀을 통해 상기 구동 박막 트랜지스터 및 스위칭 박막 트랜지스터와 전기적으로 연결되는 화소 전극을 형성하는 단계;

상기 패시베이션 층 및 화소 전극 상에 격벽을 형성하는 단계; 및

상기 격벽이 형성되지 않은 화소 전극 상에 발광 물질을 형성하는 단계를 더포함하는 표시 장치의 제조 방법.

### 청구항 30

제 28 항에 있어서,

상기 구동 반도체 층은 고상 결정화 방법을 이용하여 결정화하는 표시 장치의 제조 방법.

### 청구항 31

기판 상에 구동 반도체 층을 적층하는 단계;

상기 구동 반도체 층을 결정화하는 단계;

상기 결정화된 구동 반도체 층 상에 제 1 도전층을 적층하는 단계;

동일 마스크를 사용하여 상기 구동 반도체 층 및 제 1 도전층을 식각하는 단계;

상기 식각된 구동 반도체 층 및 제 1 도전층 상에 제 1 절연막을 형성하는 단계;

제 1 절연막 상에 구동 제어 전극 및 스위칭 제어 전극을 형성하여 구동 박막 트랜지스터를 형성하는 단계;

상기 구동 제어 전극 및 스위칭 제어 전극 상에 제 2 절연막을 형성하는 단계;

제 2 절연막 상에 스위칭 반도체 층 및 제 2 도전층을 적층하는 단계; 및

동일한 마스크를 사용하여 상기 스위칭 반도체 층 및 제 2 도전층을 식각하여 스위칭 박막 트랜지스터를 형성하는 단계를 포함하는 표시 장치의 제조 방법.

### 청구항 32

제 31 항에 있어서,

상기 스위칭 박막 트랜지스터 상에 상기 구동 제어 전극 및 상기 구동 박막 트랜지스터 및 스위칭 박막 트랜지스터의 드레인 전극을 외부에 노출시키는 컨택홀을 포함하는 패시베이션 층을 형성하는 단계;

상기 패시베이션 층 상에 상기 컨택홀을 통해 상기 구동 박막 트랜지스터 및 스위칭 박막 트랜지스터와 전기적으로 연결되는 화소 전극을 형성하는 단계;

상기 패시베이션 층 및 화소 전극 상에 격벽을 형성하는 단계; 및

상기 격벽이 형성되지 않은 화소 전극 상에 발광 물질을 형성하는 단계를 더포함하는 표시 장치의 제조 방법.

### 청구항 33

제 31 항에 있어서,

상기 구동 반도체 층은 고상 결정화 방법을 이용하여 결정화하는 표시 장치의 제조 방법.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

<21> 본 발명은 표시 장치 및 그 제조 방법에 관한 것이다.

<22> 최근 모니터 또는 텔레비전 등의 표시 장치는 경량화 및 박형화가 요구되고 있으며, 이러한 요구에 따라 음극선관(Cathode Ray Tube, CRT)이 액정 표시 장치(Liquid Crystal Display, LCD)로 대체되고 있다.

<23> 그러나, 액정 표시 장치는 비 발광 소자로서 별도의 광원이 필요할 뿐만 아니라, 응답 속도 및 시야각 등에서 많은 문제점이 있다.

- <24> 최근 이러한 문제점을 극복할 수 있는 표시 장치로서, 유기 발광 표시 장치(Organic Light Emitting Diode Display, OLED display)가 주목 받고 있다.

- <25> 유기 발광 표시 장치는 두 개의 전극과 그 사이에 위치하는 발광층을 포함하며, 하나의 전극으로부터 주입된 전자(electron)와 다른 전극으로부터 주입된 정공(hole)이 발광층에서 결합하여 여기자(exciton)를 형성하고, 여기자가 에너지를 방출하면서 발광한다.

- <26> 유기 발광 표시 장치는 자발광 소자로서 별도의 광원이 필요 없으므로 소비전력 측면에서 유리할 뿐만 아니라, 응답 속도, 시야각 및 대비비(contrast ratio)도 우수하다.

- <27> 유기 발광 표시 장치는 구동 방식에 따라 단순 매트릭스 방식의 유기 발광 표시 장치(Passive Matrix OLED display)와 능동 매트릭스 방식의 유기 발광 표시 장치(Active Matrix OLED display)로 나눌 수 있다.

- <28> 이 중, 능동 매트릭스 방식의 유기 발광 표시 장치는 신호선에 연결되어 데이터 전압을 제어하는 스위칭 박막 트랜지스터(switching thin film transistor)와 이로부터 전달받은 데이터 전압을 제어 전극으로 인가하여 발광 소자에 전류를 흘리는 구동 박막 트랜지스터(driving thin film transistor)를 포함한다.

- <29> 유기 발광 표시 장치가 최적의 특성을 나타내기 위하여 스위칭 박막 트랜지스터와 구동 박막 트랜지스터에 요구되는 특성이 서로 다르다. 스위칭 박막 트랜지스터는 높은 온/오프 전류 비(Ion/Ioff) 특성이 요구되는 반면, 구동 박막 트랜지스터는 발광 소자에 충분한 전류를 흘릴 수 있도록 높은 이동성(mobility) 및 안정성(stability)이 요구된다.

- <30> 스위칭 박막 트랜지스터에 오프 전류가 증가하는 경우 구동 박막 트랜지스터로 전달되는 데이터 전압이 감소되어 크로스 토크(cross talk)가 발생할 수 있고, 구동 박막 트랜지스터가 낮은 이동도 및 안정성을 가지는 경우 발광 소자에 흐르는 전류량이 감소하여 발광량이 감소하고 이미지 고착(image sticking) 및 수명 단축이 될 수 있다.

### 발명이 이루고자 하는 기술적 과제

- <31> 따라서 본 발명이 이루고자 하는 기술적 과제는 이러한 문제점을 해결하기 위한 것으로서 스위칭 박막 트랜지스터 및 구동 박막 트랜지스터에 요구되는 특성을 동시에 충족한 표시 장치의 구조 및 그 제조 방법을 제공하고자 한다.

### 발명의 구성 및 작용

- <32> 본 발명의 실시 예에 따른 표시 장치는 기판, 상기 기판 상에 형성되고, 채널 영역을 포함하는 제 1 반도체 층을 포함하는 구동 박막 트랜지스터, 상기 구동 박막 트랜지스터 상에 형성된 절연막, 상기 절연막 상에 형성된 채널 영역을 포함하는 제 2 반도체 층을 포함하는 스위칭 박막 트랜지스터 및 상기 구동 박막 트랜지스터 및 스위칭 박막 트랜지스터 중 적어도 하나의 소스 전극 및 드레인 전극은 채널 영역을 제외한 반도체 층 상부에 형성된 소스 전극 및 드레인 전극을 포함한다.

- <33> 상기 구동 박막 트랜지스터는 구동 전압이 인가되는 제 1 신호선에 연결되고,

- <34> 상기 스위칭 박막 트랜지스터는 데이터 신호가 인가되는 제 2 신호선에 연결된다.

- <35> 또한 상기 제 1 신호선 및 제 2 신호선 중 적어도 하나는 반도체 층 상부에 형성된다.

- <36> 상기 제 1 반도체 층 및 제 2 반도체 층은 결정 구조가 서로 다르게 형성되며, 제 1 반도체 층은 다결정 실리콘 및 미세 결정질 실리콘 중 어느 하나를 포함하고, 제 2 반도체 층은 비정질 실리콘을 포함할 수 있다.

- <37> 상기 구동 박막 트랜지스터는 게이트 전극, 제 1 신호선과 전기적으로 연결되는 소스 전극 및 화소 전극과 전기적으로 연결되는 드레인 전극을 포함한다.

- <38> 또한 상기 스위칭 박막 트랜지스터는 주사 신호를 인가하는 제 3 신호선 전기적으로 연결되는 게이트 전극, 제 2 신호선과 전기적으로 연결되는 소스 전극 및 상기 구동 박막 트랜지스터와 전기적으로 연결되는 드레인 전극을 포함한다.

- <39> 또한 상기 화소 전극과 대향하는 공통 전극 및 상기 화소 전극과 공통 전극 사이에 개재된 발광 물질을 더 포함한다.

- <40> 상기 구동 박막 트랜지스터의 구동 제어 전극은 상기 제 1 반도체 층 하부에 형성된 바텀 게이트 구조로 형성될 수 있다. 이 때 상기 구동 박막 트랜지스터의 게이트 전극과 상기 스위칭 박막 트랜지스터의 게이트 전극은 동일한 층 위에 형성될 수 있고, 상기 스위칭 박막 트랜지스터의 게이트 전극과 제 2 반도체 층 사이에는 두 층의 절연막이 개재된다.

- <41> 또한 상기 제 1 반도체 층 상부에 형성된 탑 게이트 구조로 형성될 수 있다. 이 때 상기 스위칭 박막 트랜지스터의 게이트 전극과 제 2 반도체 층 사이에는 한 층의 절연막이 개재된다.

- <42> 본 발명의 실시 예에 따른 표시 장치는 기판, 상기 기판 상에 형성되고 채널 영역을 포함하는 제 1 반도체 층 및 구동 전압을 전달하는 제 1 신호선을 포함하는 제 1 박막 트랜지스터, 제 1 박막 트랜지스터 상에 형성된 절연막 및 상기 절연막 상에 형성된 채널 영역을 포함하는 제 2 반도체 층 및 데이터 신호를 전달하는 제 2 신호선을 포함하는 제 2 박막 트랜지스터를 포함하고, 상기 제 1 신호선 및 제 2 신호선 중 적어도 하나는 하부에 상기 신호선의 폭보다 넓거나 동일한 폭을 갖는 반도체 층이 형성된다.

- <43> 상기 제 1 반도체 층 및 제 2 반도체 층의 결정 구조는 서로 다르게 형성되며, 상기 제 1 반도체 층은 다결정 실리콘 및 미세 결정질 실리콘 중 어느 하나를 포함하고 상기 제 2 반도체 층은 비정질 실리콘을 포함할 수 있다.

- <44> 제 1 박막 트랜지스터는 게이트 전극, 상기 제 1 신호선과 전기적으로 연결되는 소스 전극 및 화소 전극과 전기적으로 연결되는 드레인 전극을 포함한다. 제 2 박막 트랜지스터는 주사 신호를 제공하는 제 3 신호선과 전기적으로 연결되는 게이트 전극, 데이터 신호를 제공하는 제 2 신호선과 전기적으로 연결되는 소스 전극 및 제 1 박막 트랜지스터의 게이트 전극과 전기적으로 연결되는 드레인 전극을 포함한다.

- <45> 또한 상기 화소 전극과 대향하는 공통 전극 및 상기 화소 전극과 공통 전극 사이에 개재된 발광 물질을 더 포함한다.

- <46> 상기 제 1 박막 트랜지스터의 게이트 전극은 상기 제 1 반도체 층 하부에 형성된 바텀 게이트 구조이거나 상기 제 1 반도체 층 상부에 형성된 탑 게이트 구조로 형성될 수 있다.

- <47> 본 발명의 일 실시 예에 의한 표시 장치는 기판, 상기 기판 상에 형성되고 채널 영역을 포함하는 제 1 반도체 층을 포함하는 구동 박막 트랜지스터, 상기 구동 박막 트랜지스터 상에 형성된 절연막, 상기 절연막 상에 형성된 채널 영역을 포함하는 제 2 반도체 층을 포함하는 스위칭 박막 트랜지스터, 상기 구동 박막 트랜지스터와 연결되어 있는 제 1 전극, 제 1 전극과 마주보는 제 2 전극 및 제 1 전극과 제 2 전극 사이에 형성되어 있는 발광 부재를 포함하고, 상기 구동 박막 트랜지스터의 게이트 전극과 스위칭 박막 트랜지스터의 게이트 전극은 동일한 층 위에 형성된다.

- <48> 이 때 상기 스위칭 박막 트랜지스터 및 구동 박막 트랜지스터 중 적어도 하나의 소스 전극과 드레인 전극 전체가 채널 영역을 제외한 반도체층 상부에 형성되고, 상기 제 1 반도체 층은 다결정 실리콘 층을 포함하고, 상기 제 2 반도체 층은 비정질 실리콘 층을 포함한다.

- <49> 본 발명의 다른 실시 예에 따른 표시 장치는 기판, 상기 기판 상에 형성된 구동 반도체 층, 상기 구동 반도체 층 상부에 형성된 구동 입력 전극 및 구동 출력 전극, 상기 구동 입력 전극 및 구동 출력 전극 상에 형성된 제 1 절연막, 제 1 절연막 상에 형성되고, 상기 구동 반도체 층과 일부 중첩되는 구동 제어 전극, 상기 구동 제어 전극과 동일 층에 형성된 스위칭 제어 전극, 상기 구동 제어 전극과 스위칭 제어 전극 상에 형성된 제 2 절연막, 제 2 절연막 상에 형성되고, 상기 스위칭 제어 전극과 일부 중첩하는 스위칭 반도체 층, 상기 스위칭 반도체 층 상부에 형성된 스위칭 입력 전극 및 스위칭 출력 전극, 상기 스위칭 출력 전극과 구동 제어 전극과 전기적으로 연결된 연결 부재, 상기 연결 부재와 동일한 층에 형성되고, 구동 출력 전극과 전기적으로 연결된 화소 전극 및 상기 화소 전극 상부에 형성된 유기 발광 재료를 포함한다.

- <50> 이 때 상기 스위칭 박막 트랜지스터 및 구동 박막 트랜지스터 중 적어도 하나의 입력 전극과 출력 전극의 전 영역은 채널 영역을 제외한 반도체층 상부에 형성되고, 상기 구동 반도체 층은 다결정 실리콘 층을 포함하고, 상기 스위칭 반도체 층은 비정질 실리콘 층을 포함한다.

- <51> 본 발명의 실시 예에 따른 표시 장치의 제조 방법은 기판 상에 구동 제어 전극 및 스위칭 제어 전극을 형성하는 단계, 상기 구동 제어 전극 및 스위칭 제어 전극 상에 제 1 절연막을 형성하는 단계, 상기 제 1 절연막 상에 구동 반도체 층을 적층하는 단계, 상기 구동 반도체 층을 결정화하는 단계, 상기 결정화된 구동 반도체 층 상에 제 1 도전층을 적층하는 단계, 동일한 마스크를 사용하여 상기 결정화된 구동 반도체 층 및 제 1 도전층을 식각

하여 구동 박막 트랜지스터를 형성하는 단계, 상기 구동 박막 트랜지스터 상에 제 2 절연막을 형성하는 단계, 상기 제 2 절연막 상에 스위칭 반도체 층 및 제 2 도전층을 적층하는 단계 및 동일한 마스크를 사용하여 상기 스위칭 반도체 층 및 제 2 도전층을 식각하여 스위칭 박막 트랜지스터를 형성하는 단계를 포함한다,

<52> 그 후 상기 스위칭 박막 트랜지스터 상에 상기 구동 제어 전극 및 상기 구동 박막 트랜지스터 및 스위칭 박막 트랜지스터의 출력 전극을 외부에 노출 시키는 컨택홀을 포함하는 패시베이션 층을 형성하는 단계, 상기 패시베이션 층 상에 상기 컨택홀을 통해 상기 구동 박막 트랜지스터 및 스위칭 박막 트랜지스터와 전기적으로 연결되는 화소 전극을 형성하는 단계, 상기 패시베이션 층 및 화소 전극 상에 격벽을 형성하는 단계 및 상기 격벽이 형성되지 않은 화소 전극 상에 발광 물질을 형성하는 단계를 포함한다.

<53> 이때 상기 구동 반도체 층은 고상 결정화 방법을 이용하여 결정화할 수 있다.

<54> 본 발명의 다른 실시 예에 따른 표시 장치의 제조 방법은 기판 상에 구동 반도체 층을 적층하는 단계, 상기 구동 반도체 층을 결정화하는 단계, 상기 결정화된 구동 반도체 층 상에 제 1 도전층을 적층하는 단계, 동일 마스크를 사용하여 상기 구동 반도체 층 및 제 1 도전층을 식각하는 단계, 상기 식각된 구동 반도체 층 및 제 1 도전층 상에 제 1 절연막을 형성하는 단계, 상기 제 1 절연막 상에 구동 제어 전극 및 스위칭 제어 전극을 형성하여 구동 박막 트랜지스터를 형성하는 단계, 상기 구동 제어 전극 및 스위칭 제어 전극 상에 제 2 절연막을 형성하는 단계, 상기 제 2 절연막 상에 스위칭 반도체 층 및 제 2 도전층을 적층하는 단계 및 동일한 마스크를 사용하여 상기 스위칭 반도체 층 및 제 2 도전층을 식각하여 스위칭 박막 트랜지스터를 형성하는 단계를 포함한다.

<55> 그 후 상기 스위칭 박막 트랜지스터 상에 상기 구동 제어 전극 및 상기 구동 박막 트랜지스터 및 스위칭 박막 트랜지스터의 드레인 전극을 외부에 노출 시키는 컨택홀을 포함하는 패시베이션 층을 형성하는 단계, 상기 패시베이션 층 상에 상기 컨택홀을 통해 상기 구동 박막 트랜지스터 및 스위칭 박막 트랜지스터와 전기적으로 연결되는 화소 전극을 형성하는 단계, 상기 패시베이션 층 및 화소 전극 상에 격벽을 형성하는 단계 및 상기 격벽이 형성되지 않은 화소 전극 상에 발광 물질을 형성하는 단계를 포함한다.

<56> 이때 상기 구동 반도체 층은 고상 결정화 방법을 이용하여 결정화할 수 있다.

<57> 기타 실시예의 구체적인 사항들은 상세한 설명 및 도면들에 포함되어 있다.

<58> 본 발명의 이점 및 특징, 그리고 그것들을 달성하는 방법은 첨부되는 도면과 함께 상세하게 후술되어 있는 실시 예를 참조하면 명확해질 것이다. 그러나 본 발명은 이하에서 개시되는 실시 예에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 수 있으며, 단지 본 실시 예를 본 발명의 개시가 완전하도록 하며, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 본 발명의 범주를 완전하게 알려주기 위해 제공되는 것이며, 본 발명은 청구항의 범주에 의해 정의될 뿐이다. 명세서 전체에 걸쳐 동일 참조 부호는 동일 구성 요소를 지칭한다.

<59> 본 명세서에서 사용된 용어들은 실시예들을 설명하기 위한 것으로 본 발명을 제한하고자 하는 것은 아니다. 본 명세서에서 단수형은 문구에서 특별히 언급하지 않는 한 복수형도 포함한다. 본 명세서에서 사용되는 “포함한다(comprise)” 및/또는 “포함하는(comprising)”은 언급된 구성 요소, 단계, 동작 및/또는 소자에 하나 이상의 다른 구성 요소, 단계, 동작 및/또는 소자의 존재 또는 추가를 배제하지 않는다.

<60> 또한 본 명세서에서 층 또는 막의 “위”, “상”, “상부” 또는 “아래”, “하부”로 지칭되는 것은 중간에 다른 층 또는 막을 개재한 경우를 포함한다. 또한, 본 명세서에서 사용되는 “중첩”은 하부 구조물과 상부 구조물이 서로 공통된 중심을 갖고 겹쳐져 있는 형상을 나타내고, 하부 구조물과 상부 구조물 사이에 다른 구조물이 개재한 경우를 포함하며, 상부 구조물과 하부 구조물 중 어느 하나의 구조물은 다른 구조물에 완전히 겹쳐지는 것을 의미한다.

<61> 이하 첨부된 도면을 바탕으로 본 발명의 실시 예에 따른 표시 장치 및 그 제조 방법을 설명한다.

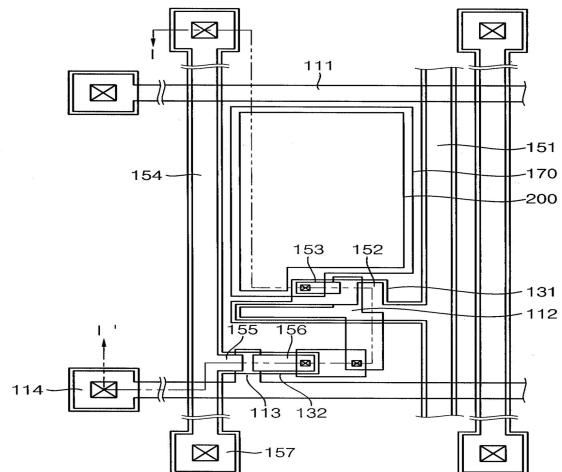

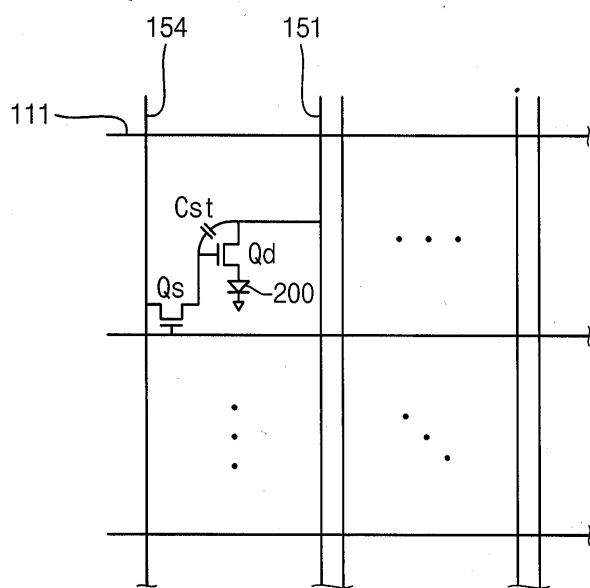

<62> 먼저 본 발명의 실시예에 따른 유기 발광 표시 장치에 대하여 도 1을 참고로 상세하게 설명한다.

<63> 도 1은 본 발명의 실시 예에 따른 표시 장치의 등가 회로도이다.

<64> 도 1을 참고하면 본 발명의 실시 예에 따른 표시 장치는 복수의 신호선(111, 151, 154)과 이들에 연결되어 있으며 대략 행렬(matrix)의 형태로 배열된 복수의 화소(pixel)를 포함한다.

<65> 상기 신호선은 케이트 신호(또는 주사 신호)를 전달하는 복수의 케이트 선(111), 데이터 신호를 전달하는 복수의 데이터 선(154) 및 구동 전압을 전달하는 복수의 구동 전압선(151)을 포함한다. 케이트선(111)은 대략 행 방향으로 뻗어 있으며 서로 거의 평행하고 데이터 선(154)과 구동 전압선(151)은 대략 열 방향으로 뻗어 있으며

서로 거의 평행하다.

- <66> 각 화소(PX)는 스위칭 트랜지스터(Switching Transistor)(Qs), 구동 트랜지스터(Driving Transistor)(Qd), 유지 축전기(Storage Capacitor)(Cst) 및 유기 발광 다이오드(Organic Light Emitting Diode, OLED)(200)를 포함한다.

- <67> 스위칭 트랜지스터(Qs)는 제어 전극(control terminal), 입력 전극(input terminal) 및 출력 전극(output terminal)을 갖는데, 상기 제어 전극은 게이트선(111)에 연결되어 있고, 상기 입력 전극은 데이터 선(151)에 연결되어 있으며, 상기 출력 전극은 구동 트랜지스터(Qd)의 제어 전극에 연결되어 있다. 이때 상기 제어 전극, 입력 전극 및 제어 전극은 일반적으로 박막 트랜지스터의 게이트 전극, 소스 전극 및 드레인 전극을 지칭한다.

- <68> 스위칭 트랜지스터(Qs)는 게이트선(111)에 인가되는 주사 신호에 응답하여 데이터 선(154)에 인가되는 데이터 신호를 구동 트랜지스터(Qd)에 전달한다.

- <69> 구동 트랜지스터(Qd) 또한 제어 전극, 입력 전극 및 출력 전극을 갖는데, 상기 제어 전극은 스위칭 트랜지스터(Qs)의 출력 전극에 연결되어 있고, 상기 입력 전극은 구동 전압선(151)에 연결되어 있으며, 상기 출력 전극은 화소 전극과 접촉하여 발광 소자(OLED)에 연결되어 있다.

- <70> 축전기(Cst)는 구동 트랜지스터(Qd)의 제어 전극과 입력 전극 사이에 연결되어 있다. 상기 축전기(Cst)는 구동 트랜지스터(Qd)의 제어 전극에 인가되는 데이터 신호를 충전하여 스위칭 트랜지스터(Qs)가 턴 오프(turn-off)된 뒤에도 이를 유지한다.

- <71> 유기 발광 소자(200)는 구동 트랜지스터(Qd)의 출력 전류의 크기에 따라서 빛의 세기를 달리함으로써 원하는 영상을 표시한다.

- <72> 스위칭 트랜지스터(Qs) 및 구동 트랜지스터(Qd)는 n-채널 전계 효과 트랜지스터(Field Effect Transistor, FET)로 형성되거나, 상기 스위칭 트랜지스터(Qs)와 상기 구동 트랜지스터(Qd) 중 적어도 하나는 p-채널 전계 효과 트랜지스터일 수 있다. 또한 상기 트랜지스터(Qs, Qd), 축전기(Cst) 및 유기 발광 소자(200)의 연결 관계가 서로 바뀔 수 있다.

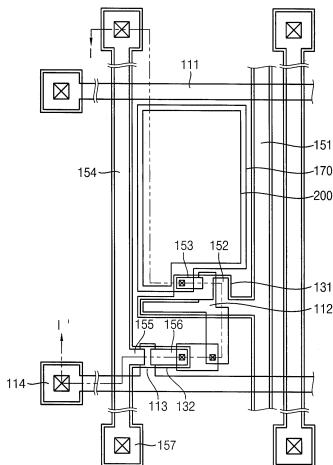

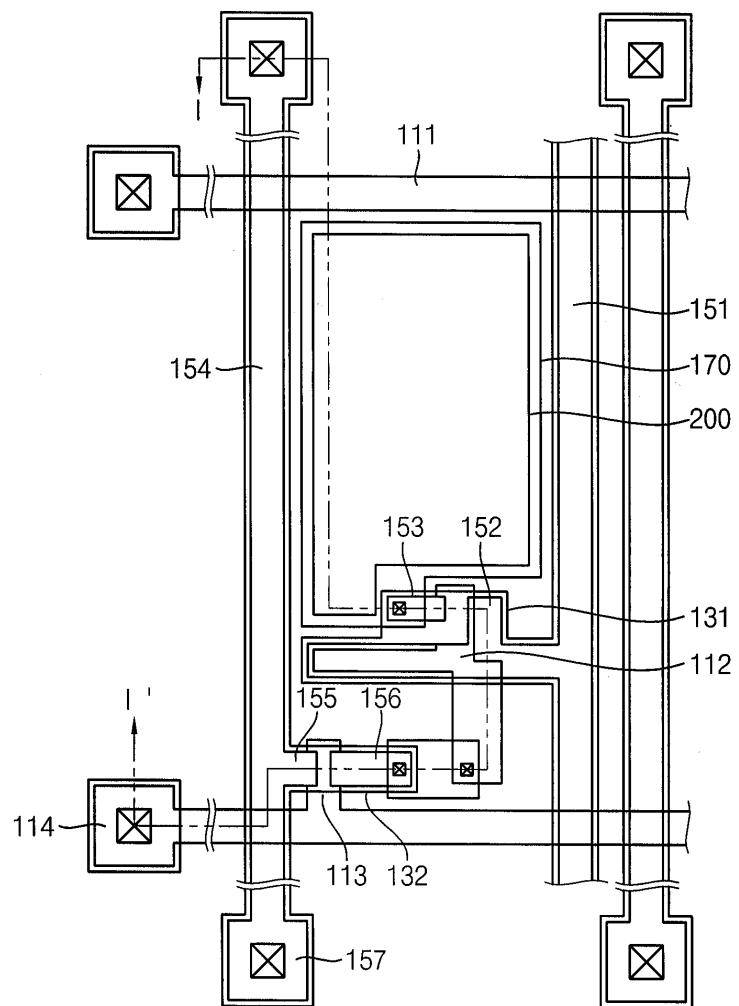

- <73> 이하 도 2 내지 도 9를 바탕으로 본 발명의 일 실시 예에 따른 표시 장치의 구조 및 그 제조 방법을 상세히 설명한다.

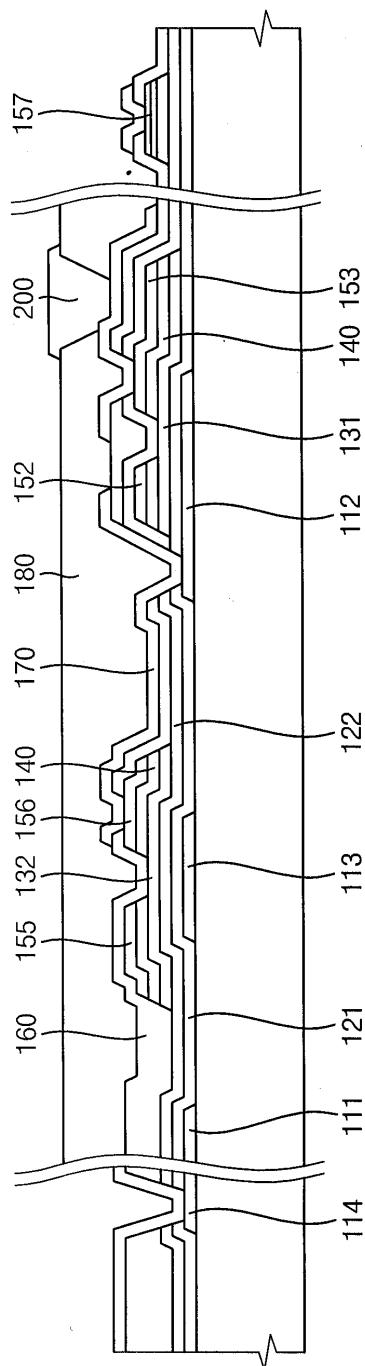

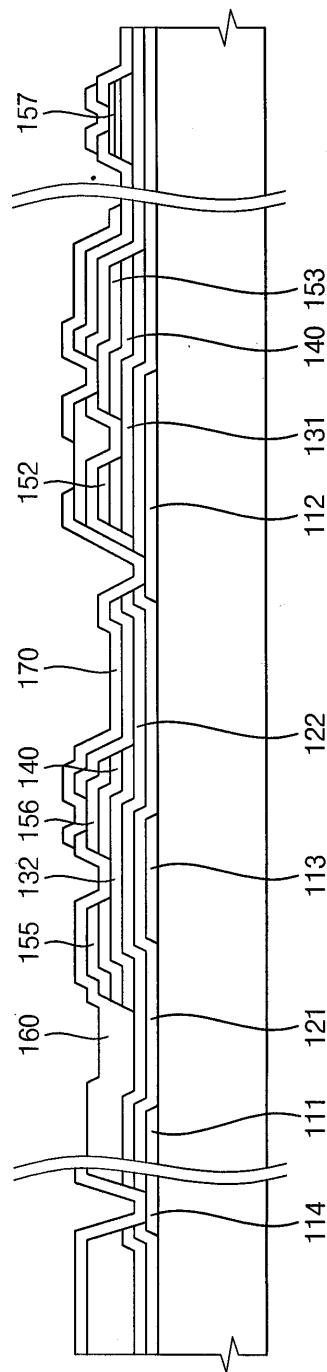

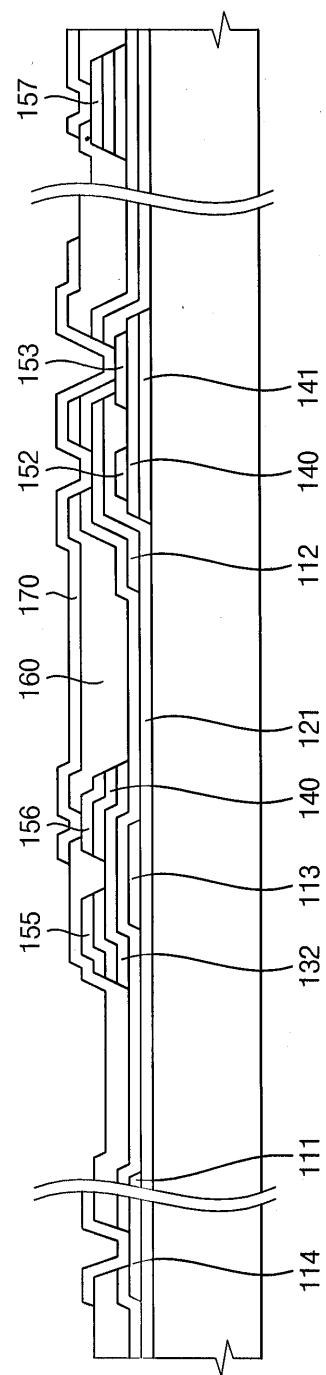

- <74> 도 2는 본 발명의 일 실시 예에 따른 표시 장치의 배치도이고, 도 3은 도 2에 도시된 표시 장치를 I-I선을 따라 자른 본 발명의 일 실시 예에 따른 표시 장치의 단면도이다.

- <75> 투명한 유리 또는 플라스틱 따위로 만들어진 기판(100) 위에 구동 제어 전극(driving control electrode)(112), 스위칭 제어 전극(switching driving control electrode)(113), 게이트 선(111) 및 게이트 패드(114)가 형성된다.

- <76> 구동 제어 전극(112)은 구동 박막 트랜지스터(Qd)의 게이트 전극 역할을 하며, 스위칭 박막 트랜지스터(Qs)를 통해 인가된 데이터 전압에 의해 상기 구동 박막 트랜지스터(Qd)의 턴 온(Turn On) 또는 턴 오프(Turn Off)를 제어한다. 또한 상기 구동 제어 전극(Qd)은 절연막을 사이에 두고 구동 박막 트랜지스터(Qs)의 입력 전극과 중첩하여 가로 방향으로 길게 뻗은 유지 전극(storage capacitor)을 형성한다.

- <77> 또한 스위칭 제어 전극(113)은 스위칭 박막 트랜지스터(Qs)의 게이트 전극 역할을 하며, 행 방향으로 다수 형성된 게이트 선(111)과 연결되어 있다. 상기 스위칭 제어 전극(113)은 상기 게이트 선(111)을 통해 전달된 주사 신호에 의해 상기 스위칭 박막 트랜지스터(Qs)를 턴 온(Turn On) 또는 턴 오프(Turn Off)를 제어한다.

- <78> 또한 게이트 패드(114)는 상기 게이트 선의 일 측 단부 또는 양 측 단부에 형성되어 외부 구동 칩 또는 패널에 실장된 게이트 구동 회로에서 인가되는 주사 신호를 상기 게이트 선에 인가해준다.

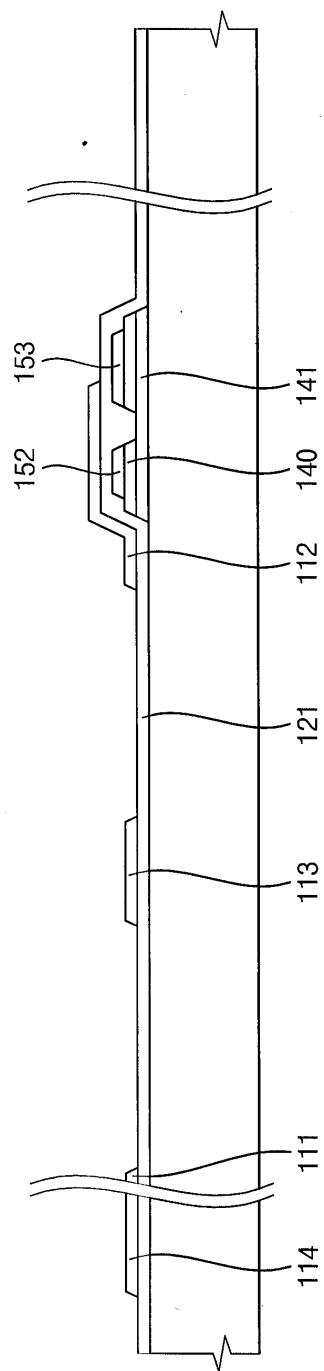

- <79> 도 3에 도시된 바와 같이, 기판 위에 상기 게이트 선(111), 구동 제어 전극(112), 스위칭 제어 전극(113)이 형성되고 그 위에 질화규소(SiNx) 또는 산화규소(SiOx) 따위로 만들어진 제 1 절연막(121)이 형성되어 있다.

- <80> 우선 도 2와 도 3를 참조하여, 표시 장치의 구동 박막 트랜지스터(Qd)부의 구조에 대하여 설명하면 다음과 같다.

- <81> 제 1 절연막(121) 위에는 미세 결정질 규소(microcrystalline silicon) 또는 다결정 규소(polycrystalline silicon)로 만들어진 구동 반도체(131)가 형성되어 있다. 상기 구동 반도체(131)는 구동 제어 전극(112)과 중

첩되어 구동 박막 트랜지스터(Qd)의 채널 영역 역할을 한다.

<82> 구동 박막 트랜지스터(Qd)의 채널 영역을 제외한 구동 반도체 층(131) 위에는 저항성 접촉 부재(140)가 형성되고 그 위에 구동 입력 전극(152), 구동 출력 전극(153)이 형성되어 있다. 또한 상기 구동 반도체 층(131) 패턴의 폭은 그 위에 형성된 상기 구동 입력 전극(152) 및 구동 출력 전극(153), 구동 전압선(151) 패턴의 폭보다 넓거나 동일하게 형성하는 것이 바람직하다.

<83> 상기 구동 입력 전극(152)은 구동 전압선(151)과 연결되어 상기 구동 박막 트랜지스터(Qd)의 소스 전극 역할을 한다. 상기 구동 출력 전극(153)은 상기 구동 입력 전극(152)과 채널 영역을 사이에 두고 서로 마주보며 형성되며, 구동 박막 트랜지스터(Qd)의 드레인 전극 역할을 한다. 또한, 상기 구동 전압선(151)은 표시 장치의 열 방향으로 형성되어 외부에서 입력되는 구동 전압을 상기 구동 박막 트랜지스터(Qd)에 전달한다.

<84> 저항성 접촉 부재(140)는 예를 들어 인(P) 따위의 n형 불순물이 고농도로 도핑되어 상기 구동 박막 트랜지스터(Qd)에서 소수 캐리어에 의한 오프 전류의 발생을 최소화시키는 역할을 한다.

<85> 도 3에 도시된 바와 같이 본 발명의 일 실시 예에 따른 표시 장치의 구동 박막 트랜지스터(Qd)는 구동 반도체 층(131) 하부에 구동 제어 전극(112)이 형성되는 바텀 게이트(bottom gate) 구조로 형성될 수 있다.

<86> 상기 구동 반도체 층(131), 구동 입력 전극(152) 및 구동 출력 전극(153) 위에는 질화규소(SiNx) 또는 산화규소(SiOx) 따위로 만들어진 제 2 절연막(122)이 형성되어 있다.

<87> 제 2 절연막(122) 위에 질화규소(SiNx) 또는 산화규소(SiOx) 따위로 만들어진 패시베이션 층(160)이 형성되어 있다.

<88> 상기 패시베이션 층(160)은 상기 구동 박막 트랜지스터(Qd)를 보호하는 역할을 한다.

<89> 다음으로, 도 2와 도 3을 참조하여 스위칭 박막 트랜지스터(Qs)의 구조를 설명하면 다음과 같다.

<90> 스위칭 박막 트랜지스터(Qs)의 스위칭 제어 전극(113)은 전술한 바와 같이 게이트 층(111) 및 구동 제어 전극(112)과 동일한 층에 형성된다. 상기 스위칭 제어 전극(113) 위에는 제 1 절연막(121) 위에 및 제 2 절연막(122)이 형성되어 있다. 제 2 절연막(122) 위에 비정질 실리콘(Amorphous Silicon)으로 만들어진 스위칭 반도체(132)가 형성된다. 상기 스위칭 반도체(132)는 스위칭 박막 트랜지스터(Qs)의 채널 영역 역할을 한다.

<91> 즉, 본 발명의 일 실시 예에 따른 표시 장치의 스위칭 제어 전극(113) 및 스위칭 반도체 층(132) 사이에는 두 층의 절연막이 개재된다.

<92> 스위칭 박막 트랜지스터(Qs)의 채널 층을 제외한 스위칭 반도체 층(132) 위에는 저항성 접촉 부재(140)가 형성되고 그 위에 스위칭 입력 전극(155), 스위칭 출력 전극(156)이 형성된다. 또한, 상기 스위칭 반도체 층 패턴의 폭은 상기 스위칭 입력 전극(155) 및 스위칭 출력 전극(156), 데이터 선(157) 패턴의 폭보다 넓거나 동일하게 형성하는 것이 바람직하다.

<93> 상기 스위칭 입력 전극(155)은 스위칭 박막 트랜지스터(Qs)의 소스 전극 역할을 한다. 상기 스위칭 출력 전극(156)은 상기 스위칭 입력 전극(155)과 채널 영역을 사이에 두고 서로 마주보며 형성되며, 스위칭 박막 트랜지스터(Qs)의 드레인 전극 역할을 한다. 상기 스위칭 출력 전극(156)은 연결 부재(171)에 의하여 상기 구동 제어 전극(112)과 연결되어 출력되는 데이터 신호에 의해 상기 구동 박막 트랜지스터(Qd)를 턴 온(Turn On) 또는 턴 오프(Turn Off) 시킨다. 상기 데이터 선(154)은 표시 장치의 열 방향으로 형성되어 외부에서 입력되는 데이터 신호를 상기 스위칭 박막 트랜지스터(Qs)에 전달하는 역할을 한다. 상기 연결 부재(171)는 후술하는 화소전극(170)과 동일한 물질로 형성된다.

<94> 상기 스위칭 반도체 층(132), 스위칭 입력 전극(155) 및 스위칭 출력 전극(156)을 포함하는 스위칭 박막 트랜지스터(Qs) 위에는 질화규소(SiNx) 또는 산화규소(SiOx) 따위로 만들어진 패시베이션 층(160)이 형성된다.

<95> 상기 패시베이션 층(160)은 상기 스위칭 박막 트랜지스터(Qs)를 보호하는 역할을 한다.

<96> 또한, 상기 패시베이션 층(160) 위에 화소 전극(170) 및 연결 부재(171)가 형성된다. 전술한 바와 같이 상기 연결 부재(171)는 컨택홀을 통해 스위칭 출력 전극(156)과 구동 제어 전극(112)과 직접 접촉하여 스위칭 박막 트랜지스터(Qs)와 구동 박막 트랜지스터(Qd)를 서로 전기적으로 연결한다. 또한 상기 화소 전극(170)은 컨택홀을 통해 구동 출력 전극(153)과 직접 접촉된다.

<97> 이러한 구조에 의하여, 상기 화소 전극(170)은 상기 구동 박막 트랜지스터(Qd)에서 출력되는 전류를 유기 발광

물질(200)에 전달 한다. 이때 상기 화소 전극(170)은 다수의 정공(hole)을 상기 유기 발광 물질(200)에 전달하는 양극(anode) 역할을 한다.

<98> 상기 패시베이션 층(160) 및 화소 전극(170) 상부에는 격벽(partition)(180)이 형성되어 있다. 상기 격벽(180)은 게이트 선(111), 구동 전압선(151), 데이터 선(154), 스위칭 박막 트랜지스터(Qs), 구동 박막 트랜지스터(Qd) 및 화소 전극(170) 중 일부 가장 자리 주변 위에 형성된다. 즉 상기 화소 전극(170) 중 격벽(180)이 형성되지 않은 개구부가 형성되고, 상기 개구부 상부에 유기 발광 물질(200)이 형성된다. 격벽(180)은 아크릴 수지(acrylic resin), 폴리이미드 수지(polyimide resin) 따위의 내열성 및 내용매성을 가지는 유기 절연물 또는 산화규소(SiO<sub>2</sub>), 산화티탄(TiO<sub>2</sub>) 따위의 무기 절연물로 만들어질 수 있으며 2층 이상일 수 있다. 격벽(180)은 또한 검정색 안료를 포함하는 감광재로 만들어질 수 있다.

<99> 전술한 바와 같이, 스위칭 반도체 층(132)는 비정질 반도체로 만들어지고, 구동 반도체 층(131)는 미세 결정질 또는 다결정 반도체로 만들어져, 스위칭 박막 트랜지스터(Qs)와 구동 박막 트랜지스터(Qd)의 채널은 결정 구조가 서로 다르게 형성된다.

<100> 구동 박막 트랜지스터(Qd)의 채널을 미세 결정질 또는 다결정 반도체에 형성함으로써 높은 전하 이동도(carrier mobility) 및 안정성(stability)을 가질 수 있다. 이에 따라 발광 소자에 흐르는 전류량을 늘릴 수 있어 표시 장치에서 출사되는 빛의 휘도를 높일 수 있다.

<101> 한편, 스위칭 박막 트랜지스터(Qs)는 특히 오프 전류(off current)에 의해 축전기(Cst)에 충전된 전하가 외부로 누출되는 것을 최소화해주어야 한다. 이에 상기 미세 결정질 또는 다결정 반도체에 비해 오프 전류(off current)가 낮은 비정질 반도체를 이용하여 상기 스위칭 박막 트랜지스터(Qs)의 채널 영역으로 사용하여야 한다.

<102> 본 실시예에서는 스위칭 박막 트랜지스터 1개와 구동 박막 트랜지스터 1개만을 도시하였지만 이들 외에 적어도 하나의 박막 트랜지스터 및 이를 구동하기 위한 복수의 배선을 더 포함함으로써, 장시간 구동하여도 유기 발광 재료(200) 및 구동 트랜지스터(Qd)가 열화되는 것을 방지하여 유기 발광 표시 장치의 수명이 단축되는 것을 방지할 수 있다.

<103> 이하에서, 도 4 내지 도 9를 참조하여 도 3에 도시한 본 발명의 일 실시 예에 따른 표시 장치를 제조하는 방법을 설명하면 다음과 같다.

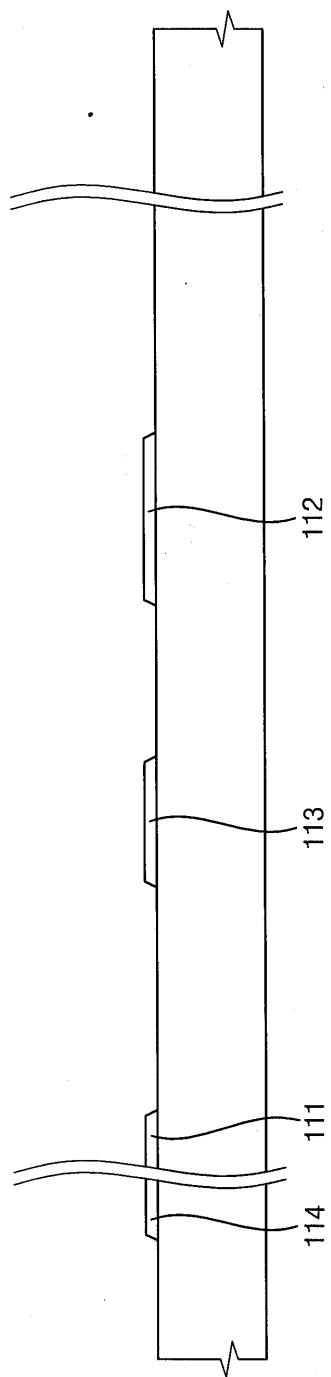

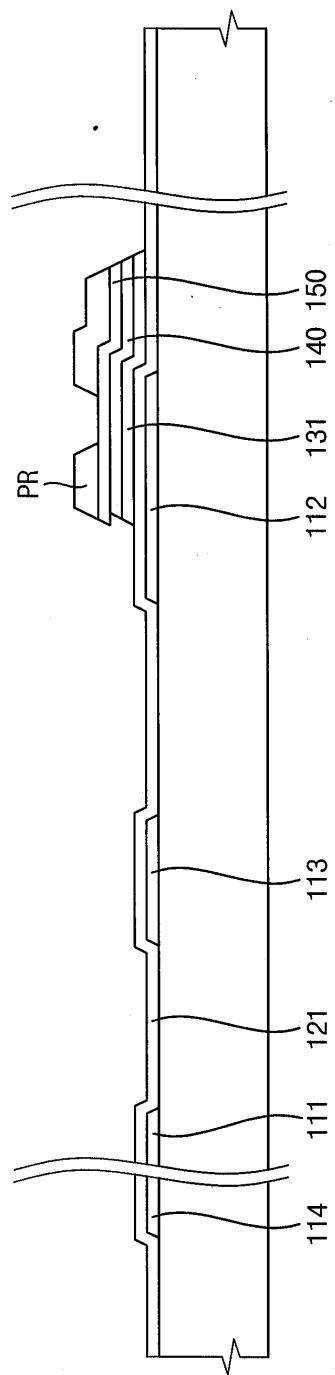

<104> 먼저, 도 4에 도시된 바와 같이, 상기 게이트 금속(110) 위에 포토 레지스트 막을 도포한 후 제 1 마스크를 사용하여 상기의 게이트 선(111), 게이트 패드(114), 구동 제어 전극(112) 및 스위칭 제어 전극(113) 패턴을 형성한다. 본 실시 예에서 상기 포토 레지스트 막은 현상 공정 후 자외선 등의 빛에 의해 노광되지 않은 부분이 잔존하는 포지티브(positive) 형을 사용하고 있으나, 노광된 영역이 잔존하는 네가티브(negative) 형이 사용될 수도 있다.

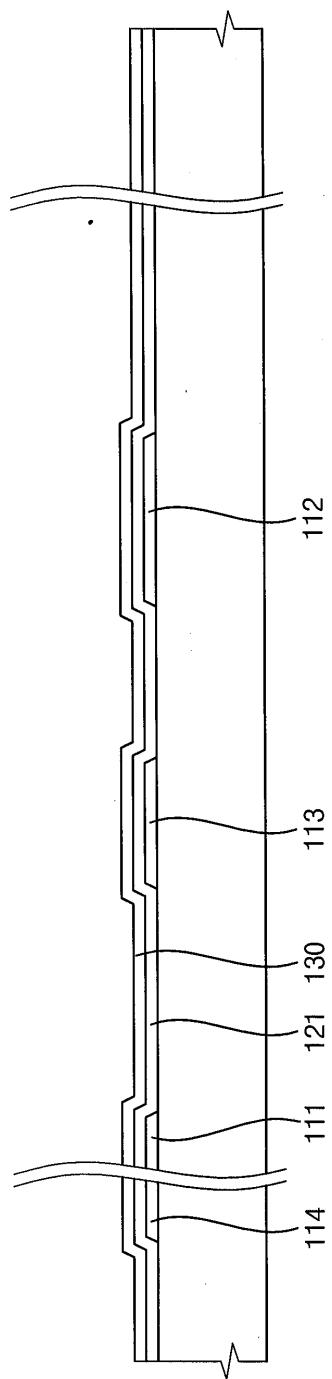

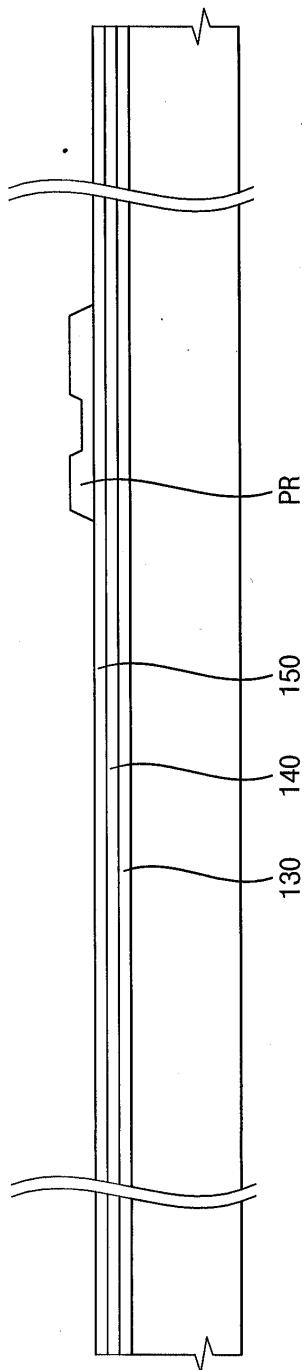

<105> 다음으로 도 5에 도시된 바와 같이, 상기 게이트 전극(111), 구동 제어 전극(112) 및 스위칭 제어 전극(113) 및 게이트 패드(114) 위에 제 1 절연막(121) 및 반도체 층(130)을 형성한다.

<106> 상기 반도체 층(130)을 증착한 후, 고상 결정화 방법(Solid Phase Crystallization, SPC), 급속 열처리 방법(Rapid Thermal Annealing, RTA) 또는 엑시머 레이저 방법(Excimer Laser Annealing, ELA)을 사용하여 상기 반도체 층(130)을 결정화할 수 있으며, 이중에서 고상 결정화 방법을 사용함이 바람직하다.

<107> 또는, 제 1 절연막(121), 반도체 층(130) 및 저항성 접촉 부재(140)를 연속적으로 도포한 후, 상기 반도체 층(130)을 결정화할 수도 있다.

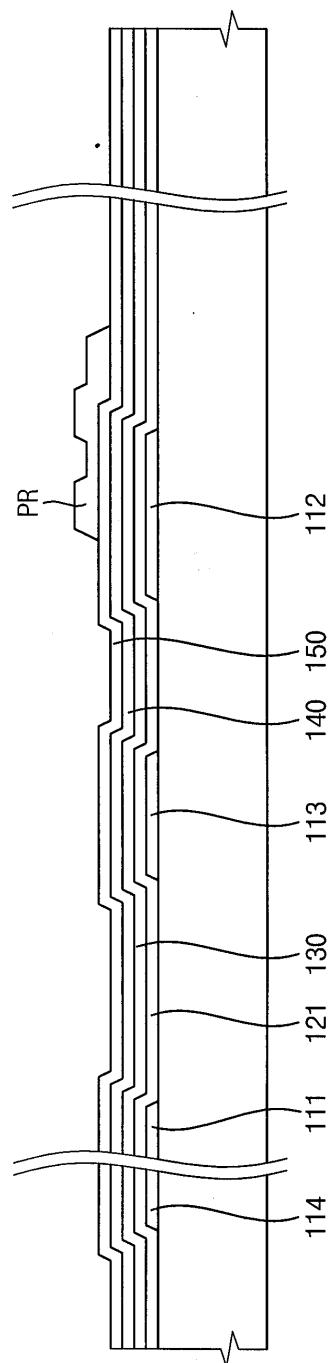

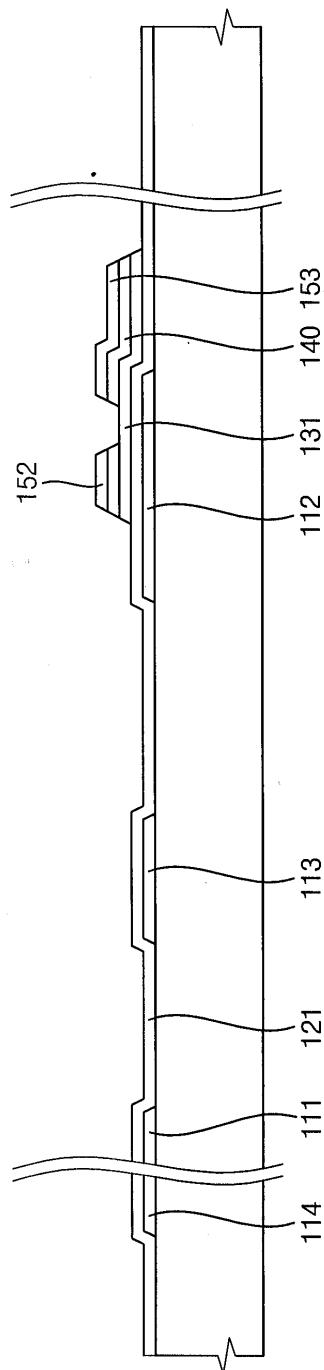

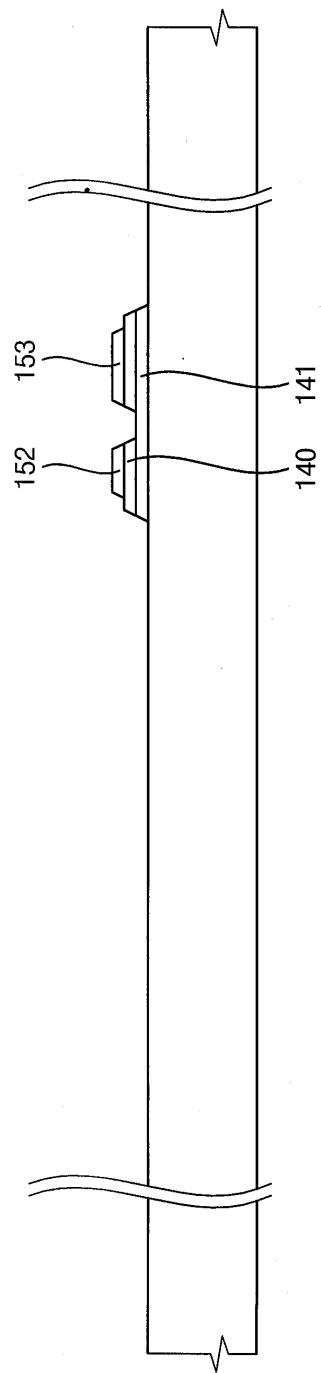

<108> 다음으로 도 6a에 도시된 바와 같이, 상기 반도체 층을 결정화 한 후, 상기 반도체 층 위에 저항성 접촉 부재(140) 및 데이터 금속(150)을 증착한다. 도 3에 도시된 상기 데이터 금속(150) 및 결정화된 구동 반도체 층(131)을 동시에 패터닝하기 위하여 상기 데이터 금속(150) 위에 포토 레지스트 막을 도포하고, 구동 박막 트랜지스터의 채널이 형성될 영역에 대응하는 부분이 슬릿(slit) 처리된 제 2 마스크를 사용하여 포토 레지스트 막(PR) 패턴을 형성한다.

<109> 이때, 제 2 마스크의 슬릿에 의하여 노광된 빛이 간섭 및 회절되기 때문에, 구동 박막 트랜지스터의 채널 형성 영역의 포토 레지스트 막 패턴의 두께는 구동 입력 전극(152), 구동 출력 전극(156) 및 구동 전압선(151)이 형성될 영역의 포토 레지스트 막 패턴의 두께보다 얇게 형성된다.

- <110> 다음으로, 도 6b에 도시된 바와 같이, 포토 레지스트 막 패턴을 이용하여 1차 식각을 하여 상기 데이터 금속(150), 저항성 접촉 부재(140) 및 반도체 층(130)을 제거한 다음, 구동 박막 트랜지스터(Qd)의 채널 형성 영역 상부의 포토 레지스트 막을 제거하는 에치 백(etch back) 공정을 진행한다. 다음으로 도 6c에 도시된 바와 같이, 상기 에치 백(etch back) 된 포토 레지스트 막을 이용하여 2 차 식각 공정을 진행하고 상기 포토 레지스트 막을 제거하면 구동 박막 트랜지스터(Qd)의 구동 입력 전극(152), 구동 출력 전극(153) 및 구동 전압선(151)과 구동 반도체 층(131)을 형성할 수 있다.

- <111> 이때, 상기 데이터 금속(150)은 구동 반도체 층(131)에 비해 한 번 더 많은 식각 공정을 거치게 되어 상기 구동 반도체 층(131)의 폭이 상기 구동 입력 전극(151), 구동 출력 전극(153) 및 구동 전압선(151)의 폭보다 넓거나 동일하게 형성된다.

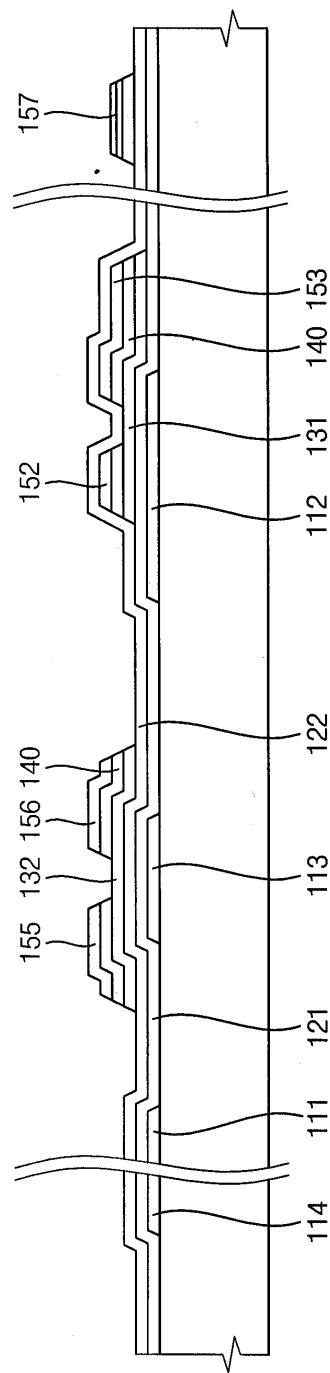

- <112> 다음으로 도 7에 도시된 박막 패턴의 형성하는 방법을 설명하면 다음과 같다. 도 6c에 의하여 형성된 박막 패턴 상에 제 2 절연막(122)을 전면 증착한다. 그 다음, 제 2 절연막(122) 위에 반도체 층, 저항성 접촉 부재 및 데이터 금속을 연속적으로 도포한다. 이때 상기 반도체 층은 별도의 결정화 공정을 거치지 않은 비정질 상태의 결정을 갖는다.

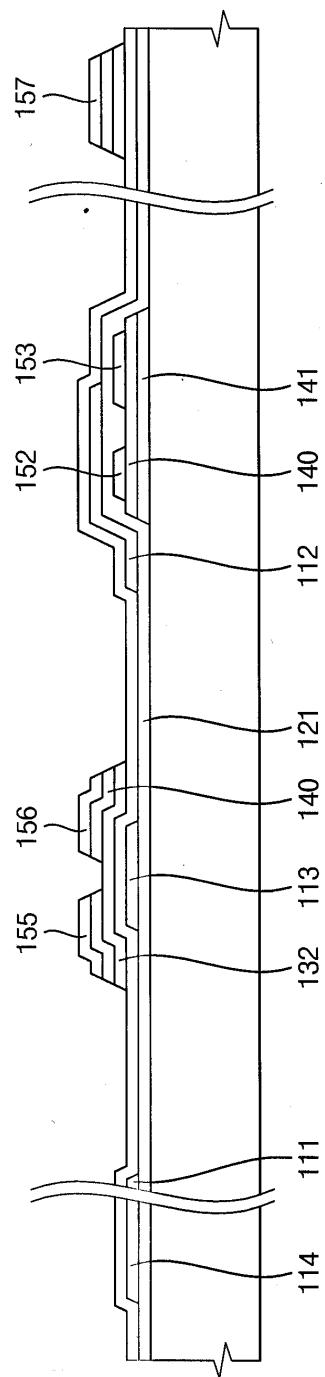

- <113> 그 후 상기 데이터 금속 상부에 포토 레지스트 막을 도포한 후 상기 구동 박막 트랜지스터(Qd)의 제조 방법과 동일하게 스위칭 박막 트랜지스터(Qs)의 채널 형성 영역에 슬릿 처리된 제 3 마스크를 사용하여 도 7에 도시된 바와 같이, 스위칭 반도체 층(132), 스위칭 입력 전극(155) 및 스위칭 출력 전극(156)을 포함하는 스위칭 박막 트랜지스터(Qs), 데이터 선(154) 및 데이터 패드(157)를 형성한다.

- <114> 상기 구동 박막 트랜지스터(Qd)와 동일하게 상기 스위칭 입력 전극(155), 스위칭 출력 전극(156) 및 데이터 패드(157)는 채널 형성 영역을 제외한 스위칭 반도체 층(132) 상에 형성된다. 또한 상기 스위칭 반도체 층(132)의 폭이 상기 스위칭 입력 전극(155), 스위칭 출력 전극(156) 및 데이터 선(154)의 폭보다 넓거나 또는 동일하게 형성된다.

- <115> 다음으로 도 8에 도시된 바와 같이, 상기 스위칭 박막 트랜지스터(Qs), 데이터 선(154) 및 데이터 패드(157) 위에 패시베이션 막(160)을 도포한 후, 제 4 마스크를 통하여 컨택홀을 포함하는 패시베이션 막(160) 패턴을 형성한다.

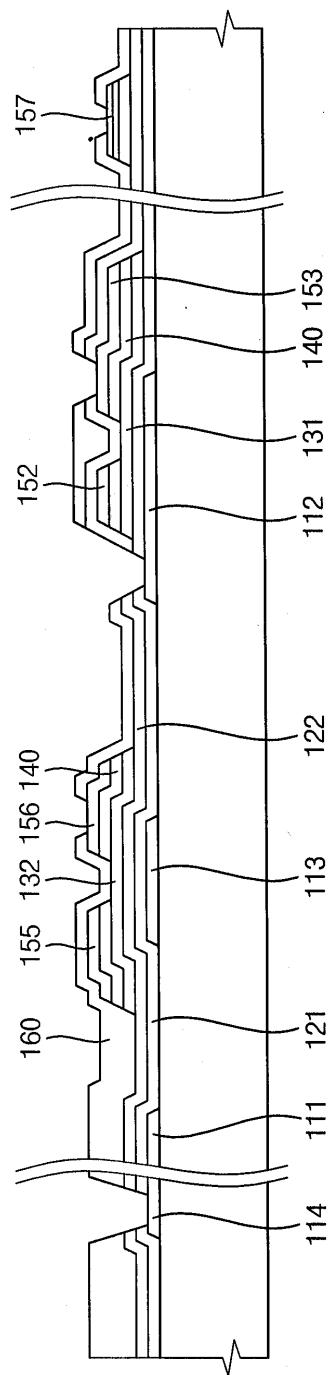

- <116> 그 후, 도 9에 도시된 바와 같이, 상기 컨택홀을 포함하는 패시베이션 층(160) 위에 화소 전극(170)을 증착하고, 제 5 마스크를 사용하여 상기 화소 전극(170)을 패터닝한다.

- <117> 다음으로 도 10에 도시된 바와 같이, 상기 패시베이션 층(160) 및 화소전극(170) 위에 제 6 마스크를 사용하여 격벽(180)을 형성한다. 상기 격벽(180)은 전술한 바와 같이 상기 화소 전극(170)의 일부가 노출되는 개구부를 제외한 화소의 전영역에 형성된다.

- <118> 그 후, 상기 화소 전극(170)의 개구부 상에 정공 수송층(비도시) 및 발광층(비도시)을 포함한 유기 발광 재료(200)를 형성한다. 상기 유기 발광 재료(200)는 잉크젯 인쇄(inkjet printing) 등의 방법으로 형성할 수 있다. 그리고 상기 화소 전극(170)과 대향하여 유기 발광 재료(200)에 전자(electron)을 제공하는 공통 전극(cathode)을 형성하여 표시 장치를 제조 한다.

- <119> 이하 도 10 내지 도 15를 바탕으로 본 발명의 다른 실시 예에 따른 표시 장치의 구조 및 그 제조 방법을 상세히 설명한다.

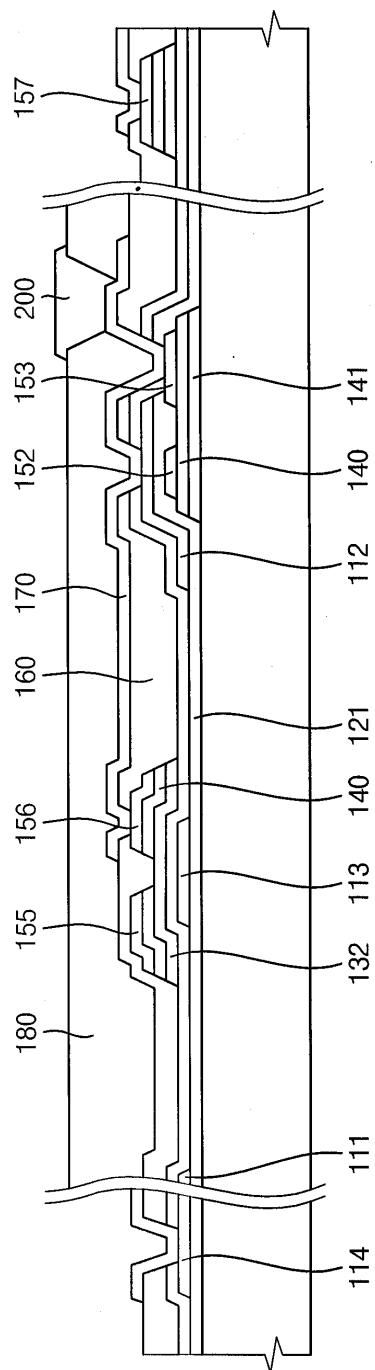

- <120> 도 10은 본 발명의 다른 실시 예에 따른 표시 장치의 구조를 나타낸 단면도이다.

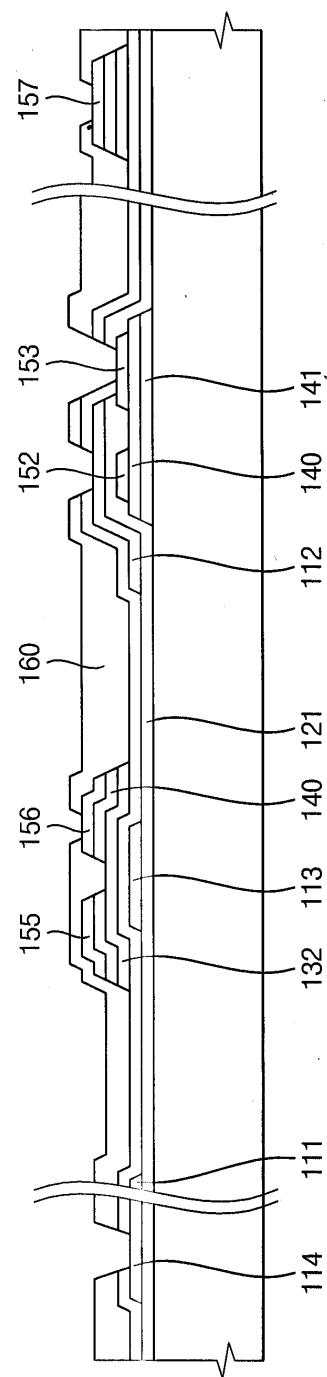

- <121> 본 발명의 다른 실시 예에 따른 표시 장치는 기판(100) 상에 구동 반도체 층(131), 저항성 접촉 부재(140), 구동 입력 전극(152) 및 구동 출력 전극(153)이 형성된다. 이때 상기 구동 반도체 층(131)은 본 발명의 일 실시 예에 따른 표시 장치의 구동 반도체 층과 동일하게 미세 결정질 규소(microcrystalline silicon) 또는 다결정 규소(polycrystalline silicon)로 형성된다. 또한 상기 구동 입력 전극(152) 및 구동 출력 전극(153)은 채널 영역을 제외한 반도체 층의 상부에 형성되고, 상기 구동 입력 전극 및 출력 전극의 폭은 상기 반도체 층의 폭보다 길거나 동일하게 형성된다.

- <122> 또한 상기 구동 반도체 층(131) 하부에는 기판으로부터 유입되는 오염원을 차단하는 블로킹 층(blocking layer, 미도시)가 형성될 수 있다. 상기 블로킹 층은 상기 구동 반도체 층(131)과 결정 구조가 유사한 산화규소(SiO<sub>x</sub>)로 형성될 수 있다.

- <123> 상기 구동 입력 전극(152) 및 구동 출력 전극(153) 위에는 제 1 절연막(121)이 형성된다. 제 1 절연막은(121)은 기판의 전면에 도포되어 상기 구동 입력 전극(152) 및 구동 출력 전극(153)과 구동 제어 전극(112)을 절연하는 역할을 한다.

- <124> 제 1 절연막(121) 위에는 구동 제어 전극(112), 스위칭 제어 전극(113), 게이트선(111) 및 게이트 패드(114)가 형성된다.

- <125> 본 발명의 다른 실시 예에 따른 표시 장치의 구동 박막 트랜지스터(Qd)는 구동 제어 전극(112)이 상기 구동 반도체 층(131) 위에 형성되는 탑 게이트(top gate) 구조로 형성된다.

- <126> 상기 구동 제어 전극(112) 및 스위칭 제어 전극(113) 위에는 제 2 절연막(122)이 형성된다. 제 2 절연막(122)은 제 1 절연막(121)의 기능과 유사하게 스위칭 제어 전극(113)과 스위칭 반도체 층(132)을 절연하는 역할을 한다.

- <127> 제 2 절연막(122) 위에는 스위칭 반도체 층(132), 저항성 접촉 부재(140), 스위칭 입력 전극(155), 스위칭 출력 전극(156)를 포함하는 스위칭 박막 트랜지스터(Qs), 데이터 선(154) 및 데이터 패드(157)가 형성된다.

- <128> 즉, 본 발명의 다른 실시 예에 따른 표시 장치의 스위칭 제어 전극(113)과 스위칭 반도체 층(132) 사이에는 한 층의 절연막이 개재된다.

- <129> 상기 스위칭 박막 트랜지스터(Qs)는 결정화가 이루어지지 않은 비정질 상태의 결정으로 형성된다. 그리고 본 발명의 일 실시 예에 따른 구동 박막 트랜지스터(Qd)와 동일하게 상기 스위칭 반도체 층(132)과 스위칭 입력 전극(155) 및 출력 전극(156)을 동일한 마스크를 사용하여 패터닝하여 스위칭 박막 트랜지스터(Qs)를 형성한다. 따라서 채널 영역을 제외한 반도체 층 상부에 상기 스위칭 입력 전극(155), 스위칭 출력 전극(156) 및 데이터 선(154)이 형성되고, 상기 반도체 층의 폭은 상기 스위칭 입력 전극, 스위칭 출력 전극 및 데이터 선의 폭보다 길거나 동일하게 형성된다.

- <130> 상기 스위칭 박막 트랜지스터(Qs) 위에는 상기 스위칭 박막 트랜지스터의 출력 전극(156), 구동 박막 트랜지스터의 제어 전극(112) 및 출력 전극이 화소 전극(170)과 전기적으로 연결되는 콘택홀을 포함하는 패시베이션 막(160)이 형성된다. 그리고 상기 패시베이션 막(180) 위에는 화소 전극(170) 및 격벽(180)이 형성된다. 상기 격벽(180)은 화소 전극(170)의 일부분이 노출되는 개구부가 형성되도록 패터닝된다.

- <131> 도 11a 내지 도 15는 본 발명의 다른 실시 예에 따른 표시 장치의 제조 방법을 나타내는 도면으로 도 10에 도시된 표시 장치를 제조하는 각 공정 단계 별 단면도이다.

- <132> 먼저, 도 11a에 도시된 바와 같이, 기판(100) 위에 반도체 층(130)을 증착한 후, 상기 반도체 층(130)을 결정화 한다. 상기 반도체 층(130)의 결정화는 고상 결정화 법(SPC), 급속 열처리 방법(Rapid Thermal Annealing, RTA) 또는 엑시머 레이저 방법(Excimer Laser Annealing, ELA)을 사용하여 상기 반도체 층(130)을 결정화할 수 있으며, 이중에서 고상 결정화 방법을 사용하는 것이 바람직하다.

- <133> 또는, 제 1 절연막(121), 반도체 층(130) 및 저항성 접촉 부재(140)를 연속적으로 도포한 후, 상기 반도체 층(130)을 결정화할 수 있다.

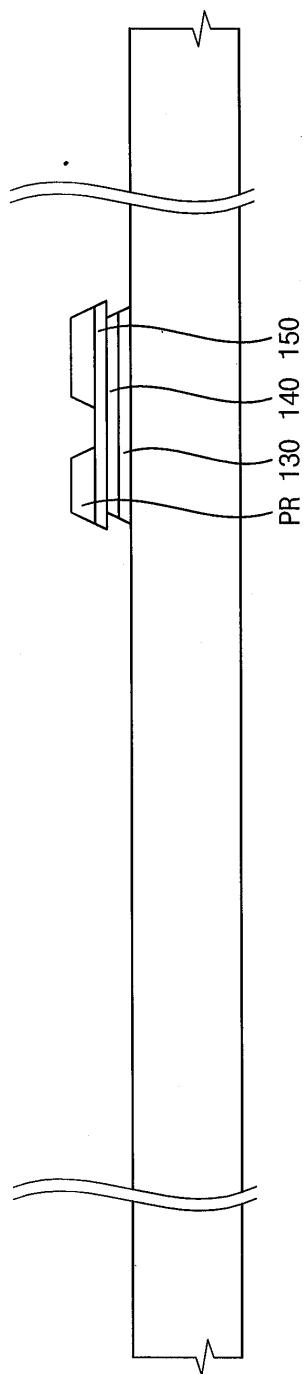

- <134> 그 다음, 본 발명의 일 실시 예에 따른 표시 장치의 구동 박막 트랜지스터(Qd)의 제조 방법과 동일하게 저항 접촉 부재(140) 및 데이터 금속(150)을 증착한다. 그리고 상기 데이터 금속(150) 위에 포토 레지스트 막(PR)을 도포한 후, 슬릿 처리된 제 1 마스크를 사용하여 포토 레지스트 막 패턴을 형성한다.

- <135> 다음으로, 도 11b에 도시된 바와 같이, 상기 포토 레지스트 막 패턴을 이용하여 1차 식각을 하여 데이터 금속(150), 저항성 접촉 부재(140) 및 반도체 층(130)을 제거한 후, 구동 박막 트랜지스터(Qd)의 채널 형성 영역 상부의 포토 레지스트 막 패턴을 제거하는 에치 백(etch back) 공정을 진행한다.

- <136> 다음으로, 도 11c에 도시된 바와 같이, 상기 에치 백(etch back) 된 포토 레지스트 막을 사용하여 2 차 식각 공정을 진행하고 상기 포토 레지스트 막을 제거하여 구동 박막 트랜지스터(Qd)의 구동 입력 전극(152), 구동 출력 전극(153) 및 구동 전압선(151)과 구동 반도체 층(131)을 형성한다.

- <137> 그 후, 상기 구동 반도체 층(131), 구동 입력 전극(152) 및 구동 출력 전극(153) 상부에 제 1 절연막(121) 및 게이트 금속(110)을 증착한 다음, 도 12에 도시된 바와 같이, 상기 게이트 금속(110)을 제 2 마스크를 사용하여 게이트선(111), 구동 제어 전극(112), 스위칭 제어 전극(113) 및 게이트 패드(114)가 형성된다.

- <138> 다음으로, 상기 스위칭 제어 전극(113) 위에 제 2 절연막(122) 및 반도체 층(130), 저항성 접촉 부재(140) 및

데이터 금속(150)을 연속 증착한다. 본 발명의 일 실시 예와 동일하게 스위칭 반도체 층(132)은 별도의 결정화 공정을 거치지 않은 비정질 실리콘 결정으로 구성된다. 또한, 도 13에 도시된 바와 같이, 본 발명의 일 실시 예에 따른 스위칭 박막 트랜지스터(Qs)의 제조 방법과 동일하게 채널 형성 영역에 대응하는 부위에 슬릿 처리된 제 3 마스크를 사용하여 상기 데이터 금속(150), 저항성 접촉 부재(140) 및 스위칭 반도체 층(132)을 패터닝하여 데이터 선(154), 데이터 패드(157) 및 스위칭 박막 트랜지스터(Qs)를 형성한다. 상기 스위칭 박막 트랜지스터의 입력 전극(155) 및 출력 전극(156), 데이터 선(154) 및 데이터 패드(157)는 스위칭 박막 트랜지스터의 채널 부위를 제외한 반도체 층 상부에 형성된다. 또한 상기 스위칭 반도체 층의 폭은 상기 스위칭 입력 전극, 스위칭 출력 전극 및 데이터 선의 폭에 비해 넓거나 동일하게 형성된다.

<139> 다음으로, 도 14에 도시된 바와 같이, 제 4 마스크를 사용하여 스위칭 출력 전극(156), 구동 제어 전극(112) 및 구동 출력 전극(152)이 화소 전극(170)과 직접 접촉할 수 있는 컨택홀을 포함하는 패시베이션 층(160)을 형성한다.

<140> 상기 패시베이션 층(160) 위에 화소 전극을 증착하고, 제 5 마스크를 사용하여 도 15에 도시된 표시 장치를 제조한다.

<141> 그 후 제 6 마스크를 사용하여 상기 패시베이션 층(160) 및 화소 전극 위에 격벽(180)을 형성한다. 상기 격벽(180)은 도 10에 도시된 바와 같이 화소 전극(170) 위에 유기 발광 재료(200)가 증착 될 수 있는 개구부를 포함한다.

<142> 그 후, 상기 화소 전극(170)의 개구부 상에 정공 수송층(도시하지 않음) 및 발광층(도시하지 않음)을 포함한 유기 발광 재료(200)를 형성한다. 그리고 상기 화소 전극(170)과 대향하여 유기 발광 재료(200)에 전자(electron)을 제공하는 공통 전극(cathode)를 형성하여 표시 장치를 제조 한다.

<143> 이상에서 설명한 본 발명의 일 실시 예 및 다른 실시 예에 따른 표시 장치의 구동 박막 트랜지스터(Qd) 및 스위칭 박막 트랜지스터(Qs)의 반도체 층과 입력 전극 및 출력 전극은 동일한 마스크를 사용하여 형성하였으나, 두 박막 트랜지스터(Qd, Qs) 중 어느 하나는 반도체 층과 입력 전극 및 출력 전극을 서로 다른 마스크를 사용하여 형성할 수 있다.

### 발명의 효과

<144> 이상에서 설명한 바와 같이 본 발명의 일 실시 예 및 다른 실시 예에 따른 표시 장치는 유기 발광 소자를 사용한 표시 장치의 스위칭 박막 트랜지스터 및 구동 박막 트랜지스터의 요구 특성을 만족한다.

<145> 또한 본 발명의 일 실시 예 및 다른 실시 예에 따른 표시 장치의 제조 방법을 사용하면 마스크 수를 감소시켜 공정을 단순화 시킬 수 있다.

### 도면의 간단한 설명

<1> 도 1은 본 발명의 실시 예에 따른 표시 장치의 등가 회로도이다.

<2> 도 2는 본 발명의 실시 예에 따른 표시 장치의 배치도이다.

<3> 도 3은 도 2에 도시된 표시 장치를 I-I선을 따라 절단한 본 발명의 일 실시 예에 따른 표시 장치의 단면도이다.

<4> 도 4 내지 도 9는 본 발명의 일 실시 예에 따른 제조 방법을 나타낸 단면도이다.

<5> 도 10은 도 2에 도시된 표시 장치를 I-I선을 따라 절단한 본 발명의 다른 실시 예에 따른 표시 장치의 단면도이다.

<6> 도 11a 내지 도 15는 본 발명의 다른 실시 예에 따른 제조 방법을 나타낸 단면도이다.

<7> <도면 부호의 설명>

<8> 100 : 기판 110 : 게이트 금속

<9> 111 : 게이트 선 112 : 구동 제어 전극

<10> 113 : 스위칭 제어 전극 114 : 게이트 패드

<11> 121 : 제 1 절연막 122 : 제 2 절연막

- <12> 130 : 반도체 층 131 : 구동 반도체 층

- <13> 132 : 스위칭 반도체 층 140 : 저항성 접촉 부재

- <14> 150 : 데이터 금속 151 : 구동 전압선

- <15> 152 : 구동 입력 전극 153 : 구동 출력 전극

- <16> 154 : 데이터 선 155 : 스위칭 입력 전극

- <17> 156 : 스위칭 출력 전극 157 : 데이터 패드

- <18> 160 : 패시베이션 층 170 : 화소 전극

- <19> 171 : 연결 부재 180 : 격벽

- <20> 200 : 유기 발광 재료

## 도면

### 도면1

## 도면2

도면3

도면4

도면5

도면6a

도면6b

도면6c

도면7

도면8

도면9

도면10

도면11a

도면11b

도면11c

도면12

도면13

도면14

도면15

|                |                                                                                                   |         |            |

|----------------|---------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置及其制造方法                                                                                        |         |            |

| 公开(公告)号        | <a href="#">KR1020070095620A</a>                                                                  | 公开(公告)日 | 2007-10-01 |

| 申请号            | KR1020060026031                                                                                   | 申请日     | 2006-03-22 |

| [标]申请(专利权)人(译) | 三星显示有限公司                                                                                          |         |            |

| 申请(专利权)人(译)    | 三星显示器有限公司                                                                                         |         |            |

| 当前申请(专利权)人(译)  | 三星显示器有限公司                                                                                         |         |            |

| [标]发明人         | CHOI JAE BEOM<br>최재범<br>CHANG YOUNG JIN<br>장영진<br>JUNG KWAN WOOK<br>정관욱<br>SHIM SEUNG HWAN<br>심승환 |         |            |

| 发明人            | 최재범<br>장영진<br>정관욱<br>심승환                                                                          |         |            |

| IPC分类号         | H01L51/52 H01L29/786 H01L51/50                                                                    |         |            |

| CPC分类号         | H01L27/3262 H01L27/1288 H01L29/04 H01L27/1229                                                     |         |            |

| 代理人(译)         | PARK , YOUNG WOO                                                                                  |         |            |

| 其他公开文献         | KR101277606B1                                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                         |         |            |

### 摘要(译)

本发明包括基板，驱动薄膜晶体管，包括形成在基板上并包括沟道区的半导体层，以及形成在驱动薄膜晶体管上的绝缘层和包括第二半导体的开关薄膜晶体管包括形成在绝缘层上的沟道区的层。并且，在驱动薄膜晶体管之间设置至少一个源电极，包括源电极的显示装置，其中漏电极整体形成在除沟道区和漏电极之外的半导体层的上部中并切换薄膜晶体管。本发明提供一种显示装置的结构，其同时满足开关薄膜晶体管和驱动薄膜晶体管所需的性能及其制造方法的有机发光显示装置。有机发光器件，半导体，晶态，电荷迁移率，截止电流，发射电流。